Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

55results about How to "Improve trade-offs" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

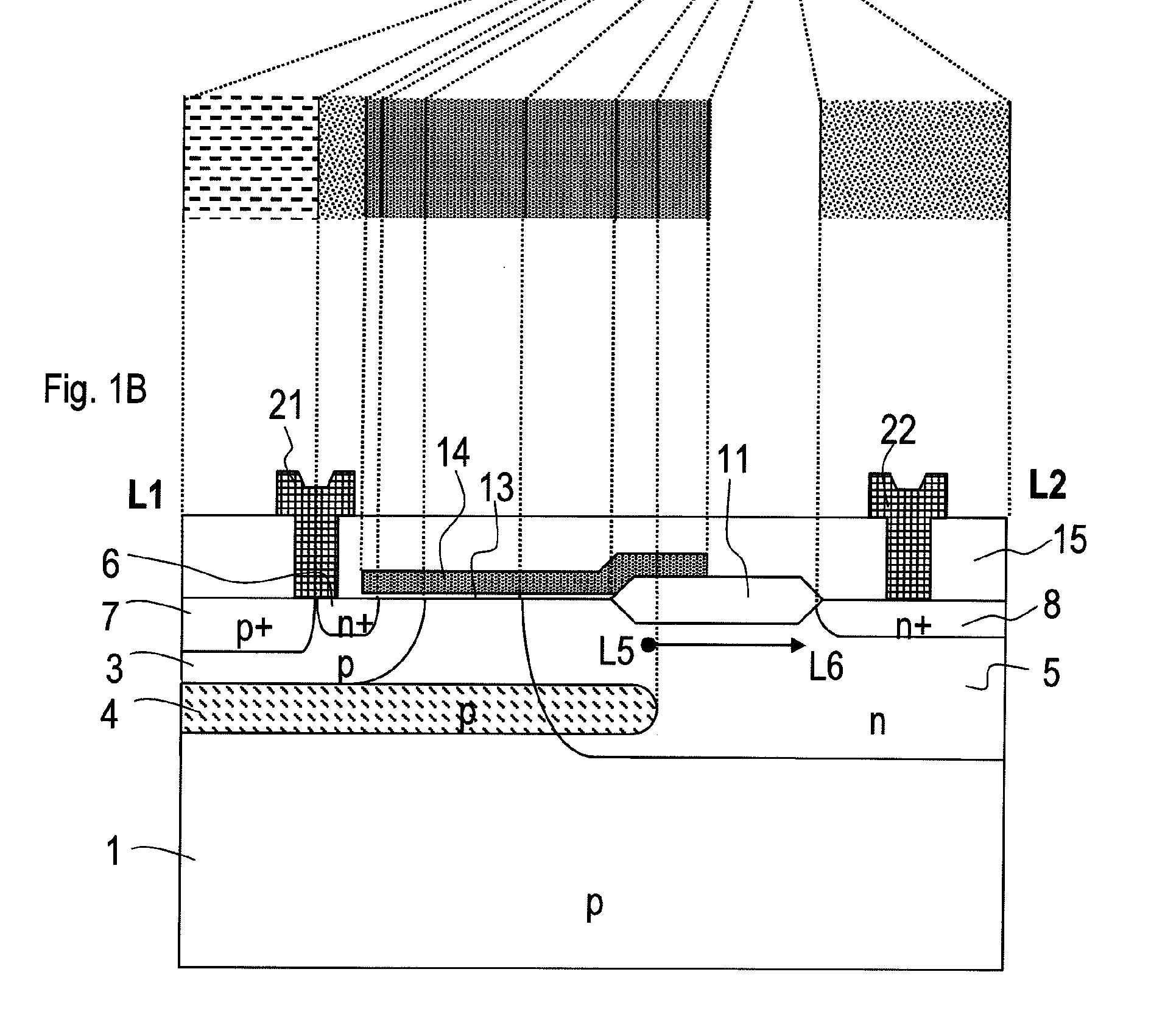

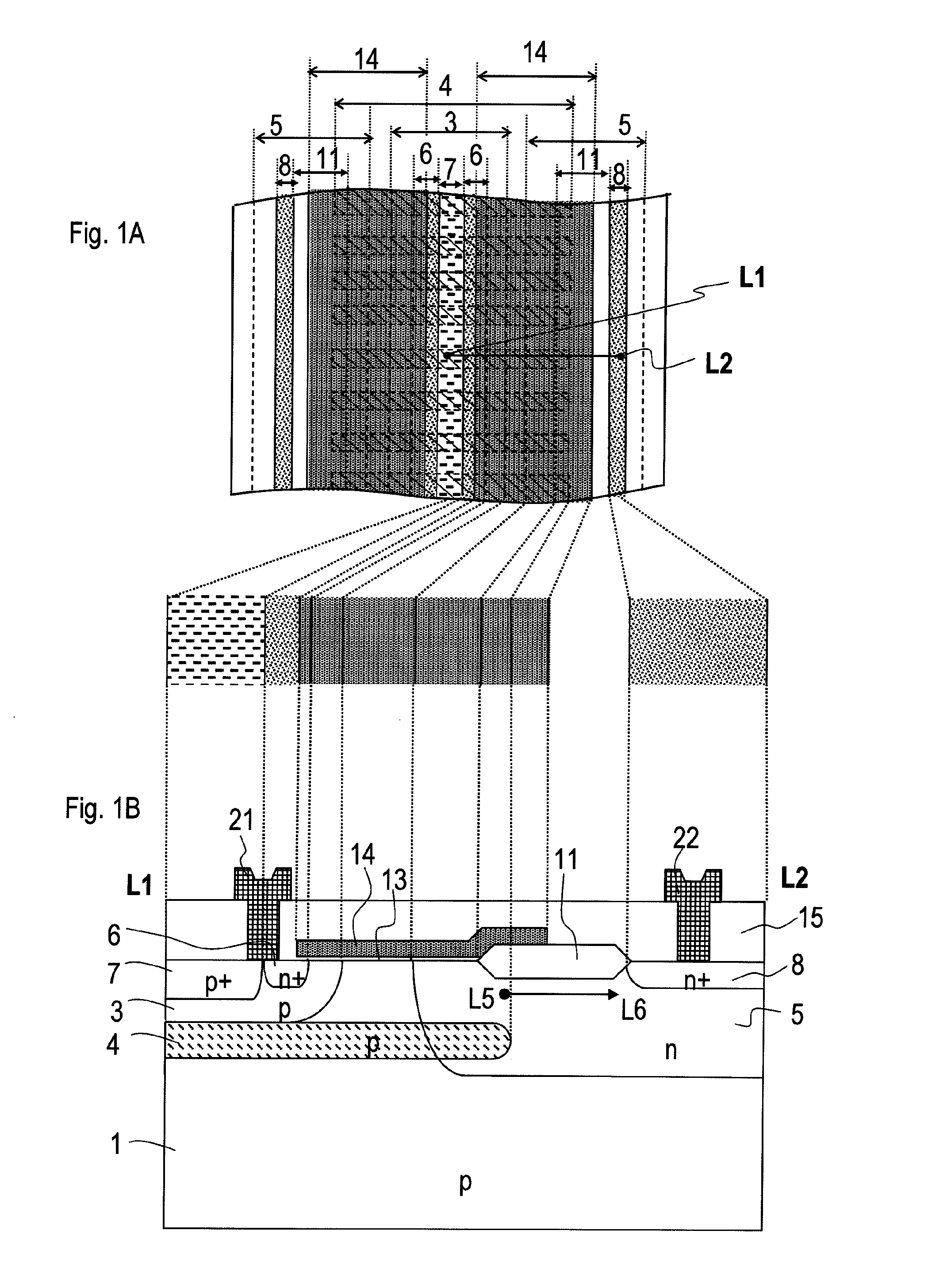

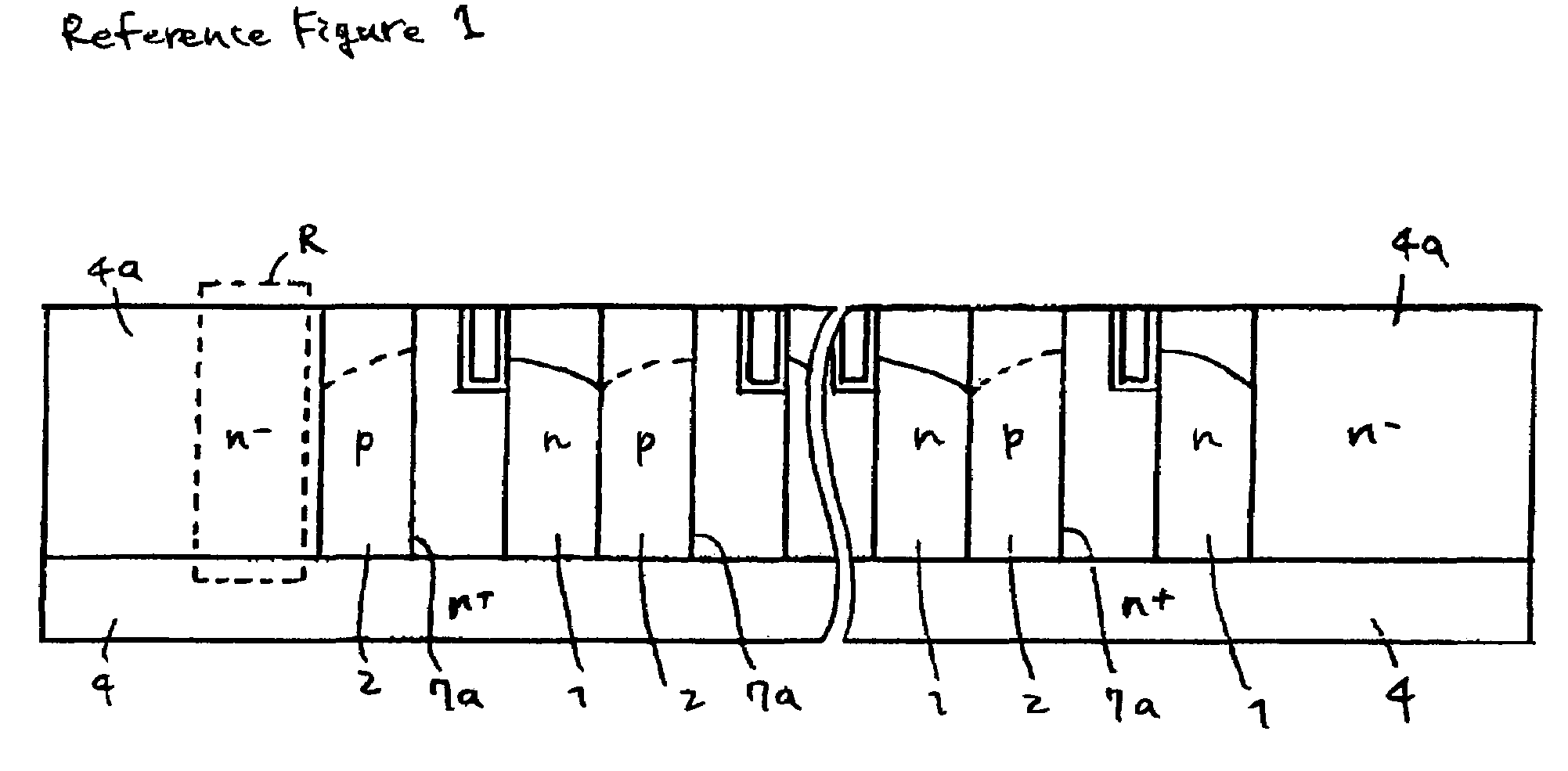

Semiconductor device and manufacturing method for the same

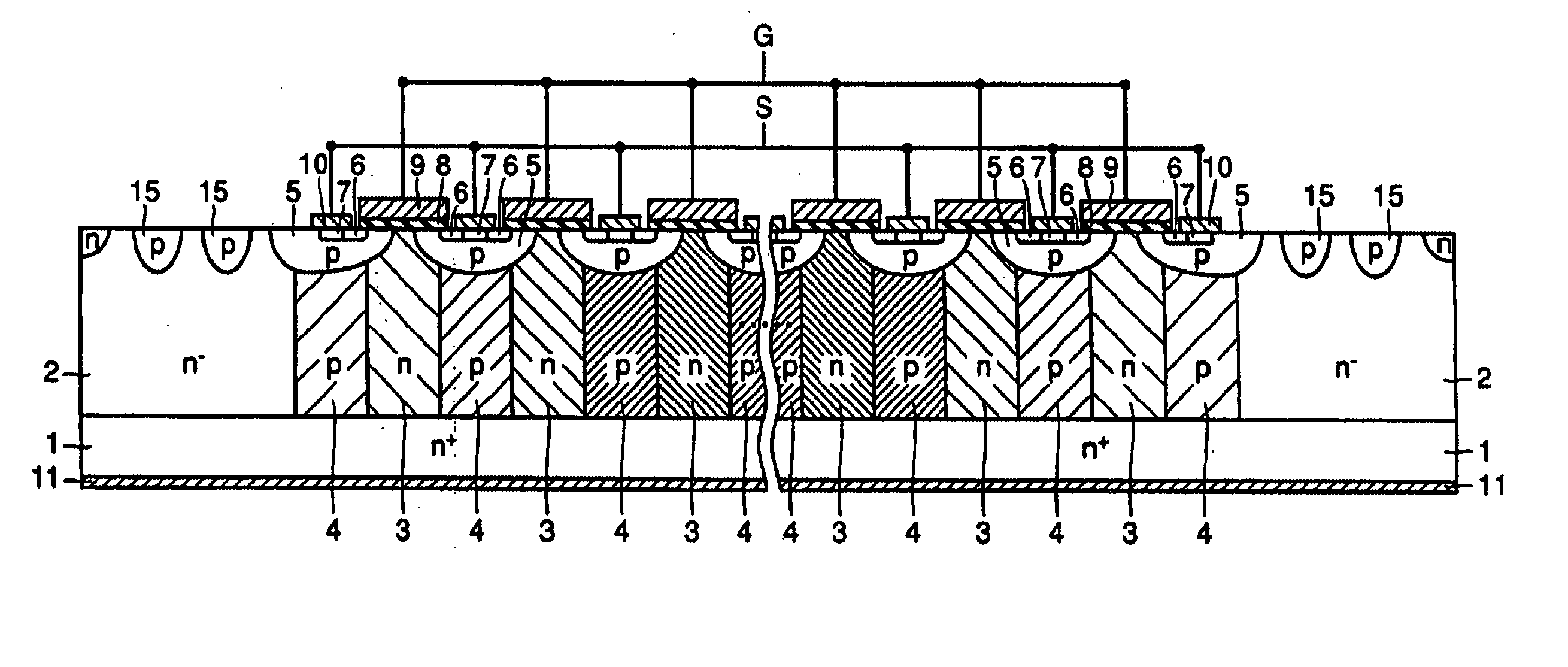

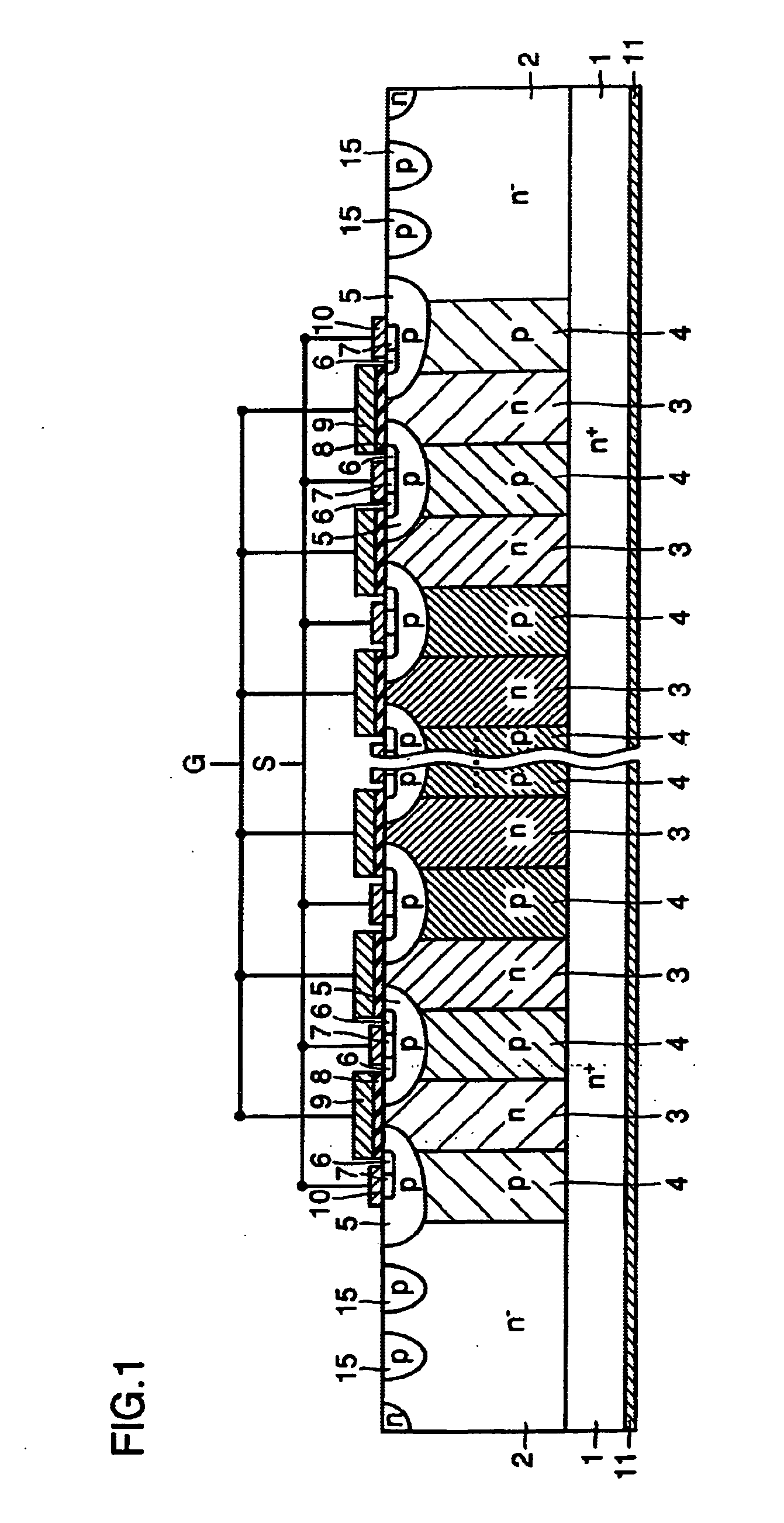

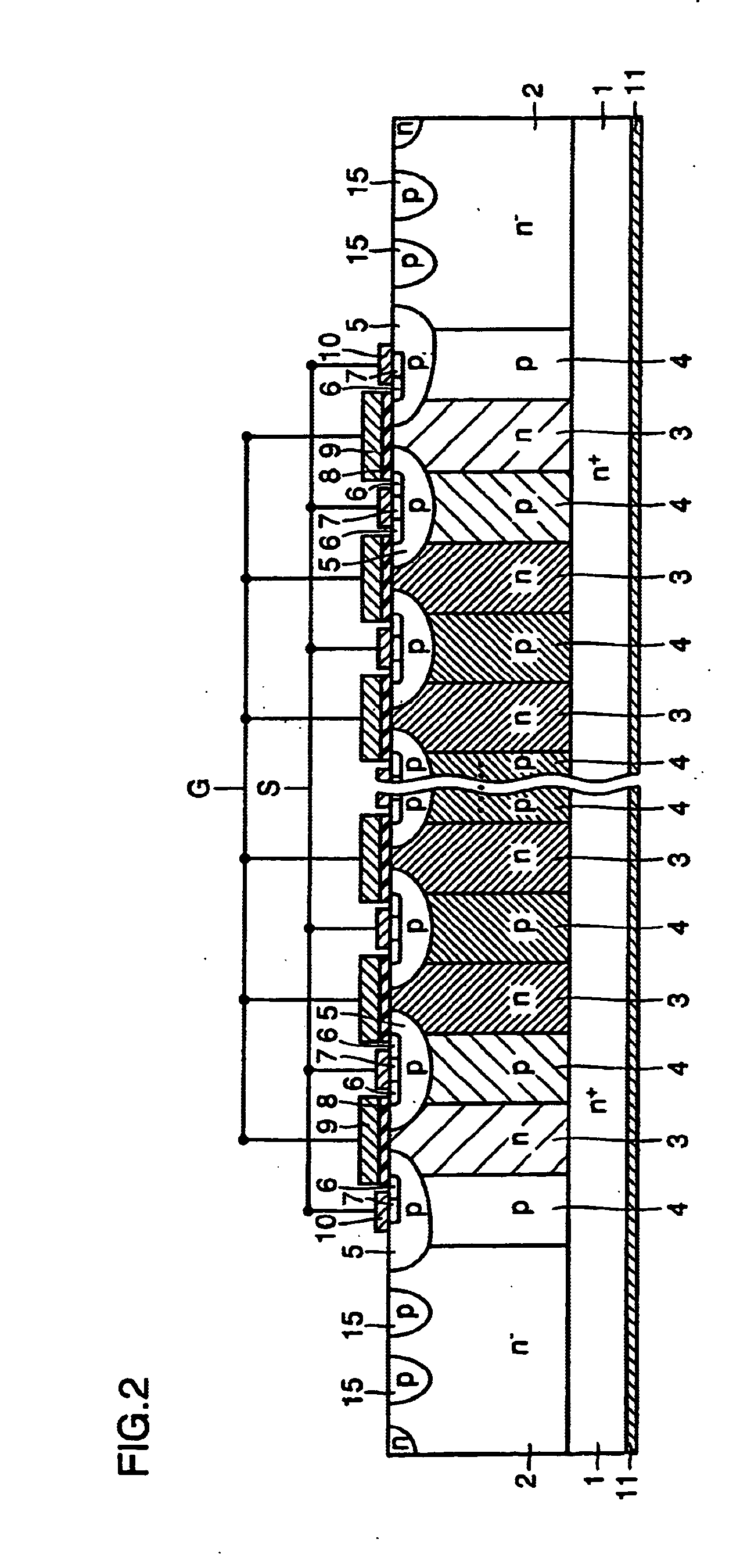

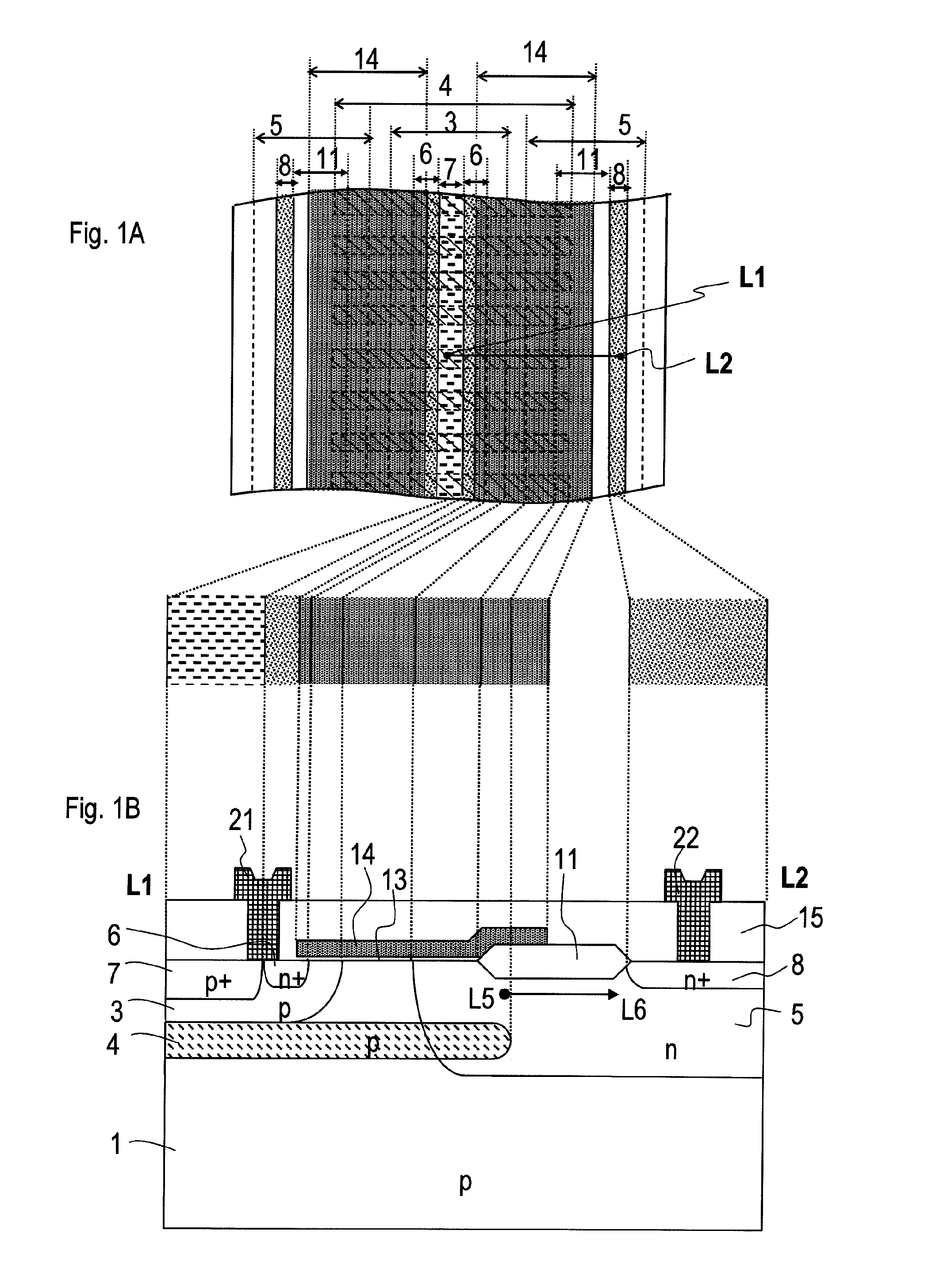

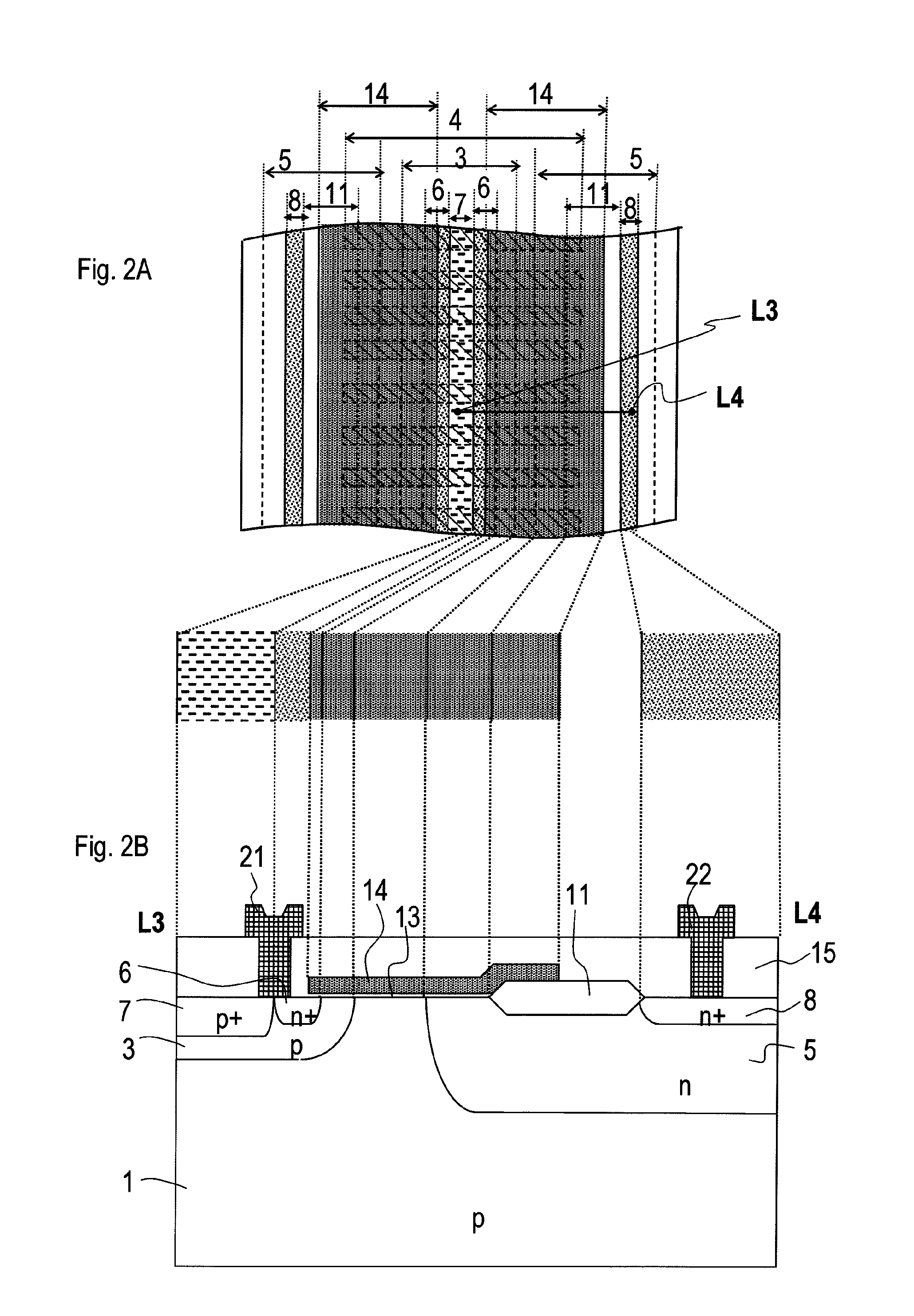

InactiveUS20050048701A1Improve trade-offsSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingElectrical resistance and conductancePower semiconductor device

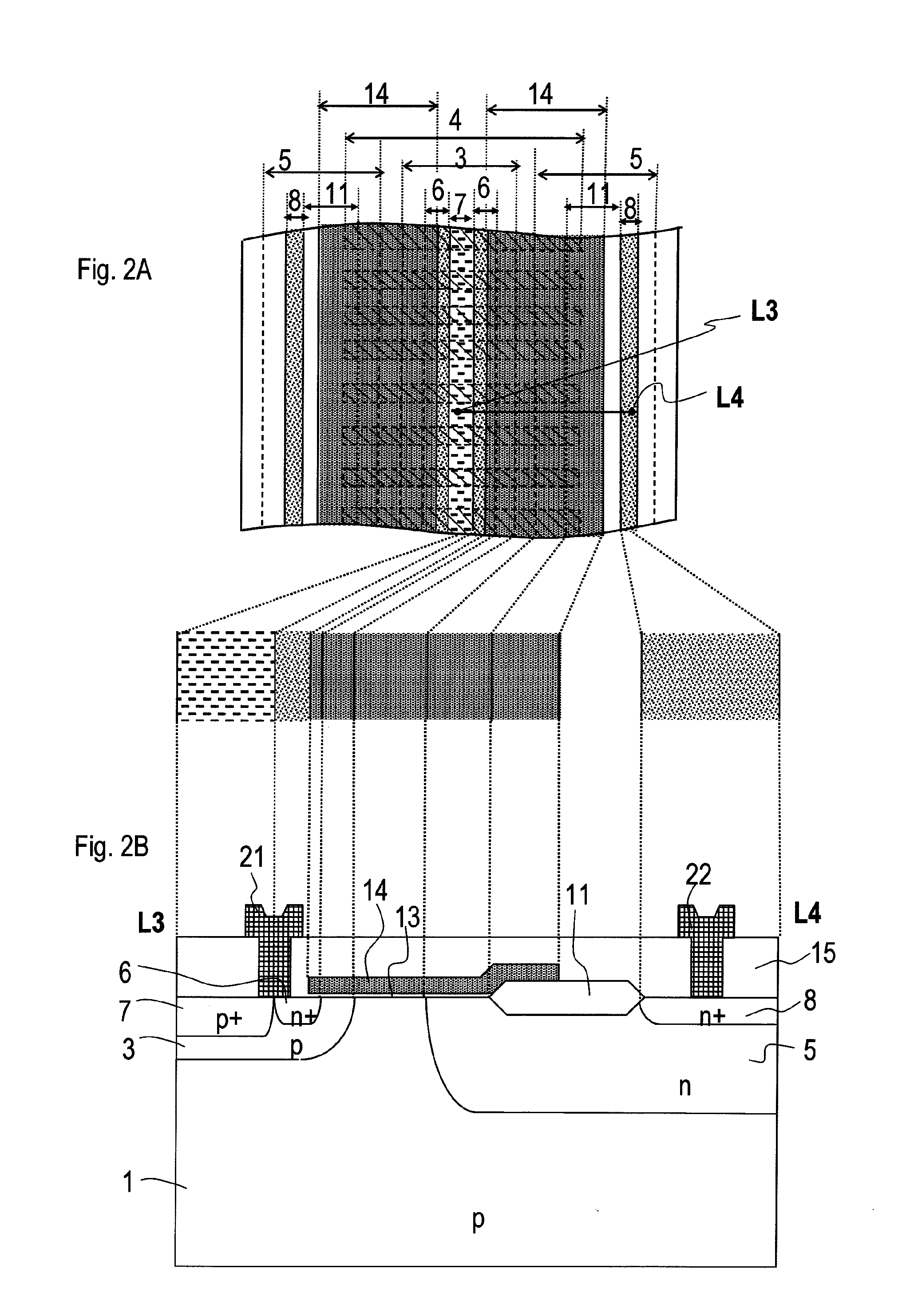

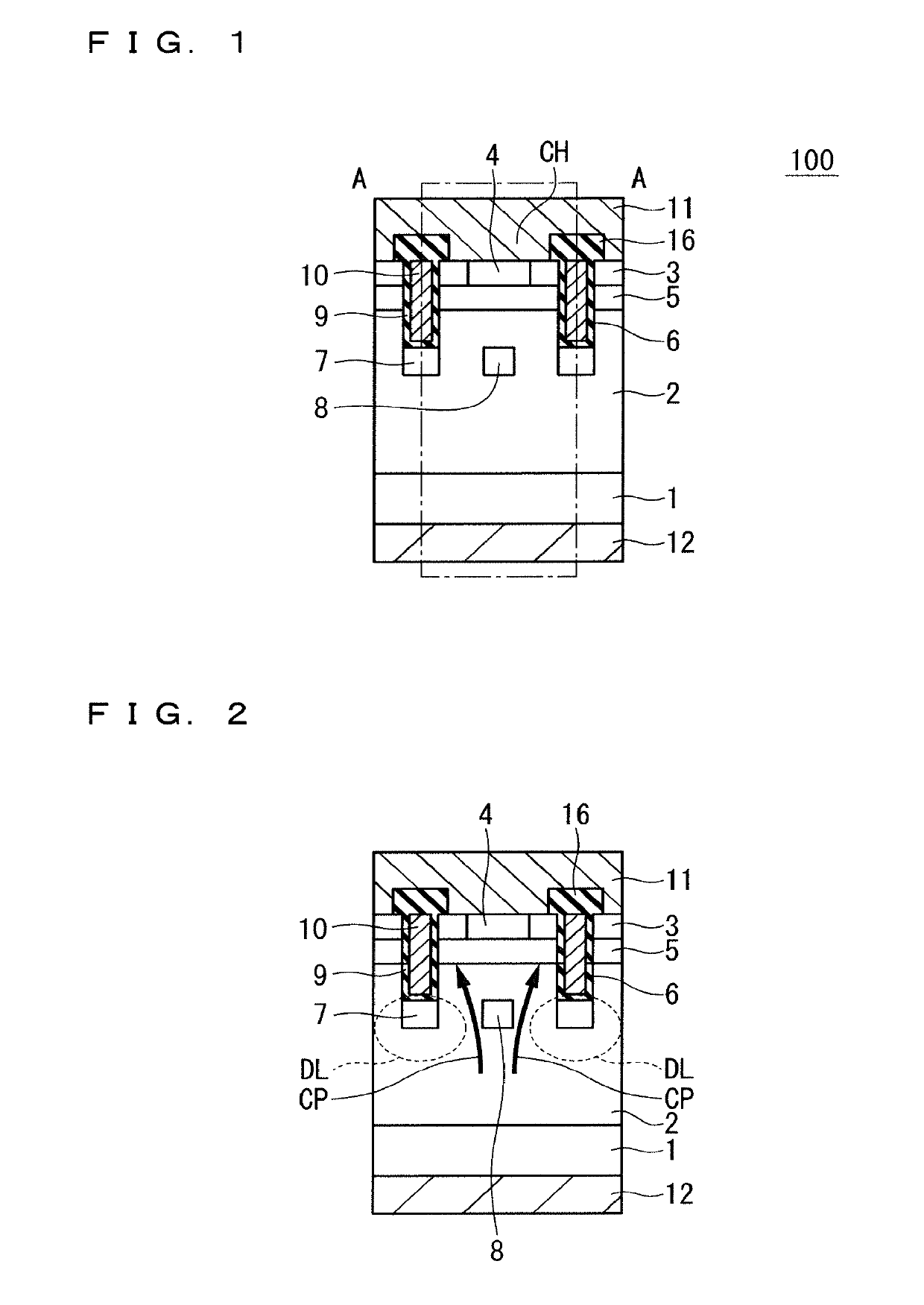

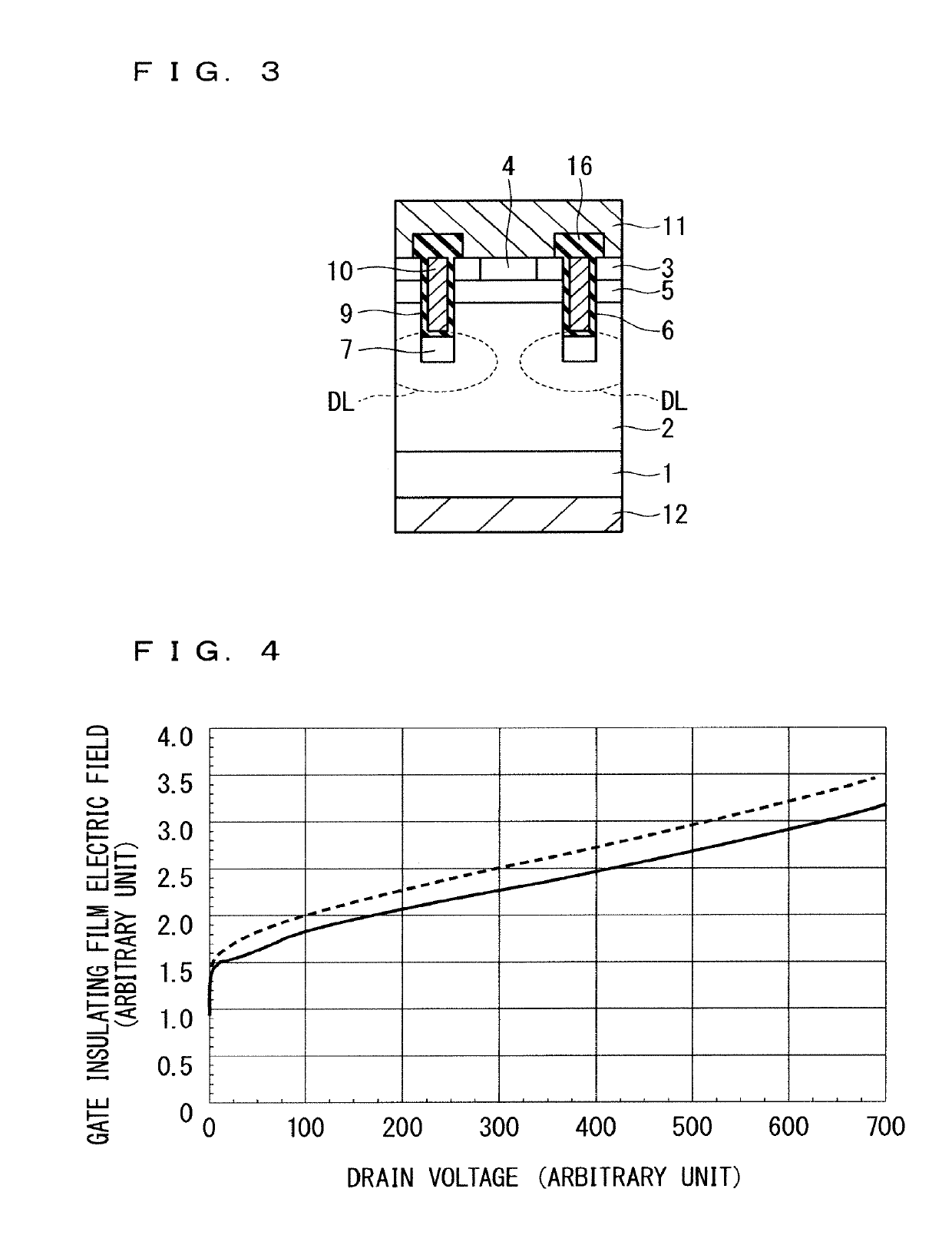

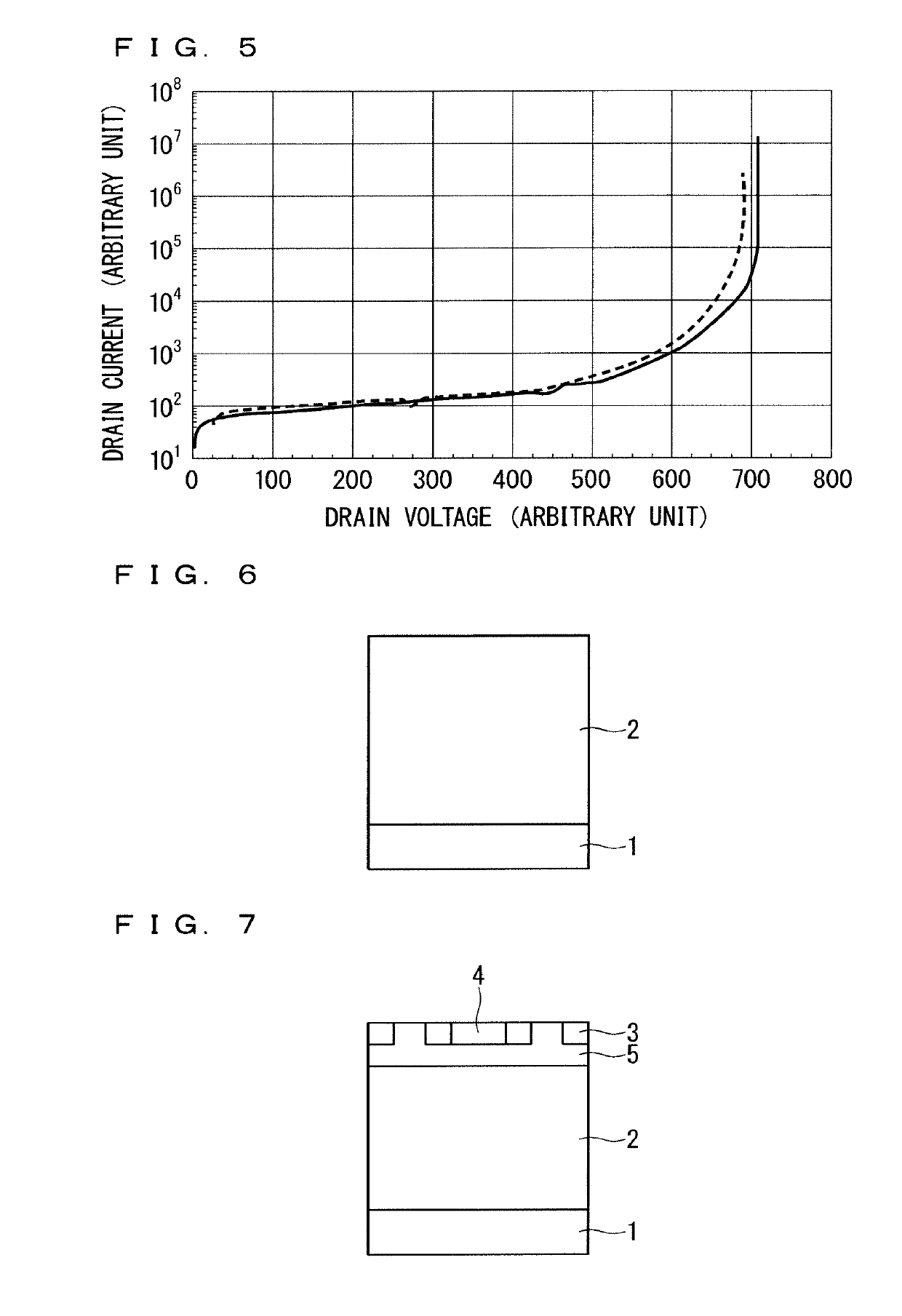

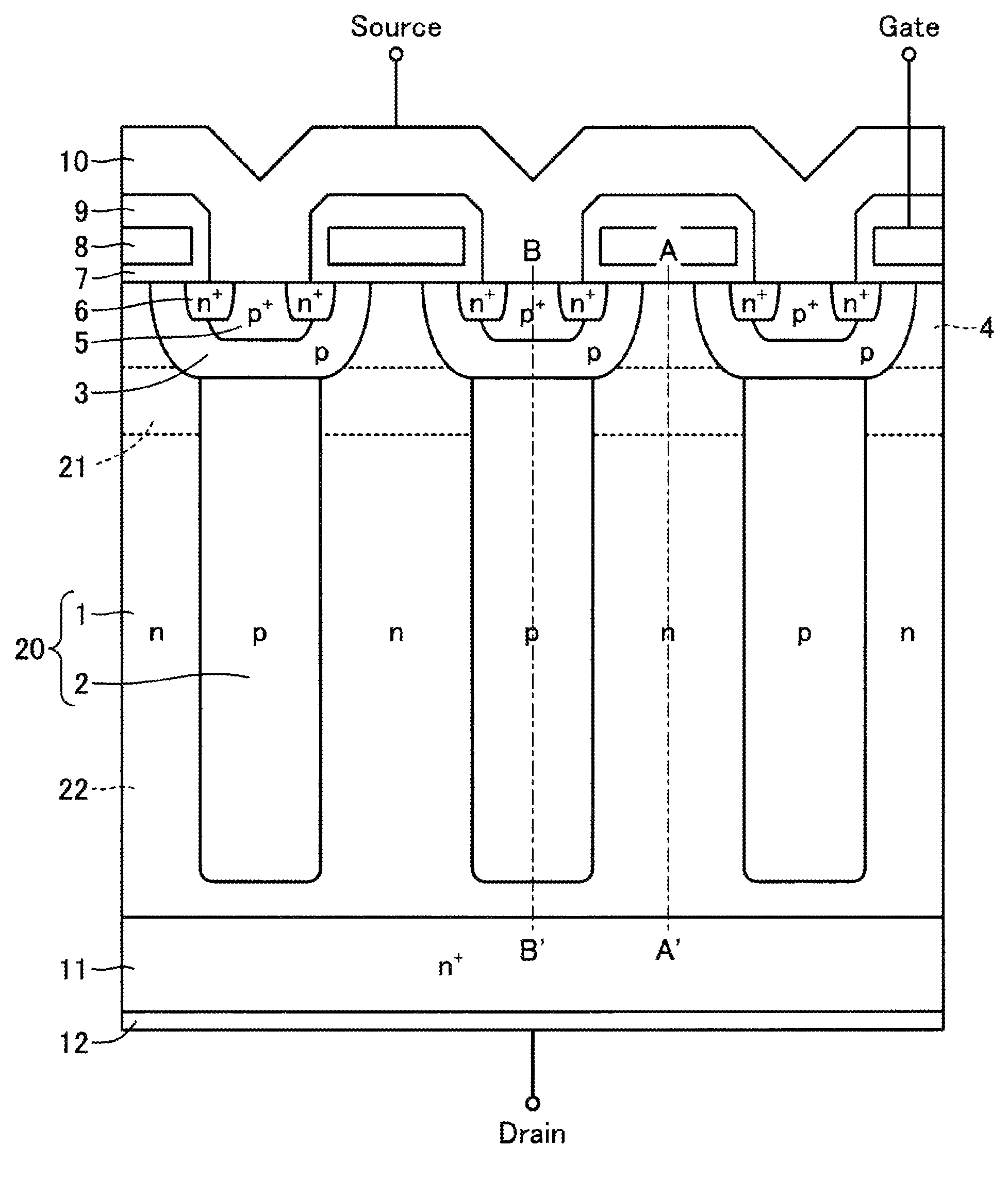

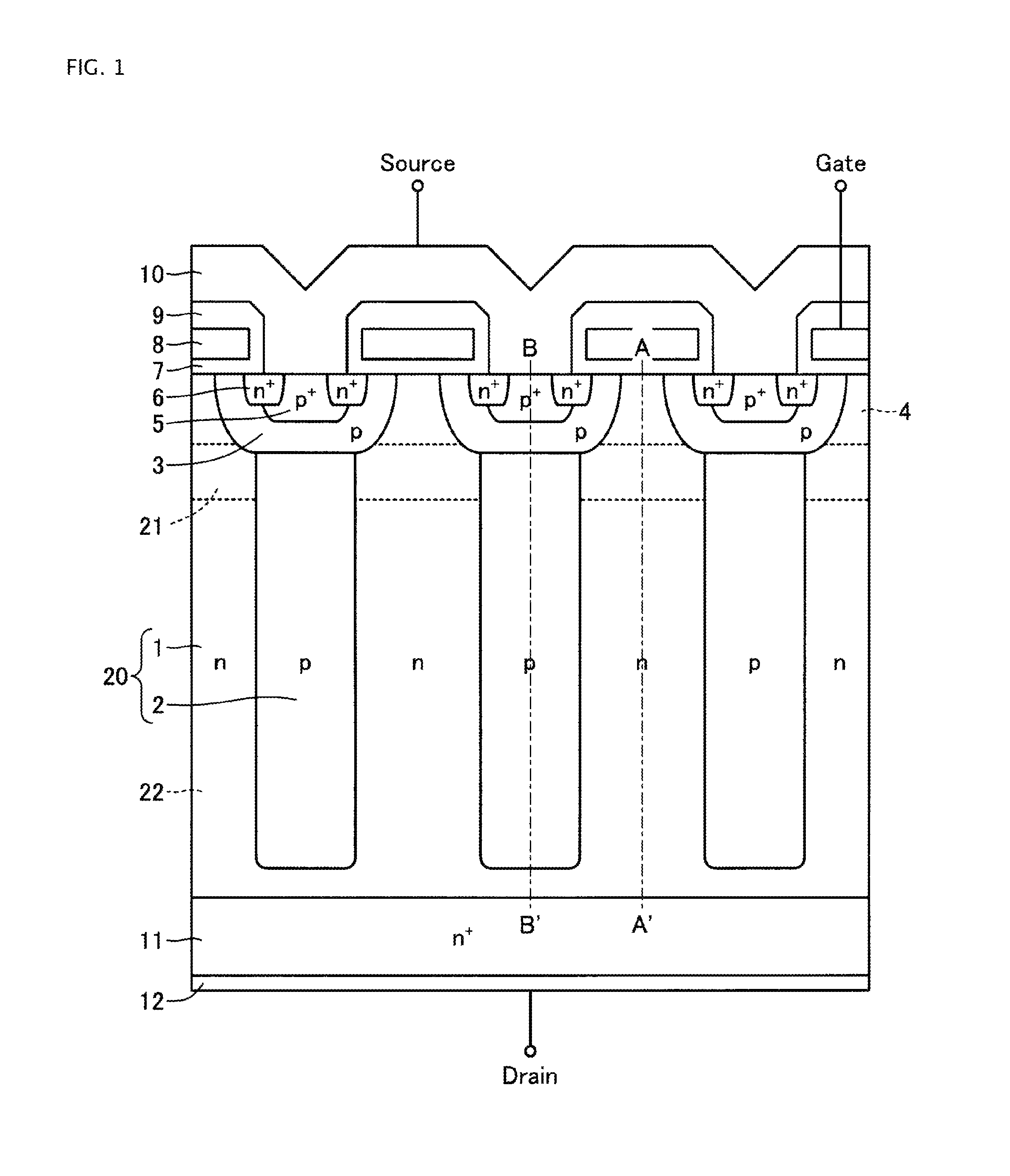

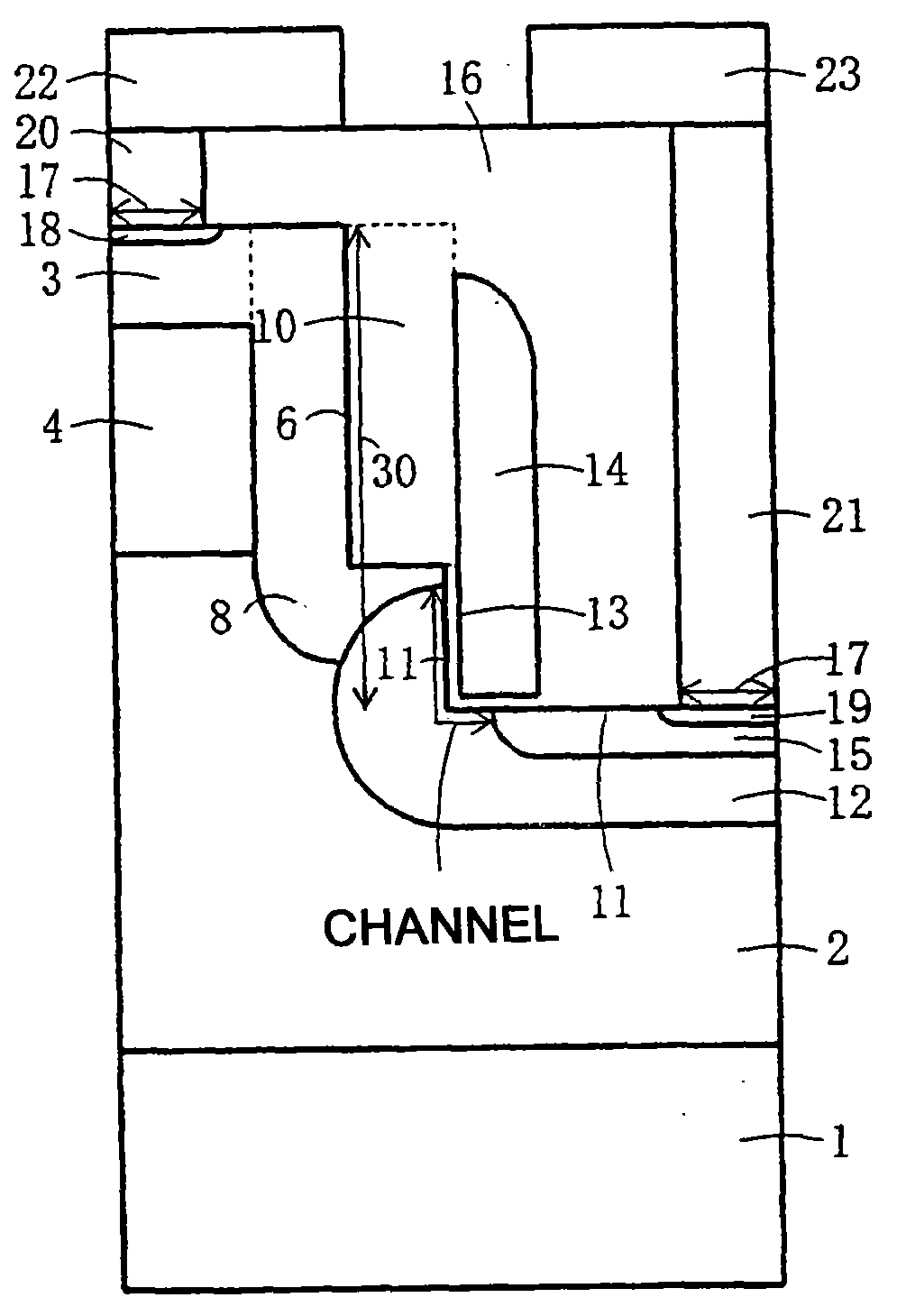

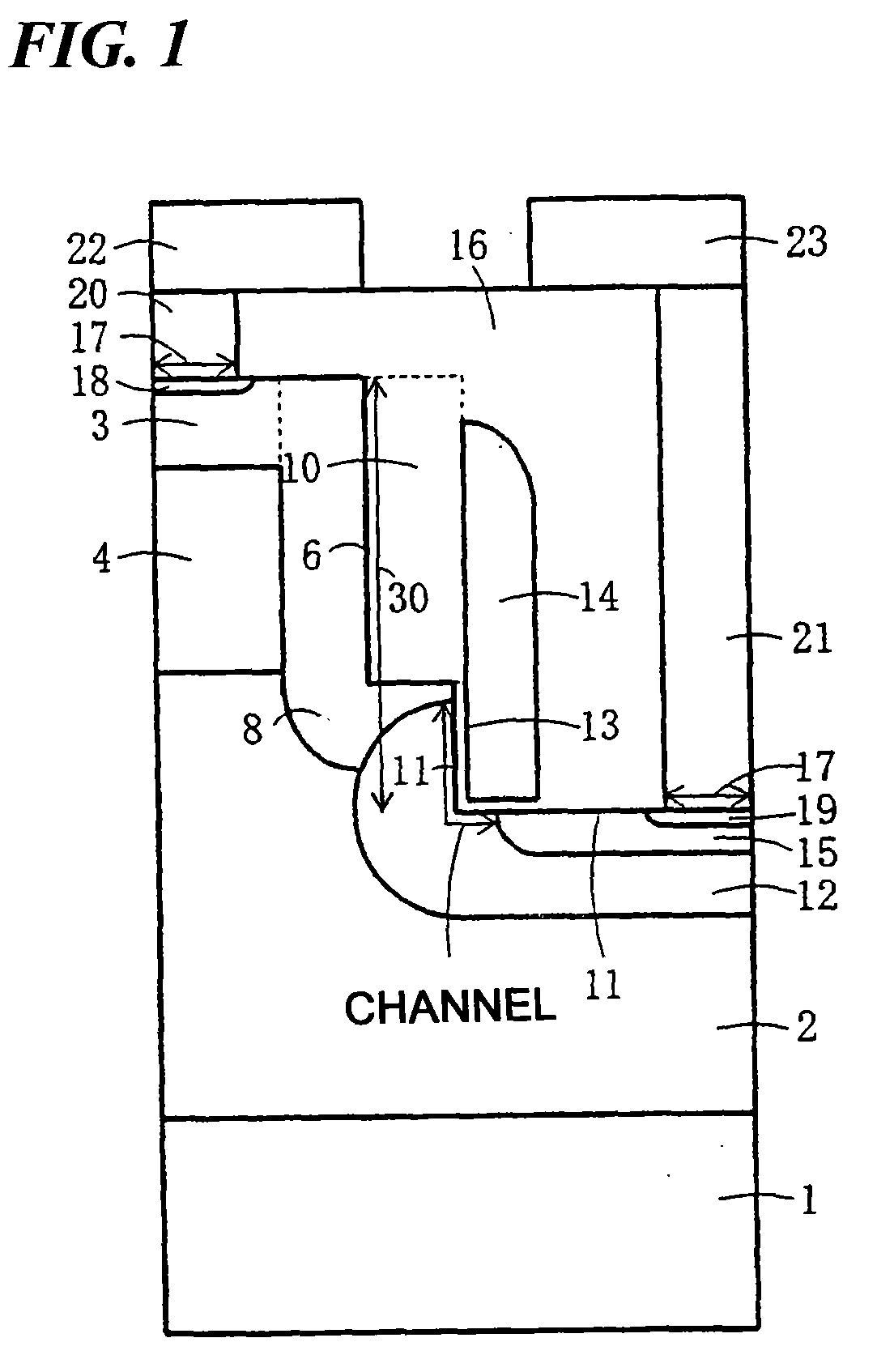

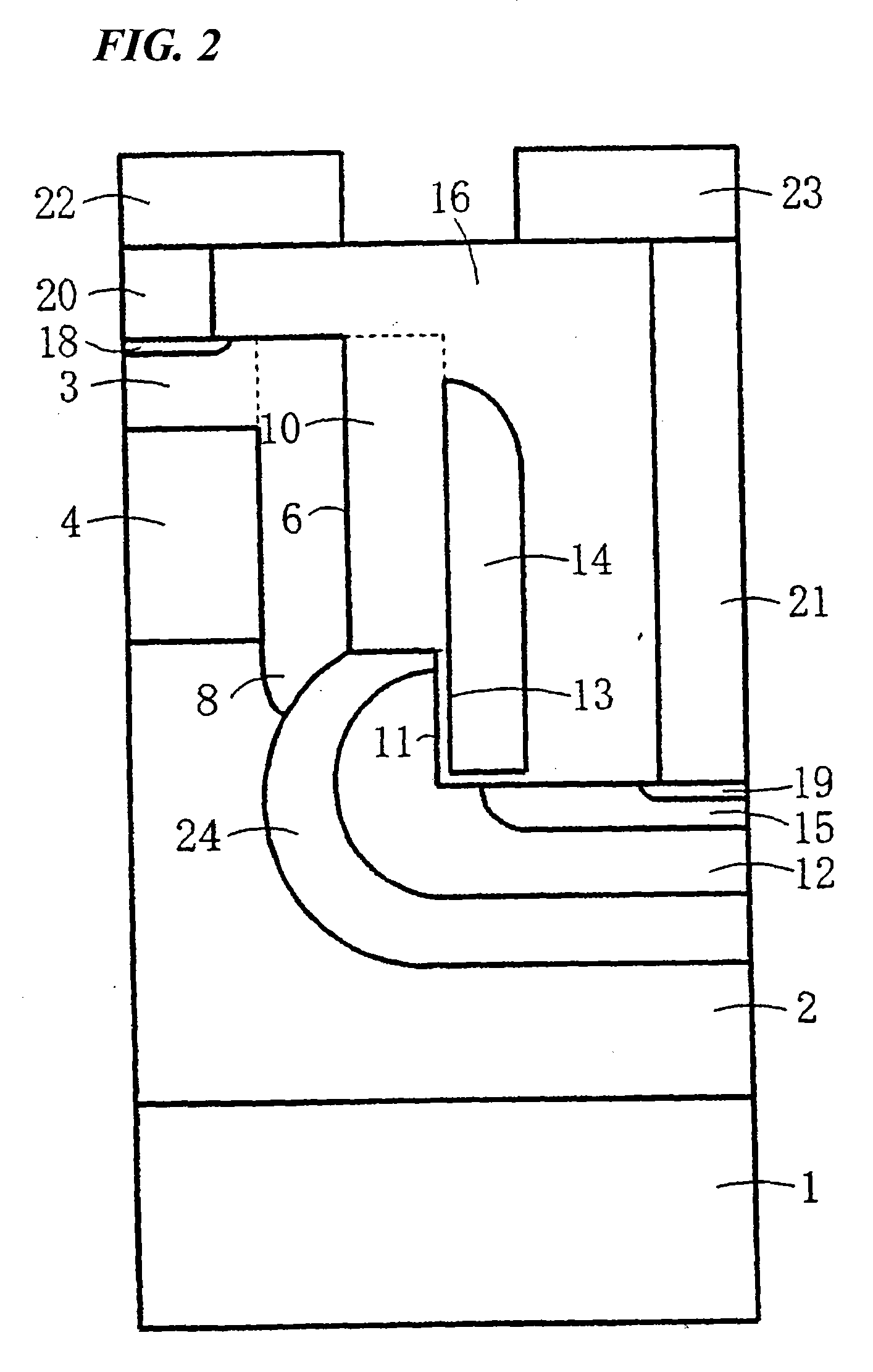

A semiconductor device of the present invention has a pn-repeating structure that a structure in which a p-type impurity region (4) and an n-type drift region (3) are aligned side by side is repeated twice or more, and a low concentration region which is either p-type impurity region (4) or n-type drift region (3) located at the outermost portion of this pn-repeating structure has the lowest impurity concentration or has the least generally effective charge amount among all the p-type impurity regions (4) and n-type drift regions (3) forming the pn-repeating structure. Thereby, the main withstand voltage of a power semiconductor device to which a three dimensional multi-RESURF principle is applied, wherein the element withstand voltage is specifically in the broad range of 20 to 6000 V, can be improved and the trade-off relationship between the main withstand voltage and the ON resistance can also be improved, so that an inexpensive semiconductor device of which the power loss is small and of which the size of the chip is small can be obtained. In addition, a trench of a dotted line trench (DLT) structure and a manufacturing method corresponding to this can be used, so that a semiconductor device with a good yield can be obtained at low cost.

Owner:MITSUBISHI ELECTRIC CORP

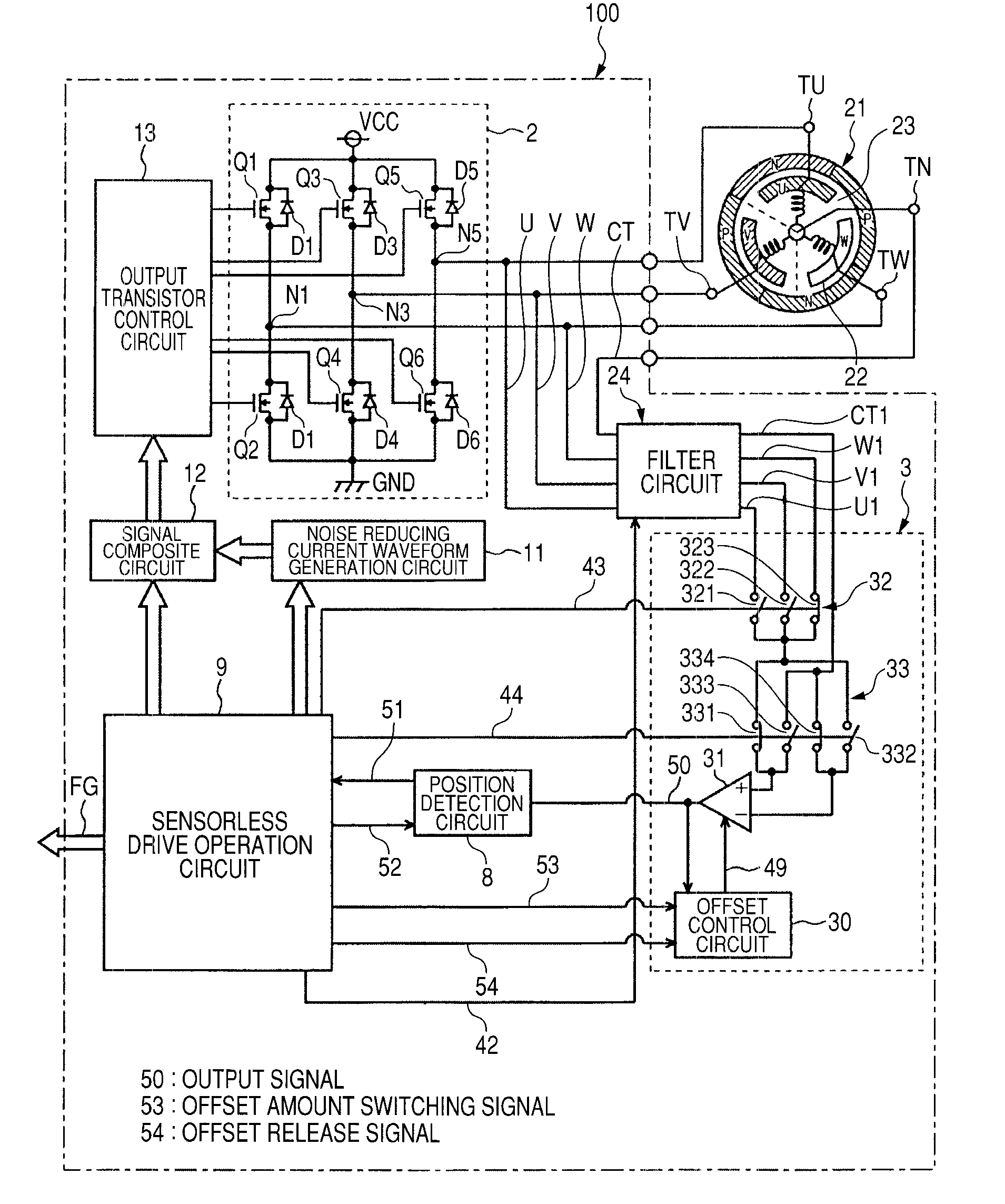

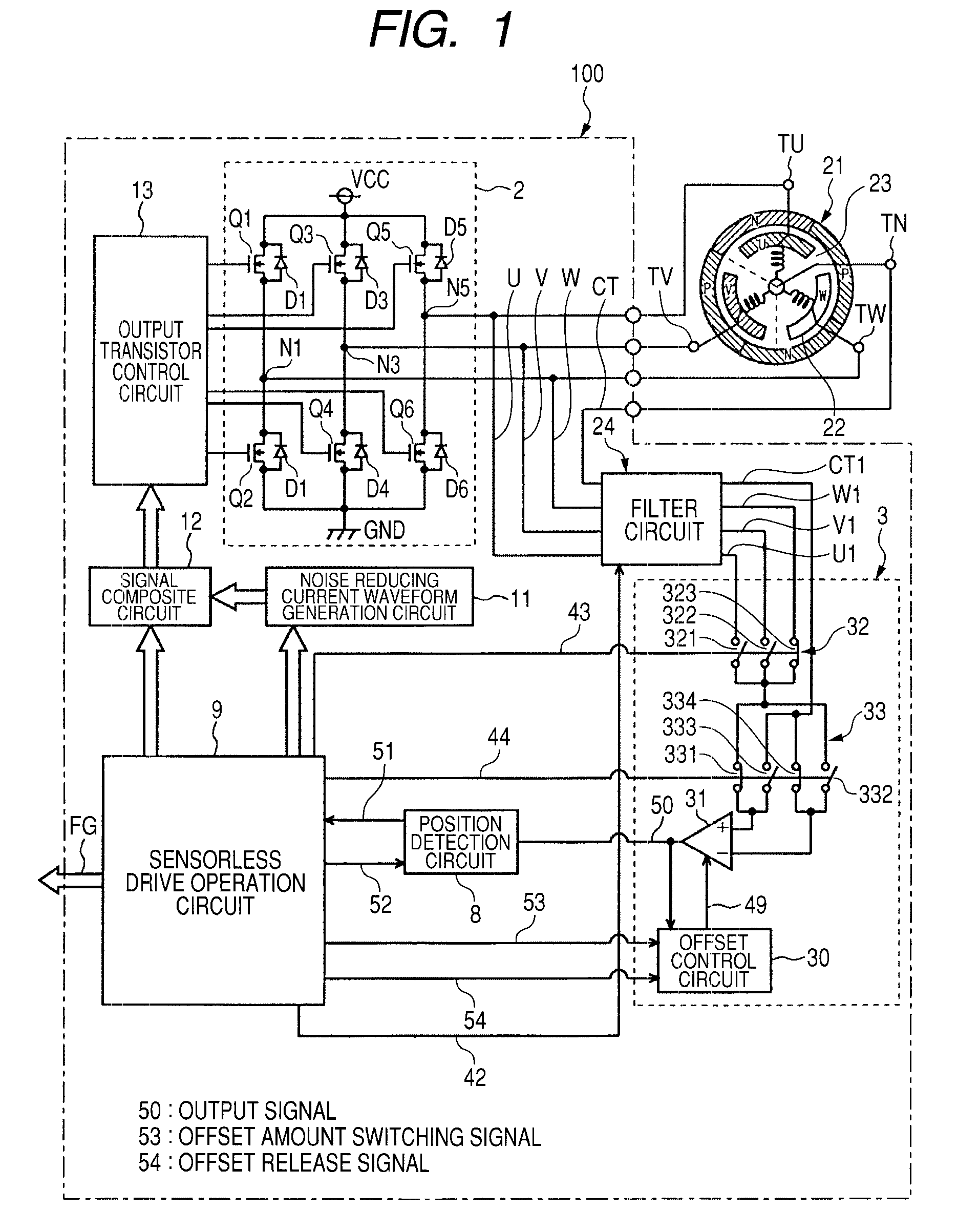

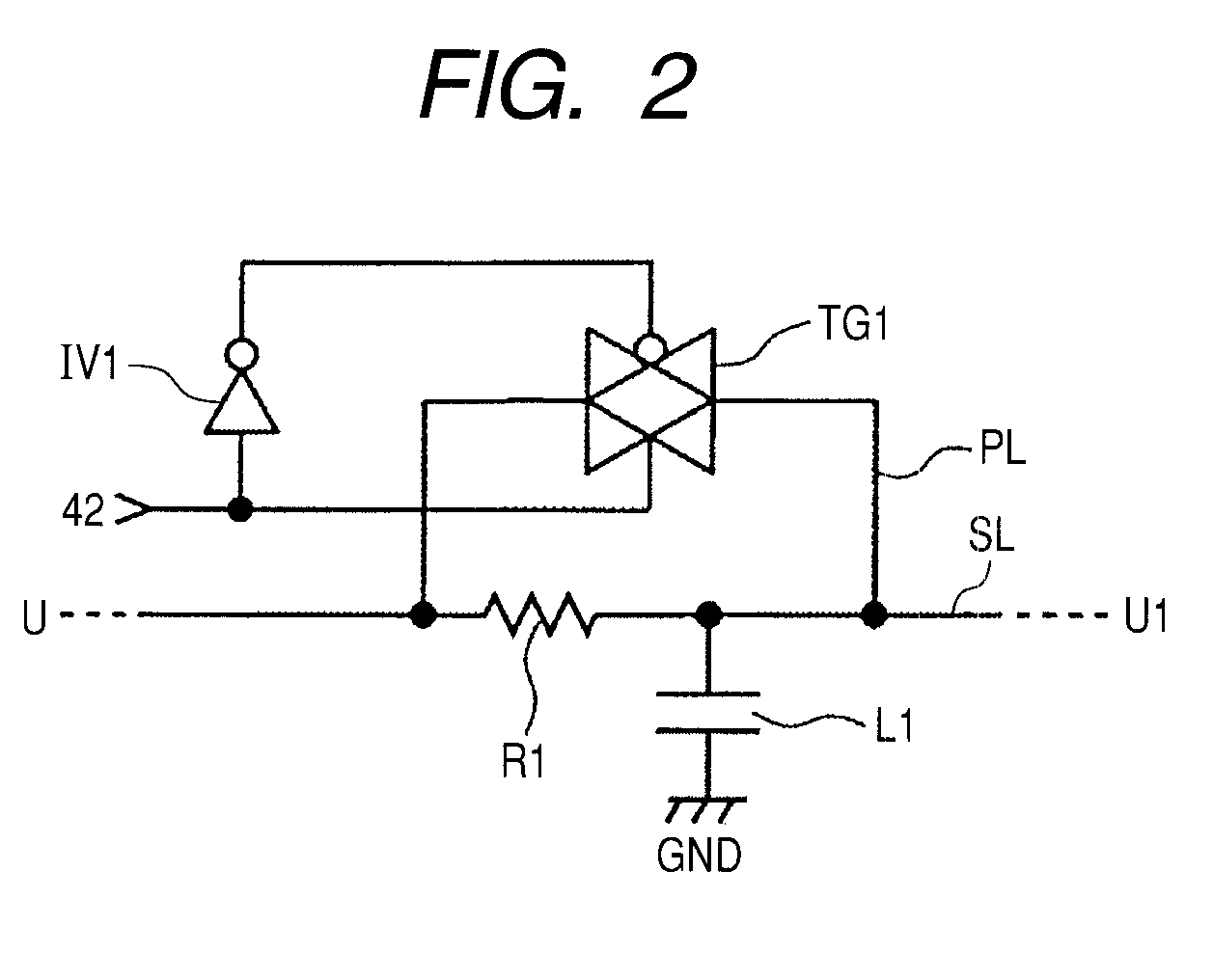

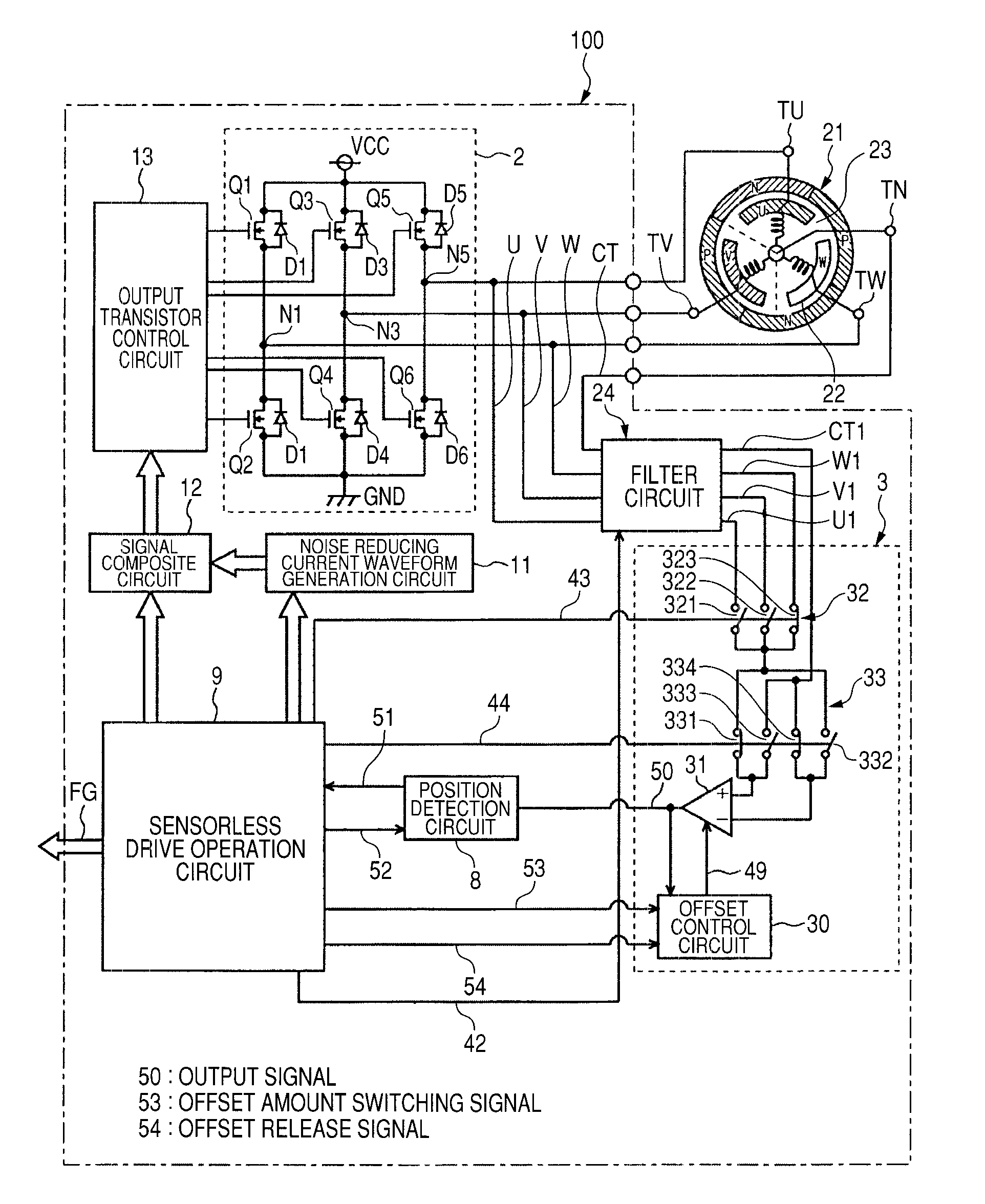

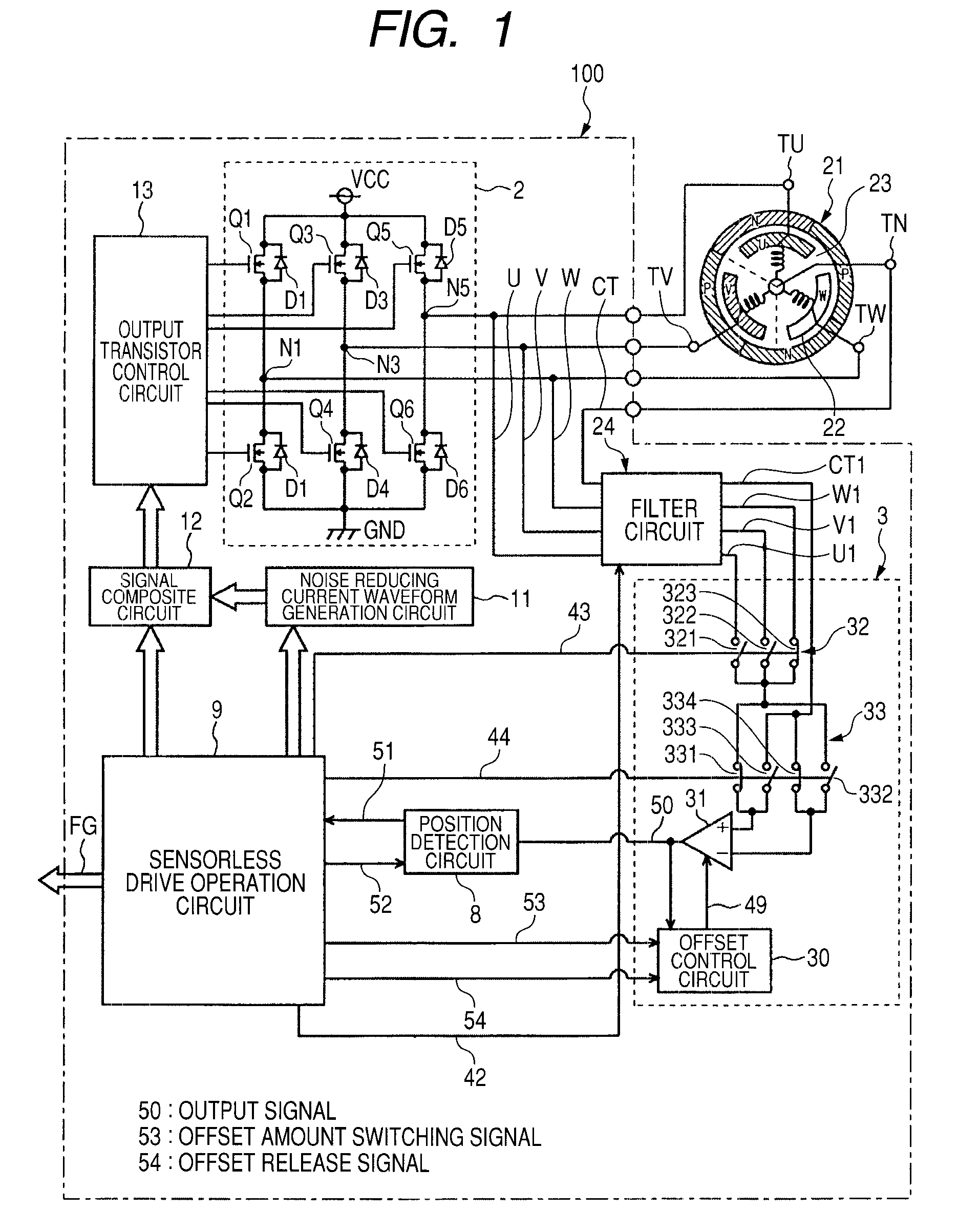

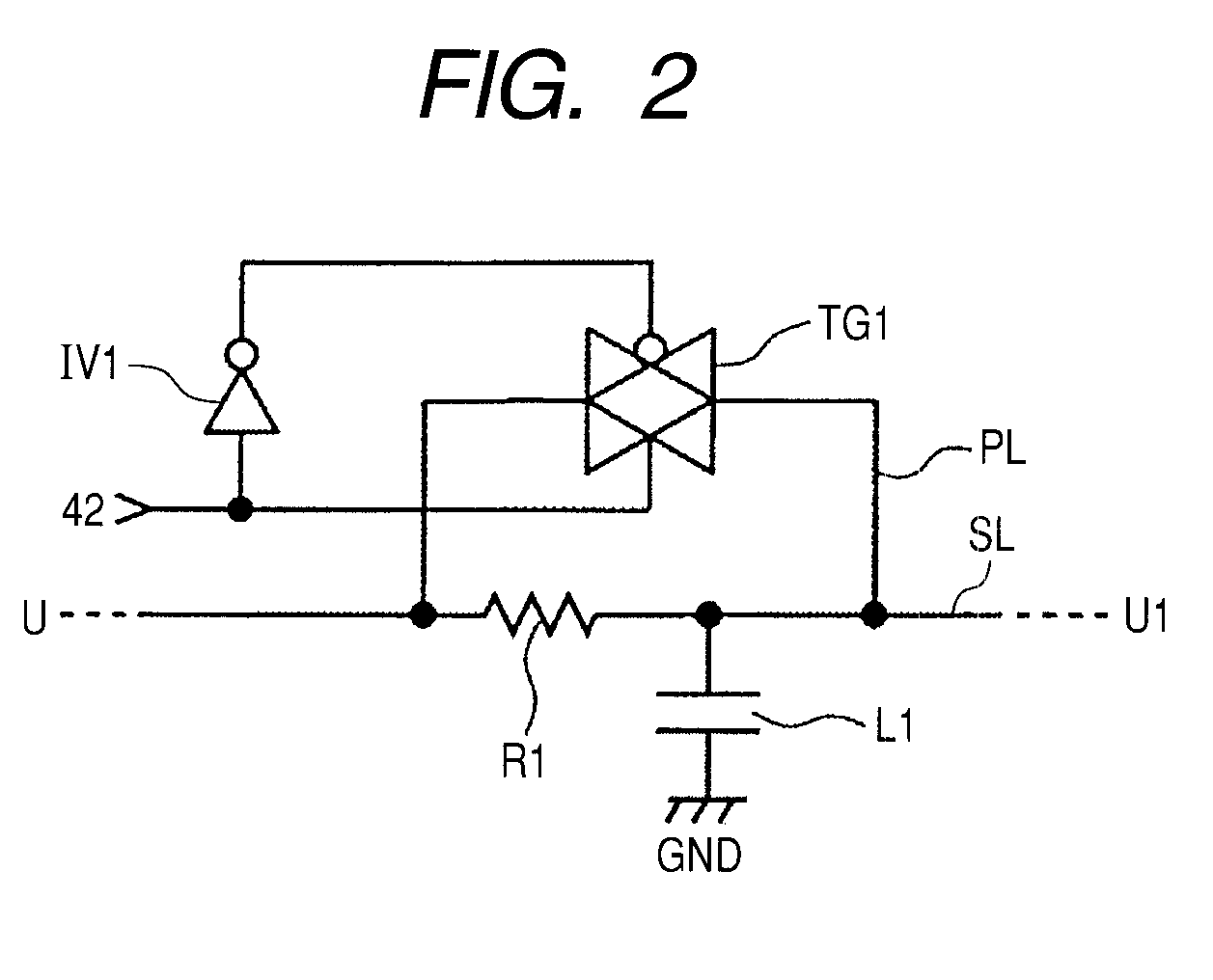

Motor drive apparatus

InactiveUS20090153086A1Stable position detectionReduce noiseSingle-phase induction motor startersDC motor speed/torque controlLocation detectionDriving current

The present invention provides a motor drive apparatus which improves a trade-off relation between a stable position detection and noise at its driving. A sensorless drive operation circuit calculates by operation a zero cross point (point p) of a voltage of a position detection phase at the next interval, using time information measured based on an output signal from a comparison circuit at the previous interval and the present interval. After the point p has been calculated, points a and b are detected by interrupting a predetermined time drive current.

Owner:RENESAS ELECTRONICS CORP

Semiconductor device and method for producing the same

ActiveUS20110101454A1Lower resistanceHigh off-breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionSubstrate surface

A P type semiconductor substrate includes a P type body region, an N type drift region formed away from the P type body region in a direction parallel to a substrate surface, an N type drain region formed in a region separated by a field oxide film in the N type drift region so as to have a concentration higher than the N type drift region, an N type source region formed in the P type body region so as to have a concentration higher than the N type drift region. A P type buried diffusion region having a concentration higher than the N type drift region is formed of a plurality of parts each of which is connected to a part of the bottom surface of the P type body region and extends parallel to the substrate surface and its tip end reaches the inside of the drift region.

Owner:SHARP KK

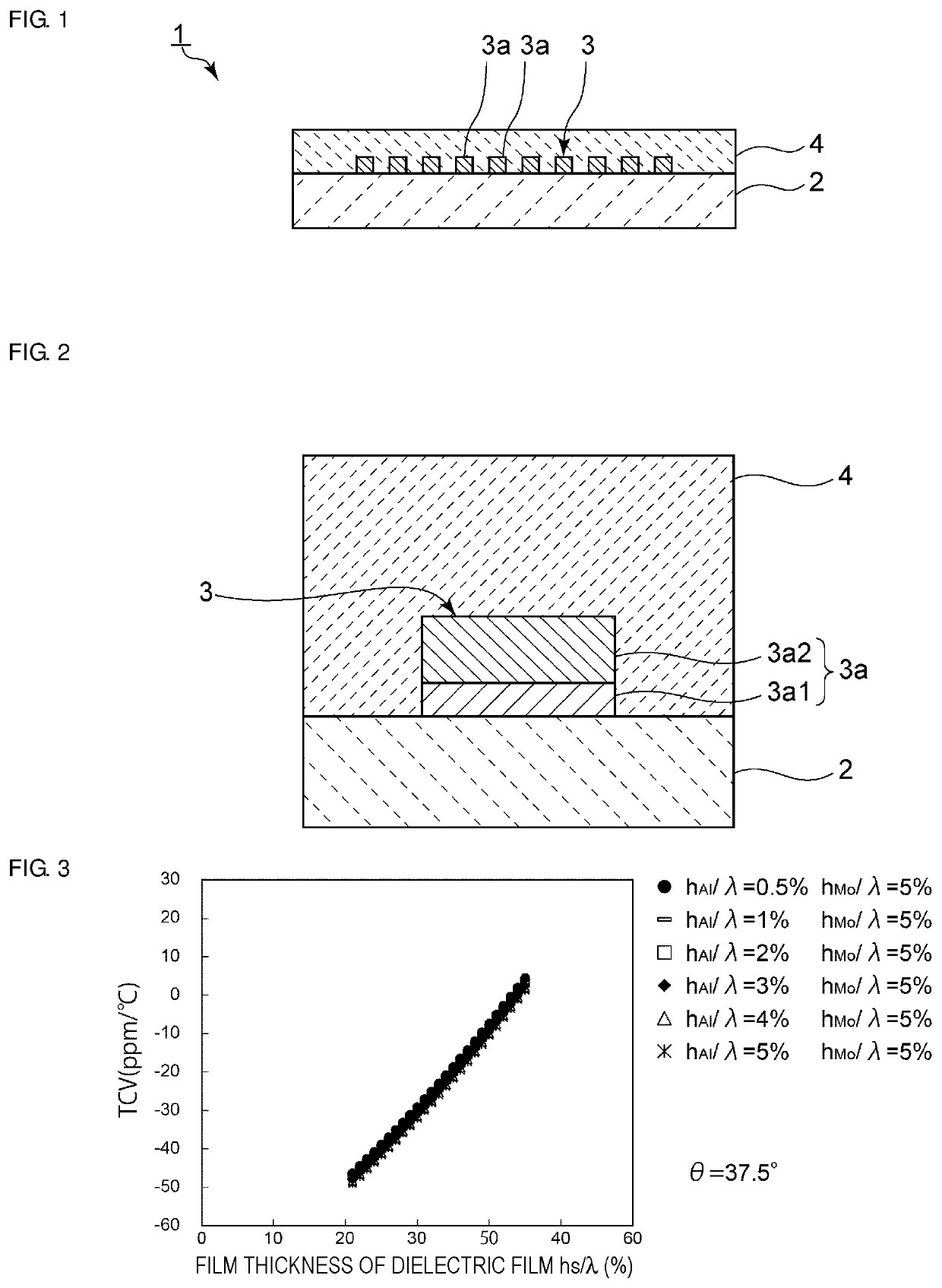

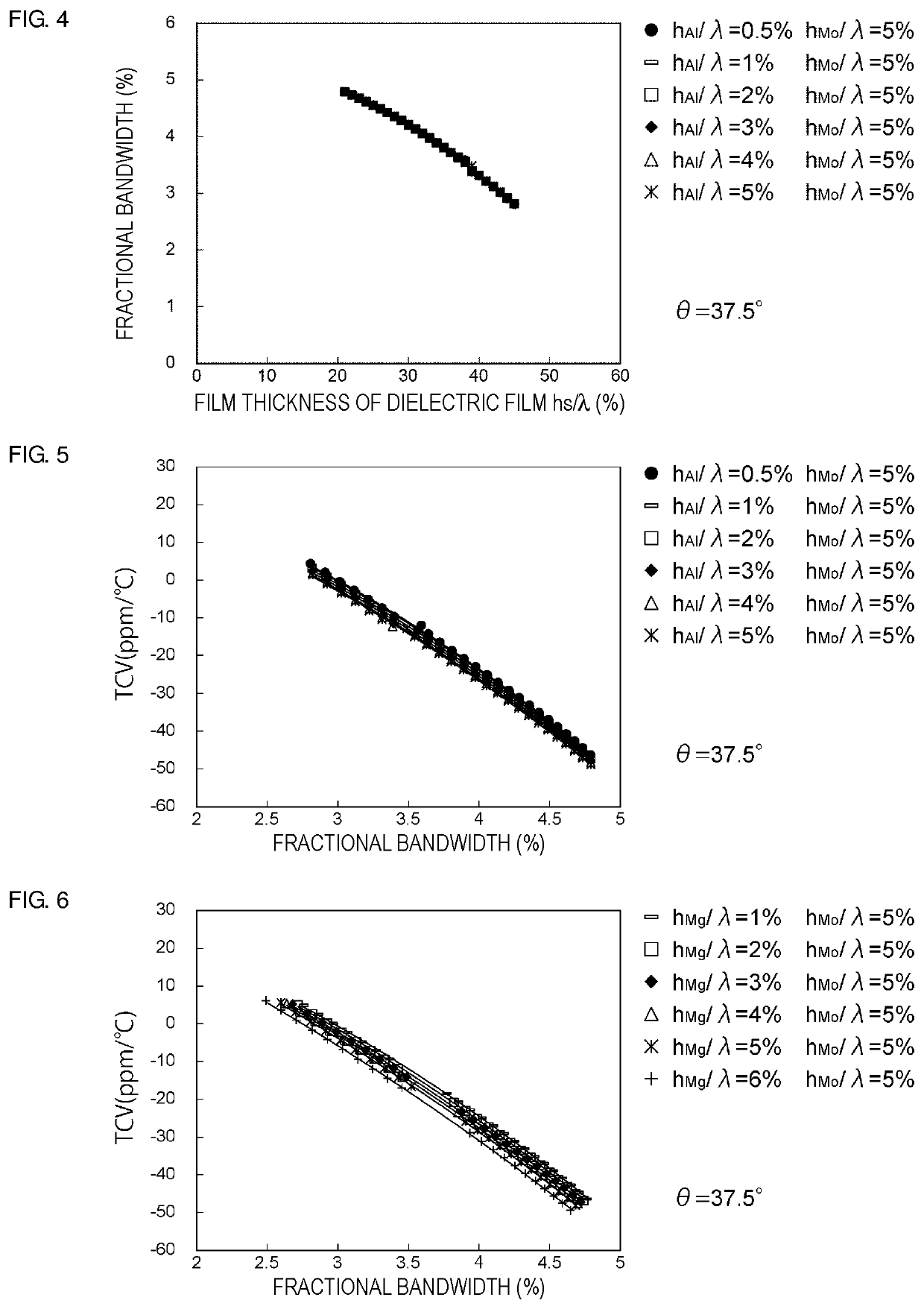

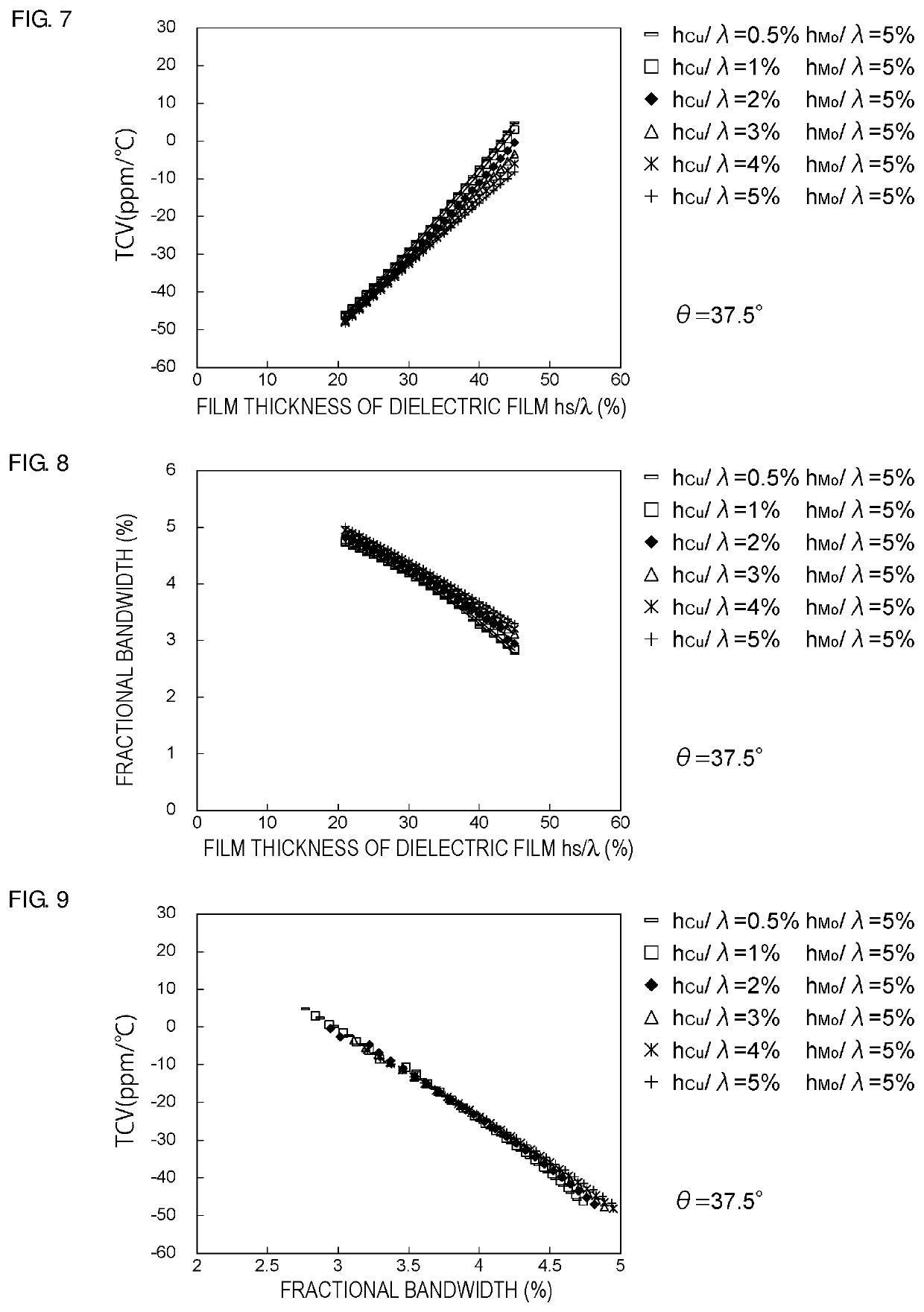

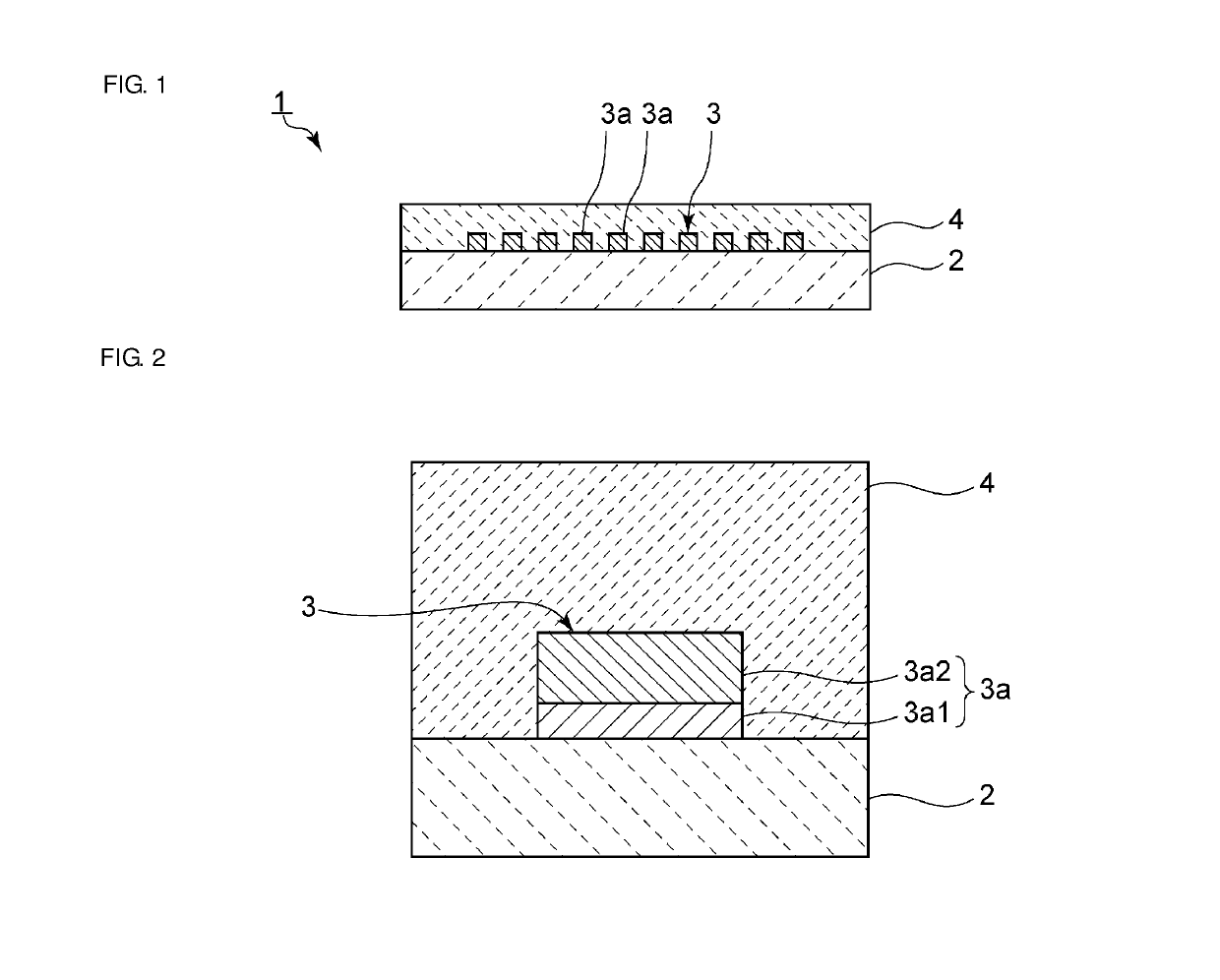

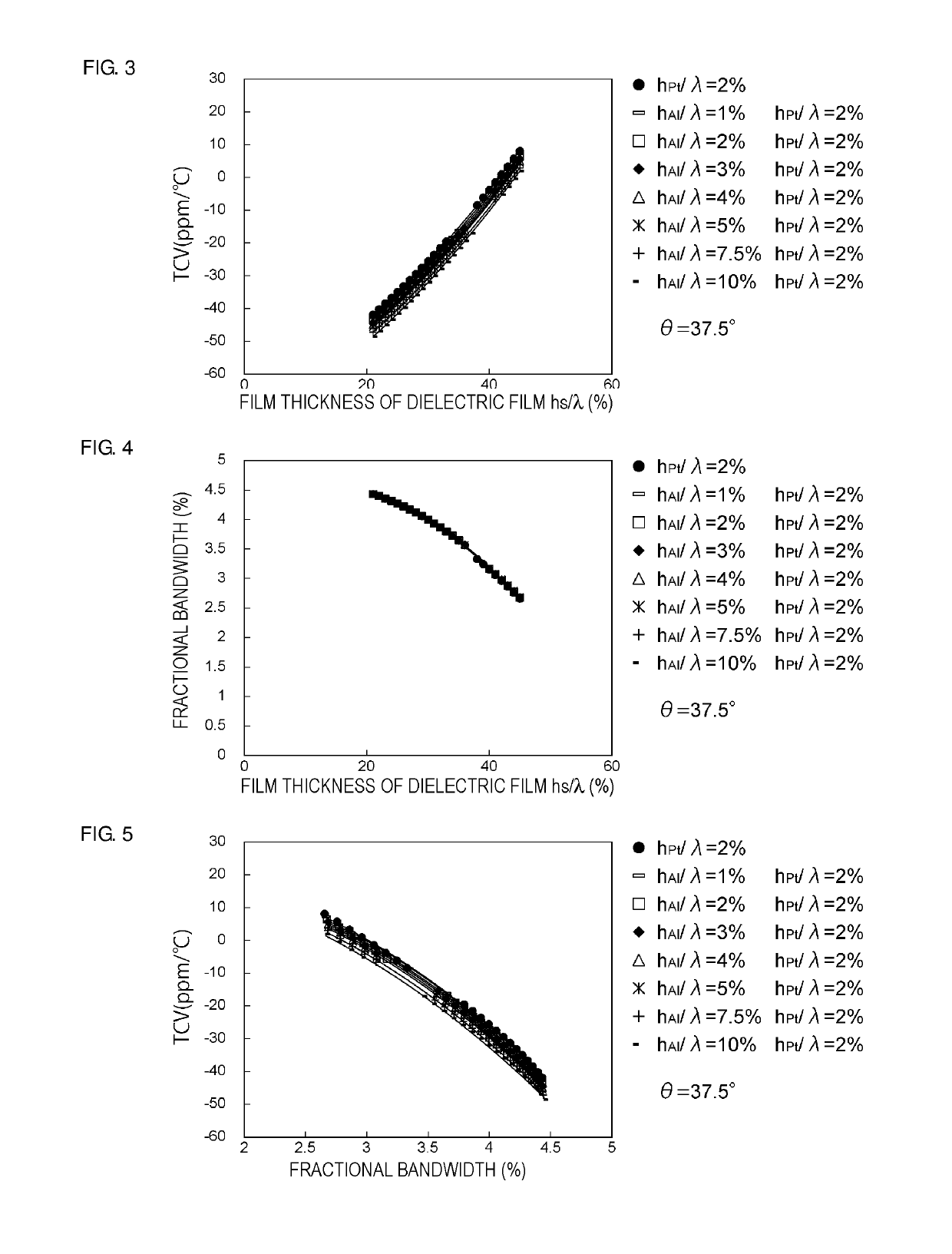

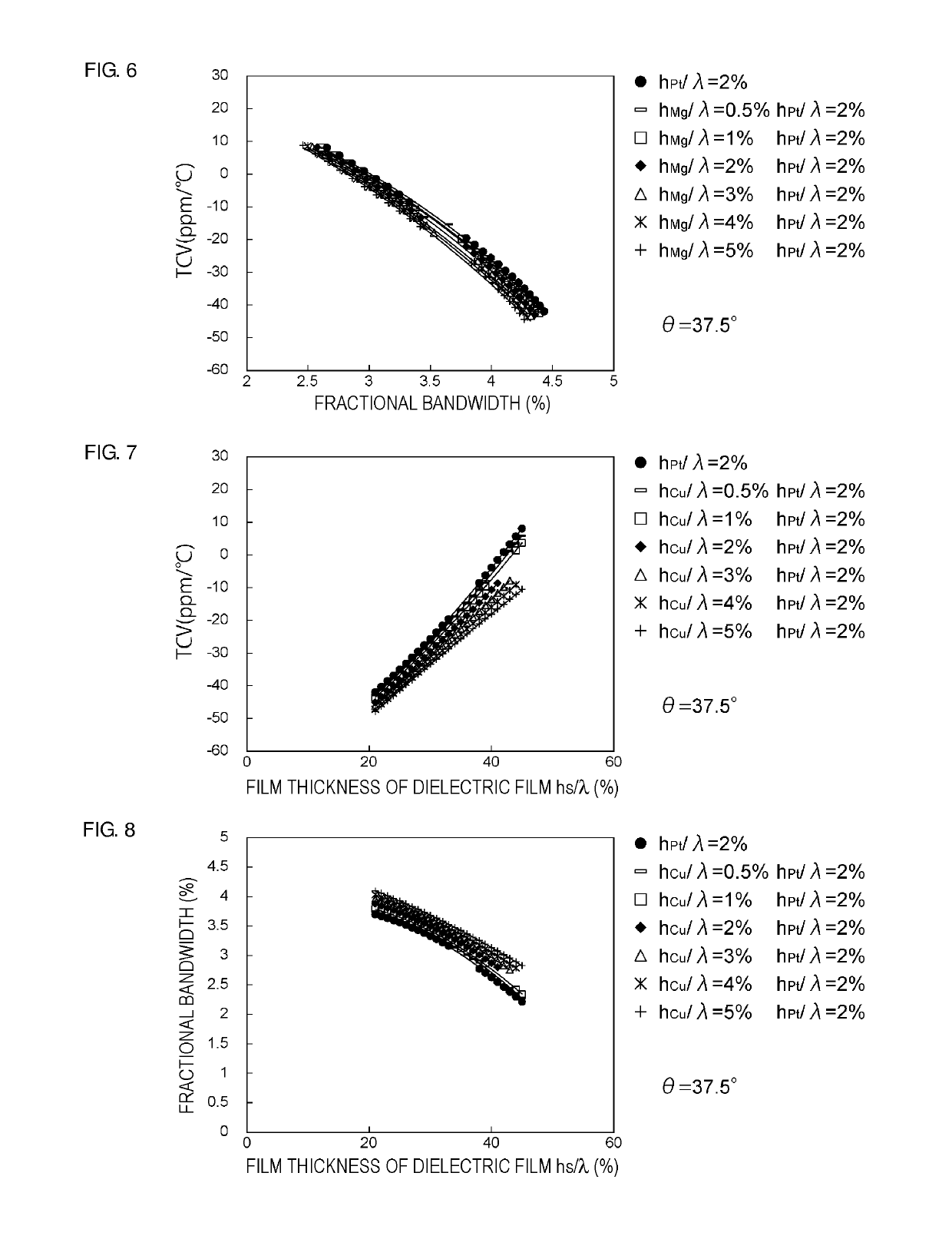

Elastic wave device, high-frequency front end circuit, and communication apparatus

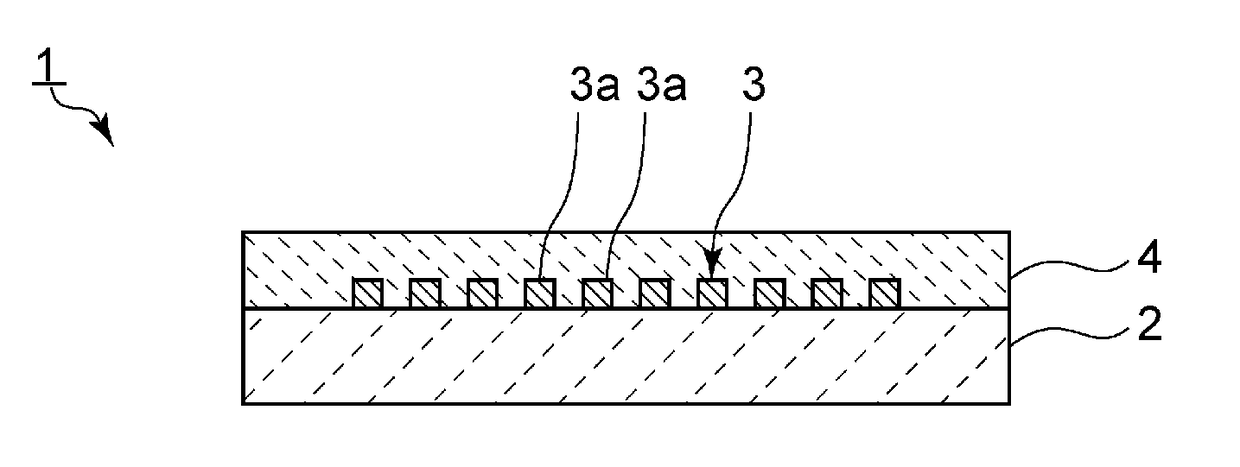

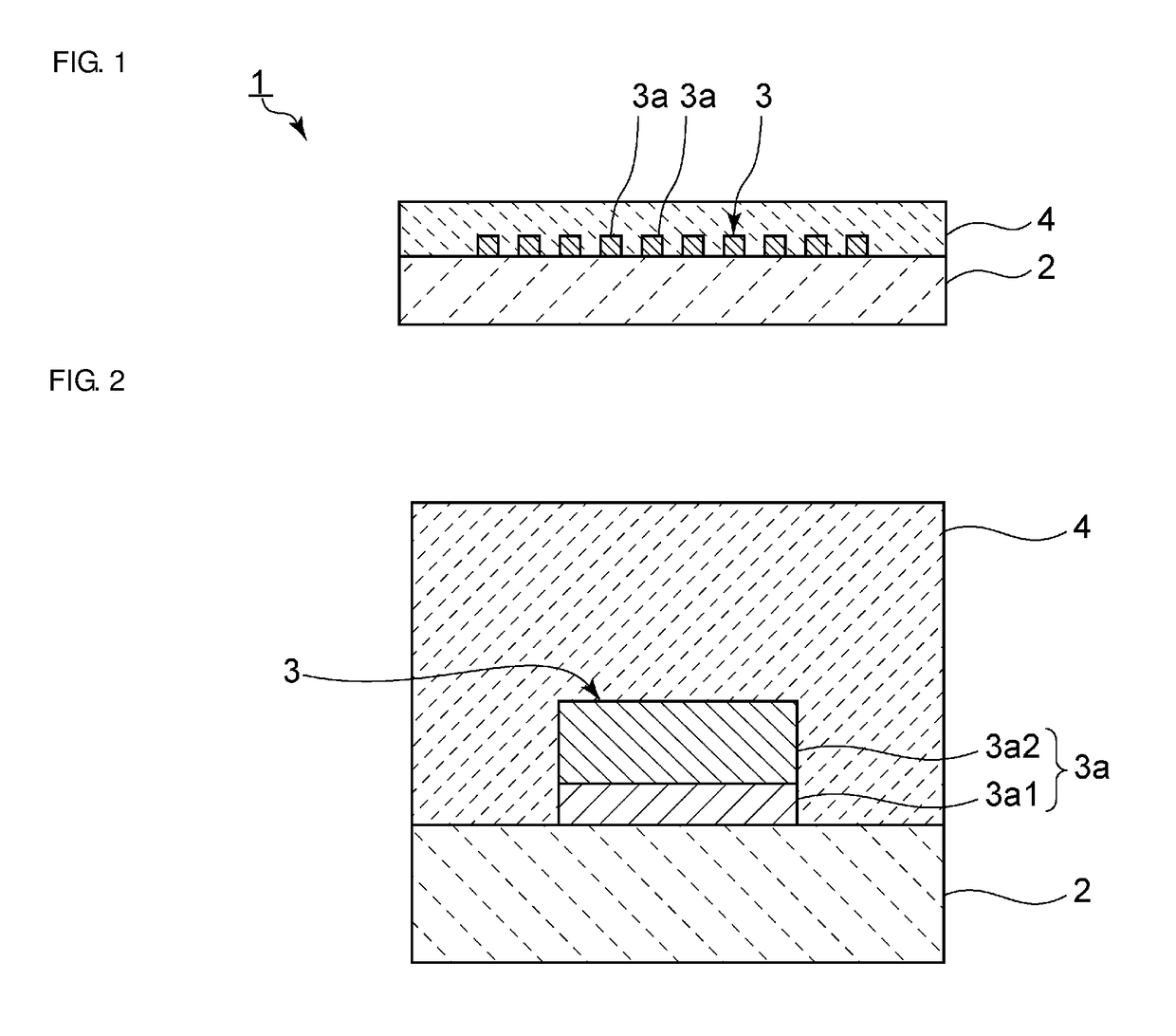

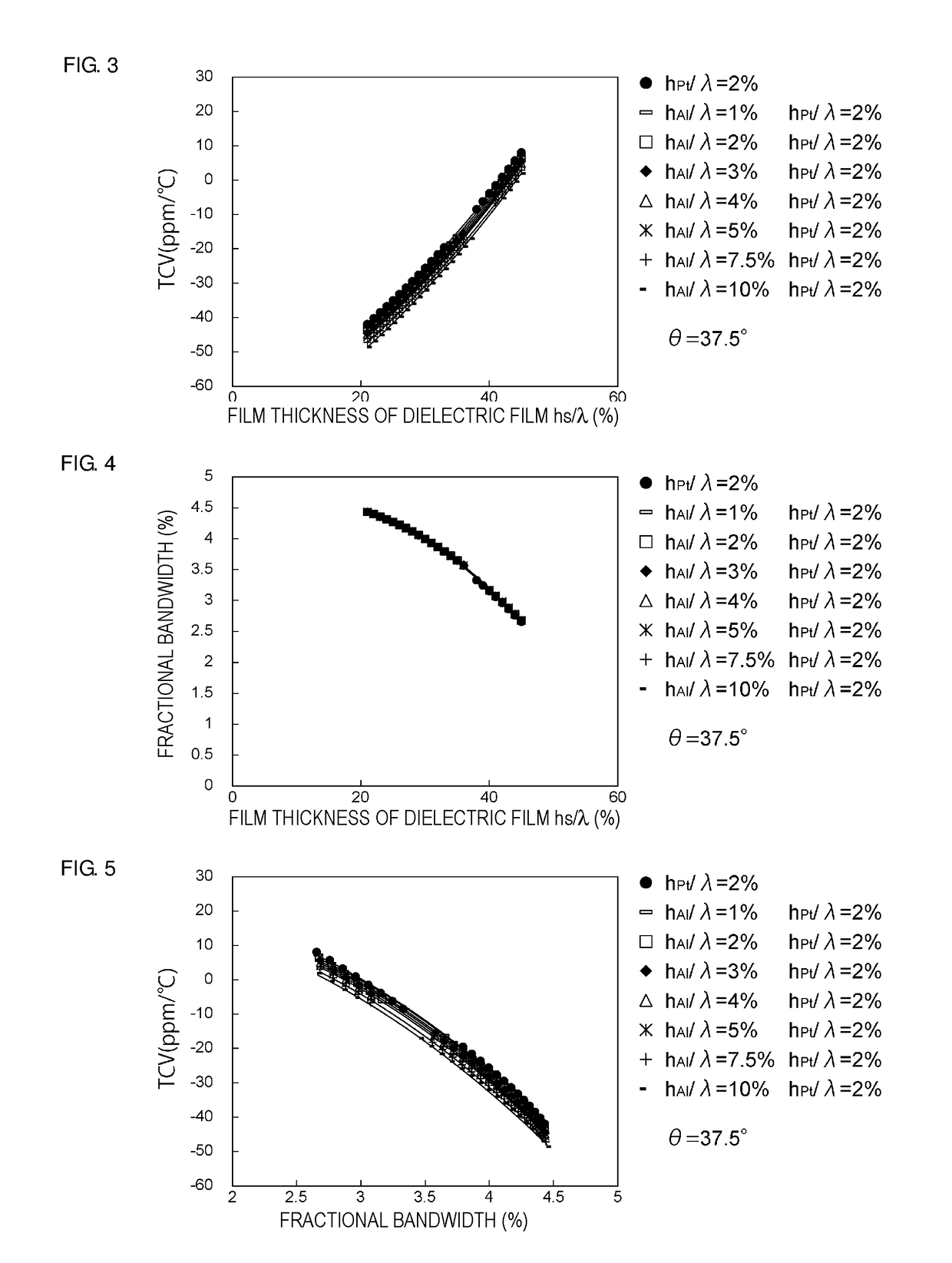

ActiveUS20180145658A1Improve trade-offsReduce resistanceImpedence networksPiezoelectric/electrostrictive/magnetostrictive devicesOptoelectronicsSilicon oxide

An elastic wave device includes a piezoelectric substrate, an IDT electrode including a first electrode layer which is provided on the piezoelectric substrate and contains Pt as a main component and a second electrode layer which is laminated on the first electrode layer and contains Cu as a main component, and a dielectric film that is provided on the piezoelectric substrate and covers the IDT electrode. The piezoelectric substrate is made of lithium niobate. The dielectric film is made of silicon oxide. The elastic wave device uses Rayleigh waves propagating along the piezoelectric substrate.

Owner:MURATA MFG CO LTD

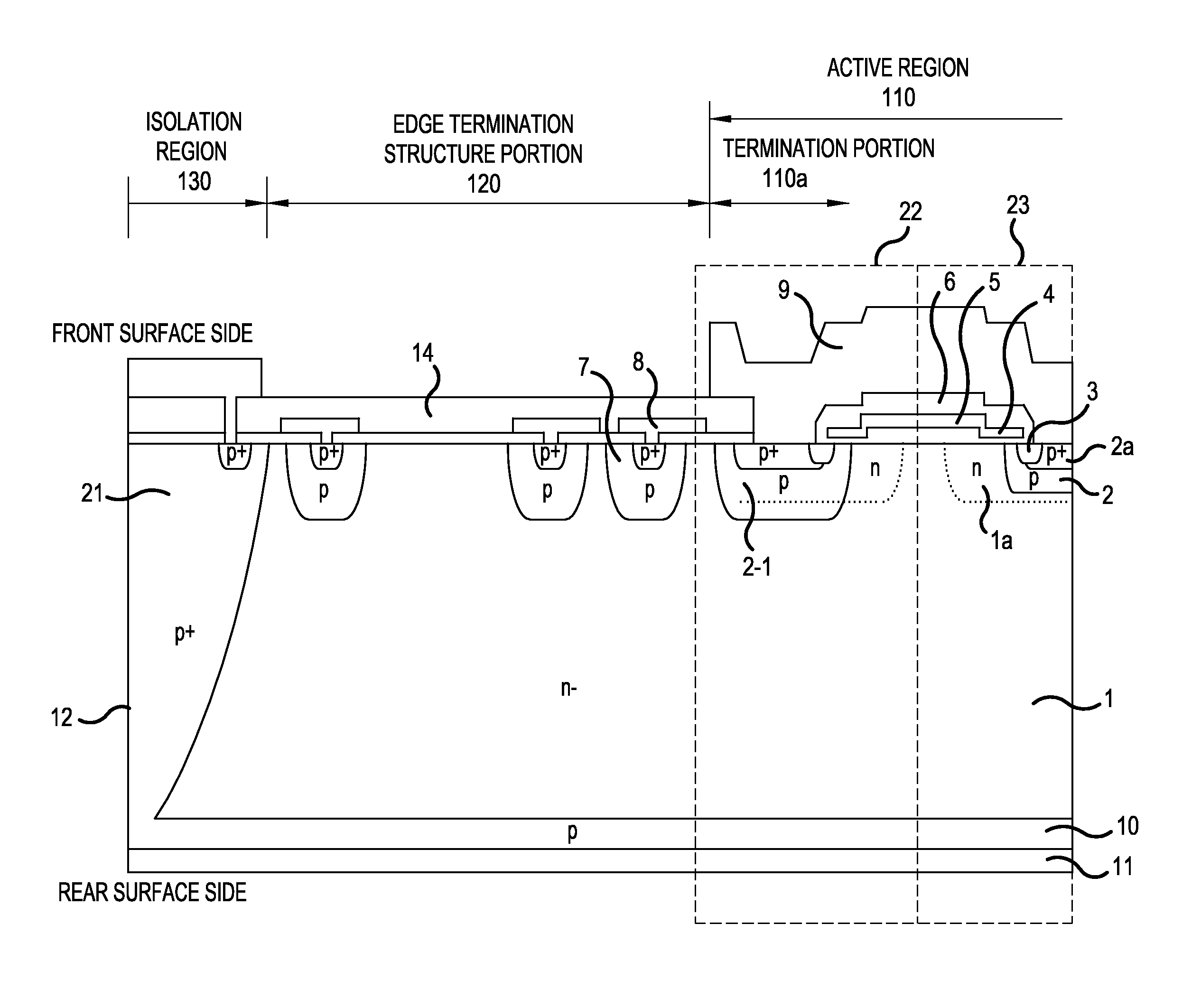

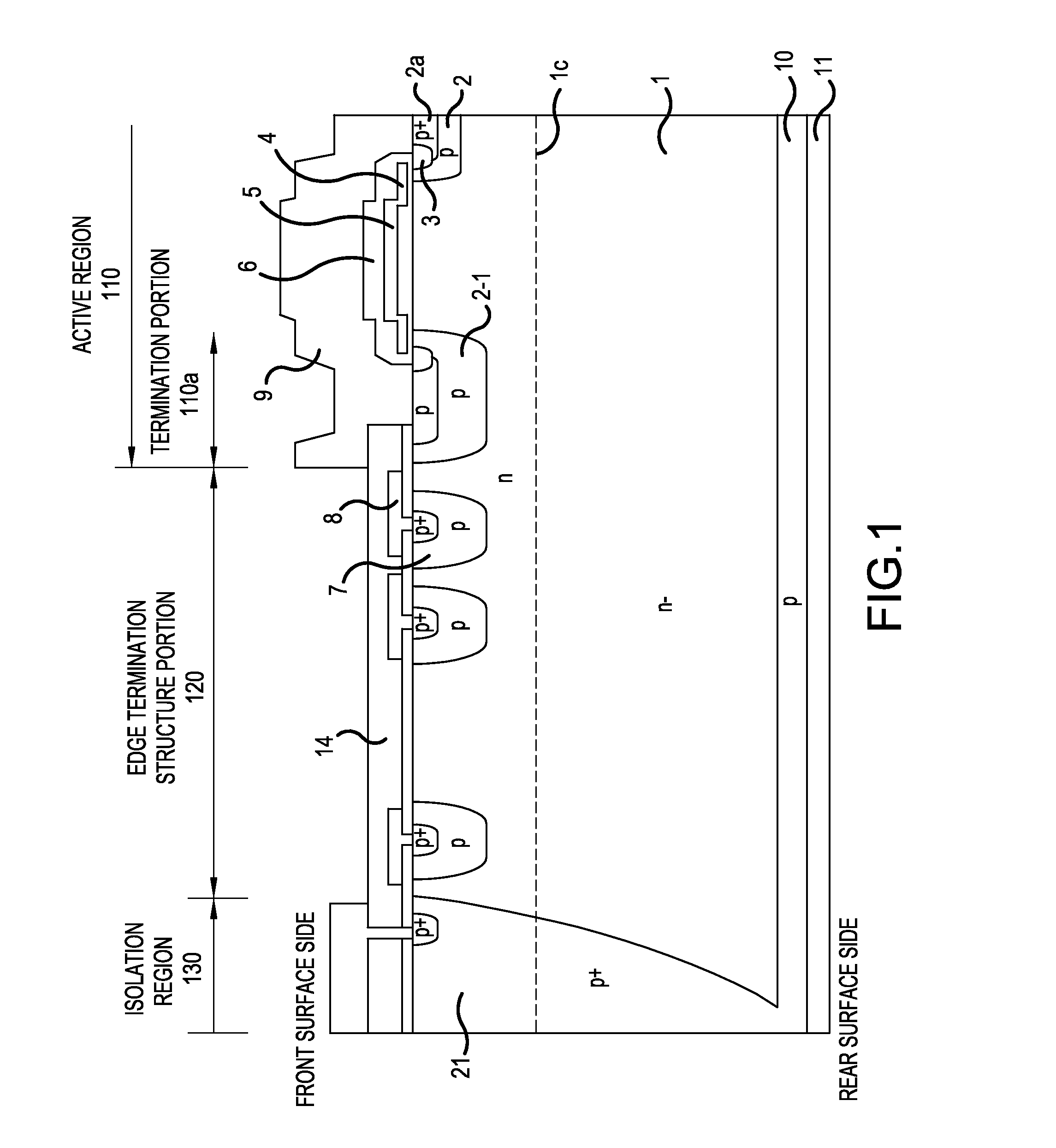

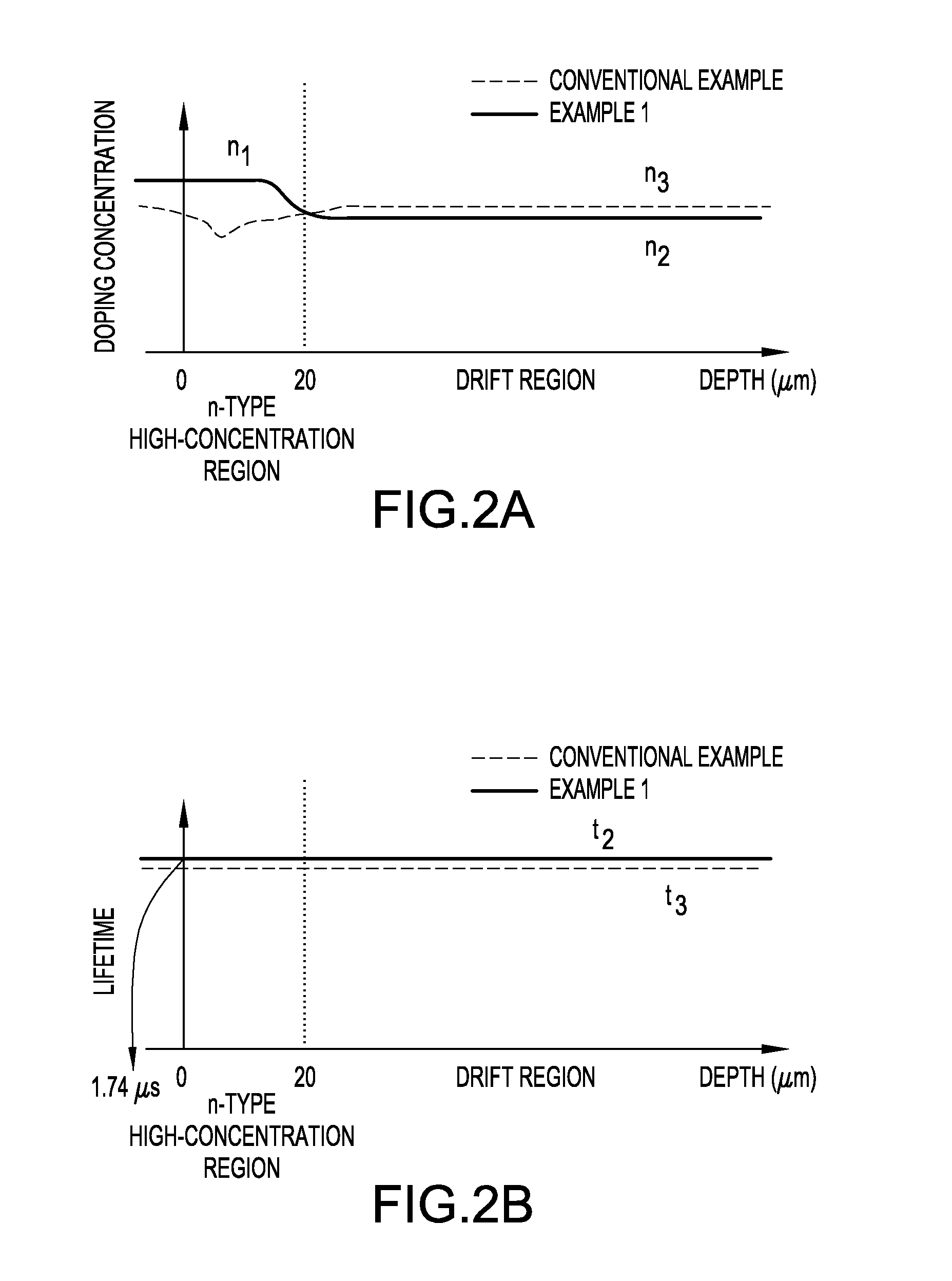

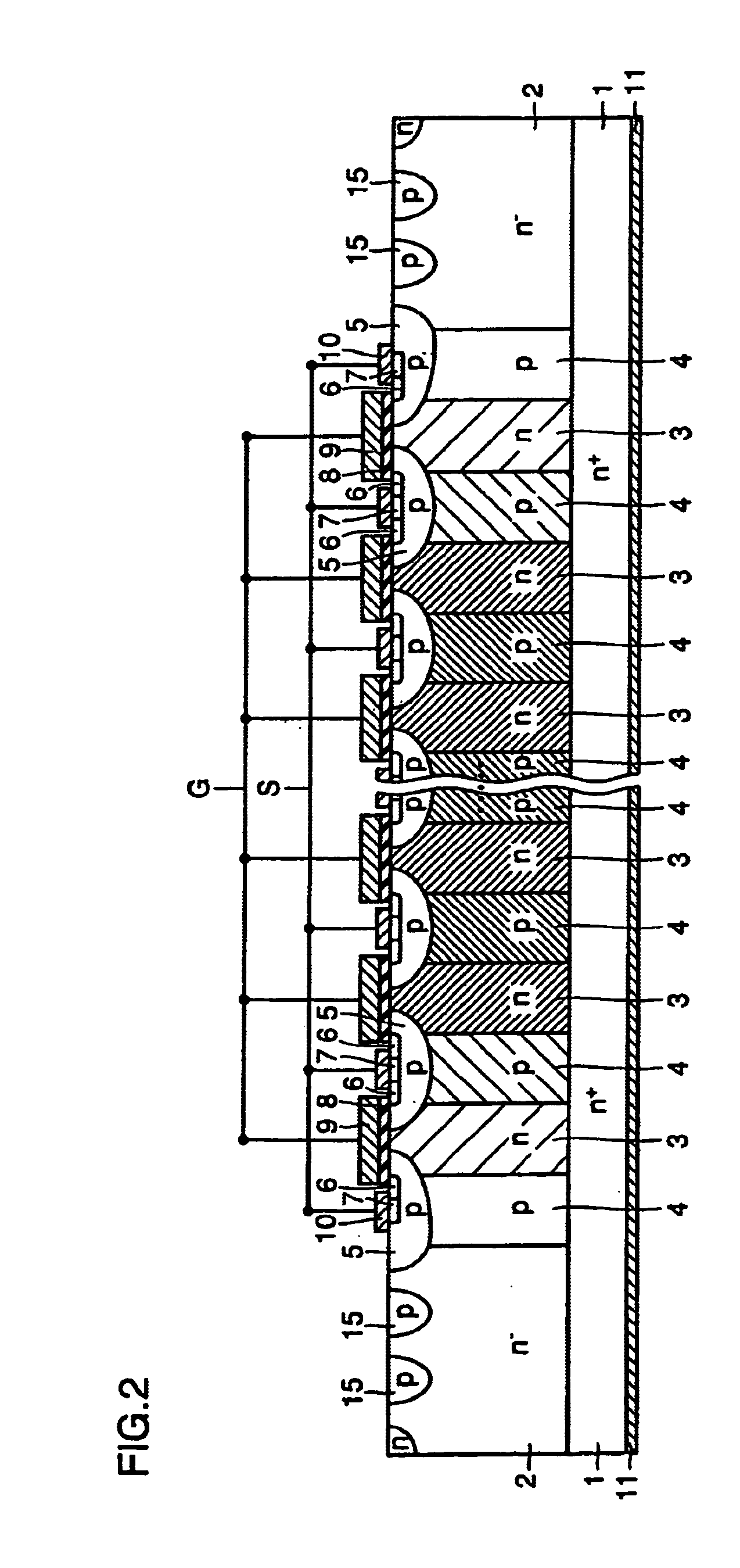

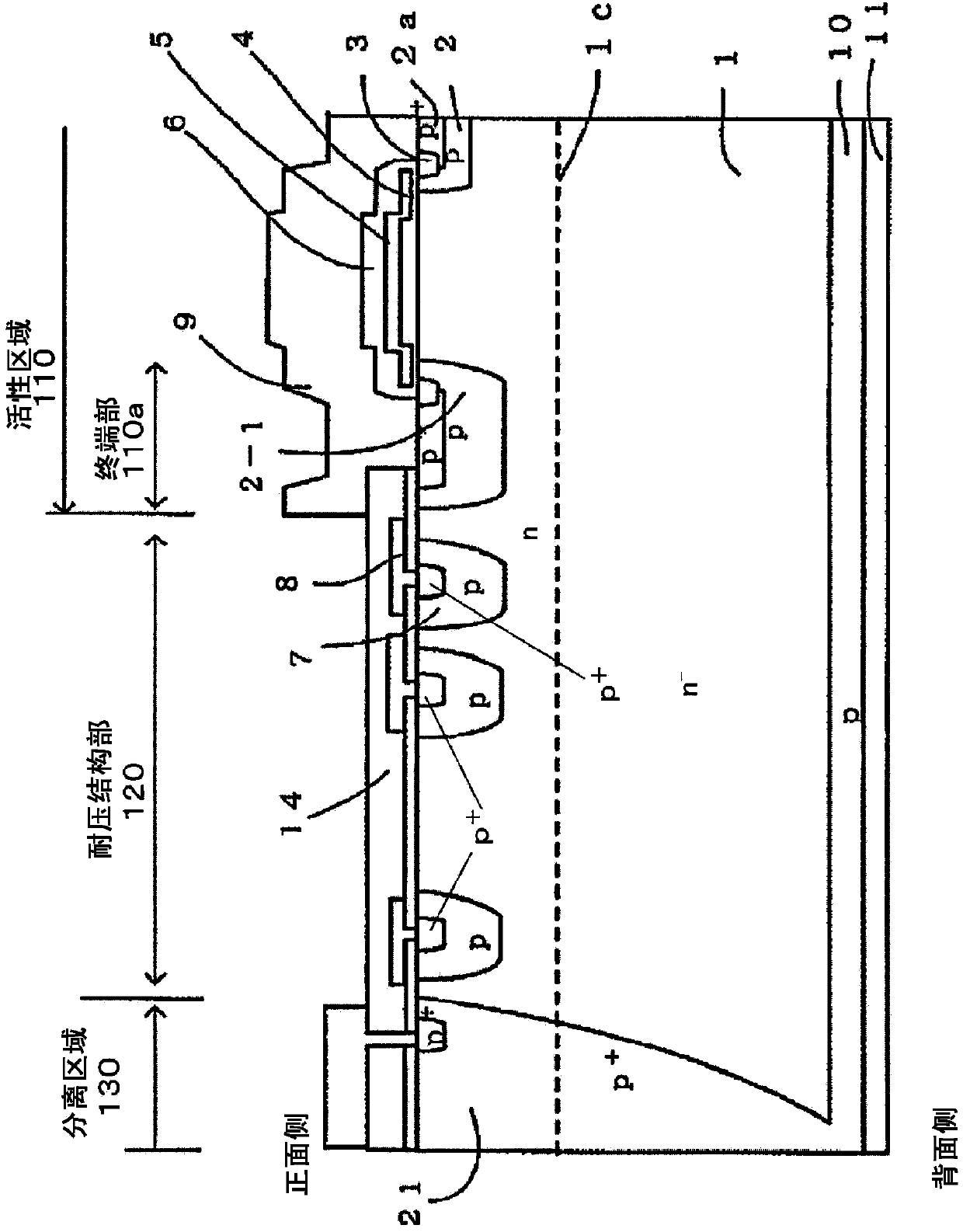

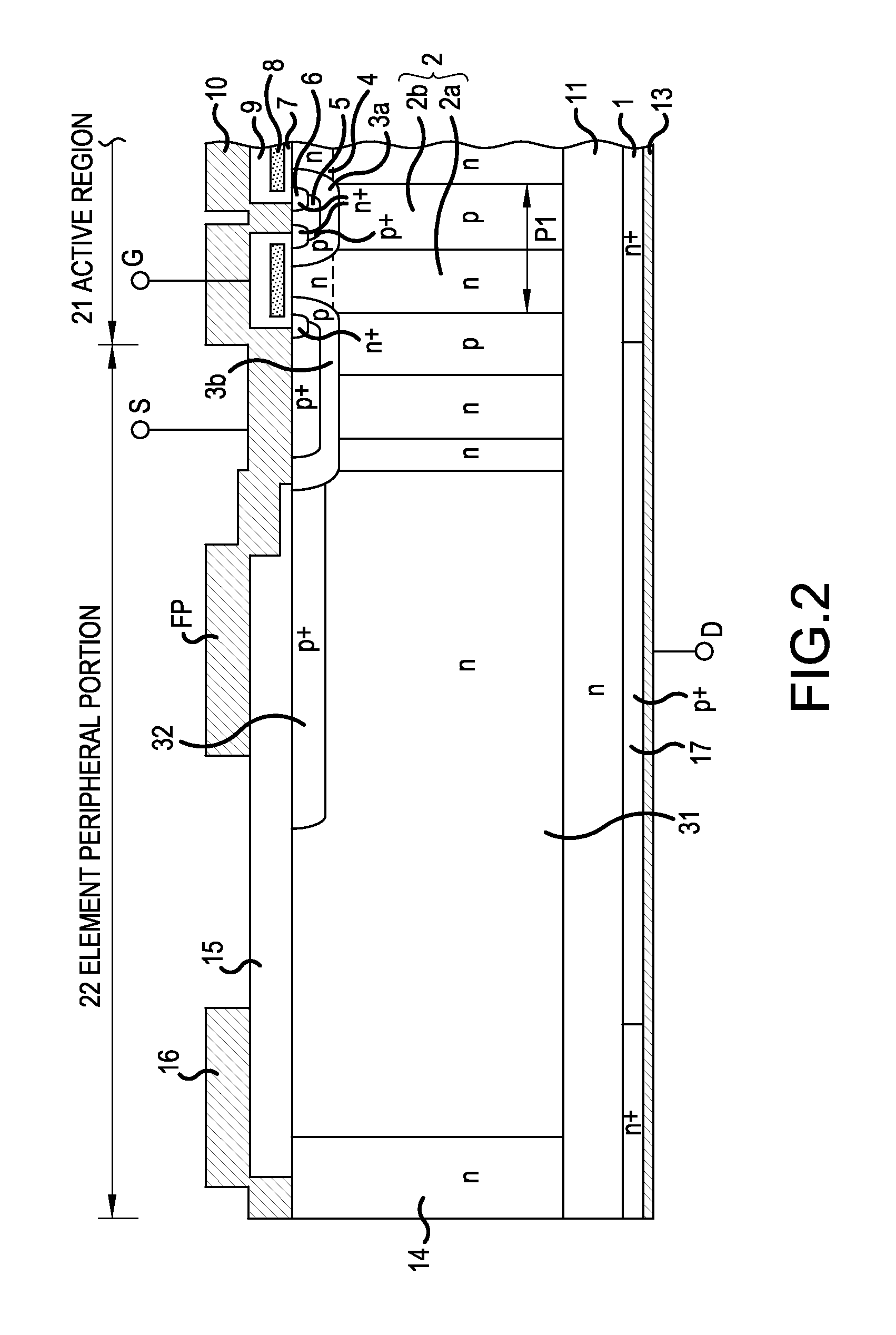

Semiconductor device and production method for semiconductor device

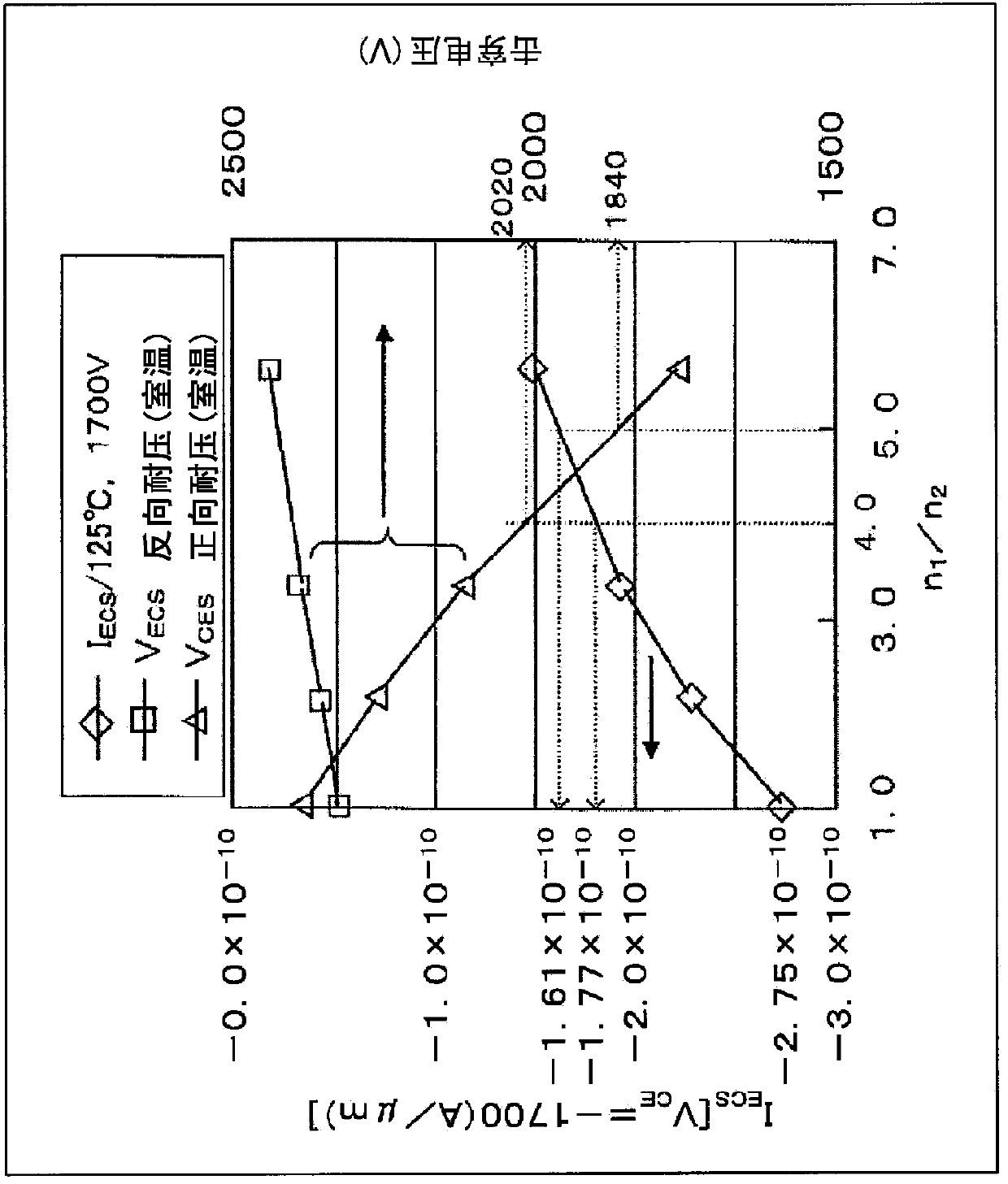

InactiveUS20150014742A1Improve trade-off relationshipImprove resistanceTransistorSemiconductor/solid-state device manufacturingPeak valueVoltage

Depth of a termination p base region provided in a termination portion of an active region close to an edge termination structure portion is more than depth of a p-type base region provided inside the termination p base region. An n-type high-concentration region is provided from one main surface of the semiconductor substrate in the entire surface layer of one surface of a semiconductor substrate within a depth of 20 μm or less below the bottom of the termination p base region. Ratio of the impurity concentration n1 of the n-type high-concentration region (1c) to the impurity concentration n2 of an n− drift region satisfies 1.0<n1 / n2≦5.0. Reverse leakage current when operation temperature of an element is high can be reduced and trade-off between on-state voltage and switching loss can be improved. Rising peak voltage of collector voltage when a semiconductor device is off is reduced.

Owner:FUJI ELECTRIC CO LTD

Motor drive apparatus

InactiveUS8018189B2Improve trade-offsReduce interruptionsSingle-phase induction motor startersAC motor controlDriving currentTime information

Owner:RENESAS ELECTRONICS CORP

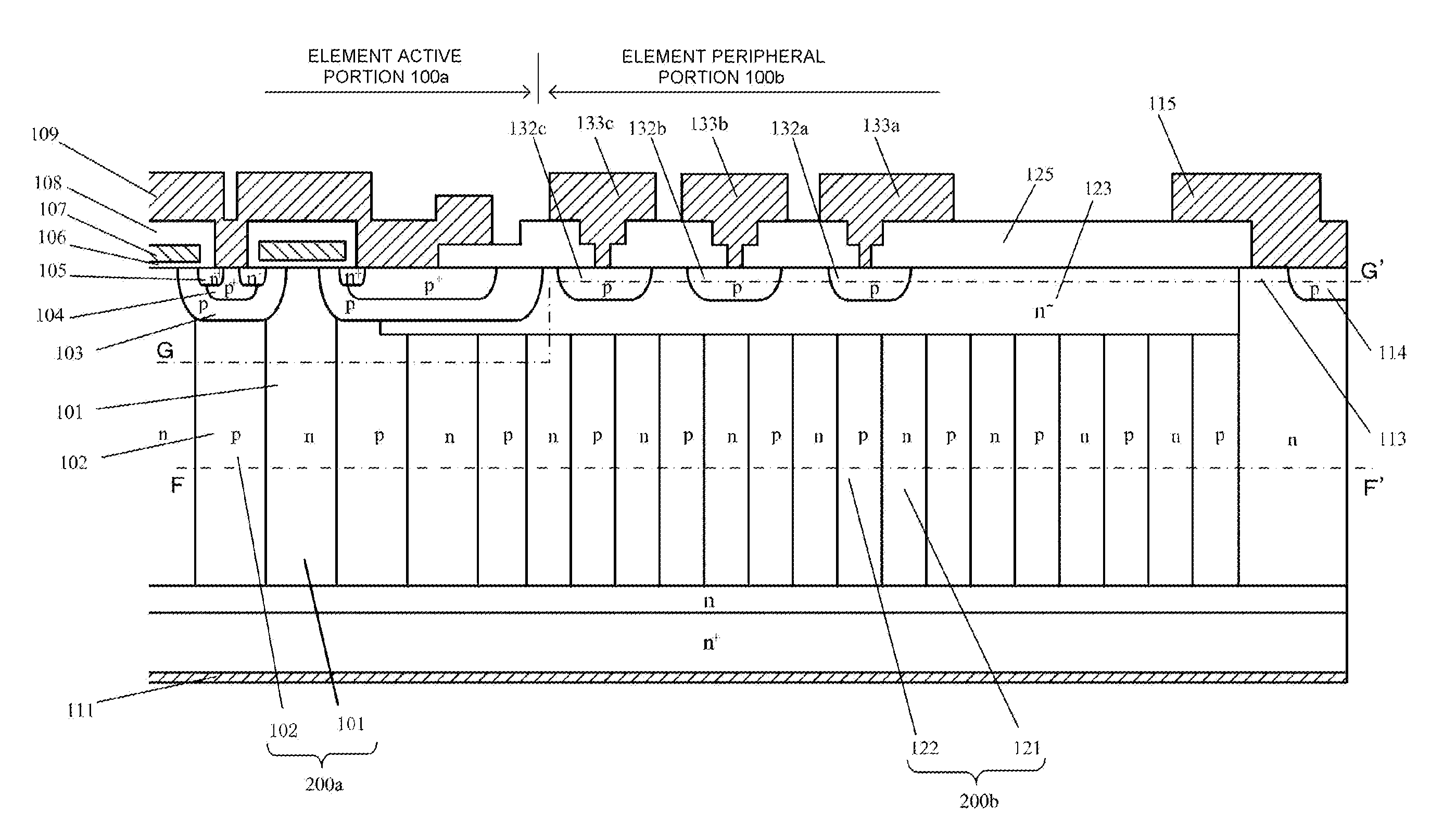

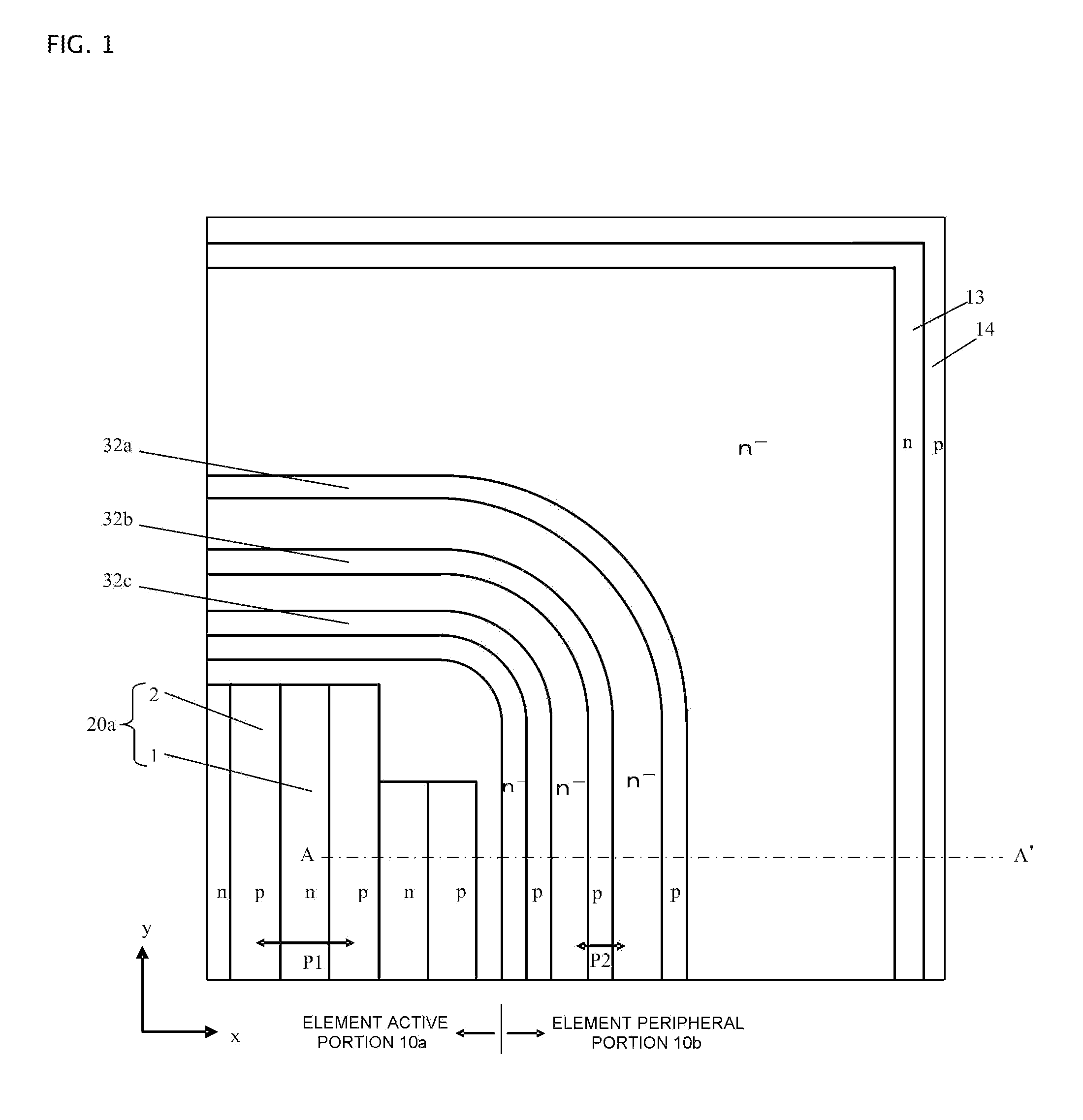

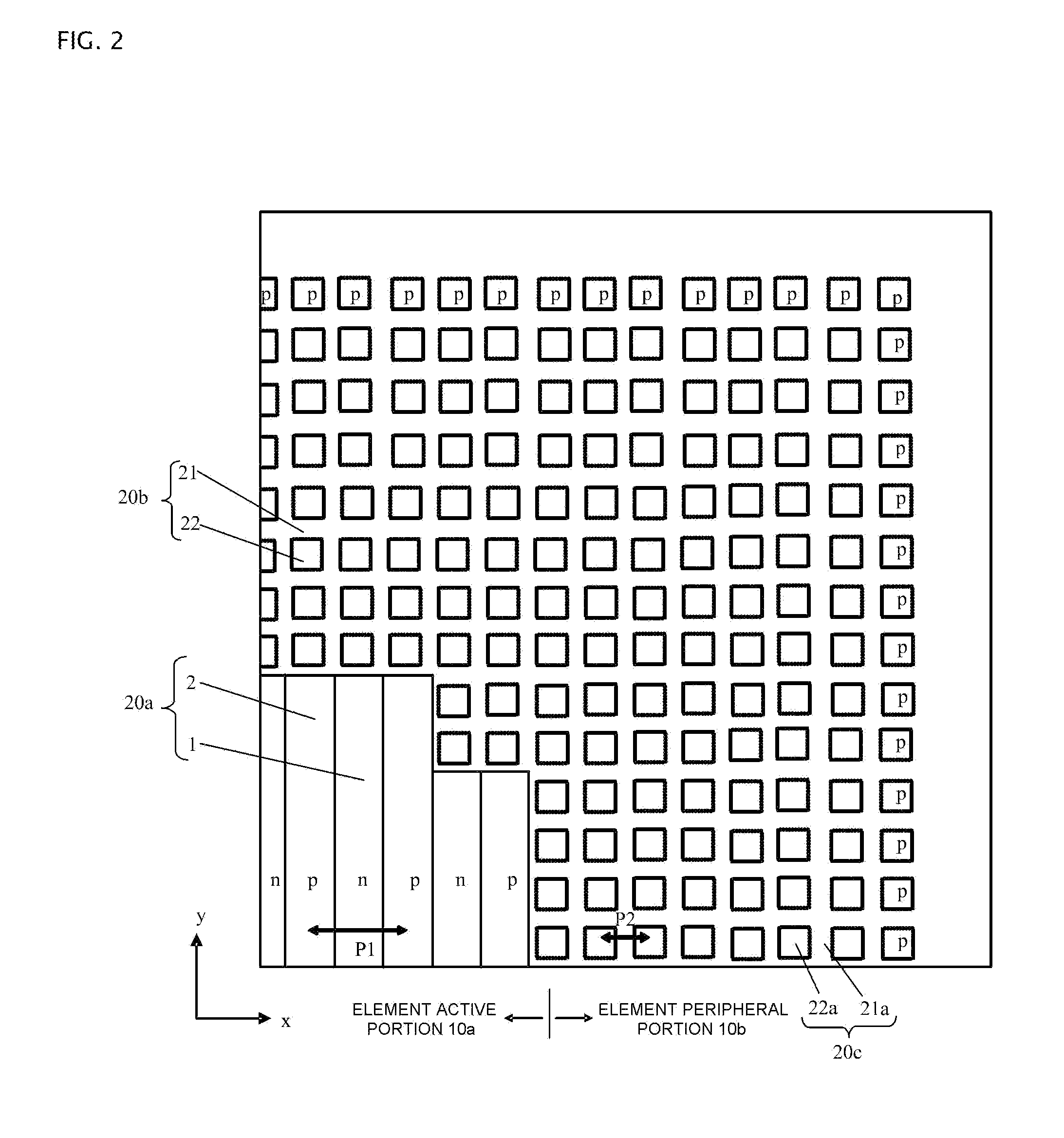

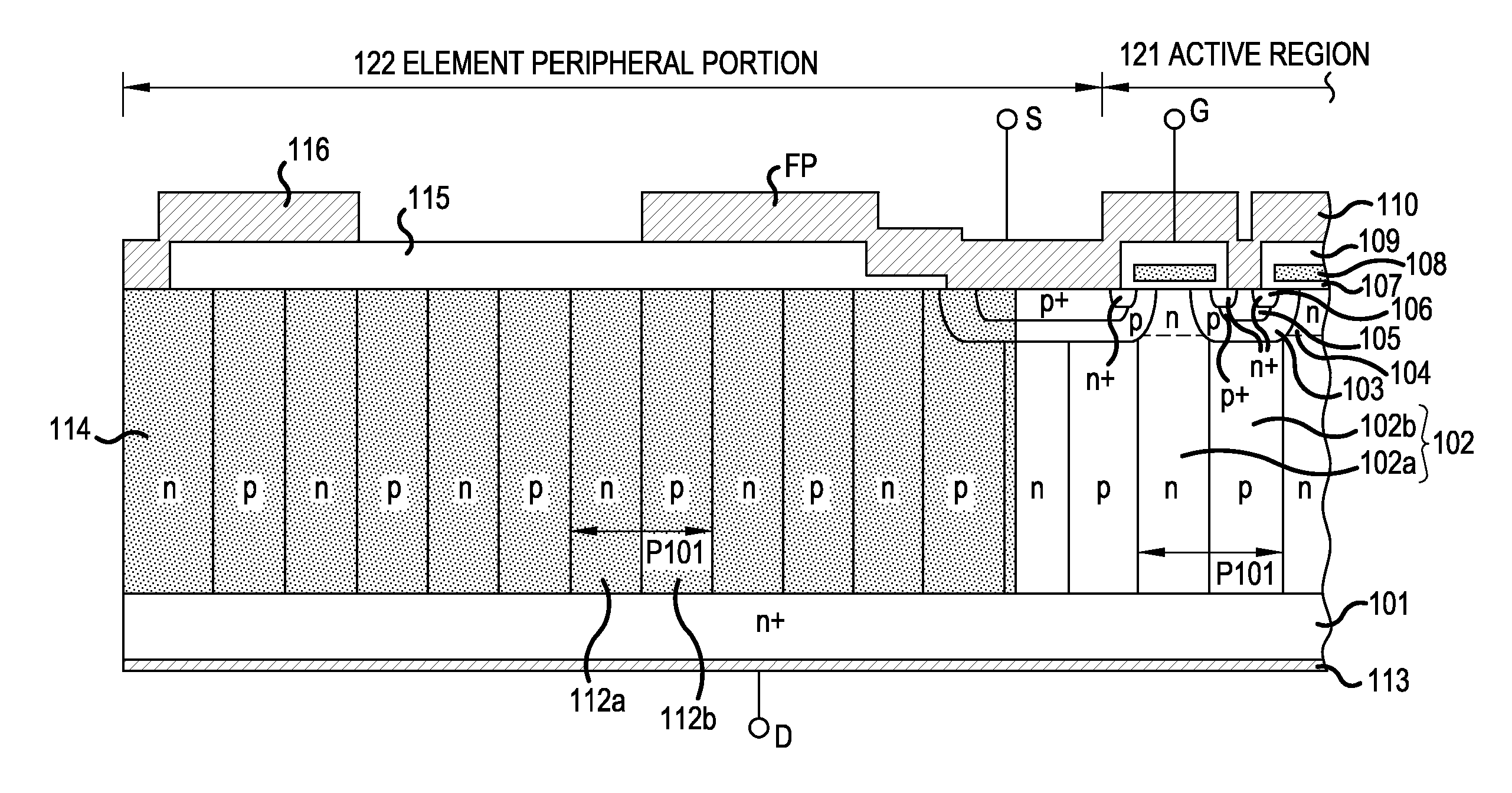

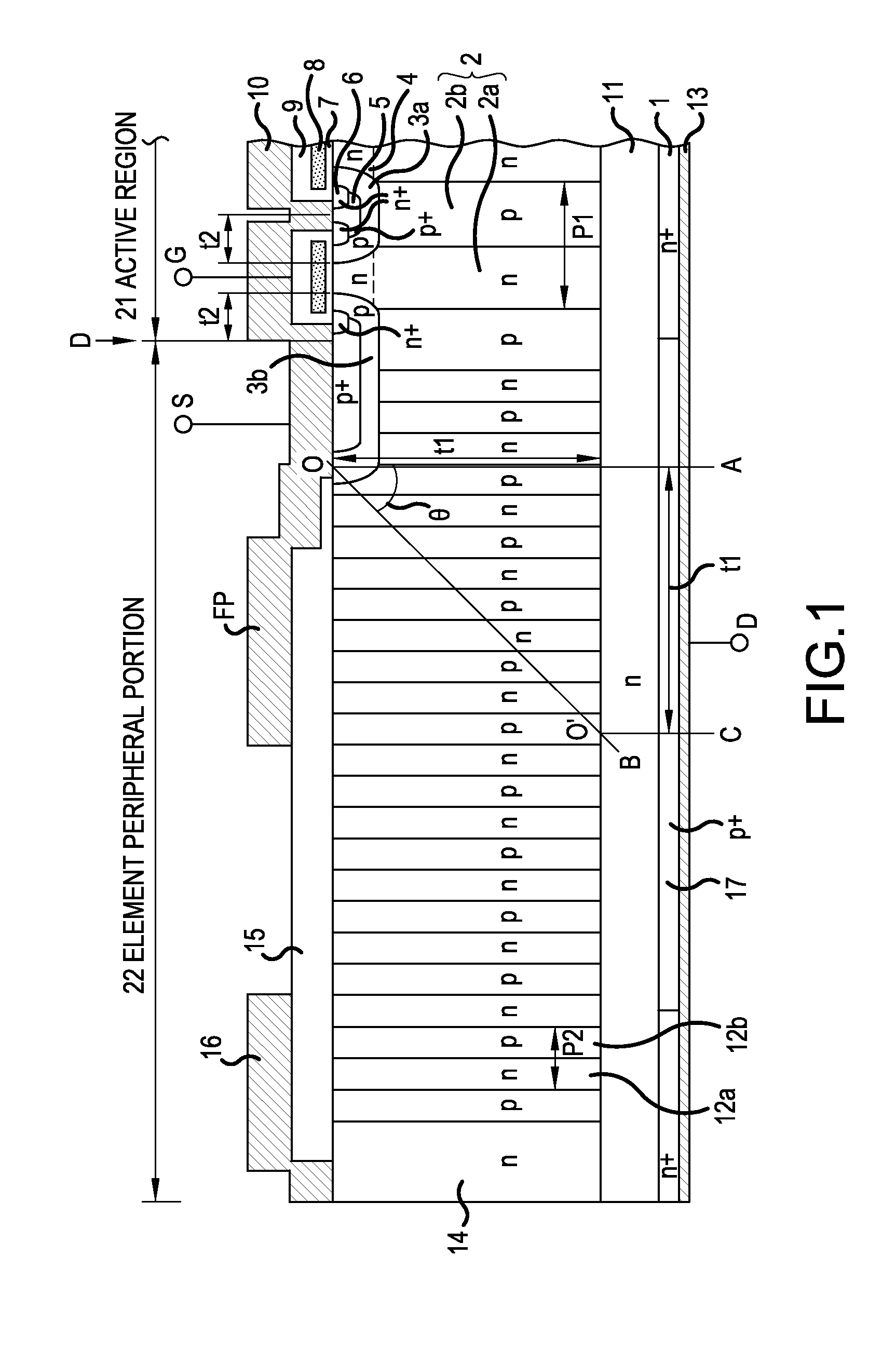

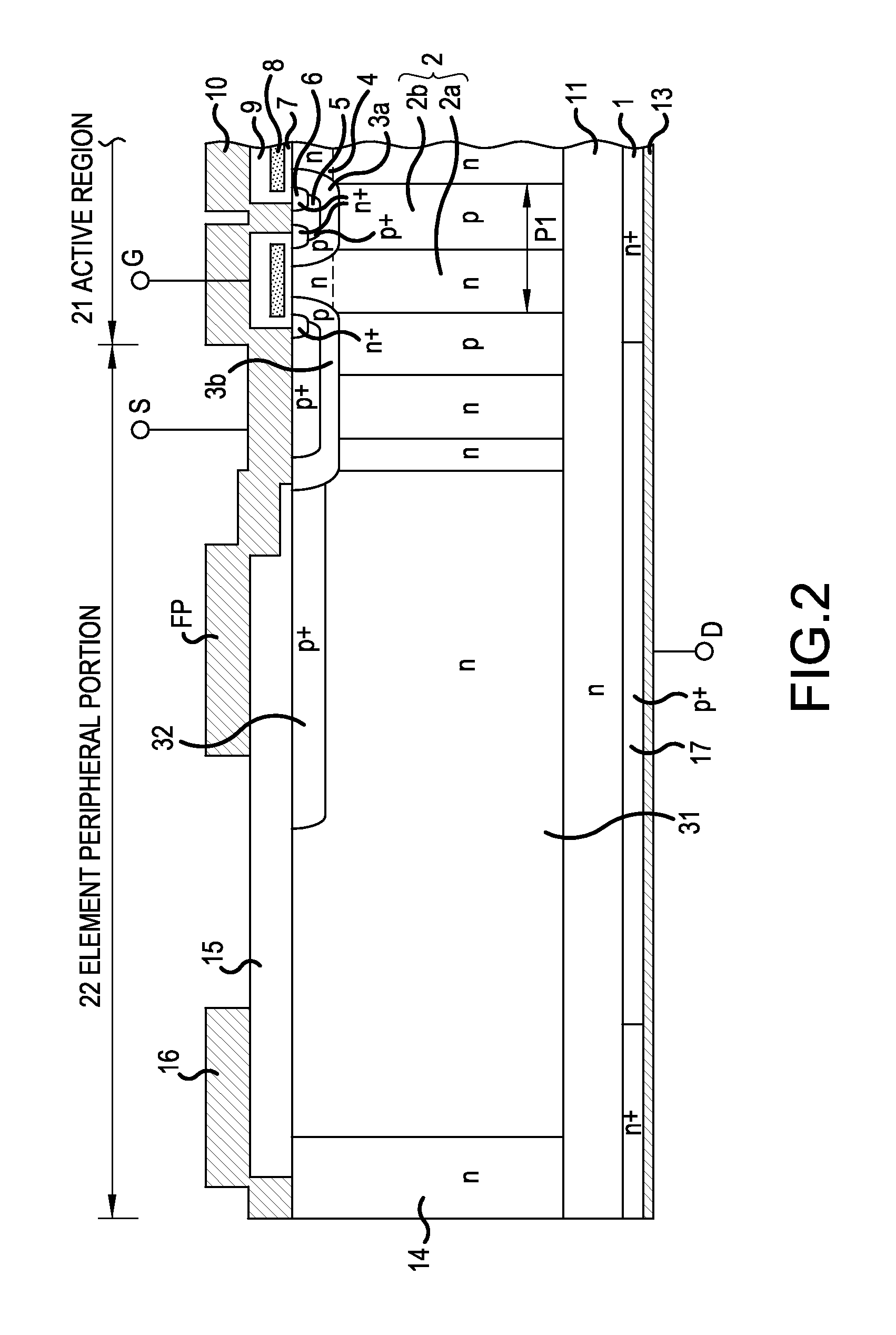

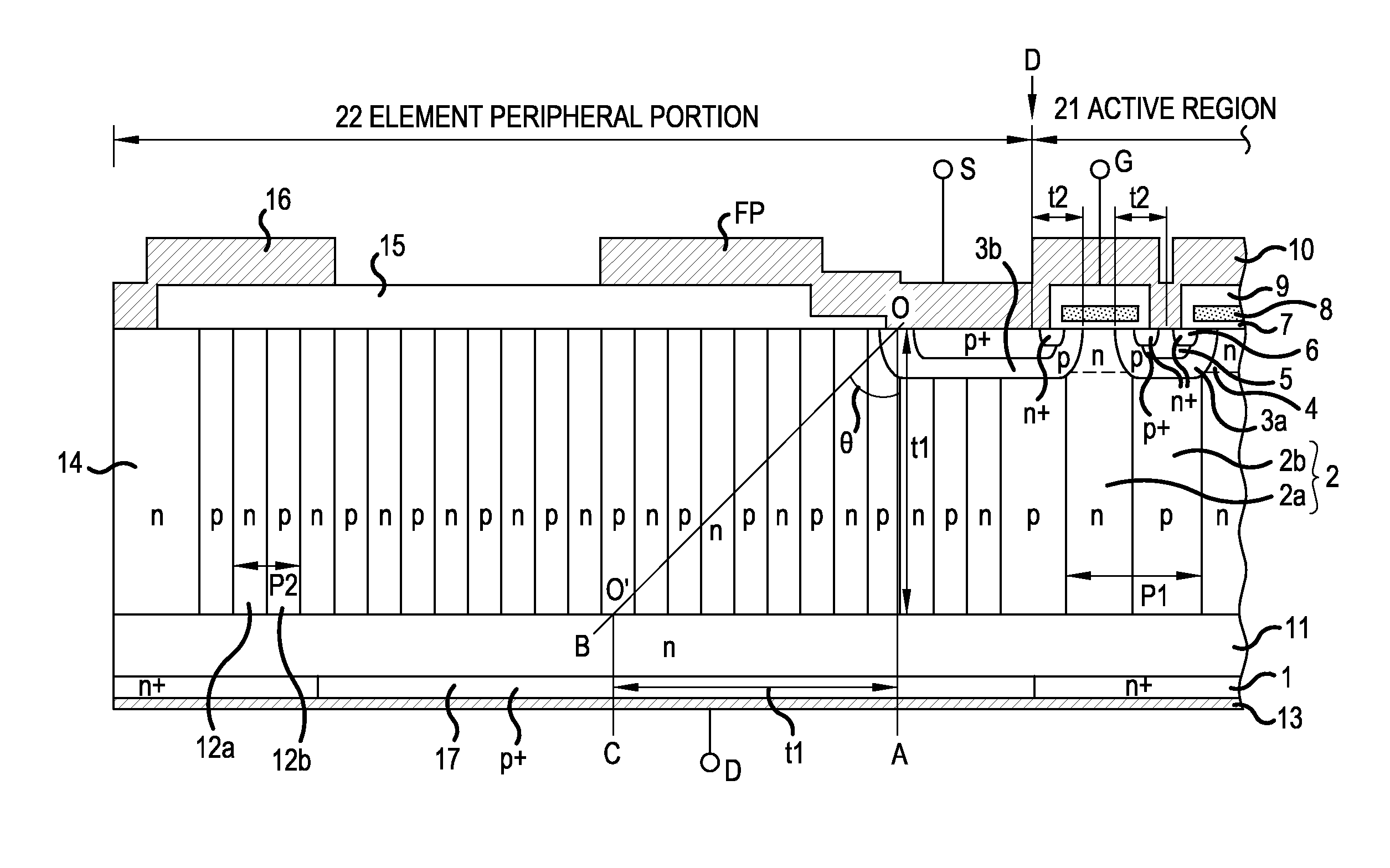

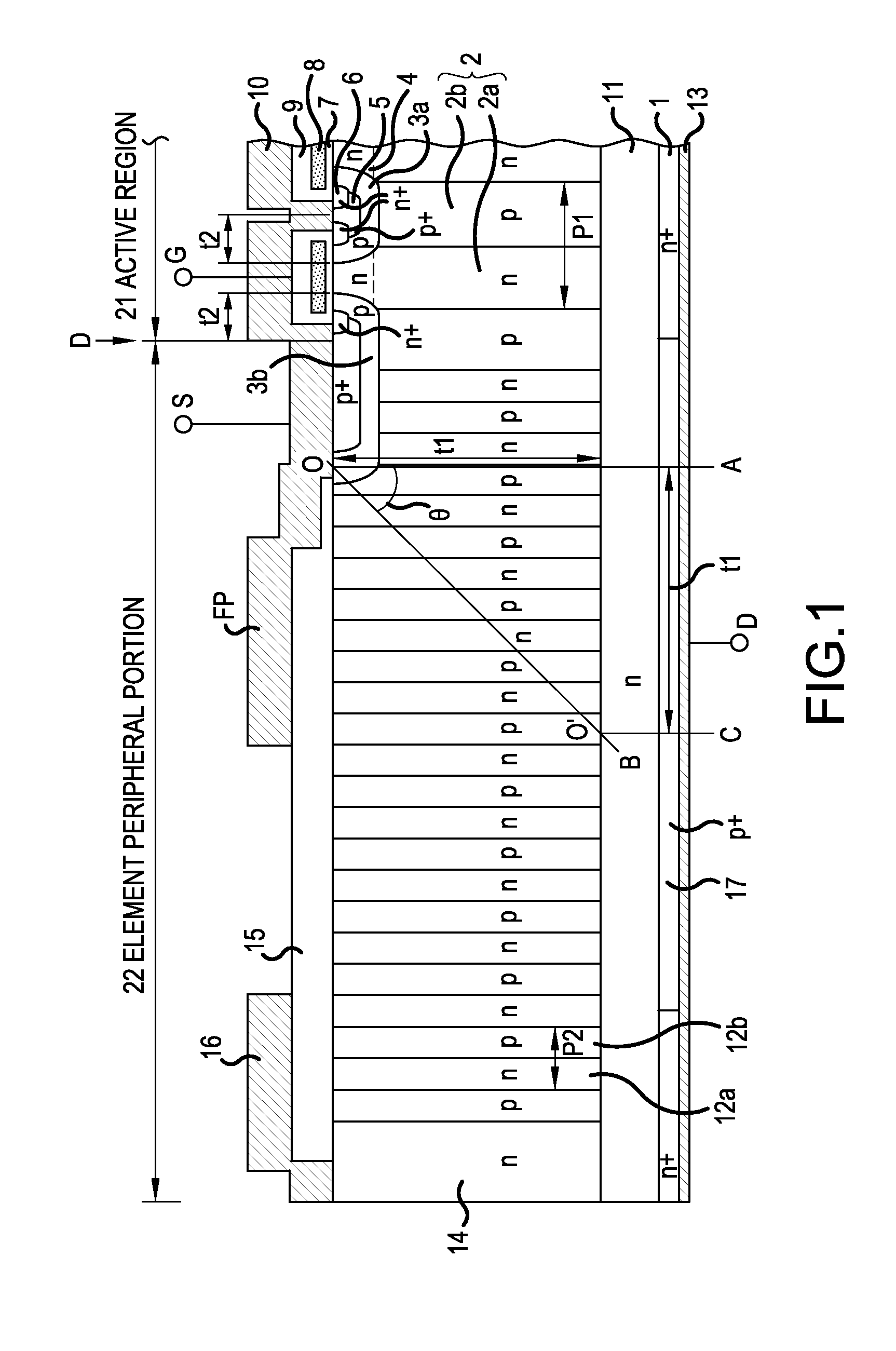

Superjunction semiconductor device

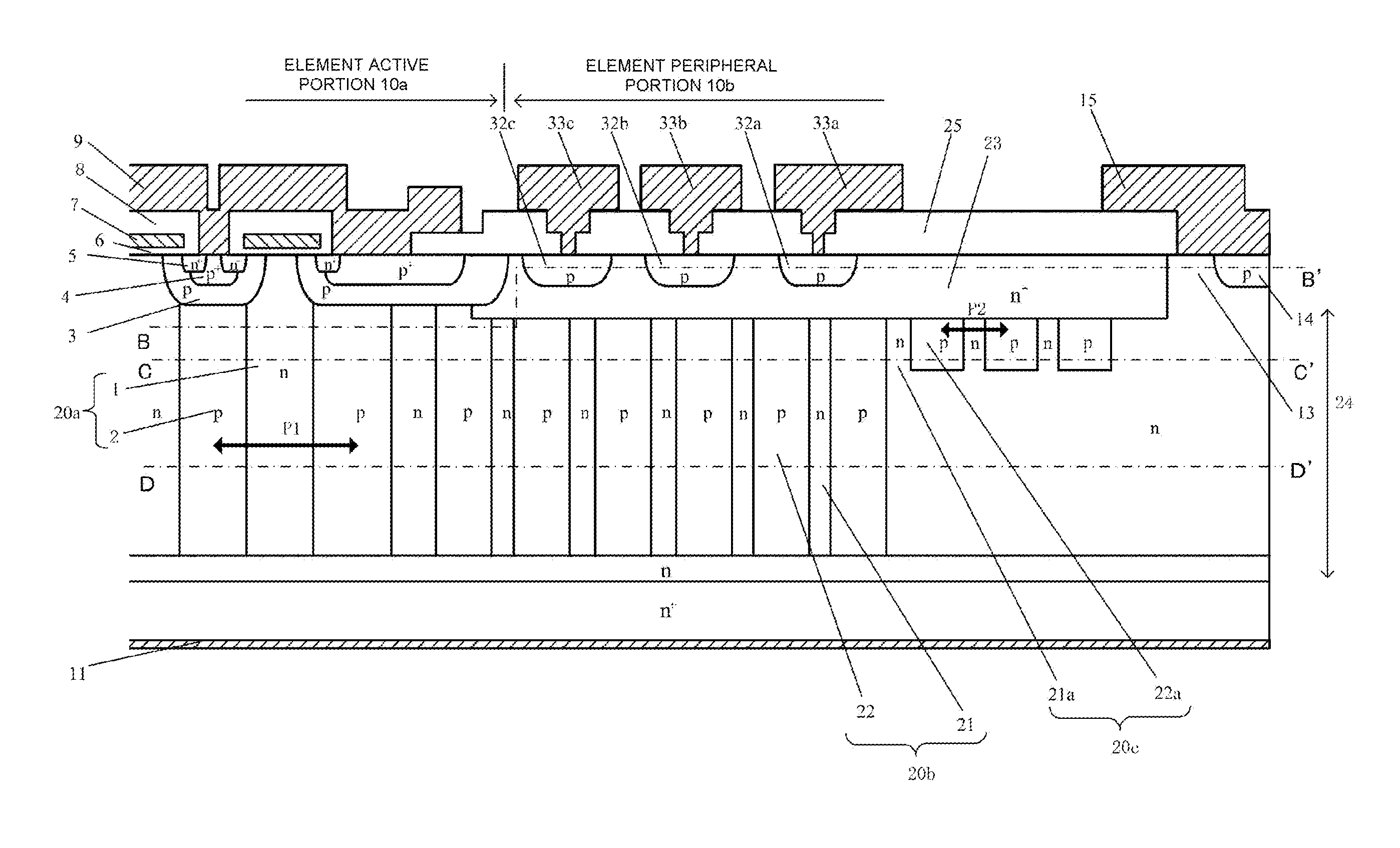

ActiveUS20130099347A1Trade-off relationshipImprove charge resistanceSemiconductor devicesVoltage dropEngineering

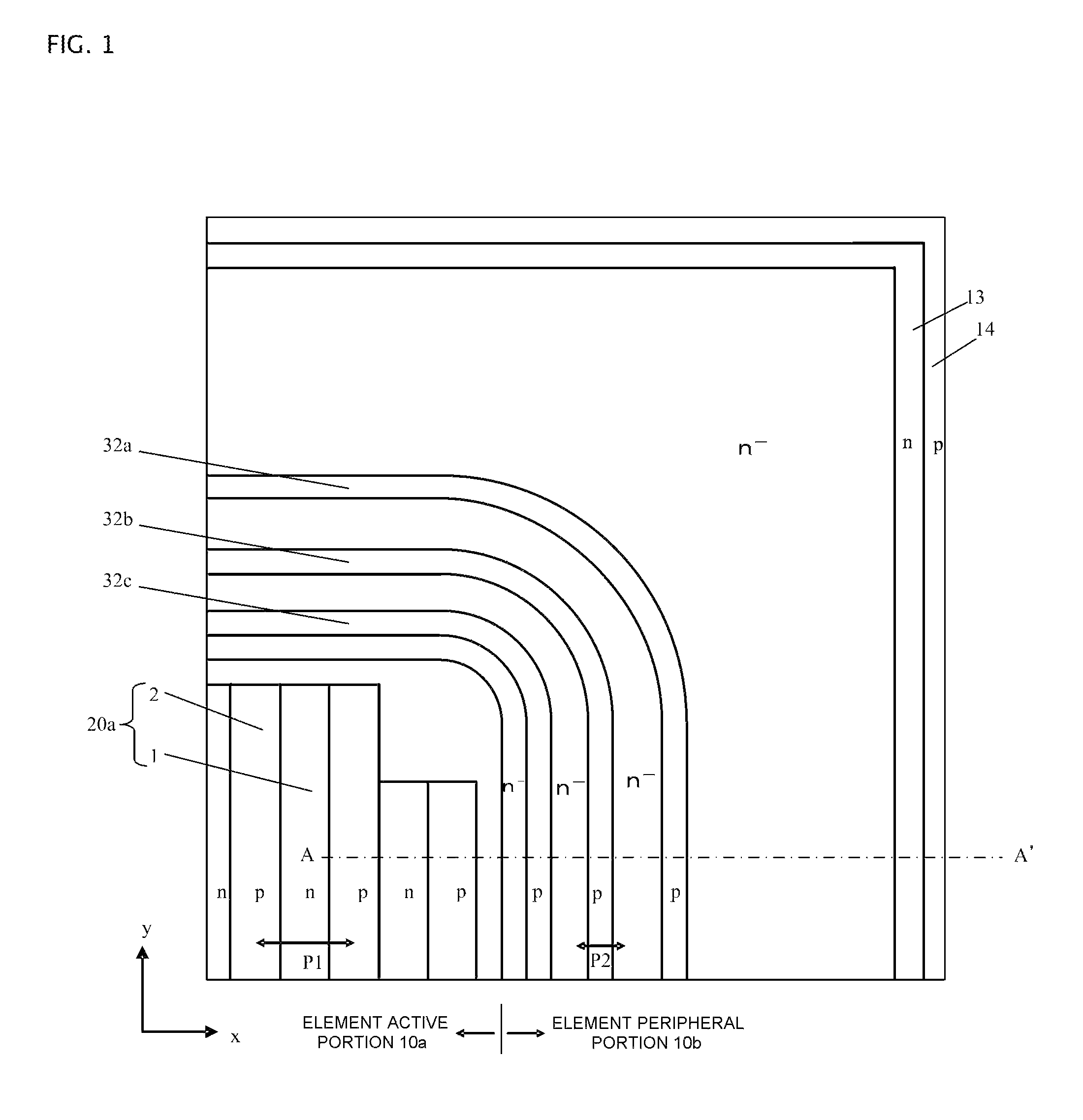

A superjunction semiconductor device is disclosed in which the trade-off relationship between breakdown voltage characteristics and voltage drop characteristics is considerably improved, and it is possible to greatly improve the charge resistance of an element peripheral portion and long-term breakdown voltage reliability. It includes parallel pn layers of n-type drift regions and p-type partition regions in superjunction structure. PN layers are depleted when off-state voltage is applied. Repeating pitch of the second parallel pn layer in a ring-like element peripheral portion encircling the element active portion is smaller than repeating pitch of the first parallel pn layer in the element active portion. Element peripheral portion includes low concentration n-type region on the surface of the second parallel pn layer. The depth of p-type partition region of an outer peripheral portion in the element peripheral portion is smaller than the depth of p-type partition region of an inner peripheral portion.

Owner:FUJI ELECTRIC CO LTD

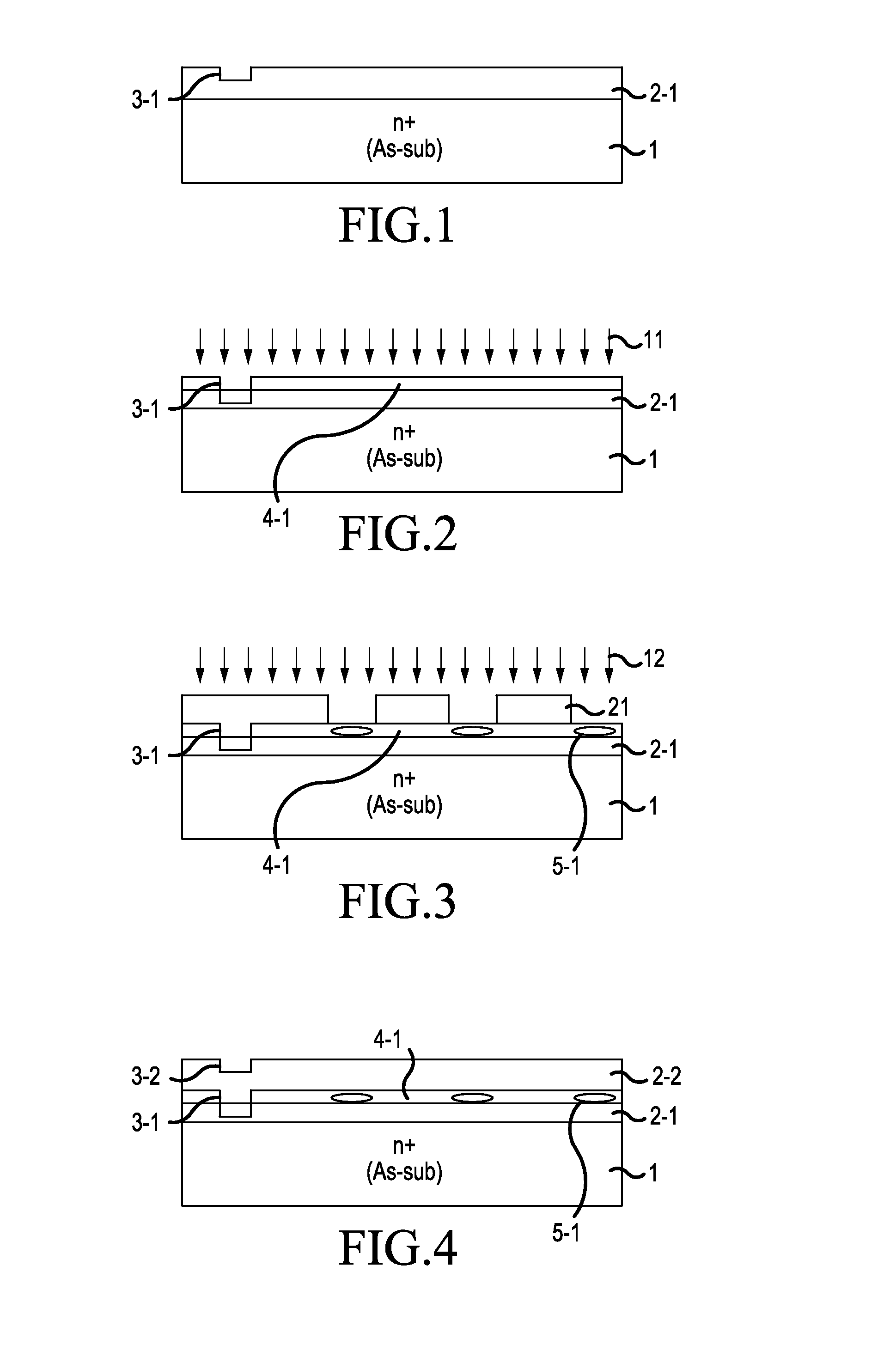

Semiconductor device and manufacturing method for the same

InactiveUS7105387B2Improve trade-offsSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceChip size

A semiconductor device of the present invention has a pn-repeating structure that a structure in which a p-type impurity region (4) and an n-type drift region (3) are aligned side by side is repeated twice or more, and a low concentration region which is either p-type impurity region (4) or n-type drift region (3) located at the outermost portion of this pn-repeating structure has the lowest impurity concentration or has the least generally effective charge amount among all the p-type impurity regions (4) and n-type drift regions (3) forming the pn-repeating structure.Thereby, the main withstand voltage of a power semiconductor device to which a three dimensional multi-RESURF principle is applied, wherein the element withstand voltage is specifically in the broad range of 20 to 6000 V, can be improved and the trade-off relationship between the main withstand voltage and the ON resistance can also be improved, so that an inexpensive semiconductor device of which the power loss is small and of which the size of the chip is small can be obtained.In addition, a trench of a dotted line trench (DLT) structure and a manufacturing method corresponding to this can be used, so that a semiconductor device with a good yield can be obtained at low cost.

Owner:MITSUBISHI ELECTRIC CORP

Semiconductor device and power conversion device

ActiveUS20190206987A1Improve trade-offsLower on-resistanceAC motor controlAc-dc conversionProtection layerTrench gate

A semiconductor device including: a trench gate; a trench-bottom protecting layer of a second conductivity type provided in a semiconductor layer of a first conductivity type while contacting a bottom of trenches; and a depletion suppressing layer of the first conductivity type provided between adjacent trench-bottom protecting layers, wherein the depletion suppressing layer includes an intermediate point that is horizontally equidistant to the adjacent trench-bottom protecting layers and is formed of a size to contact neither the trenches nor the trench-bottom protecting layers, and an impurity concentration of the depletion suppressing layer is set higher than an impurity concentration of the semiconductor layer.

Owner:MITSUBISHI ELECTRIC CORP

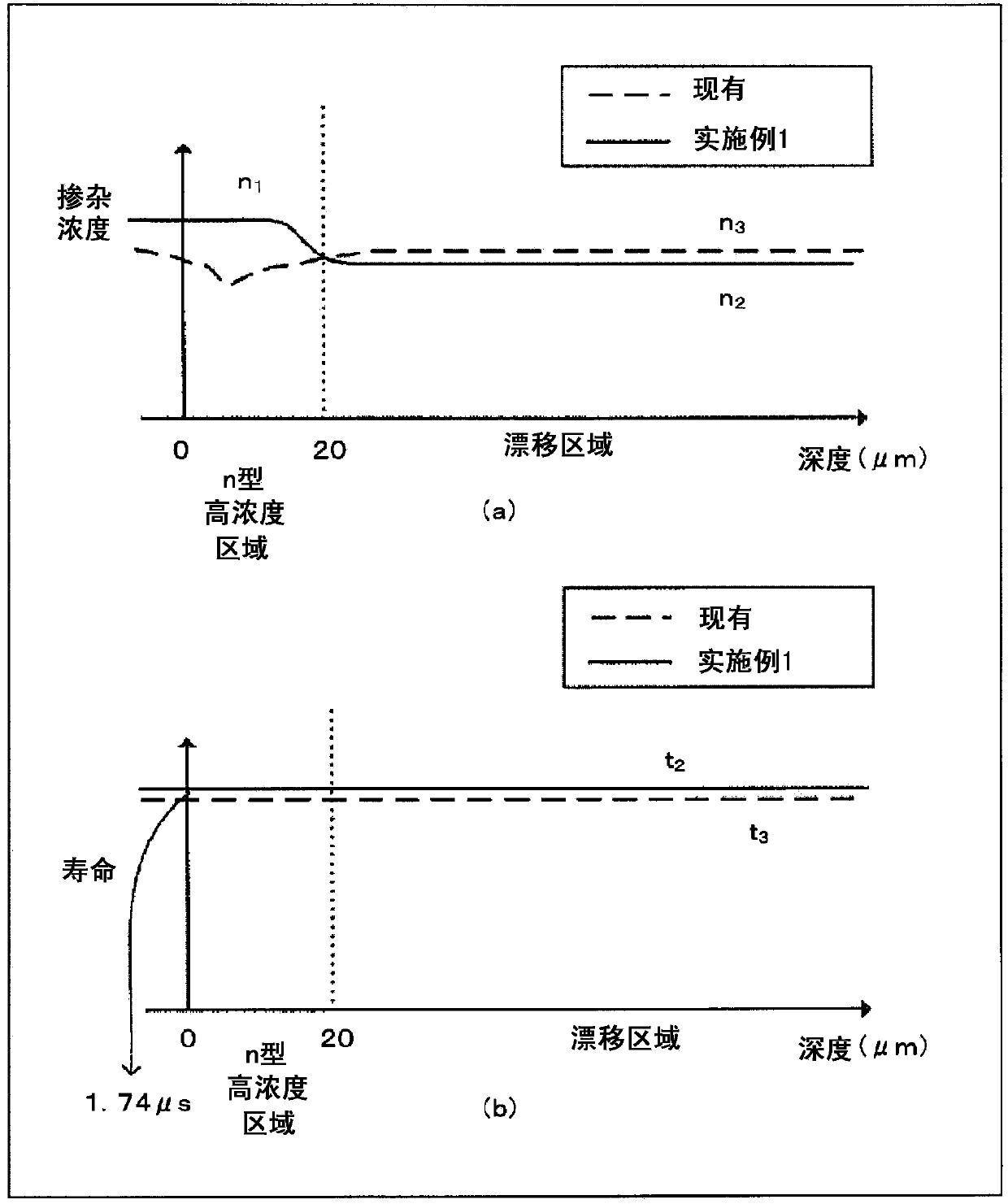

Semiconductor device manufacturing method

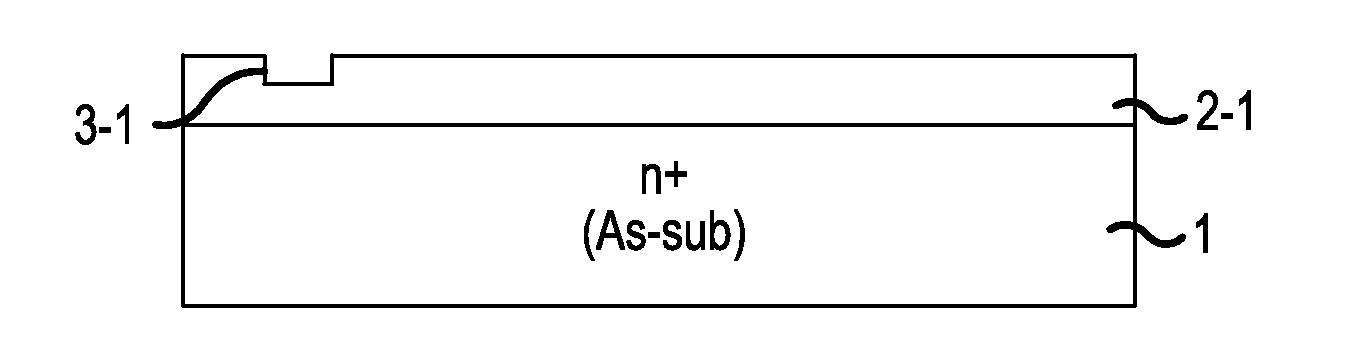

InactiveUS20140106520A1Preventing auto-dopingAvoid alignmentSemiconductor/solid-state device detailsSolid-state devicesProduction rateTrade offs

A semiconductor device manufacturing method with high productivity is disclosed with improved trade-off relationship between auto-doping and breakdown in alignment mark form. First to sixth epitaxial layers are grown sequentially on Si {100} main surface of an arsenic doped substrate using multilayer epitaxial technology. Epitaxial growth conditions of the first to sixth epitaxial layers are growth at atmospheric pressure and a temperature of 1,150° C. to 1,180° C., with epitaxial growth rate of 2.2 to 2.6 μm / minute. An alignment mark of depressed form whose bottom surface is the Si {100} plane is formed in the arsenic doped substrate. Every time one of the first to sixth epitaxial layers is grown on the main surface of the arsenic doped substrate, an alignment mark of depressed form is formed in the outermost epitaxial layer by a portion above the alignment mark of the layer below being transformed.

Owner:FUJI ELECTRIC CO LTD

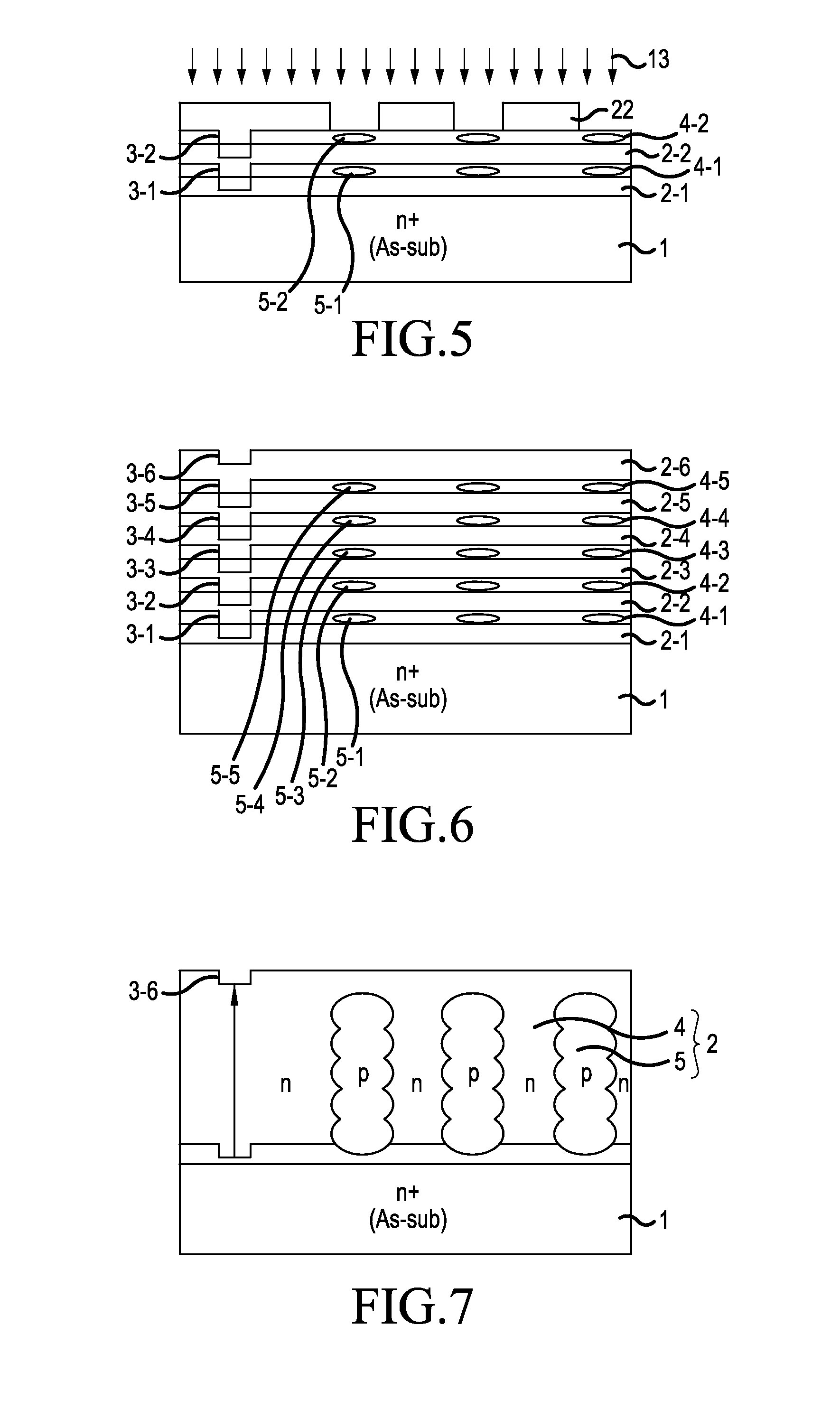

Semiconductor device and production method for semiconductor device

InactiveCN104221152AImprove toleranceImprove trade-offsTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceSurface layer

The invention provides a semiconductor device and a production method for the semiconductor device. The depth of a terminal end p base region (2-1) provided in a terminal end section (110a) on the withstand voltage structure (120) side of an active region (110) is greater than the depth of a p-type base region (2) further on the inside than the terminal end p base region (2-1). An n-type high-density region (1c) is provided in the entire surface layer of one main surface of a semiconductor substrate, said region (1c) having a depth of no more than 20 [mu]m, from one main surface of the semiconductor substrate to the lower part of the floor section of the terminal end p base region (2-1). The ratio between the impurity concentration (n1) in the n-type high-density region (1c) and the impurity concentration (n2) in an n-type drift region (1) fulfills 1.0<n1 / n2<=5.0. As a result, the inverse leakage current when element operation temperatures are high can be reduced, the trade-off between the on voltage and switching loss can be improved, and overshoot peak voltages in collector voltages during turn off can be suppressed.

Owner:FUJI ELECTRIC CO LTD

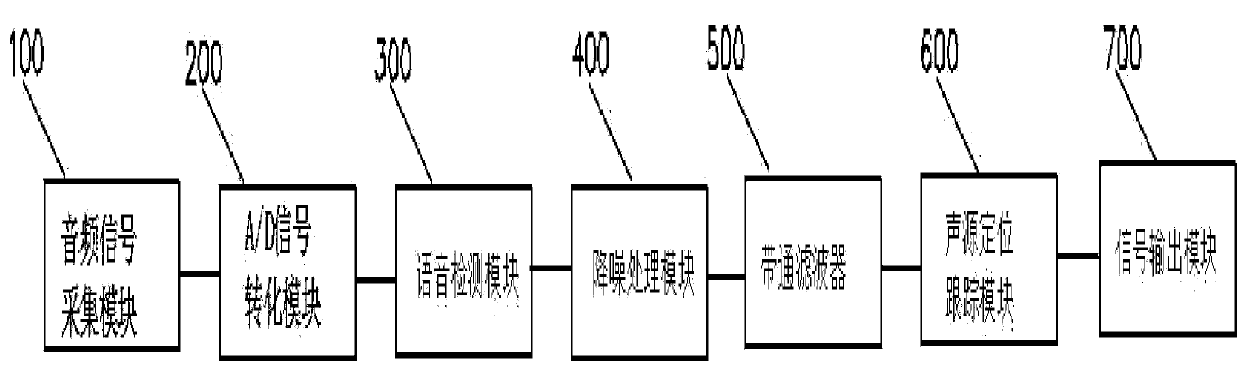

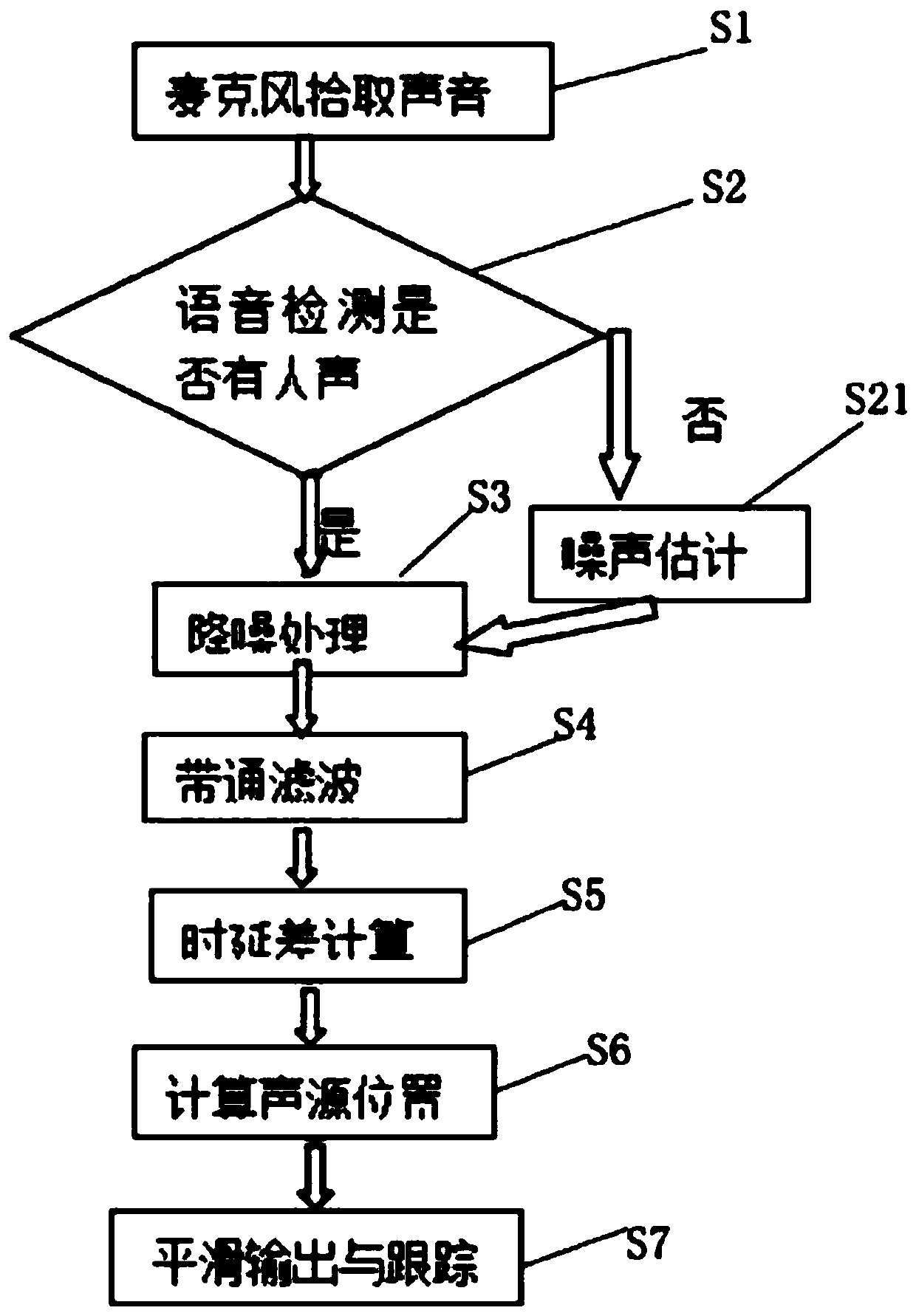

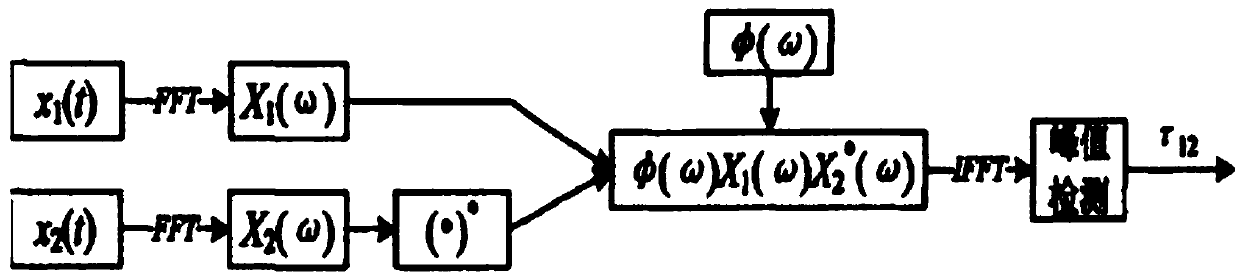

Sound source localization tracking device and method based on microphone cross ring array

InactiveCN109669159AImprove trade-offsGood value for moneyPosition fixationSound source locationSound sources

The invention discloses a sound source localization tracking device and method based on a microphone cross ring array. The sound source localization tracking device comprises an audio signal acquisition module, an A / D signal conversion module, a speech detection module, a noise reduction processing module, a band-pass filter, a sound source localization tracking module and a signal output module,wherein the audio signal acquisition module transmits a signal to the speech detection module through the A / D signal conversion module; and then the signal is transmitted to the sound source localization tracking module through the noise reduction processing module and the band-pass filter and is then outputted through the signal output module. The method comprises the following steps: 1, pickingup an analog sound signal; 2, detecting a speech endpoint; 5, carrying out noise reduction processing on a speech signal; 4, carrying out filtering processing on the speech signal; 5, calculating delay inequality; 6, acquiring a sound source position; and 7, outputting the speech signal. The invention aims at providing the sound source localization tracking device and method with high positioningaccuracy, fast tracking reaction, low implementation cost and high reliability based on the microphone cross ring array.

Owner:深圳市友杰智新科技有限公司

Semiconductor device and method for manufacturing semiconductor device

InactiveUS20160149029A1Reduce thicknessReduce channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionSemiconductor

A semiconductor device includes a semiconductor substrate including a trench, a gate insulating layer, and a gate electrode. A step is arranged in a side surface of the trench. The semiconductor substrate includes first and second regions, a body region, and a side region. The body region extends from a position being in contact with the first region to a position located on the lower side with respect to the step. The body region is in contact with the gate insulating layer at a portion of the upper side surface located on a lower side with respect to the first region. The second region is located on a lower side of the body region and in contact with the gate insulating layer at the lower side surface. The side region is in contact with the gate insulating layer at the step surface and connected to the second region.

Owner:TOYOTA JIDOSHA KK

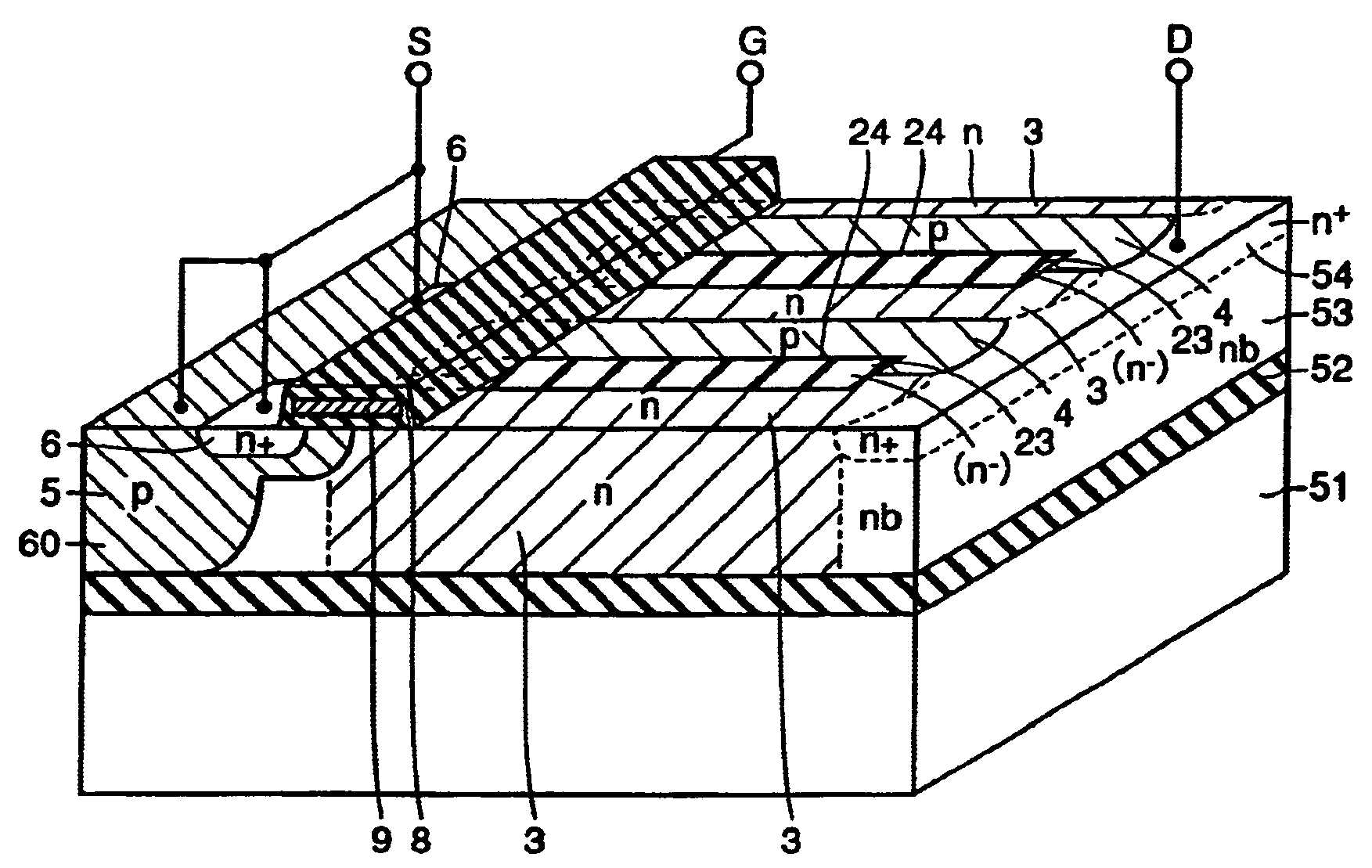

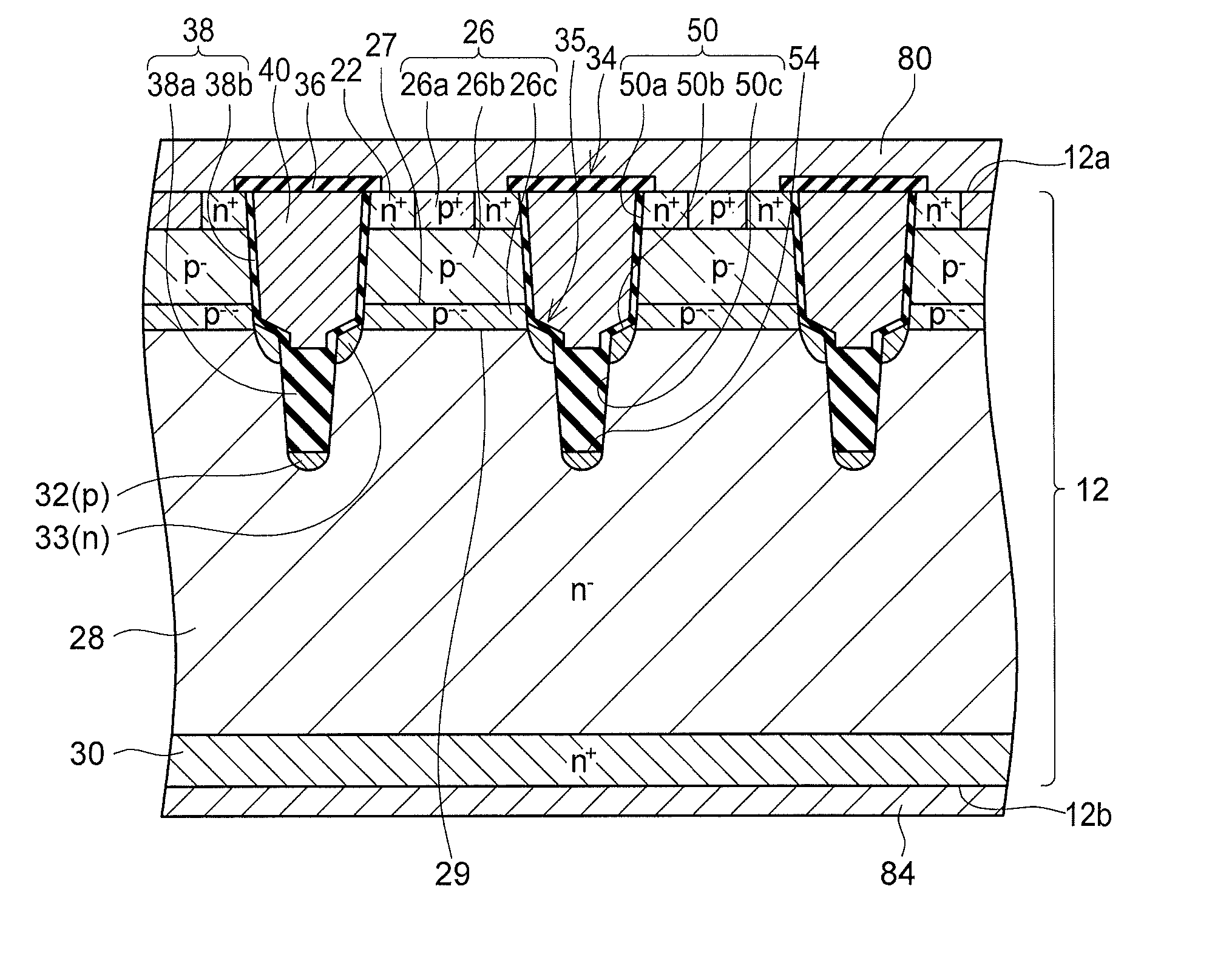

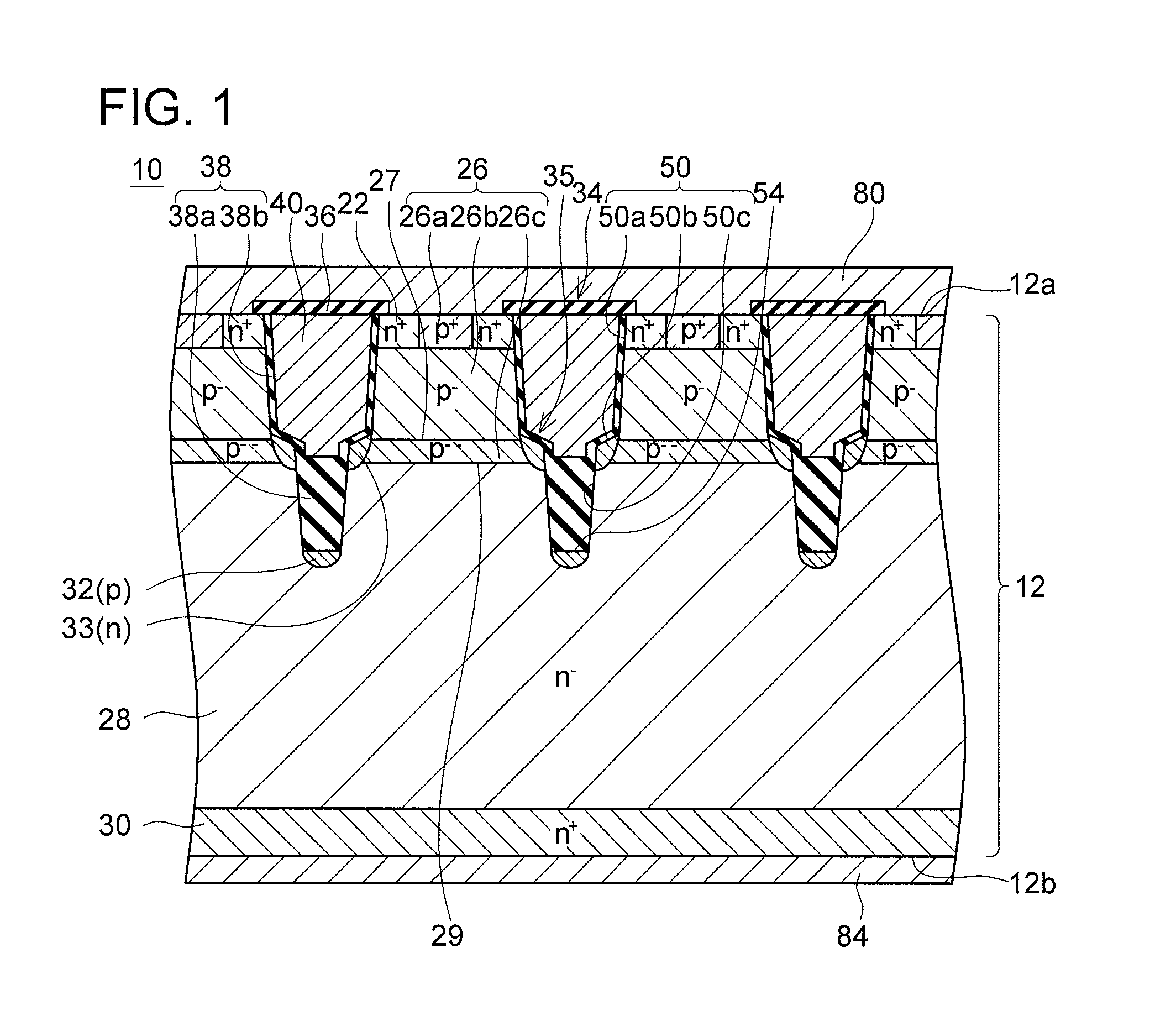

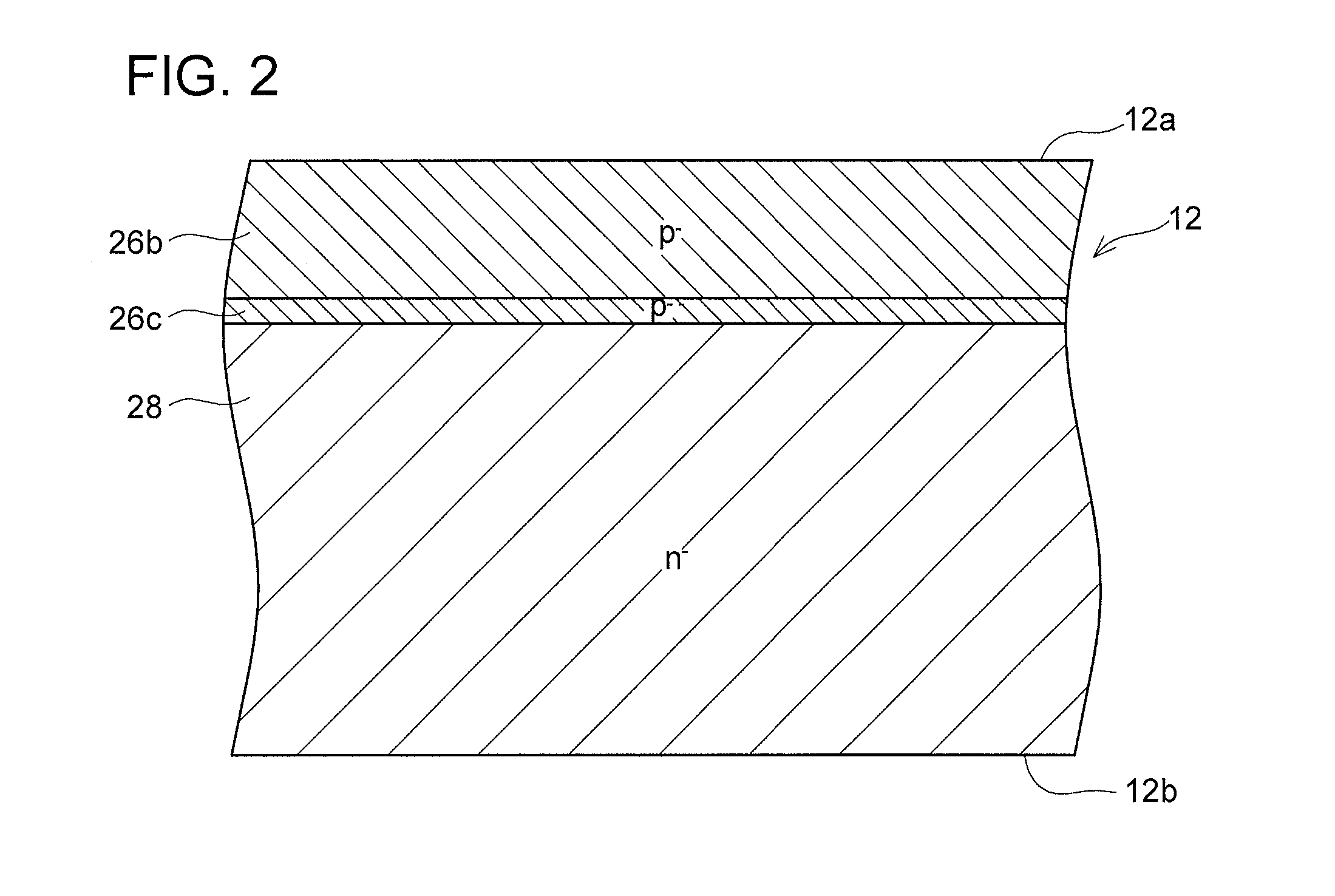

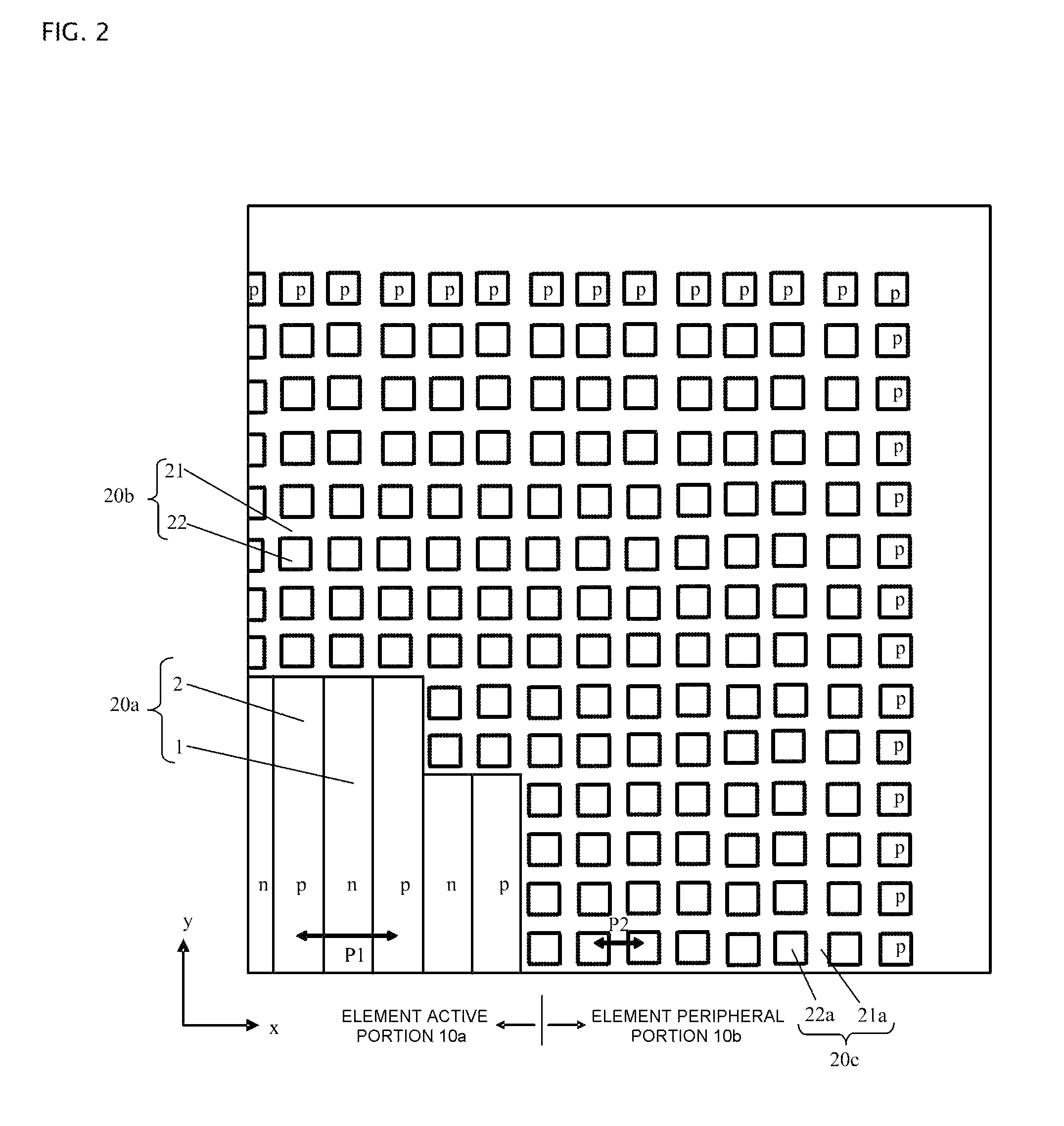

Superjunction semiconductor device with reduced switching loss

ActiveUS9087893B2Improve trade-offsImprove avalanche resistanceSemiconductor devicesHigh concentrationAtomic physics

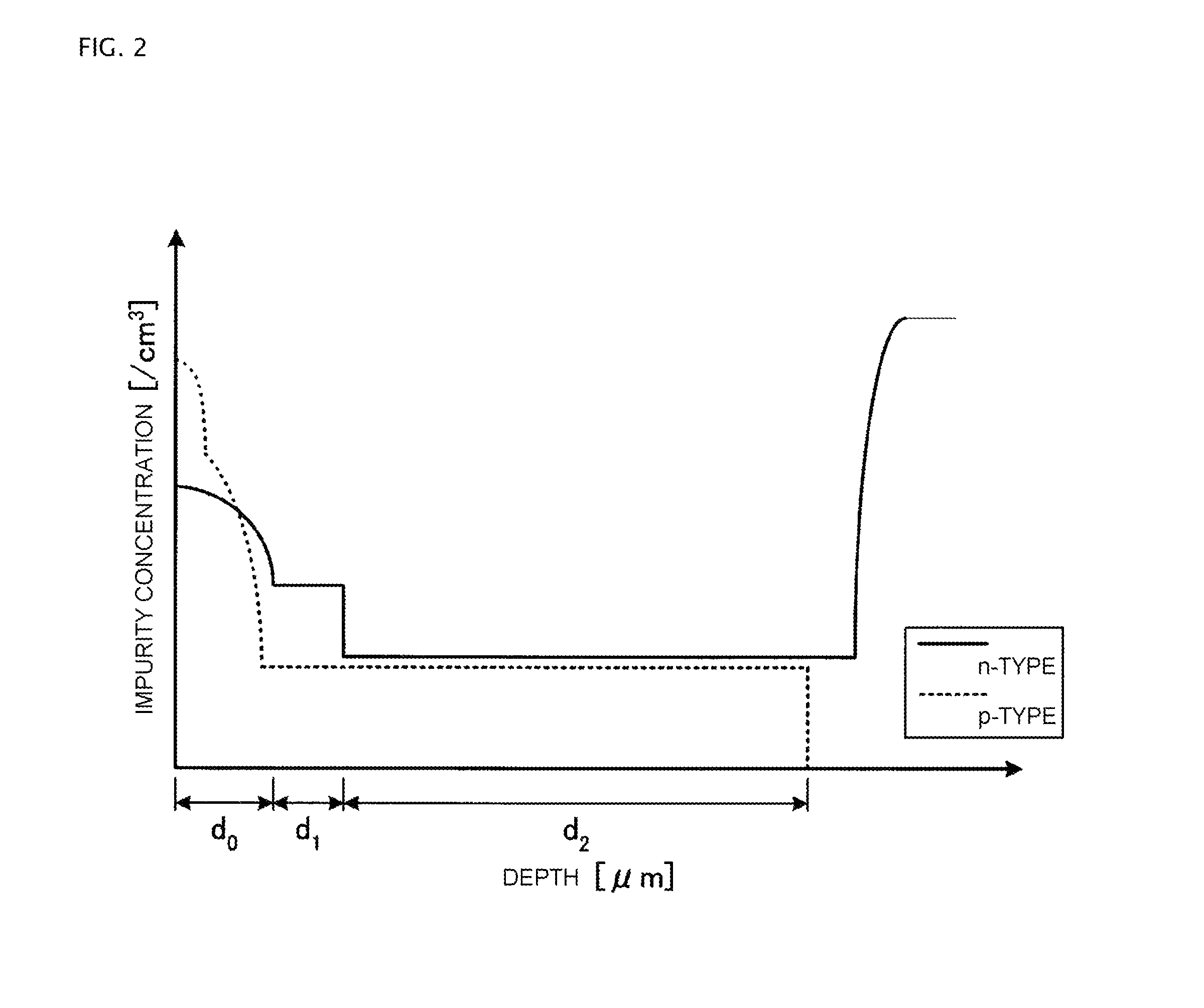

A parallel p-n layer (20) is provided as a drift layer between an active portion and an n+ drain region (11). The parallel p-n layer (20) is formed by an n-type region (1) and a p-type region (2) being repeatedly alternately joined. An n-type high concentration region (21) is provided on a first main surface side of the n-type region (1). The n-type high concentration region (21) has an impurity concentration higher than that of an n-type low concentration region (22) provided on a second main surface side of the n-type region (1). The n-type high concentration region (21) has an impurity concentration 1.2 times or more, 3 times or less, preferably 1.5 times or more, 2.5 times or less, greater than that of the n-type low concentration region (22). Also, the n-type high concentration region (21) has one-third or less, preferably one-eighth or more, one-fourth or less, of the thickness of a region of the n-type region (1) adjacent to the p-type region (2).

Owner:FUJI ELECTRIC CO LTD

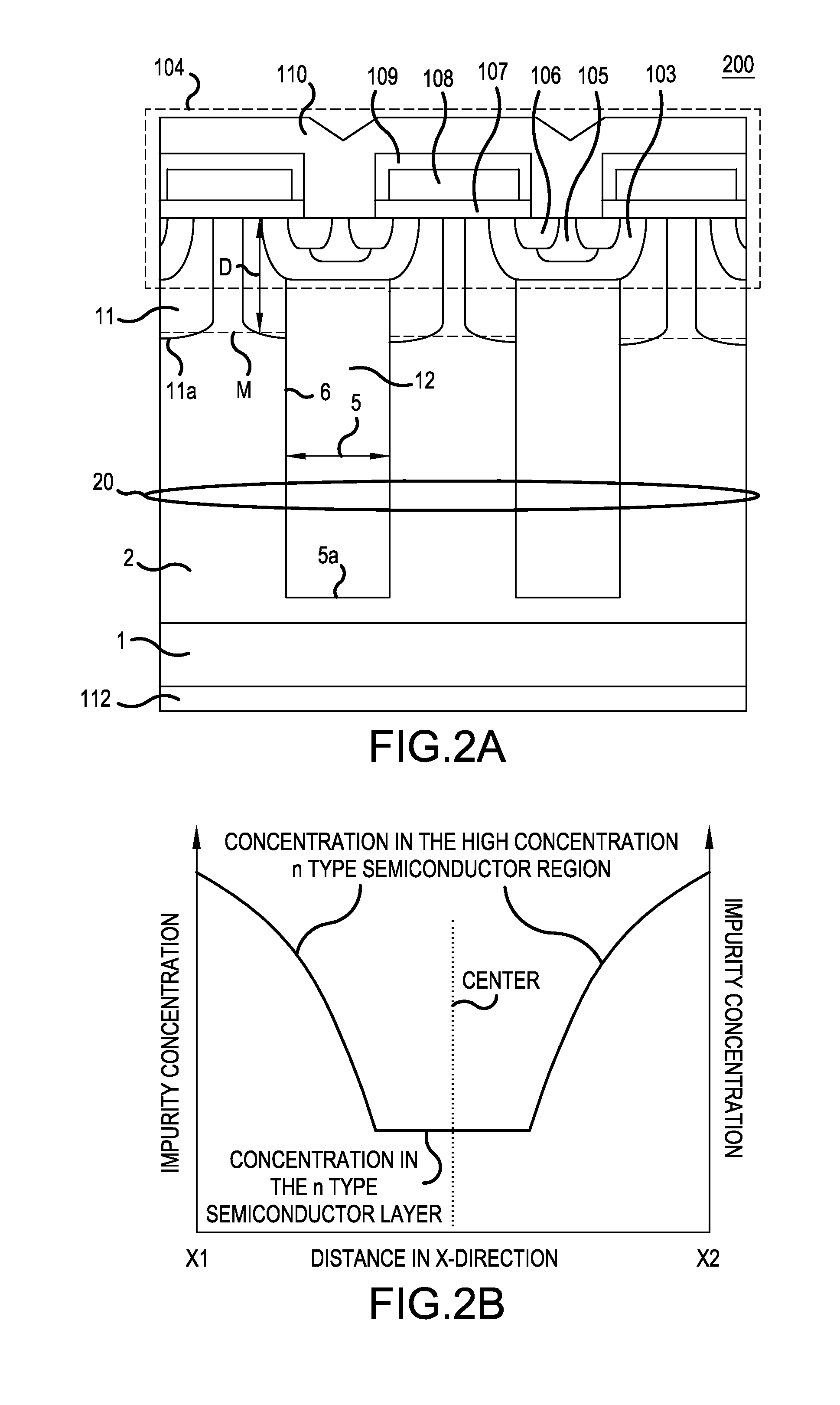

Semiconductor device and method of manufacturing the same

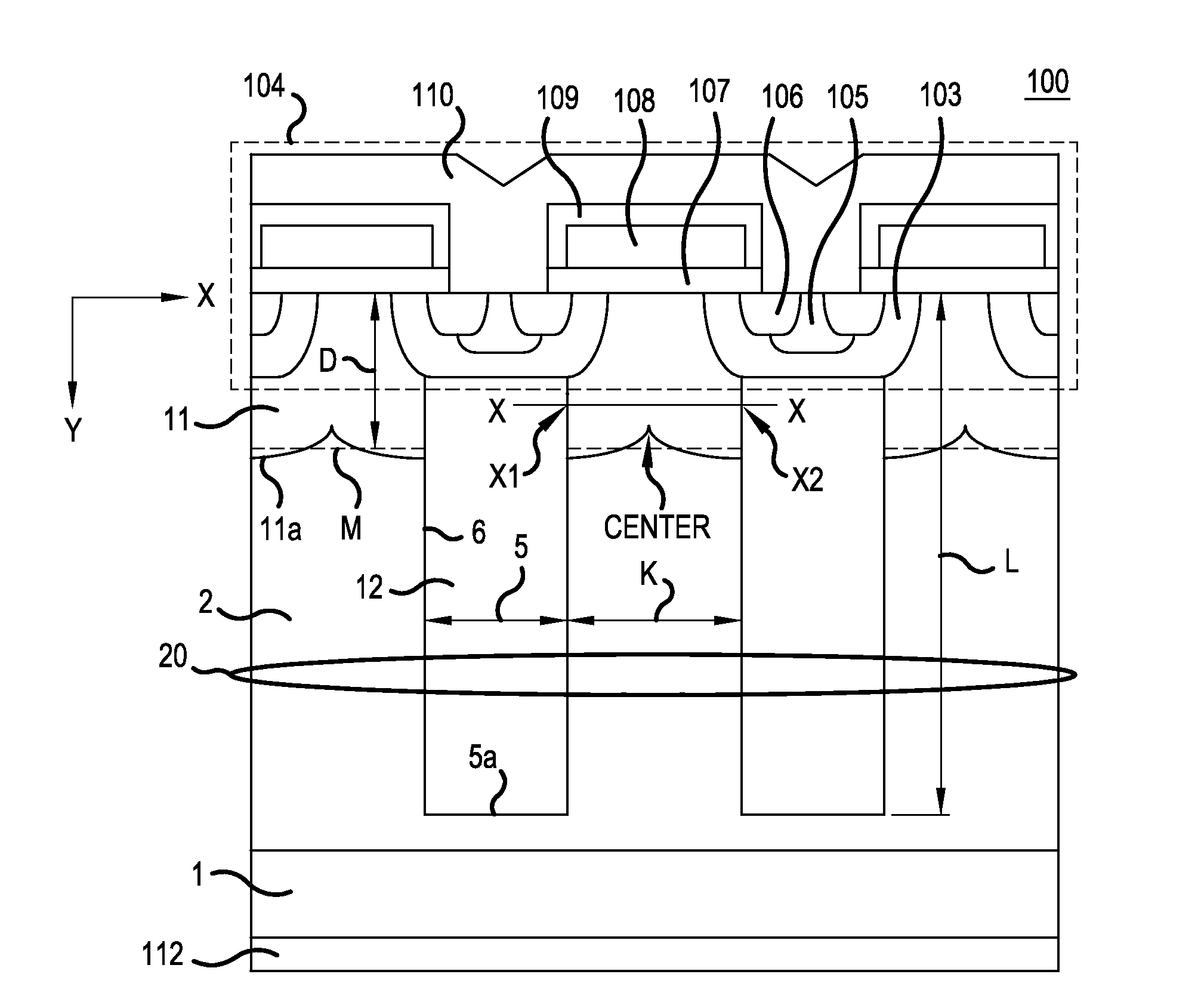

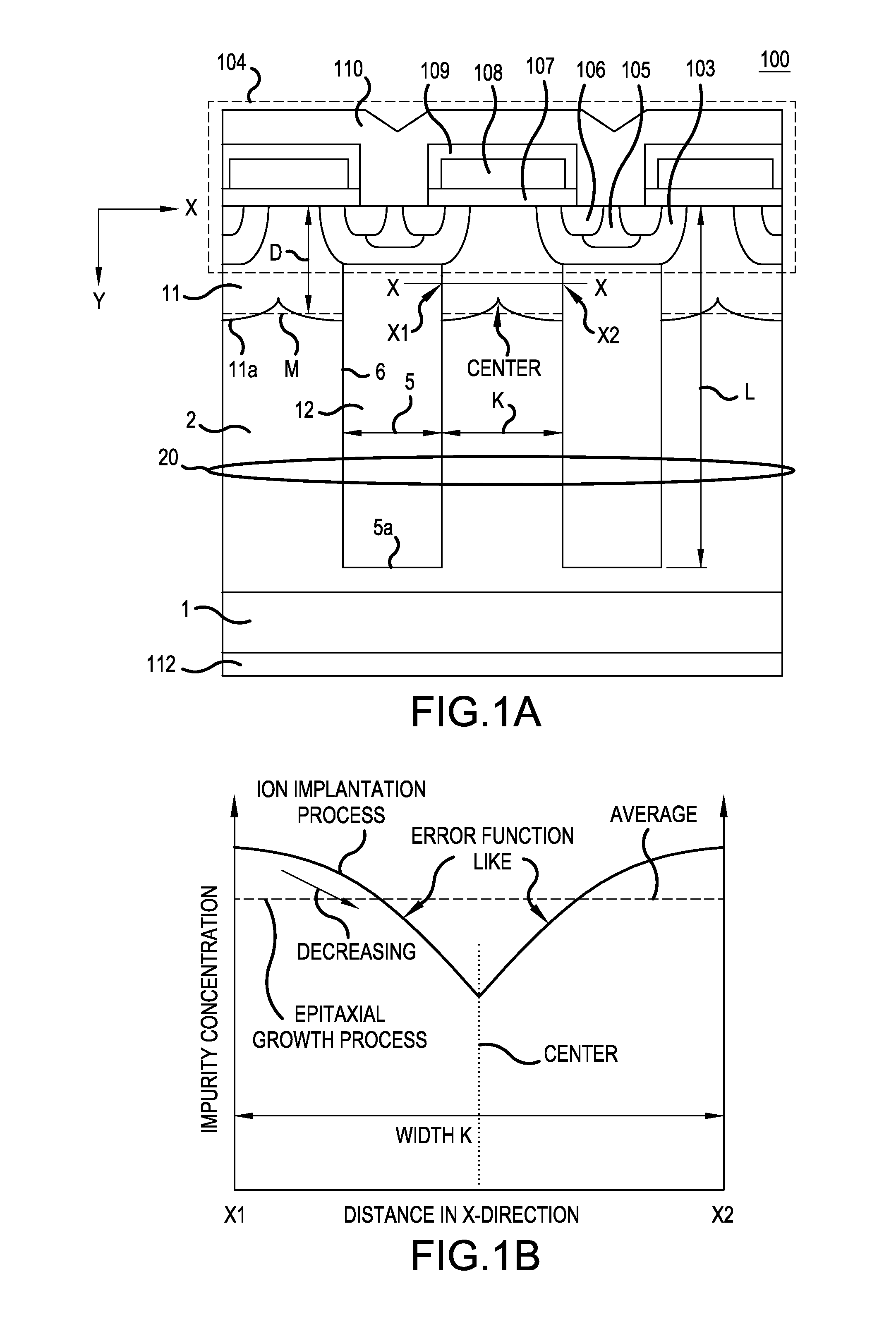

InactiveUS20140225217A1Improve trade-offsReduction procedureSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationDevice material

A semiconductor device and method of manufacturing the semiconductor device is disclosed in which the tradeoff relationship between the Eoff and the turning OFF dV / dt is improved at a low cost using a trench embedding method. The method comprises a step of forming a parallel pn layer that is a superjunction structure using a trench embedding method and a step of ion implantation into an upper part of an n type semiconductor layer, i.e., an n type column, forming a high concentration n type semiconductor region. This method improves the trade-off relationship between the Eoff and the turning OFF dV / dt as compared with a high concentration n type semiconductor region formed of an epitaxial layer. This method achieves shorter process time and lower cost in manufacturing because it eliminates the redundant repeating of steps performed in the conventional method of forming a superjunction structure through multi-stage epitaxial growth.

Owner:FUJI ELECTRIC CO LTD

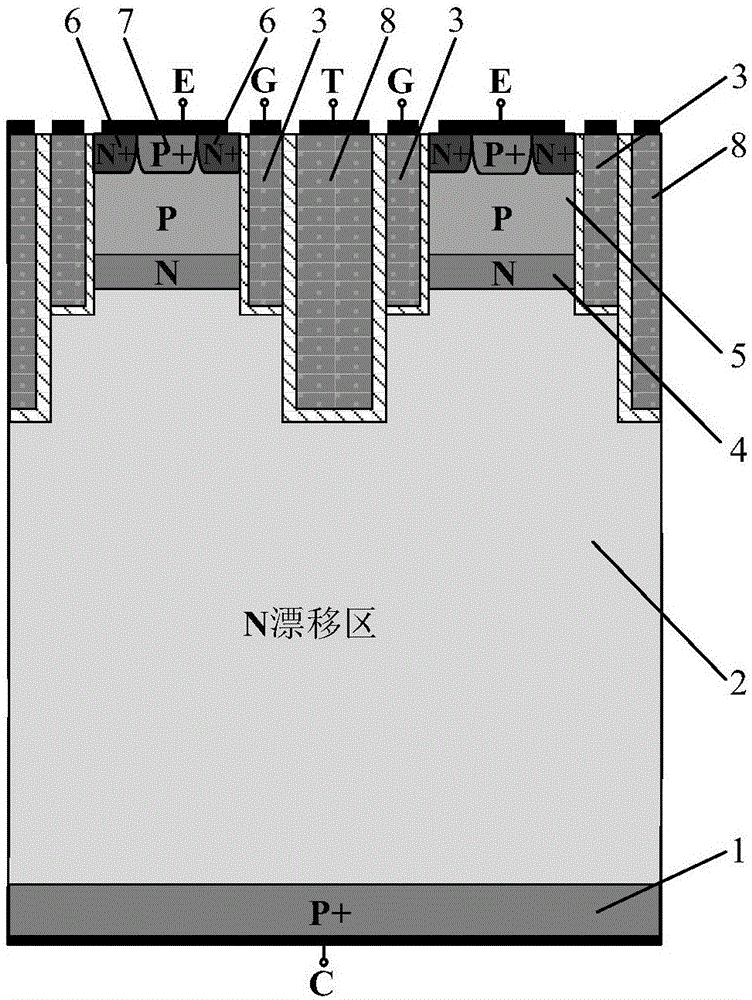

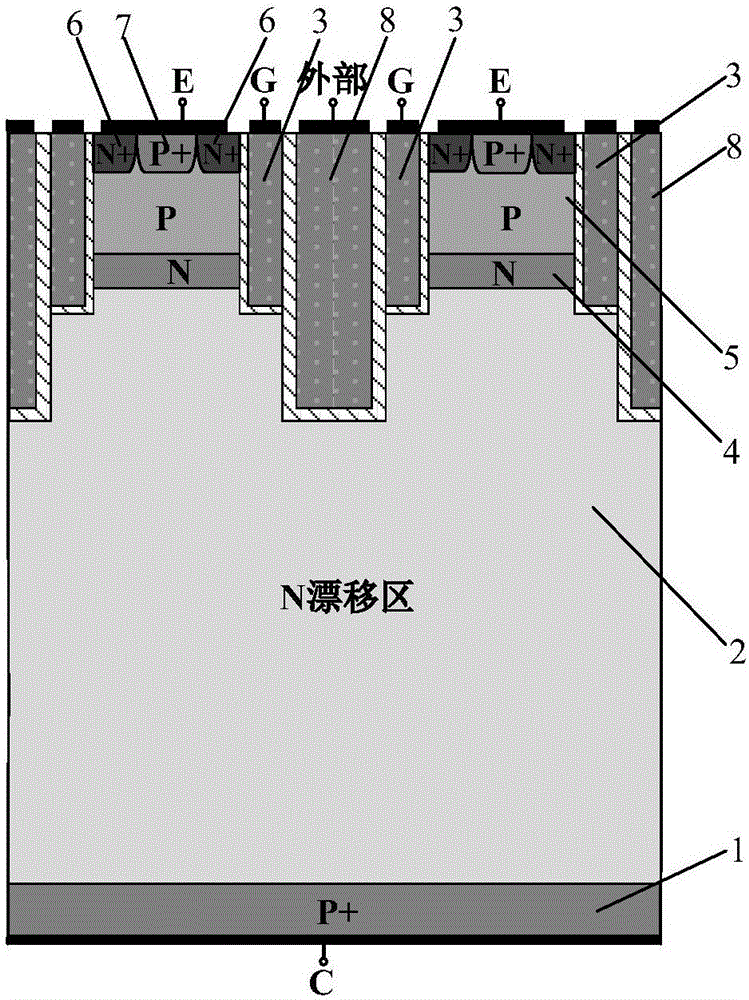

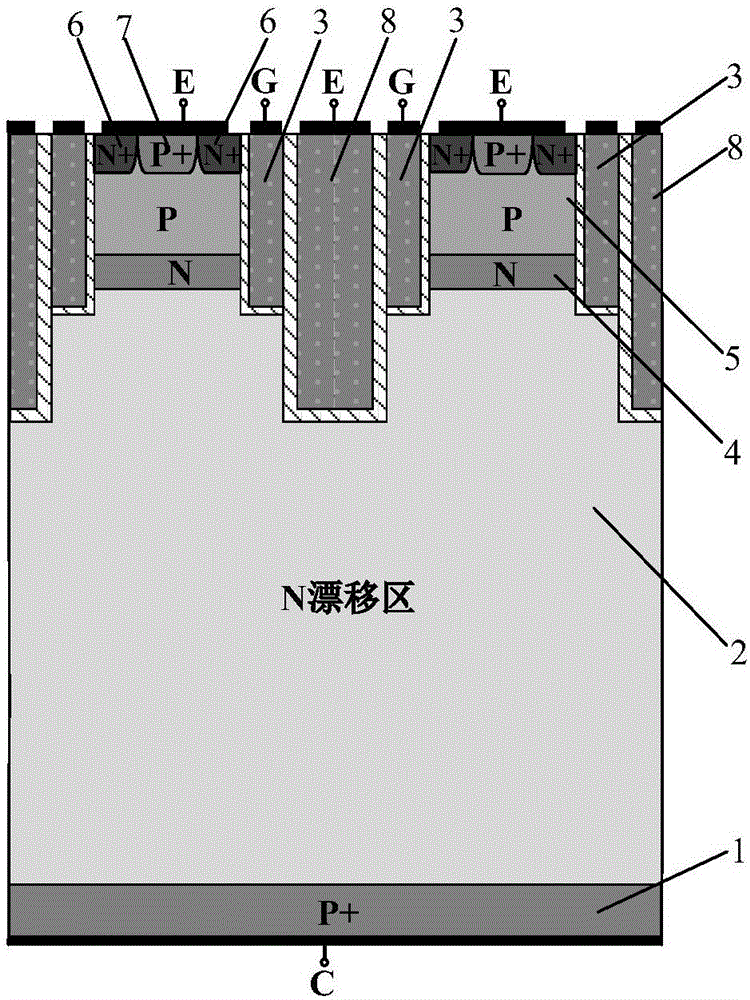

Carrier storage type grooved-gate IGBT (insulated gate bipolar transistor)

InactiveCN106356400AImprove pressure resistanceImprove trade-offsSemiconductor devicesElectric fieldPeak value

The invention belongs to the technical field of semiconductors and relates to a carrier storage type grooved-gate IGBT (insulated gate bipolar transistor). The carrier storage type IGBT is structurally provided with two split gates and a deep groove; when a device is in a closed state, a carrier storage layer of the device is exhausted by adopting assistance of a deep groove, and meanwhile, the deep grove and the split gates form a stepped structure to weaken the peak value of an electric field of an emitter, so that voltage endurance capability of the device under higher carrier storage layer concentration is obviously improved. In addition, when the device is in an open state, a layer of the carriers can be further accumulated on the surface of a deep-groove structure 8, and conduction pressure of the device is further reduced.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

Semiconductor element

ActiveUS20150187930A1Reduce concentrationImproved reverse recovery capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDepth directionSemiconductor components

A drain drift portion is a first parallel p-n structure, largely corresponding to a portion directly below a p-type base region forming an active region, formed by first n-type regions and first p-type regions being alternately and repeatedly joined. The periphery of the drain drift portion is an edge termination region formed of a second parallel p-n structure aligned contiguously to the first parallel p-n structure and formed by second n-type regions and second p-type regions being alternately and repeatedly joined. An n-type buffer layer is provided between the first and second parallel p-n structures and an n+ type drain layer. A p+ type drain region is selectively provided inside the n+ type drain layer in the edge termination region, penetrating the n+ type drain layer in the depth direction.

Owner:FUJI ELECTRIC CO LTD

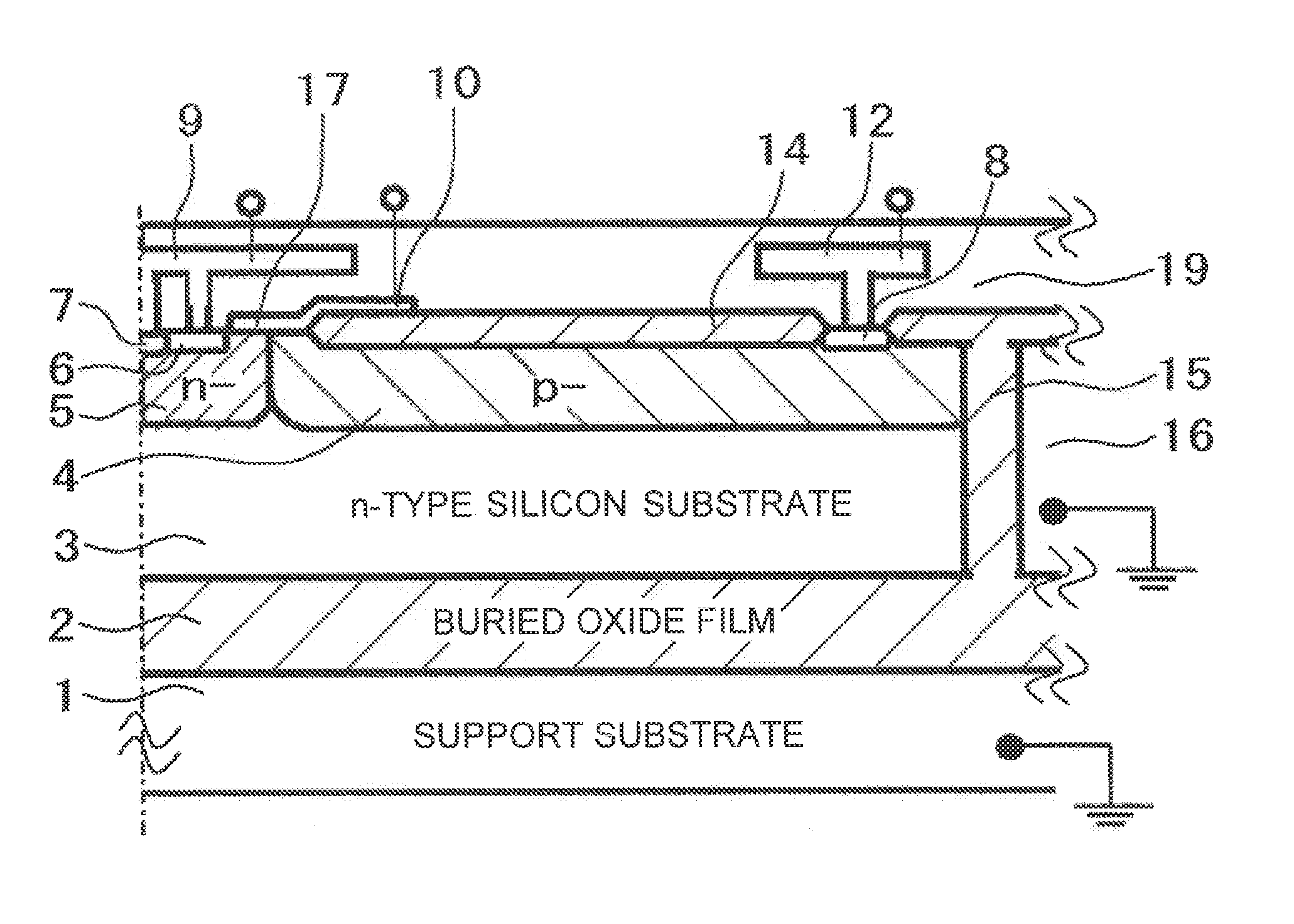

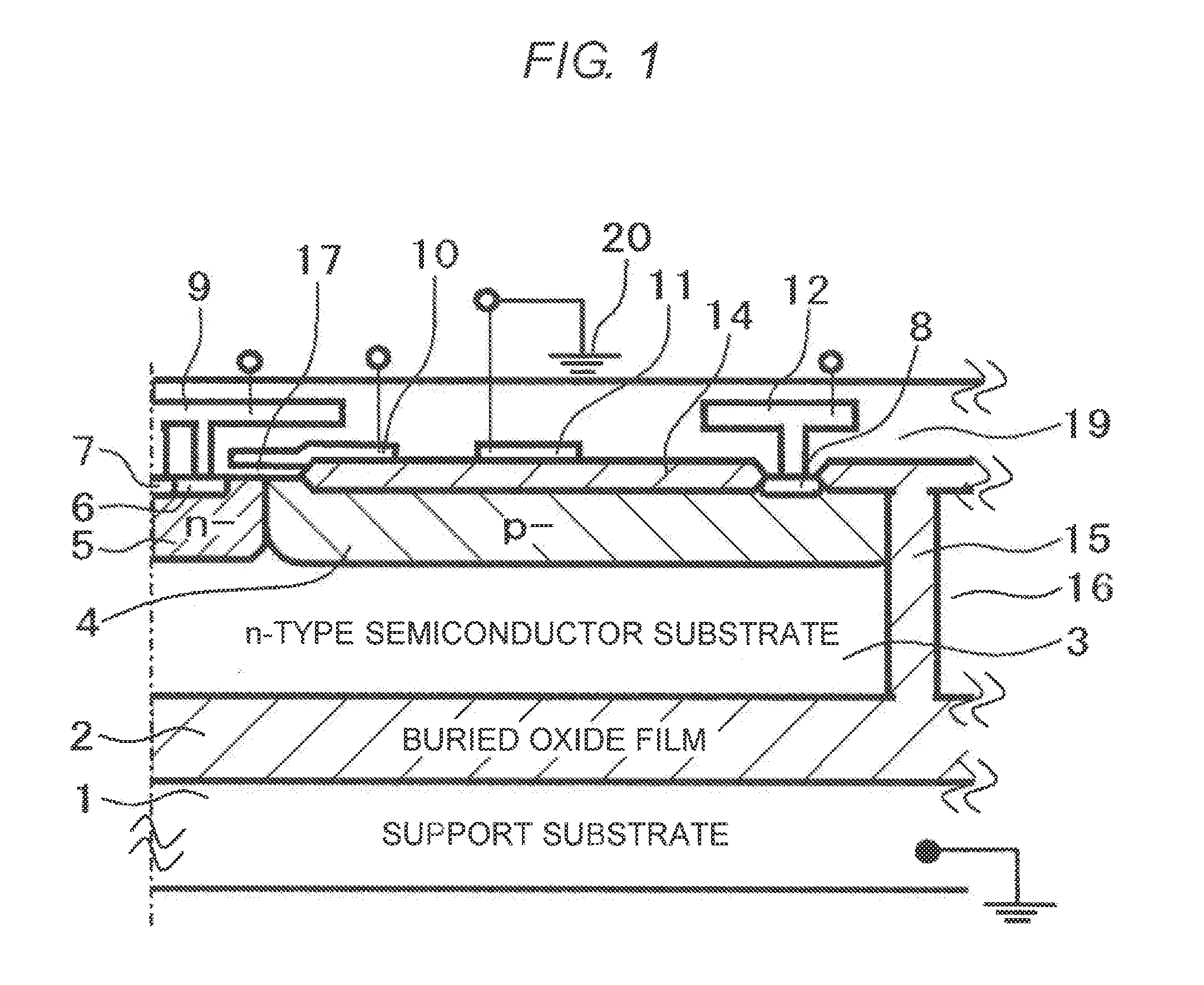

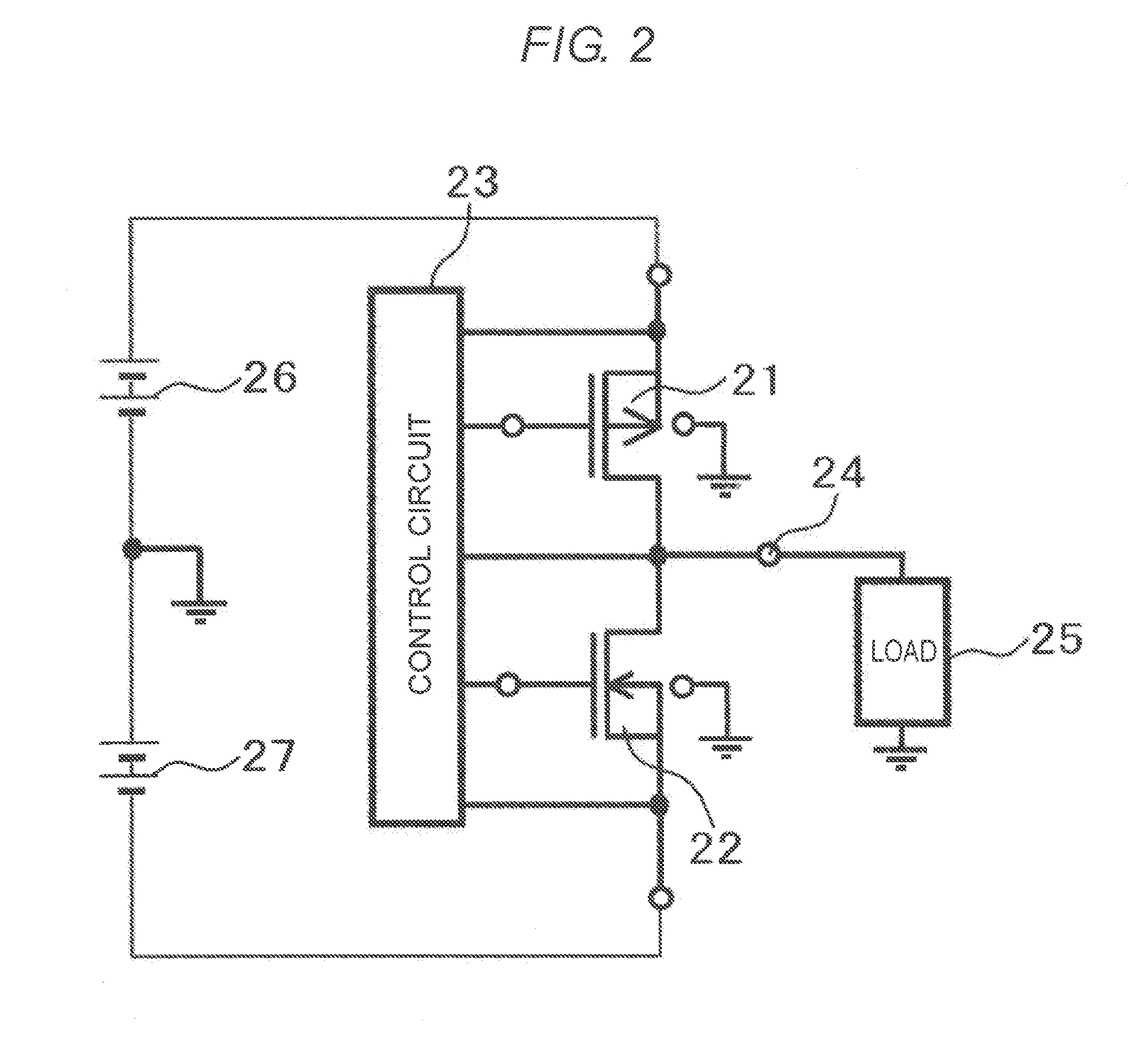

Semiconductor device and semiconductor integrated circuit device using the same

InactiveUS20140070314A1Increase resistanceImprove pressure resistanceTransistorSolid-state devicesMOSFETEngineering

There is provided an MOSFET having a large current density, which can be mixed with a logic circuit, and is used in a circuit that conducts the operation of applying a negative voltage to a drain electrode. An electrode surrounded by an insulating film is formed, at an intermediate position of a gate electrode and a drain of the MOSFET formed on an SOI substrate having a drain electrode applied with a negative voltage, and the electrode is connected to the ground to prevent a withstand voltage from being lowered which is caused by an increase in impurity concentration of a drift region. A drift resistance is lowered to improve the current density.

Owner:HITACHI LTD

Semiconductor element including active region, low resistance layer and vertical drift portion

ActiveUS9437727B2Improve trade-offsIncrease breakdown withstandSemiconductor/solid-state device manufacturingSemiconductor devicesVertical driftDepth direction

A drain drift portion is a first parallel p-n structure, largely corresponding to a portion directly below a p-type base region forming an active region, formed by first n-type regions and first p-type regions being alternately and repeatedly joined. The periphery of the drain drift portion is an edge termination region formed of a second parallel p-n structure aligned contiguously to the first parallel p-n structure and formed by second n-type regions and second p-type regions being alternately and repeatedly joined. An n-type buffer layer is provided between the first and second parallel p-n structures and an n+ type drain layer. A p+ type drain region is selectively provided inside the n+ type drain layer in the edge termination region, penetrating the n+ type drain layer in the depth direction.

Owner:FUJI ELECTRIC CO LTD

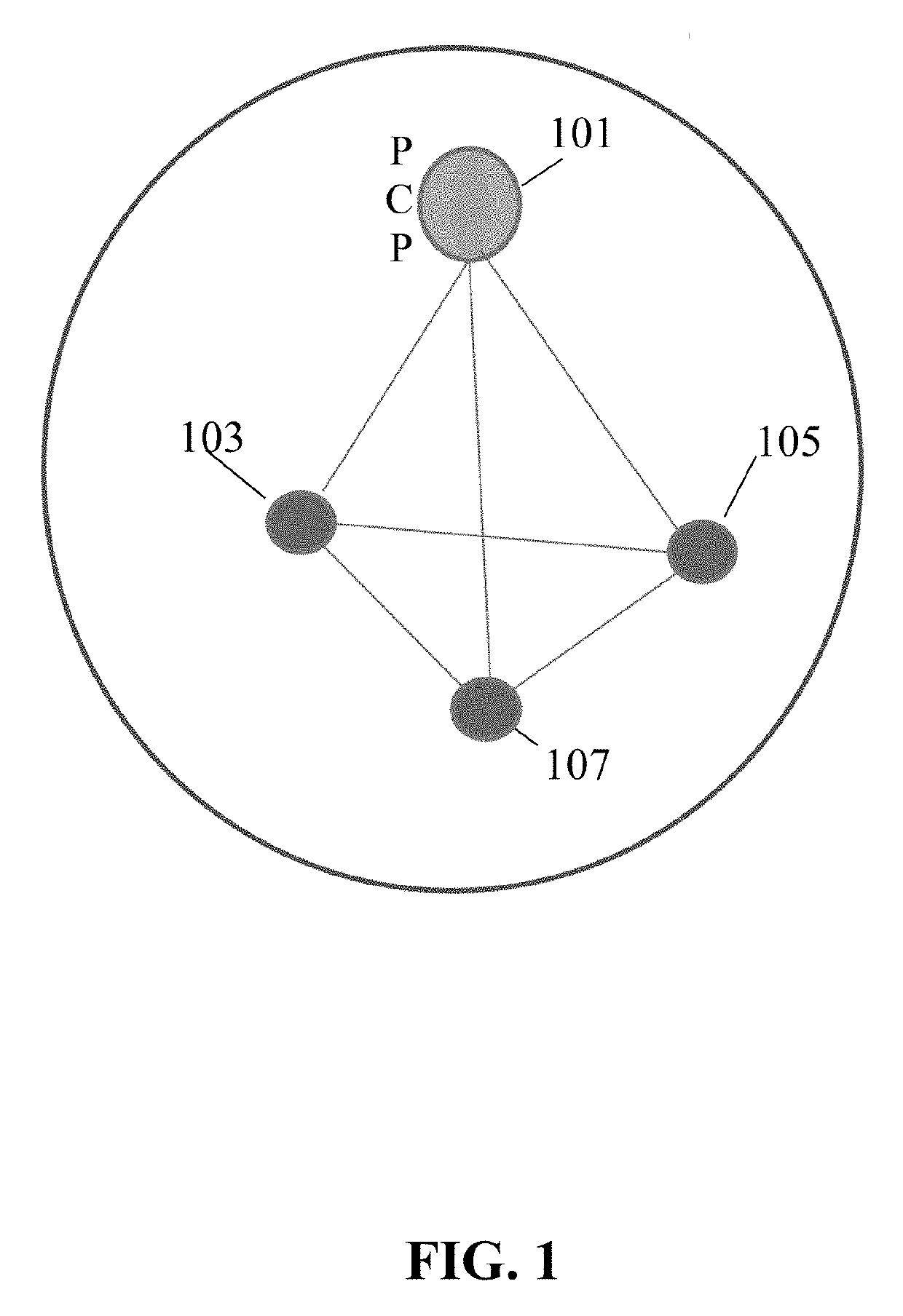

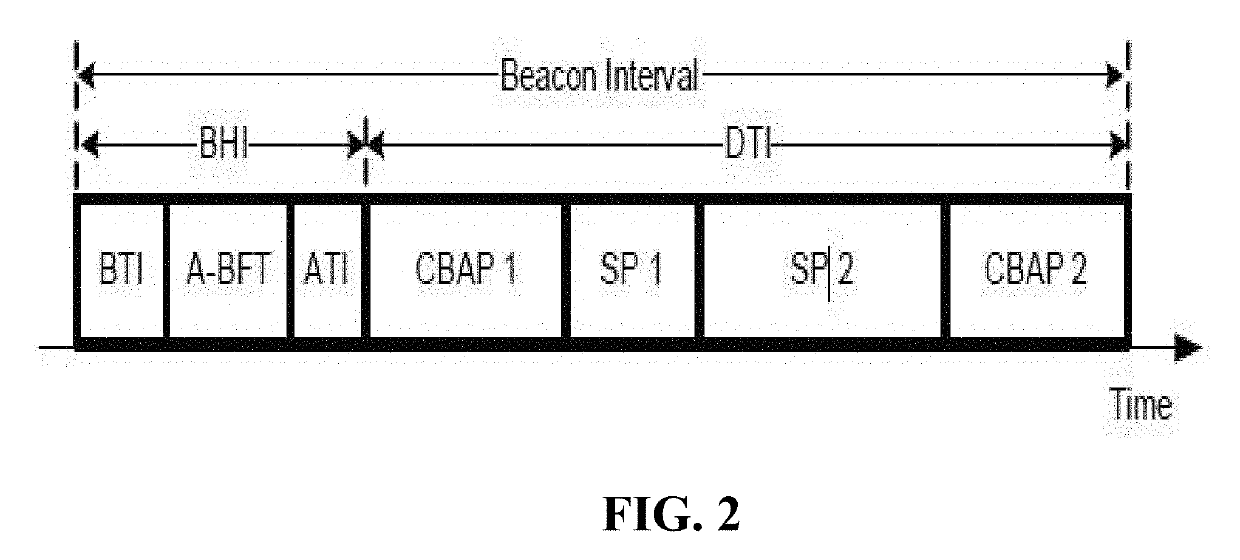

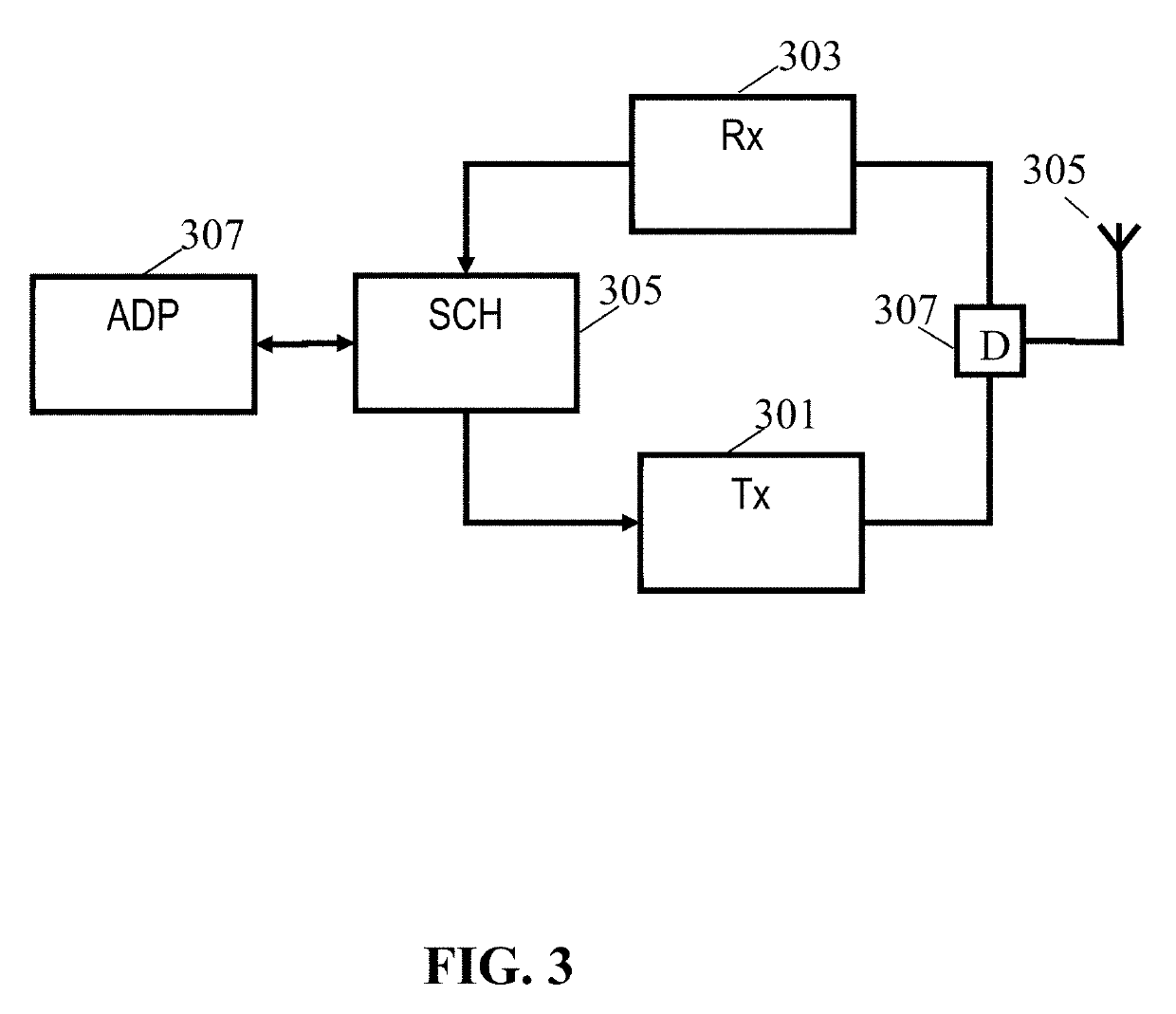

Apparatus and method for scheduling communications in a wireless communication system

ActiveUS20190335455A1Improve schedulingImprove performanceNetwork traffic/resource managementNetwork topologiesTime division multiple accessCommunications system

An apparatus schedules communications in a wireless communication system comprising a plurality of wireless stations (103-107) operable to communicate wirelessly with each other in accordance with a time division multiple access scheme. The apparatus comprises a receiver (303) for receiving resource requests from the plurality of wireless stations (103-107). A scheduler (305) schedules air interface resource to communications between the plurality wireless stations by allocating time intervals in repeating scheduling intervals. A transmitter (301) transmits scheduling messages providing indications of the scheduling to the plurality of wireless stations (103-107). An adapter (307) adapts a duration of at least one scheduling interval of the repeating scheduling intervals in response to the resource requests from the plurality of wireless stations (103-107).

Owner:BLUWIRELESS TECH

Semiconductor device and the method of manufacturing the same

InactiveUS20090224314A1Improve breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringPower MOSFET

A power MOSFET exhibits a high breakdown voltage and low ON-state resistance. The device includes a trench formed in a semiconductor substrate, a gate electrode located along a side wall of the trench and a bottom wall of the trench near a side wall thereof, a pillar section, a first drain region of a first conductivity type in the pillar section, a base region of a second conductivity type in contact with the side wall of the trench in a bottom portion thereof and the bottom wall of the trench, a source region of the first conductivity type in a surface portion of the base region, a RESURF region of the second conductivity type in the pillar section, the RESURF region being formed in contact with the first drain region; and a second drain region of the first conductivity type in a side wall surface portion of the pillar section.

Owner:FUJI ELECTRIC SYST CO LTD

Superjunction semiconductor device

ActiveUS9123561B2Easy to chargeImprove breakdown voltageSemiconductor devicesElectrical resistance and conductancePower semiconductor device

A superjunction semiconductor device is disclosed in which the trade-off relationship between breakdown voltage characteristics and voltage drop characteristics is considerably improved, and it is possible to greatly improve the charge resistance of an element peripheral portion and long-term breakdown voltage reliability. It includes parallel pn layers of n-type drift regions and p-type partition regions in superjunction structure. PN layers are depleted when off-state voltage is applied. Repeating pitch of the second parallel pn layer in a ring-like element peripheral portion encircling the element active portion is smaller than repeating pitch of the first parallel pn layer in the element active portion. Element peripheral portion includes low concentration n-type region on the surface of the second parallel pn layer. The depth of p-type partition region of an outer peripheral portion in the element peripheral portion is smaller than the depth of p-type partition region of an inner peripheral portion.

Owner:FUJI ELECTRIC CO LTD

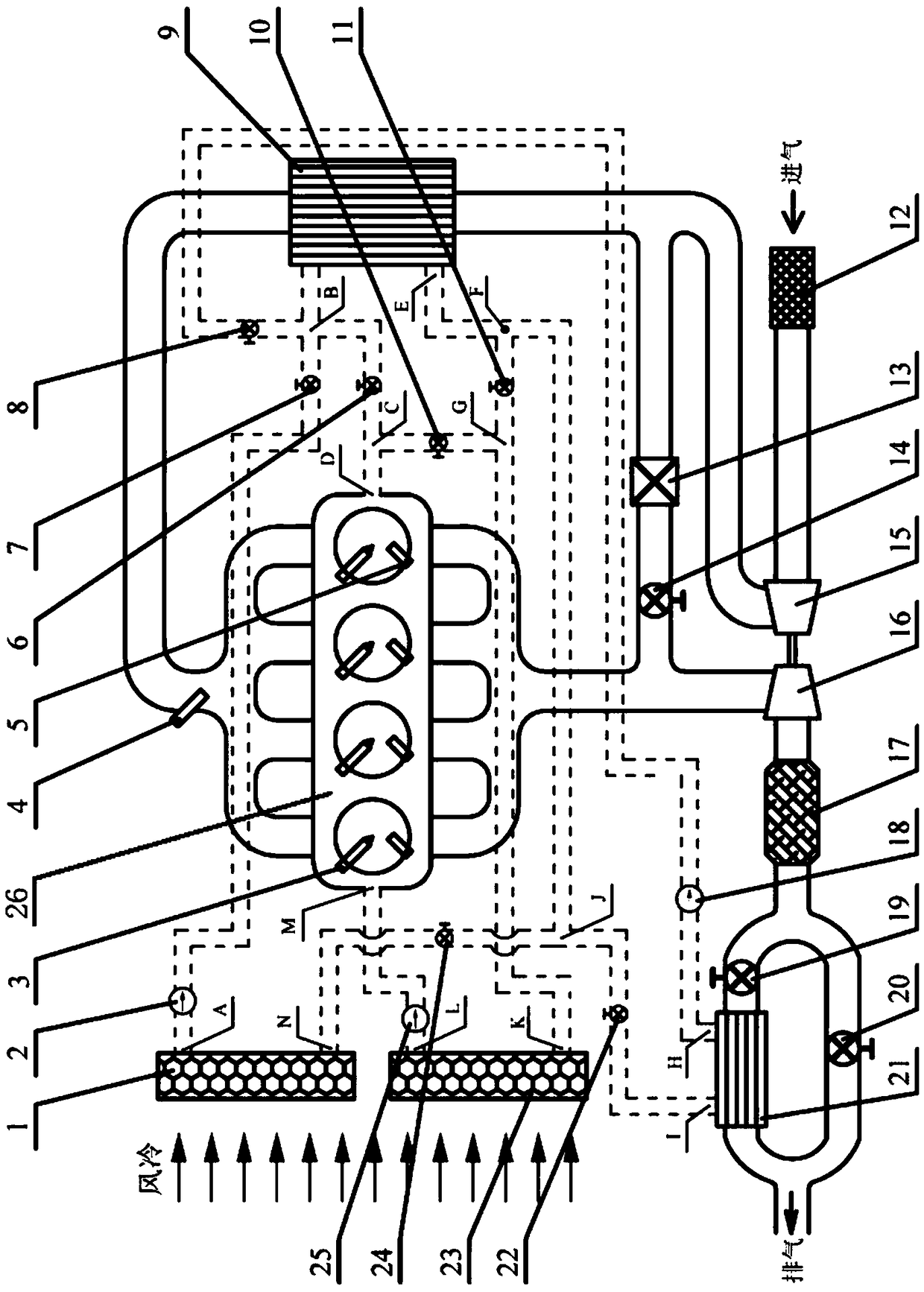

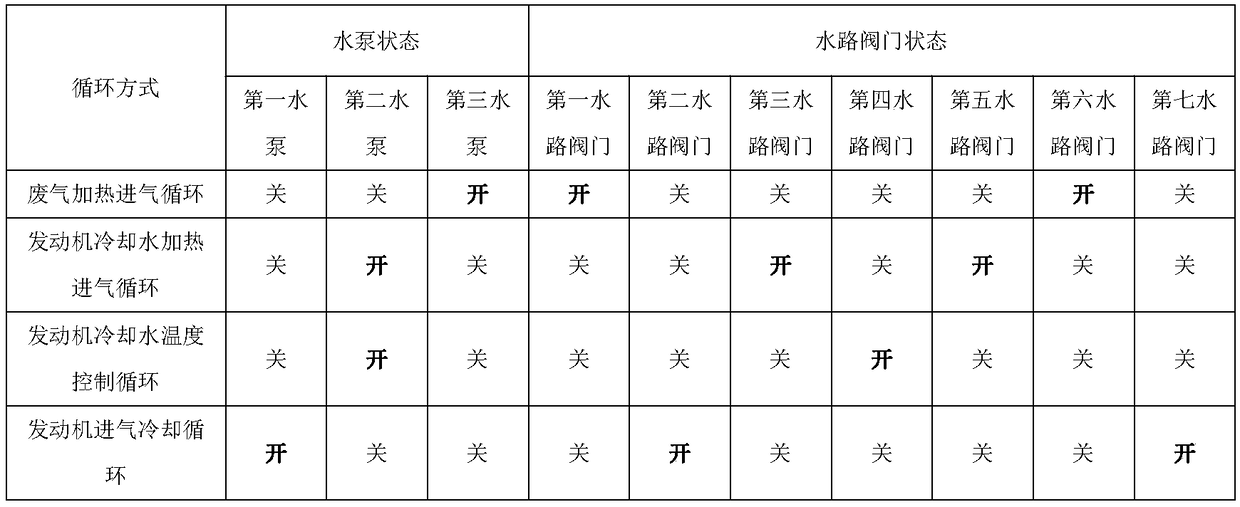

Intake temperature control system to meet intake temperature requirement of gasoline compression ignition full conditions

ActiveCN109252990AIncrease profitImprove combustion stability and combustion efficiencyInternal combustion piston enginesThermal treatment of fuelIntercoolerEngineering

The invention discloses an intake temperature control system to meet intake temperature requirement of gasoline compression ignition full conditions. An intake port of a dual-variable-valve mechanismis connected with an intake master tube that is connected with a gas compressor; an exhaust port of the dual-variable-valve mechanism is connected with an exhaust master tube; the exhaust master tubeis connected with a turbine that is connected with a post-processor; the intake master tube is provided with an intercooler; an exhaust port of the post-processor is connected with two exhaust branches; one exhaust branch is provided with a second exhaust valve, and the other exhaust branch is provided with a first exhaust valve and an exhaust heat exchanger; a shell side water outlet of the exhaust heat exchanger is connected with a shell side water inlet of the intercooler; a shell side water inlet of the exhaust heat exchanger is connected with a shell side water outlet of the intercooler;the shell side water inlet of the intercooler is connected with a water inlet of a first radiator; the shell side water outlet of the intercooler is connected with a water inlet of the first radiator;the shell side water outlet of the intercooler is connected with a water inlet of the second radiator; the shell side water inlet of the intercooler is connected with a water outlet of a cooling water passage of an engine; a water outlet of the second radiator is connected with a water inlet of the cooling water passage of the engine.

Owner:TIANJIN UNIV

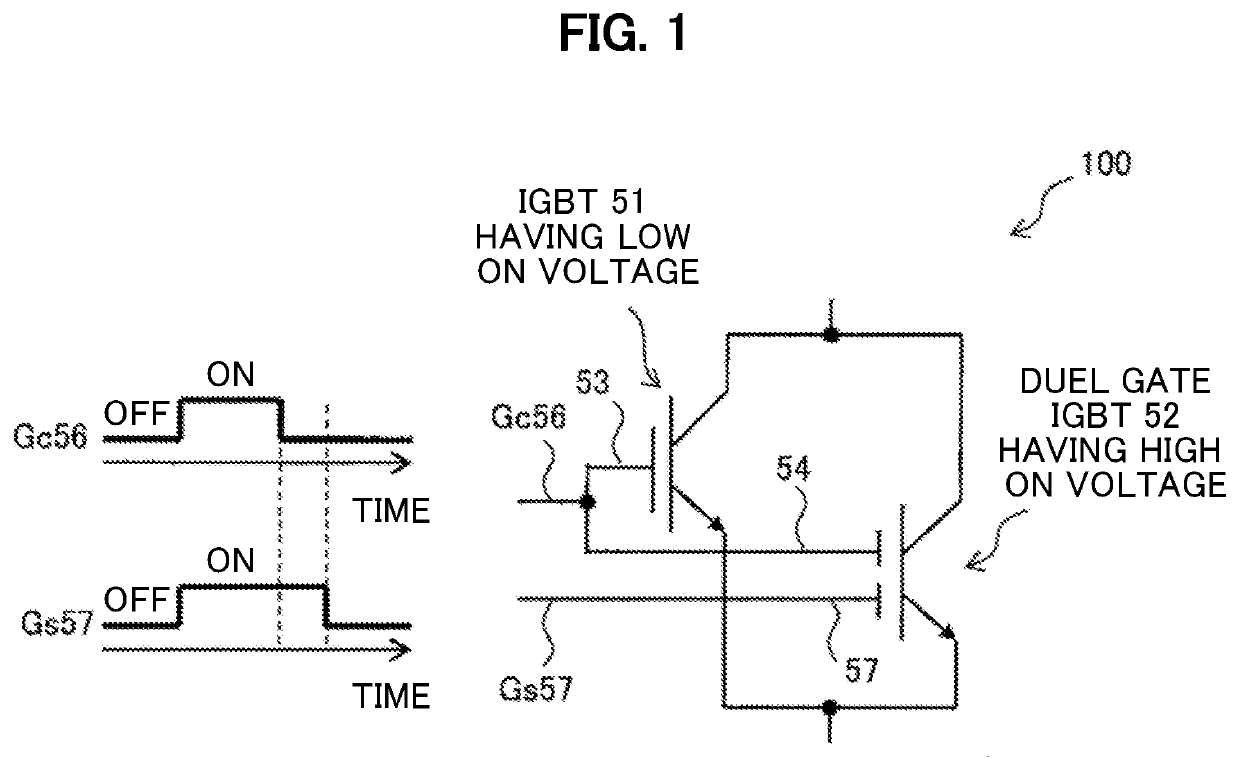

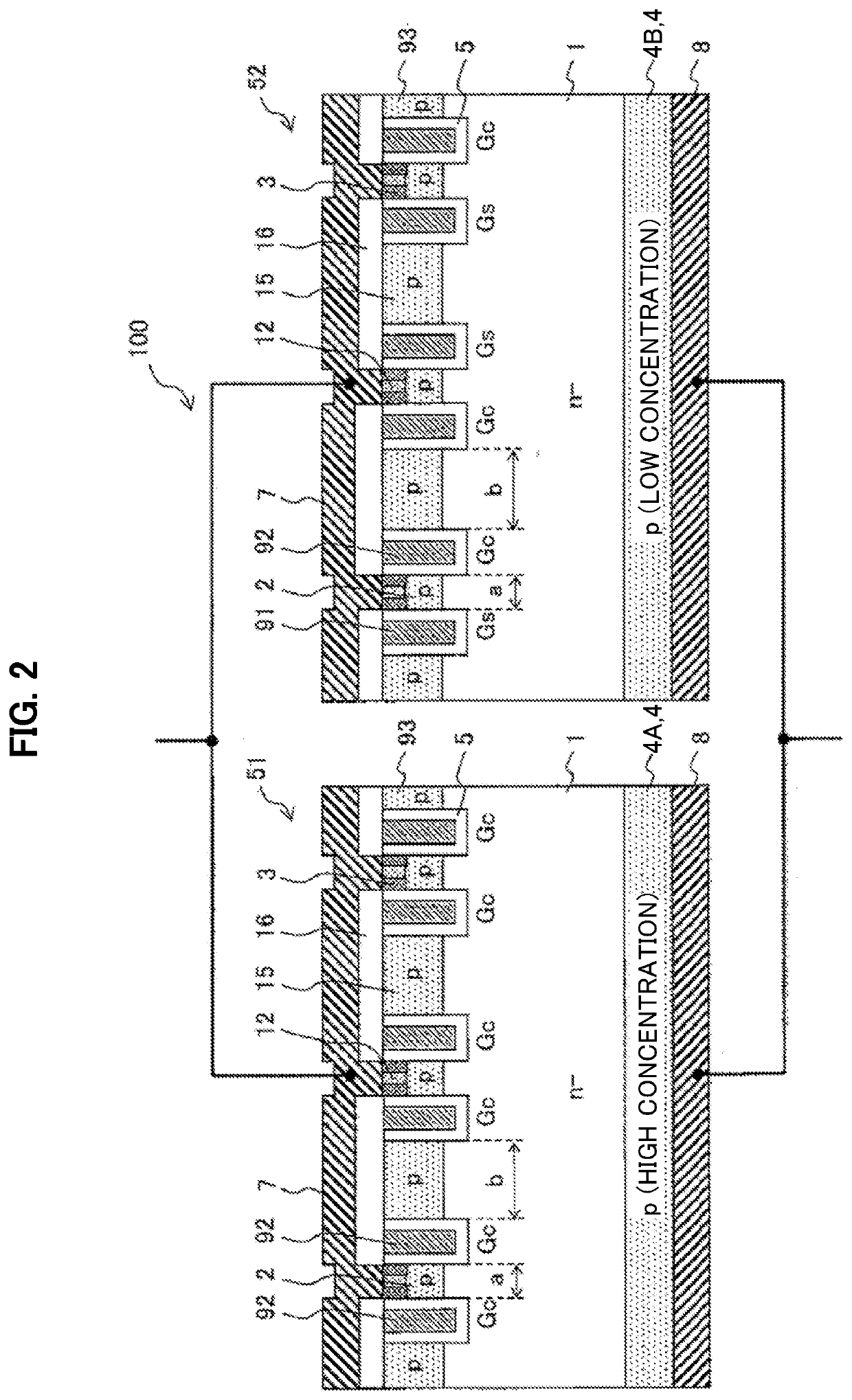

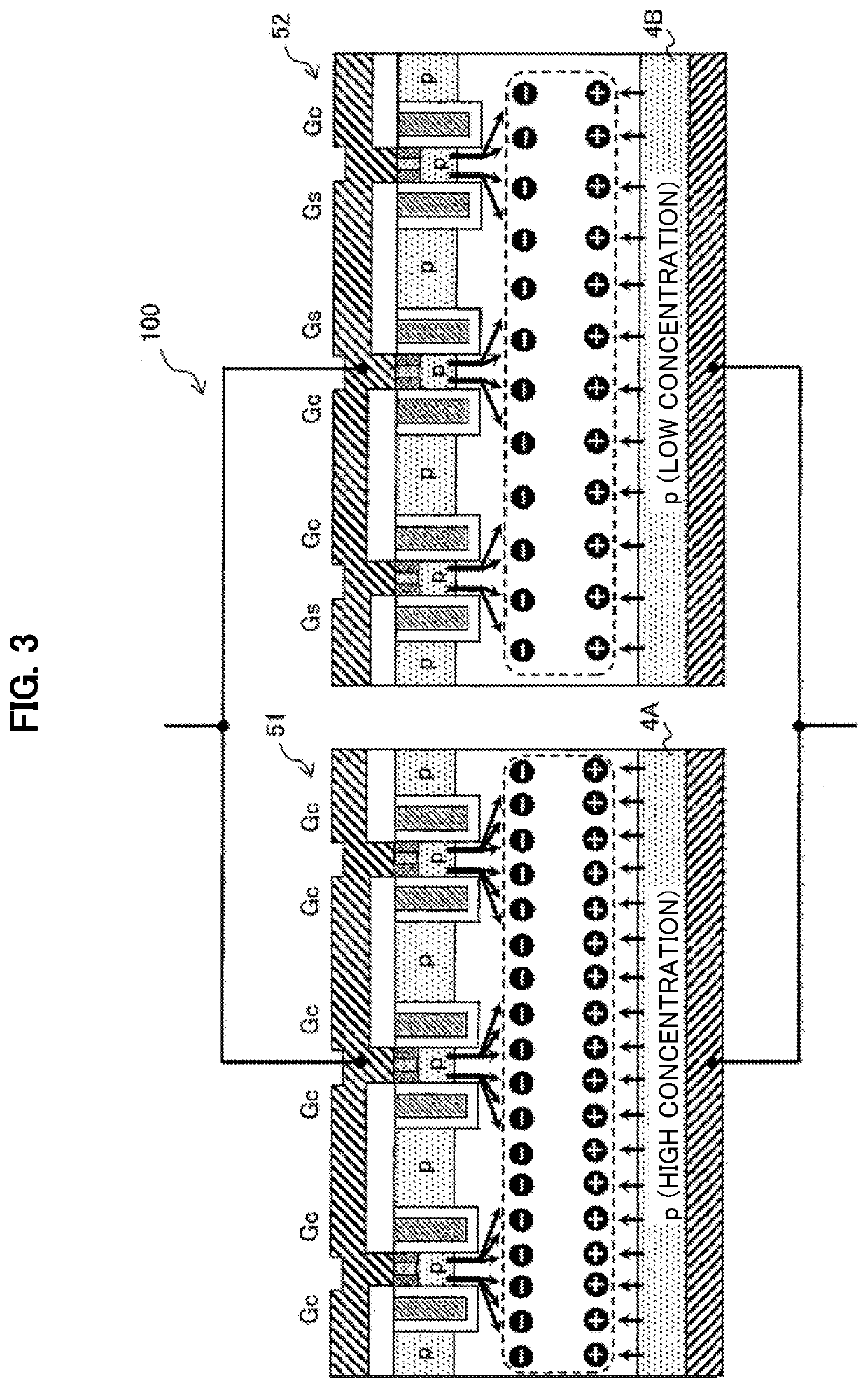

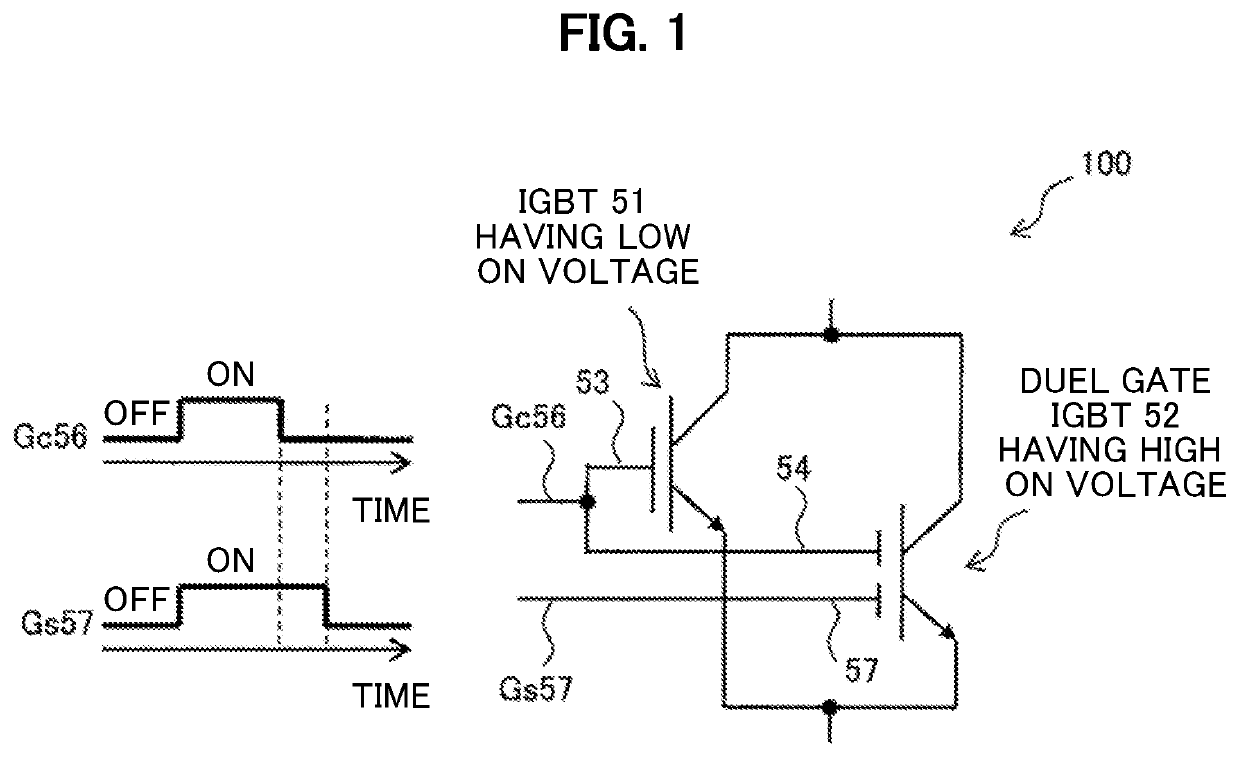

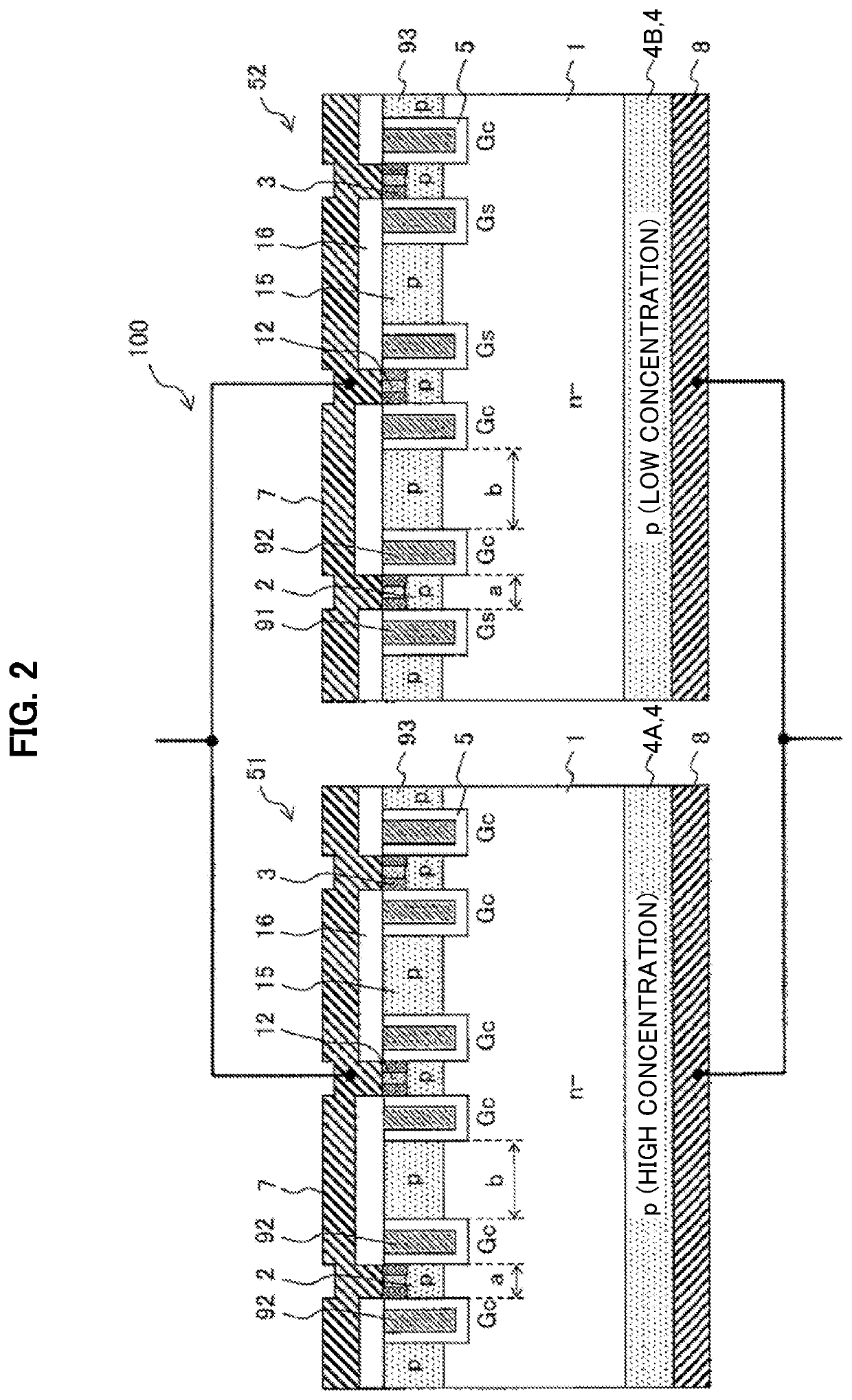

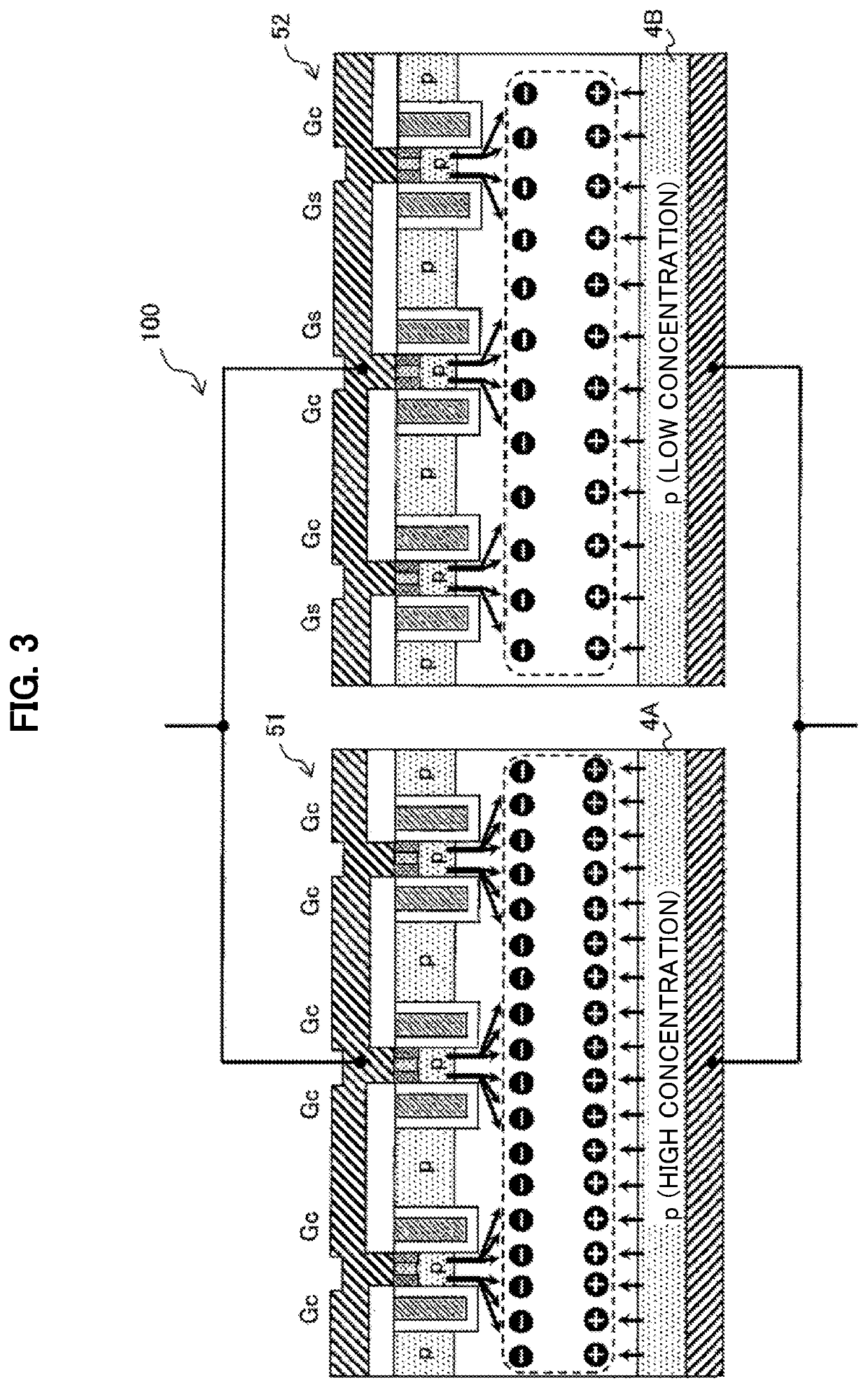

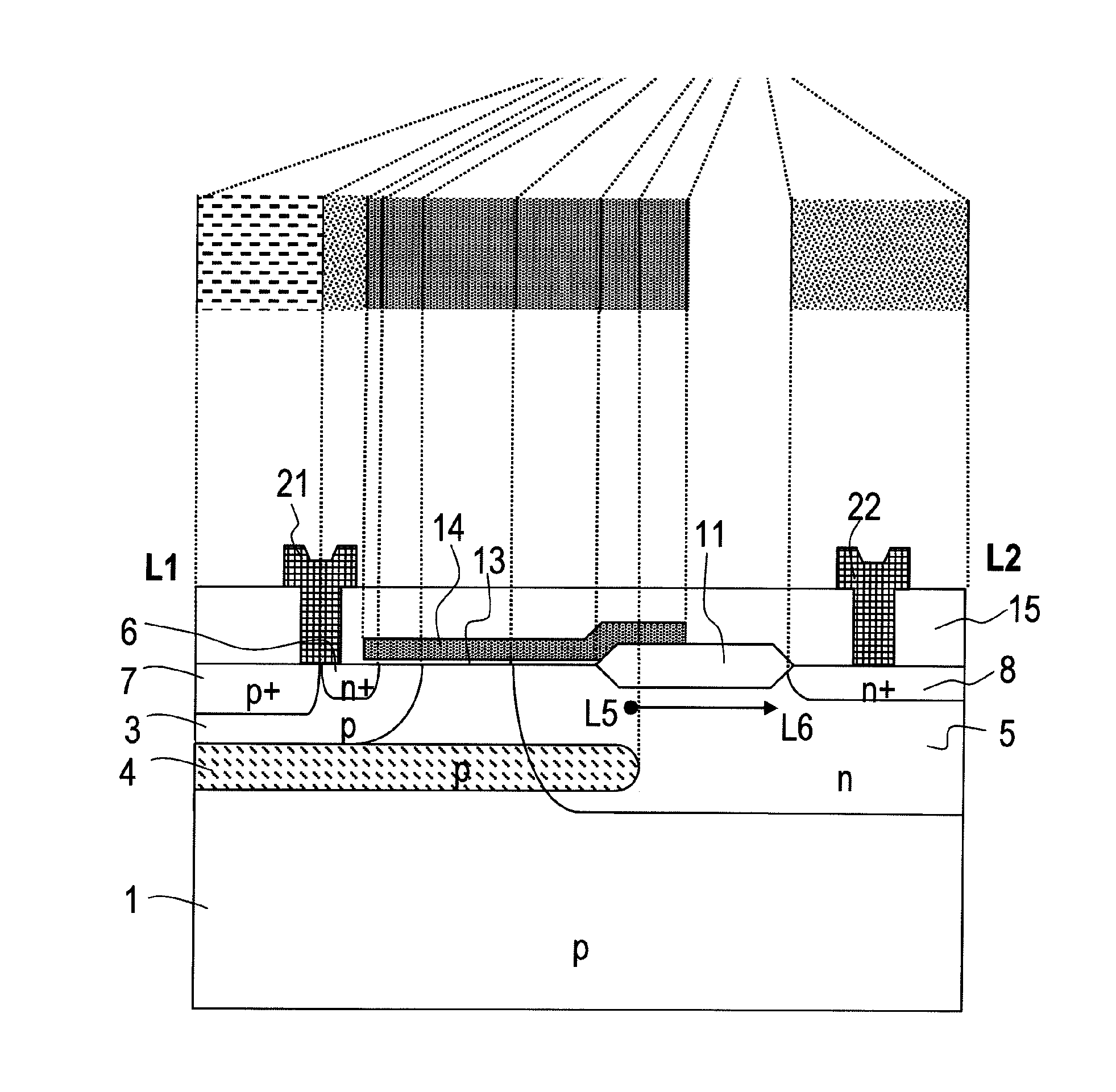

Semiconductor Device and Power Conversion Device

ActiveUS20210091217A1Improve trade-offsReduce conduction lossSolid-state devicesSemiconductor devicesConvertersDevice material

A current switching semiconductor device to be used in a power conversion device achieves both a low conduction loss and a low switching loss. The semiconductor device includes the IGBT in which only Gc gates are provided and an impurity concentration of the p type collector layer is high, and the IGBT in which the Gs gates and the Gc gates are provided and an impurity concentration of the p type collector layer is low. When the semiconductor device is turned off, the semiconductor device transitions from a state in which a voltage lower than a threshold voltage is applied to both the Gs gates and the Gc gates to a state in which a voltage equal to or higher than the threshold voltage is applied to the Gc gates prior to the Gs gates.

Owner:HITACHI POWER SEMICON DEVICE

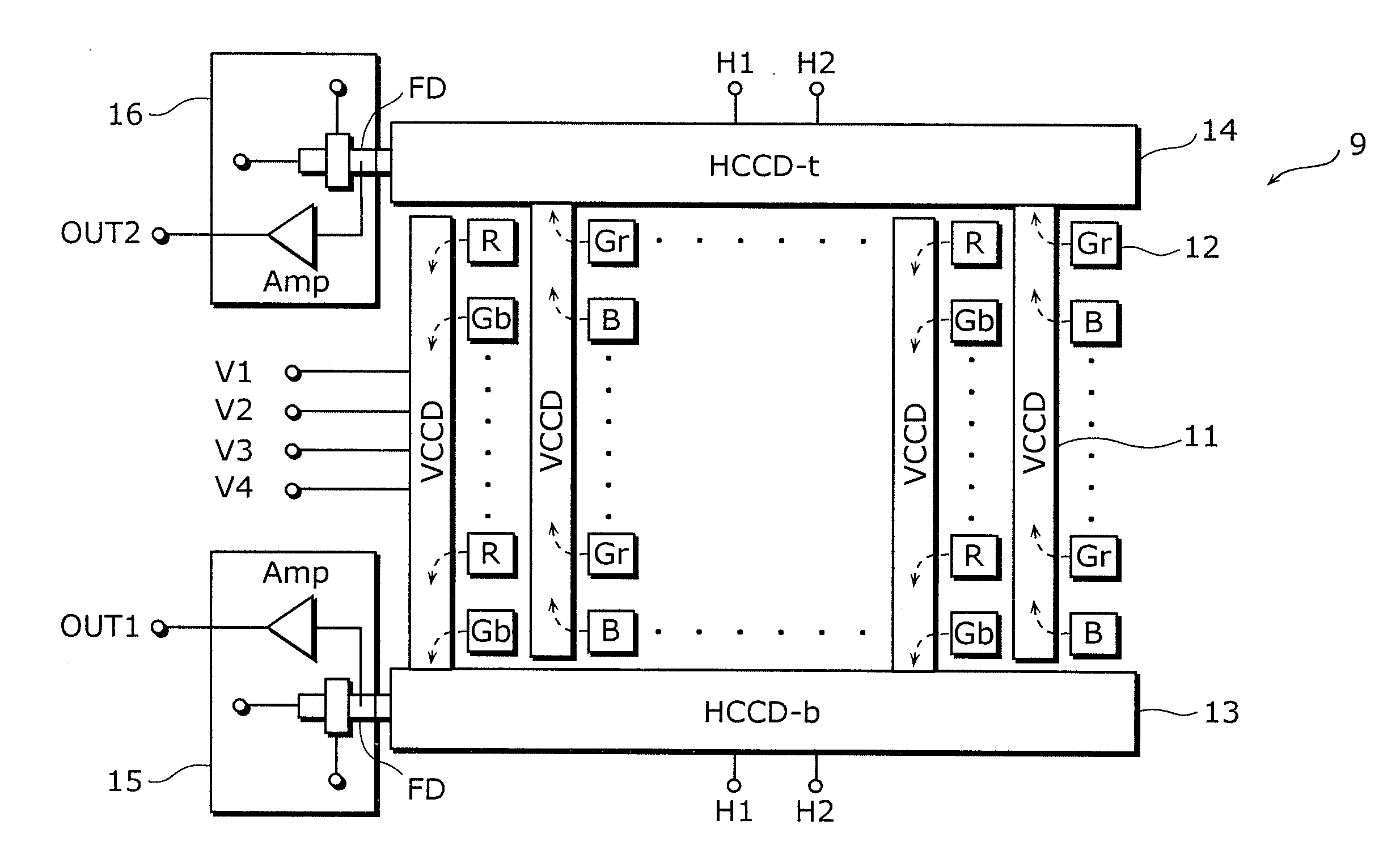

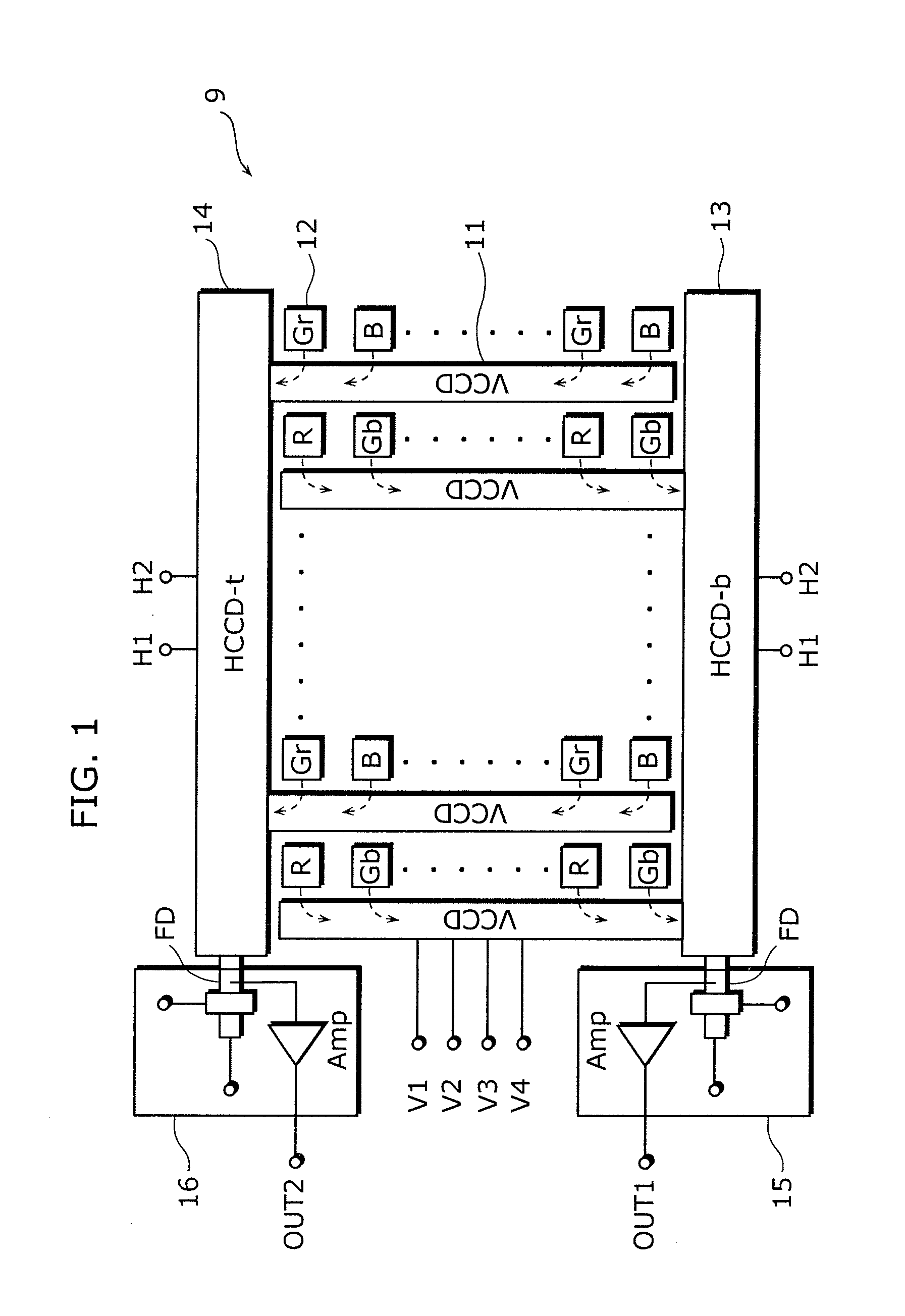

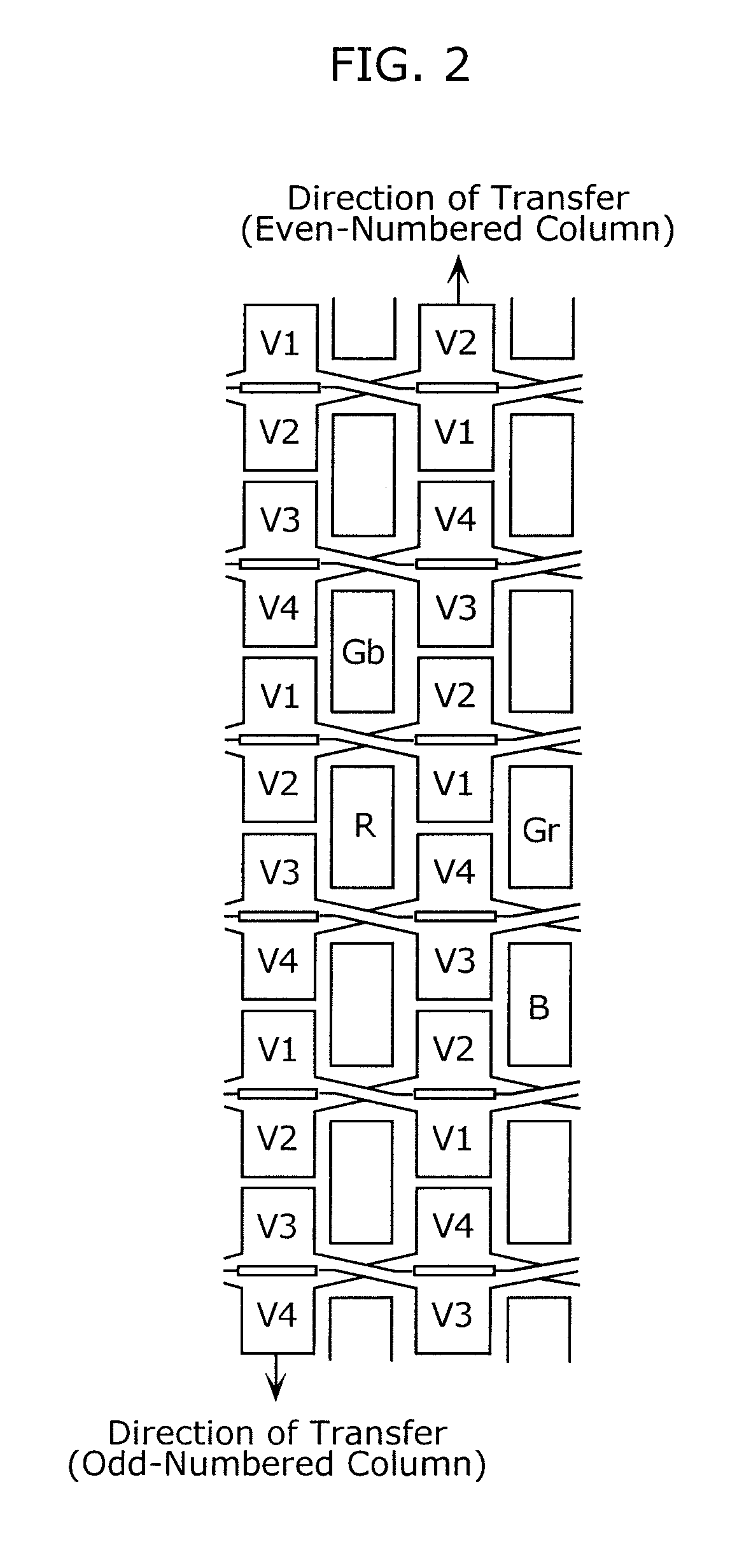

Solid-state imaging device

InactiveUS20100182477A1Improve balanceImprove dynamic rangeTelevision system detailsTelevision system scanning detailsPhotodiodeBiomedical engineering

In a solid-state imaging device, photodiodes (12) are classified into a plurality of fields, and each one of driving pulses (V1A, V1B, V2, V3A, V3B, V4) is applied to corresponding one of the photodiodes via a plurality of electrodes (17). Of the electrodes, a plurality of electrodes used to control readout of the signal charges from the photodiodes to the charge-coupled devices (11) are interconnected such that each one of a plurality of independent driving pulses (V1A, V1B, V3A, V3B) is applied to the corresponding one of the electrodes in accordance with the number of fields into which the photodiodes are classified.

Owner:PANASONIC CORP

Elastic wave device, high-frequency front end circuit, and communication apparatus

ActiveUS11367829B2Improve trade-offsReduce resistancePolycrystalline material growthImpedence networksHemt circuitsEngineering

An elastic wave device includes a piezoelectric substrate, an IDT electrode including a first electrode layer located on the piezoelectric substrate and including one of Mo and W as a main component and a second electrode layer laminated on the first electrode layer and including Cu as a main component, and a dielectric film located on the piezoelectric substrate and covering the IDT electrode. The piezoelectric substrate is made of lithium niobate. The dielectric film is made of silicon oxide. The elastic wave device utilizes Rayleigh waves propagating along the piezoelectric substrate.

Owner:MURATA MFG CO LTD

Elastic wave device, high-frequency front end circuit, and communication apparatus

ActiveUS10250226B2Improve trade-offsReduce resistanceImpedence networksPiezoelectric/electrostrictive/magnetostrictive devicesSilicon oxideOptoelectronics

An elastic wave device includes a piezoelectric substrate, an IDT electrode including a first electrode layer which is provided on the piezoelectric substrate and contains Pt as a main component and a second electrode layer which is laminated on the first electrode layer and contains Cu as a main component, and a dielectric film that is provided on the piezoelectric substrate and covers the IDT electrode. The piezoelectric substrate is made of lithium niobate. The dielectric film is made of silicon oxide. The elastic wave device uses Rayleigh waves propagating along the piezoelectric substrate.

Owner:MURATA MFG CO LTD

Semiconductor device and power conversion device

ActiveUS11296212B2Improve trade-offsReduce conduction lossSolid-state devicesSemiconductor devicesConvertersDevice material

A current switching semiconductor device to be used in a power conversion device achieves both a low conduction loss and a low switching loss. The semiconductor device includes the IGBT in which only Gc gates are provided and an impurity concentration of the p type collector layer is high, and the IGBT in which the Gs gates and the Gc gates are provided and an impurity concentration of the p type collector layer is low. When the semiconductor device is turned off, the semiconductor device transitions from a state in which a voltage lower than a threshold voltage is applied to both the Gs gates and the Gc gates to a state in which a voltage equal to or higher than the threshold voltage is applied to the Gc gates prior to the Gs gates.

Owner:HITACHI POWER SEMICON DEVICE

Semiconductor device and method for producing the same

ActiveUS8334568B2Improve breakdown voltageIncrease the on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionSemiconductor

A P type semiconductor substrate includes a P type body region, an N type drift region formed away from the P type body region in a direction parallel to a substrate surface, an N type drain region formed in a region separated by a field oxide film in the N type drift region so as to have a concentration higher than the N type drift region, an N type source region formed in the P type body region so as to have a concentration higher than the N type drift region. A P type buried diffusion region having a concentration higher than the N type drift region is formed of a plurality of parts each of which is connected to a part of the bottom surface of the P type body region and extends parallel to the substrate surface and its tip end reaches the inside of the drift region.

Owner:SHARP KK

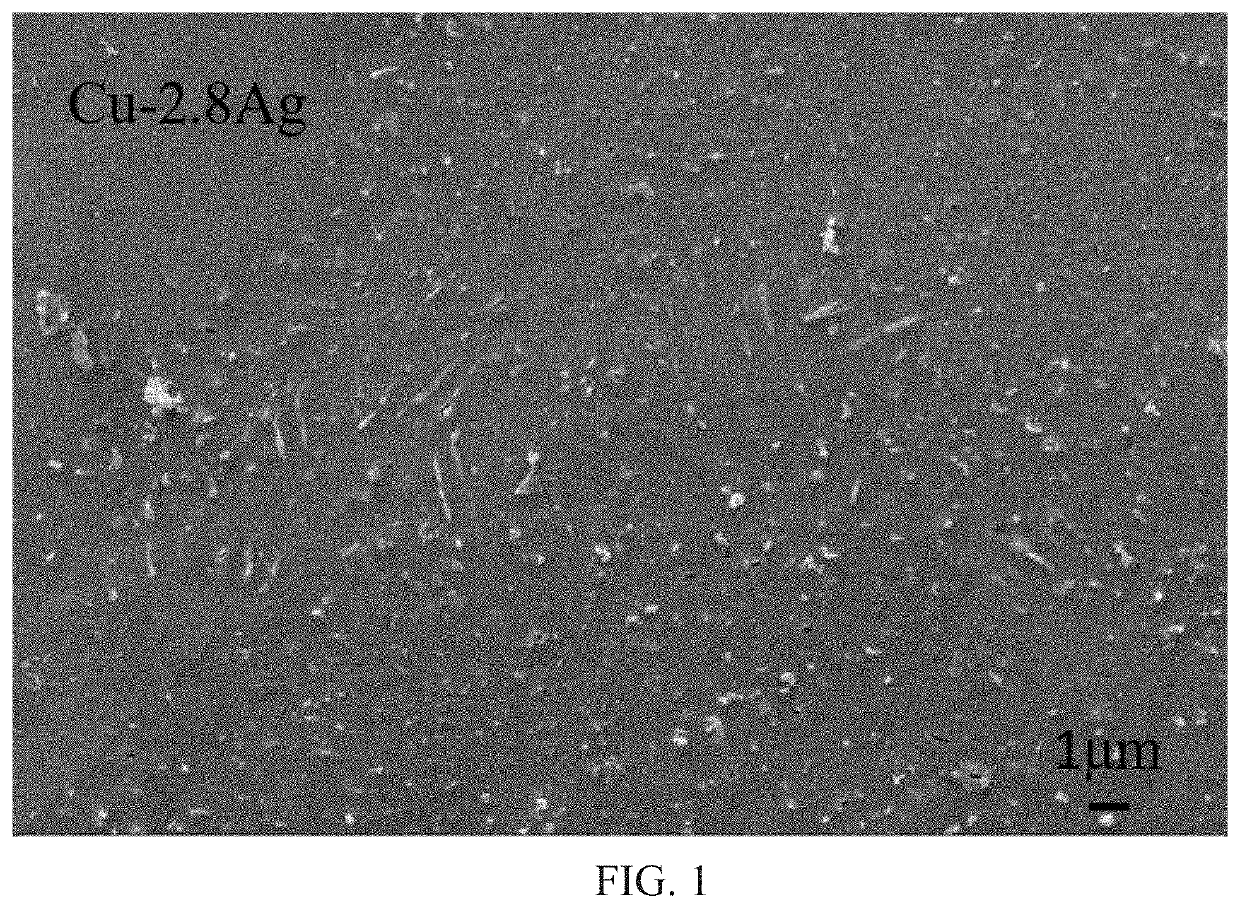

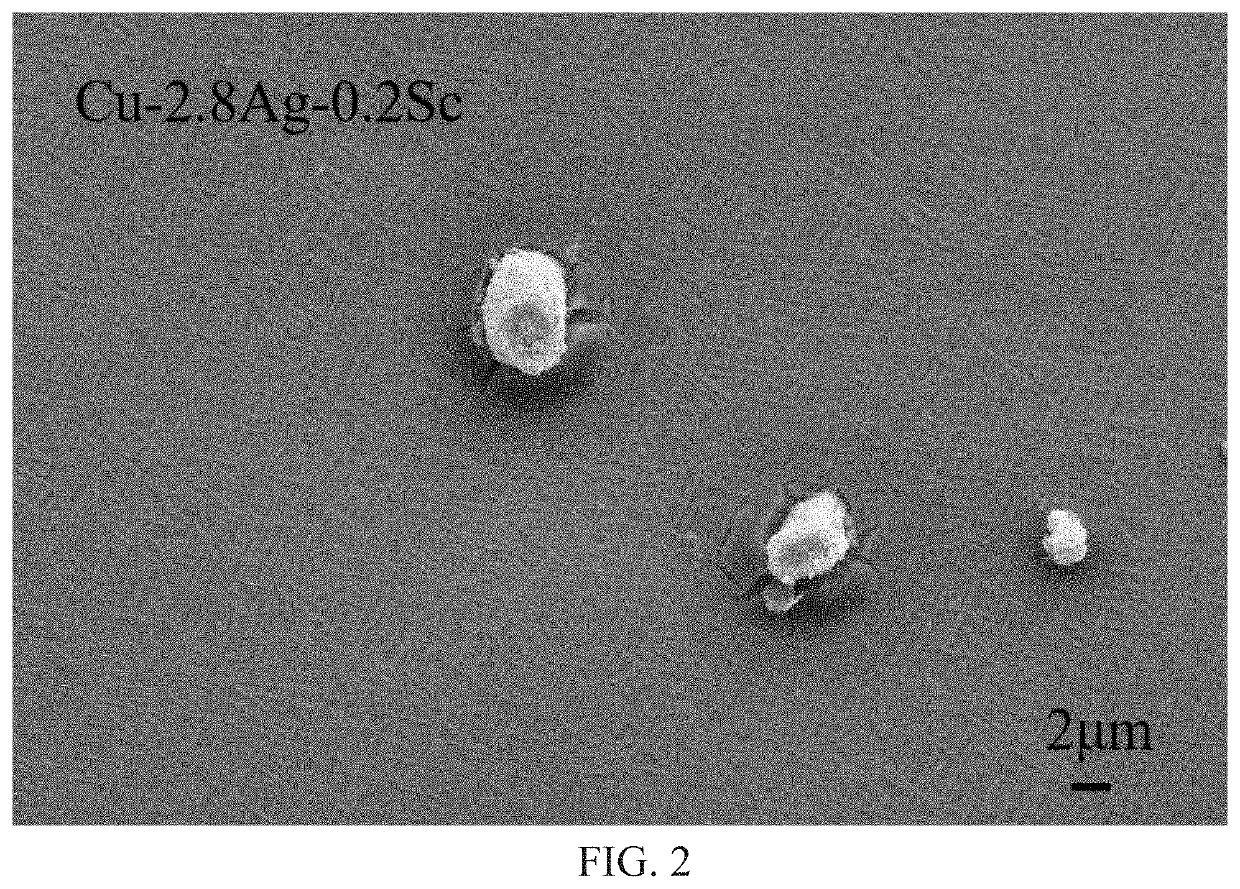

High-strength and high-conductivity cu-ag-sc alloy and preparation method thereof

ActiveUS20210340658A1Improve conductivityImprove balanceIncreasing energy efficiencyElectric arc furnaceIngot

Provided are a high-strength and high-conductivity Cu—Ag—Sc alloy and a preparation method thereof. The preparation method includes the following steps: (1) placing metal Ag and metal Sc in an electric-arc furnace and performing smelting under a vacuum condition, performing cooling to normal temperature in the furnace to obtain an Ag—Sc intermediate alloy; (2) placing the Ag—Sc intermediate alloy, an electrolytic copper and the metal Ag in an induction furnace and performing heating to 1200-1300° C. under a vacuum condition, keeping at the temperature for 10-60 min for smelting, then performing casting and cooling to normal temperature in the furnace to obtain ingots; (3) heating the ingots to 700-850° C. under an inert atmosphere, then performing water quenching to normal temperature to obtain heat-treated ingots; and (4) heating the heat-treated ingots to 400-500° C. under an inert atmosphere, then performing air cooling to normal temperature to obtain the high-strength and high-conductivity Cu—Ag—Sc.

Owner:NORTHEASTERN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com