Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

44results about How to "Good statistical properties" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

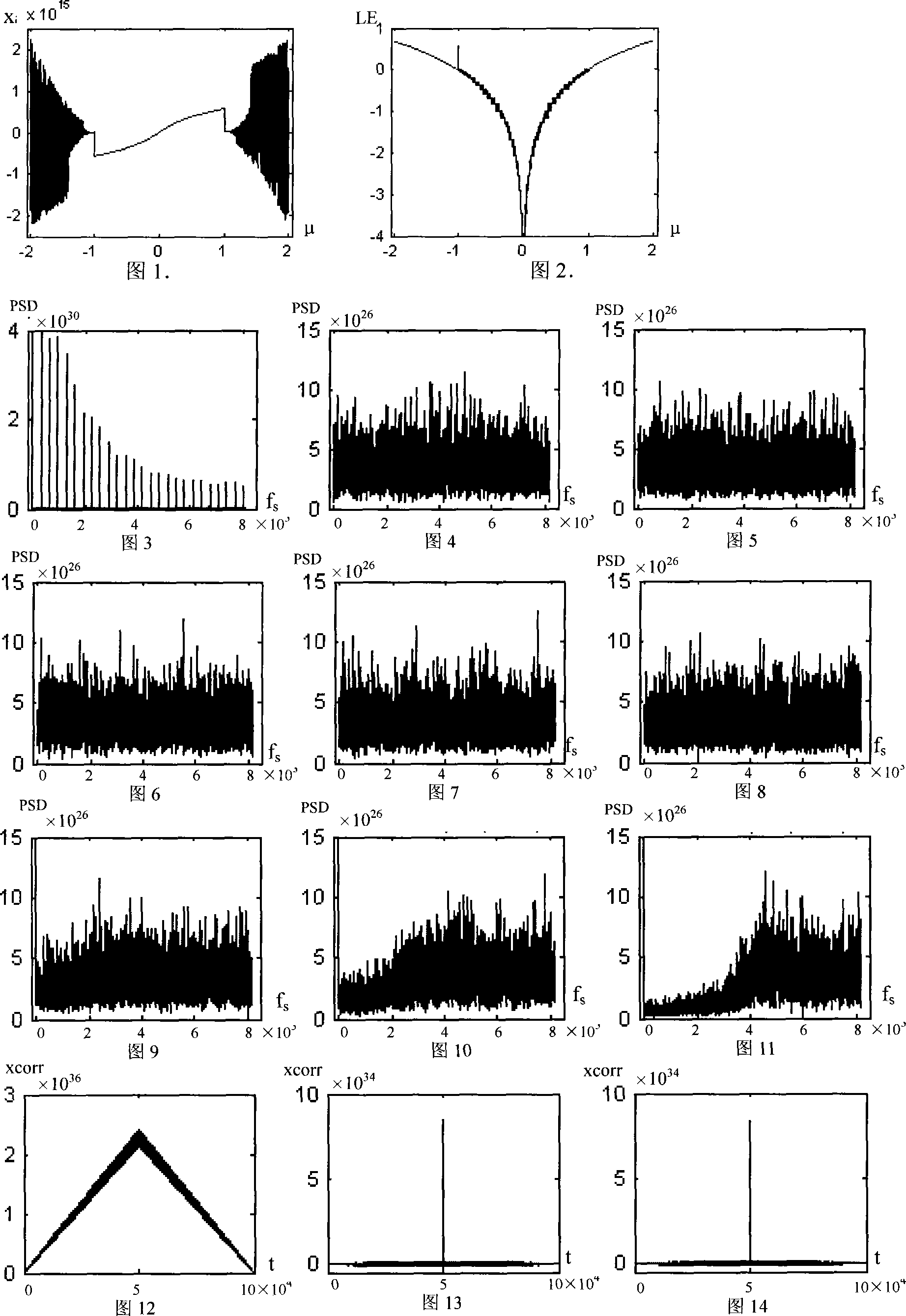

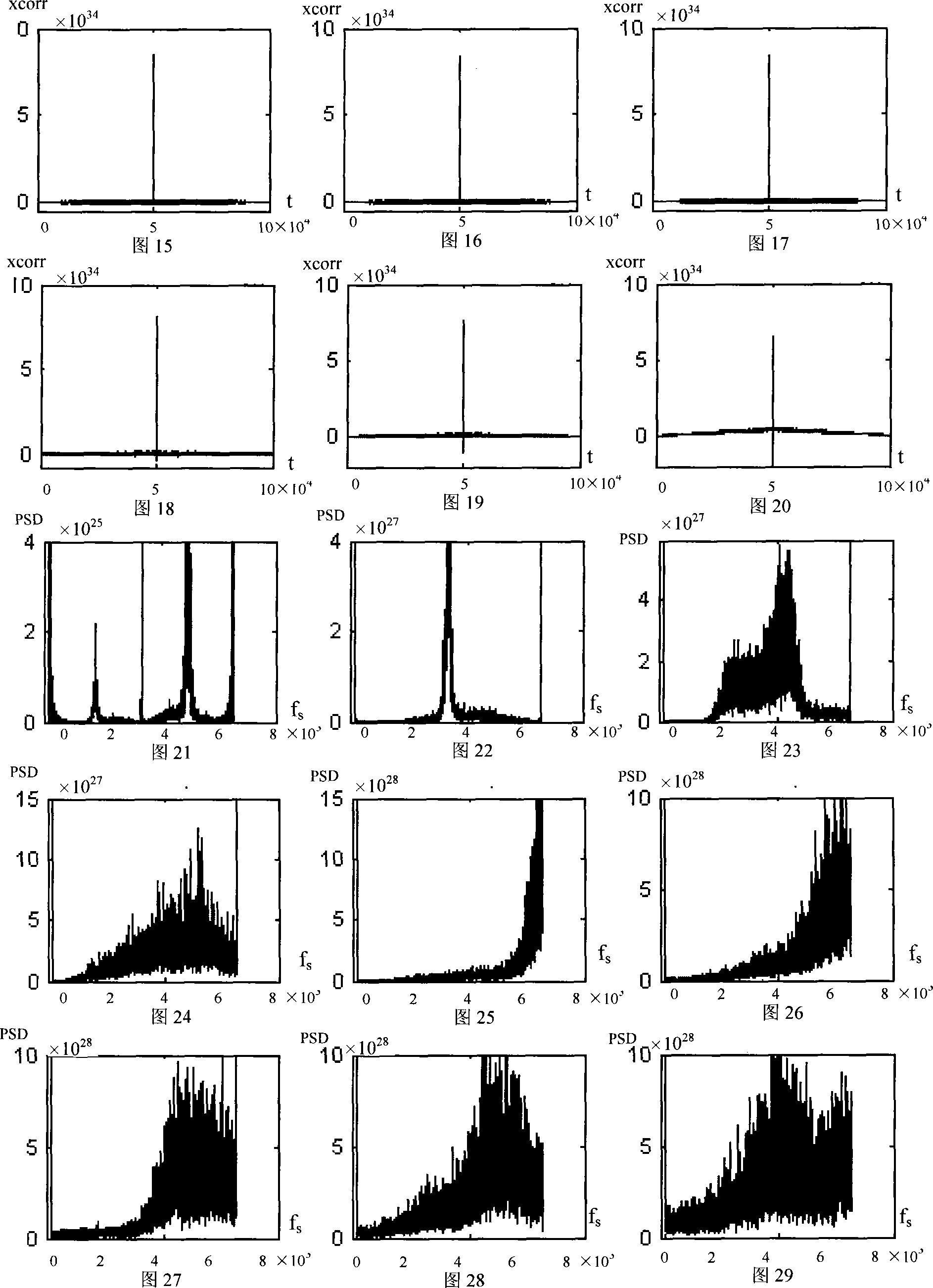

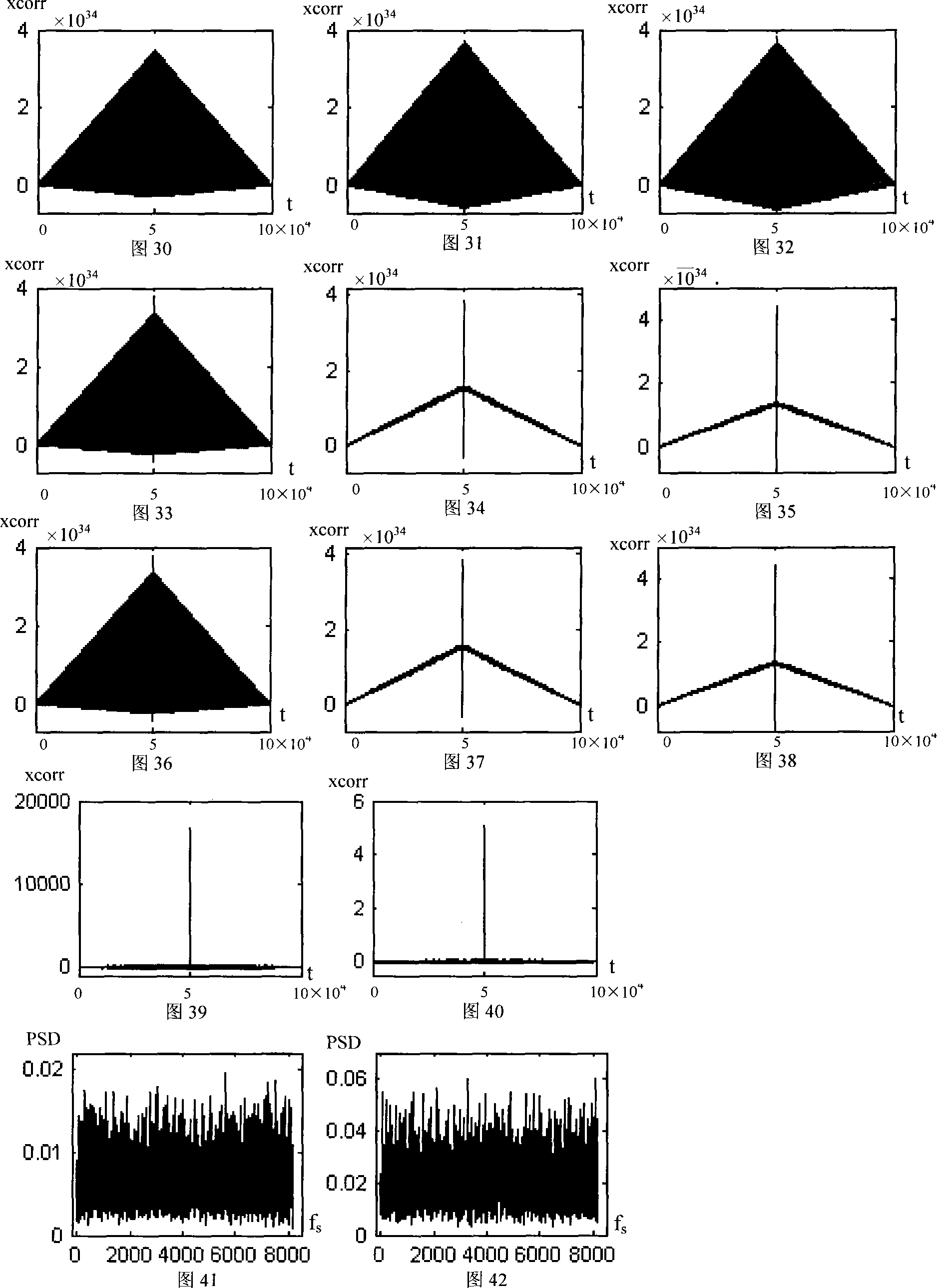

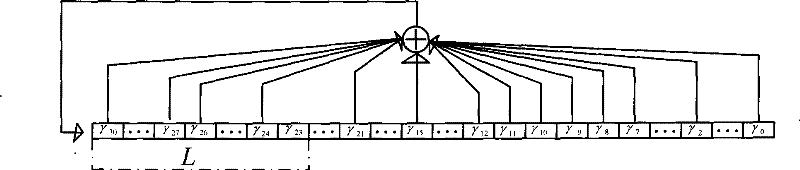

Chaotic sequence generation method and sequence generator of high speed high-precision chaotic function

InactiveCN101222318AGood statistical propertiesOvercome short cycle responseSecuring communicationComplex mathematical operationsPlaintextMultiplexer

The invention discloses a chaotic sequence generation method and a sequence generator for high-speed high-accuracy chaotic functions. An initial key circuit stores the initial value of a chaotic latch unit, a u value key circuit stores a sequence ui value; each cp chaotic function finishes one-time interactive operation: a bitwise conversion circuit outputs a bitwise XOR to the chaotic latch unit, the bitwise XOR is used to realize a subtraction operation N minus one and minus the absolute value of xi and so on; a shift data selector takes the ui as an address code of the data selector, the data is shifted with a plurality of bits toward right, then the subtraction is used to realize a multiplication that the ui is multiplied by the data; the subtraction result is stored into the chaotic latch unit at the rising edge of the cp, each cp generates a 160-bit chaotic output; the randomness is good due to the existence of an initial key and a u value key; the precision is far greater than that of the double type, the cycle of the cp can reach 90ns, the encryption of a 128-bit plaintext needs 1.7us; the invention can be realized by using FPGAs, GPLDs and ASICs and so on, and is used in the network security technical field, particularly in the wireless networks and the wireless sensor networks.

Owner:HEILONGJIANG UNIV

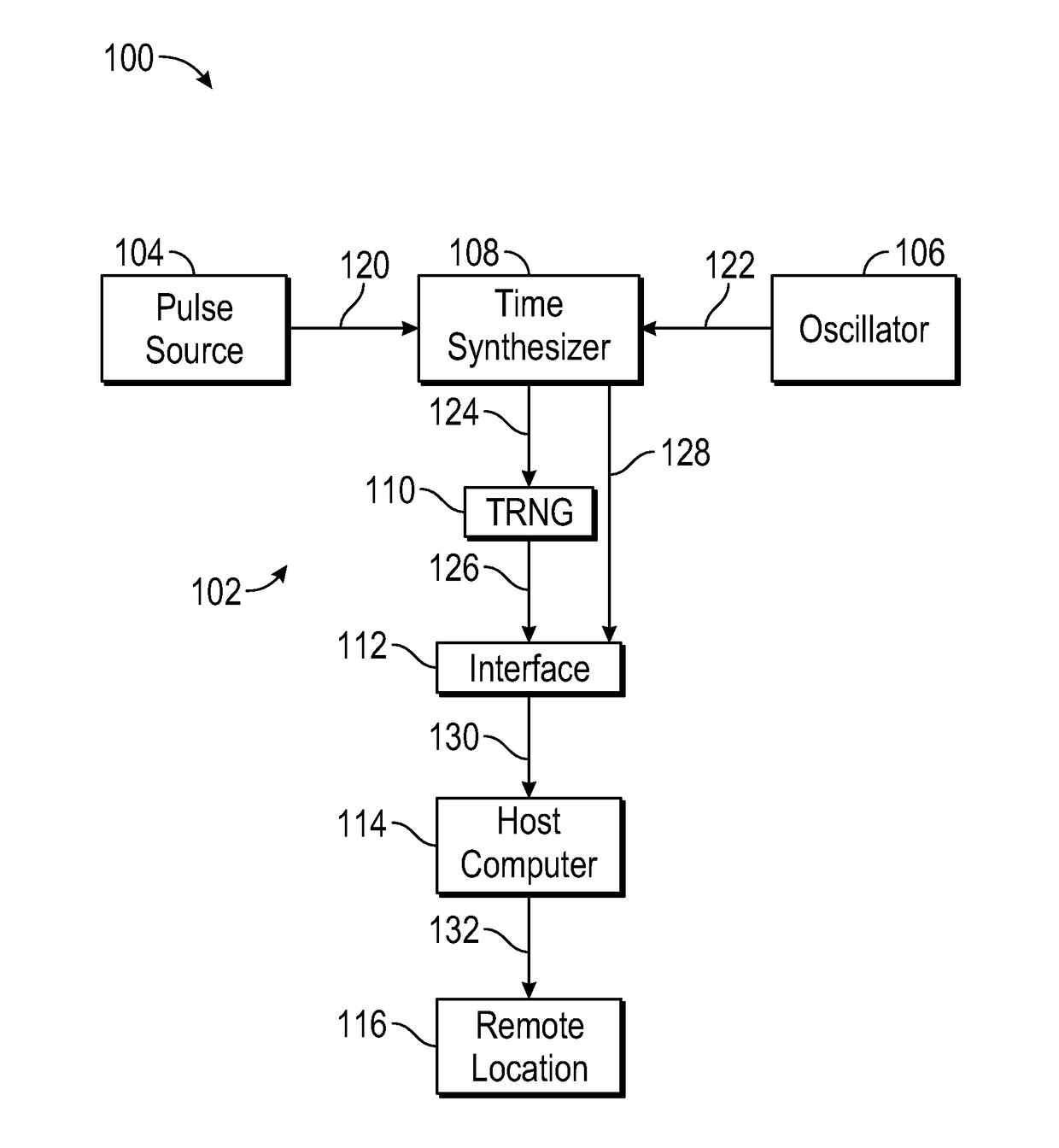

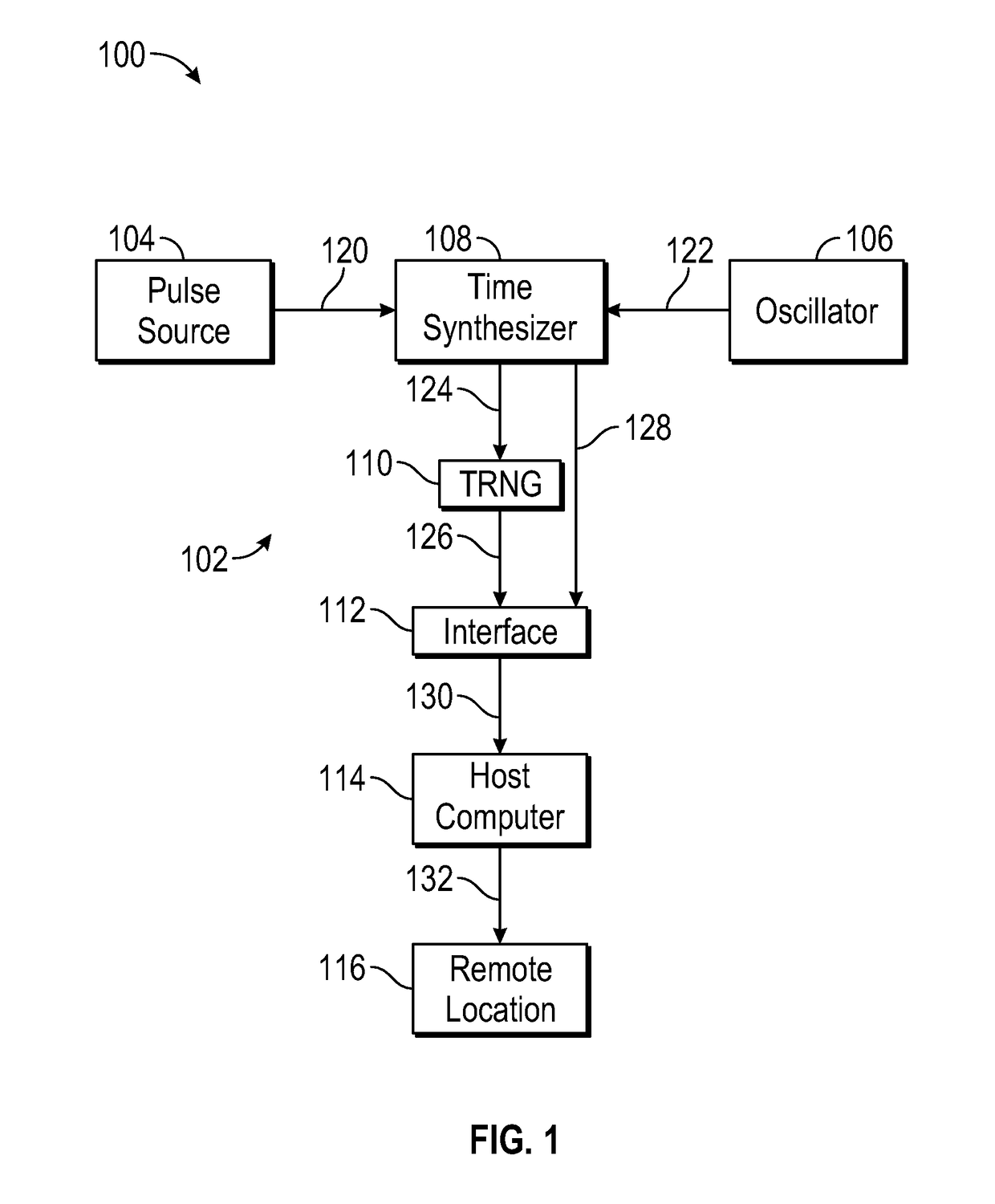

Synchronized True Random Number Generator

ActiveUS20180039485A1Good statistical propertyEasy to useRandom number generatorsLight sourceVoltage noise

A synchronized true random number generator (SRNG) includes a pulse source that provides a synchronized pulse signal synchronized with a known time, an oscillator to make a clock signal, a time synthesizer, and a triggerable true random number generator (TRNG). Another embodiment includes a plurality of independent triggerable TRNGs, separated by a separation distance, that produce free TRNG output. A separation distance is a distance greater than the product of the speed of light (C) multiplied by the generation period. A generation period of a TRNG is the period from the start of generating a random number until the random number can be determined. A triggerable single-photon-detector TRNG comprises first and second single-photon detectors, a light source, first and second pulse-generator circuits, and a first-pulse detector. A triggerable photon-shot-noise TRNG contains a photonic detector comprising two photodiodes connected back-to-back, and light source (e.g., an LED) providing illumination to the two photodiodes; a current-to-voltage converter; an amplifier; and a comparator for converting the amplified voltage noise to a binary random bit output.

Owner:WILBER SCOTT A

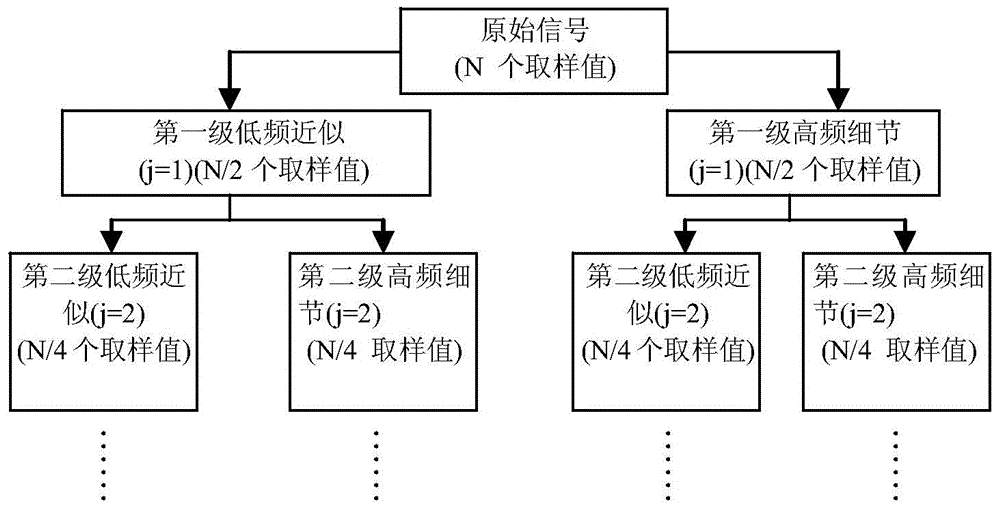

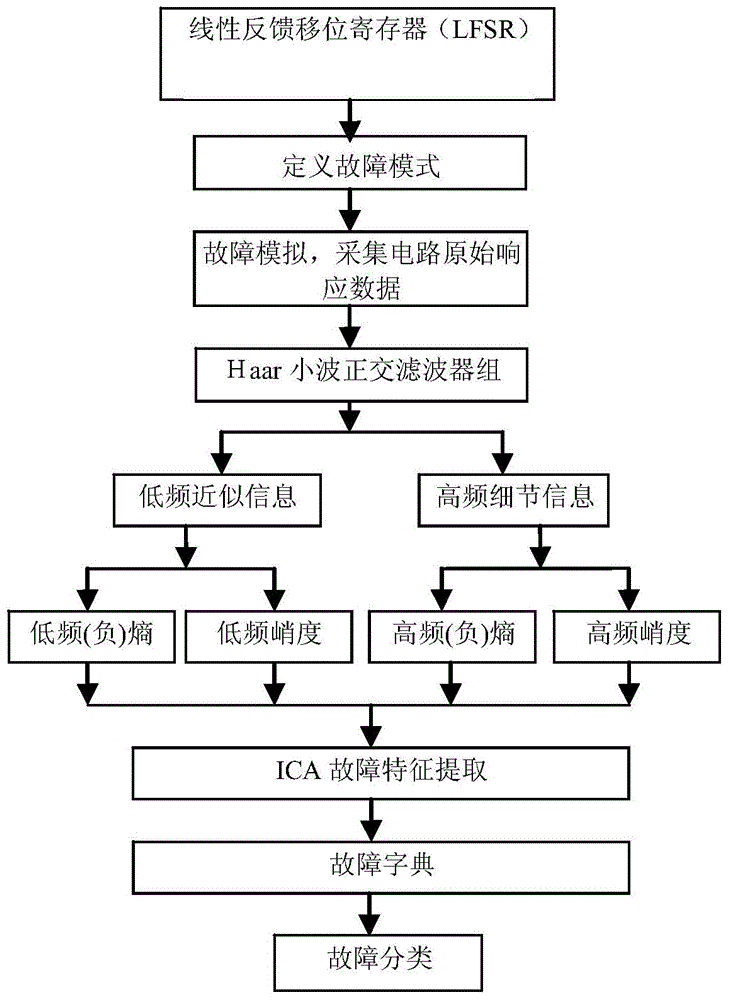

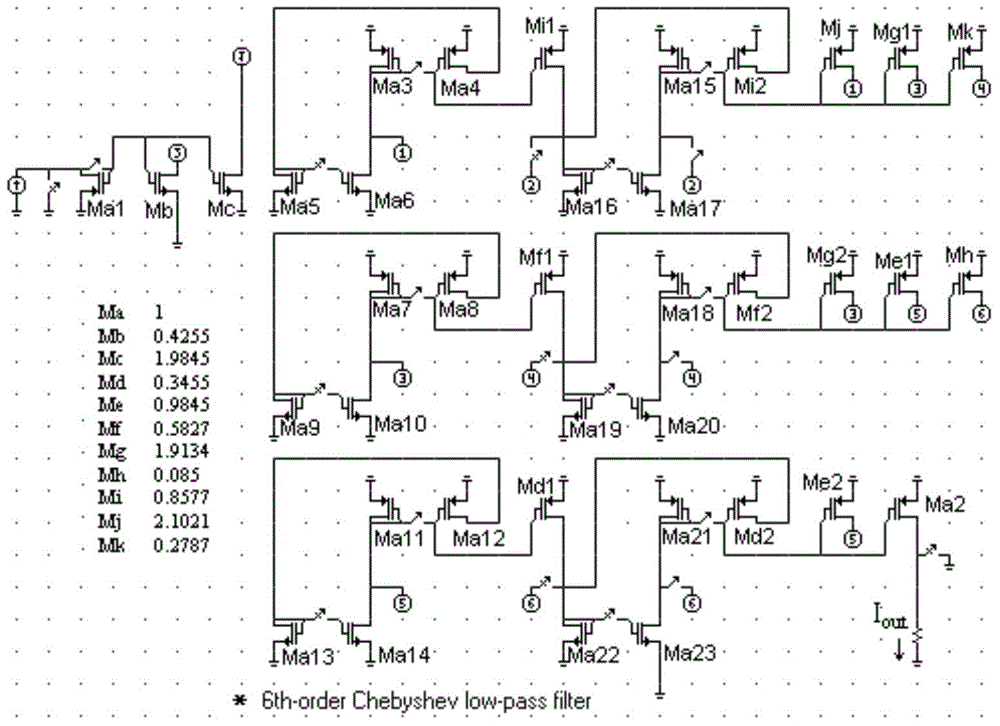

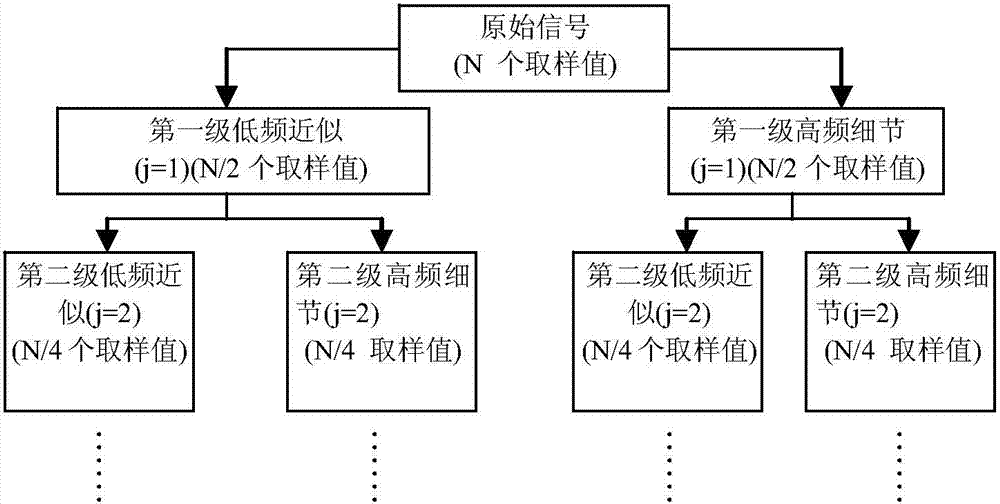

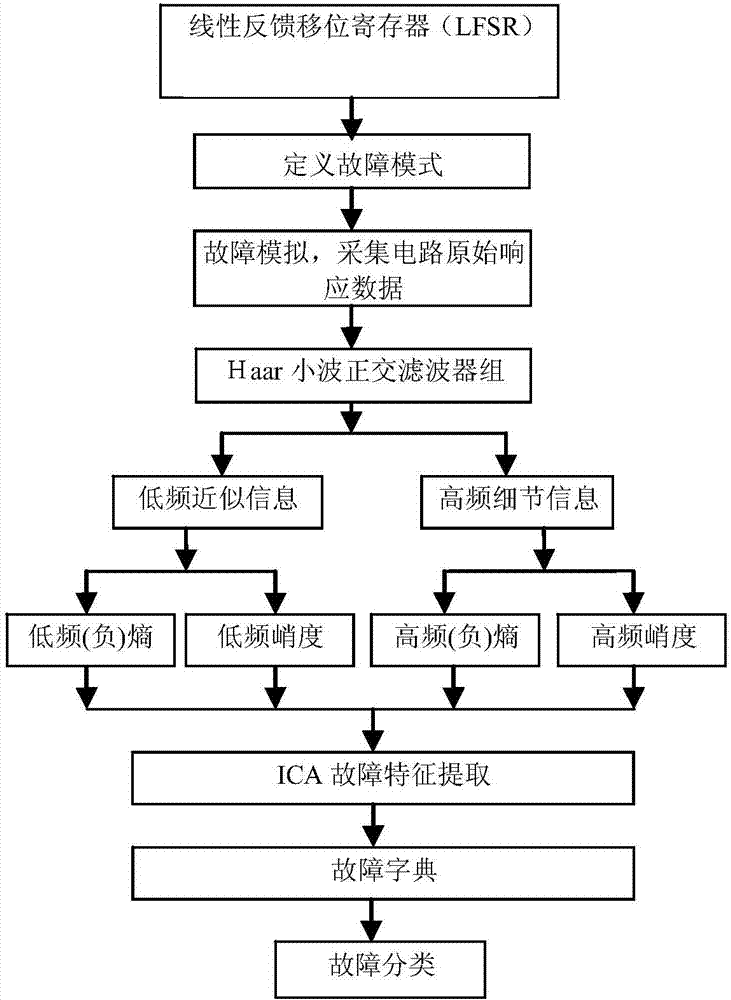

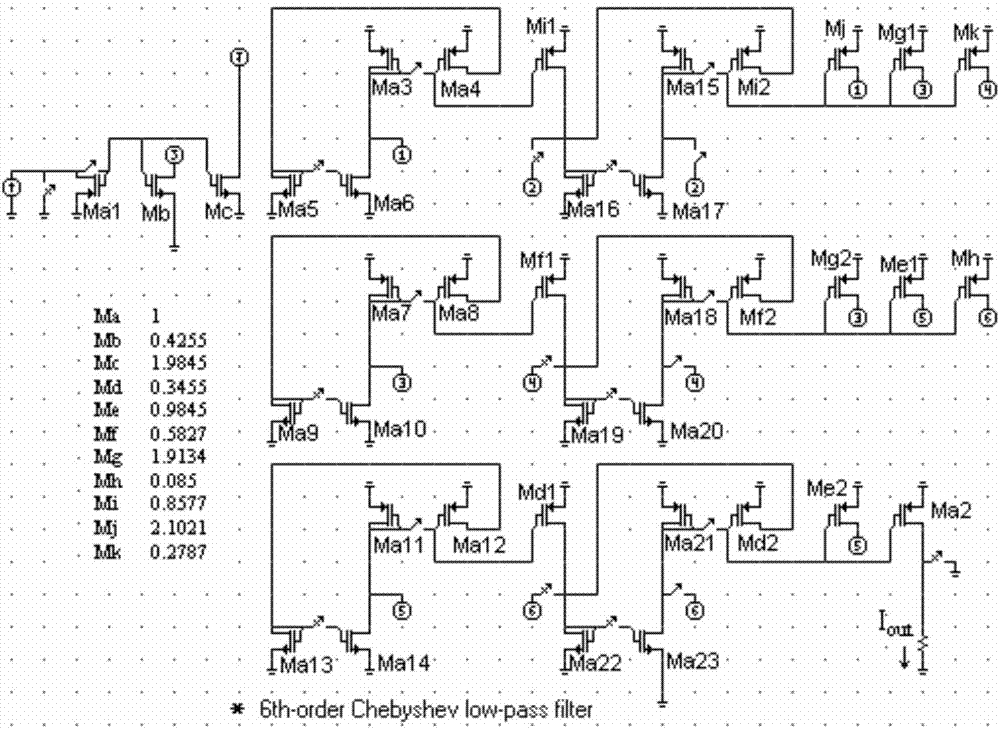

Switched circuit fault diagnosis method based on wavelet transformation and ICA (independent component analysis) feature extraction

InactiveCN104793124AThe classification result is accurateAccurate diagnosisElectronic circuit testingFeature extractionSwitched current

The invention discloses a switched circuit fault diagnosis method based on wavelet transformation and ICA (independent component analysis) feature extraction. The switched circuit fault diagnosis method includes the steps of firstly, performing classifier training and fault dictionary construction, namely, based on circuit simulation, acquiring feature parameters by a method based on wavelet transformation and ICA feature extraction, and constructing a fault dictionary and a training classifier based on the feature parameters; secondly, performing fault diagnosis, namely, acquiring the feature parameters aiming at a switched current circuit to be diagnosed by referring to the fault dictionary and by the method based on wavelet transformation and ICA feature extraction, inputting the feature parameters into a trained classifier, and subjecting the switched current circuit to be diagnosed to fault diagnosis to obtain output signals of the classifier, namely, fault diagnosis results. The switched circuit fault diagnosis method based on wavelet transformation and ICA feature extraction has the advantages of ingenious concept, easiness in implementation, simulation proving and capability of distinguishing various fault types more accurately as compared with an existing method.

Owner:CHANGSHA UNIVERSITY

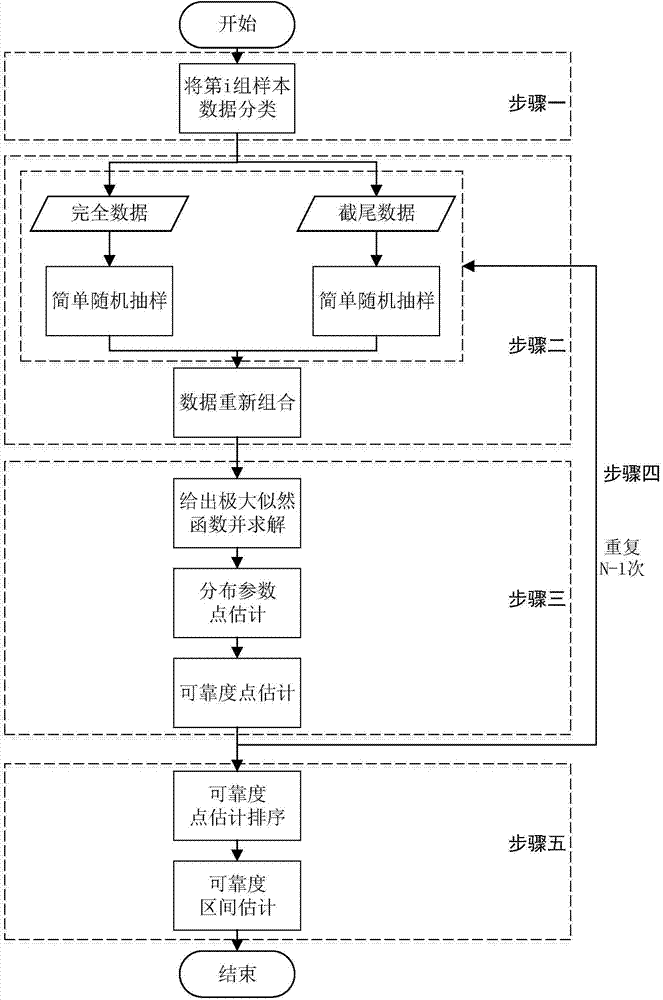

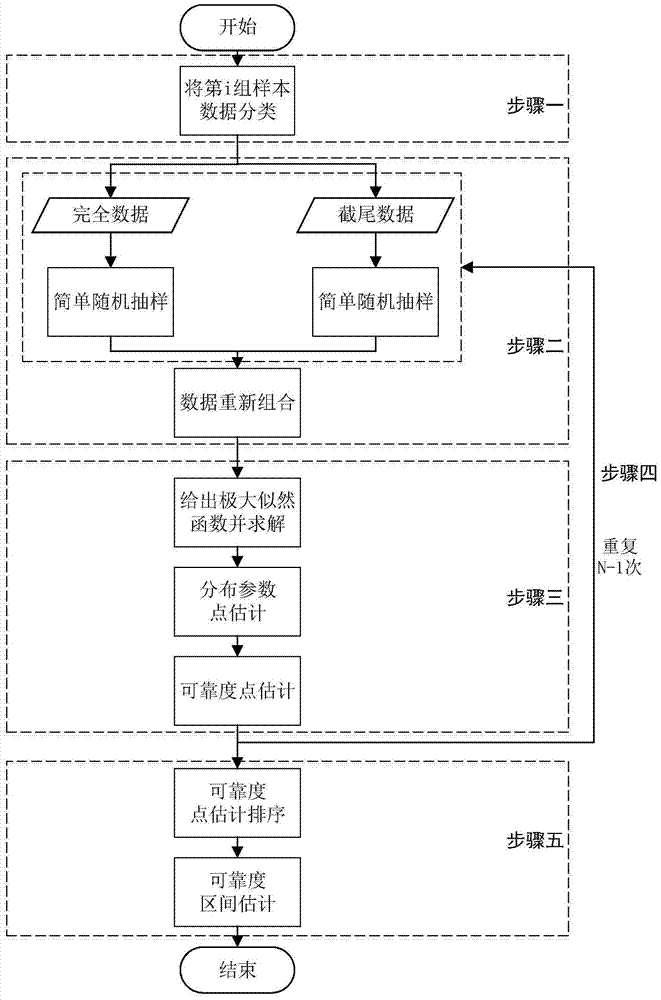

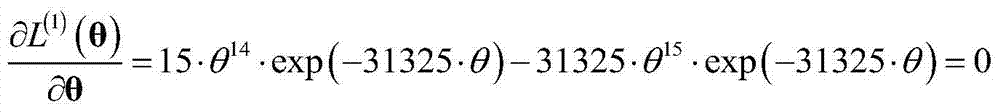

Reliability interval estimation method based on proportion grouping re-sampling

InactiveCN104750982AGuaranteed uptimeAvoid problemsSpecial data processing applicationsComplete dataLife time

The invention discloses a high-proportion censored data reliability interval estimation method based on proportion grouping re-sampling. The method includes the steps that firstly, life test data are grouped into complete data and censored data; secondly, repeated sampling is conducted according to a specific proportion; thirdly, distribution parameters and reliability point estimations are obtained; fourthly, repeated re-sampling is conducted by the adoption of a Bootstrap method, and corresponding distribution parameters and reliability point estimations are calculated; fifthly, the obtained reliability point estimations are sequenced, and then the reliability interval estimation is obtained. The method avoids appearance of zero-failure data in the process of repeated re-sampling, and normal operation of the method is guaranteed; the method needs less theoretical knowledge, is easy and convenient to calculate, is easy to implement, facilitates use of engineering technicians and has good application value.

Owner:BEIHANG UNIV

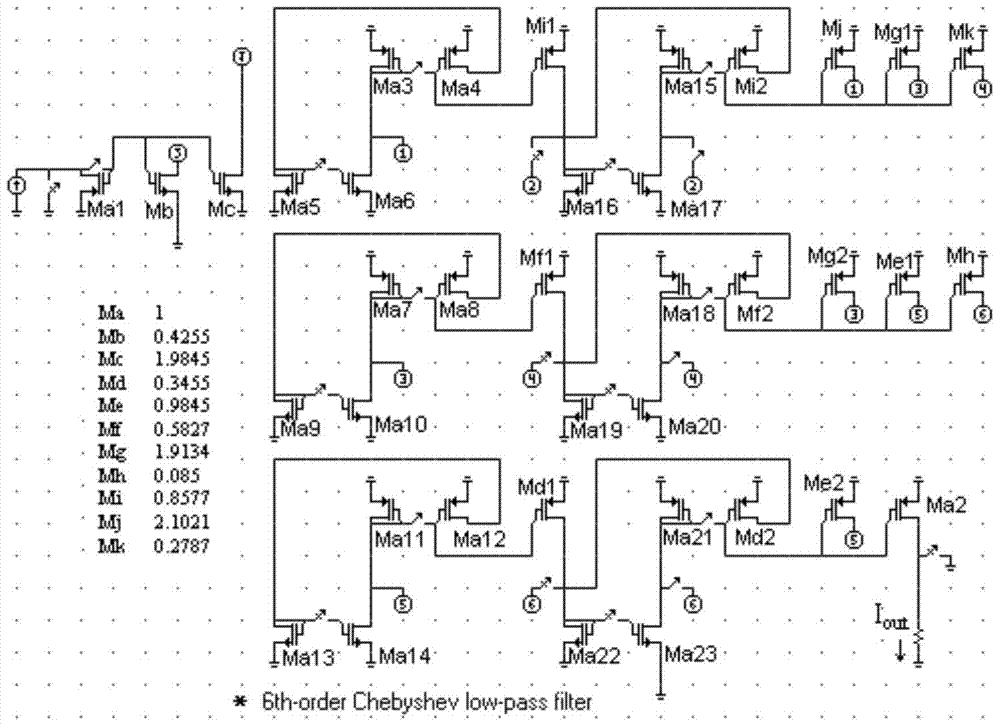

Switching circuit fault classifying method based on wavelet transform and ICA feature extraction

InactiveCN104714171AThe result is accurateHigh fault classification accuracyElectronic circuit testingCircuit interrupters testingFeature extractionAlgorithm

The invention discloses a switching circuit fault classifying method based on wavelet transform and ICA feature extraction. The method comprises the following steps: (1) generating a pseudo random signal as a test stimulation signal; (2) defining a fault mode; (3) acquiring the original response data of the circuit; (4) pre-treating the original response data by a Haar wavelet orthogonal filter; (5) extracting the fault feature parameters, and calculating the entropy and kurtosis as well as fuzzy sets thereof of low-frequency approximate information and high-frequency detail information for the pre-treated signal respectively; and (6) constructing a fault dictionary based on the extracted fault feature parameters so as to realize fault classification of the switching circuit. The method disclosed by the invention has the advantages of skillful concept, easiness in implementation and simulation proof and can distinguish the fault types more accurately than the existing method.

Owner:CHANGSHA UNIVERSITY

Quick parallel generating method for multidimensional pseudo-random sequence with uniform distribution characteristics

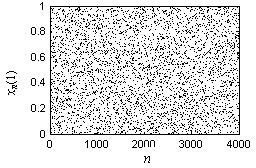

InactiveCN102684871ADisassociationSuppression of short-period phenomenaSecuring communicationTent mapTheoretical computer science

The invention discloses a quick parallel generating method for a multidimensional pseudo-random sequence with uniform distribution characteristics, wherein the quick parallel generating method improves a classic coupled map lattice (CML) model according to the security requirement of the cryptography, cancels diffusion coefficients thereof, increases constant terms, limits the grid value to be within [0, 1] through modular operation, and achieves a novel coupled tent map lattice system with the uniform distribution characteristics; and in addition, the pseudo-random sequence is generated through user key conversion and initial vector conversion by utilizing a coupled tent map lattice system model with the uniform distribution characteristics. The quick parallel generating method inherits the coupling diffusion mechanism and the parallel iteration characteristics of the CML model, leads system state tendency to achieve ergodicity through the stretching and folding of the local grid tent map as well as the double nonlinear action of the modular operation, overcomes the defect of the CML model on security, and can generate the multidimensional pseudo-random sequence with the uniform distribution characteristics in a parallel and quick manner.

Owner:BEIJING INSTITUTE OF PETROCHEMICAL TECHNOLOGY

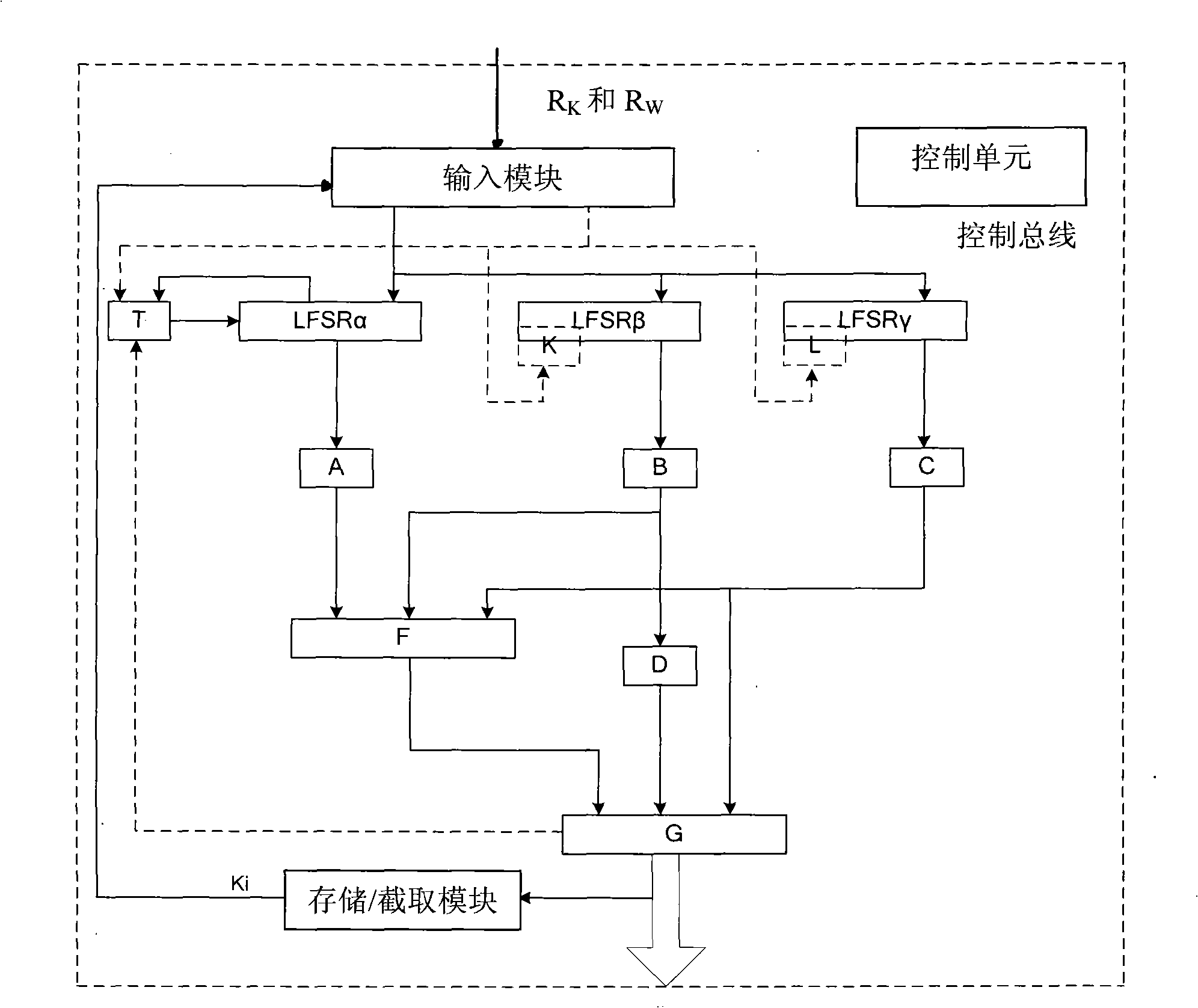

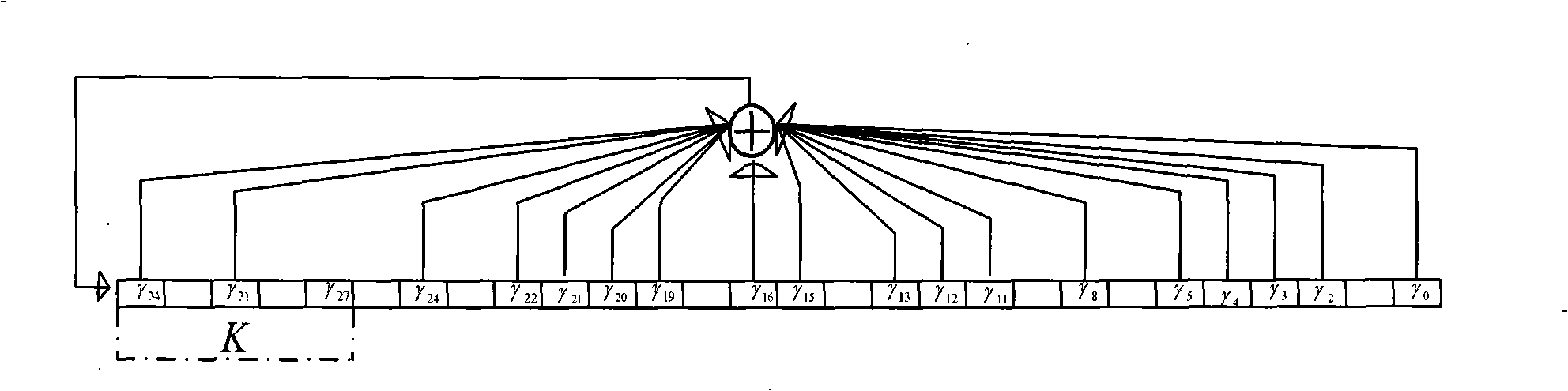

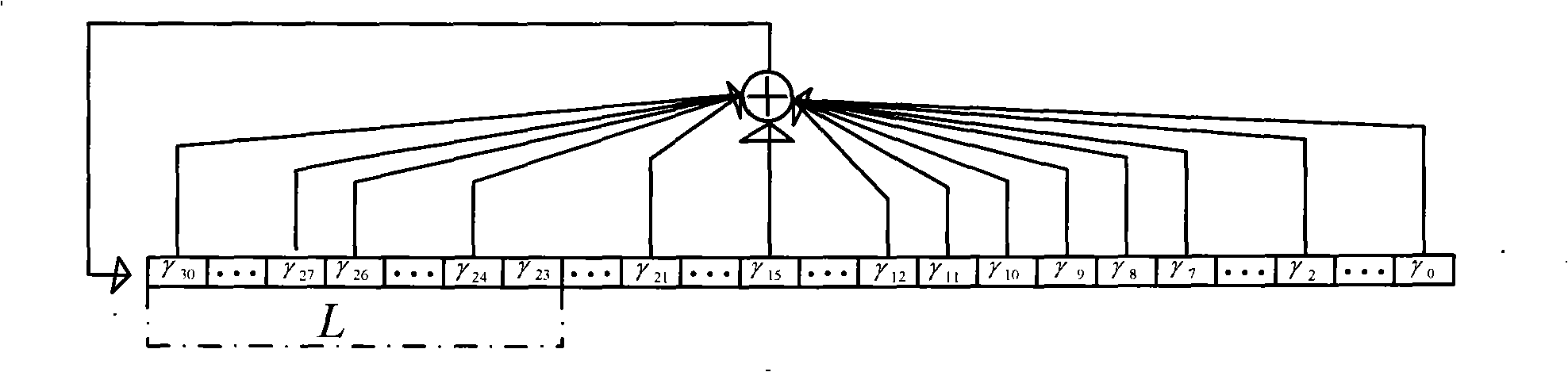

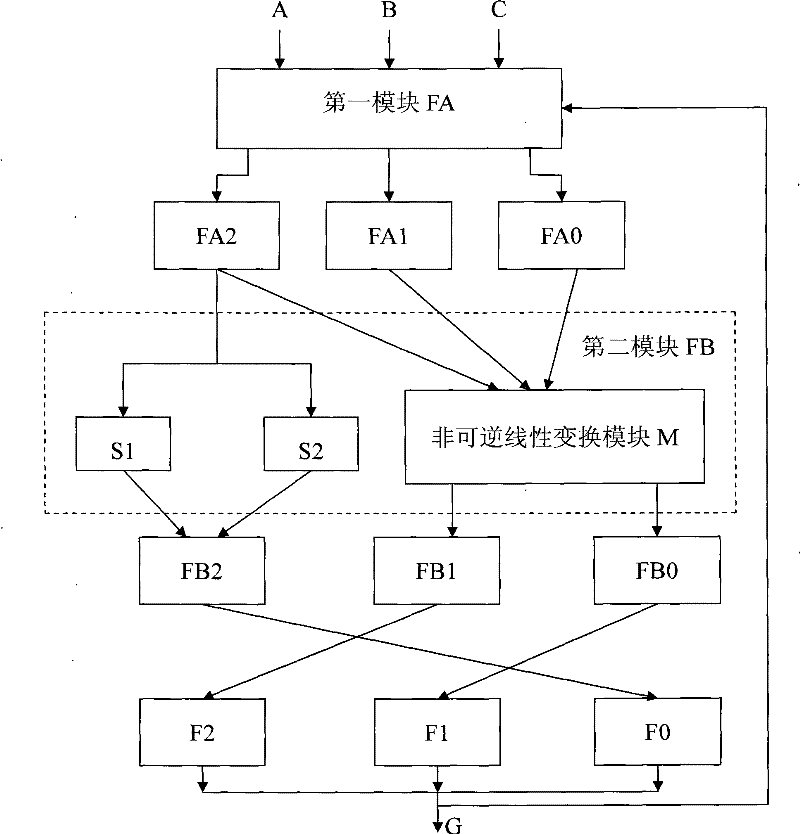

Stream cipher generator

InactiveCN101340280AGood statistical propertiesImprove statsKey distribution for secure communicationBroadcast systems controlS-boxComputer science

The invention discloses a stream cipher generator; wherein, in the present framework, a first module of a linear transformation module F is used for compression transformation of numbers read by a state reading list module A, B and C and output numbers of the linear transformation module F and outputting the numbers which are suitable for input by a second module; the second module comprises a non-reversible linear transformation module and two S boxes which are connected in parallel and the numbers input from the first module is output after being transformed in the non-reversible linear transformation module; the location of the numbers input from the first module is selected as the input of the two S boxes, in which table search transformation is carried out, and the output thereof is combined with the output of the non-reversible linear transformation module as the output of the linear transformation module F; the S boxes randomly generate an S box pool and the S box pool is obtained by optimal selecting by analyzing the cipher characteristics with an evolutionary algorithm. The cipher characteristics of the S boxes of the invention are greatly improved, and the S boxes with high security intensity are obtained so as to improve the security intensity of the stream cipher generator.

Owner:SICHUAN PANOVASIC TECH

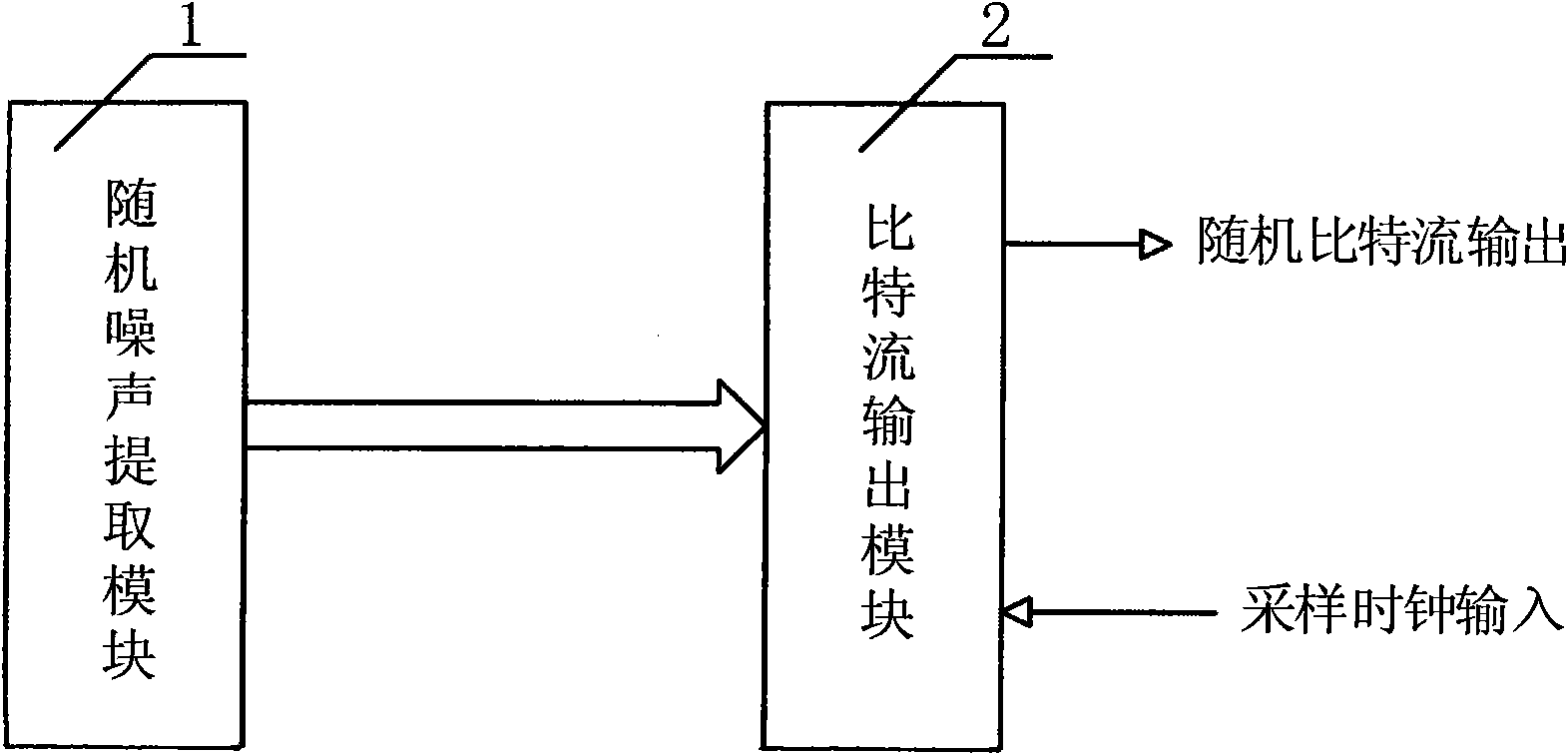

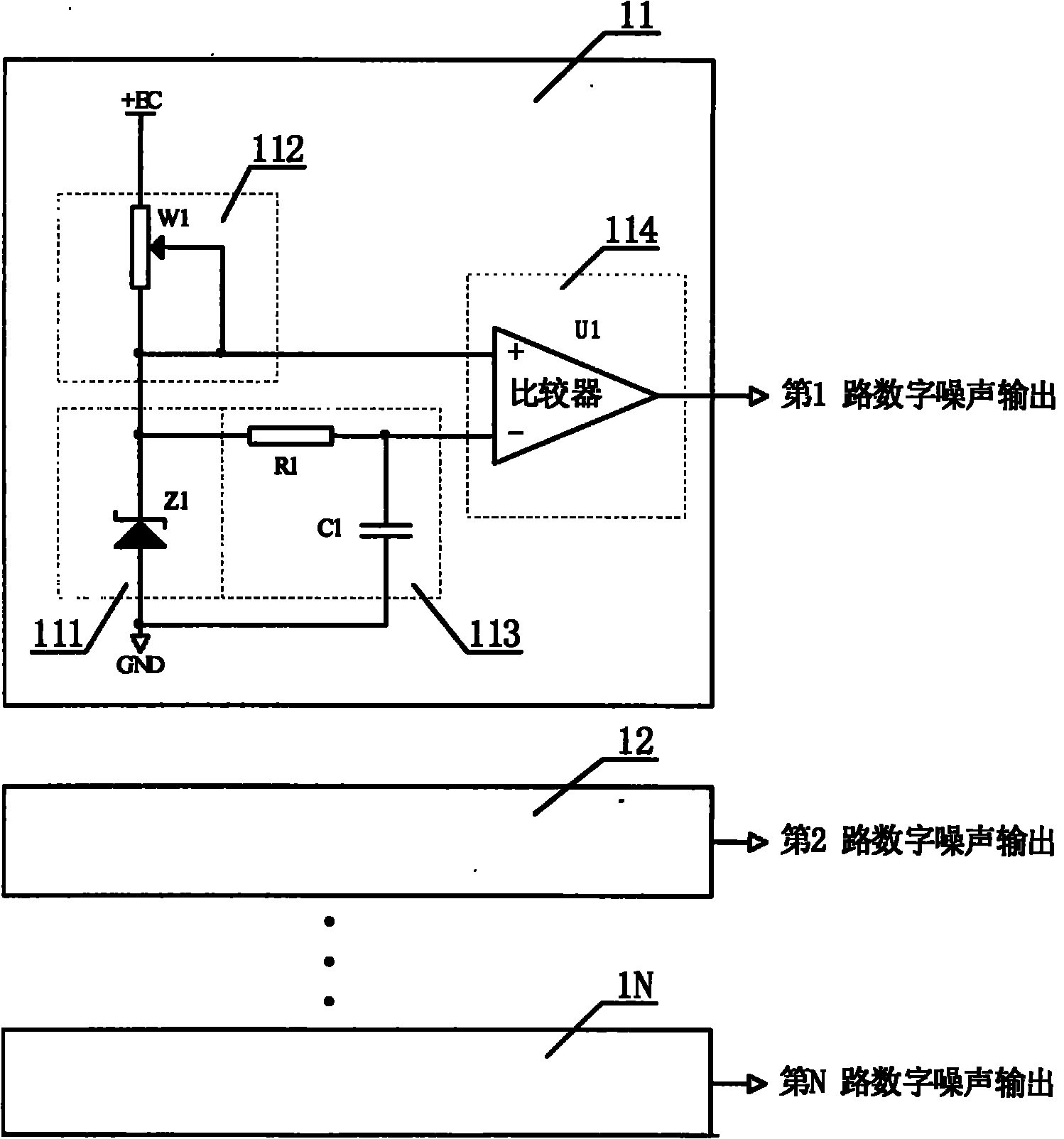

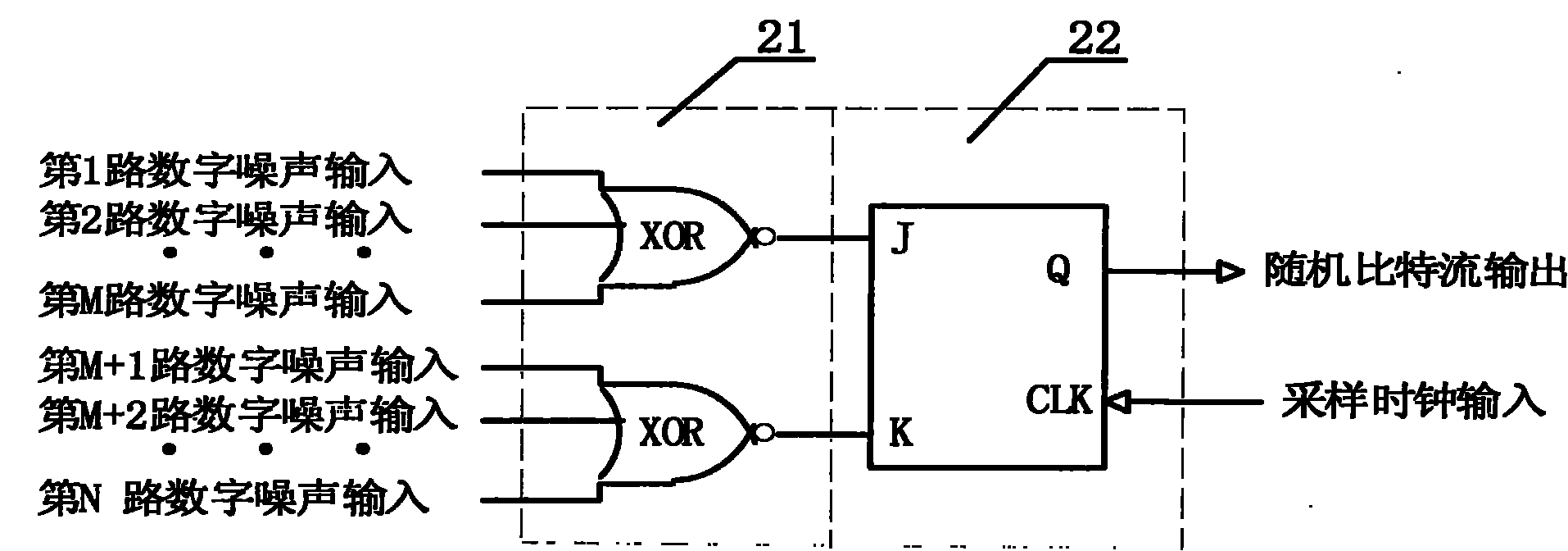

True random bit stream generator

InactiveCN101882062ALight in massIncrease randomnessRandom number generatorsRandom noiseComputer science

The invention relates to a true random bit stream generator, which comprises a random noise extraction module and a bit stream output module. The random noise extraction module is used for extracting the noise at two ends of a voltage-regulator diode and generating a random digital noise signal to the bit stream output module; and the bit stream output module processes the random digital noise and outputs the true random bit stream. Due to the adoption of a multi-path noise extraction method, the randomness of the output bit streams is further improved, and the generated random data has good statistical property before postprocessing.

Owner:房慧龙

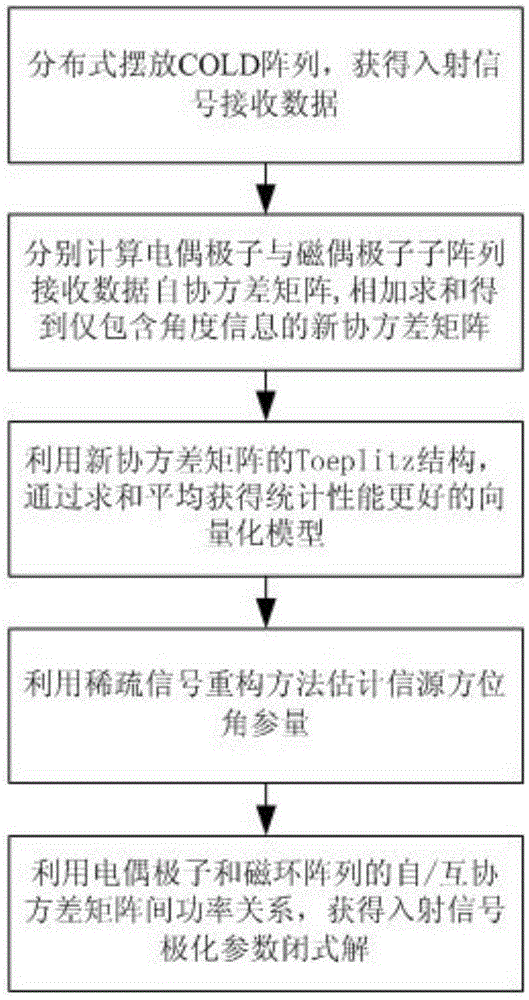

Method for multi-parameter joint estimation of distributed type electromagnetic vector sensor array

ActiveCN105334489AReduce the influence of mutual coupling effectImprove estimation performanceRadio wave direction/deviation determination systemsComputation complexityArray element

The invention relates to a method for multi-parameter joint estimation of a distributed type electromagnetic vector sensor array and belongs to the field of array signal processing. Received data of the distributed type electromagnetic vector sensor array are constructed, covariance matrixes are performed on received data of an electric dipole and a magnetic dipole respectively and adding summation is performed, a covariance matrix sum only containing an information source azimuth parameter is obtained, a sparse signal reconstruction method is utilized to estimate the information source incident azimuth; and the estimation of polarization parameters is obtained by utilizing maxtrix relations of autocovariance and cross covariance of an electric dipole array and a magnetic dipole array. According to the method, the joint estimation of multi-dimensional parameters is converted into substep estimation of a plurality of one-dimensional parameters, the calculation complexity of the method is lowered; by distributed placing of electric dipole and magnetic dipole sensors, not only is the cross coupling influence between array elements reduced, but also the array physical pore diameter is extended effectively, and the parameter estimation accuracy is improved greatly.

Owner:JILIN UNIV

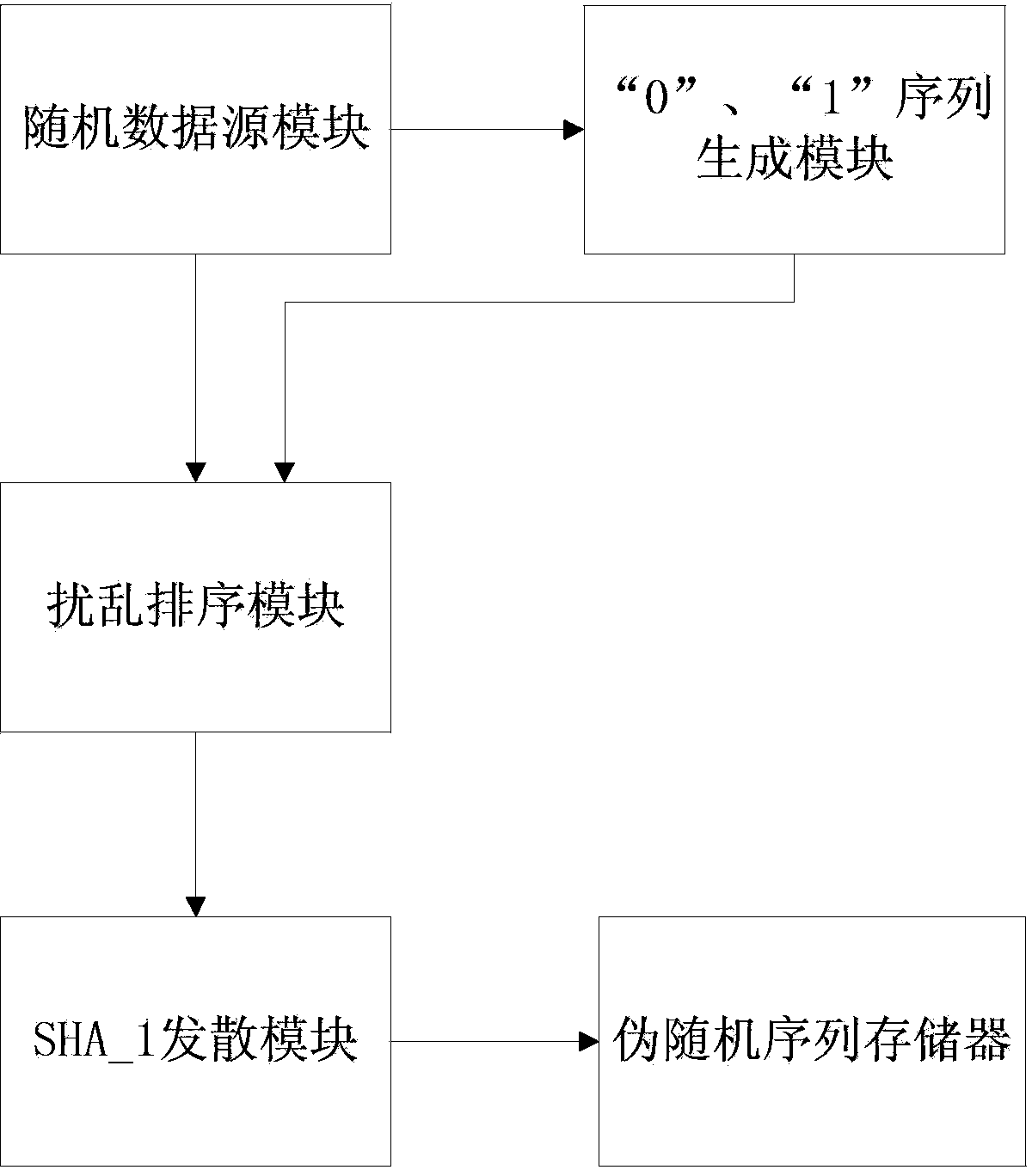

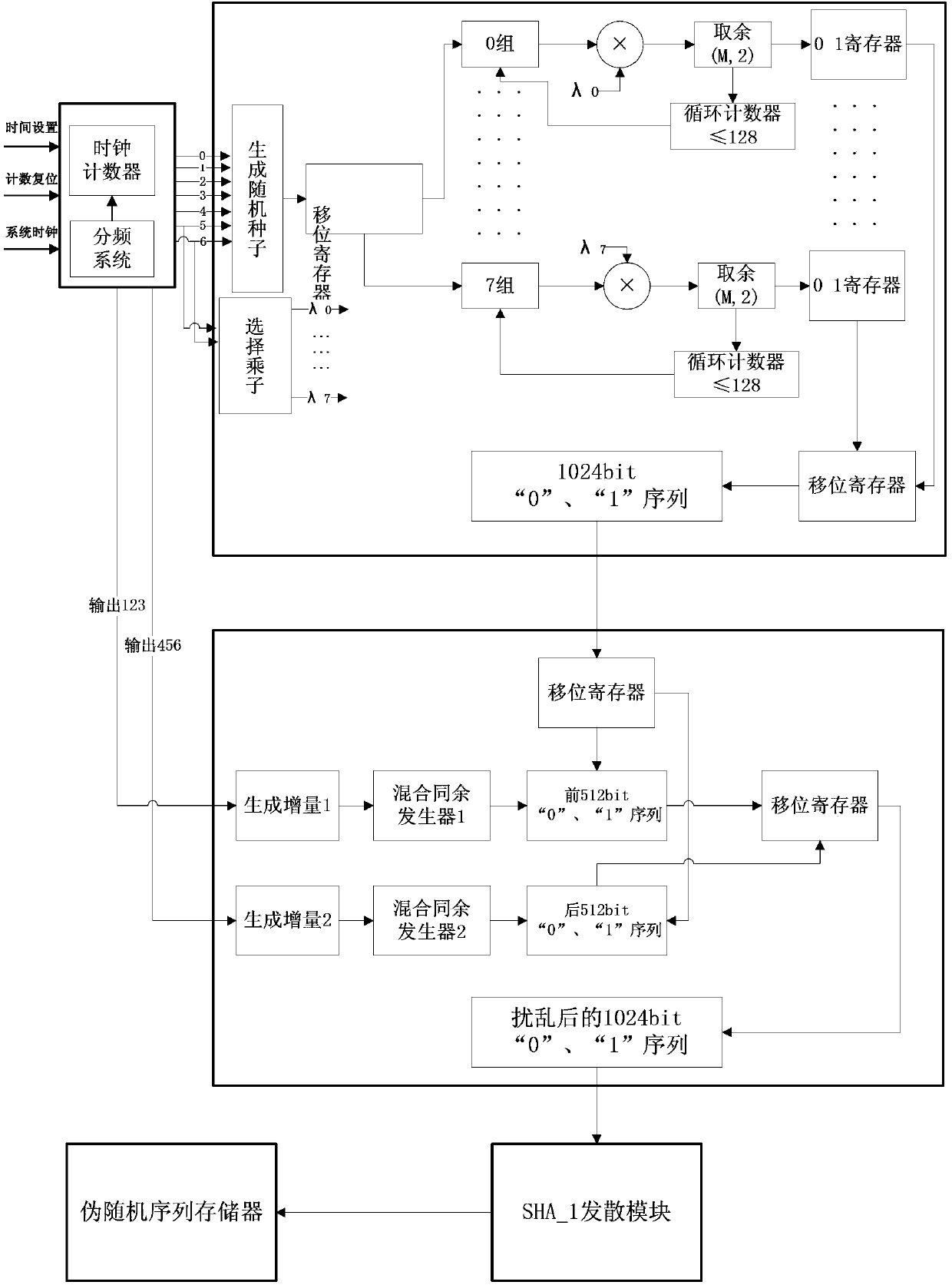

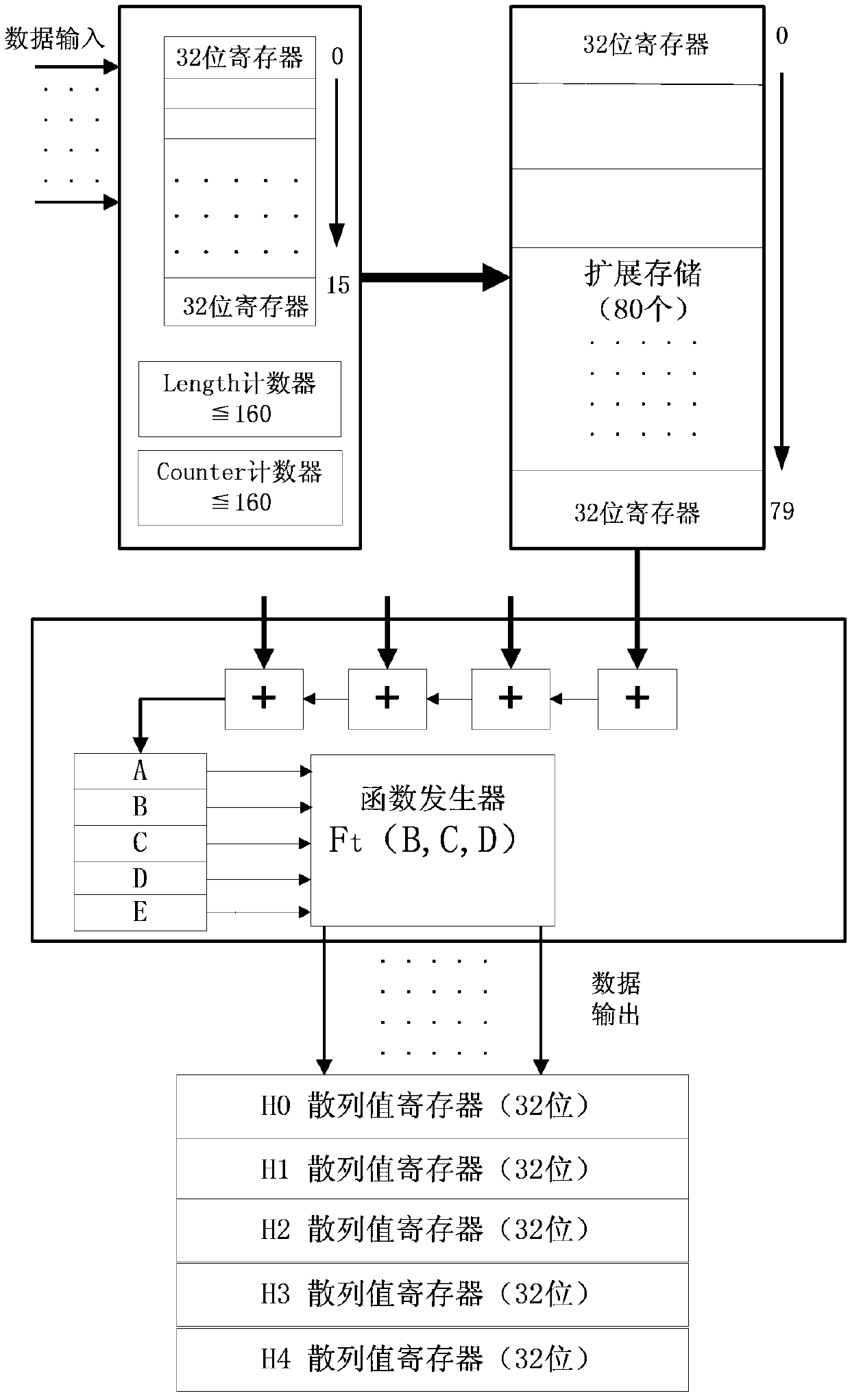

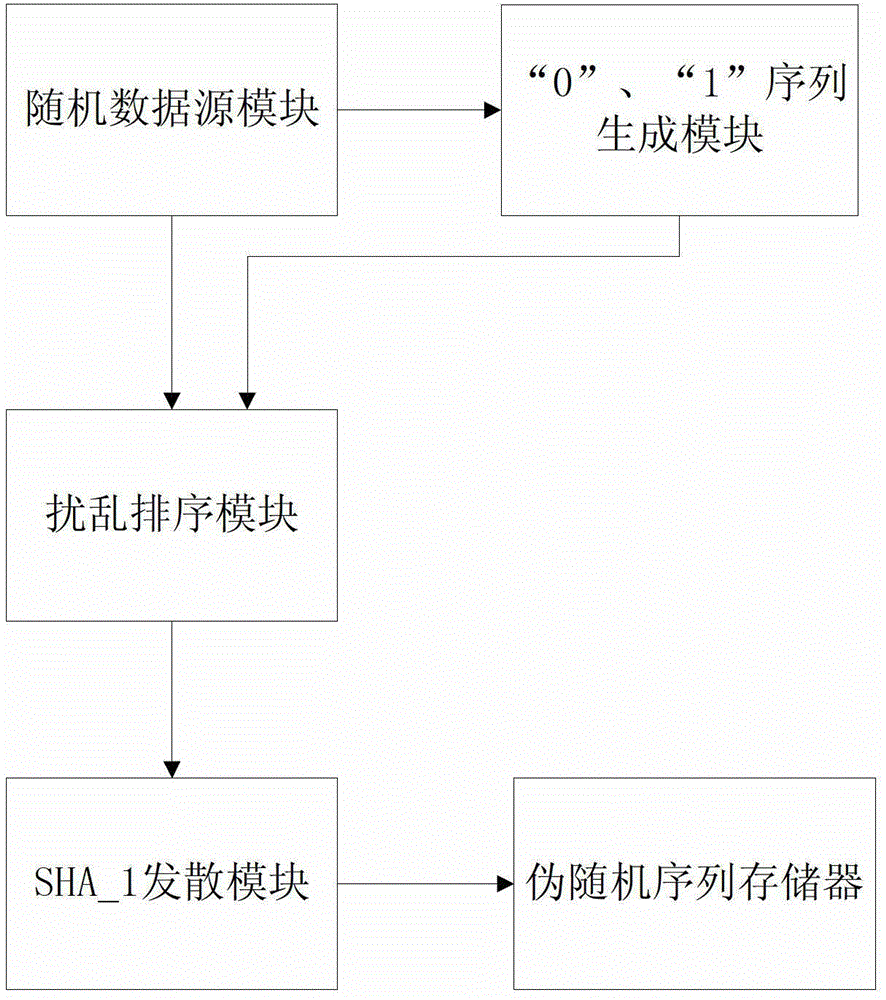

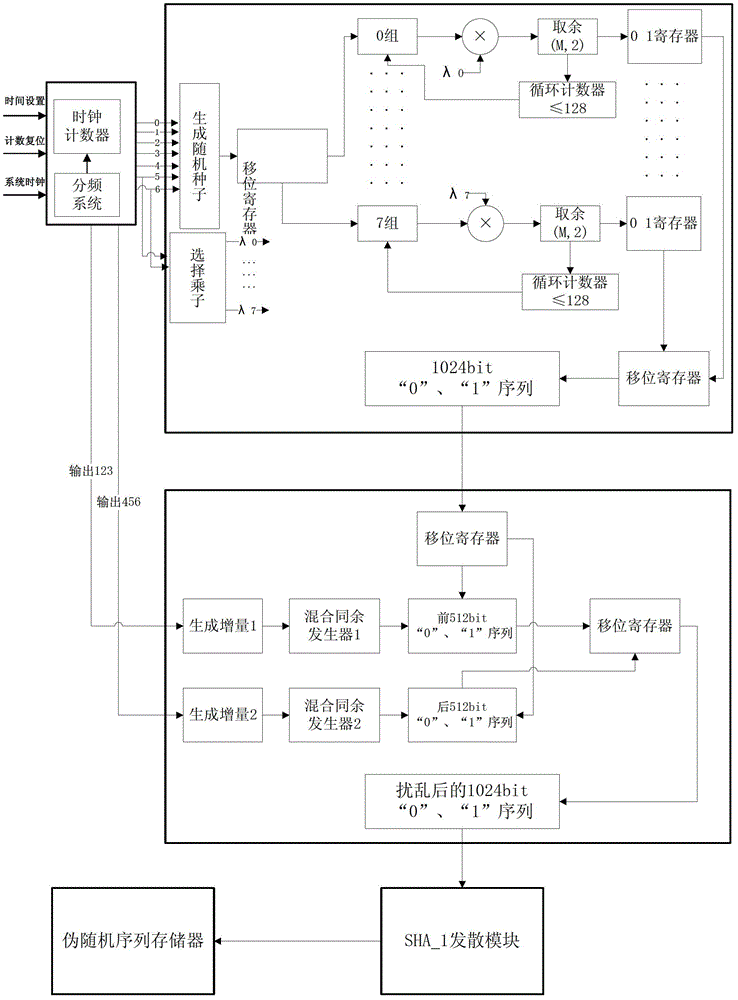

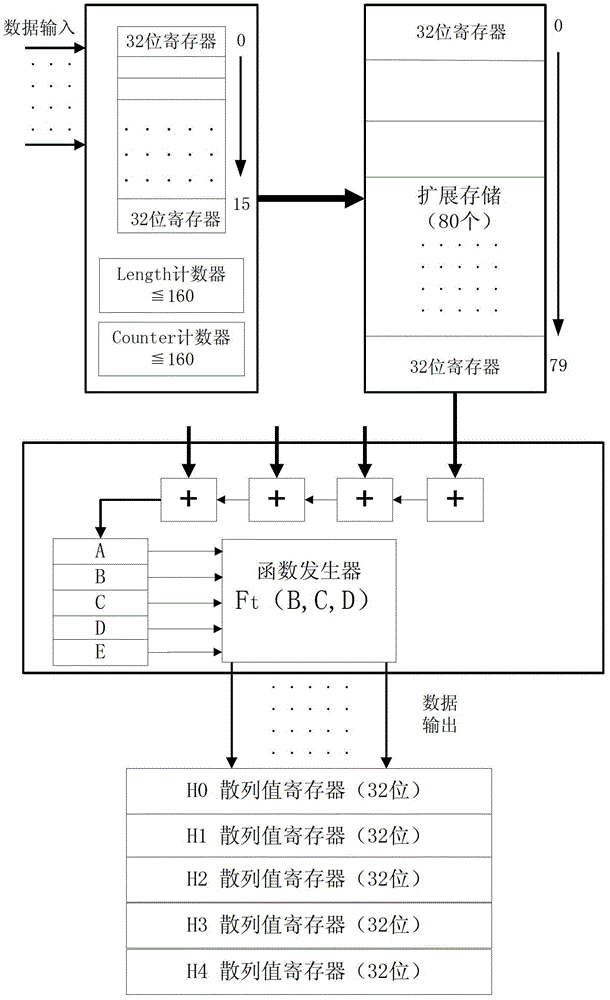

Streamlined combined-type pseudo-random number generator

ActiveCN103399726AGood statistical propertiesImprove securityRandom number generatorsData sourceNumber generator

The invention belongs to the field of high-speed generation of pseudo-random number sequences, and particularly relates to a streamlined combined-type pseudo-random number generator. The streamlined combined-type pseudo-random number generator comprises a random data source module, a 0 and 1 sequence generating module, an order disrupting module, an SHA_1 divergence module and a pseudo-random sequence storage module. Tests on the pseudo-random number generator prove that the generator can generate random number sequences with better statistical properties and higher safety, design cost is low, and efficiency of application in the fields like chip encryption and computer simulation can be improved.

Owner:HARBIN ENG UNIV

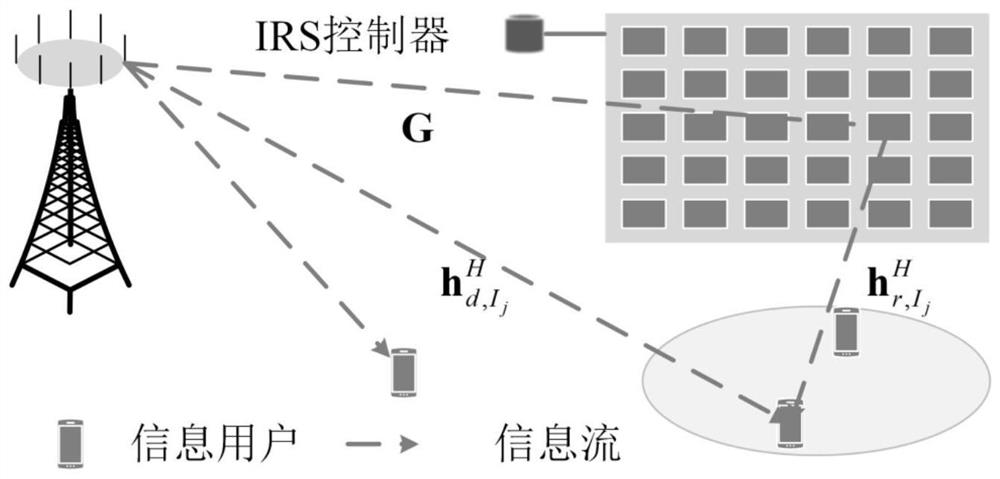

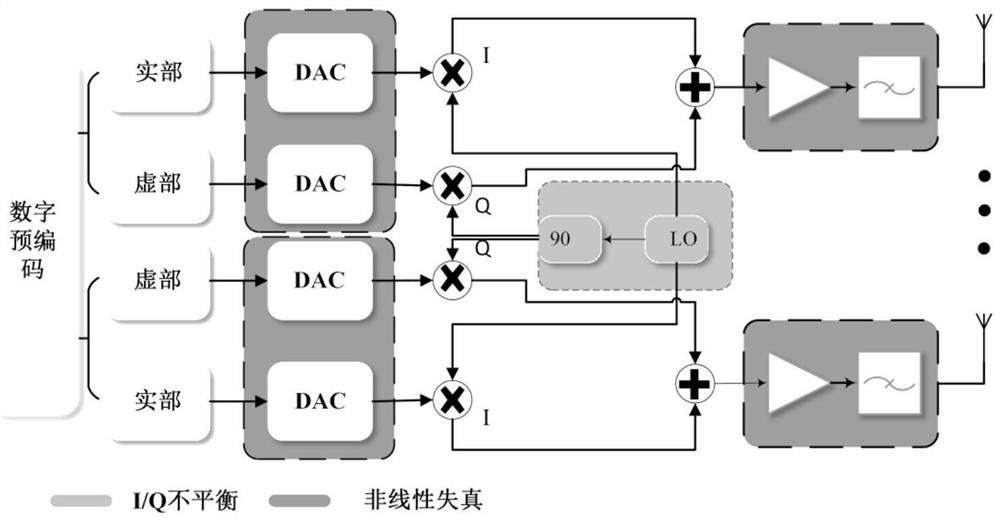

IRS-assisted MISO system performance optimization method for hardware distortion

ActiveCN113364494AGood statistical propertiesReduce reachable rateTransmission monitoringRadio transmissionGaussian signalBroadcasting

The invention discloses an IRS-assisted MISO system performance optimization method for hardware distortion, and the method comprises the steps that a multi-antenna base station wide linear precodes messages of M information users, generates a baseband transmission signal, processes the baseband transmission signal into an asymmetric Gaussian signal, and generates an output signal through a high-power amplifier; with the assistance of an intelligent reflecting surface, the multi-antenna base station transmits the output signal generated by the high-power amplifier in a broadcasting manner, and controls the phase shift of a reflecting element in real time through a controller on the intelligent reflecting surface; the rates of M information users are decoded; and by taking the rates of the M information users as performance evaluation, a base station beam forming vector and a phase shift vector at an intelligent reflecting surface are optimized under the condition of satisfying the total power constraint of the base station, and the minimum reachable rates of the information users are maximized to complete performance optimization. According to the invention, the IGS is used for transmission, so that the reachable rate of the information user is further improved.

Owner:XI AN JIAOTONG UNIV

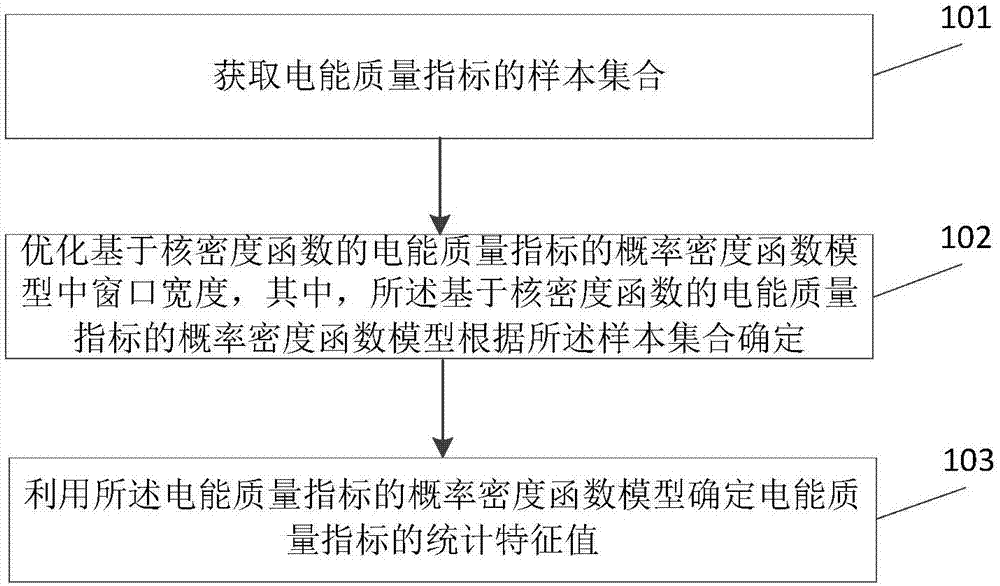

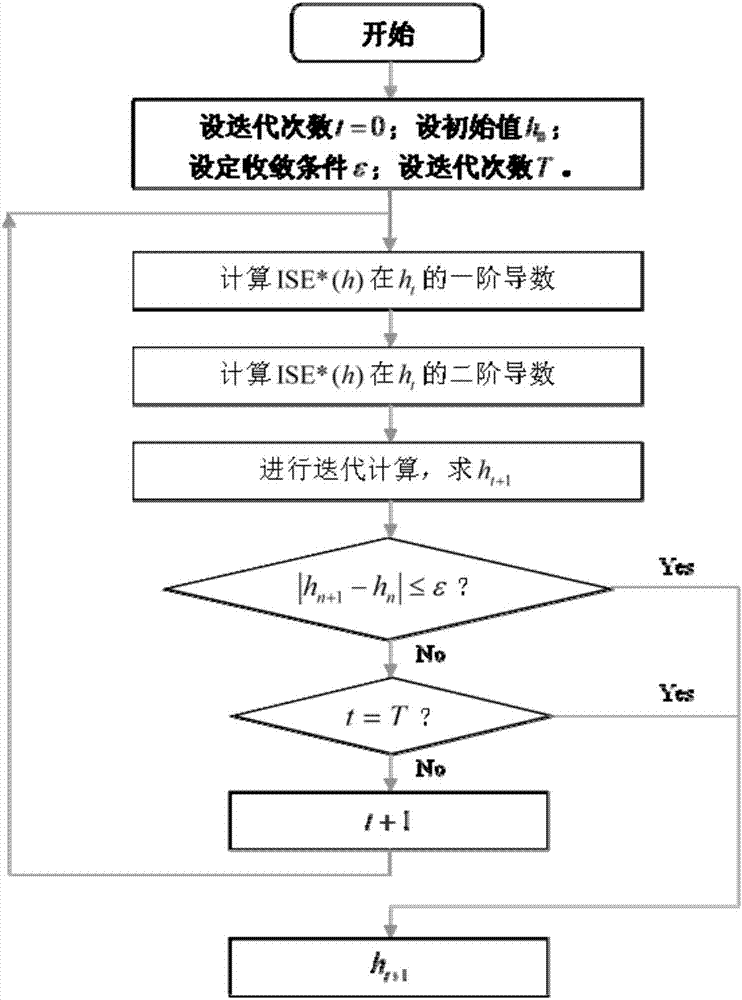

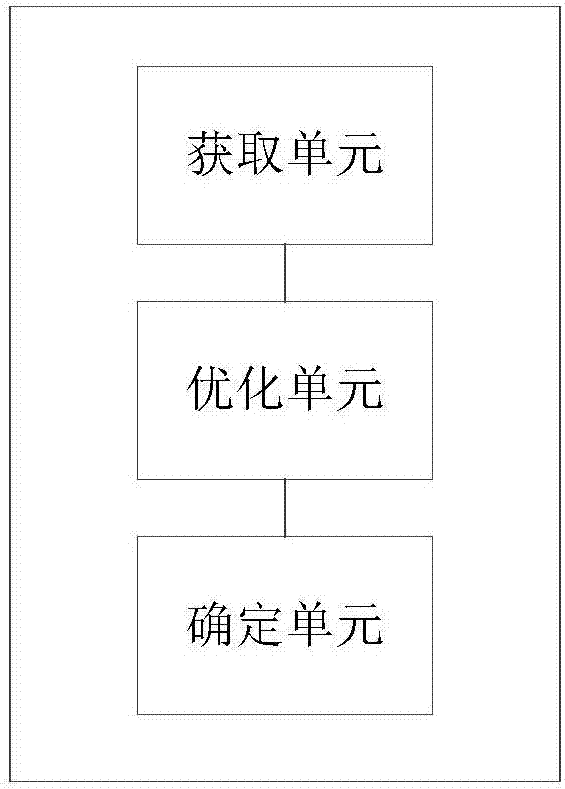

Method and device for analyzing power quality of distributed power supply access grid

ActiveCN107505519AGood statistical propertiesReduce conditions that exceed national standardsMeasuring interference from external sourcesEnvironmental/reliability testsPower qualityElectric energy

The invention relates to a method and a device for analyzing the power quality of a distributed power supply access grid. The method includes the following steps: acquiring a sample set of power quality indexes; optimizing the width of window in a probability density function model of power quality indexes based on a kernel density function, wherein the probability density function model of power quality indexes based on a kernel density function is determined according to the sample set; and using the probability density function model of power quality indexes to determine the statistical characteristic values of power quality indexes. According to the technical scheme provided by the invention, power quality indexes are analyzed using a kernel density estimation method, a probability density distribution function of the power quality indexes is calculated based on the kernel density estimation method, and a statistical analysis is made of the power quality indexes according to the probability density function.

Owner:CHINA ELECTRIC POWER RES INST +2

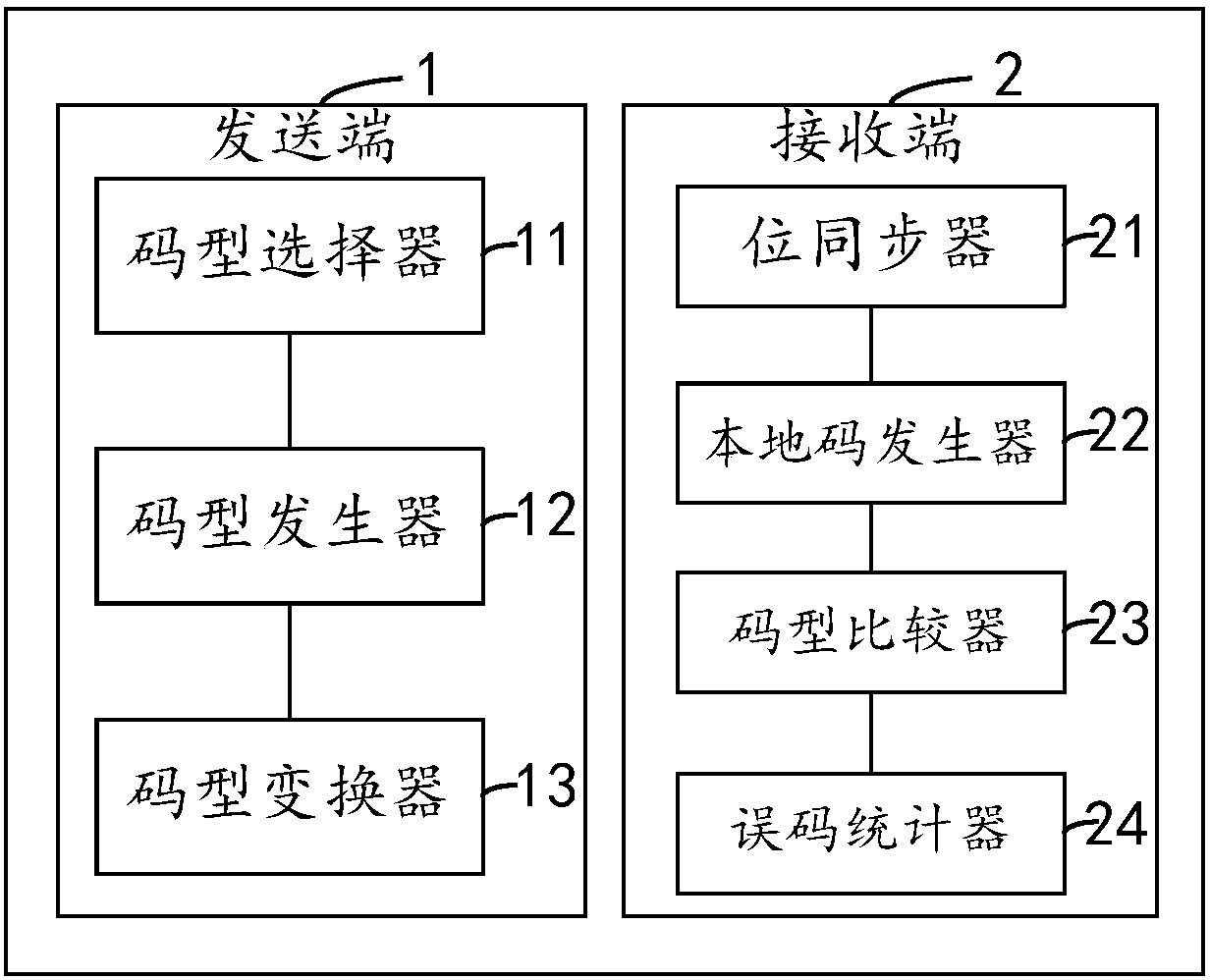

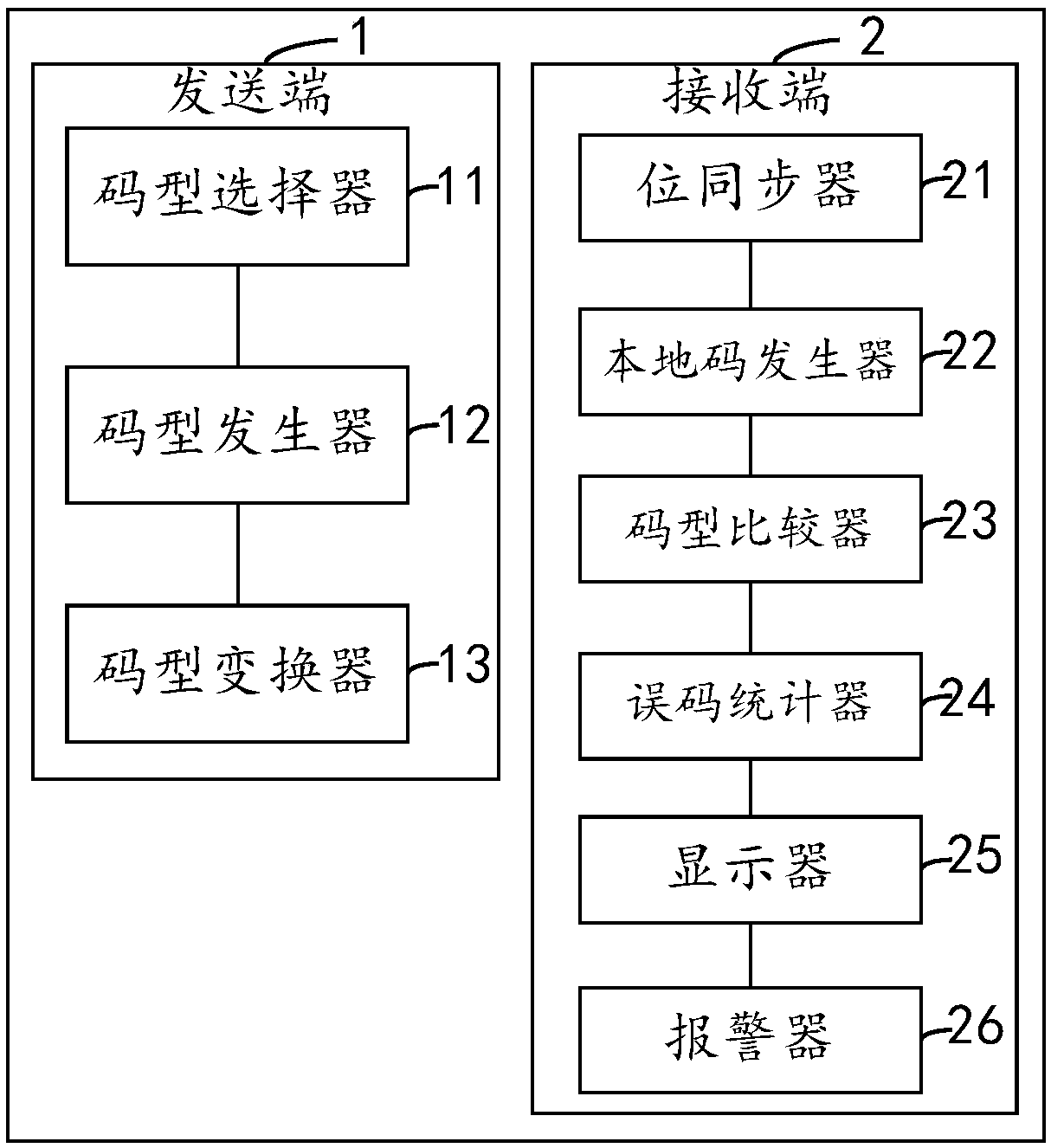

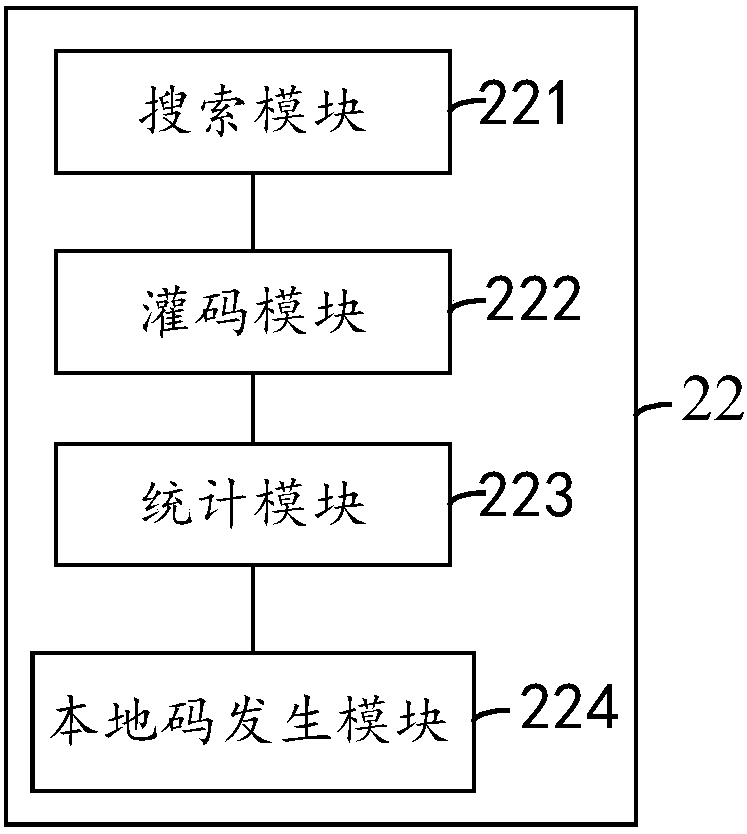

Error code detection device

ActiveCN108242981AGood autocorrelationGood statistical propertiesTransmitters monitoringReceivers monitoringComputer hardwareSelf correlation

The invention provides an error code detection device, which belongs to the technical field of communication detection. The error code detection device comprises a transmitting end and a receiving end, wherein the transmitting end is used for transmitting a test pseudorandom sequence code obtained through converting and processing a pseudorandom sequence code to a test device; and the receiving end is used for receiving a test sequence code outputted by the test device for error code detection, and the test sequence code is the sequence code outputted when the pseudorandom sequence code is transmitted through a to-be-detected device. The pseudorandom sequence code has good self correlation and good statistical properties. By using the pseudorandom sequence code as a standard test signal, the error code detection accuracy can be improved.

Owner:AEROSPACE INFORMATION

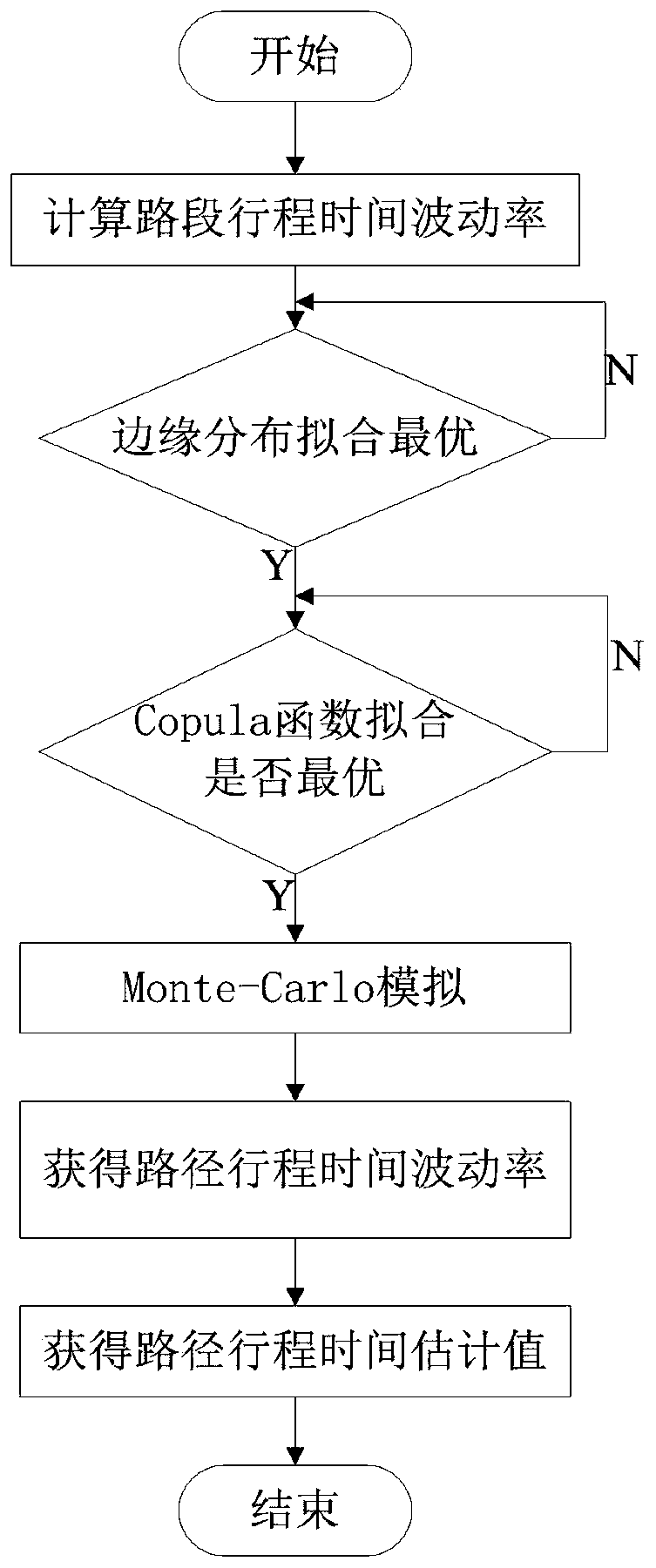

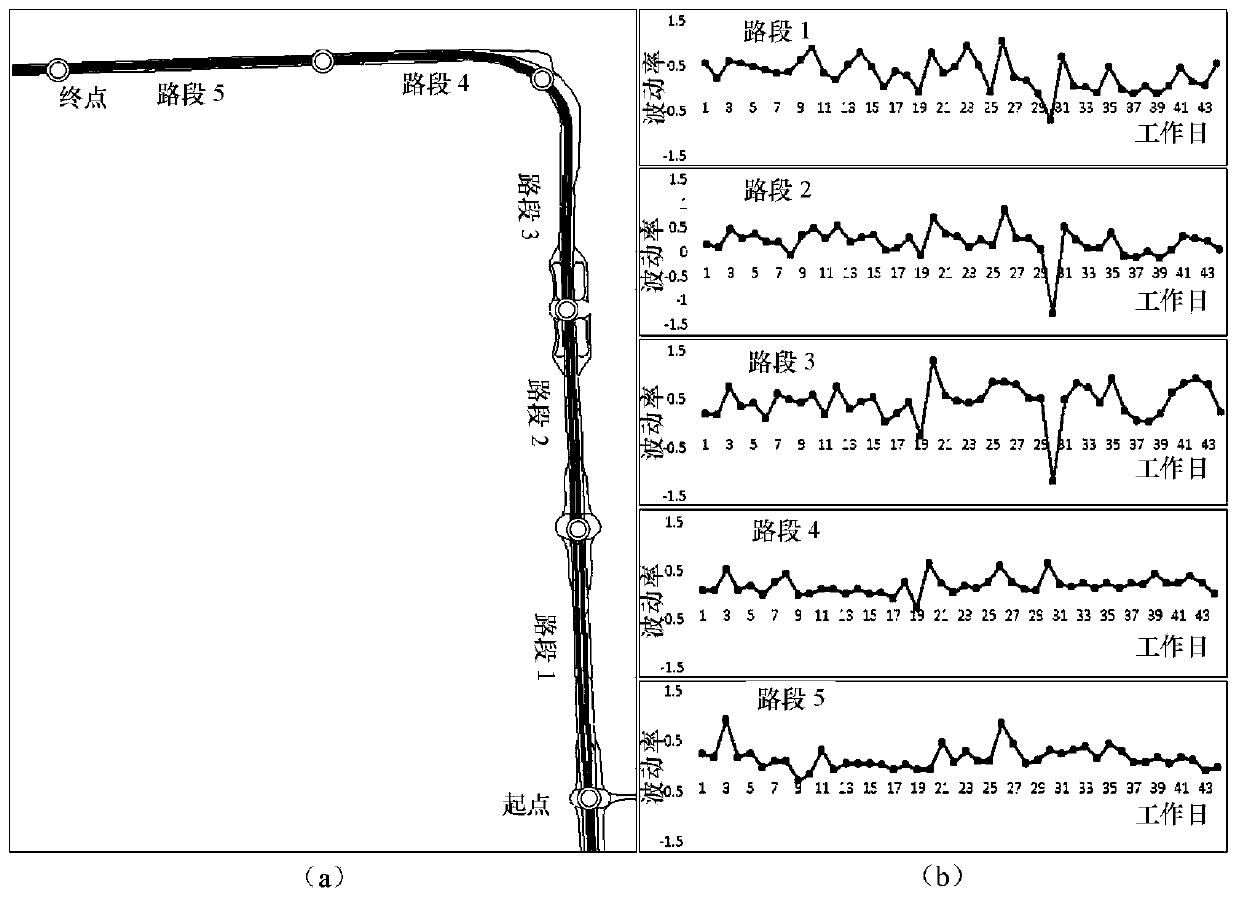

Copula and Monte-Carlo simulation based path stroke time estimation method

ActiveCN109712389AReduce distractionsImprove applicabilityDetection of traffic movementConfidence intervalRatio Sequence

The invention discloses a Copula and Monte-Carlo simulation based path stroke time estimation method. The method comprises the steps that S1) the fluctuation ratio of path stroke time of different segments in a path is obtained; S2) edge distribution fitting is carried out on the fluctuation ratio of path stroke time of different segments by means of maximum likelihood estimation; S3) a Copula theory is used to fit a path stroke time fluctuation ratio distribution function on the basis of a distribution function of the fluctuation ratio of path stroke time of different segments; S4) Monte-Carlo simulation is used to obtain a path stroke time fluctuation ratio sequence on the basis of the Copula function; S5) a confidence interval in certain confidence level is determined, and an expected value of the path stroke time fluctuation ratio is calculated; and S6) the expected value of the path stroke time fluctuation ratio is combined with path stroke time in the last period to estimate thepath stroke time of the present period. Sequential fluctuation of stroke time of the different segments as well as spatial relation between the segment stroke time is taken into consideration, time-space characteristic of the stroke time is dug deeply, and the precision and reliability are higher.

Owner:BEIHANG UNIV

Parallel implementation method of real-time Gaussian white noise hardware generator

InactiveCN106774624ALong cycleHigh bandwidthDigital function generatorsBinary multiplierFpga implementations

The invention discloses a parallel implementation method of a real-time Gaussian white noise hardware generator. By the parallel implementation method, the Gaussian white noise hardware generator can generate high-speed and parallel high-quality Gaussian white noise in real time, at high speed and in parallel. According to the parallel implementation method, first, through high-speed parallel FPGA (field programmable gate array) implementation of uniform white noise based on a cellular automata theory, a method for calculating N-th initial vectors required by parallel implementation as well as a recursive function relationship of a cellular automata parallel generation algorithm are given; then, a low-complexity approach method based on a Box_Muller algorithm is given, the Box_Muller algorithm is simplified into simple multiplication and addition and CORDIC operation, and during FPGA implementation, a small number of multipliers and a small quantity of logical resources are needed, so that in case of relatively low consumption of the FPGA resources, long-cycle, large-bandwidth and good-quality Gaussian white noise can be generated in real time and at high speed.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY +1

Parallel implementation method of real-time phase noise hardware generators

The invention discloses a parallel implementation method of real-time phase noise hardware generators. By the adoption of the method, real-time, high-speed and parallel phase noise simulation can be achieved at an FPGA processor. According to the method, firstly, on the basis of the FPGA high-speed and parallel implementation method of uniform white noise of a cellular automaton theory, a calculation method of N-way initialization vectors needed by the parallel implementation and a recurrence function relation of the parallel generating algorithm of the cellular automaton are given; then, on the basis of real-time parallel generation of white noise, parallel first-order IIR filter banks are designed, and by setting a gain value at a corner frequency, noise output which meets features of a power law spectrum is achieved by filtering; finally, an equivalent form of the phase noise is obtained from the white noise, and is superposed with effective signals to complete the phase noise simulation. Under the condition of low FPGA source consumption, the method rapidly generates white noise which is long in cycle, large in band width and good in quality in real time, and on this basis, a parameter-controllable phase-noise simulation hardware generator is achieved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY +1

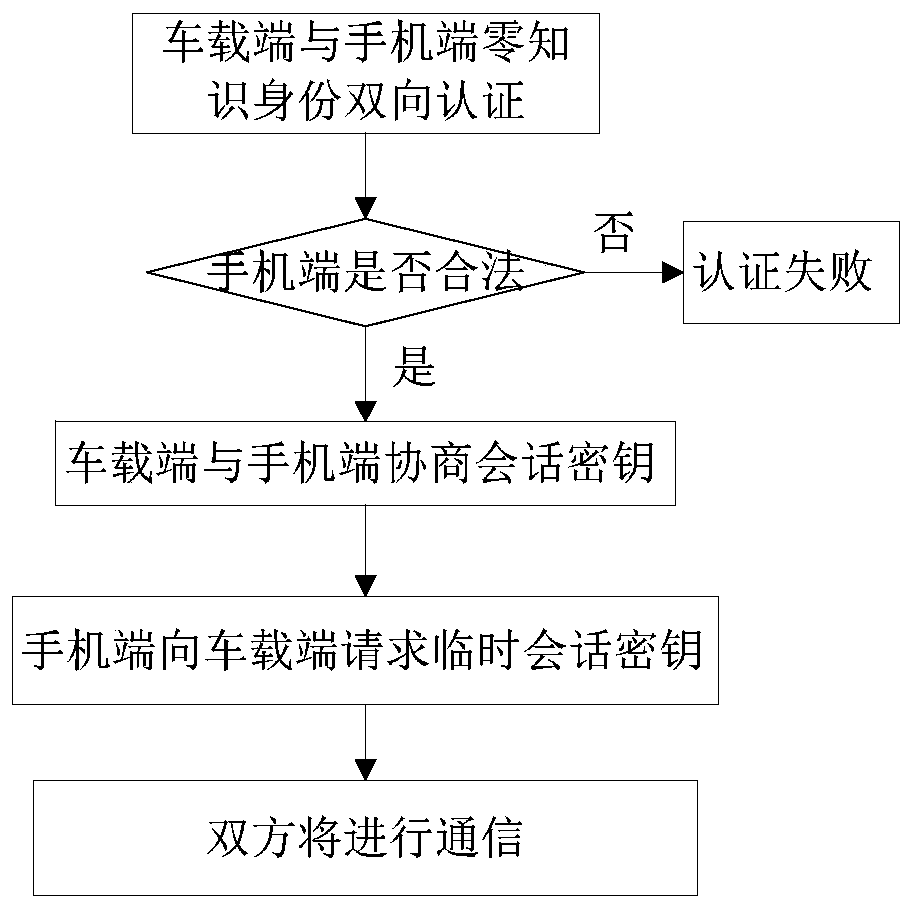

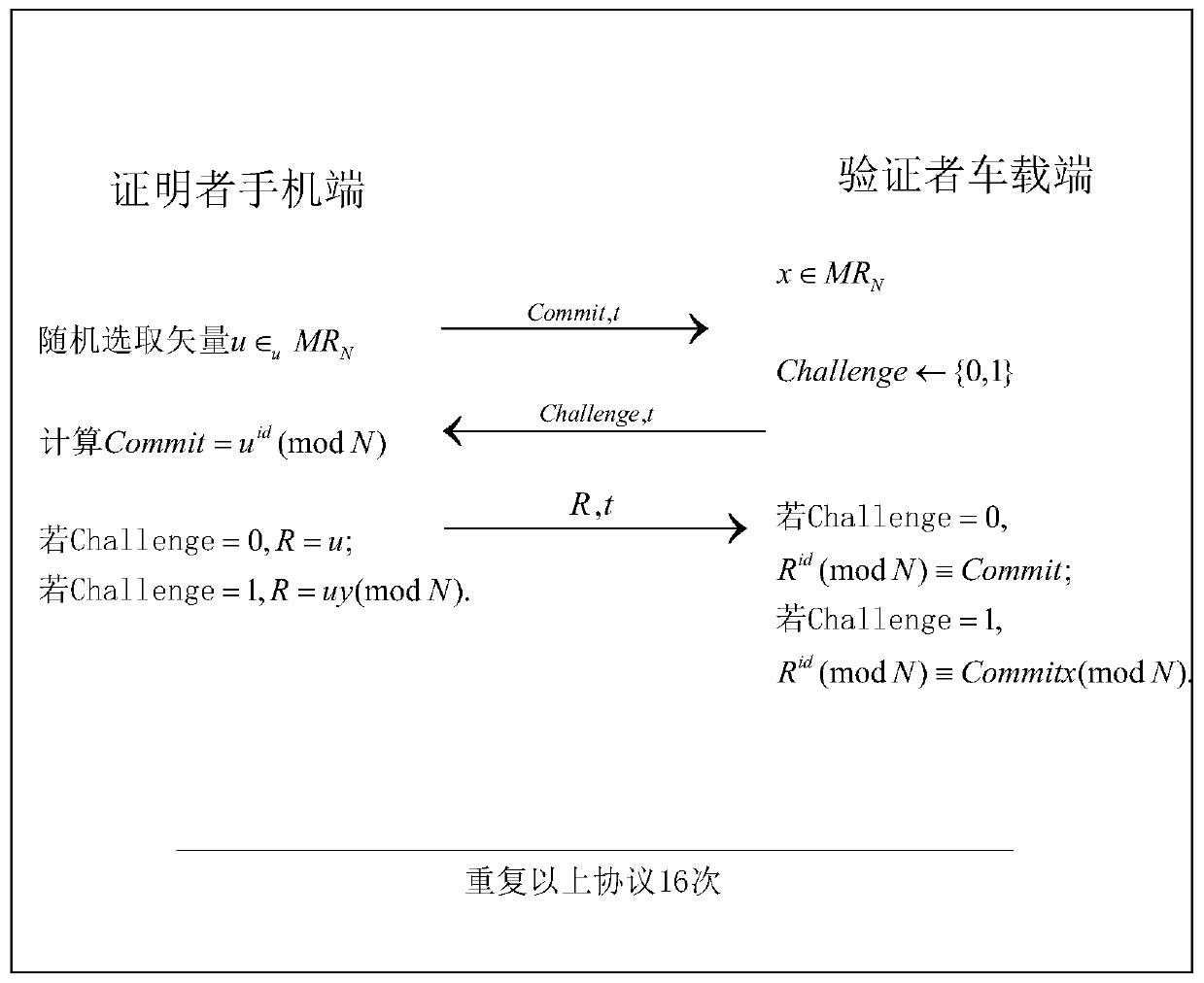

Vehicle-mounted virtual key communication method

ActiveCN110932846AGood statistical propertiesKey distribution for secure communicationParticular environment based servicesEmbedded systemIn vehicle

Owner:NANJING AUTOMOBILE GROUP CORP +1

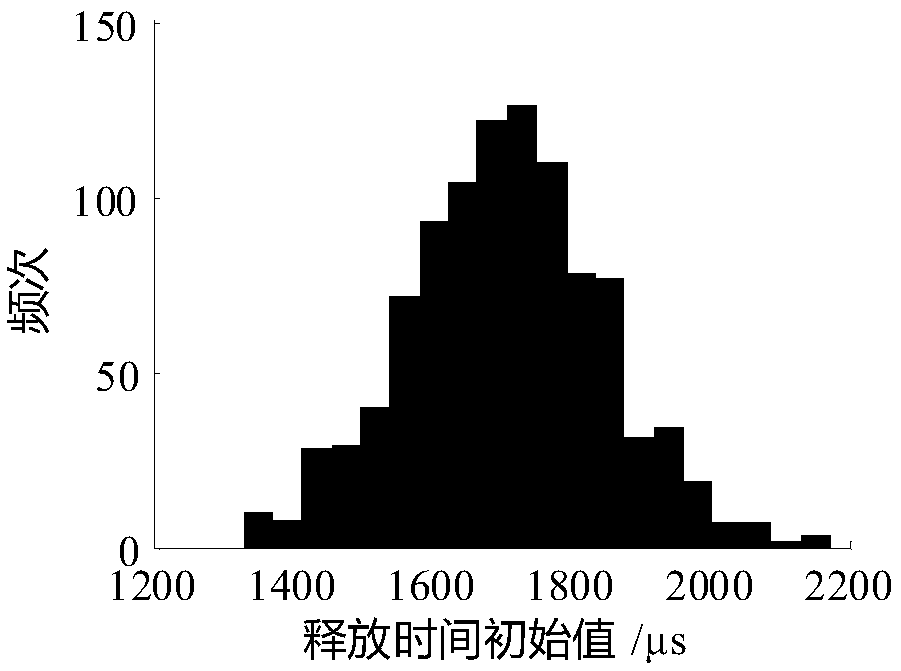

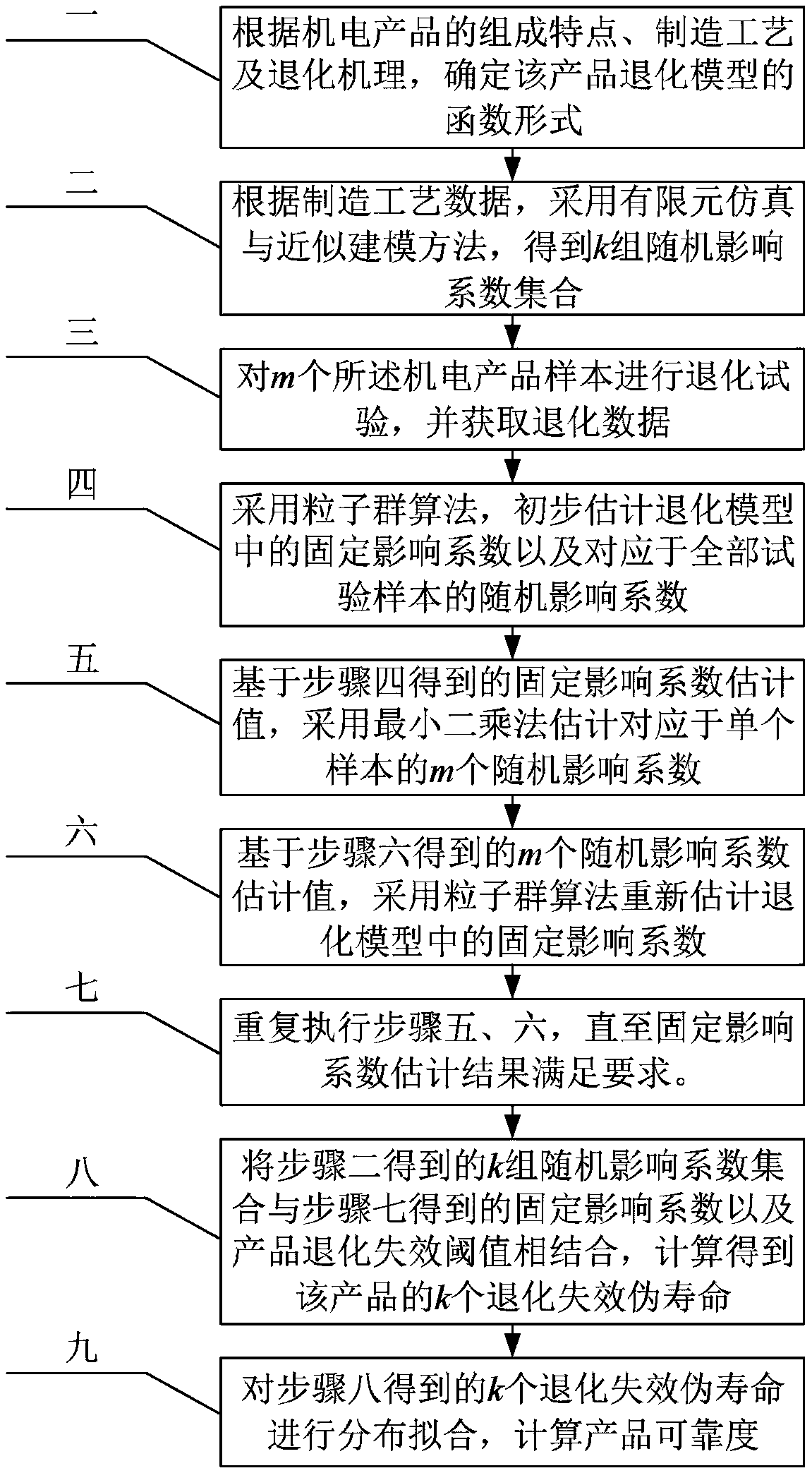

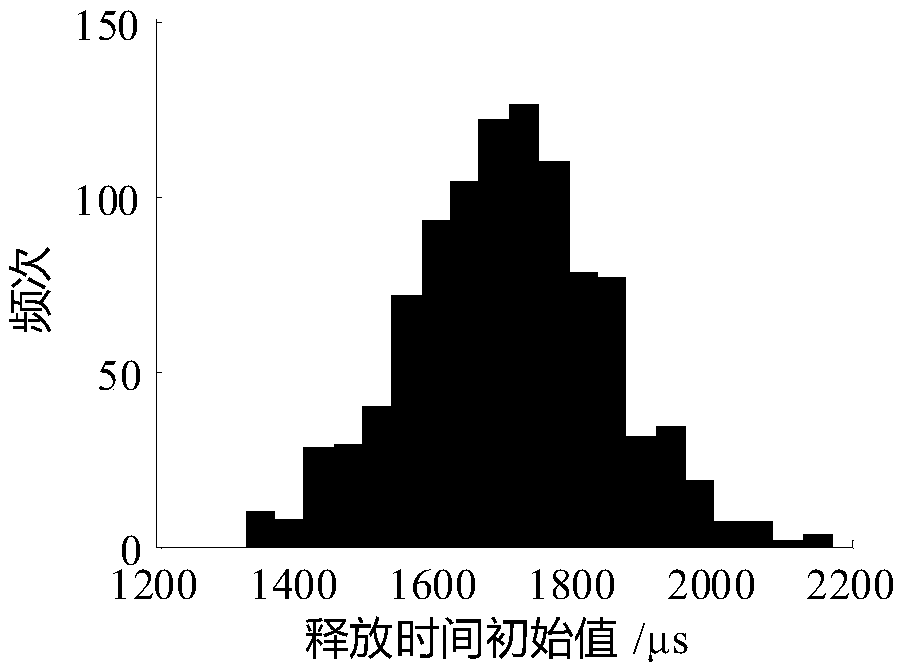

Electromechanical product degradation modeling method which combines with manufacturing process data

ActiveCN108647458AGood statistical propertiesWell describe statistical propertiesDesign optimisation/simulationSpecial data processing applicationsTest sampleEngineering

The invention discloses an electromechanical product degradation modeling method which combines with manufacturing process data. The method comprises the steps of determining the function form of an electromechanical product output characteristic degradation model according to the composition characteristics, the manufacturing process data and the degradation mechanism of the electromechanical product; determining the distribution of stochastic influence coefficients in the degradation model by a finite element simulation and approximate modeling method based on the manufacturing process dataof the electromechanical product; estimating the value of the fixed influence coefficient in the degradation model based on the degradation data of mechanical and electrical products test samples; andcompleting electromechanical product degradation modeling which combines with manufacturing process data according to the determined function form of the degradation model, stochastic influence coefficient and fixed influence coefficient. The electromechanical product degradation modeling method solves the problem that a current degradation modeling method needs to make subjective assumptions about the distribution of the stochastic influence coefficient determined by the manufacturing process because the stochastic influence coefficient can not be expressed quantitatively.

Owner:HARBIN INST OF TECH

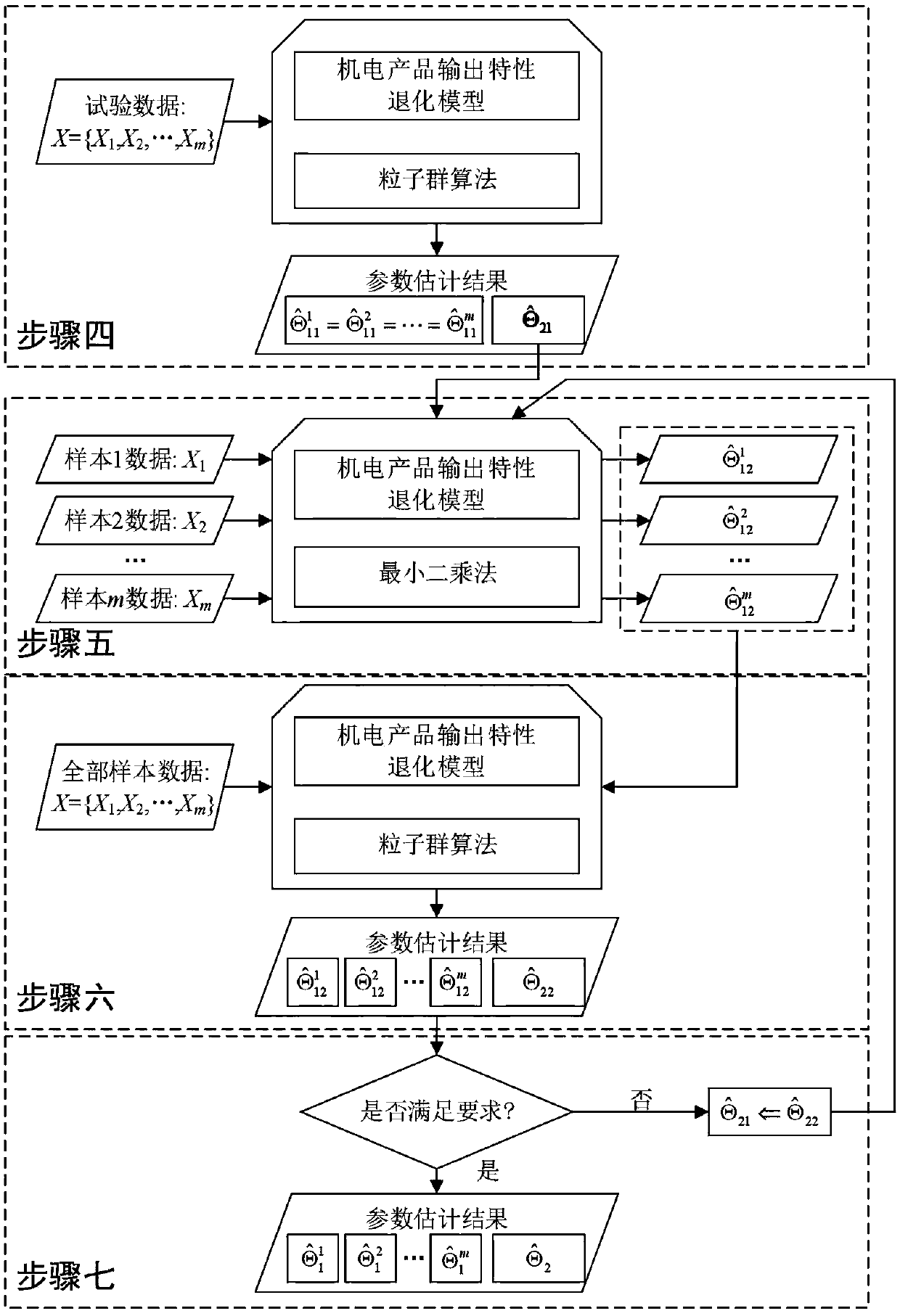

Method for evaluating reliability of mechanical and electrical products based on combination of manufacturing process data

ActiveCN108710745ASolve the problem of simultaneous estimationGood statistical propertiesDesign optimisation/simulationSpecial data processing applicationsSmall sampleTest sample

The invention discloses a method for evaluating reliability of mechanical and electrical products based on combination of manufacturing process data. The method comprises the following steps: firstly,determining a functional form of an output characteristic degradation model according to composition characteristics, the manufacturing process data and a degradation mechanism; subsequently, obtaining k sets of random influence coefficients in the degradation model through finite element simulation and approximate modeling methods based on the manufacturing process data of the mechanical and electrical products; simultaneously, estimating values of fixed influence coefficients in the degradation model by means of multi-iteration based on the degradation data of test samples of the mechanicaland electrical products; subsequently, obtaining k degradation failure pseudo-life of the product according to the k groups of random influence coefficient sets, fixed influence coefficient estimation values and degradation failure threshold values of the mechanical and electrical products; and finally, calculating and giving out the reliability of the mechanical and electrical products at each moment based on the obtained degradation failure pseudo-life. According to the method for evaluating the reliability of the mechanical and electrical products based on combination of the manufacturingprocess data disclosed by the invention, an effective means is provided for solving the problem of reliability evaluation of batch products under small sample conditions.

Owner:哈尔滨宇高电子技术有限公司

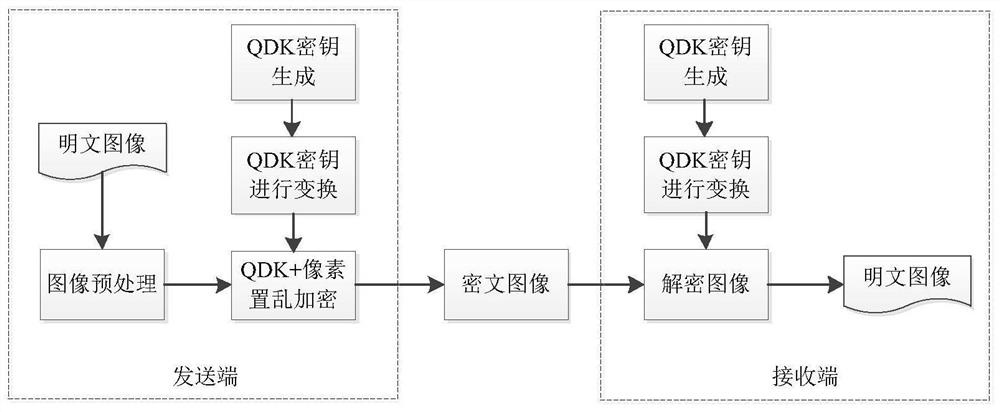

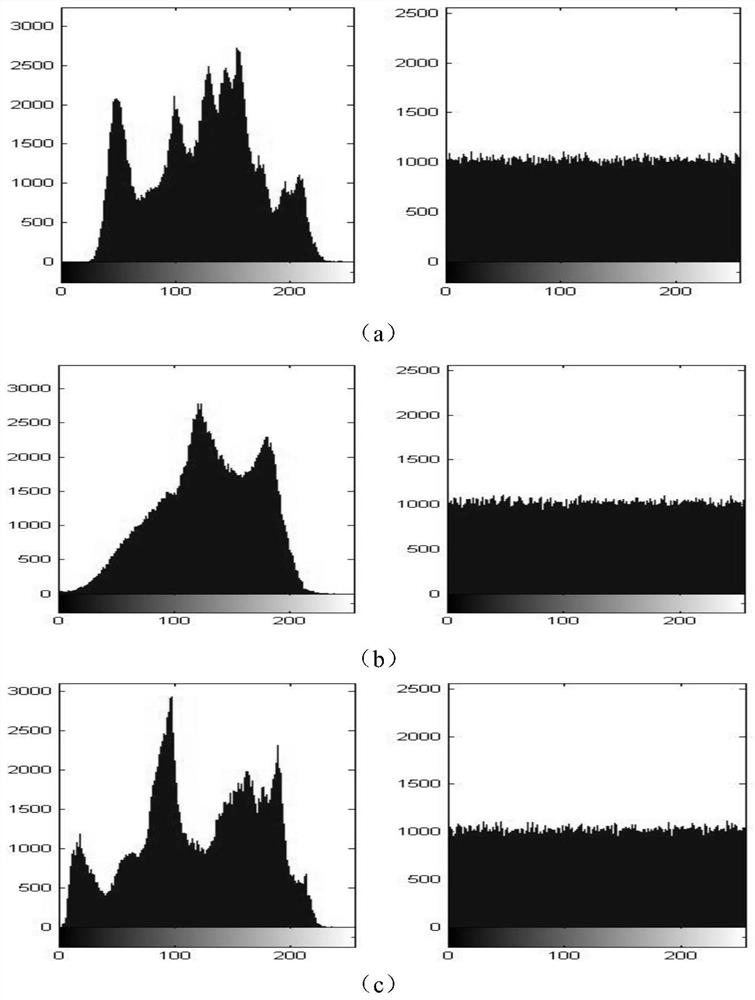

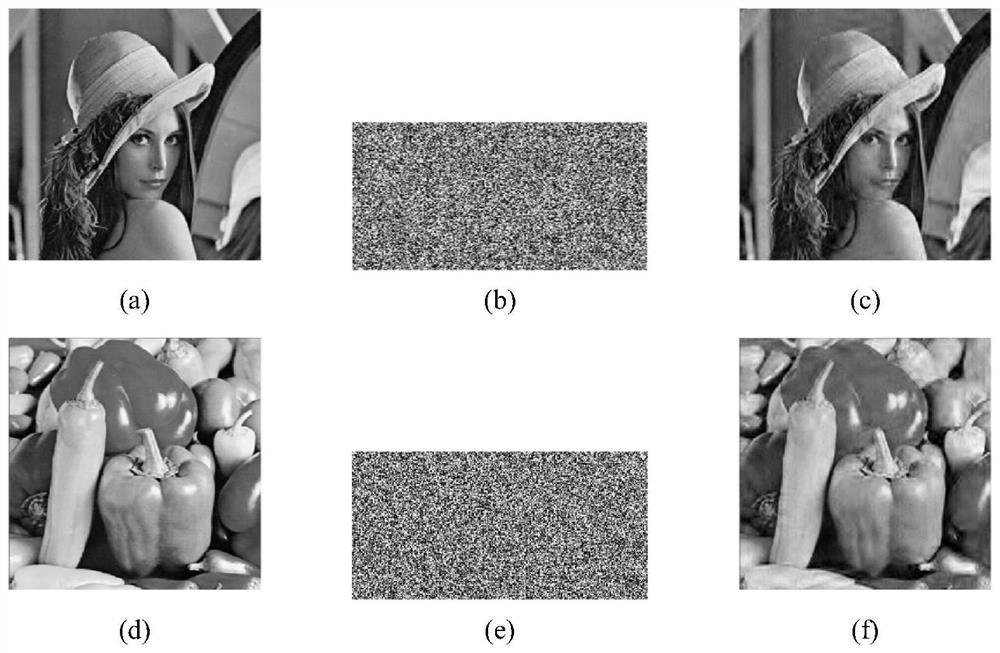

Image encryption method based on quantum key distribution and pixel scrambling

PendingCN114579993AGood statistical propertiesImprove securityKey distribution for secure communicationDigital data protectionAdvantageQuantum key distribution

The invention discloses an image encryption method based on quantum key distribution and pixel scrambling in the technical field of information security. The method comprises the following steps: S1, image preprocessing; s2, generating a QKD key; s3, carrying out pixel scrambling and QKD encryption on the image; s4, carrying out decryption by utilizing the generated QDK key; s5, restoring the pixels; s6, obtaining an original image; the key used in the image encryption algorithm based on quantum key distribution is generated by a quantum key distribution protocol, compared with other classic image encryption algorithms, the algorithm has the greatest advantage of high security, and the algorithm is good in statistical property and can effectively prevent statistical attack through performance analysis of the encryption algorithm; the correlation of the encrypted image in three directions is very weak, so that an attacker cannot obtain useful information by using the correlation; the pixel difference between the plaintext image and the ciphertext image is larger; the information entropy of the ciphertext image is very close to an ideal value, and the attack of the information entropy can be resisted.

Owner:ENG UNIV OF THE CHINESE PEOPLES ARMED POLICE FORCE

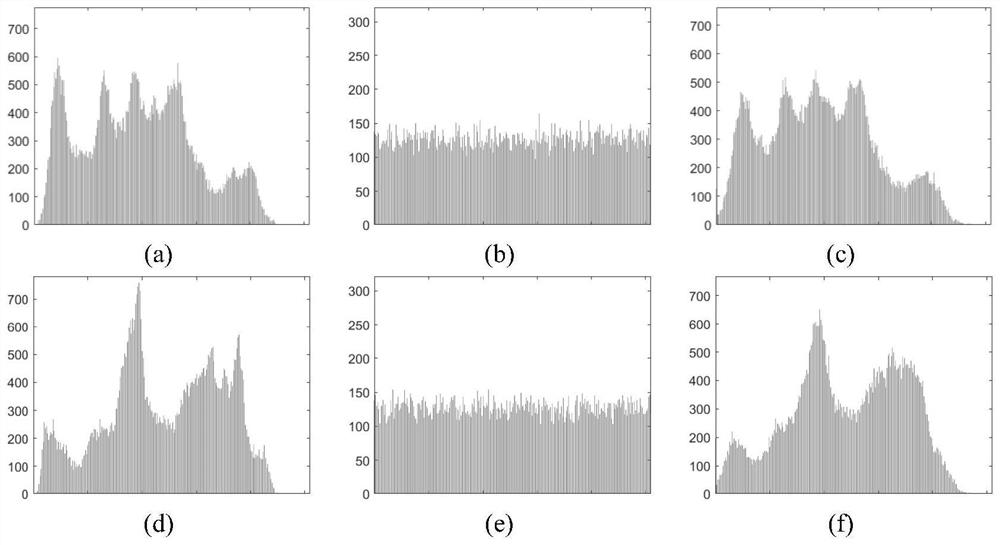

Image compression encryption method based on compressed sensing and fractional order chaos

PendingCN113746997ALarge key spaceGood statistical propertiesSecuring communication by chaotic signalsPictoral communicationKey spaceTheoretical computer science

The invention discloses an image compression encryption method based on compressed sensing and fractional order chaos, and belongs to the technical field of multimedia information security. The invention provides an image compression encryption method based on compressed sensing and fractional order chaos to solve the problem that an image compression and encryption scheme based on a low-dimensional integer order chaos system is insufficient in safety. According to the method, a new three-dimensional fractional order chaotic system is constructed to provide a random sequence required by an image compression encryption algorithm, and the complexity and key space of the algorithm are greatly expanded. An image is compressed by adopting a compressed sensing algorithm, and a novel measurement matrix is constructed according to a random sequence. Meanwhile, the scheme follows a classical confusion and diffusion structure, and a Josephus problem principle and annular diffusion are used as image scrambling and diffusion algorithms respectively. Theoretical analysis and experimental results show that the algorithm is high in safety and has wide application prospects and practical value.

Owner:HARBIN INST OF TECH AT WEIHAI

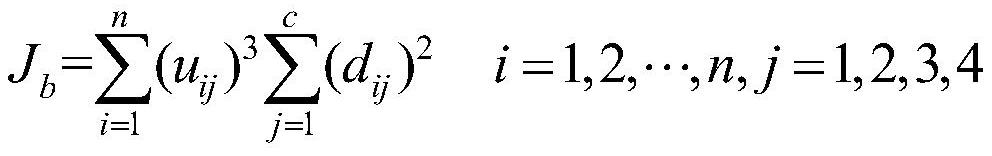

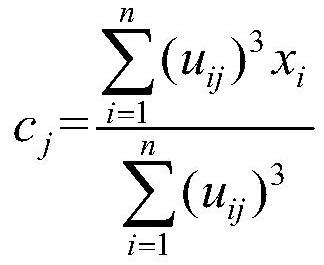

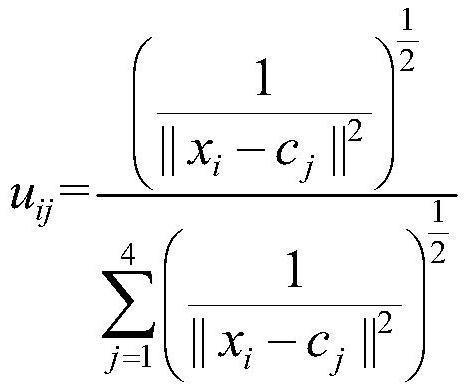

Seismic oscillation record selection method based on clustering analysis

InactiveCN113791444AFast cluster classificationGood statistical propertiesCharacter and pattern recognitionSeismic signal recordingCluster algorithmResponse spectrum

The invention relates to a seismic oscillation record selection method based on clustering analysis. The method comprises the following steps: 1, selecting seismic oscillation records based on a strong earthquake database; 2, selecting an earthquake magnitude and epicentral distance strip range, and giving specific earthquake information of each seismic oscillation record; 3, according to a fuzzy C-mean value clustering algorithm, taking the mean value of the magnitude and the epicentral distance of each seismic oscillation record as a clustering center, repeatedly modifying the clustering center and a data membership degree through an iteration process, and giving a preliminary trial calculation clustering analysis result; 4, introducing a simulated annealing algorithm to converge to global optimal clustering analysis; and 5, on the basis of carrying out clustering analysis according to the magnitude and the epicentral distance, giving a response spectrum curve of each group of seismic oscillation records under different site category conditions in combination with the soil layer shear wave velocity and the site covering soil layer thickness. According to the method, adaptive classification of the seismic oscillation record database is realized, and technical support is provided for subsequent dynamic time history analysis.

Owner:JIANGSU UNIV OF SCI & TECH

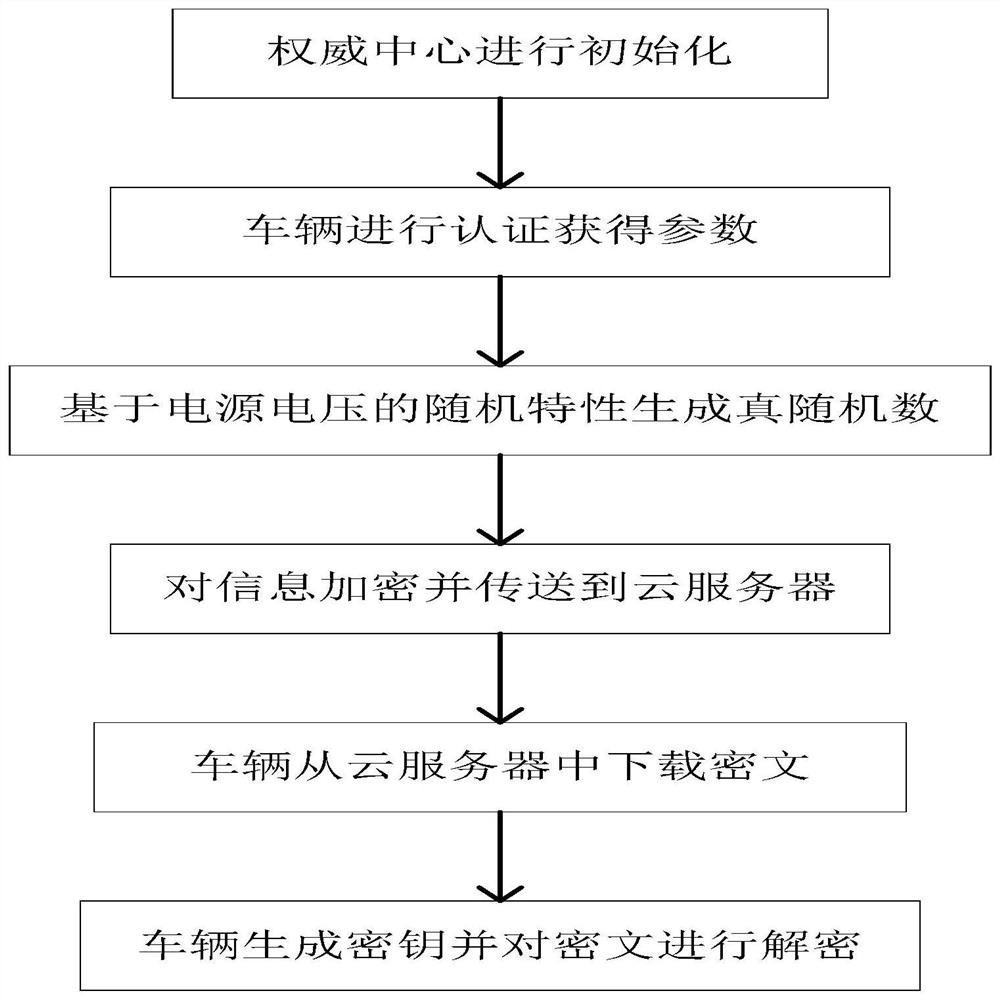

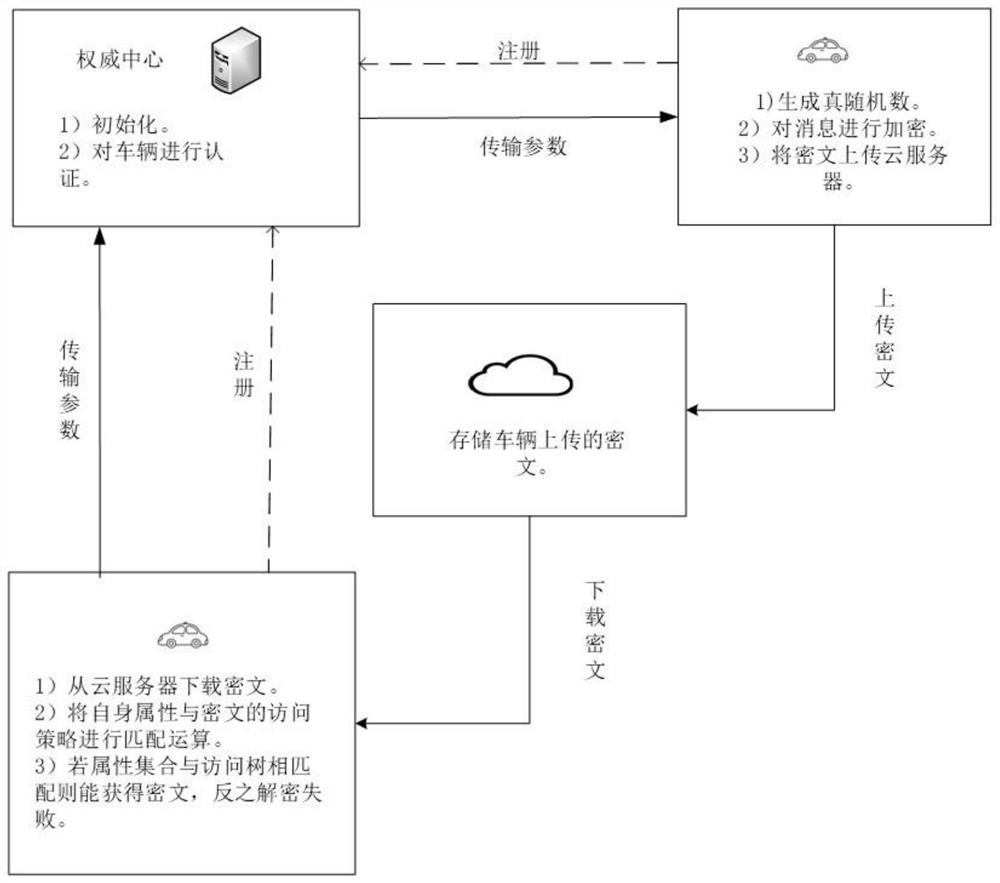

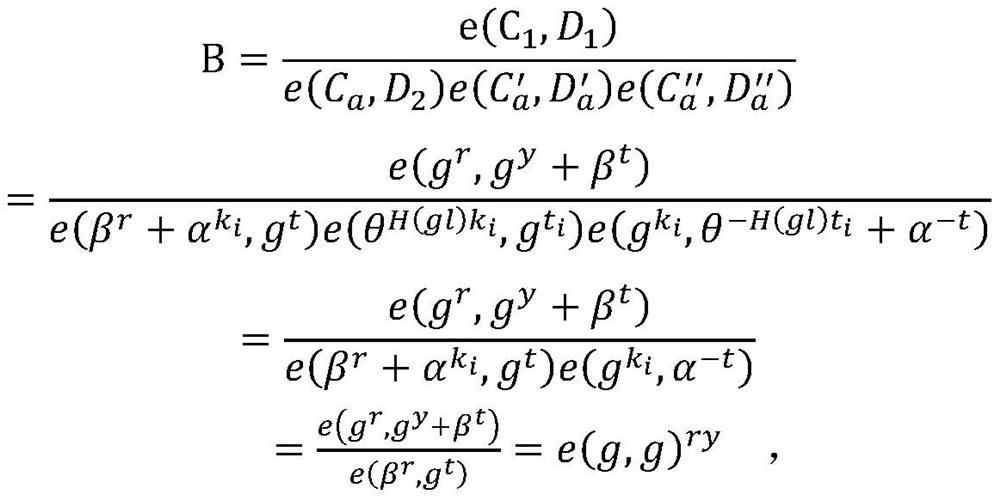

Internet of vehicles privacy protection communication method based on true random number

ActiveCN113141344AGood statistical propertiesMeet the unpredictabilityKey distribution for secure communicationEncryption apparatus with shift registers/memoriesIn vehiclePrivacy protection

The invention provides an Internet of Vehicles privacy protection communication method based on a true random number, and the method mainly comprises the following steps: 1), carrying out the initialization of an authority center, and generating necessary parameters; 2) the vehicle performing registration application to the authority center to obtain important parameters; 3) encrypting the information by using a true random number generated by the vehicle-mounted power supply voltage and the obtained parameters, and uploading the information to a cloud server; and 4) other vehicles downloading the ciphertext from the cloud server and decrypt the ciphertext to obtain data. True random numbers not only have good statistical characteristics but also meet unpredictability, the true random numbers extracted on the basis of the vehicle-mounted power supply voltage are used as important parameters for generating the ciphertext and have very high safety, and a ciphertext attribute-based encryption scheme with an access strategy hidden is designed to hide the attributes of the vehicle. And the effect of protecting the privacy of the vehicle is achieved.

Owner:JIANGSU UNIV

Fault Diagnosis Method of Switching Circuit Based on Wavelet Transform and ICA Feature Extraction

InactiveCN104793124BThe classification result is accurateAccurate diagnosisElectronic circuit testingTreatment failureFeature extraction

The invention discloses a switching circuit fault diagnosis method based on wavelet transform and ICA feature extraction, step 1: classifier training and constructing a fault dictionary, based on circuit simulation, adopting a method based on wavelet transform and ICA feature extraction to obtain characteristic parameters, based on The characteristic parameters construct the fault dictionary and train the classifier; Step 2: Fault diagnosis: refer to the fault dictionary, use the method based on wavelet transform and ICA feature extraction to obtain the characteristic parameters for the switching current circuit to be diagnosed, and input the characteristic parameters into the training Fault diagnosis is carried out in the classifier of the switch current circuit to be tested, and the output signal of the classifier is the fault diagnosis result. The invention has an ingenious concept and is easy to implement. The simulation proves that compared with the existing method, various fault types can be more accurately distinguished .

Owner:CHANGSHA UNIVERSITY

A Pipelined Combined Pseudo-Random Number Generator

ActiveCN103399726BGood statistical propertiesImprove securityRandom number generatorsData sourceNumber generator

The invention belongs to the field of high-speed generation of pseudo-random number sequences, and particularly relates to a streamlined combined-type pseudo-random number generator. The streamlined combined-type pseudo-random number generator comprises a random data source module, a 0 and 1 sequence generating module, an order disrupting module, an SHA_1 divergence module and a pseudo-random sequence storage module. Tests on the pseudo-random number generator prove that the generator can generate random number sequences with better statistical properties and higher safety, design cost is low, and efficiency of application in the fields like chip encryption and computer simulation can be improved.

Owner:HARBIN ENG UNIV

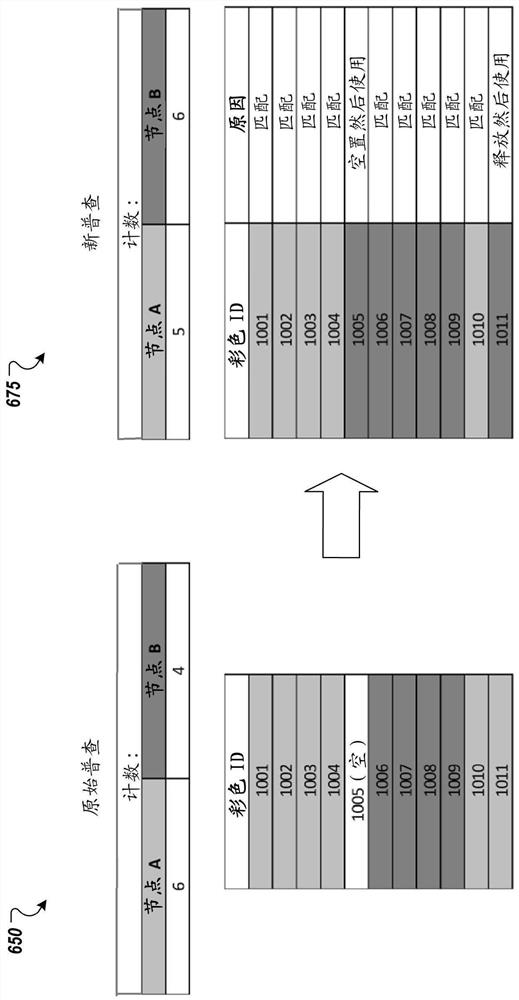

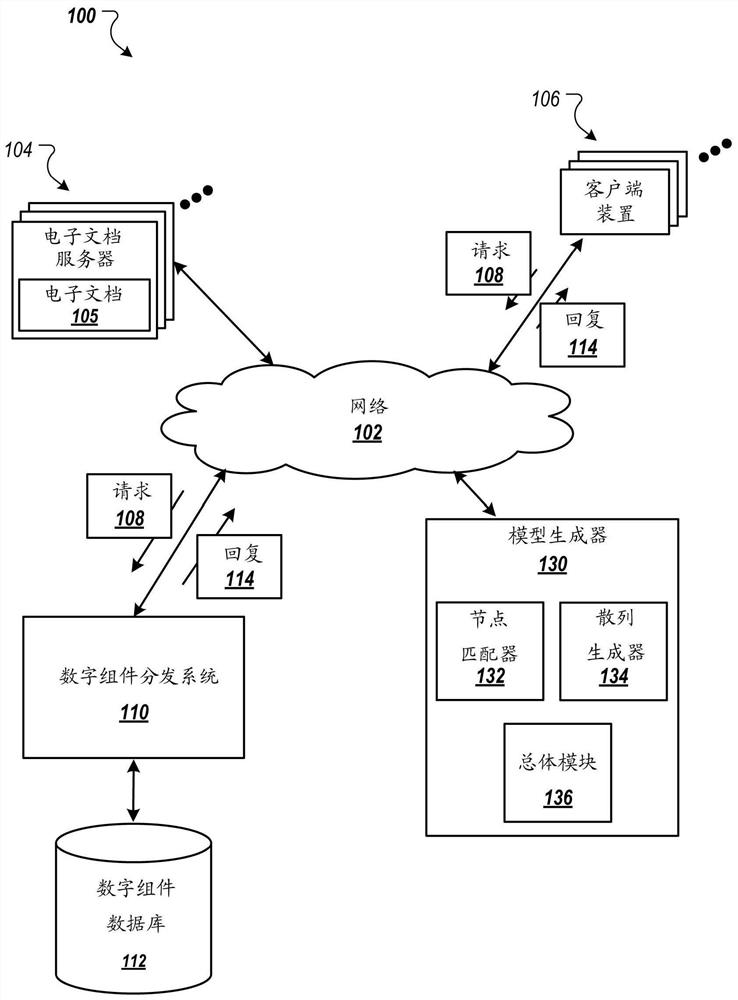

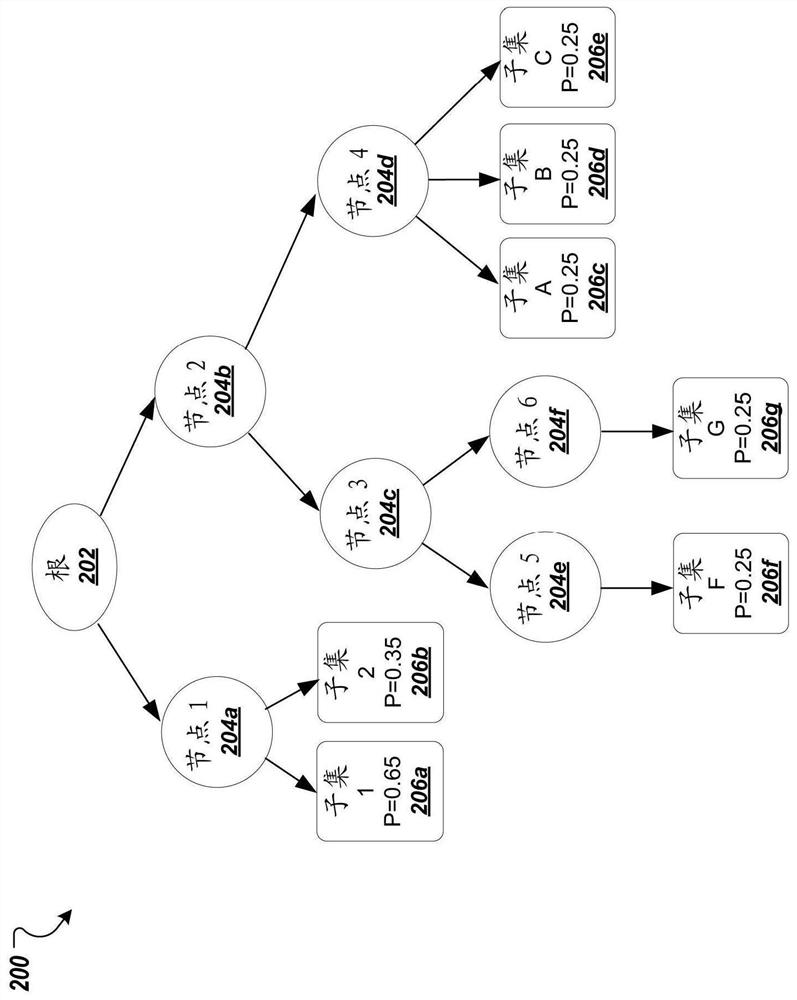

Reducing errors introduced by model updates

PendingCN111699481AReduce reallocationReduce inaccuracyEnsemble learningRelational databasesStructural classificationEngineering

Methods, systems, and computer readable medium for reducing inconsistencies in output between an original model and a new model. The method includes receiving an original model and a new model, mapping structures of the new model to structures of the original model, classifying each structure of the new model as belonging to a group of the original model, an unused group not in the original model,a subset of a group of the original model, or a merged set of a first and a second, different group of the original model, generating a merged model based on the mapping and classifying, and classifying a unique entities, using the merged model, by applying consistent hashing to each of the unique entities.

Owner:GOOGLE LLC

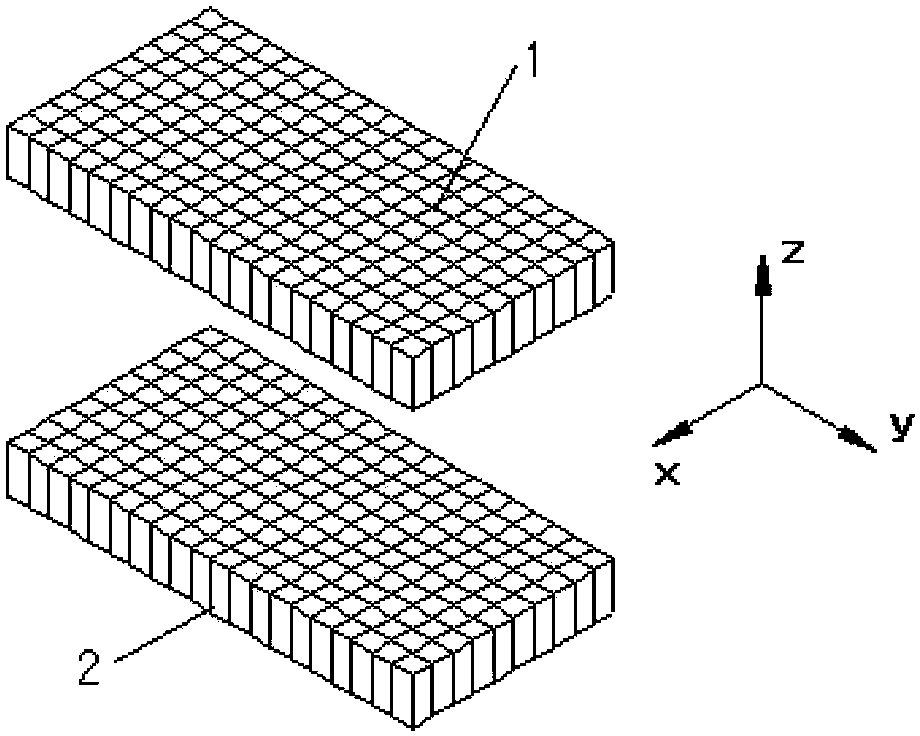

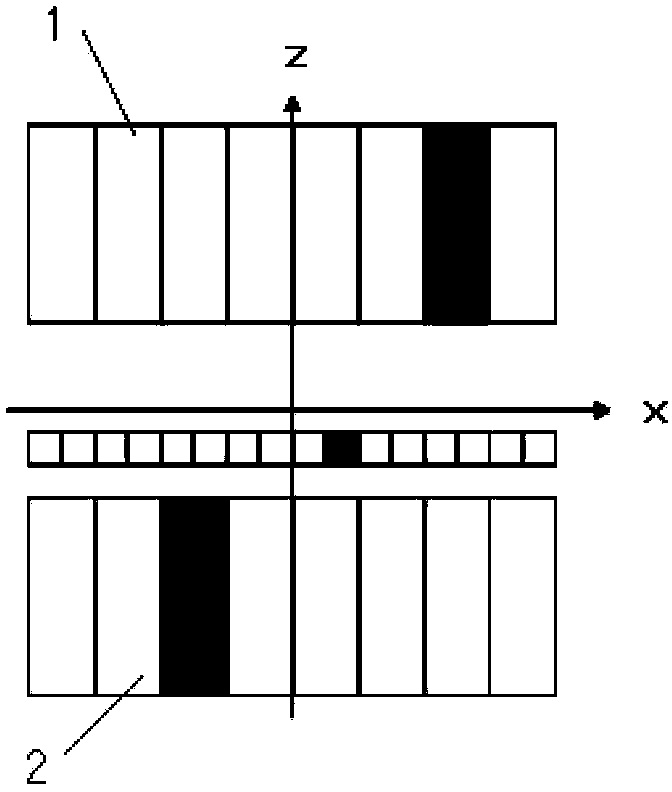

Image reconstruction method for dual panel position-emission tomography (PET) detector

ActiveCN103099637BAchieve compressionGood statistical propertiesComputerised tomographsTomographyLines of responseEvent type

The invention relates to an image reconstruction method for a dual panel position-emission tomography (PET) detector. The image reconstruction method for the dual panel PET detector comprises the following steps: conducting simulation on image process of a dual panel PET detection structure by using simulation software; recording line of response (LOR) information corresponding to all coincidence events and voxels where annihilation events lay; judging the type of one coincidence event according to positions of photon pairs in the annihilation events, considering the coincidence event as a true coincidence event if the occurring positions of the pair of photons corresponding to the coincidence event are consistent, considering the coincidence event as a random coincidence event if the occurring positions are inconsistent and removing the random coincidence event; expanding the range of the voxels; obtaining a compressed system response matrix through calculation by using symmetry of the structure the dual panel PET detector; reconstructing an image by using the obtained system response matrix. The image reconstruction method for the dual panel PET detector can be widely in the image reconstruction of the PET detector with the dual panel PET detection structure.

Owner:TSINGHUA UNIV

A Reliability Interval Estimation Method Based on Proportional Grouping Resampling

InactiveCN104750982BGuaranteed uptimeAvoid problemsSpecial data processing applicationsLife timeRepeated failure

The present invention provides a reliability interval estimation method based on proportionate grouping and resampling. ① firstly group life test data according to complete data and censored data; Point estimation of parameters and reliability, ④ use the self-service method (Bootstrap method) to repeatedly re-sample, and calculate the corresponding distribution parameters and point estimates of reliability, ⑤ sort the obtained reliability point estimates, and obtain the interval estimate of reliability . This method avoids the occurrence of non-failure data during repeated re-sampling, ensures the normal operation of the method, requires less theoretical knowledge, is simple to calculate, easy to implement, and is convenient for engineering and technical personnel to use, and has good application value.

Owner:BEIHANG UNIV

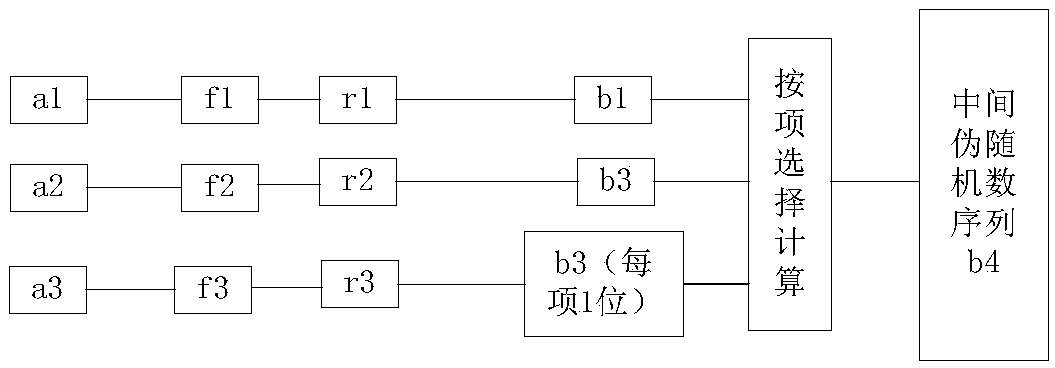

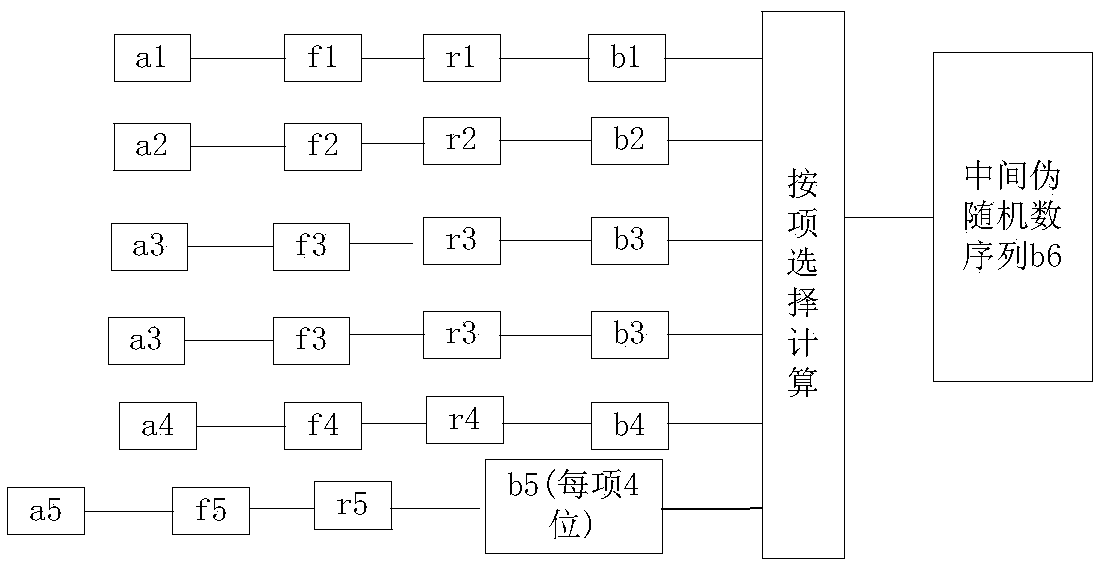

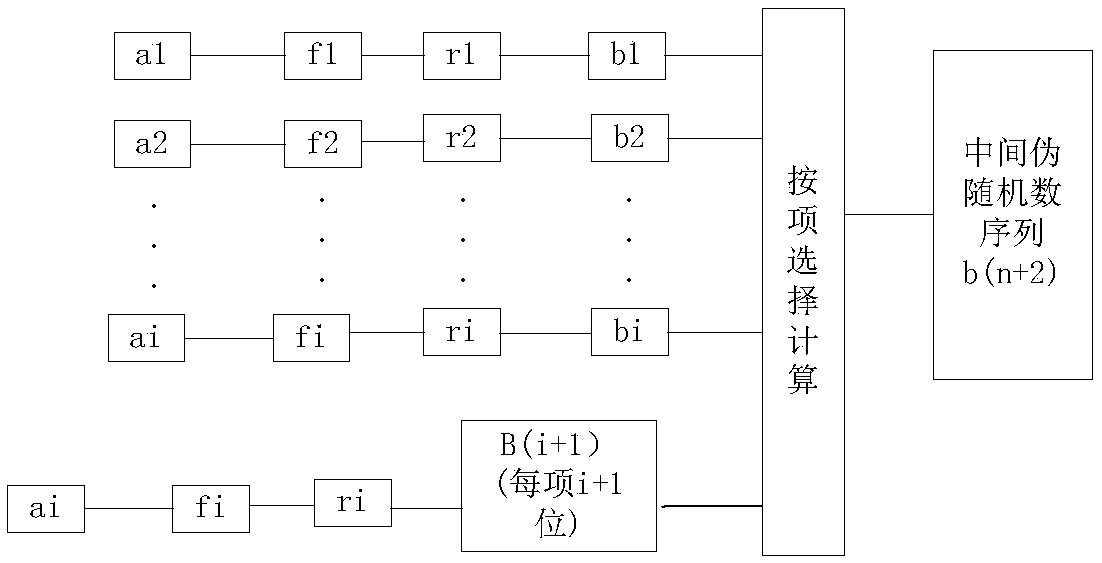

Pseudo-random number generation method based on chaotic function combination selection

PendingCN109582285AIncreased confusionGood statistical propertiesRandom number generatorsSecuring communication by chaotic signalsPseudo random number generationComputer science

The invention relates to a pseudo-random number generation method based on chaotic function combination selection, comprising the following steps: S1, initializing n chaotic functions f1, f2, f3-fi, fn to generate n initial function value sequences r1, r2, r3-ri-rn, where n is greater than or equal to 3; S2, simplifying each of the n initial function value sequences r1, r2, r3-ri-rn into an initial pseudo-random number sequence b1, b2, b3,-bn which only contains 0 or 1 through calculation; S3, dividing the n initial pseudo-random number sequences b1, b2, b3-bn into M levels cj; And S4, carrying out item-by-item selection on the pseudo-random number sequences with the same level or low level through the high-level pseudo-random number sequences so as to generate an ultimate pseudo-random number sequence bf. According to the pseudorandom number generation method, the new pseudorandom number sequence is generated through mutual item-by-item selection among the chaotic functions, and compared with the pseudorandom number sequence generated through column-by-column selection in the prior art, the combined selection method is higher in precision.

Owner:XIDIAN UNIV

Stream cipher generator

InactiveCN101340280BGood statistical propertiesImprove statsKey distribution for secure communicationBroadcast systems controlS-boxComputer science

The invention discloses a stream cipher generator; wherein, in the present framework, a first module of a linear transformation module F is used for compression transformation of numbers read by a state reading list module A, B and C and output numbers of the linear transformation module F and outputting the numbers which are suitable for input by a second module; the second module comprises a non-reversible linear transformation module and two S boxes which are connected in parallel and the numbers input from the first module is output after being transformed in the non-reversible linear transformation module; the location of the numbers input from the first module is selected as the input of the two S boxes, in which table search transformation is carried out, and the output thereof is combined with the output of the non-reversible linear transformation module as the output of the linear transformation module F; the S boxes randomly generate an S box pool and the S box pool is obtained by optimal selecting by analyzing the cipher characteristics with an evolutionary algorithm. The cipher characteristics of the S boxes of the invention are greatly improved, and the S boxes with high security intensity are obtained so as to improve the security intensity of the stream cipher generator.

Owner:SICHUAN PANOVASIC TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com