Error code detection device

A bit error detection and bit error technology, which is applied in the direction of synchronization device, error detection/prevention using signal quality detector, digital transmission system, etc., can solve the problem that the bit error tester cannot meet the bit error test, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

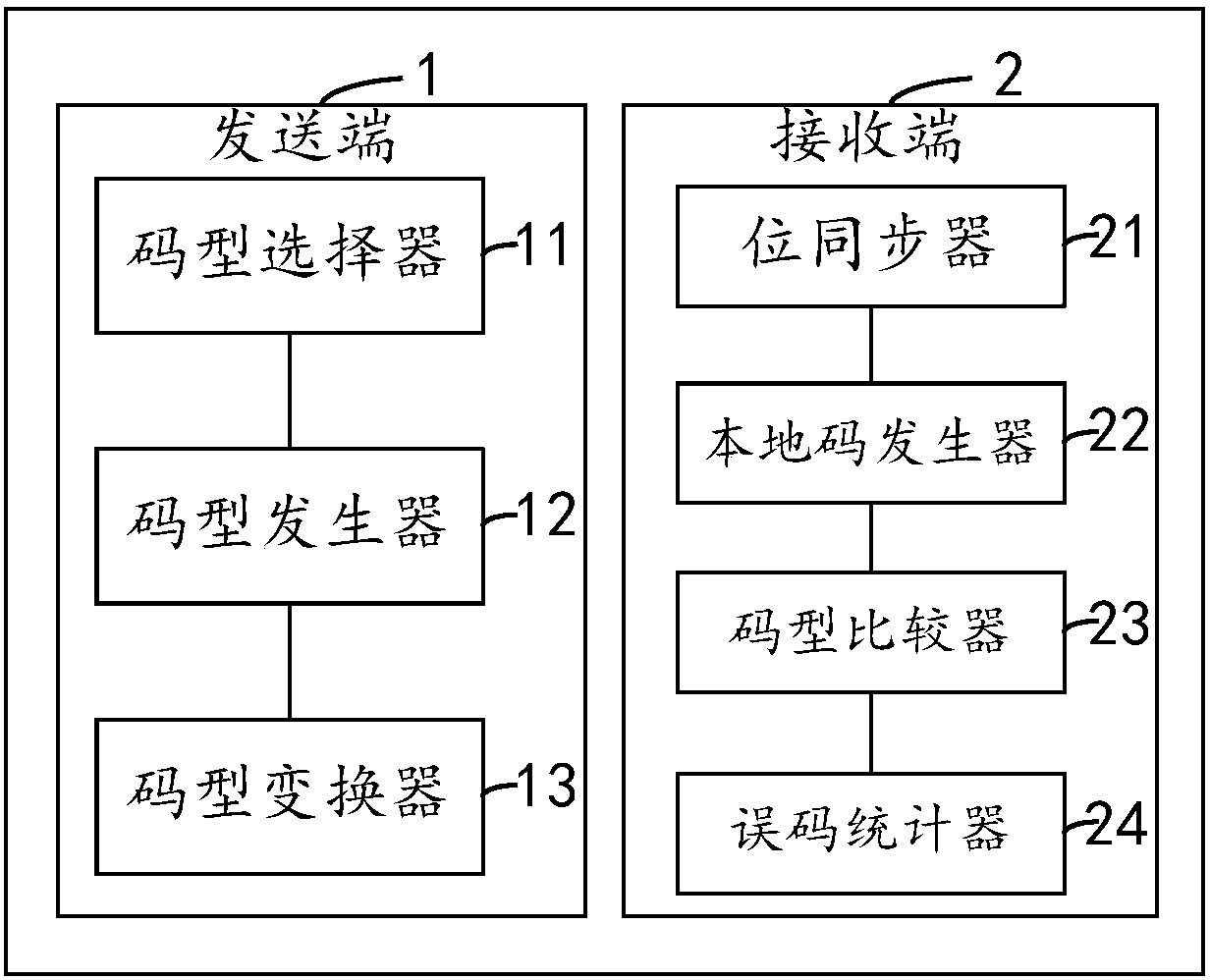

[0045] figure 1 It is a schematic structural diagram of an error detection device provided by an embodiment of the present invention. Such as figure 1 As shown, the error detection device provided in this embodiment includes:

[0046] Transmitter 1 is used to transmit the test pseudo-random sequence code obtained by transforming the pseudo-random sequence code to the test equipment;

[0047] The receiving end 2 is used to receive the test sequence code output by the test equipment for error detection, and the test sequence code is the sequence code outputted by the pseudo-random sequence code transmitted by the equipment under test.

[0048] Specifically, pseudo-random sequence code is a code stream generated by imitating the random characteristics of random sequence, which has good self-correlation and good statistical characteristics. In this embodiment, the transmitting terminal 1 transmits the test pseudo-random sequence code obtained by transforming the pseudo-random sequence c...

Embodiment 2

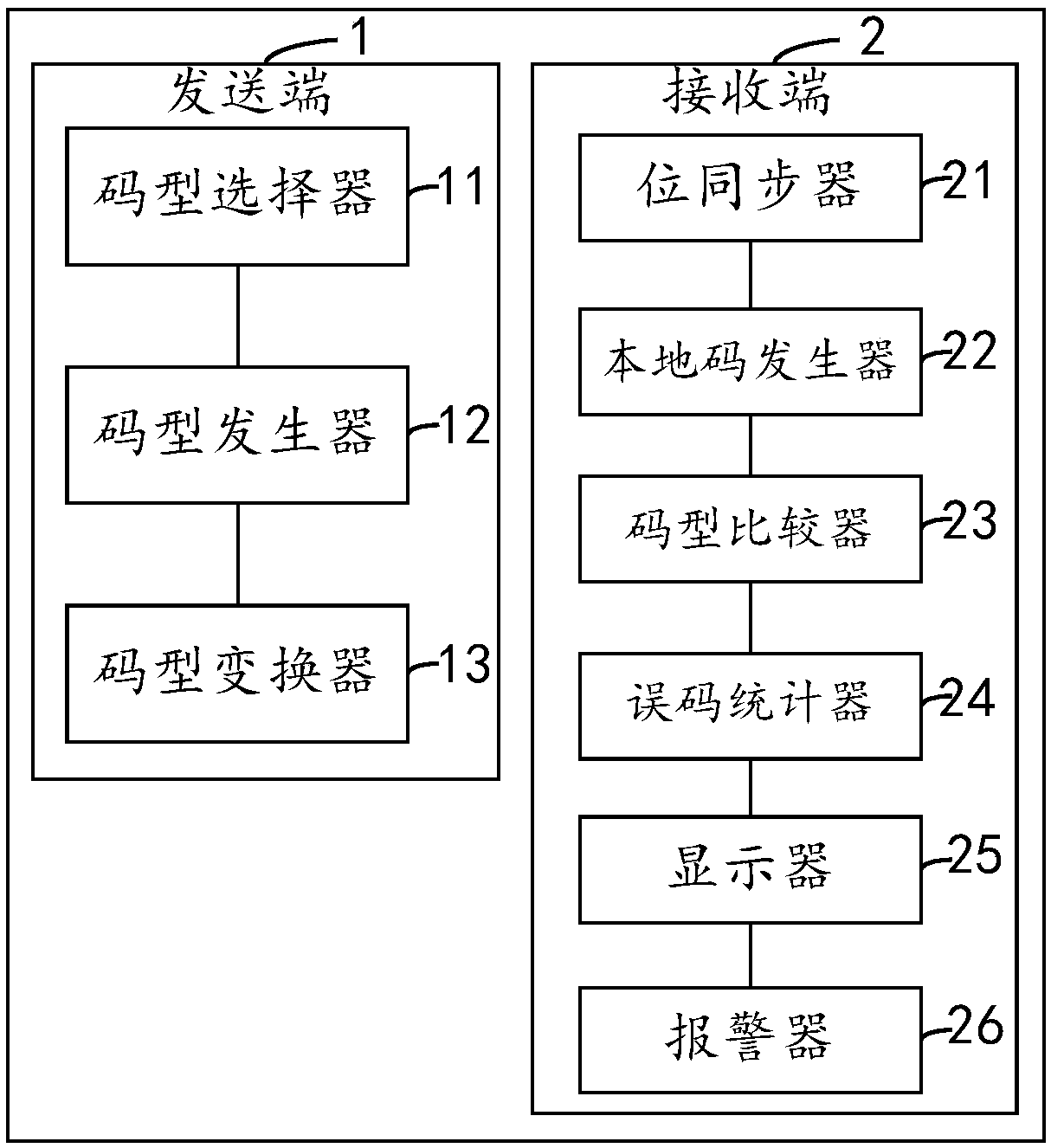

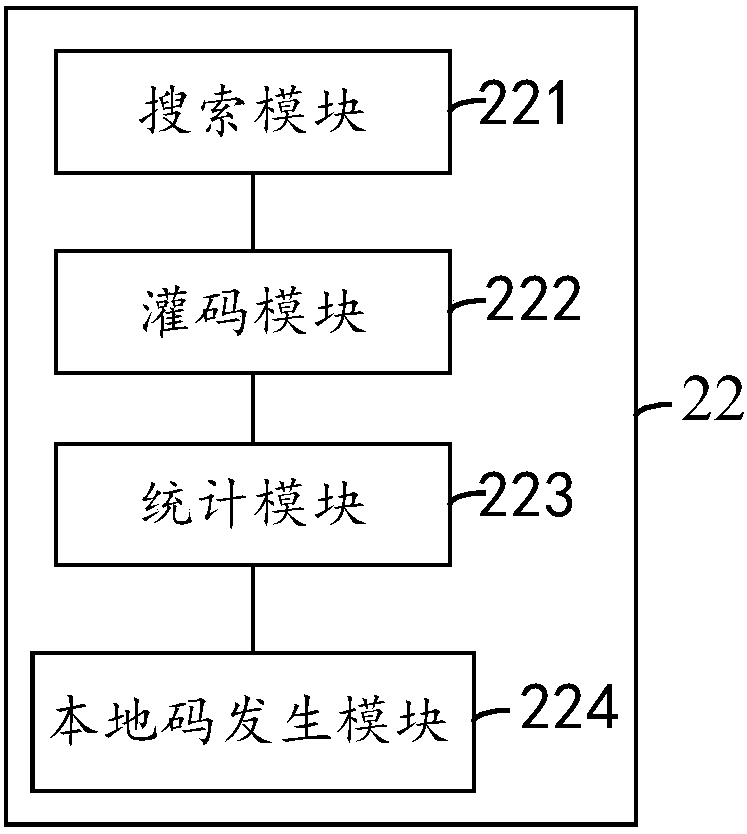

[0054] This embodiment is a supplementary explanation to the above embodiment. figure 2 It is a schematic structural diagram of an error detection device according to another embodiment of the present invention. image 3 It is a schematic structural diagram of the bit synchronizer 21 in the error detection device according to another embodiment of the present invention. Figure 4 It is a schematic structural diagram of the local code generator 22 in the error detection device according to another embodiment of the present invention. This embodiment mainly supplements the bit synchronizer 21, the local code generator 22, etc. of the above embodiment.

[0055] Specifically, the bit synchronizer 21 includes: a transition edge capture module 211, a status register 212, and a controllable counter 213. For example, the bit synchronizer 21 first extracts the clock signal of the test sequence code and the test pseudo-random sequence code obtained from the transmitter 1 and inputs them to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com