Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

90 results about "Logistic function" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A logistic function or logistic curve is a common "S" shape (sigmoid curve), with equation: f(x)=L/(1+e⁻ᵏ⁽ˣ⁻ˣ₀⁾) where e = the natural logarithm base (also known as Euler's number), x₀ = the x-value of the sigmoid's midpoint, L = the curve's maximum value, and k = the logistic growth rate or steepness of the curve. For values of x in the domain of real numbers from −∞ to +∞, the S-curve shown on the right is obtained, with the graph of f approaching L as x approaches +∞ and approaching zero as x approaches −∞.

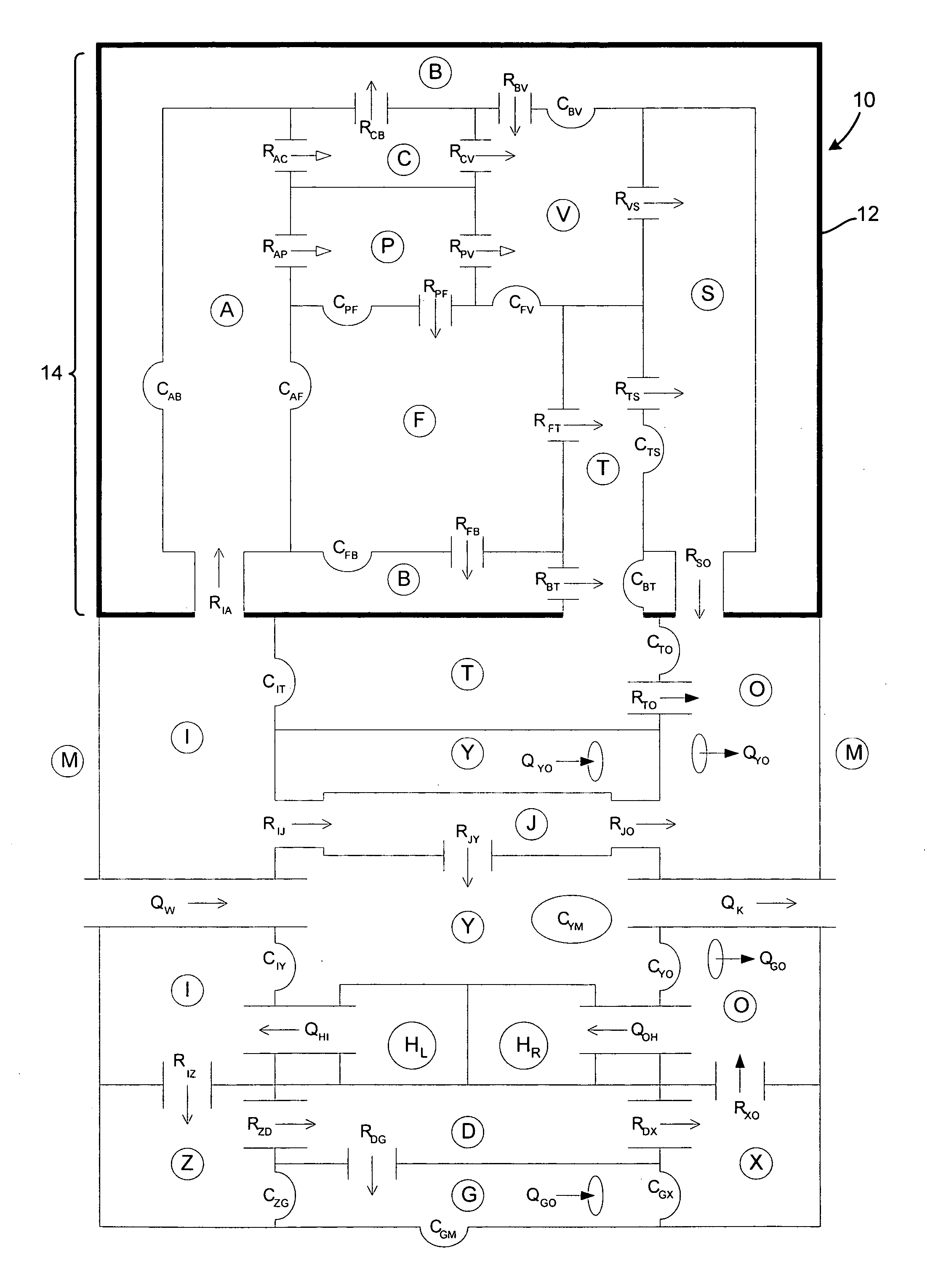

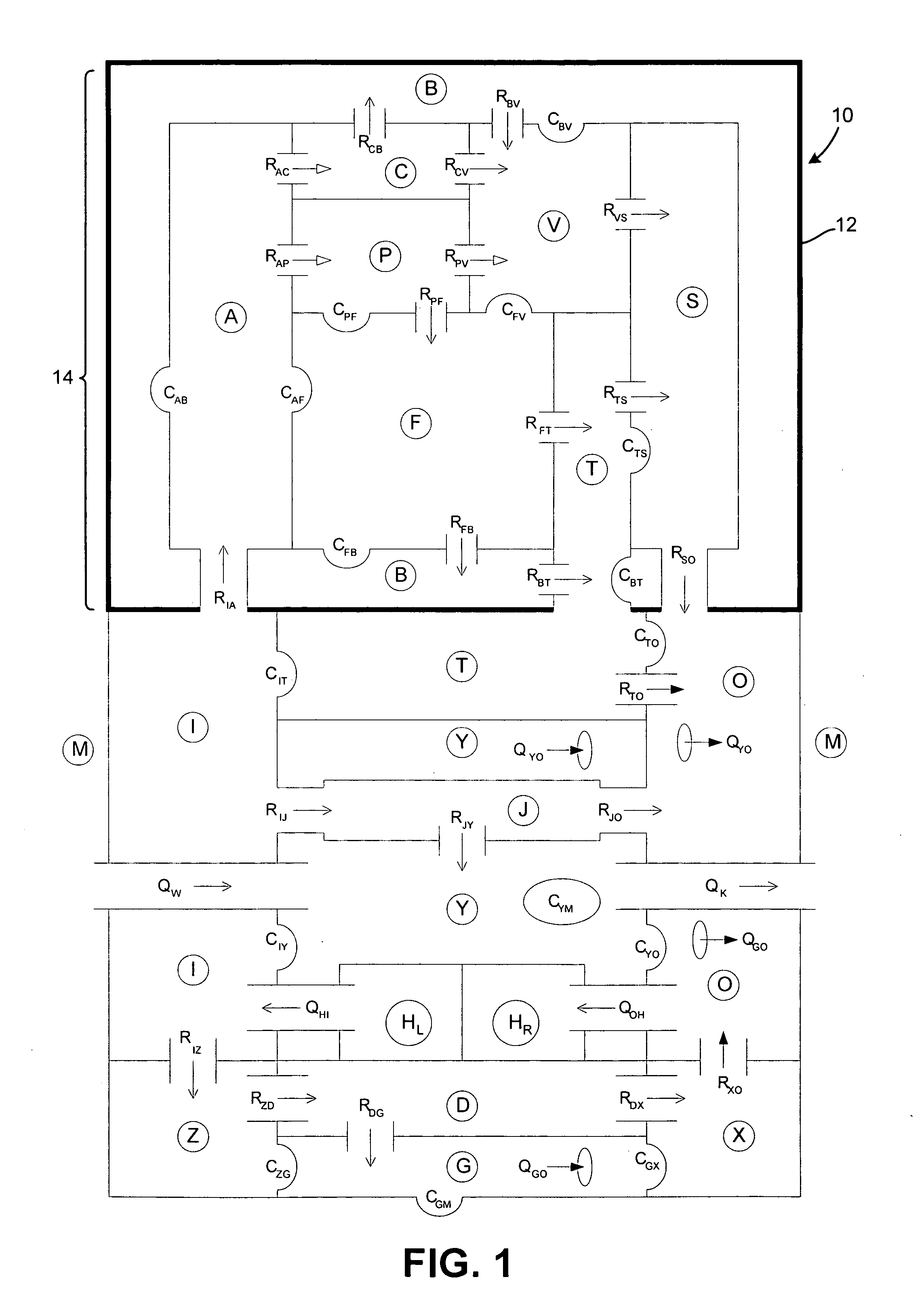

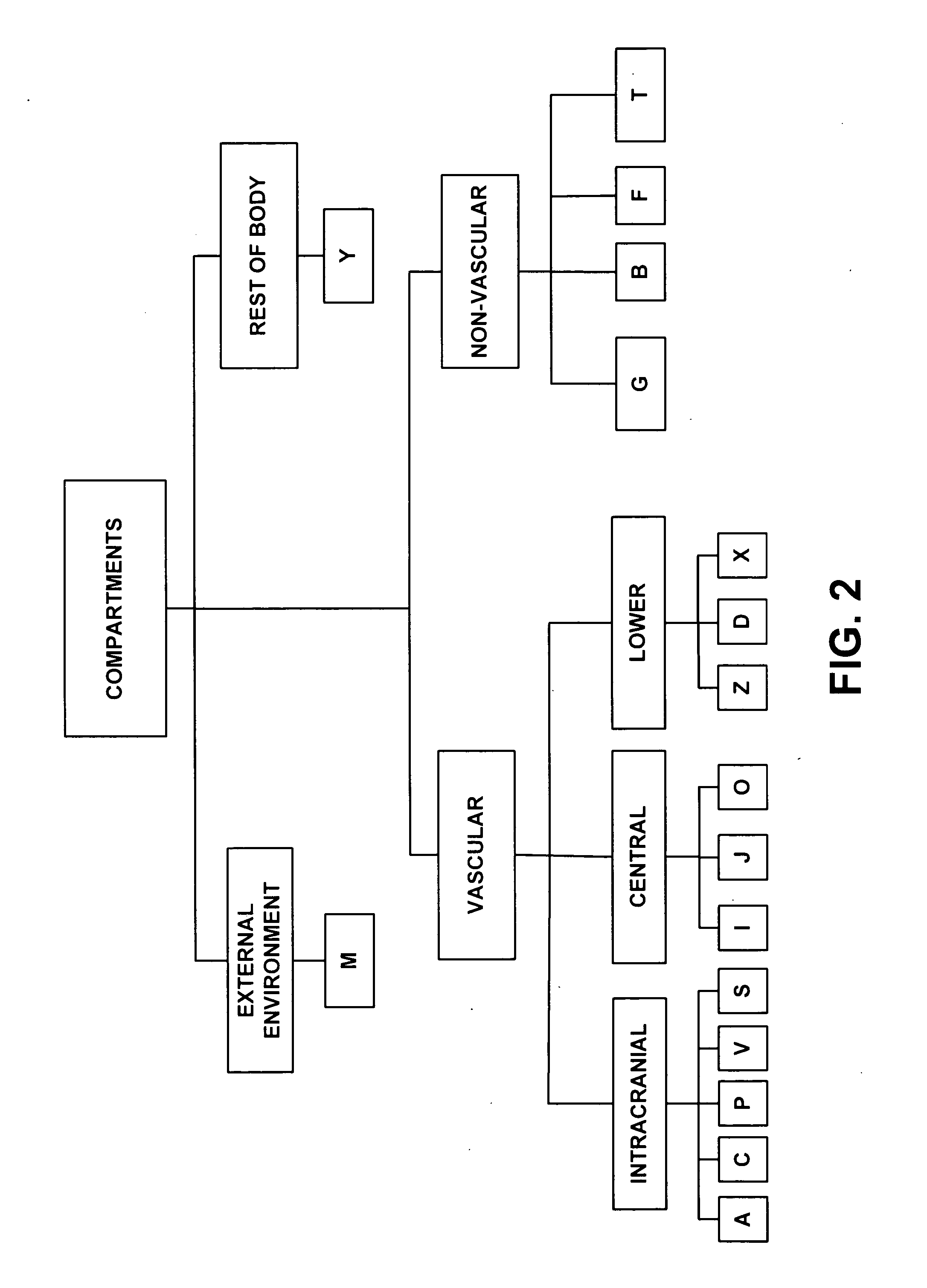

Mathematical circulatory system model

InactiveUS20060166176A1Medical simulationAnalogue computers for chemical processesSmooth muscleLogistic function

A system and method of modeling a circulatory system including a regulatory mechanism parameter. In one embodiment, a regulatory mechanism parameter in a lumped parameter model is represented as a logistic function. In another embodiment, the circulatory system model includes a compliant vessel, the model having a parameter representing a change in pressure due to contraction of smooth muscles of a wall of the vessel.

Owner:UNIVERSITY OF VERMONT

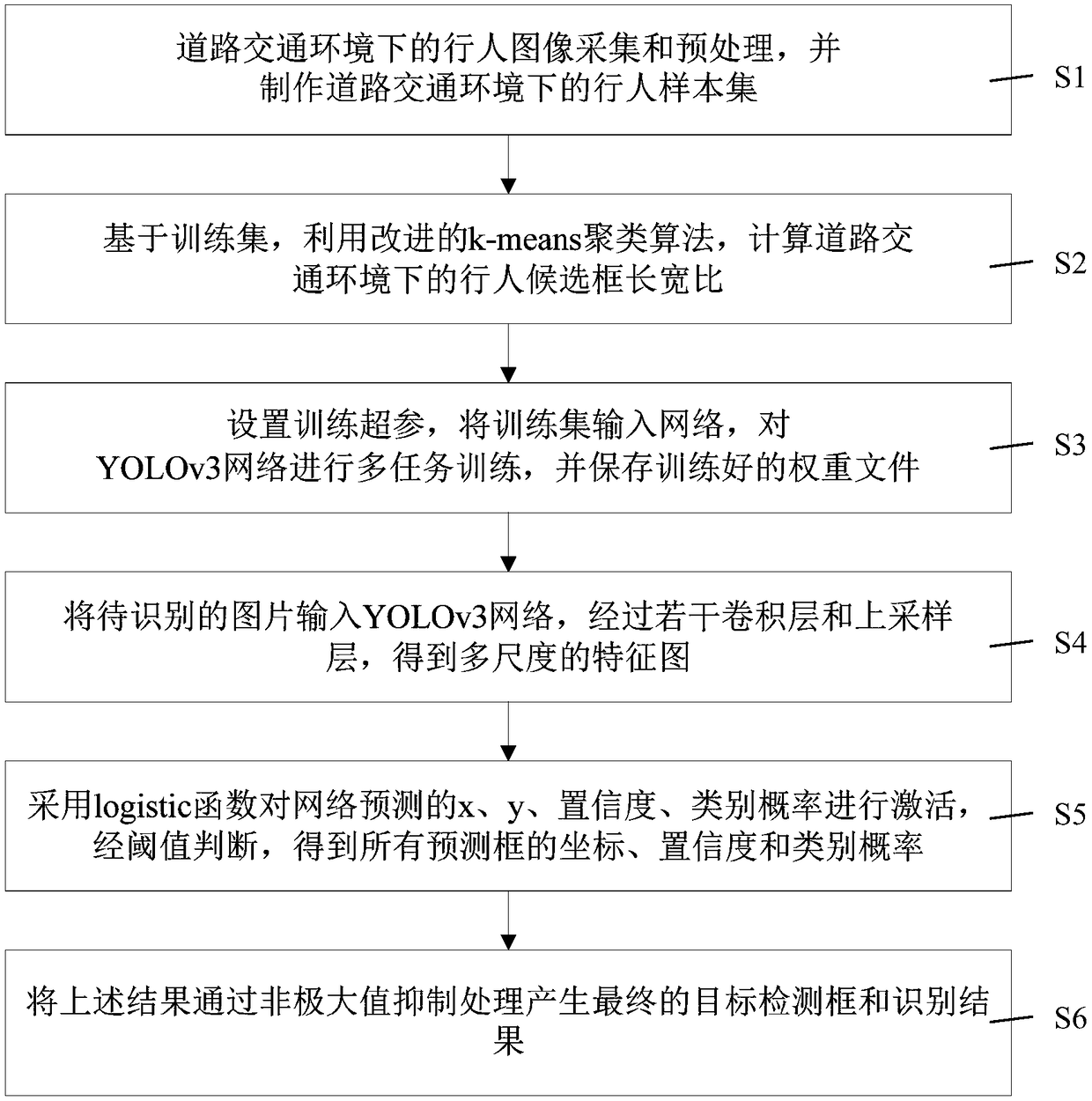

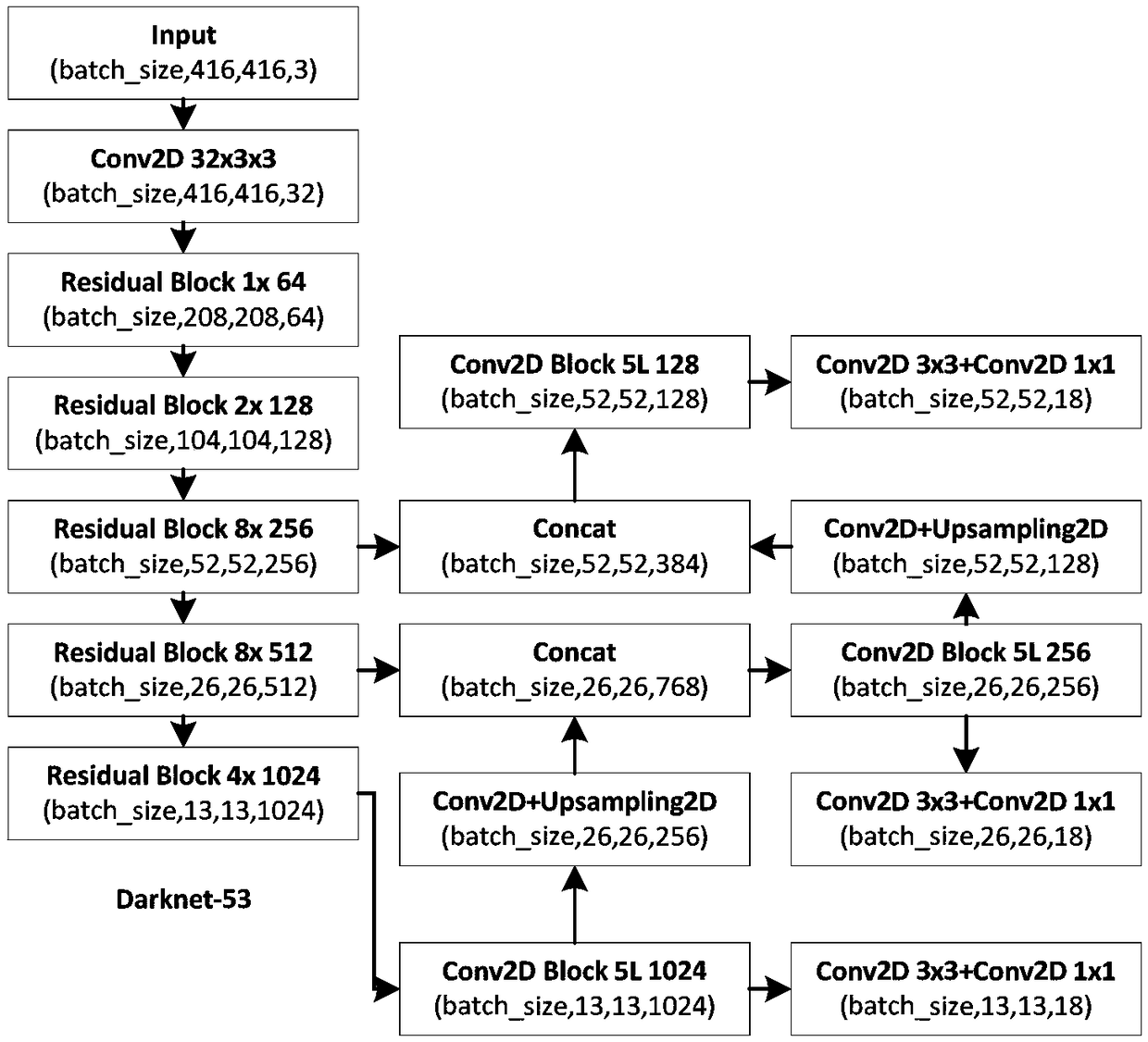

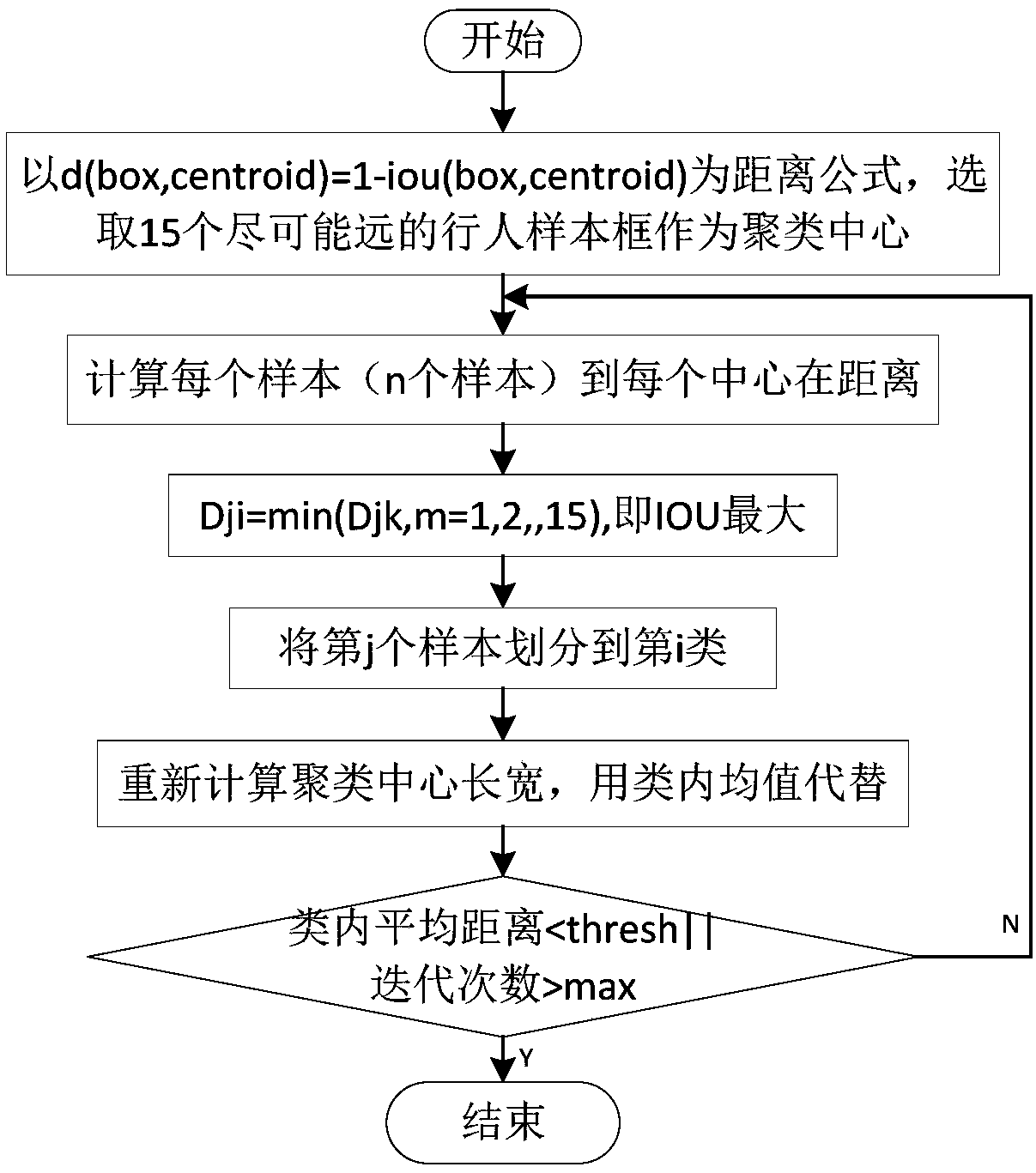

Pedestrian identification method under road traffic environment based on improved YOLOv3.

InactiveCN109325418AVerify the recognition effectSolve the problem of difficult and slow target detectionBiometric pattern recognitionCluster algorithmRoad traffic

The invention discloses a pedestrian identification method under a road traffic environment based on improved YOLOv3. The method comprises the following steps of: S1, acquiring and pre-processing an image, and making a pedestrian sample set; 2, calculating the length-width ratio of the pedestrian candidate frames by using a clustering algorithm and the training set; 3, inputting the training set into the YOLOv3 network for multi-task training and saving the trained weight file; S4, inputting a picture to be recognized into the YOLOv3 network to obtain a multi-scale characteristic map; S5, using a logistic function to activate the x, y, confidence degree and category probability of the network prediction, and obtaining the coordinates, confidence degree and category probability of all prediction frames by judging the threshold value; S6, generating a final target detection frame and a recognition result by carrying out the non-maximum value suppression processing on the above result. The method of the invention solves the problem of low detection accuracy of the prior method, realizes the multi-task training, does not need additional storage space, and is high in detection accuracyand fast in speed.

Owner:SOUTH CHINA UNIV OF TECH

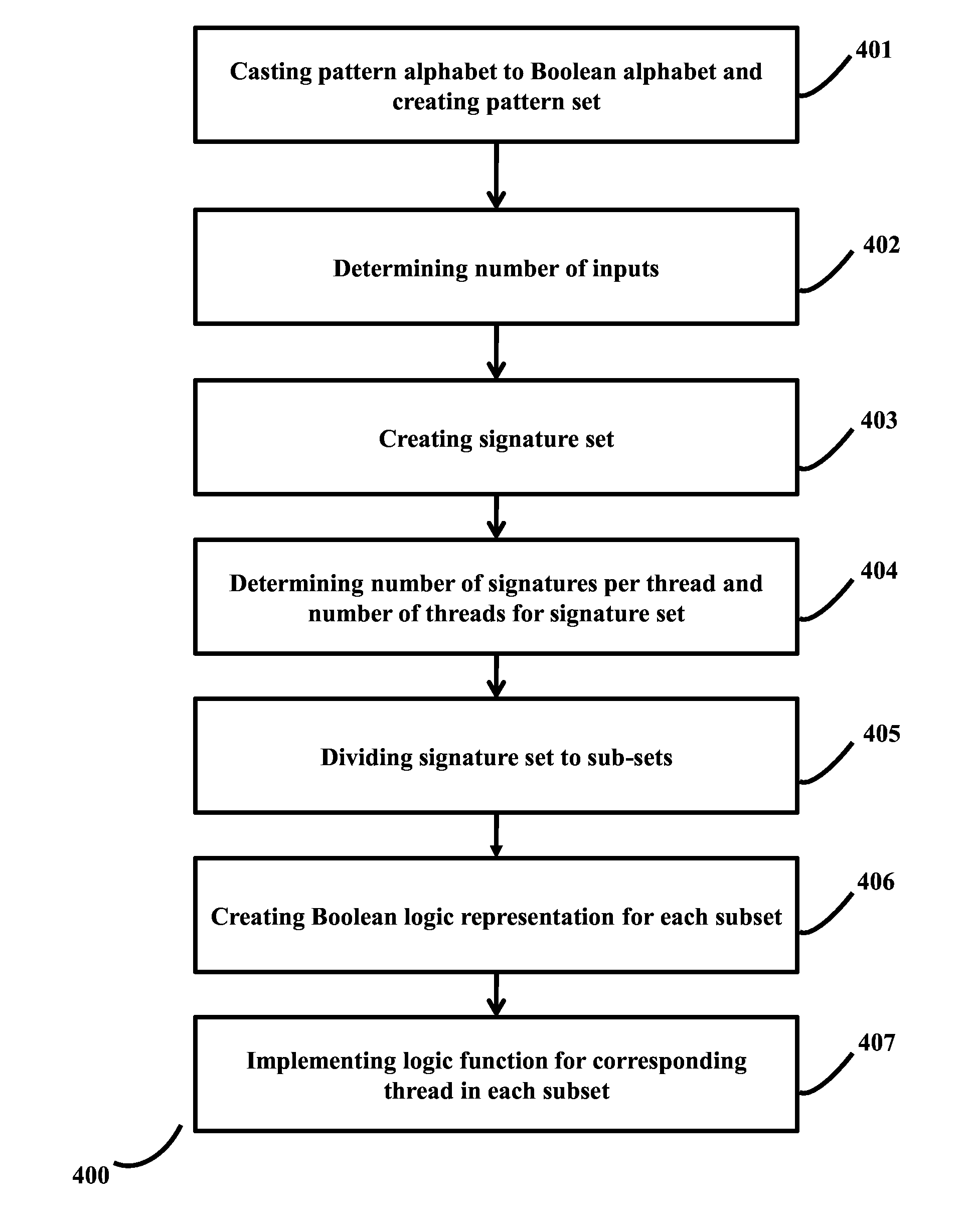

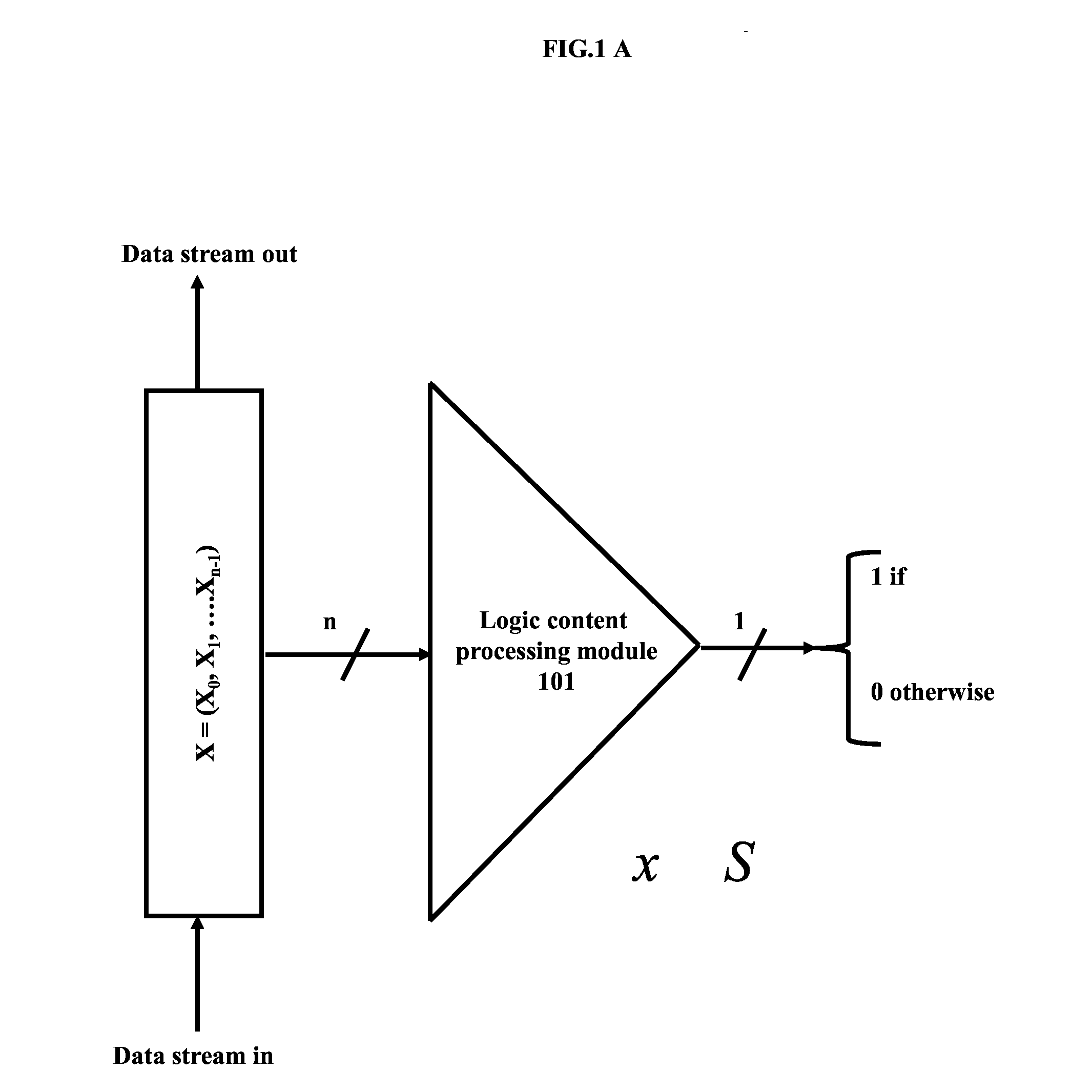

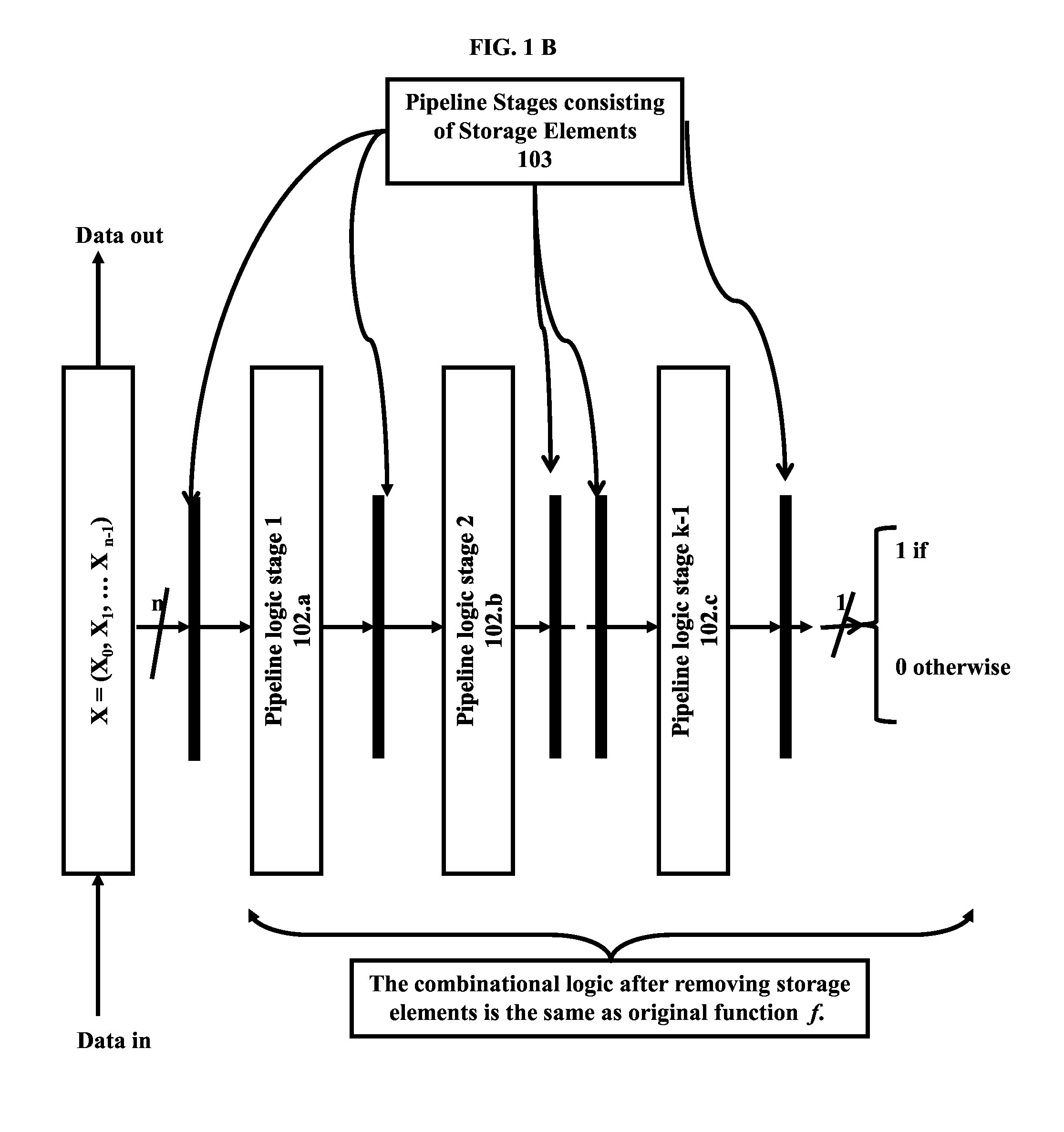

Logic Content Processing for Hardware Acceleration of Multi-Pattern Search

InactiveUS20140019486A1Digital data information retrievalDigital data processing detailsData streamType conversion

The embodiments herein relate to multi pattern searching and, more particularly, to multi pattern search or multi pattern matching using logic content processing. The input pattern is type cast to a Boolean alphabet and is then processed to create a corresponding signature set. Further, the signature set is divided into subsets and a Boolean logic function representing each signature subset is created. Further, the values of each subset are simultaneously compared with windows of an input data steam or data file to find a match. If a match is found, the system returns a hit, else a miss. Parallel stages may be added to enhance performance of the system, as multiple inputs may be processed at a time.

Owner:MAJUMDAR AMITAVA

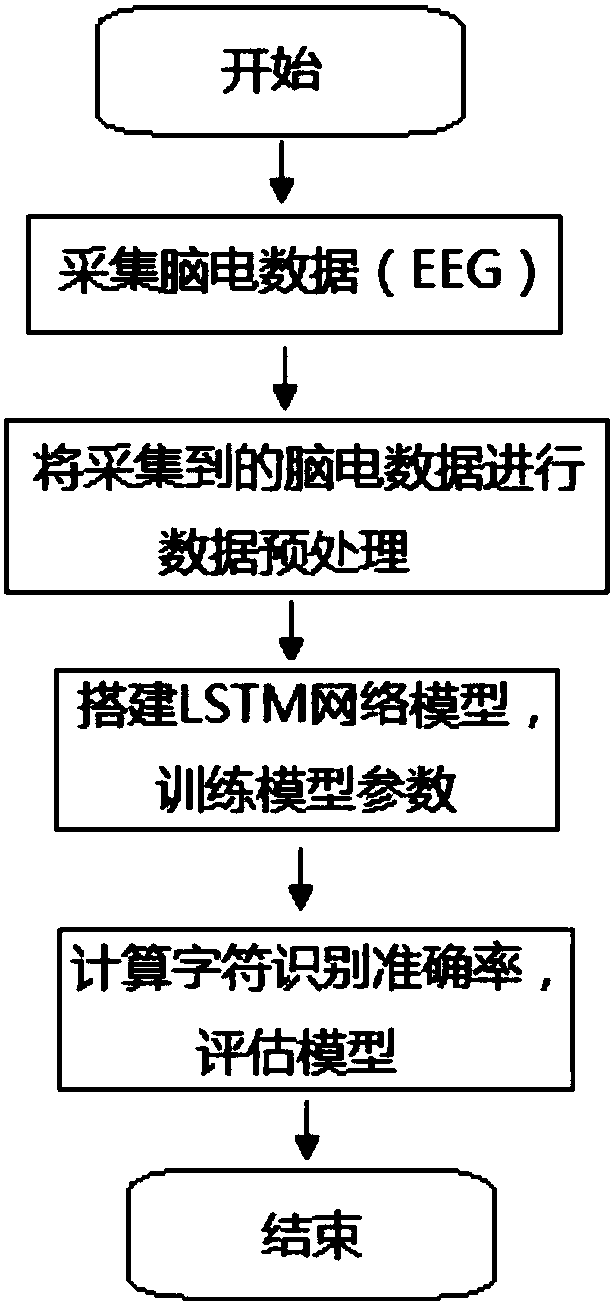

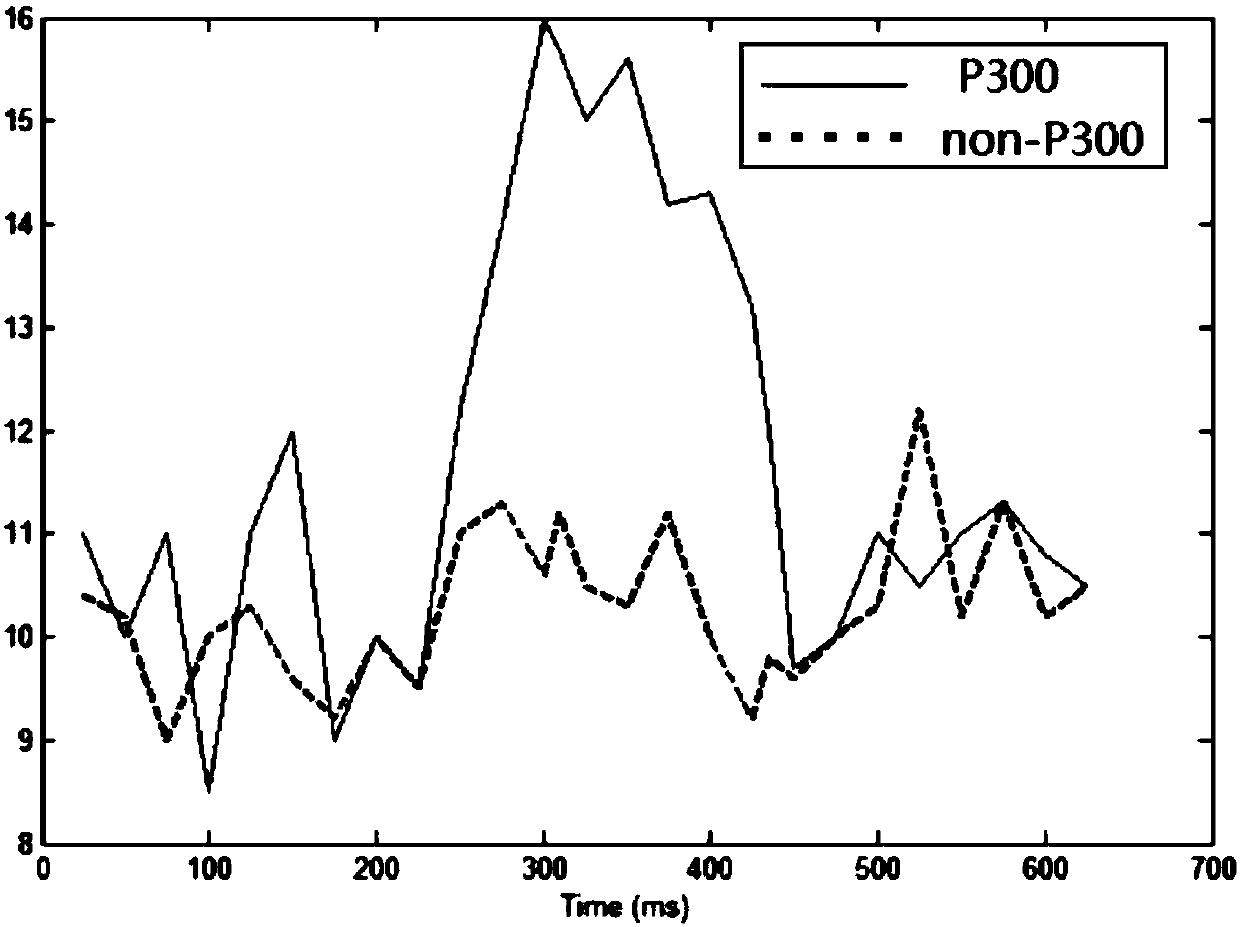

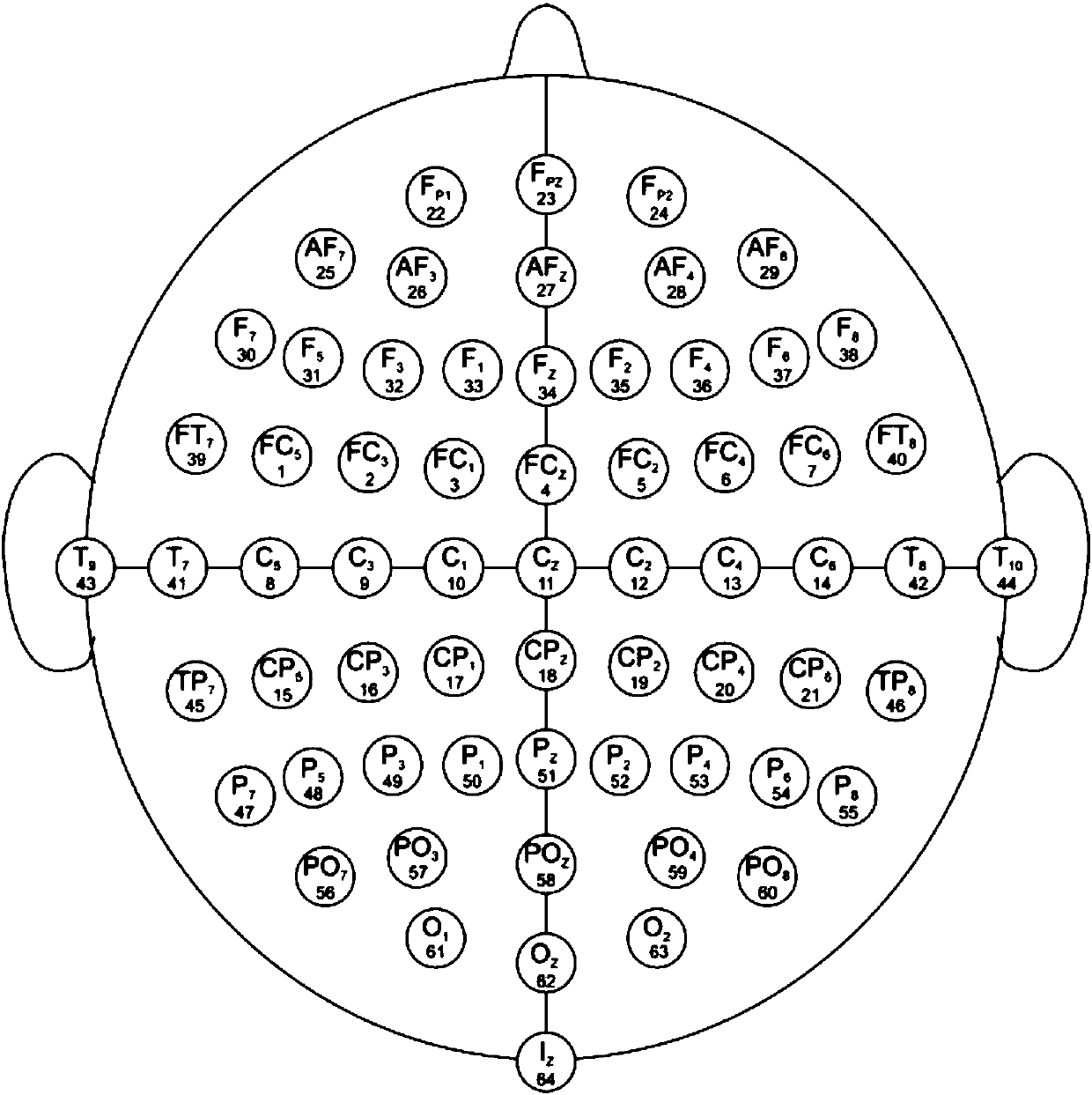

P300 signal detection method based on LSTM network

ActiveCN108304917AImprove recognition accuracyImprove generalization abilityInput/output for user-computer interactionNeural architecturesData setEeg data

The invention discloses a P300 signal detection method based on an LSTM network. The method comprises the following steps: step one, an experiment is carried out by using a P300 character speller andEEG signals are extracted to form a training set and a testing set; step two, preprocessing is carried out on the collected data and the processed data are used as an input data set of a model; step three, an LSTM layer is designed as a spatio-temporal filter of the EEG data set, an all-connection layer is added after a least time step of the LSTM layer, a Softmax layer is added to convert a network output value into a probability form, and then the network is trained and a model parameter is determined, wherein the Softmax layer is a generalized form of the logic function; and step four, a model evaluation index and a testing set character recognition rate are calculate to verify the performance of the model. The method has the following characteristics: no manual feature extraction is needed; the recognition performance is good; the generalization ability is high; and the good information conversion rate is realized. The P300 signal detection method is a good P300 classification algorithm.

Owner:GUANGZHOU GUANGDA INNOVATION TECH CO LTD

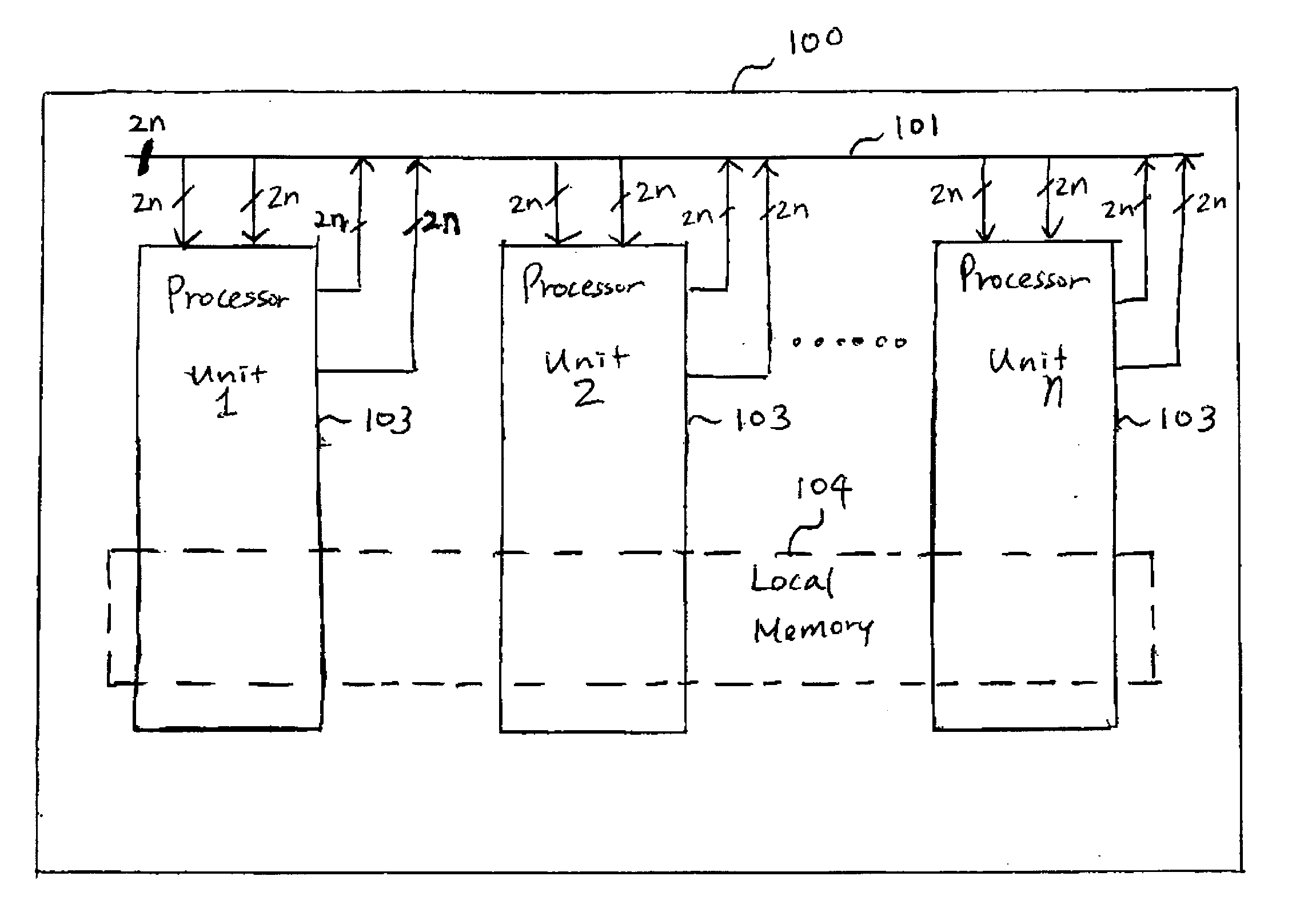

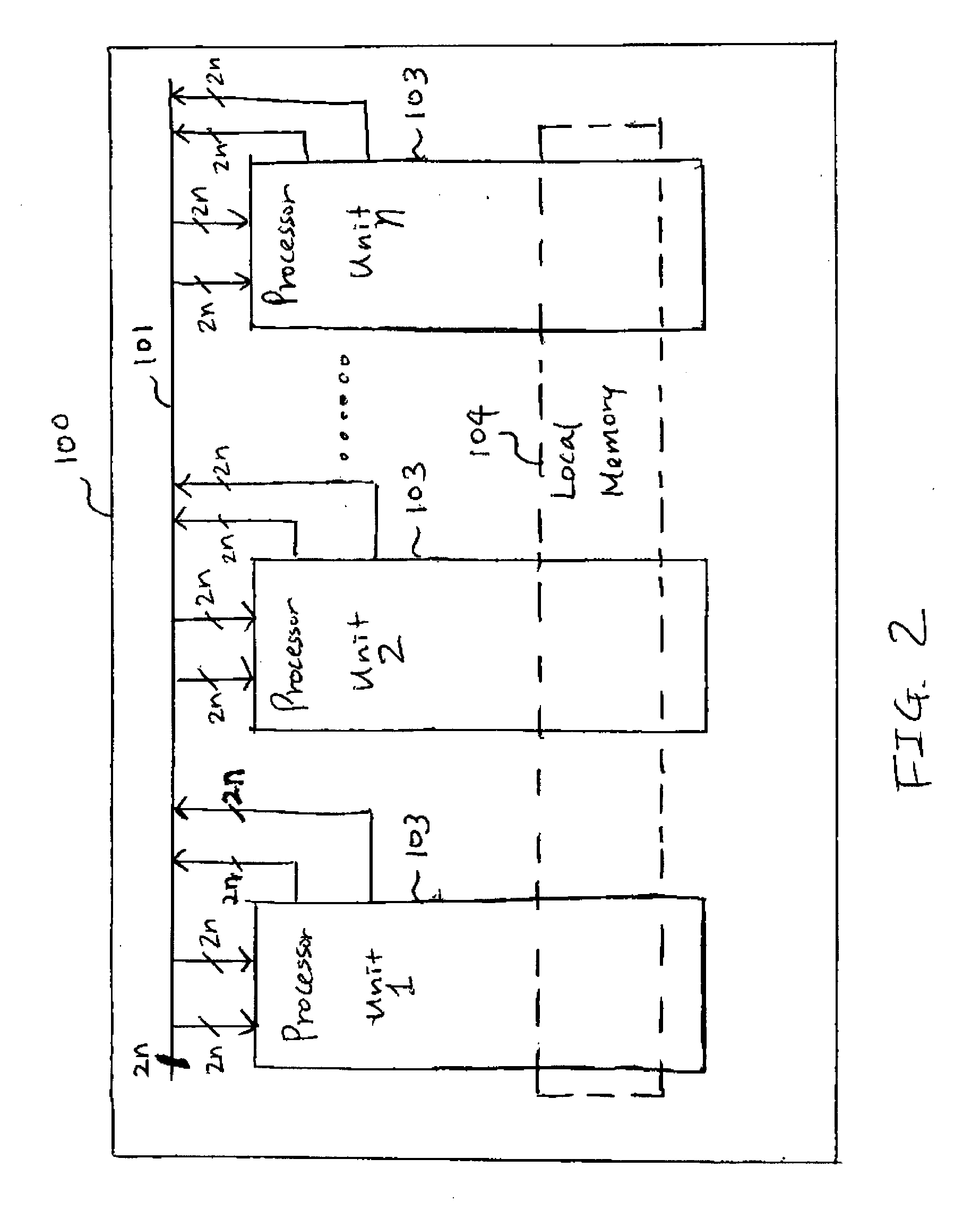

VLIW Acceleration System Using Multi-state Logic

InactiveUS20070074000A1Instruction analysisGeneral purpose stored program computerSemiconductor chipLogic simulation

A logic simulation processor uses multi-state logic (e.g., in 4-state, signals may take the values 0, 1, X or Z in the simulation of a semiconductor chip design). Typically a reduced number of basic multi-state logic functions are selected for the instruction set of the processor. Logic functions that are not part of the basic set are simulated by constructing them from combinations of the basic logic functions. In this way, the instruction length remains a manageable size but all logic functions that may occur can be simulated. The basic VLIW architecture can be extended to other applications.

Owner:LIGA SYST

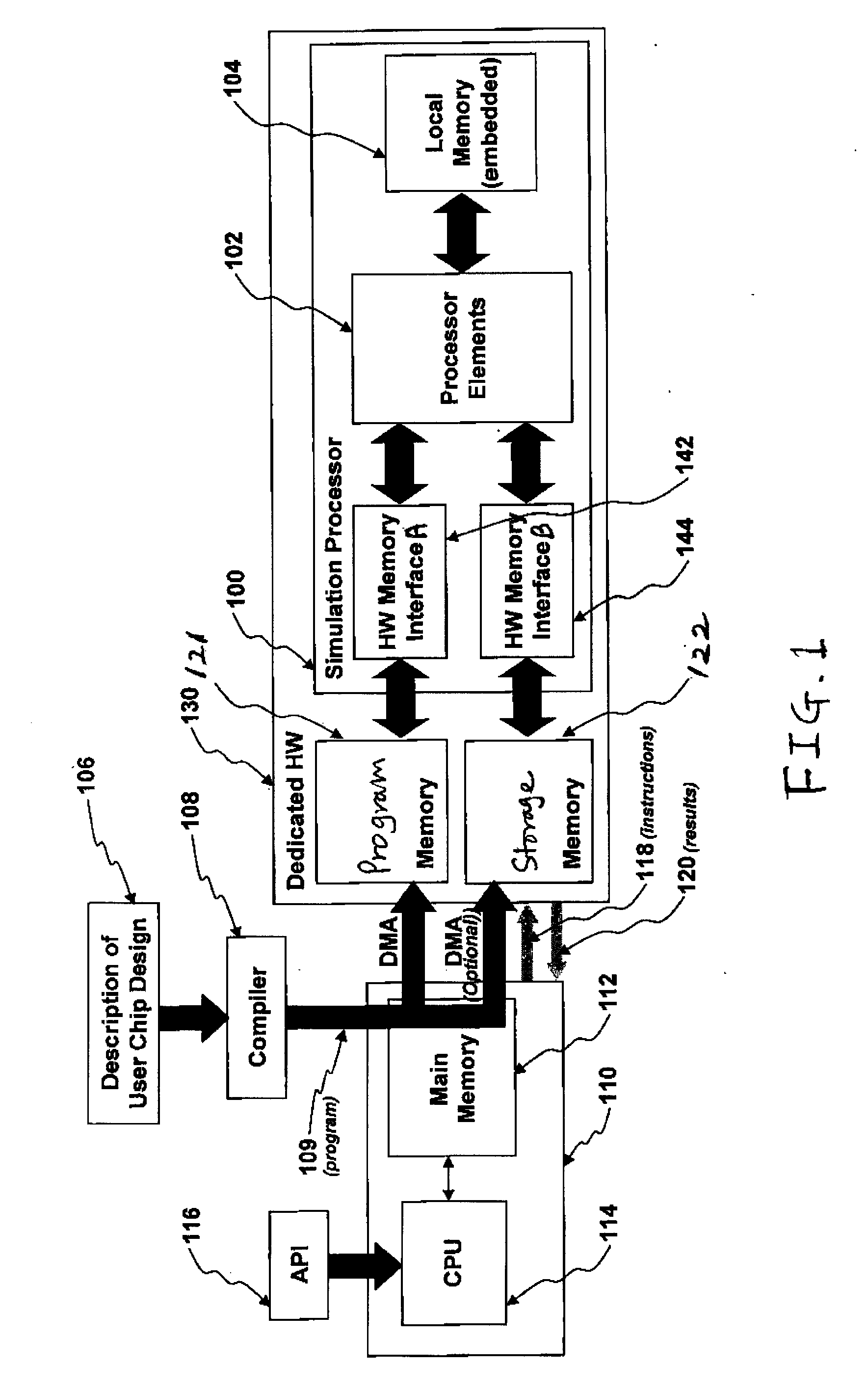

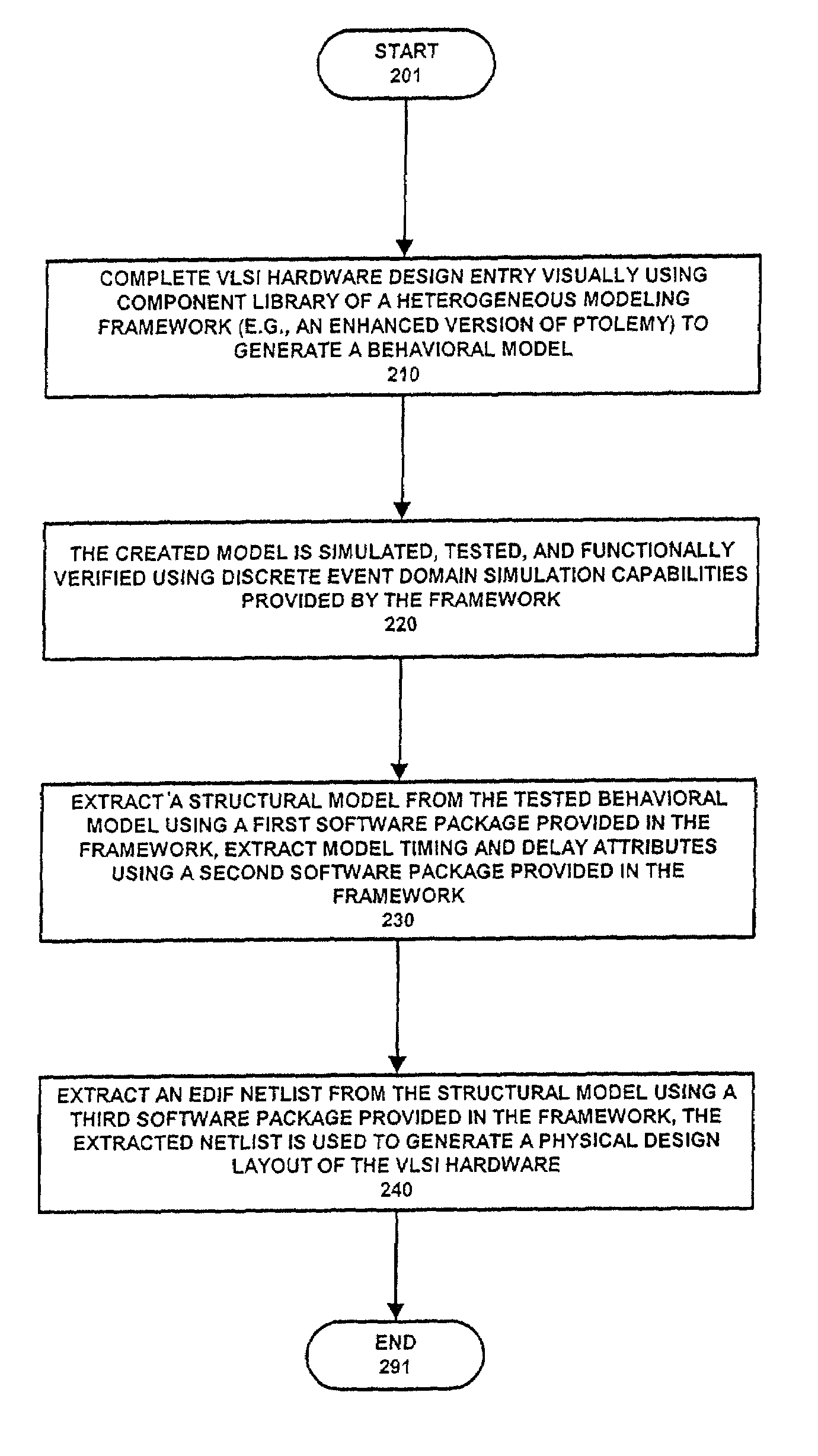

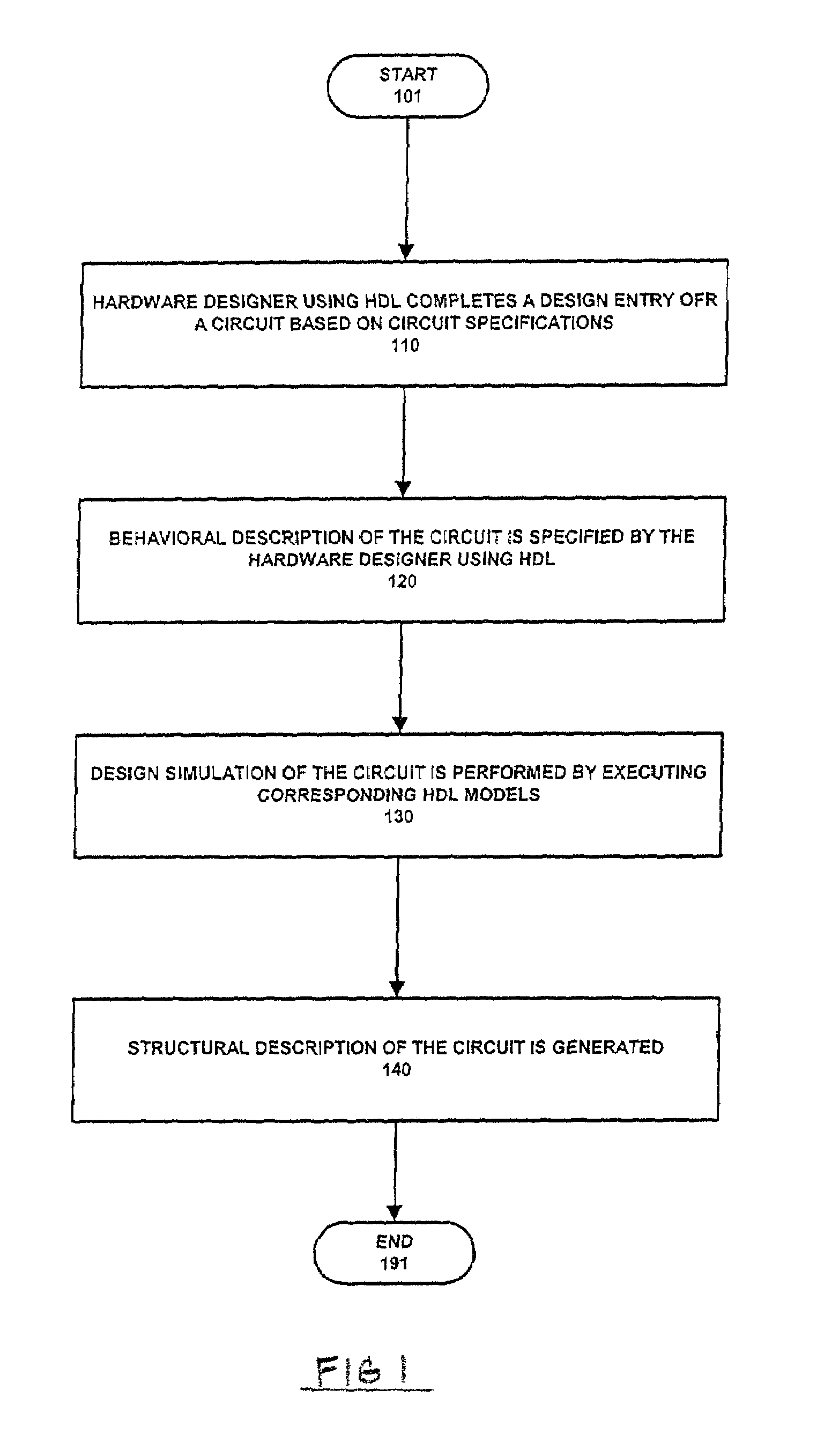

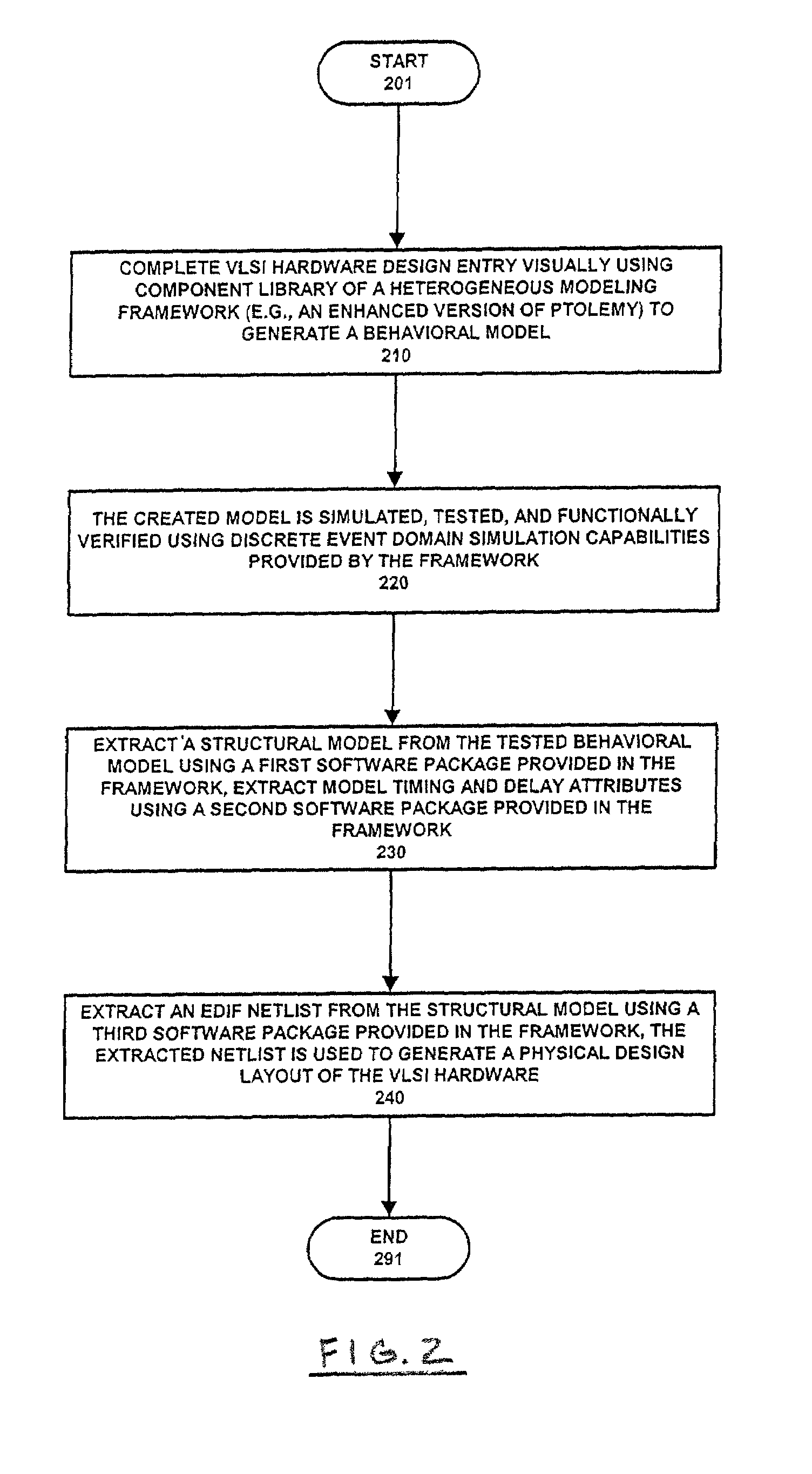

Method, apparatus, and system for hardware design and synthesis

ActiveUS6938237B1CAD circuit designSoftware simulation/interpretation/emulationHardware structureTheoretical computer science

According to one embodiment of the present invention, a method and system for VLSI hardware design and synthesis is provided in which components provided by a heterogeneous modeling framework are interconnected, based on design specifications of a VLSI, to create a corresponding behavioral VLSI model. The heterogeneous modeling framework contains a first component library including logic functions that can be used to build hardware structural models and a second component library including numeric standard. The created model is simulated, tested, and functionally verified using discrete event domain simulation capabilities provided by the heterogeneous framework. A corresponding structural model is extracted from the tested behavioral VLSI model using a software tool provided by the heterogeneous modeling framework.

Owner:OSTENDO TECH INC

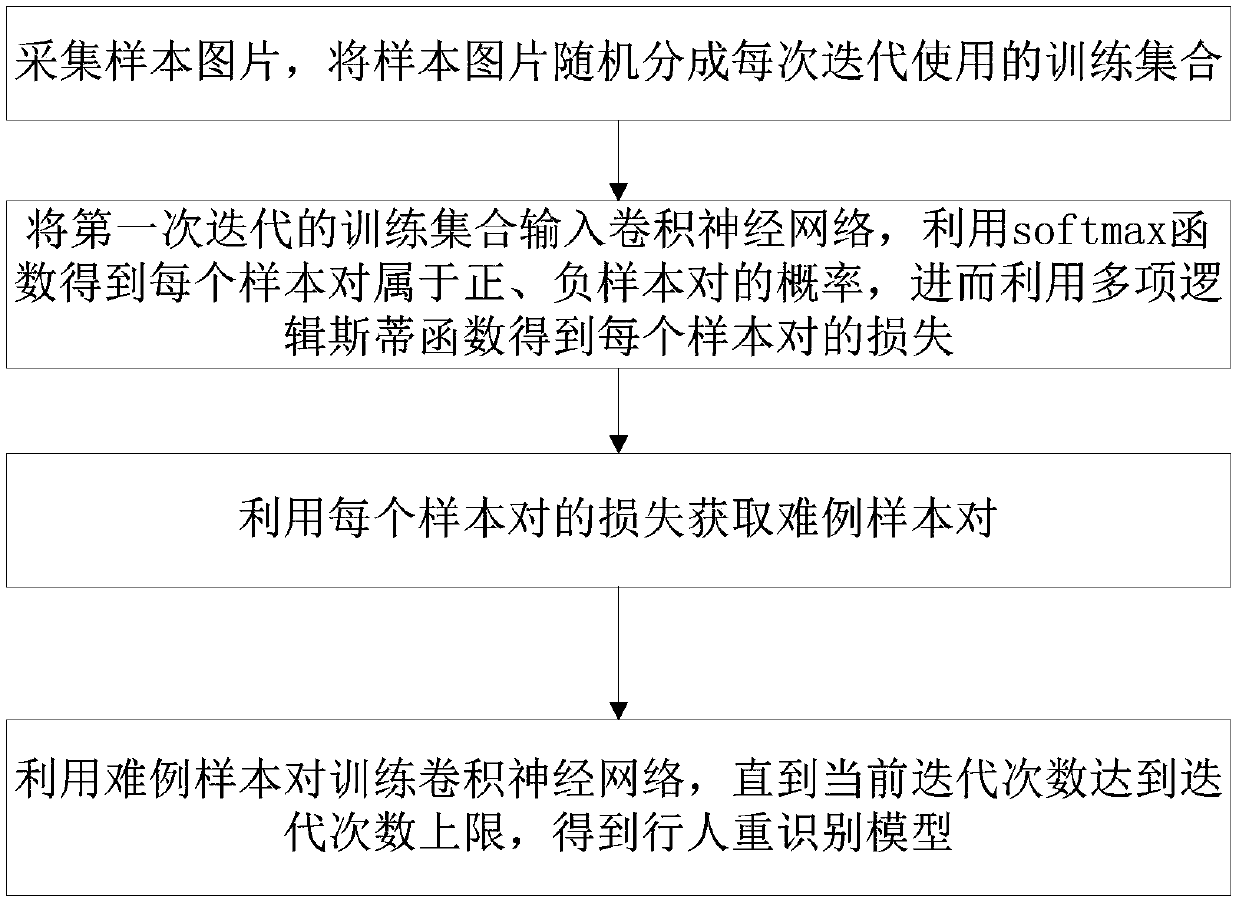

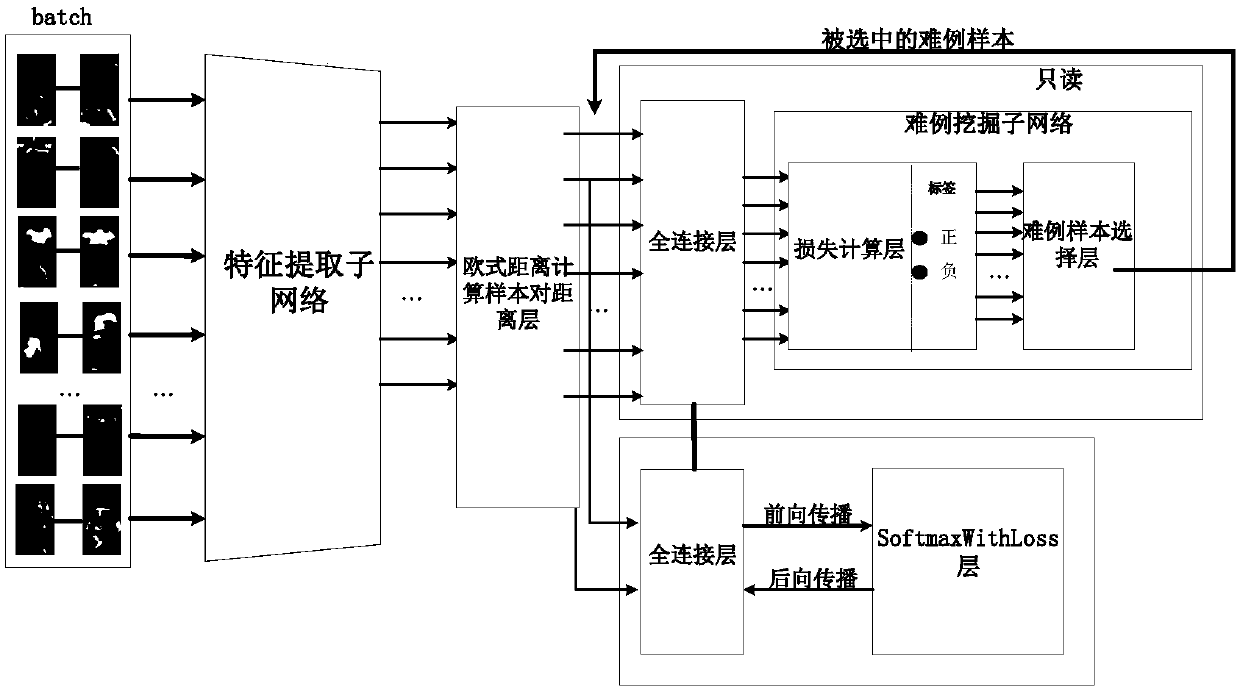

Pedestrian re-identification model, method and system for adaptive difficulty mining

InactiveCN108647577AChoose sciencePrevent overfittingCharacter and pattern recognitionModel extractionSample image

The invention discloses a pedestrian re-identification model, method and system for adaptive difficulty mining. The identification method comprises the steps of: randomly dividing sample pictures intoa training set used for each iteration, inputting the training set into a convolutional neural network, obtaining the probability that each sample pair belongs to a positive or negative sample pair by using a softmax function, and then obtaining the loss of each sample pair by using a multinomial logistic function; obtaining a difficult sample pair by using the loss of each sample pair; and training the convolutional neural network by using the difficult sample pair until the current number of iterations reaches the upper limit of the number of iterations, thus obtaining the pedestrian re-identification model. The pedestrian re-identification model is used to extract features of each picture in a picture set to be identified, and then a similarity order of the sample pairs in the pictureset to be identified is obtained. The pedestrian re-identification model, method and system avoid over-fitting and under-fitting, and have high recognition accuracy.

Owner:HUAZHONG UNIV OF SCI & TECH

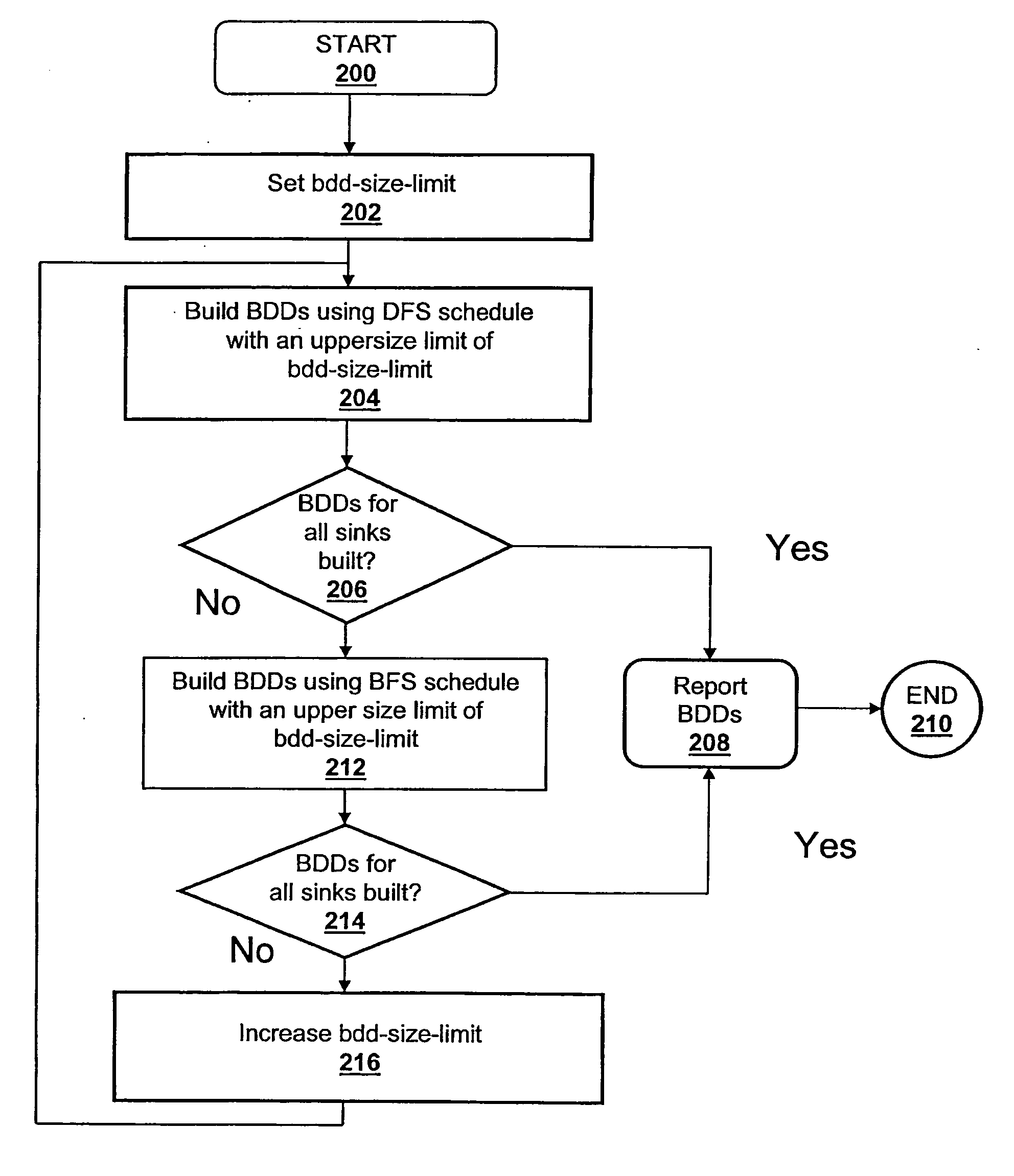

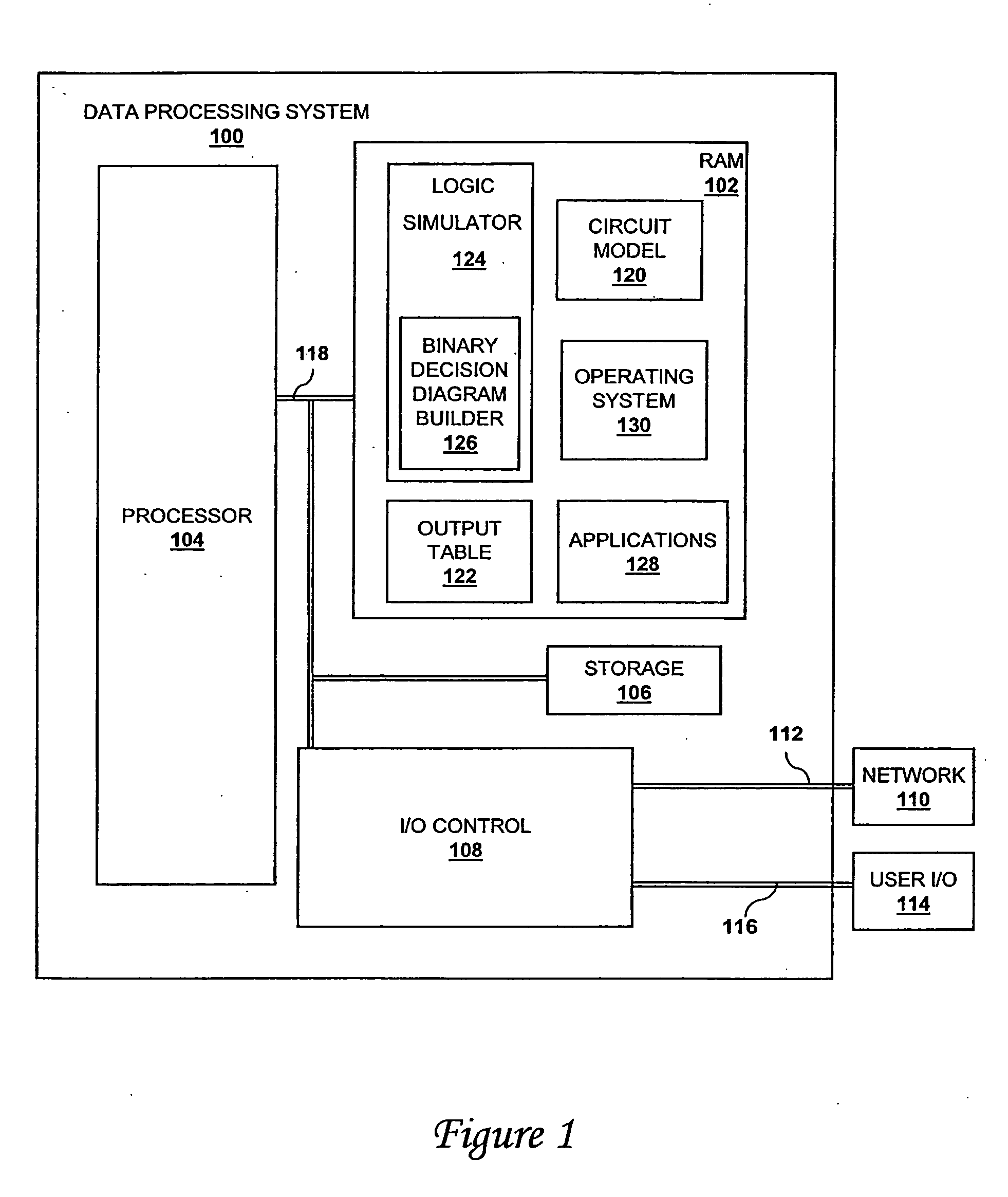

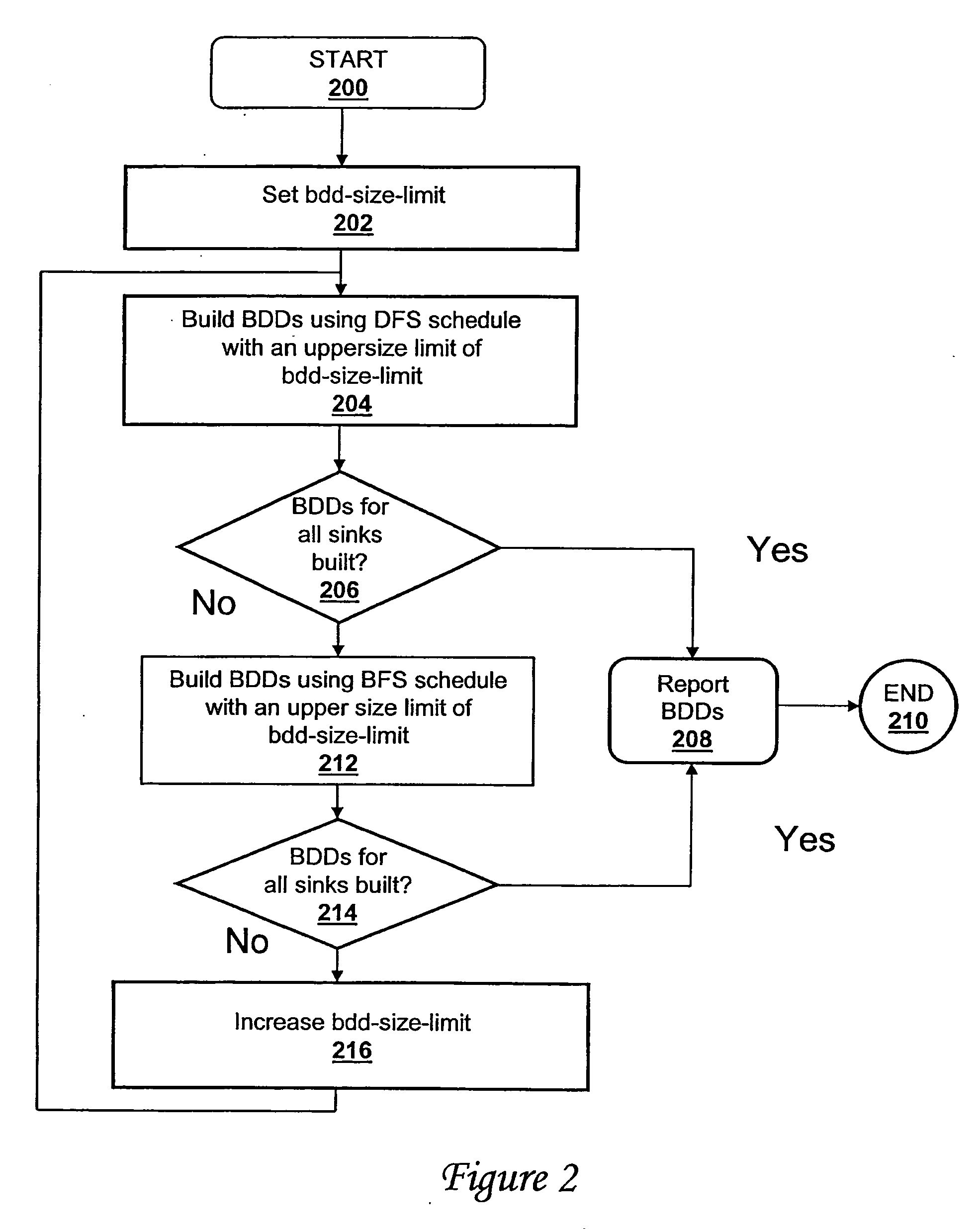

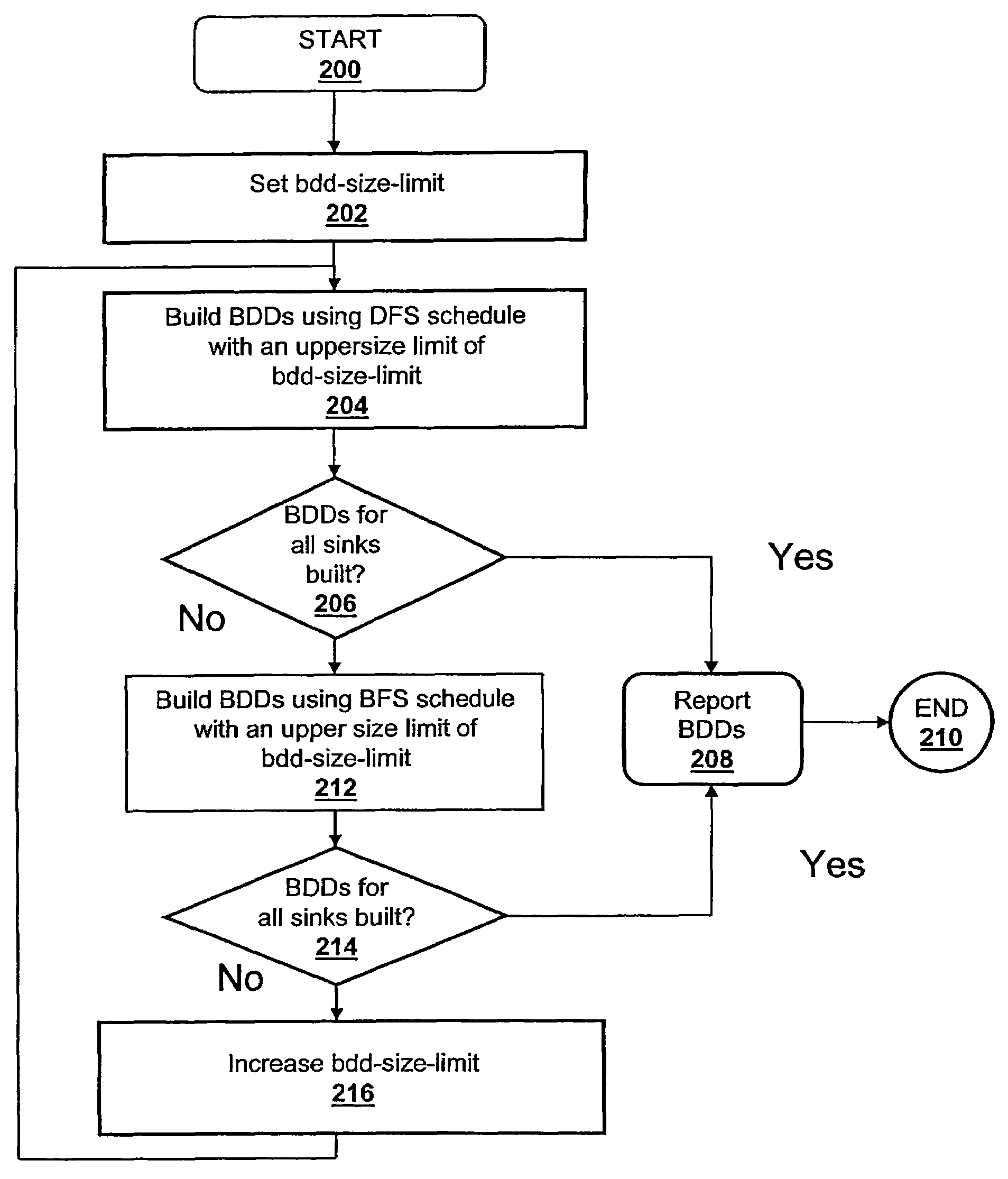

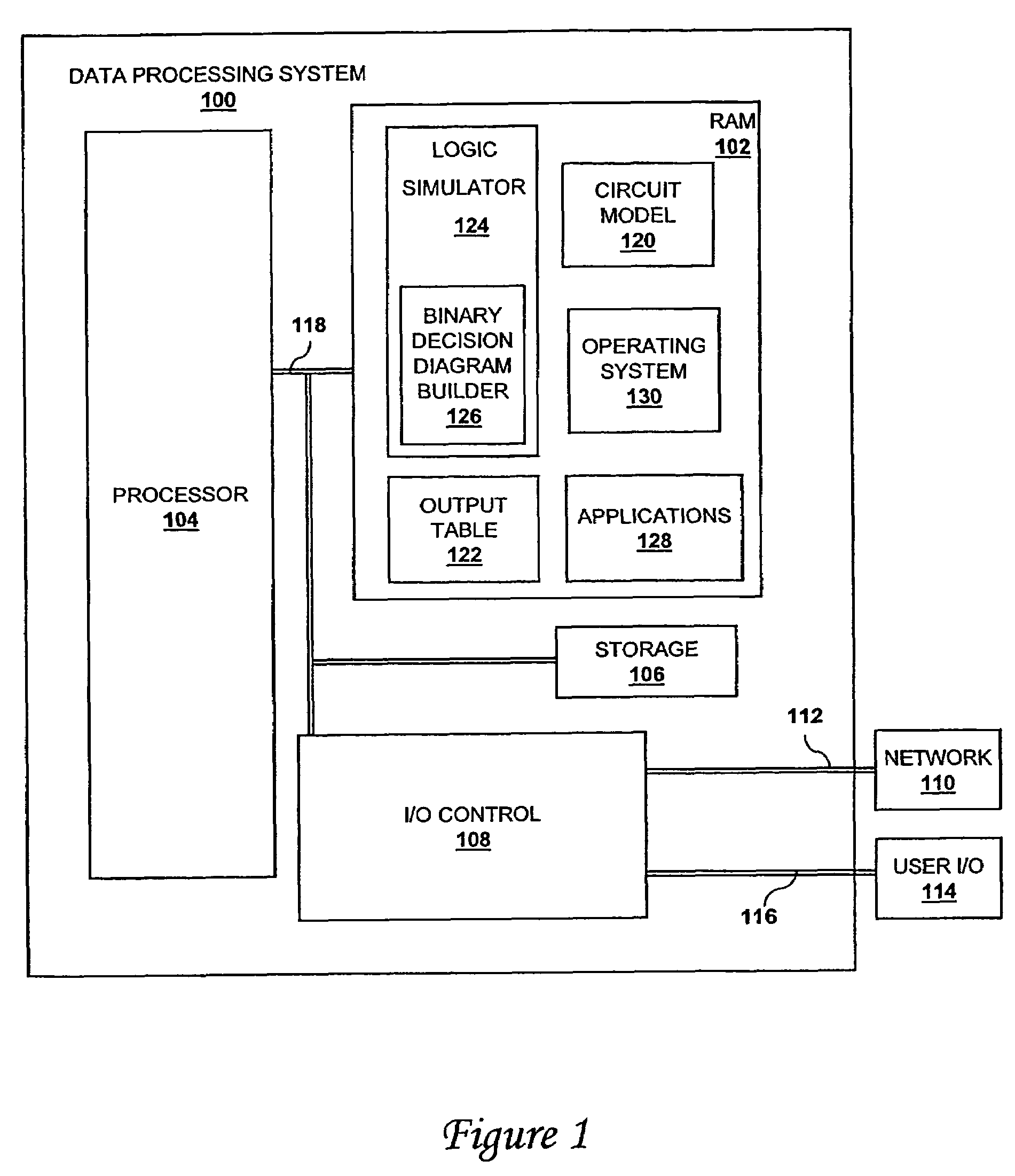

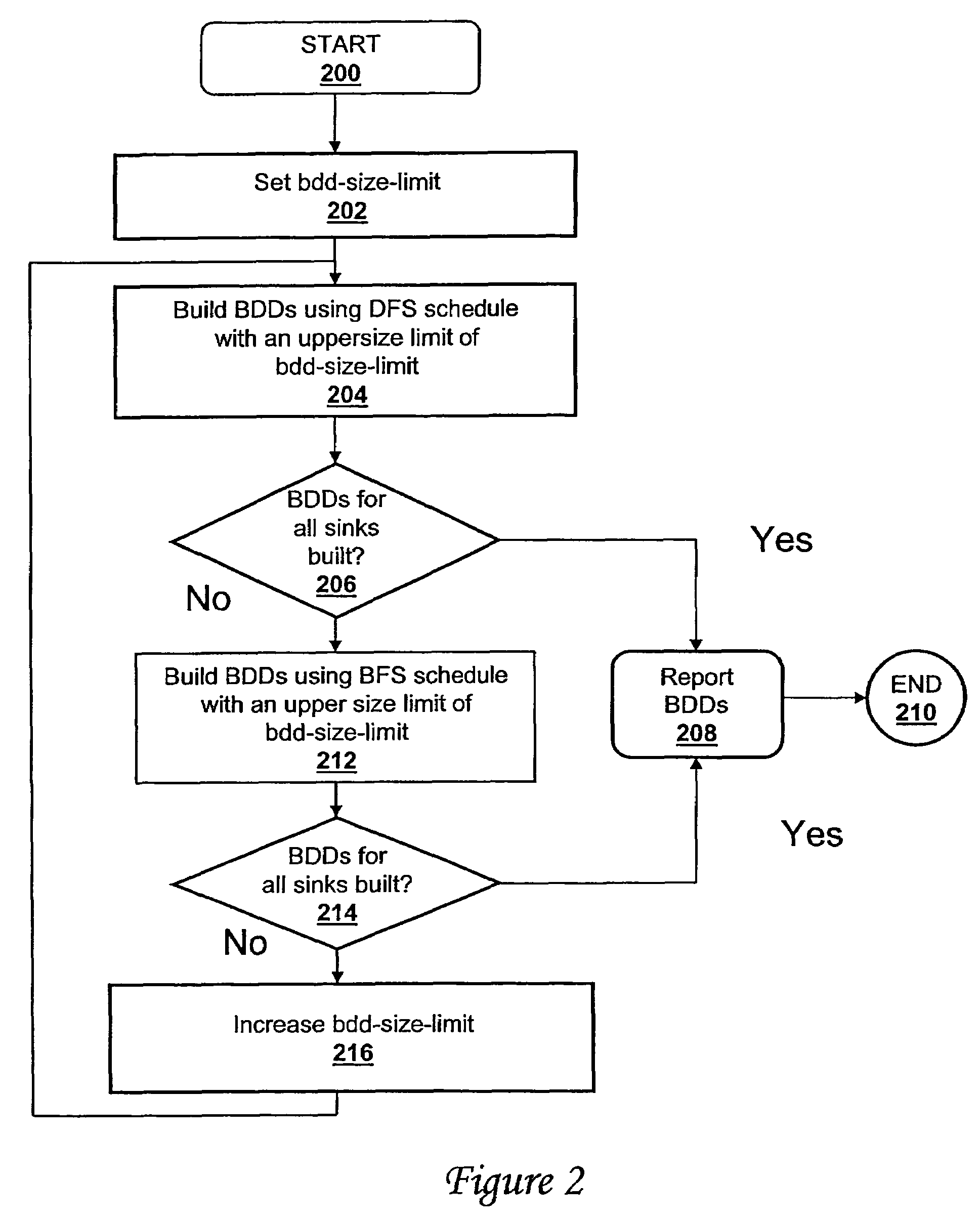

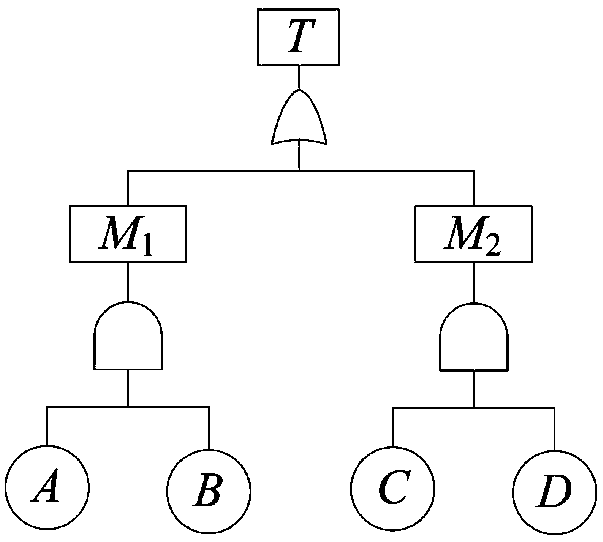

Method and system for building binary decision diagrams efficiently in a structural network representation of a digital circuit

ActiveUS20060047680A1Digital data information retrievalData processing applicationsDepth-first searchDynamic resource

A method, system and computer program product for building decision diagrams efficiently in a structural network representation of a digital circuit using a dynamic resource constrained and interleaved depth-first-search and modified breadth-first-search schedule is disclosed. The method includes setting a first size limit for a first set of one or more m-ary decision representations describing a logic function and setting a second size limit for a second set of one or more m-ary decision representations describing a logic function. The first set of m-ary decision representations of the logic function is then built with one of the set of a depth-first technique or a breadth-first technique until the first size limit is reached, and a second set of m-ary decision representations of the logic function is built with the other technique until the second size limit is reached. In response to determining that a union of first set and the second set of m-ary decision representations do not describe the logic function, the first and second size limits are increased, and the steps of building the first and second set are repeated. In response to determining that the union of the first set of m-ary decision representations and the second set of m-ary decision representations describe the logic function, the union is reported.

Owner:GLOBALFOUNDRIES US INC

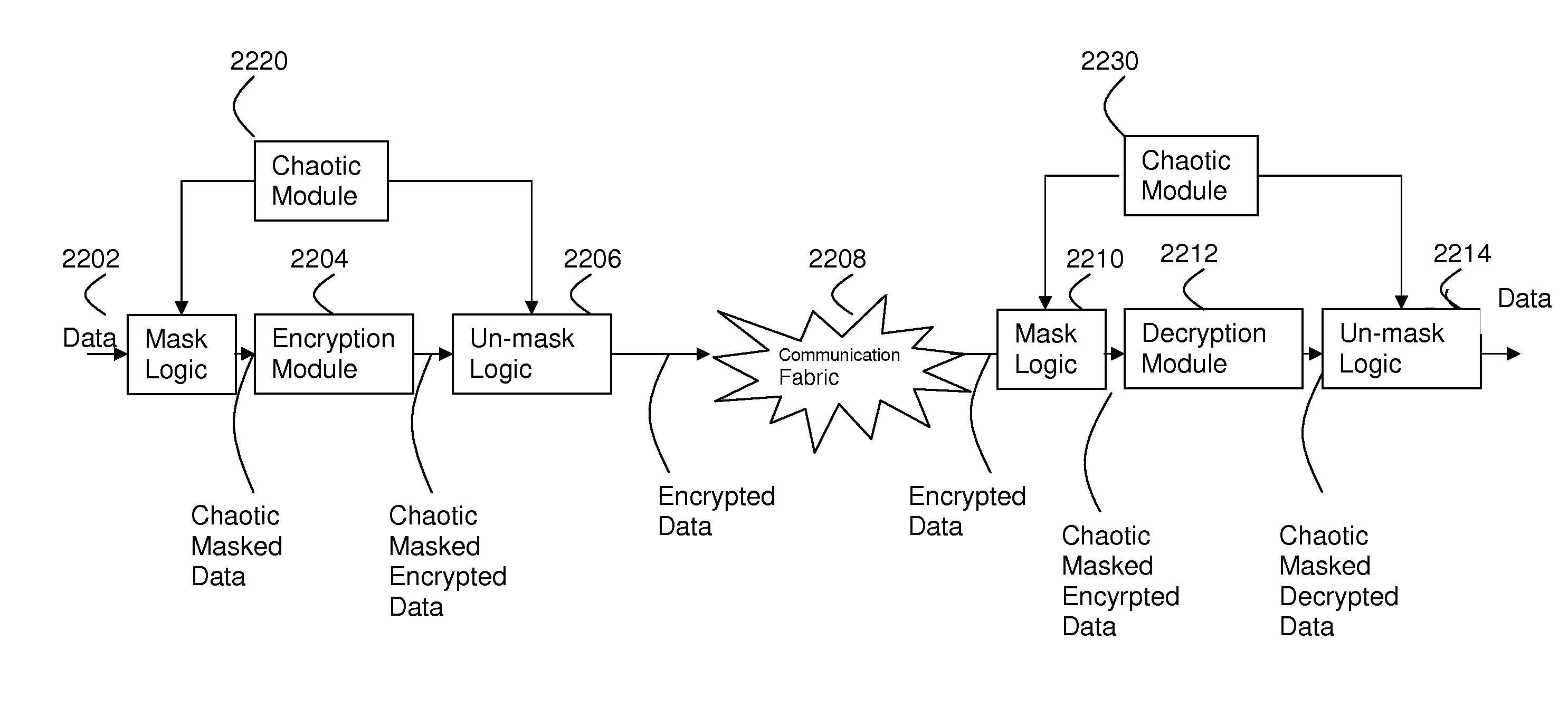

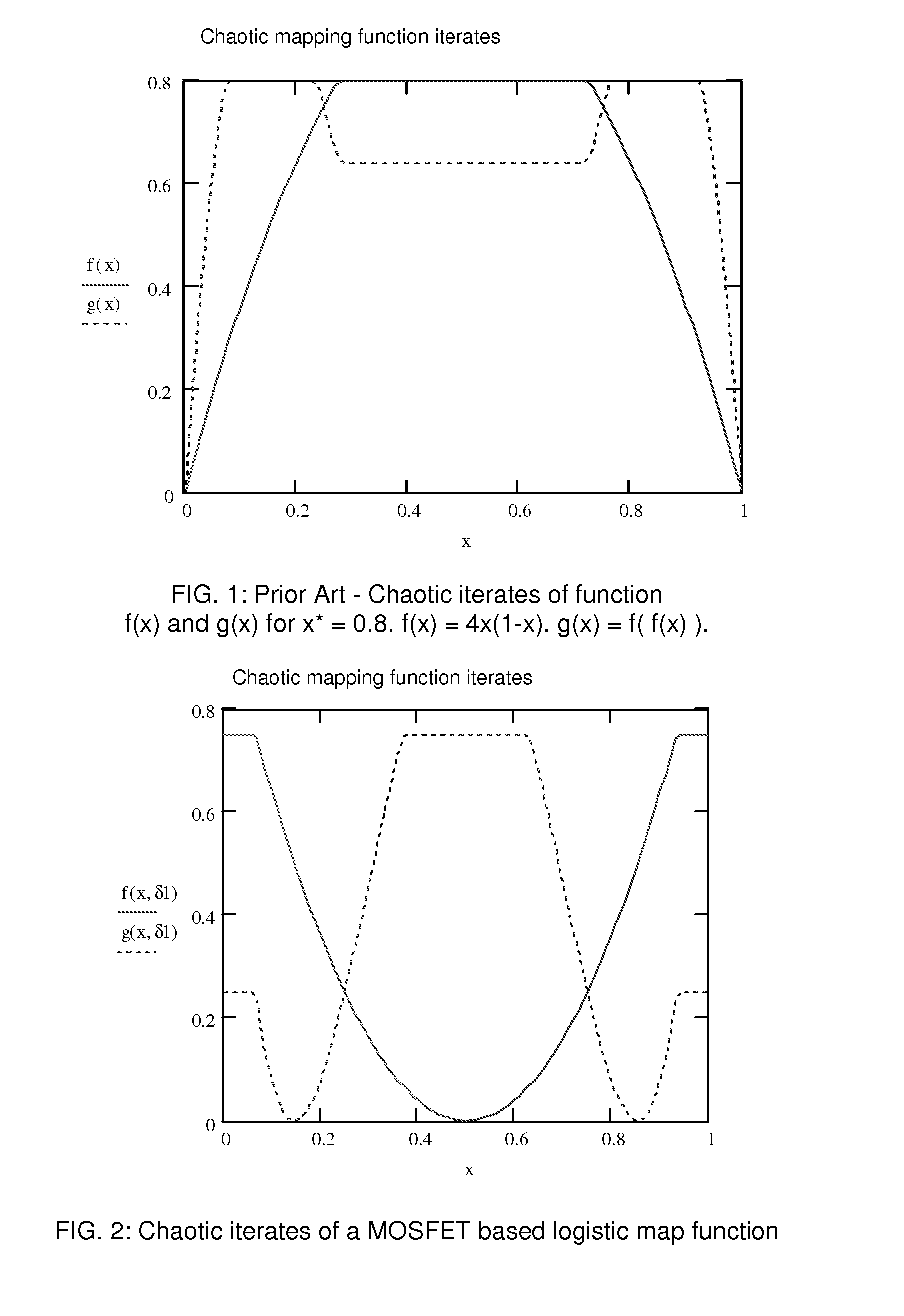

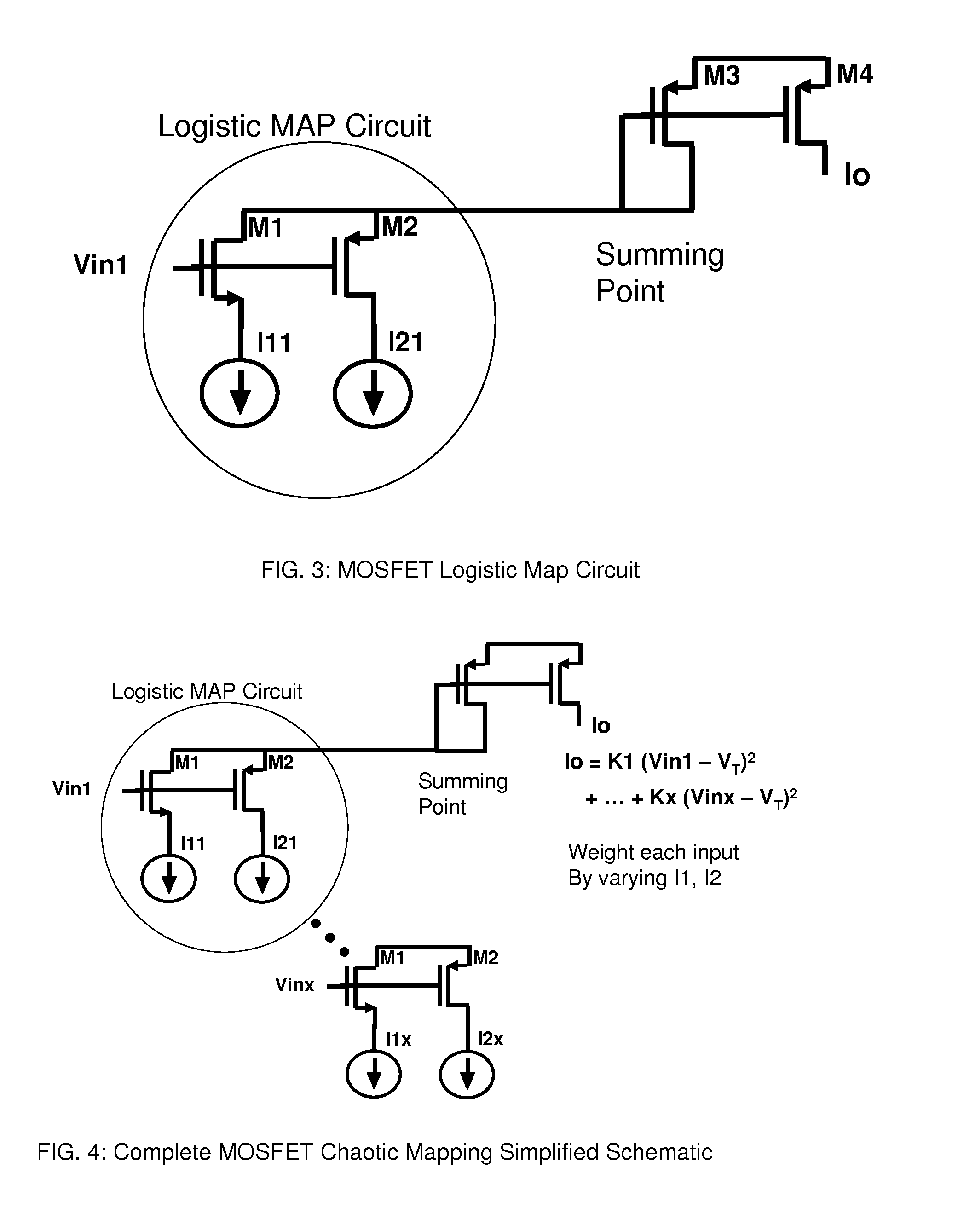

High utilization universal logic array with variable circuit topology and logistic map circuit to realize a variety of logic gates with constant power signatures

ActiveUS20110085662A1Avoid detectionPower reduction in field effect transistorsLogic circuits characterised by logic functionMulti inputConstant power

Disclosed is a novel circuit able to generate any logic combination possible as a function of the input logic signals. The circuit is described as a 2 input logistic map circuit but may be expanded to 3 or more inputs as required. Further disclosed is a universal logic array with variable circuit topology. A metallization layer and / or a via interconnection between cells in the array elements produce a circuit topology that implements a Boolean function and / or chaotic function and / or a logic function. The novel circuit provides a circuit topology for secure applications with no obvious physical correspondence between control signal values and input to output mapping. Further disclosed is a network which has a power signature independent of input signal state and output transition. This provides a very useful circuit to protect data from decryption from power signature analysis in secure applications.

Owner:CHAOLOGIX INC

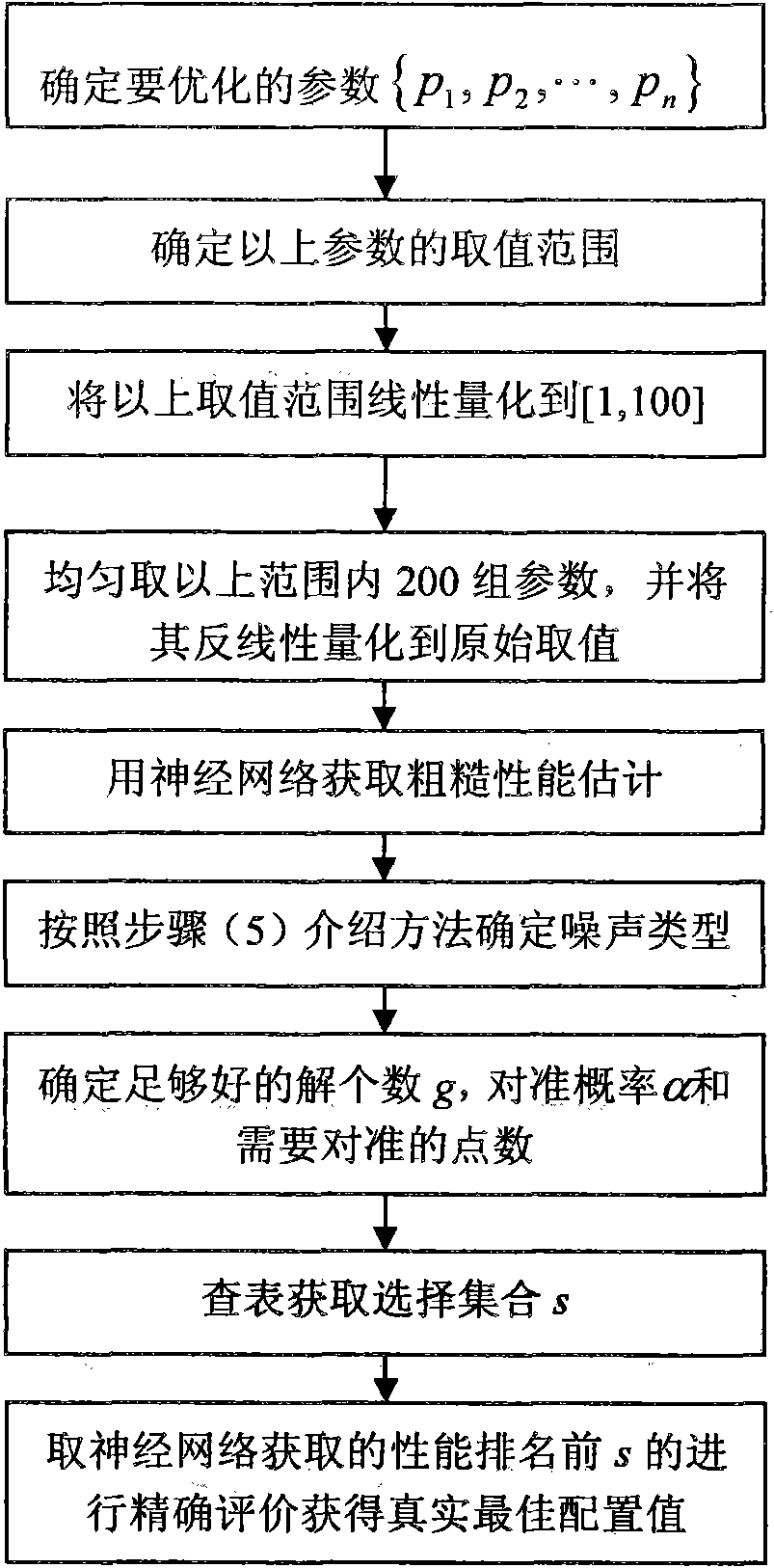

Method for improving performance tuning speed of distributed system

ActiveCN101609416AShorten test timeBiological neural network modelsMultiprogramming arrangementsPerformance tuningNetwork model

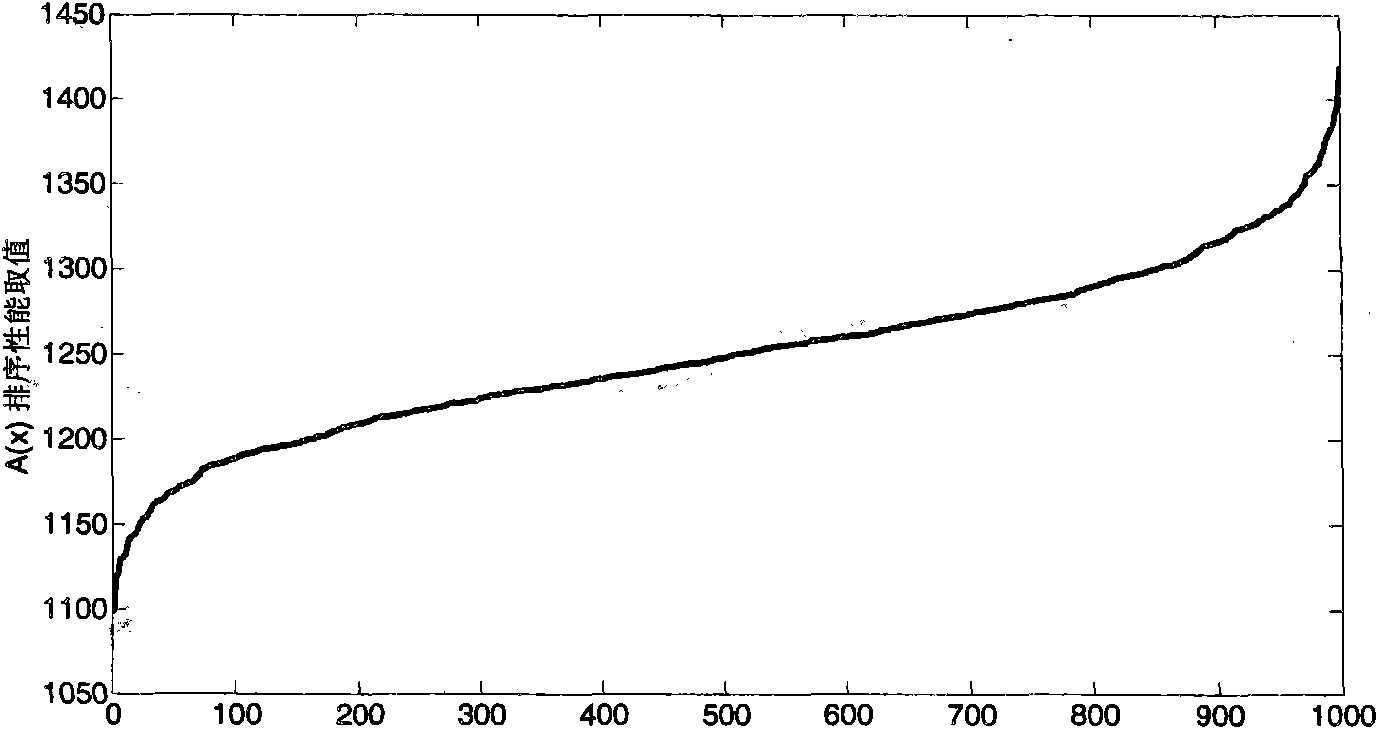

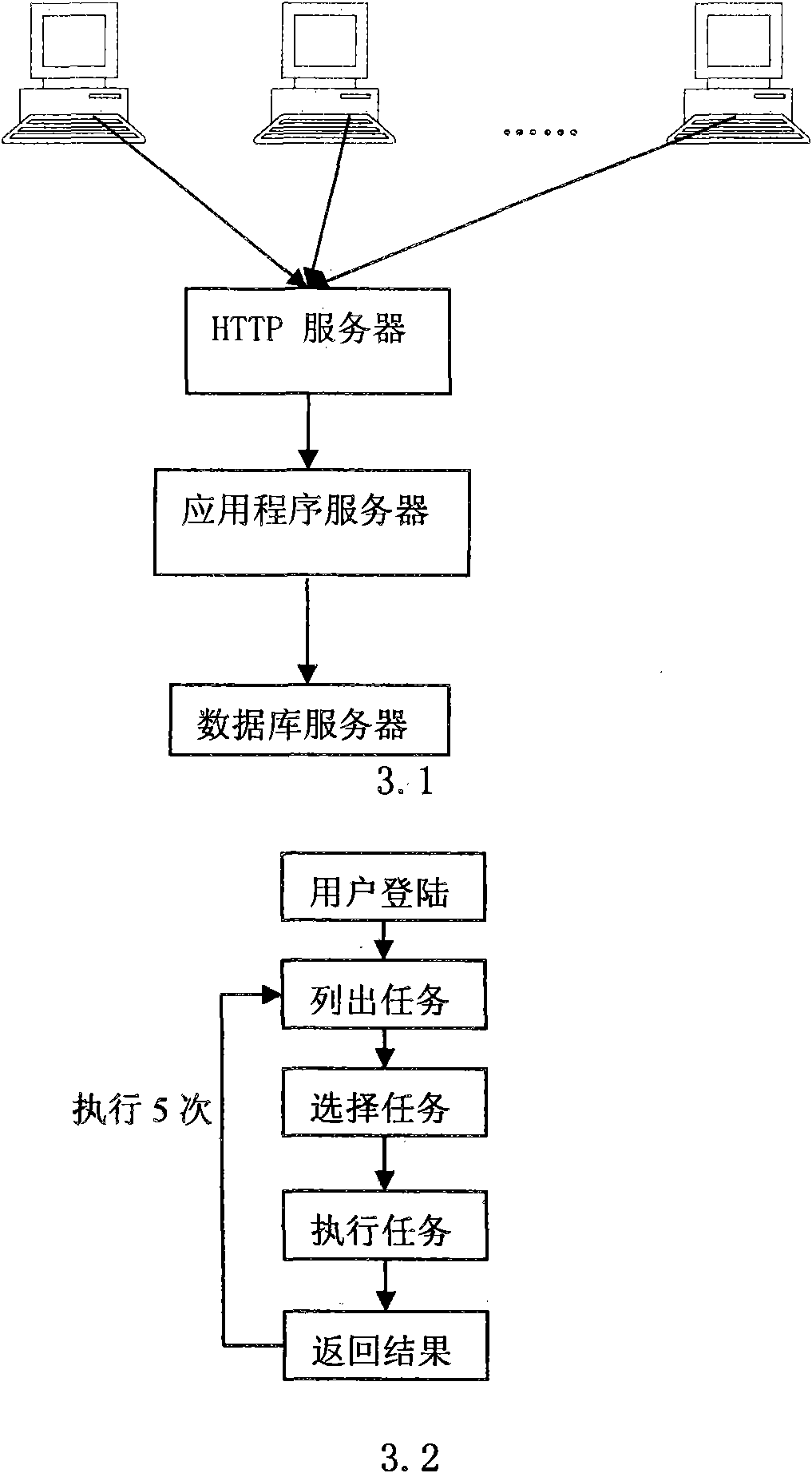

A method for improving performance tuning speed of a distributed system belongs to the technical category of performance optimization of a distributed computer system. The method is characterized by comprising the steps of quantizing the parameters with respective numeric area as a uniform parameter set in the distributed system including a web page server, an application programme server and a database server and composed of three-layer servers, obtaining the parameter set through uniform sampling, training by using a three-layer neural network model which comprises two hidden layers and of which each node is a logistic function, then repeatedly sampling, testing new parameters in the neural network to obtain rough response time and rough throughput rate, determining the sequencing performance curve and noise grade of the neural network based on the requirements of the system performance optimization, and finally obtaining the parameters of a regression function according to the set relative performance requirements so as to obtain the desired optimal parametric solution. The invention has the advantages that the invention improves the system performance and synchronously reduces test time.

Owner:CERTUS NETWORK TECHNANJING

Network logistics

InactiveCN101639889ASolving Comprehensive Integration ProblemsData processing applicationsData switching by path configurationShortest distanceGeneral purpose computer

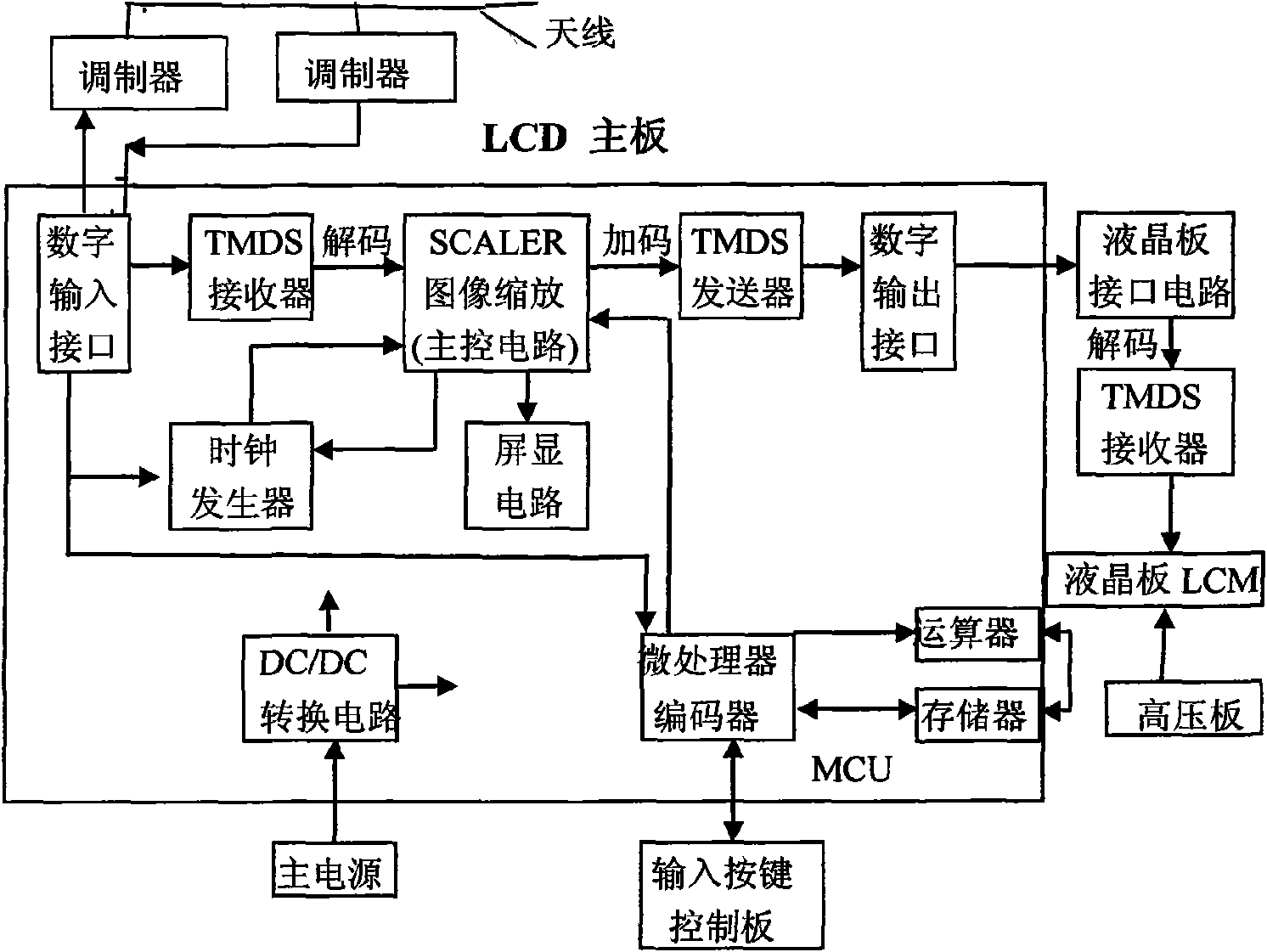

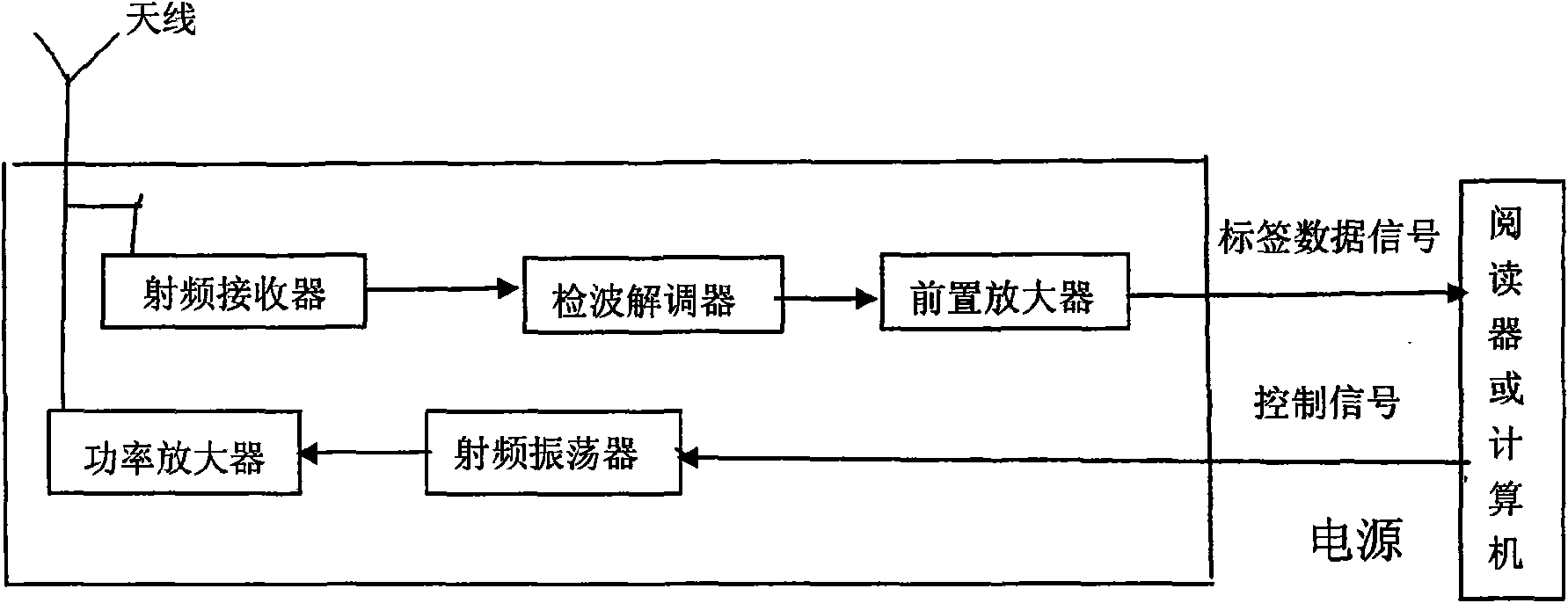

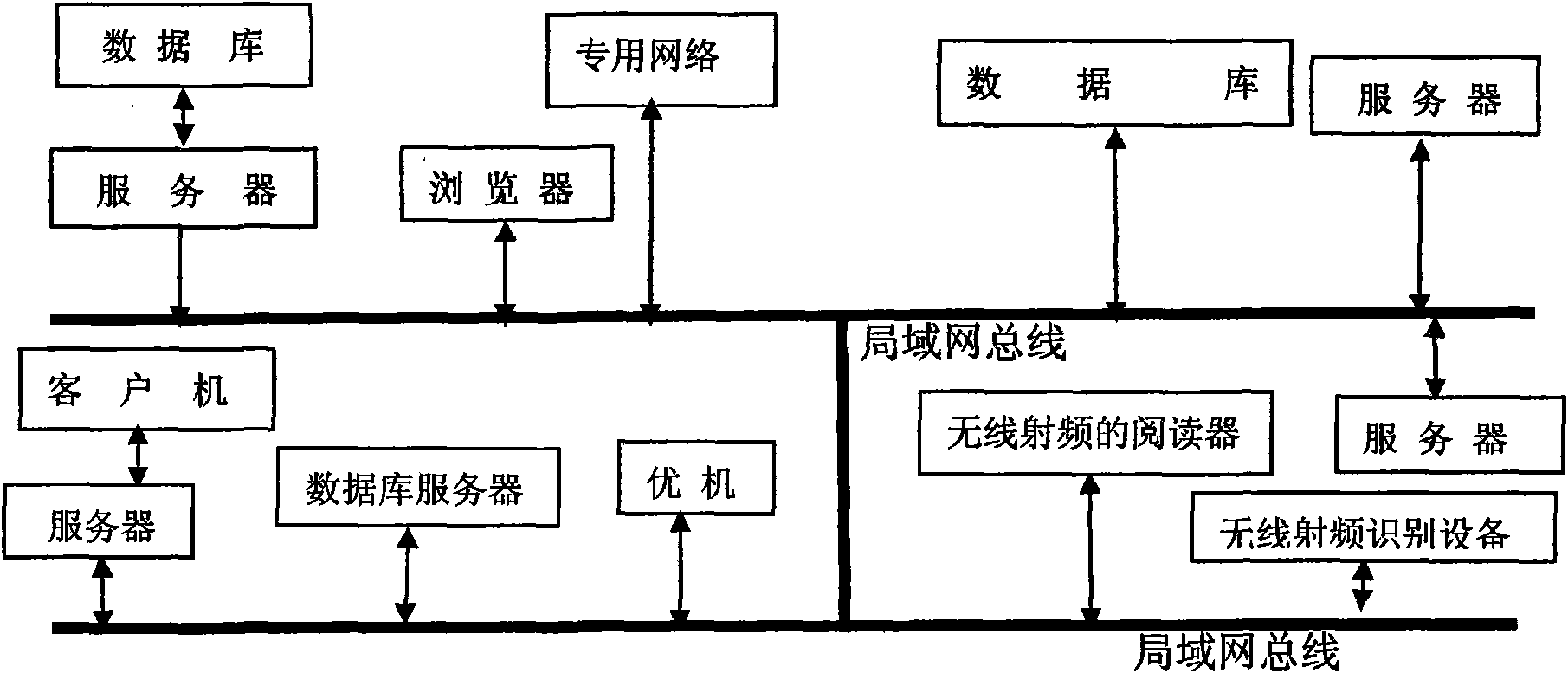

Network logistics and network business are mutually integrated. In order to realize the sharing of logistics information and logistics functions among logistics enterprises, industrial and commercialenterprises and logistics supervision government departments, the network logistics has to be interconnected, intercommunicated and interoperated with network government affairs. The problem of logistics information comprehensive integration among logistics enterprises, industrial and commercial enterprises, financial institutions and government supervision departments in logistics can be effectively solved by means of the government affairs. Network logistics systems are closely related to the network business, the network government affairs, network intelligent traffic systems and the like.The network logistics is based on the network business, the network government affairs, the network intelligent traffic systems and the like. A plurality of identification facilities and a general purpose calculator are mutually connected in a short distance through transmission media according to physical topological structures of a local area network (in a star shape, a ring shape, a tree shapeor a bus shape and the like) to form a logistics network unit. Each identification facility is fixedly distributed in a monitoring area and respectively takes an identification task of cargoes and thelike of the monitoring area in the logistics system.

Owner:刘文祥

Urban trunk road travel time estimation method based on variable weight mixed distribution

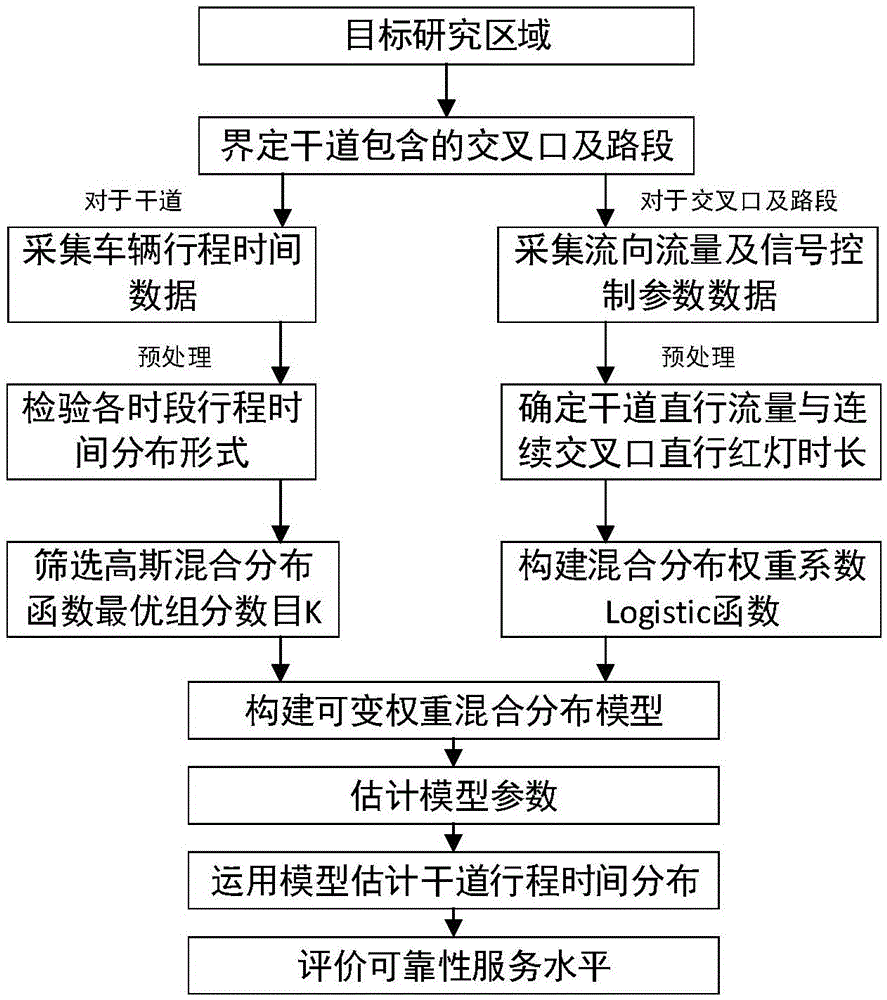

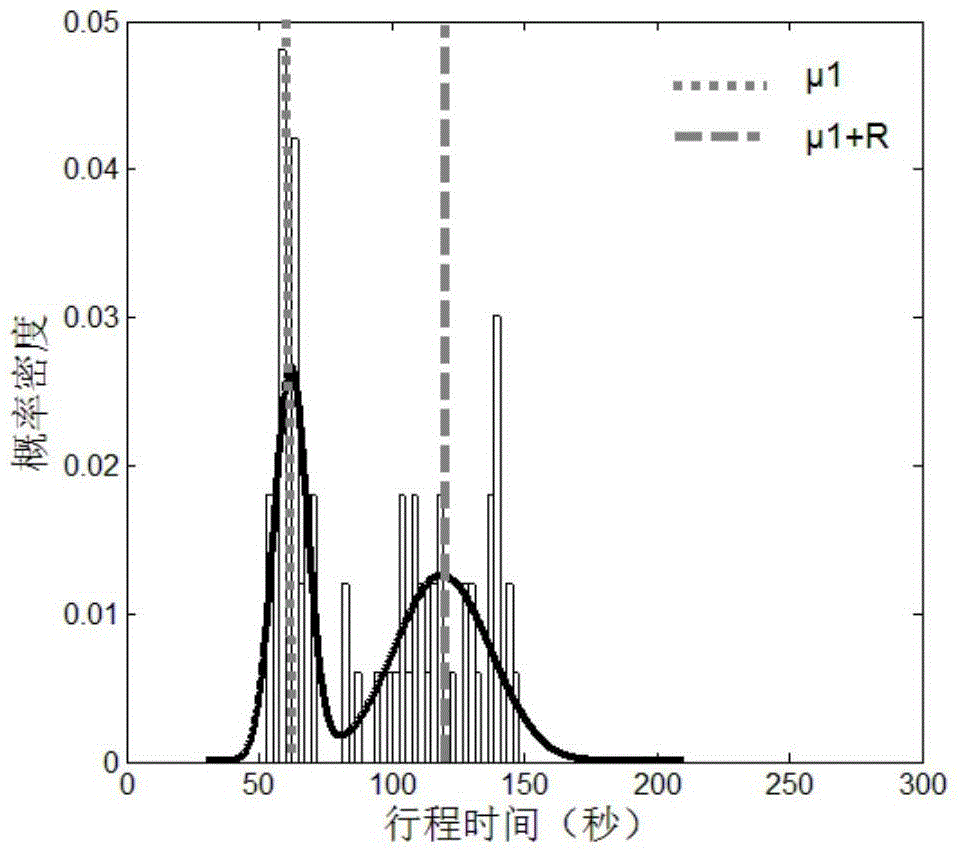

ActiveCN105679025AOvercoming portabilityOvercoming adaptabilityDetection of traffic movementWeight coefficientEngineering

The invention discloses an urban trunk road travel time estimation method based on variable weight mixed distribution, and belongs to the technical field of intelligent traffic. The method comprises the steps: collecting a trunk road travel time parameter of a trunk road in a target research region, preprocessing and verifying the distribution mode of the trunk road travel time in all time periods, building a Gaussian mixed distribution model with a fixed weight, and determining an optimal component number K; collecting the flow in all flowing direction and a signal control parameter for an intersection and an road segment, and building a mixed distribution weight coefficient Logistic function with K components; building a variable weight mixed distribution model, estimating an unknown parameter in the variable weight mixed distribution model, and finally carrying out the estimation of trunk road travel time distribution and the estimation of reliability service level. Compared with a conventional single-distribution-function and fixed weight mixed distribution model, the method irons out the defects that the transplantability and the adaptability are poor, and can achieve the more accurate estimation and reliability evaluation of the trunk road travel time distribution.

Owner:BEIHANG UNIV

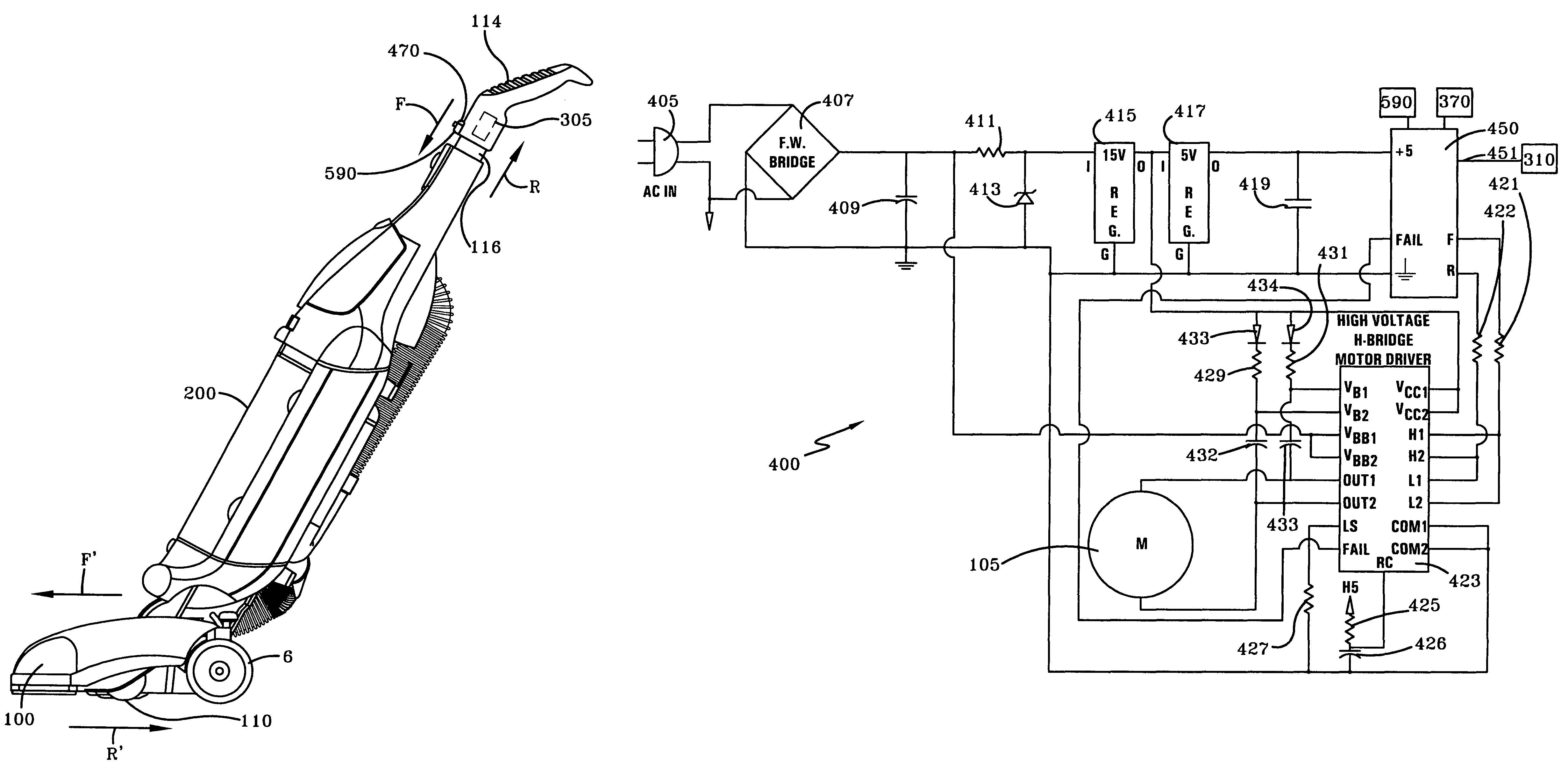

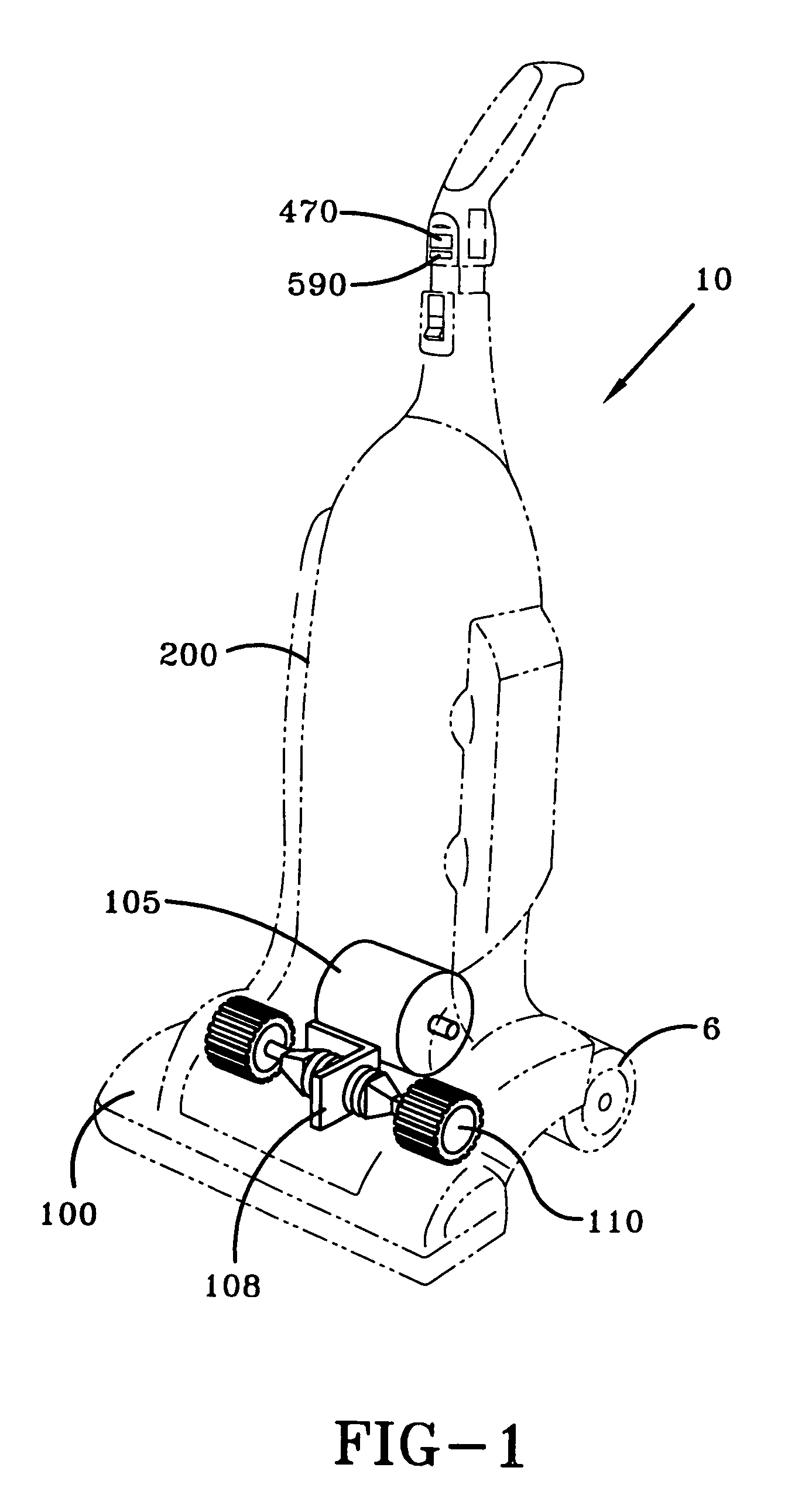

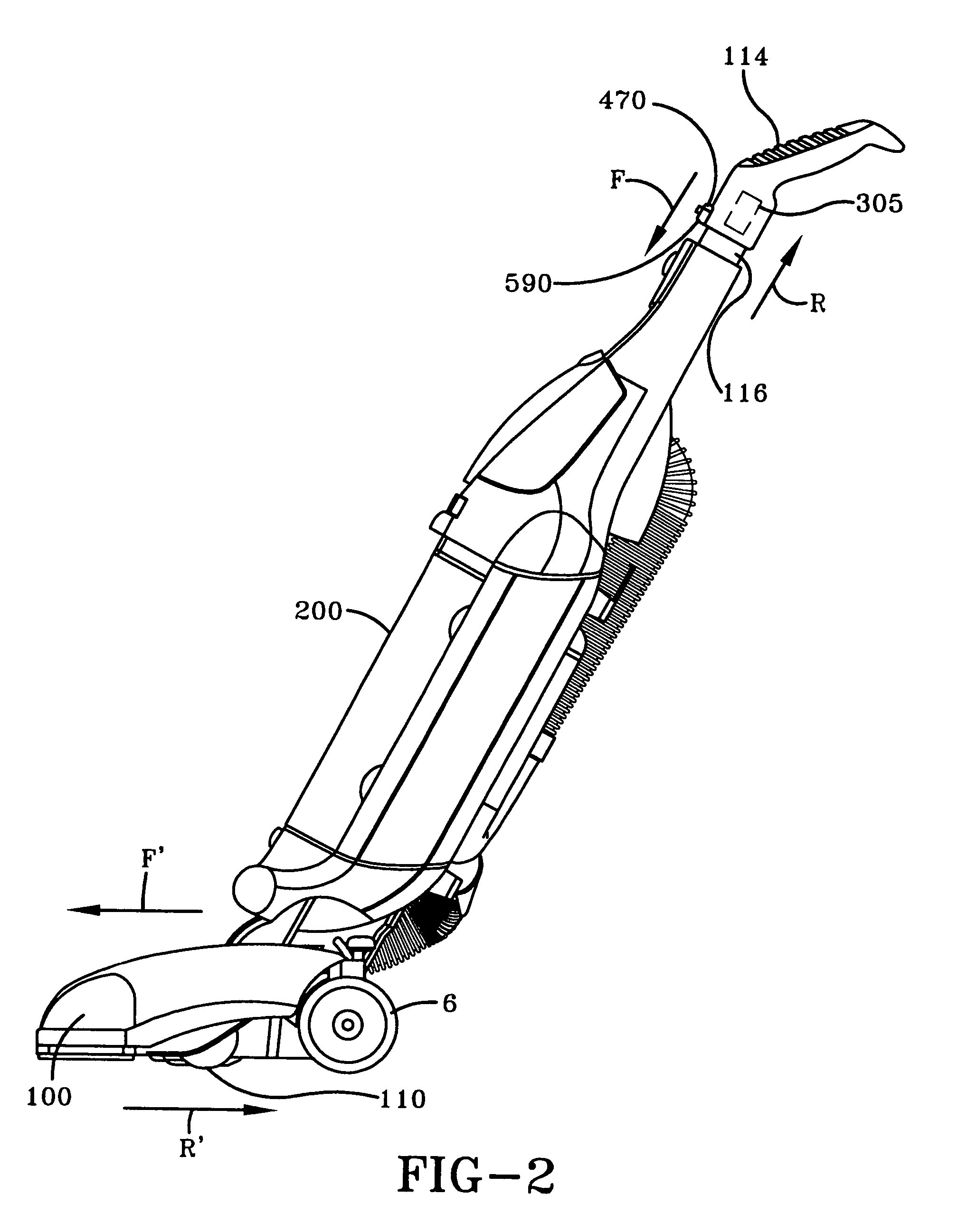

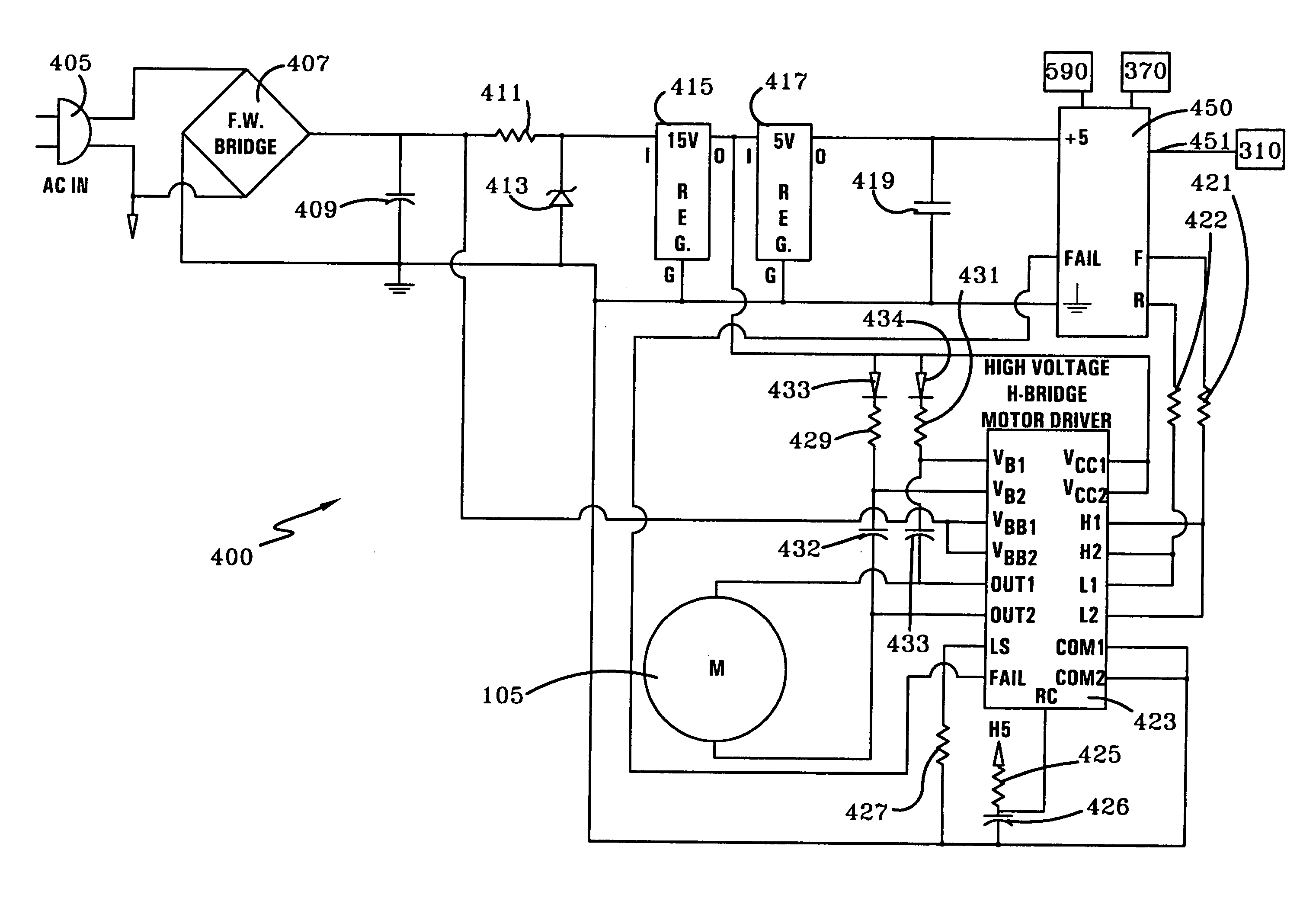

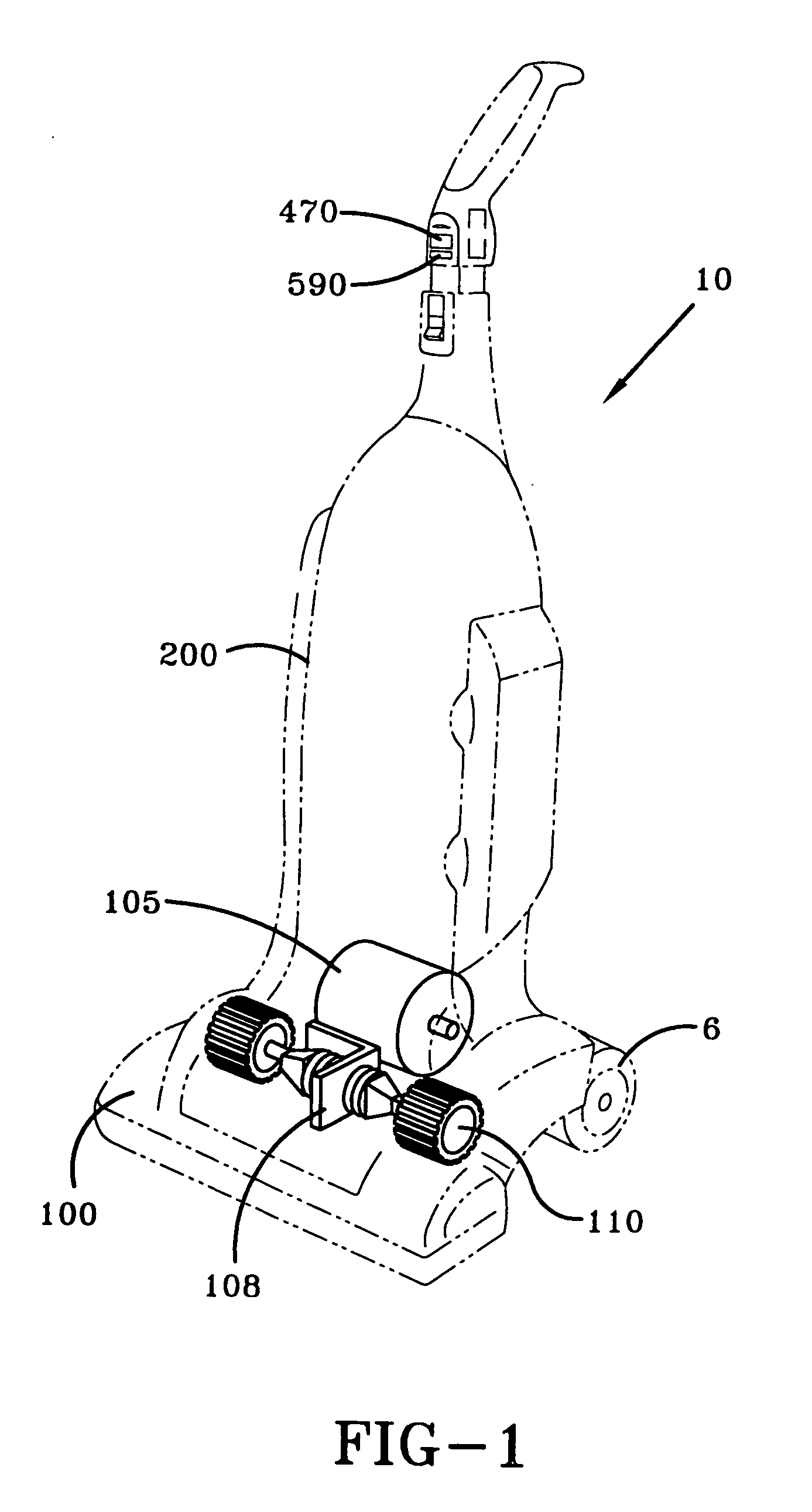

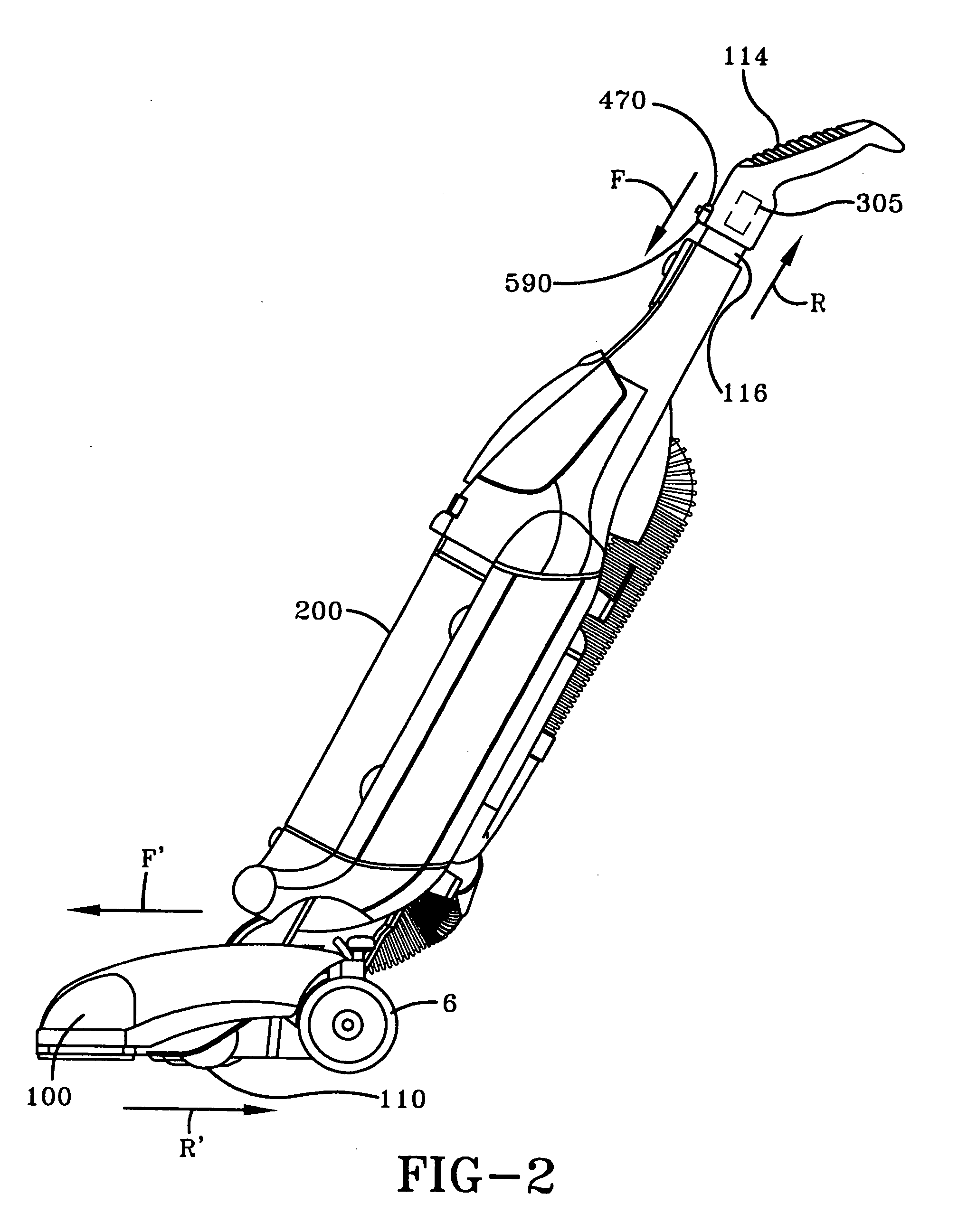

Control arrangement for a propulsion unit for a self-propelled floor care appliance

A self propelled upright vacuum cleaner is provided with a Hall effect sensor to provide a Hall voltage that varies according to the position of a handgrip maintained by the vacuum cleaner. A microprocessor generates a PWM control signal to control the movement of the vacuum based on the magnitude of the Hall voltage with respect to various response characteristics, including a non-linear logistic function. As such, the vacuum cleaner imparts a user-friendly responsiveness to the user during the operation of the vacuum cleaner.

Owner:TECHTRONIC FLOOR CARE TECH LTD

Control arrangement for a propulsion unit for a self-propelled floor care appliance

A self propelled upright vacuum cleaner is provided with a Hall effect sensor to provide a Hall voltage that varies according to the position of a handgrip maintained by the vacuum cleaner. A microprocessor generates a PWM control signal to control the movement of the vacuum based on the magnitude of the Hall voltage with respect to various response characteristics, including a non-linear logistic function. As such, the vacuum cleaner imparts a user-friendly responsiveness to the user during the operation of the vacuum cleaner.

Owner:TECHTRONIC FLOOR CARE TECH LTD

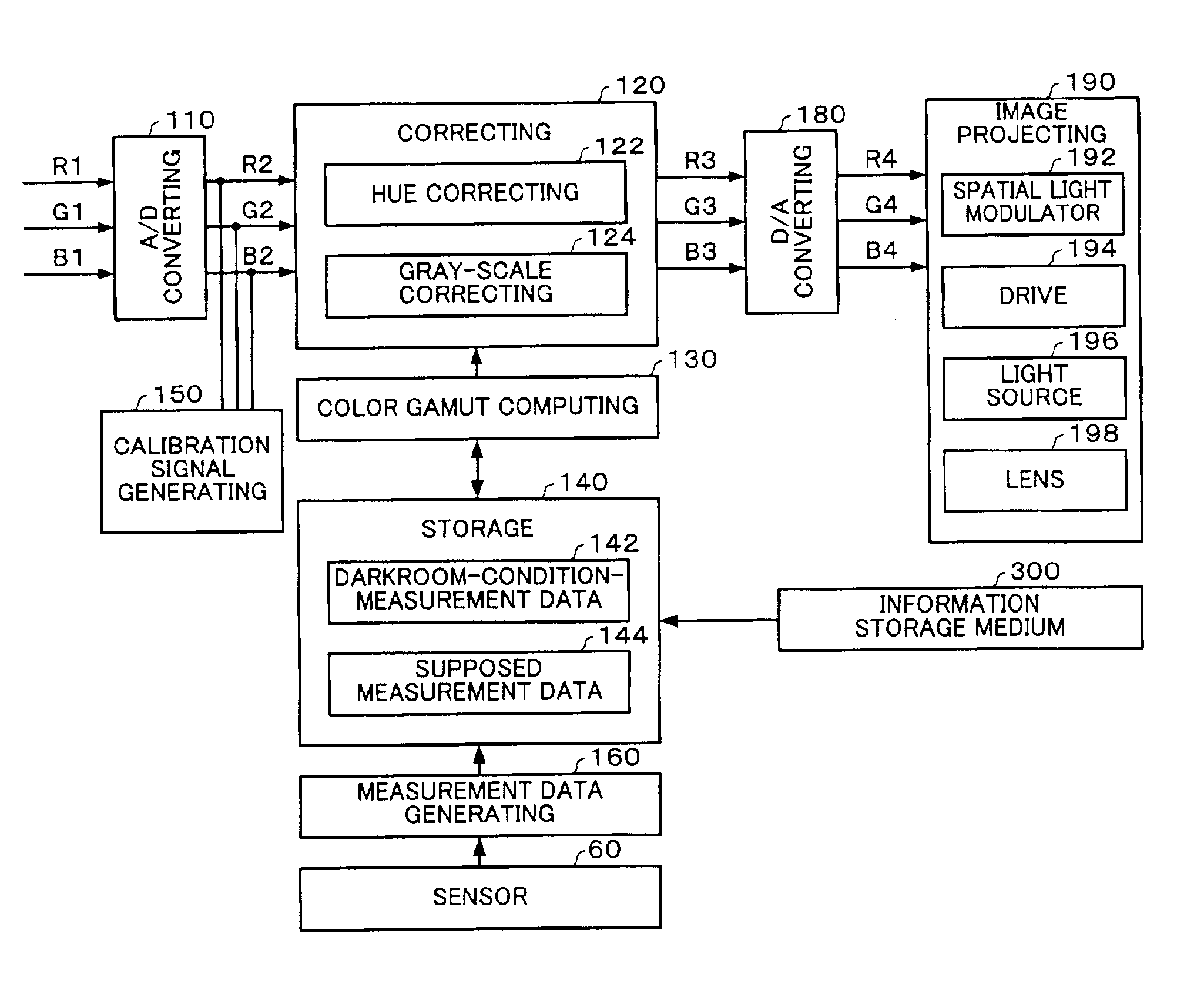

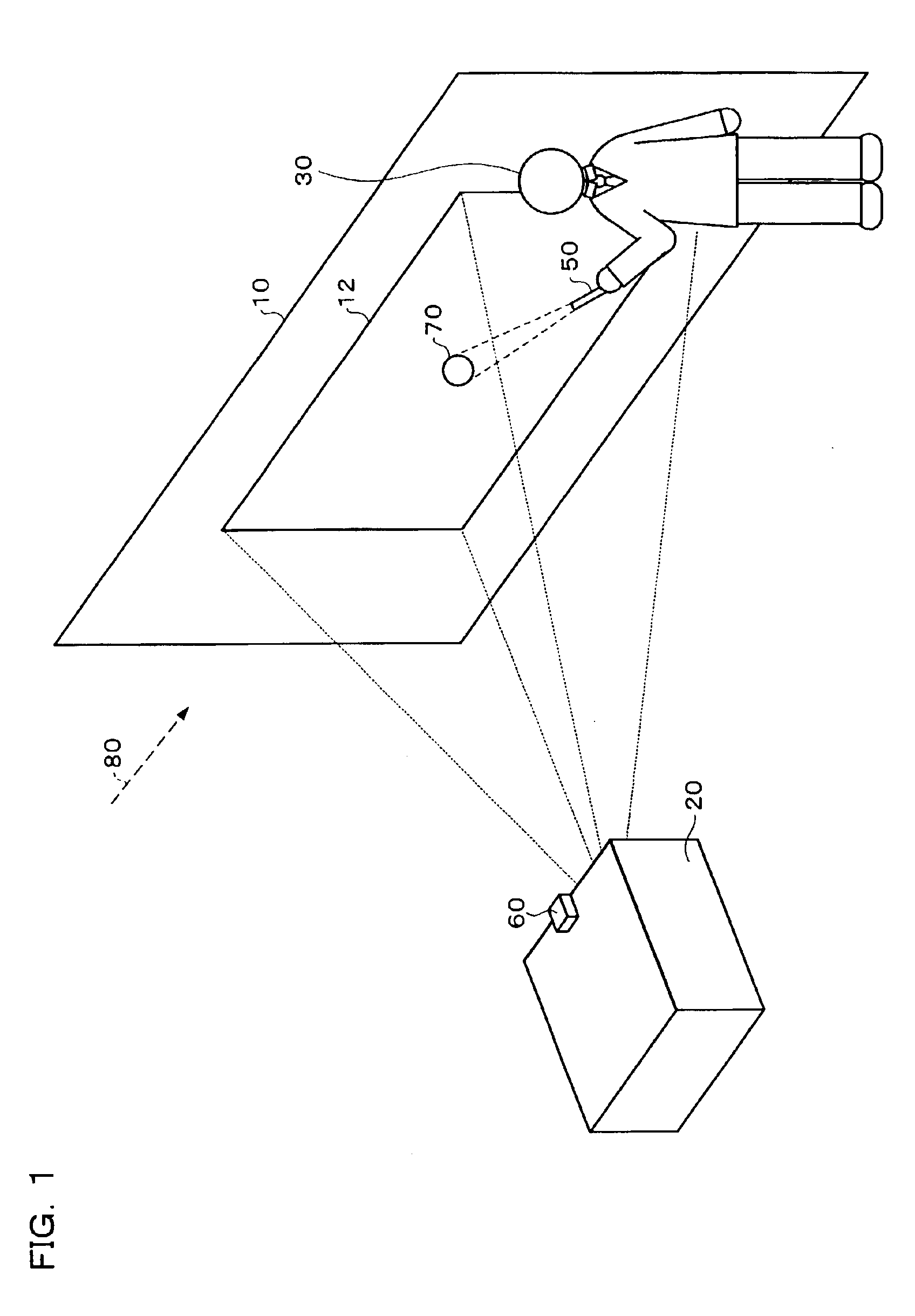

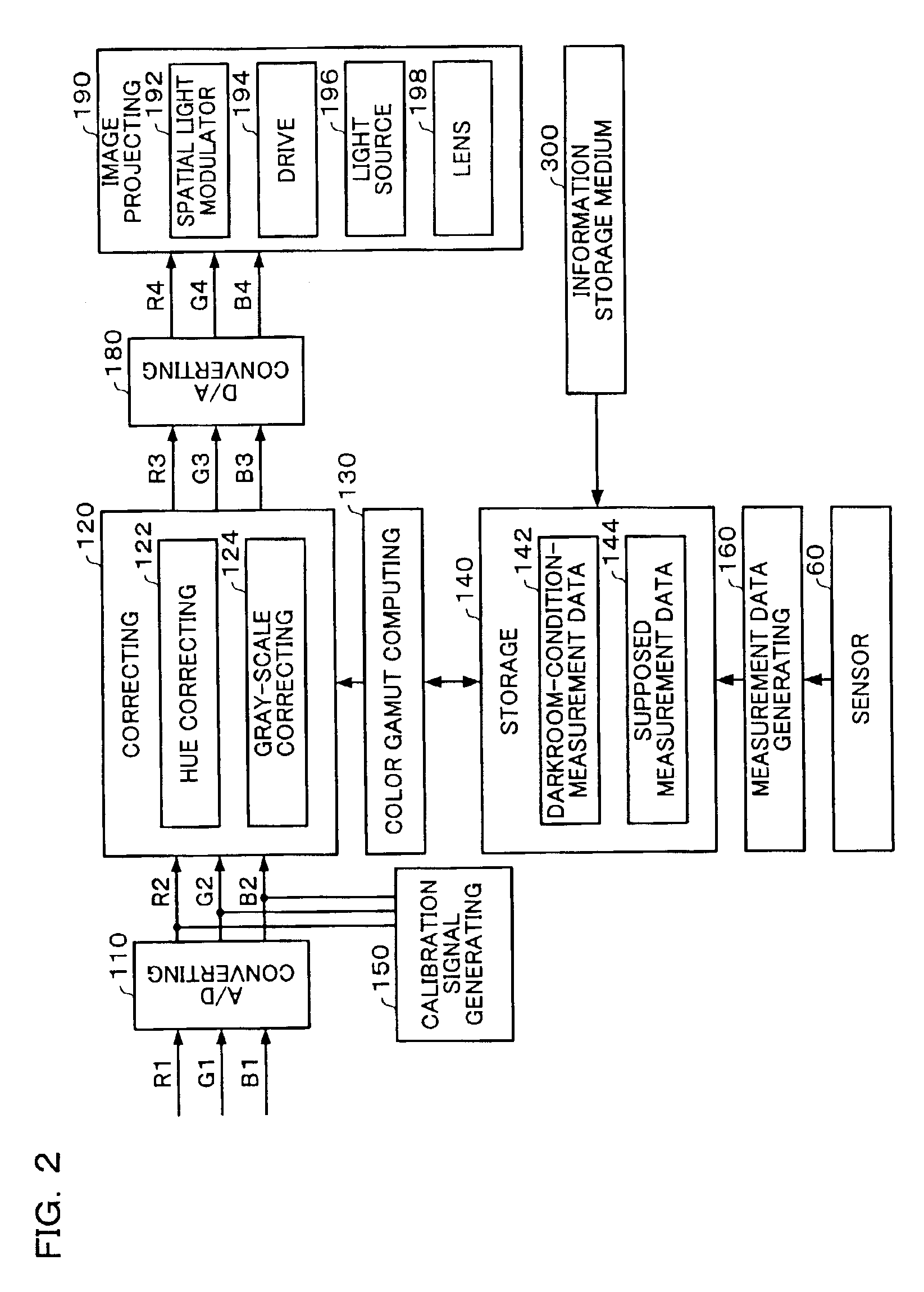

Image processing system, projector, program, information storage medium, and image processing method

InactiveUS7011413B2Shorten the timeTelevision system detailsImage enhancementImaging processingGamut

An image processing system that shorten calibration time includes a storage section which stores darkroom-condition-measurement data obtained by measuring a display region on which a plurality of calibration images having different colors are displayed under a darkroom condition through a sensor; a measurement data generating section which generates supposed measurement data based on a viewing-environment-measurement data obtained by measuring one of the plurality of calibration images through the sensor under a viewing environment and the darkroom-condition-measurement data; a color gamut computing section which computes an area ratio between a color gamut based on the darkroom-condition-measurement data and a color gamut based on the supposed measurement data; and a correcting section which corrects an image correcting data to correct a hue and gray scale of an image using a logistic function with a parameter based on the area ratio and also corrects image information for displaying an image.

Owner:SEIKO EPSON CORP

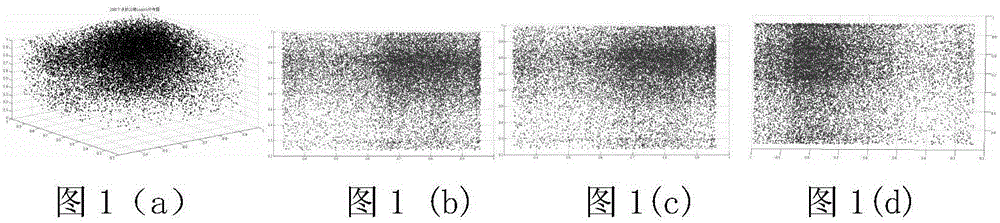

Image duel scrambling method based on three-dimensional Logistic mapping

InactiveCN103606126ADouble reset implementationSimple methodImage data processing detailsDigital signal processingLogistic map

An image duel scrambling method based on three-dimensional Logistic mapping belongs to the field of digital image processing. The image positive scrambling process comprises the steps that firstly an IMAGE to be scrambled with the size of M*N is obtained, 5*M*N three-dimensional Logistic mapping function values are respectively obtained according to a three-dimensional Logistic mapping formula, the Logistic function values of last M first dimensions, last N second dimensions, and last M*N third dimensions of the 5*M*N three-dimensional Logistic mapping function values are obtained and sorted in an ascending mode respectively, and position sequences of an index 1, an index 2 and an index 3 are obtained; pixel position scrambling is conducted on the IMAGE by utilizing the sequences of the index 1 and the index 2, and an Image is obtained and converted into a single-dimensional image; an xor operation is conducted on the image and a result obtained through a reminder operation of the index 3 and 255, an image pixel value is changed to obtain an image fig, and the size of the fig is converted into the size of the IMAGE to obtain an image FIG which is a scrambling image. According to the image duel scrambling method based on three-dimensional Logistic mapping, the function value sequences of the three-dimensional Logistic mapping are utilized to respectively change the pixel position and the pixel value of the scrambling image, dual scrambling to the image is achieved, and the image duel scrambling method has the advantages of being high in generality and good in safety.

Owner:LIAONING UNIVERSITY

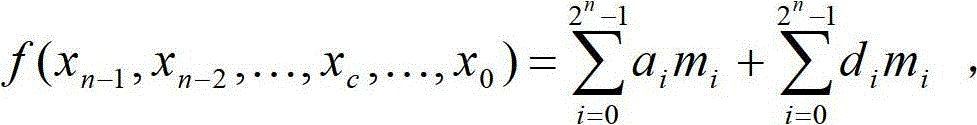

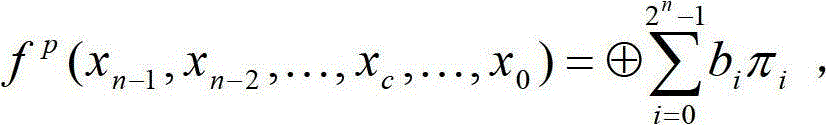

Fixed polarity conversion method for design of digital circuit

ActiveCN102982205AThe quick list technique establishes the minimum area respectivelyReduce areaSpecial data processing applicationsElectrical polarityFunctional expression

The invention discloses a fixed polarity conversion method for design of a digital circuit. The method comprises the following steps of: firstly reading in an SOP (Sum-of-Products) expansion of a Boolean logic function containing irrelative items; respectively establishing a minterm index table and an irrelative item index table by utilizing a quick list technology; and finally, searching the optimal irrelative item for choice, selecting an appropriate irrelative item to be read in an FPRM (Fixed Polarity Reed Muller) functional expression to obtain an FPRM expansion with lest and items. The method has the advantages that the conversion of fixed polarity from the SOP expansion of the Boolean logic function containing the irrelative items to an RM expansion in the design process of the digital circuit is realized; through the test of ten 10 MCNC (microelectronics center of north carolina) Benchmark circuits, the result shows that: compared with the fixed polarity conversion method which does not consider the irrelative items, the method has the advantages that the FPRM expansion can be effectively simplified, and the RM logic circuit with smaller area, lower power consumption and faster speed is obtained.

Owner:NINGBO UNIV

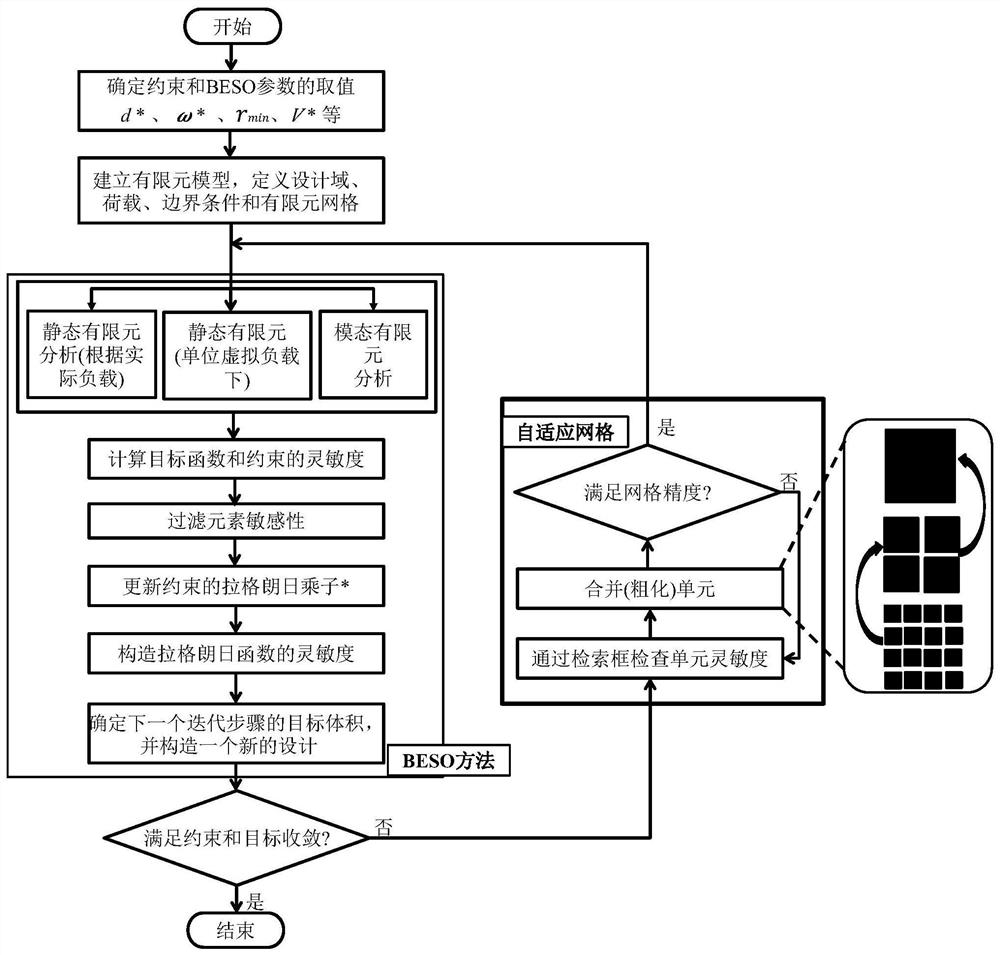

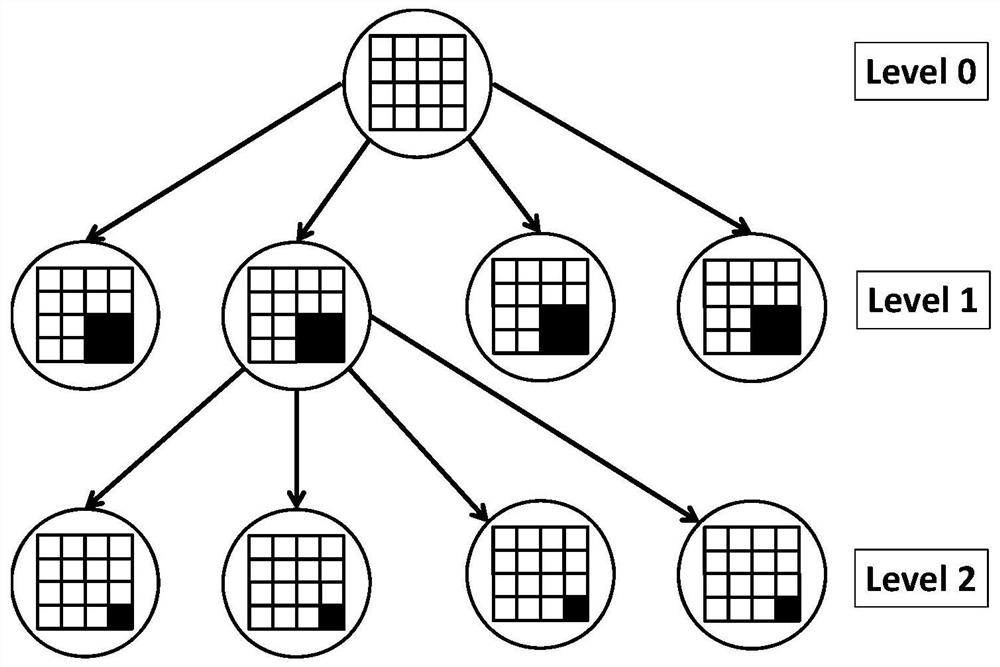

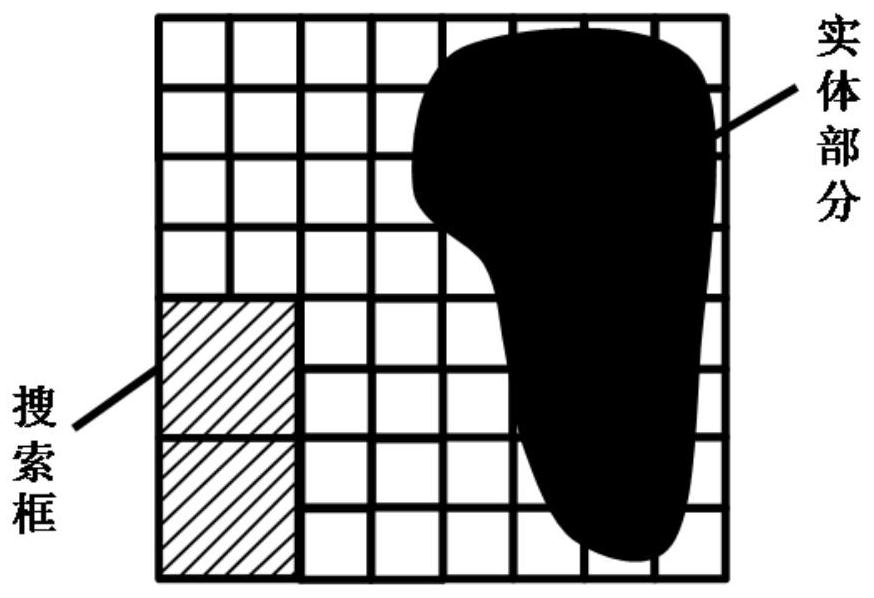

BESO topological optimization method based on dynamic evolution rate and adaptive grid and application of BESO topological optimization method

ActiveCN111737839ASmall amount of calculationImprove calculation accuracyGeometric CADDesign optimisation/simulationElement modelElement analysis

The invention discloses a BESO topological optimization method based on a dynamic evolution rate and an adaptive grid and application thereof, and the method comprises the steps: building a finite element model for a to-be-topologically optimized basic structure, and defining a design domain, a load, a boundary condition and a grid size; determining a constraint value and BESO necessary parameters; performing finite element analysis on the structure after mesh division, and calculating unit sensitivity under a target function and a constraint condition; filtering the unit sensitivity and updating the constrained Lagrange multiplier, and constructing the sensitivity of a Lagrange function; determining an evolution rate of the current iterative step based on a dynamic evolution rate functionof a Logistic function according to the volume rate of the current iterative step; and updating a design variable according to a set constraint function, judging whether constraint conditions and convergence conditions are met or not, if not, performing grid adaptive updating, then performing unit updating, and stopping iteration until the constraint conditions and the convergence conditions aremet. According to the invention, the calculation amount of single finite element analysis and the number of iterations required by topological optimization are effectively reduced while high calculation precision is ensured, so that the total calculation time consumption of topological optimization is greatly reduced.

Owner:GUANGZHOU UNIVERSITY

Method and system for building binary decision diagrams efficiently in a structural network representation of a digital circuit

ActiveUS7340473B2Data processing applicationsDigital data information retrievalDepth-first searchDynamic resource

Owner:GLOBALFOUNDRIES U S INC

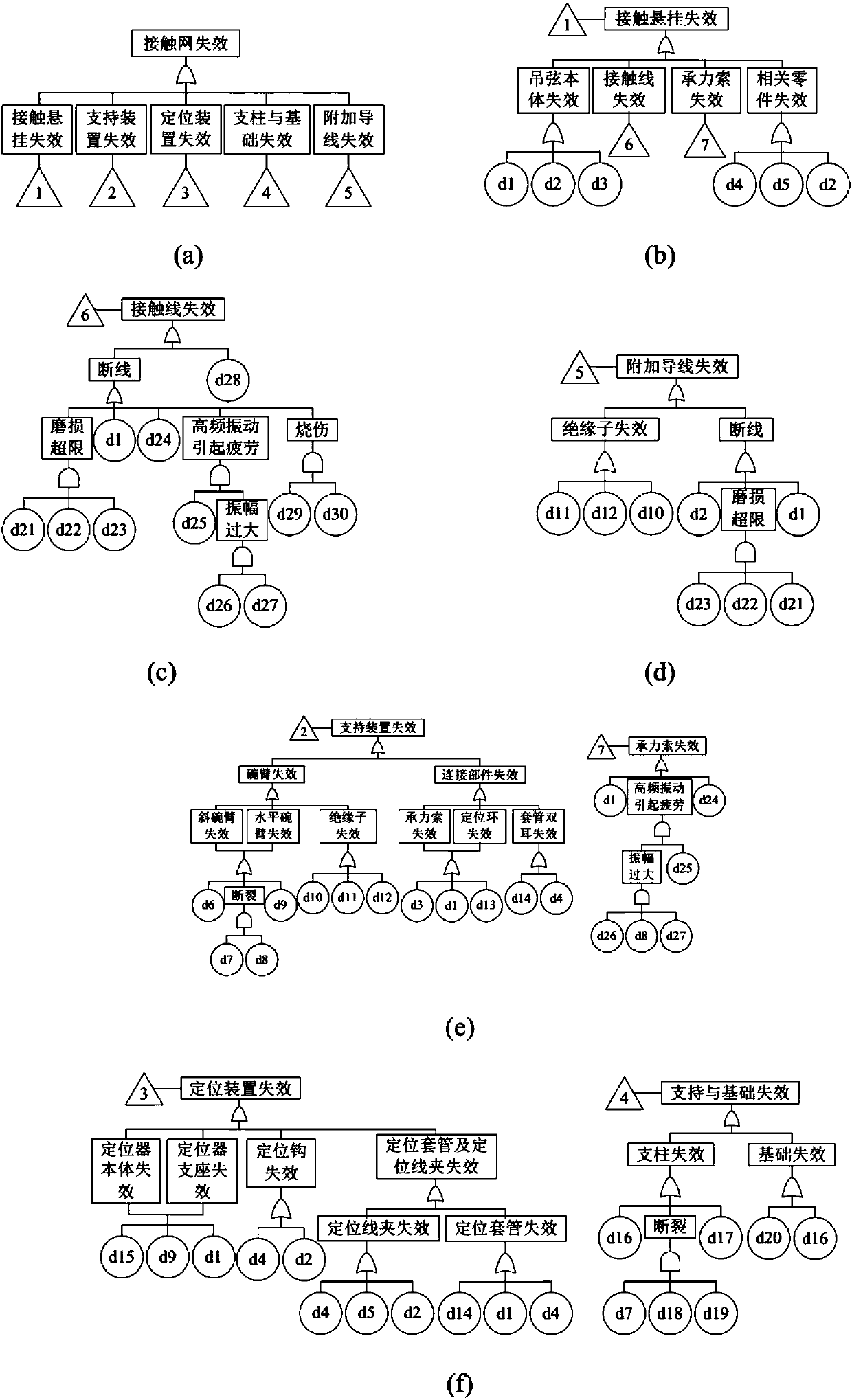

Contact network failure risk assessment method based on binary decision graph algorithm

PendingCN108596511ASolving combinatorial explosionsSolve complexityResourcesComplex mathematical operationsContact networkDecision graph

The invention discloses a contact network failure risk assessment method based on a binary decision graph algorithm, comprising the steps of: (1) generating a BDD structure, determining system boundaries, basic events and top events, establishing and normalizing a fault tree, and generating a BDD structure, wherein the corresponding BDD nodes may be directly created by ITE operations for basic events; and ITE operations may be performed on basic events or other intermediate events to obtain the BDD structure of the original intermediate event for intermediate events; (2) calculating the accident rate of the contact network failure risk, generating a Boolean logic expression by the fault tree, and generating a Boolean logic function corresponding to the fault tree top event, wherein when the true value is obtained, the probability of occurrence of the top event or any intermediate event may be obtained; and (3) measuring the event importance. The invention applies the BDD method to thefailure risk assessment of the contact network, which simplifies the calculation process, and solves the problems such as the combined explosion and the complicated solving process encountered by thecut set method in the contact network failure fault tree analysis.

Owner:CHINA RAILWAYS CORPORATION +1

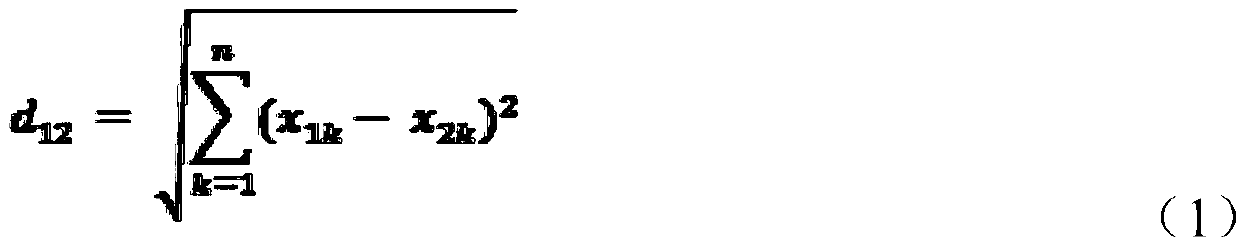

Pedestrian re-identification method based on triple convolutional neural network

ActiveCN109635695AImprove re-identification performanceImprove the performance of joint optimizationCharacter and pattern recognitionNeural architecturesNerve networkRe identification

The invention discloses a pedestrian re-identification method based on a triple convolutional neural network. The method comprises the steps of 1, forming a small batch of samples; 2, outputting global features and local features of each pedestrian image; 3, calculating the distance between the global features of every two pedestrian images in the small-batch samples and the distance between the local features of the corresponding body parts; 4, forming P x K pairs of triple samples; 5, using a Log-logistic function to replace a hinge function to improve a triple convolutional neural network loss function; 6, obtaining a trained triple convolutional neural network; asnd step 7, identifying the target pedestrian image by using the trained triple convolutional neural network, and further avoiding mismatching between the target pedestrian image and the pedestrian image to be identified by combining a confidence measurement mechanism. According to the pedestrian re-identification method based on the triple convolutional neural network, pedestrian re-identification can be accurately carried out, and mismatching between different pedestrians is avoided.

Owner:XIAN UNIV OF TECH

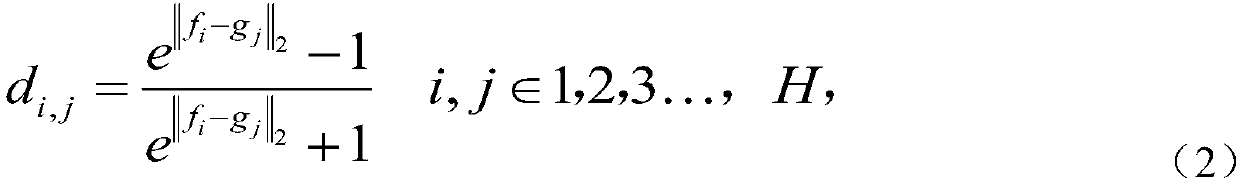

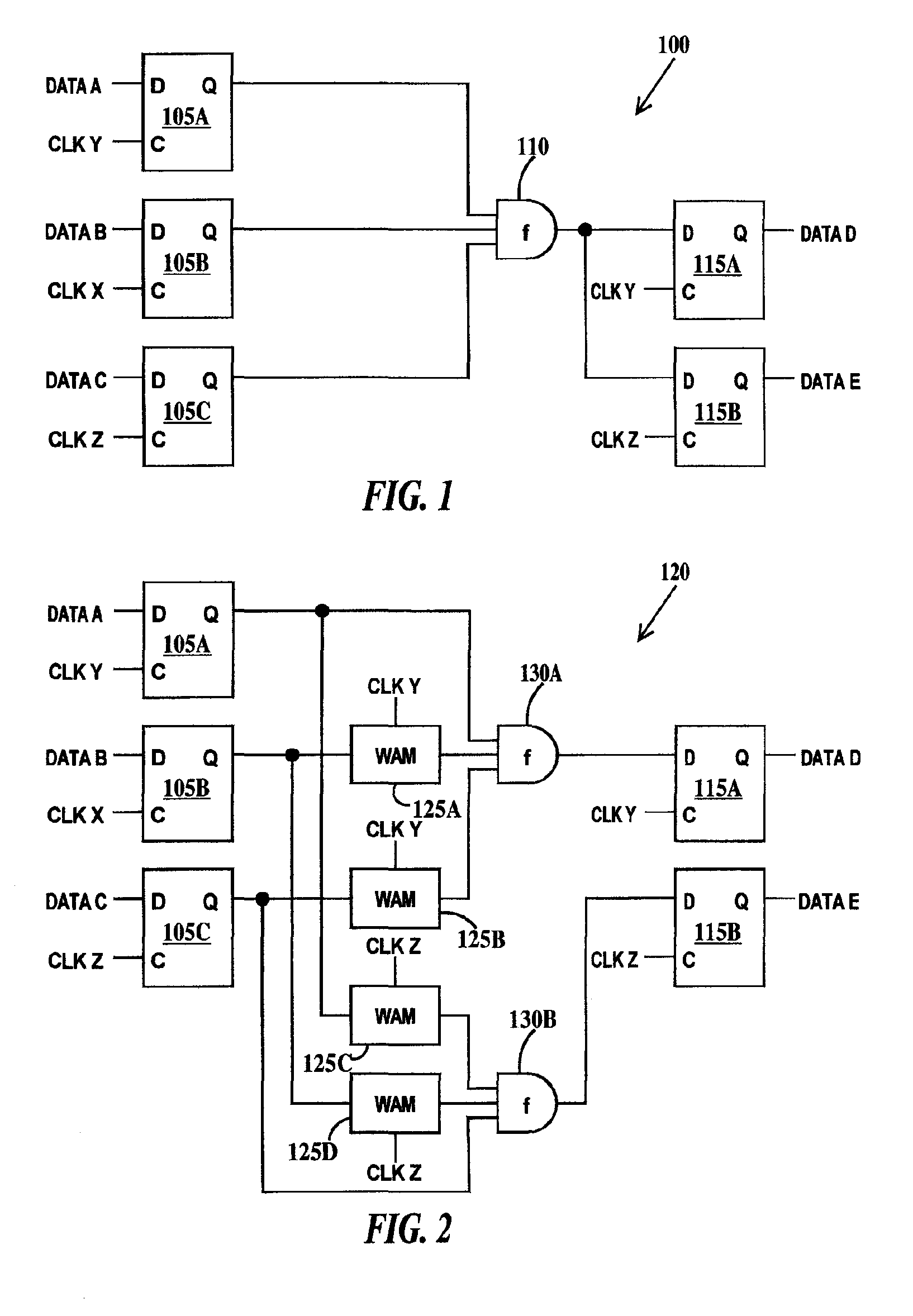

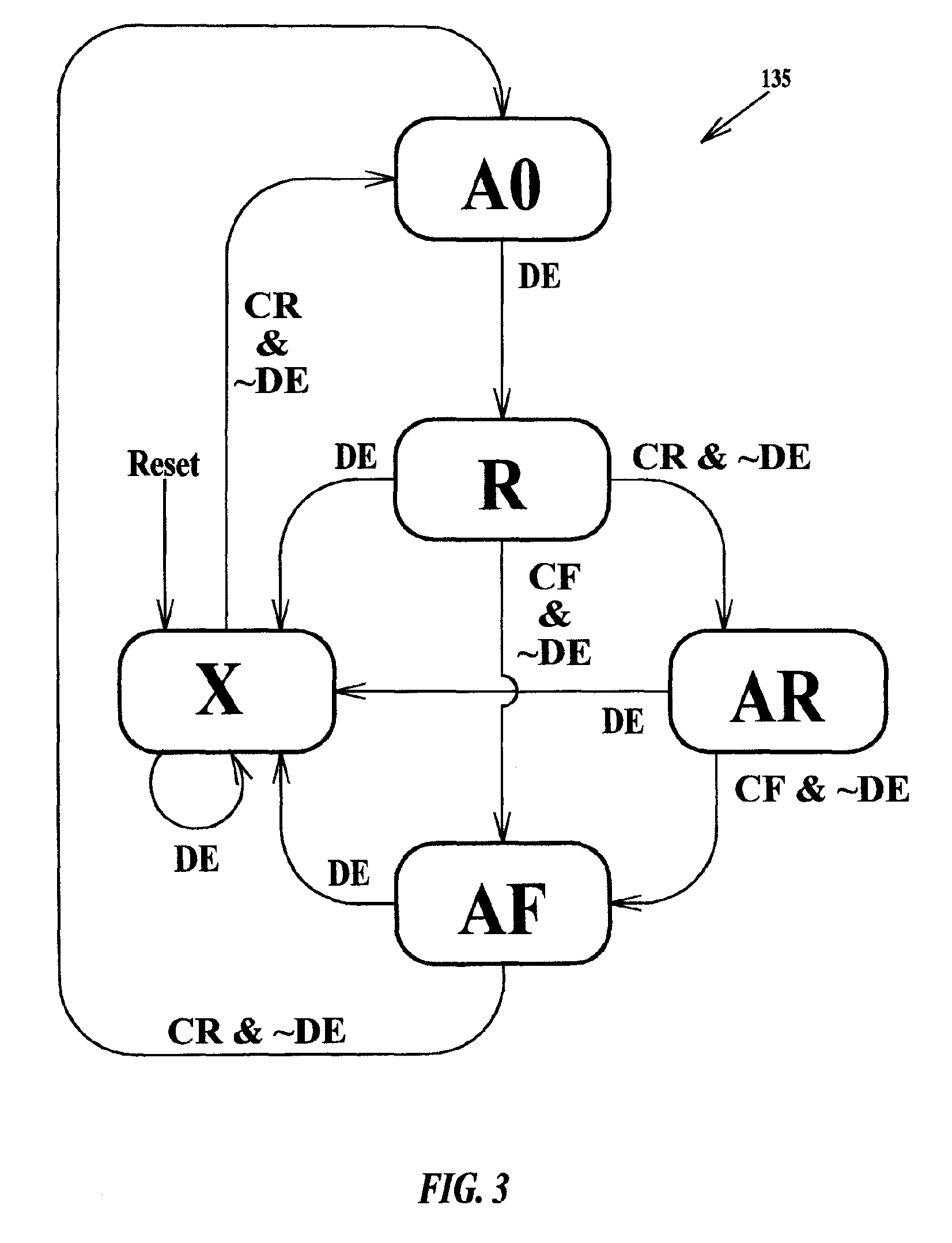

Simulation testing of digital logic circuit designs

InactiveUS20060090149A1Computer aided designSoftware simulation/interpretation/emulationComputer architectureSimulation testing

A method and system for testing a circuit design. The method including generating a simulation model of the circuit design, the circuit design comprising one or more source latches, one or more destination latches and a logic function connected between the source latches and the destination latches; generating a modified simulation model of the simulation model by inserting random skew between an output of each source latch and an input of the logic function only in asynchronous data paths between the source latches and the destination latches of the simulation model; and running the modified simulation model.

Owner:GLOBALFOUNDRIES INC

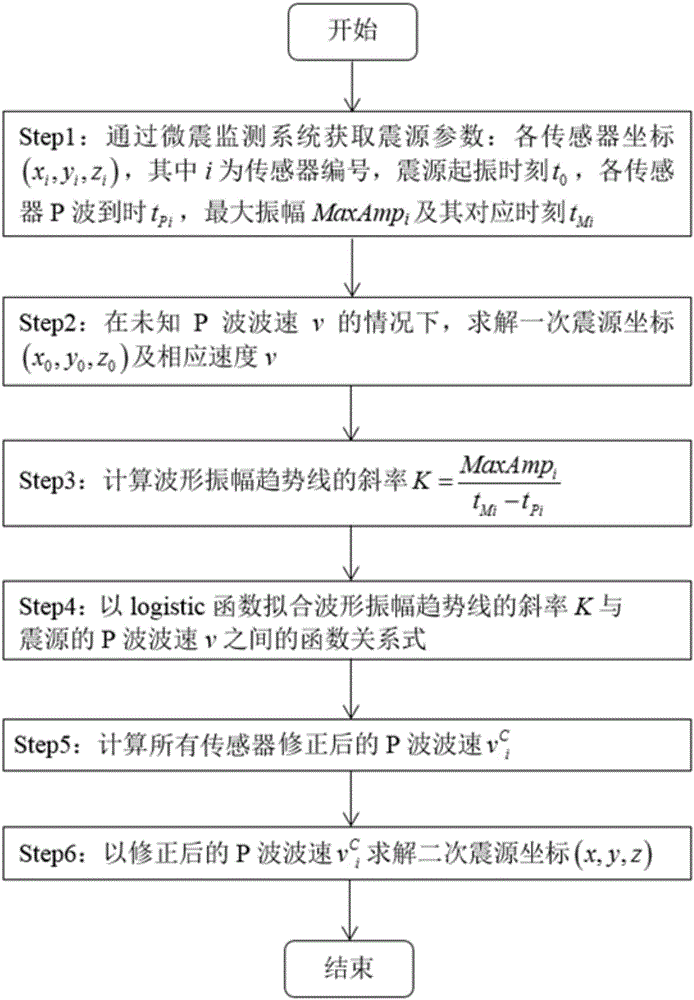

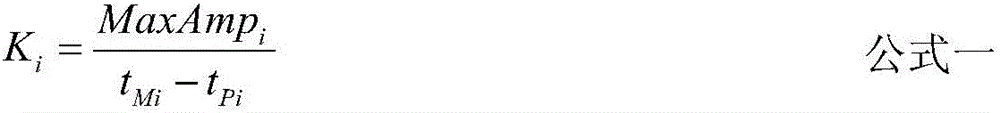

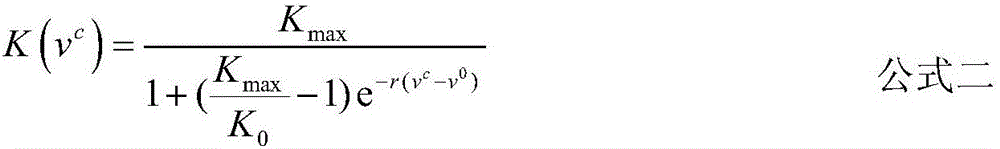

Seismic source positioning method based on P-wave arrival time and waveform amplitude

ActiveCN106680871AClear resultImprove applicabilitySeismic signal processingMonitoring systemArrival time

The invention discloses a seismic source positioning method based on P-wave arrival time and waveform amplitude. The method comprises following steps of step 1, acquiring seismic source parameters through a micro-seismic monitoring system; step 2, in case of unknown P-wave wave speed v, solving a primary seismic source coordinate (x0, y0, z0) and corresponding speed v; step 3, calculating the slope K of a waveform amplitude trend line, wherein K is defined in the description; step 4, using the logistic function to fit the function relation expression between the slope K of the waveform amplitude trend line and the P-wave wave speed v of each seismic source; step 5, calculating the P-wave wave speed v<c> of each corrected sensor; and step 6, using the P-wave wave speed v<c> of each corrected sensor to solve a secondary seismic source coordinate (x, y, z). The method is characterized by high adaptability and precision.

Owner:CENT SOUTH UNIV

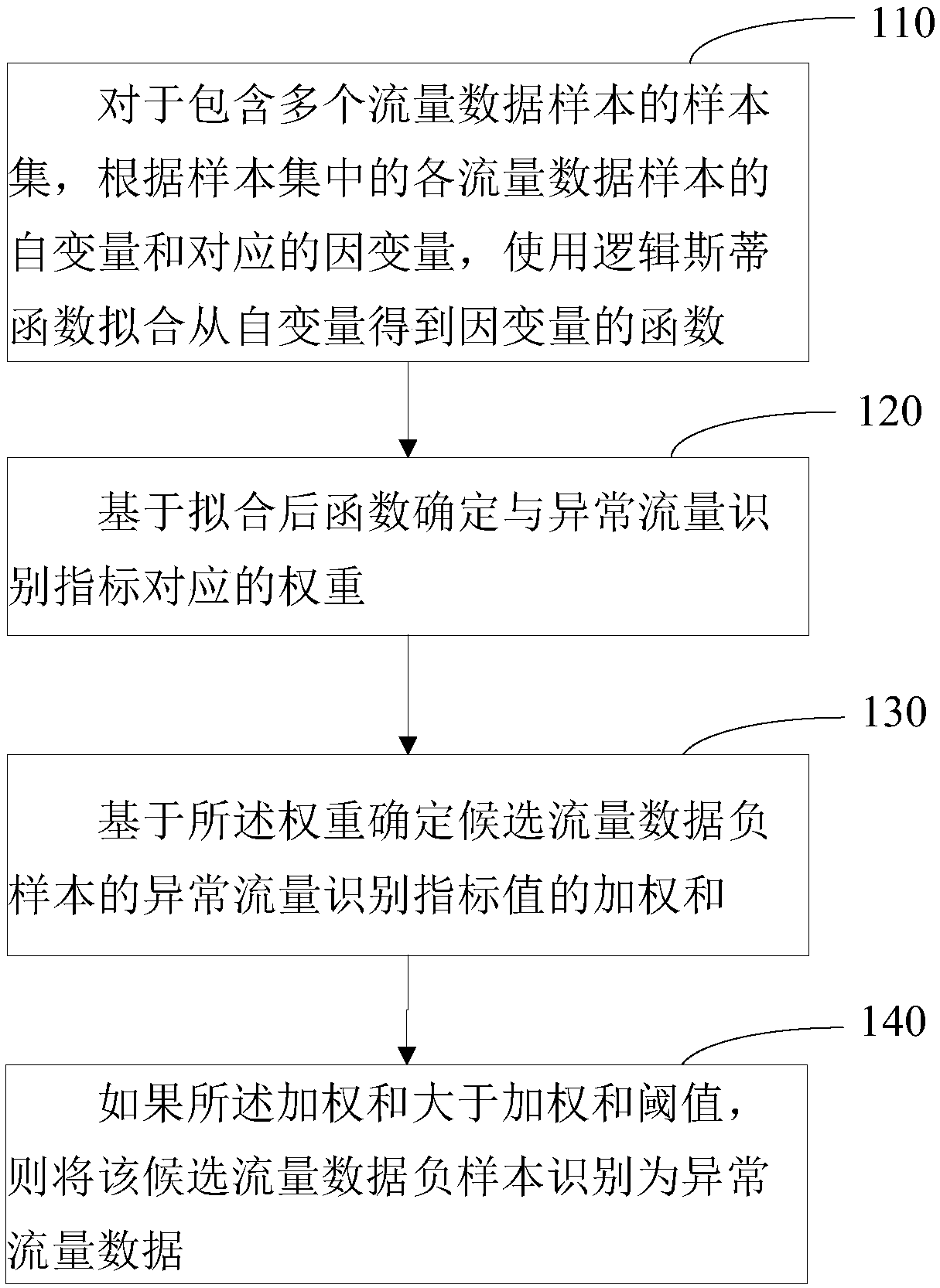

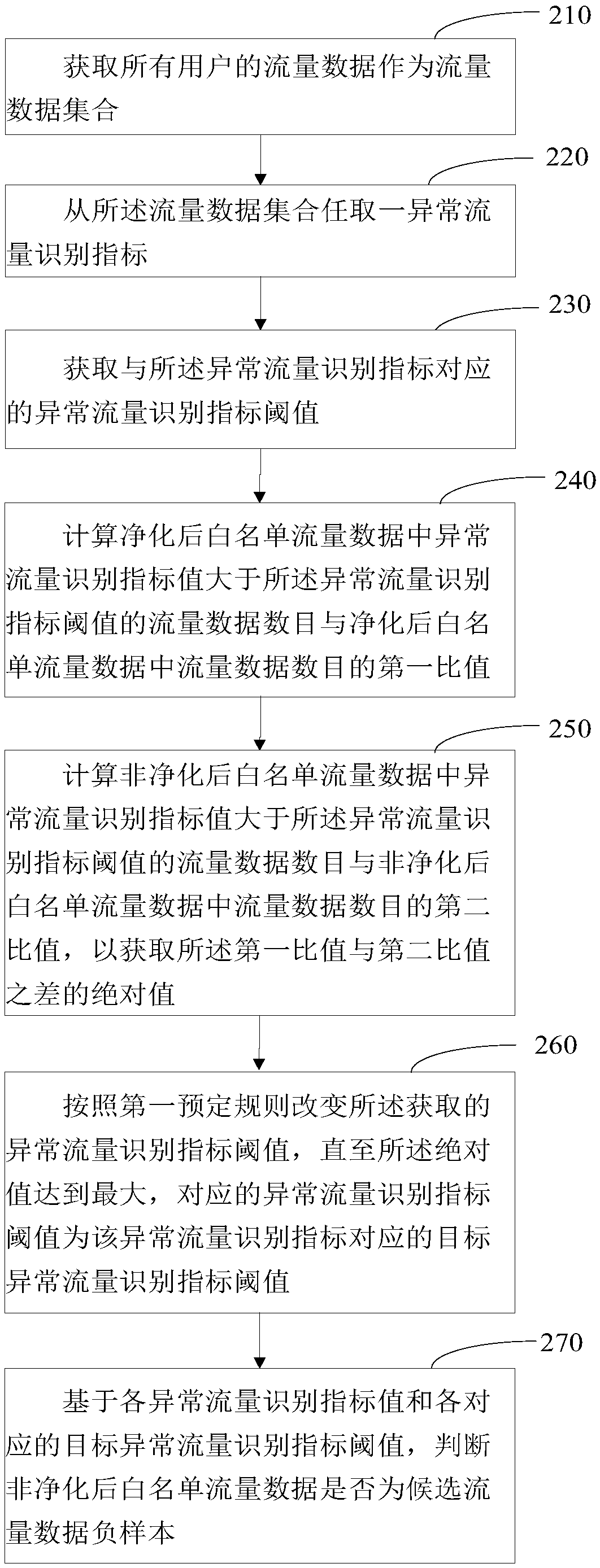

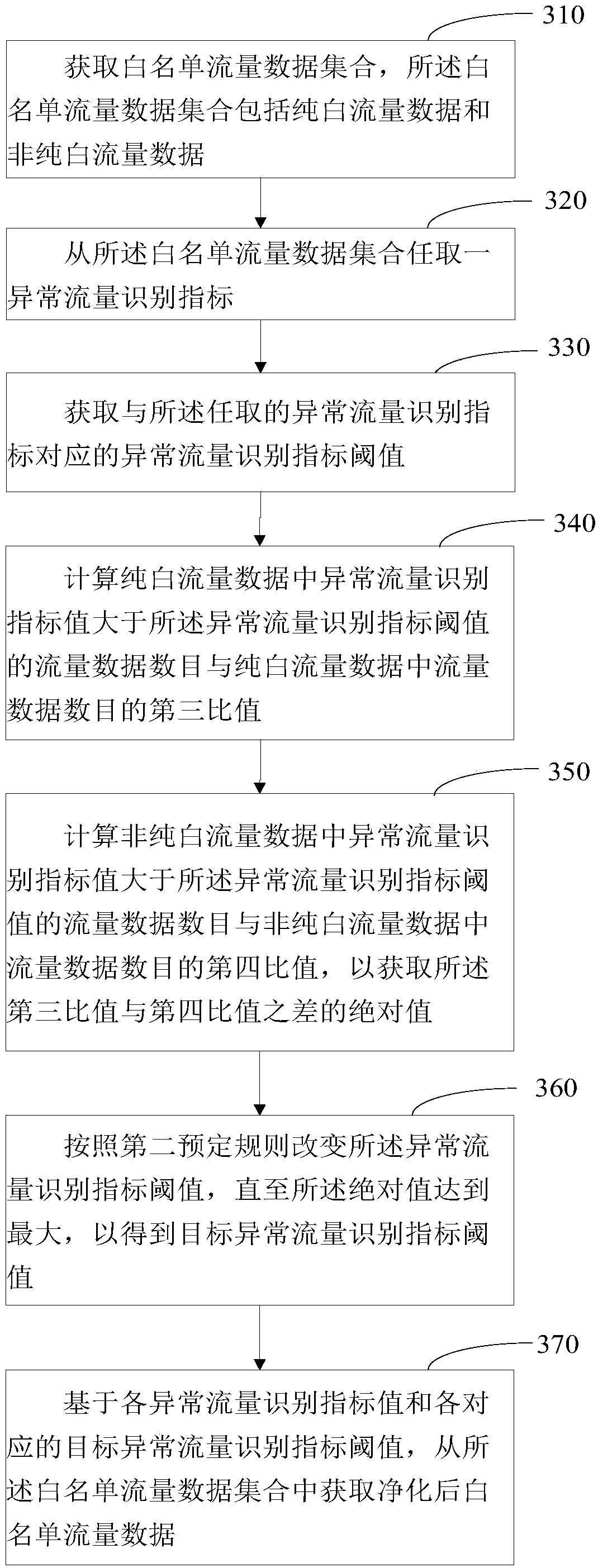

Abnormal traffic data identification method and device, medium, and electronic equipment

The invention relates to the field of information security, and discloses an abnormal traffic data identification method and device, a medium, and electronic equipment. The method comprises the following steps: for a sample set comprising a plurality of traffic data samples, according to independent variables and corresponding dependent variables of the traffic data samples in the sample set, carrying out fitting through a logistic function to obtain a function which is used to obtain the dependent variables from the independent variables; determining weights corresponding to abnormal trafficidentification indicators based on the function obtained through the fitting; determining the weighted sum of abnormal traffic identification indicator values of a candidate negative traffic data sample based on the weights; and if the weighted sum is larger than a weighted sum threshold, identifying the candidate negative traffic data sample as abnormal traffic data. The method disclosed by the invention has the advantages that different importance degrees of the multiple abnormal traffic identification indicators in an abnormal traffic data identification process are fully considered, so that intrusions can be prevented based on network security, and the abnormal traffic identification accuracy can be improved.

Owner:PING AN TECH (SHENZHEN) CO LTD

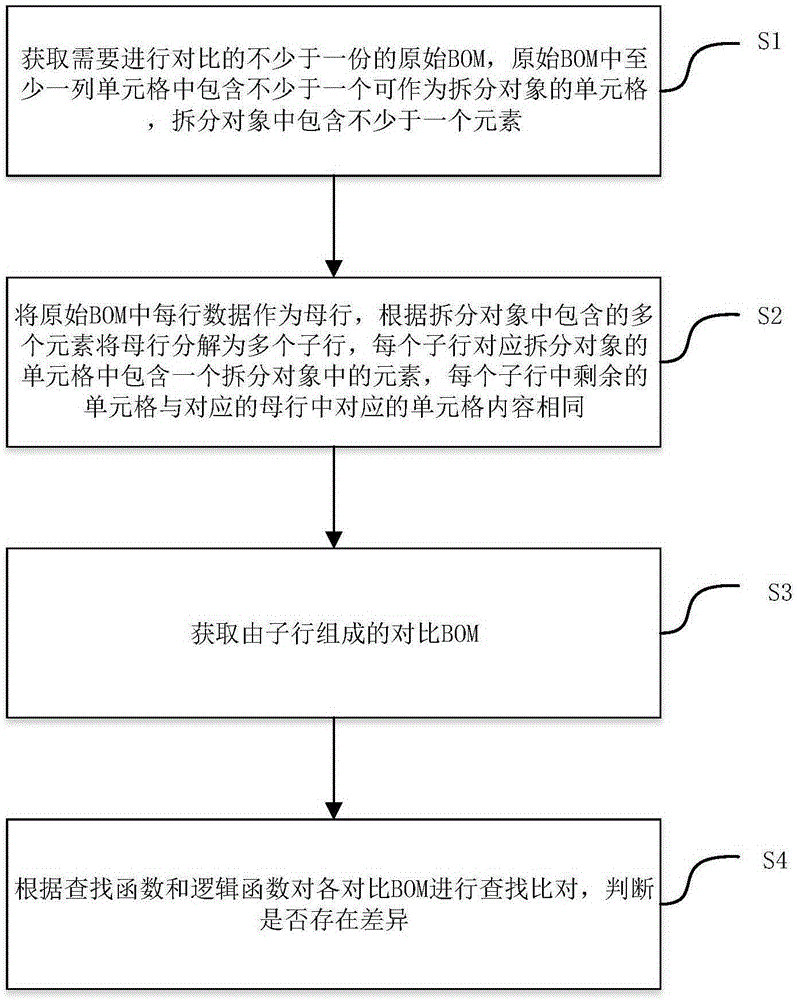

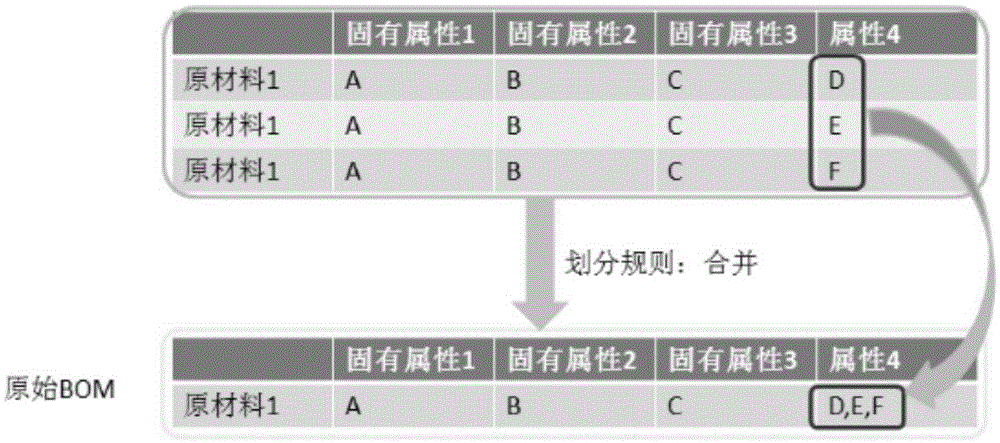

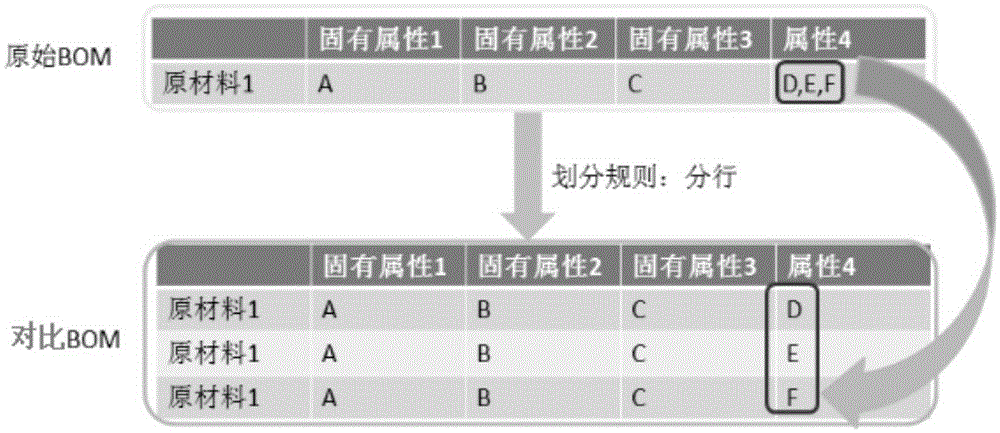

Method for fast BOM comparison

InactiveCN105302781AQuick searchFast and accurate total dosageText processingSpecial data processing applicationsTheoretical computer scienceManufacturing enterprises

The invention discloses a method for fast BOM comparison. The method includes the following steps that S1, not less than one original BOM needing to be compared is acquired; S2, each row of data in the original BOM serve as a mother row, each mother row is decomposed into a plurality of sub-rows according to a plurality of elements contained a corresponding splitting object, a cell of the splitting object corresponding to each sub-row contains elements in the splitting object, and remaining cells in each sub-row and corresponding cells of the corresponding mother row are the same in content; S3, comparison BOMs composed of the sub-rows are acquired; S4, searching comparison of the comparison BOMs is performed according to a searching function and a logic function, and whether a difference exists or not is judged. According to the method for fast BOM comparison, the difference of two BOMs can be efficiently and fast compared, BOM accuracy is checked, it is guaranteed that accurate BOMs are made, and unnecessary loss of manufactured products caused by BOM errors are avoided. The method can be applied to production and manufacturing enterprises.

Owner:合肥宝龙达光电技术有限公司

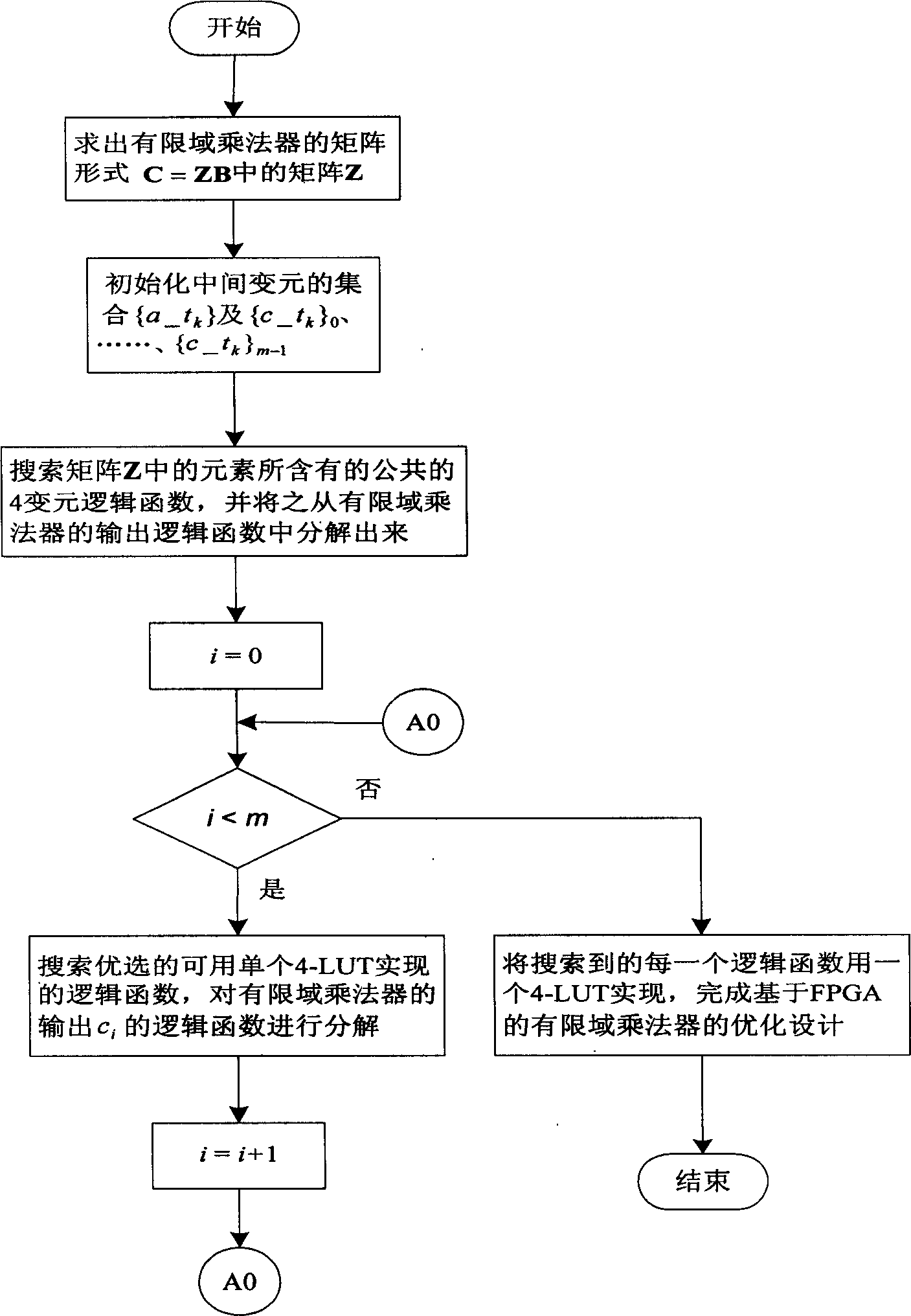

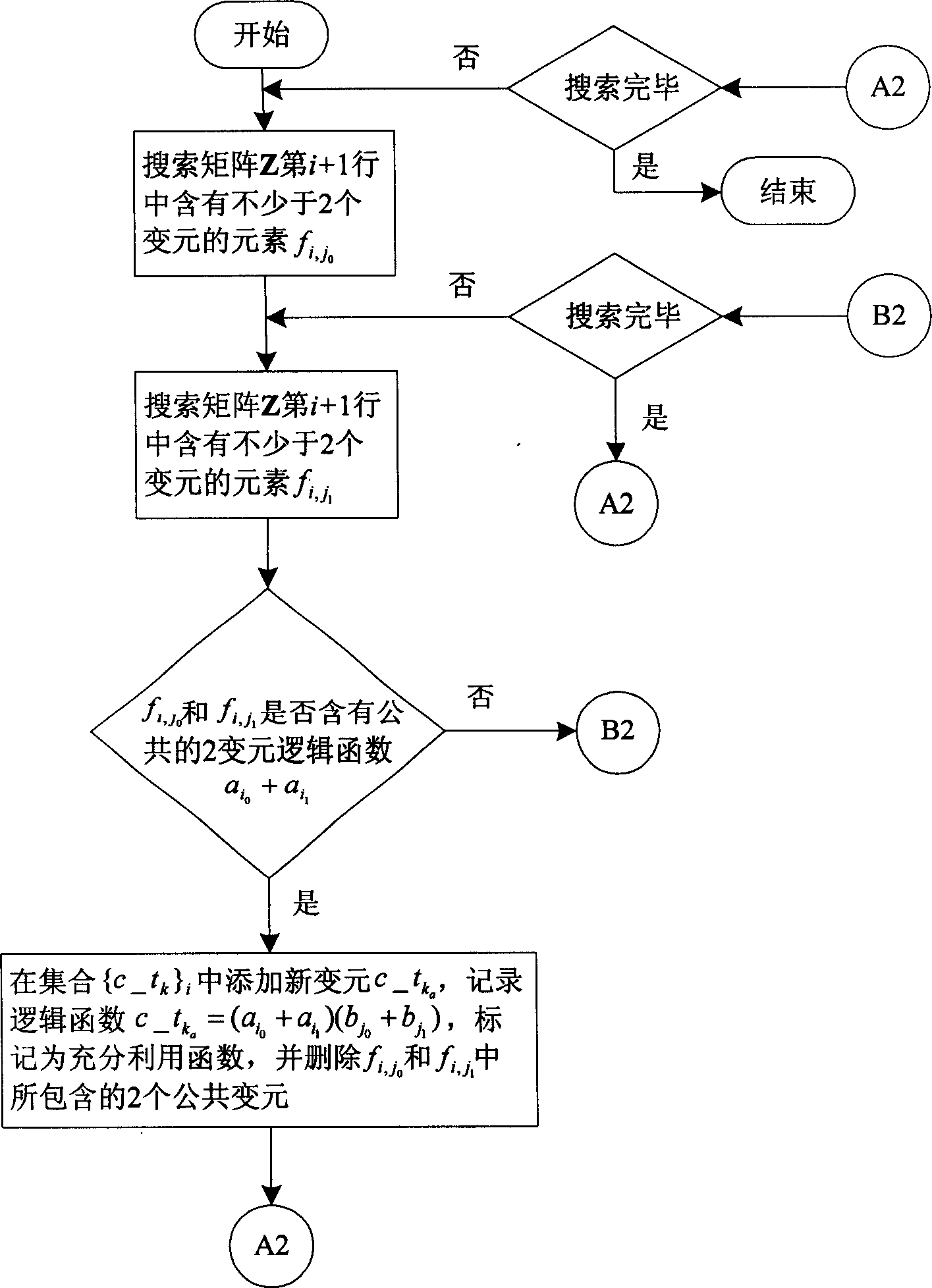

Optimization design method based on FPGA finite field multipier

InactiveCN1658200AShorten the lengthReduce resource usageSpecial data processing applicationsTheoretical computer scienceCritical path method

This invention discloses a optimum design method for the finite field multiplier on the base of FPGA. This invention defines those logic functions which can be realized with a single 4-LUT into 7 styles, and it will follow some steps to realize the optimization for the finite field multiplier. Firstly, it figures out the matrix form of the finite field multiplier according to the generator polynomial and initialize the integration of middle variables. Secondly, it will repeatedly search for the common logic functions in the elements in the Matrix Z, bringing in a new middle variable, and it will use this new middle variable to represent the output variable of those logic functions, modifying the Matrix Z. Finally, it will find out preferred logic functions that can be realized by a single 4-LUT. Then those logic functions will be decomposed into a series of logic functions that can be realized by a single 4-LUT, and Matrix Z and the integration of middle variables will be modified. After all above, we finally get a optimized finite field multiplier on the base of FPGA. The advantages are short key route and time delay.

Owner:XIDIAN UNIV

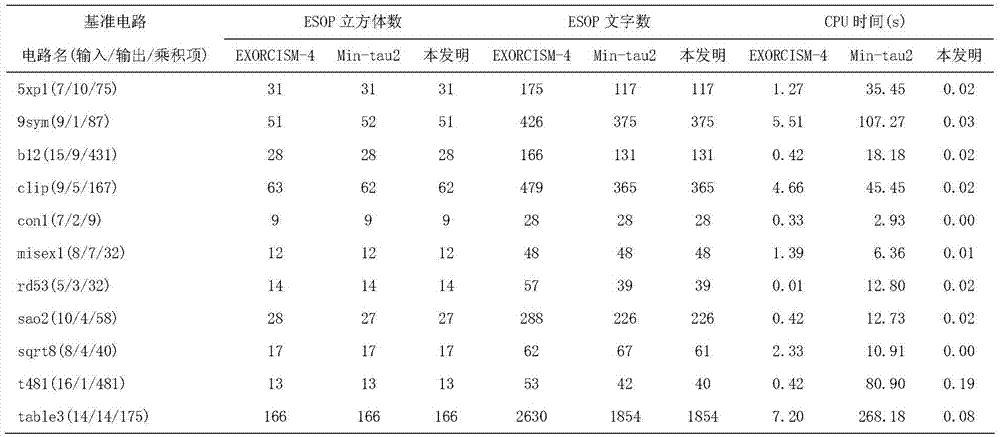

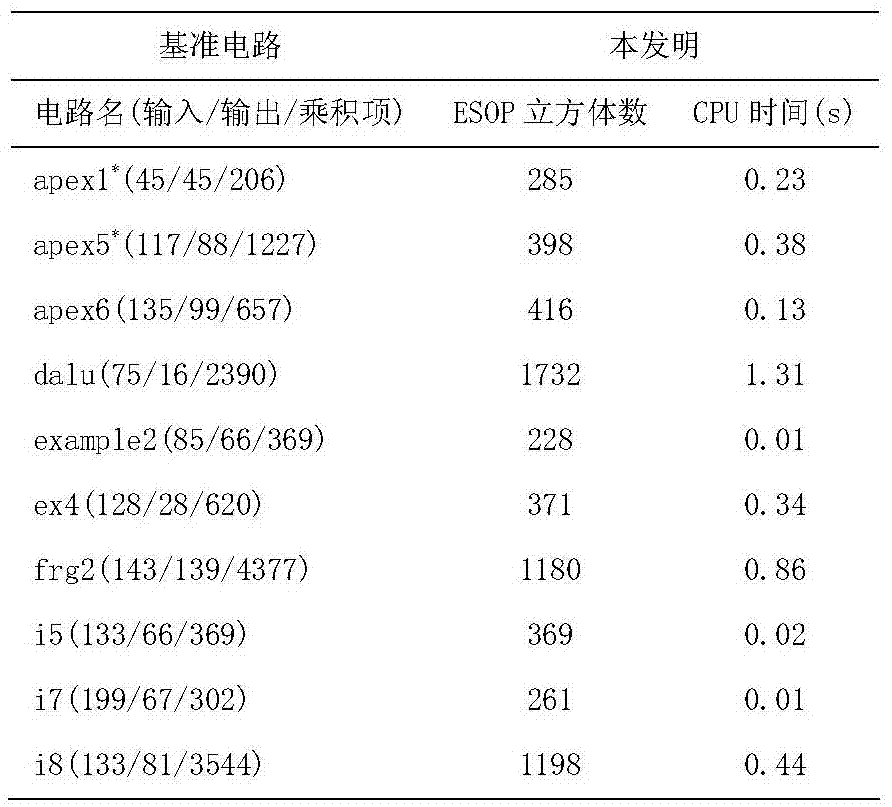

ESOP minimization method for logic function

InactiveCN105447241AMinimizeGet rid of constraintsComputer aided designSpecial data processing applicationsSearch problemRound complexity

The present invention discloses an ESOP minimization method for a logic function. By converting the optimal coverage searching problem of a 3n global space in the ESOP minimization process of an n variable logic function into the simplest connection problem in a plurality of cube blocks, a search space is reduced, thereby breaking away from a constraint of a variable scale; moreover, a cube set is directly operated without being converted into a minterm set, so that limitation to a product term number is avoided; and in order to achieve accurate minimization of rapid ESOP, a minimized conversion algorithm of a cube EXOR conversion diagram is adopted to improve operation efficiency so as to effectively reduce calculation complexity and a memory occupied quantity, and the characteristics that calculation time is insensitive to the number of input variables and is only related to the number of product terms included by the logic function and intersection can effectively achieve an effect that random n variables totally regulate the ESOP minimization of the logic function. The ESOP minimization method has the advantages of no limitation to the number of the product items and the number of the variables in the logic function and capacity of carrying out minimization processing on an ESOP of a random logic function.

Owner:ZHEJIANG WANLI UNIV

Space load predication method with consideration of cellular development degree

InactiveCN105825295AAchieve forecastSolve the accuracy problemForecastingCellular developmentComputer science

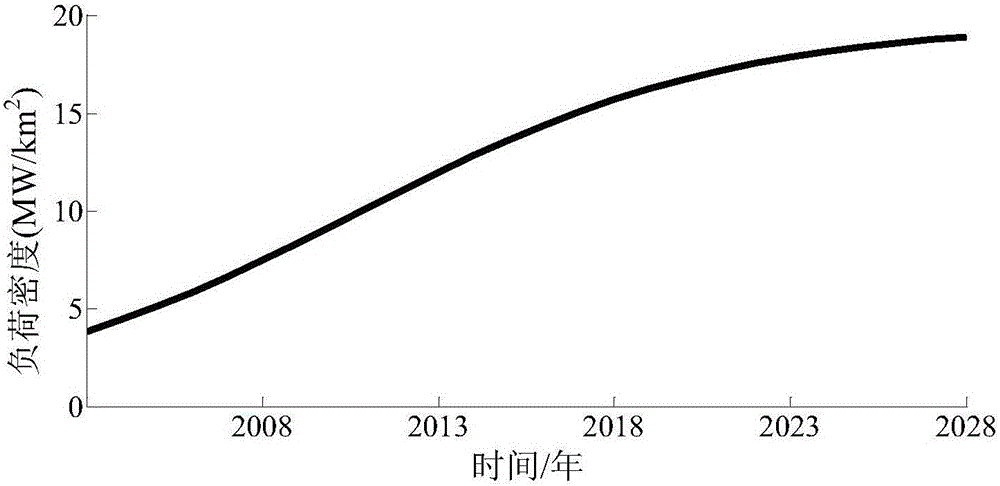

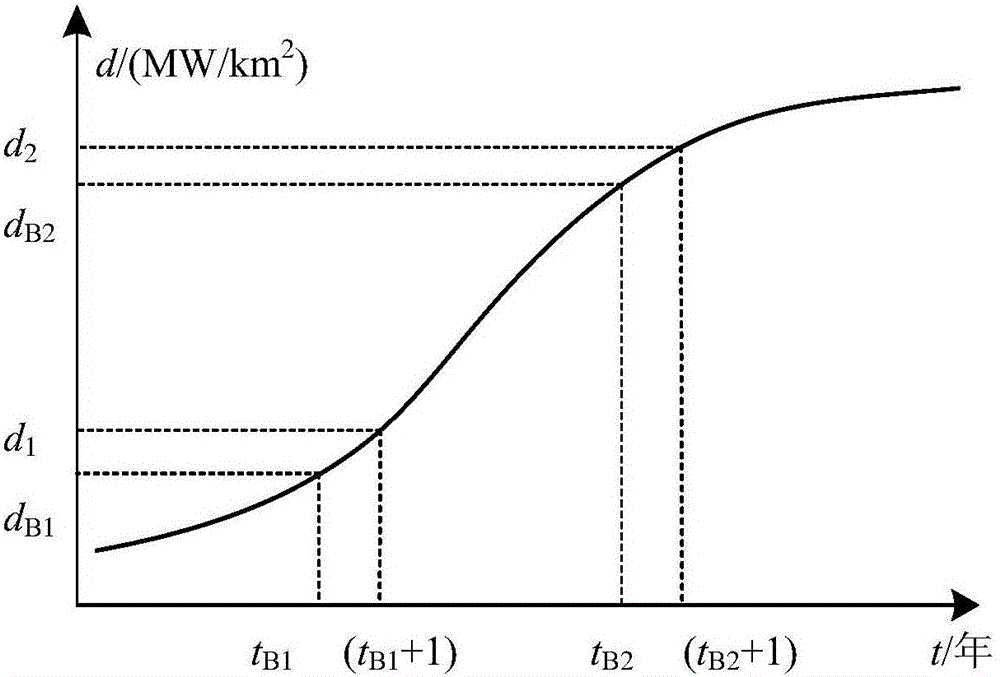

The invention relates to a space load predication method with consideration of a cellular development degree. The method comprises: a power geographic information system (GIS) is established, and integration of land information, a power supply range of a 10-kV feeder line, and classification load data is realized; cellular units are generated in the GIS in the power supply range of the 10-kV feeder line; changing situations of classification load densities are described by using a logistic function, and regular curves corresponding to all classification load density development trends are generated respectively; development degrees of classification load densities in all cellular units in a current year are determined, and thus positions of classification load densities in all cellular units in a current year on the load density development rule curves of the classes are found; and a cellular load value of a target year is predicted, a classification load density index in the cellular unit at the target year is determined by combining the classification load density development rule curves according to the classification load density development degrees in all cellular units at the current year, and then multiplication by areas corresponding to all kinds of loads in the cellular units to realize prediction of cellular load values.

Owner:NORTHEAST DIANLI UNIVERSITY

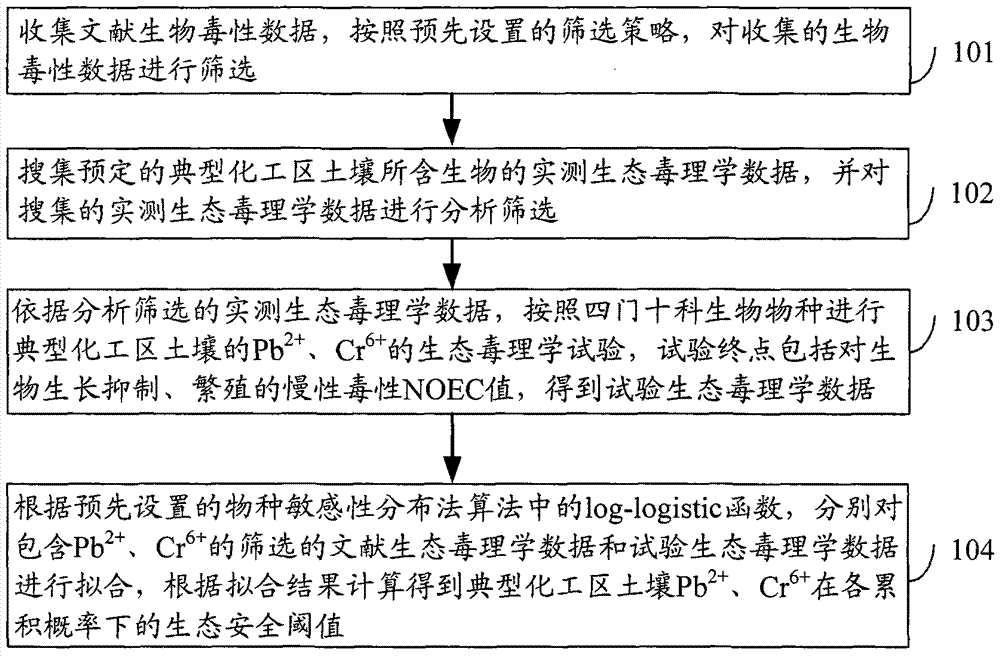

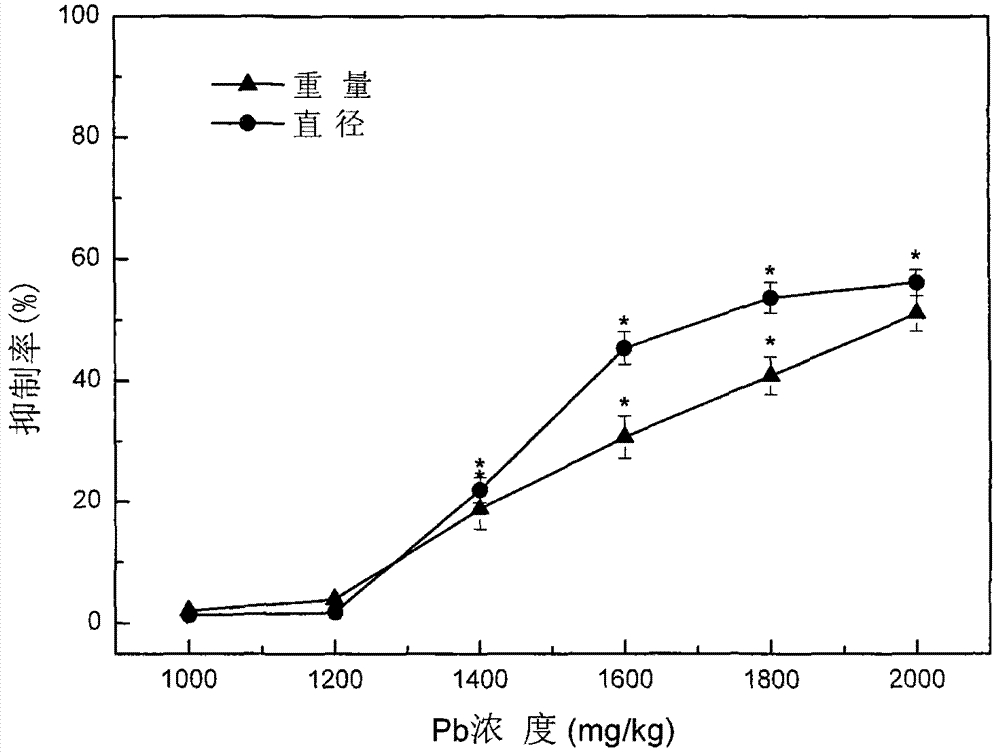

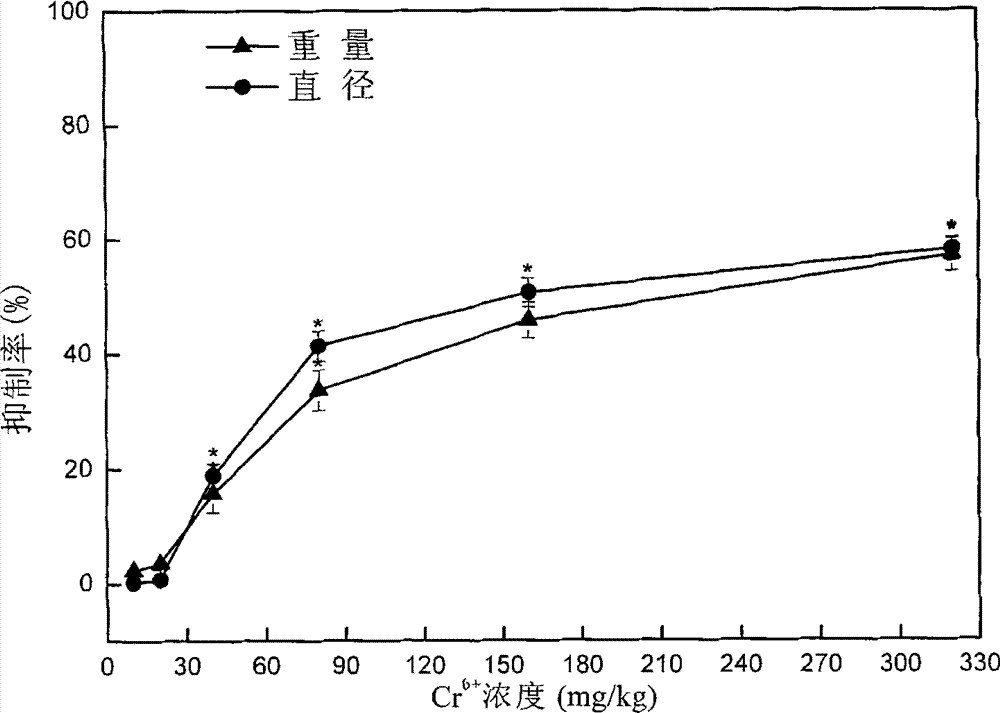

Four phyla and ten families based method for obtaining ecological safety thresholds of lead and chromium in soil

The invention discloses a four phyla and ten families based method for obtaining ecological safety thresholds of lead and chromium in soil. The method includes the steps of: screening the collected biological toxicity data; analyzing and screening the collected measured ecotoxicological data; according to the screened and analyzed measured ecotoxicological data, conducing ecotoxicological tests of Pb<2+> and Cr<6+> in the soil of a typical chemical industry zone and endpoints in accordance with four phyla and ten families, wherein test terminal points include chronic toxicity NOEC values on biological growth inhibition and reproduction; and according to a log-logistic function in a preset species sensitivity distribution method, respectively fitting the screened literature ecotoxicological data and ecotoxicological test data, and calculating the ecological safety threshold values of Pb<2+> and Cr<6+> in the soil of the typical chemical industry zone under each cumulative probability according to the fitting results. The method of the invention can effectively evaluate the soil ecological risk caused by heavy metal pollutants.

Owner:CHINESE RES ACAD OF ENVIRONMENTAL SCI

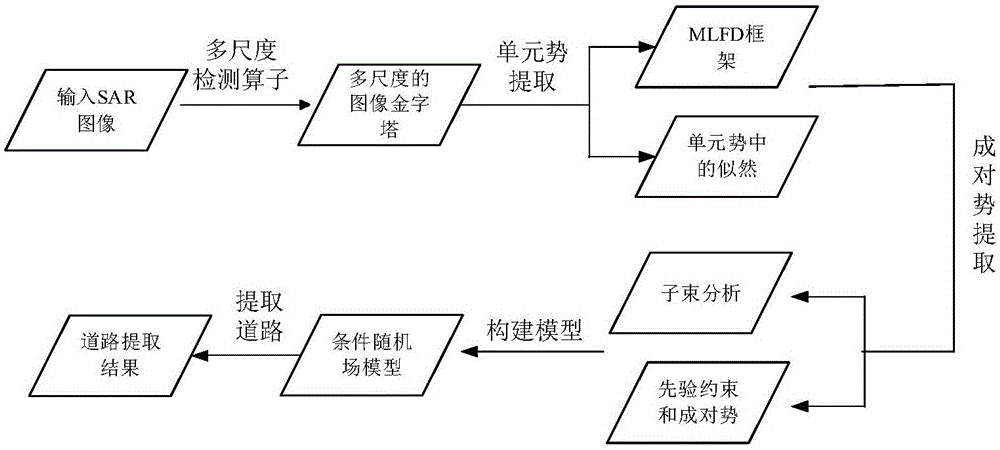

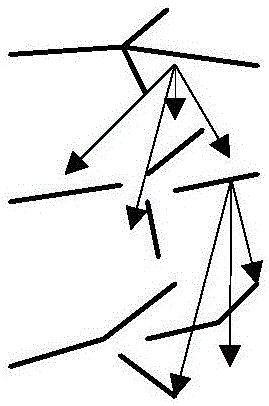

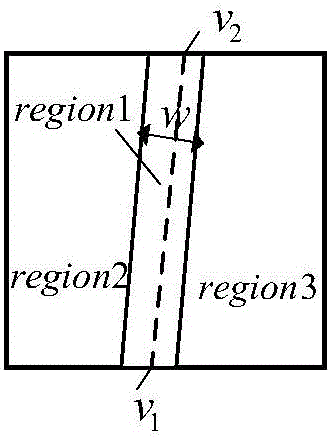

Polarization SAR image road extraction method based on conditional random field

ActiveCN106709465AImprove efficiencyGood precisionCharacter and pattern recognitionConditional random fieldDecomposition

The invention provides a polarization SAR image road extraction method based on a conditional random field. A conditional random field framework is built to realize road extraction. The method comprises the following steps: building a pyramid for an input SAR image through use of a multi-scale line feature detection MLFD operator to get a multi-scale image pyramid; carrying out modeling through CRF, and introducing context information; modeling a cell potential function through a logistic function; adopting a Beamlet decomposition mode to look for optimal partitioning according to potential functions in pair; using relevant constraints to group and mark road elements, describing potential functions in pair, and merging information obtained from global data; and normalizing characteristic matrixes in a unified manner. By using the technical scheme, road extraction is efficient and precise. The method is suitable for popularization.

Owner:WUHAN UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com