Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

80 results about "Design language" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A design language or design vocabulary is an overarching scheme or style that guides the design of a complement of products or architectural settings. Designers wishing to give their suite of products a unique but consistent look and feel define a design language for it, which can describe choices for design aspects such as materials, colour schemes, shapes, patterns, textures, or layouts. They then follow the scheme in the design of each object in the suite.

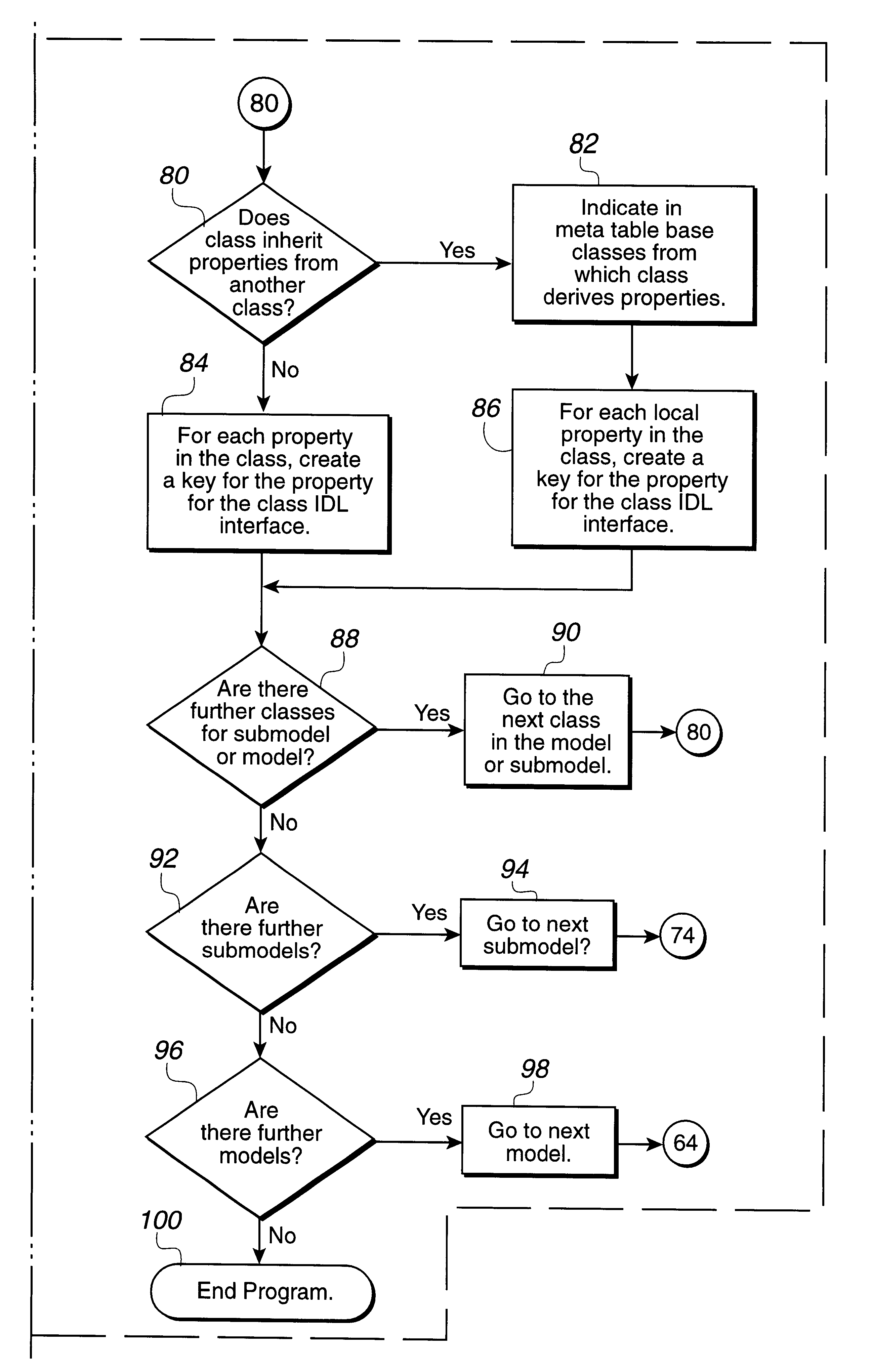

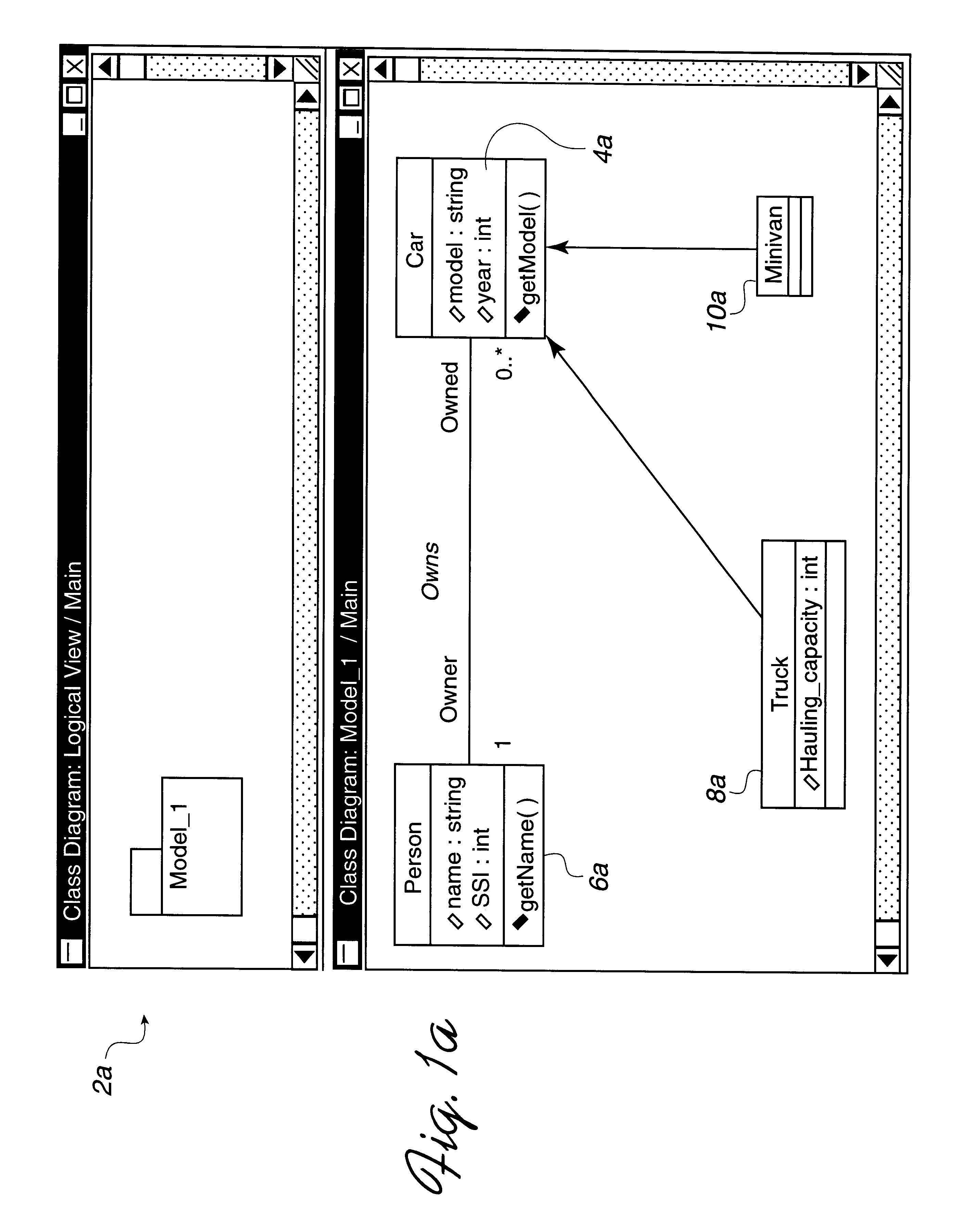

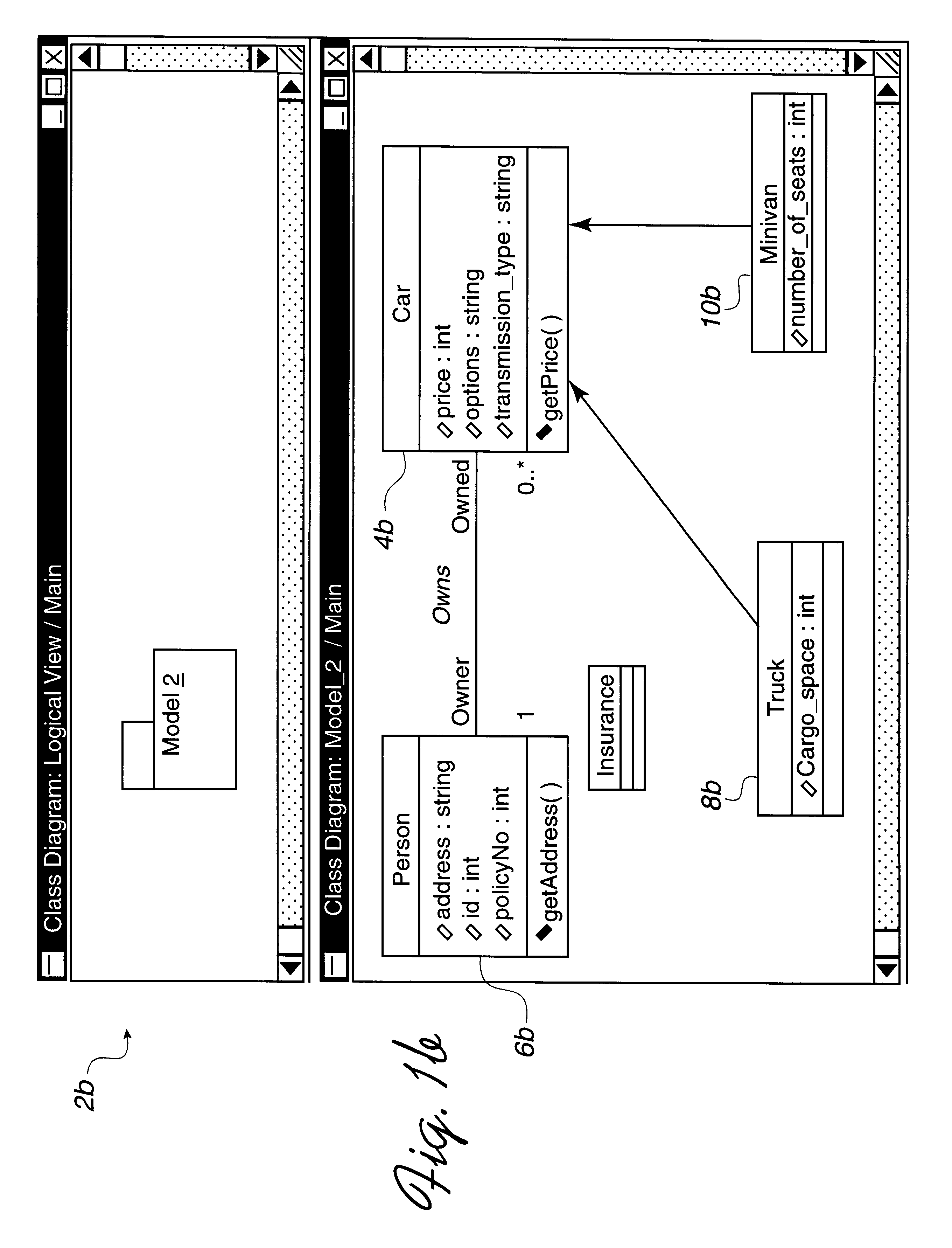

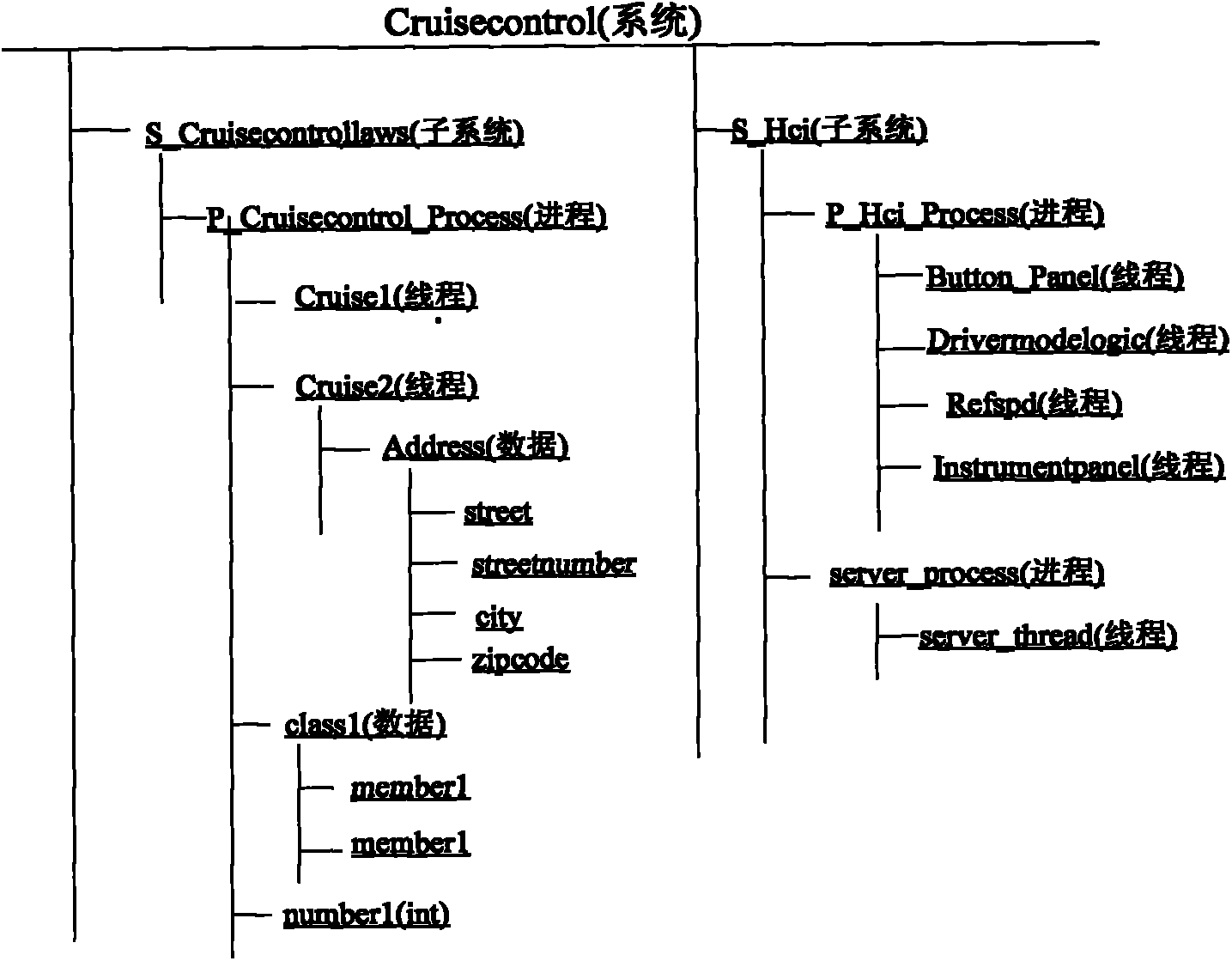

System and method for mapping a design model to a common repository with context preservation

InactiveUS6343265B1Improved GUIEasy to understandData processing applicationsSoftware designModeling languageData structure

Disclosed is a system for mapping objects defined in a design model, such as an object oriented design model defined using a design language such as the Universal Modeling Language (UML), to a data model accessible to an application development tool. A design model is provided that includes at least two models. A first model includes a first class and a second model includes a second class. The first class and second class have the same name, and the first class and second class have at least one different attribute and method. The first model, the first class, and attributes and methods therein are mapped to a first data structure that indicates that the first class is included with the first model. The second model, the second class, and attributes and methods therein are mapped to a second data structure that indicates that the second class is included with the second model. In this way, the first class and the second class are distinguished according to their model in the data structures.

Owner:IBM CORP

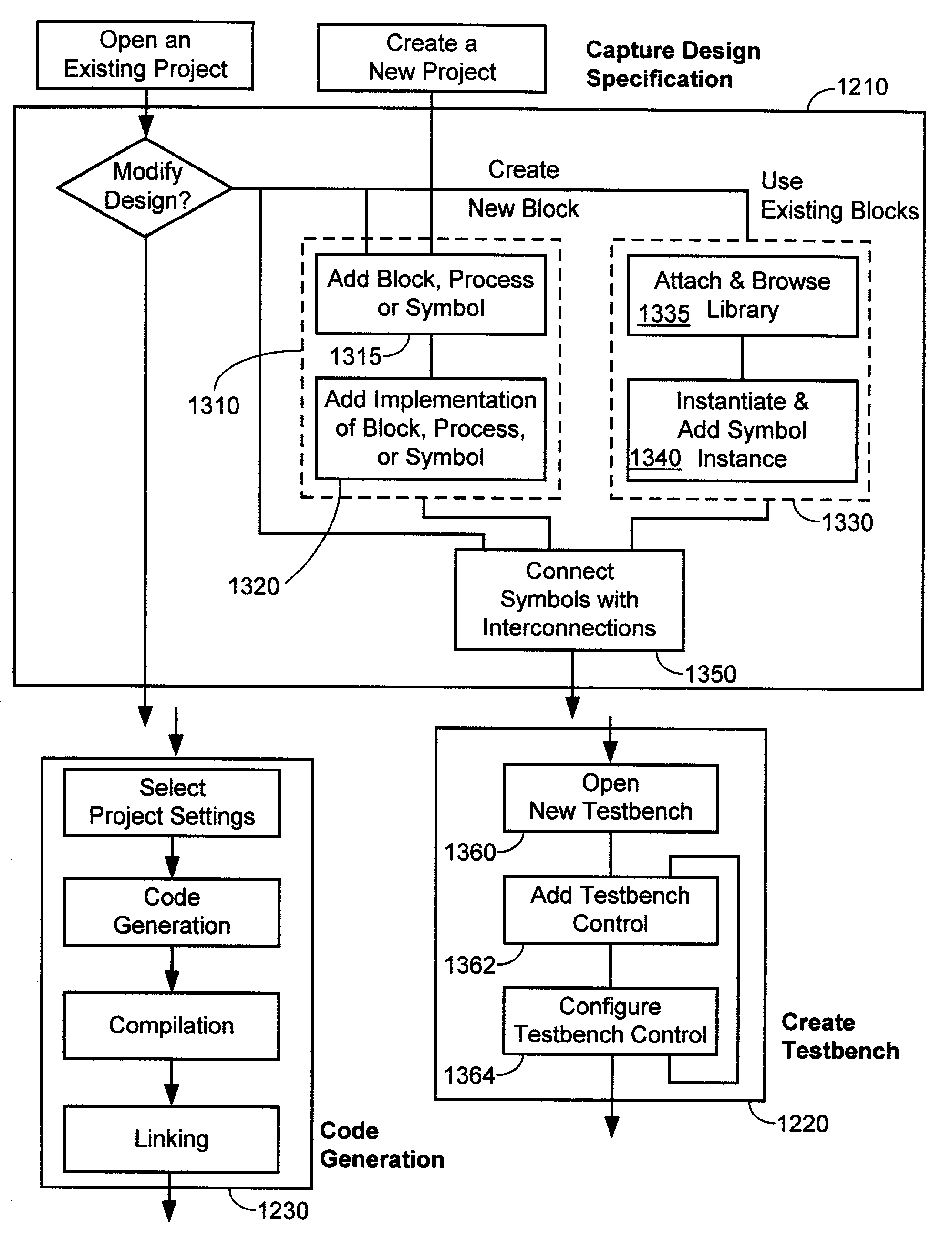

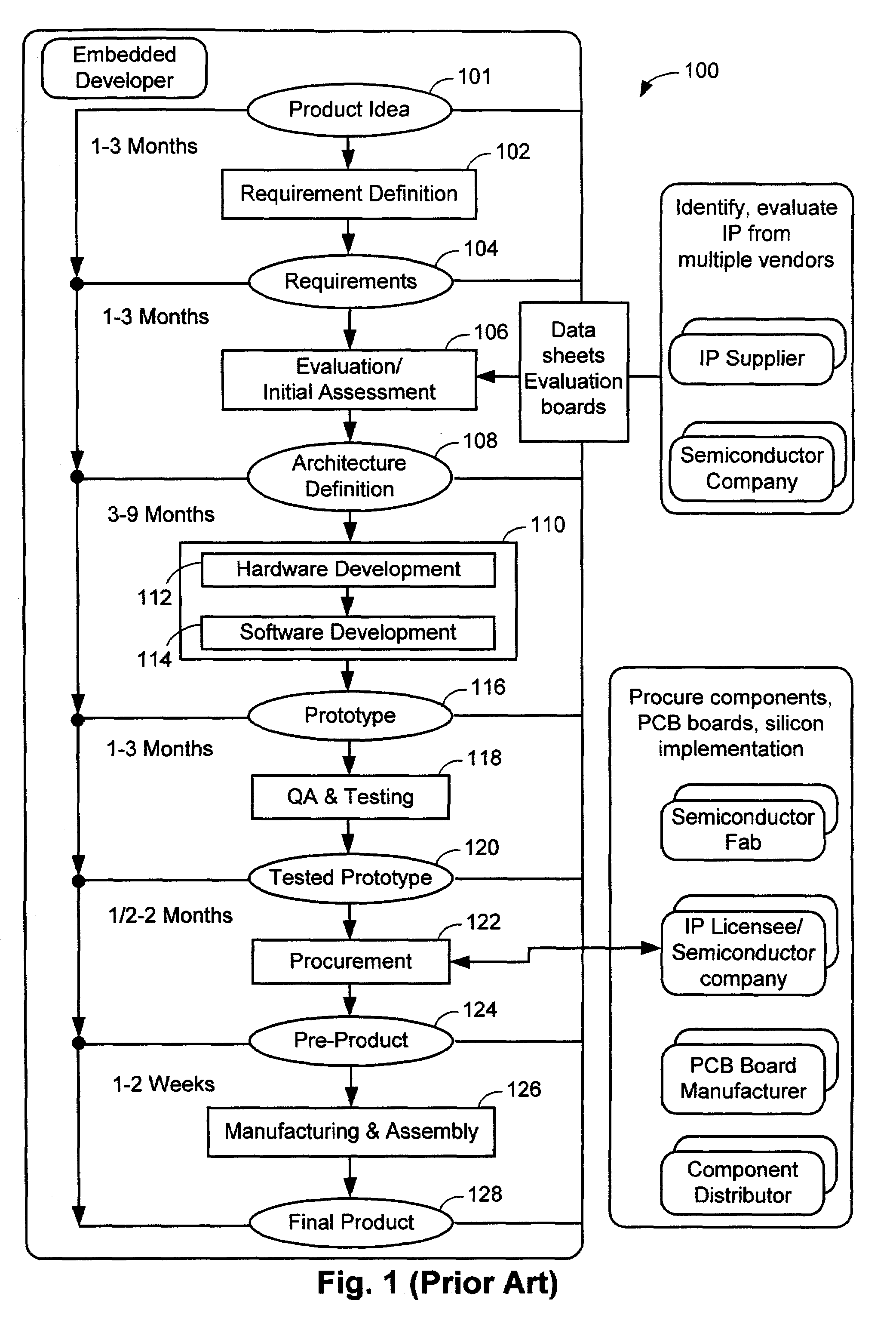

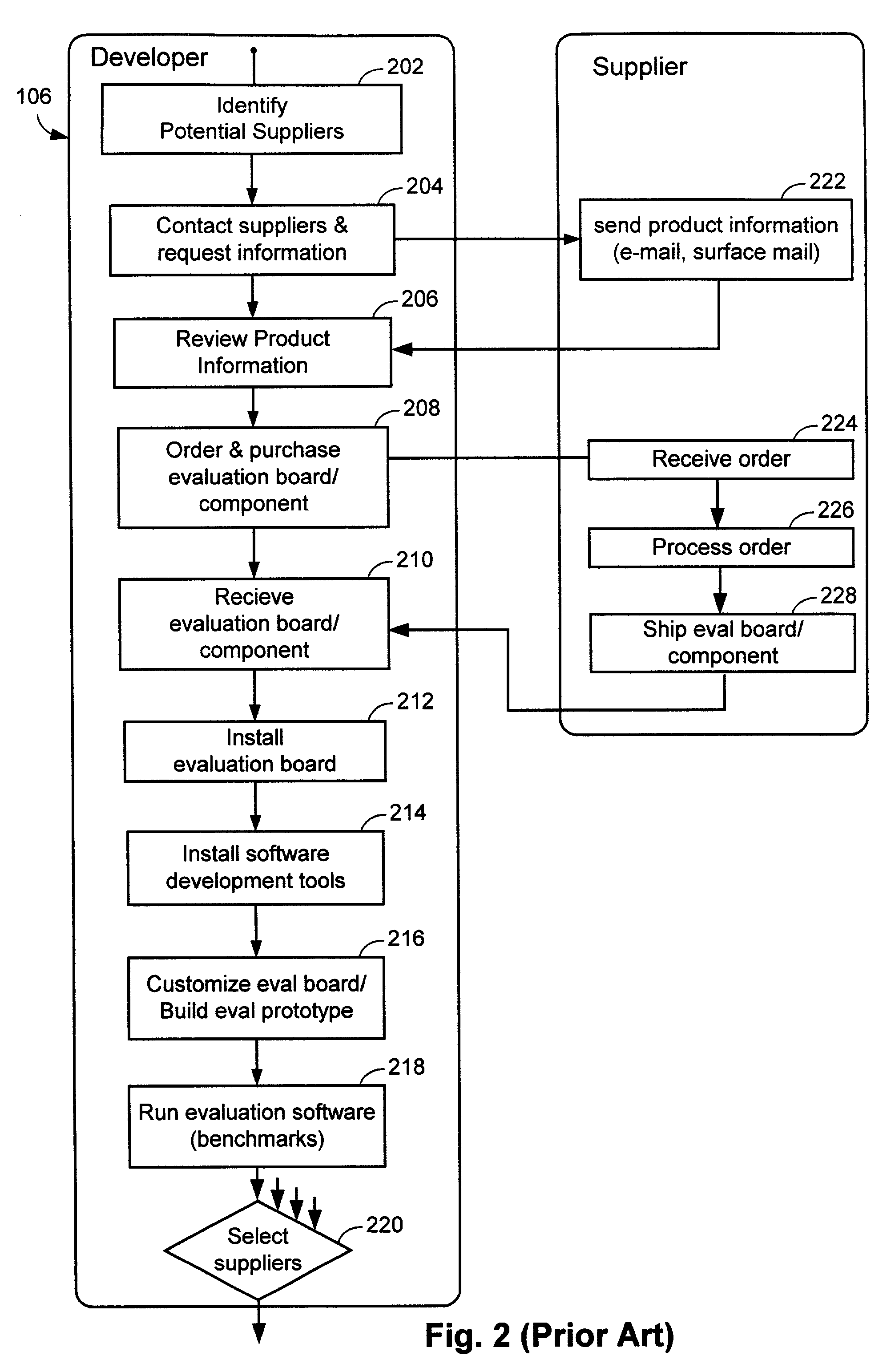

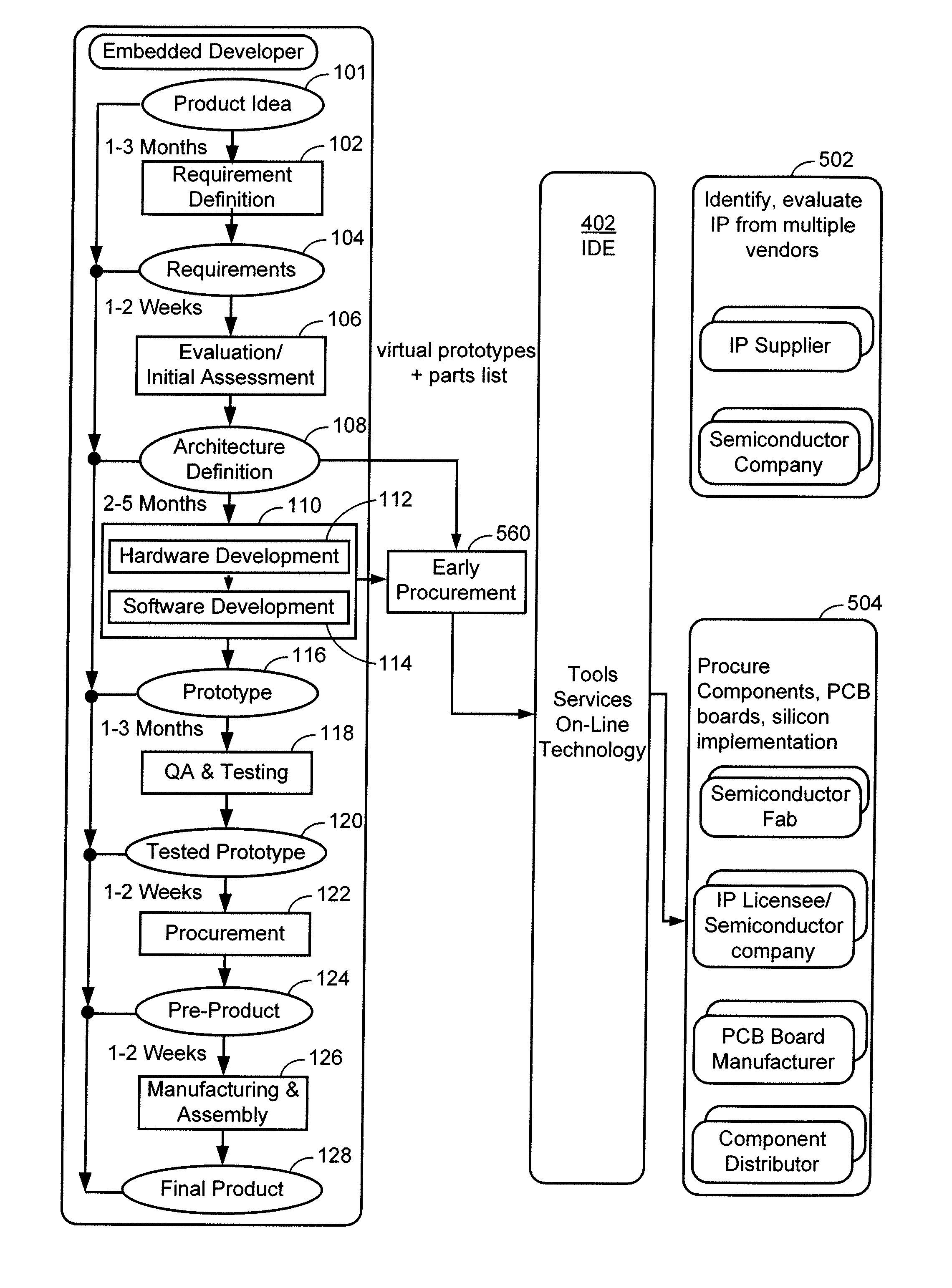

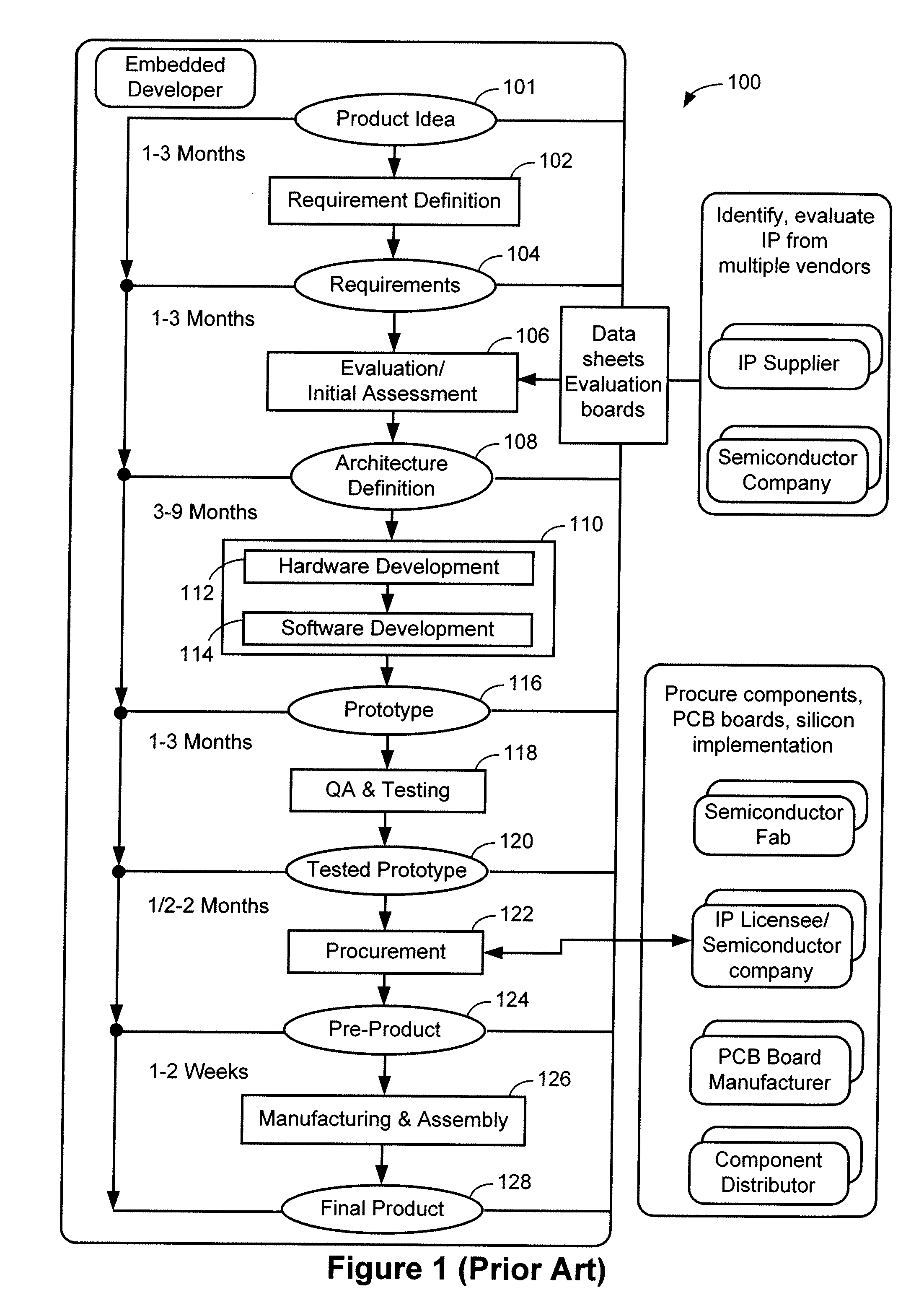

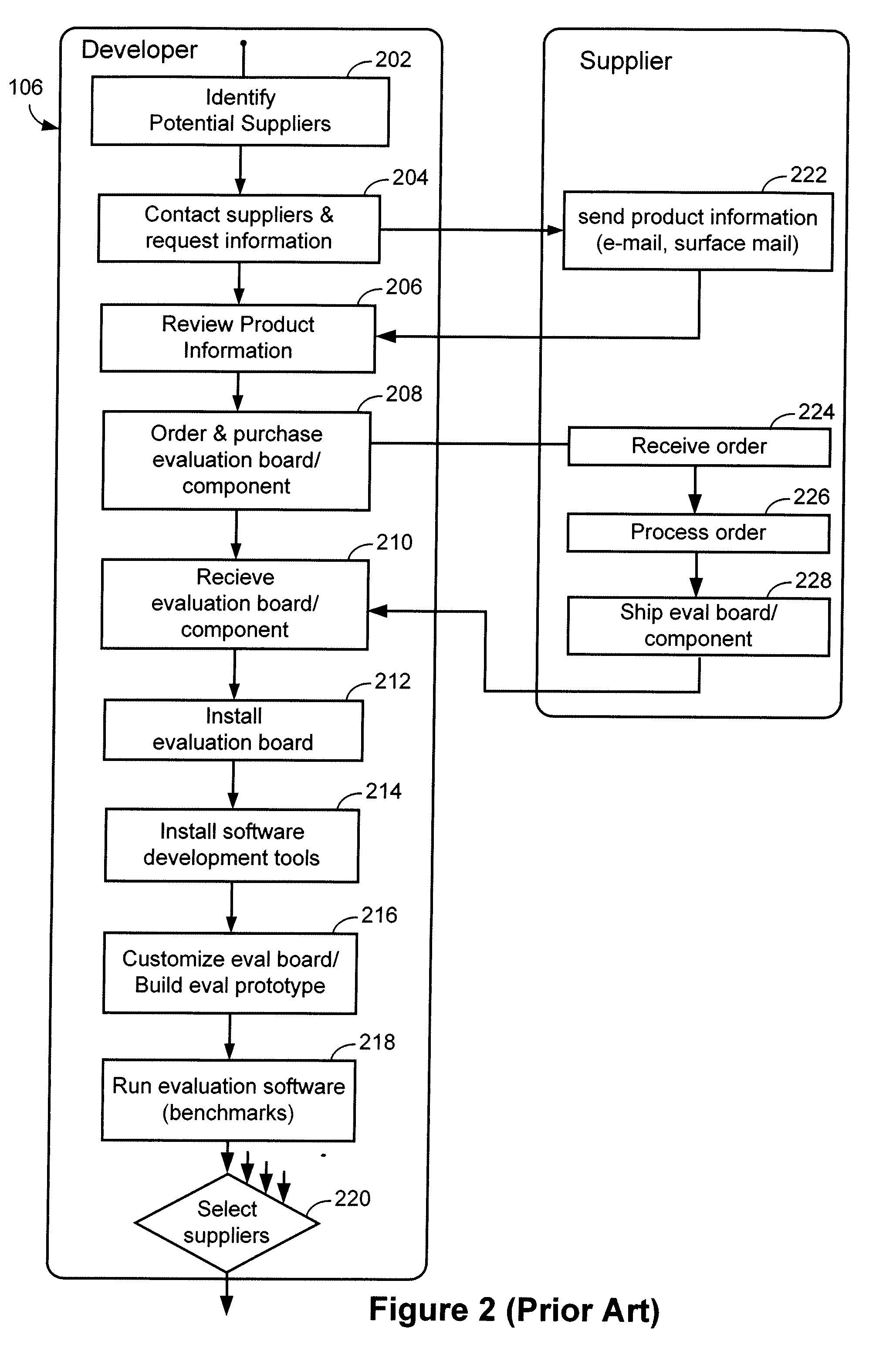

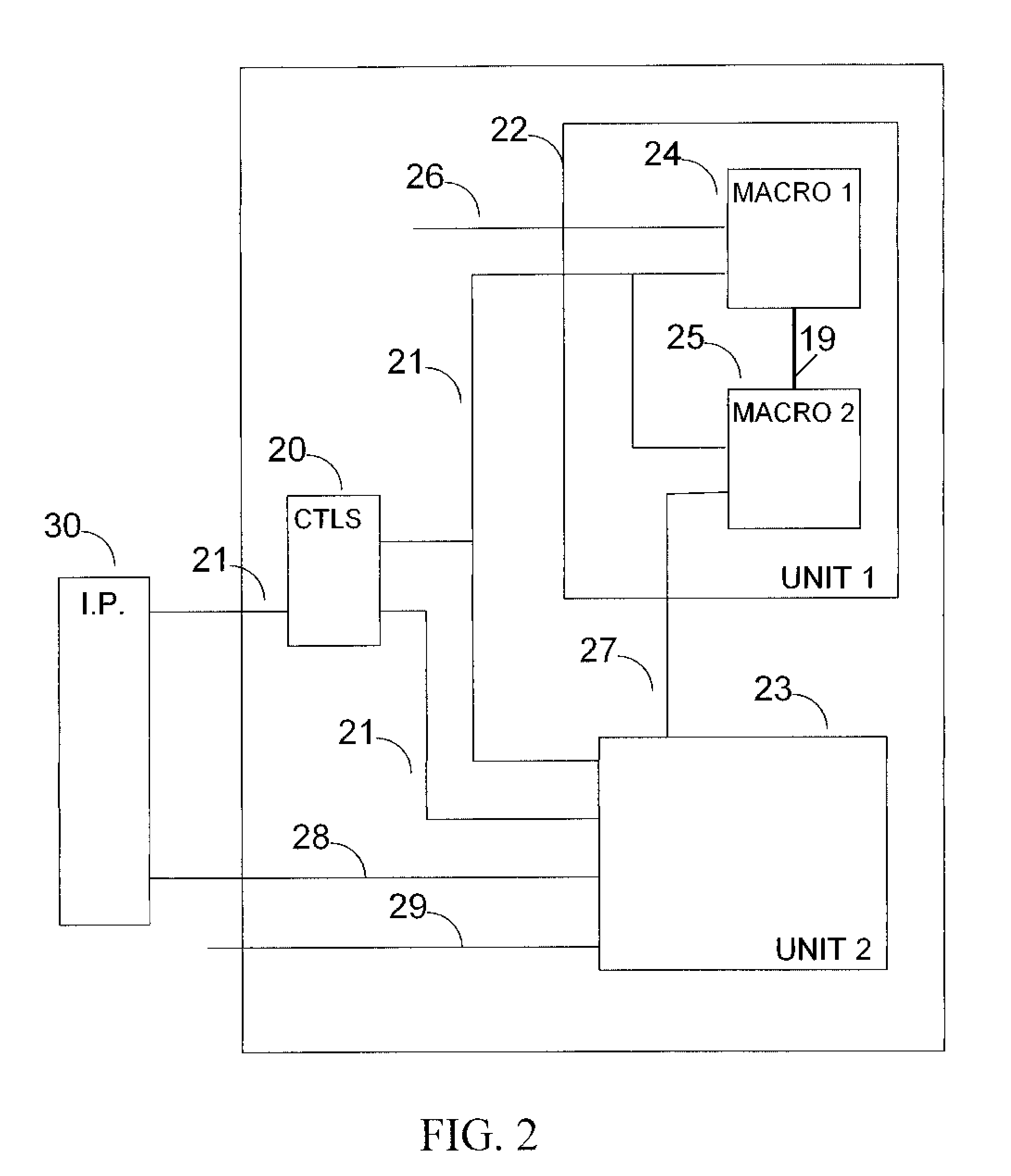

Method and system for virtual prototyping

ActiveUS7613599B2Reduce simulation overheadFast executionElectronic circuit testingError detection/correctionHuman–machine interfaceComputer architecture

An integrated design environment (IDE) is disclosed for forming virtual embedded systems. The IDE includes a design language for forming finite state machine models of hardware components that are coupled to simulators of processor cores, preferably instruction set accurate simulators. A software debugger interface permits a software application to be loaded and executed on the virtual embedded system. A virtual test bench may be coupled to the simulation to serve as a human-machine interface. In one embodiment, the IDE is provided as a web-based service for the evaluation, development and procurement phases of an embedded system project. IP components, such as processor cores, may be evaluated using a virtual embedded system. In one embodiment, a virtual embedded system is used as an executable specification for the procurement of a good or service related to an embedded system.

Owner:SYNOPSYS INC

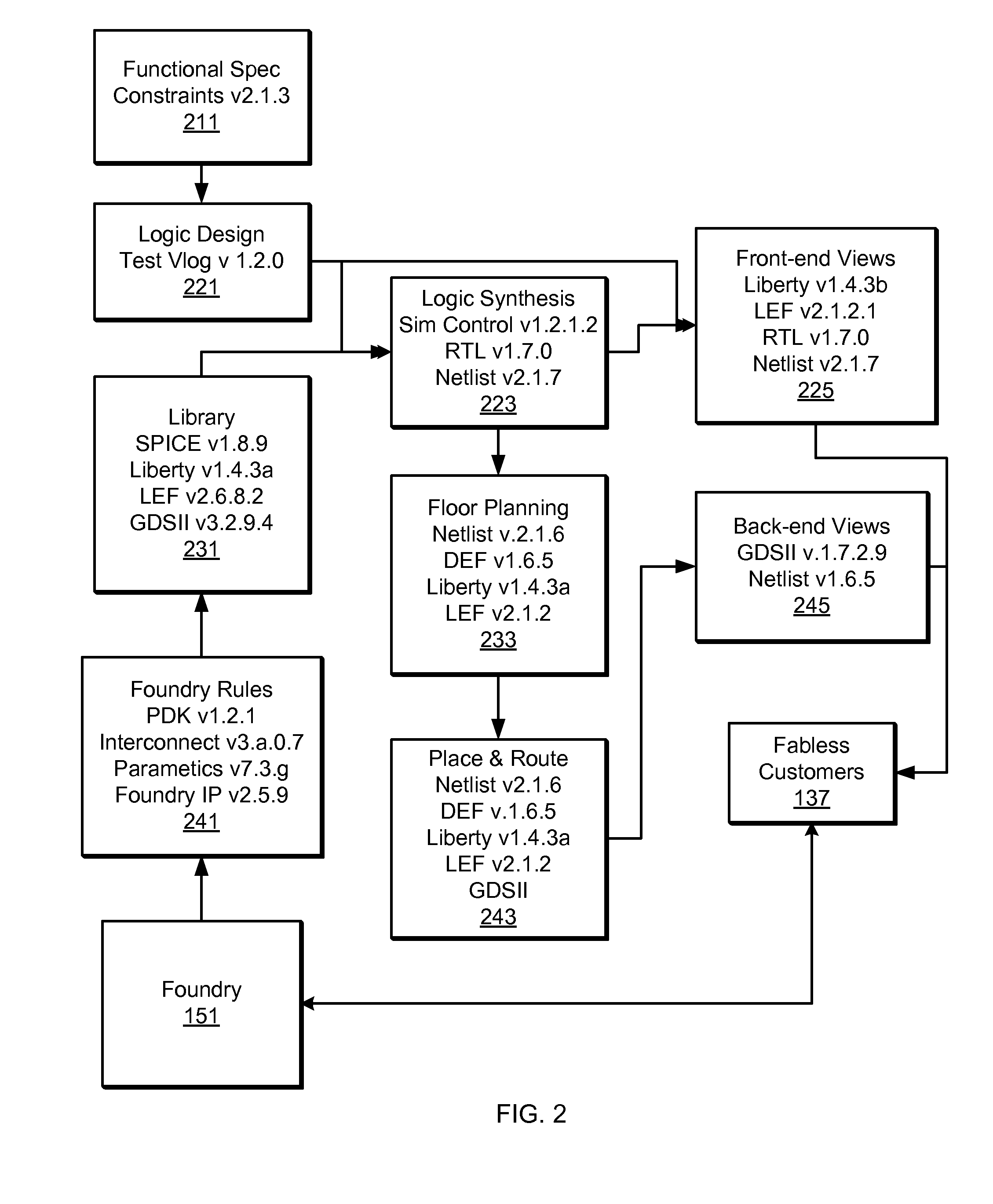

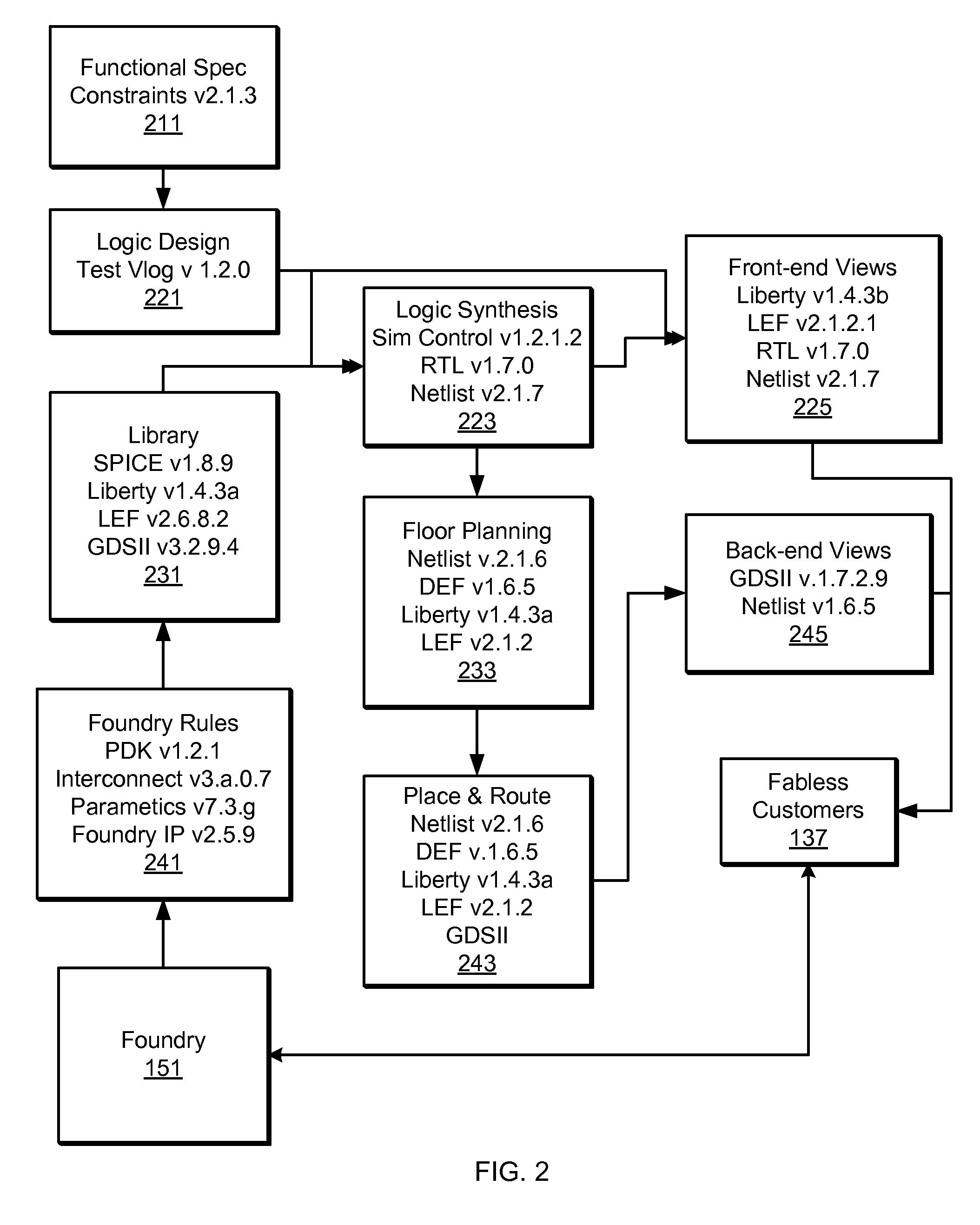

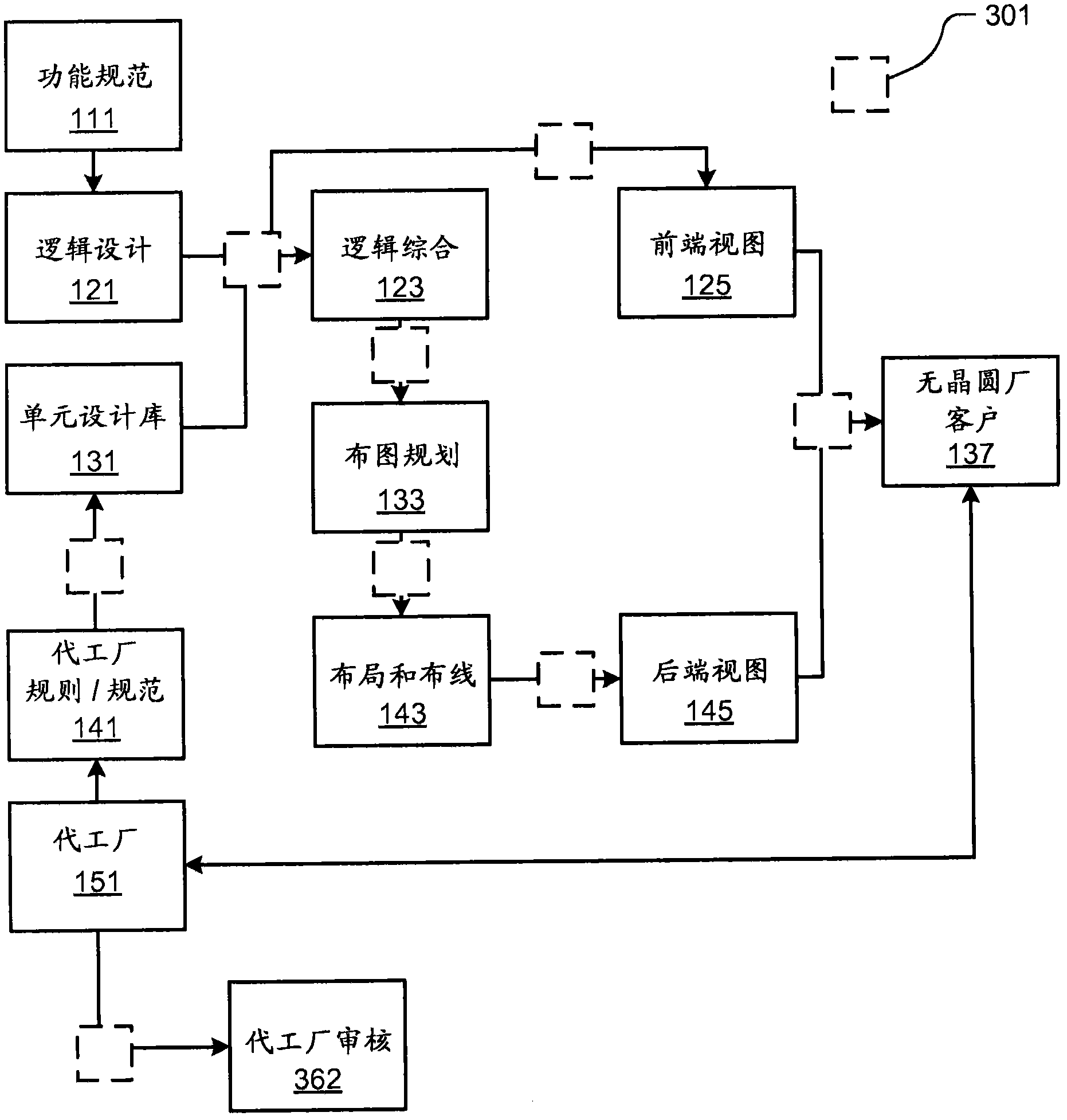

Methods and Devices for Independent Evaluation of Cell Integrity, Changes and Origin in Chip Design for Production Workflow

ActiveUS20090307640A1Reduce sensitivityDetecting faulty computer hardwareCAD circuit designCell integrityFunctional impact

The technology disclosed relates to granular analysis of design data used to prepare chip designs for manufacturing and to identification of similarities and differences among parts of design data files. In particular, it relates to parsing data and organizing into canonical forms, digesting the canonical forms, and comparing digests of design data from different sources, such as designs and libraries of design templates. Organizing the design data into canonical forms generally reduces the sensitivity of data analysis to variations in data that have no functional impact on the design. The details of the granular analysis vary among design languages used to represent aspects of a design. For various design languages, granular analysis includes partitioning design files by header / cell portions, by separate handling of comments, by functionally significant / non-significant data, by whitespace / non-whitespace, and by layer within a unit of design data. The similarities and differences of interest depend on the purpose of the granular analysis. The comparisons are useful in many ways.

Owner:OASIS TOOLING

Method And System for Virtual Prototyping

InactiveUS20100017185A1Analogue computers for electric apparatusCAD network environmentHuman–machine interfaceComputer architecture

An integrated design environment (IDE) is disclosed for forming virtual embedded systems. The IDE includes a design language for forming finite state machine models of hardware components that are coupled to simulators of processor cores, preferably instruction set accurate simulators. A software debugger interface permits a software application to be loaded and executed on the virtual embedded system. A virtual test bench may be coupled to the simulation to serve as a human-machine interface. In one embodiment, the IDE is provided as a web-based service for the evaluation, development and procurement phases of an embedded system project. IP components, such as processor cores, may be evaluated using a virtual embedded system. In one embodiment, a virtual embedded system is used as an executable specification for the procurement of a good or service related to an embedded system.

Owner:SYNOPSYS INC

Methods and devices for independent evaluation of cell integrity, changes and origin in chip design for production workflow

ActiveUS7685545B2Reduce sensitivityDetecting faulty computer hardwareCAD circuit designCell integrityFunctional impact

The technology disclosed relates to granular analysis of design data used to prepare chip designs for manufacturing and to identification of similarities and differences among parts of design data files. In particular, it relates to parsing data and organizing into canonical forms, digesting the canonical forms, and comparing digests of design data from different sources, such as designs and libraries of design templates. Organizing the design data into canonical forms generally reduces the sensitivity of data analysis to variations in data that have no functional impact on the design. The details of the granular analysis vary among design languages used to represent aspects of a design. For various design languages, granular analysis includes partitioning design files by header / cell portions, by separate handling of comments, by functionally significant / non-significant data, by whitespace / non-whitespace, and by layer within a unit of design data. The similarities and differences of interest depend on the purpose of the granular analysis. The comparisons are useful in many ways.

Owner:OASIS TOOLING

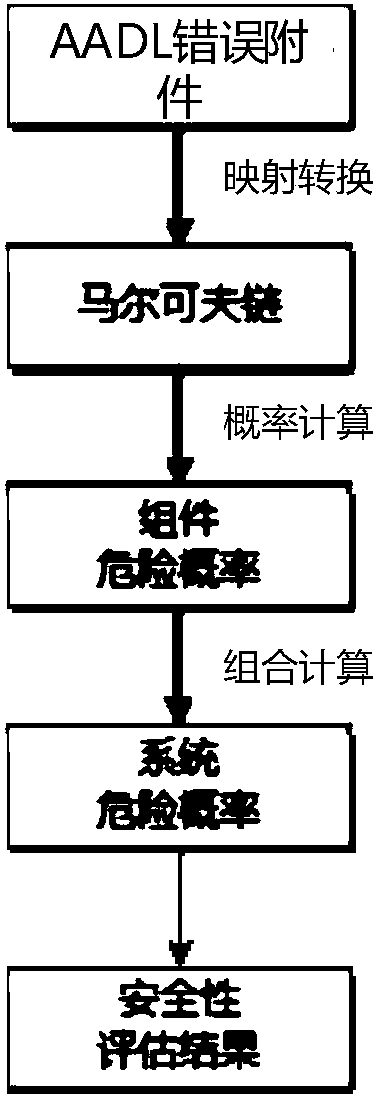

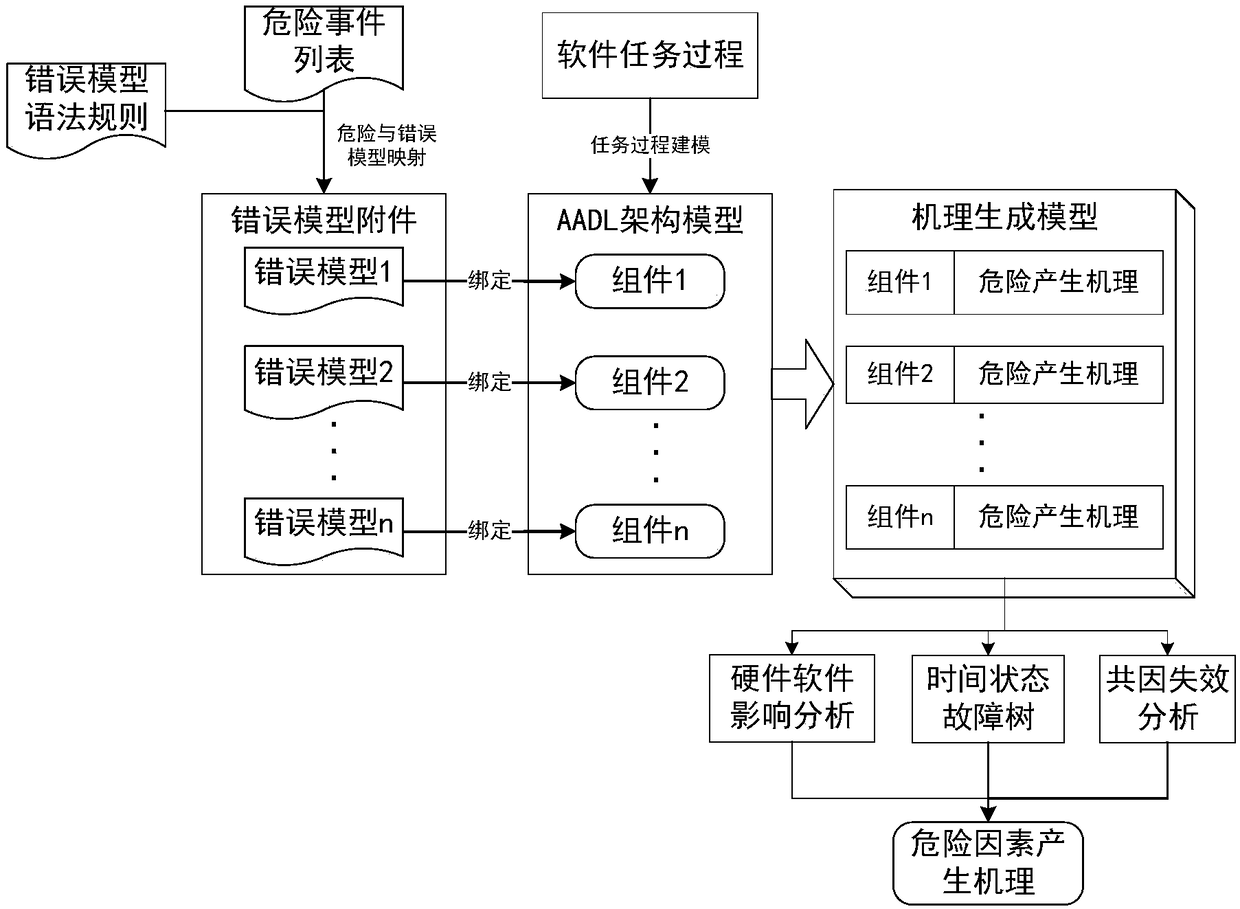

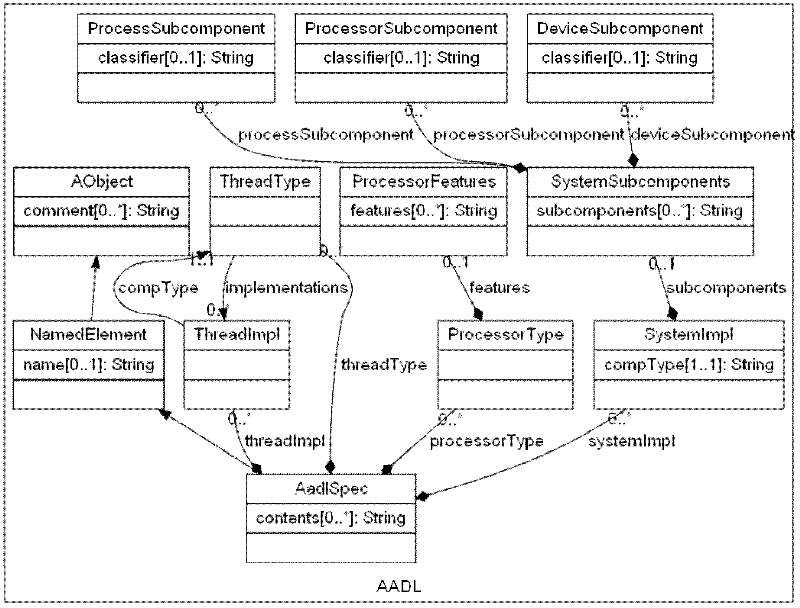

AADL (architecture analysis and design language) model extension based software system security verification and assessment method

ActiveCN108376221AImplement security assessmentImprove assessment accuracyPlatform integrity maintainanceSoftware systemAutomaton

The invention relates to an AADL (architecture analysis and design language) model extension based software system security verification and assessment method, which is provided in order to overcome defect of difficulty in direct processing of system models, high computation cost and high redundancy in computation in existing AADL model based verification and assessment. The method includes: establishing relationship between risk factors and an AADL architecture model to form a mechanism generating model; extracting model elements, generating a time state fault tree, a hardware software impactanalysis tree and a common cause time-dependent analysis tree according to the model elements, and backstepping a risk generation route according to the tree structure from bottom to top; setting physical resource properties and capacity of each physical device; calculating the failure probability of each physical device according to labeled risk factor probability of each physical device; converting an AADL security model into a timed automata; calling a formal verification tool UPPAAL for analysis and verification of the timed automata. The method is applicable to security assessment of software and hardware systems.

Owner:HARBIN INST OF TECH

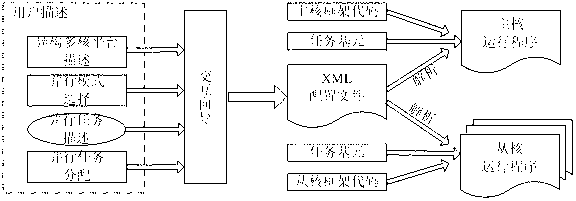

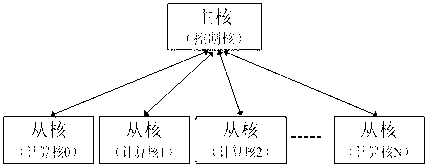

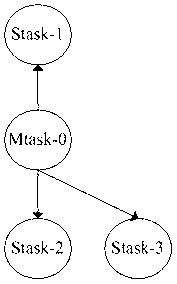

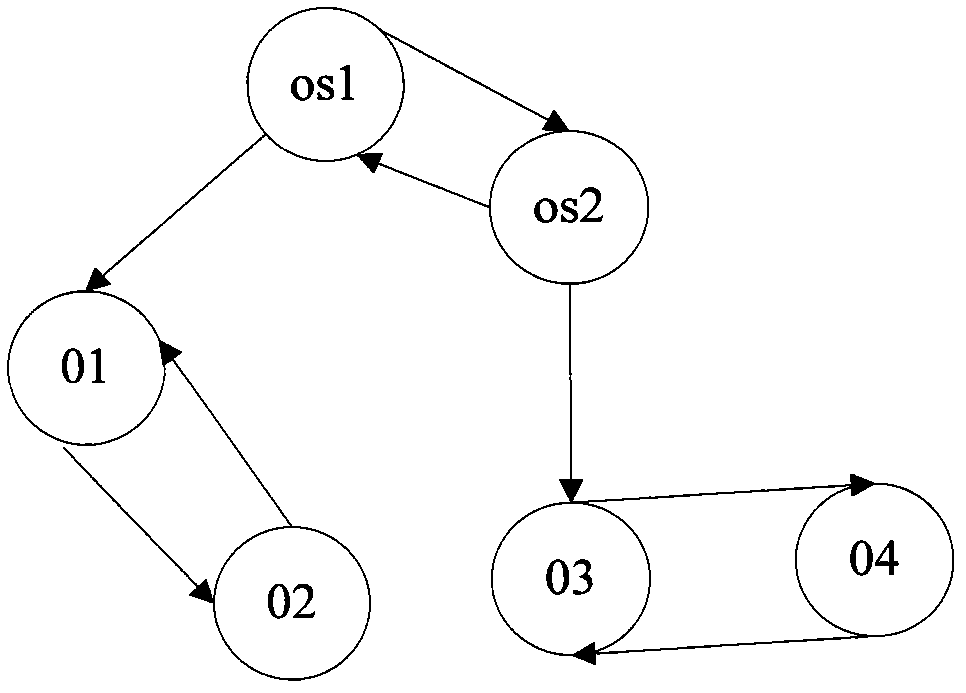

User description based programming design method on embedded heterogeneous multi-core processor

InactiveCN102707952AOutstanding FeaturesHighlight significant progressSpecific program execution arrangementsPerformance computingParallel programming model

The invention relates to a user description based programming design method on an embedded heterogeneous multi-core processor. The method includes the steps that a user configures a guide through an image interface to perform description of a heterogeneous multi-core processor platform and a task, a parallel mode is set, an element task is established and registered, a task relation graph (directed acyclic graph (DAG)) is generated, the element task is subjected to a static assignment on the heterogeneous multi-core processor, and processor platform characteristics, parallel demands and task assignment are expressed in a configuration file mode (extensible markup language (XML)). Then the element task after a configuration file is subjected to a parallel analysis is embedded into a position of a heterogeneous multi-core framework code task label, a corresponding serial source program is constructed, a serial compiler is invoked, and finally an executable code on the heterogeneous multi-core processor can be generated. By means of the user description based programming design method on the embedded heterogeneous multi-core processor, parallel programming practices such as developing a parallel compiler on a general personal computer (PC) or a high-performance computing platform, establishing a parallel programming language and porting a parallel library are effectively avoided, the difficulty of developing a parallel program on the heterogeneous multi-core processor platform in the embedded field is greatly reduced, the purpose of parallel programming based on the user description and parallelization interactive guide is achieved.

Owner:SHANGHAI UNIV

Methods and devices for independent evaluation of cell integrity, changes and origin in chip design for production workflow

ActiveUS20090307639A1Reduce sensitivityDetecting faulty computer hardwareCAD circuit designCell integrityFunctional impact

The technology disclosed relates to granular analysis of design data used to prepare chip designs for manufacturing and to identification of similarities and differences among parts of design data files. In particular, it relates to parsing data and organizing into canonical forms, digesting the canonical forms, and comparing digests of design data from different sources, such as designs and libraries of design templates. Organizing the design data into canonical forms generally reduces the sensitivity of data analysis to variations in data that have no functional impact on the design. The details of the granular analysis vary among design languages used to represent aspects of a design. For various design languages, granular analysis includes partitioning design files by header / cell portions, by separate handling of comments, by functionally significant / non-significant data, by whitespace / non-whitespace, and by layer within a unit of design data. The similarities and differences of interest depend on the purpose of the granular analysis. The comparisons are useful in many ways.

Owner:OASIS TOOLING

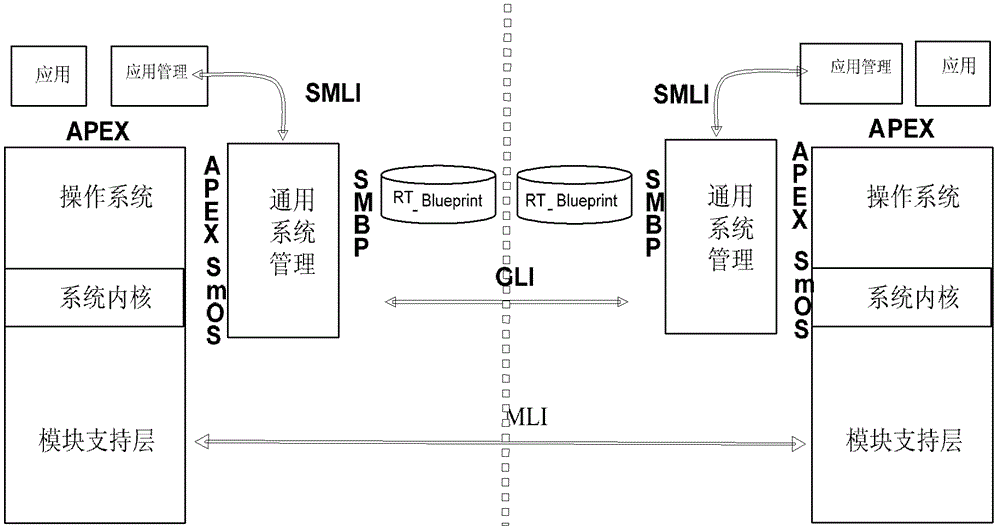

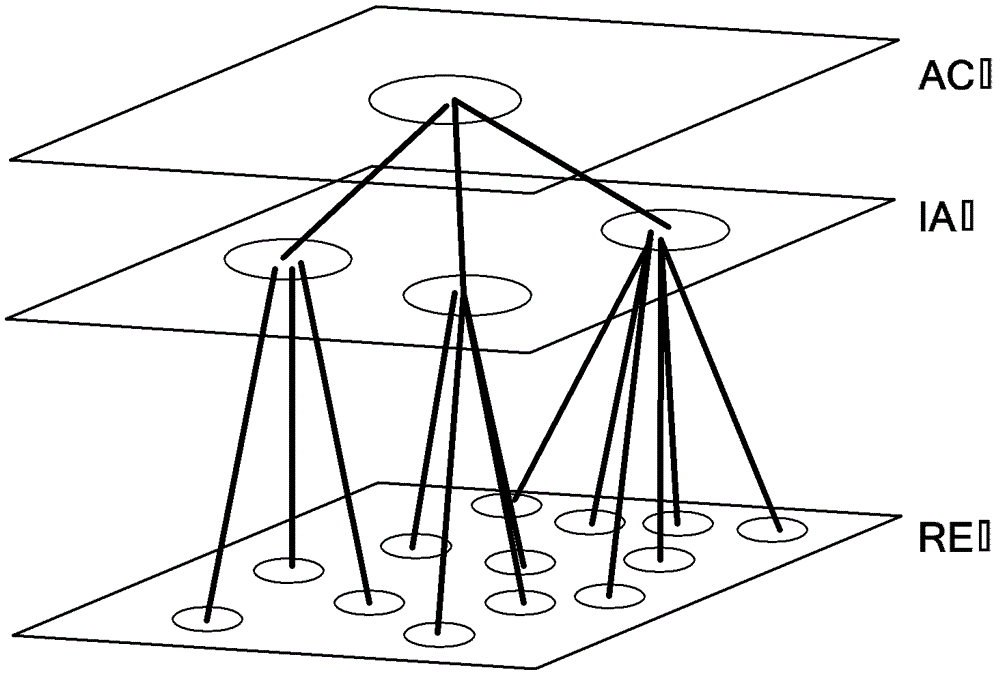

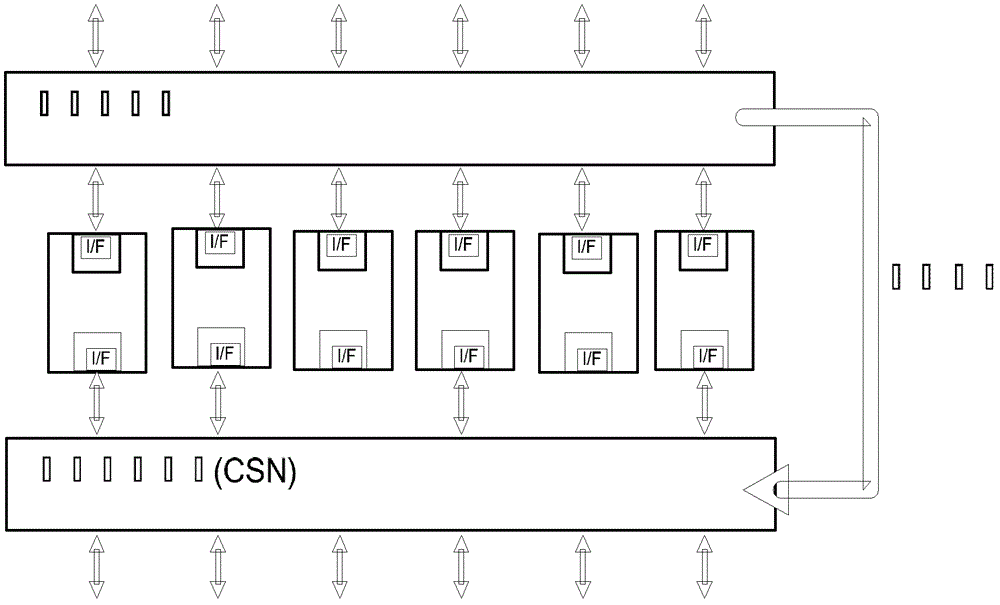

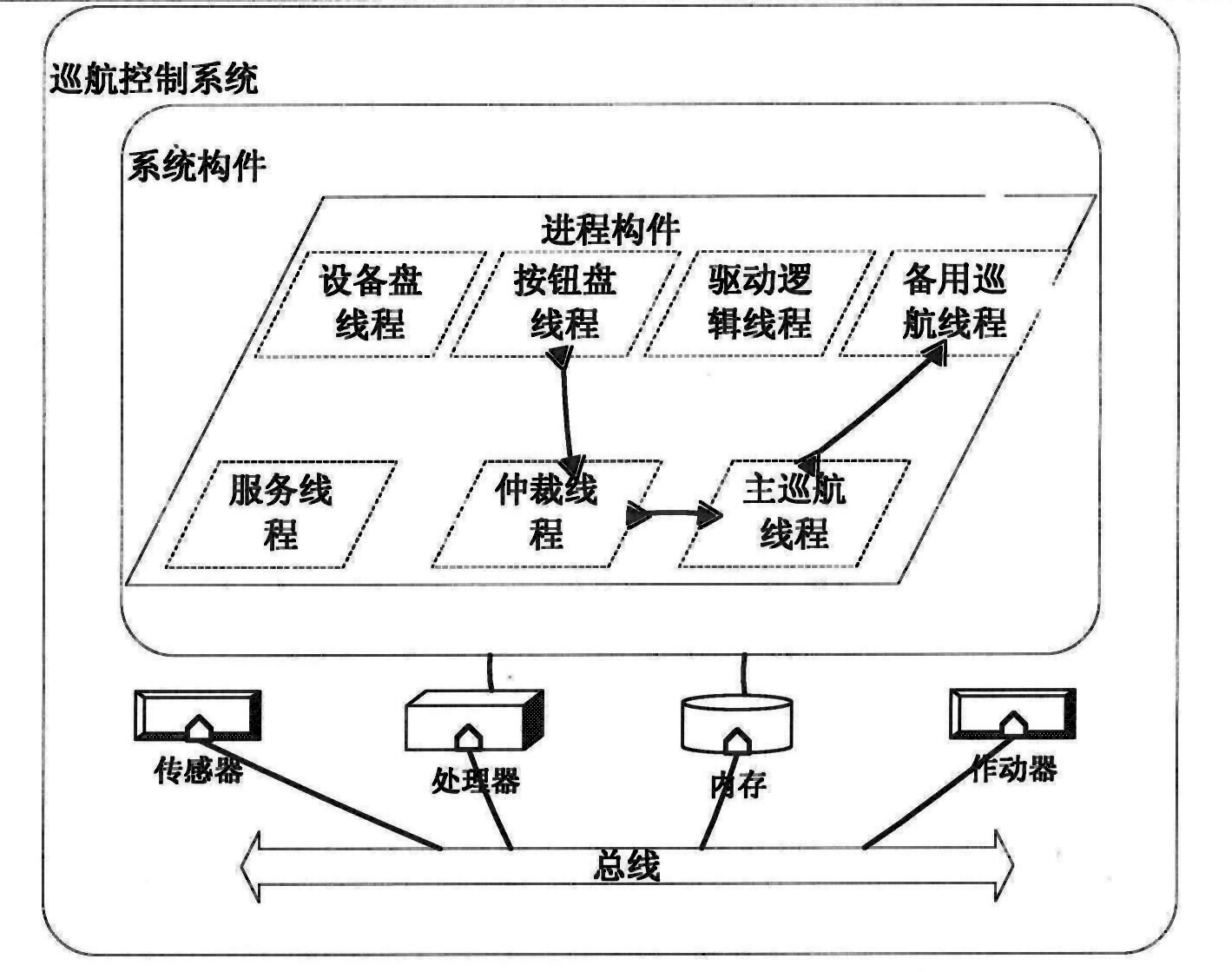

Blueprint generating method for integrated avionic system model aiming at architecture analysis and design language (AADL) description

ActiveCN102750301AImprove production efficiencyAvoid manually writingSpecial data processing applicationsElectricityHardware structure

The invention relates to a blueprint generating method for an integrated avionic system model aiming at architecture analysis and design language (AADL) description. The blueprint generating method includes the following steps: 1 modeling: building the avionic system model from bottom to top in an AADL modeling environment: 1.1 modeling a hardware structure; 1.2 modeling a software structure; 1.3 building a mapping relation model from software to hardware; 1.4 building a distributed system model which comprises a distributed software model, a distributed hardware model and the mapping relation model from software to hardware; 2 automatically generating a blueprint according to the avionic system model; and 3 enabling a user to upload a blueprint file to a target machine. The blueprint generating method solves the technical problem that time and labor are wasted and errors can be caused easily when the current users manually edit the blueprint file, automatically generates the blueprint in operation aiming at the avionic system model established by the AADL, prevents the users from manually editing the blueprint file and improves blueprint generating efficiency.

Owner:AVIC NO 631 RES INST

Graphical Internet Search System and Methods

InactiveUS20080097859A1Easy to listEfficient communicationWeb data indexingBuying/selling/leasing transactionsInternet searchingGraphics

Owner:ROSETTA HLDG

AADL2TASM (Architecture Analysis and Design Language-to-Timed Abstract State Machine) model transformation method

The invention relates to an AADL2TASM model transformation method, which is used for transforming an AADL model into a TASM model. KM3 is used for describing the meta-model of the source language AADL and the meta-model of the target language TASM, and aimed at a thread component, a dispatcher, mode conversion and a scheduler in the AADL model, a transformation method for the thread component, a transformation method for the dispatcher component, a transformation method for the mode conversion and a transformation method for the scheduler component are respectively used for transforming the AADL model into the TASM model.

Owner:BEIHANG UNIV

Embedded software testing method based on AADL (Architecture Analysis and Design Language) mode transformation relationship

InactiveCN102053910ASolve the "Oracle problemGuaranteed reliabilitySoftware testing/debuggingSoftware designMetamorphic testing

The invention relates to an embedded software testing method based on AADL (Architecture Analysis and Design Language) mode transformation relationship, which has the following steps of: constructing a mode transition diagram on the basis of mode information in an AADL model, and converting the diagram into a mode relationship tree required by a transformation test according to the improved depth-first traversing algorithm; constructing a source test case in the mode transformation relationship by traversing the mode relationship tree, generating a subsequent test case by means of the mode transformation relationship in the AADL model, and verifying the mode transformation relationship to obtain the conclusion of the transformation test. The embedded software testing method based on AADL mode transformation relationship solves the 'Oracle' problem existing in the embedded software test, is convenient for a user to test the embedded software at an early stage of software design and ensures the reliability of software at a system architecture level. If the model architecture can not meet corresponding requirements, the architecture of the software can be modified at an early stage of development, thus the development cost is saved, and meanwhile, the development cycle can also be shortened.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

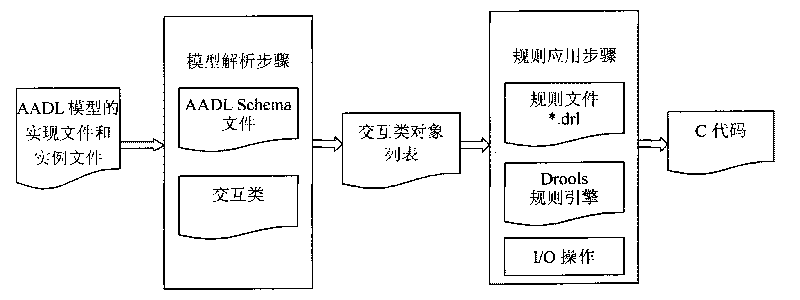

Automatic code generation method of architecture analysis and design language (AADL) model

InactiveCN101739258AConvenient and Feasible Generation MethodSpecific program execution arrangementsSystem structureHuman language

The invention discloses an automatic code generation method of an architecture analysis and design language (AADL) model, which comprises the steps of: analyzing implementation files and instance files in the AADL model, extracting information of each component, storing in an AADL interactive object; when generating the interactive object, triggering corresponding I / O (input / output) operations by using a Drools rule engine according to different model forms of the interactive object; and generating C codes meeting normative hierarchical structures and corresponding formats by the I / O operations according to the regulations in an attachment of an AADL standard society of automotive (SAE) AS5506 / 1 and the requirements of the standard C code regulations. The automatic code generation method of the AADL model can generate the codes meeting the regulations in the attachment of the AADL standard society of automotive (SAE) AS5506 / 1 and the standard C code regulations through reading in the implementation files and the instance files of the AADL model by using the processing of the two steps, and realizes the conversion between descriptive frame language and executable platform language which are designed and analyzed in a system structure.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

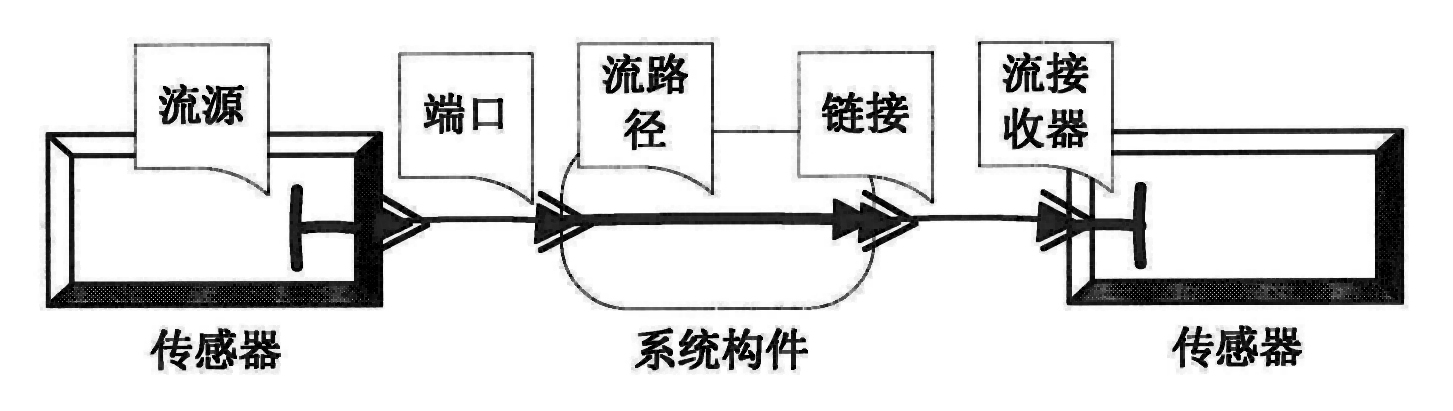

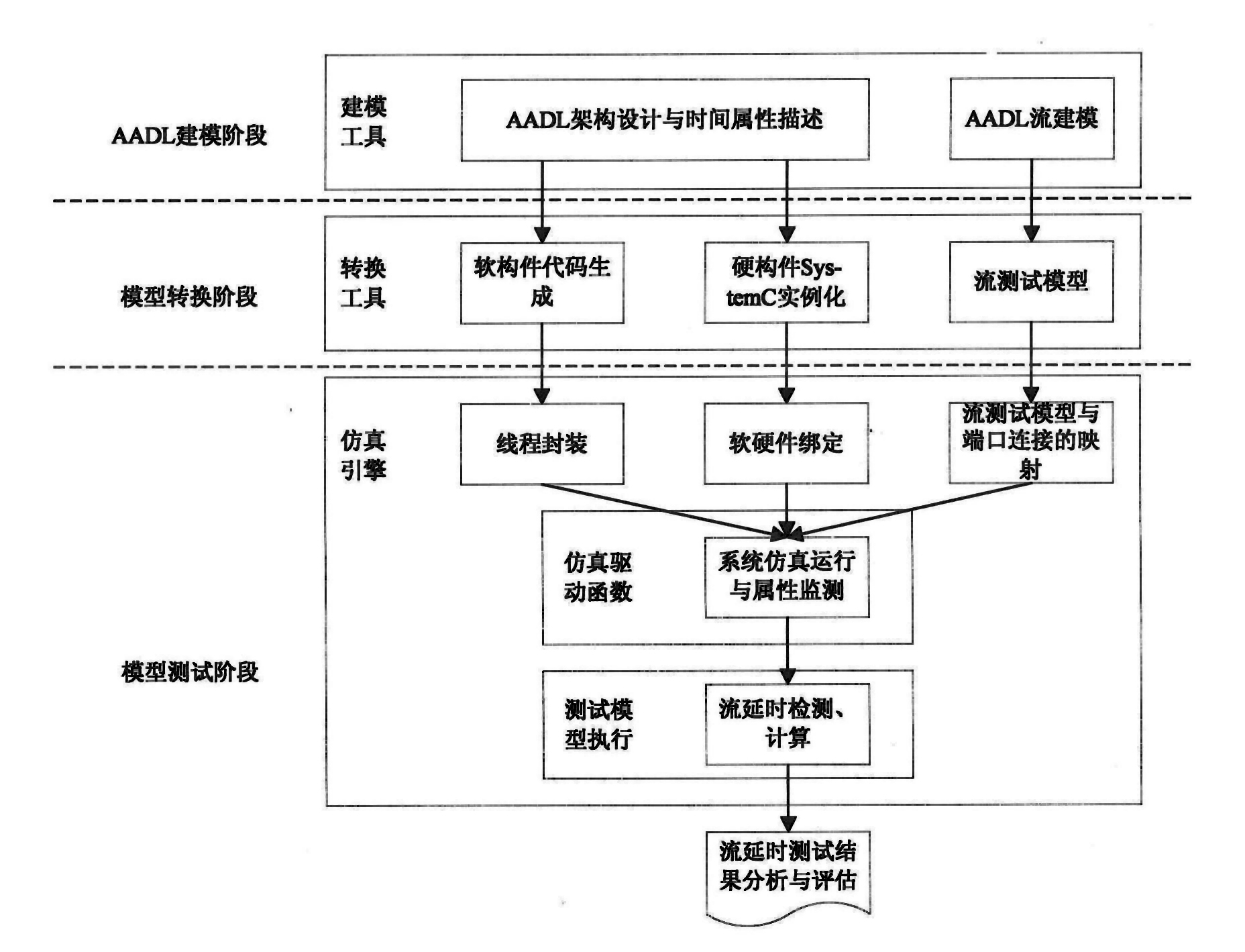

Method for testing delay attribute of embedded system stream based on model

InactiveCN102073585AImprove development efficiencySoftware testing/debuggingTest platformDesign stage

The invention discloses a method for testing a delay attribute of an embedded system stream based on a model, which is characterized by comprising the steps of: building an AADL (Architecture Analysis and Design Language) model simulation test platform based on a System C hardware description language, converting an AADL model into a system example executed by the test platform, abstracting and mapping a member sequence and a port sequence during the convection, converting a stream in the AADL model into a test model described by C++, completing the test of the delay attribute of the AADL stream in a process of executing the simulation of the system example, and analyzing and estimating a test result. The method can be used for dynamically testing the delay attribute of the stream of the AADL model in the design stage of the model, and iteratively constructing and fining the design model according to the test result, thereby being convenient for finding the problem in the design modeland improving the development efficiency of the design early stage of the AADL model.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Embedded software testing method based on AADL (Architecture Analysis and Design Language) mode time automata model

InactiveCN102063369AShorten the development cycleReduce development costsSoftware testing/debuggingSoftware designEmbedded software design

The invention relates to an embedded software testing method based on an AADL (Architecture Analysis and Design Language) mode time automata model, which is technically characterized by comprising the steps of: generating an AADL system member tree with mode information according to an AADL architecture model file, and constructing a time automata model of an AADL model through carrying out breadth-first traversal on the member tree. The correctness and the time attribute of converting the AADL model mode are verified by using a verifying tool of the traditional time automata. The method provided by the invention is used for testing the model in an early state of designing the embedded software so as to find whether the correctness and the real time of the software model meet the design requirement or not as soon as possible and immediately correct the design scheme, thereby shorting the period of developing the embedded real-time system and saving the development cost.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

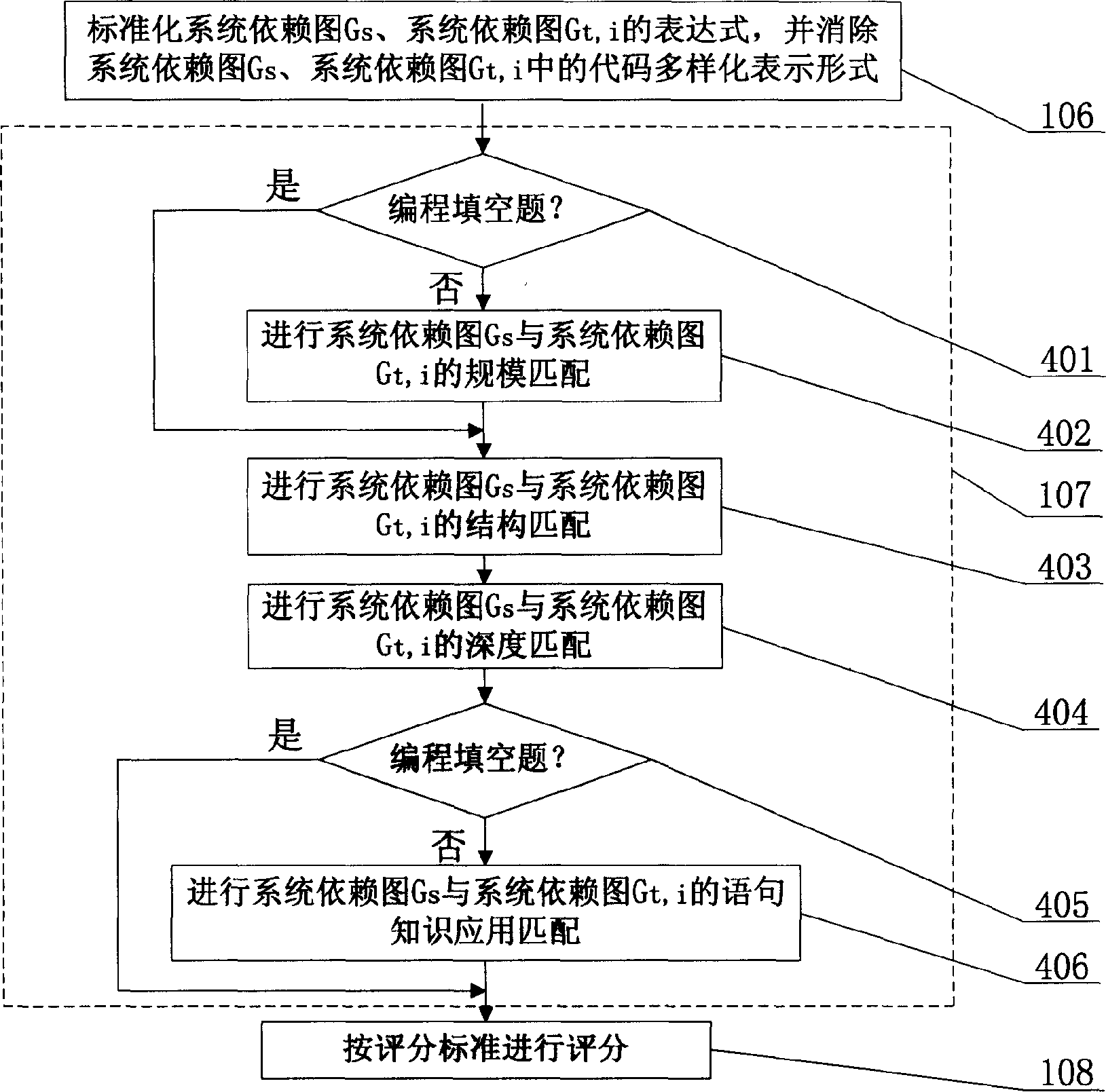

Method of automatic grading program design language editor topic

InactiveCN1598809AEliminate diverse representationsOvercome the limitations of grammatical errorsSpecial data processing applicationsTheoretical computer scienceProgram Design Language

The invention discloses an automatic grading method used in C, Pascal, Fortran and Basic programming subjects. Its steps include: input program (S) designed by students and standard key; respectively analyze grammar and accidence of program (S) and standard key (Ti) and generate system dependency graph (Gs), (Gt.i); Normalize the two graphs; represent the two graphs in syntax tree to eliminate code diversification; match process result in scale, construction, depth and knowledge application four layers; give once matching score (108) and select the highest score from all matching results of (S) and (Ti) as the final score (110). With a full consideration of kinds of grading factors, the invention has a higher precision than manual grading.

Owner:HARBIN INST OF TECH

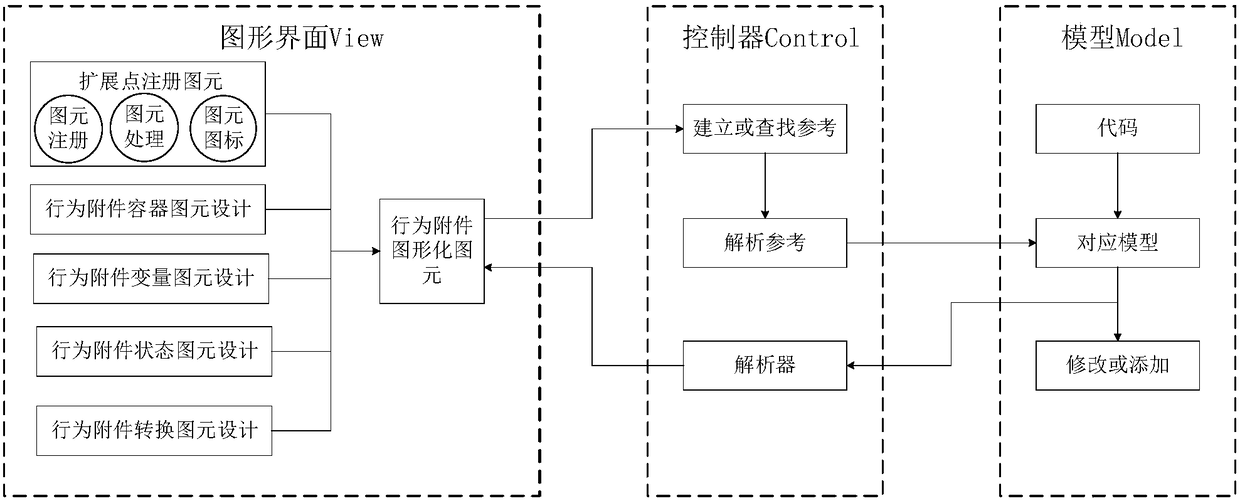

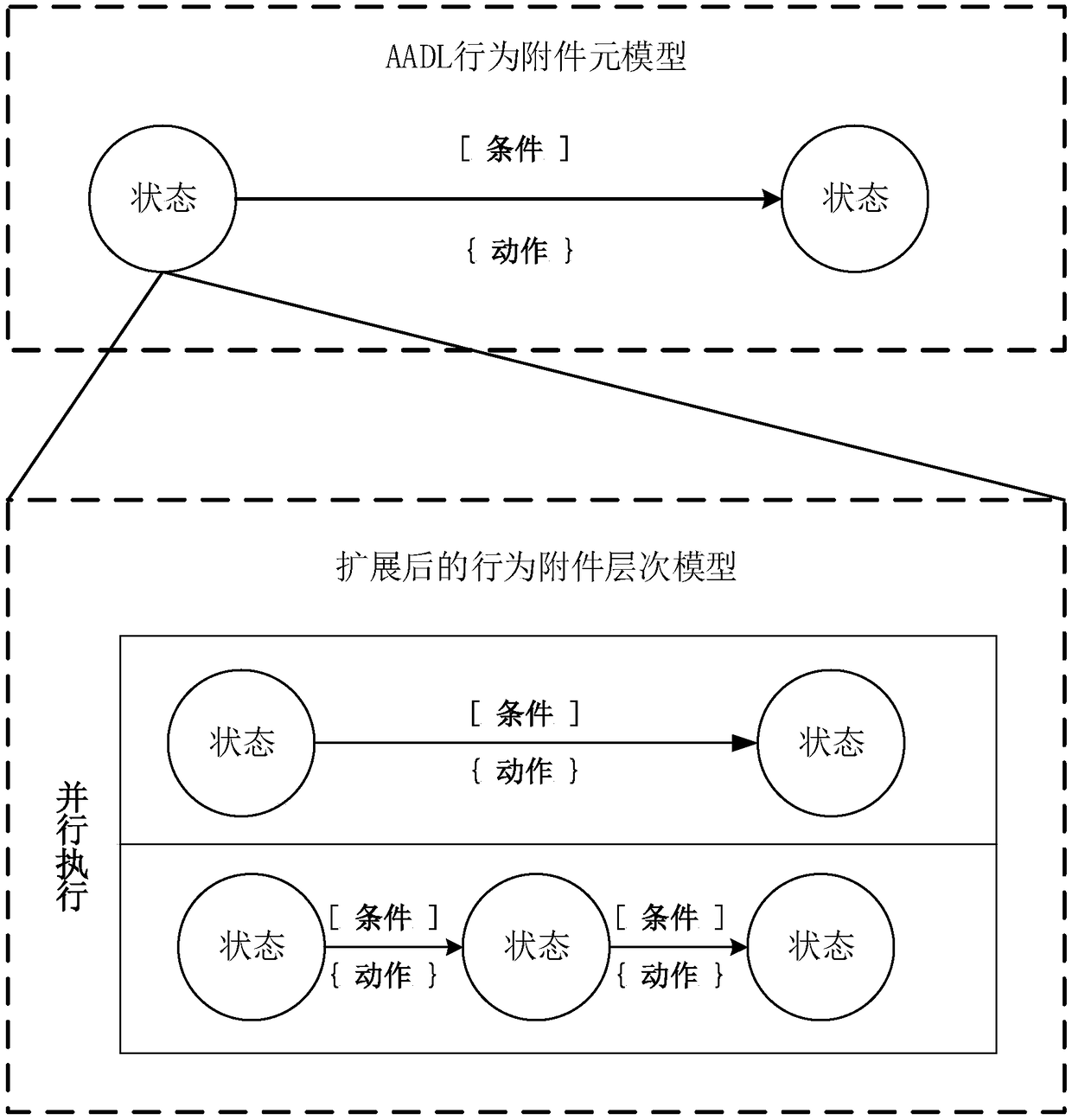

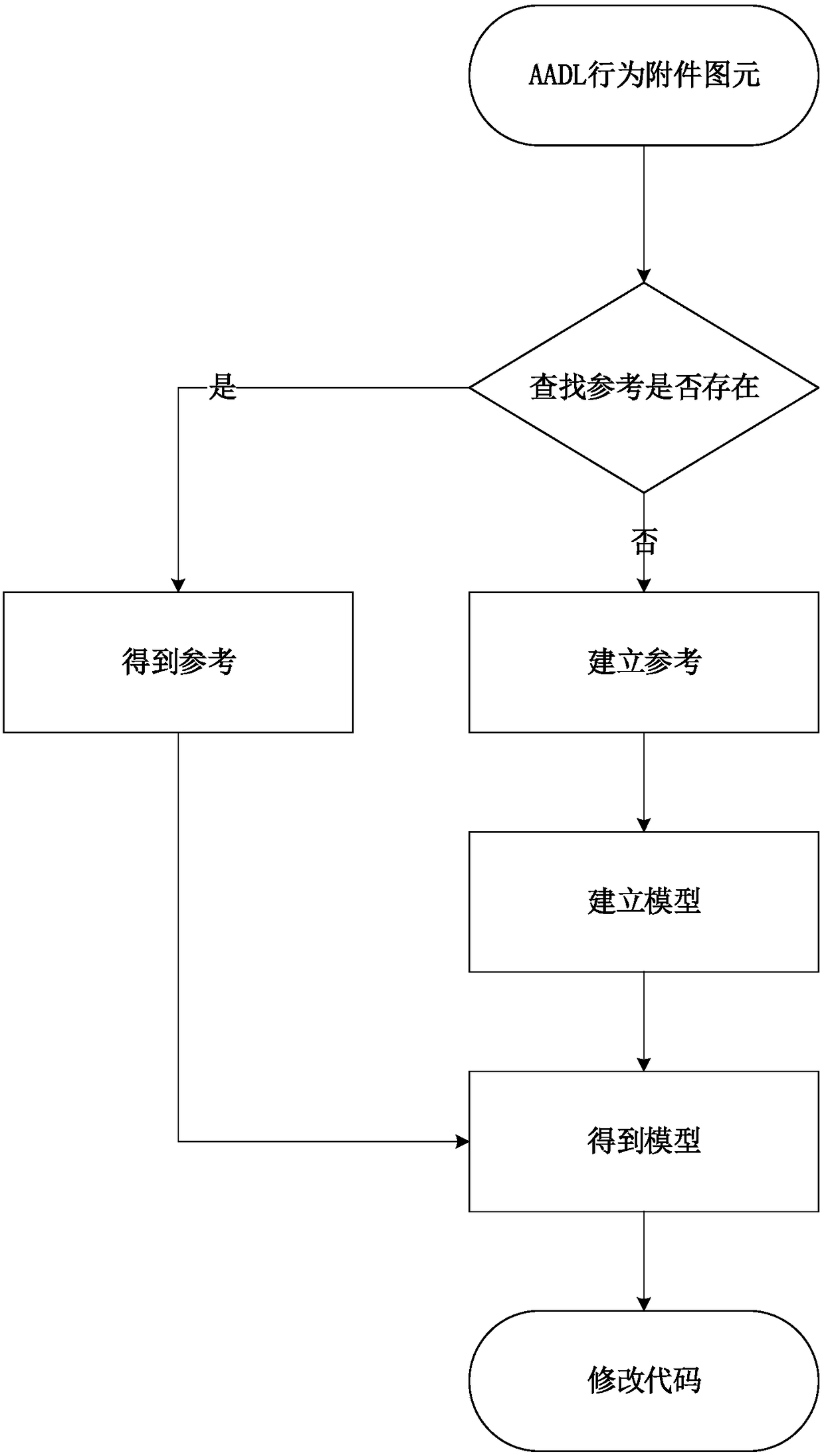

Graphical AADL (Architecture Analysis and Design Language) function behavior modeling method

ActiveCN108491196AEnhance expressive abilityRich modeling methodsVisual/graphical programmingTheoretical computer scienceOpen source

The invention discloses a graphical AADL (Architecture Analysis and Design Language) function behavior modeling method. The method is characterized by including the following steps: 1) carrying out graph element definition on each component of AADL behavior annexes; 2) using Eclipse plug-in development technology and plug-in extension point extension technology to realize graph element registration; 3) carrying out graphical modification on the AADL behavior annexes, and then carrying out checking; and 4) carrying out hierarchical extension on the AADL behavior annexes. The method achieves theadvantages that the method realizes hierarchical expression of the AADL function behaviors through AADL metamodel extension; complete graphical conversion of the AADL behavior annexes is realized through GEF (Graphical Editing Framework) technology, and the same is integrated into an AADL open-source tool OSATE (Open Source AADL Tool Environment); hierarchical expression of the AADL function behaviors enhances expression ability of an AADL; and graphical conversion of the behavior annexes enriches modeling manners of the AADL behavior annexes, and satisfies actual needs that engineers are accustomed to using graphical modeling in actual modeling processes.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

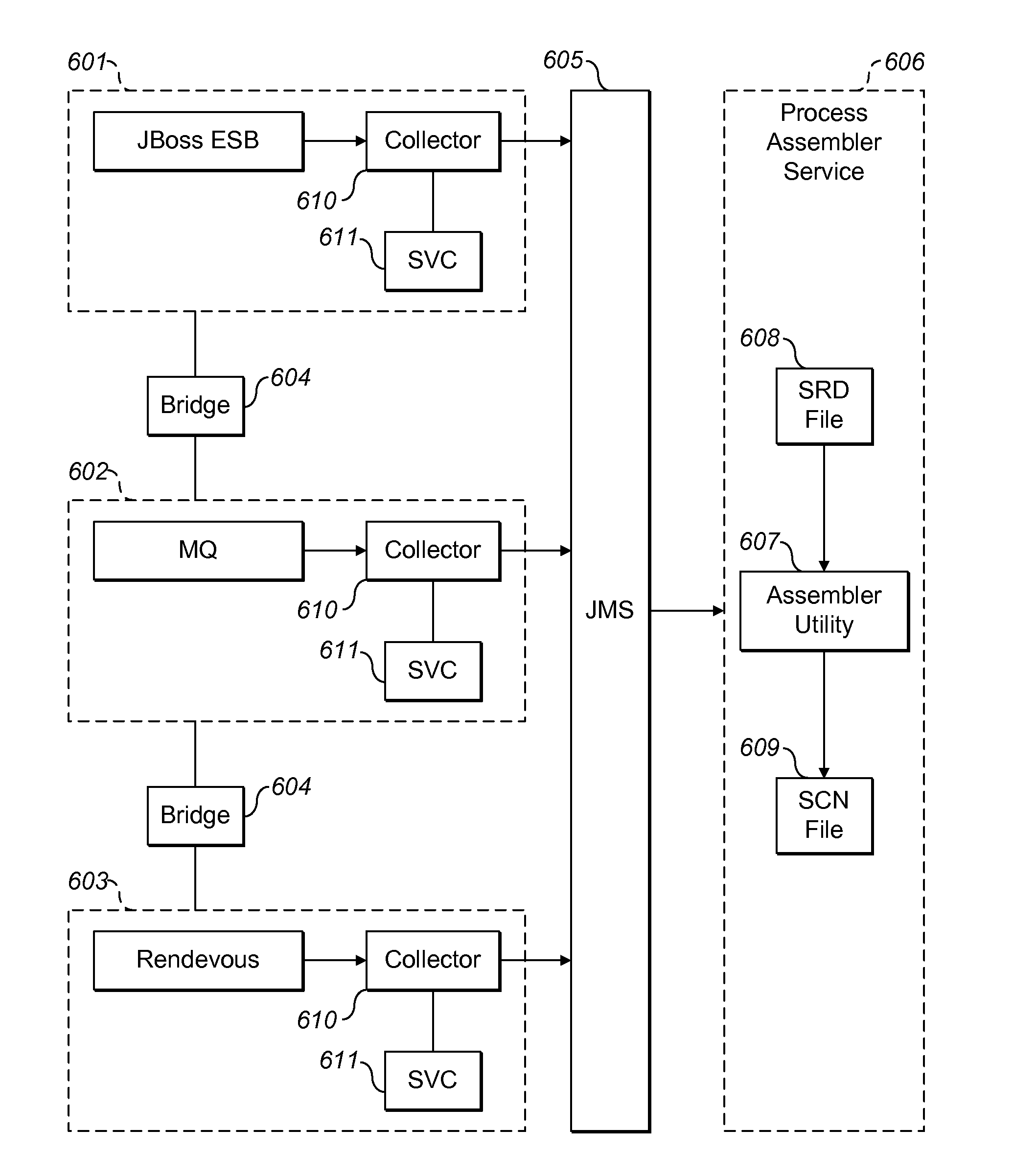

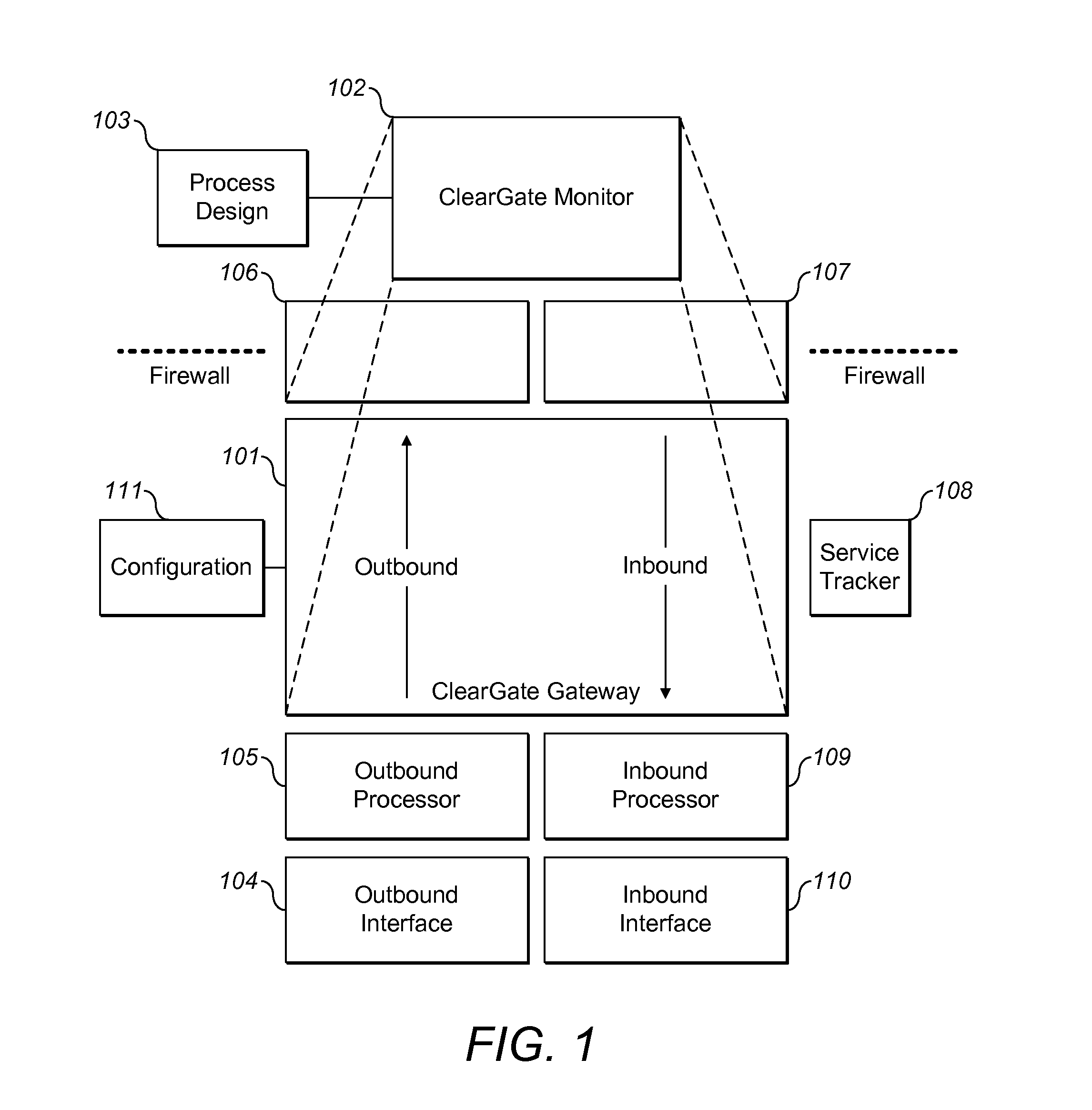

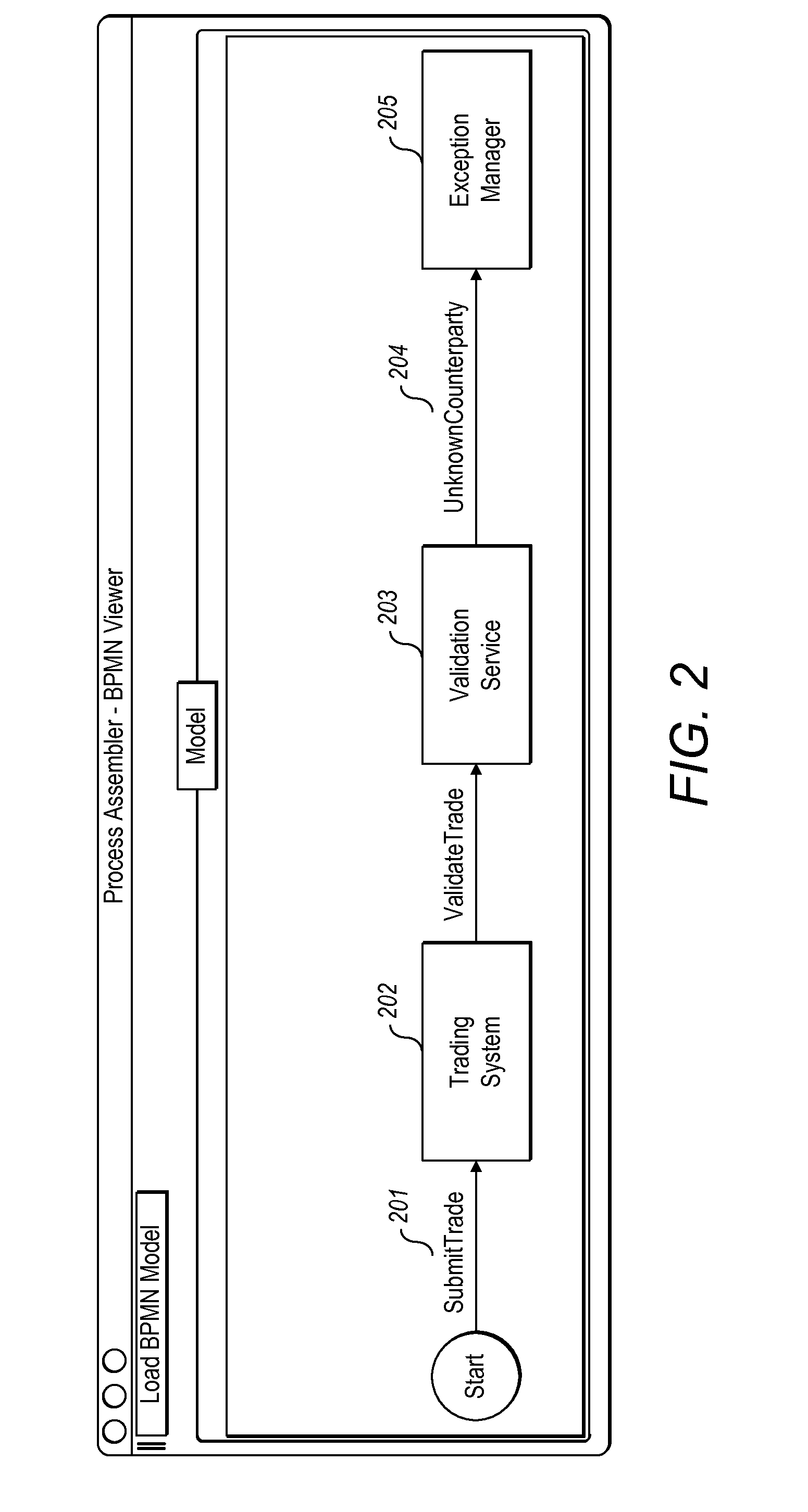

Automated process assembler

ActiveUS20110179046A1Reduce in quantitySpeed of Capture-theDigital data processing detailsDigital computer detailsDocumentation procedureMessage passing

A method and system for automatically assembling a complete machine readable description of a process by observing and filtering digital messages executing on one or more message bus and that relate to the process. Message details are stored and a tracker record published in a common format. The stored message details are processed into a set of service execution path descriptions, which in turn are processed into the complete machine readable description of the process, using a suitable process design language. The invention automates the capture and documentation of a process, regardless of the complexities of the underlying messaging environment, and produces a complete and unambiguous description of the end-to-end process, free of errors, omissions and interpretation, thereby addressing a key need in any process re-engineering project, including the delivery of SOA implementations and other forms of agile and adaptable systems.

Owner:ANQUIRO HLDG LTD

Methods and devices for independent evaluation of cell integrity, changes and origin in chip design for production workflow

ActiveCN102112988AReduce sensitivityCAD circuit designSpecial data processing applicationsFunctional impactCell integrity

The technology disclosed relates to granular analysis of design data used to prepare chip designs for manufacturing and to identification of similarities and differences among parts of design data files. In particular, it relates to parsing data and organizing into canonical forms, digesting the canonical forms, and comparing digests of design data from different sources, such as designs and libraries of design templates. Organizing the design data into canonical forms generally reduces the sensitivity of data analysis to variations in data that have no functional impact on the design. The details of the granular analysis vary among design languages used to represent aspects of a design. For various design languages, granular analysis includes partitioning design files by header / cell portions, by separate handling of comments, by functionally significant / non-significant data, by whitespace / non-whitespace, and by layer within a unit of design data. The similarities and differences of interest depend on the purpose of the granular analysis. The comparisons are useful in many ways.

Owner:OASIS TOOLING

Methods and structure for improved testing of embedded systems

InactiveUS7385927B2Shorten the timeImprove uniformityError preventionFrequency-division multiplex detailsConfiguration languageSystem under test

Methods and structure for standardized communication between a test operator, a host system, and an embedded system under test. Test program instructions are designed, written for, and executed on, an embedded system under test in accordance with standard API functions for message exchange. Still further, the invention provides for standards in the user interface to select a desired test, to start the test with defined parameters and to present reply and status information to the test operator. These user interactions are defined in a test configuration language of the present invention and preferably incorporated with the executable image file to define an integral test vehicle file. The present invention thereby reduces test sequence development time by providing standard API functions for message exchange between a host system test application and the system under test and provides for standardized user interaction in a flexible, easily maintained design language.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Determining a quality parameter for a verification environment

Determining a quality parameter for a verification environment for a register-transfer level hardware design language description of a hardware design. A netlist is generated from the hardware design language description. A list of hardware design outputs is generated, and logical paths in the netlist are generated based on the list of hardware design outputs. Furthermore, a modified netlist involving logical paths is generated by determining whether a gate is selected as an insertion point, and selecting a fault type, which is part of the efficiency vector for the selected gate in the netlist and inserting a mutant. Additionally, a fault simulation is performed and the quality parameter for the verification environment is determined from the fault simulation and the simulation result data.

Owner:IBM CORP

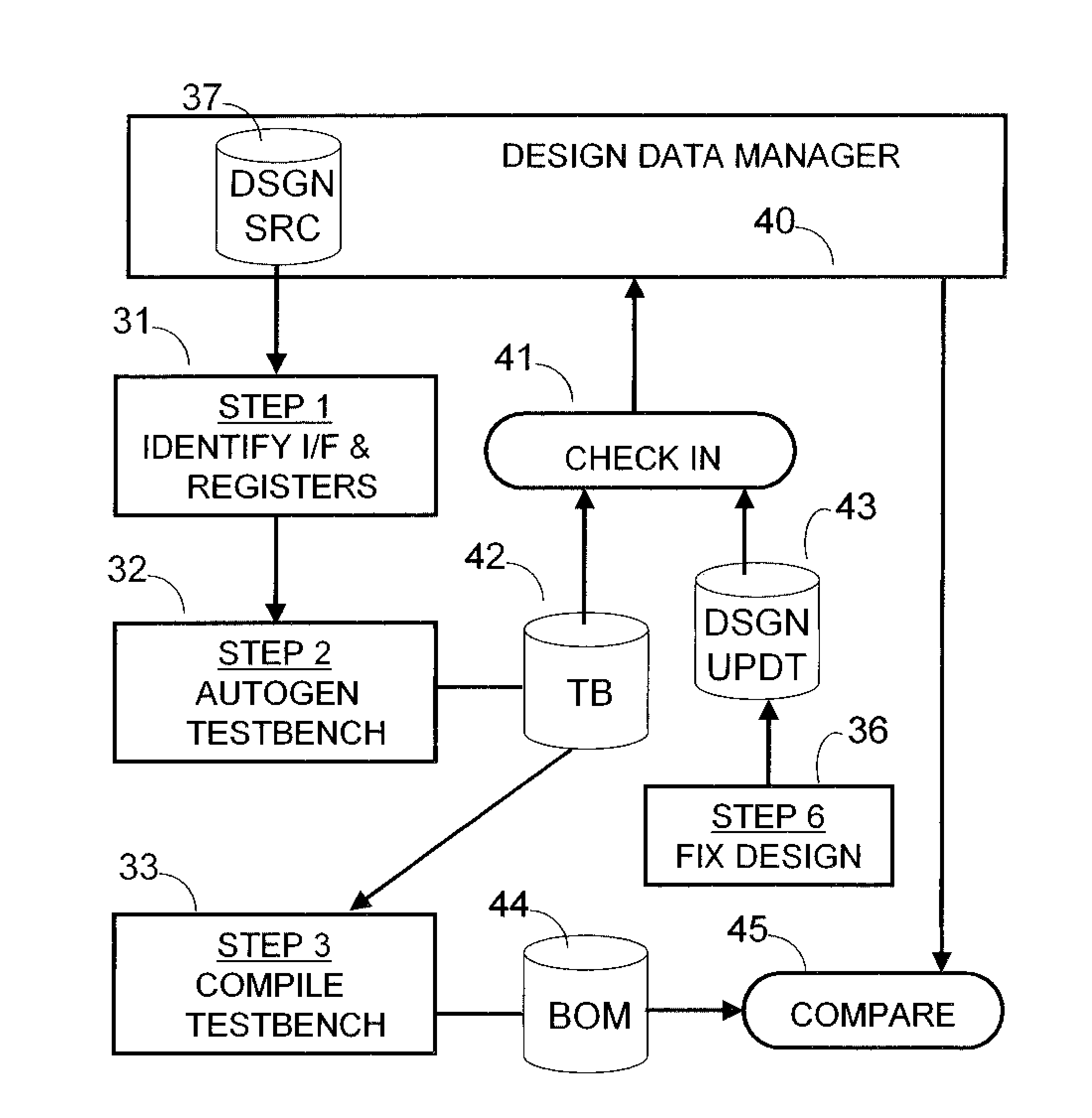

Method, System, and Program Product for Automated Verification of Gating Logic Using Formal Verification

InactiveUS20080059925A1Improve rendering capabilitiesExpand coverageComputer aided designSoftware simulation/interpretation/emulationValidation methodsTest bench

As described herein the automated verification methodology parsing scripts auto generate test bench hardware design langaue, such as VHDL or Verilog, from the design source VHDL or Verilog. A formal verification model is then built comprising the testbench VHDL and the design under test. The resulting design verification tool then provides proofs and counterexamples for all of the rules, e.g., auto-generated rules, in the test bench.

Owner:GLOBALFOUNDRIES INC

Rapid reliability evaluation method for SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array)

InactiveCN104598352AReduce processingReduce computing timeFunctional testingStatic random-access memoryIntegrated software

The invention specifically provides a rapid reliability evaluation method for an SRAM (Static Random Access Memory) type FPGA (Field Programmable Gate Array). The method comprises the following steps: (1) dividing a to-be-processed VHD (Virtual Hard Disk) source program into L modules according to a module division criterion determined according to a VHDL (Very High Speed Integrated Circuit Hardware Description Language) hardware language; (2) performing integration, mapping, layout wiring and XDL (Xilinx Design Language) file generation operation on the L modules in combination with a hardware design tool ISE (Integrated Software Environment) in sequence; (3) performing rough calculation by using a probability analysis method to obtain the soft error rate of each module and adding the soft error rates to a rough calculation set C1; (4) selecting a threshold value delta for the C1 by using a maximum between-class variance algorithm OSTU; adding the module with the soft error rate of being greater than the delta into an accurate calculation set C2; (5) performing accurate calculation on the soft error rate SER for each module in the accurate calculation set C2 by using a monte carlo method respectively, and saving the results in a protection set S from big to small. While the calculation accuracy is guaranteed, the calculation time in the reliability evaluation process of the SRAM type FPGA can be reduced as much as possible.

Owner:XIAN INSTITUE OF SPACE RADIO TECH +1

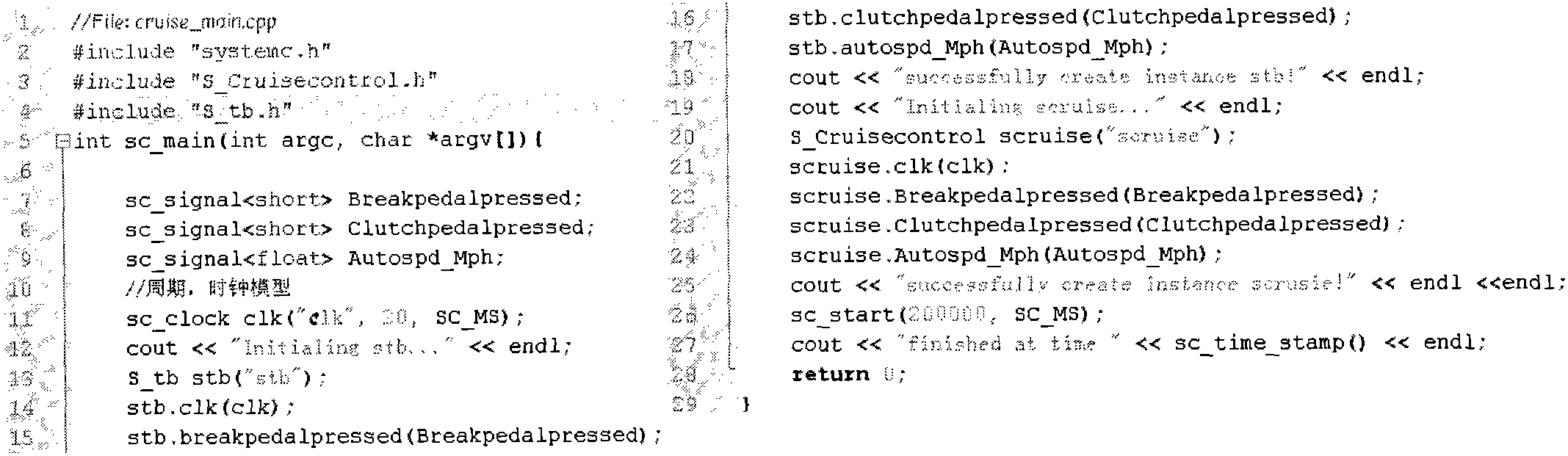

Method for generating simulation test example of AADL (Architecture Analysis and Design Language) software component model based on SystemC

InactiveCN102231132AQuality assuranceImprove reliabilitySoftware testing/debuggingInclusion relationSystemC

The invention provides a method for generating a simulation test example of an AADL (Architecture Analysis and Design Language) software component model based on SystemC. The method comprises the following steps of: firstly, providing a conversion technology for converting data components, ports and connections into a SystemC simulation test example; then, according to inclusion relations of the components, providing a conversion technology for converting each component into the SystemC simulation test example step by step from a bottom layer (sub-program) of a component tree to an intermediate layer (thread and progress) of the tree; and finally, providing a conversion technology of a sub-system and a system component. By means of the method disclosed by the invention, users can realize the simulations of the AADL software component based on the SystemC; the simulations include simulations of interactions, execution times and thread schedulings between software components and the like; the users can also combine the method disclosed by the invention with the simulation of an AADL execution platform component based on the SystemC; software and hardware can be subjected to cooperative simulation; in addition, according to a simulation result, a construction is iterated and a design model is refined so that problems existing in the design model is found out as soon as possible and the quality of the design model is ensured.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

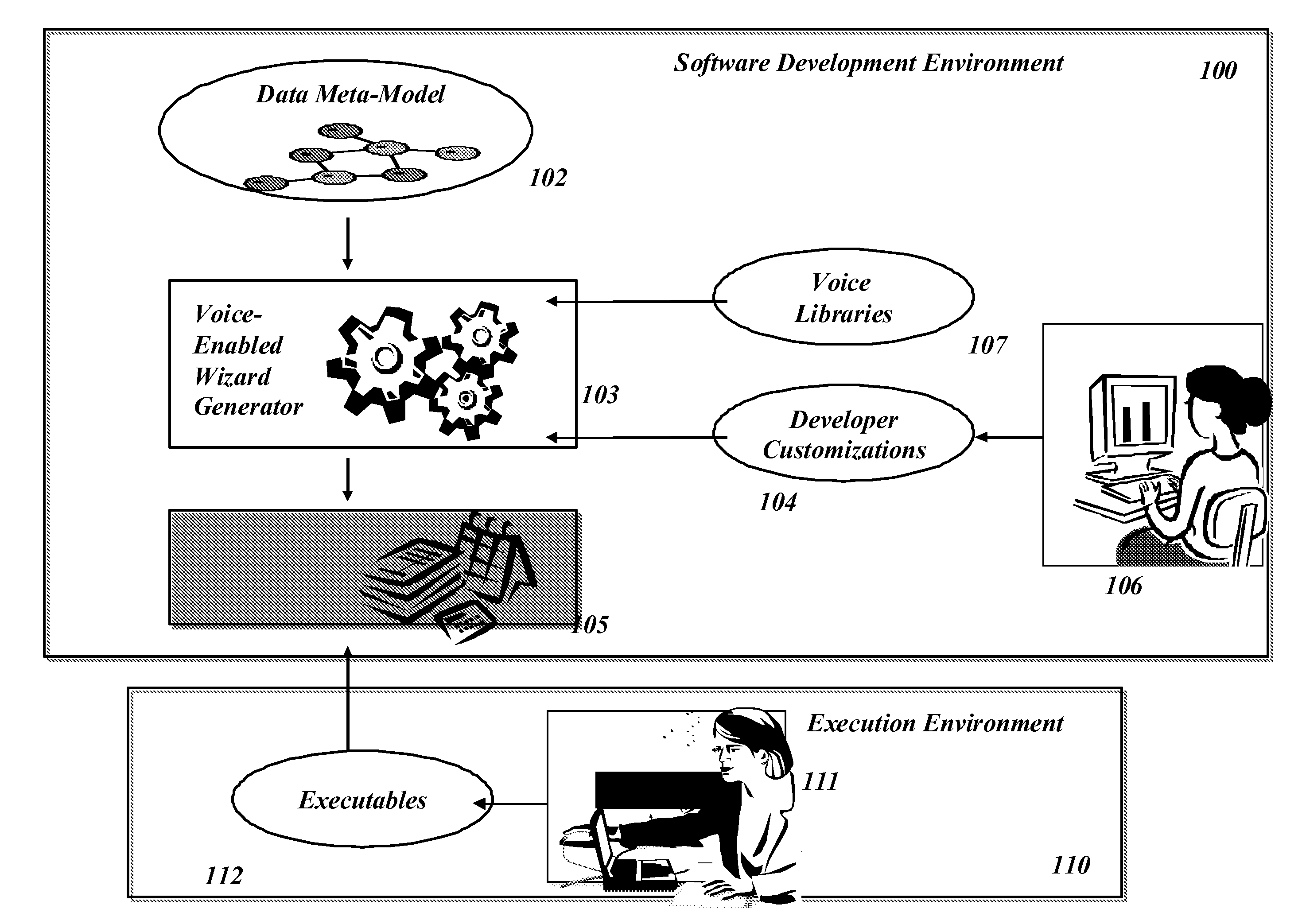

Method and system for generating vocal user interface code from a data metal-model

InactiveUS20110252398A1Advantage of usabilitySoftware engineeringSpeech recognitionUnified Modeling LanguageApplication software

A method, computer program and system for generating code of the vocal interface of a software application by reading the persistent data of an application designed by a data meta model using a design language such as UML (Unified Modeling Language) defining a hierarchical organization of classes, their attributes and the relations between classes.Similarly to the wizard for graphical user interface the vocal interface code comprises dialog unit code, which is Forms when VoiceXML language is used, to allow at execution time, entry of data for the application in a guided way.

Owner:IBM CORP

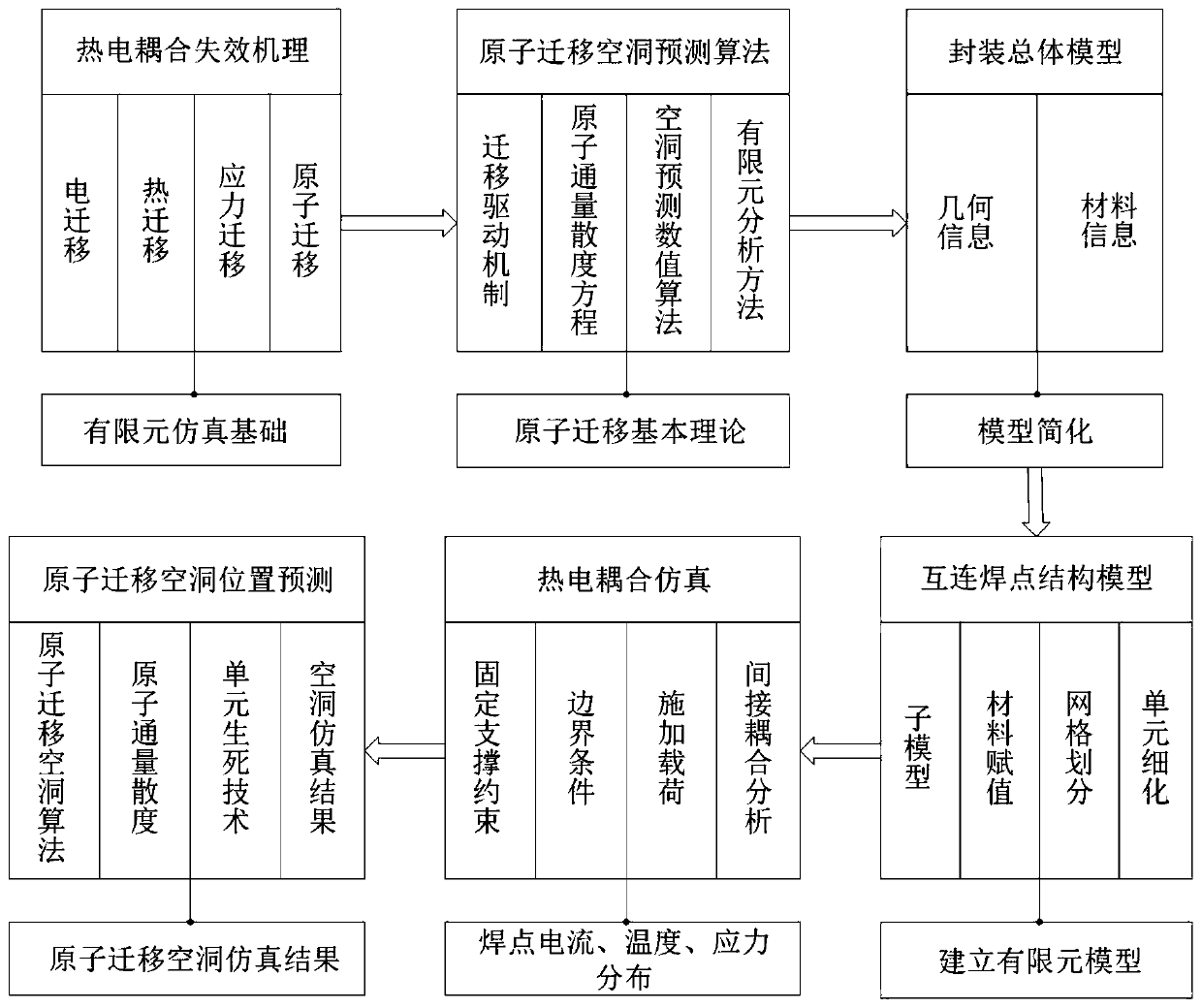

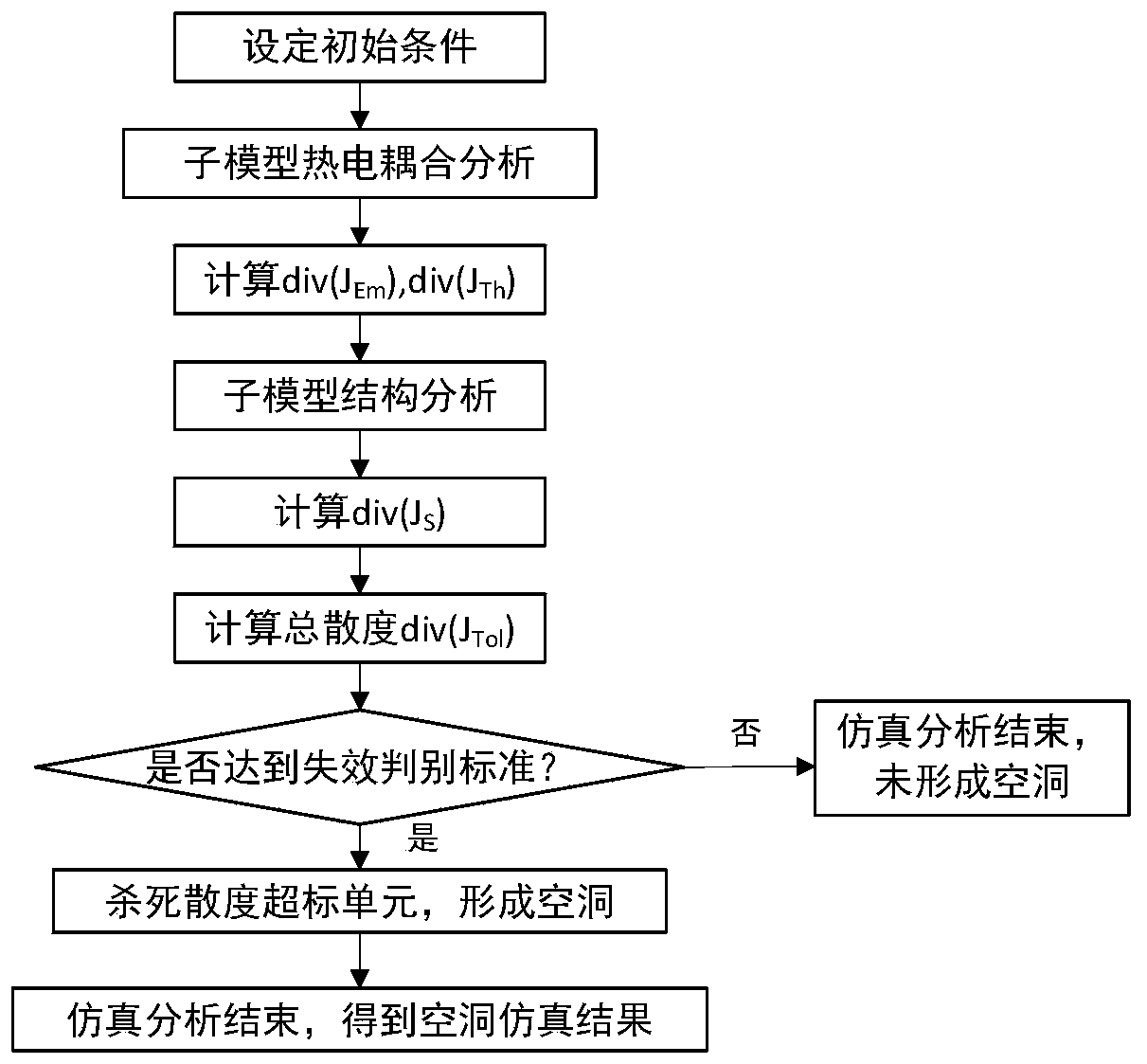

Lead-free component interconnection welding spot thermoelectric coupling simulation method

InactiveCN110287639AImprove use reliabilityEasy to operateElectronic circuit testingDesign optimisation/simulationPrediction algorithmsElement analysis

The invention relates to a lead-free component interconnection welding spot thermoelectric coupling simulation method. The method comprises the following steps that step 1, analyzing a lead-free component interconnection welding spot thermoelectric coupling failure mechanism; step 2, researching an atomic migration hole prediction algorithm; step 3, establishing an overall packaging model; step 4, carrying out simulation modeling of the interconnection welding spot structure; step 5, performing thermoelectric coupling simulation analysis; and step 6, predicting the position of the atomic migration cavity. Based on the basic theory of atomic migration, three driving mechanisms of electromigration, thermal migration and stress migration generated by thermal stress gradient are comprehensively considered, and an atomic migration cavity prediction numerical algorithm is obtained. On the basis, an ANSYS parameterized design language and a Matlab program are used as carriers to form a finite element analysis method for predicting atomic migration cavities of the interconnection welding spots of the lead-free component, and simulation study is carried out on cavity failures of the interconnection welding spots under the thermoelectric coupling condition. The method belongs to the technical field of lead-free component interconnection welding spot thermoelectric coupling reliability simulation.

Owner:BEIHANG UNIV

Finite element-based full-parameterization gear meshing analysis method

PendingCN113868901AAll-in-one modelingEasy to set upGeometric CADDesign optimisation/simulationGear geometryGear wheel

The invention discloses a finite element-based full parameterized gear meshing analysis method, which comprises the following steps that: a user interaction interface is established by using an ansys parameterized design language (APDL), the initial parameters of a gear is identified, parameters which influence the geometrical shape and material of the gear are confirmed, then a tooth profile is obtained based on an involute and a transition curve parameter equation, and a complete gear tooth profile and a three-dimensional gear solid model are generated; and then, APDL implementation of parameterized mapping grids is carried out, end faces are segmented, proper grid units are selected to generate a complete gear parameterized model, after the parameterized model is obtained, assembly and contact analysis of the two gears are considered, initial contact of the gears is defined, corresponding boundary conditions are applied, and finally solving is carried out to obtain gear meshing results required by tooth surface contact stress, contact slippage, von Mises stress diagrams, deformation diagrams and the like.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

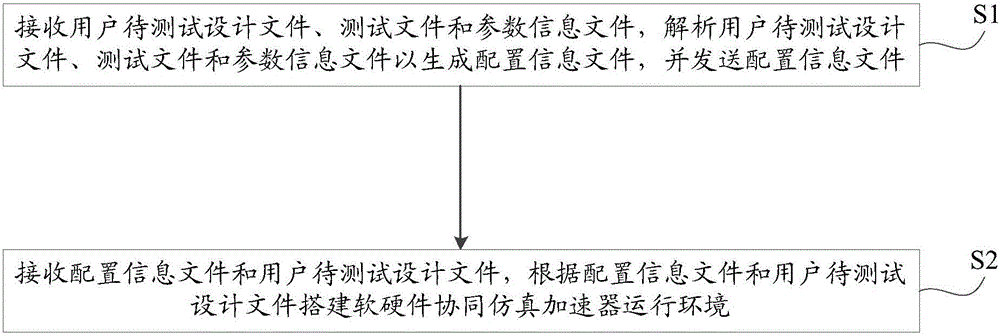

Method and device for constructing operating environment of software and hardware co-simulation accelerator

ActiveCN106202685AFacilitate data exchangeImprove processing efficiencyDesign optimisation/simulationSpecial data processing applicationsTest designCo-simulation

The invention provides a method and device for constructing an operating environment of a software and hardware co-simulation accelerator. The method comprises the steps of receiving a user's to-be-tested design file, a test file and a parameter information file, analyzing the user's to-be-tested design file, the test file and the parameter information file to generate a configuration information file, and sending the configuration information file; receiving the configuration information file and the user's to-be-tested design file, and constructing the operating environment of the software and hardware co-simulation accelerator according to the configuration information file and the user's to-be-tested design file. According to the method and device for constructing the operating environment of the software and hardware co-simulation accelerator, an SCE-MI protocol can be completely unified on the basis of a current design language, an interface of the software and hardware co-simulation accelerator is standardized conveniently, and data exchange between the test file and the user's to-be-tested design file is facilitated. An SCE-MI parameter file to a large extent enables the implementation of a follow-up software interface to be separated from hardware. The operating environment of the software and hardware co-simulation accelerator can be constructed automatically, and the software and hardware co-simulation treatment efficiency and technical development are greatly accelerated.

Owner:HEFEI HAIBENLAN TECH

Method for nondestructively converting AADL (architecture analysis and design language) into XML (extensible markup language)

InactiveCN103793458AEasy to readSpecific program execution arrangementsSpecial data processing applicationsEllipseModelling analysis

The invention relates to a method for nondestructively converting AADL (architecture analysis and design language) into XML (extensible markup language), and belongs to the field of language conversion technologies. The method includes converting an AADL description model into an XML format; describing grammar of the AADL by the aid of Xtext; describing a meta model of the AADL by the aid of an EMF (ellipse modeling framework); creating mapping relations among the grammar of the AADL and the meta model of the AADL in the Xtext so as to convert the AADL model into an object model; fixing the object model into an XML format by the aid of a fixing mechanism provided by the EMF and storing the XML format. The method has the advantages that a special tool for serializing models can be designed by the aid of the method step by step, so that model files represented by ASCII (American standard codes for information exchange) can be converted into XML files, model information can be conveniently read by other tools, and a foundation can be laid for heterogeneous model interaction, model analysis and simulation.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

Method for checking operation state and demand consistency of AADL (Architecture Analysis and Design Language) model

ActiveCN102184136AImprove accuracyReduced settling timeSoftware testing/debuggingTheoretical computer scienceNetwork model

The invention provides a method for checking operation state and demand consistency of an AADL (Architecture Analysis and Design Language) model, which comprises the steps of: 1, constructing the AADL model according to state in demand and state transition, wherein mode and mode transition in the AADL model respectively correspond to the state in demand and the state transition; 2, converting the mode and the mode transition in the AADL mode into a Petri network model; 3, calculating an incidence matrix C of the Petri network mode; and 4, judging whether the operation state of the constructed AADL mode is consistent with the demand by using a state equation of the Petri network model. In the invention, the mode and the mode transition in the AADL model are mapped to place and transition in the Petri network model, and the Petri network model is used as a measured model, an accessible state set of the AADL model is calculated by combining with properties of the Petri network model and characteristics of the AADL model, therefore, the purpose of judging whether the operation state of the constructed AADL model is consistent to the demand is achieved, the correctness of the constructed AADL model is improved, the system building time is shortened, and the system building cost is saved.

Owner:中国航天科技集团公司第七一〇研究所

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com