Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

114 results about "Cmos switch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Matching network

InactiveUS20070155347A1Quick switchImproving Impedance MatchingMultiple-port networksResonant long antennasAudio power amplifierHigh frequency power

A matching network for matching an antenna to a transmitter or receiver comprises an input port for receiving high-frequency power, an output port and a switchable impedance transformation circuit, which is connected between the input port and the output port. The impedance transformation circuit comprises a CMOS switch in a high-frequency path, which has a first switching state and a second switching state. The impedance transformation circuit is implemented to match a first impedance applied to the output port to a first predetermined impedance in the first switching state, and to match a second impedance applied to the output port to a second predetermined impedance in the second switching state. The inventive matching network allows a particularly good utilization of power provided by a transmitting amplifier or an antenna.

Owner:INFINEON TECH AG

Matching network

InactiveUS7831219B2Easy to useMultiple-port networksMultiple input and output pulse circuitsHigh frequency powerAudio power amplifier

A matching network for matching an antenna to a transmitter or receiver comprises an input port for receiving high-frequency power, an output port and a switchable impedance transformation circuit, which is connected between the input port and the output port. The impedance transformation circuit comprises a CMOS switch in a high-frequency path, which has a first switching state and a second switching state. The impedance transformation circuit is implemented to match a first impedance applied to the output port to a first predetermined impedance in the first switching state, and to match a second impedance applied to the output port to a second predetermined impedance in the second switching state. The inventive matching network allows a particularly good utilization of power provided by a transmitting amplifier or an antenna.

Owner:INFINEON TECH AG

Programmable attenuator using digitally controlled CMOS switches

A programmable attenuator includes a resistor ladder having a plurality of taps to provide a coarse gain control. Coupled to each tap is a plurality of switches. Control logic activates or deactivates individual switches in the plurality of switches to provide a fine gain control. More specifically, a set of activated switches provides fine gain control by determining an overall attenuation level interpolated between an adjacent pair of taps.

Owner:AVAGO TECH INT SALES PTE LTD

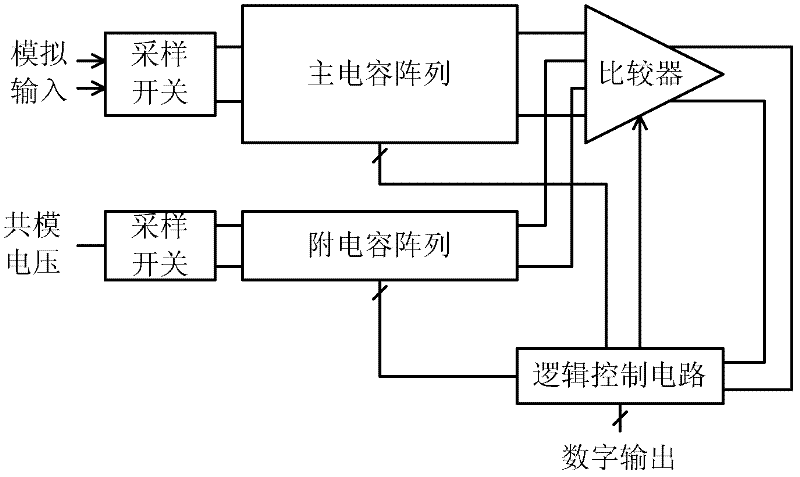

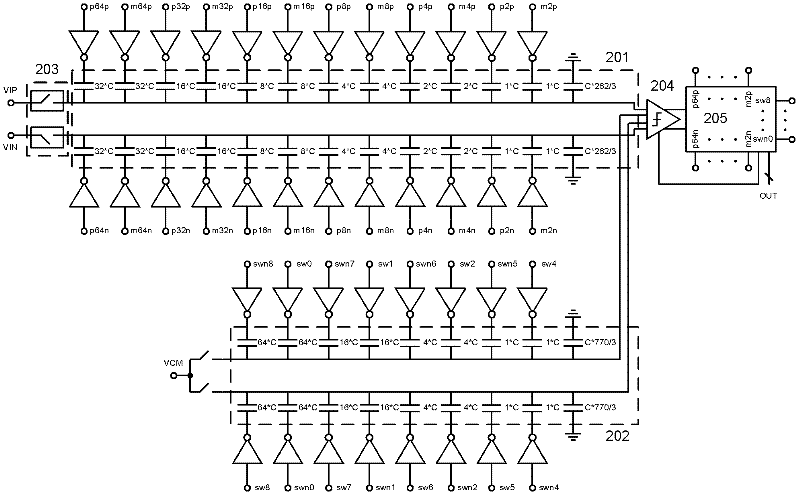

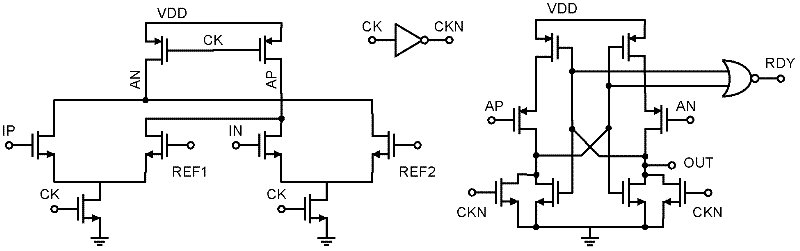

Asynchronous successive approximation analog-to-digital converter and conversion method

InactiveCN102386923AReduce power consumptionImprove power efficiencyAnalogue/digital conversionElectric signal transmission systemsCapacitanceLow voltage

The invention discloses an asynchronous successive approximation analog-to-digital converter and a conversion method. The asynchronous successive approximation analog-to-digital converter comprises: a sampling network, a main capacitor array, an auxiliary capacitor array, a comparator and a logic control circuit. The sampling network of the main capacitor array uses a bootstrap switch. The sampling network of the auxiliary capacitor array uses a CMOS switch. Each two same capacitors in the main capacitor array are in a group. A capacitance value size is reduced as two times relationship. Top crowns of all the capacitors and the bootstrap switch are connected and output to the comparator. The each two same capacitors in the auxiliary capacitor array are in one group. The capacitance value size is reduced as four times relationship. The top crowns of all the capacitors and the CMOS switch are connected and output to the comparator. The comparator comprises a preamplifier and a latch and compares the size of an output voltage of the main capacitor array and the auxiliary capacitor array. The logic control circuit uses an asynchronous sequential control capacitor array to successively complete switching. A power consumption efficiency of the analog-to-digital converter can be effectively raised. And demands of capacitor coupling and a peripheral circuit can be reduced. The method is suitable for a deep-submicron low voltage design.

Owner:BEIJING UNIV OF TECH

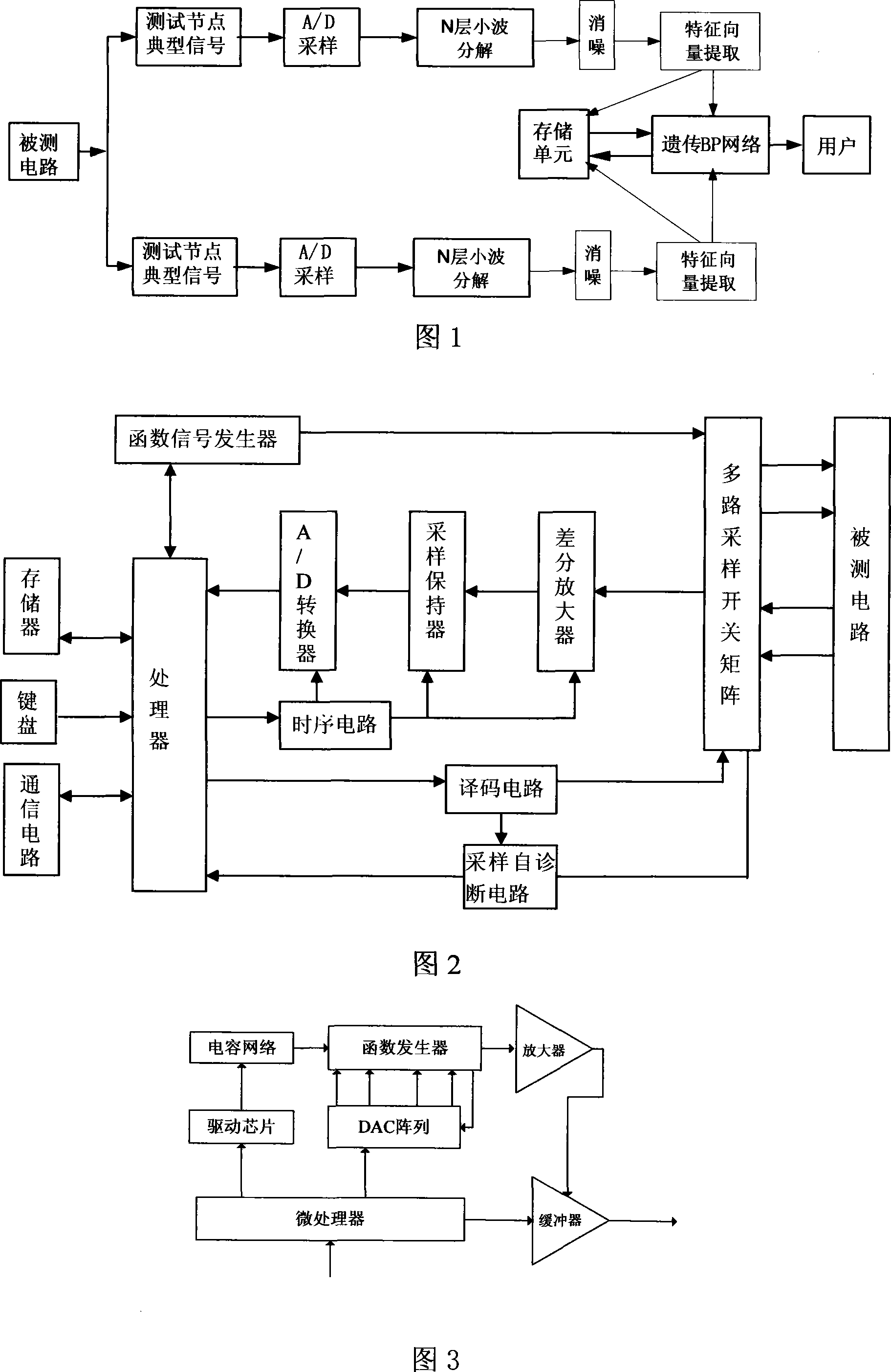

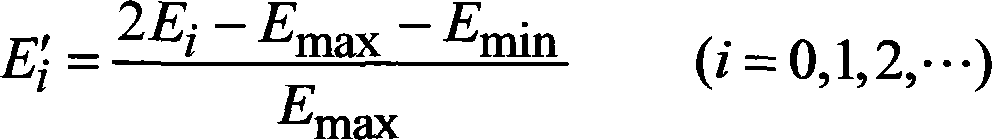

Analog PCB intelligent test system based on neural network

InactiveCN101246200ARealize acquisitionRealize transmissionAnalog circuit testingPhysical realisationNerve networkPrincipal component analysis

The invention discloses a simulating PCB intelligent test system which is based on nerve network, which includes main control PC machine, processor, storage, communication circuit, function signal generator, multi-channel sampling switch matrix, sequential circuit, decoding circuit, A / D converter, sampling retainer, differential amplifier, function signal generator under the control of processor outputs stimulating signal to the stimulating node of the tested circuit, the responding signal of the tested circuit is transmited to the processor by multi-channel sampling circuit, then is transmitted to the main control PC machine by communication circuit, the main control PC machine treats the sampling signal with wavelet packet transform de-noising treatment, and with principal component analysis and normalization processing for obtaining fault feature vector; the fault feature vector is inputted into the trained BP nerve network, the output of the BP nerve network is fault type. The invention can position the PCB test fault to the component level effectively, and improve the scalability of system greatly with the simple and effective test method of CMOS switch array.

Owner:HUNAN UNIV

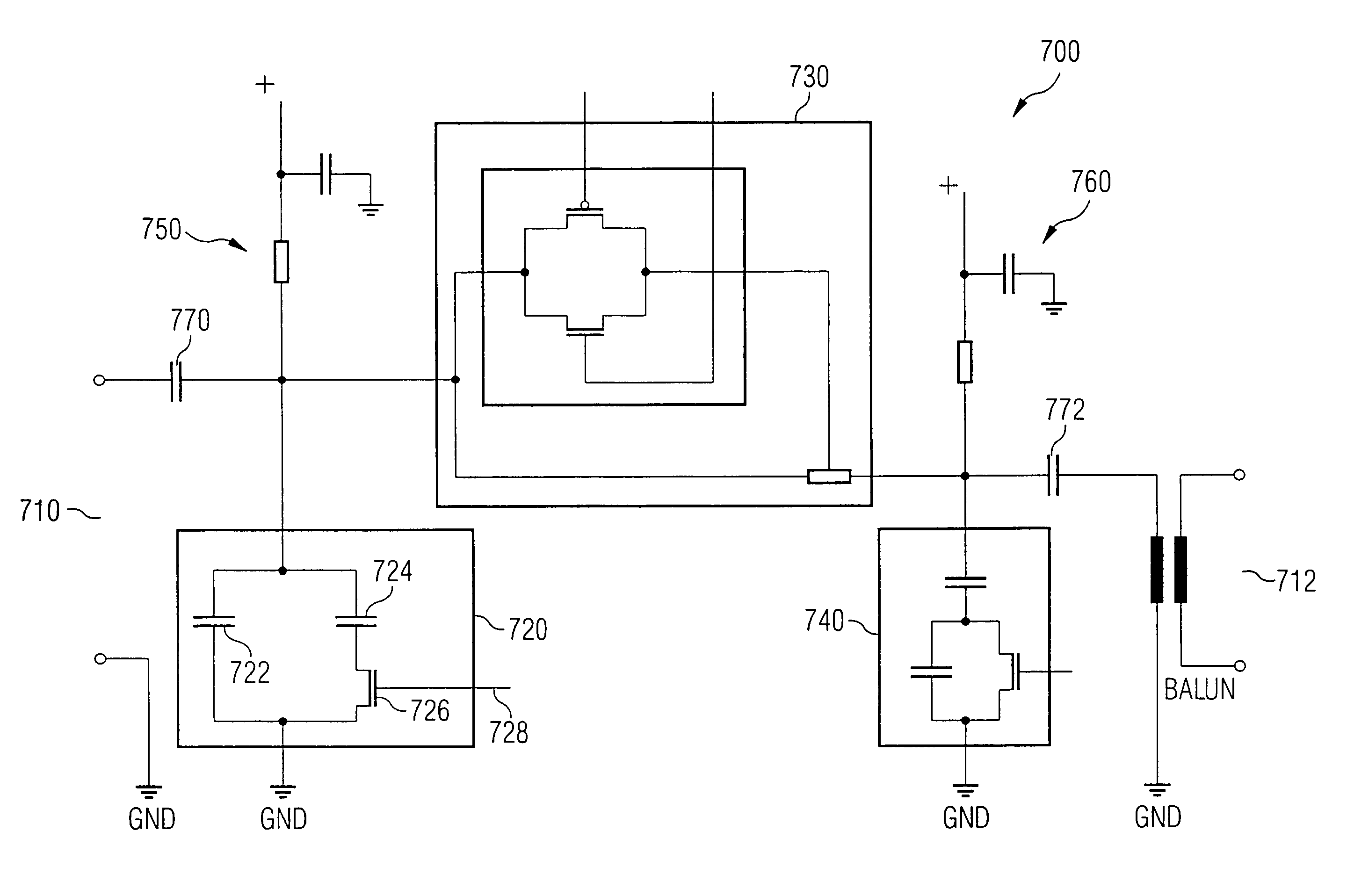

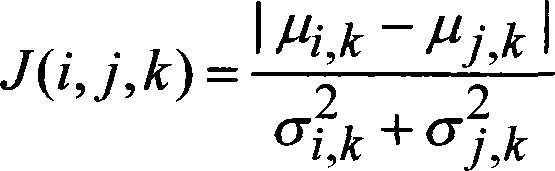

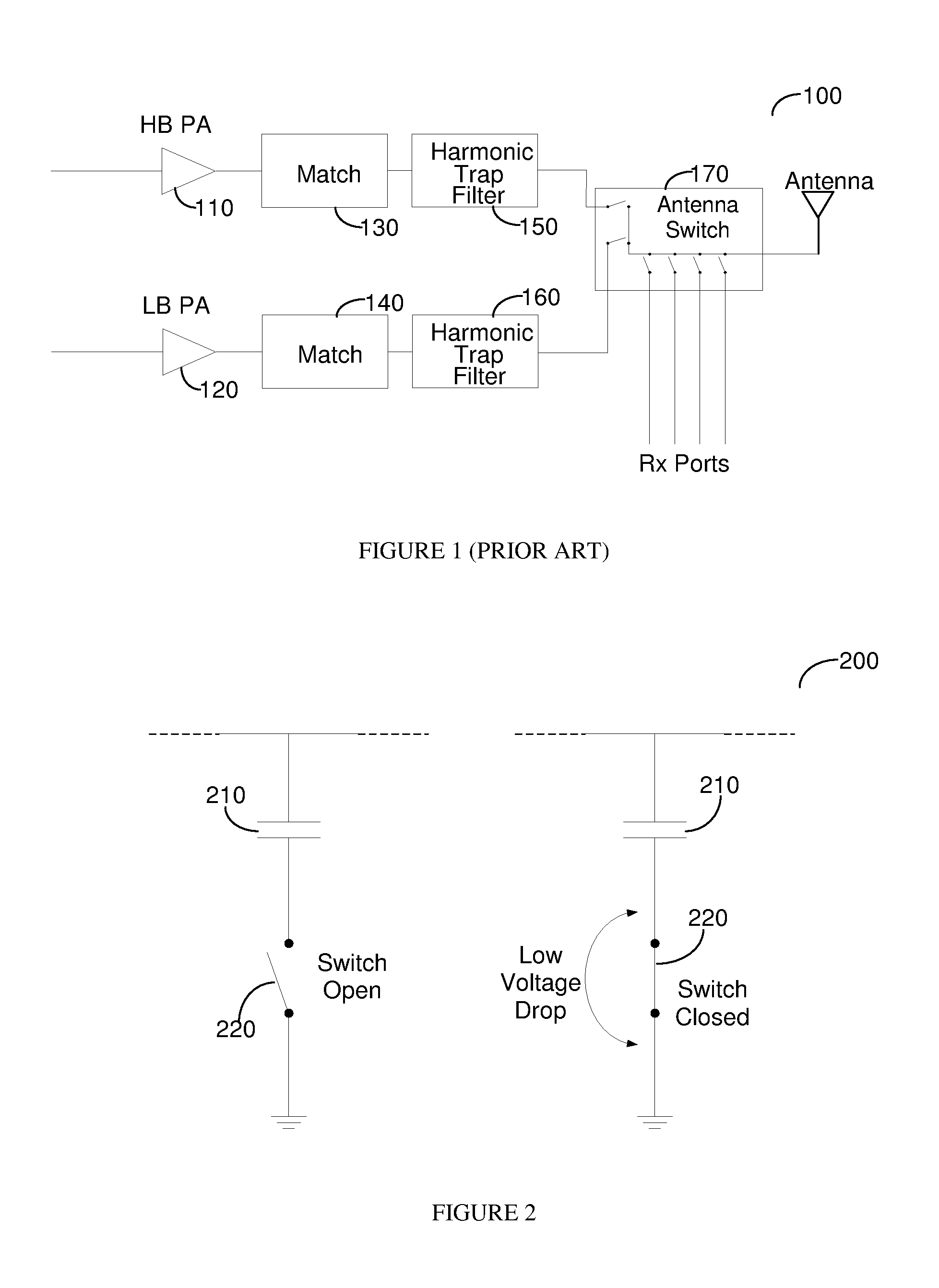

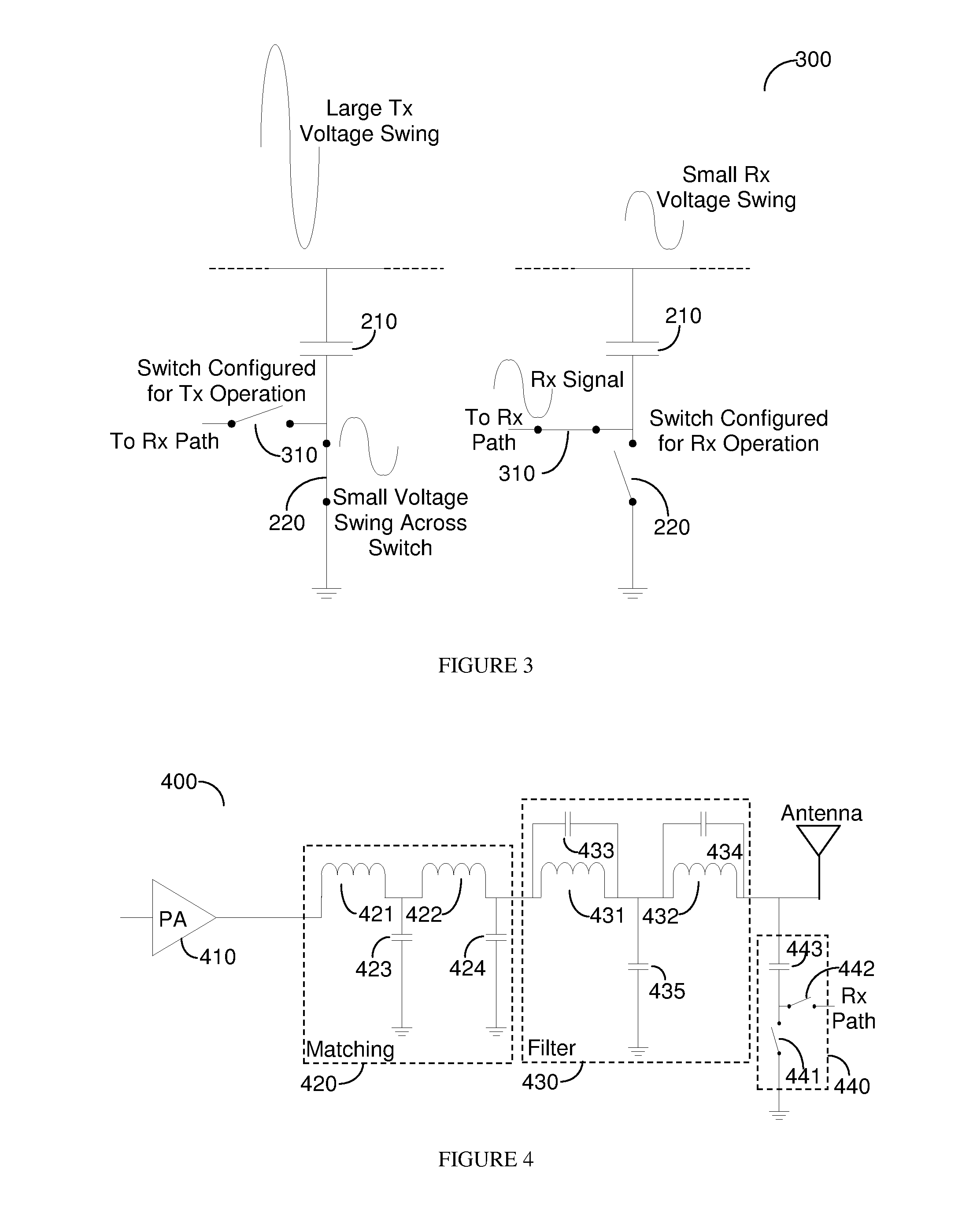

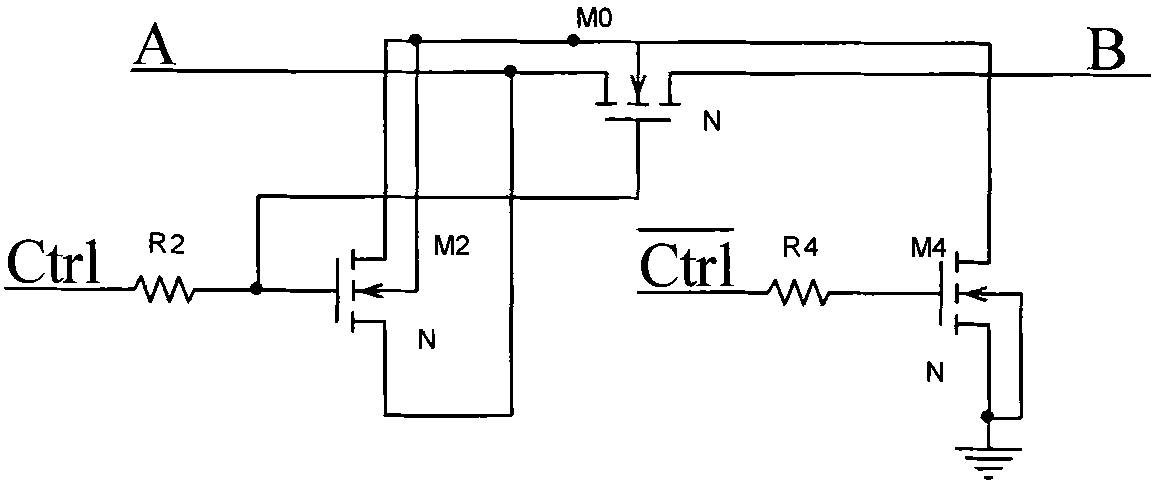

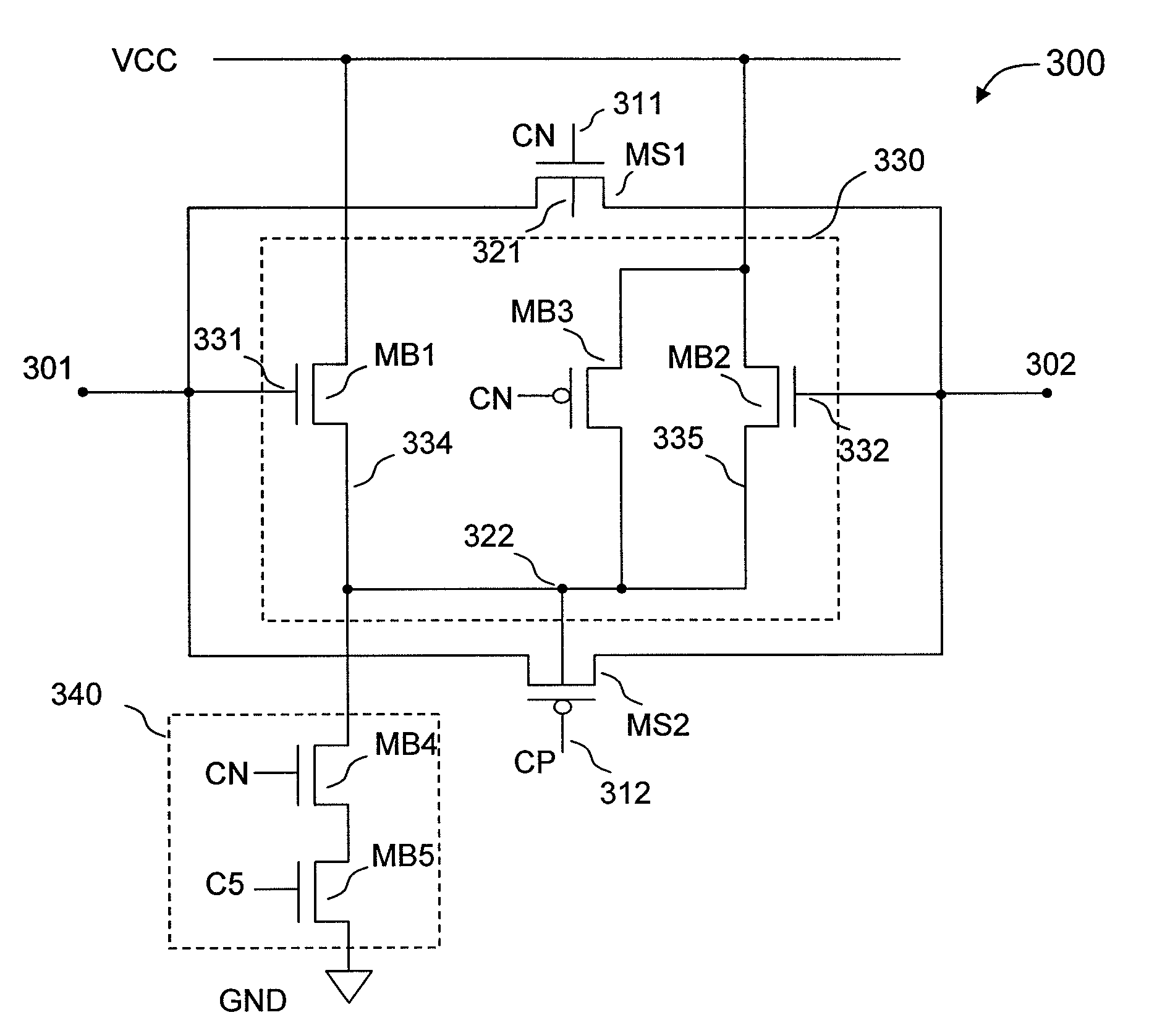

CMOS Switching Circuitry of a Transmitter Module

ActiveUS20140009208A1Gated amplifiersElectronic switchingCode division multiple accessSynchronization code division multiple access

Transmit modules typically constitute passive matching circuitry, harmonic trap filters and an antenna switch to provide isolation between the transmit bands as well as between transmit and receive functions. In complementary metal-oxide semiconductor (CMOS) processes the switch function is difficult to implement as a large voltage swing may result in breakdown of the MOS oxide, drain diode, source diode as well as substrate diodes. Therefore a switching function is provided at a node that has low impedance during transmit that limits the voltage swing that the MOS switches experience. The approach is particularly useful, but not limited to, half duplex transmissions such as those used in global system for mobile (GSM) communication, enhanced data for GSM Evolution (EDGE), and time division synchronous code division multiple access (TDSCDMA).

Owner:QORVO INT PTE LTD

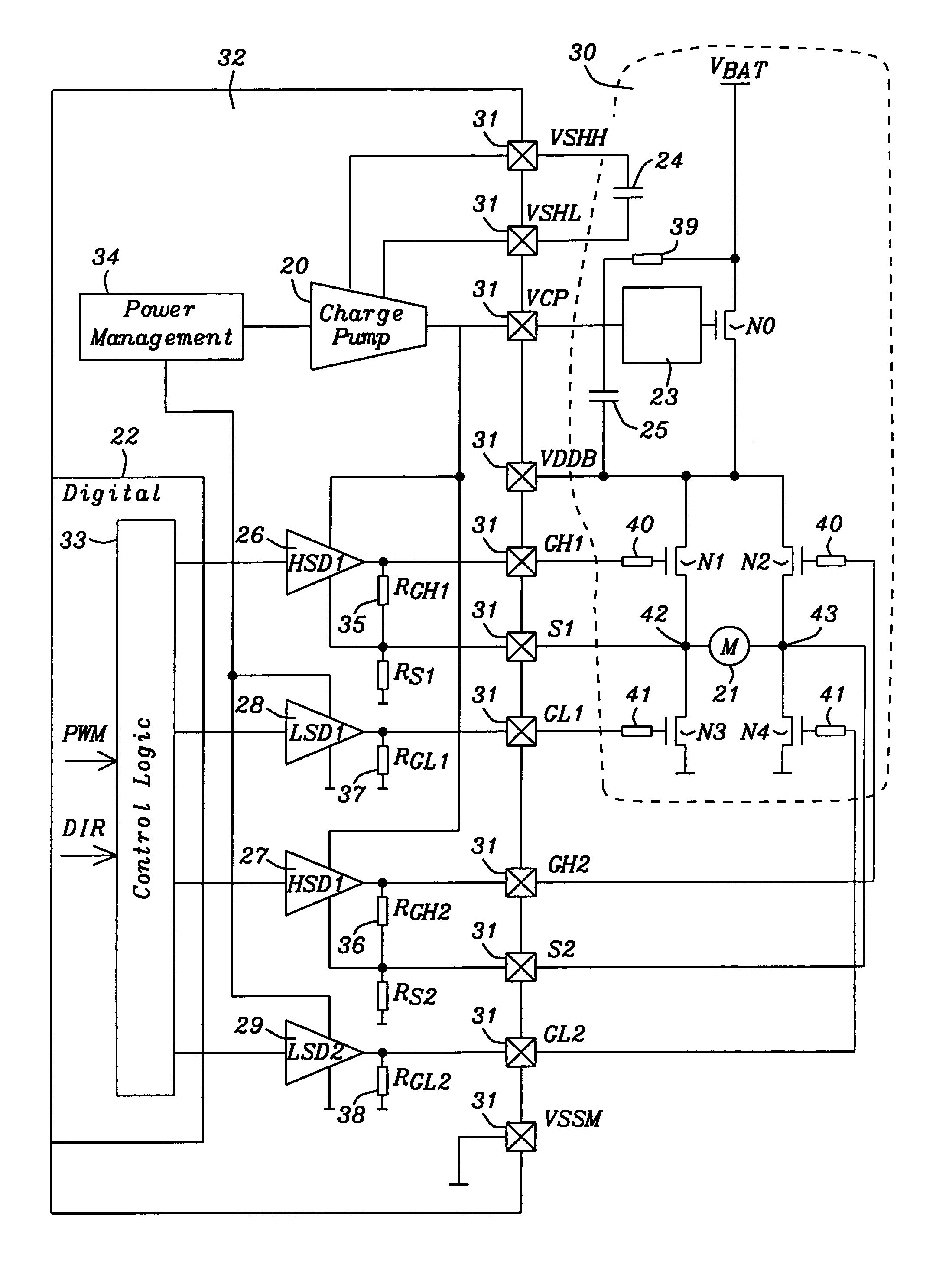

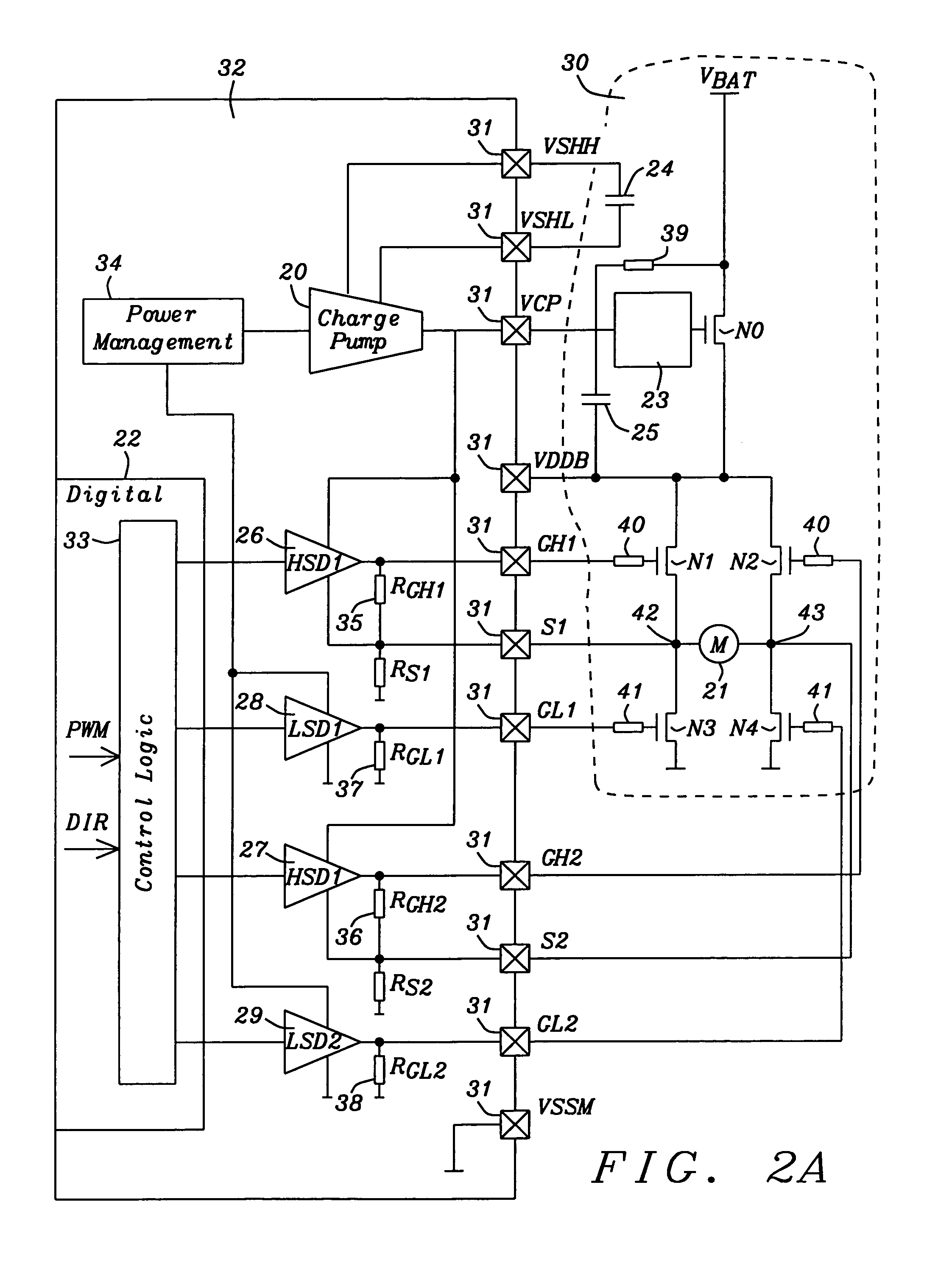

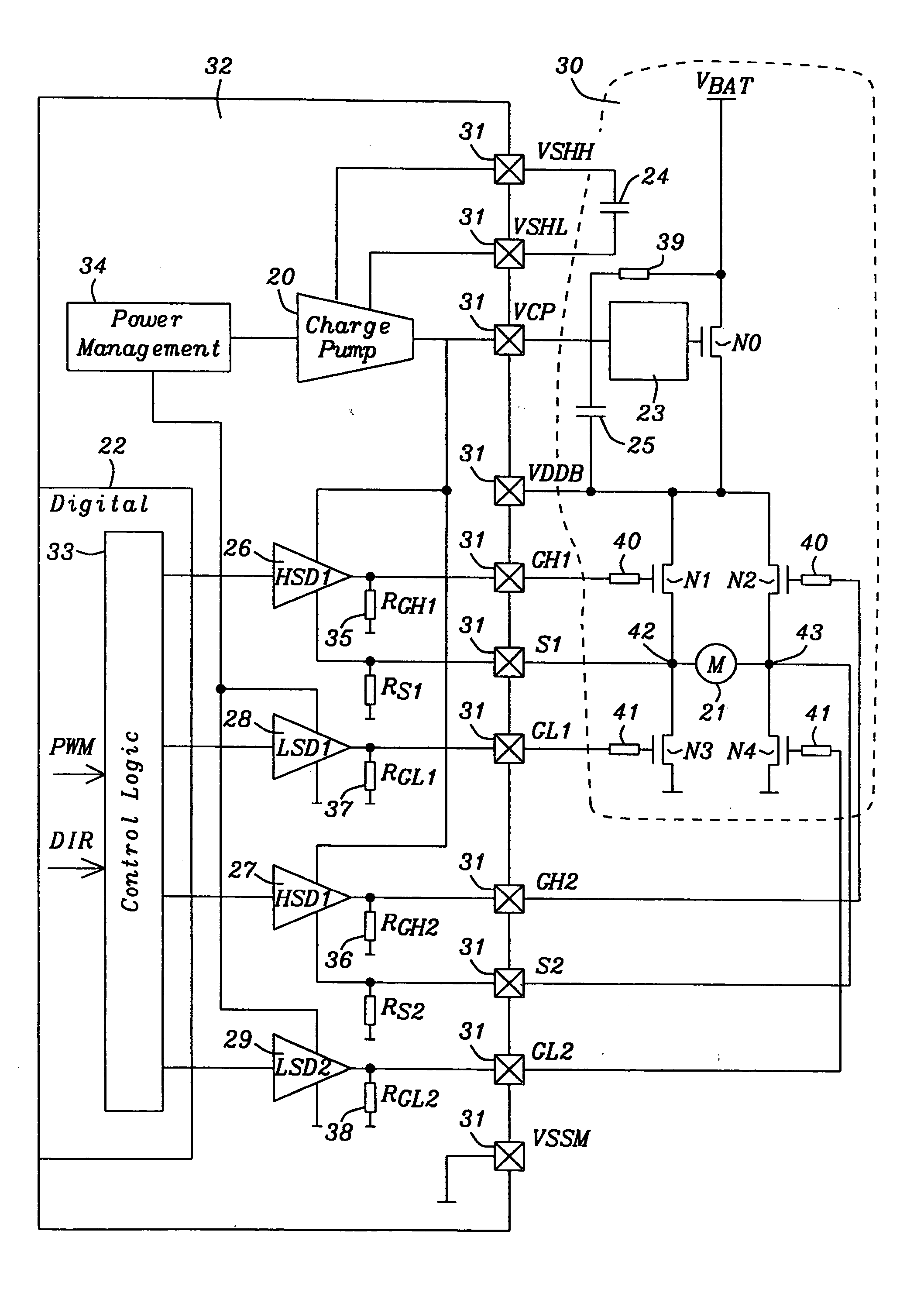

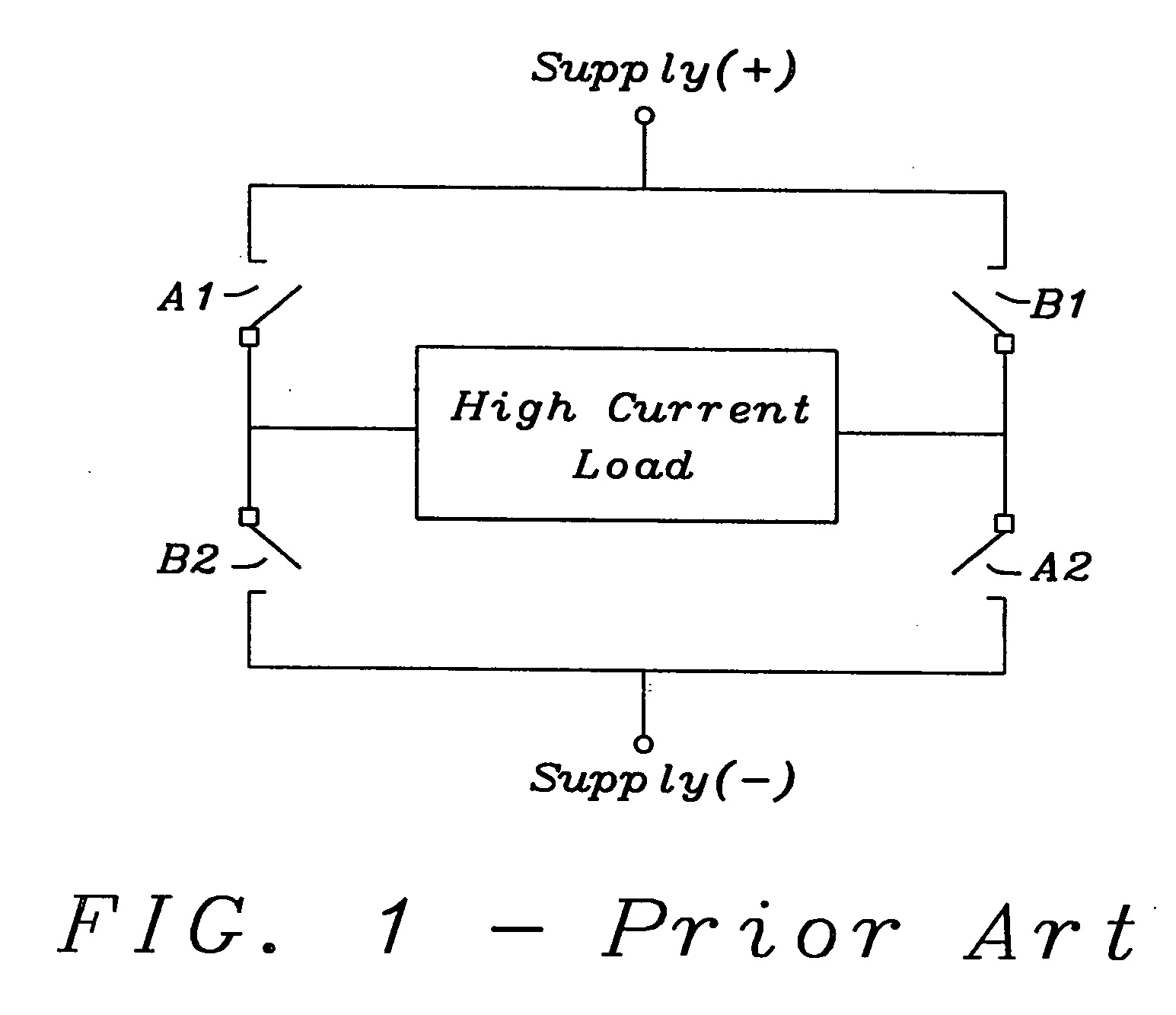

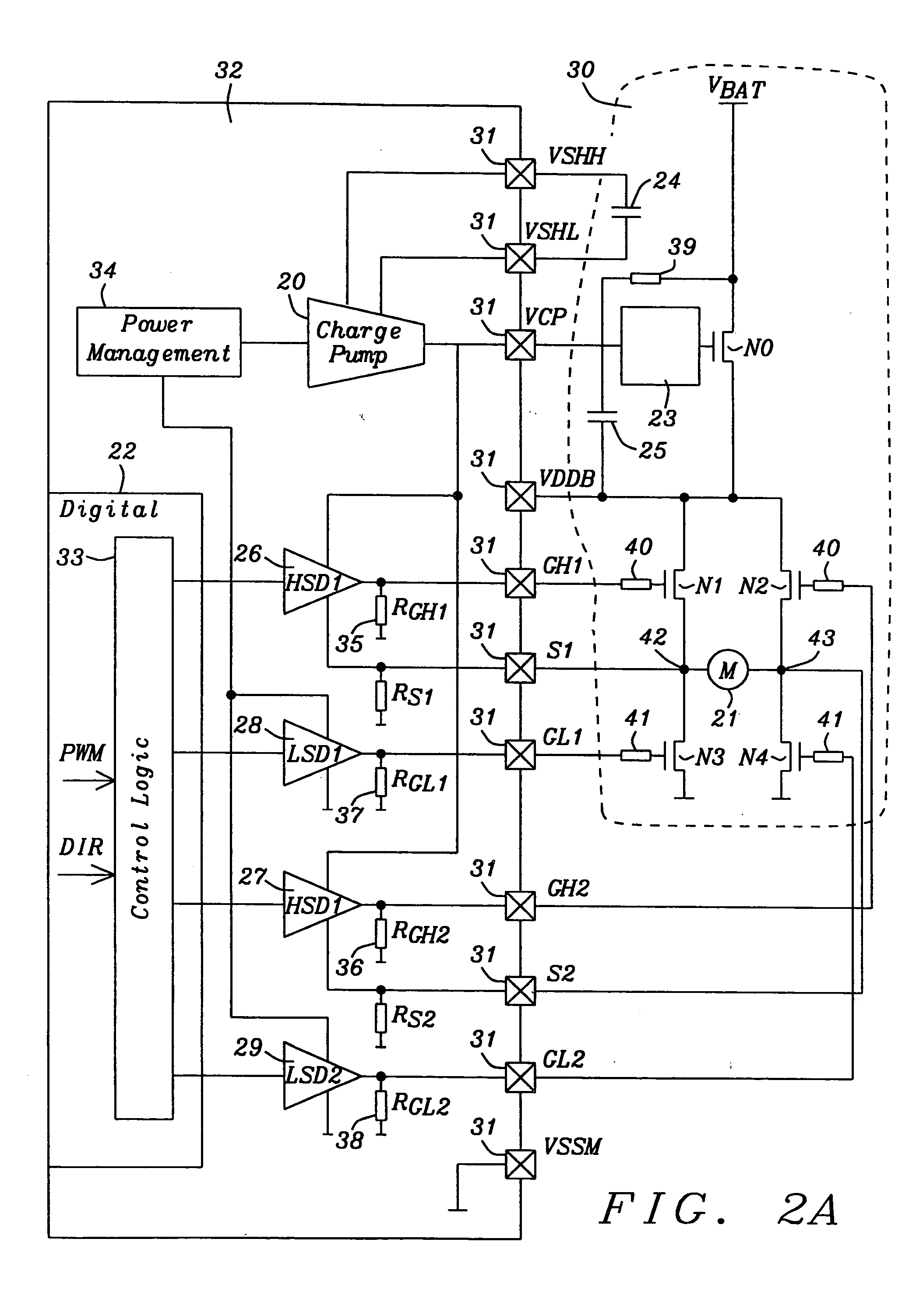

32V H-bridge driver with CMOS circuits

InactiveUS6977533B2Switching is accurate and fastAC motor controlSynchronous motors startersCMOSCmos switch

A motor bridge driver interlace, implemented in an ASIC using cost-efficient CMOS technology, is designed to control four external MOS power transistors in a H-bridge configuration for DC-motor driving to achieve accurate and fast switching. Main components of the interface are a charge pump for generating the control voltage for the high-side N-channel MOS transistors, high-side (HSD) circuits, low-side (LSD) circuits and a complex digital interlace for supplying the control signals in a programmable timing scheme. A “strong” charge pump is used to realize a simple CMOS switch to steer the output to the high-side transistors of said H-bridge. The motor bridge is connected to the battery supply by an additional N-channel MOS transistor to implement a reverse supply protection.

Owner:DIALOG SEMICON GMBH

Switch-capacitor integrator

InactiveCN101621292ARelax requirementsOptimize topologyElectric pulse generator detailsLogic circuitsCapacitanceIntegrator

The invention discloses a switch-capacitor integrator adopting novel C-class inverters and a switch-capacitor integrator realizing form of a pseudodifferential structure. The switch-capacitor integrator in a pseudodifferential structure comprises two novel C-class inverters (60) and capacitors such as a sampling capacitor CS, a compensation capacitor CC, an integrating capacitor CI, and the like, switches such as an NMOS switch S2, an NMOS switch S4, an NMOS switch S7, an NMOS switch S8, a CMOS switch S3, a CMOS switch S5, a bootstrap NMOS switch S1, a bootstrap NMOS switch S6, a bootstrap NMOS switch S9, and the like and a common mode feedback circuit (61) in the prior art, wherein the two novel C-class inverters (60) are respectively positioned in a positive branch and a negative branch of the integrator and differentially symmetrized to be in the pseudodifferential structure. The invention overcomes the effects of indexes of working efficiency, establishing time, integrating accuracy, power consumption, and the like on the switch-capacitor integrator by technical deviation through the bulk potential modulation effect of a bulk potential modulator in the novel C-class inverters and greatly improves the stability and the robustness of the integrator without obviously increasing the power consumption.

Owner:ZHEJIANG UNIV

SOI (Silicon on Insulator) CMOS (Complementary Metal Oxide Semiconductor) RF (Radio Frequency) switch and RF transmitter front-end module comprising same

The invention relates to an SOI (Silicon On Insulator) CMOS (Complementary Metal Oxide Semiconductor) RF (Radio Frequency) switch and an RF transmitter front-end module comprising the same. The SOI CMOS RF switch comprises a plurality of DC-blocking capacitors, a plurality of resistors and a plurality of switching tubes, wherein the switching tubes are SOI CMOS switching tubes, the drain electrode of each switching tube is connected to a channel control voltage through a resistor, the source electrode of each switching tube is connected to the channel control voltage through another resistor and connected with an antenna, and the channel control voltage is larger than 0 V and smaller than the difference of a high level and a threshold voltage of the switching tube. At the same moment, only one switching tube has a control signal at a high-level voltage, and the other switching tubes have control signals at the voltage of 0 V. The technical scheme provided by the invention simplifies the structure of the RF switch; and the RF switch can work under a signal power supply to ensure that the control signal voltage in a switching transistor in each SOI CMOS RF switch can be higher than the safe voltage of the transistor, thus the reliability of the RF switch is improved.

Owner:RDA MICROELECTRONICS BEIJING

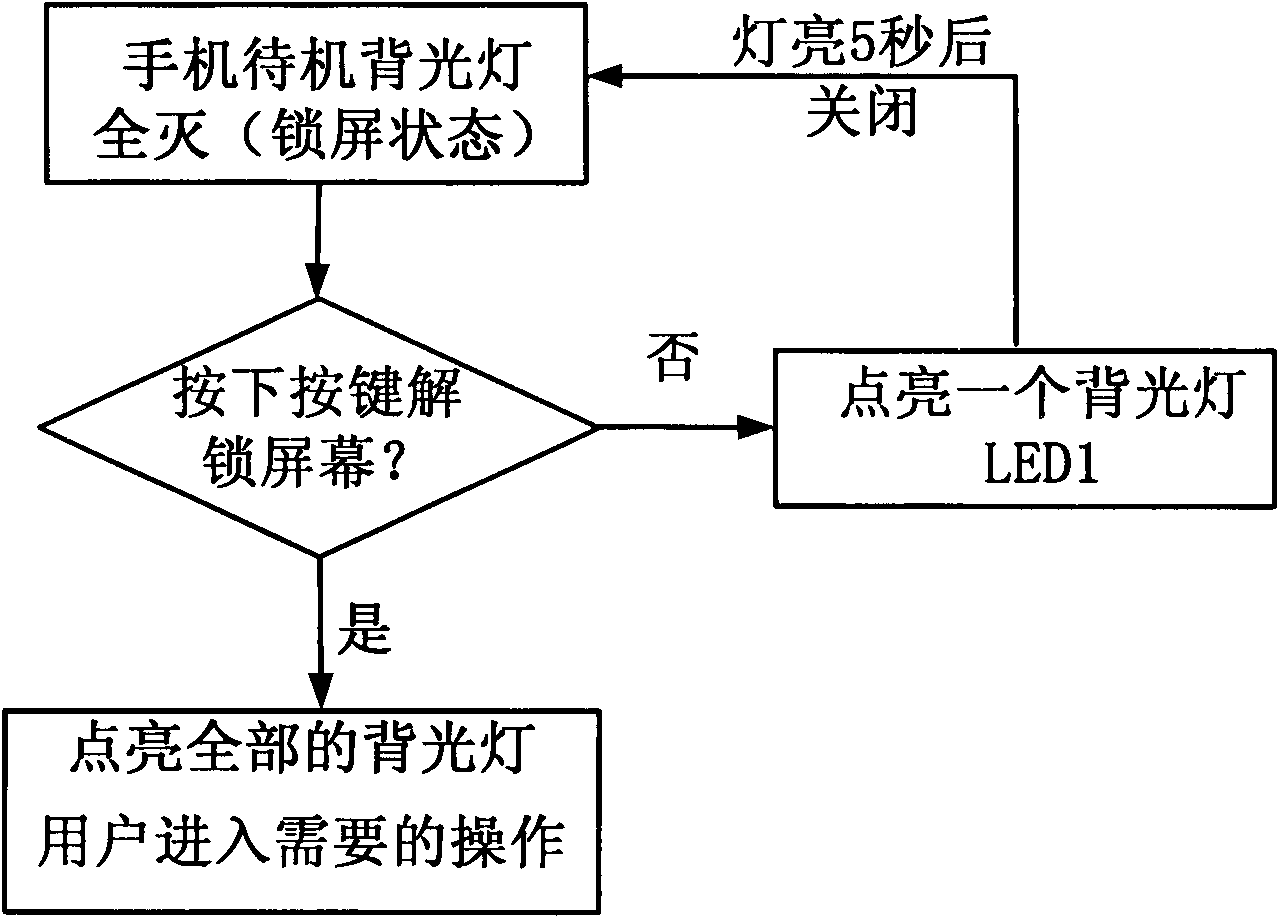

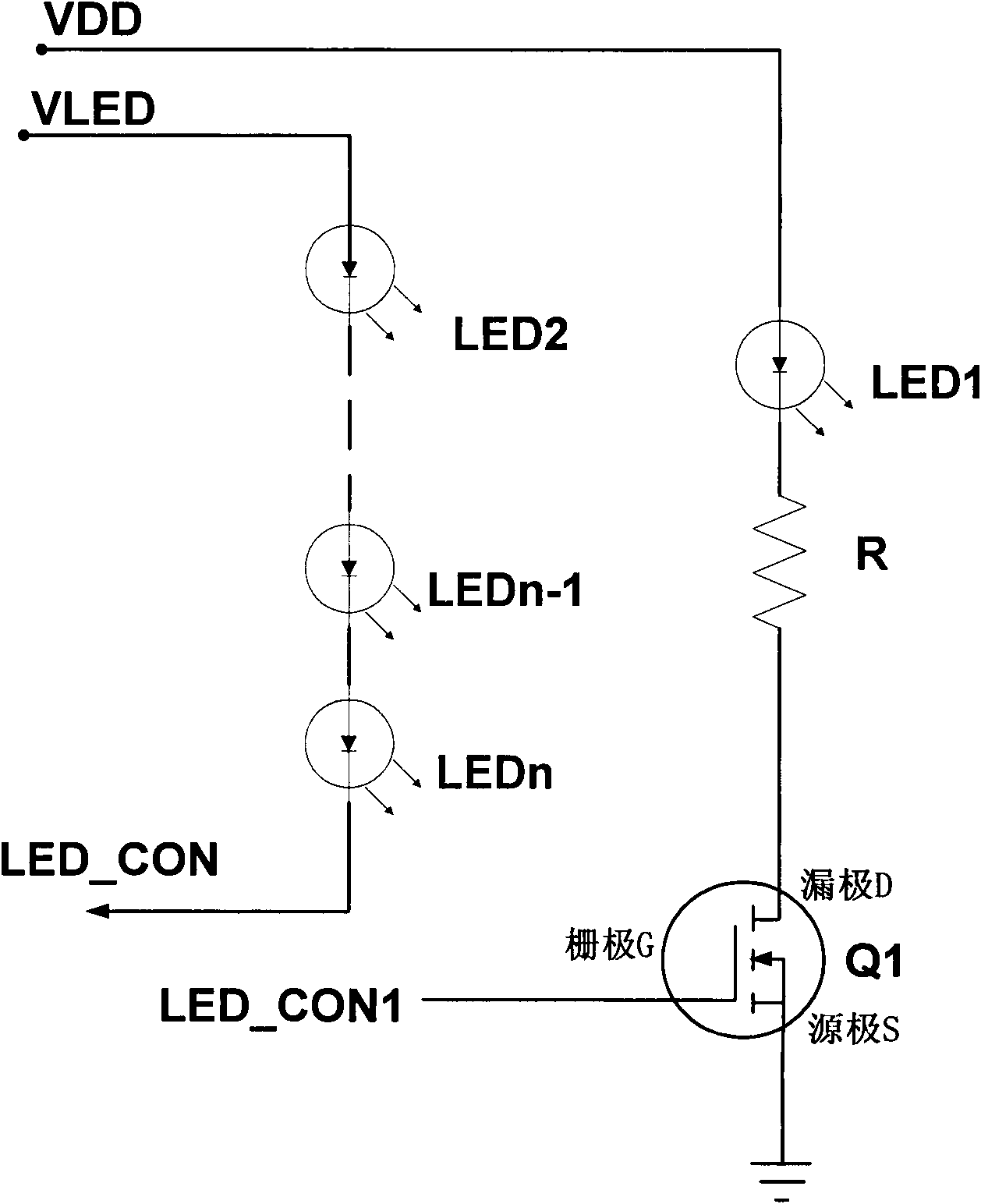

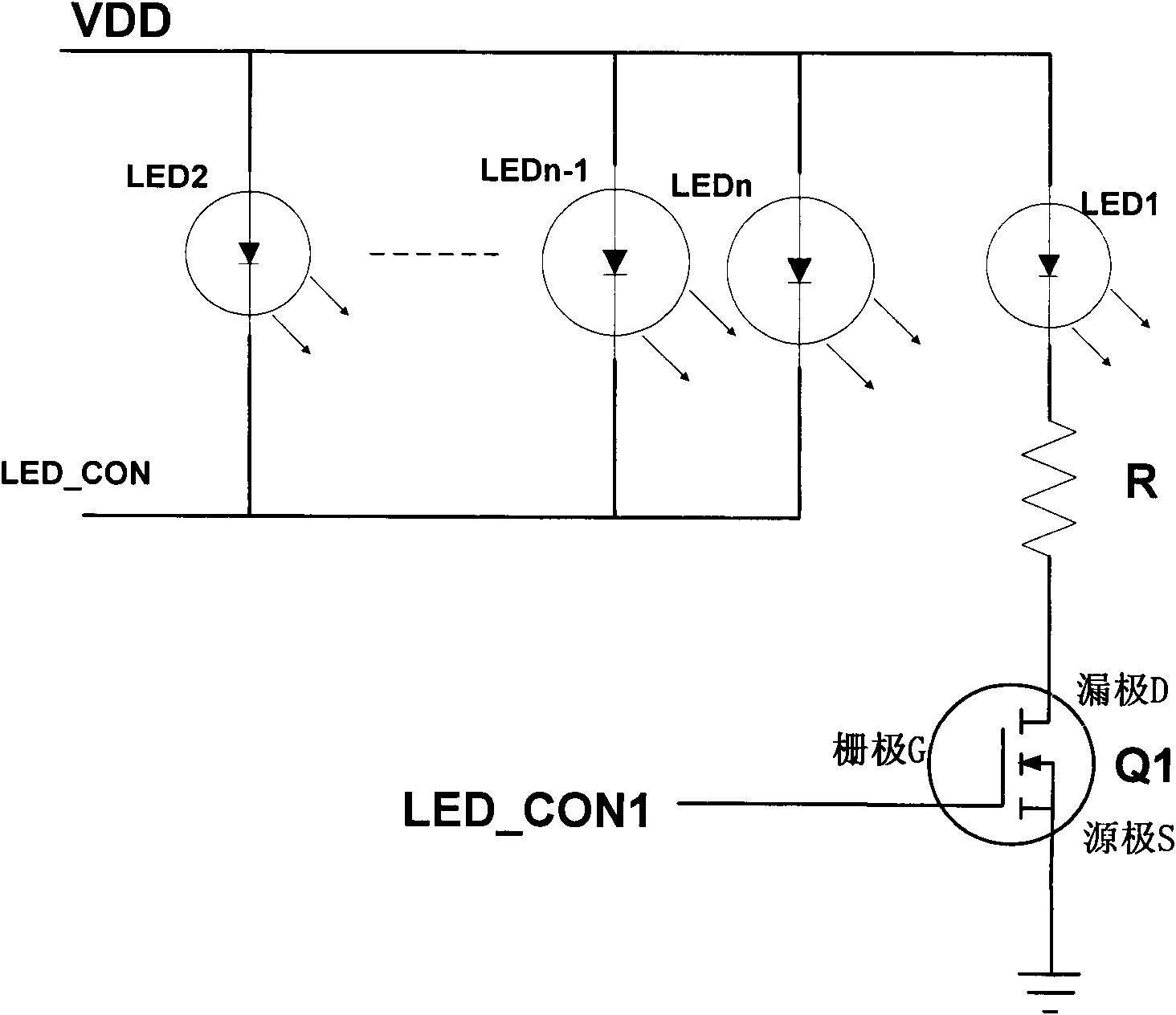

Method for reducing consumption of mobile phone battery and mobile phone thereof

InactiveCN101977271AReduce consumptionExtend standby timeCurrent supply arrangementsElectric light circuit arrangementElectricityCMOS

The invention discloses a method for reducing consumption of a mobile phone battery and a mobile phone thereof. The method comprises the steps of: when the mobile phone enters a standby and screen-locking state, simultaneously extinguishing all backlights on a screen; monitoring the operation of a user, judging whether the operation is a screen-unlocking operation; and if the operation is a screen-locking operation, conducting an NMOS (N-Mental-Oxide-Semiconductor) pipe, lighting an appointed backlight used for looking the time, the unread message or missed call. Because the NMOS pipe is adopted for conducting the appointed backlight when the mobile phone is in the standby and screen-locking state, the newly added backlight or the original LCD backlight is utilized for looking the time and finding whether the unread message or missed call exists or not under special demands, and one appointed backlight is only opened through a control signal and a CMOS (Complementary Metal Oxide Semiconductor) switching element additionally arranged on a hardware circuit without opening all LCD backlights, thus the consumption of the mobile phone battery is reduced, and the function of saving electricity is obtained, and the standby time of the mobile phone is prolonged.

Owner:HUIZHOU TCL MOBILE COMM CO LTD

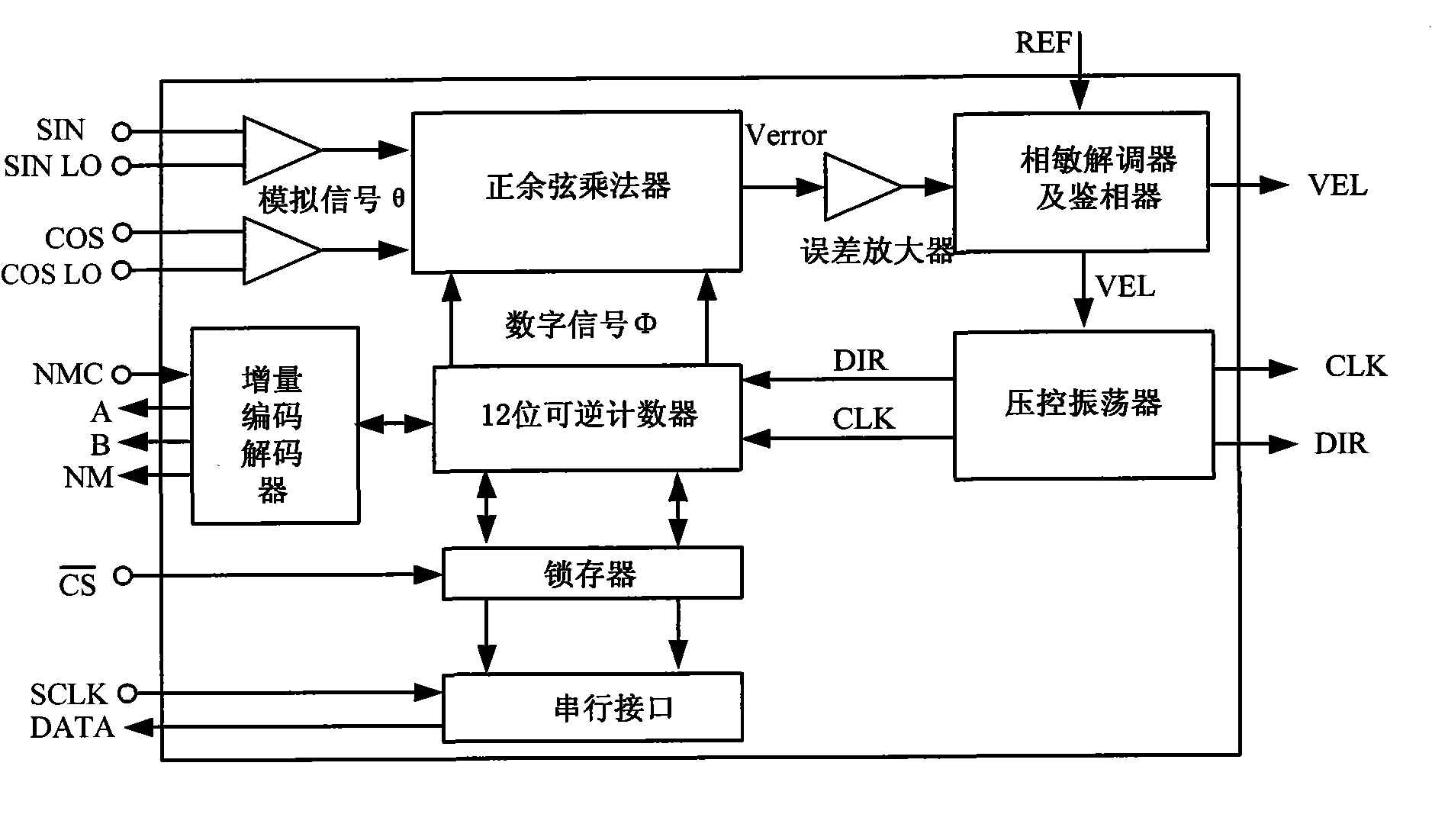

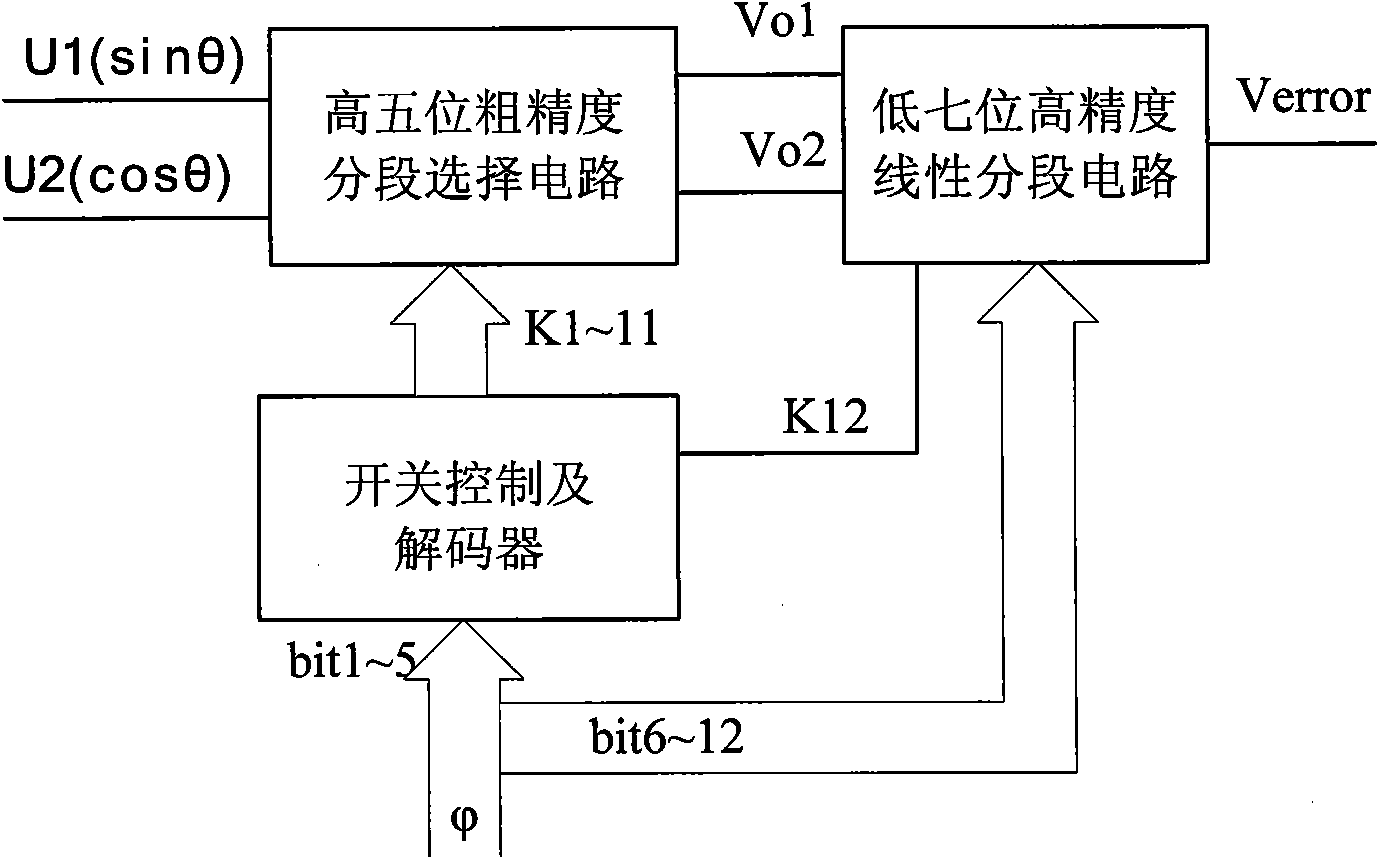

Signal-digit converter of low-temperature drift rotary transformer

ActiveCN101788307AAchieve uniform angular velocity error-free tracking outputHigh precisionConverting sensor output electrically/magneticallyCapacitanceTime delays

The invention discloses a signal-digit converter of a low-temperature drift rotary transformer. The signal-digit converter is characterized by consisting of a sine and cosine multiplier, an error amplifier, a phase-sensitivity demodulating and phase discriminating device, a voltage-controlled oscillator, a 12-bit reversible counter, a latch, an incremental codec and a serial interface. In the invention, a linear compatible CMOS (Complementary Metal-Oxide-Semiconductor Transistor) process is used; and by adopting a temperature self-compensated bootstrap mirror image current reference source, the invention realizes the output of reference current which is irrelative with mains voltage and near-zero temperature drift near 300K. The sampling precision can be improved by adopting a CMOS switch capacitance technology. All peripheral assemblies are integrated inside an integrated circuit and the most tidy pin definition is formed, so that track conversion from the angle to digital quantity can be realized without extra assemblies. The low-temperature drift can be realized by adopting a zero temperature drift reference source. The wide work frequencies of an input signal and a reference signal can be realized by adopting a dynamic time-delay technology. The high track speed can be realized by adopting a technology of high performance operational amplifier, switch and linear combination and high-speed dynamic parameter design.

Owner:连云港杰瑞电子有限公司

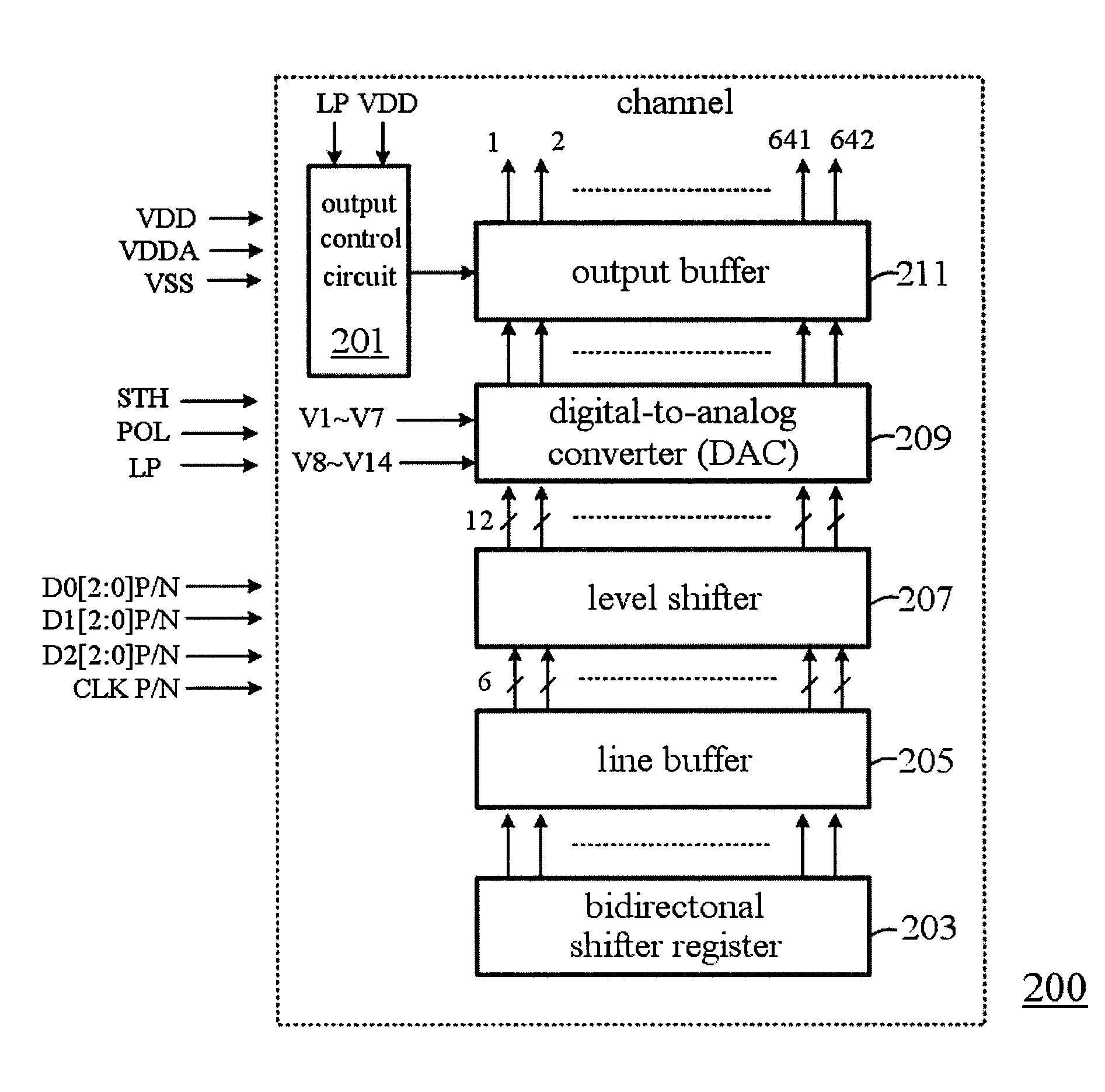

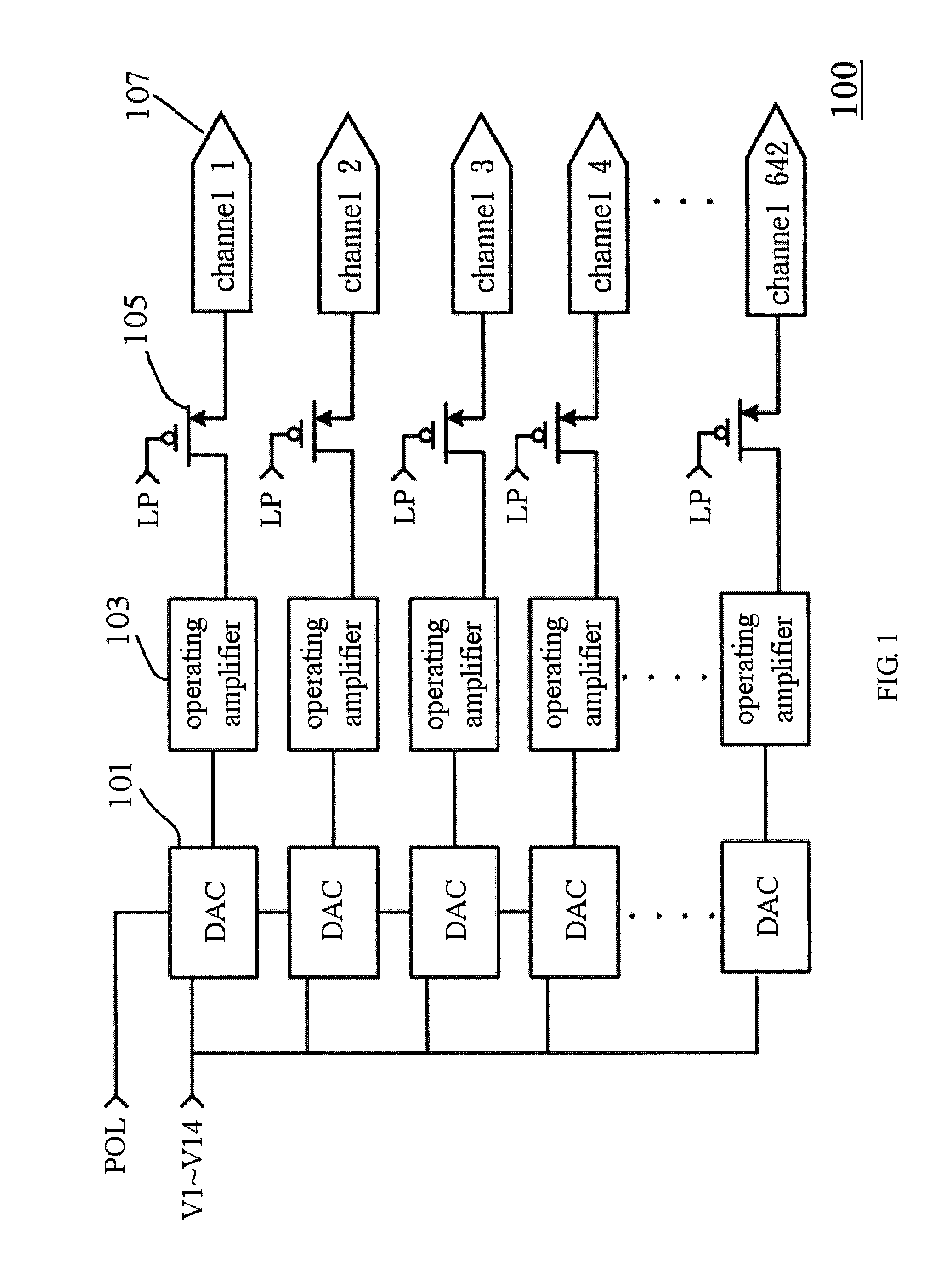

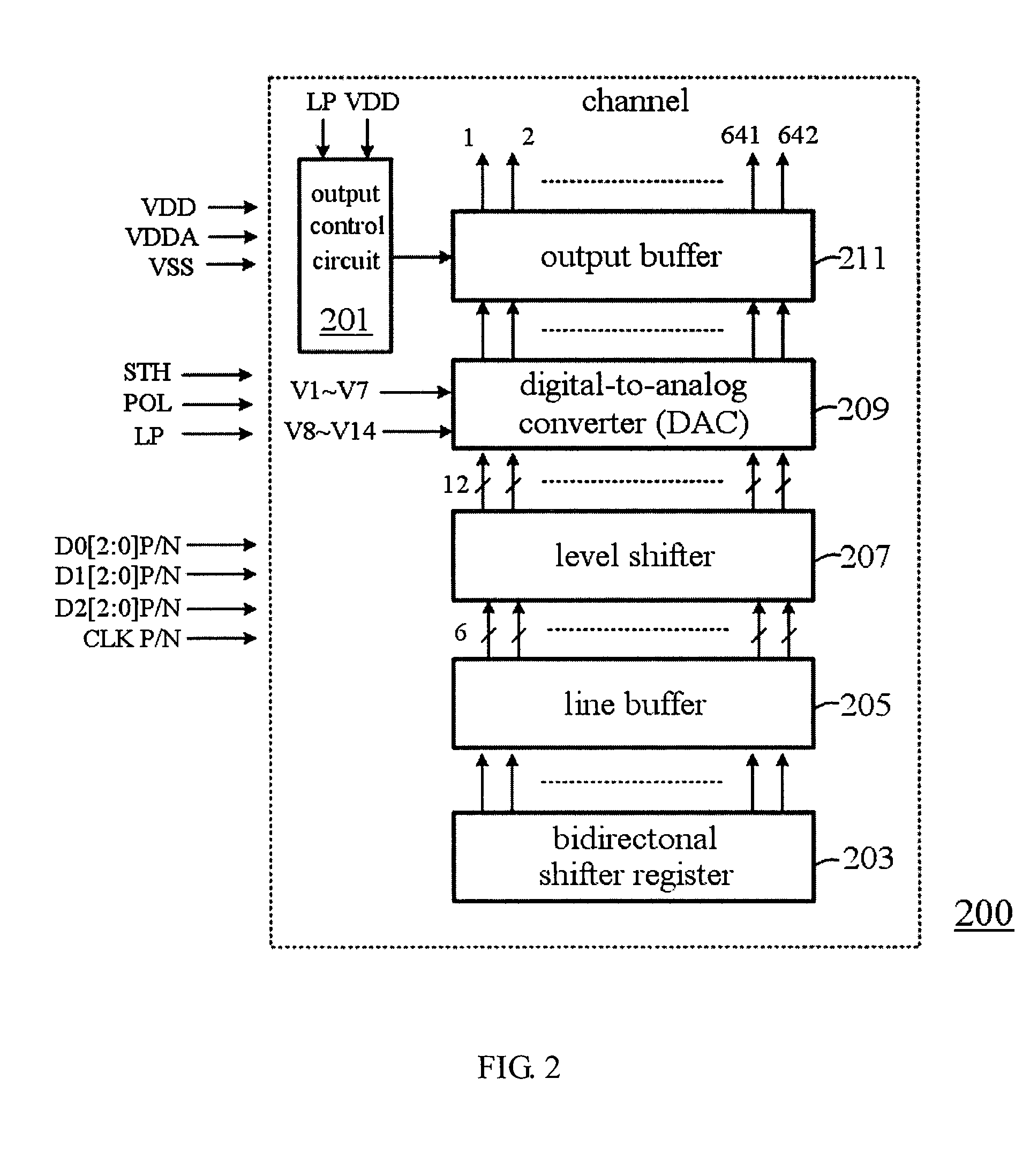

Source driver structure for display and output control circuit thereof

ActiveUS20100103315A1Increase production costSolve the noiseTelevision system detailsStatic indicating devicesShift registerDisplay device

The present invention discloses an source driver circuit scheme for displayer, which comprises a shifter register to register data signal, a line buffer coupled with said shifter register to latch the data signal, a level shifter coupled with line buffer to level output electrical potential, a digital-to-analog converter (DAC) to convert digital signal to analog signal, an output buffer coupled with said digital-to-analog converter (DAC) to output converted signal, and an output control circuit coupled with output buffer. Said output control circuit comprises a D flip-flop and CMOS switching element to output a LP_out signal and control the data signal output of the source driver IC to avoid the power-on noise of the displayer.

Owner:CHUNGHWA PICTURE TUBES LTD

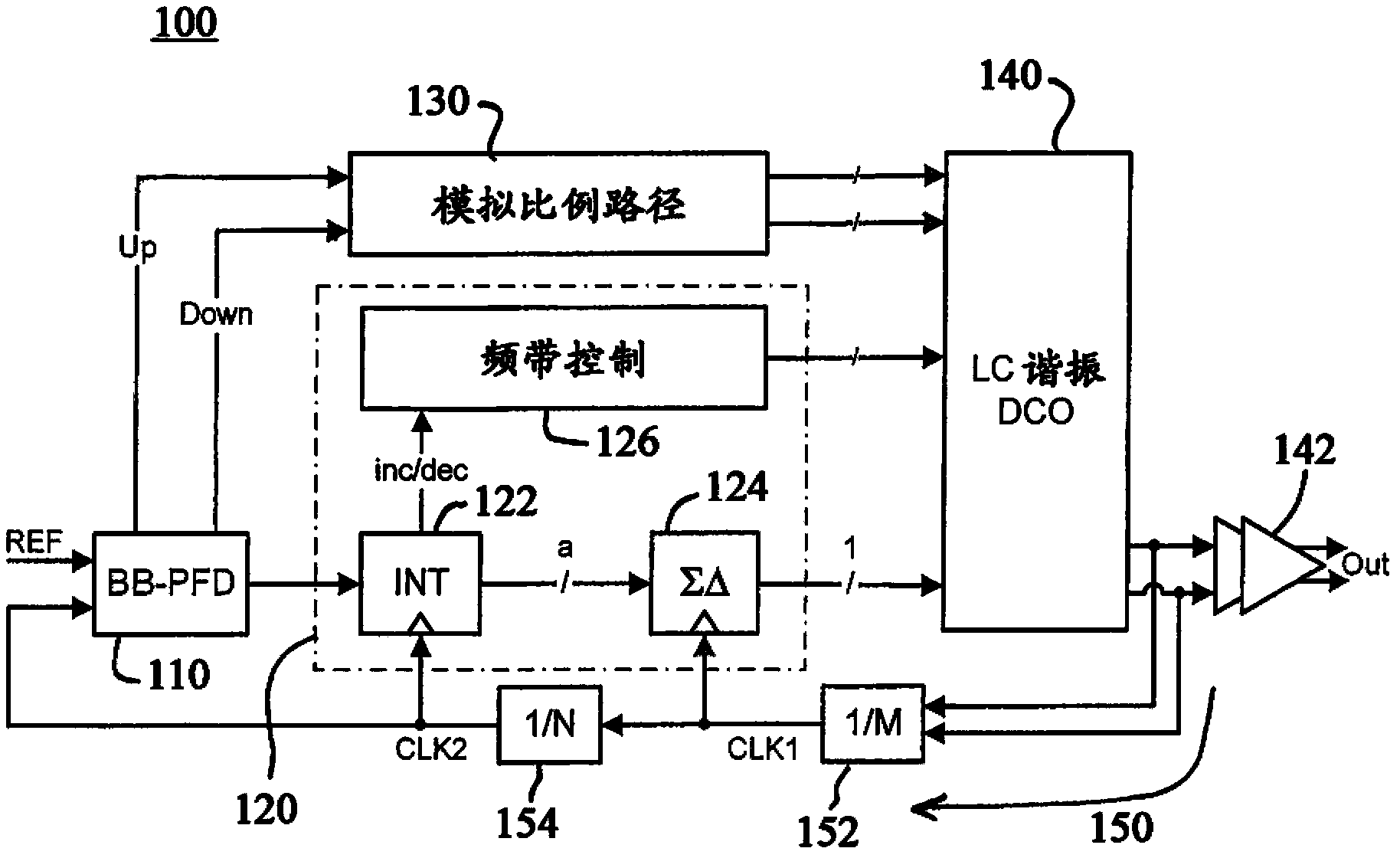

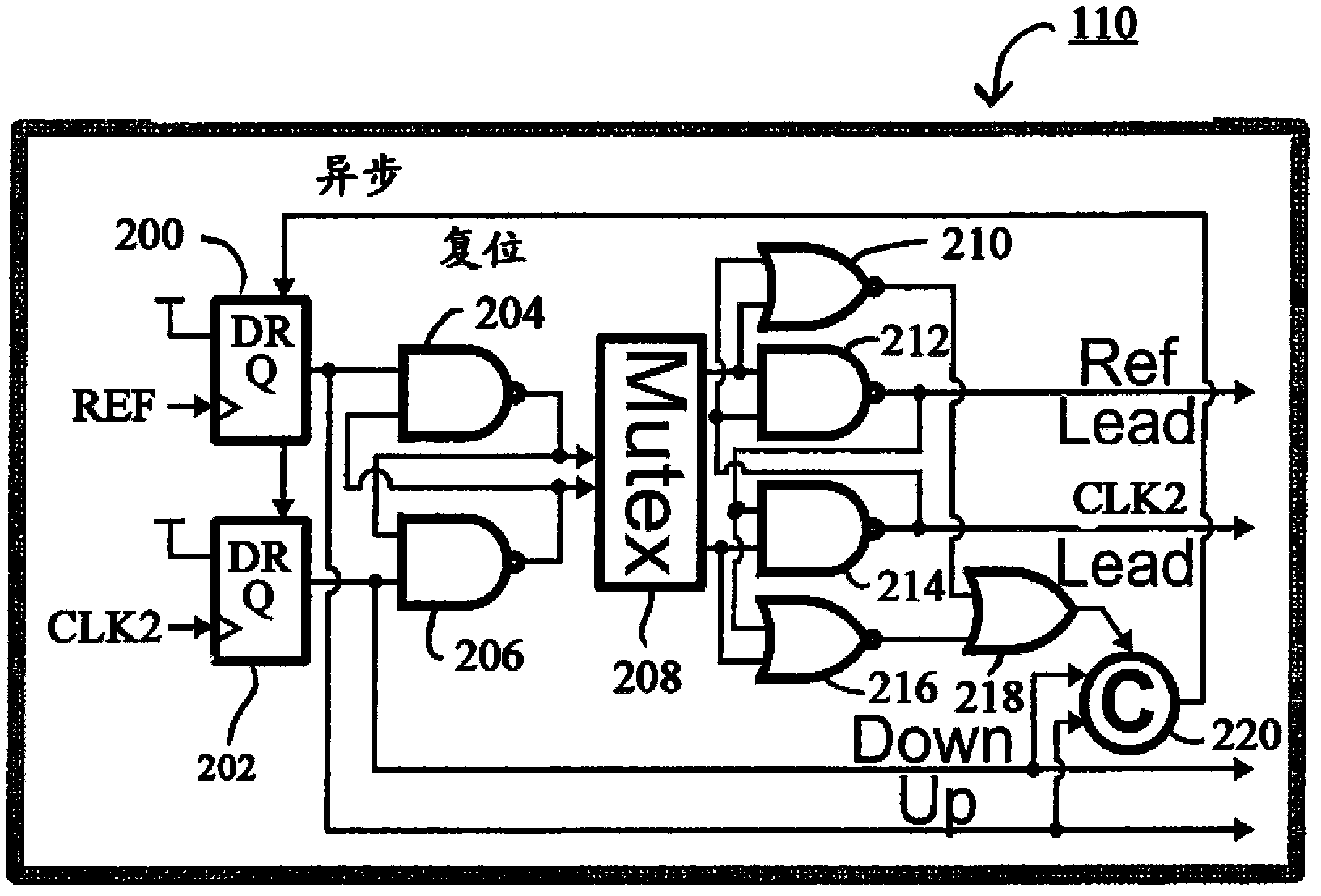

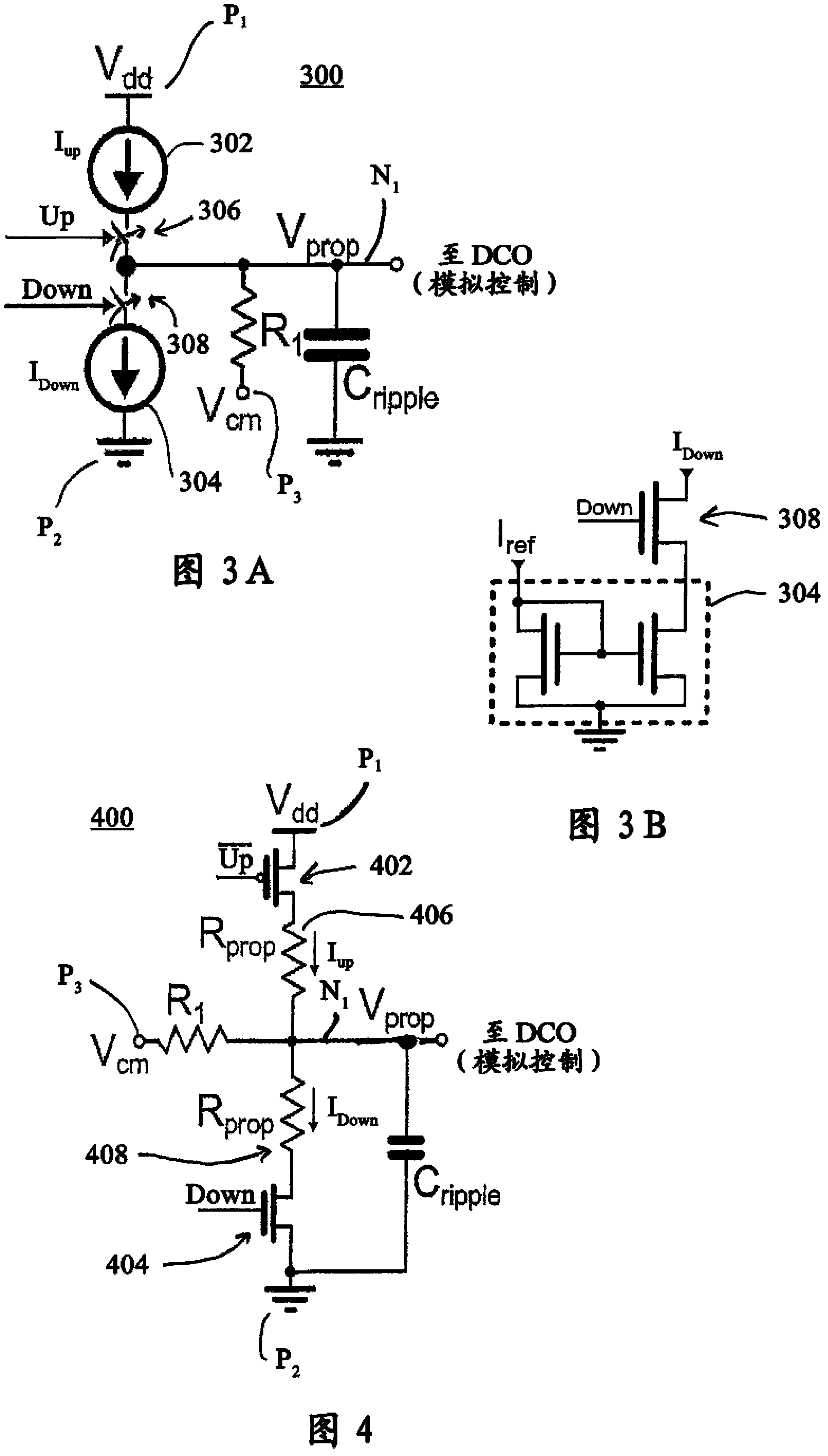

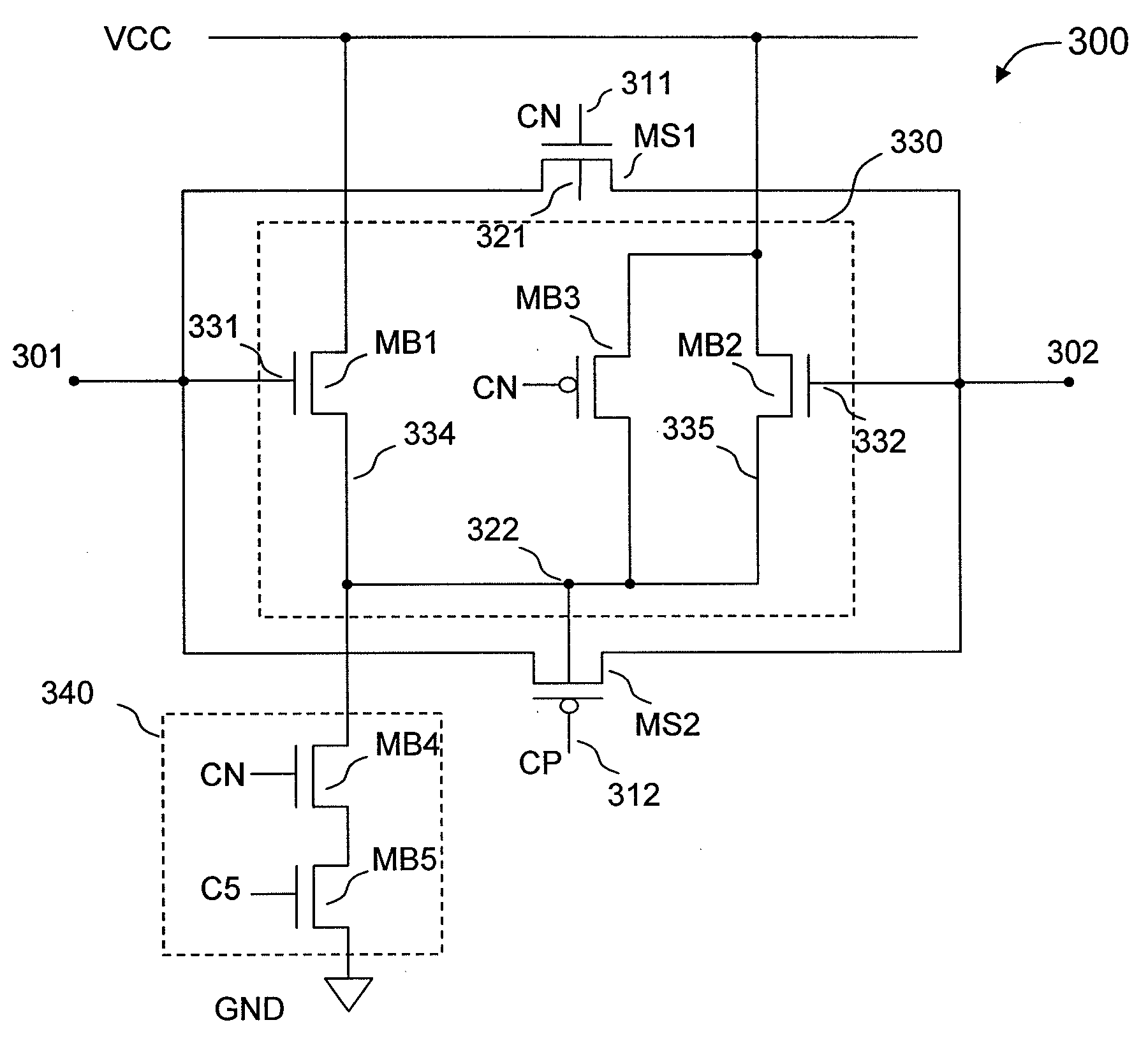

Phase locked loop circuit and method of generating clock signals using the phase locked loop

The invention refers to a phase locked loop circuit and a method of generating clock signals using the phase locked loop. Phase locked loop (PLL) architectures are provided such as hybrid PLL architectures having separate digital integrating control paths and analog proportional control paths. An analog proportional control path can be implemented with a charge pump circuit that includes resistors in series with CMOS switches to generate control currents (e.g., Up / Down control currents) which are used to adjust a control voltage applied to a digitally controlled oscillator. A digital integrating control path can be implemented with a series of sigma-delta modulators that operate at different frequencies to convert higher bit data signals to lower bit data signals along the digital integrating control path. A single phase frequency detector may be implemented to generate control signals that separately control the analog proportional and digital integrating control paths.

Owner:GLOBALFOUNDRIES INC

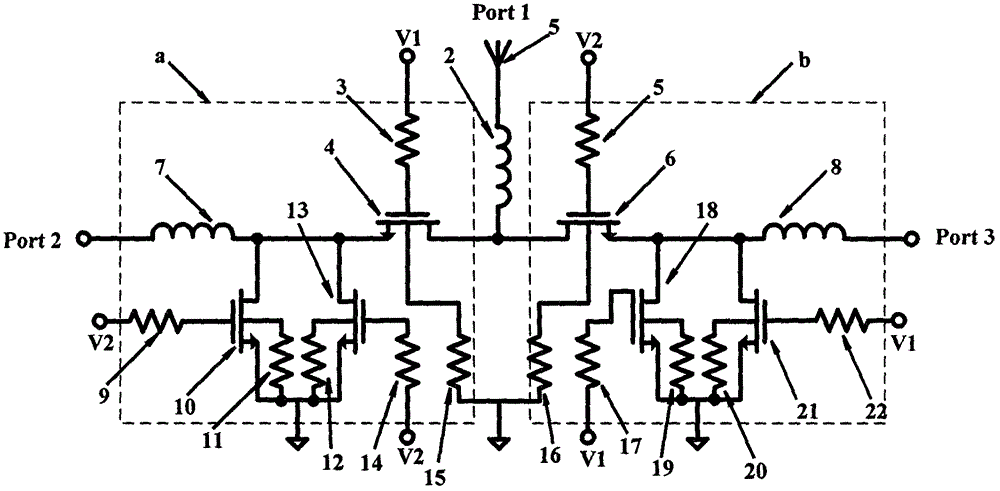

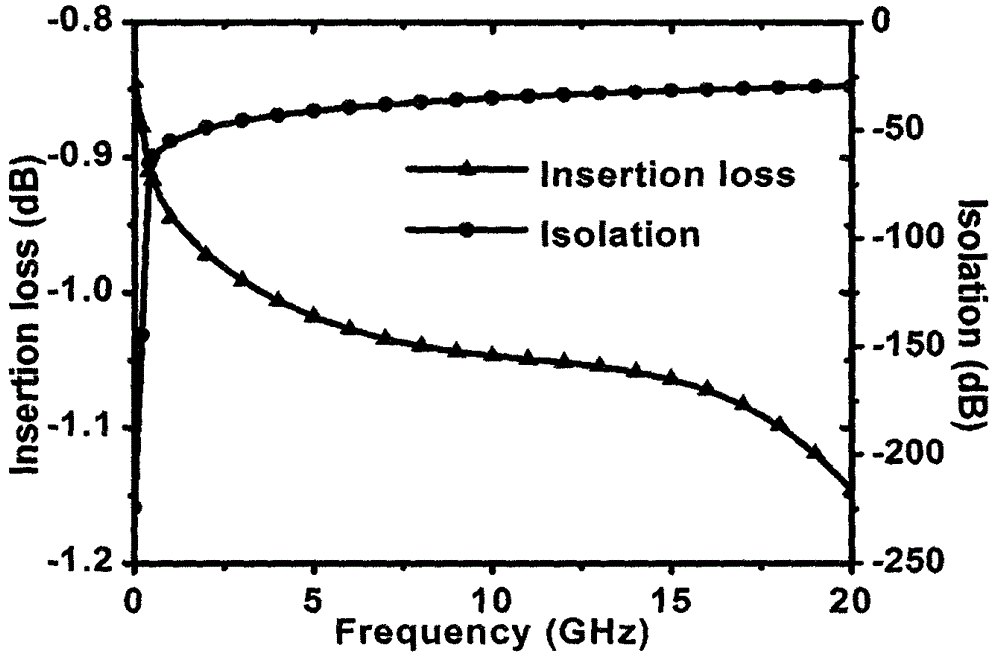

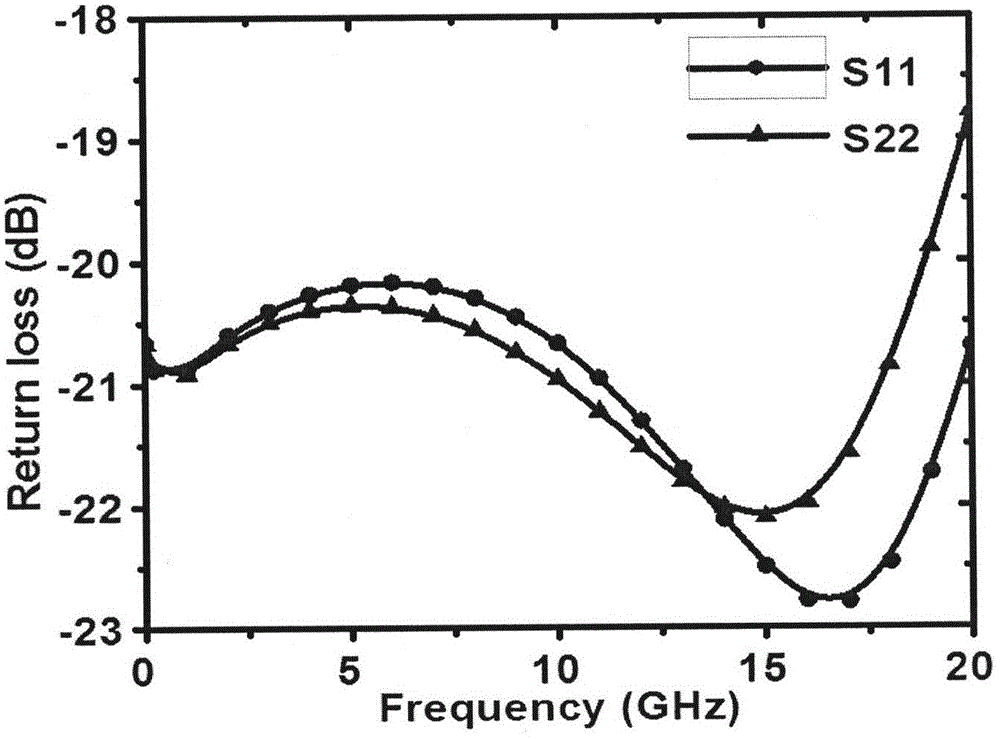

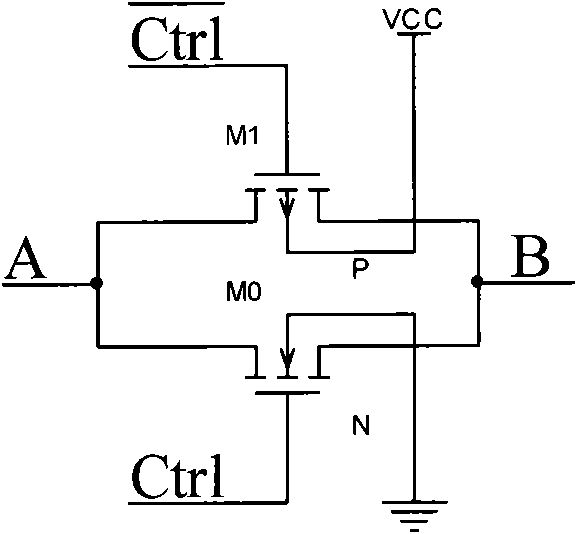

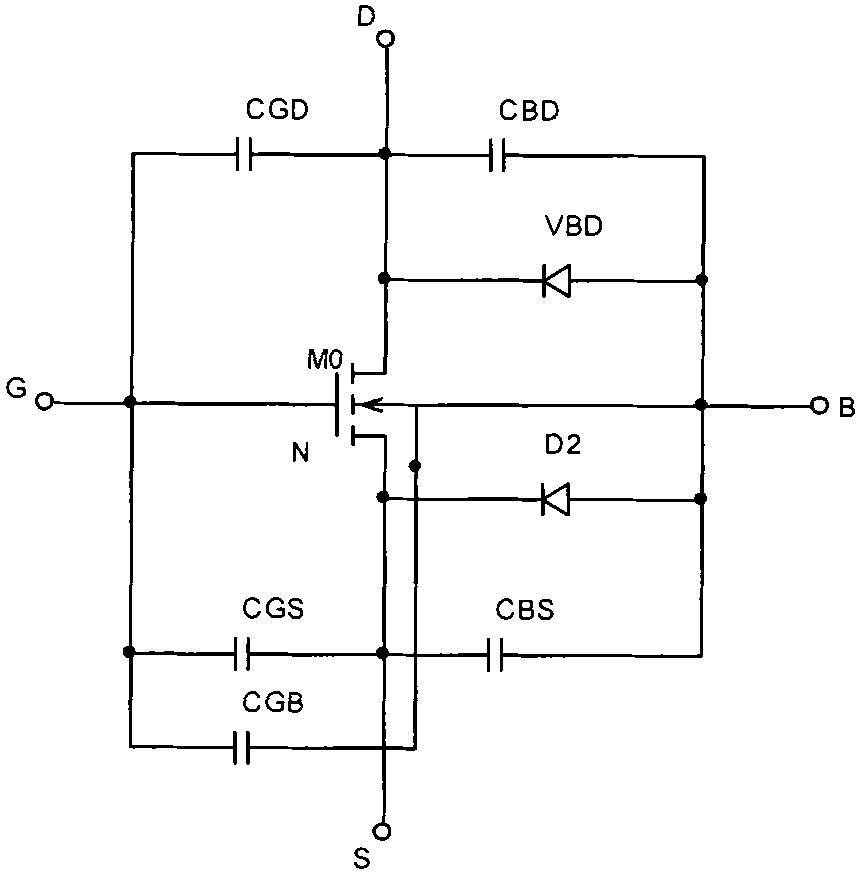

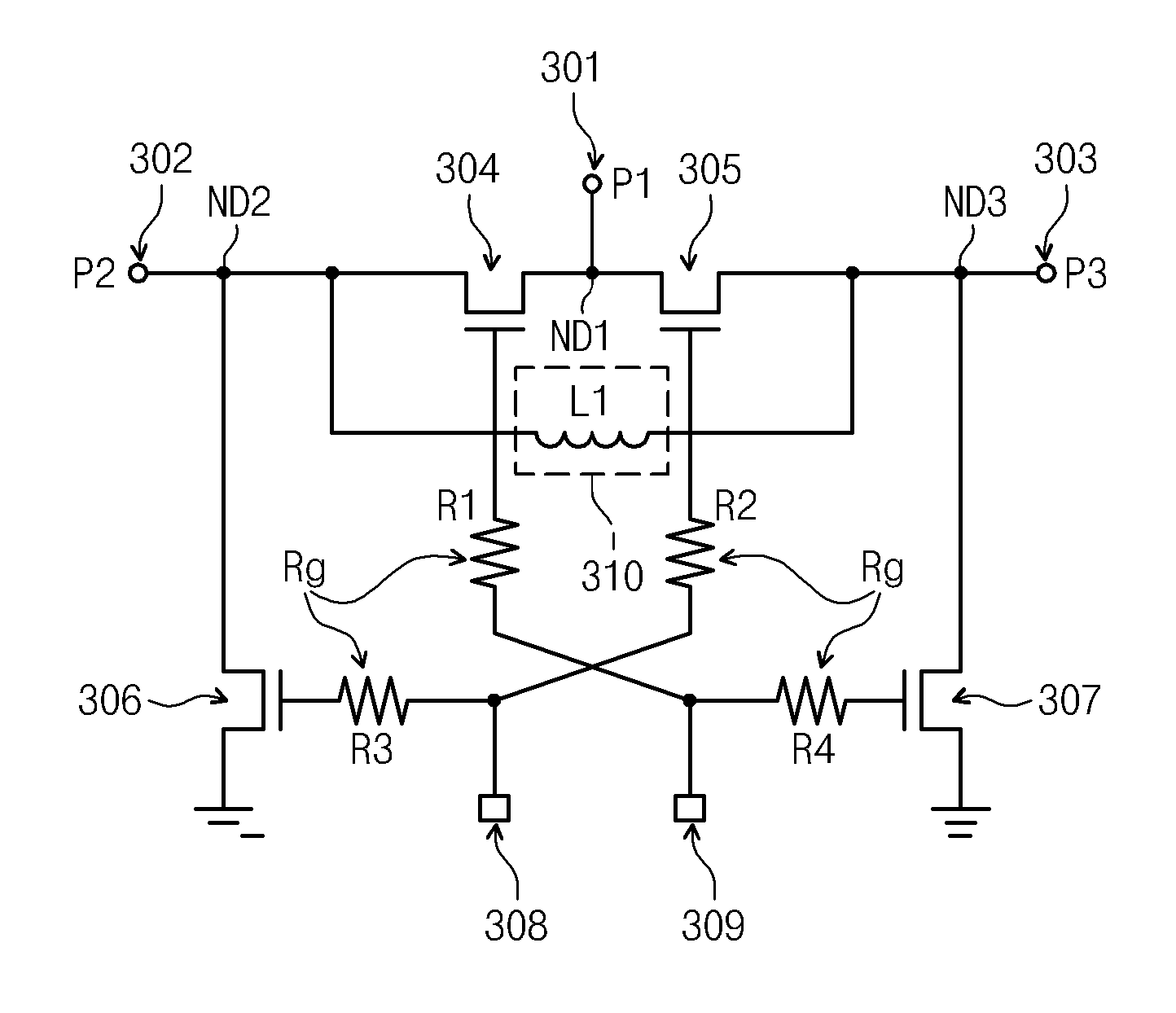

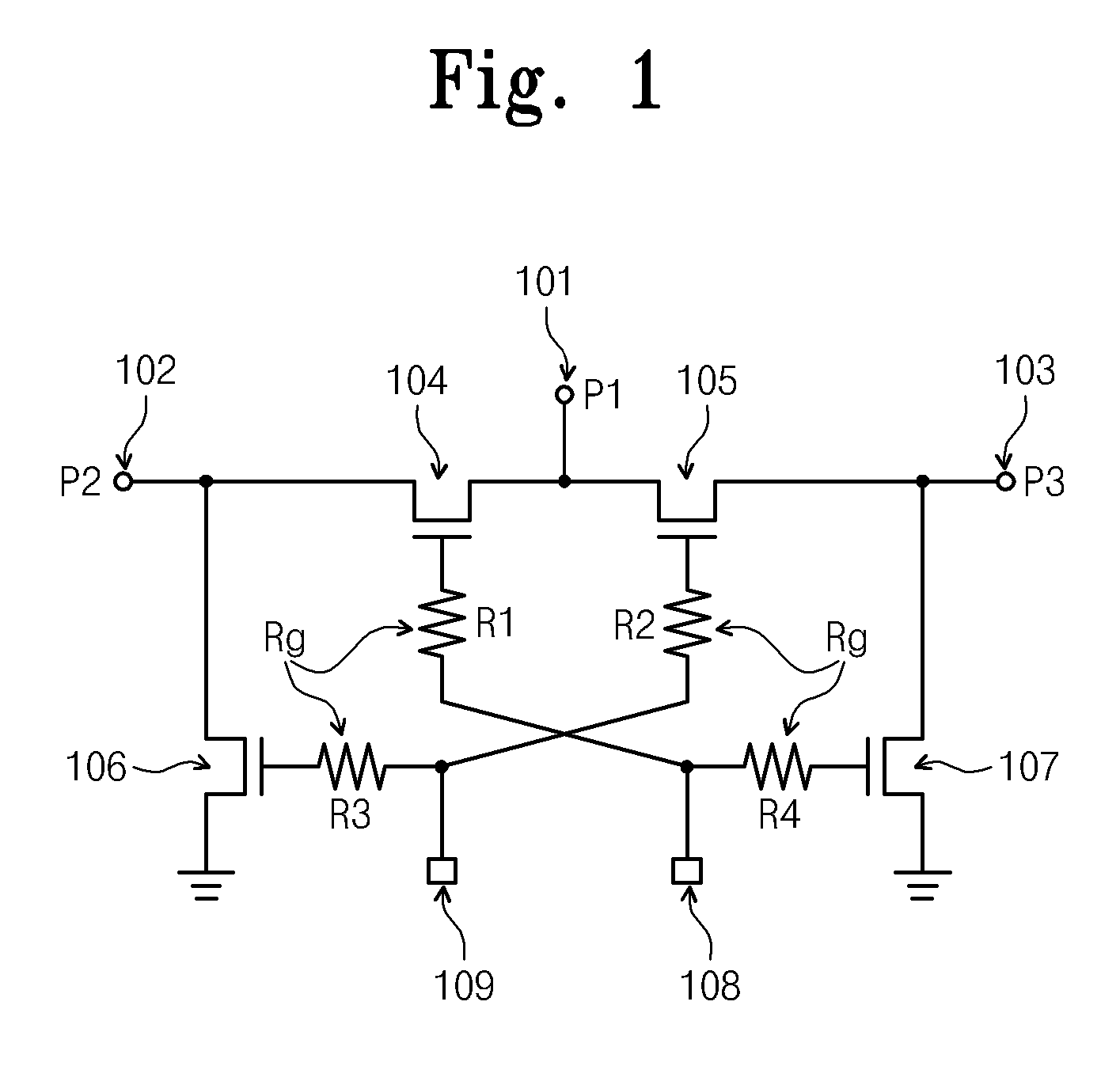

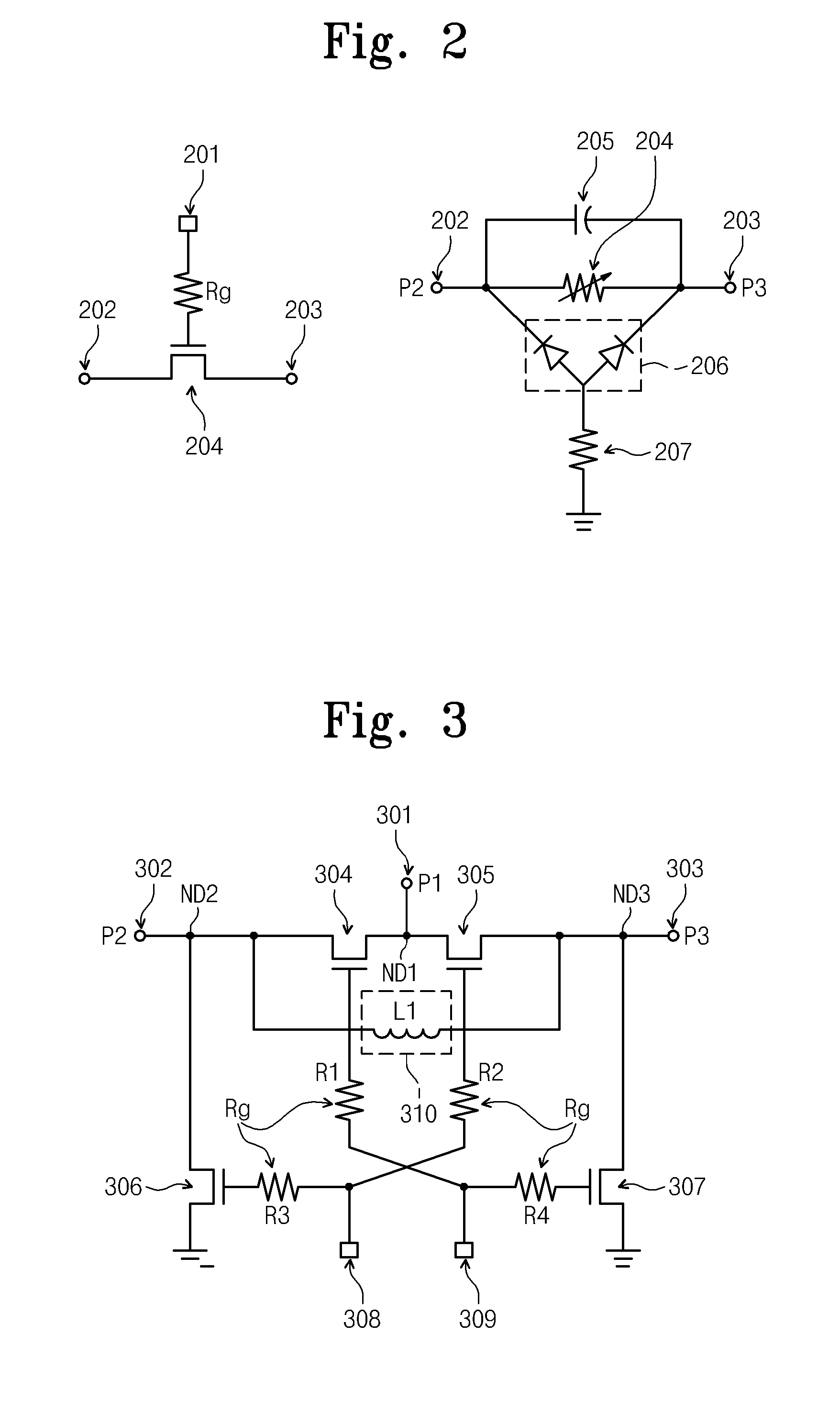

CMOS switching circuit

The invention belongs to the technical field of integrated circuits, and specifically provides a CMOS single pole double throw transceiver switch, which has low insertion loss, a high isolation degree and a low input and output reflection coefficient. The CMOS single pole double throw transceiver switch comprises a receiving switch and a transmitting switch. The CMOS single pole double throw transceiver switch provided by the invention adopts the deep N well technology, the bodies of all the transistors are connected to the ground, and N wells are connected with a supply voltage to minimize the capacitance between the bodies and a matrix; the CMOS single pole double throw transceiver switch provided by the invention adopts the inductance matching technology to achieve impedance matching at three ports; and in the CMOS single pole double throw transceiver switch provided by the invention, the grid electrodes of all the transistors are serially connected with a substrate. The CMOS single pole double throw transceiver switch provided by the invention can effectively reduce the leakage of a low radio frequency signal, reduce the insertion loss of the switch, and can increase the isolation degree of the switch at the same time. The CMOS single pole double throw transceiver switch provided by the invention can be integrated to a system-on-chip Soc or an application-specific integrated circuit ASCI or the like under a low voltage of 1.8V and working frequency of 0-20GHz.

Owner:WENZHOU UNIVERSITY

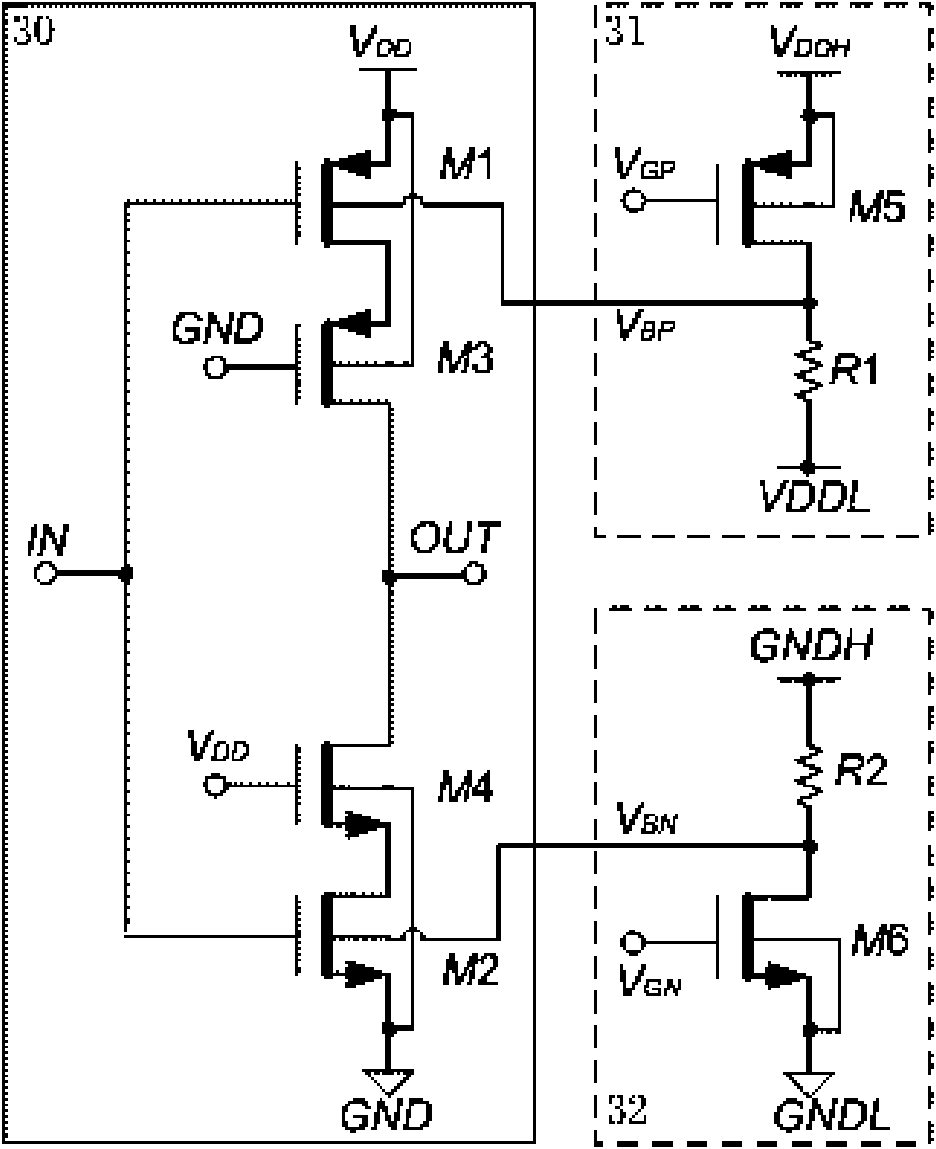

High-bandwidth high-isolation low on-resistance CMOS analog switch circuit and realizing mode thereof

InactiveCN101931387AImprove transmission bandwidthDoes not affect isolationElectronic switchingGrid impedanceEngineering

The invention provides a CMOS switch circuit with wider bandwidth, high isolation and low on-resistance, which is used for multi-path high-frequency analog signal switching. By adopting the technology of floating trap and grid impedance control, the problem that the on-resistance and the transmission bandwidth of the traditional CMOS analog switch circuit are restricted with each other can be solved, so that the signal transmission bandwidth of the CMOS switch under the same on-resistance and isolation can be greatly improved.

Owner:上海英联电子科技有限公司

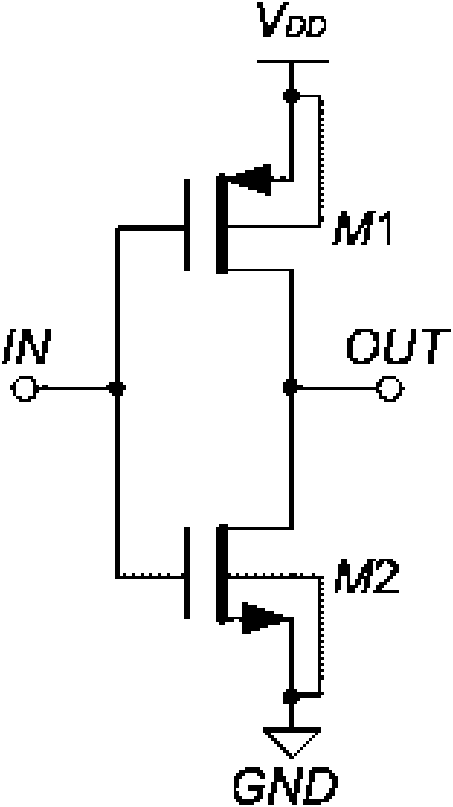

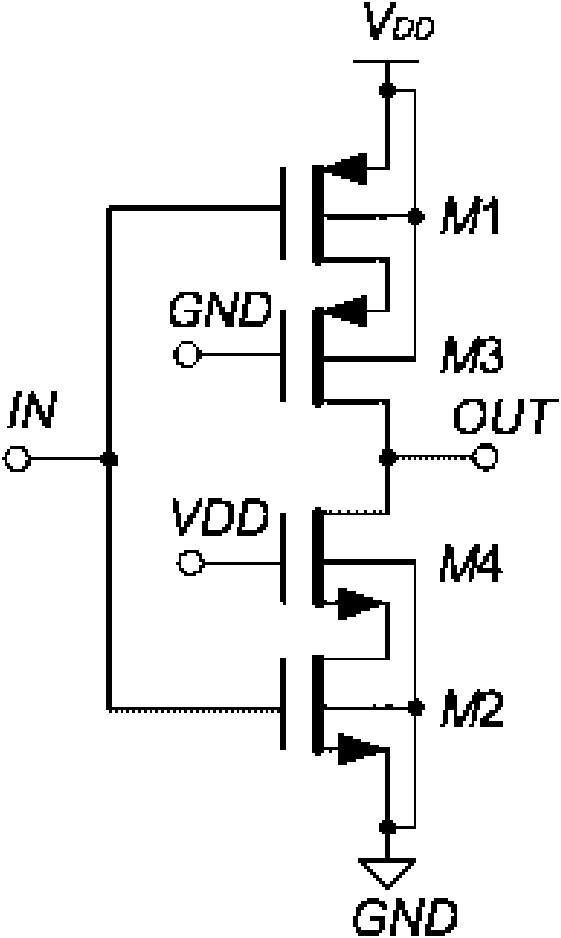

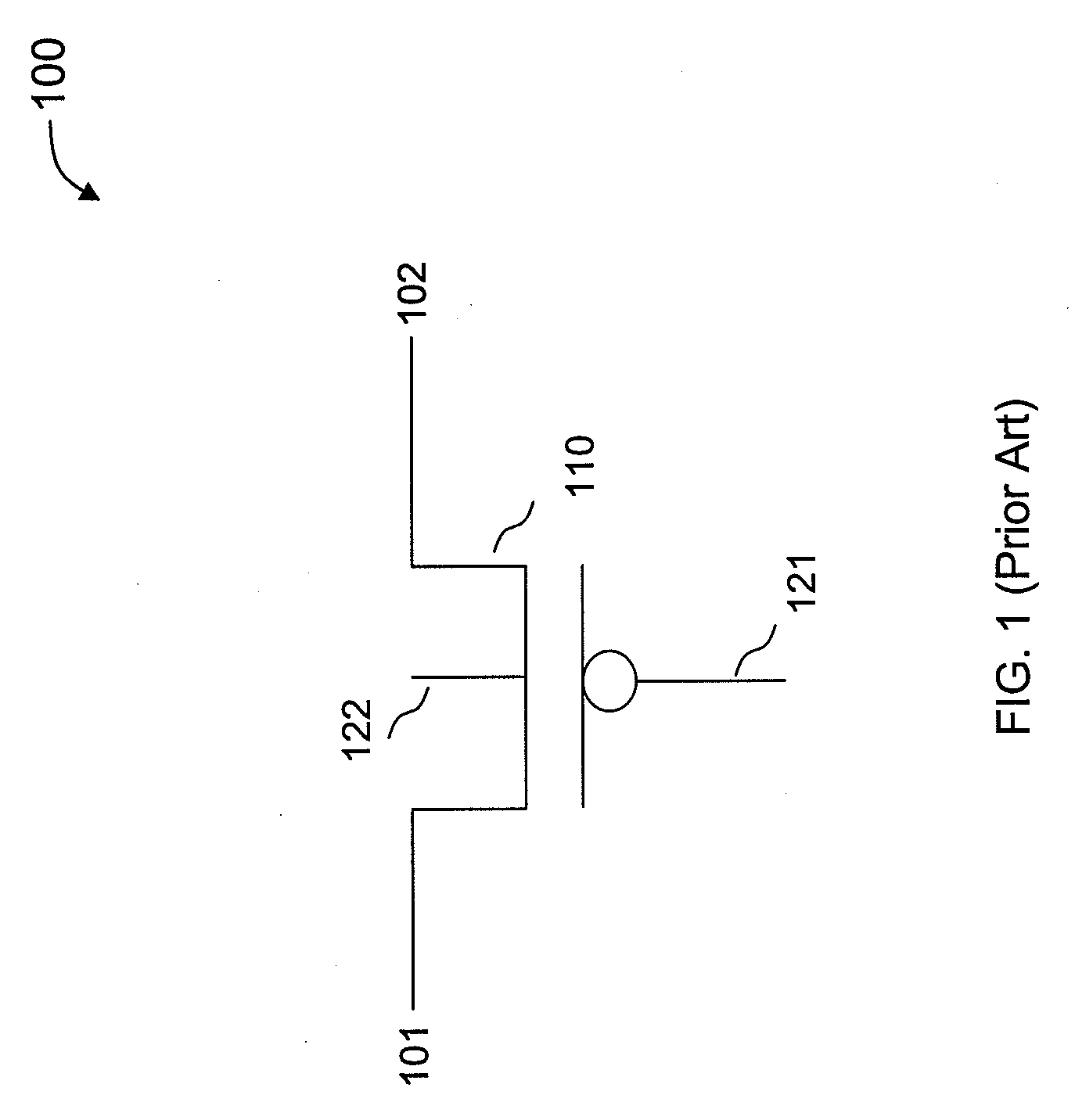

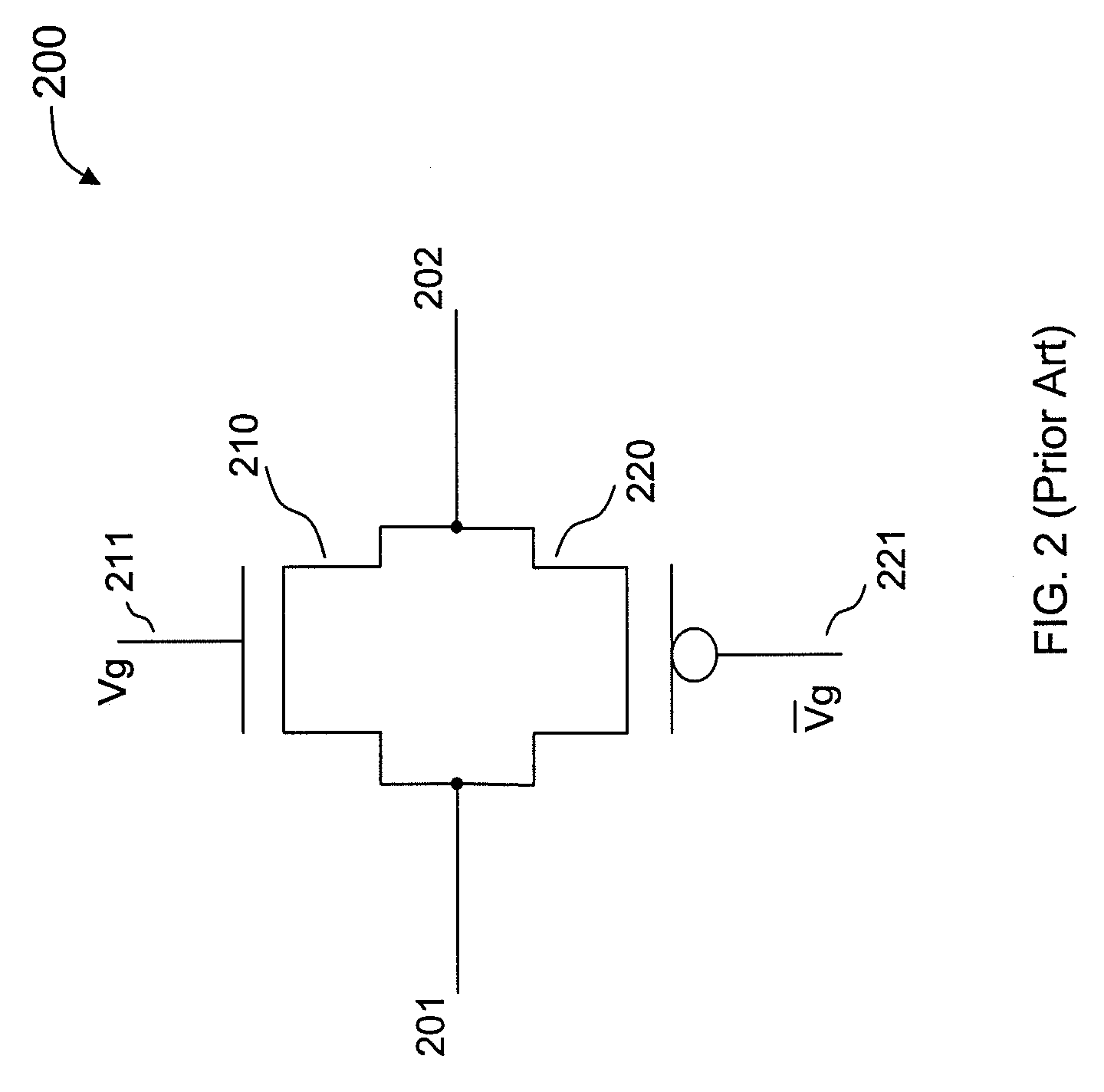

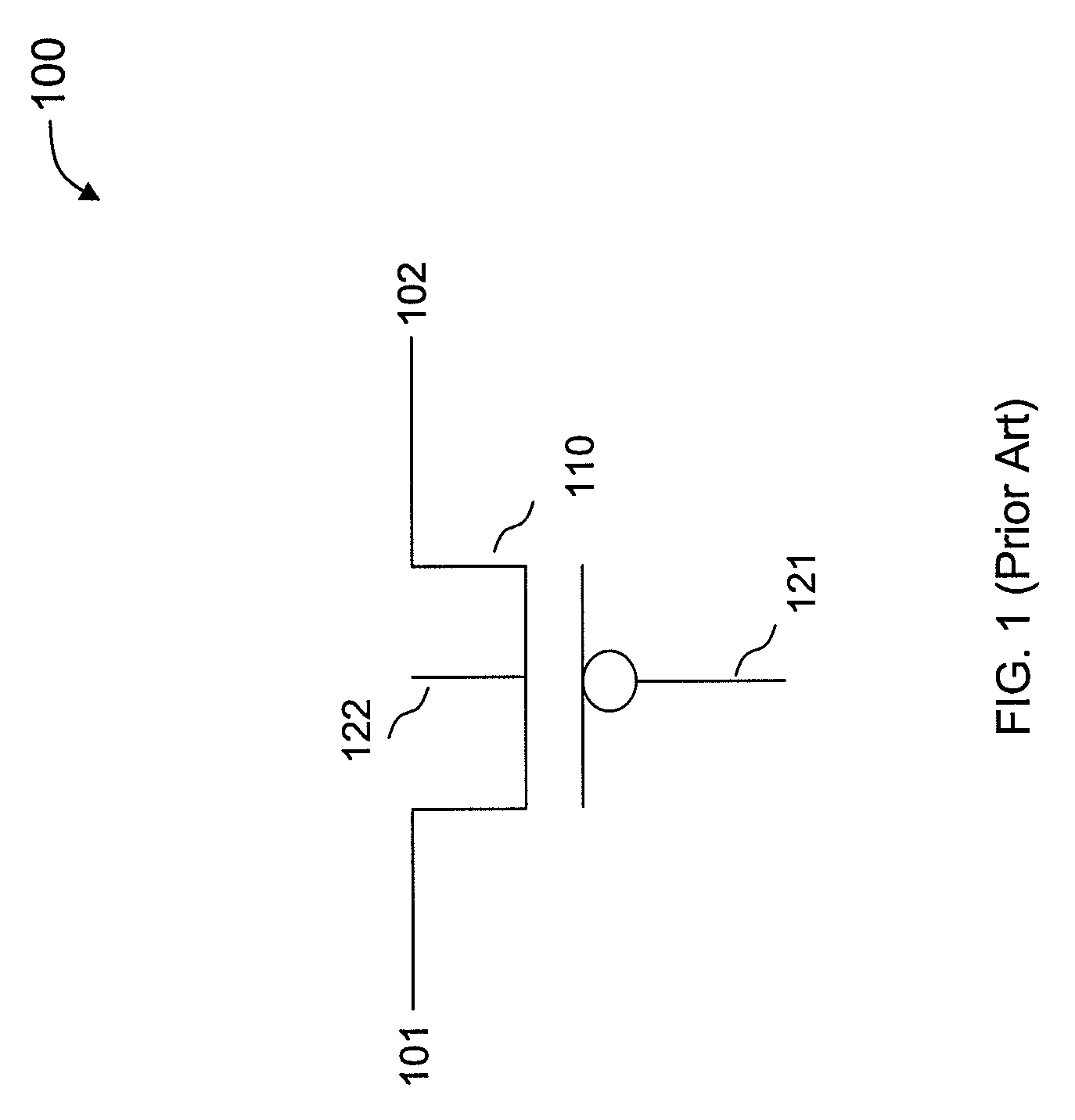

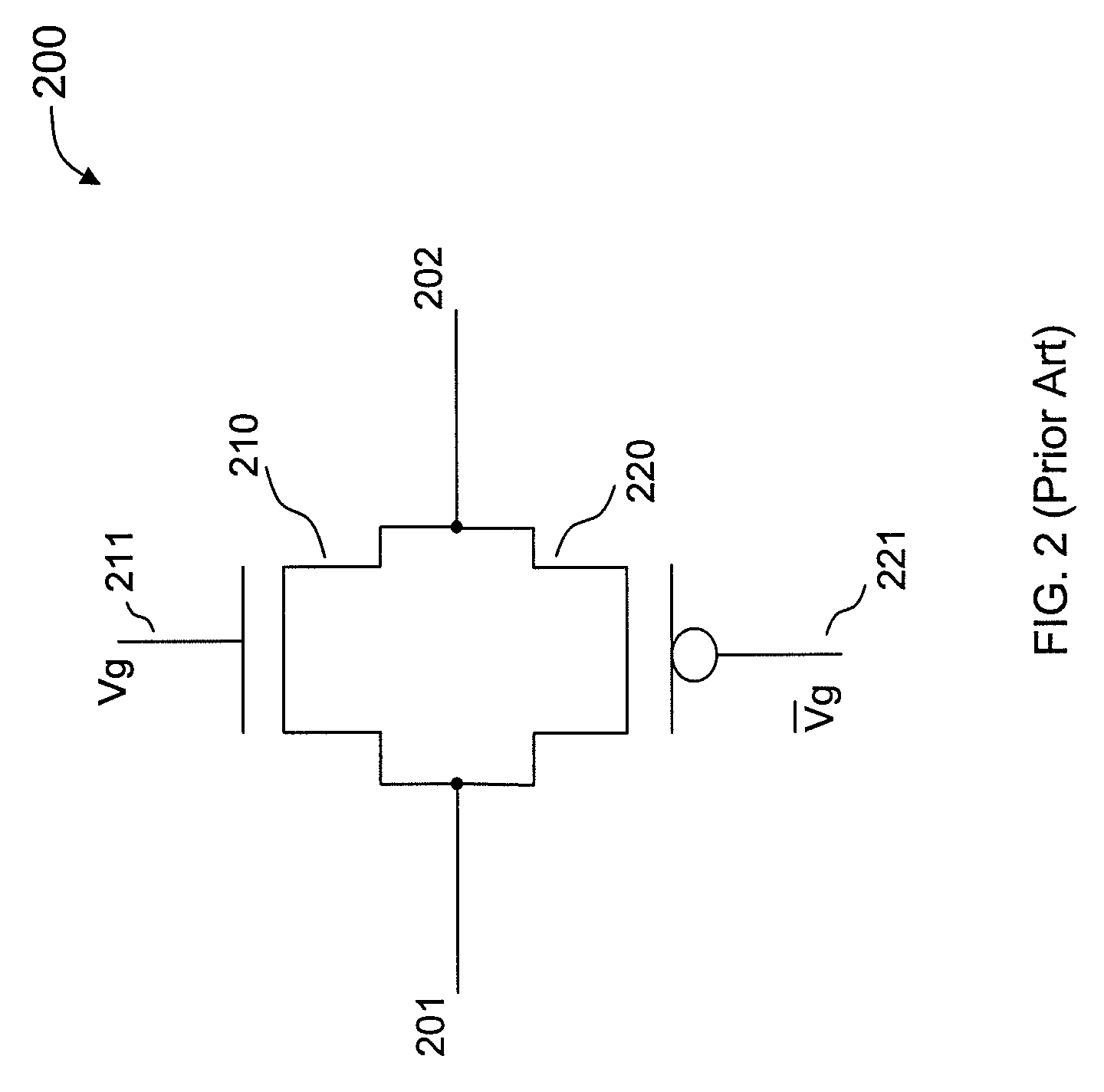

Low voltage analog CMOS switch

ActiveUS20100148851A1Simple and cost-effective techniqueImprove leakageTransistorElectronic switchingCMOSLow voltage

A CMOS analog switch circuit includes an NMOS switch transistor, a PMOS switch transistor, and a bias circuit. In an embodiment, the bias circuit includes a first and a second native bias transistors having their gate terminals coupled to a first and a second terminals of the CMOS switch circuit, respectively. The source terminals of the first and the second native bias transistors are coupled together and are also coupled to the body terminal of the PMOS switch transistor. In an configuration, the first and the second native bias transistors are characterized by substantially 0V threshold voltages, and the PMOS switch transistor is configured to exhibit a lower on-resistance in response to the greater of the voltages of the first terminal and the second terminal of the CMOS analog switch circuit.

Owner:NUVOTON

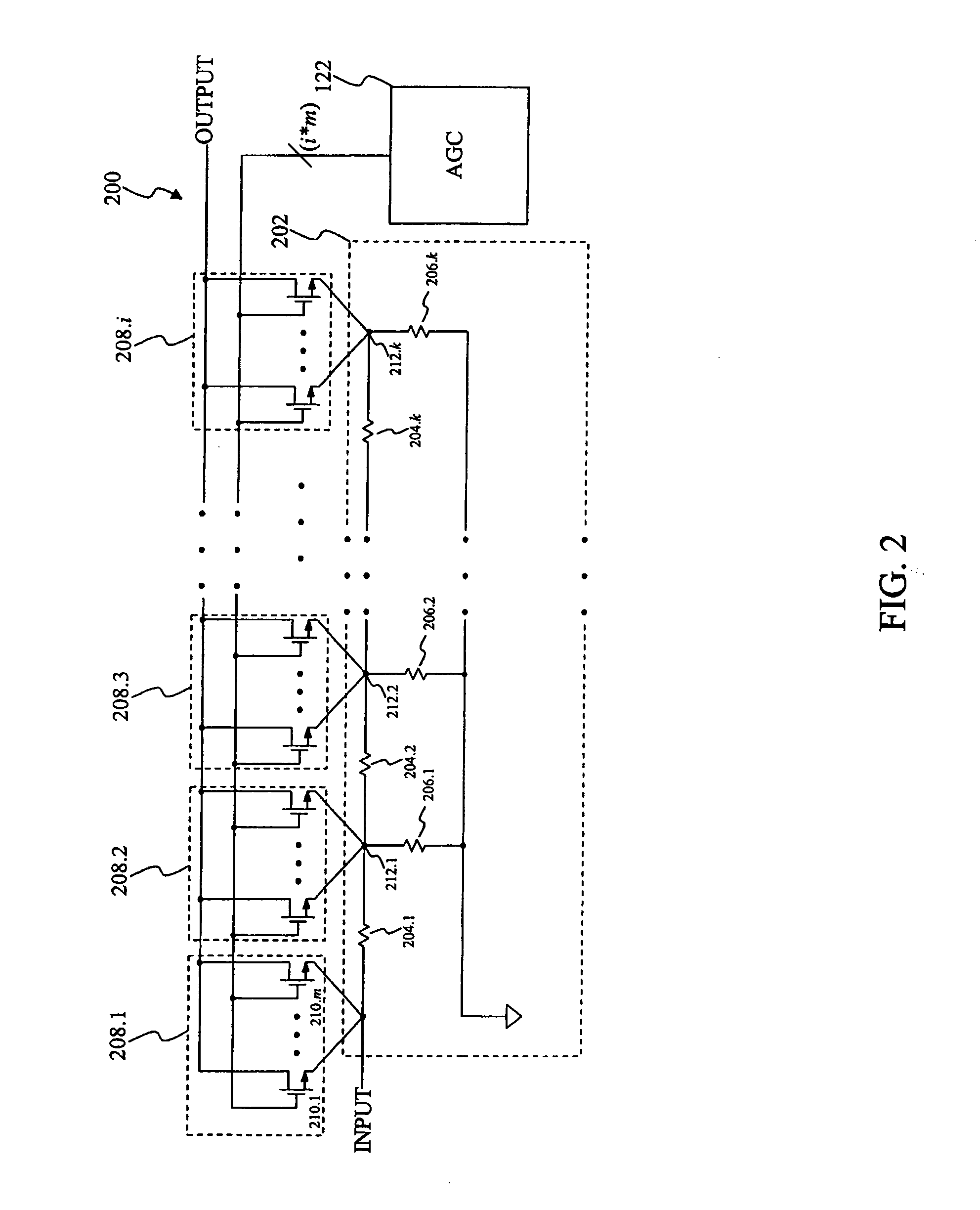

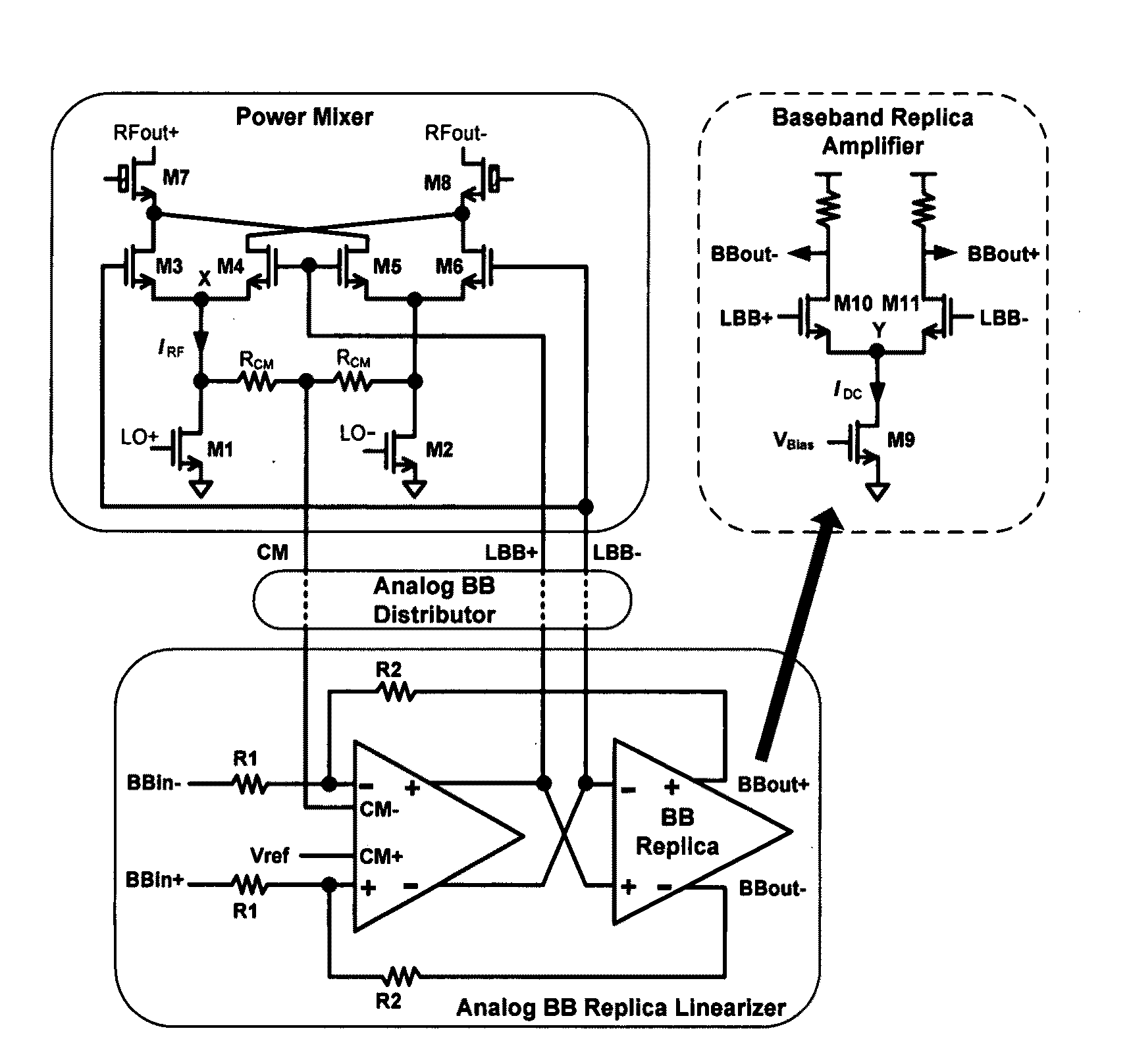

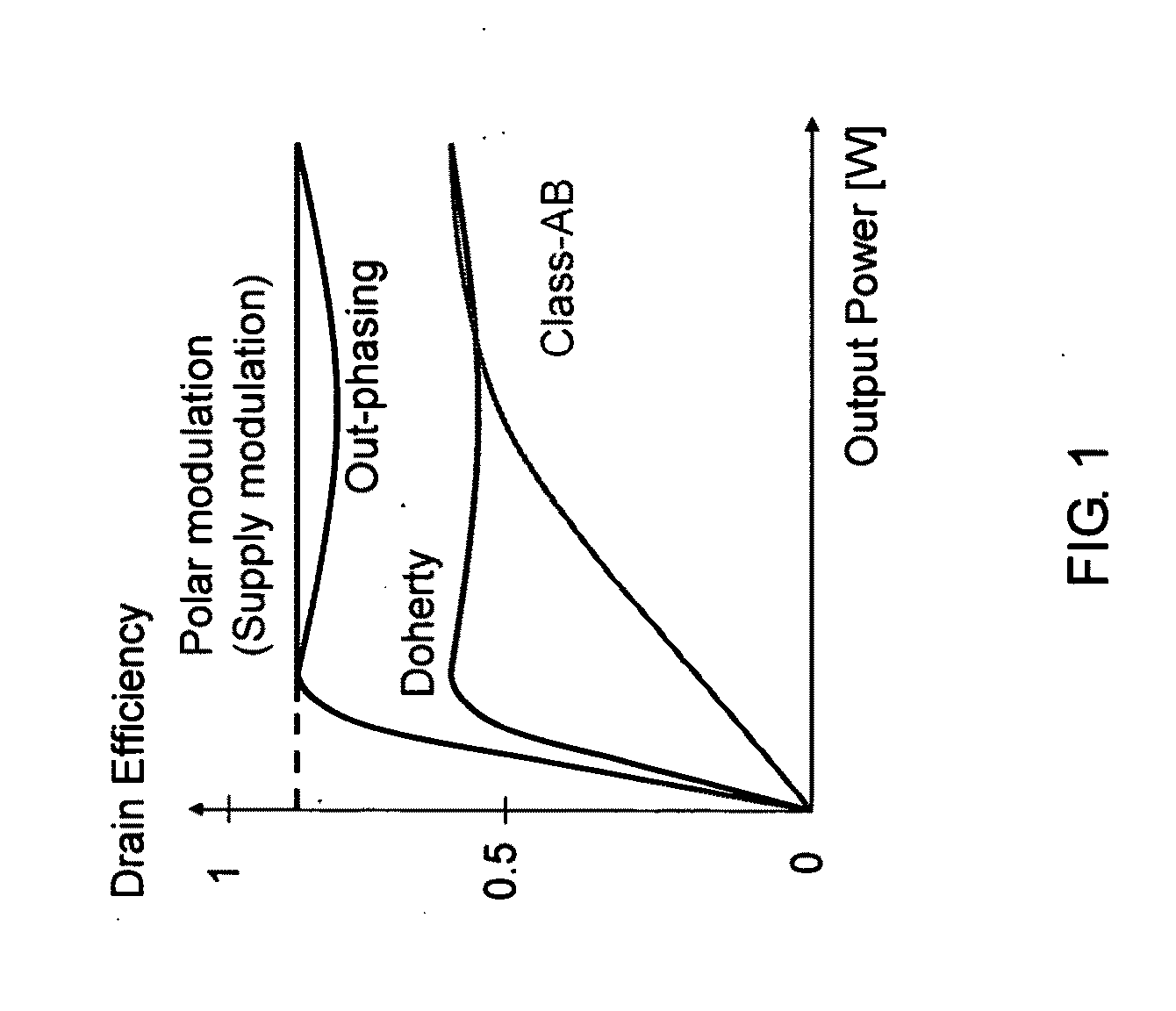

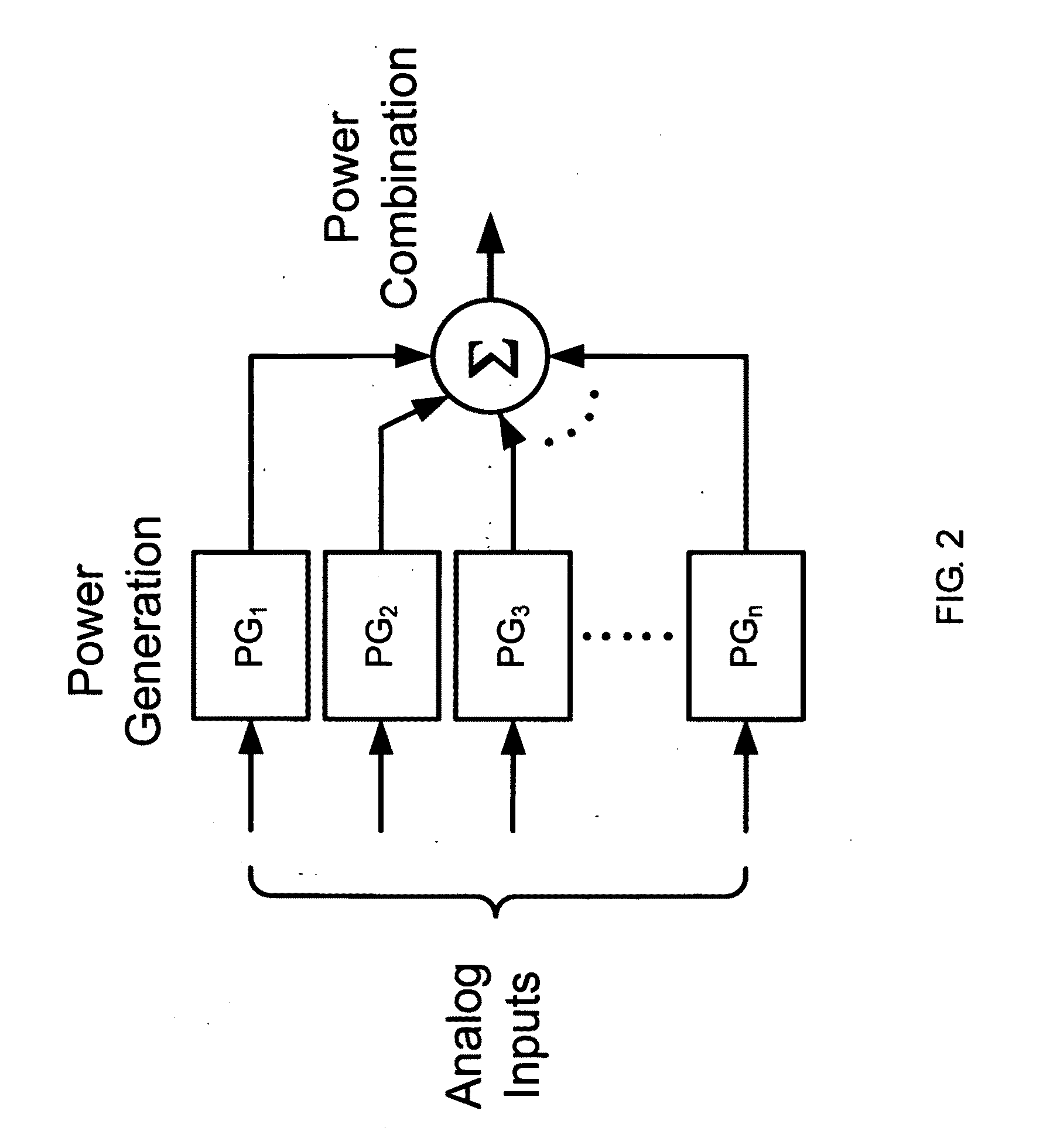

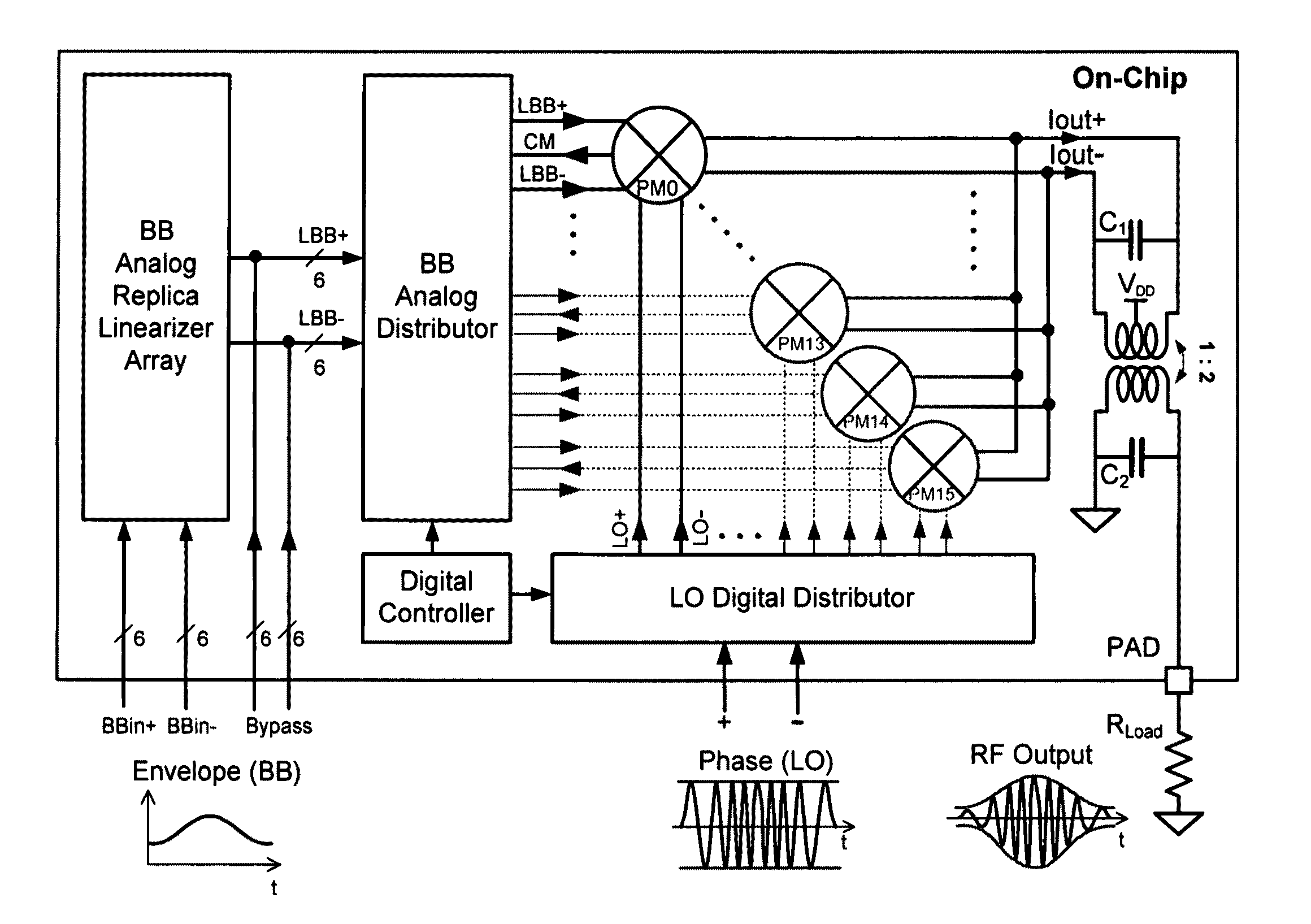

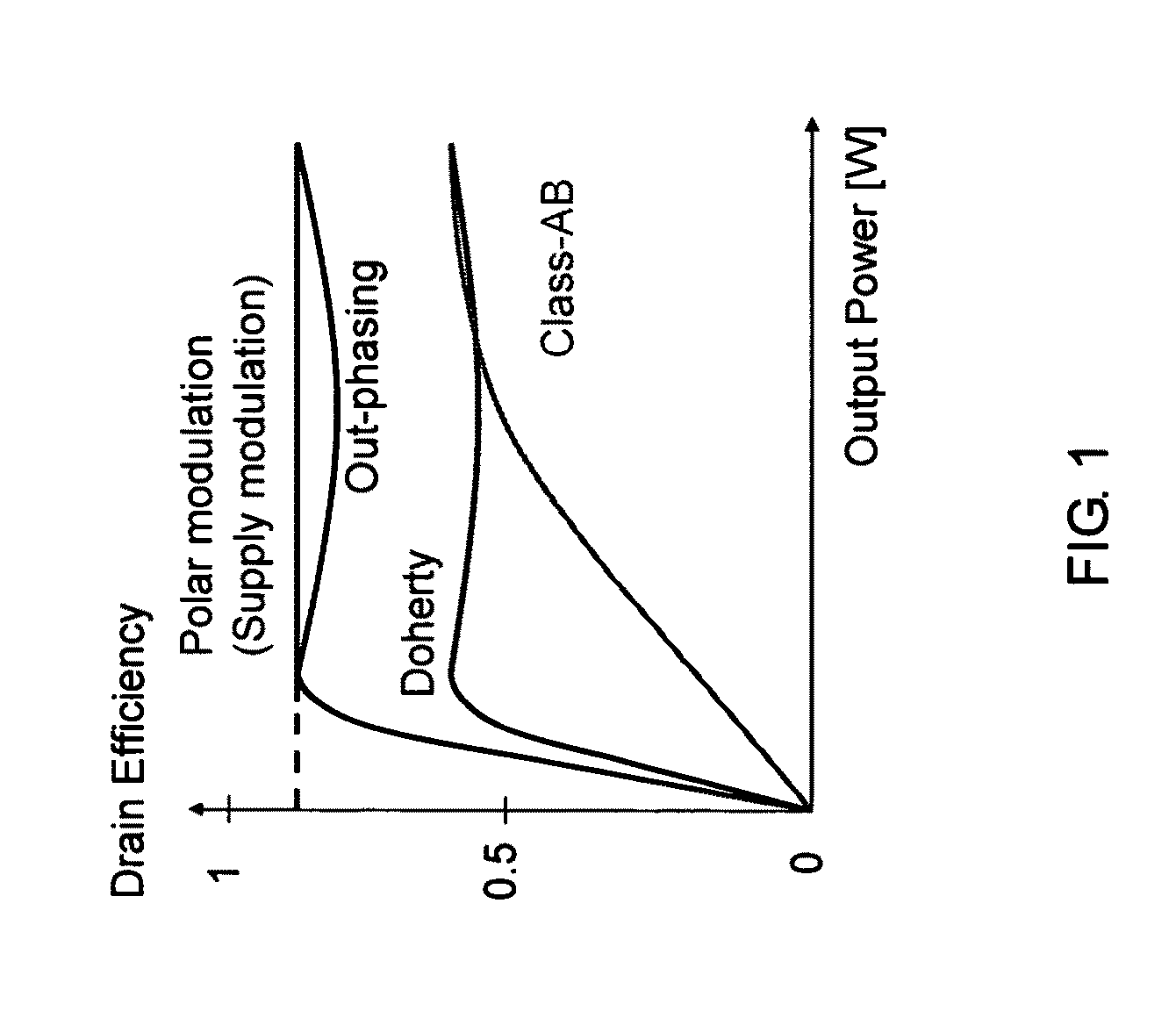

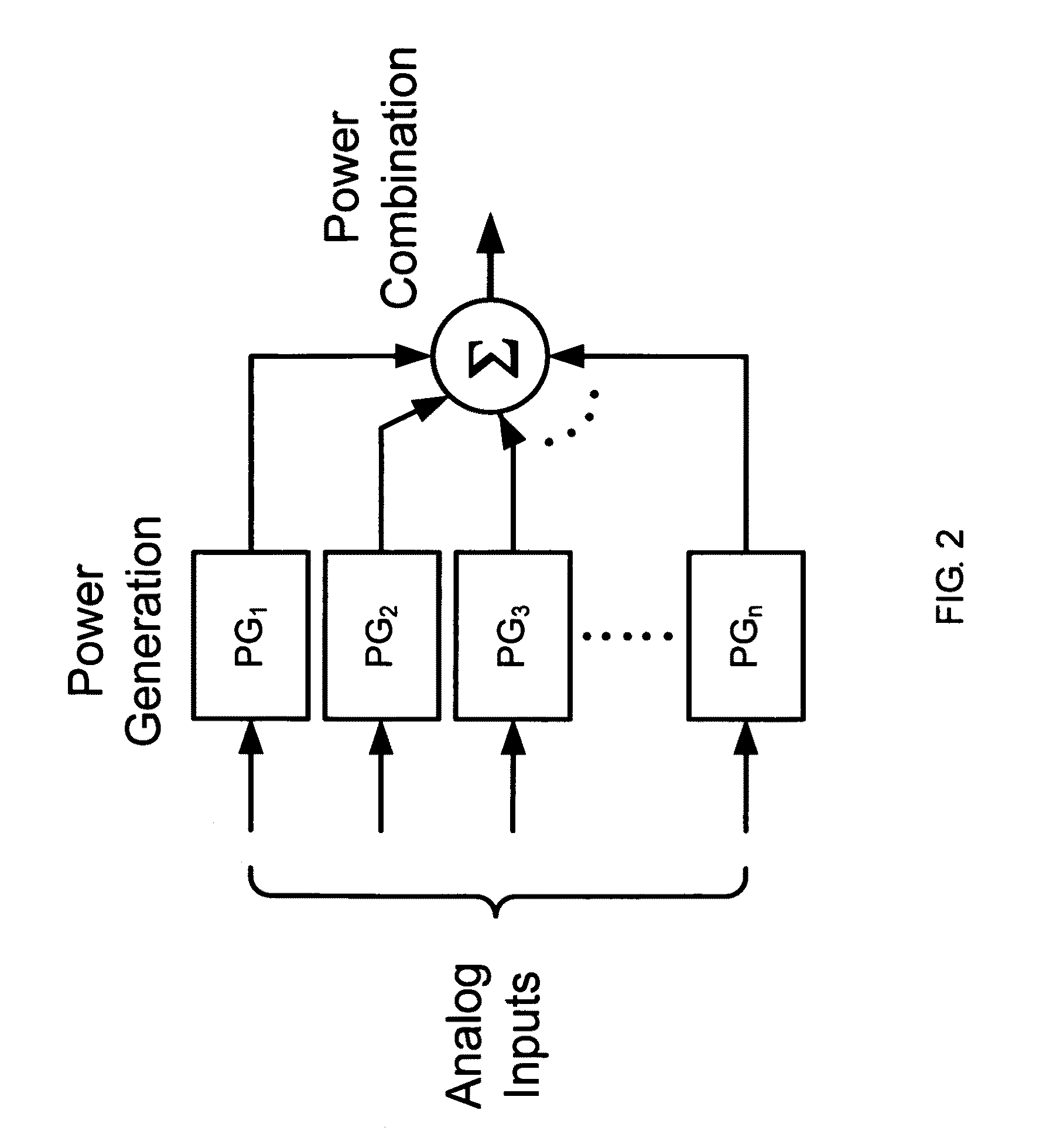

Octave-range, watt-level, fully-integrated CMOS switching power mixer array for linearization and back-off-efficiency improvement

ActiveUS20100090745A1Computations using contact-making devicesComputing operations for multiplication/divisionPower-added efficiencyCMOS

Power mixer arrays for providing watt-level power in mobile systems. In one embodiment, a fully-integrated octave-range CMOS power mixer that occupies only 2.6 mm2 using a 130 nm semiconductor process has been demonstrated. The power mixer provides an output power of +31.5 dBm into an external 50 Ω load with a power added efficiency (PAE) of 44% at 1.8 GHz and a full power gain compression of only 0.4 dB.

Owner:CALIFORNIA INST OF TECH

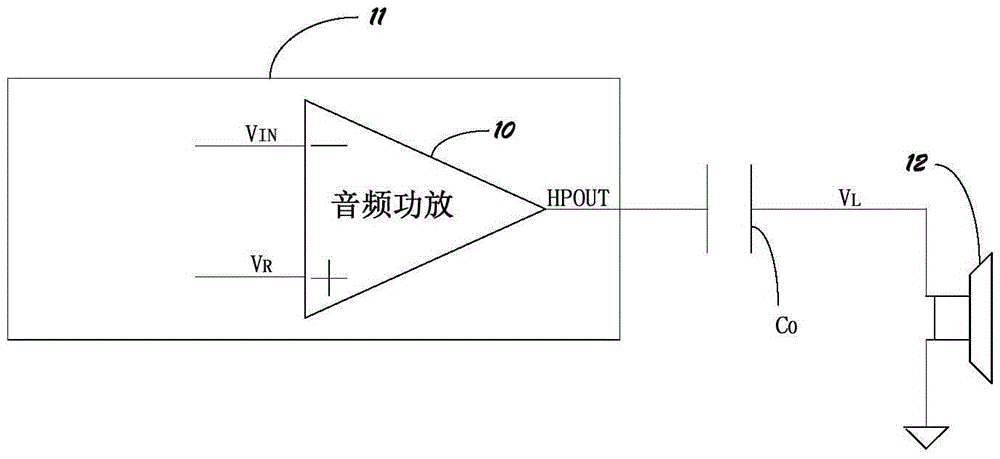

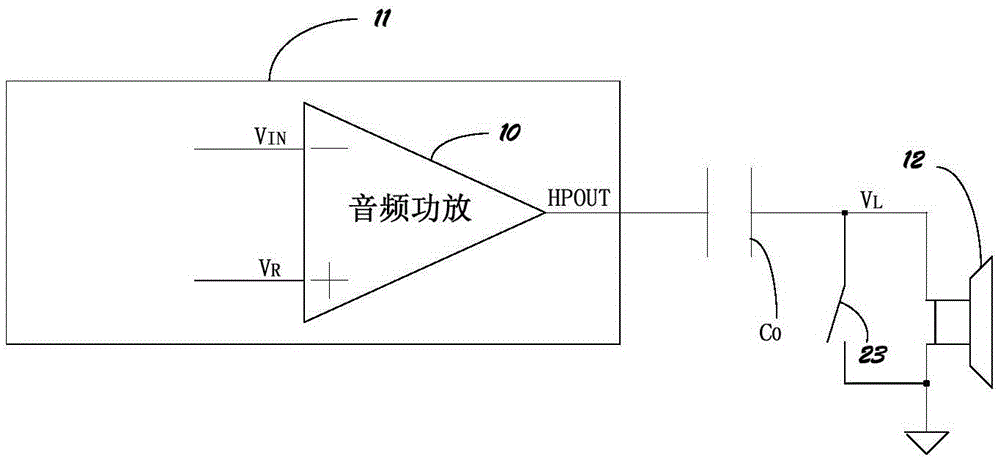

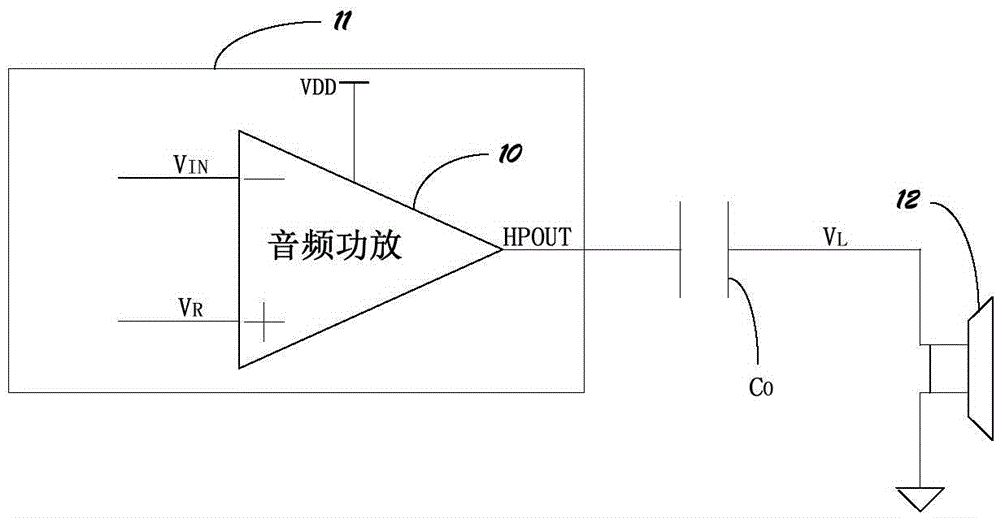

Audio output POP (Post Office Protocol) sound eliminating circuit

ActiveCN105554634AEliminate pop soundImprove hearing experienceMicrophonesTransducer circuitsCapacitanceCMOS

The invention discloses an audio output POP (Post Office Protocol) sound eliminating circuit, which comprises a reference voltage generation module, a voltage follower and an audio amplifier; the reference voltage generation module is connected to the first input end of the voltage follower, and is grounded via a decoupling capacitor C1; the second input end of the voltage follower is connected to the output end of the voltage follower and the forward output end of the audio amplifier; the reverse input end of the audio amplifier is used for inputting audio signals; the output end of the audio amplifier is connected to one end of a direct current blocking capacitor C0; the other end of the direct current blocking capacitor C0 is used for connecting an audio player; the output end of the voltage follower and the output end of the audio amplifier are connected via a first CMOS (Complementary Metal Oxide Semiconductor) switch; and the first input end of the voltage follower and the output end of the audio amplifier are connected via a second CMOS switch. According to the audio output POP sound eliminating circuit disclosed by the invention, all POP sounds generated in power supply and outage process of the audio output as well as in startup and shutdown process of the audio amplifier can be completely eliminated, the auditory feeling is improved, the structure is simple and the cost is low.

Owner:芯动科技(珠海)有限公司

32V H-bridge driver with CMOS circuits

InactiveUS20050127859A1Switching is accurate and fastAC motor controlSynchronous motors startersCMOSControl signal

A motor bridge driver interface, implemented in an ASIC using cost-efficient CMOS technology, is designed to control four external MOS power transistors in a H-bridge configuration for DC-motor driving to achieve accurate and fast switching. Said driver interface is comprising a charge pump for generating the control voltage for the high-side N-channel MOS transistors, high-side (HSD) circuits, low-side (LSD) circuits and a complex digital interface for supplying the control signals in a programmable timing scheme. A “strong” charge pump is used to realize a simple CMOS switch to steer the output to the high-side transistors of said H-bridge. The motor bridge is connected to the battery supply by an additional N-channel MOS transistor to implement a reverse supply protection.

Owner:DIALOG SEMICONDUCTOR GMBH

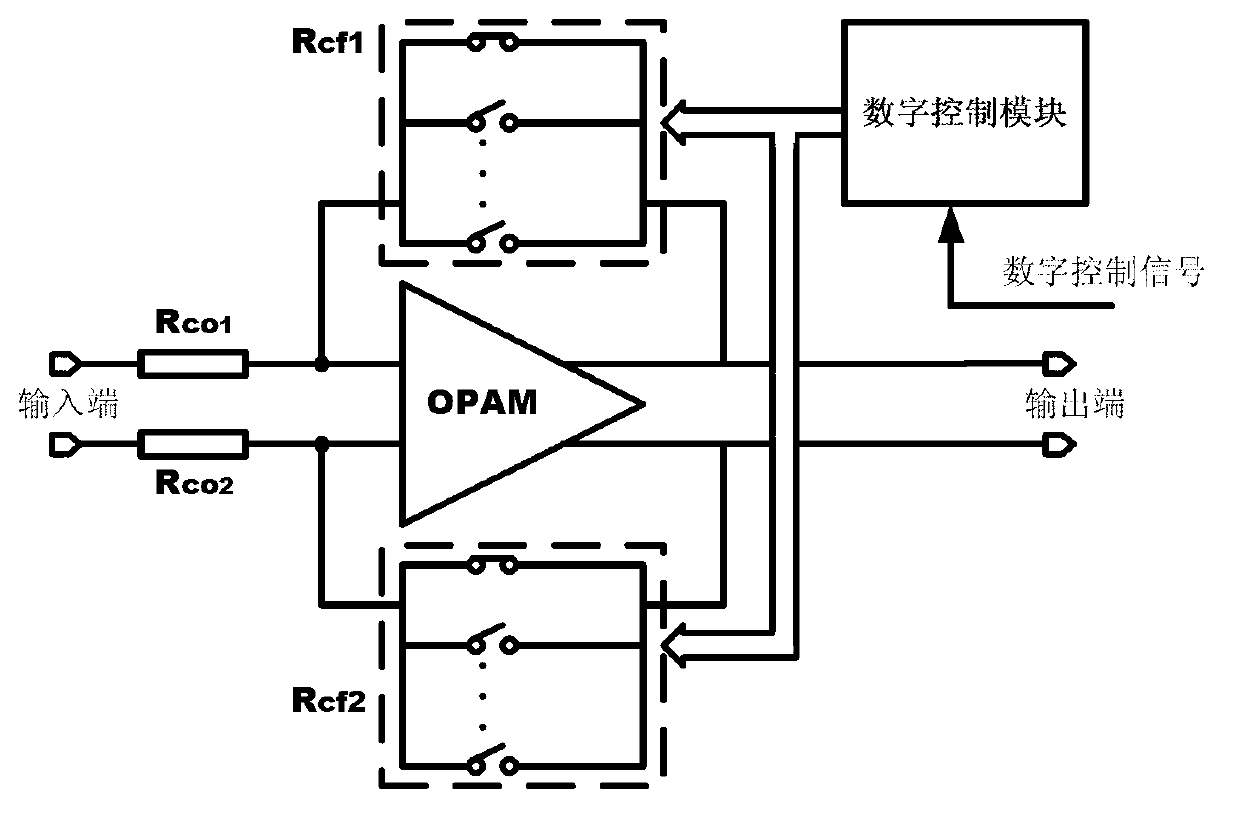

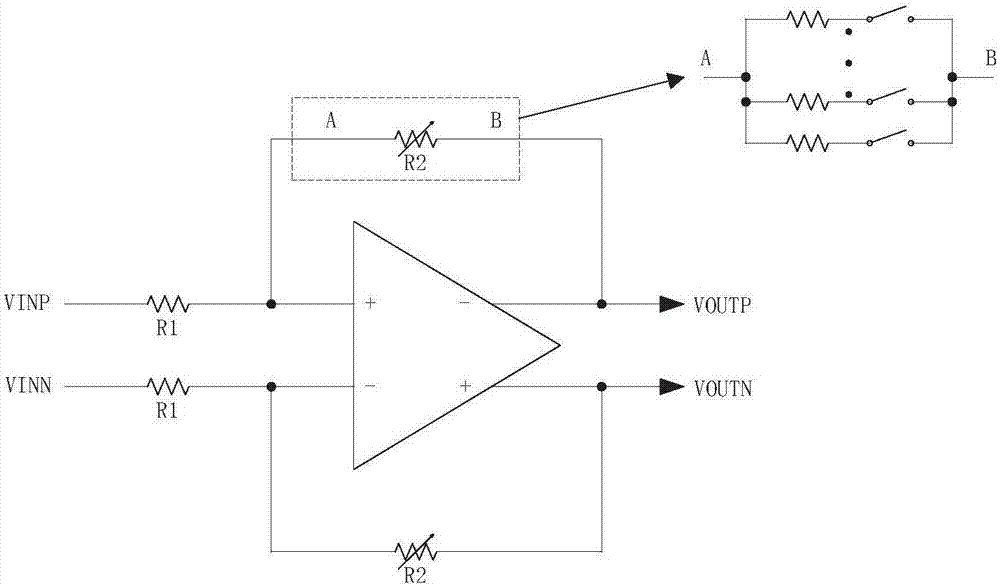

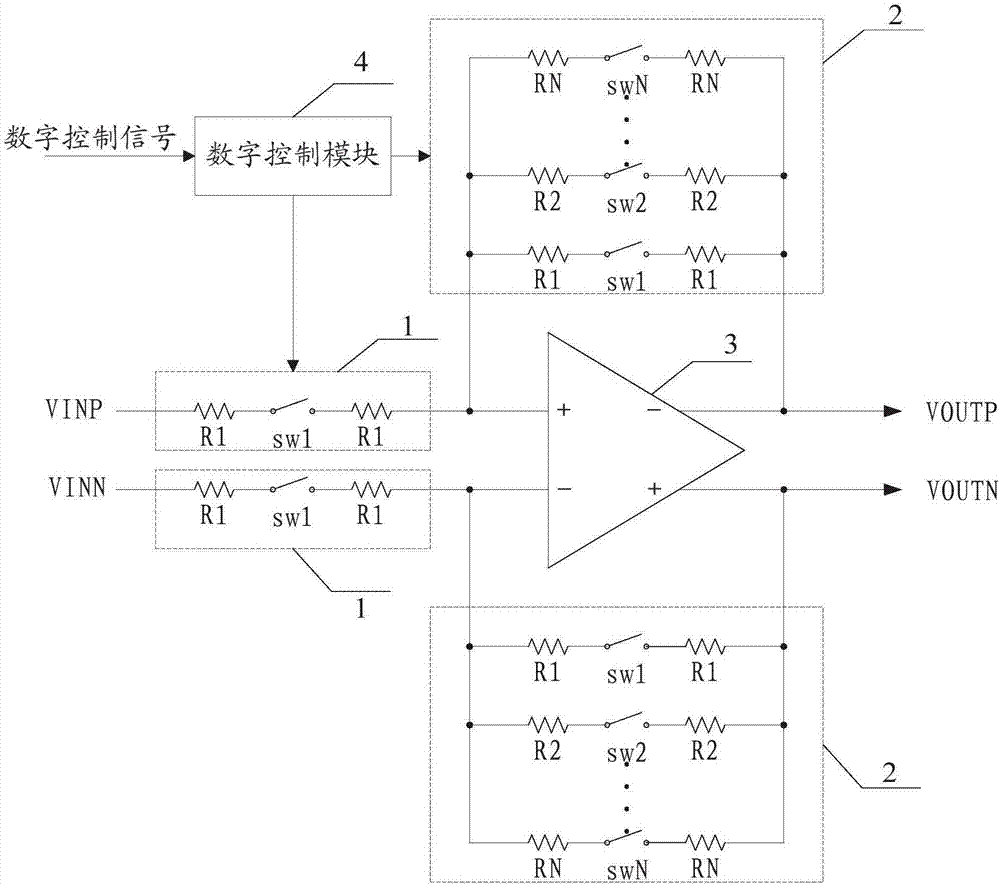

Programmable gain amplifier

ActiveCN103107790ARealize precise regulationReduce parasitic capacitanceGain controlCapacitanceAudio power amplifier

The invention relates to a programmable gain amplifier. The programmable gain amplifier comprises an operational amplifier, at least one first complementary metal oxide semiconductor (CMOS) switch array, and a digital control module, wherein the operational amplifier comprises two input ends and at least one output end, at least one input end is in tandem connection with a resistor unit, the operational amplifier is used for amplifying and outputting output signals of the gain amplifier, the first CMOS switch array is composed of a plurality of CMOS switches which are in parallel connection with each other, the first CMOS switch array is connected between one input end and one output end of the operation amplifier in a bridging mode, and the digital control module is used for controlling on-off of all CMOS switches according to digital control signals so as to adjust the first CMOS switch array. The programmable gain amplifier realizes accurate regulation of gain, and is favorable to reducing stray capacitance.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

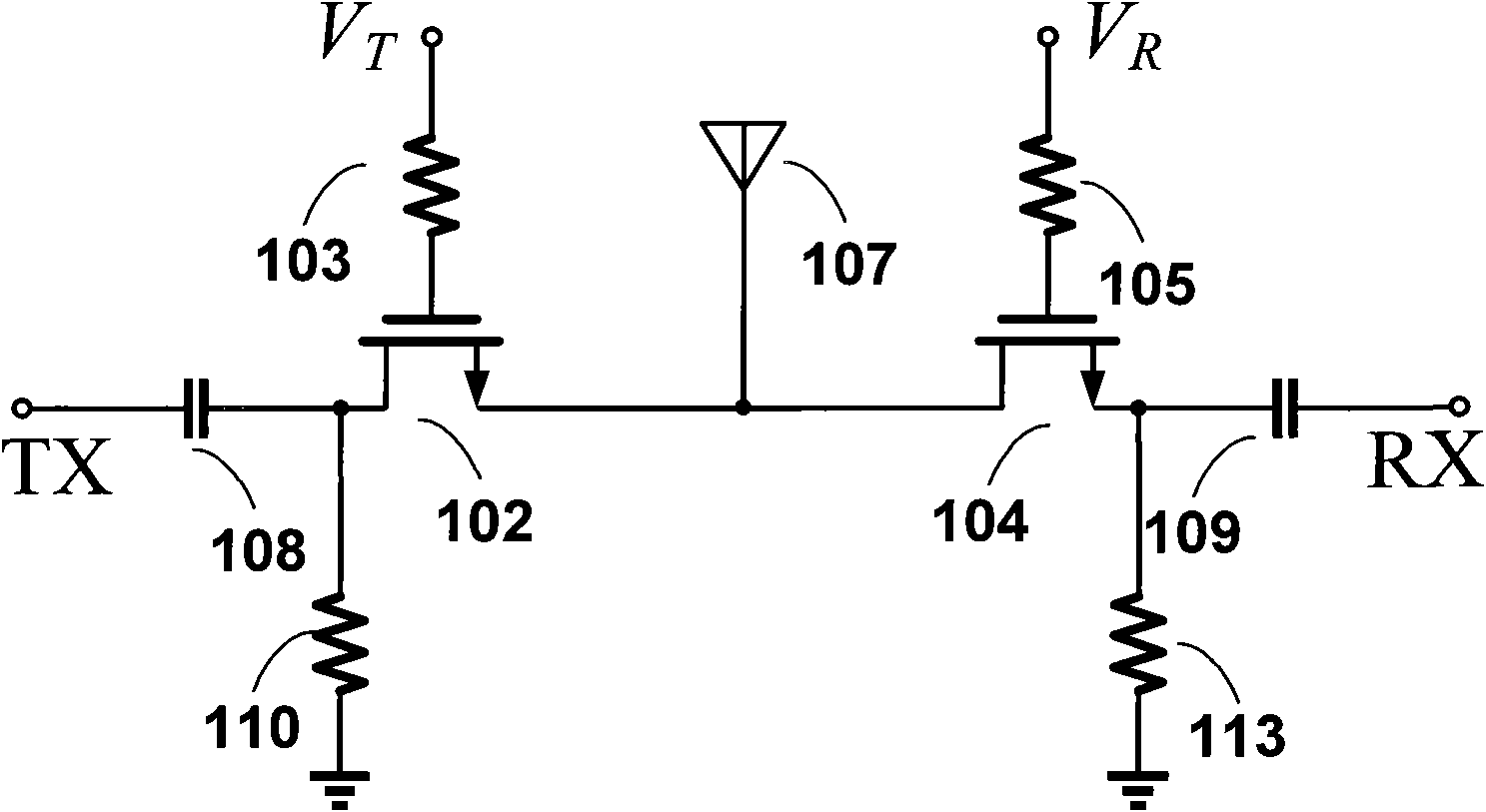

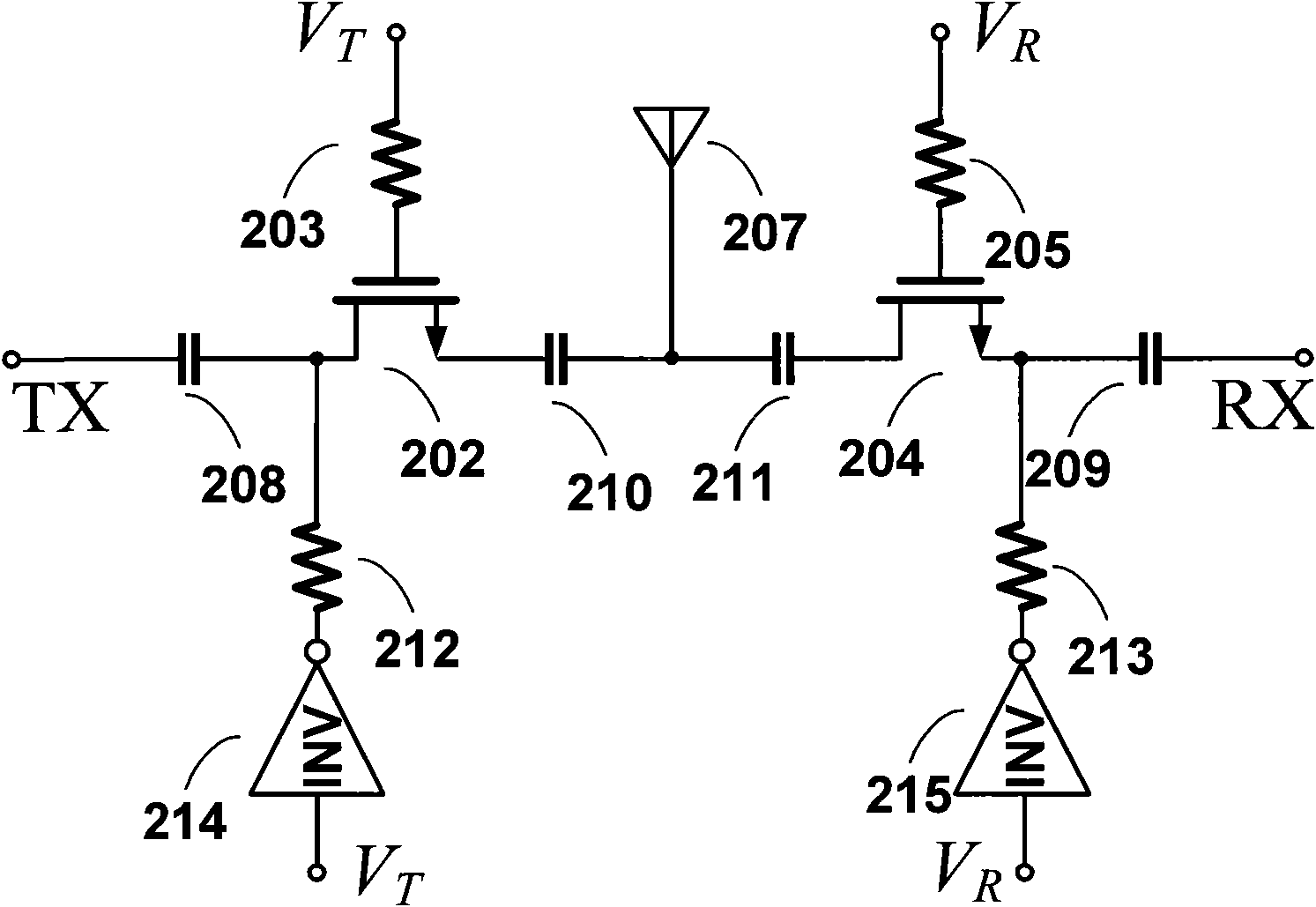

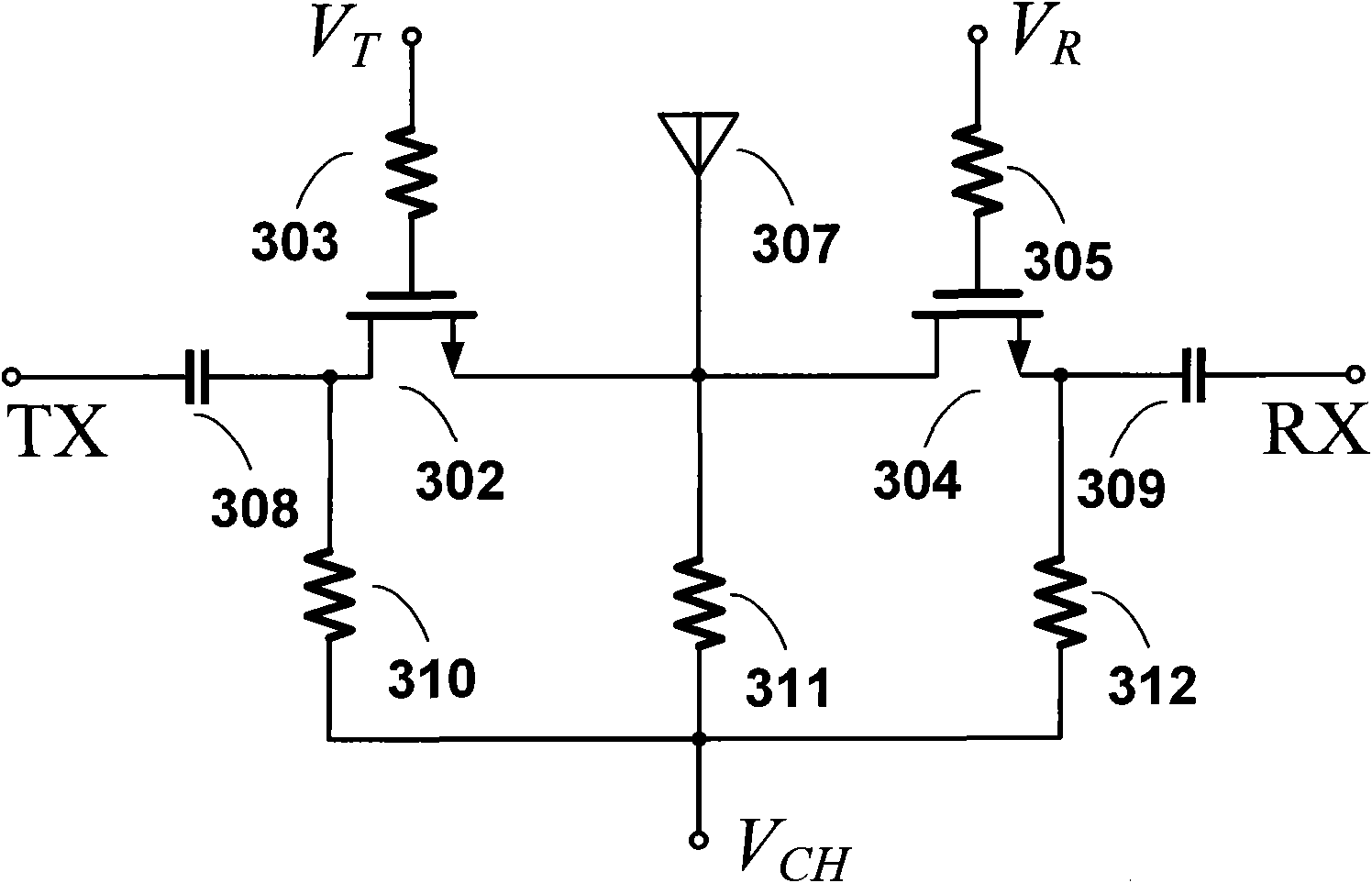

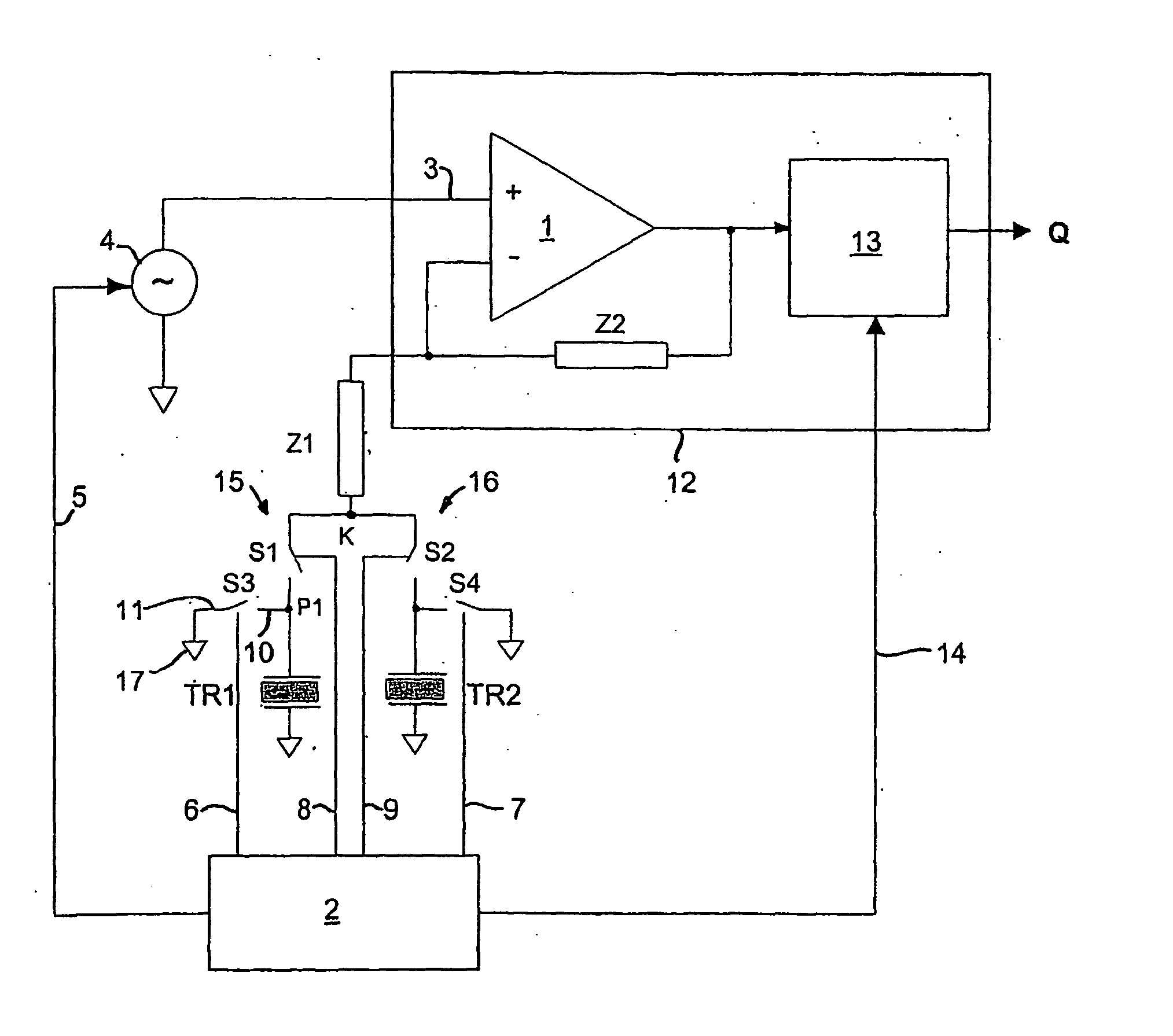

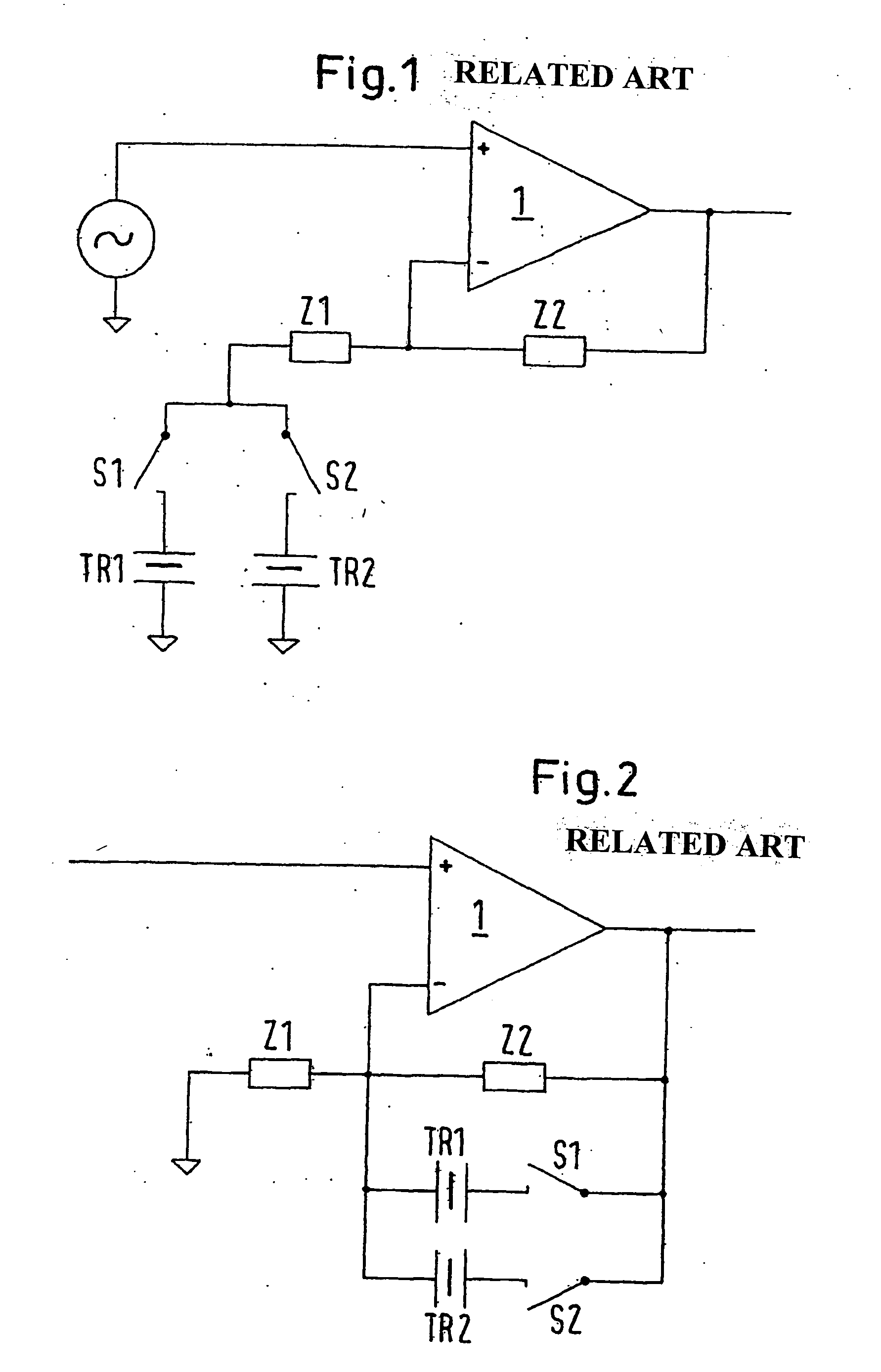

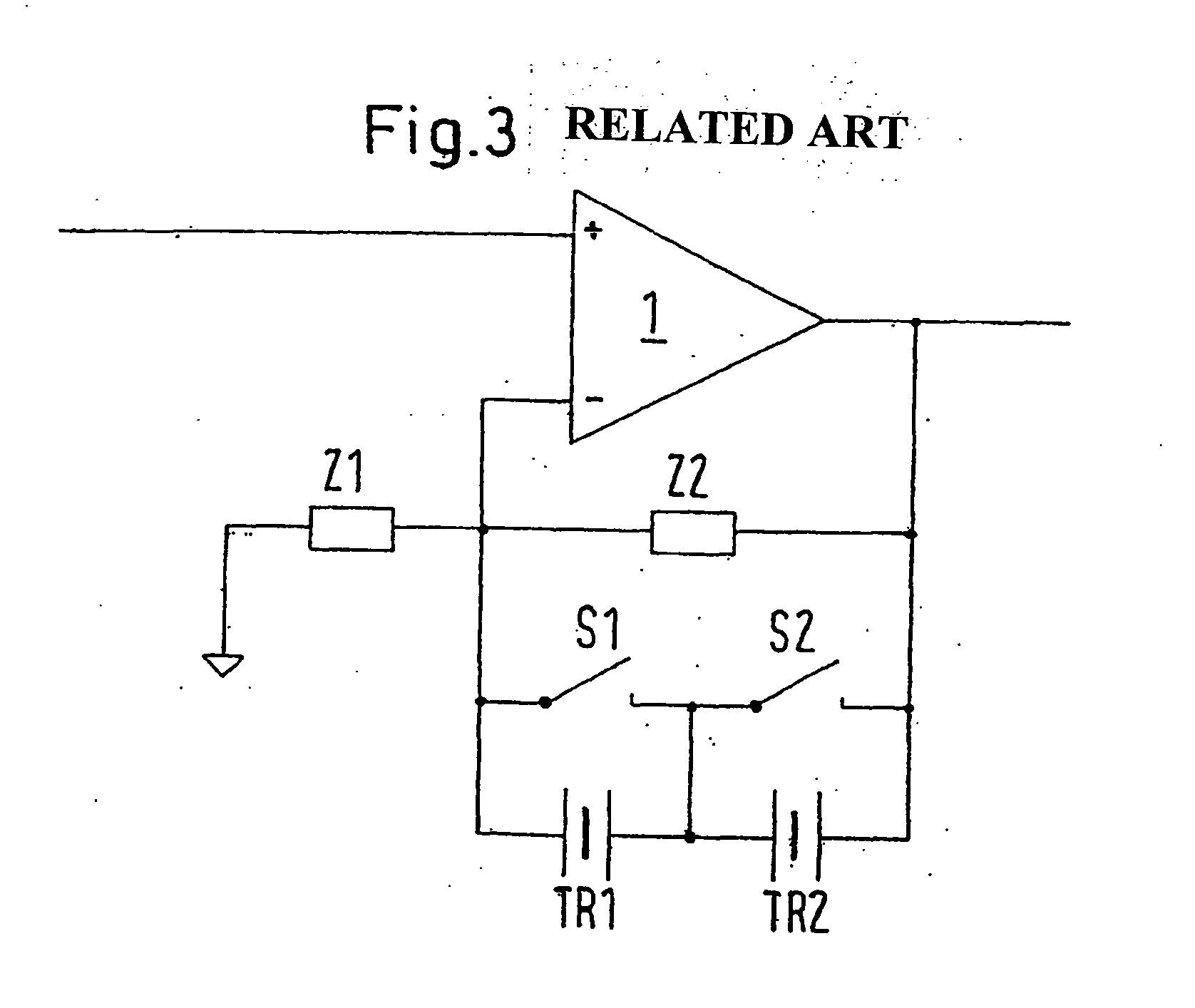

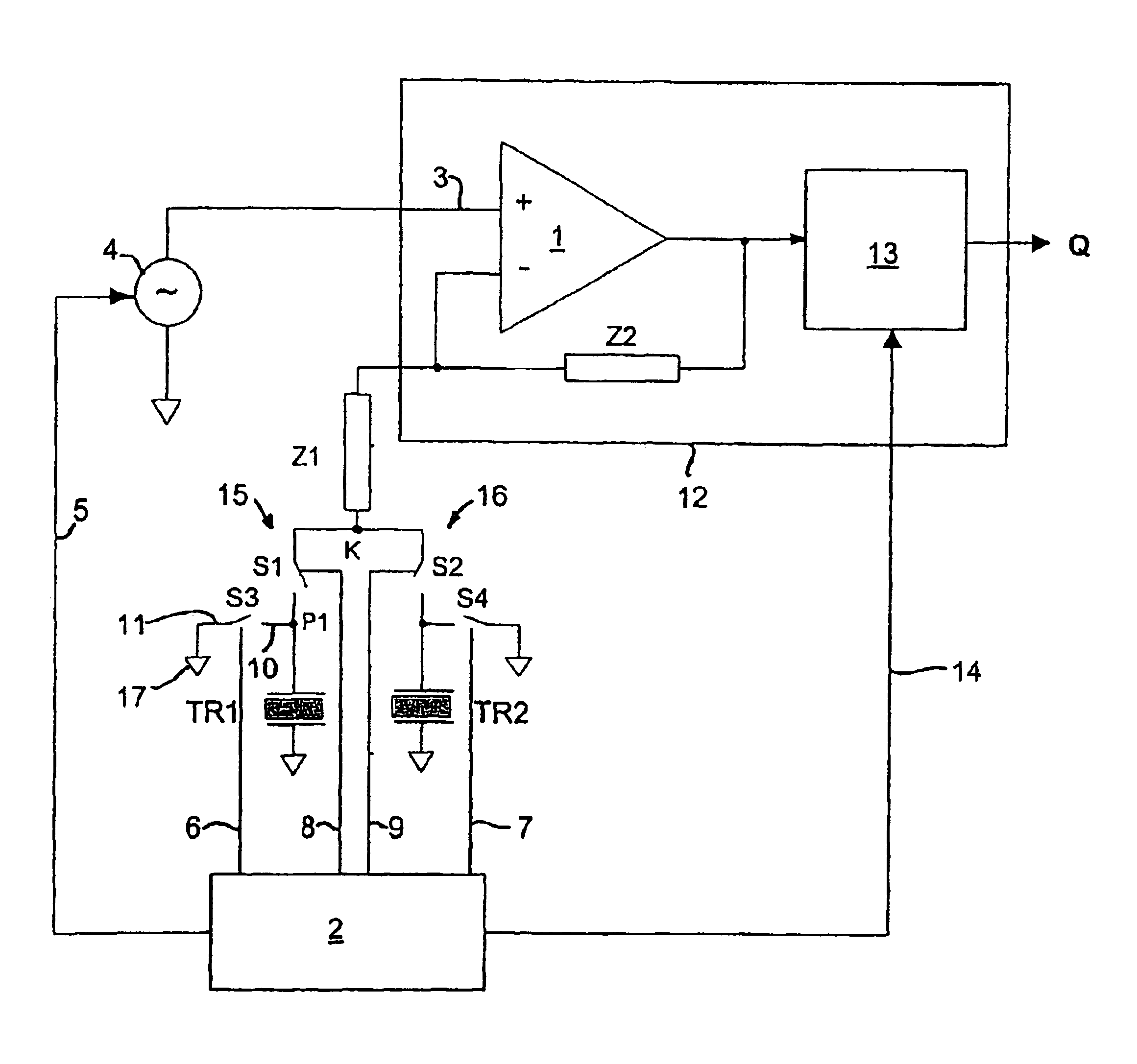

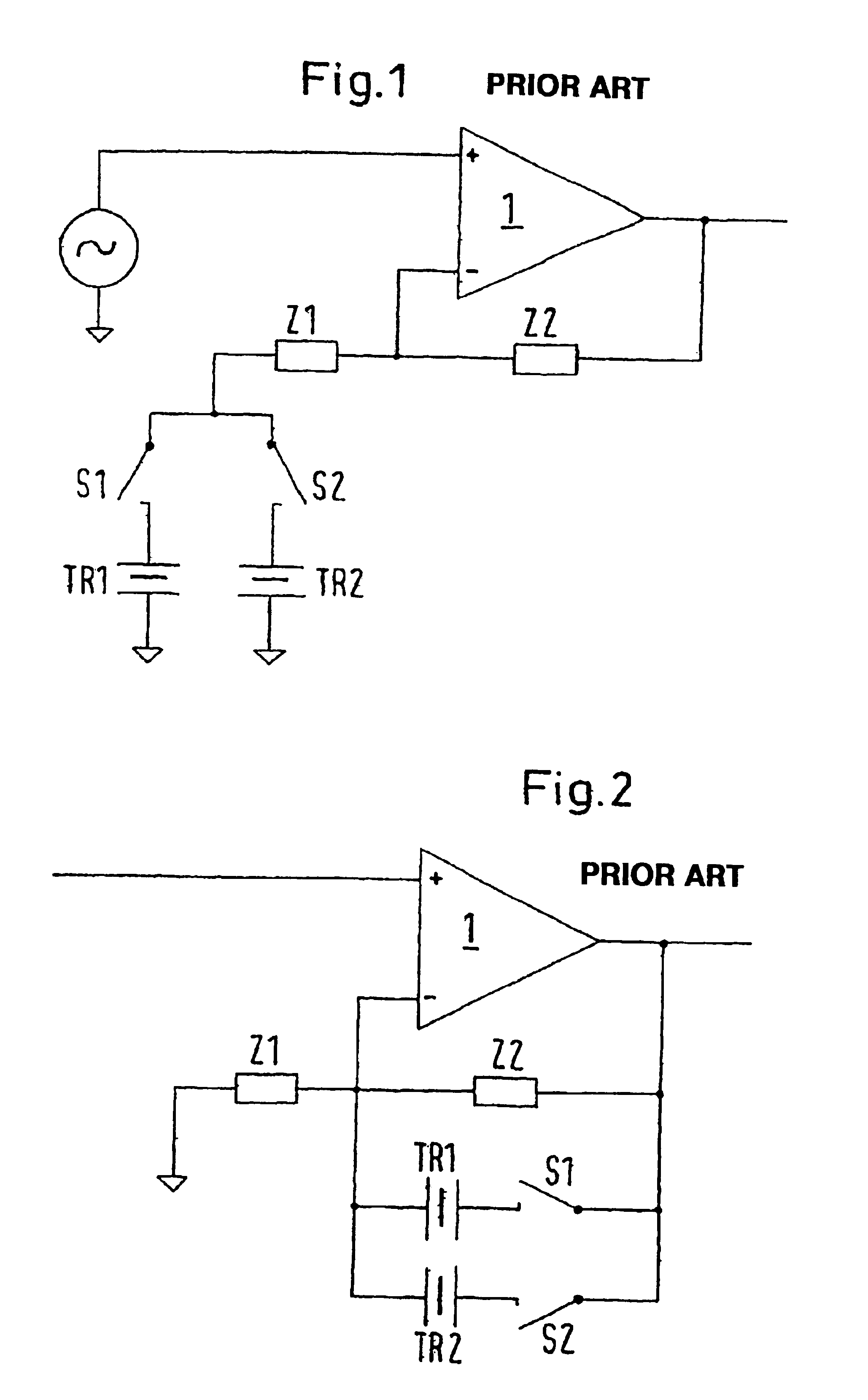

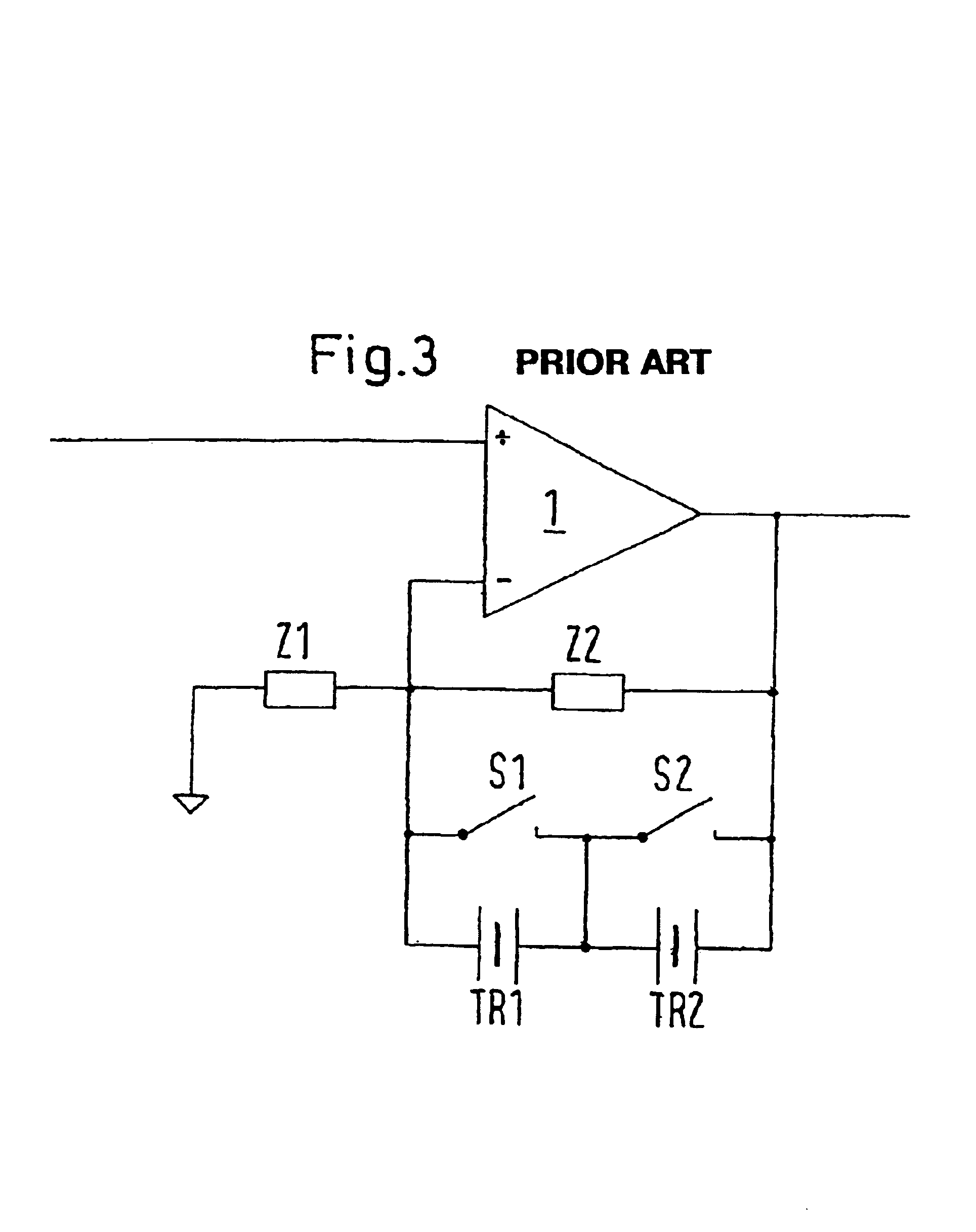

Transceiver circuit for an ultrasonic flowmeter

InactiveUS20050061085A1Reduce couplingSimple transmitting and receivingVolume/mass flow by dynamic fluid flow effectVolume flow measuring devicesCMOSRing down

A transmitting and receiving circuit for an ultrasonic flowmeter. In such circuits, an ultrasonic transducer is typically used as both transmitter and receiver. This is obtained by using switching means, for example in the form of CMOS switches. However, problems arise with ringings of a transducer when having acted as a transmitter. This unwanted ringing makes the crystal of the transducer act as an additional signal generator, and the signal is coupled via parasitic capacitances in a switching means to the receiving ultrasonic transducer. This problem is solved by connecting one pole of a short circuit switch (S3, S4) to the ultrasonic transducer (TR1, TR2) or to the switching means (S1, S2) and the other pole of the short circuit switch to ground. Keeping the short circuit switch closed when the switching means is open, and open when the switching means is closed, creates a decoupling path for the unwanted signal, thereby improving the accuracy of the transmitting and receiving circuit.

Owner:SIEMENS FLOW INSTR +1

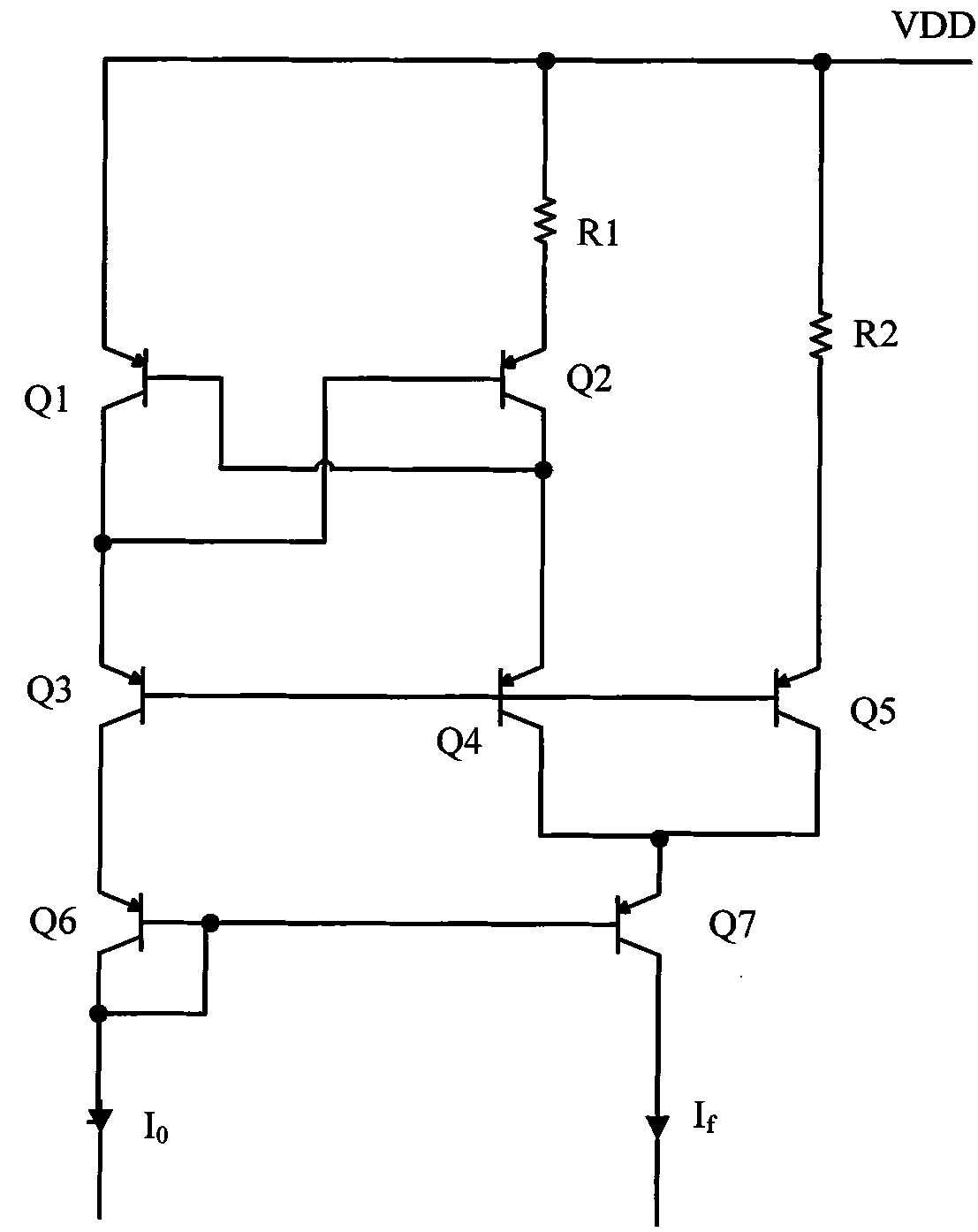

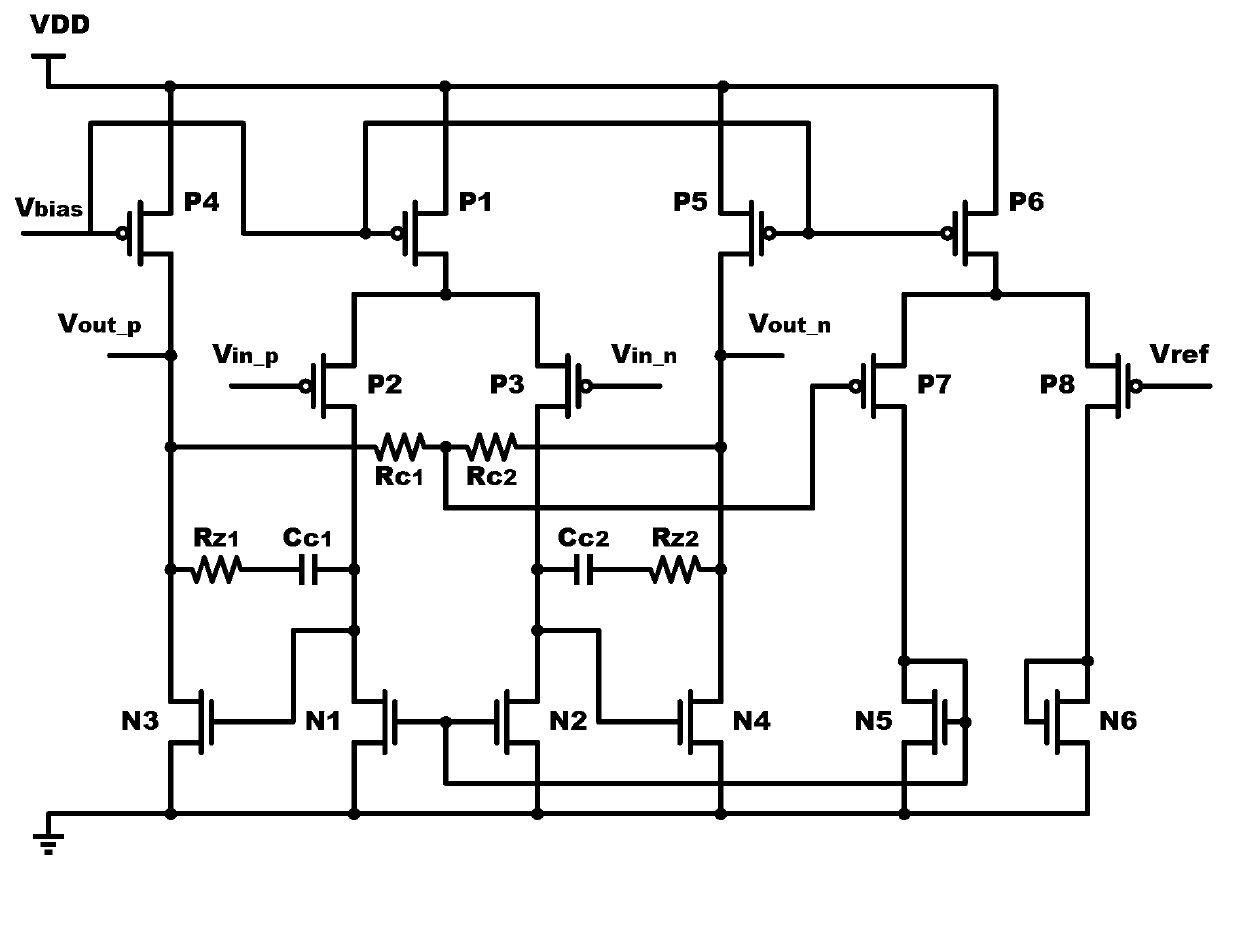

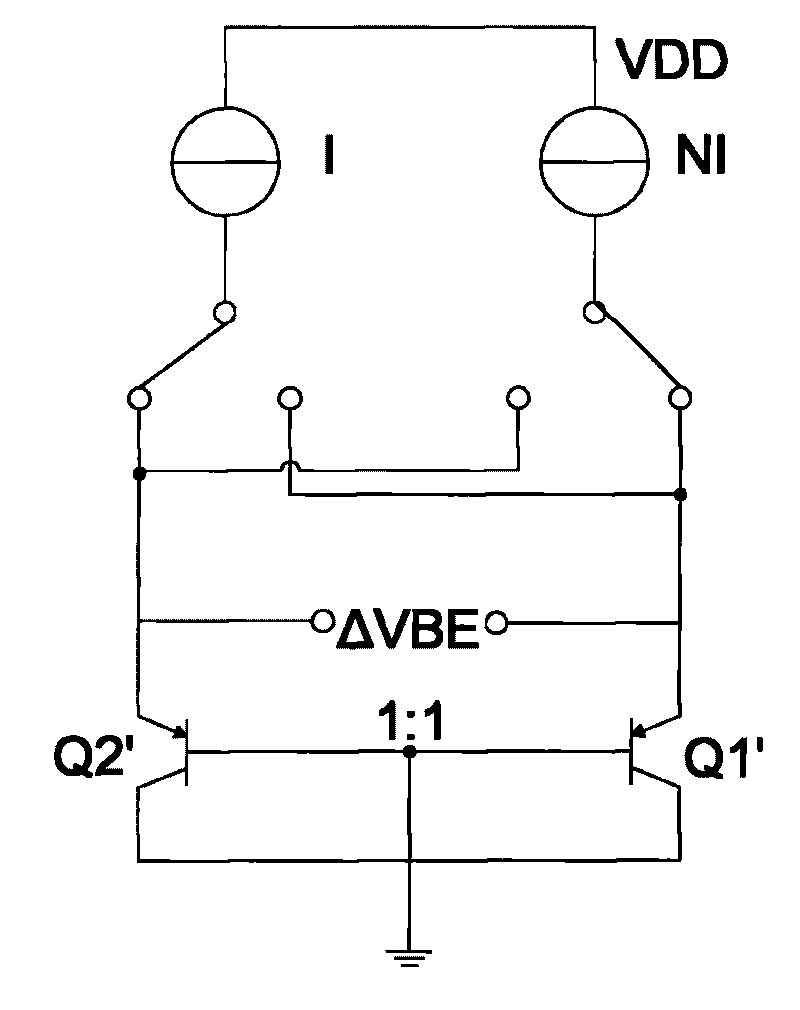

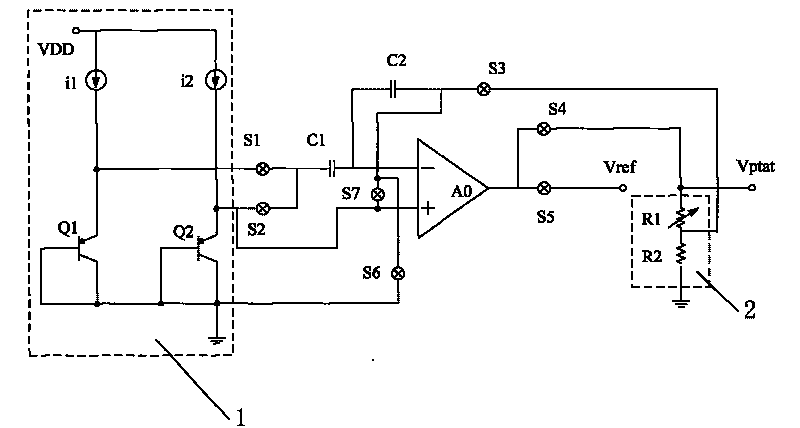

Current temperature sensor circuit for CMOS switch and control method thereof

ActiveCN101762336AImprove temperature detection accuracyThermometers using electric/magnetic elementsUsing electrical meansCapacitanceAudio power amplifier

The present invention relates to a current temperature sensor circuit for CMOS switch and control method thereof. The sensor circuit comprises a voltage generation circuit, an operational amplifier, an input capacitor, a feedback capacitor, a resistance voltage divider, a control circuit and several MOS switches. The voltage generation circuit is connected with an external power supply to output the first interelectrode voltage and the second interelectrode voltage. An out-phase input of the operational amplifier is connected with the voltage generation circuit through the input capacitor to receive the first interelectrode voltage while the in-phase input receives the second interelectrode voltage; and the output of the operational amplifier is divided into two paths which respectively output reference voltage and positive temperature coefficient voltage. By utilizing dynamic element matching technique, the current temperature sensor circuit can generate an accurate amplifying coefficient for a small voltage difference delta Vbe, and generate accurate reference voltage independent of temperature and positive temperature coefficient voltage varying in direct proportion to temperature, thus effectively improving temperature detection accuracy of the temperature sensor.

Owner:SHANGHAI BEILING

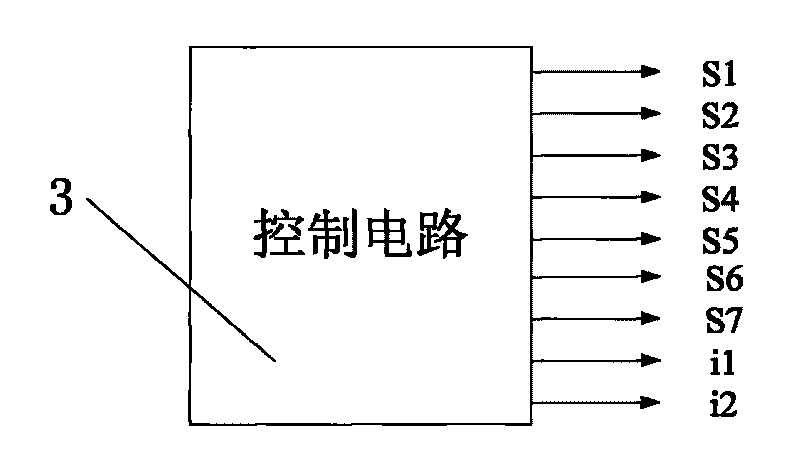

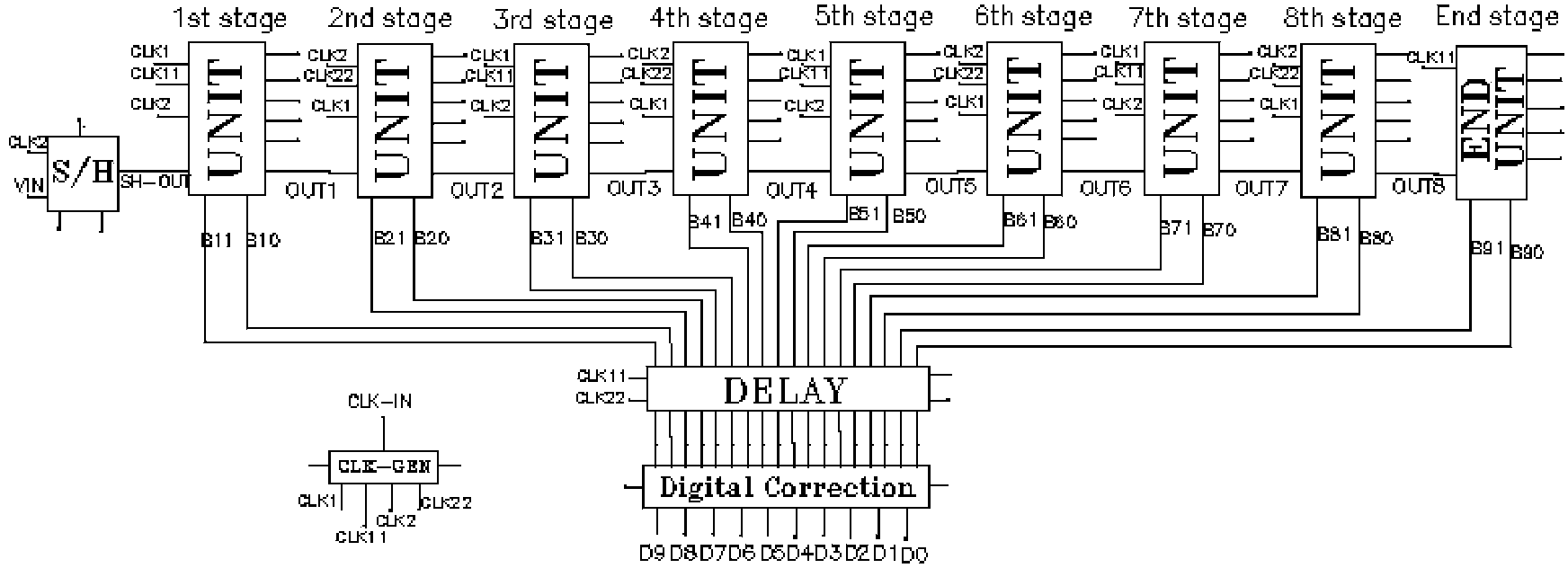

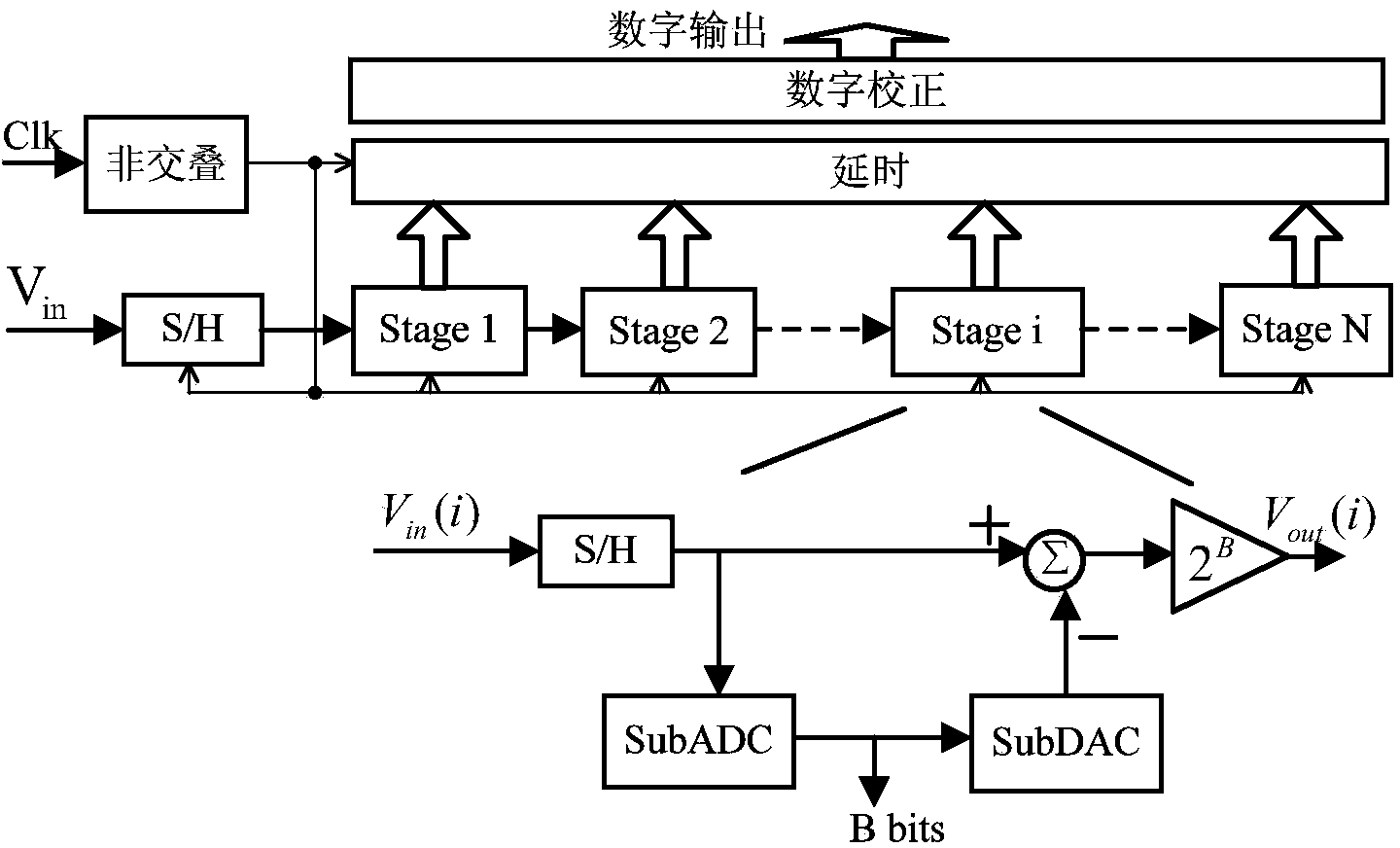

Nine-stage ten-bit pipelined ADC circuit

InactiveCN103905046AAnalogue-digital convertersAnalogue/digital conversion calibration/testingCapacitanceCmos switch

The invention discloses a nine-stage ten-bit pipelined ADC circuit. During the designing of a modular circuit, to avoid nonlinearity caused by on-resistance change of an ordinary CMOS switch, firstly, a nine-stage pipelined unit is adopted for the overall structure of an ADC, identical 1.5-bit structures are adopted by all the nine stages, so that modularization of the circuit is improved, and the figure adjustment technique is adopted to reduce the designing requirements of a sub-analog-digital converter (SubADC) and reduce the influence of non-ideal factors; secondly, optimal design is conducted on the modular circuit to reduce the error of the ADC. According to the nine-stage ten-bit pipelined ADC circuit, due to the fact that a single-capacitor sampling hold circuit and a bootstrapped switch are used, sampling linearity and accuracy are improved; due to the fact that an operational amplifier detuning eliminated type switched capacitor MDAC circuit structure is adopted, margin amplification accuracy is improved; a full-adder circuit is used for achieving figure adjustment, and the structure is simple.

Owner:XINXIANG UNIV

Transceiver circuit for an ultrasonic flowmeter

InactiveUS6947851B2Reduce couplingSimple transmitting and receivingVolume/mass flow by dynamic fluid flow effectVolume flow measuring devicesCMOSRing down

A transmitting and receiving circuit for an ultrasonic flowmeter. In such circuits, an ultrasonic transducer is typically used as both transmitter and receiver. This is obtained by using switching means, for example in the form of CMOS switches. However, problems arise with ringings of a transducer when having acted as a transmitter. This unwanted ringing makes the crystal of the transducer act as an additional signal generator, and the signal is coupled via parasitic capacitances in a switching means to the receiving ultrasonic transducer. This problem is solved by connecting one pole of a short circuit switch (S3, S4) to the ultrasonic transducer (TR1, TR2) or to the switching means (S1, S2) and the other pole of the short circuit switch to ground. Keeping the short circuit switch closed when the switching means is open, and open when the switching means is closed, creates a decoupling path for the unwanted signal, thereby improving the accuracy of the transmitting and receiving circuit.

Owner:SIEMENS FLOW INSTR +1

CMOS switch for use in radio frequency switching and isolation enhancement method

InactiveUS20110140764A1Improve isolationEasy to switchElectronic switchingTransmissionCMOSElectricity

Provided is a CMOS switch for use in RF switching having improved isolation properties. The CMOS switch includes a serial switching unit having first and second CMOS switches, a switching isolation unit for allowing an unselected output terminal of two output terminals to be electrically isolated from a common input terminal when the serial switching unit operates and an isolation enhancement unit. The isolation enhancement unit is connected in parallel to the first and the second CMOS switches between the two output terminals forming a parallel resonance circuit together with a parasitic capacitor of the serial switching unit. The CMOS switch for use in RF switching according to the present invention has a simple circuit structure and excellent operating properties at the MF or higher band. Also, the CMOS switch having high isolation properties is realized.

Owner:ELECTRONICS & TELECOMM RES INST

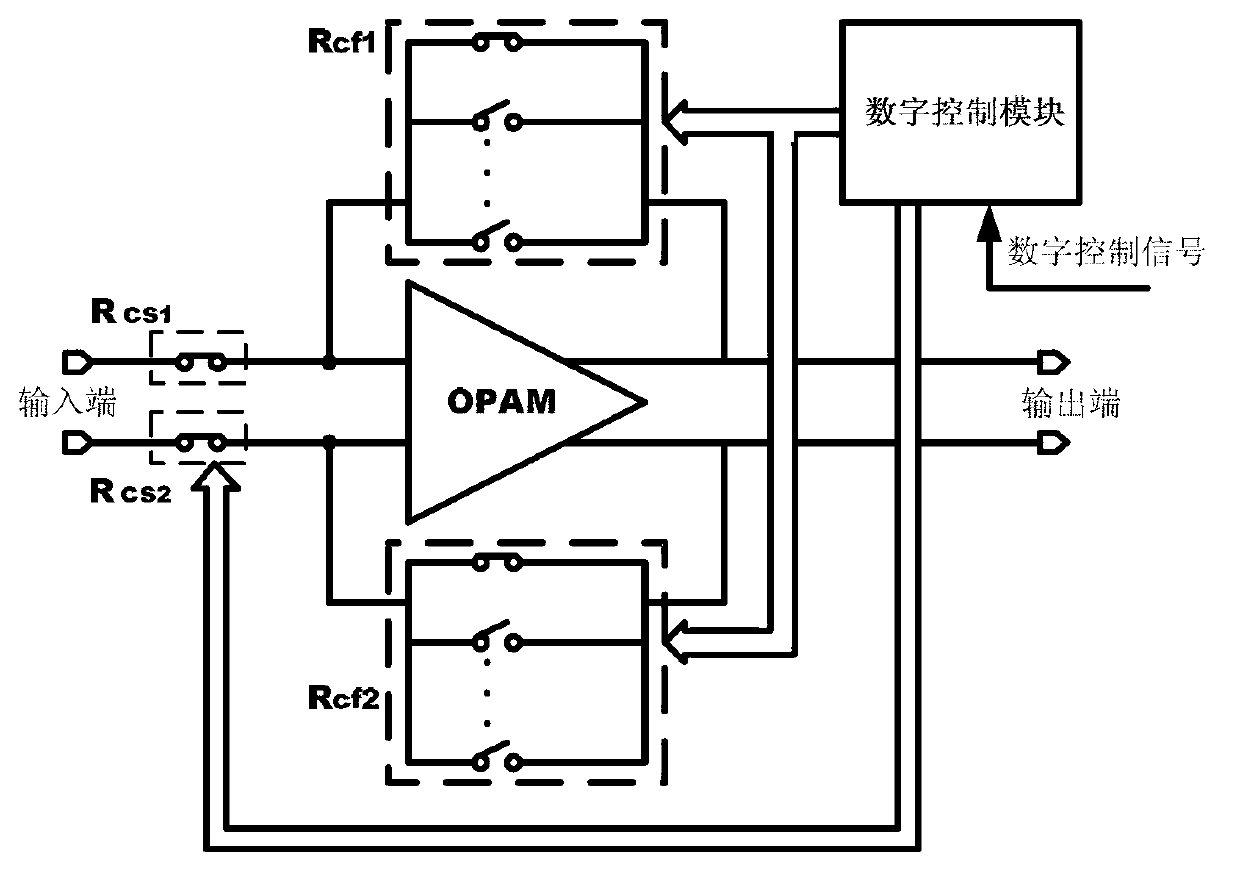

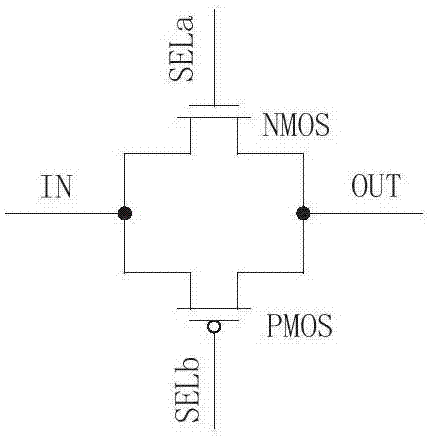

High precision broadband programmable gain amplifier

ActiveCN107370465AHigh gain accuracyHigh bandwidthGain controlDifferential amplifiersAudio power amplifierCmos switch

The invention discloses a high precision broadband programmable gain amplifier comprising two input resistor arrays, two feedback resistor arrays, an operational amplifier and a digital control module, wherein the digital control module is electrically connected with each input resistor array and each feedback resistor array; the operational amplifier comprises two input / output interfaces, each input / output interface comprises an input end and an output end, the feedback resistor array crosses over the input end and the output end, and the input end is connected with the input resistor array; and each input resistor array comprises two resistors R1 and a CMOS switch SW1 arranged between the two resistors R1, each feedback resistor array comprises N branches connected in parallel, and the i-th branch comprises two resistors Ri and a CMOS switch SWi arranged between the two resistors Ri, i is not more than N and not less than 1, and on resistance of the CMOS switch SWi is RSWi. According to the high precision broadband programmable gain amplifier provided by the invention, gain precision and broadband of the programmable gain amplifier are improved.

Owner:芯与物(上海)技术有限公司

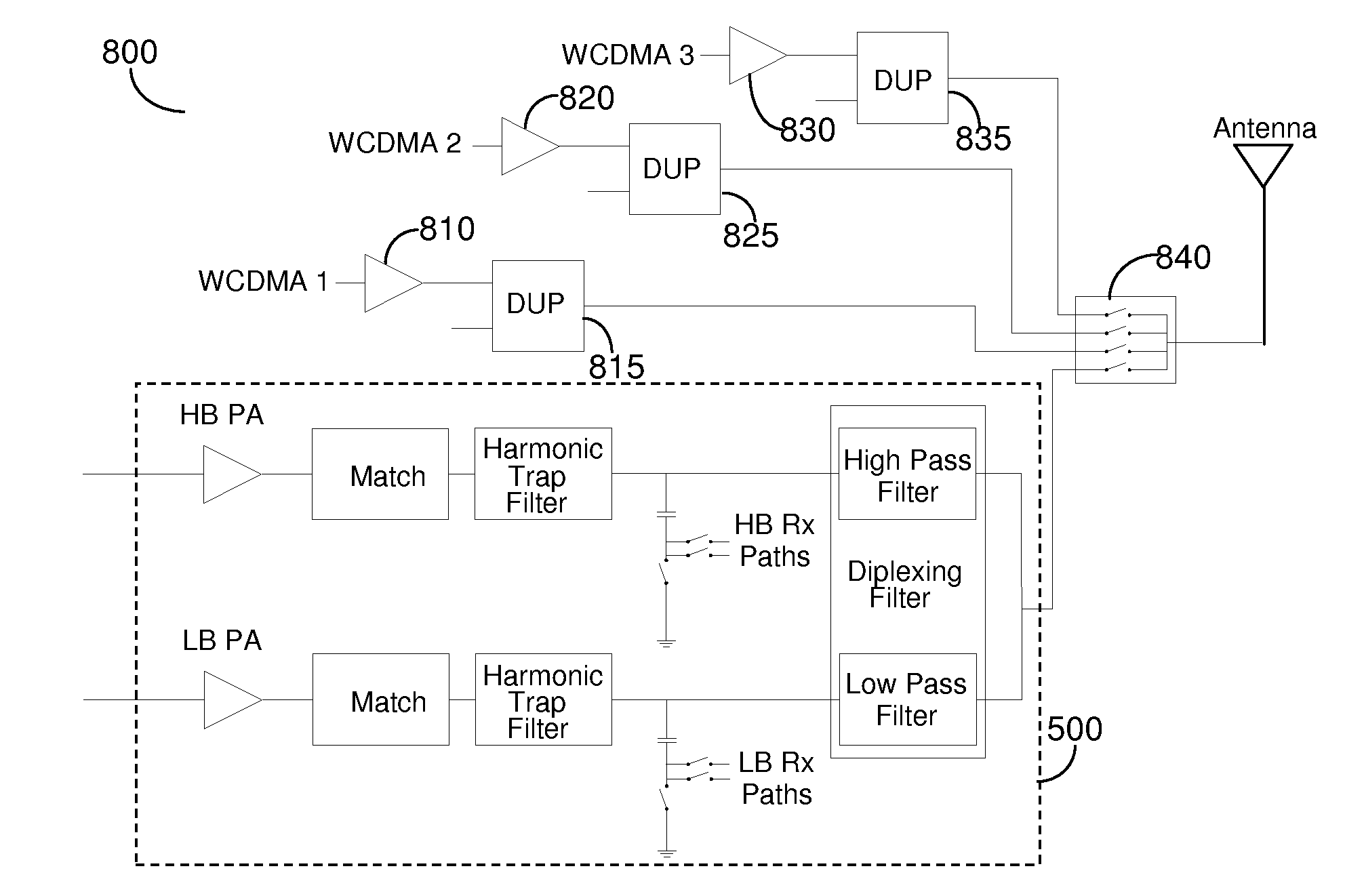

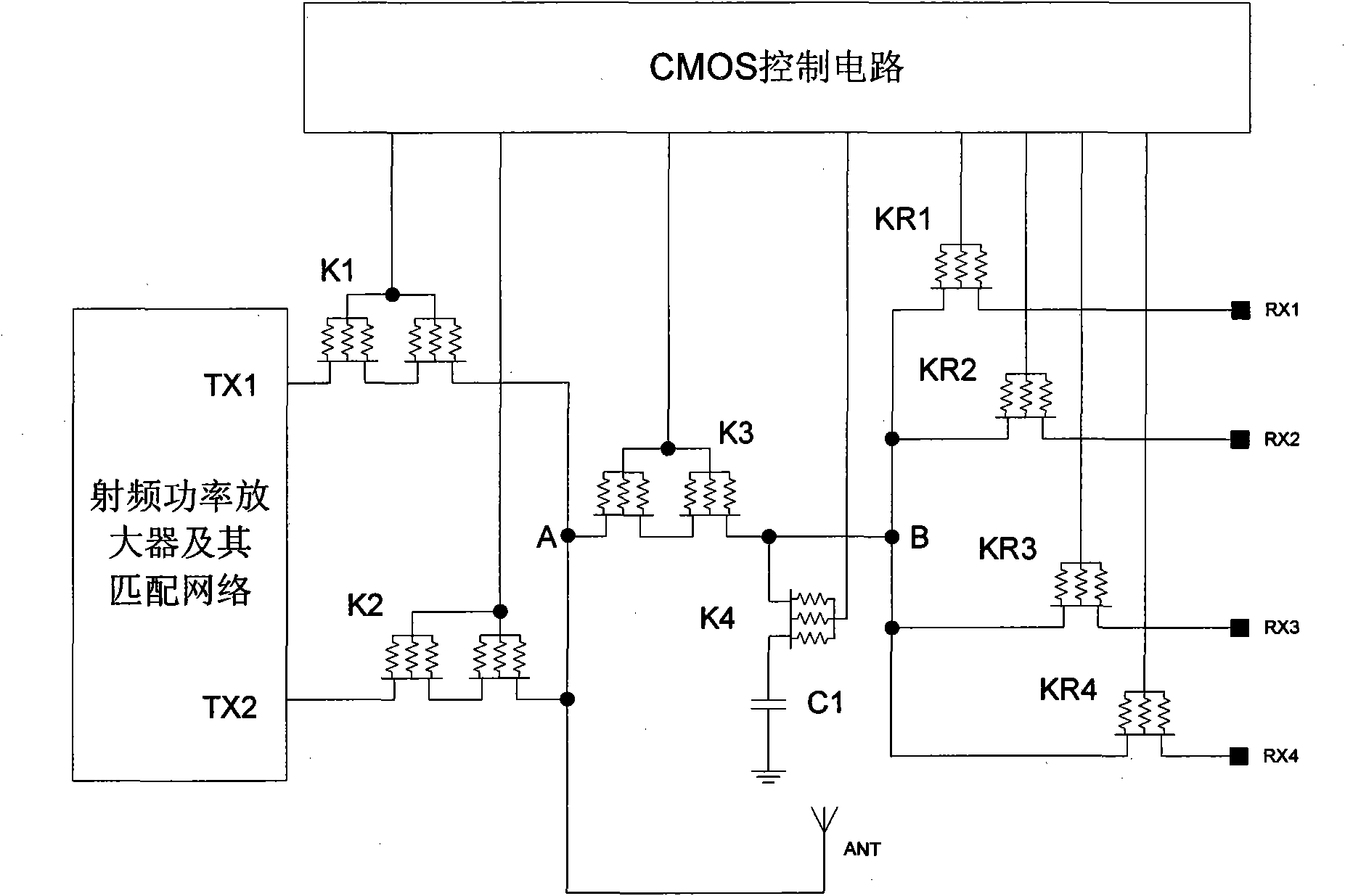

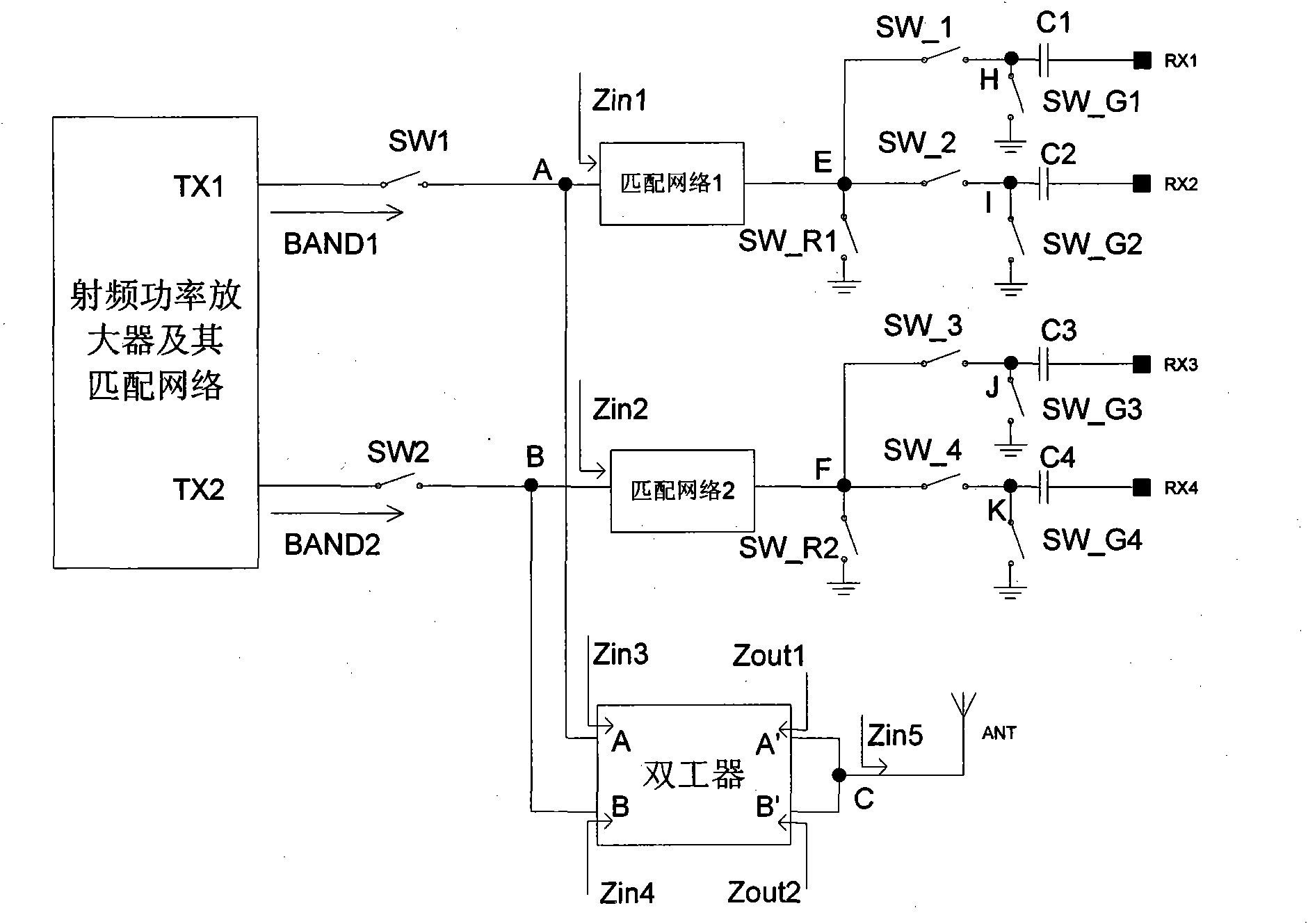

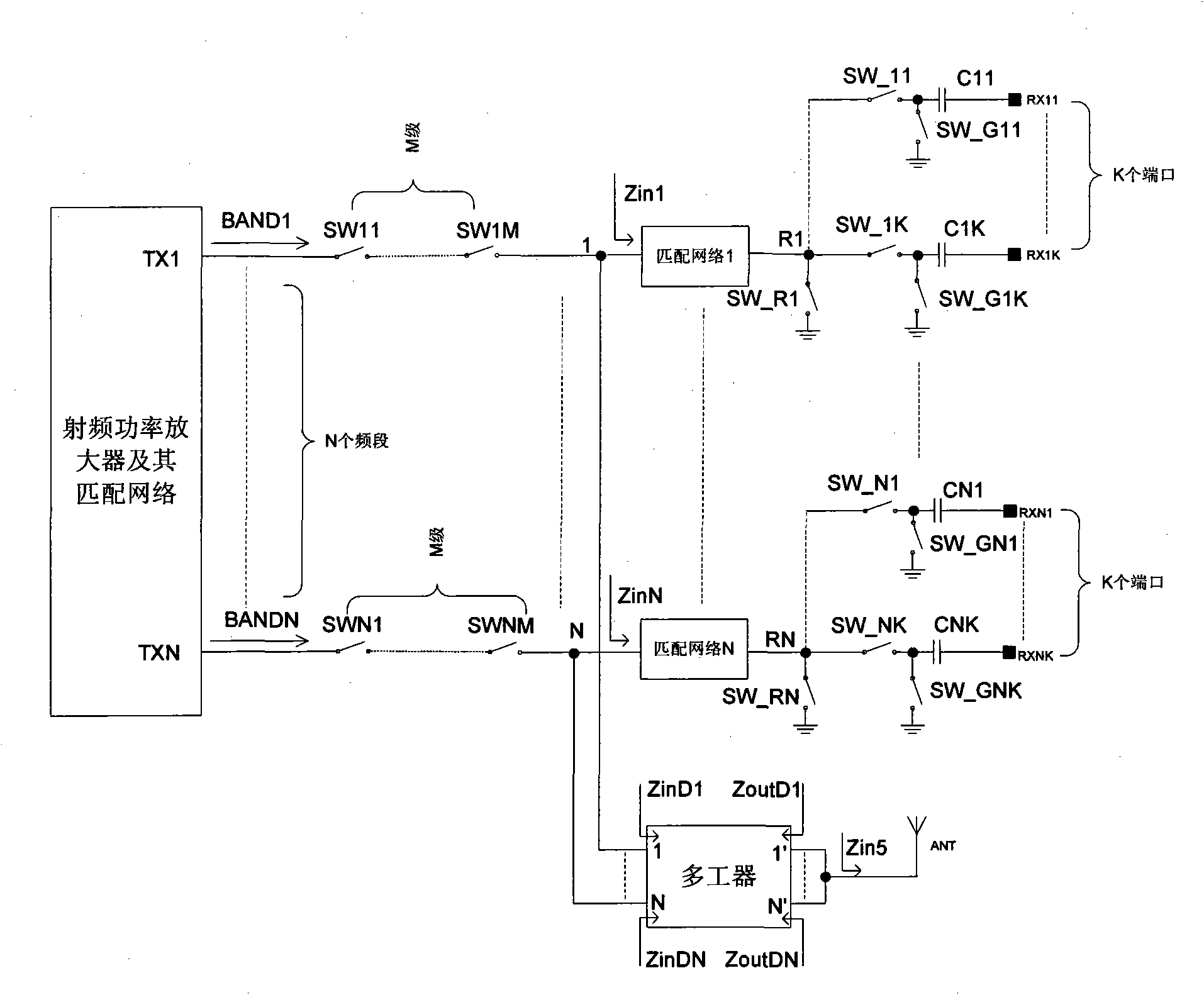

Radio-frequency power composite circuit

ActiveCN101667854AImprove the ability to resist voltage breakdownHighly integratedHigh frequency amplifiersTransmission control/equalisingCMOSAudio power amplifier

The invention discloses a radio-frequency power composite circuit applied to the composite control of multi-frequency band power signals of a radio-frequency power amplifier and sending the signals by an antenna. The circuit comprises a switching device group I connected with the radio-frequency power amplifier and a matching network signal output end and a switching device group II connected with a signal receiving end, wherein the switching device group I is connected with the antenna by a duplexer and simultaneously and respectively connected with the switching device group II by a matching network; and the switching devices are CMOS devices. The circuit adopts technology using the matching network or the duplexer having filtering function to combine with and isolate from the switchingdevices, thus effectively improving the voltage breakdown resisting performance of the CMOS switching devices; the combined circuit is applied to the power composite circuit, thus ensuring higher integration degree and lower cost of a chip of the radio-frequency power amplifier; and simultaneously, the circuit also improves the isolation degree and flexibility of a wireless communication system and reduces insertion loss of the wireless communication system when a receiving end receives the radio-frequency signals.

Owner:北京昂瑞微电子技术股份有限公司

Low voltage analog CMOS switch

ActiveUS7760007B2Simple and cost-effective techniqueImprove leakageTransistorElectronic switchingCMOSLow voltage

Owner:NUVOTON

Octave-range, watt-level, fully-integrated CMOS switching power mixer array for linearization and back-off-efficiency improvement

ActiveUS8378732B2Computations using contact-making devicesComputing operations for multiplication/divisionPower-added efficiencyCMOS

Power mixer arrays for providing watt-level power in mobile systems. In one embodiment, a fully-integrated octave-range CMOS power mixer that occupies only 2.6 mm2 using a 130 nm semiconductor process has been demonstrated. The power mixer provides an output power of +31.5 dBm into an external 50 Ω load with a power added efficiency (PAE) of 44% at 1.8 GHz and a full power gain compression of only 0.4 dB.

Owner:CALIFORNIA INST OF TECH

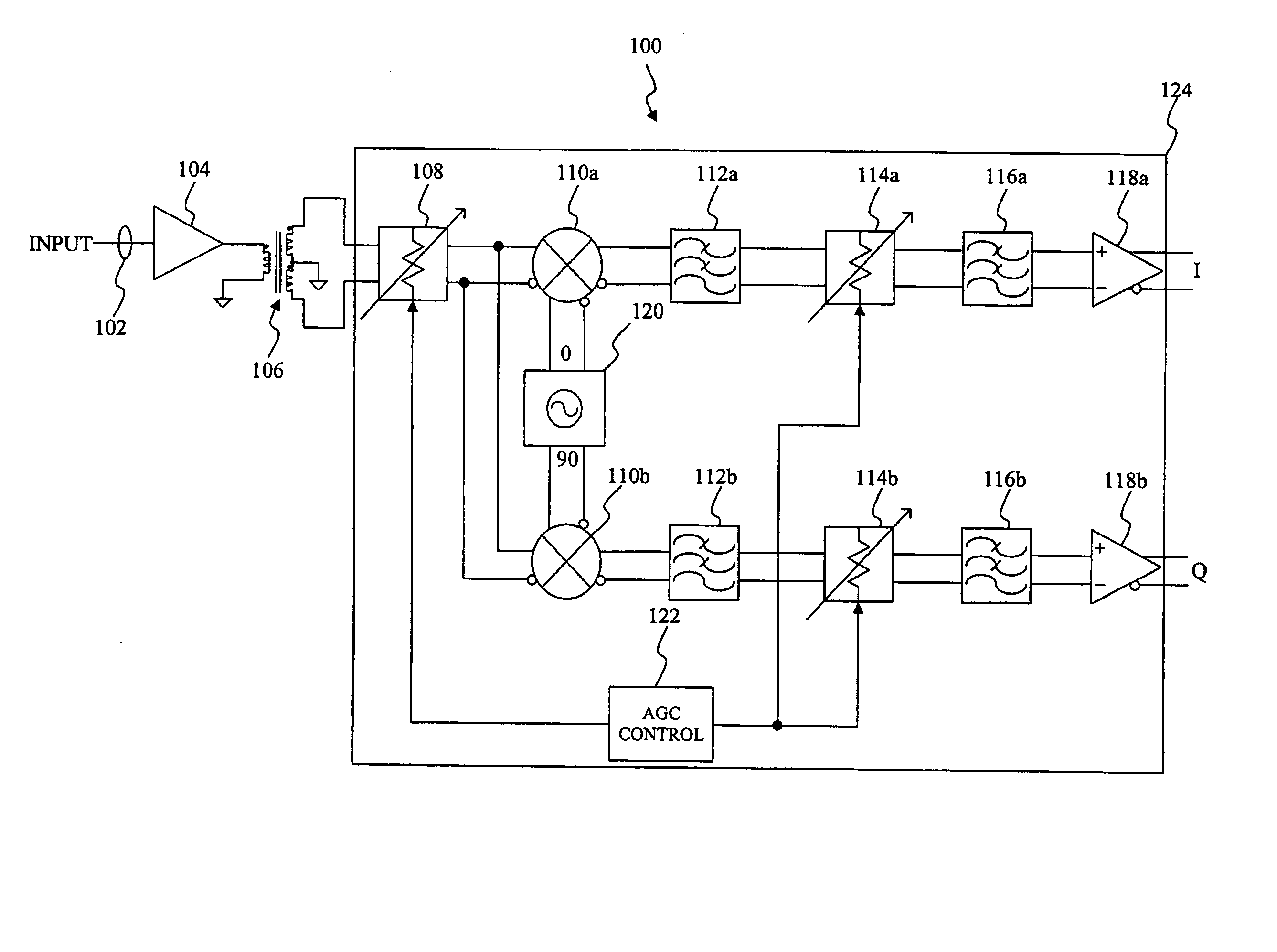

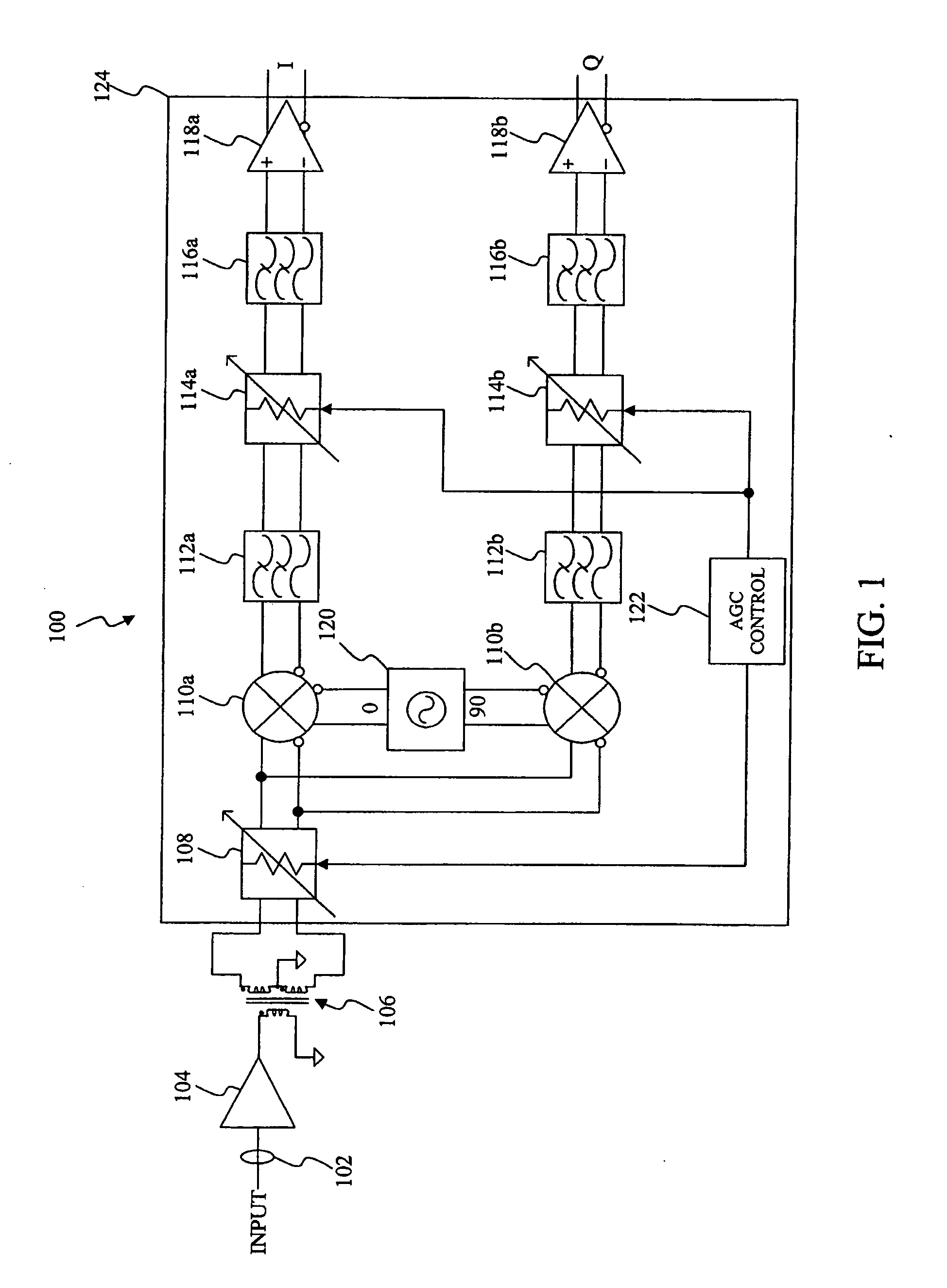

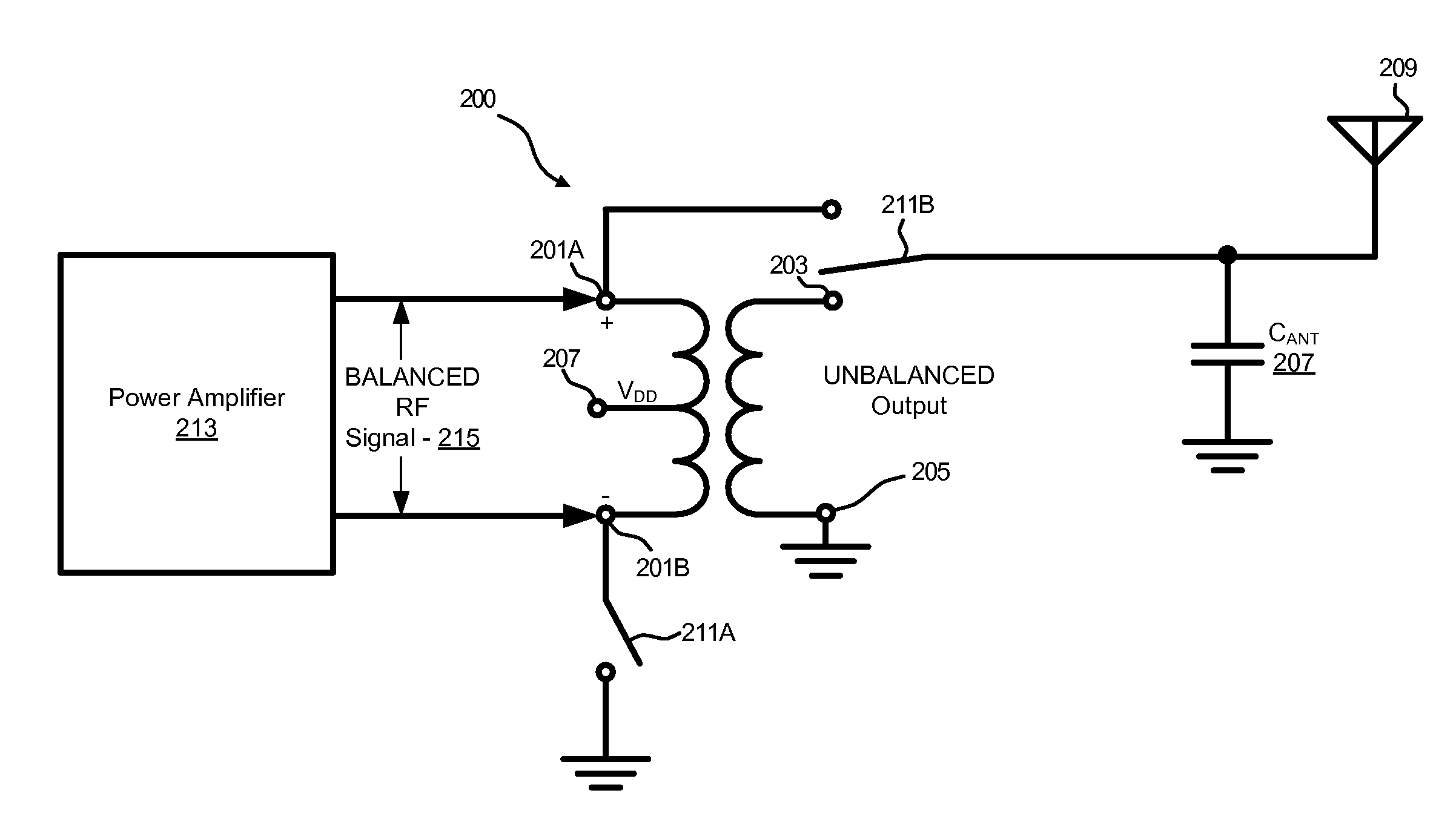

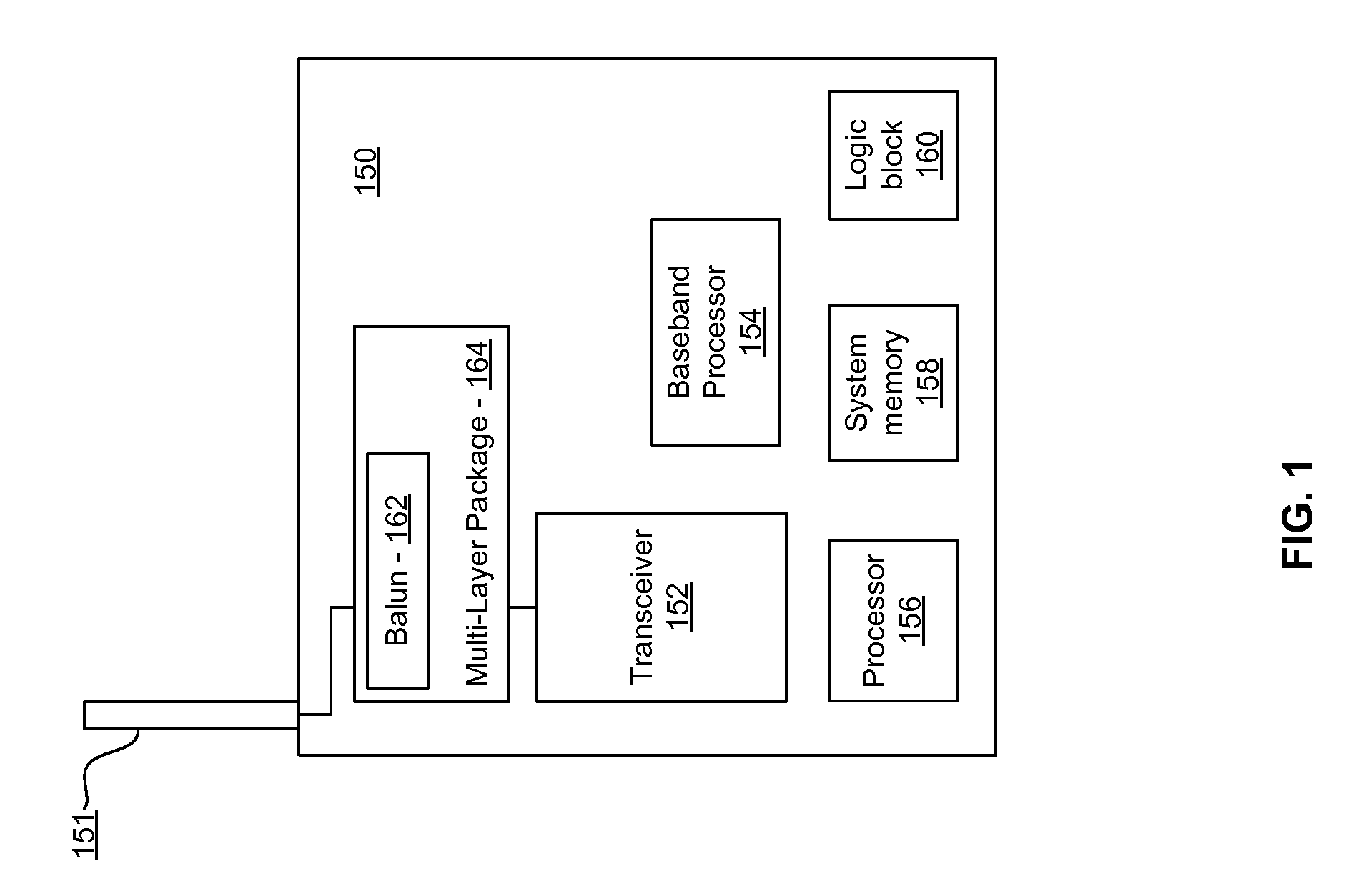

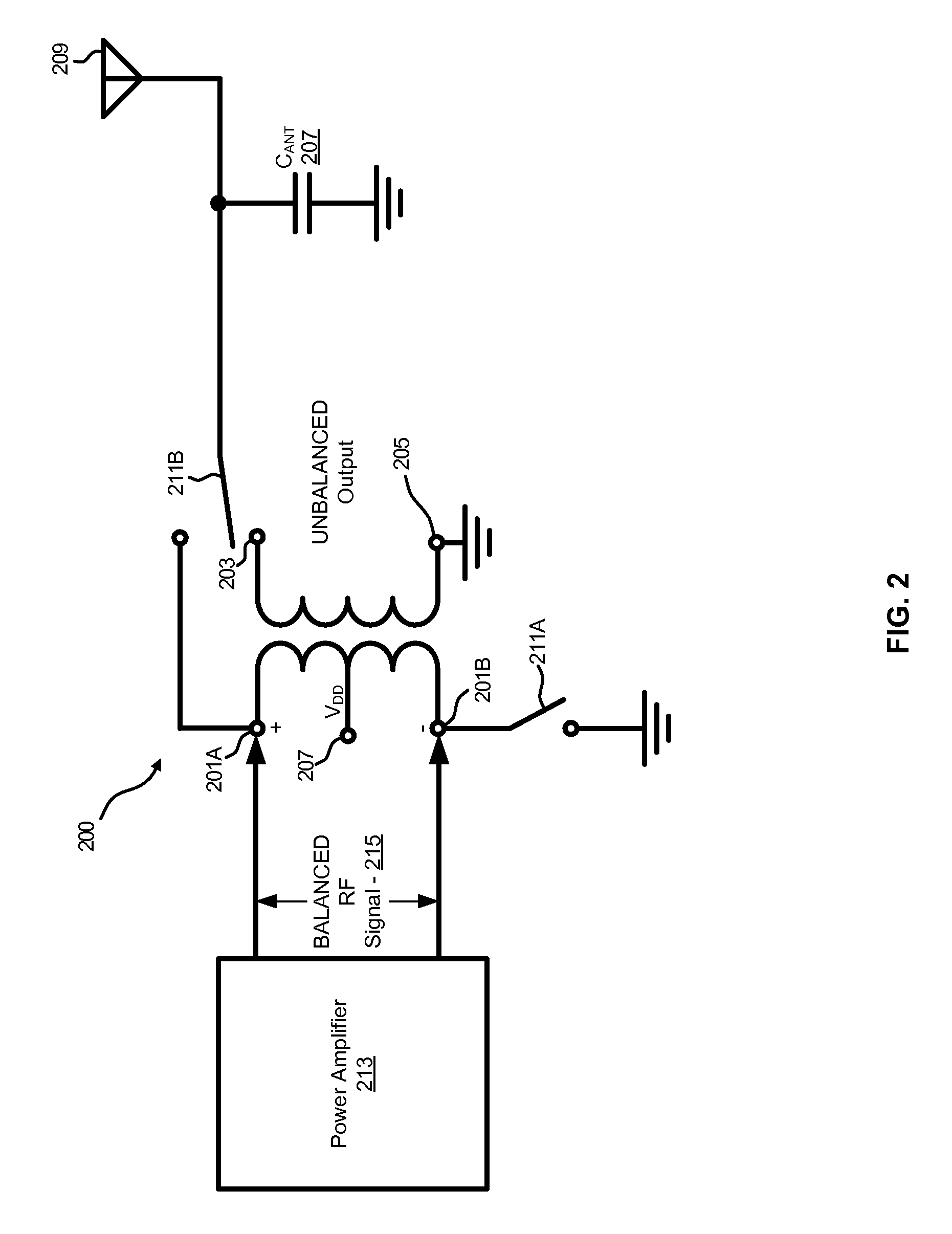

Method and system for a balun embedded in an integrated circuit package

Methods and systems for a balun embedded in an integrated circuit package are disclosed and may include a multi-layer package bonded to an integrated circuit. The multi-layer package may include an integrated balun which may be enabled to process RF signals received from and / or communicated to an antenna. The integrated circuit may be flip-chip bonded to the multi-layer package. The balun may include ferromagnetic layers integrated in the multi-layer package, and may be bypassed via bypass switches integrated in the multi-layer package. The switches integrated in the multi-layer package may include MEMS switches. The balun may be bypassed via bypass switches in the integrated circuit. The switches in the integrated circuit may include CMOS switches. The balun may be impedance matched to the integrated circuit via surface mount devices, which may be coupled to the multi-layer package.

Owner:AVAGO TECH INT SALES PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com