High-bandwidth high-isolation low on-resistance CMOS analog switch circuit and realizing mode thereof

A low on-resistance, high-isolation technology, applied in electronic switches, electrical components, pulse technology, etc., to achieve the effect of improving transmission bandwidth, wide bandwidth, and low on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

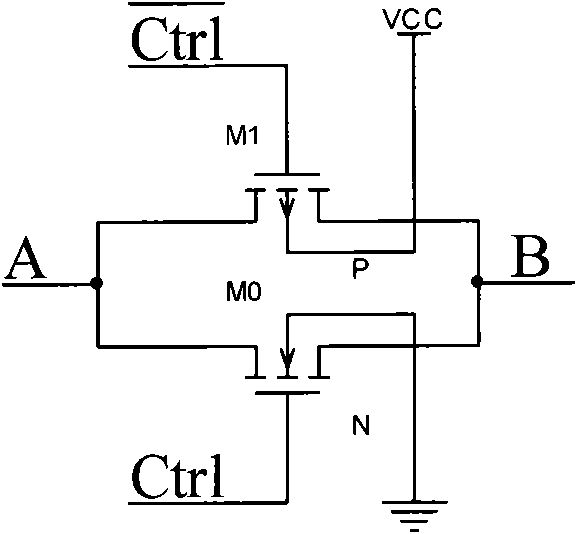

[0011] As shown in Figure 1, the traditional CMOS analog switch circuit is composed of paired NMOS and PMOS in parallel. Its gate is connected to control signal, and its substrate is grounded and power supply respectively.

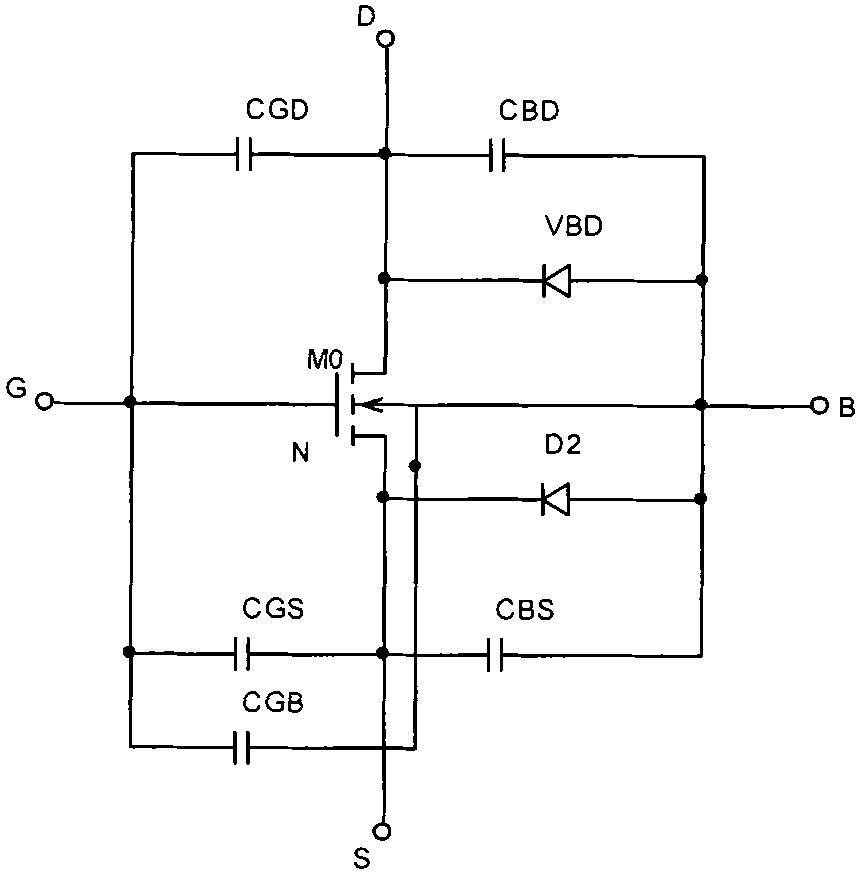

[0012] As shown in Figure 2, the traditional CMOS analog switch transmits signals through C GD 、C GS 、C GB 、C BD 、C BS Receive the AC signal ground respectively. As the size of the CMOS analog switch increases, the on-resistance decreases, and the C GD 、C GS 、C GB 、C BD 、C BS It is increasing, which affects the transmission of high-frequency signals.

[0013] Due to the separation of B and S in the traditional CMOS analog switch, there is a lining offset effect, which affects V T

[0014] V T = V T 0 + γ ( 2 | φ F | ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com