Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

123results about How to "Shorten the verification cycle" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A highly automated intelligent contract formal verification system and method

ActiveCN108985073ASave time and costShorten the verification cycleFinancePlatform integrity maintainanceSpecification documentAutomaticity

The invention discloses a highly automated intelligent contract formal verification system and method. The method includes the following steps: step 001, converting an intelligent contract function requirement description document into an intelligent contract function requirement specification document described in a non-natural language, wherein the content of intelligent contract function requirement specification document includes target contract function specification description and security attribute description; step 002, creating a formal validation rule model library; step 003, automatically modeling the contract source code and / or bytecode by an automated modeling tool; step 004, parsing the abstract syntax tree generated in step 003, and allocating memory addresses for constantsand variables in the code; step 005, performing formal proof. The invention is adapted to program codes written in a plurality of high-level programming languages and also adapted to a plurality of formal languages, and simultaneously provides two automatic modeling modes of source code modeling and bytecode modeling, so that modeling can be carried out according to different modeling requirements of users, and the verification efficiency is further improved.

Owner:成都链安科技有限公司

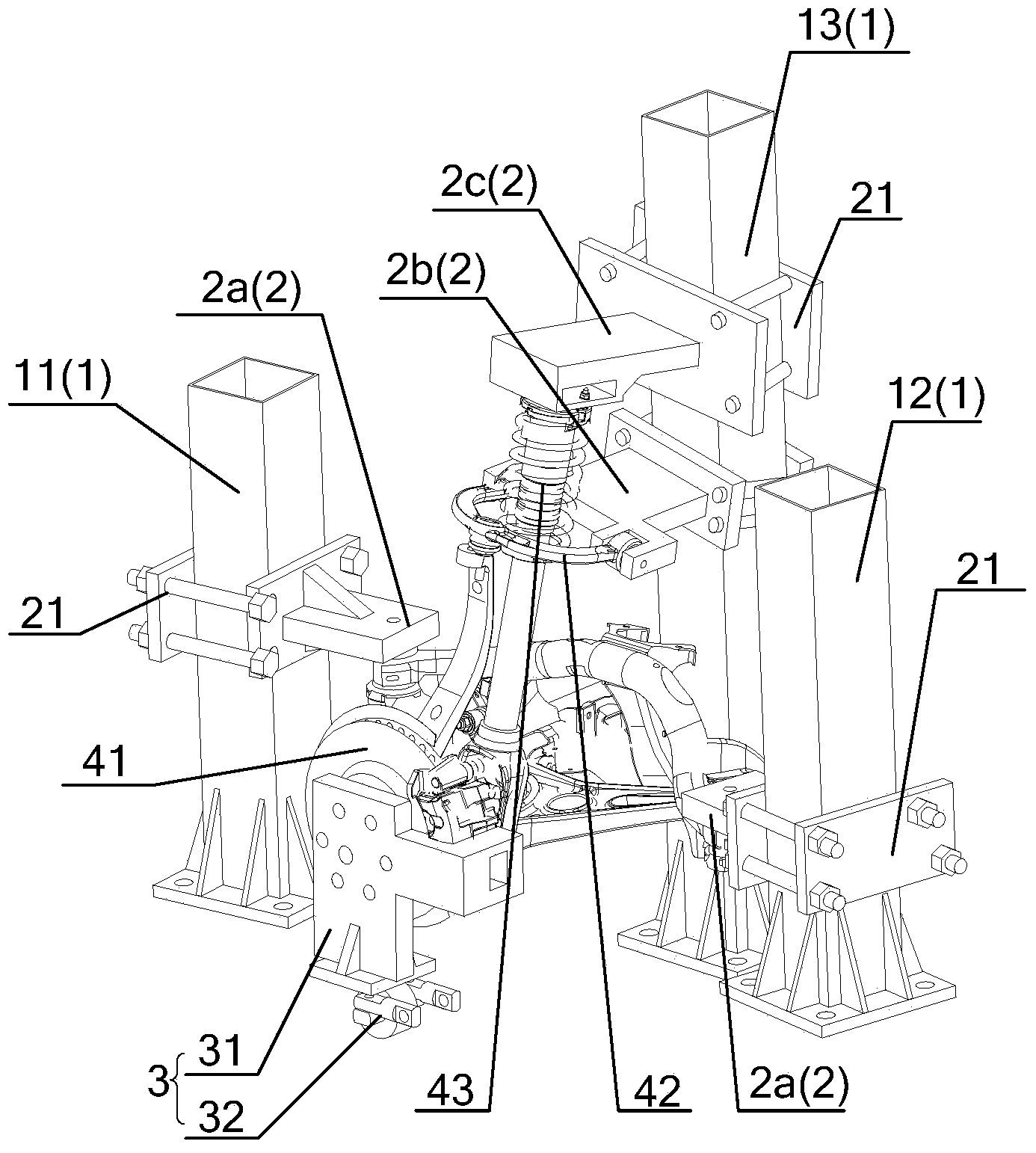

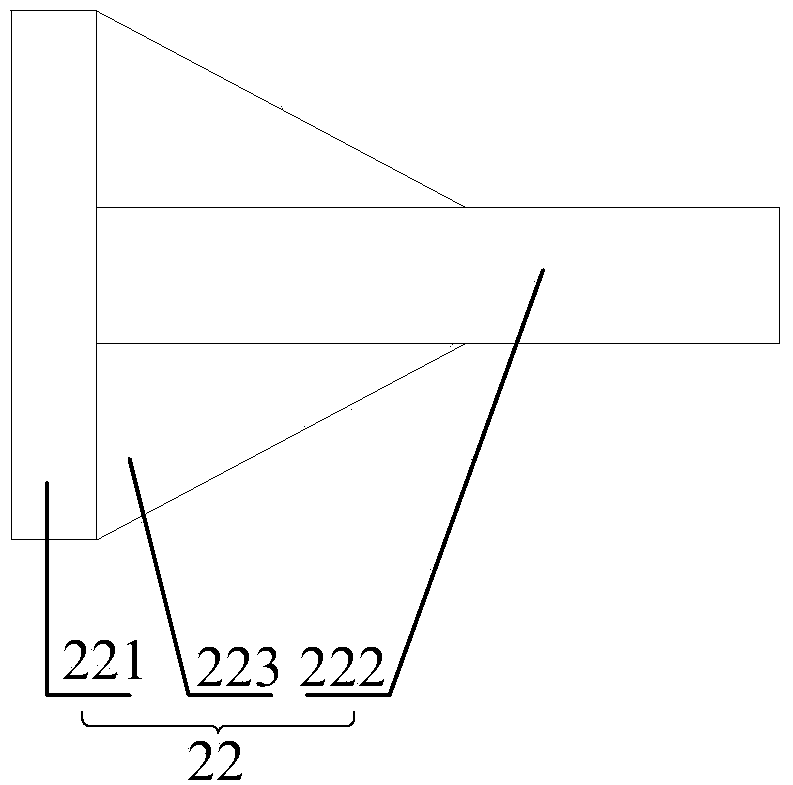

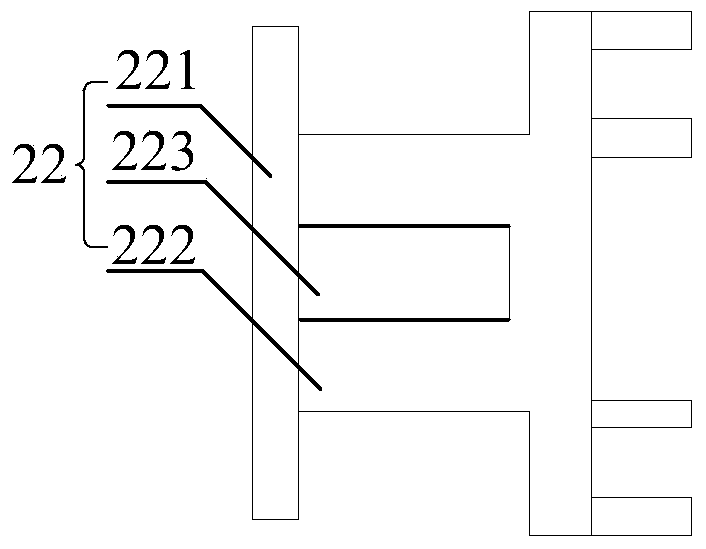

Automotive suspension test bed

ActiveCN103954459AShorten the design and development cycleHigh strengthVehicle suspension/damping testingVehicle frameUltimate tensile strength

The invention discloses an automotive suspension test bed, relates to the technical field of fatigue verification for an automotive suspension and provides the automotive suspension test bed which is simple in structure, high in strength and capable of shortening the development and verification period of the automotive suspension and reducing test expenditures. The automotive suspension test bed comprises a plurality of stand columns, wherein a clamp plate with the height and the angle adjustable is installed on each stand column, and a calibrating mark is further arranged on each stand column and used for calibrating the installation position of the corresponding clamp plate. The automotive suspension test bed further comprises a loading mechanism used for being connected with a loading device, the stand columns are assembled with an automotive frame through the clamp plates in a matched and connected mode, the loading mechanism is connected with a brake disc on the frame, and the direction of the loading device is controlled so that the loading mechanism can perform suspension endurance verification under different working conditions. The automotive suspension test bed is mainly used in tests of fatigue verification for the automotive suspension.

Owner:GREAT WALL MOTOR CO LTD

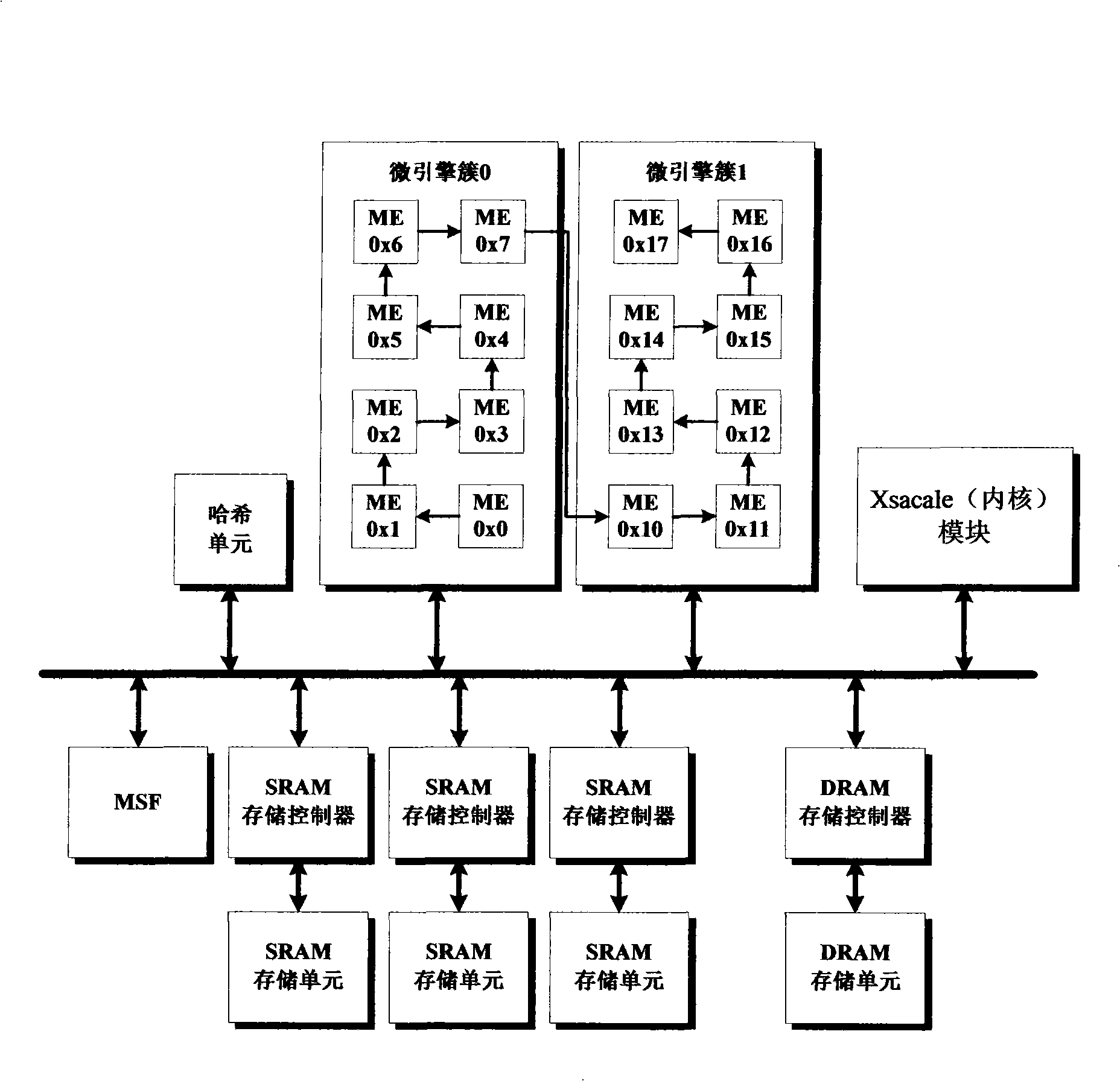

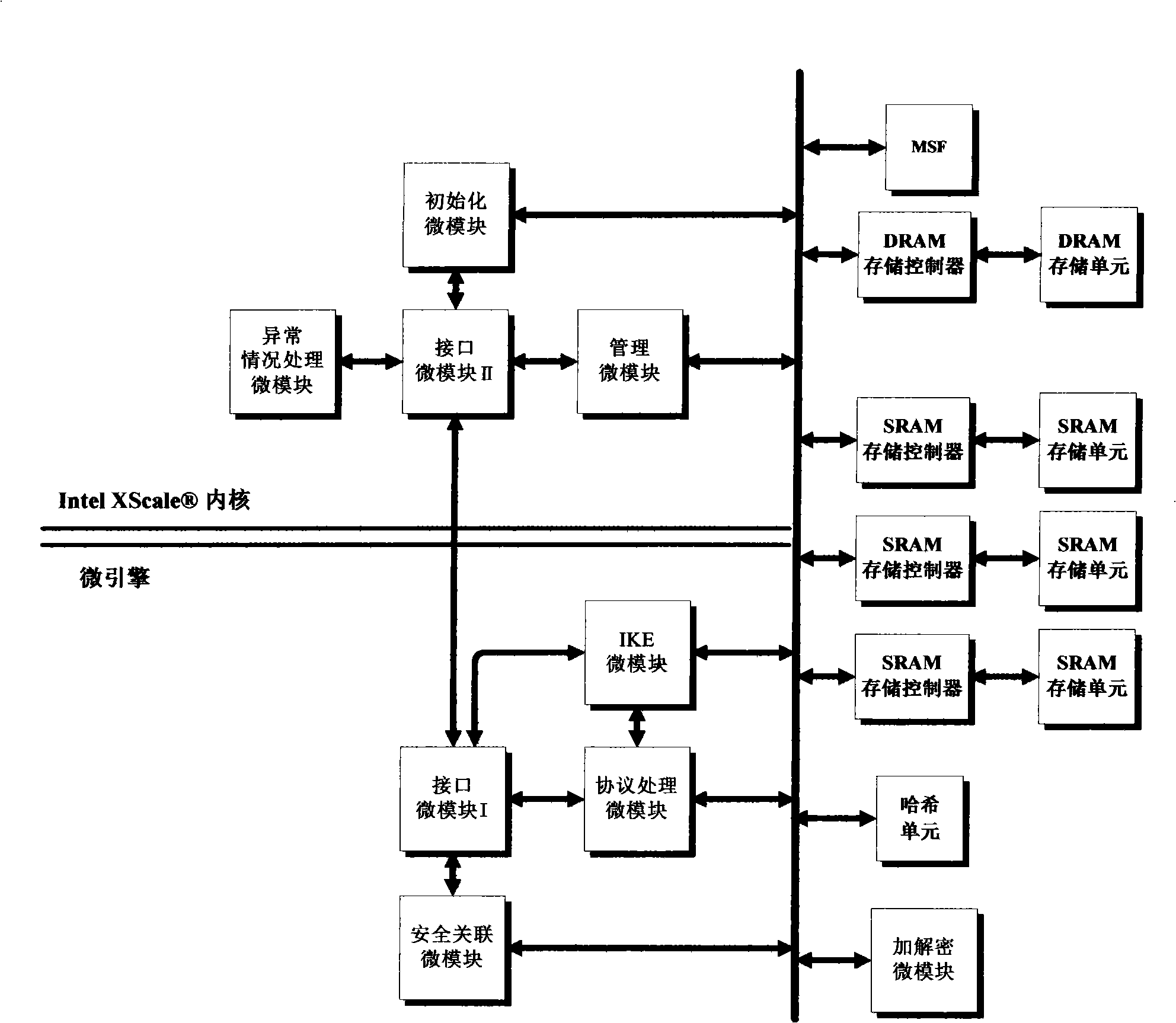

High-speed secure virtual private network channel based on network processor and its realization method

InactiveCN101262405AShorten the verification cycleHigh-speed encryption and decryption processingNetworks interconnectionSecuring communicationPrivate networkControl store

The invention provides a high-speed and secure VPN channel which is based on a network processor. The VPN channel comprises micro engine clusters, a kernel module, at least one SRAM and a memory controller thereof, at least one DRAM and a memory controller thereof, an MSF module and a Hash unit, wherein, two micro engine clusters are connected in sequence and each micro engine cluster consists of eight micro engines in sequence; two micro engine clusters, the kernel, the MSF and the hash unit are respectively connected with a PCI bush; each SRAM and DRAM are connected with the PCI bush through the respective memory controller and the PCI bush is connected with an administrative system module of an upper computer. The invention adopts a network processor IXP2850 to realize the VNP functions, and effectively shortens the period of the encoding, decoding and verifying of effective loads by sufficiently utilizing a quick-slow data channel formed by the micro engine-kernel and the kernel which is specially for encoding and decoding, and is highly integrated with a router and a firewall, thereby effectively relieving the conflict between the security requirement and the data processing rate.

Owner:SOUTH CHINA UNIV OF TECH

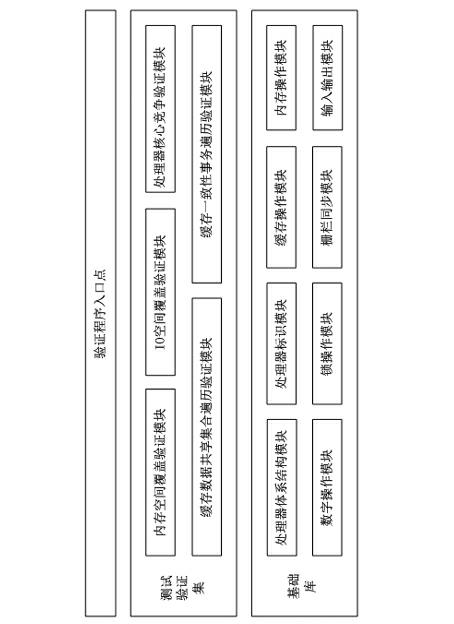

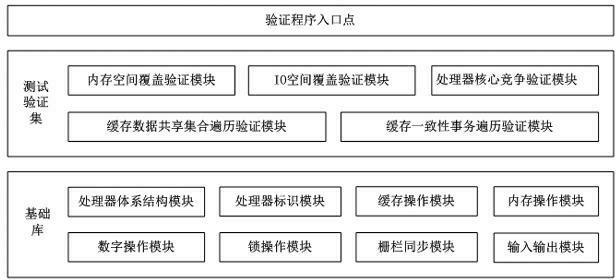

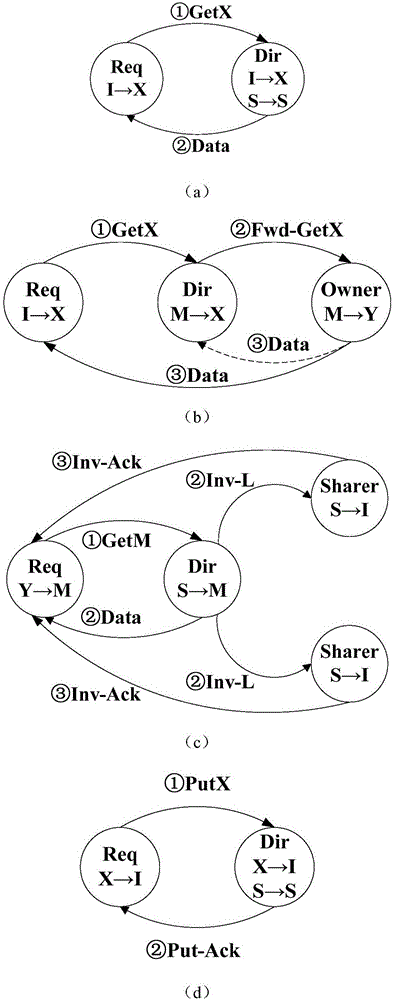

Correctness verifying method of cache consistency protocol

ActiveCN102681937AMake up for efficiencyMake up for poor verification coverageDigital computer detailsMultiprogramming arrangementsOperational systemTerm memory

The invention provides a correctness verifying method of a cache consistency protocol. After a computer enters an operating system, the complexity of a core and the application of the operating system is higher; the action of a processor is not easy to control accurately; therefore, in order to keep verification correctness, a verifying program for the cache consistency protocol is necessary to embed in a systematic procedure; the program is embedded in a BIOS (basic input / output system) code; after the initialization of a memory subsystem is completed at the initialization initial stage of the system, the verifying program is started to be executed; the verifying program needs to be capable of accurately controlling actions of each processor of the system, supports a user to select a verification item to be particularly executed, and feeds back a verification result to the user; by using the method, the verification of the correctness of the cache consistency protocol is realized at a system level; all application scenes of a real system can be completely covered; the disadvantages that a conventional verifying method based on an analog way is low in efficiency and poor in verification coverage rate are made up; the design period and the verifying period of an inter-domain cache consistency chip of the processor can be shortened; the one-time taping-out mission success rate of the chip can be guaranteed effectively; and therefore, the correctness verifying method has an extremely wide development prospect and an extremely high technical value.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

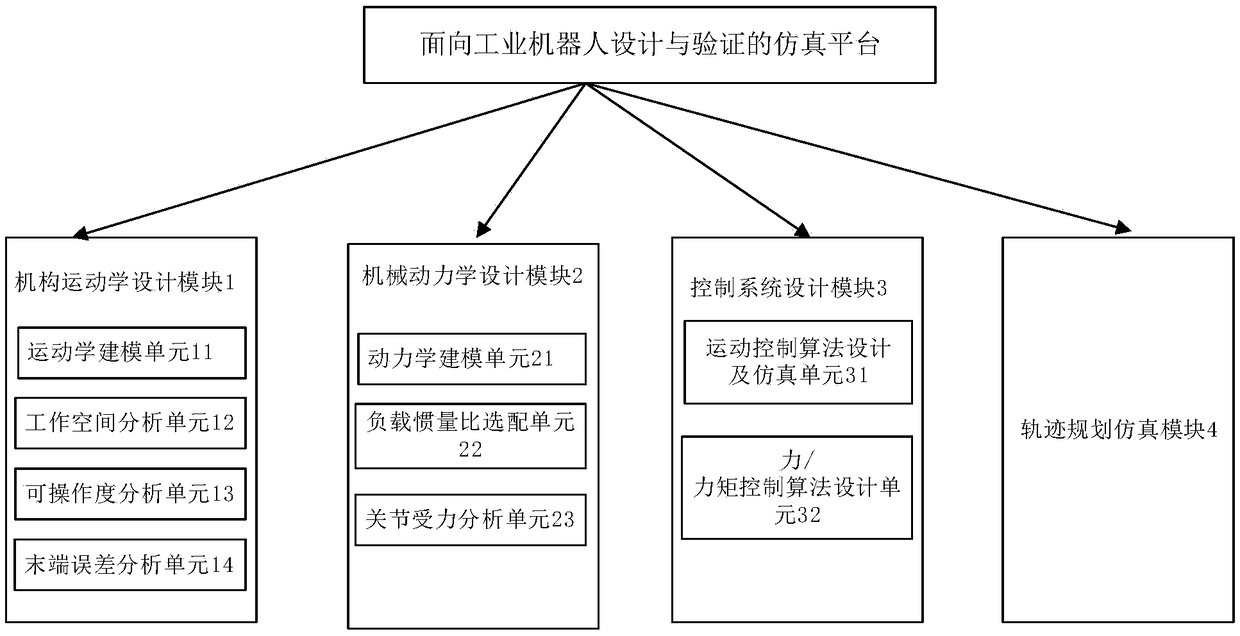

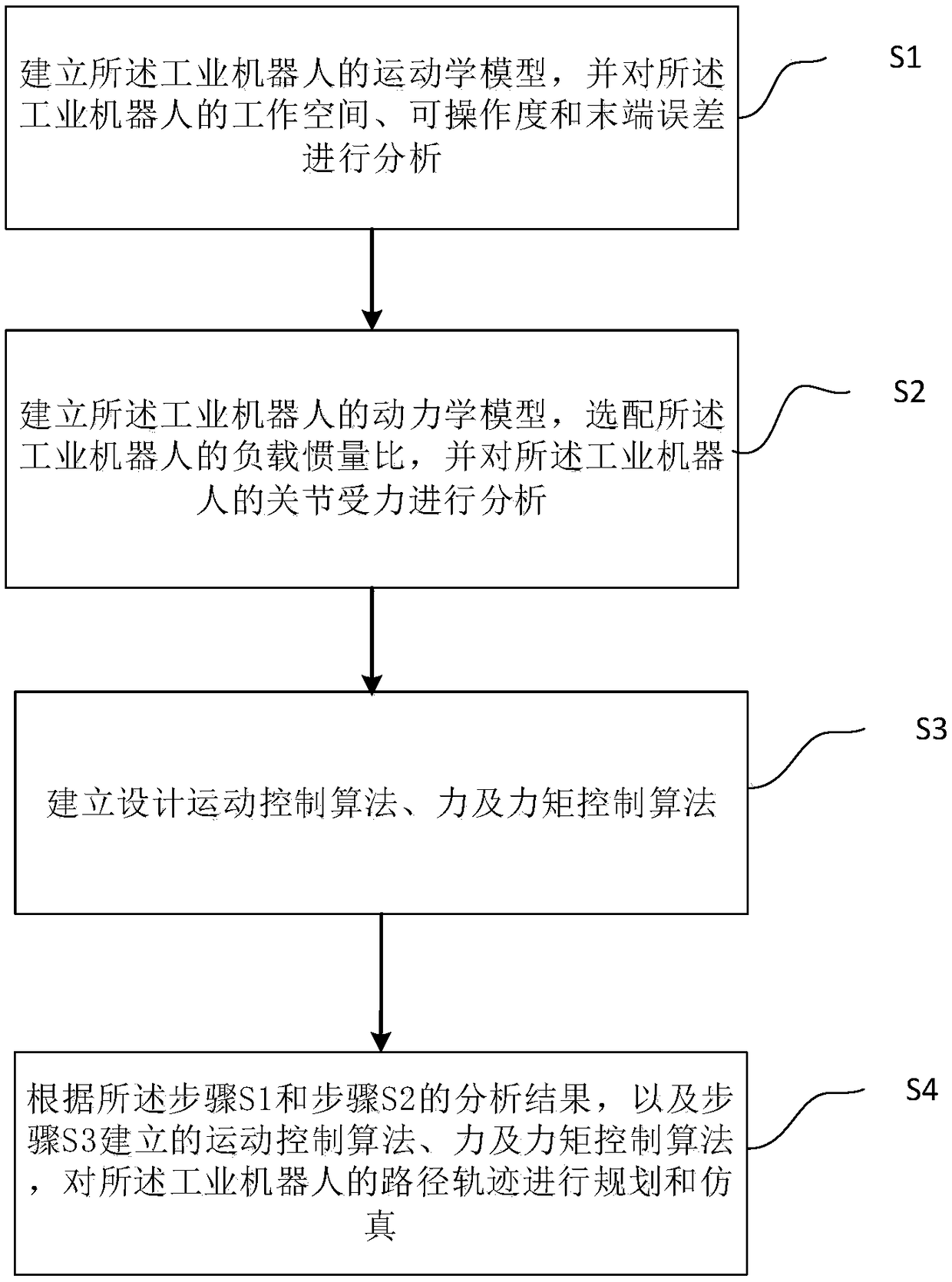

Industrial robot design and verification-oriented simulation platform and method

InactiveCN108595888ARealize integrated designImprove efficiencyGeometric CADProgramme-controlled manipulatorDynamic modelsControl system design

The invention provides an industrial robot design and verification-oriented simulation platform and method. The platform comprises a mechanism kinematics design module used for building a kinematics model of an industrial robot and performing analysis on working space, operability and end errors of the industrial robot, a mechanical dynamics design module used for building a dynamics model of theindustrial robot, selecting and configuring a load inertia ratio of the industrial robot and performing analysis on a joint stress of the industrial robot, a control system design module used for establishing a design motion control algorithm and a force and moment control algorithm, and a track planning simulation module used for performing planning and simulation on a path track of the industrial robot. The integrated design of the robot can be realized, so that the research development design efficiency and quality of the robot are effectively improved.

Owner:ROKAE SHANDONG INTELLIGENT TECH CO LTD

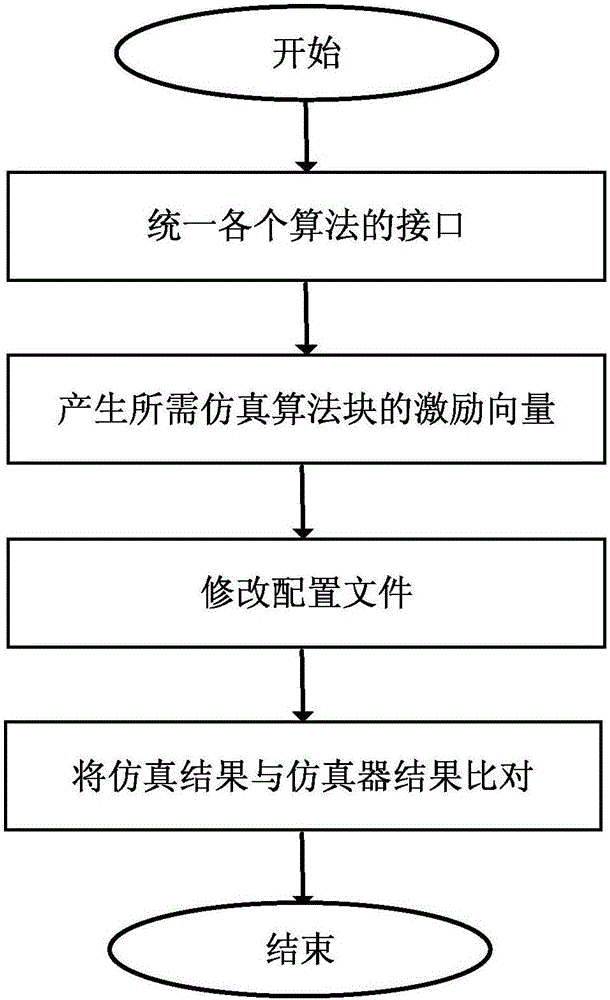

FPGA-based algorithm library simulation and verification platform implementation method

InactiveCN106777729ATo achieve the purpose of automatic simulationSimulation automationCAD circuit designSpecial data processing applicationsNuclear powerControl system

The invention provides an FPGA-based algorithm library simulation and verification platform implementation method. The implementation method comprises the following steps: firstly, according to requirements of nuclear power station safety level control system application, implementing all the algorithm blocks through FPGA basically; secondly, producing a simulation excitation vector of each algorithm block; thirdly, if an algorithm block needs to be added, only adding algorithm block content and a corresponding simulation vector on the verification platform, and then modifying a configuration file; and fourthly, carrying out comparison analysis on a simulation result output by a simulation tool and a result generated by a simulator. The implementation method provided by the invention has the advantages that all the algorithm blocks are unified into the same interface, and the algorithm blocks can be automatically called only by modifying the configuration file once the algorithm block or the simulation vector needs to be added, so that the aim of automatic simulation is achieved.

Owner:CHINA NUCLEAR CONTROL SYST ENG

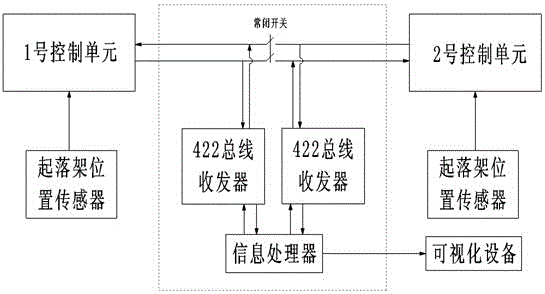

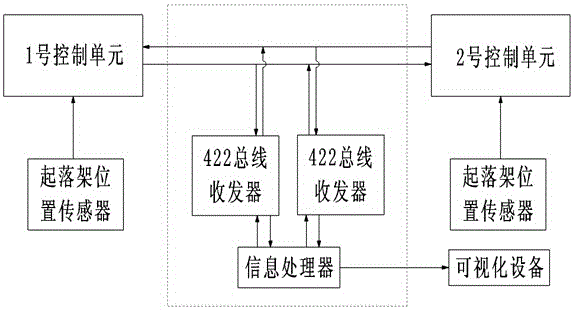

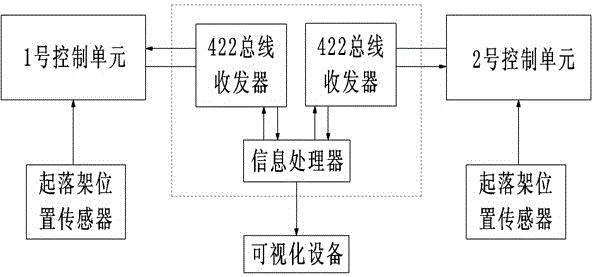

Method and device for verifying RS422 bus data of aircraft landing gear system

ActiveCN106742048AShorten the verification cycleAvoid safety hazardsDetecting faulty computer hardwareAircraft components testingReal time acquisitionEmbedded system

The invention discloses a method and device for verifying the RS422 bus data of an aircraft landing gear system. The device comprises a normally closed switch, two RS422 bus data receivers and an information processor. The RS422 bus data between two equipment in the landing gear system mainly transmits landing gear positions and the working states and current parameters of the equipment, and whether the responding conditions of the whole system satisfy design requirements or not when the landing gear positions and control unit parameters change can be verified by the receiving, reconstruction and transferring of the RS422 data between two mutual-backup control units. The method and device has the advantages that the bus data between the equipment is collected in real time, and the safety and integrity of system verification are guaranteed.

Owner:LANDING GEAR ADVANCED MFG

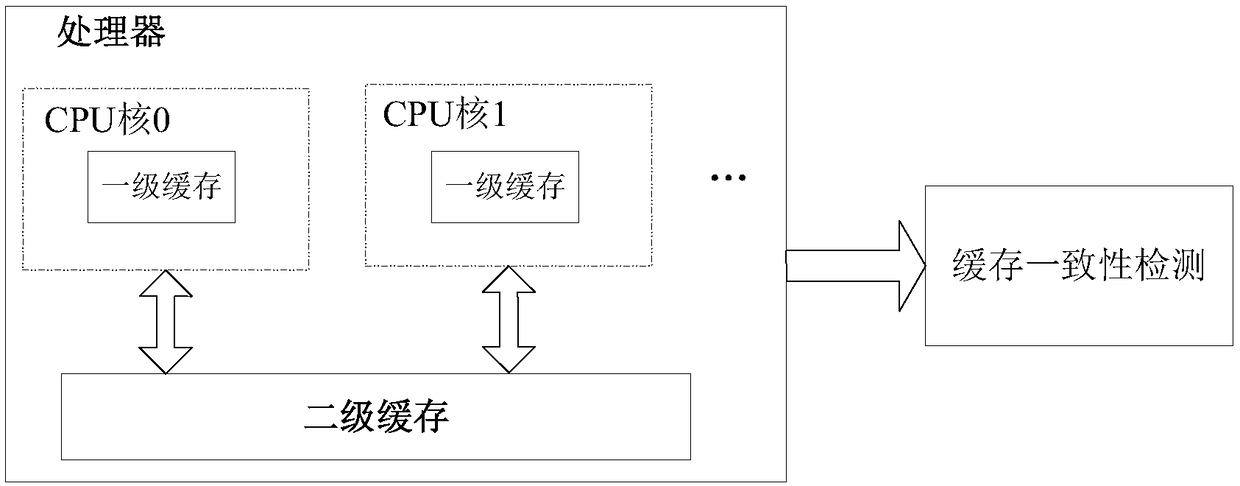

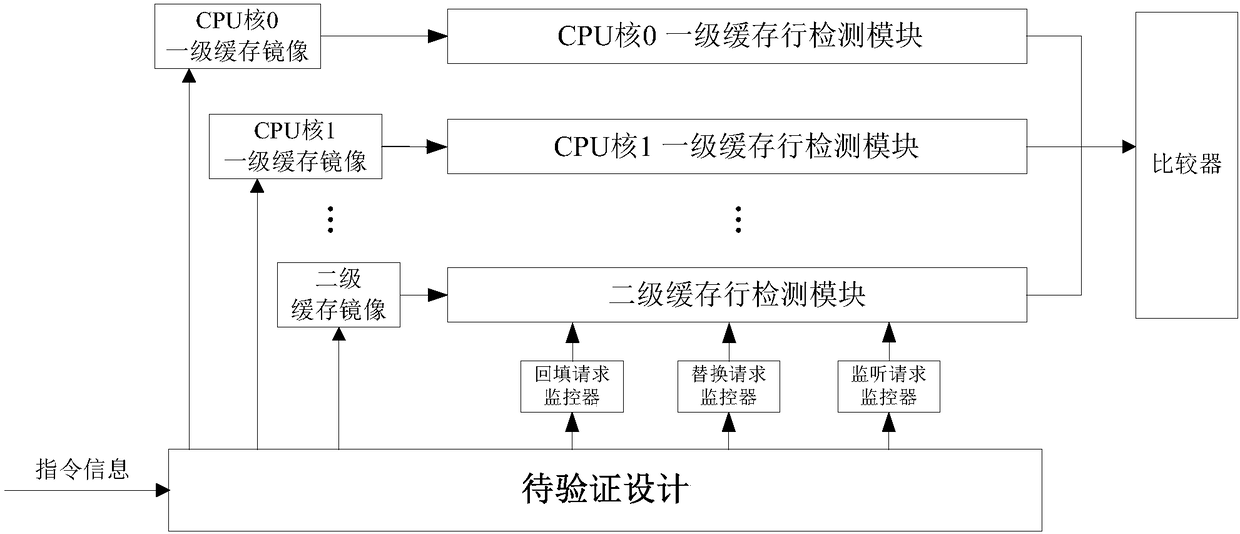

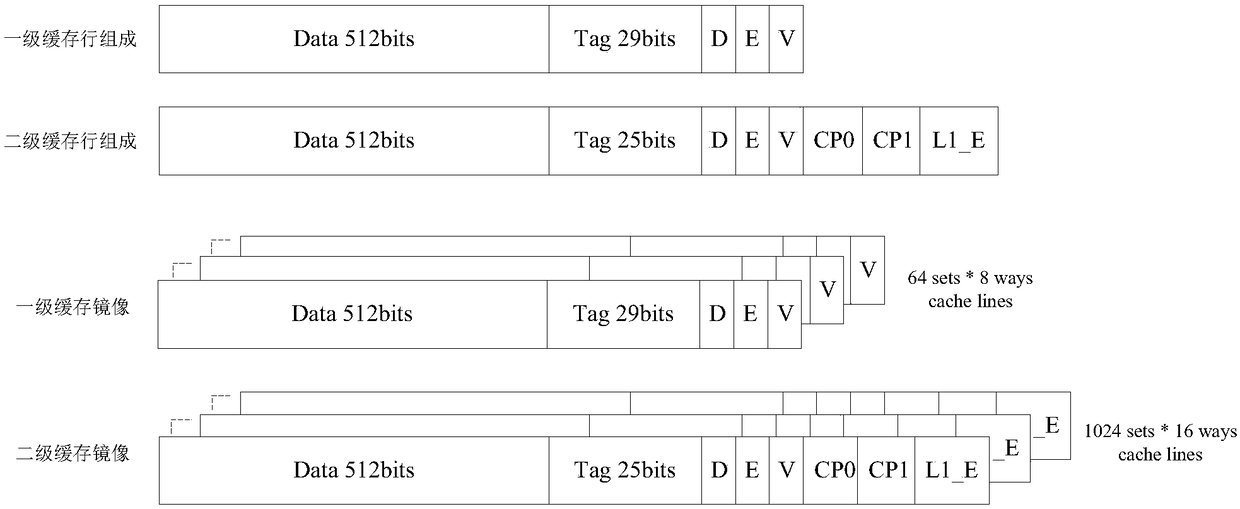

Cache consistency detection system and method

ActiveCN109213641AShorten the verification cycleGuarantee the success rate of one shotDetecting faulty computer hardwareHardware monitoringReal systemsParallel computing

The invention provides a cache consistency detection system and method. The system comprises a plurality of CPU core first-level cache mirror images, first-level cache row detection modules in one-to-one corresponding to the CPU core first-level cache mirror images, a second-level cache mirror image, a second-level cache row detection module corresponding to the second-level cache mirror image, abackfill request monitor, a replacement request monitor, a snoop request monitor and a comparator. The invention can dynamically cover the detection of all application scenes of the real system in real time, and improves the efficiency of cache consistency detection.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

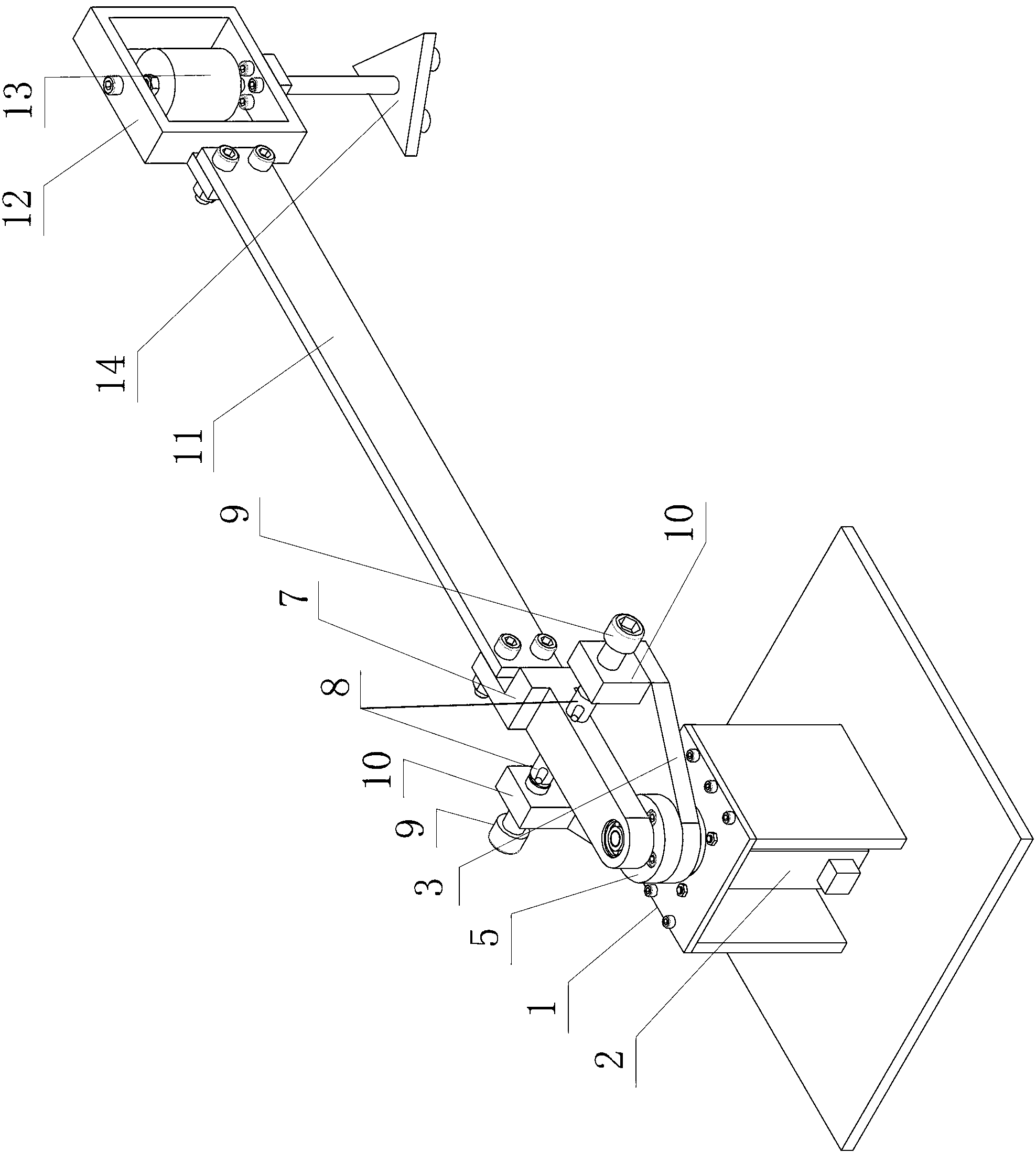

Flexible joint analog device with adjustable gaps of space manipulator

InactiveCN103158150AFlexible withGuaranteed zero-gravity simulation state in spaceProgramme-controlled manipulatorFixed frameEngineering

The invention discloses a flexible joint analog device with adjustable gaps of a space manipulator and relates to a flexible joint analog device. The flexible joint analog device with adjustable gaps of the space manipulator solves the problems that an existing space manipulator flexible joint analog device is difficult in achieving an analog test with large flexible loads and adjustable joint gaps, and a test verification period is long and cost is huge. One end of a driving connection rod is connected with a plate-shaped extending shaft in a rotating mode, and the other end of the driving connection rod is fixedly connected with one end of a flexible shrapnel. The other end of the flexible shrapnel is fixedly connected with the side wall of a load fixed frame, and heavy articles are arranged in the load fixed frame which is fixed on the upper end face of an air floating foot. Two screw fixed seats are symmetrically arranged on the upper end face of a gap adjusting plate with the driving connection rod as a symmetry axis, and each screw fixed seat is provided with a gap adjusting inner hexagon screw. Two force sensors are symmetrically arranged on two side walls of the driving connection rod, and the two force sensors are coaxially arranged with the two gap adjusting inner hexagon screws. The flexible joint analog device with adjustable thee gaps of the space manipulator is used for verifying mechanical properties of the flexible joint analog device.

Owner:HARBIN INST OF TECH

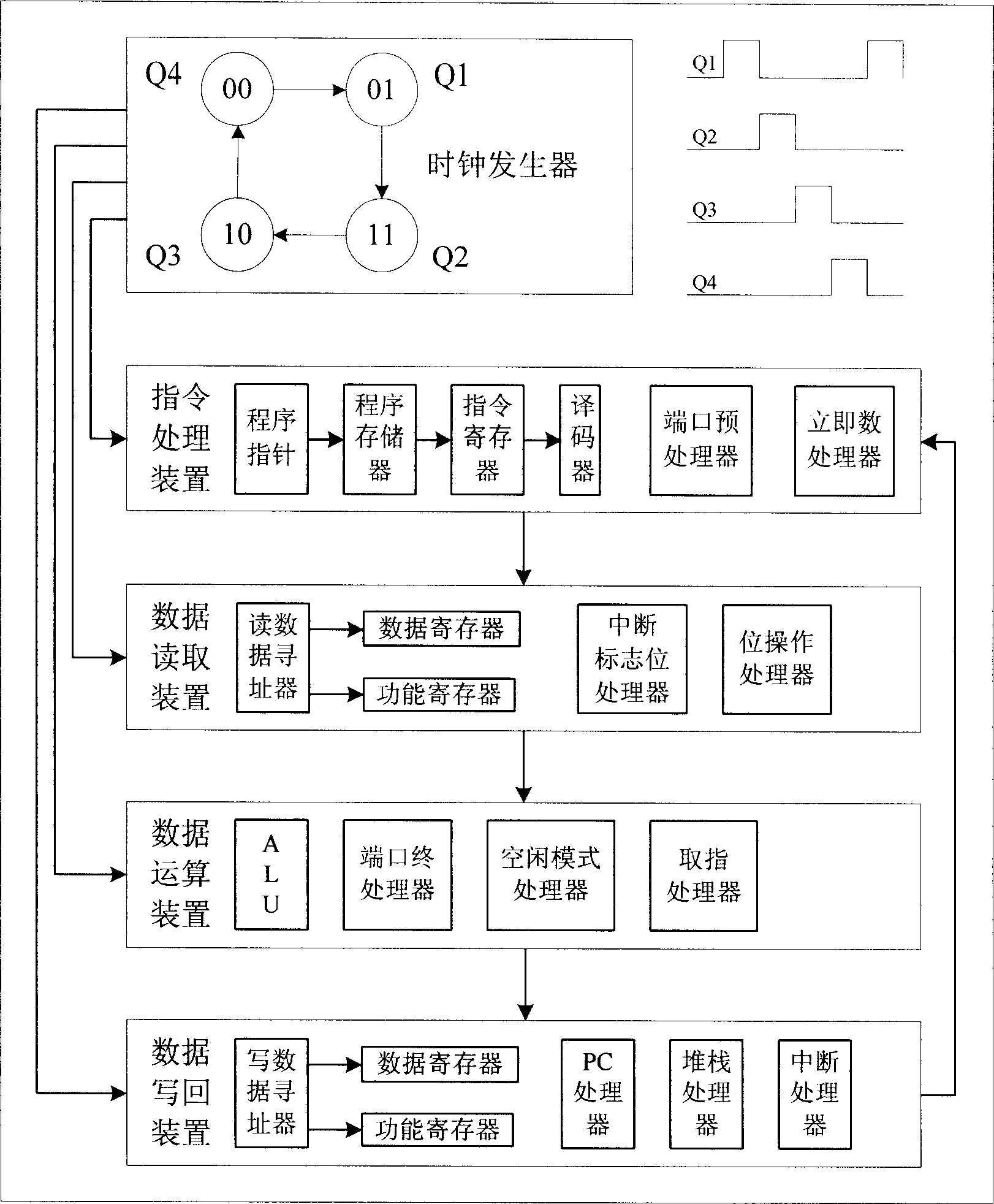

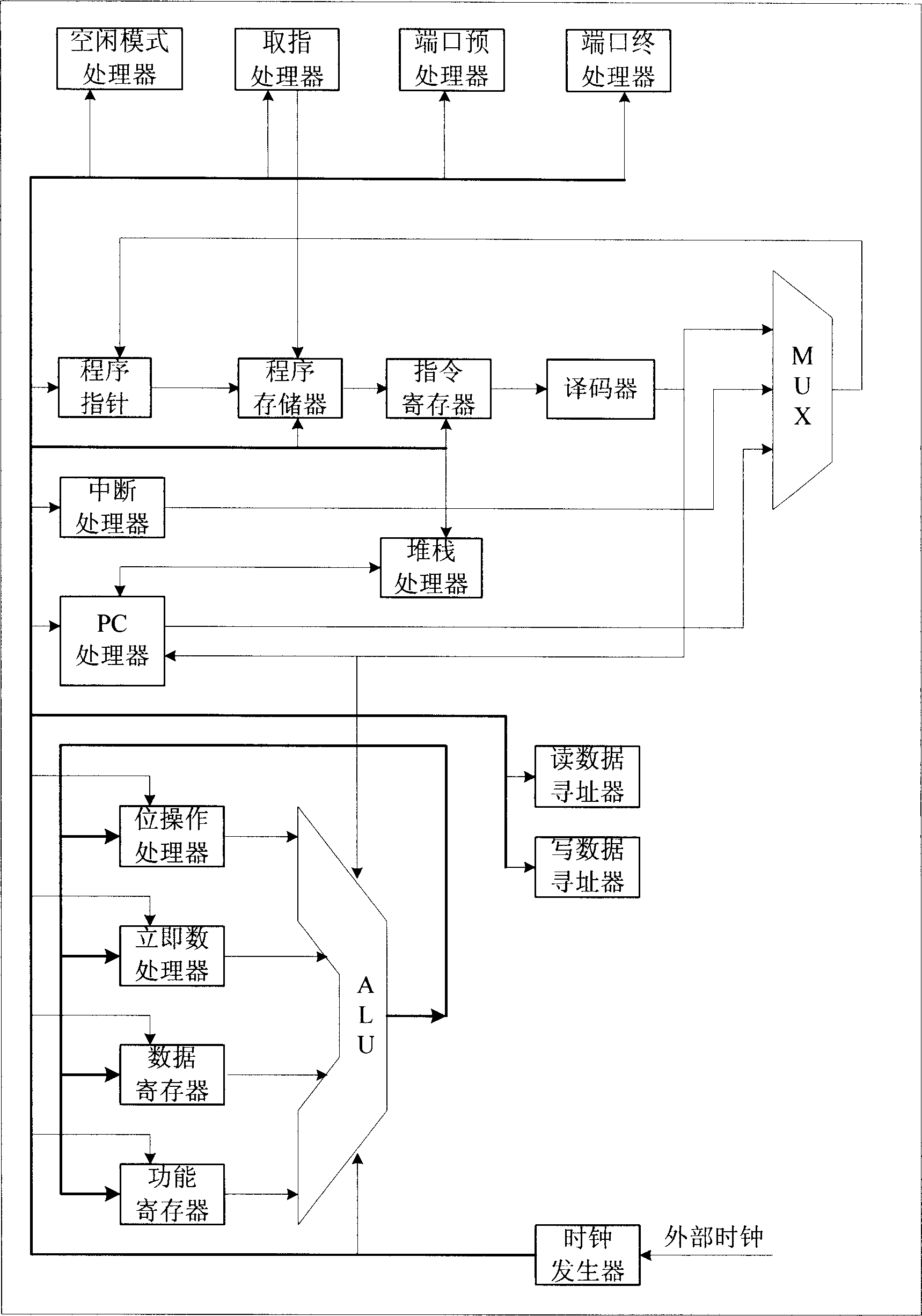

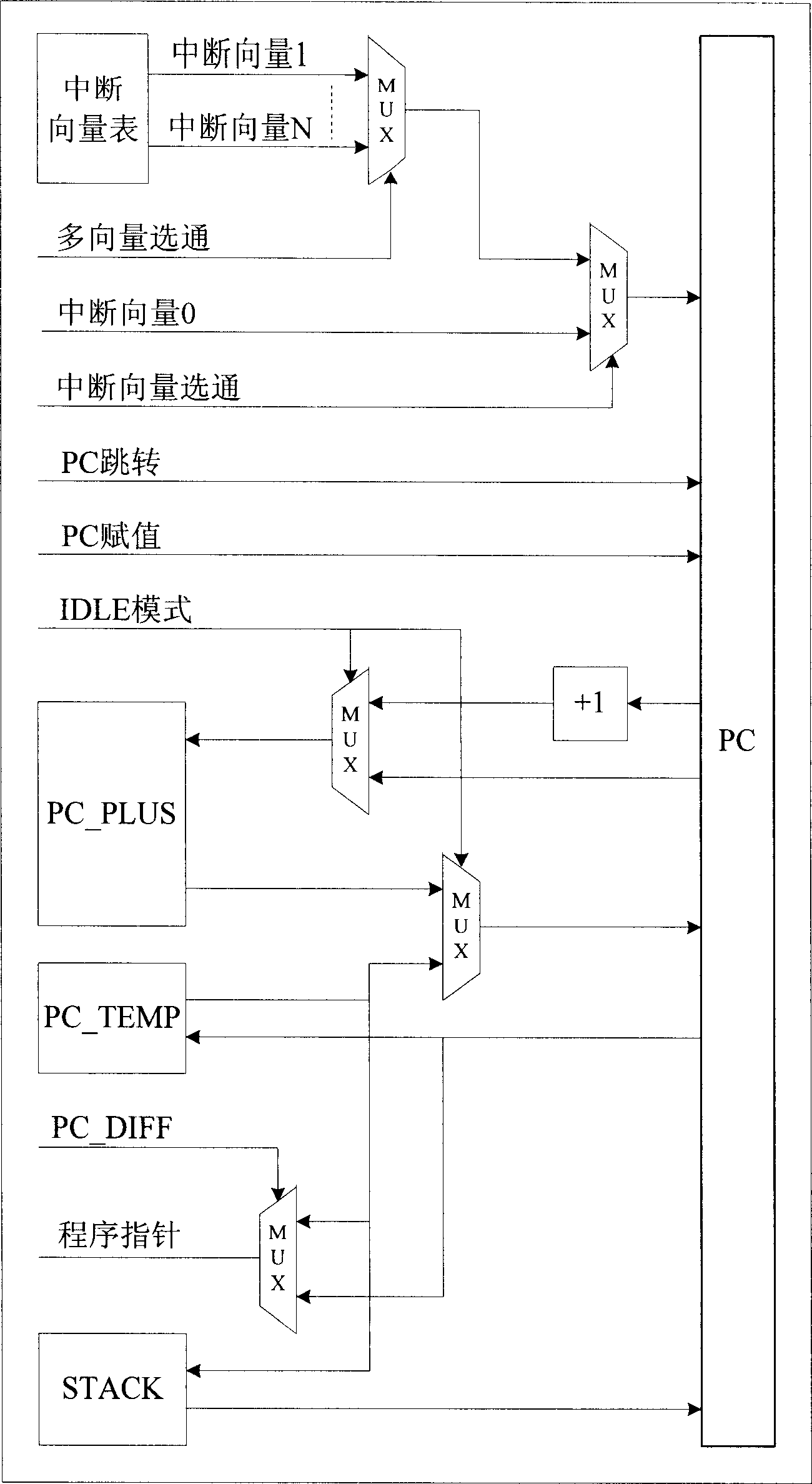

Novel 8 digit RISC micro controller frame

ActiveCN1737750AEfficient interrupt handlingEasy to handleConcurrent instruction executionMemory systemsClock generatorComputer science

This invention discloses one new eight bit RISC micro controller frame, which is characterized by the following: the second degree four section streamline structure comprises order process device, data reading device, data computing device, data writing back device and clock generator. The technique achievements are ad following: making each clock non-crossing coupling to ensure the stable clock; each device relies on each other and to pre-process data to improve the structure to realize the high productivity.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

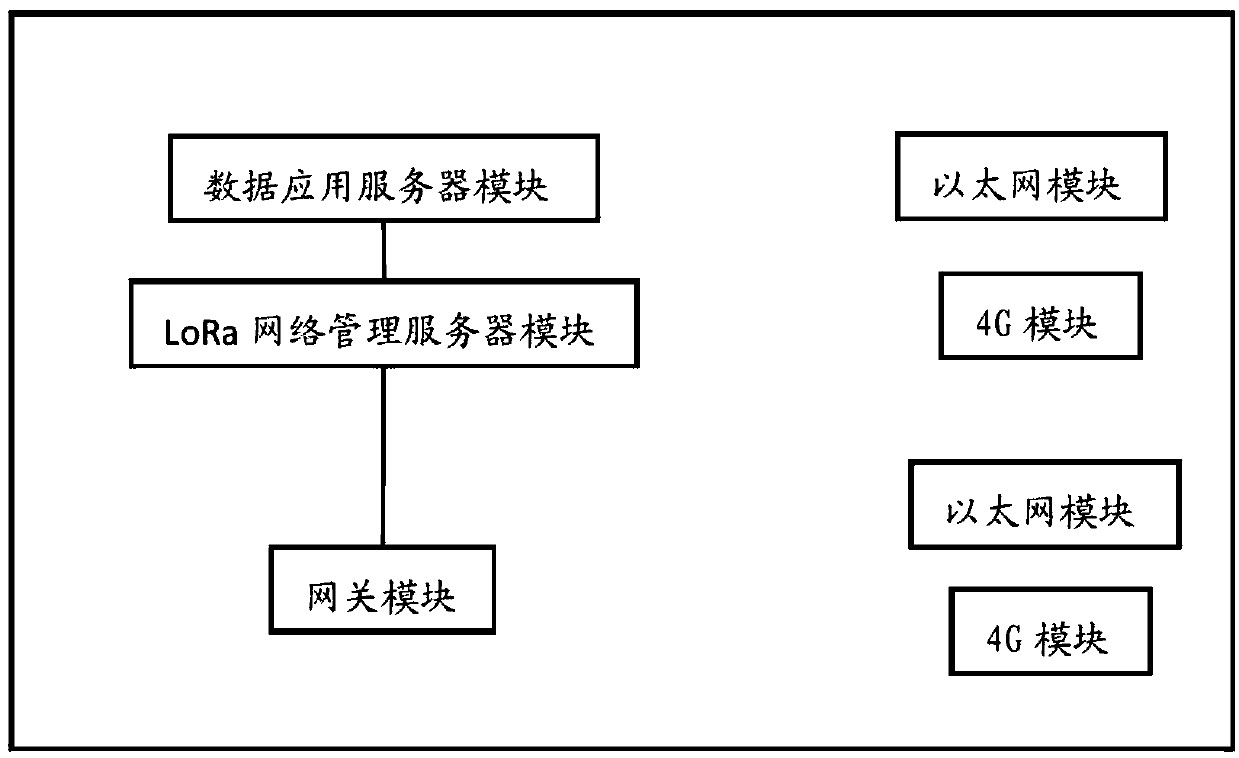

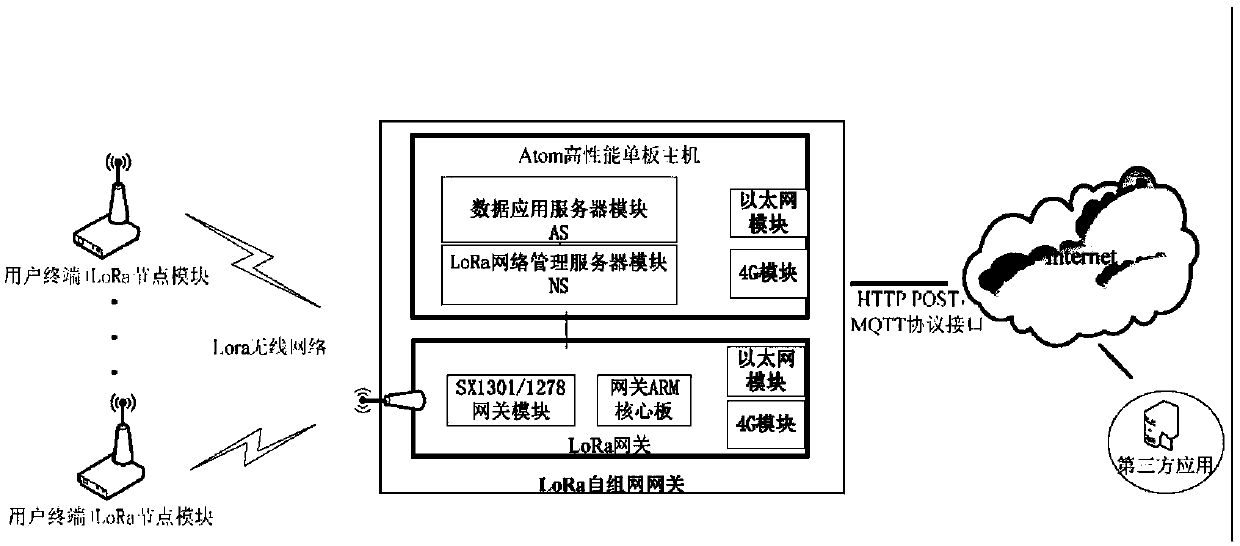

LoRa ad hoc network method and system

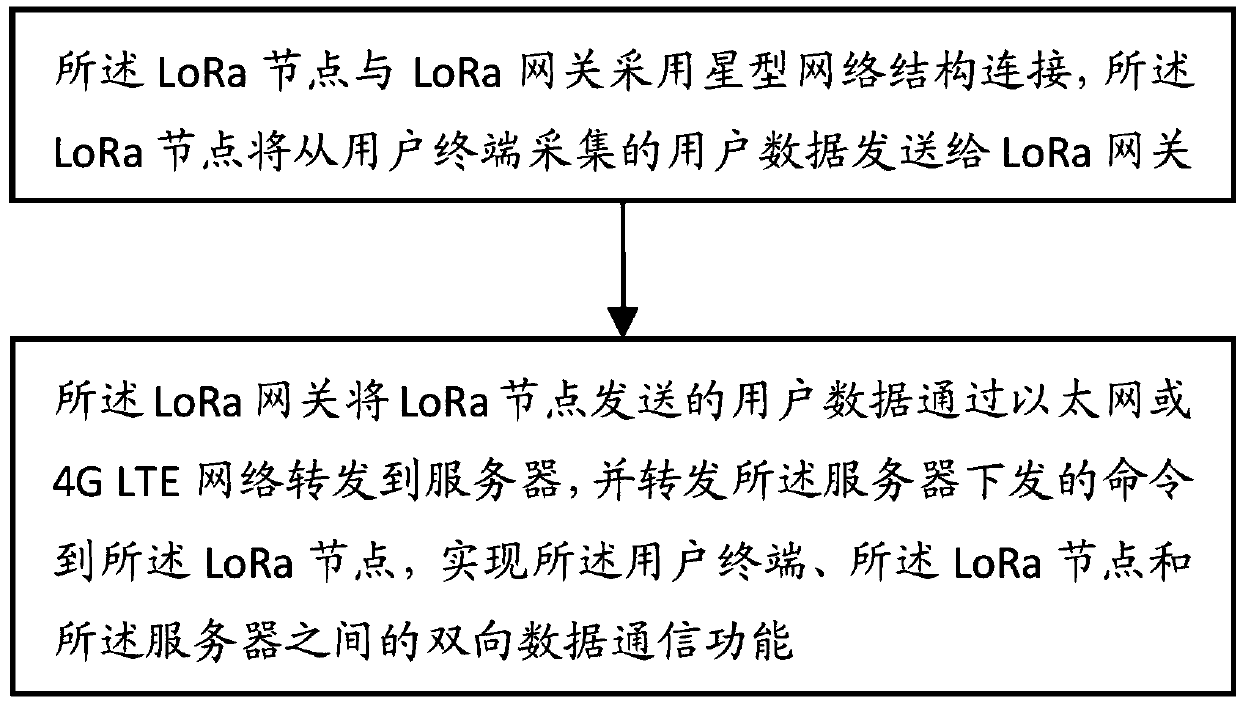

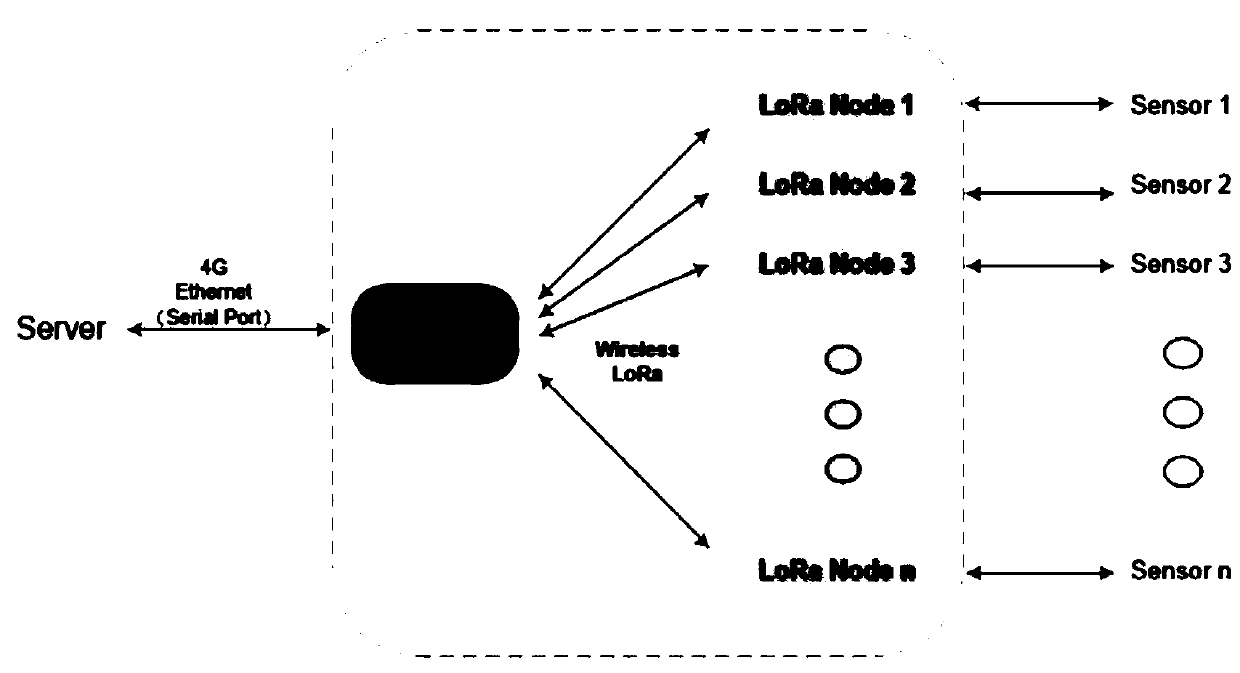

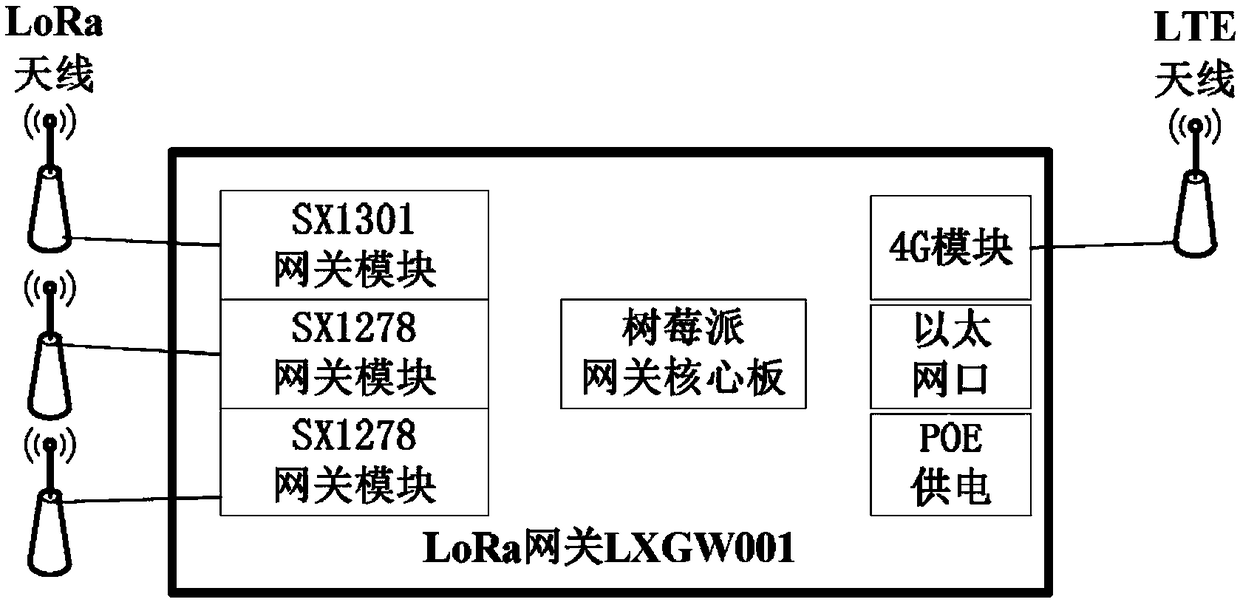

InactiveCN109587023AImprove experienceShorten the time periodNetwork topologiesStar/tree networksStar networkEthernet

The invention discloses a LoRa ad hoc network method and system. The method comprises the following steps: a LoRa node and a LoRa gateway are connected by adopting a star network structure, and the LoRa node transmits user data acquired from a user terminal to the LoRa gateway; the LoRa gateway forwards the user data transmitted by the LoRa node to a server through Ethernet or a 4G LTE network, acommand issued by the server is forwarded to the LoRa node, and a bidirectional data communication function among the user terminal, the LoRa node and the server is realized. Through the embodiment ofthe invention, the user does not need to care about the specific construction process of a LoRa / LoRaWAN wireless network, a standard interface provided by the LoRa ad hoc network only needs to be called to quickly generate the own wireless application solution, the user product development time and the verification cycle are greatly shortened, and the experience of teh user is improved.

Owner:凌犀工业互联网科技(广州)有限公司

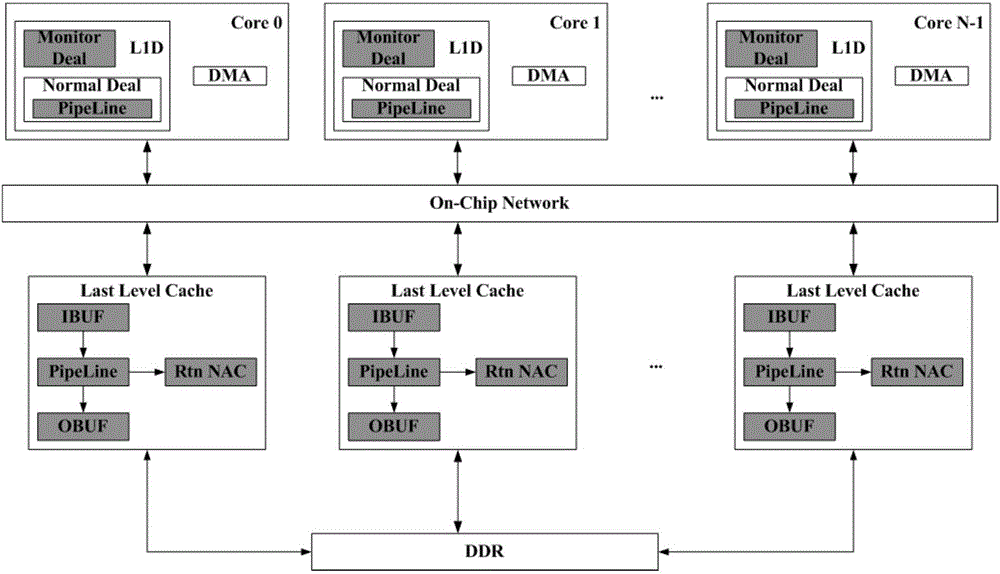

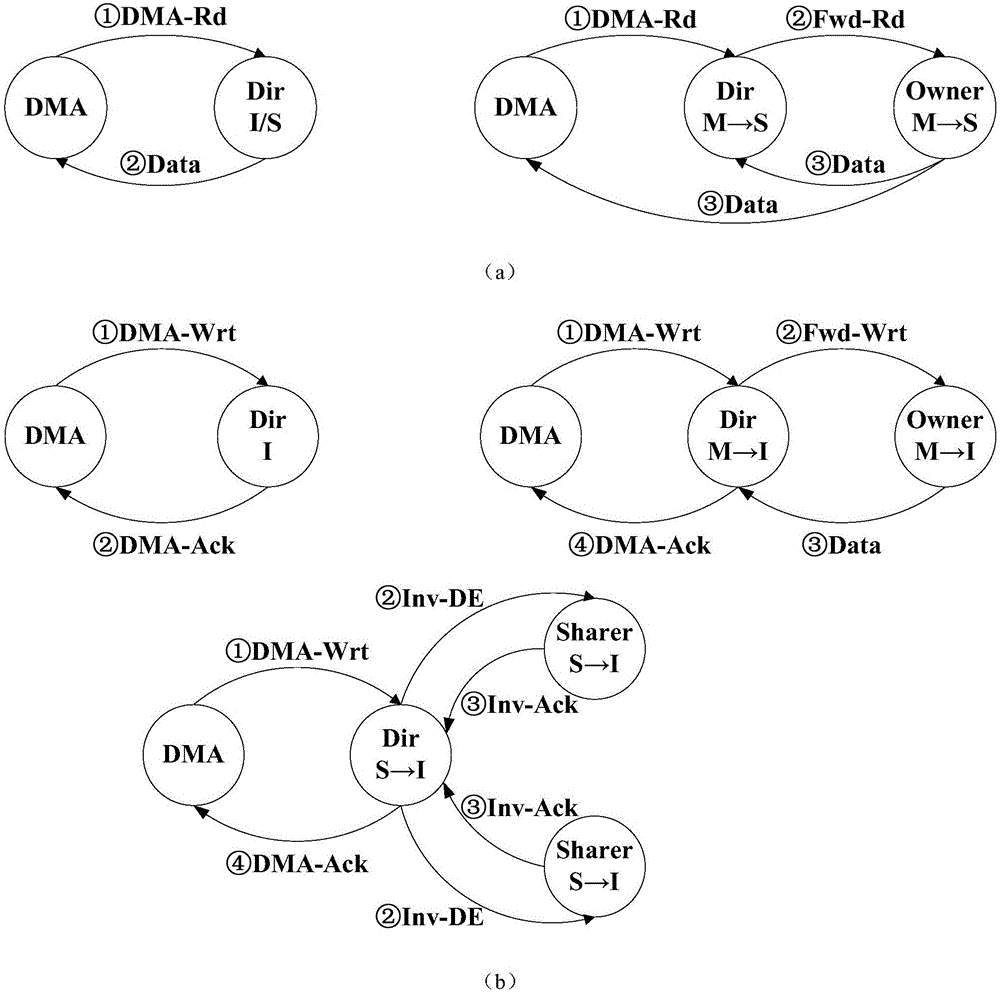

GPDSP framework-oriented multi-kernel directory consistency apparatus

ActiveCN106201939AThe principle is simpleEasy to operateElectric digital data processingMulti kernelLevel data

The invention discloses a GPDSP (General-Purpose Digital Signal Processor) framework-oriented multi-kernel directory consistency apparatus. The apparatus comprises kernels, an on-chip last-level Cache, an off-chip memory DDR and an on-chip interconnection network. Each kernel comprises DMA and L1D, wherein L1D is a first-level data Cache; the DMA is used for finishing transfer of data between a peripheral and the kernel; the L1D comprises two parallel processing units of Normal Deal and Monitor Deal; the Normal Deal processing unit finishes processing of load and store instructions; and the Monitor Deal processing unit is used for making a response to a monitoring request arrived at any moment, and the processing process is not influenced by the Normal Deal processing unit. The on-chip last-level Cache is connected to the on-chip interconnection network in a distributed way. Data in the off-chip memory DDR is cached in the L1D and the on-chip last-level Cache. The on-chip interconnection network is used for receiving a network request, performing decoding processing first to obtain a destination node and a destination device after receiving the network request, and sending the request to a corresponding position. The apparatus has the advantages of simple principle, convenient operation, high flexibility, wide application range and the like.

Owner:NAT UNIV OF DEFENSE TECH

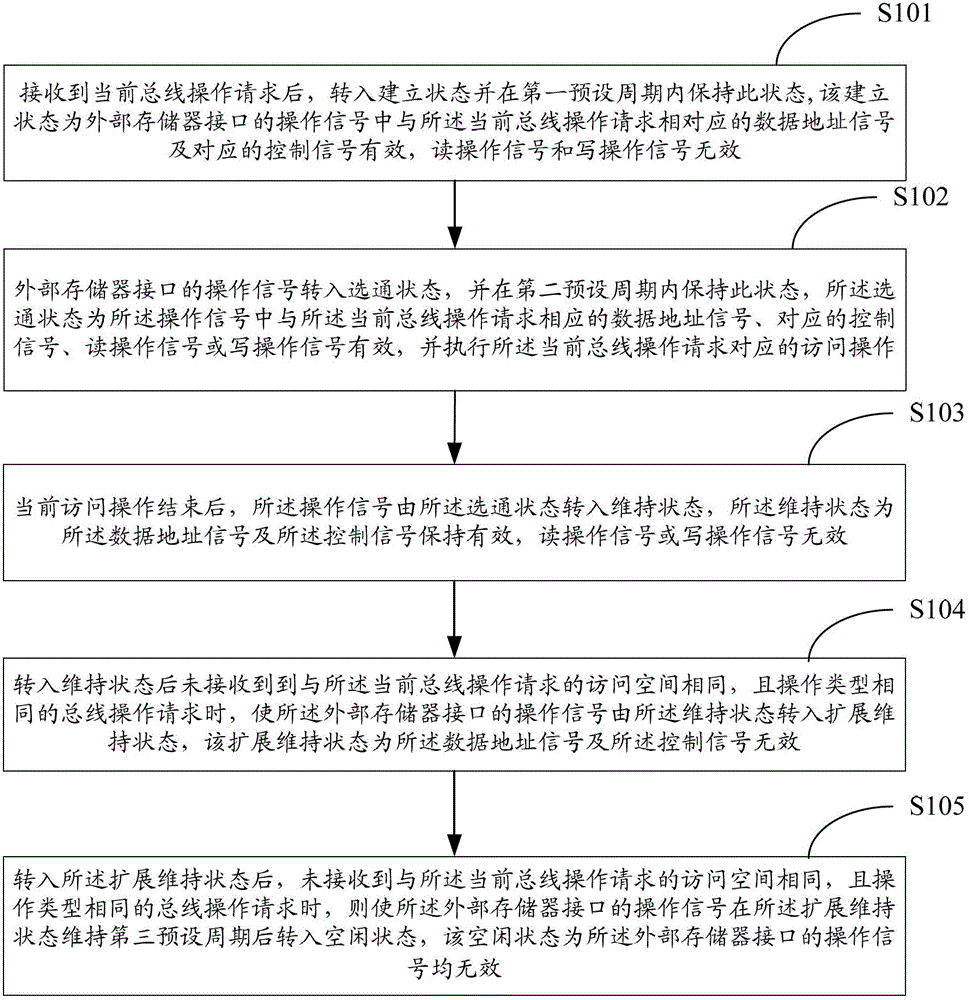

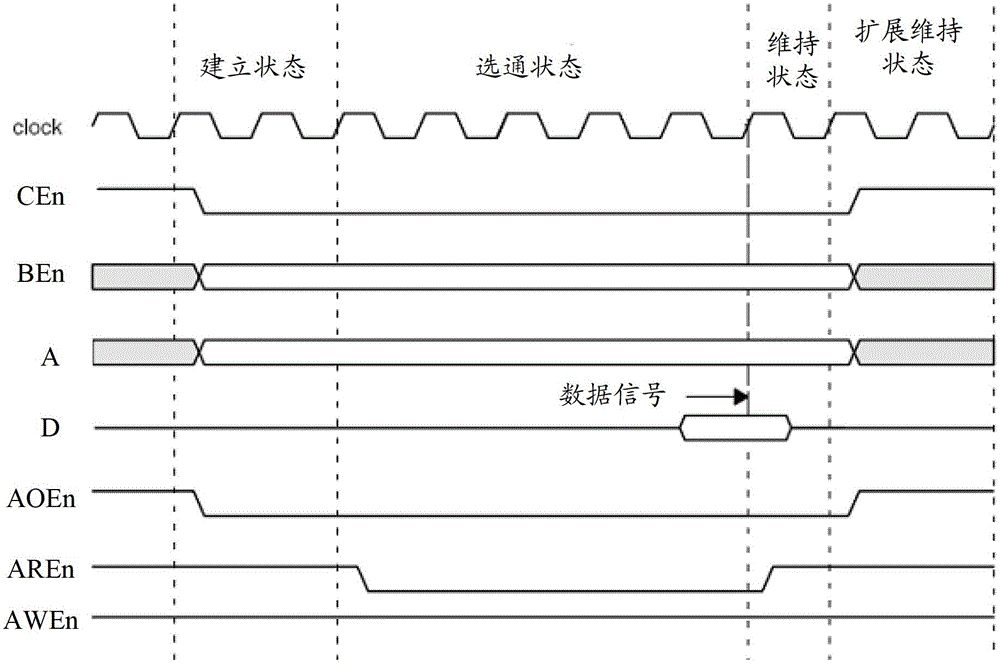

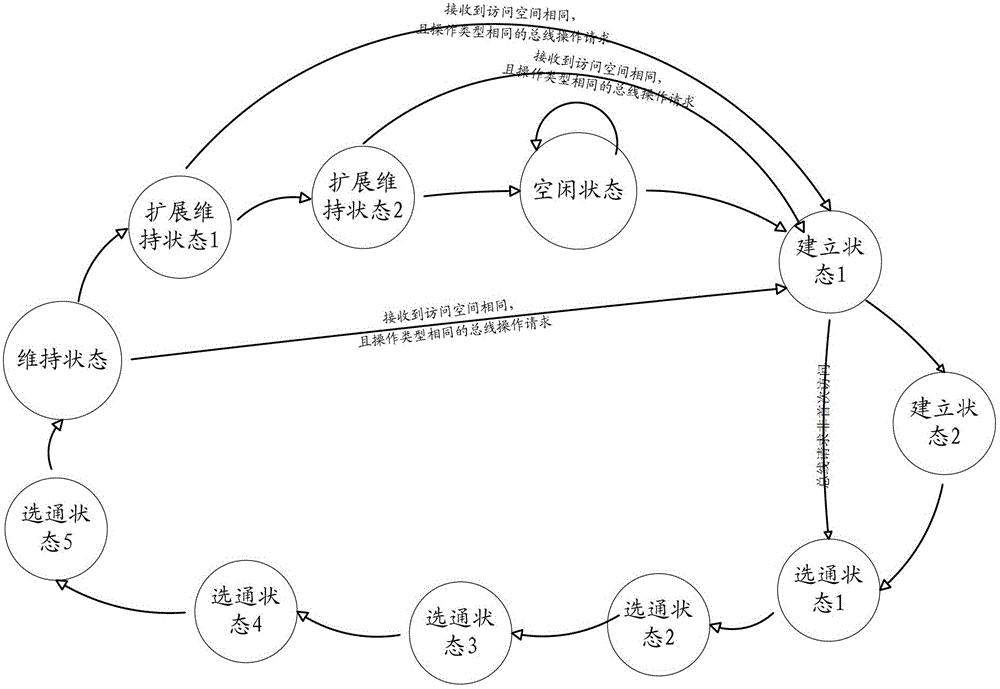

Bus interface conversion method and bus bridging device

ActiveCN102722457AShorten the verification cycleLow costElectric digital data processingAdvanced Microcontroller Bus ArchitectureComputer module

The invention discloses a bus interface conversion method and a bus bridging device. The bus interface conversion method is specifically characterized by comprising the steps of generating operation signals according with the timing sequence states of an interface of an external memory according to the received bus operating requirements, and executing the corresponding operation so as to establish the communication between a system on a chip on the basis of the bus and a wireless communication module based on the interface of the external memory, wherein the timing sequence states of the interface of the external memory comprise an idle state, an establishment state, a gating state, a maintenance state, and an extended maintenance state. In this way, when a wireless communication module processed verified by FPGA (field programmable gate array) is transplanted to the system on the chip on the basis of an AMBA (advanced microcontroller bus architecture) bus, bus read-write operation requirements can be converted into the read-write operation time sequence of the interface of the external memory, the redesign to the AMBA bus interface of the wireless communication module can be avoided, the verification period is shortened after the wireless communication module is integrated to the system on the chip on the basis of the AMBA bus, and the cost of the system on the chip on the basis of the AMBA bus is lowered.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

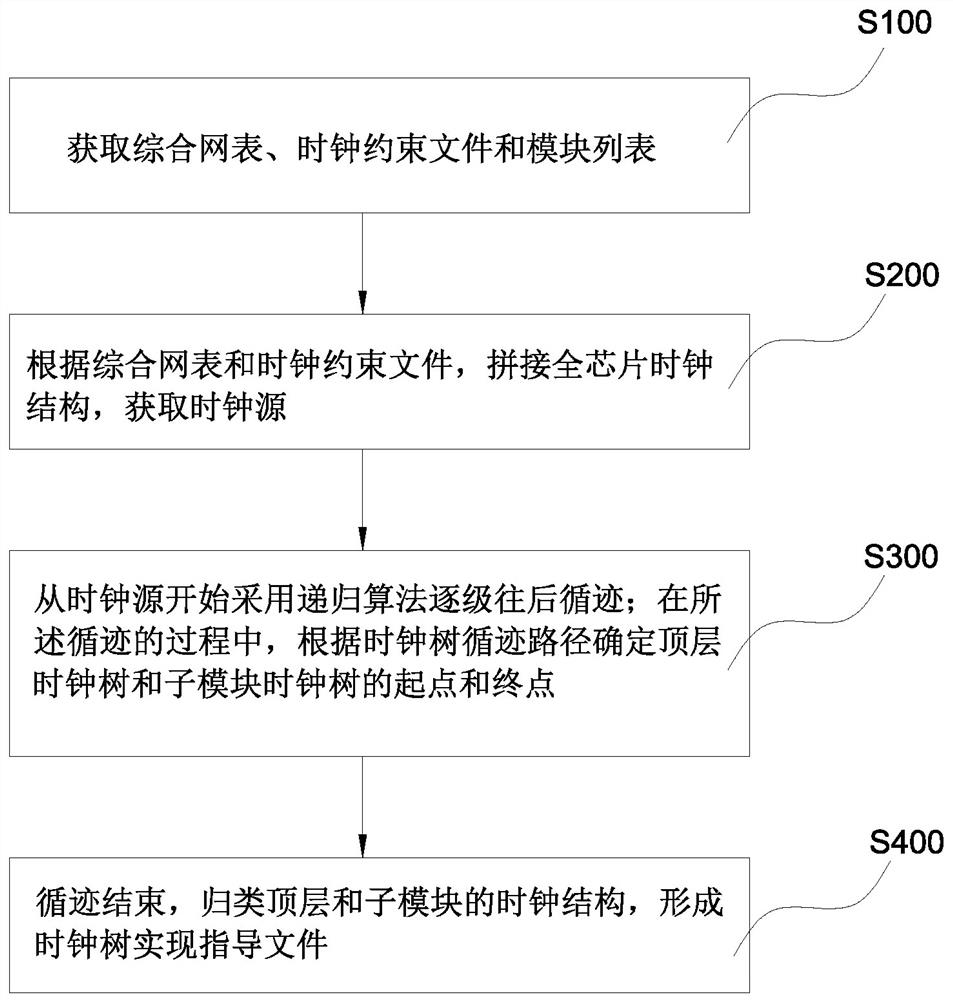

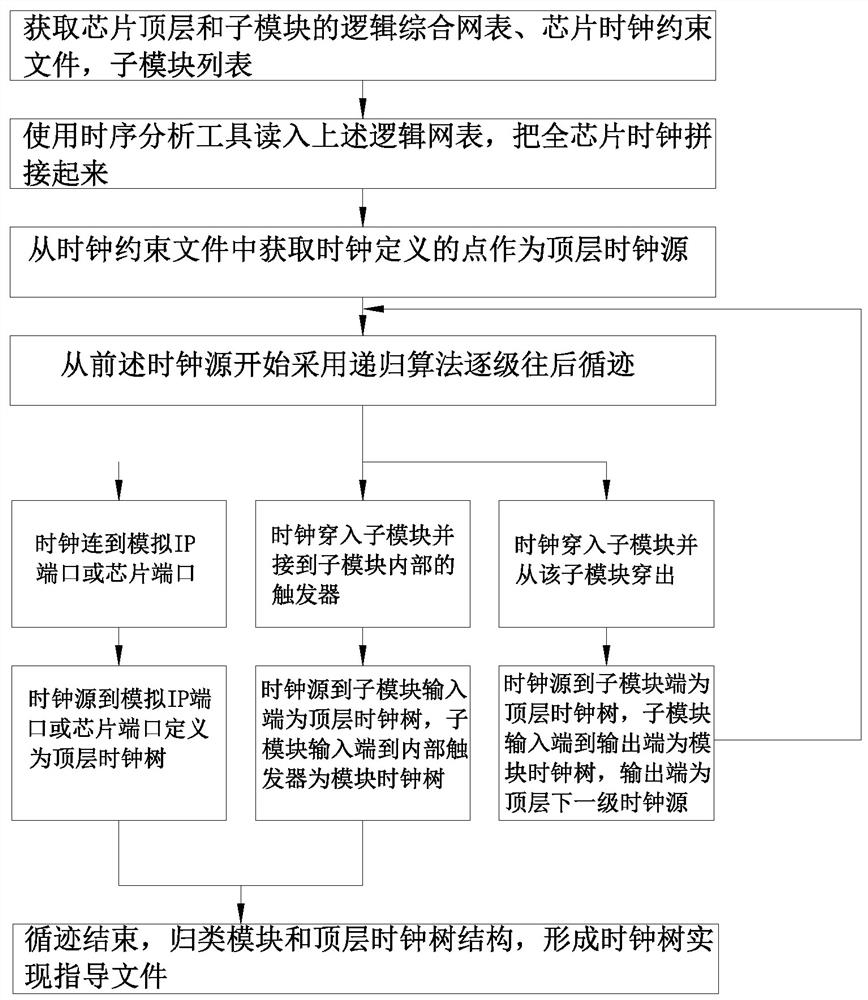

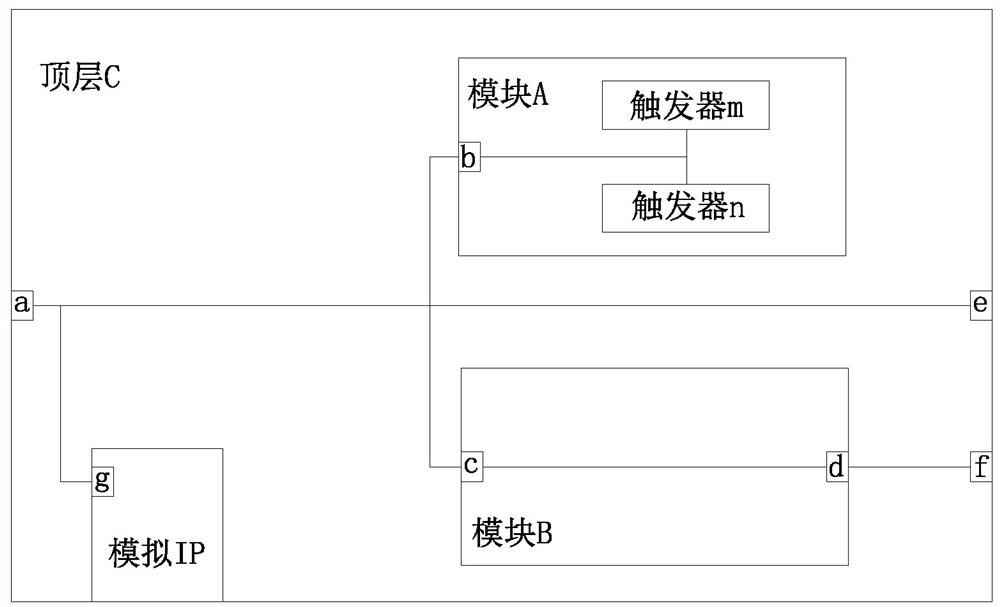

Method for extracting clock tree based on comprehensive netlist in chip design and application

PendingCN113569524AReduce workloadShorten the verification cycleCAD circuit designConstraint-based CADIntegrated circuitCircuit design

The invention discloses a method for extracting a clock tree based on a comprehensive netlist in chip design and application, and relates to the technical field of integrated circuit design. The method comprises the following steps: in a logic synthesis step, obtaining logic synthesis netlist information of a chip top layer and a sub-module, and module information and clock constraint file information of chip segmentation; splicing a clock structure of the whole chip according to the obtained information, and obtaining a clock source from a clock constraint file; based on full-chip clock structure information, performing tracking backwards step by step from a clock source by adopting a recursive algorithm to form a full-chip clock tree network; in the tracking process, determining starting points and ending points of the top-layer clock tree and the sub-module clock tree according to the clock tree tracking path; and after the tracking is finished, classifying the clock structures of the top layer and the sub-modules to form a clock tree implementation guidance file. According to the method, the clock tree verification period is shortened, and the efficiency and correctness of clock tree implementation work are improved.

Owner:MOLCHIP TECH (SHANGHAI) CO LTD

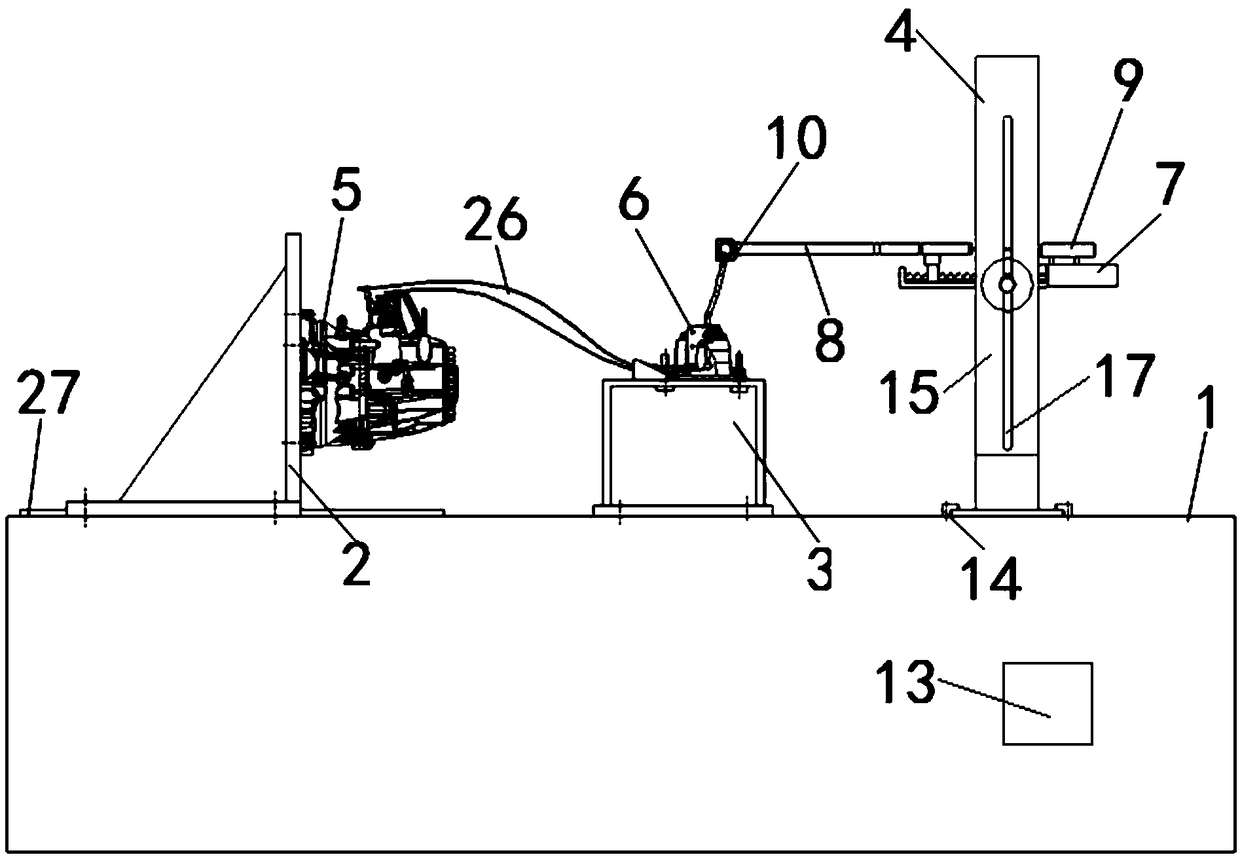

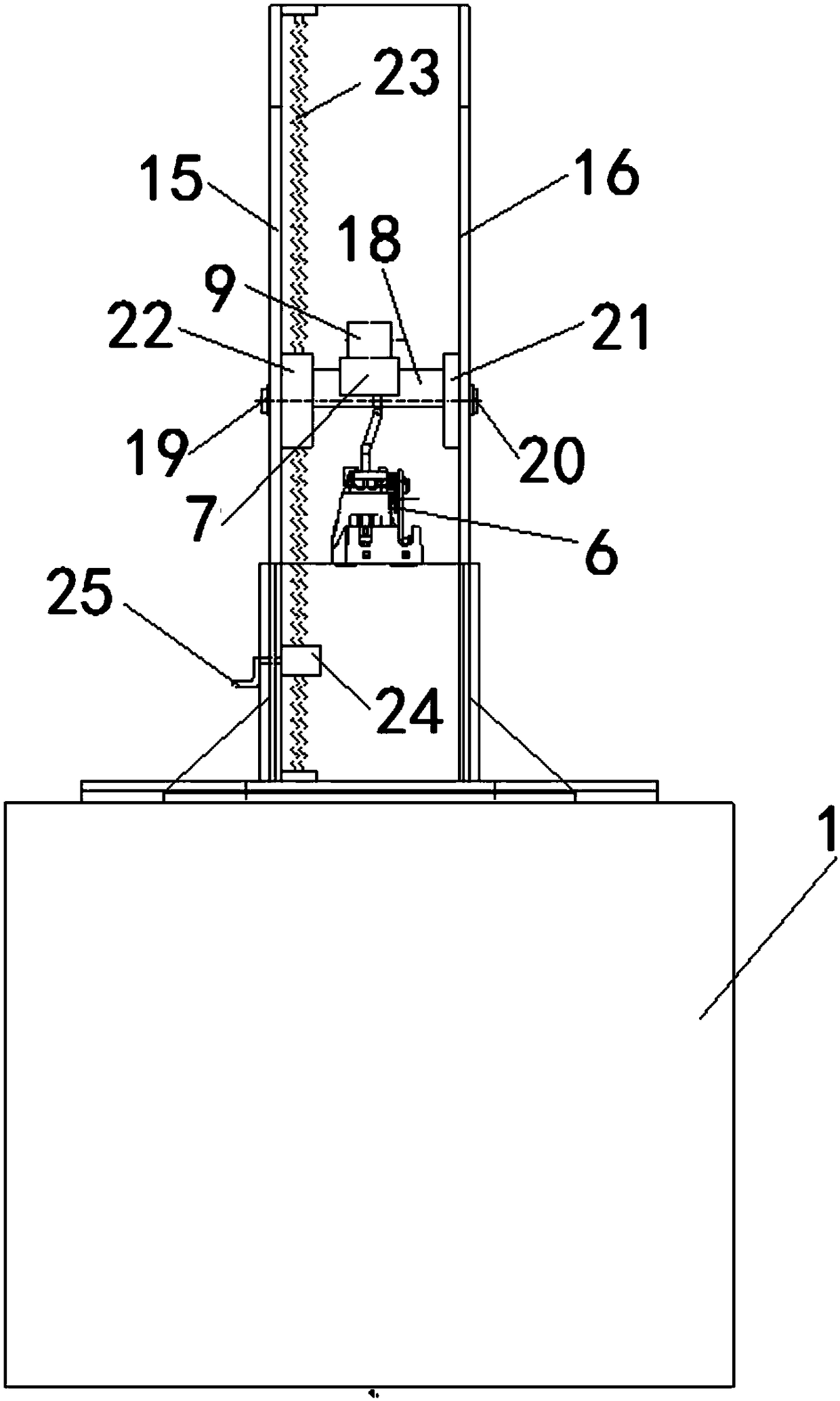

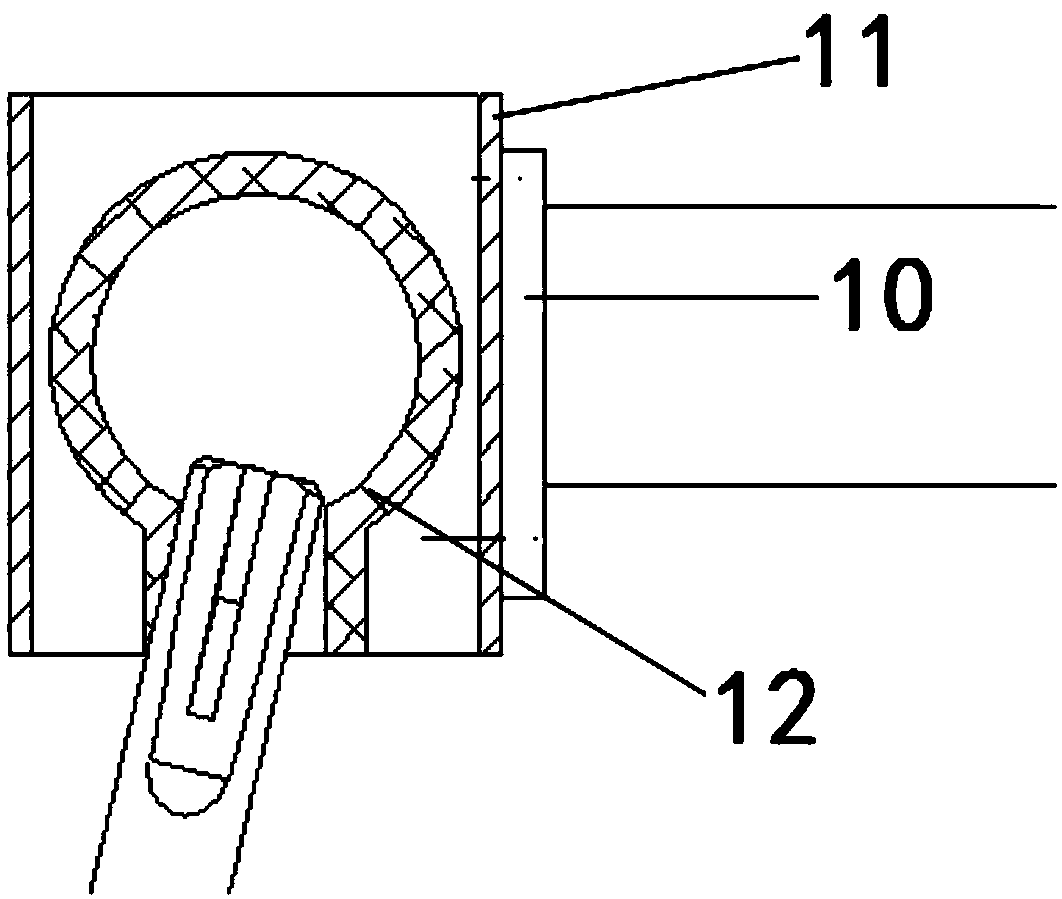

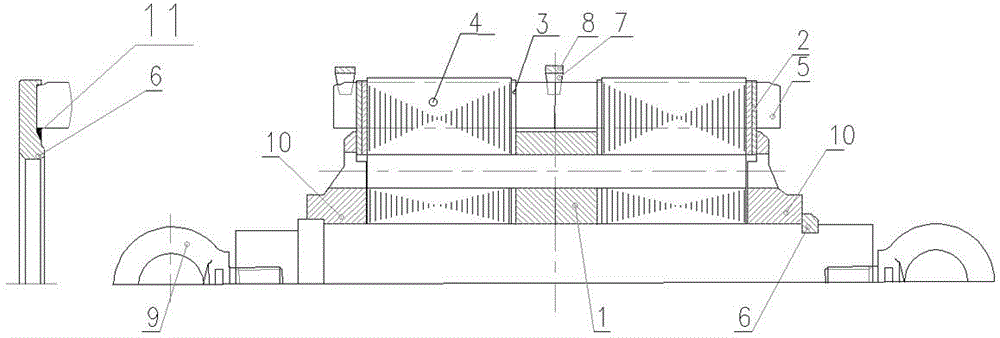

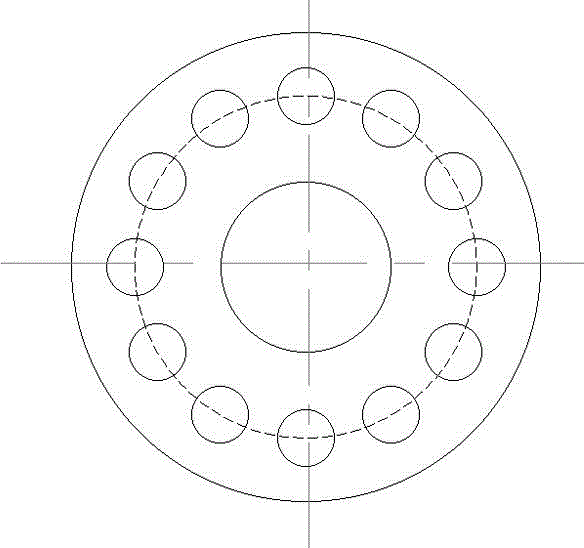

Automobile power system shift performance test device and shift performance test method

The present invention provides an automobile power system shift performance test device applied to the technical field of power system performance test. The present invention provides an automobile power system shift performance test method. A test substrate (1) of the automobile power system shift performance test device is provided with a gearbox mounting bracket (2), a shift mechanism installation bracket (3) and a servo drive support (4), a servo motor (7) on the servo drive support (4) is connected with one end of an execution mechanism (8), the servo motor (7) is provided with a pull lever displacement sensor (9), the other end of the execution mechanism (8) is provided with a pull-press force sensor (10), and the pull-press force sensor (10) is connected with a shift casing pipe (11). The automobile power system shift performance test device can conveniently and accurately simulate the state of the whole vehicle to allow the vehicle selection and shift performance test operationto be simple and improve the product shift quality.

Owner:ZOTYE INT AUTOMOBILE TRADING CO LTD

Motor rotor end ring-guide bar medium-frequency induction brazing verifying tooling and method

ActiveCN104022605AEffective Quality VerificationImprove labor productivityManufacturing stator/rotor bodiesPunchingMedium frequency

The invention relates to a motor rotor end ring-guide bar medium-frequency induction brazing verifying tooling, comprising a rotor separator, rotor end plates I and rotor end plates II, wherein the rotor separator is arranged in the middle of a rotor core punching plate, and divides the rotor core punching plate and a guide bar into two parts; the outer diameter of the rotor separator is smaller than the inner diameter of a circle on which the guide bar is located; the rotor end plates I with pre-pressing curved radians are respectively arranged at the sides of the end rings at two sides; the rotor end plates II are respectively arranged at two sides of the rotor separator. The end ring-guide bar component after being brazed is smoothly taken out by adopting a split structure by combining with the structure characteristics of a traditional motor rotor, the manufacturing period is short, time and labor are saved, just the end rings, the guide bar, a silver solder and a welding agent need to be fed, the motor rotor end ring-guide bar medium-frequency induction brazing verifying tooling can be repeatedly utilized, and is large in operation space, and convenient to maintain, and verification of the performance of the actual motor rotor end ring-guide bar medium-frequency induction brazing product is met.

Owner:CRRC YONGJI ELECTRIC CO LTD

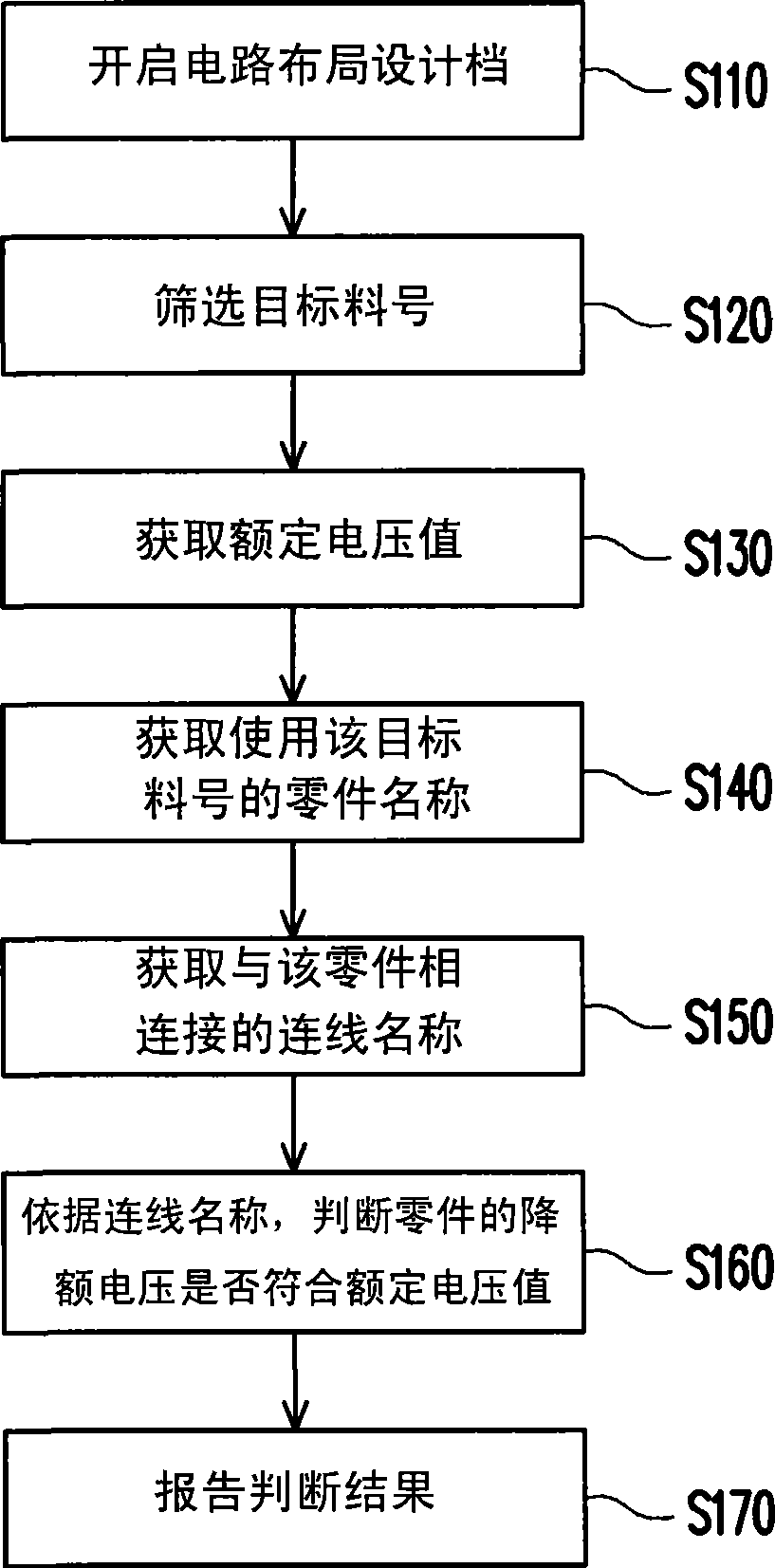

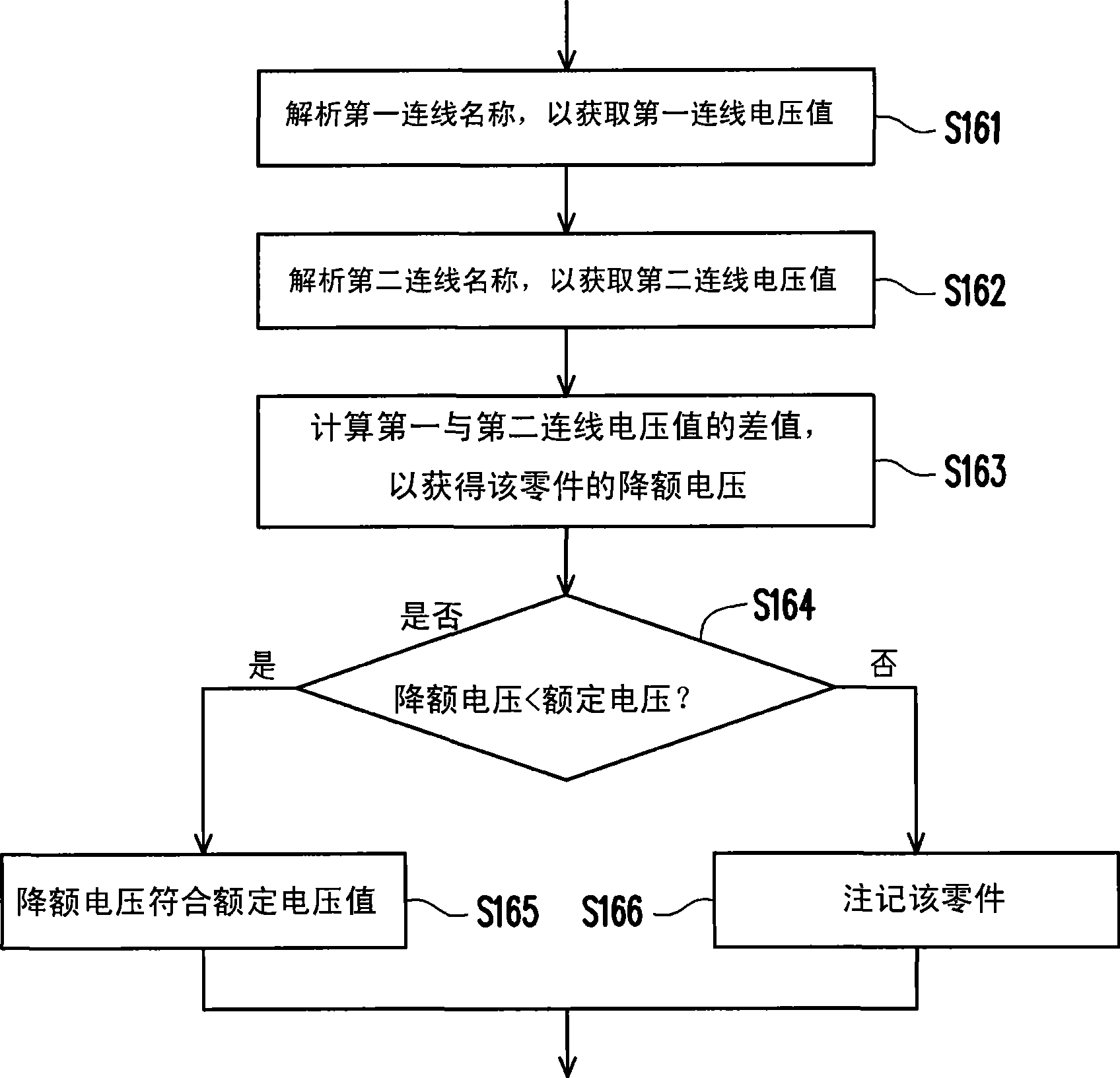

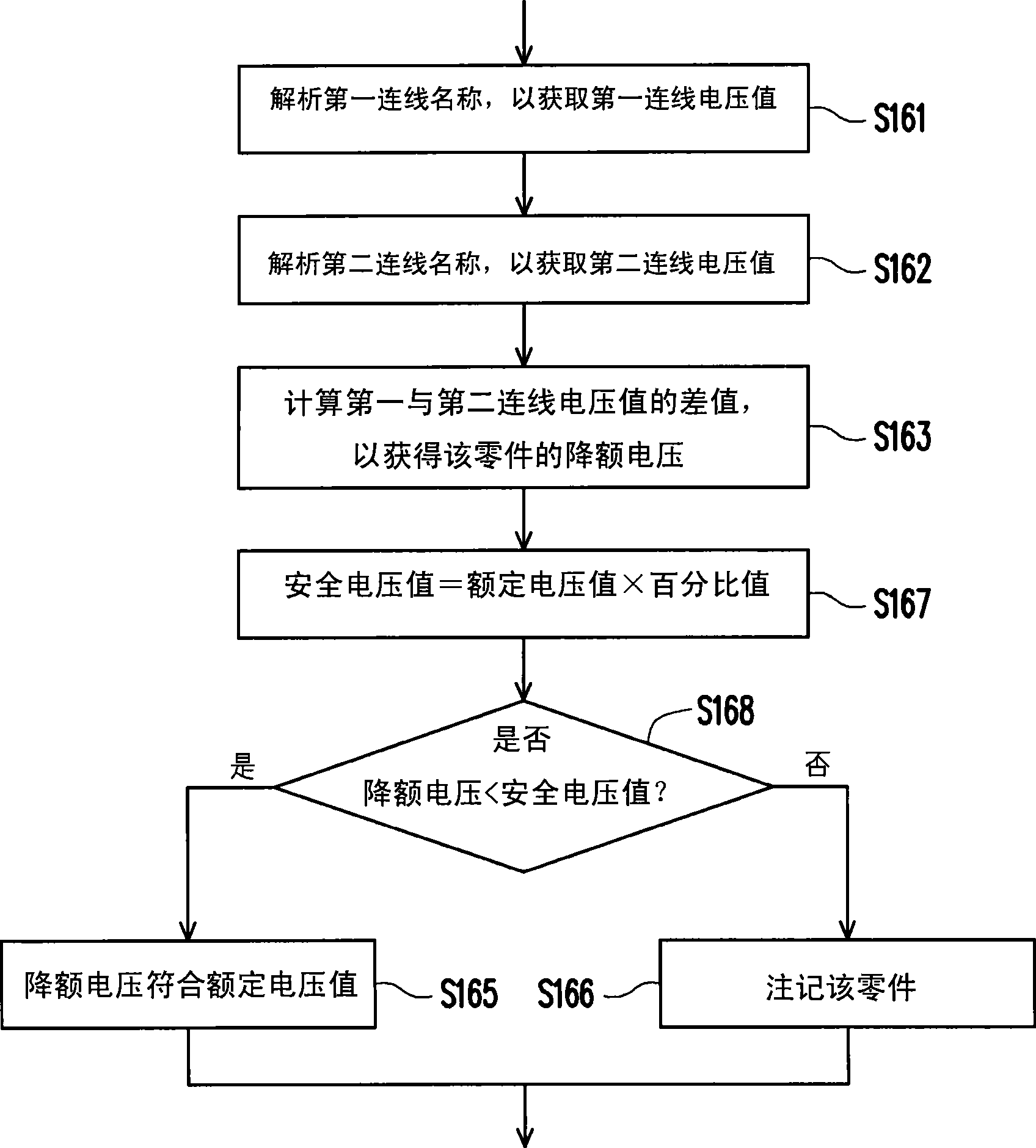

Derating checking method and computer-readable storage medium

InactiveCN101470763ASave man hoursShorten the verification cycleSpecial data processing applicationsVoltage ratingInspection method

The invention discloses a derating inspection method, which comprises opening a circuit layout design gear, screening at least one target part number belonging to the target class from a plurality of part numbers (parts number) used in the circuit layout design gear, obtaining the rated voltage value according to the target part number, obtaining the element number of at least one element using the target part number in the circuit layout design gear according to the target part number, obtaining a first connection name (net name) and a second connection name respectively connected with the two ends of the element according to the element name, and judging whether the derating voltage of the element fits for the rated voltage value according to the first connection name and the second connection name.

Owner:INVENTEC CORP

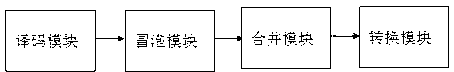

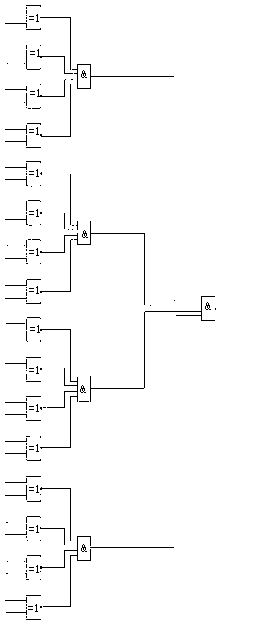

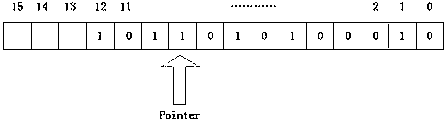

Message filtering system and message filtering method of high-speed interconnection bus

The invention discloses a message filtering system and a message filtering method of a high-speed interconnection bus. The message filtering system comprises a decoding module, a bubbling module connected with the decoding module, a combining module connected with the bubbling module and a converting module connected with the combining module. By the aid of the message filtering system of the high-speed interconnection bus, data transmitted on the high-speed interconnection bus are decoded, effective data messages are kept, invalid information in the data is filtered, and a data stream after filtering is subjected to clock domain conversion by means of asynchronous FIFO (first in first out) and further is converted from a high-frequency clock domain of the high-speed interconnection bus to a lower-frequency clock domain of an FPGA (field programmable gate array) chip core logic, so that requirements on frequency and resources are lowered, the problem about limitation of an FPGA verification system is solved, and design flexibility of the high-speed interconnection bus is improved. By means of reducing risks and difficulty of an FPGA prototype system, a product verification cycle is shortened, and the success rate of chip putting is increased.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

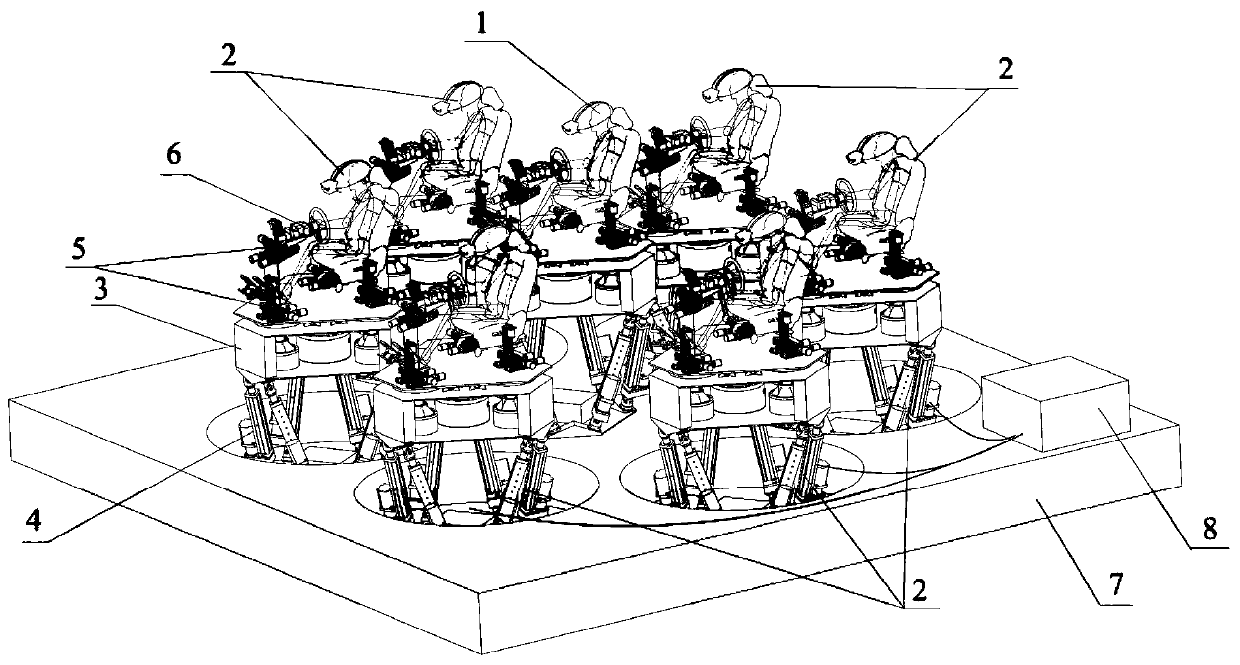

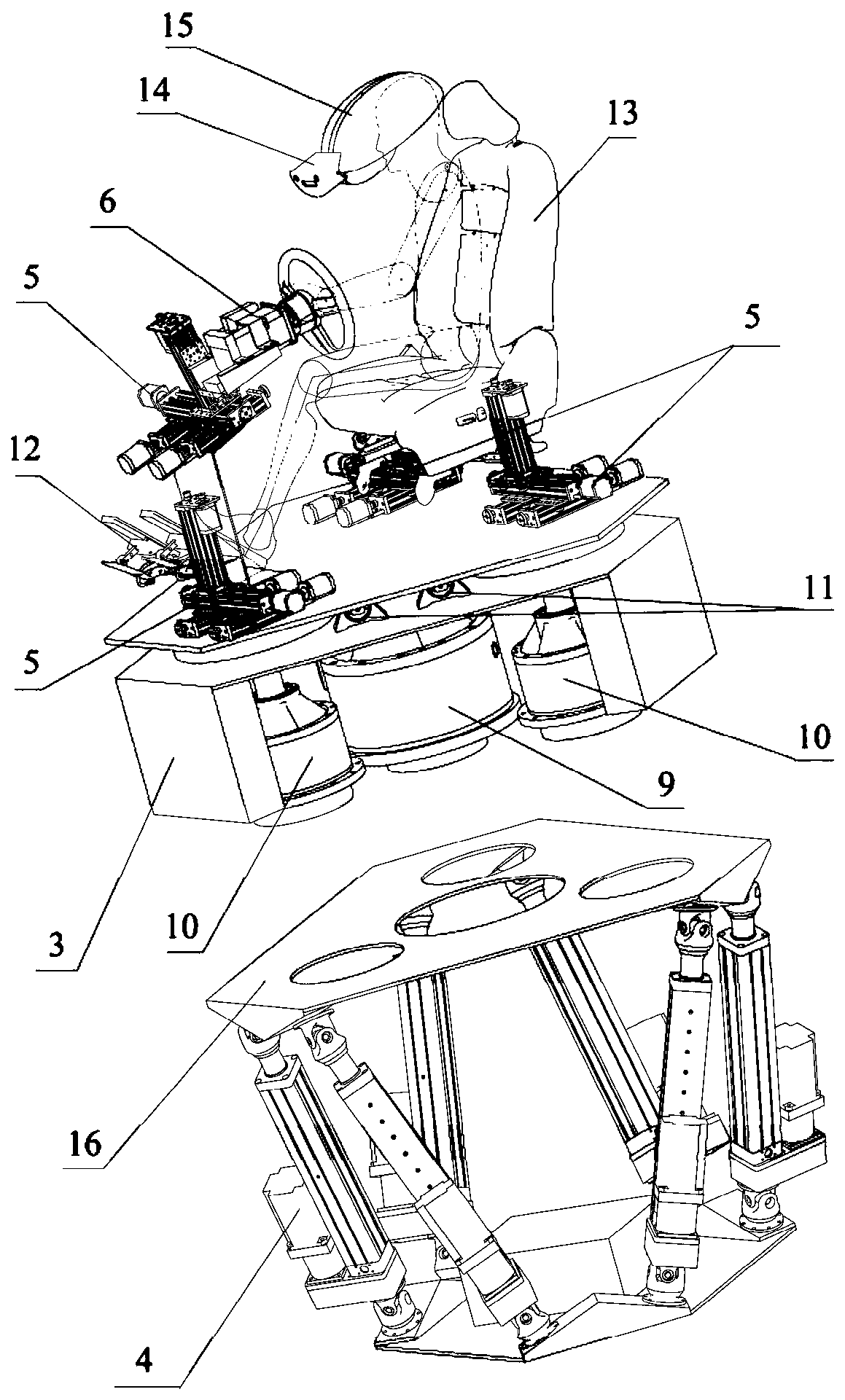

High-precision virtual reality intelligent driving simulator group for universal vehicle types and driving scenes

ActiveCN109785709AHigh simulationImprove test resultsVehicle testingCosmonautic condition simulationsElectricityActuator

The invention discloses a high-precision virtual reality intelligent driving simulator group for universal vehicle types and driving scenes, wherein the simulator group comprises a main vehicle simulator single unit, a plurality of traffic vehicle simulator single units, a controller assembly, a sensor in-ring assembly and an actuator in-ring assembly, the main vehicle simulator single unit and the traffic vehicle simulator single unit have the same mechanical structures and are fixedly connected with the ground infrastructure through a lower motion platform assembly, the plurality of trafficvehicle simulator single units are arranged around the main vehicle simulator single unit, the main vehicle simulator single unit and the plurality of traffic vehicle simulator single units are tangent to each other in an enveloping space formed in the space motion limit of the part above the ground infrastructure, the controller assembly is electrically connected with the main vehicle simulator single unit, the plurality of traffic vehicle simulator single units, the sensor in-ring assembly and the actuator in-ring assembly respectively, and the simulator group has the advantages that the corresponding materials of the parts are reasonably selected, and the service life is higher; the test and verification period based on large-scale road tests is shortened.

Owner:HENAN UNIV OF SCI & TECH

LED (Light Emitting Diode) display screen control device and control method capable of randomly arranging pixels

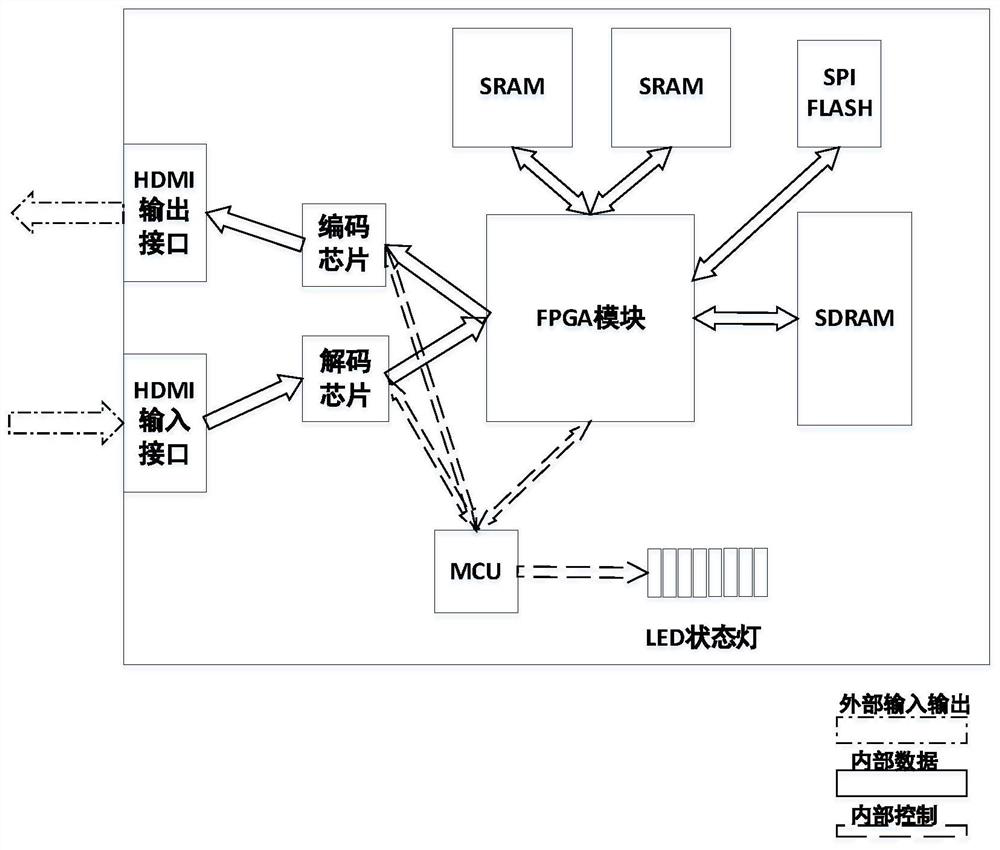

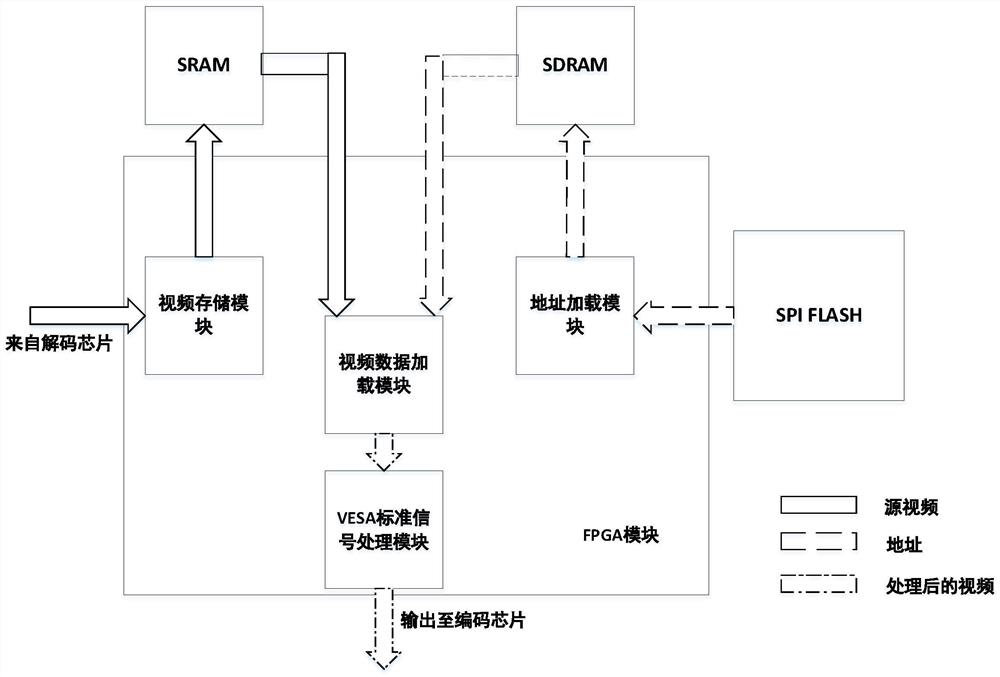

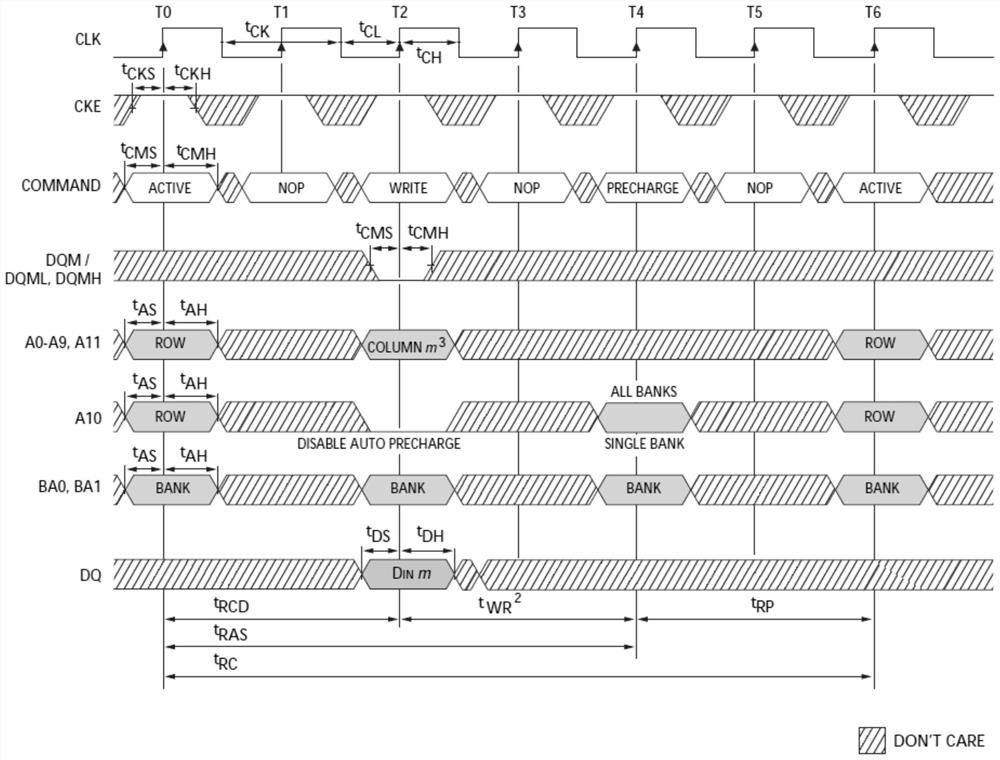

ActiveCN112967666AImprove bandwidth characteristicsMeet display needsStatic indicating devicesLED displayHigh bandwidth

The invention provides an LED display screen control device and control method capable of carrying out pixel random arrangement, and the device comprises a decoding chip which is used for decoding a video source signal into a TTL video signal; a coding chip which is used for coding the VESA standard signal into a differential signal; a SRAM array which is used for storing TTL video signals; a SPIFLASH which is used for storing an address table; a SDRAM which is used for transferring the address table; an FPGA module which is used for randomly reading the video pixel data stored in the SRAM array according to the address table; and a MCU which is used for configuring and monitoring the coding chip, the decoding chip and the FPGA module. According to the method, the high-bandwidth characteristic of the SDRAM during continuous access and the high-bandwidth characteristic of the SRAM during random access are fully combined, the output picture is changed in the mode that the address table is issued through software, and the display requirement of multi-scene change is met.

Owner:南京磊积科技有限公司

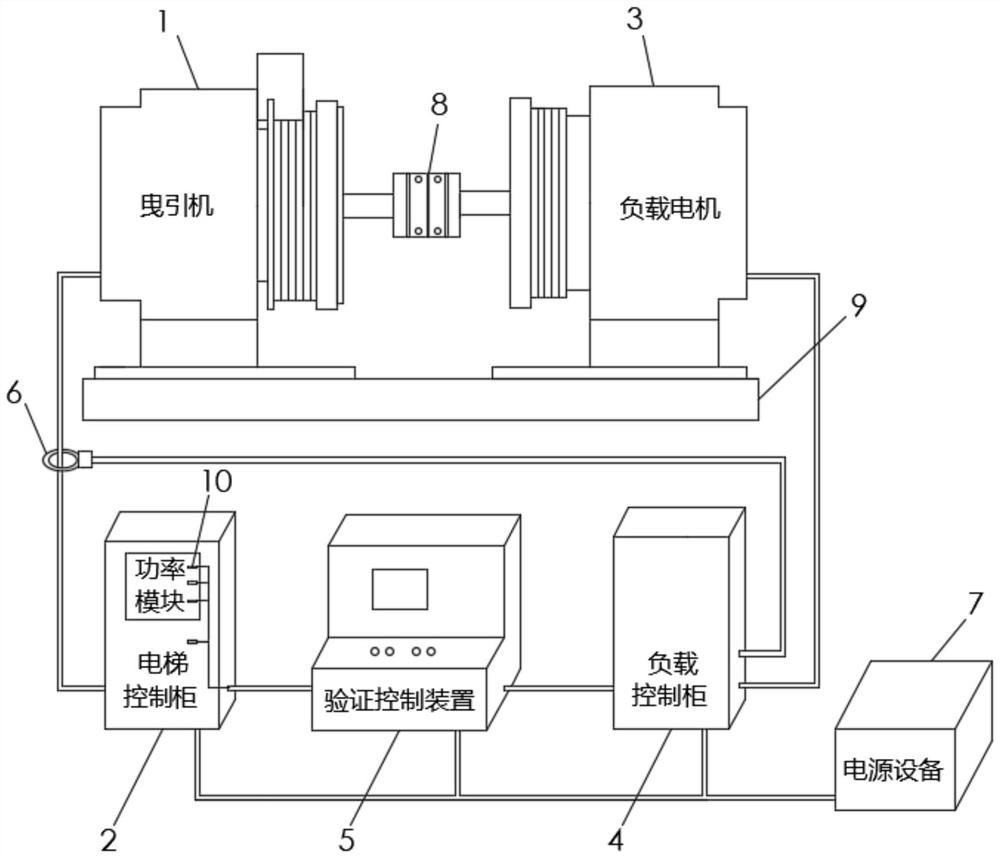

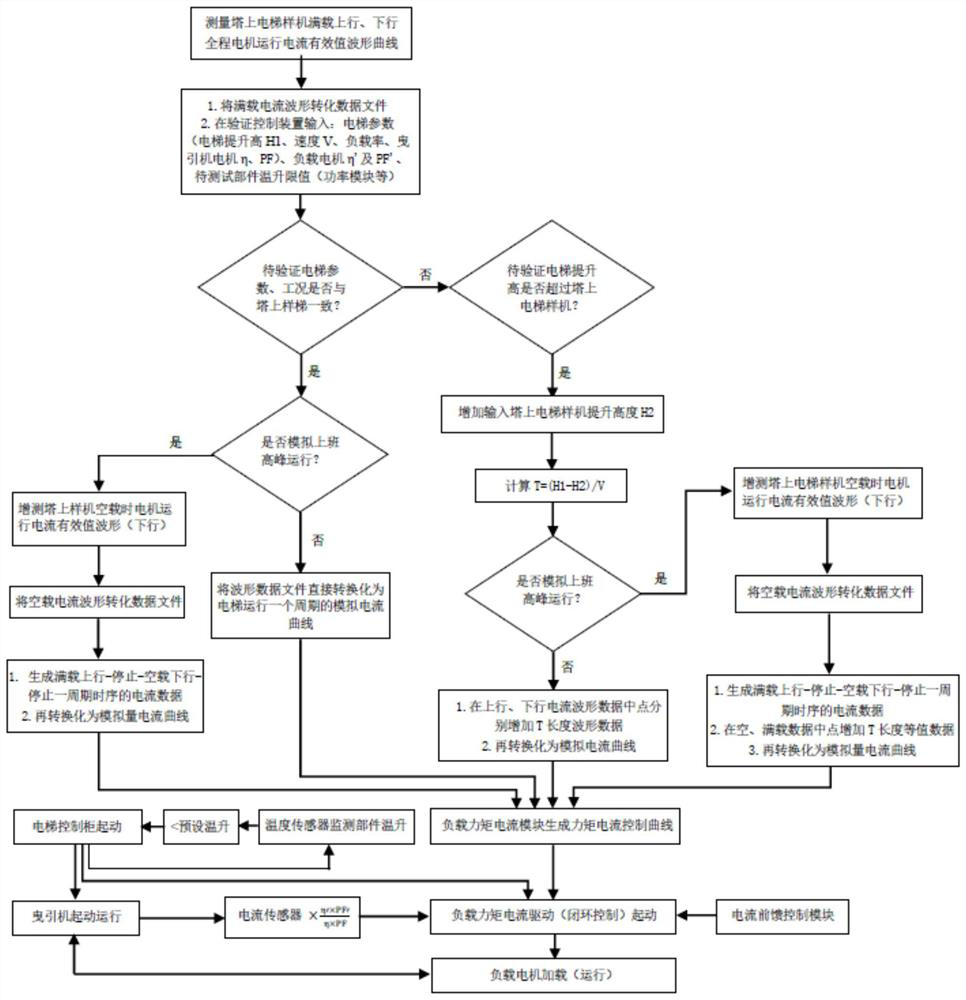

Elevator control cabinet reliability ground equivalent verification system and method

ActiveCN112978523AReduce consumptionReduce LF turn-on timeElevatorsBuilding liftsCurrent transducerPower cycle

The invention discloses an elevator control cabinet reliability ground equivalent verification system and method. The system comprises a to-be-verified device, a load simulation device and a verification control device. The to-be-verified device comprises an elevator control cabinet and an elevator traction machine, and the load simulation device comprises a load control cabinet and a load motor. The load control cabinet is in closed-loop connection with a current sensor. The load motor is in transmission connection with the power output end of the elevator traction machine. The verification control device is electrically connected with the elevator control cabinet and the load control cabinet. The elevator control cabinet sends a starting or stopping instruction to the verification control device and the load control cabinet, and the load simulation device synchronously achieves loading and stopping of the load according to the instruction. Simulation of elevator operation conditions can be completed on the ground in a high-precision mode, matching verification of reliability of the control cabinet in development is achieved, especially verification of performance such as the power cycle and the thermal cycle life of a power module in a main loop of the control cabinet is achieved, hoistway resources are not occupied, the verification period is shortened, and resource consumption is reduced.

Owner:HITACHI ELEVATOR CHINA +1

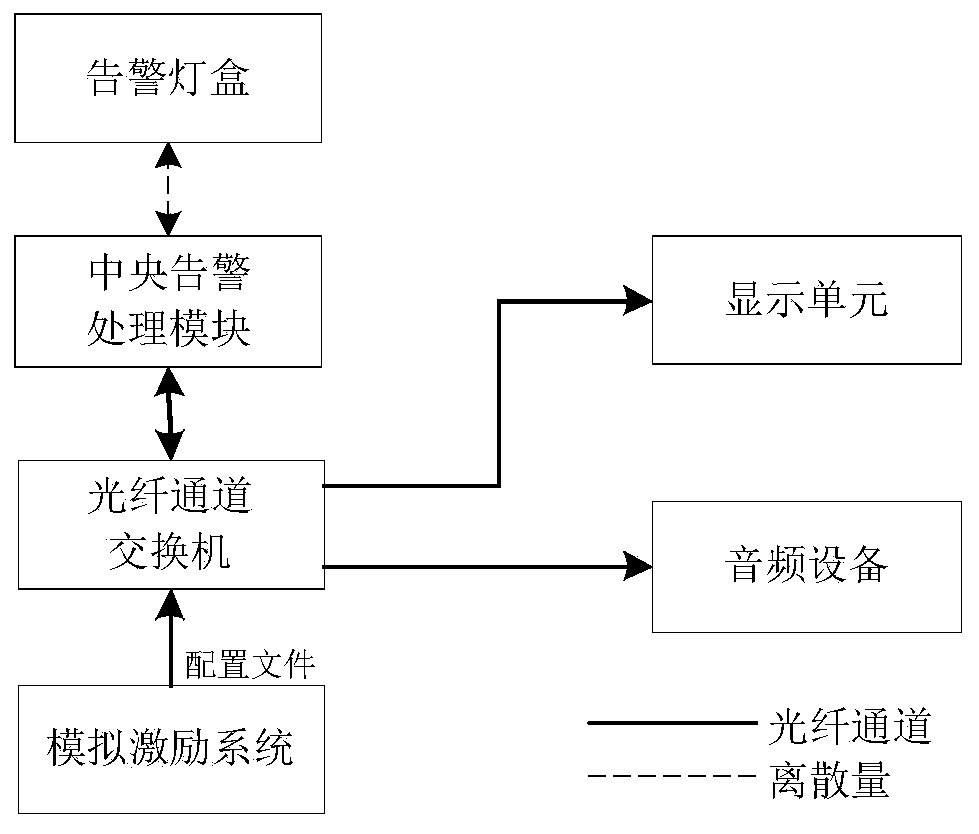

Central alarm verification method under comprehensive modular avionics architecture

ActiveCN111208744ASimplify Test Verification ConfigurationReduce the difficulty of verificationSimulator controlElectronic systemsChannel network

The invention belongs to the field of avionics systems, and provides a central alarm verification method under a comprehensive modular avionics architecture. The central alarm verification method comprises the following steps: S1, enabling the system to have a fiber channel network node simulation capability; S2, enabling the system to have the capability of simulating flight state information andwarning information of all airborne optical fiber channel network nodes; S3, connecting a simulation excitation system with a certain standby port outside the airborne fiber channel switch to realizephysical connection between the system and the airborne network; S4, compiling a network configuration file according to an airborne network configuration file compiling rule so that the system has amessage transmission capability; S5, simulating a plurality of pieces of alarm information of different alarm levels in a certain non-alarm-suppression flight state, and correspondingly checking alarm display, voice and light processes; and S6, simulating different flight state information to drive to generate different flight stages, simulating a plurality of pieces of alarm information as required in each flight state, and correspondingly checking suppression processing results of different flight stages.

Owner:XIAN AIRCRAFT DESIGN INST OF AVIATION IND OF CHINA

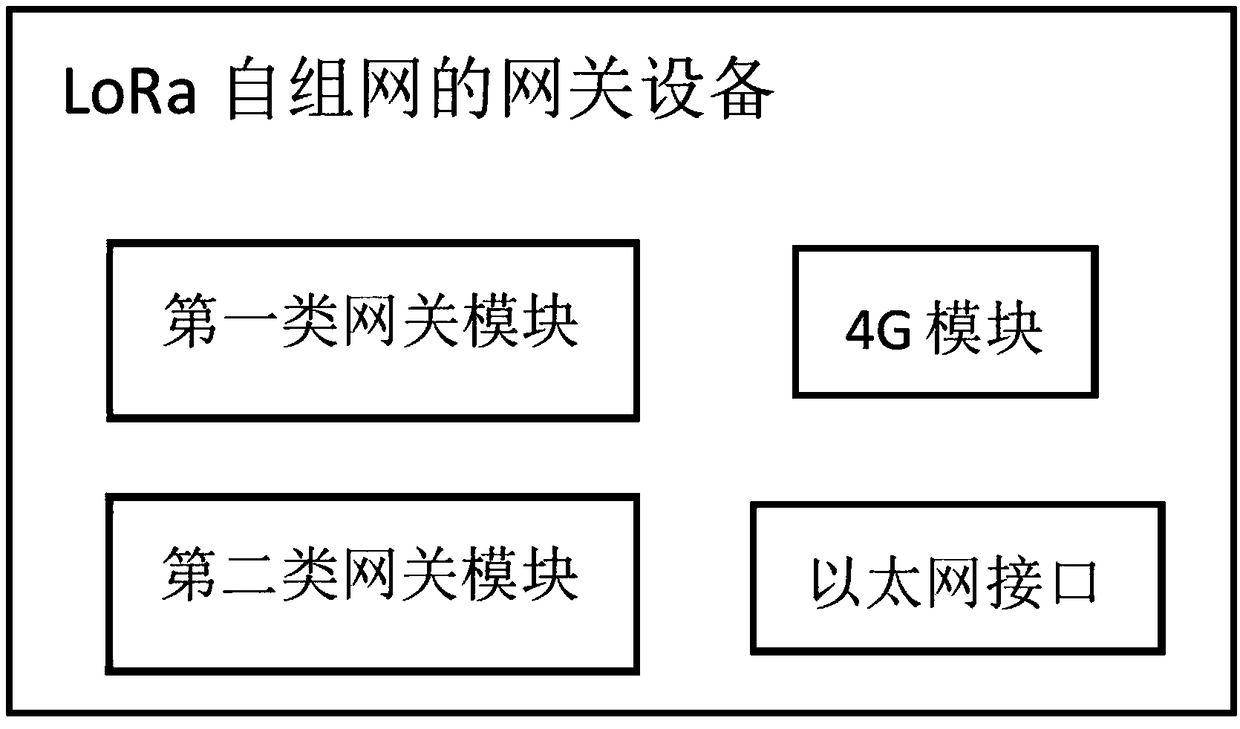

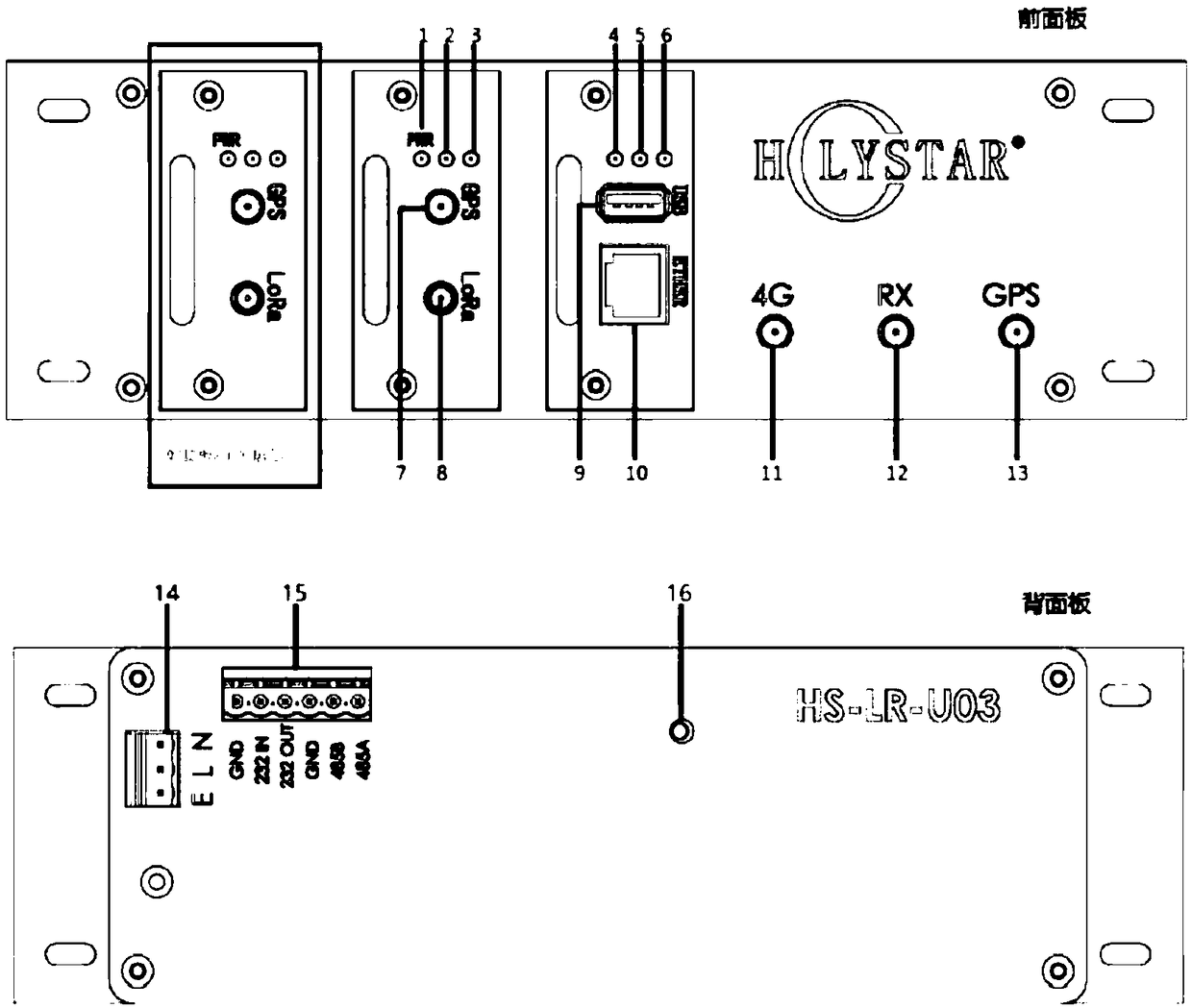

LoRa gateway equipment

InactiveCN109639497AImprove experienceShorten the time periodNetwork topologiesData switching networksThird partyNetwork management

The invention discloses LoRa gateway equipment. The gateway equipment comprises a gateway module, wherein the gateway module is wirelessly connected with LoRa terminal nodes through adoption of a starnetwork structure, and receives user data from the LoRa terminal nodes; a LoRa network management server module, wherein the LoRa network management server module provides a UI interface, configuresthe gateway module, and carries out connectivity management, authentication management and grouping management on the LoRa terminal nodes; and a data application server module, wherein the data application server module provides data push service and message subscription and release service for a third party application platform. Through utilization of the gateway equipment, a user does not need to care about a specific establishment process of a LoRa / LoRaWAN wireless network and can rapidly generate own wireless application solution only through call of a standard interface provided by a LoRaad-hoc network, so user product development time and verification period are greatly reduced, and user experience is improved.

Owner:凌犀工业互联网(深圳)有限公司

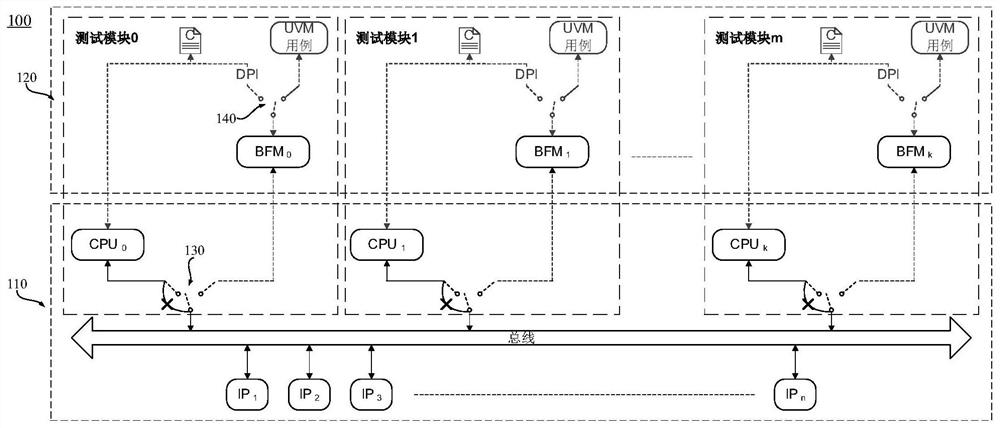

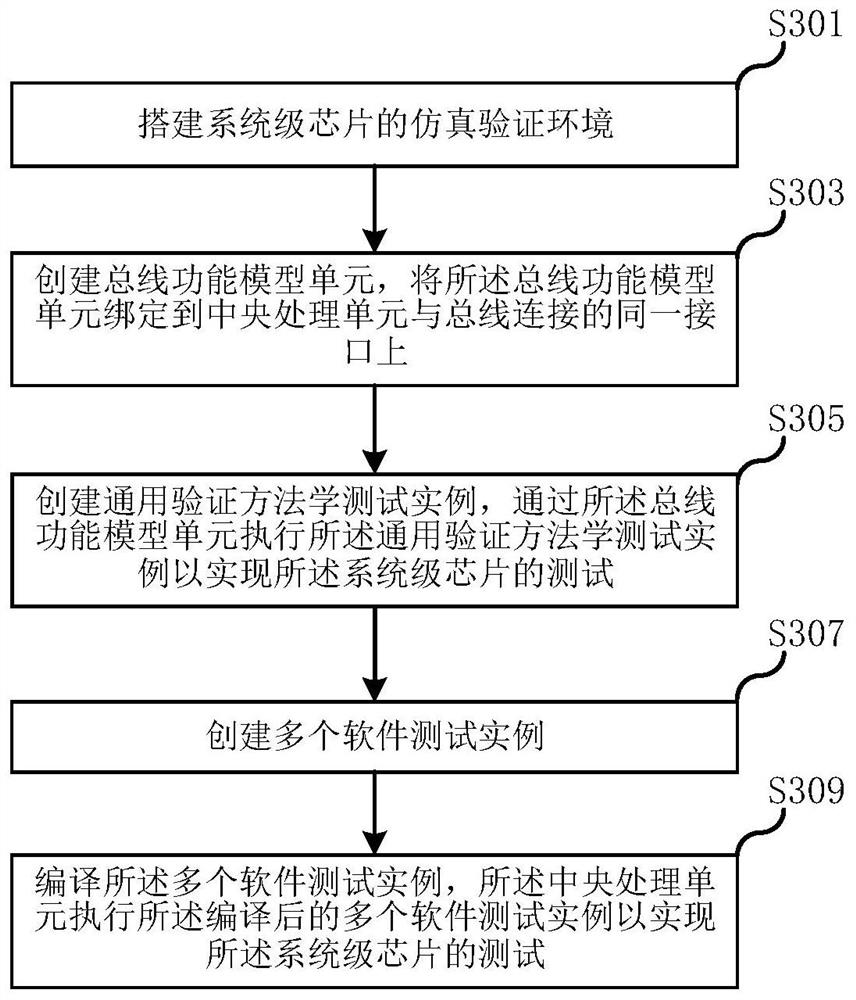

System-level verification method and system of chip and related device

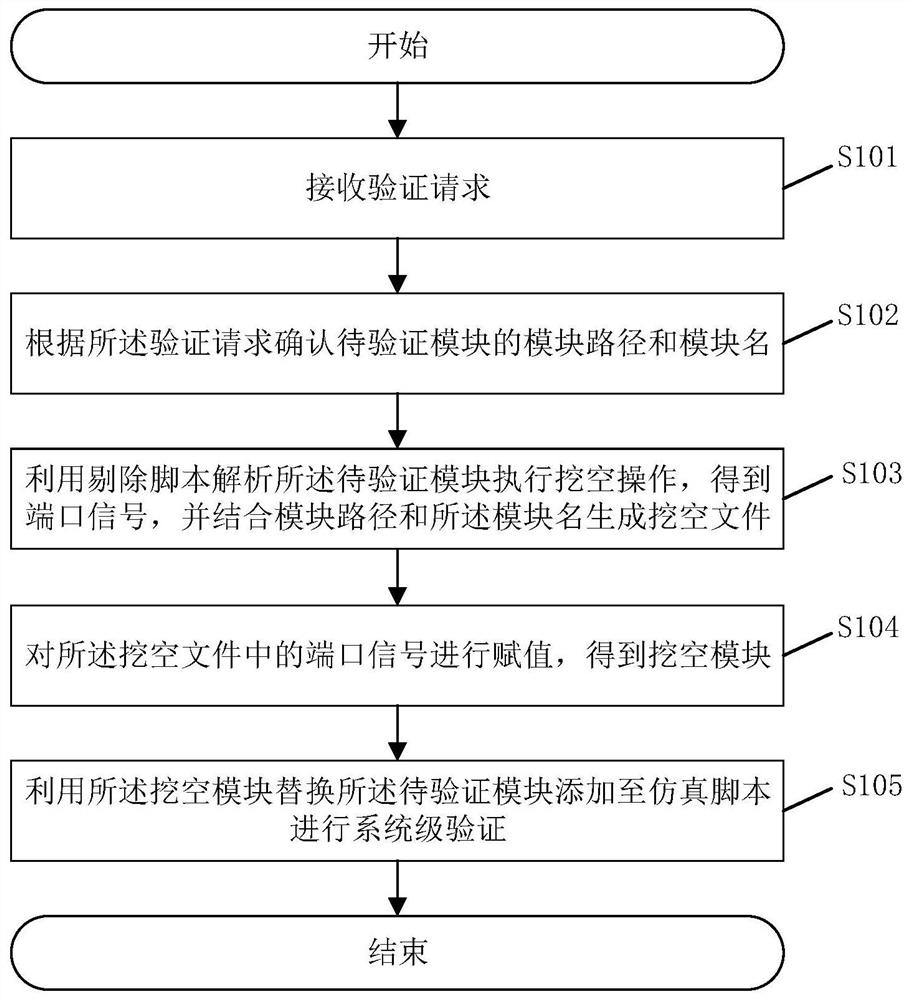

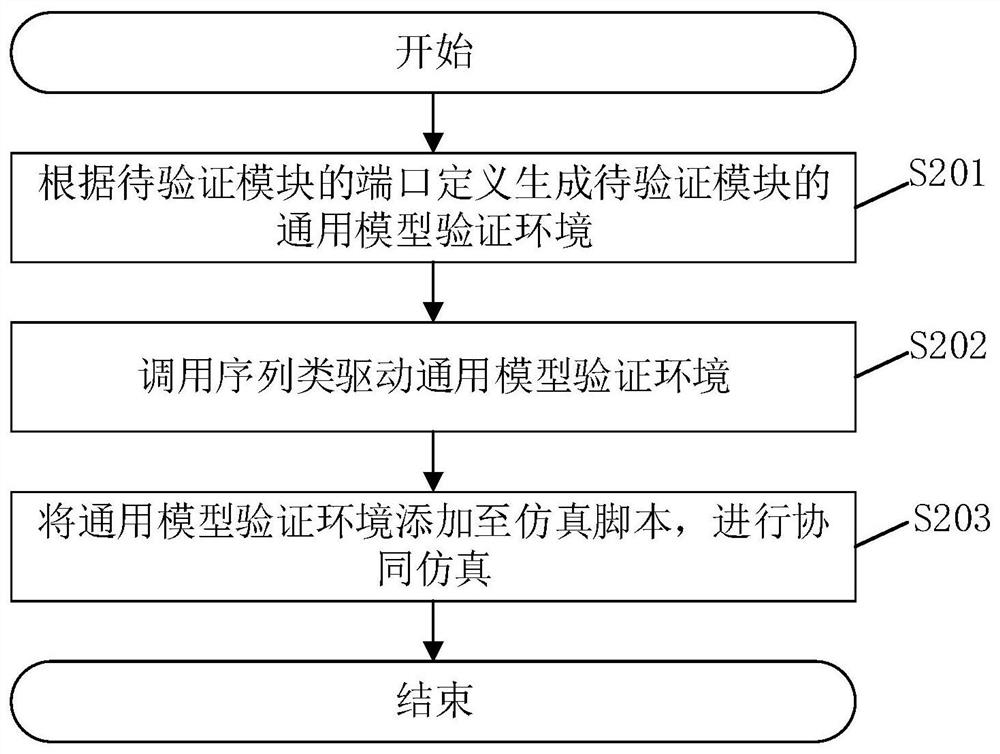

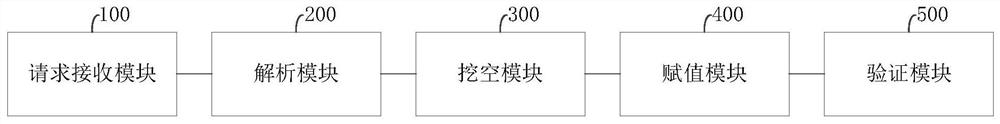

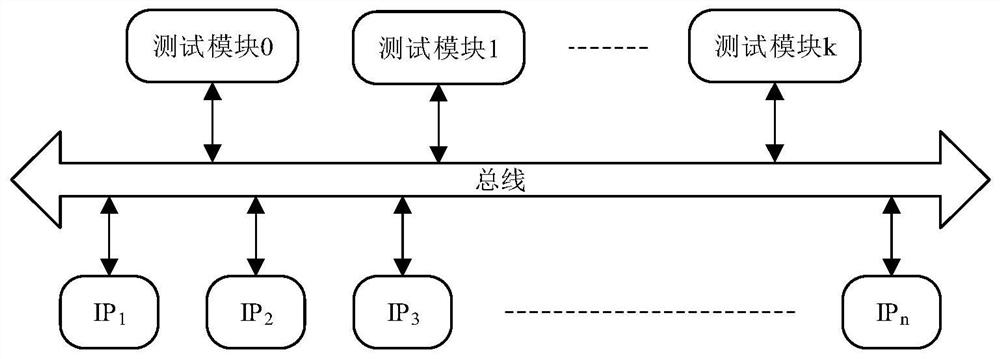

PendingCN112733490AReduce verification impactSolve the problem that cannot be verified by cooperationCAD circuit designSpecial data processing applicationsComputer hardwareVerification

The invention provides a system-level verification method of a chip. The system-level verification method comprises the steps of receiving a verification request; confirming a module path and a module name of a to-be-verified module according to the verification request; wherein the to-be-verified module comprises a to-be-rejected module and a to-be-replaced module; analyzing the to-be-verified module by utilizing a rejection script to execute a hollowing operation to obtain a port signal, and generating a hollowing file in combination with the module path and the module name; assigning a value to a port signal in the hollowed-out file to obtain a hollowed-out module; and replacing the to-be-verified module with the hollow module, and adding the to-be-verified module to a simulation script for system-level verification. The verification influence on other modules can be reduced when the to-be-verified module is not completed, and the verification period is shortened. The invention further provides a system-level verification system of the chip, a computer readable storage medium and electronic equipment, which have the above beneficial effects.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

Verification platform and verification method of system-on-chip

PendingCN113866586AGuaranteed coverageReduce complexityElectronic circuit testingError detection/correctionComputer architectureEngineering

Owner:MONTAGE TECH CHENGDU CO LTD

Gateway equipment for LoRa self-organized network

InactiveCN109511112AShorten development time and verification cycleImprove experienceNetwork topologiesSecurity arrangementSpreading factorTTEthernet

The invention discloses gateway equipment for a LoRa self-organized network. The gateway equipment comprises a first class of gateway module for receiving data in parallel through eight LoRa uplink channel multi-spreading factors; at least one second class of gateway module for sending data in parallel through a LoRa downlink channel; a 4G module and an Ethernet interface for connecting the internet and connecting the NS / AS server of the cloud side through a wire way and a wireless way. Through the gateway equipment provided by the invention, a user can quickly generate the own wireless application solution by only calling a standard interface provided by the LoRa self-organized network without concerning the specific construction process of the LoRa / LoRaWAN wireless network, the user product development time and the verification cycle are greatly shortened, and the user experience is improved.

Owner:凌犀工业互联网(深圳)有限公司

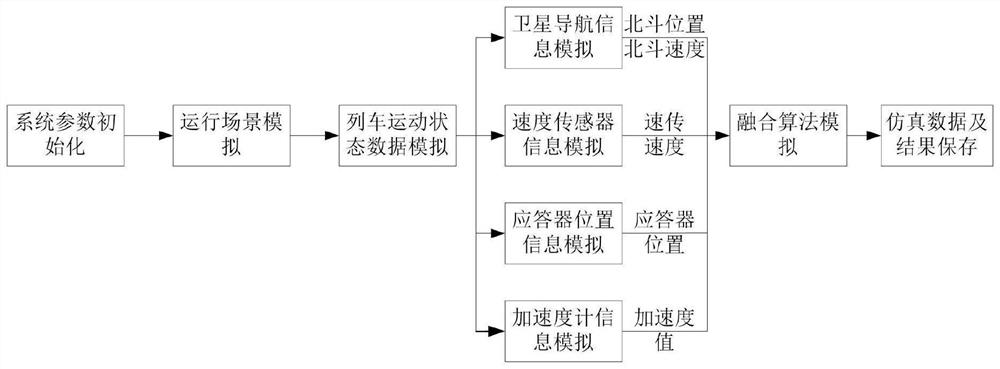

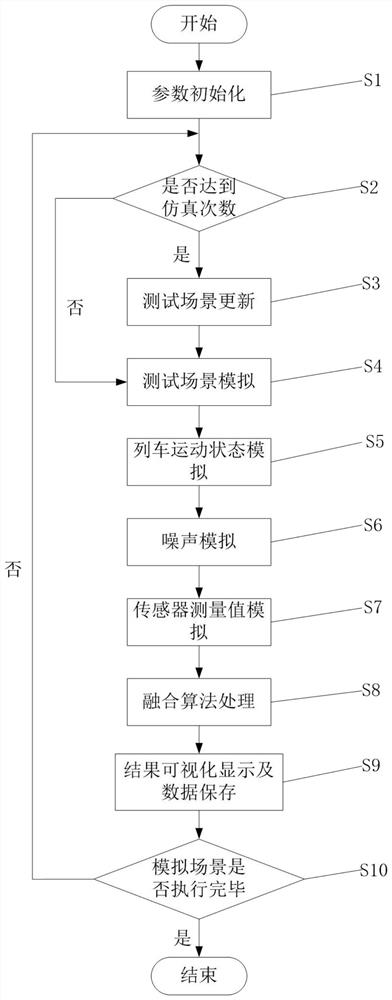

Train positioning analysis method and system based on Monte Carlo simulation

PendingCN114013478AShorten the verification cycleFast iterationRailway traffic control systemsAccelerometerAlgorithm

The invention discloses a train positioning analysis method and system based on Monte Carlo simulation. The method comprises the steps of initializing simulation parameters, simulating an operation scene, simulating train motion state data according to the operation scene, simulating satellite navigation information, speed sensor information, transponder position information and accelerometer information according to the train motion state data, designing a fusion algorithm, and carrying out fusion filtering processing on the simulated satellite navigation information, the speed sensor information, the transponder position information and the accelerometer information, and saving the above simulation data and results. According to the method, the test data are generated through simulation software without depending on hardware equipment, preliminary testing is carried out when system functions are not completed, the verification period of a positioning algorithm is greatly shortened, and rapid iteration of the train positioning algorithm is facilitated.

Owner:CASCO SIGNAL +1

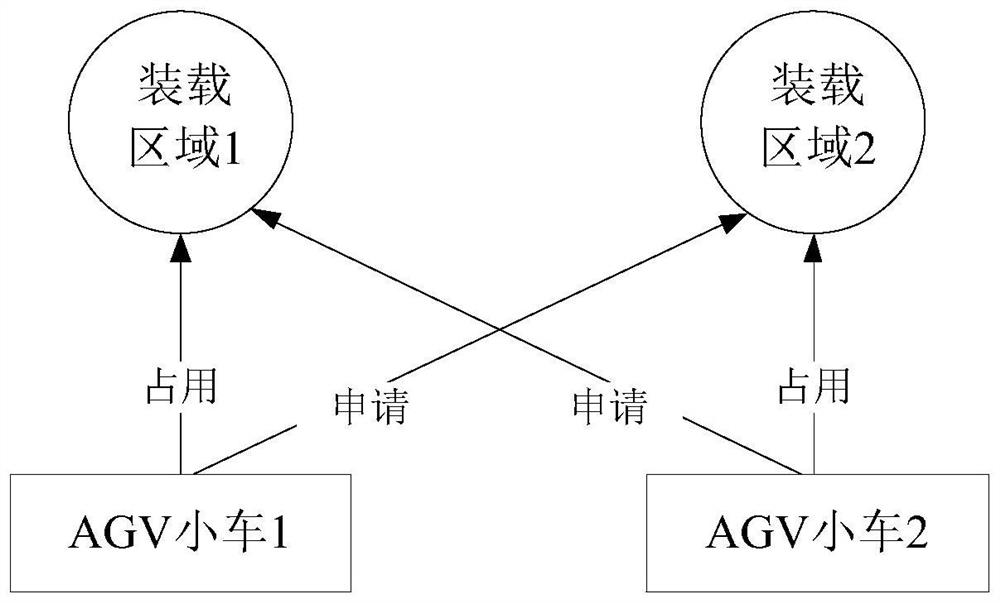

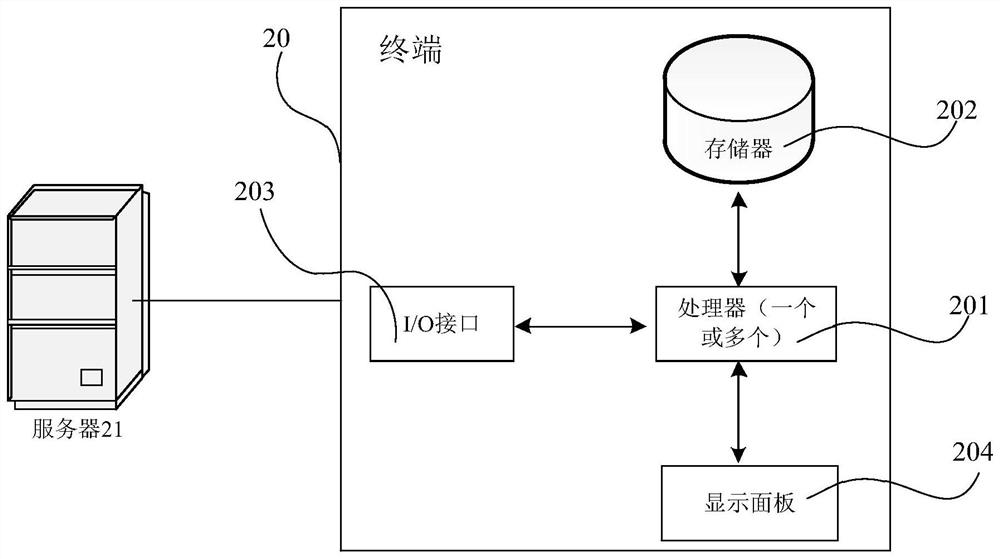

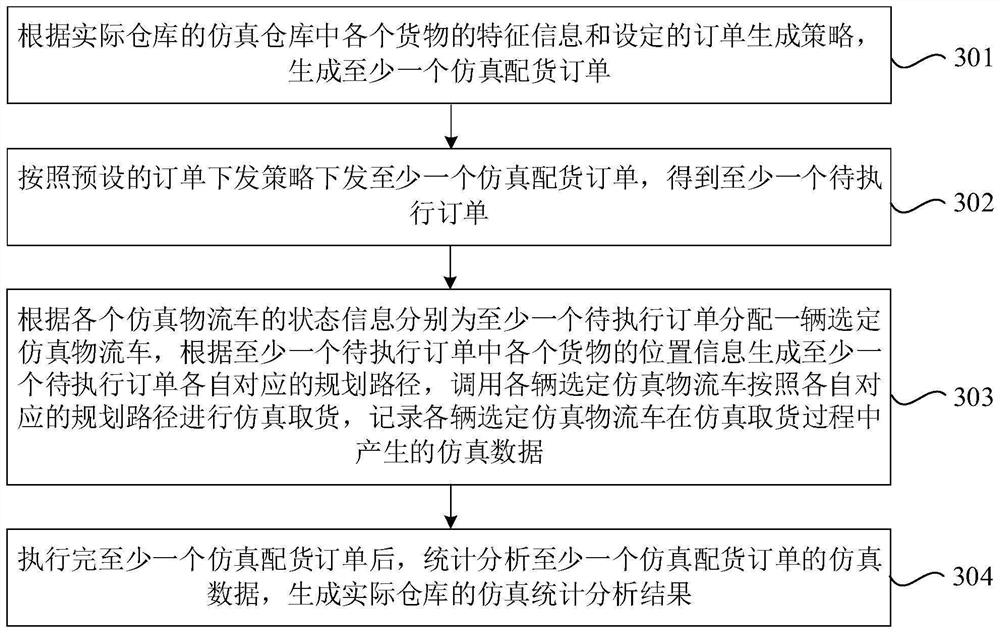

Warehouse logistics simulation method, device and equipment and storage medium

PendingCN114219276AShorten the verification cycleReduce riskResourcesLogisticsLogistics managementStatistical analysis

The invention provides a warehouse logistics simulation method, device and equipment and a storage medium, relates to the technical field of computers, and is used for reducing the fulfillment cost of cargo orders and meeting diversified requirements of customers through simulation analysis of warehouse logistics. The method comprises the following steps: issuing at least one generated simulation cargo allocation order according to a preset order issuing strategy to obtain at least one order to be executed; according to the state information of each simulation logistics vehicle, allocating a selected simulation logistics vehicle to at least one order to be executed, and according to the position information of each cargo in the at least one order to be executed, generating a planning path corresponding to the at least one order to be executed, calling each selected simulation logistics vehicle to carry out simulation goods taking according to the respective corresponding planning path; and after the at least one simulation cargo allocation order is executed, recording and statistically analyzing simulation data of the at least one simulation cargo allocation order, and generating a simulation statistical analysis result of the actual warehouse.

Owner:RUIJIE NETWORKS CO LTD

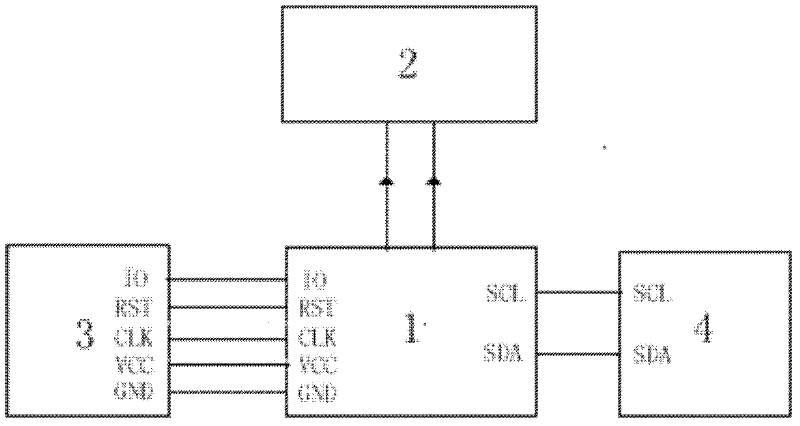

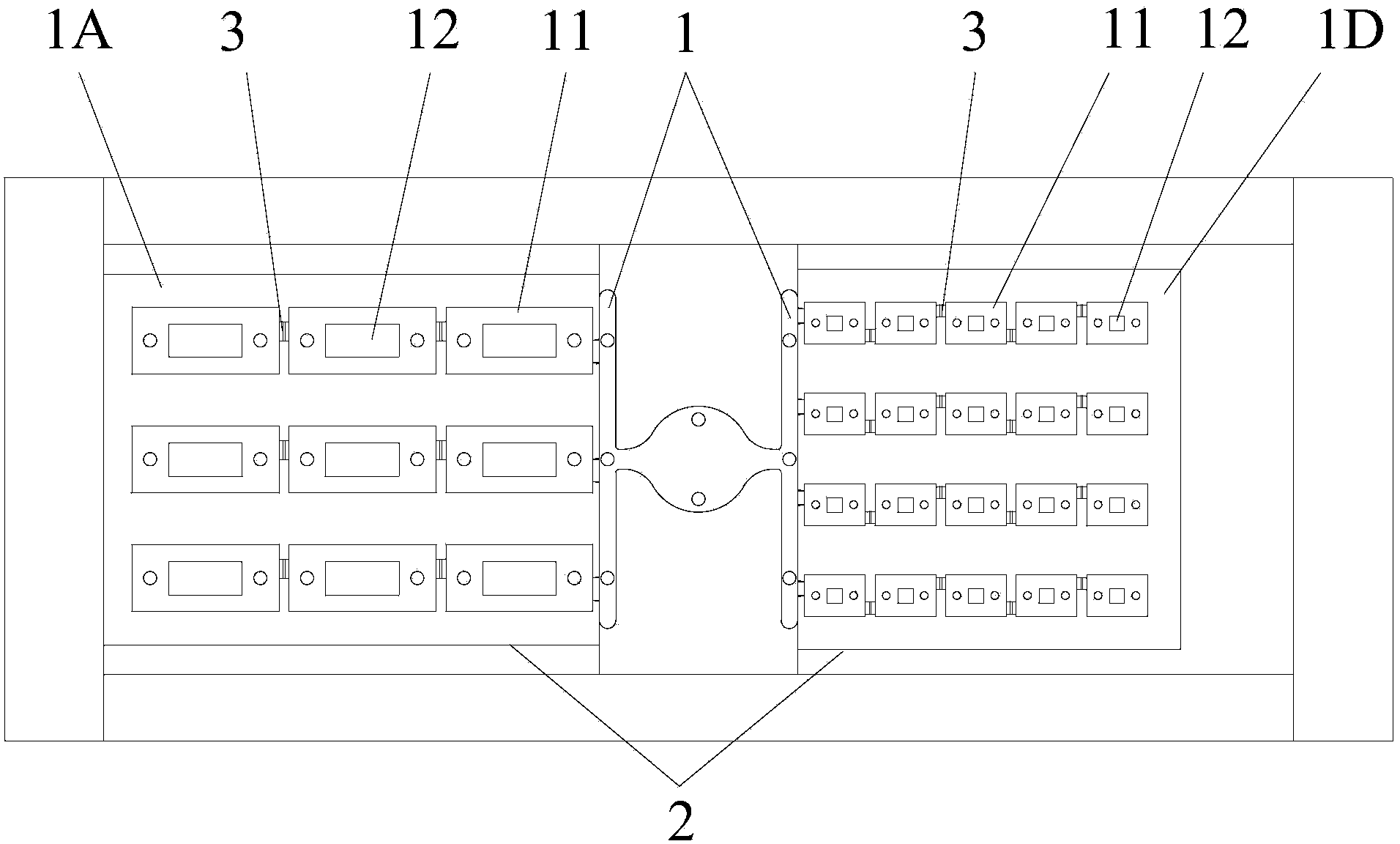

Design method of contact type card verification system based on FPGA (field programmable gate array)

InactiveCN102495913AImprove reliabilityShorten the verification cycleSpecial data processing applicationsReconfigurabilitySoftware emulation

A design method of a contact type card verification system based on an FPGA (field programmable gate array) belongs to the technical field of verification of integrated circuit chips, aims to solve problems of high complexity of verification operation, slow simulation speed of software, insufficient reliability and the like of verification of integrated circuits in the prior art, and is applied to integrated circuit design. The verification system based on the FPGA adopts the design of a contact type card as a verification object, and has the advantages of high reliability, fast simulation speed, high portability and reconfigurability and the like, problems of high test complexity, slow simulation speed, insufficient reliability, complication in modification and the like in traditional verification of the integrated circuits are solved, and a new solution can be provided for verification technology of the integrated circuit design.

Owner:SHANDONG UNIV

Mold for detecting mold flow marks of epoxy molding plastic

The invention provides a mold for detecting mold flow marks of epoxy molding plastic, relates to the field of detecting the mold flow marks and solves the problems that the detection of the existing mold flow marks needs to be matched with a frame, different sealing manners need different molds to perform a simulation test, the number of mold operating times is large, and the verifying effect is not obvious. The mold for detecting the mold flow marks of the epoxy molding plastic comprises a mold main body, wherein the mold main body comprises an upper module and a lower module, wherein the upper module is provided with an upper module panel; the lower module is provided with a lower module panel which is matched with the upper module panel for application; the lower module panel consists of a glue inlet passage and a traveling cavity part; the traveling cavity part is divided into a plurality of traveling cavity part function areas; the lower module panel adopts any traveling cavity part function area or a plurality of traveling cavity part function areas. The mold disclosed by the invention can be used for verifying the conditions of the mold flow marks of the epoxy molding plastic in different sealing modes in a disposable manner, the material consumption cost is reduced, the number of the mold operating times is reduced, the labor intensity is reduced, the verifying efficiency is improved, the verifying period is greatly shortened, and the verifying effect is very obvious.

Owner:ETERNAL ELECTRONICS MATERIALS (KUNSHAN) CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com