Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

31results about How to "Reduce the probability of electric leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

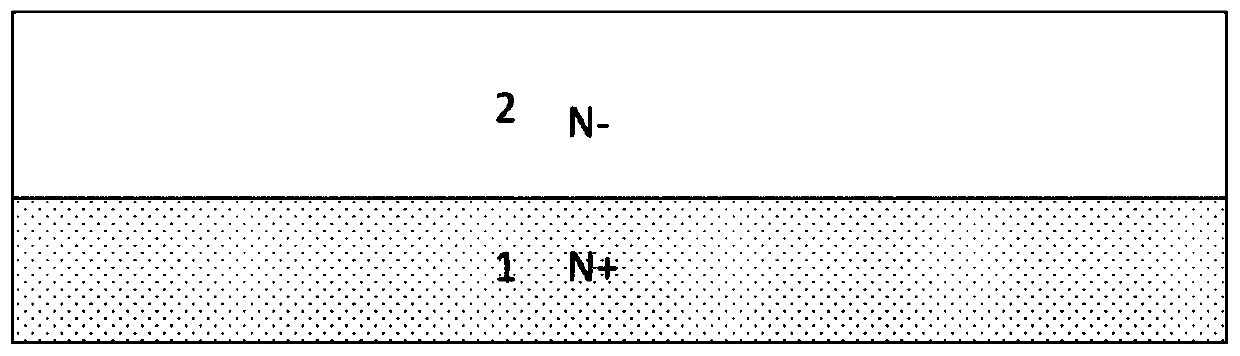

Efficient heterojunction solar cell and preparation method thereof

InactiveCN112289894ALow content of metal impuritiesImprove conversion efficiencyFinal product manufactureSemiconductor devicesElectrical batteryPhysical chemistry

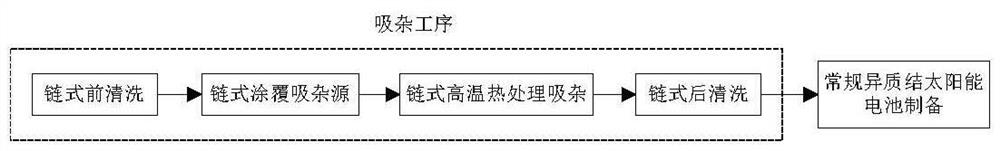

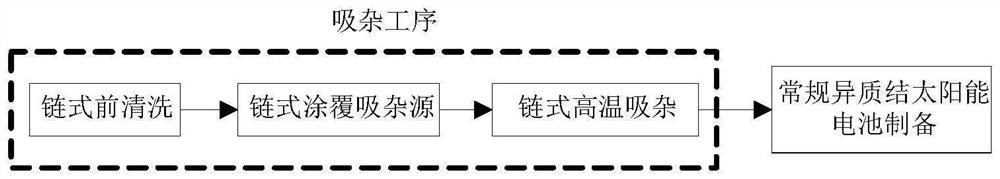

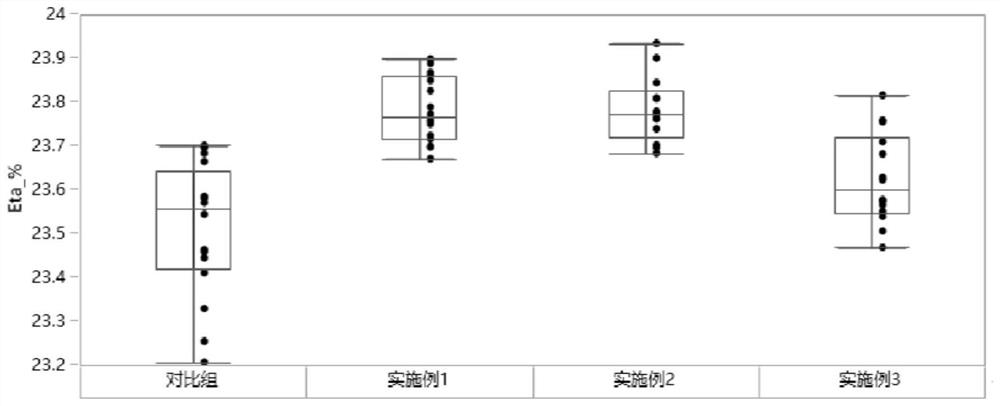

The invention discloses an efficient heterojunction solar cell and a preparation method thereof, and the preparation method is characterized in that a gettering process is added before a conventionalheterojunction solar cell preparation process, and the gettering process is completed through a full-chain process; the full-chain process comprises the following steps: coating a gettering source ona silicon wafer in a chain manner; and performing chained high-temperature gettering. According to the preparation method, the conversion efficiency of the efficient heterojunction solar cell is improved by reducing the metal impurity content of the N-type silicon wafer; the efficiency distribution of the prepared efficient heterojunction solar cell is more centralized, and the product consistencyis greatly improved; the battery edge electric leakage rate is reduced, and the battery yield is improved; the full-chain gettering process shortens the circulation time of the silicon wafer in the manufacturing process, reduces the pollution probability of the silicon wafer, improves the conversion efficiency of the battery to a certain extent, and is short in time consumption, low in energy consumption, high in automation degree and beneficial to industrial popularization and application.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

Capacitor structure, semiconductor device and capacitor structure preparation method

PendingCN111834529AImprove stabilityAvoid destructionSolid-state devicesCapacitorsCapacitanceDevice material

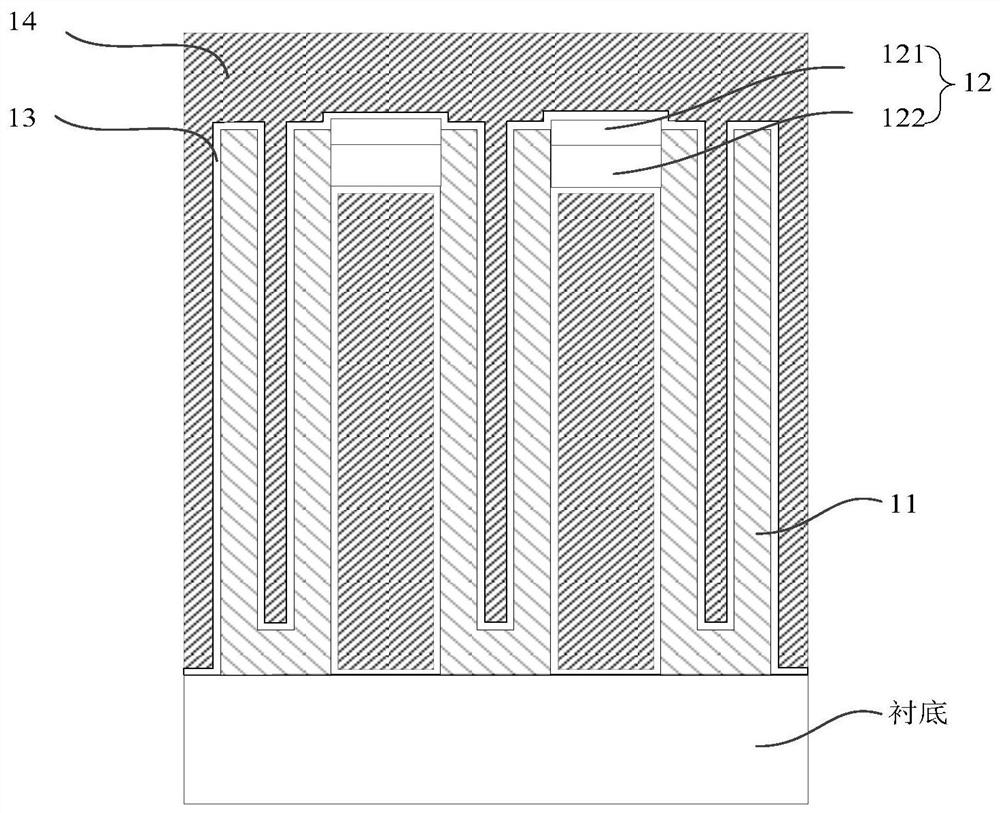

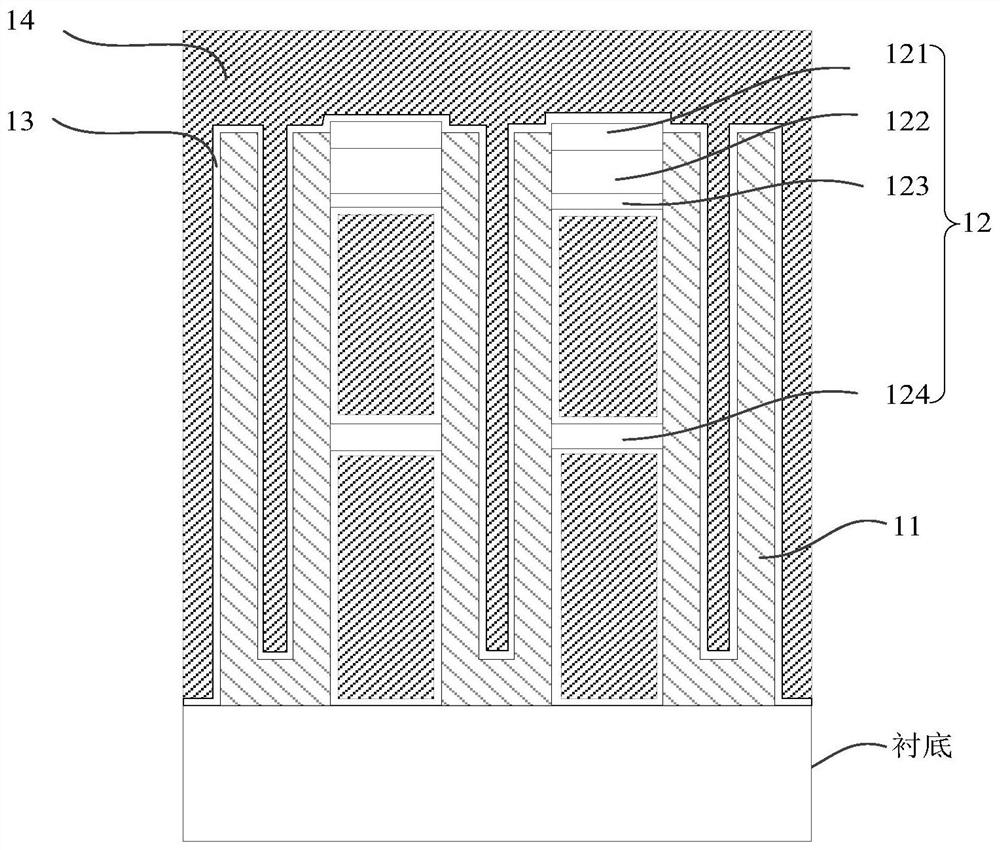

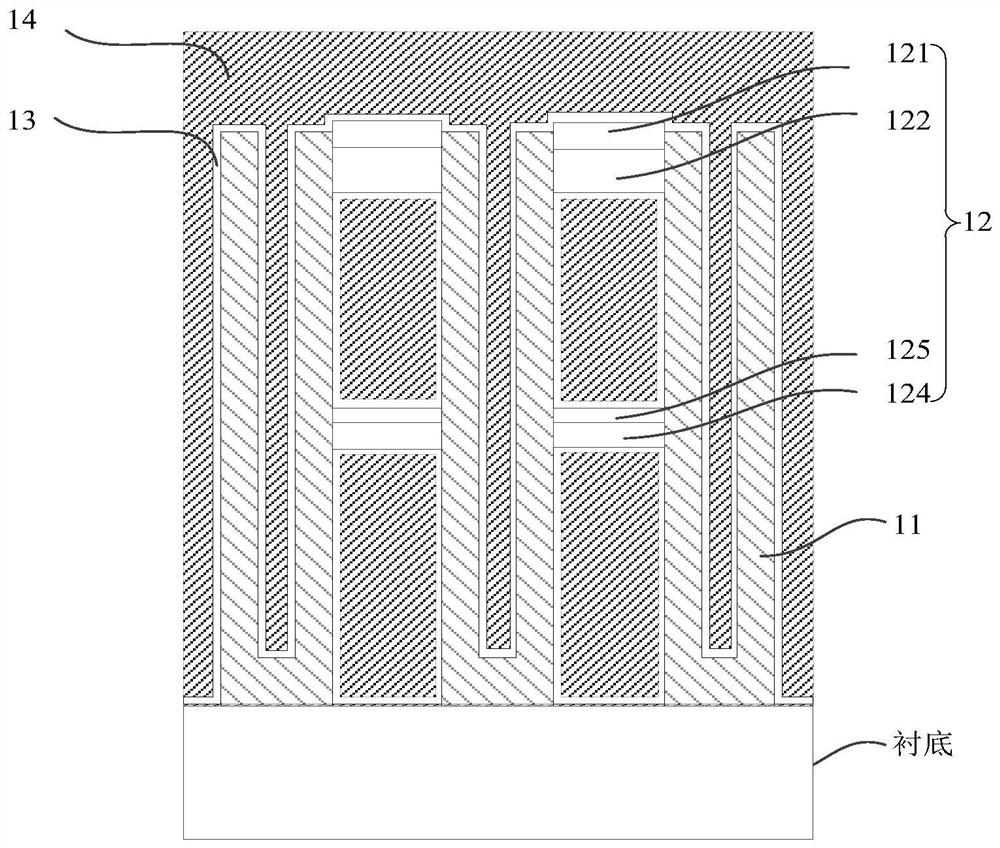

The invention discloses a capacitor structure, a semiconductor device and a capacitor structure preparation method. A supporting structure is arranged on the outer side wall of a lower electrode of acolumnar structure; the supporting structure comprises a top supporting structure for supporting the upper area of the lower electrode; the top supporting structure at least comprises a first supporting layer and a second supporting layer made of a material different from that of the first supporting layer. The lower surface of the first supporting layer is arranged to be in contact with the uppersurface of the second supporting layer, the contact interface of the first supporting layer and the second supporting layer is lower than the top of the lower electrode, and the upper surface of thefirst supporting layer is higher than the top of the lower electrode; a capacitor dielectric layer covering the lower electrode and the support structure and an upper electrode covering the capacitordielectric layer are formed, so the electric leakage rate can be reduced while the extending height of the lower electrode in the vertical direction is met, the supporting structure at the position needing to be reserved is prevented from being damaged in the patterning process of the top supporting structure of the lower electrode, and the stability of the lower electrode and the performance of the capacitor structure can be effectively improved.

Owner:FUJIAN JINHUA INTEGRATED CIRCUIT CO LTD

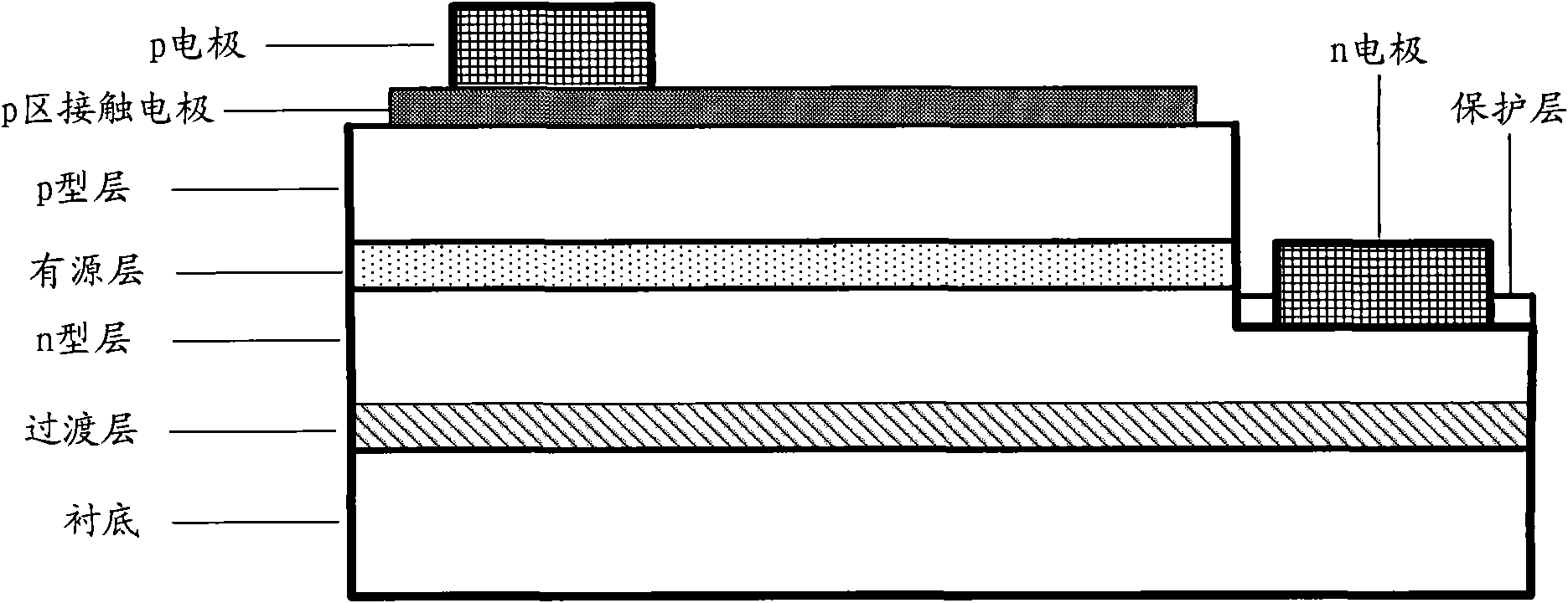

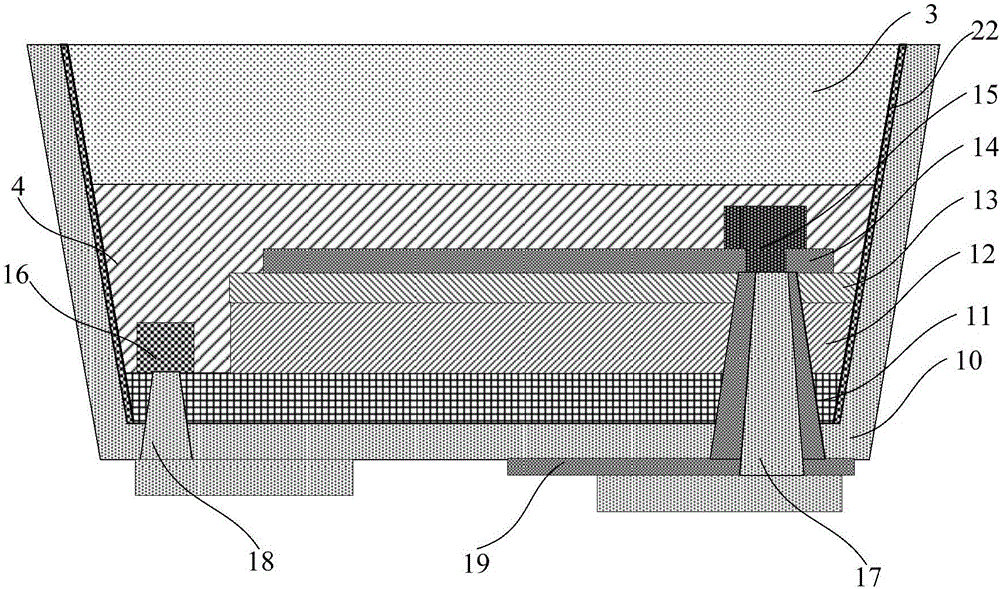

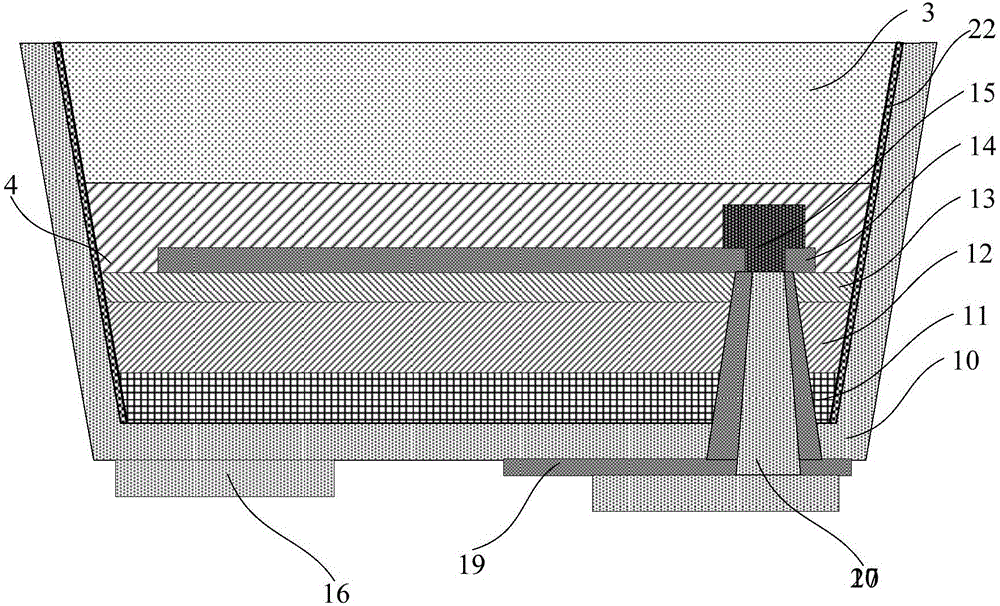

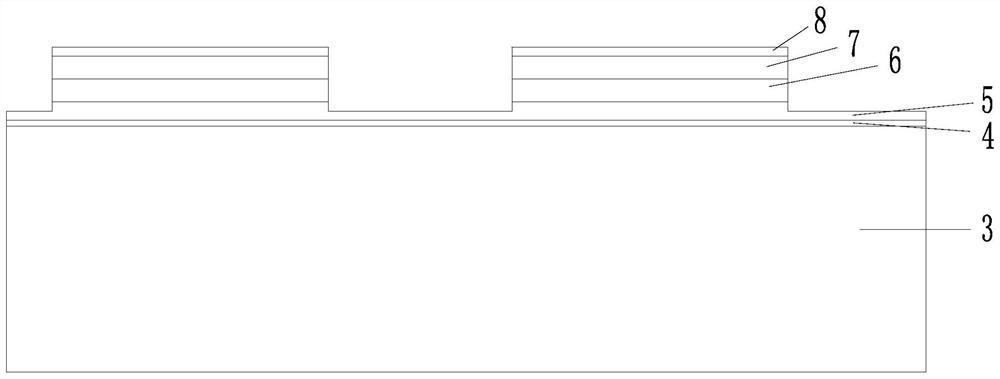

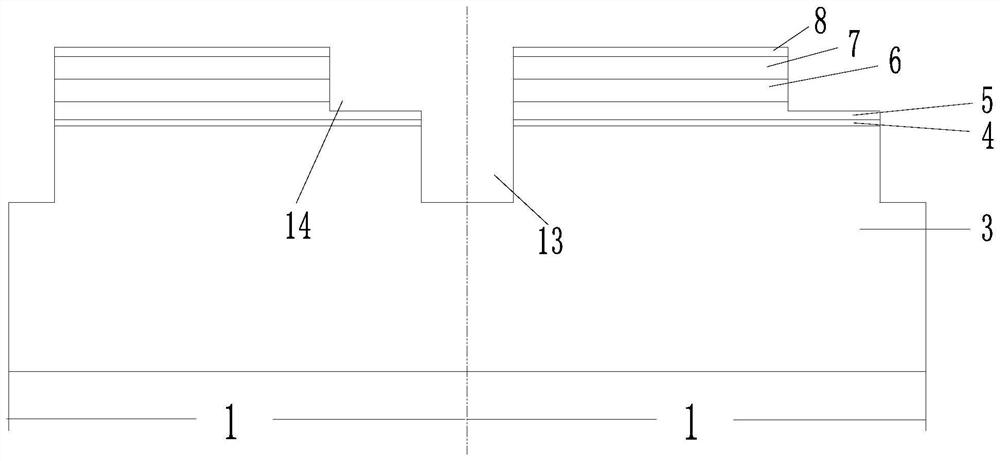

Reflector, manufacturing method thereof and luminescent device applying same

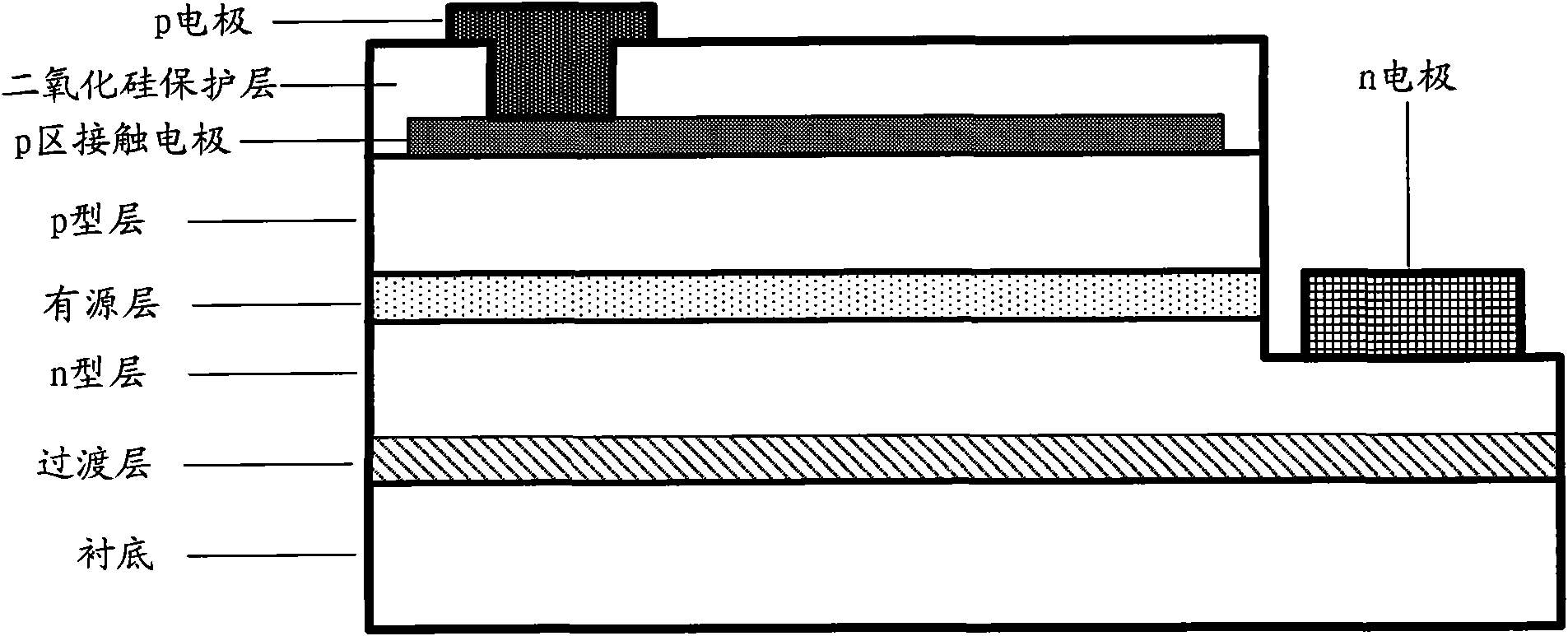

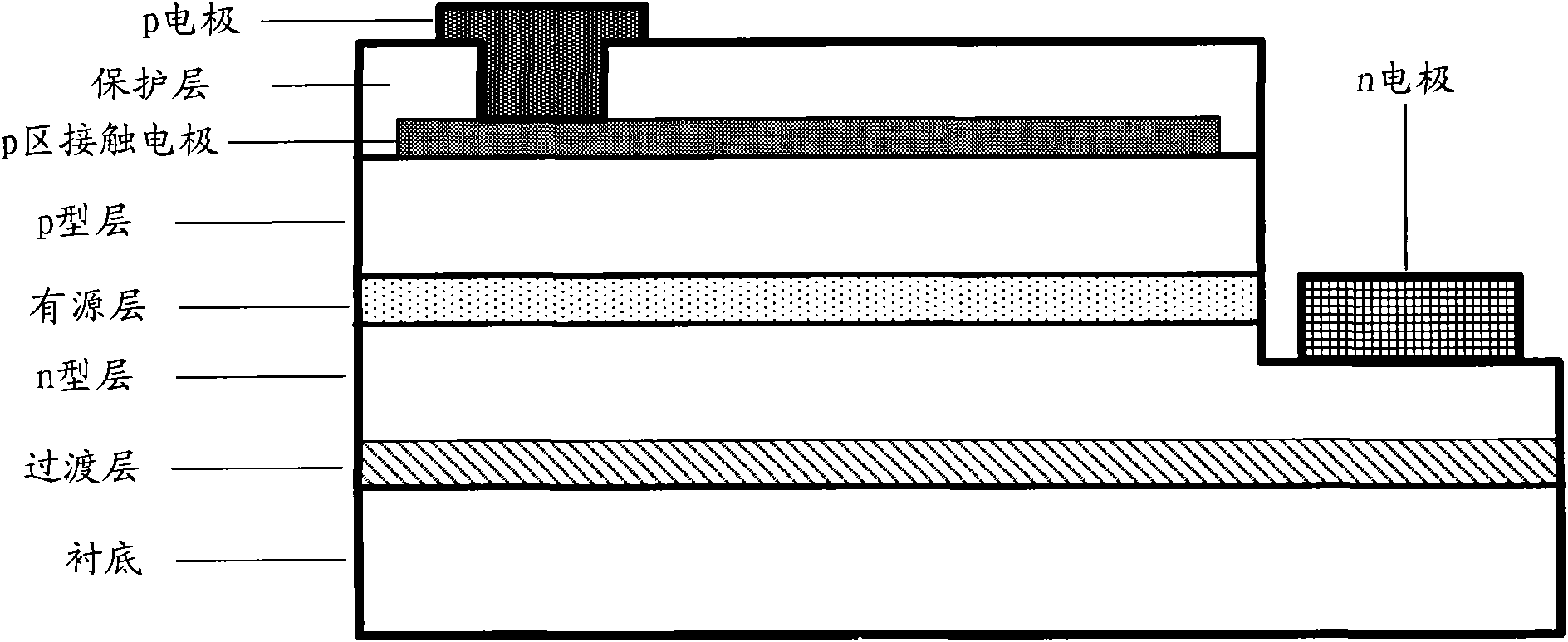

ActiveCN102054916APrevent penetrationReduce the probability of electric leakageSemiconductor devicesWhiskersReflective layer

The invention discloses a reflector used for a gallium nitride-based luminescent device and a manufacturing method thereof and a luminescent device applying the reflector. The reflector is formed on a P-type gallium nitride-based epitaxial layer and comprises whisker crystals and a metal reflecting layer, wherein the whisker crystals are made from undoped gallium nitride, distributed in a certain density, formed on the surface of the P-type gallium nitride-based epitaxial layer in a position corresponding to a dislocation defect of the epitaxial layer; and the metal reflecting layer is formed on the P-type gallium nitride-based epitaxial layer and the whisker crystals. Undoped gallium nitride-based whisker crystals are arranged on the dislocation defect of the P-type GaN-based epitaxial layer, thus an Ag reflecting layer can be separated from the dislocation defect of the P-type GaN-based epitaxial layer, Ag is effectively inhibited from permeating into the inside of the dislocation defect in an electromigration way and electric leakage probability of the luminescent device comprising an Ag reflector can be greatly decreased.

Owner:QUANZHOU SANAN SEMICON TECH CO LTD

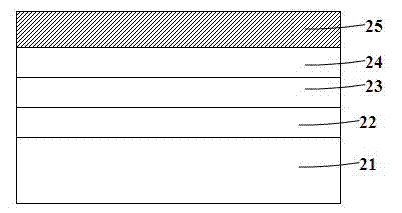

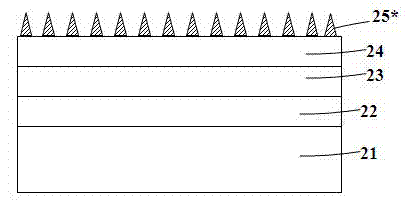

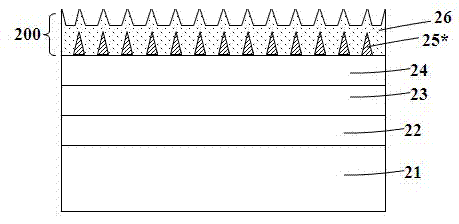

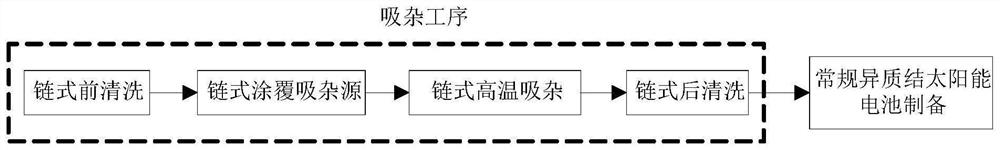

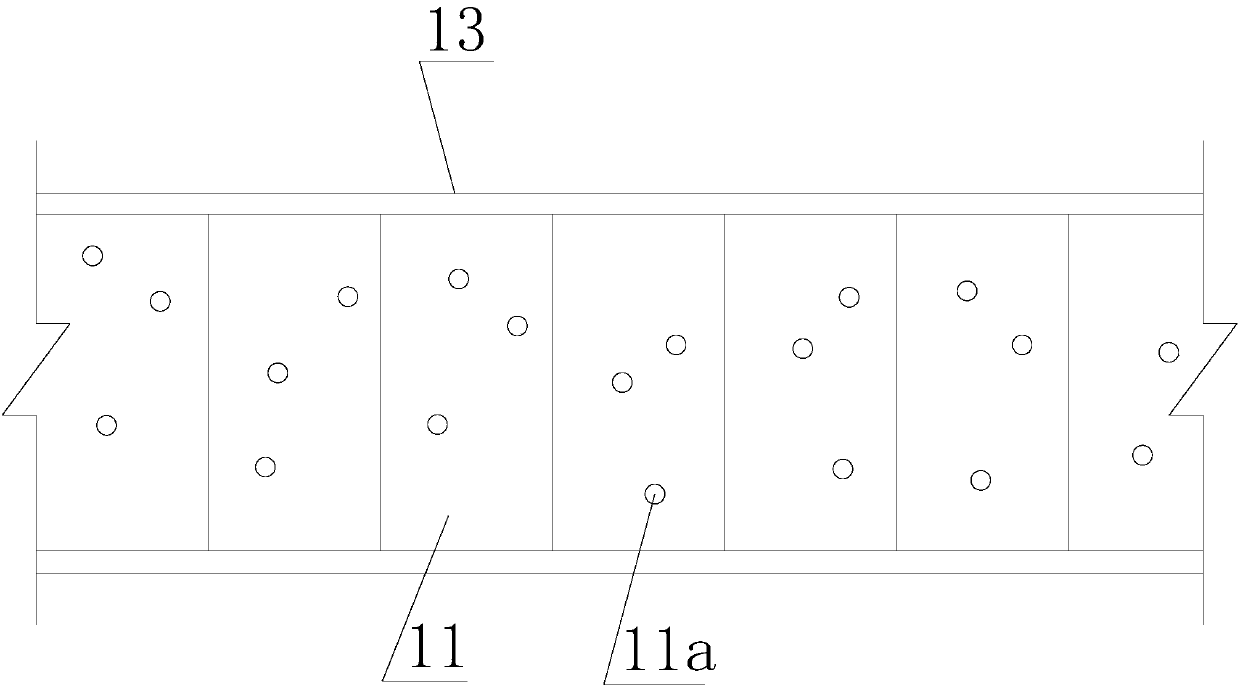

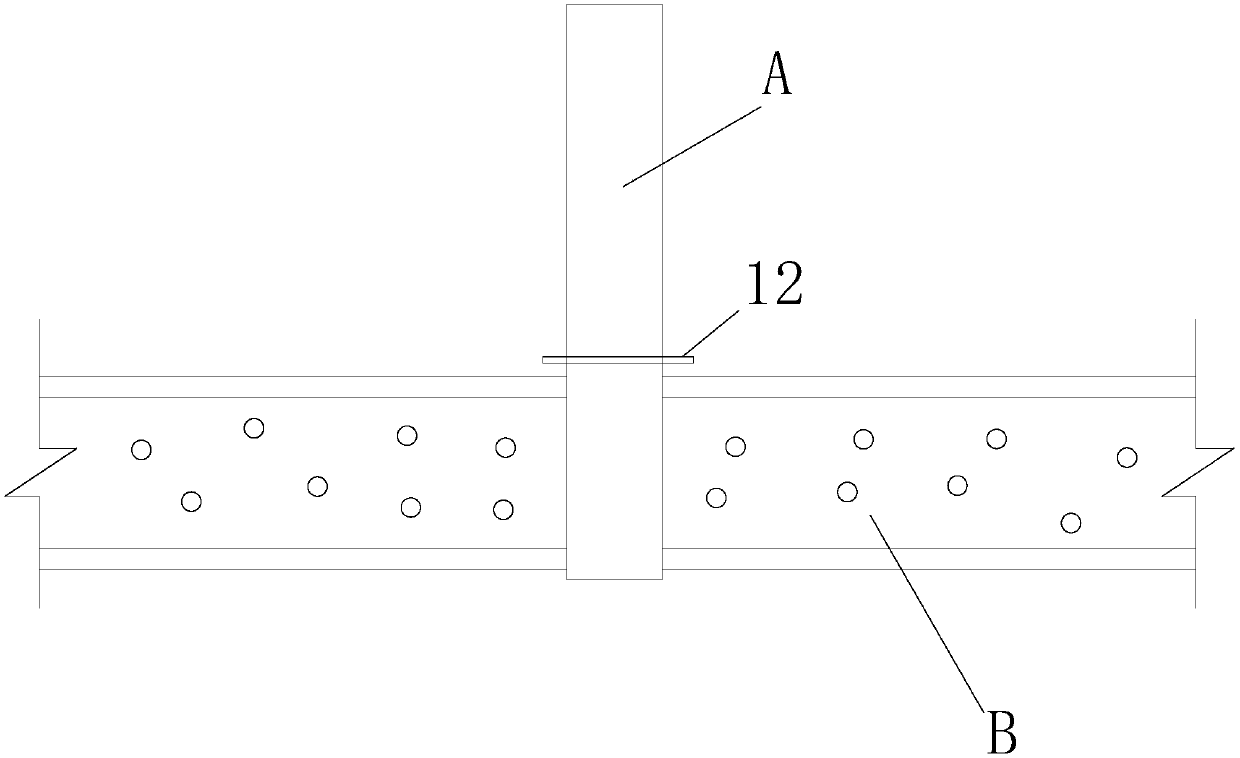

High-efficiency heterojunction solar cell and preparation method thereof

ActiveCN114551636ALow content of metal impuritiesImprove quality levelFinal product manufactureSemiconductor devicesHeterojunctionPhysical chemistry

The invention discloses a high-efficiency heterojunction solar cell and a preparation method thereof, and the preparation method is characterized in that a gettering process is added before a conventional heterojunction solar cell preparation process, and the gettering process is completed through a full-chain gettering process; the full-chain gettering process comprises the following steps: carrying out chain pre-cleaning on a silicon wafer; coating a gettering source on the surface of the silicon wafer in a chained manner; and carrying out chained high-temperature gettering on the silicon wafer. According to the preparation method, by reducing the metal impurity content of the N-type monocrystalline silicon wafer, the quality level of the silicon wafer is improved, the difference between the silicon wafers is reduced, and the conversion efficiency of the heterojunction solar cell is improved; the quality of the N-type monocrystalline silicon wafer tends to be consistent, the efficiency distribution of the prepared heterojunction solar cell is more concentrated, the discreteness of the efficiency distribution is reduced, and the product consistency is greatly improved.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

Light-emitting diode with gradually changed refractive index of light-emitting layer

InactiveCN101916818AAchieving Gradient Refractive IndexImprove luminous efficiencySemiconductor devicesRefractive indexLight-emitting diode

The invention relates to a light-emitting diode with gradually changed refractive index of a light-emitting layer. The refractive index of the light-emitting layer is gradually changed by arranging a protective layer outside the light-emitting layer of the light-emitting diode, wherein the refractive index of the material of the protective layer is between that of the material of the light-emitting layer and that of the packaging material of the light-emitting diode. The luminescent efficiency of the light-emitting diode can be improved and the leakage rate of the light-emitting diode can be reduced.

Owner:AQUALITE CO LTD

A kind of manufacturing method of p-type double-sided crystal silicon battery

InactiveCN107359112BUniform sheet resistanceGuaranteed not to intermixFinal product manufactureSemiconductor/solid-state device manufacturingSilver electrodeEngineering

The invention discloses a method for manufacturing a P-type double-sided crystalline silicon battery. Firstly, the silicon chip is made of double-sided texture by using the traditional texture-making process, and then the slurry printing process and the chain level are adopted with the solid impurity source as the main component. Diffusion process, followed by double-sided coating, double-sided printing of front silver electrodes and sintering. The process of preparing double-sided batteries by the method of the present invention is simpler than that of conventional double-sided batteries, especially the double-sided printing process and chain diffusion process, which ensures that different diffusion sources at the edge are not doped with each other, and at the same time reduces the leakage rate of the finished battery ; The diffusion time of the chain diffusion process is greatly shortened compared with the traditional tubular diffusion process, and the production efficiency is improved.

Owner:河北兆能新能源科技有限公司

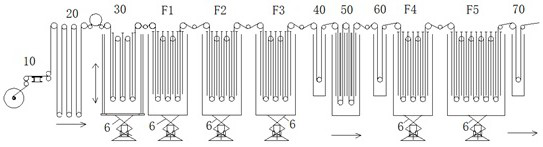

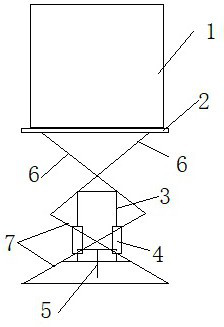

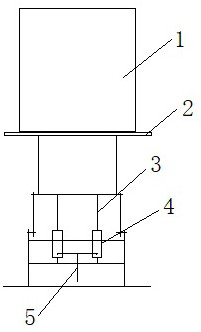

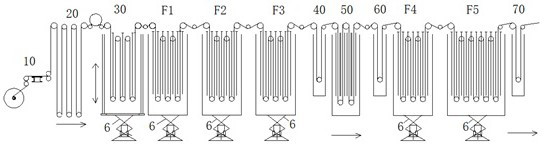

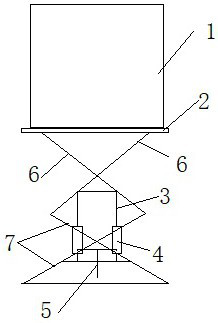

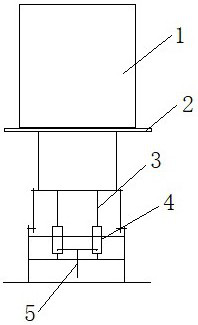

5G signal transmitter capacitor formed foil multistage oxidation treatment process and production line thereof

ActiveCN112490007AHigh ripple current resistanceReduce leakageElectrolytic capacitorsCapacitor manufactureOXALIC ACID DIHYDRATECapacitance

The invention discloses a 5G signal transmitter capacitor formed foil multistage oxidation treatment process and a production line thereof, the process at least comprises five formation processes of first-stage formation, second-stage formation, third-stage formation, fourth-stage formation and fifth-stage formation of an aluminum foil, and the first-stage formation and the second-stage formationare both carried out in an aqueous solution containing oxalic acid, phosphoric acid and ammonium dihydrogen phosphate; the third-stage formation is carried out in an aqueous solution containing ammonium dihydrogen phosphate, boric acid and ammonium pentaborate; and the fourth-stage formation and the fifth-stage formation are both carried out in an aqueous solution containing boric acid and ammonium pentaborate. The first-stage to fifth-stage formation processes of the production line are respectively carried out in corresponding liftable grooves, so that the working hours for converting product specifications are shortened, the reaction time of oxidation in the aluminum foil and the liftable grooves can be conveniently changed, the overall process equipment is simple and convenient to operate, time-saving, labor-saving and energy-saving, the performance parameters of the product are improved, the capacitor meeting the technical requirements of the 5G signal transmitter is manufactured,and the cost is low.

Owner:新疆金泰新材料技术股份有限公司

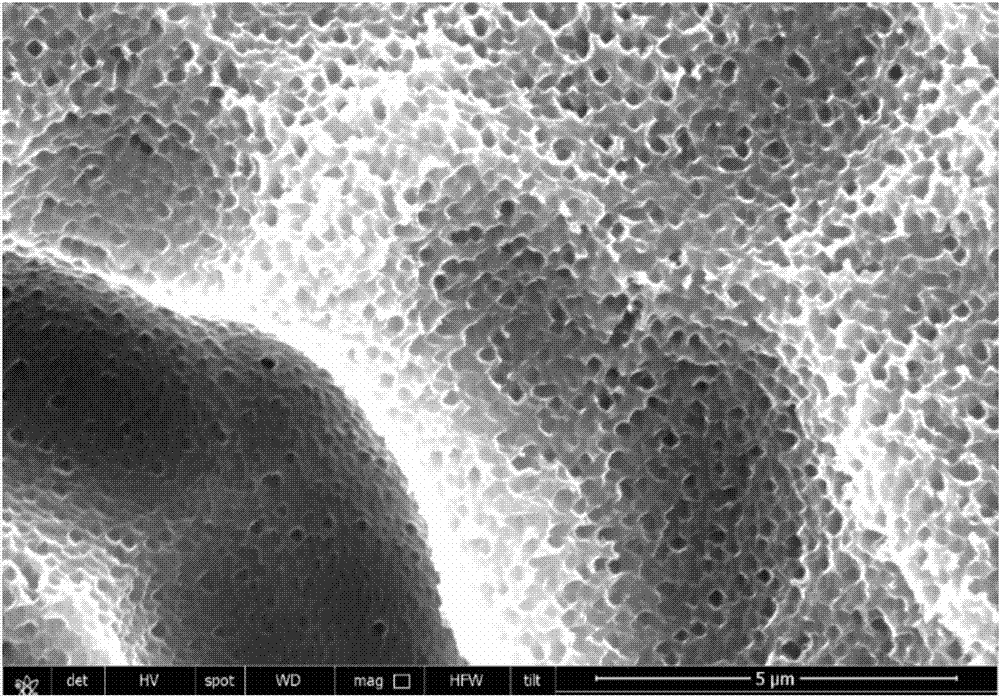

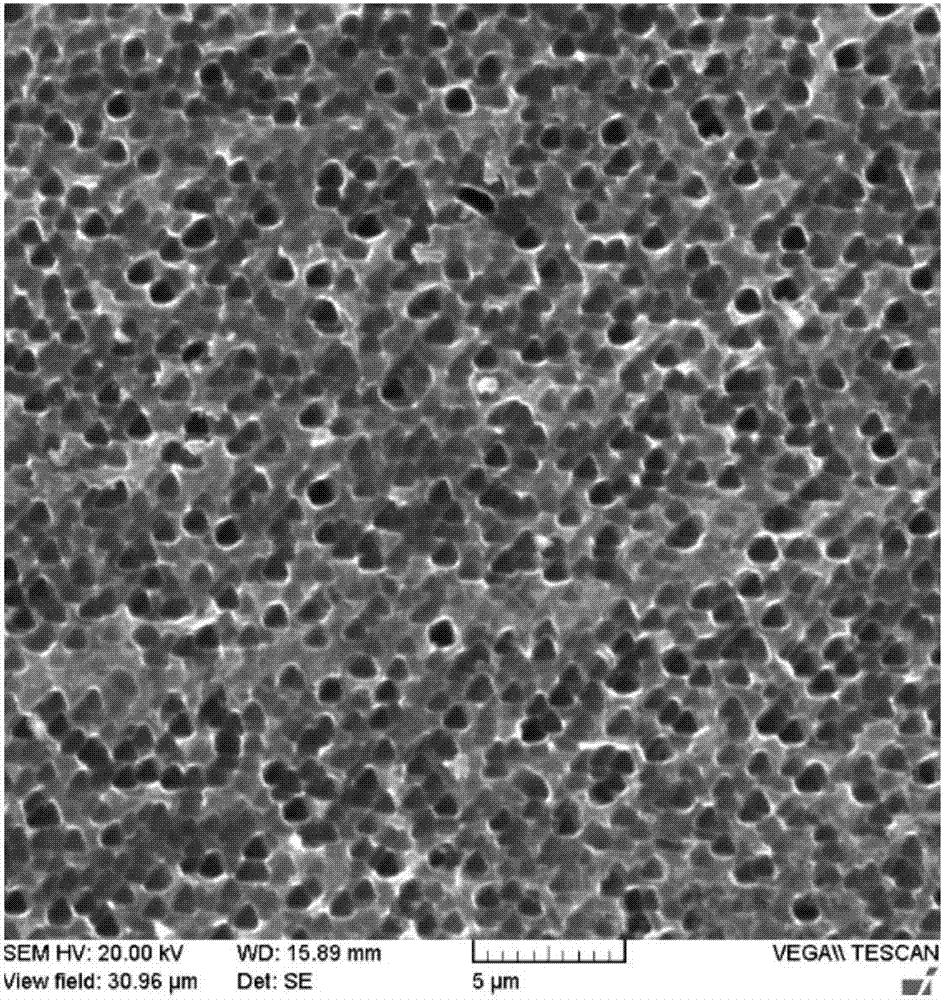

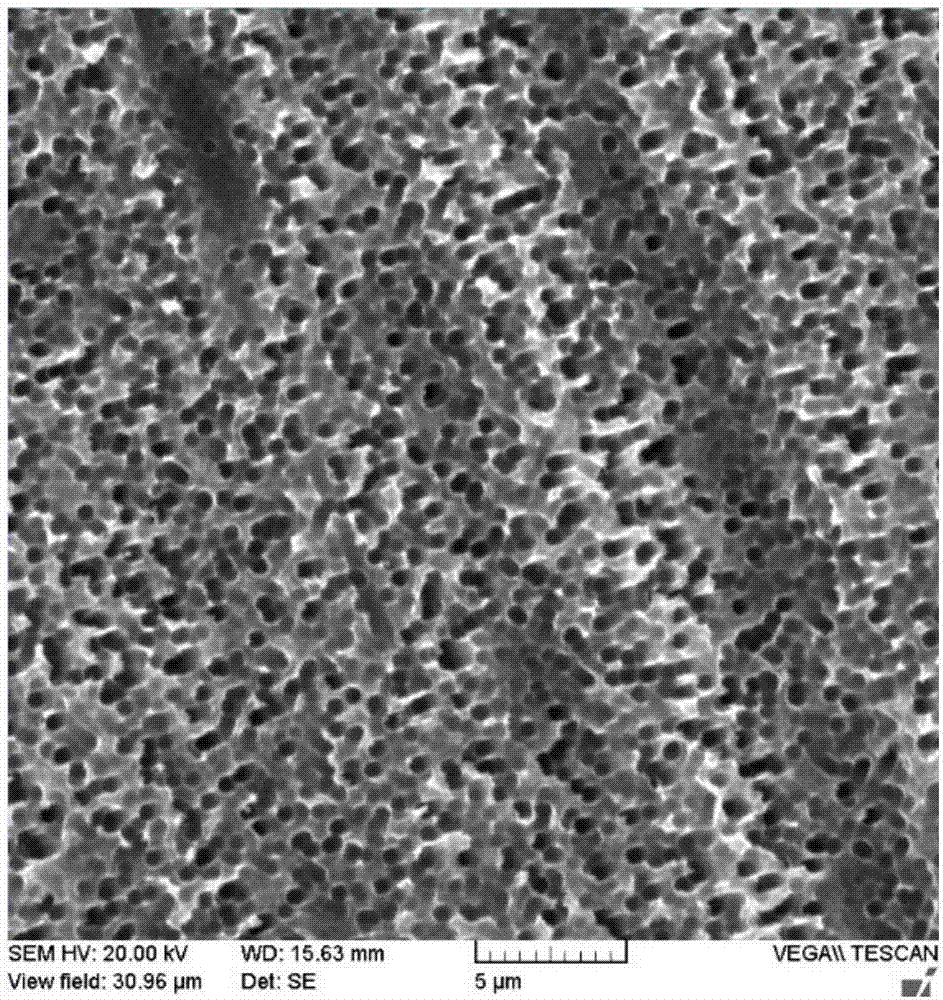

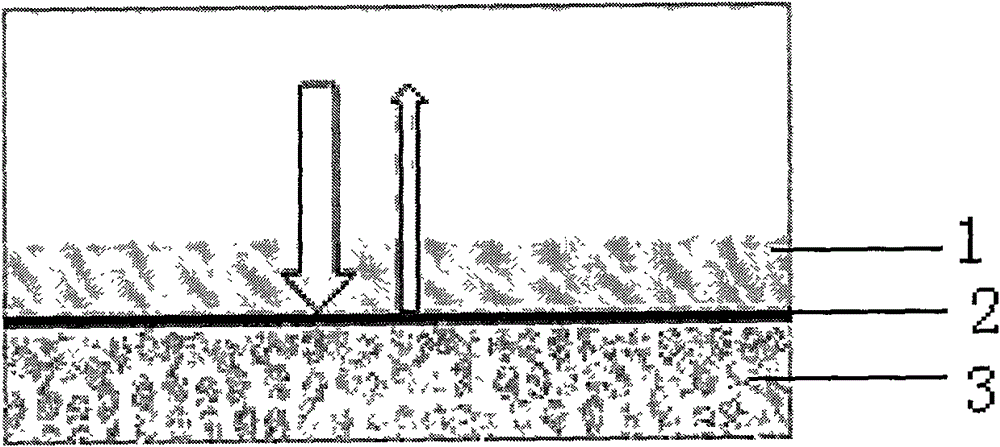

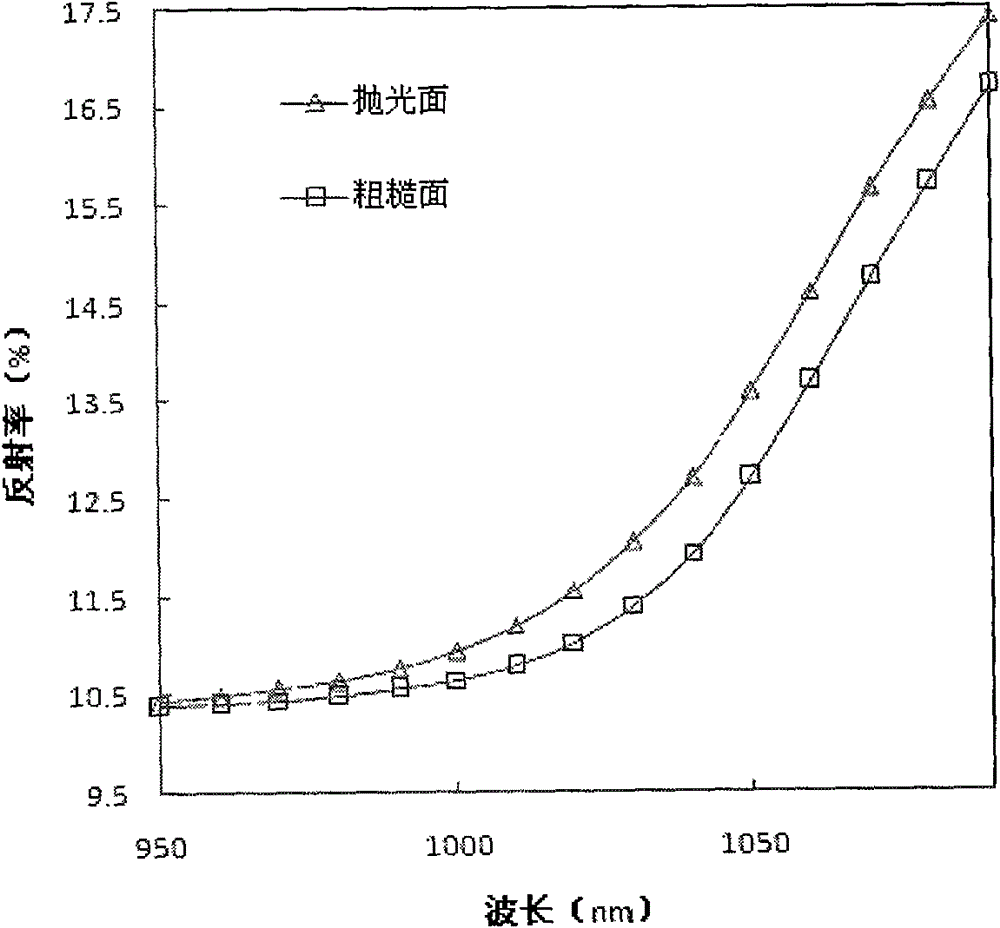

One-step wet process black silicon preparation and surface treatment method

ActiveCN106024988BReduce the probability of electric leakageImprove absorption efficiencyAfter-treatment detailsFinal product manufactureElectrical batteryCell leakage

Owner:湖州叁峰能源新材料有限公司

Industrialized production process of crystalline silicon solar battery

ActiveCN101840961BReduce the probability of electric leakageReduce process stepsFinal product manufactureSemiconductor devicesSpectral responseBack surface field

The invention discloses an industrialized production process of a crystalline silicon solar battery, which comprises the following steps of: selecting a silicon chip; performing front surface matte making, phosphorous diffusion, the removal of phosphorosilicate glass formed on the surface during the phosphorous diffusion, and the deposition of silicon nitride on the front surface through PECVD inturn, and then putting an anti-reflecting film protected silicon ship provided with the front surface silicon nitride into heated alkali liquor to perform back polishing so as to remove a diffusion layer on the back surface; and washing and drying the silicon chip, and printing and sintering the silicon chip by adopting a bending-resistant aluminum paste silk screen. The process adopts a chemicalmethod to replace a plasma etching process, realizes non-contact of a matte surface of the silicon chip in the whole production flow, avoids matte surface damages caused by silicon chip friction, so the probability of electric leakage after facade silver paste sintering is reduced; the flat and clean back surface is favorable for the reaction of aluminum and silicon during the sintering to form amore uniform aluminum back surface field; and a polished surface has a stronger reflex action compared with an irregular matte surface, and can increase the absorption of incident light, improve the spectral response of the long-wavelength of a battery chip, and significantly improve a short-circuit current and an open-circuit voltage.

Owner:JA YANGZHOU SOLAR PHOTOVOLTAIC ENG

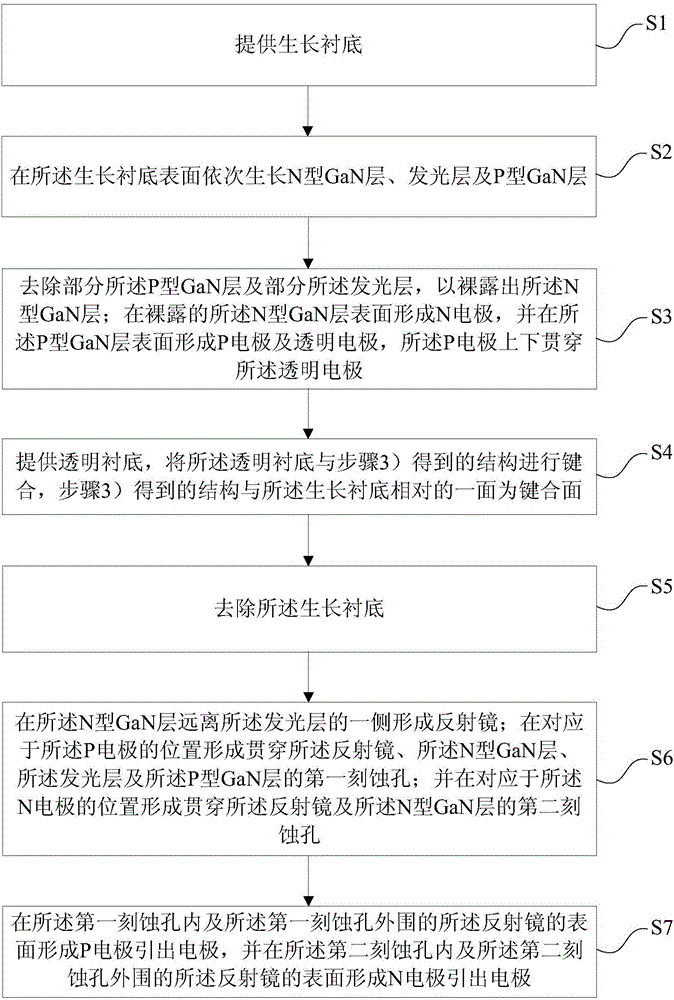

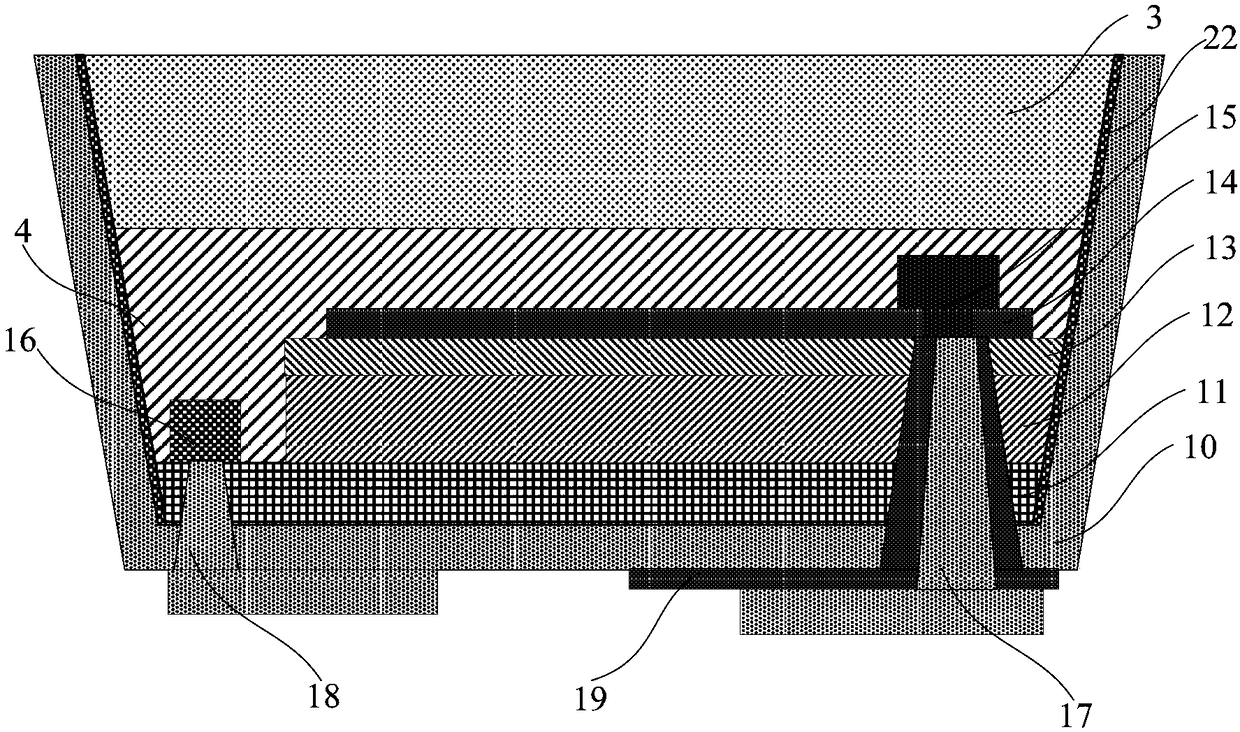

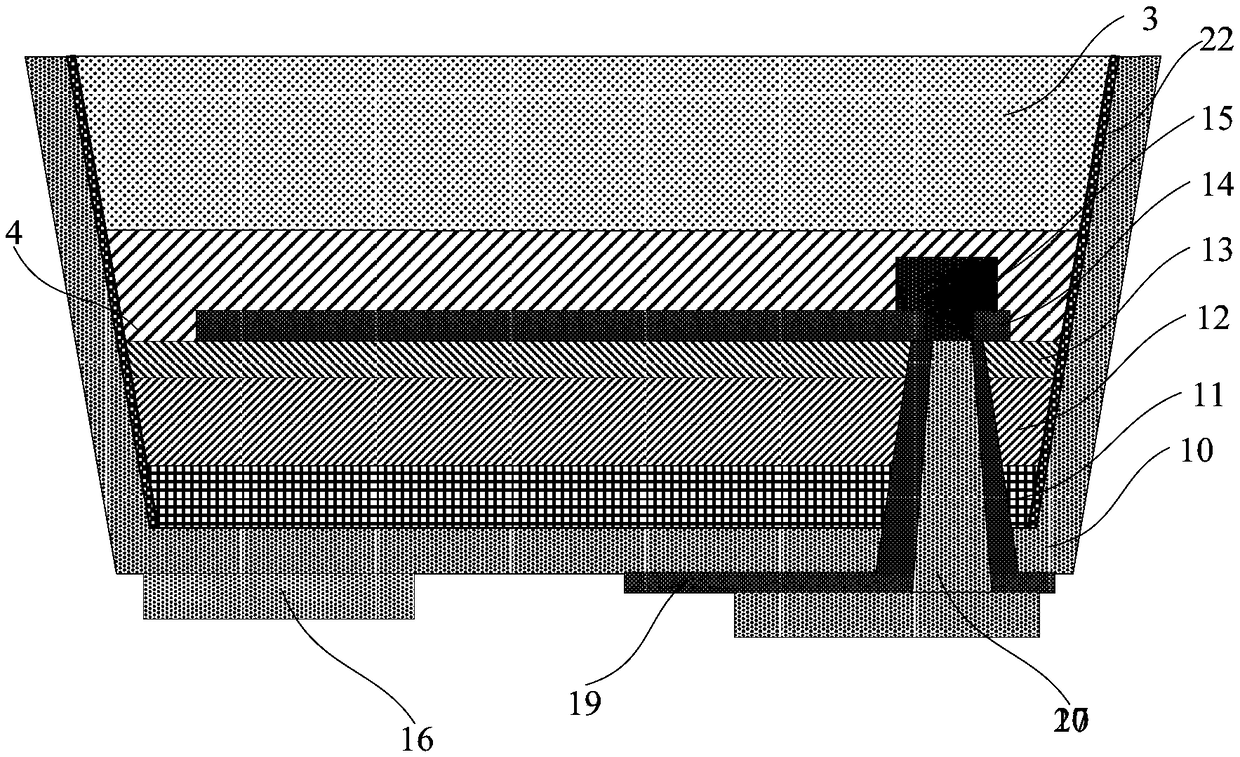

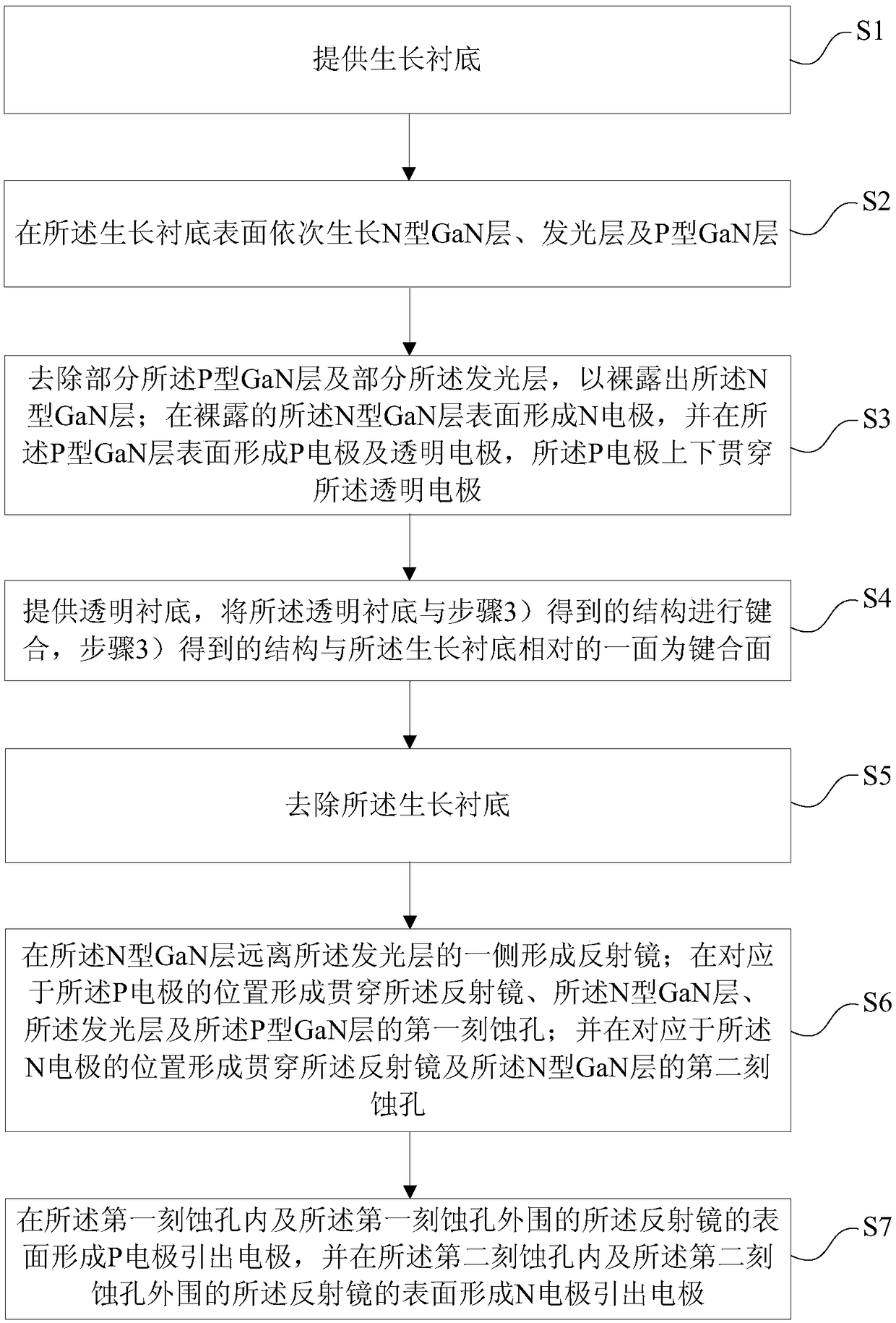

Packaging-free high-luminance LED chip structure and manufacturing method therefor

ActiveCN106531859AImprove qualityHigh quality and high efficiencySemiconductor devicesEngineeringHigh luminance

The invention provides a packaging-free high-luminance LED chip structure and a manufacturing method therefor. The packaging-free high-luminance LED chip structure comprises a GaN-based LED structure and a transparent substrate, wherein the GaN-based LED structure comprises a reflecting mirror, an N type GaN layer, a light-emitting layer, a P type GaN layer, a transparent electrode, a P electrode, an N electrode and a P electrode extraction electrode; the reflecting mirror, the N type GaN layer, the light-emitting layer, the P type GaN layer and the transparent electrode are stacked from the bottom up in sequence; one surface, far from the reflecting mirror, of the GaN-based LED structure is a P surface; the P electrode runs through the transparent electrode and is in contact connection with the P type GaN layer; the N electrode is positioned on the surface of the N type GaN layer or on the surface of the reflecting mirror; one end of the P electrode extraction electrode is connected with the P electrode while the other end runs through the P type GaN layer, the light-emitting layer, the N type GaN layer and the reflecting mirror and extends to the surface of the reflecting mirror; and the transparent substrate is bonded on the P surface of the GaN-based LED structure. The LED chip structure provided by the invention has the advantages of low electric leakage rate, capability of realizing the packaging-free effect, high luminous efficiency and the like.

Owner:SHANGHAI XINYUANJI SEMICON TECH

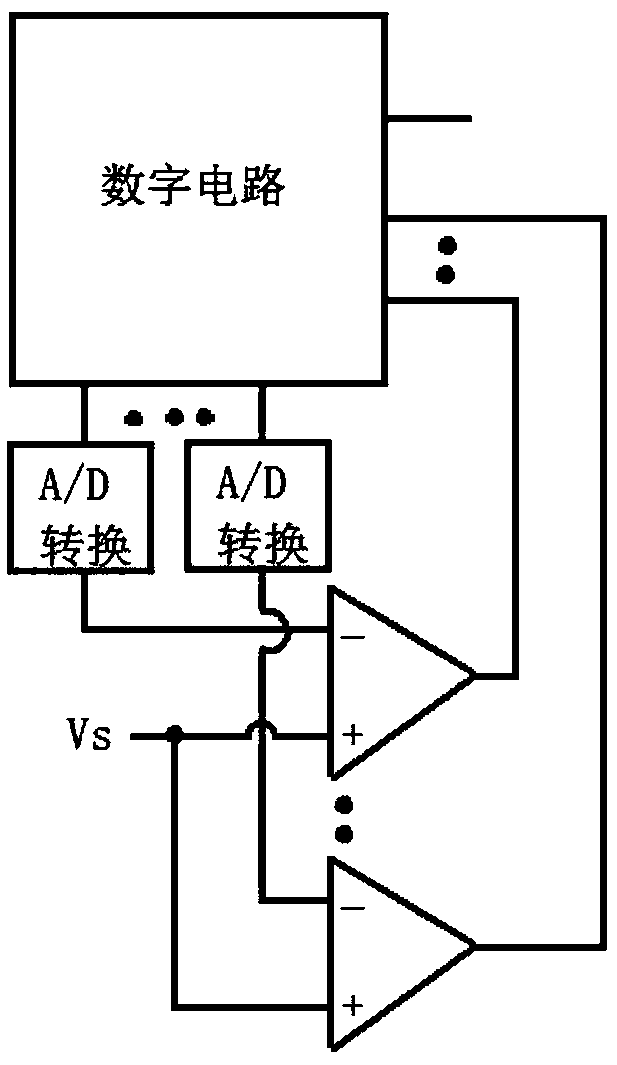

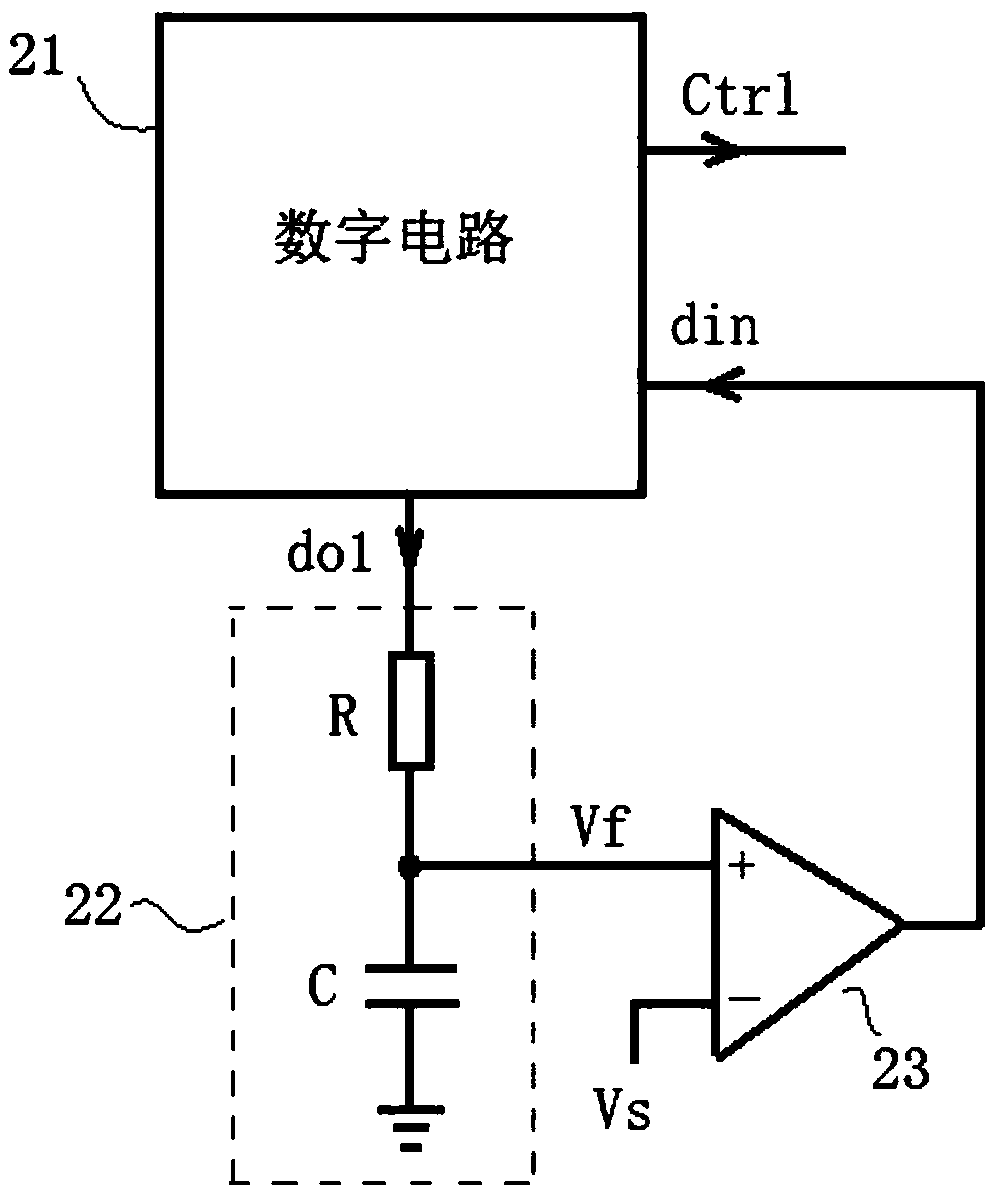

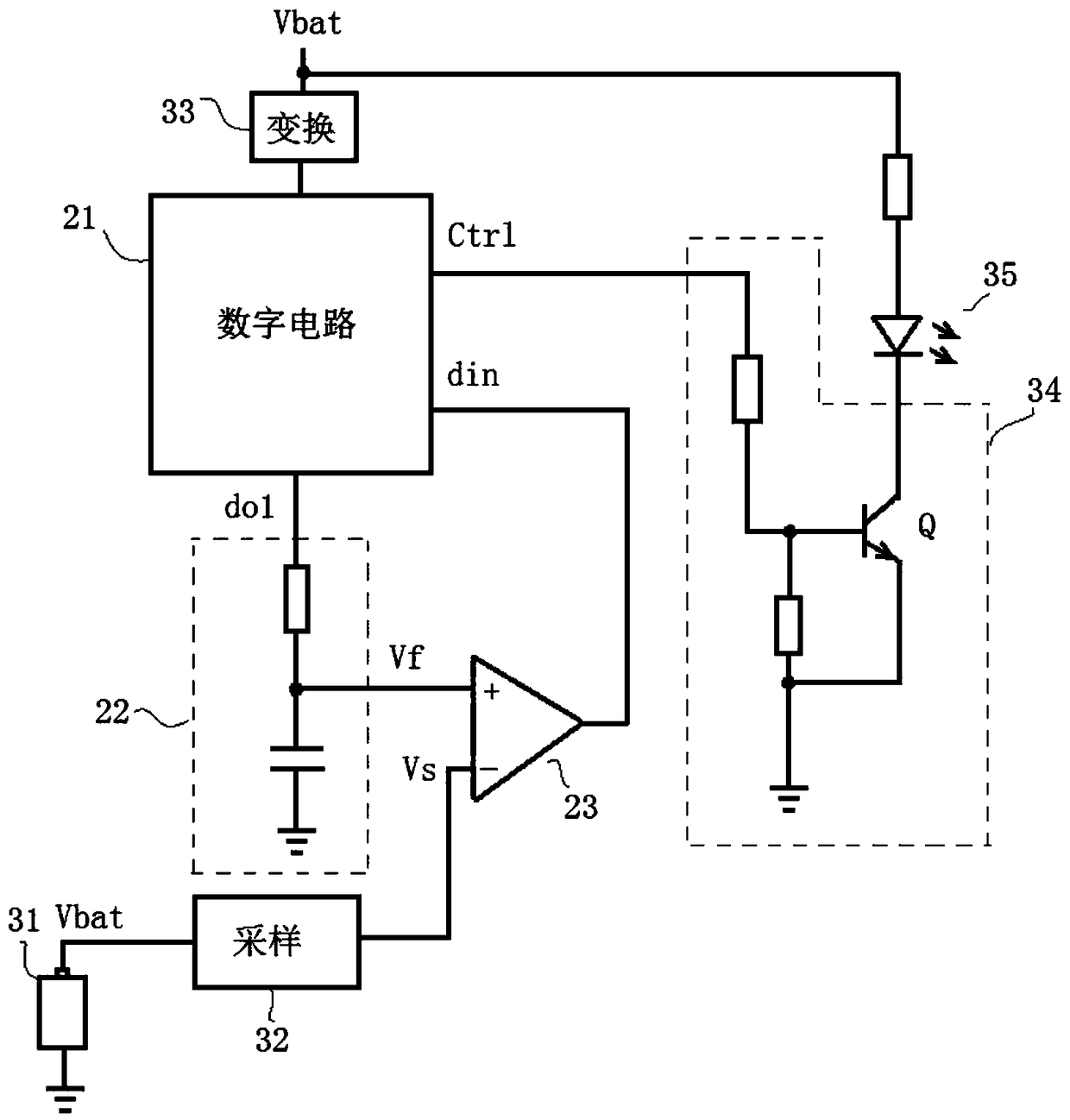

Voltage detecting circuit, battery power prompting system and voltage detecting method

PendingCN109298339AImprove scalabilityReduce in quantityElectrical testingMeasurement using digital techniquesSystem integrationControl signal

The invention provides a voltage detecting circuit, a battery power prompting system and a voltage detecting method. The voltage detecting circuit based on a digital circuit comprises a digital circuit, a conversion circuit and a comparison circuit. The digital circuit has a first output end, an input end and a second output end. The first output end outputs a digital signal. The input end of theconversion circuit is coupled to the first output end of the digital circuit. The first input end of the comparison circuit receives a voltage signal representative of the to-be-detected voltage. Thesecond input end of the comparison circuit is coupled to the output end of the conversion circuit. The output end of the comparison circuit is coupled to the input end of the digital circuit. The digital circuit obtains a to-be-detected voltage level based on the output signal of the comparison circuit, and provides a control signal at the second output end of the digital circuit, wherein the control signal is generated based on the to-be-detected voltage level. According to the voltage detecting circuit, the battery power prompting system and the voltage detecting method in the embodiment, the detection can be realized only by occupying two pins of the digital circuit, so that extension of other functions of the digital circuit is facilitated; meanwhile, the complexity, the volume and thecost of the system are reduced, so that the system integration is facilitated, thereby improving the reliability of a portable electric tool in a relatively poor working environment.

Owner:HANGZHOU BOON ELECTRONICS CO LTD

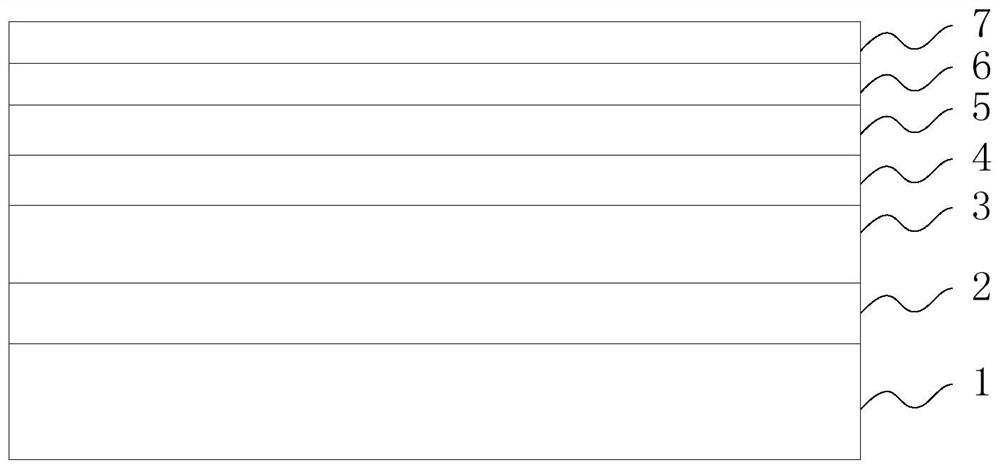

A kind of n-type high-efficiency solar cell and preparation method thereof

ActiveCN112289895BLow content of metal impuritiesImprove life expectancyFinal product manufactureSemiconductor devicesHeterojunctionElectrical battery

The invention discloses an N-type high-efficiency heterojunction solar cell and a preparation method thereof. The N-type high-efficiency solar cell is an N-type high-efficiency heterojunction solar cell made of an N-type silicon wafer; N-type silicon wafers undergo gettering treatment, and then complete the conventional production of heterojunction solar cells; the gettering treatment includes the following steps: (1) Cleaning the silicon wafer; (2) Coating or depositing a layer on the front and back of the silicon wafer gettering source; (3) heat-treat the silicon wafer coated or deposited with the gettering source through a chain annealing furnace to complete the gettering, and form a layer of gettering layer on the surface of the silicon wafer; (4) etch and remove the silicon wafer surface gettering layer. The invention reduces the metal impurity content in the silicon wafer, improves the minority carrier life of the silicon wafer, and finally improves the conversion efficiency of the battery; makes the efficiency distribution of the battery more concentrated, and improves product consistency; reduces the edge leakage rate of the battery, and improves the battery efficiency. Battery yield.

Owner:CHANGZHOU SHICHUANG ENERGY CO LTD

Vertical epitaxial structure LED chip and preparation method thereof

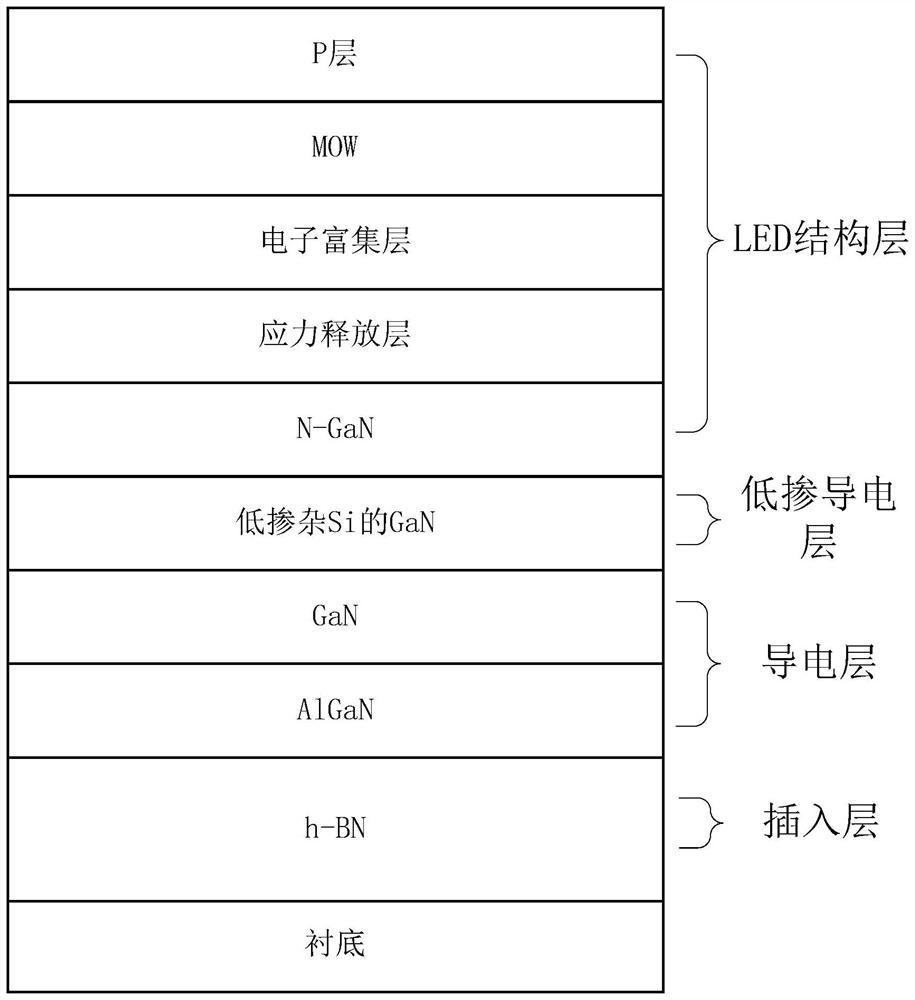

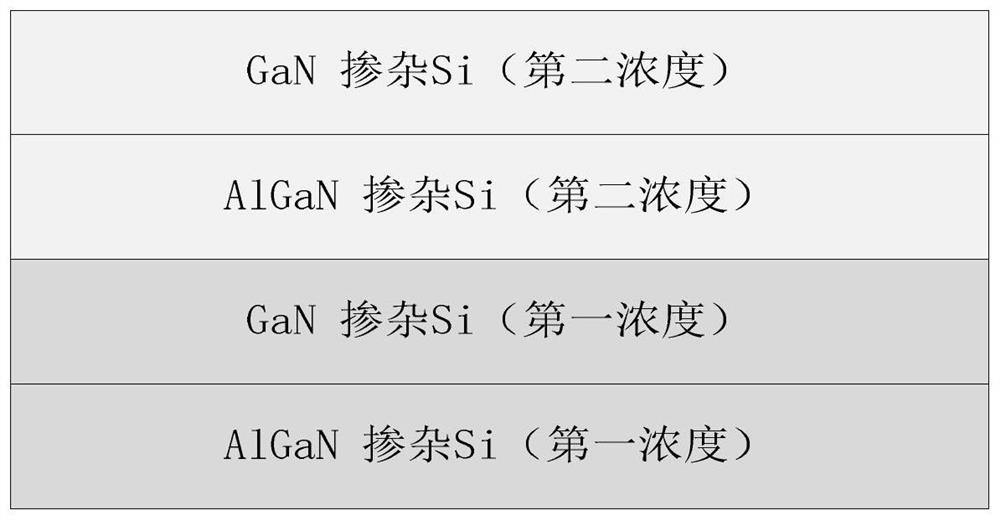

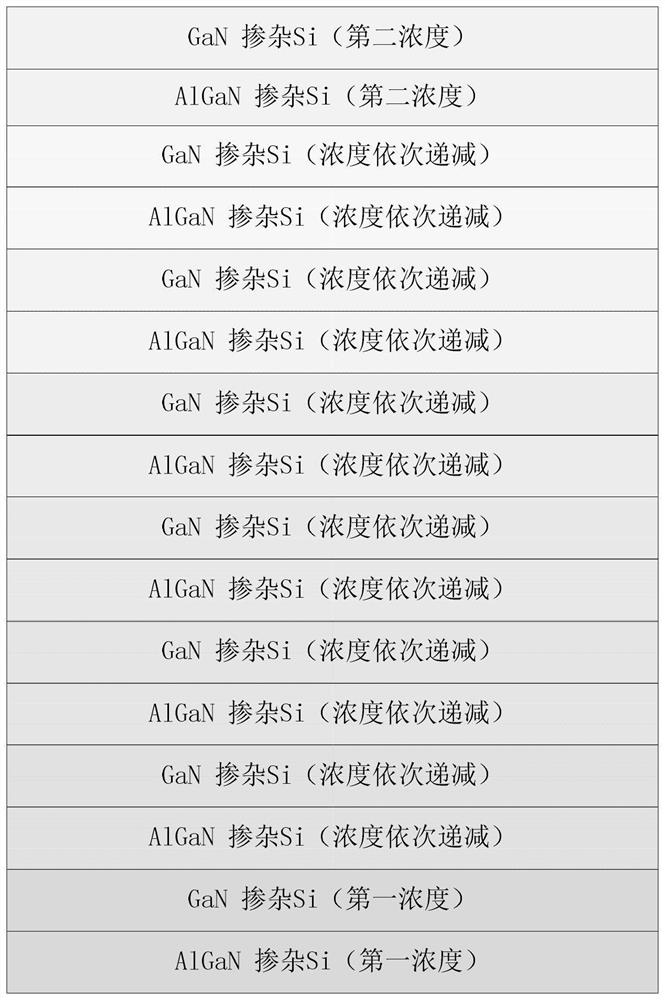

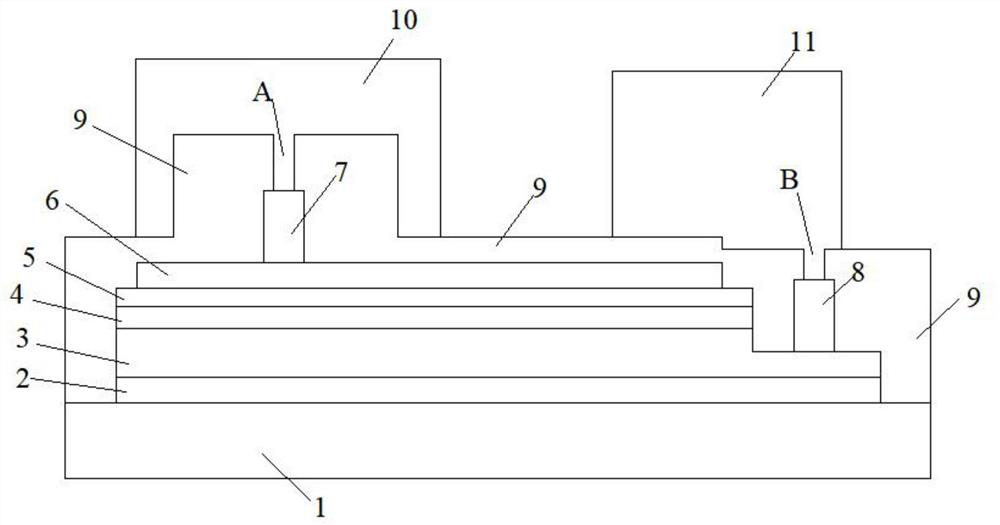

PendingCN114784158ADoes not affect electrical performanceImprove yieldSemiconductor devicesHeterojunctionHexagonal boron nitride

The invention provides a vertical epitaxial structure LED chip and a preparation method thereof, the vertical epitaxial structure LED chip comprises a substrate, an insertion layer, a conductive layer, a low-doped conductive layer and an LED structure layer which are sequentially arranged in a laminated manner, and the insertion layer is a hexagonal boron nitride layer; the conductive layer comprises a plurality of gallium nitride aluminum / gallium nitride heterojunction layers. The mutual acting force between the hexagonal boron nitride layered structures is small, and the damage of stripping to the upper epitaxial structure is small. And by utilizing the layered structure characteristic of the hexagonal boron nitride, the laser lift-off technology cannot damage the structure on the hexagonal boron nitride layer, so that the yield of the LED chip is improved. The gallium nitride aluminum / gallium nitride heterojunction structure can play a role similar to a chip DBR (Distributed Bragg Reflector) due to different materials. Moreover, through the design that the silicon-doped concentration of the gallium aluminum nitride / gallium nitride heterojunction layer is gradually reduced, the gallium aluminum nitride / gallium nitride heterojunction layer can be well matched with an electrode, and has good conductive and ohmic contact effects.

Owner:JUCAN PHOTOELECTRIC TECH (SUQIAN) CO LTD

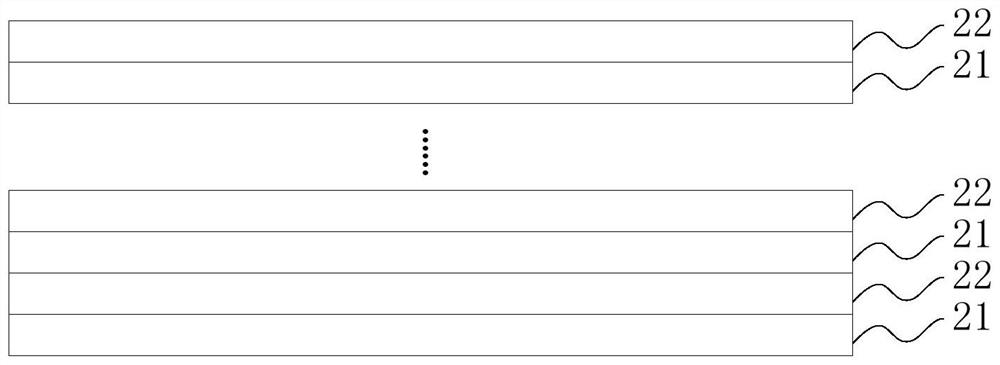

Simple eutectic LED chip structure and manufacturing method thereof

PendingCN113838953AReduce the difficulty of eutecticLow costSemiconductor devicesEngineeringElectrical and Electronics engineering

The invention provides a simple eutectic LED chip structure and a manufacturing method thereof. The LED chip structure comprises a P electrode, an N electrode, a Bragg reflection layer, a P welding layer, and an N welding layer, wherein the P electrode is arranged below the Bragg reflection layer and is connected with the P welding layer through a first through hole penetrating through the Bragg reflection layer; the N electrode is arranged below the Bragg reflection layer and is connected with the N welding layer through a second through hole penetrating through the Bragg reflection layer; and the electrode structures of the P welding layer and the N welding layer are respectively a Cr layer, an Al layer, (Ti layer / Pt layer)n, an Au layer and a Sn layer which are sequentially stacked on the Bragg reflection layer, and n represents the number of repetition times of the Ti layer and the Pt layer which are stacked. The manufacturing method comprises the steps of manufacturing a step structure, manufacturing a single wafer, manufacturing a P electrode and an N electrode, manufacturing a Bragg reflection layer, and manufacturing a P welding layer and an N welding layer. According to the invention, the eutectic difficulty is greatly reduced.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

Insulation protection flip LED chip structure and manufacturing method thereof

PendingCN114156385AImprove yieldImprove light extraction efficiencySemiconductor devicesThin membraneEngineering

The invention discloses a flip LED chip structure with insulation protection and a manufacturing method thereof, and the flip LED chip structure with insulation protection is characterized in that an LED chip epitaxial structure is grown on a chip substrate, a chip current layering structure and N and P bonding pad regions are manufactured, a compact insulating film is deposited on a sliced chip unit to serve as an insulating protection layer, and the insulating protection layer is formed on the chip substrate. And the insulating protection layer wraps and covers the chip structure except the N and P bonding pad areas, and comprises the front surface, the back surface and the side surface of the chip unit. The surrounding type insulation protection LED chip structure is adopted, the compact insulation film is deposited on the sliced chip unit to serve as the insulation protection layer, the electric leakage rate can be reduced, the yield of the chip can be improved, meanwhile, the light emitting efficiency is enhanced, the reliability of long-term use of a device is enhanced, and water vapor erosion is restrained.

Owner:普瑞(无锡)研发有限公司

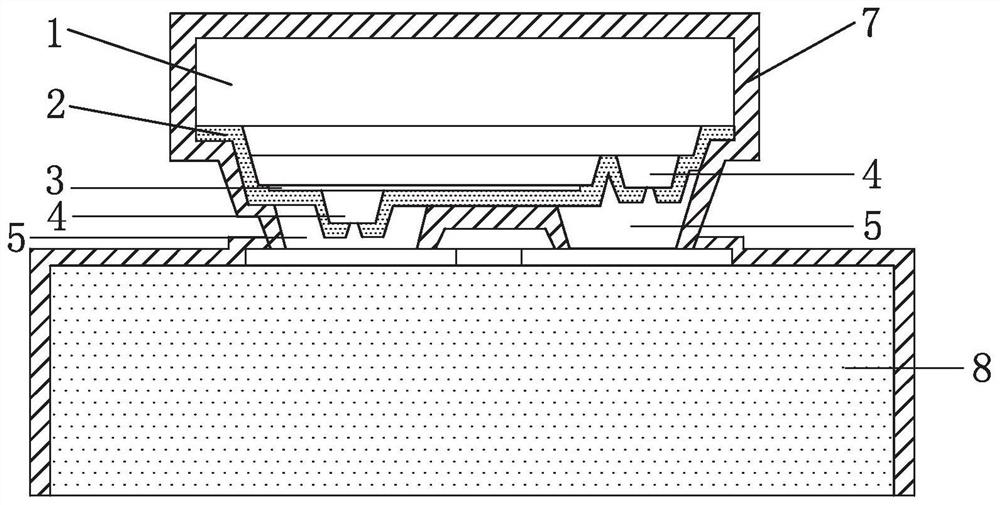

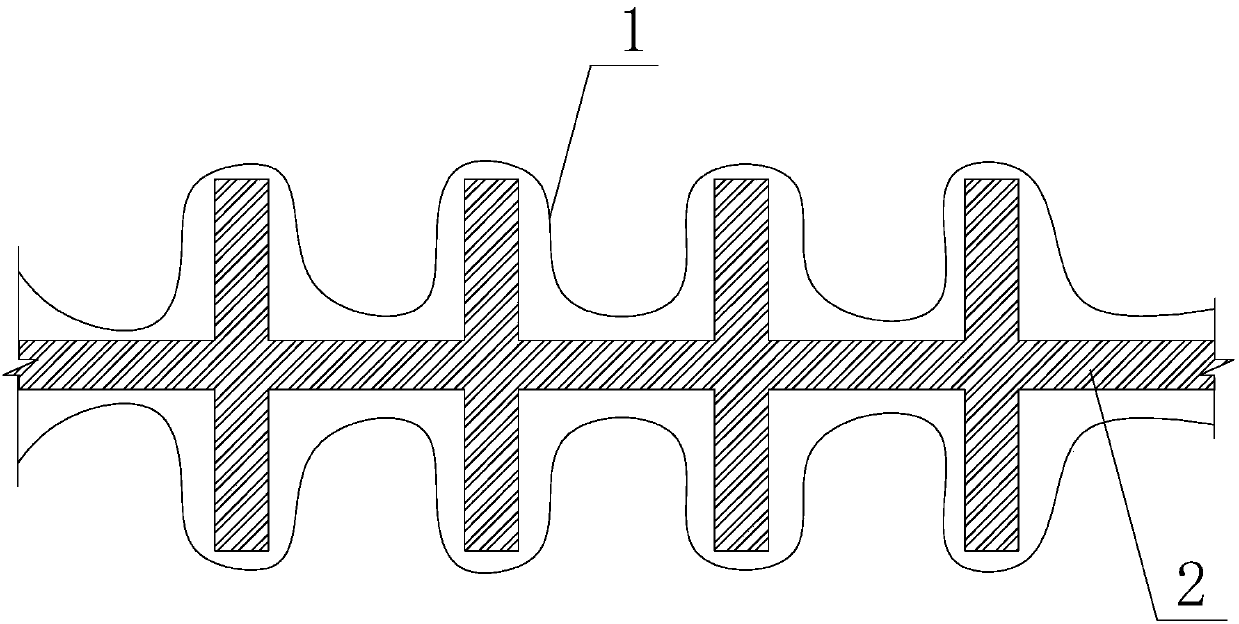

Filter tube and super-soft soil solidifying device provided with same

PendingCN107761709ANo need to worry about flatteningAvoid lostSoil preservationSoil scienceMechanical engineering

Owner:CCCC SHANGHAI DREDGING +1

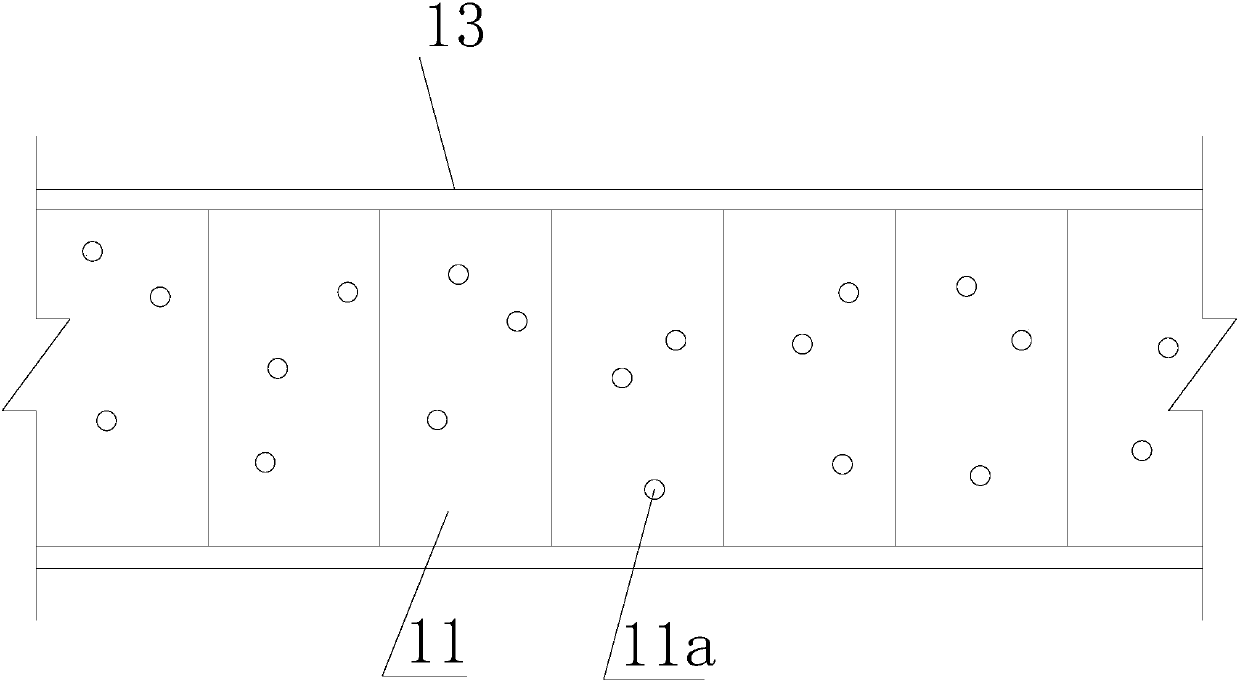

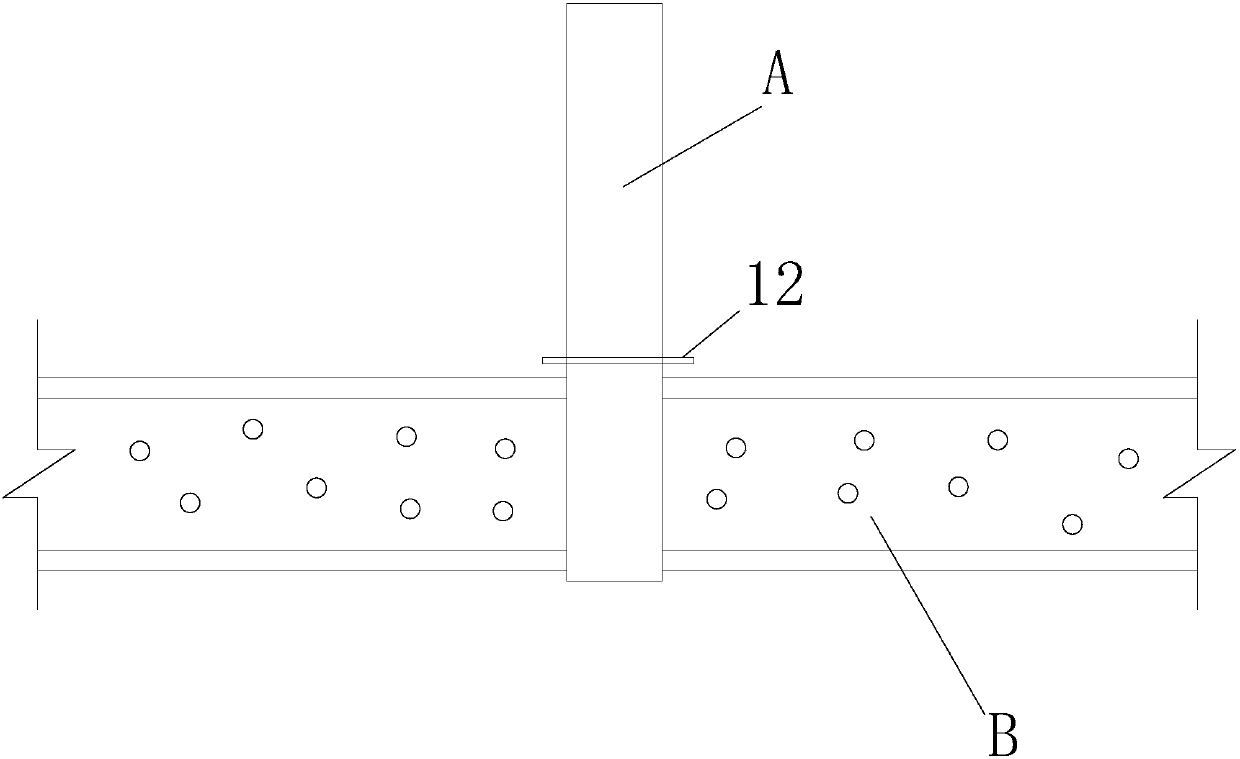

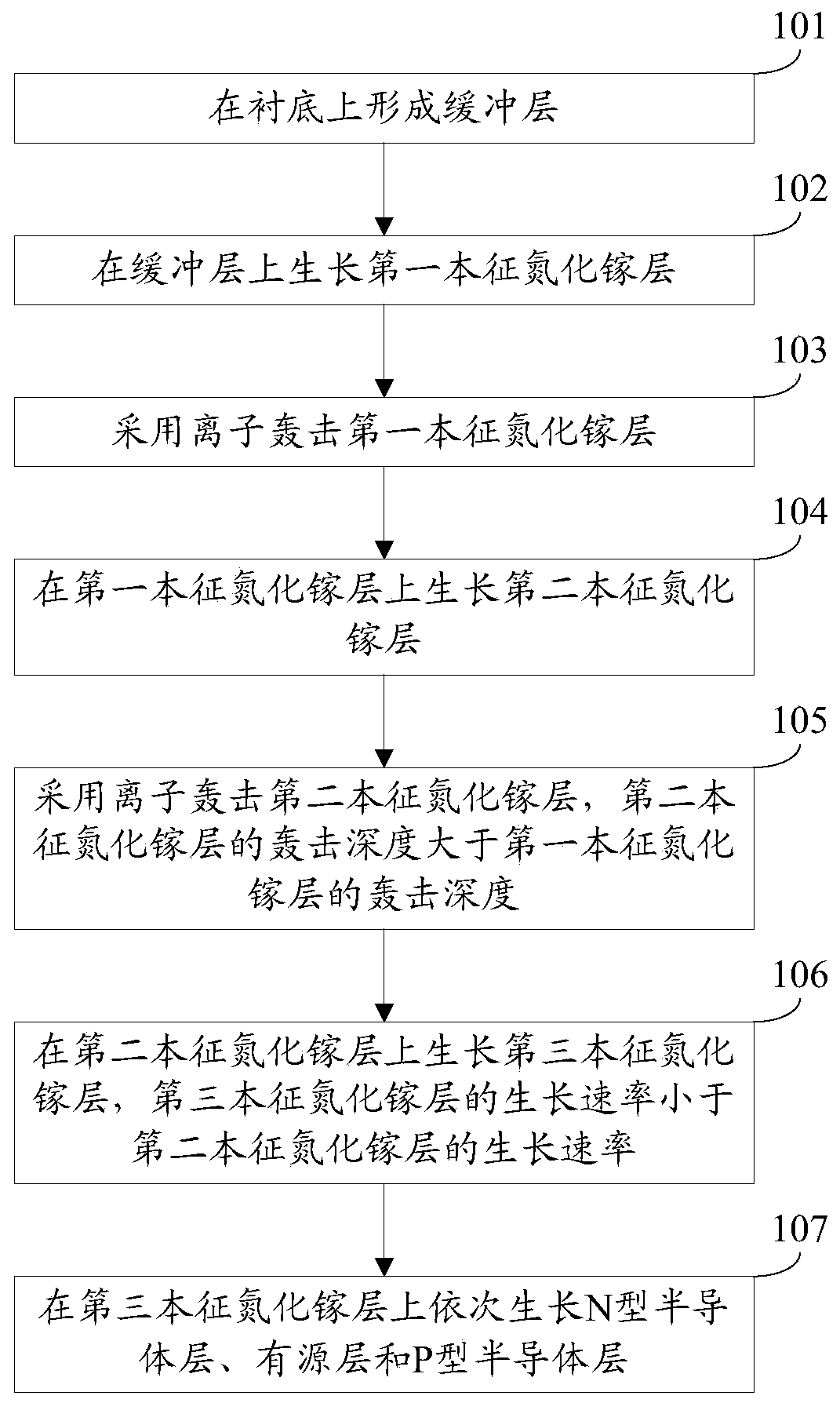

A method for growing light-emitting diode epitaxial wafers

ActiveCN109768124BQuality improvementImprove flatnessSemiconductor devicesGallium nitrideActive layer

Owner:HC SEMITEK ZHEJIANG CO LTD

A kind of solid capacitor negative electrode carbon foil and preparation method thereof

The invention discloses solid-state capacitance negative carbon foil. The solid-state capacitance negative carbon foil comprises a corrosion aluminum foil layer, wherein the corrosion aluminum foil layer is provided with upper and lower rough surfaces, upper and lower metal transition layers with high affinity to aluminum and graphite are plated on the upper and lower rough surfaces of the corrosion aluminum foil layer respectively through a magnetron sputtering manner, and upper and lower graphite layers are plated on outer surfaces of the upper and lower metal transition layers respectively through a magnetron sputtering manner. A manufacture method of the solid-state capacitance negative carbon foil includes the following steps of taking corrosion aluminum foil with the upper and lower rough surfaces, subsequently performing sputtering plating of the upper and lower metal transition layers with high affinity to aluminum and graphite on the upper and lower surfaces of the corrosion aluminum foil by means of a magnetron sputtering manner under a vacuum condition, and finally performing sputtering plating of a graphite layer on the outer surfaces of the upper and lower metal transition layers through a magnetron sputtering manner again. According to the solid-state capacitance negative carbon foil, the graphite layer is not prone to fall off, and the solid-state capacitance negative carbon foil has the advantages of being long in service life, large in electric capacity, low in leakage rate, small in impedance, and the like.

Owner:辽宁北宇真空科技有限公司

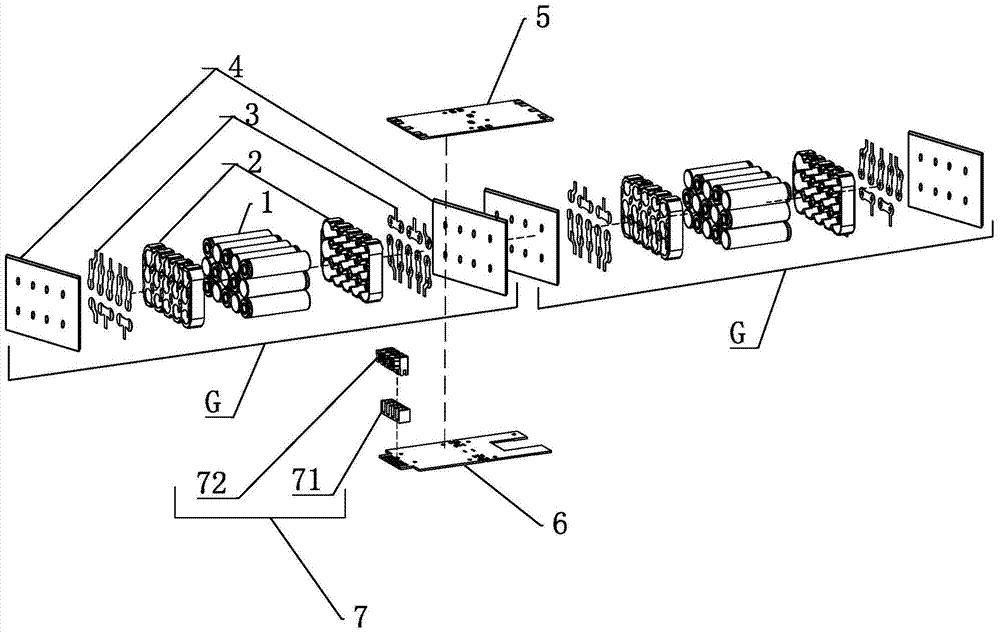

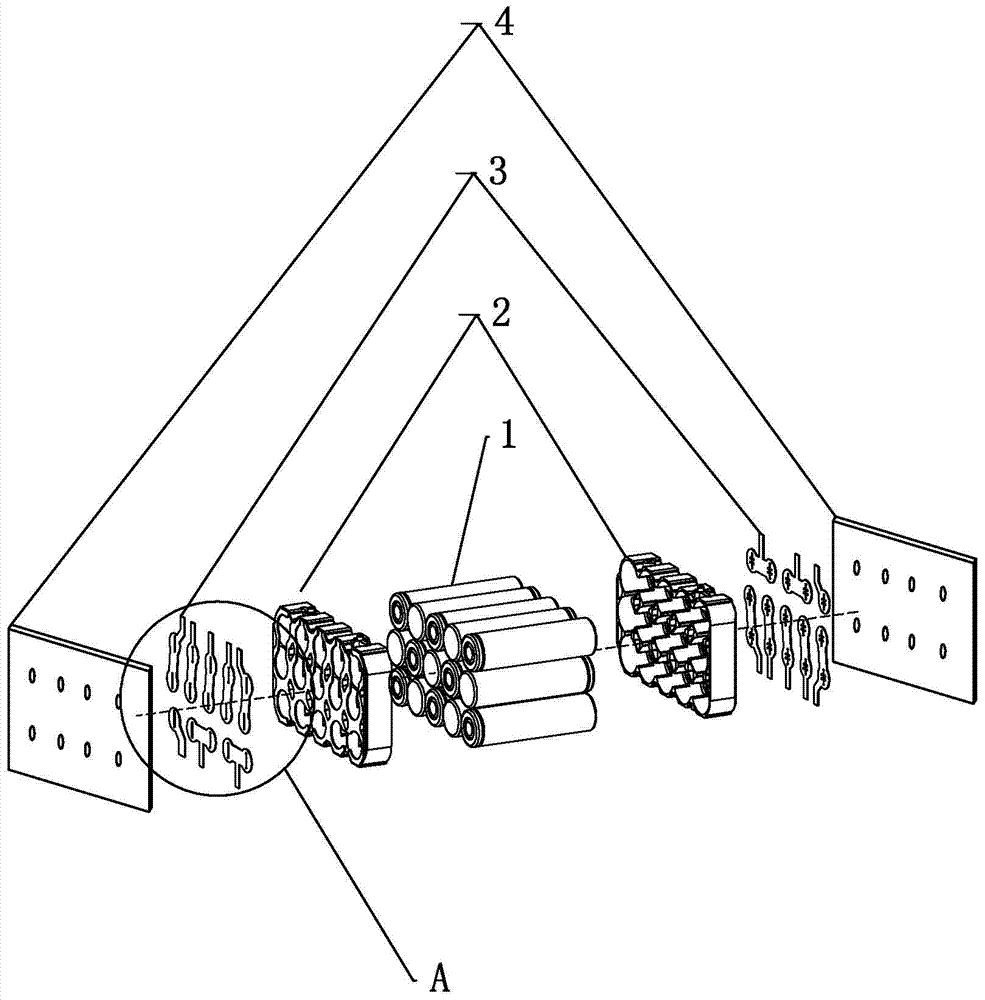

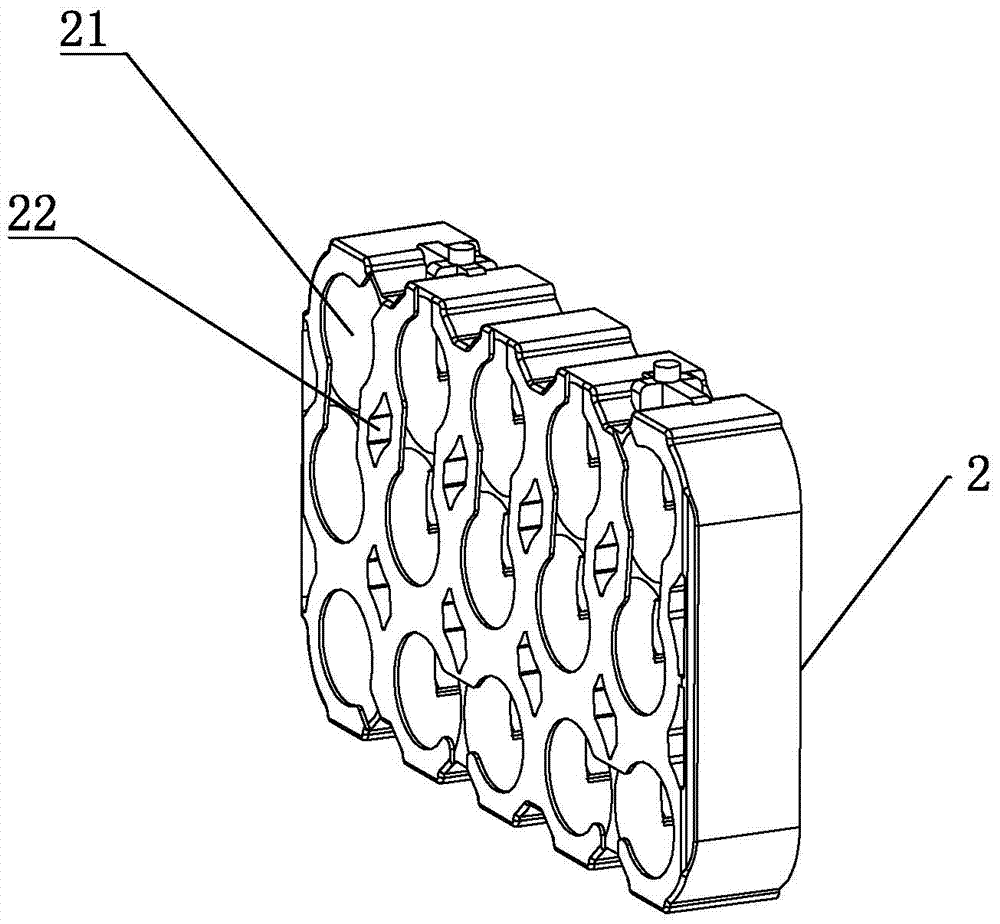

a battery pack

ActiveCN105390654BReduce volumeImprove cooling effectCurrent conducting connectionsSecondary cellsMechanical engineeringBattery cell

The invention discloses a battery pack, which comprises an upper PCB fixing plate, a lower PCB fixing plate, and two battery units connected in series between the upper and lower PCB fixing plates, and the battery units include a plurality of rectangular arrays. Arranged batteries, the placement direction of each adjacent two batteries is opposite, and the two ends of the battery are provided with conductive sheets that connect the batteries in each battery unit in series, and the front and rear ends of the battery are fixed with rectangular Skeleton, the frame is provided with clamping holes for fixing the end of the battery, and a heat dissipation hole is provided at the center of each adjacent four rectangularly arranged clamping holes on the skeleton, and the heat dissipation holes are arranged on the skeleton to connect with the batteries arranged in a rectangular shape. The passages formed between the batteries under the four adjacent rectangular arrays together form a heat dissipation passage, which greatly increases the heat dissipation performance of the battery pack and provides a prerequisite for the large-scale battery pack to work.

Owner:宁波瑞霖机械科技有限公司

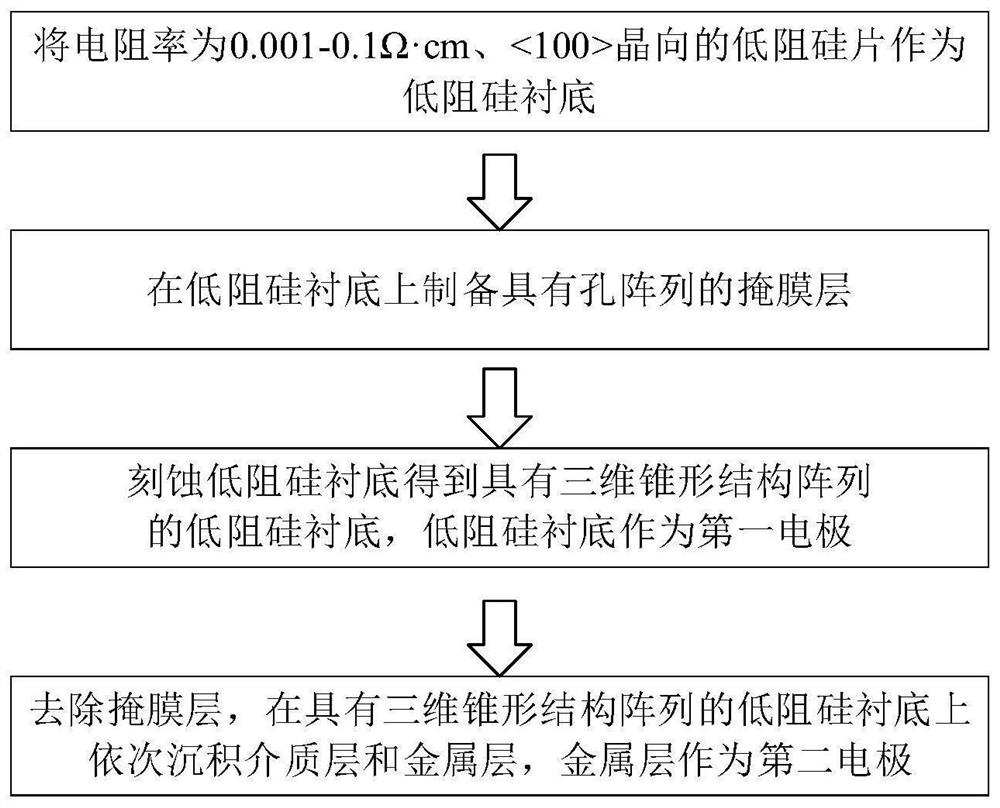

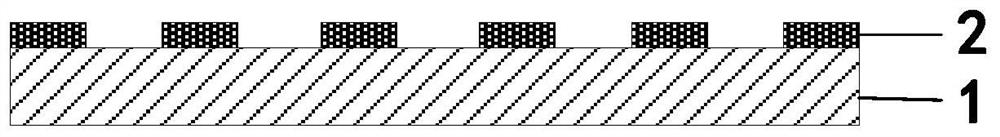

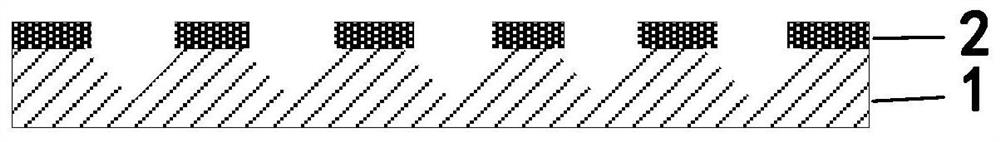

A kind of memristor and preparation method thereof

ActiveCN110797458BClear on and off statesGuaranteed continuityElectrical apparatusDevice materialEngineering

The invention discloses a memristor and a preparation method thereof, which belong to the technical field of micro-nano processing of semiconductor devices. The method comprises using a low-resistance silicon chip whose resistivity satisfies the first threshold condition and whose crystal orientation is <100> as a low-resistance silicon lining. bottom; prepare a mask layer with hole arrays on the low-resistance silicon substrate; etch the low-resistance silicon substrate to obtain a low-resistance silicon substrate with a three-dimensional cone structure array, the three-dimensional cone structure The low-resistance silicon substrate of the array is used as the first electrode layer; the mask layer is removed, and a dielectric layer and a metal layer are sequentially deposited on the low-resistance silicon substrate with a three-dimensional tapered structure array, and the metal layer is used as the second electrode layer. Two electrode layers. The invention introduces a three-dimensional tapered structure array into both the low-resistance silicon substrate and the metal layer, so that the on and off states of the memristor are more obvious and easier to control, and the low-resistance silicon substrate is directly used as the lower electrode, reducing the The memristor film layer reduces the probability of leakage of the memristor and increases the area of the memristor array.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

5g signal transmitter capacitor forming foil multi-stage oxidation treatment process and its production line

ActiveCN112490007BHigh ripple current resistanceReduce leakageElectrolytic capacitorsCapacitor manufactureOXALIC ACID DIHYDRATECapacitance

The invention discloses a 5G signal transmitter capacitor forming foil multi-stage oxidation treatment process and a production line thereof. The process includes at least one-stage forming, two-stage forming, three-stage forming, four-stage forming, and five-stage forming five-stage forming processes of aluminum foil, wherein : Both primary and secondary formation are carried out in an aqueous solution containing oxalic acid, phosphoric acid and ammonium dihydrogen phosphate; tertiary formation is carried out in an aqueous solution containing ammonium dihydrogen phosphate, boric acid and ammonium pentaborate. Both the quaternary formation and the 5th formation are carried out in an aqueous solution containing boric acid and ammonium pentaborate. The first-level to fifth-level chemical formation processes of the production line are carried out in their corresponding liftable tanks, which shortens the man-hours for changing product specifications, and can easily change the reaction time between aluminum foil and the oxidation in the liftable tank. The equipment is easy to operate, saves time and effort, saves energy, and improves the performance parameters of the product, and produces a capacitor that meets the technical requirements of the 5G signal transmitter, and the cost is low.

Owner:新疆金泰新材料技术股份有限公司

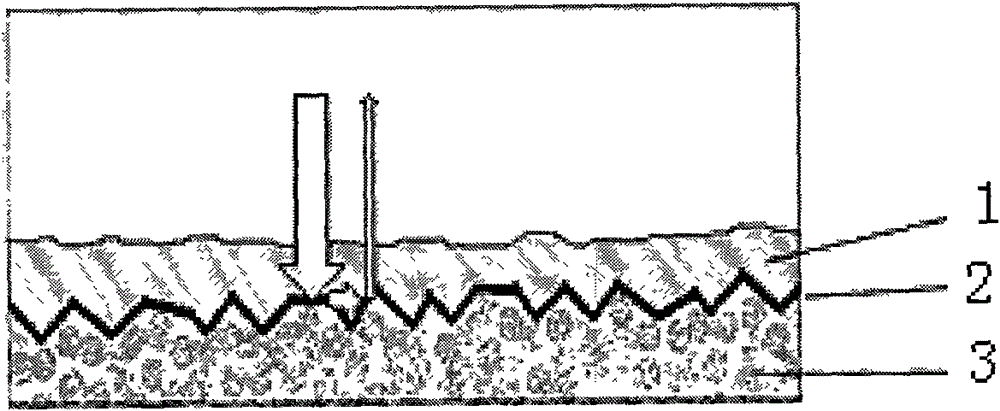

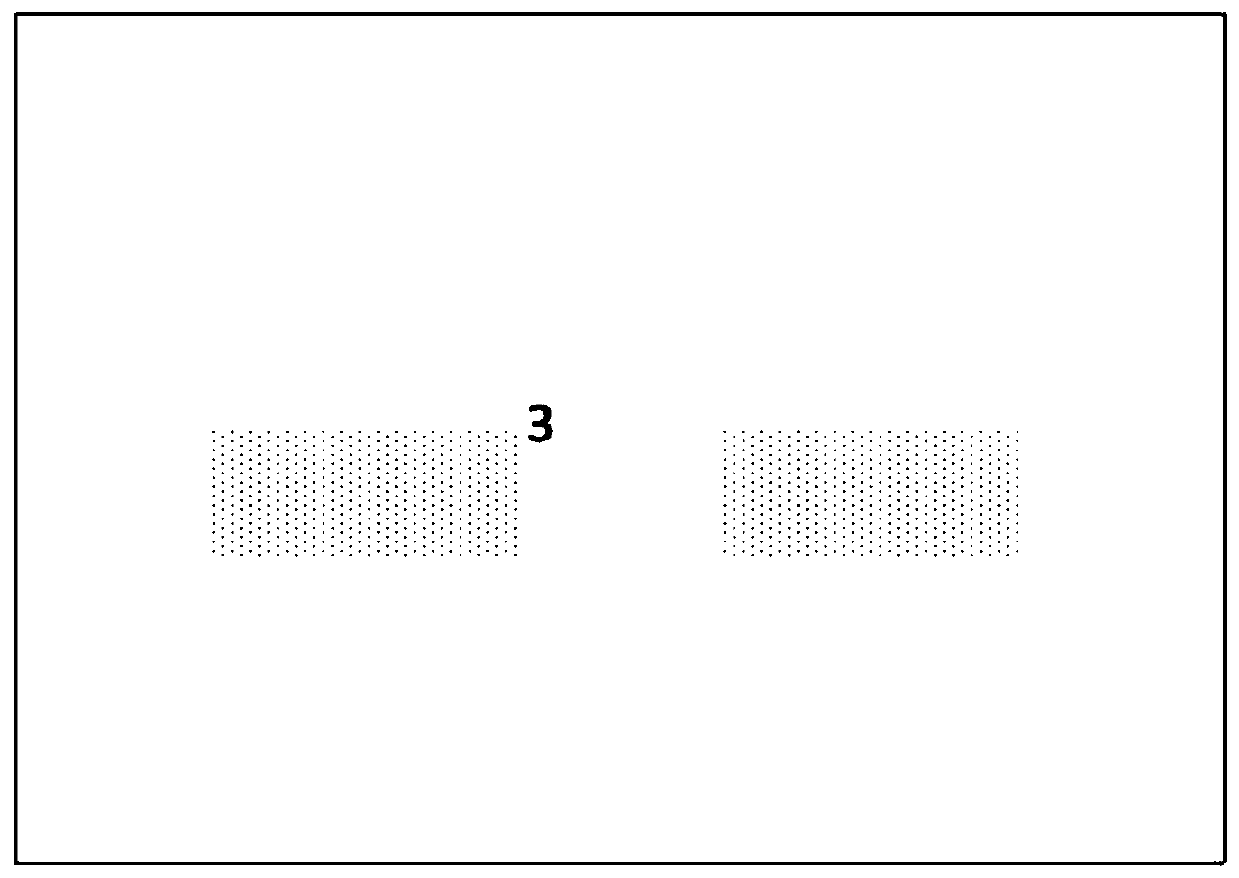

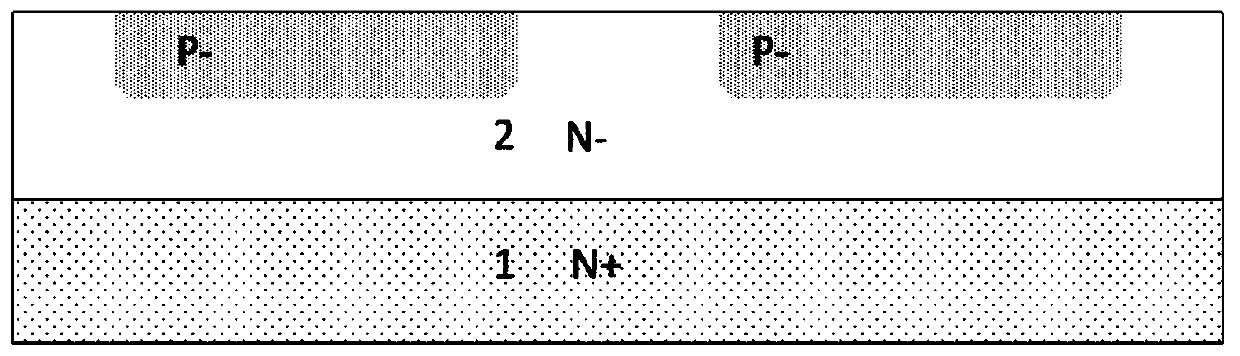

Manufacturing method for high reliability VDMOS power device

InactiveCN110473786AReduce the probability of electric leakageSimple processing technologySemiconductor/solid-state device manufacturingSemiconductor devicesControllabilitySilicon dioxide

The invention discloses a manufacturing method for a high reliability VDMOS power device, and belongs to the technical field of integrated circuit design. The method includes growing an epitaxial silicon layer on a silicon substrate; depositing a shielding layer on the epitaxial silicon layer; designing a photomask of a P-well pattern, performing corrosion, and removing the redundant shielding layer; manufacturing a P well; depositing a silicon dioxide layer on the surface to perform corrosion to form two side triangular structures; manufacturing a contact end and a source end; and taking outthe contact end and the source end. Through the increasing of the shielding layer and the silicon dioxide layer of a power VDMOS device, the fixing of the effective dimension of a channel can be realized, so that the probability of the occurrence of electric leakage can be reduced; and the method is simple in processing technology and strong in controllability, and has strong maneuverability.

Owner:58TH RES INST OF CETC

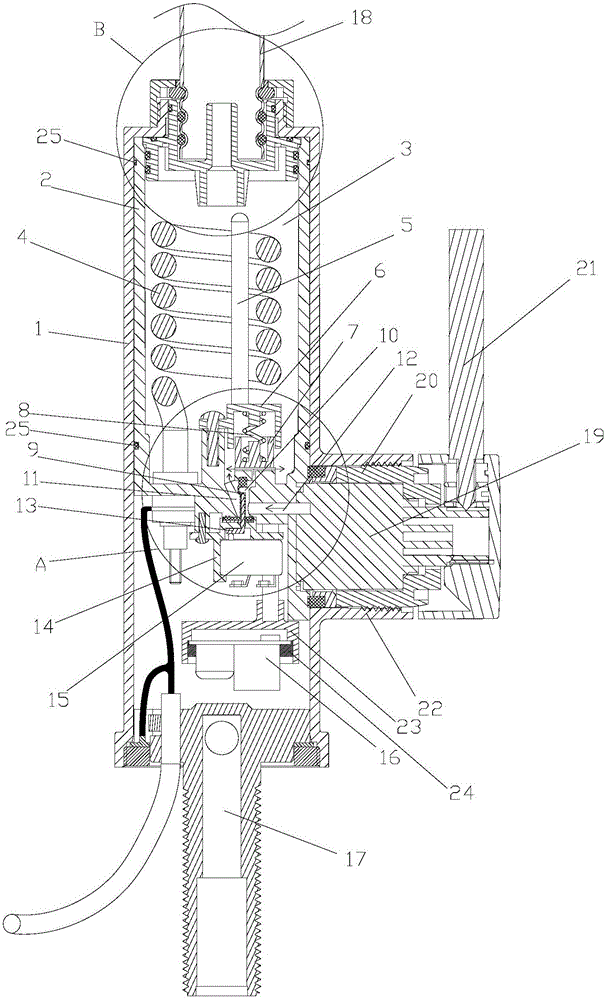

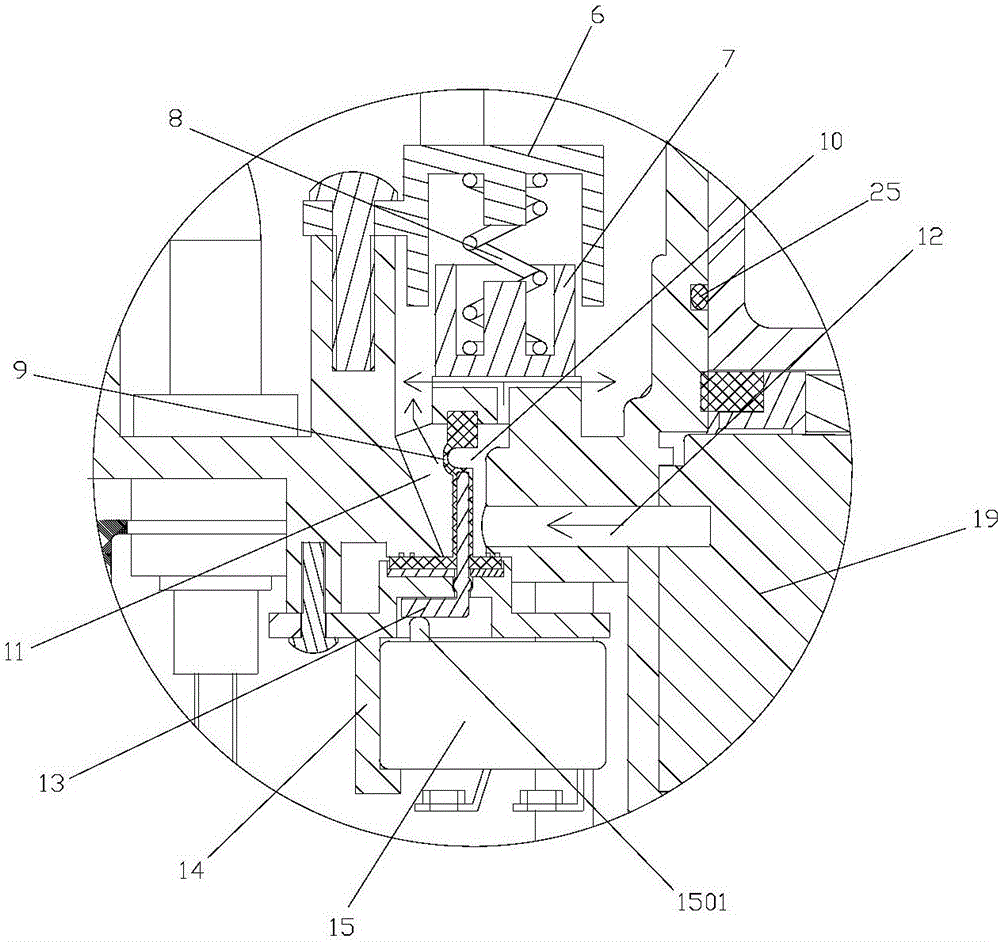

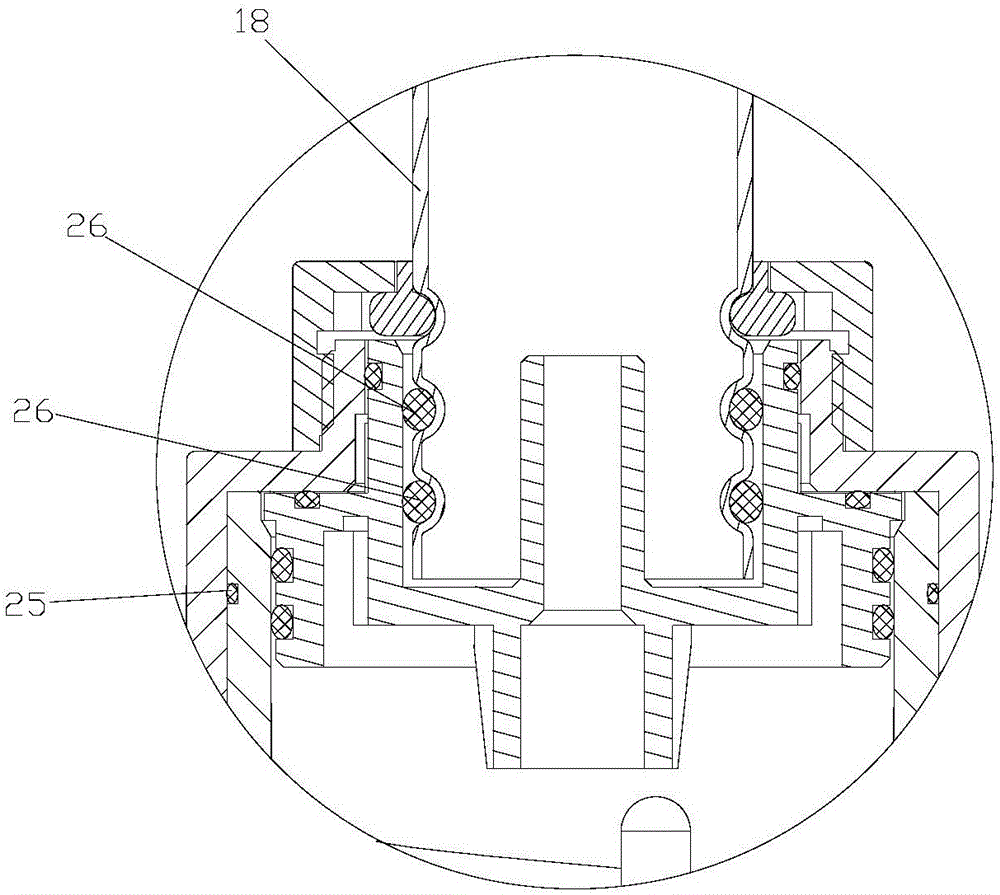

Electric heating faucet with waterproof function

ActiveCN106641433AReduce the probability of leakageWith waterproof functionValve members for heating/coolingDamp environmentElectric heating

The invention discloses an electric heating faucet with a waterproof function. The electric heating faucet comprises a shell, a base arranged in the shell and internally provided with a heating cavity, an electric heating body arranged in the heating cavity, a side barrel welded to one side of the shell in a vertical manner in the radial direction, a water inlet channel communicated with the heating cavity and used for supplying water to the heating cavity, a water outlet channel communicated with the heating cavity and enabling the water in the heating cavity to flow out through the water outlet channel and a switching valve arranged in the side barrel and used for controlling on and off of the water inlet channel, wherein the heating cavity is formed in the base, and two first sealing rings are arranged between the shell and the base at intervals. According to the electric heating faucet with the waterproof function, the two first sealing rings are arranged between the shell and the base, so that the water cannot enter a gap between the shell and the base, the electric leakage probability of the faucet is reduced, and the condition that a damp environment is provided for rusting and corrosion after the water enters the position between the shell and the base is effectively prevented.

Owner:宁波惠荣电器有限公司

Solid-state capacitance negative carbon foil and manufacture method thereof

InactiveCN104103418AMeet quality requirementsImprove bindingFixed capacitor electrodesCapacitanceRough surface

The invention discloses solid-state capacitance negative carbon foil. The solid-state capacitance negative carbon foil comprises a corrosion aluminum foil layer, wherein the corrosion aluminum foil layer is provided with upper and lower rough surfaces, upper and lower metal transition layers with high affinity to aluminum and graphite are plated on the upper and lower rough surfaces of the corrosion aluminum foil layer respectively through a magnetron sputtering manner, and upper and lower graphite layers are plated on outer surfaces of the upper and lower metal transition layers respectively through a magnetron sputtering manner. A manufacture method of the solid-state capacitance negative carbon foil includes the following steps of taking corrosion aluminum foil with the upper and lower rough surfaces, subsequently performing sputtering plating of the upper and lower metal transition layers with high affinity to aluminum and graphite on the upper and lower surfaces of the corrosion aluminum foil by means of a magnetron sputtering manner under a vacuum condition, and finally performing sputtering plating of a graphite layer on the outer surfaces of the upper and lower metal transition layers through a magnetron sputtering manner again. According to the solid-state capacitance negative carbon foil, the graphite layer is not prone to fall off, and the solid-state capacitance negative carbon foil has the advantages of being long in service life, large in electric capacity, low in leakage rate, small in impedance, and the like.

Owner:辽宁北宇真空科技有限公司

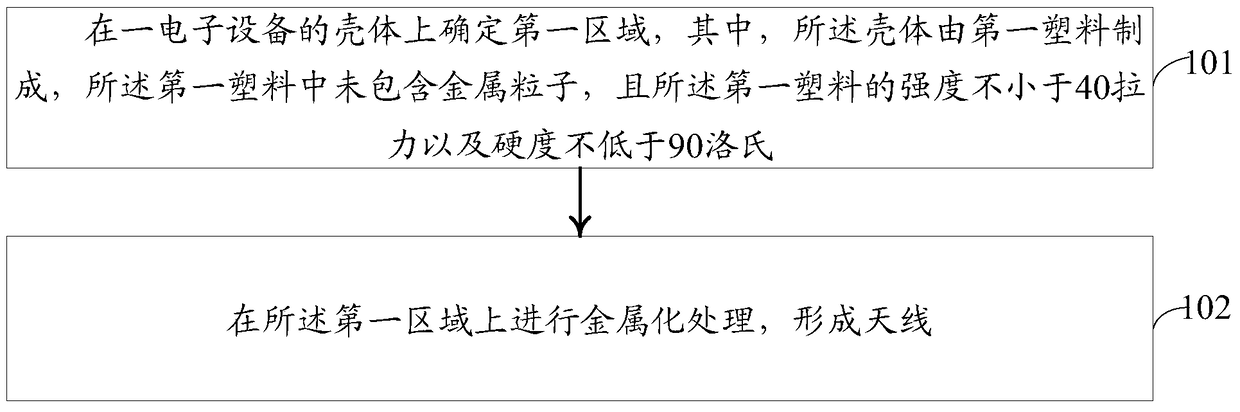

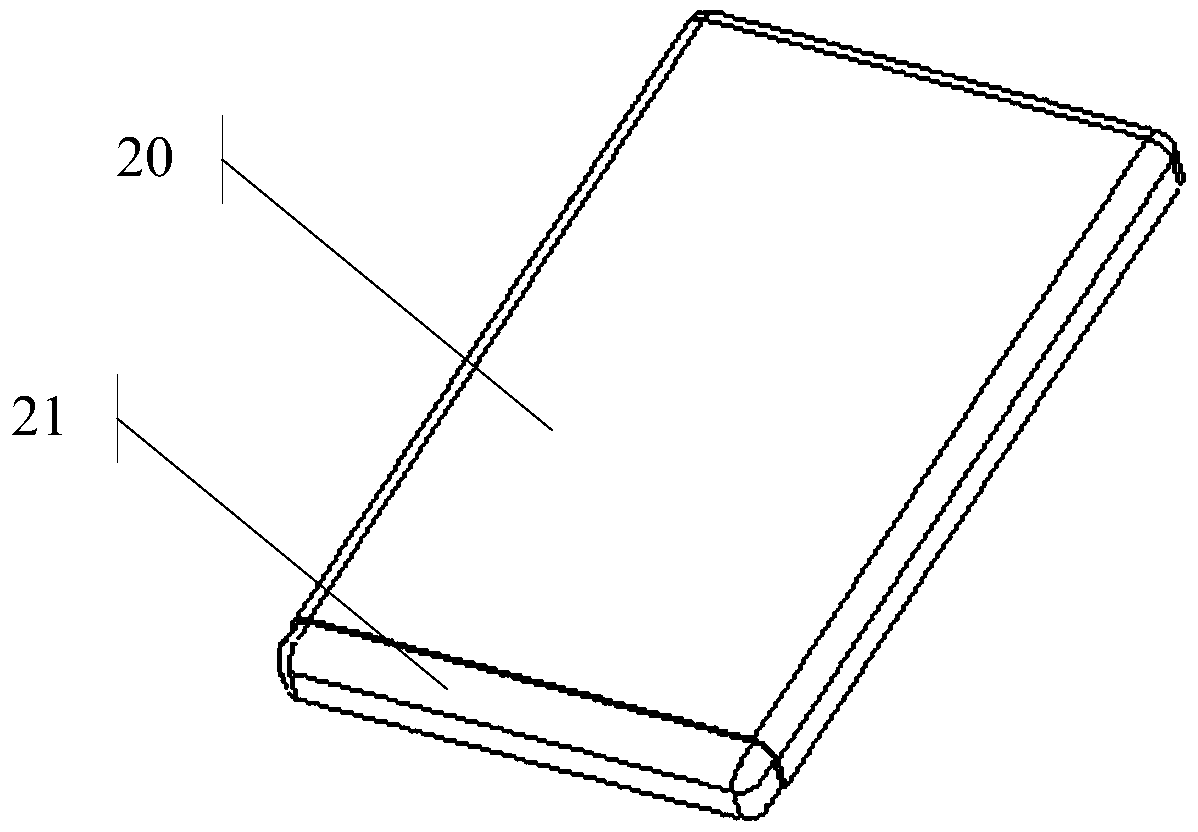

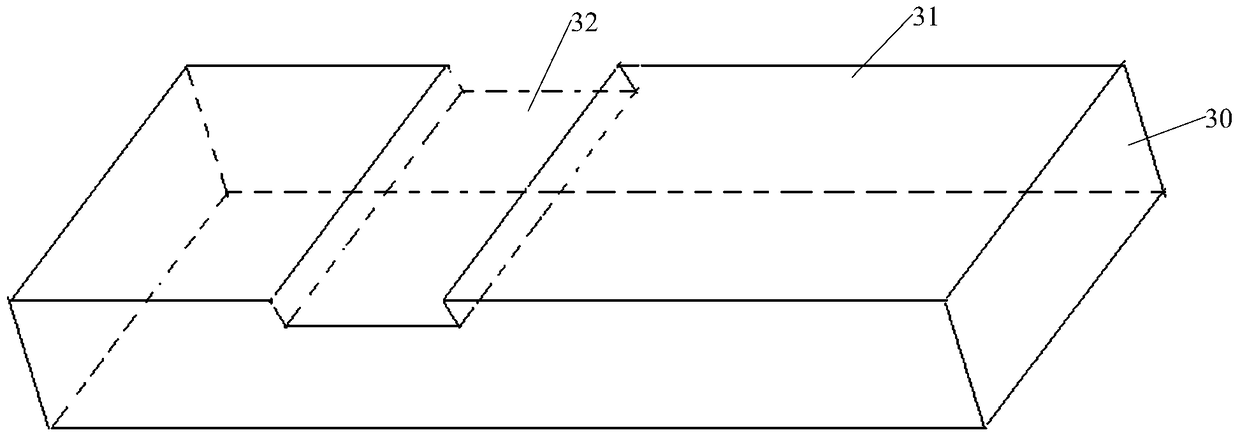

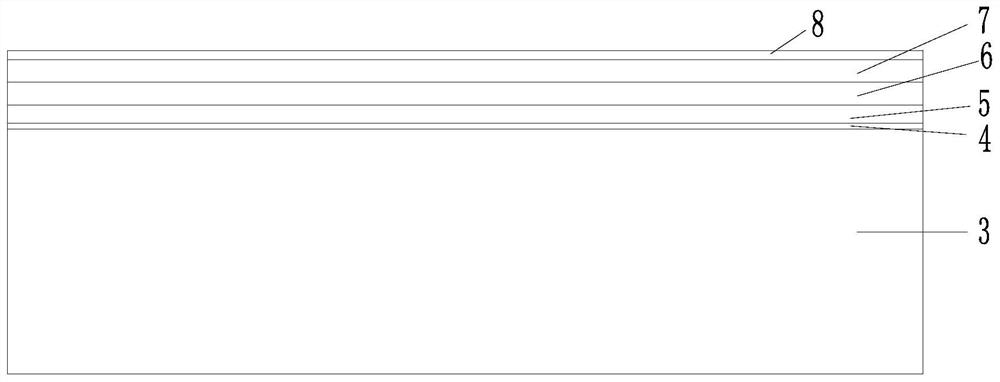

Method and electronic device for making antenna

ActiveCN104466370BSmall mechanical propertiesImprove mechanical propertiesAntenna supports/mountingsRadiating elements structural formsMetal particleElectron

The application discloses an antenna making method and an electronic device; a first zone is determined on a housing of the electronic device; the housing is made of first plastic having no metal particles; metallization processing is carried out on the first zone so as to form the antenna.

Owner:LENOVO (BEIJING) LTD

A kind of gan-based led microdisplay device and manufacturing method thereof

ActiveCN109560100BImprove luminous brightnessIncrease contrastSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceMaterials science

The invention belongs to the technical field of LED micro-displays, and provides a front-mounted GaN-based LED micro-display device and a manufacturing method thereof. The display units are separated by insulating SU glue; the LED micro-display unit includes a buffer layer on a sapphire substrate, an N-GaN layer, a multiple quantum well, a P-GaN layer and a transparent conductive layer. N electrode, a SiO insulating layer is arranged on the N electrode and the insulating SU glue, a P electrode is placed on the SiO insulating layer, and the P electrode passes through the SiO insulating layer and contacts the transparent conductive layer; a Bragg reflector DBR is arranged on the back of the sapphire substrate; The inventive microdisplay device is filled with thicker insulating SU8 glue in the LED unit isolation groove, which avoids the open circuit caused by electrode stress factors and ensures the stability of the LED microdisplay device; at the same time, the Bragg reflector DBR is used on the back to make the device The light output rate is better.

Owner:JIANGSU XINGUANGLIAN TECH +1

Encapsulation-free high-brightness LED chip structure and manufacturing method thereof

ActiveCN106531859BImprove qualityHigh quality and high efficiencySemiconductor devicesEngineeringLead structure

The invention provides a packaging-free high-luminance LED chip structure and a manufacturing method therefor. The packaging-free high-luminance LED chip structure comprises a GaN-based LED structure and a transparent substrate, wherein the GaN-based LED structure comprises a reflecting mirror, an N type GaN layer, a light-emitting layer, a P type GaN layer, a transparent electrode, a P electrode, an N electrode and a P electrode extraction electrode; the reflecting mirror, the N type GaN layer, the light-emitting layer, the P type GaN layer and the transparent electrode are stacked from the bottom up in sequence; one surface, far from the reflecting mirror, of the GaN-based LED structure is a P surface; the P electrode runs through the transparent electrode and is in contact connection with the P type GaN layer; the N electrode is positioned on the surface of the N type GaN layer or on the surface of the reflecting mirror; one end of the P electrode extraction electrode is connected with the P electrode while the other end runs through the P type GaN layer, the light-emitting layer, the N type GaN layer and the reflecting mirror and extends to the surface of the reflecting mirror; and the transparent substrate is bonded on the P surface of the GaN-based LED structure. The LED chip structure provided by the invention has the advantages of low electric leakage rate, capability of realizing the packaging-free effect, high luminous efficiency and the like.

Owner:SHANGHAI XINYUANJI SEMICON TECH

Semiconductor structure and formation method thereof

InactiveCN108735576AImprove stabilityNot easy to loseSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureDielectric layer

The invention provides a semiconductor structure and a formation method thereof. The formation method comprises the following steps: providing a substrate; carrying out plasma sulfurizing treatment onthe substrate; and after the plasma sulfurizing treatment is carried out on the substrate, forming a high-K dielectric layer on the substrate. Electrical properties of the semiconductor structure formed by adopting the formation method of the invention are improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

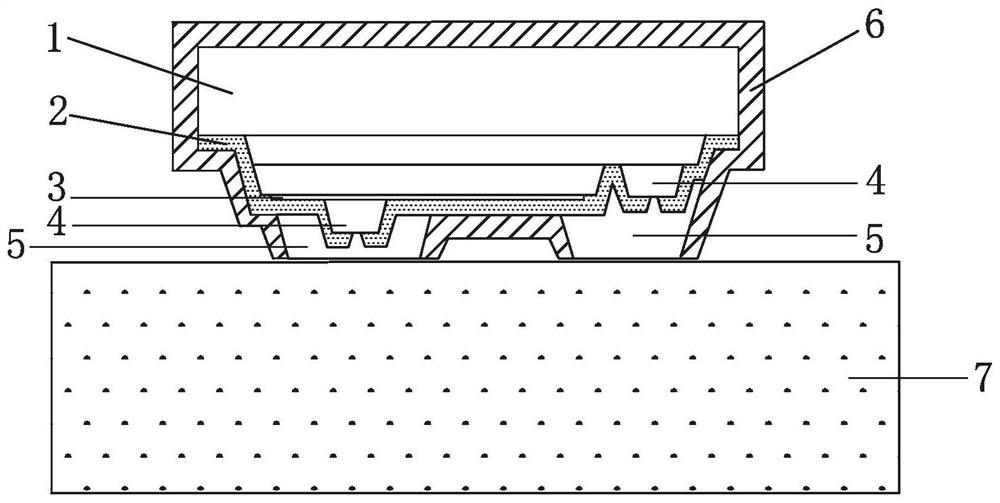

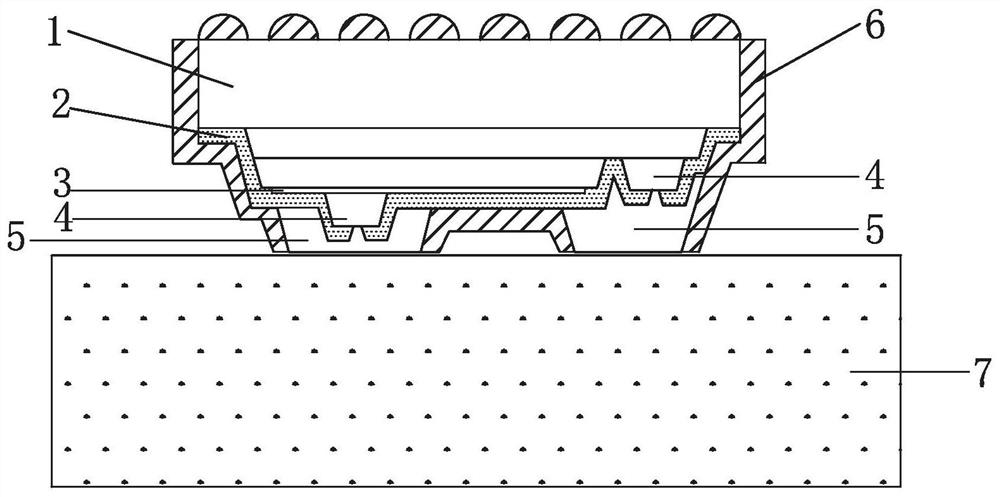

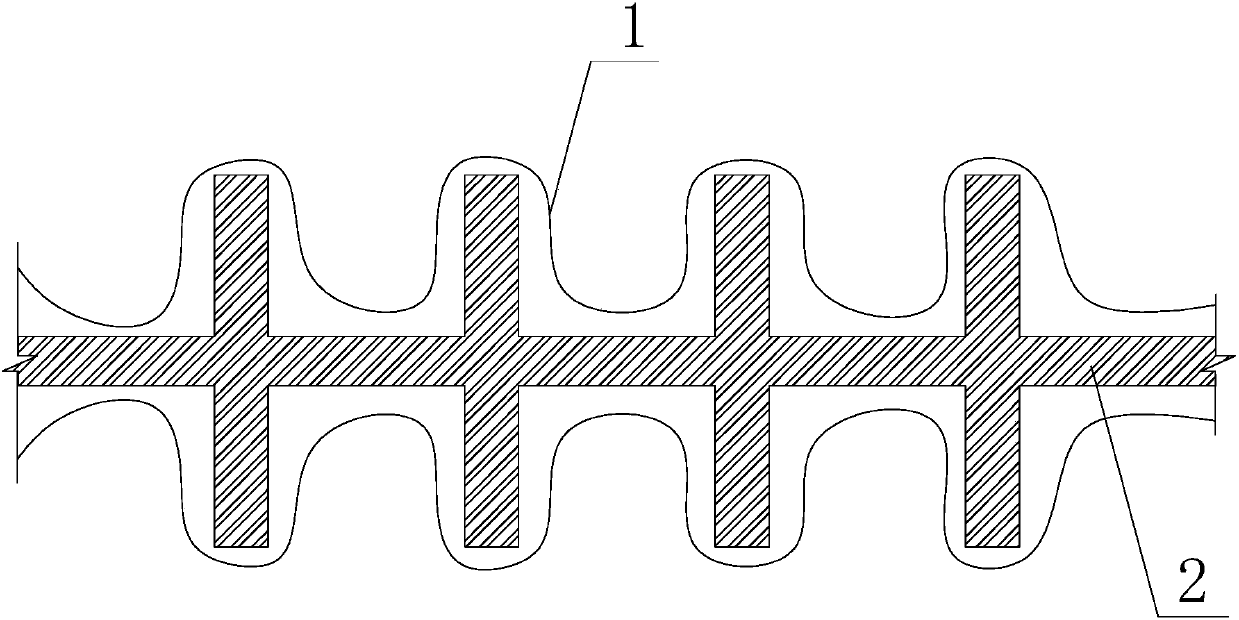

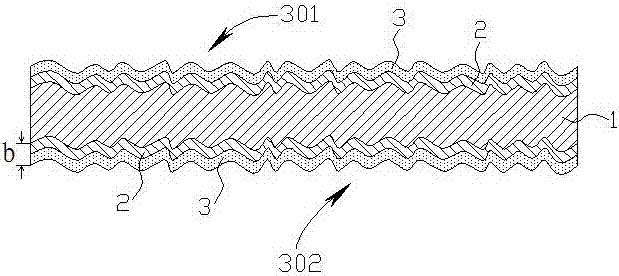

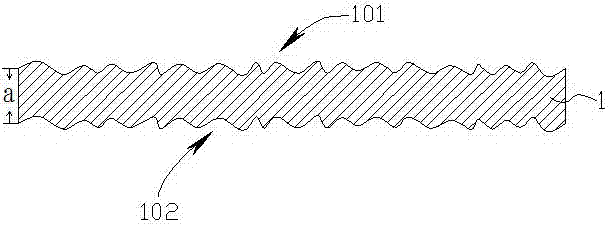

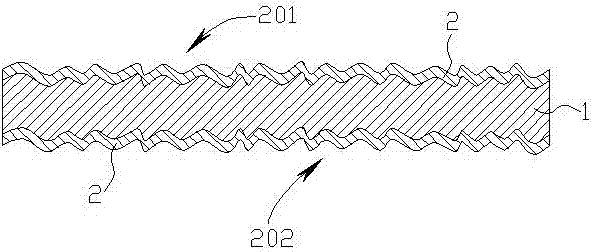

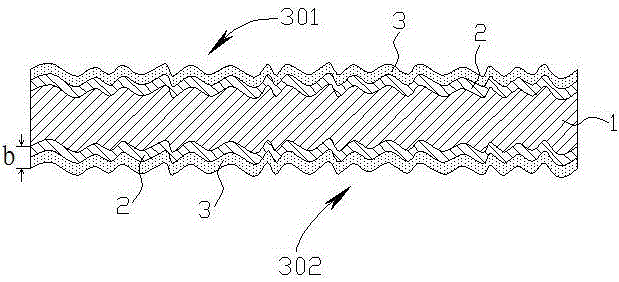

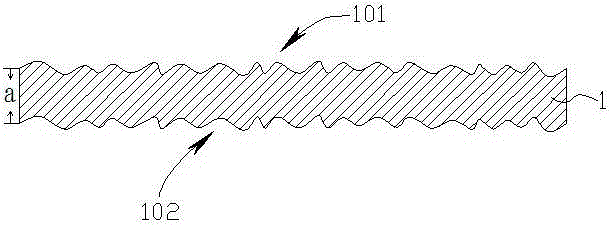

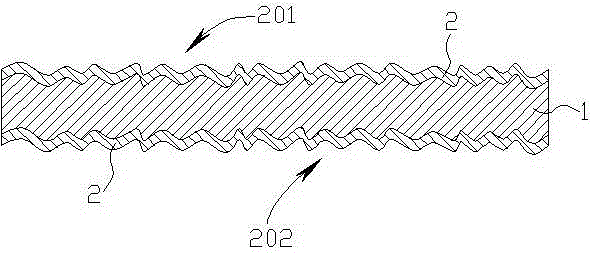

Draining board and ultra-soft soil curing device with draining board

InactiveCN107761710AIncreased ring stiffnessNo need to worry about flatteningSoil preservationSoil scienceHigh energy

The invention provides a draining board and an ultra-soft soil curing device with the draining board. The draining board comprises a board core, a filter membrane and a draining channel, wherein the draining channel is formed between the board core and the filter membrane, and the board core is fixedly connected with the filter membrane. The ultra-soft soil curing device has the advantages of lowprice, high energy utilization rate, no need of sand bed and good curing effect, the curing treatment on new blow filling ultra-soft soil can be preferably performed, the board core of the draining board is fixedly connected with the filter membrane, the filter membrane is connected with the board core all the time and cannot be disengaged from the board core under the action of extrusion of soiland negative pressure, and the draining channel is open all the time.

Owner:CCCC SHANGHAI DREDGING

Epitaxial structure provided with Bragg reflector, preparation method thereof and LED chip

PendingCN114242857AReduce light lossImprove light extraction efficiencySemiconductor devicesEngineeringQuantum well

The invention discloses an epitaxial structure provided with a Bragg reflector, a preparation method thereof and an LED chip, the epitaxial structure comprises a GaN composite layer, the Bragg reflector, an N-GaN layer, a stress release layer, a quantum well layer, a P-AlGaN layer and a P-GaN layer which are arranged in sequence, the Bragg reflector is composed of a plurality of periods of AlN layers / GaN layers, and the stress release layer is composed of a plurality of periods of N layers / GaN layers. The growth temperature of the AlN layer and the growth temperature of the GaN layer in the Bragg reflector are the same and range from 900 DEG C to 1200 DEG C. The epitaxial structure is high in luminous efficiency and good in antistatic performance, and surface cracks of the Bragg reflector are few.

Owner:FOSHAN NATIONSTAR SEMICON

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com