Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

305results about How to "Improve execution speed" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

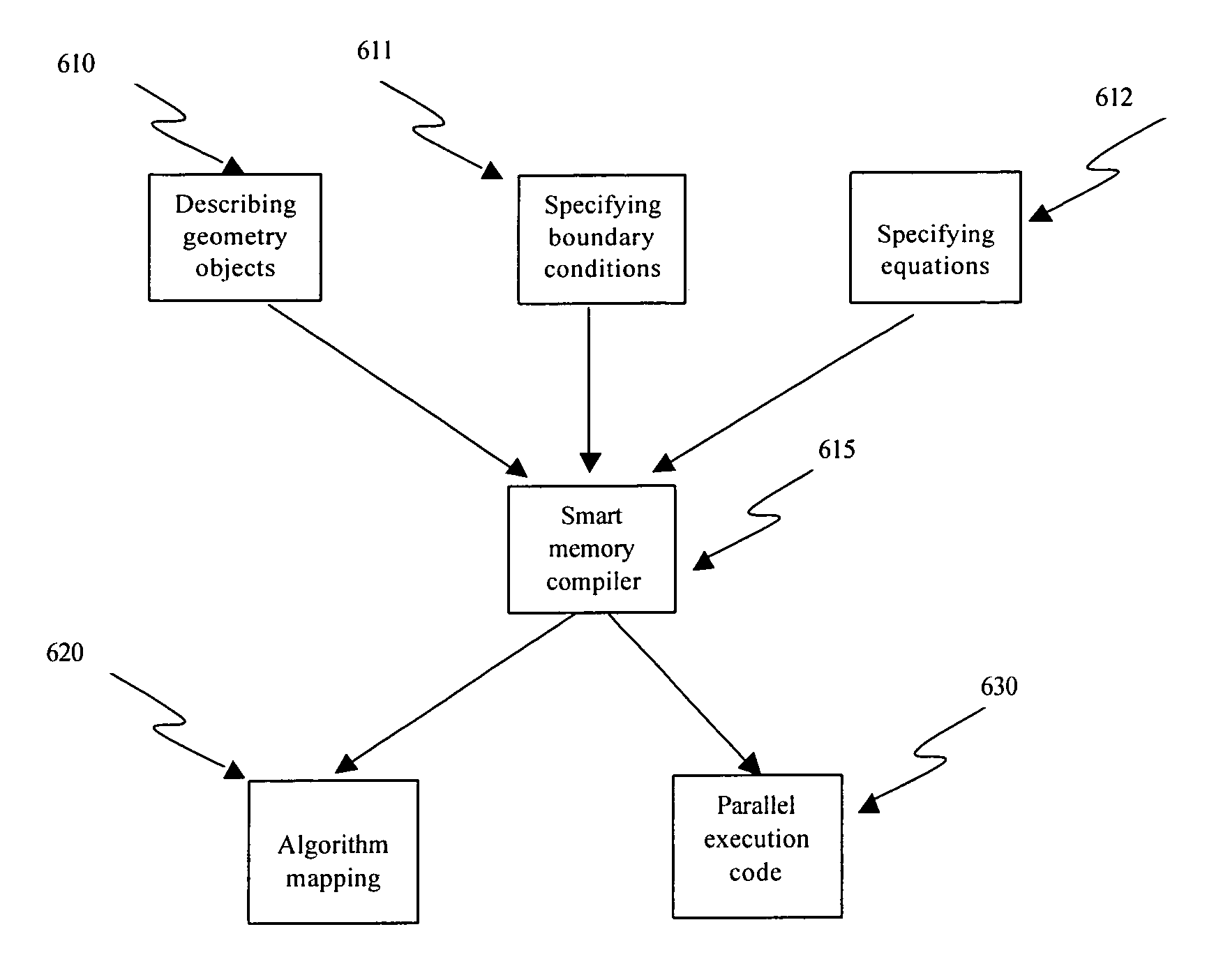

Algorithm mapping, specialized instructions and architecture features for smart memory computing

InactiveUS7546438B2Improve performanceLow costMultiplex system selection arrangementsDigital computer detailsSmart memoryExecution unit

A smart memory computing system that uses smart memory for massive data storage as well as for massive parallel execution is disclosed. The data stored in the smart memory can be accessed just like the conventional main memory, but the smart memory also has many execution units to process data in situ. The smart memory computing system offers improved performance and reduced costs for those programs having massive data-level parallelism. This smart memory computing system is able to take advantage of data-level parallelism to improve execution speed by, for example, use of inventive aspects such as algorithm mapping, compiler techniques, architecture features, and specialized instruction sets.

Owner:STRIPE INC

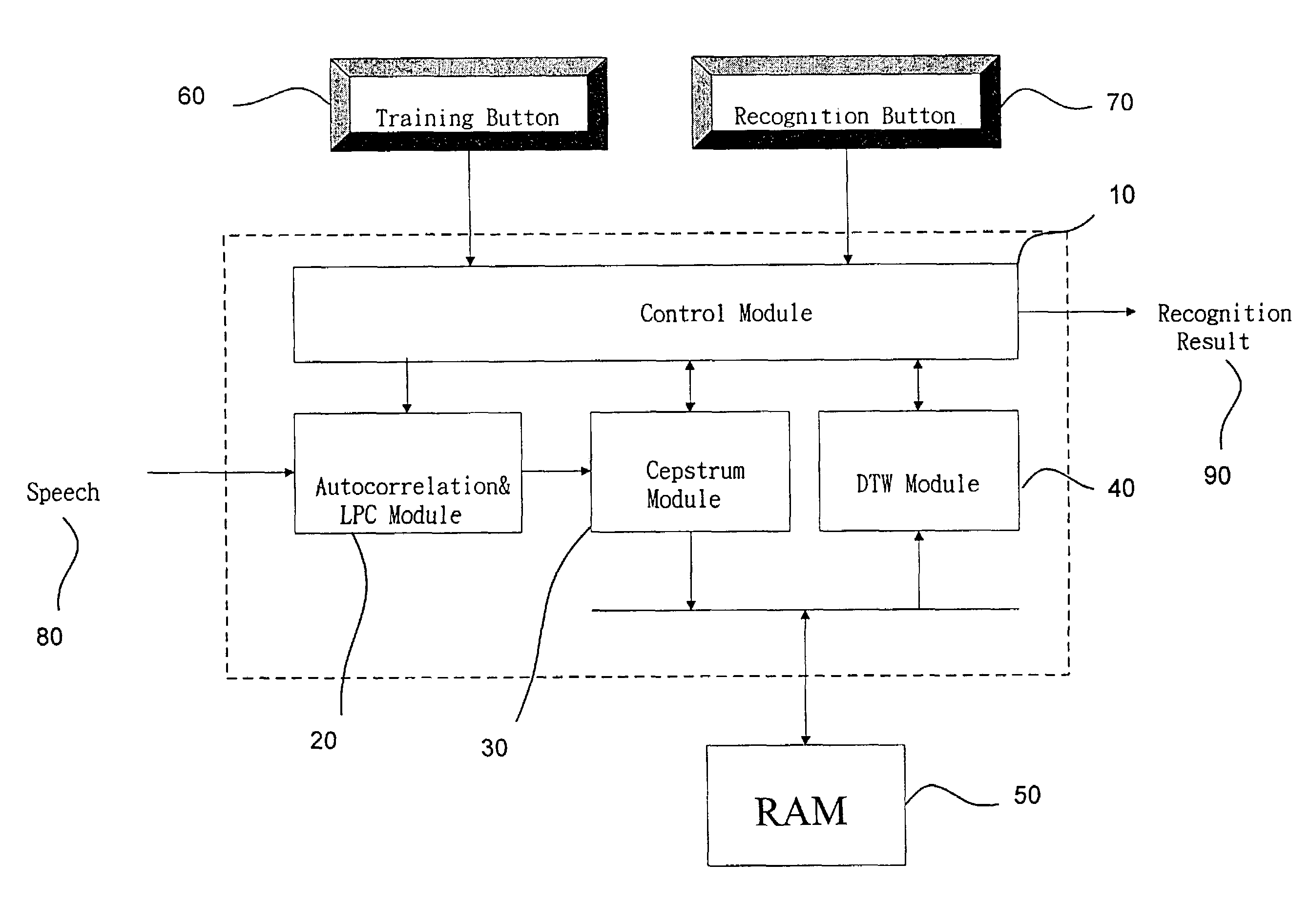

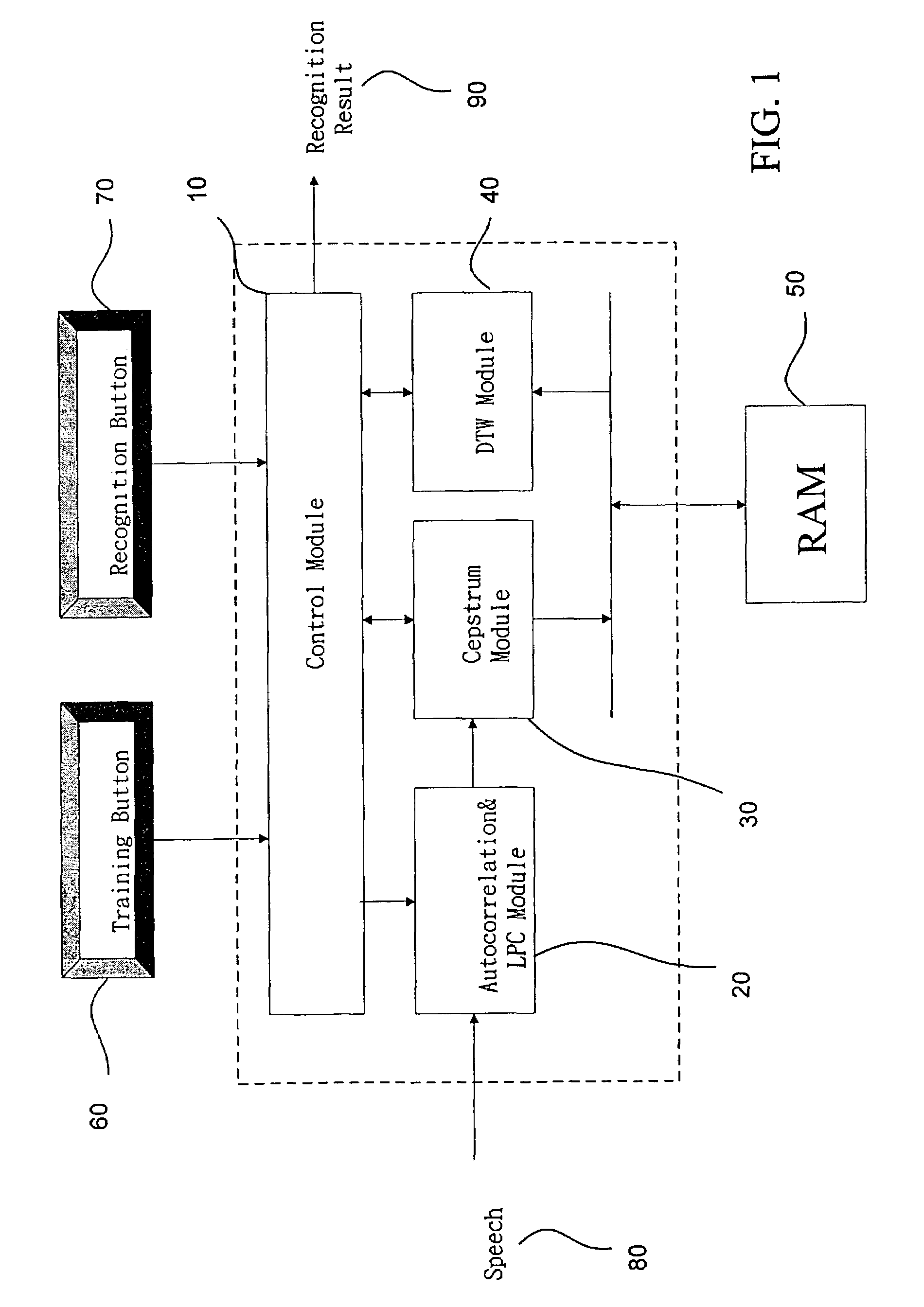

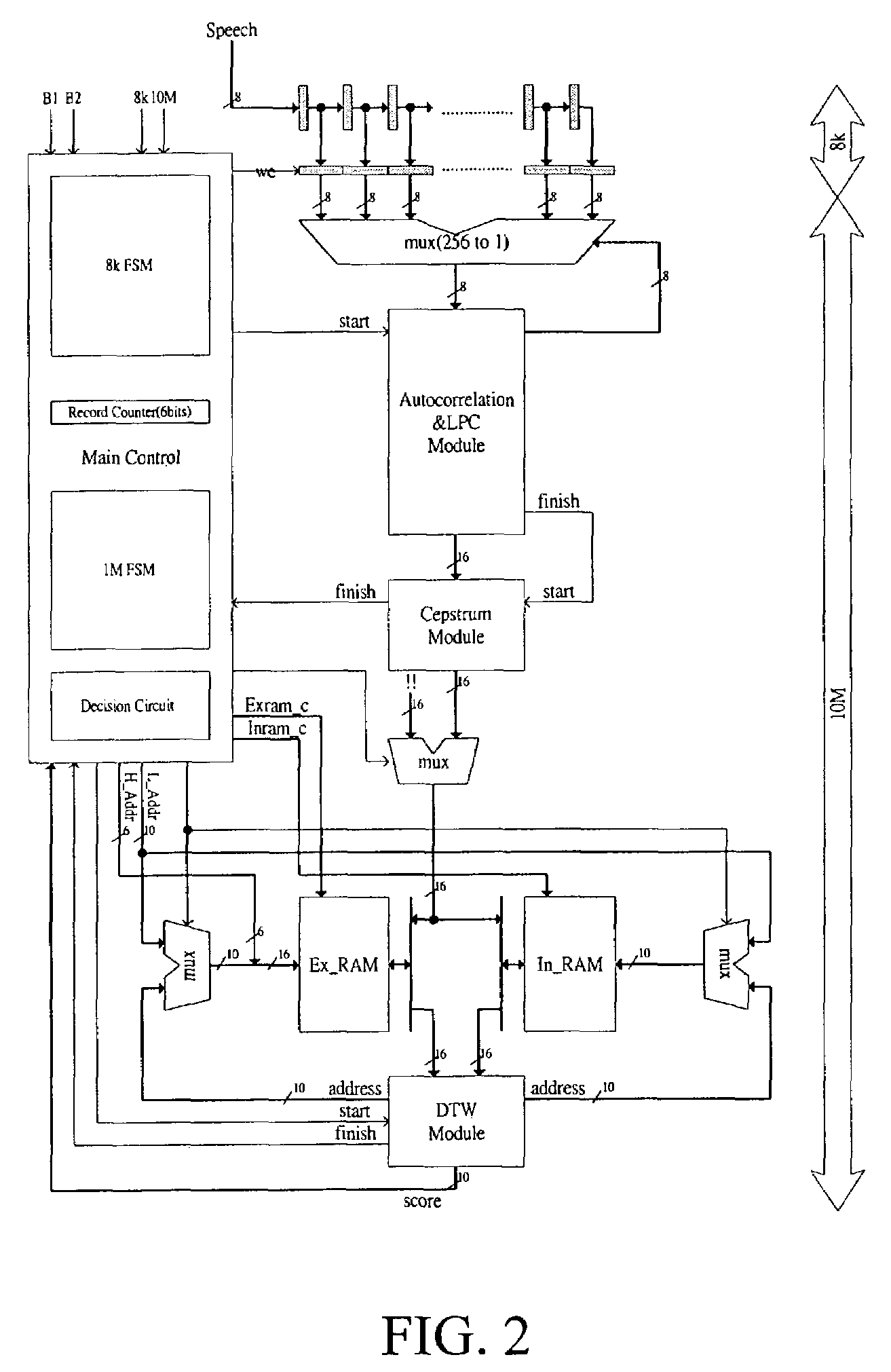

Speech recognition system

InactiveUS7266496B2Improve execution speedLow costSpeech recognitionLinearityLinear prediction coefficient

The present invention discloses a complete speech recognition system having a training button and a recognition button, and the whole system uses the application specific integrated circuit (ASIC) architecture for the design, and also uses the modular design to divide the speech processing into 4 modules: system control module, autocorrelation and linear predictive coefficient module, cepstrum module, and DTW recognition module. Each module forms an intellectual product (IP) component by itself. Each IP component can work with various products and application requirements for the design reuse to greatly shorten the time to market.

Owner:NAT CHENG KUNG UNIV

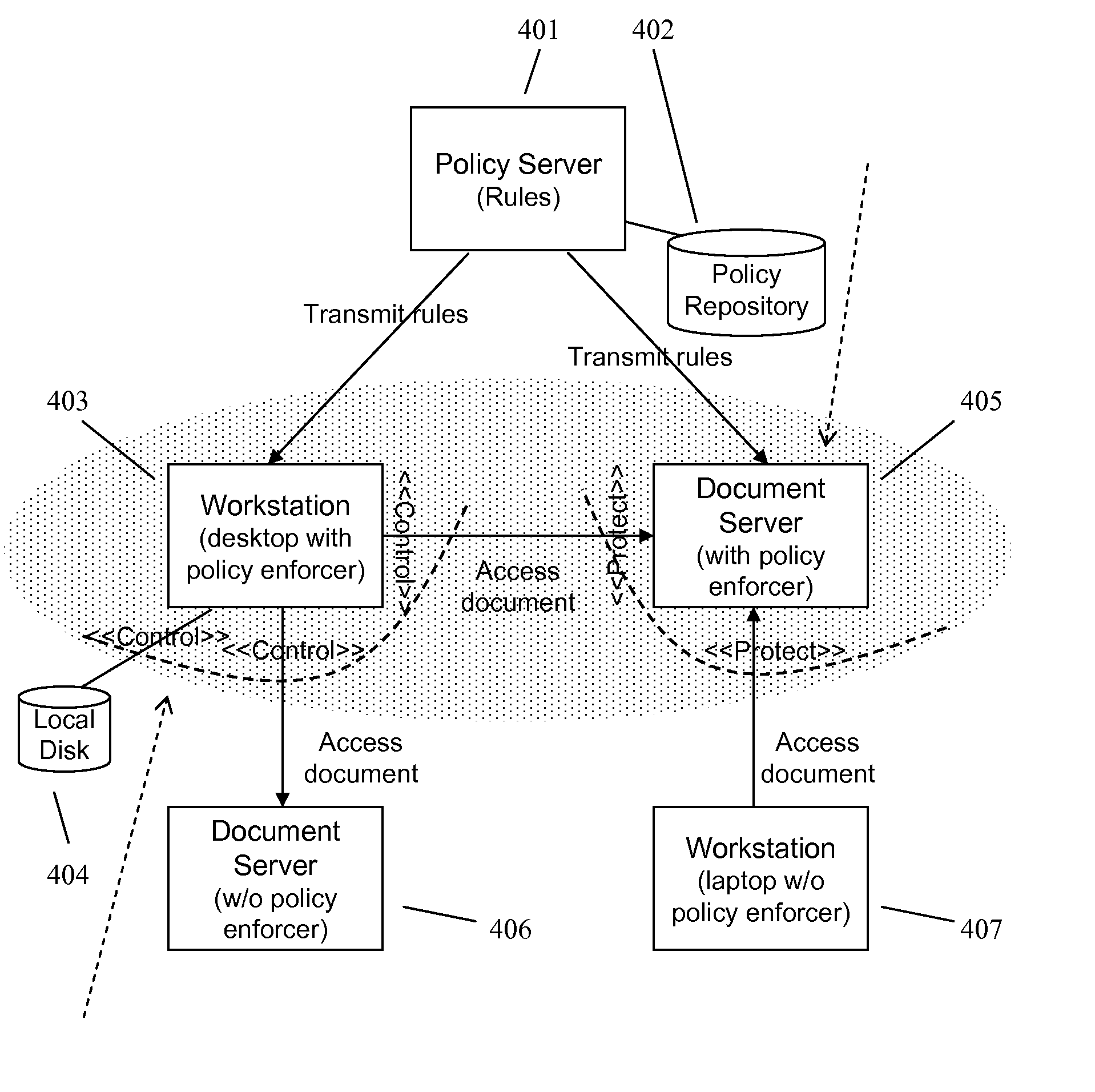

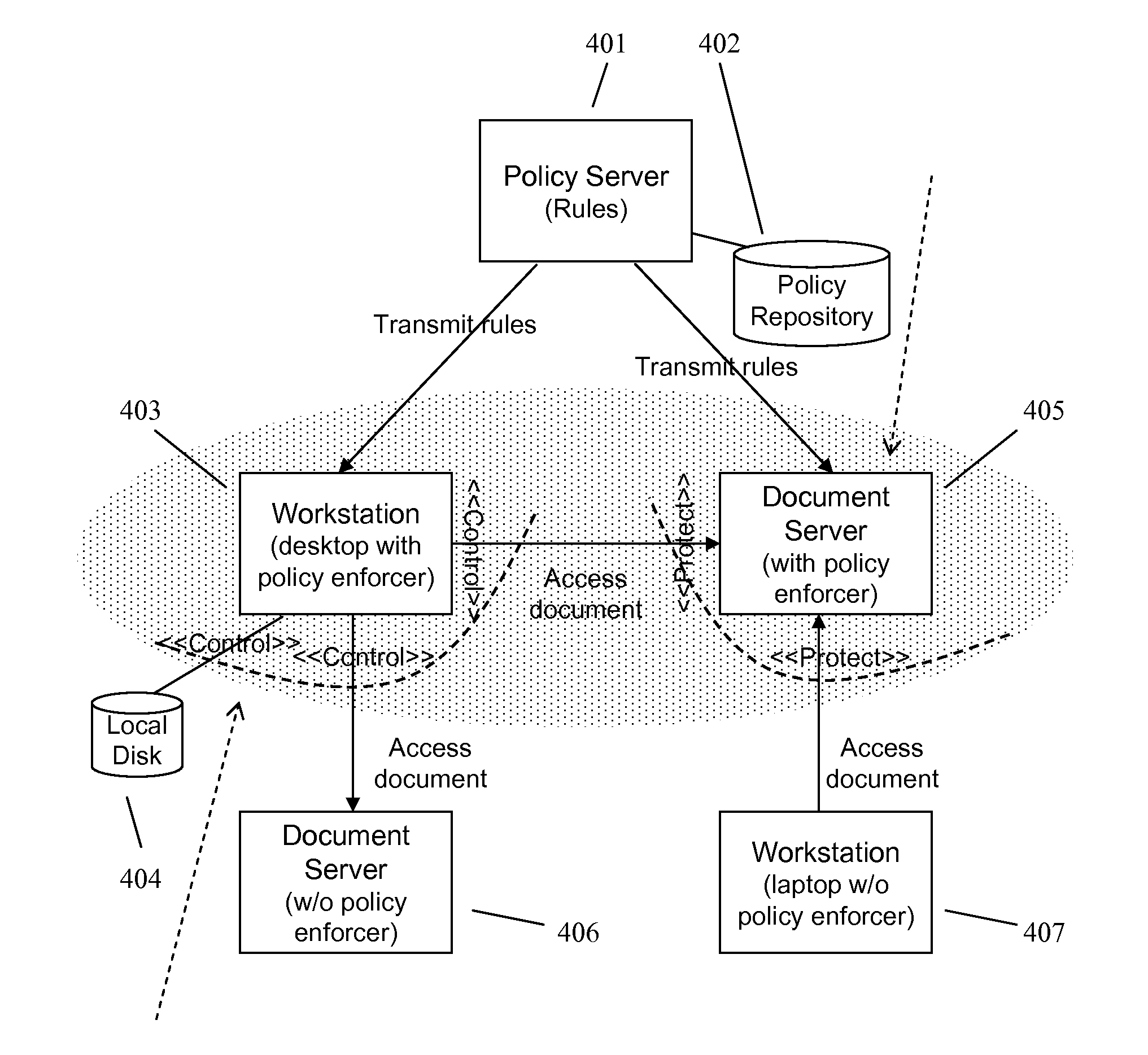

Techniques and system to deploy policies intelligently

ActiveUS7716240B2Reduce the amount requiredImprove execution speedDigital data processing detailsComputer security arrangementsSpace requirementsOperating system

In an information management system, relevant policies are deployed to targets while policies which are not relevant are not. By deploying relevant policies, this reduces the amount of space requirements at the target to store the policies and the amount of data that needs to be sent to the target. Also, execution speed at the target may increase since the target does not need to evaluate policies that are not relevant.

Owner:NEXTLABS

Physical resynthesis of a logic design

InactiveUS7337100B1Simple designMinimize time delayElectronic circuit testingAnalogue computers for electric apparatusThird partyVisibility

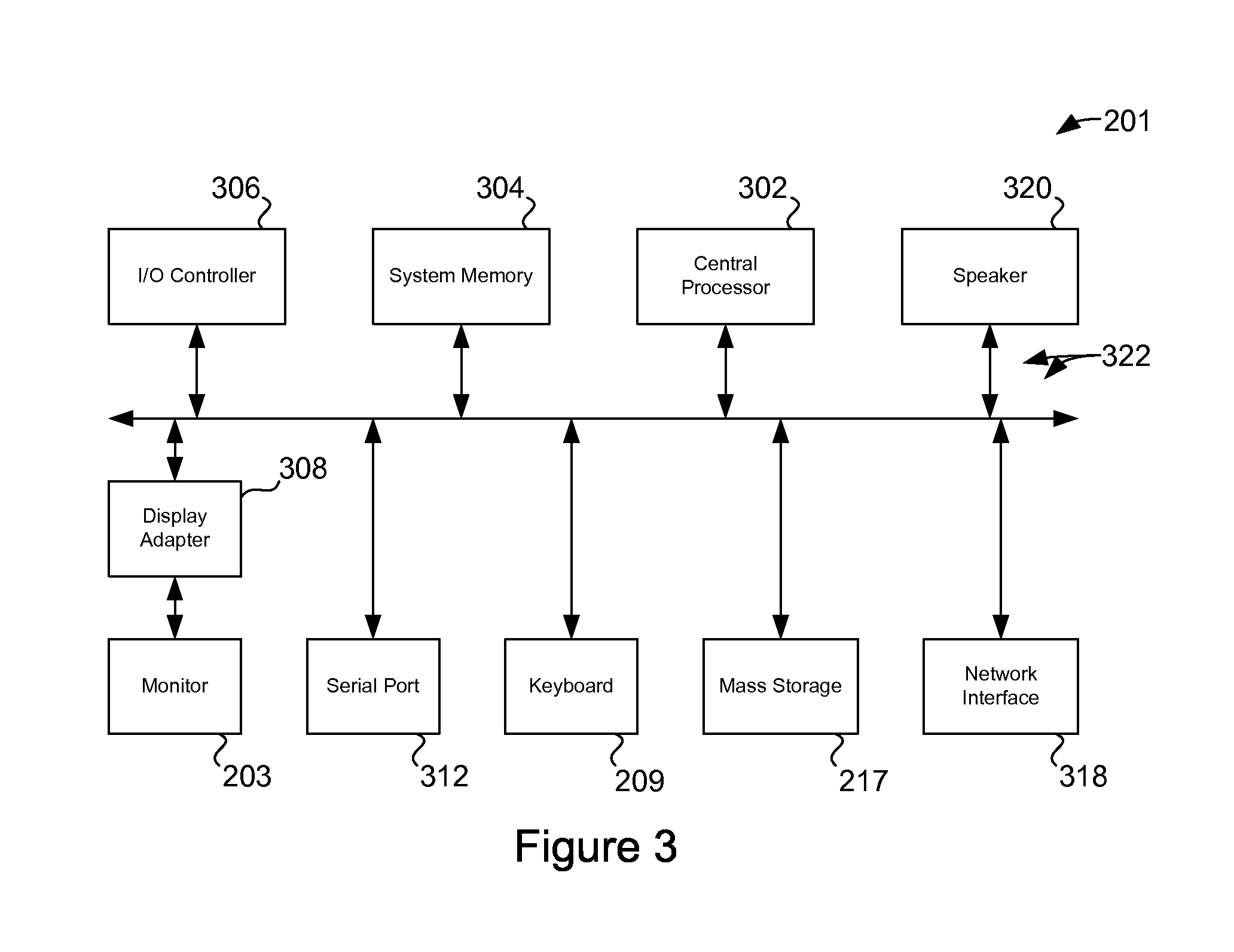

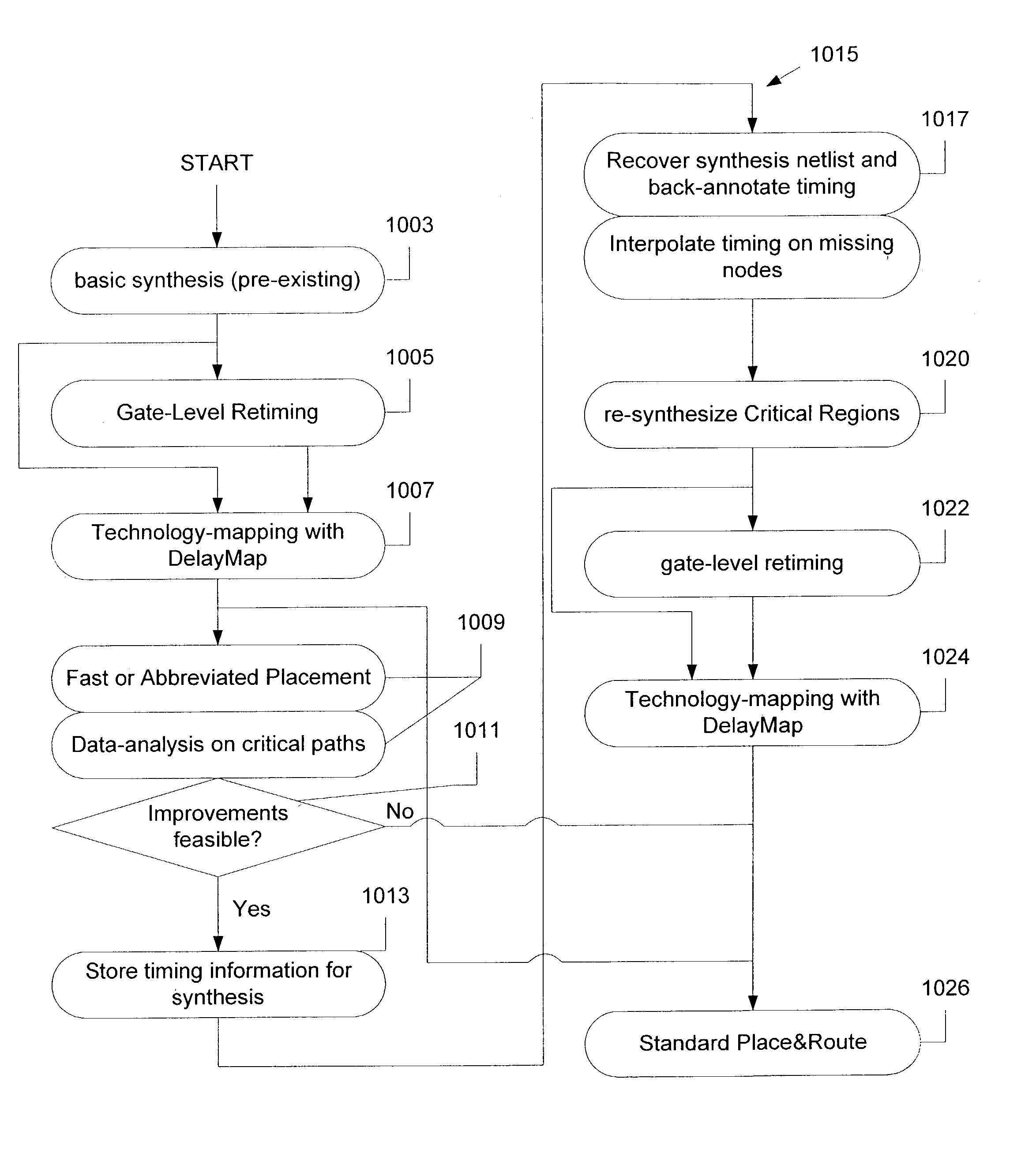

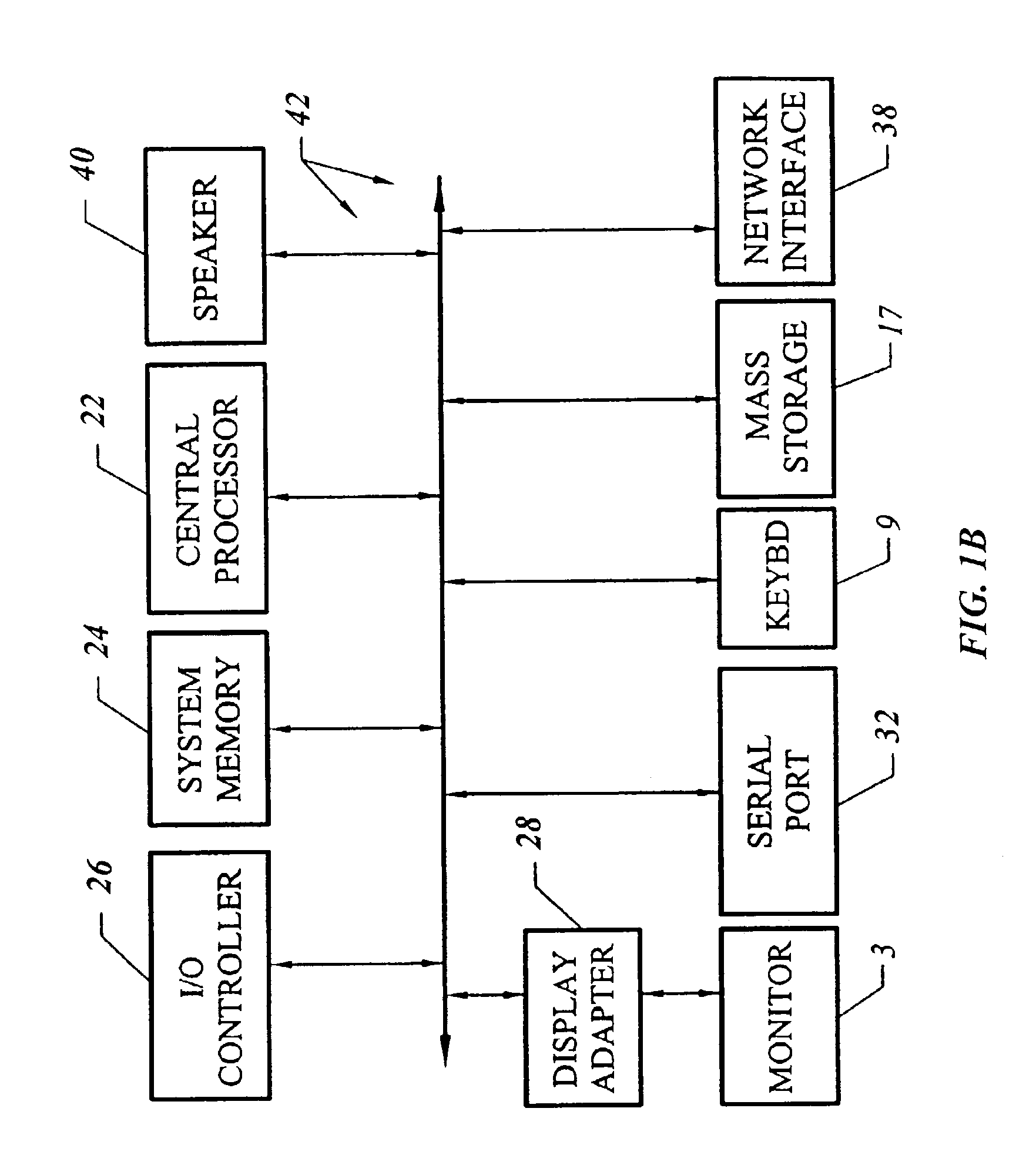

A multiple-pass synthesis technique improves the performance of a design. In a specific embodiment, synthesis is performed in two or more passes. In a first pass, a first synthesis is performed, and in a second or subsequent pass, a second synthesis or resynthesis is performed. During the first synthesis, the logic will be mapped to for example, the logic structures (e.g., logic elements, LUTs, synthesis gates) of the target technology such as a programmable logic device. Alternatively a netlist may be provided from a third party. Before the second synthesis, a fast or abbreviated fit may be performed of the netlist to a specific device (e.g., specific programmable logic device product). Before the second synthesis, the netlist obtained from the first synthesis (or provided by a third party) is unmapped and then the second synthesis is performed. Since a partial fit is performed, the second synthesis has more visibility and optimize the logic better than by using a single synthesis pass. After the second synthesis pass, a more detailed fit is performed.

Owner:ALTERA CORP

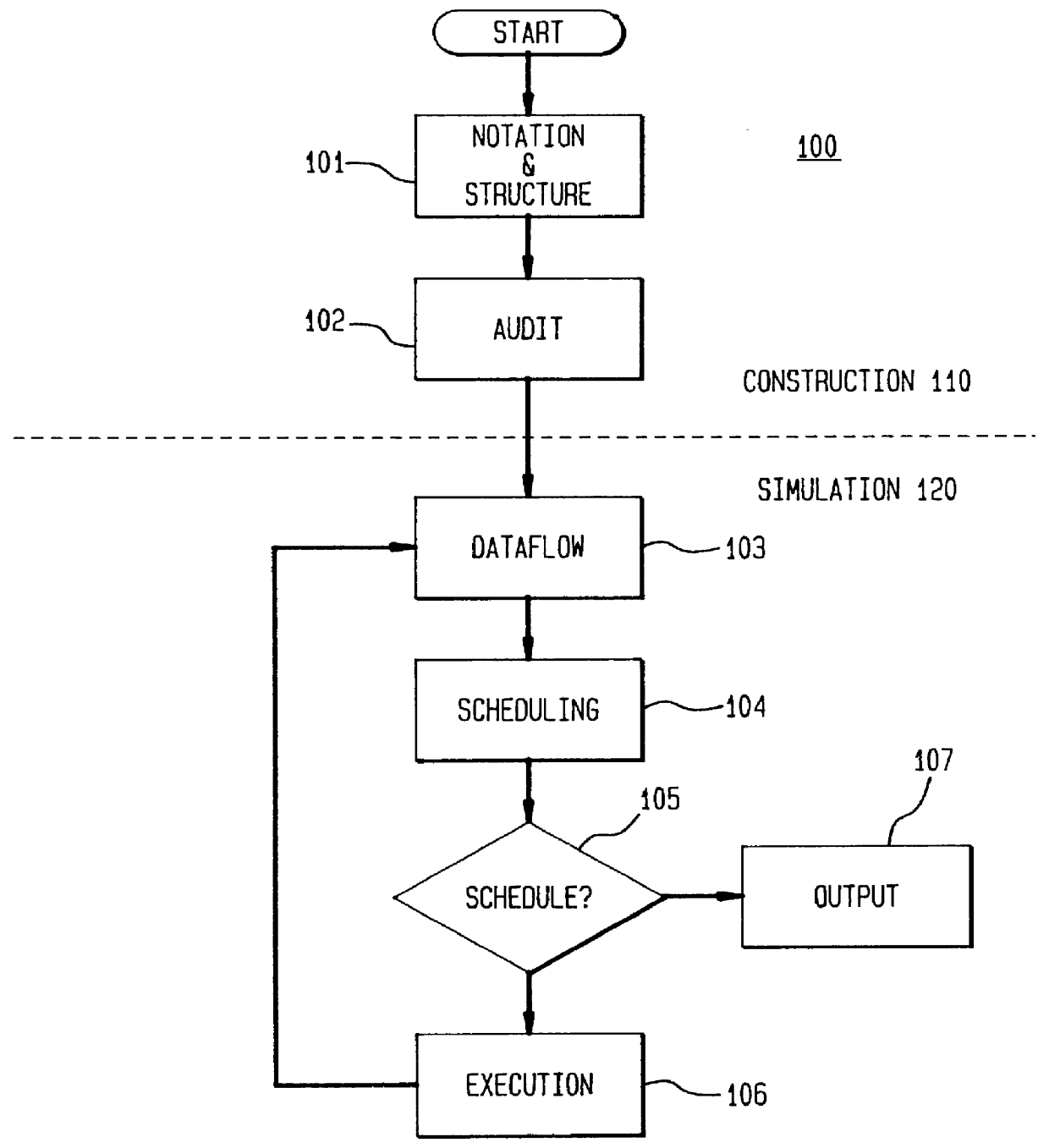

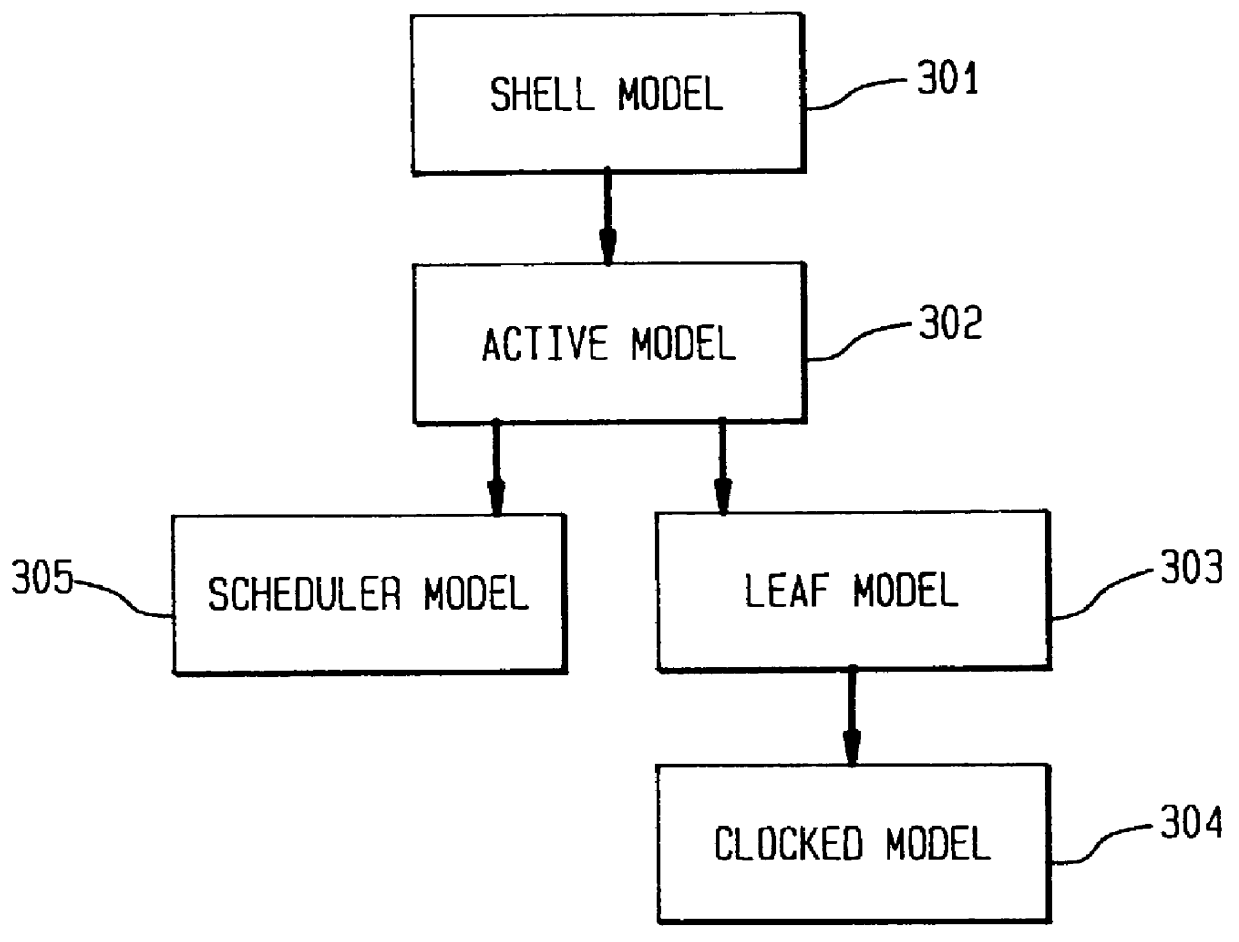

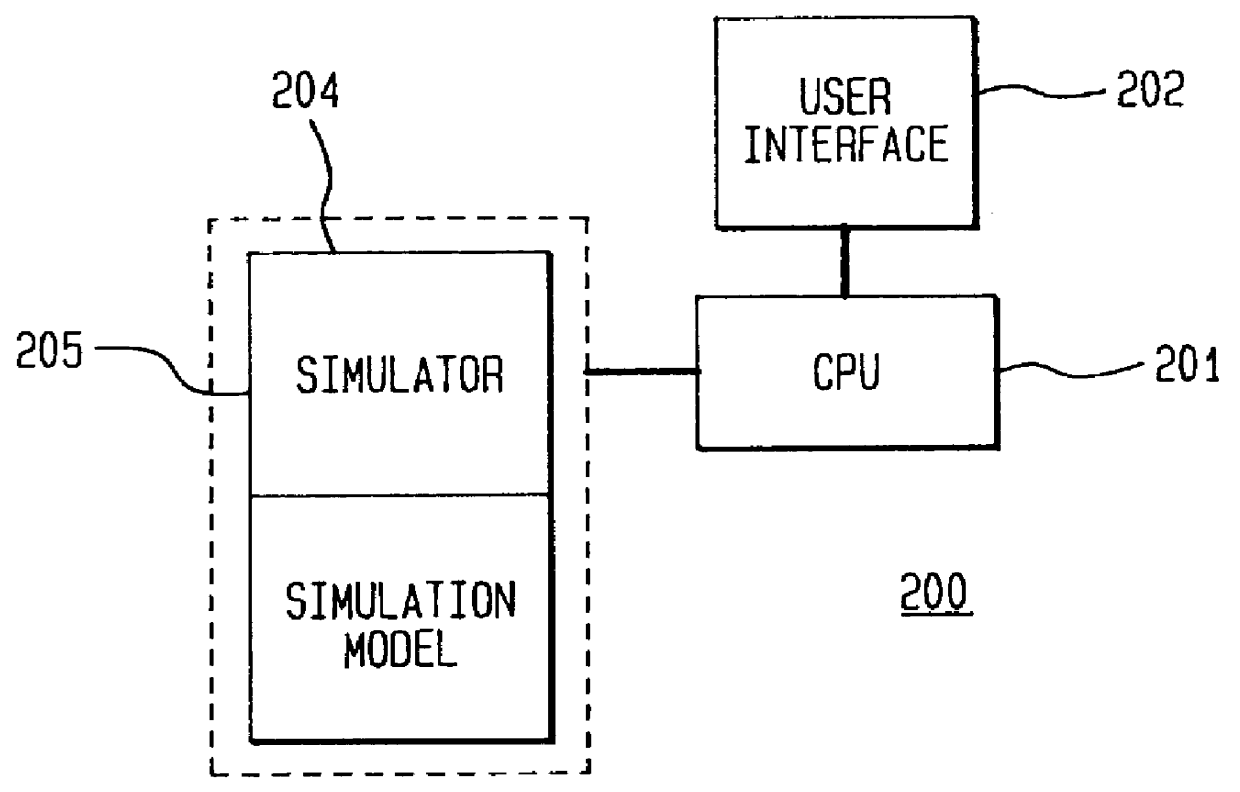

Simulation model using object-oriented programming

InactiveUS6053947AIncrease execution speedEfficiency and flexibilityAnalogue computers for electric apparatusCAD circuit designComputer basedPriority scheduling

A method, apparatus and system for simulating the operation of a circuit using a computer-based simulator comprising: (a) distributing at least one signal upon to one or more simulation model subcircuit functions, which use the signal, upon a change in the signal; (b) scheduling one or more subcircuit functions that use the signal for execution according to a priority assigned to each subcircuit function; and (c) providing an output value to the simulator when no subcircuit functions are scheduled, otherwise, executing one or more subcircuit functions with the highest priority and returning to step (a) to repeat the process.

Owner:BELL SEMICON LLC

Decoder-side motion vector restoration for video coding

PendingUS20180192071A1Improve execution speedImprove efficiencyDigital video signal modificationMotion vectorVideo encoding

The techniques described herein relate to methods, apparatus, and computer readable media configured to determine motion vectors. The techniques relate to both encoders and decoders. For example, a decoder receives compressed video data related to a set of frames. The decoder calculates, using a decoder-side predictor refinement technique, a new motion vector for a current frame from the set of frames, wherein the new motion vector estimates motion for the current frame based on one or more reference frames. The calculation includes retrieving a first motion vector associated with the current frame, executing a first portion of the decoding process using the first motion vector, retrieving a second motion vector associated with the current frame that is different than the first motion vector, and executing a second portion of the decoding process using the second motion vector.

Owner:HFI INNOVATION INC

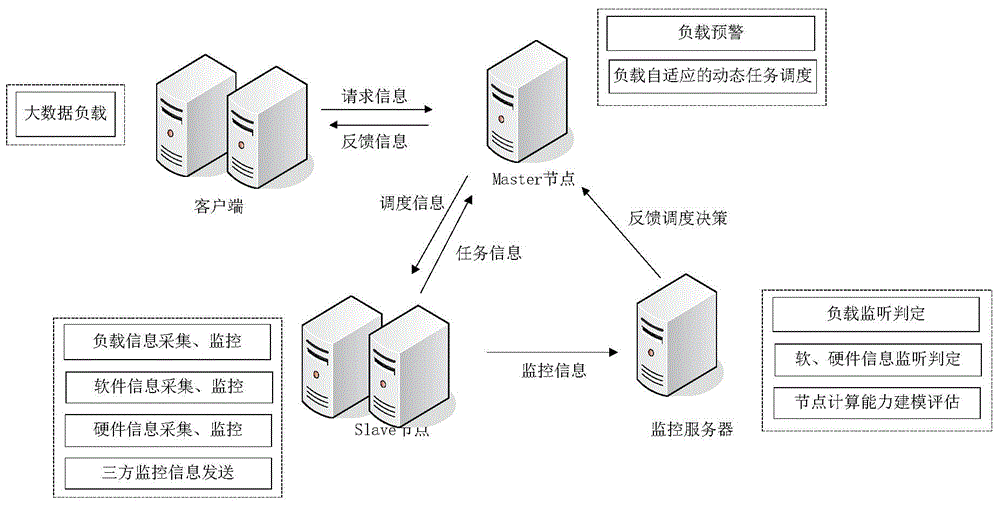

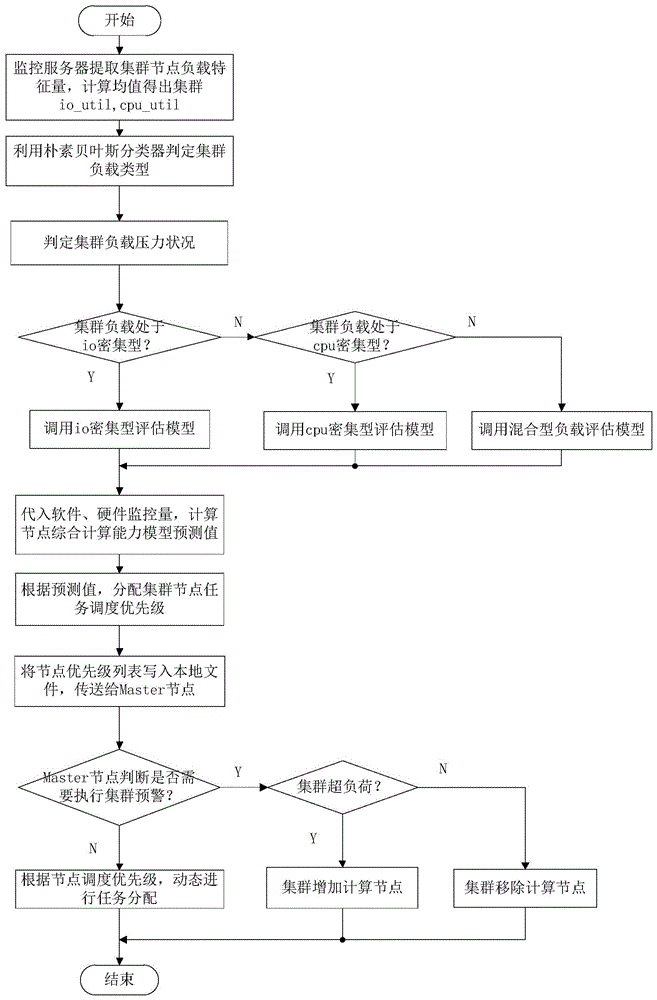

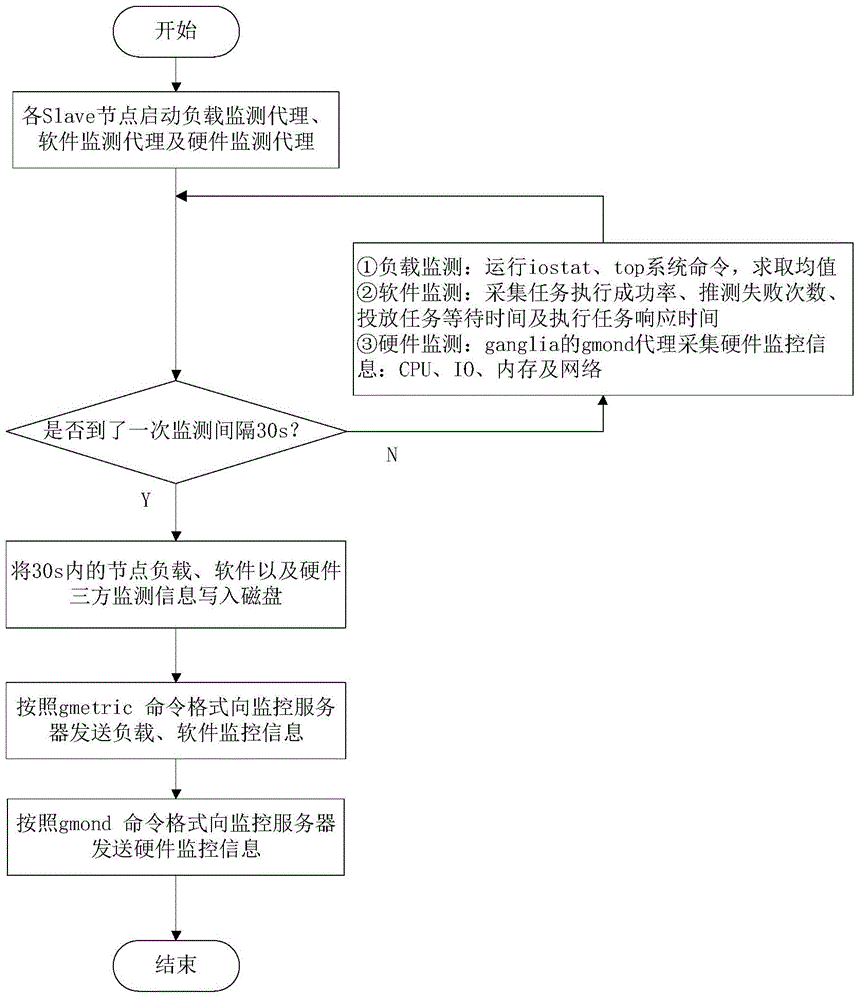

MapReduce based load self-adaptive task scheduling method

ActiveCN104317658AImprove applicabilityAccurately measure the computing power of execution nodesResource allocationSelf adaptiveSoftware

The invention discloses a MapReduce based load self-adaptive task scheduling method, which comprises the following steps: (1) dynamically monitoring a Hadoop cluster load condition; (2) dynamically monitoring software information generated in the task execution process of each execution node in the cluster; (3) dynamically monitoring hardware information generated in the task execution process of each execution node in the cluster; (4) summarizing load monitoring information, software monitoring information and hardware monitoring information of each execution node in the cluster collected in the steps (1), (2) and (3), and modeling and computing the computing power of each execution node in the cluster; (5) executing a cluster load pre-warning function, and carrying out the intelligent task scheduling according to the computing power of each execution node in the cluster. The MapReduce based load self-adaptive task scheduling method provided by the invention solves the problems that the existing Hadoop scheduler has low perceptibility to cluster resources and unreasonable task allocation, and provides a load self-adaptive and more scientific and effective task scheduling scheme.

Owner:HUAZHONG UNIV OF SCI & TECH

Pattern-based motion vector derivation for video coding

ActiveUS20180041769A1Improve execution speedImprove efficiencyDigital video signal modificationFrame basedVideo encoding

The techniques described herein relate to methods, apparatus, and computer readable media configured to receive compressed video data, wherein the compressed video data is related to a set of frames. A decoder-side predictor refinement technique is used to calculate a new motion vector for a current frame from the set of frames, wherein the new motion vector estimates motion for the current frame based on one or more reference frames. An existing motion vector associated with a different frame from a motion vector buffer is retrieved. The new motion vector is calculated based on the existing motion vector using a decoder-side motion vector prediction technique, such that the existing motion vector is in the motion vector buffer after calculating the new motion vector.

Owner:HFI INNOVATION INC

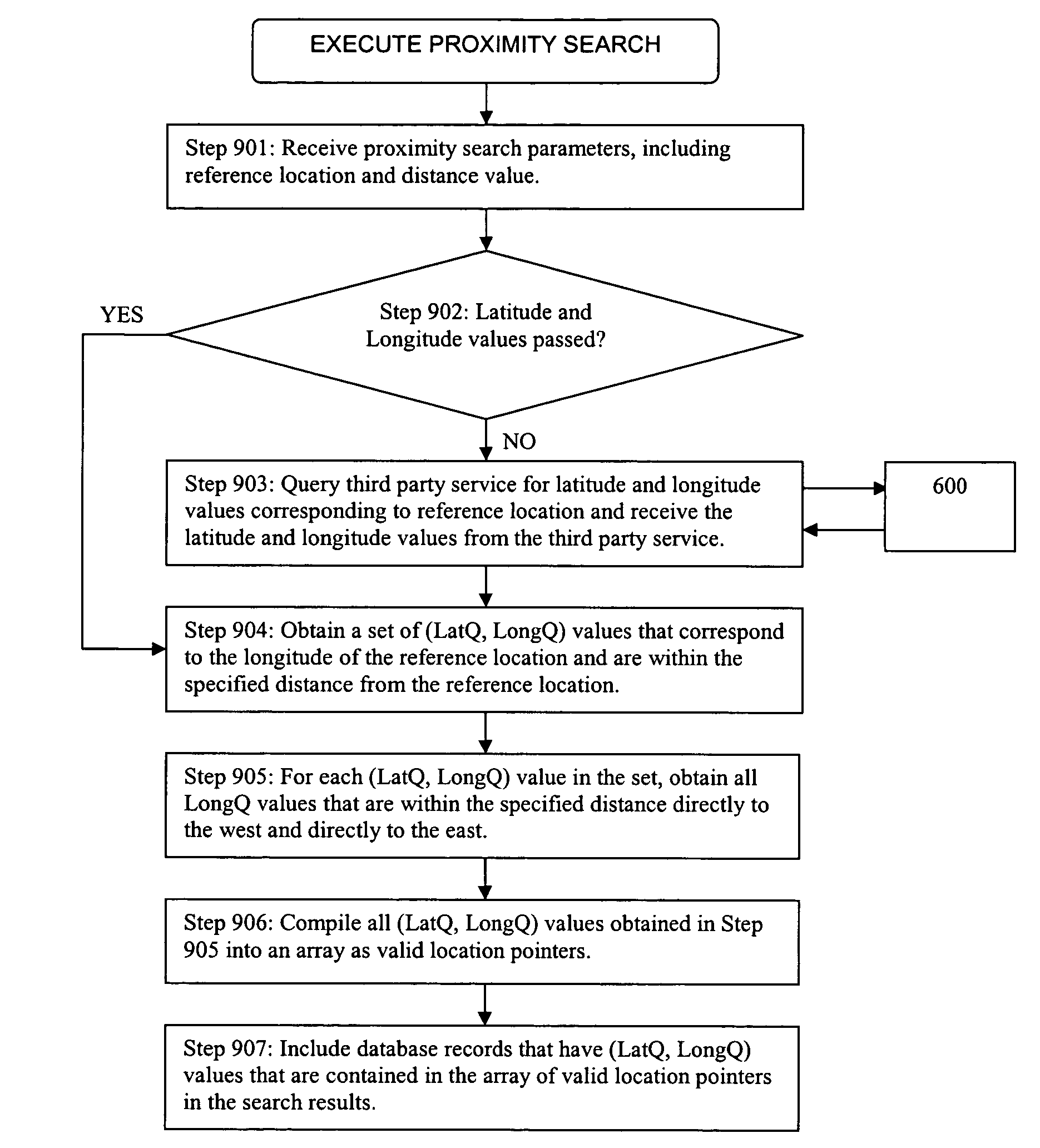

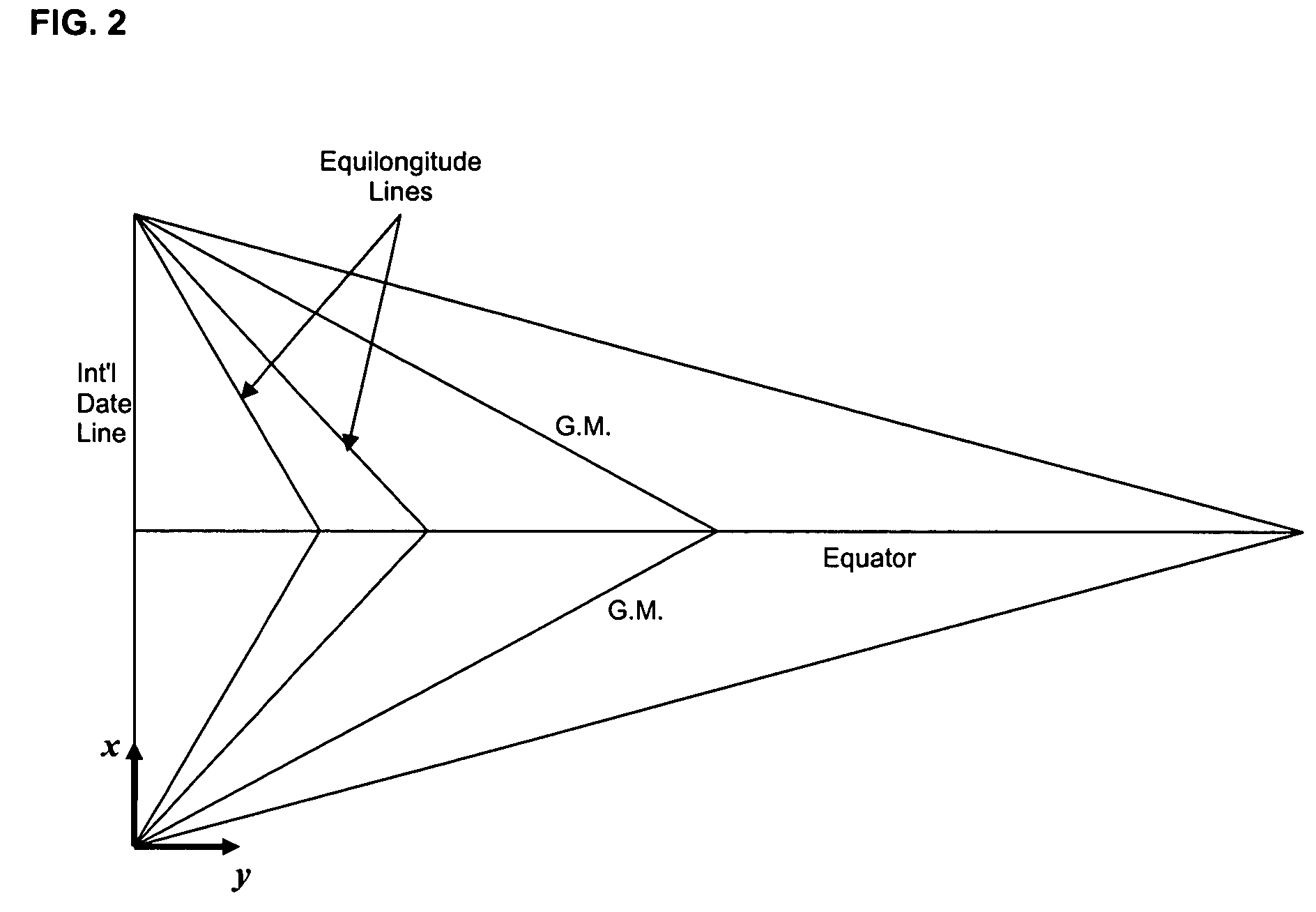

Proximity search methods using tiles to represent geographical zones

ActiveUS7606687B2Reduce in quantityImprove execution speedRoad vehicles traffic controlNavigation instrumentsGeographical zoneComputer science

A proximity search engine for carrying out a proximity search with respect to a reference location uses as a reference frame the earth divided into tiles, which are predefined geographic regions of substantially equal areas. Records that are searched based on proximity to a reference location include location pointers, each of which identifies a particular tile that encompasses the physical location indicated by the corresponding record. When the proximity search is carried out, the tiles that are within a specified distance from the reference location are obtained and records having location pointers corresponding to such tiles are selected for inclusion in the search results.

Owner:META PLATFORMS INC

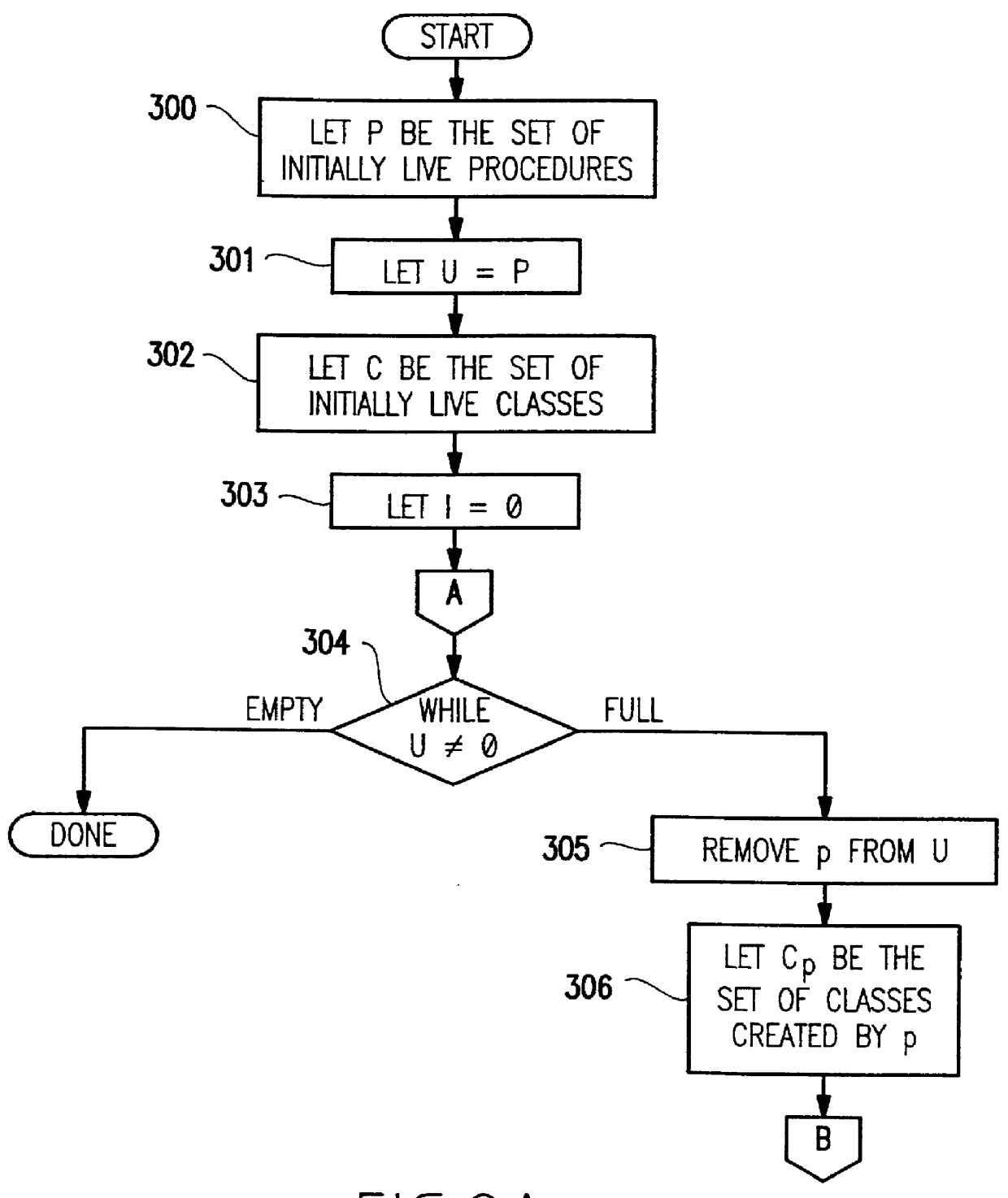

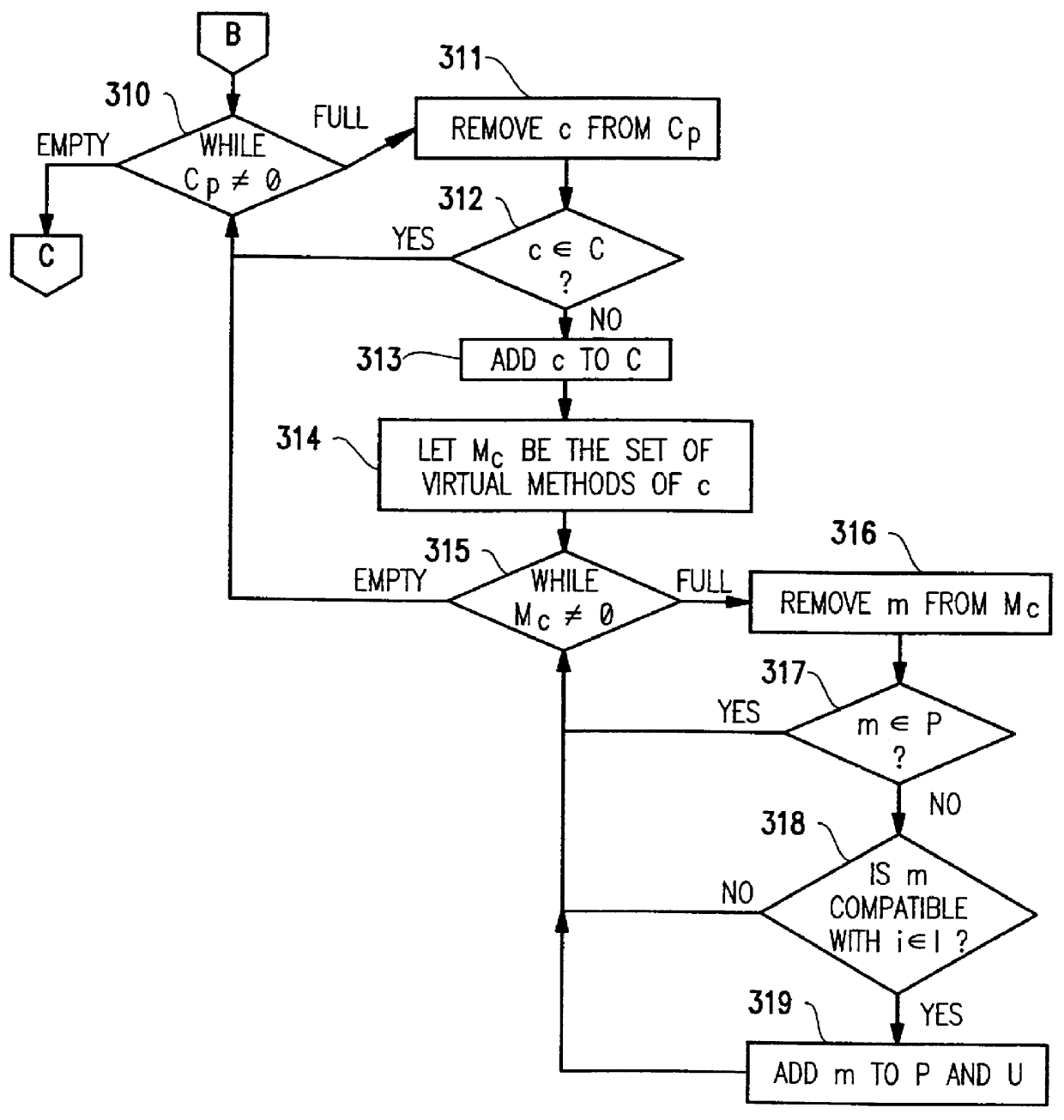

Object oriented dispatch optimization

InactiveUS6041179AFast and simple type-inference processReduce settingsSoftware engineeringSpecific program execution arrangementsProgram codeProgramming language

An object oriented dispatch optimization method determines statically which body of code will be executed when a method is dispatched. The program code is examined to identify all procedure bodies that can be invoked for a given class and a given method. An identified procedure body is analyzed to determine whether a method invocation on a pointer can invoke only one procedure body. Based on this analysis, either the procedure body or the invocation mechanism is changed so a unique procedure is directly called without a test or dispatch being used.

Owner:IBM CORP

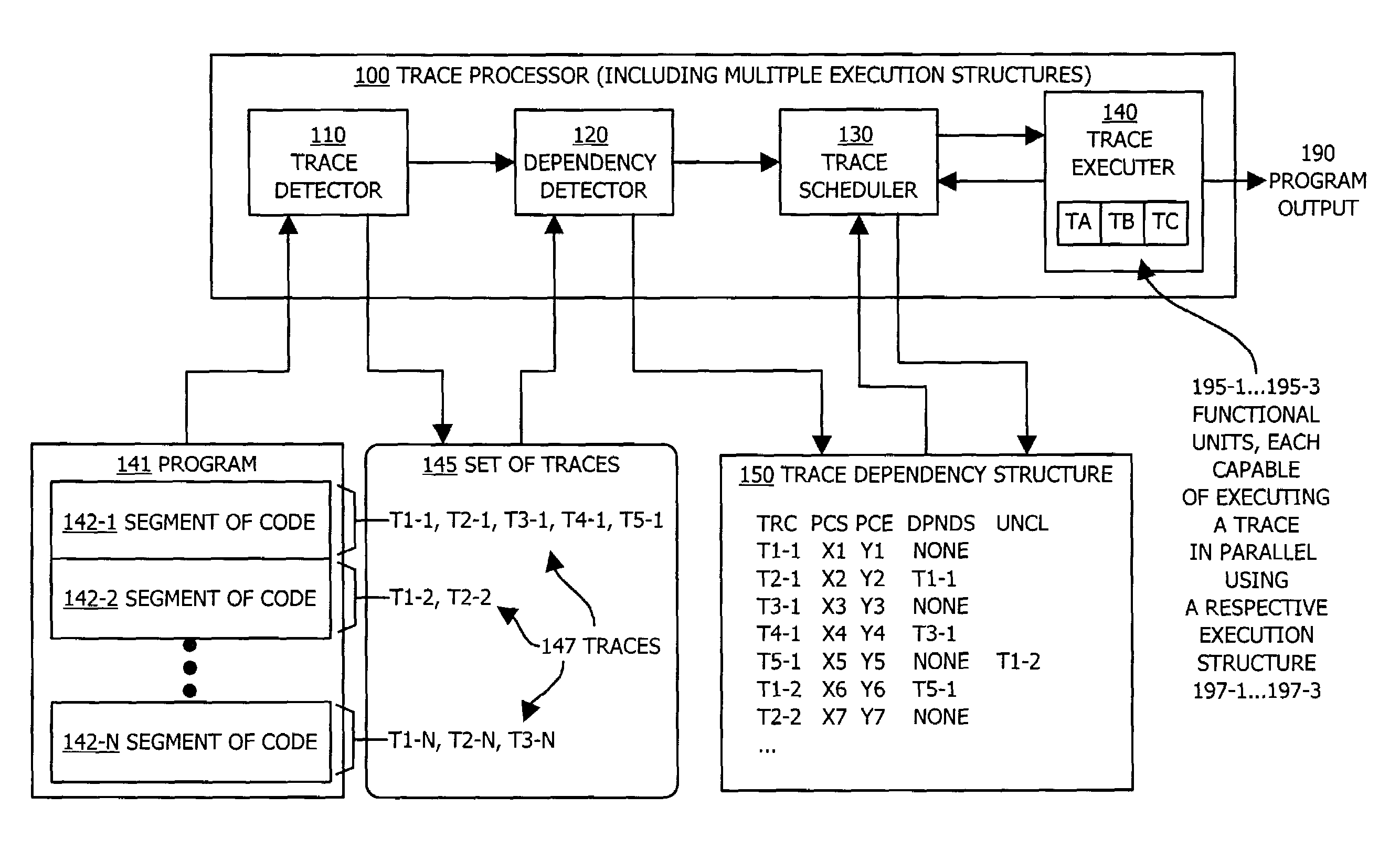

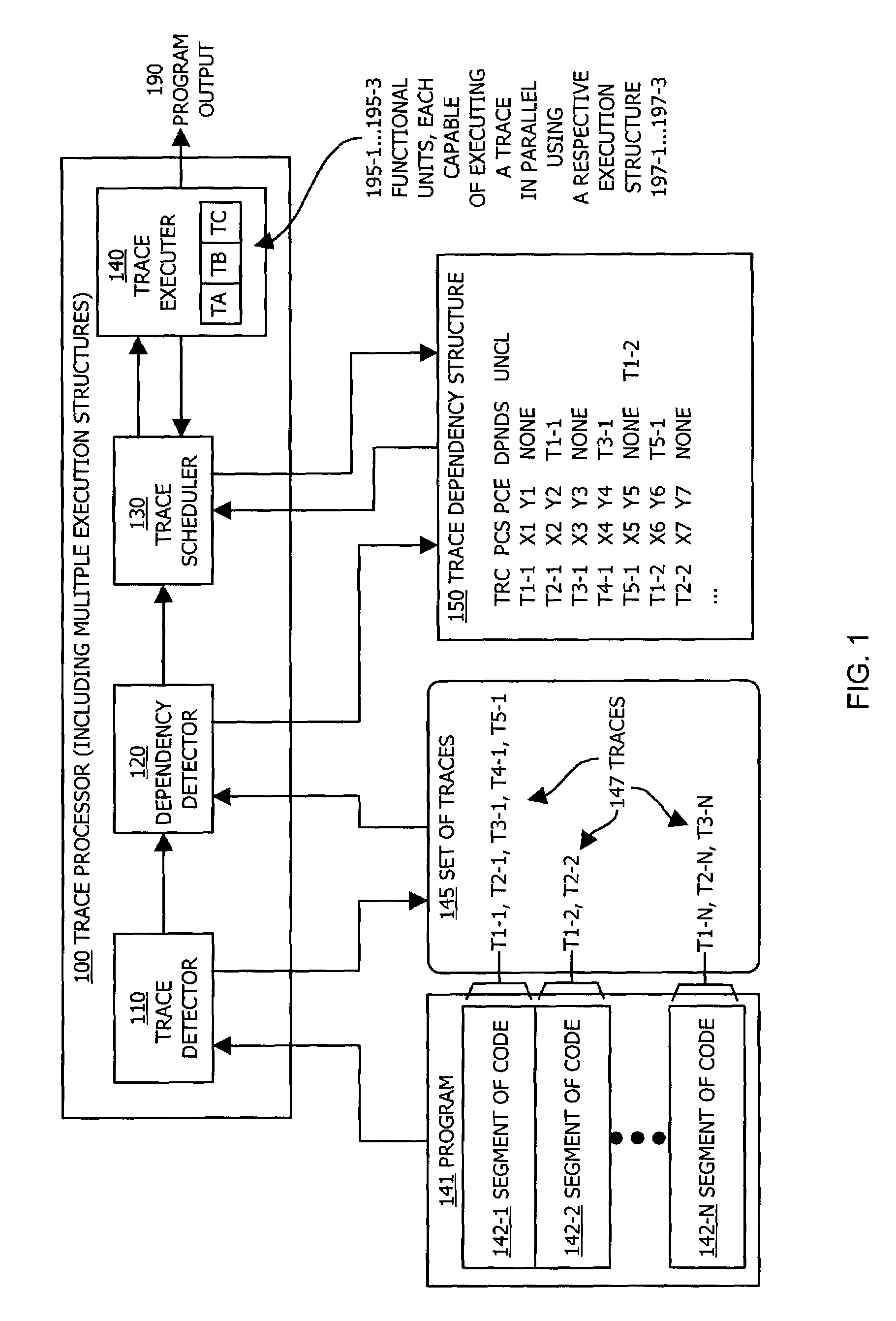

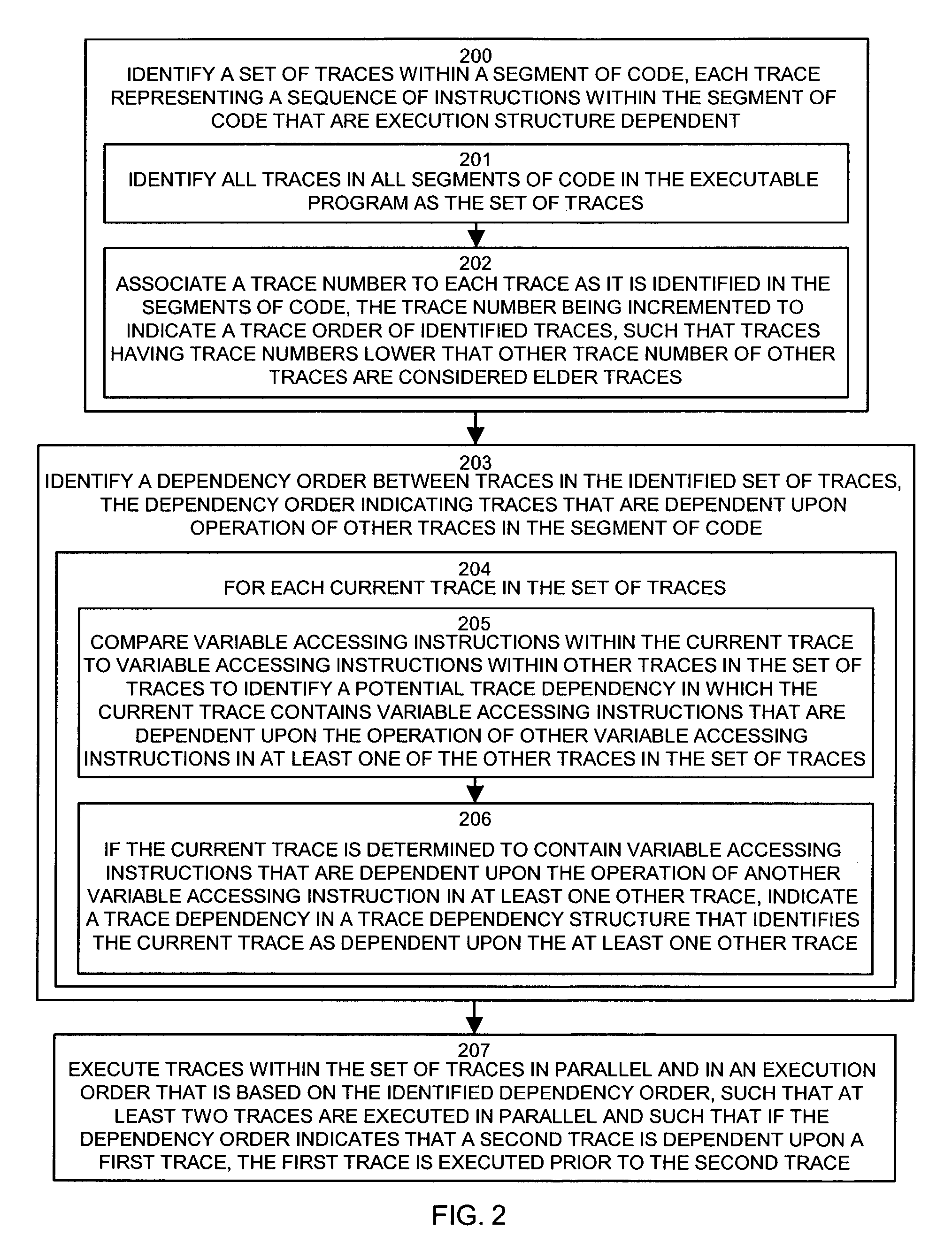

Methods and apparatus for executing instructions in parallel

ActiveUS7210127B1Eliminate operationLimited abilitySpecific program execution arrangementsMemory systemsParallel computingJava bytecode

A system, method and apparatus for executing instructions in parallel identify a set of traces within a segment of code, such as Java bytecode. Each trace represents a sequence of instructions within the segment of code that are execution structure dependent, such as stack dependent. The system, method and apparatus identify a dependency order between traces in the identified set of traces. The dependency order indicates traces that are dependent upon operation of other traces in the segment of code. The system, method and apparatus can then execute traces within the set of traces in parallel and in an execution order that is based on the identified dependency order, such that at least two traces are executed in parallel and such that if the dependency order indicates that a second trace is dependent upon a first trace, the first trace is executed prior to the second trace. This system provides bytecode level parallelism for Java and other applications that utilize execution structure-based architectures and identifies and efficiently eliminates Java bytecode stack dependency.

Owner:ORACLE INT CORP

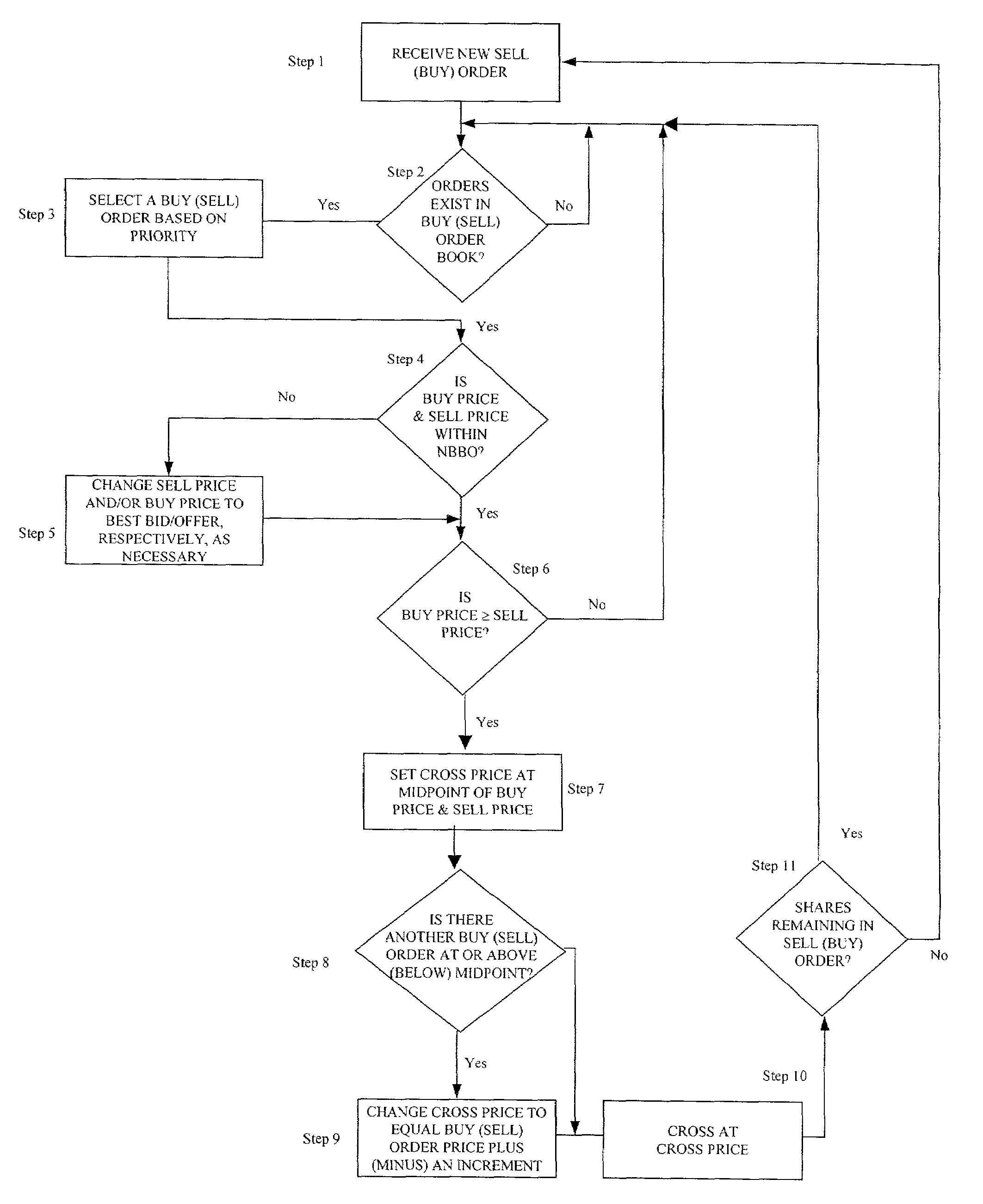

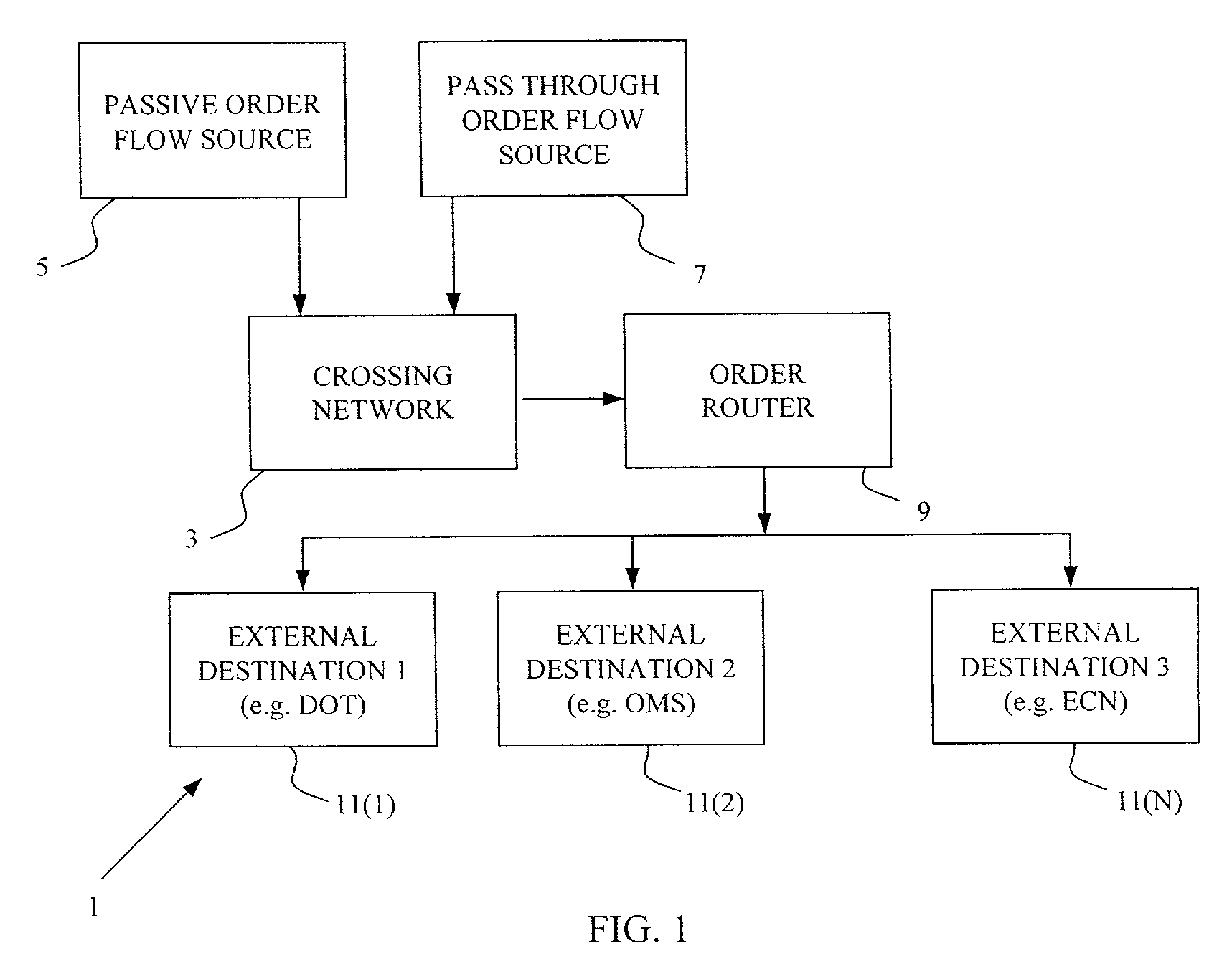

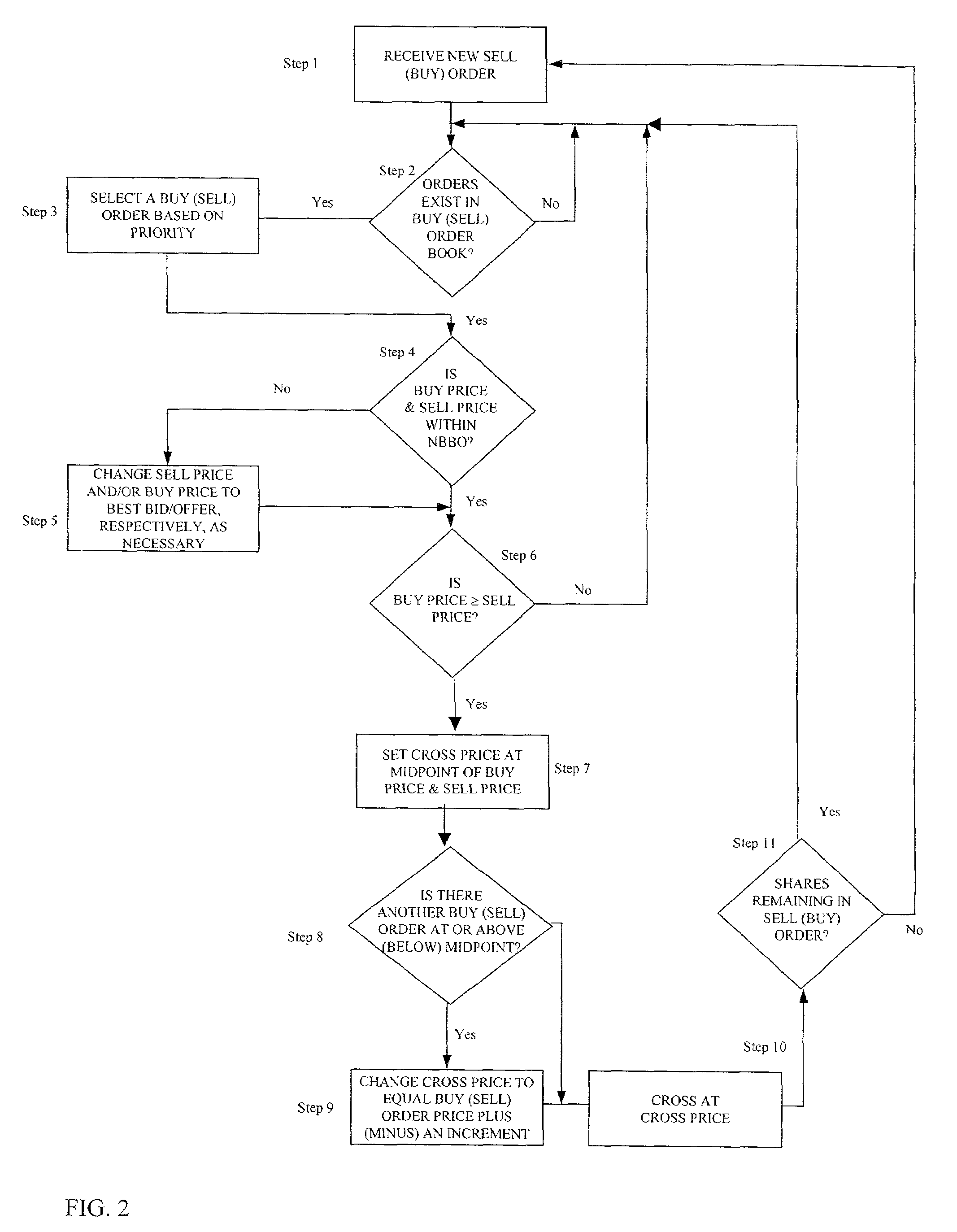

Price improvement crossing system

InactiveUS7558753B2Maintain confidentialityOrder flow through the crossing networkFinanceBuying/selling/leasing transactionsIndustrial engineering

Owner:MORGAN STANLEY

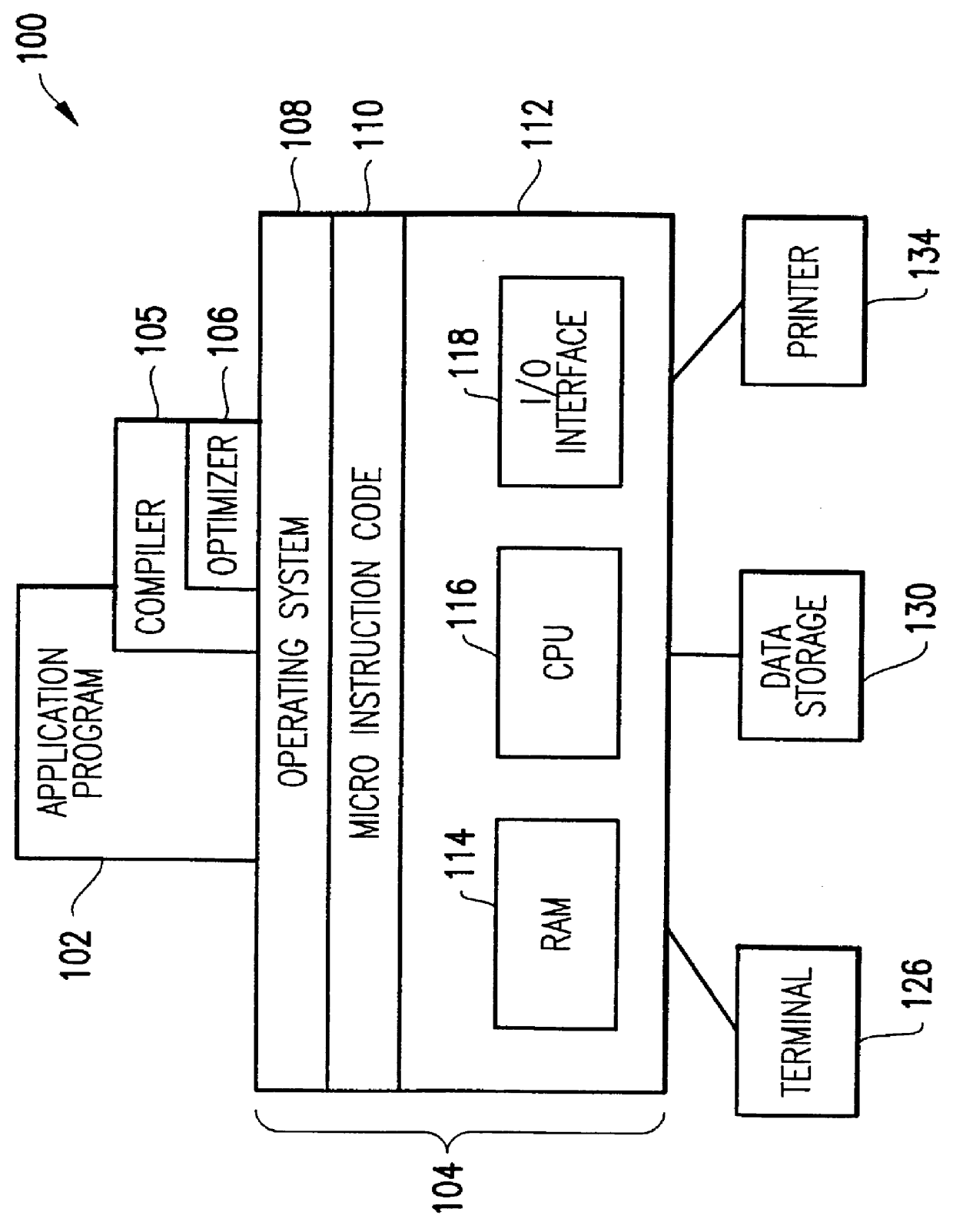

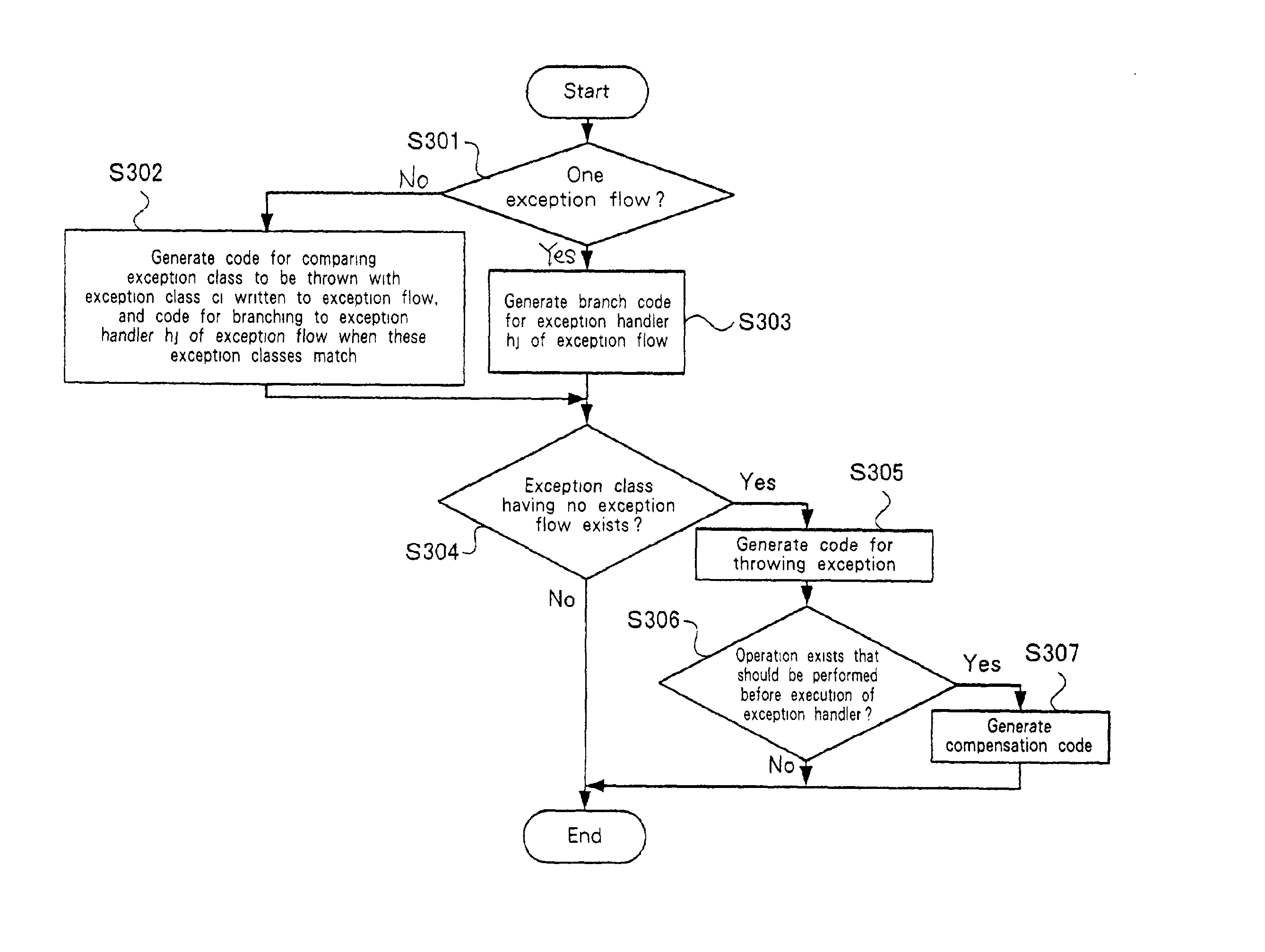

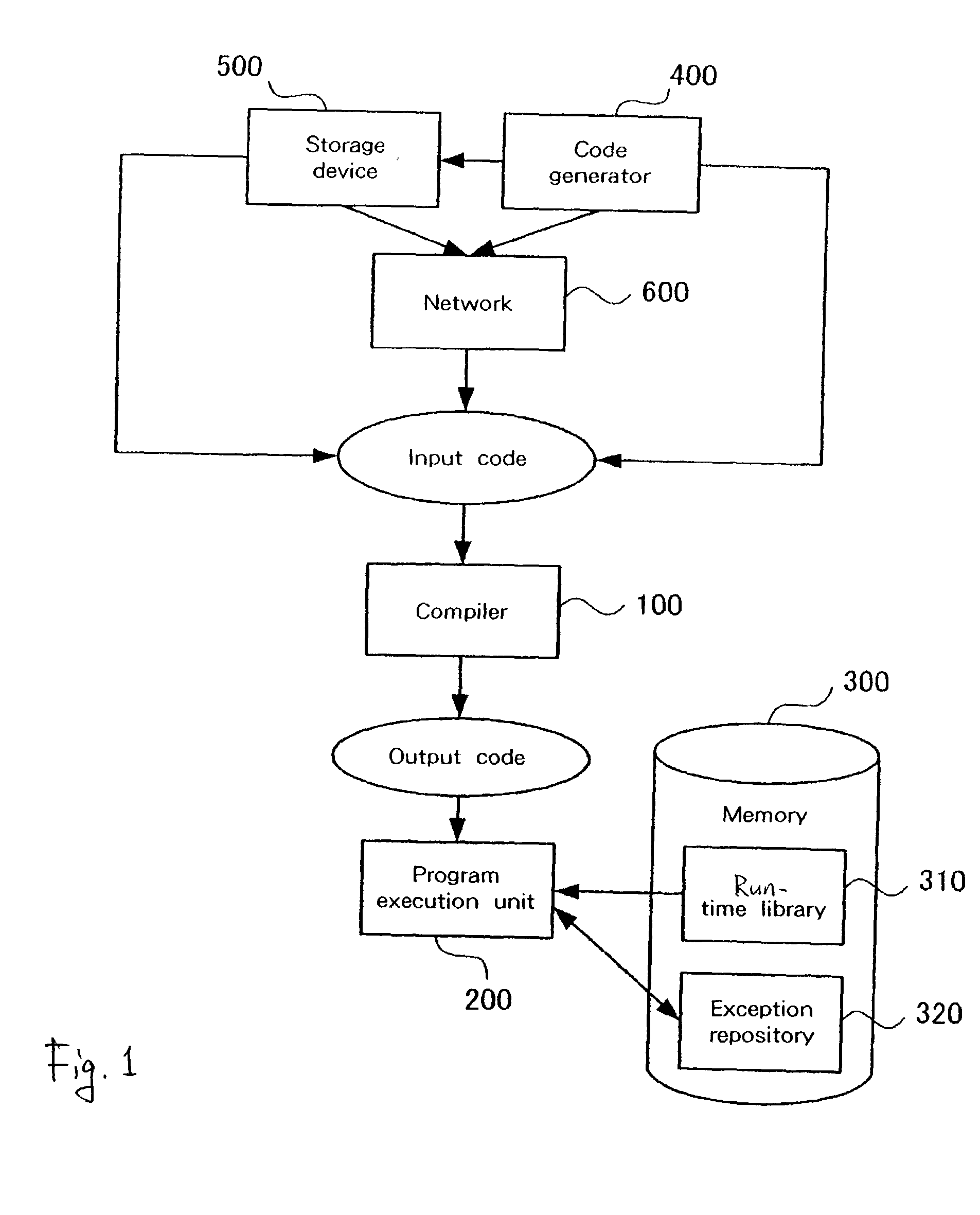

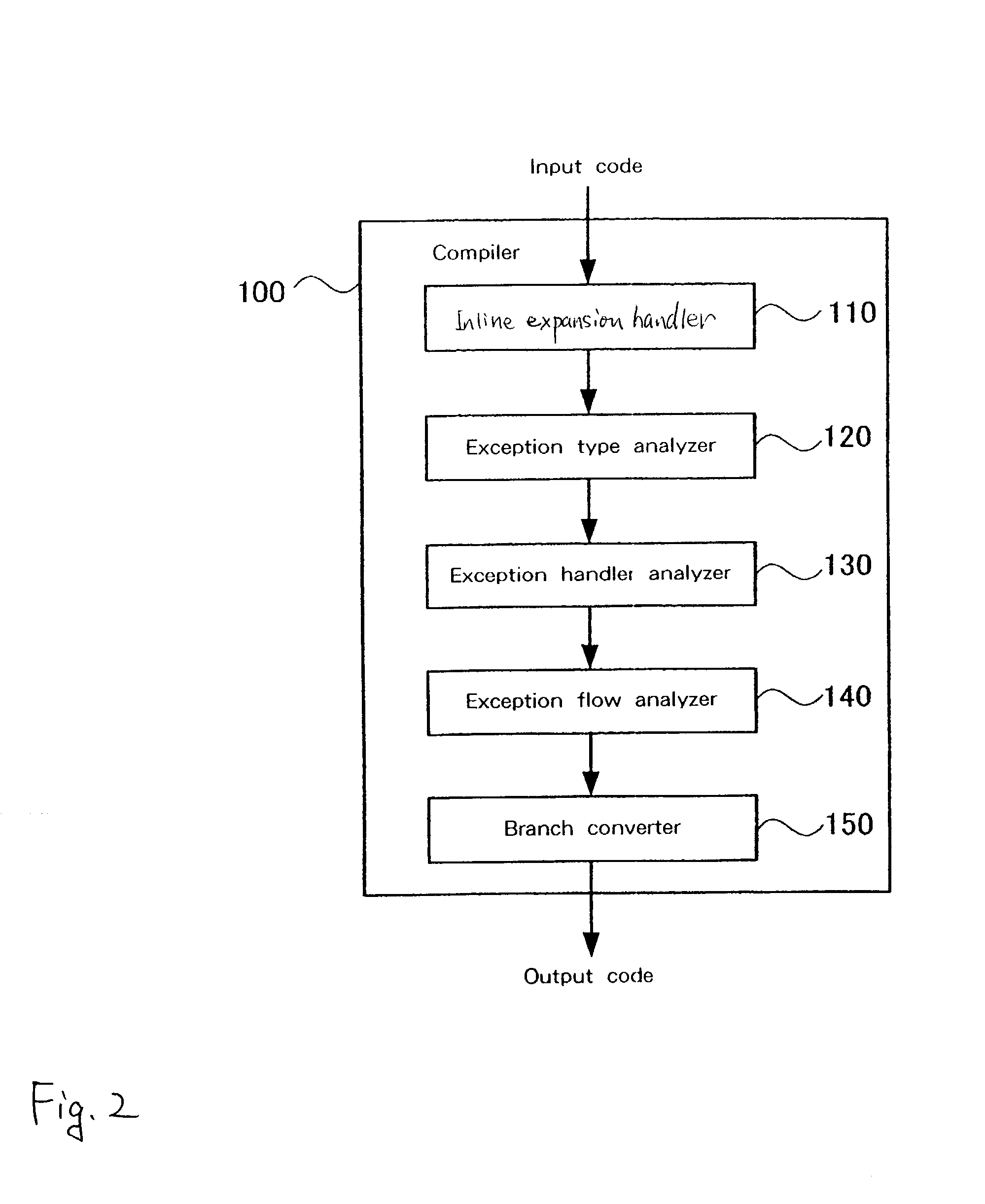

System and method for handling an exception in a program

ActiveUS20030018961A1Improve execution speedReduce search costsSoftware engineeringProgram controlComputerized systemExecution unit

A technique for improving the execution speed of a computer system by effectively reducing the costs to perform a search operation for an exception handler during the exception handling process is established. A computer system comprises 1) a compiler for compiling a program written in a programming language having an exception handling mechanism and 2) an execution unit for executing the compiled program. The execution unit calculates an occurrence frequency of an execution context in which a search operation for an exception handler is performed for execution handling, and determines the execution context to be optimized based on the frequency data. The compiler determines the exception handler for handling an exception that occurs in the above execution context, and generate a code describing a process path from a point that throw the exception in said execution context to the exception handler. Specifically, the compiler deletes the code that throws the exception, and generates a code that branches to the corresponding exception handler.

Owner:GOOGLE LLC

Techniques and System to Deploy Policies Intelligently

ActiveUS20100223287A1Reduce the amount requiredImprove execution speedDigital data processing detailsComputer security arrangementsSpace requirementsOperating system

In an information management system, relevant policies are deployed to targets while policies which are not relevant are not. By deploying relevant policies, this reduces the amount of space requirements at the target to store the policies and the amount of data that needs to be sent to the target. Also, execution speed at the target may increase since the target does not need to evaluate policies that are not relevant.

Owner:NEXTLABS INC

File system consistency checking in a distributed segmented file system

ActiveUS7546319B1Improve scalabilityImprove execution speedData processing applicationsDigital data information retrievalObject pointFile system

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

Amphibious mechanical crab step control device and control method

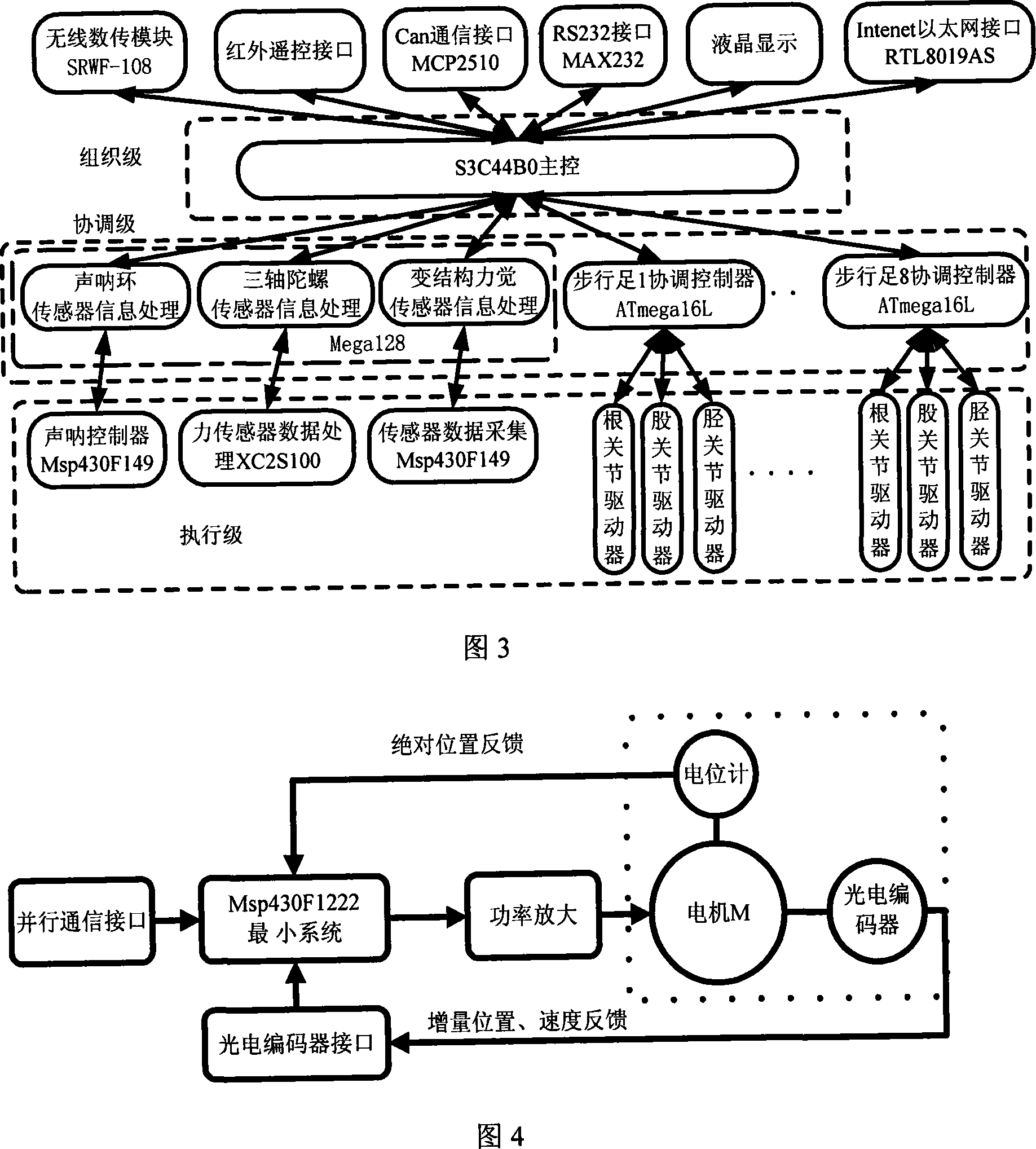

InactiveCN101216711AClear division of laborFast operationElectric controllersTotal factory controlControl signalNetwork Communication Protocols

The invention provides a hierarchical control device for an amphibian machinery crab and a control method thereof. The device comprises a superstructure-level control part composed of a B3C44B0-cored ARM system, a coordination-level control part composed of an AVR single chip computer ATmega128L, eight walking-leg drive modules and an execution-level control part which is composed of a multi-sensor signal collecting module; wherein control signals are input to the superstructure-level control part; the coordination-level control part is connected between the superstructure-level control part and the execution-level control part; and the execution-level control part communicates with joint drive units through bus communication protocols. The invention divides the system into superstructure level, monitoring coordination level and execution level based on the design principle of hierarchical distribution, each dispersed controller not only can work independently but also can communicate and exchange information with a higher level controller or a peer level controller through communication circuits. The hierarchical structure has the advantages of a centralized structure and a dispersed structure, thereby overall and partial control performances are high, and the operation is reliable.

Owner:HARBIN ENG UNIV

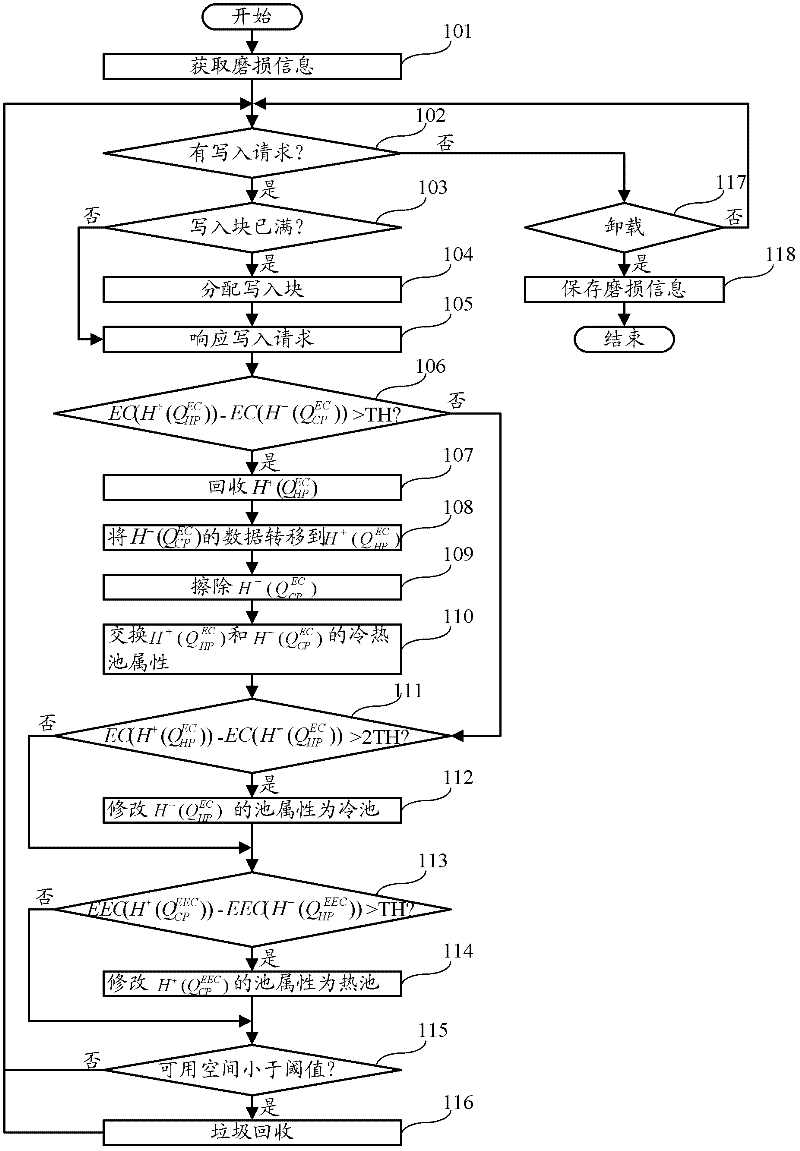

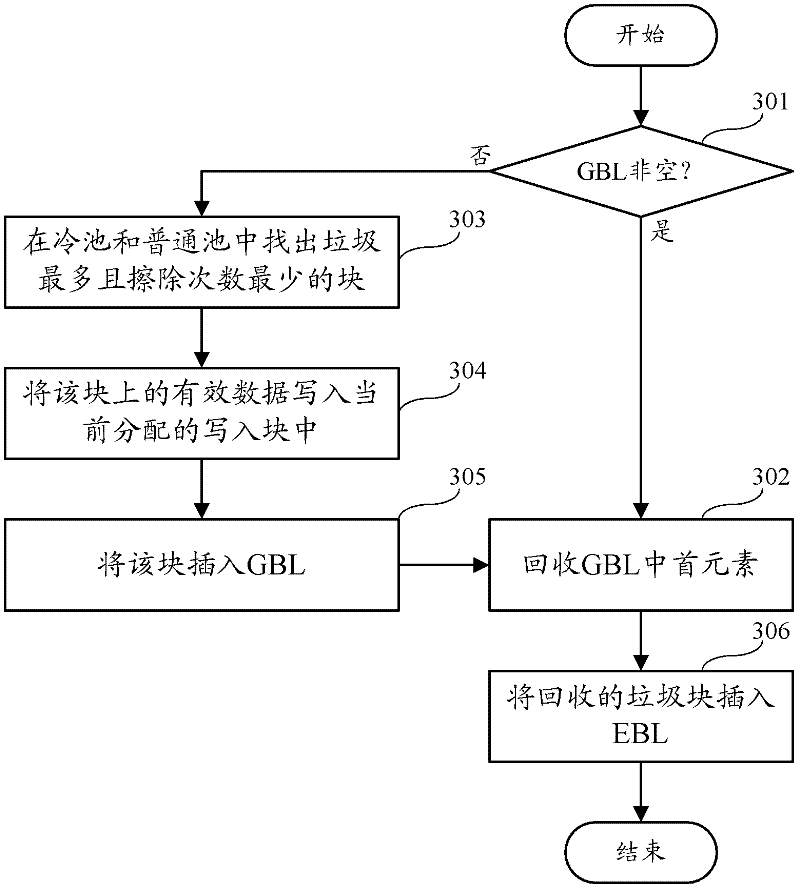

Abrasion equilibrium method and device

ActiveCN102222046AReduce wearGood wear levelingMemory adressing/allocation/relocationComputer science

The invention discloses an abrasion equilibrium method comprising a pool mask of each physical block according to erasing times of each physical block, wherein for different erasing times, the pool mask of the physical block is determined as CPM (Cold Pool Mask), NPM (Normal Pool Mask) or HPM (Hot Pool Mask); when the pool mask of the physical block becomes into HPM from NPM, data in the physicalblock in which any pool mask is CPM is copied onto the physical block in which the pool mask is HPM, and the physical block in which the pool mask is CPM is recycled as rubbish. The invention furtherdiscloses an abrasion equilibrium device, and the method and the device can reduce the extra abrasion caused by abrasion equilibrium.

Owner:TSINGHUA UNIV

Method and system for improving performance of Java virtual machine

InactiveUS20050160415A1Improve execution speedImprove performanceSoftware simulation/interpretation/emulationMemory systemsParallel computingByte

A method and system for improving the performance of a Java virtual machine includes extracting a byte-code of a method constituting a Java class; combining the extracted byte-code to generate a second code with a predetermined byte size and allocating the second code to a data structure of a predetermined type; and executing the second code by an execution engine employed in the Java virtual machine.

Owner:SAMSUNG ELECTRONICS CO LTD

Program execution control device, program execution control method, control program, and recording medium

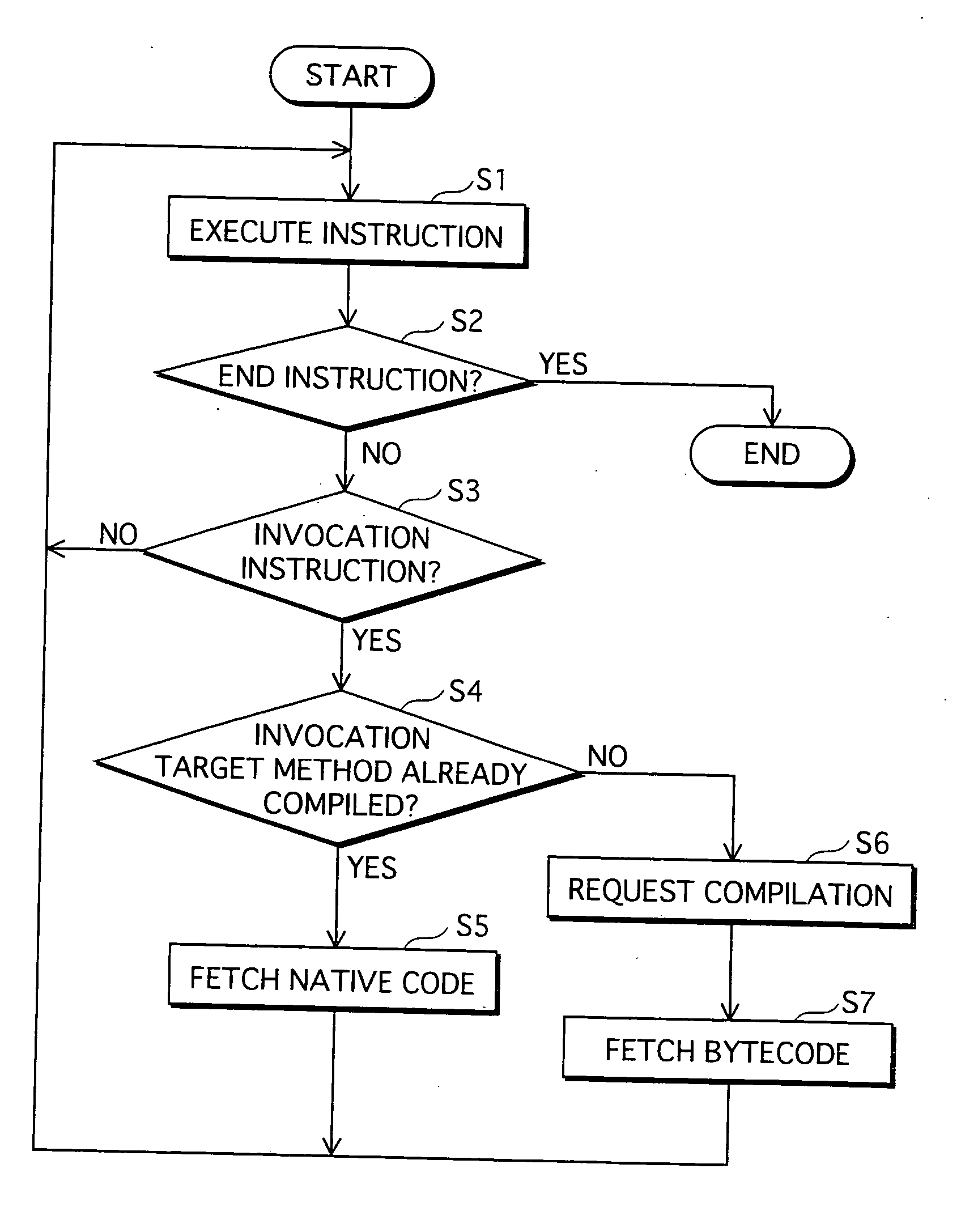

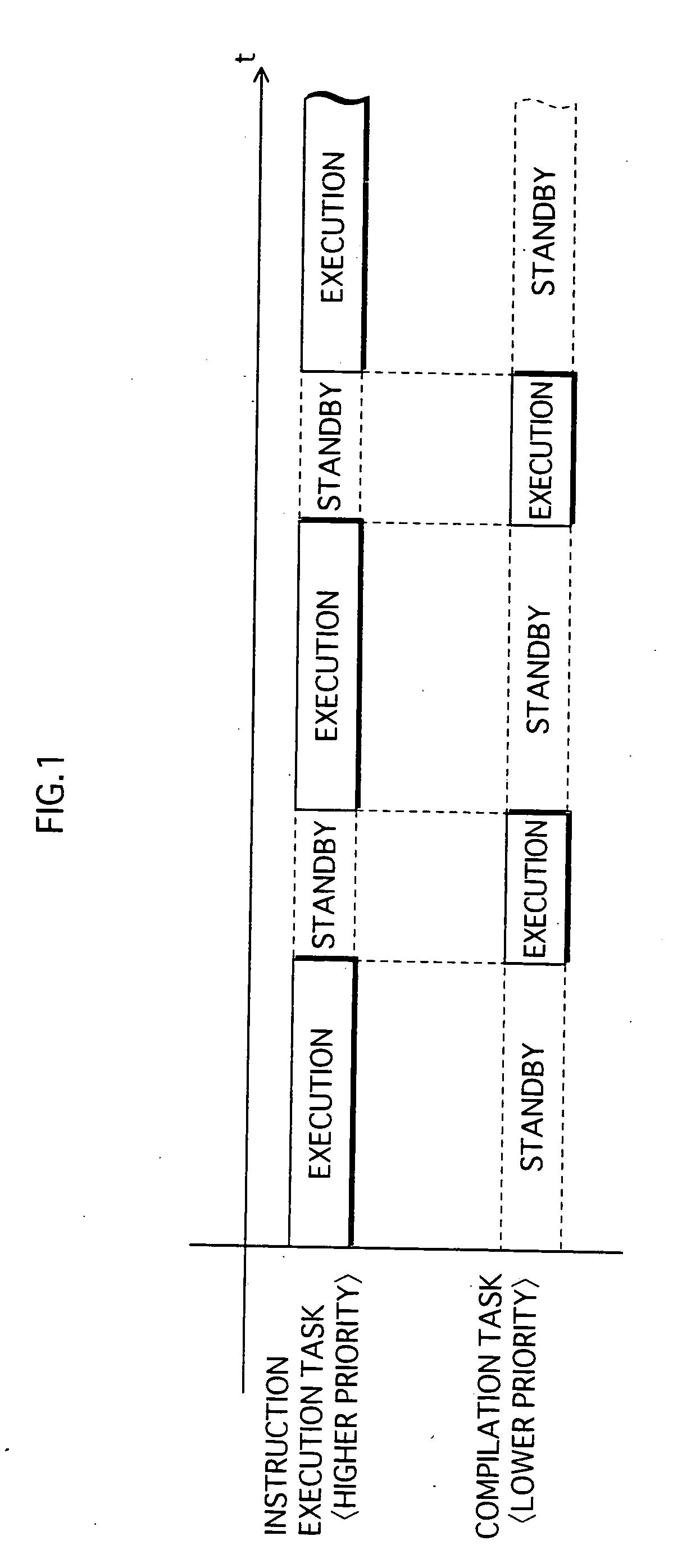

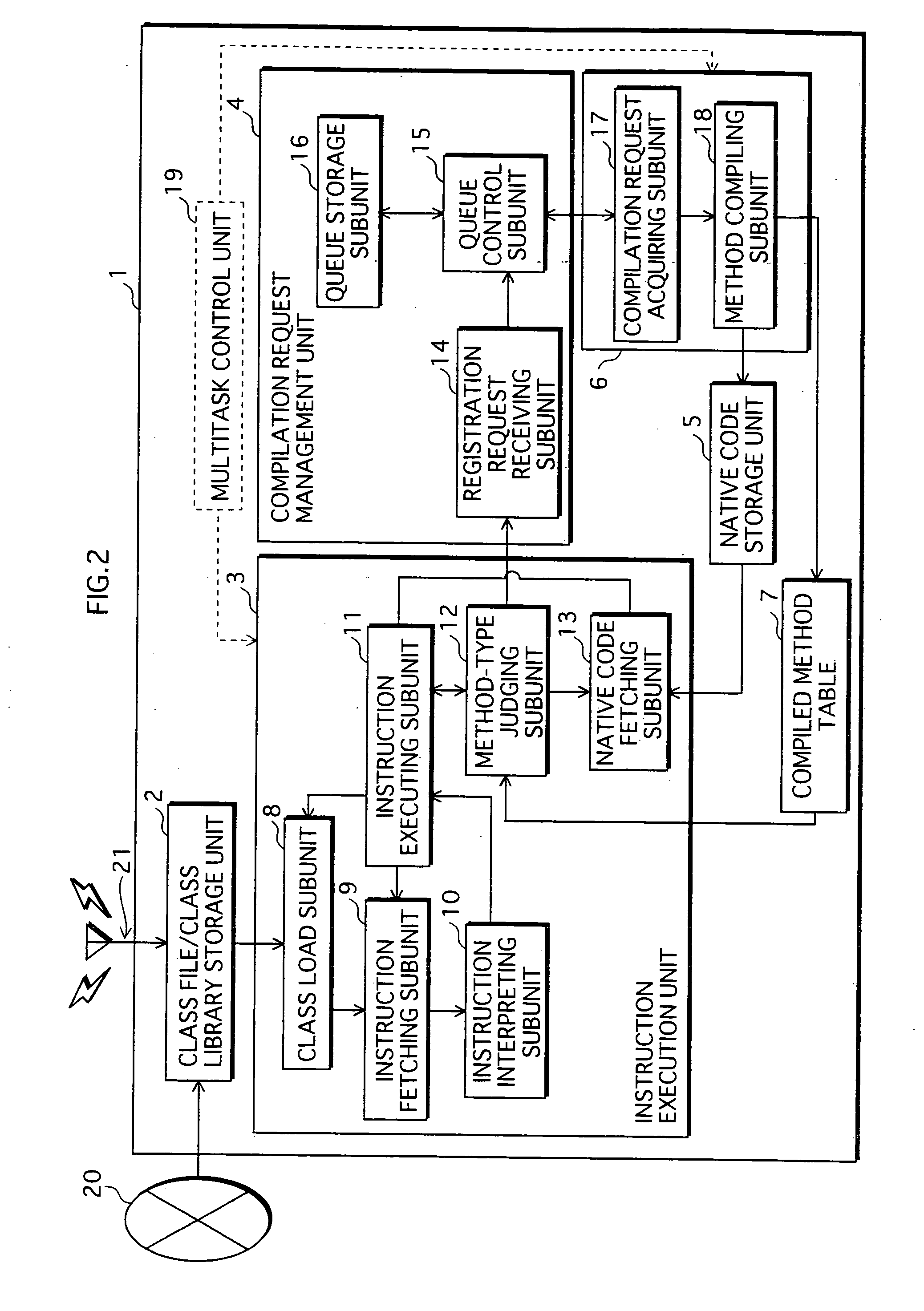

ActiveUS20070226714A1Suppressing reduction of execution speedSuppress execution speedTransformation of program codeSoftware simulation/interpretation/emulationParallel computingExecution control

When a home appliance equipped with a processor implementing a conventional JVM with a JIT compiler executes uncompiled methods, the execution speed is slower because the methods are compiled at runtime. To suppress the execution speed reduction, a program execution control device judges, on invocation of a method during program execution, whether a method invoked has previously been compiled. If the method is uncompiled, the device executes the method by interpreting associated bytecodes, and also issues a compilation request for the method. If the method is compiled, the device executes native code having been generated by compiling the method. Compilation of a method requested is executed as a separate task from tasks of instruction execution such as interpreter execution or native code execution.

Owner:PANASONIC CORP

Formal sequential lagrangian algorithm for large scale resource scheduling optimization

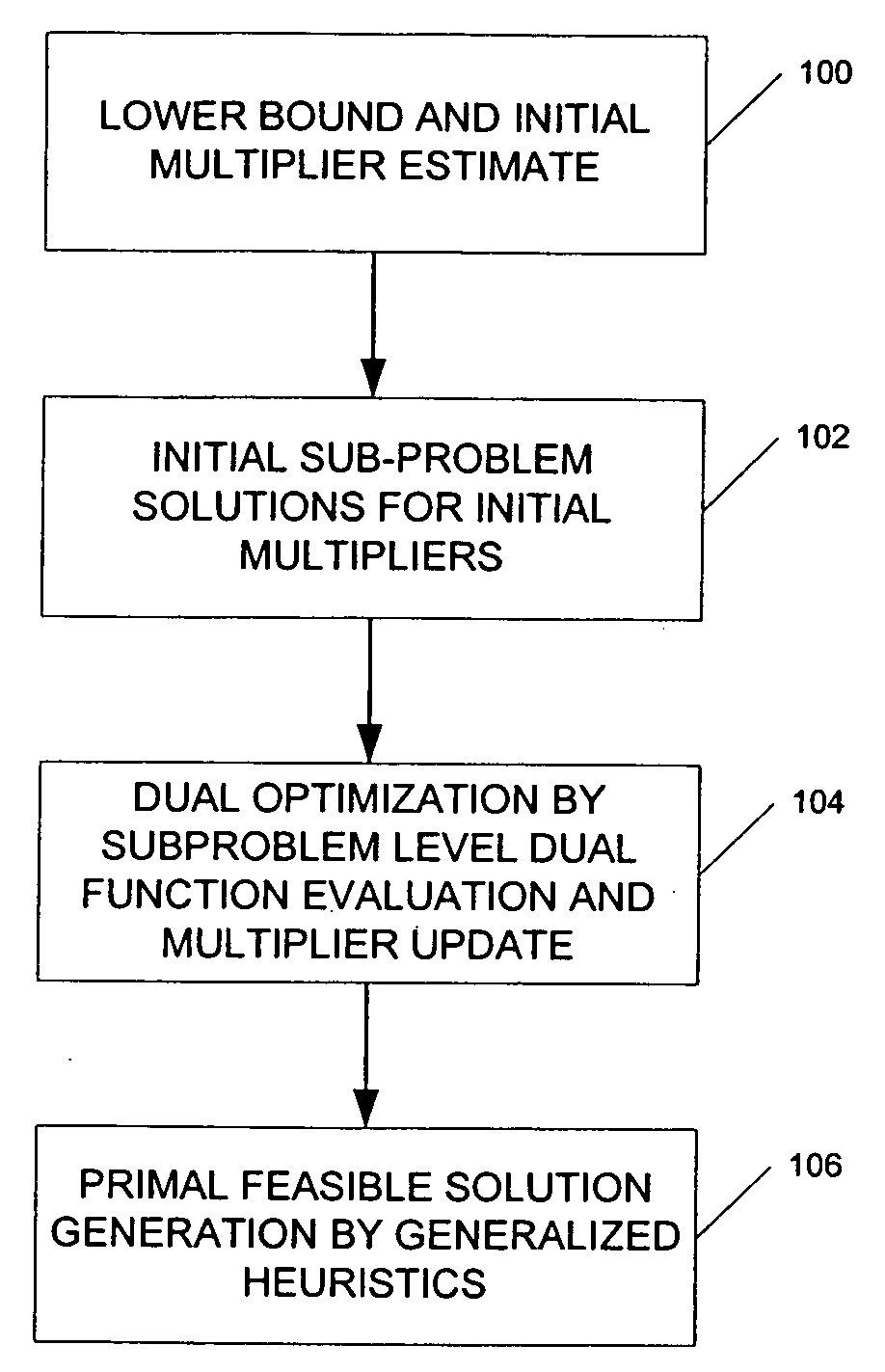

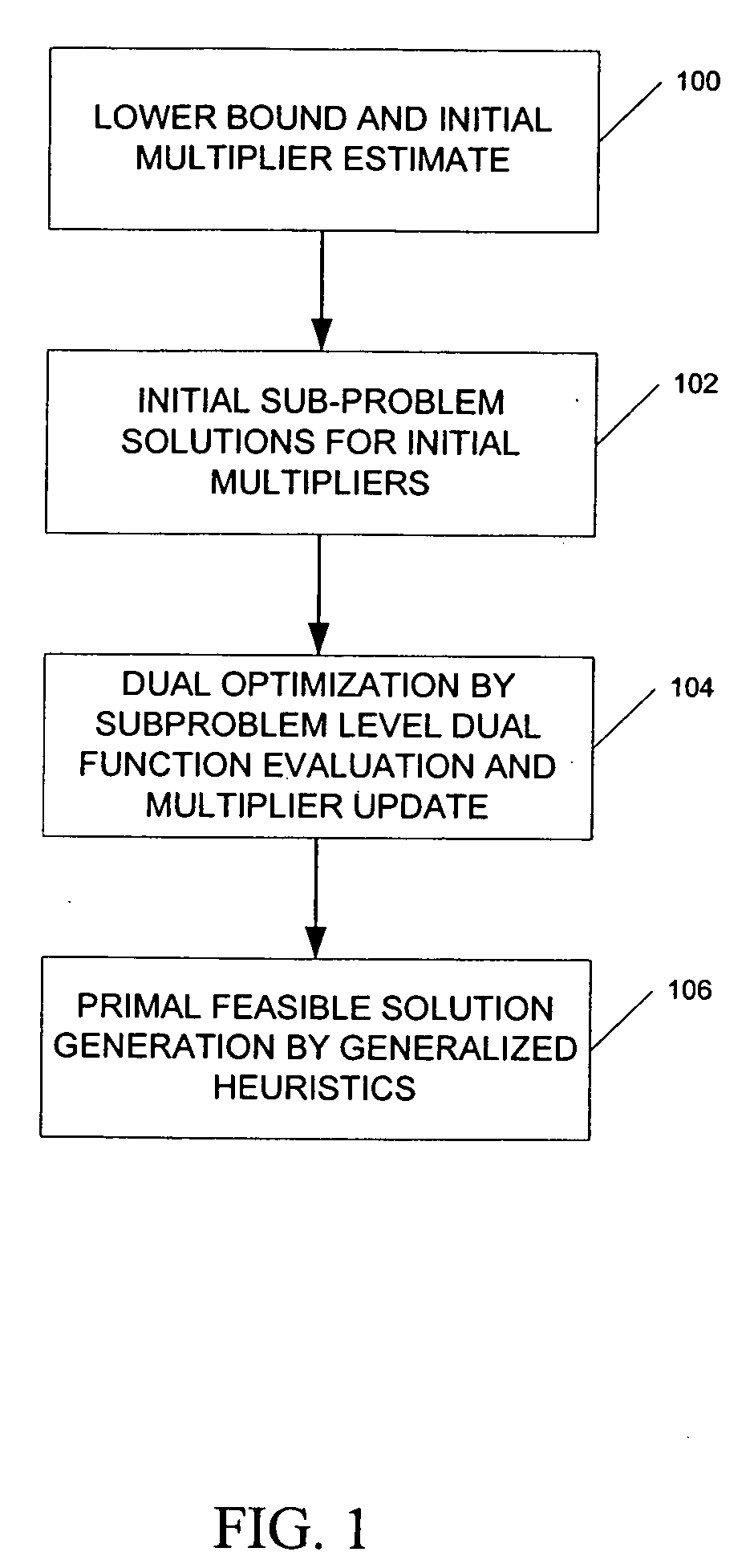

ActiveUS20060089864A1Reduce operating costsFast dual optimization—obtainingDigital computer detailsForecastingProblem domainAlgorithm

A method and computer program product for optimization of large scale resource scheduling problems. Large scale resource scheduling problems are computationally very hard and extremely time consuming to solve. This invention provides a Lagrangian relaxation based solution method. The method has two distinct characteristics. First, the method is formal. It is completely structure-based and does not use any problem domain specific knowledge in the solution process, either in the dual optimization or the primal feasibility enforcement process. Second, updating the Lagrangian multipliers after solution of every sub-problem without using penalty factors results in fast and smooth convergence in the dual optimization. The combination of high quality dual solution and the structure-based primal feasibility enforcement produces a high quality primal solution with very small solution gap. An optimal solution is first found to the dual of the resource scheduling problem by sequentially finding a solution to a plurality of sub-problems and updating a set of values used in the dual problem formulation after each sub-problem solution is obtained. Coupling constraint violations are systematically reduced and the set of values are updated until a feasible solution to the primal resource scheduling problem is obtained. An initial set of multiplier values is further determined by solving a relaxed version of the primal problem where most of the local constraints except the variable bounds are relaxed.

Owner:HITACHI ENERGY SWITZERLAND AG

Organization method of client directory cache in distributed file system

InactiveCN102541985AAvoid multiple communicationsImprove execution speedSpecial data processing applicationsDistributed File SystemData access

The invention discloses an organization method of a client directory cache in a distributed file system, wherein the distributed file system adopts a multi-metadata server framework, i.e. contents of a single directory are distributed on a plurality of metadata servers. The reason why the multi-metadata framework is adopted is mainly that the pressure of metadata access can be decentralized and the concurrency can be improved. According to the method, aiming at the characteristic that people write less but read more in network application, contents of a directory item and corresponding index nodes are remained in the cache of a client side, thereby avoiding the client side from communicating with the servers for multiple times when reading repeatedly; meanwhile when a directory is accessed for the first time, the directory items of the directory distributed on different metadata servers are pre-read, and the file index nodes and the file contents are pre-read according to a default pre-reading strategy or a pre-reading strategy issued by an application program. Consequently when the application program needs to access a certain file under the directory items, the metadata and data of the file are pre-read into the local cache of the client side already, so that the execution speed of the application program is accelerated greatly.

Owner:DAWNING INFORMATION IND BEIJING

Wear leveling method and device

ActiveCN102508785AGood wear levelingReduced speed when searching for physical blocksMemory adressing/allocation/relocationComputer scienceWear leveling

The invention discloses a wear leveling method, which comprises the following steps of: determining a pool mask of each physical block according to an erasing count of each physical block, wherein the pool mask of the physical block is determined as a cold pool mask (CPM), a normal pool mask (NPM) or a hot pool mask (HPM) according to different erasing counts; and when a pool mask of a certain physical block is changed from the NPM to the HPM, copying the data of any physical block with the pool mask of CPM into the physical block with the pool mask of HPM, and performing spam collection by taking the physical block with the pool mask of CPM as a spam block, wherein a cold pool, a hot pool and a normal pool are divided according to a value of a reference erasing count counter (RECC) and a threshold (TH) value, the value of the RECC is equal to an erasing count of a physical block with the smallest erasing count in the physical blocks, and the preset TH value is changed along with the wear condition of the physical block. The invention also discloses a wear leveling device. By the method and the device, additional wear caused by wear leveling can be reduced.

Owner:TSINGHUA UNIV

Inductive monitoring system constructed from nominal system data and its use in real-time system monitoring

ActiveUS7383238B1Avoid complexityAvoid expensesComputer controlDigital computer detailsOperational systemMonitoring system

The present invention relates to an Inductive Monitoring System (IMS), its software implementations, hardware embodiments and applications. Training data is received, typically nominal system data acquired from sensors in normally operating systems or from detailed system simulations. The training data is formed into vectors that are used to generate a knowledge database having clusters of nominal operating regions therein. IMS monitors a system's performance or health by comparing cluster parameters in the knowledge database with incoming sensor data from a monitored-system formed into vectors. Nominal performance is concluded when a monitored-system vector is determined to lie within a nominal operating region cluster or lies sufficiently close to a such a cluster as determined by a threshold value and a distance metric. Some embodiments of IMS include cluster indexing and retrieval methods that increase the execution speed of IMS.

Owner:NASA

Method to create optimized machine code through combined verification and translation of JAVA TM bytecode

InactiveUS20050091650A1Improve execution speedShorten the timeBinary to binaryProgram loading/initiatingParallel computingByte

The present invention is a new method and apparatus to perform combined compilation and verification of platform independent bytecode instruction listings into optimized machine code. More specifically, the present invention creates a new method and apparatus in which bytecode compilation instructions are combined with bytecode verification instructions, producing optimized machine code on the target system in fewer programming steps than traditionally known. The new method, by combining the steps required for traditional bytecode verification and compilation, increases speed and applicability of platform independent bytecode instructions.

Owner:MYRIAD GROUP

Method of recognizing and indexing documents

InactiveUS7319799B2Low costImprove execution speedData processing applicationsImage data processing detailsPointing deviceLibrary science

A method of recognizing and indexing documents, using a scanner connected to a computer, the method including scanning the documents, then using a pointing device or member of the computer to designate an arbitrary point P in at least one box of the documents, and finally recognizing by OCR the characters in the box so as to store them in a first database connected to the computer to enable documents scanned in this way to be indexed. The designation step comprises a step of searching for and identifying the box of the document containing the point P designated by the user.

Owner:OCE IND

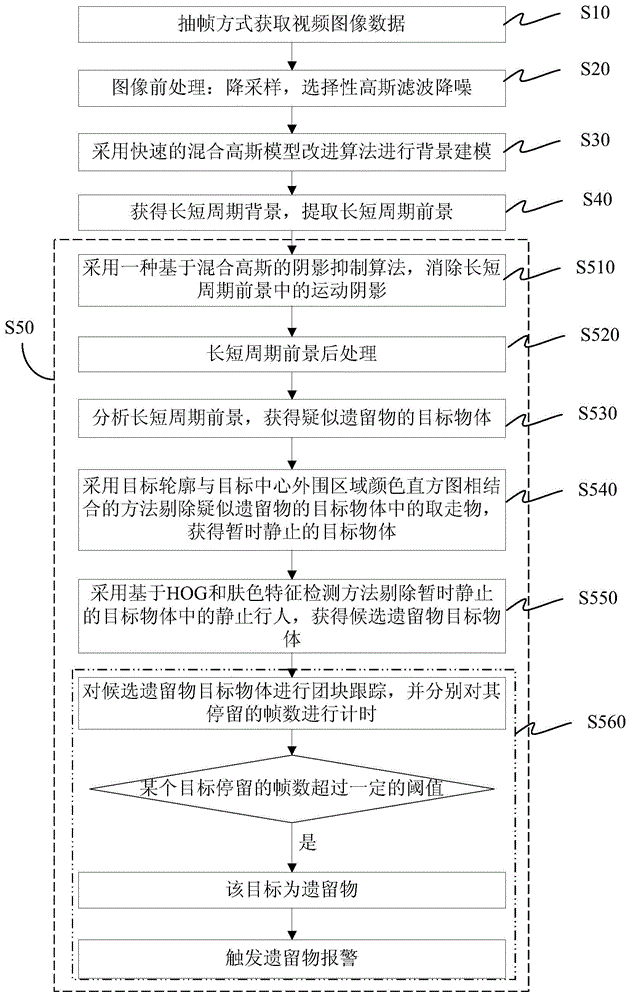

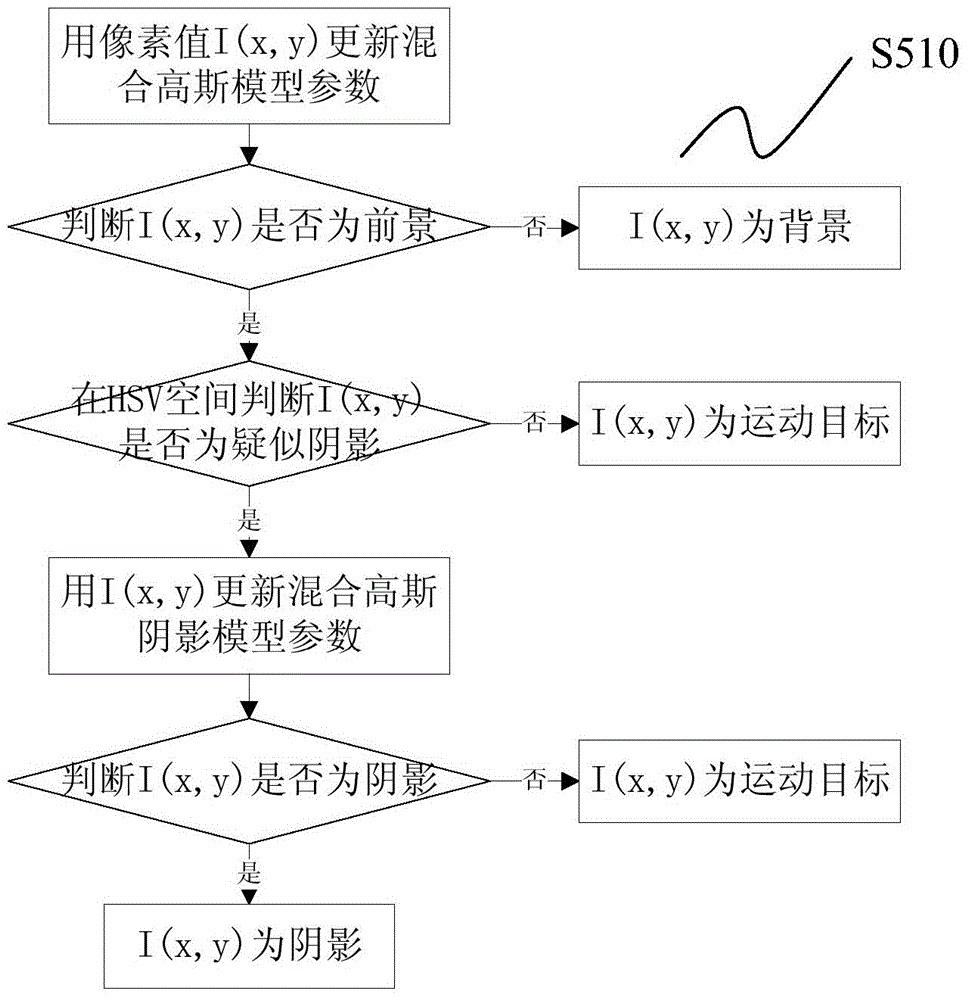

Real-time detection method for object left behind

ActiveCN105404847AReduce workloadImprove real-time performanceImage analysisCharacter and pattern recognitionImproved algorithmVideo image

The invention discloses a real-time detection method for an object left behind. The method comprises the steps of acquiring video image data; carrying out background modeling of the video image by using a Gaussian mixture model improved algorithm, and establishing a long-period background model and a short-period background model respectively, the background being divided into a stable region and a dynamic region; obtaining a long-period prospect FL by subtracting the long-period background model from a current video frame, and obtaining a short-period prospect FS by subtracting the short-period background model from the current video frame; analyzing the long-period prospect FL and the short-period prospect FS, detecting an object left behind, marking the object left behind and sending out an alarm. The invention adopts the fast Gaussian mixture model improved algorithm for modeling the background which is divided into the stable region and the dynamic region, the detection accuracy of the object left behind is improved, and the execution speed of the algorithm is also increased.

Owner:BEIJING INST OF COMP TECH & APPL +1

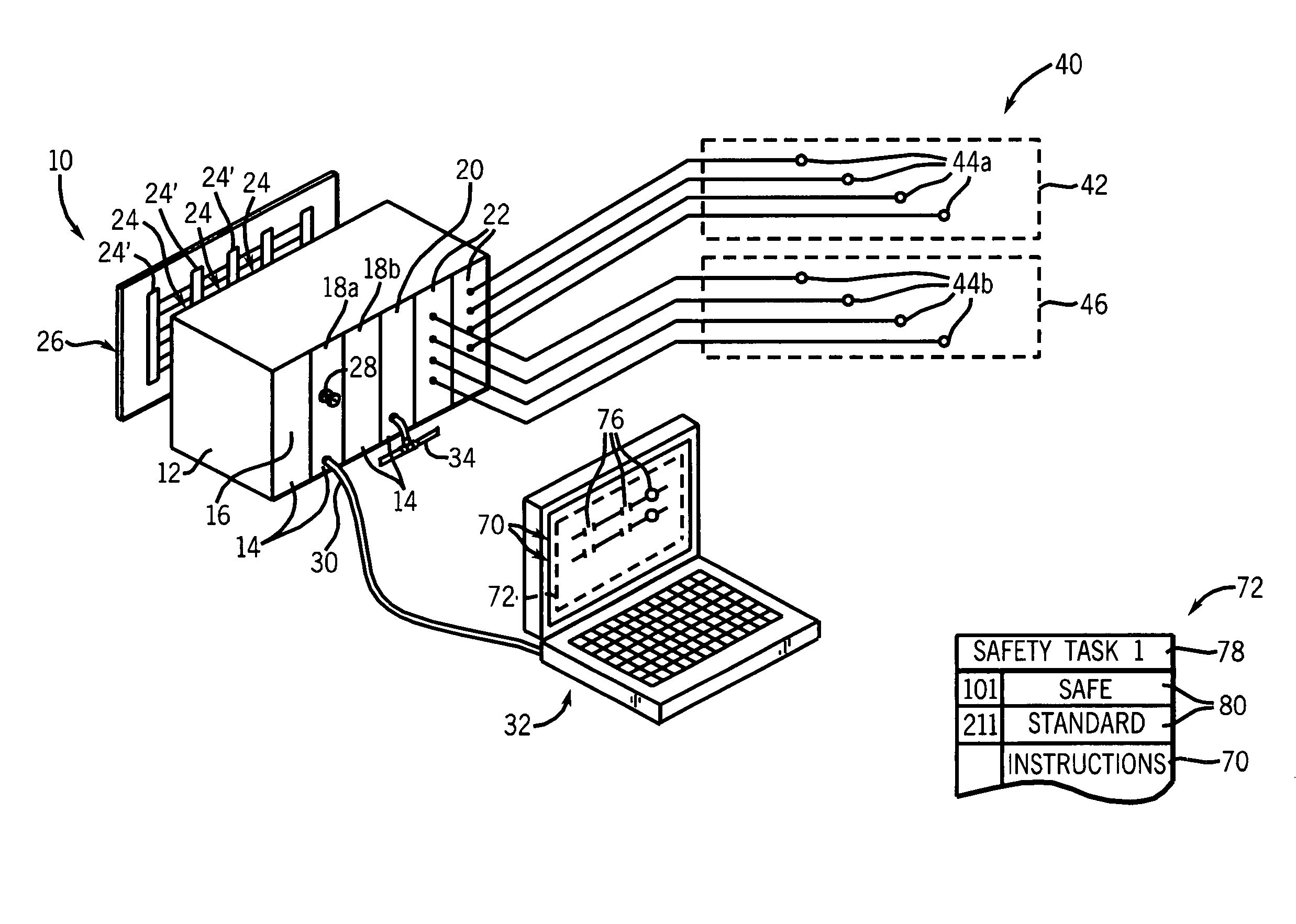

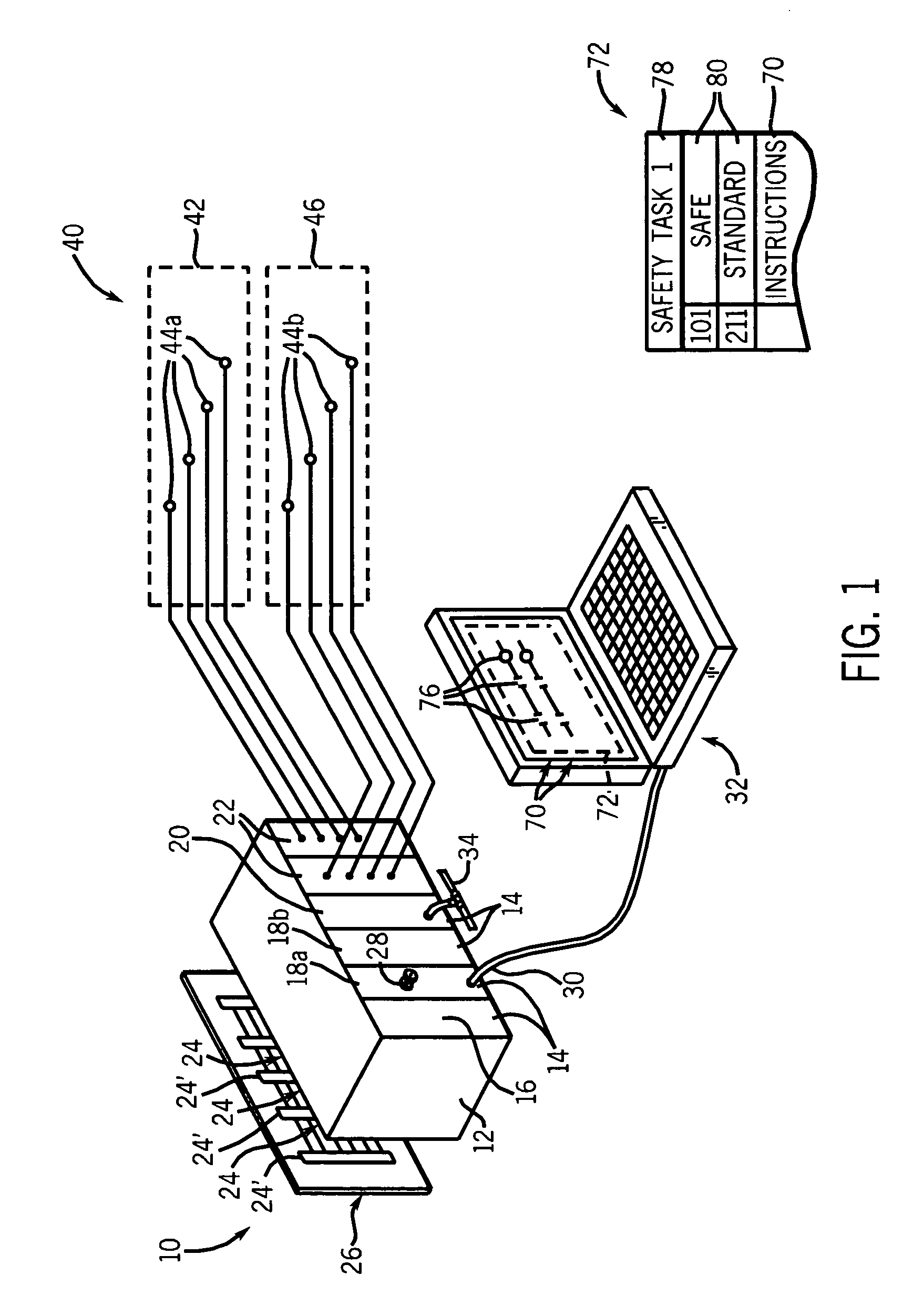

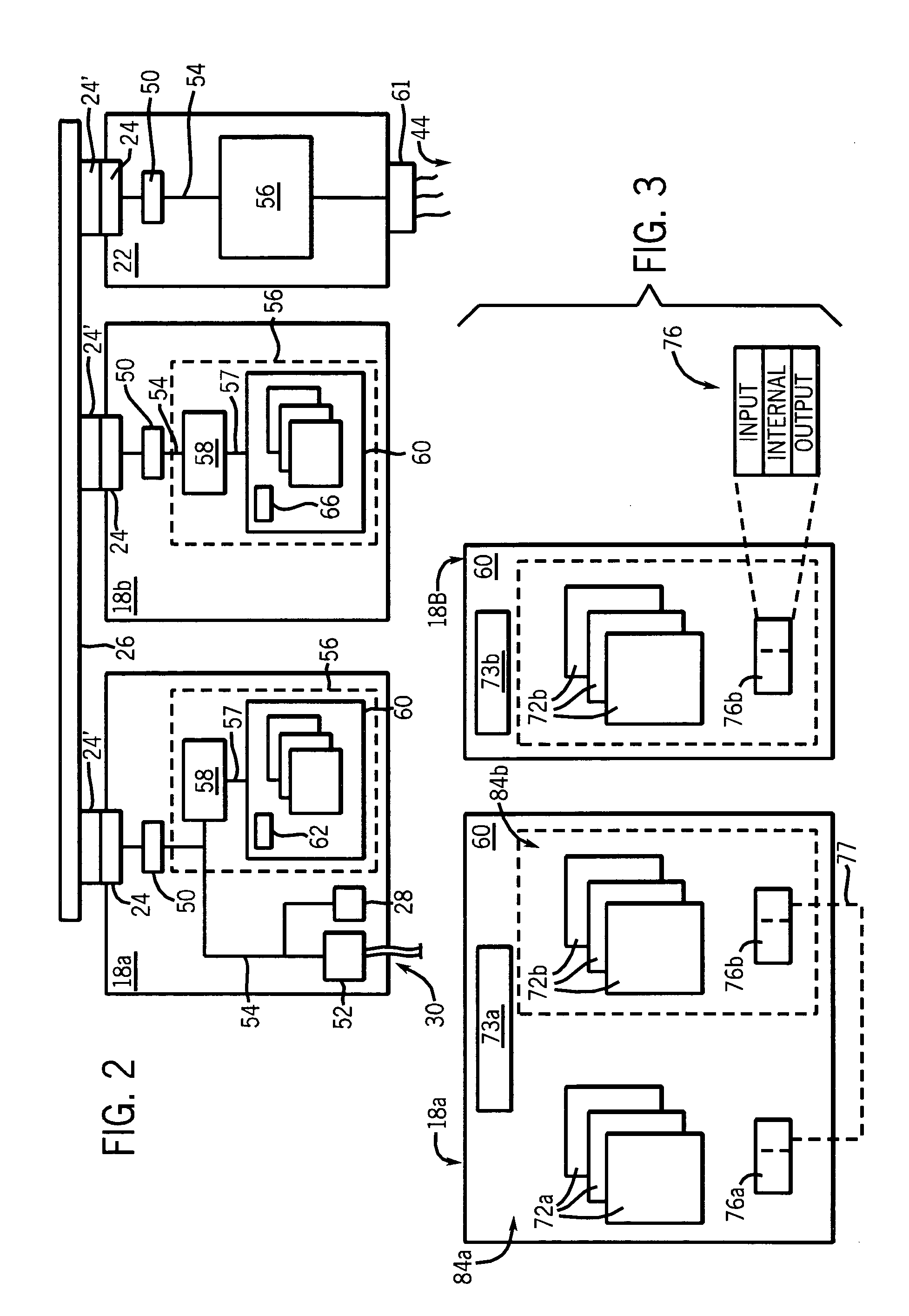

High speed synchronization in dual-processor safety controller

ActiveUS20050060605A1Fast executionImprove execution speedProgramme controlSafety arrangmentsParallel computingProcessing element

A safety controller executes a control program in two processing units to detect processor failure by comparison of the execution in each unit. This comparison is made rapid by synchronizing the input variables at the beginning of the task and comparing output variables at a conclusion of the task, avoiding line-by-line comparison of input and output variables. Intermediate variables, that are neither input nor output values, are compared at a less frequent interval.

Owner:ROCKWELL AUTOMATION TECH

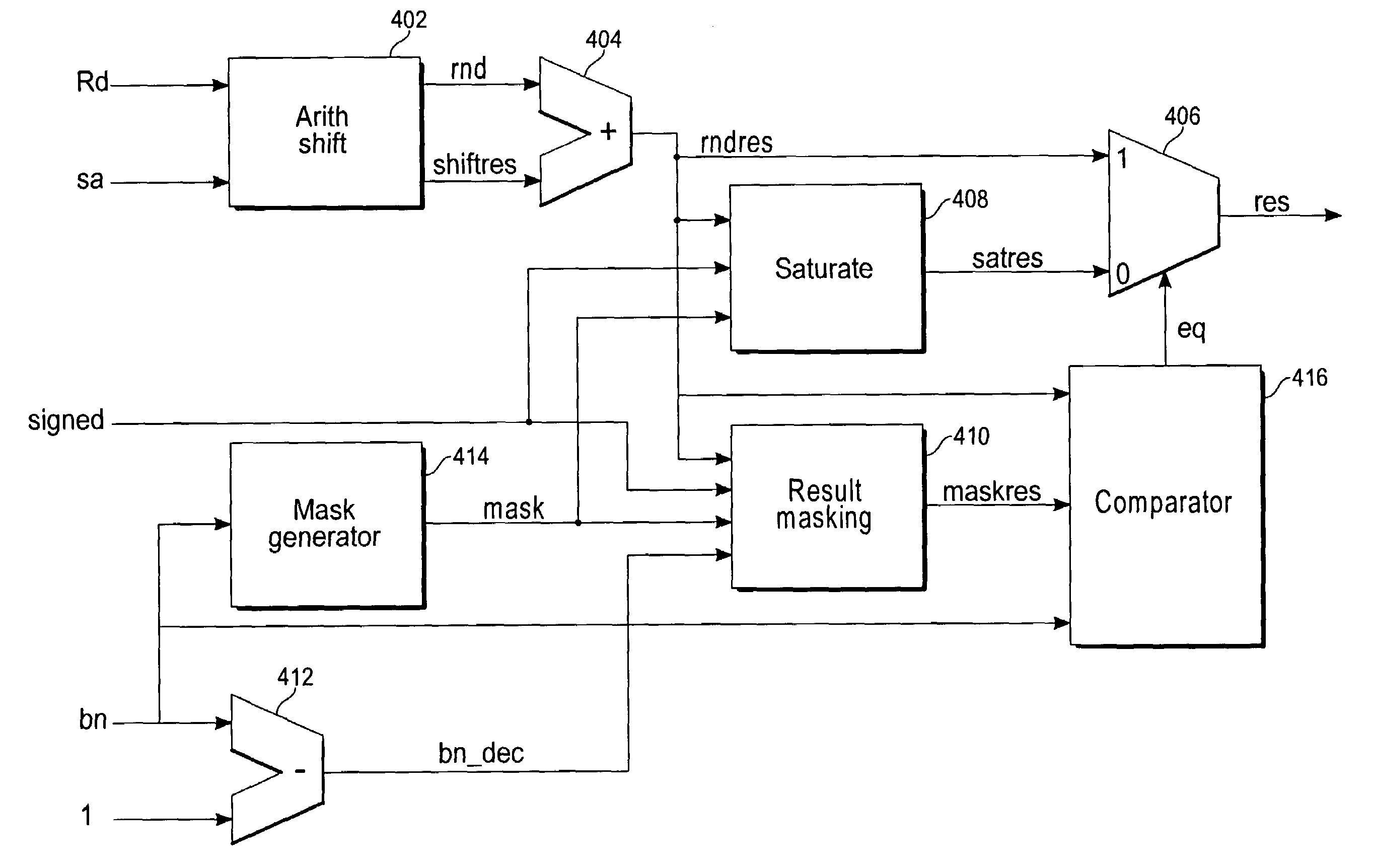

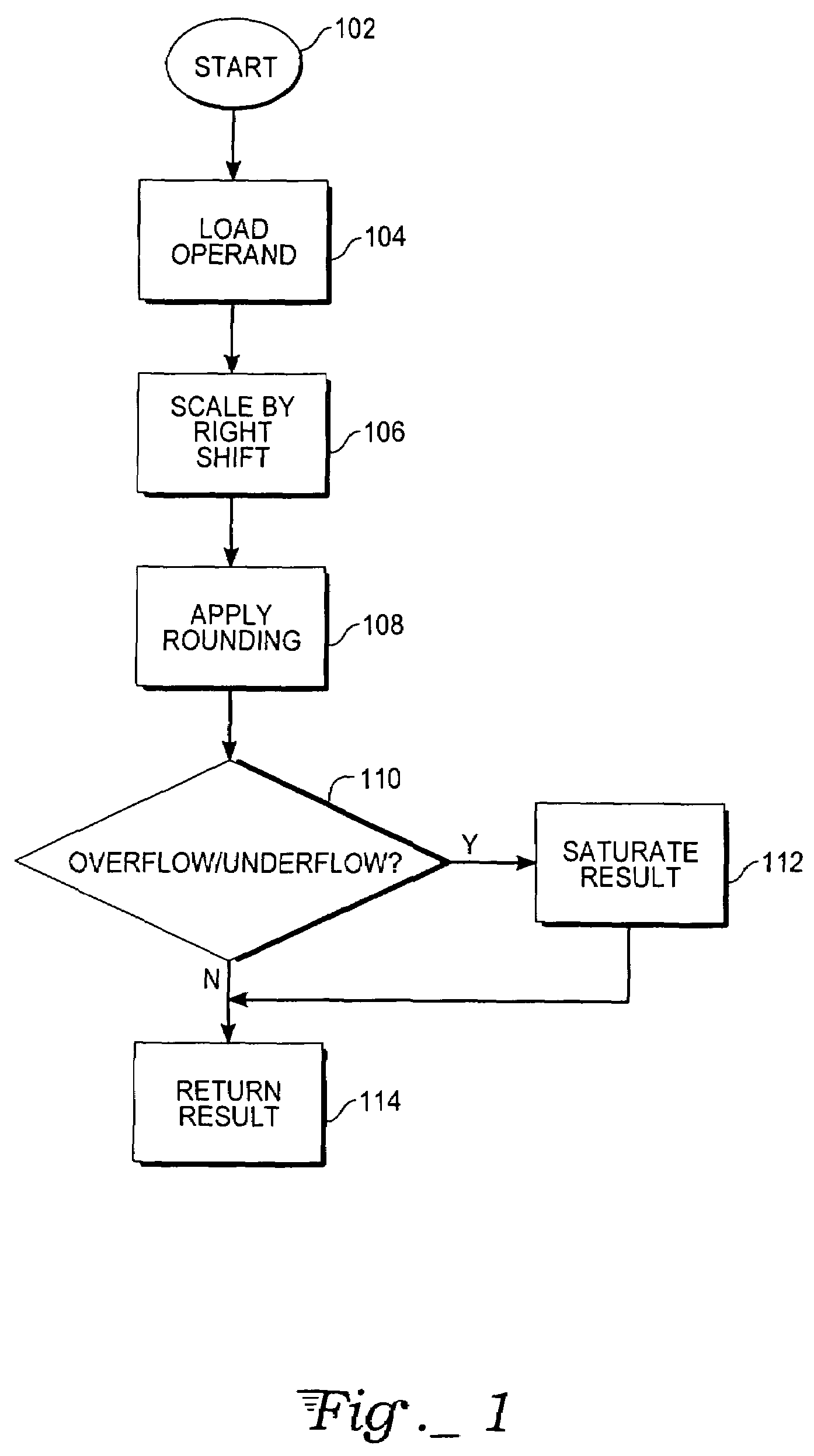

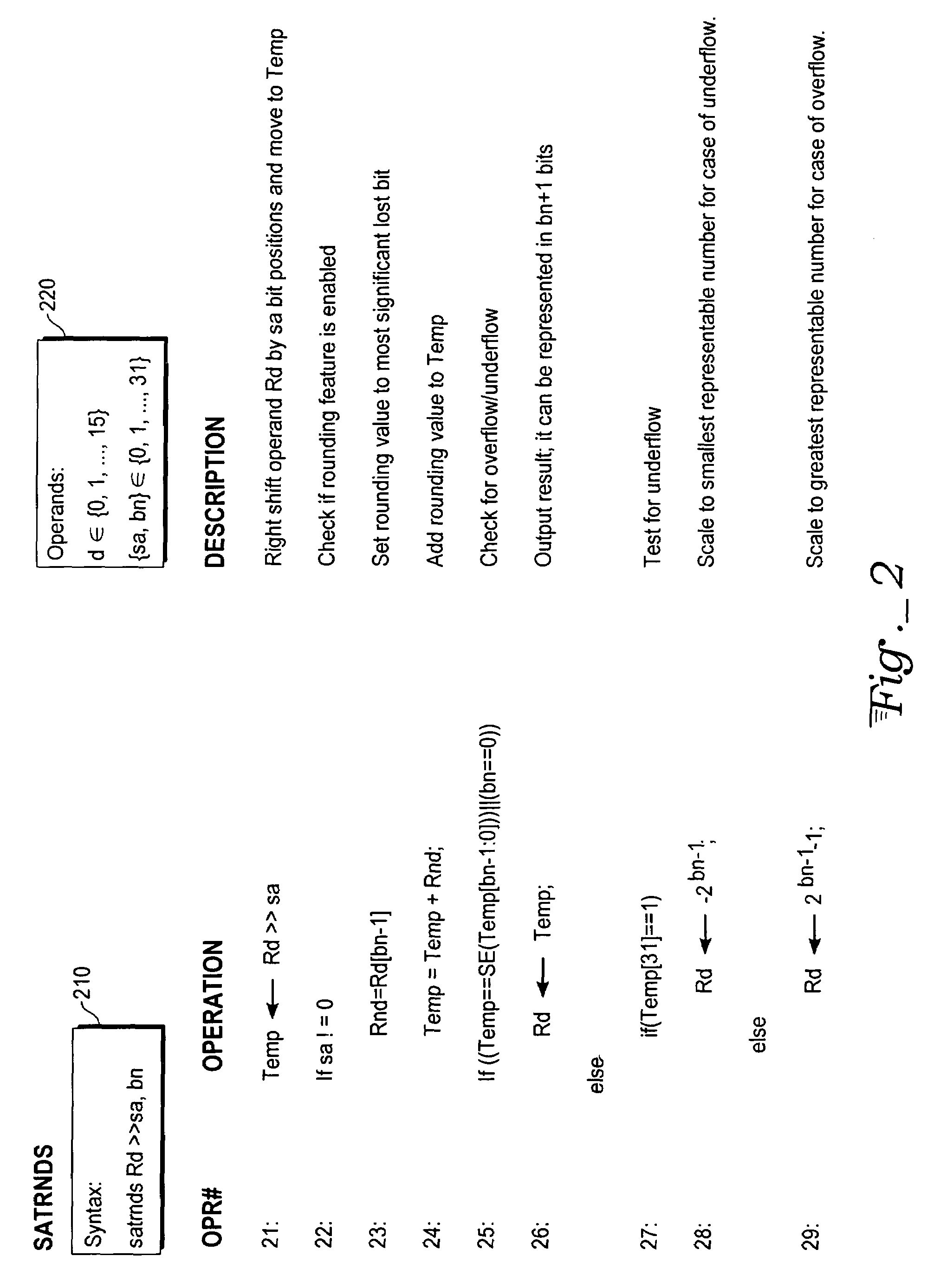

Method and apparatus for formatting numbers in microprocessors

ActiveUS7689640B2Improve execution speedResult is avoidedDigital computer detailsComputation using denominational number representationRight shiftOperand

An apparatus for scaling numbers comprises register means for storing an operand to be scaled, bit shifting means for performing a right shift operation on the operand, rounding means, and decision means to test for the existence of at least one of an overflow and an underflow condition.

Owner:ATMEL CORP

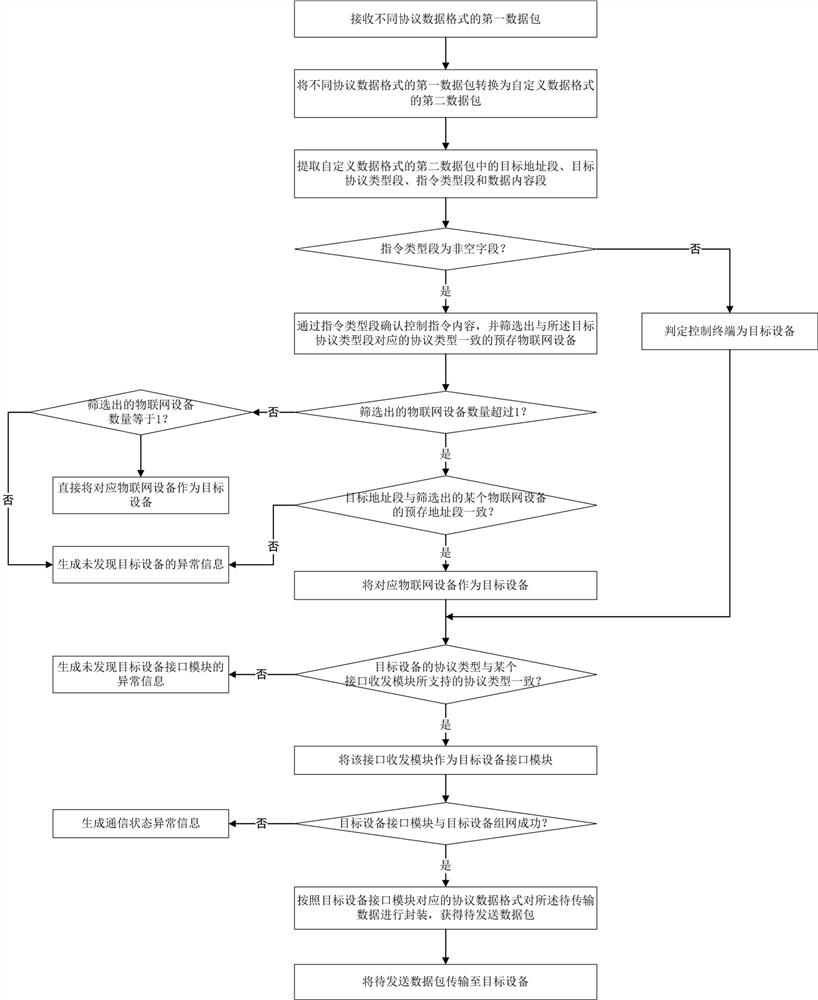

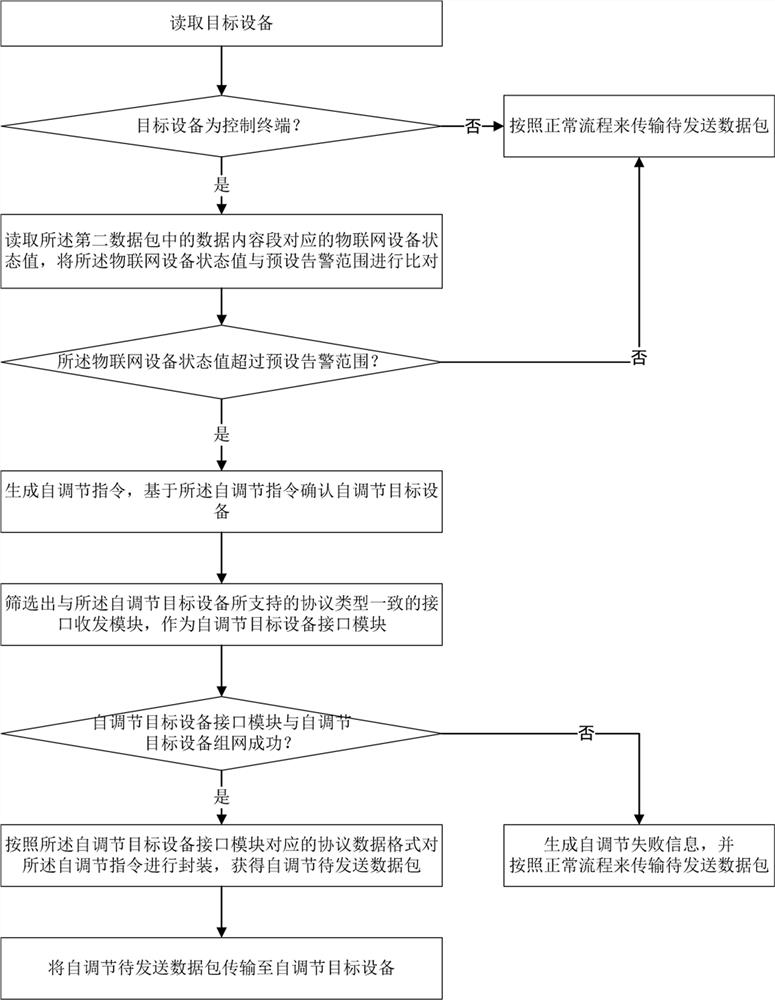

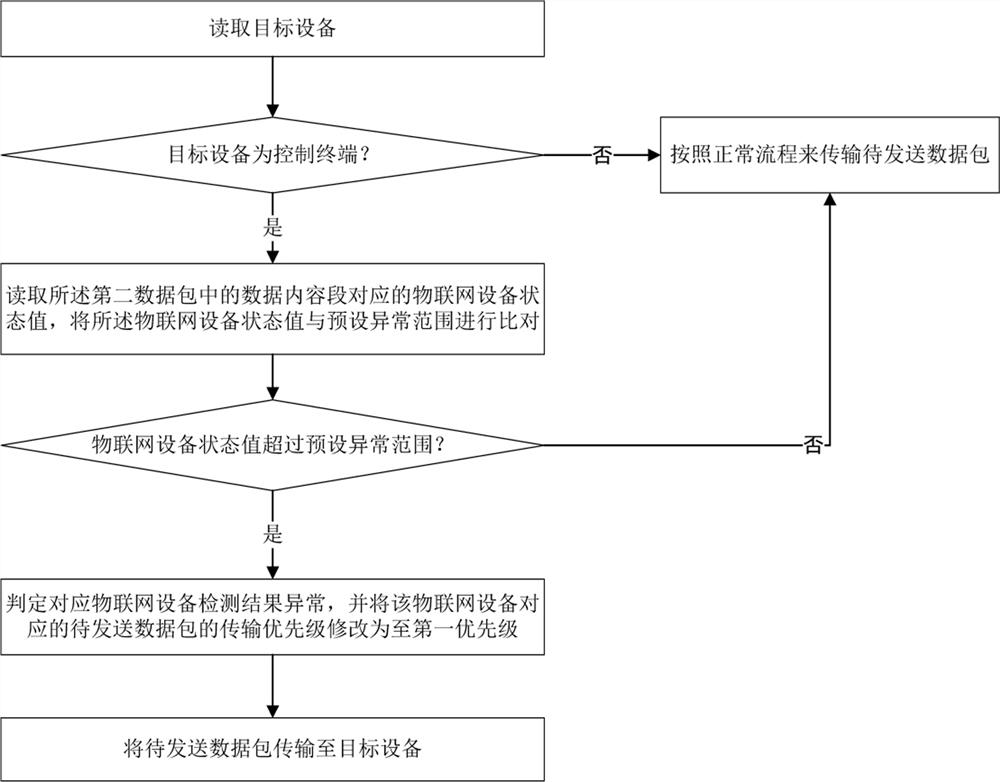

Multi-protocol communication method, smart home gateway and multi-protocol communication system

ActiveCN112087441AHighlight substantiveSignificant progressDigital data authenticationNetwork connectionsData packCommunications system

The invention provides a multi-protocol communication method, a smart home gateway and a multi-protocol communication system. The method comprises the the steps of receiving first data packets of different protocol data formats; converting the first data packets of different protocol data formats into second data packets of a self-defined data format; extracting a target address segment, a targetprotocol type segment, an instruction type segment and a data content segment in the second data packet with the self-defined data format; and if the extracted instruction type segment is a non-emptyfield, determining the content of the control instruction through the instruction type segment, screening out pre-stored Internet of Things devices and the like consistent with the protocol type corresponding to the target protocol type segment, and if the number of the screened Internet of Things devices is equal to 1, directly taking the corresponding Internet of Things device as a target deviceand the like. According to the invention, while the compatibility and universality of the gateway are improved, the design and development difficulty of a gateway application layer is reduced, the multi-protocol communication efficiency is improved, and the operation cost of the multi-protocol gateway is reduced.

Owner:郑州信大先进技术研究院

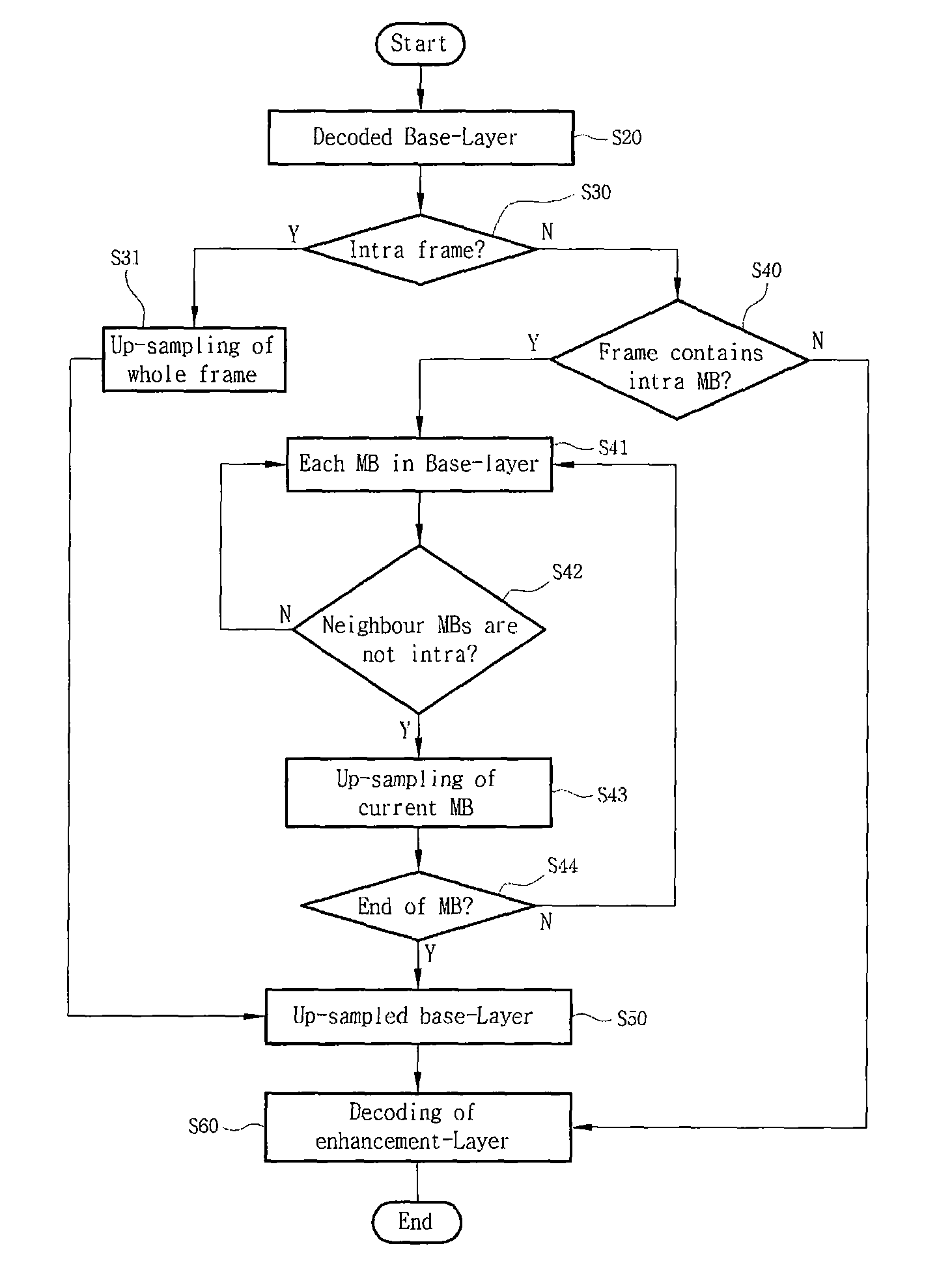

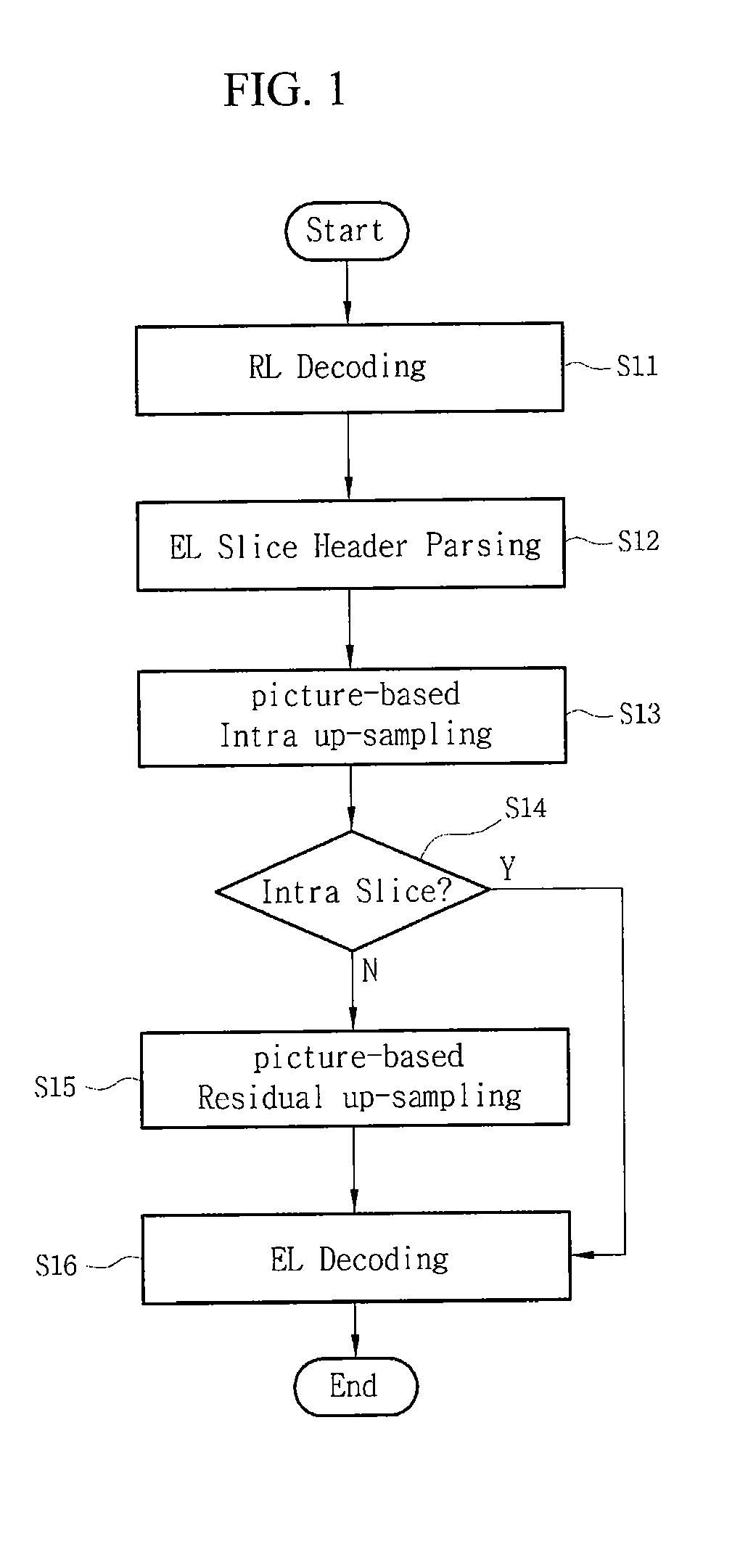

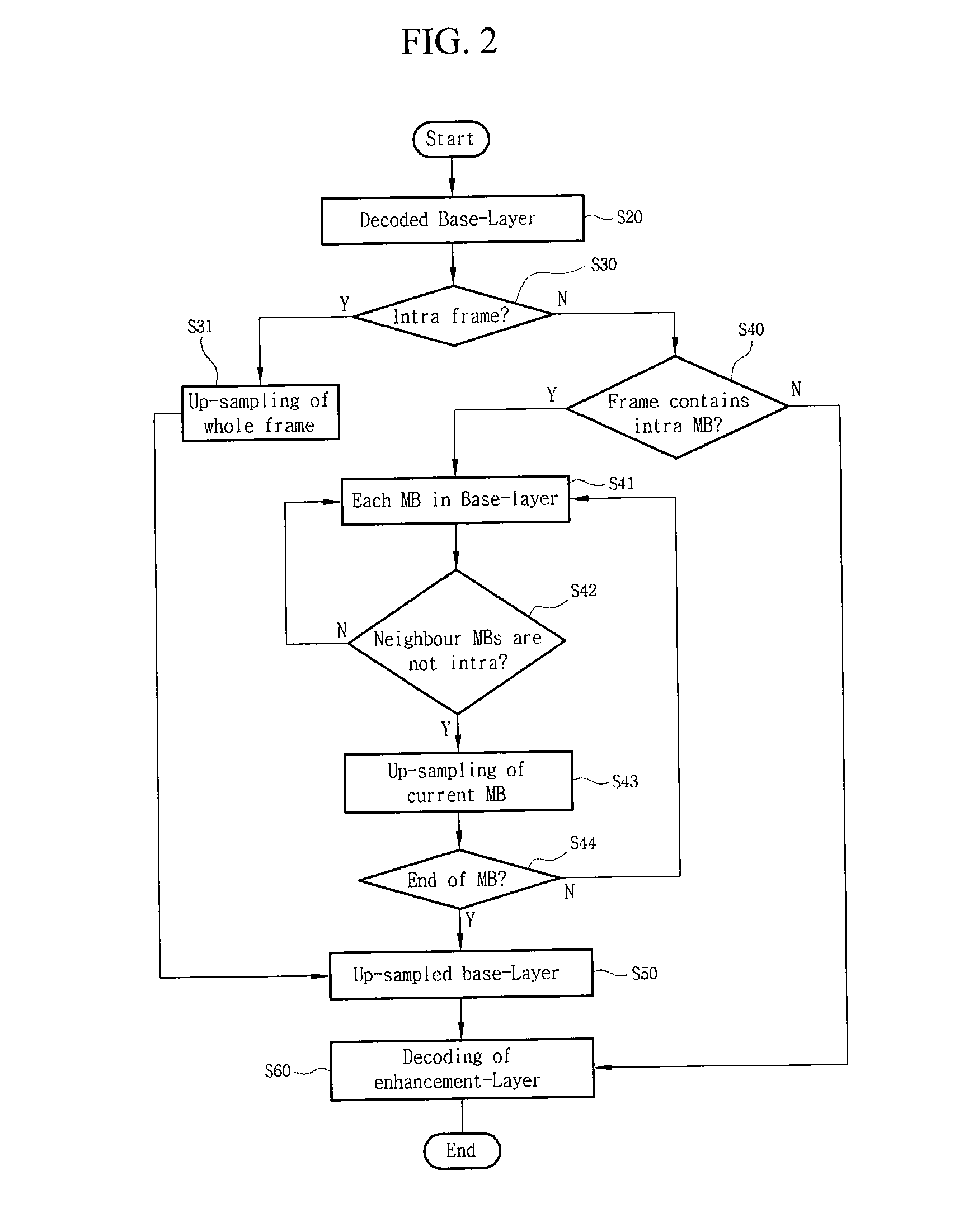

Method and apparatus for scalable video coding

ActiveUS20110110426A1High speedReduce memoryColor television with pulse code modulationPulse modulation television signal transmissionComputer architectureInter layer

Owner:KOREA ELECTRONICS TECH INST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com