Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

424results about How to "Control consumption" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

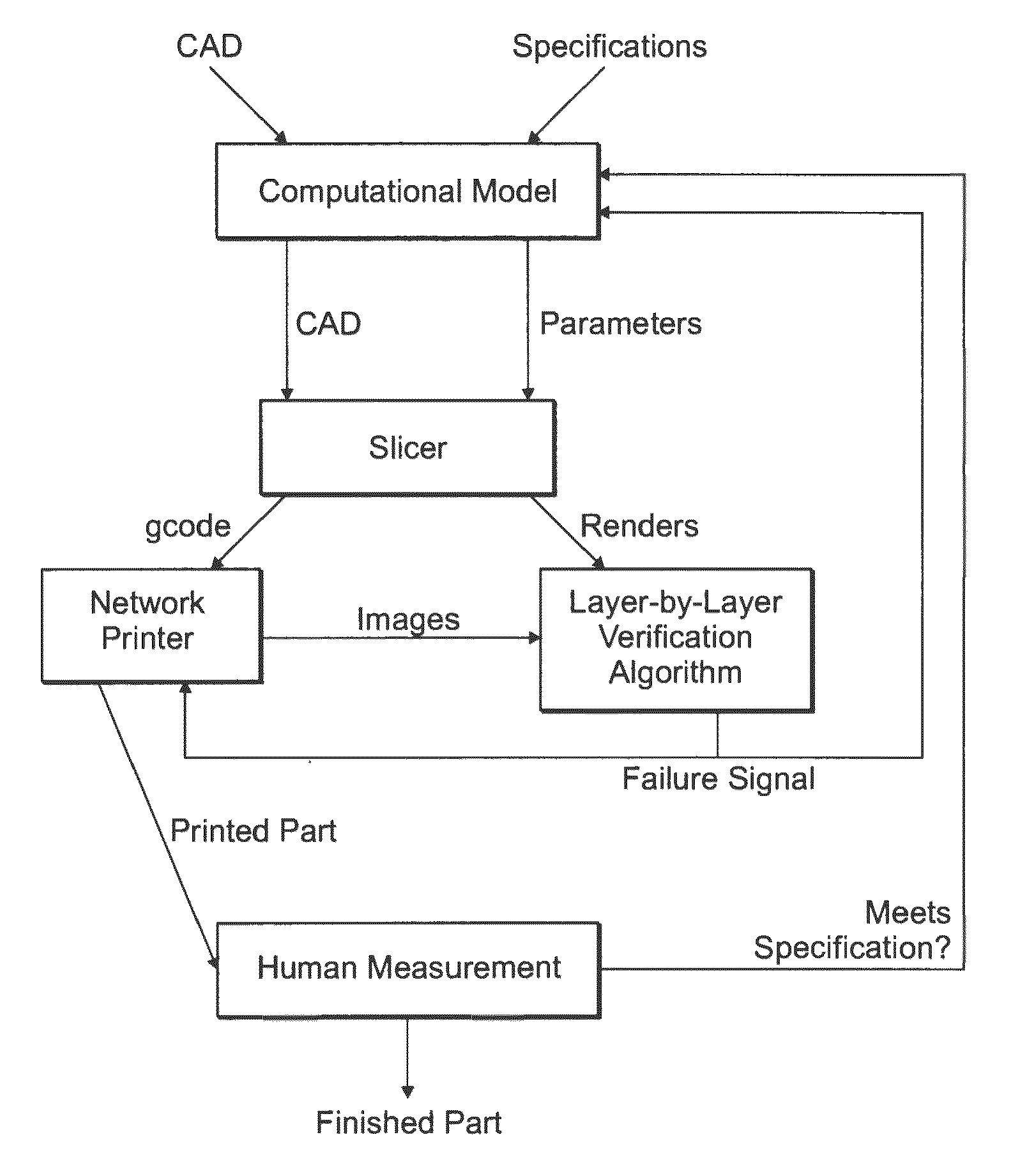

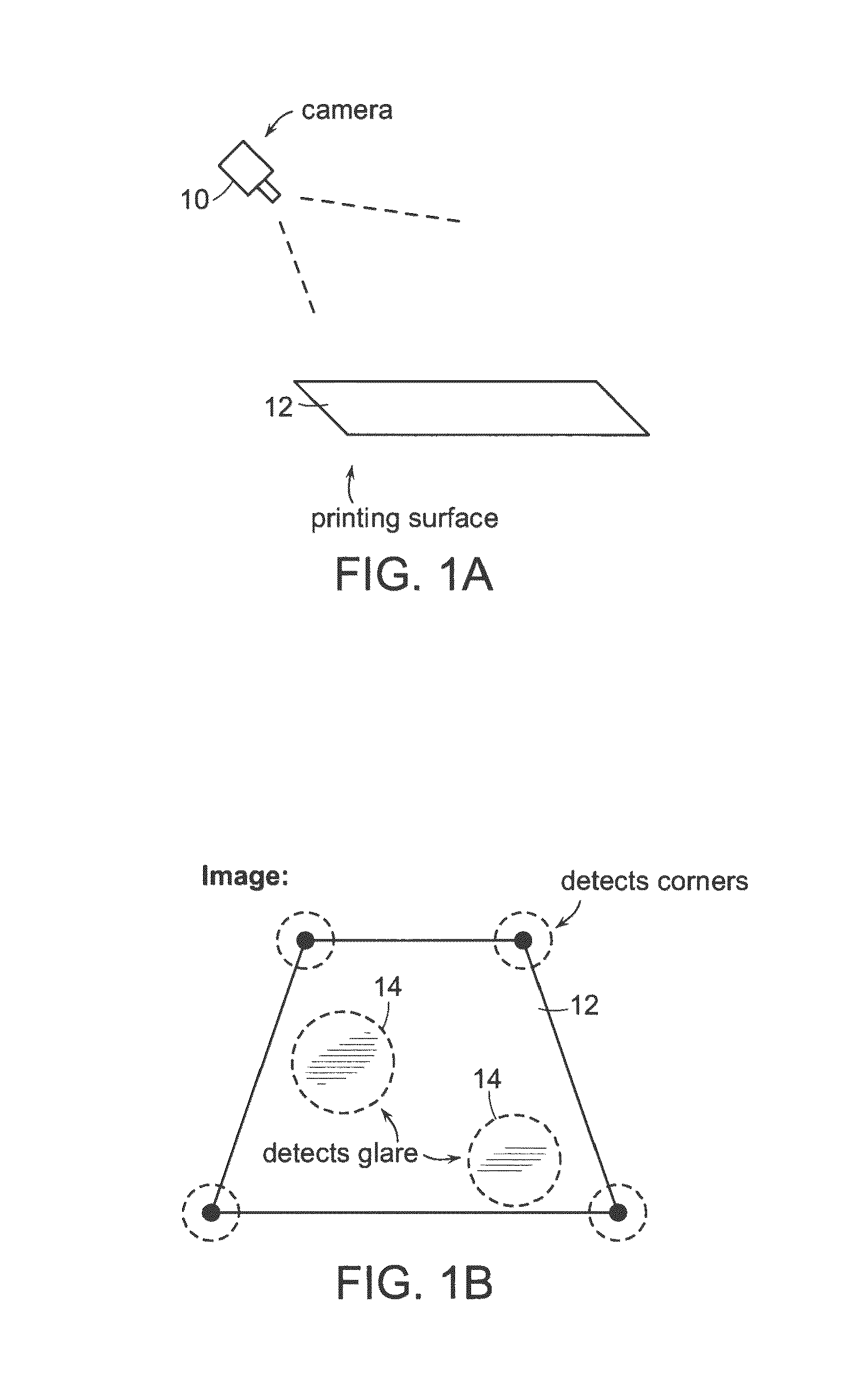

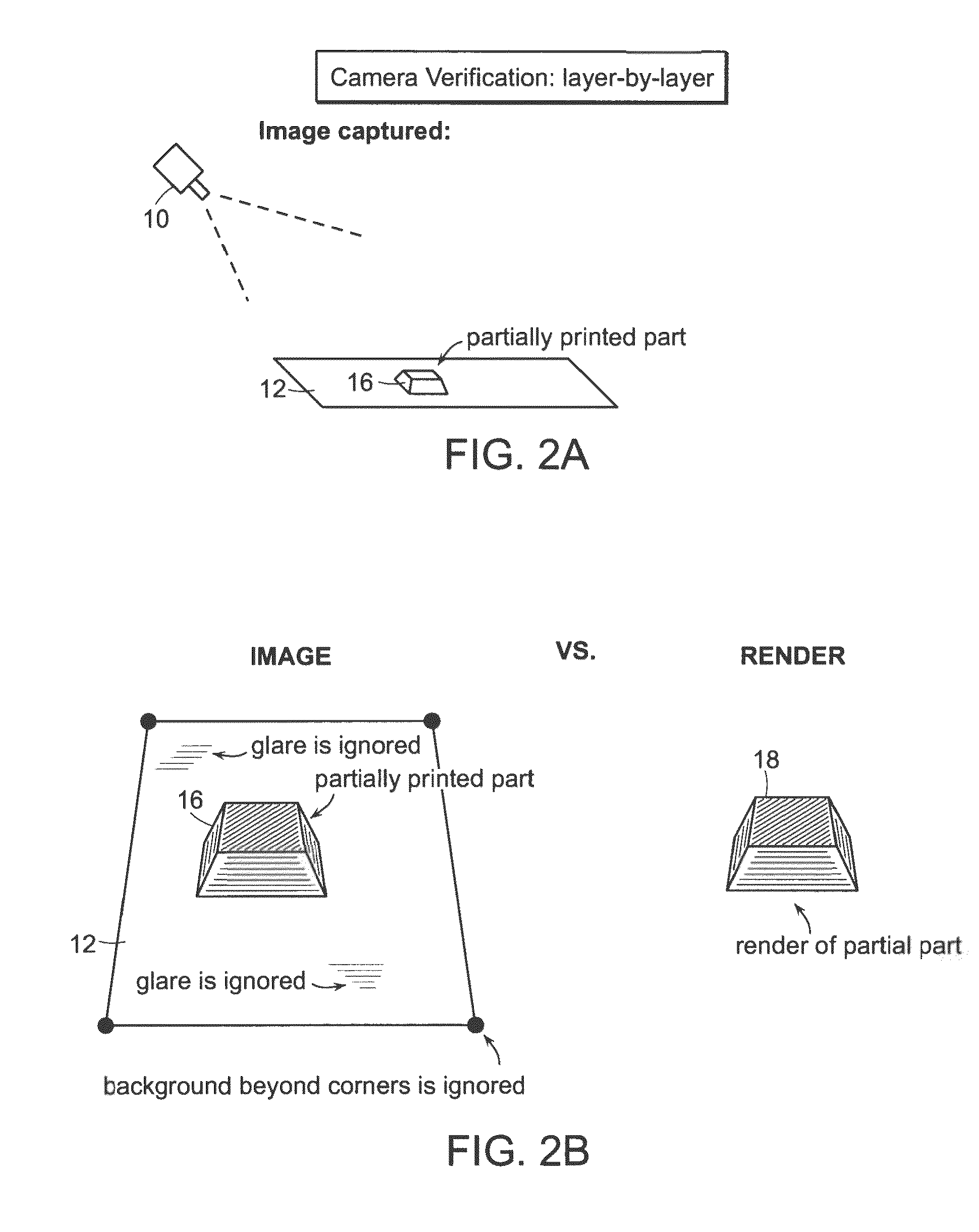

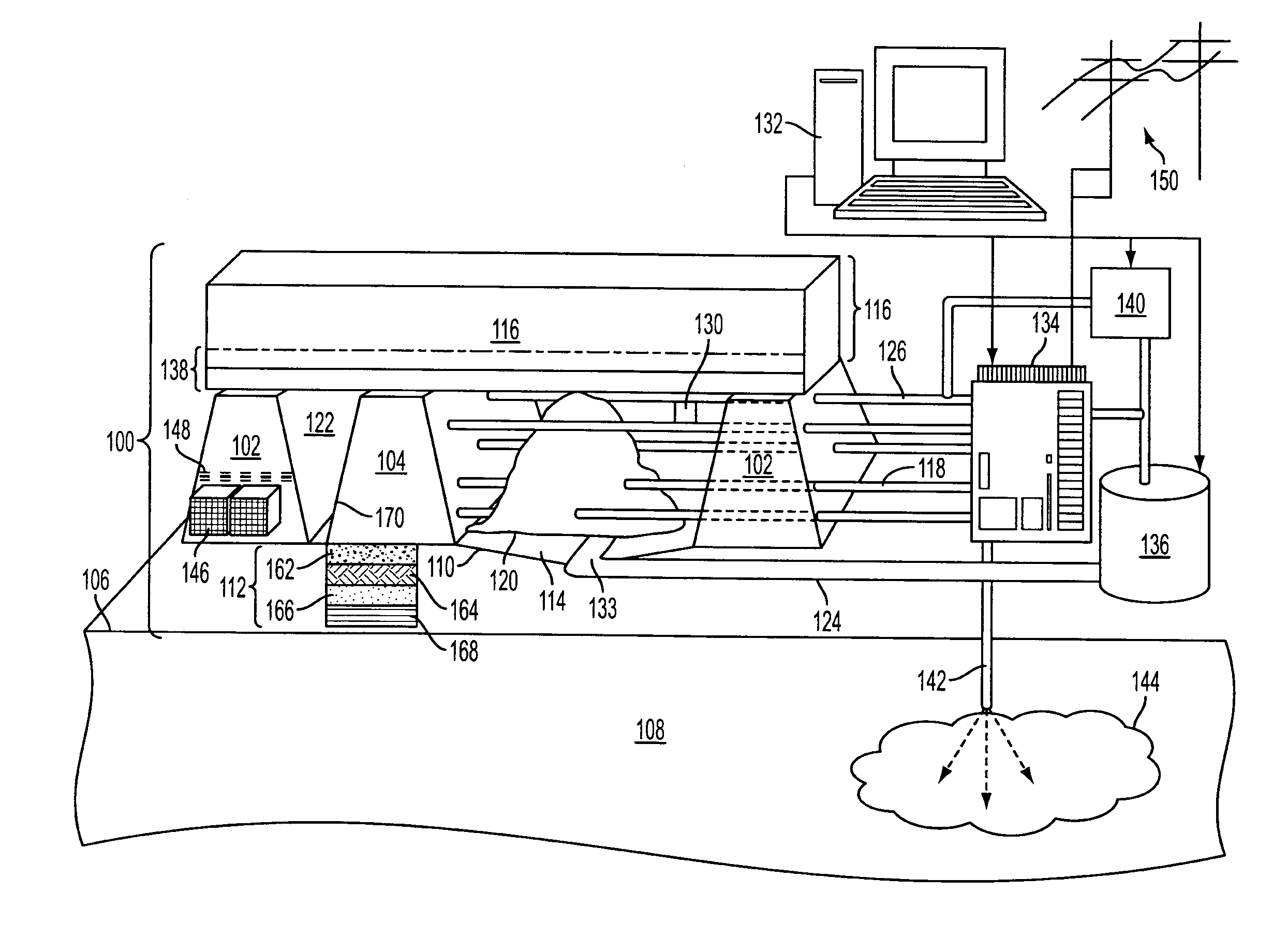

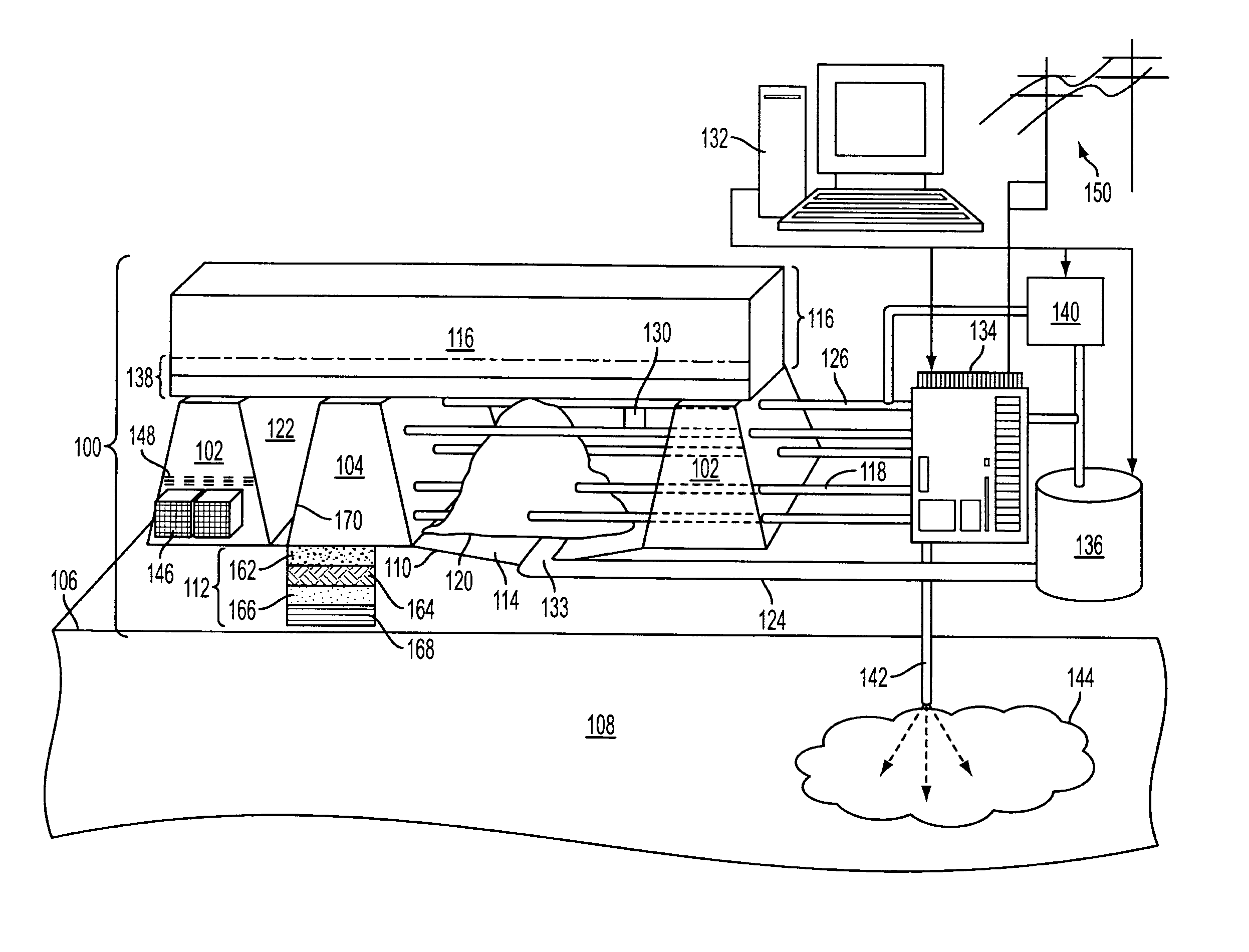

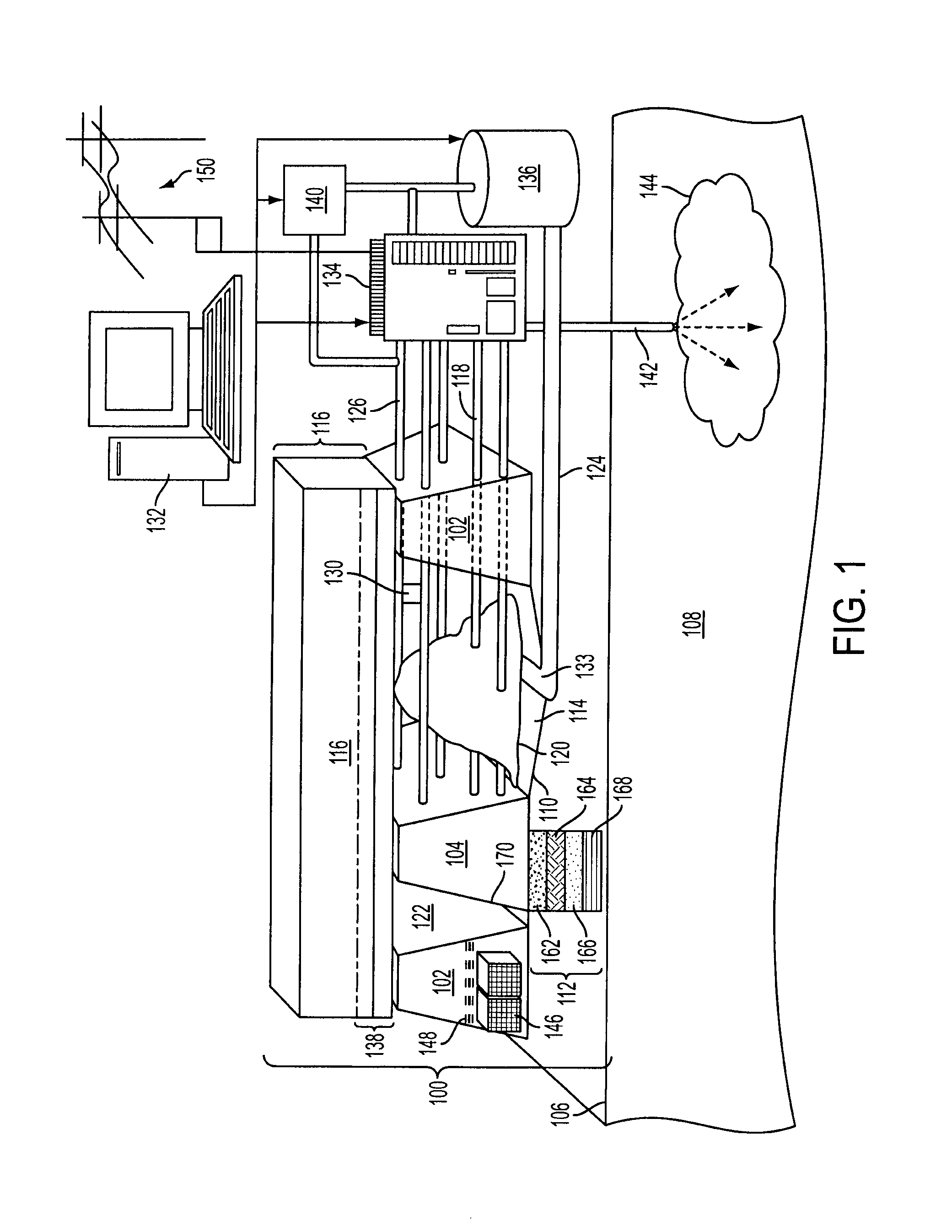

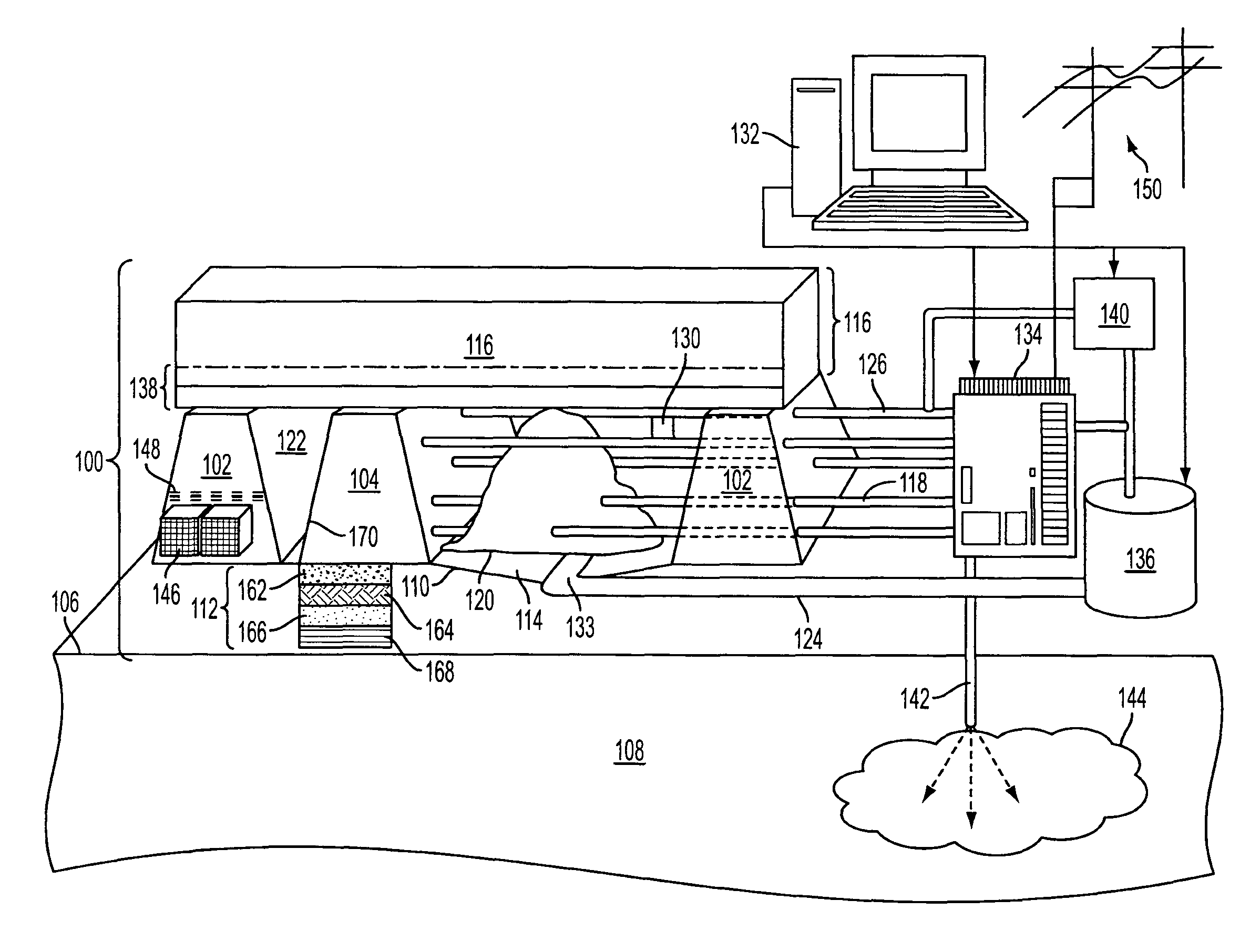

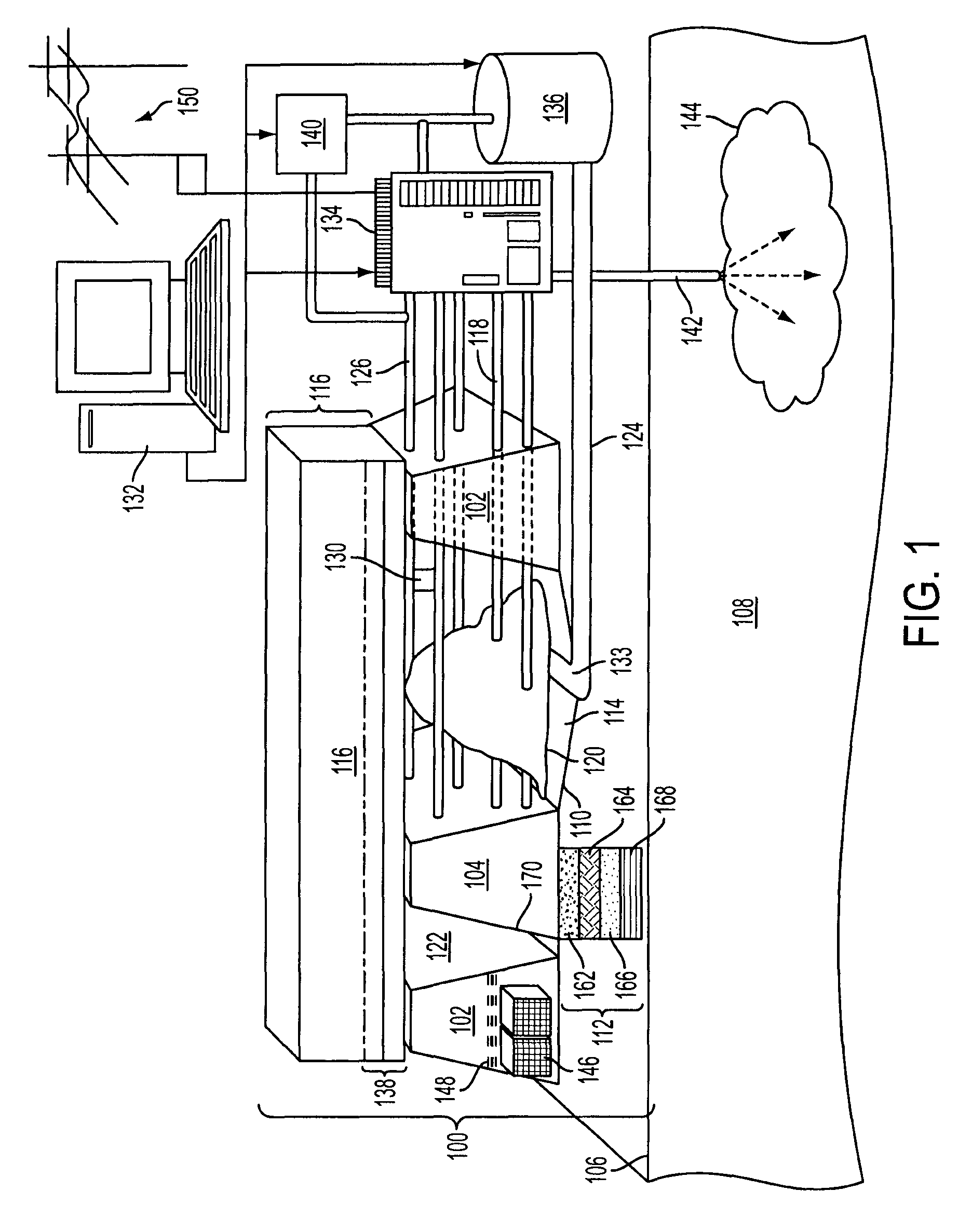

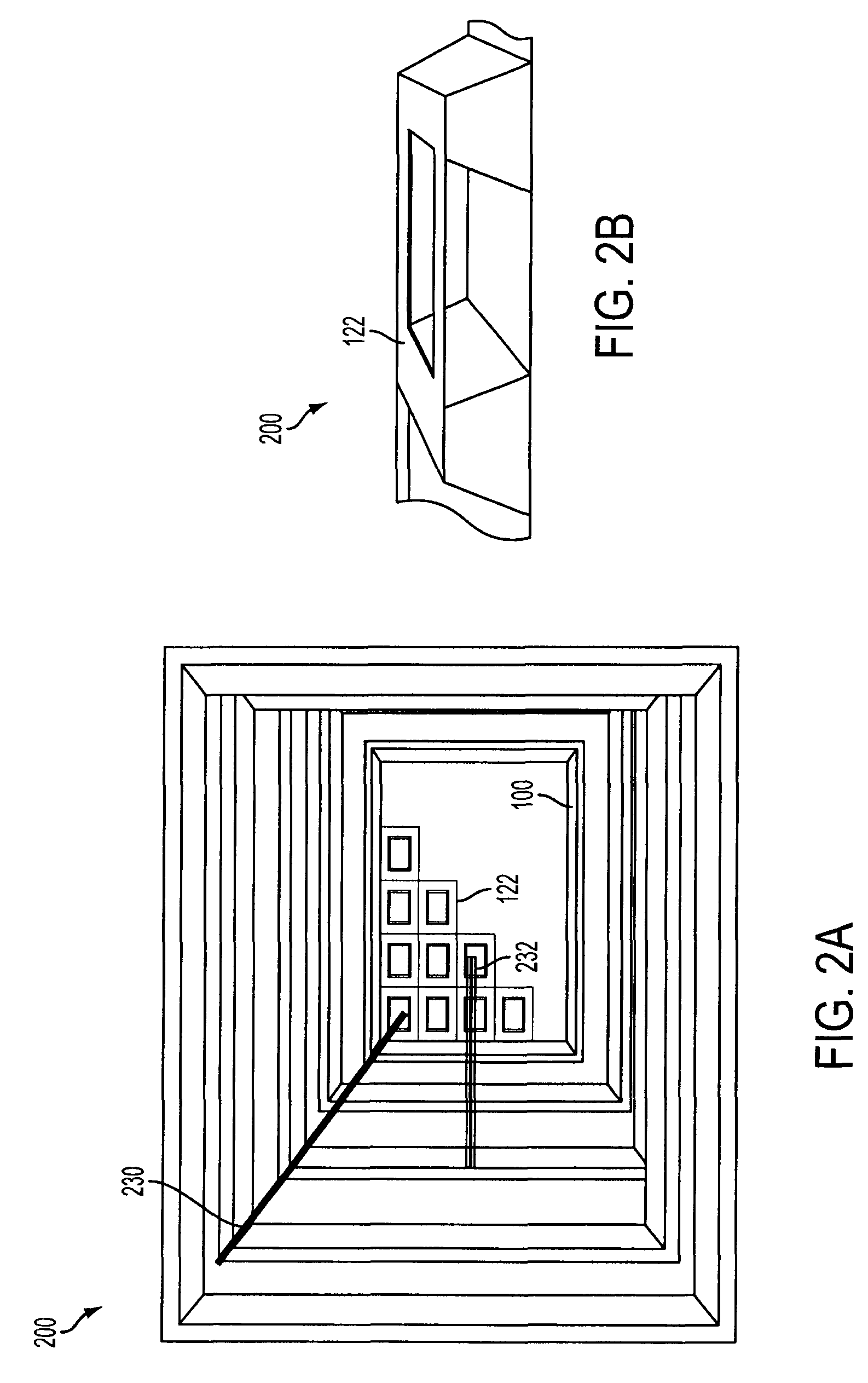

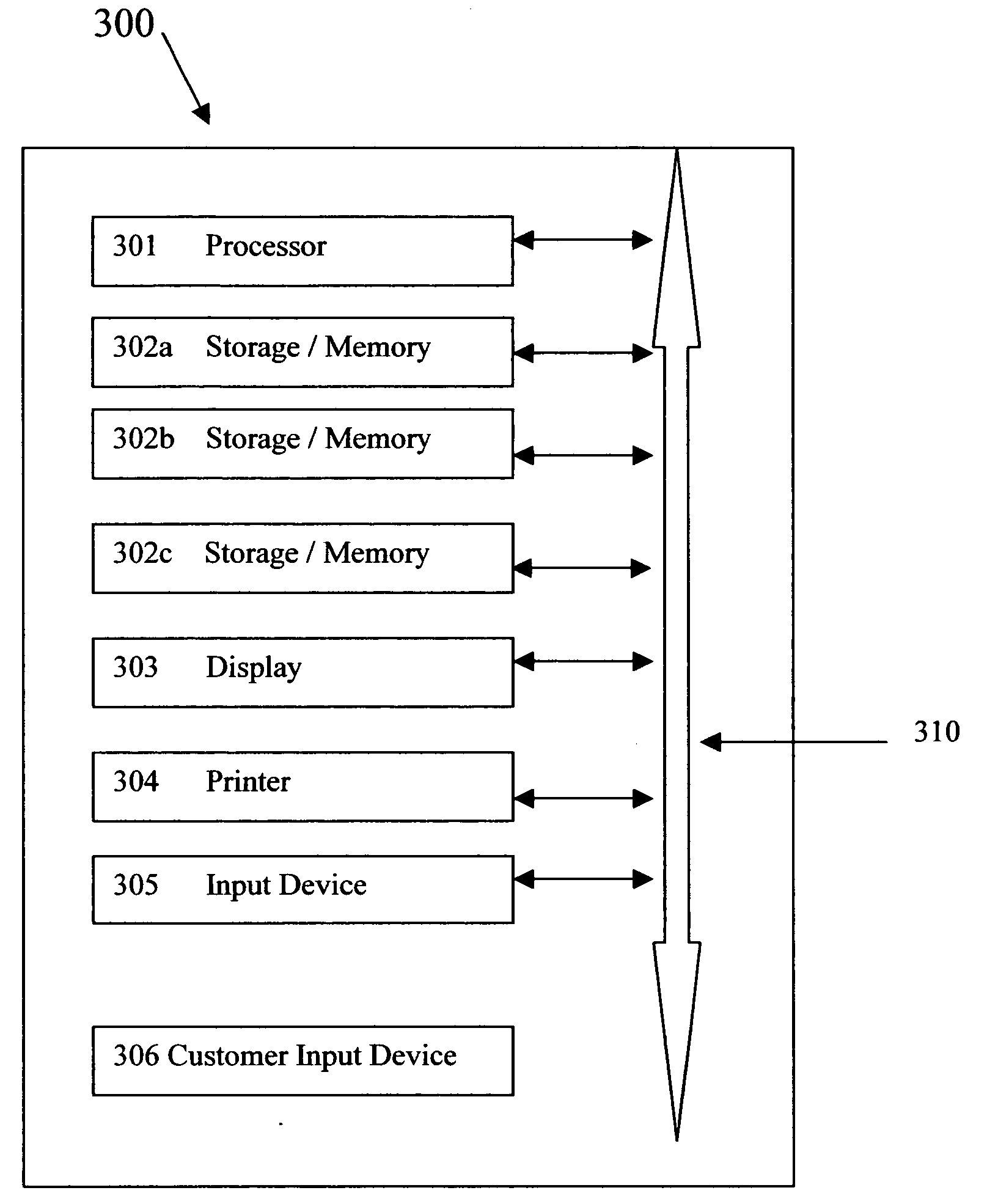

Automatic Process Control of Additive Manufacturing Device

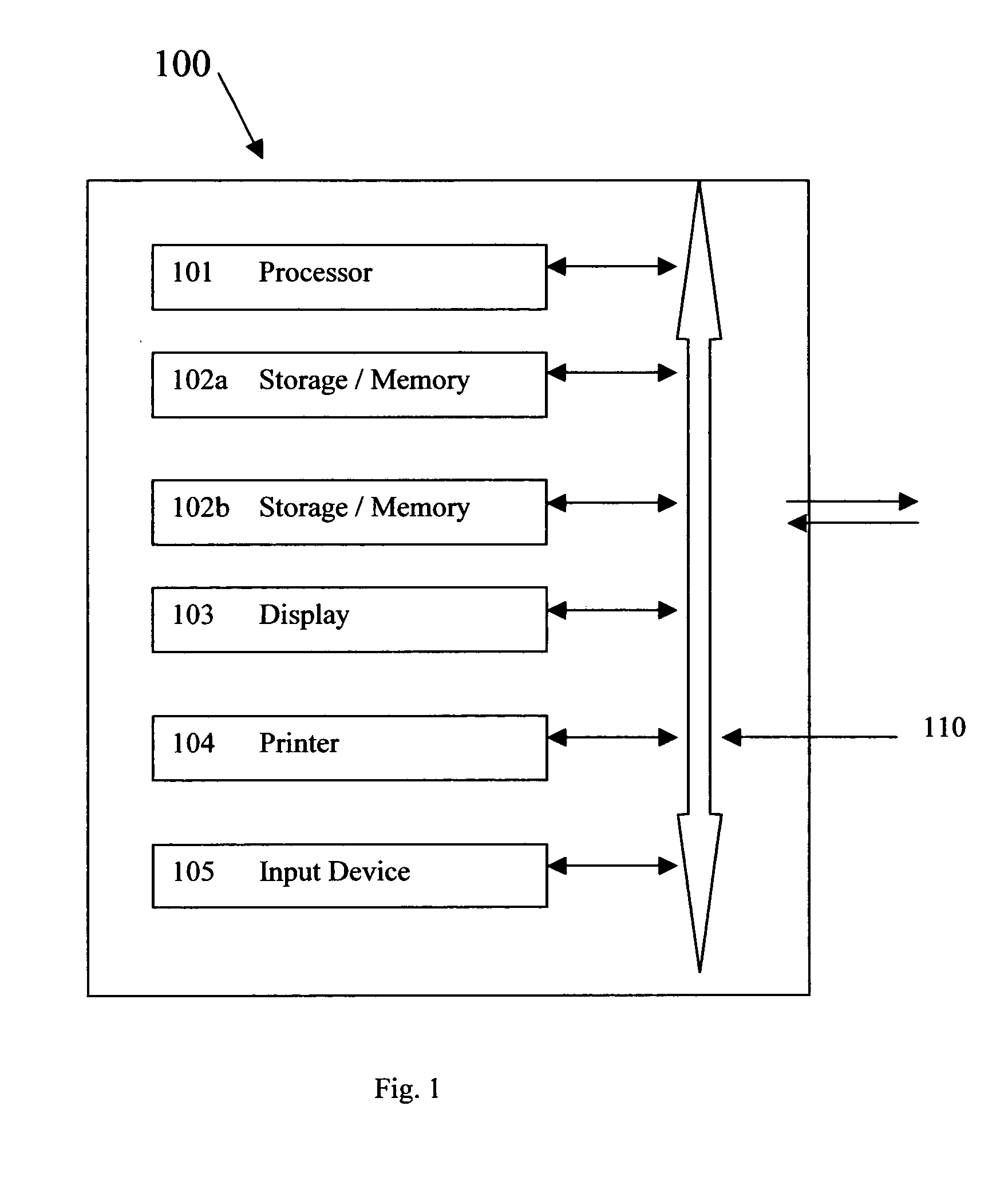

ActiveUS20150045928A1Minimize the numberImprove efficiencyAdditive manufacturing apparatusComputing modelsAutomatic process controlAccessible image

Automatic process control of additive manufacturing. The system includes an additive manufacturing device for making an object and a local network computer controlling the device. At least one camera is provided with a view of a manufacturing volume of the device to generate network accessible images of the object. The computer is programmed to stop the manufacturing process when the object is defective based en the images of the object.

Owner:MASSACHUSETTS INST OF TECH

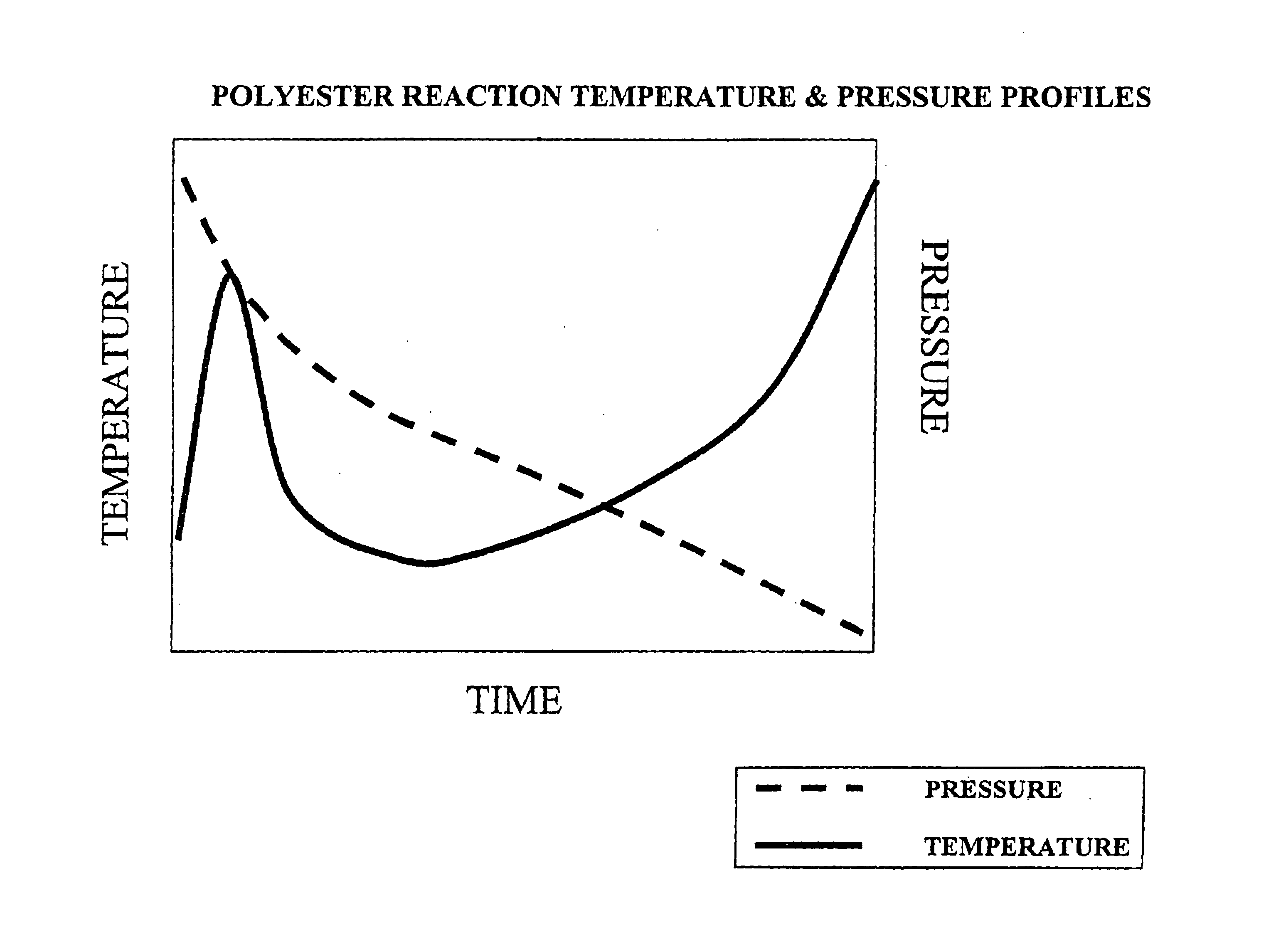

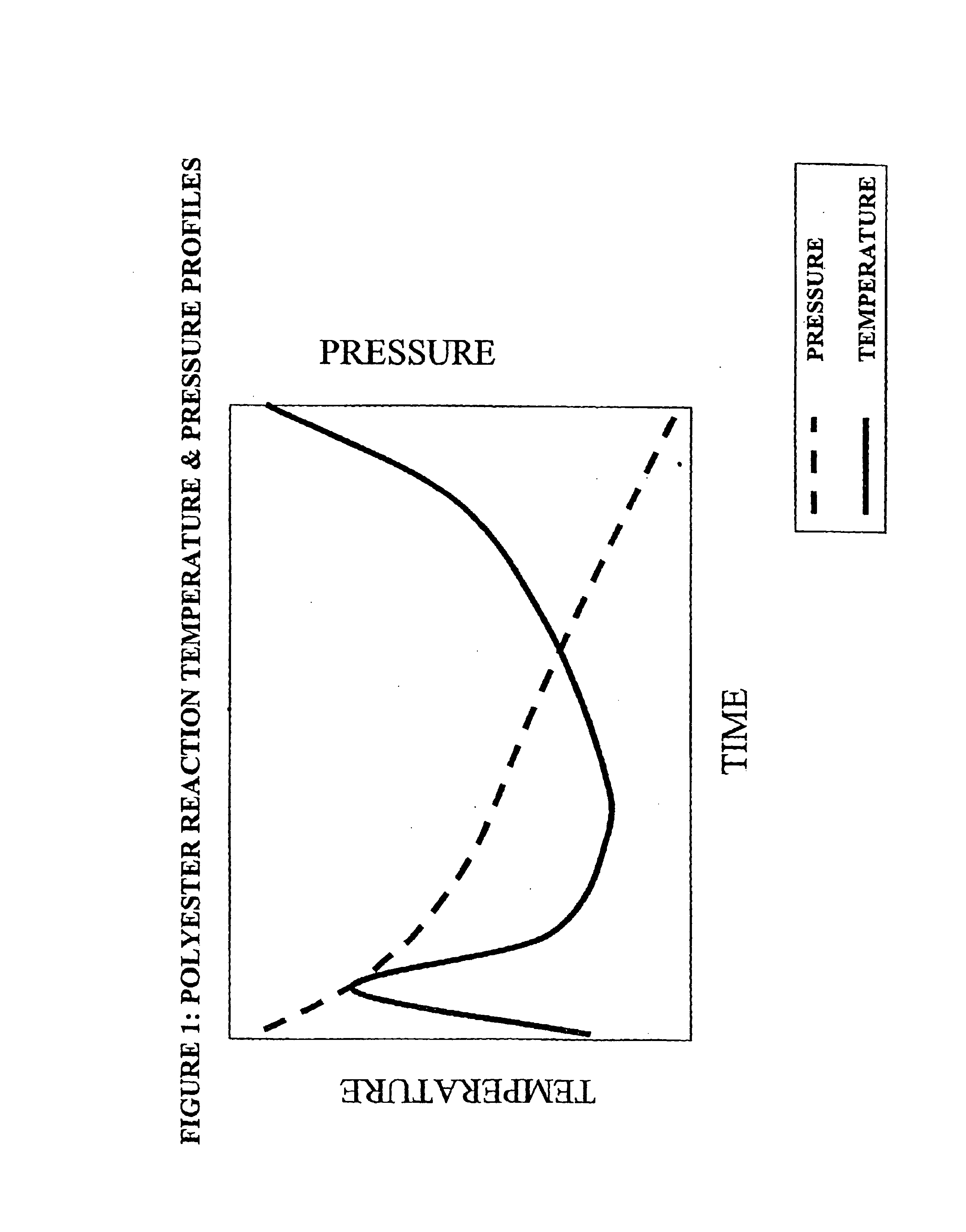

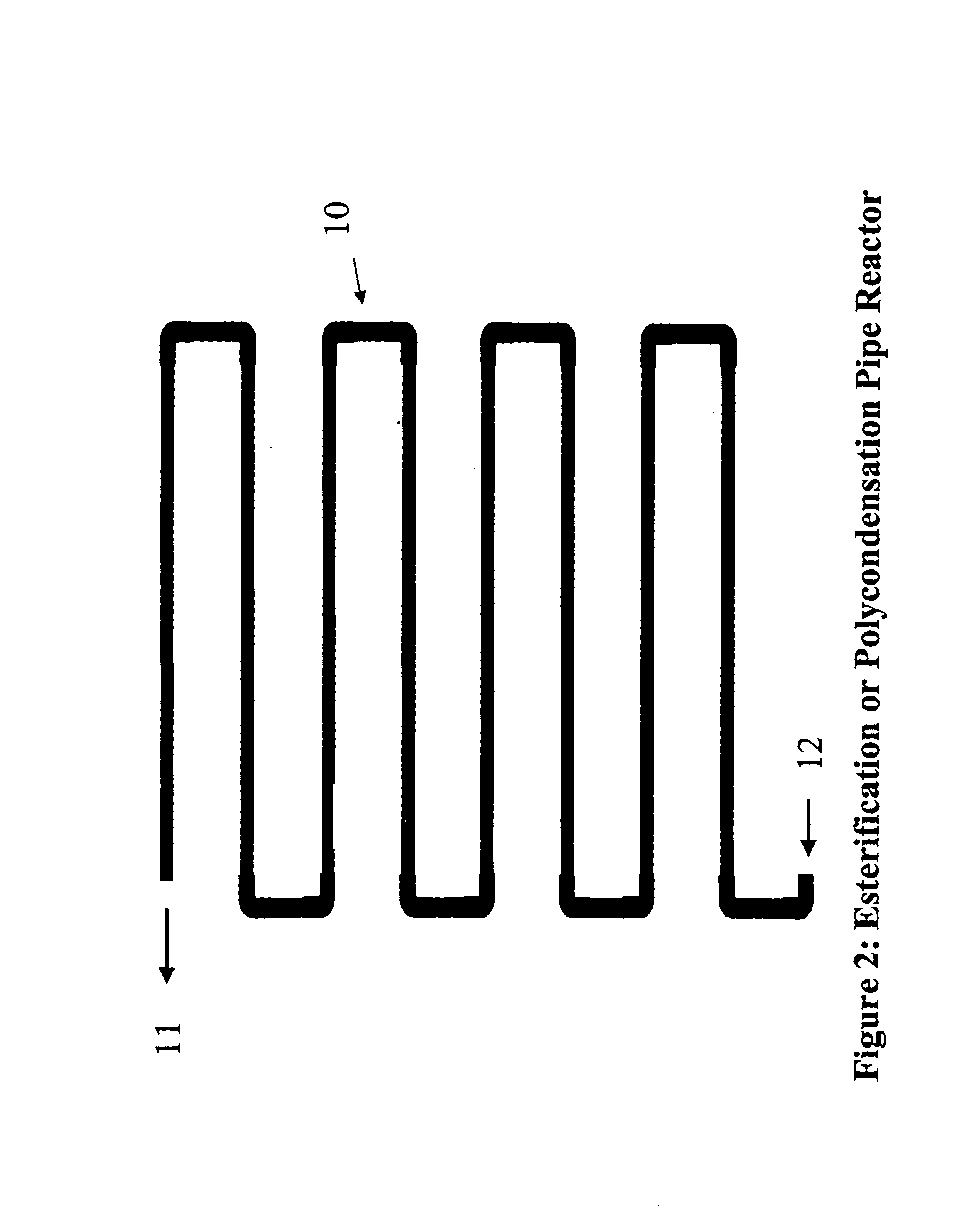

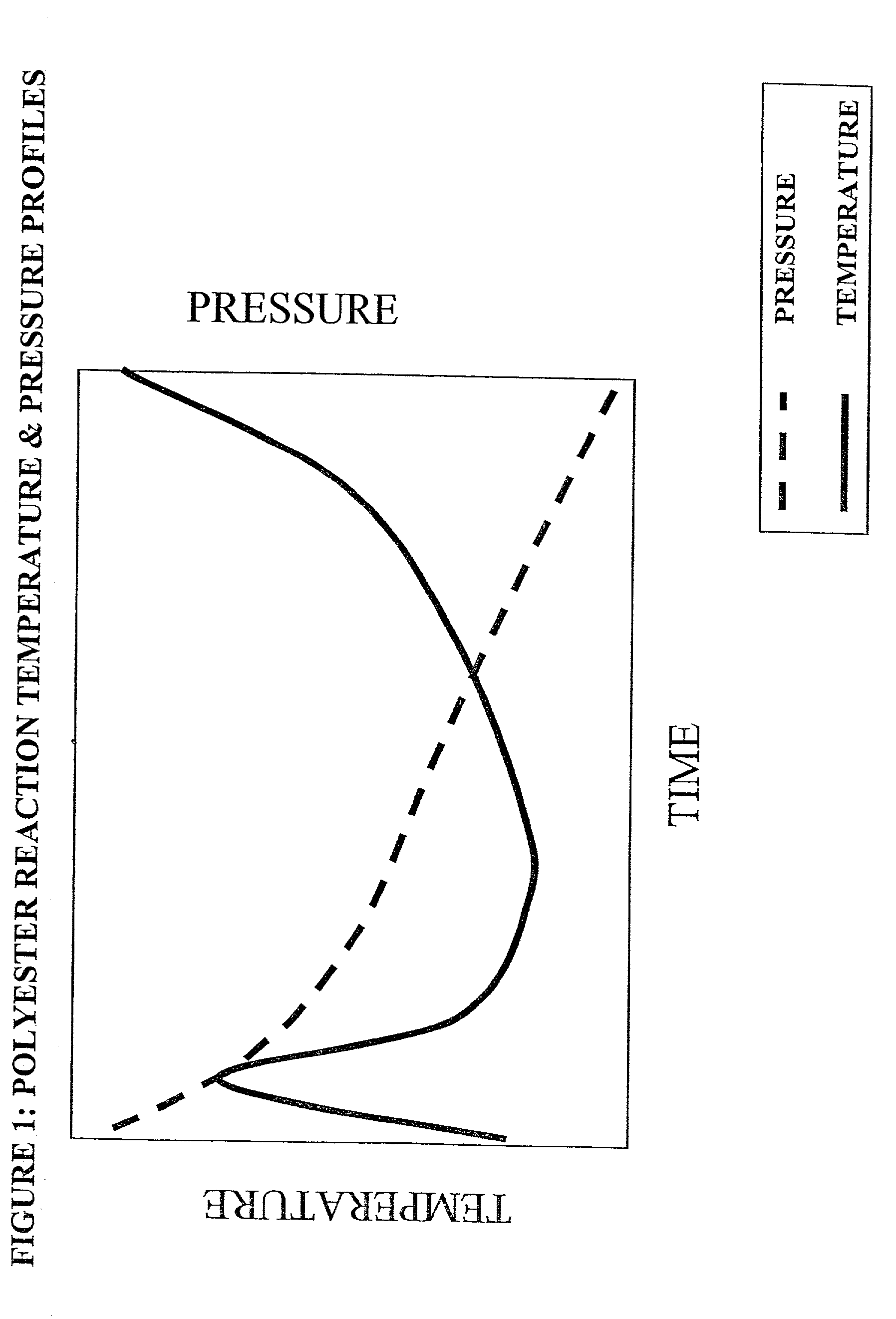

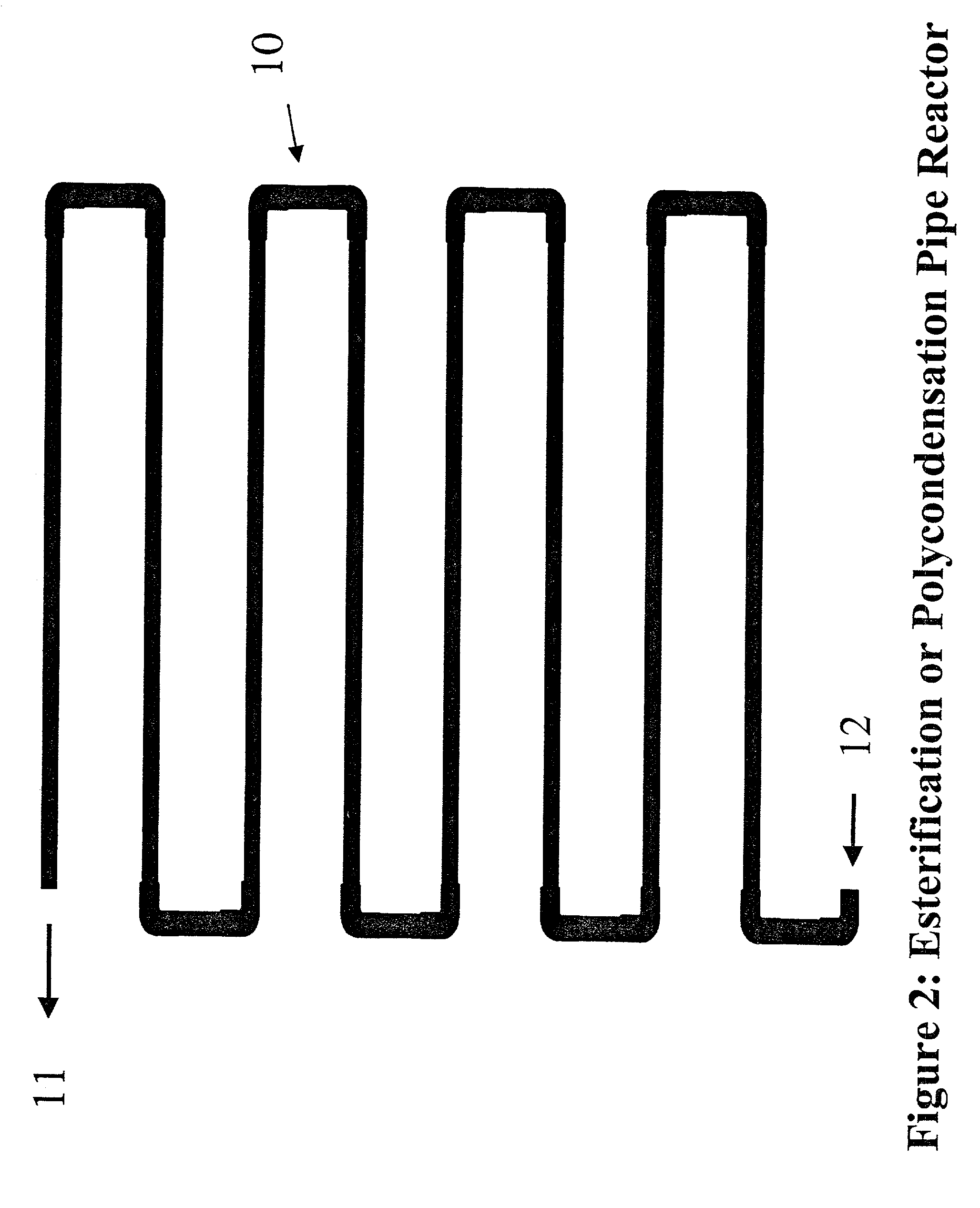

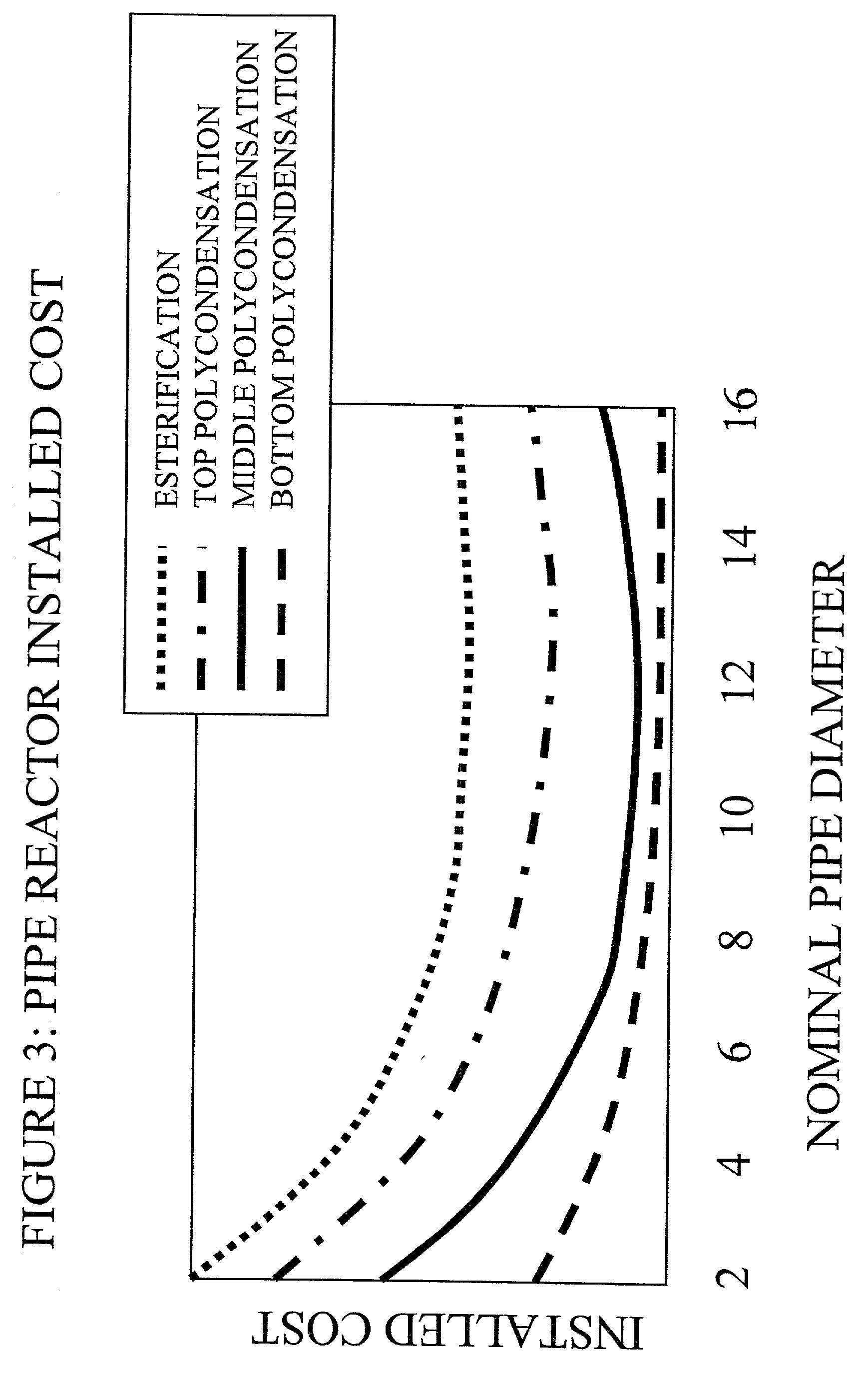

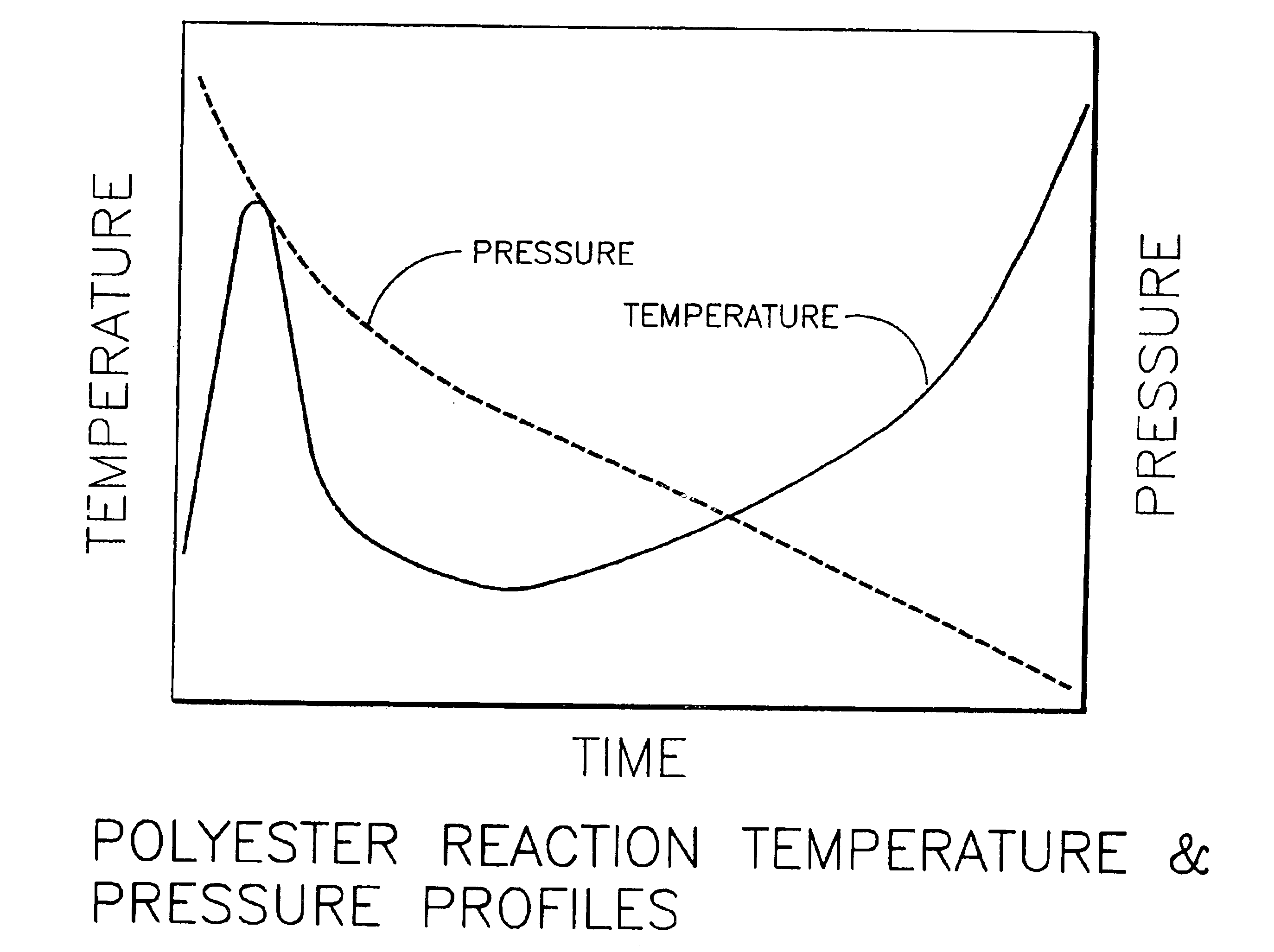

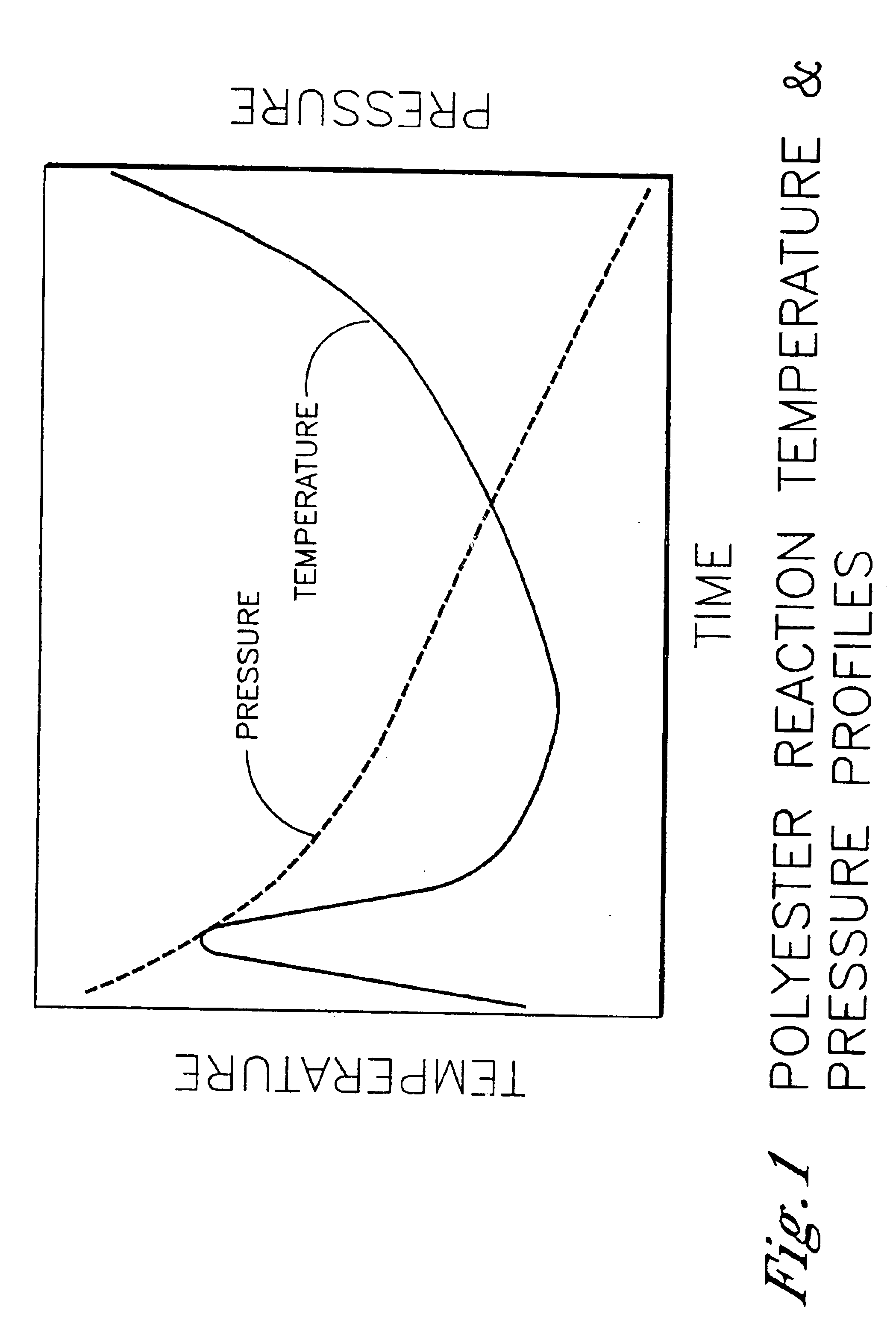

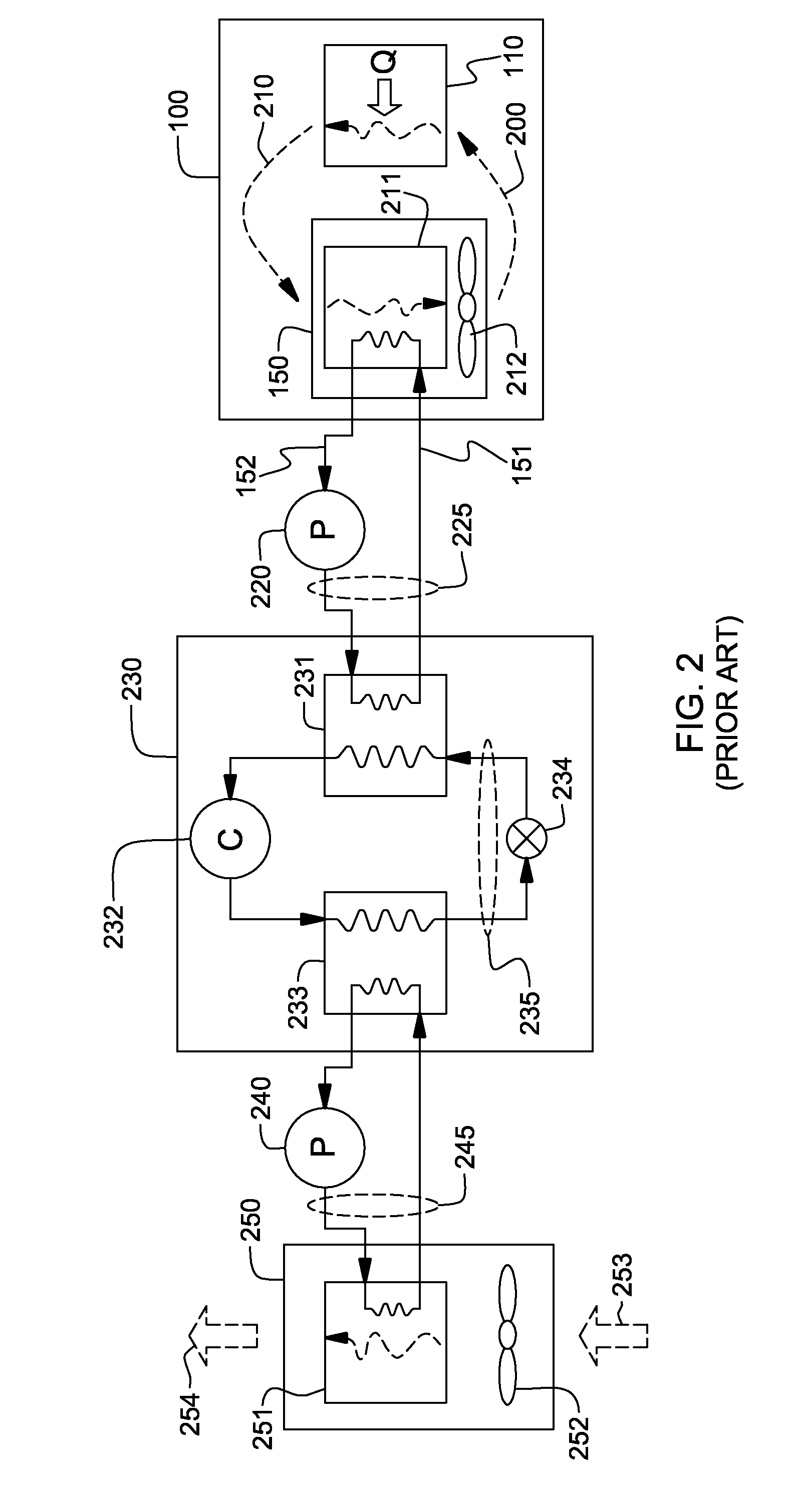

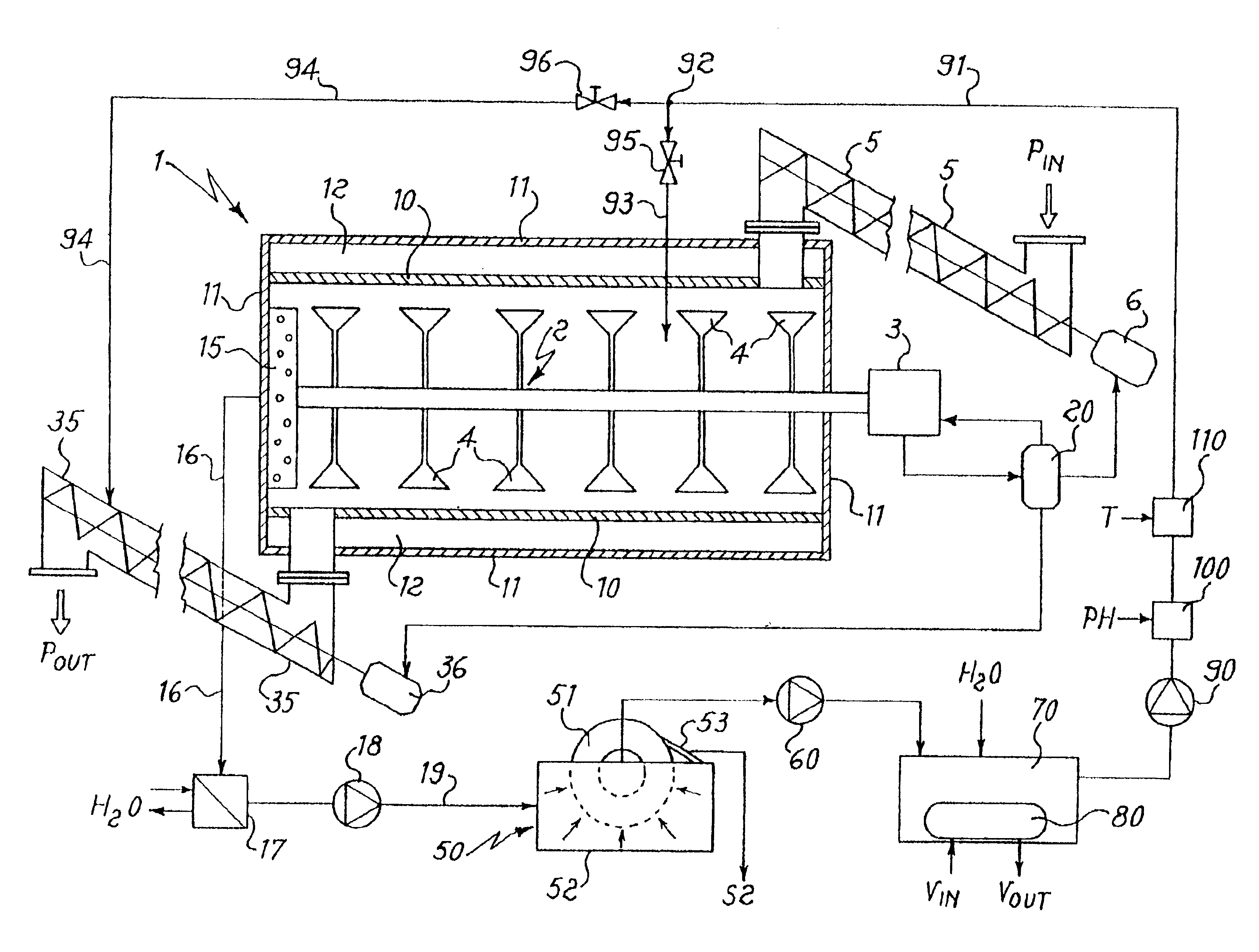

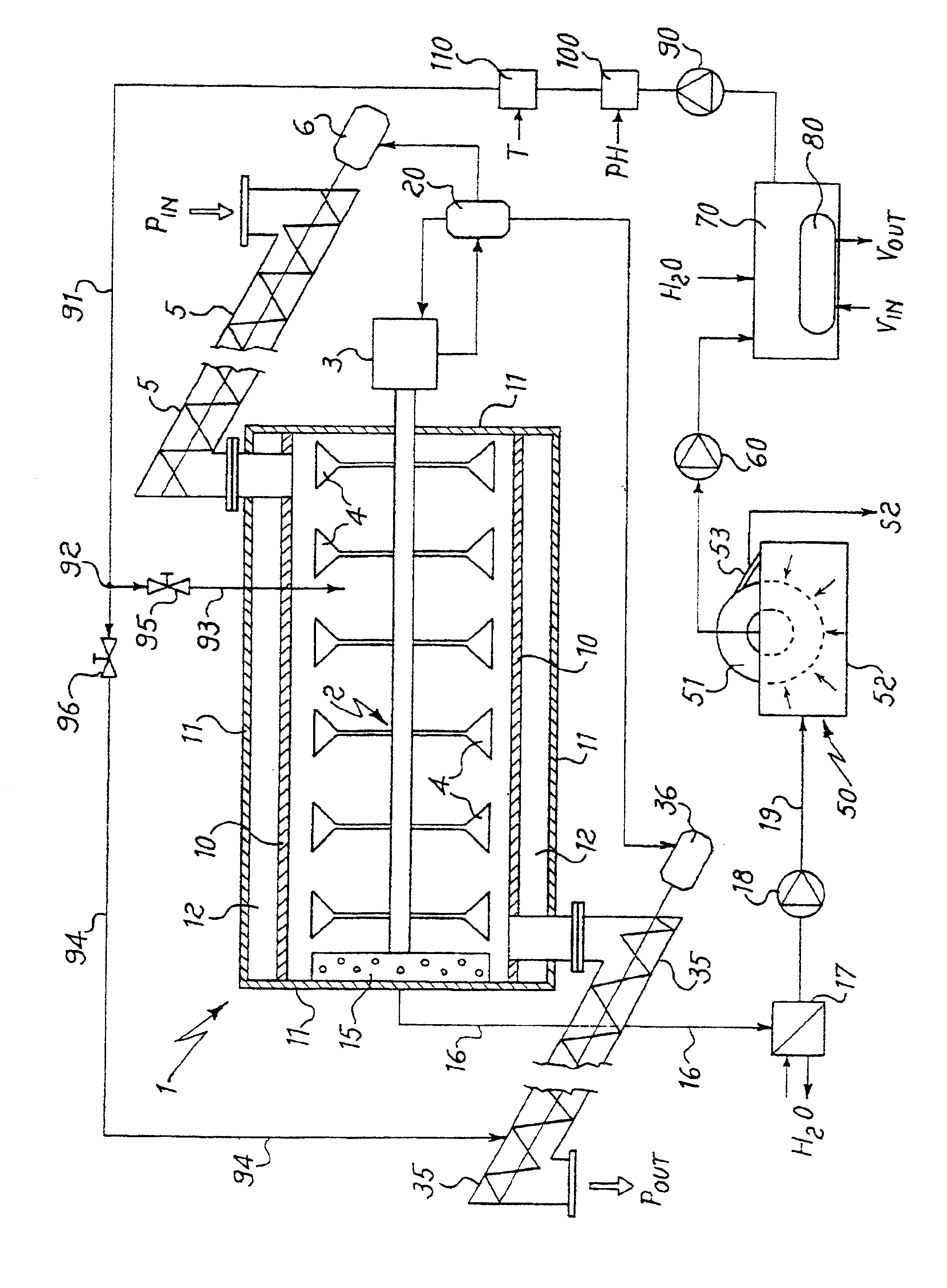

Polyester process using a pipe reactor

InactiveUS6861494B2Reduce pressureEliminate needLiquid degasificationFlow mixersProcess engineeringPolyester resin

Owner:ALPEK POLYESTER SA DE CV

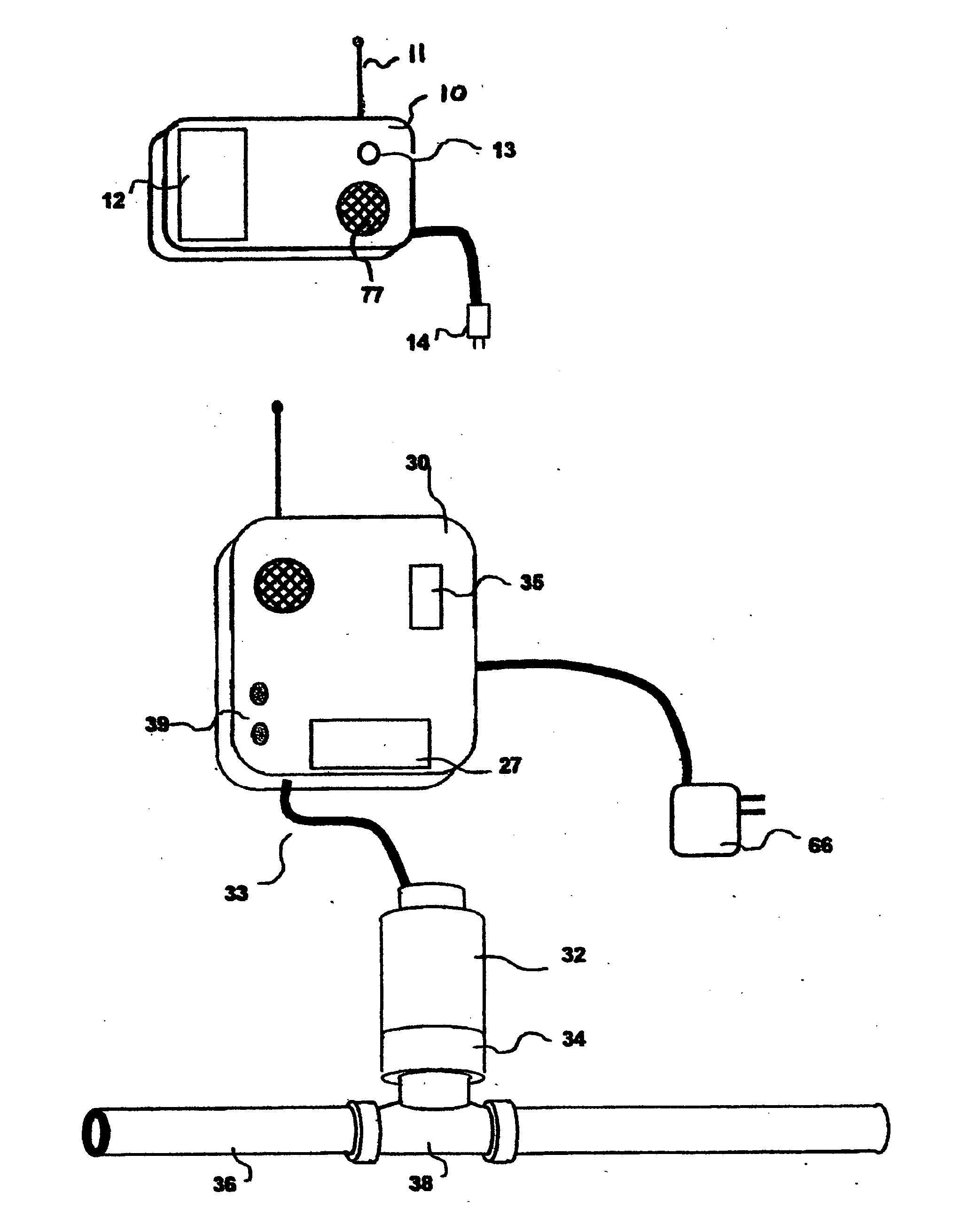

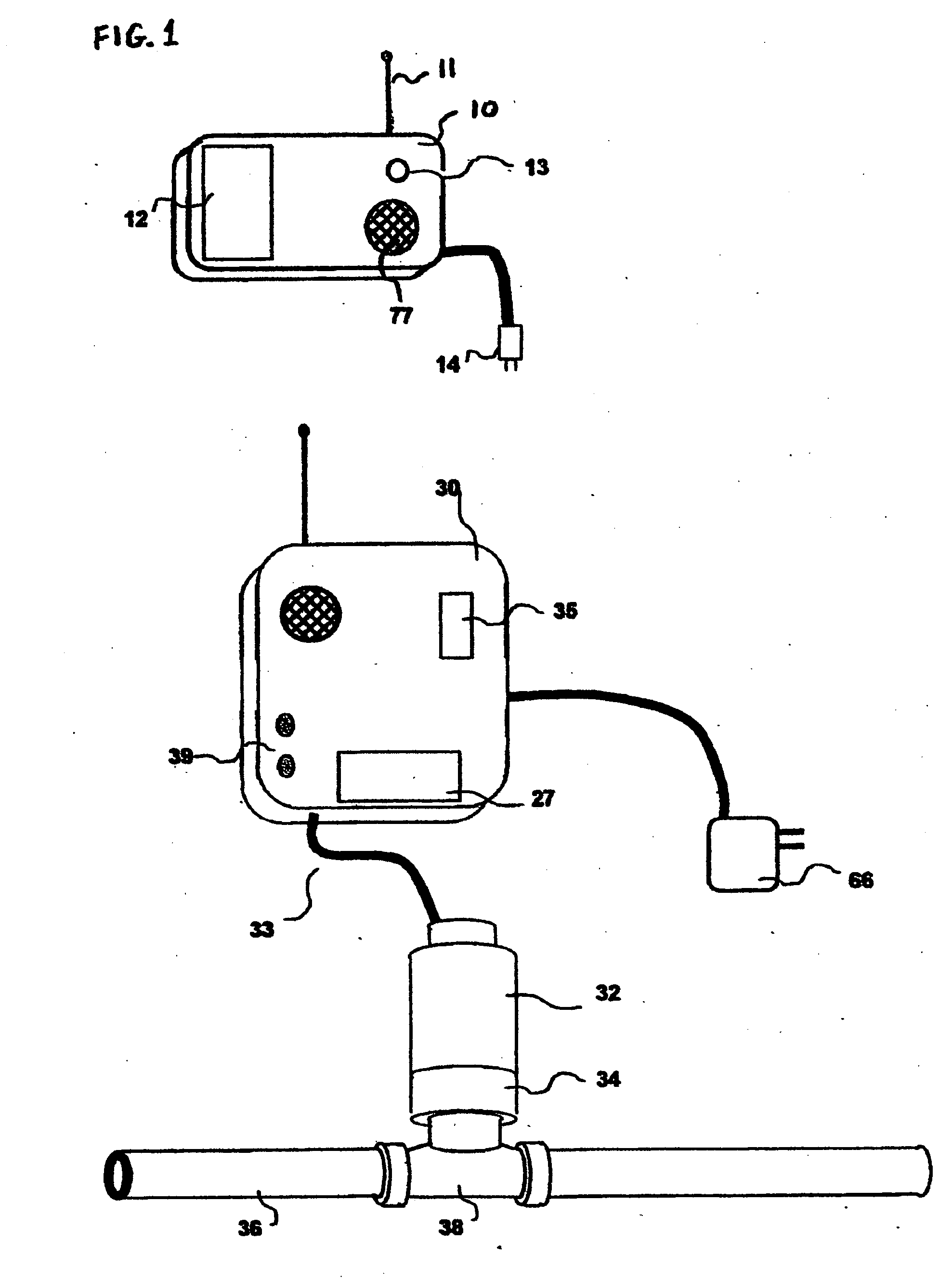

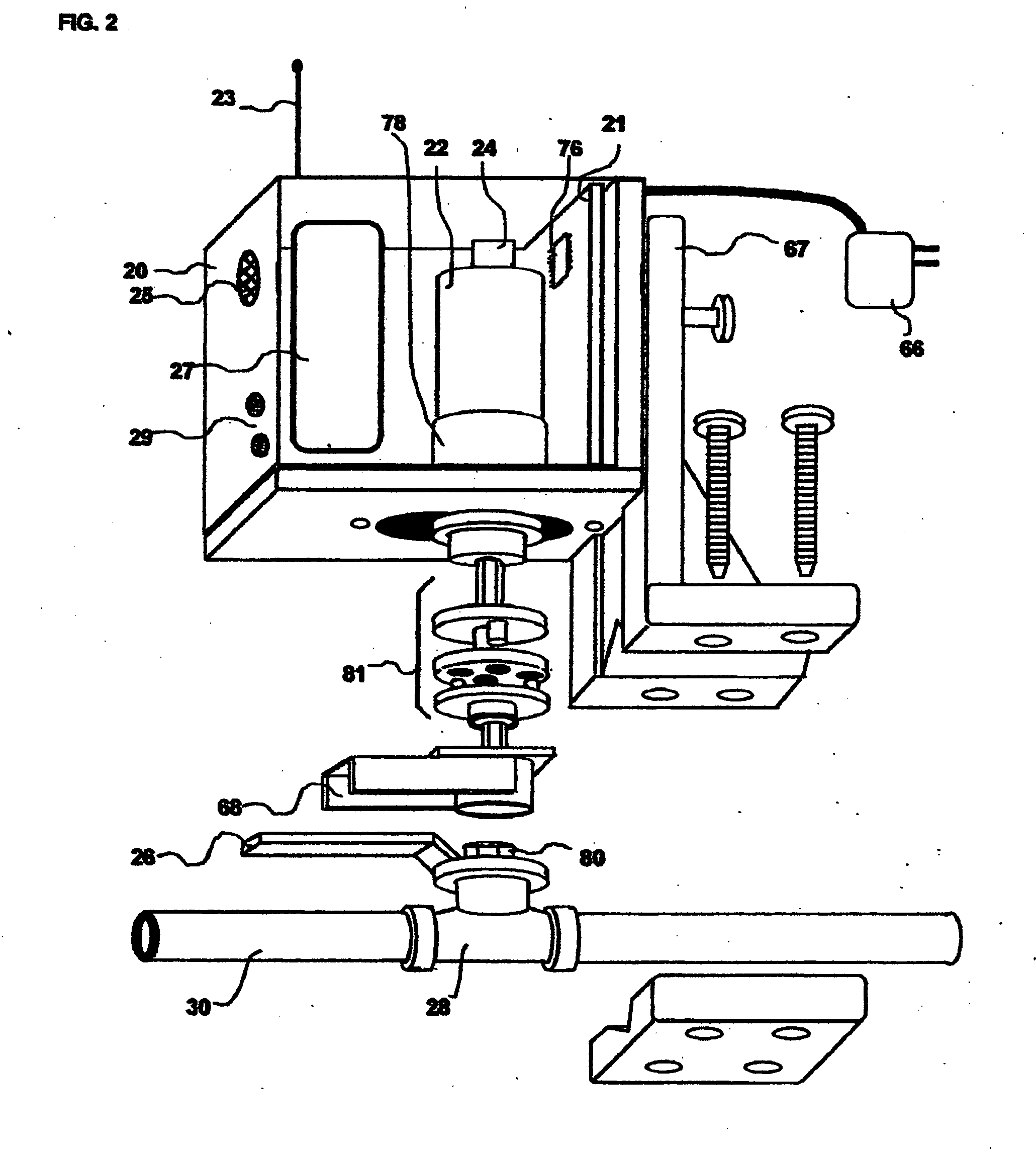

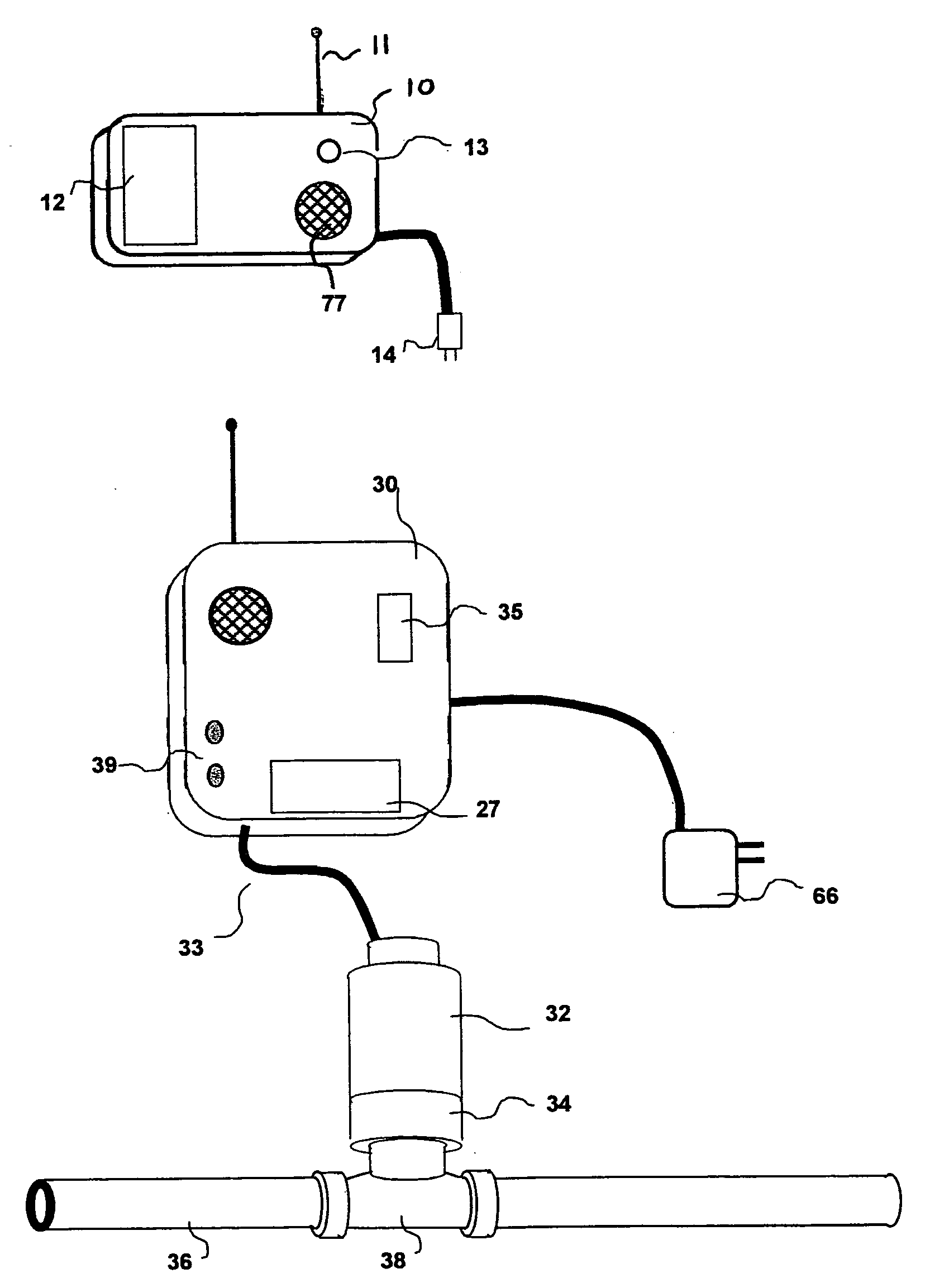

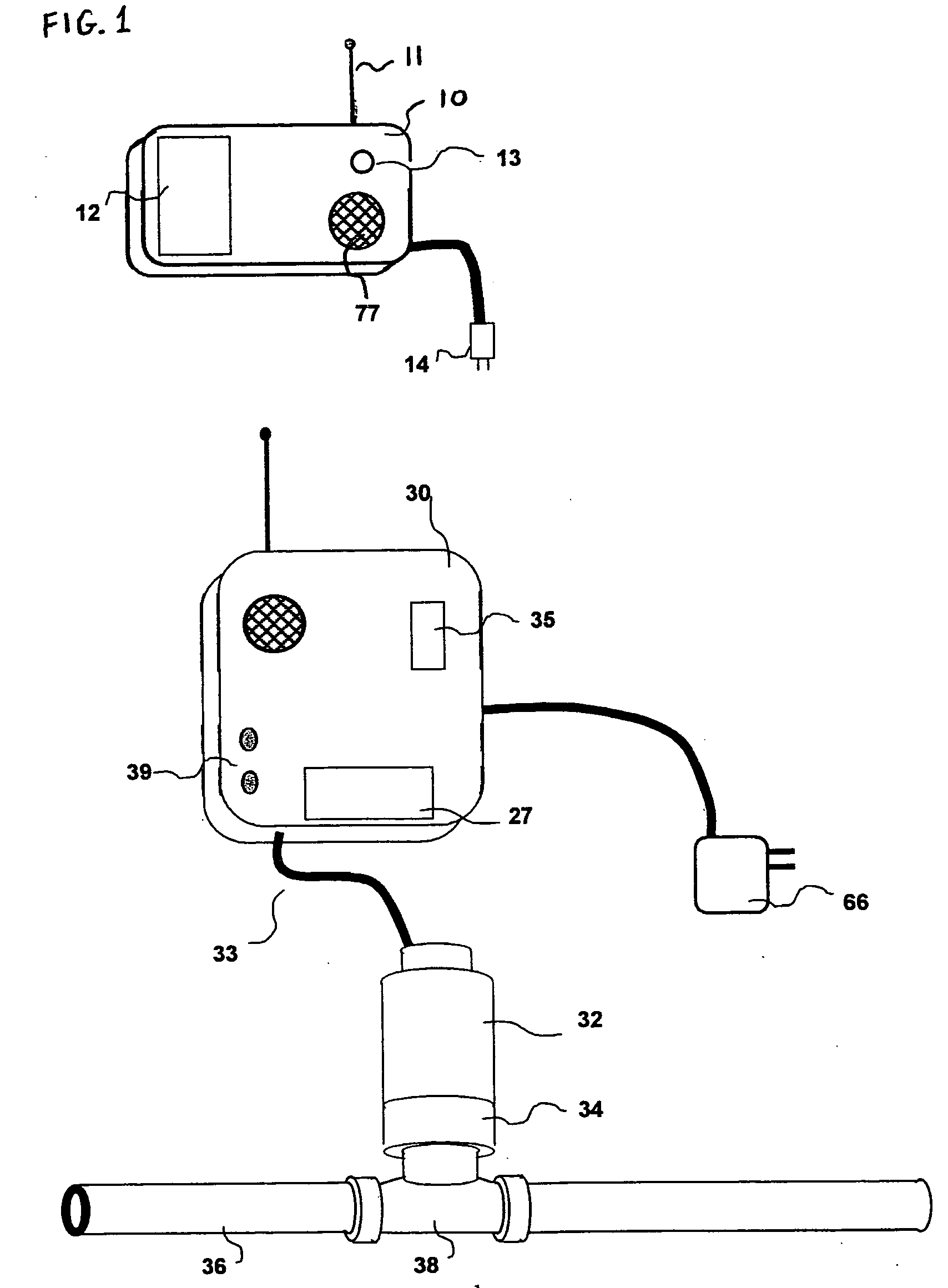

Secure wireless leak detection system

InactiveUS20070289635A1Easy to installReduce power consumptionDetection of fluid at leakage pointOperating means/releasing devices for valvesTransceiverMotor control

Supervised wireless leak detection system, having a leak detection sensor unit, capable of transmitting a uniquely coded signal in response to a detected leak, a supervised wireless valve control transceiver unit having a receiver, capable of receiving said uniquely coded signal, and a transmitter for feeding the uniquely coded signal within the system, a valve shut-off mechanism in communication with said valve control transceiver unit said valve shut-off mechanism having a motor attached to a valve, said motor creating a rotation pulse used to close and open said valve, and a processor having an electronic circuitry containing sensor(s), detecting said motor rotation pulse count during a motorized valve closure or open process. Said processor functions in a setup process to memorize (learn) said motor rotation pulse count, required, to close and or to open the valve. Wherein said processor upon receipt of said uniquely coded signal in response to a detected leak, applies power to the motor to close the valve, the motor controlled to stop turning the valve in response to a processor received motor rotation pulse count number, substantially equal to a previously stored number needed to close or open said valve. A digital, voice, or SMS text message phone dialer is add to dispatch the detected leak signals, and notify monitoring personnel supervised system operation, end provide user access to turn on or off a valve(s) from a remote location(s).

Owner:RUGGIERI MONICA L +1

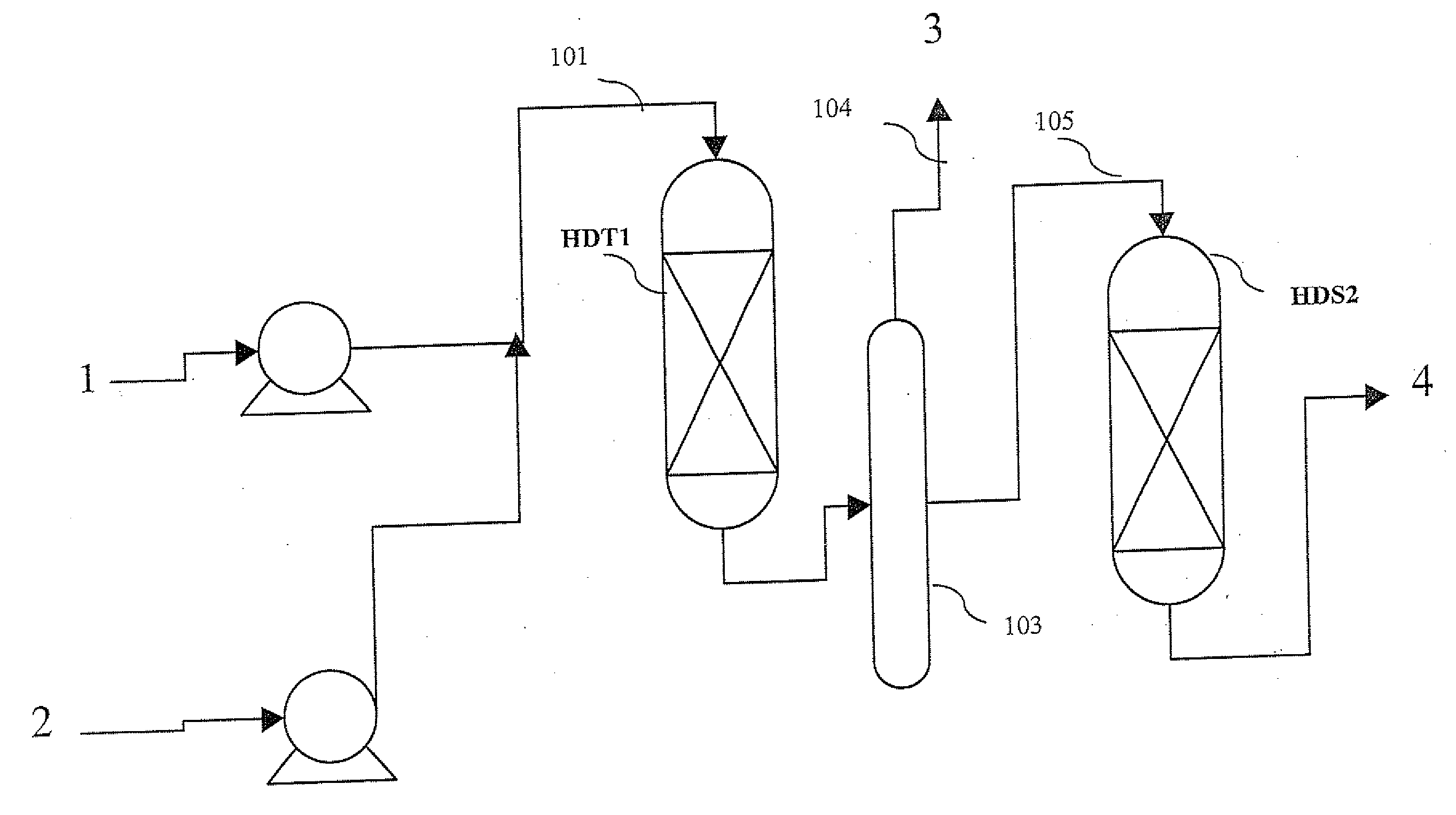

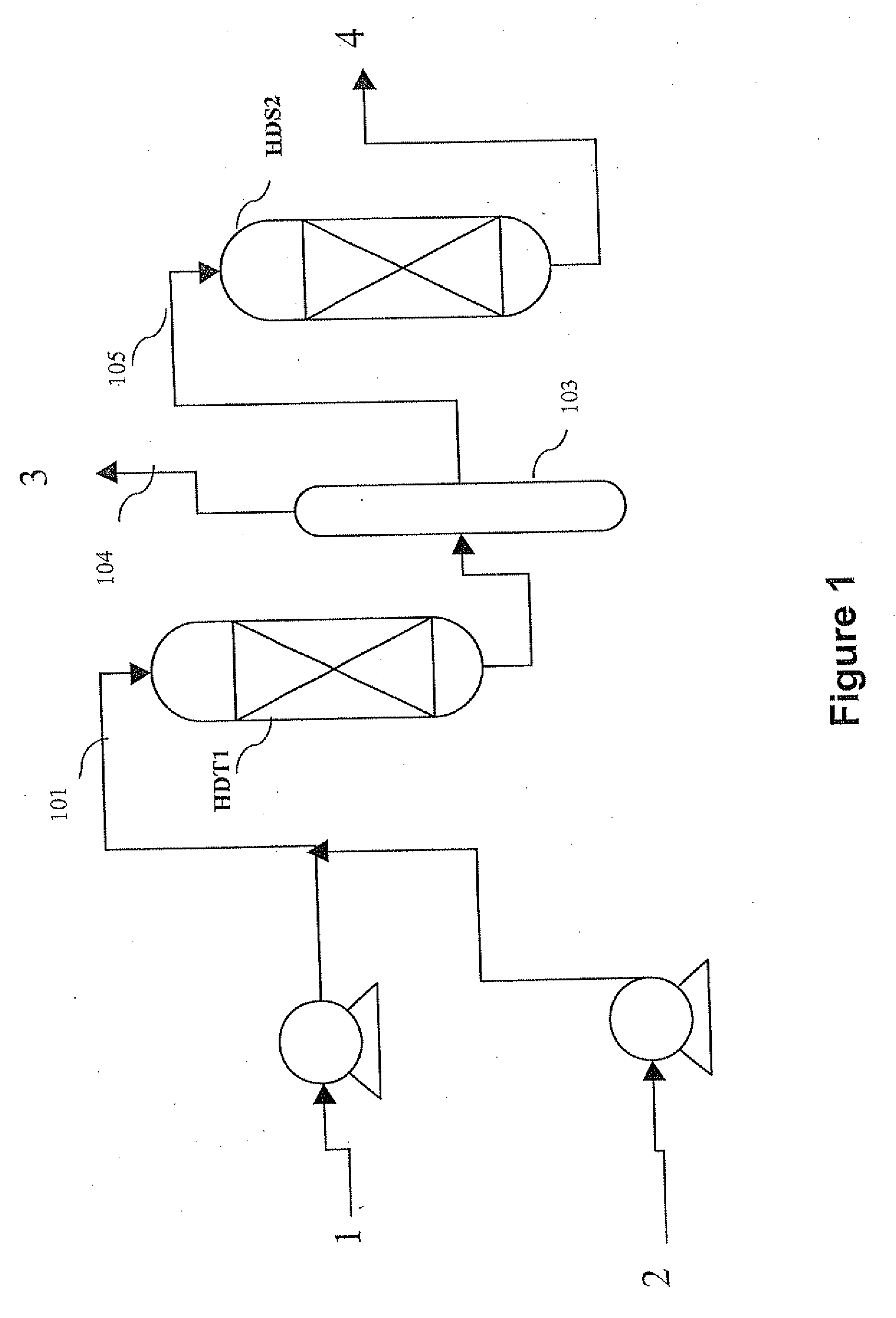

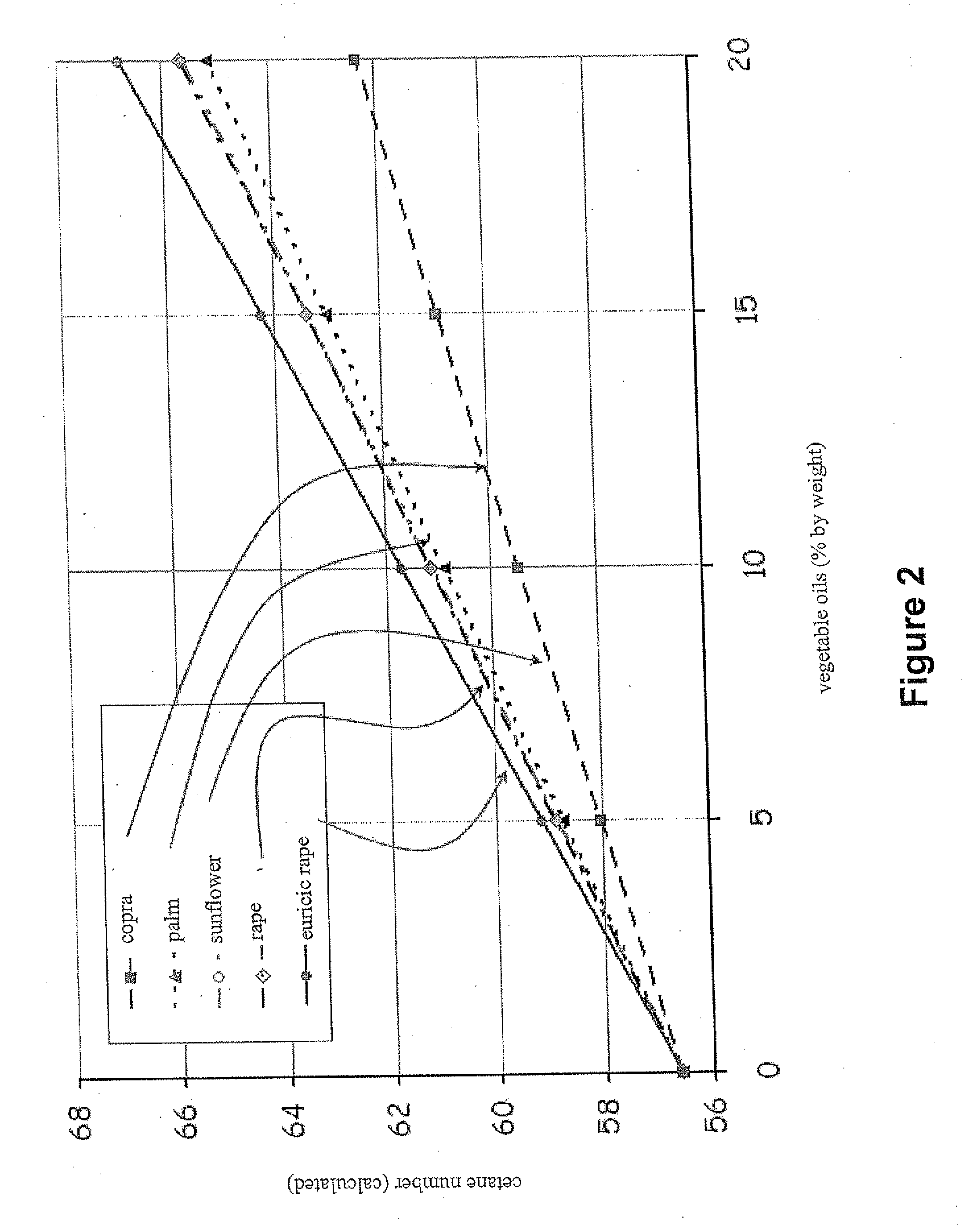

Methods of hydrotreating a mixture made up of oils of animal or vegetable origin and of petroleum cuts with intermediate stripping

ActiveUS20080161614A1Low costLimit consumption of hydrogenThermal non-catalytic crackingCatalytic crackingVegetable oilVolumetric Mass Density

The invention relates to a hydrotreating method (HDT) using two plants working under different operating conditions with an intermediate stripping for co-treating a mixture made up of oils of vegetable or animal origin and petroleum cuts (gas oil cuts (GO) and middle distillates) in order to produce gas oil fuel bases meeting specifications. The first plant (HDT1) is more particularly dedicated to the reactions concerning oils of vegetable or animal origin in comixture while pretreating the hydrocarbon feed, whereas the second plant (HDS2) works under more severe conditions to obtain diesel fuel according to standards, in particular in terms of effluent sulfur content, density and cold properties. The process economy, the activity and the stability of the catalyst of the second plant are greatly improved by the intermediate stripping.

Owner:INST FR DU PETROLE

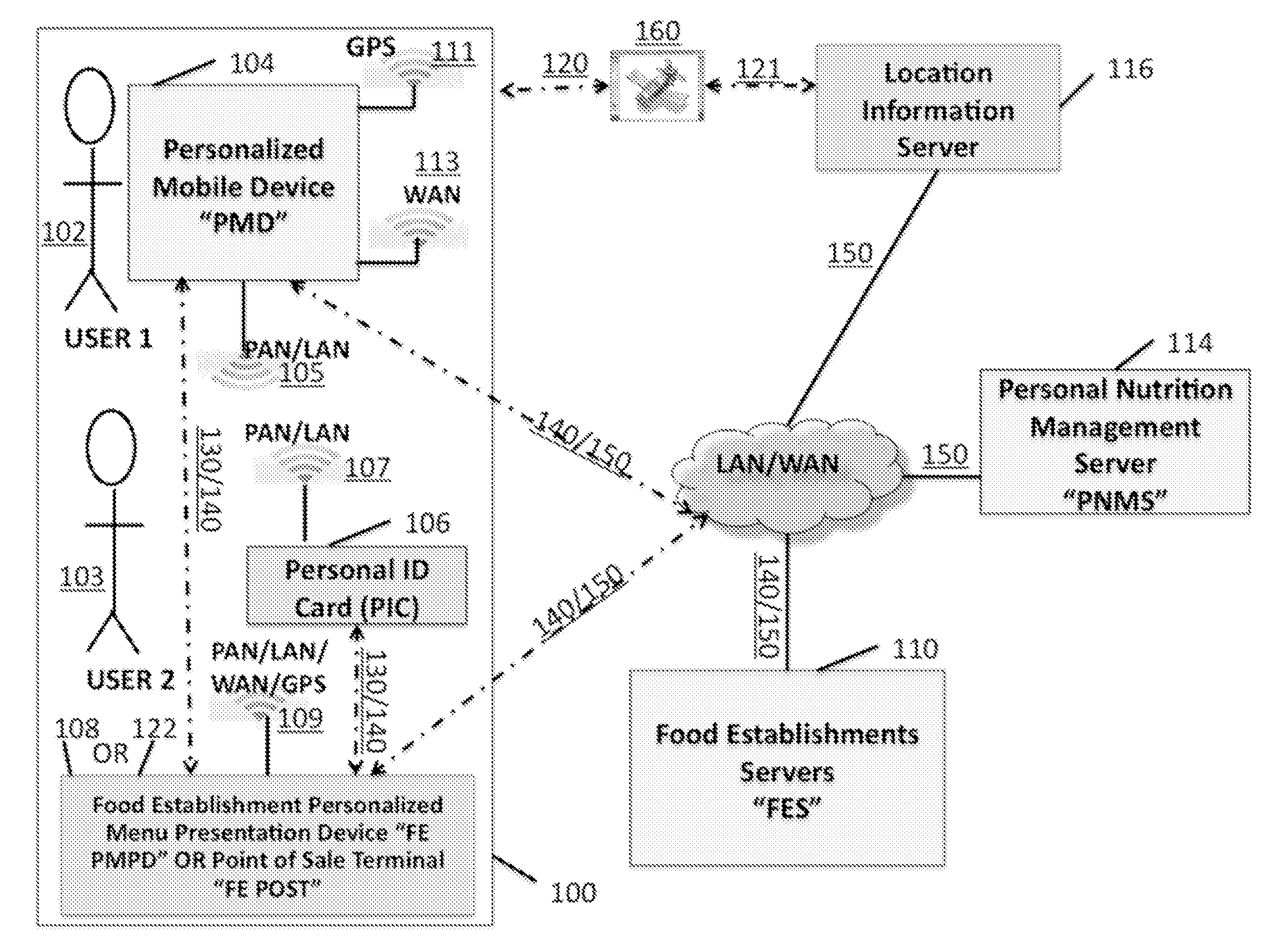

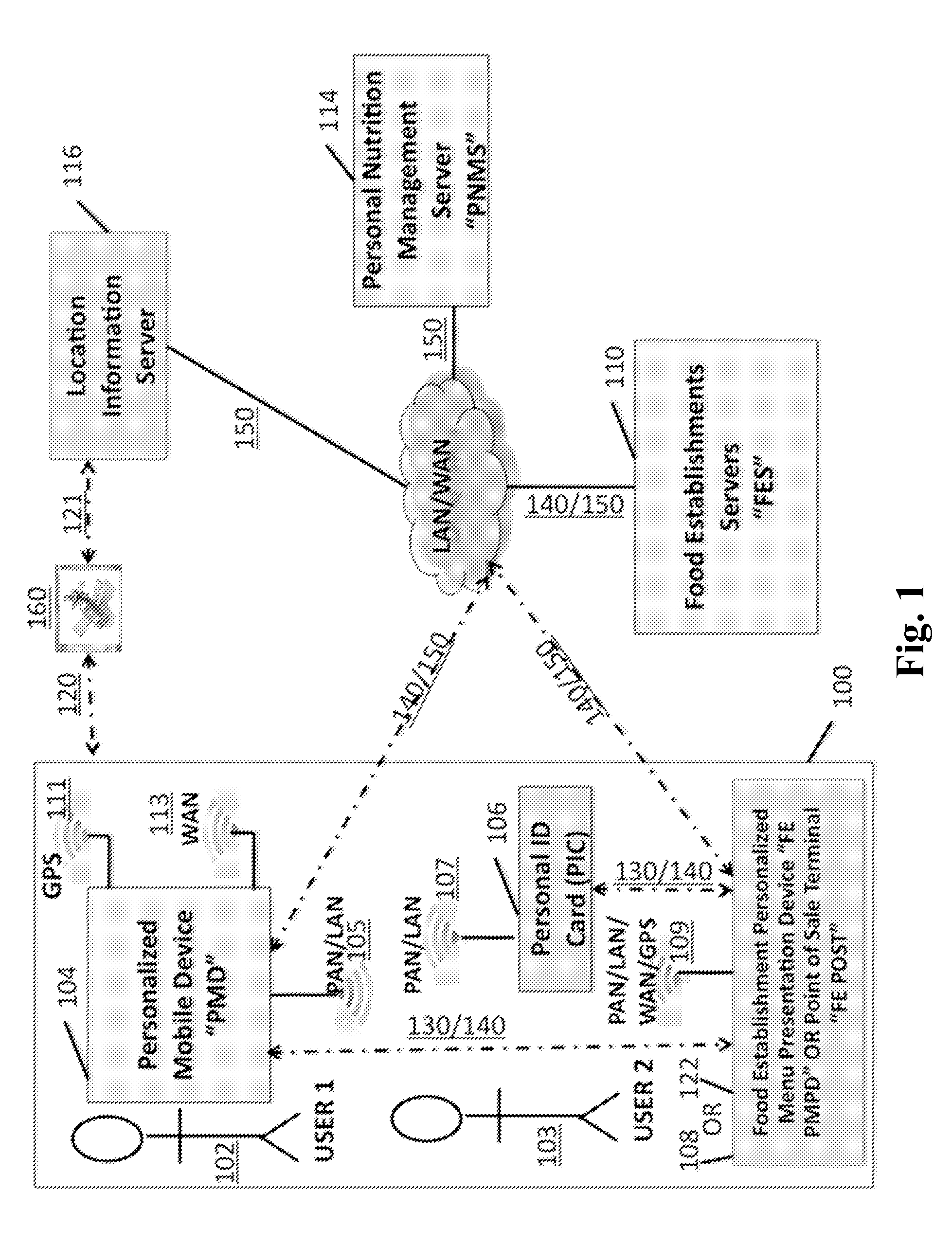

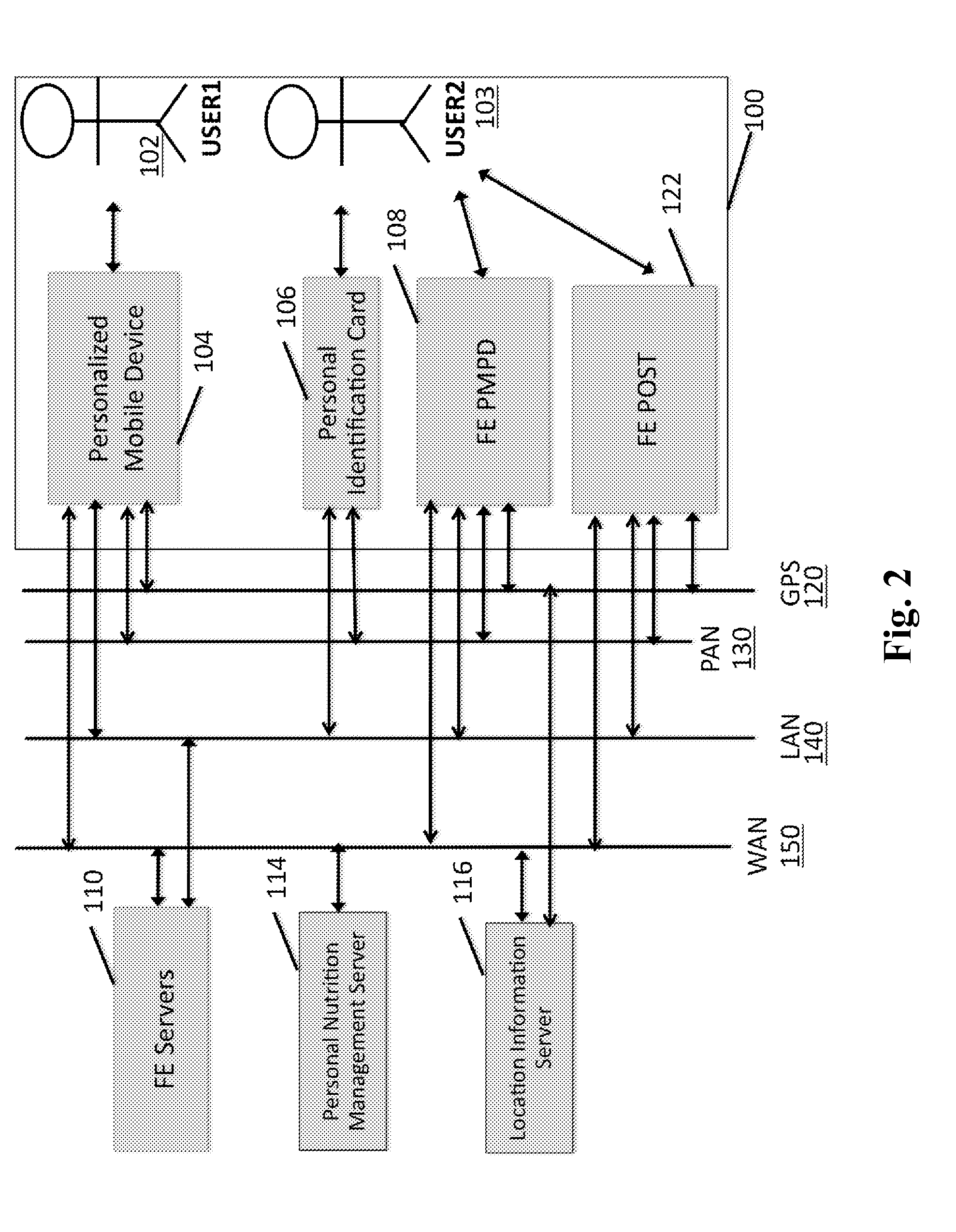

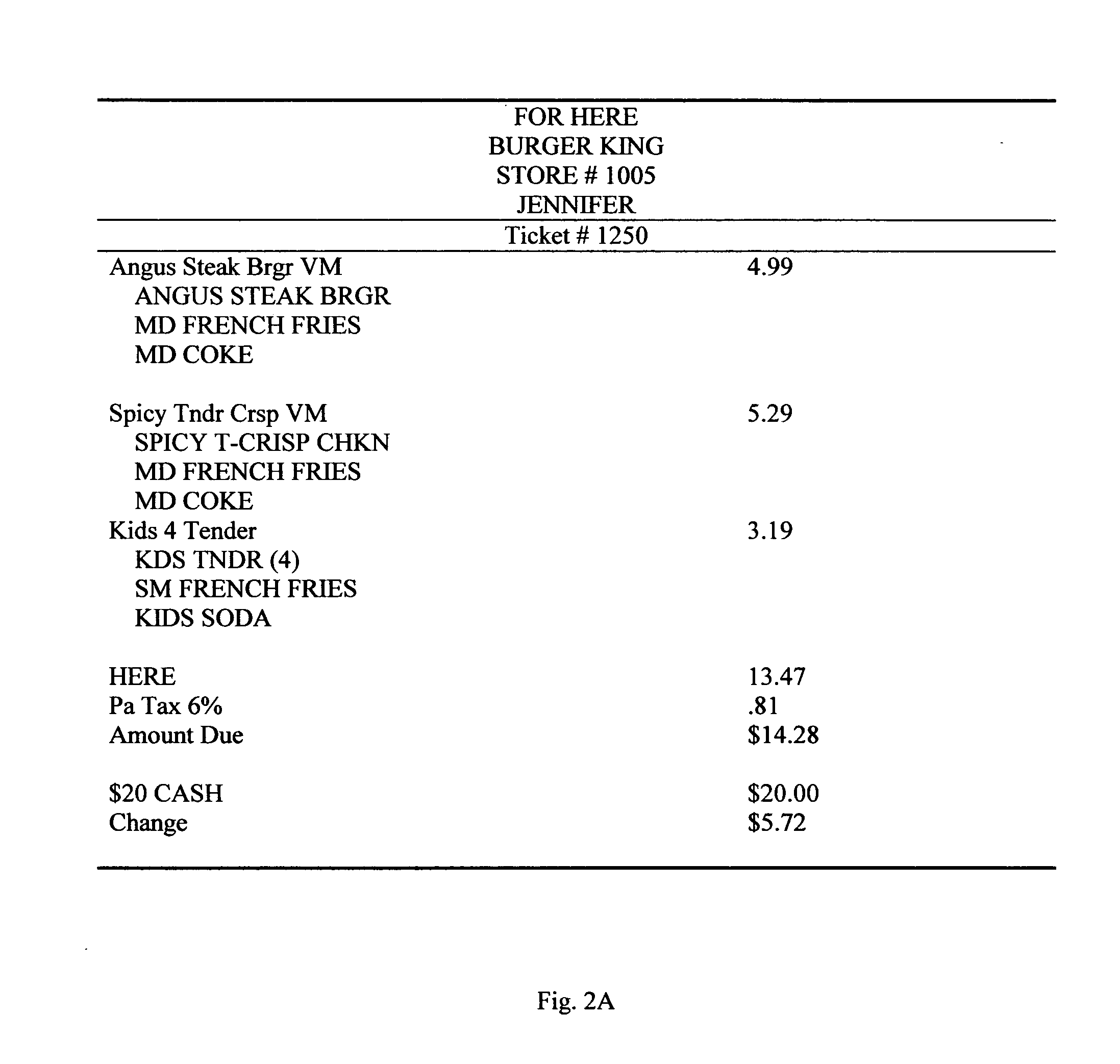

Personal Menu Generator

InactiveUS20120233002A1Maintain balanceImprovement in user ' long-term health outcomeNutrition controlResourcesPortion sizeDietary supplement

Personal menu generator method, system, and autonomous mobile device will assist users in the selection of the most affordable and beneficial subset of food items to order at food serving establishments by composing and presenting to each guest an individualized subset of menu items and recommended portion sizes out of the larger set of available food items usually listed on the menus of food serving establishments; the presented individualized subset of food items is selected based on one or more of a multitude of criteria, such as the remaining daily balances of each user's macronutrient and micronutrient budgets, each available food item price, ingredients and energy and nutrient contents, the names, doses, and timing of medications and dietary supplements taken by each individual, favorite and restricted foods and ingredients, monetary spending limit for food, and healthcare provider recommendations.

Owner:ABUJBARA NABIL M

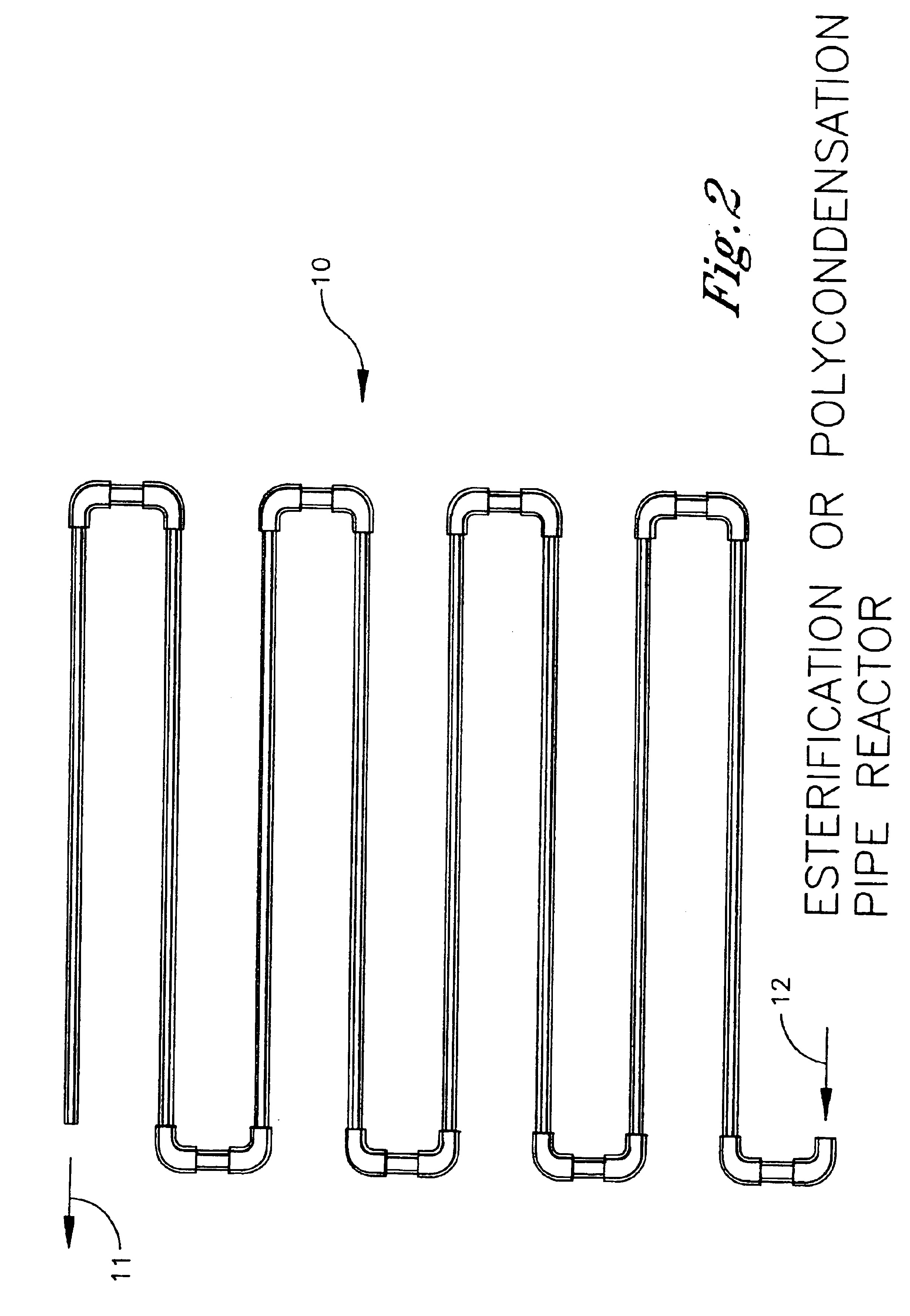

Low cost polyester process using a pipe reactor

InactiveUS20020137877A1Reduce pressureEliminate needLiquid degasificationFlow mixersProcess engineeringVolume control

The invention is directed to polyester processes that utilizes a pipe reactor in the esterification, polycondensation, or both esterification and polycondensation processes. Pipe reactor processes of the present invention have a multitude of advantages over prior art processes including improved heat transfer, volume control, agitation and disengagement functions. The pipe reactor processes and apparatus of the present invention are built and operated at a much lower cost than conventional polyester processes.

Owner:ALPEK POLYESTER SA DE CV

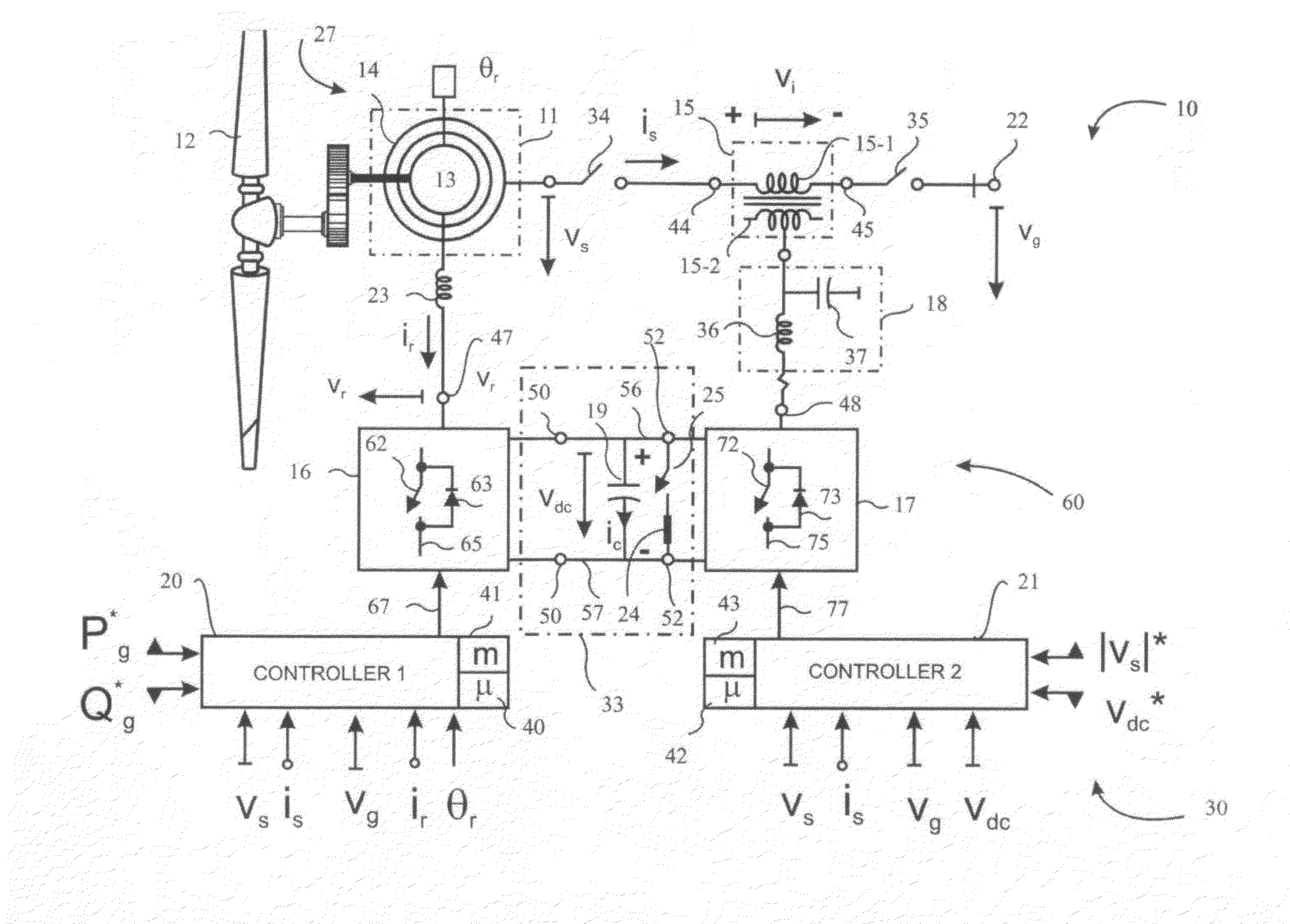

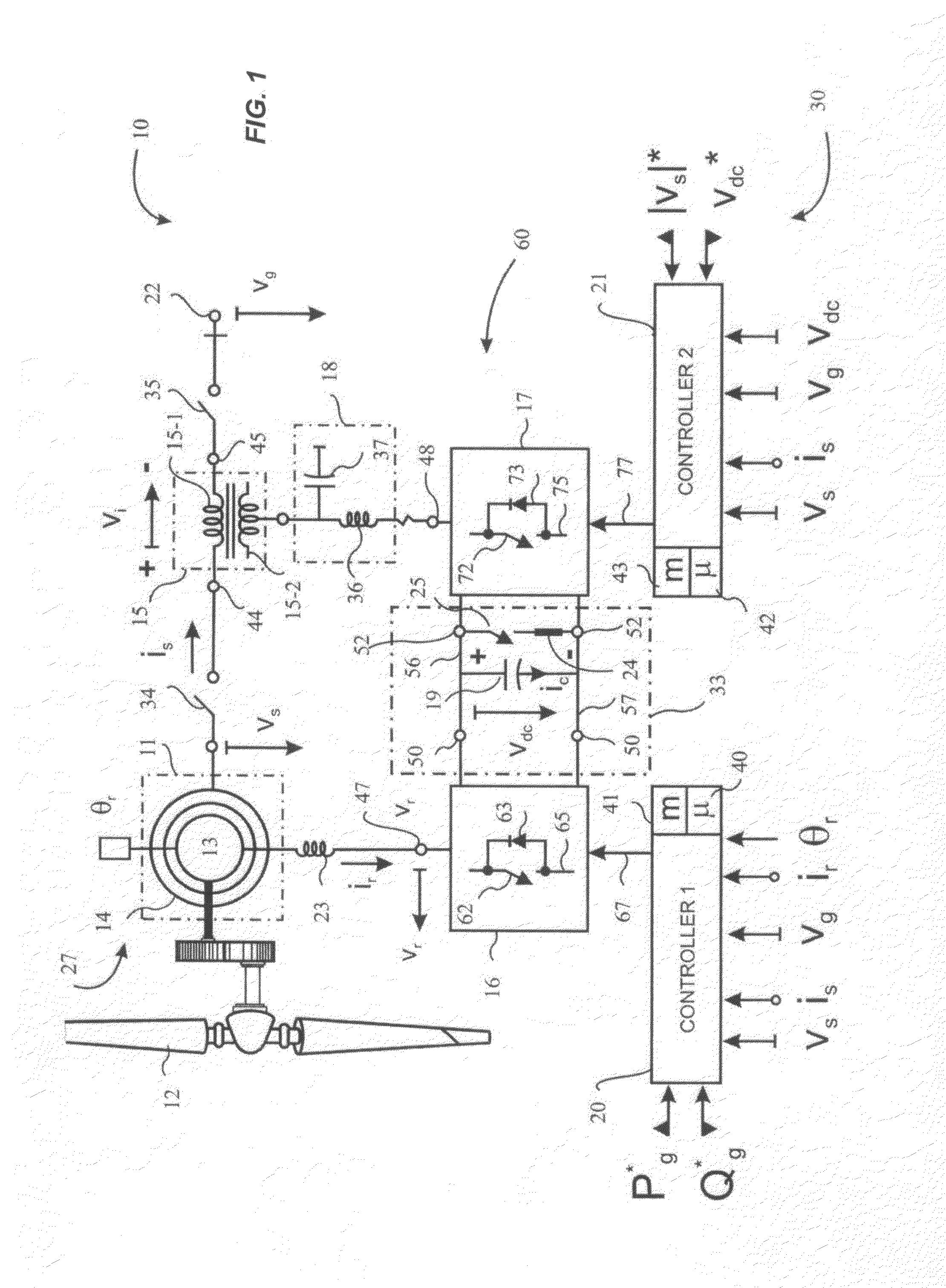

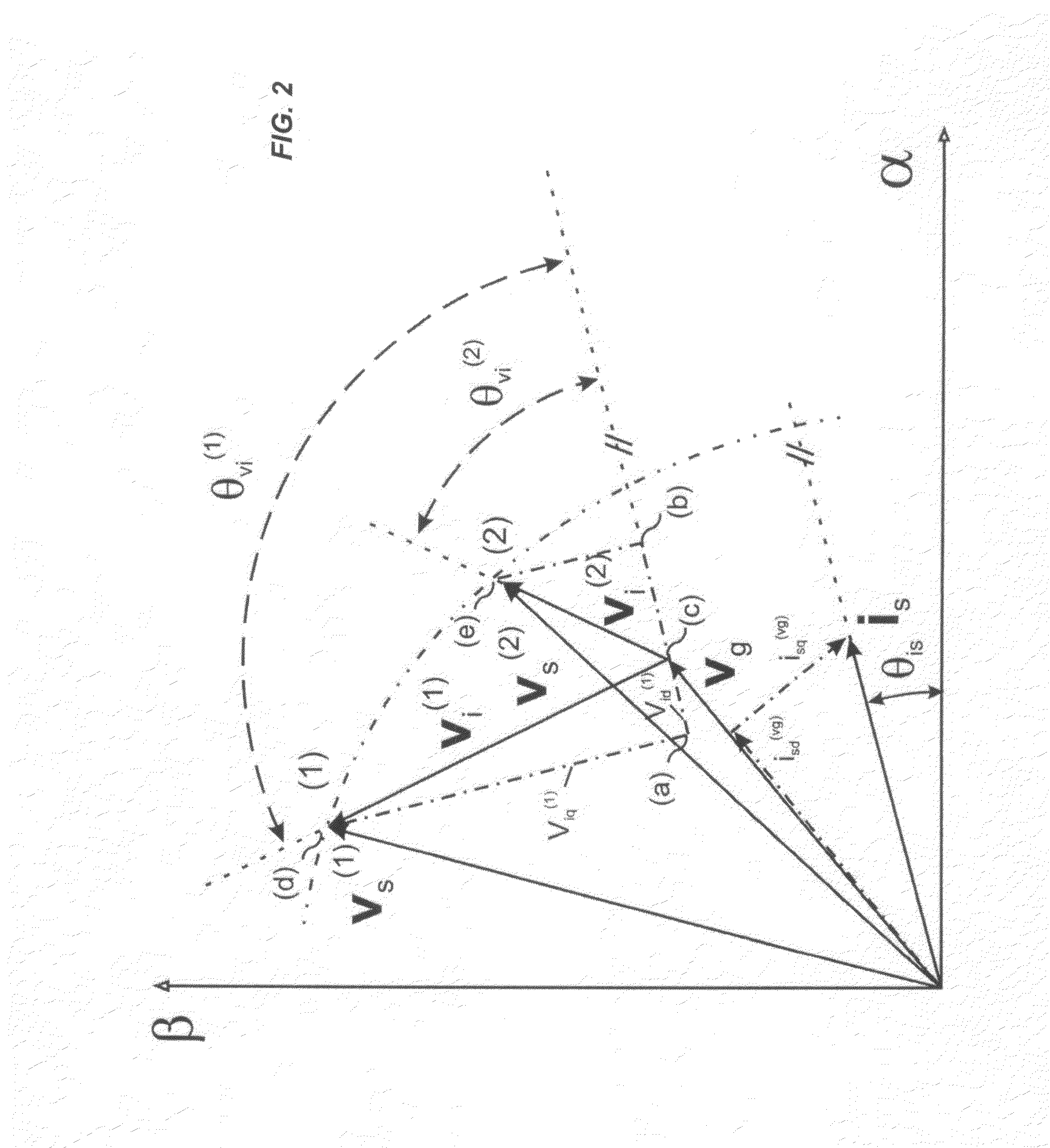

Doubly-controlled asynchronous generator

InactiveUS20080150285A1Avoid problemsReduce settingsGenerator control circuitsWind motor controlTransformerElectric power distribution

An electric power generator system or a motor comprising a doubly-fed asynchronous generator or motor comprising a stator and a rotor, a transformer having a first winding and a second winding, the first winding having a first end and a second end; and wherein the stator and the transformer are connectable in series with an electric power distribution grid.

Owner:WIND TO POWER SYST

Polyester process using a pipe reactor

InactiveUS6906164B2Reduce pressureEliminate needLiquid degasificationFlow mixersPolyesterPolymer science

Owner:ALPEK POLYESTER SA DE CV

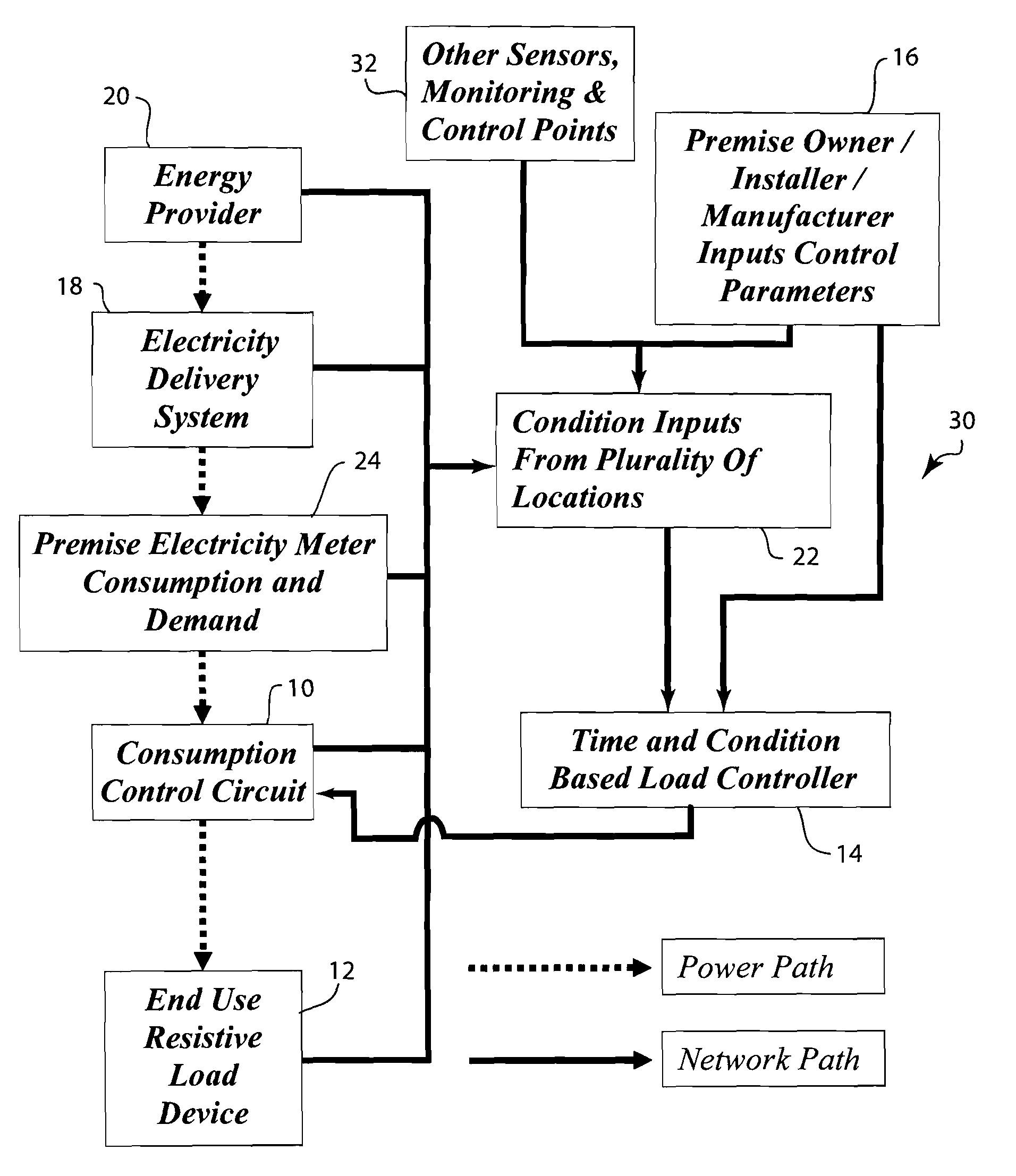

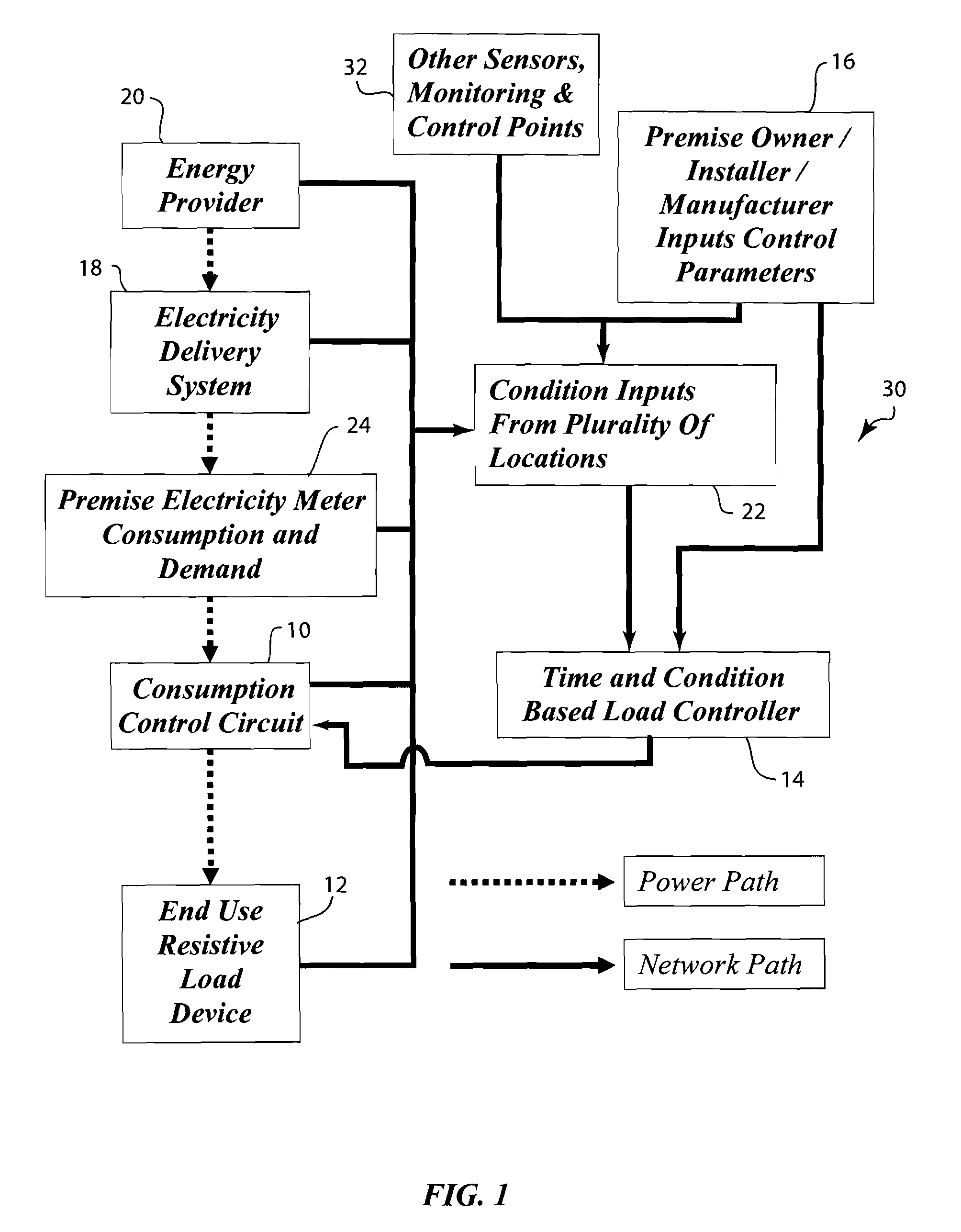

System and method for demand limiting resistive load management

ActiveUS20070213880A1Control consumptionReduce the amount requiredLevel controlDc source parallel operationElectricity meterThird party

An electricity demand limiting system for limiting the electricity consumption of at least one resistive load device. The demand limiting system includes a consumption controller associated with the resistive load device that is operable to infinitely vary the amount of electricity being consumed by the load device. The consumption control device is in operative communication with a load controller such that the load controller can generate a control signal to affect the operation of the consumption control circuit. Preferably, the consumption control circuit is a triac-based circuit that receives the control signal from the load controller and limits the amount of electricity consumed by the resistive load device. The load controller can receive input signals from sensors monitoring the electricity delivery system or from the premise electricity meter. Further, the load controller can receive external inputs from a third party that determine the operation of the load controller in limiting the electricity demands of the resistive load device.

Owner:INVENSYS SYST INC +1

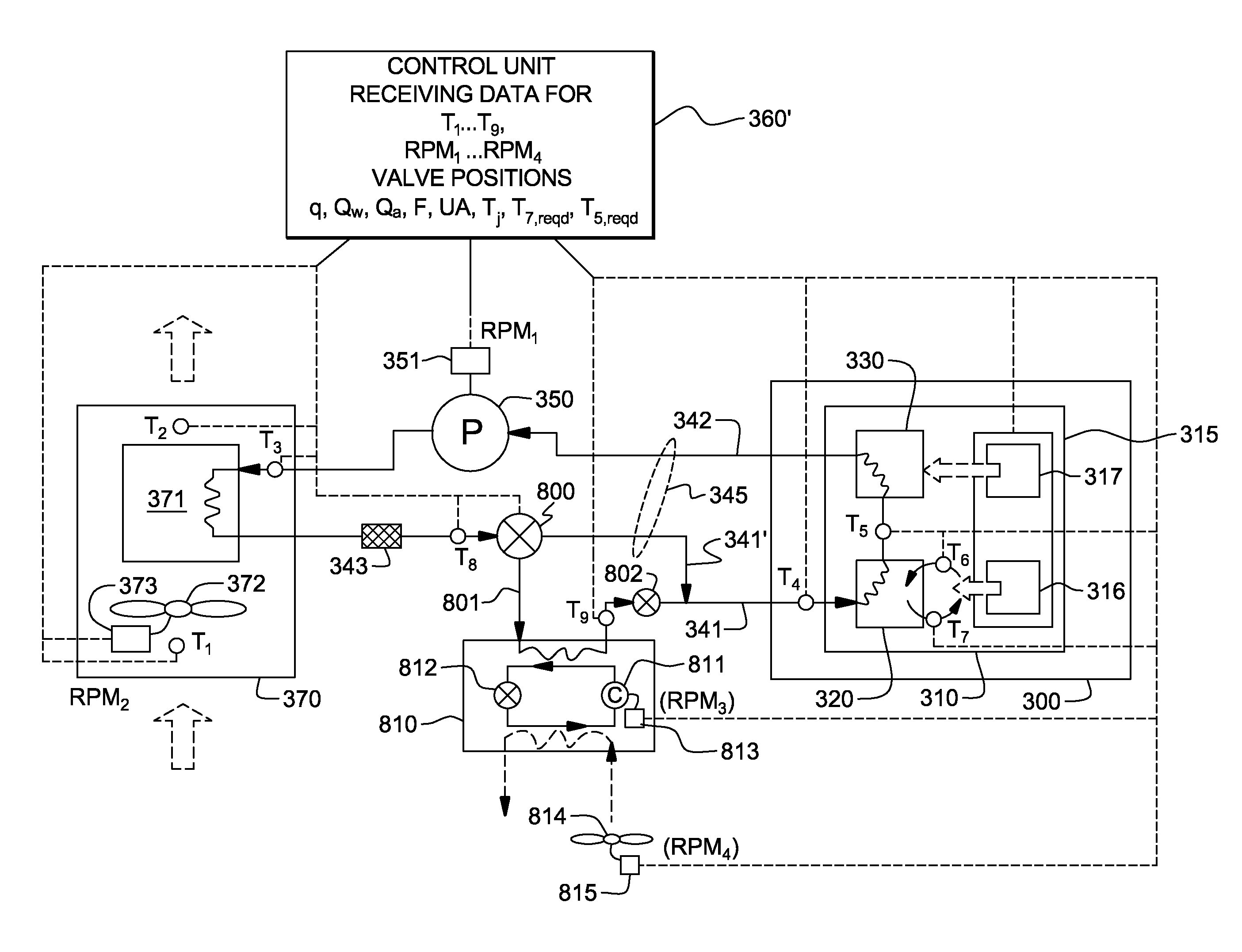

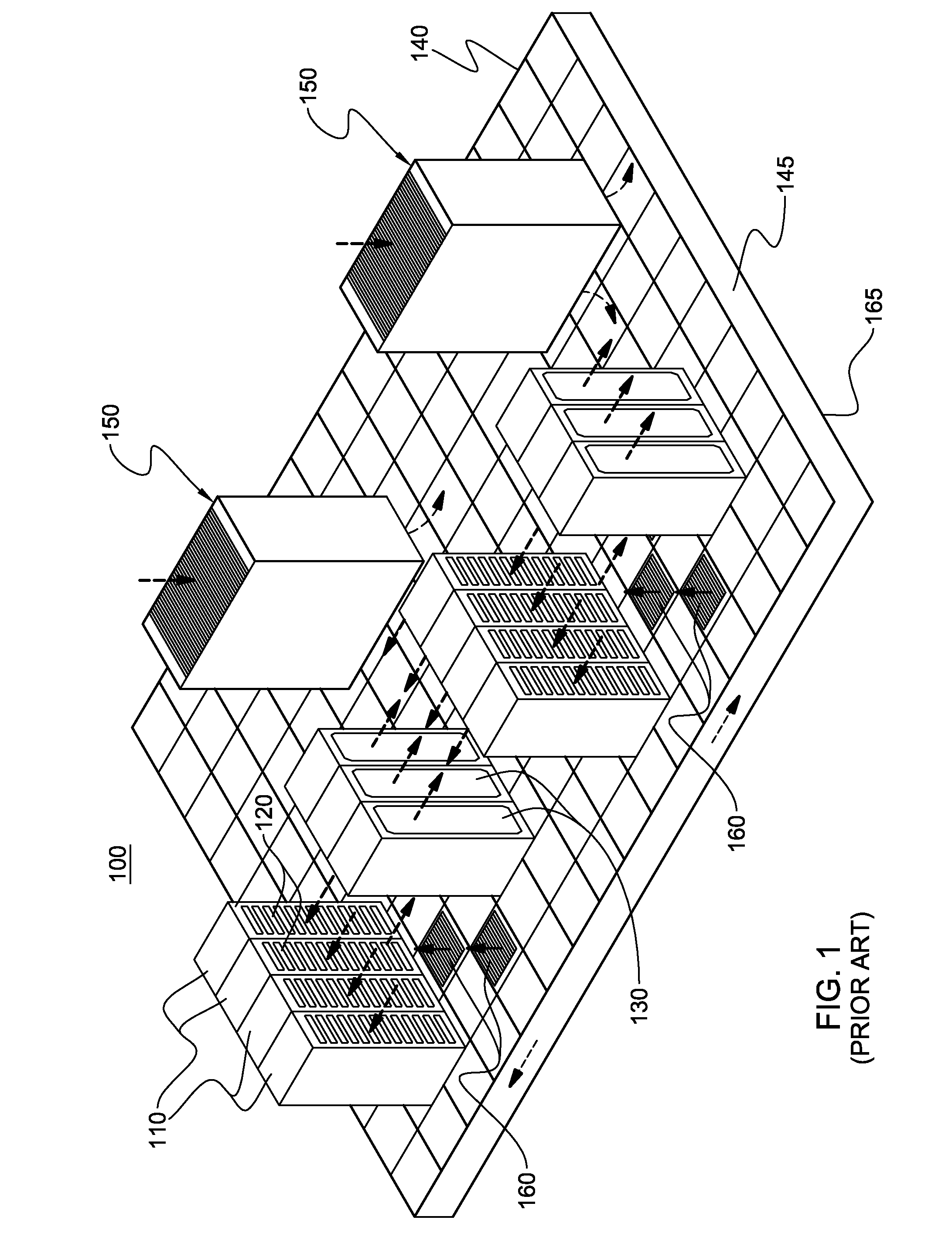

Energy efficient apparatus and method for cooling an electronics rack

InactiveUS7791882B2Overcomes shortcomingImprove cooling effectDomestic cooling apparatusDigital data processing detailsNuclear engineeringEnergy expenditure

Apparatus and method are provided for cooling an electronics rack in an energy efficient, dynamic manner. The apparatus includes one or more extraction mechanisms for facilitating cooling of the electronics rack, an enclosure, a heat removal unit, and a control unit. The enclosure has an outer wall, a cover coupled to the outer wall and a central opening sized to surround the electronics rack and the heat extraction mechanism. A liquid coolant loop couples the heat removal unit in fluid communication with the heat extraction mechanism, which removes heat from liquid coolant passing therethrough. The control unit is coupled to the heat removal unit for dynamically adjusting energy consumption of the heat removal unit to limit its energy consumption, while providing a required cooling to the electronics rack employing the liquid coolant passing through the heat extraction mechanism.

Owner:INT BUSINESS MASCH CORP

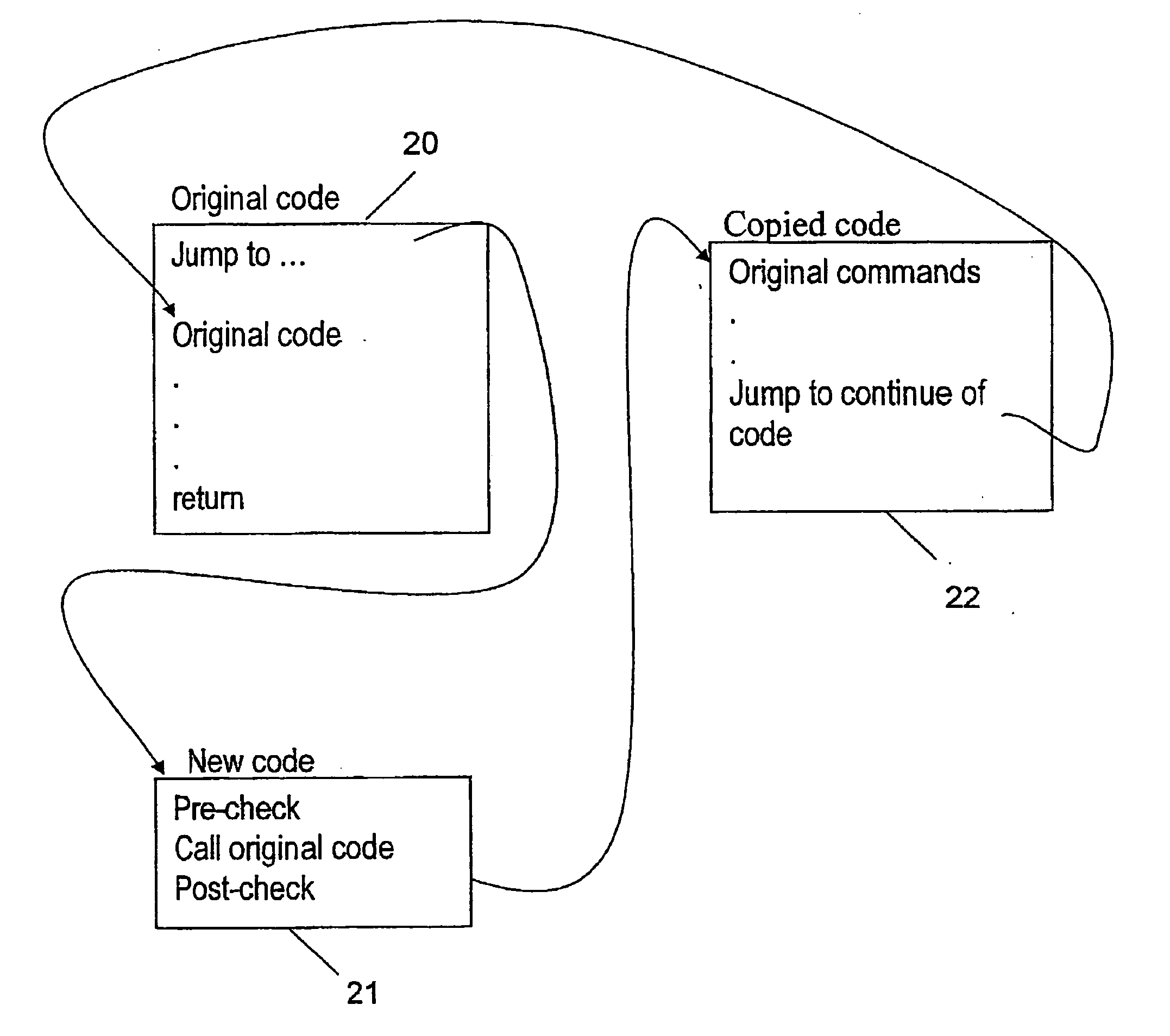

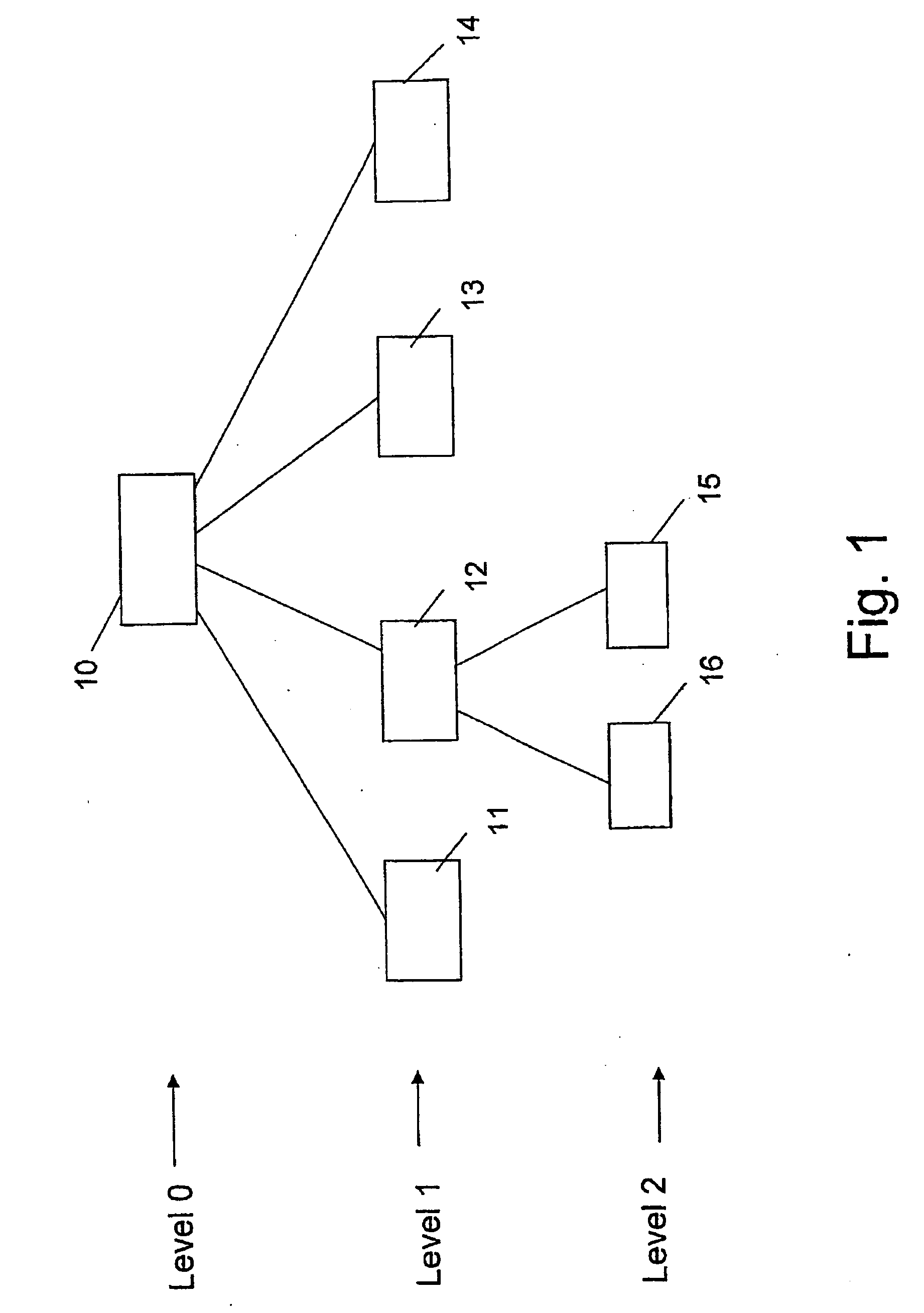

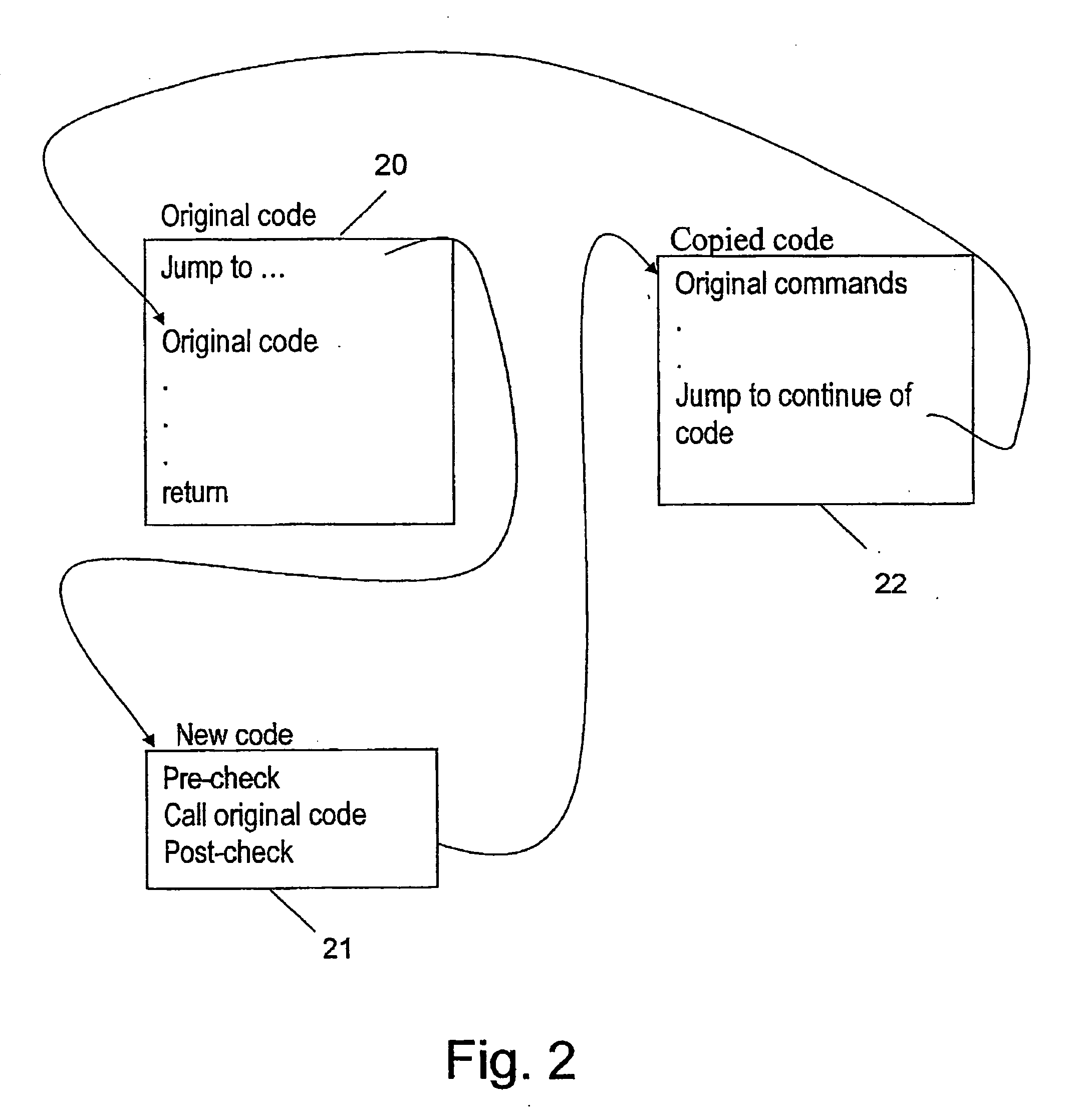

Method for dynamically allocating and managing resources in a computerized system having multiple consumers

InactiveUS20050246705A1Control resource consumptionControl consumptionData processing applicationsResource allocationMemory addressVirtual memory

Method for dynamically allocating and managing resources in a computerized system managed by an operating system (OS) and having multiple accounts of consumers. Portions of the virtual memory address space are allocated, whenever desired, in a swap file, for each account associated with a consumer. The memory address space is limited for each account. The CPU usage is divided between the tasks requested from each account, and segments in the original code of the OS are changed by locating one or more specific procedures in the original code, and modifying the specific procedures to operate according to the allocation and / or the limitation of the memory address space and / or the limitation of the number of processes and / or the divided CPU usage.

Owner:PARALLELS IP HLDG

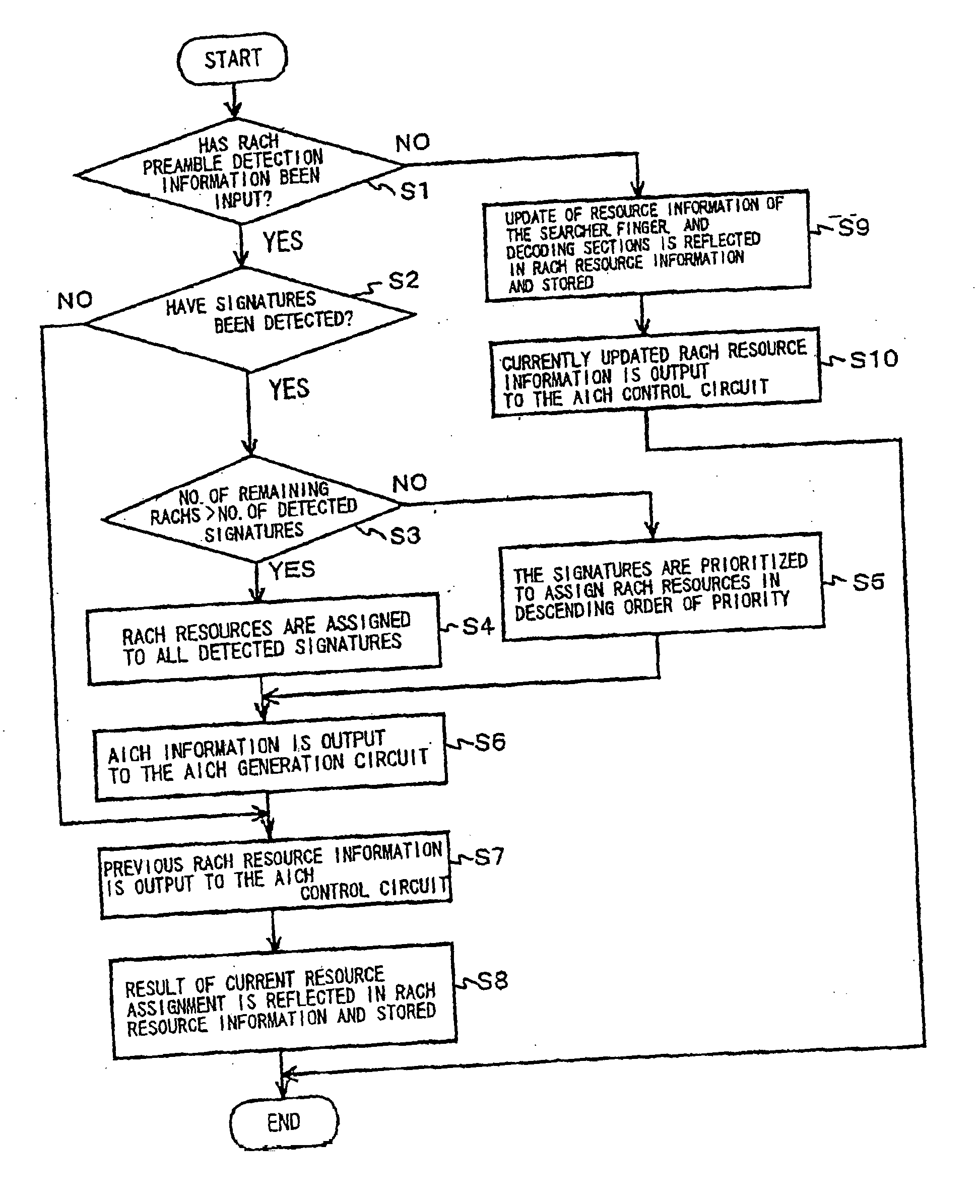

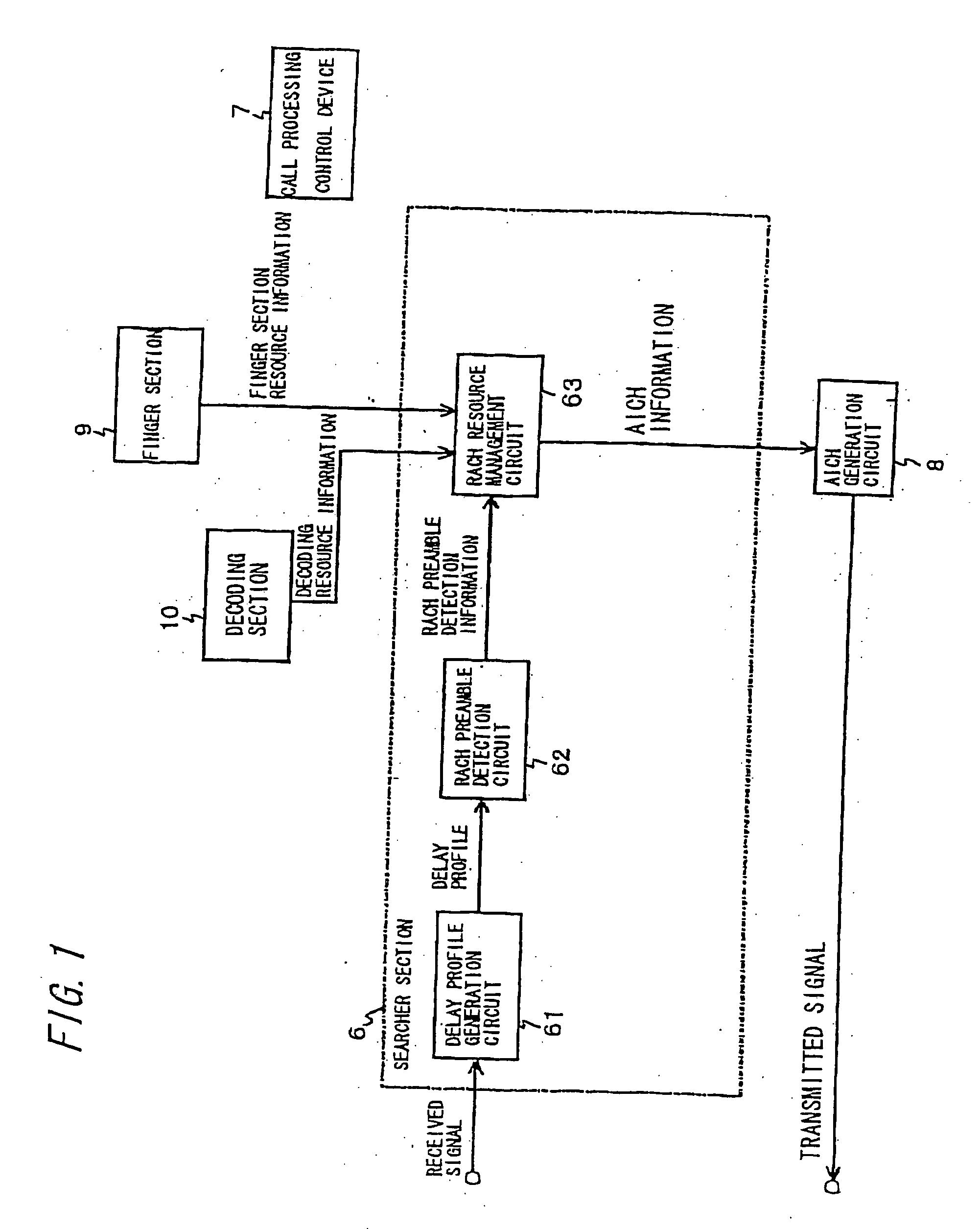

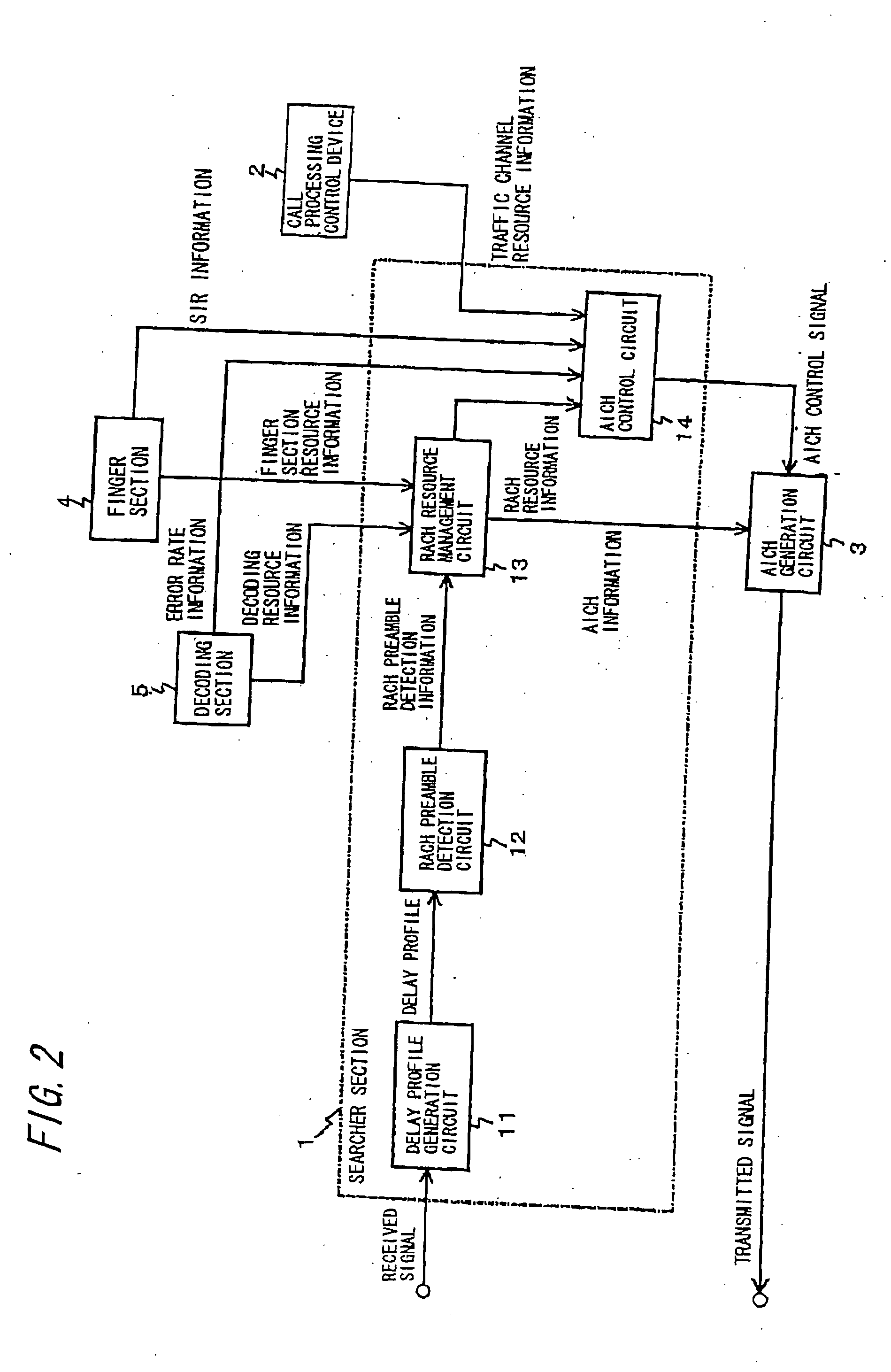

Mobile communication system, radio base station apparatus and random access control method used in them

InactiveUS20050232158A1Control consumptionImprove communication qualityError preventionFrequency-division multiplex detailsResource informationControl signal

An AICH control circuit (14) outputs, to an AICH generating Circuit (3), RACH resource information from an RACH resource management circuit (13), SIR information from a finger part (4), error rate information from a decoding part (5), and a call processing control signal. The AICH generating circuit (3) uses AICH information from the RACH resource management circuit (13) and an AICH control signal.

Owner:NEC CORP

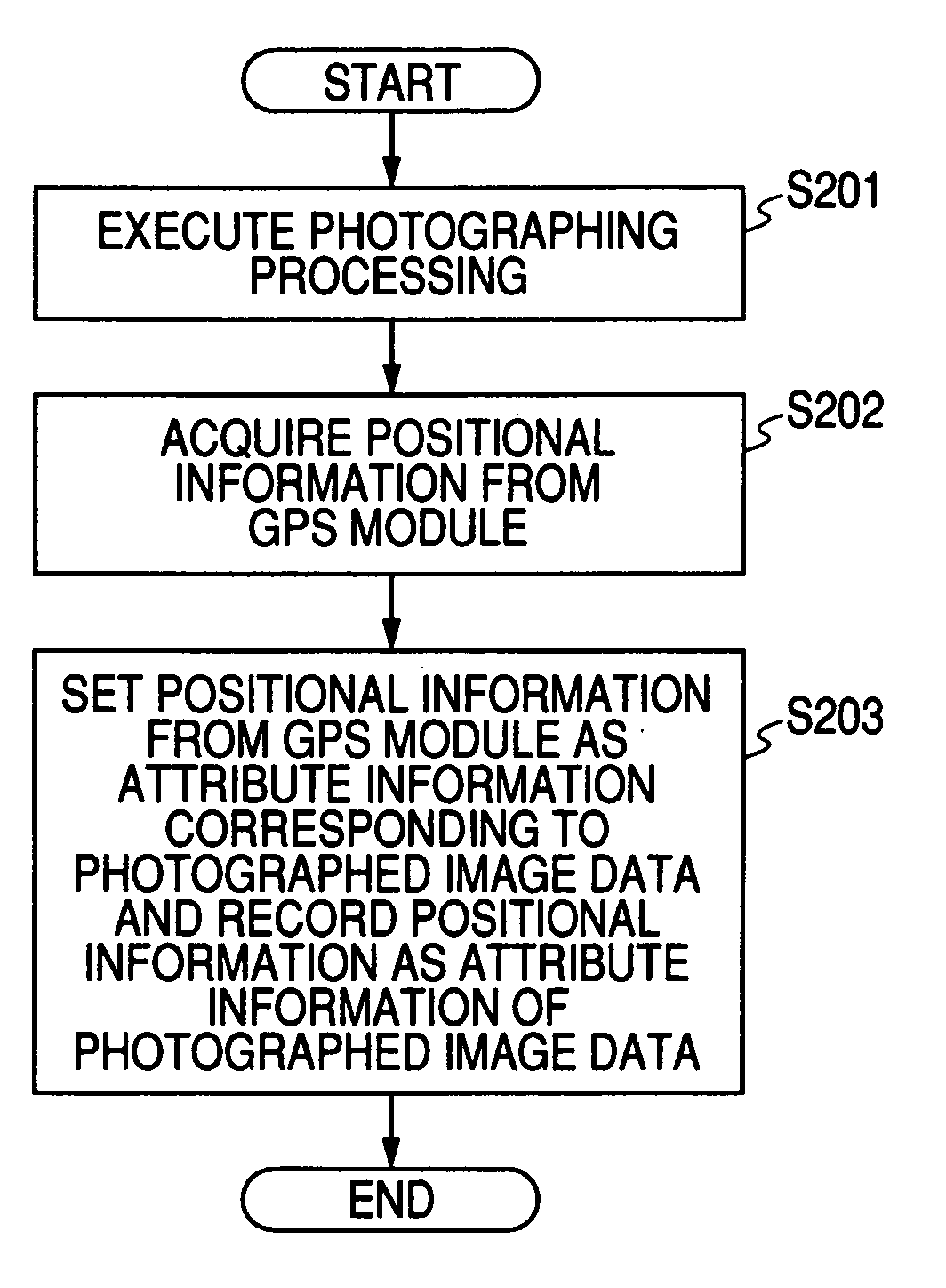

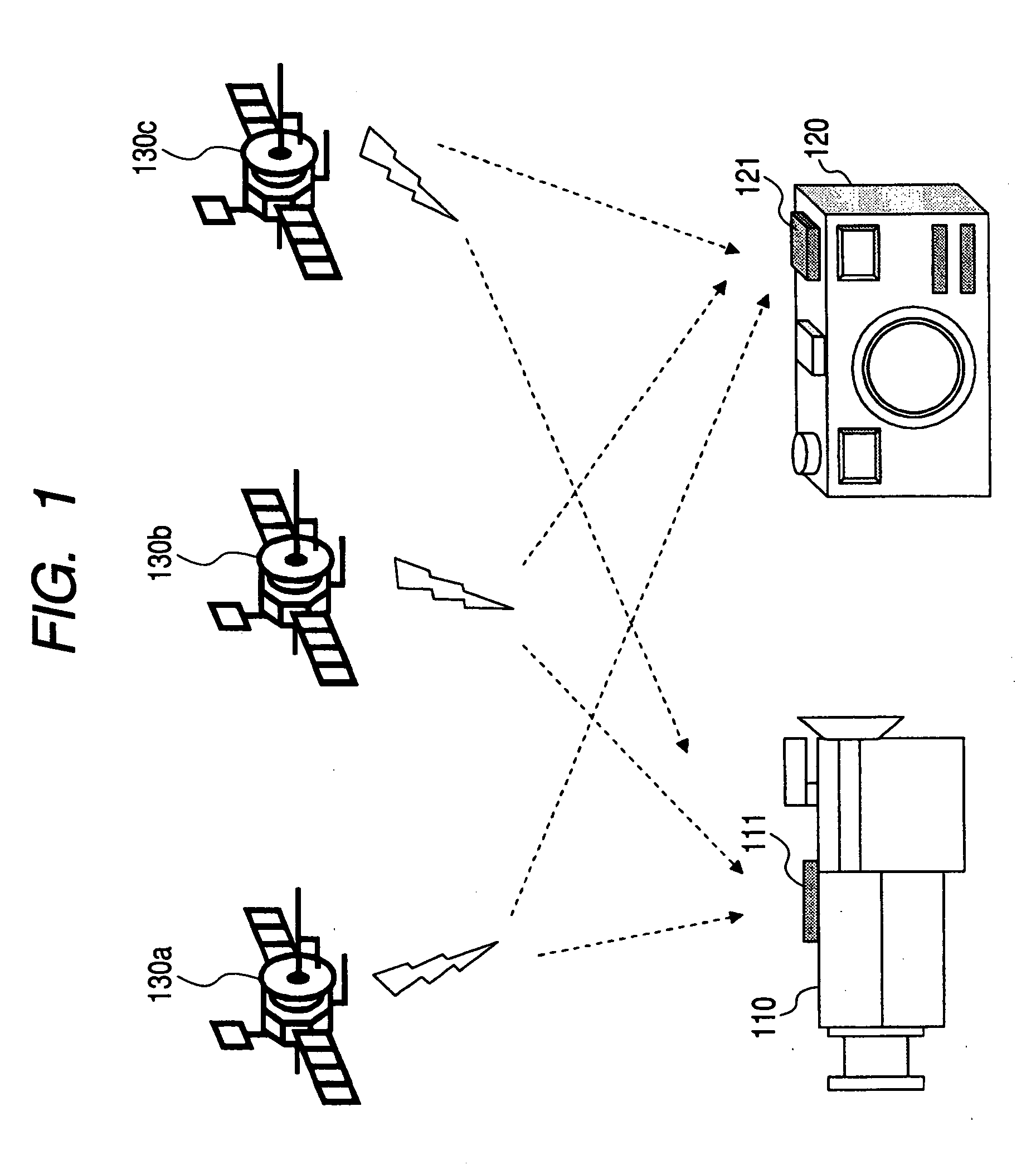

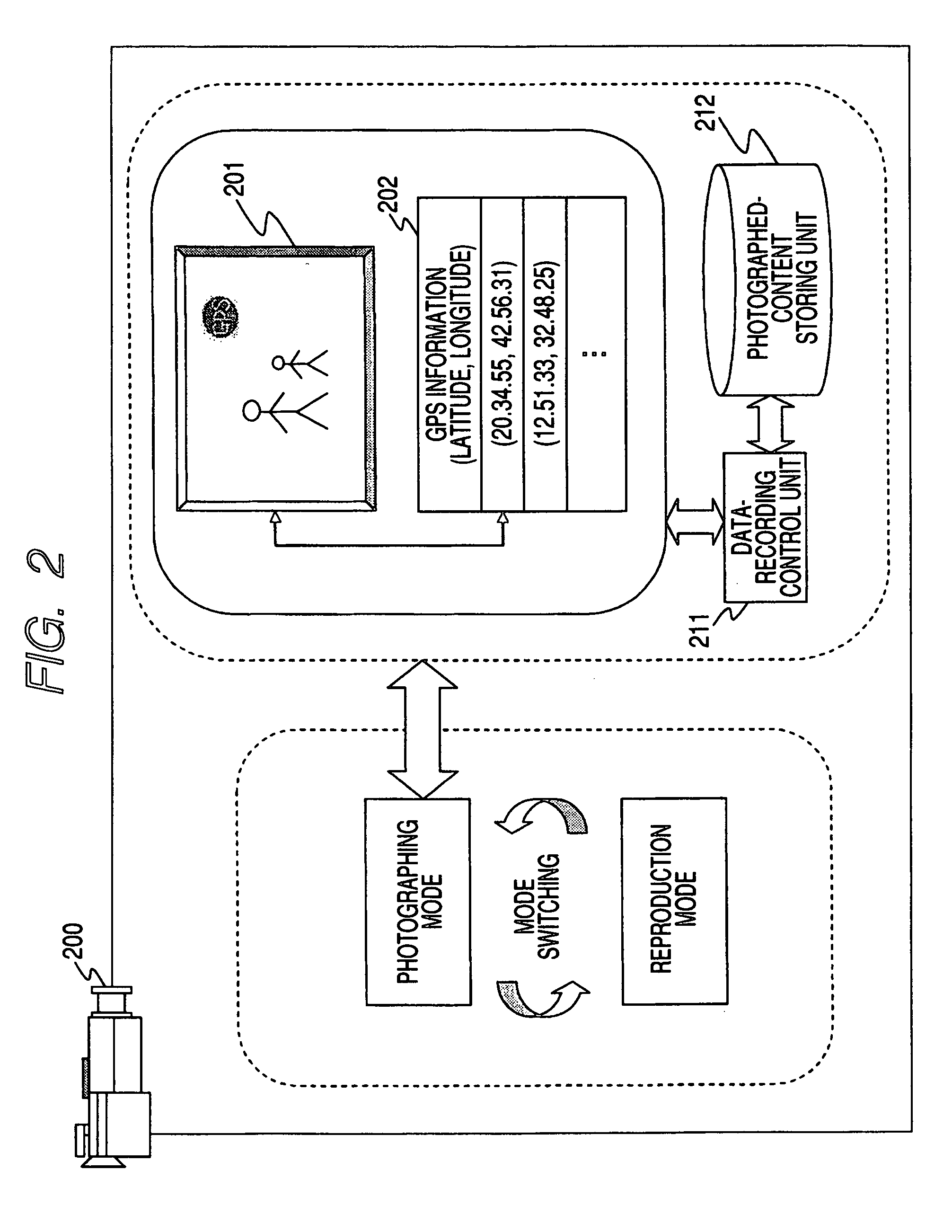

Imaging apparatus, data recording method and data-display control method, and computer program

InactiveUS20080094499A1Efficient display information generation processingAvoid wasting electricityTelevision system detailsPosition fixationData displayData recording

An imaging apparatus includes an imaging unit configured to execute processing to capture an image; a GPS (Global Positioning System) device configured to execute position calculation processing based on data received from a satellite; a power-supply control unit configured to control power supply to the GPS device; an apparatus control unit configured to monitor a state of photographing by a user to calculate a frequency of use of the imaging unit per unit time, and to cause the power-supply control unit to intermittently supply power to the GPS device when the calculated use frequency is lower than a predetermined threshold; and a data-recording control unit configured to generate photographed data attribute information in which positional information acquired in the GPS device is set as attribute information of an acquired image in the imaging unit, and to execute processing to store the photographed data attribute information in a storing unit.

Owner:SONY CORP

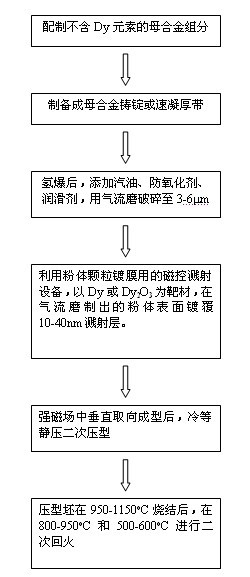

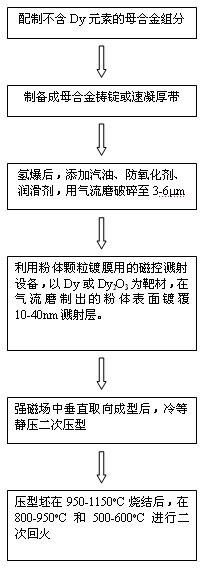

A preparation method of high-performance sintered NdFeB with low dysprosium content

The invention discloses a method for preparing sintered NdFeB with low dysprosium (Dy) content and high performance; the method comprises the following steps of: sputtering and plating the Dy element on the surface of jet mill powder by using the powder plate technology based on magnetron sputtering on the basis of preparing NdFeB powder, and then sufficiently dispersing the Dy element to micron-sized NdFeB crystal particles by dispersing the Dy element at high temperature in the sintering and tempering process, thereby achieving the effect of improving magnetic performance of the sintered NdFeB. Compared with the introduction of the Dy element in the proportioning process of the prior art, the method disclosed by the invention has the advantages: the low dysprosium content and high performance is limited in the nano-size by adopting the physical gas-phase deposition, the consumption quantity of the Dy element during the production process is controlled effectively and the preparationof sintered NdFeB with low dysprosium content and high performance is realized. Compared with the sintered NdFeB of the same components prepared by the traditional casting and powder metallurgy process, both the intrinsic coercivity and the maximum magnetic energy product of the sintered NdFeB rare-earth permanent magnetic material obtained according to the invention are improved obviously; compared with the sintered NdFeB with the same performance prepared by the traditional casting and powder metallurgy process, the dosage of the dysprosium element is reduced remarkably. The method can be widely applicable to producing and manufacturing sintered NdFeB with high performance.

Owner:NANJING UNIV OF SCI & TECH +1

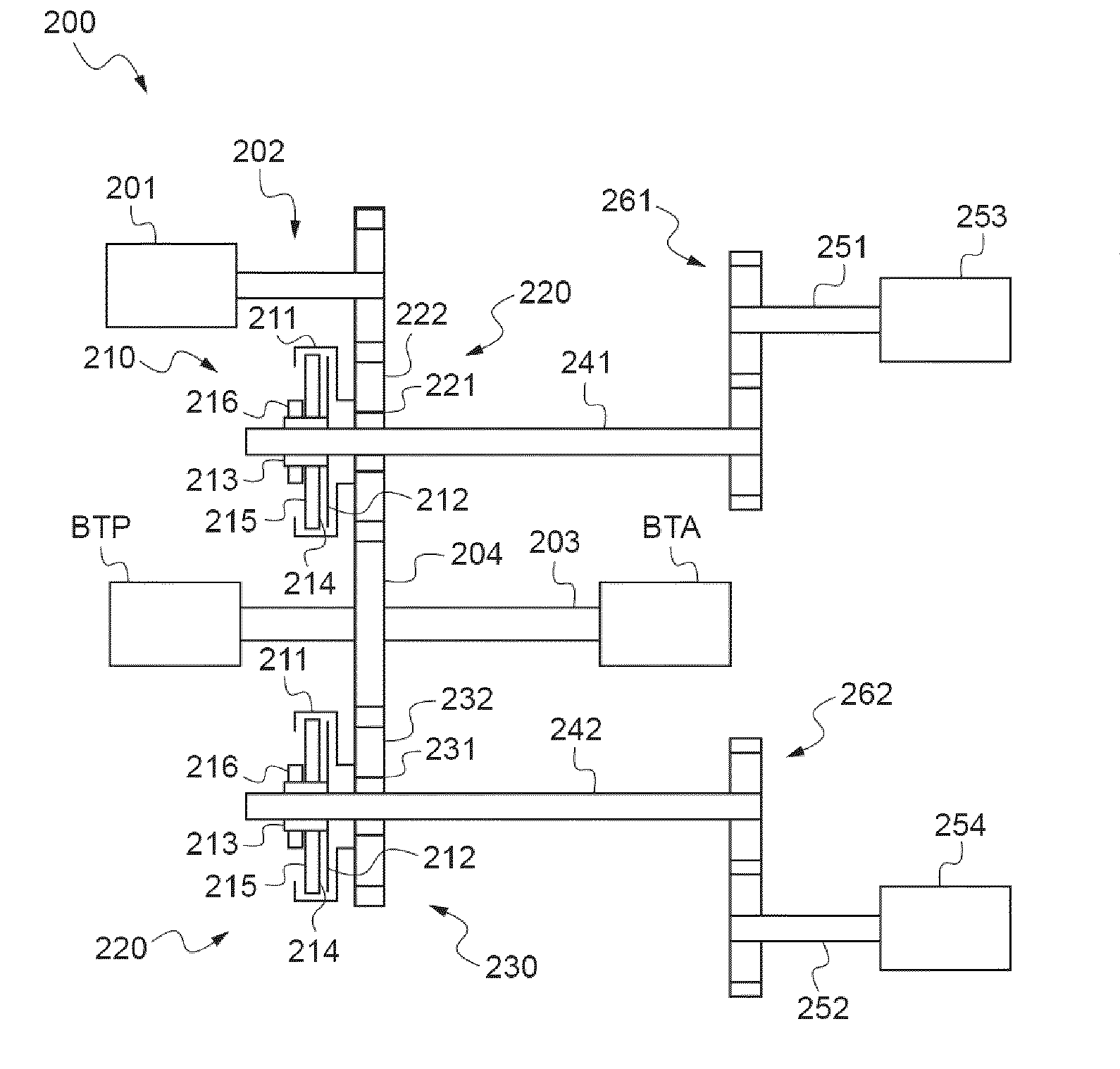

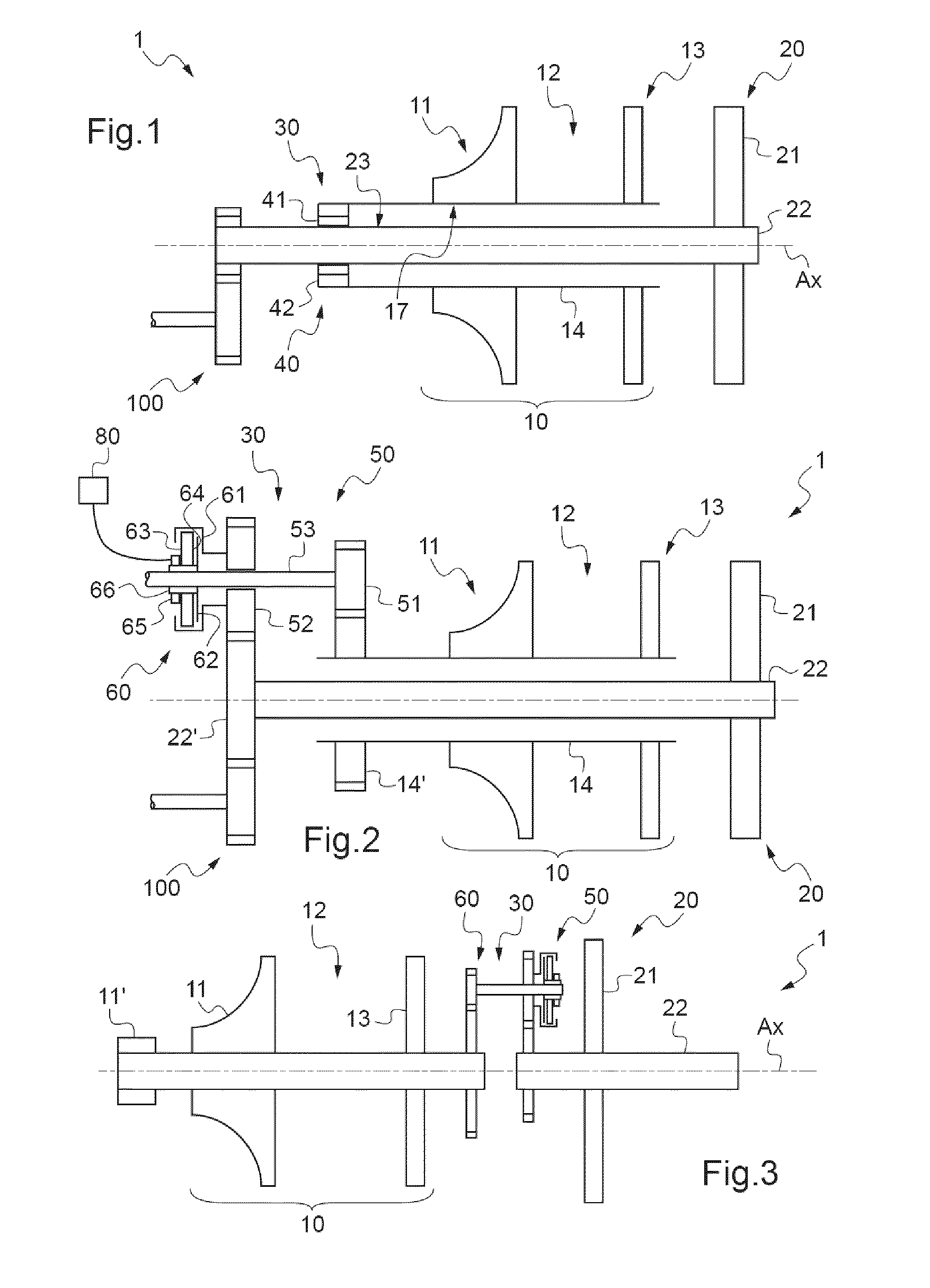

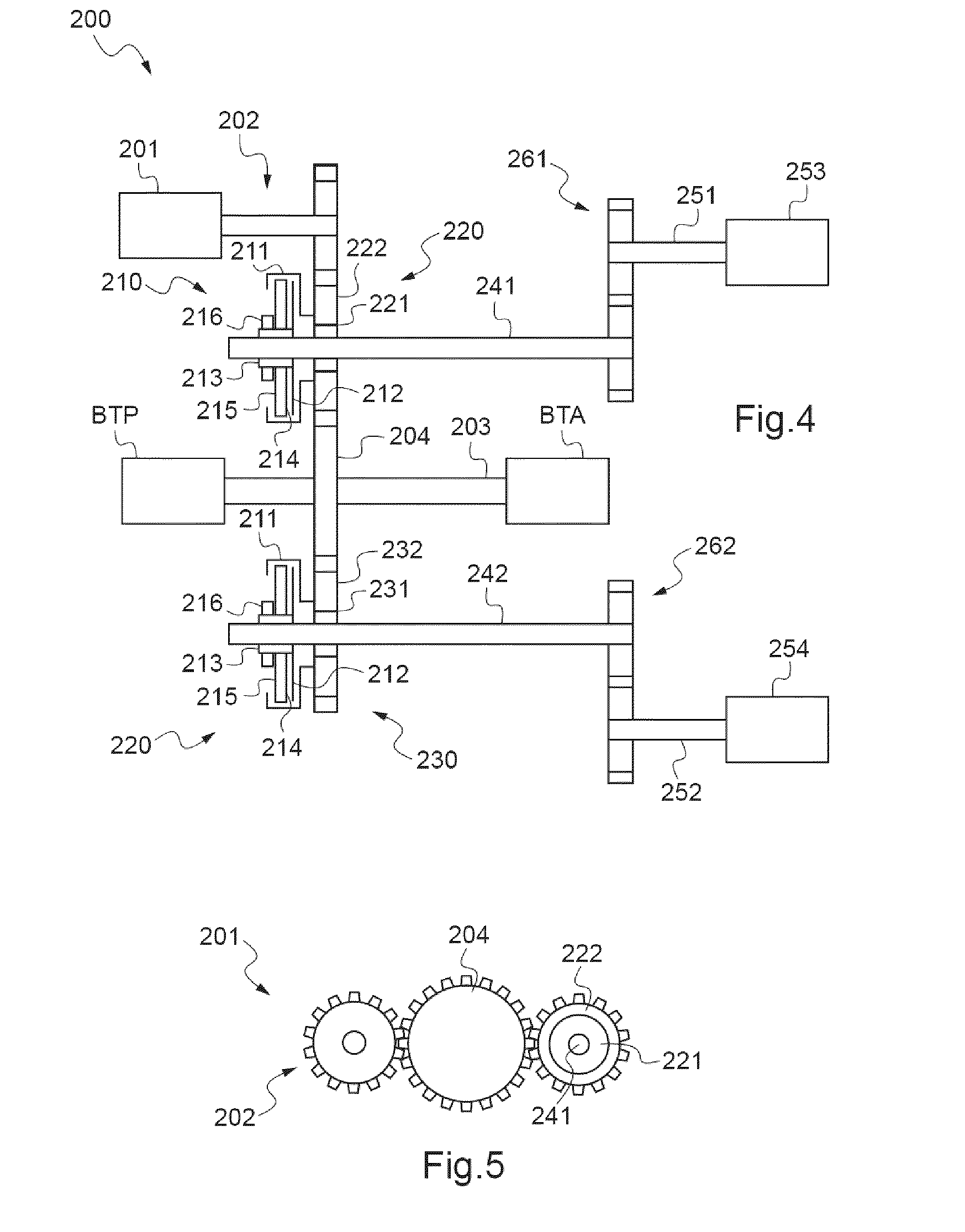

Hybrid engine installation and a method of controlling such an engine installation

ActiveUS20100013223A1Control fuel consumptionControl consumptionElectric motor startersPlural diverse prime-mover propulsion mountingDriven elementGas turbines

A hybrid engine installation (200) includes drive element (204) suitable for driving a mechanical element (BTP, BTA) in rotation. In addition, the hybrid engine installation is remarkable in that it includes at least one gas turbine (253, 254) and at least one electric motor (201) mechanically linked to the drive element (204) to drive it in rotation.

Owner:EUROCOPTER

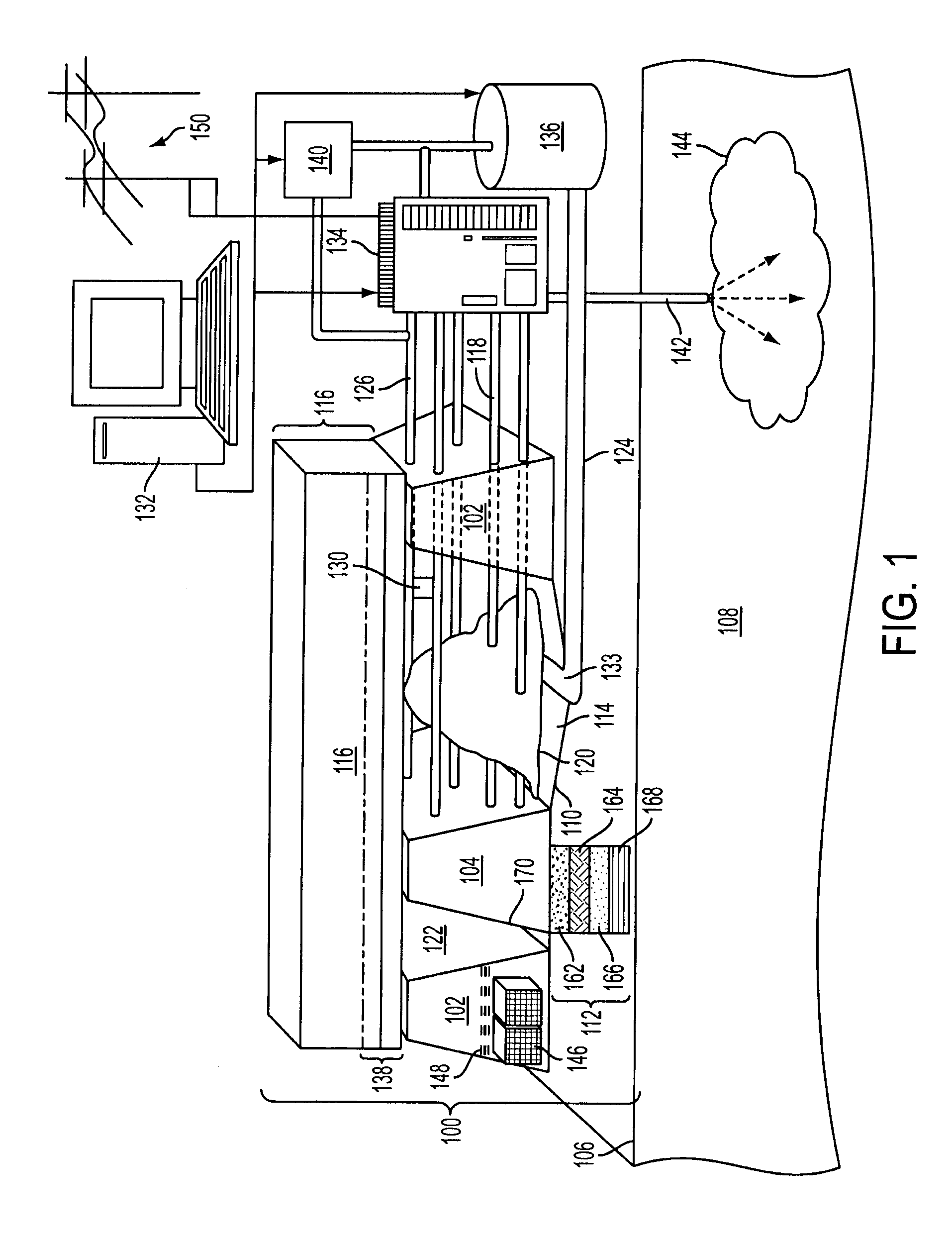

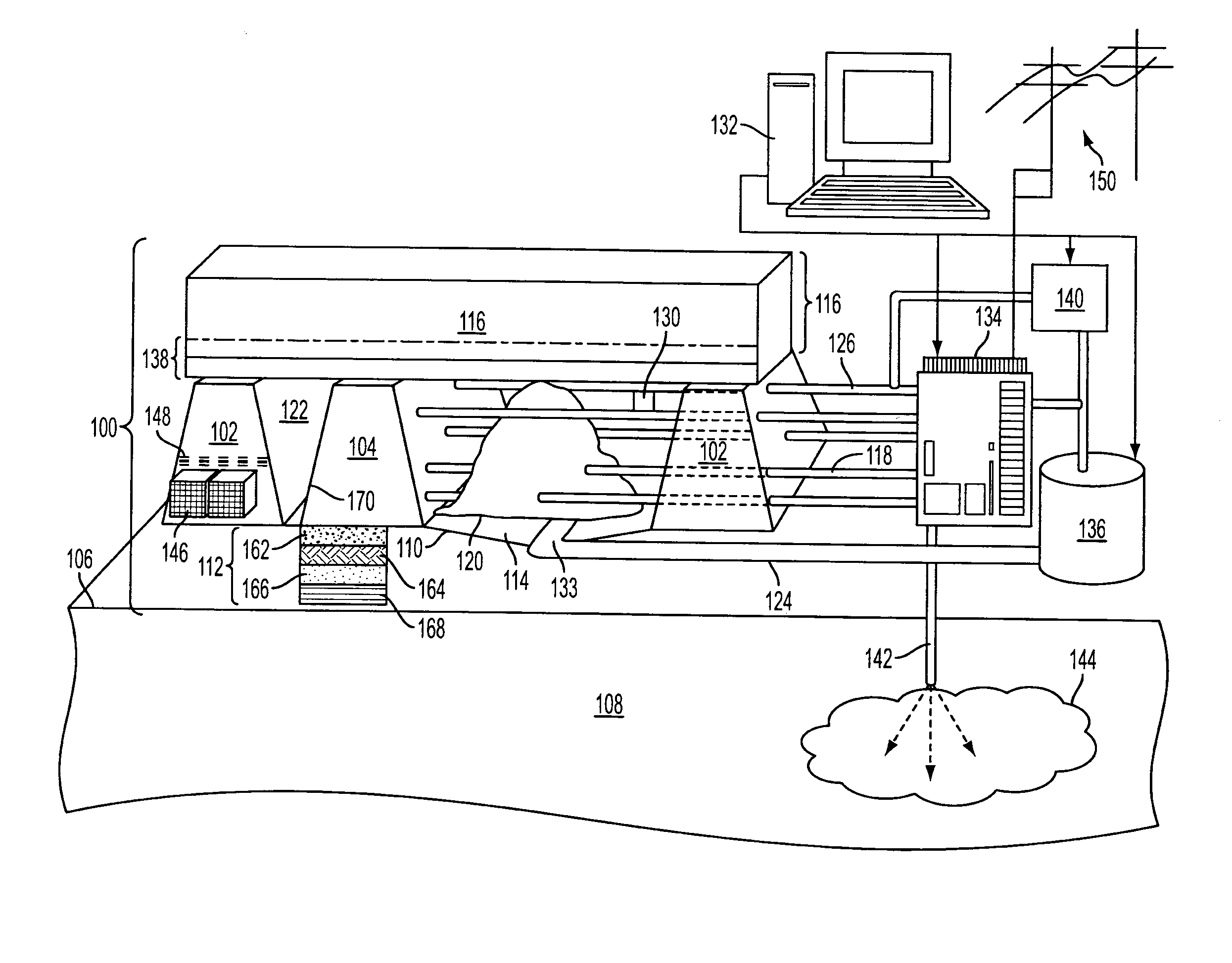

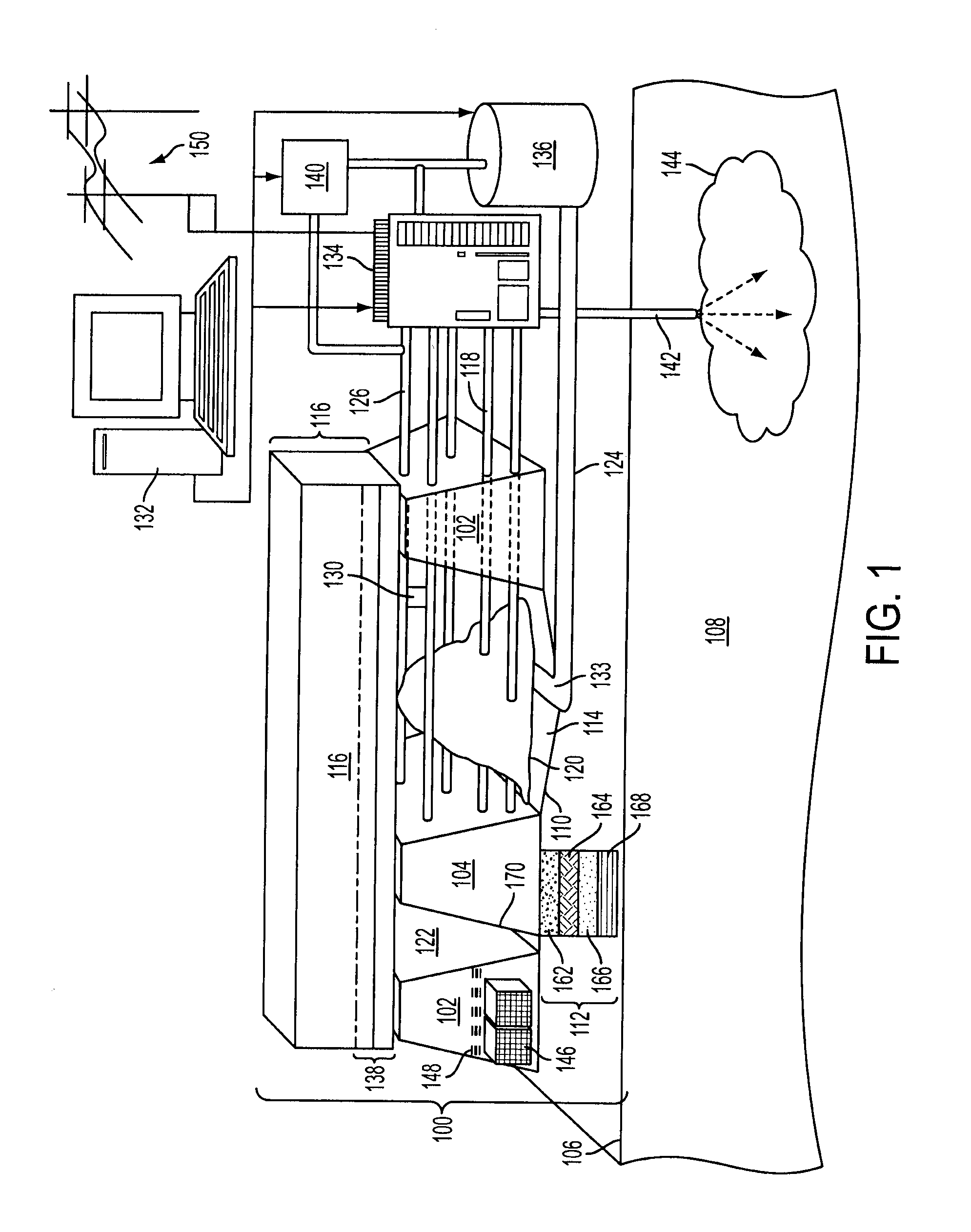

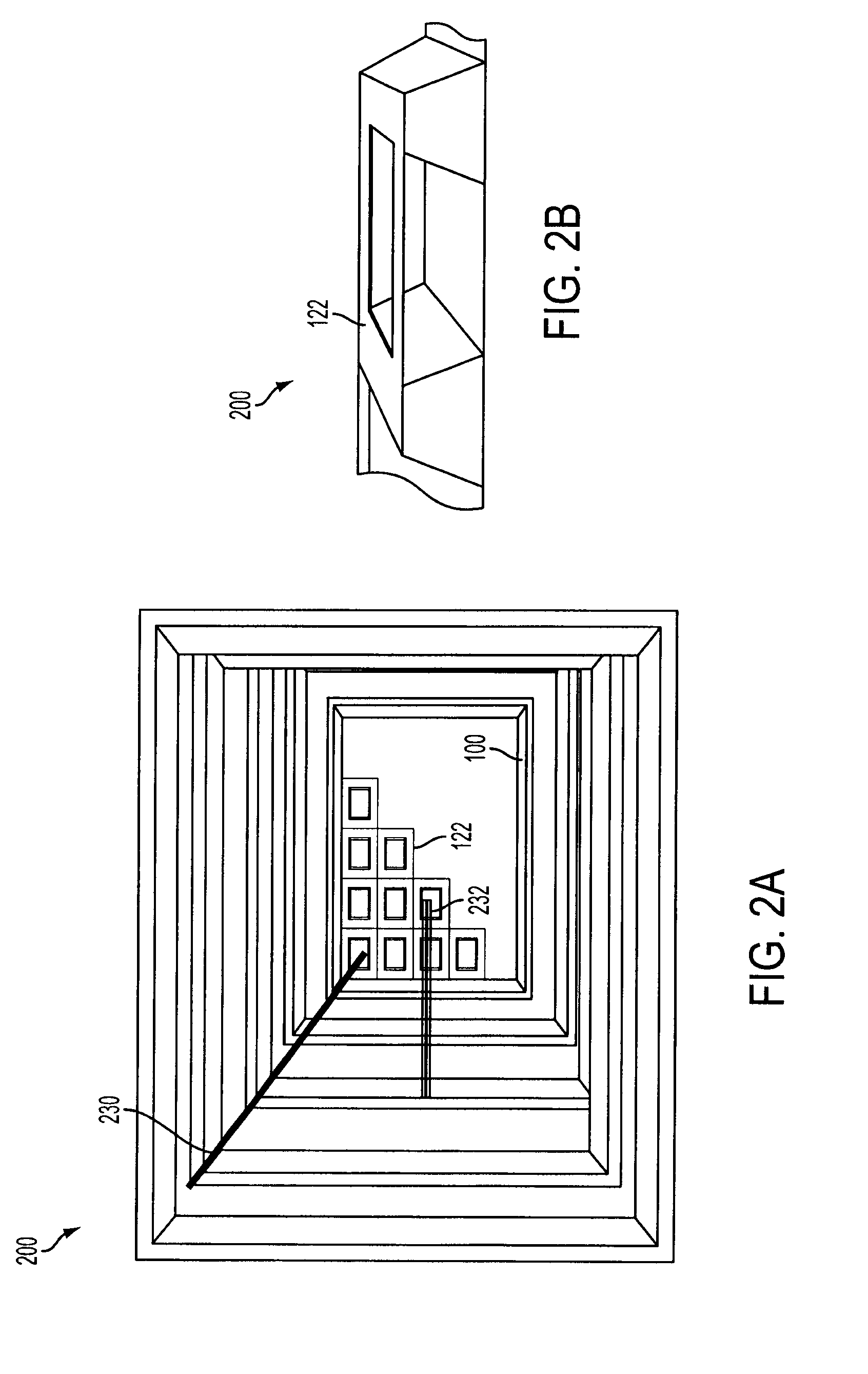

Methods of recovering hydrocarbons from hydrocarbonaceous material using a constructed infrastructure and associated systems

ActiveUS20080190818A1Reduce processing costsIncrease volume outputThermal non-catalytic crackingSolid waste disposalEngineeringHydrocarbon

A method of recovering hydrocarbons from hydrocarbonaceous materials can include forming a constructed permeability control infrastructure. This constructed infrastructure defines a substantially encapsulated volume. A comminuted hydrocarbonaceous material can be introduced into the control infrastructure to form a permeable body of hydrocarbonaceous material. The permeable body can be heated sufficient to remove hydrocarbons therefrom. During heating the hydrocarbonaceous material is substantially stationary as the constructed infrastructure is a fixed structure. Removed hydrocarbons can be collected for further processing, use in the process, and / or use as recovered.

Owner:RED LEAF RESOURCES

Methods of recovering hydrocarbons from water-containing hydrocarbonaceous material using a constructed infrastructure and associated systems

ActiveUS20080190813A1Reduce processing costsIncrease volume outputThermal non-catalytic crackingUnderground chambersEngineeringHydrocarbon

A method of recovering hydrocarbons from water-containing hydrocarbonaceous materials can include forming a constructed permeability control infrastructure. This constructed infrastructure defines a substantially encapsulated volume. A mined or separately collected water-containing hydrocarbonaceous material can be introduced into the control infrastructure to form a permeable body of hydrocarbonaceous material. The permeable body can be heated sufficient to initially remove water therefrom as a water vapor. The water vapor can be removed from the infrastructure via an outlet which can be controlled or shut off when the permeable body is sufficiently dewatered. The dewatered permeable body can be heated sufficient to remove hydrocarbons therefrom. During heating the hydrocarbonaceous material is substantially stationary as the constructed infrastructure is a fixed structure. Removed hydrocarbons can be collected for further processing, use in the process, and / or use as recovered.

Owner:RED LEAF RESOURCES

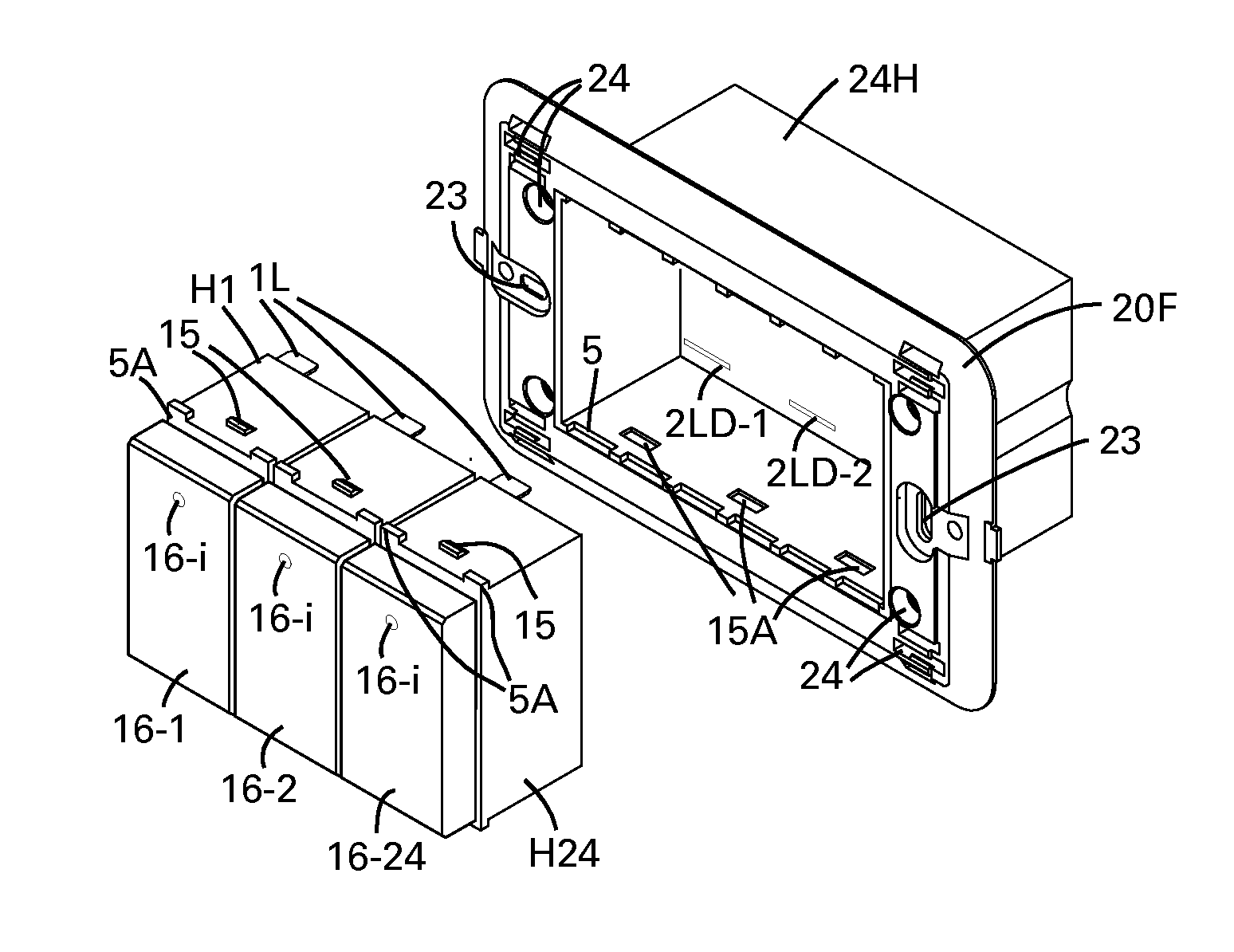

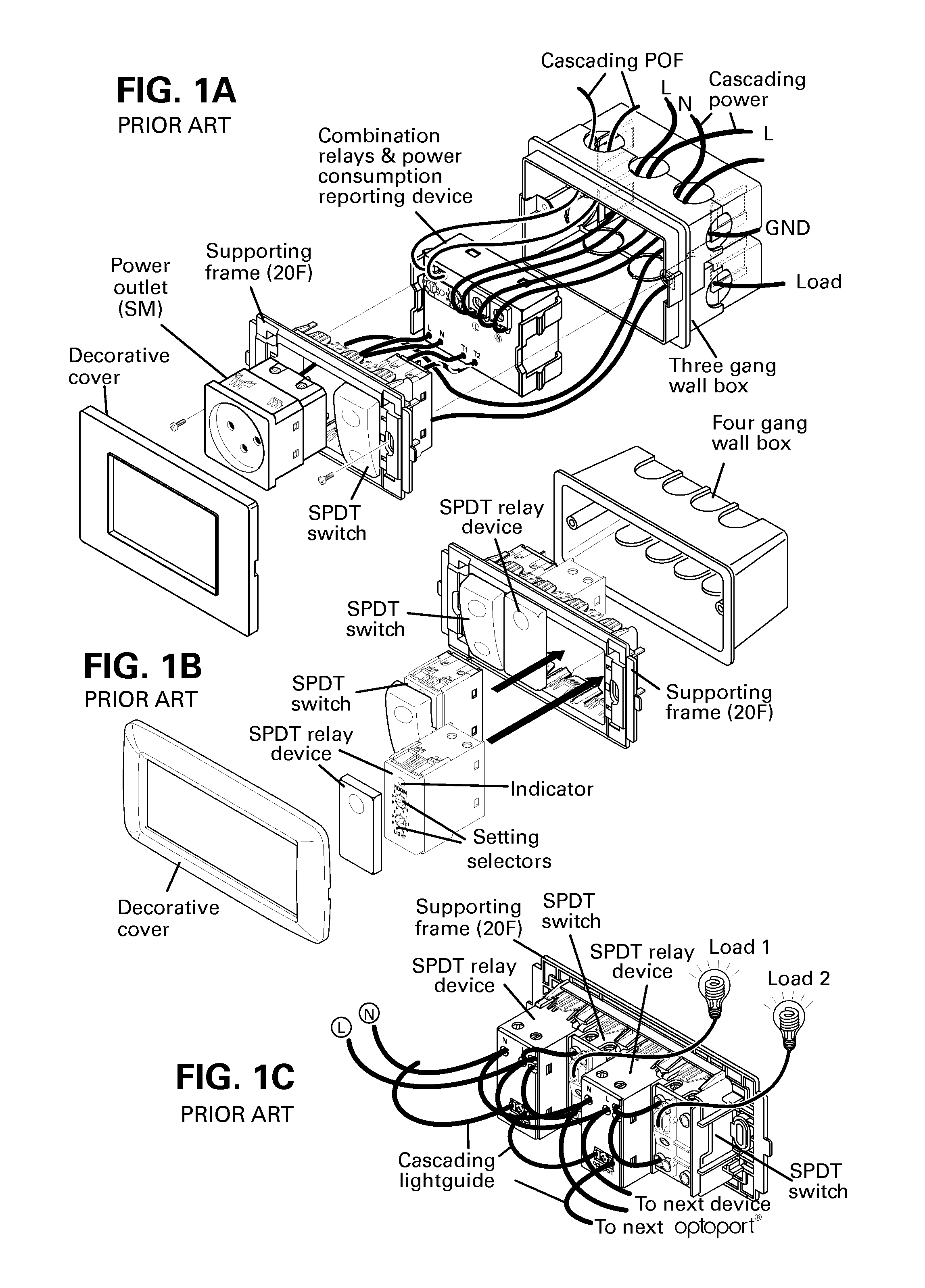

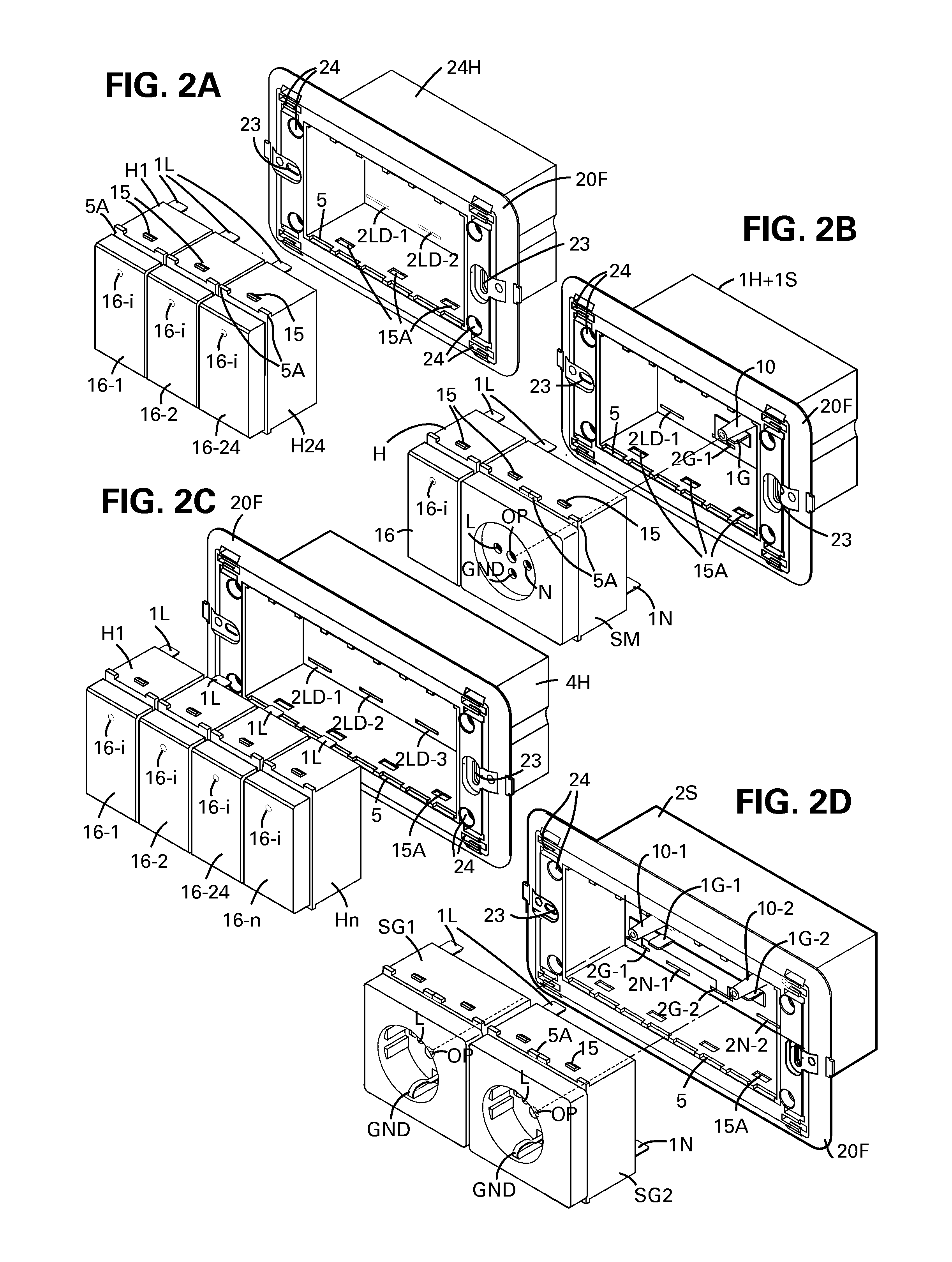

Intelligent Support Box for Electric Hybrid Switches, Power Outlets and Combinations Thereof

ActiveUS20150280410A1Control consumptionNumber of controlLine/current collector detailsNon-electrical signal transmission systemsCommand and controlEngineering

A method and apparatus for attaching at least one wiring device comprising AC outlet, switch, relay, hybrid switch-relay and hybrid switch to a support box using pins and receptacle including locking structure for attaching by introduction of the device into the box. The box including intelligent control and communication circuits including RF, RFID, optical via POF and IR in line of sight for communicating commands and control including power consumption reporting from every outlet and device. The power outlets include rear opening for introduction of RFID sensor, optical sensor and setting selector for identifying the appliance or the load powered via the outlet.

Owner:ELBEX VIDEO LTD

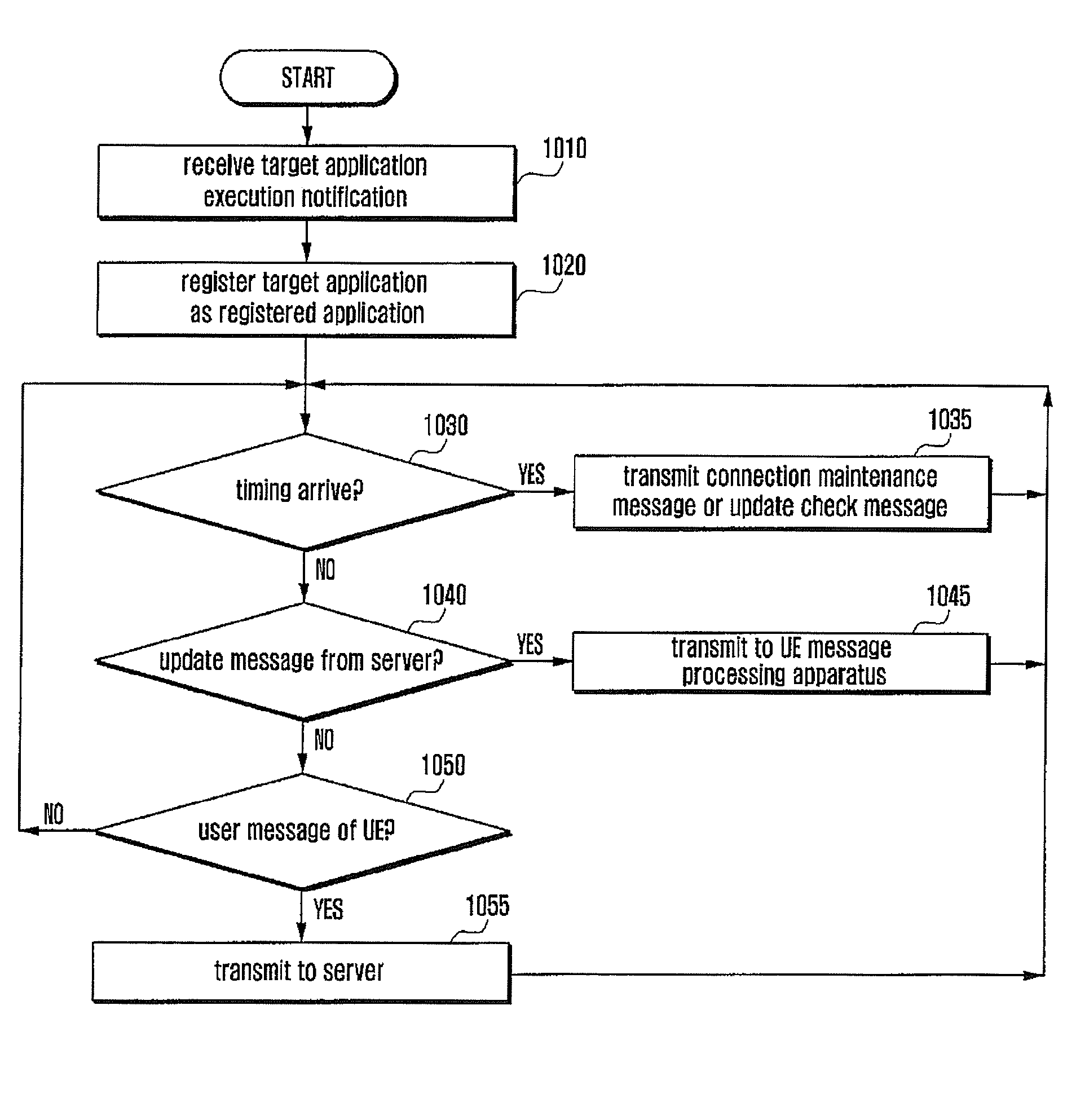

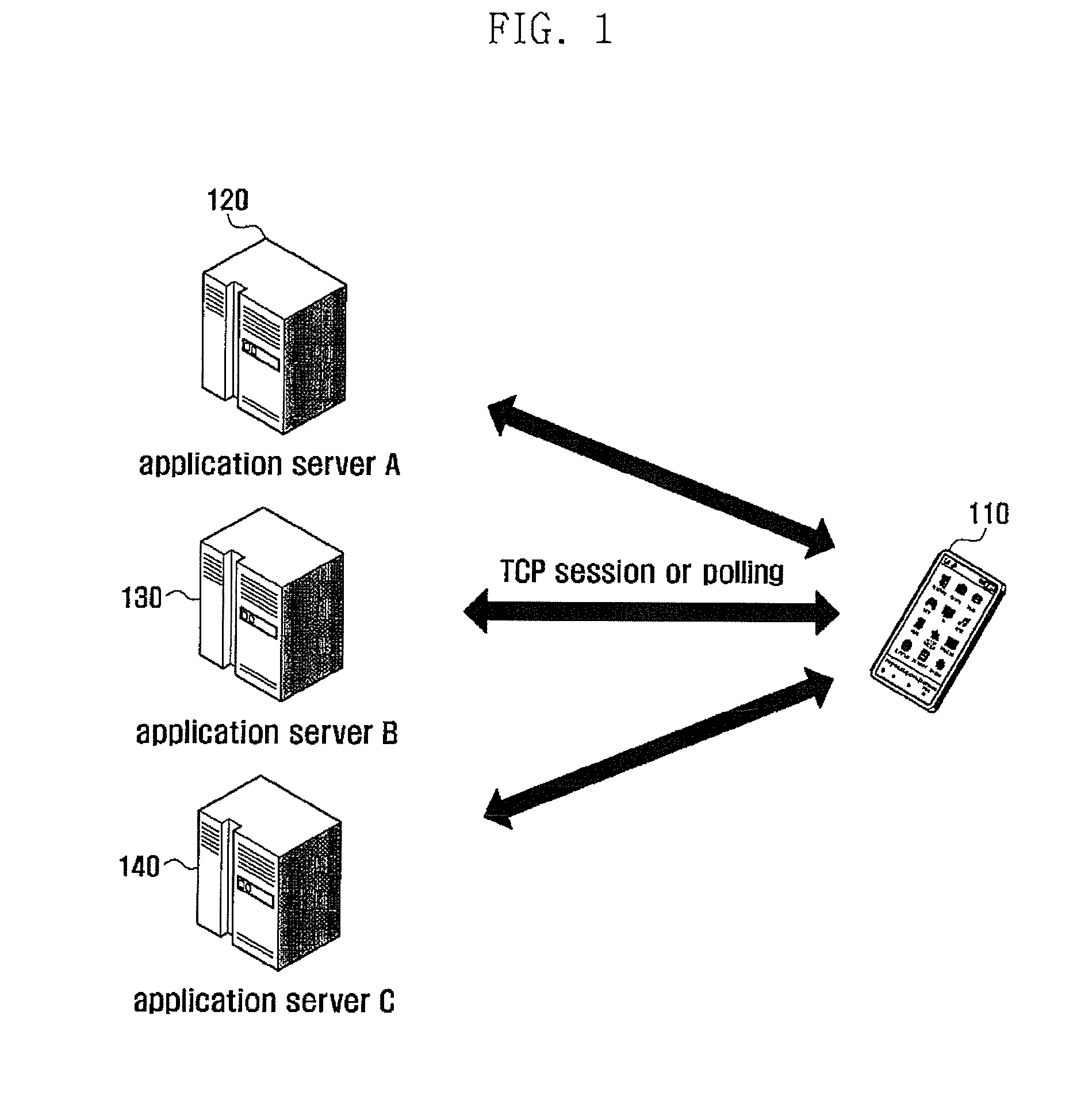

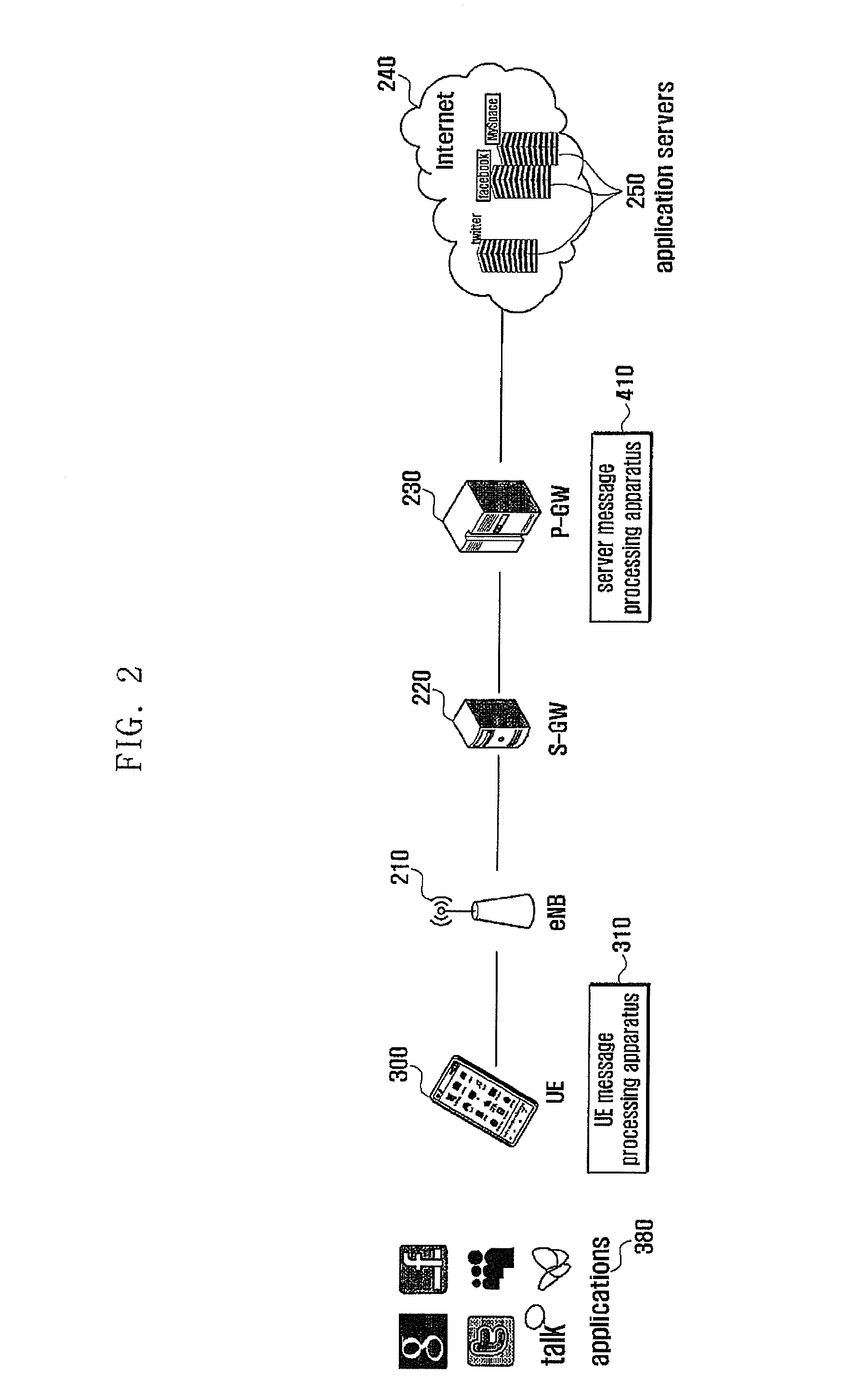

Method and apparatus for processing messages

ActiveUS20150019723A1Reduce decreaseControl consumptionPower managementDigital computer detailsComputer hardwareMessage processing

The present disclosure relates to a method and apparatus for processing messages. The terminal message processing method According to one embodiment of the present disclosure, the method for processing terminal messages used by the apparatus for processing terminal messages can include the steps of: receiving a message from an application of the terminal; determining whether the message is from a pre-registered registration application; when the message is from the registration application, determining whether the message is a control message; and when the message is not from the registration application, transmitting the message to a device for processing server messages. According to one embodiment of the present disclosure, a message processing apparatus and method for reducing the transmission and reception of a control message for an application are provided, and battery consumption is reduced.

Owner:SAMSUNG ELECTRONICS CO LTD

Methods of recovering hydrocarbons from hydrocarbonaceous material with reduced non-carbonaceous leachate and co2 and associated systems

ActiveUS20080190816A1Avoid insufficient heatingInhibition formationThermal non-catalytic crackingUnderground chambersLeachateMaterials science

A method of recovering hydrocarbons from hydrocarbonaceous materials can include forming a stationary permeability control infrastructure. This constructed infrastructure defines a substantially encapsulated volume. A comminuted hydrocarbonaceous material can be introduced into the control infrastructure to form a permeable body of hydrocarbonaceous material. The permeable body can be heated sufficient to remove hydrocarbons therefrom within a temperature range which is sufficient to substantially avoid formation of carbon dioxide or non-hydrocarbon leachates. During heating the hydrocarbonaceous material is substantially stationary as the constructed infrastructure is a fixed structure. Removed hydrocarbons can be collected for further processing, use in the process, and / or use as recovered.

Owner:RED LEAF RESOURCES

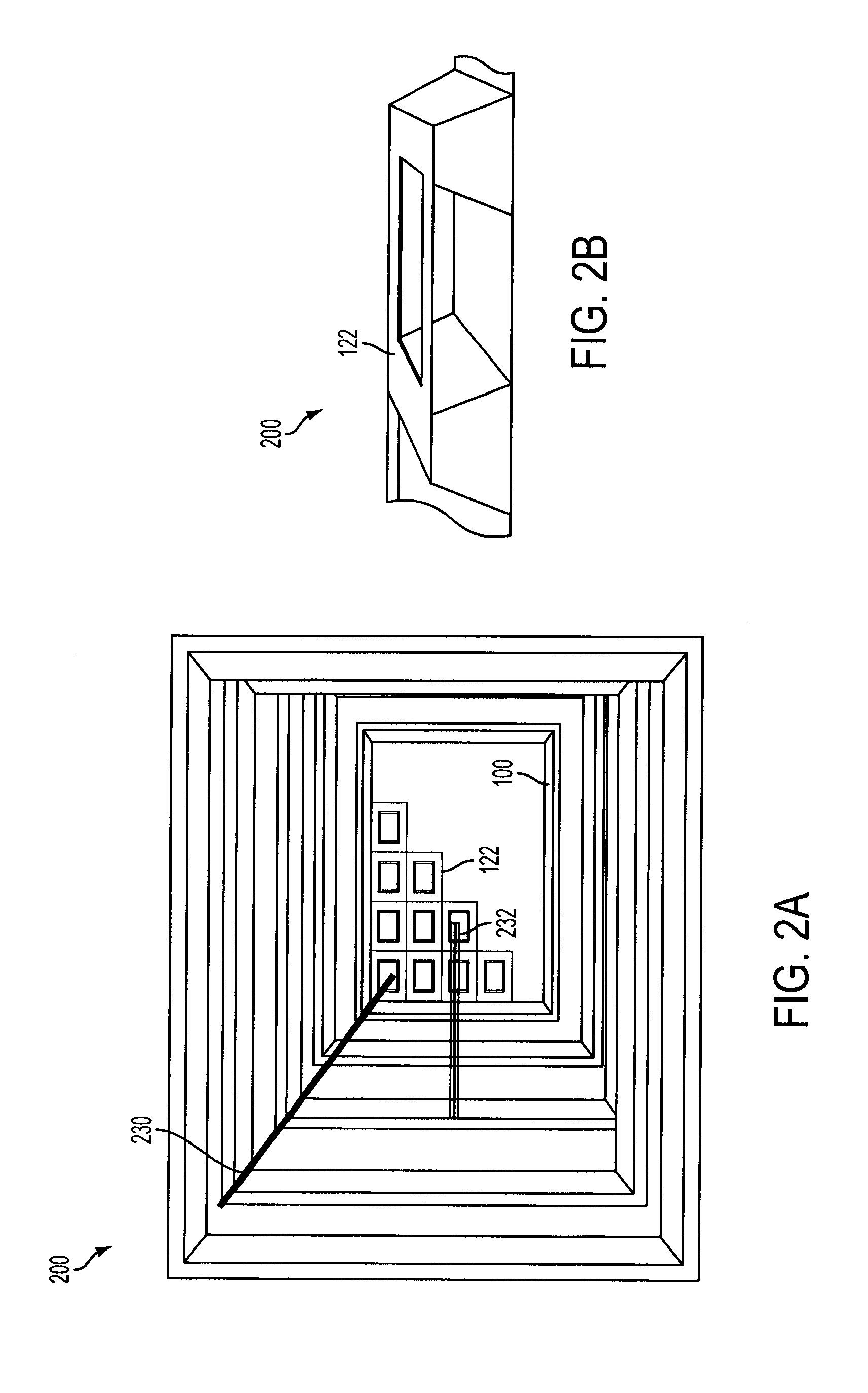

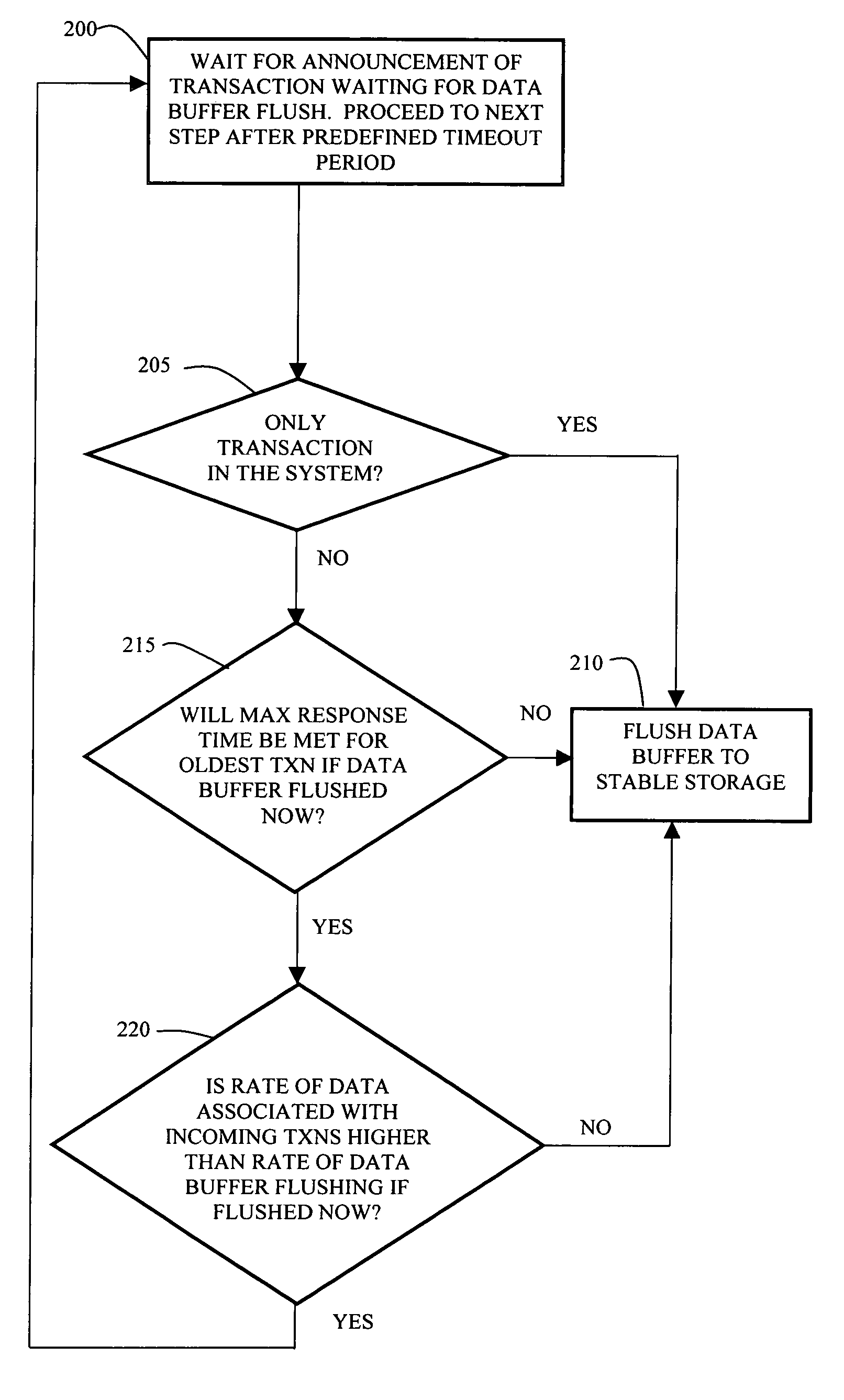

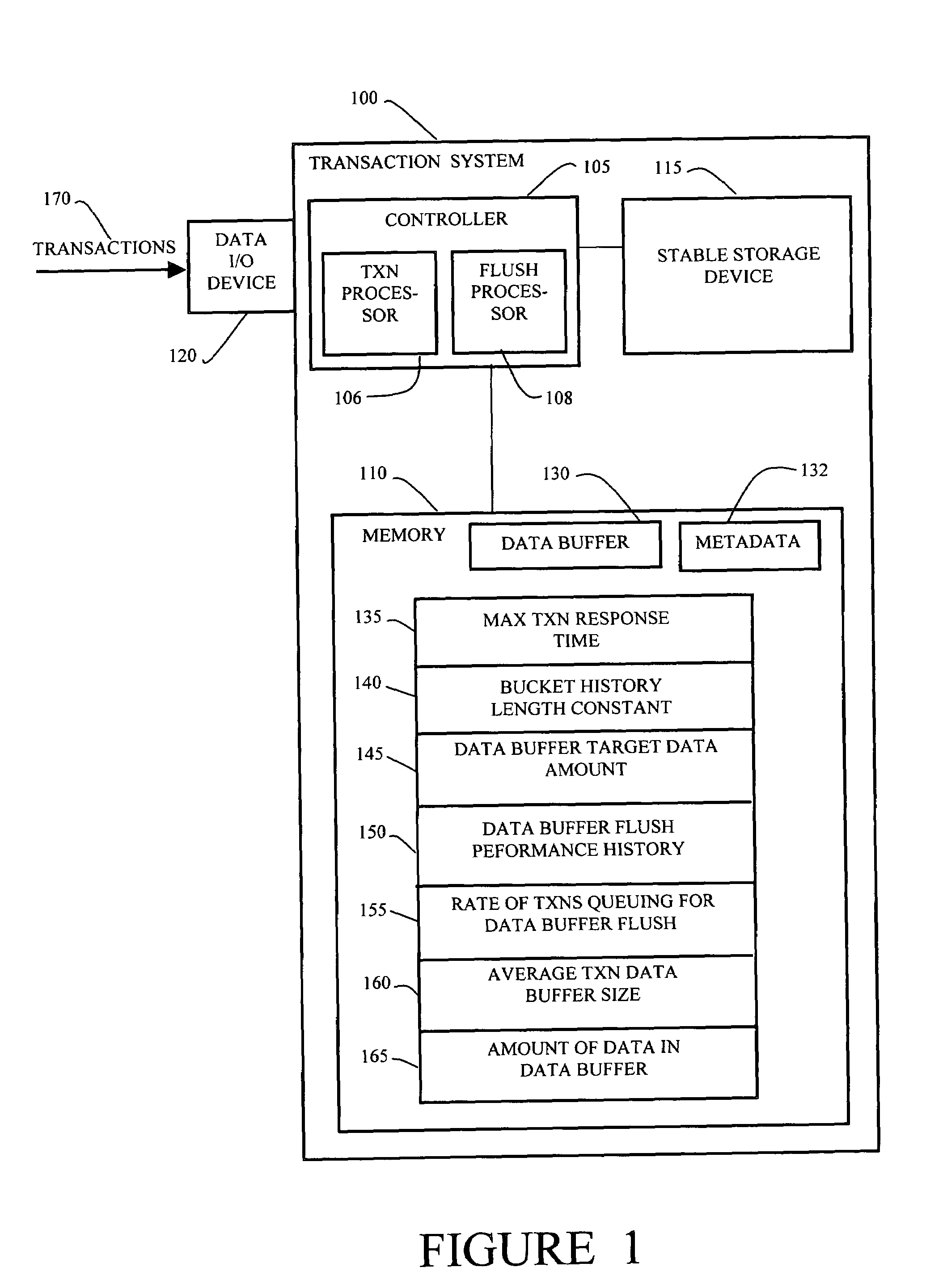

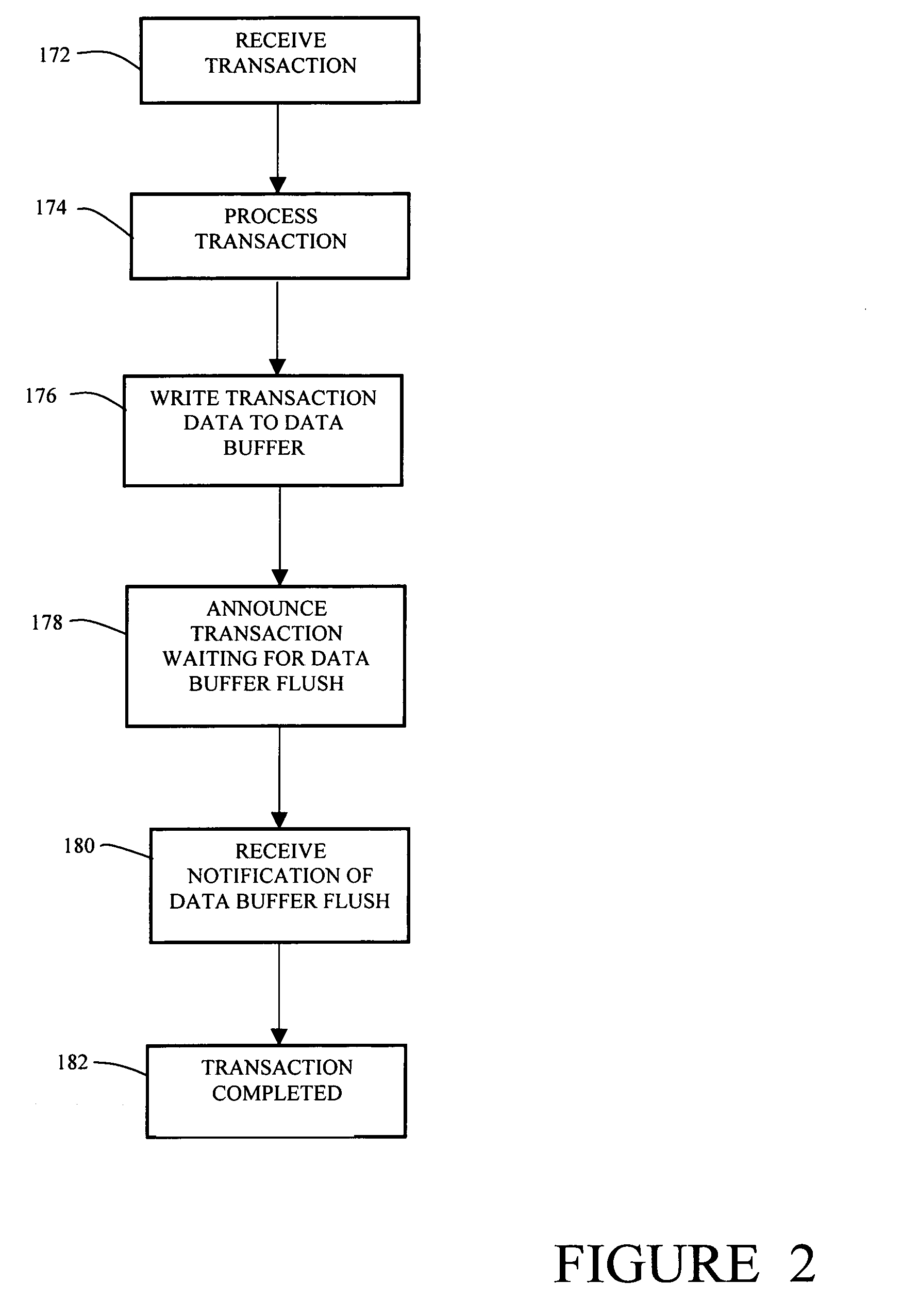

Method and apparatus for self-tuning transaction batching

InactiveUS7165129B1Improve responseImprove throughputMemory architecture accessing/allocationSpecial data processing applicationsSelf-tuningPeak value

In a transaction system, a dynamic batching process enables efficient flushing of data in a data buffer to a stable storage device. The transaction system uses constant values and dynamic values and a system performance history to adjust the rate of flushing data and also to adjust the amount of data flushed in each flush operation. The transaction system is able to respond to both spikes in rate of received transactions as well as more gradual changes in the rate of received transactions and to automatically adapt to stable storage device performance variations.

Owner:CISCO TECH INC

Methods of recovering hydrocarbons from hydrocarbonaceous material using a constructed infrastructure and associated systems

ActiveUS7862705B2Low costHigh outputThermal non-catalytic crackingSolid waste disposalEngineeringHydrocarbon

A method of recovering hydrocarbons from hydrocarbonaceous materials can include forming a constructed permeability control infrastructure. This constructed infrastructure defines a substantially encapsulated volume. A comminuted hydrocarbonaceous material can be introduced into the control infrastructure to form a permeable body of hydrocarbonaceous material. The permeable body can be heated sufficient to remove hydrocarbons therefrom. During heating the hydrocarbonaceous material is substantially stationary as the constructed infrastructure is a fixed structure. Removed hydrocarbons can be collected for further processing, use in the process, and / or use as recovered.

Owner:RED LEAF RESOURCES

Nutrition / diet control system

InactiveUS20080033827A1Conveniently placed anywhereControl consumptionNutrition controlMedical equipmentDiet controlledControl system

The present invention relates to a system for diet control; more specifically, to an autonomous portable electronic device, which allows the user easily, input a nutrition facts data about the food he or she takes into the device. The device can extract, display, and store in a cumulative fashion the nutrition facts he or she takes, and possibly give a warning message when the user takes more nutrition facts than their needs, and possibly give a suggestion helping the user to select to meal. Also, the device can easily send the user's nutrition information to the restaurant / food store when they buy the food so the restaurant / food store can make the food based on the user's nutrition requirement. Also, the device can count the energy consumed by the user, and give the user a hint on how to adjust his or her nutrition / diet control.

Owner:KUANG SHAOBO +1

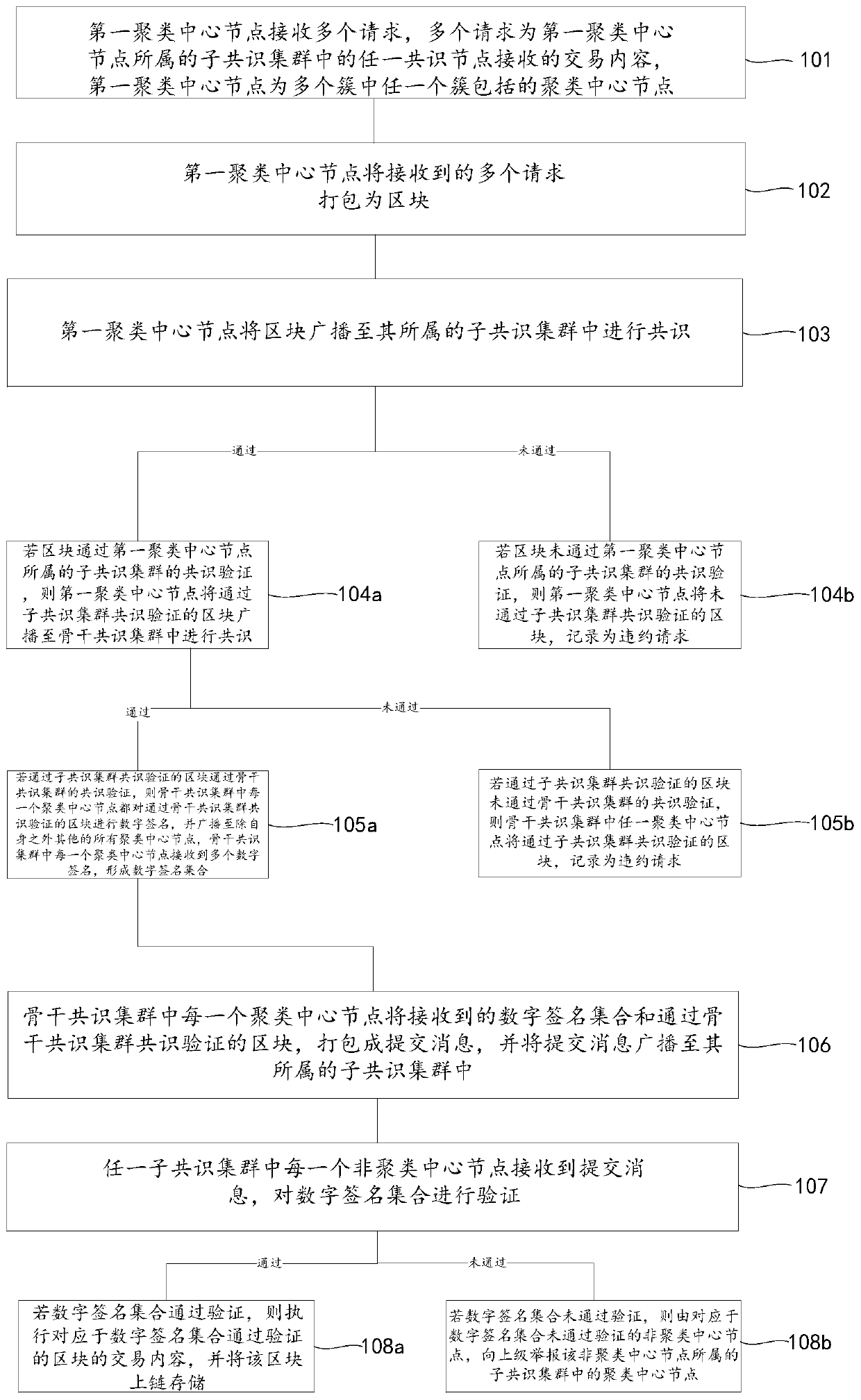

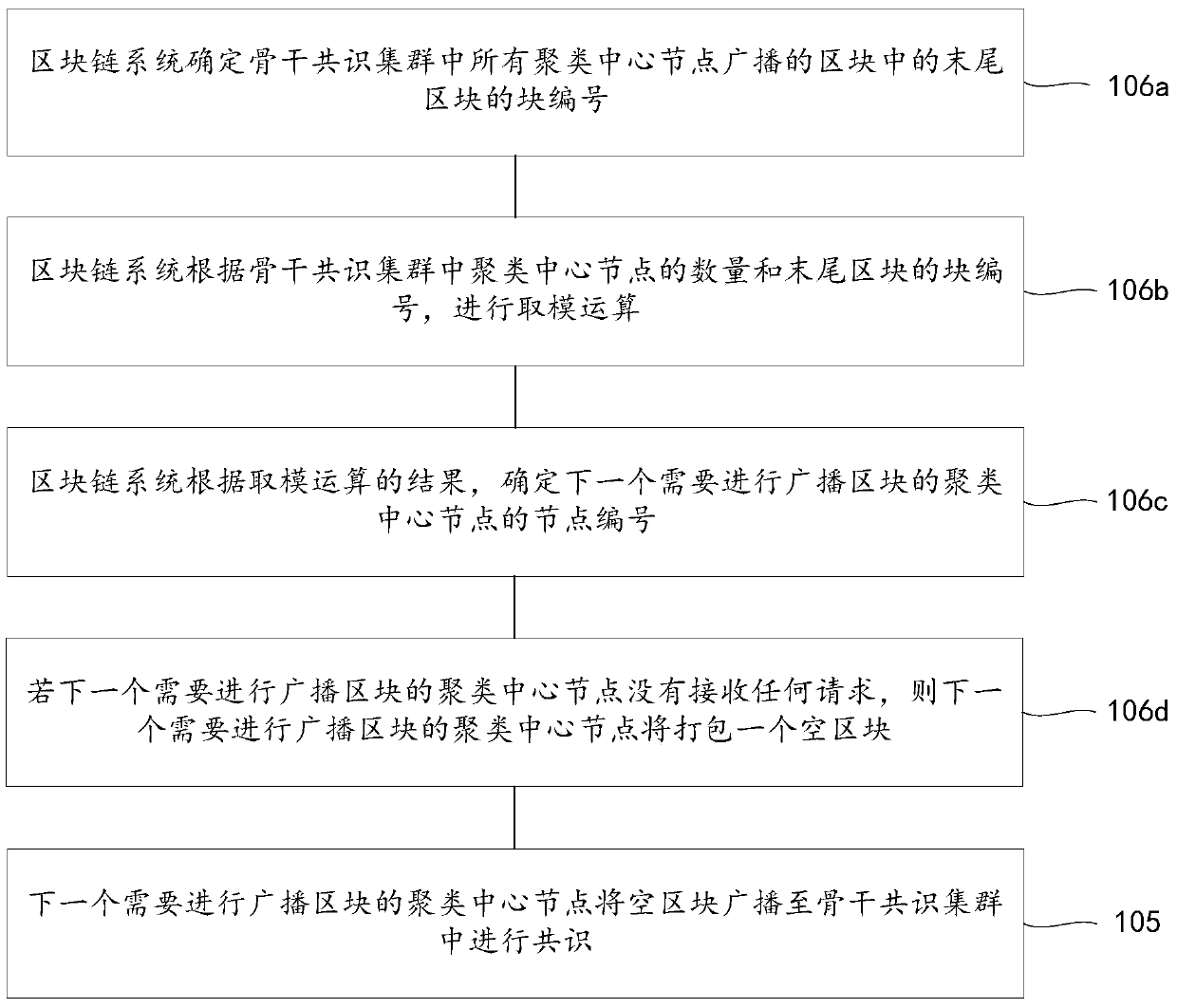

Block chain system consensus method and device based on improved clustering algorithm

ActiveCN110113388AImprove work efficiencyControl consumptionUser identity/authority verificationCanopy clustering algorithmCluster algorithm

The invention discloses a block chain system consensus method and device based on an improved clustering algorithm. The invention relates to the field of block chains. The method comprises the following steps: enabling the first clustering center node to receive a plurality of requests, packaging the plurality of requests into blocks; broadcasting to the subconsensus cluster to which the subconsensus cluster belongs for consensus; if the block passes the consensus, enabling the block to pass the consensus, broadcasting the blocks to a backbone consensus cluster for consensus; if the consensusof the backbone consensus cluster is passed, enabling each clustering center node to digitally sign and broadcast the block; packaging the received digital signature set and the block into a submission message, broadcasting the submission message to a sub-consensus cluster to which the submission message belongs, receiving the submission message by each non-clustering center node, verifying the digital signature set, and if the transaction content of the block is verified and executed, storing the block in a chain. According to the block chain system consensus based on the improved clusteringalgorithm, the communication frequency and the data transmission amount required by single consensus are reduced, and the working efficiency of the whole block chain system is greatly improved.

Owner:SICHUAN UNIV

Secure wireless leak detection system

InactiveUS20060124171A1Easy to installReduce power consumptionDetection of fluid at leakage pointOther washing machinesTransceiverMagnetic valve

A method utilizing a wireless leak detection and prevention system, used for preventing property damage and personal injury caused by liquid or gas leak. The system comprised of a wireless, battery operated apparatus having sensor(s) incorporated with an RF transmitter, used for detecting liquid or gas leaks, and transmits signal(s) to a wireless valve shutoff control unit. The valve shutoff control unit containing an RF transceiver and a processor designed to receive the detected signals and activate a supervised solenoid or motorized valve shut-off mechanism to stop the detected leak. In a preferred embodiment of the invention, the wireless valve control unit is connected to a motor, which is mounted on manual shutoff valve. Wherein the valve control unit activates the motor to produce torque to turn the valve towards a close position in response to a received detected leak signal from a sensor. An electronic or electromechanical circuitry is provided, to detect motor or gear turn cycles. The motor rotation is being controlled by the valve control unit processor, which stops motor rotation in response to a detected preset number of motor turn cycles. A digital, voice, SMS text message phone dialer is add to dispatch the detected leak signals, and notify monitoring personnel of the supervised system operation status. And provide user access to turn on or off a valve(s) from a remote location.

Owner:RUGGIERI MONICA L +1

Method of recovery copper, nickel and noble metal in waste water and slag by combined technology of wet method and fire method

A process for recovering the copper, Ni and noble metals from the sewage and dregs by the combination of wet method and fire method includes the wet process including extracting, Cu-Ni separation, removing Fe, extracting, and refining nickel carbonate, and the fire process including sintering and smelting to produce nickel matte and black copper. Its advantages are high recovery rate of Ni, Cu, Au, Ag and Pd, and no secondary pollution.

Owner:孙涛 +1

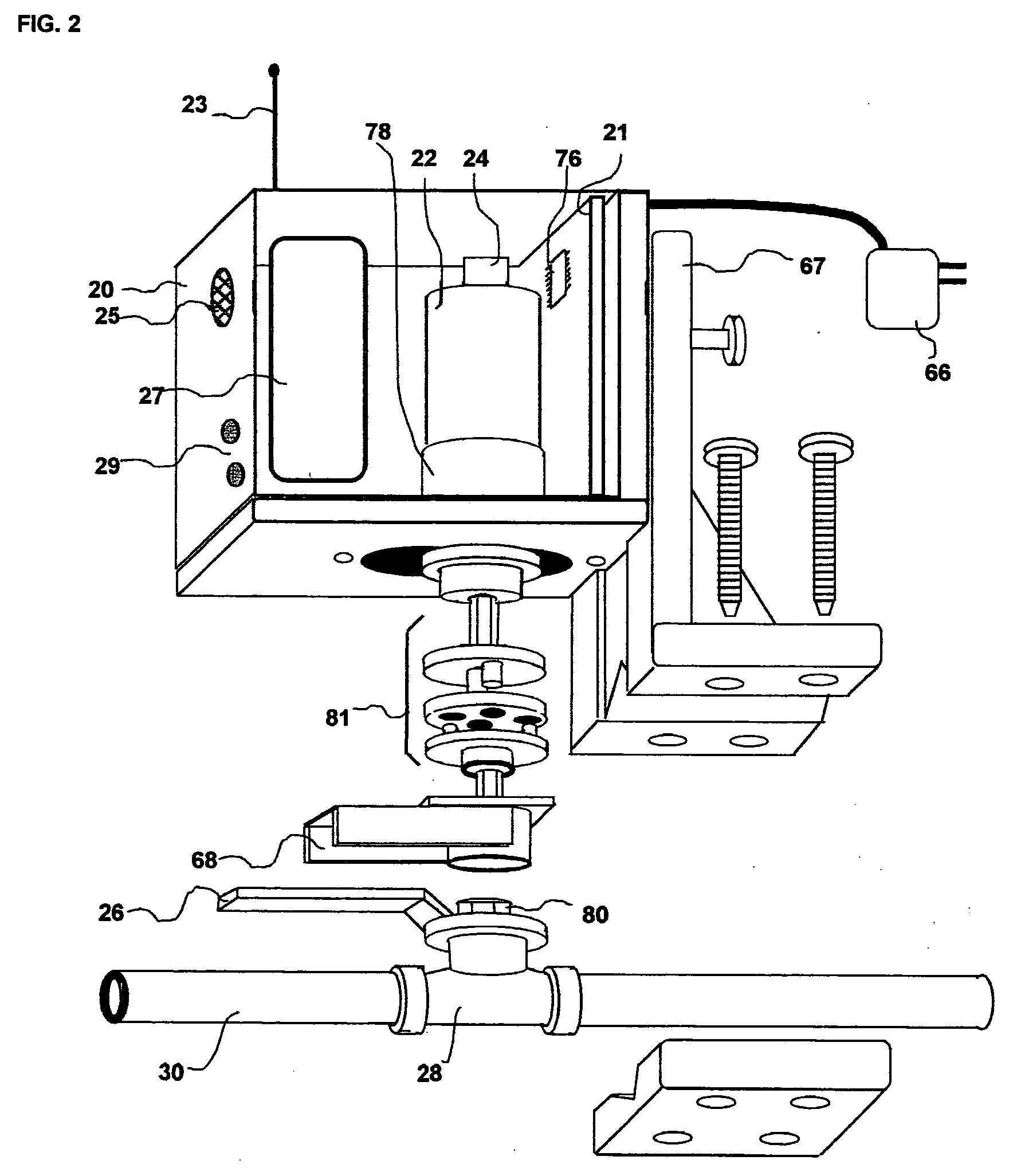

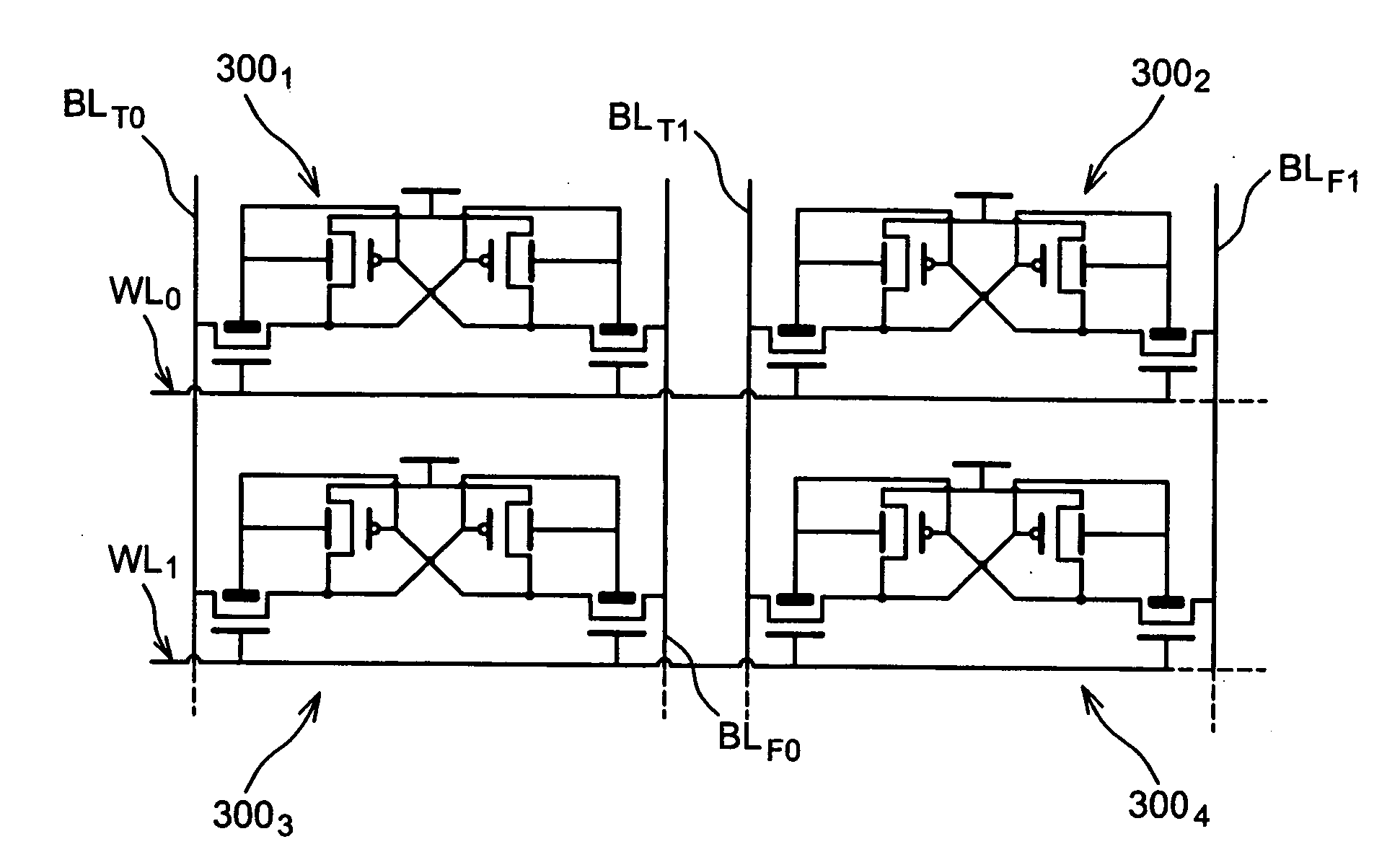

Memory cell provided with dual-gate transistors, with independent asymmetric gates

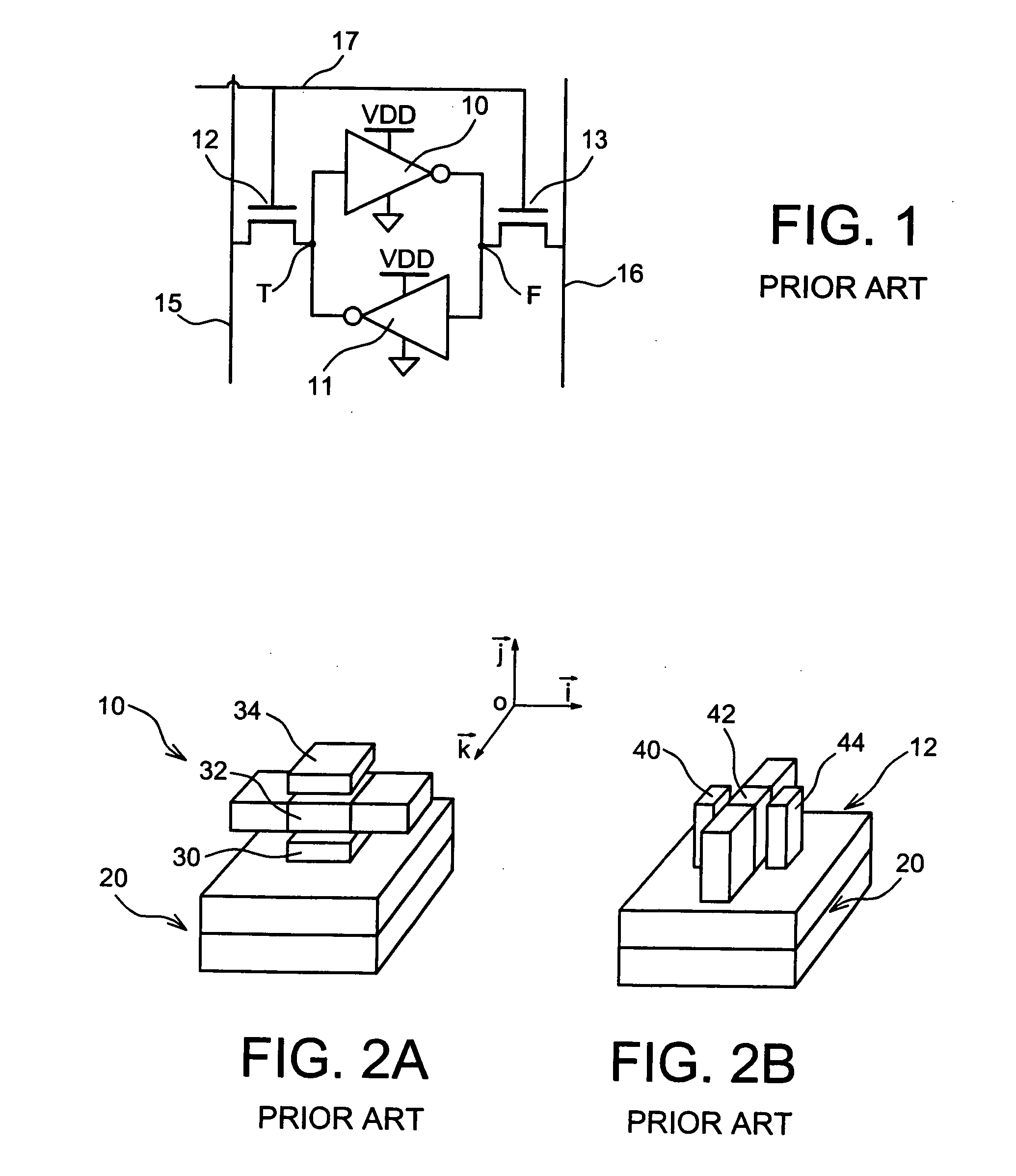

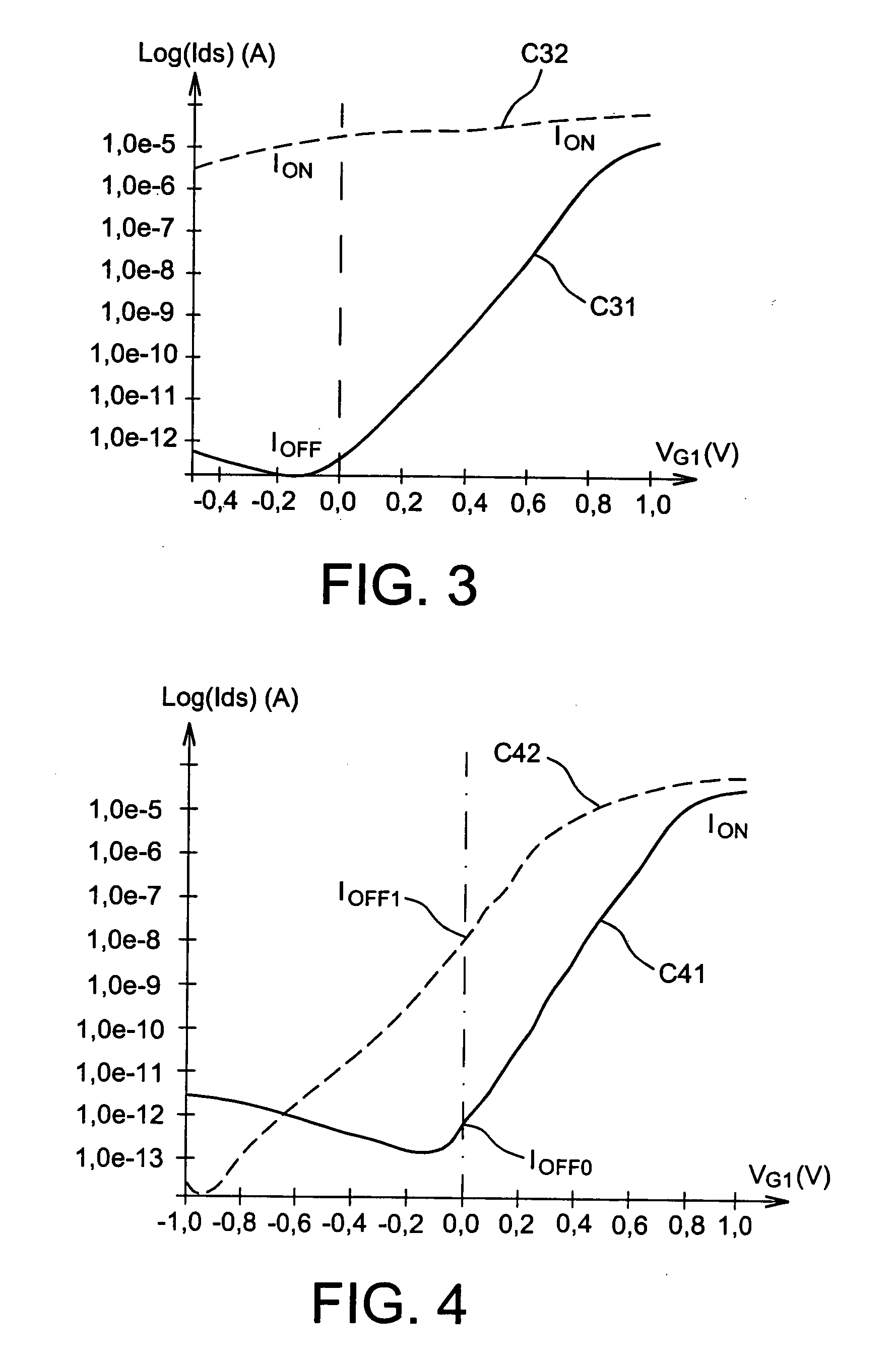

InactiveUS20080175039A1Control consumptionIncrease read and retention stabilityTransistorSolid-state devicesEngineeringBit line

The invention concerns a random access memory cell comprising:at least one first plurality of symmetrical dual-gate transistors (TL1T, TL1F, TD1T, TD1F, TL2T, TL2F) forming a flip-flop,at least a first asymmetric dual-gate access transistor (TA1T, TAW1T) and at least a second asymmetric dual-gate access transistor (TA1F, TAW1F) disposed respectively between a first bit line (BLT, WBLT) and a first storage node (T), and between a second bit line (BLF, WBLF) and a second storage node (F), a first gate of the first access transistor (TA1T, TAW1T) and a first gate of the second access transistor (TA1F, TAW1F) being connected to a first word line (WL, WWL) able to route a biasing signal, a second gate (TA1F, TAW1F) of the first access transistor connected to the second storage node (F) and a second gate of the second access transistor connected to the first storage node (T).

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

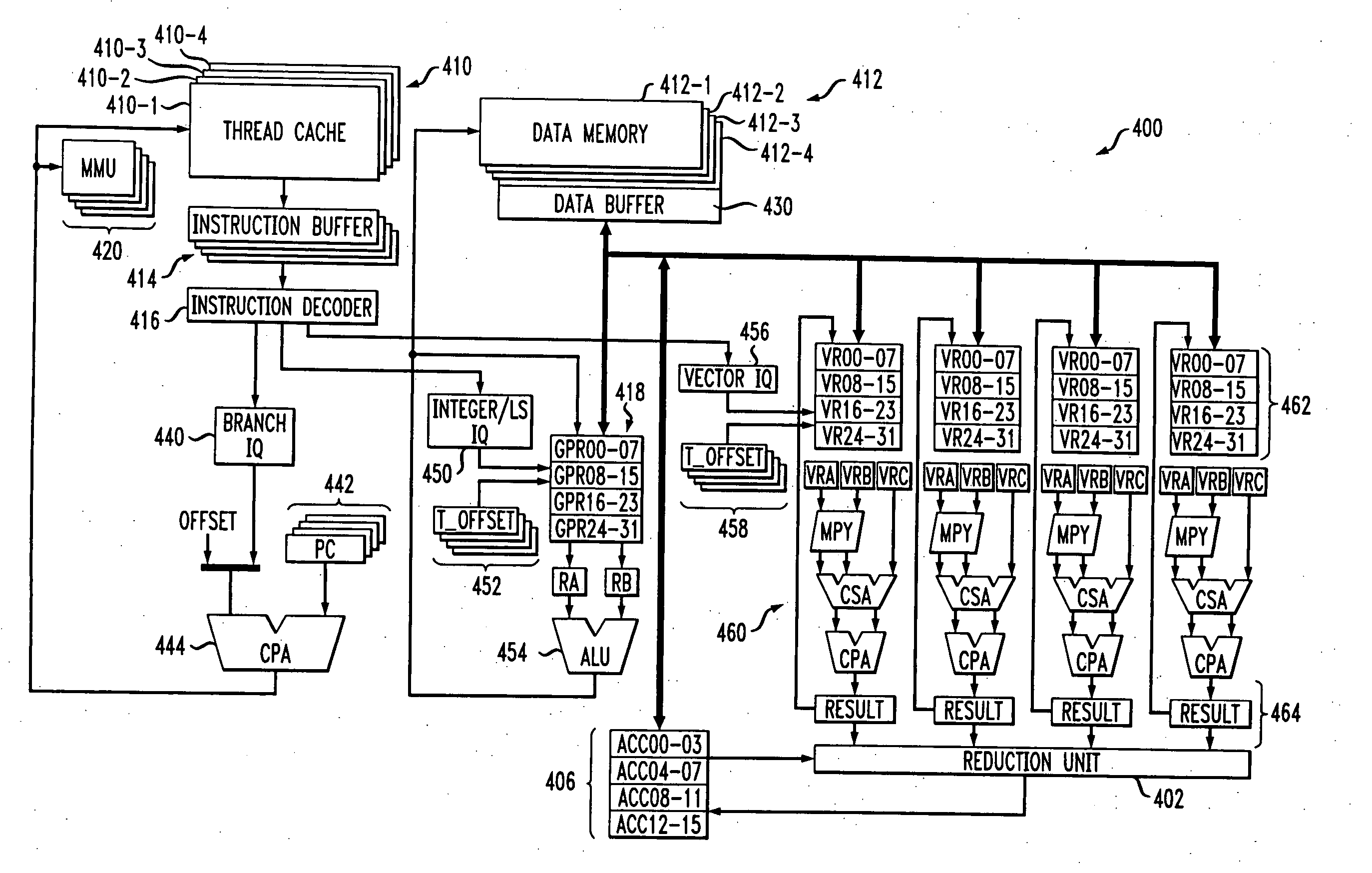

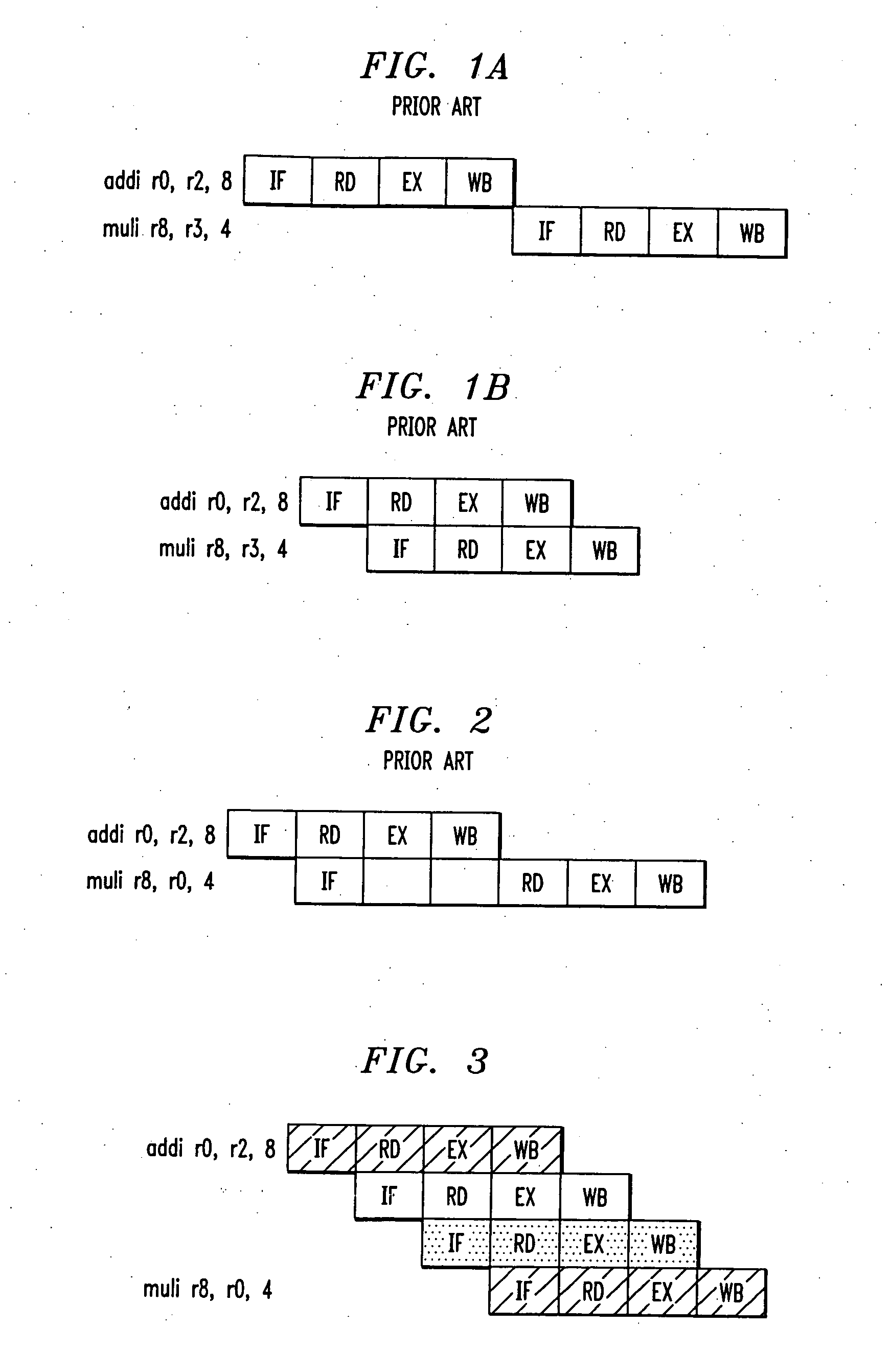

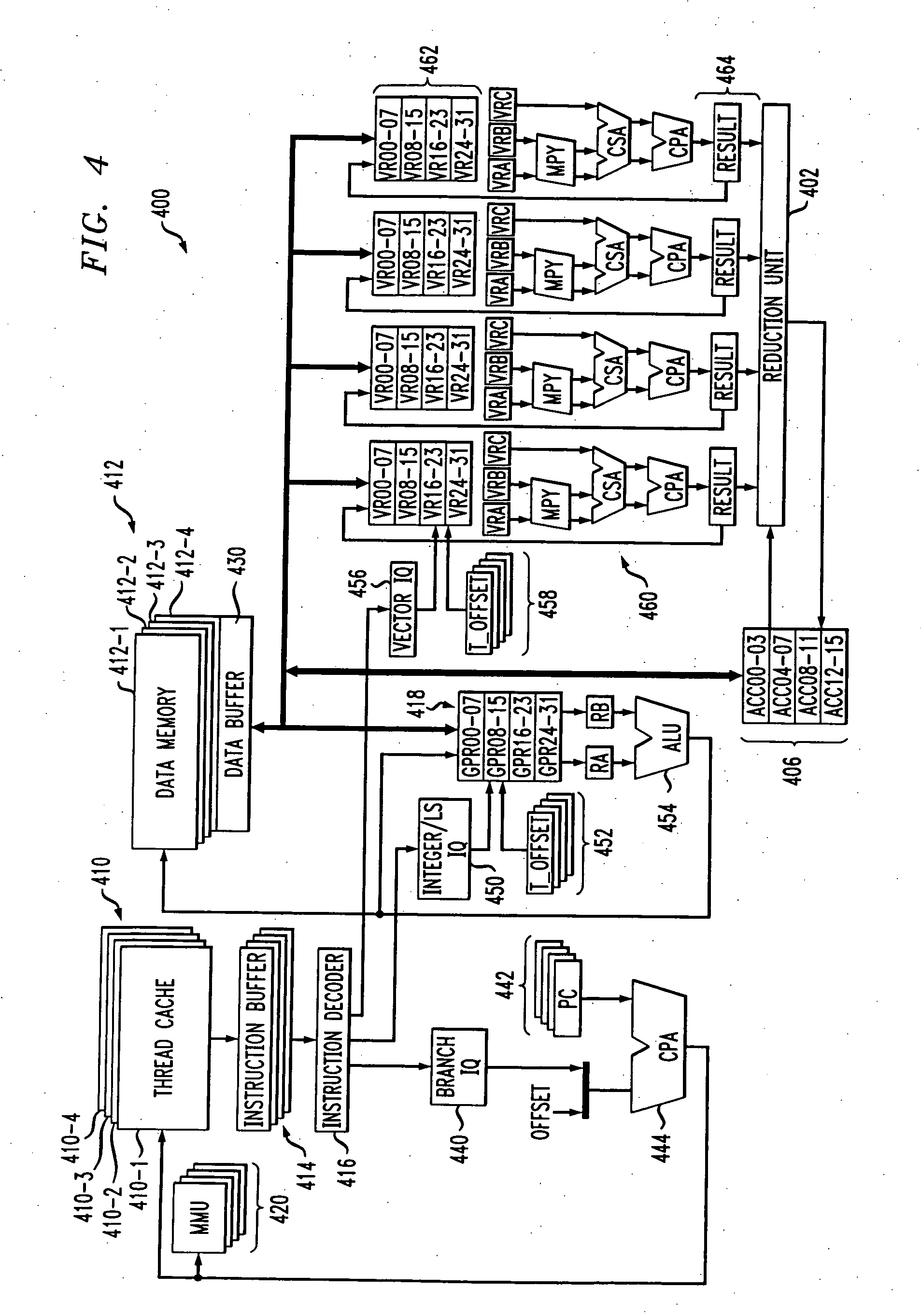

Multithreaded processor with multiple concurrent pipelines per thread

ActiveUS20060095729A1Improve concurrencyControl consumptionGeneral purpose stored program computerConcurrent instruction executionHardware threadExecution unit

A multithreaded processor comprises a plurality of hardware thread units, an instruction decoder coupled to the thread units for decoding instructions received therefrom, and a plurality of execution units for executing the decoded instructions. The multithreaded processor is configured for controlling an instruction issuance sequence for threads associated with respective ones of the hardware thread units. On a given processor clock cycle, only a designated one of the threads is permitted to issue one or more instructions, but the designated thread that is permitted to issue instructions varies over a plurality of clock cycles in accordance with the instruction issuance sequence. The instructions are pipelined in a manner which permits at least a given one of the threads to support multiple concurrent instruction pipelines.

Owner:QUALCOMM INC

Plant for washing plastic material

InactiveUS6797073B1Control consumptionLow costHollow article cleaningPlastic recyclingWaste management

A plant for the continuous washing of plastic material in scales. The plant having a washing apparatus, at least one filtering unit connected to the apparatus for purifying the washing fluid and means for varying the time the scales remain in the washing apparatus as a function of the quantity of scales contained at that same moment in the same apparatus.

Owner:AMUT SPA

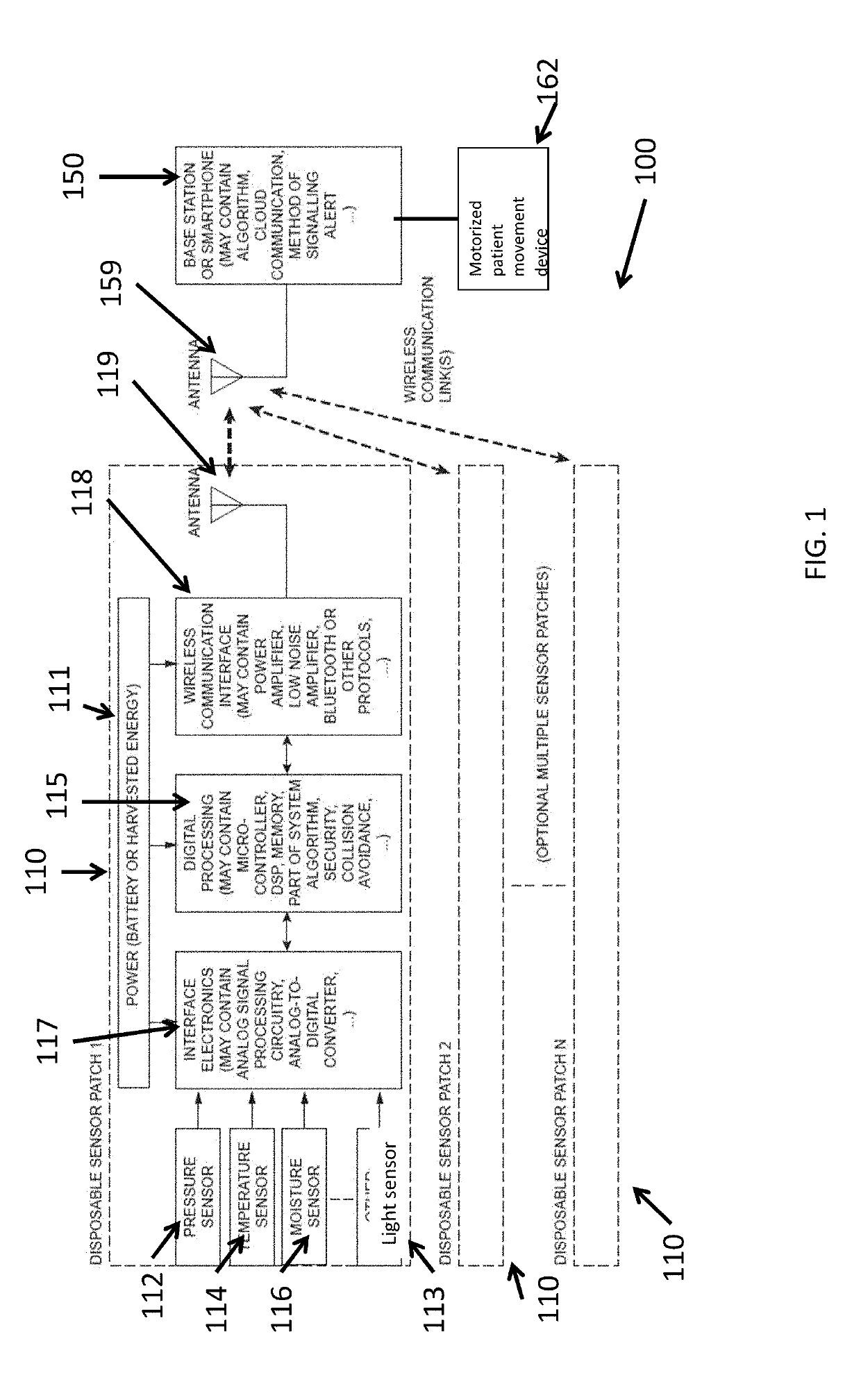

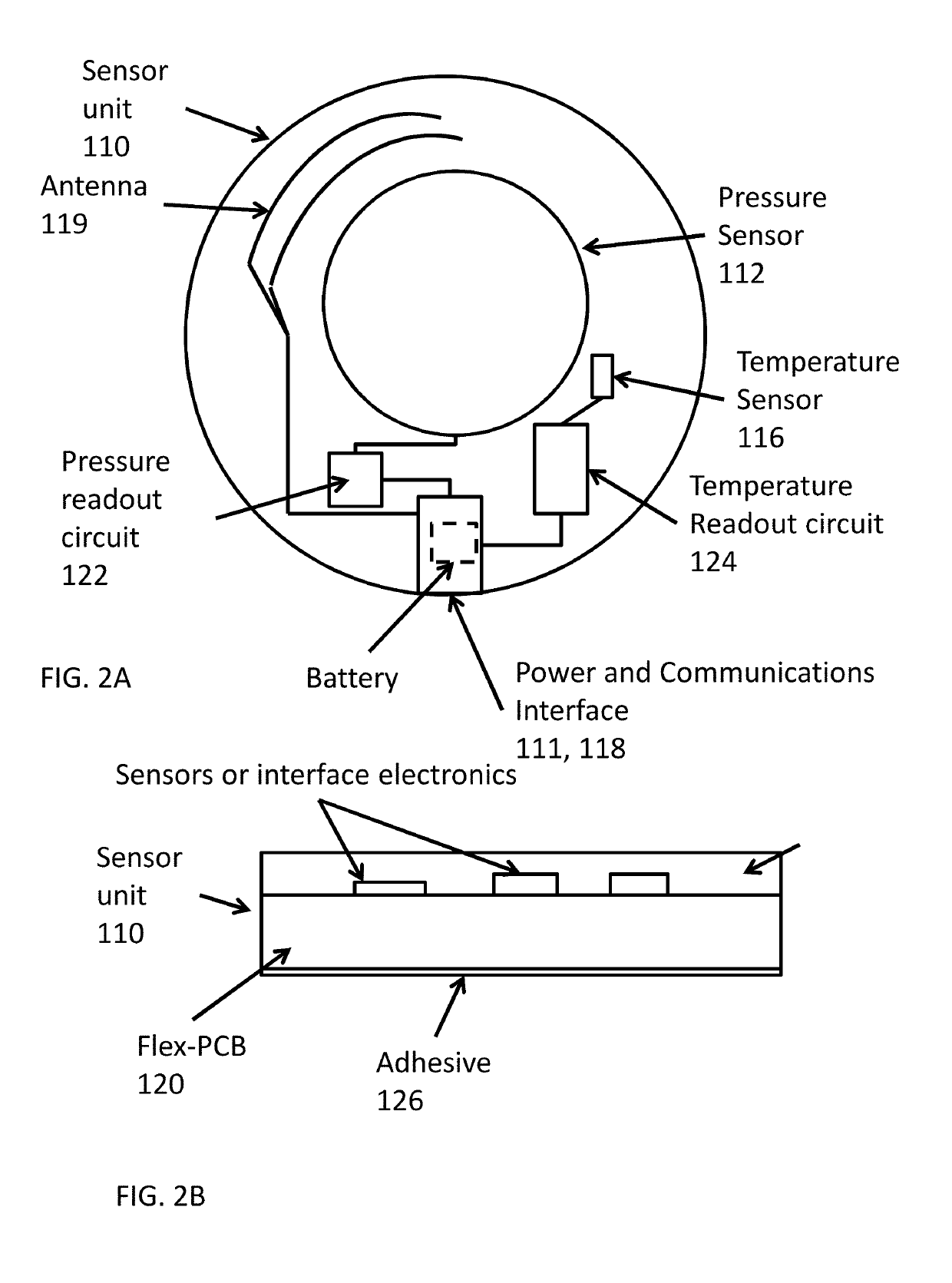

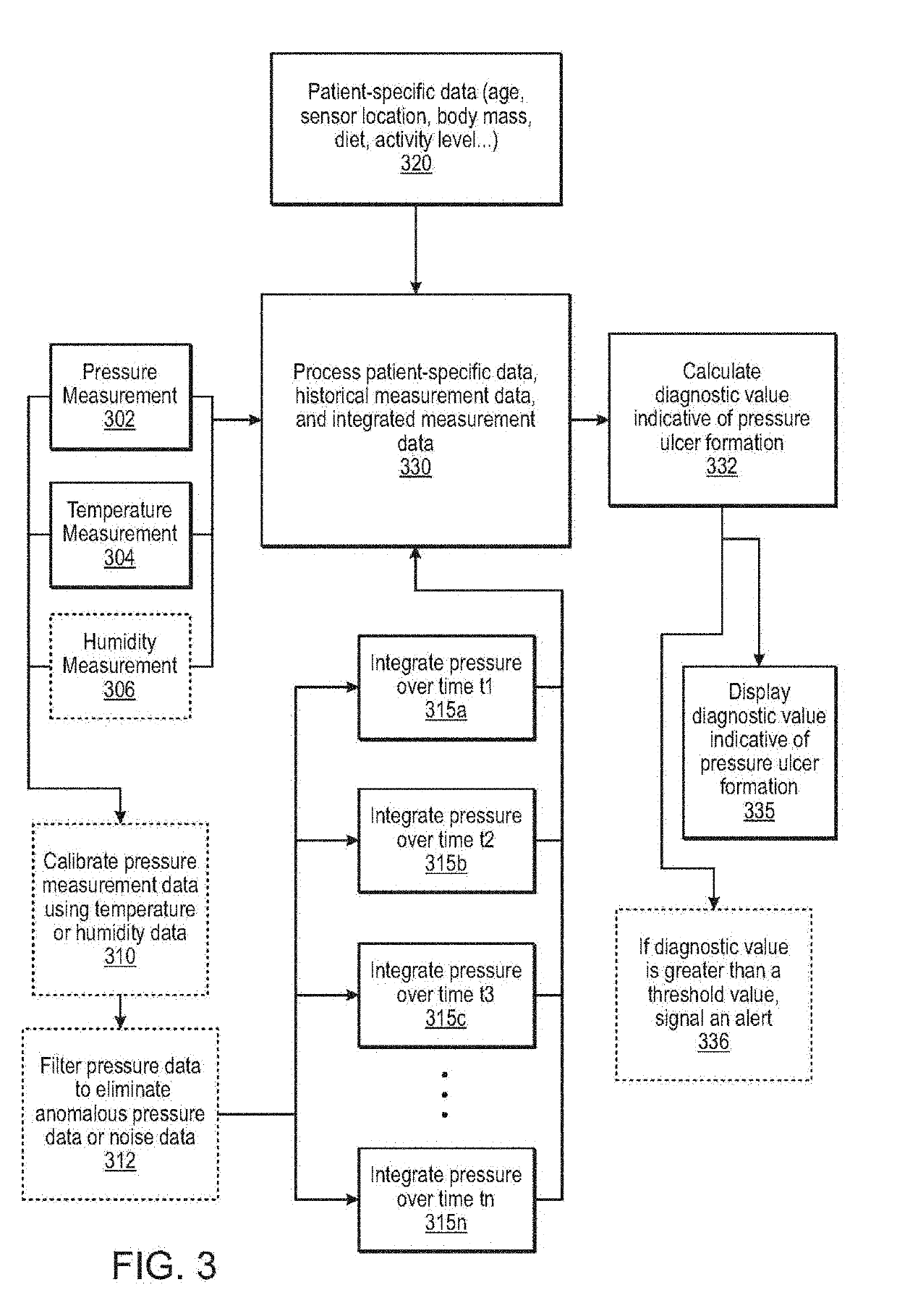

Systems and methods for prevention of pressure ulcers

PendingUS20190104982A1Limit consumption of battery powerControl consumptionMedical data miningHumidity sensorsPressure Sores/UlcersPhysical therapy

Systems, devices, and methods of the present application relate to the diagnostic measurement of condition for pressure ulcers. Preferred embodiments utilize pressure measurements at body locations to determine a diagnostic pressure ulcer value. A pressure sensor device generates patient pressure data that is processed by a data processor which utilizes a diagnostic function to determine the diagnostic value that indicates whether corrective action is needed to prevent pressure ulcer formation. One or more sensor devices can be attached to a patient to measure to transmit data for further processing.

Owner:UNIV OF MASSACHUSETTS +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com