Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

47results about "Network simulating resistances" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

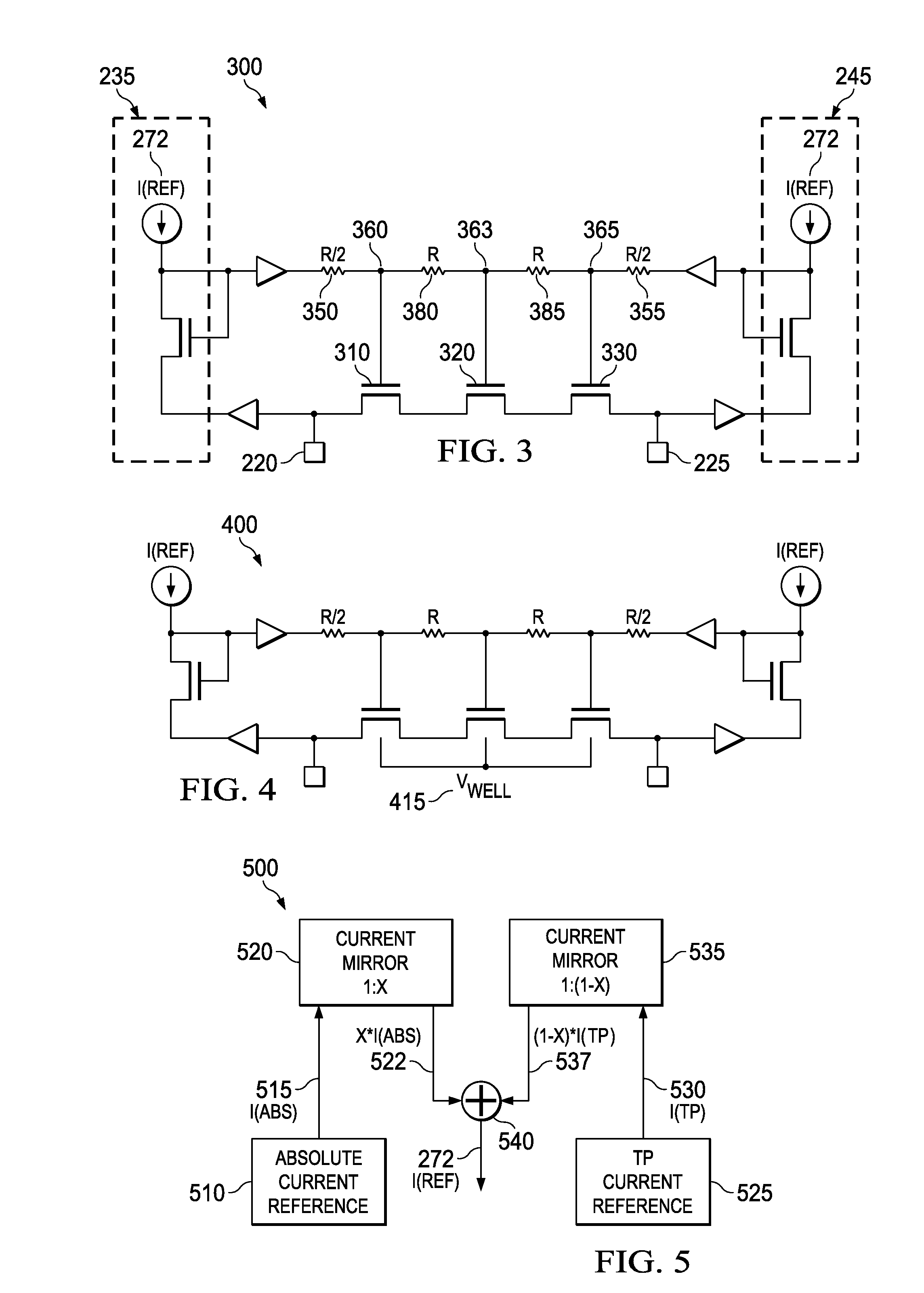

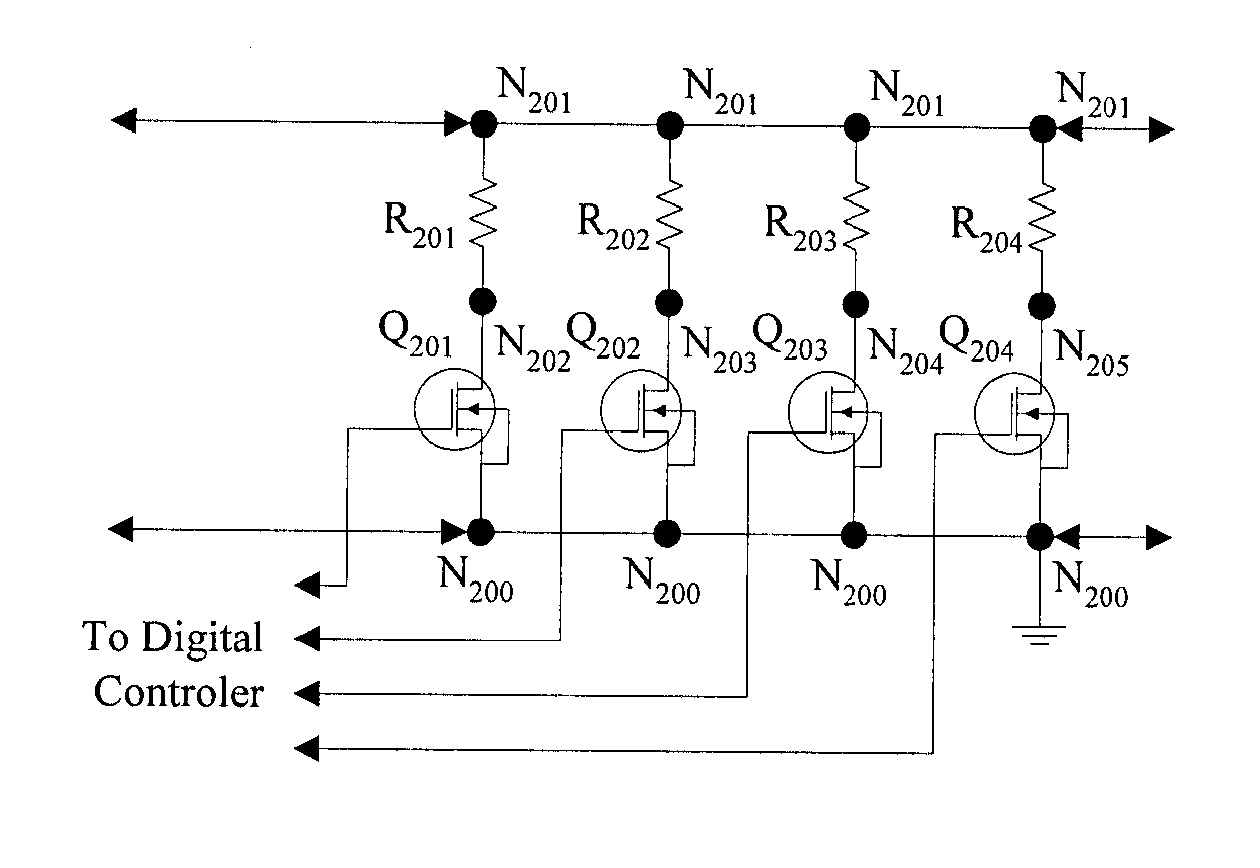

Systems and methods for controlling termination resistance values for a plurality of communication channels

ActiveUS7196567B2Reliability increasing modificationsPulse automatic controlElectrical resistance and conductanceAnalog signal

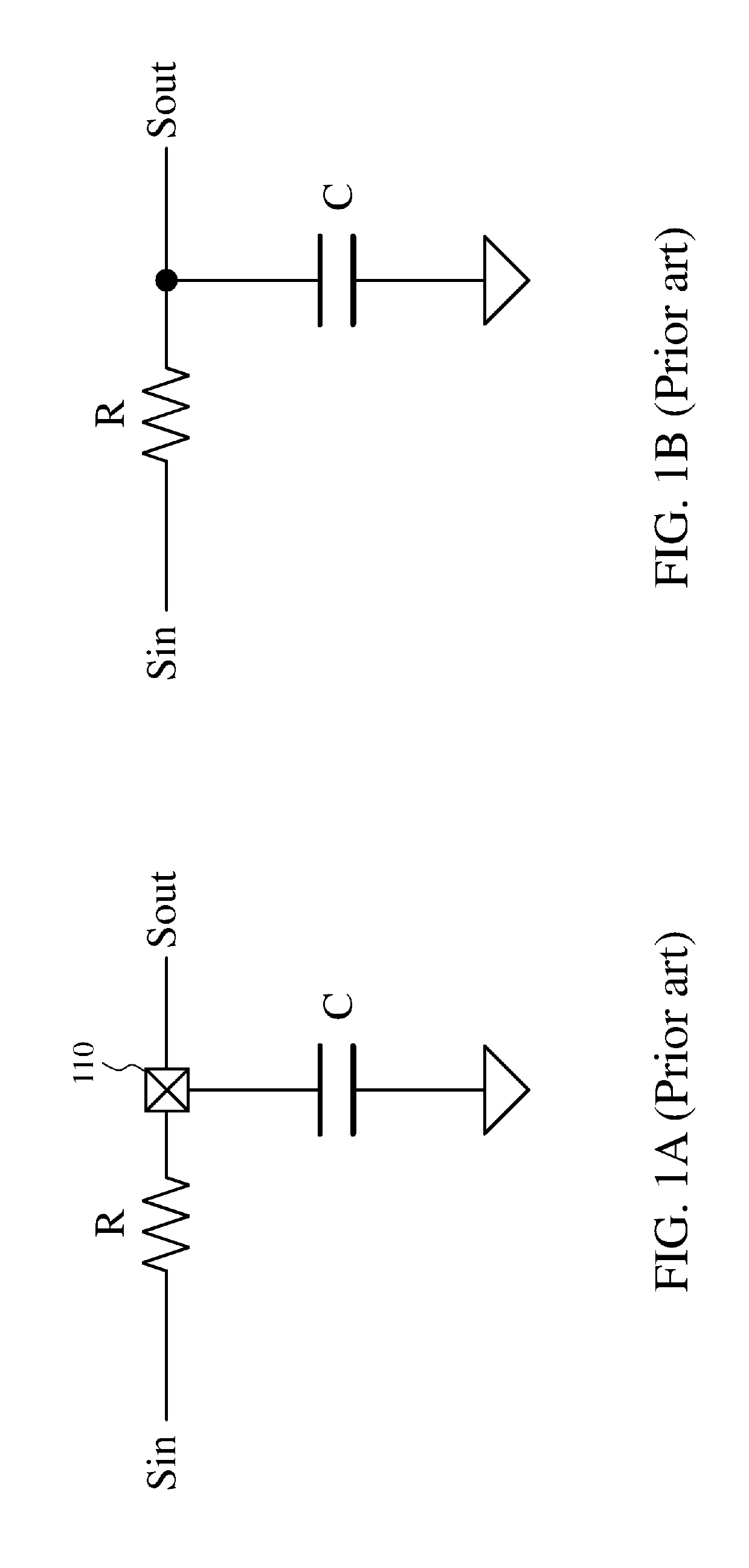

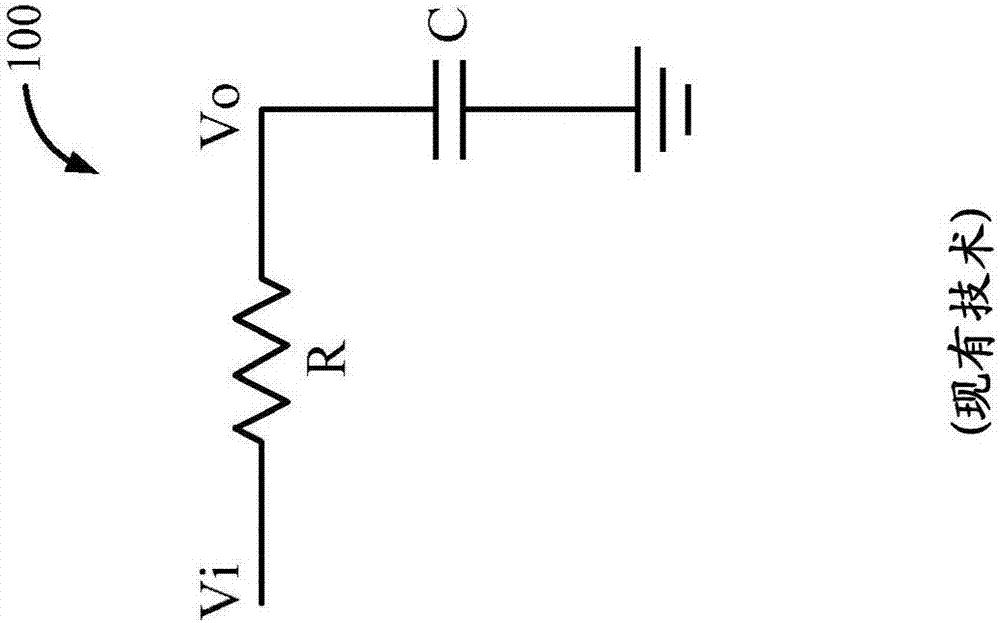

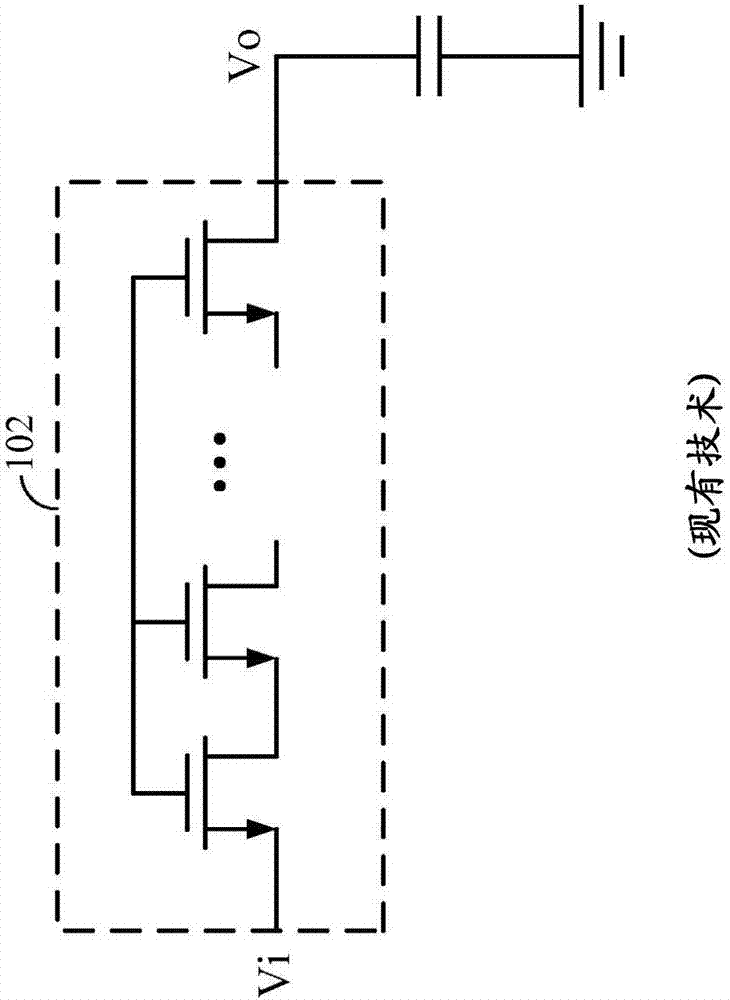

Described are controllable termination impedances that may be adjusted collectively by a combination of digital and analog signals. Each adjustable impedance, responsive to the digital signals, establishes a gross termination resistance for one of a plurality of communication channels by enabling one or more of a plurality of parallel-coupled impedance legs. Each leg includes at least one transistor for controlling the impedance of the leg over a continuous range. An analog compensation voltage is level shifted and the resulting level-shifted signal is applied to the control terminals of the transistors of the selected impedance legs. The compensation voltage, and consequently the level-shifted signal, varies with supply-voltage and temperature fluctuations in a manner that causes the collective impedance of the selected legs for each channel to remain stable despite the fluctuations. The combination of digital and analog impedance control provides for coarse impedance adjustments, such as to compensate for process variations, and additionally provides fine, adaptive adjustments to maintain the selected impedance despite changes in the supply voltage and temperature.

Owner:RAMBUS INC

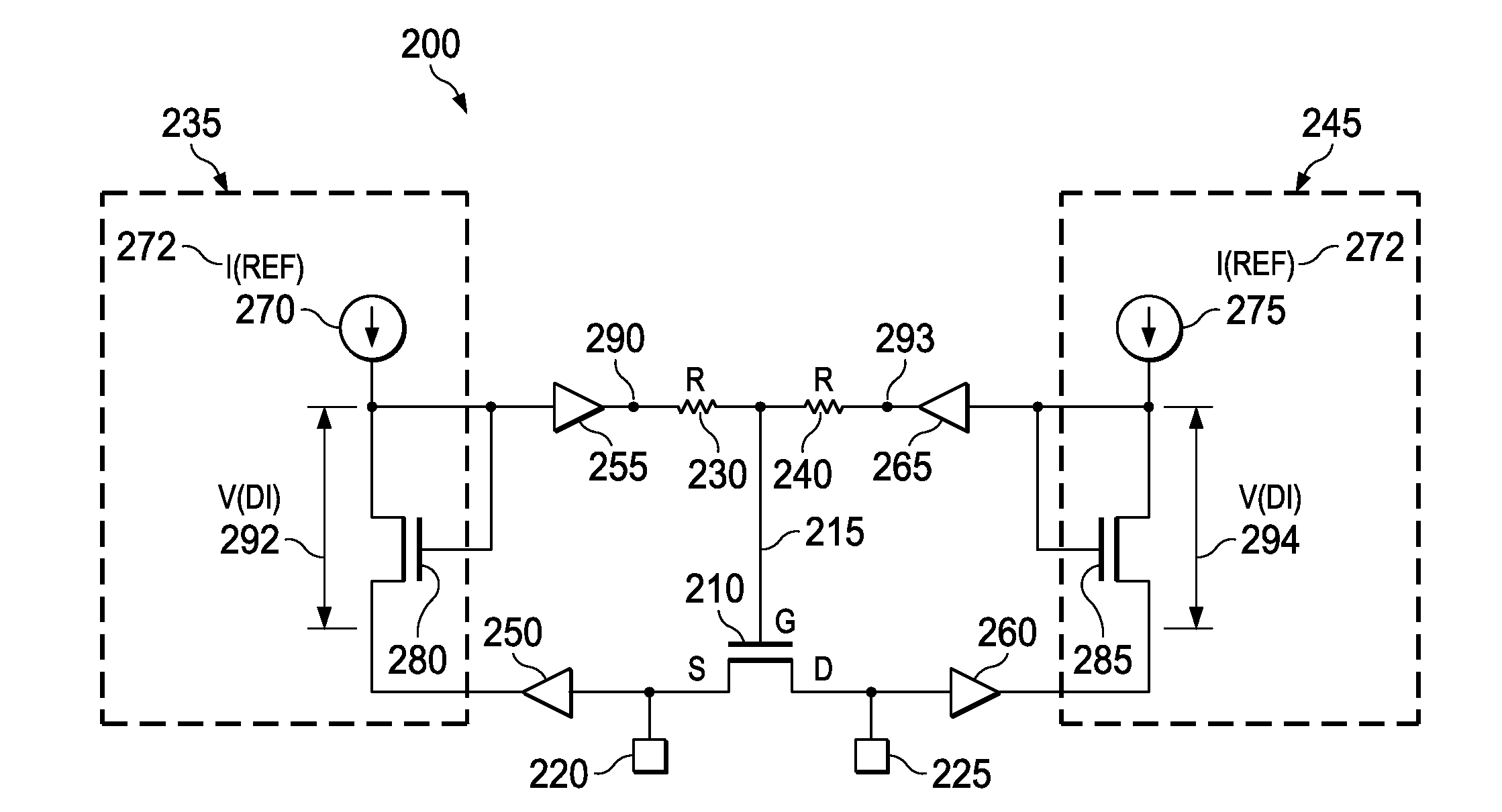

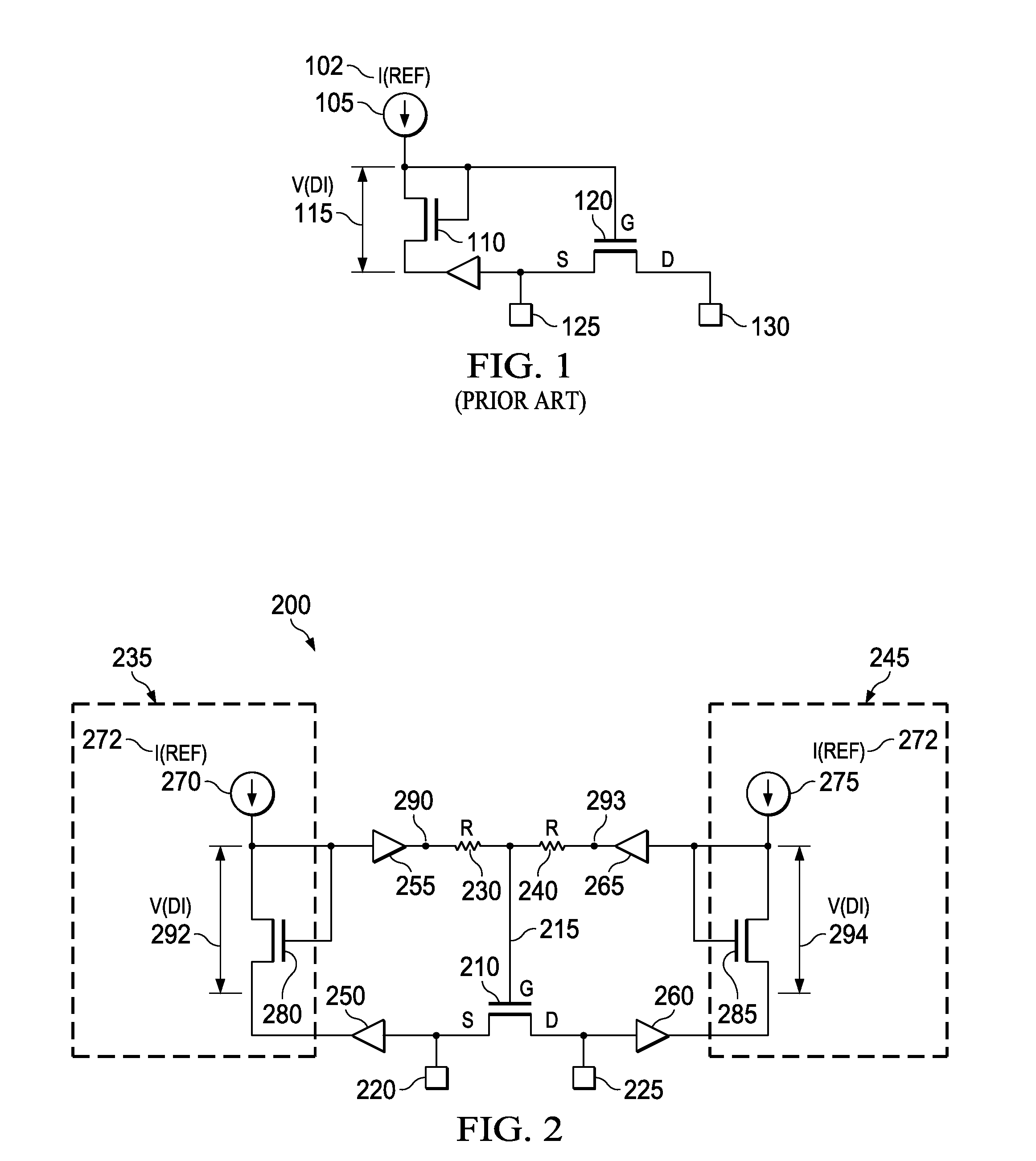

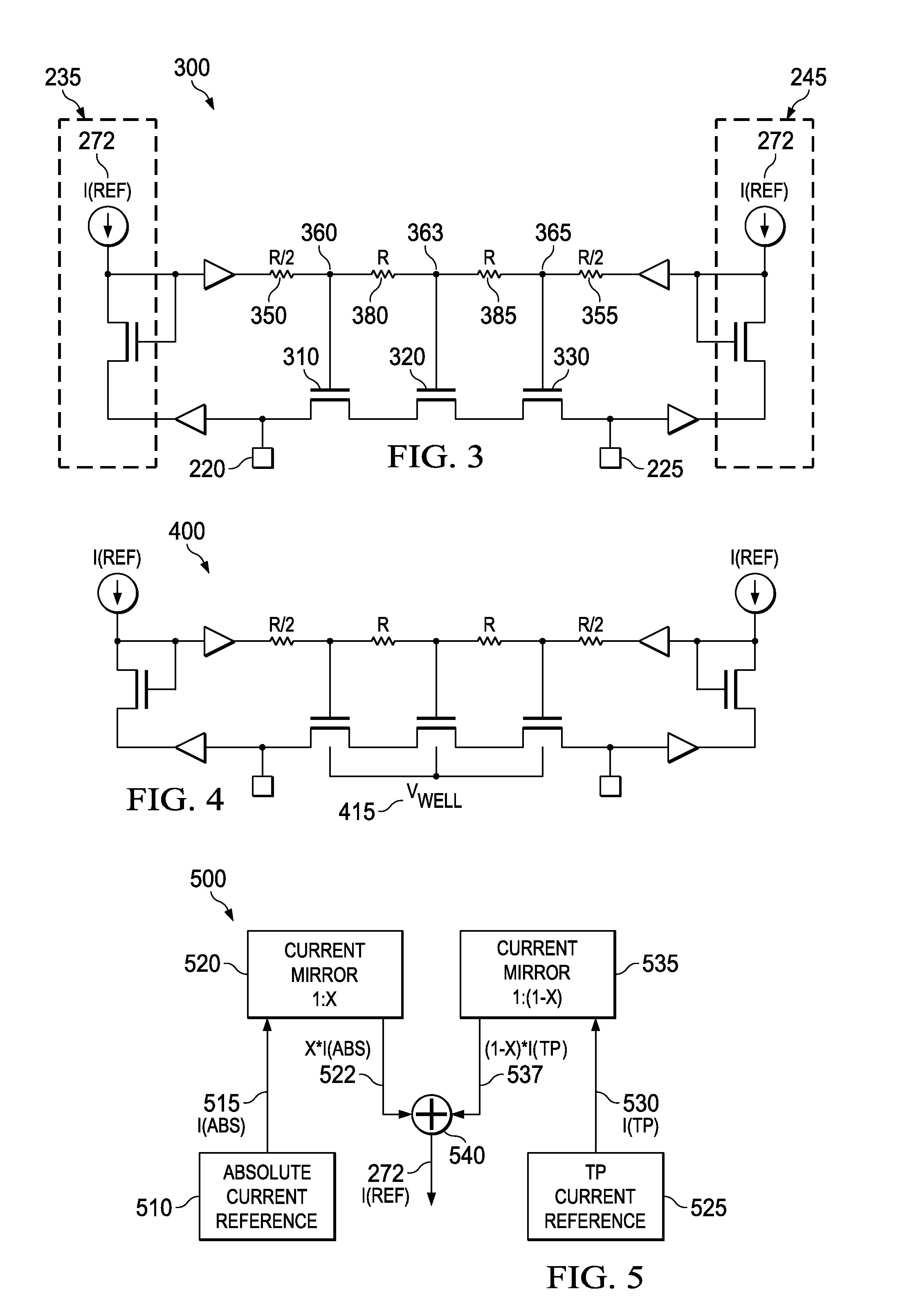

Mos resistor apparatus and methods

Apparatus and methods disclosed herein implement a MOS resistor using the current channel of a MOS transistor. The MOS resistance R(DS) is dependent upon MOS transistor geometry and nominal gate voltage. MOS resistor terminal-to-gate voltages are averaged and applied to the MOS transistor gate such as to maintain the MOS resistor terminal voltage to current ratio, resulting in a substantially constant R(DS). R(DS) is also compensated for temperature and process variations by adjusting gate voltages via negative feedback methods.

Owner:TEXAS INSTR INC

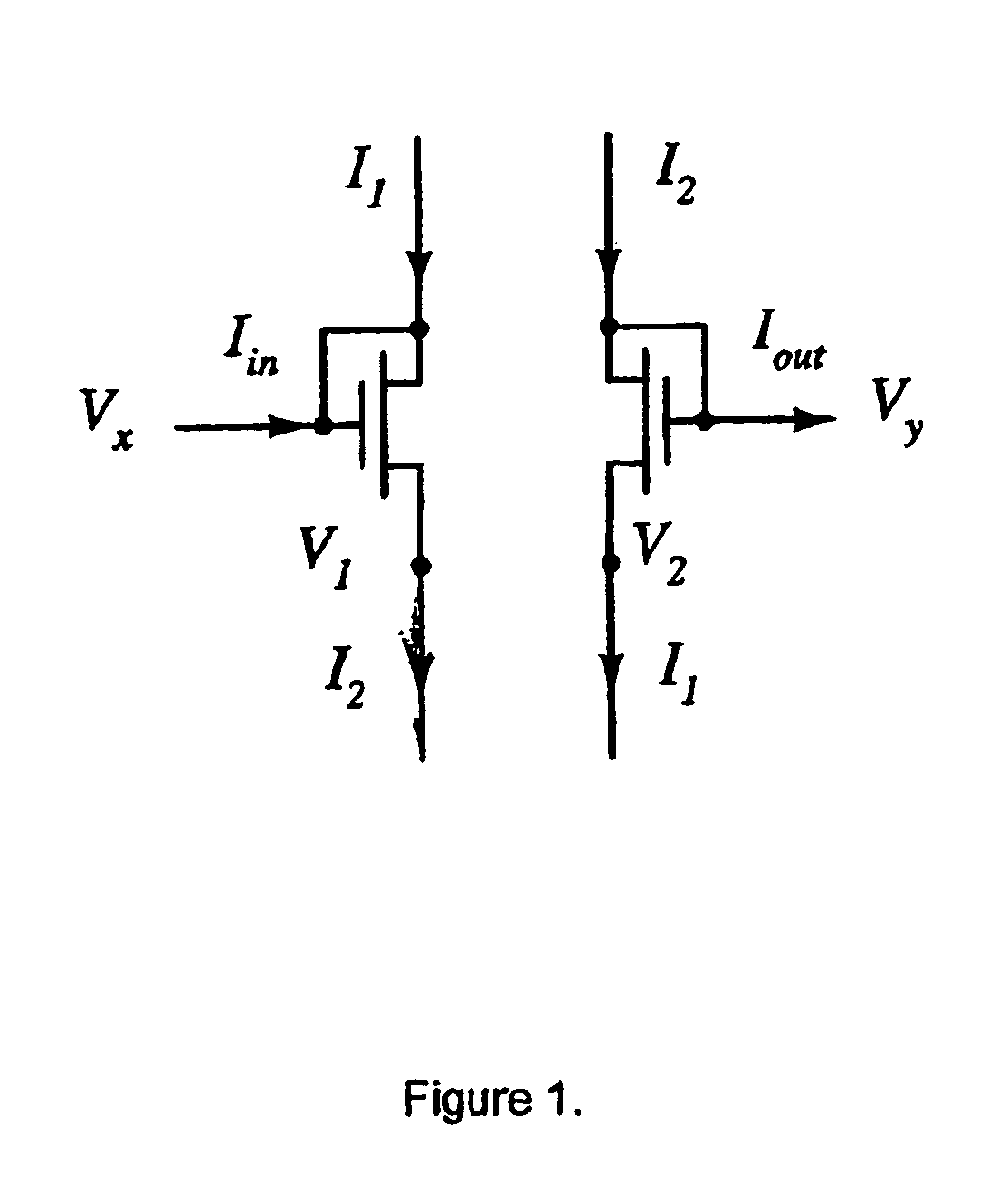

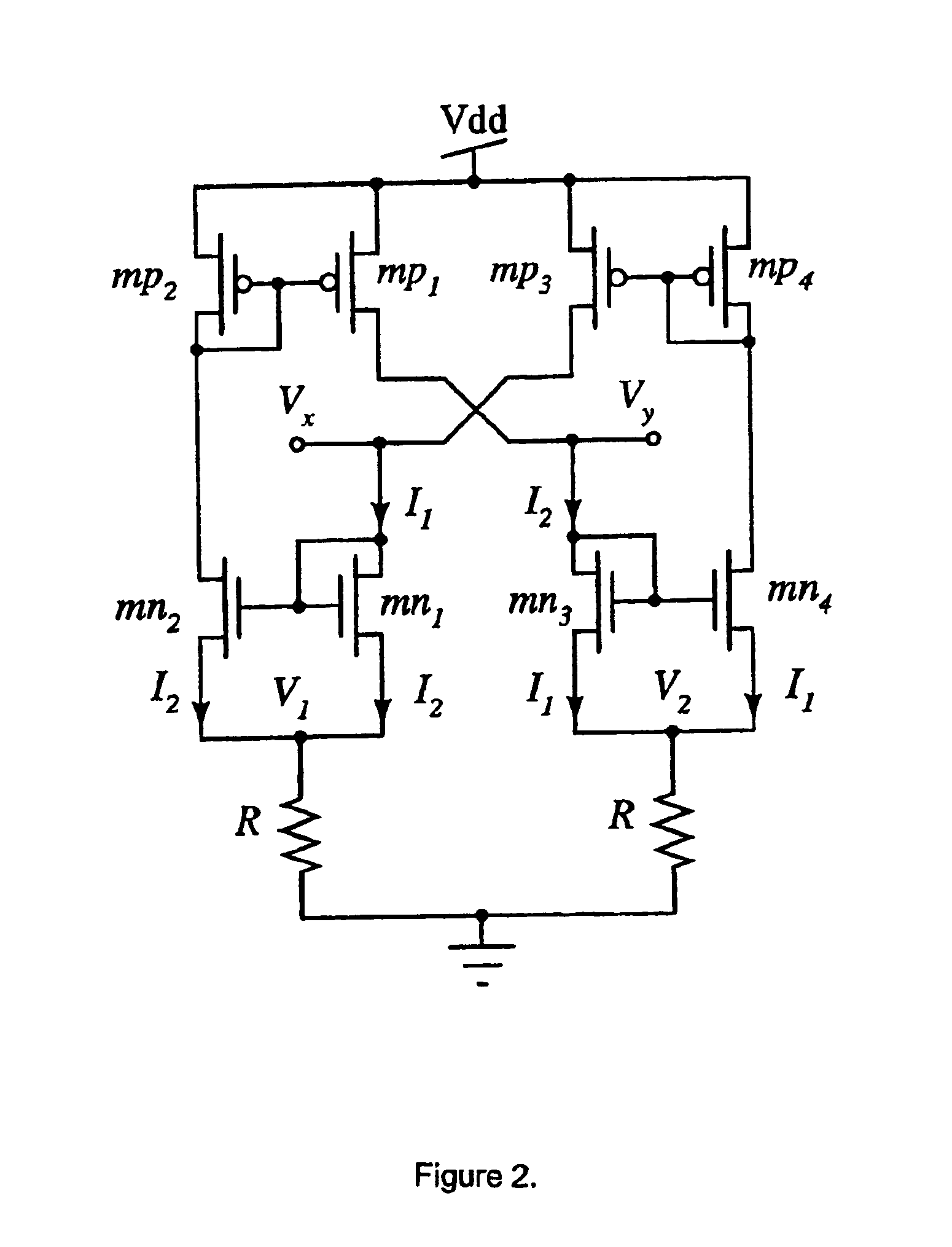

Electrically controlled very high value floating CMOS resistor

InactiveUS6897528B2Valid conversionSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLinearity

The present invention provides a circuit arrangement to convert fixed, or grounded resistors, to floating resistors. In particular, the circuit arrangement provides for the coupling of active electrical resistance devices to provide a relatively high value electrical resistance between two non-grounded nodes of the circuit arrangement in the order of Giga-ohms. The invention further provides for the magnitude of the floating electrical resistance to be determined by the magnitude of electrical current supply thus providing a means to select the magnitude of the floating electrical resistance by selecting by selecting the magnitude of electrical current supply. The circuit arrangement requires relatively few active devices and consumes a relatively small amount of electrical power in operation. The floating resistor of the present invention may be used in applications where a relatively high value resistor consuming a relatively small area of silicon, exhibiting relatively good linearity and wide dynamic range are required. Applications for such a device include neural networks, image processing and vision systems.

Owner:SARAWI SAID

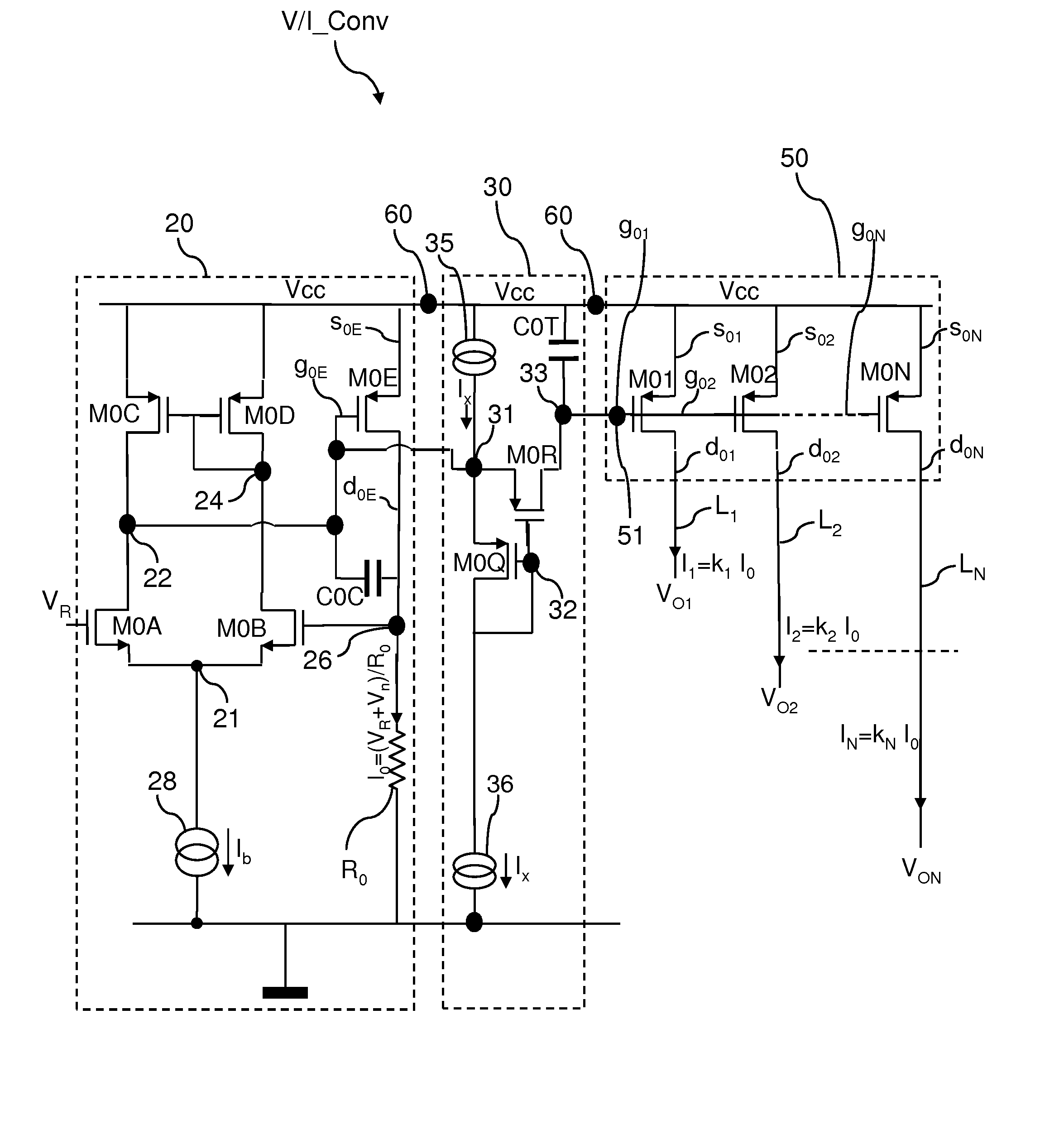

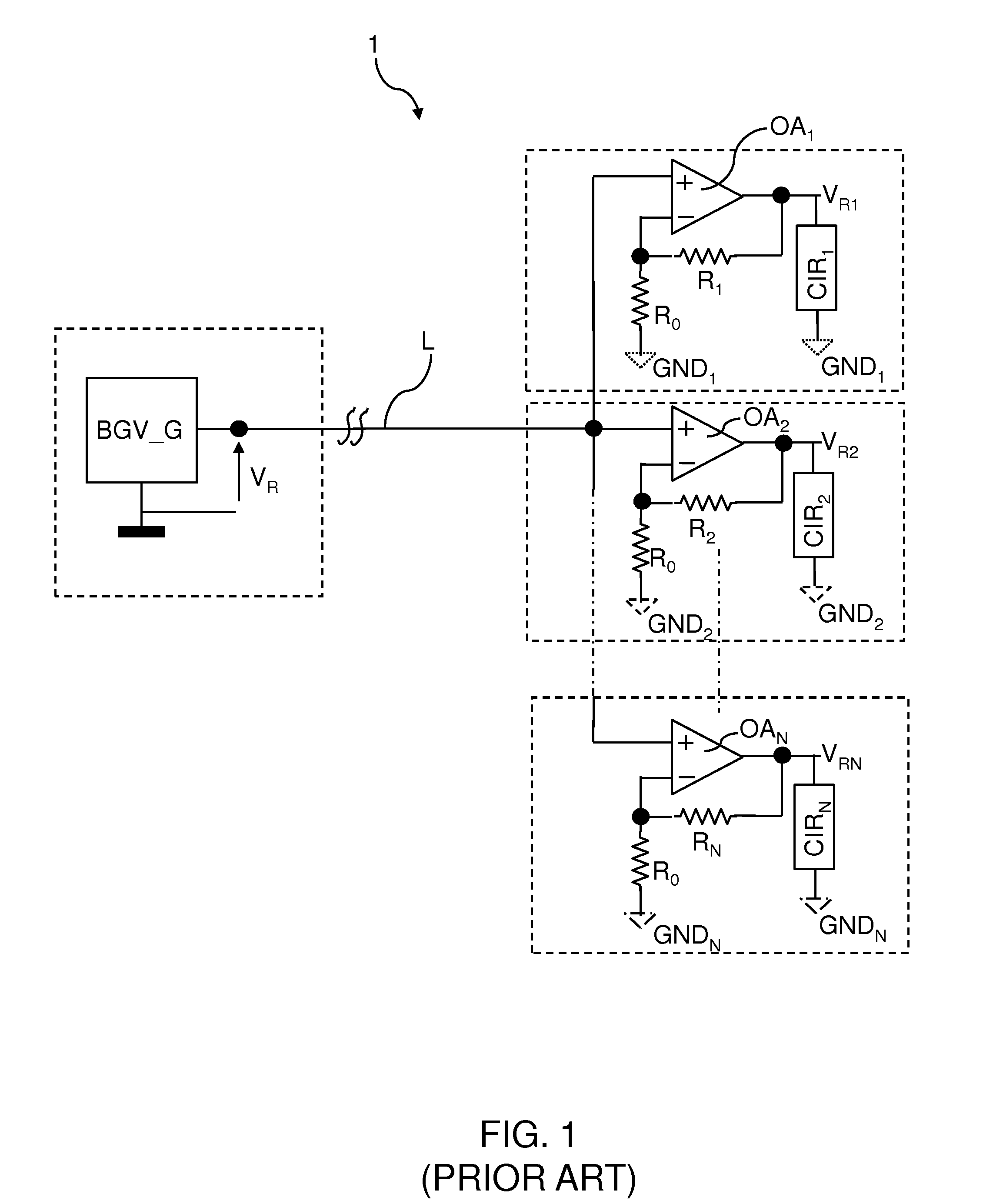

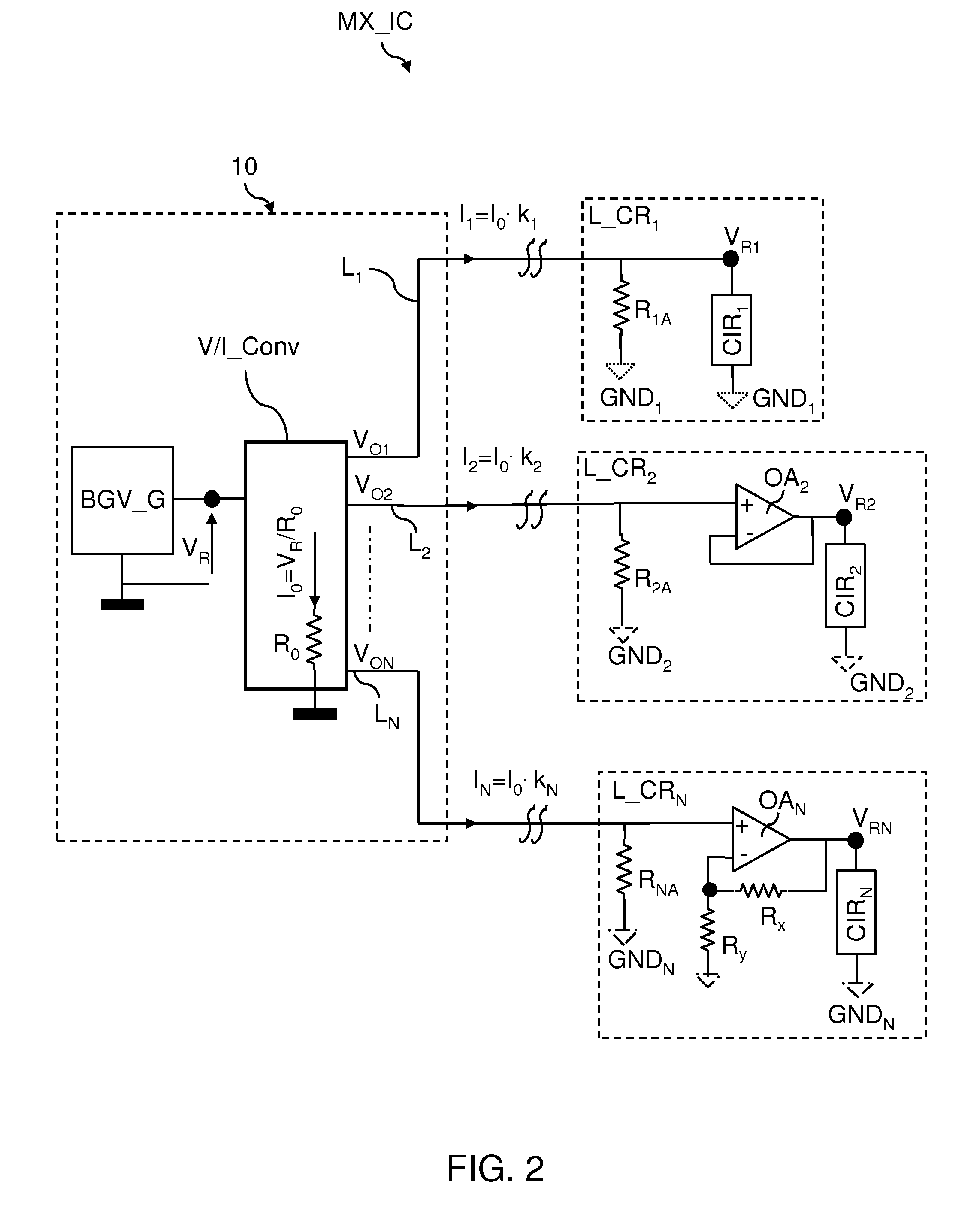

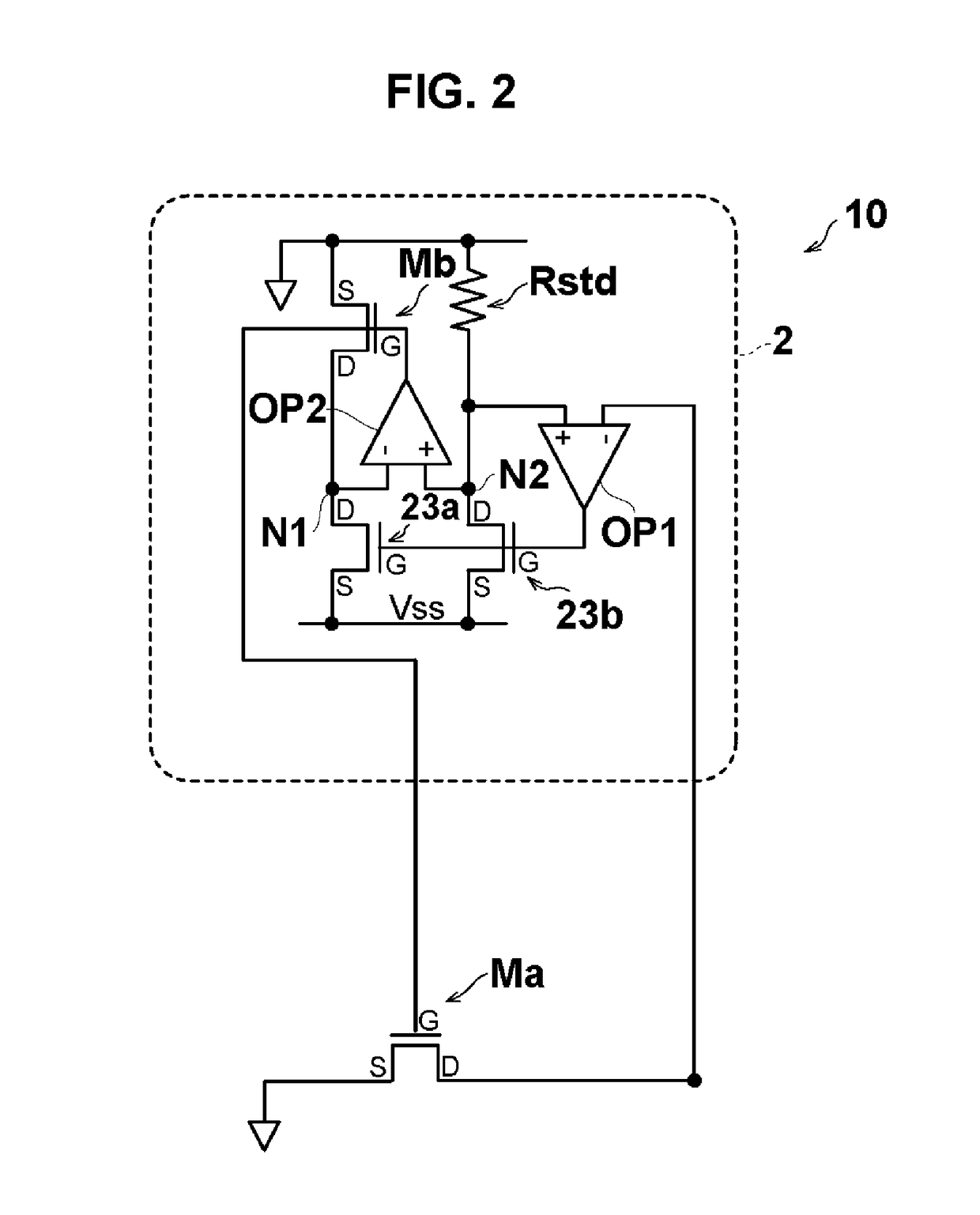

Low-Noise Reference Voltages Distribution Circuit

ActiveUS20150035591A1Increase of areaIncrease of consumptionMultiple-port networksElectric variable regulationLow noiseLow-pass filter

A low-noise reference voltages distribution circuit (10) is disclosed, comprising a multi-output voltage to current converter (V / I_Conv) adapted to receive an input reference voltage (VR) for providing a plurality of output reference currents (I1, . . . , IN) to be converted into a plurality of local reference voltages (V01, V0N) at corresponding receiving circuits (LCR1, LCRN) adapted to be connected to said reference voltages distribution circuit (10). The multi-output voltage to current converter (V / I_Conv) comprises: -an input section (20) adapted to generate on the basis of said input reference voltage (VR) a reference current (I0), the input section (20) comprising a current mirror input transistor (M0E) having a voltage controlled input terminal (g0E); -an output section (50) comprising a plurality of current mirror output transistors (M01, M0N) each adapted to provide a corresponding output reference current of said plurality of reference currents (I1, . . . , IN), each of said current mirror output transistors (M01, M0N) comprising a voltage controlled input terminal (g01, . . . , g0N), the output section (50) comprising a common input node (51) to which voltage controlled input terminals (g01, g0N) of said current mirror output transistors (M01, M0N) are connected. The voltage to current converter (V / I_Conv) comprises a low-pass filter (30) having an input node (31) connected to said voltage controlled input terminal (g0E) of the current mirror input transistor (M0E) and an output node (33) connected to said common input node (51).

Owner:TELEFON AB LM ERICSSON (PUBL)

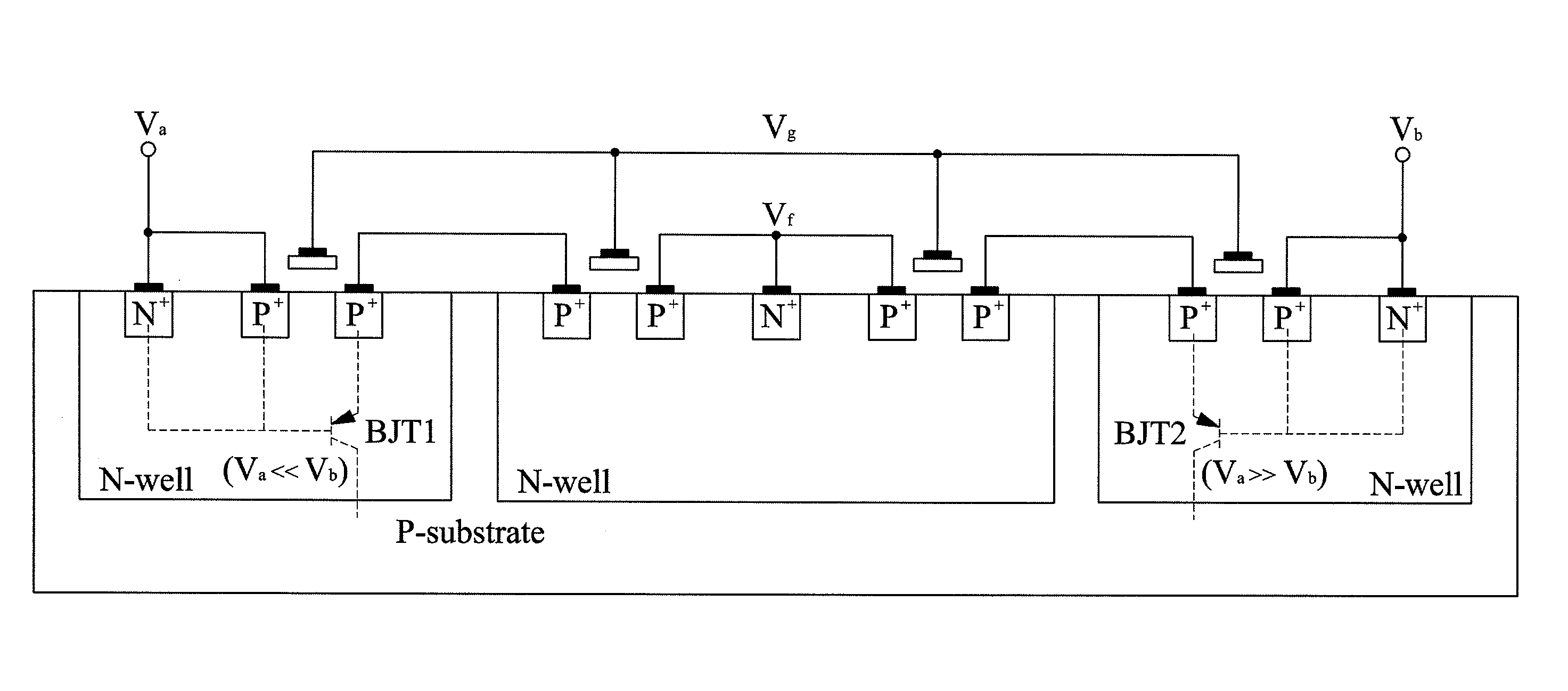

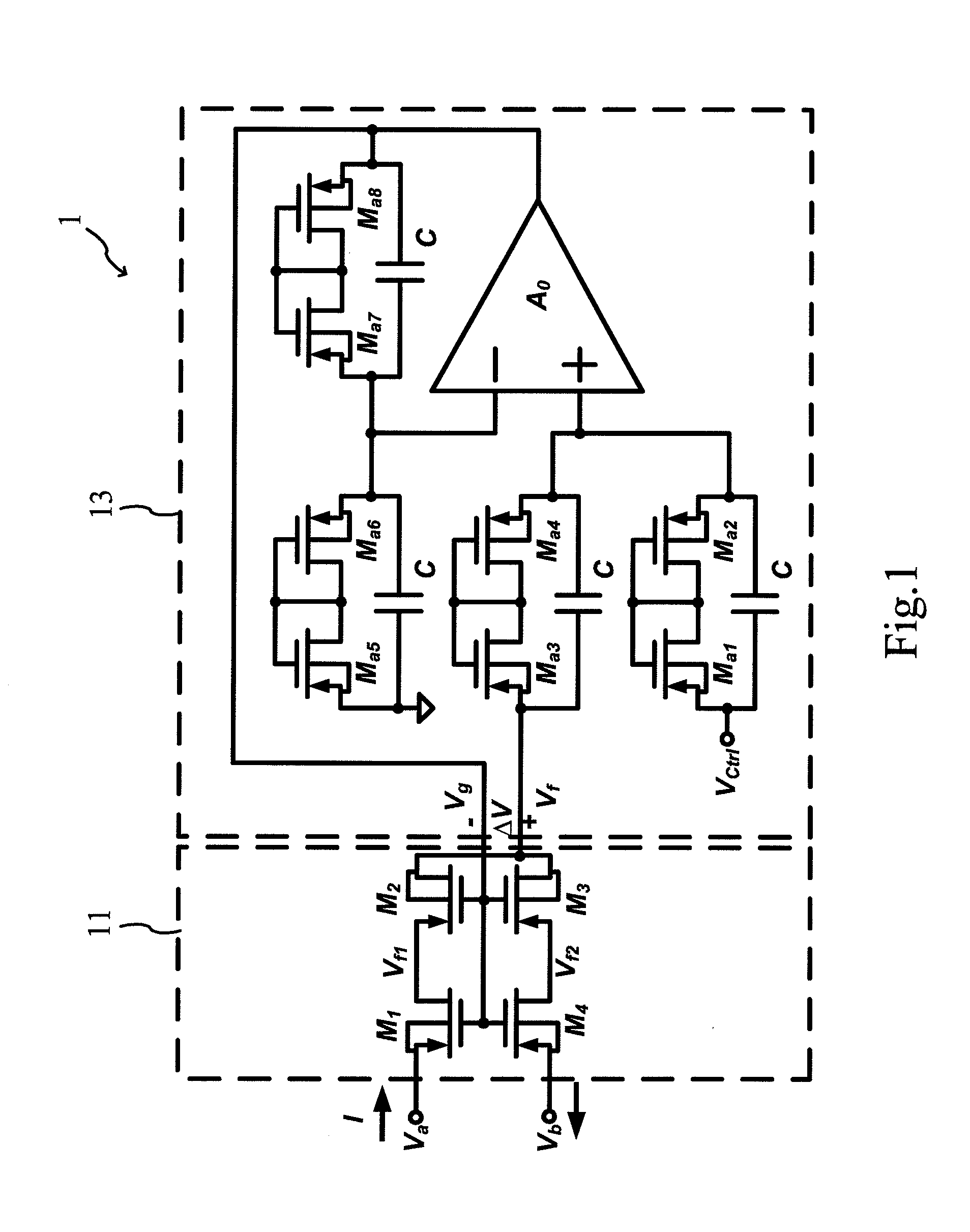

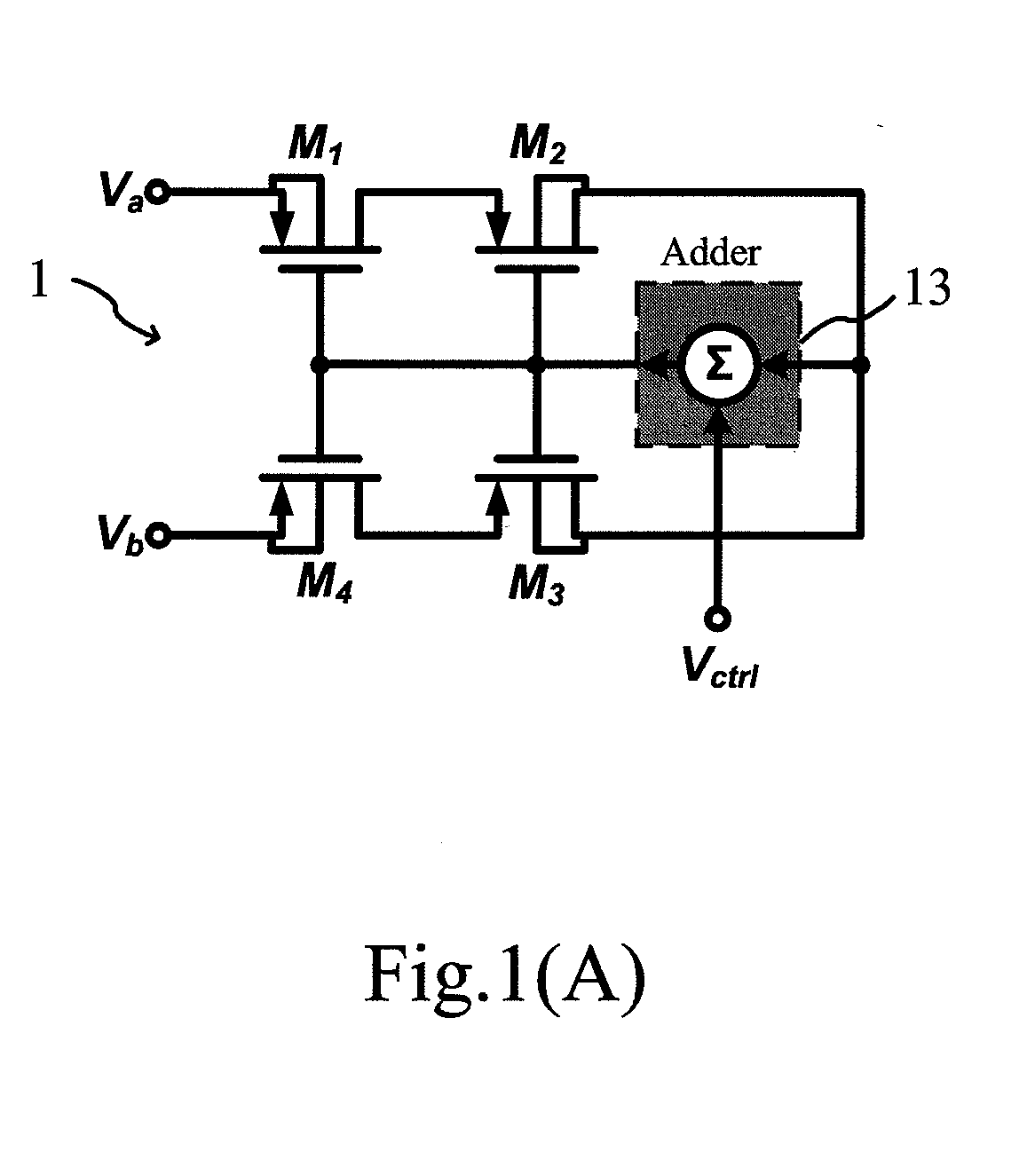

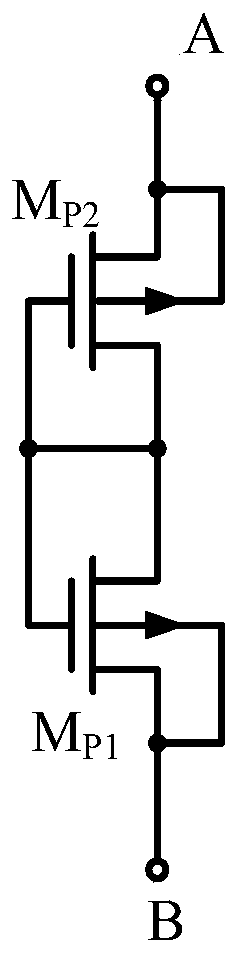

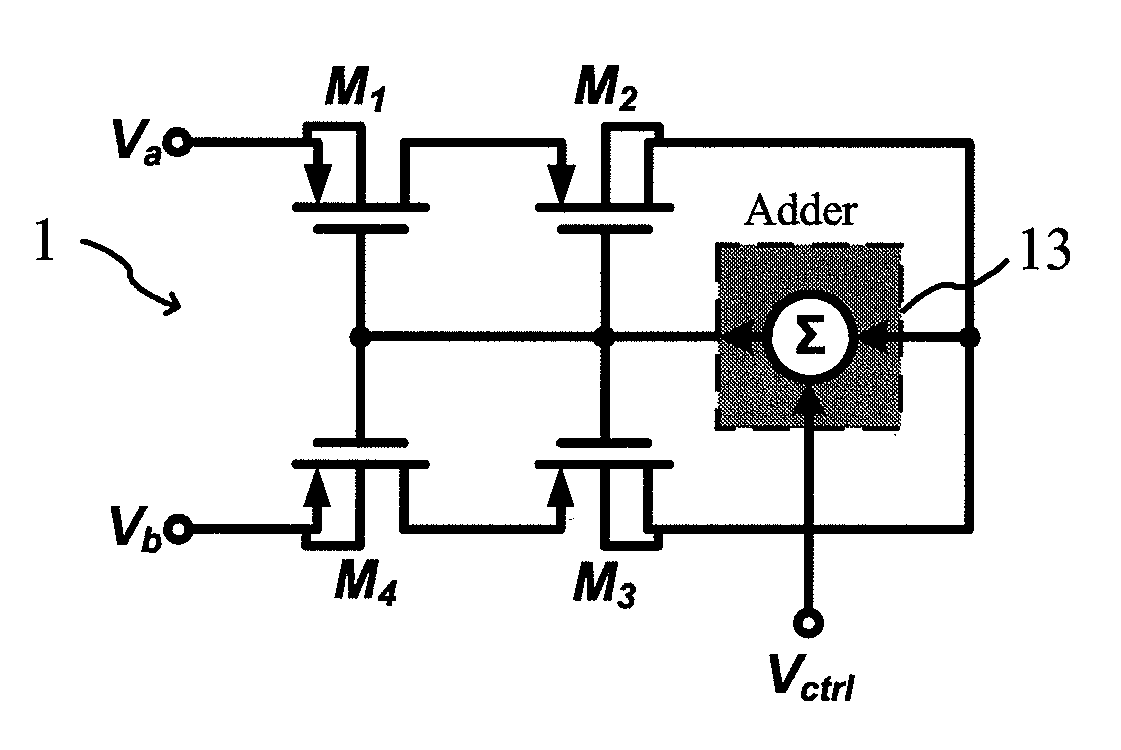

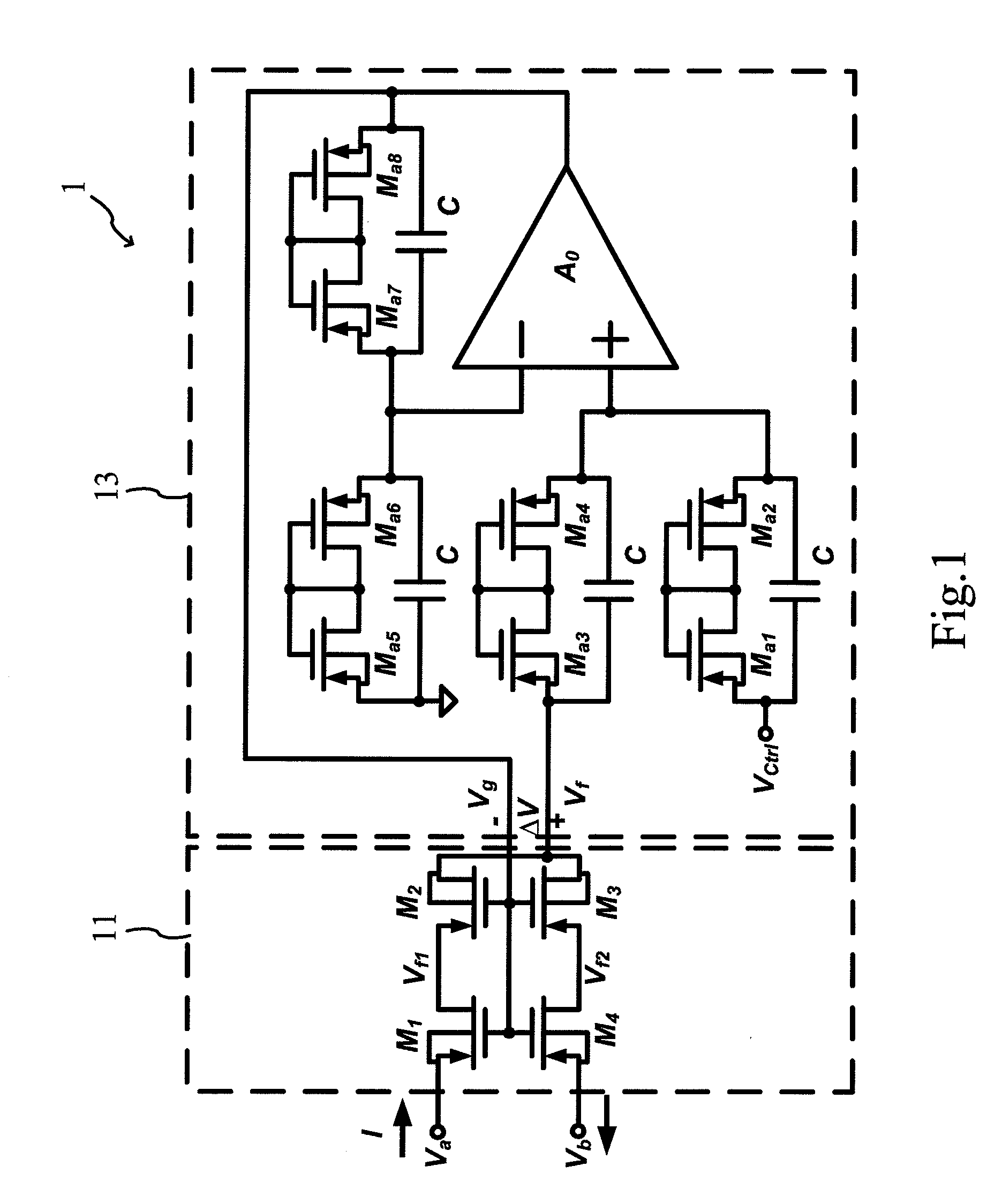

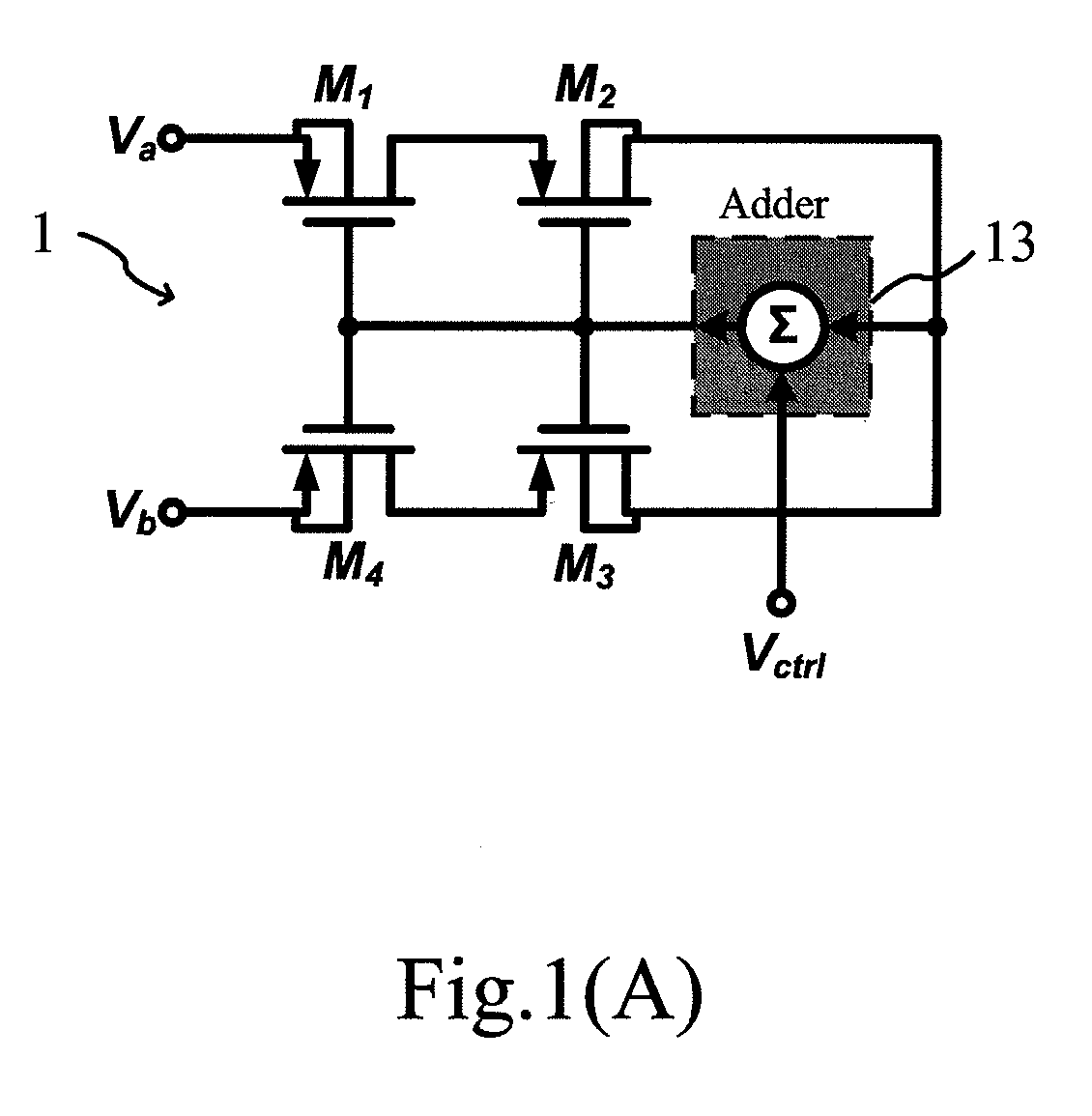

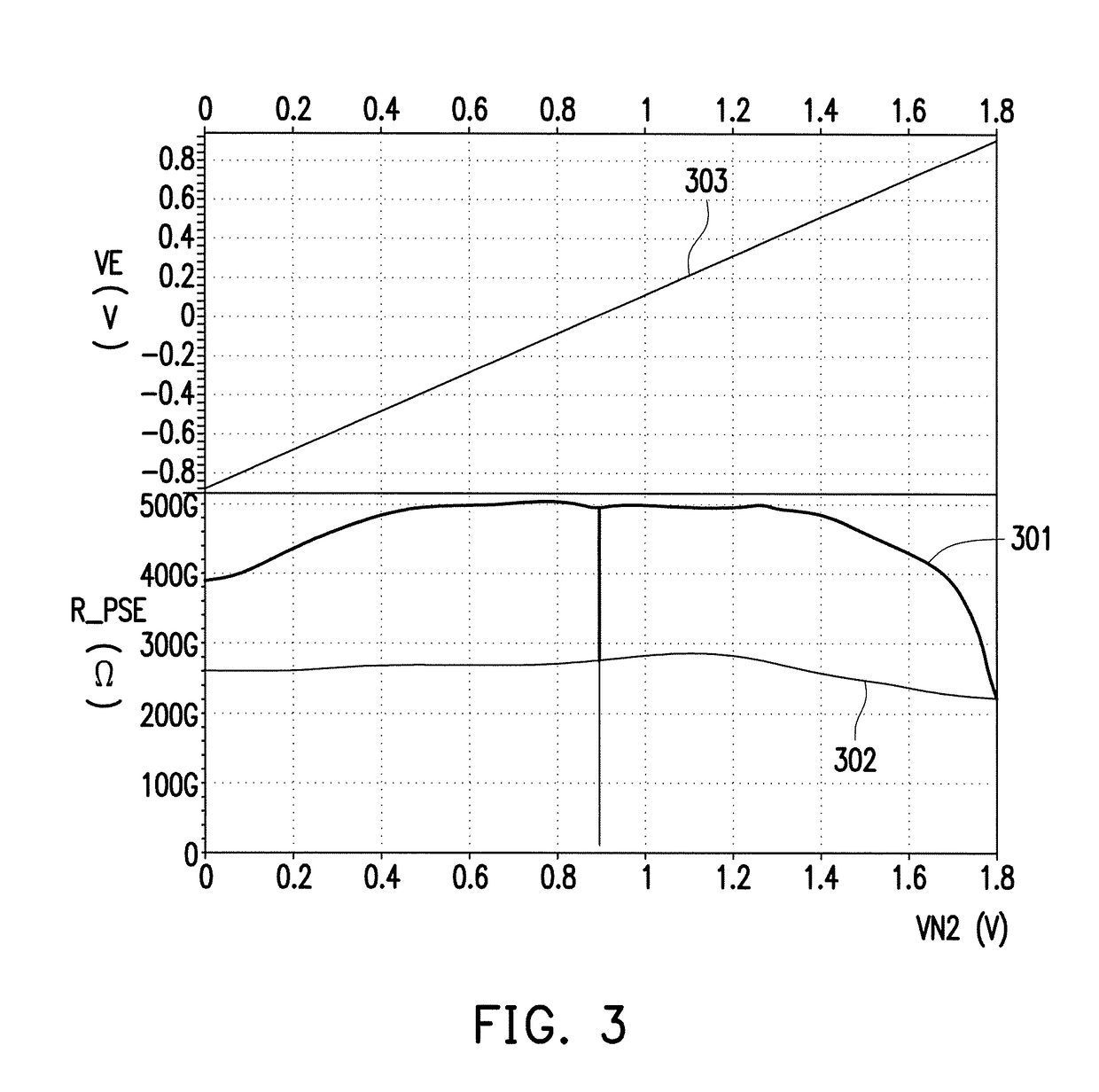

Tunable voltage-controlled pseudo-resistor

InactiveUS20130069716A1Low costReduce power consumptionNetwork simulating resistancesFrequency-independant attenuatorsCompensation effectEngineering

A tunable voltage-controlled pseudo-resistor structure, comprising: a symmetric PMOS transistor circuit and an auto-tuning circuit connected in series. Input of the auto-tuning circuit is connected to a central position Vf of the PMOS transistor circuit having its output Vg, with its purpose of keeping Vg−Vf at a constant value. The PMOS transistor circuit may produce body effect through various different bulk voltages. Through the auto-tuning circuit, Vg and Vf are kept constant to make current of transistor to produce compensation effect, such that regardless of Va>Vb or Va<Vb, a large resistance is maintained. Through utilizing the tunable voltage-controlled pseudo-resistor structure, constant resistance can be maintained under high input voltage, hereby reducing drifting of common-mode voltage, in achieving a superior resistance effect.

Owner:NAT CENT UNIV

MOS resistor apparatus and methods

Apparatus and methods disclosed herein implement a MOS resistor using the current channel of a MOS transistor. The MOS resistance R(DS) is dependent upon MOS transistor geometry and nominal gate voltage. MOS resistor terminal-to-gate voltages are averaged and applied to the MOS transistor gate such as to maintain the MOS resistor terminal voltage to current ratio, resulting in a substantially constant R(DS). R(DS) is also compensated for temperature and process variations by adjusting gate voltages via negative feedback methods.

Owner:TEXAS INSTR INC

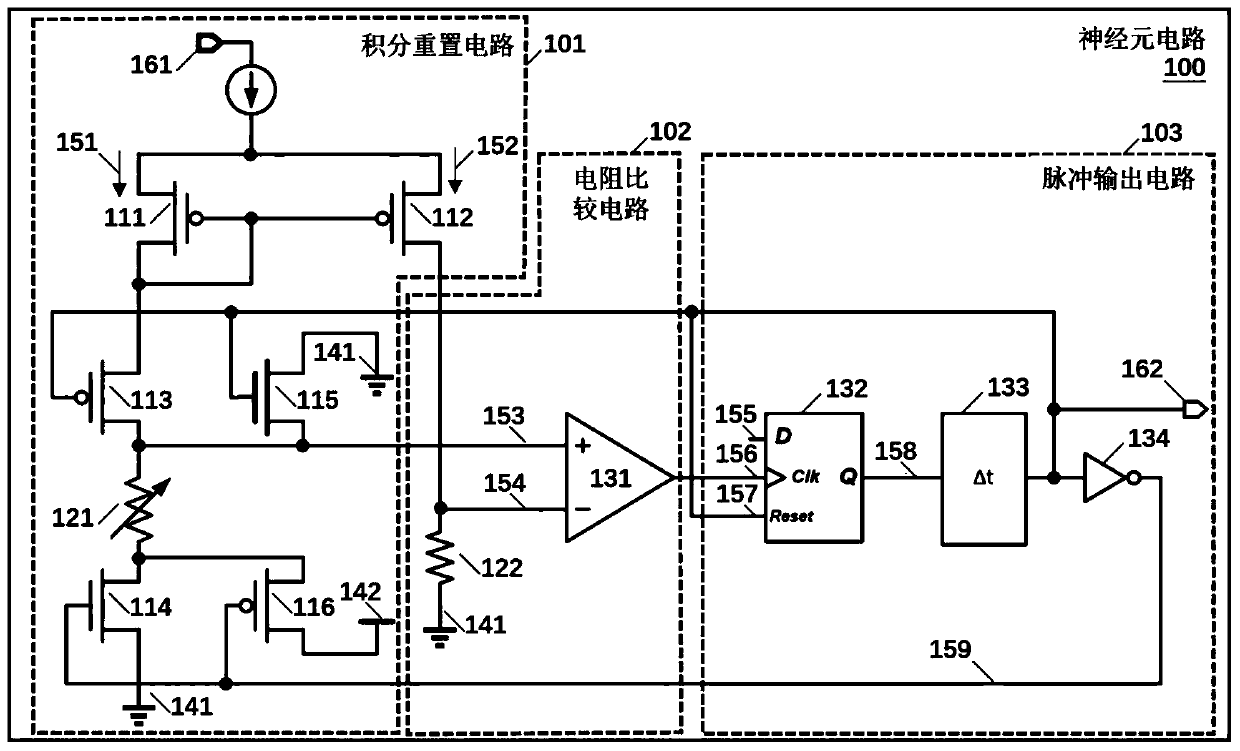

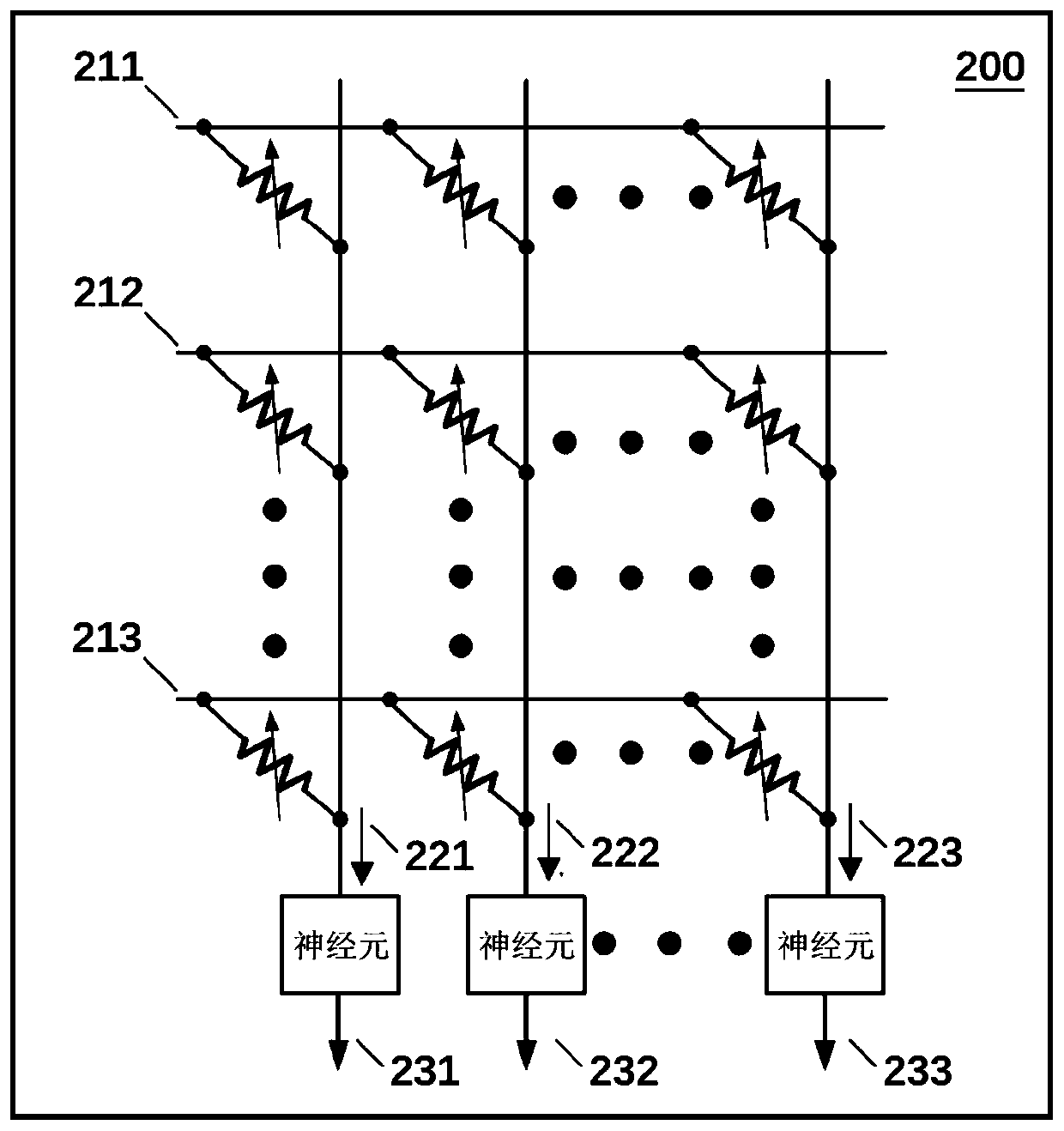

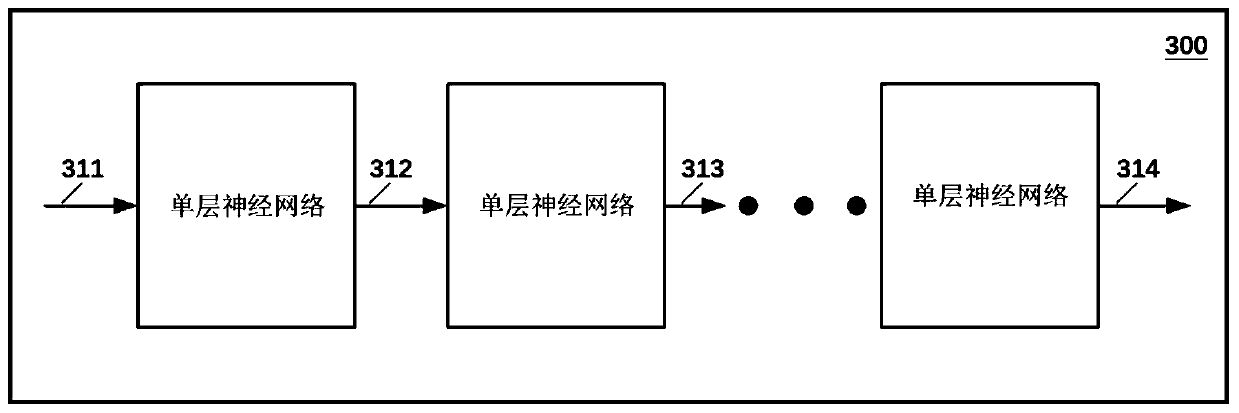

Neuron circuit based on memristor

ActiveCN110991629AReduce error rateImprove real-time performanceNetwork simulating resistancesEnergy efficient computingHemt circuitsNeuron circuit

The invention belongs to the technical field of neural components, and particularly relates to a neuron circuit based on a memristor. The neuron circuit comprises an integral reset circuit, a resistance comparison circuit and a pulse output circuit, the integral reset circuit takes the current of an external circuit as the input, realizes the integration of the input current through the reset or setting operation of the memristor, and takes the monitoring voltage of the real-time resistance value of the memristor as the output. The resistance comparison circuit receives the real-time monitoring voltage, compares the real-time monitoring voltage with a voltage signal of a reference resistor, and outputs a resistance comparison result to the pulse output circuit; when the real-time monitoring voltage exceeds a threshold value, the pulse output circuit outputs a neural pulse signal to an external circuit and sends a feedback signal to the integral reset circuit, so that the memristor resistance of the integral reset circuit is reset. The method has the advantages of being low in area cost after integration, good in real-time performance and low in misoperation rate.

Owner:FUDAN UNIV

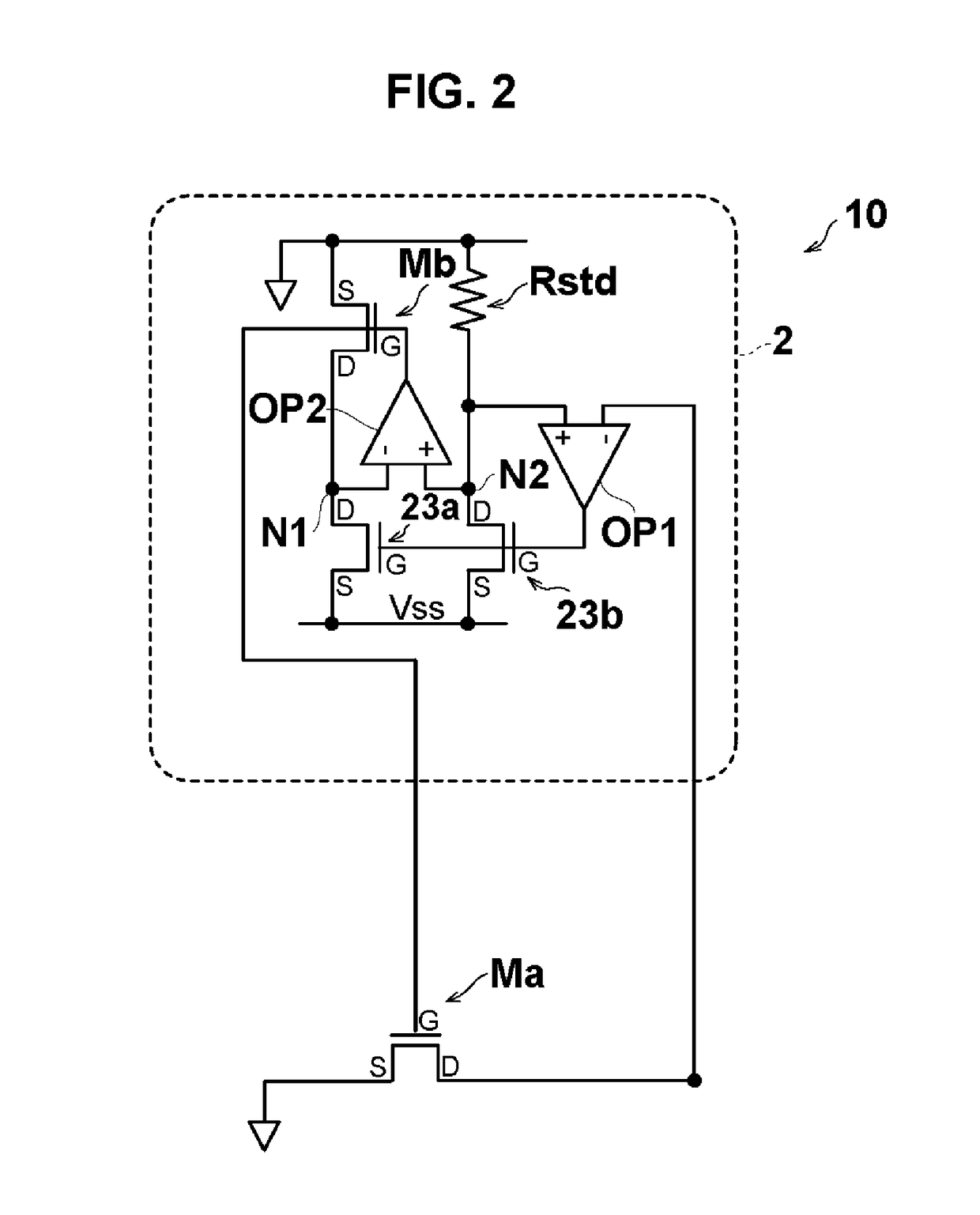

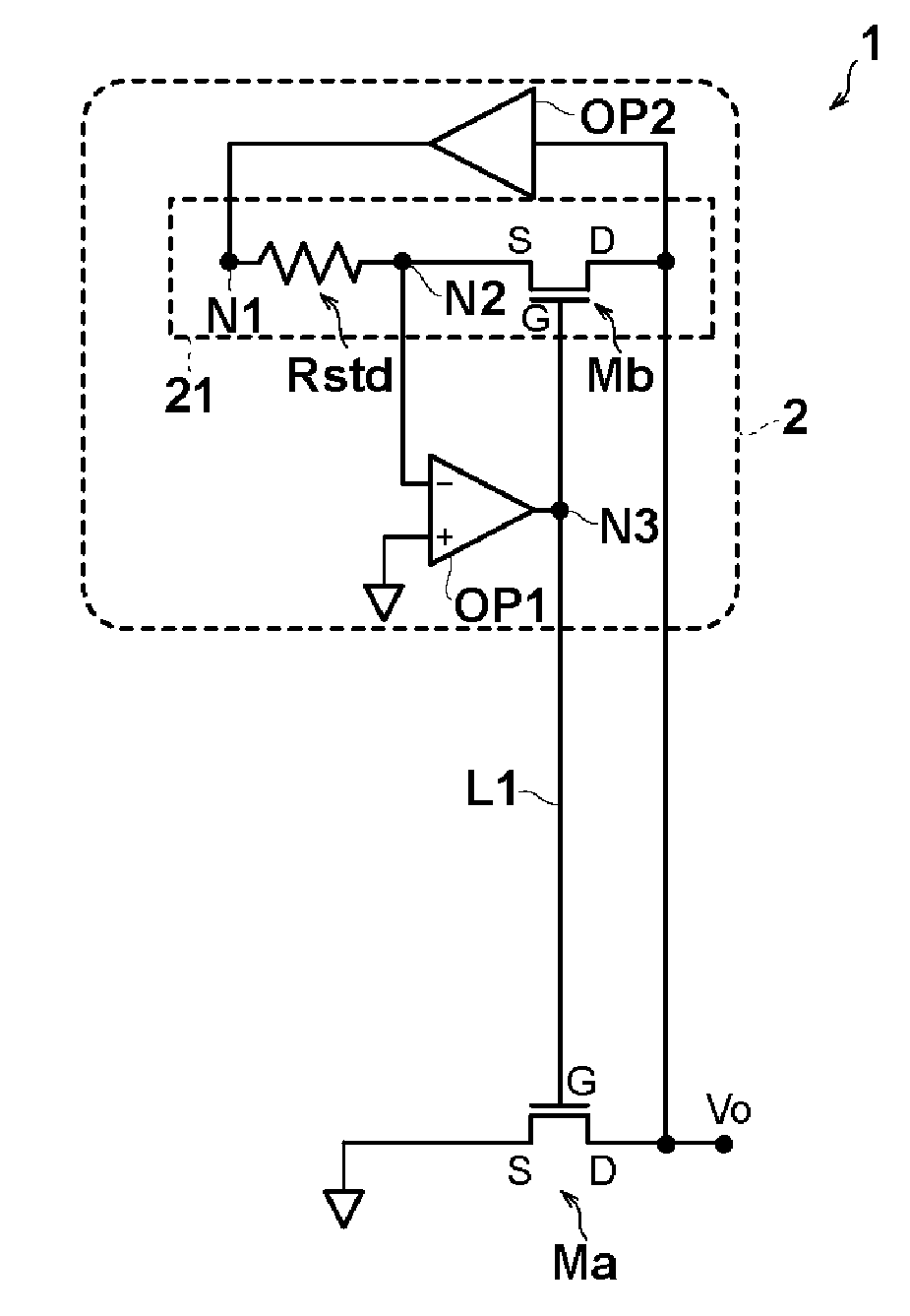

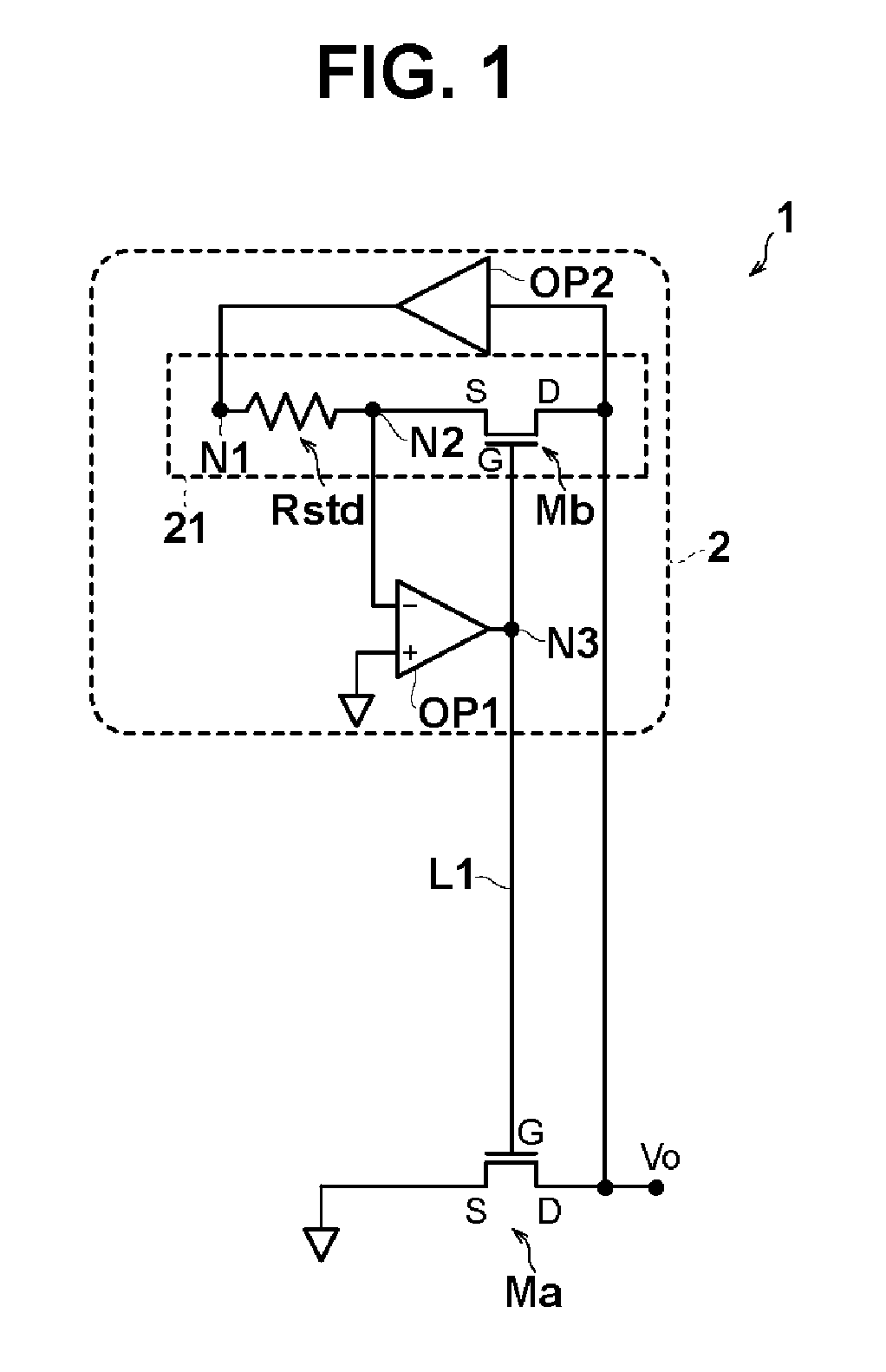

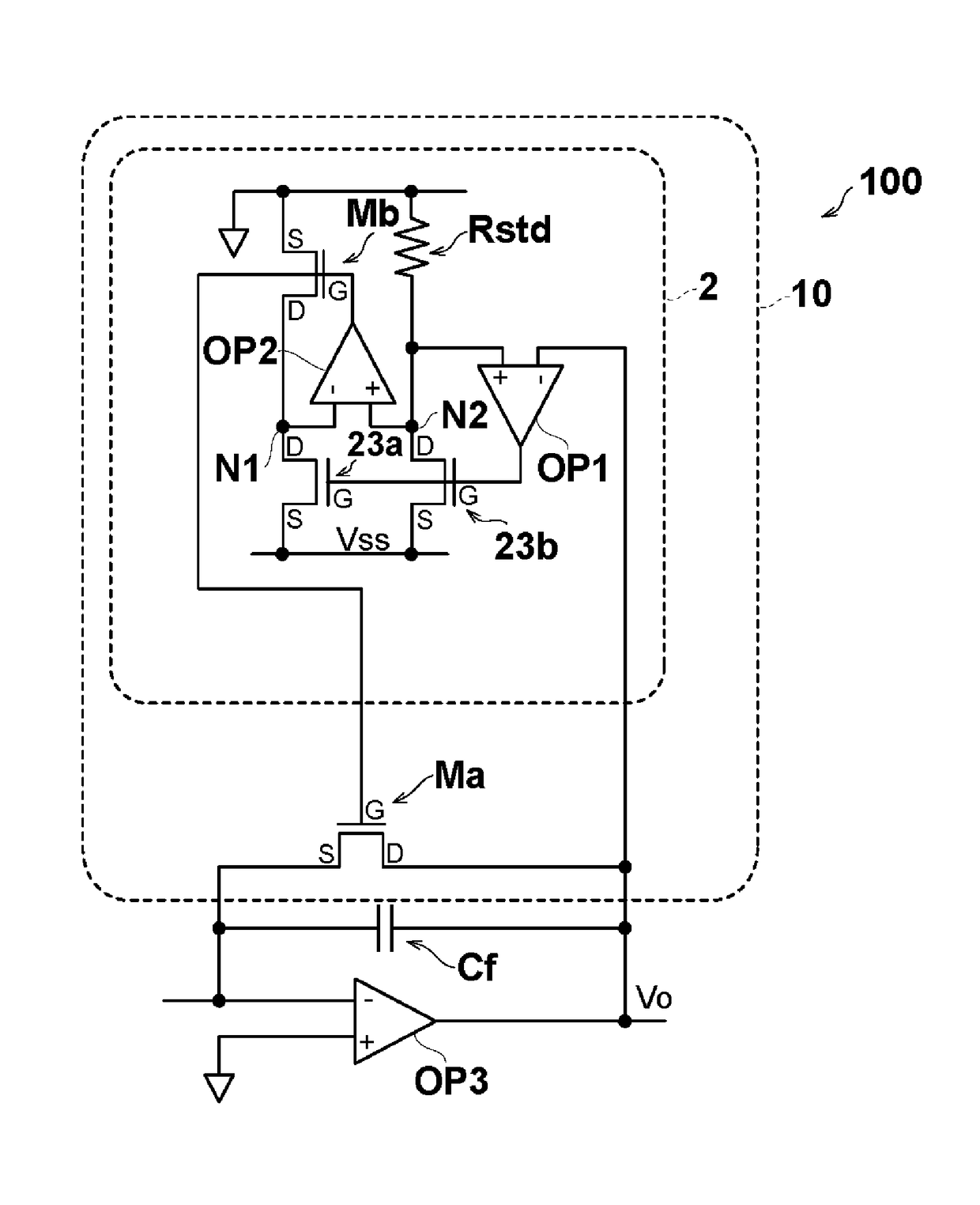

Psuedo resistor circuit and charge amplifier

ActiveUS20160020734A1Low temperature dependenceLower gate voltageNegative-feedback-circuit arrangementsCharge amplifiersAudio power amplifierDividing circuits

A pseudo resistor circuit and a charge amplifier include a first field effect transistor; a second field effect transistor having electrical characteristics matched with electrical characteristics of the first field effect transistor; and a voltage dividing circuit with terminal of a reference resistor electrically connected to a source terminal of the second field effect transistor. Further, a first operational amplifier with an output terminal is connected to a gate terminal of the first field effect transistor and a gate terminal of the second field effect transistor and in which midpoint voltage of the voltage dividing circuit is input into either an inverting or non-inverting input terminal and reference voltage is input into the other of the inverting and non-inverting input terminal. Furthermore, a second operational amplifier supplies voltage resulting from inversion and amplification of drain voltage of the first field effect transistor into the other terminal of the resistor.

Owner:MURATA MFG CO LTD

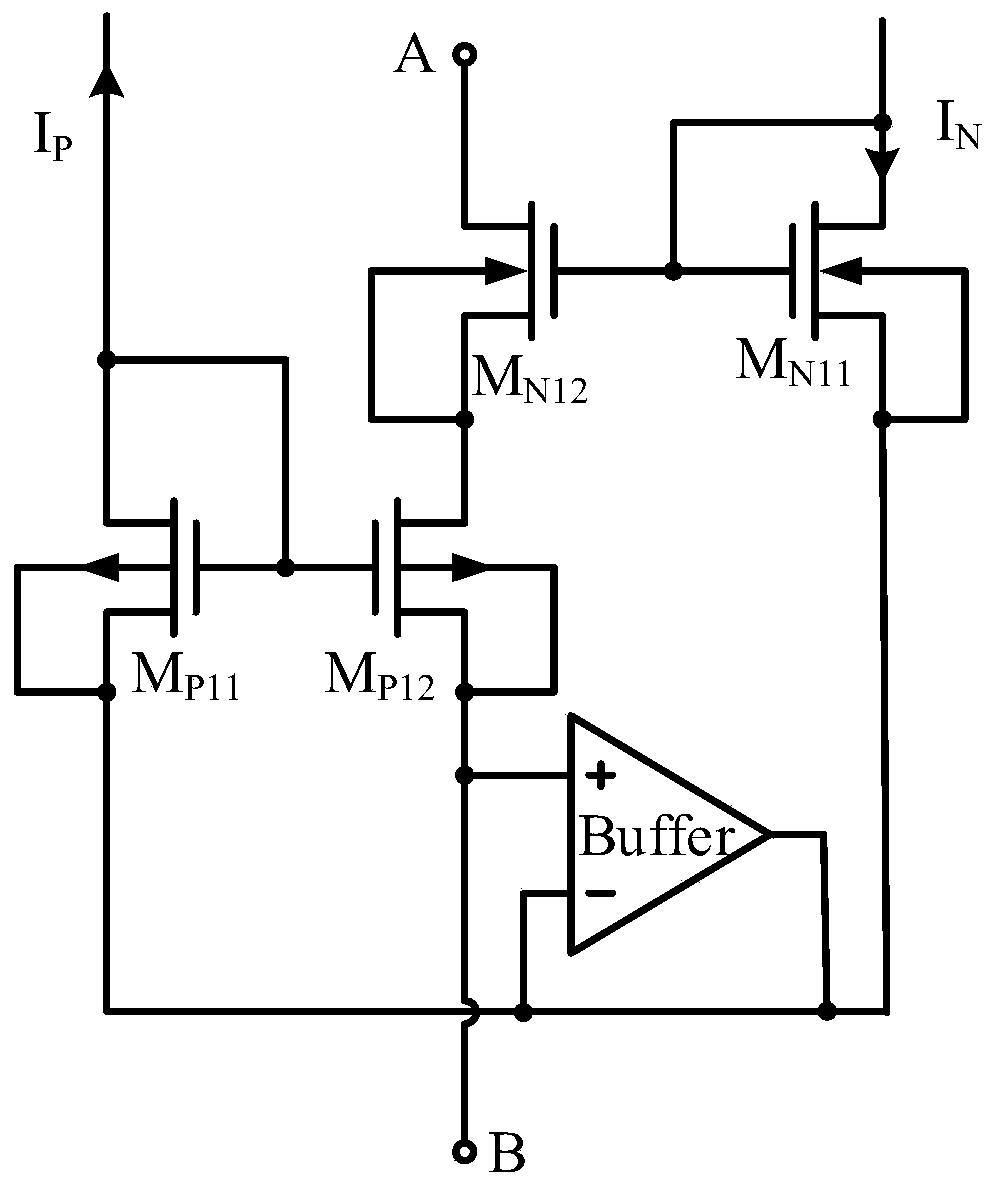

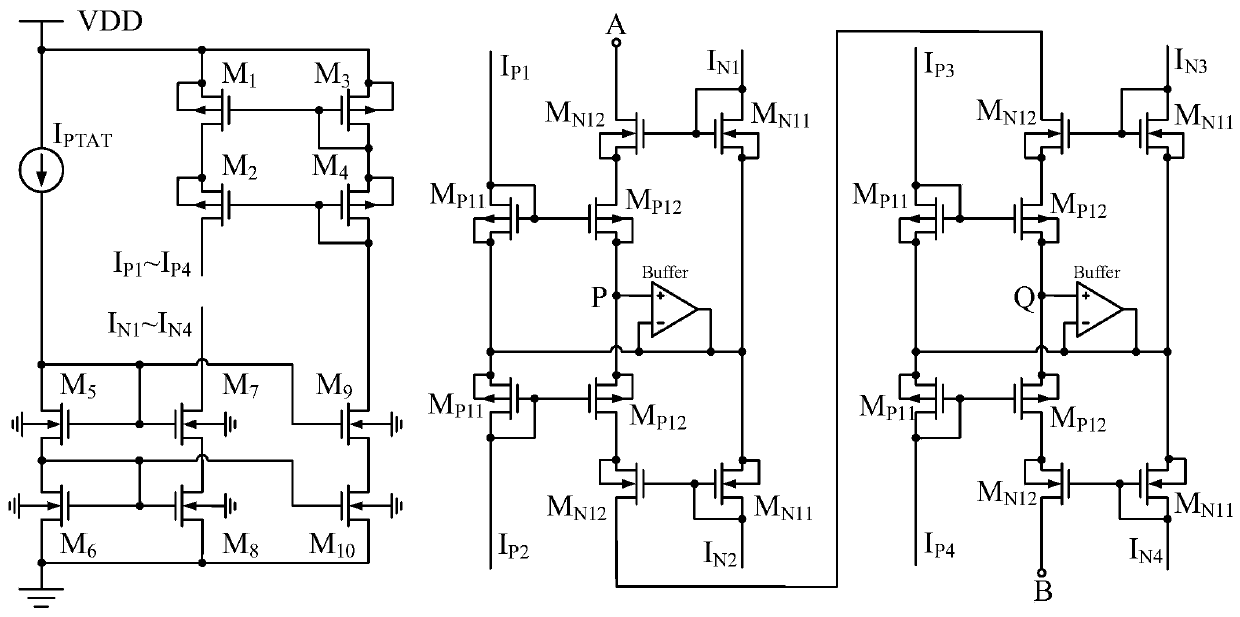

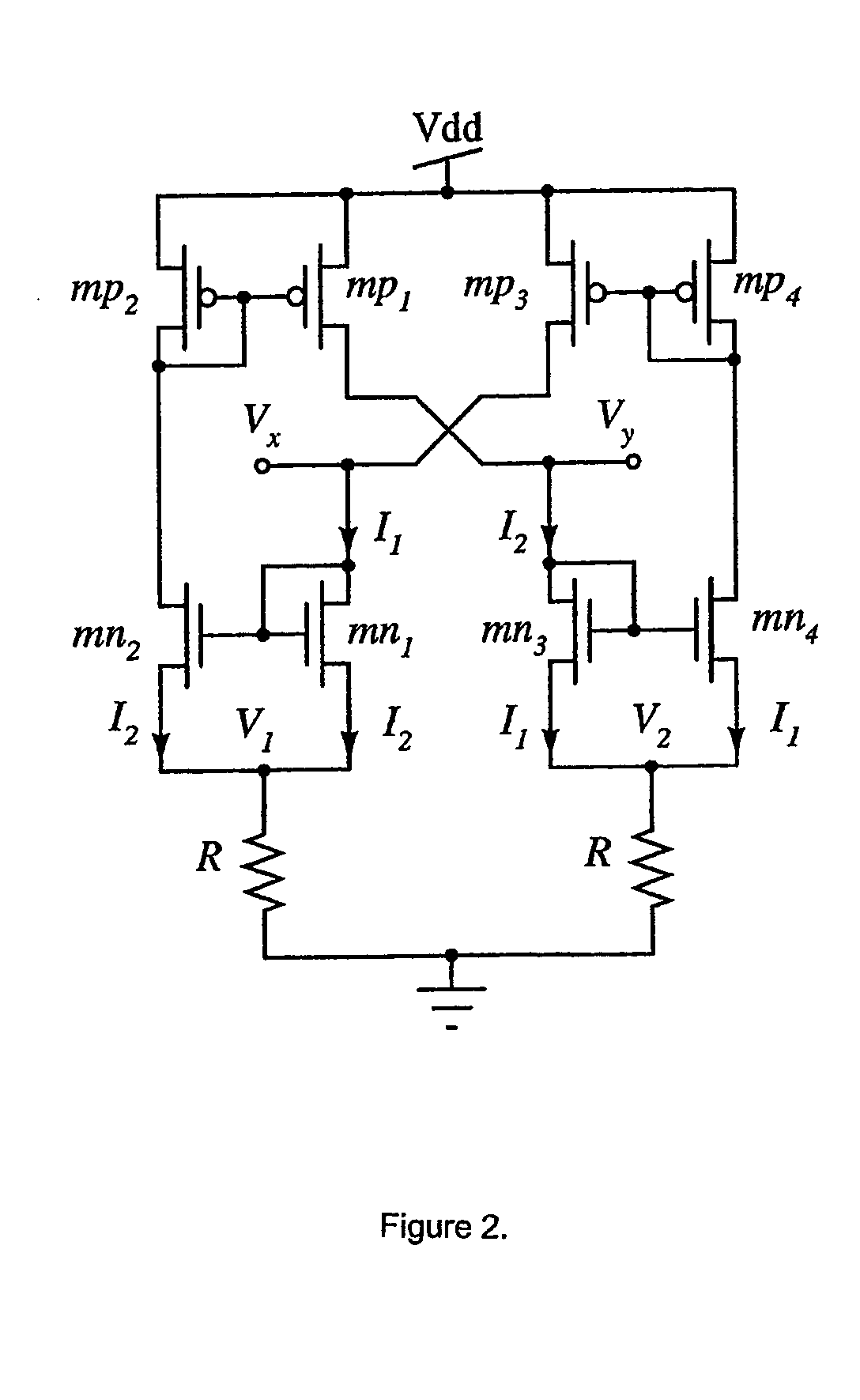

Dual-current bias type CMOS (Complementary Metal Oxide Semiconductor) pseudo resistor

PendingCN110752834AImprove robustnessInhibit injectionNetwork simulating resistancesCMOSMaterials science

The invention relates to a dual-current bias type CMOS (Complementary Metal Oxide Semiconductor) pseudo resistor, which comprises a first PMOS transistor, a second PMOS transistor, a first NMOS transistor, a second NMOS transistor and a buffer. The drain electrode of the first PMOS transistor is connected with the grid electrode of the first PMOS transistor. A substrate is connected with the source electrode of the first PMOS transistor, the grid electrode is connected with the grid electrode of the second PMOS transistor, and the source electrode is connected with the source electrode of thefirst NMOS transistor; the substrate of the second PMOS transistor is connected with the source electrode of the second PMOS transistor, the drain electrode of the second PMOS transistor is connectedwith the source electrode of the second NMOS transistor, and the source electrode serves as the first end of the CMOS pseudo resistor; the drain of the first NMOS transistor is connected with the grid of the first NMOS transistor, the substrate is connected with the source of the first NMOS transistor, and the grid is connected with the grid of the second NMOS transistor; the substrate of the second NMOS transistor is connected with the source of the second NMOS transistor, and the drain of the second NMOS transistor is used as the second end of the CMOS pseudo resistor; the non-inverting input end of the buffer is connected with the source electrode of the second PMOS tube, the inverting input end of the buffer is connected with the source electrode of the first PMOS tube, and the outputend of the buffer is connected with the source electrode of the first NMOS tube. The resistance value of the dual-current bias CMOS pseudo resistor is basically not affected by the process, temperature change and sub-threshold leakage current, and the robustness is good.

Owner:XIDIAN UNIV

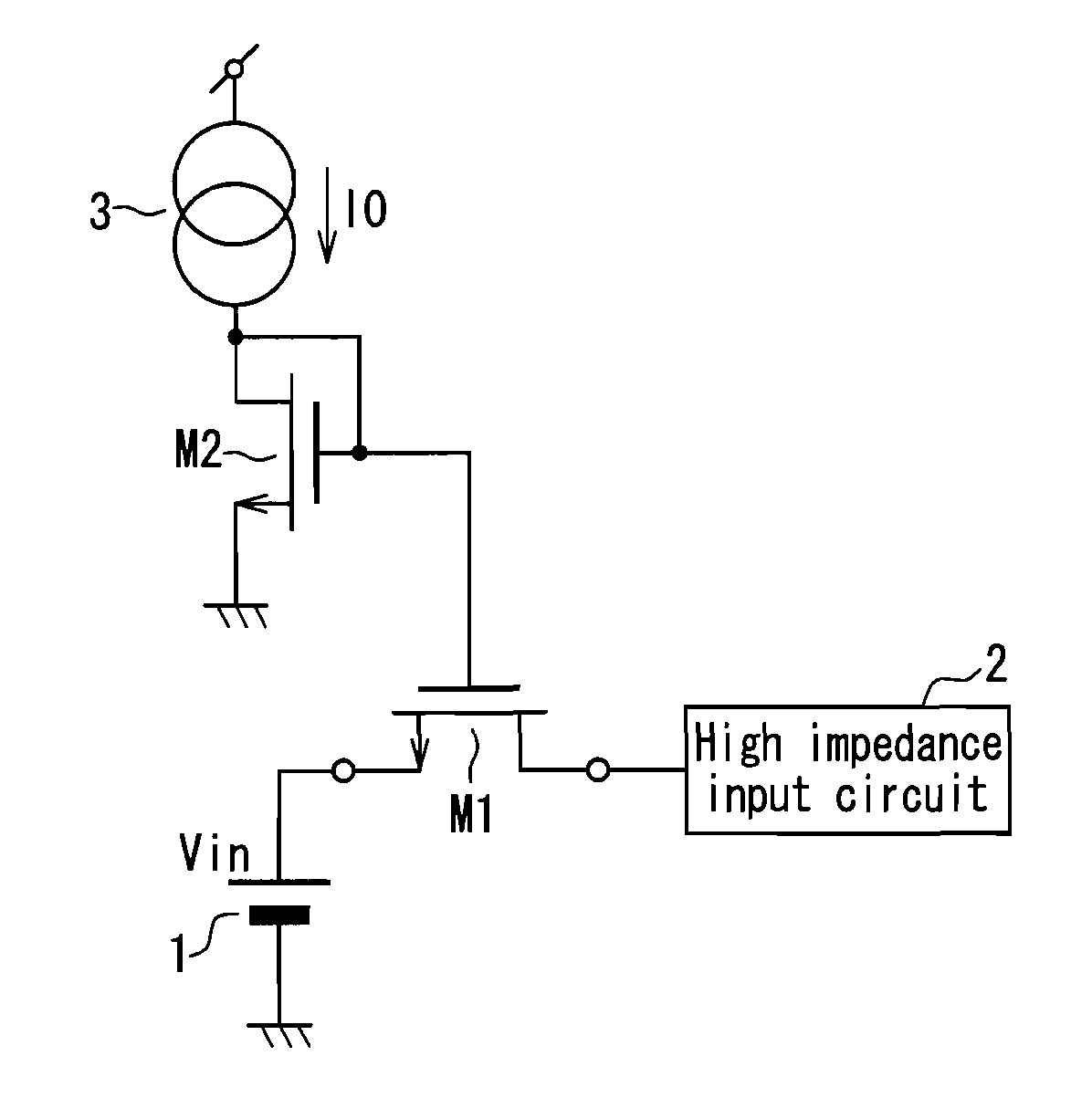

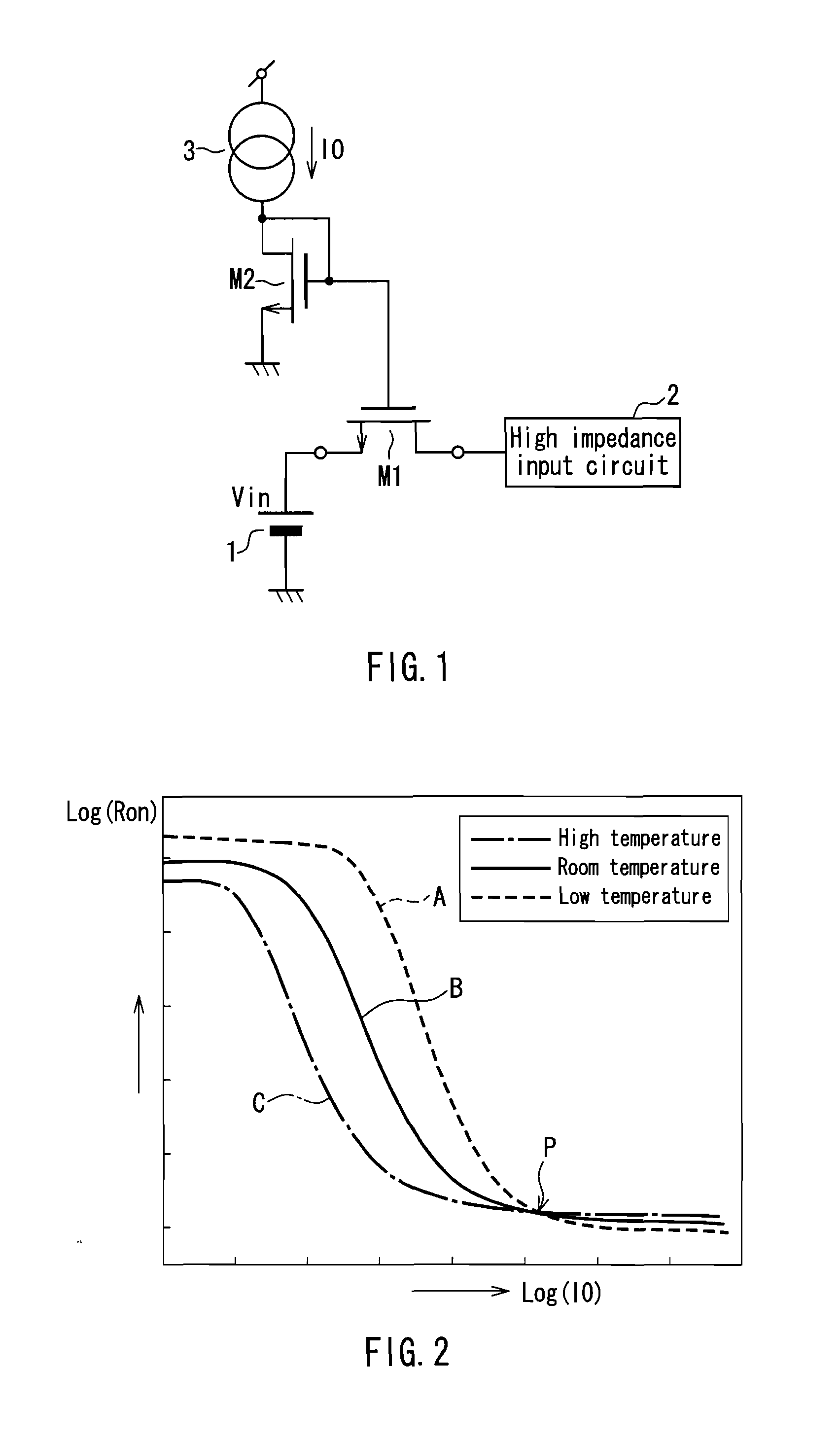

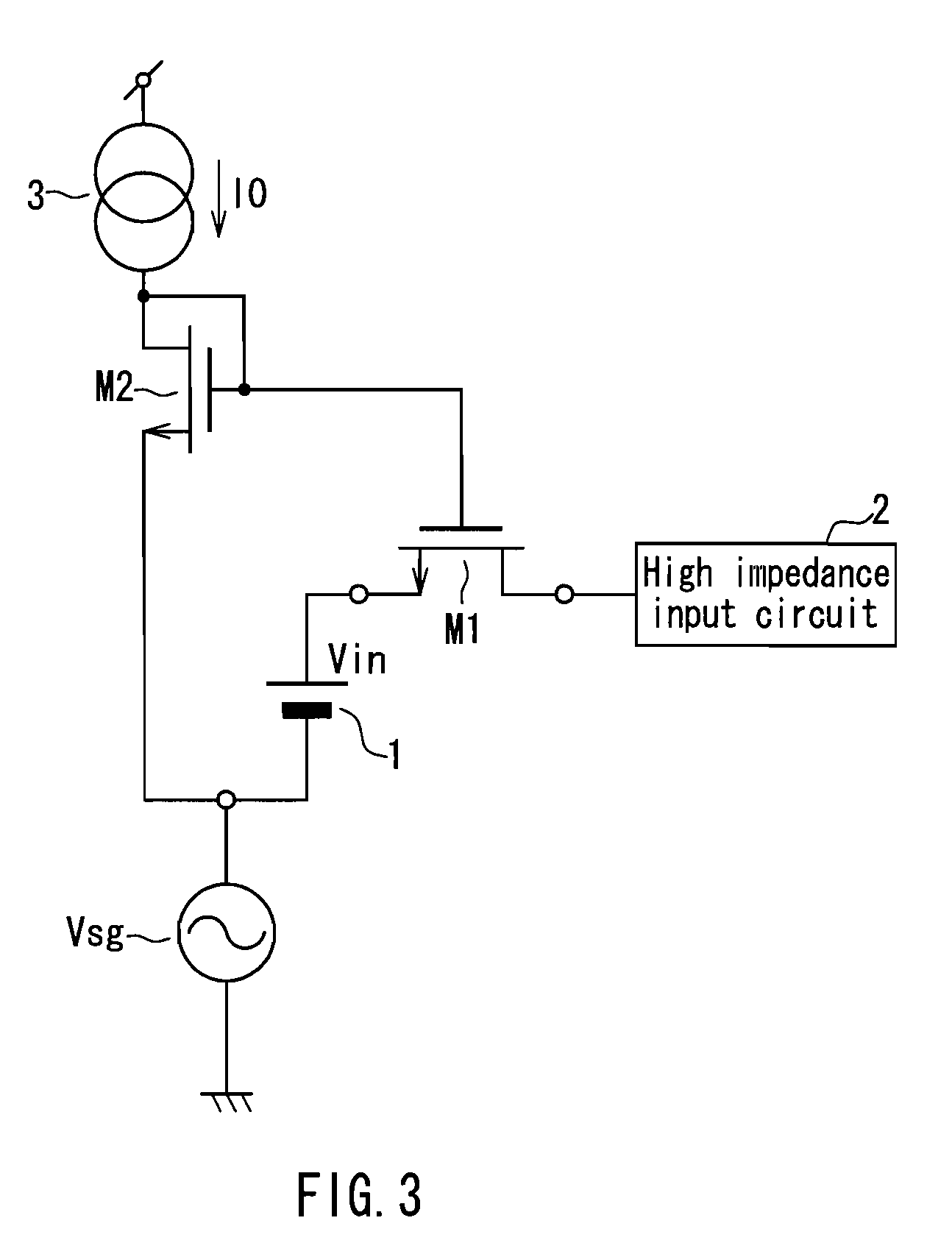

Mos transistor resistor, filter, and integrated circuit

InactiveUS20110095813A1Good temperature characteristicsLower the resistance valueTransistorSolid-state devicesEngineeringManufacturing variation

A MOS transistor including a first MOS transistor M1 to be used as a resistor; an input voltage source 1 connected to the source of the first MOS transistor for applying an input voltage Vin; and a gate voltage source 6 connected to the gate of the first MOS transistor for applying a gate voltage Vg. The gate voltage Vg and the input voltage Vin are set within a range where a gate-source voltage and source-drain voltage of the first MOS transistor cause the first MOS transistor to operate in a non-saturation region and also are set to avoid the first MOS transistor operating in an operation region with leakage current. Fluctuations of the resistance value resulting from a change in leakage current due to manufacturing variations are reduced and favorable temperature characteristics are obtained.

Owner:PANASONIC CORP

Tunable voltage-controlled pseudo-resistor

InactiveUS8659340B2High resistanceIncrease resistanceMultiple-port networksPulse automatic controlCompensation effectTransistor circuits

A tunable voltage-controlled pseudo-resistor structure, comprising: a symmetric PMOS transistor circuit and an auto-tuning circuit connected in series. Input of the auto-tuning circuit is connected to a central position Vf of the PMOS transistor circuit having its output Vg, with its purpose of keeping Vg−Vf at a constant value. The PMOS transistor circuit may produce body effect through various different bulk voltages. Through the auto-tuning circuit, Vg and Vf are kept constant to make current of transistor to produce compensation effect, such that regardless of Va>Vb or Va<Vb, a large resistance is maintained. Through utilizing the tunable voltage-controlled pseudo-resistor structure, constant resistance can be maintained under high input voltage, hereby reducing drifting of common-mode voltage, in achieving a superior resistance effect.

Owner:NAT CENT UNIV

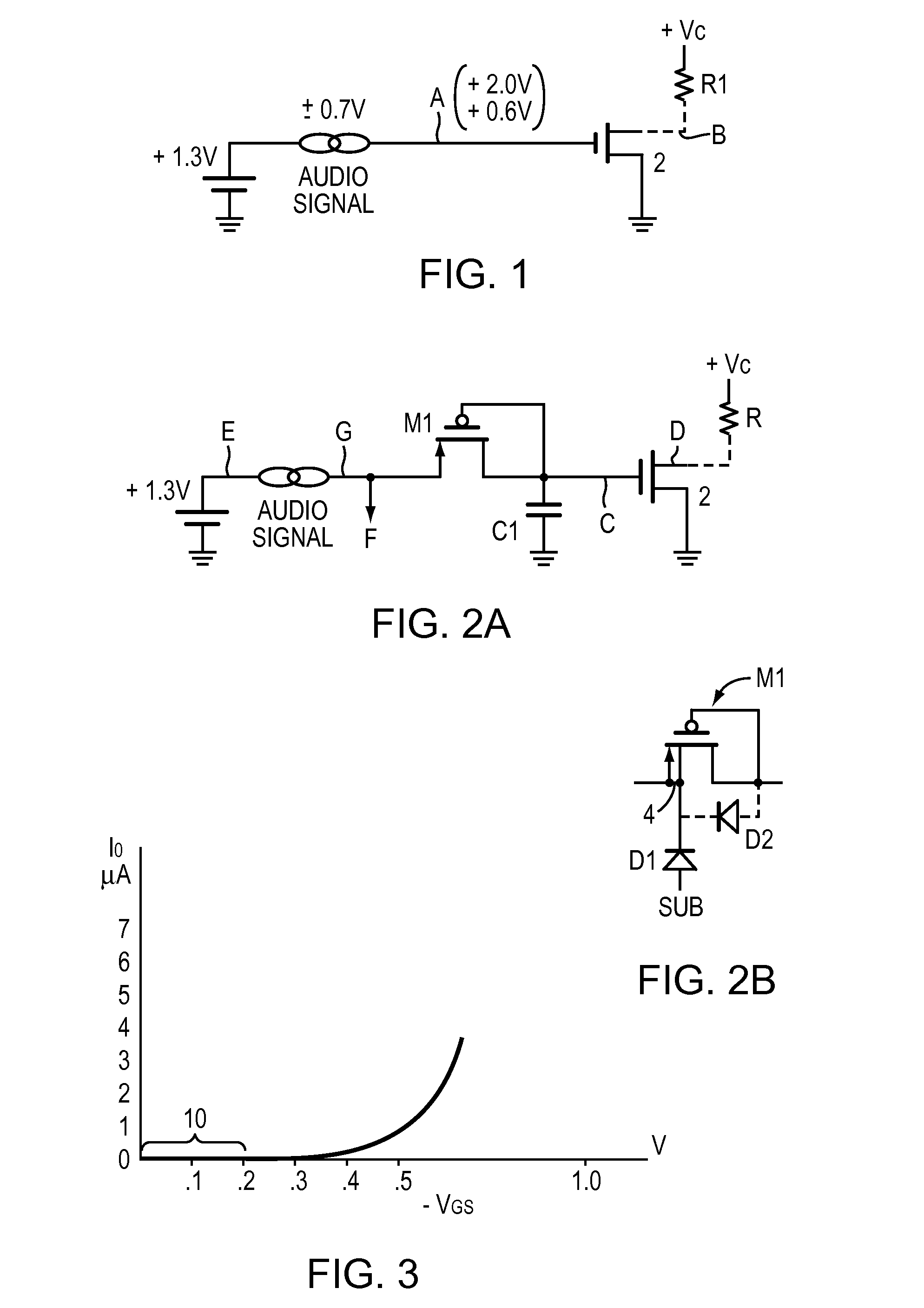

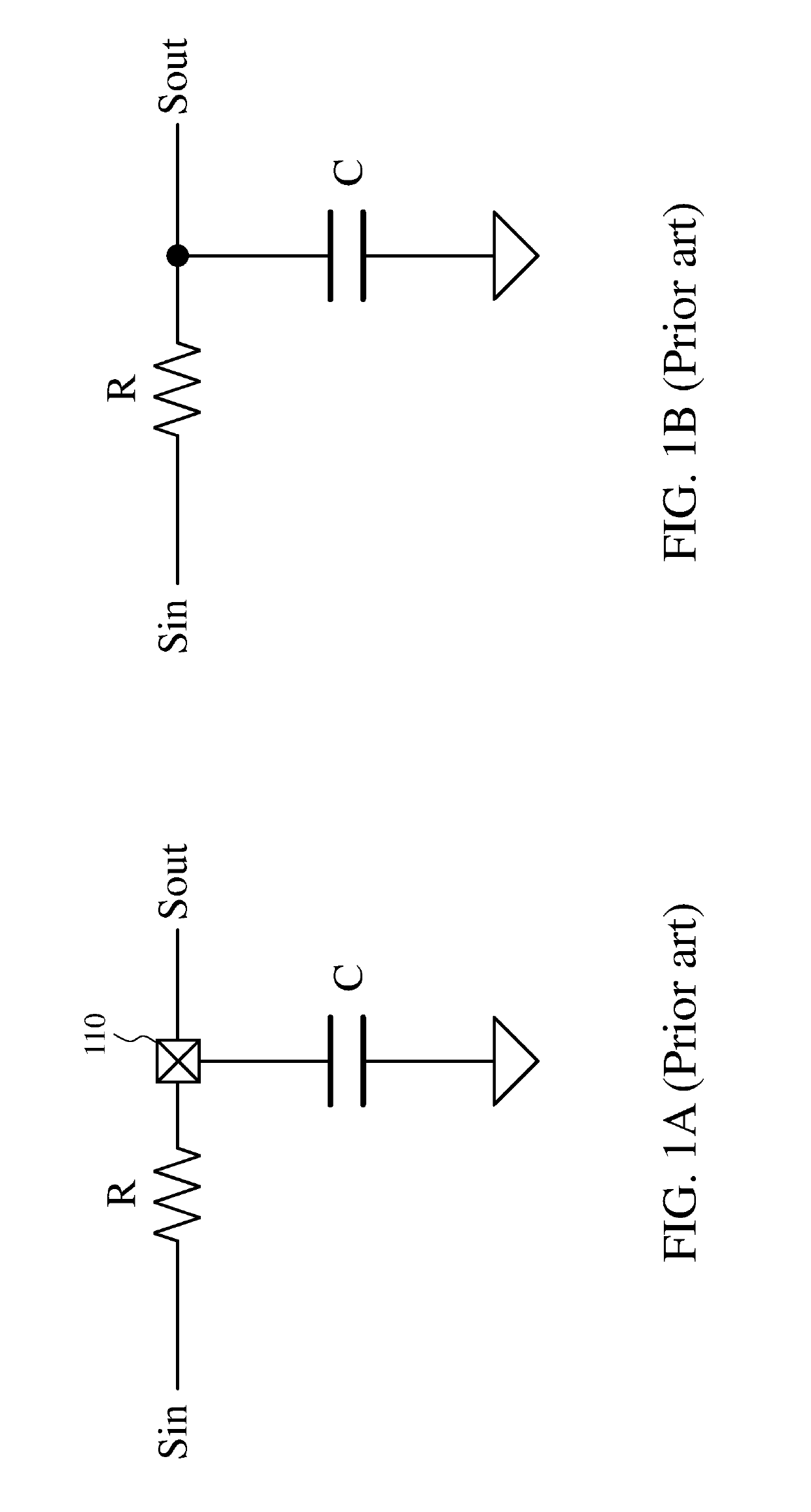

Audio filter using a diode connected mosfet

InactiveUS20080136509A1High value resistanceDegrade audio signalNetwork simulating resistancesOscillations generatorsMOSFETLow-pass filter

A diode connected P-type CMOS transistor is operated in the sub-threshold area and, with a bypass capacitor, operates as a low pass audio filter. The equivalent resistance of the CMOS transistor in the sub-threshold range is very high—in the gigaOhm range. With this size resistor, a capacitor in the 1-25 pF range may be used to provide filtering capabilities with break points in the 1-10 Hz frequency range. Such a filter provides an effective low pass filter that attenuates audio frequency signals. The 1-25 pF capacitors use little chip area making the arrangement practical for integrating on an IC with the audio signals. In one embodiment, a digital signal and the audio signals share one pin, where the audio signal appears only when the digital signal is high. In this case, the audio signal filtered out from the digital high signal. The filtered digital signal drives digital circuitry while the audio signal is directed to other audio circuitry.

Owner:SEMICON COMPONENTS IND LLC

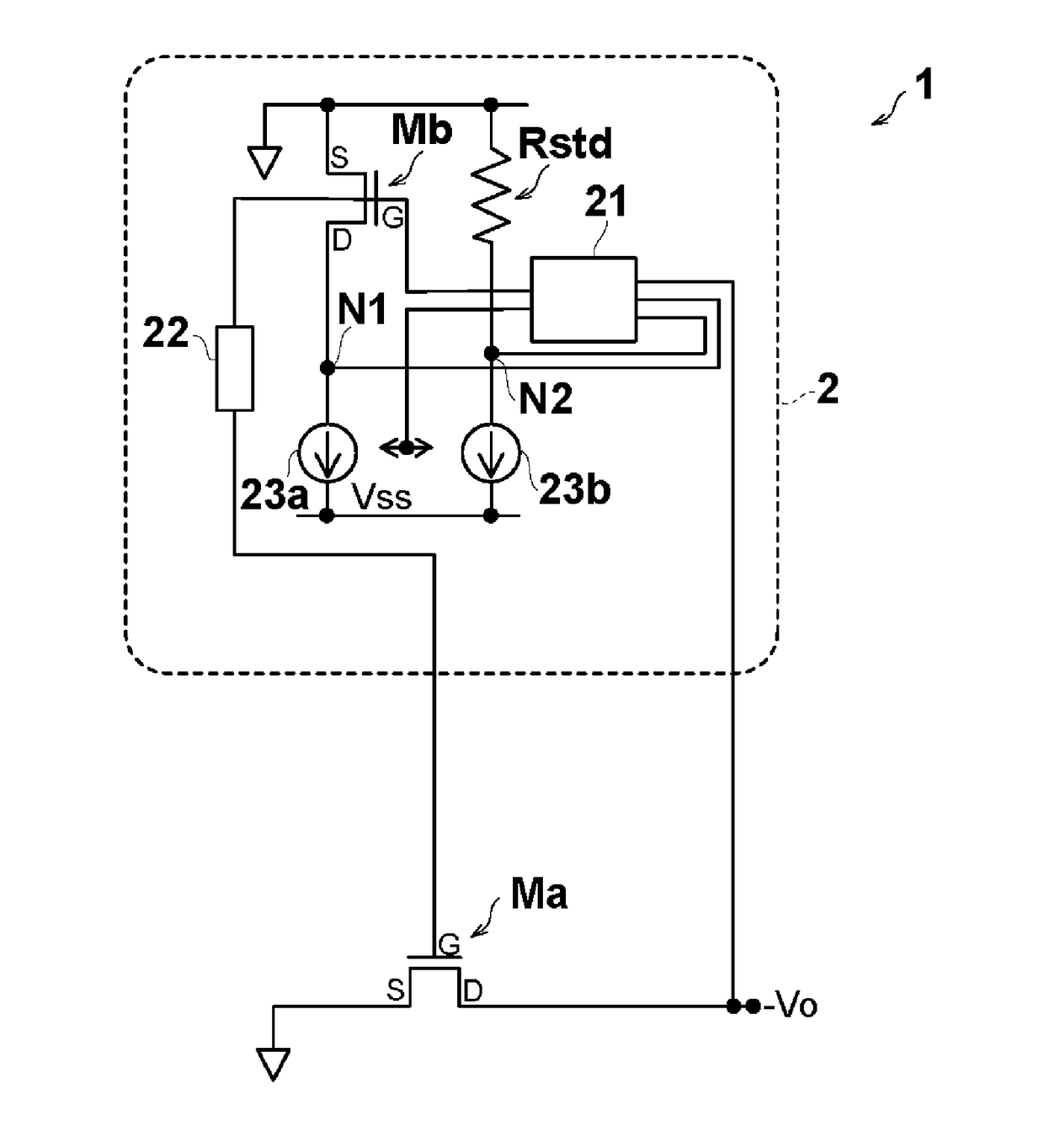

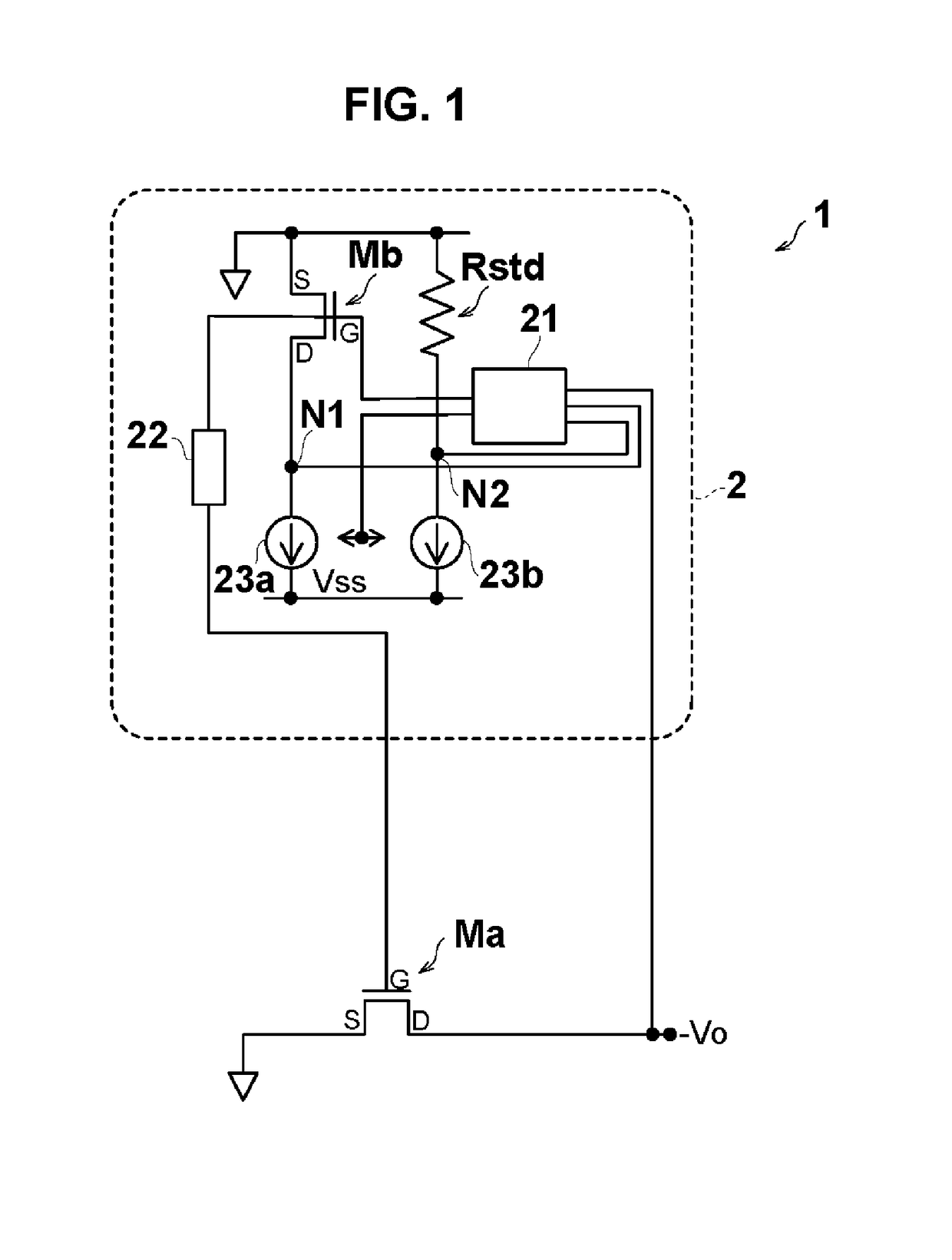

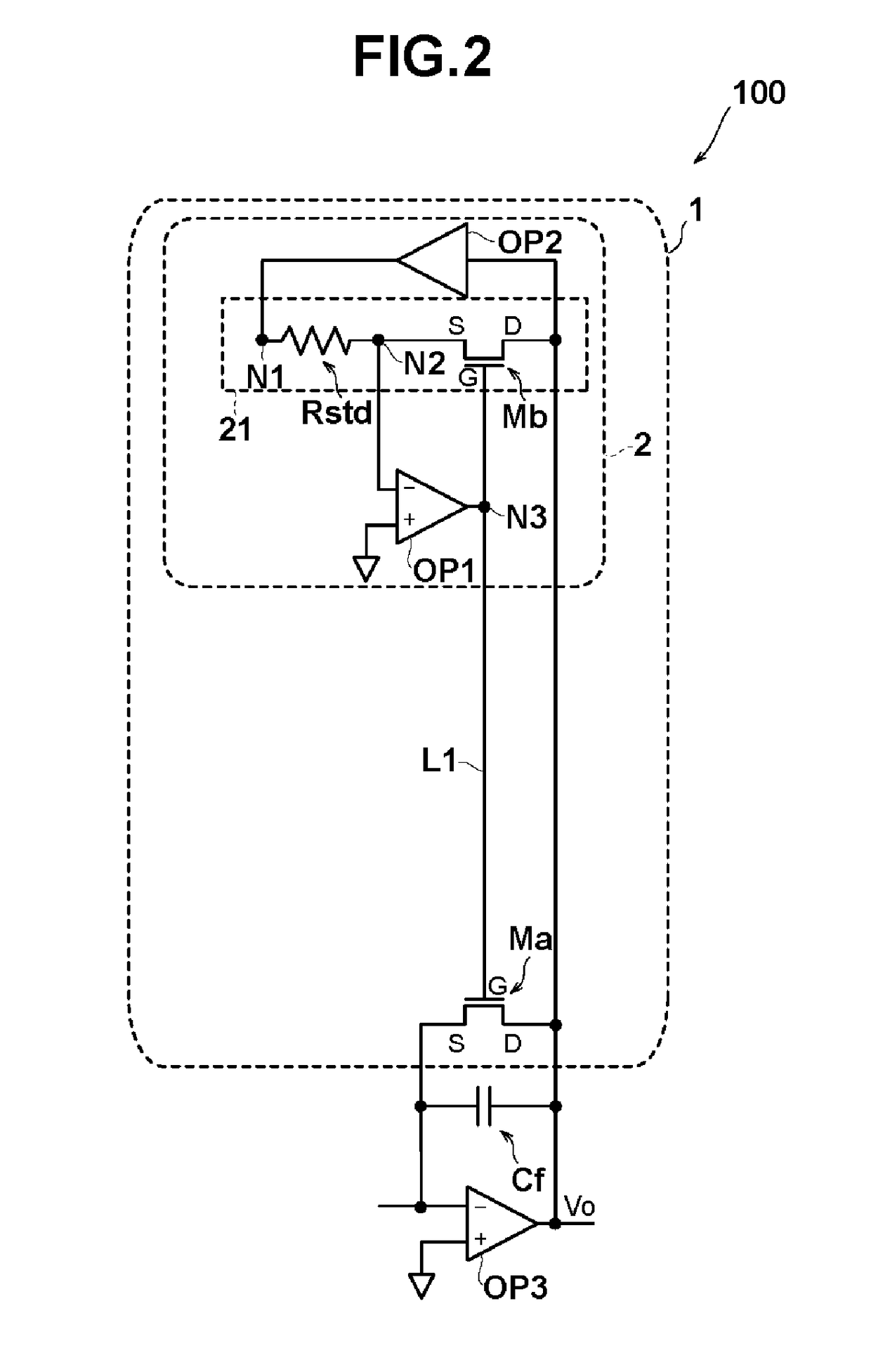

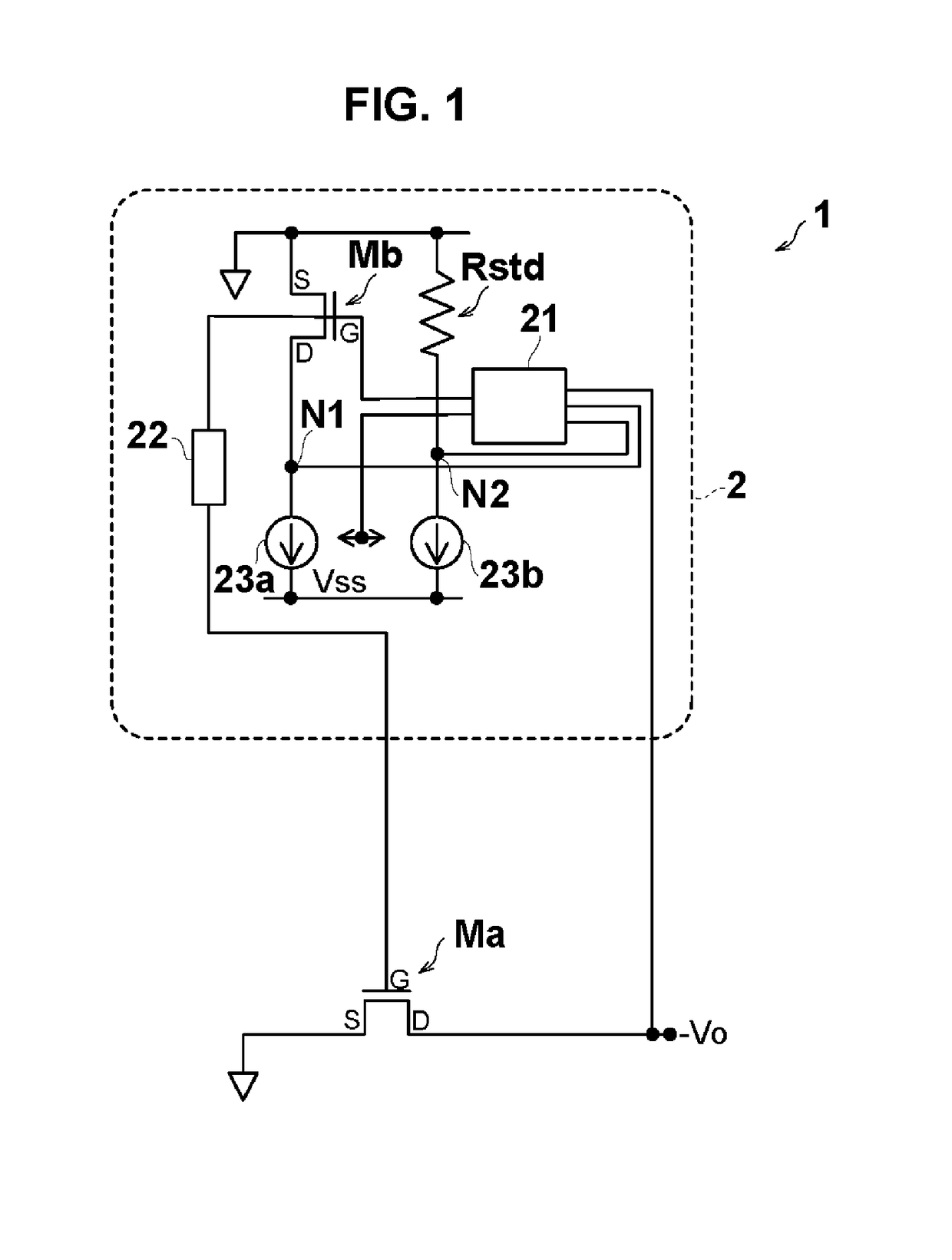

Pseudo resistance circuit and charge detection circuit

ActiveUS20170070209A1Low temperature dependenceAdjustable resistanceSolid-state devicesAmplifier with semiconductor-devices/discharge-tubesResistive circuitsCharge detection

A pseudo resistance circuit includes a first gate voltage adjustment circuit that adjusts respective currents of first and second current sources and also adjusts a gate voltage of a second field effect transistor to equalize or substantially equalize a drain voltage of the second field effect transistor and a voltage of a first end portion of a reference resistance element and controls a drain voltage of a first field effect transistor and the drain voltage of the second field effect transistor to maintain a constant or substantially constant relationship with each other; and a second gate voltage adjustment circuit that adjusts a gate voltage of the first field effect transistor to control the gate voltage of the second field effect transistor and the gate voltage of the first field effect transistor to maintain a constant or substantially constant relationship with each other.

Owner:MURATA MFG CO LTD

Adaptive mosfet resistor

Owner:MARYLAND SEMICON

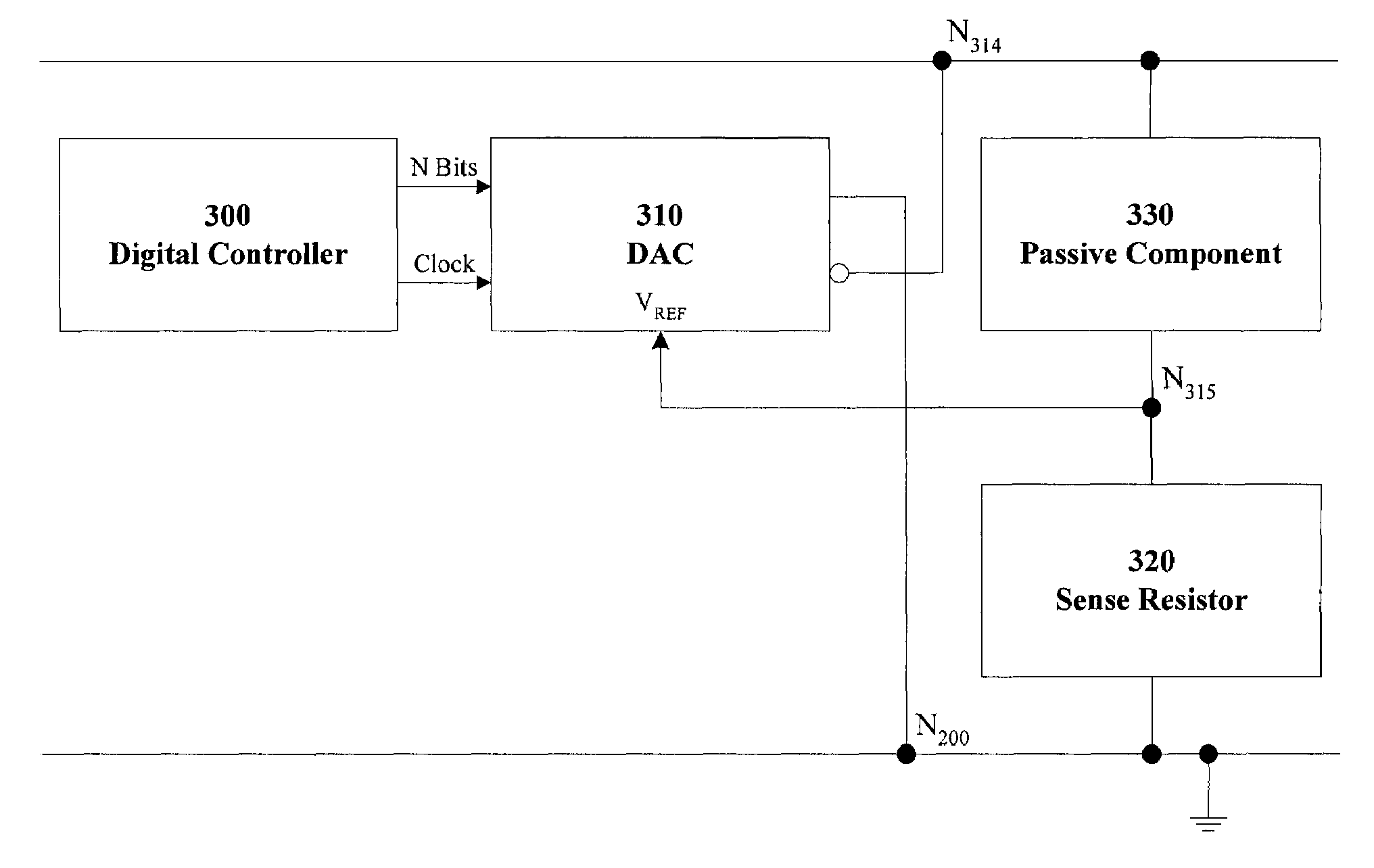

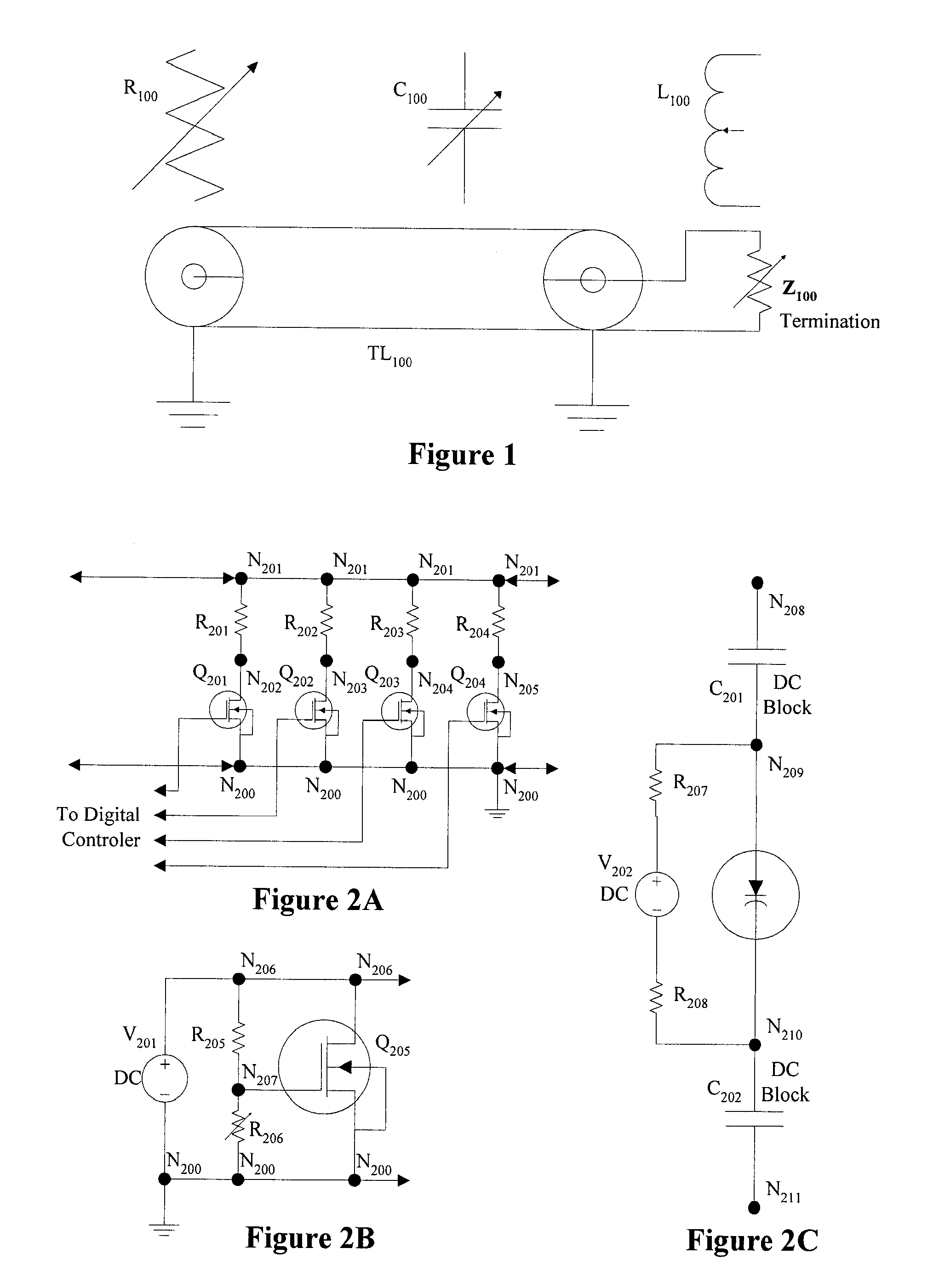

Variable passive components with high resolution value selection and control

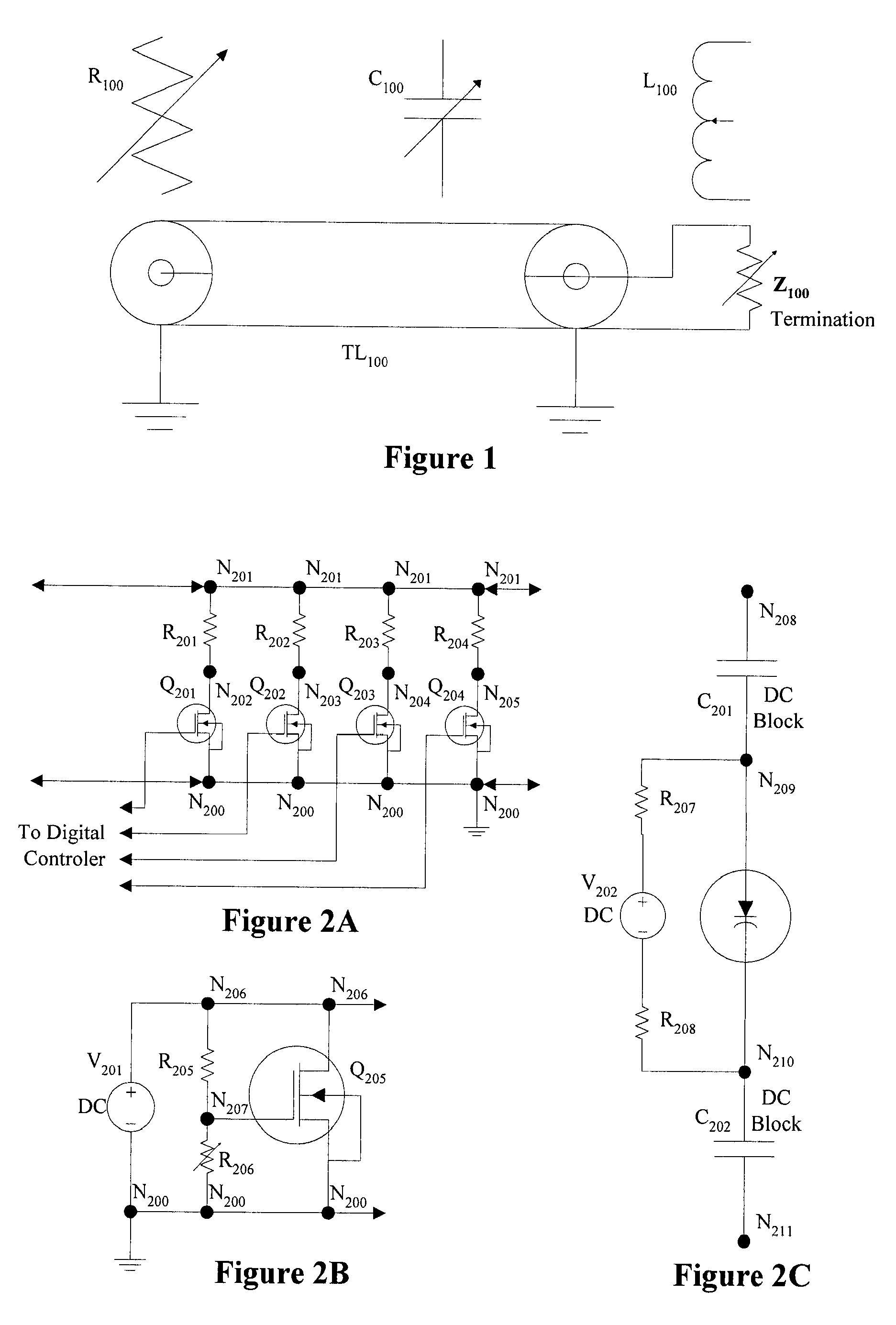

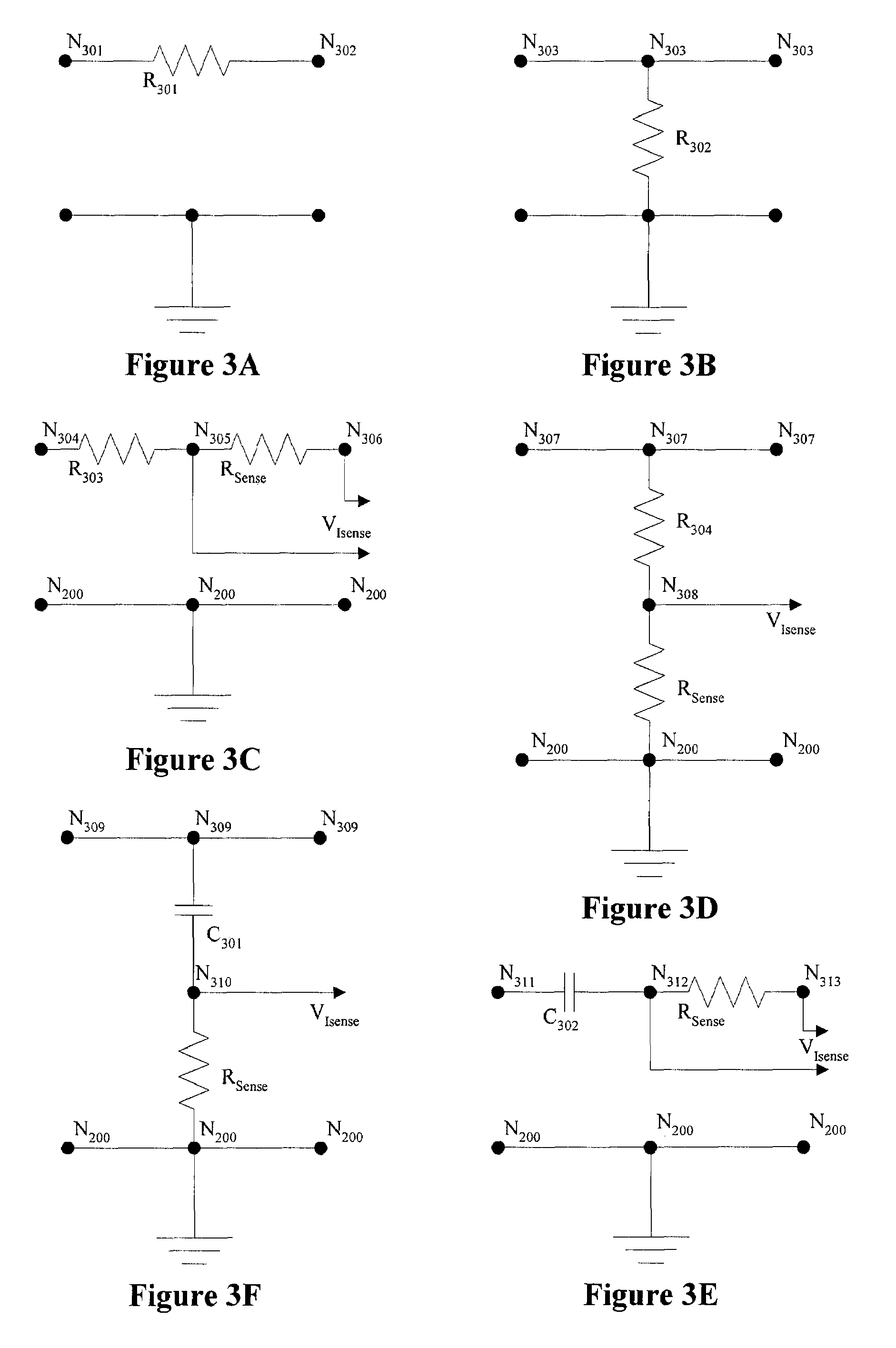

The present system provides a method for varying the value of passive components in electronic circuits. Passive components can range from basic resistors, capacitors, and inductors to complex, structures such as transmission lines and resonant cavities. Value selection and variation can either be dynamically performed during circuit operation or as a one-time part of the manufacturing process as determined by the requirements of the specific application. A digital-to-analog converter (DAC) circuit is used to input value selection data digitally, and control value selection with value resolution dependent on the resolution of the DAC. An alternate embodiment is provided for high frequency operation.

Owner:MASHHOON HAMID R +1

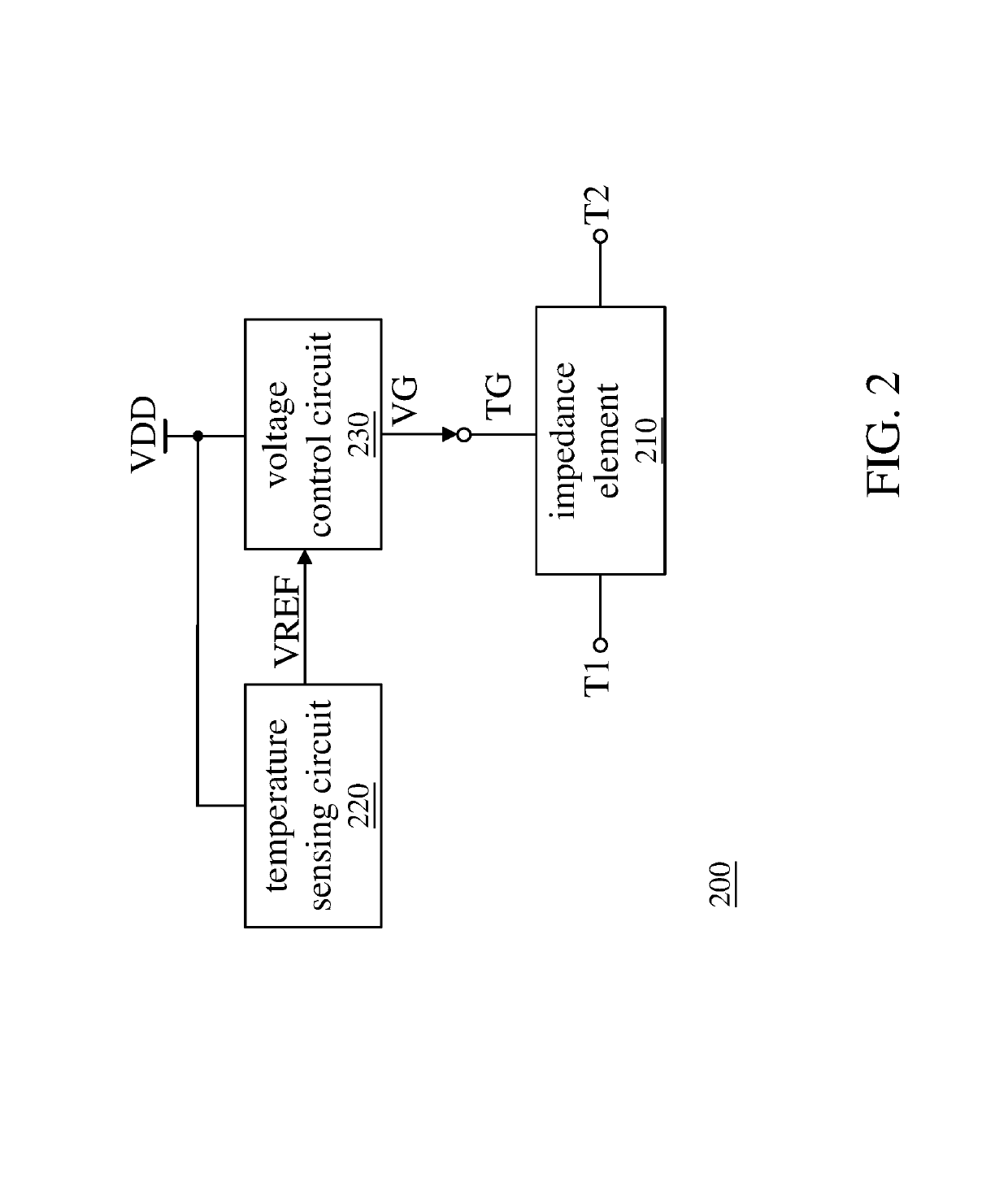

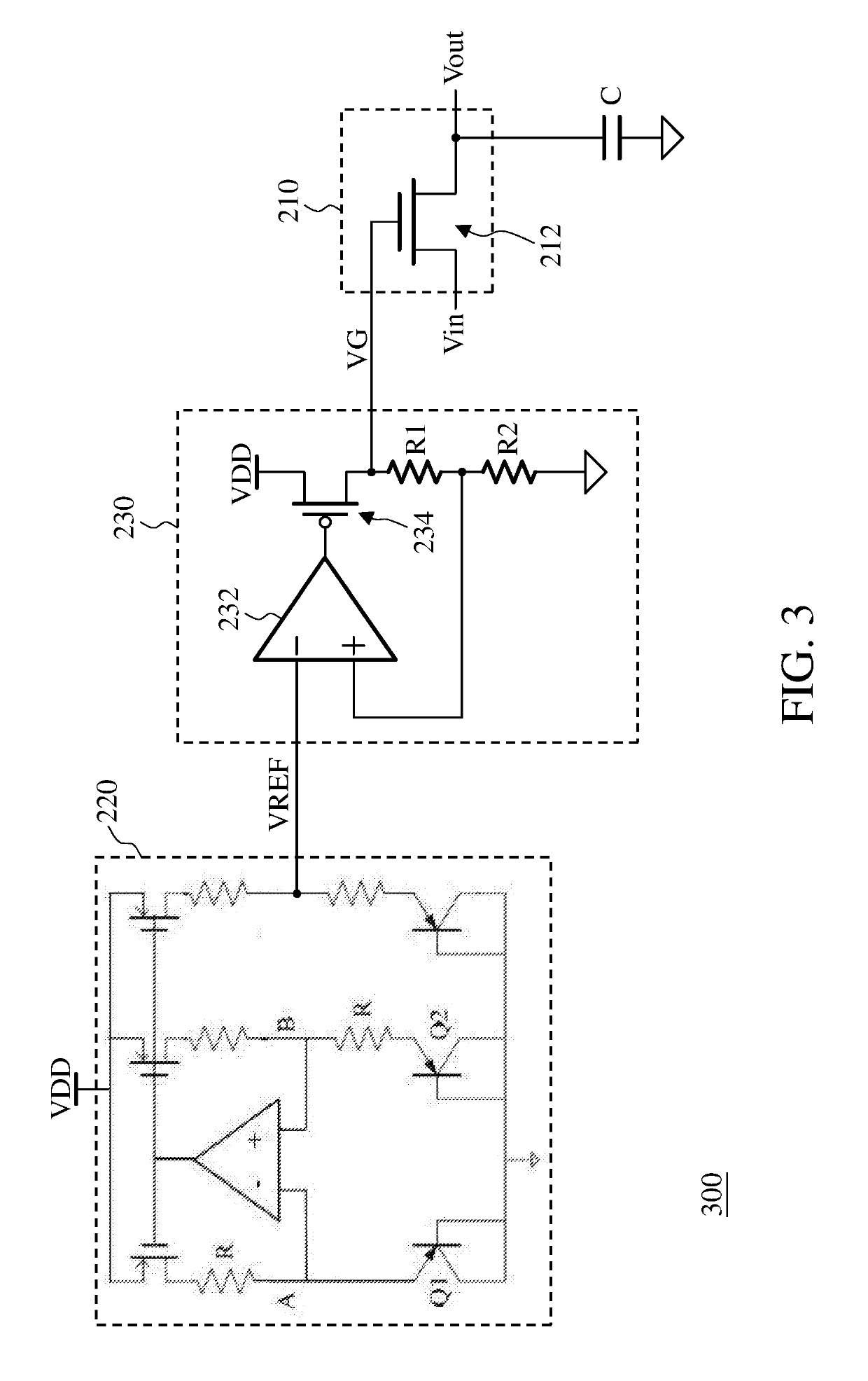

Active load generation circuit and filter using same

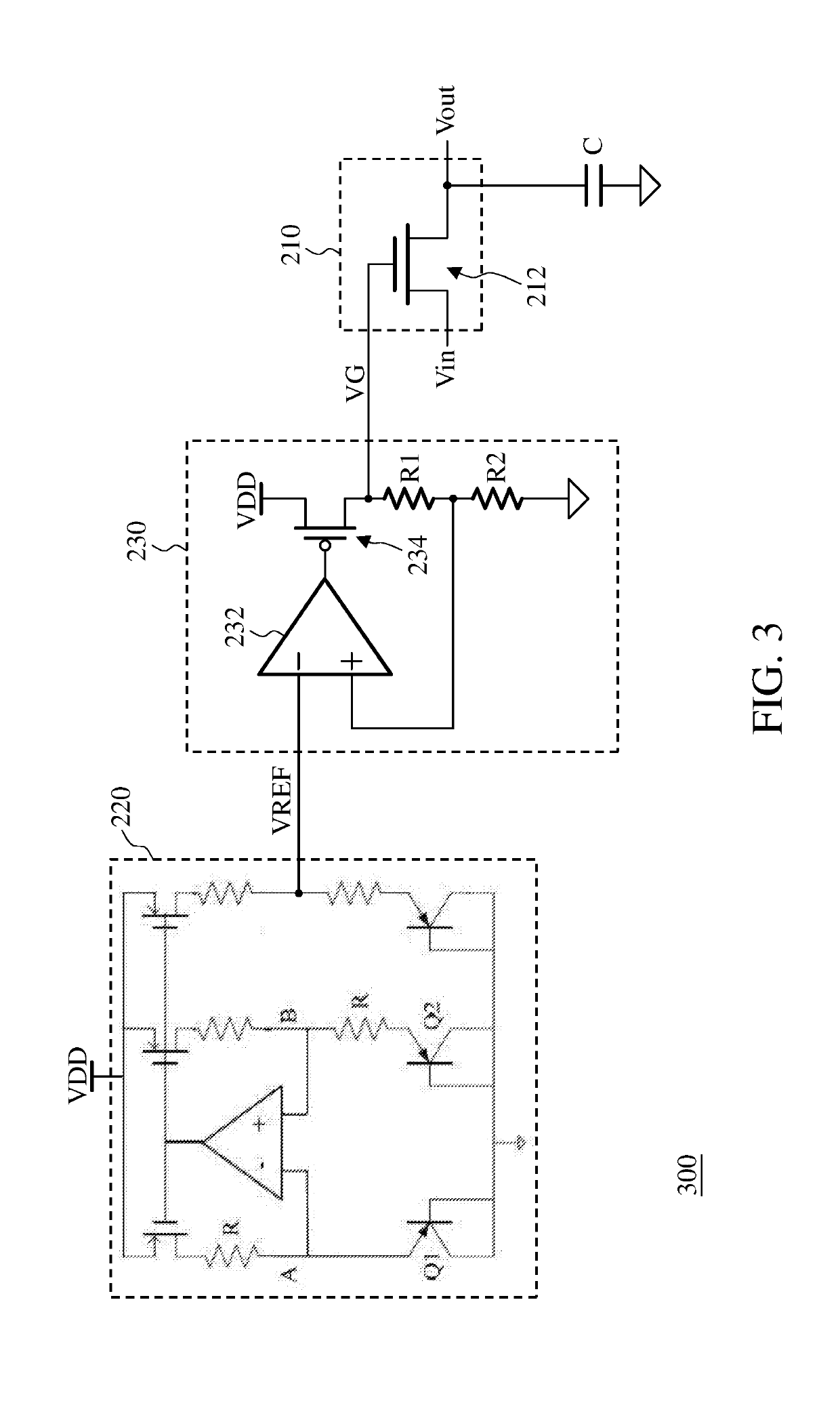

ActiveUS20190149146A1High impedanceReduce areaInput/output impedence modificationSemiconductor/solid-state device detailsEngineeringVoltage reference

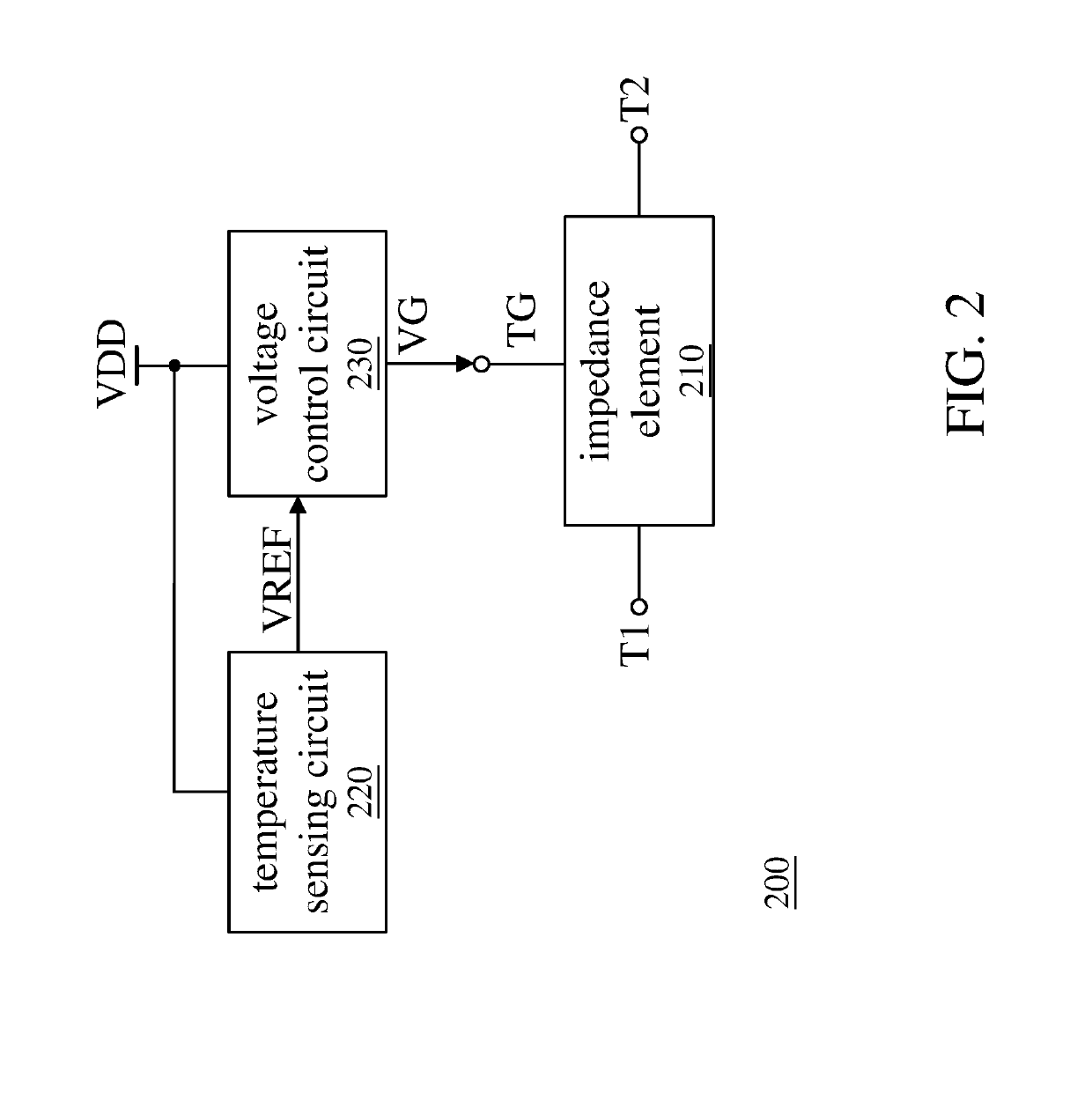

This invention discloses an active load generation circuit and a filter. The active load generation circuit includes a transistor, a voltage control circuit, a voltage offset and tracking circuit, and a temperature sensing circuit. The transistor provides an impedance and includes a control terminal and an input terminal. The control terminal receives a control voltage, the input terminal receives an input signal, and the impedance is associated with the control voltage. The voltage control circuit generates an intermediate voltage according to a power supply voltage and a first reference voltage. The voltage offset and tracking circuit generates the control voltage according to the input signal and the intermediate voltage such that the control voltage varies with the input signal. The temperature sensing circuit senses an ambient temperature of the active load generation circuit and adjusts the first reference voltage according to the ambient temperature.

Owner:REALTEK SEMICON CORP

Variable passive components with high resolution value selection and control

InactiveUS20070194813A1Impedence matching networksMultiple-port networksResonant cavityImage resolution

The present system provides a method for varying the value of passive components in electronic circuits. Passive components can range from basic resistors, capacitors, and inductors to complex, structures such as transmission lines and resonant cavities. Value selection and variation can either be dynamically performed during circuit operation or as a one-time part of the manufacturing process as determined by the requirements of the specific application. A digital-to-analog converter (DAC) circuit is used to input value selection data digitally, and control value selection with value resolution dependent on the resolution of the DAC. An alternate embodiment is provided for high frequency operation.

Owner:MASHHOON HAMID R +1

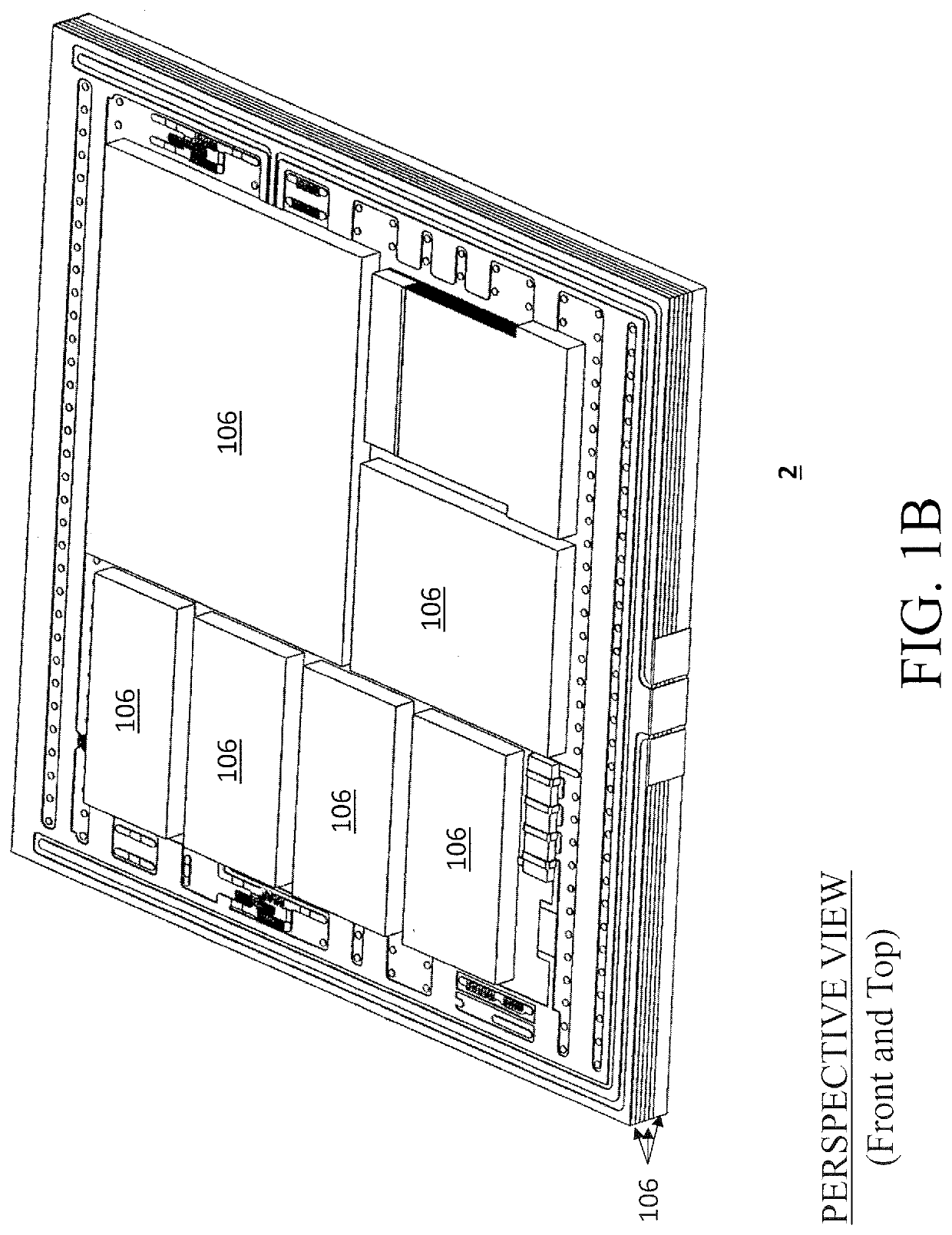

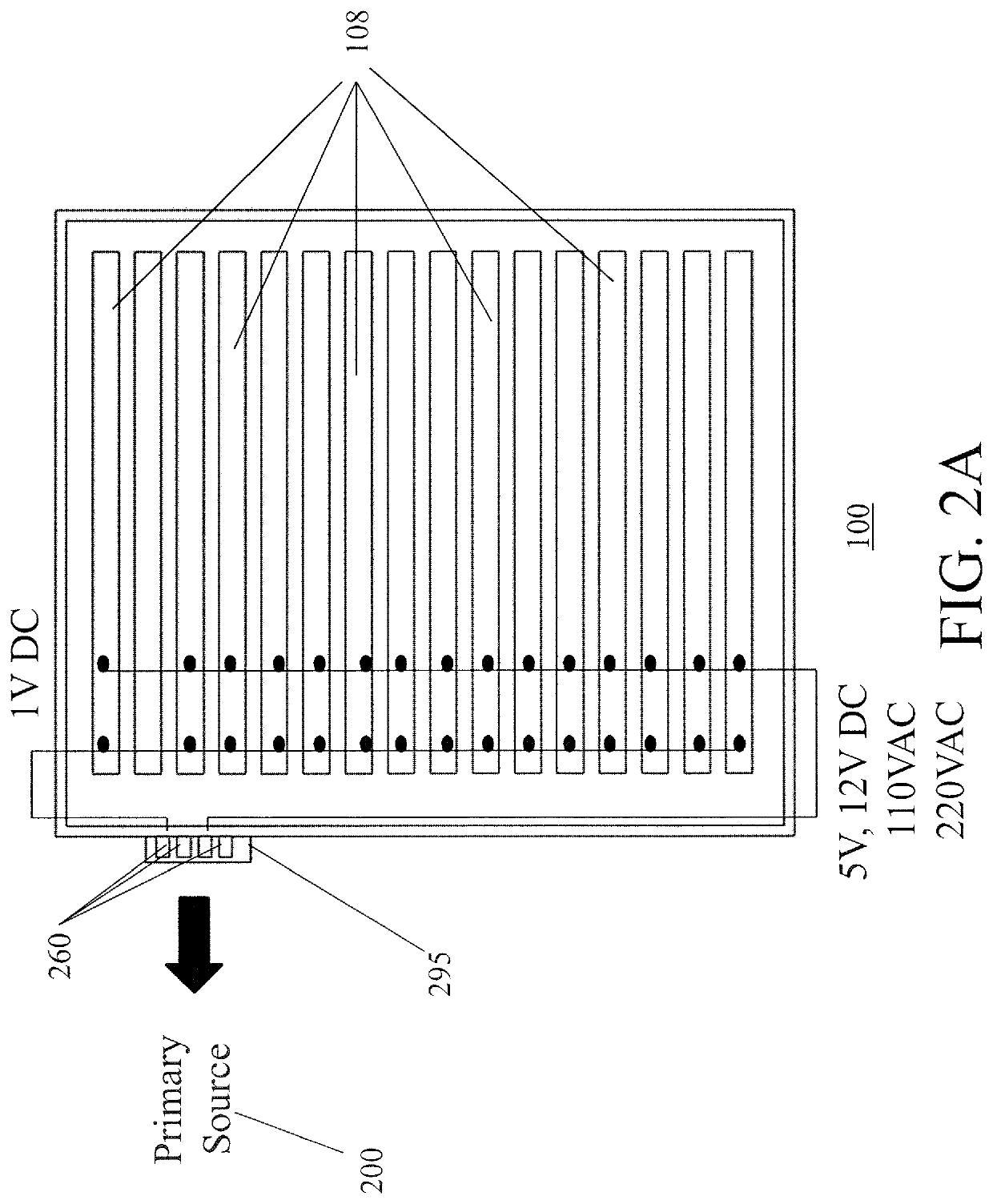

High speed / low power server farms and server networks

ActiveUS20200033931A1Large permeabilityMinimal magnetic core lossesImpedence convertorsDigital data processing detailsSemiconductor chipLow power dissipation

A server farm has servers with at least one hybrid computing module operating at a system clock speed that optimally matches the intrinsic clock speed of a semiconductor die embedded within a high speed semiconductor chip stack or mounted upon the semiconductor carrier.

Owner:DE ROCHEMONT L PIERRE

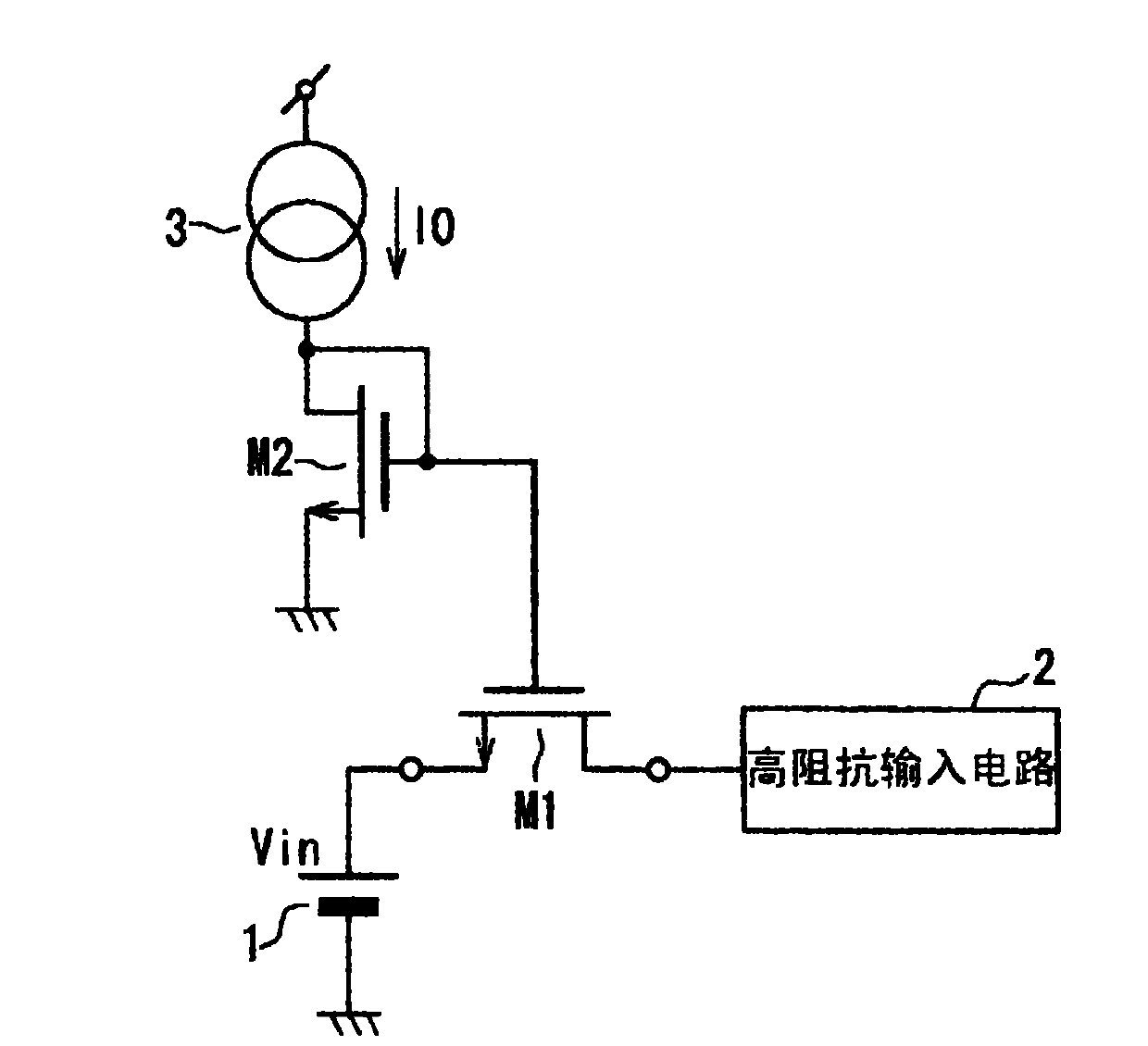

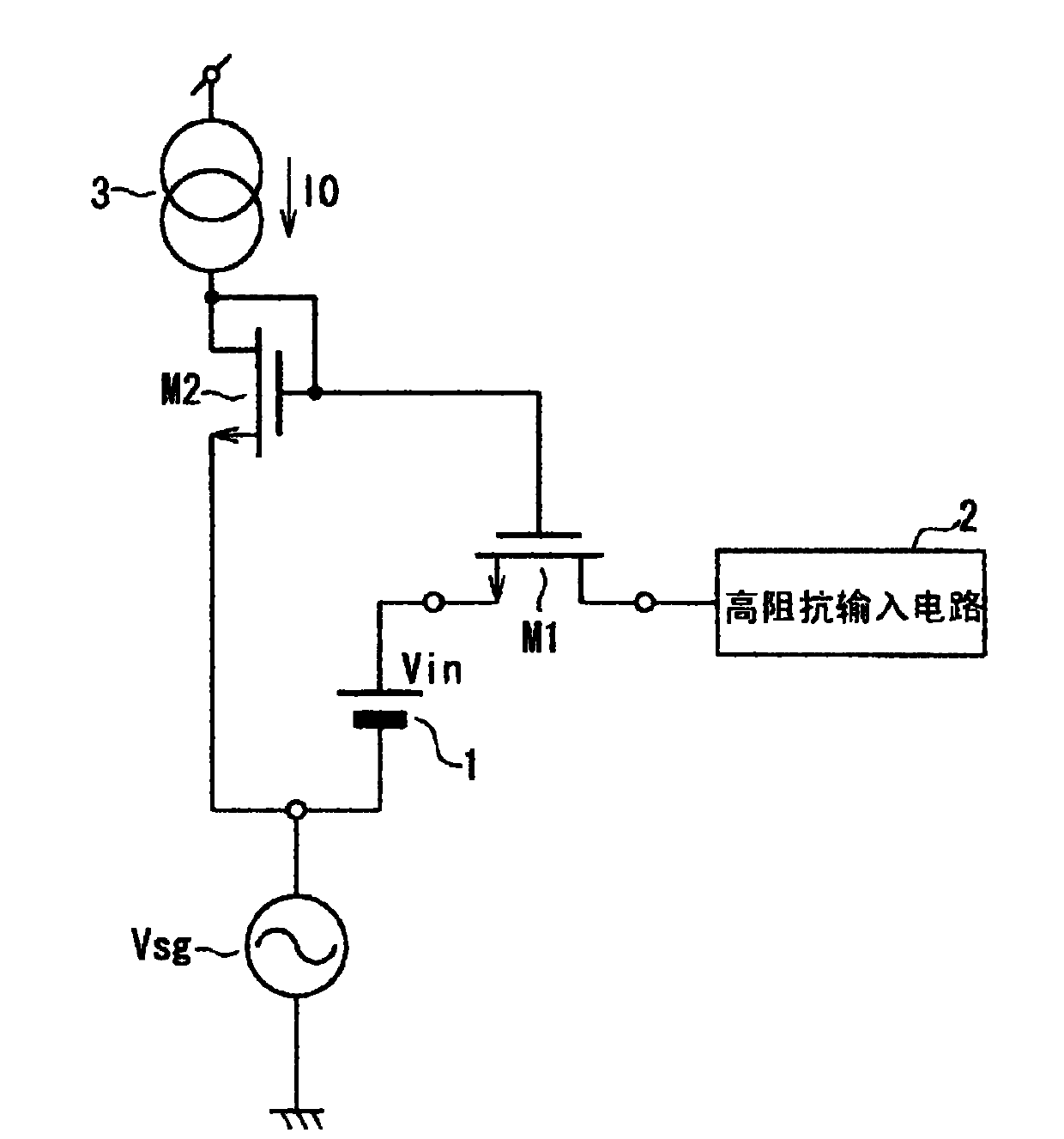

MOS transistor resistor, filter, and integrated circuit

InactiveCN102089971ALittle changeGood temperature characteristicsTransistorSolid-state devicesEngineeringVoltage source

Disclosed is a MOS transistor resistor that is equipped with a first MOS transistor (M1), which is used as a resistor, an input voltage source (1), which is connected, and applies an input voltage (Vin), to the source of the first MOS transistor, and a gate voltage source (6), which is connected, and applies a gate voltage (Vg), to the gate of the first MOS transistor. The gate voltage (Vg) and input voltage (Vin) are set in a range to cause the first MOS transistor to operate with the gate-source voltage and the source-drain voltage in the first MOS transistor in the unsaturated zone, and are set so that the temperature characteristics at the resistance value of the first MOS transistor become constant. Fluctuations in resistance value, which are caused by changes in leakage current due to manufacturing variances, are decreased and excellent temperature characteristics are obtained.

Owner:PANASONIC CORP

Psuedo resistor circuit and charge amplifier

ActiveUS9660592B2Reduce distortionReduce necessityCharge amplifiersAmplifier modifications to reduce temperature/voltage variationAudio power amplifierDividing circuits

Owner:MURATA MFG CO LTD

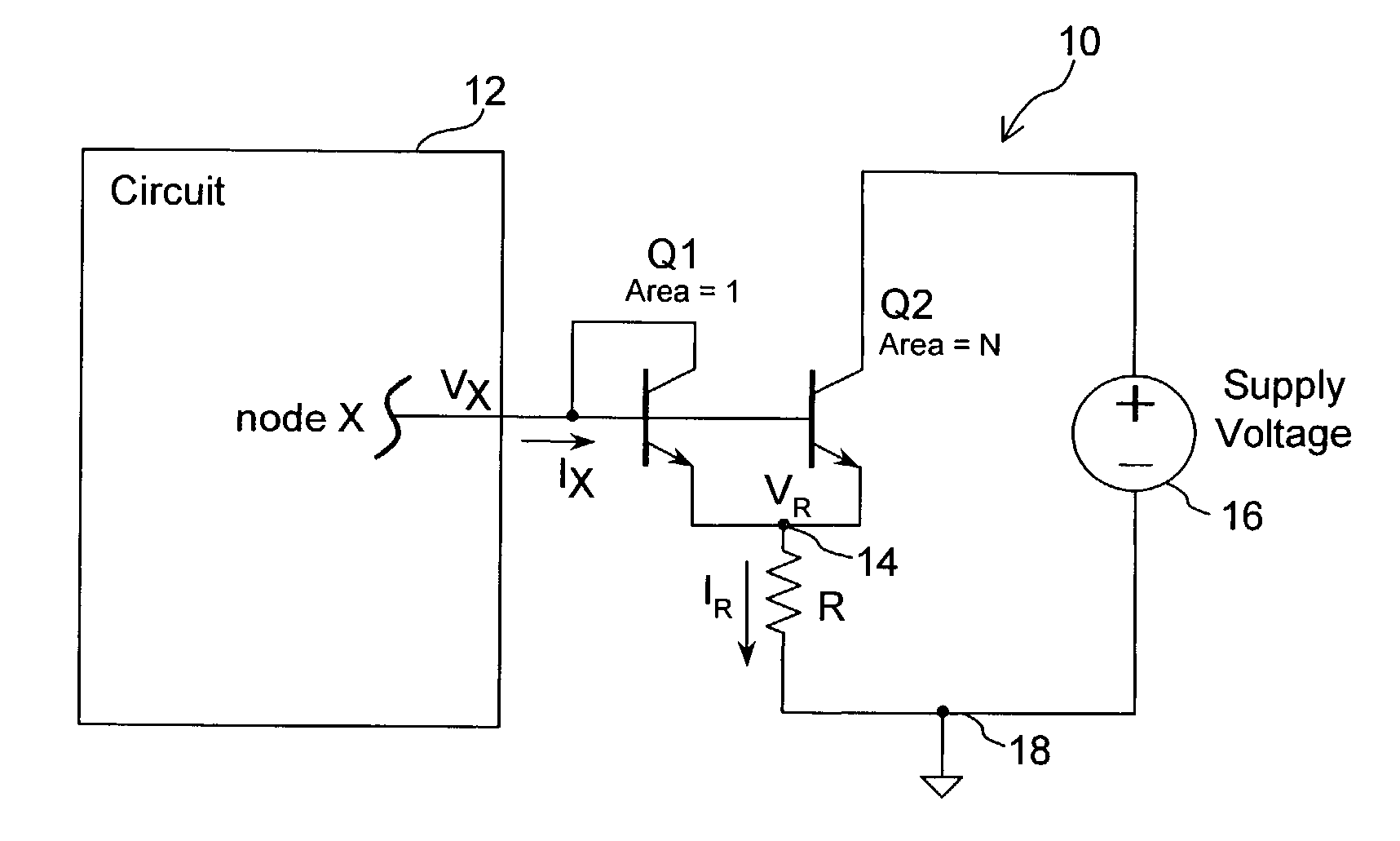

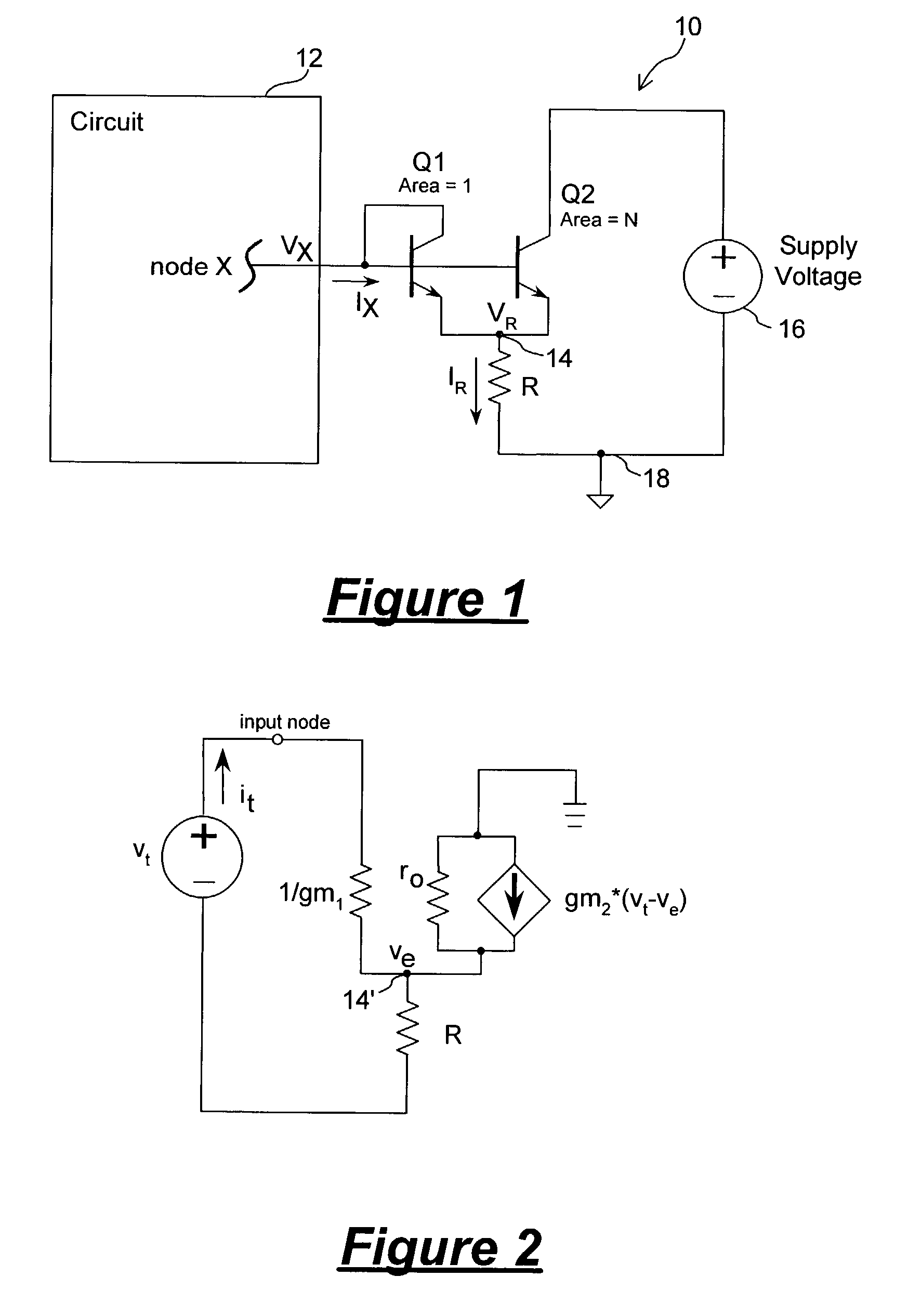

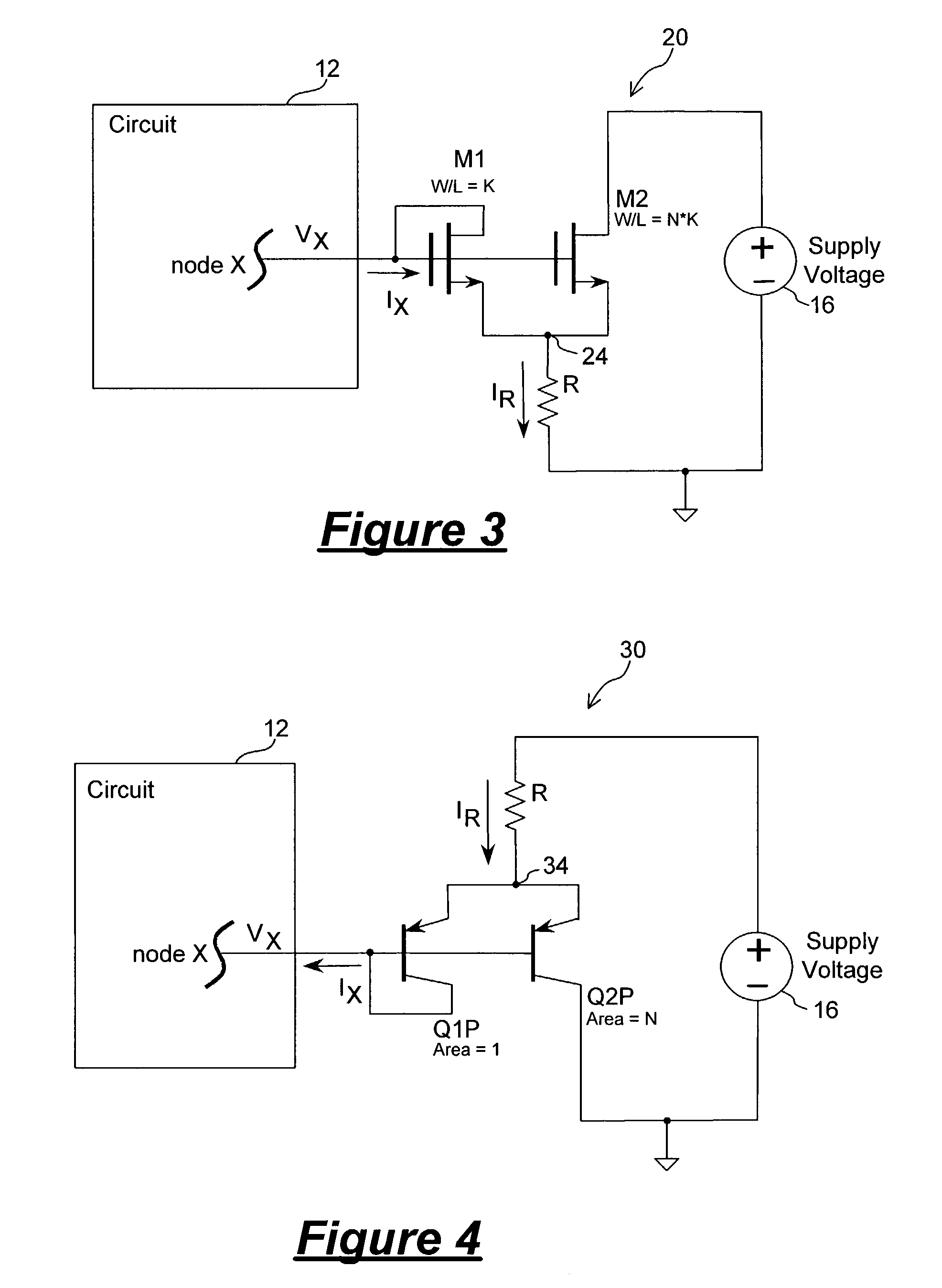

Resistance multiplier circuit and compact gain attenuator

A resistance multiplier circuit coupled to a first node of a first circuit for providing a high-value resistance at the first node includes a first transistor, a second transistor being N times larger than the first transistor, and a resistor. In one embodiment, the first and second transistors are NPN bipolar transistors. The first transistor has its base and collector terminals coupled to the first node and an emitter terminal coupled to a second node. The second transistor has a base terminal coupled to the first node, a collector terminal coupled to a positive supply voltage, and an emitter terminal coupled to the second node. The resistor is coupled between the second node and a virtual ground node. When a voltage is applied to the first node, the resistance at the first node is (N+1) times the resistance of the resistor.

Owner:MICREL

Pseudo resistance circuit and charge detection circuit

ActiveUS9887689B2Reduce distortionIncrease valueSolid-state devicesSemiconductor/solid-state device manufacturingPower flowCharge detection

A pseudo resistance circuit includes a first gate voltage adjustment circuit that adjusts respective currents of first and second current sources and also adjusts a gate voltage of a second field effect transistor to equalize or substantially equalize a drain voltage of the second field effect transistor and a voltage of a first end portion of a reference resistance element and controls a drain voltage of a first field effect transistor and the drain voltage of the second field effect transistor to maintain a constant or substantially constant relationship with each other; and a second gate voltage adjustment circuit that adjusts a gate voltage of the first field effect transistor to control the gate voltage of the second field effect transistor and the gate voltage of the first field effect transistor to maintain a constant or substantially constant relationship with each other.

Owner:MURATA MFG CO LTD

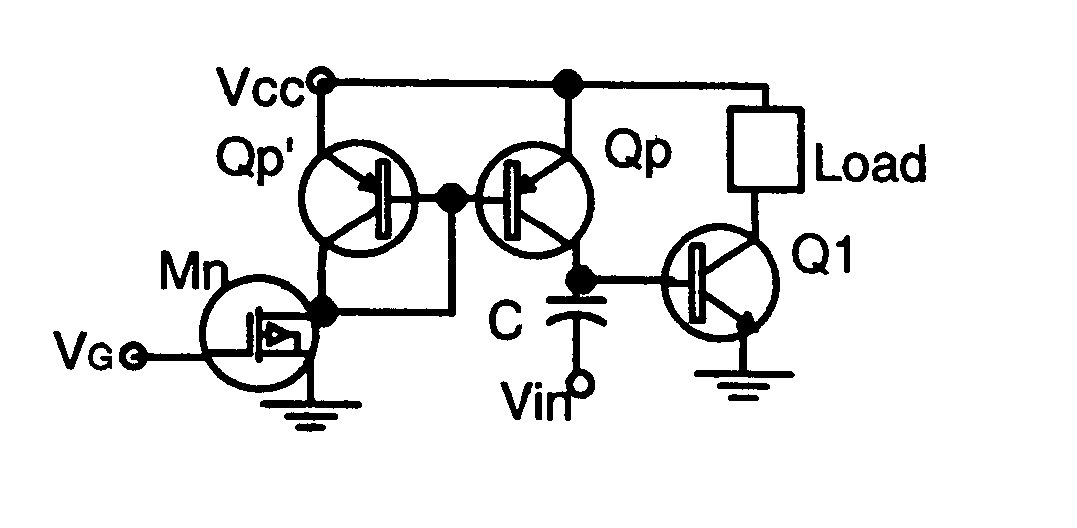

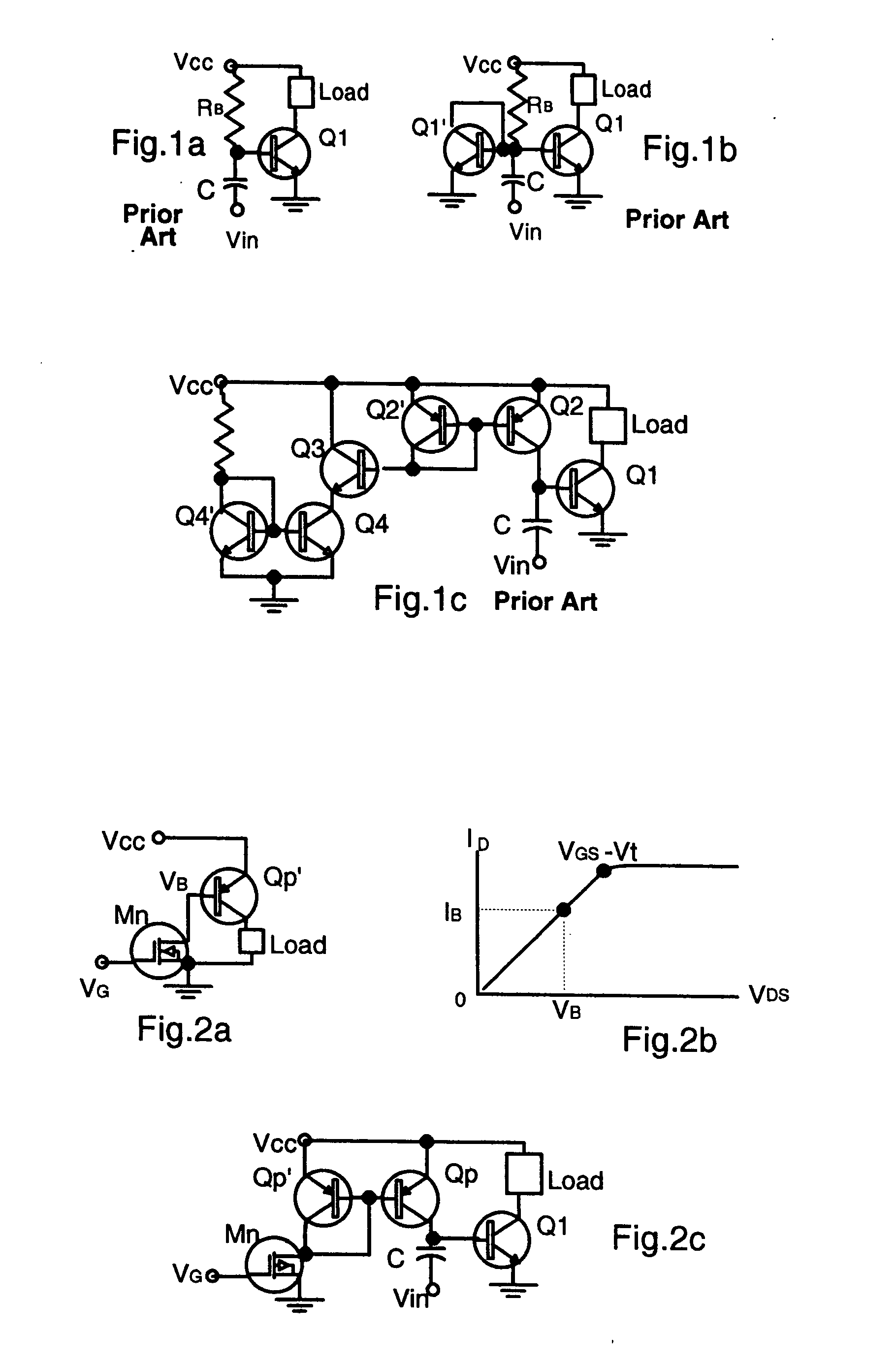

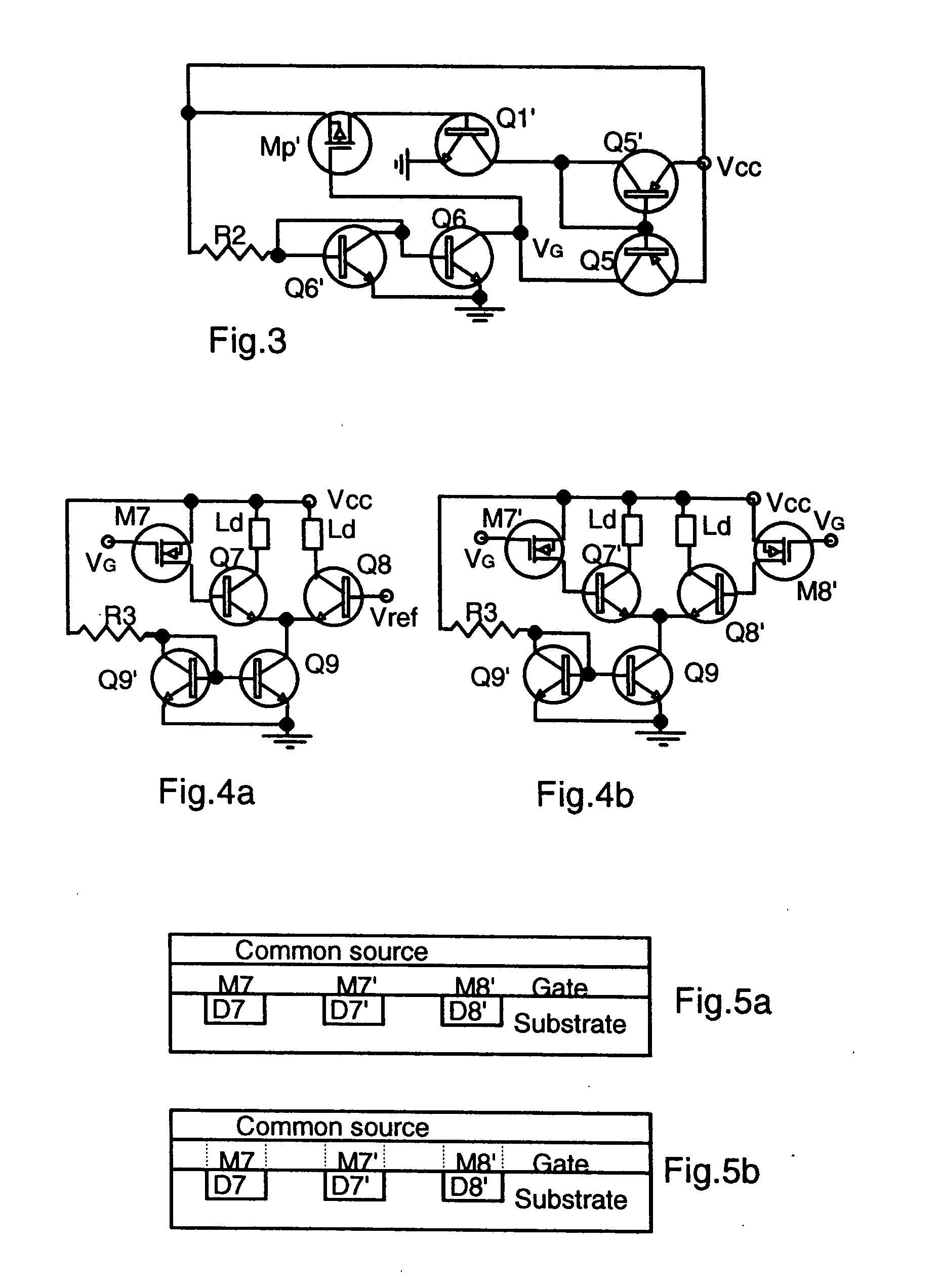

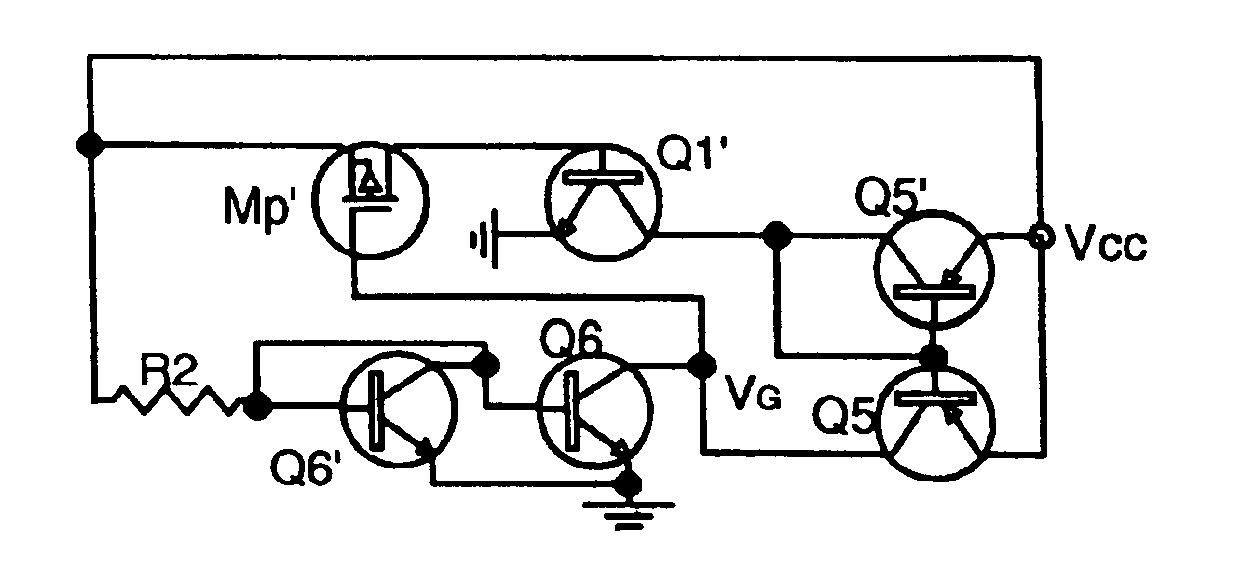

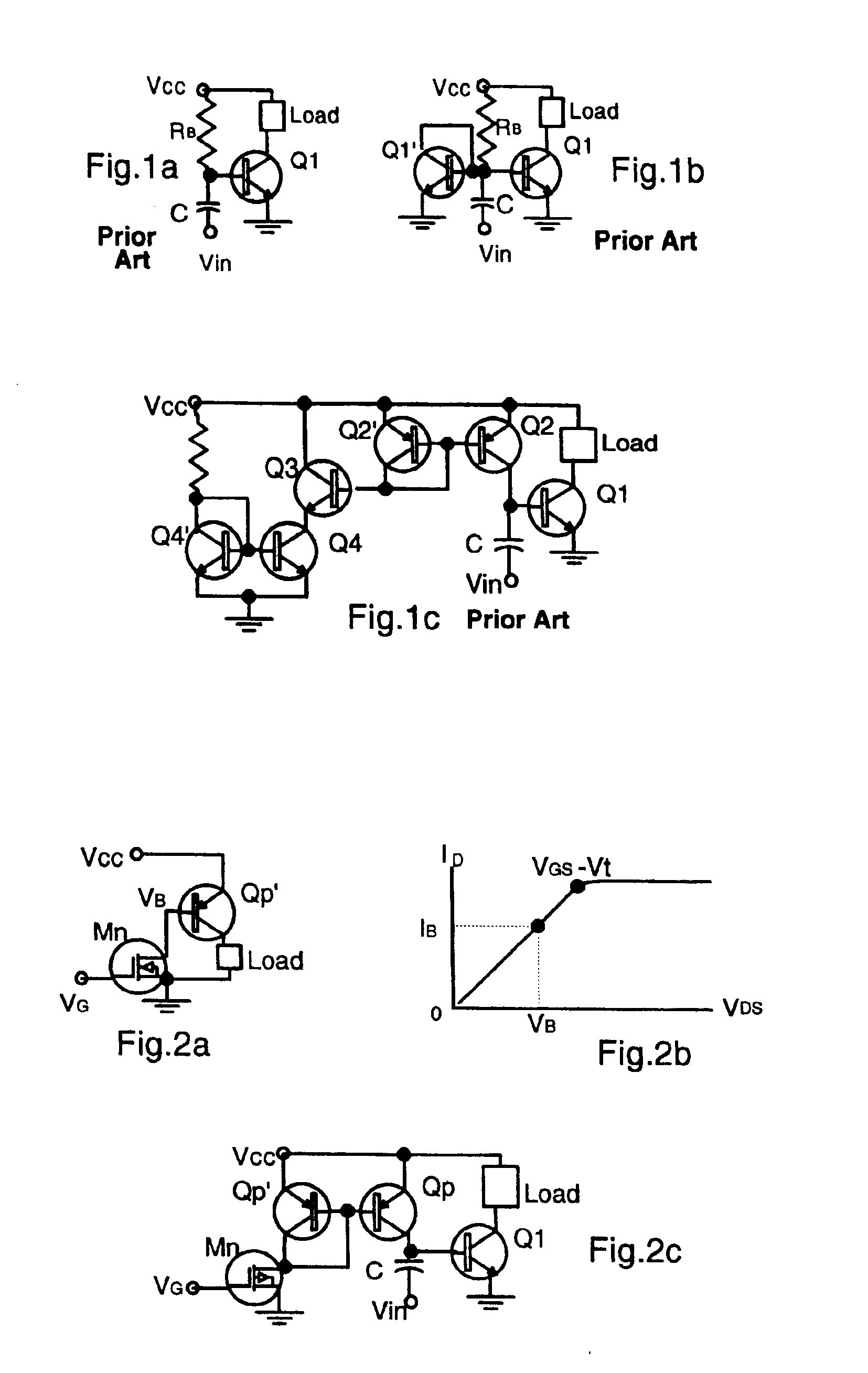

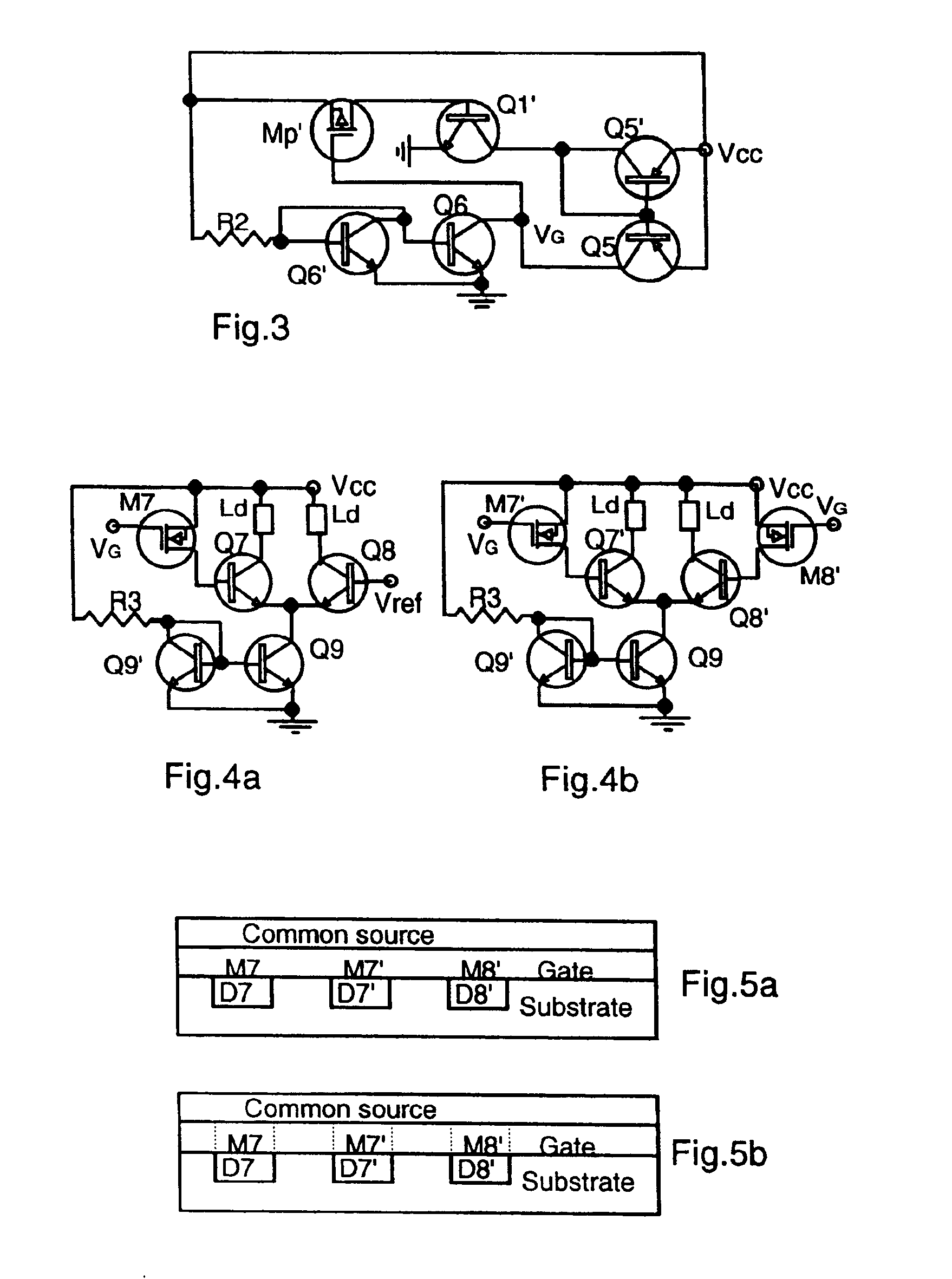

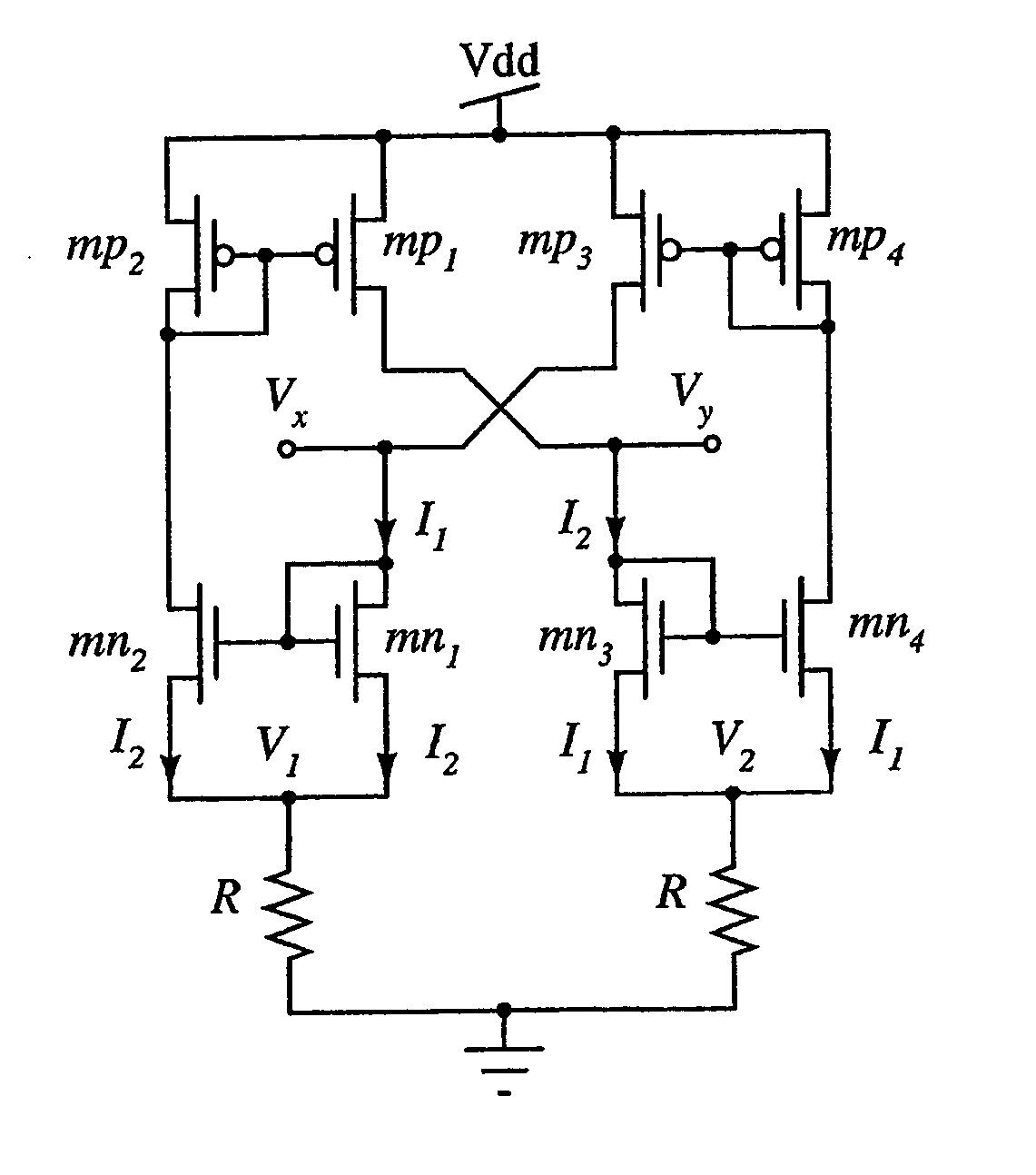

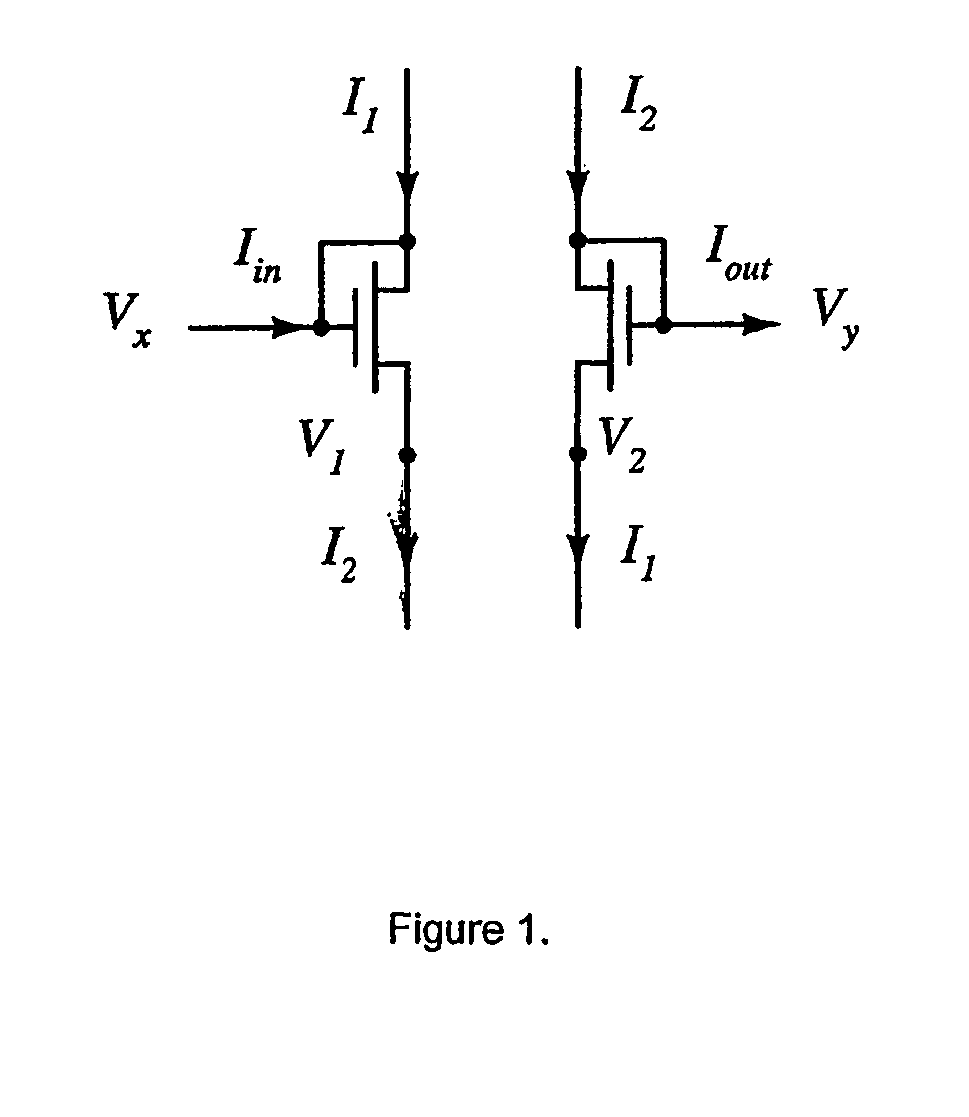

Adaptive MOSFET resistor

InactiveUS6873202B1Reduced footprintReduce power supply voltageTransistorNetwork simulating reactancesMOSFETDc current

A MOSFET can operate as a resistor by operating in the linear or ohmic region of the drain V-I characteristics. This region can be obtained by floating the gate of the MOSFET, when the dc current and the voltage drop are given. Multiple resistors can be duplicated (or mirrored) by sharing the same source and floating gate. The floating gate voltage can be simulated using a closed loop equivalent circuit. Alternatively, the gate voltage can also be derived from the given drain-to-source voltage and the given current in a feedback loop. With this adaptive MOSFET resistor, the minimum supply voltage can be as low as the sum of the BJT threshold and the complementary BJT saturation voltage, e.g. VCC≧VBE+Vsat (e.g. 0.8+0.15<1.0V). The threshold voltage Vt should be less than VBE.

Owner:MARYLAND SEMICON

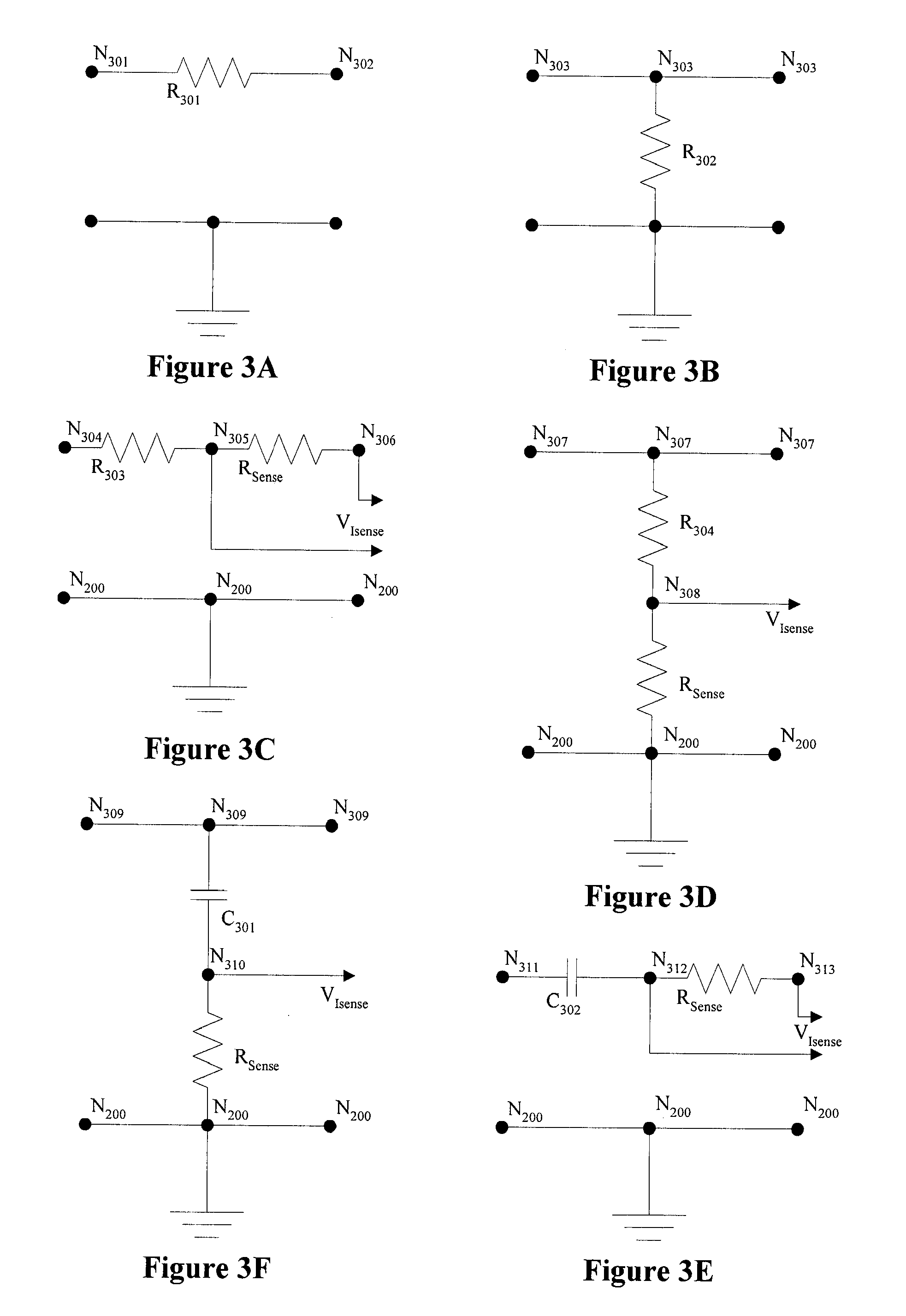

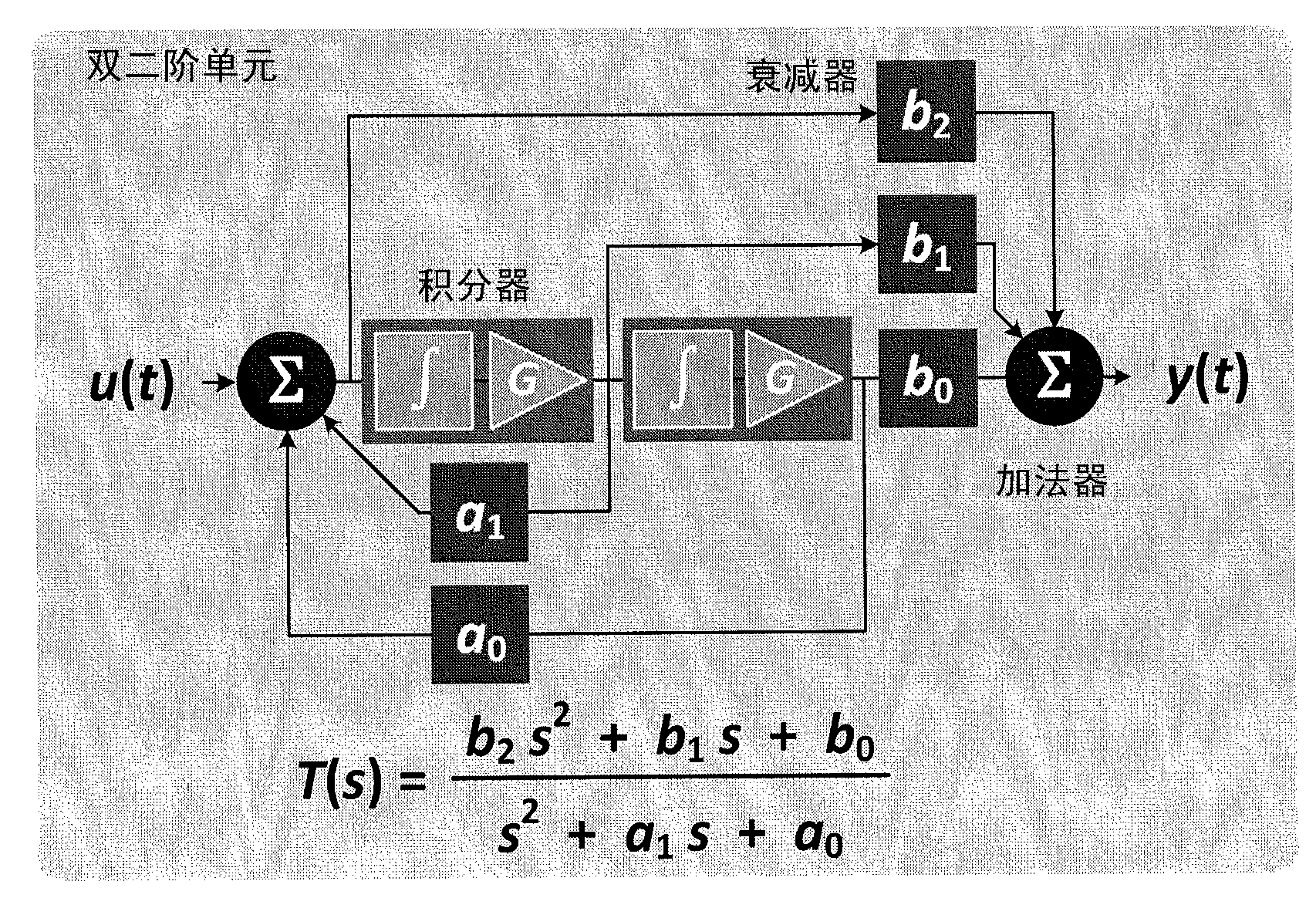

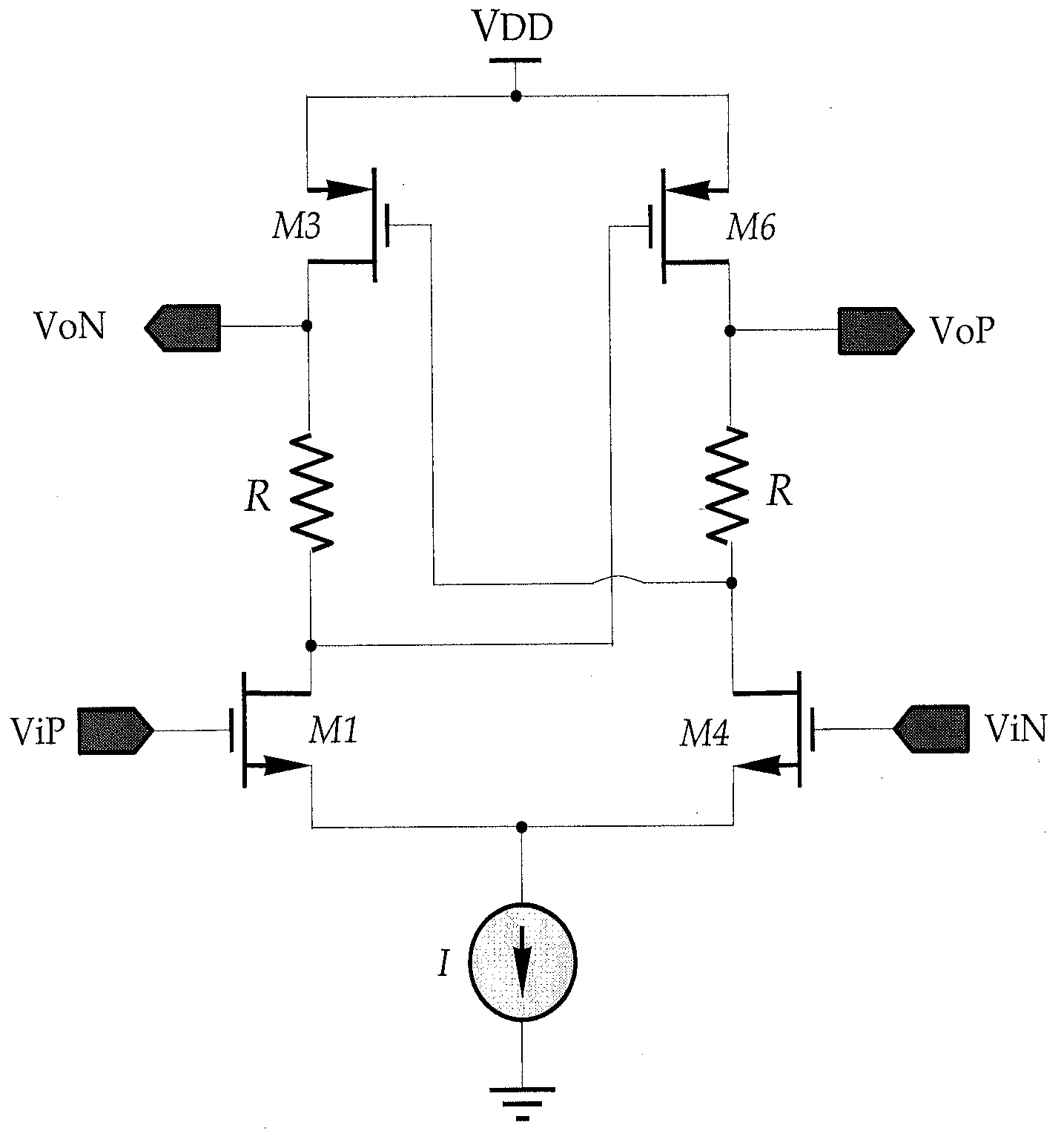

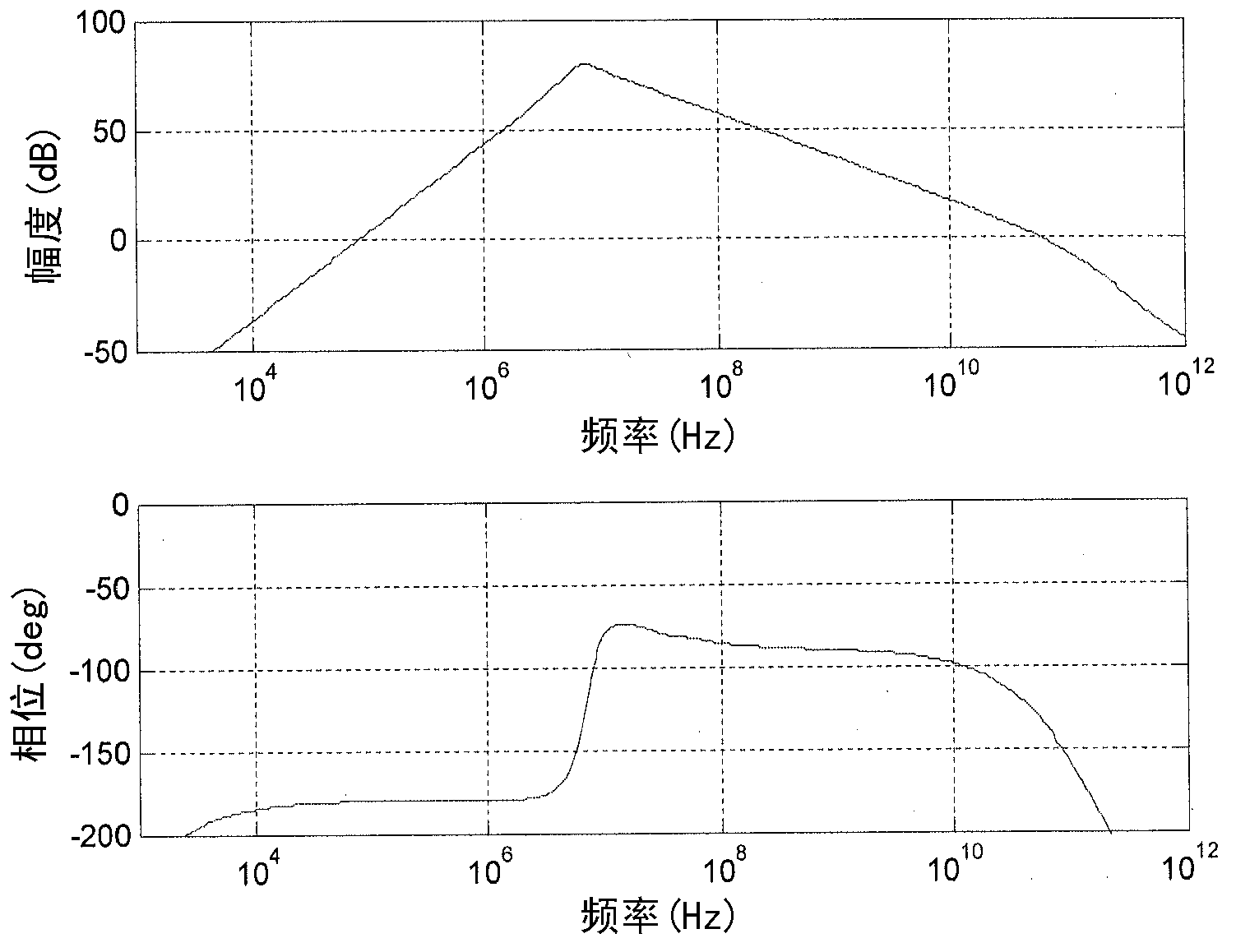

Broadband analog radio-frequency components

InactiveCN102835027AEasy to makeEasy to operateMultiple-port networksHigh frequency amplifiersCMOSIntegrator

Broadband analog radio-frequency devices can be used to create building blocks for scalable analog signal processors that operate over bandwidths of 50 MHz to 20 GHz or more. Example devices include integrators (transconductors), digitally controlled attenuators, buffers, and scalable summers implemented using deep sub-micron CMOS technology. Because the devices are implemented in CMOS, the ratio of trace / component size to signal wavelength is about the same as that of low-frequency devices implemented in printed circuit boards. Combining this scaling with high gain / high bandwidth enables implementation of feedback and programmability for broadband analog signal processing.

Owner:斯佩罗设备有限公司

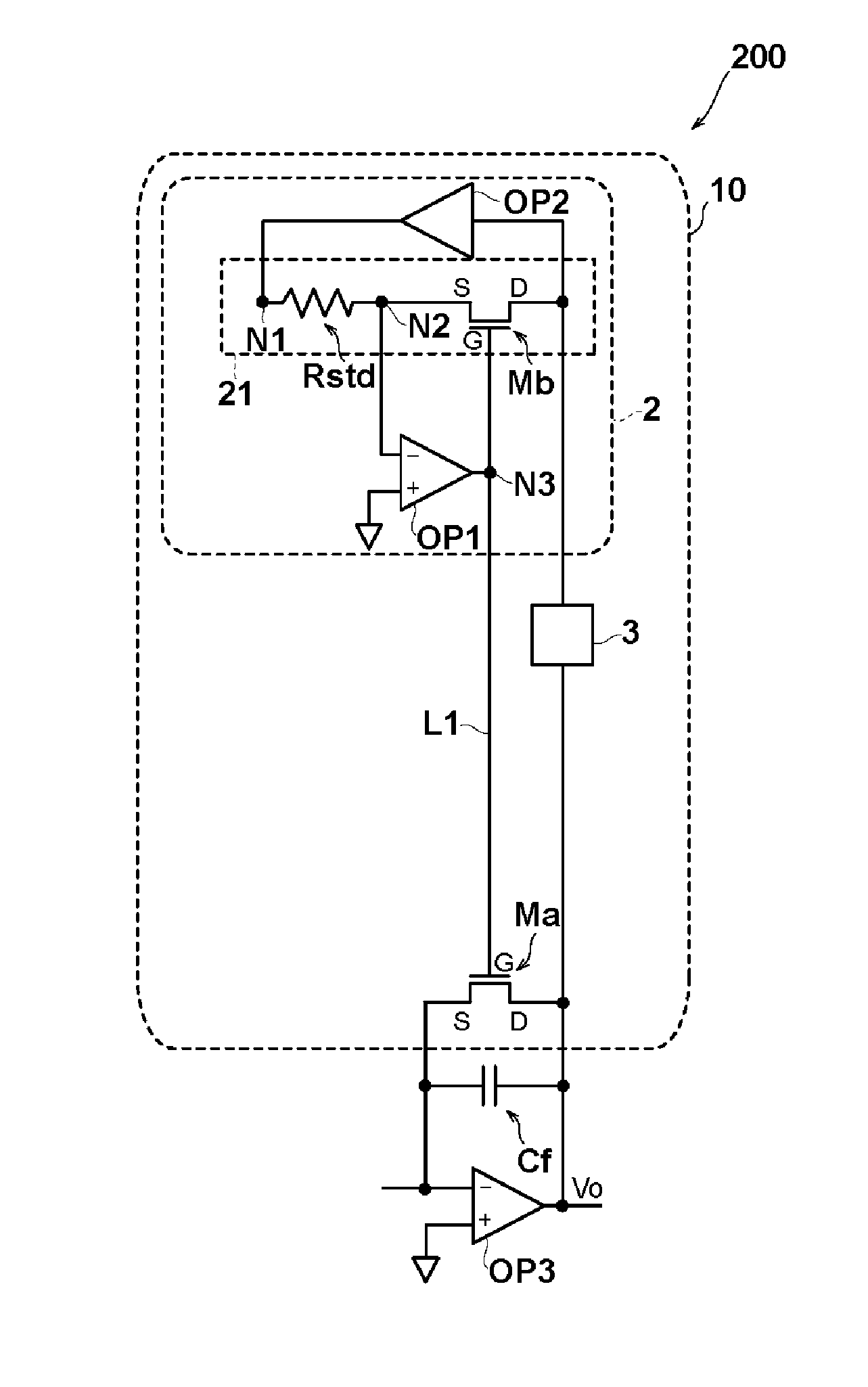

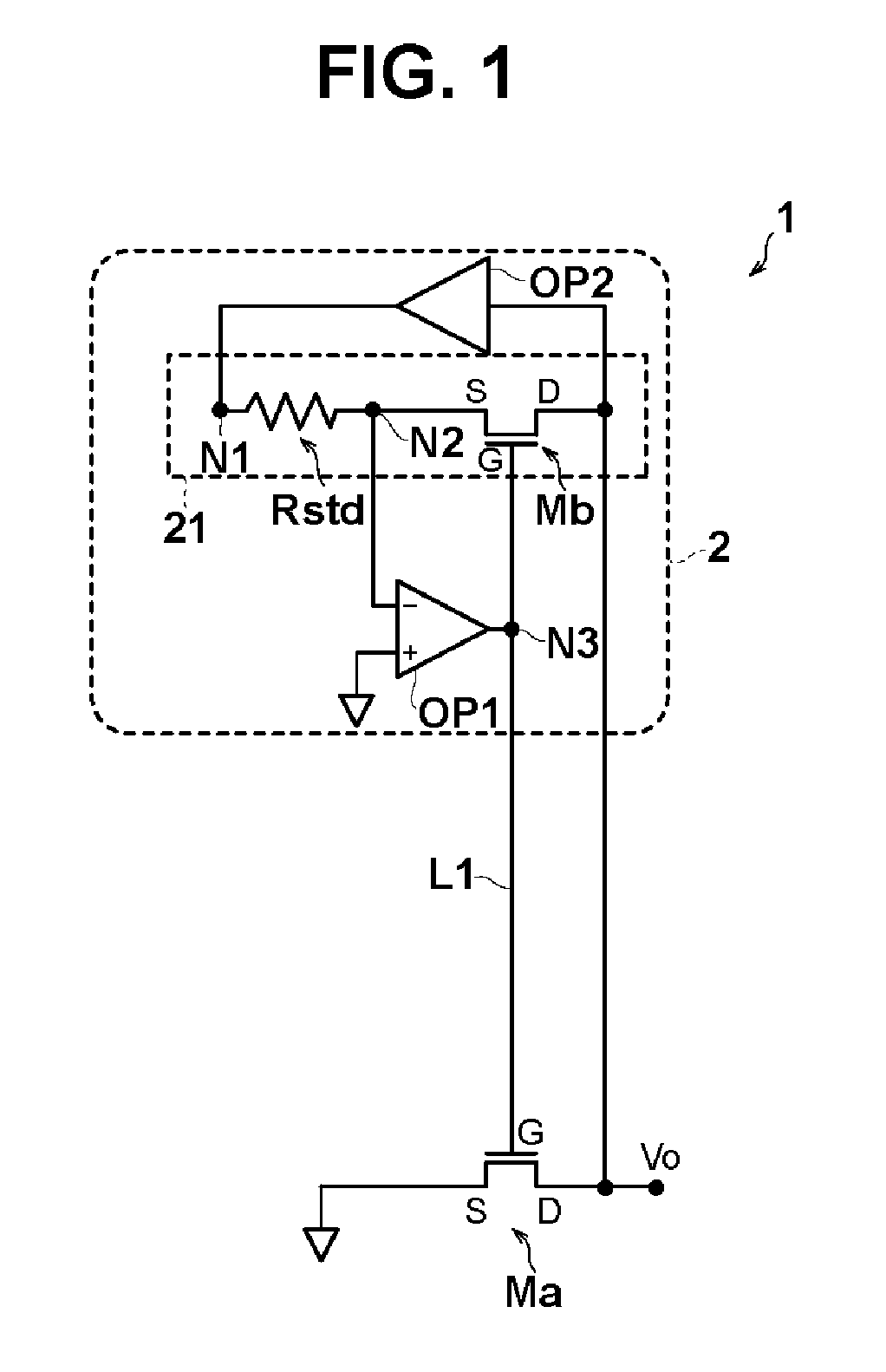

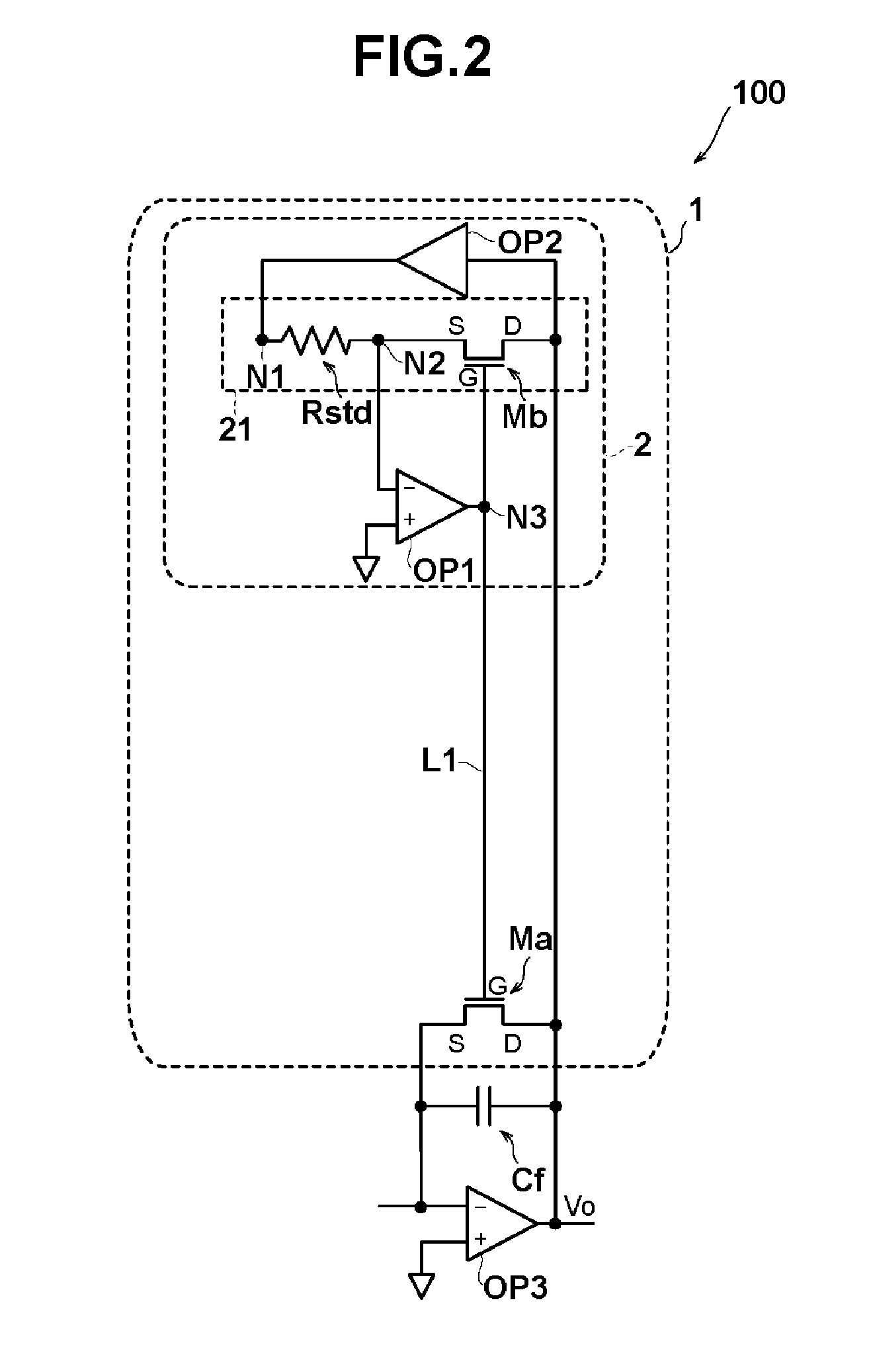

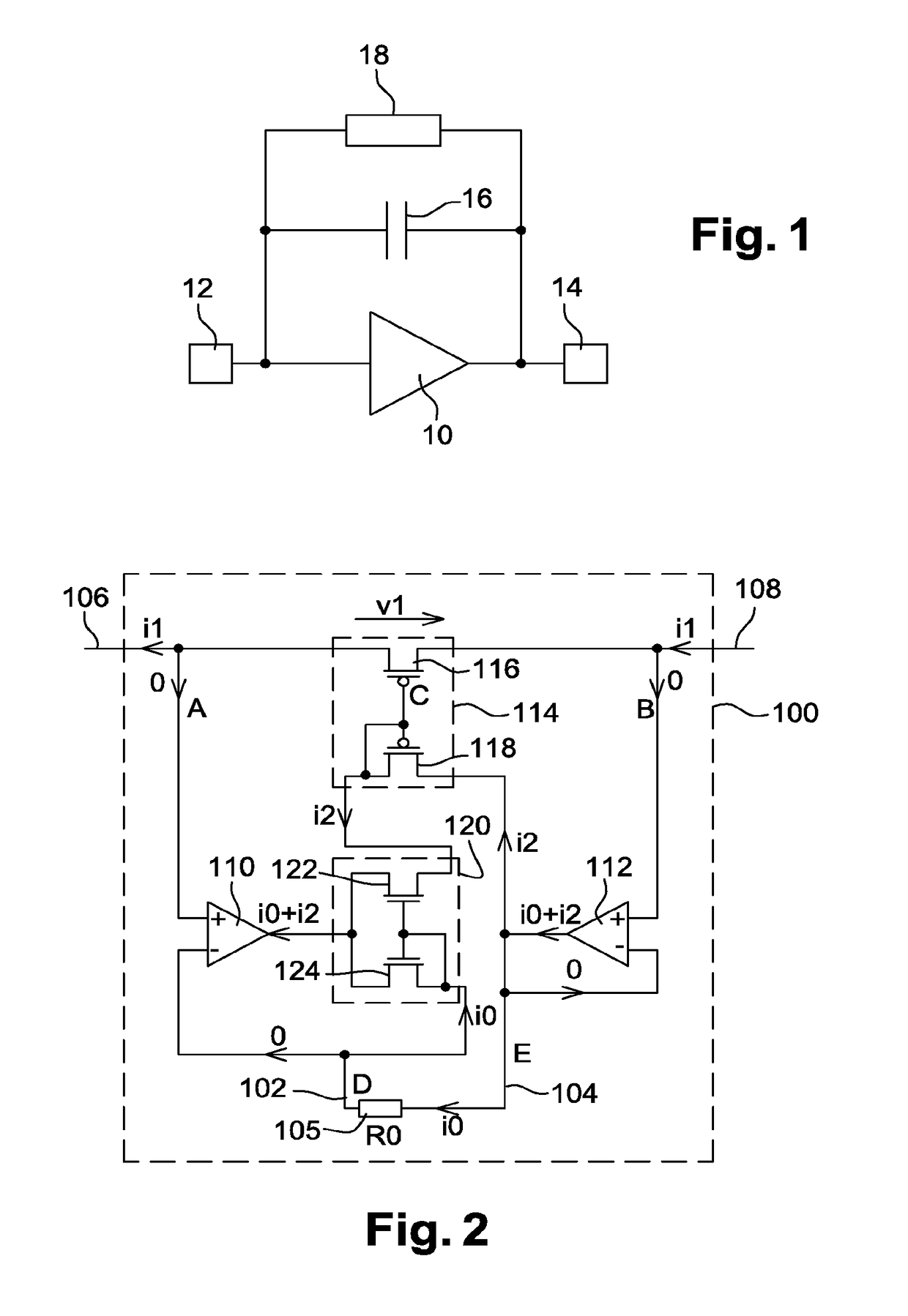

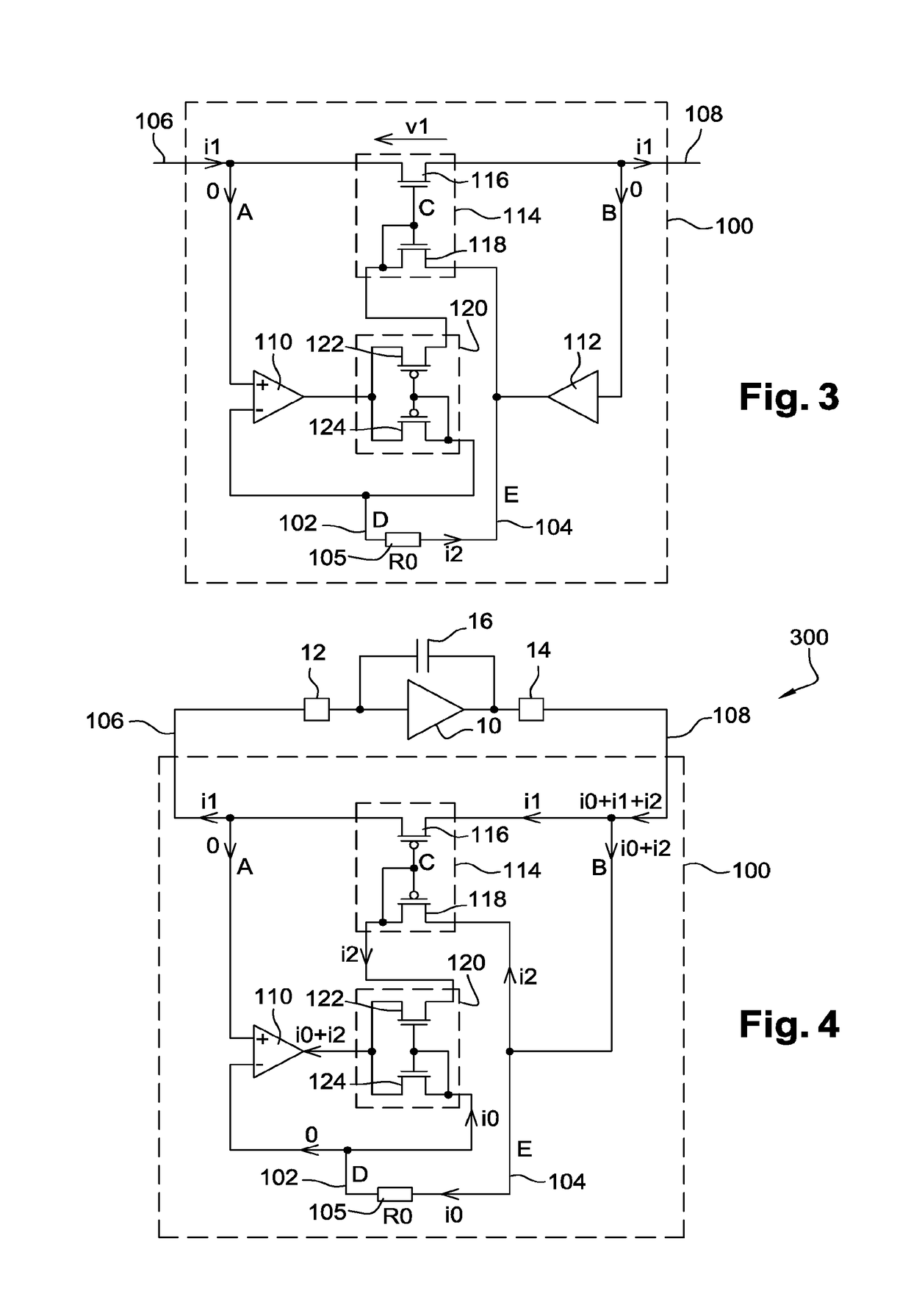

Device modifying the impedance value of a reference resistor

ActiveUS20190081625A1Raise the ratioEasy to getCharge amplifiersNetwork simulating resistancesEngineeringResistor

An electronic device including at least:a reference resistor;two first terminals between which the reference resistor is connected, and two second terminals between which a modified impedance value of the reference resistor is intended to be obtained;a first circuit configured to apply between the two second terminals a voltage substantially equal to that between the two first terminals;a second circuit configured to flow between the two second terminals a second current the value of which corresponds to a fraction of a first current for flowing in the reference resistor between the two first terminals.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES

Pseudo resistor with tunable resistance

ActiveUS20180234081A1Wide range of applicationsReduce the impactNetwork simulating resistancesAmplifiersEngineeringTransistor

A pseudo resistor with tunable resistance including a first transistor and a second transistor is provided. The first transistor has a first terminal, a second terminal and a control terminal. The first terminal of the first transistor serves as a first terminal of the pseudo resistor. The control terminal of the first transistor receives a control voltage. The first transistor is controlled by the control voltage, such that the first transistor operates in a weak inversion region. The second transistor has a first terminal, a second terminal and a control terminal. The first terminal of the second transistor is coupled to the second terminal of the first transistor. The second terminal of the second transistor and the control terminal of the second transistor are coupled to each other to serve as a second terminal of the pseudo resistor with tunable resistance. The second transistor operates in the weak inversion region.

Owner:WINBOND ELECTRONICS CORP

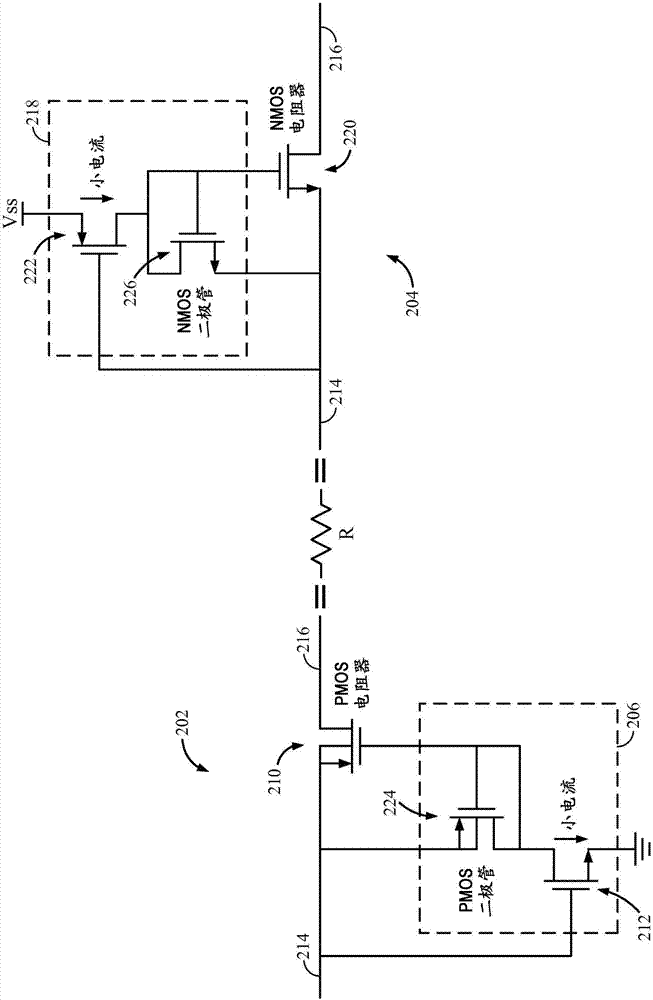

Subthreshold metal oxide semiconductor for large resistance

Certain aspects of the present disclosure generally relate to generating a large electrical resistance. One example circuit generally includes a first transistor 210, 220 having a gate, a source connected with a first node 214 of the circuit, and a drain connected with a second node 216 of the circuit. The circuit may also include a voltage-limiting device 224, 226 connected between the gate and the source of the first transistor, wherein the device, if forward biased, is configured to limit a gate-to-source voltage of the first transistor such that the first transistor operates in a sub-threshold region. The circuit may further include a second transistor 212, 222 configured to bias the voltage-limiting device with a current, wherein a drain of the second transistor is connected with the gate of the first transistor, a gate of the second transistor is connected with the first node, and a source of the second transistor is connected with an electric potential.

Owner:QUALCOMM INC

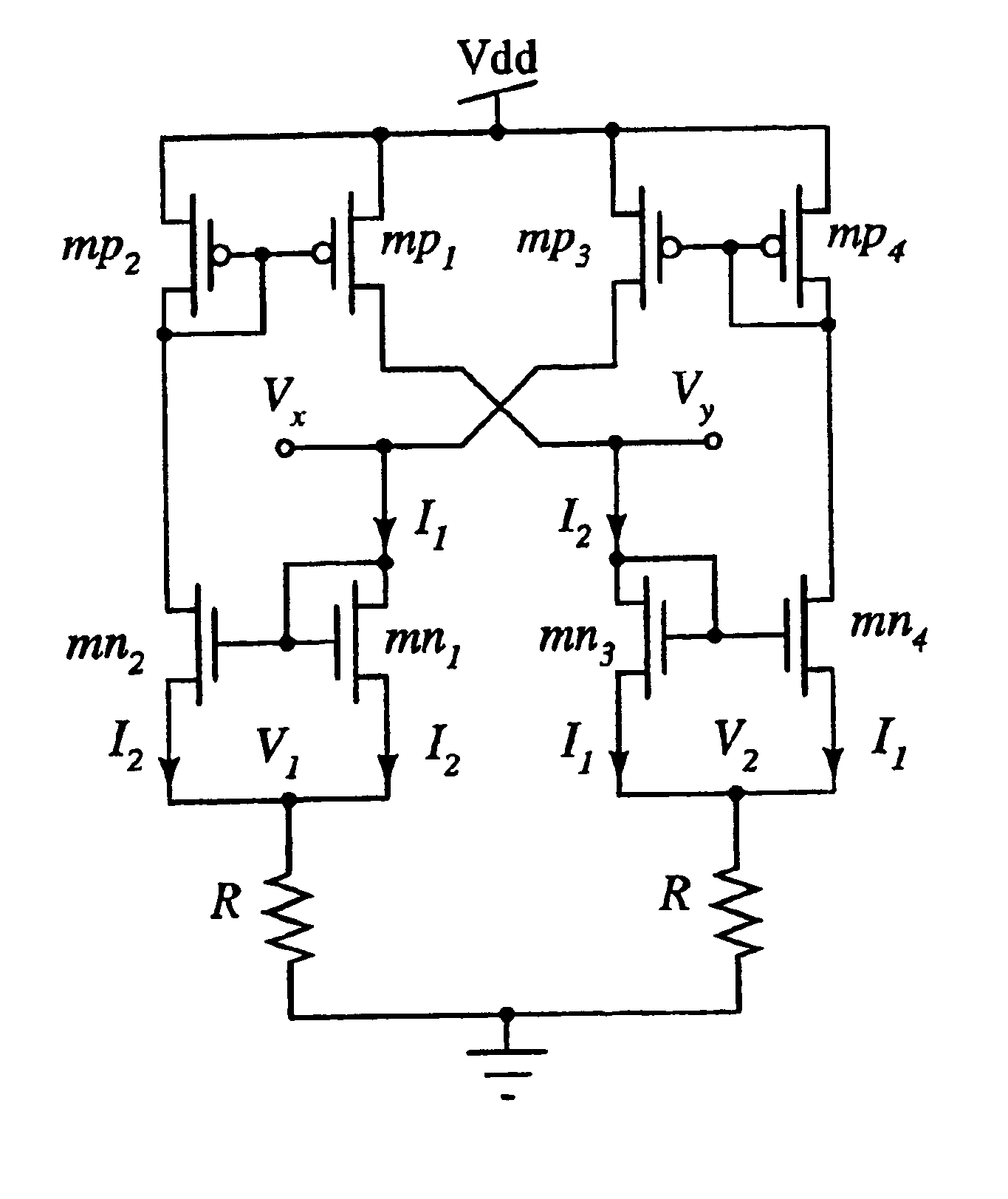

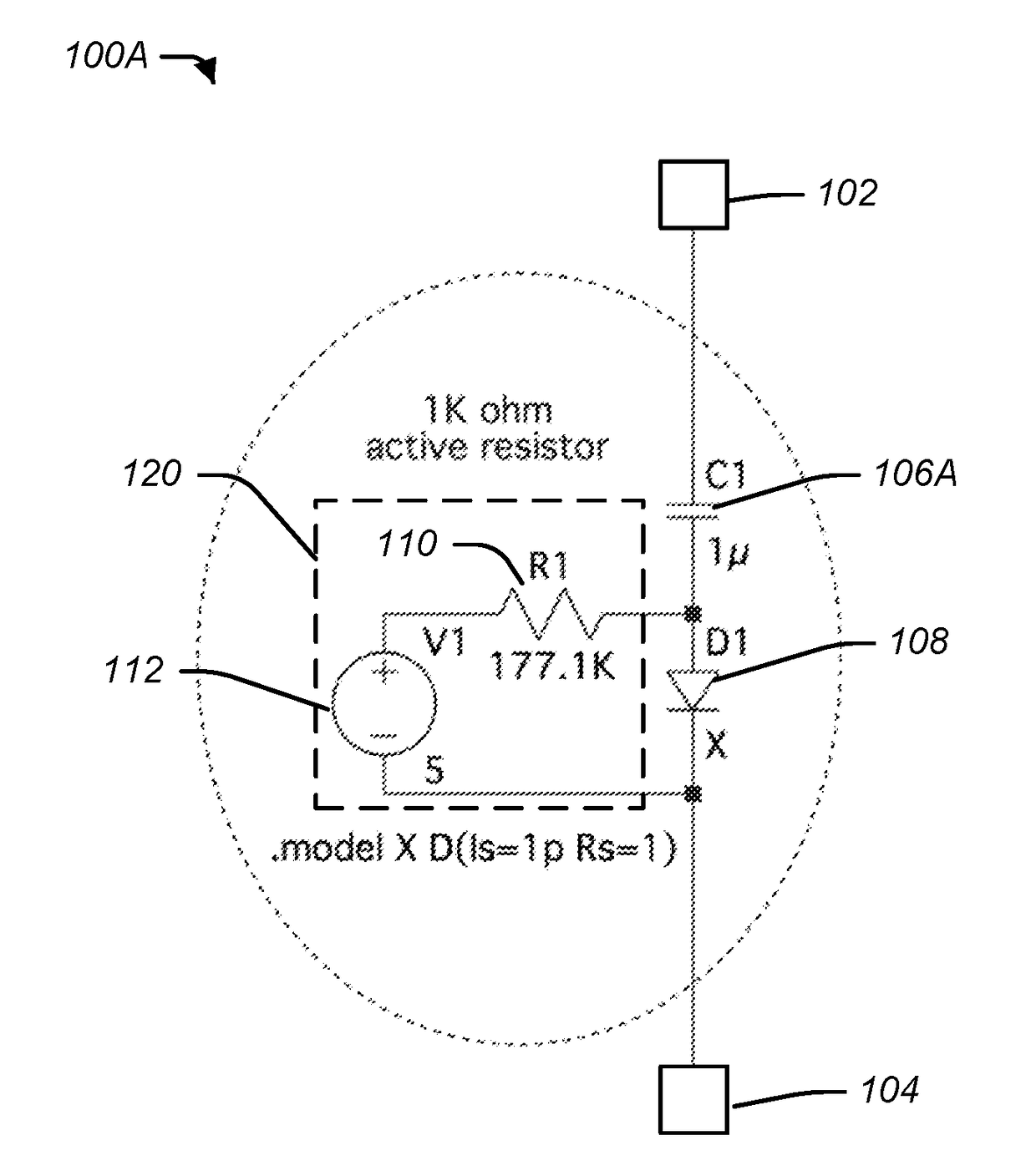

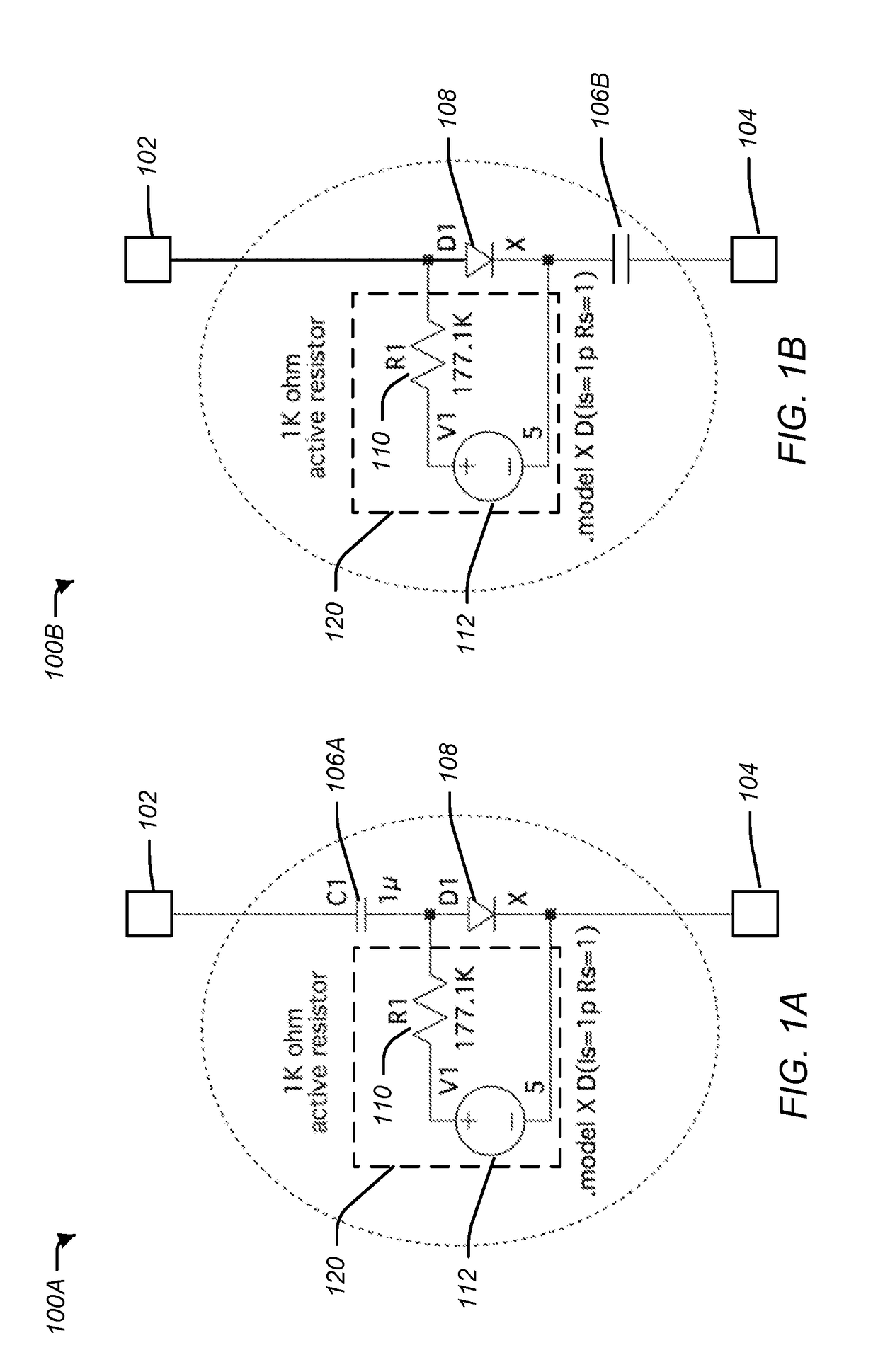

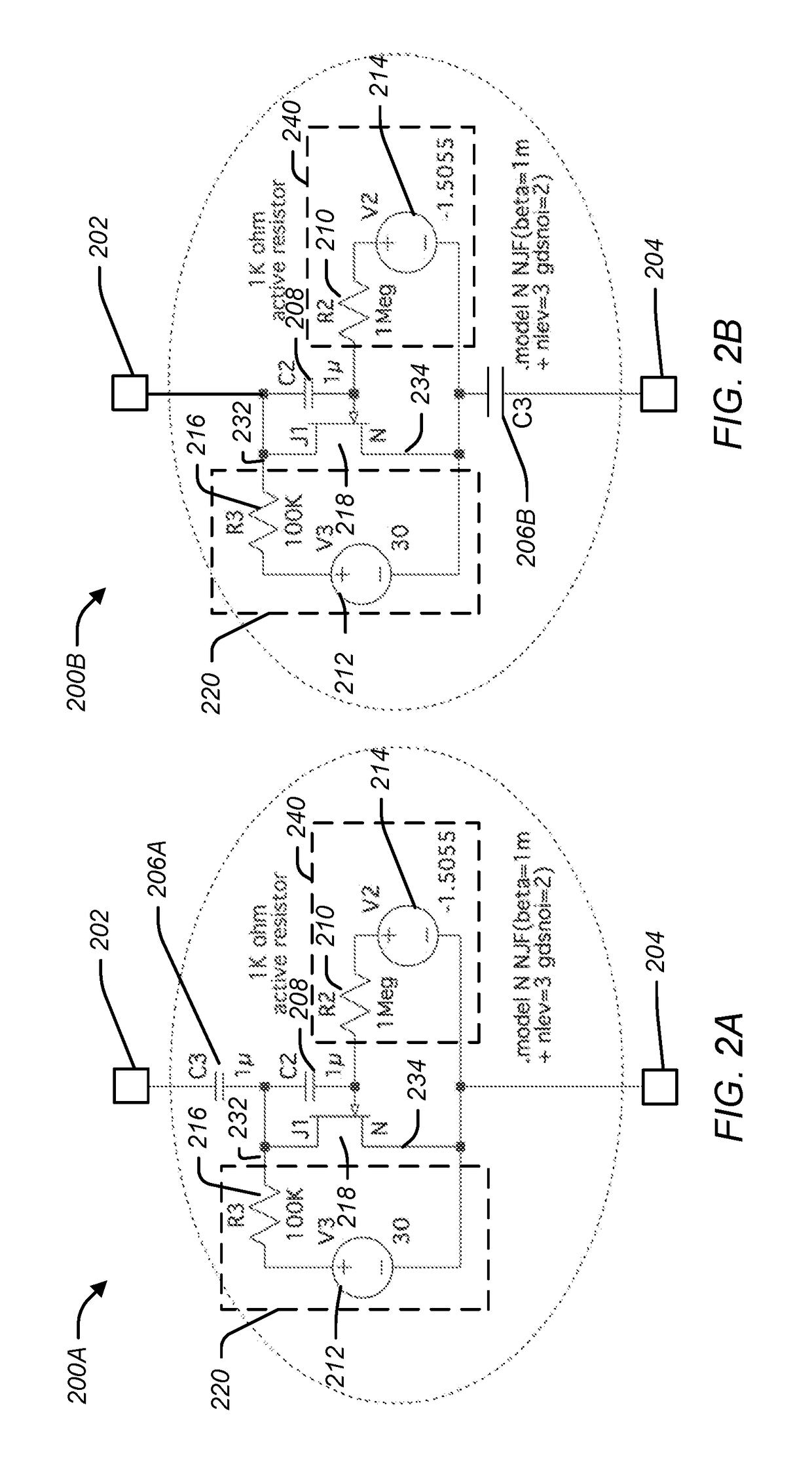

Active differential resistors with reduced noise

ActiveUS9866245B2Network simulating resistancesElectronic switchingSoftware engineeringMechanical engineering

A method and system of providing an active differential resistor. The active differential resistor includes a diode having a first node and a second node. There is a capacitor coupled in series between the first node of the diode and an input of the active differential resistor. There is a current source coupled across the first node and the second node of the diode and configured to forward bias the diode such that a Johnson-Nyquist noise of the active differential resistor is replaced by a shot noise.

Owner:ANALOG DEVICES INT UNLTD

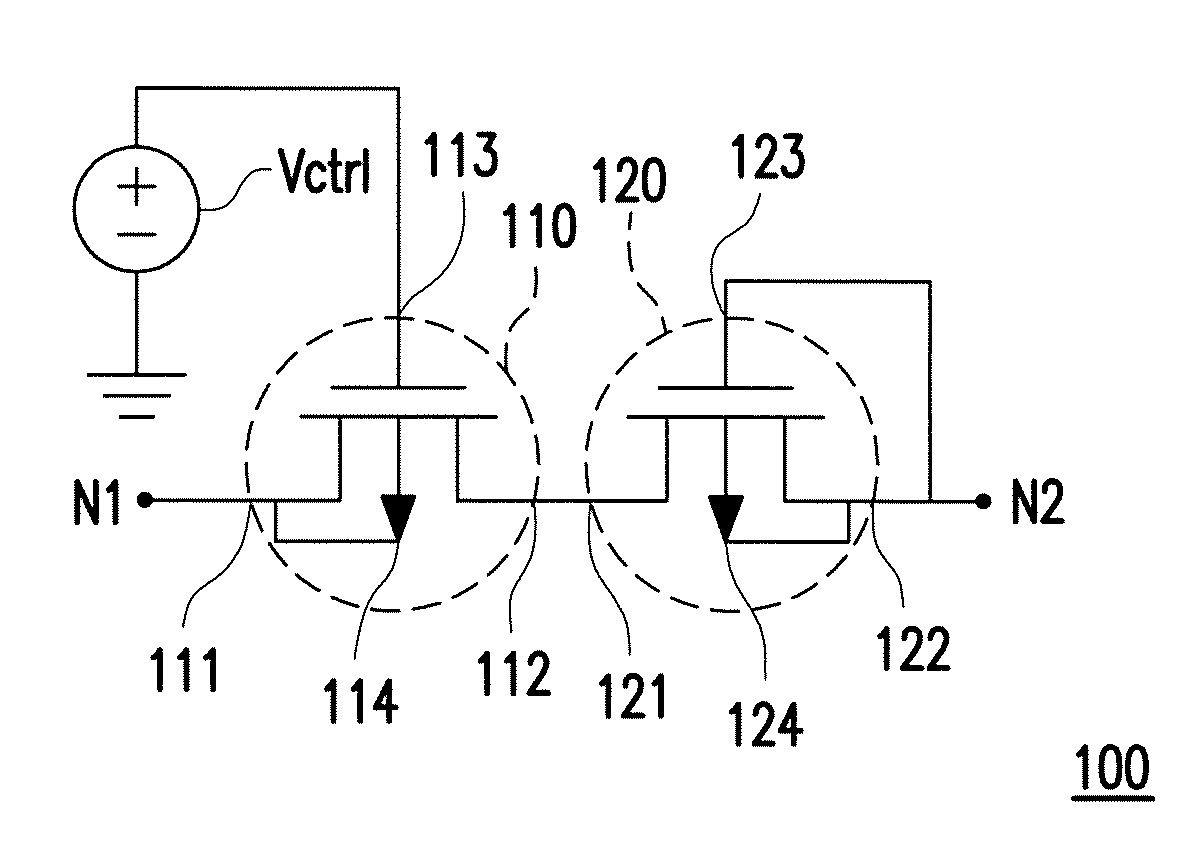

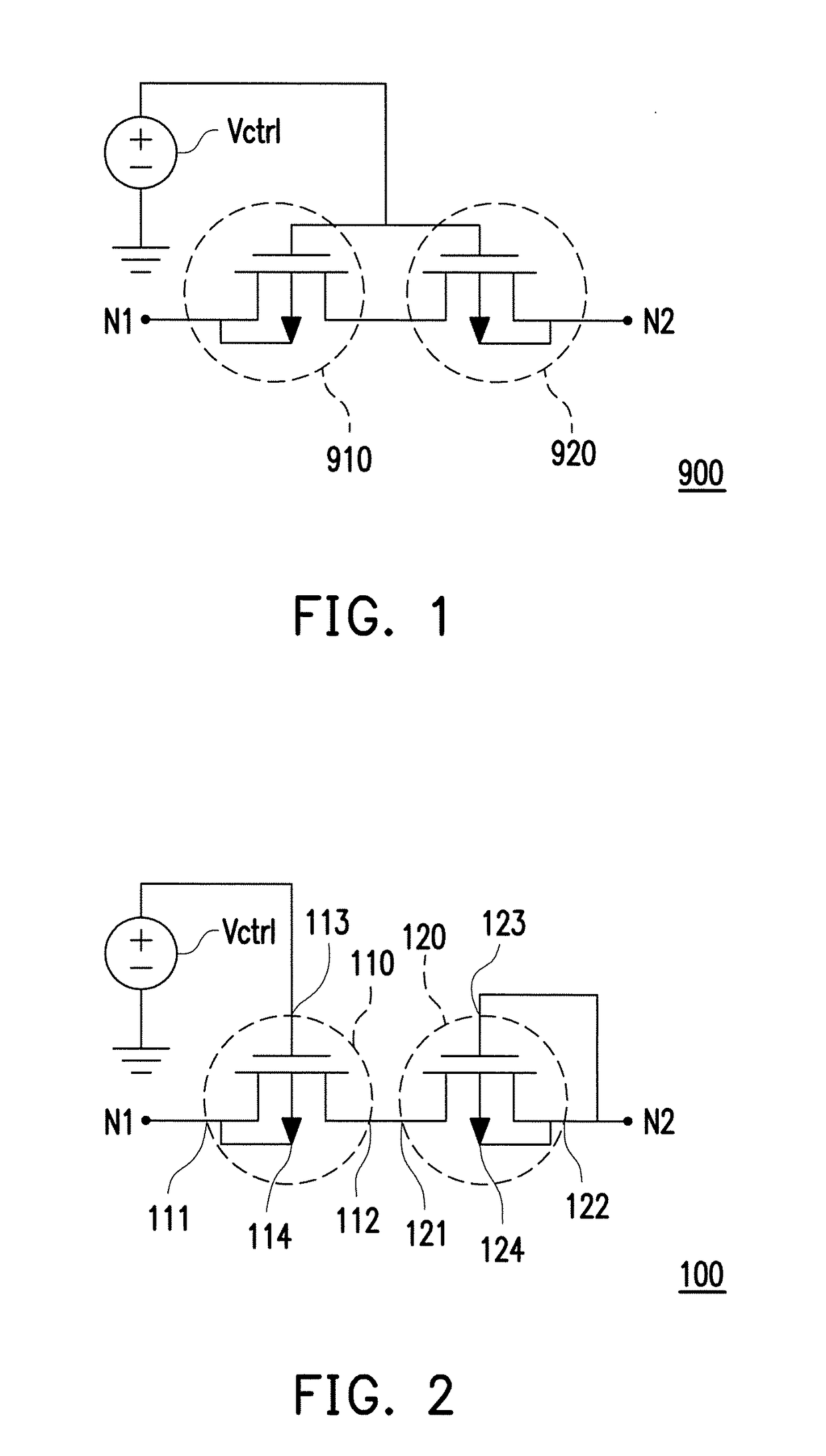

Electrically controlled very high value floating cmos resistor

InactiveUS20040256695A1Valid conversionSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringLinearity

The present invention provides a circuit arrangement to convert fixed, or grounded resistors, to floating resistors. In particular, the circuit arrangement provides for the coupling of active electrical resistance devices to provide a relatively high value electrical resistance between two non-grounded nodes of the circuit arrangement in the order of Giga-ohms. The invention further provides for the magnitude of the floating electrical resistance to be determined by the magnitude of electrical current supply thus providing a means to select the magnitude of the floating electrical resistance by selecting by selecting the magnitude of electrical current supply. The circuit arrangement requires relatively few active devices and consumes a relatively small amount of electrical power in operation. The floating resistor of the present invention may be used in applications where a relatively high value resistor consuming a relatively small area of silicon, exhibiting relatively good linearity and wide dynamic range are required. Applications for such a device include neural networks, image processing and vision systems.

Owner:SARAWI SAID

Active load generation circuit and filter using same

ActiveUS10461734B2Save areaHigh impedanceInput/output impedence modificationSemiconductor/solid-state device detailsEngineeringVoltage reference

This invention discloses an active load generation circuit and a filter. The active load generation circuit includes a transistor, a voltage control circuit, a voltage offset and tracking circuit, and a temperature sensing circuit. The transistor provides an impedance and includes a control terminal and an input terminal. The control terminal receives a control voltage, the input terminal receives an input signal, and the impedance is associated with the control voltage. The voltage control circuit generates an intermediate voltage according to a power supply voltage and a first reference voltage. The voltage offset and tracking circuit generates the control voltage according to the input signal and the intermediate voltage such that the control voltage varies with the input signal. The temperature sensing circuit senses an ambient temperature of the active load generation circuit and adjusts the first reference voltage according to the ambient temperature.

Owner:REALTEK SEMICON CORP

Popular searches

Amplifier input/output impedence modification Semiconductor devices Frequency selective two-port networks Physical realisation Amplifier modifications to reduce detrimental impedence Electrical measurements Amplifiers with semiconductor devices only Electric pulse generator details Transmission Pulse manipulation

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com