Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

74 results about "Process architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Process architecture is the structural design of general process systems. It applies to fields such as computers (software, hardware, networks, etc.), business processes (enterprise architecture, policy and procedures, logistics, project management, etc.), and any other process system of varying degrees of complexity.

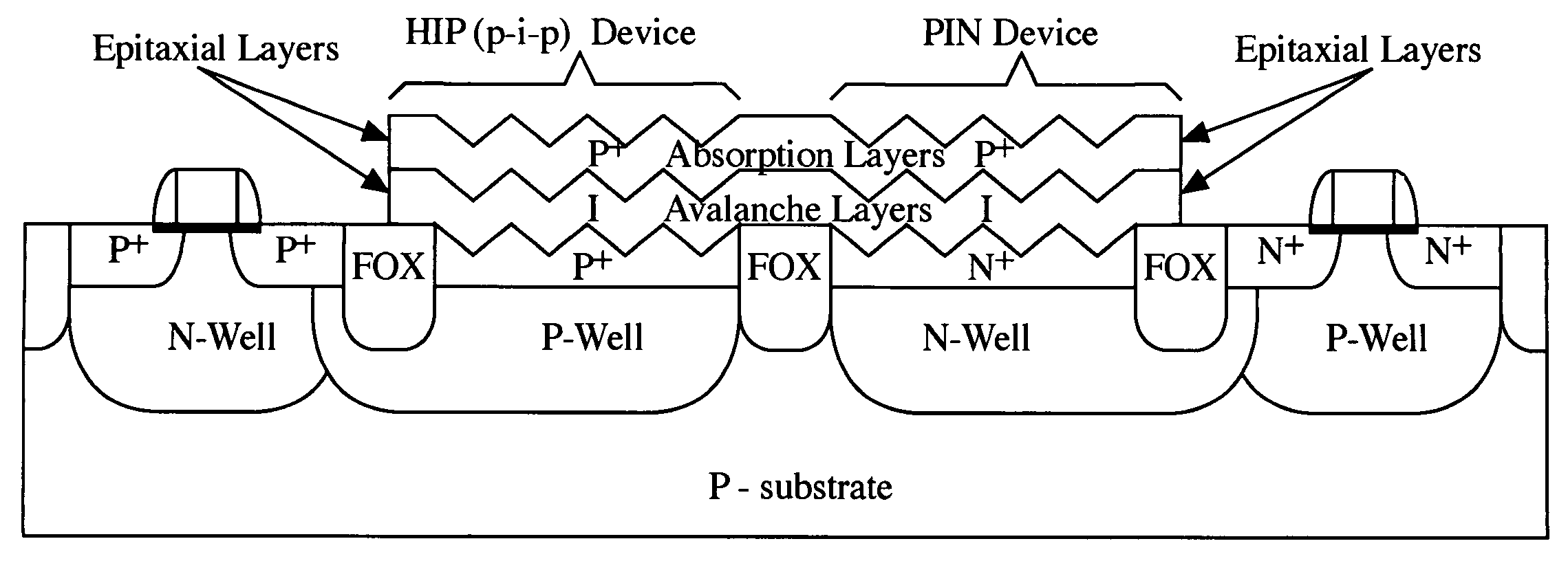

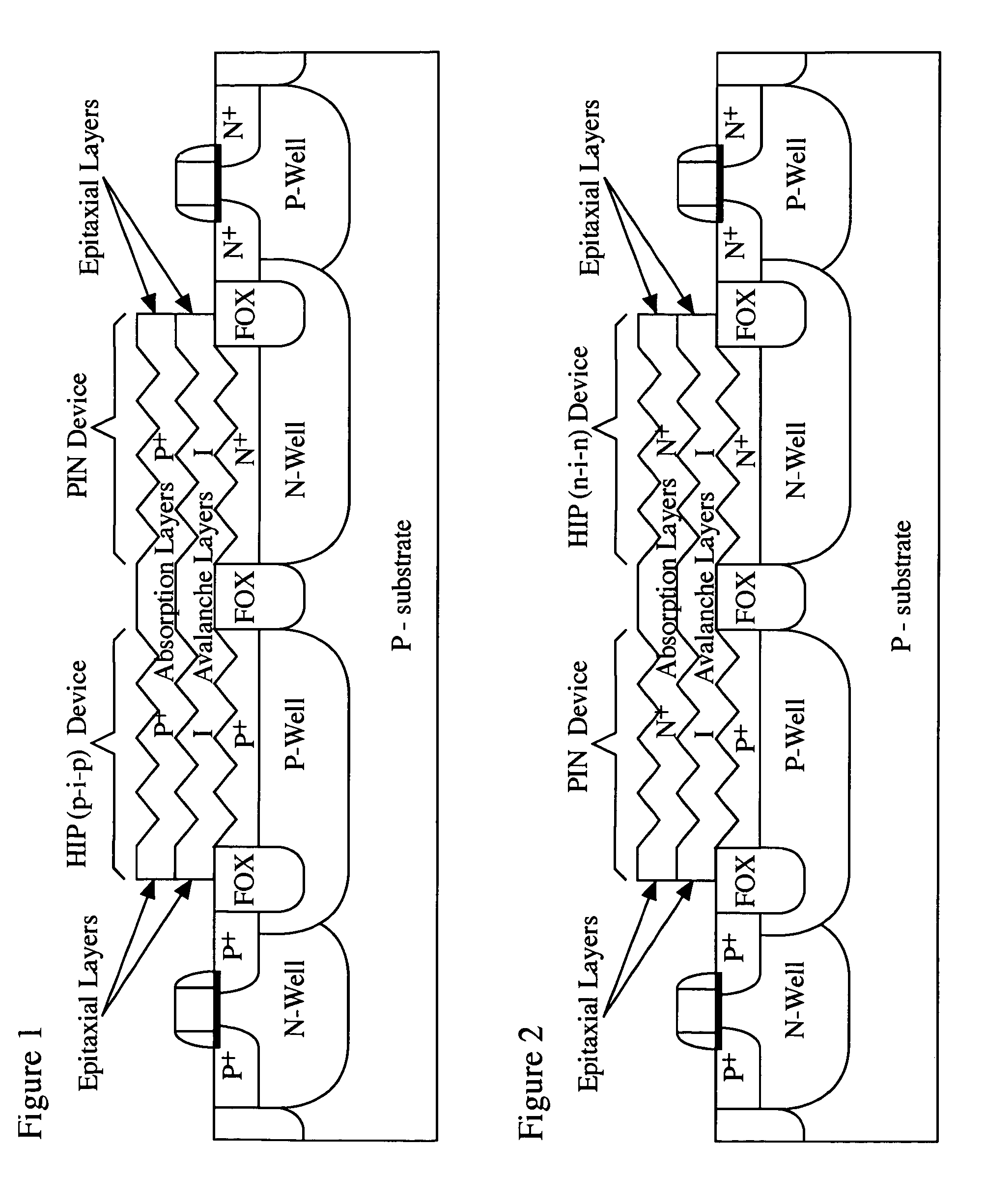

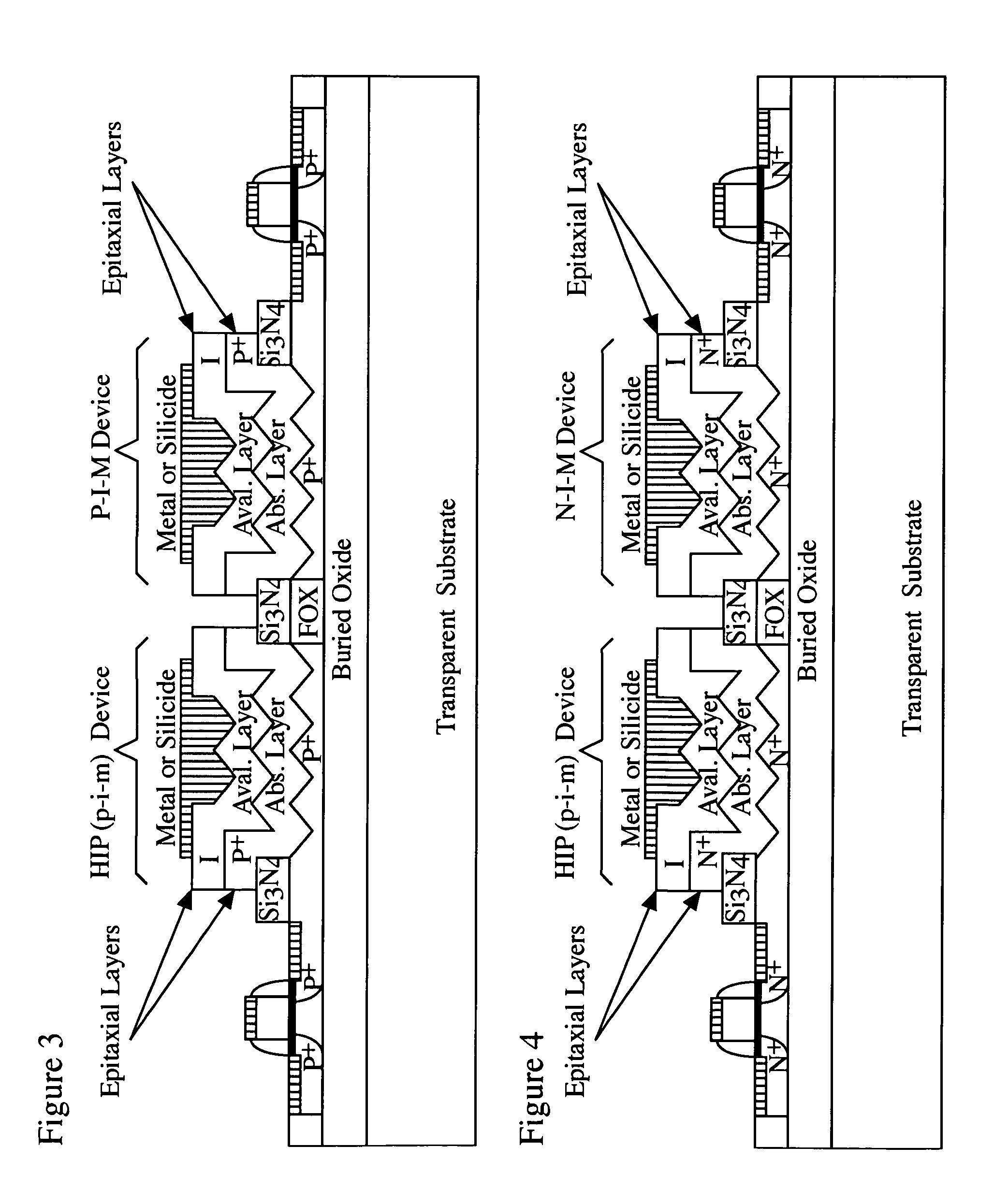

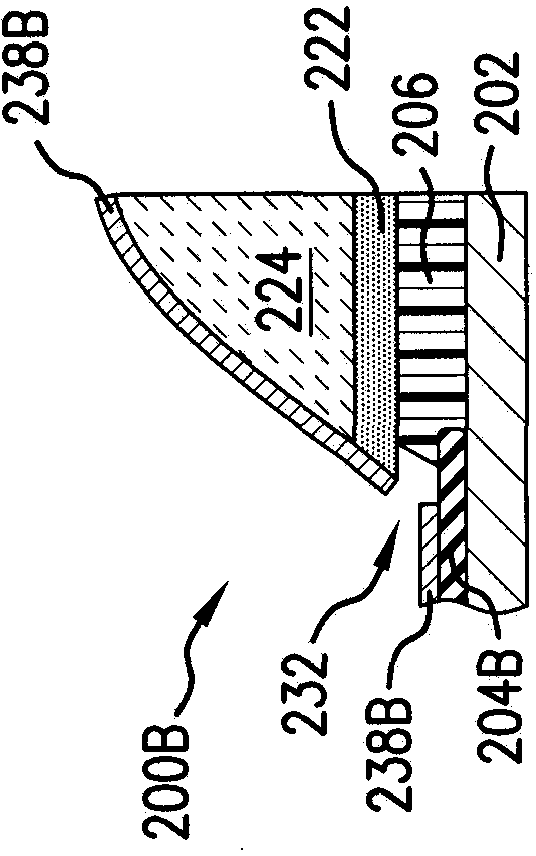

Light-sensing device

ActiveUS7521737B2Solid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionPixel density

A method of fabricating light-sensing devices including photodiodes monolithically integrated with CMOS devices. Several types of photodiode devices (PIN, HIP) are expitaxially grown in one single step on active areas implanted in a common semiconductor substrate, the active areas having defined polarities. The expitaxially grown layers for the photodiode devices may be either undoped or in-situ doped with profiles suitable for their respective operation. With appropriate choice of substrate materials, device layers and heterojunction engineering and process architecture, it is possible to fabricate silicon-based and germanium-based multi-spectral sensors that can deliver pixel density and cost of fabrication comparable to the state of the art CCDs and CMOS image sensors. The method can be implemented with epitaxially deposited films on the following substrates: Silicon Bulk, Thick-Film and Thin-Film Silicon-On-Insulator (SOI), Germanium Bulk, Thick-Film and Thin-Film Geranium-On-Insulator (GeOI).

Owner:QUANTUM SEMICON

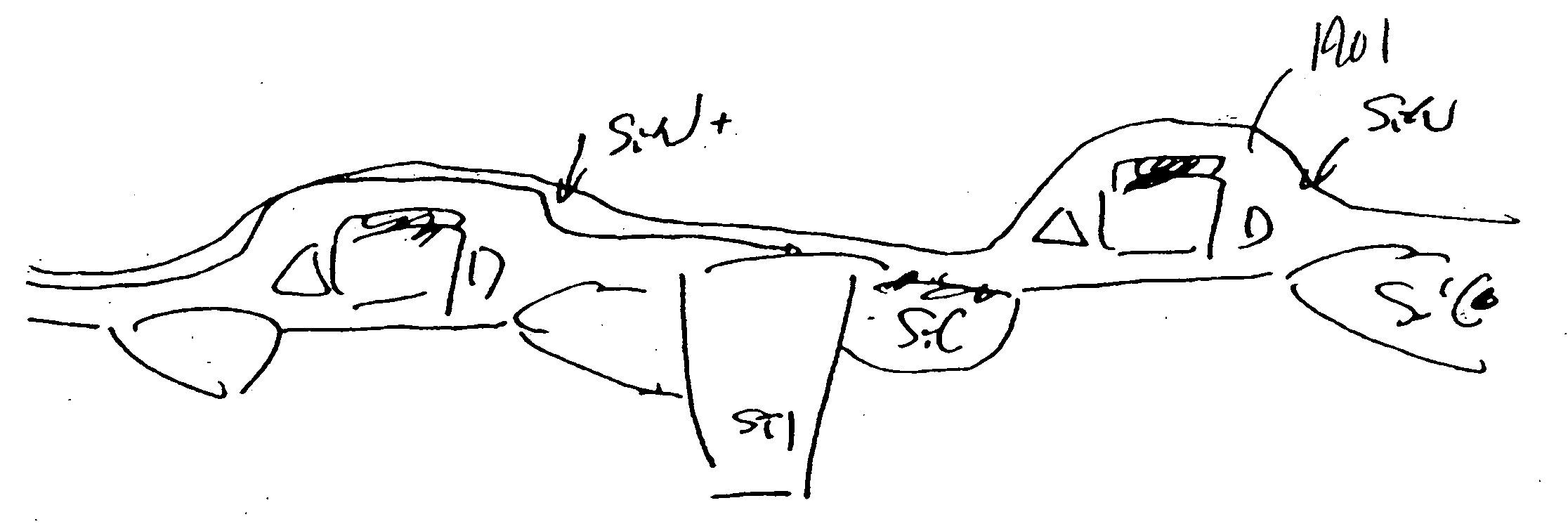

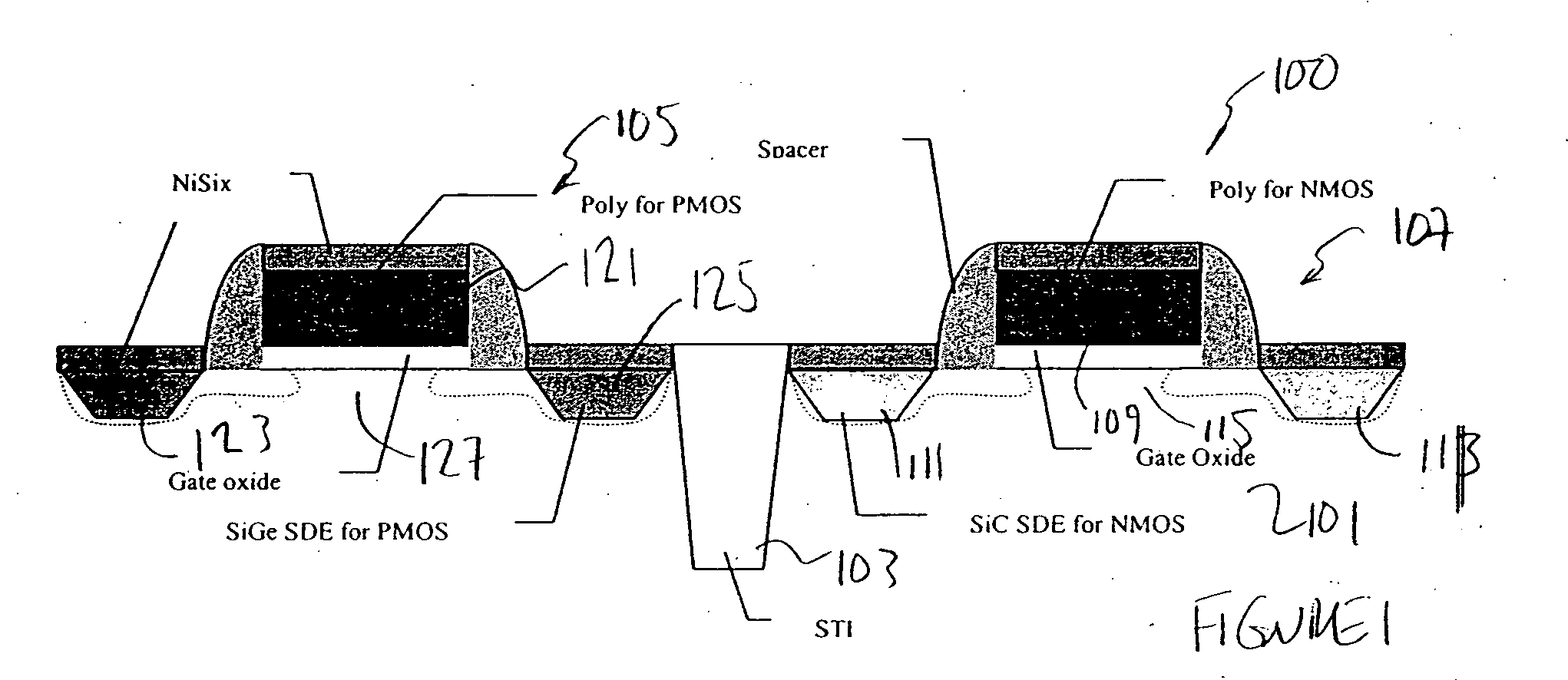

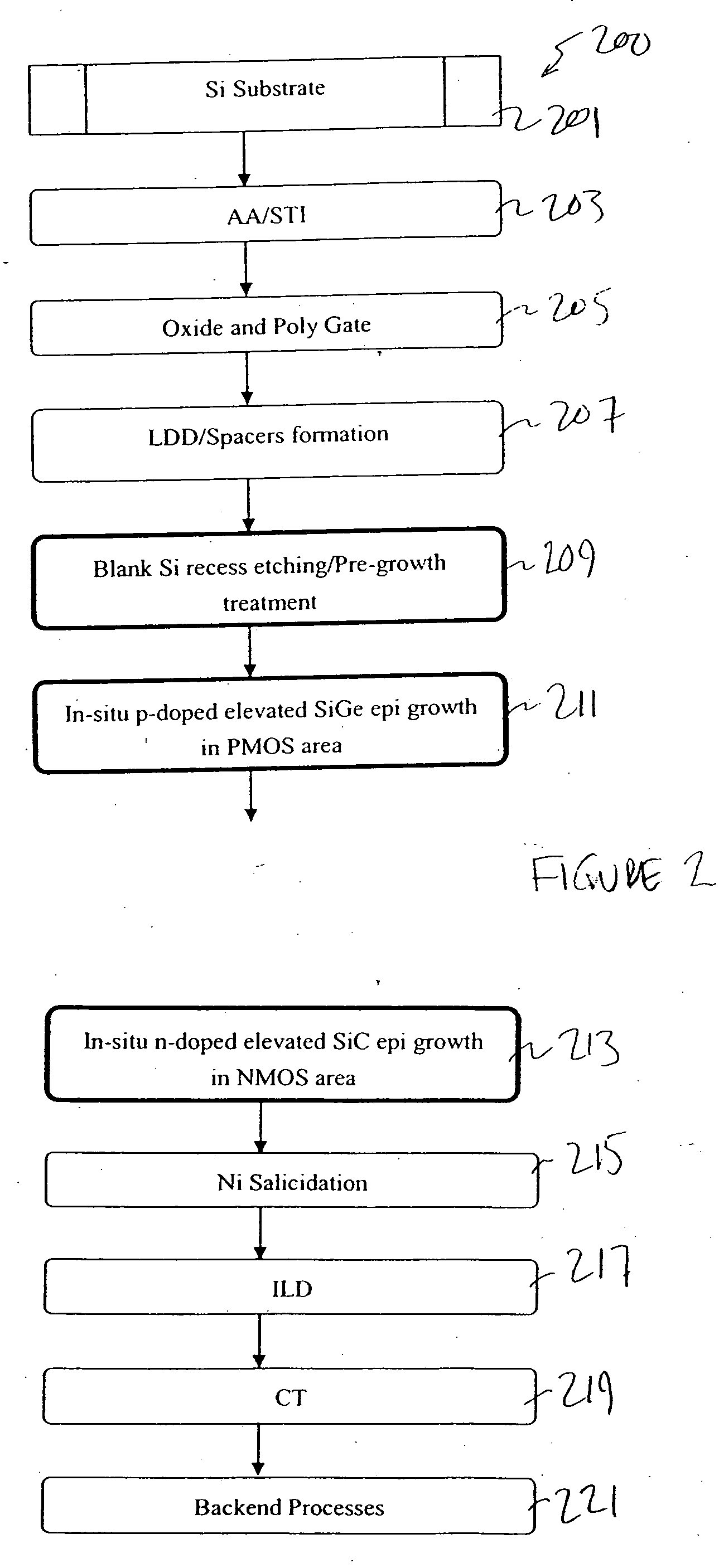

Strained-induced mobility enhancement nano-device structure and integrated process architecture for CMOS technologies

InactiveUS20070072376A1Easy to useHigh device yieldTransistorSemiconductor/solid-state device manufacturingCMOSNano-device

A CMOS semiconductor integrated circuit device. The CMOS device includes an NMOS device comprising a gate region, a source region, and a drain region and an NMOS channel region formed between the source region and drain region. A silicon carbide material is formed within the source region and formed within the drain region. The silicon carbide material causes the channel region to be in a tensile mode. The CMOS device also has a PMOS device comprising a gate region, a source region, and a drain region. The PMOS device has a PMOS channel region formed between the source region and the drain region. A silicon germanium material is formed within the source region and formed with in the drain region. The silicon germanium material causes the channel region to be in a compressive mode.

Owner:SEMICON MFG INT (SHANGHAI) CORP

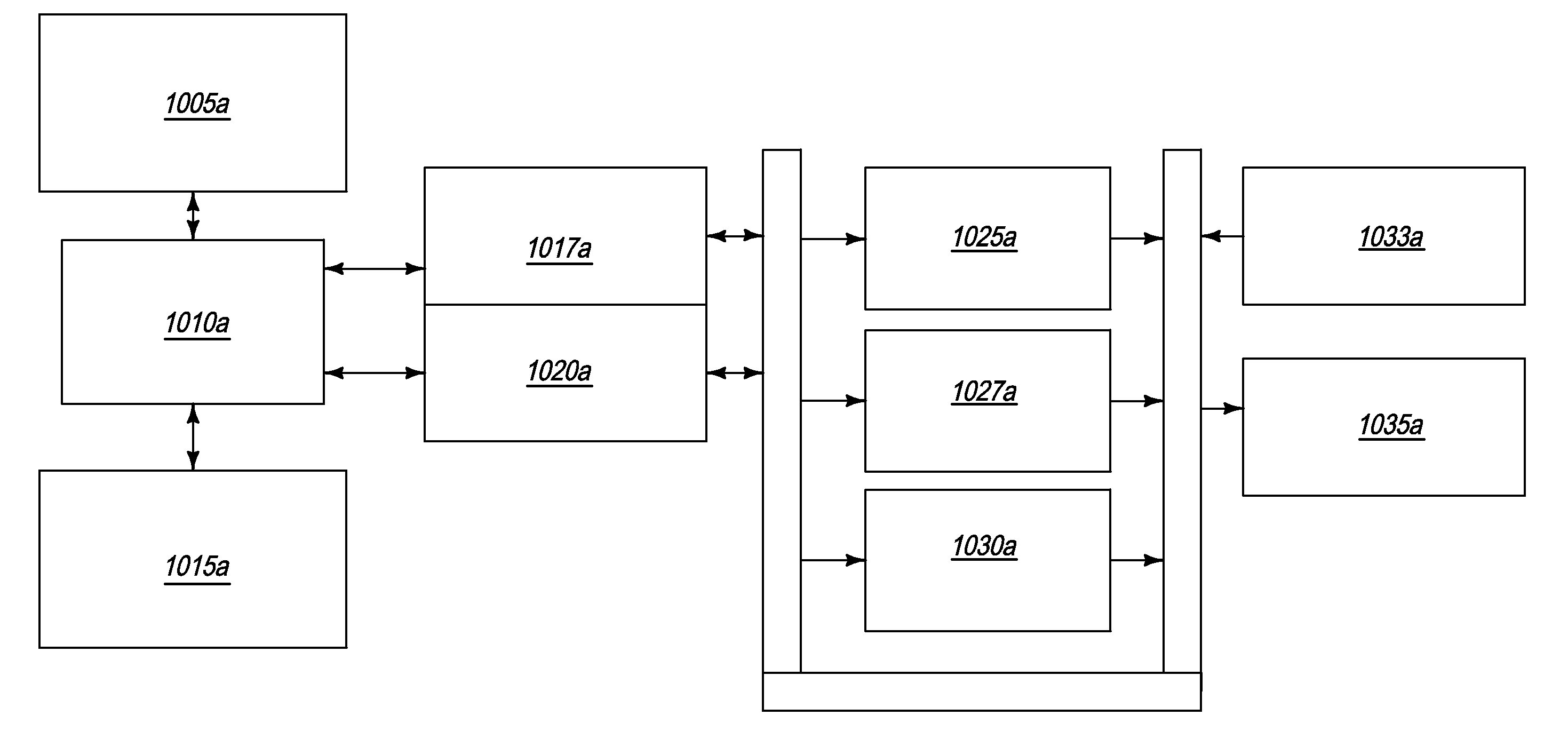

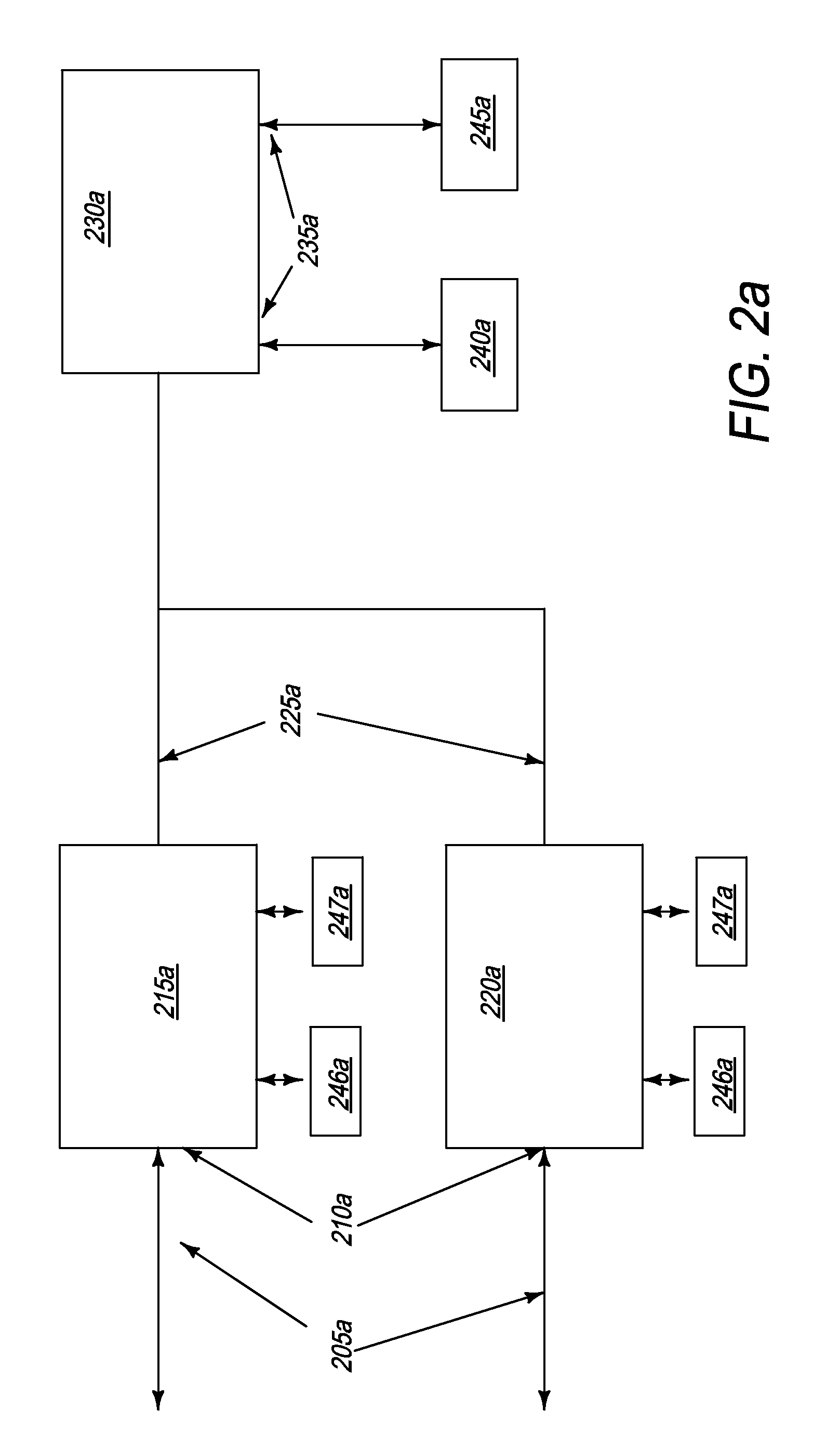

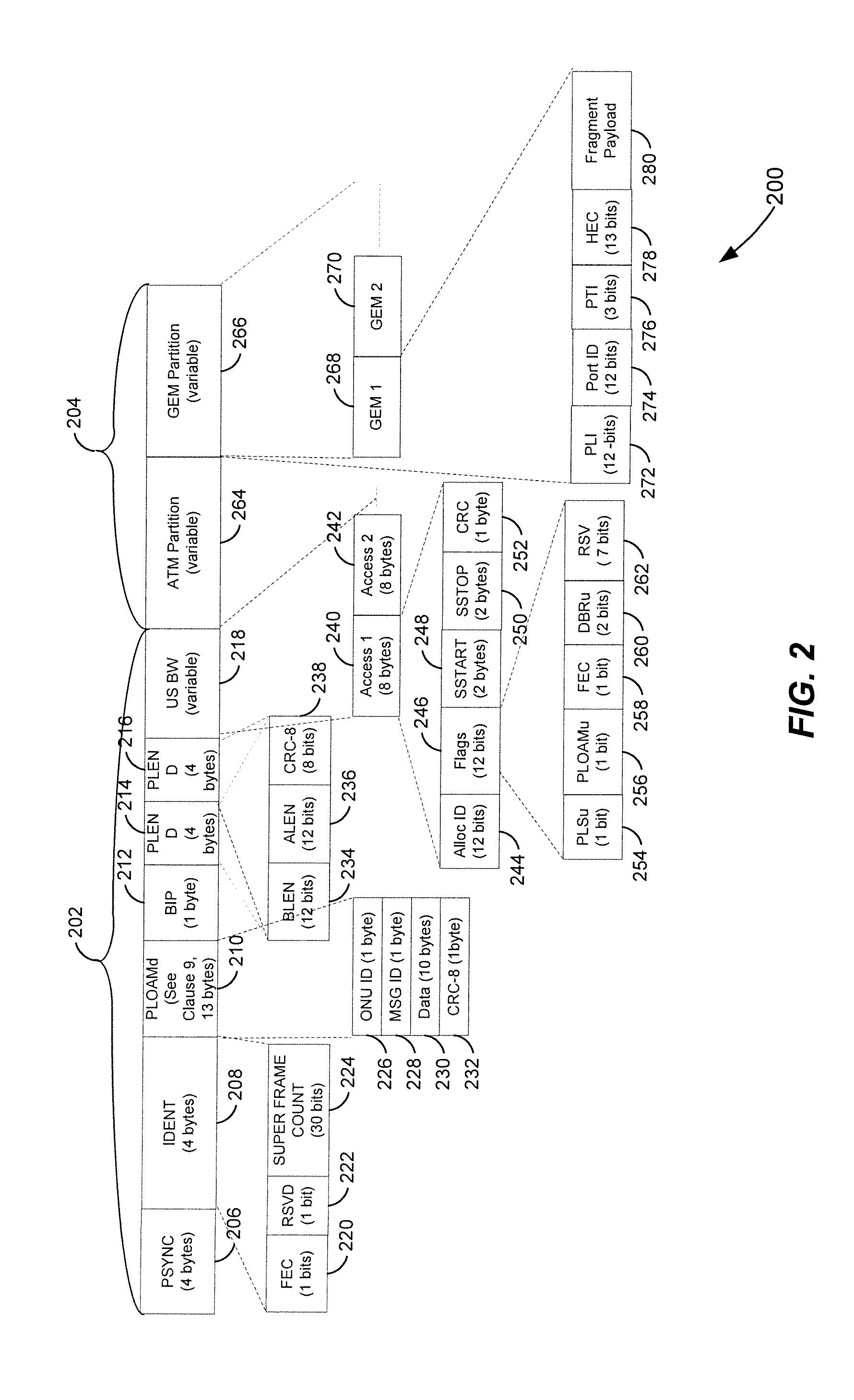

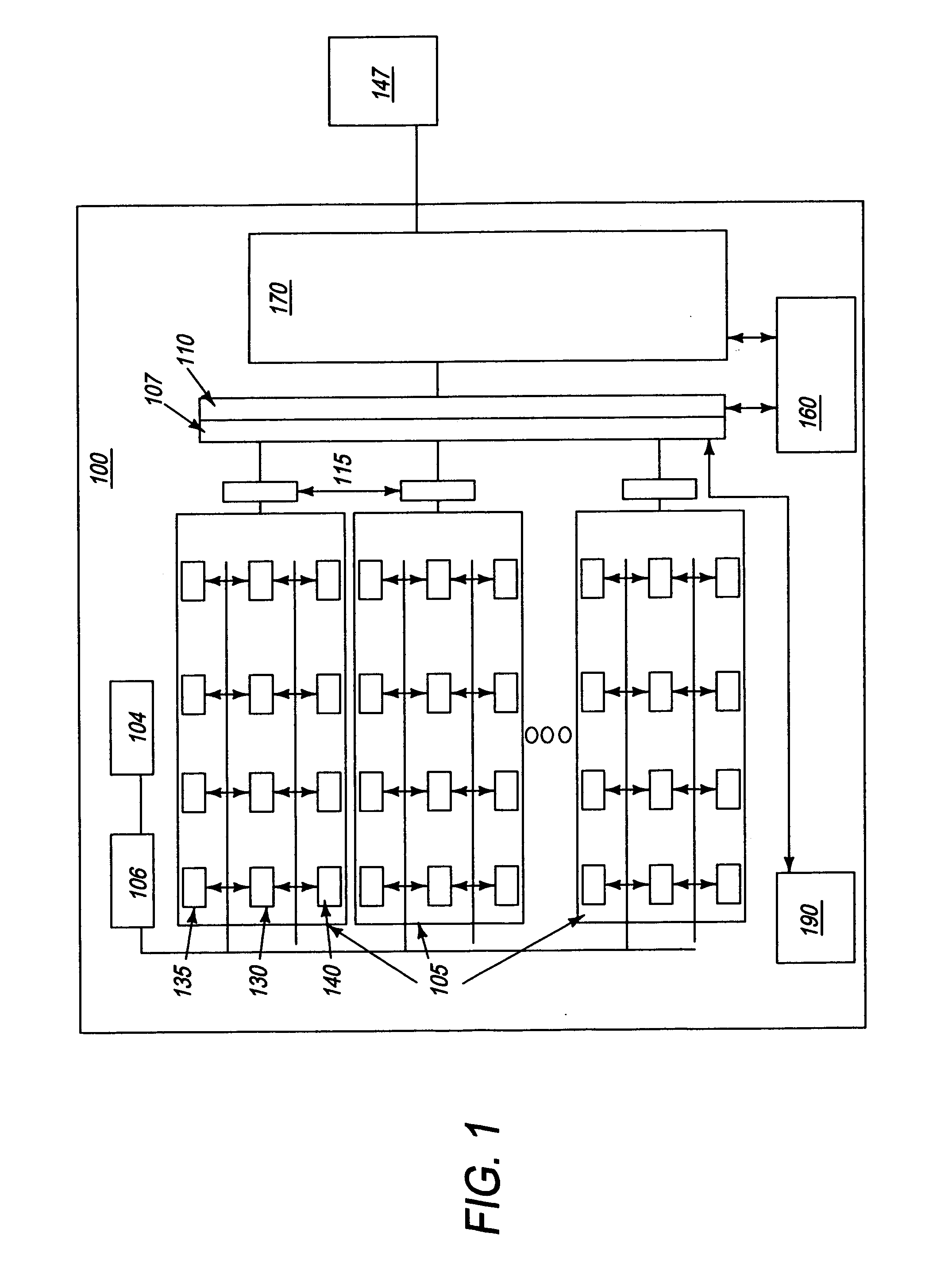

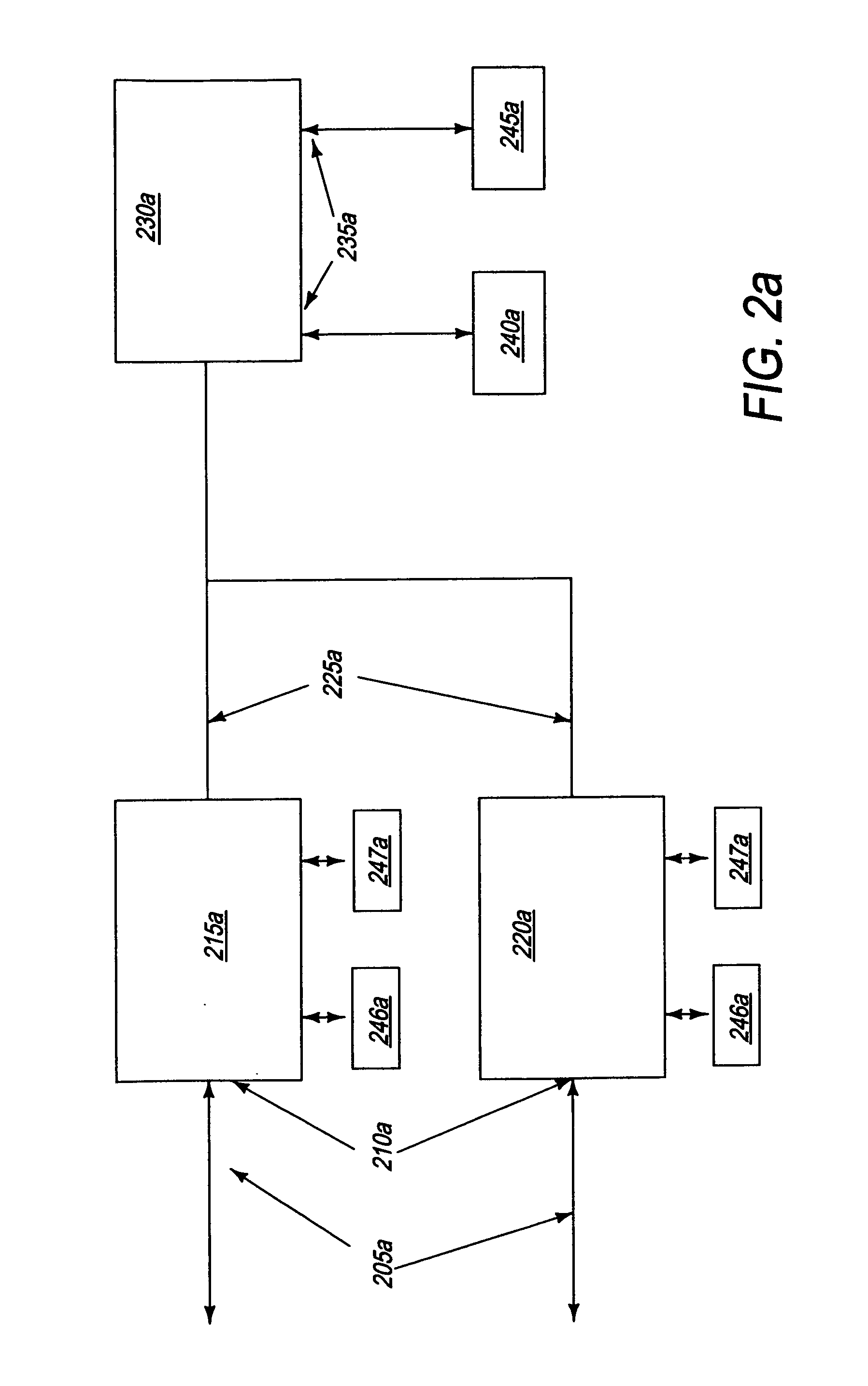

Distributed Processing Architecture With Scalable Processing Layers

The present invention is a system on chip architecture having scalable, distributed processing and memory capabilities through a plurality of processing layers. In a preferred embodiment, a distributed processing layer processor comprises a plurality of processing layers, a processing layer controller, and a central direct memory access controller. The processing layer controller manages the scheduling of tasks and distribution of processing tasks to each processing layer. Within each processing layer, a plurality of pipelined processing units (PUs), specially designed for conducting a defined set of processing tasks, are in communication with a plurality of program memories and data memories. One application of the present invention is in a media gateway that is designed to enable the communication of media across circuit switched and packet switched networks. The hardware system architecture of the said novel gateway is comprised of a plurality of DPLPs, referred to as Media Engines that are interconnected with a Host Processor or Packet Engine, which, in turn, is in communication with interfaces to networks. Each of the PUs within the processing layers of the Media Engines are specially designed to perform a class of media processing specific tasks, such as line echo cancellation, encoding or decoding data, or tone signaling.

Owner:QUARTICS

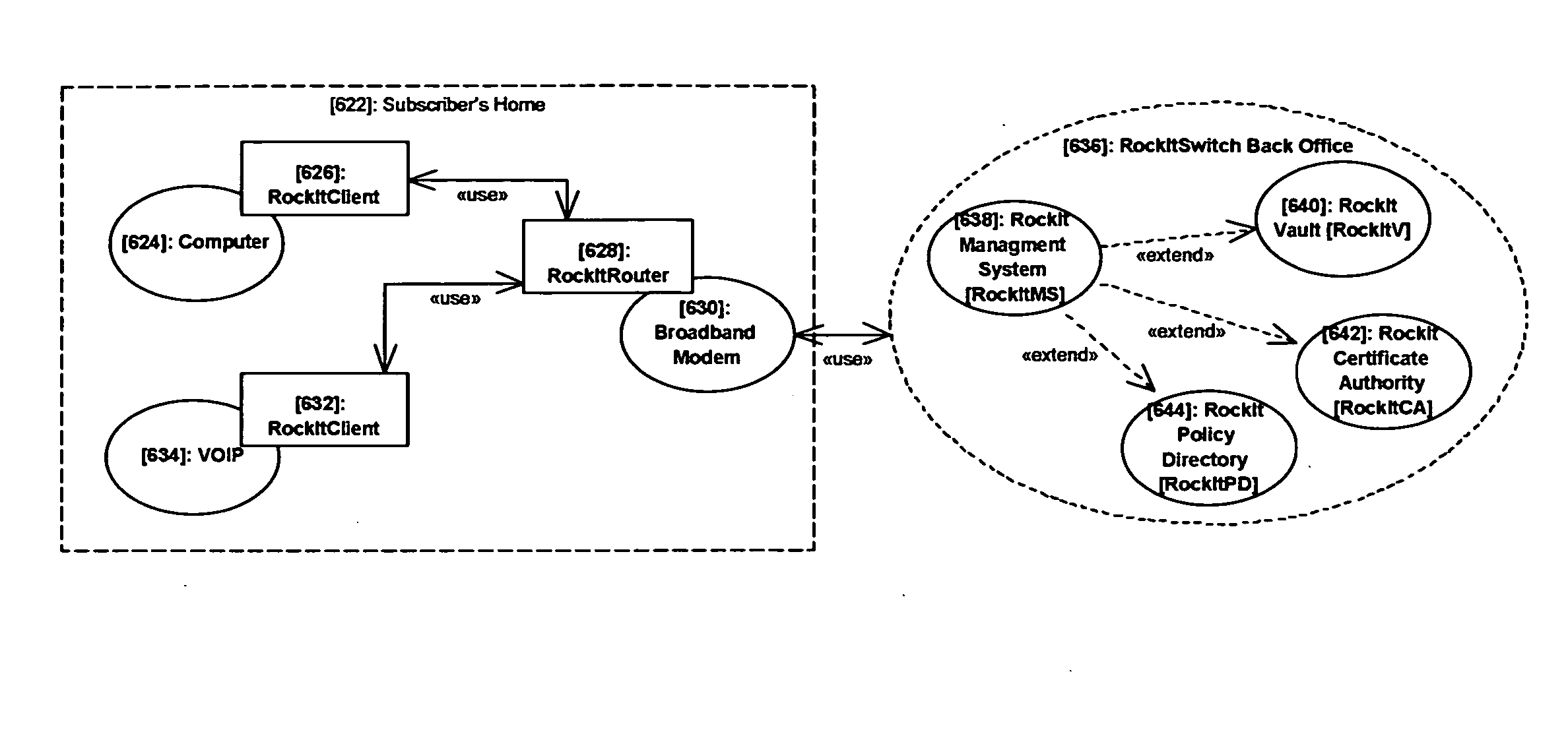

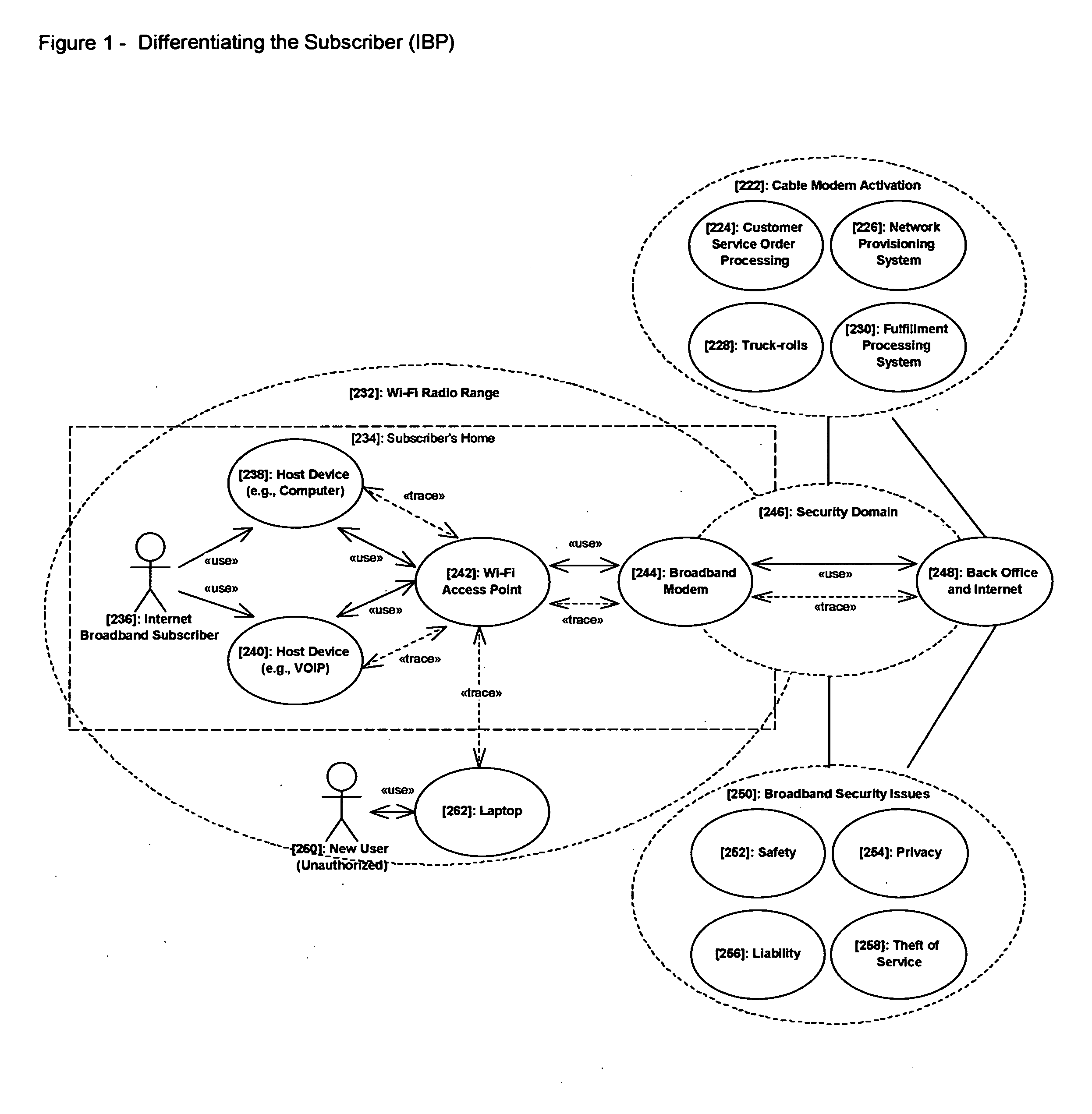

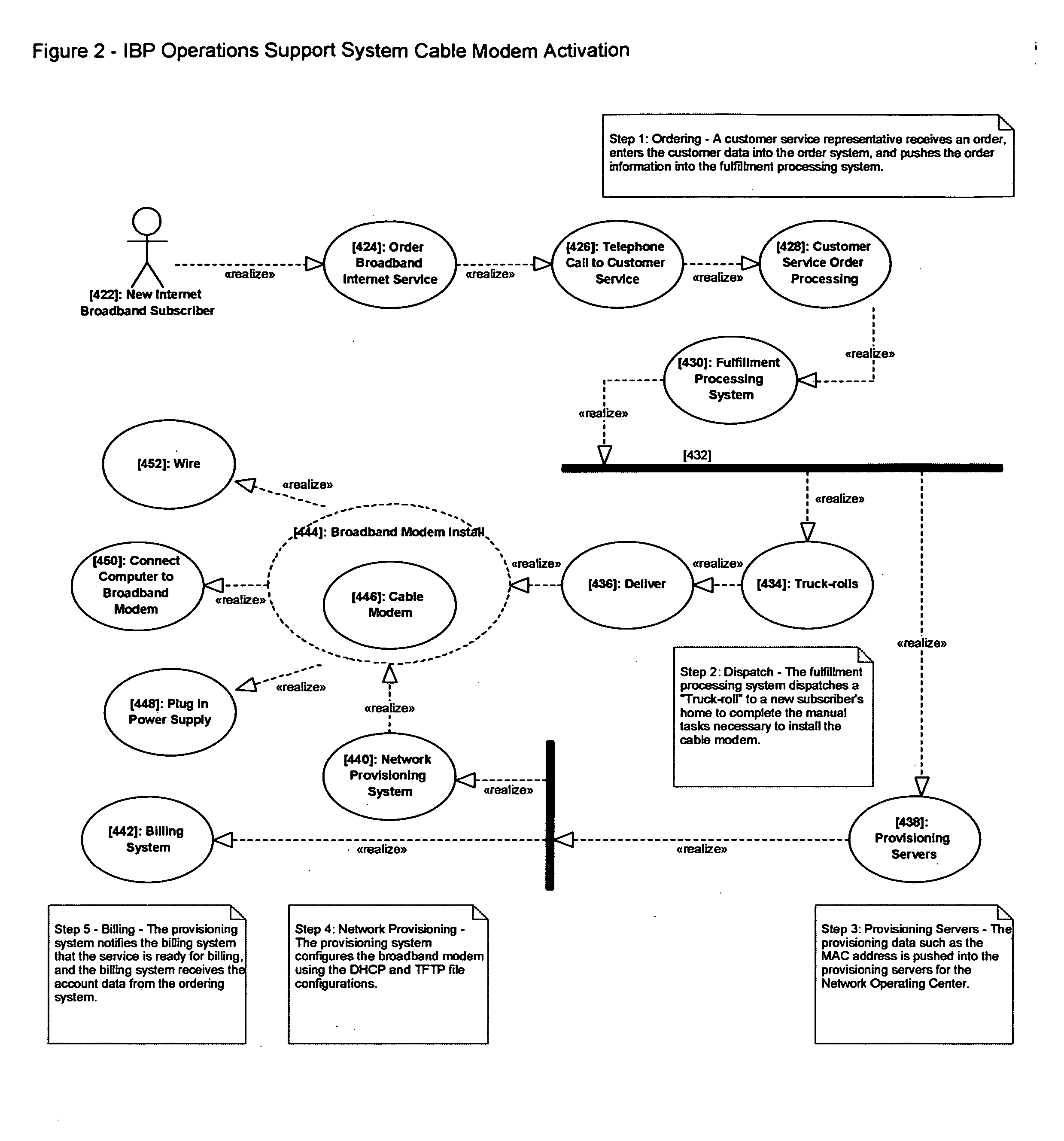

Broadband network security and authorization method, system and architecture

InactiveUS20070199049A1Digital data processing detailsUser identity/authority verificationModem deviceOrder fulfillment

A systems and process architecture which mandates, automates and manages network security and authorization for Internet broadband provider broadband modems and their customer's connectable host device(s), and provides and facilitates real-time automation of service order fulfillment and account processing. An Internet broadband IPsec, PKC, and QoS systems and process architecture which mandates, automates, and manages IPsec, PKC, and QoS for Internet broadband provider broadband modems and their customer's connectable host device(s). A systems and process architecture for determining broadband customer type including one of new, expired, roaming and current.

Owner:UBIQUITYNET

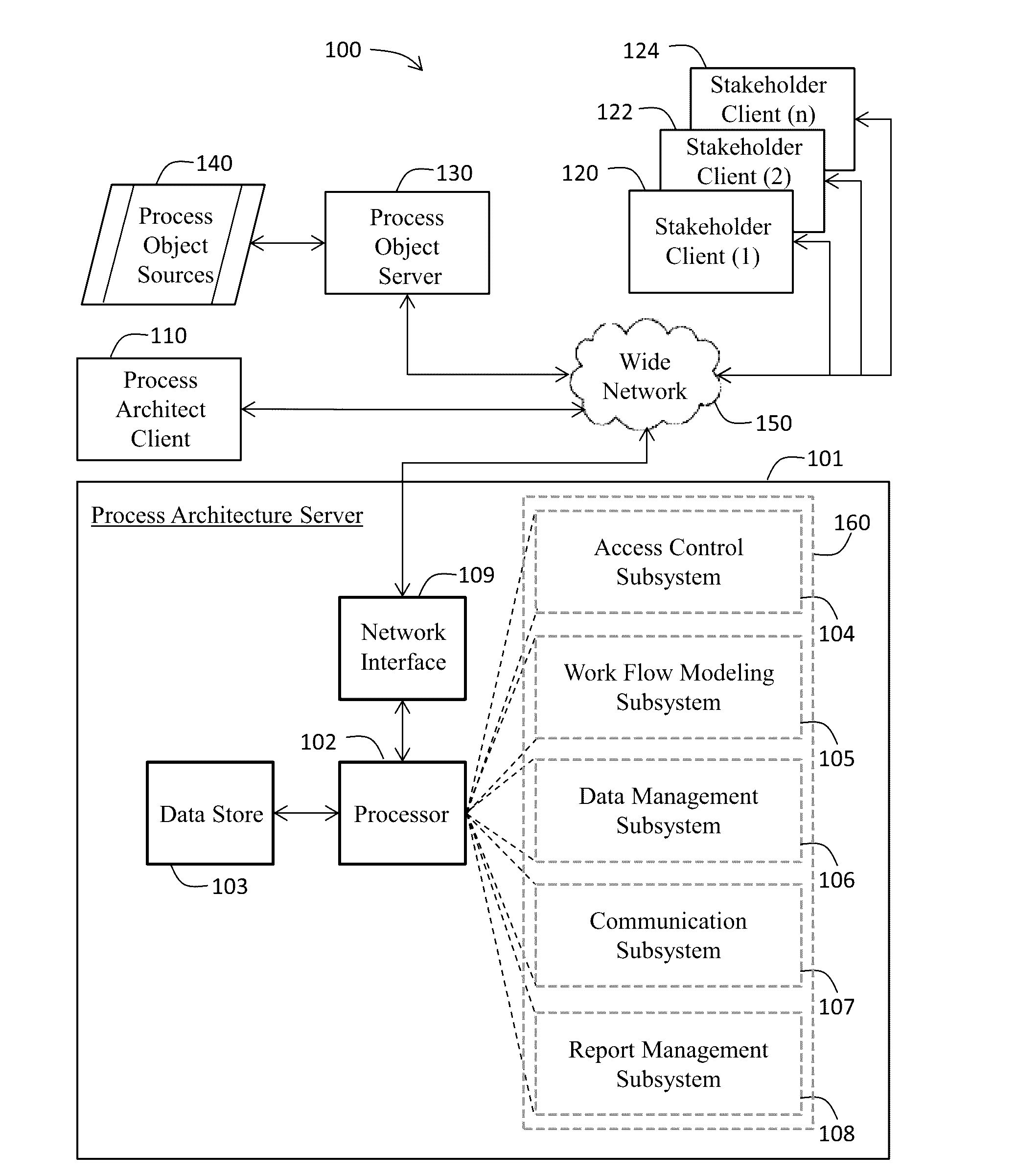

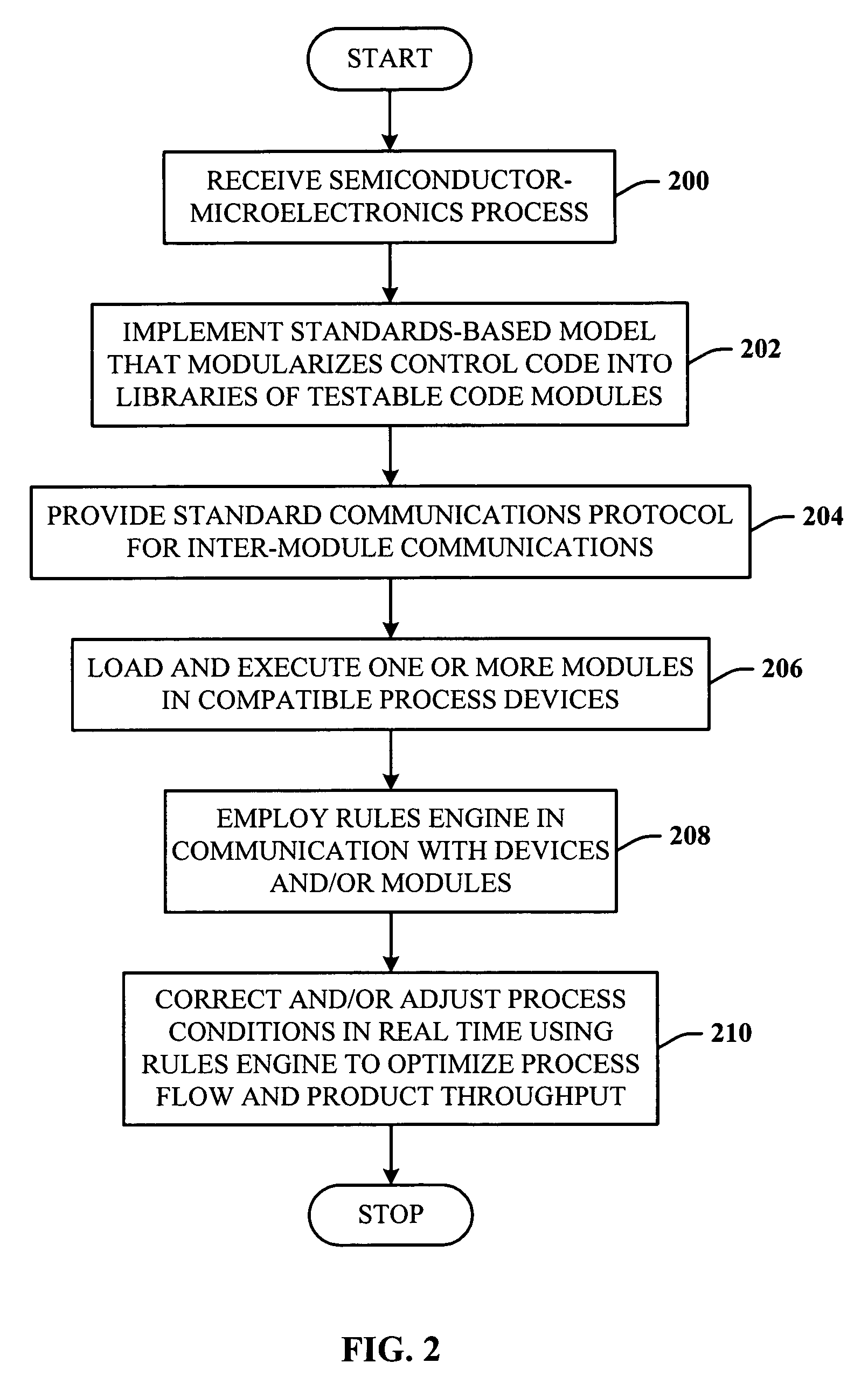

Method and computer program product for creating enterprise management systems

ActiveUS20160328217A1Software maintainance/managementModel driven codeDashboardRole-based access control

A computer program product for creating an enterprise management dashboard program, and comprising a process architecture server, a process architect client, a stakeholder client, and / or a process object server. The process architecture server includes a compiler characterized by an access control subsystem (receives role-base access control definition data), a work flow modeling subsystem (receives process model definition data), a data management subsystem (receives data structure definition data), a communication subsystem (receives communication protocol definition data), and a report management subsystem (receives report content definition data). The compiler uses the aforementioned data to create executable computer code for the enterprise management dashboard program based on modeling constructs including project sites, task pages, interface templates, report templates, and / or third-party process content. The resultant enterprise management dashboard program may be used to create and save process objects such as projects, tasks, artifacts (e.g., digital files), and process metrics.

Owner:CRAIG TECHNICAL CONSULTING INC

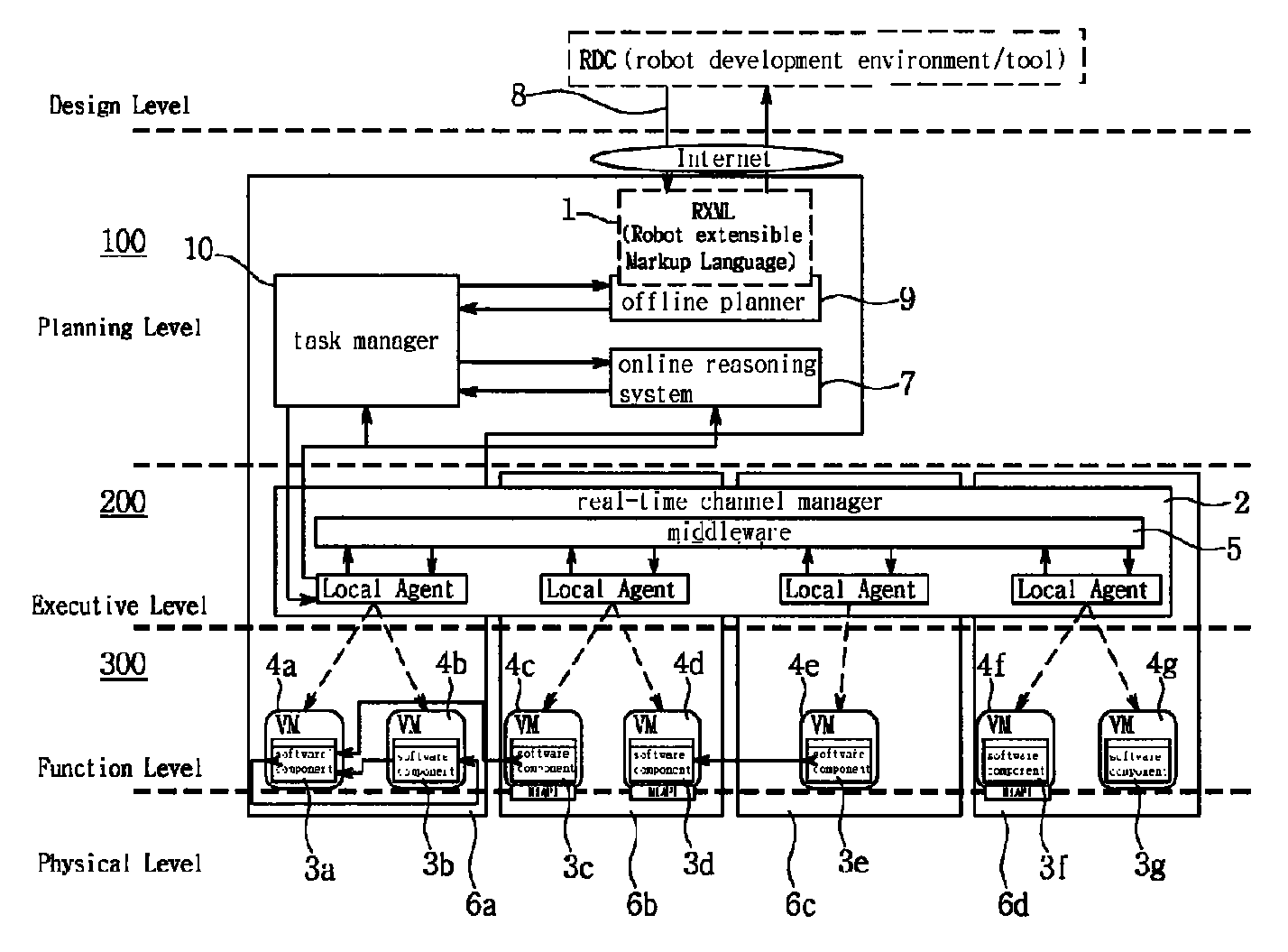

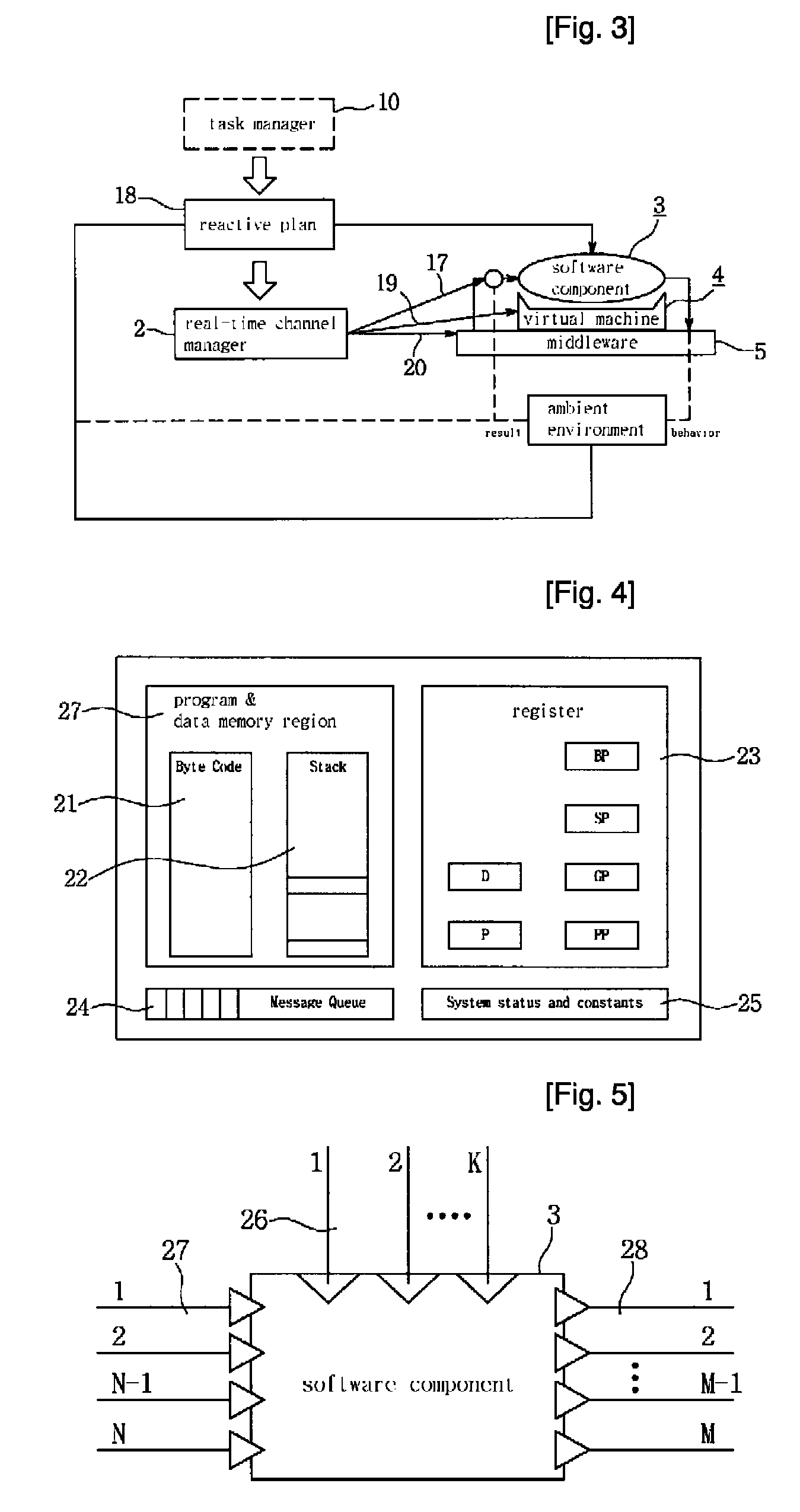

Robot Control Software Framework in Open Distributed Process Architecture

ActiveUS20080141220A1Advancing technology developmentIncrease heightProgramme-controlled manipulatorProgram control using stored programsTechnology developmentComputer architecture

An open distributed processing structured robot control software architecture is enclosed, which makes it possible to manufacture a user-oriented robot through combination of independent heterogeneous functional modules. The invention involves an open software framework for integrated operation and production of distributed software of the modules, and an autonomous robot control architecture suitable for distributed environments. The software framework indicates underlying software components for robot control and service creation. The invention makes it possible to mass-produce autonomous robots in units of interoperable functional modules. It is also possible to meet various demands of consumers, achieve specialization, and accelerate technology development since the development procedures are specialized in an independent manner and are suitable for manufacturing a wide variety of robot products in small quantities.

Owner:KOREA INST OF IND TECH

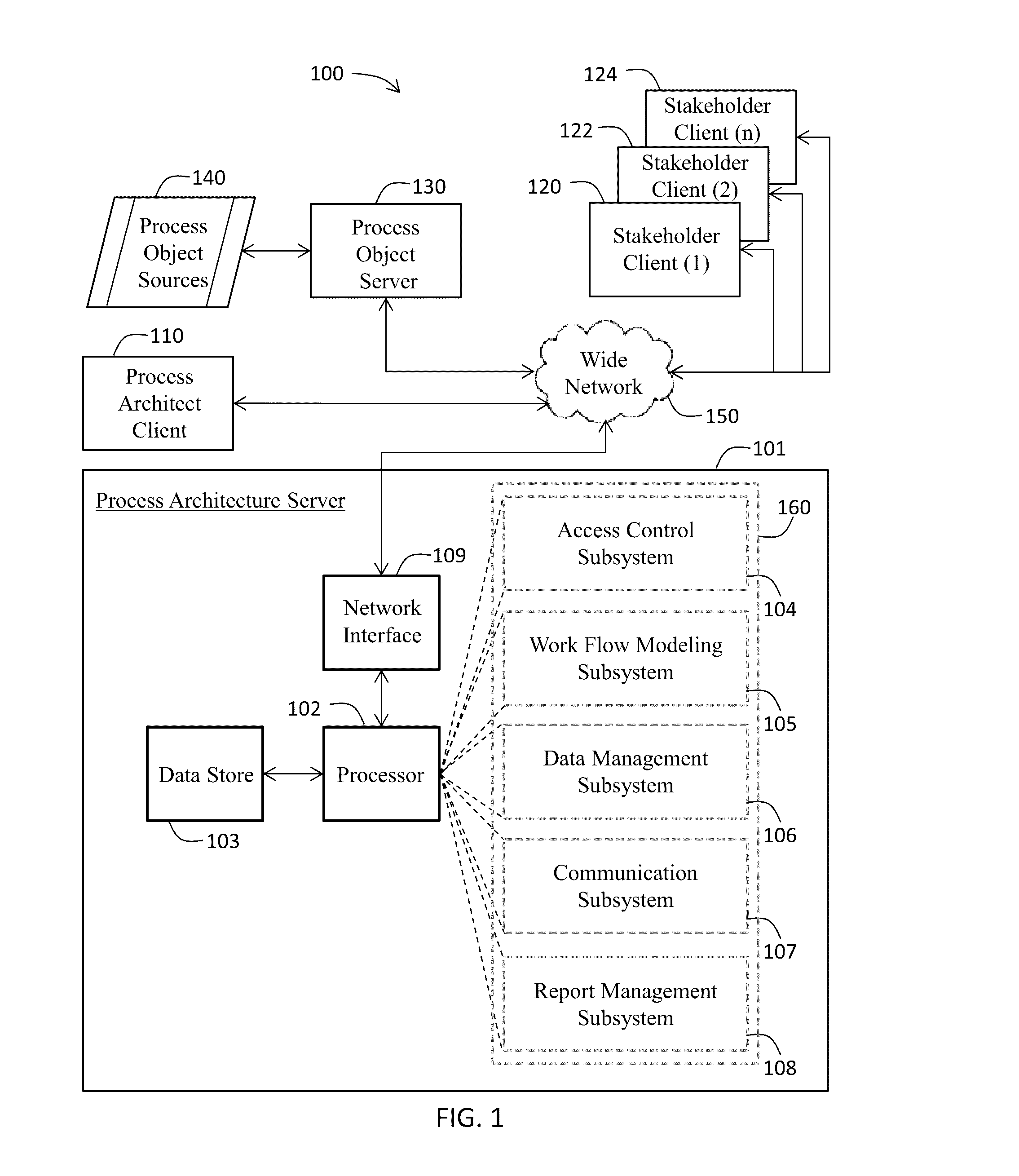

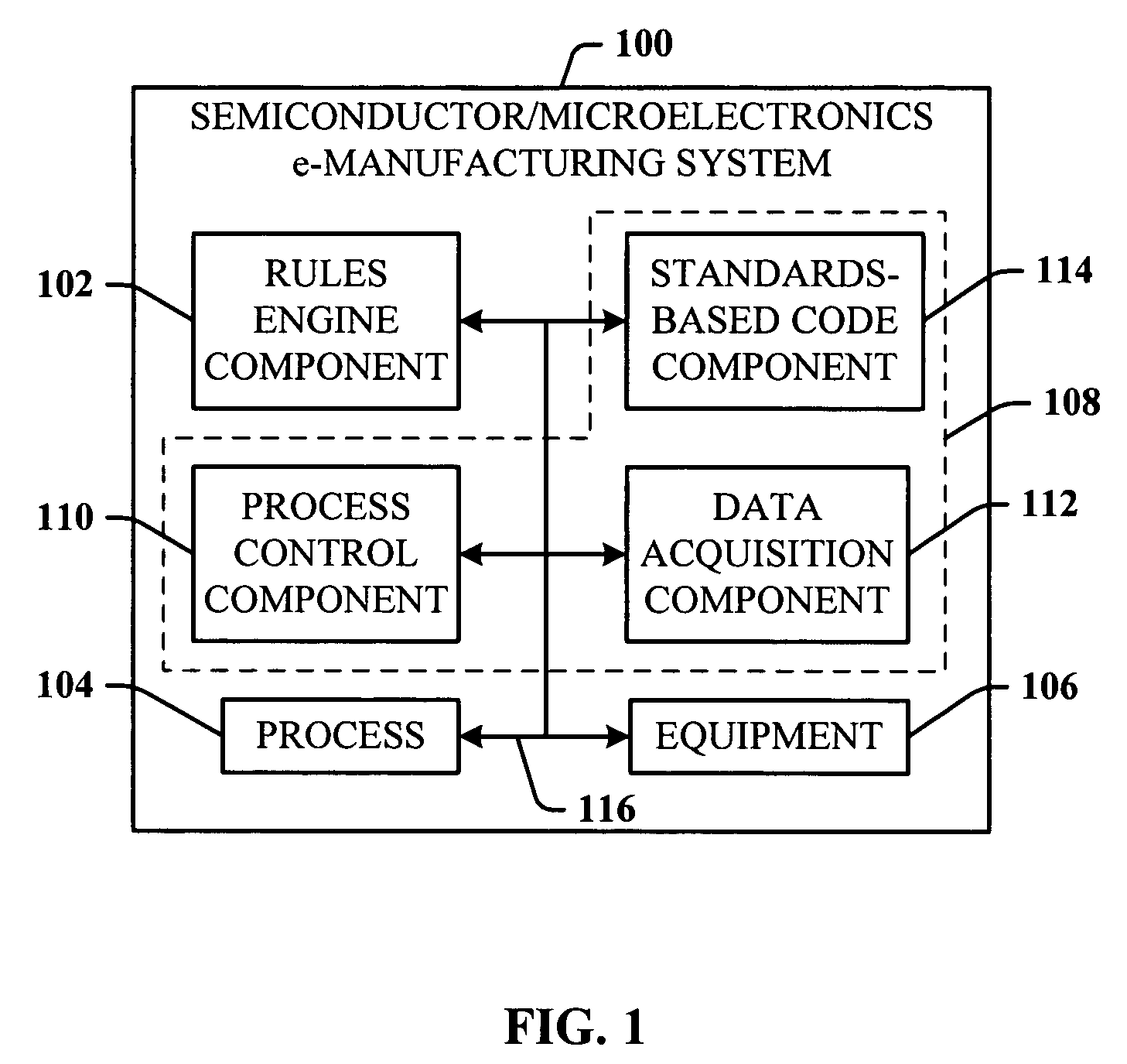

E-manufacturing in semiconductor and microelectronics processes

InactiveUS7242995B1Addressing slow performanceIncrease speedResourcesTotal factory controlModularityProcess efficiency

Architecture that facilitates management of a semiconductor and / or microelectronics manufacturing process. A manufacturing component in communication with the semiconductor and / or microelectronics process operates according to process conditions to output a product, which manufacturing component at least one of monitors and controls the process using modularized code. A rules engine component processes one or more rules in association with the modularized code to control the process conditions in realtime by balancing process efficiency criteria to arrive at an optimal result.

Owner:ROCKWELL AUTOMATION TECH

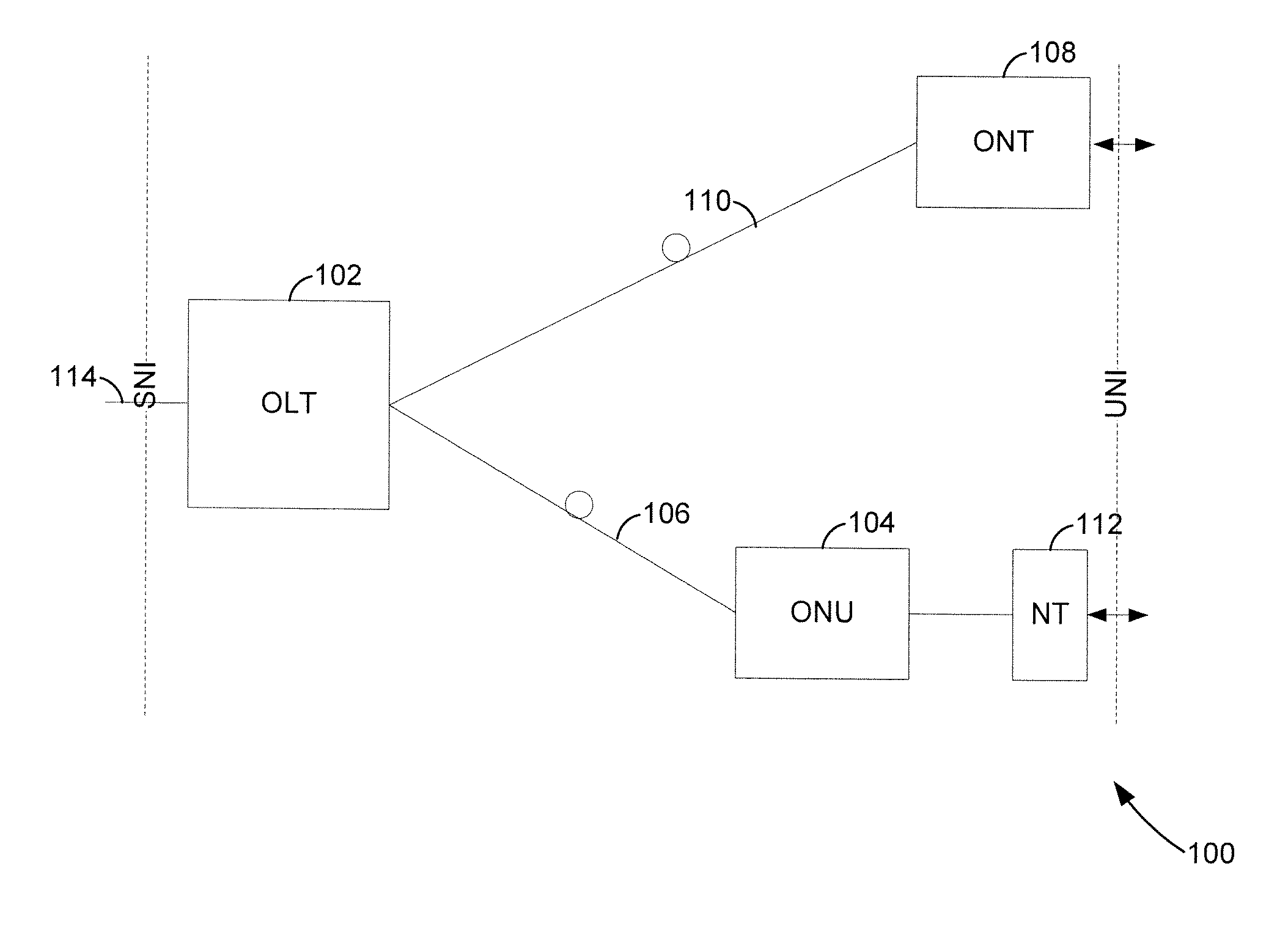

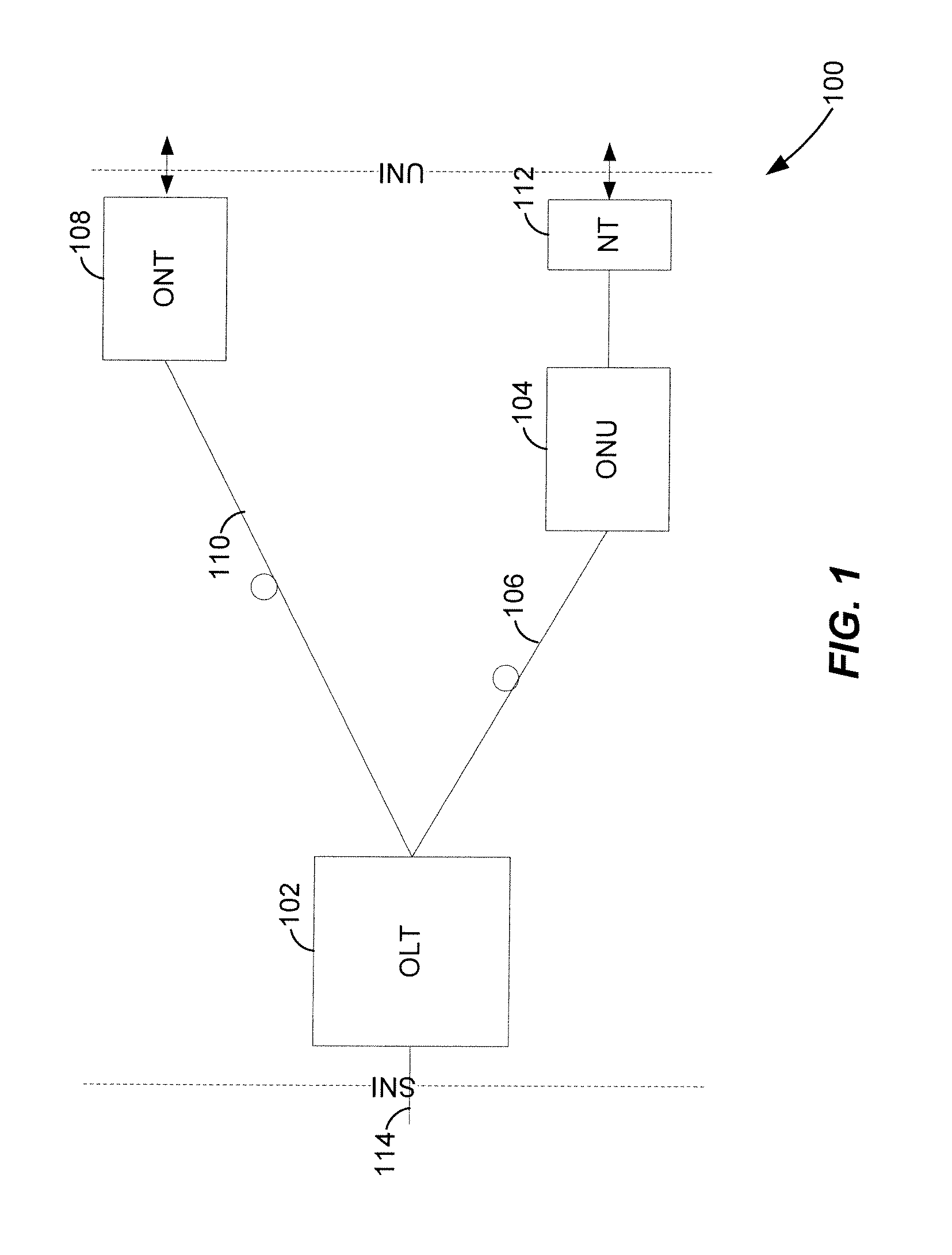

Processing architecture for passive optical network

InactiveUS8718087B1Energy efficient ICTSubstation remote connection/disconnectionNetwork terminationEmbedded system

In a network termination device integrated circuit in a point-to-multipoint network, a receiver receives a downstream transmission from a line termination unit within the point-to-multipoint network, a transmitter transmits an upstream transmission to the line termination unit within the point-to-multipoint network, and an internal processor operatively coupled to the receiver processes sub-fields within the overhead field of the downstream transmission. The internal processor is also operatively coupled to the transmitter to assemble the overhead field of the upstream transmission. The downstream transmission is an downstream transmission convergence frame format having an overhead field and a payload field, and the upstream transmission is an upstream transmission convergence frame format having an overhead field and a payload field.

Owner:MARVELL INT LTD

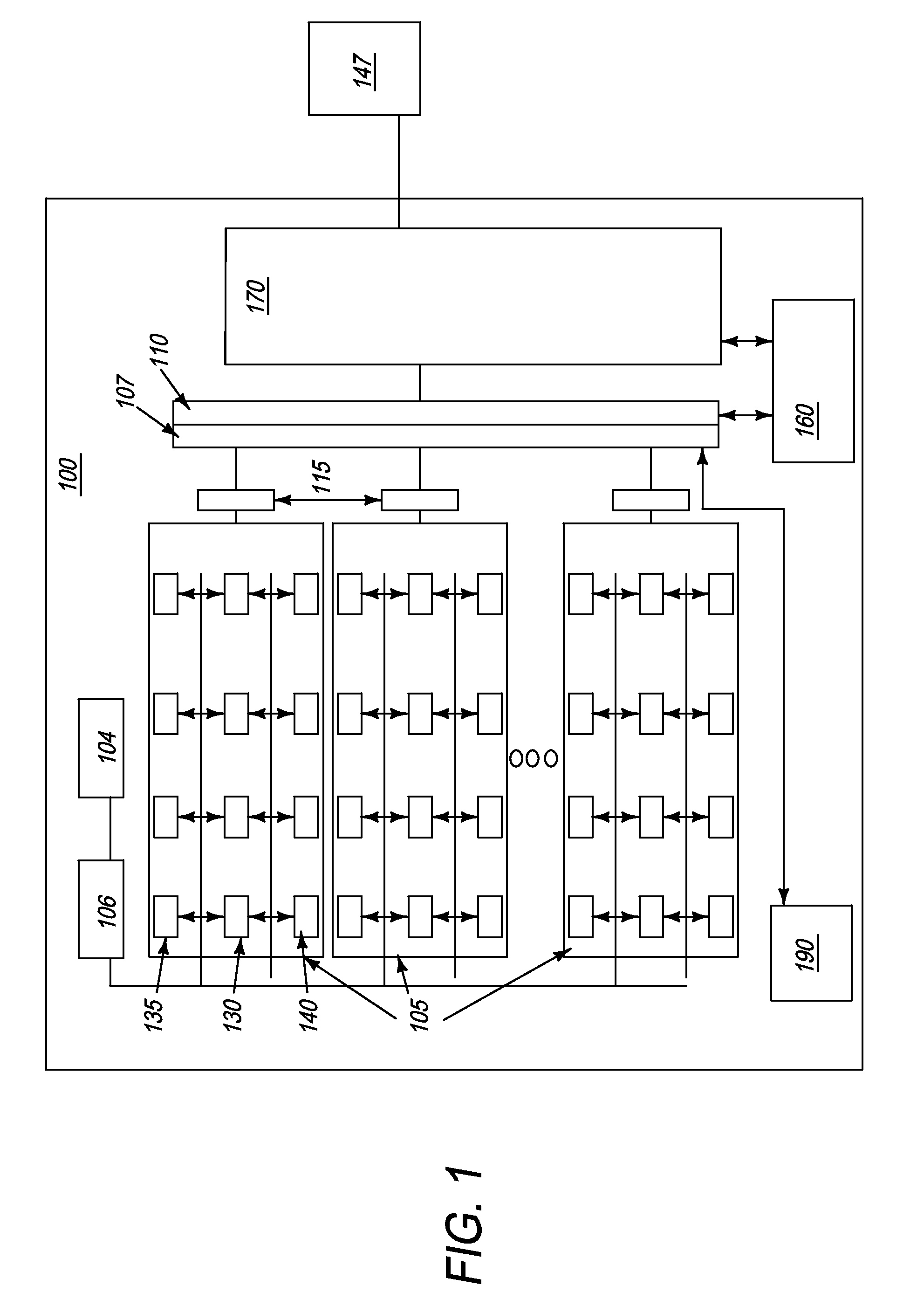

Distributed processing architecture with scalable processing layers

InactiveUS20060287742A1Program initiation/switchingError preventionDirect memory accessParallel computing

The present invention is a system on chip architecture having scalable, distributed processing and memory capabilities through a plurality of processing layers. In a preferred embodiment, a distributed processing layer processor comprises a plurality of processing layers, a processing layer controller, and a central direct memory access controller. The processing layer controller manages the scheduling of tasks and distribution of processing tasks to each processing layer. Within each processing layer, a plurality of pipelined processing units (PUs), specially designed for conducting a defined set of processing tasks, are in communication with a plurality of program memories and data memories. One application of the present invention is in a media gateway that is designed to enable the communication of media across circuit switched and packet switched networks. The hardware system architecture of the said novel gateway is comprised of a plurality of DPLPs, referred to as Media Engines that are interconnected with a Host Processor or Packet Engine, which, in turn, is in communication with interfaces to networks. Each of the PUs within the processing layers of the Media Engines are specially designed to perform a class of media processing specific tasks, such as line echo cancellation, encoding or decoding data, or tone signaling.

Owner:QUARTICS

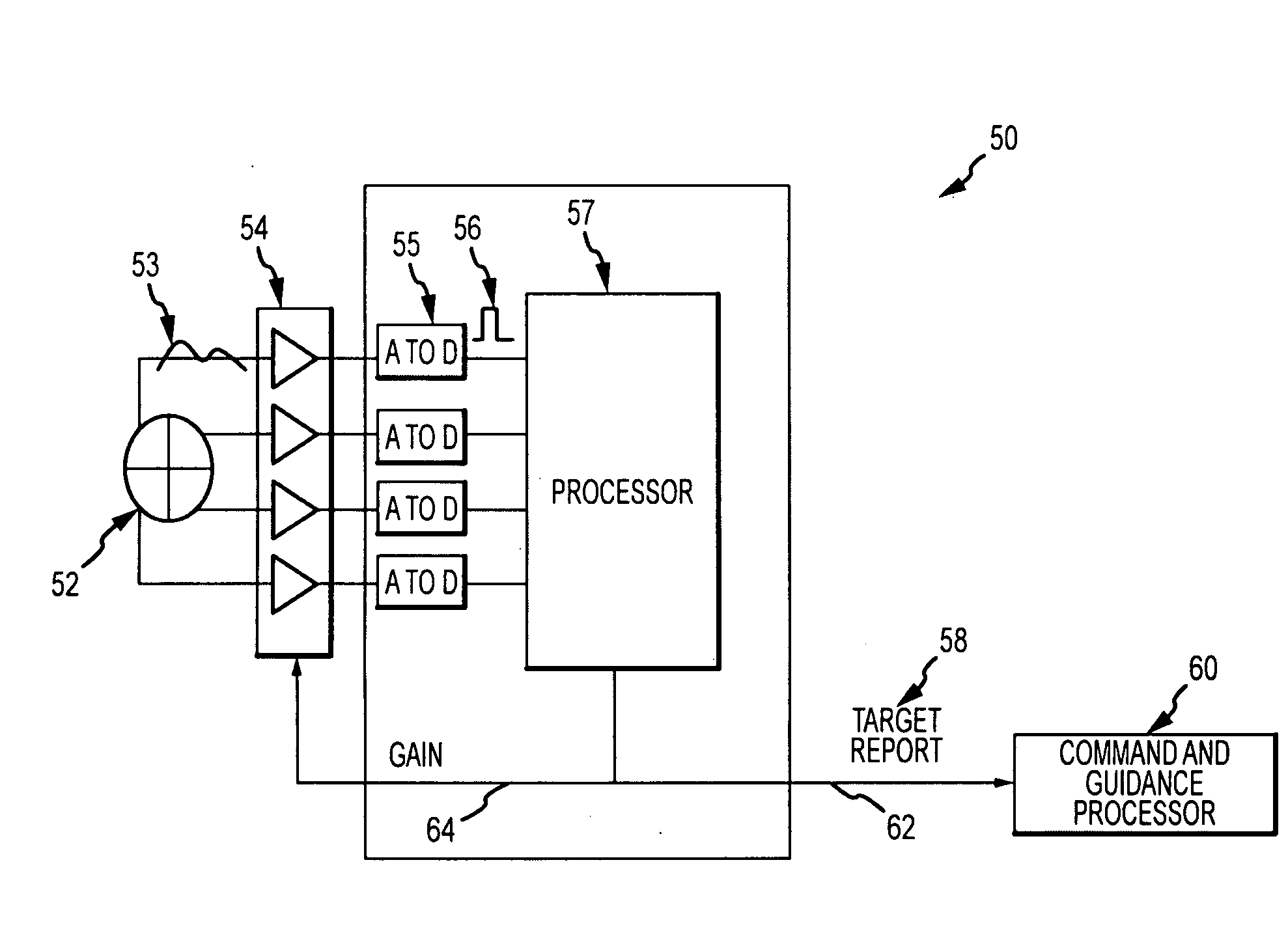

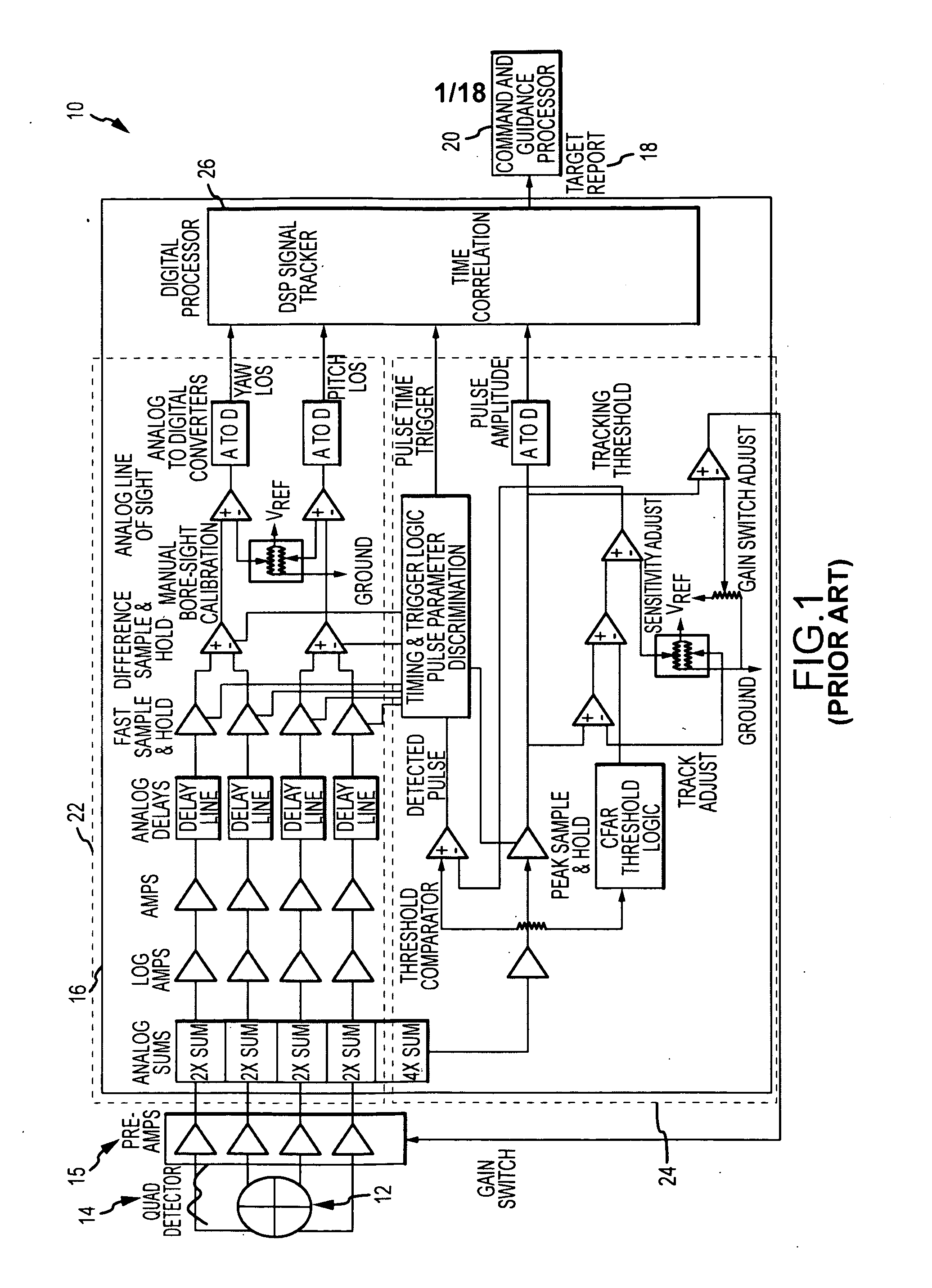

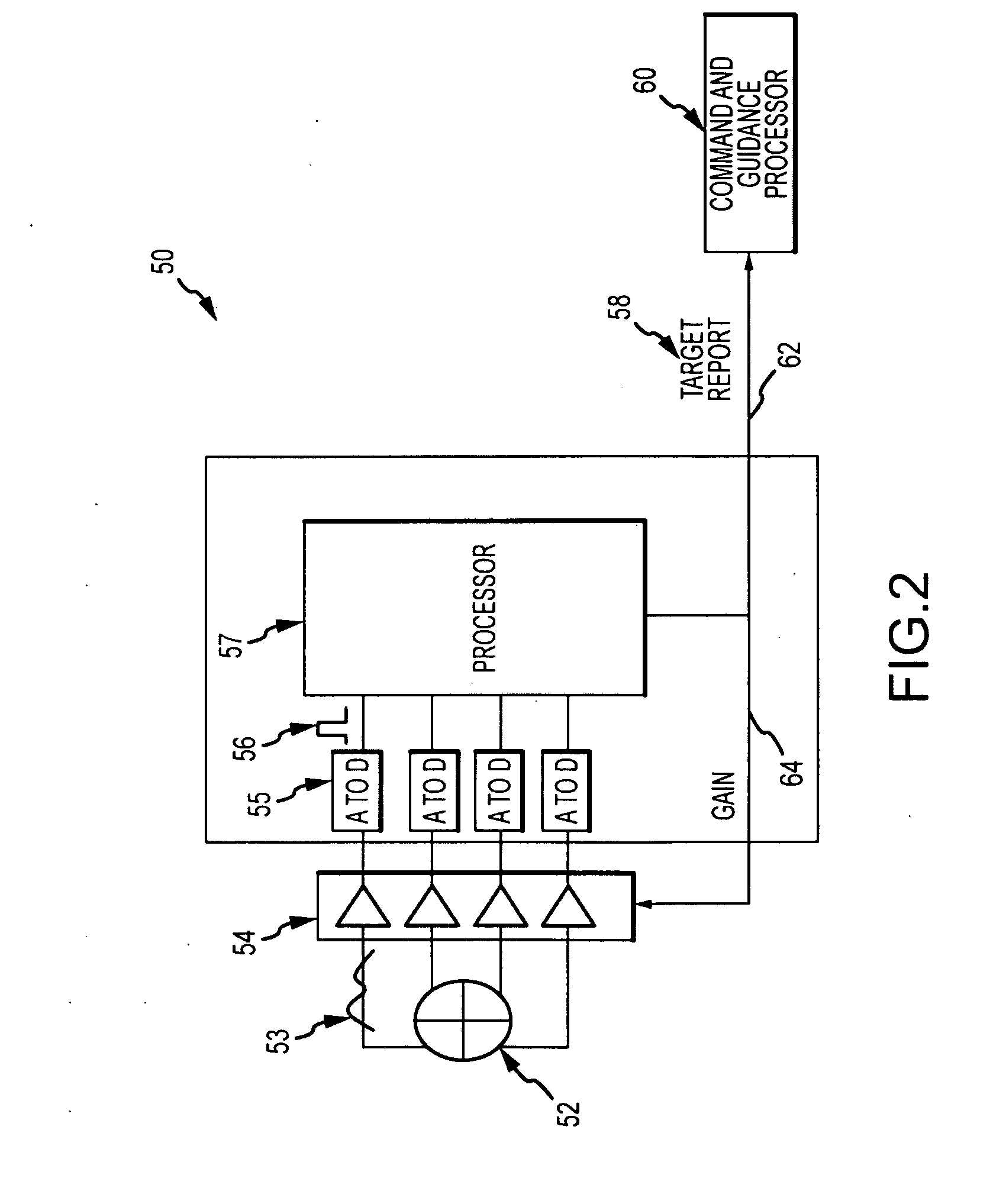

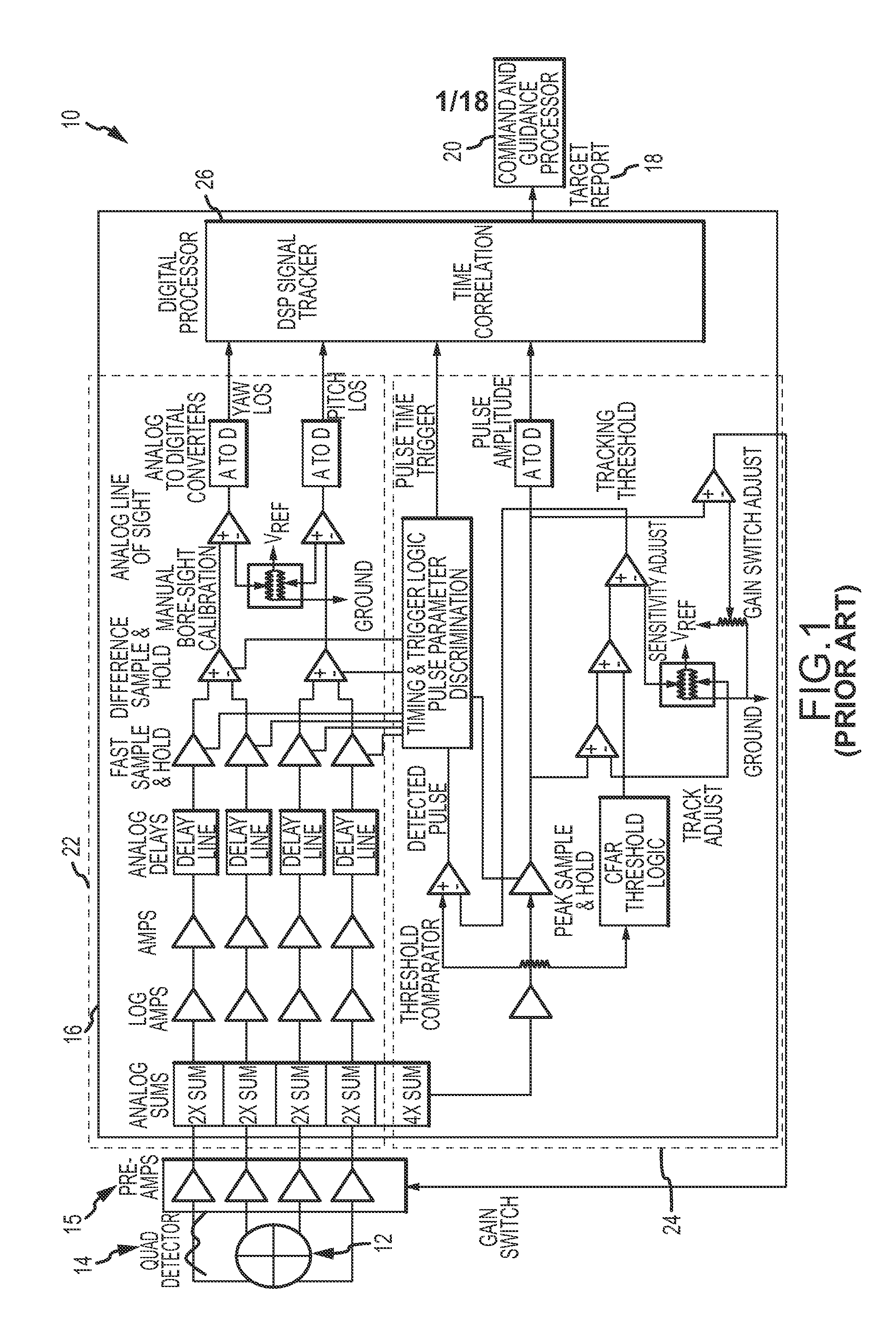

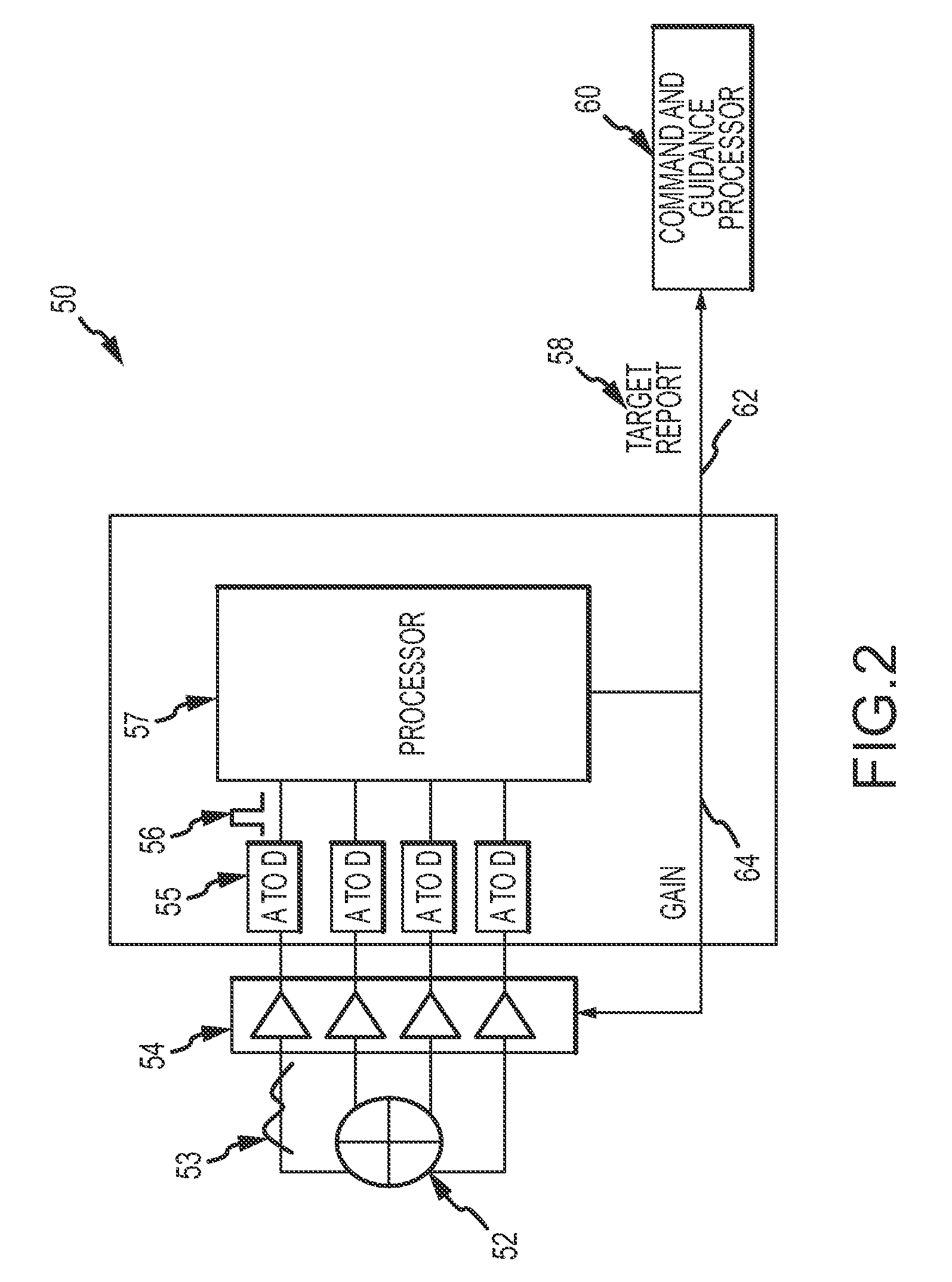

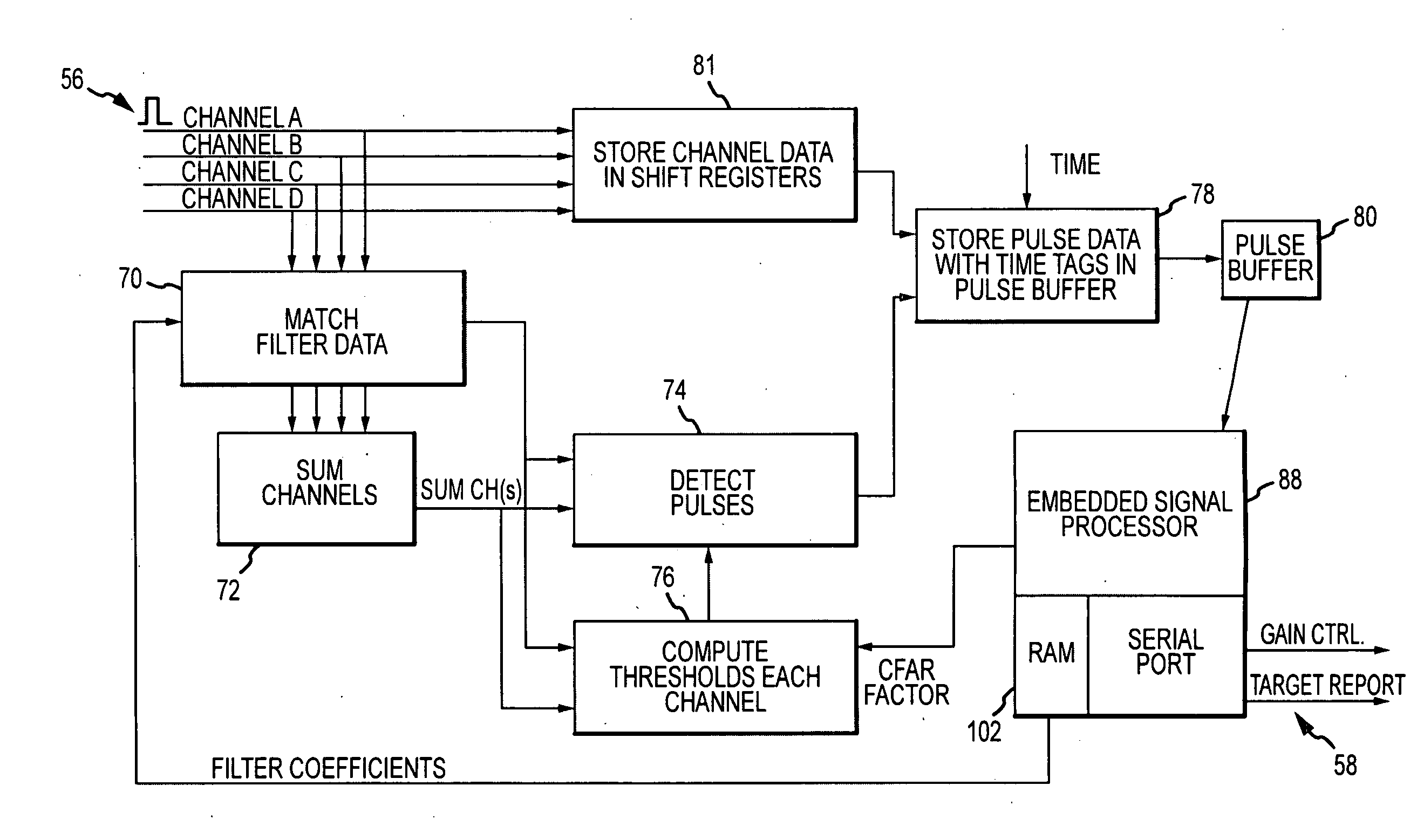

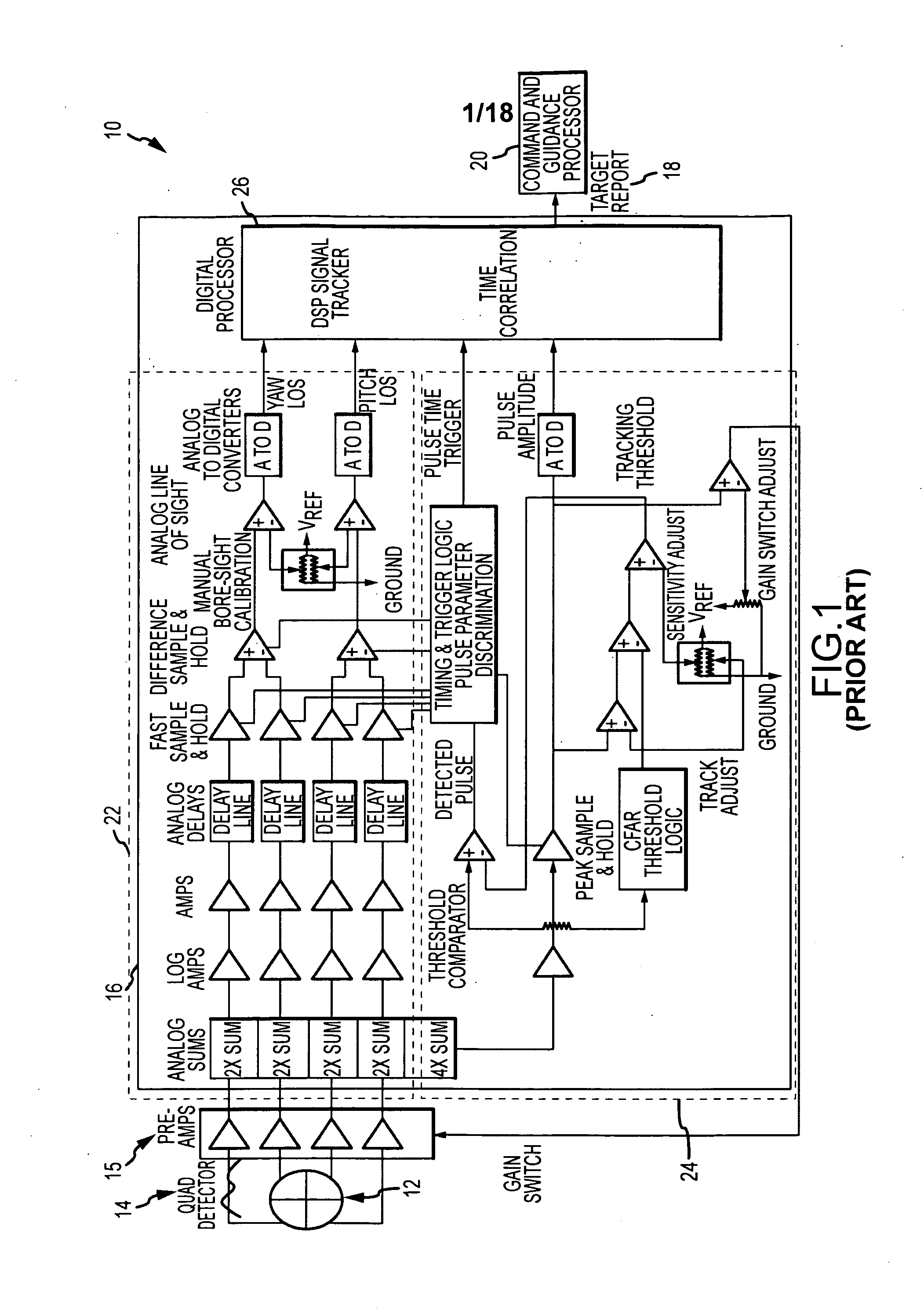

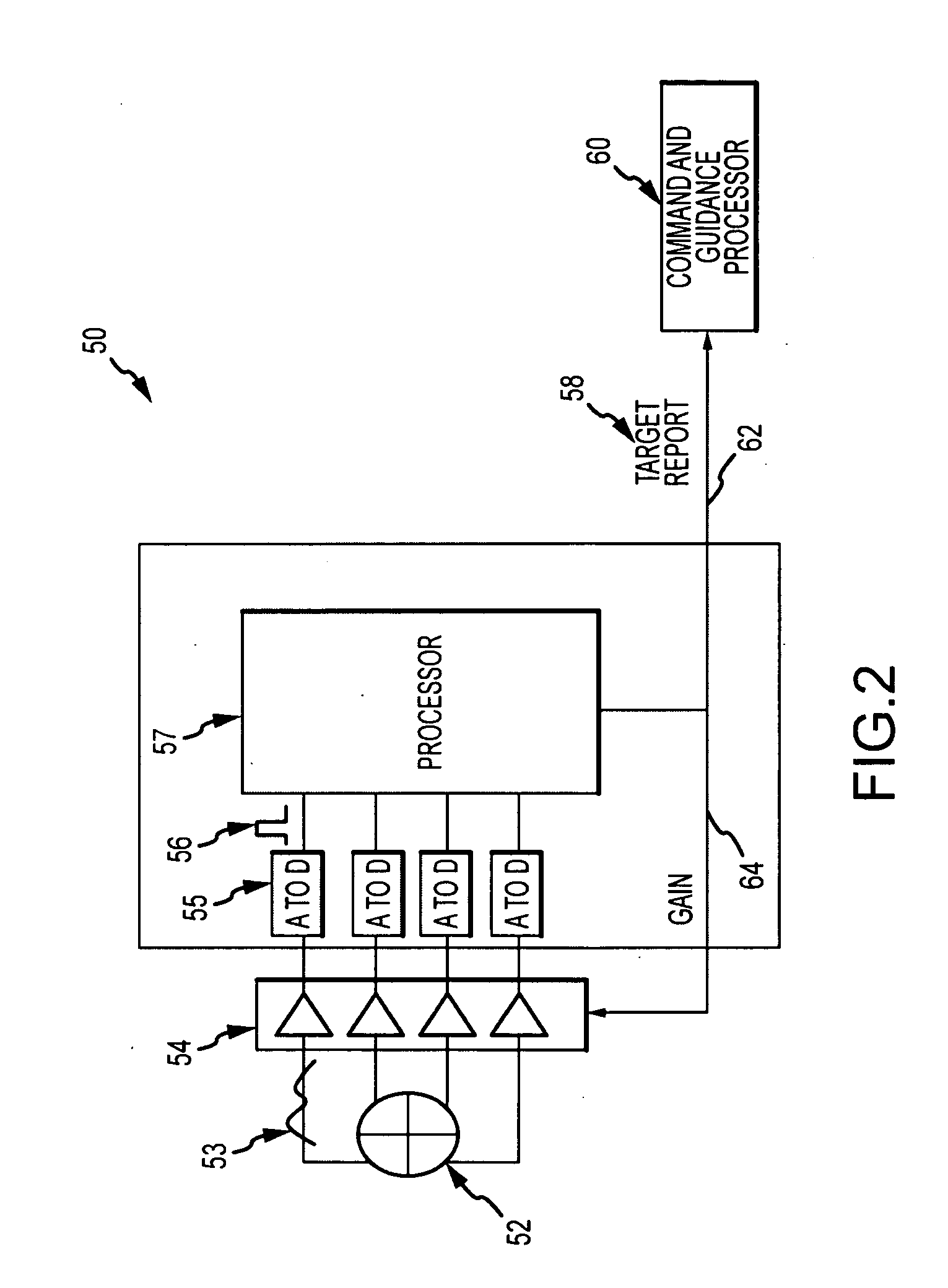

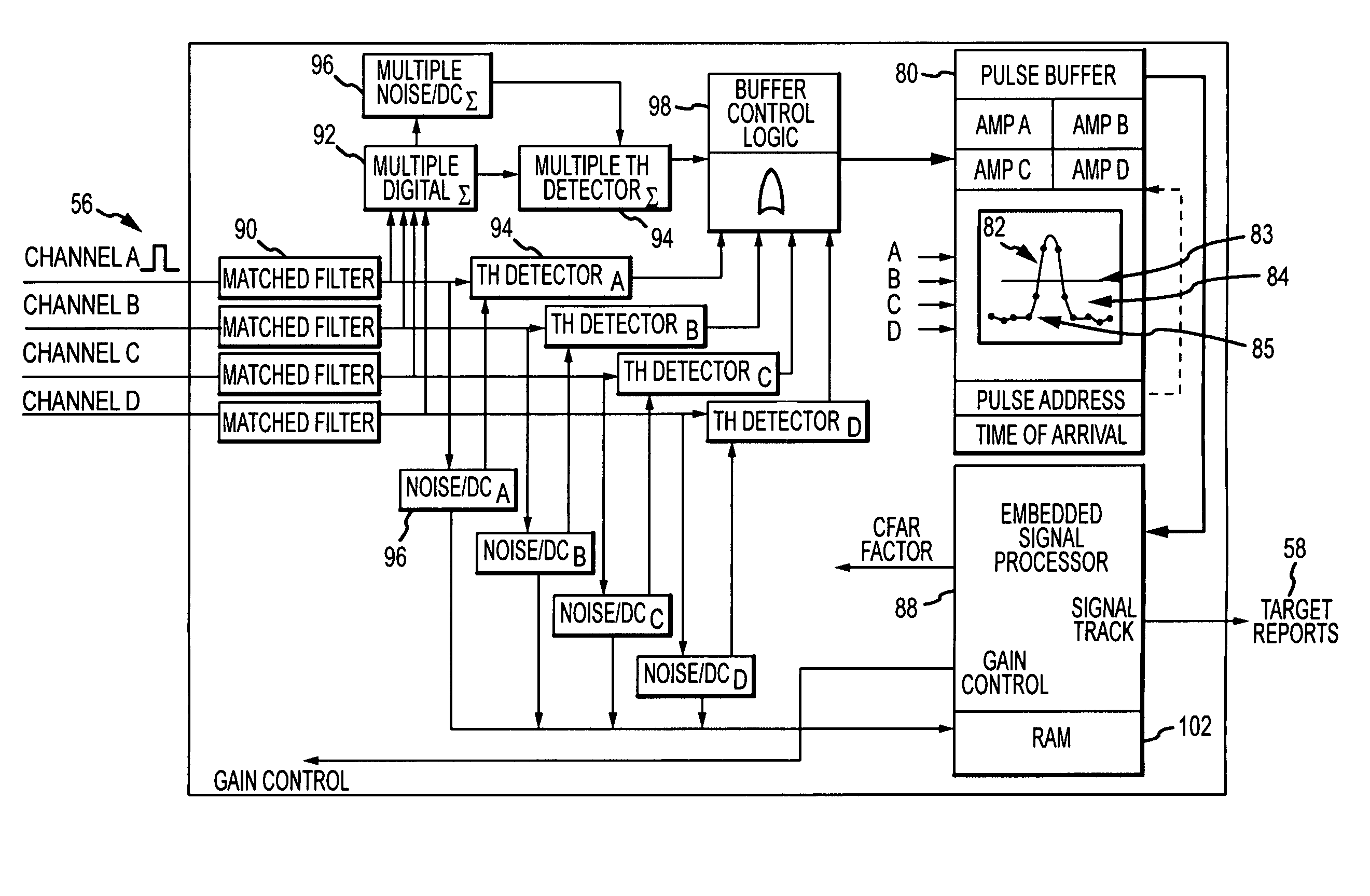

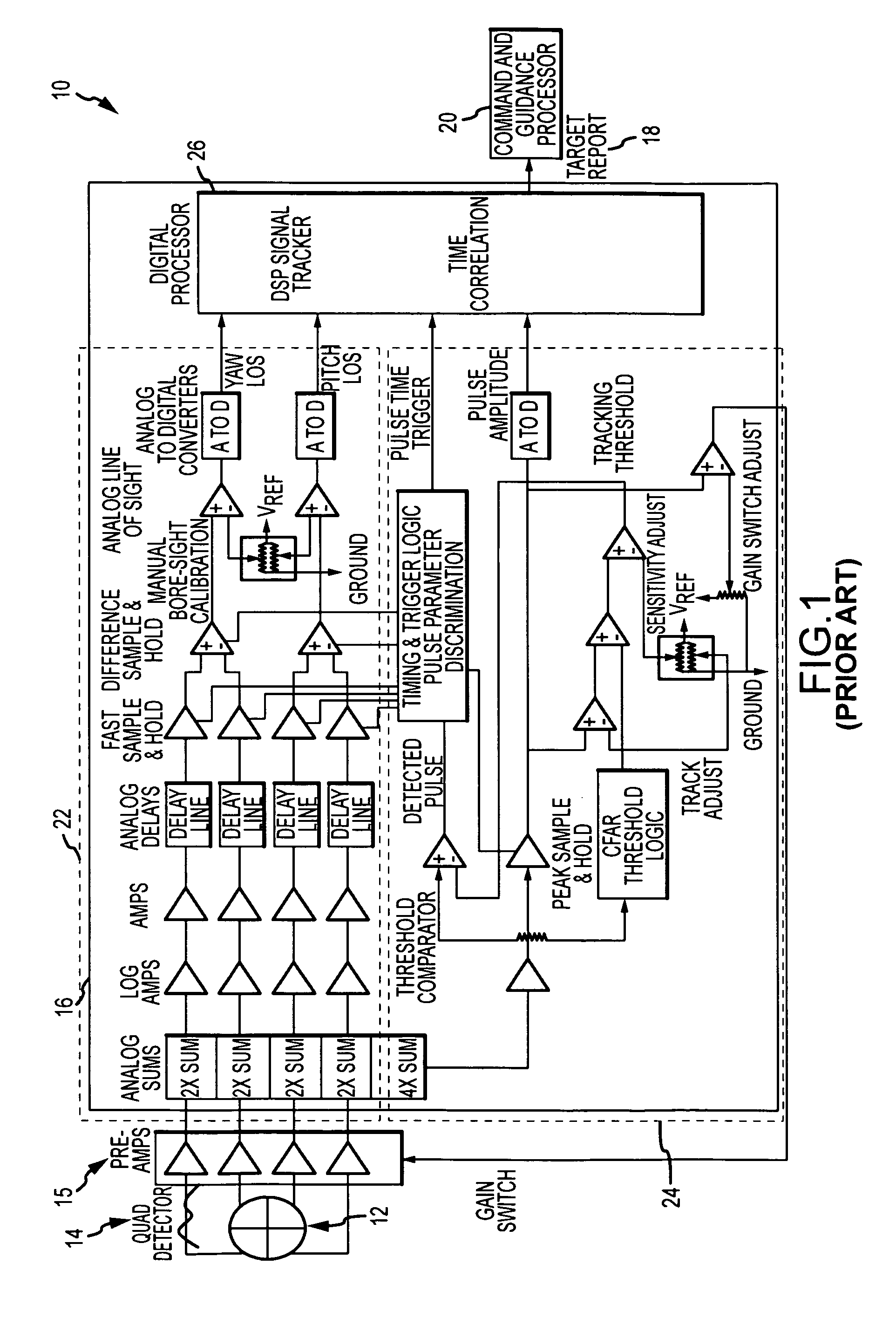

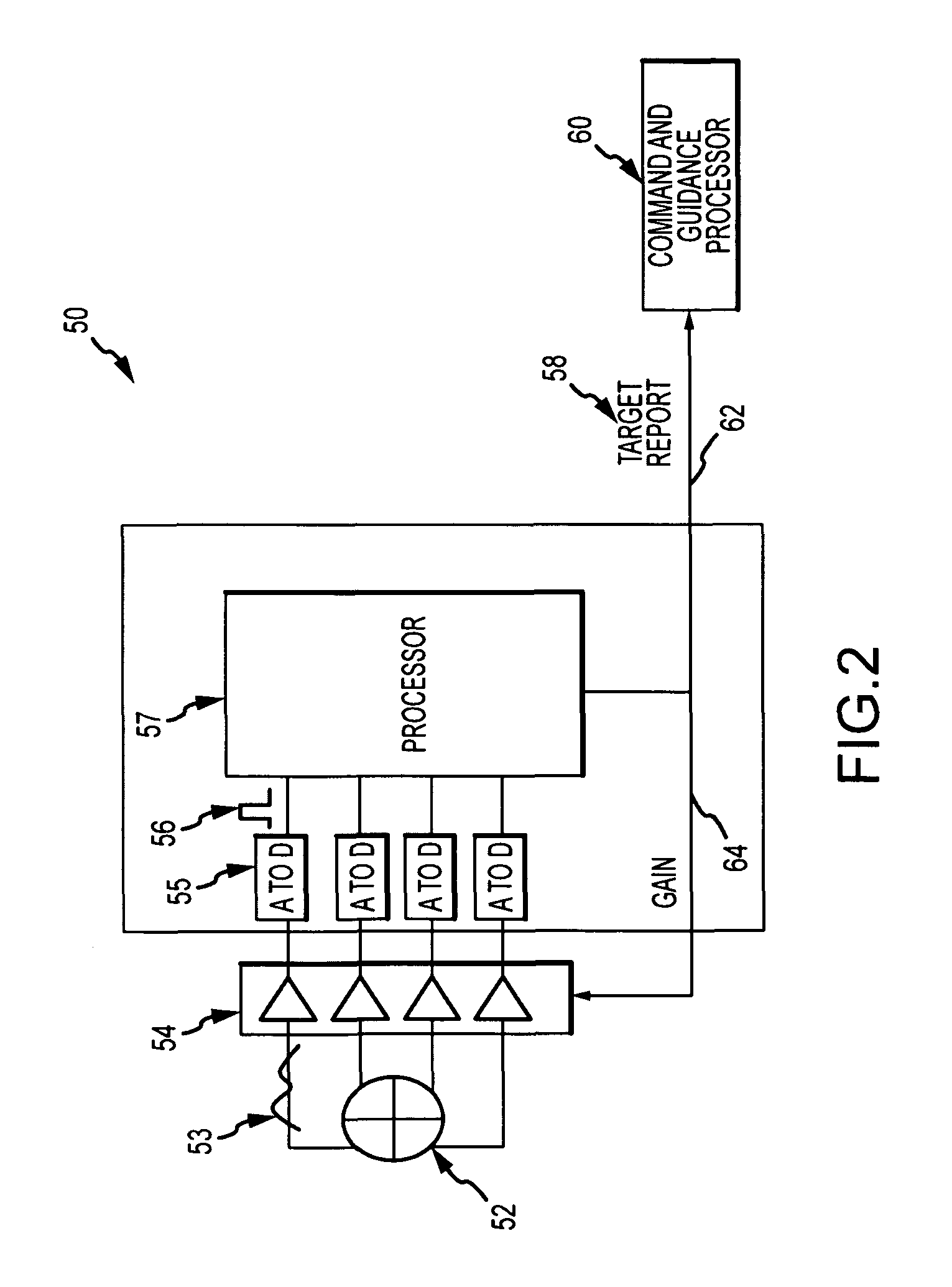

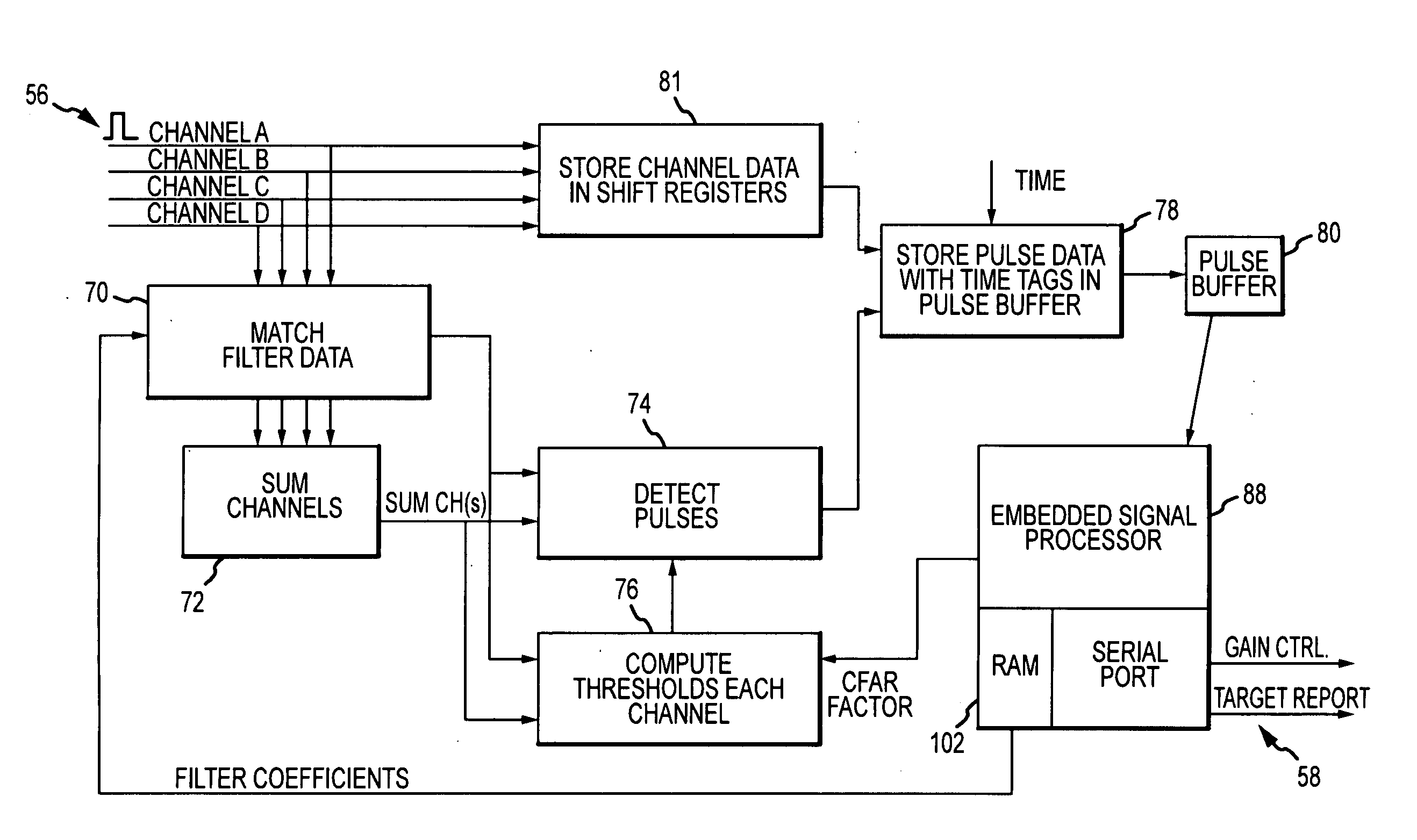

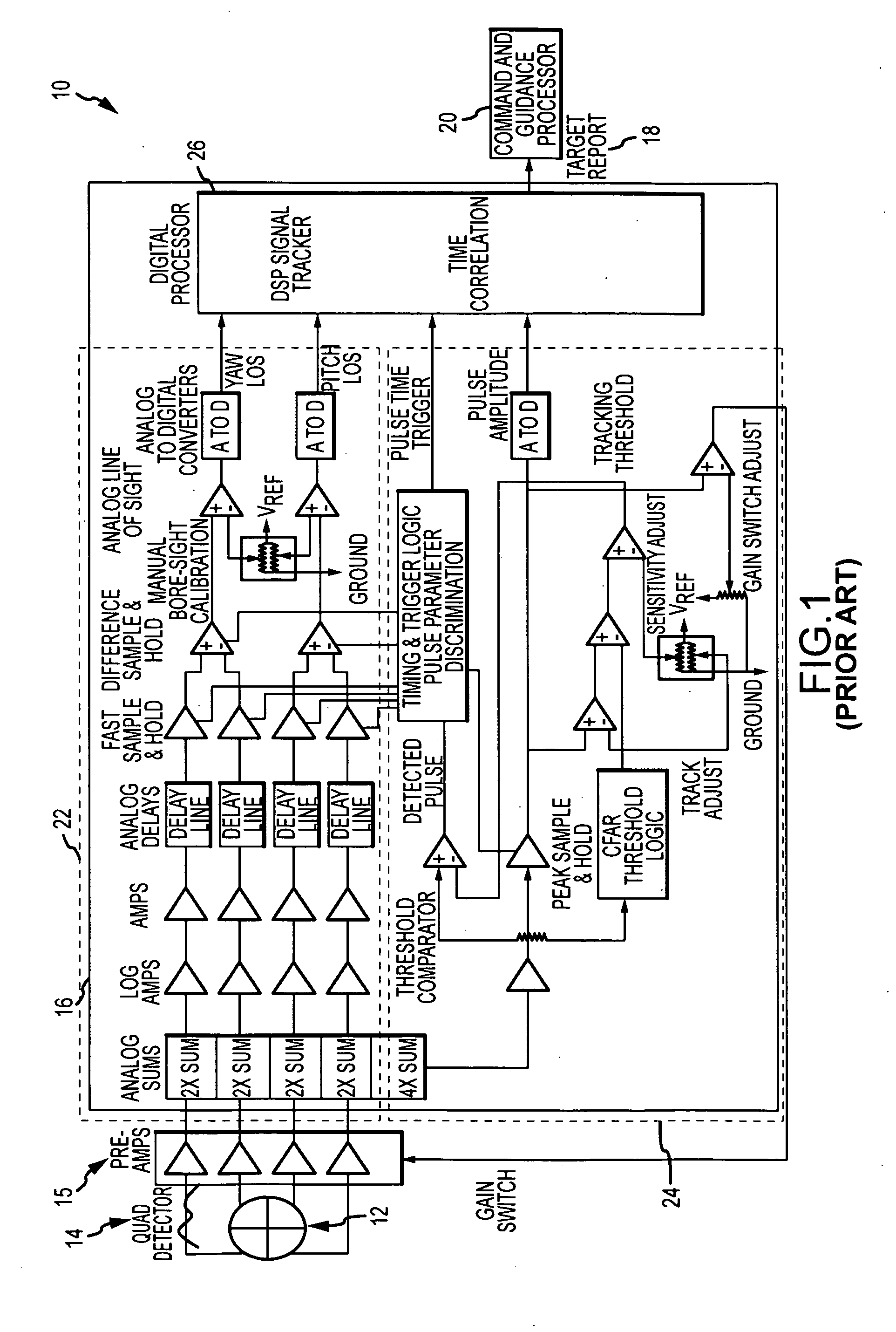

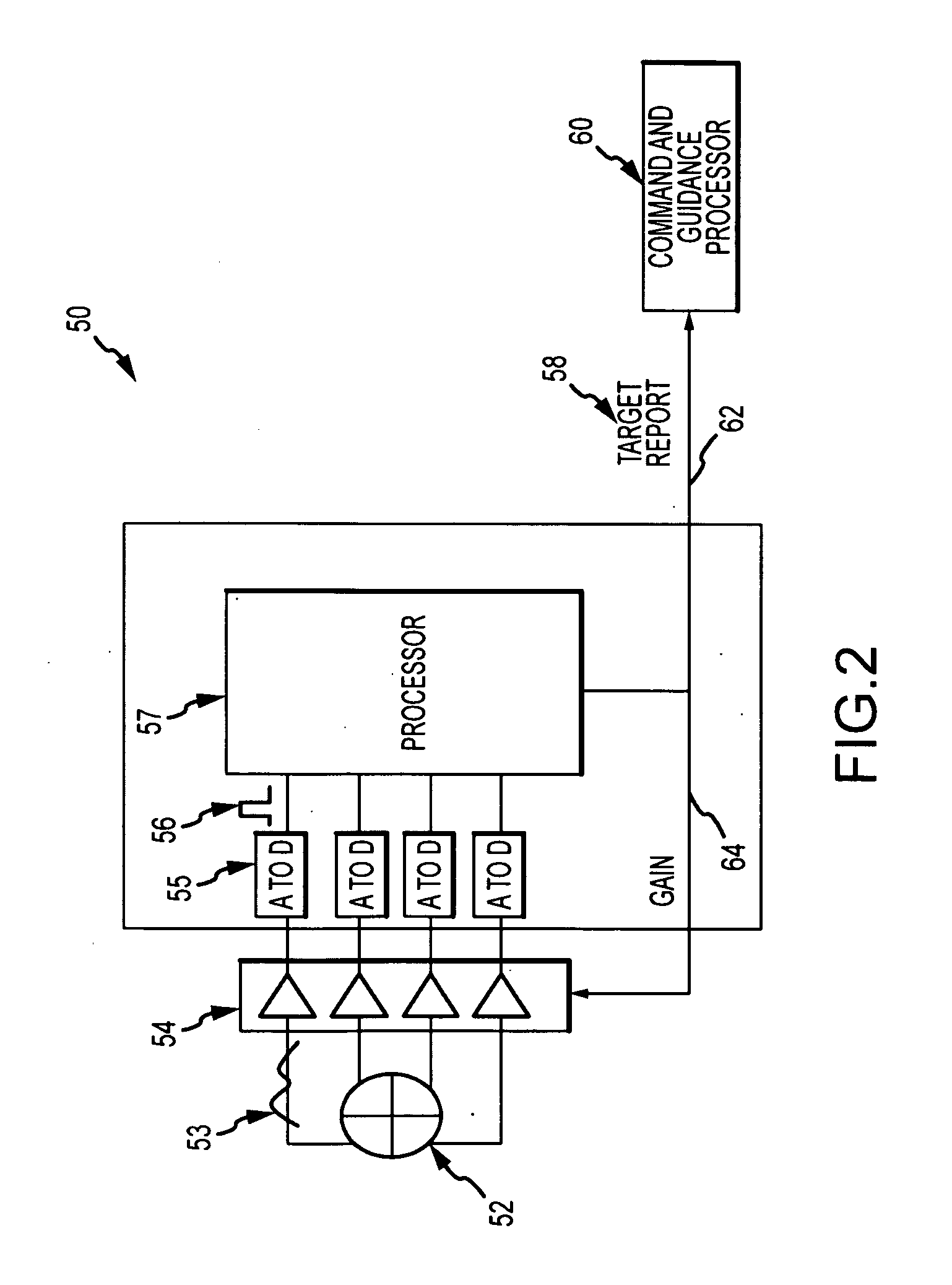

Enhanced countermeasures for all-digital line-of-sight (LOS) processor

ActiveUS20100067608A1Improved pulse detectionSmall sizeDirection controllersModulated-carrier systemsSemi activeWide field

An all-digital line-of-sight (LOS) process architecture addresses the size, weight, power and performance constraints of a receiver for use in semi-active or active pulsed electromagnetic (EM) targeting systems. The all-digital architecture provides a platform for enhanced techniques for sensitive pulse detection over a wide field-of-view, adaptive pulse detection, LOS processing and counter measures.

Owner:RAYTHEON CO

All-digital line-of-sight (LOS) processor architecture

ActiveUS20100066597A1Improved pulse detectionSmall sizeDirection findersElectromagnetic wave reradiationSemi activeWide field

An all-digital line-of-sight (LOS) process architecture addresses the size, weight, power and performance constraints of a receiver for use in semi-active or active pulsed electromagnetic (EM) targeting systems. The all-digital architecture provides a platform for enhanced techniques for sensitive pulse detection over a wide field-of-view, adaptive pulse detection, LOS processing and counter measures.

Owner:RAYTHEON CO

Agent interworking protocol and call processing architecture for a communications system

InactiveUSH1941H1Software engineeringMultiprogramming arrangementsCommunications systemProtocol for Carrying Authentication for Network Access

A call processing architecture treats a call connection as having two halves an originating half and a terminating half. An agent is associated with each call half, the originating agent being assigned by a switching center of a telecommunications system to establish the originating half of a call. The originating agent interacts with a translator and router to process the dated digits for a call to route the call to a terminating agent, the terminating agent establishing the terminating half of the call to complete the call connection. An agent interworking protocol (AIP) provides a generic superset protocol containing the common elements and unique elements for all call types so that an originating agent converts its call messages to the AIP and is connected to a terminating agent via an AIP connector, the terminating agent converting the AIP formatted call messages to the native protocol of the terminating agent. Agents for different call types are each able to convert call messages to or translate call messages from the agents's unique protocol to the AIP format and each type of agent does not need to know the type of agent being connected to as communication with other agents is via the AIP.

Owner:DSCCELCORE

Internal control management system capable of applying response type shared application architecture

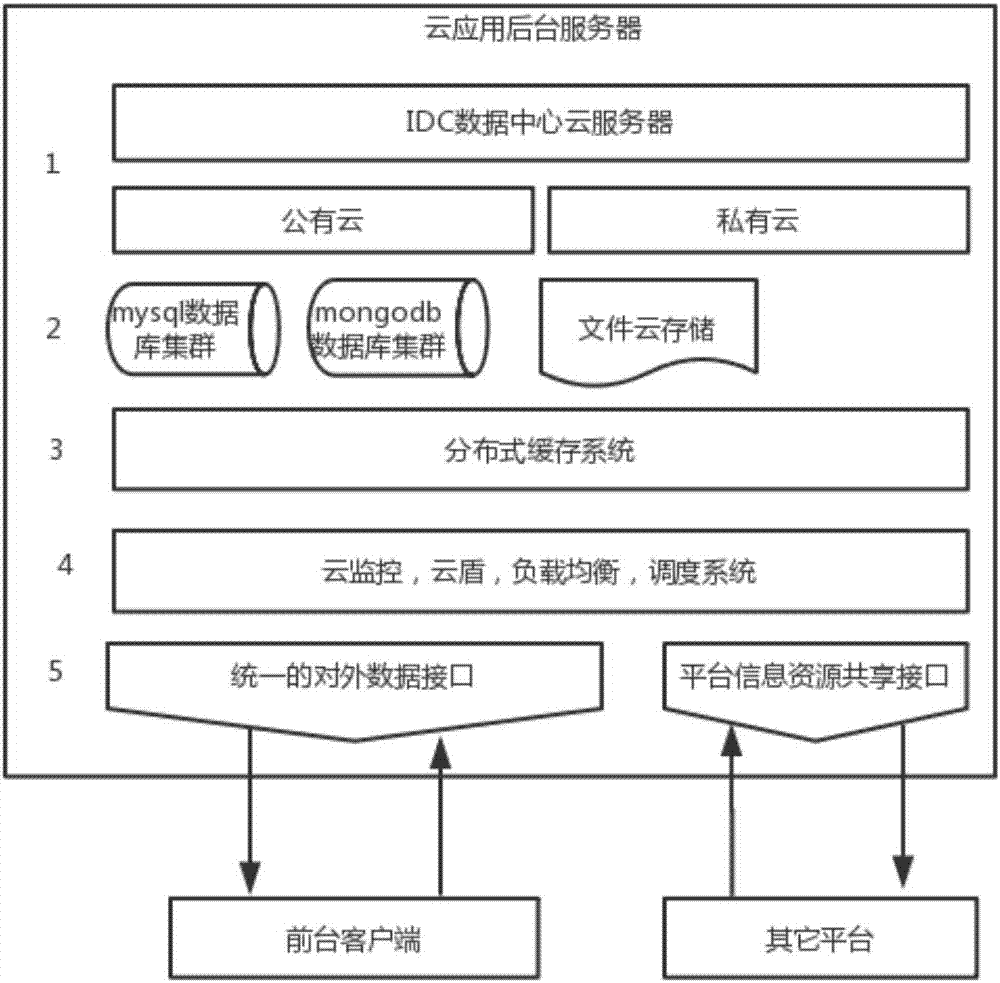

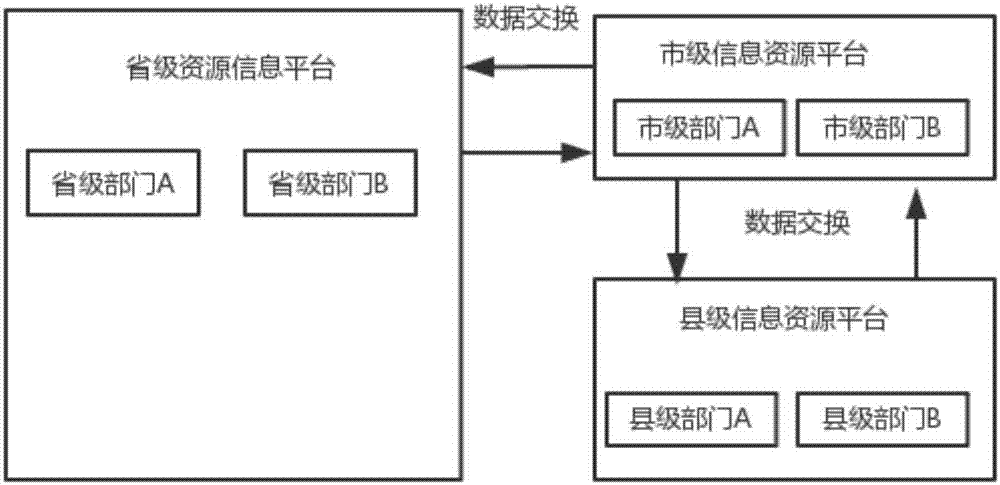

ActiveCN107301048AEasy to controlEnsure safetySoftware designSpecific program execution arrangementsApplication serverProcess architecture

The invention puts forward an internal control management system capable of applying response type shared application architecture so as to carry out standardized processing on business selection, process selection, risk point selection and risk control measure suggestion through the definition and the modeling of basic process architecture on the basis of taking the clear responsibility of organization structures, departments and posts as a basis. The internal control management system comprises an application server side and a Web application front side, wherein the application server side and the Web application front side are communicated; the application server side comprises an IDC (Internet Content Provider) data center cloud server, a database cluster, a distributed cache system, a safety management and internal scheduling system and a data processing and application interface system; and the Web application front side comprises a data storage system, a data model system, a route control and Template rendering system and a response type page system. By use of the system, a uniform dedicated cloud and big data platform is constructed to realize uniform resource pooling, all government departments of the platform resource pool can share resources, and platform resources are utilized to a maximum degree.

Owner:北京中泰合信管理顾问有限公司 +1

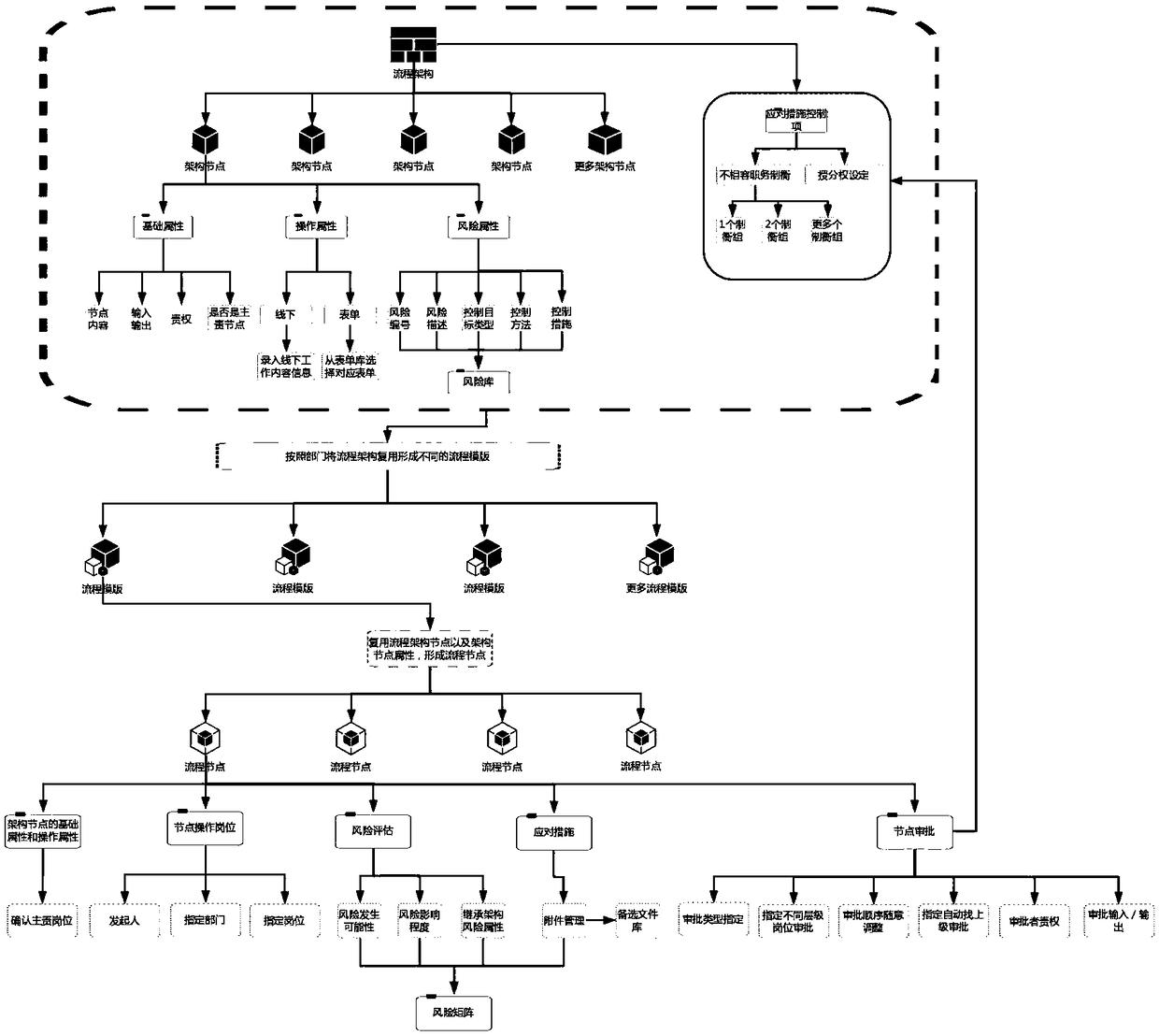

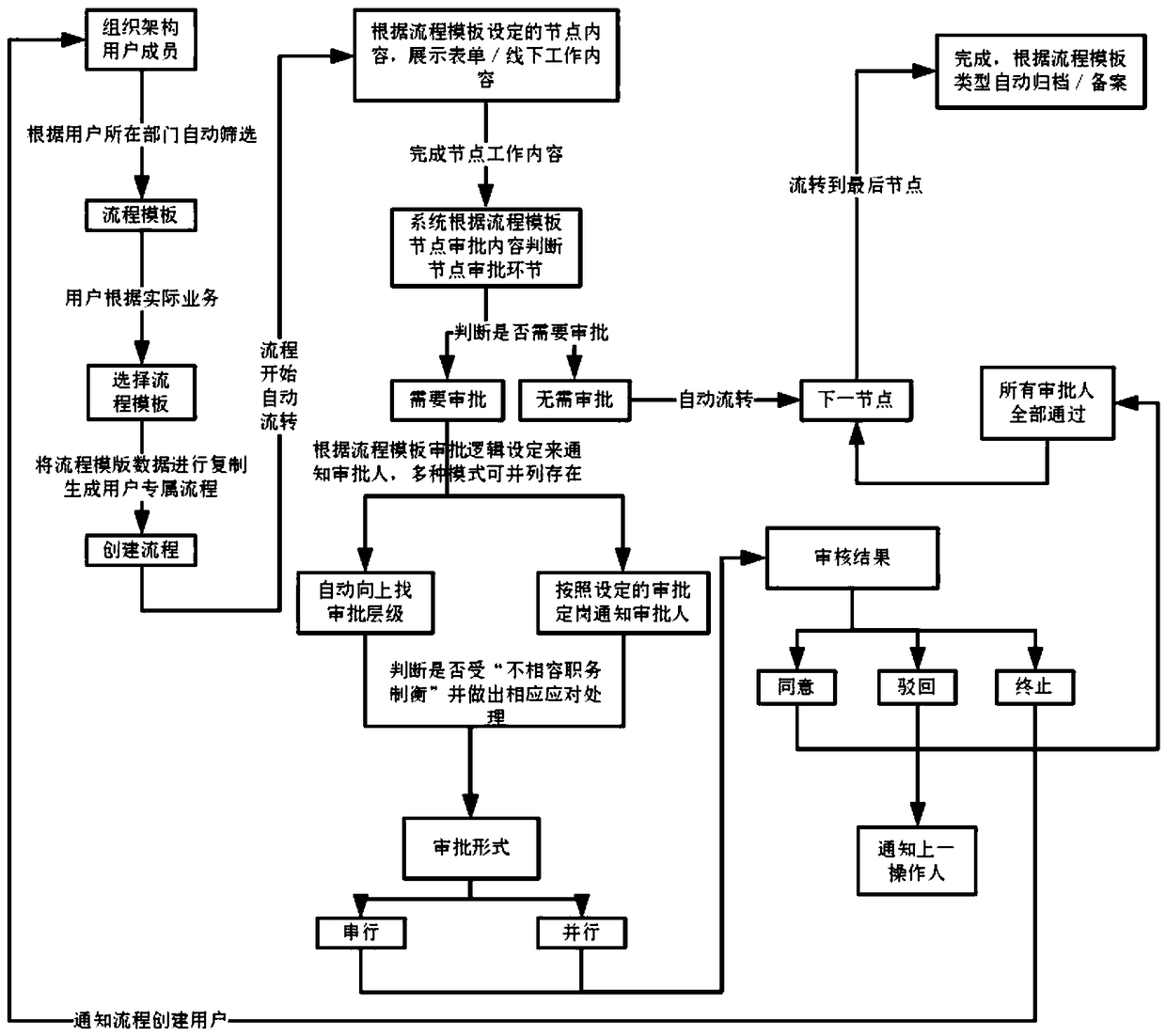

An internal control system management method with a process structure as a core

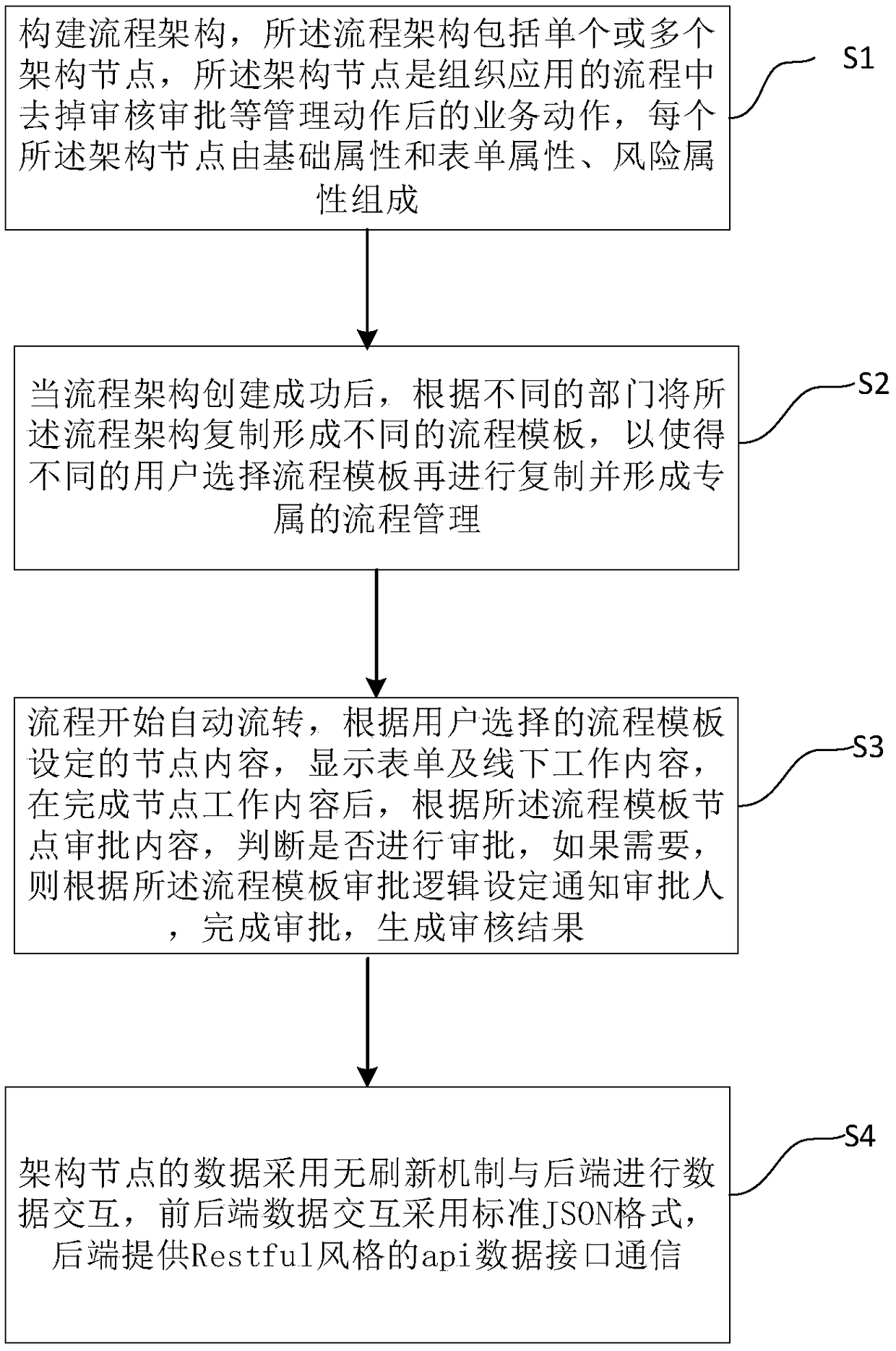

InactiveCN109034602AQuick buildFast implementation of constructionResourcesSystems managementWork content

The invention provides an internal control system management method with a process structure as a core, which includes: constructing a process architecture, wherein the process architecture includes single or multiple architecture nodes, the architecture node is the business action after the management actions such as approval and approval are removed from the process of organization application,and each architecture node is composed of basic attribute, form attribute and risk attribute; when the process architecture is created successfully, copying the process architecture into different process templates according to different departments, so that different users can select the process templates to copy and form the proprietary process management; The process starts to flow automatically. After completing the work content of the node, whether to approve or not is judged according to the approval content of the process template node. The data of the architecture node is exchanged with the back-end by using no-refresh mechanism. The invention realizes the combination of process management and internal control management in software, realizes the management duplication quickly, andsimplifies the examination and approval process.

Owner:北京中泰合信管理顾问有限公司 +1

Enhanced line-of-sight (LOS) processing for all-digital los processor

ActiveUS20100066596A1Improved pulse detectionSmall sizeDirection controllersOptical rangefindersSemi activeCountermeasure

An all-digital line-of-sight (LOS) process architecture addresses the size, weight, power and performance constraints of a receiver for use in semi-active or active pulsed electromagnetic (EM) targeting systems. The all-digital architecture provides a platform for enhanced techniques for sensitive pulse detection over a wide field-of-view, adaptive pulse detection, LOS processing and counter measures.

Owner:RAYTHEON CO

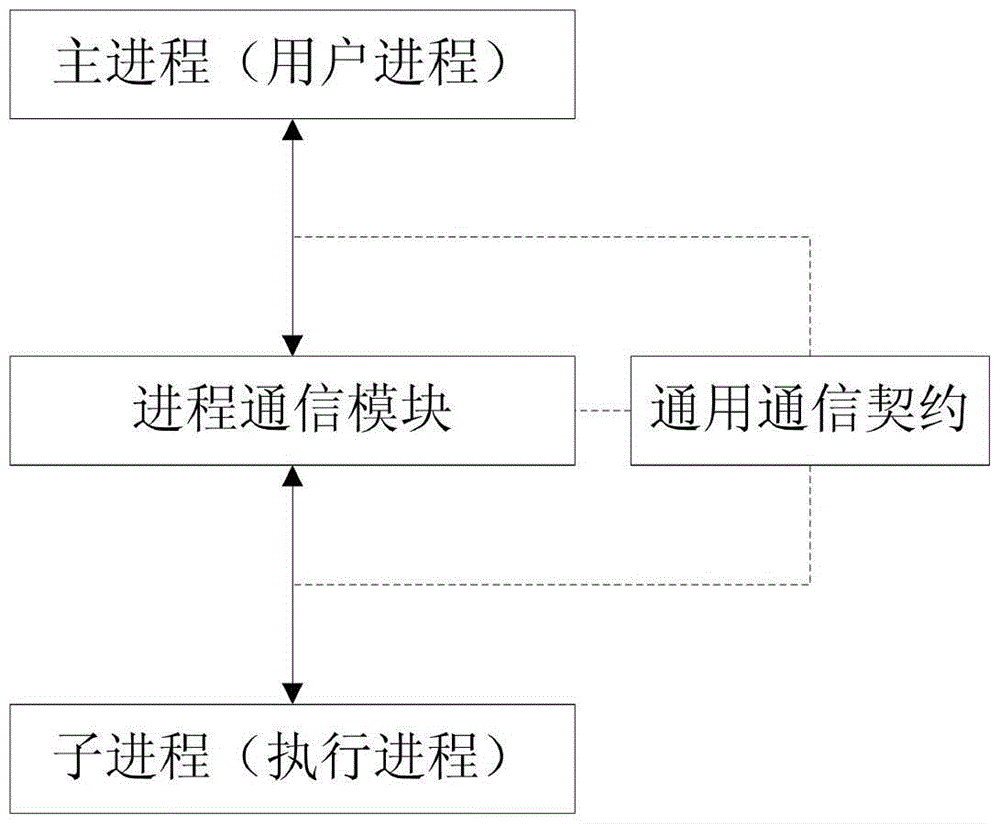

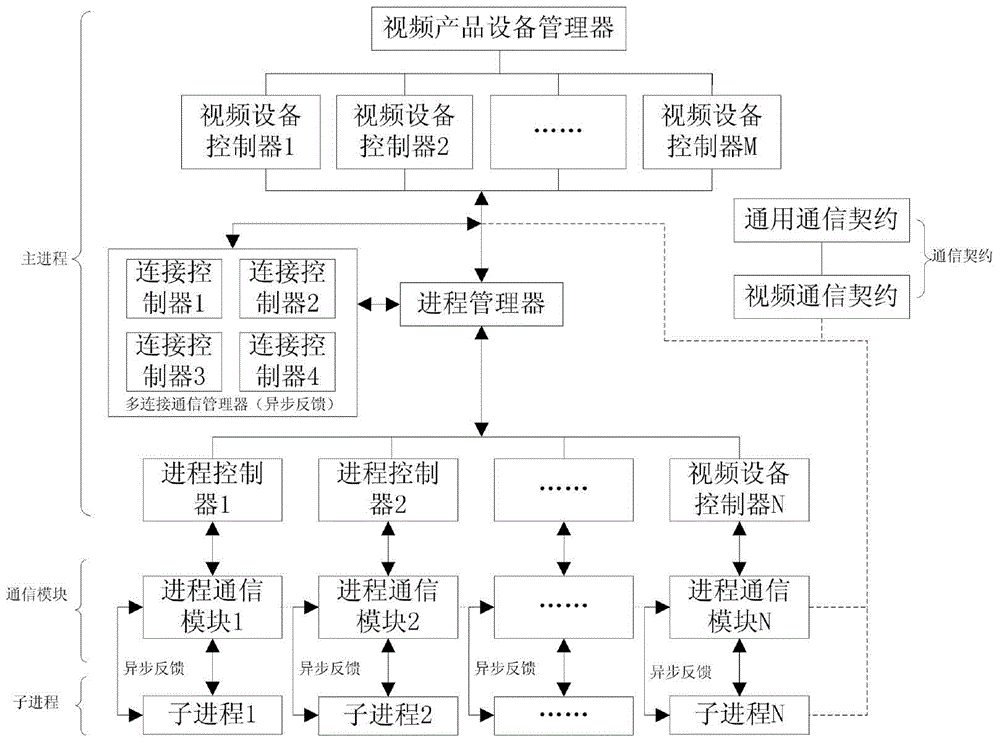

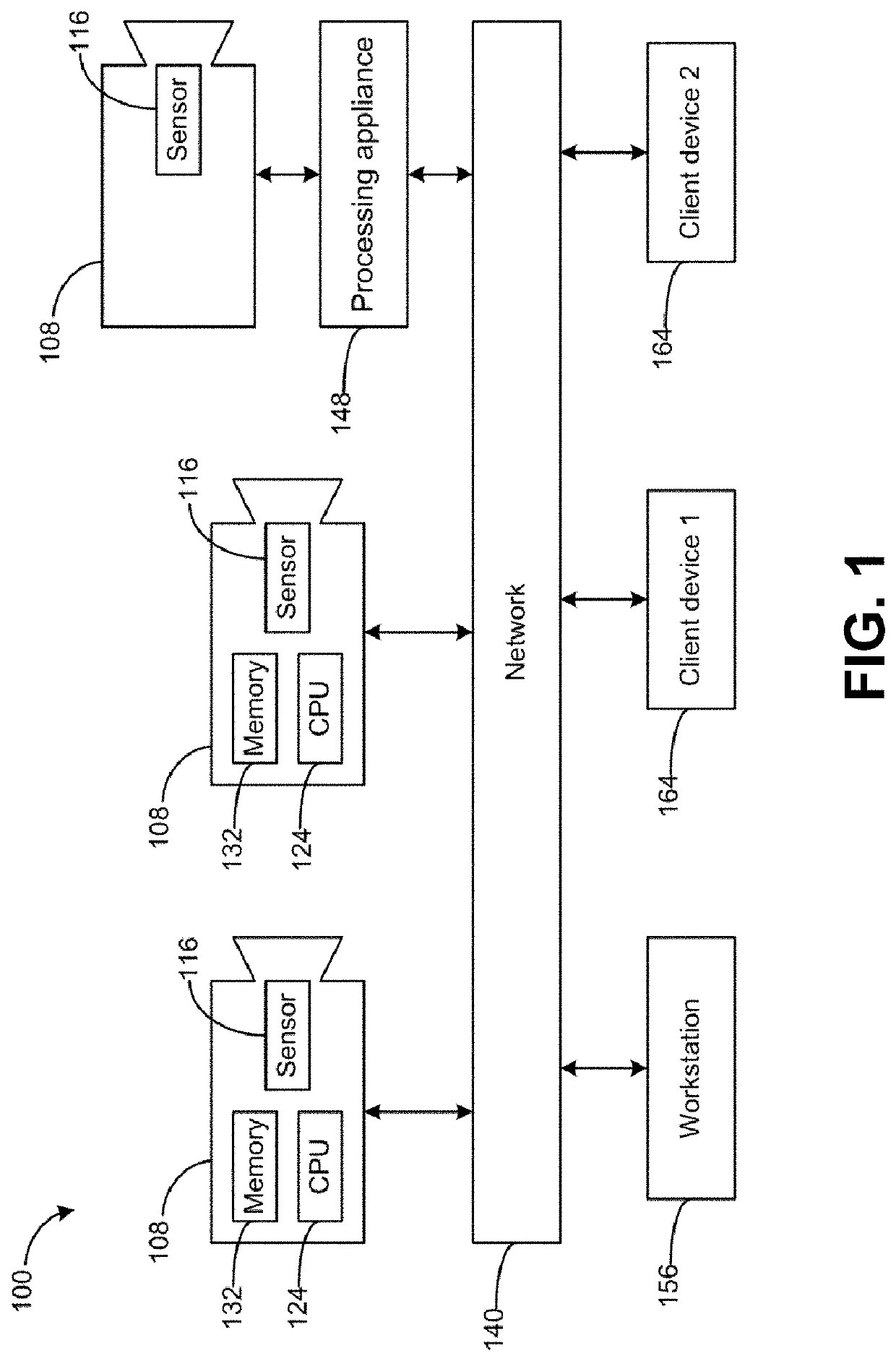

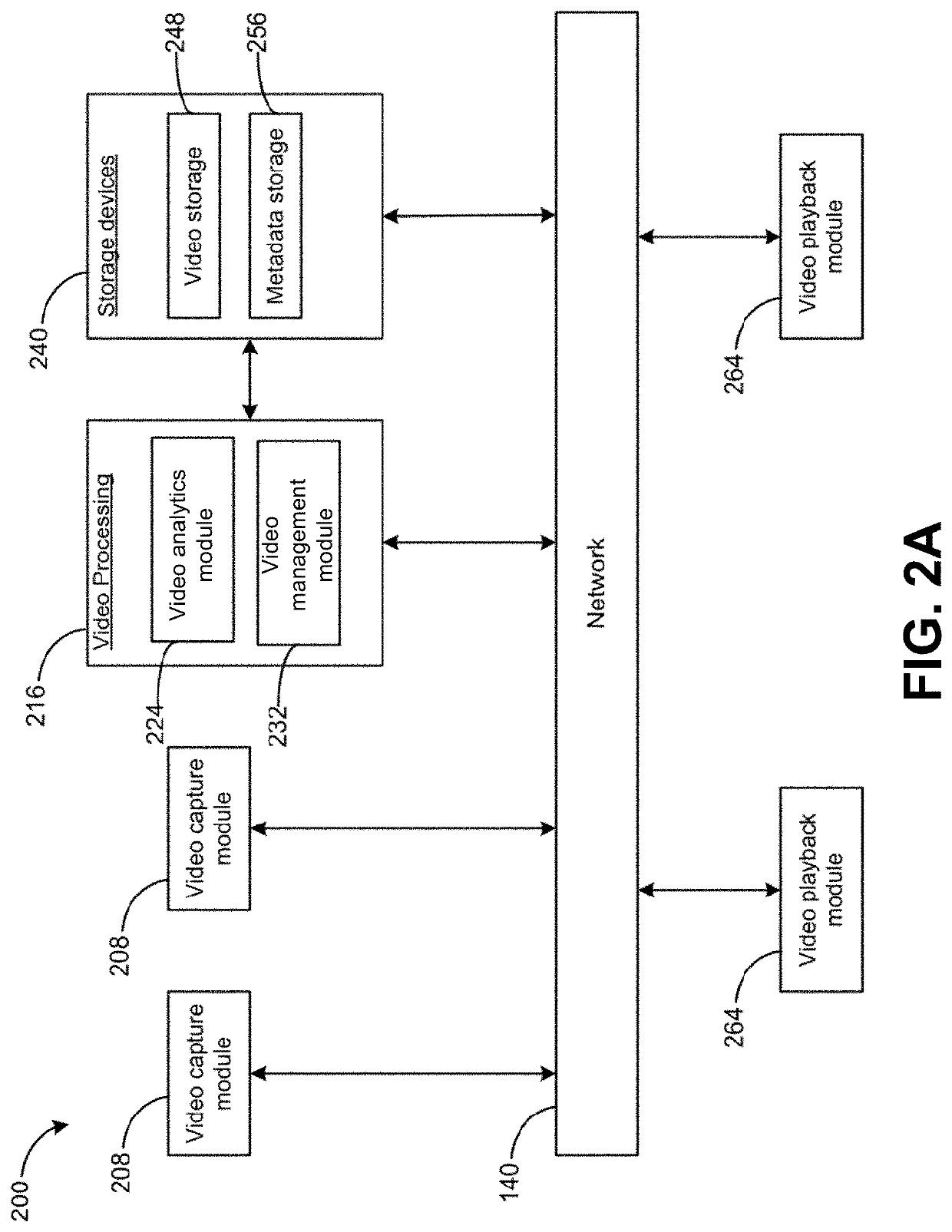

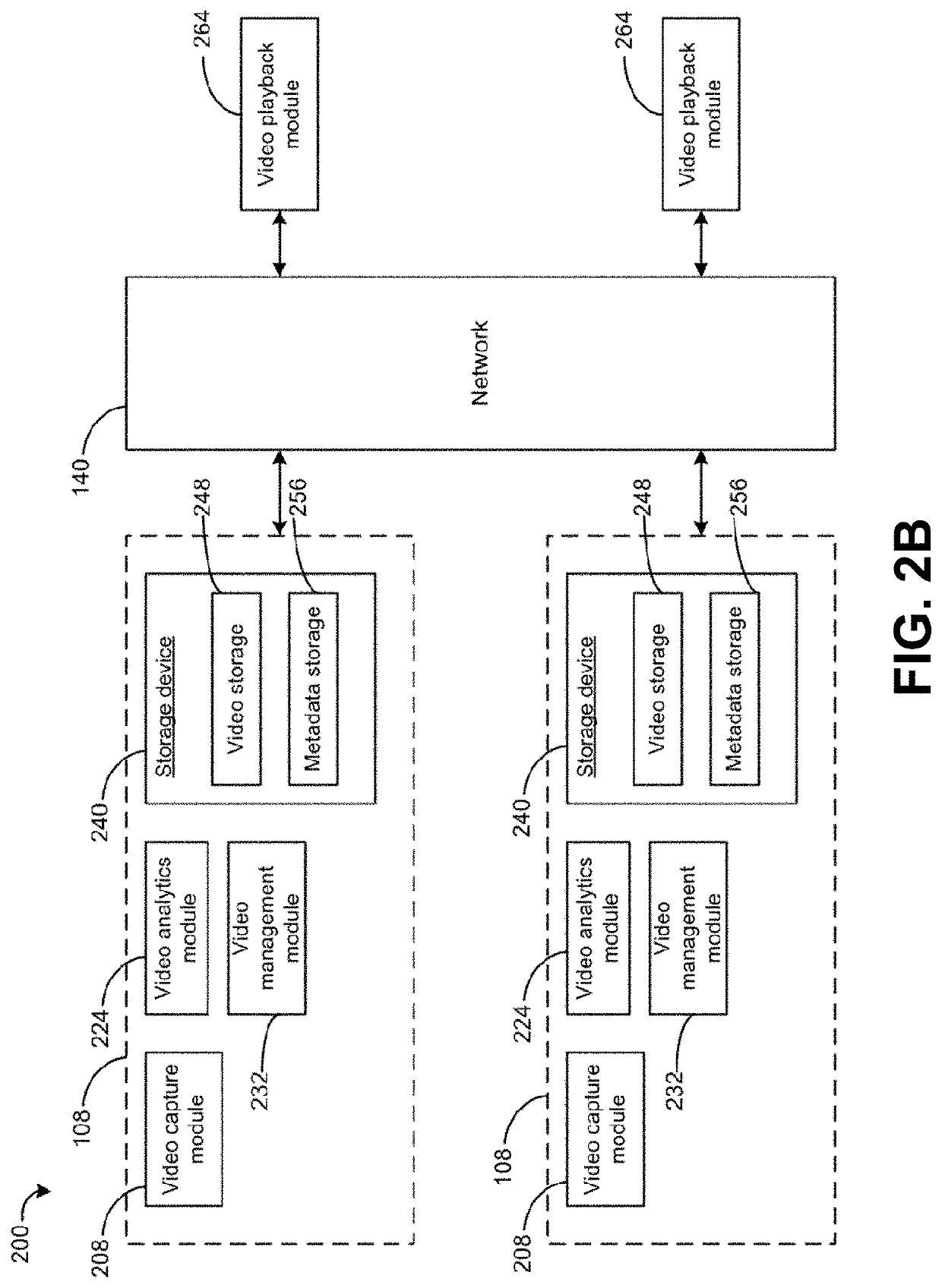

Method for designing video monitoring client side based on multi-process architecture

ActiveCN105721831APrevent crashAvoid confictClosed circuit television systemsClassified informationProduct type

The invention belongs to the field of monitoring of multi-process communication technologies and video monitoring client sides, and in particular relates to a method for designing a video monitoring client side based on a multi-process architecture. A multi-process architecture technology is adopted in the invention; a universal video equipment interface management list is searched in a sub-process according to equipment numbers; if the management list is not searched, the SDK of a manufacturer of video equipment corresponding to classified information is dynamically loaded according to the number of the manufacturer, the product type and the production model; then, a plug-in is encapsulated; a universal video equipment operation interface and an object are generated according to the equipment number; the fact that SDKs of different video equipment manufacturers are separately loaded into different sub-processes can be ensured; the problem that a program is overall collapsed due to the SDK problem of a single manufacturer can be avoided; and simultaneously, conflict of the SDKs of different video equipment manufacturers is also avoided.

Owner:ANHUI SUN CREATE ELECTRONICS

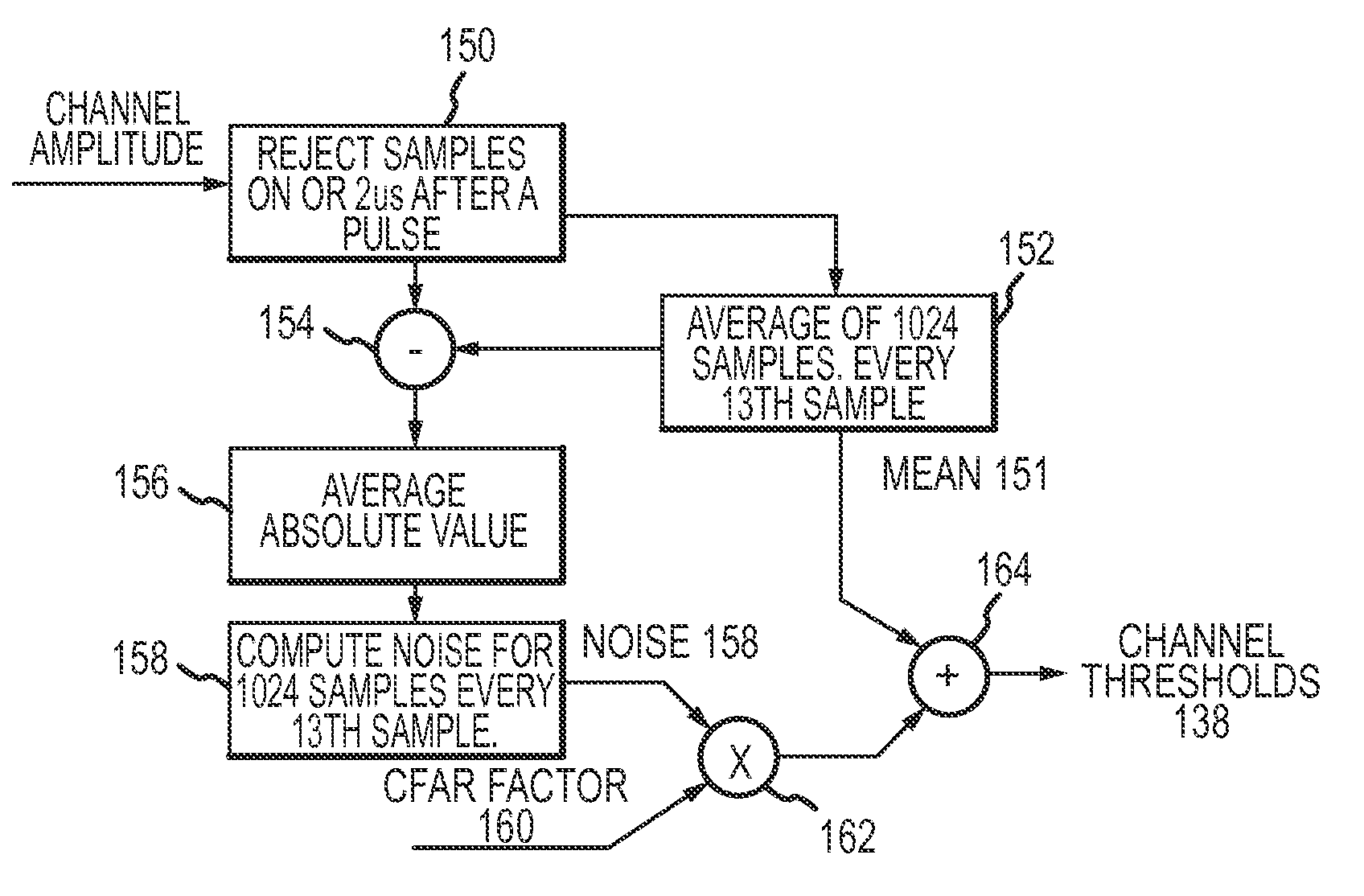

Adaptive pulse detection for all-digital line-of-sight (LOS) processor

ActiveUS7764222B2Simple technologyEasy to detectDirection controllersModulated-carrier systemsWide fieldEngineering

An all-digital line-of-sight (LOS) process architecture addresses the size, weight, power and performance constraints of a receiver for use in semi-active or active pulsed electromagnetic (EM) targeting systems. The all-digital architecture provides a platform for enhanced techniques for sensitive pulse detection over a wide field-of-view, adaptive pulse detection, LOS processing and counter measures.

Owner:RAYTHEON CO

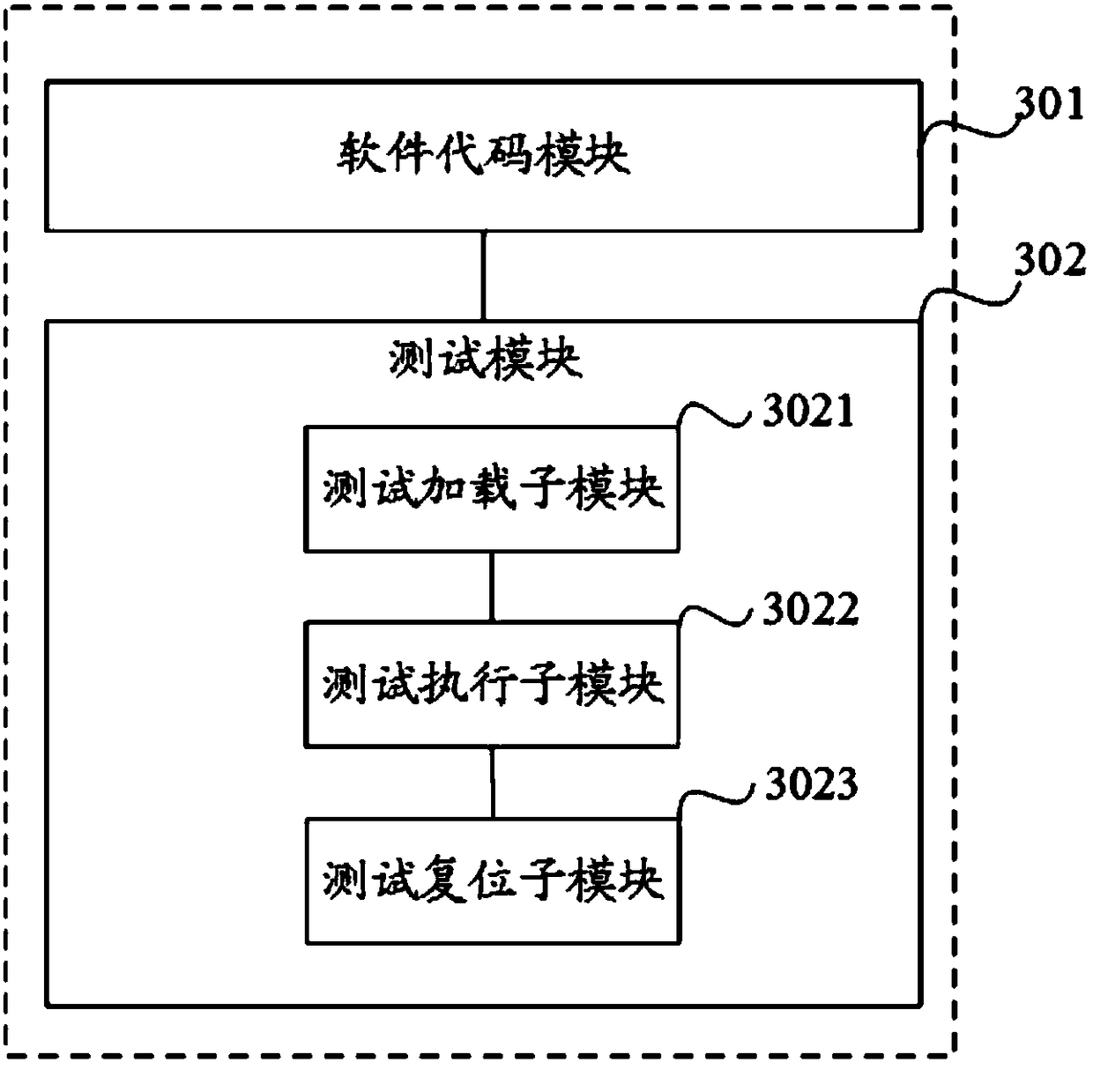

Computing device with multiple progress structure for operating inserter program code module

ActiveCN1965281ADigital data processing detailsPlatform integrity maintainanceCode moduleComputer architecture

The invention discloses a computing device with a multiple process architecture for running plug-in code modules in their own dedicated processes for increasing both the security and reliability of software systems using plug-in design patterns.

Owner:NOKIA TECHNOLOGLES OY

Adaptive pulse detection for all-digital line-of-sight (LOS) processor

ActiveUS20100067587A1Improved pulse detectionSmall sizeDirection controllersModulated-carrier systemsSemi activeWide field

An all-digital line-of-sight (LOS) process architecture addresses the size, weight, power and performance constraints of a receiver for use in semi-active or active pulsed electromagnetic (EM) targeting systems. The all-digital architecture provides a platform for enhanced techniques for sensitive pulse detection over a wide field-of-view, adaptive pulse detection, LOS processing and counter measures.

Owner:RAYTHEON CO

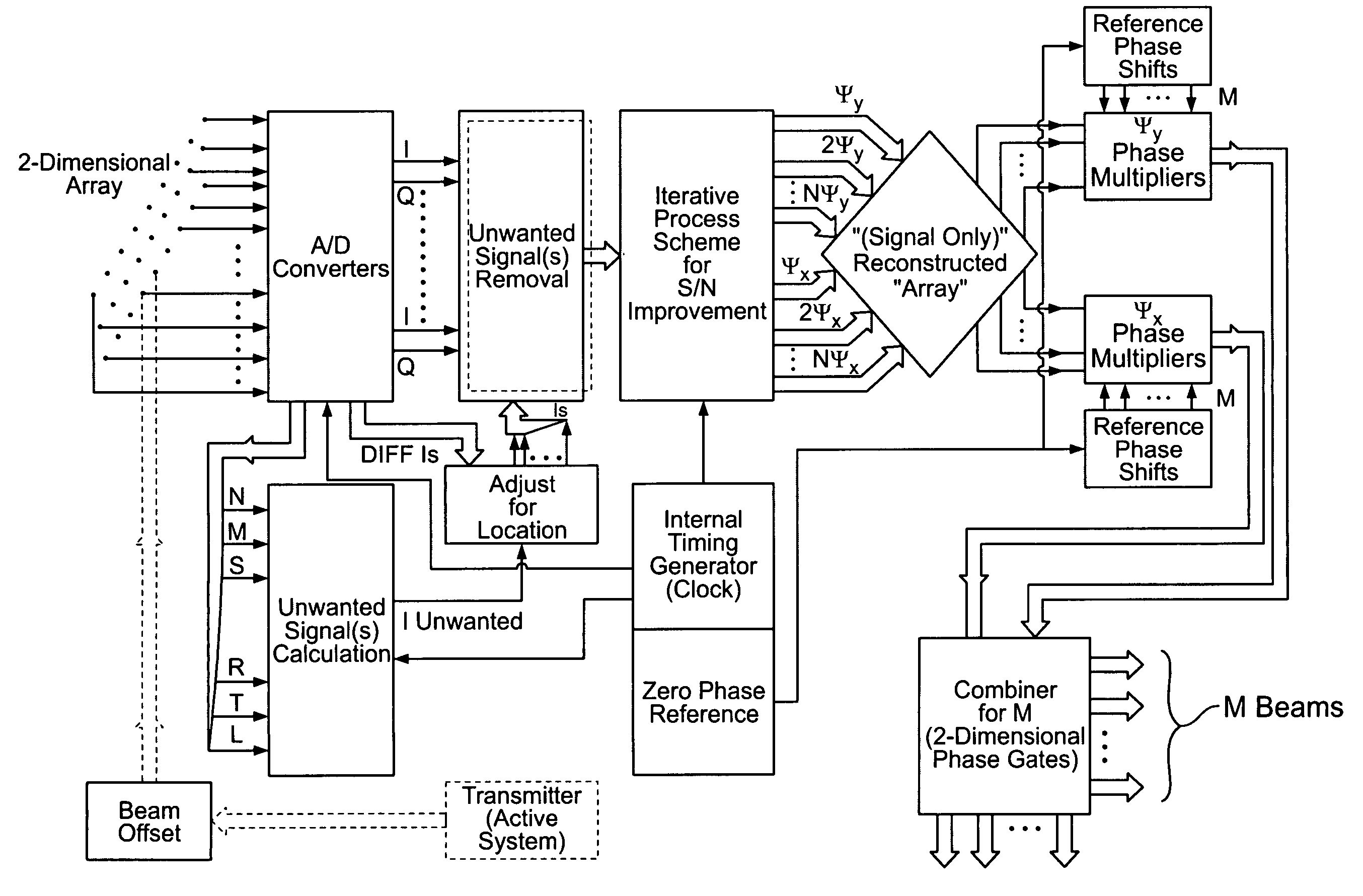

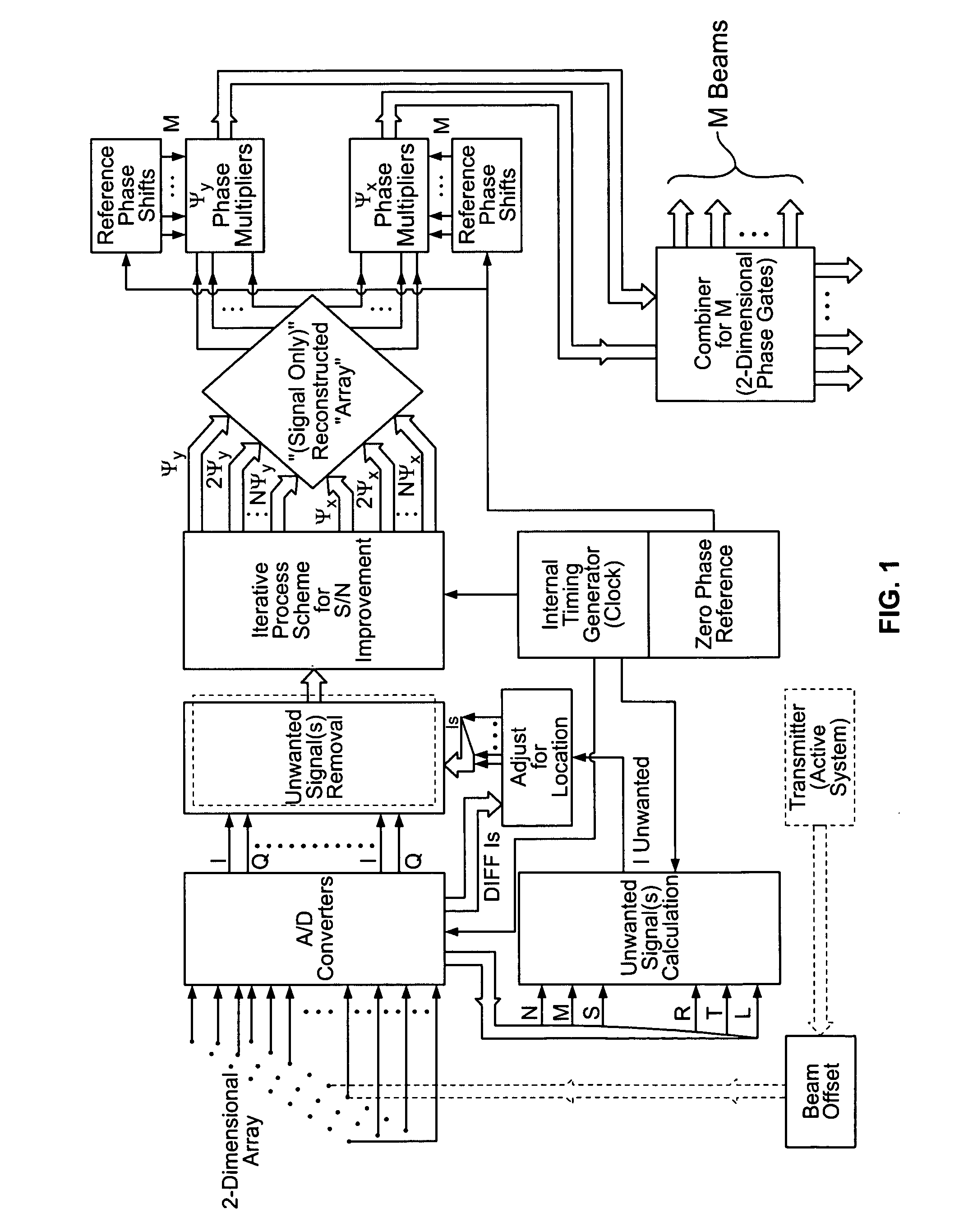

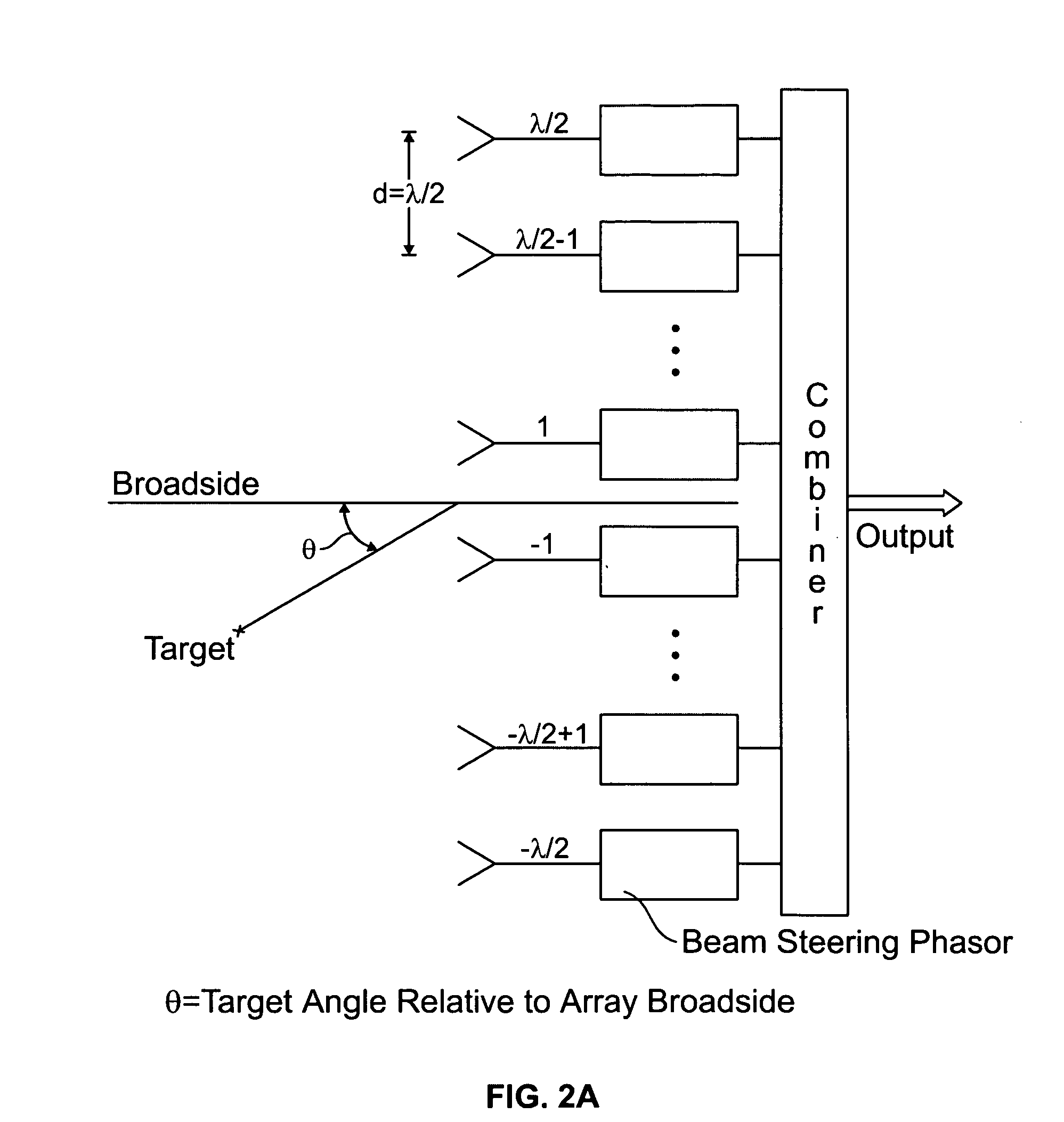

Processing architecture for a receiving system with improved directivity and signal to noise ratio

InactiveUS20060079192A1Improve signal-to-noise ratioSame performanceRadio transmissionTransmission noise suppressionSignal-to-noise ratio (imaging)Image resolution

A receive system providing enhanced directivity in the form of a narrowed receive beam and a relatively small antenna with performance comparable to a much larger antenna at similar frequencies. Received signals are converted to digital values and stored in a manner which enables subsequent processing directed to improving the resolution of the received signals and to reduce the associated noise corresponding to the received data samples. The Signal-to-Noise ratio of the received data signals is improved as a result of processing techniques made possible by the configuration of the antenna and the digitally stored nature of the received data.

Owner:CALLAHAN CELLULAR L L C

Robot control software framework in open distributed process architecture

ActiveUS7823126B2Low costExpand the robot marketProgramme-controlled manipulatorProgram control using stored programsTechnology developmentComputer architecture

An open distributed processing structured robot control software architecture is enclosed, which makes it possible to manufacture a user-oriented robot through combination of independent heterogeneous functional modules. The invention involves an open software framework for integrated operation and production of distributed software of the modules, and an autonomous robot control architecture suitable for distributed environments. The software framework indicates underlying software components for robot control and service creation. The invention makes it possible to mass-produce autonomous robots in units of interoperable functional modules. It is also possible to meet various demands of consumers, achieve specialization, and accelerate technology development since the development procedures are specialized in an independent manner and are suitable for manufacturing a wide variety of robot products in small quantities.

Owner:KOREA INST OF IND TECH

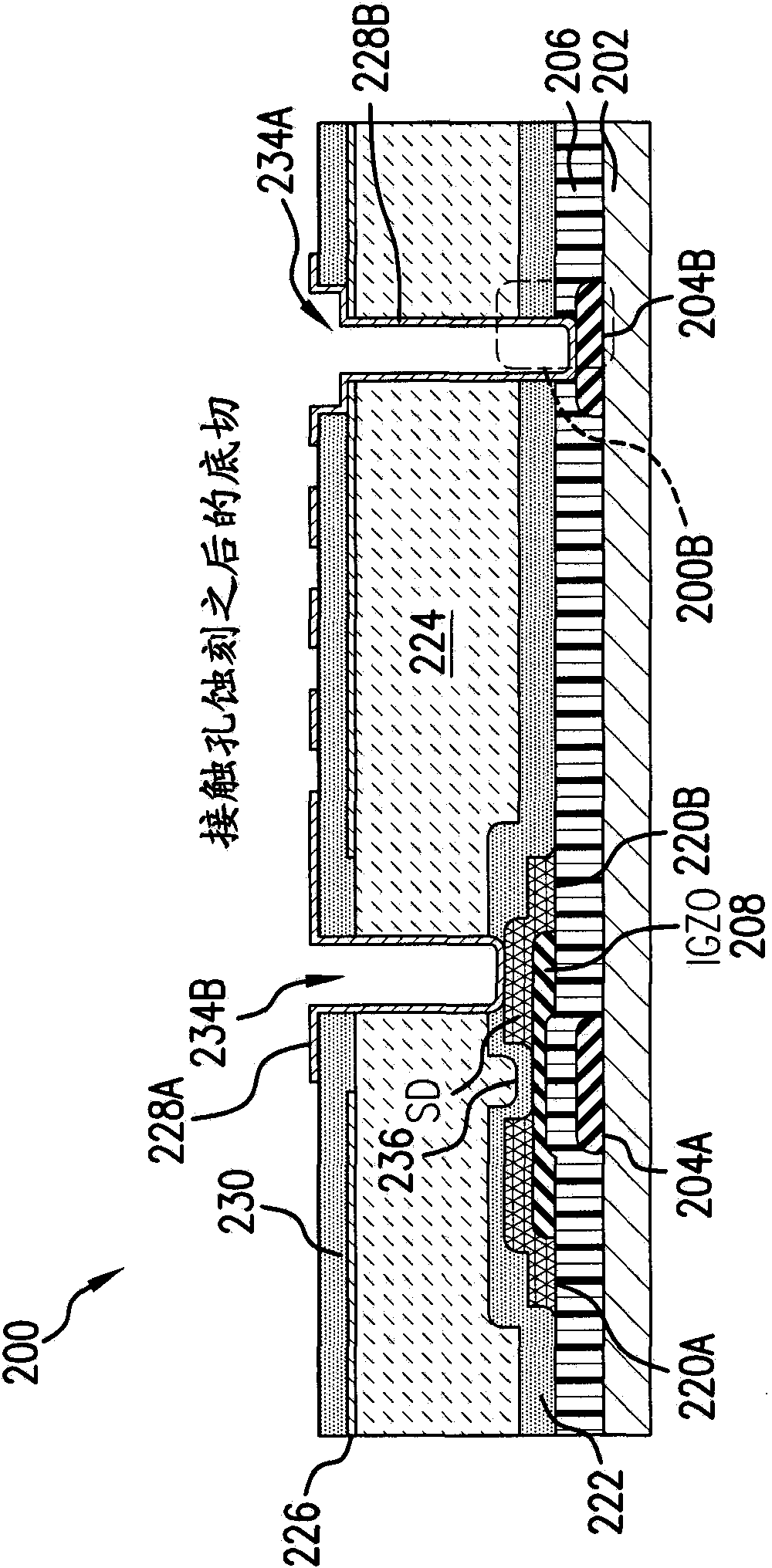

Back channel etching oxide thin film transistor process architecture

The disclosure relates to a back channel etching oxide thin film transisto process architecture. A method for fabricating a back channel etching (BCE) oxide thin film transistor (TFT) for a liquid crystal display is provided. The method includes forming a first metal layer having a first portion and a second portion over a substrate, depositing a gate insulator over the first metal layer, and disposing a semiconductor layer over the gate insulator. The method also includes depositing a half-tone photoresist to cover a first portion of the semiconductor layer and the first portion of the first metal layer. The half-tone photoresist has a first portion and a second portion thicker than the first portion. The first portion has a through hole above the second portion of the first metal layer. The second portion of the half-tone photoresist covers the first portion of the first metal layer. The method further includes etching a portion of the gate insulator through the via hole such that the second portion of the first metal layer is exposed, removing the first portion of the half-tone photoresist while remaining the second portion of the half-tone photoresist, and etching to remove a second portion of the semiconductor layer that is not covered by the half-tone photoresist.

Owner:APPLE INC

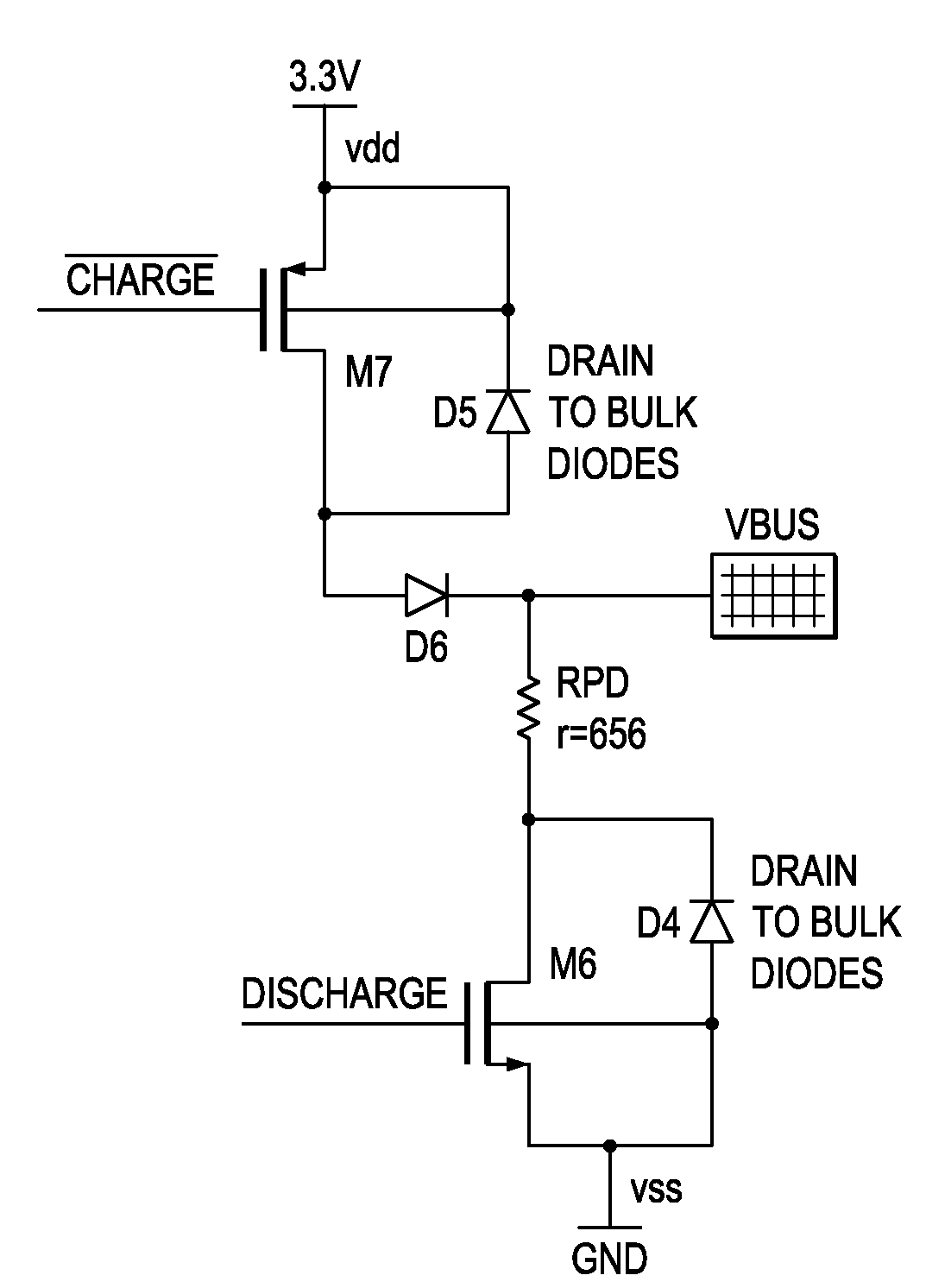

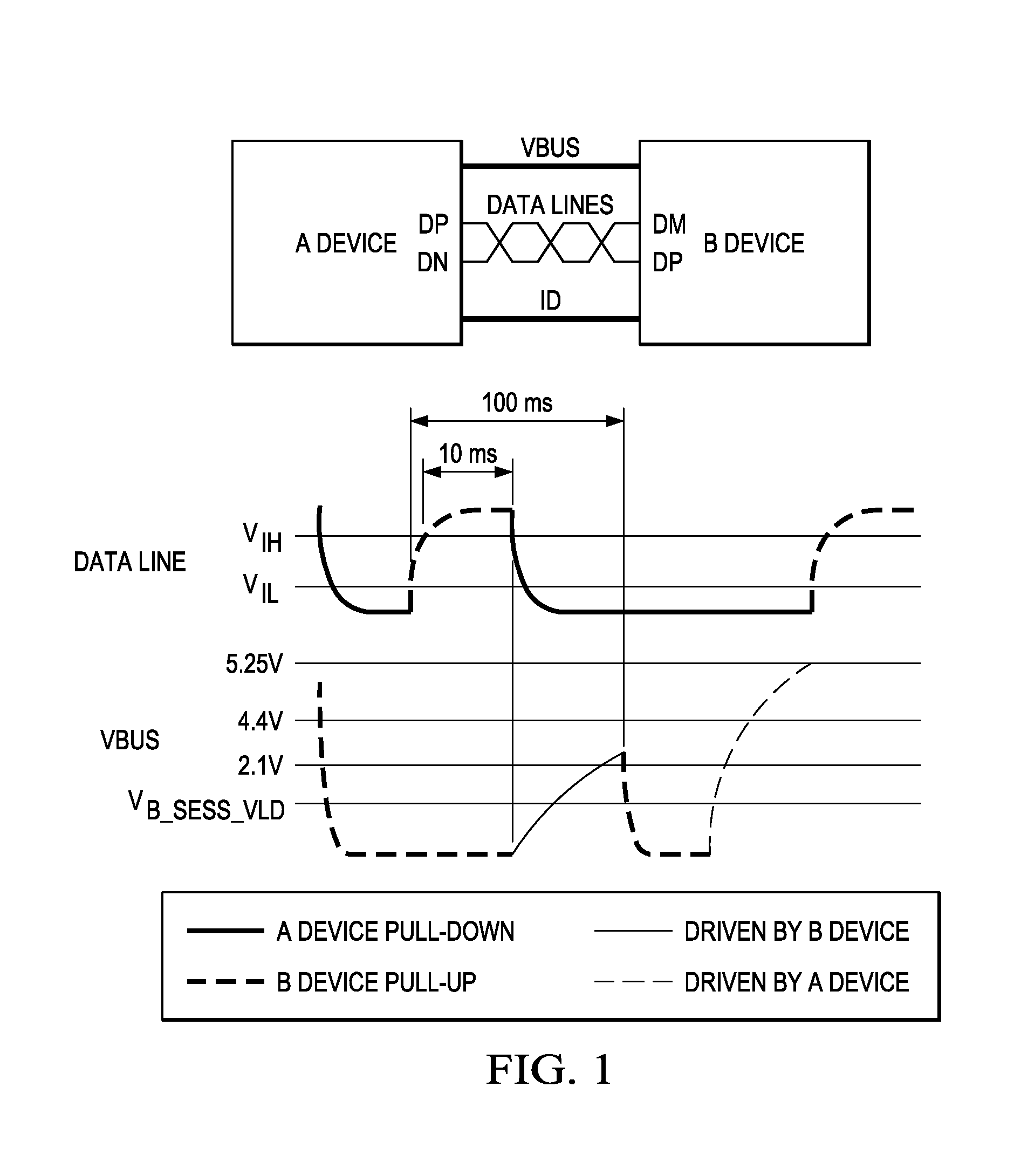

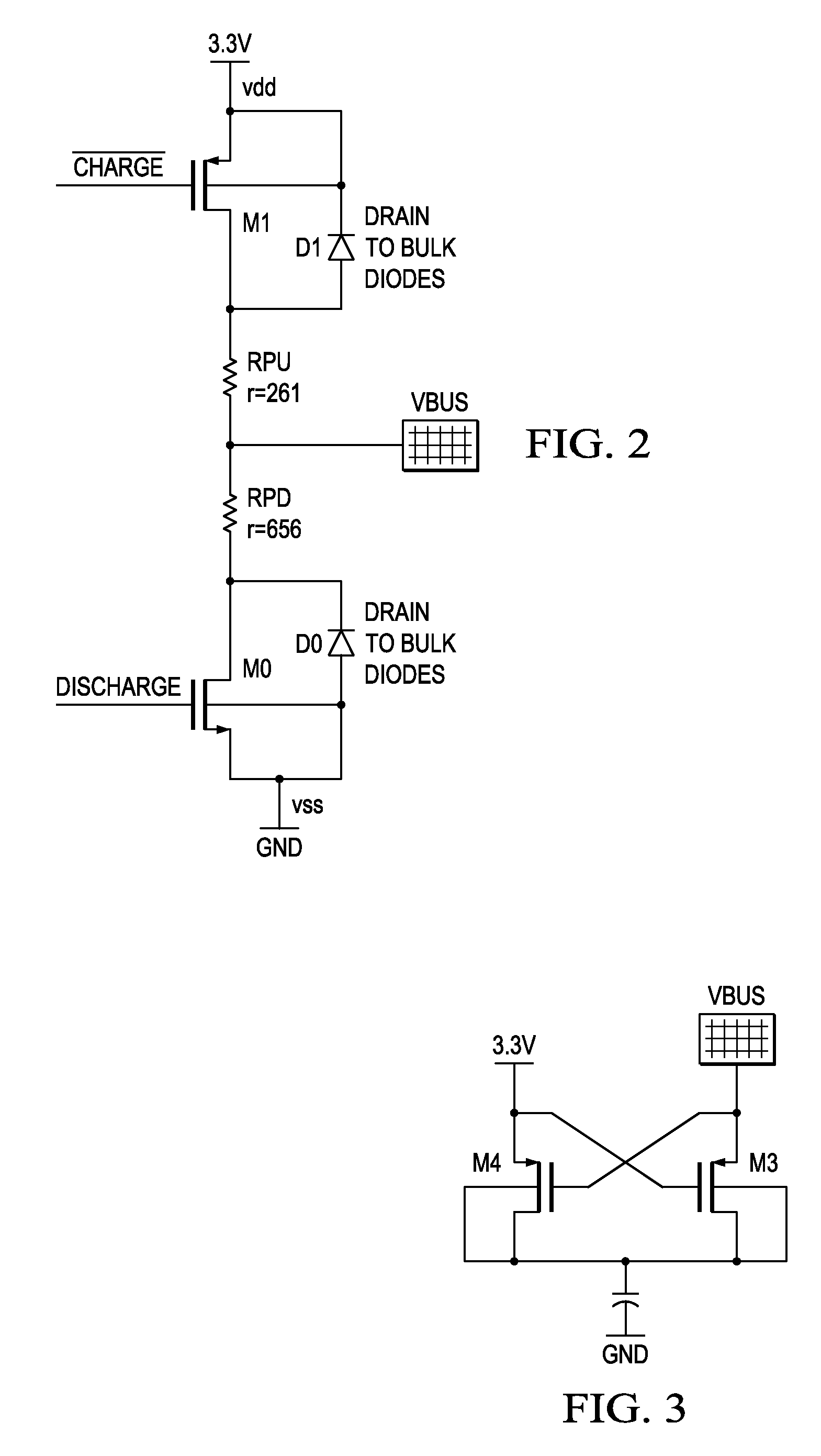

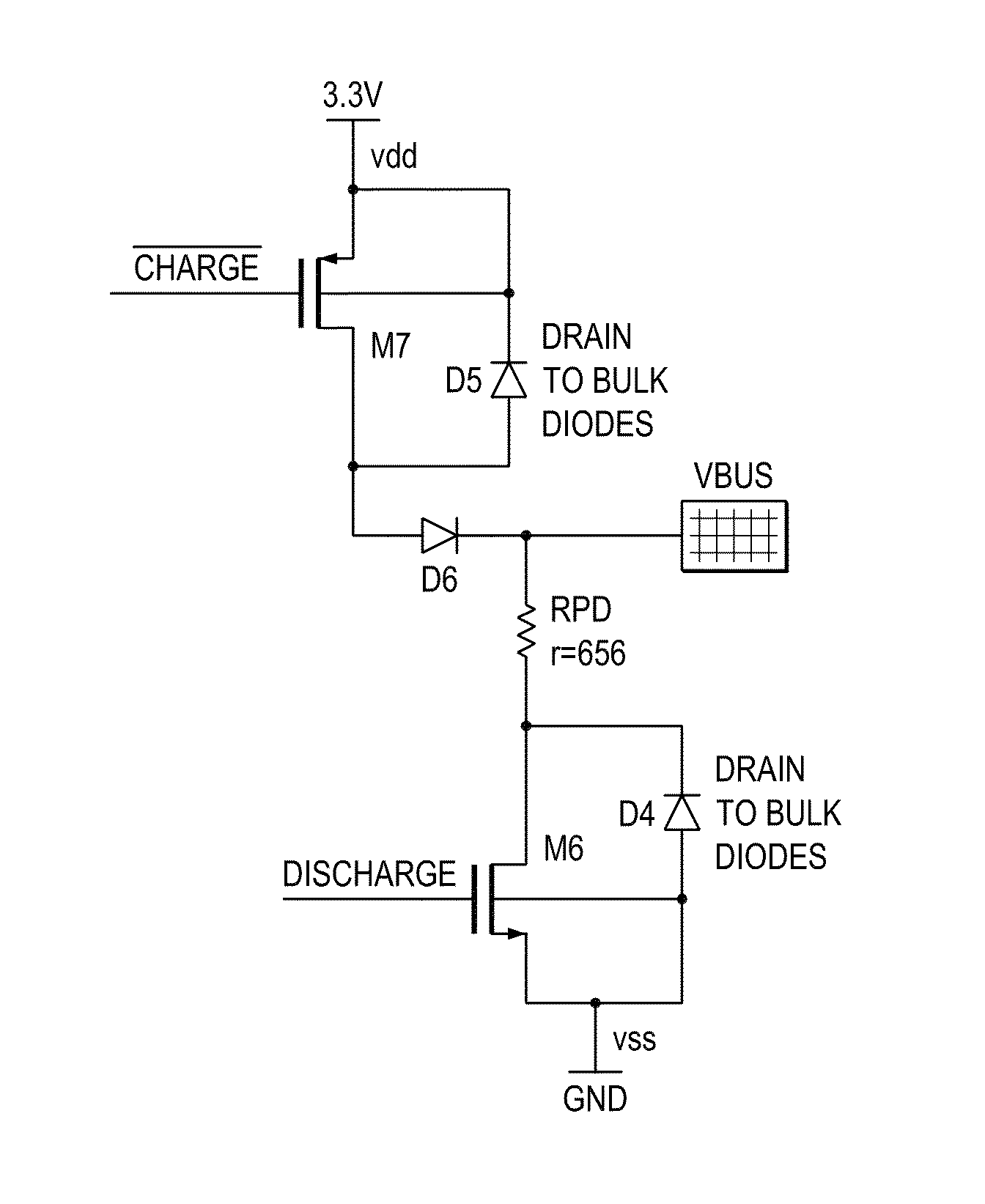

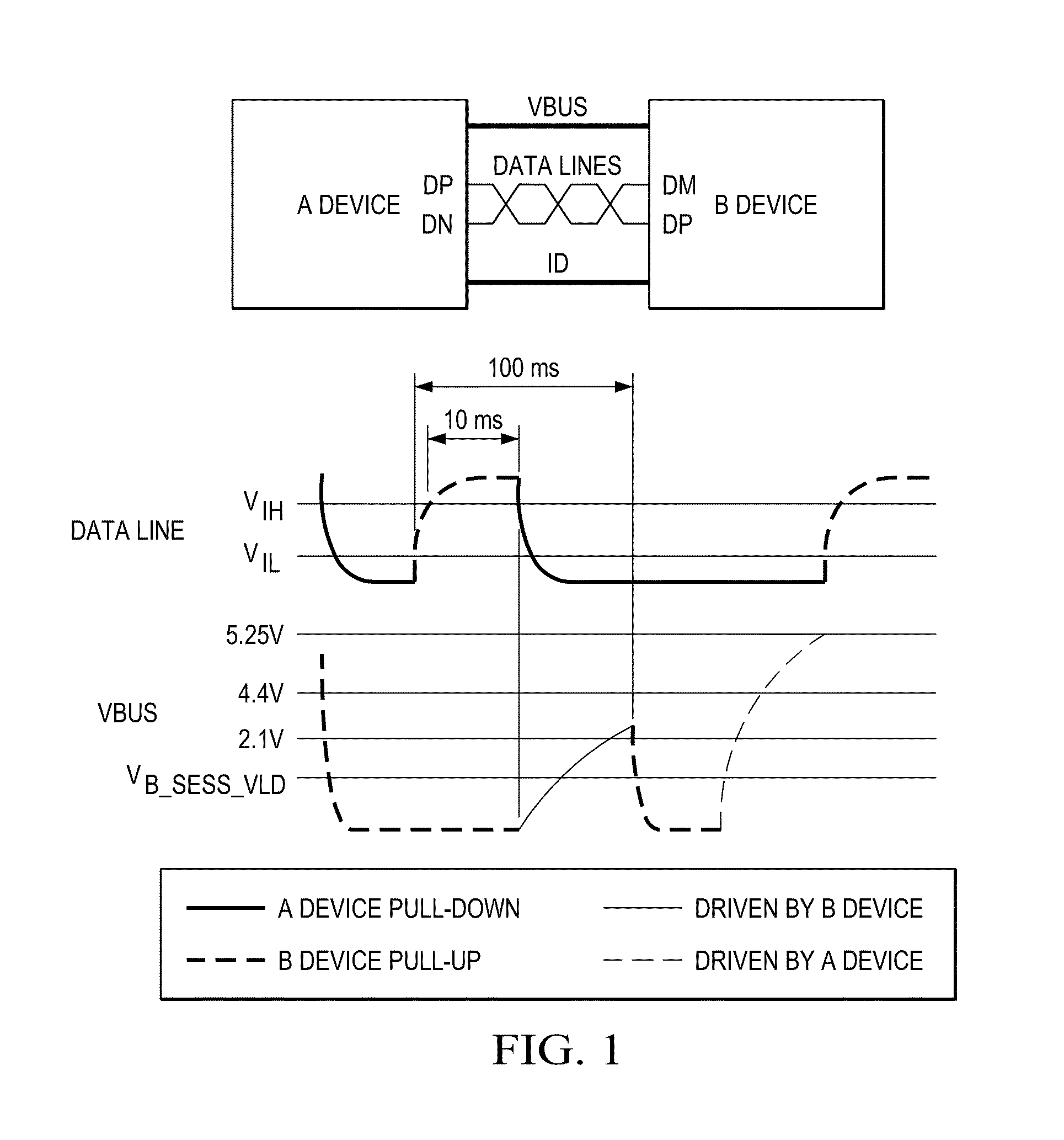

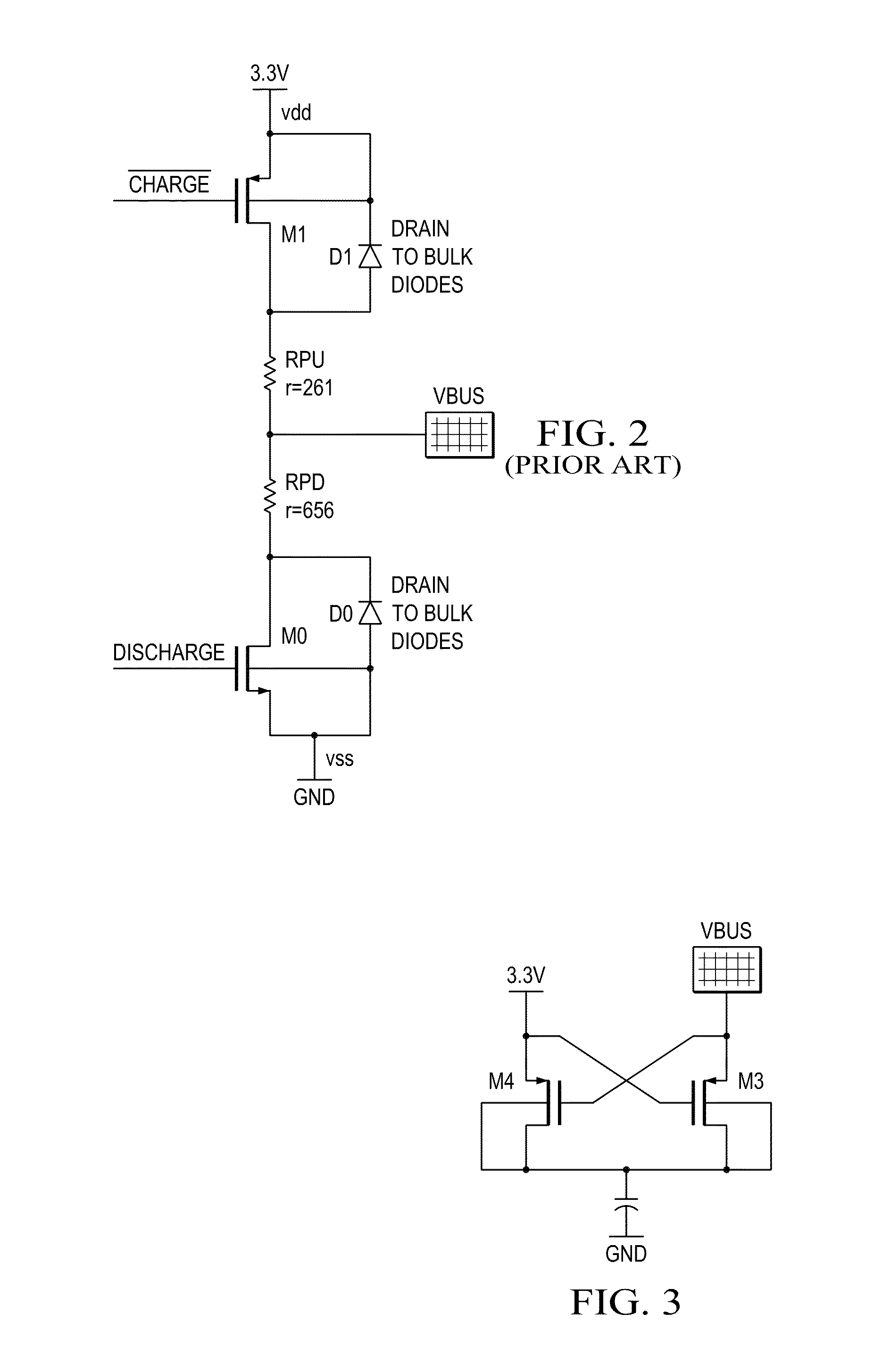

Architecture for vbus pulsing in udsm processes

ActiveUS20090140772A1Batteries circuit arrangementsLogic circuits coupling/interface using field-effect transistorsEngineeringUSB

Architecture for VBUS pulsing in an Ultra Deep Sub Micron (UDSM) process for ensuring USB-OTG (On The Go) session request protocol, the architecture being of the type wherein at least a charging circuit is deployed, uses a diode-means connected in a forward path of the charging circuit. The architecture might include a diode-divider including nodes and connected from VBUS in said charging circuit. One embodiment uses both charging and discharging circuits comprising transistors. The charging circuit transistor might comprise a PMOS transistor and the discharging circuit transistor might comprise a NMOS transistor. The architecture might include a three resistance string of a total resistance value approximating 100K Ohms connected between said VBUS and ground, wherein the discharging circuit transistor might comprise a drain extended NMOS transistor. The charging and discharging circuit transistors have VDS and VGD of about 3.6V, whereby high VGS transistors are not needed.

Owner:TEXAS INSTR INC

Architecture for VBUS pulsing in UDSM processes

ActiveUS8704550B2Batteries circuit arrangementsLogic circuits coupling/interface using field-effect transistorsUSBCharge and discharge

Architecture for VBUS pulsing in an Ultra Deep Sub Micron (UDSM) process for ensuring USB-OTG (On The Go) session request protocol, the architecture being of the type wherein at least a charging circuit is deployed, uses a diode-means connected in a forward path of the charging circuit. The architecture might include a diode-divider including nodes and connected from VBUS in said charging circuit. One embodiment uses both charging and discharging circuits comprising transistors. The charging circuit transistor might comprise a PMOS transistor and the discharging circuit transistor might comprise a NMOS transistor. The architecture might include a three resistance string of a total resistance value approximating 100K Ohms connected between said VBUS and ground, wherein the discharging circuit transistor might comprise a drain extended NMOS transistor. The charging and discharging circuit transistors have VDS and VGD of about 3.6V, whereby high VGS transistors are not needed.

Owner:TEXAS INSTR INC

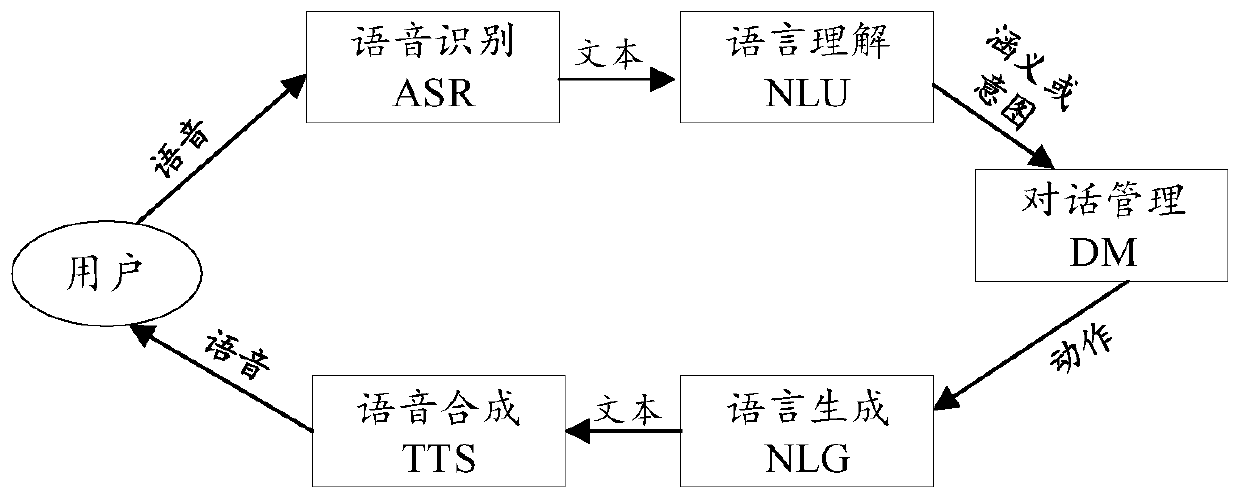

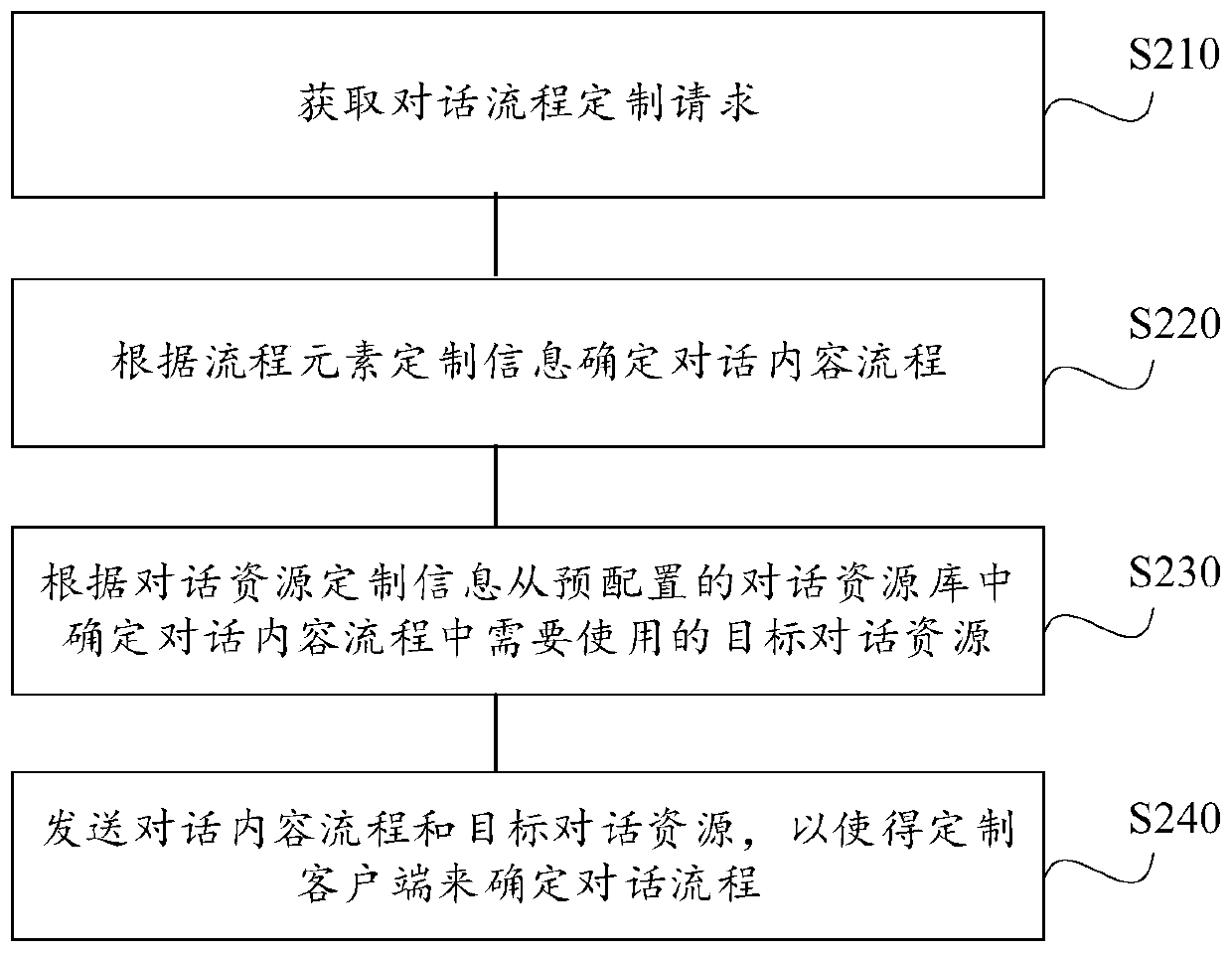

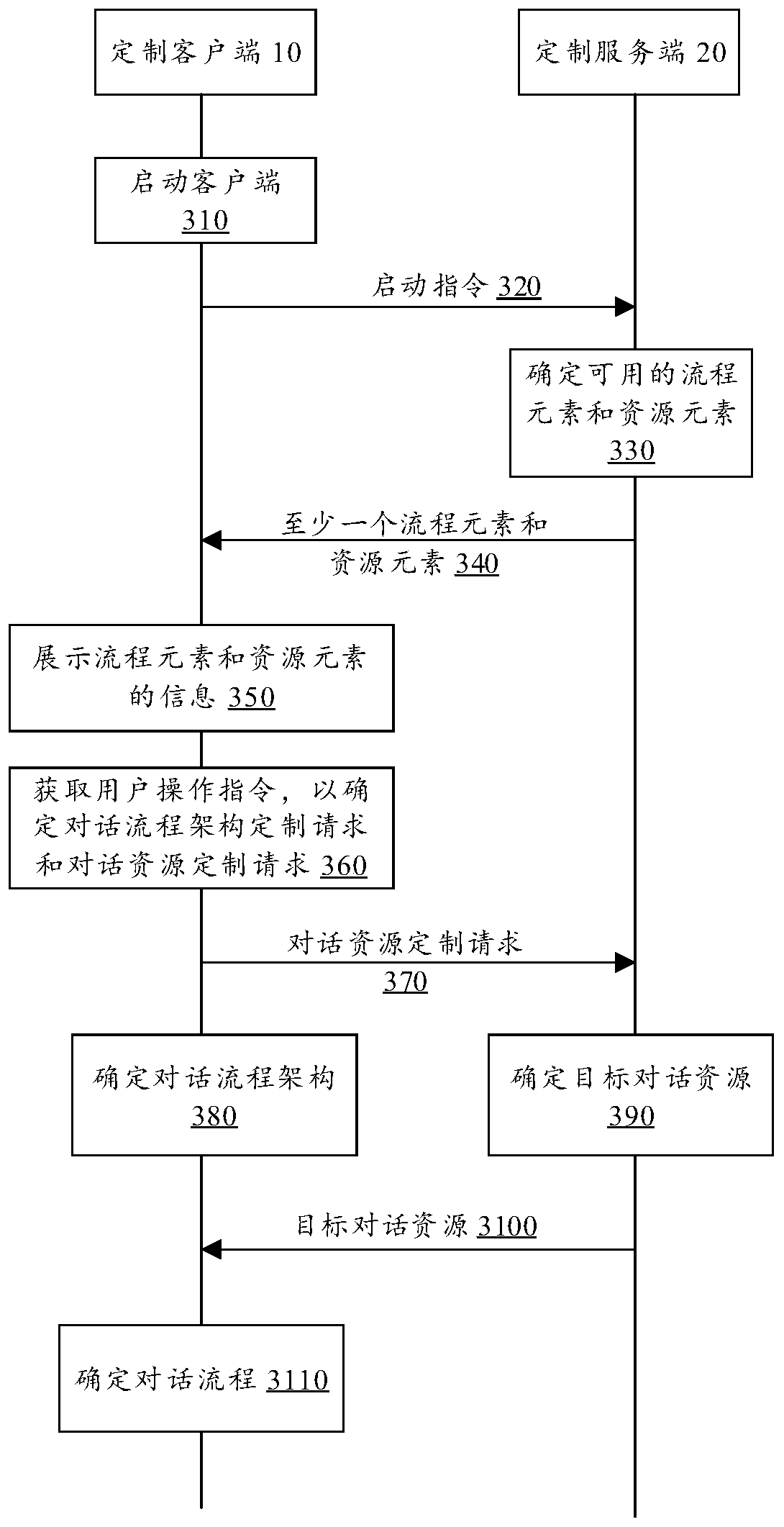

Conversation process customization method and device

ActiveCN111145745AMeet the requirements of privatization deploymentMany degrees of freedomDigital data information retrievalSoftware testing/debuggingHuman–computer interactionComputer engineering

The invention discloses a dialogue process customization method and a device. In the dialogue process customization method, a dialogue resource customization request is acquired by a customization server, a target dialogue resource from a pre-configured dialogue resource library is determined according to dialogue resource customization information, and then the target dialogue resource is sent, so that a customization client can configure the target dialogue resource into a dialogue process architecture to determine a dialogue process. By means of the dialogue process customization method, non-professional users can customize the dialogue process more freely, and the dialogue process customization method can be suitable for numerous dialogue customizing scenes.

Owner:AISPEECH CO LTD

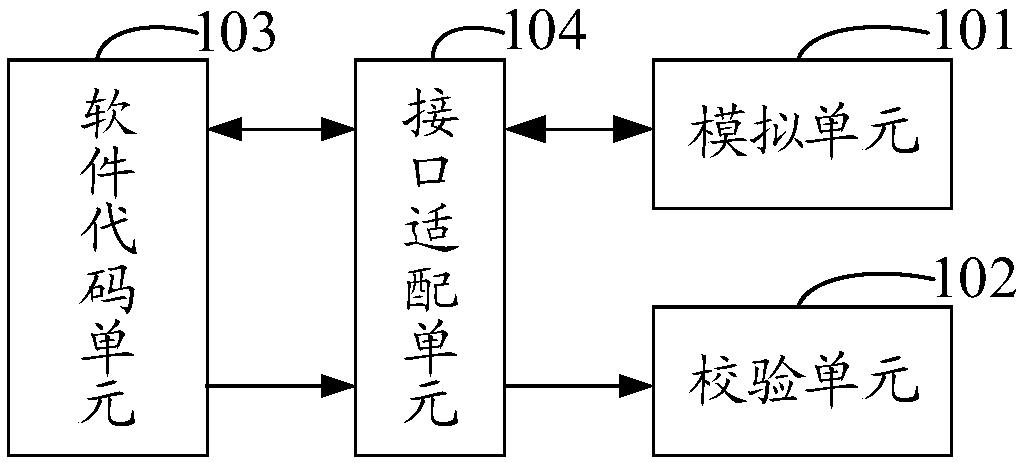

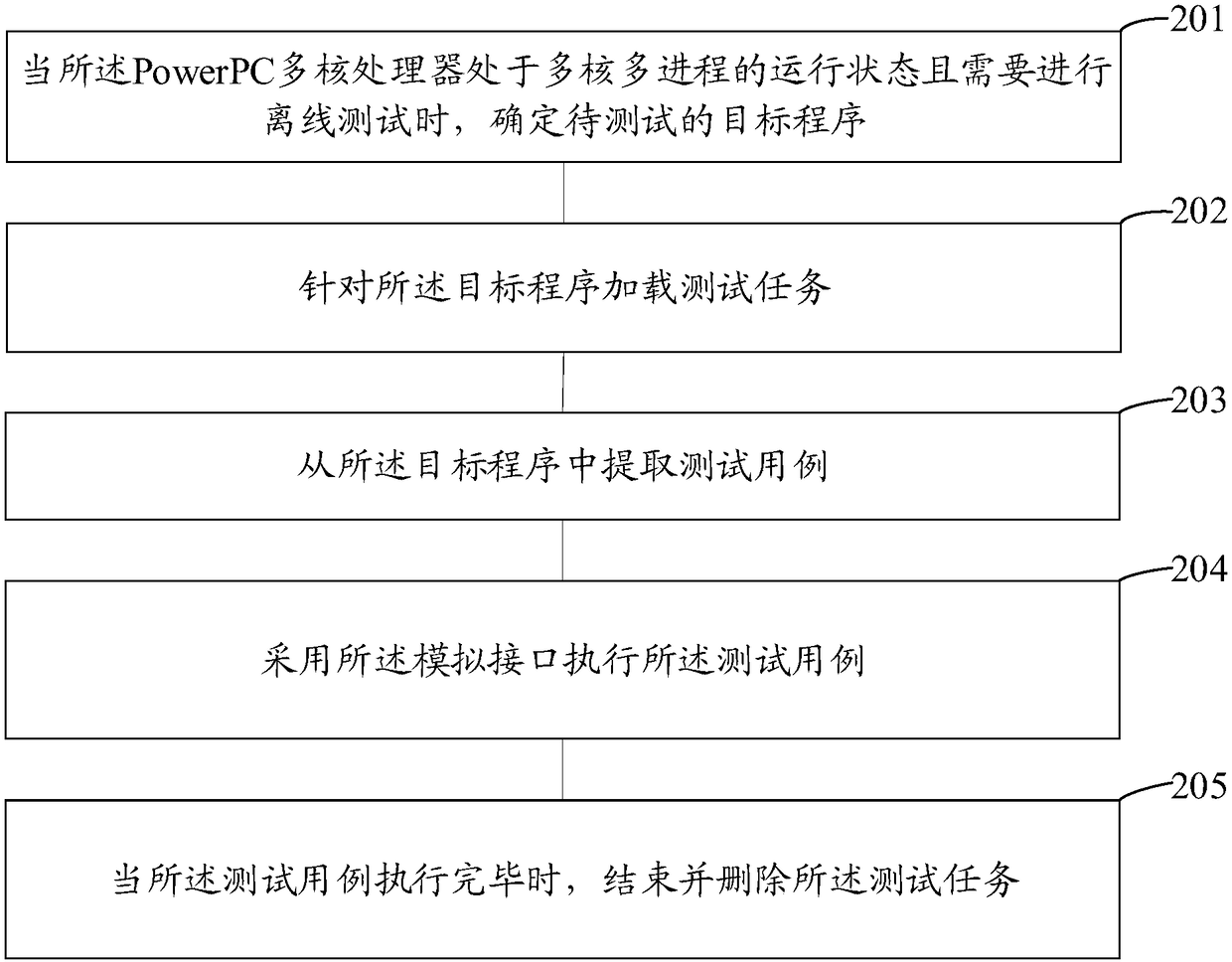

Offline test method and device based on PowerPC multi-core processor

ActiveCN108572892AGuaranteed completenessFunctional testingFaulty hardware testing methodsPowerPCMulti-core processor

An embodiment of the invention provides an offline test method and device based on a PowerPC multi-core processor. The method includes determining a target program to be tested when the PowerPC multi-core processor is in the multi-core multi-process running state and needs to be tested off line; loading a test task for the target program; extracting a test case from the target program; executing the test case using a simulation interface; ending and deleting the test task when the test case is executed. The method solves the problem in the prior art that software compiling loading consumes long time and the multi-core multi-process timing sequence cannot be simulated or tested due to the fact that repeated compiling, linking and loading of the program must be performed when the test case not passed is executed singly. The working efficiency of an embedded program system is improved in the multi-core multi-process architecture mode, and the completeness and the reliability of the test are also ensured.

Owner:DATANG MOBILE COMM EQUIP CO LTD

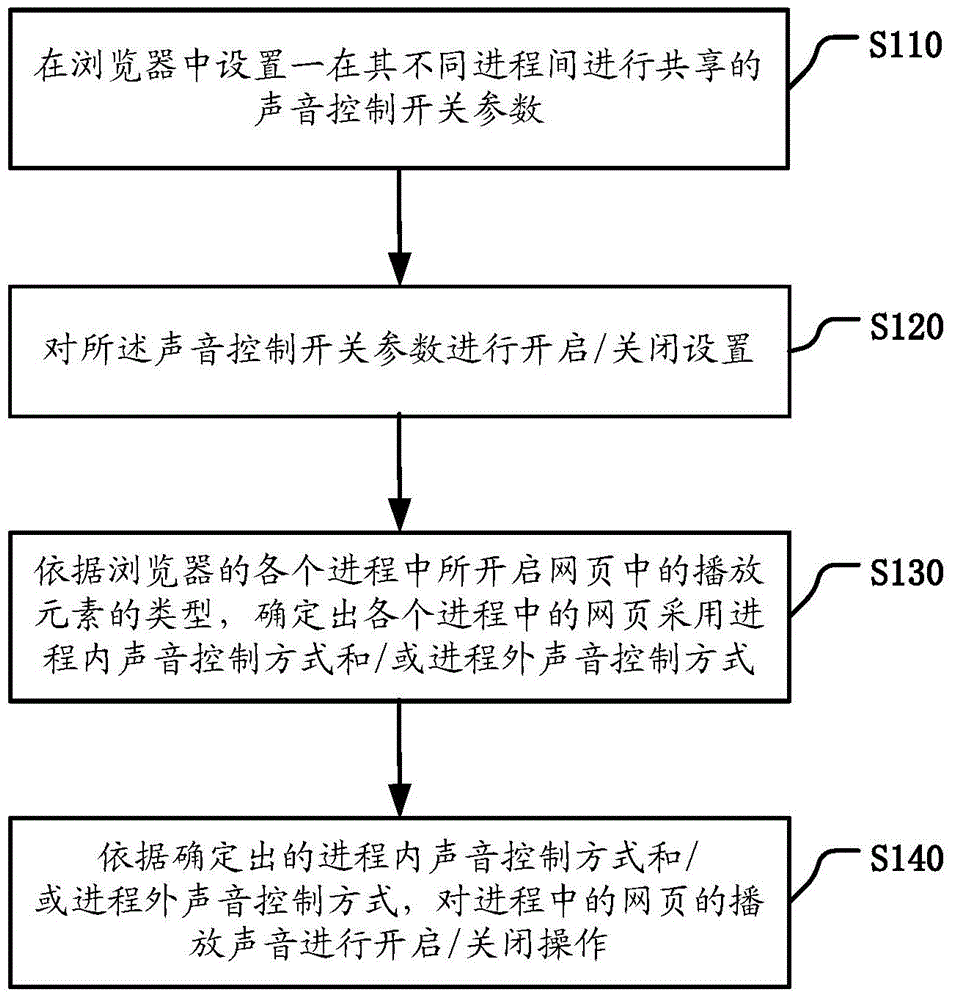

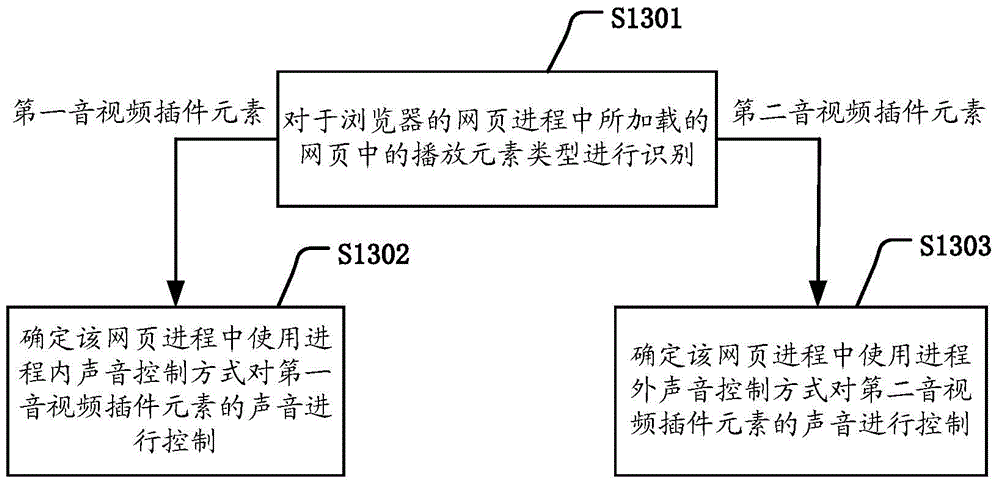

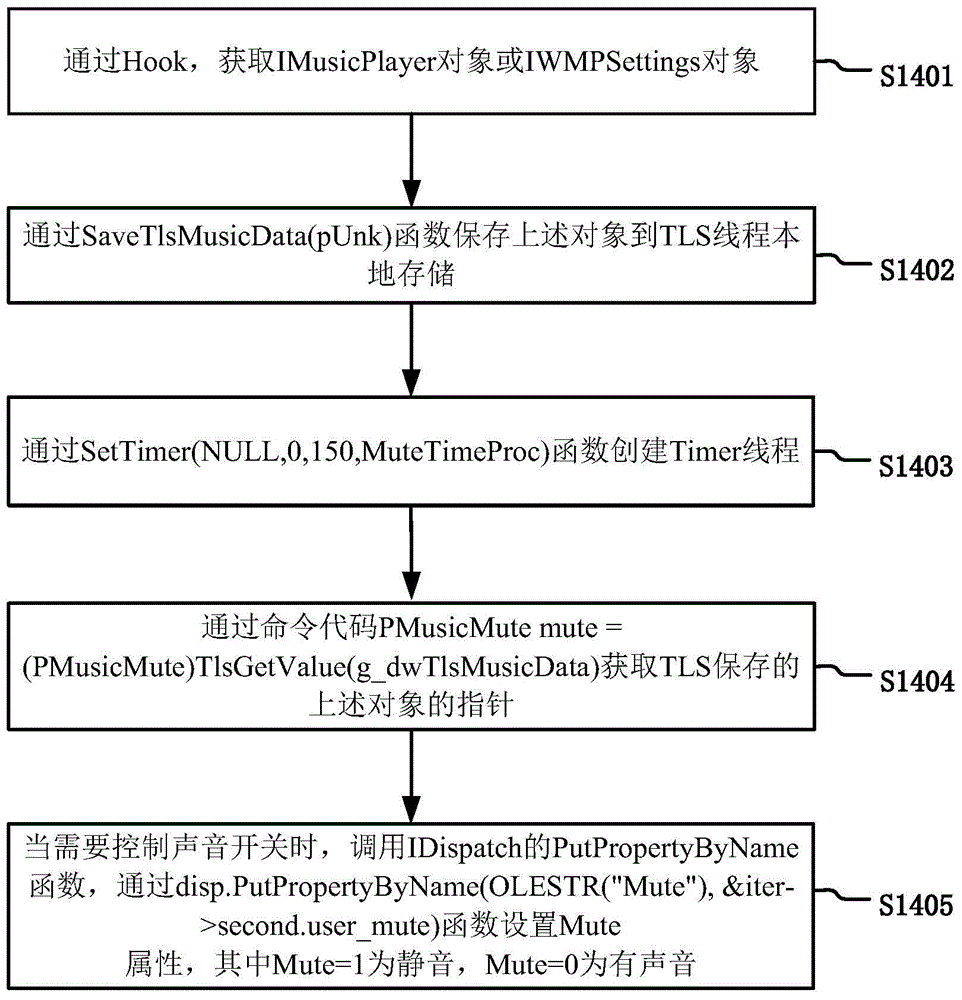

Method and device for carrying out sound control in browser

ActiveCN104133849AMeet individual needsImprove experienceSound input/outputExecution for user interfacesControl switchWeb page

The invention discloses a method and a device for carrying out sound control in a browser. The method comprises the following steps that: a sound control switch parameter for carrying out sharing among different processes is arranged in the browser; the sound control switch parameter is subjected to on / off setting; according to the types of playing elements in a web page opened in each process of the browser, an in-process sound control mode and / or an out-of-process sound control mode adopted by the web page in each process are / is determined; and the playing sound of the web page in each process is subjected to on / off operation according to the determined in-process sound control mode and / or the out-of-process sound control mode. The invention provides a solution for carrying out the sound control on the browser of a multi-process architecture; the simultaneous control on the playing sound of a plurality of processes of the browser is realized; and the playing sound in browser framework processes or browser web page processes can be subjected to on / off operation at any time.

Owner:BEIJING QIHOO TECH CO LTD

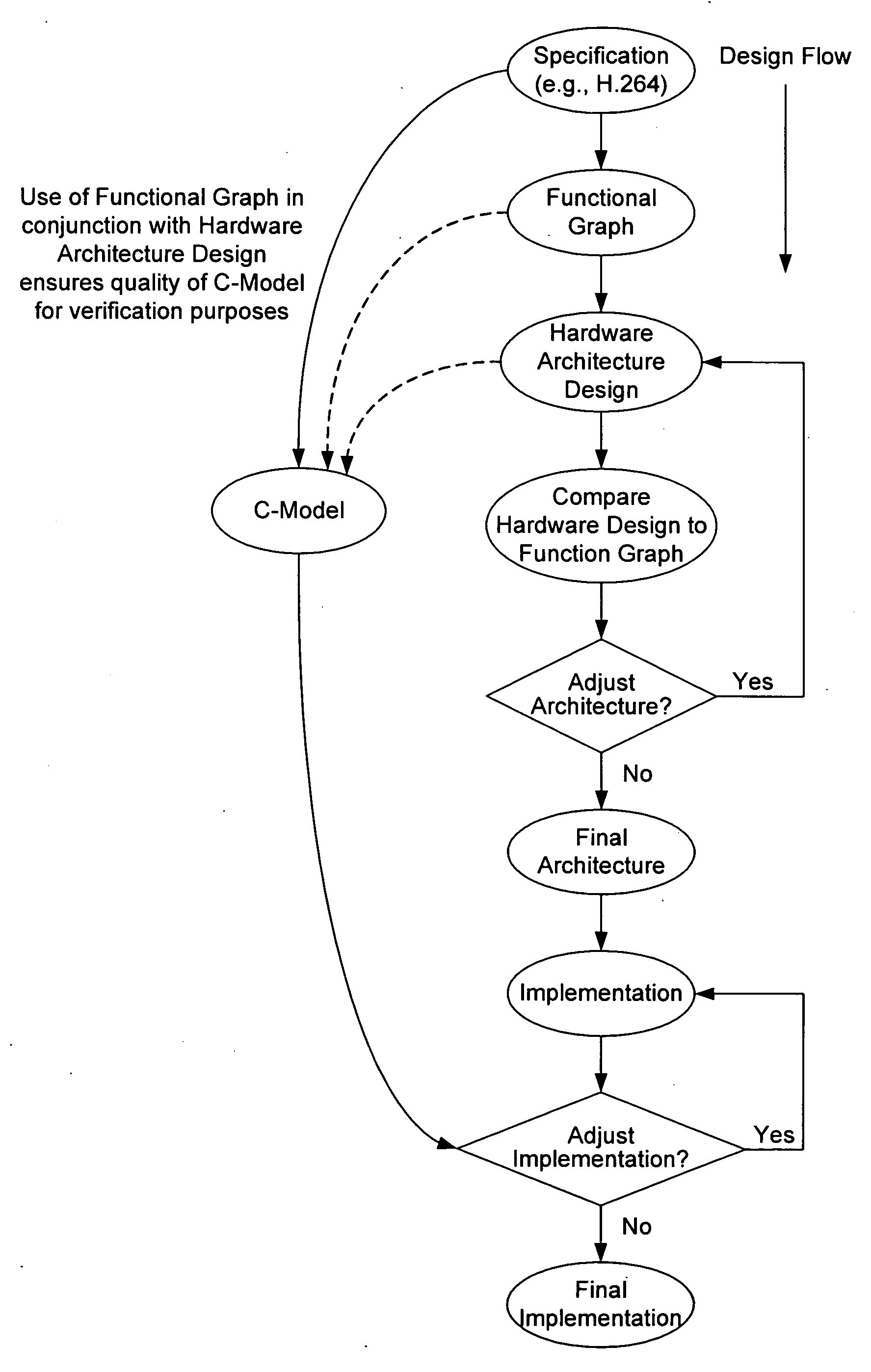

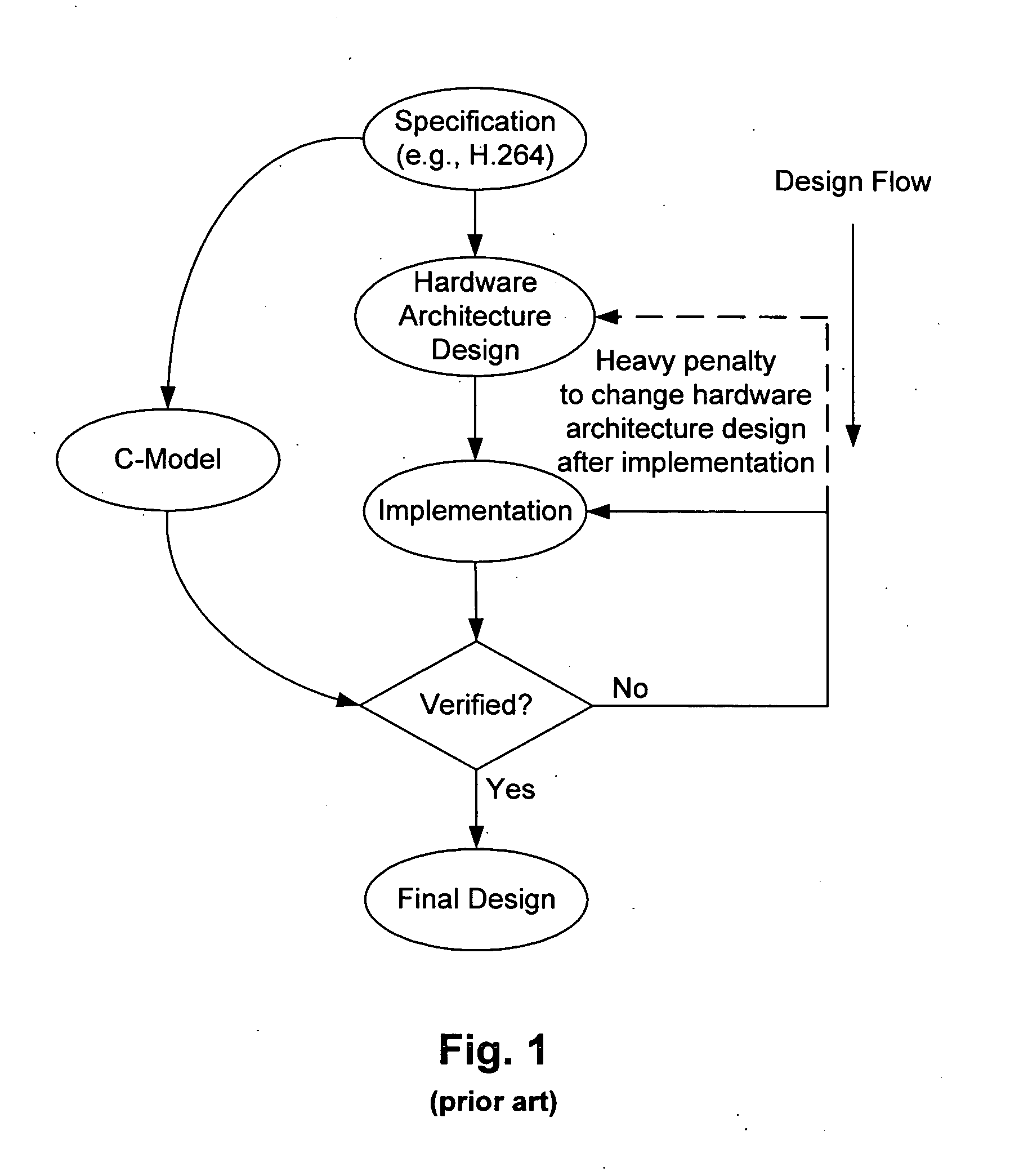

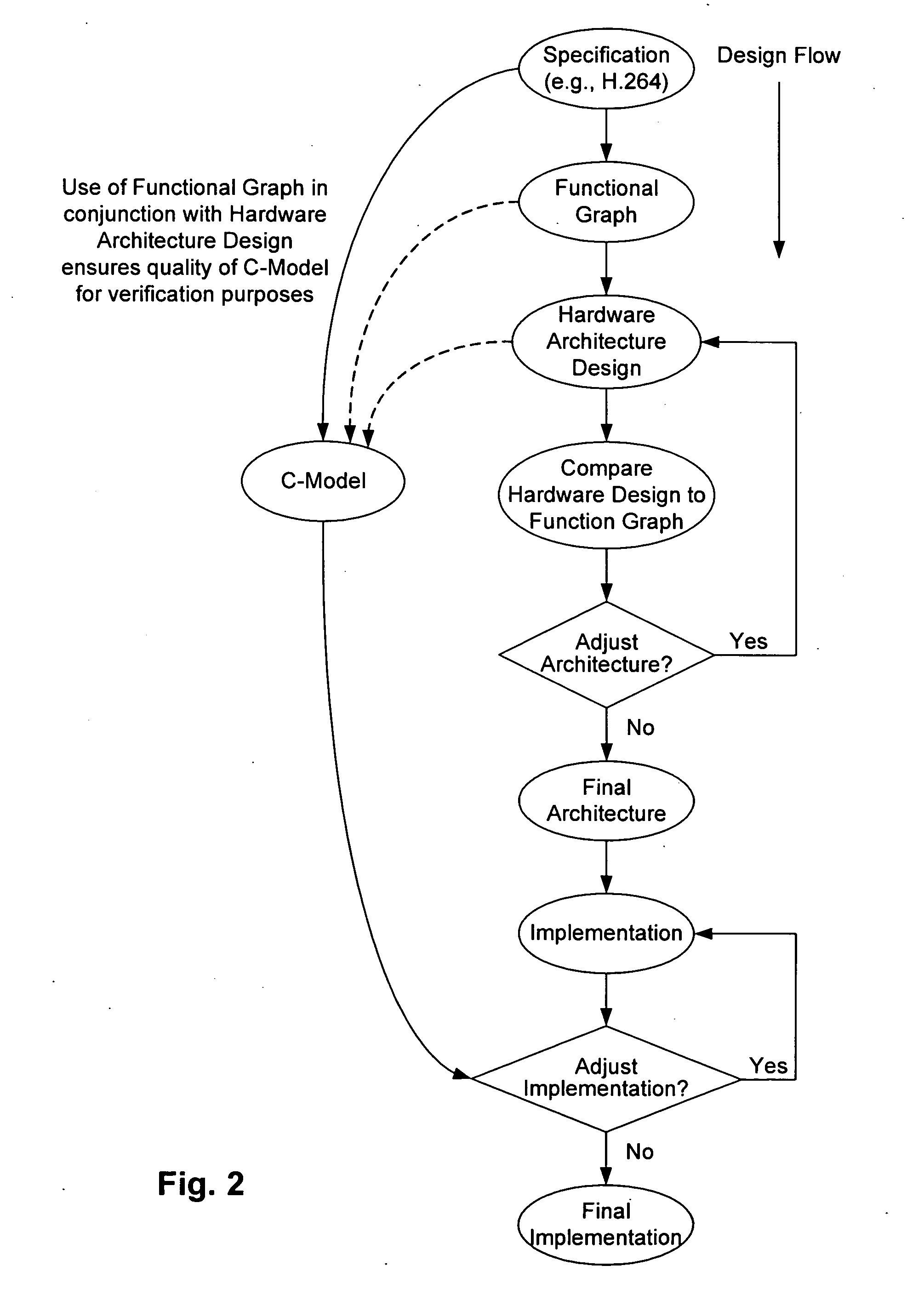

Video processing architecture definition by function graph methodology

InactiveUS20060143588A1CAD circuit designSoftware simulation/interpretation/emulationComputer architectureHardware architecture

A design technique is disclosed that allows video processing hardware designers to effectively employ the requirements of a video processing standard (e.g., H.264 specification or other such standard) during the hardware architecture design phase of the design process. The technique eliminates or otherwise reduces costly multiple passes through the resource intensive implementation and verification portions of the design process, and allows designers to make changes to the hardware architecture design, thereby ensuring verification at the implementation phase.

Owner:MICRONAS

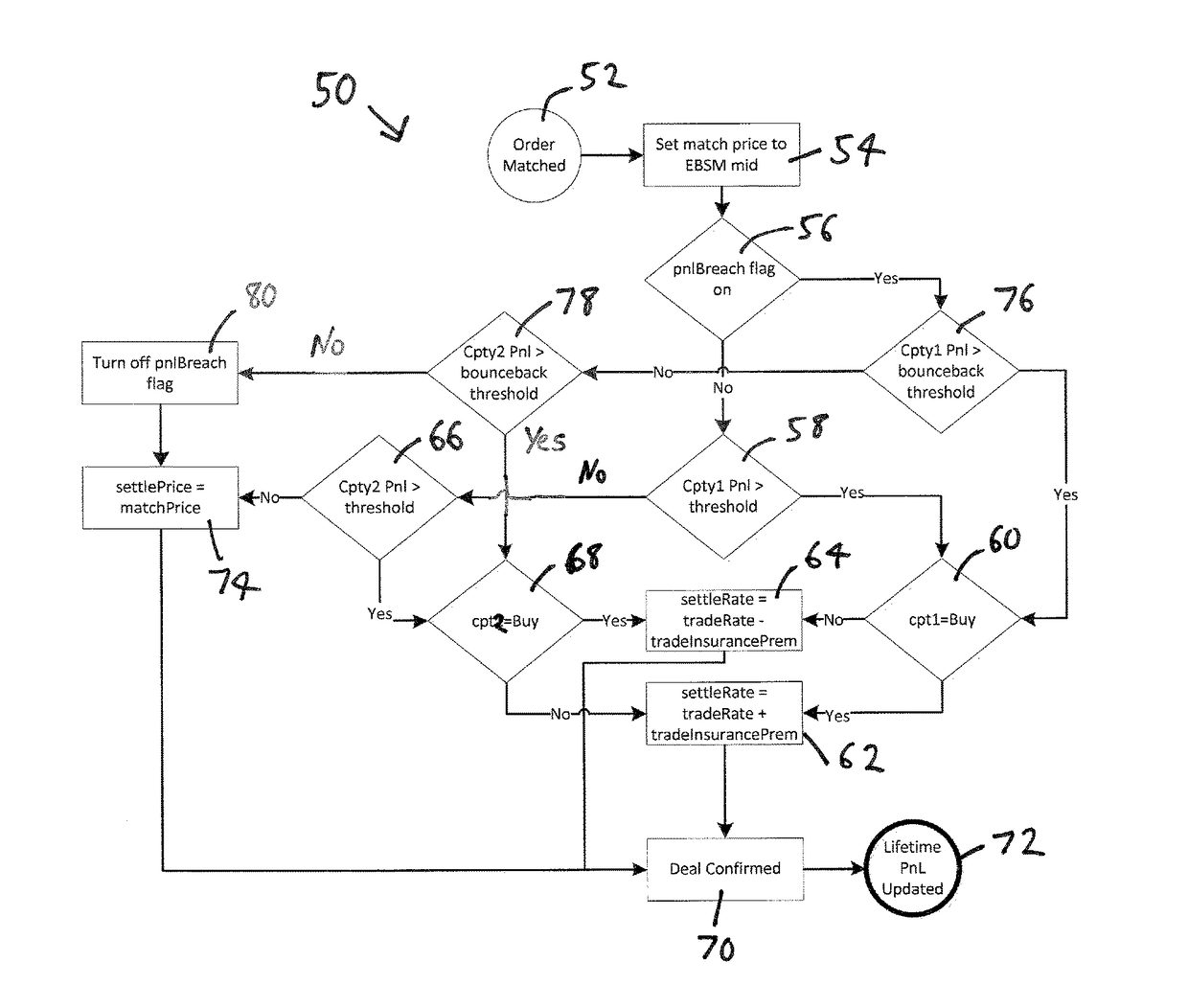

Electrical computer system processing architecture

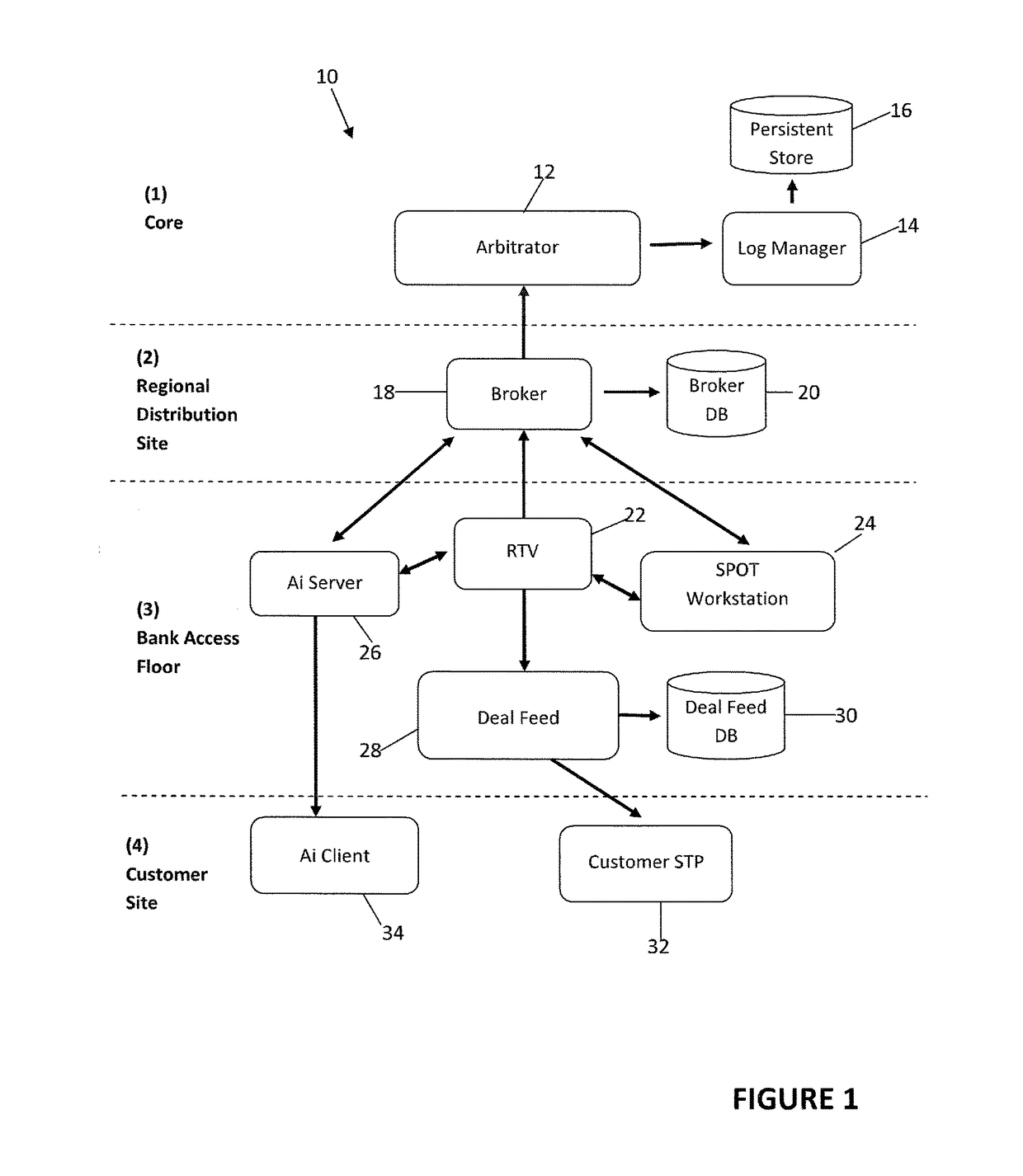

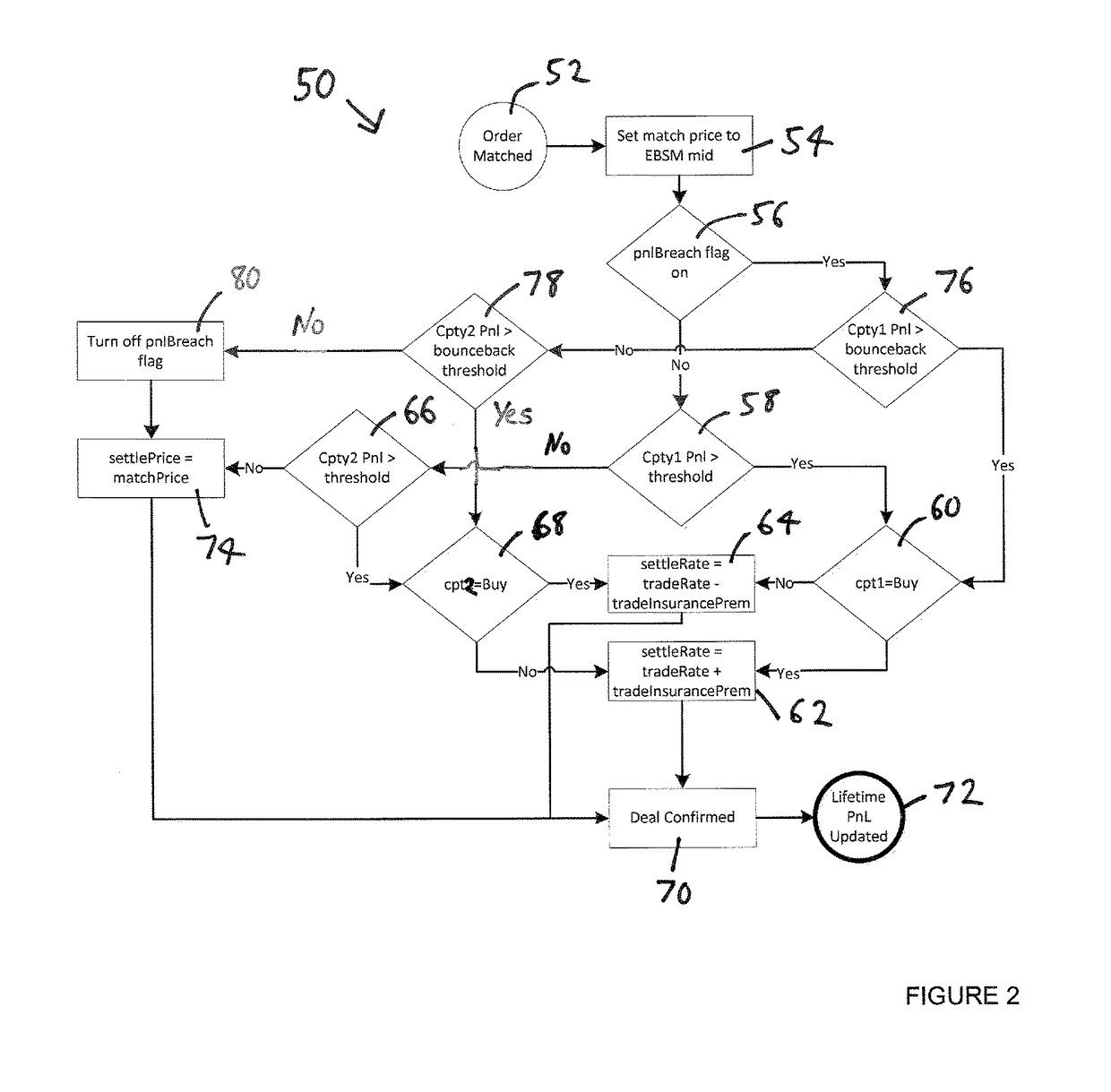

ActiveUS20170257325A1Fairness amongst client computersEliminate the effects ofFinanceData switching networksComputerized systemClient machine

An electrical computer system processing architecture for providing fairness amongst client computers of the computer system is disclosed. The electrical computer system processing architecture comprises a plurality of client computers connected to at least one server by a computer network. Each of the client computers is configured to provide requests to the at least one server. The or each server comprises a store for storing requests provided by the plurality of client computers. The or each server is configured to: match complementary requests from the plurality of client computers stored in the store; following matching of complementary requests, assign an indication of how well the requests have been met compared to requests of other client computers of the computer system; accumulate the indications to form an accumulation of indications; and when the accumulation exceeds a predetermined threshold, match future requests in favour of the client computer whose requests have not been met as favourably with requests of other client computers of the computer system, thereby providing fairness amongst client computers of the computer system.

Owner:ICAP SERVICES NORTH AMERICA LLC

Secured multi-process architecture

ActiveUS20200081754A1Random number generatorsInterprogram communicationInter-process communicationChannel use

Methods, systems, infrastructures and techniques for operating a multi-process application are described. The method includes starting a master process and the master process instantiating a first child process and a first inter-process communication (IPC) channel; and instantiating a second child process and a second IPC channel. The method further includes the master process instantiating a third IPC channel used for a direct peer-to-peer (P2P) communication; and providing first and second handles of the third IPC channel to the first and second child processes, using the first and second IPC channels, respectively. The first child process and the second child process can communicate directly using the received first and second handles of the third IPC channel.

Owner:MOTOROLA SOLUTIONS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com