Back channel etching oxide thin film transistor process architecture

A technology of oxide thin film and back channel, which is applied in the field of back channel etching oxide thin film transistor process architecture, which can solve the problems of increasing production time, reducing output, and interrupting conductive materials

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present disclosure can be understood by referring to the following detailed description in conjunction with the accompanying drawings described below. Note that for clarity of illustration, some elements in the various figures may not have been drawn to scale.

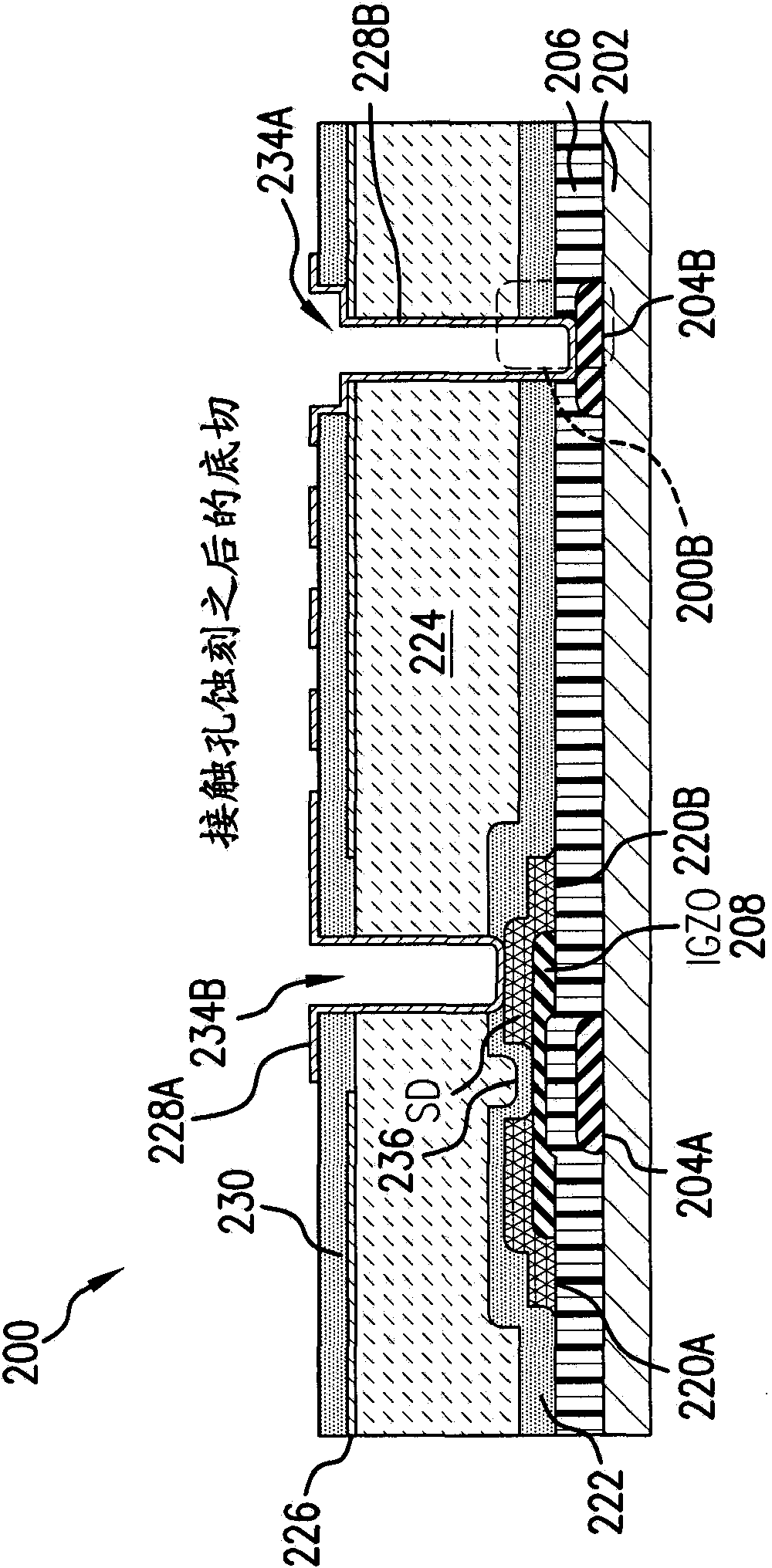

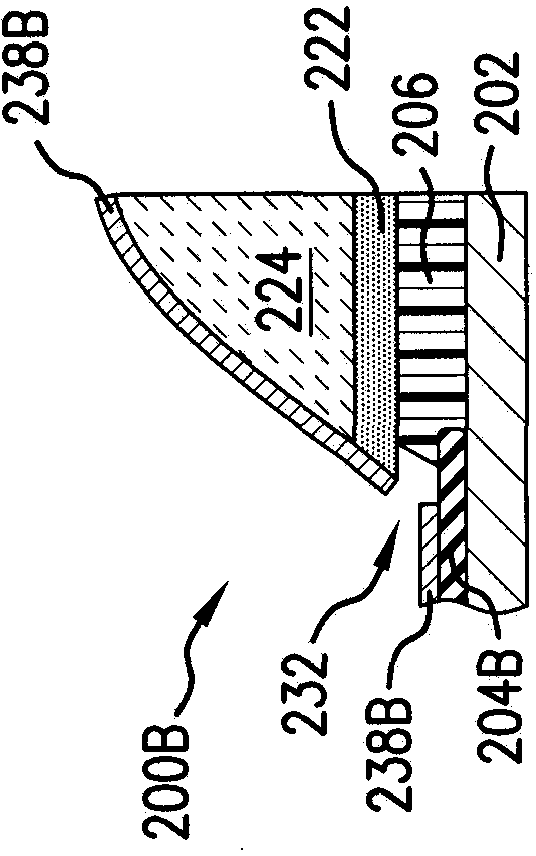

[0042] Figure 2A A cross-sectional view of an oxide TFT for an AMLCD according to an embodiment of the present disclosure is shown. The oxide TFT 200 includes a substrate 202 , a first metal layer disposed on the substrate 202 including a gate electrode 204A and a metal common electrode 204B. The oxide TFT 200 also includes a gate insulator 206 disposed on the gate electrode 204A and the metal common electrode 204B. Oxide TFT 200 also includes a semiconductor such as IGZO layer 208 disposed on gate insulator 206 above gate electrode 204A. The oxide TFT 200 also has a second metal layer including a source electrode 220A and a drain electrode 220B provided on the IGZO 208 . The source and drain electrodes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com