Strained-induced mobility enhancement nano-device structure and integrated process architecture for CMOS technologies

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] According to the present invention, techniques for processing integrated circuits for the manufacture of semiconductor devices are provided. More particularly, the invention provides a method and structures for manufacturing MOS devices using strained silicon structures for CMOS advanced integrated circuit devices. But it would be recognized that the invention has a much broader range of applicability.

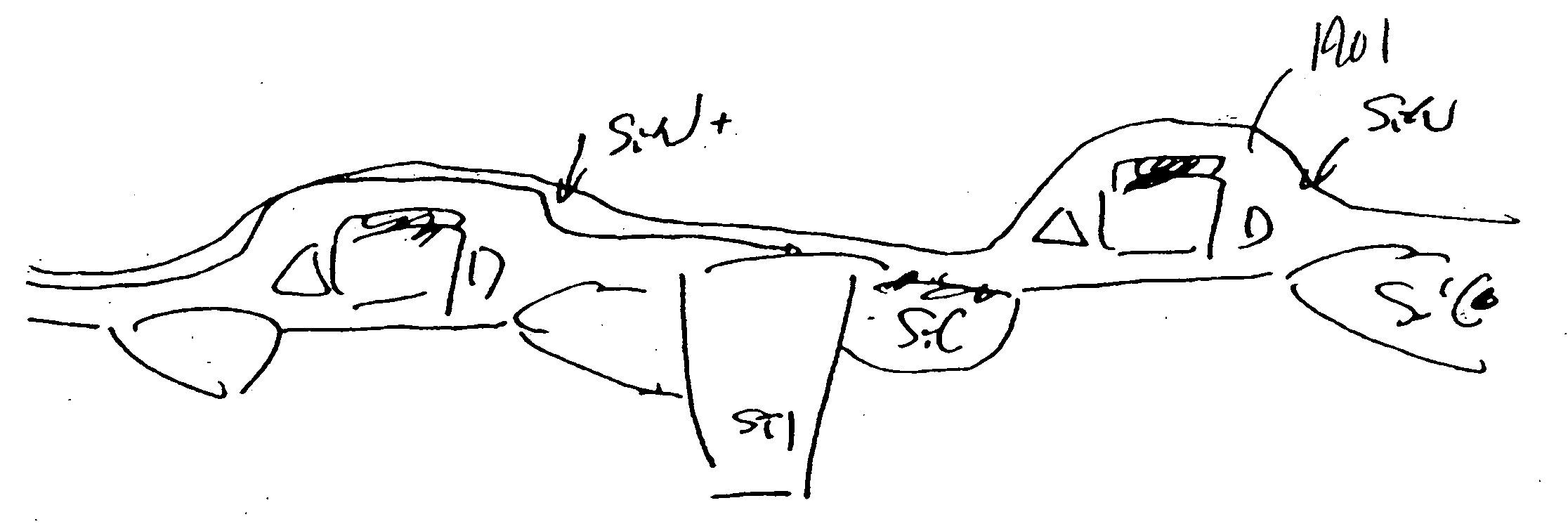

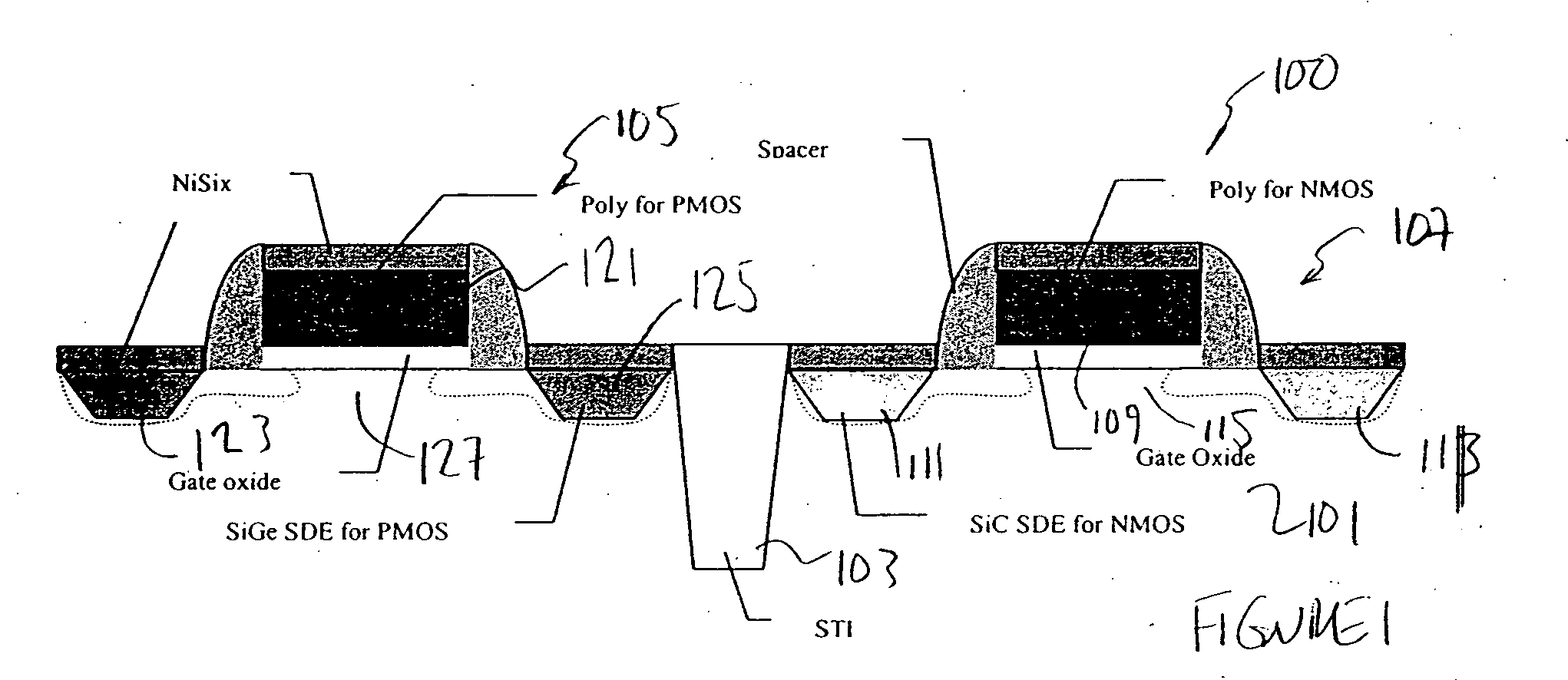

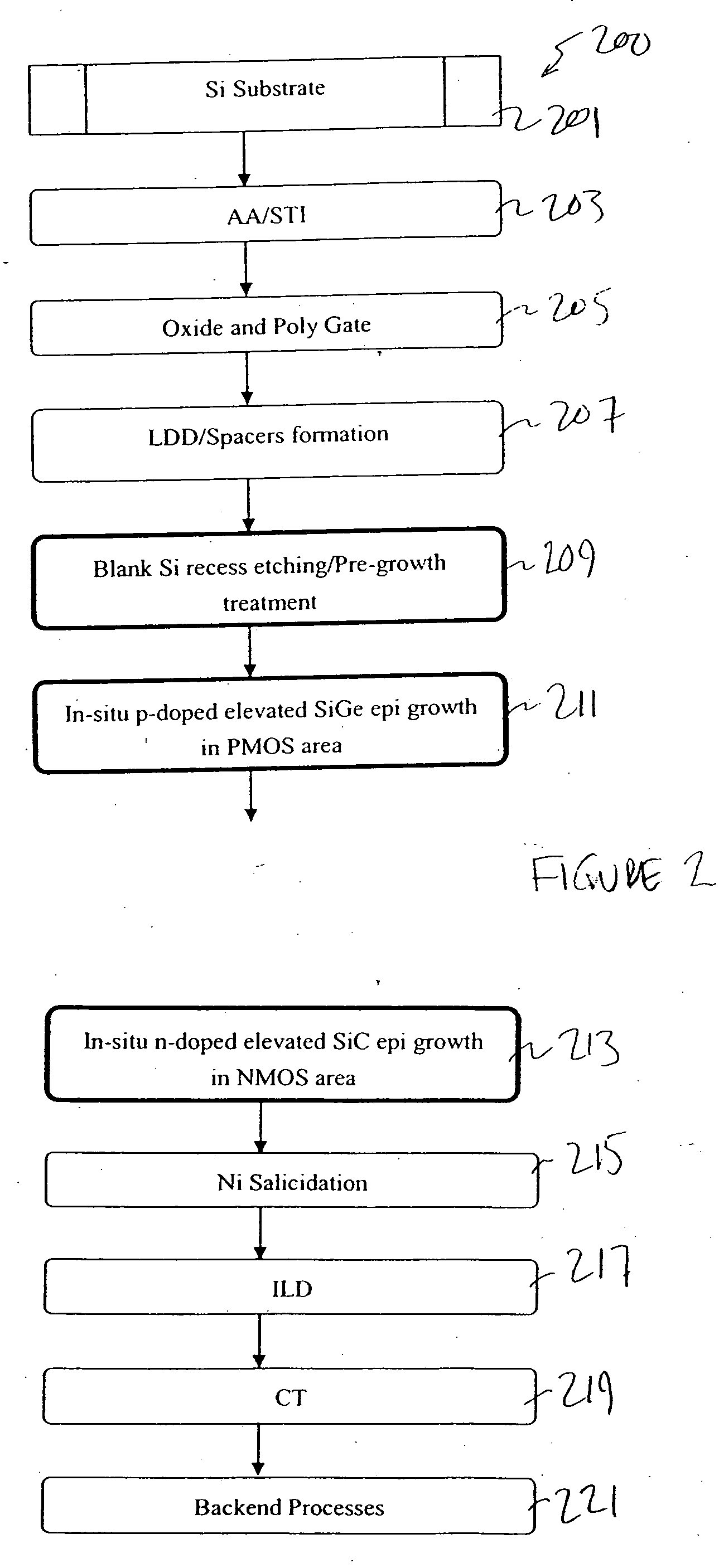

[0020]FIG. 1 is a simplified cross-sectional view diagram of a CMOS device 100 according to an embodiment of the present invention. This diagram is merely an example, which should not unduly limit the scope of the claims herein. One of ordinary skill in the art would recognize many variations, alternatives, and modifications. As shown, the CMOS device includes an NMOS device 107 comprising a gate region 109, a source region 111, a drain region 113 and an NMOS channel region 115 formed between the source region and drain region. Preferably, the channel region has width of less t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com