Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

89 results about "Nios II" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Nios II is a 32-bit embedded-processor architecture designed specifically for the Altera family of field-programmable gate array (FPGA) integrated circuits. Nios II incorporates many enhancements over the original Nios architecture, making it more suitable for a wider range of embedded computing applications, from digital signal processing (DSP) to system-control.

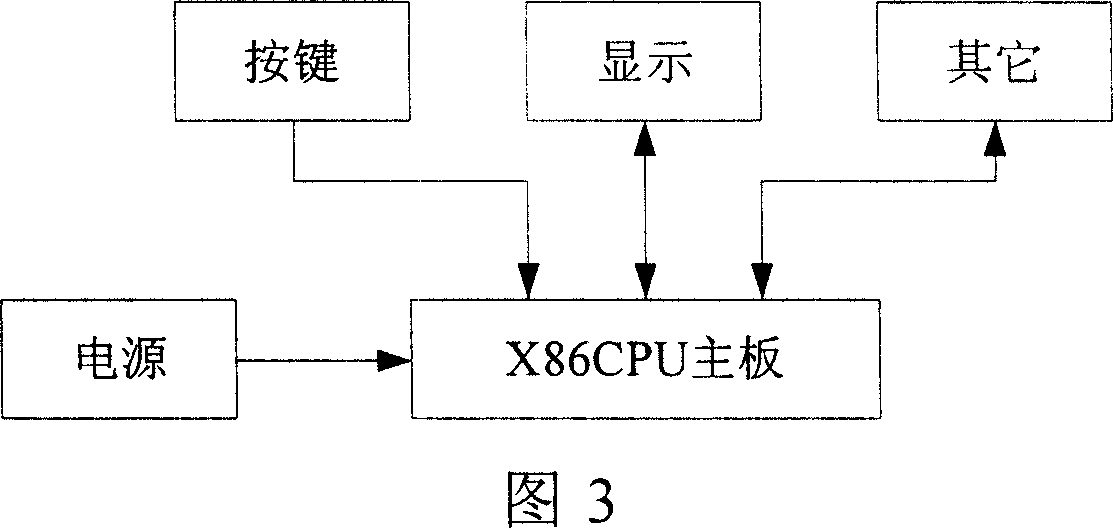

Embedded multinuclear main controller of modular robot based on FPGA (Field Programmable Gata Array)

InactiveCN102393656AReduce volumeReduce energy consumptionProgramme control in sequence/logic controllersDigital signal processingJoint Test Action Group

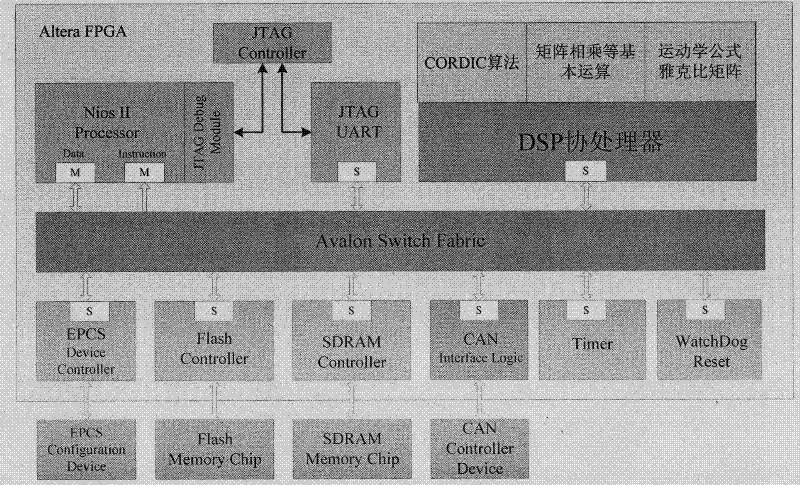

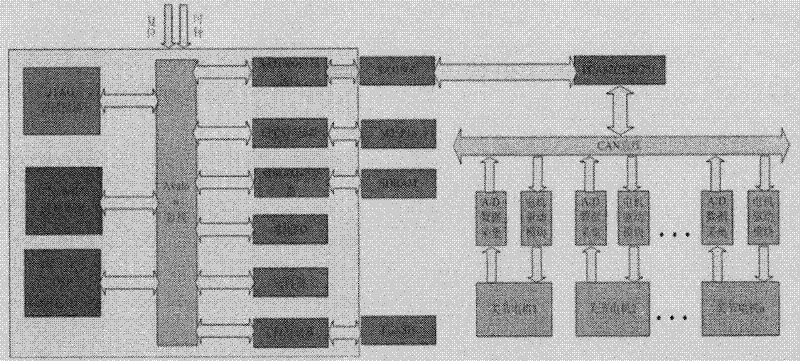

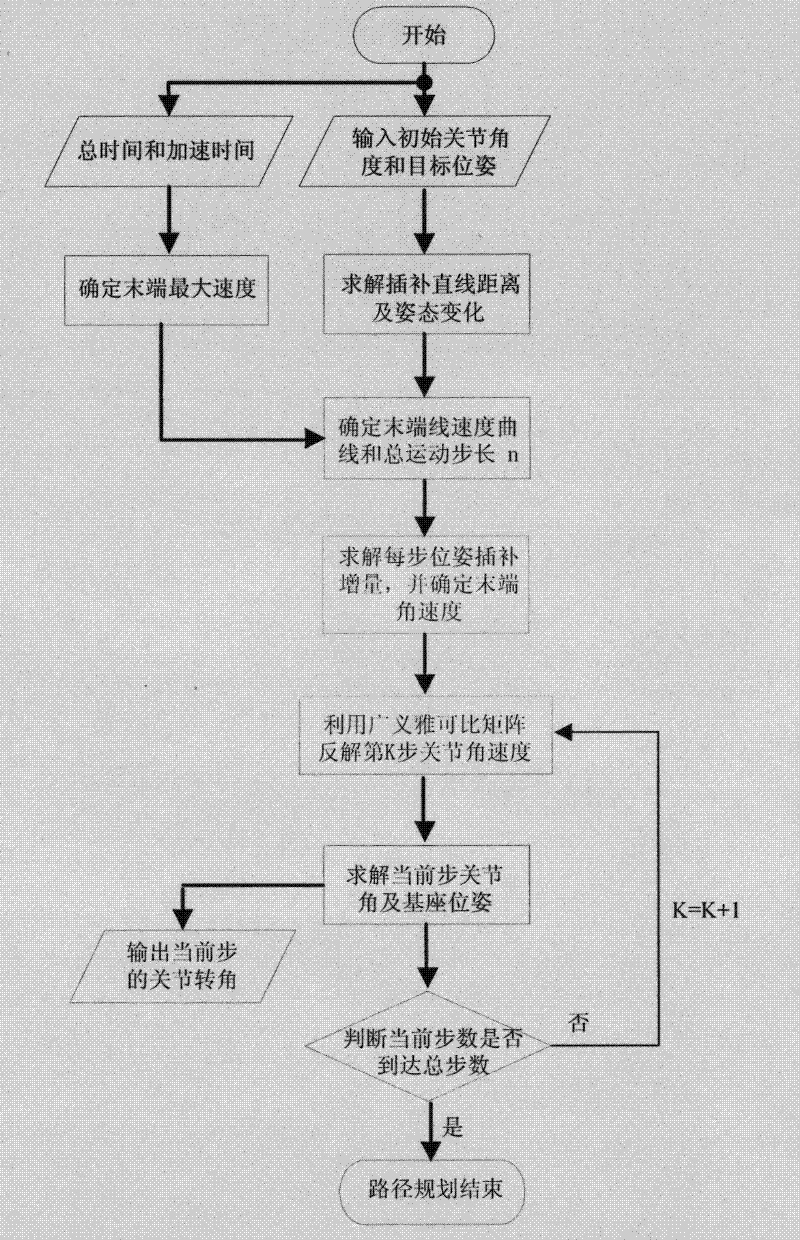

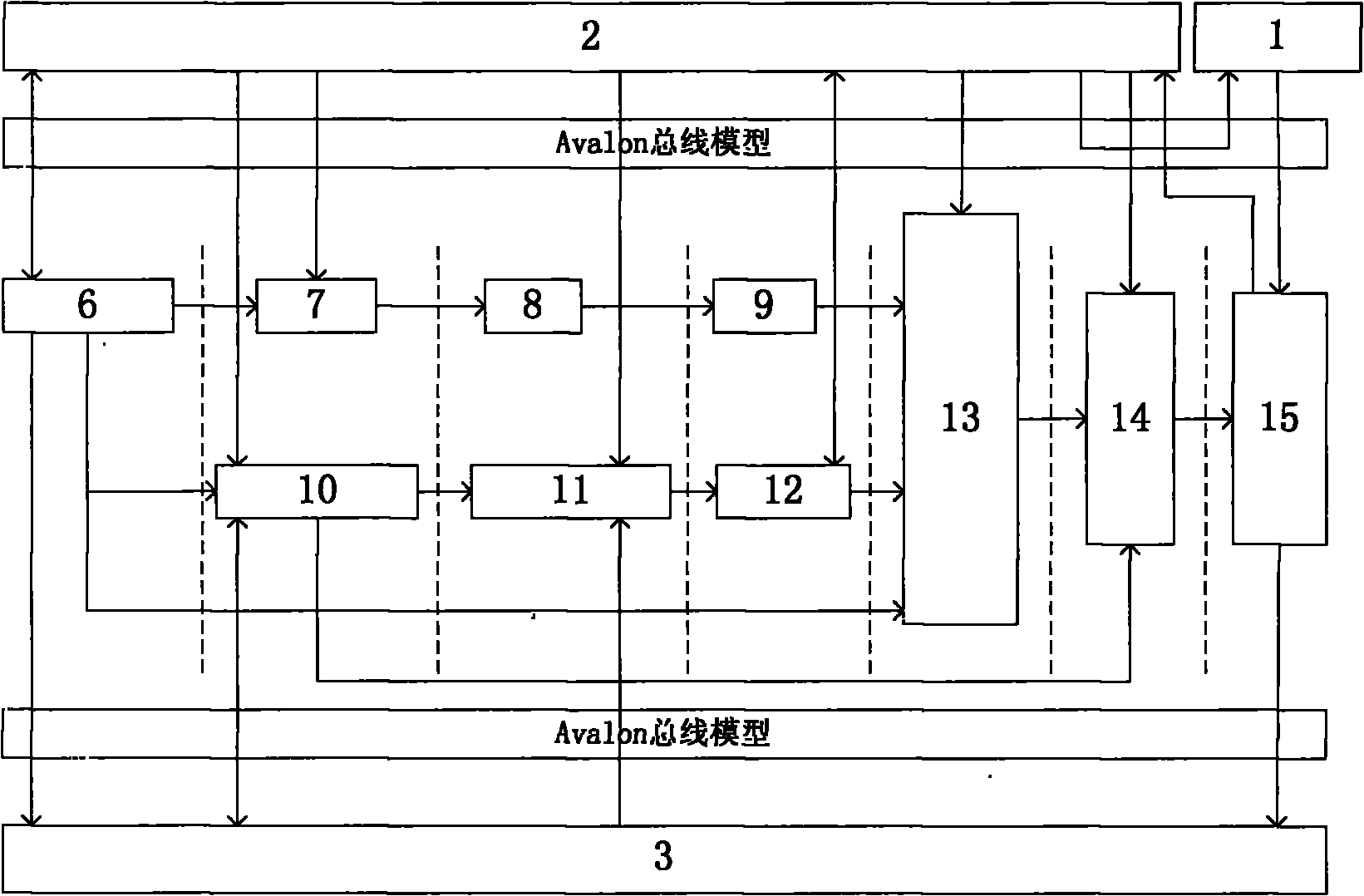

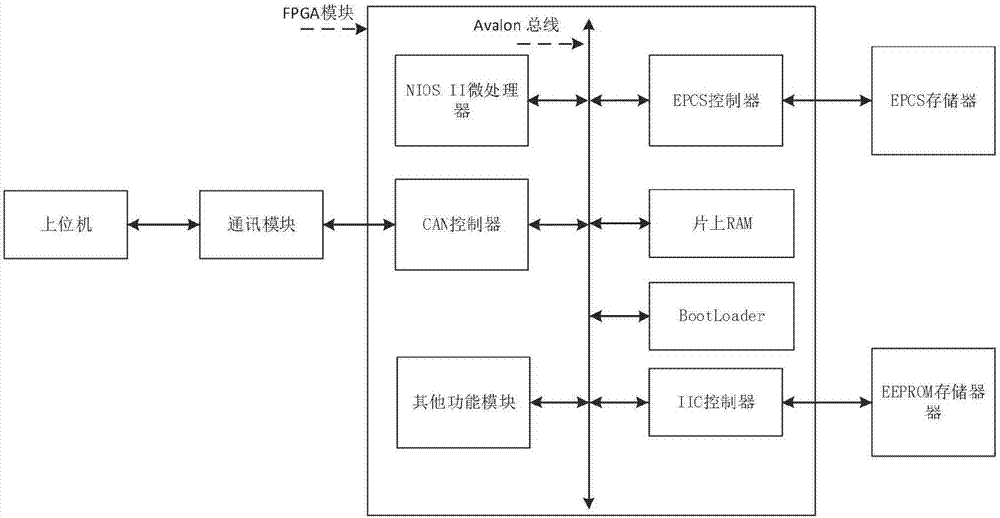

The invention discloses an embedded multinuclear main controller based on an FPGA (Field Programmable Gata Array) chip in the technical field of robot control. The main controller integrates two main modules, namely a Nios II soft core processor and a DSP (Digital Signal Processing) coprocessor, wherein the Nios II soft core processor communicates with a system clock module, a watchdog and resetting system module, a JTAG interface module, a CAN serial bus control module and a memorizer control module by an Avalon bus module; as a hardware computing core, the DSP coprocessor communicates with a Nios II soft core by the Avalon bus module; and the Nios II soft core is responsible for the movement planning of a robot and the communication of each controller at each joint, and the coprocessor is responsible for kinetic resolving. The embedded multinuclear main controller adopts the Nios II soft core as a communication core and the coprocessor as a computing core to realize the rapid and stable control and reduce energy consumption and the volume.

Owner:BEIJING UNIV OF POSTS & TELECOMM

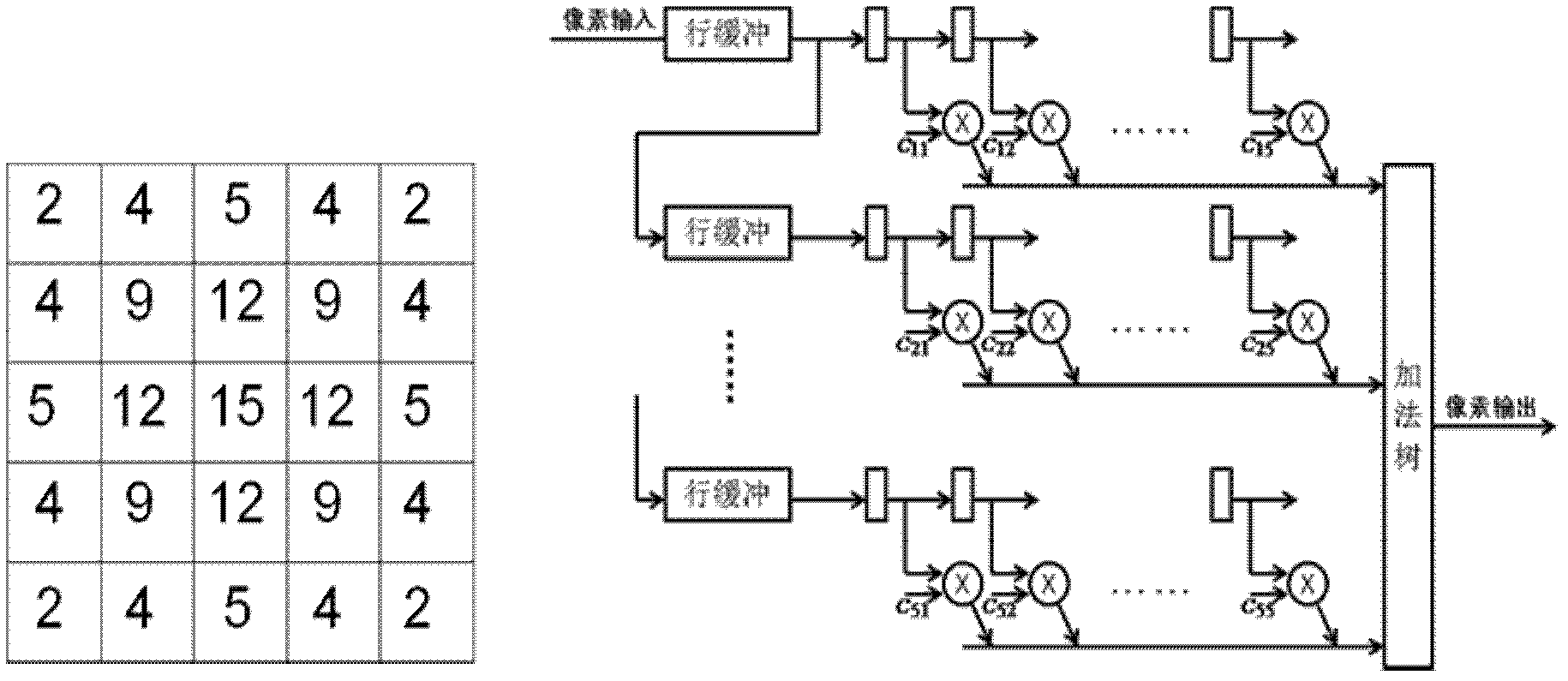

Image acquiring and processing method based on FPGA (field programmable gate array) serving as control core

InactiveCN102663758AImprove signal-to-noise ratioImprove detection accuracyImage analysisCMOSGraphics

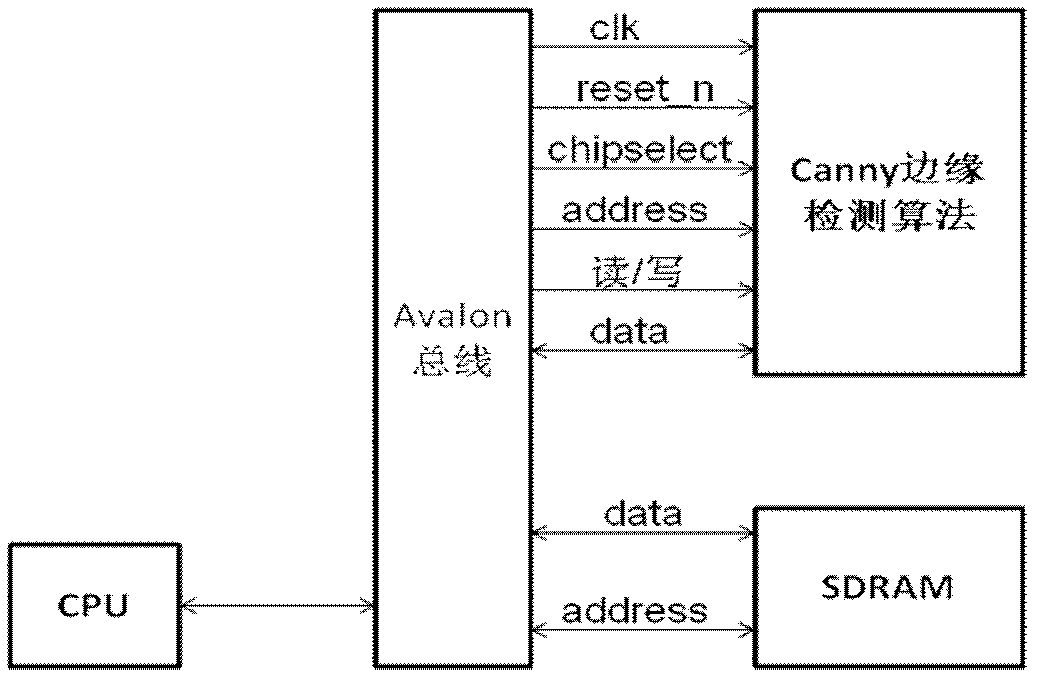

The invention belongs to the field of image acquiring and processing, and particularly relates to an image acquiring and processing method based on an FPGA (field programmable gate array) serving as a control core. The method mainly includes building an image acquiring and processing SOPC (system on programmable chip) system comprising a Nios II soft-core processor module, a CMOS (complementary metal-oxide-semiconductor transistor) image sensing controller module, an FIFO (first in first out) controller module, an SDRAM (synchronous dynamic random access memory) controller module, a Canny edge detection algorithm module and a VGA (video graphic array) controller module. Firstly, images are acquired and then cached in the FIFO controller module; secondly, image data in the FIFO controller module are transmitted to an off-chip SDRAM chip by FPGA software and are stored in the off-chip SDRAM chip; thirdly, images in a memory are processed by means of an image processing algorithm, 'ping pong operation' is realized during processing, and the processing images are stored in the SDRAM again; and finally, the acquired edge images are displayed through a VGA interface after being processed.

Owner:BEIJING UNIV OF TECH

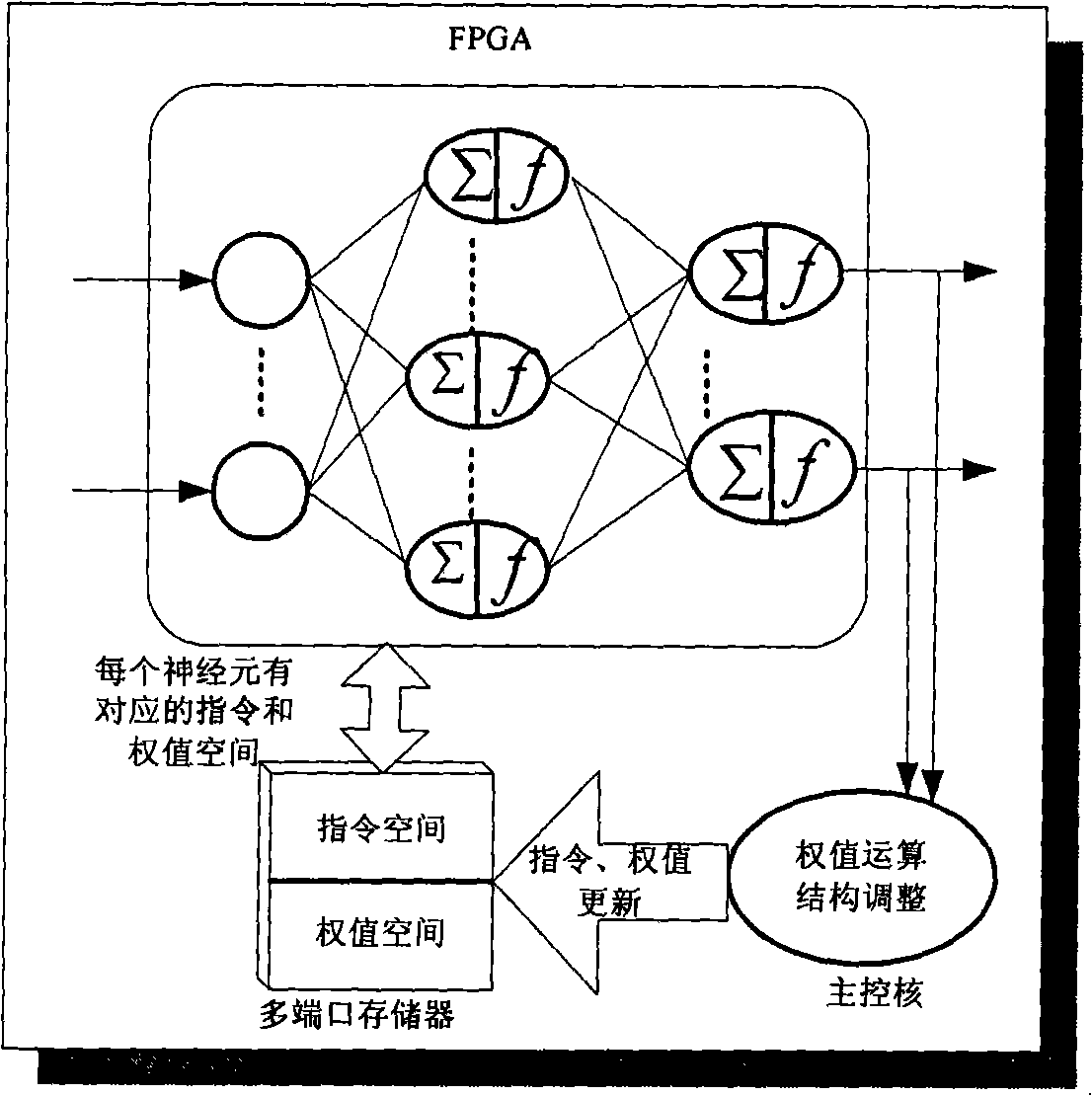

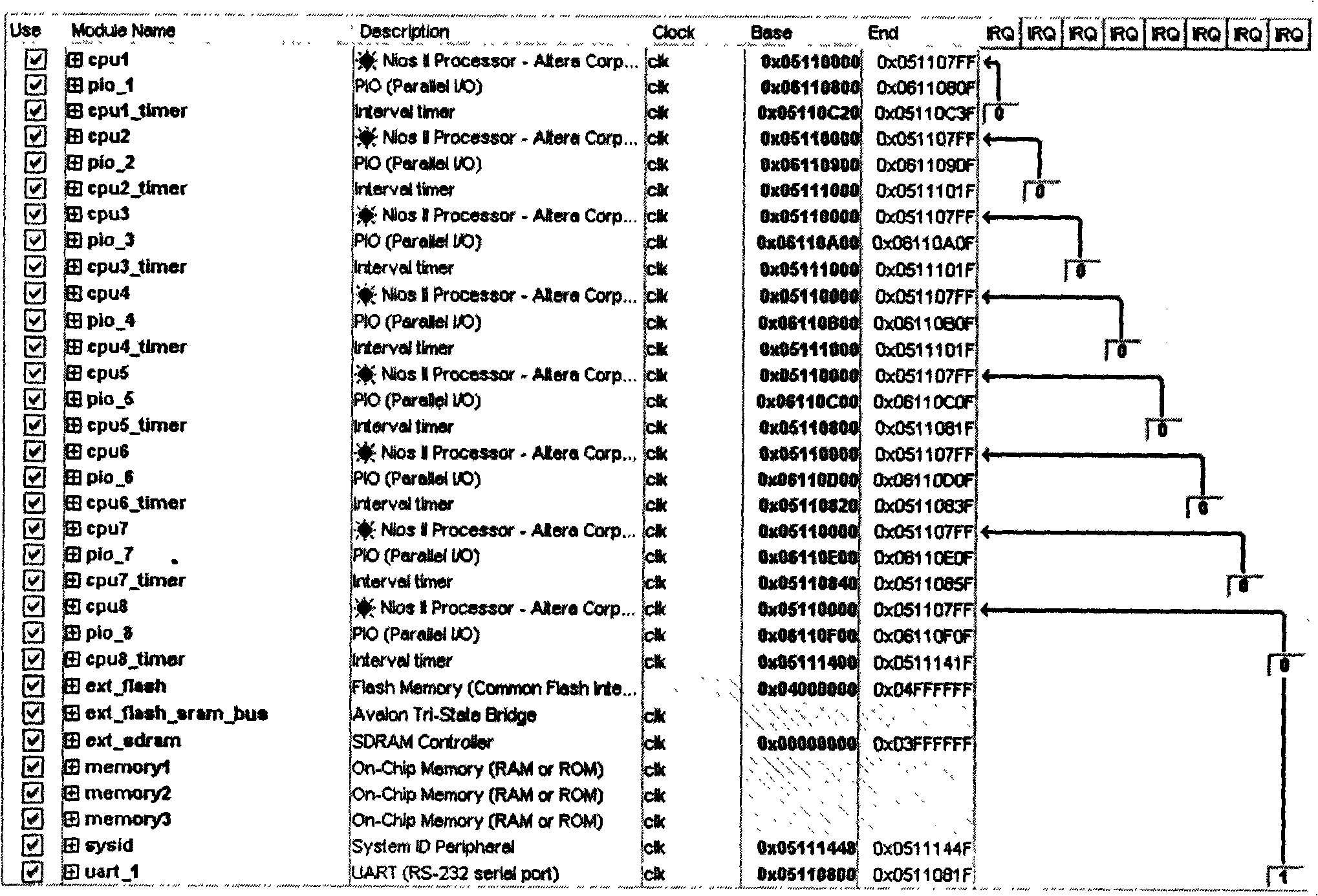

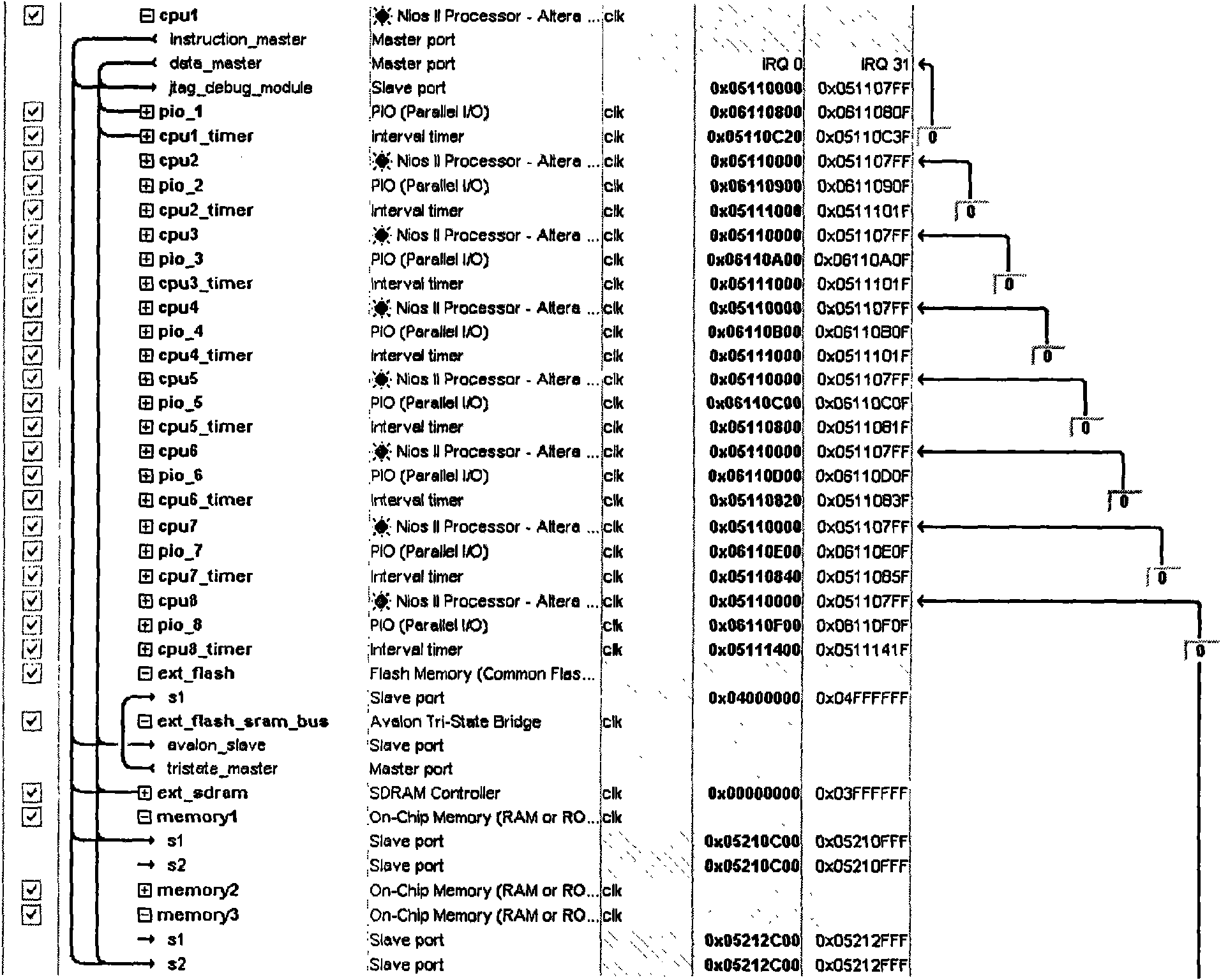

Feedforward neural network hardware realization method based on multicore technology

The invention discloses a feedforward neural network hardware realization method based on multicore technology, relating to a computer system based on a specific calculation model. The invention adopts an NIOS II soft core processor and utilizes Quartus II software in an FPGA development system thereof to build a multicore processor system, the number of processor cores is only limited by chip scale, each processor core can be independently programmed, and multiple processor cores can simultaneously run respective program and simulate the characteristics of nerve cells of any kind by performing programming of one single core; in the network studying process, the single cores calculate output amount in a parallel mode and finish the adjustment of corresponding weights and thresholds; the input and output of each single core are performed with data exchange via a multiport memory to stimulate feedforward neural network with any structure, which realizes the purposes of high speed, distribution and parallel calculation of the neural network.

Owner:王连明

Device for online detecting and locating cable fault based on SOPC (System On Programmable Chip) technology

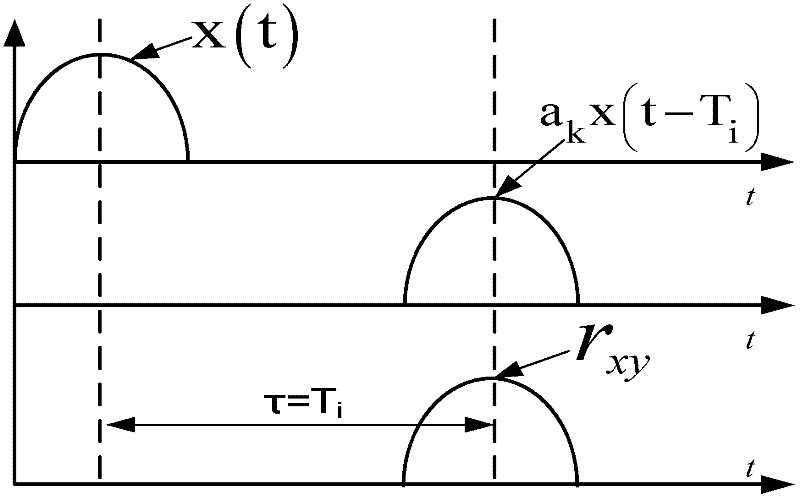

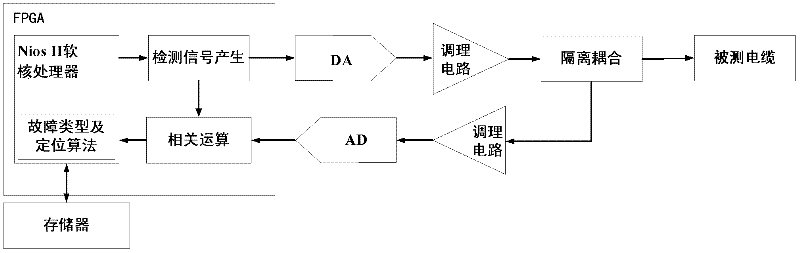

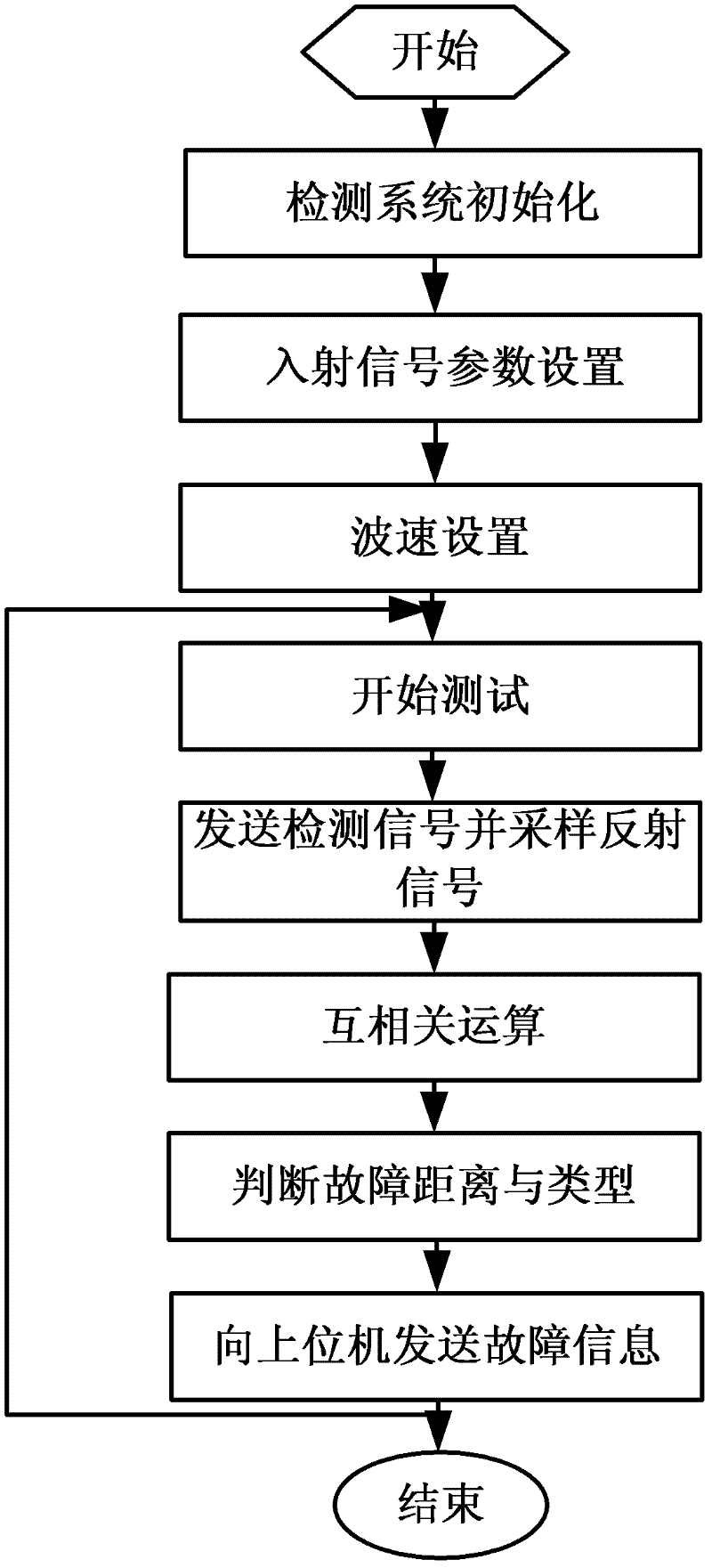

InactiveCN102435916AWith programmableIncrease flexibilityFault location by pulse reflection methodsInterference resistanceSignal conditioning

The invention discloses a device for online detecting and locating cable fault based on SOPC (System On Programmable Chip) technology, which comprises an FPGA (Field Programmable Gate Array) module with a NIOS II soft core, a high-speed DA module, a signal conditioning module, a separating coupling module and a high-speed AD module, wherein the FPGA (Field Programmable Gate Array) module generates detecting signals for detecting cable faults; the detecting signals are converted into analog signals by the high-speed DA module; then the analog signals are converted into detecting signals with proper amplitude by the signal conditioning module; the detecting signals are coupled into the detected cable in working state by the separating coupling module; meanwhile, the feedback signals from the cable fault points are received from the separating coupling module; the feedback signals are converted into digital signals by the high-speed AD module and the digital signals are sent to the FPGA (Field Programmable Gate Array) module with NIOS II soft core; and the fault type and fault distance information of the tested cable is acquired by the digital signals through relative calculation and fault detecting and locating algorithm. The cable fault can be detected and located in real time by the device. In addition, the device has advantages of accurate test, high test precision, strong interference resistance, high integration level and the like.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

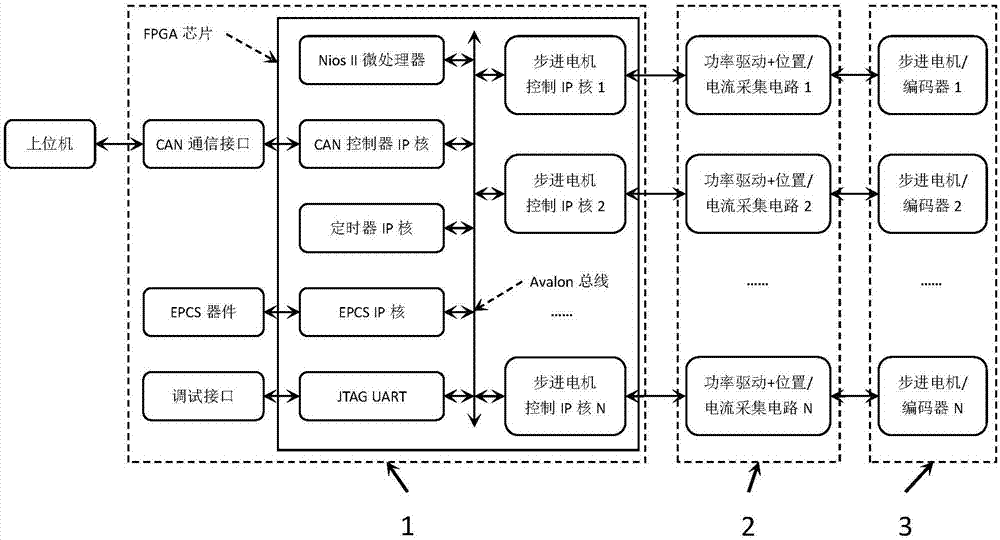

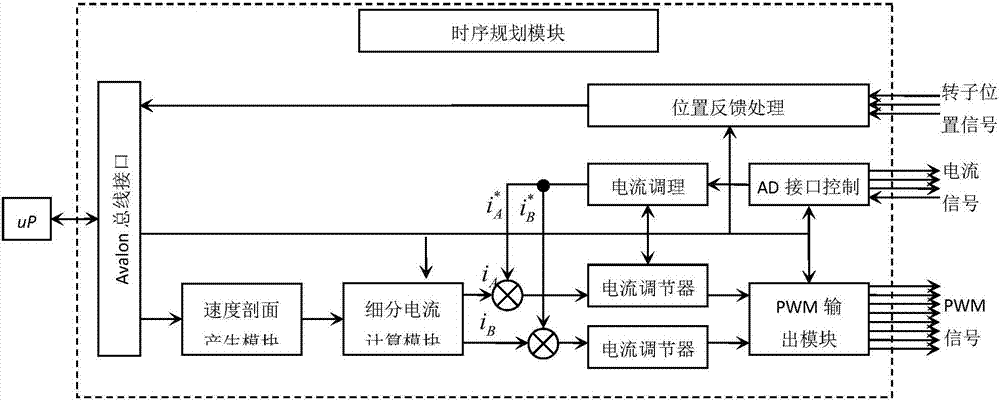

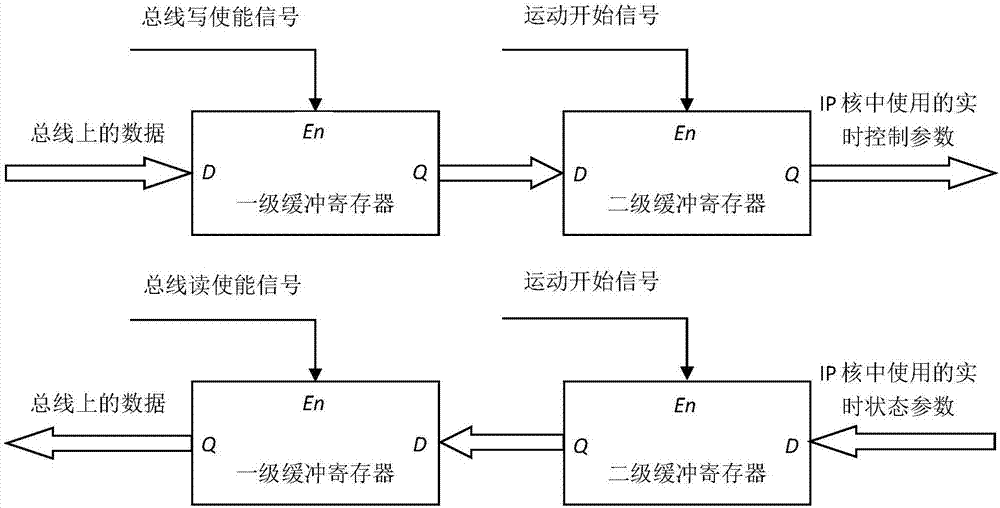

Multi-shaft stepping motor controller system based on FPGA chip

InactiveCN107124125AResolve synchronizationAchieve high integrationProgramme controlComputer controlControl theoryProgrammable hardware

The invention relates to a multi-shaft stepping motor controller system based on an FPGA chip. The system comprises an FPGA control module and a multi-channel power drive and signal acquisition module. The FPGA control module comprises a Nios II microprocessor, a CAN controller IP core, a multi-channel stepping motor control IP core and the like. The stepping motor control IP core is used for the control of the stepping motor current subdivision drive and the trajectory motion. Each channel of stepping motor control IP core is connected with a channel of power drive and signal acquisition module, and then is connected with a channel of stepping motor / encoder. According to the invention, the control architecture has the characteristics of FPGA-rich programmable hardware resources and parallel processing; precision control of multi-channel (up to 25) stepping motors is realized through a single chip; and the multi-shaft stepping motor controller system has the advantages of miniaturization, low cost, high flexibility and the like.

Owner:SOUTHWEST JIAOTONG UNIV

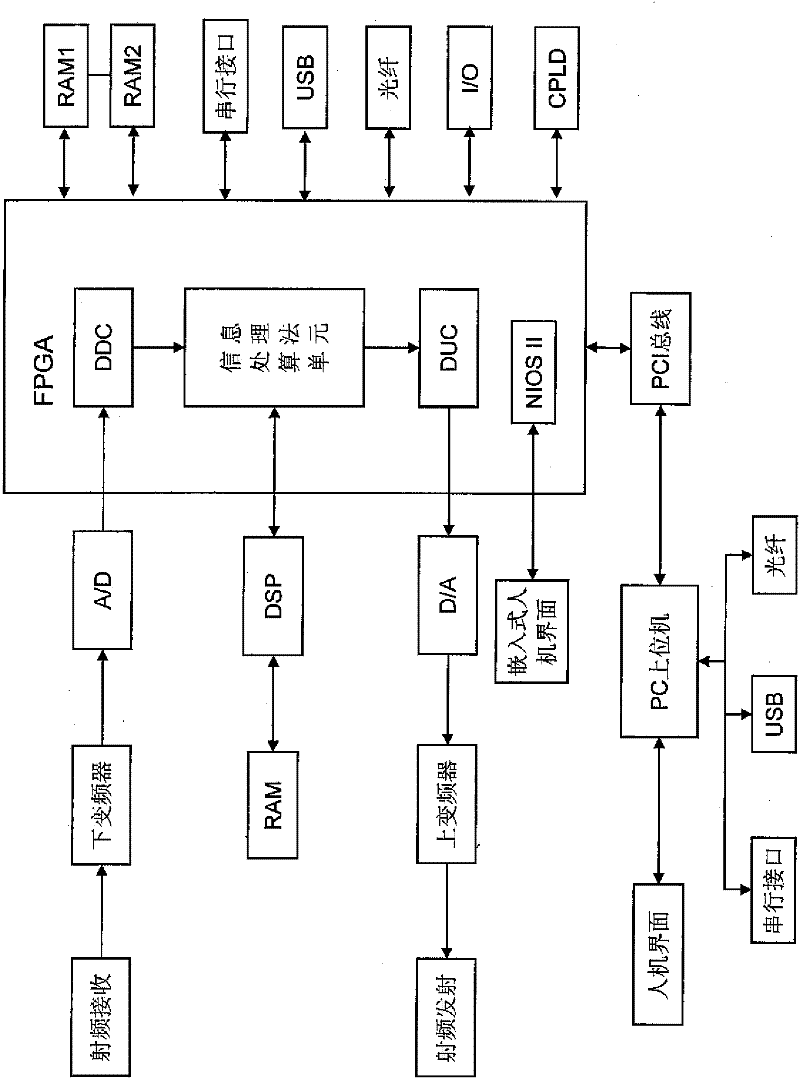

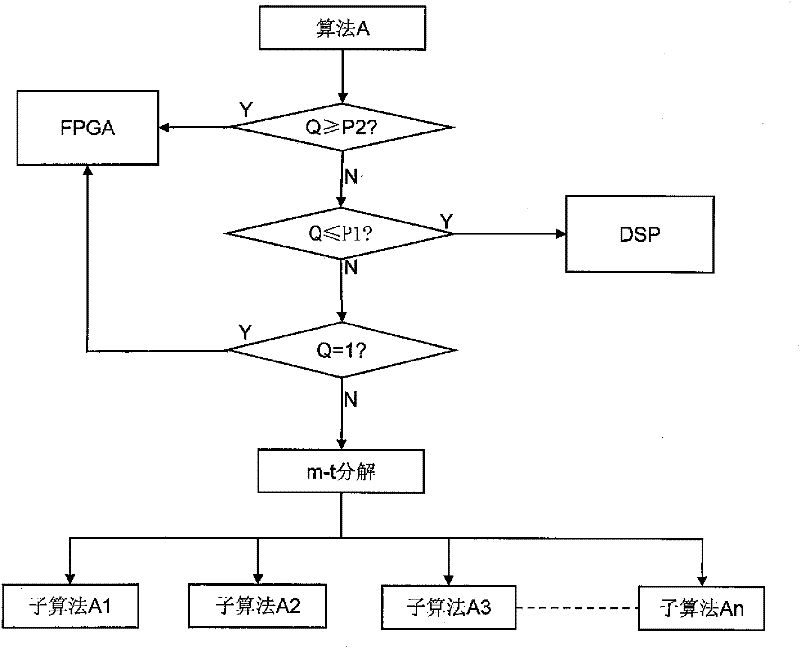

Linear frequency-modulated continuous wave automobile anti-collision radar system and using method thereof

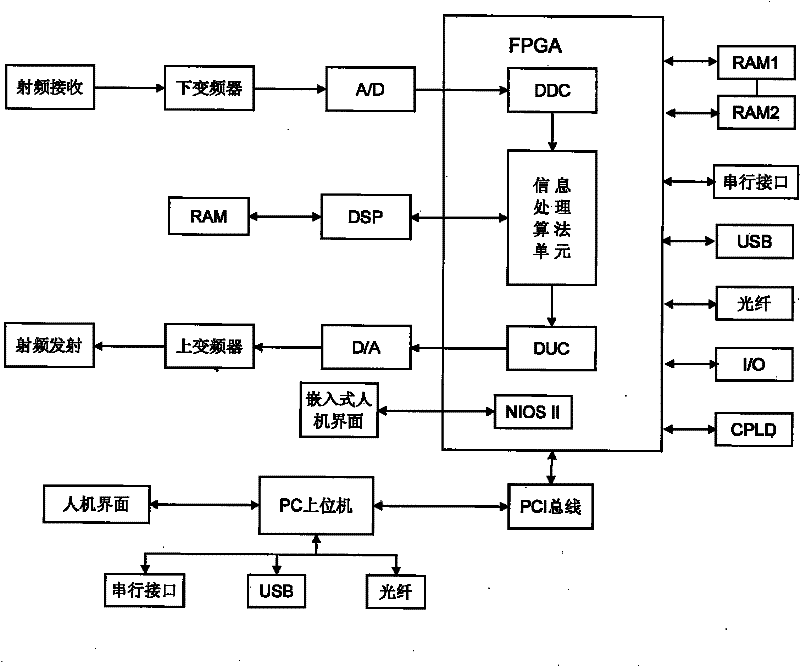

InactiveCN102353954AImprove execution efficiencyGuaranteed continuityRadio wave reradiation/reflectionInformation processingHuman–machine interface

The invention relates to a linear frequency-modulated continuous wave automobile anti-collision radar system and a using method thereof. An information processing platform of the radar system comprises a dual processor formed by a DSP and an FPGA. An information processing algorithm unit of the FPGA contains a space-time complexity rate distribution module. The DSP has an RAM and the FPGA has twoRAMs, so that an operating speed is improved. A serial port, a USB, an I / O, a PCI bus and a fiber interface are configured to the FPGA. An NIOS II can be embedded into the FPGA. And the FPGA is connected with a host computer having a human-computer interface; and the host computer can be connected with an alarm device and / or an automatic brake device and the like. According to the method providedin the invention, an information processing platform carries out calculation processing on real-time data to obtain real-time data of positions and speeds of front objects, and then the real-time data are displayed at an human-computer interface; a space-time complexity rate distribution method is employed to carry out m-t decomposition according to a space-time complexity rate Q for processing radar signal algorithms; and the various algorithms are respectively sent to an FPGA and a DSP for completion according to an upper threshold and a lower threshold. Therefore, advantages of the FPGA and the DSP are fully utilized; the work is done smoothly; the efficiency is high; images front the automobile can be reflected in real time; safe driving can be assisted; and anti-collision performancecan be well realized.

Owner:GUILIN UNIV OF ELECTRONIC TECH

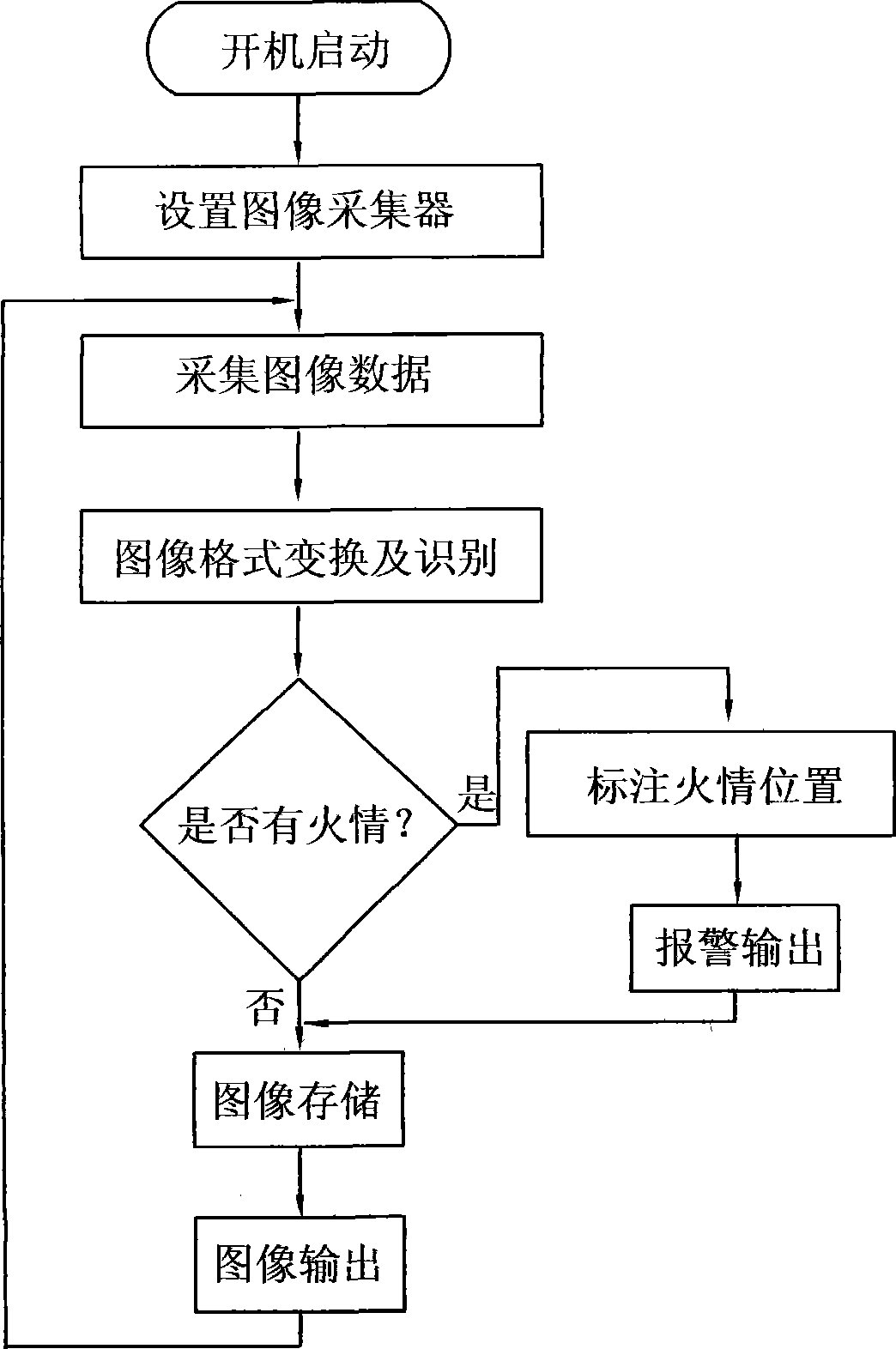

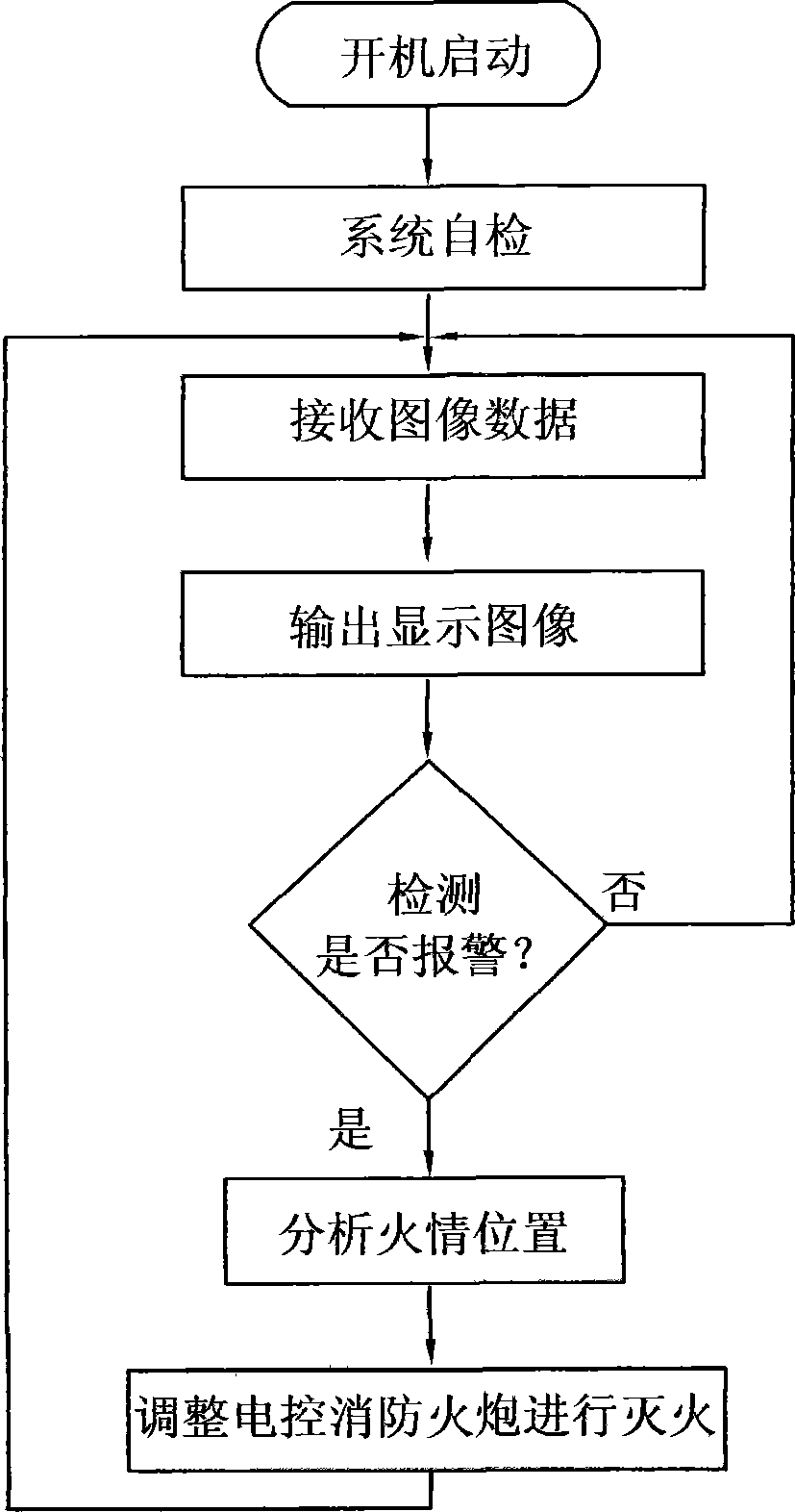

Automatic fire-extinguishing system based on NiosII video image recognition

InactiveCN101502707ASolve the problem of low accuracy of automatic fire extinguishing workSimple structureCharacter and pattern recognitionFire rescueVideo image processorWater monitor

The invention discloses an automatic fire extinguishing system of Nios II-based video image identification, comprising a camera, an image collector, an Nios II-based video image processor, a controller based on embedded ARM and an electrically controlled fire water monitor; the invention is characterized in that: the camera is connected with the image collector which is connected to a corresponding external function pin of the Nios II-based video image processor, the corresponding function pin of the Nios II-based video image processor is connected with a corresponding function pin of the controller based on embedded ARM and the corresponding external function pin of the controller based on embedded ARM is connected with the electrically controlled fire water monitor; the controller based on embedded ARM receives the fire condition position signal and the impingement position signal of the water column, the difference of the fire condition position and the impingement position of the water column is calculated, the movement of driving the electrically controlled fire water monitor is controlled, thus causing the impingement position of the water column and the fire condition position to be overlapped, and achieving the aim of fast and precise fire extinguishing.

Owner:许如臣 +2

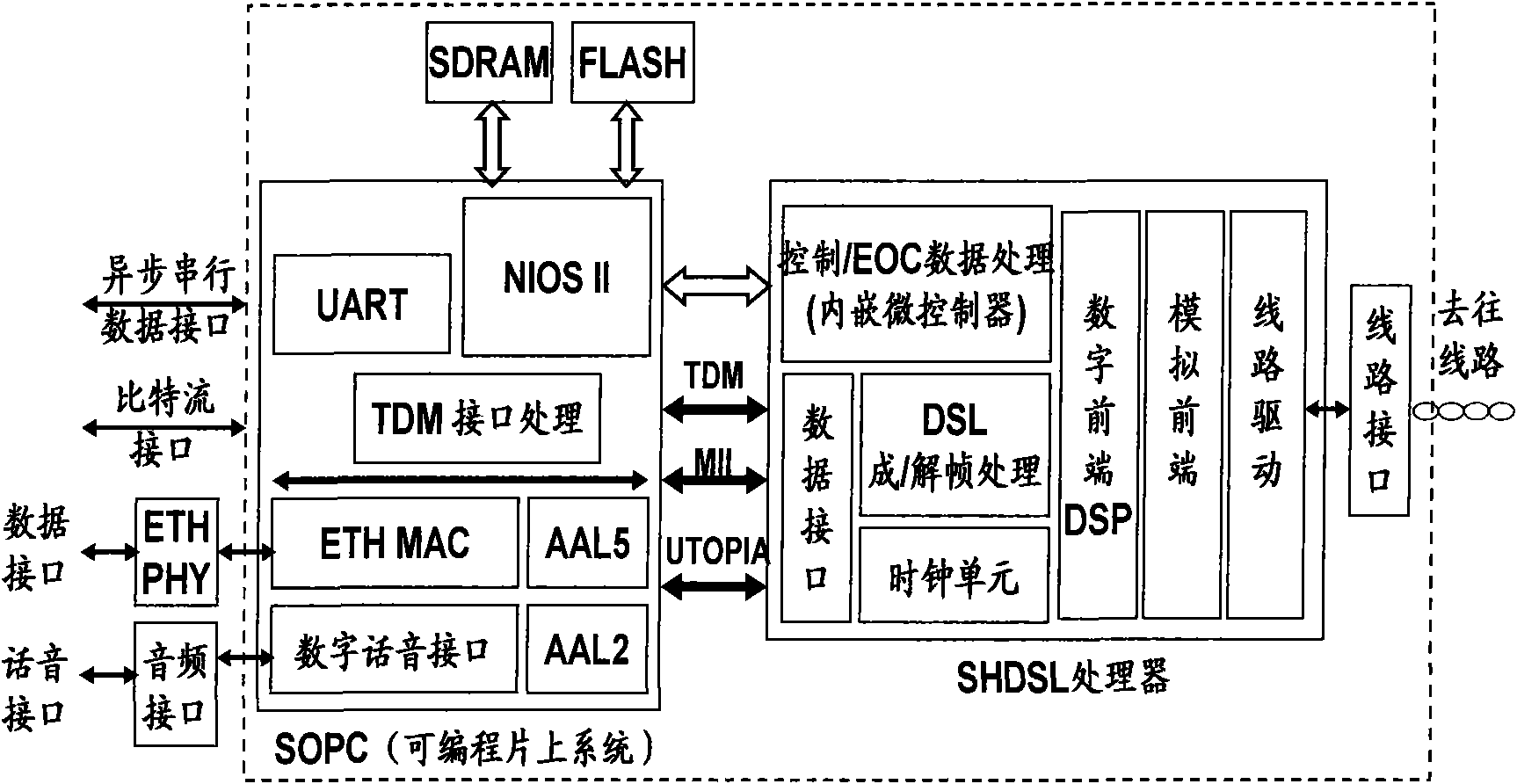

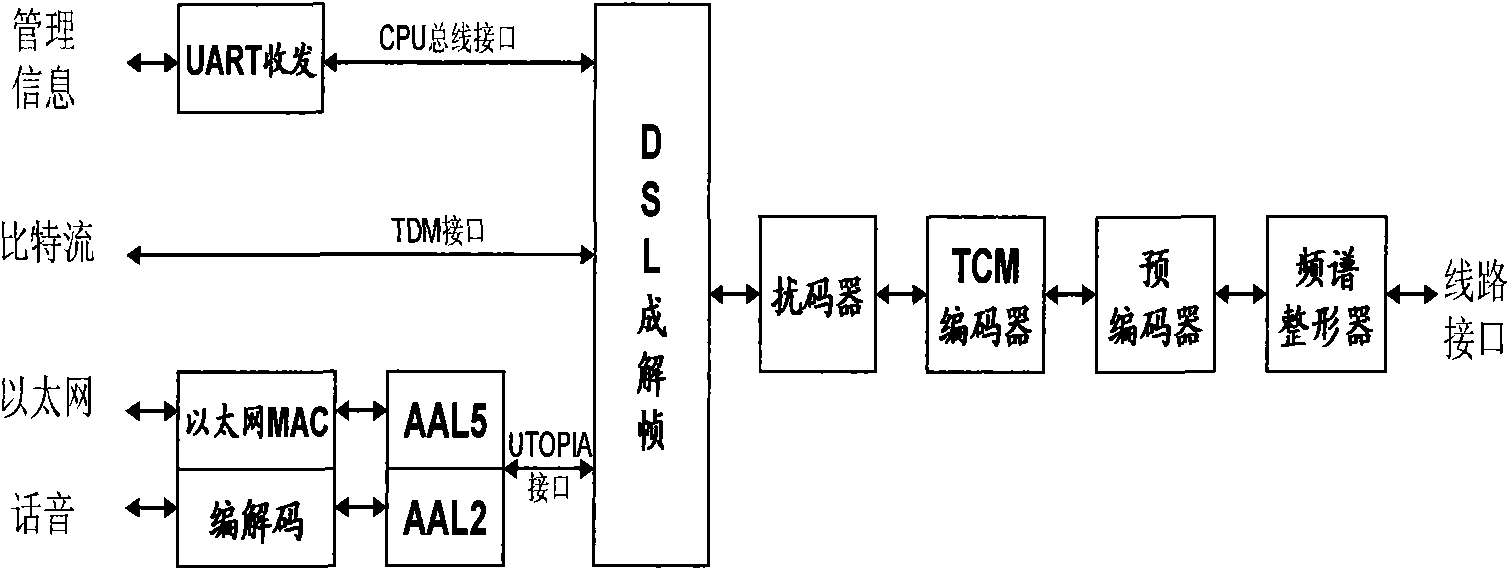

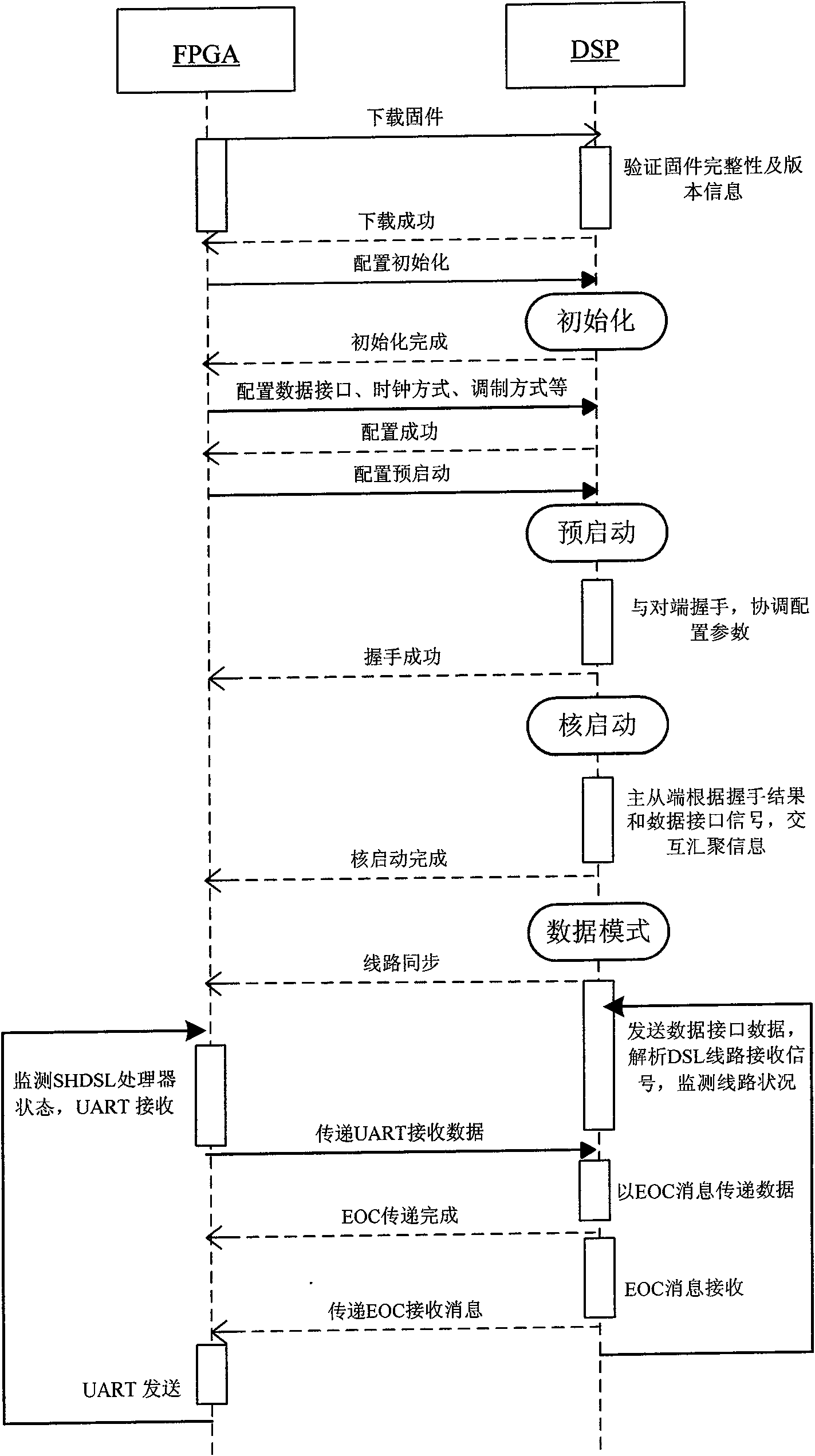

Full-speed wired remote-transmission module

InactiveCN101594363ATo solve the need to adopt SHDSLSolving the Deficiencies of the Two Technologies of VDSLTransmissionData interfaceComputer science

The invention discloses a full-speed wired remote-transmission module, which comprises two parts of an SOPC and an SHDSL processor, wherein the SOPC is in charge of finishing the interaction with the SHDSL process through a CPU soft-core NIOS II, processing forwarding management information, controlling the logic of the entire remote-transmission module from a starting state to a synchronous state, and providing three service data interfaces and a route of management information interface for a user; and the SHDSL is in charge of finishing the extended TC-PAM modulation based on G.991.2, G.994.1 and G.997.1 protocols of an ITU organization at a digital front end, and achieving twisted-pair transmission at a bidirectional symmetrical load rate of between 128 and 8,192 kbit / s per second. The full-speed wired remote-transmission module has the following advantages: the problems that the conventional remote-transmission module has the defect caused by adopting two techniques of the SHDSL and a VDSL and line interference and can hardly finish the interlocking of clocks at a master end and a slave end are solved; and in the aspect of transmission distance, the remote-transmission moduleimproves the transmission distance to a large extent compared with the conventional remote-transmission module when the transmission rate is same, thus the full-speed wired remote-transmission modulecan reach the transmission distance of between 1 and 10 kilometers through a light coated wire.

Owner:CHONGQING JINMEI COMM

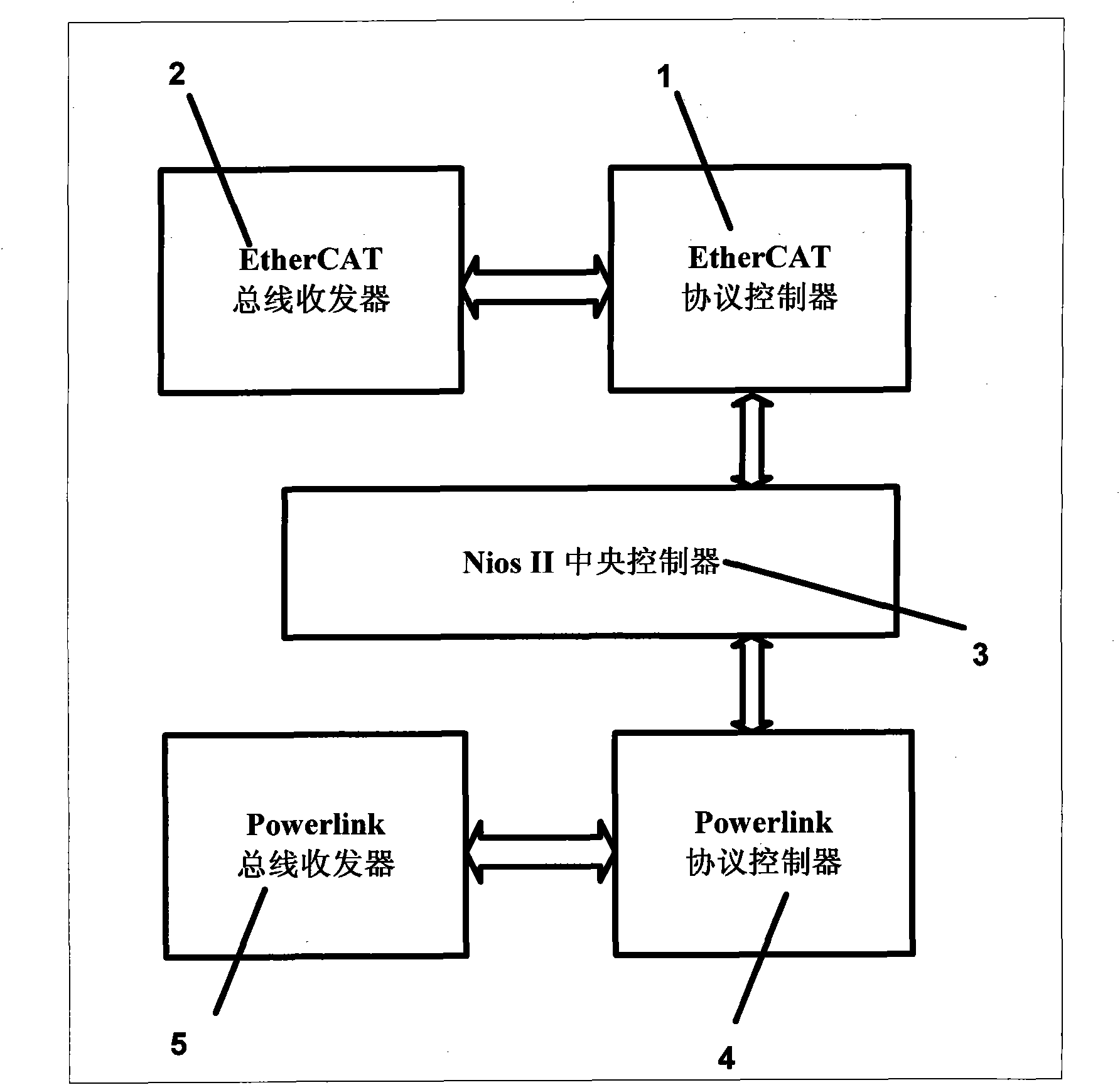

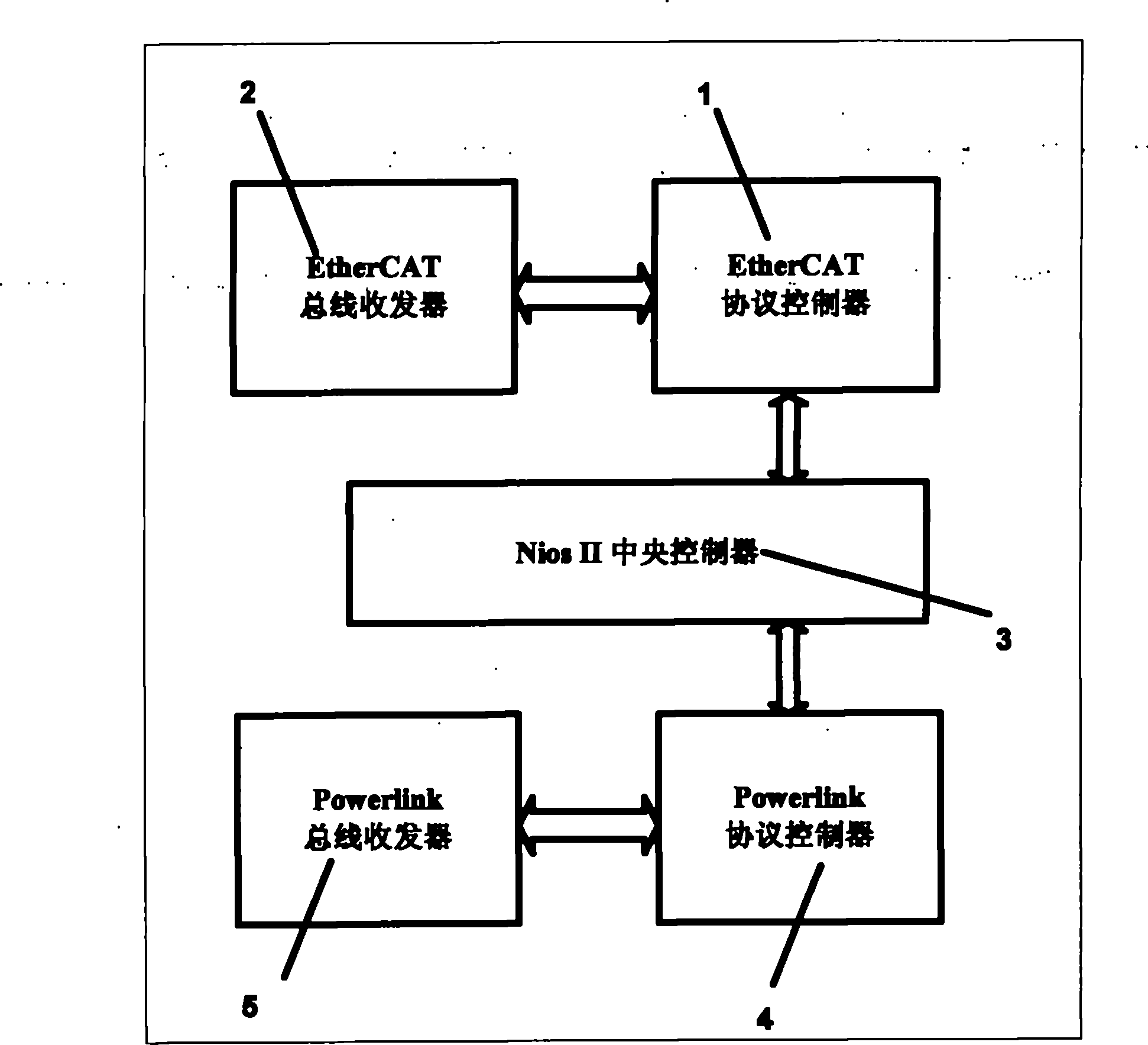

EtherCAT Ethernet gateway and working method thereof

InactiveCN101917321ARealize data exchangeSolve interconnection problemsNetwork connectionsBus networksTransceiverEtherCAT

The invention discloses an EtherCAT Ethernet gateway and a working method thereof. The gateway comprises an EtherCAT bus protocol controller, an EtherCAT bus transceiver, a Nios II central controller, a Powerlink bus protocol controller, and a Powerlink bus transceiver, wherein the Nios II central controller is respectively connected to the EtherCAT bus protocol controller and the Powerlink bus protocol controller in two directions, and the Powerlink bus protocol controller is connected to the Powerlink bus transceiver in two directions. Through the Nios II central controller, the invention realizes the data exchange between the EtherCAT bus protocol controller and the Powerlink bus protocol controller, which solves the communication problem between the EtherCAT and Powerlink in a train communication network.

Owner:CHINA CNR LIMITED DALIAN ELECTRIC TRACTION R&D CENT

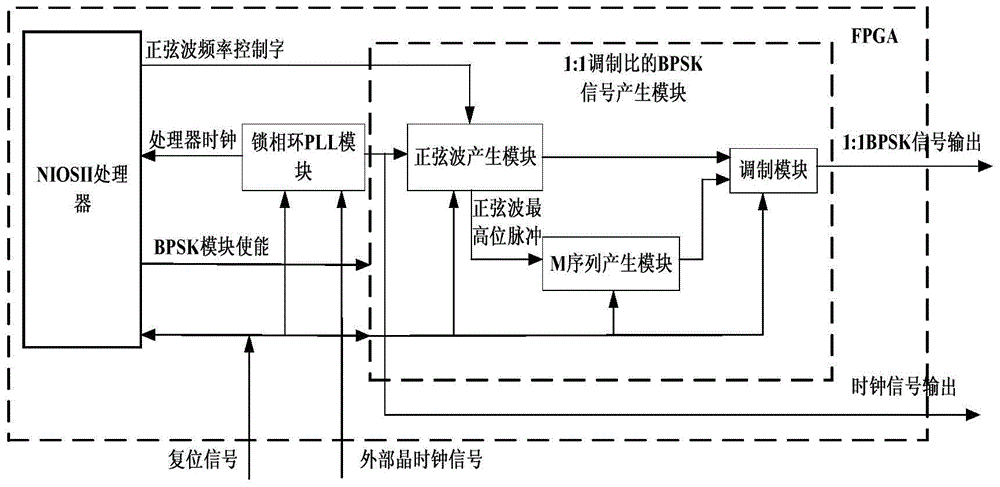

Cable fault on-line detecting and positioning device

InactiveCN104977504AOnline detection does not affectLow signal to noise ratioFault locationComputer moduleSoft core processor

The invention discloses a cable fault on-line detecting and positioning device. The device includes an FPGA module with an NIOS II soft core processor, a high-speed DA module, an isolation coupling module, a high-speed AD module and a conditioning circuit. The FPGA module provides clocks needed by all modules, generates a detection signal formed by modulation of an m sequence and sine waves, performs related operation processing of the detection signal and a reflection signal, and positions cable faults. The high-speed DA module is used for digital analog conversion of the detection signal generated by the FPGA module. The isolation coupling module isolates an output signal of the high-speed DA module and couples the output signal to a cable, and also isolates a reflection signal in the cable and couples the reflection signal to a detection positioning device. The high-speed AD module carries out analog-to-digital conversion of the reflection signal in the cable and then sends the signal to the FPGA module for processing. The conditioning circuit is used for conditioning the output signal of the high-speed DA module and an input signal of the high-speed AD module. The device has an on-line detection function, is high in positioning precision, and exhibits a high anti-interference capability.

Owner:SHANDONG INST OF AEROSPACE ELECTRONICS TECH

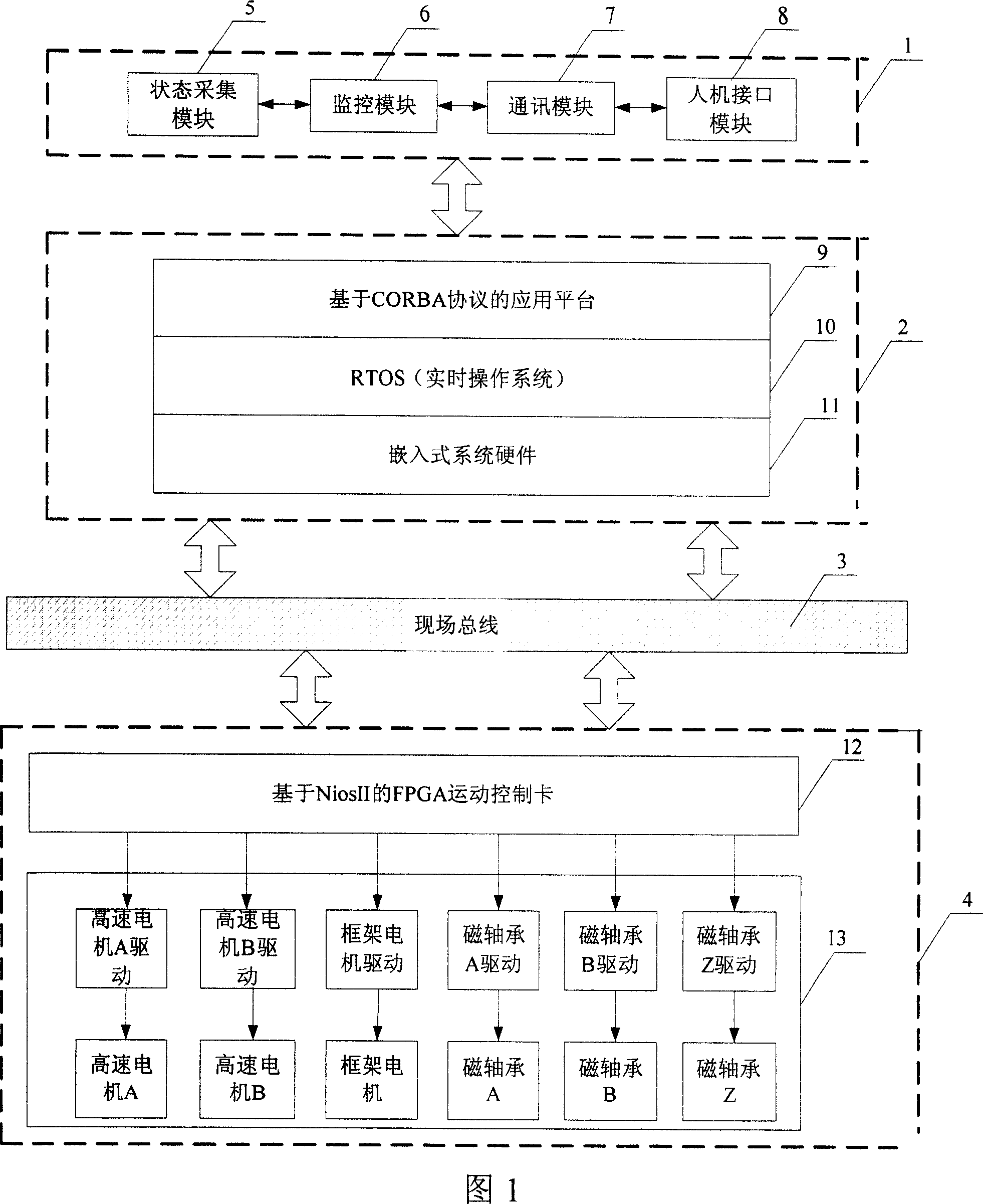

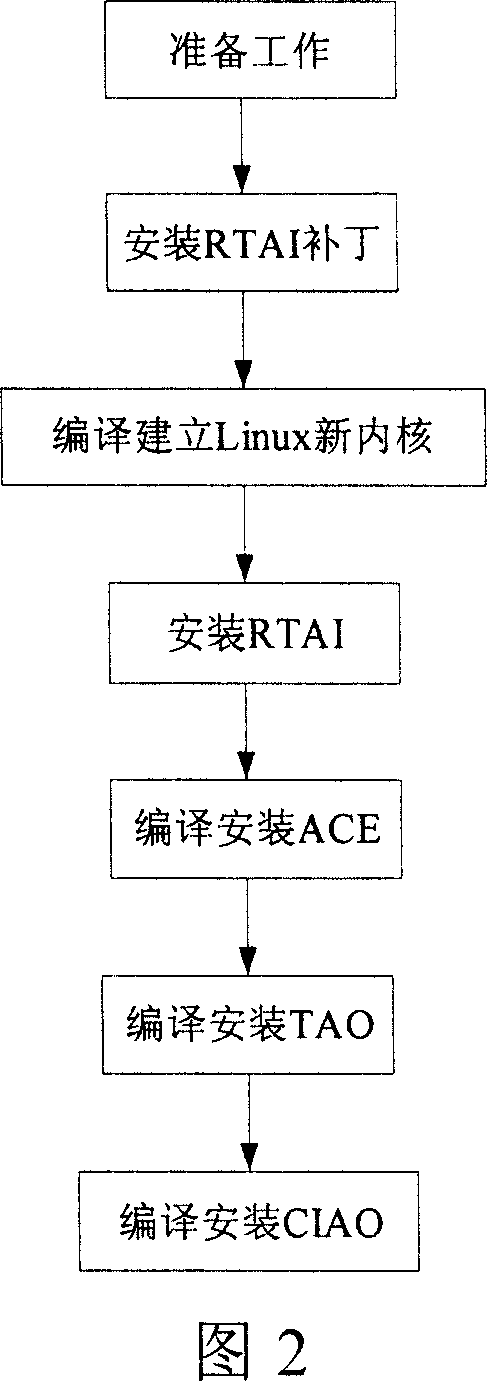

Integrated magnetically suspended control moment gyroscope control platform

InactiveCN1974326AEasy to handle relationshipsEasy to controlSpacecraft guiding apparatusAviationControl layer

The integrated magnetically suspended control moment gyroscope control platform for the integrated control of the magnetically suspended control moment gyroscope system includes mainly an application layer, a system layer, a field bus and a control layer. The application layer on the control layer completes the signal data acquisition, complicated algorithm calculation and monitoring, and includes a state acquisition module, a monitoring module, a communication module and a man-machine interface module. The system layer providing the application layer with operation platform and real-time datum includes an application platform based on CORBA protocol, a RTOS and an embedded hardware system. The control layer completes the control on the current loop of the controlled parts, including FPGA motion control card based on Nios II, high speed motor, frame motor, etc. The system layer communicates with the control layer through the field bus.

Owner:BEIHANG UNIV

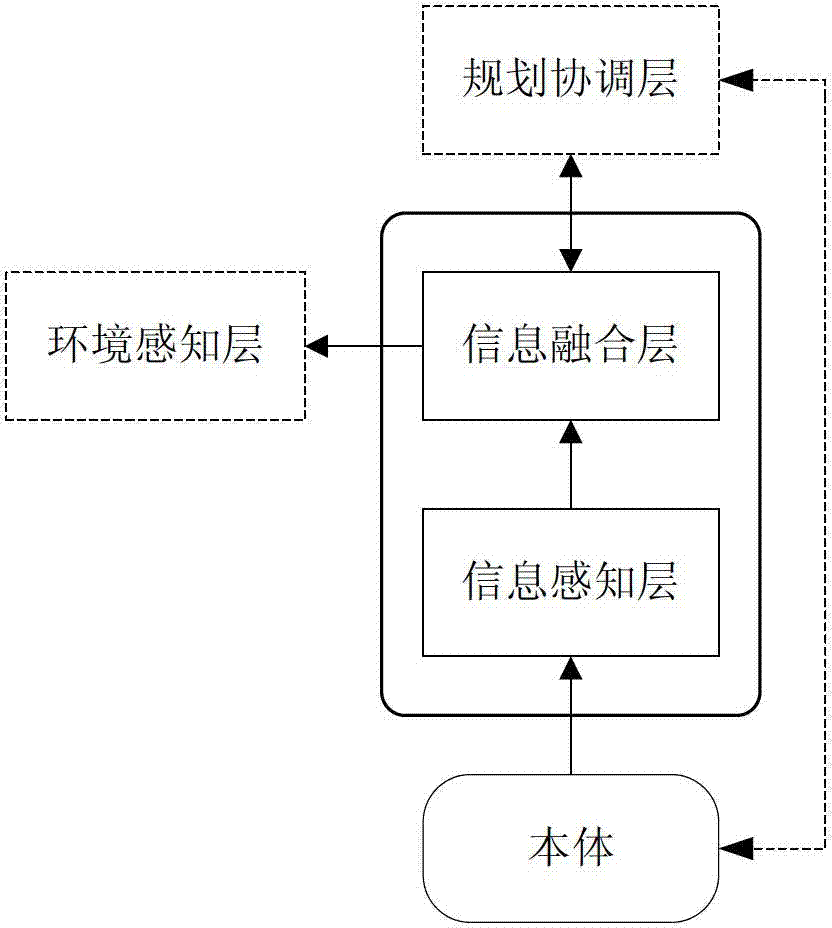

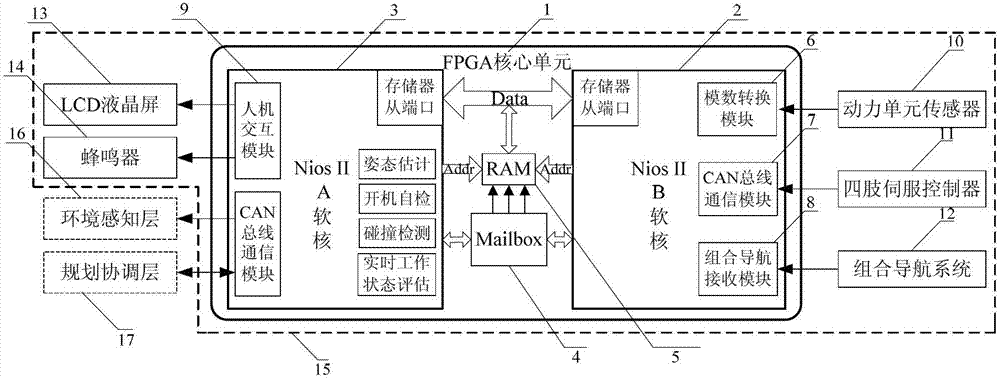

Legged robot state sensing system based on dual core processing technology

InactiveCN102853831ACompleteness checkComplete collectionNavigation instrumentsReal-time dataDual core

The present invention discloses a legged robot state sensing system based on a dual core processing technology, wherein a dual core system structure is adopted, and a SOPC technology is adopted to embed two RISC embedded processor NIOS II soft cores in a chip based on a FPGA core unit to achieve the structure. One soft core is used to establish a data acquisition kernel having a data acquisition function, and the other soft core is used to establish a data processing kernel having a data processing and communication function. Data interaction of the two kernels is achieved through a mailbox kernel Mailbox and a shared RAM memory. With the NIOS II B soft core, complete information acquisition can be achieved, while the NIOS IIA soft core performs a data fusion treatment based on the data acquired by the NIOS II B soft core. According to the present invention, a state sensing technology facing the complex legged robot is adopted, and characteristics of information completeness detection, high speed data parallel processing, real-time data communication, high reliability, and the like are provided.

Owner:CENT SOUTH UNIV

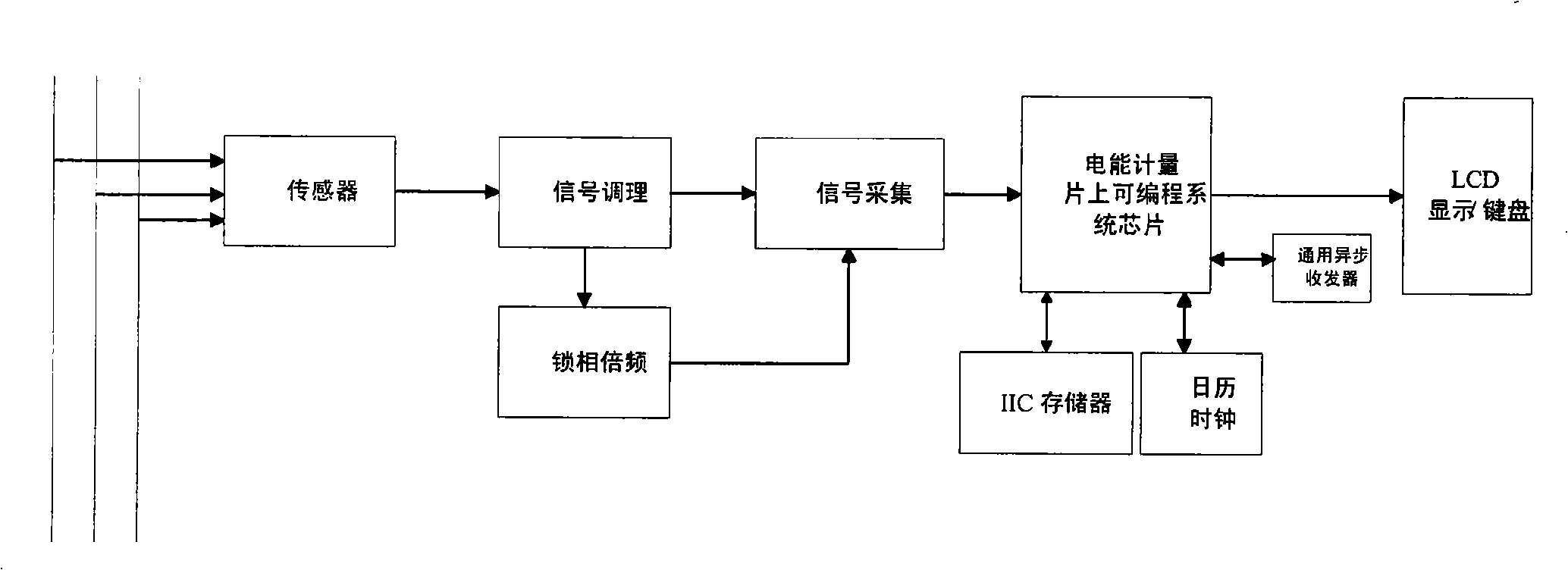

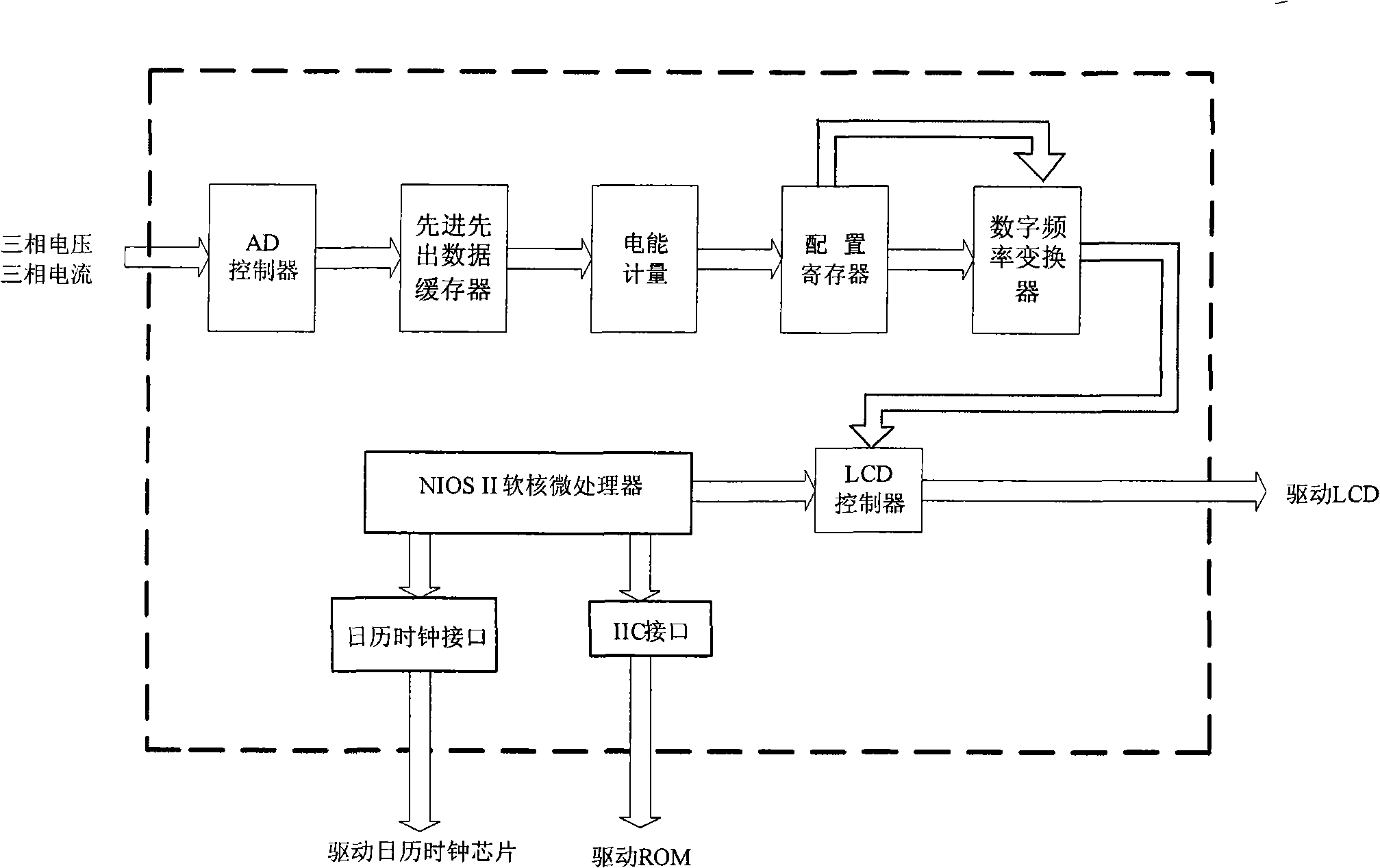

Three-phase electric energy meter based on NIOS II microprocessor

InactiveCN101256210AReduce volumeHighly integratedElectric signal transmission systemsPower measurement by digital techniqueReconfigurabilityElectricity

The invention provides a three-phase electric energy gauge based on NIOS II microprocessor, comprising: sensor, output terminal connected with signal conditioning module; signal conditioning module, input terminal connected with output terminal; signal collecting module, input terminal connected with input terminal of signal conditioning module; electric energy measuring SOPC chip connected with the signal collecting module, being the core of the whole electric energy gauge; phase-lock multiple frequency connected with the signal conditioning module and signal collecting module; general asynchronism transceiver for realizing the communication of electric energy gauge and host computer or meter reading system using RS-232 interface mode; LCD display / keyboard module for connecting the electric energy measuring SOPC chip; calendar clock module connected with the electric energy measuring SOPC chip; IIC memorizer connected with the electric energy measuring SOPC chip. The bulk of electric energy gauge is small and the integration lever is high, and the reliability is high, with reconfigurability.

Owner:CAPITAL NORMAL UNIVERSITY

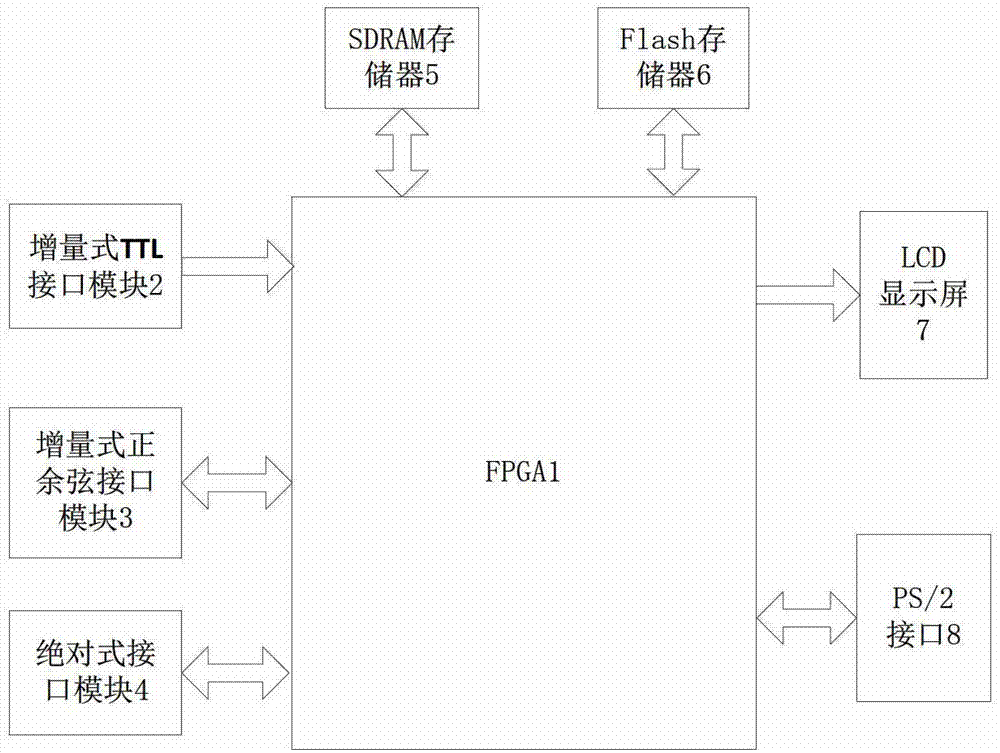

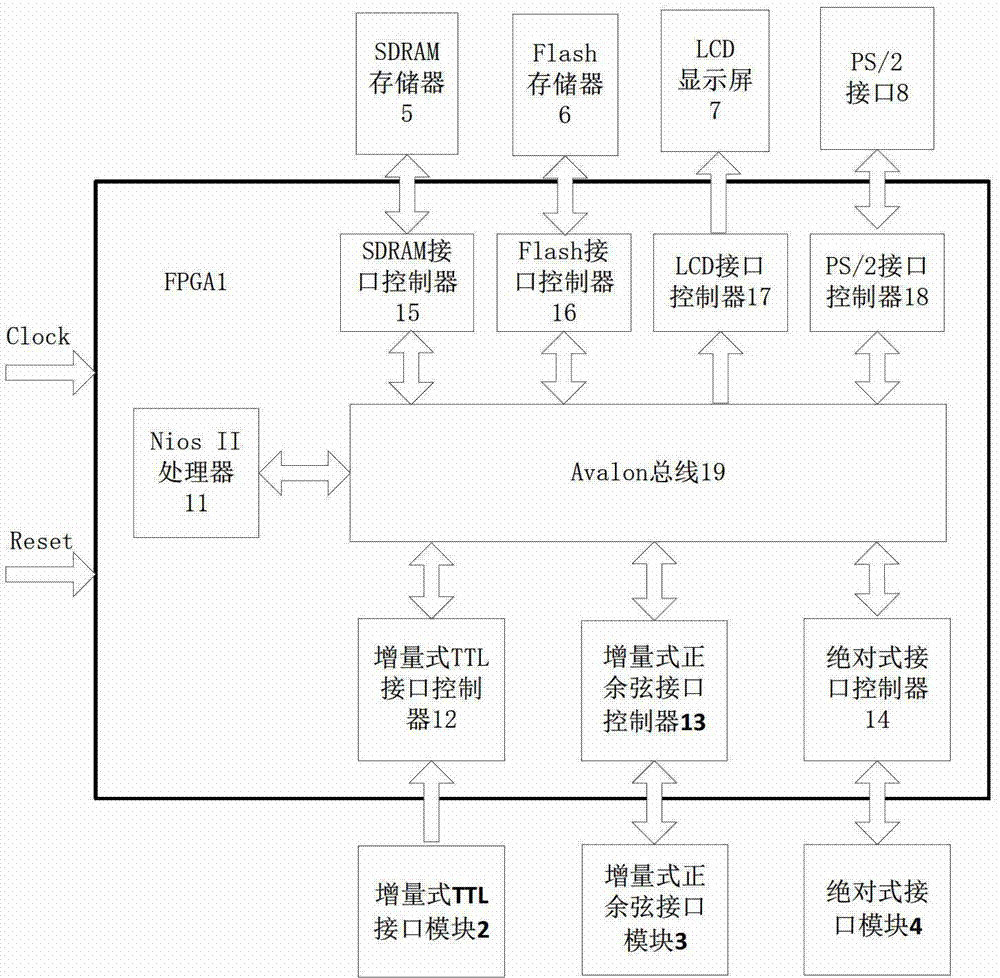

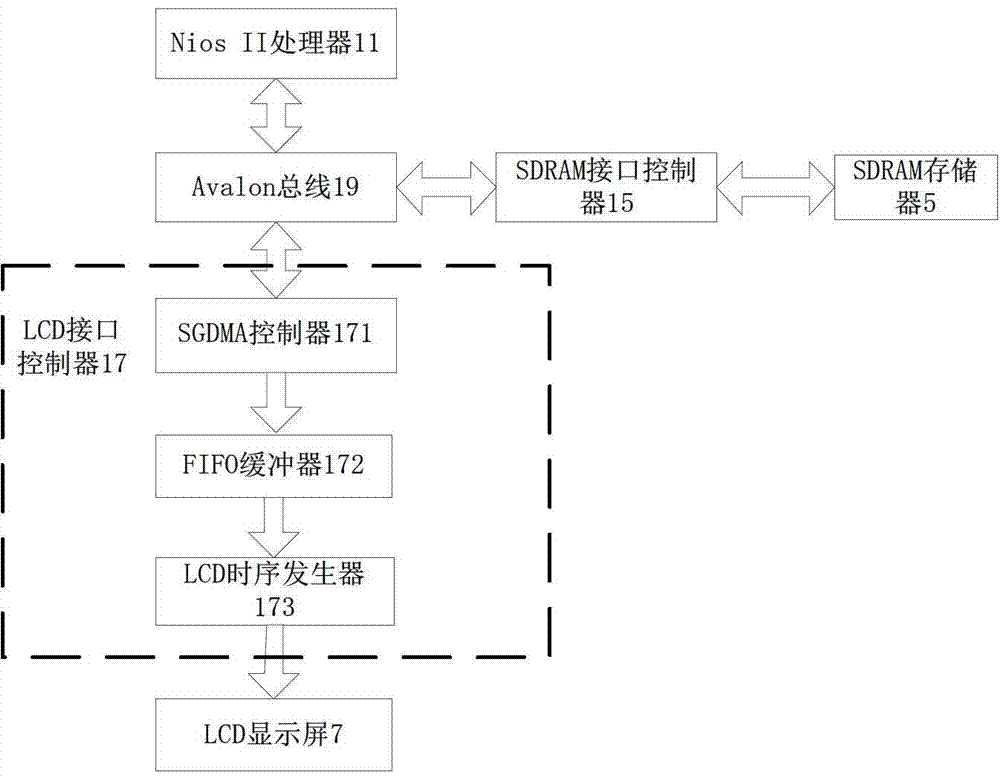

Coder interface testing device based on Nios II processor

InactiveCN102967326AHighly integratedReduce volumeInstrumentsTransistor–transistor logicDifferential signaling

The invention discloses a coder interface testing device based on a Nios II processor. The device comprises an FPGA (Field Programmable Gate Array) chip, an incremental TTL (Transistor Transistor Logic) interface module, an incremental sine and cosine interface module, an absolute interface module, a display screen and a PS (Poly Styrene) / 2 interface device, wherein the incremental TTL interface module, an incremental sine and cosine interface module, an absolute interface module, a display screen and a PS / 2 (Purple Green) interface device are connected with the FPGA chip; the incremental TTL interface module is used for being connected with the coder of an incremental TTL interface type, the incremental sine and cosine interface module is used for being connected with the coder of an incremental sine and cosine interface type, the absolute interface module is used for being connected with an absolute coder so that a serial digital signal output by the absolute interface module is transformed between a differential signal and a single-end signal, and the FPGA chip comprises a Nios II processor embedded in a chip, and the Nios II processor is used for processing an input signal and realizing the testing of coder interfaces. The Nios II processor-based coder interface testing device can be used for solving the problems that the coder interfaces in the existing coder testing platform can not be mutually compatible and are inconveniently carried, and has the characteristics of low cost, strong function, small volume, compact structure and high integration.

Owner:SUZHOU TIANCHENMA INTELLIGENT EQUIP +1

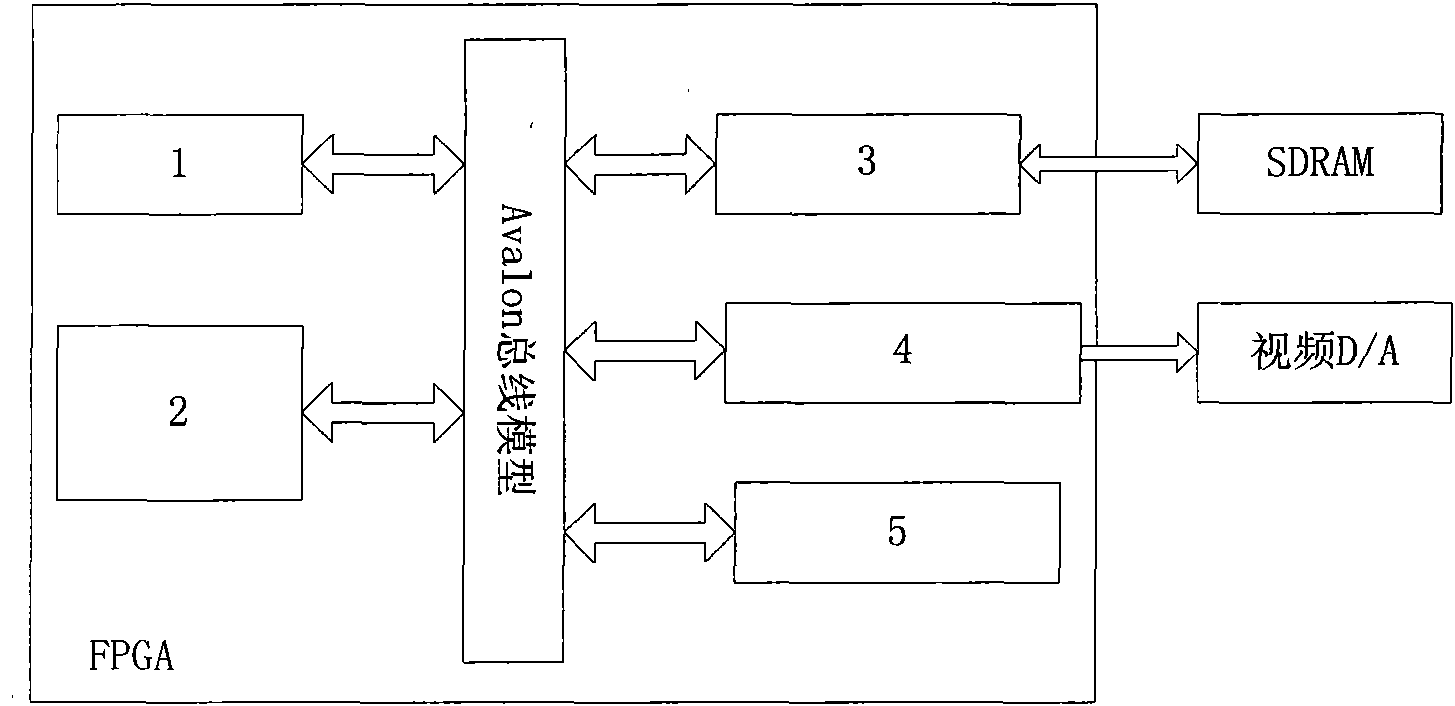

Device and method for implementation of AVS video decoding by using SOPC

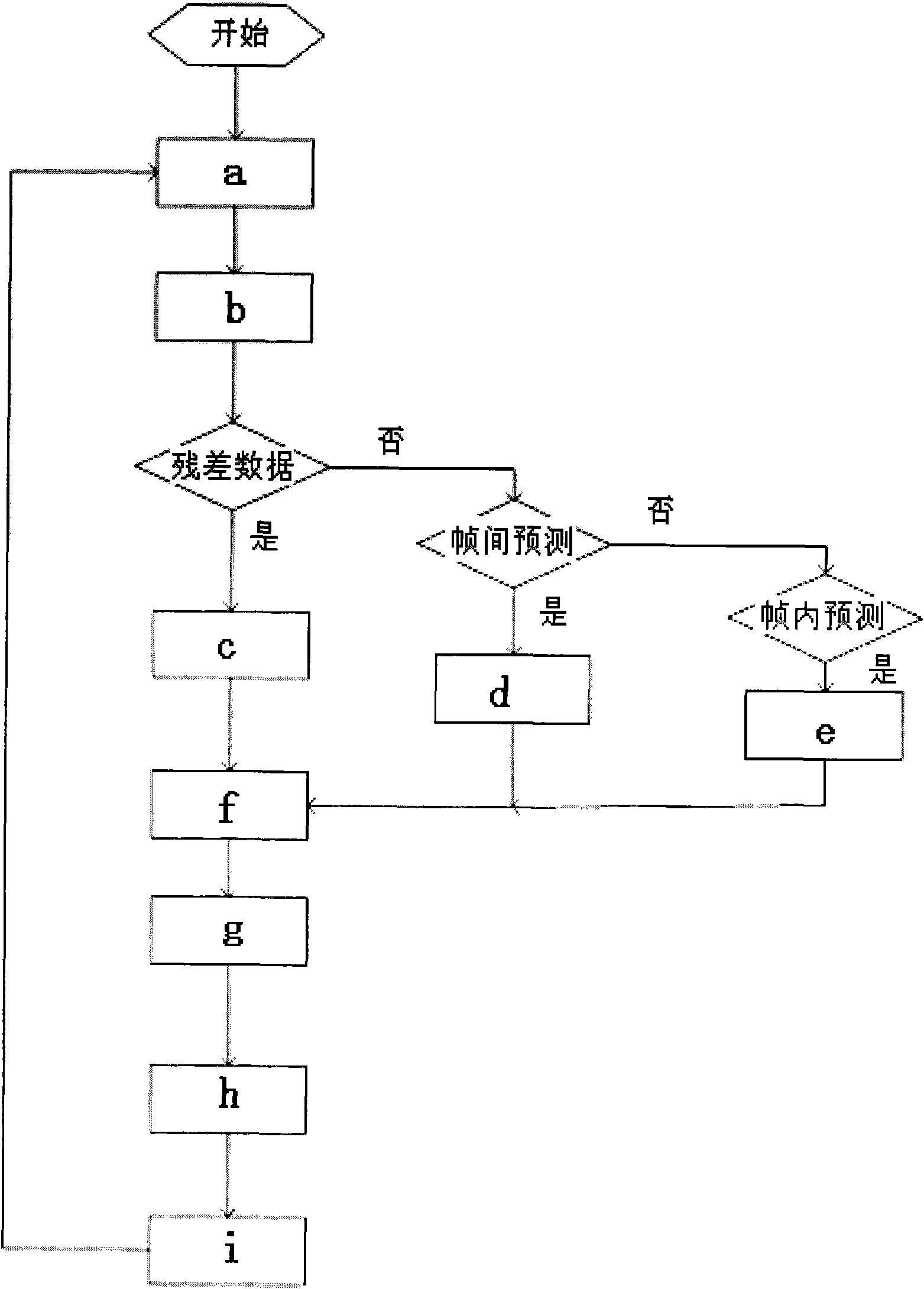

InactiveCN101790093AEnsure orderly operationControl normal operationTelevision systemsDigital video signal modificationModularityVideo decoding

The invention discloses a device and a method for the implementation of AVS video decoding by using SOPC, belonging to the field of video decoding. The device comprises an Nios II microprocessor module and other modules. The Nios II microprocessor module is connected with a DMA controller module and other modules; a SDRAM controller module is connected with the DMA controller module and other modules as well as SDRAM; a video output controller module is connected with the SDRAM controller module and a video output module; the DMA controller module is connected with an AVS co-processing module. The Nios II microprocessor module executes software decoding control, the AVS co-processing module executes AVS hardware decoding, other modules executes auxiliary decoding, and all the modules are hung on a bus and packaged in FPGA for data interaction. The device is reasonable in software / hardware division, capable of varying software decoding procedures by modularized design and of supporting the design with other standards by hanging other co-processor cores, and has high expandability, universality and flexibility.

Owner:SHANDONG UNIV

Indoor intelligent video monitoring system based on SOPC

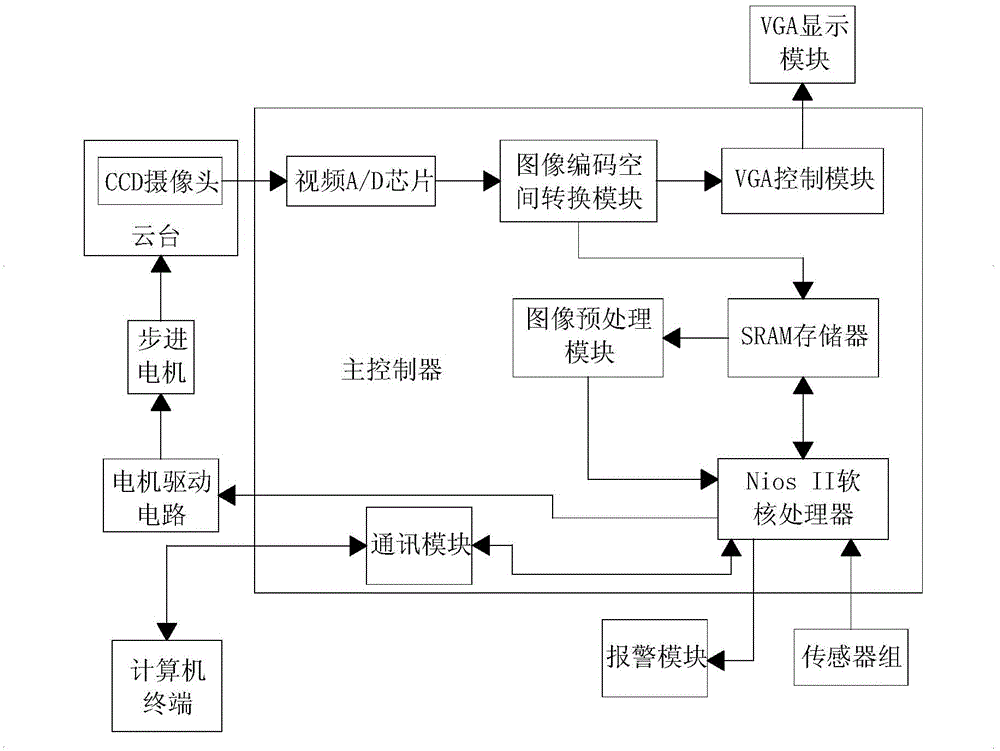

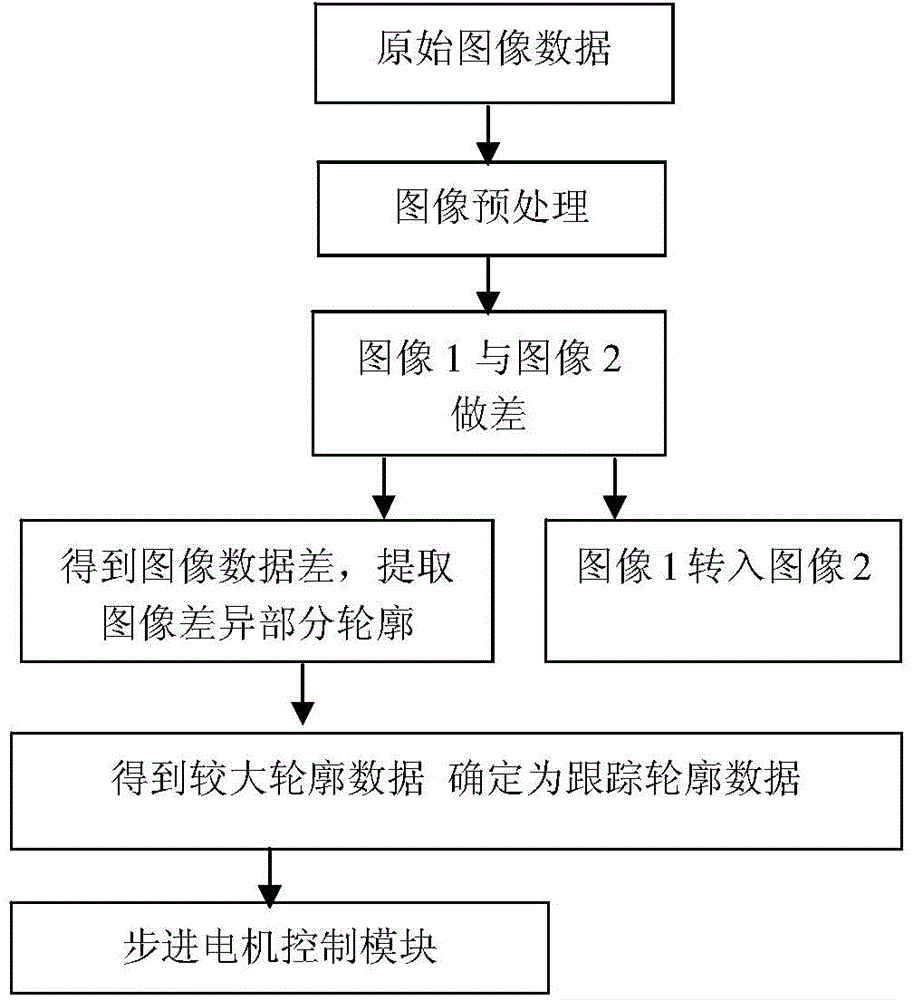

InactiveCN104935886AEasy to upgradeSupport remote network monitoringClosed circuit television systemsBurglar alarmVideo monitoringCyclone

The invention discloses an indoor intelligent video monitoring system based on SOPC, comprising a CCD camera, a holder, a stepping motor, a motor-drive circuit, a sensor group, a master controller combined by a Nios II soft core processor and a Cyclone II, a VGA display module, an alarm module and a computer terminal. The indoor intelligent video monitoring system is a platform for tracking an object and alarming by basing on a robot vision technology of the SOPC technology and the sensor technology, and is capable of alarming according to the setting values of temperature, humidity, smog and people activity and transmitting the alarm information to the remote user. The indoor intelligent video monitoring system based on the SOPC is a monitoring system which can finish the mission in the short time according to the user customization, can support the remote network monitoring, and is applicable to the household, the shopping mall and the library.

Owner:NINGXIA UNIVERSITY

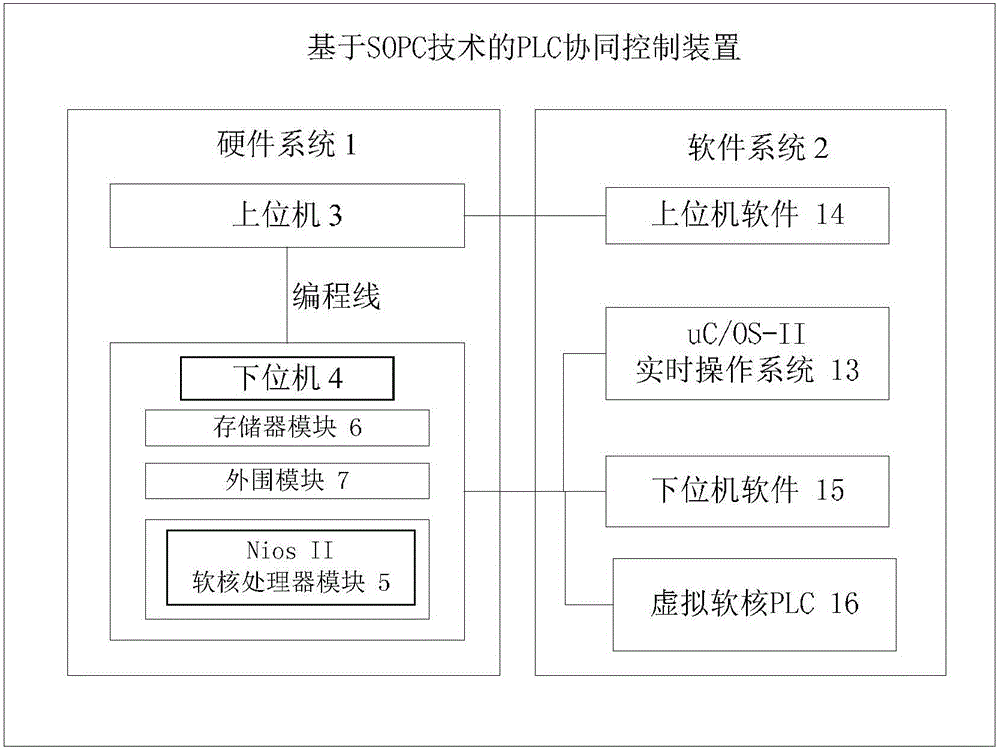

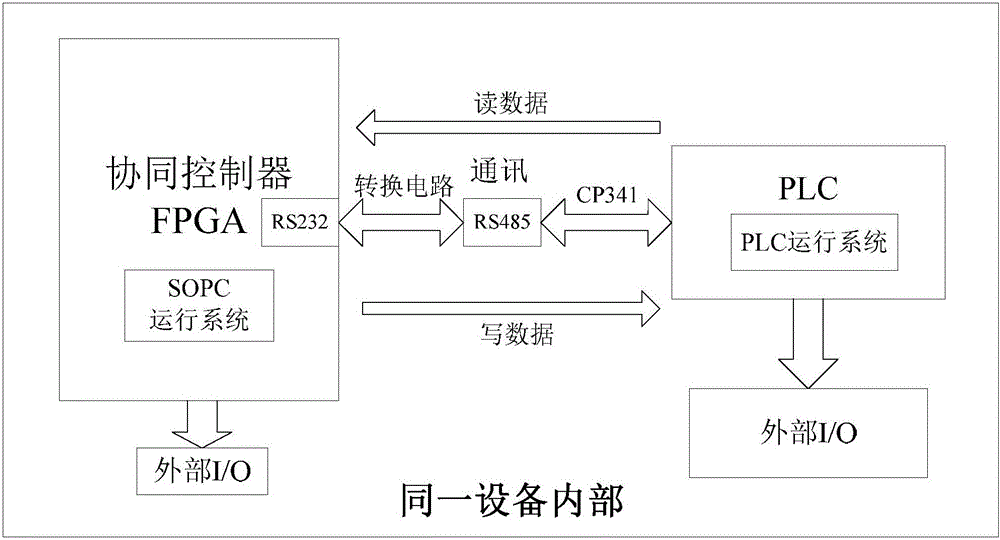

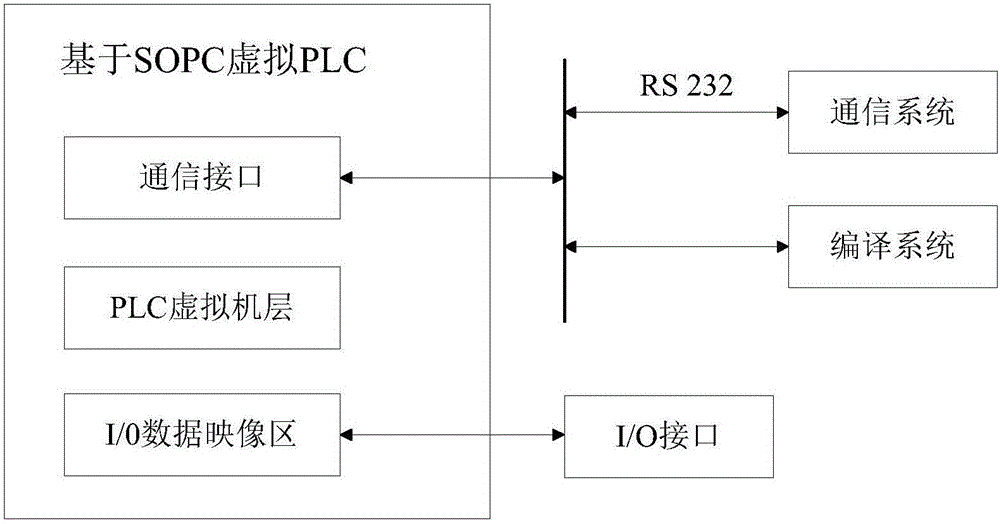

PLC cooperative control device based on SOPC technology

InactiveCN105137800AHigh densityIncrease or decrease quantityProgramme controlComputer controlOperational systemSoftware system

The invention relates to a PLC cooperative control device based on an SOPC technology. The device comprises two parts, a hardware system and a software system. The hardware system comprises an upper computer and a lower computer. The upper computer is formed by a Nios II soft core processor module, a memory module and a peripheral module, wherein the Nios II soft core processor module is composed of a CPU module, a TIMER0 module, a TIMER1 module, an UART module and a JTAG module. The software system comprises an embedded uC / OS-II real-time operating system, upper computer software, lower computer software and a virtual soft core PLC. The PLC cooperative control device is high in modifiability and transportability; the uC / OS-II real-time operating system is added, the operation real-time performance of the system is ensured, customized IP cores can be compiled according to specific requirements, and the required specific functions can be added freely; in addition, the number of I / O ports can be conveniently increased or reduced, so that the system is high in expansion and maintenance performance.

Owner:CHINA TOBACCO ZHEJIANG IND

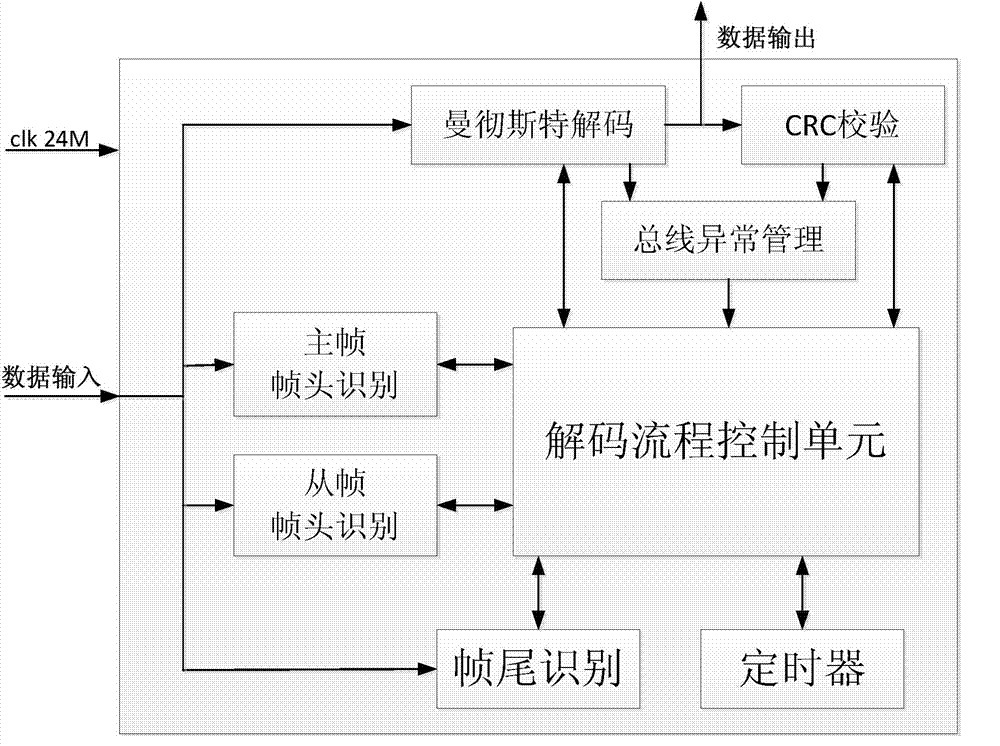

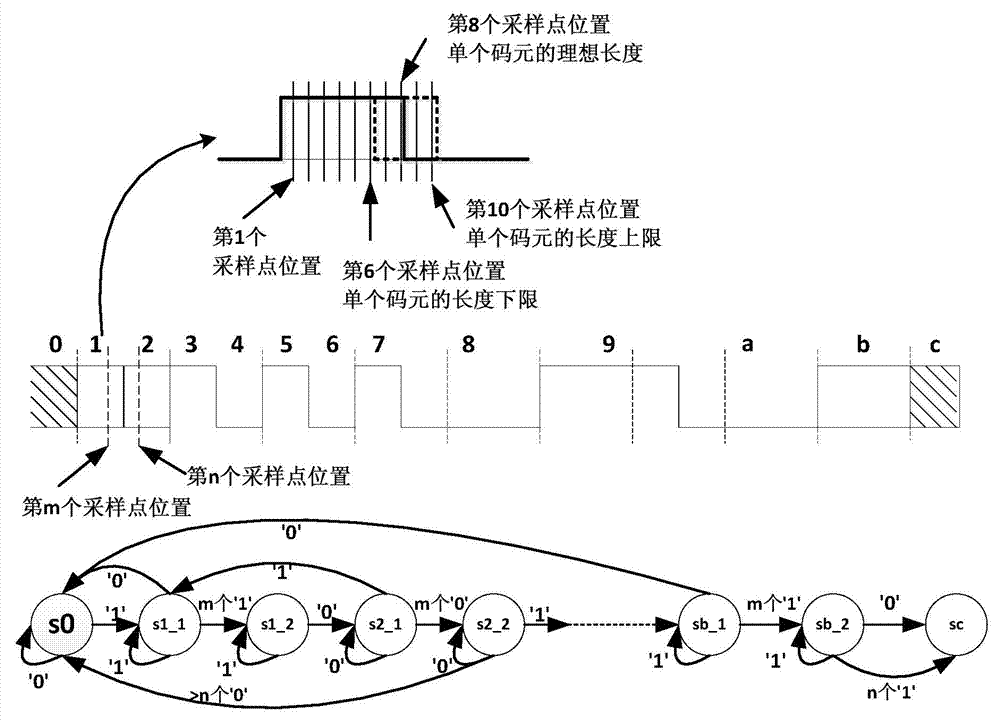

MVB (Multifunction Vehicle Bus) bus decoding and on-vehicle recording system based on SOPC technology

ActiveCN104282054AParsing is intuitiveImprove reliabilityRegistering/indicating working of vehiclesFrequency multiplierFpga chip

The invention relates to an MVB (Multifunction Vehicle Bus) bus decoding and on-vehicle recording system based on an SOPC technology. The system comprises an FPGA chip, an EPCS serial FLASH chip, an SDRAM chip, an SRAM chip, an SD card and an MVB level switching circuit, wherein the FPGA chip comprises an NIOS-II soft-core processor, a phase-locked loop frequency multiplier, an MVB decoder, an SRAM read / write controller, an SPI switching module and an SPI; the NIOS-II soft-core processor is connected with the EPCS serial FLASH chip, the SDRAM chip, the phase-locked loop frequency multiplier, the MVB decoder, the SRAM read / write controller and the SPI; the MVB decoder is connected with the phase-locked loop frequency multiplier, the MVB level switching circuit and the SRAM read / write controller; and the SPI switching module is connected with the SPI interface, the SRAM read / write controller and the SD card. Compared with the prior art, the MVB bus decoding and on-vehicle recording system disclosed by the invention has the advantages of software and hardware integration, high reliability, convenience in operation, high real-time property and the like.

Owner:SHANGHAI JIAO TONG UNIV

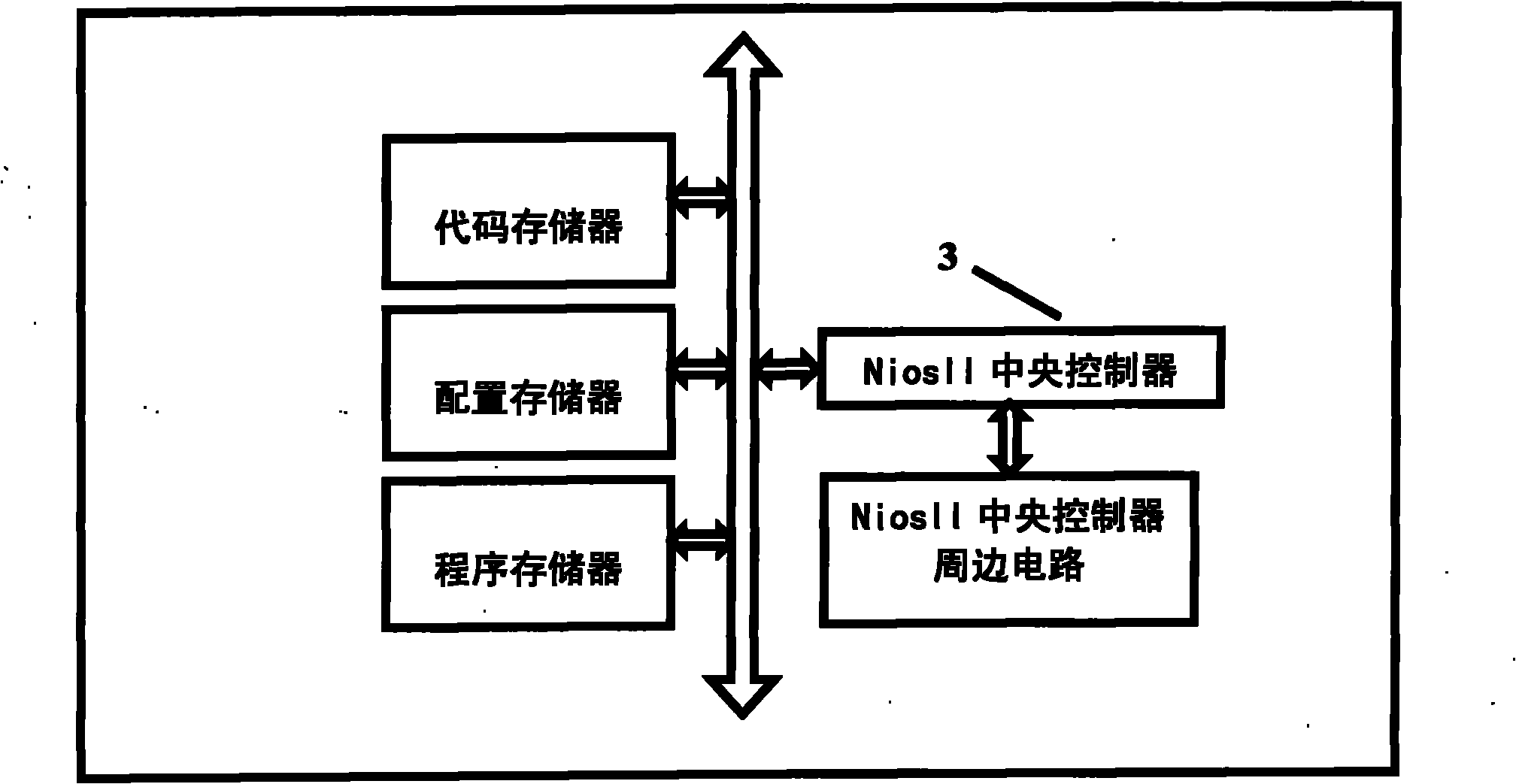

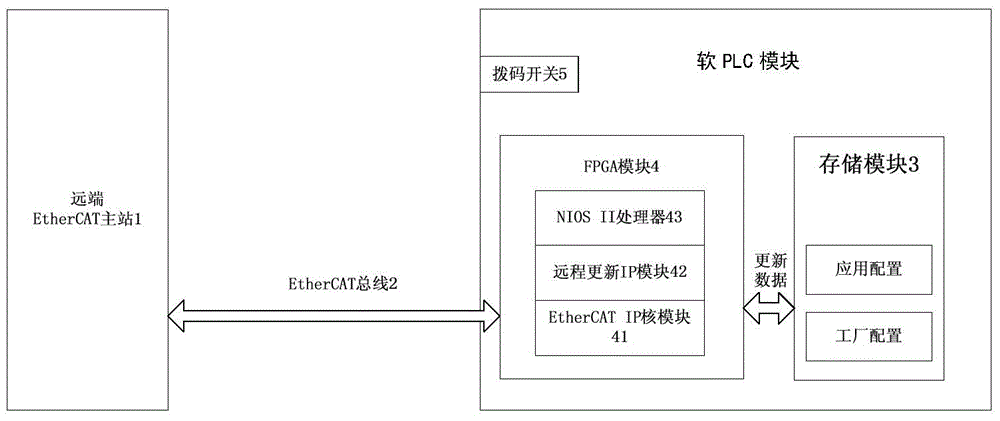

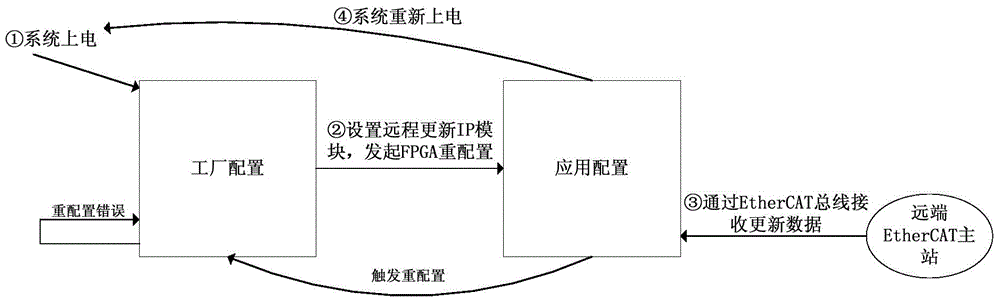

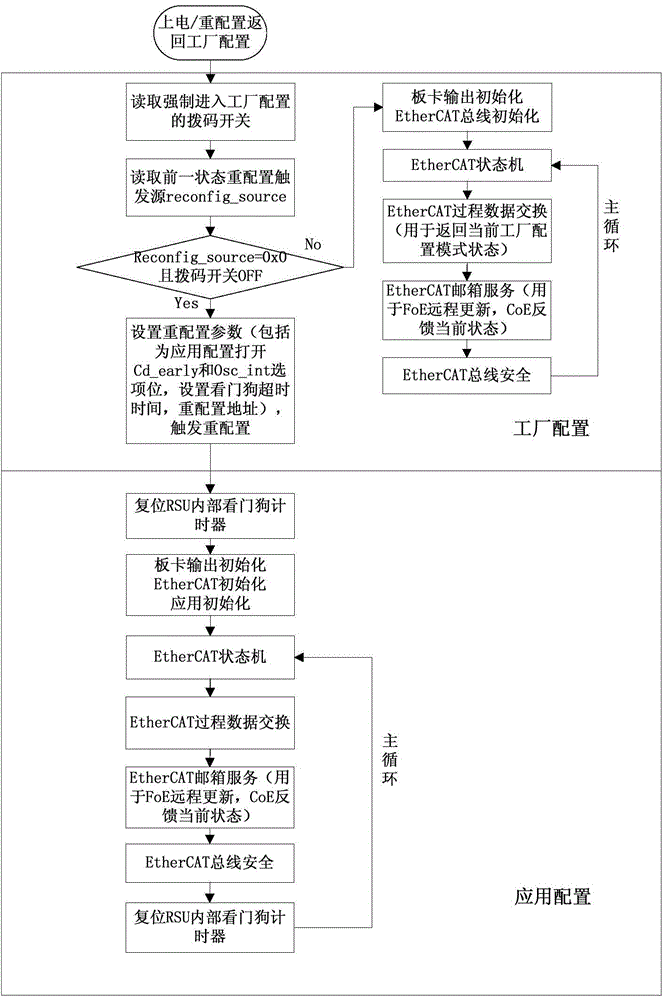

Remote online data updating system and method of soft PLC module

InactiveCN105467921AImprove update efficiencyEasy maintenanceProgramme control in sequence/logic controllersComputer moduleEtherCAT

The invention provides a remote online data updating system of a soft PLC module. The system comprises a far-end EtherCAT main station, an EtherCAT bus, a storage module and an FPGA module. The invention also provides a remote online data updating method of the soft PLC module. The method comprises that the far-end EtherCAT main station sends update data upgraded remotely, an EtherCAT IP core module receives the update data transmitted by the EtherCAT bus, an NIOS II processor writes the update data in the storage module, and controls remote updating of the IP module, reconfiguration of the FPGA is initiated, and the FPGA is reconfigured by utilizing the update data.

Owner:SHENYANG MACHINE TOOLGRP RES & DESIGN INST CO LTD SHANGHAI BRANCH

All-dimensional visual system based on SOPC

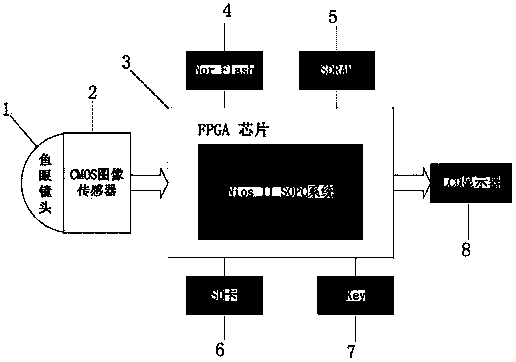

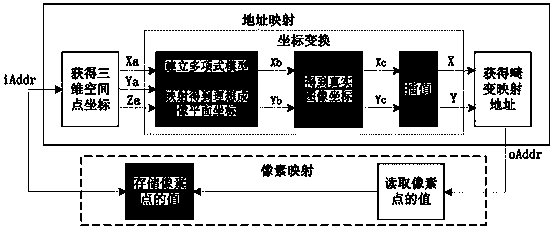

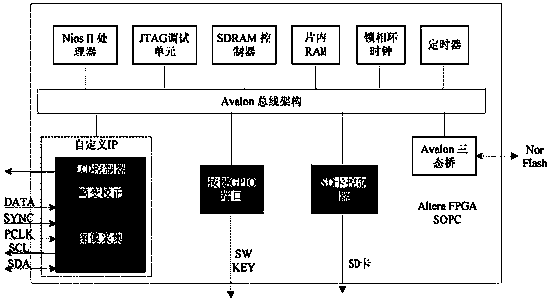

InactiveCN104243781ASimple and convenient human-computer interaction interfaceHighly integratedTelevision system detailsColor television detailsHuman–computer interactionVisual perception

The invention discloses an all-dimensional visual system based on an SOPC. According to the all-dimensional visual system based on the SOPC, (1) a fish-eye lens and a CMOS image sensor are used for obtaining all-dimensional visual image information of a view field larger than a hemisphere; (2) a Nios II / SOPC system is established in an FPGA chip by configuring an IP module based on the SOC technology and FPGA programmable features, and a user-defined IP is designed to achieve system core functions such as real-time collection, distortion correction and display of all-dimensional visual images; (3) a Nor Flash is used for storing FPGA configuration files and system software, an SD card is used for storing image files, and an SDRAM serves as an internal storage device of the system; (4) keys and an LCD displayer serve as a man-machine interaction unit of the system. The all-dimensional visual system solves the problems that the real-time collection, correction, storage and display of images cannot be achieved in small embedded devices through an existing all-dimensional visual system establishing method. The all-dimensional visual system has the advantages of being small in size, low in cost and high in function expandability.

Owner:SUN YAT SEN UNIV +1

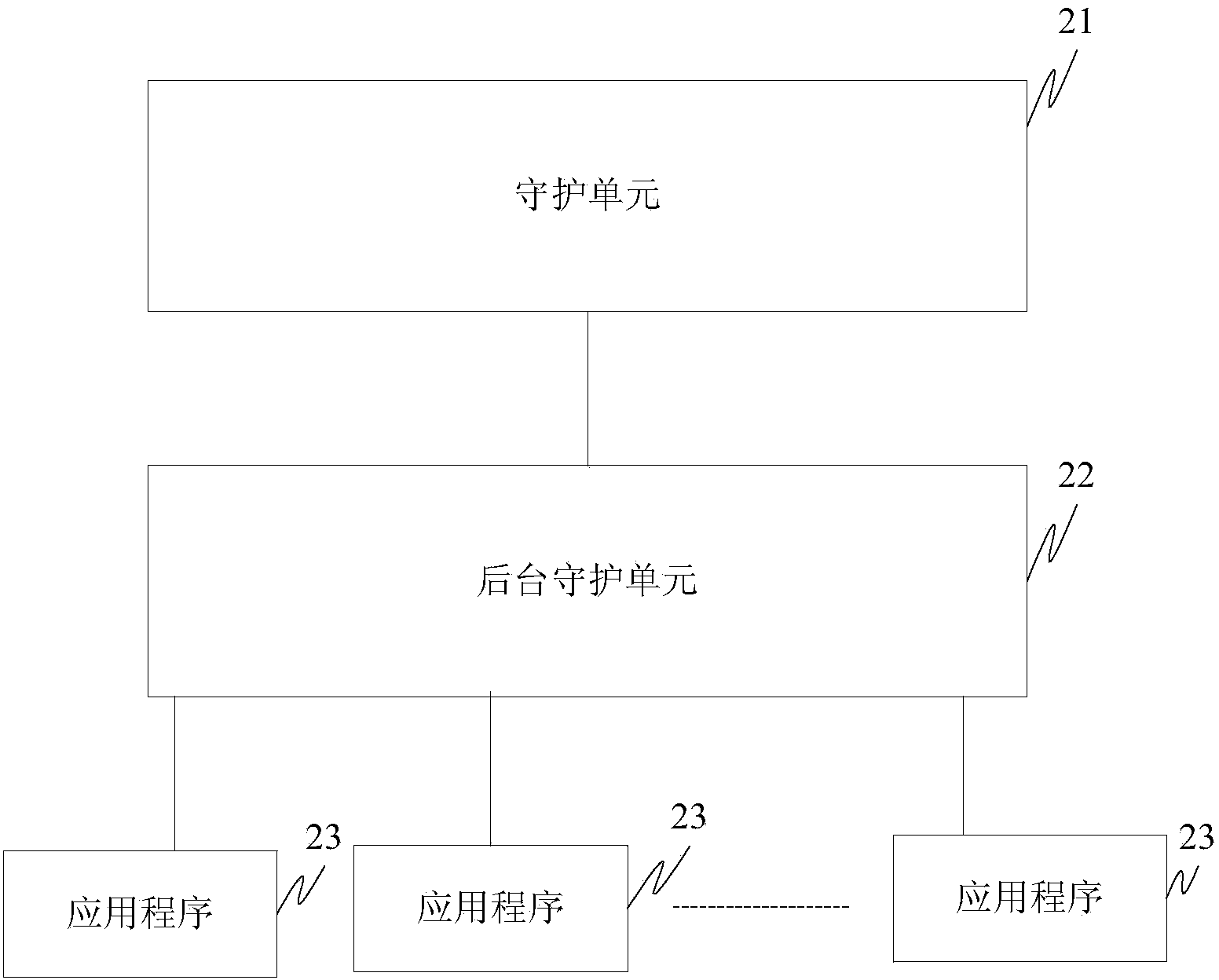

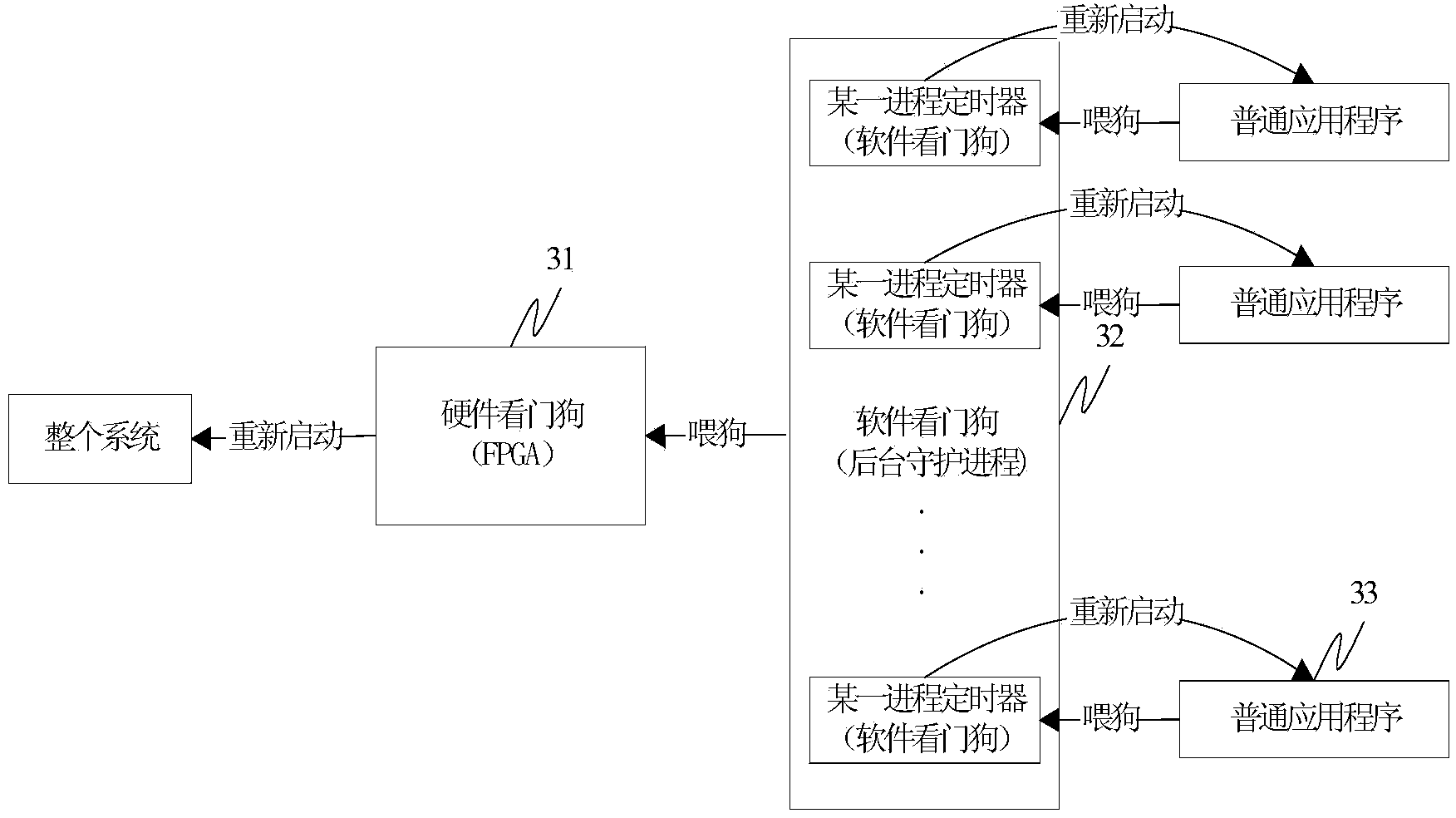

Watch-dog implementation method and device based on Nios II system

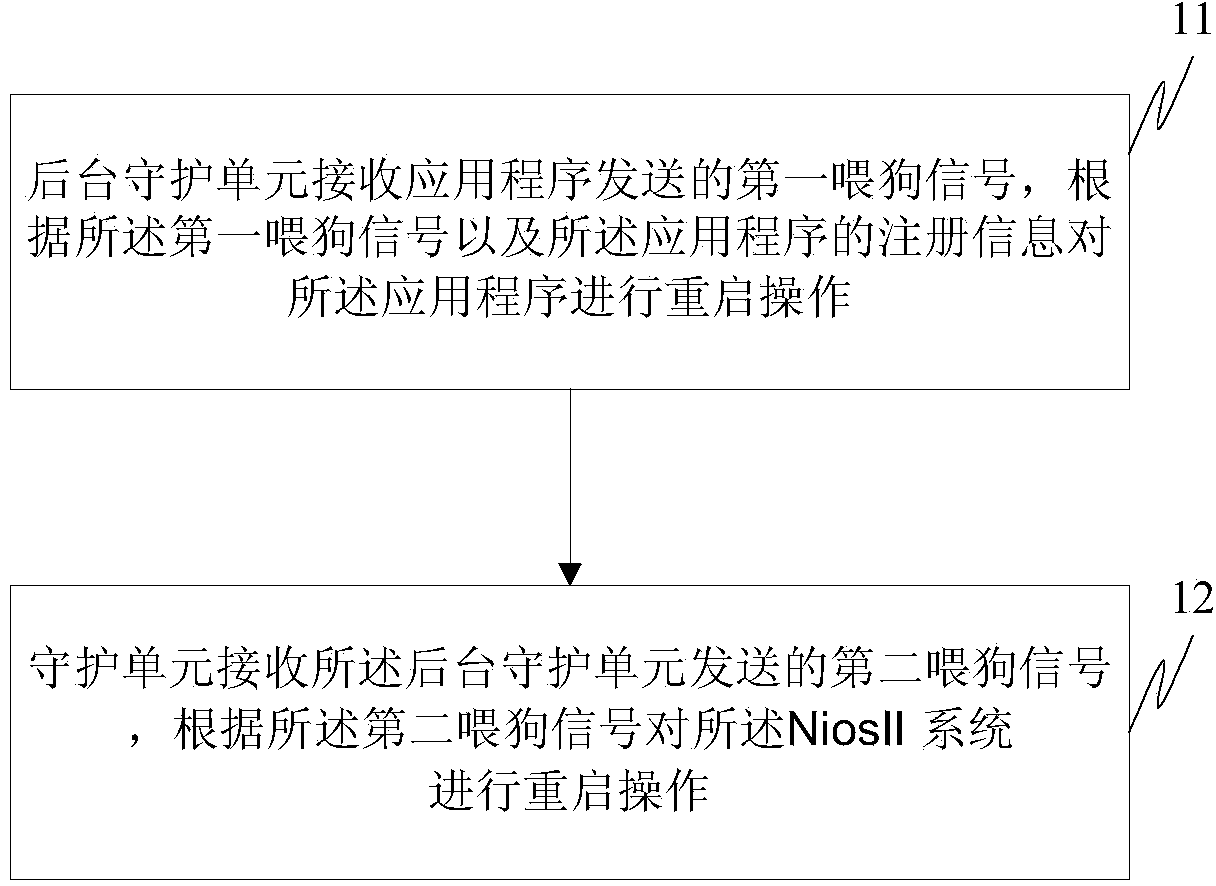

InactiveCN103645962AImprove stabilityImprove general performanceFault responseSystem stabilitySystem structure

An embodiment of the invention provides a watch-dog implementation method and device based on a Nios II system. The watch-dog implementation method based on the Nios II system comprises the steps as follows: a background guard unit receives a first dog feeding signal sent by an application program, and performs restart operation on the application program according to the first dog feeding signal and registration information of the application program; and the guard unit receives a second dog feeding signal sent by the background guard unit, and performs restart on the Nios II system according to the second dog feeding signal. According to the watch-dog implementation method and device based on the Nios II system, the watch-dog system with a multi-task processing system structure is realized, the universality is high, the method and the device can be applicable to various operation systems, and the system stability is improved.

Owner:BEIJING HUAHUAN ELECTRONICS

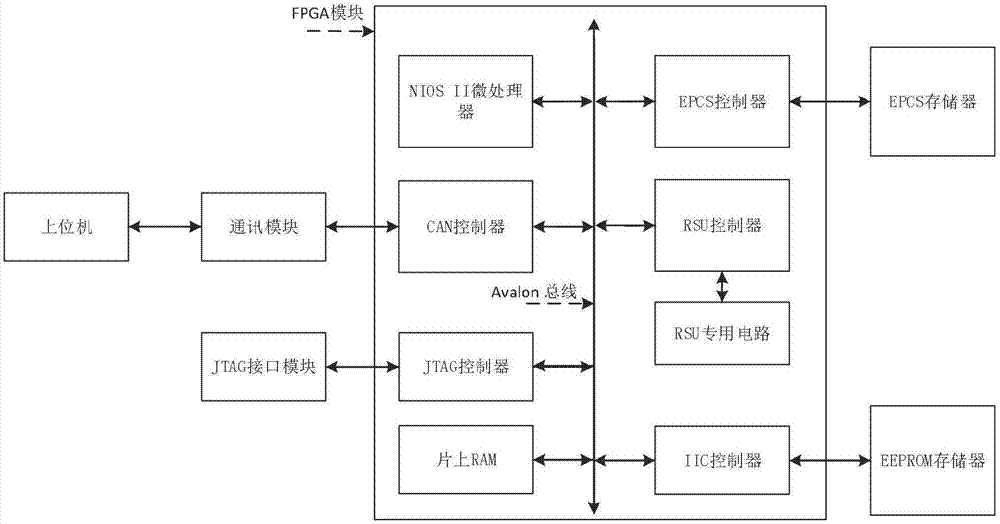

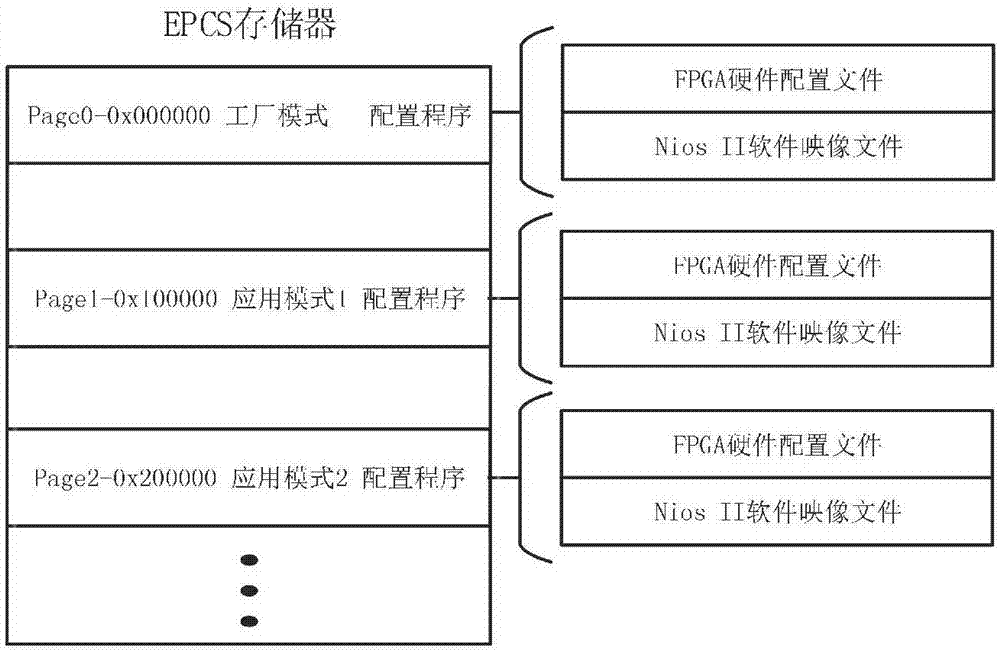

SoPC program remote updating system and method

ActiveCN107273170AAvoid disassemblyReal-time online updateProgram loading/initiatingElectricityCommunications protocol

The invention provides an SoPC program remote updating system and method. The method comprises the steps that a hardware configuration file of an FPGA and a software mapping file of Nios II are generated through compiling, merged and converted into a binary file; a Nios II microprocessor writes an application mode configuration program transmitted from an external communication module into an in-chip RAM for temporary storage according to a preset communication protocol instruction; the Nios II microprocessor erases data in a designated address of an EPCS memory and programs the temporarily stored configuration program into the designated address of the EPCS memory; and when power-on is performed again, the FPGA gets into a factory mode first, and then the stored corresponding application mode configuration program is automatically loaded according to configuration of an RSU-dedicated circuit. Through the SoPC program remote updating system and method, remote updating of an SoPC program by a single FPGA chip is realized, the system is simple, the method is flexible, and switching between multiple configuration programs is easy to realize.

Owner:SOUTHWEST JIAOTONG UNIV

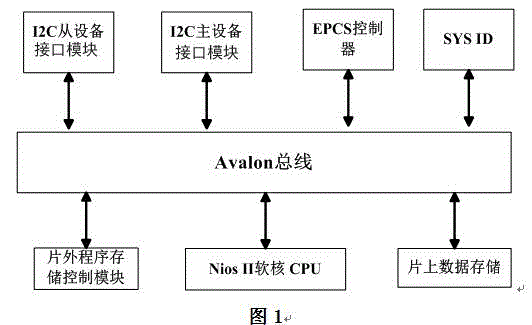

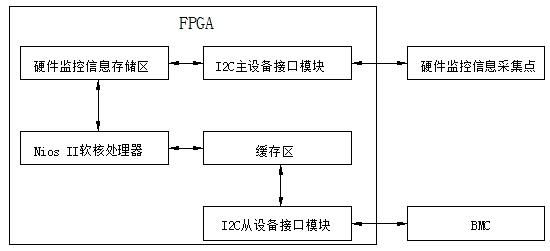

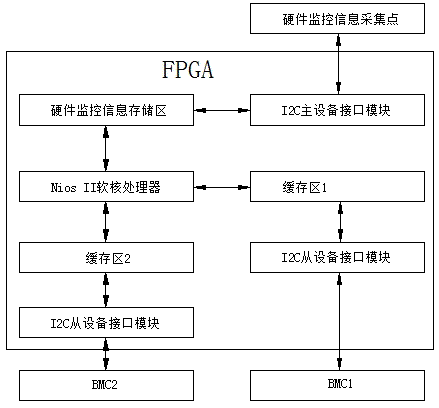

Method for acquiring monitoring information of computer system structure based on NUMA (Non Uniform Memory Access)

The invention discloses a method for acquiring monitoring information of a computer system structure based on NUMA (Non Uniform Memory Access). The method comprises the following steps: constructing an interface function module of a Nios II soft-core processor by utilizing FPGA programmable logic resources and an IP soft core; constructing a Nios II soft-core system by using Qsys in Quartus II software, and adding the Nios II soft-core processor, an I2C master equipment interface module, an I2C slave equipment interface module and other IP cores; acquiring the monitoring information through the I2C master equipment interface module, processing the monitoring information by virtue of the Nios II soft-core processor, and transmitting the processed information to the I2C slave equipment interface module; and accessing the I2C slave equipment interface module to acquire hardware monitoring information by using BMC. According to the method, the hardware monitoring information of the system is acquired in a unified mode by virtue of the FPGA, the integration level of the system is improved, and the design of an external hardware circuit is simplified; and moreover, the hardware information can be independently monitored without influence by the BMC under the multiple physical layer partitions in the system, and the stability and real-time property of the system are improved.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

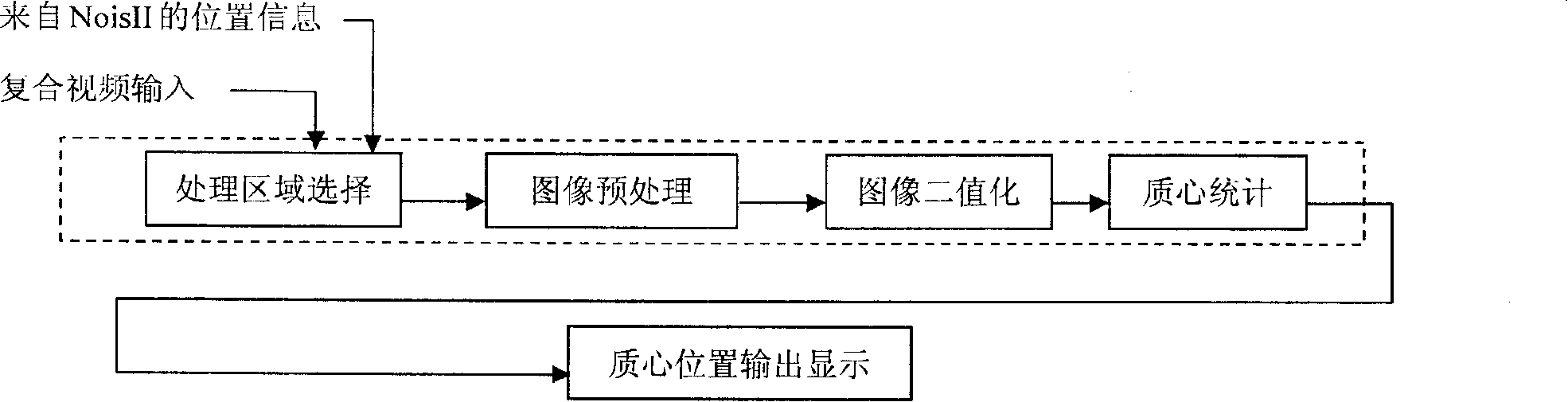

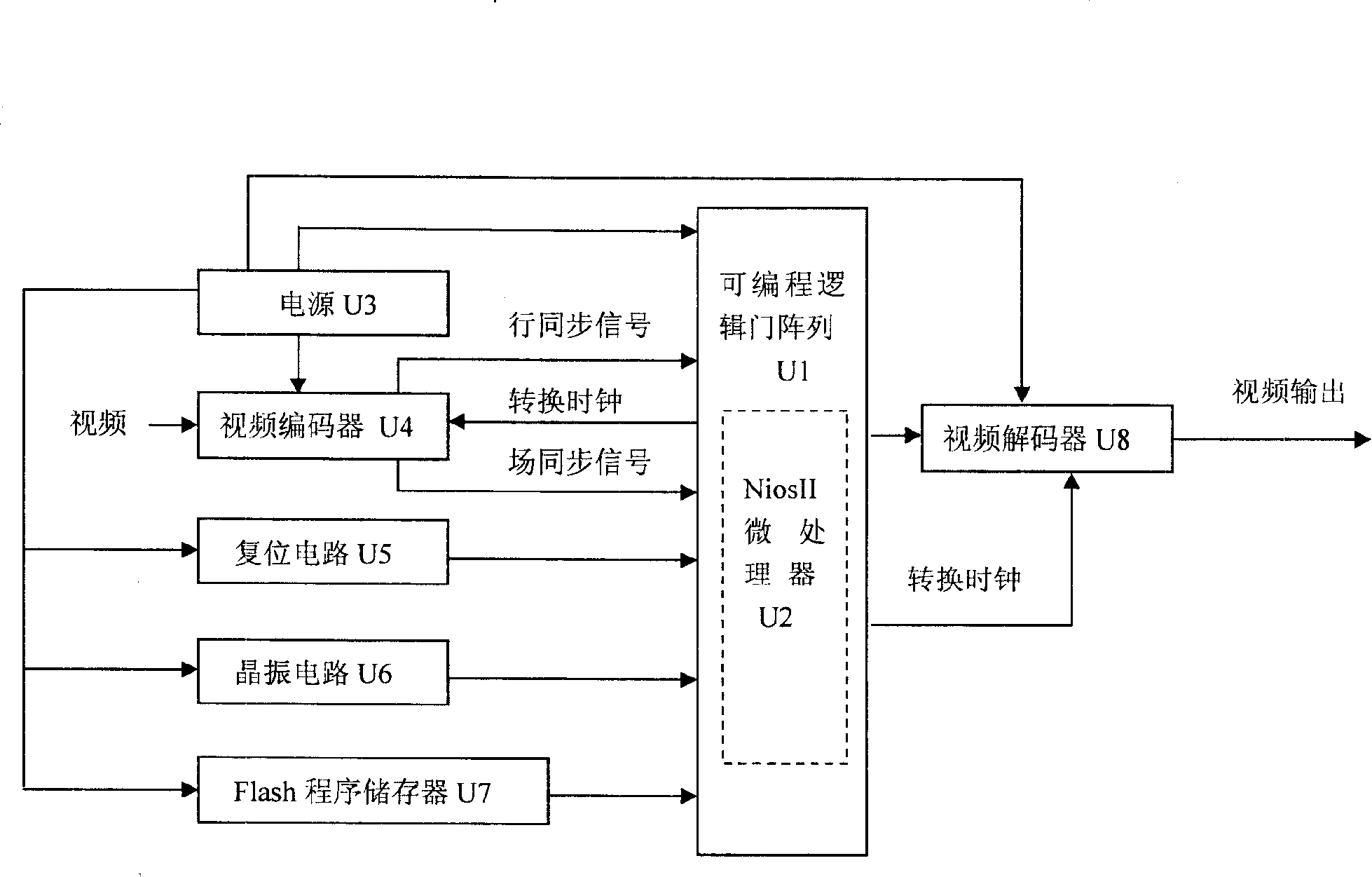

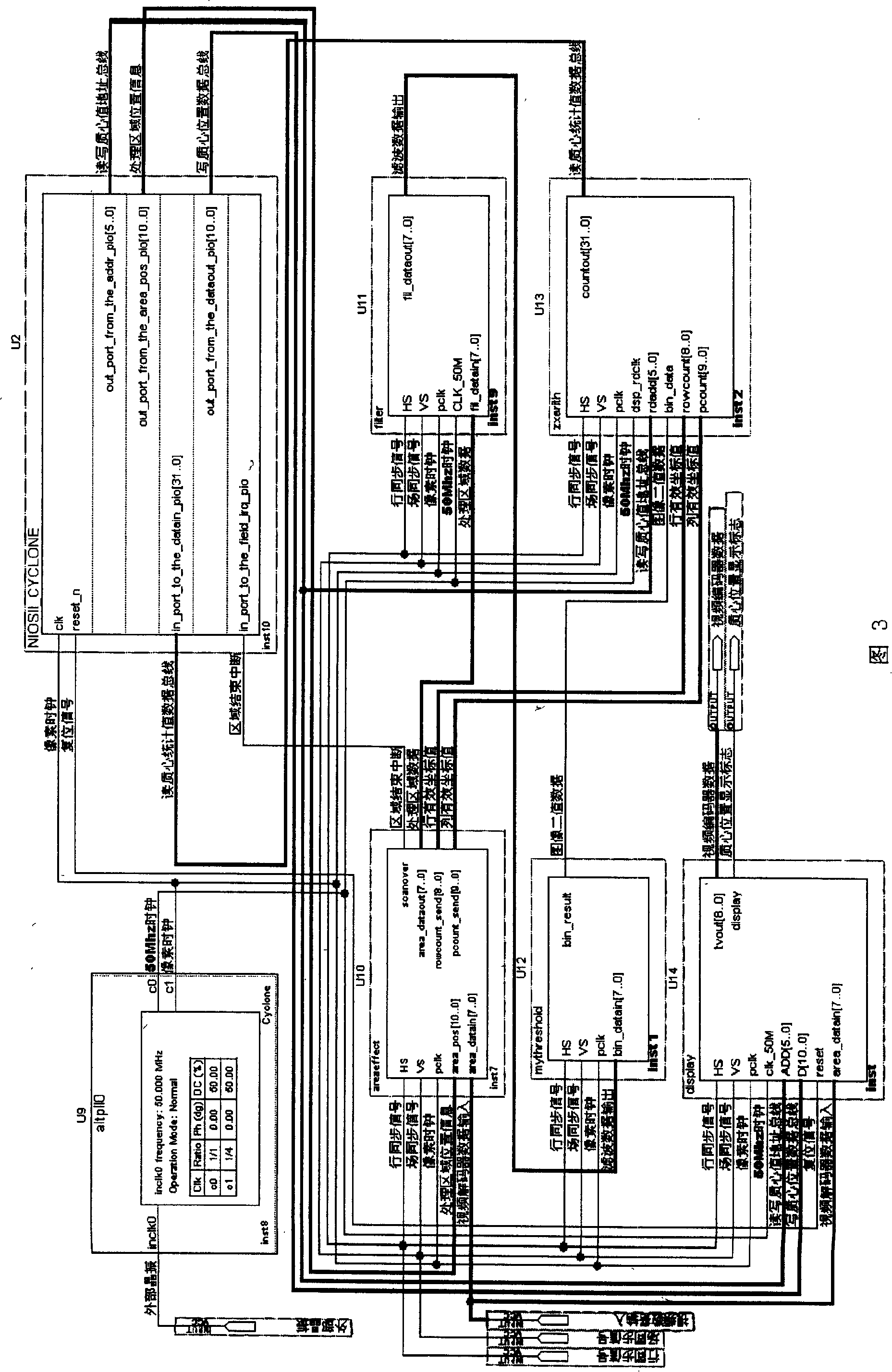

An image centroid computing method and implementation device

InactiveCN101193286ASimple structureRun robustlyImage analysisTelevision systemsStructure functionProcess region

The invention discloses a calculating method and a realization apparatus for image centroid. The invention insets a Nios II microprocessor into the interior of a programmable logic gate array to form a system on a programmable chip. By utilizing the characteristic of the programmable logic gate array on applicability to completing the concurrent structure function, the functions such as selection of the image treatment areas, image enhancement, binary image, image centroid statistics can be completed by the programmable logic gate array. The programmable logic gate array connects each function unit in the form of pipeline structure in the process of completing the image centroid statistic, thus achieving the goal of real-time treatment. By utilizing the characteristic of convenience and flexibility of free customization in the Nios II microprocessor, the size of the image treatment area can be selected according to the actual requirements in the process of treatment, and the bit width and the direction of a data interface bus can be designed thereby without limitations of the prefabricated processor technology.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

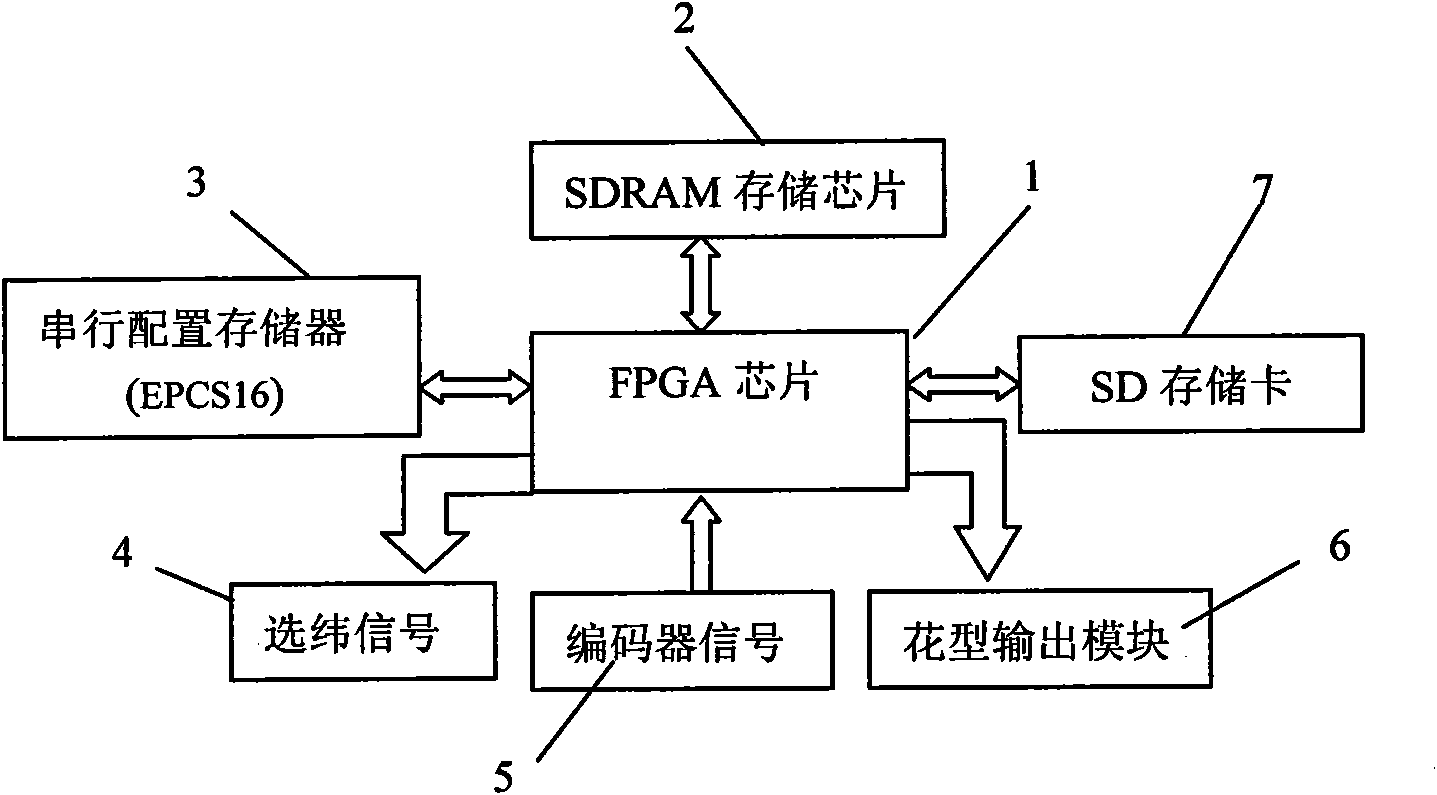

Electronic jacquard machine control system based on FPGA

InactiveCN101634071AFlexible designFlexible commissioningJacquardsProgramme control in sequence/logic controllersMachine controlControl signal

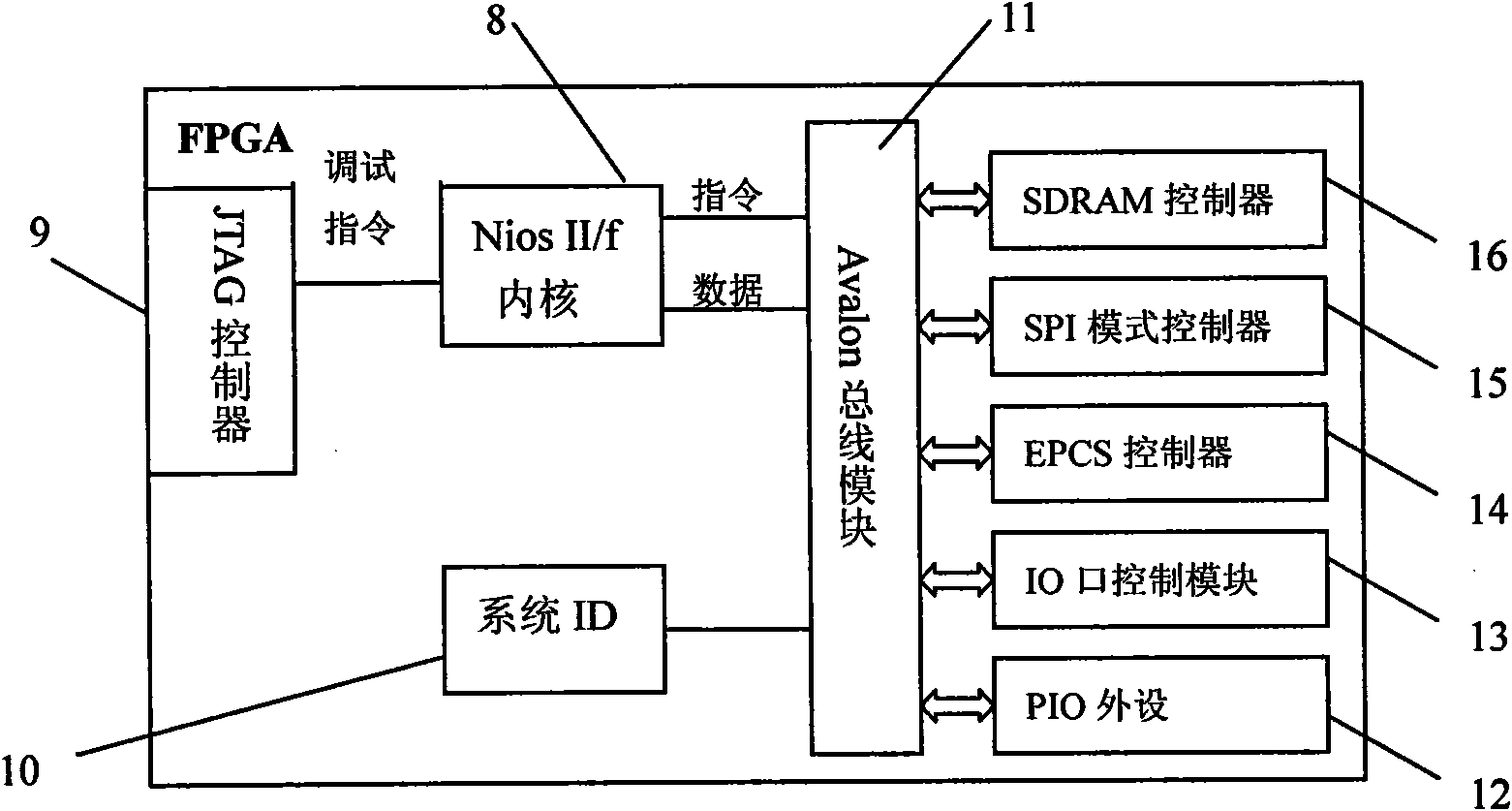

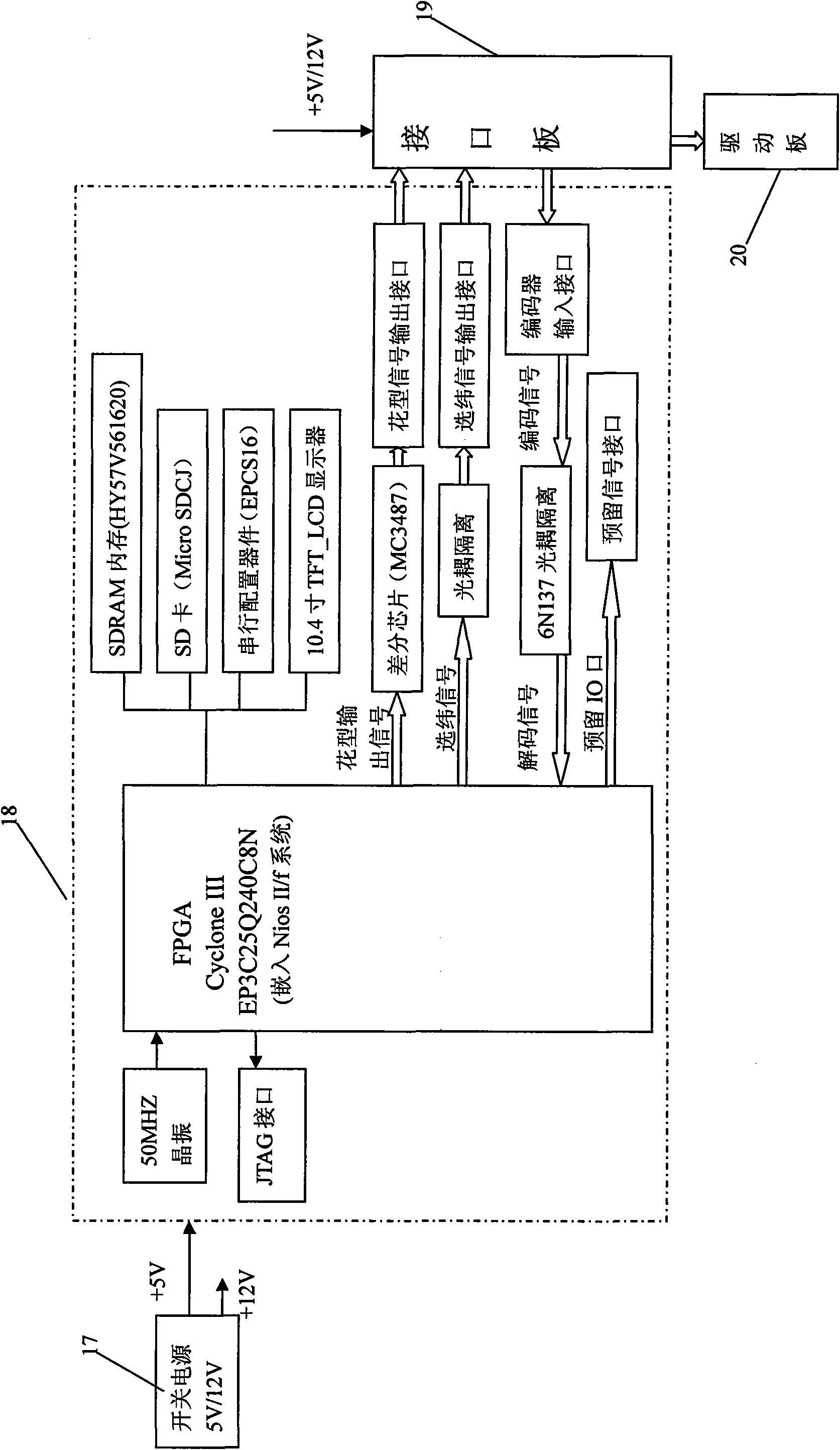

The invention discloses an electronic jacquard machine control system based on an FPGA. An SDRAM controller in an FPGA chip is connected to an SDRAM storage chip by an address, data and a control signal; a corresponding pin of the FPGA chip is connected with a serial configuration memory EPCS16; both a weft selecting signal and a coder signal are directly connected with the FPGA chip by one general I / O pin; and a pattern output module and an SD storage card are respectively connected with the FPGA chip by the other I / O pin. A Nios II / f kernel embedded with the FPGA is interactive with PIO peripheral equipment, an IO port control module, an EPCS controller, an SPI mode controller and an SDRAM controller by an Avalon bus. The electronic jacquard machine control system adopting the FPGA embedded into a Nios II / f system, a serial configuration device, the SD storage card and the pattern output module as kernels has flexible hardware design and short development period, solves the problem of low data transmission speed and pattern file storage content of the prior jacquard machine control system and realizes electronic jacquard weaving at large stitch and high speed.

Owner:ZHEJIANG SCI-TECH UNIV

Direct digital frequency synthesis (DDS)-based signal source

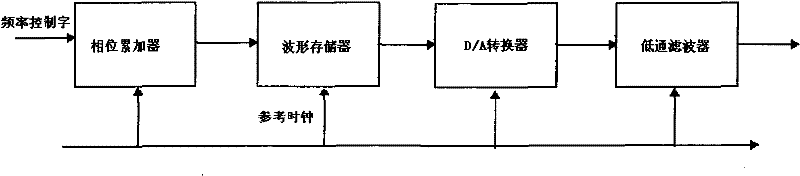

InactiveCN102447470ALow costShorten the design cycleLogic circuits using elementary logic circuit componentsEngineeringDigital signal

A direct digital frequency synthesis (DDS)-based signal source relates to a signal source which is based on the DDS technology. The DDS-based signal source comprises a phase-locked loop clock circuit, a key shake-removal interface circuit, a control circuit, a DDS modular circuit and other parts, wherein the DDS generates digital signal through a field programmable gate array (FPGA), the digital signal is converted into a continuous adjustable sine wave with the frequency being between 30-100Hz and the phase being between 0-360 degrees, the control circuit uses a Nios II system, so the core part of the whole system is completed on an FPGA chip. The DDS-based signal source is used for signal simulation, simulates the signal required by electronic equipment with the same characteristics as the practical environment, tests the performance of the equipment, and is used as a standard source to calibrate or compare with the common signal.

Owner:卢珊

Three-phase electrical energy computation chip based on NIOS II microprocessor

InactiveCN101256209AHighly integratedStrong reliabilityPower measurement by digital techniquePower measurement by current/voltageElectricityEnergy metering

The invention provides a three-phase electric energy gauge based on NIOS II microprocessor, comprising: AD controller, first-in first-out data buffer, electric energy measuring and configurating register, NIOS II flexible core microprocessor, calendar clock interface, digital frequency transformer, IIC interface and LCD controller. Input of AD controller is collected three phase voltage and three phase current, namely serial data of six channels. The AD controller transfers the serial data into parallel data and stores the parallel data in the first-in first-out dada buffer. The first-in first-out data buffer stores the AD data. The electric energy measuring module realizes power active, reactive and apparent energy metering. The configurating register stores configuration data, history electric quantity data, freezing data. The NIOS II flexible core microprocessor dispatches the electric energy measuring chip. The calendar clock interface is connected with the outside calendar clock chip. The digital frequency transformer transfers the electric energy into pulse to output. The IIC interface controls the outside IIC read-only memory. The LCD controller drives the outside LCD.

Owner:CAPITAL NORMAL UNIVERSITY

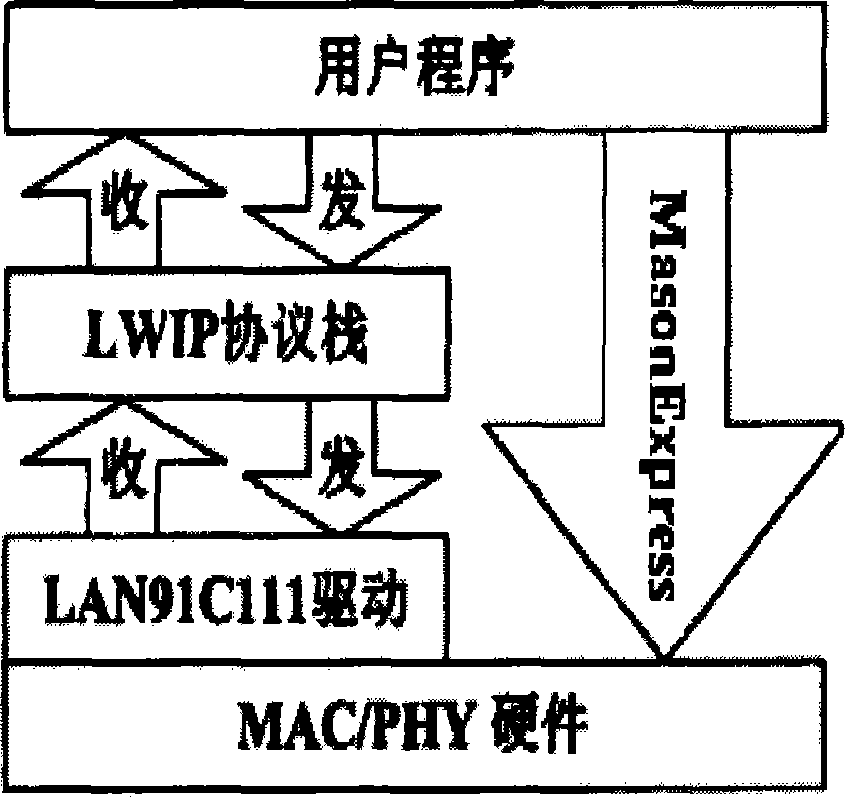

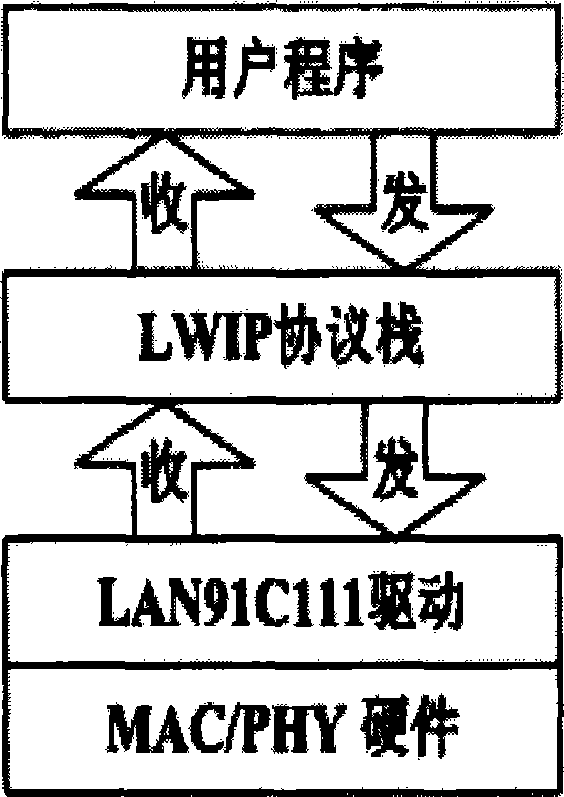

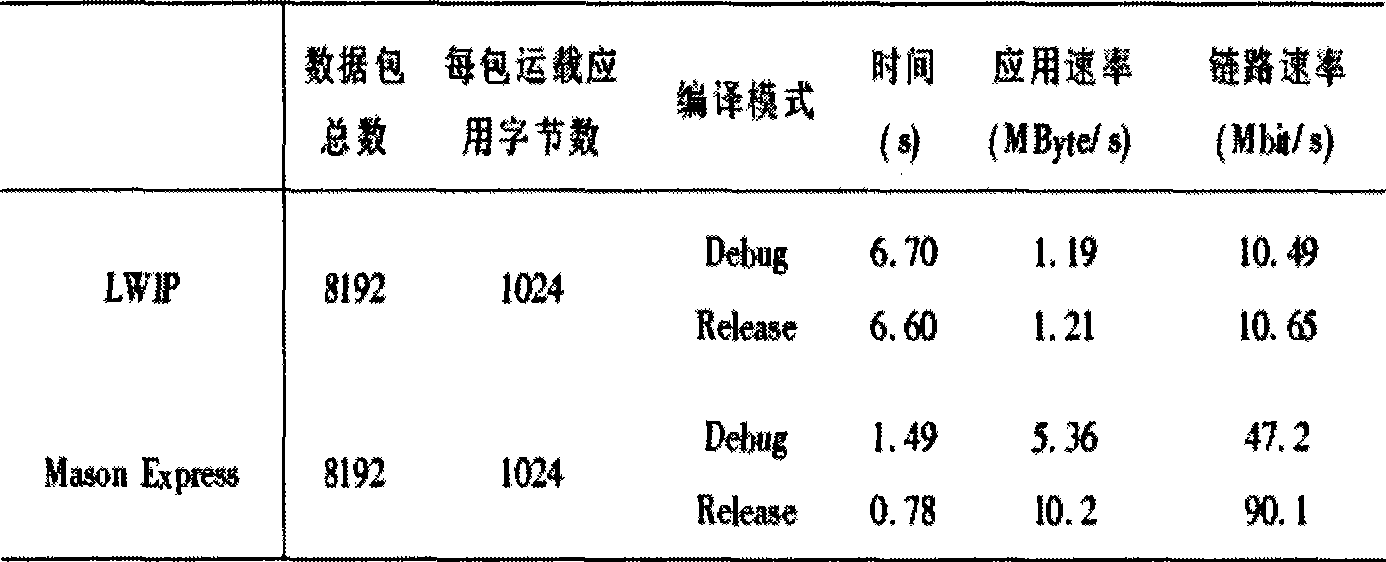

Method for acquiring and transmitting mass data in astronomical telescope control system

InactiveCN101387883AProtect Intellectual InvestmentEnsure safetyTransmissionTotal factory controlNetworking protocolControl system

A method for collecting or transmitting a mass of data in an astronomical telescope control system belongs to the automation control field, which includes steps as following: step 1, preparing protocol headers of protocols of each layer when starting the procedure of astronomical data collection, utilizing the Mason Express function to manually produce a required protocol header, and skirting an LWIP protocol stack running in a Nios II embedded system, step 2, setting a global pointer in the Mason Express function for the skirted LMIP protocol stack, obtaining a semaphore handle from the inside of the LWIP protocol stack, simultaneously, enabling data to be sent by the LWIP protocol stack to be kept in a waiting status before the Mason Express function sending data, and thereby avoiding safety hazards resulting in thread conflicts. By manually producing the required net protocol header, the invention can realize a data transfer rate higher than 90MB / s from an embedded system to a data collecting computer.

Owner:SHANGHAI JIAO TONG UNIV

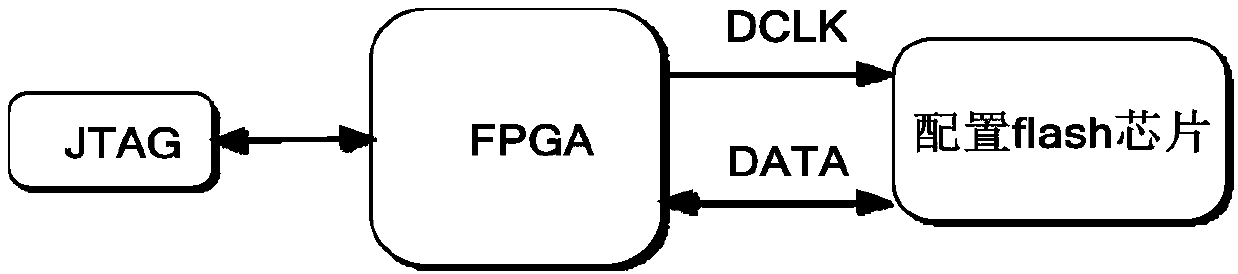

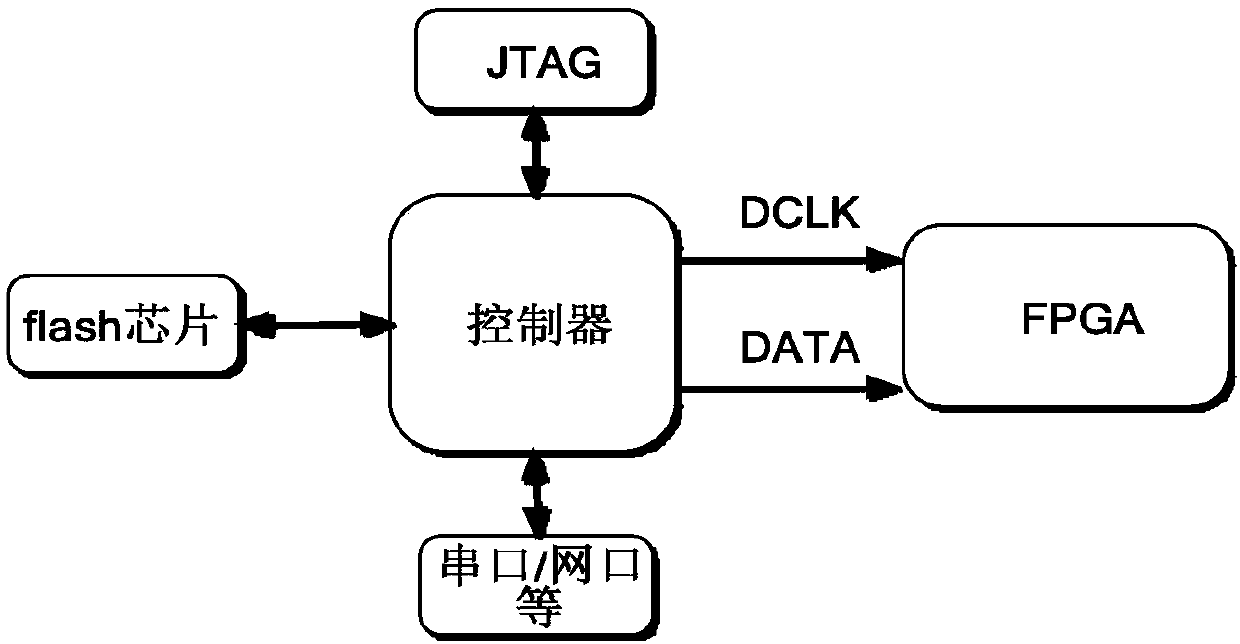

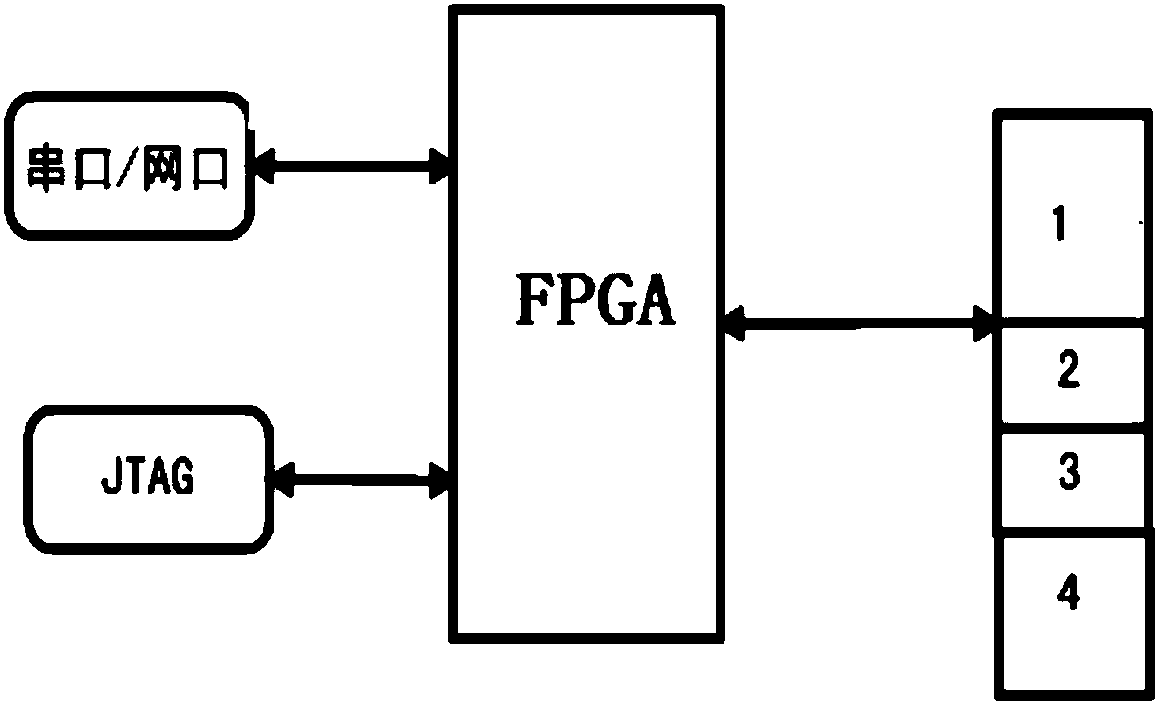

FPGA online upgrading method based on NIOS II

ActiveCN108037943AAvoid the hassle of developingMake the most of storage spaceSoftware engineeringElectricityInternet access

The invention relates to the field of FPGA chips, and discloses an FPGA online upgrading method based on NIOS II. An FPGA can be reconfigured without the assistance of external controller chips underan AS configuration mode online. An IP of a NIOS II processor is embedded into the FPGA to serve as a controller, and an external serial port and an internet access are integrated; when the system iselectrified or reset, the NIOS II processor starts a locator, a waterdog program is closed, if the data NIOS II processor does not receive data from the serial port or the internet access within a limited time, then FPGA configured file data is read from a configured FLASH chip, and then the system enters a user mode; if the data is received and is upgraded data, then the upgraded data is writteninto the configured FLASH chip, the watchdog program is started after the upgraded data is received and written, system restoration is triggered, and online upgrading of the FPGA is completed. The FPGA online upgrading method is applicable to FPGA configuration.

Owner:成都华力创通科技有限公司

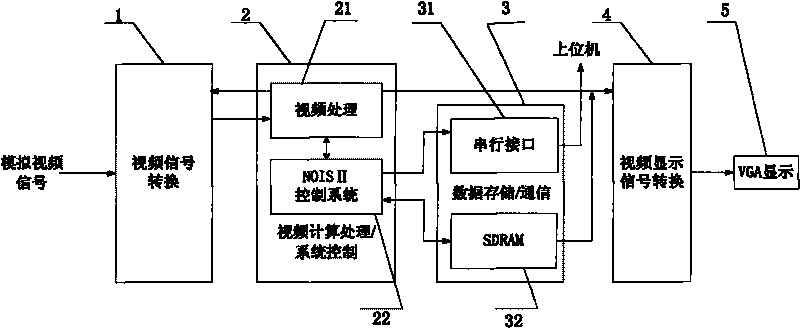

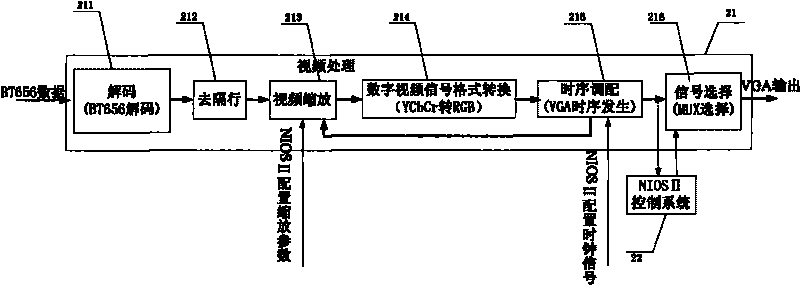

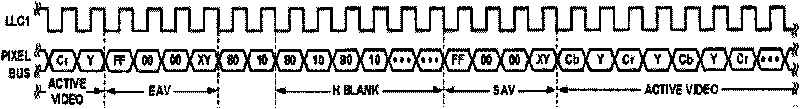

NIOS II-based video monitoring method

InactiveCN101742264AHighly integratedEasy to updateColor signal processing circuitsClosed circuit television systemsVideo monitoringDigital video

The invention provides an NIOS II-based video monitoring method, which belongs to the technical field of embedded video monitoring. The method comprises the following steps: a, converting an analogue video signal into a digital video signal and a synchronizing signal I; b, processing a video to output an RGB digital video signal and a synchronizing signal II; c, real time displaying, or storing or uploading the RGB digital video signal and the synchronizing signal II to an upper computer; and d, outputting an analogue RGB digital video signal to a VGA for displaying and outputting. The method solves the problems that the video monitoring method in the prior art cannot realize real-time monitoring, acquisition, storage and transmission at the same time. Therefore, the method has the advantages of high integration level and fast image data transmission speed.

Owner:XIAN UNIV OF POSTS & TELECOMM

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com