FPGA online upgrading method based on NIOS II

A processor and area technology, applied in instruments, electrical digital data processing, computing, etc., can solve the problems of large configuration data, increased complexity, time-consuming and laborious, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

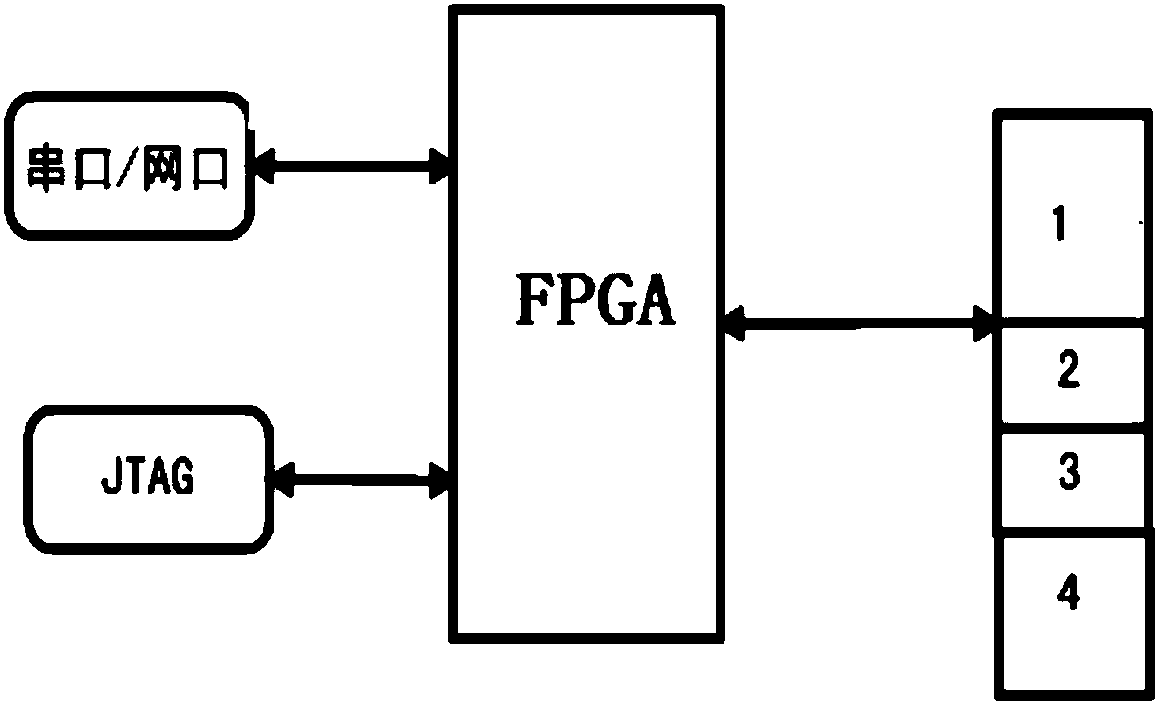

[0020] The embodiment provides a kind of FPGA online upgrade method based on NIOS II, and the IP core of the NIOS II processor is embedded in the embodiment FPGA as a controller, and integrates peripherals such as serial port and network port; FPGA adopts the form of secondary loader to start and upgrade ,Such as image 3 As shown, the FPGA divides the configuration FLASH chip into four storage areas, and the four storage areas are area 1, 2, 3, and 4 respectively. Area 1 stores the configuration file of the FPGA secondary loader program (factory mode program), area 2 stores FPGA configuration file 1, area 3 stores FPGA configuration file 2, and area 4 stores user data. The steps of FPGA online upgrade are as follows: Figure 4 Shown: When the system is powered on or reset, the NIOS II processor starts the timer and closes the watchdog program; Area 2 reads FPGA configuration file 1 and enters user mode 1; if data is received, and the received data is instruction data for sw...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com