Method for acquiring monitoring information of computer system structure based on NUMA (Non Uniform Memory Access)

A technology for monitoring information and architecture, applied in the computer field, can solve the problem of not being able to provide I2C bus interface to store hardware monitoring information, and achieve the effect of simplifying hardware circuit design, improving integration, and improving stability and real-time performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

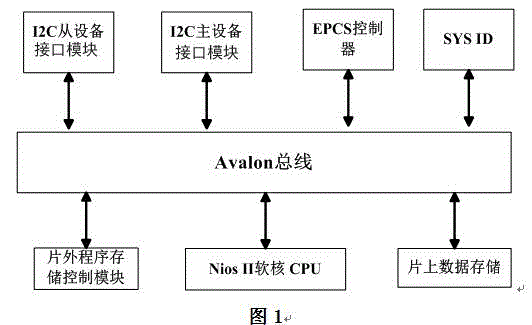

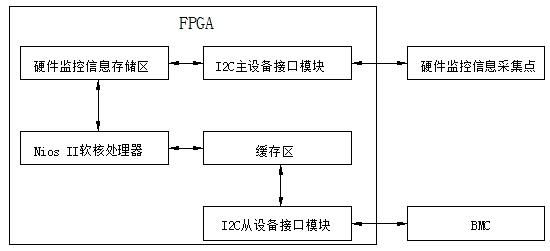

[0015] When the system has no partition work settings, use the monitoring information collection method based on the NUMA computer architecture described in this embodiment, as attached figure 2 As shown, the hardware monitoring information collection point is connected to the I2C master interface module inside the FPGA, and the system hardware collection information is transmitted to the FPGA hardware monitoring information storage area through the I2C bus. The Nios II soft-core processor packs the external hardware monitoring information and passes it through the Avalon The bus is stored in the buffer area of the system, and the buffer area corresponds to the area under the I2C slave device interface module connected to the BMC; when the BMC sends a command to read hardware monitoring information, the BMC collects the hardware monitoring information stored in the buffer area through the I2C bus information.

[0016] In the monitoring information collection method describe...

Embodiment 2

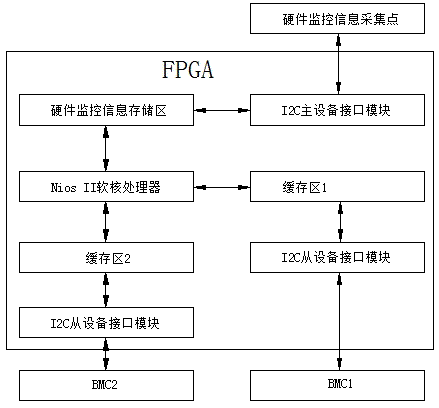

[0018] When the multi-partition work of the system is set, it is divided into multiple independent systems, using the monitoring information collection method based on the NUMA computer architecture described in this embodiment, as attached image 3 As shown, in the present embodiment, taking two partitions as an example, the number of physical partitions is detected by the FPGA, and divided into double buffer areas according to the number of partitions, and the system hardware acquisition information is transmitted to the FPGA hardware monitoring information storage area through the I2C bus. The Nios II soft-core processor packs the external hardware monitoring information, and stores the hardware monitoring information of each partition in its corresponding buffer area through the Avalon bus, that is, buffer area 1 corresponds to the hardware monitoring information under partition 1, and the buffer area 2 corresponds to the hardware monitoring information under partition 2; e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com