Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

45 results about "Co implantation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Co-Implantation. ドーパント原子と共に炭素(C)、窒素(N)、フッ素(F)等の原子を注入することにより、熱処理時のドーパントの拡散が抑制される効果が得られる。浅い接合を形成するために用いられることがある。 PAI(Pre-Amorphization Implantation)

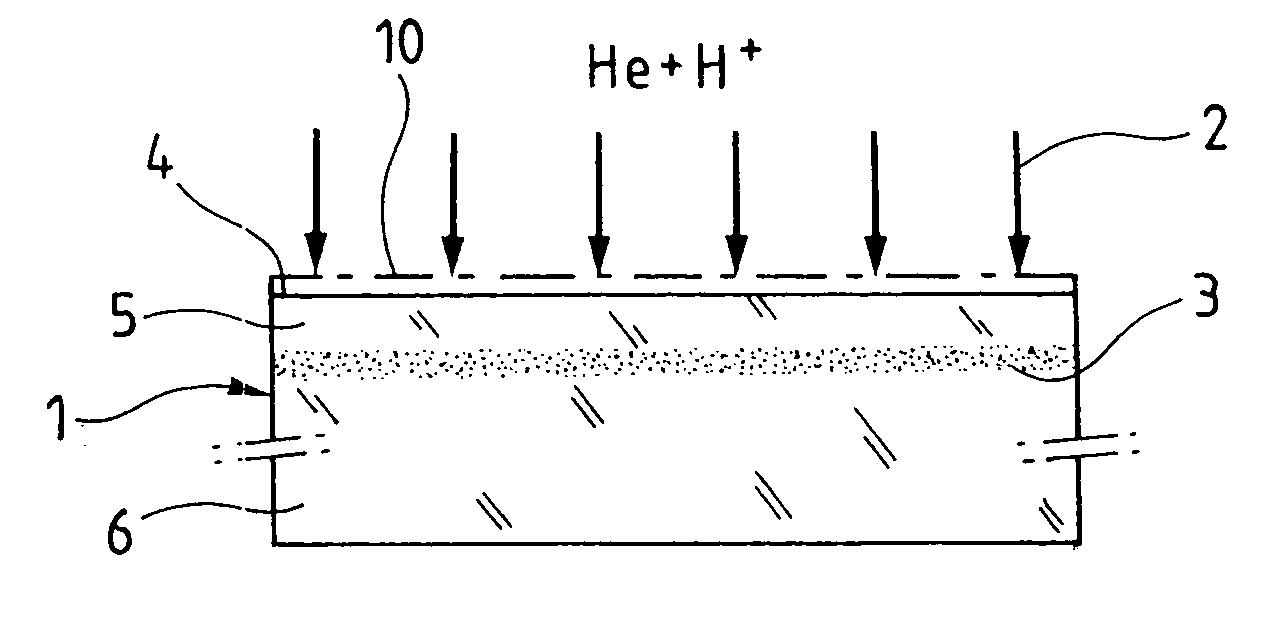

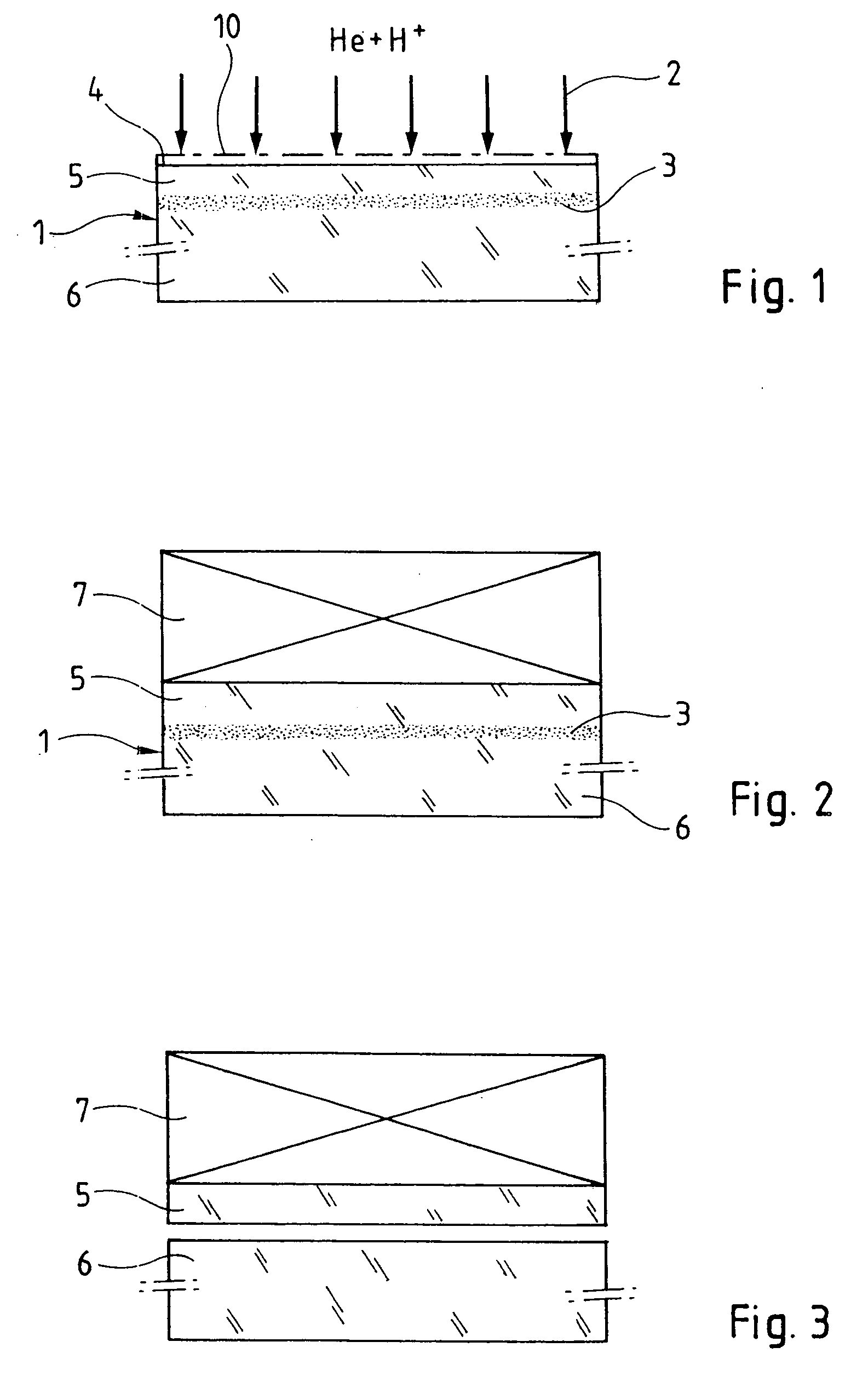

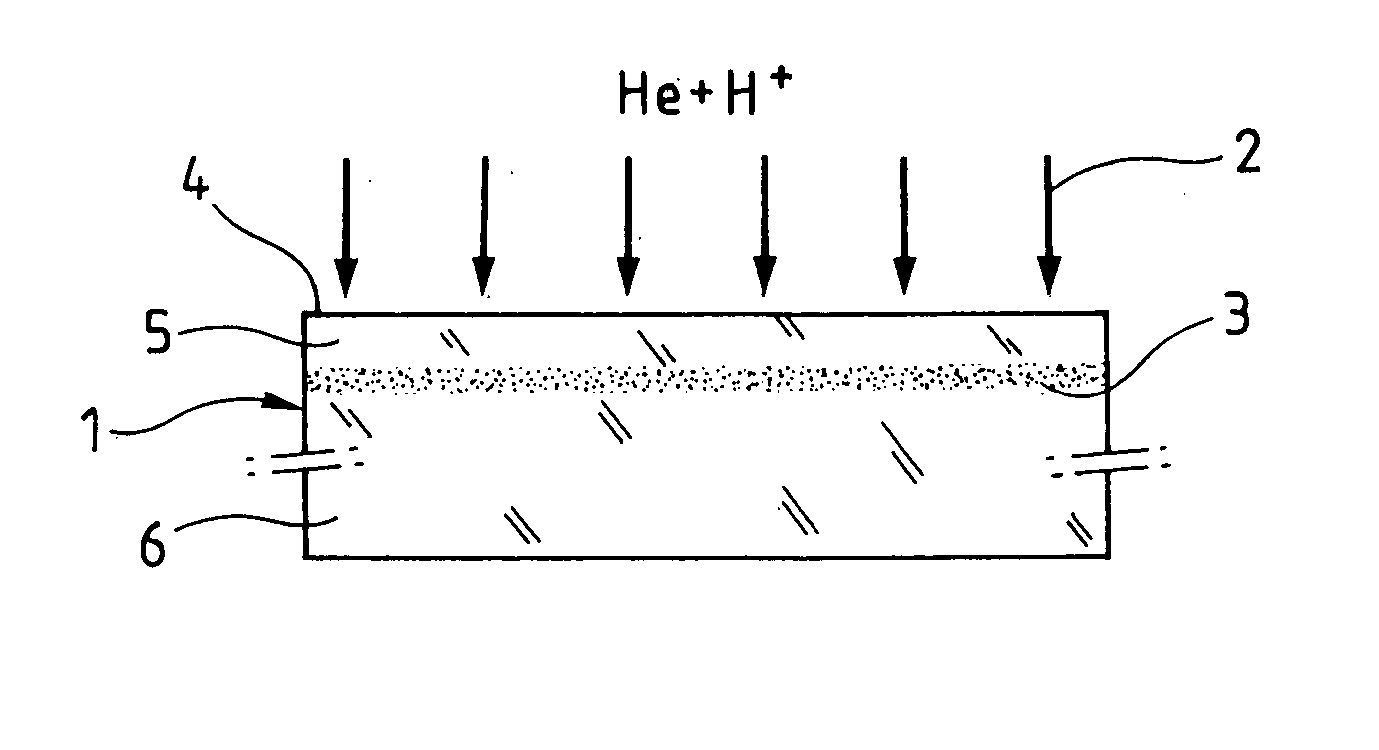

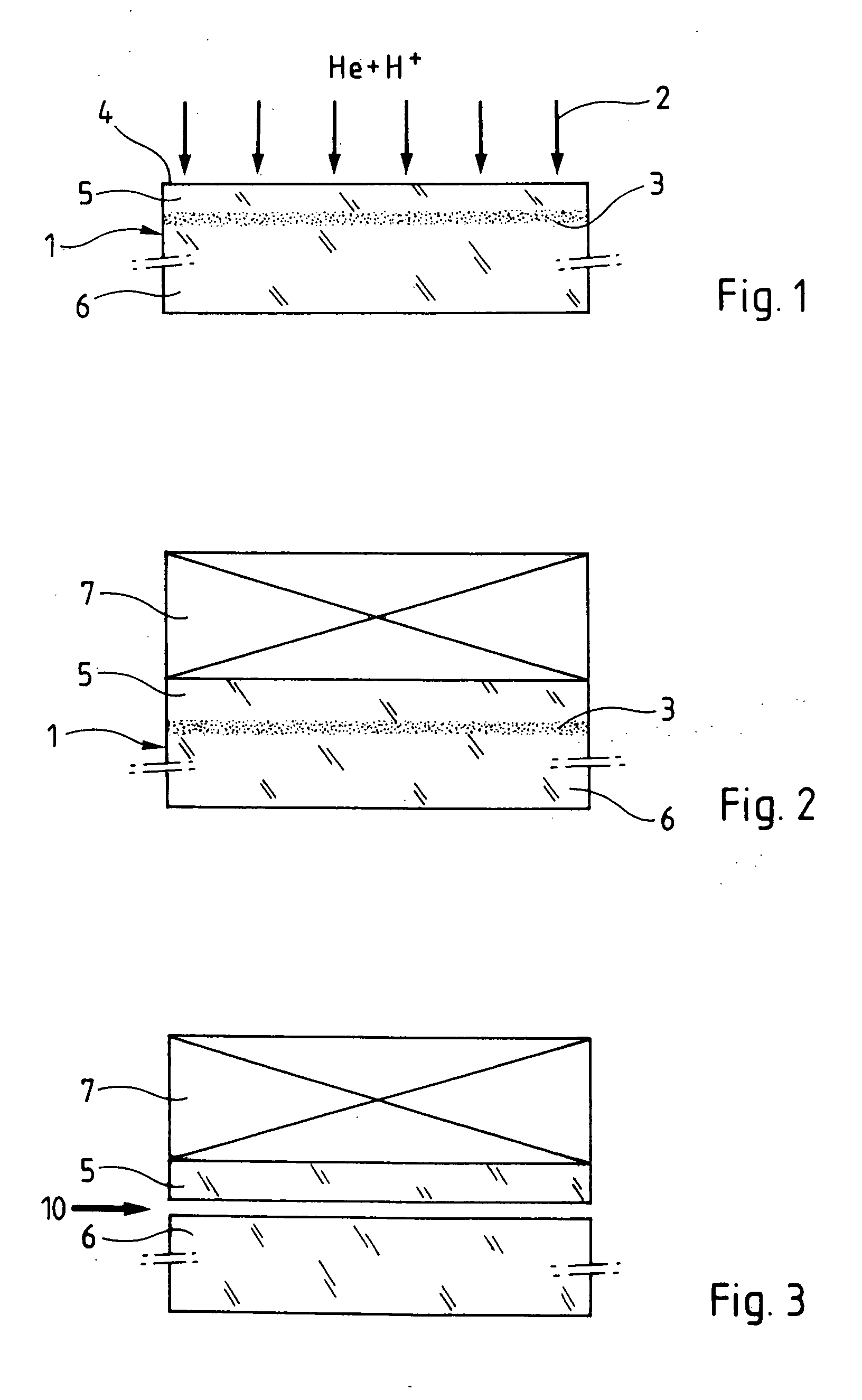

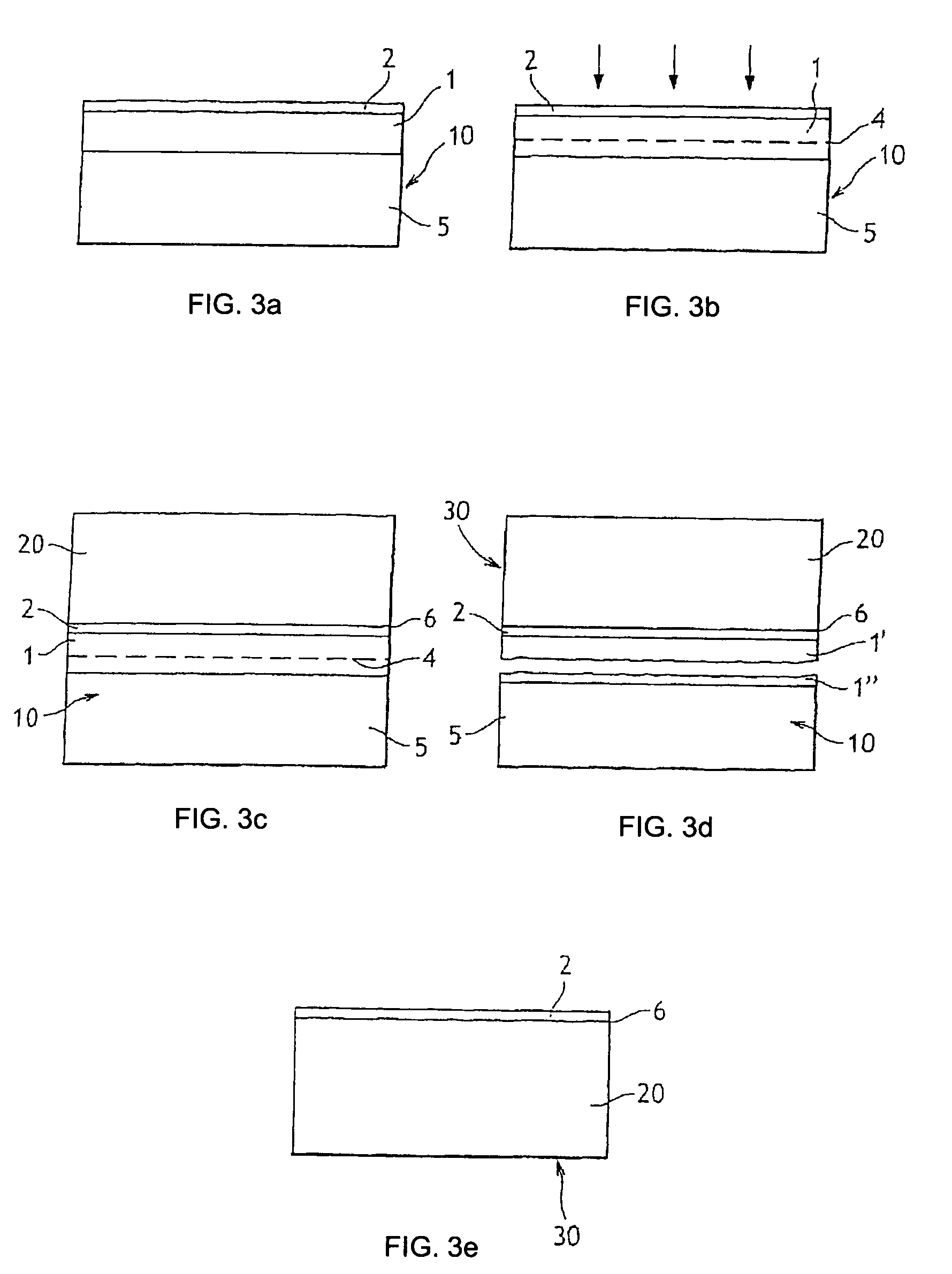

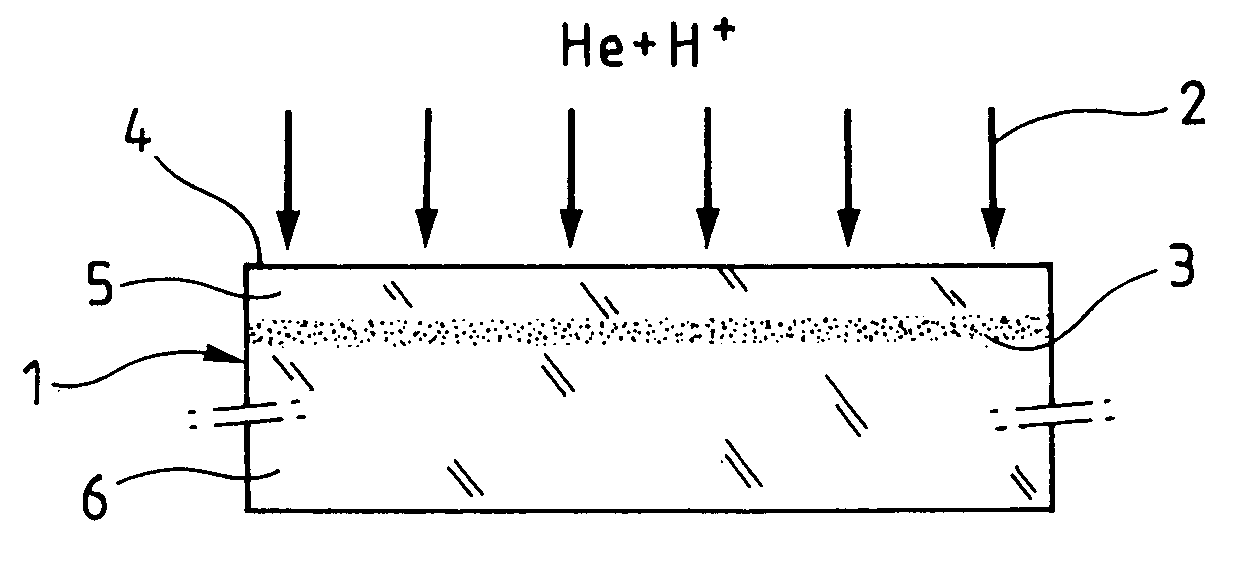

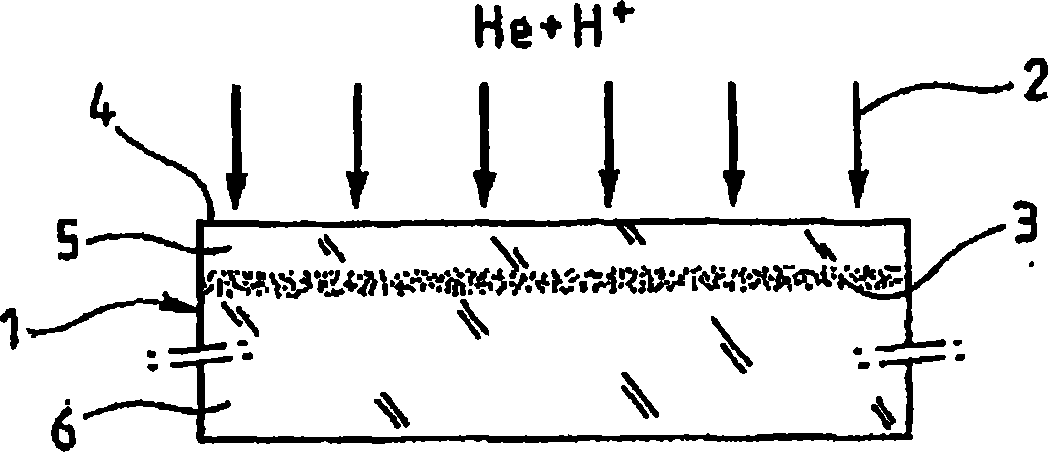

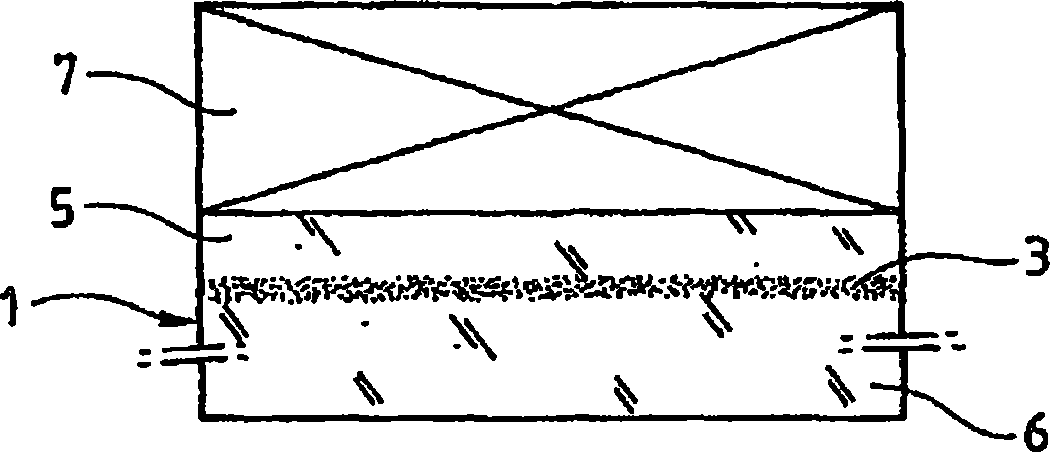

Method of detaching a thin film at moderate temperature after co-implantation

ActiveUS20040171232A1Increase internal pressureEasy to reinforceSemiconductor/solid-state device manufacturingAmount of substanceCo implantation

A method of detaching a thin film from a source substrate comprises the following steps: implanting ions or gaseous species in the source substrate so as to form therein a buried zone weakened by the presence of defects; splitting in the weakened zone leading to the detachment of the thin film from the source substrate. Two species are implanted of which one is adapted to form defects and the other is adapted to occupy those defects, the detachment being made at a temperature lower than that for which detachment could be obtained with solely the dose of the first species.

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

Method of catastrophic transfer of a thin film after co-implantation

ActiveUS20050148163A1Reduce roughnessHigh mechanical stressSemiconductor/solid-state device manufacturingCo implantationAtomic physics

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

Atomic implantation and thermal treatment of a semiconductor layer

ActiveUS20050245049A1Minimize surface roughnessOvercome problemsSemiconductor/solid-state device manufacturingElectrical conductorSemiconductor structure

Methods for forming a semiconductor structure are described. In an embodiment, the technique includes providing a donor wafer having a first semiconductor layer and a second semiconductor layer on the first layer and having a free surface; coimplanting two different atomic species through the free surface of the second layer to form a zone of weakness zone in the first layer; bonding the free surface of the second layer to a host wafer; and supplying energy to detach at the zone of weakness a semiconductor structure comprising the host wafer, the second layer and a portion of the first layer. Advantageously, the donor wafer includes a SiGe layer, and the co-implantation of atomic species is conducted according to implantation parameters adapted to enable a first species to form the zone of weakness in the SiGe layer, and to enable a second species to provide a concentration peak located beneath the zone of weakness in the donor wafer to thus minimize surface roughness resulting from detachment at the zone of weakness.

Owner:SOITEC SA

Thermal treatment of a semiconductor layer

InactiveUS20060014363A1Shorten the durationReduce economic costsSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor package

A method for forming a structure that includes a layer that is removed from a donor wafer that has a first layer made of a semiconductor material containing germanium. The method includes the steps of forming a weakness zone in the thickness of the first layer; bonding the donor wafer to a host wafer; and supplying energy so as to weaken the donor wafer at the level of the zone of weakness. The zone of weakness is formed by subjecting the donor wafer to a co-implantation of at least two different atomic species, while the bonding is carried out by performing a thermal treatment at a temperature between 300° C. and 400° C. for a duration of from 30 minutes to four hours.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES

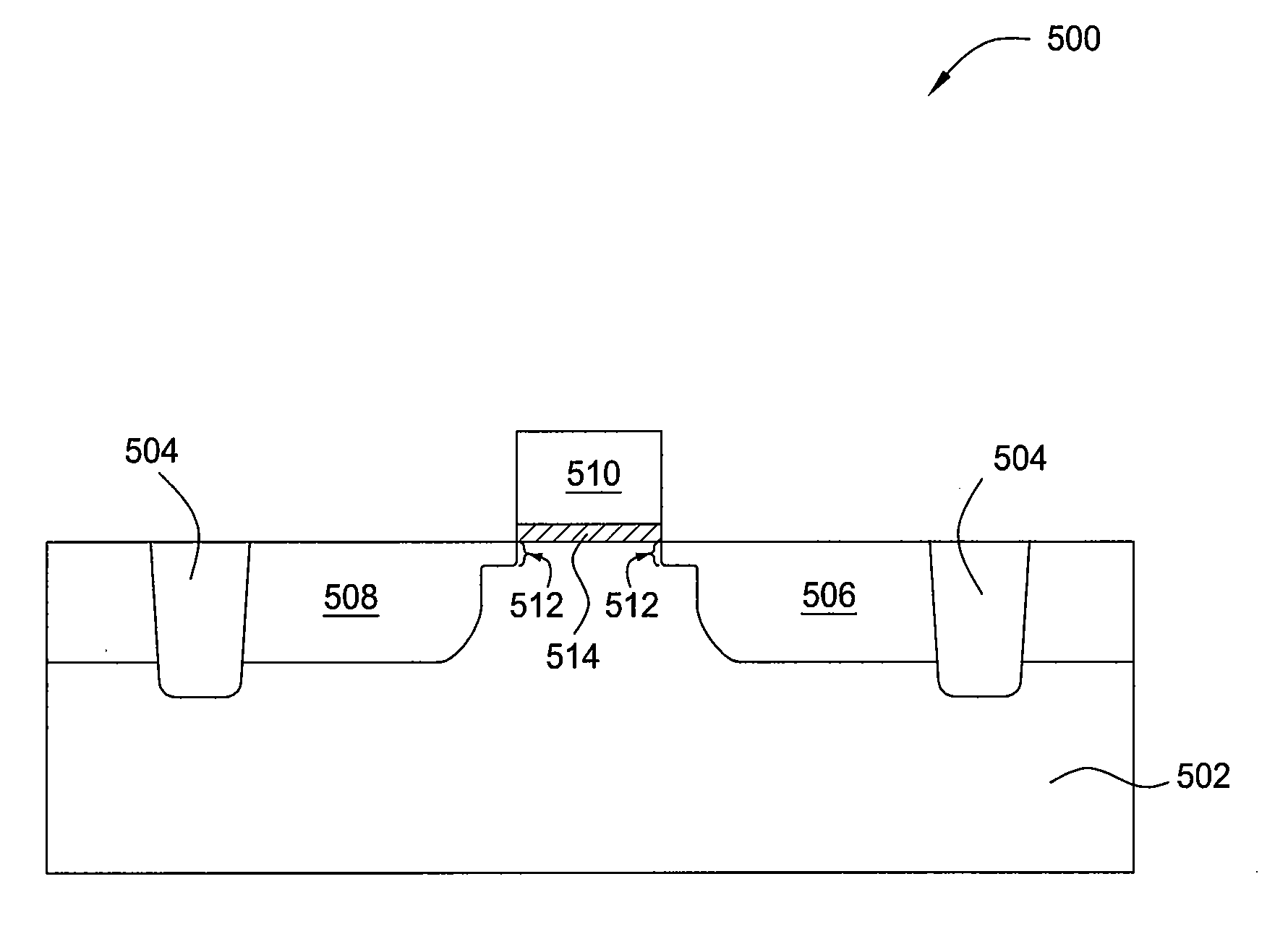

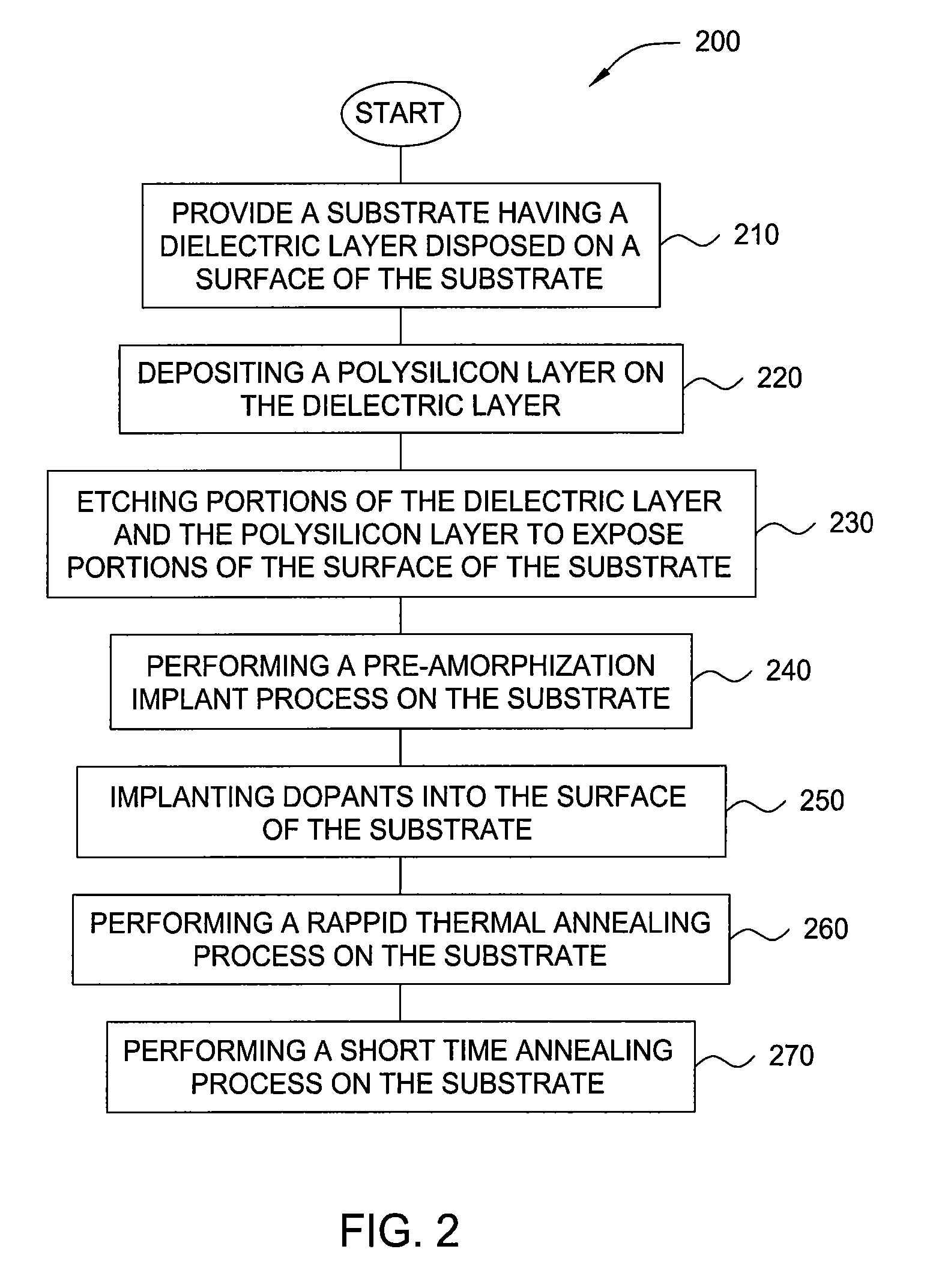

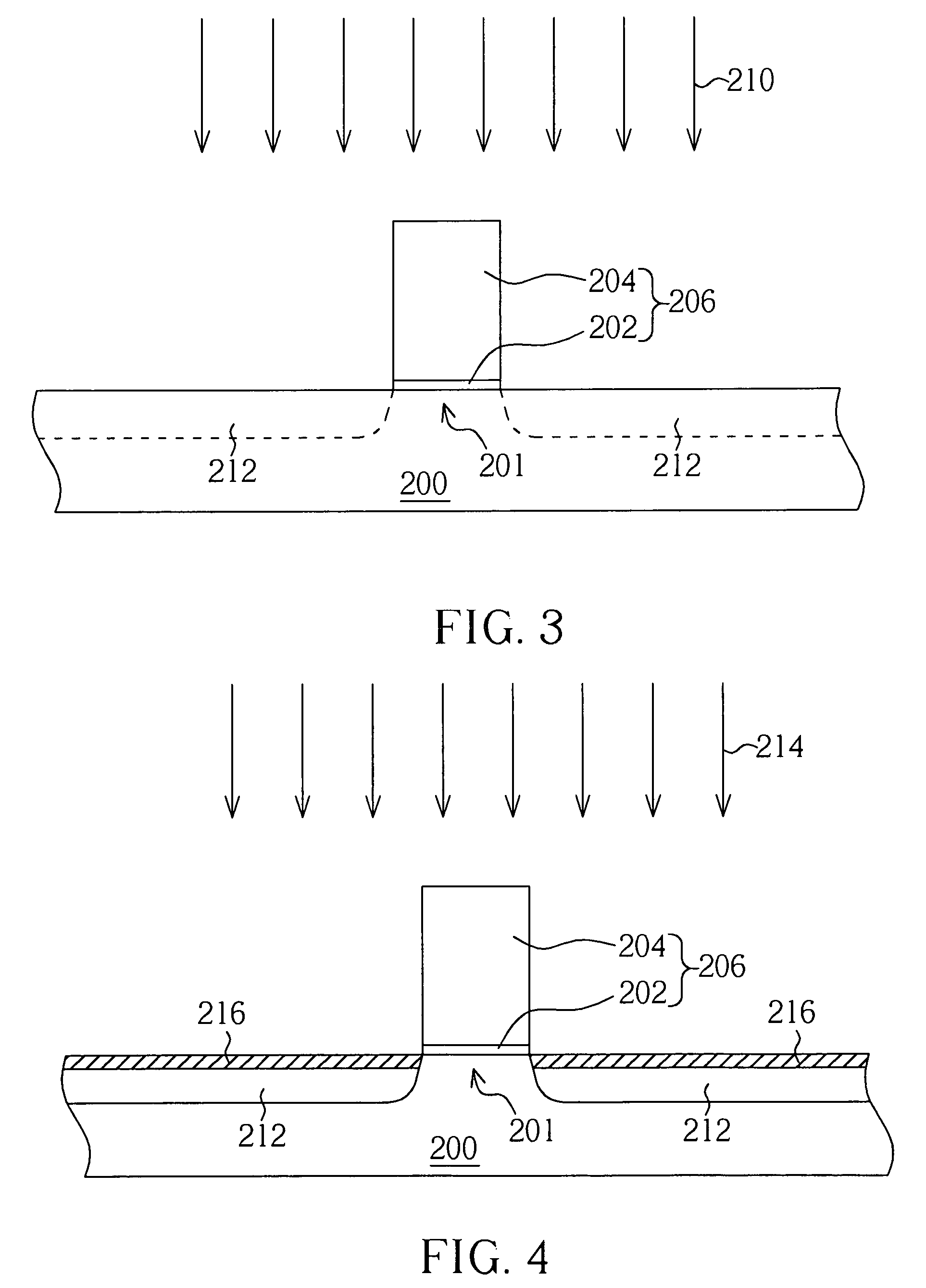

Use of carbon co-implantation with millisecond anneal to produce ultra-shallow junctions

InactiveUS20080023732A1Short timeShort time thermal annealTransistorSemiconductor/solid-state device manufacturingDopantRapid thermal annealing

Embodiments of the present invention include methods for forming an ultra-shallow junction in a substrate. In one embodiment, the method includes providing a silicon substrate, co-implanting the silicon substrate with carbon and a dopant to form a doped silicon substrate, and exposing the silicon substrate to a short time thermal anneal. In certain embodiments, the silicon substrate is exposed to a rapid thermal anneal after co-implanting the silicon substrate but prior to exposing the silicon substrate to a short time thermal anneal. In certain embodiments, the pre-amorphization implant is performed on the silicon substrate prior to implanting the silicon substrate with carbon and a dopant. In certain embodiments, the silicon substrate is a monocrystalline silicon substrate.

Owner:APPLIED MATERIALS INC

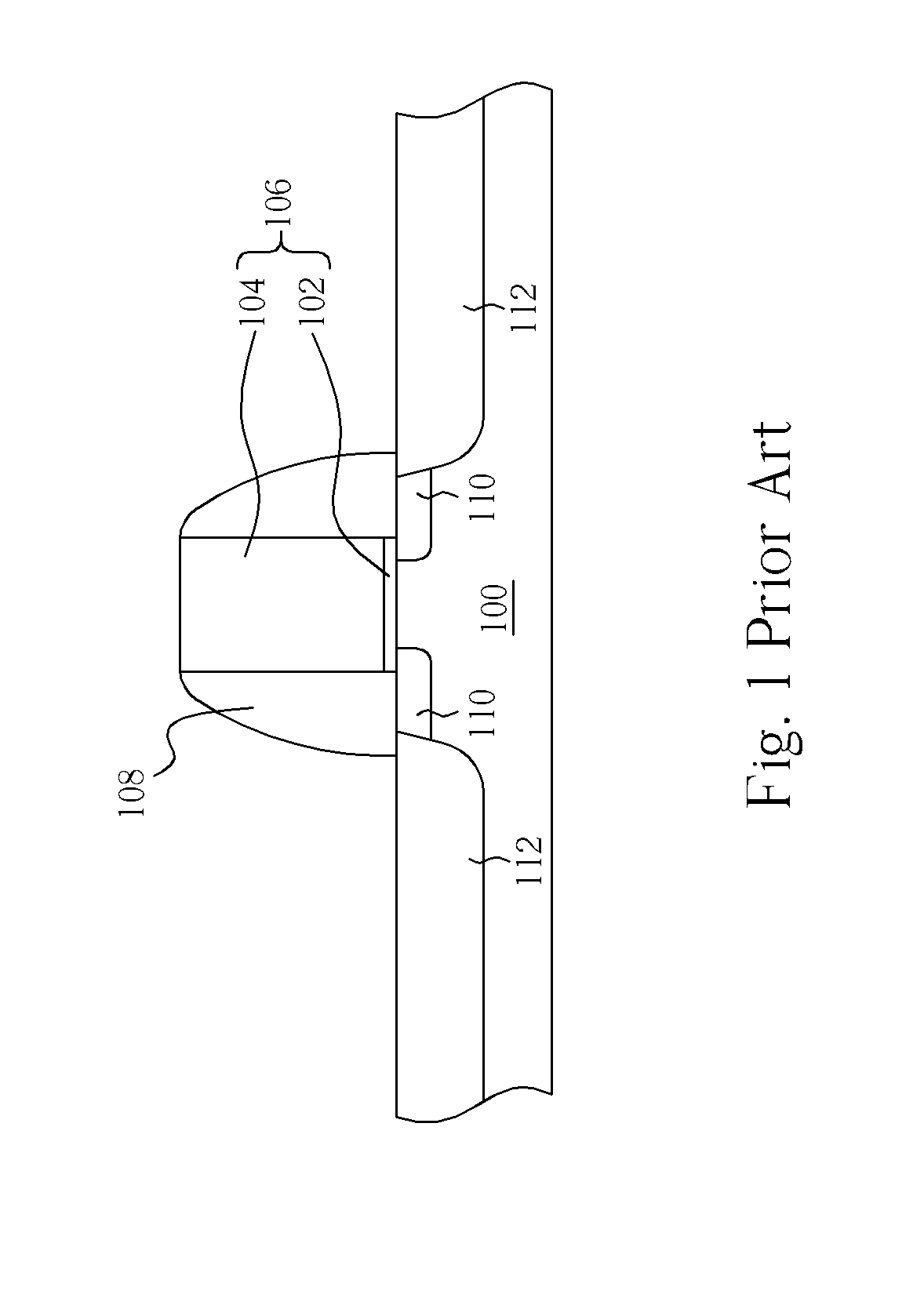

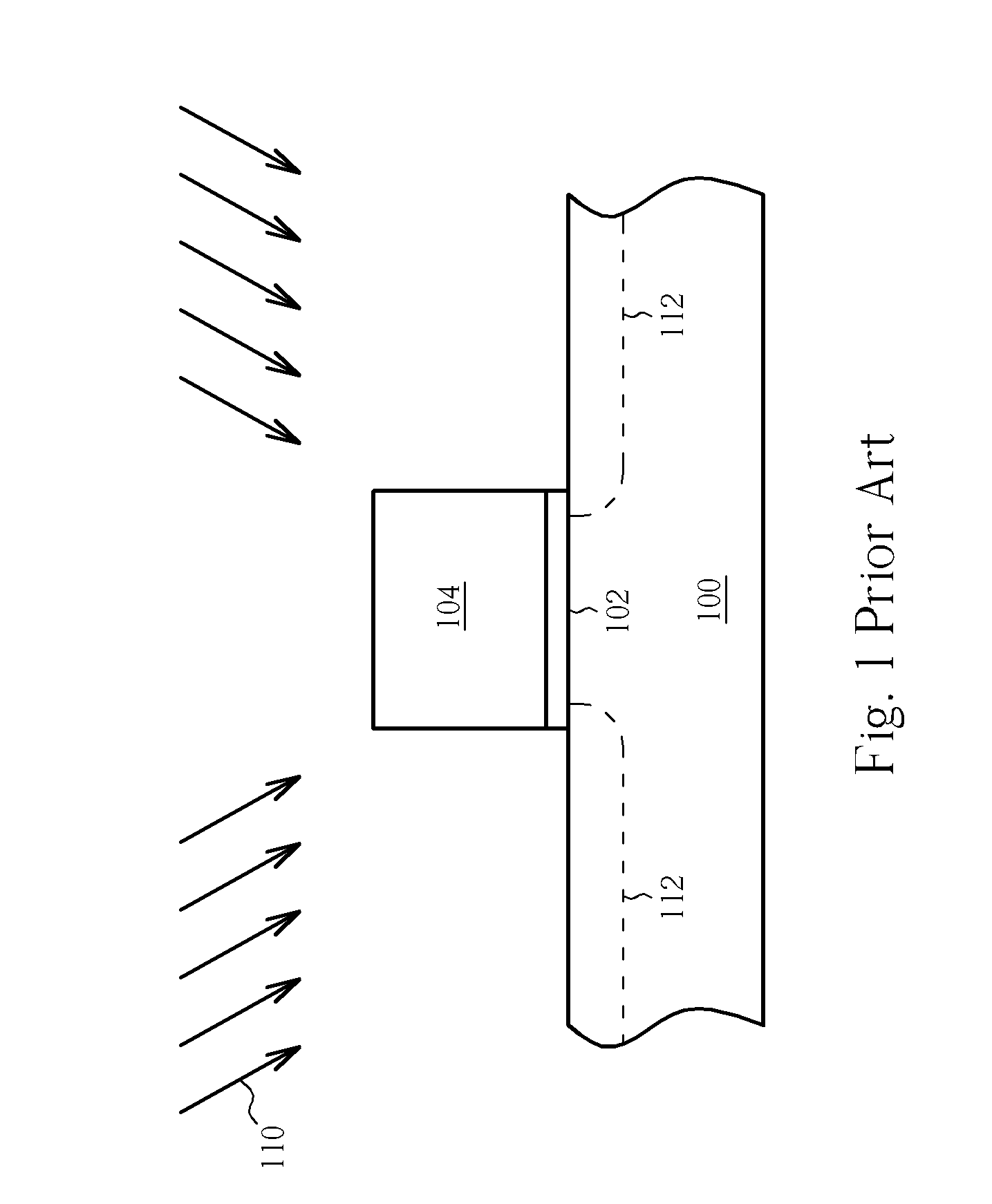

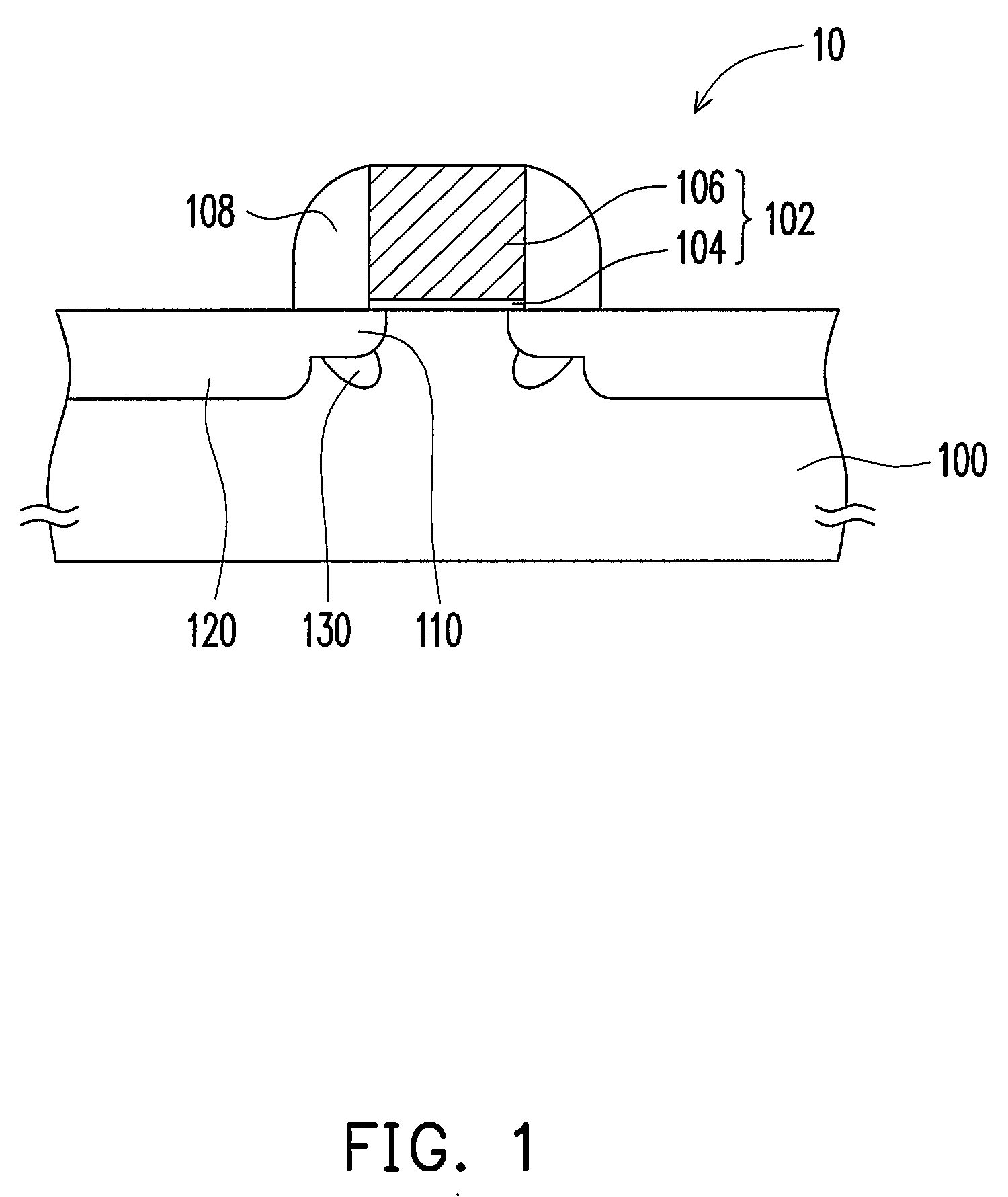

Method of forming a MOS transistor

ActiveUS20070238234A1Improve short channel effectFacilitated DiffusionTransistorSemiconductor/solid-state device manufacturingDopantEngineering

A method of forming a MOS transistor, in which a co-implantation is performed to implant an implant into a source region and a drain region or a halo implanted region to effectively prevent dopants from over diffusion in the source region and the drain region or the halo implanted region, for obtaining a good junction profile and improving short channel effect. The implant comprises carbon, a hydrocarbon, or a derivative of the hydrocarbon, such as one selected from a group consisting of C, CxHy+, and (CxHy)n+, wherein x is a number of 1 to 10, y is a number of 4 to 20, and n is a number of 1 to 1000.

Owner:MARLIN SEMICON LTD

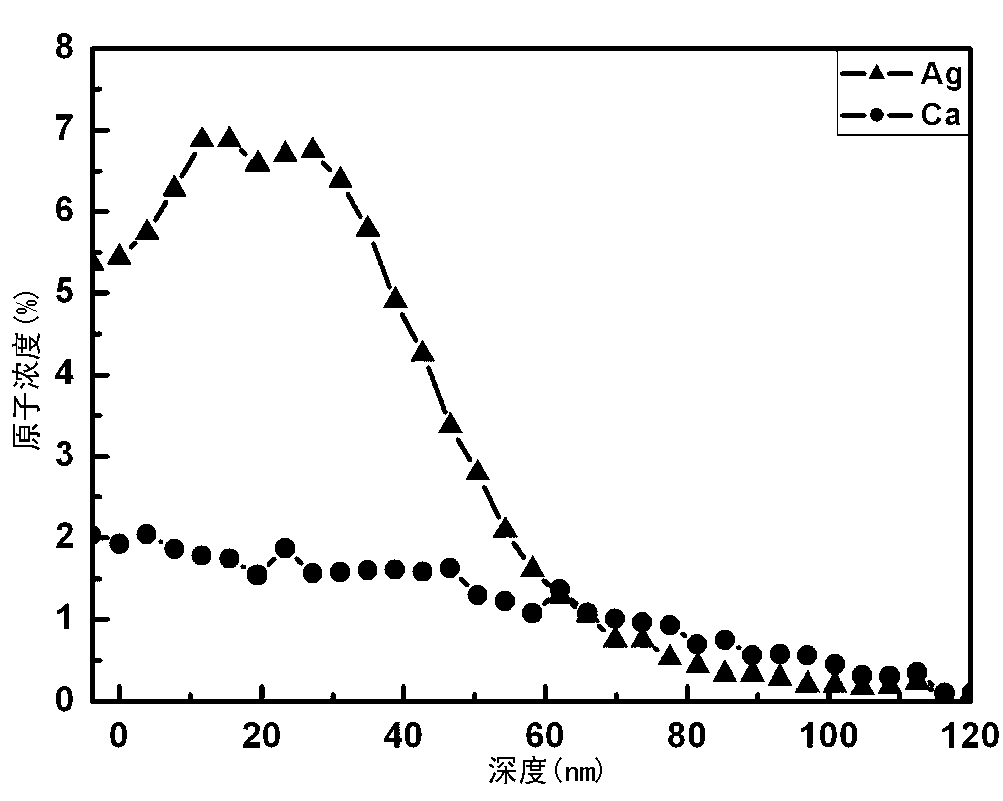

Modification method for titanium surface with osteogenic performance and antibacterial performance

ActiveCN103014646AEnhanced inhibitory effectPromote osteogenesisVacuum evaporation coatingSputtering coatingEscherichia coliMedical equipment

The invention relates to a modification method for a titanium surface with osteogenic performance and antibacterial performance. The modification method adopts a plasma-immersion ion implantation treatment process to co-implant silver ion and calcium ion to the surface of a titanium base material, wherein the co-implantation simultaneously arouse two cathode impulse arc sources, which respectively adopt pure silver and pure calcium as a cathode, to carry out plasma-immersion ion implantation treatment process. The silver-calcium co-implantation method provided by the invention can be used for improving the osteogenic performance and antibacterial performance of the surface (for example an artificial bone, an artificial joint and a dental implant) which can be implanted to medical equipment. The prepared modified material has a remarkable inhibitory effect to the escherichia coli and staphylococcus aureus, and a remarkable promotion to adhesion and proliferation of relevant osteoblast (BMSCs, MG63 cells).

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

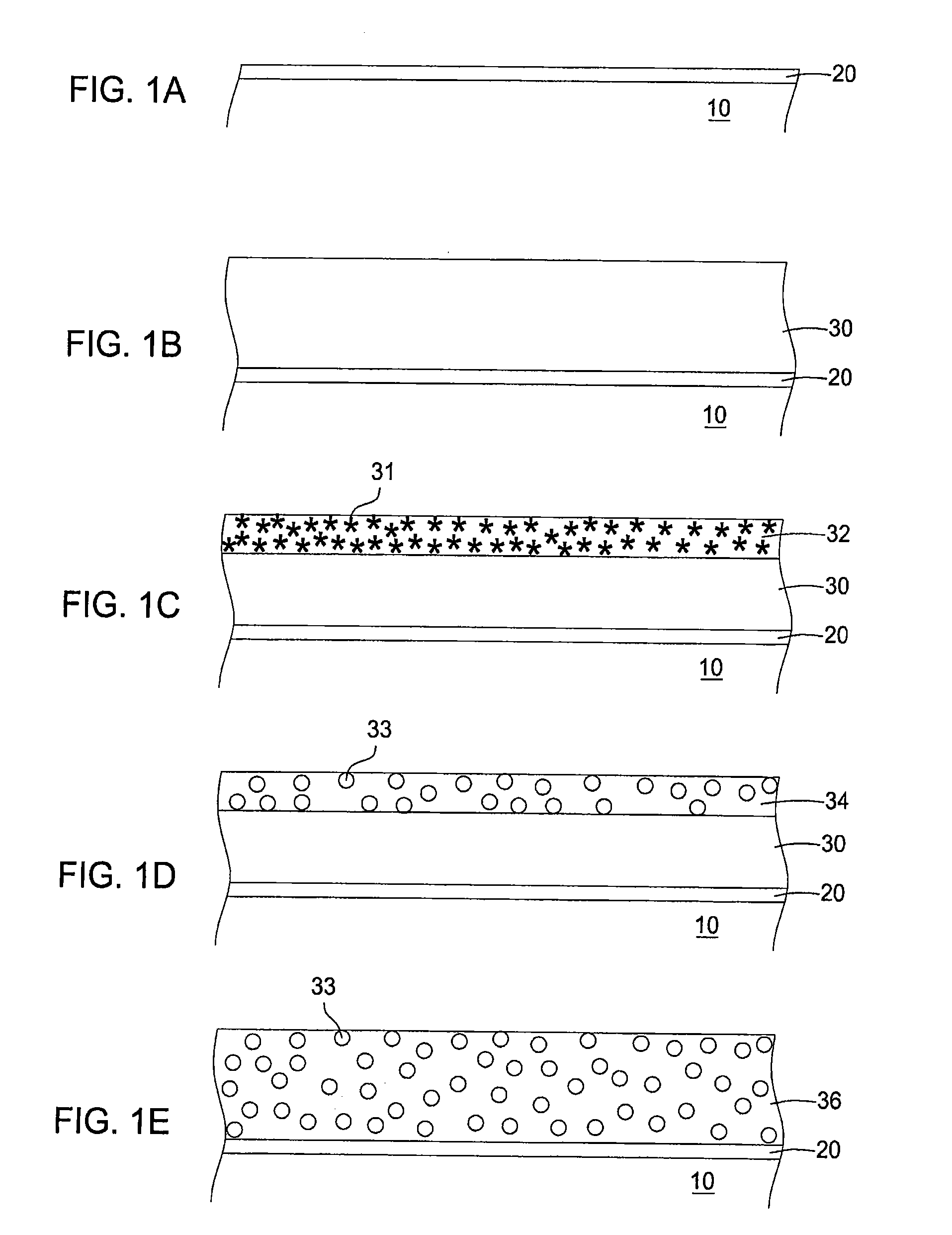

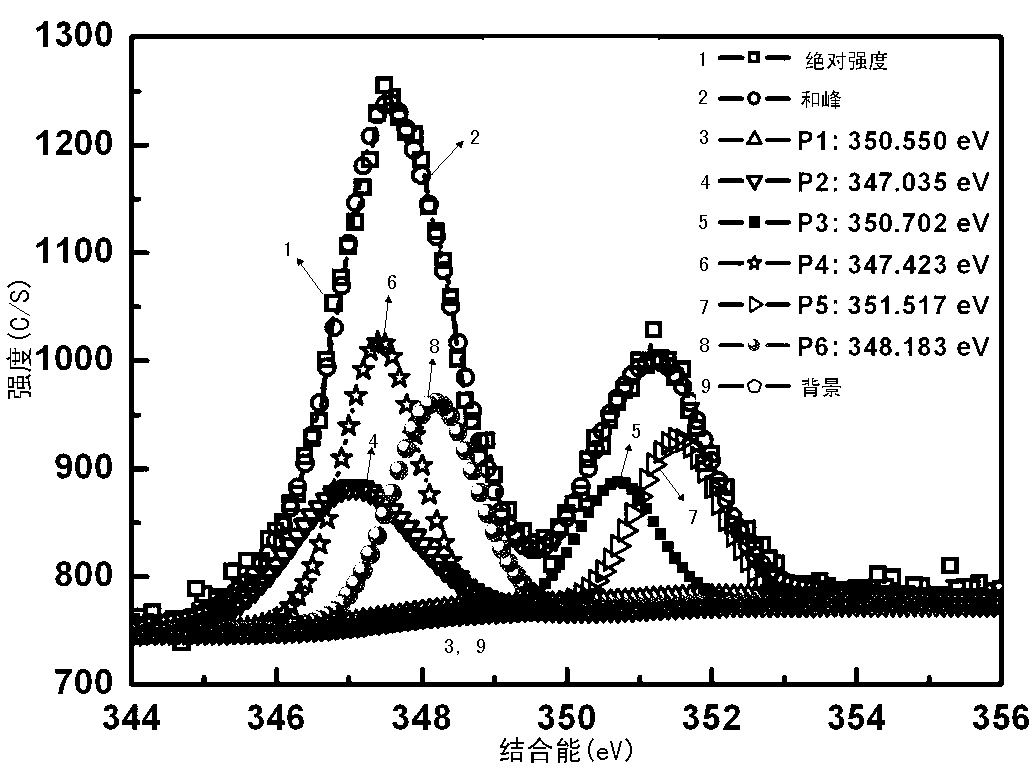

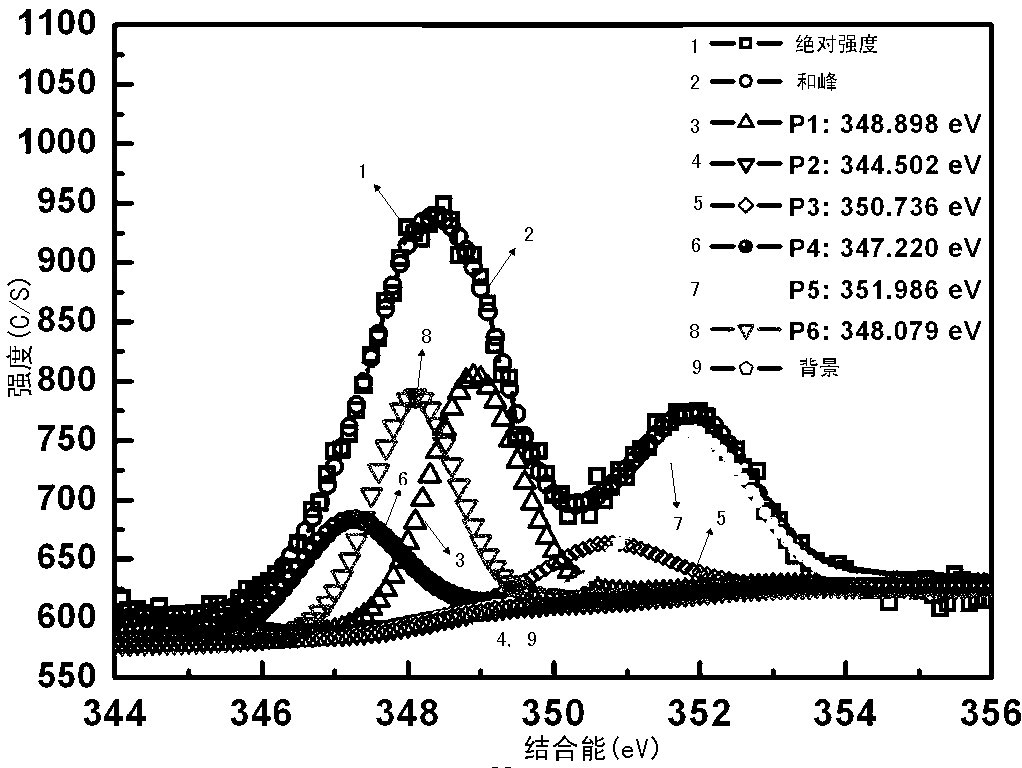

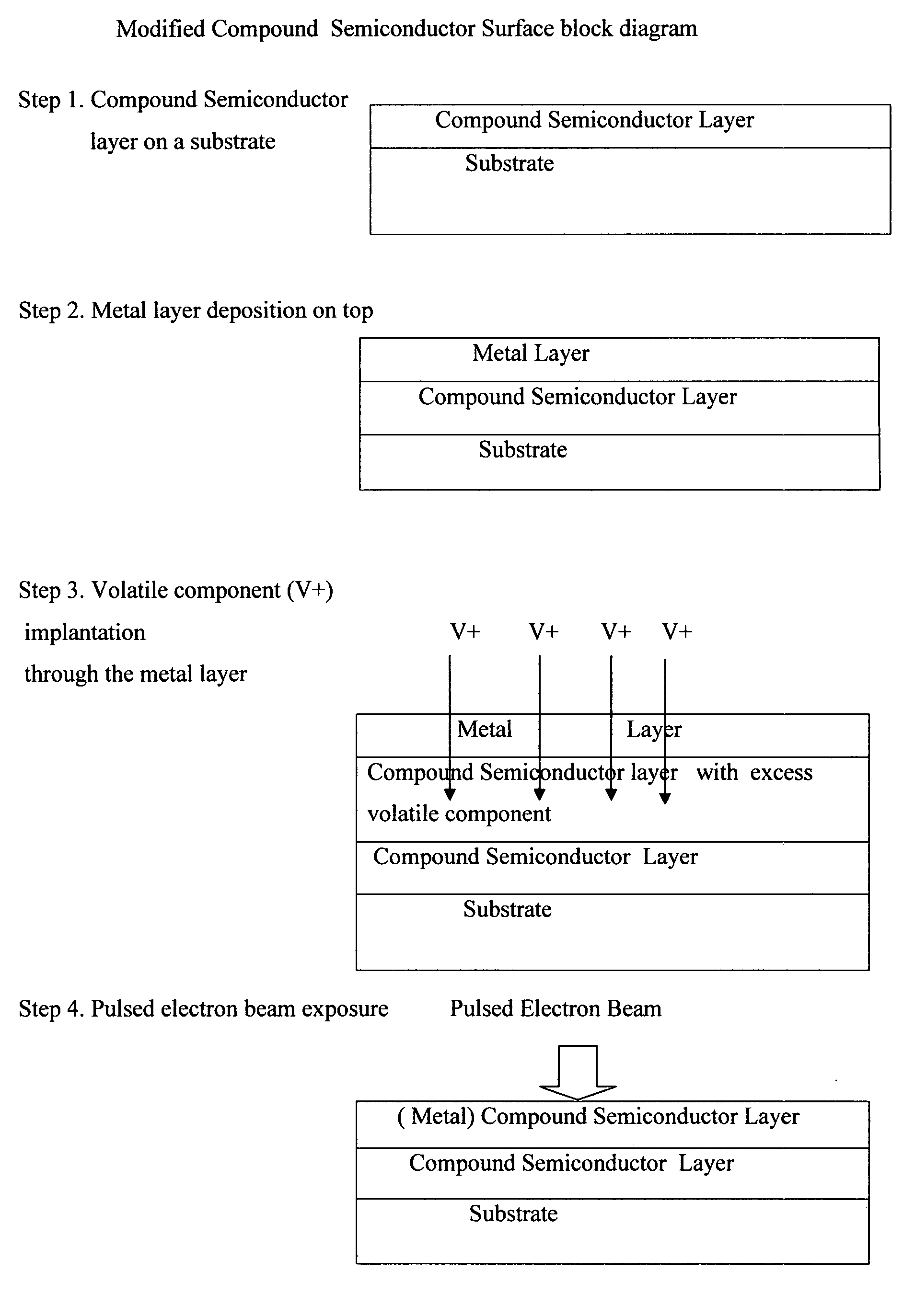

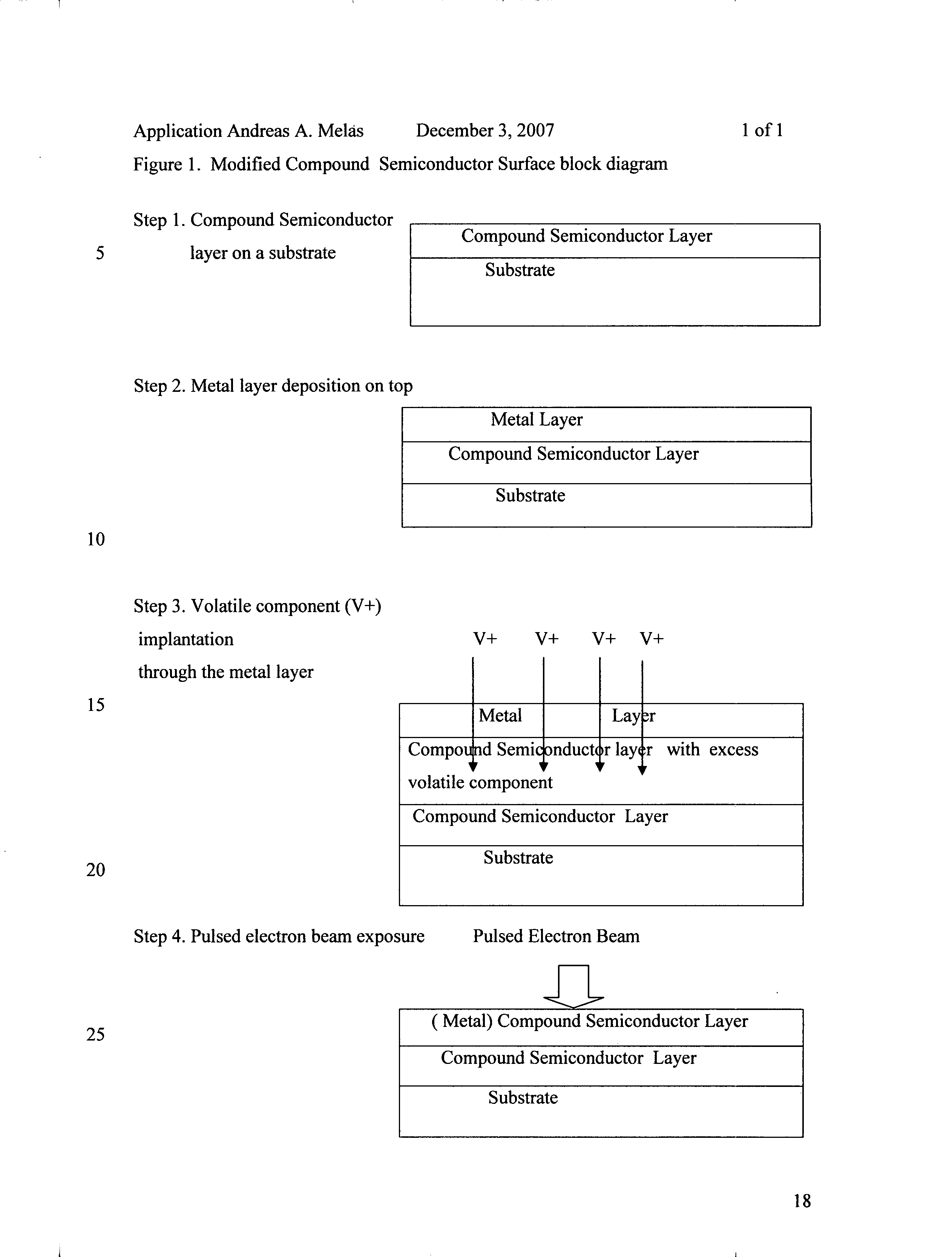

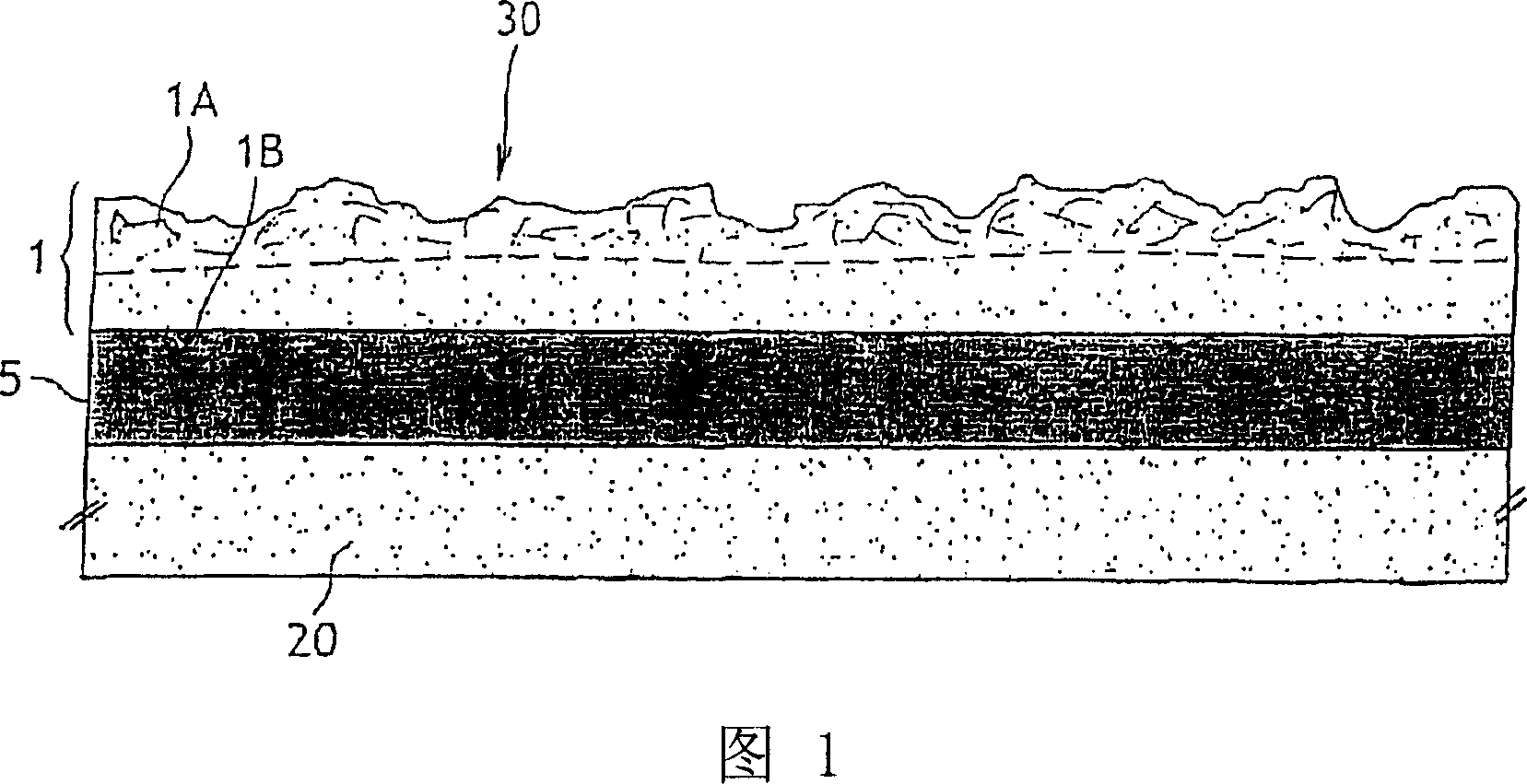

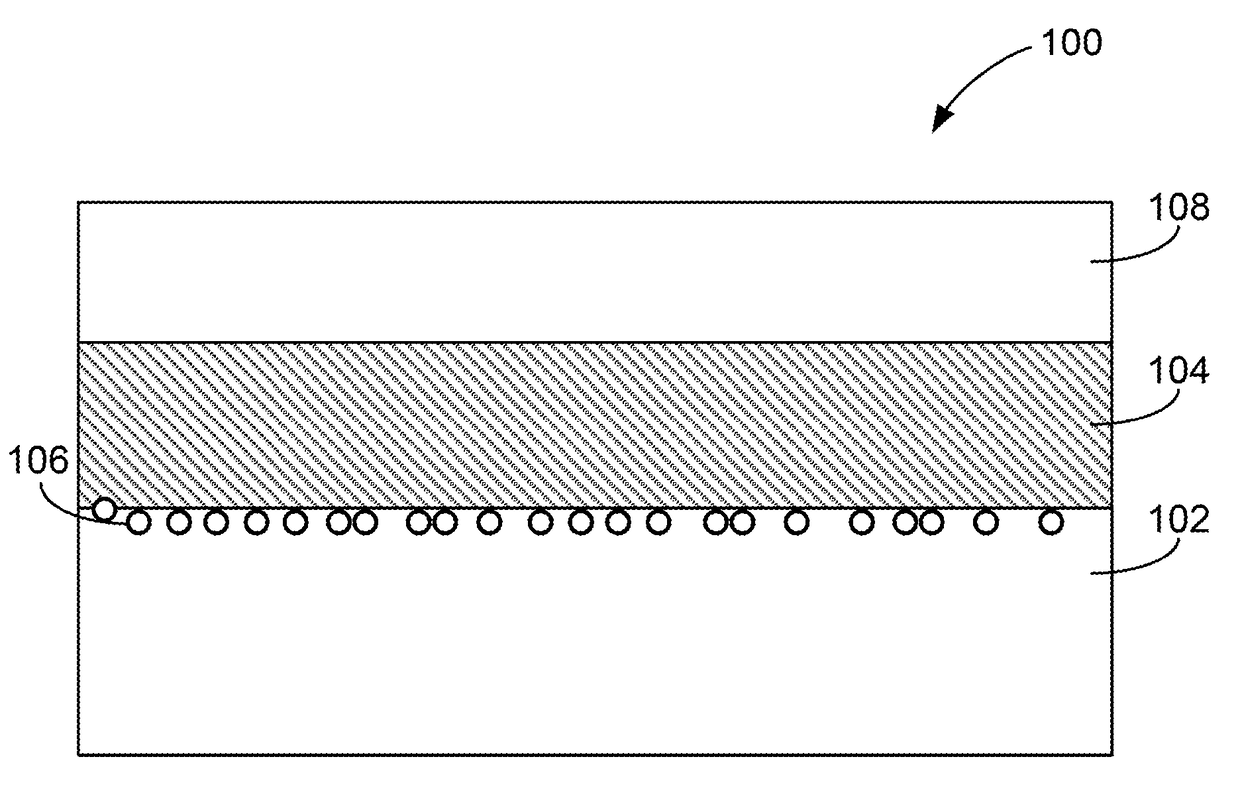

Compound semiconductor modified surface by use of pulsed electron beam and ion implantation through a deposited metal layer

InactiveUS20080087984A1Polycrystalline material growthDiffusion/dopingSingle crystalCrystallographic defect

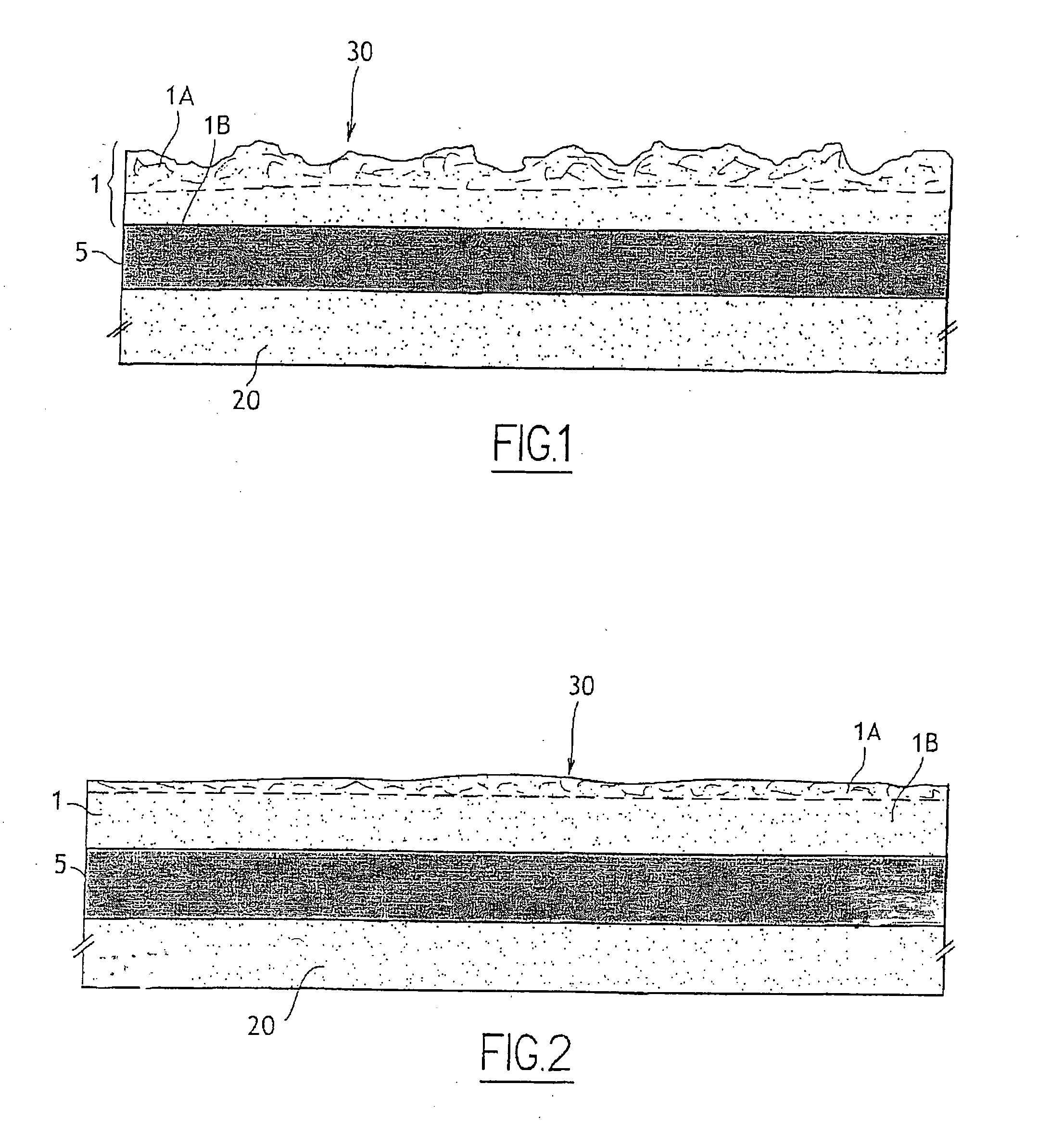

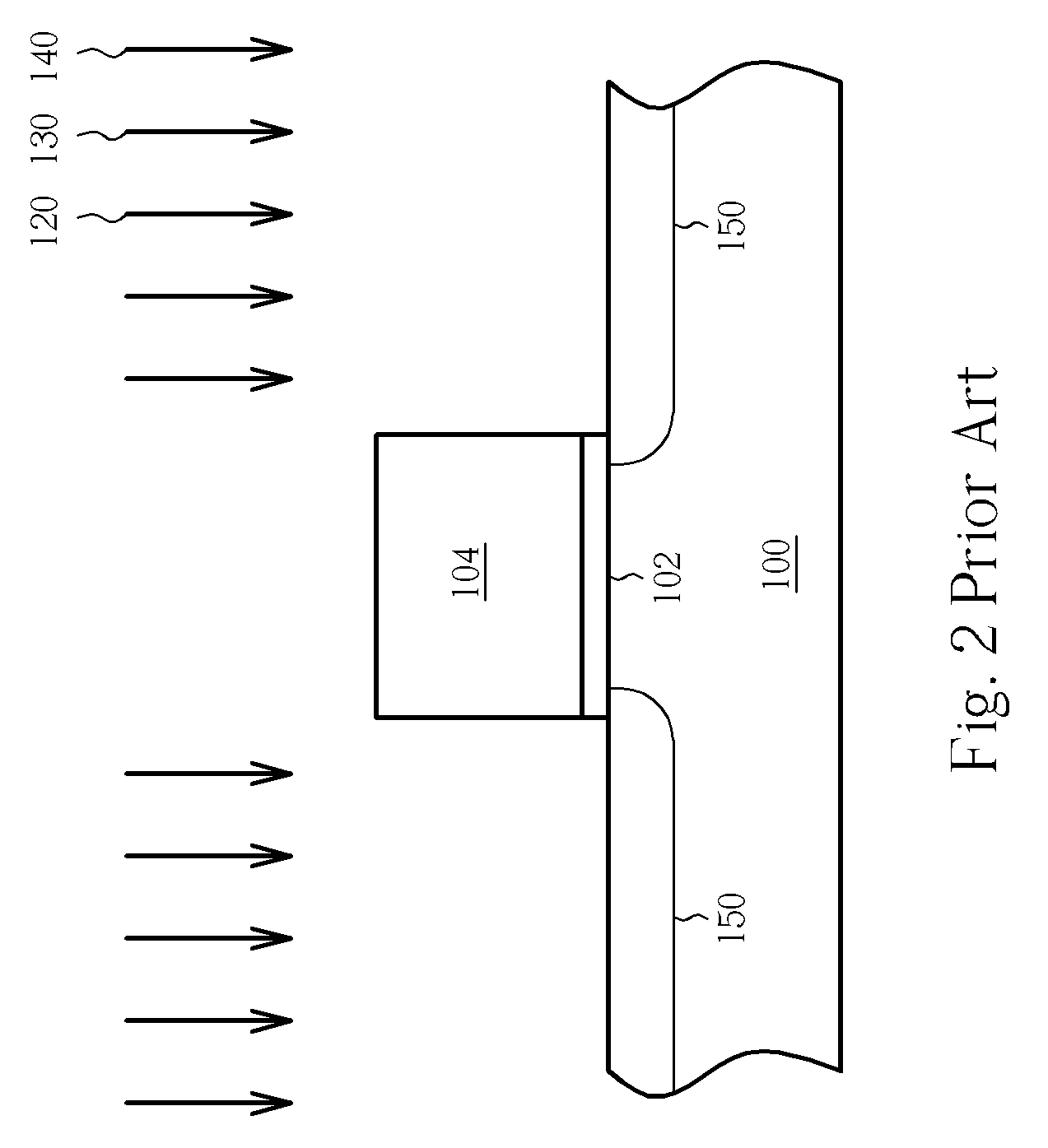

Thermally sensitive at elevated, near melting point temperature, compound semiconductor materials single crystals including Group III-Nitride, other Group III-V, Group II-VI and Group IV-IV are produced by a variety of methods. When produced as single crystal layers by epitaxy methods or is necessary to expose them to elevated temperatures or ion implanted to the non crystalline state, or their electrical or optical properties are modified, large numbers of crystal defects on the atomic or macro scale may be produced, which limit the yield and performance of opto- and electronic devices constructed out of and grown on top of these layers. It is necessary to be able to improve the crystal quality of such materials after being exposed to elevated temperature or ion implanted or modified by the presence of impurities. It is necessary, particularly for opto- and electronic devices that only the surface of such materials is processed, improved and thus the modified surface product. Generally, as shown in FIG. 1, the thermally sensitive compound semiconductor layer is first coated with a metal layer of approximate thickness of 0.1 microns. Next, the volatile component of the compound semiconductor is ion implanted through the metal layer so as to occupy mostly the top 0.1 to 0.5 microns of the compound semiconductor layer. Co-implantation may be used as well to improve the surface. Finally, through a pulsed directed energy beam of electrons with a fluence of approximately 1 Joule / cm2, the top approximately 0.5 microns acquire a level of the deposited metal and are converted into a single crystal with improved properties such as reduced defect density and or electrical dopant (FIG. 1).

Owner:MELAS ANDREAS A

Method of catastrophic transfer of a thin film after co-implantation

ActiveUS7772087B2Reduce roughnessHigh mechanical stressSemiconductor/solid-state device manufacturingCo implantationAtomic physics

Owner:COMMISSARIAT A LENERGIE ATOMIQUE ET AUX ENERGIES ALTERNATIVES +1

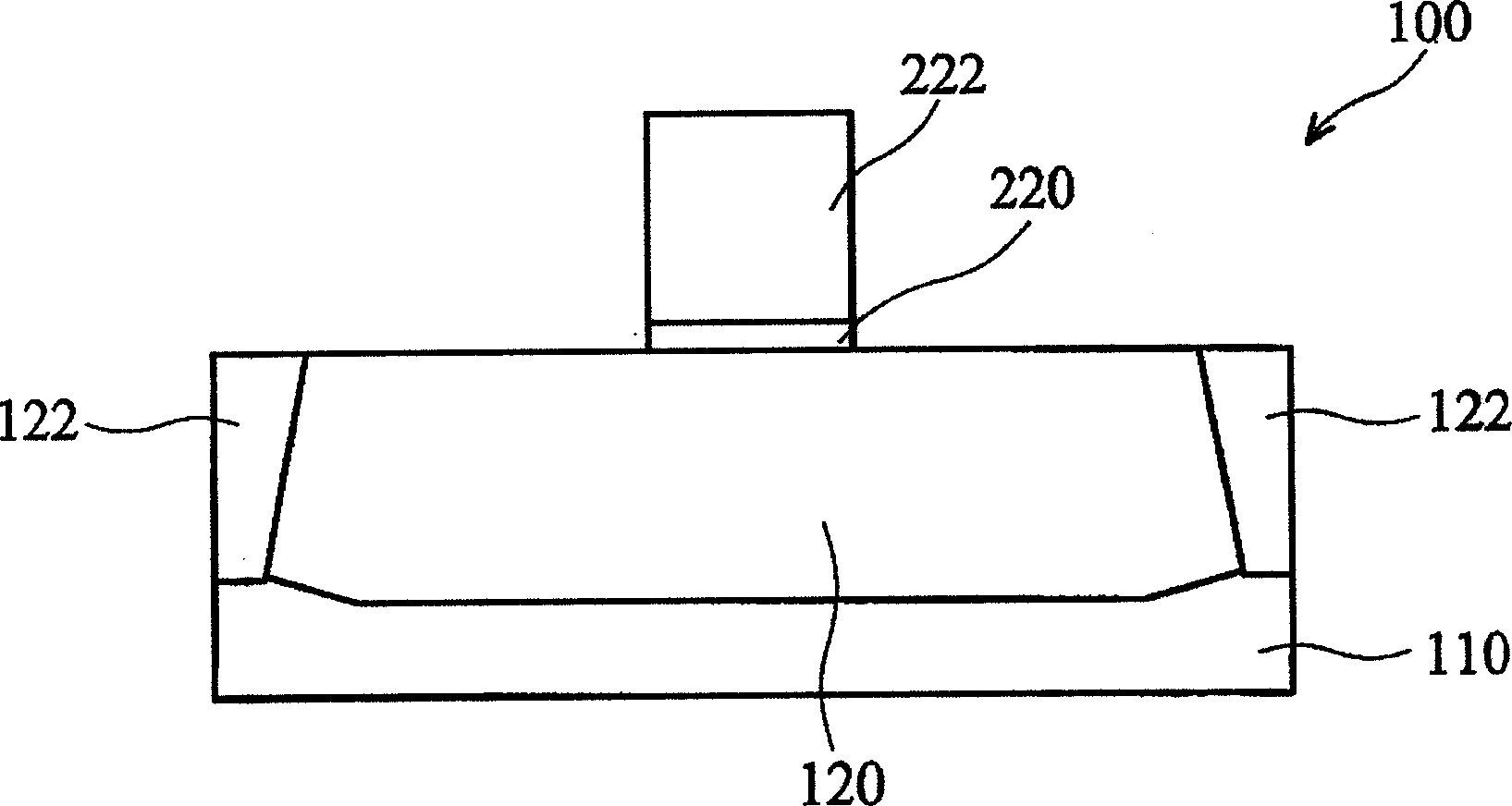

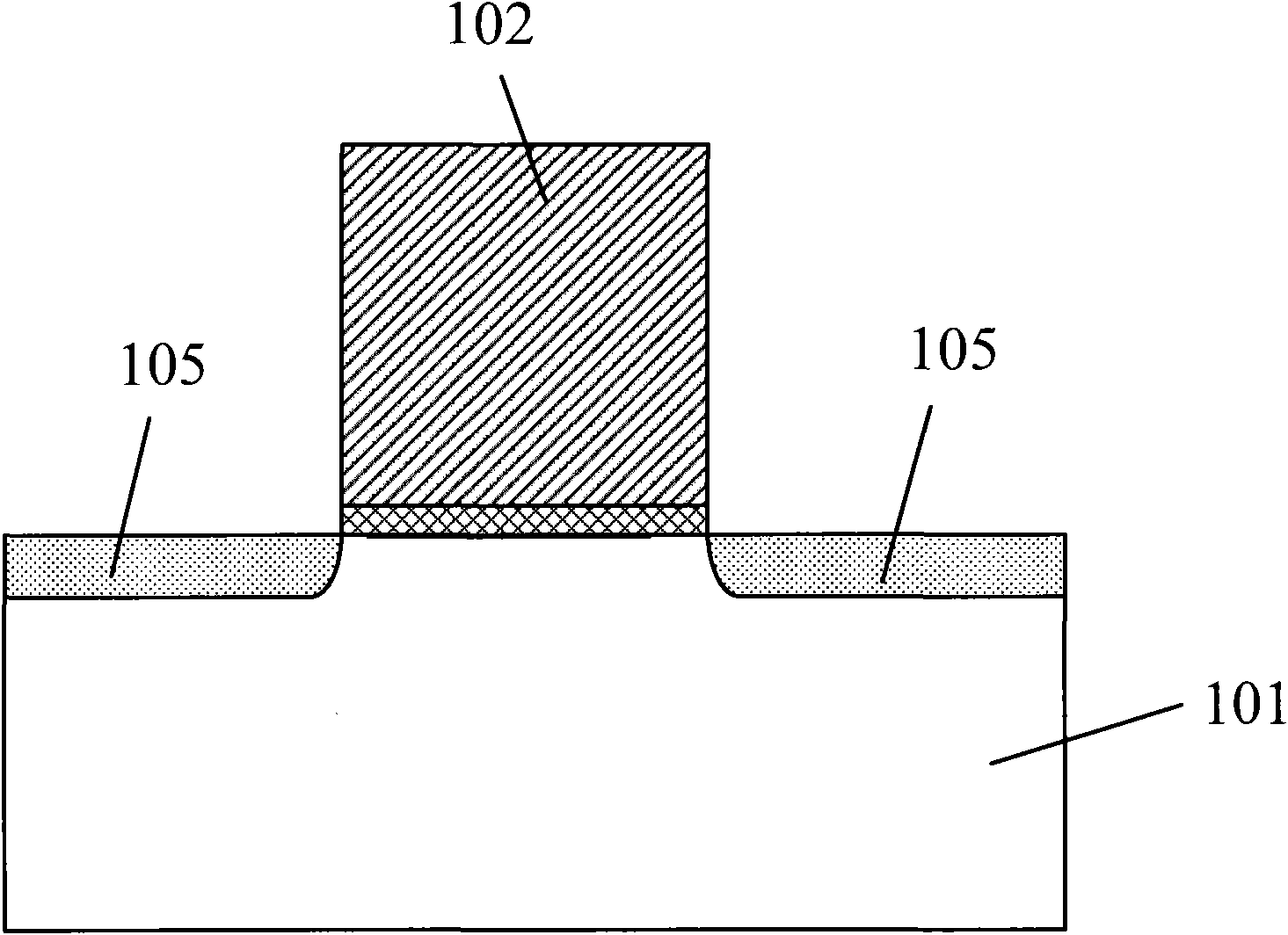

Method for forming MOS transistor

ActiveUS7700450B2Reducing TED effect and short channel effectReduce diffuseTransistorSemiconductor/solid-state device manufacturingEngineeringRapid thermal annealing

Owner:UNITED MICROELECTRONICS CORP

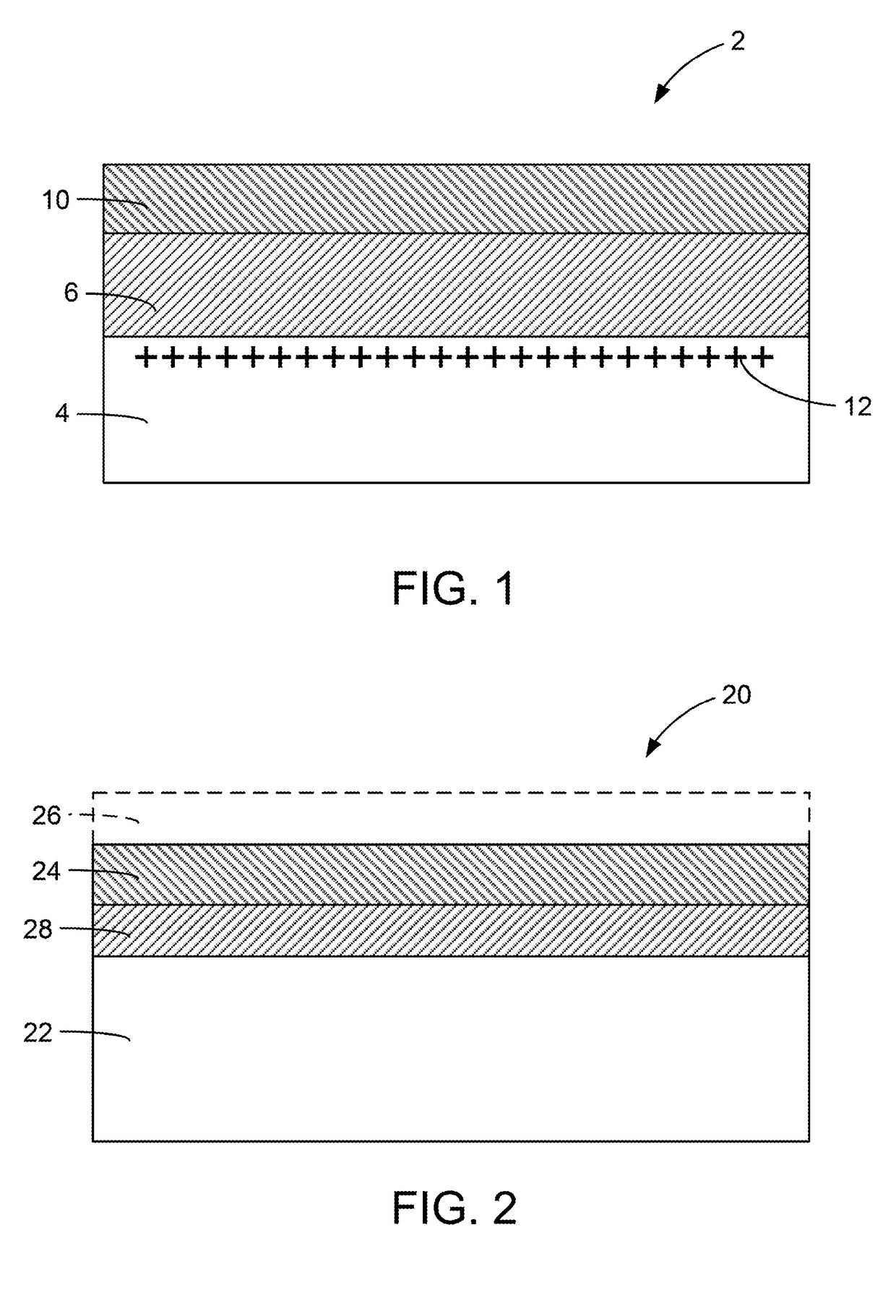

Thin layer transfer method utilizing co-implantation to reduce blister formation and to surface roughness

ActiveUS7326628B2Minimizing formationMinimizing in roughnessSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureThin layer

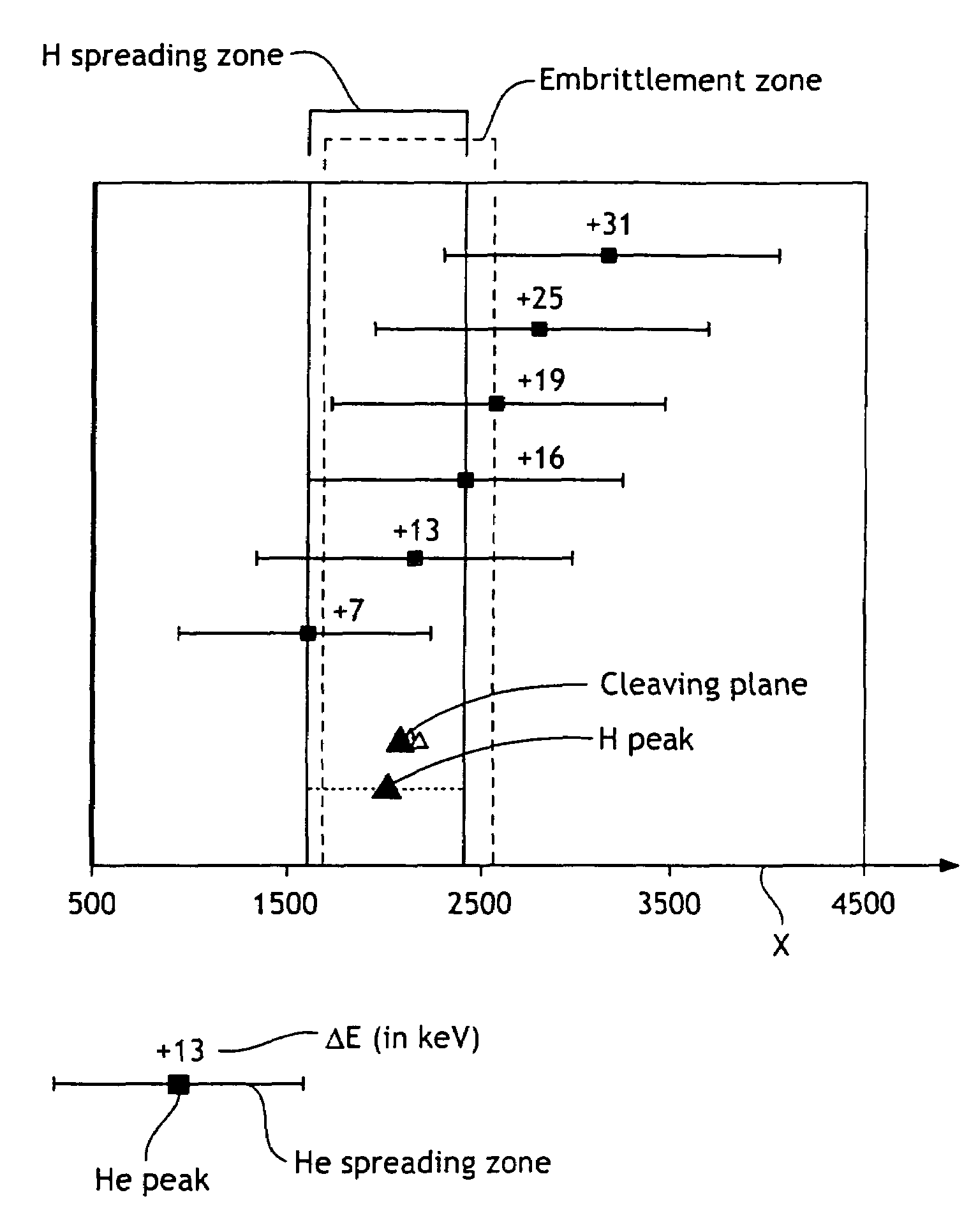

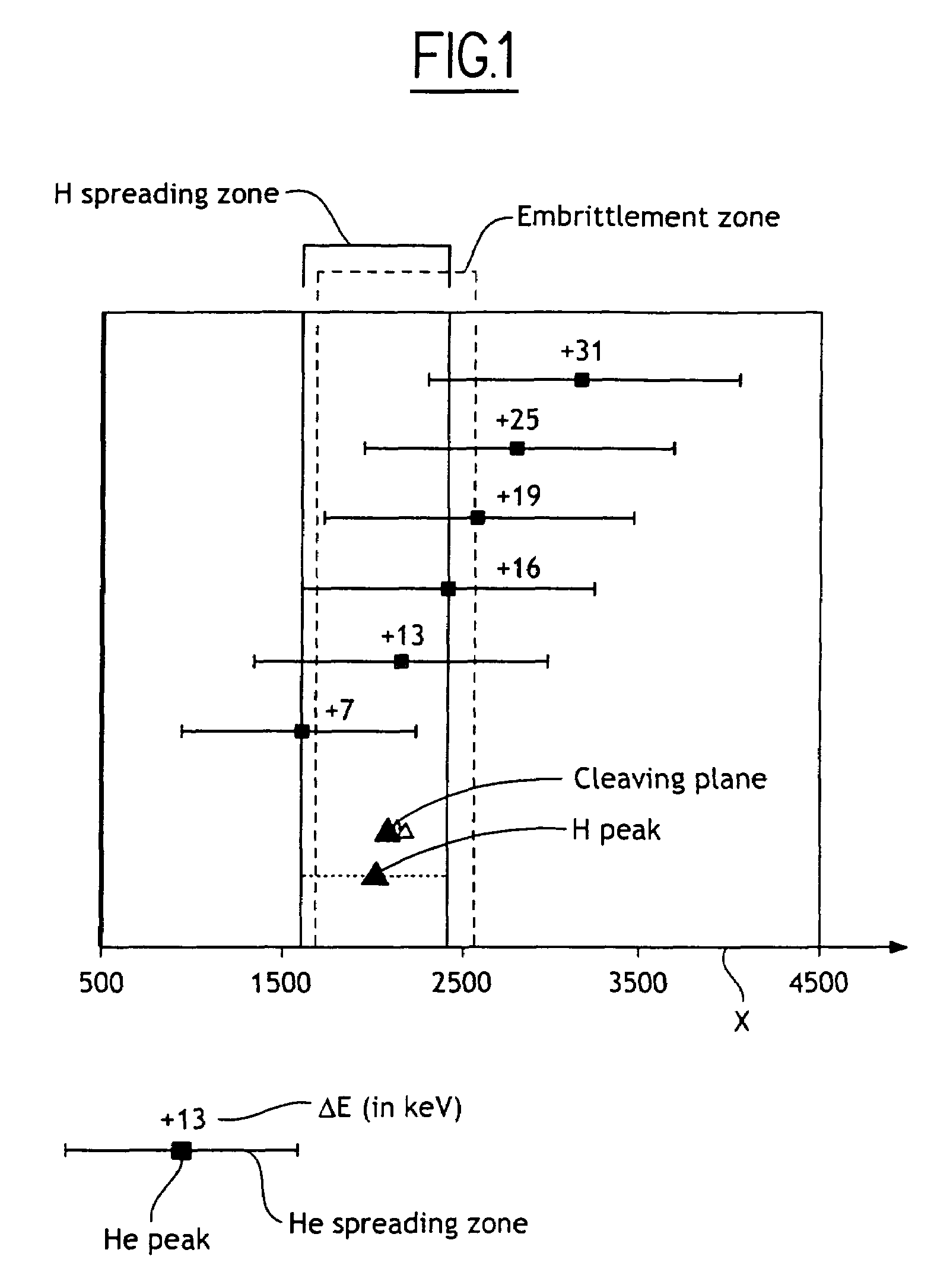

A method for producing a semiconductor structure by conducting controlled co-implanting of at least first and second different atomic species into a donor substrate to create an embrittlement zone which defines a thin layer of donor material to be transferred. Implantation energies are selected so that the first and second species are respectively distributed in the donor wafer according to a repartition profile that presents a spreading zone in which each species is mainly distributed at a maximum concentration peak. The implantation doses and energies of the first and second species are selected such that the second species is implanted deeper in the embrittlement zone than the first species spreading zone. The donor substrate is detached at the embrittlement zone to transfer the thin layer to the support substrate while minimizing blister formation in and surface roughness of the transferred layer. Preferably, the implantation dose of the first species is between about 40 to 60 percent of all implantation doses. This method is preferably utilized for forming or producing SeOI (Semiconductor On Insulator) structures.

Owner:SOITEC SA

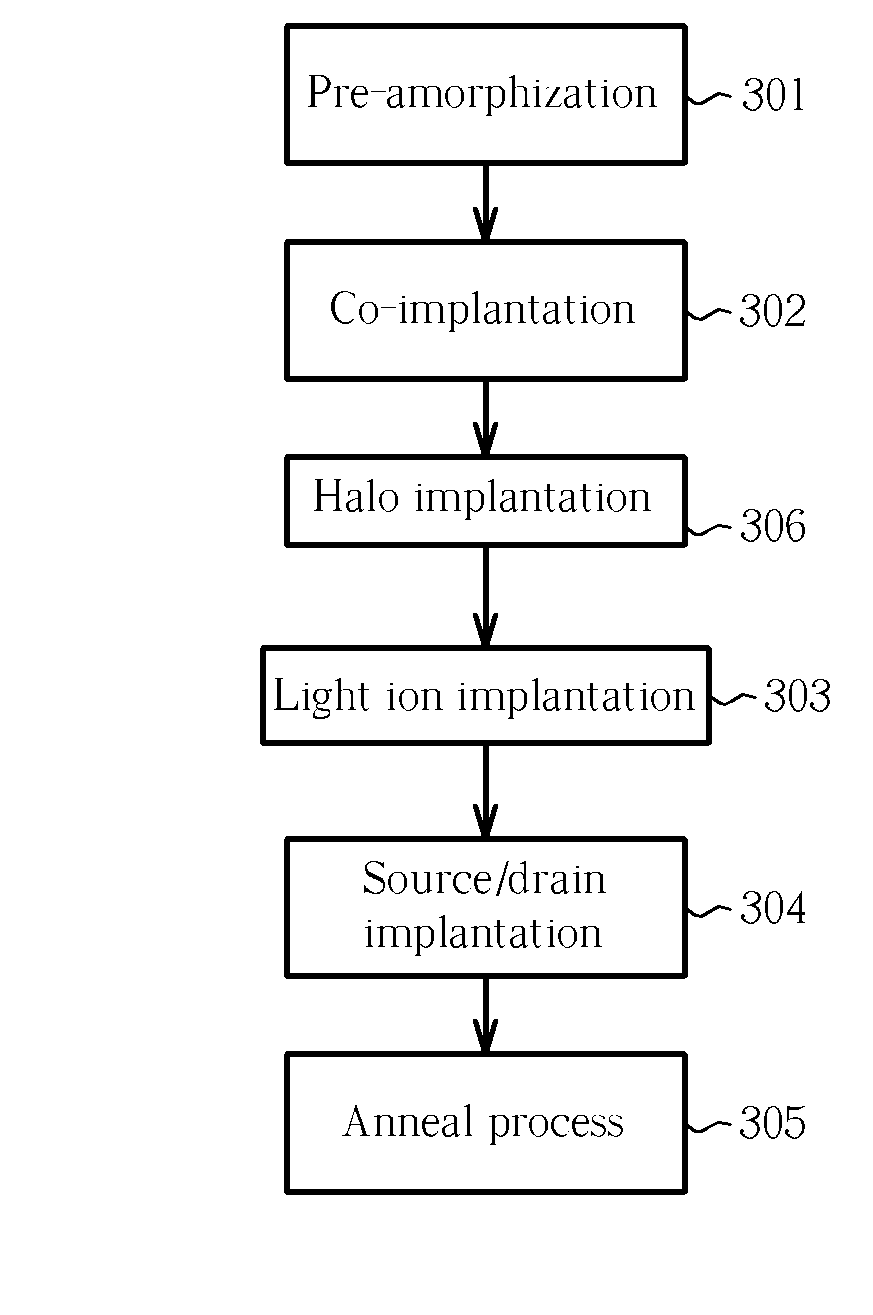

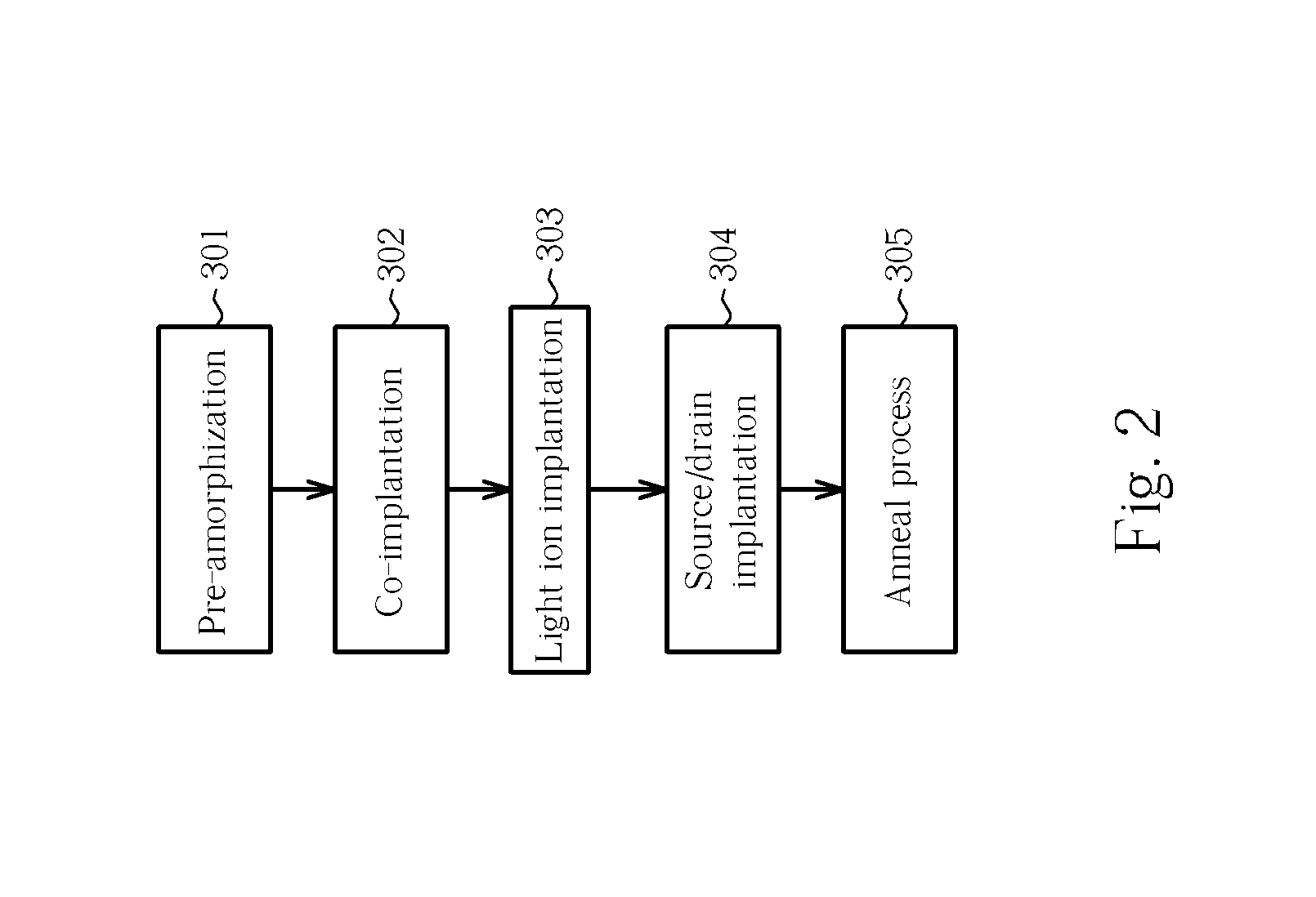

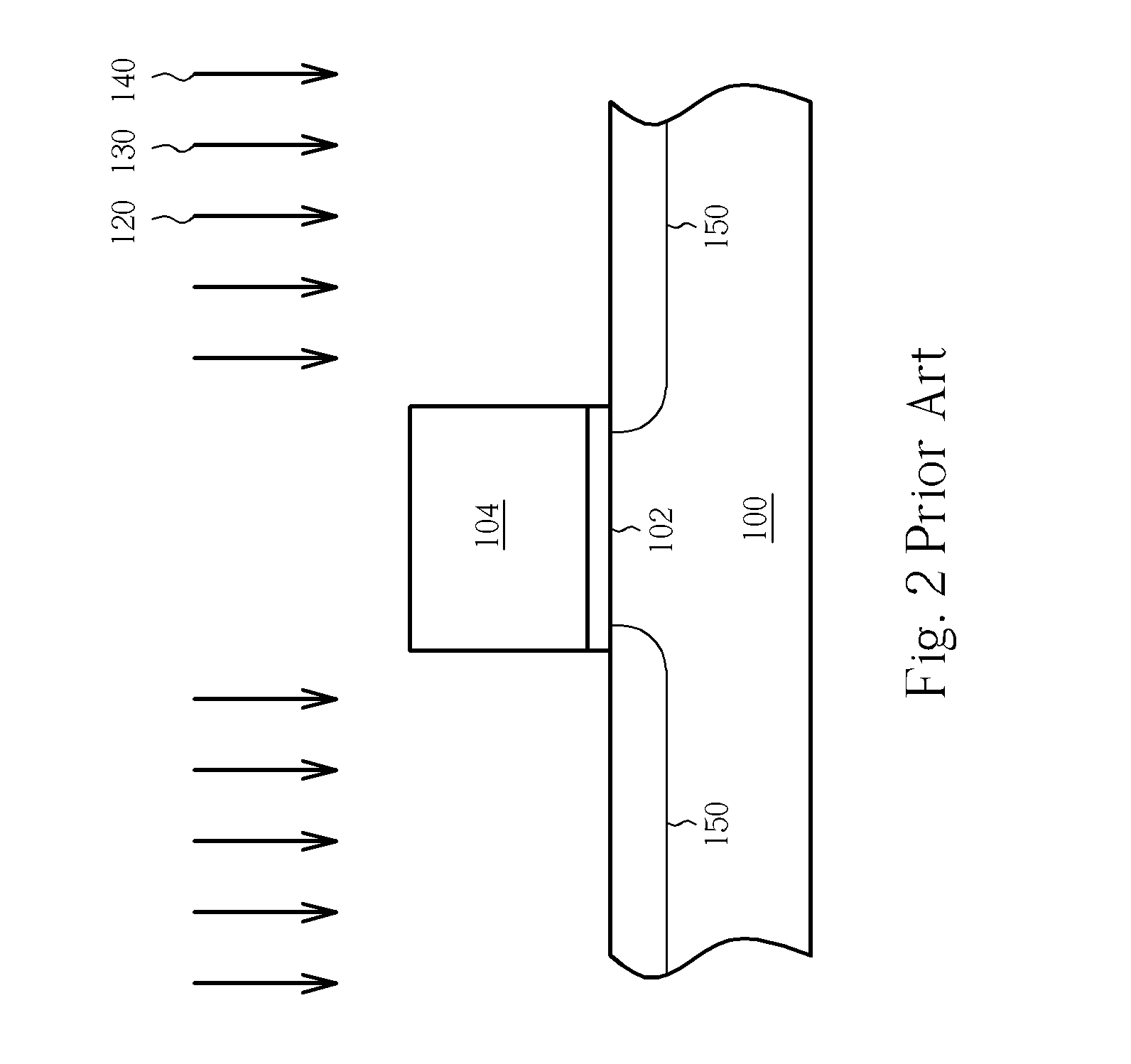

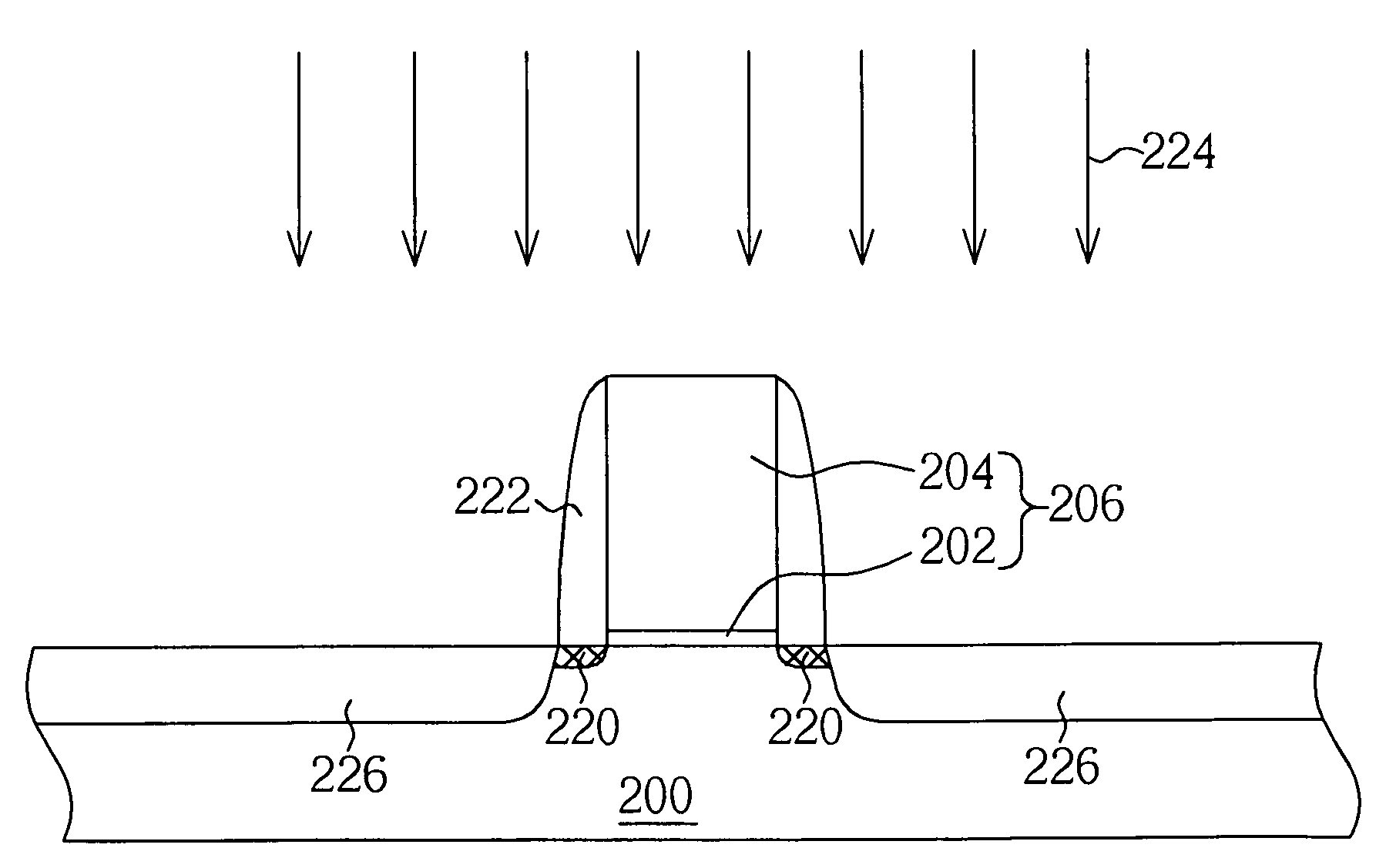

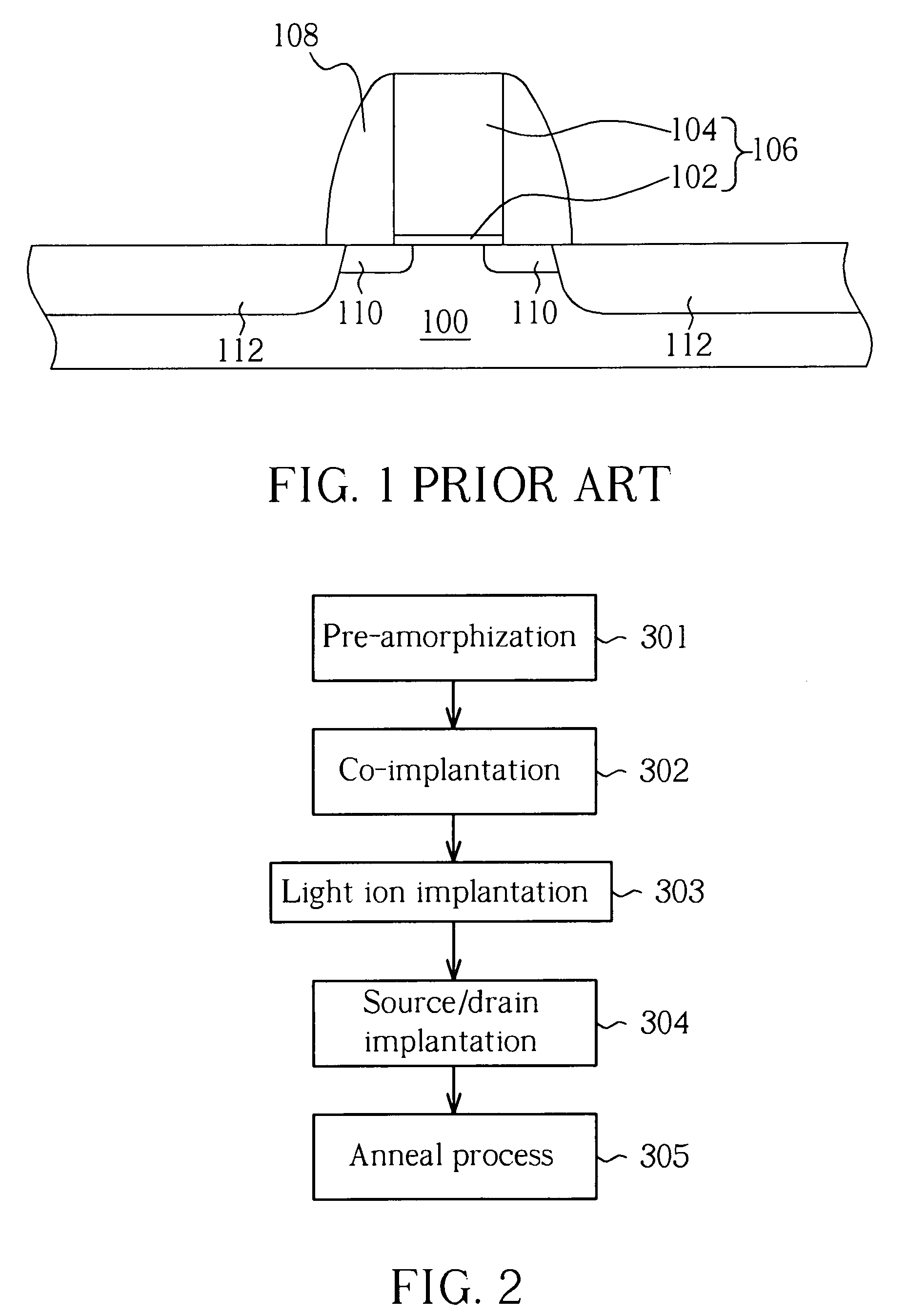

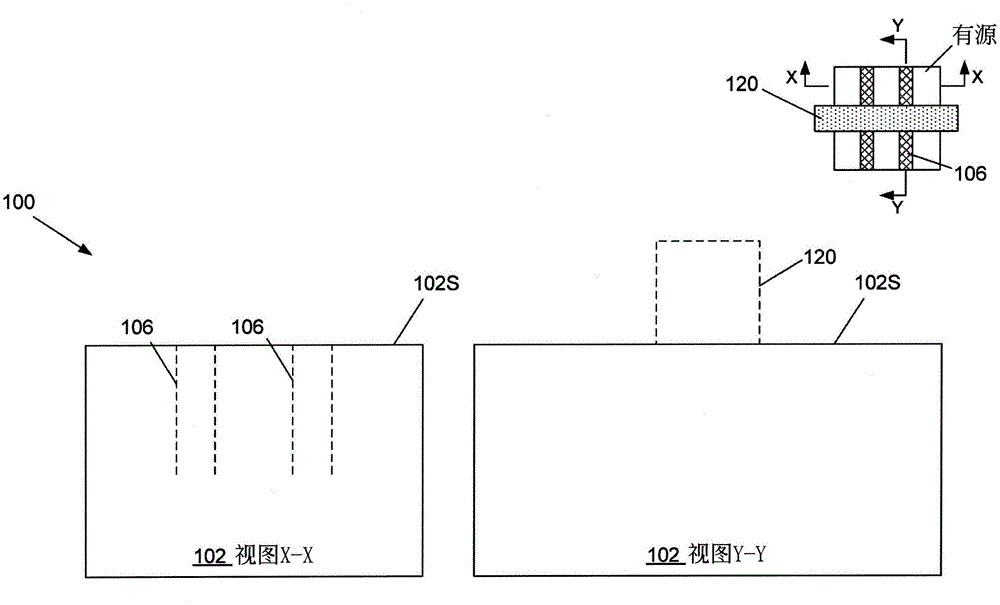

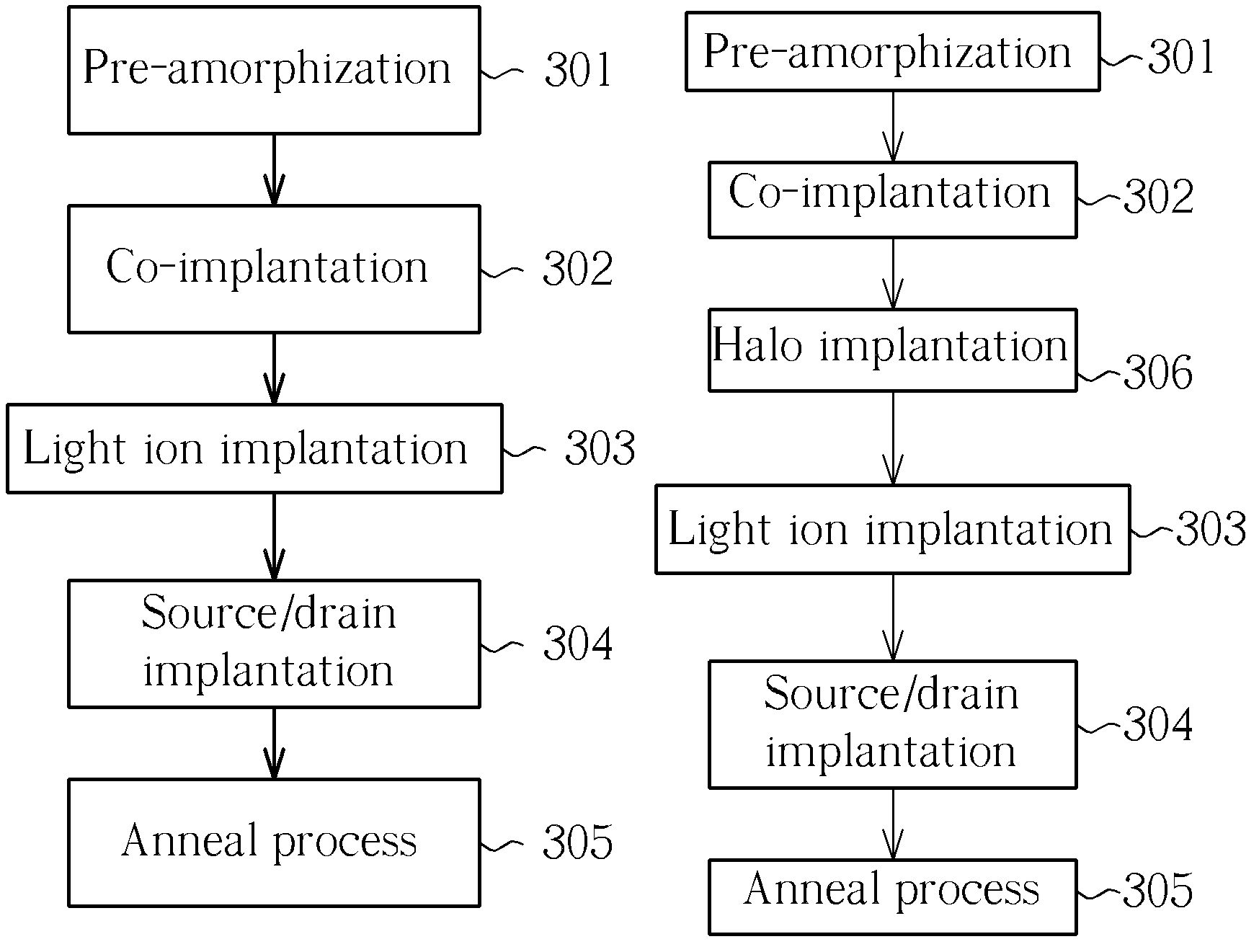

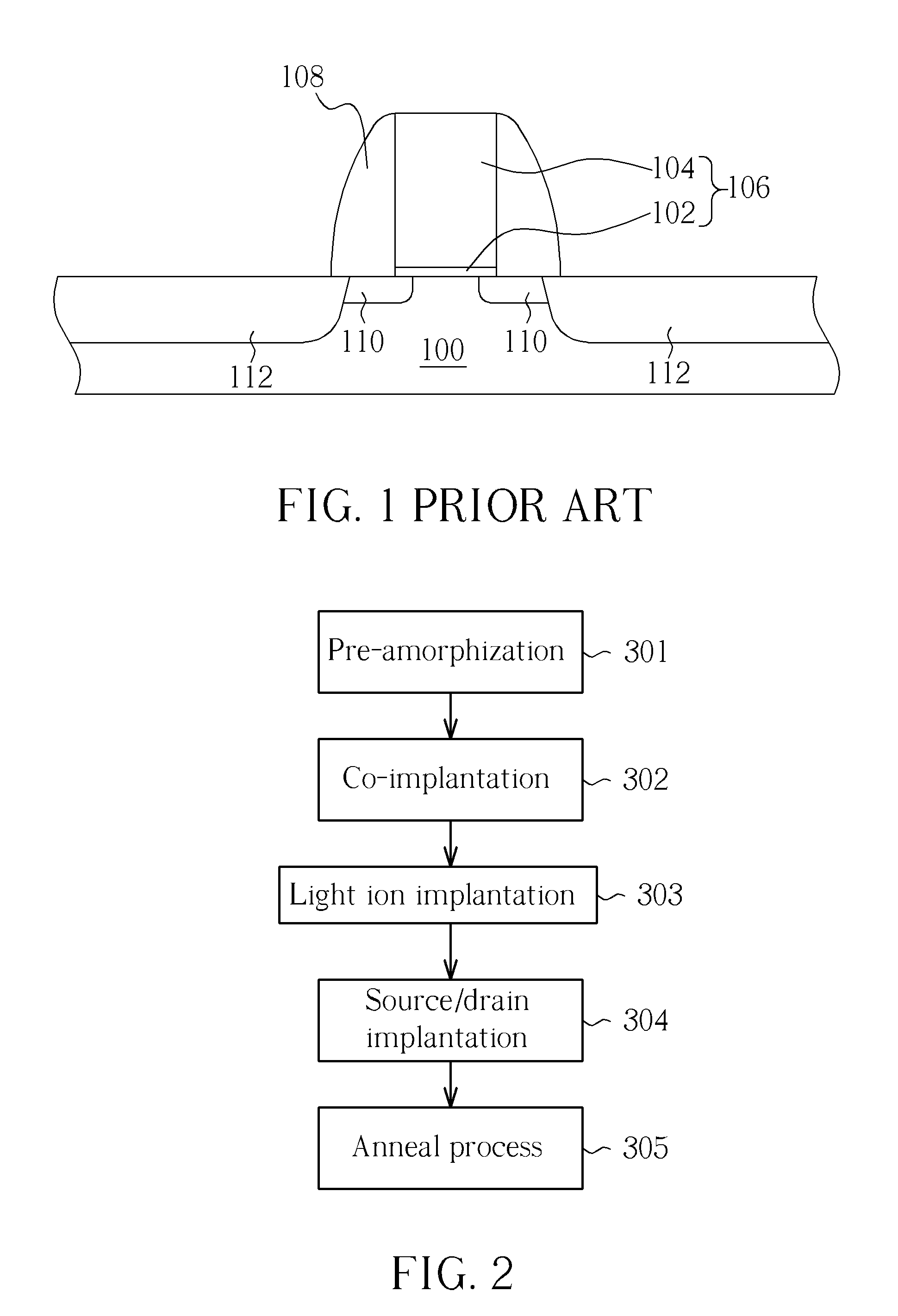

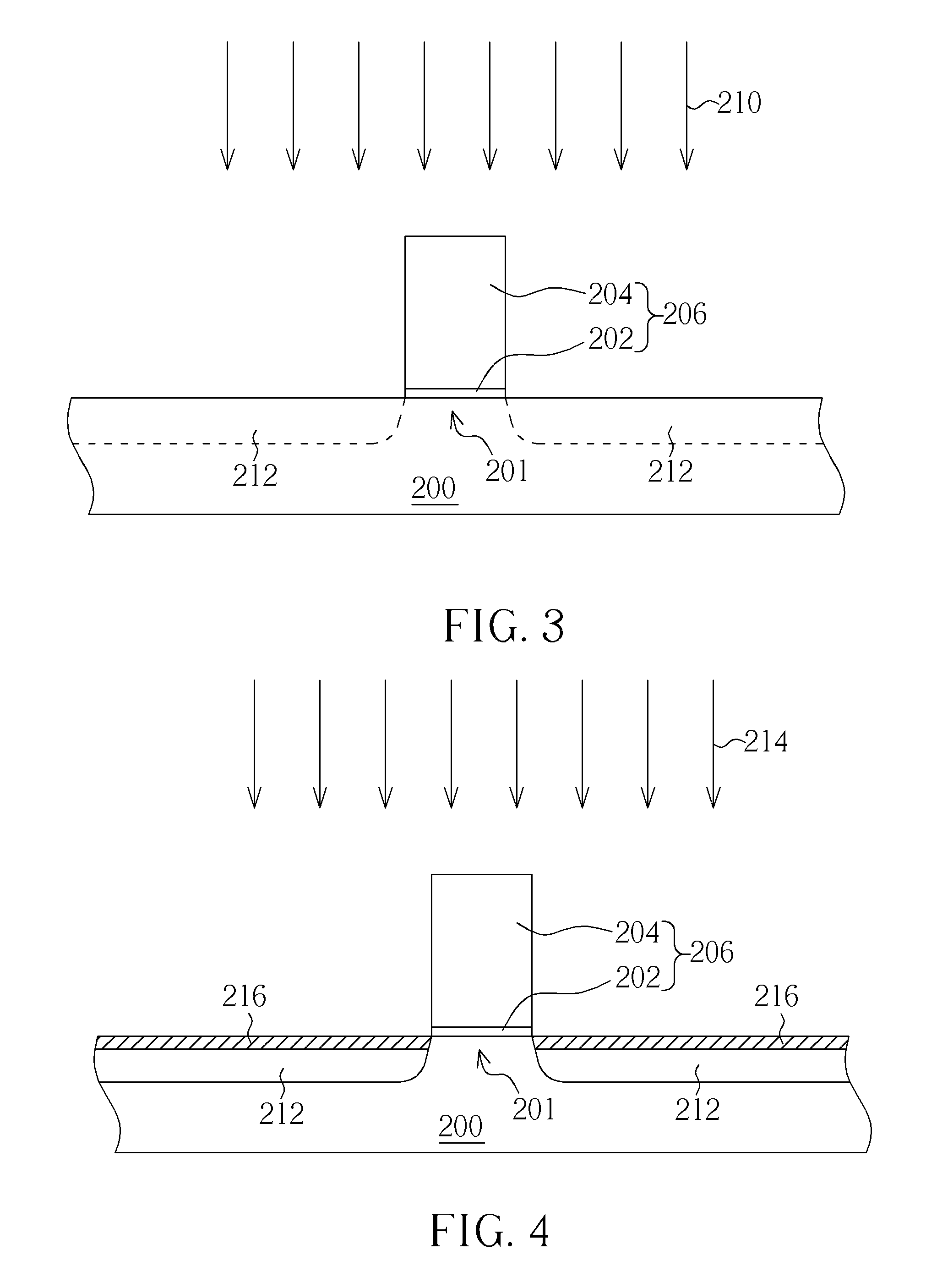

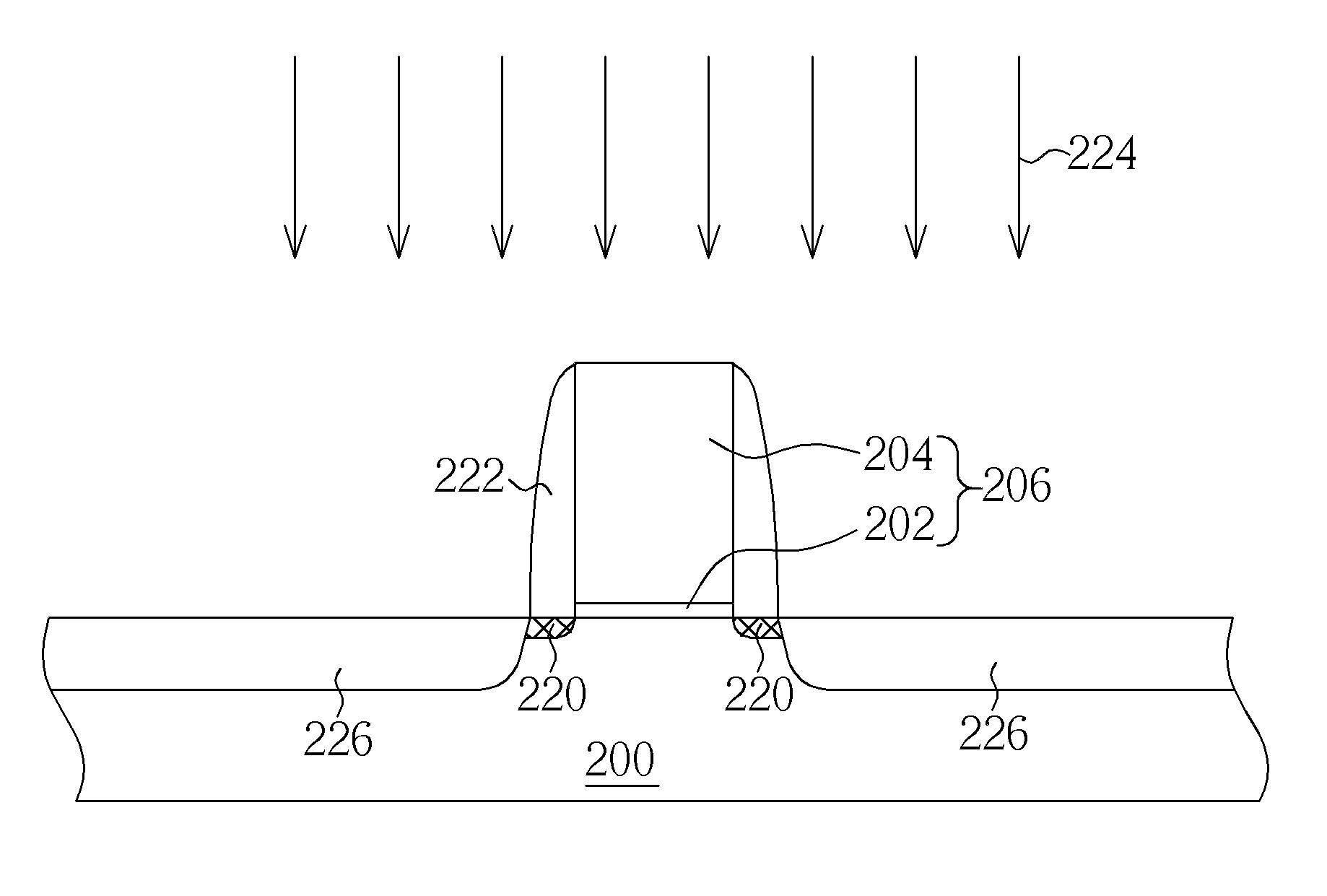

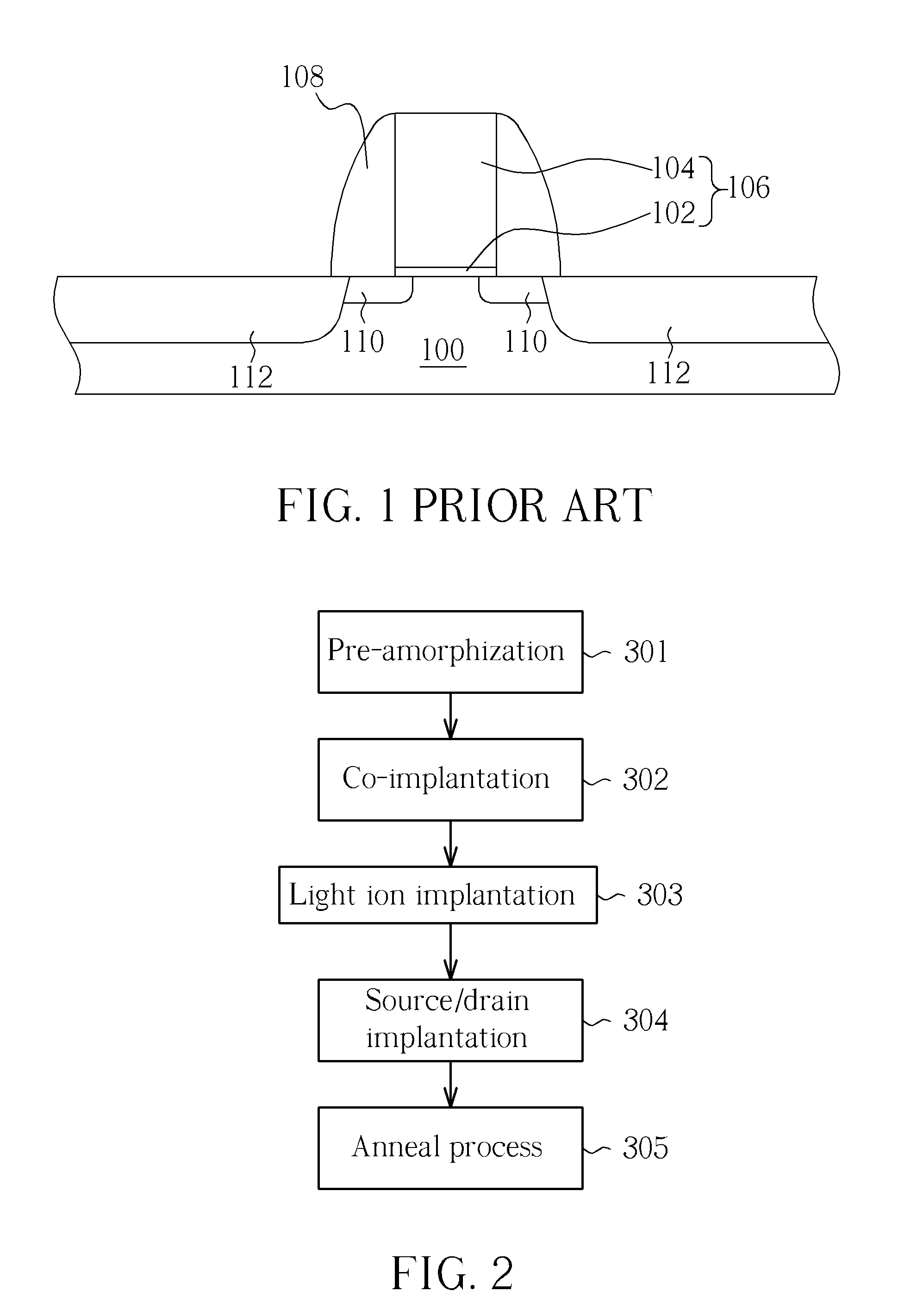

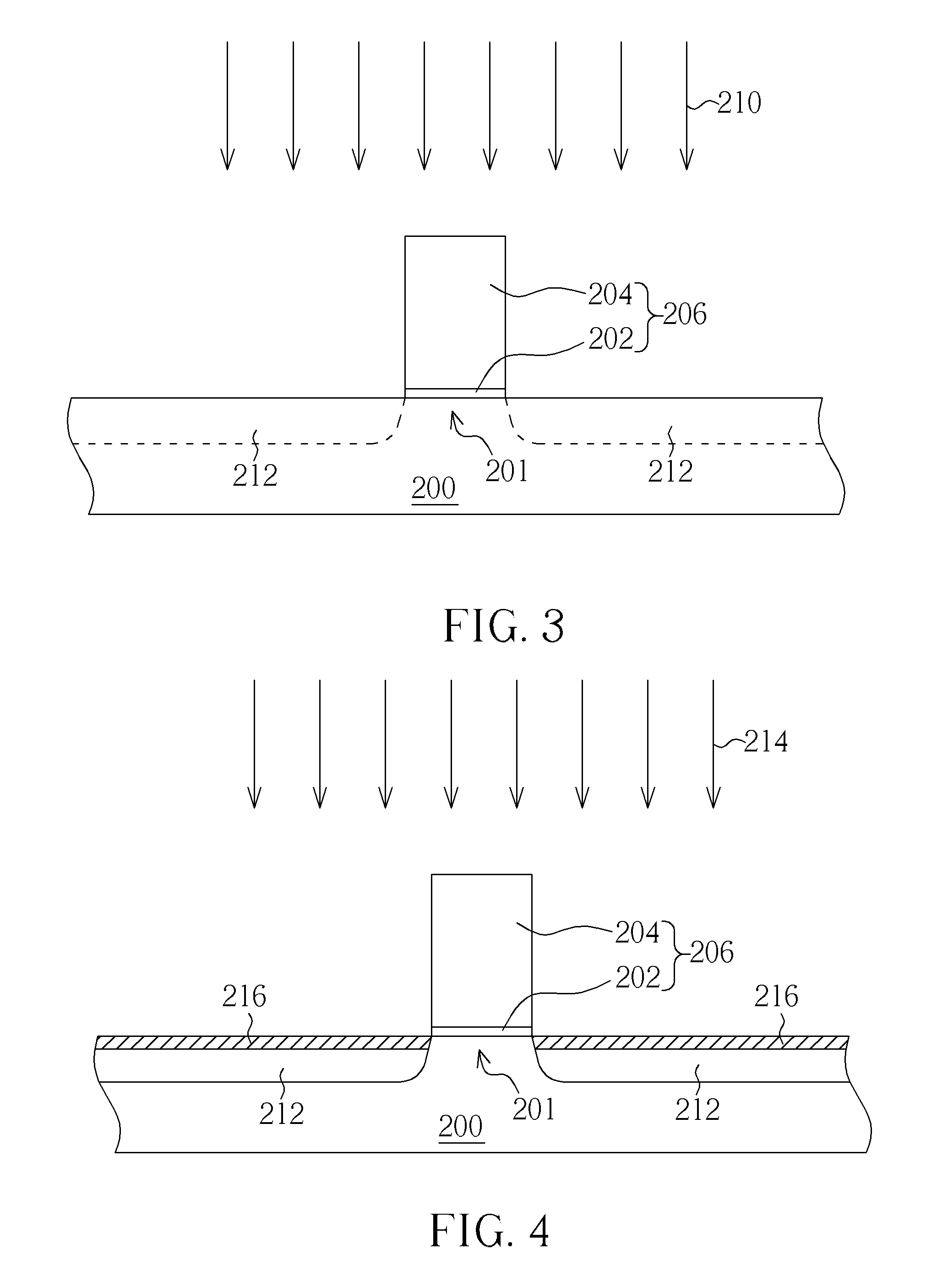

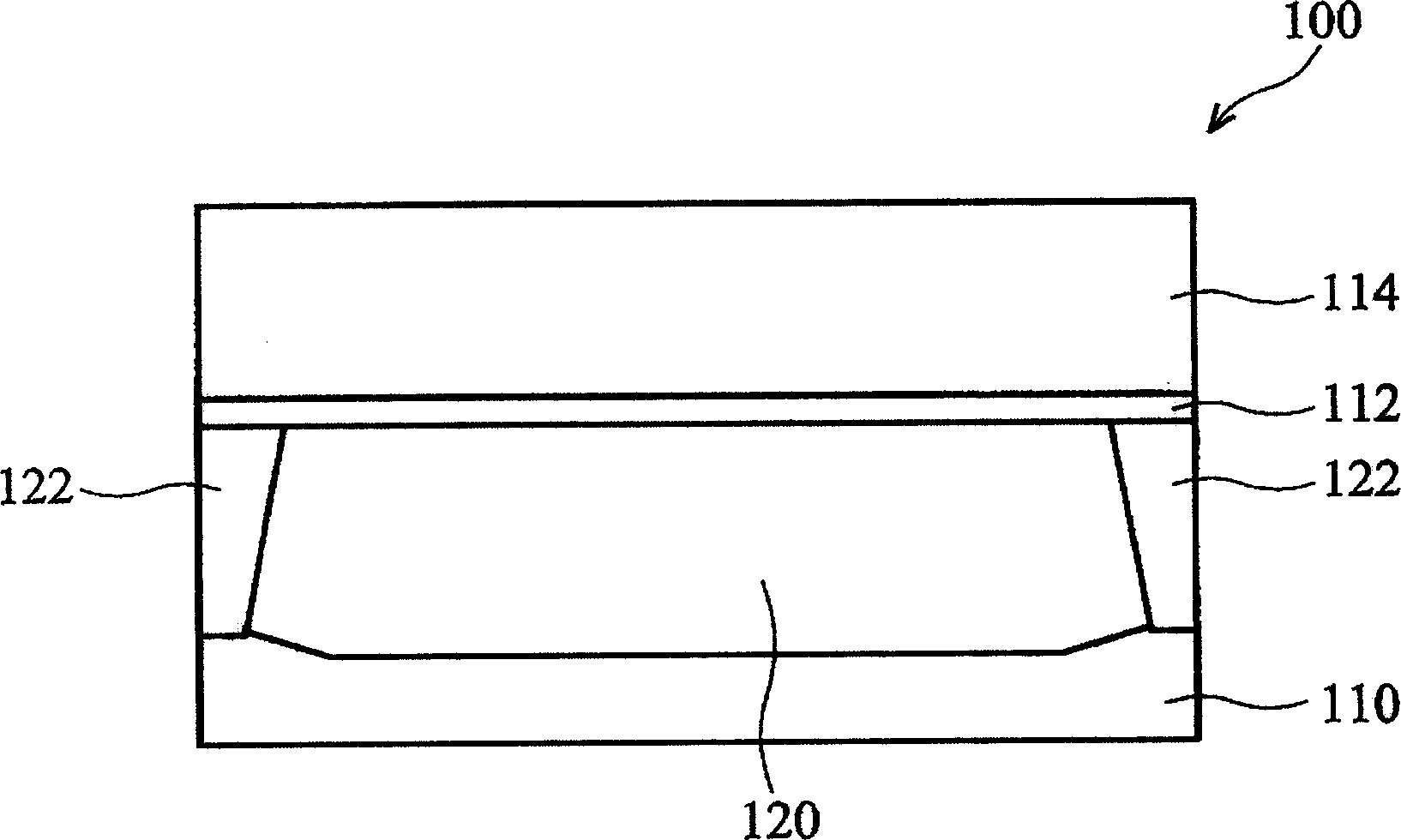

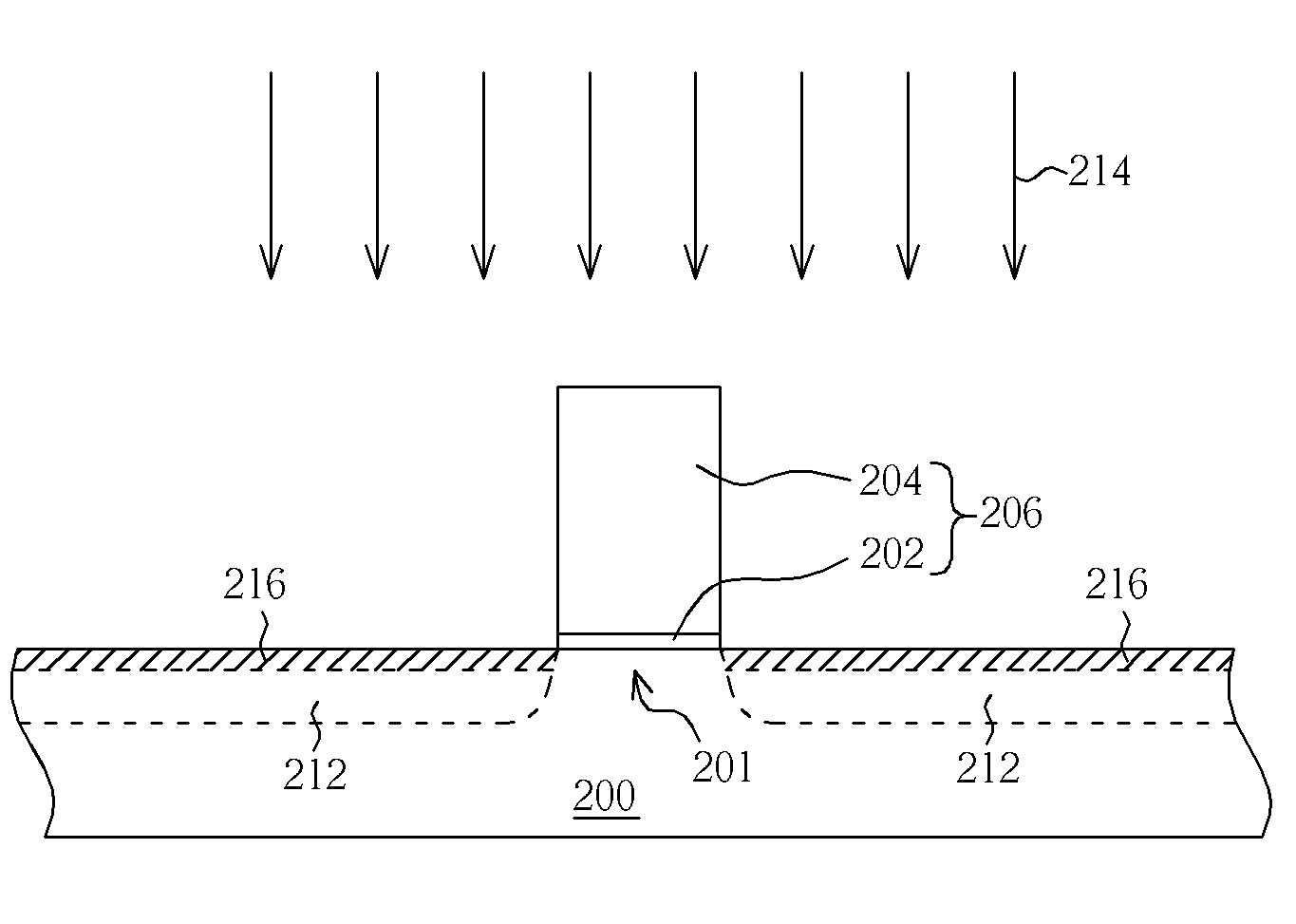

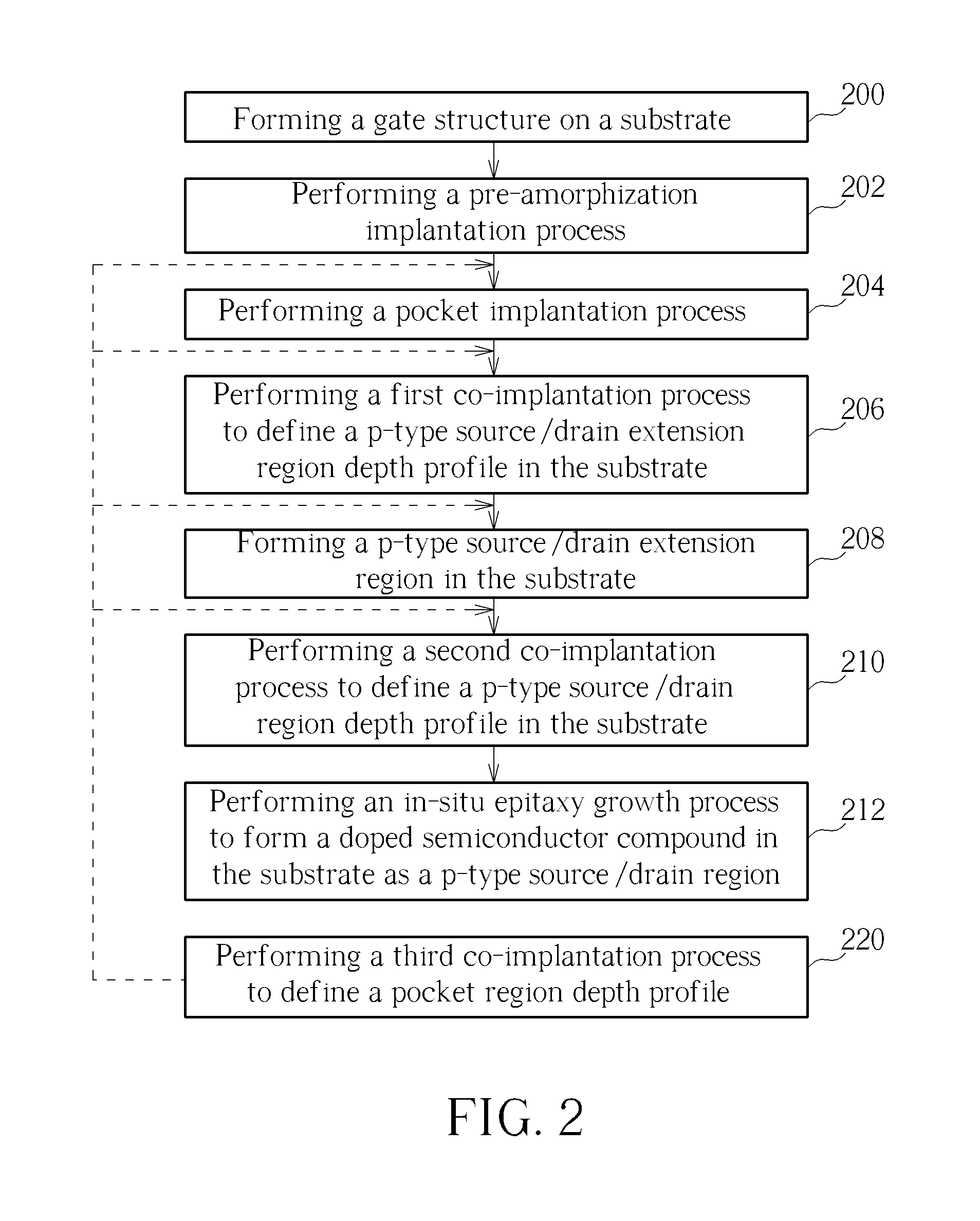

Method for forming mos transistor

ActiveUS20080102588A1Good junction profileSuppression of short channel effectsTransistorSemiconductor/solid-state device manufacturingEngineeringRapid thermal annealing

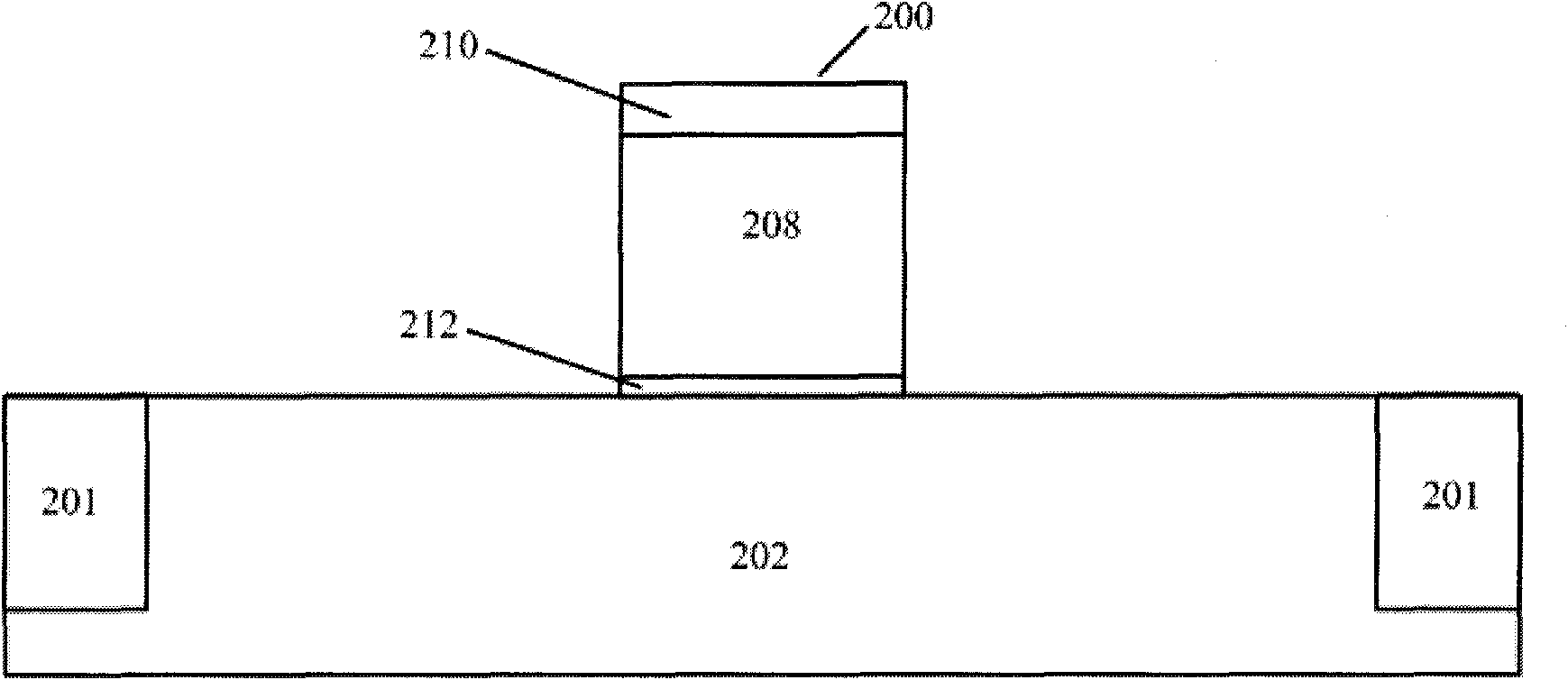

A method for forming a MOS transistor includes providing a substrate having at least a gate structure formed thereon, performing a pre-amorphization (PAI) process to form amorphized regions in the substrate, sequentially performing a co-implantation process, a first ion implantation process, and a first rapid thermal annealing (RTA) process to form lightly doped drains (LDDs), forming spacers on sidewalls of the gate structure, and forming a source / drain.

Owner:UNITED MICROELECTRONICS CORP

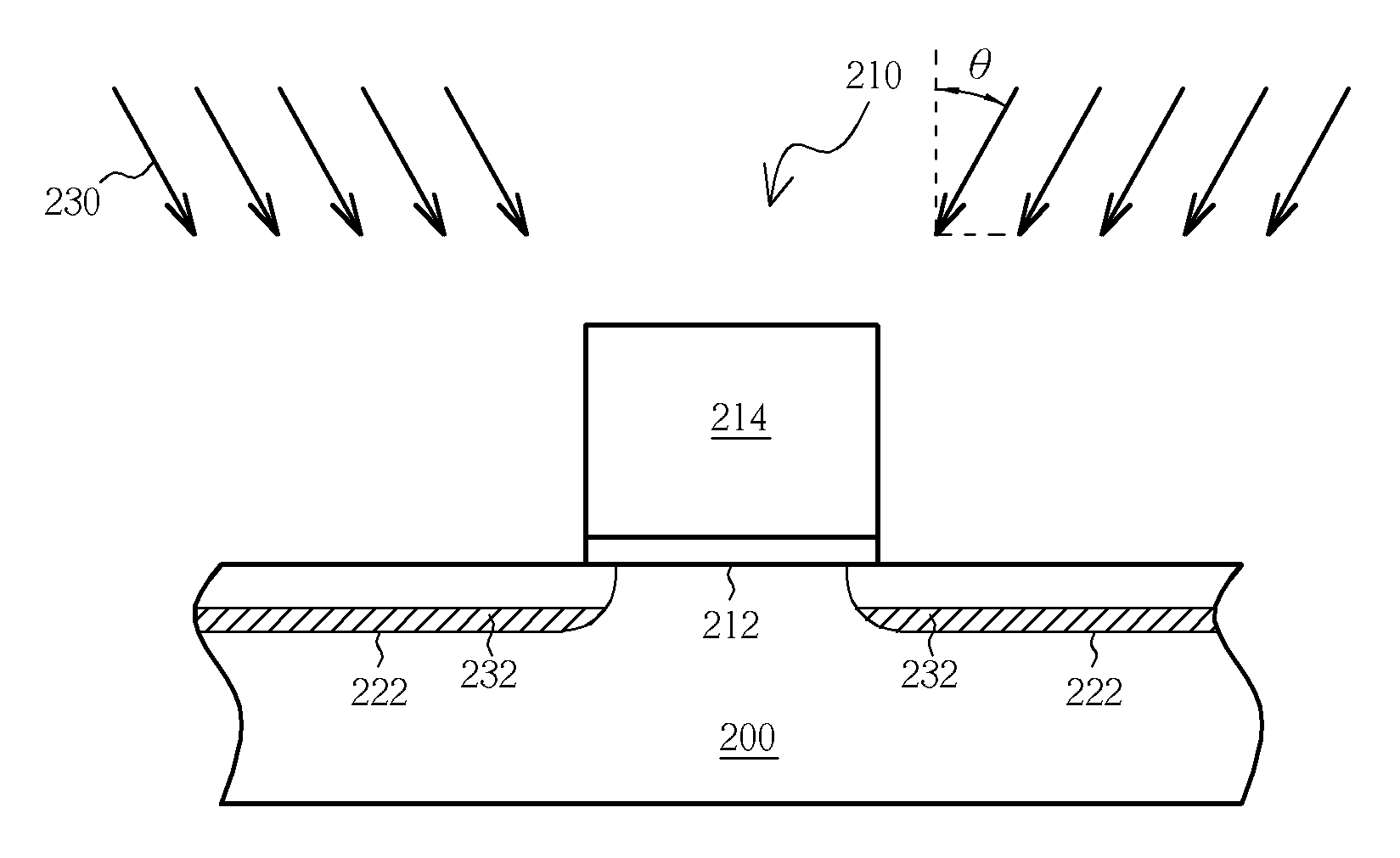

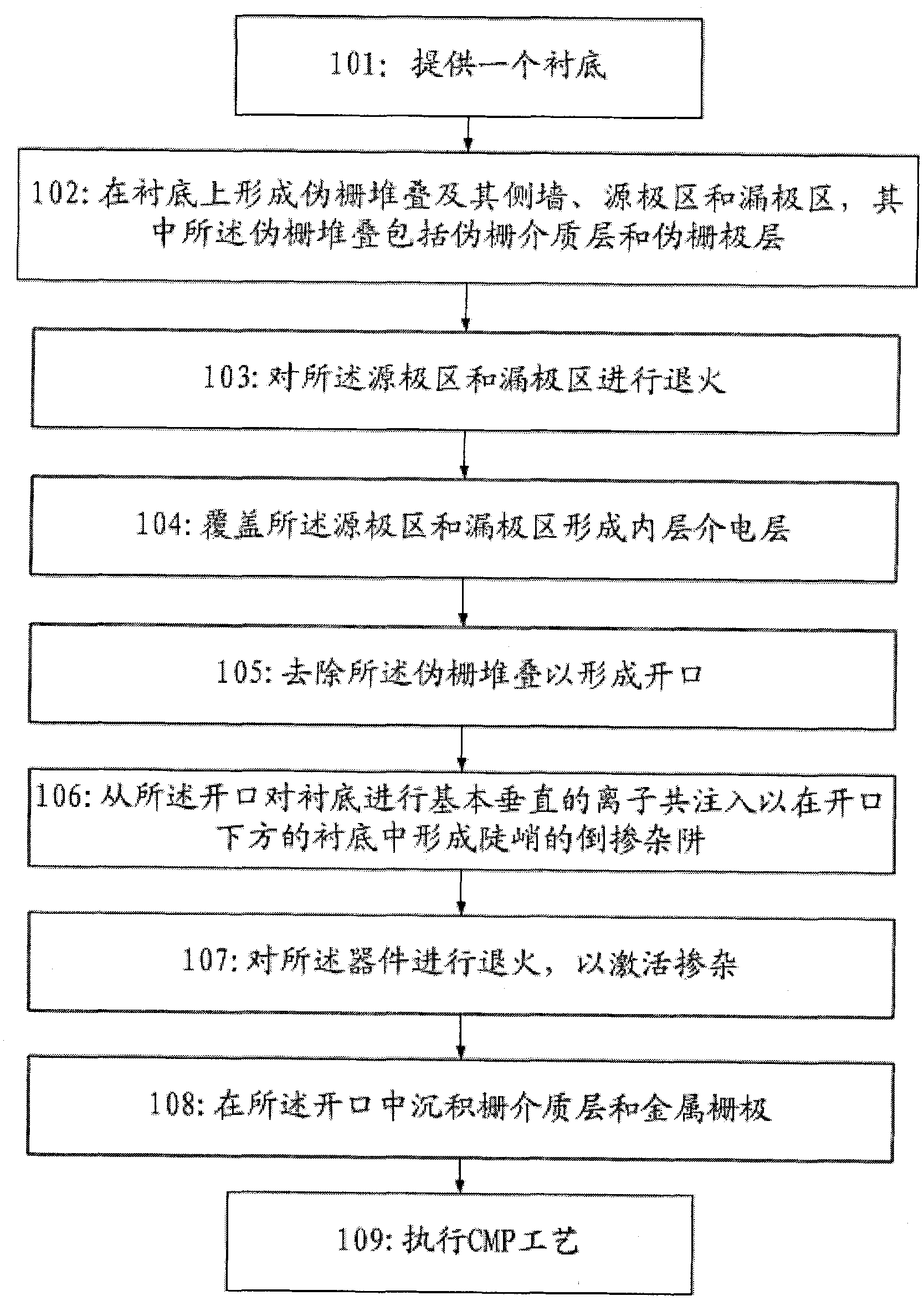

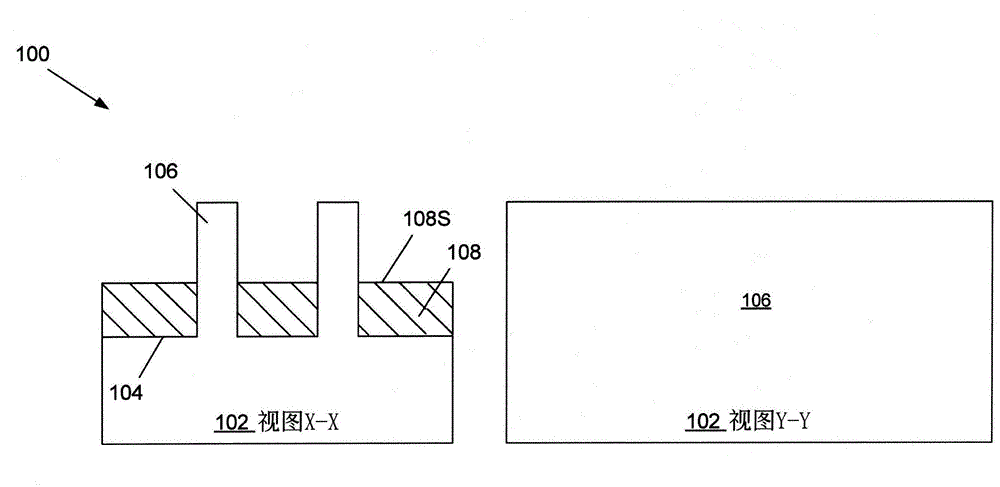

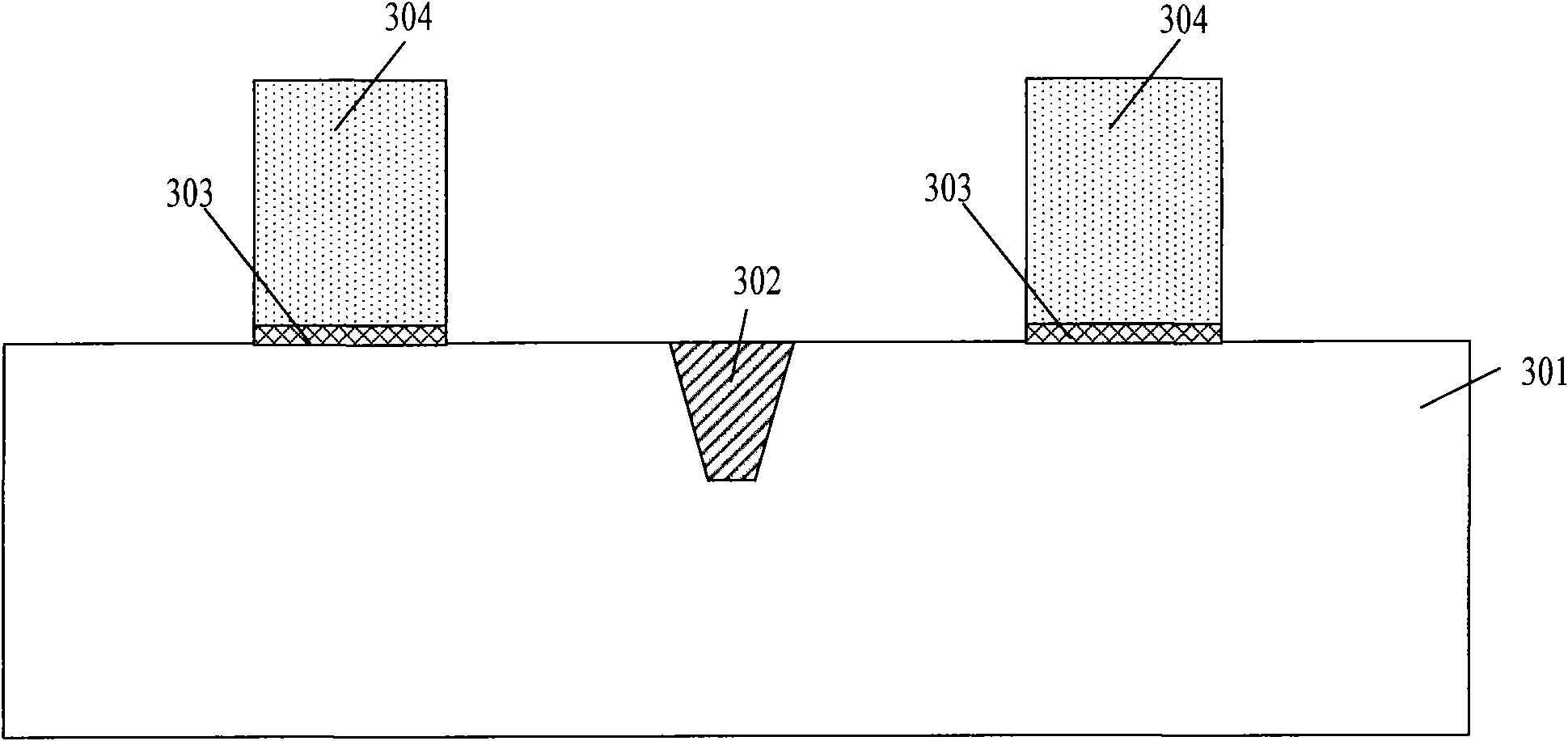

High-performance semiconductor device and manufacturing method thereof

ActiveCN102157379ASemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceMOSFET

The invention provides a method for manufacturing a semiconductor device, comprising the following steps of: firstly forming a false gate stack and a side wall thereof, a source electrode region and a drain electrode region by utilizing a gate alternative process; annealing the source electrode region and the drain electrode region, and then removing the false gate stack; carrying out basically vertical ion co-implantation and / or slant ion co-implantation on a substrate to form a steep inverted dopant well in the substrate positioned below an opening and / or respectively form ion implantation regions near the source electrode region and the drain electrode region by utilizing the opening formed by removing the false gate stack, and then annealing the semiconductor device to activate doping; and depositing a gate dielectric layer and a metal gate electrode in the opening. Thus, the increase of tape-to-tape leakage currents and source drain junction capacitances of an MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device are inhibited and the breakdown of a source electrode and a drain electrode is prevented, thereby the performance of the semiconductor device is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method of forming a MOS transistor

InactiveUS20080258178A1Improve short channel effectFacilitated DiffusionTransistorSolid-state devicesDopantEngineering

A method of forming a MOS transistor, in which a co-implantation is performed to implant an implant into a source region and a drain region or a halo implanted region to effectively prevent dopants from over diffusion in the source region and the drain region or the halo implanted region, for obtaining a good junction profile and improving short channel effect. The implant comprises carbon, a hydrocarbon, or a derivative of the hydrocarbon, such as one selected from a group consisting of CO, CO2, CxHy+, and (CxHy)n+, wherein x is a number of 1 to 10, y is a number of 4 to 20, and n is a number of to 1000.

Owner:UNITED MICROELECTRONICS CORP

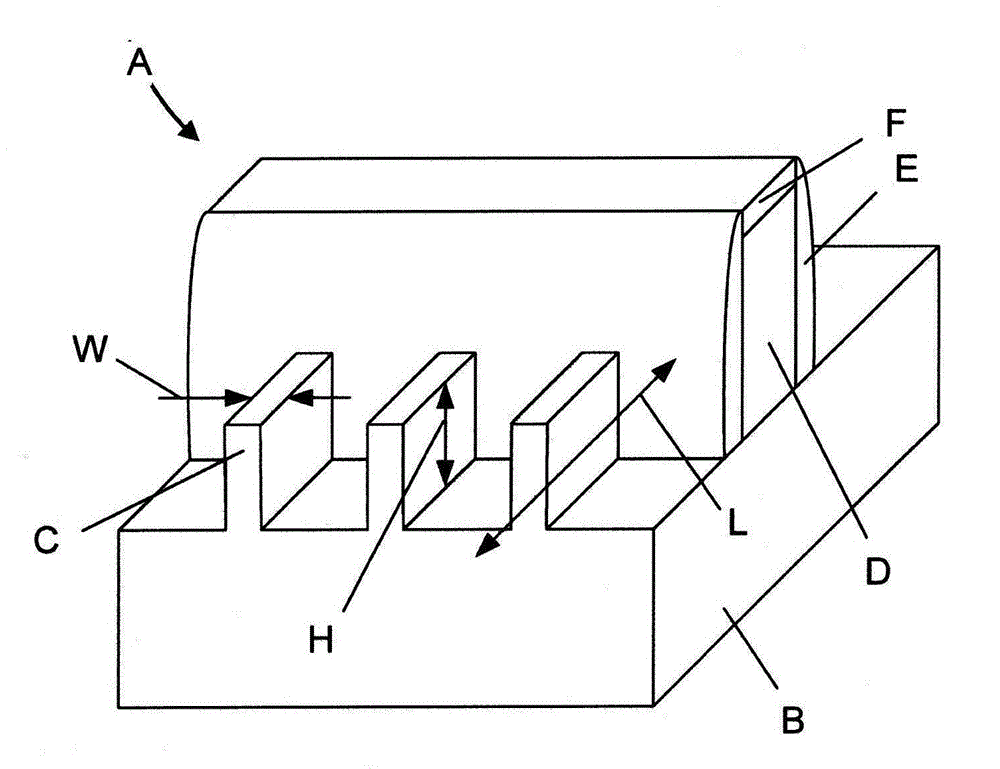

Methods to improve FinFet semiconductor device behavior using co-implantation under the channel region

ActiveCN104900498ASemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringBiomedical engineering

One illustrative method disclosed includes, among other things, forming a fin in a substrate, forming a well implant region in at least the substrate, forming a punch-stop implant region in the fin, performing at least one neutral implantation process with at least one neutral implant material to form a neutral boron-diffusion-blocking implant region in the fin, wherein an upper surface of the neutral boron-diffusion-blocking implant region is positioned closer to an upper surface of the fin than either the punch-stop implant region or the well implant region and, after forming the well implant region, the punch-stop implant region and the neutral boron-diffusion-blocking implant region, forming a gate structure above the fin.

Owner:GLOBALFOUNDRIES U S INC MALTA

Method of forming a MOS transistor

ActiveUS7795101B2Improve short channel effectFacilitated DiffusionTransistorSemiconductor/solid-state device manufacturingDopantEngineering

A method of forming a MOS transistor, in which, a co-implantation is performed to implant a carbon co-implant into a source region and a drain region or a halo implanted region to effectively prevent dopants from over diffusion in the source region and the drain region or the halo implanted region, for obtaining a good junction profile and improving short channel effect, and the carbon co-implant is from a precursor comprising CO or CO2.

Owner:MARLIN SEMICON LTD

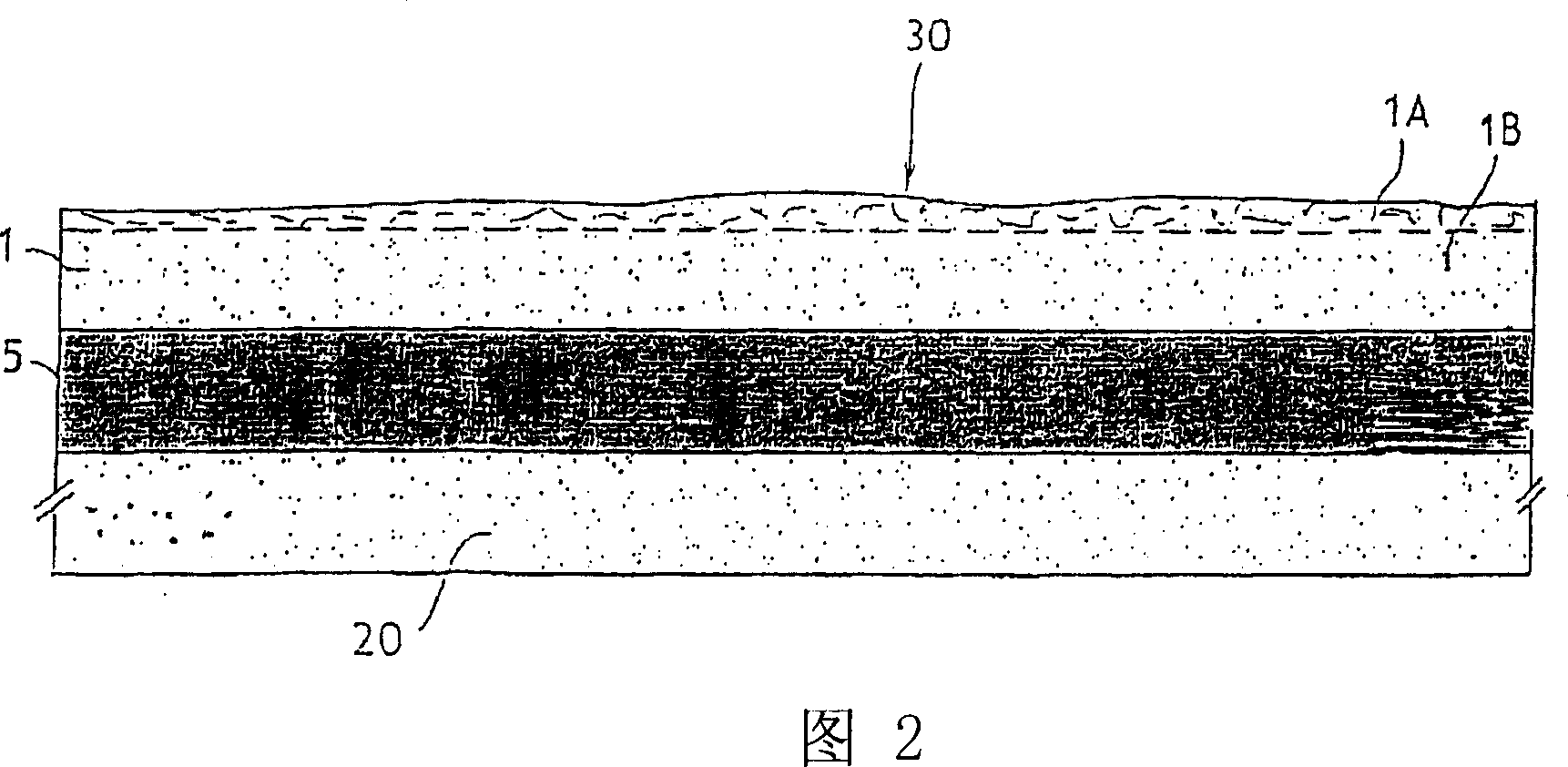

Heat treatment for improving the quality of a taken thin layer

InactiveCN1930674AFinal product manufactureSemiconductor/solid-state device manufacturingSemiconductor materialsThin layer

A method for forming a structure that includes a layer that is removed from a donor wafer that has a first layer made of a semiconductor material containing germanium. The method includes the steps of forming a weakness zone in the thickness of the first layer; bonding the donor wafer to a host wafer; and supplying energy so as to weaken the donor wafer at the level of the zone of weakness. The zone of weakness is formed by subjecting the donor wafer to a co-implantation of at least two different atomic species, while the bonding is carried out by performing a thermal treatment at a temperature between 300 DEG C. and 400 DEG C. for a duration of from 30 minutes to four hours.

Owner:SOITEC SA

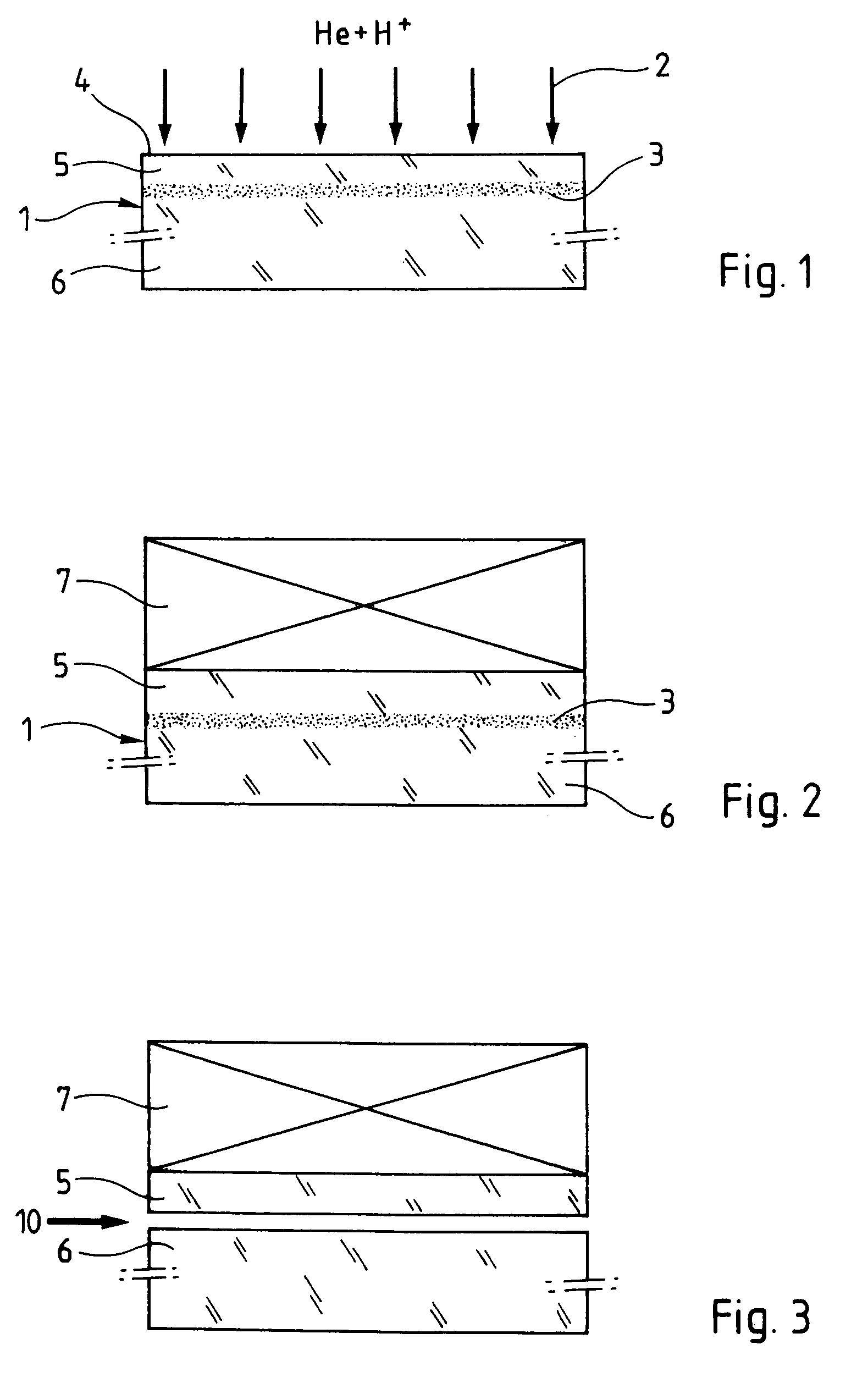

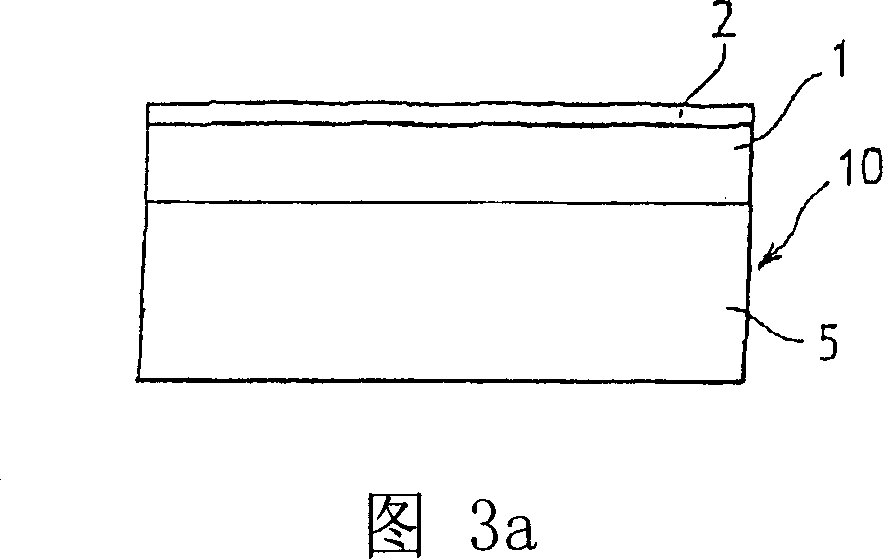

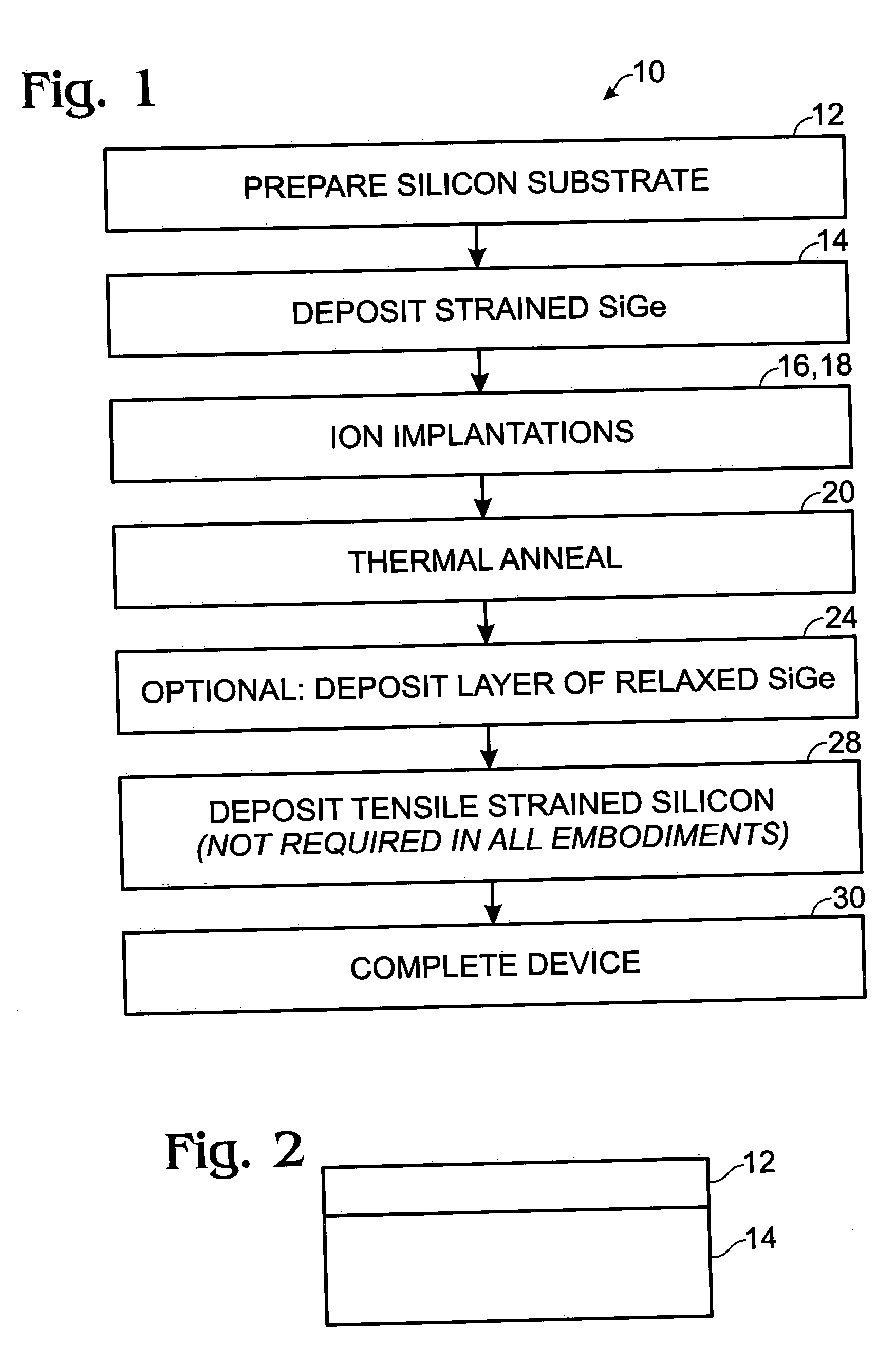

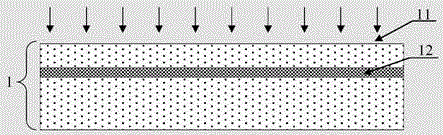

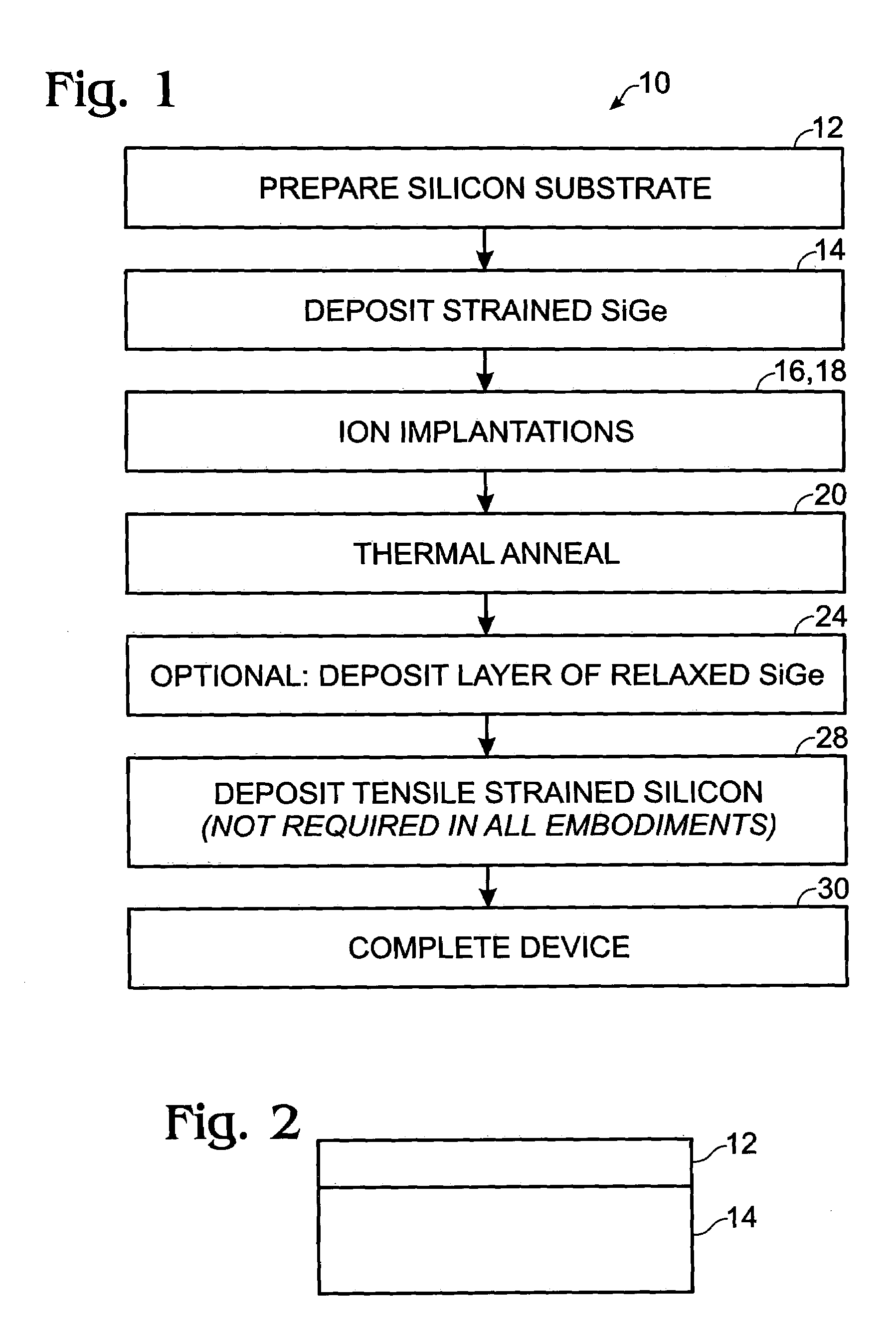

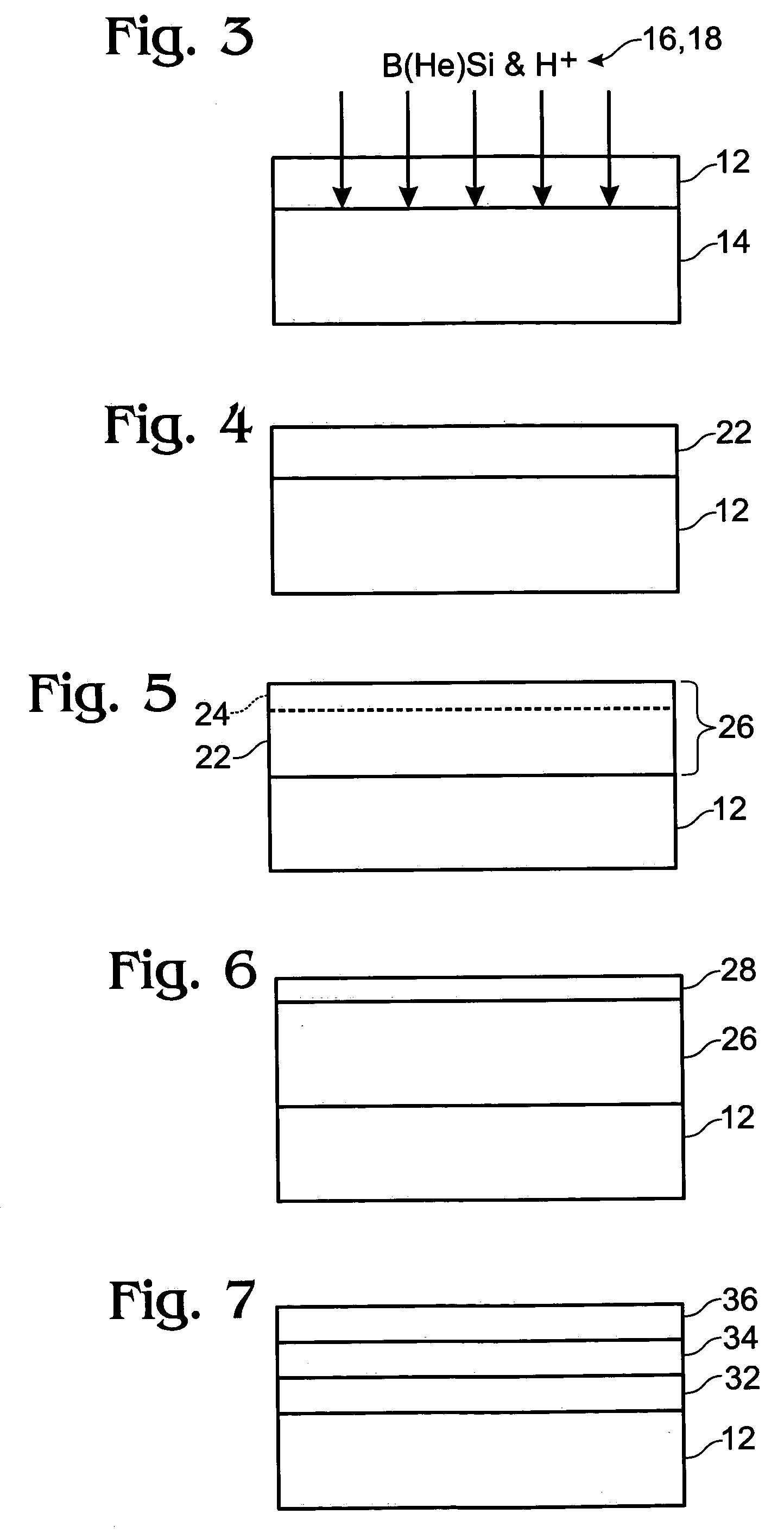

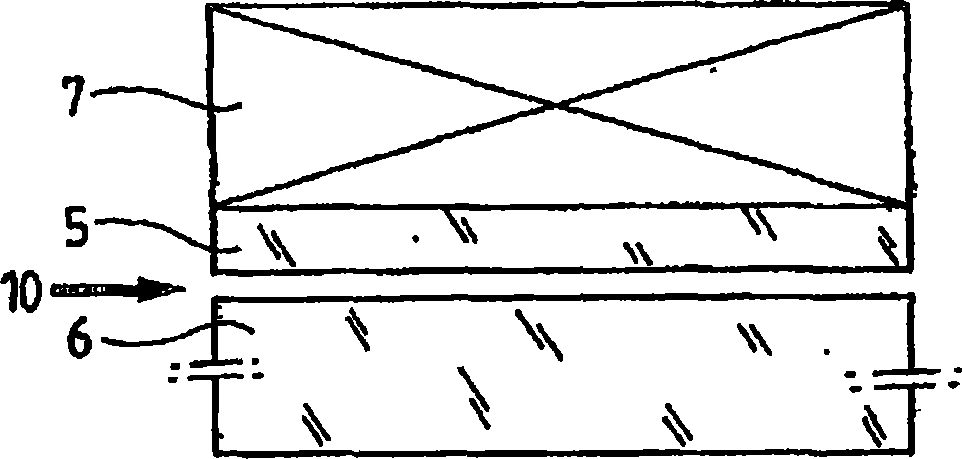

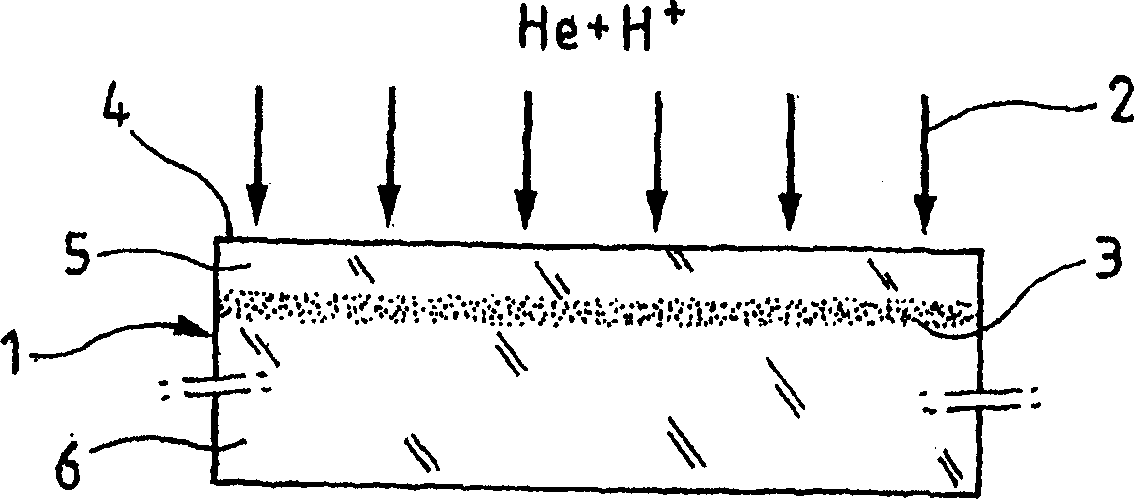

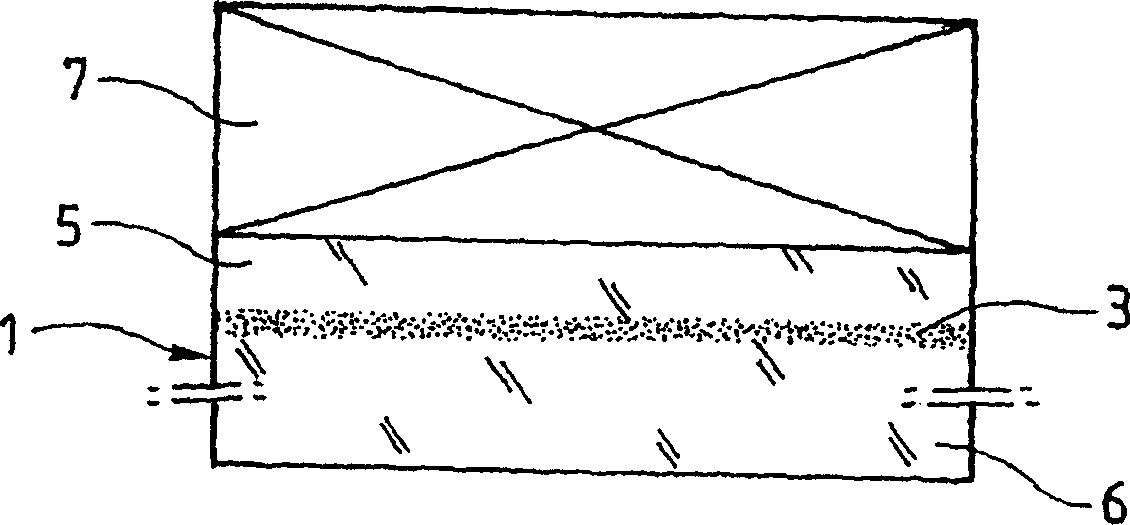

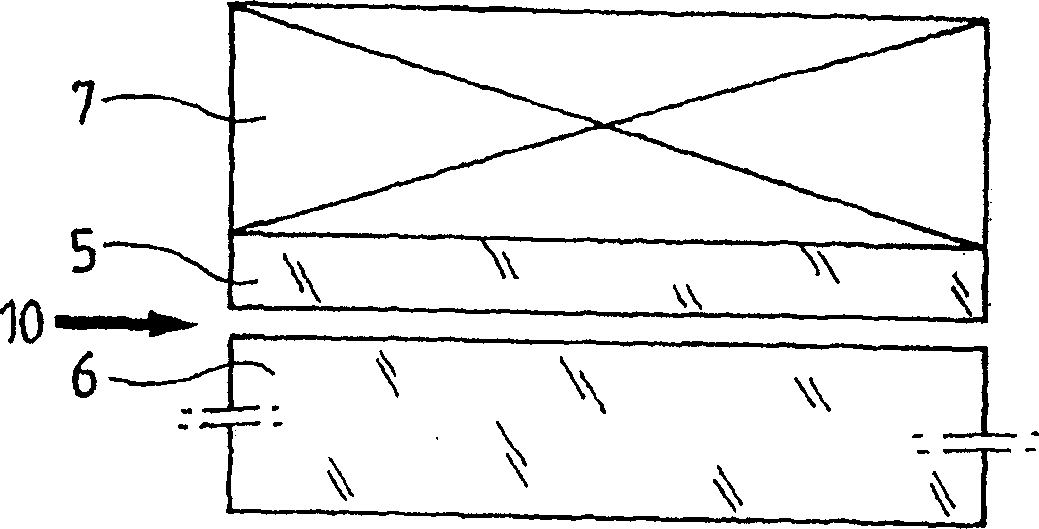

Method to form relaxed SiGe layer with high Ge content using co-implantation of silicon with boron or helium and hydrogen

InactiveUS20060051960A1Low costImprove film propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenDevice material

A method of forming a relaxed SiGe layer having a high germanium content in a semiconductor device includes preparing a silicon substrate; depositing a strained SiGe layer; implanting ions into the strained SiGe layer, wherein the ions include silicon ions and ions selected from the group of ions consisting of boron and helium, and which further includes implanting H+ ions; annealing to relax the strained SiGe layer, thereby forming a first relaxed SiGe layer; and completing the semiconductor device.

Owner:SHARP KK

Method of forming a MOS transistor

ActiveUS20100144110A1Good junction profileImprove short channel effectTransistorSemiconductor/solid-state device manufacturingDopantEngineering

A method of forming a MOS transistor, in which, a co-implantation is performed to implant a carbon co-implant into a source region and a drain region or a halo implanted region to effectively prevent dopants from over diffusion in the source region and the drain region or the halo implanted region, for obtaining a good junction profile and improving short channel effect, and the carbon co-implant is from a precursor comprising CO or CO2.

Owner:MARLIN SEMICON LTD

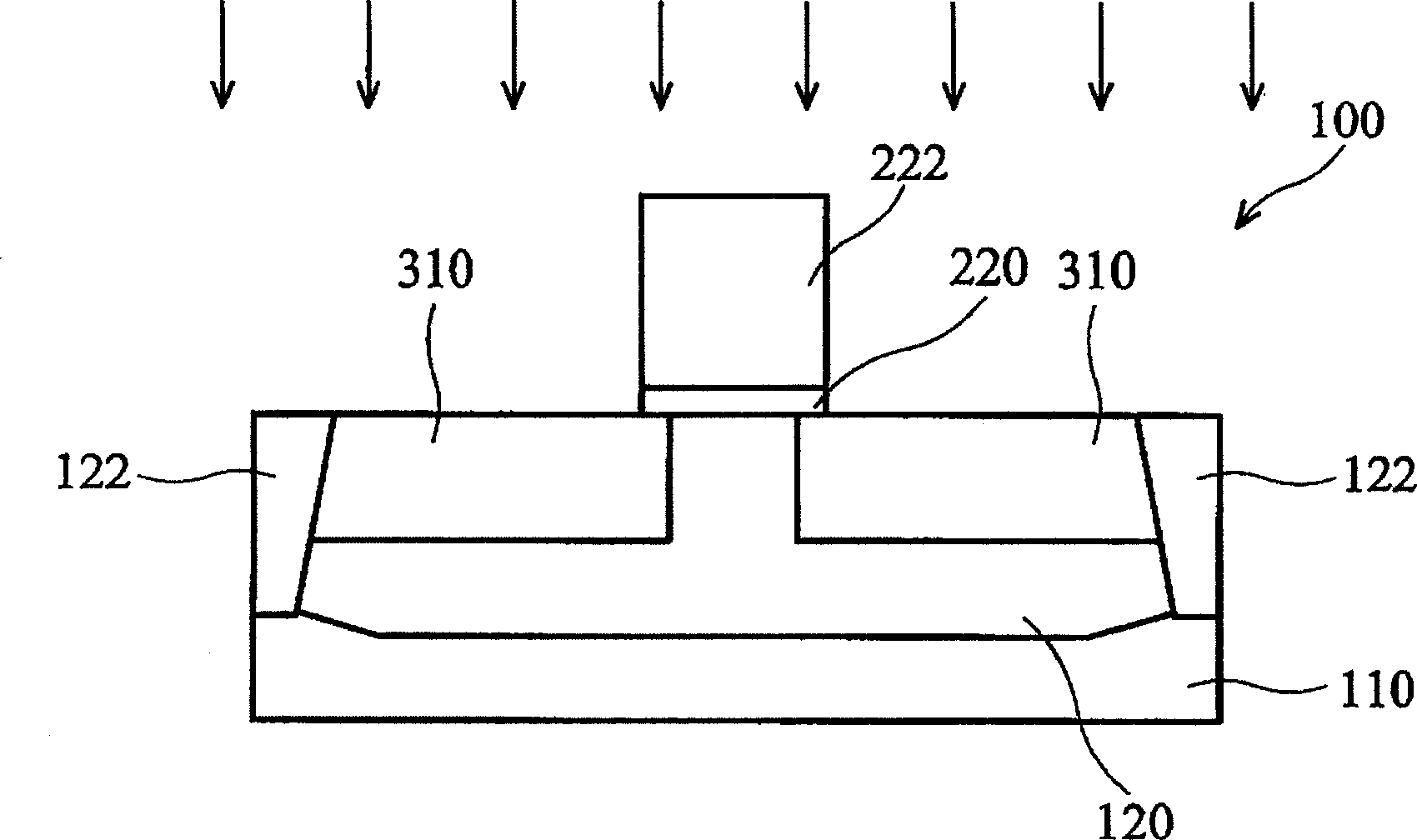

Method for manufacturing semiconductor element

ActiveCN1913112AShow technicalityTransistorSemiconductor/solid-state device manufacturingEngineeringCo implantation

The invention proposes a method for manufacturing a semiconductor element which has shallow, high-dopant concentration source / drain regions. The manufacturing method is provided that, a gate electrode is formed on a substrate, and the source / drain regions of the substrate are transformed into an amorphous state by implanting ions. A co-implantation process is performed to implant ions in the source / drain regions. Thereafter, one or more implants may be performed to form the LDD and source / drain regions and the substrate is recrystallized. The amorphous regions and the co-implantation regions effectively confine or reduce the diffusion of the ions used to form the LDD and source / drain regions.

Owner:TAIWAN SEMICON MFG CO LTD

MOS transistor

InactiveUS20070228464A1Good junction profileImprove short channel effectTransistorSemiconductor/solid-state device manufacturingDopantHydrocotyle bowlesioides

A method of forming a MOS transistor, in which a co-implantation is performed to implant an implant into a source region and a drain region or a halo implanted region to effectively prevent dopants from over diffusion in the source region and the drain region or the halo implanted region, for obtaining a good junction profile and improving short channel effect. The implant comprises carbon, a hydrocarbon, or a derivative of the hydrocarbon, such as one selected from a group consisting of C, CxHy+, and (CxHy)n+, wherein x is a number of 1 to 10, y is a number of 4 to 20, and n is a number of 1 to 1000.

Owner:UNITED MICROELECTRONICS CORP

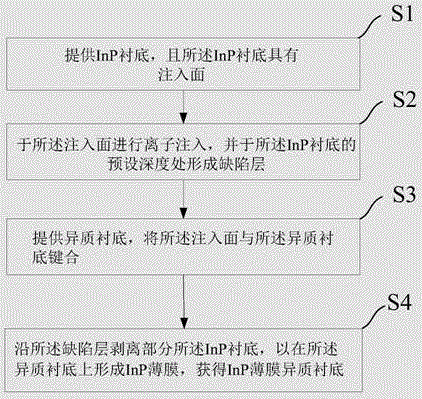

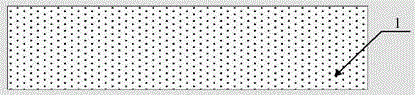

Method for preparing InP thin film heterogeneous substrate

InactiveCN106711026ASolve the problem that the peeling cannot be achievedReduce ion implantation doseSolid-state devicesSemiconductor/solid-state device manufacturingBond interfaceOptoelectronics

The invention provides a method for preparing a InP thin film heterogeneous substrate. The method at least comprises the steps of providing an InP substrate which has an injection plane; carrying out ion co-implantation on the injection plane to form a defect layer at a preset depth of the InP substrate; providing a heterogeneous substrate, bonding the InP substrate and the heterogeneous substrate, and taking the injection plane of the InP substrate as a bonding interface; peeling part of the InP substrate along the defect layer, getting a part of the InP substrate transferred onto the heterogeneous substrate to form an InP thin film on the heterogeneous substrate to obtain the InP thin film heterogeneous substrate. By the scheme, the dosage of unitary ion injection required by peeling and transferring InP thin film cam be effectively reduced, the adoption of a sub-zero low temperature injection method to peel an InP material, which is reported in literature, is avoided simultaneously, then the preparation period is shortened, and the cost of production is saved; and low-temperature or high-temperature injection is not required, so that the additional energy consumption required by controlling injection temperature can be reduced.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Method to form relaxed SiGe layer with high Ge content using co-implantation of silicon with boron or helium and hydrogen

InactiveUS7241670B2Low costImprove film propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenBoron

A method of forming a relaxed SiGe layer having a high germanium content in a semiconductor device includes preparing a silicon substrate; depositing a strained SiGe layer; implanting ions into the strained SiGe layer, wherein the ions include silicon ions and ions selected from the group of ions consisting of boron and helium, and which further includes implanting H+ ions; annealing to relax the strained SiGe layer, thereby forming a first relaxed SiGe layer; and completing the semiconductor device.

Owner:SHARP KK

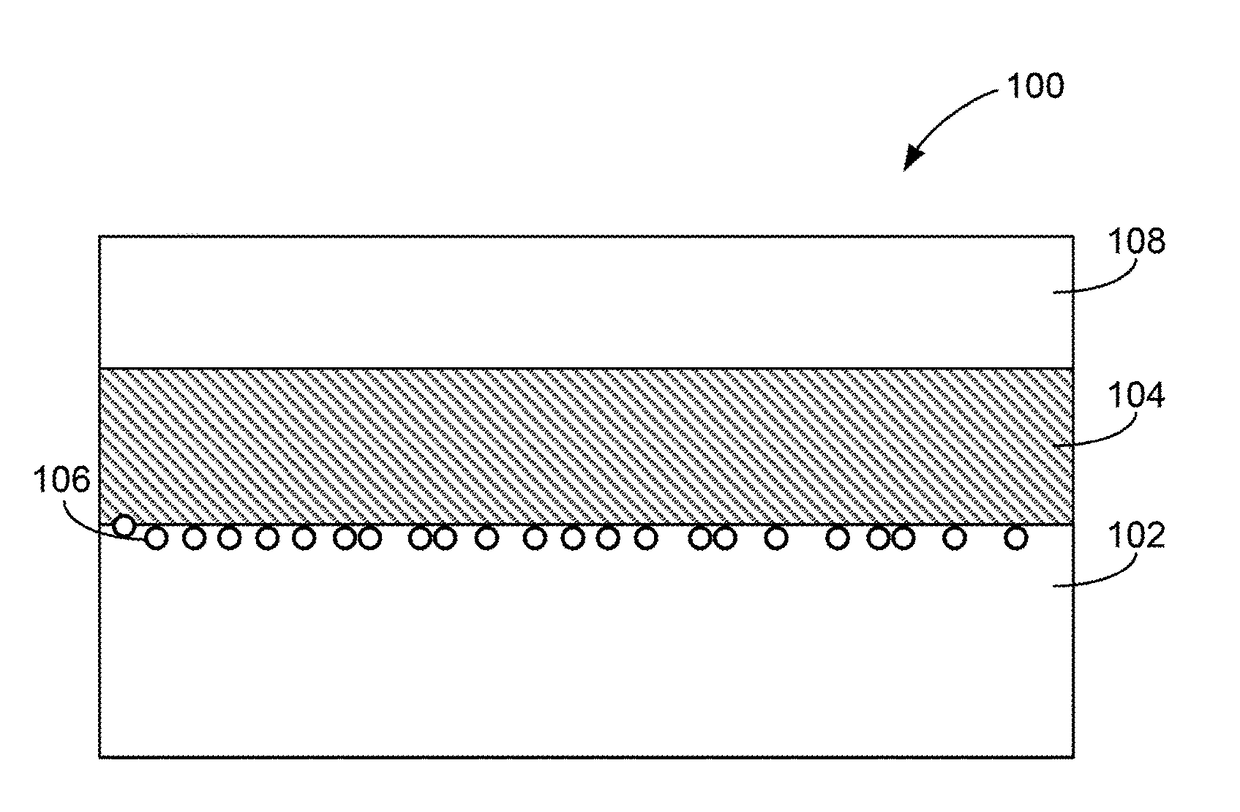

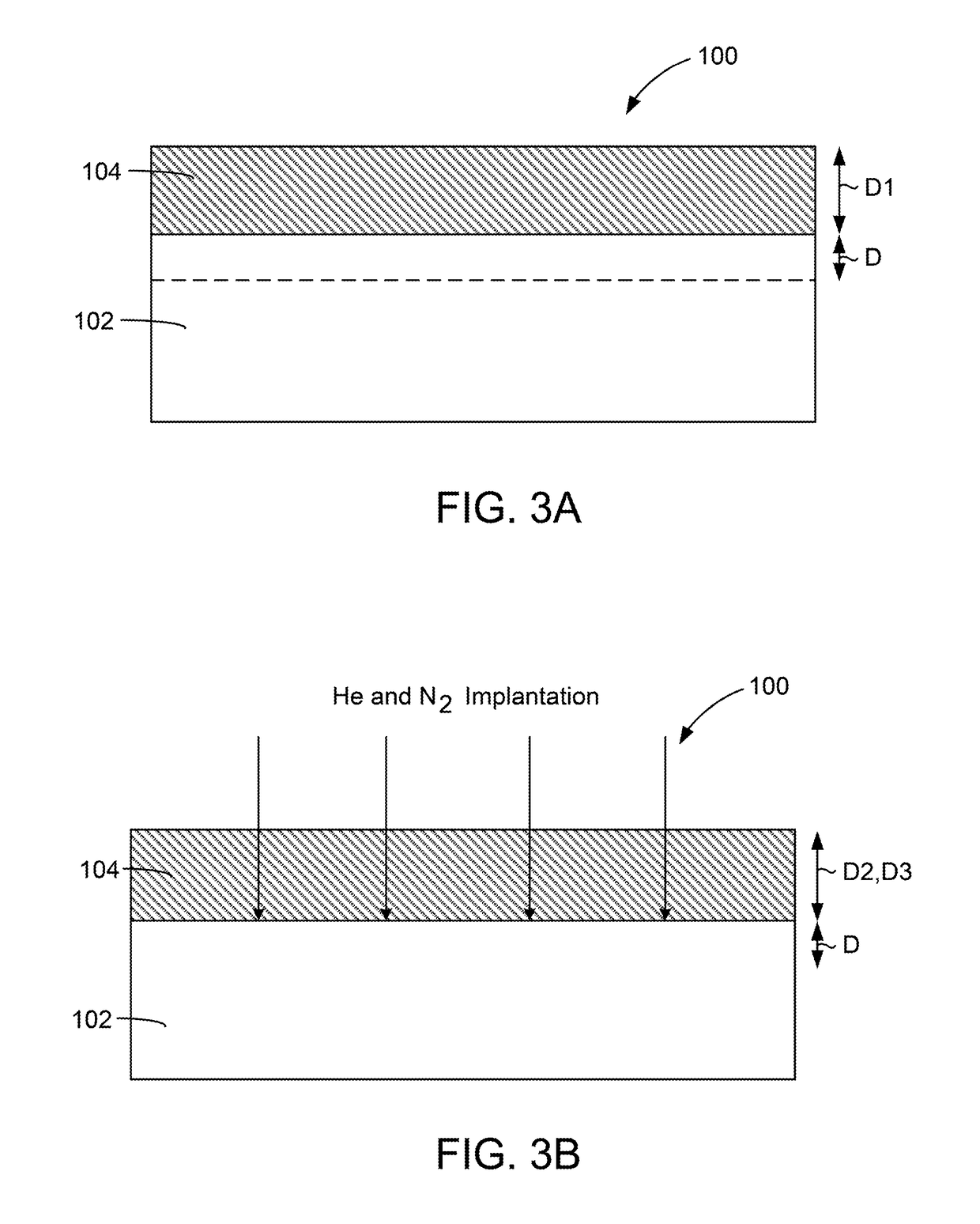

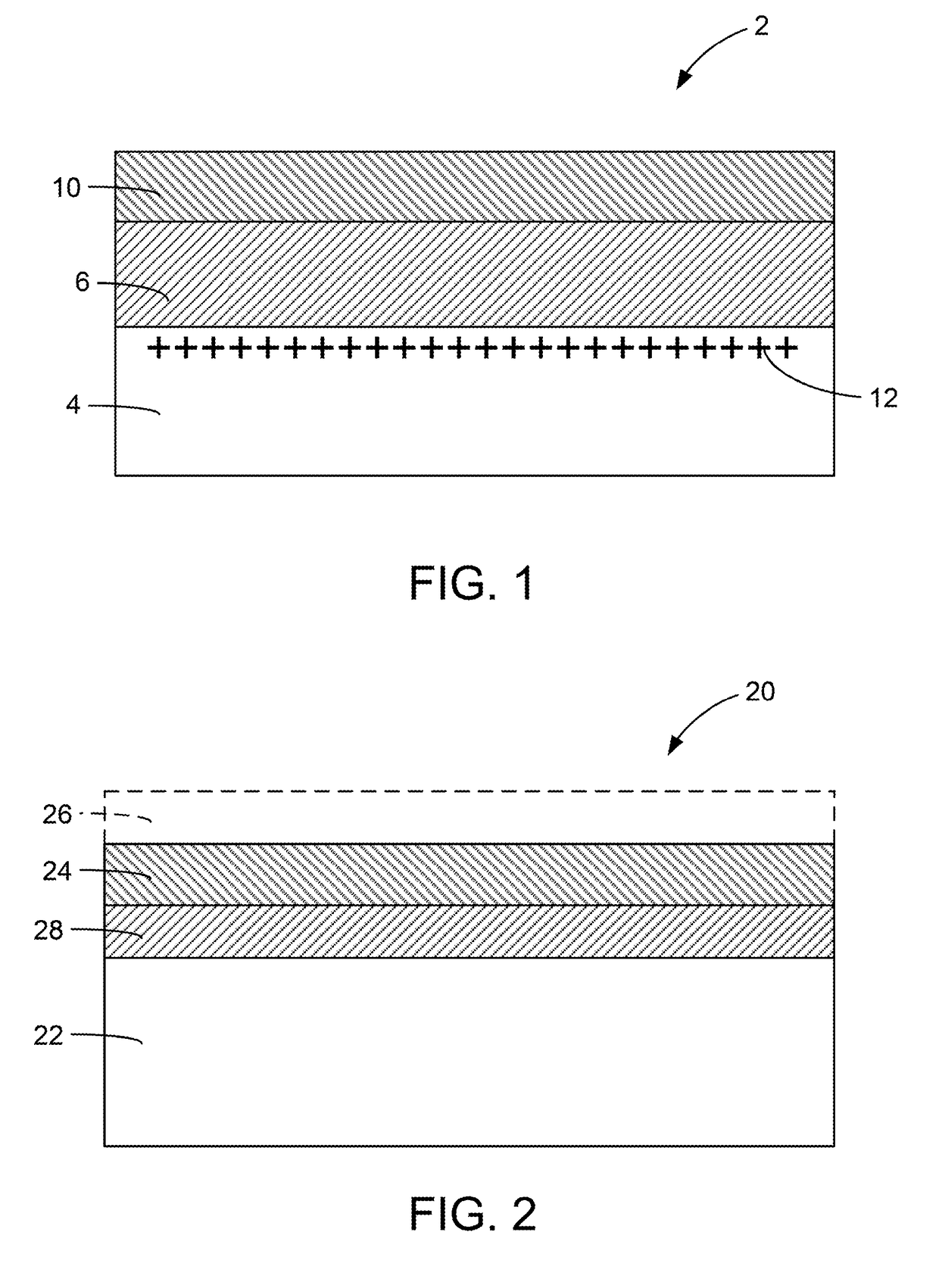

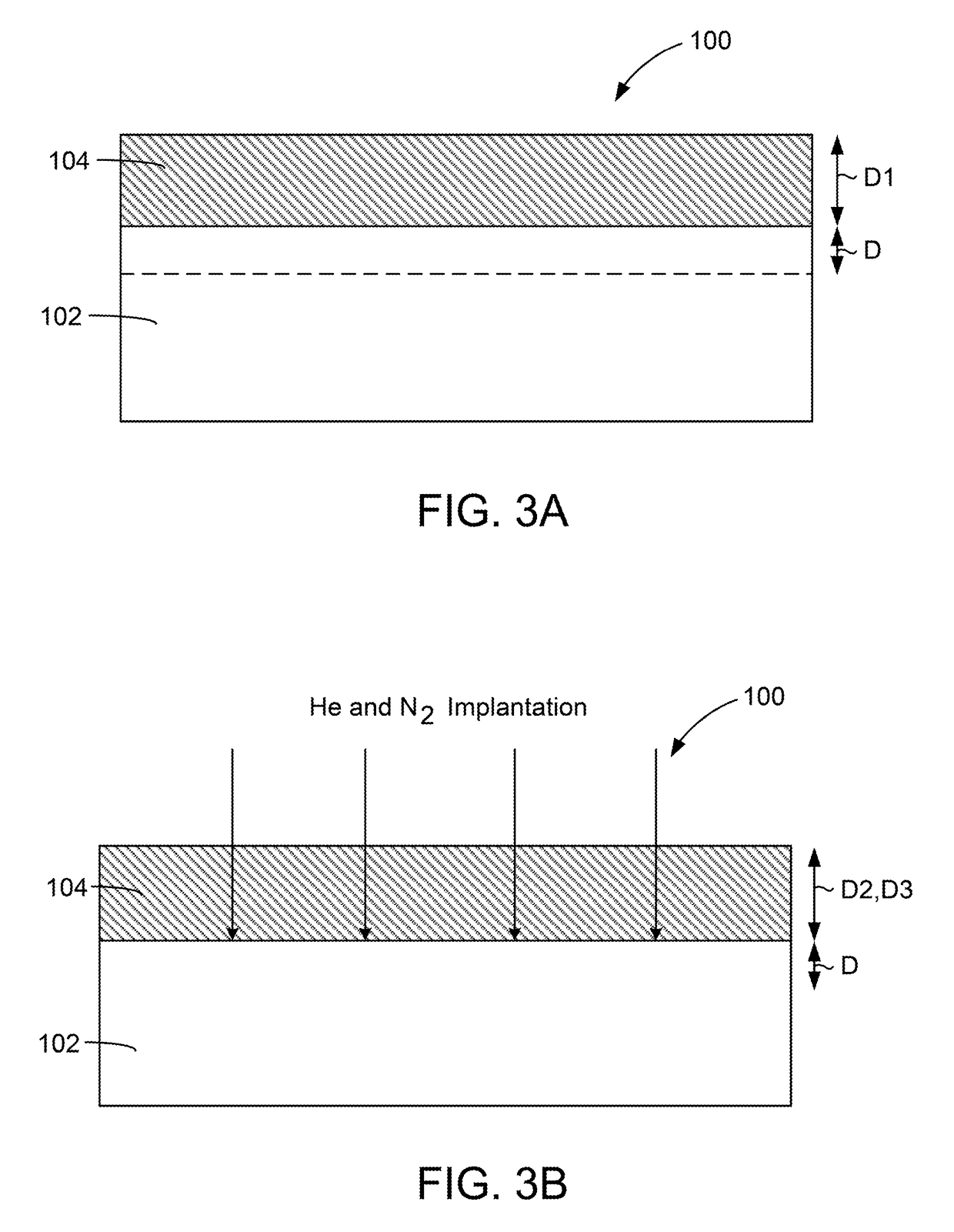

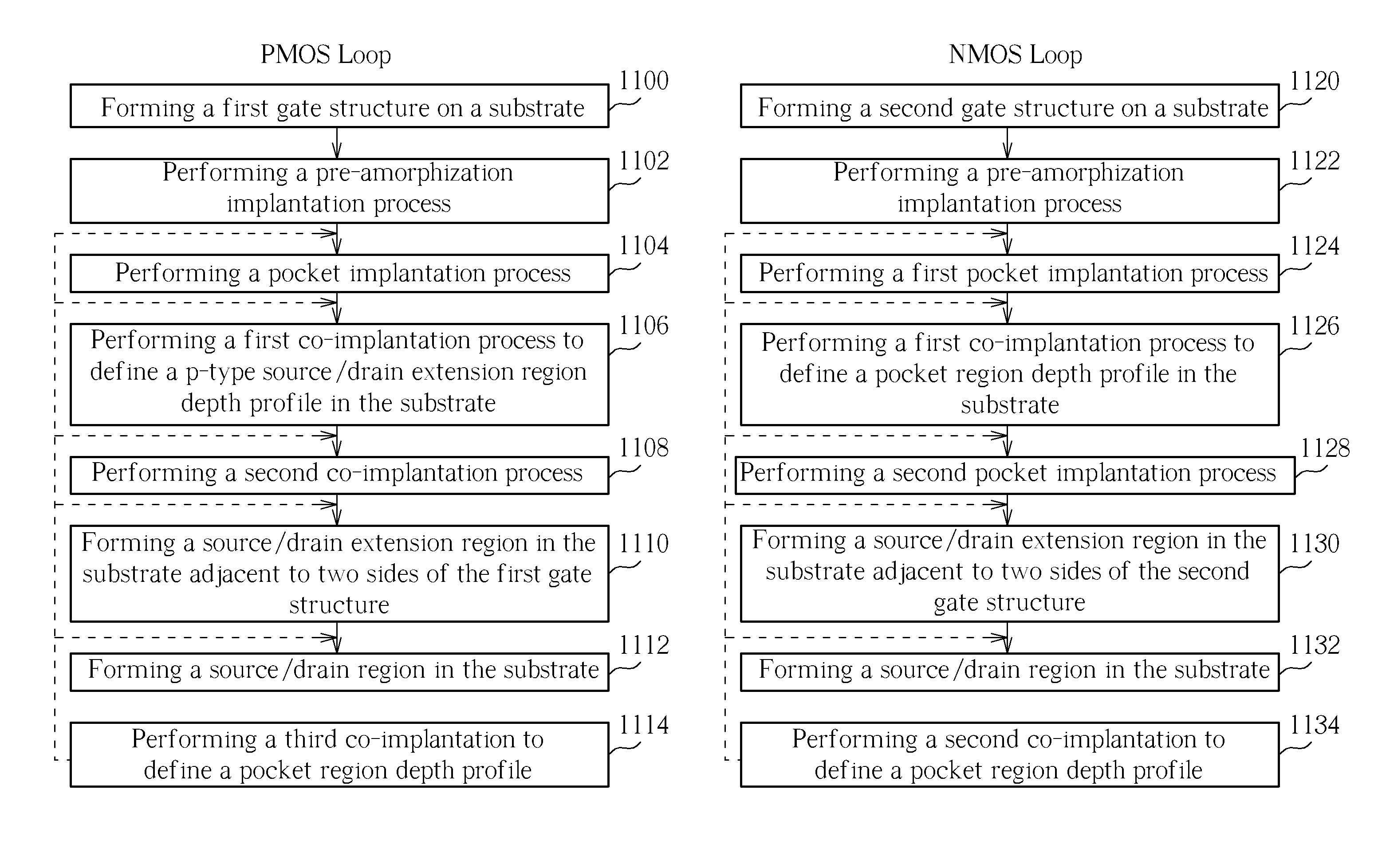

High resistivity silicon-on-insulator substrate comprising a charge trapping layer formed by he-n2 co-implantation

A multilayer composite structure and a method of preparing a multilayer composite structure are provided. The multilayer composite structure comprises a semiconductor handle substrate having a minimum bulk region resistivity of at least about 500 ohm-cm and comprises a region of nitrogen-reacted nanovoids in the front surface region; a silicon dioxide layer on the surface of the semiconductor handle substrate; a dielectric layer in contact with the silicon dioxide layer; and a semiconductor device layer in contact with the dielectric layer.

Owner:GLOBALWAFERS CO LTD

Method for fabricating P-channel field-effect transistor (FET)

ActiveUS7888223B2Increased injected energyTransistorSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

Owner:MARLIN SEMICON LTD

Method for the catastrophic transfer of a thin layer after co-implantation

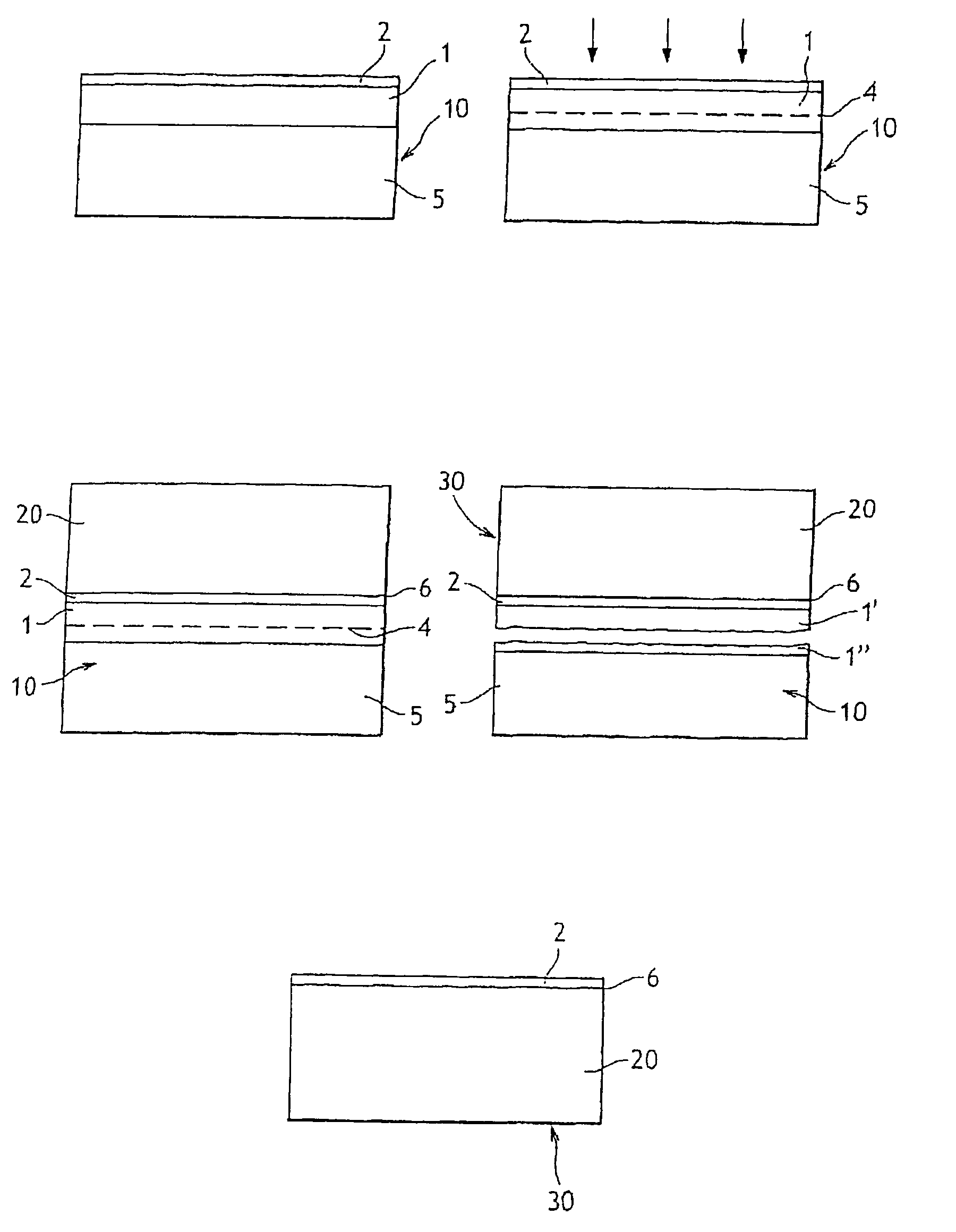

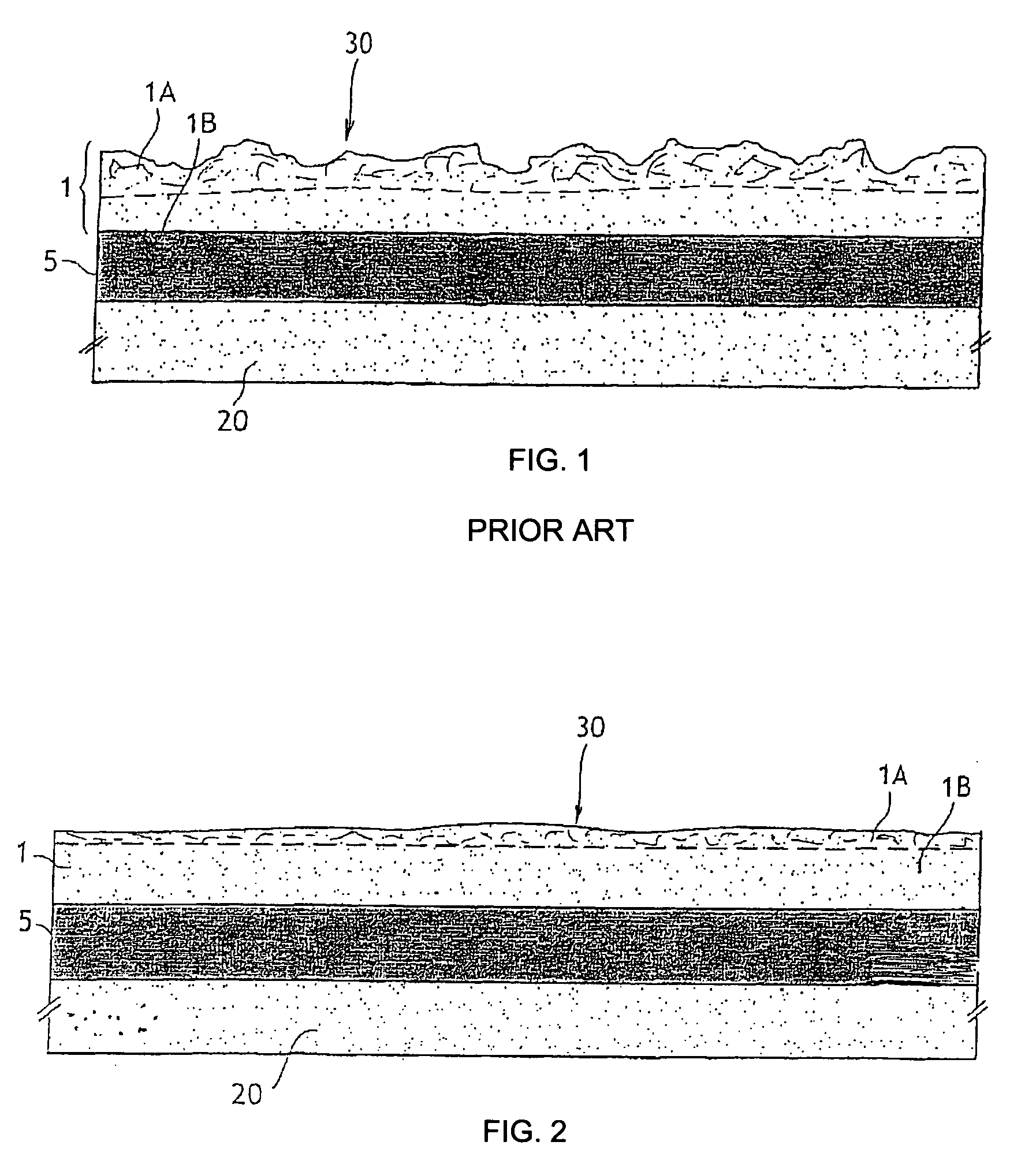

ActiveCN1868053ASemiconductor/solid-state device manufacturingMicrostructural devicesThin layerOptoelectronics

The invention relates to a thin-layer self-sustaining transfer method, according to which - ions of at least one species are implanted in a source substrate at a given depth relative to a surface of the source substrate at a certain dose, - bringing a stiffener into intimate contact with the source substrate, - applying heat treatment to the source substrate at a given temperature for a given time to create a weakened buried region substantially at a given depth, and without inducing thermal detachment of the thin layer, - applying a controlled pulse of energy to the source substrate in a temporally localized manner so as to induce The rest of the self-sustaining detachment.

Owner:SOITEC SA +1

Catastrophic transfer of thin film after co-implantation

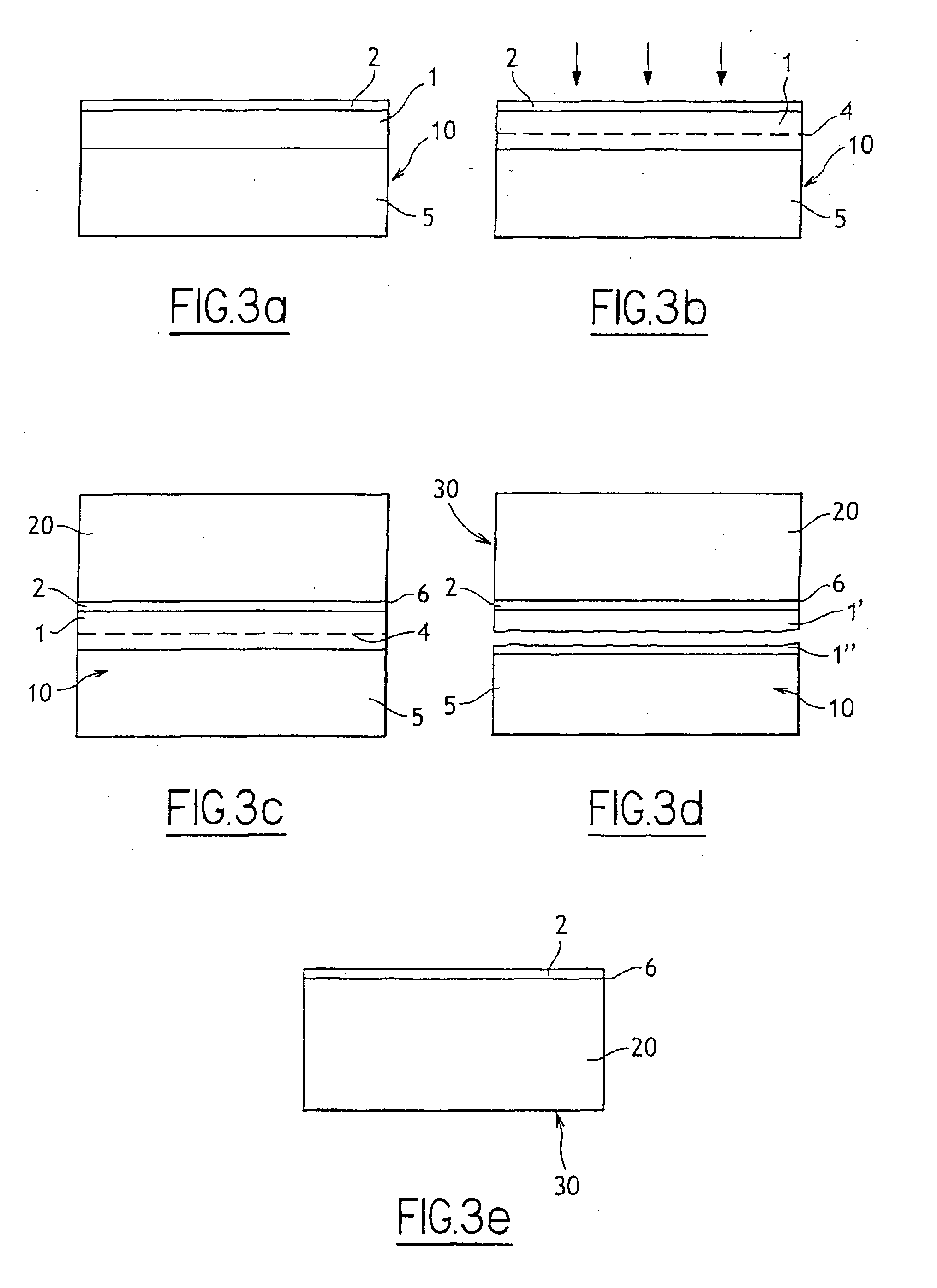

ActiveCN1864256AEasy to industrializeImprove topologySemiconductor/solid-state device manufacturingMicrostructural devicesRugosityProduct gas

The catastrophic transfer of a thin film comprises: - (a) preparing a source substrate; - (b) implanting a first species of ions or gas, in a first dose to a given depth, and a second species of ions or gas in a second dose, the first species being able to generate defects and the second species being able to occupy these defects; - (c) applying a stiffener in intimate contact with the source substrate; - (d) heat treating the source substrate to a given temperature for a given time, to create a buried fragile zone without initiating the thermal detachment of the thin film; and - (e) applying a localized energy contribution to provoke the catastrophic detachment of the thin film delimited between the surface and the buried fragile layer, this thin film having a surface with a rugosity below a given threshold.

Owner:S O I TEC SILICON ON INSULATOR THECHNOLOGIES +1

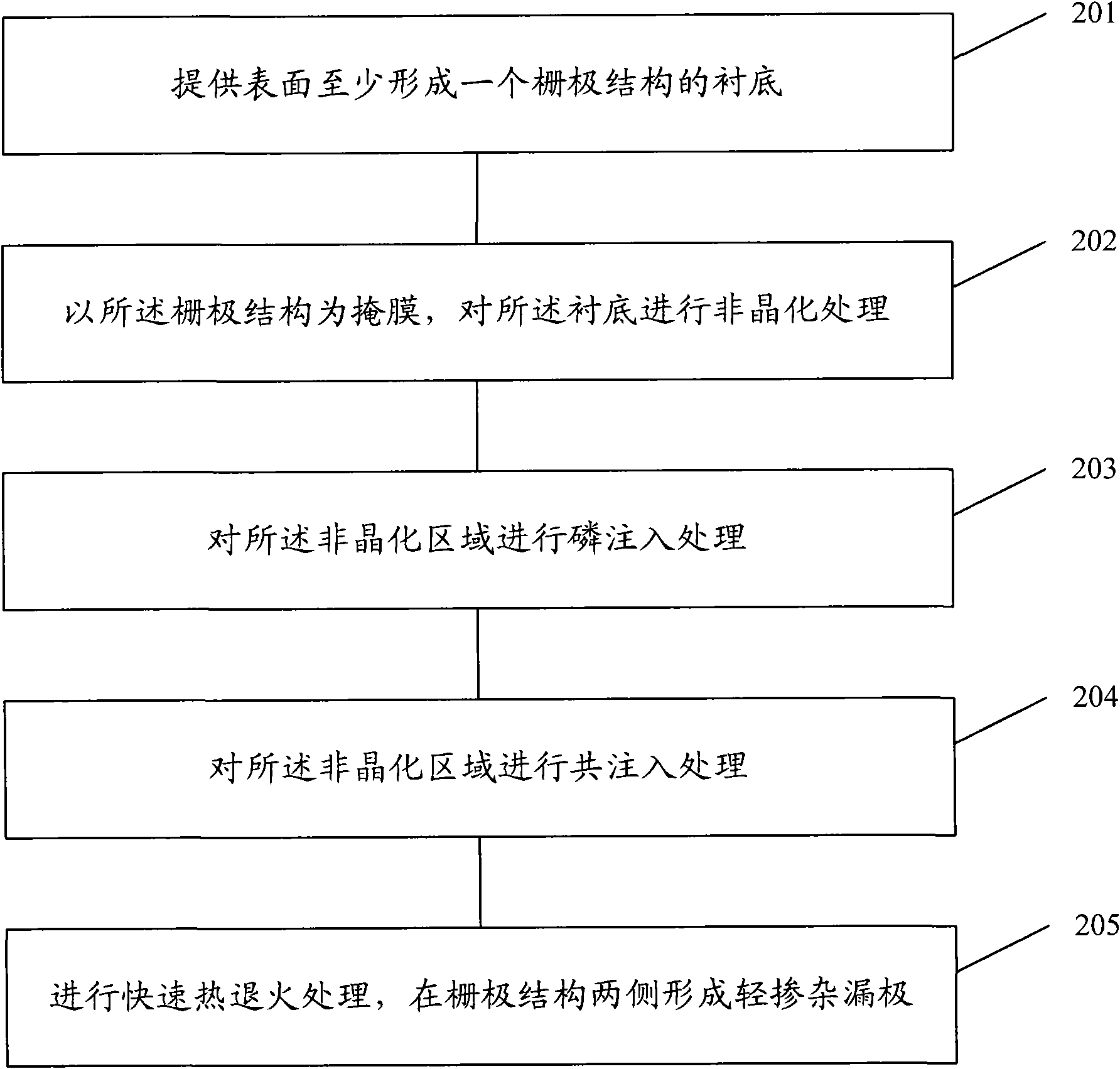

Method for forming lightly doped drain

ActiveCN101770950ASuppression of Transient Enhancement Diffusion EffectsLower thermal budgetSemiconductor/solid-state device manufacturingElectrical performanceRapid thermal annealing

The invention discloses a method for forming a lightly doped drain, which comprises the following steps: providing a substrate on the surface of which at least one grid structure is formed; using the grid structure as a mask and performing a de-crystallization treatment on the substrate to form a amorphous region; performing a phosphorus implantation treatment on the amorphous region; performing a co-implantation treatment on the de-crystallization region; and performing a quick thermal annealing treatment to form lightly doped drains on both sides of the grid structure. The thermal budget of an apparatus is lowered, a small junction depth is maintained and excellent electrical performance of the apparatus is obtained. The method is particularly beneficial for the manufacture of small-size apparatuses.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

HIGH RESISTIVITY SILICON-ON-INSULATOR SUBSTRATE COMPRISING A CHARGE TRAPPING LAYER FORMED BY He-N2 CO-IMPLANTATION

A multilayer composite structure and a method of preparing a multilayer composite structure are provided. The multilayer composite structure comprises a semiconductor handle substrate having a minimum bulk region resistivity of at least about 500 ohm-cm and comprises a region of nitrogen-reacted nanovoids in the front surface region; a silicon dioxide layer on the surface of the semiconductor handle substrate; a dielectric layer in contact with the silicon dioxide layer; and a semiconductor device layer in contact with the dielectric layer.

Owner:GLOBALWAFERS CO LTD

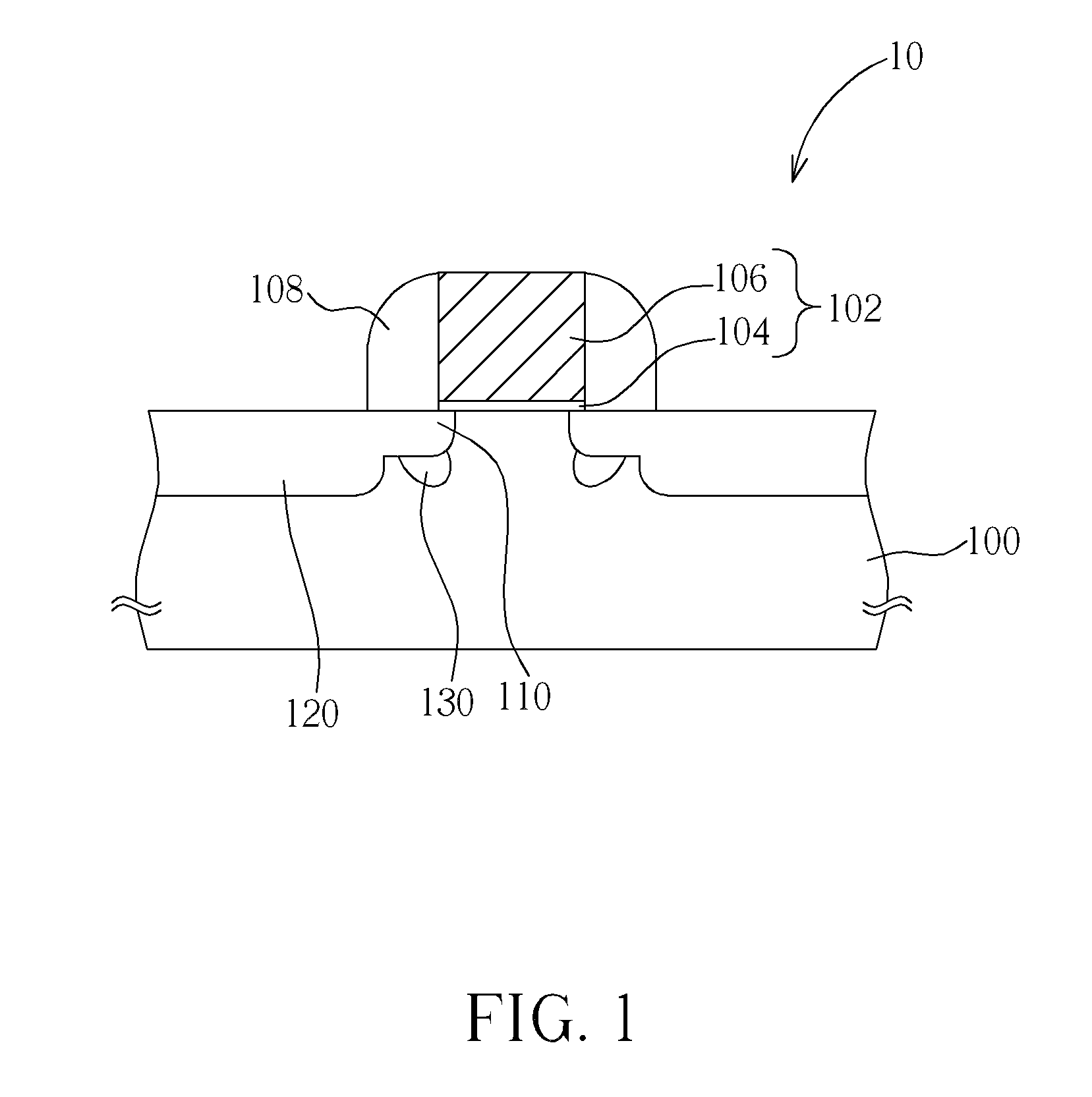

Method for fabricating field-effect transistor

ActiveUS8664073B2TransistorSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

A method for fabricating complimentary metal-oxide-semiconductor field-effect transistor is disclosed. The method includes the steps of: (A) forming a first gate structure and a second gate structure on a substrate; (B) performing a first co-implantation process to define a first type source / drain extension region depth profile in the substrate adjacent to two sides of the first gate structure; (C) forming a first source / drain extension region in the substrate adjacent to the first gate structure; (D) performing a second co-implantation process to define a first pocket region depth profile in the substrate adjacent to two sides of the second gate structure; (E) performing a first pocket implantation process to form a first pocket region adjacent to two sides of the second gate structure.

Owner:MARLIN SEMICON LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com