Method for manufacturing semiconductor element

A technology of semiconductors and components, applied in the field of source/drain regions of complementary metal oxide semiconductor transistors, which can solve the problems of reducing the drive current of PMOS components, easily increasing source/drain resistance, and depleting gate depletion

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The methods for making and using the current commonly used embodiments of the present invention will be described in detail below. The present invention presents many implementable innovative concepts that can be implemented in a wide variety of specific situations. The specific embodiments discussed herein are intended merely to illustrate specific ways to make and practice the invention, and do not limit the invention to the specific scope.

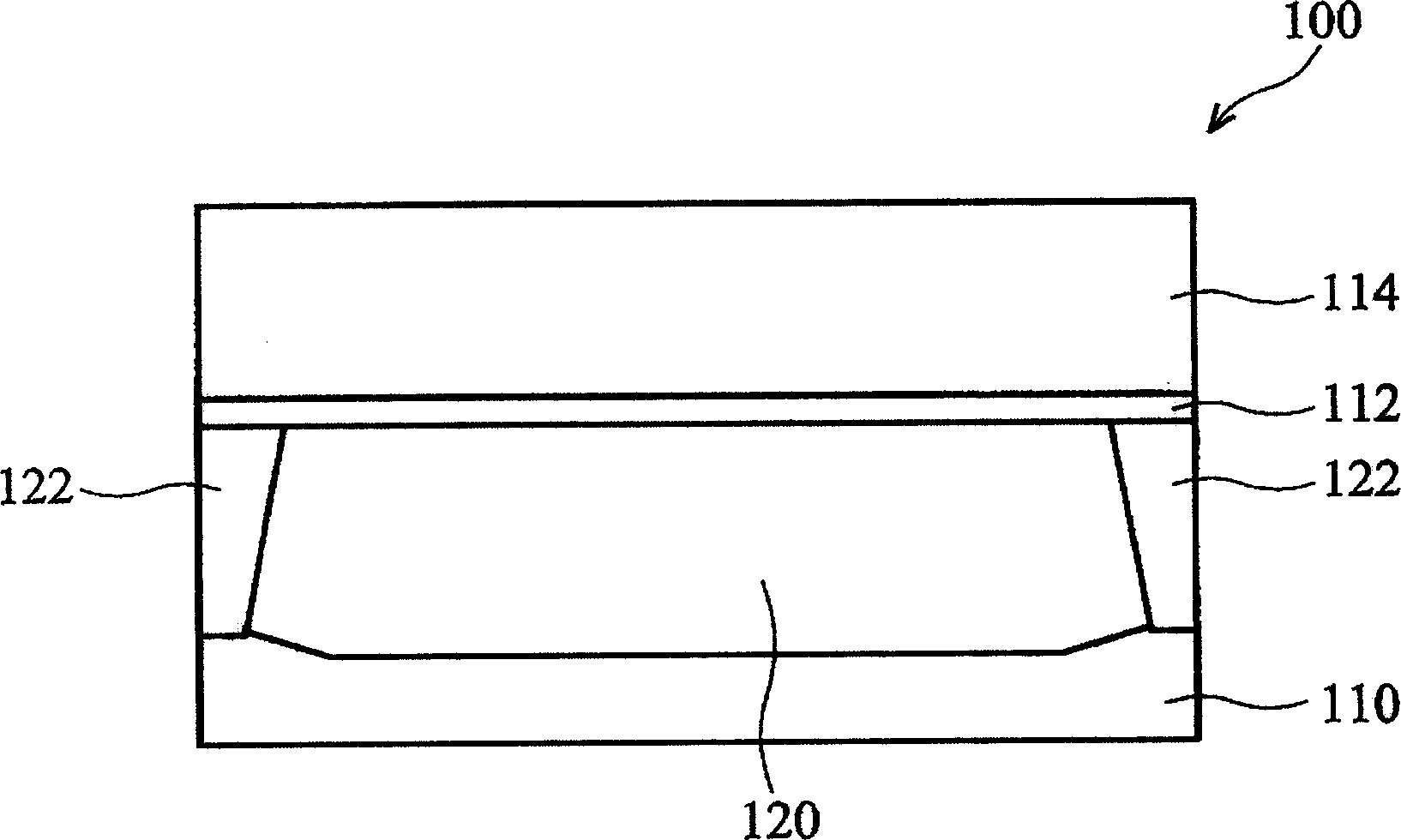

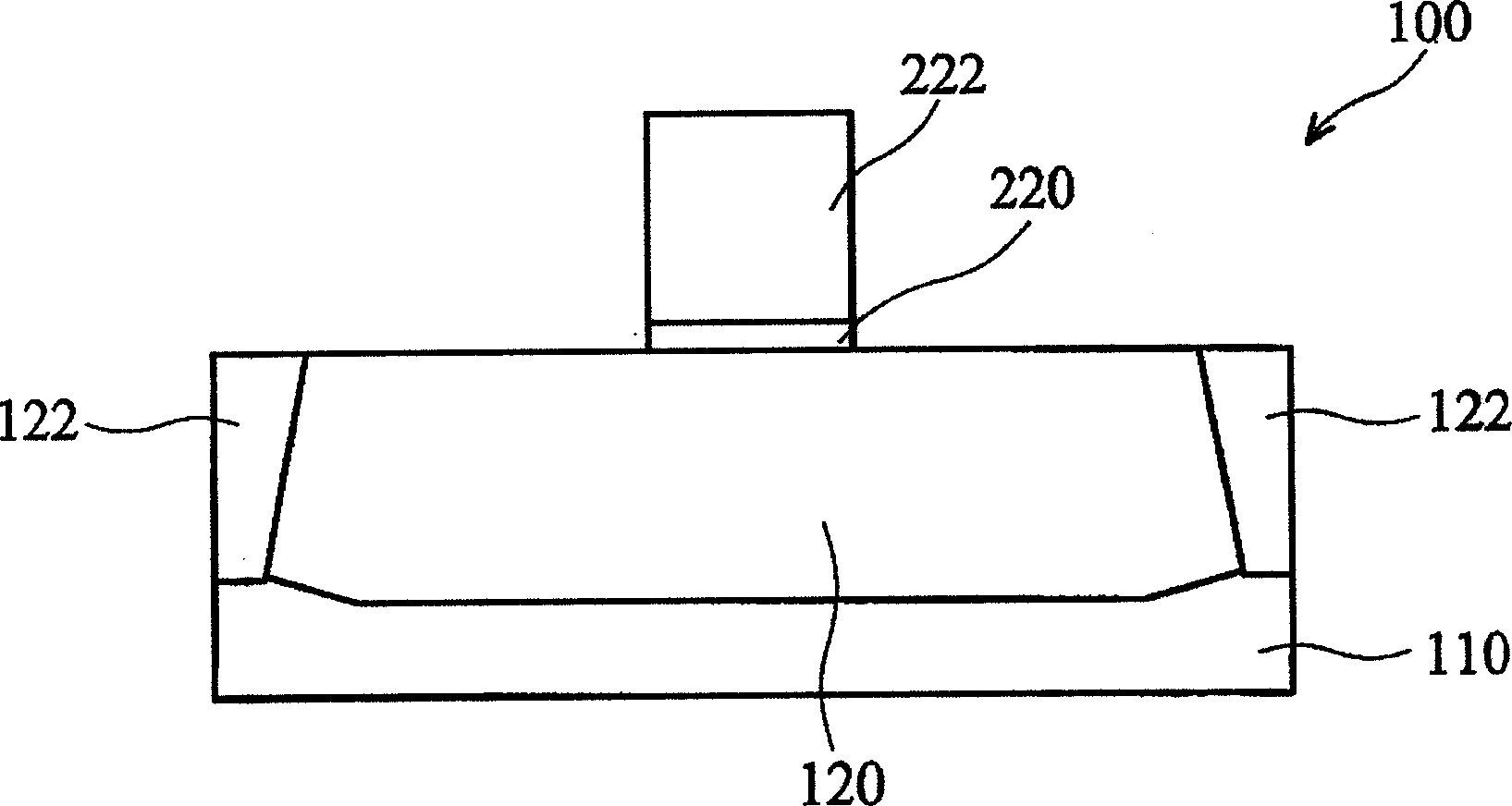

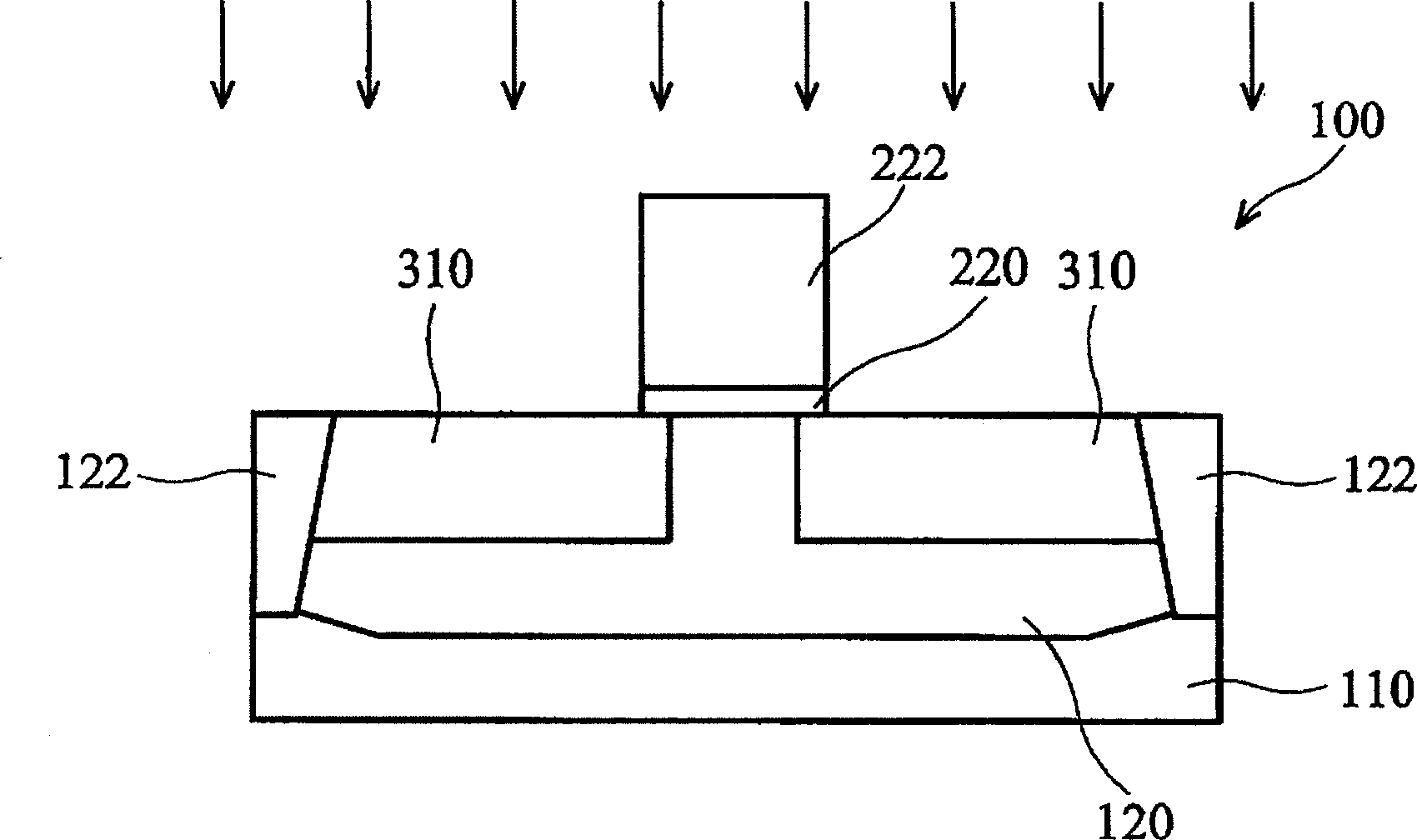

[0043] Figure 1 to Figure 6 An embodiment is described, wherein an amorphization process and a co-implant process are used to fabricate p-type metal oxide semiconductor (PMOS) transistors according to an embodiment of the present invention. Amorphization and simultaneous implantation processes have been found to limit lateral / vertical diffusion of source / drain implants. Therefore, higher dopant concentrations can be used to create shallower source / drain regions while reducing or eliminating short channel effects. For the conv...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com