Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

129 results about "Channel rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

System and method for multiple channel statistical re-multiplexing

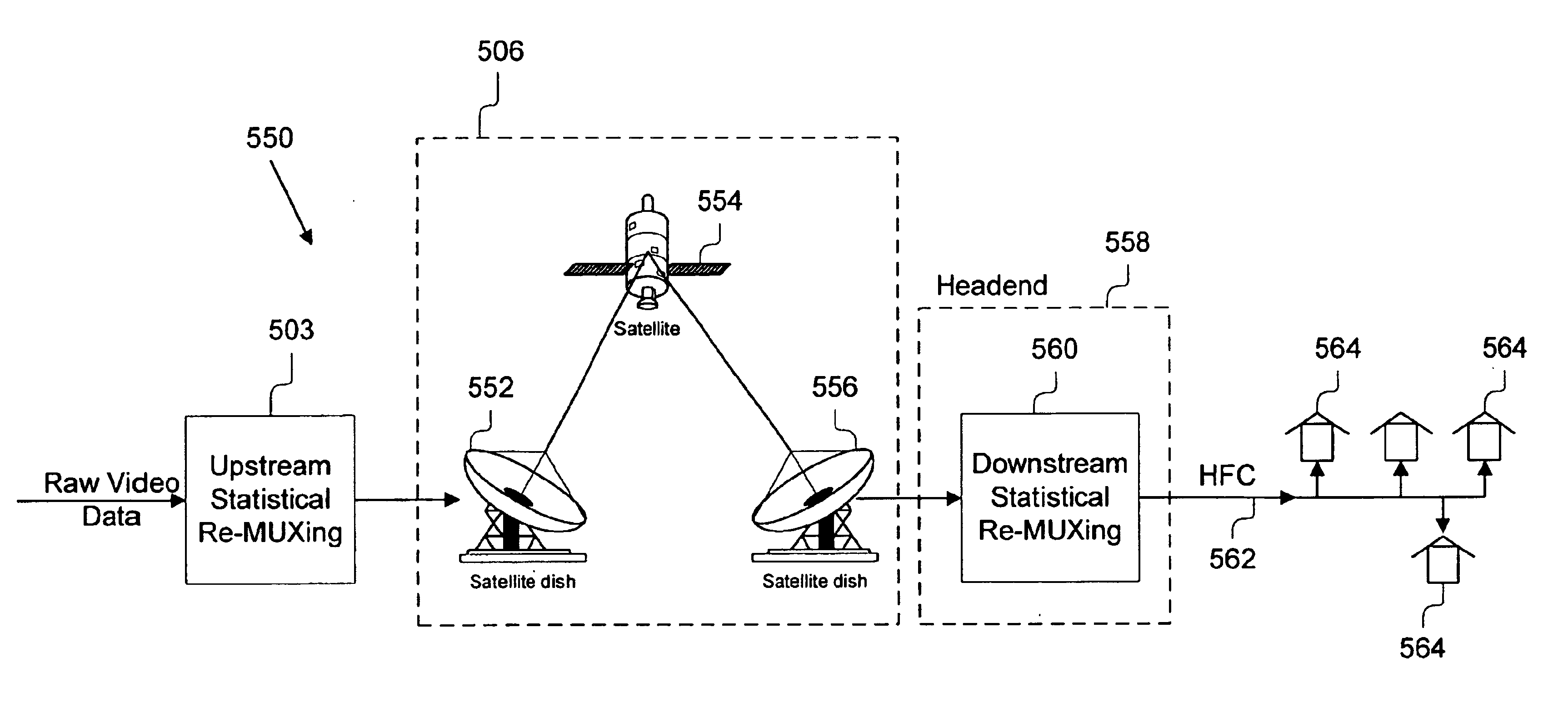

Methods and apparatus are provided for statistical re-multiplexing of multiple channels. Mechanisms are provided to manipulate and / or recode multiple compressed bit streams such that a resulting bit stream has a rate matching adjusted based on the allowable output channel rate. Loss-less transmission of compressed video bit streams can be output in real-time. In one example, the system includes encoders and demultiplexers on multiple channels. The demultiplexers are connected to a scheduler and multiplexer to provide an output bit stream at a given channel rate.

Owner:CISCO TECH INC

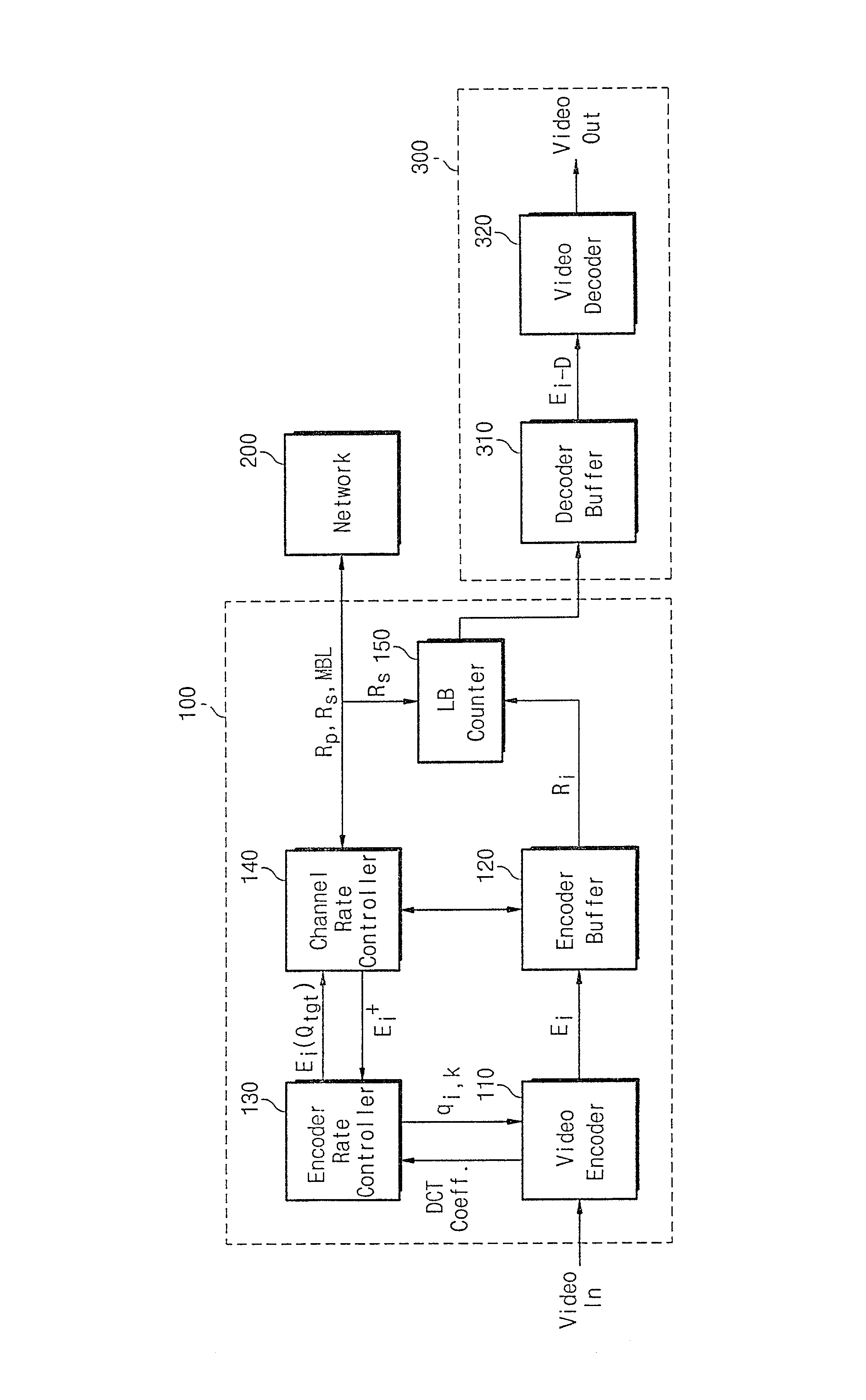

System for real time transmission of variable bit rate MPEG video traffic with consistent quality

InactiveUS20020090029A1Quality improvementPicture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningReal time transmissionTransmission system

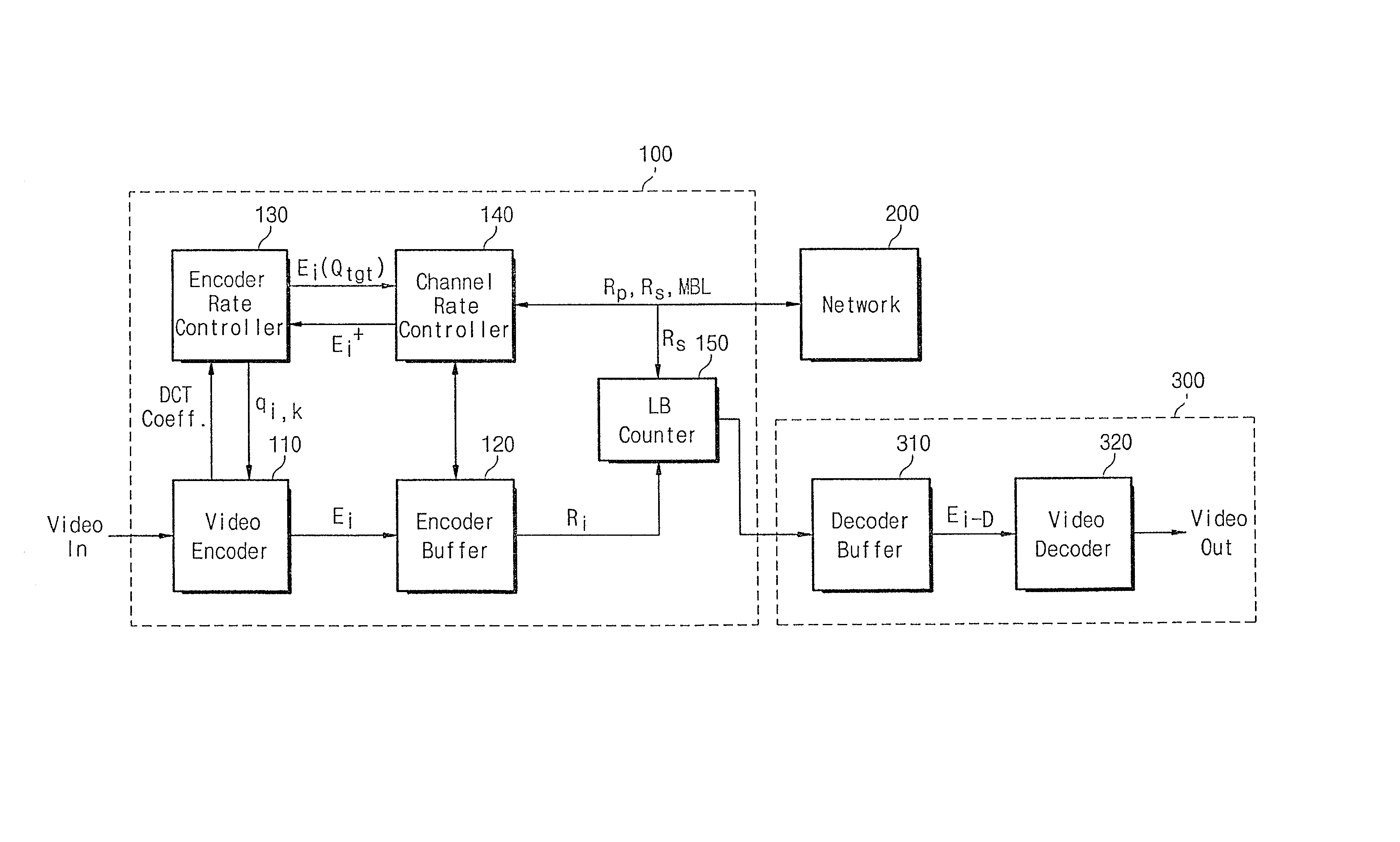

A system and method for real time transmission of variable bit rate MPEG video traffic with consistent quality, wherein each frame is encoded with quantization parameter generated from an encoder rate controller, and encoded data is transmitted to an encoder buffer. Transmission rate about each frame interval is determined by a channel rate controller at the beginning of the frame interval. Data transmission buffered at the encoder buffer is first regulated by Leaky Bucket counter, and the regulated data is transferred to a decoder buffer in a video receiving system through network. The encoder rate controller and channel rate controller included in the VBR video transmission system control the transmission rate generated from the video encoder and that from the network with satisfying imposed constrained conditions, respectively.

Owner:SAMSUNG ELECTRONICS CO LTD

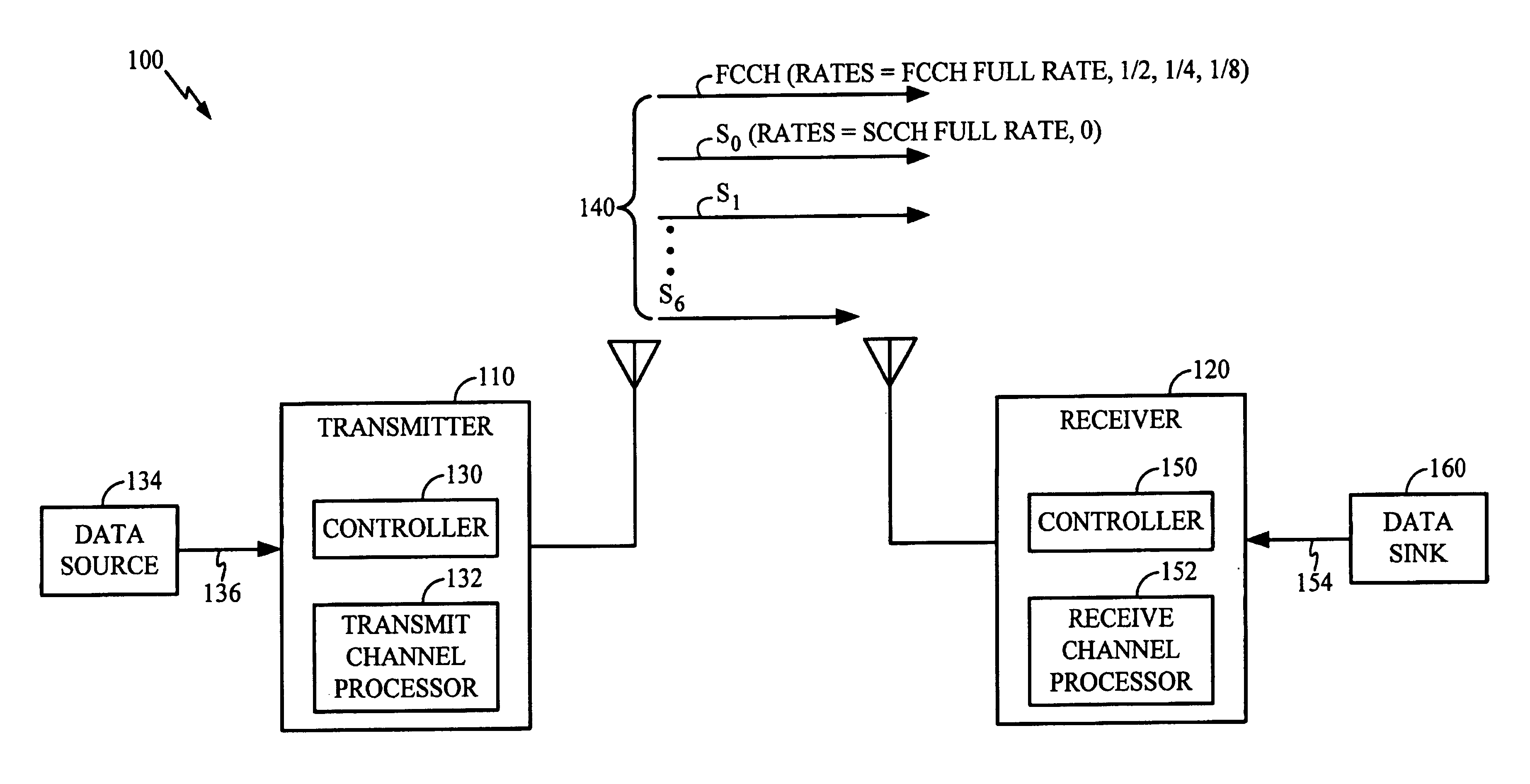

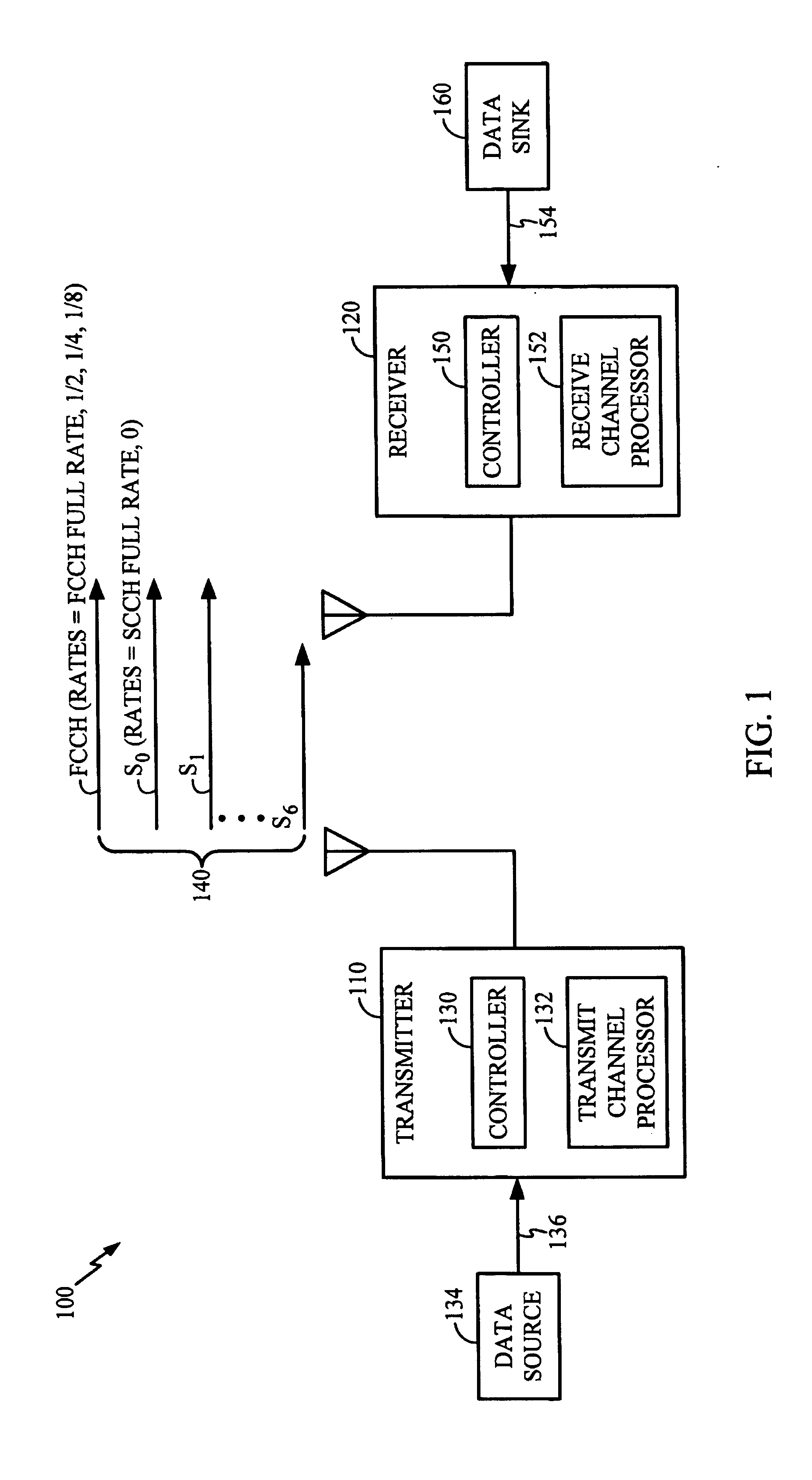

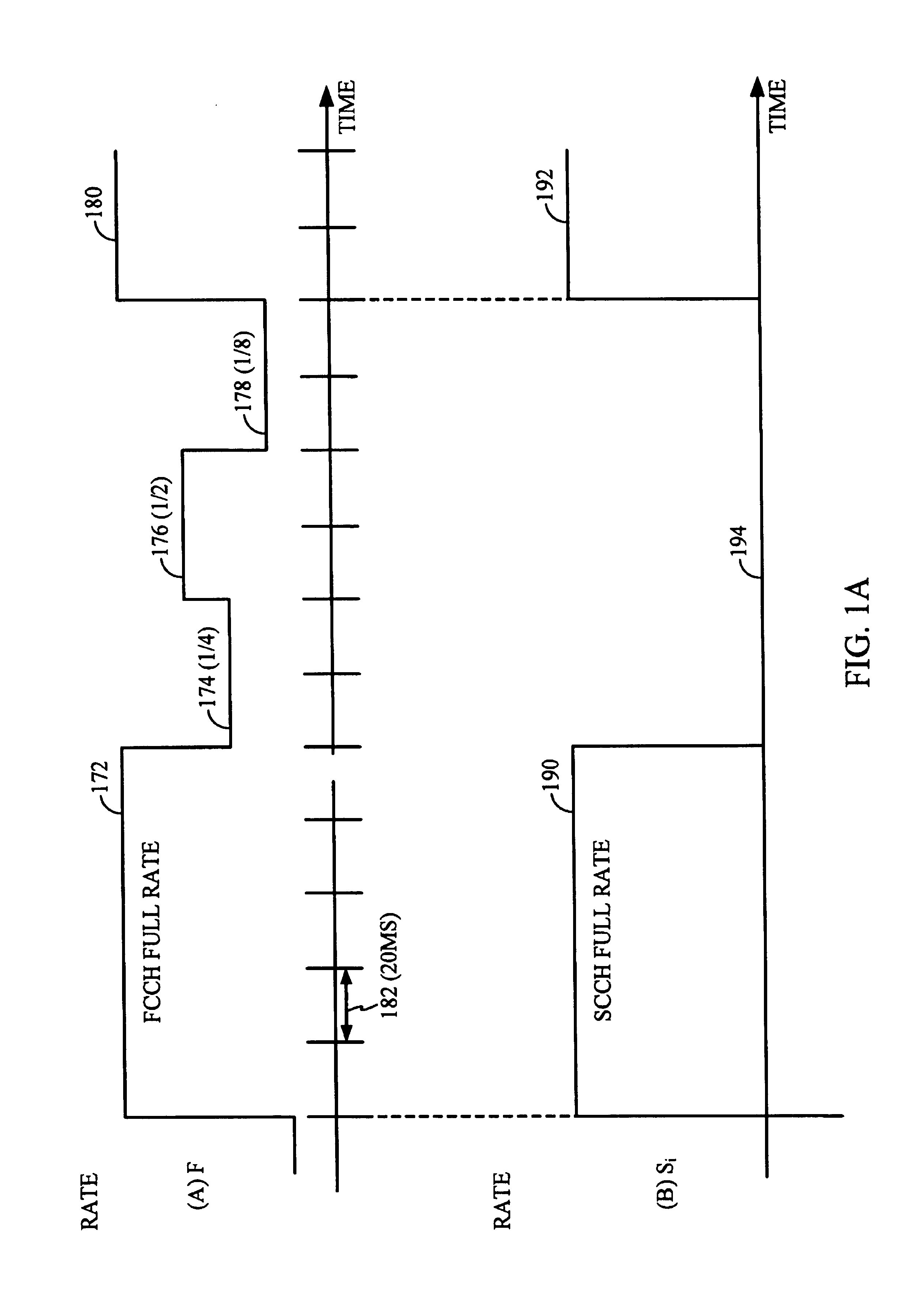

Method and apparatus for IS-95B reverse link supplemental code channel frame validation and fundamental code channel rate decision improvement

InactiveUS6975868B2Accurately determineReduce invalid dataNetwork traffic/resource managementRadio/inductive link selection arrangementsTransmission protocolCommunications system

The present invention provides a method and apparatus for maximizing throughput of a data call in a wireless communication system in which data is transmitted from a wireless station, such as a mobile station, on multiple assigned channels in accordance with a known transmission standard, such as IS-95B. The multiple assigned channels include a fundamental channel and at least one supplemental channel. Data is formatted into variable rate data frames and transmitted on the fundamental channel and the supplemental channel. A wireless receiver, such as a base station, receives the multiple assigned channels. The wireless receiver demodulates and decodes data frames associated with each of the multiple assigned channels. The wireless receiver determines a likely initial data rate for each demodulated and decode data frame. The wireless receiver correlates all of the likely data rates, by comparison to one another and to a relevant transmission protocol standard, to determine a maximum likelihood combination of data rates. The maximum likelihood combination of data rates includes a maximum likelihood data rate corresponding to each likely data rate. Decoded data frames are invalidated and erased when the likely data frame rates do not match corresponding maximum likelihood data rates.

Owner:QUALCOMM INC

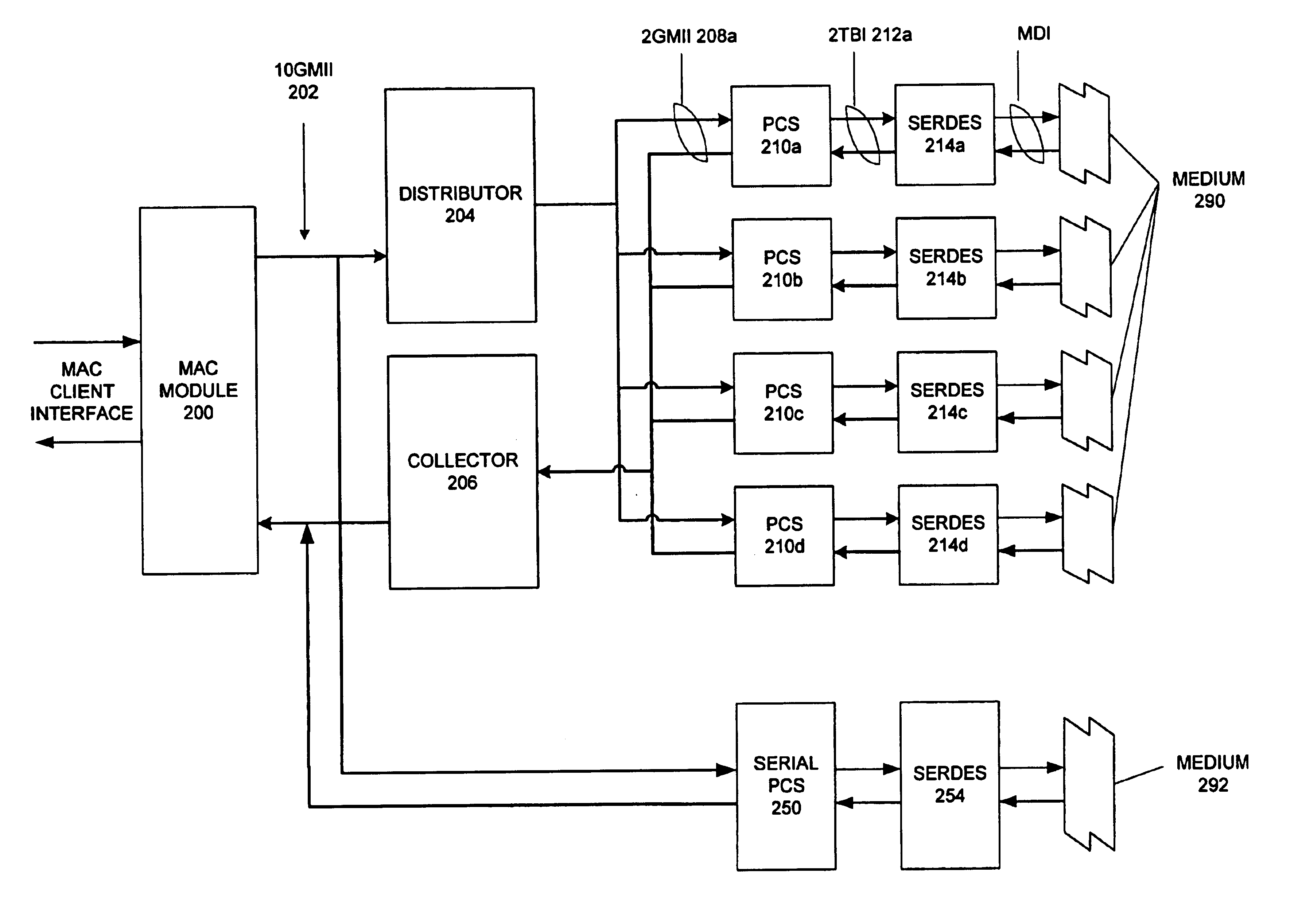

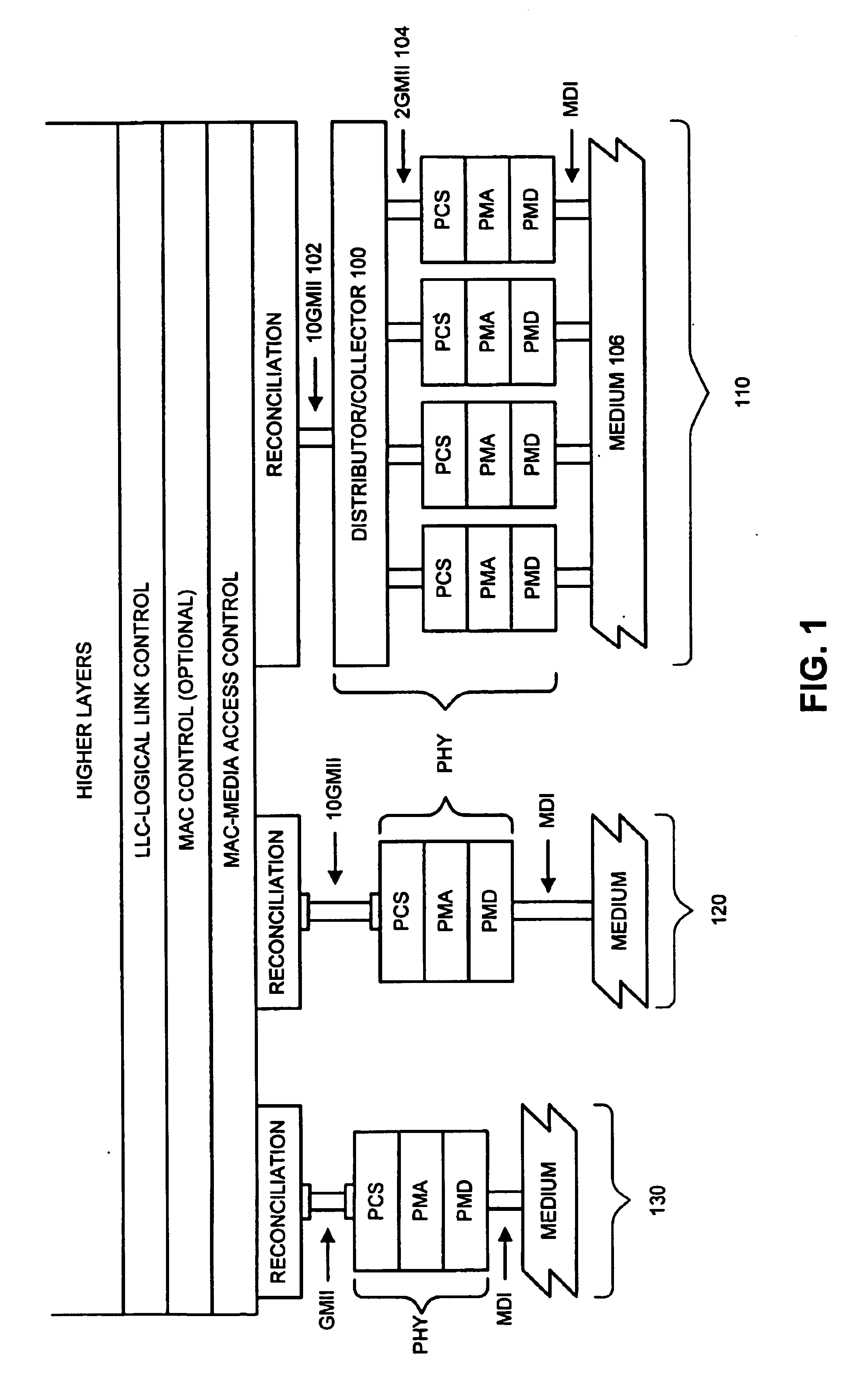

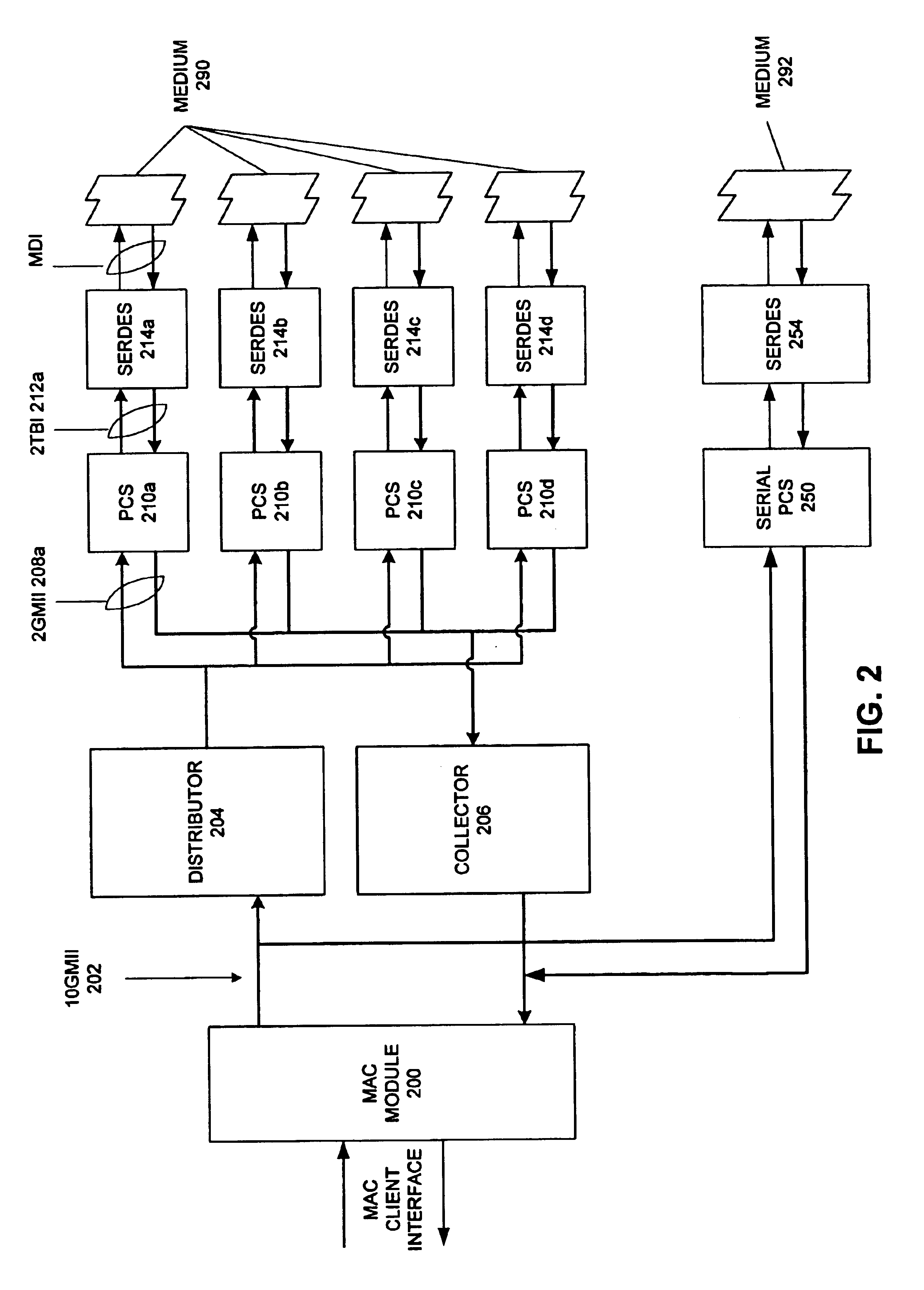

Method and apparatus for a multi-gigabit ethernet architecture

InactiveUS6873630B1Communication speed be lowerTime-division multiplexNetwork connectionsMultiplexingPropagation delay

An Ethernet architecture is provided for connecting a computer system or other network entity to a dedicated Ethernet network medium. The network interface enables the transmission and receipt of data by striping individual Ethernet frames across a plurality of logical channels and may thus operate at substantially the sum of the individual channel rates. Each channel may be conveyed by a separate conductor (e.g., in a bundle) or the channels may be carried simultaneously on a shared medium (e.g., an electrical or optical conductor that employs a form of multiplexing). On a sending station, a distributor within the sender's network interface receives Ethernet frames (e.g., from a MAC) and distributes frame bytes in a round-robin fashion on the plurality of channels. Each “mini-frame” is separately framed and encoded for transmission across its channel. On a receiving station, the receiver's network interface includes a collector for collecting the multiple mini-frames (e.g., after decoding) and reconstructing the frame's byte stream (e.g., for transfer to the receiver's MAC). The first and last bytes of each frame and mini-frame are marked for ease of recognition. Multiple unique idle symbols may be employed for transmission during inter-packet gaps to facilitate the collector's synchronization of the multiple channels and / or enhance error detection. A maximum channel skew is specified, and each received channel may be buffered with an elasticity that is proportional to the maximum skew so that significant propagation delay may be encountered between channels without disrupting communications.

Owner:ORACLE INT CORP

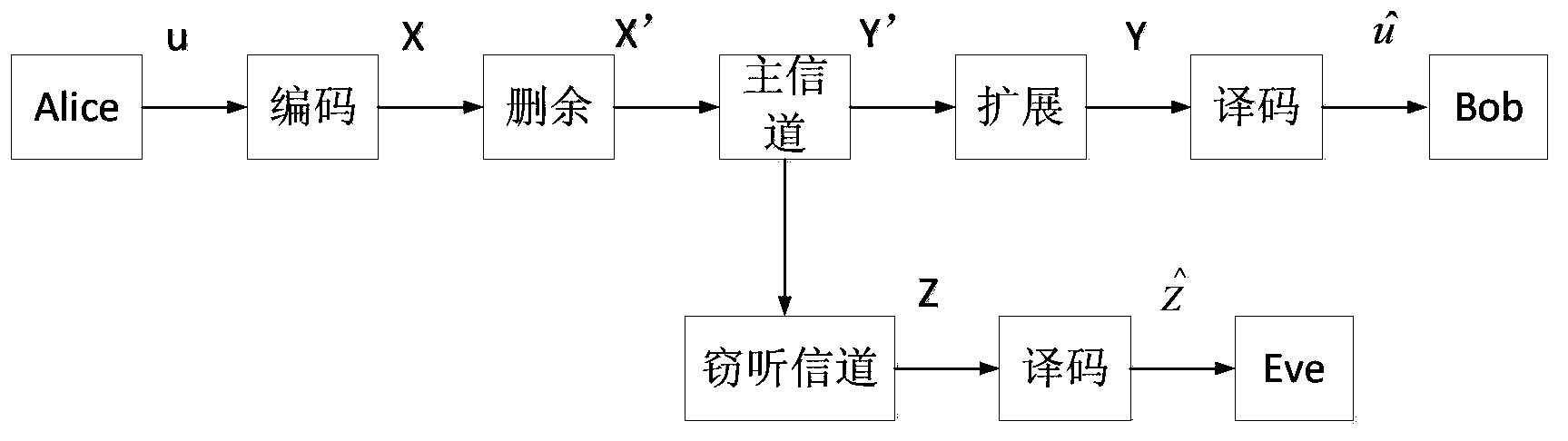

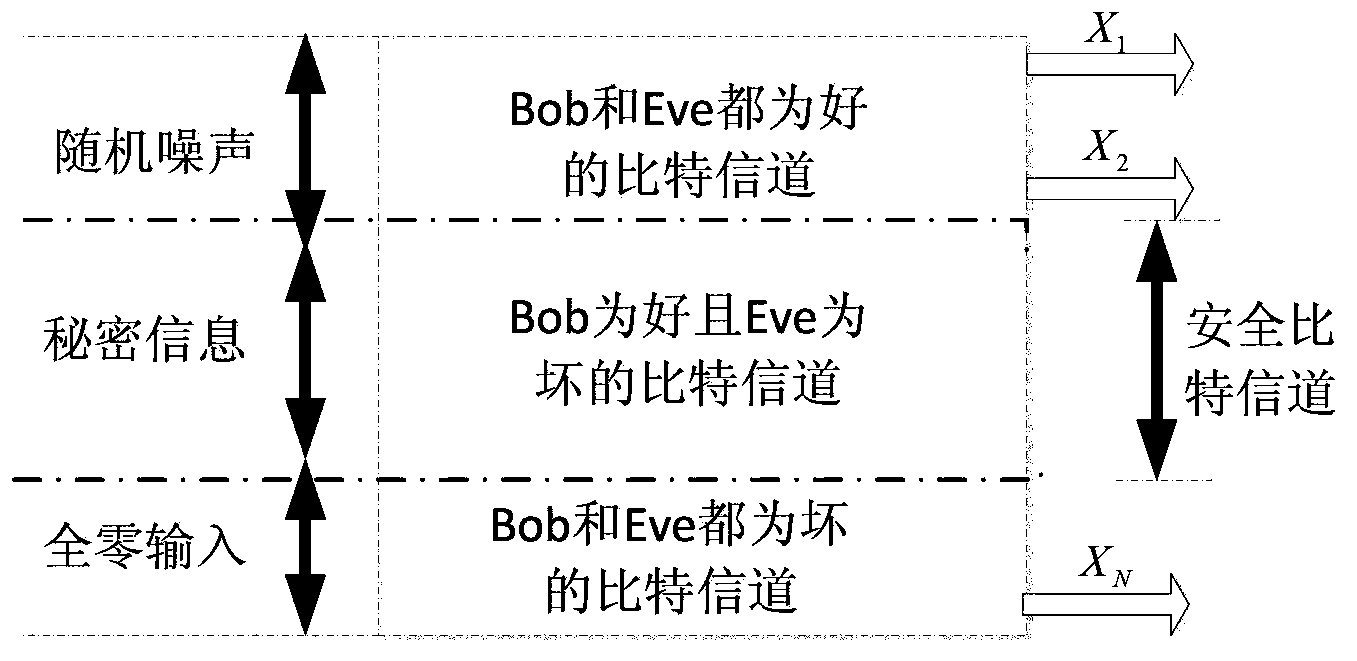

Degraded eavesdropping channel rate compatible method based on Polar code

InactiveCN103414540AIncrease safety capacityEnsure safetyError preventionEavesdroppingComputer science

The invention discloses a degraded eavesdropping channel rate compatible method based on a punctured Polar code. According to the method, the punctured Polar code is combined with a degraded eavesdropping channel model; according to construction features of the Polar code, a safe bit-channel used for transmitting information is given; according to channel rate requirements of a degraded eavesdropping channel, a proper puncturing matrix is built, and the degraded eavesdropping channel rate compatible method based on the Polar code is achieved; because eavesdroppers do not know the puncturing matrix, the coded code word length is reduced through puncturing operation, information is hidden through the puncturing operation, the complexity that the eavesdroppers recover original information through code words received through wiretapping is increased, and system safety is guaranteed; furthermore, the puncturing method ensures that all codes in the same group of rate-compatible codes can be achieved through the same group of encoders, and therefore the complexity of emitters and receivers is greatly reduced.

Owner:NANJING UNIV OF POSTS & TELECOMM

Source and channel rate adaptation for VoIP

A coding system and method for a terminal including a multi-rate codec is disclosed. The terminal includes a multi-rate adaptive coder that is capable of transmitting a continuous voice stream transmission at a source code bit rate and a channel code bit rate. A quality of service probing module probes an end-to-end network path of the continuous voice stream transmission to obtain at least one quality of service parameter. A quality of service management module determines at least one constraint associated with the continuous voice stream transmission. An adaptive bit rate algorithm module dynamically adjusts the source code bit rate and the channel code bit rate as a function of the quality of service parameter and the constraint to obtain a maximum value of perceived user performance during the continuous voice stream transmission.

Owner:NTT DOCOMO INC

Packet communication apparatus

InactiveUS20060176862A1Error prevention/detection by using return channelFrequency-division multiplex detailsPacket communicationTimer

Mobile terminal 100 has: operator 251 that calculates the generation interval of ACK packets based on the size of the ACK packet that is to be transmitted and the channel rate of the transmitting channel, held in controller 250; delay ACK timer 223 that repeats counting the calculated ACK packet generation interval as one period and outputs an expiration signal every time the one period expires; and data packet receiver 221 that, every time the expiration signal is input, generates an ACK packet containing the latest reception confirmation information relating to data packets received while the expiration signal was being received, and transmits the ACK packet to transmission buffer 240 via IP section 210.

Owner:PANASONIC CORP

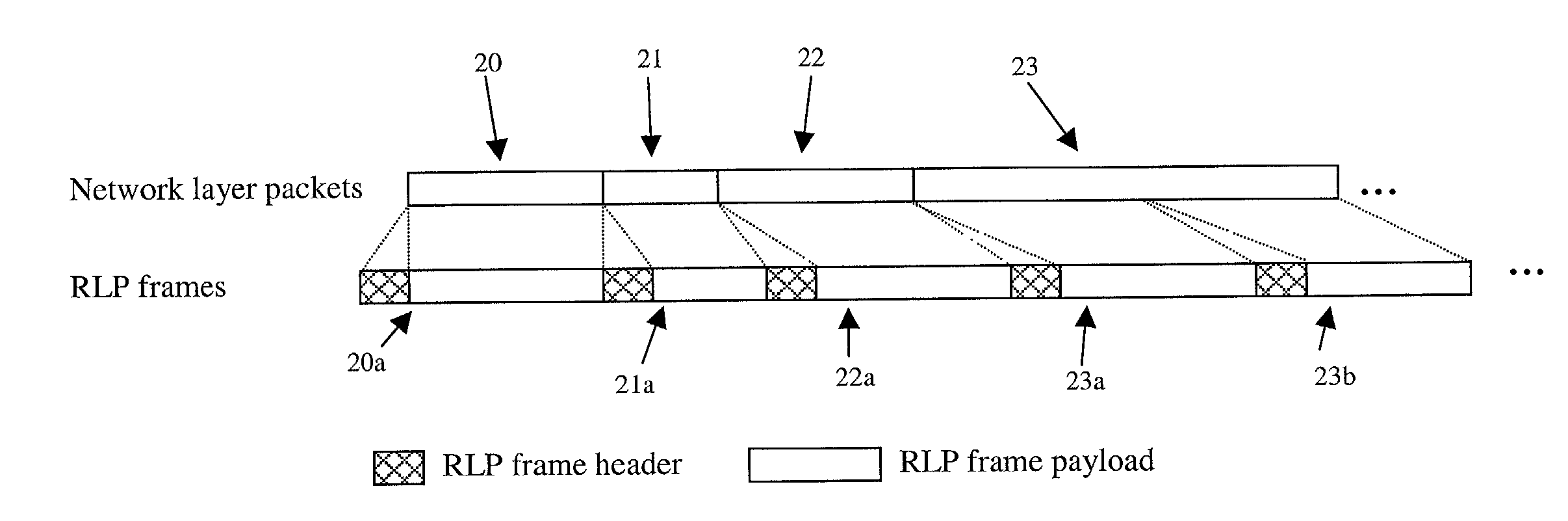

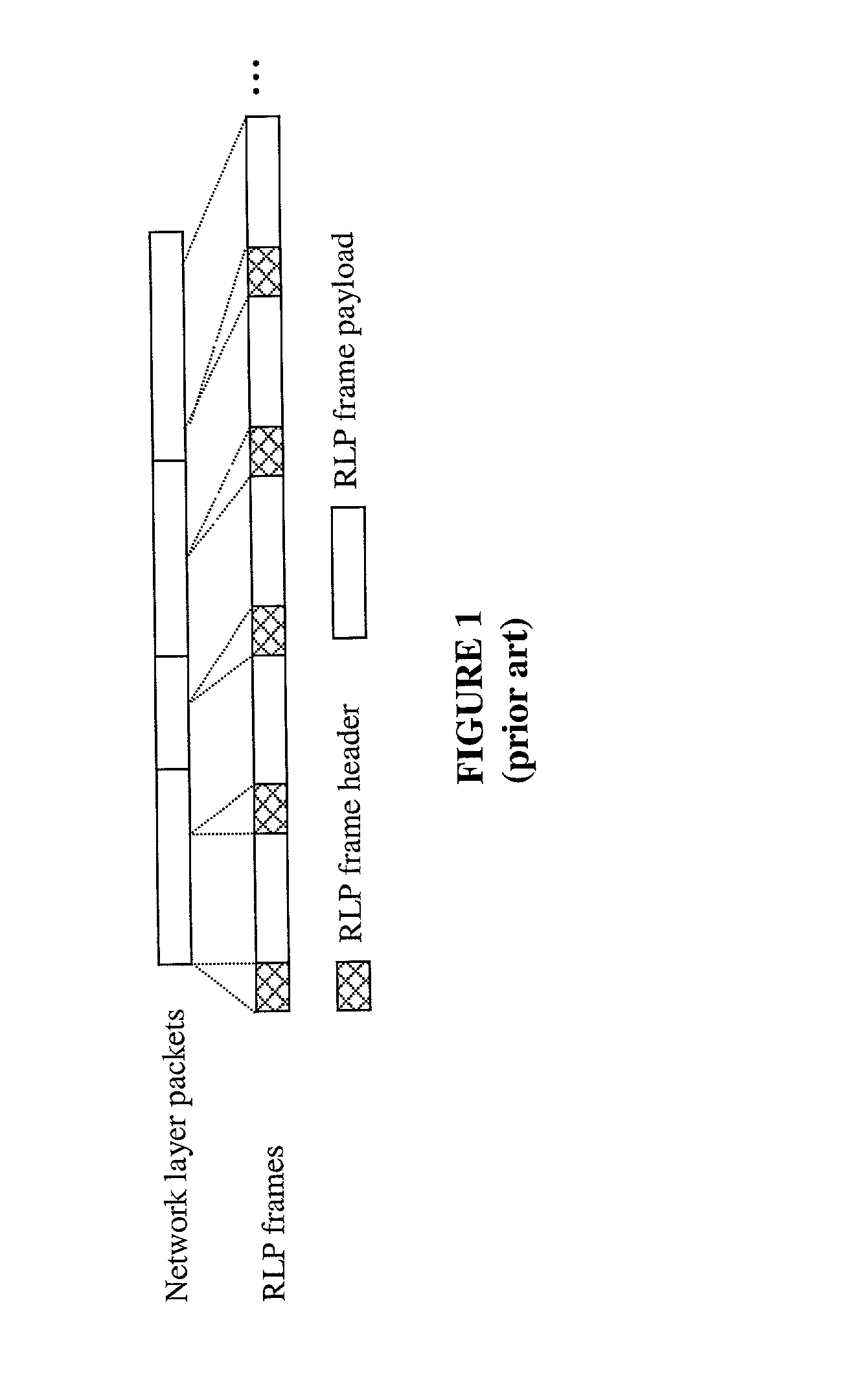

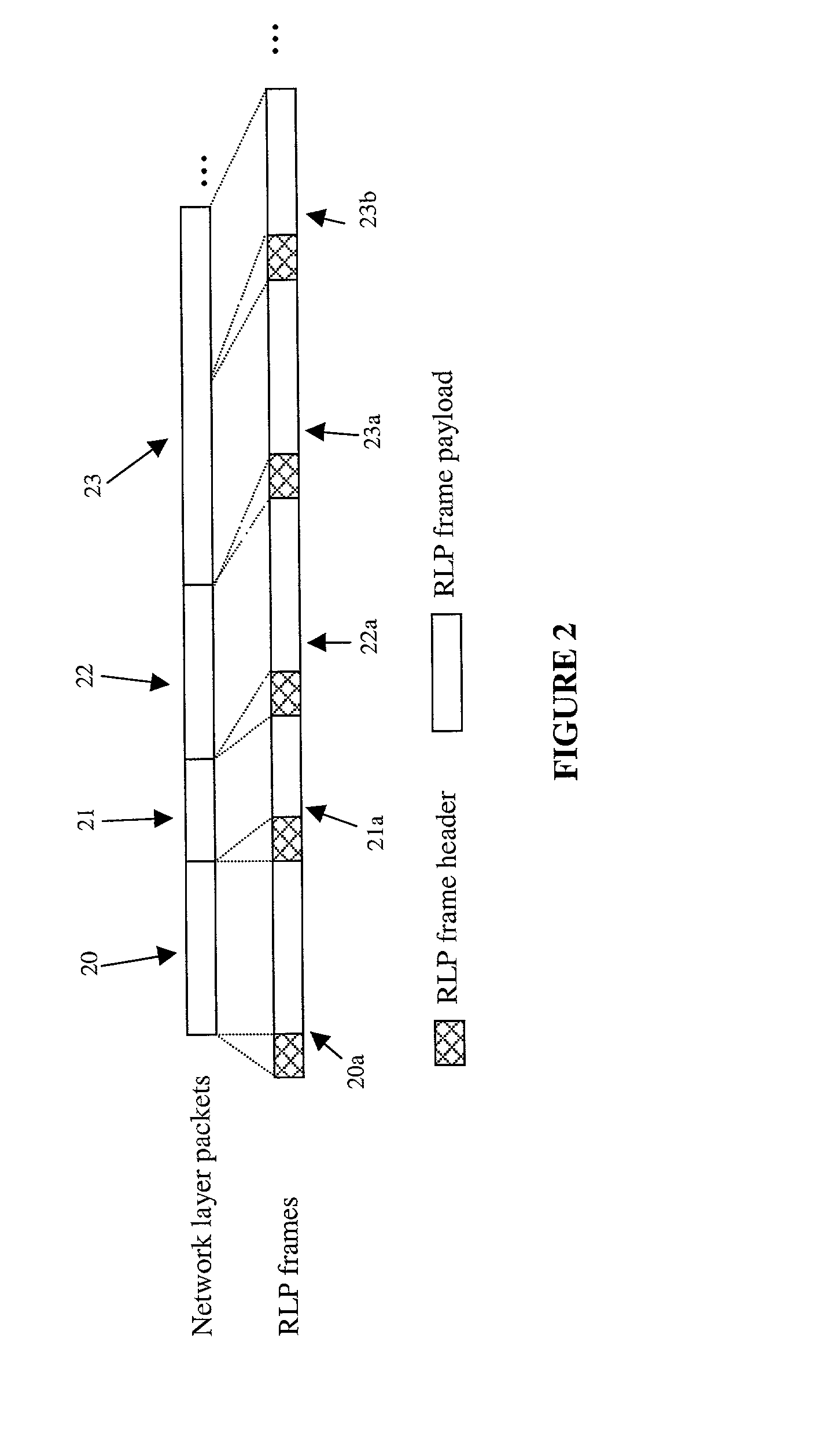

Network layer protocol aware link layer

InactiveUS7085291B2Enhances conventional RLP designResolution problemError prevention/detection by using return channelNetwork traffic/resource managementAccess networkWireless mesh network

An enhanced radio link protocol (RLP) in a wireless access network that is network aware is disclosed. The RLP increases radio link quality by various ARQ mechanisms. The RLP framing structure is included that supports and enables at least network layer packet boundary detection, dynamic and adaptive ARO schemes for QoS support on a per-packet basis, and a flexible RLP frame structure for fast adaptation to physical layer channel rate / RLP frame sizes. Optional uses include supporting negative acknowledgment (NAK) based ARQ.

Owner:APPLE INC

Fast flow control methods for communication networks

InactiveUS7221653B2Reduce distractionsMaximize capacityError preventionNetwork traffic/resource managementTraffic capacityLink data

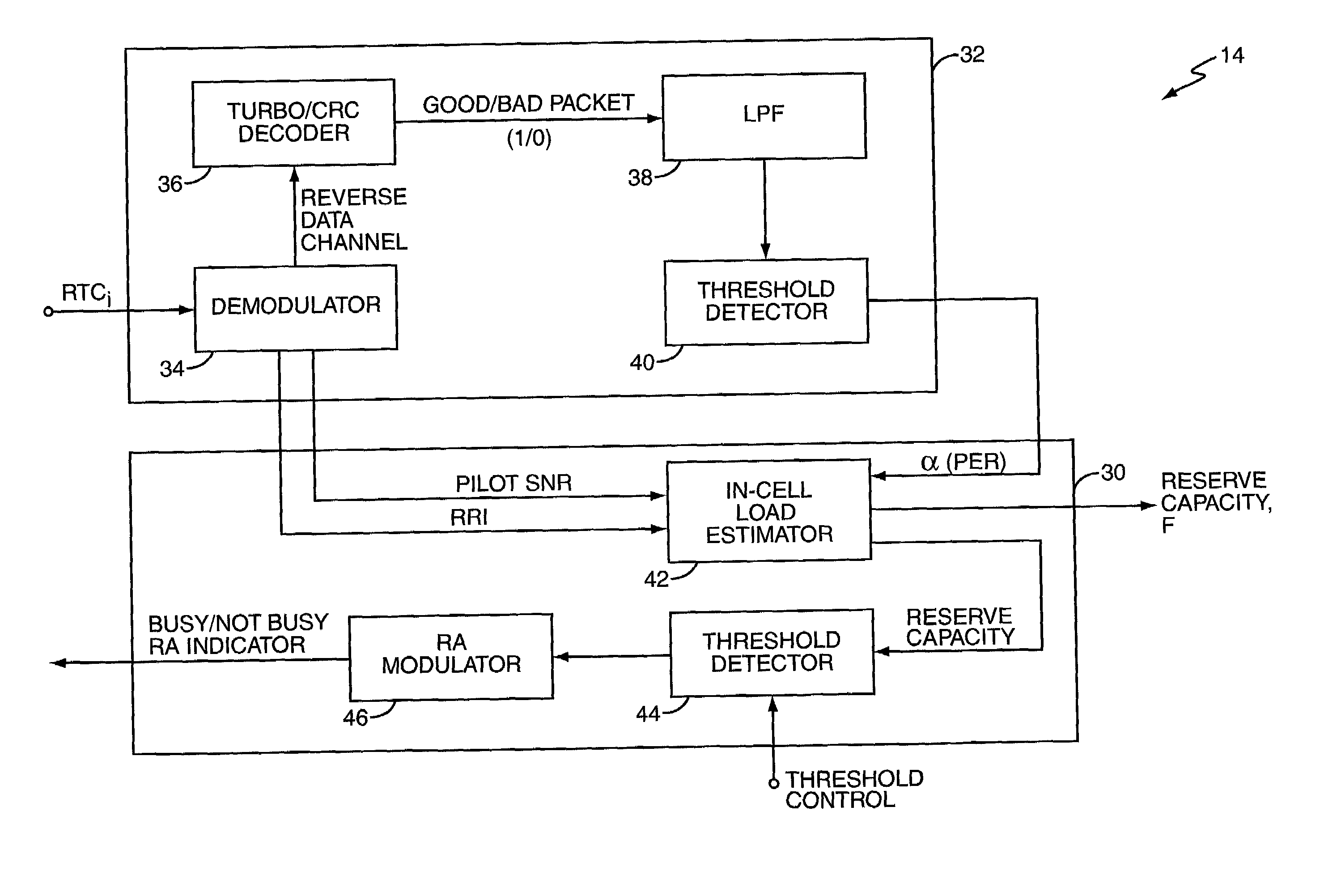

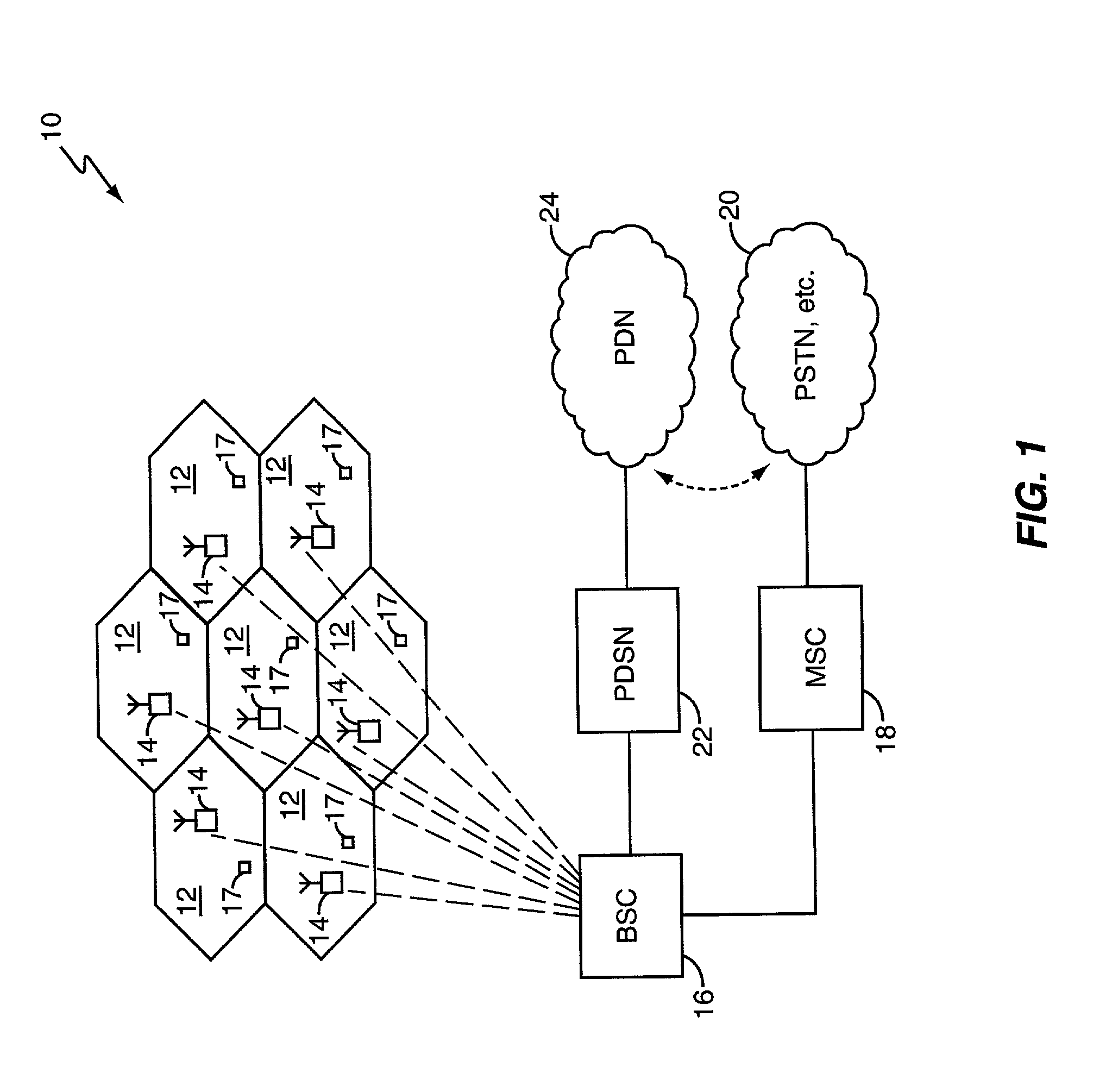

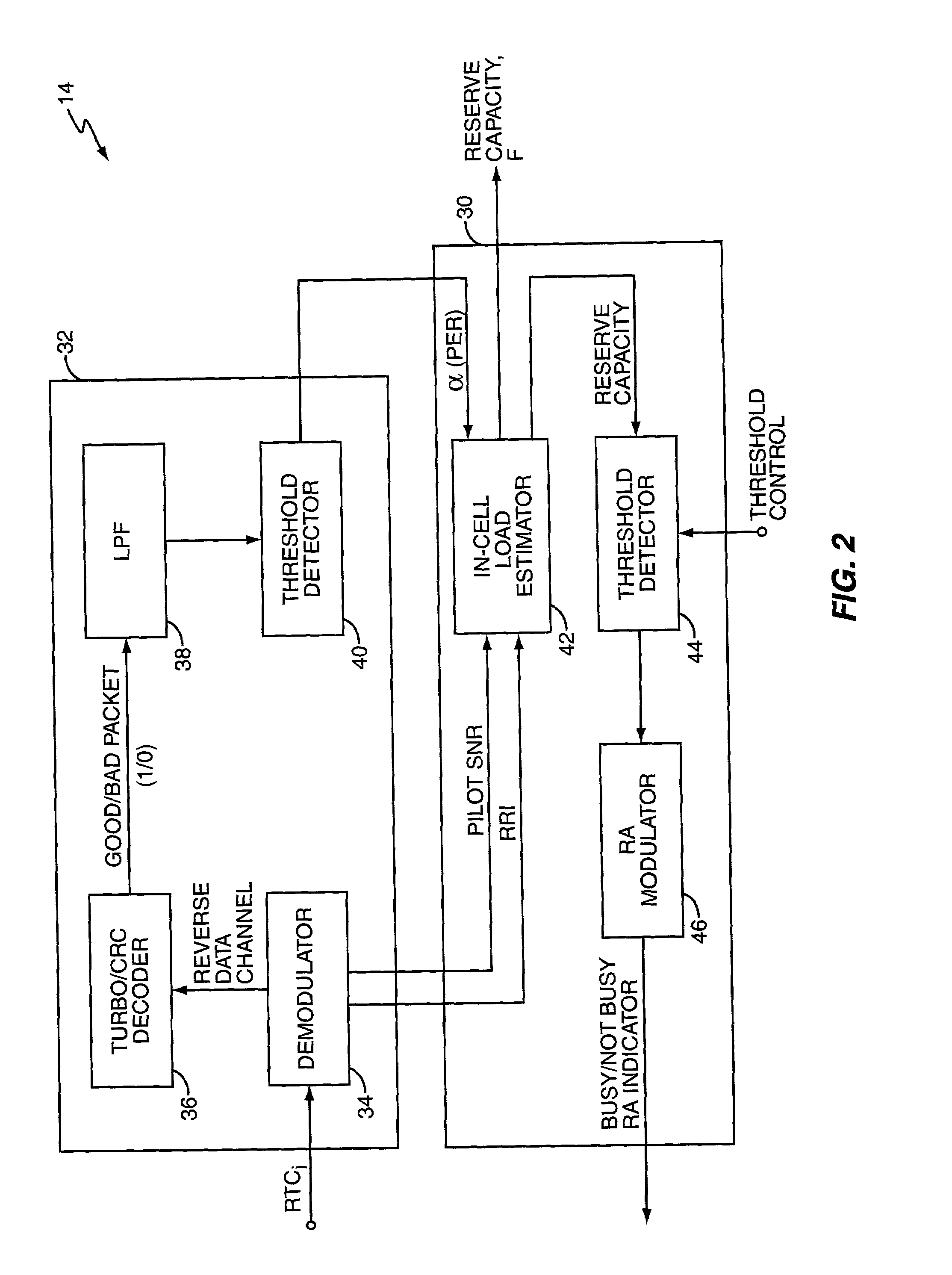

Reverse link flow control in a high data rate network determines current reverse link data channel rates for access terminals served by a network sector to identify corresponding defined channel gains, which are used to rapidly and reliably estimate total sector interference on the reverse link. Total sector interference indicates reverse link capacity utilization, and when remaining capacity approaches a defined threshold, the sector sets an activity indicator to a busy state indicating reverse link congestion. This action causes at least some access terminals to reduce their reverse link data channel rate. Interference calculation techniques preferably involve baseband digital processing using defined channel gains, permitting rapid evaluation of reverse link capacity and quick, reliable activity indicator updating, which increases reverse link capacity utilization. These techniques may be applied to inter-sector control, wherein the reverse activity indicator status for one sector depends on interference in one or more other sectors.

Owner:OPTIS WIRELESS TECH LLC

System and method for implementing an end-to-end error-correcting protocol in a voice band data relay system

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

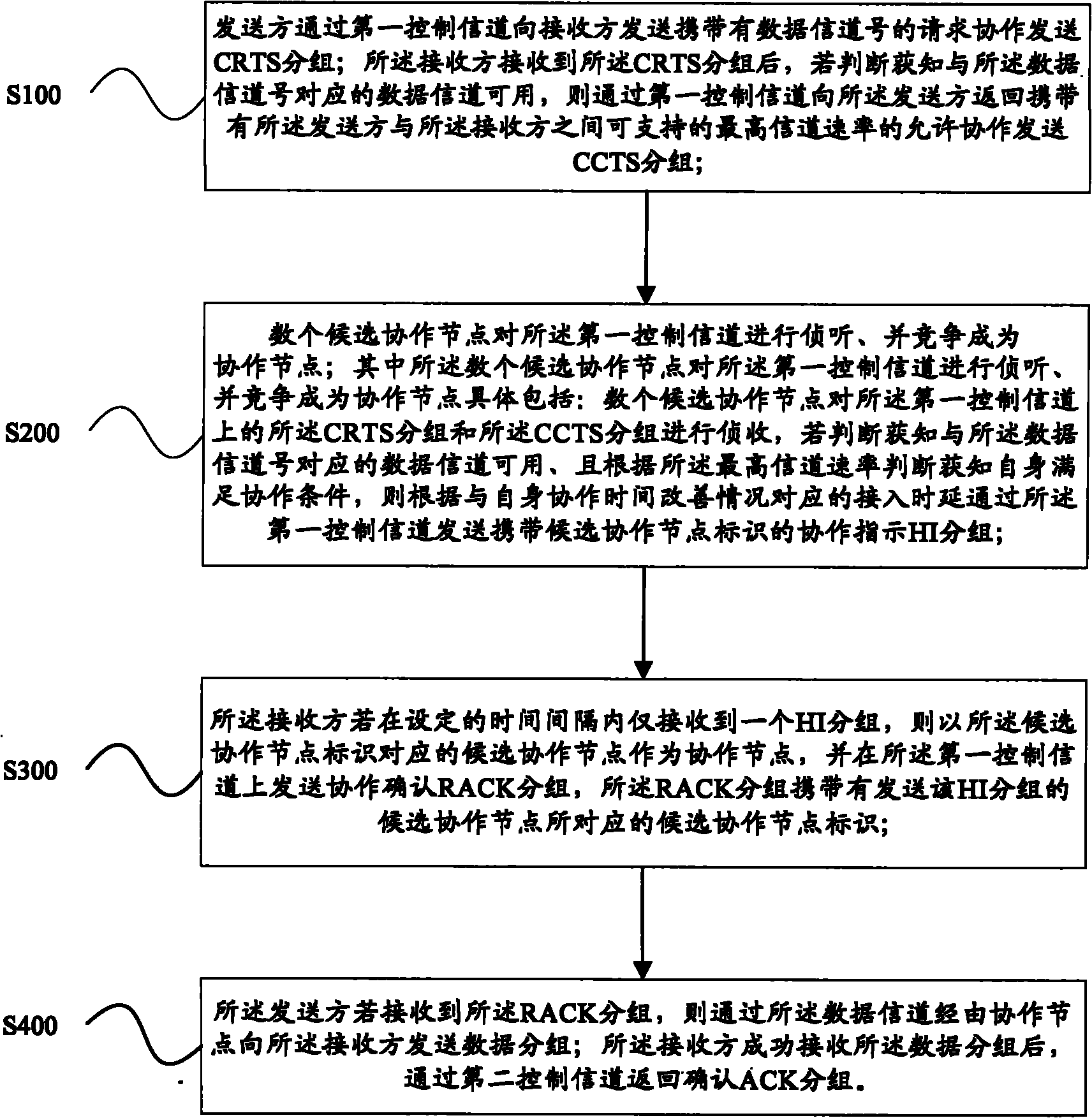

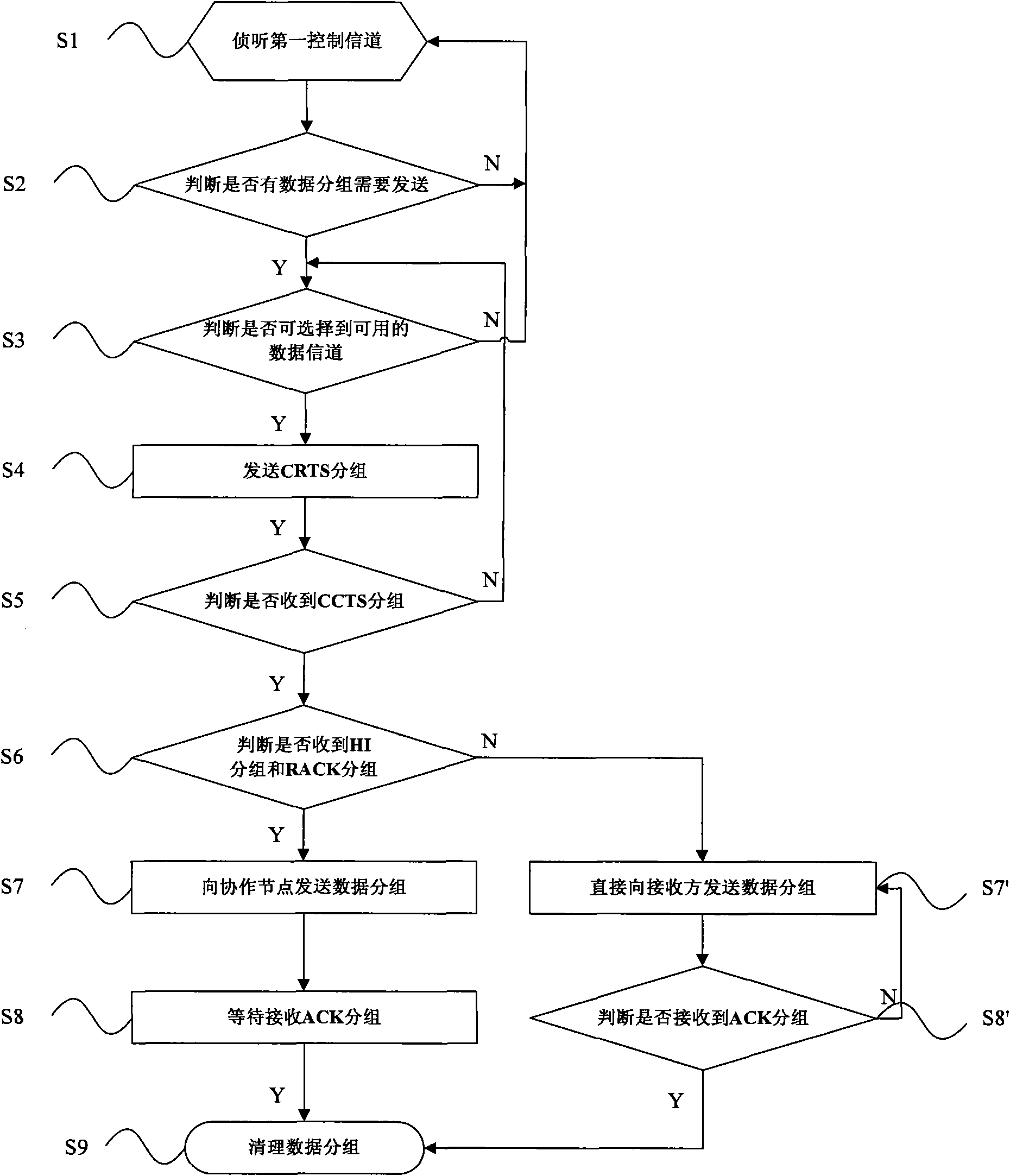

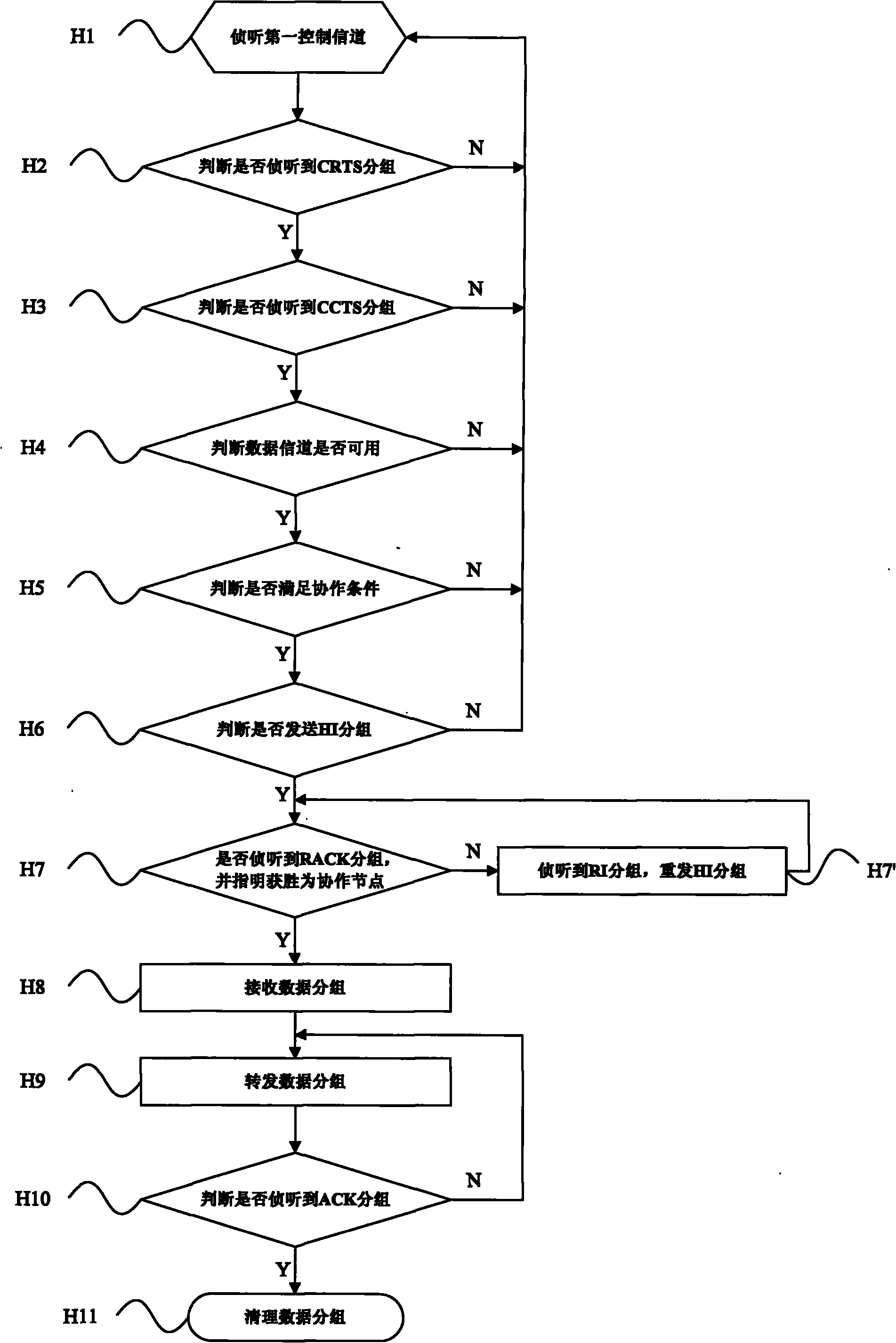

Multichannel cooperative data transmission method and system

InactiveCN102006630AIncrease profitImprove accuracyNetwork traffic/resource managementError prevention/detection by transmission repeatClear to sendAccess time

The invention discloses a multichannel cooperative data transmission method and system. The method of the invention comprises the following steps: a sender sends a cooperative request-to-send (CRTS) packet carrying a data channel number to a receiver through a first control channel; after the receiver receives the CRTS packet, if the acquired data channel is judged to be usable, the receiver returns a conditional clear-to-send (CCTS) packet carrying the highest channel rate between the receiver and the sender to the sender; a candidate cooperative node intercepts the CRTS packet and the CCTS packet, and if the acquired data channel is judged to be usable and the cooperation condition is met, the candidate cooperative node sends a high (HI) packet according to access time delay; if the receiver only receives the HI packet, the receiver sends a relay acknowledgement (RACK) packet on the first control channel to disclose the cooperative node; if the sender receives the RACK packet, the sender sends a data packet to the receiver through the cooperative node; and after the receiver successfully receives the data packet, the receiver returns an acknowledgement packet through a second control channel. The invention can be used to realize efficient and reliable data transmission.

Owner:BEIHANG UNIV

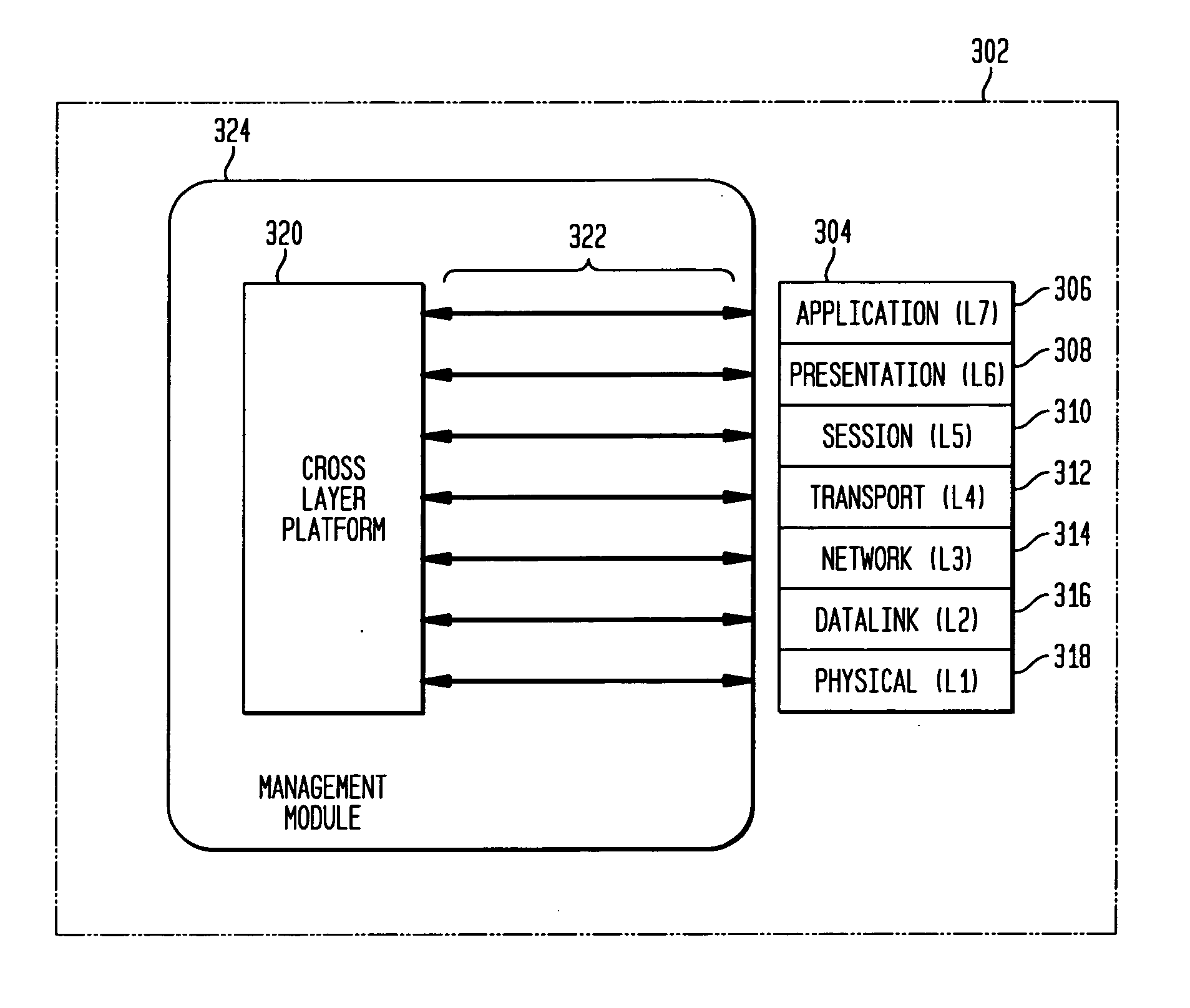

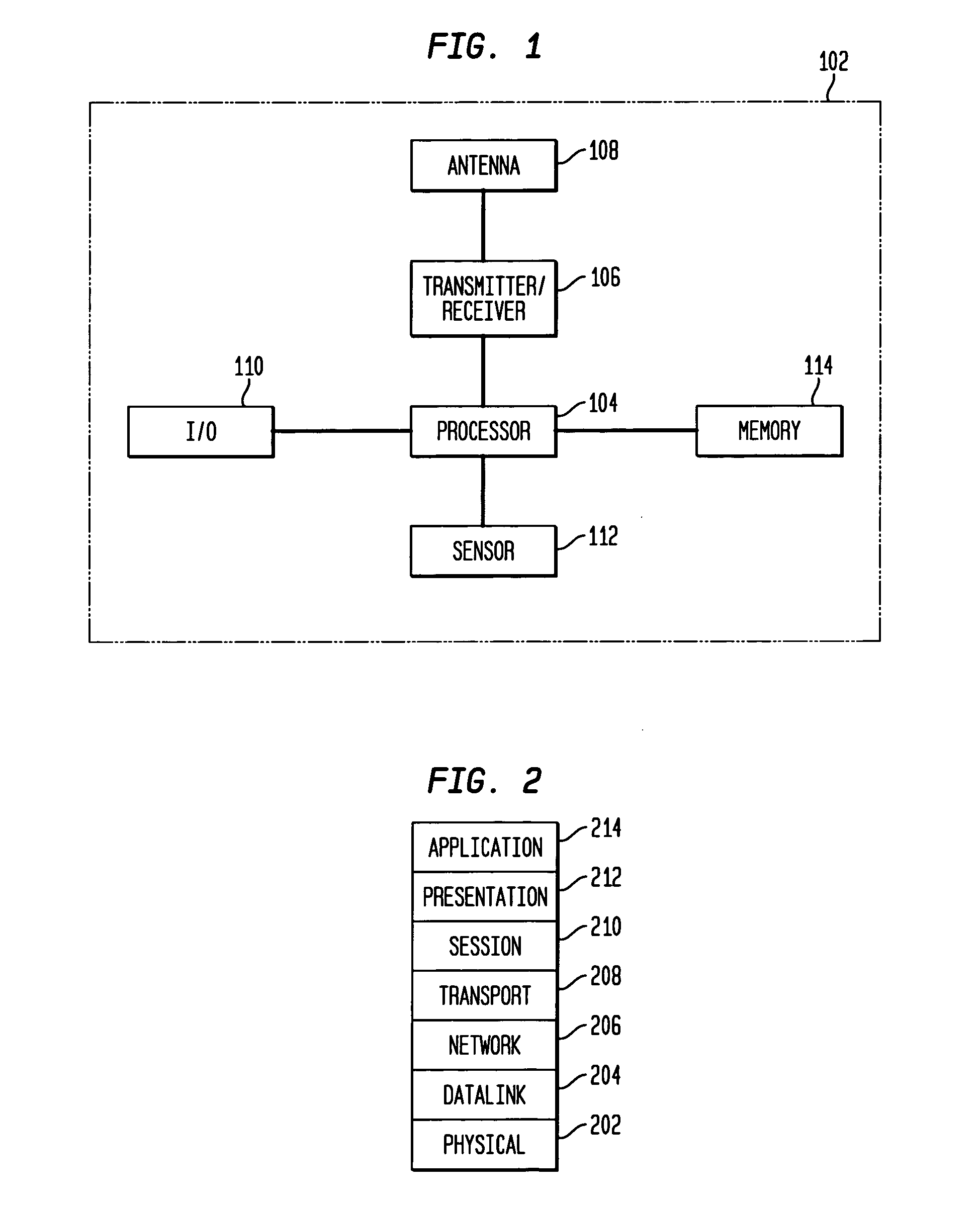

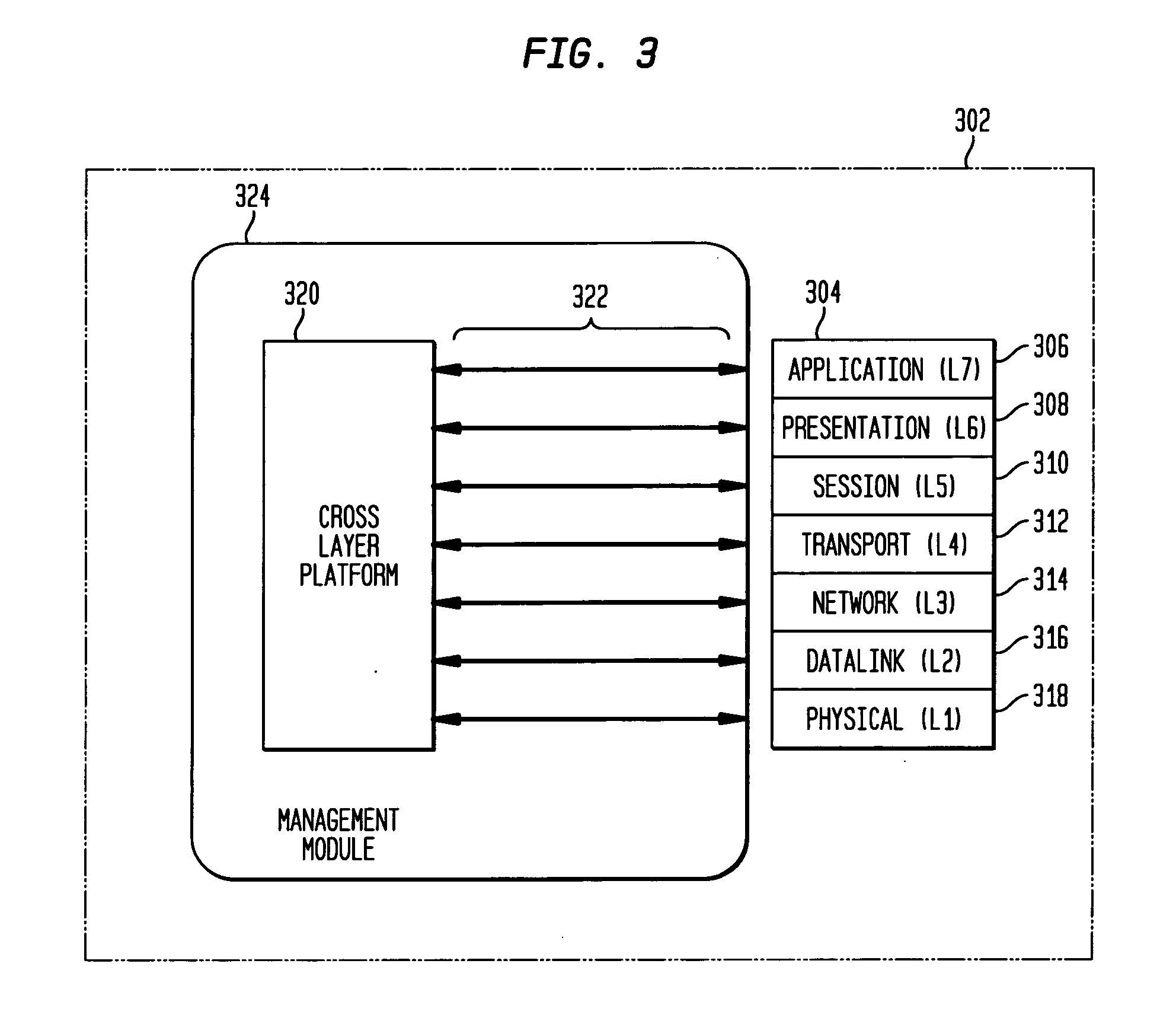

Cross-layer self-healing in a wireless ad-hoc network

ActiveUS20060239216A1Improve self-healing abilityEnhanced network operationPower managementNetwork topologiesSuccessful transmissionWireless ad hoc network

Disclosed is a method and apparatus for improved self-healing in a mobile ad-hoc wireless network in which network communication functions are divided into a plurality of functional layers. The system utilizes cross-layer self-healing techniques. Network data from at least one of the functional layers is stored, for example in a storage unit of the network node. The stored network data is then used to modify the functioning of at least one of the other layers. In one embodiment, a management module manages the storage and use of the network data. In particular embodiments, the stored network data relates to successful transmission rates and / or clear channel rates, and this stored data is used to adjust the transmission power of the network node. In another embodiment, the stored data may be used to generate a table of interchangeable network nodes, which may then be used to reroute a data packet to a network node other than an originally specified destination node. In yet another embodiment, the stored data may be used to generate a list of recent neighbor nodes, which data may be used to reroute data packets to intermediate network nodes.

Owner:TELCORDIA TECHNOLOGIES INC

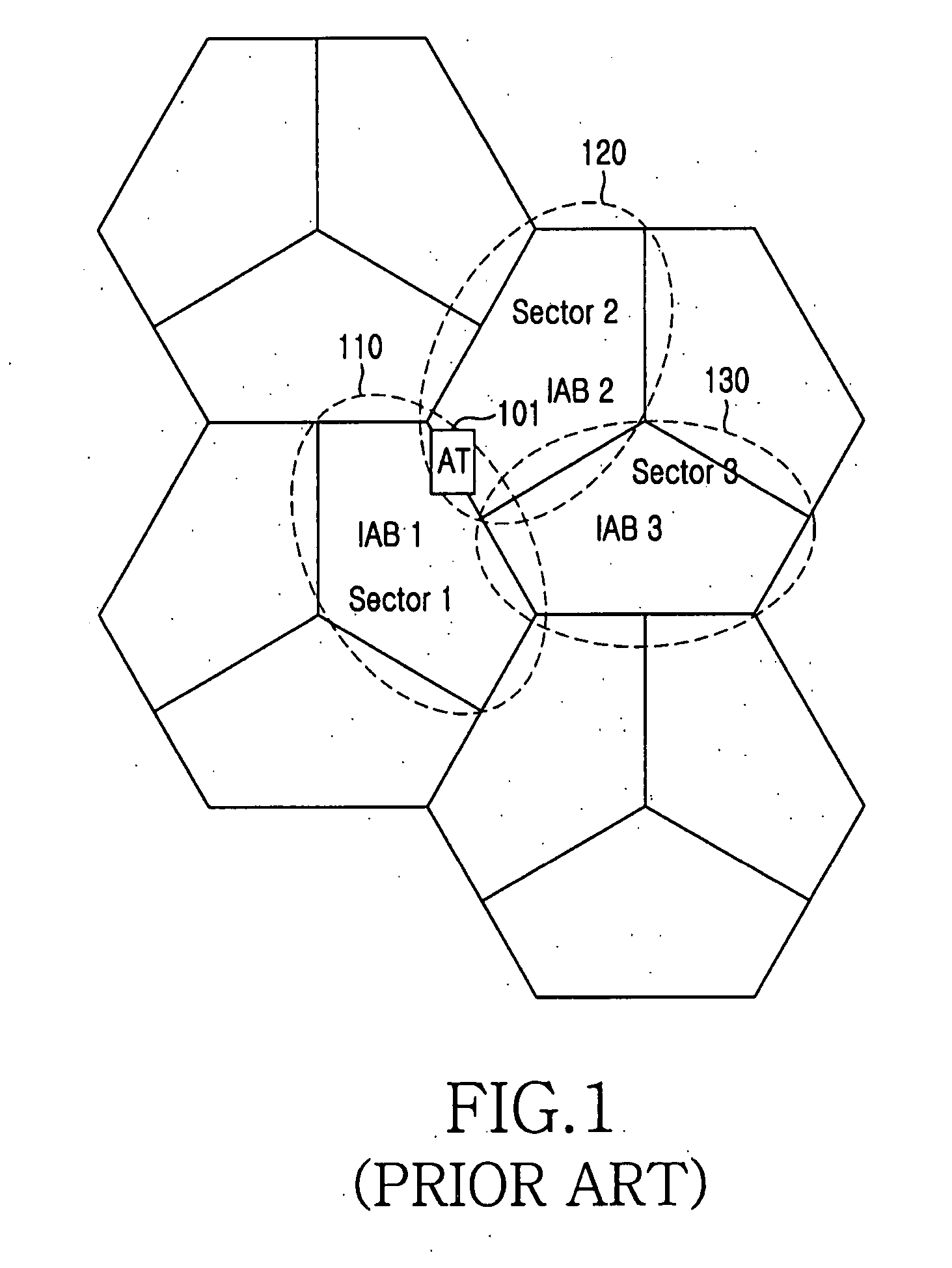

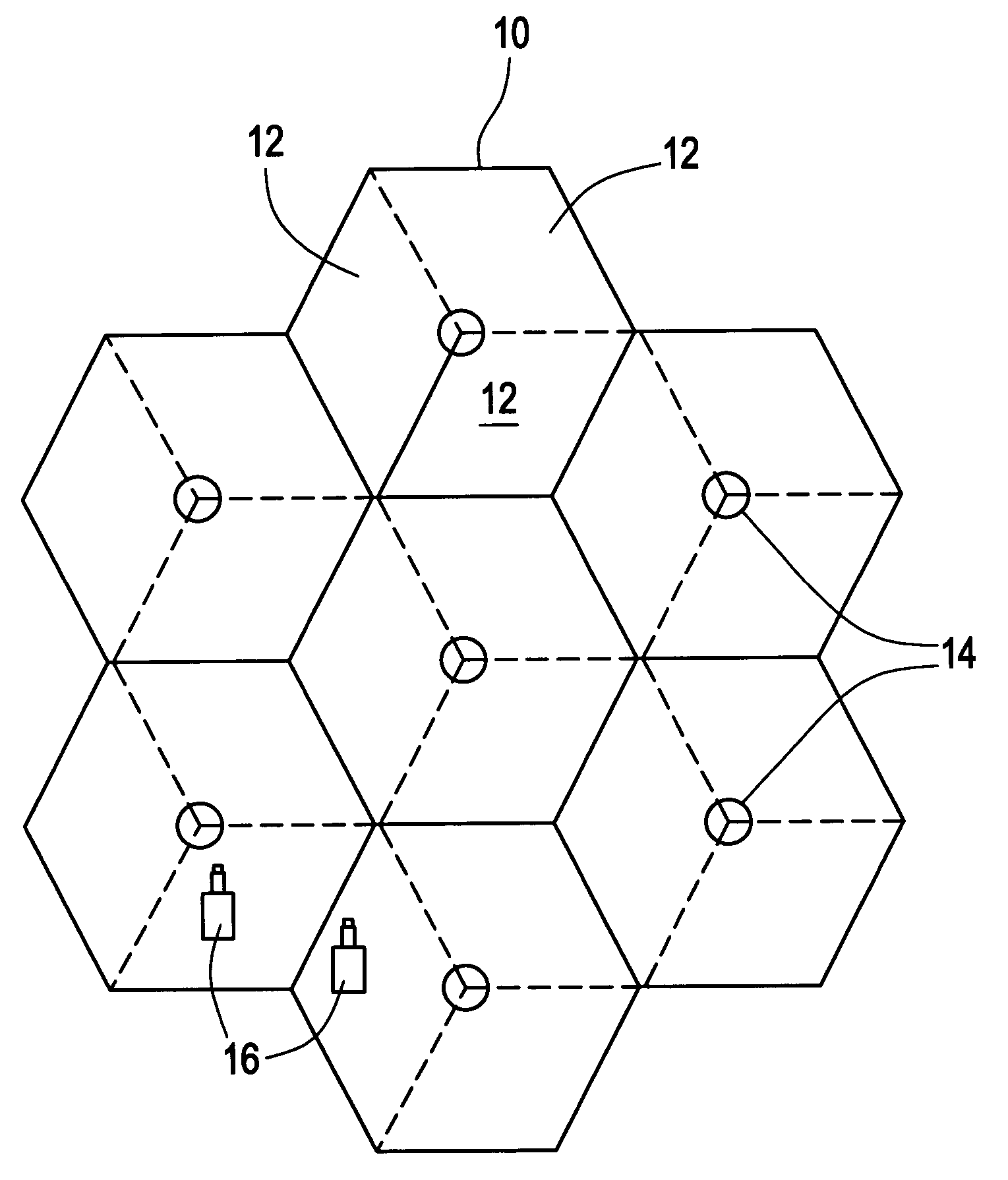

Method for controlling reverse channel rate in a cellular mobile communication system and system thereof

InactiveUS20070213011A1Improve throughputPower managementRadio transmissionMobile communication systemsBackward channel

Disclosed is a method for controlling reverse transmission power in a cellular mobile communication system. A base station measures interference in a cell divided into a plurality of beamforming areas, determines an Interference Availability Bit (IAB) of a specific area where the measured interference is greater than or less than a threshold, and forms a beam so as to transmit the determined IAB to a beamforming area including the specific area. A terminal receiving the formed beam receives the IAB, and controls reverse transmission power according to the received IAB.

Owner:SAMSUNG ELECTRONICS CO LTD

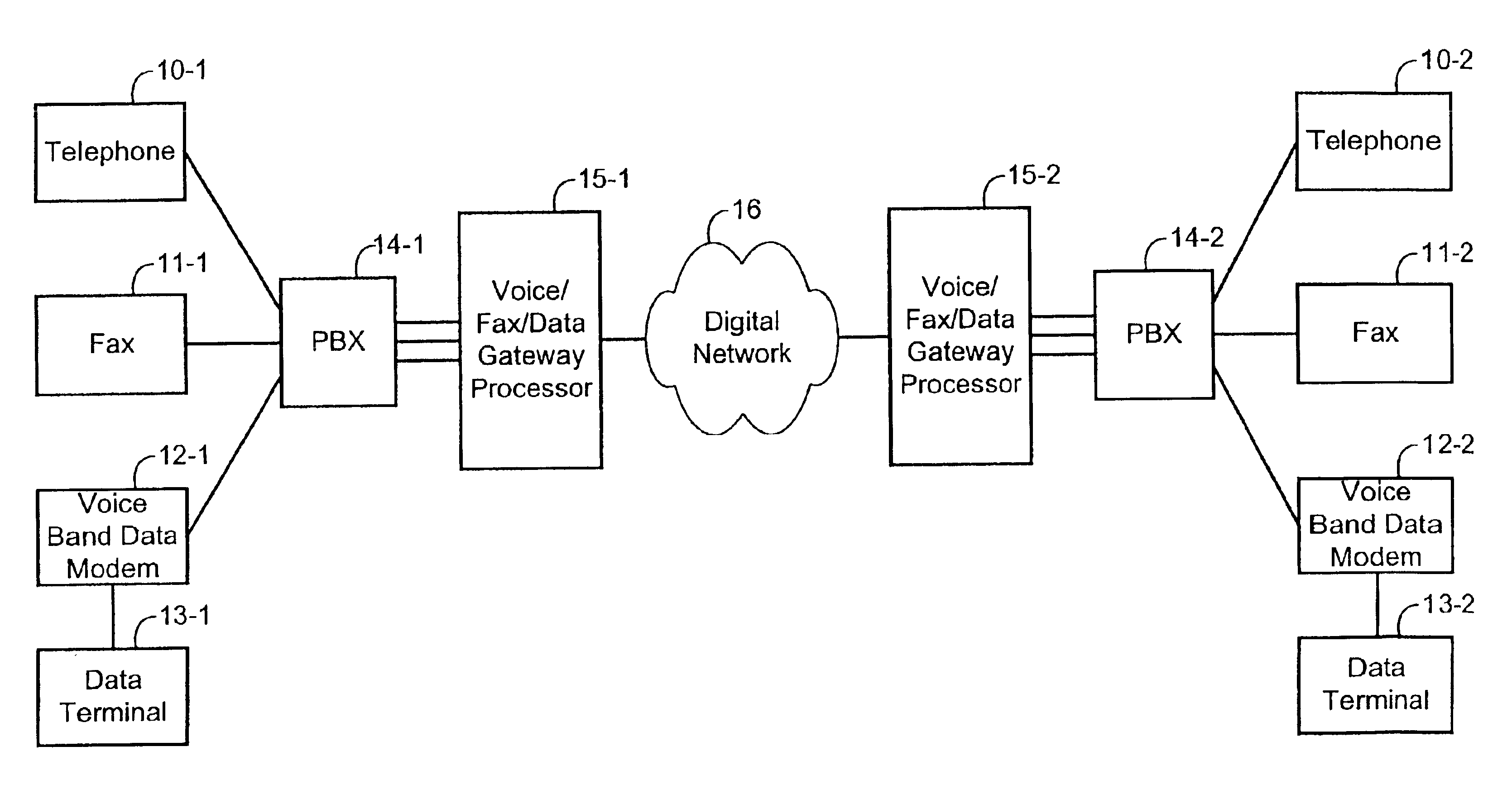

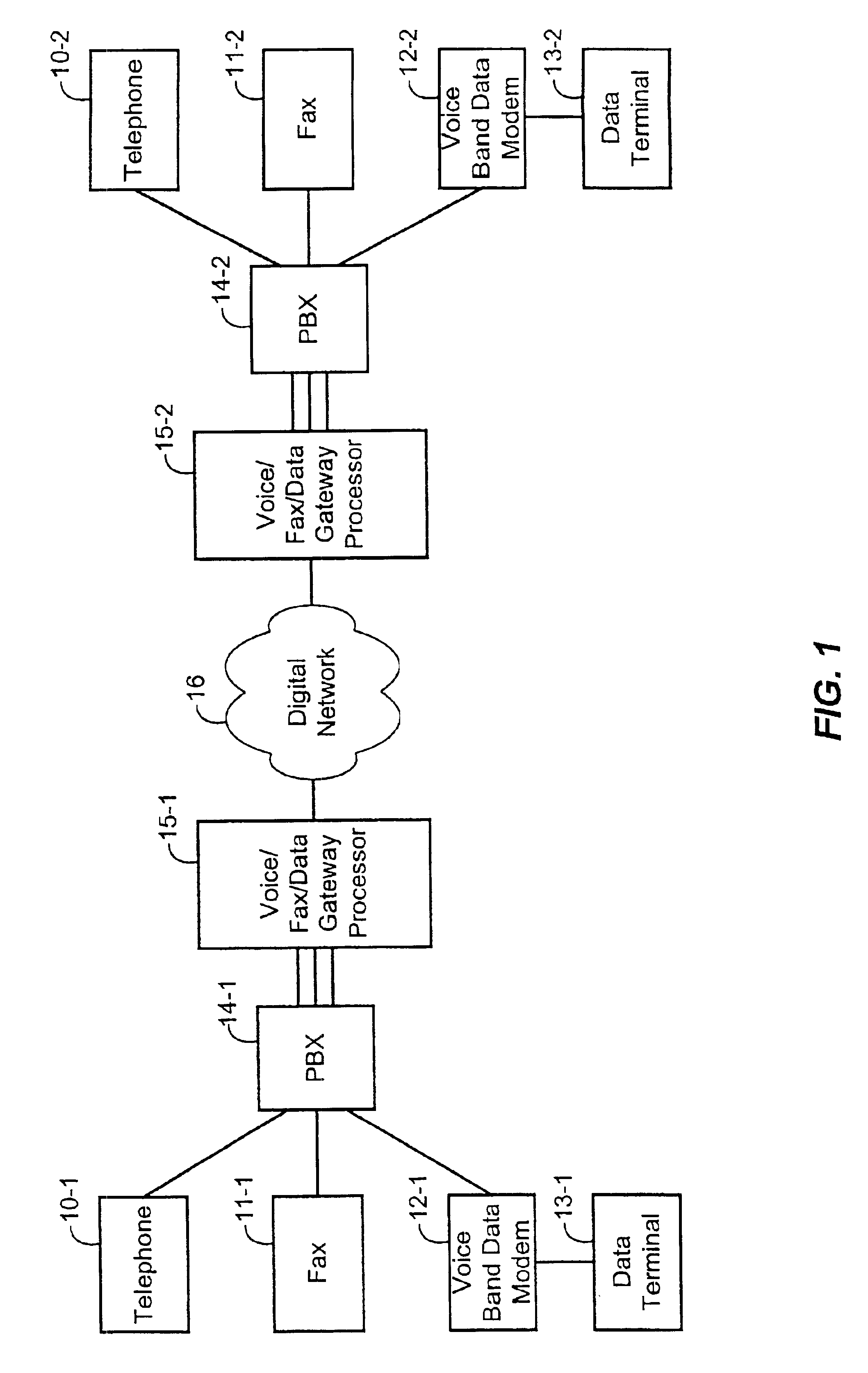

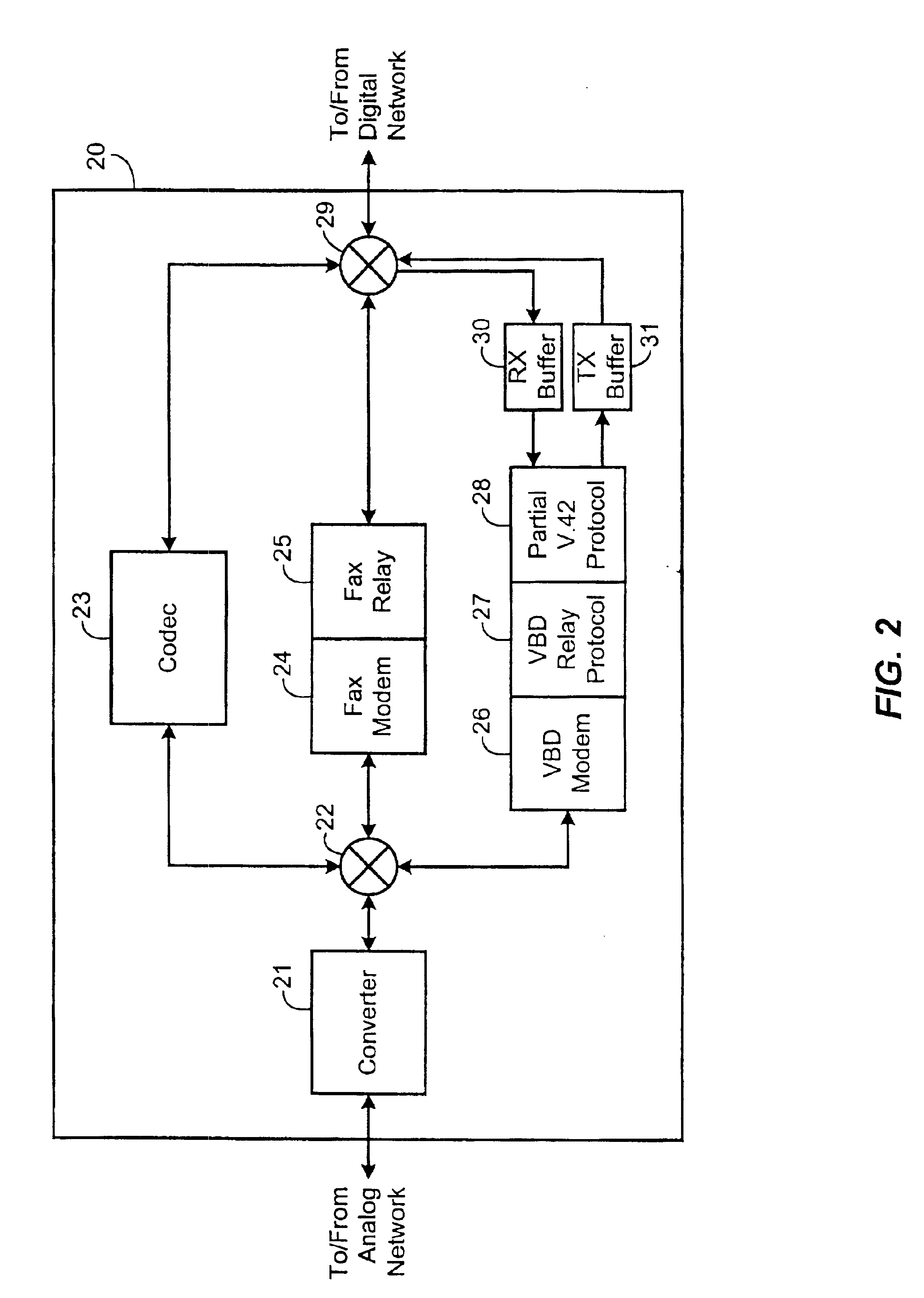

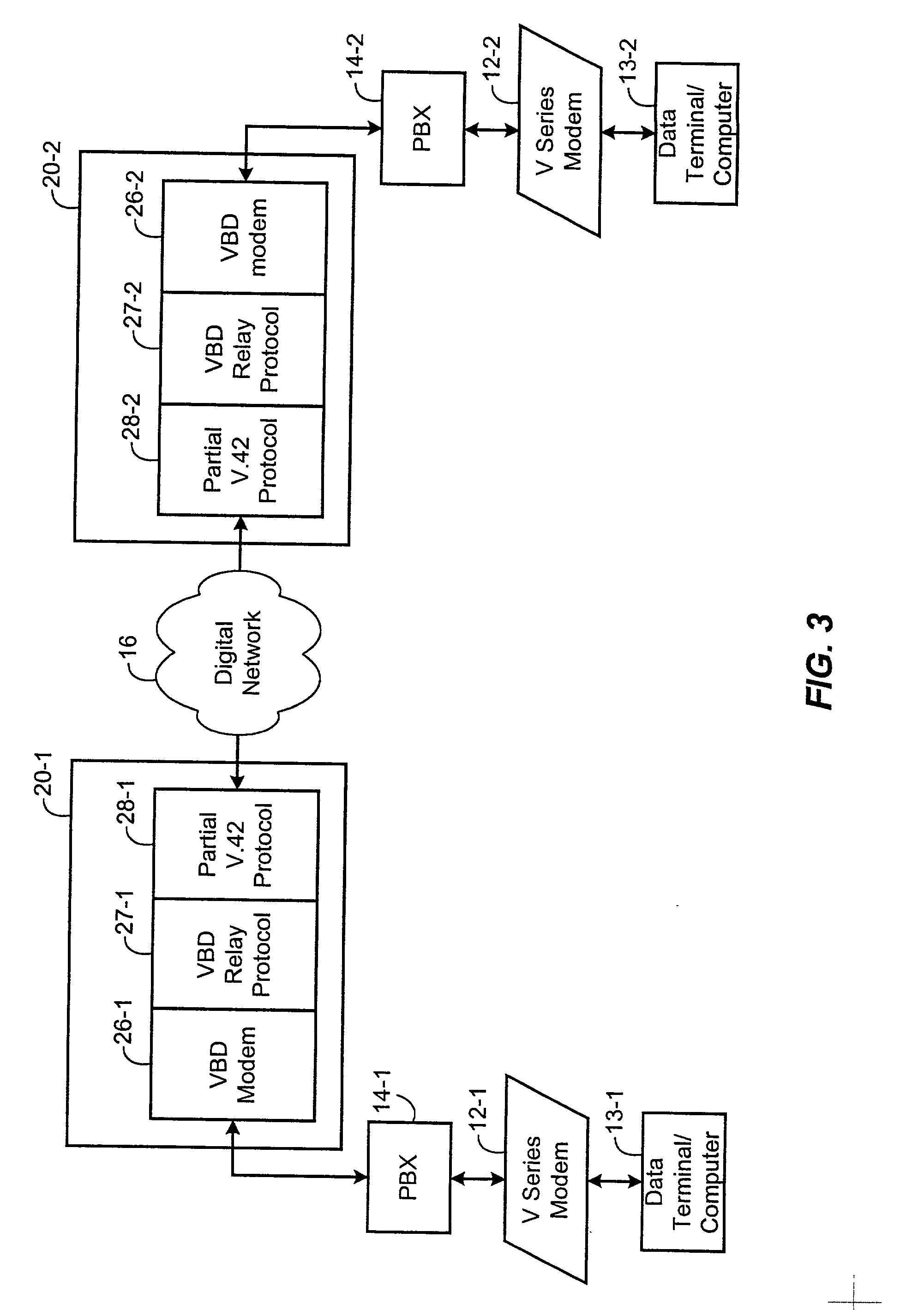

System and method for implementing an end-to-end error-correcting protocol in a voice band data relay system

InactiveUS20010046259A1Error preventionFrequency-division multiplex detailsModem deviceError correcting

A system and method to establish an end-to-end error correcting protocol between two voice band data modems over a network including voice band data relay gateways, where part of the end-to-end connection is via low data rate narrowband network. Using a partial implementation of V.42 LAPM protocol within the data relay gateways, the system allows the independent selection of modulation schemes at each gateway as well as increased user data throughput by removing non-informational data. Flow control of the user data to match the channel rate of the narrowband network may also be provided.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

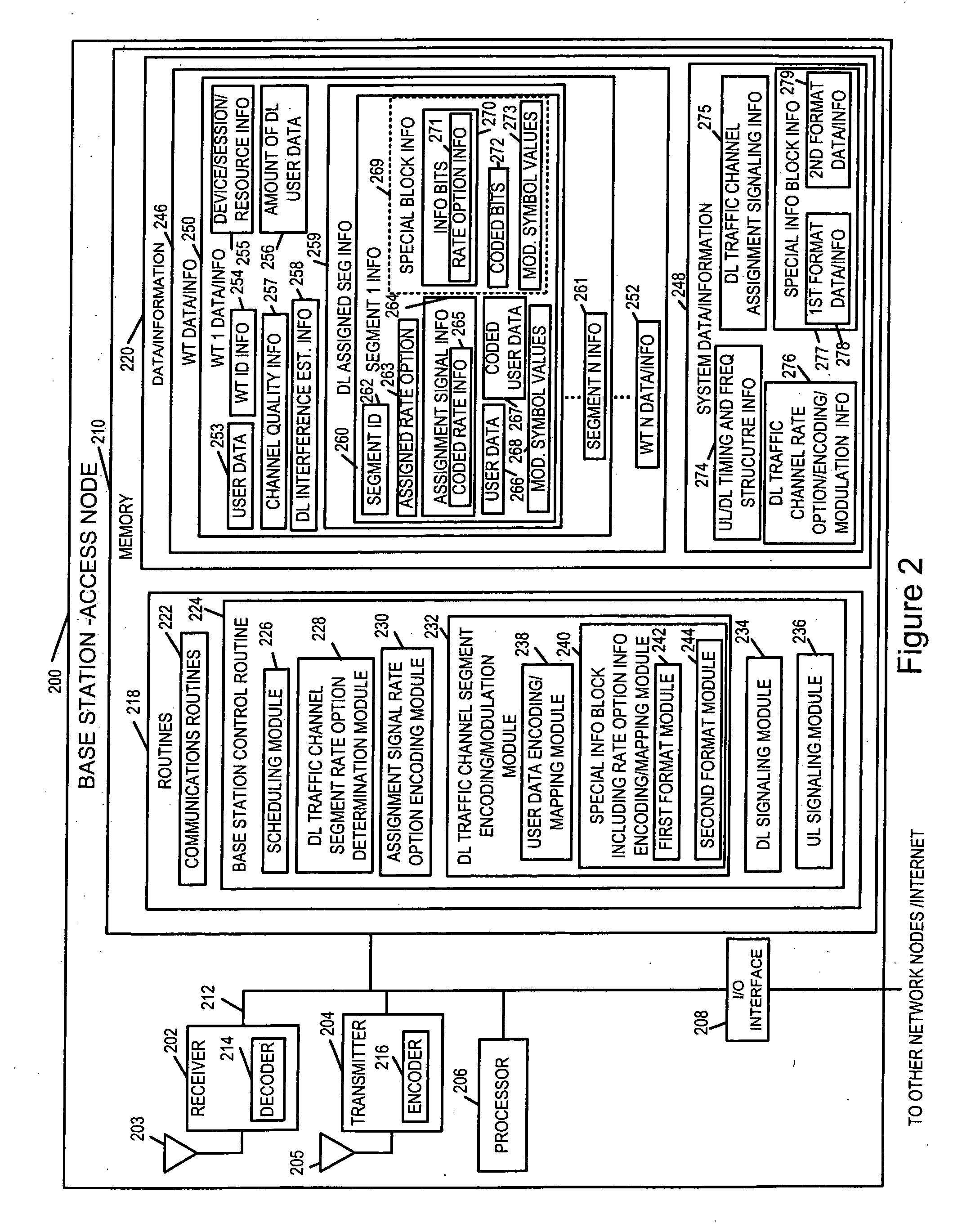

In-band rate indicator methods and apparatus

InactiveUS20070019583A1Accurate explanationMultiple modulation transmitter/receiver arrangementsModulation type identificationData rateComputer science

Downlink traffic channel data rate options and methods of indicating to a wireless terminal a utilized downlink data rate option are described. The downlink traffic channel rate option for a segment is conveyed using an assignment signal and / or a block in the downlink traffic channel segment which is not used for user data. Downlink segment assignment signals in some implementations allocate fewer bits for rate option indication than are required to uniquely identify each option. In some implementations low rate options, e.g., using QPSK, are uniquely identified via assignment signals. Higher rate options, e.g., using QAM16 modulation, are conveyed via the distinct information block in the downlink traffic segment using a first coding / modulation method. Still higher rate options, e.g., using QAM16, QAM64, or QAM256, are conveyed via the information block in the segment using a second coding / modulation method which is applied to the rate option information.

Owner:QUALCOMM INC

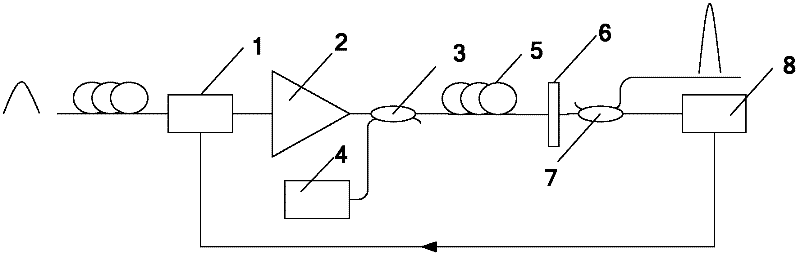

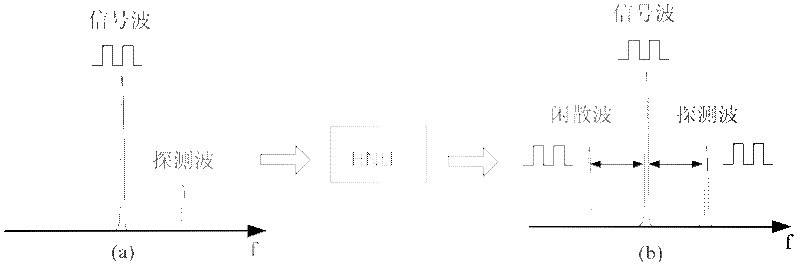

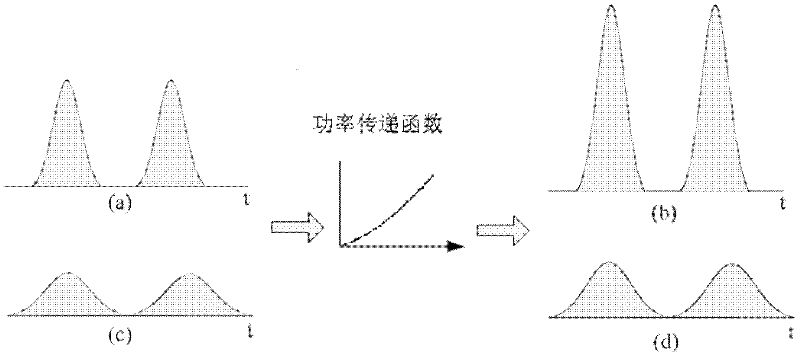

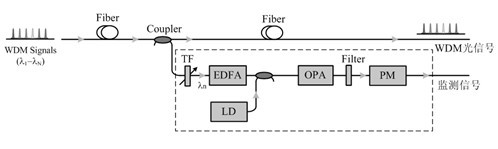

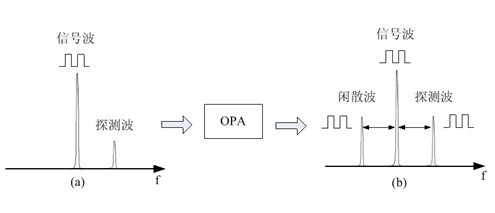

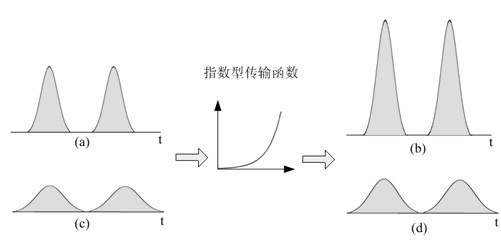

Multifunctional optical signal processing system

InactiveCN102347797AAchieving Dynamic Dispersion CompensationTransparent rateDistortion/dispersion eliminationOptical power meterTransport system

The invention relates to a multifunctional optical signal processing system. In the system, continuous detection light and signal light are combined through a first coupler and injected into a high nonlinear optical fiber; idle light generated in the high nonlinear optical fiber due to a fourwave mixing effect is divided into two paths through an optical filter and an optical coupler and are output, wherein one output path is connected to an optical power meter, the optical power output performs feedback control on a tunable dispersion compensator so as to realize dynamic dispersion compensation, while the other output path is used as a system output signal to generate an optical signal with high extinction ratio and no dispersion; and the wavelength of the output optical signal is changed by regulating the wavelength of the detection light, so that tunable wavelength conversion is realized. The multifunctional optical signal processing system can realize HNLF (High Nonlinear Fiber), dispersion detection, extinction ratio enhancement and wavelength conversion, has the advantages of multifunction integration, high response speed, high sensitivity of dispersion detection, wide working wave band and transparency to signal speed and modulation format and can be applied to an optical transmission system with channel rate of over 40Gb / s.

Owner:HUAZHONG UNIV OF SCI & TECH

Selective intra and/or inter prediction video encoding

ActiveUS20120307884A1Energy efficient ICTPicture reproducers using cathode ray tubesVideo encodingData rate

Selective intra and / or inter-prediction video encoding. Based upon anticipation of a future communication channel rate (e.g., actual physical layer channel rate) or video data rate of a communication channel, a given prediction mode for video encoding may be adaptively selected. Prediction of a future or expected value corresponding to at least one parameter associated with the communication channel (e.g., channel rate, video data rate, etc.) can drive operational mode selection / adaptation in accordance with video coding. Alternatively, one or more actual measured values corresponding to at least one parameter can drive operational mode selection / adaptation in accordance with video coding. In some instances, neither intra-prediction nor inter-prediction is performed in accordance with a non-feedback operational mode, and an input video signal undergoes compression (e.g., without intra-prediction and / or inter-prediction). Transitioning between various video coding operational modes may be made in different manners and based on different criteria as desired in various given applications.

Owner:AVAGO TECH INT SALES PTE LTD

All-optical dispersion monitor based on optical parameter amplifier

InactiveCN101841368ATransparent rateTransparent modulation formatTransmission monitoring/testing/fault-measurement systemsNon-linear opticsIdle waveOptical power meter

Owner:HUAZHONG UNIV OF SCI & TECH

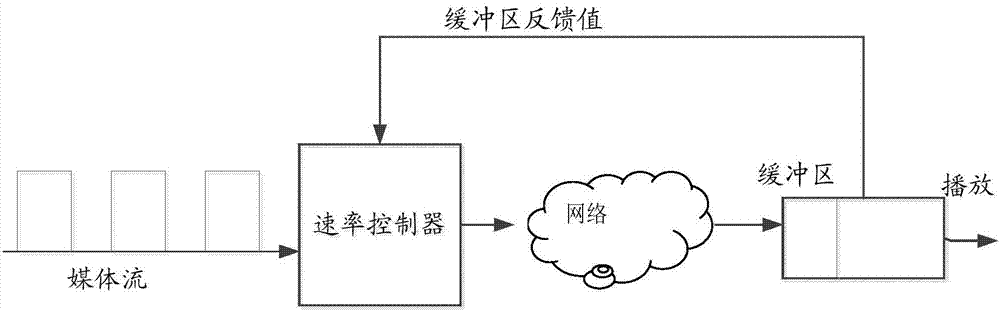

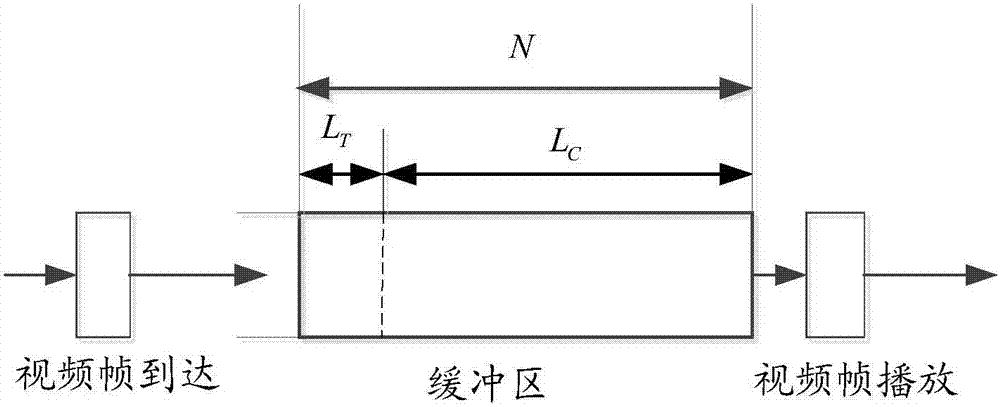

Playing method and device of videos issued by server

InactiveCN107205160AIncrease playback rateQuick adjustment of playback rateSelective content distributionChannel rateLower threshold

The invention discloses a playing method and device of videos issued by a server, so that the playing quality of the videos is improved. The method comprises the following steps: acquiring an upper threshold and a lower threshold of a buffer area used for storing video frames, wherein the upper threshold and the lower threshold are determined according to the channel rate of a network; if the current buffer data volume in the buffer area is less than the lower threshold, decreasing the playing rate of the video frames, wherein if the buffer data volumes in the buffer area at adjacent moments are unequal and are both less than the lower threshold, the change rate of the playing rates of the video frames at the adjacent moments is in direct proportion to the size of the buffer data volume in the buffer area; if the current buffer data volume in the buffer area is more than the upper threshold, increasing the playing rate of the video frames, wherein if the buffer data volumes in the buffer area at the adjacent moments are unequal and are both more than the upper threshold, the change rate of the playing rates of the video frames at the adjacent moments is in direct proportion to the size of the buffer data volume in the buffer area.

Owner:HISENSE VISUAL TECH CO LTD

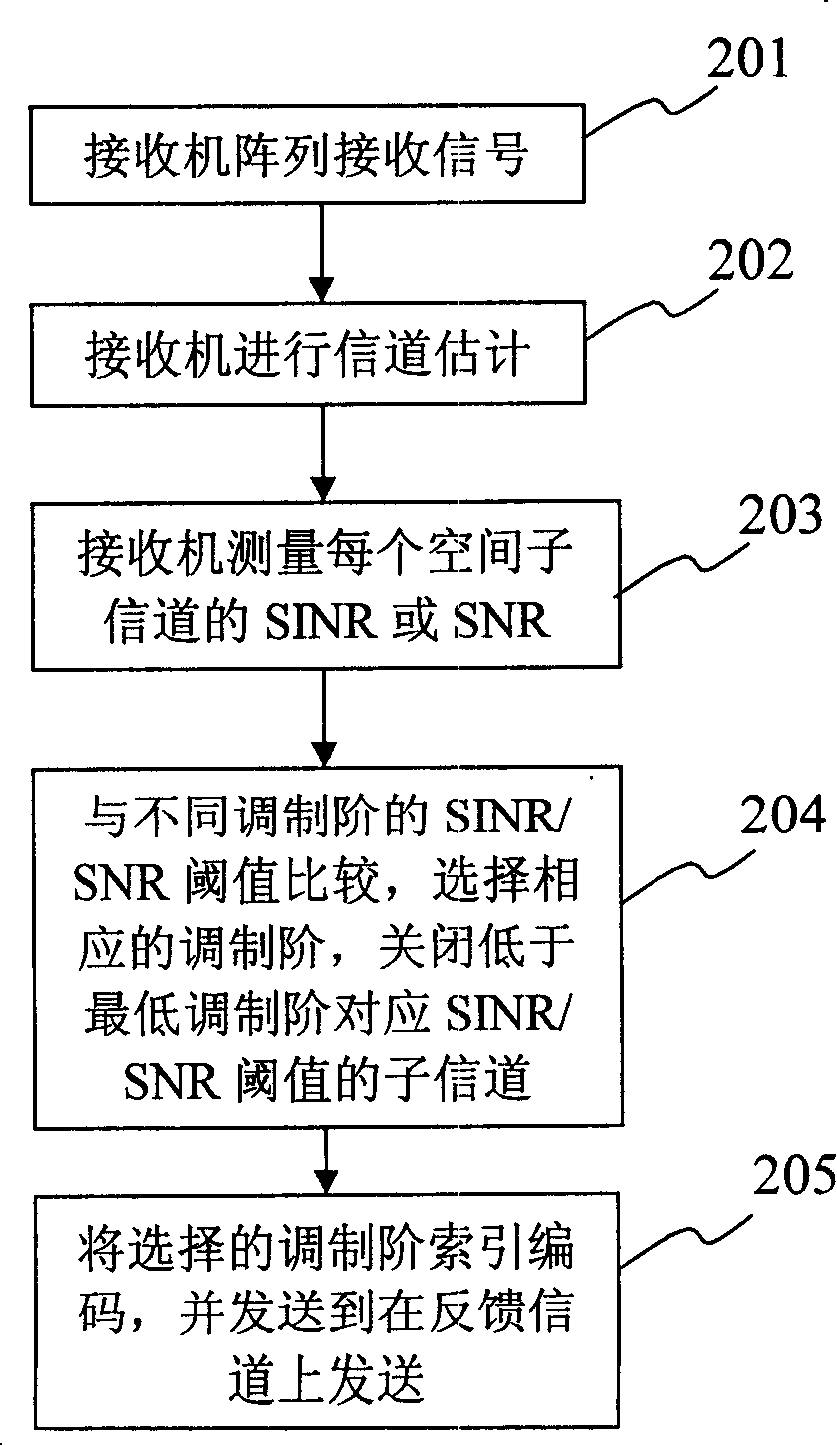

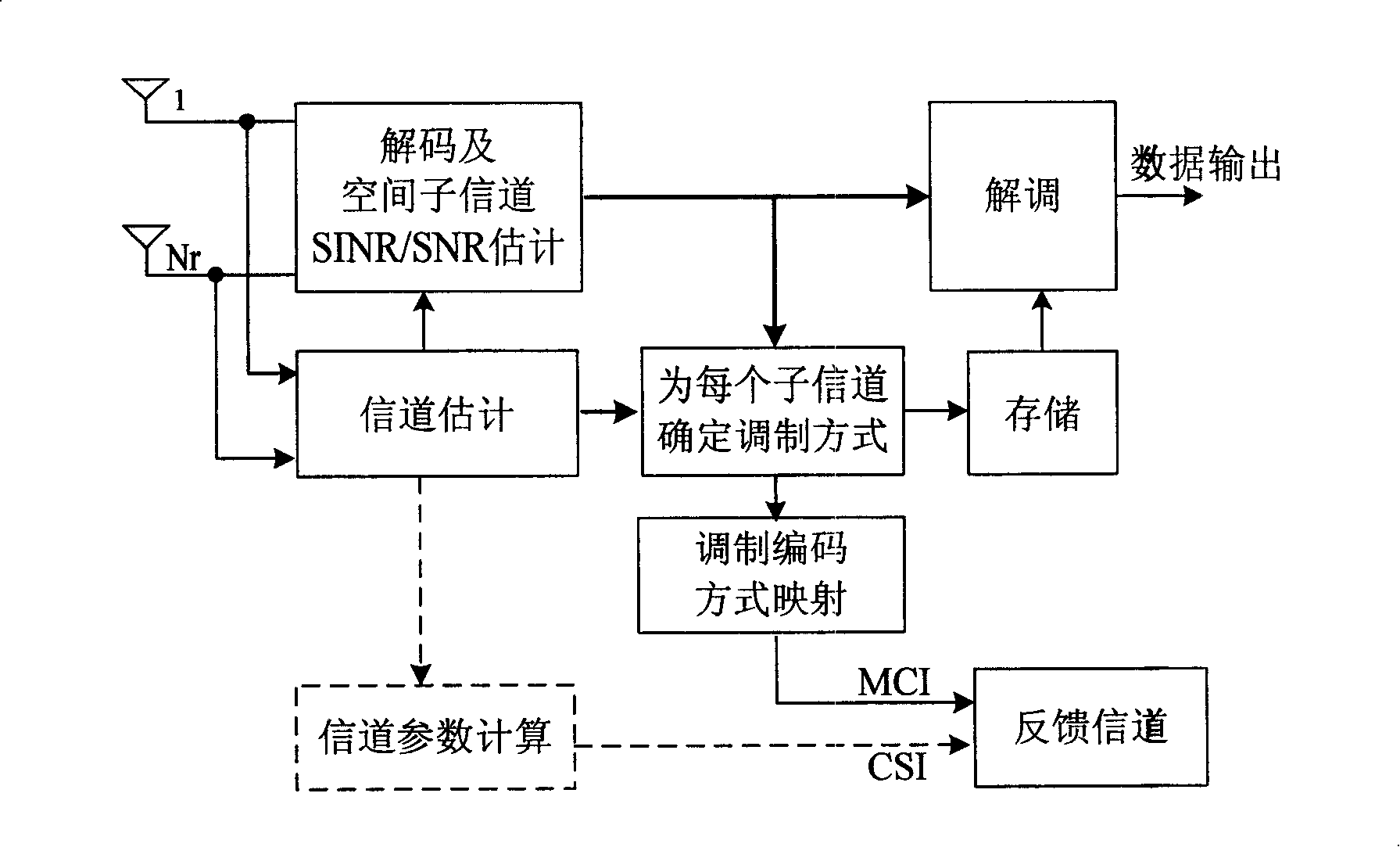

A space sub-channel rate and power control method and its control device

InactiveCN101242205AAccurately reflectReduce bandwidth requirementsPower managementSpatial transmit diversityChannel state informationPrecoding

The invention discloses a control method and a device of every space subchannel rate and power, the method comprises: receiver determinates modulation coding chose by every space subchannel according to the receiver side channel state information; the modulation coding which is chosen by the receiver is noticed to transmitter with index; pre-coding is carried out by the receiver According to channel state information statistics and the subchannel modulation coding. The invention returns only the 'index', not the channel state information real-time, thus reducing bandwidth demand of feedback channel. The invention pre-cods using channel state information statistical information, such as mean, variance matrix or related matrix parameters, thus reducing sensitivity pre-coding system performance to channel state information error.

Owner:LENOVO (BEIJING) CO LTD

Method and apparatus for IS-95B reverse link supplemental code channel frame validation and fundamental code channel rate decision improvement

InactiveUS20050250521A1Accurately determineImprove accuracyNetwork traffic/resource managementRadio/inductive link selection arrangementsTransmission protocolCommunications system

The present invention provides a method and apparatus for maximizing throughput of a data call in a wireless communication system in which data is transmitted from a wireless station, such as a mobile station, on multiple assigned channels in accordance with a known transmission standard, such as IS-95B. The multiple assigned channels include a fundamental channel and at least one supplemental channel. Data is formatted into variable rate data frames and transmitted on the fundamental channel and the supplemental channel. A wireless receiver, such as a base station, receives the multiple assigned channels. The wireless receiver demodulates and decodes data frames associated with each of the multiple assigned channels. The wireless receiver determines a likely initial data rate for each demodulated and decode data frame. The wireless receiver correlates all of the likely data rates, by comparison to one another and to a relevant transmission protocol standard, to determine a maximum likelihood combination of data rates. The maximum likelihood combination of data rates includes a maximum likelihood data rate corresponding to each likely data rate. Decoded data frames are invalidated and erased when the likely data frame rates do not match corresponding maximum likelihood data rates.

Owner:JOSHI ABHAY +2

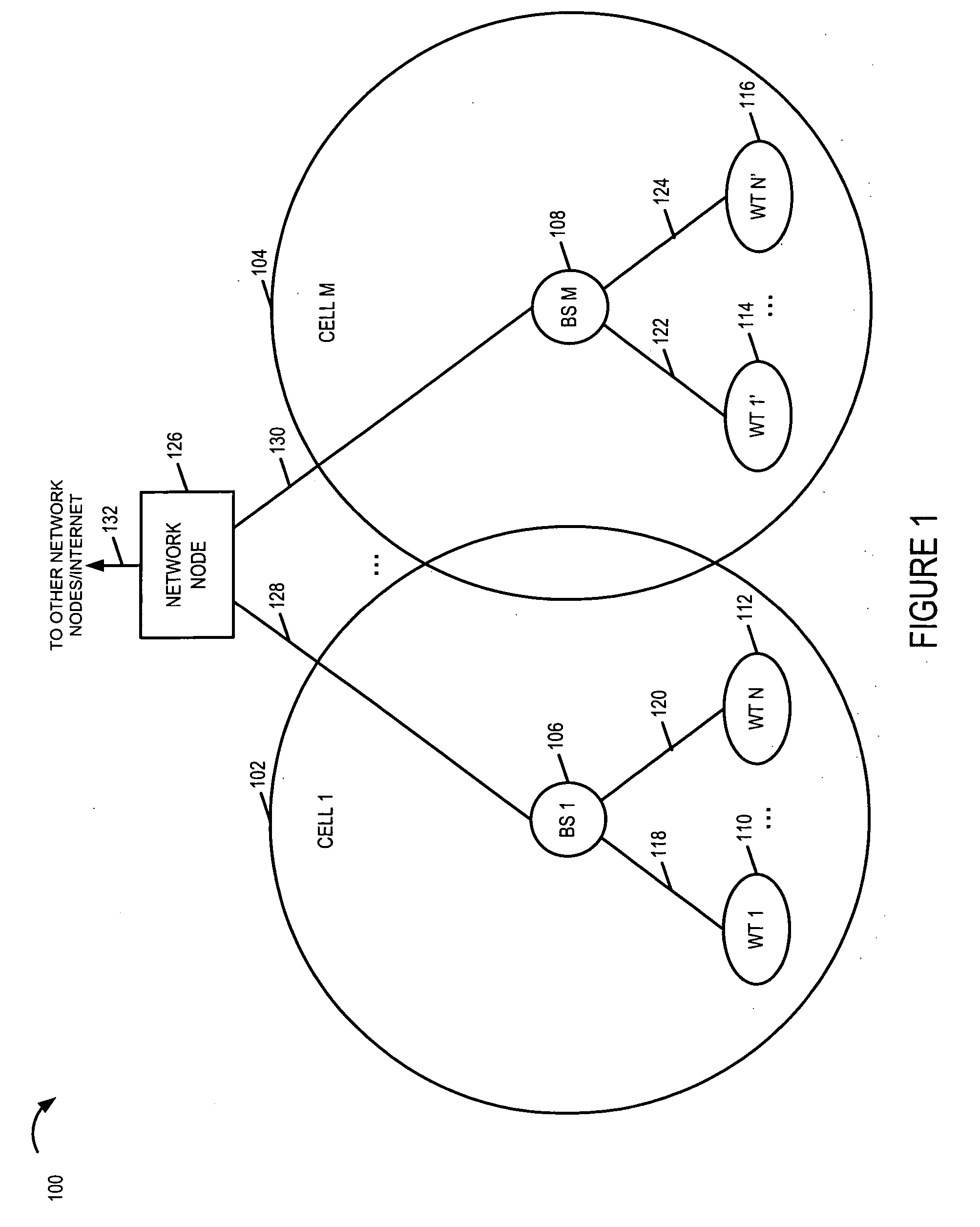

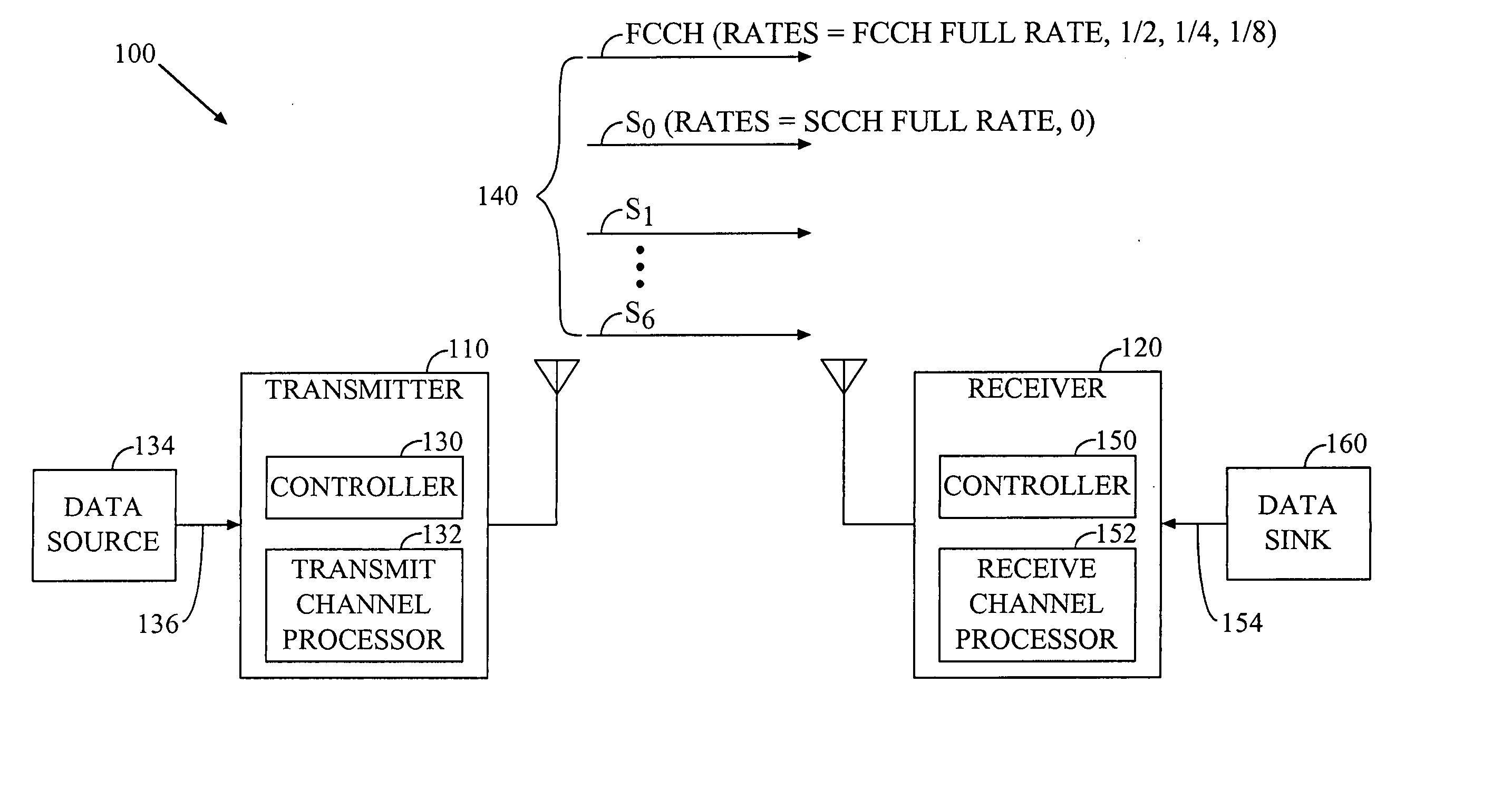

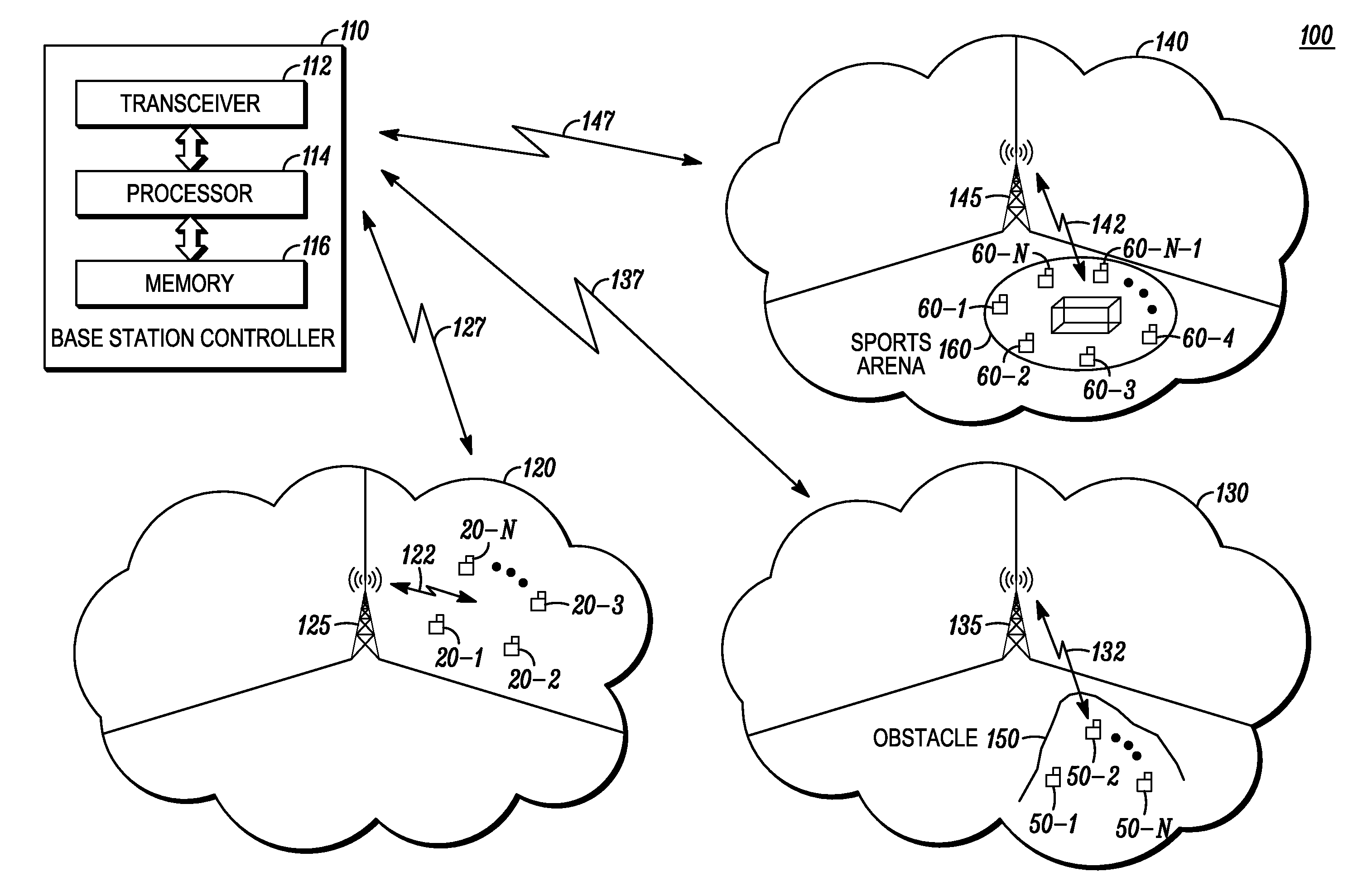

Channel rate and physical channel selection in wireless communications networks

ActiveUS7236789B2Increase network capacityLow costNetwork traffic/resource managementRadio/inductive link selection arrangementsTelecommunicationsMobile station

In the method for selecting a channel rate, link quality between the serving portion of the network and a mobile station is determined from at least one signal strength measurement. A channel rate is then selected based on the determined link quality. Also, a physical channel is assigned to the mobile station on a prioritized basis with respect to the selected channel rate.

Owner:LUCENT TECH INC

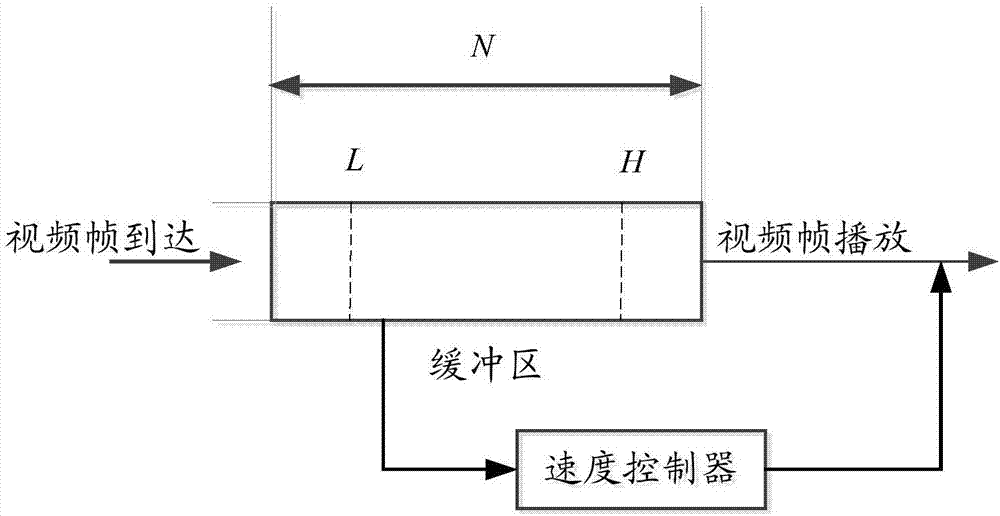

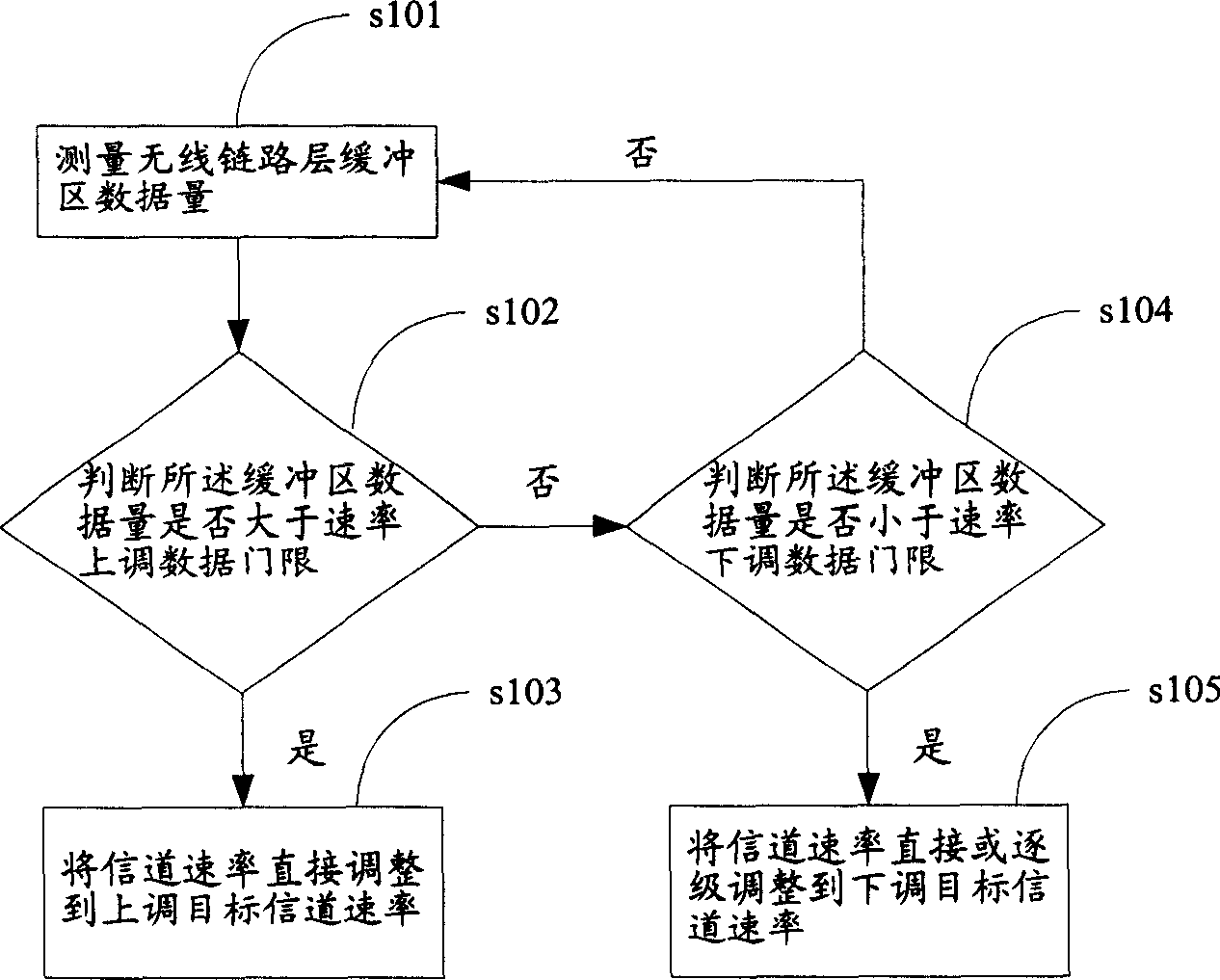

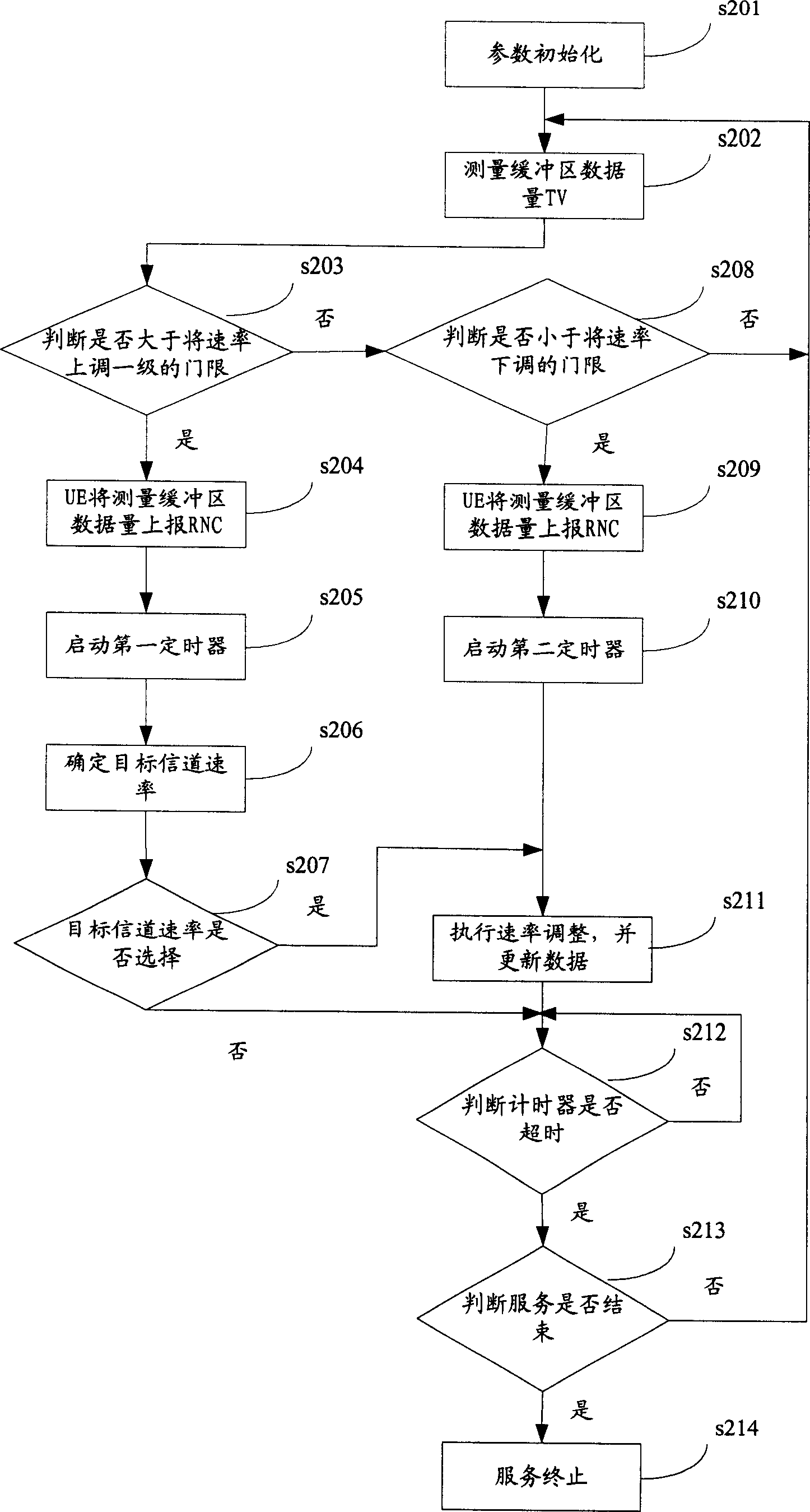

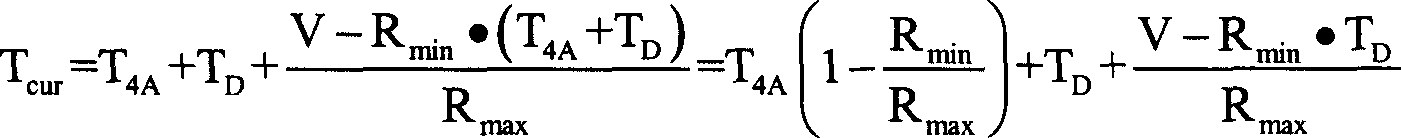

Channel rate adjusting method for packet data service of general mobile communication system

ActiveCN1866783AIncrease profitImprove deteriorationRadio/inductive link selection arrangementsRadio transmission for post communicationCommunications systemMobile communication systems

The invention discloses a channel rate adjustment method of moving communication system sectionalization data service, which comprises the following steps: measuring buffer area data bulk of wireless links inlay; deciding whether the buffer area data bulk is bigger than upper data threshold; adjusting the channel rate on the upper goal channel rate if the buffer area data bulk is bigger than upper data threshold; deciding whether the buffer area data bulk is smaller than downward datathreshold; adjusting the channel rate to downward goal channel rate, if the buffer area data bulk is smaller than downward datathreshold; going to check data bulk if buffer area data bulk isn't smaller than downward datathreshold. The invention reduces the signaling cost of current scheme, which improves the system resource availability.

Owner:DATANG MOBILE COMM EQUIP CO LTD

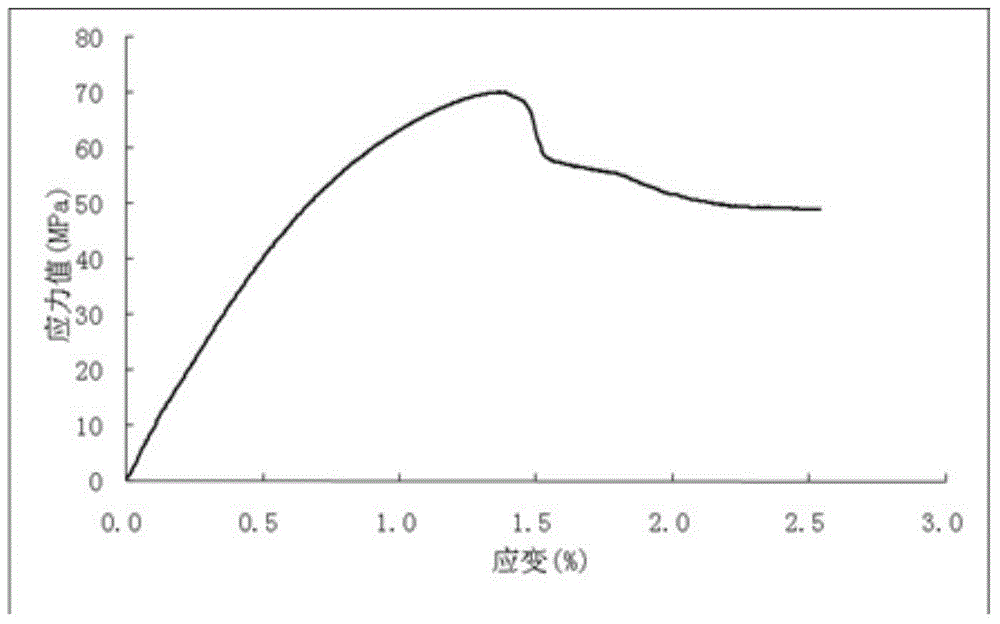

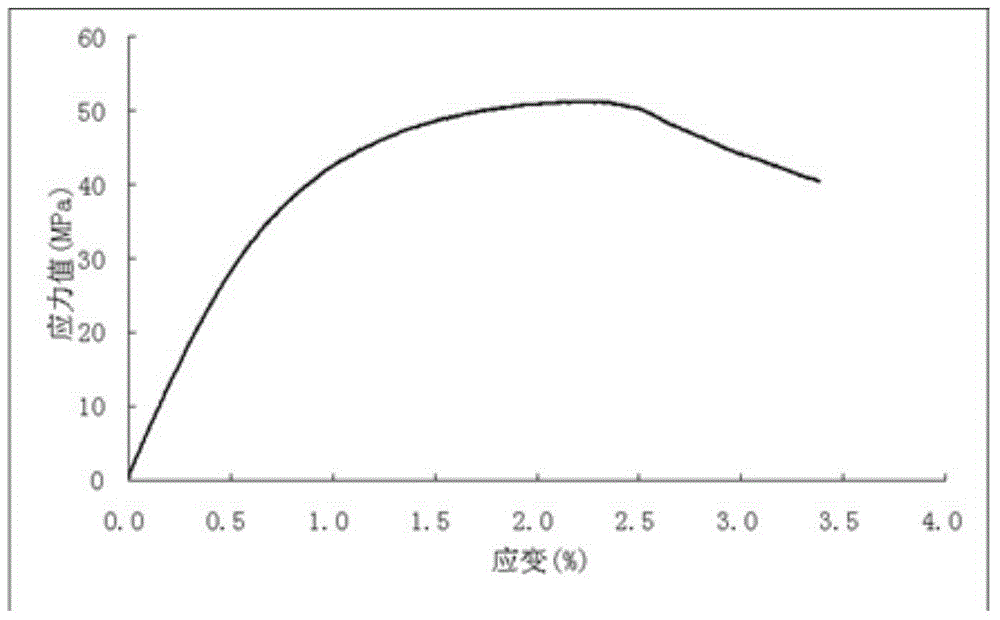

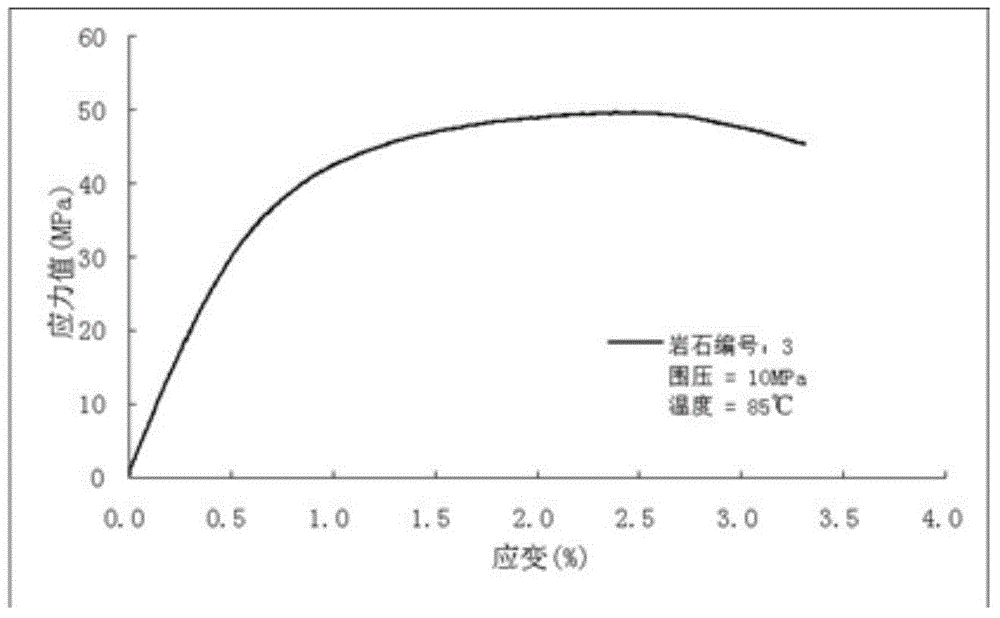

Horizontal well cement paste

ActiveCN104650836AZero analysis waterReduce dehydrationDrilling compositionStress–strain curveYoung's modulus

The invention provides a horizontal well cement paste, which comprises the following components in percentage by weight: 0.5%-2.5% of a flexibilizer GZR, 1%-3% of a GFC expansion agent, 0.04%-0.08% of a GH retarder and the balance of cement, zero free water and low-loss water, wherein the formed set cement does not shrink, and has a certain expansion rate and good mechanical property, and shows excellent tenacity. The set cement is high in breaking strength, and small in crumbly coefficient; the tenacity coefficient is increased; the young modulus of the set cement is decreased; the poisson ratio is increased; the bending radius of the set cement is reduced; a triaxial stress strain curve shows good elastoplasticity; the anti-channeling ability is improved; the thickening time is shortened; the time and the fluid channeling rate of a formation fluid intruding into the cement paste are reduced; the paste is uniform, stable and good in mobility; reduction of annular flow resistance is facilitated; and the displacement efficiency is improved.

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

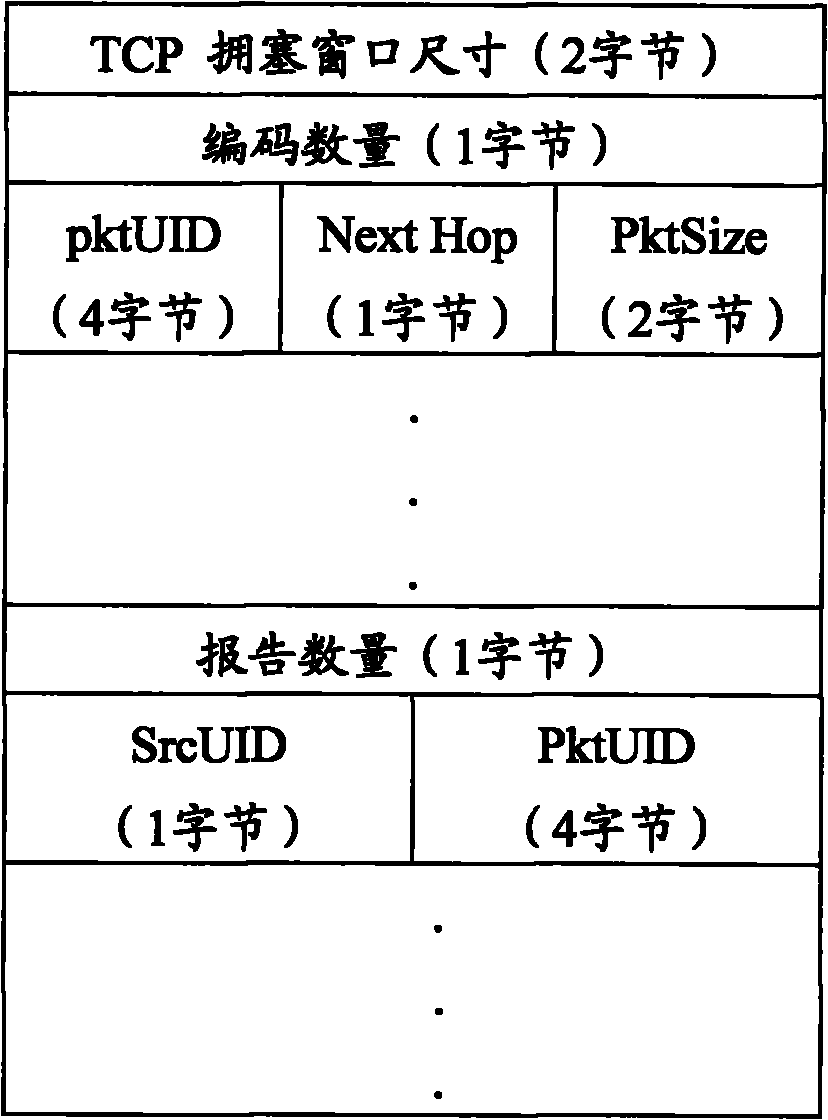

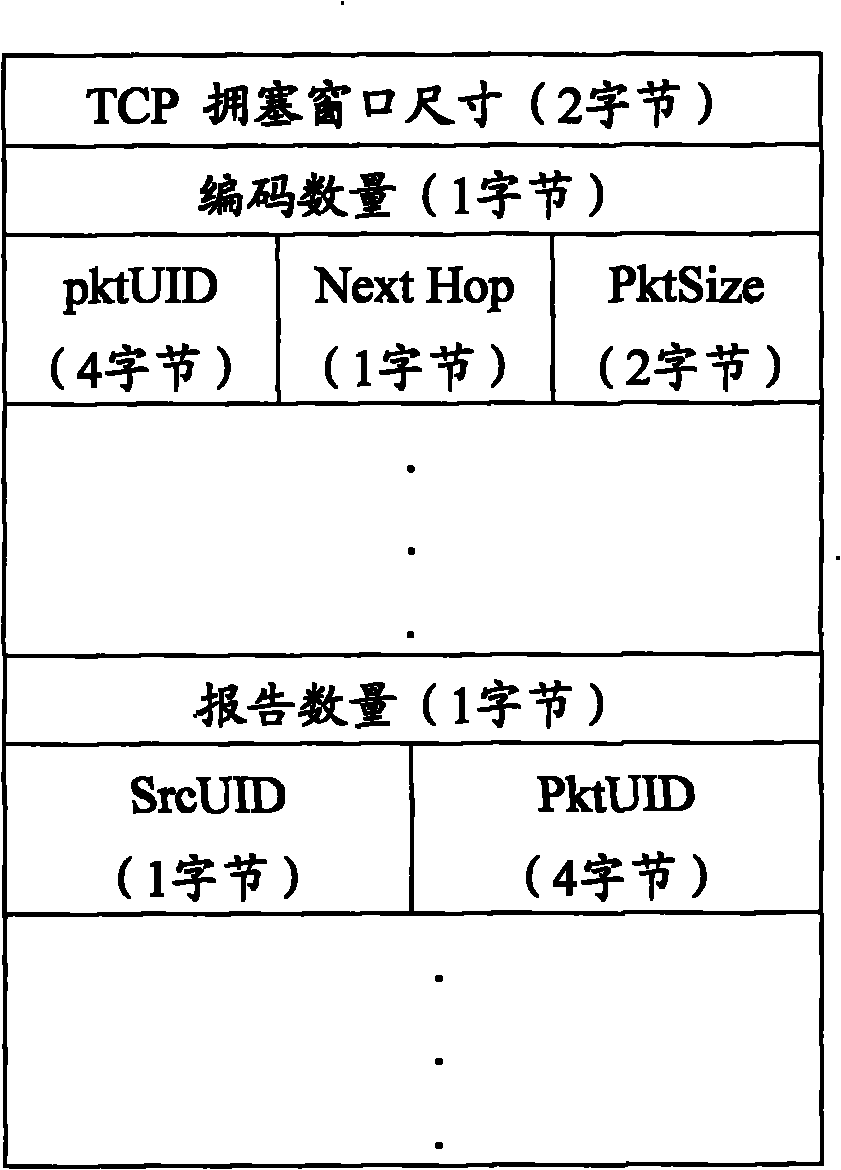

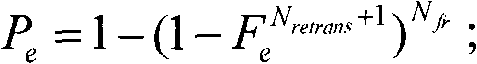

Method for realizing scheduling control of network encoding perceived by transmission control protocol in wireless network

ActiveCN102111820AReduce congestionImprove throughputError preventionNetwork traffic/resource managementWireless mesh networkTransport control protocol

The invention relates to a method for realizing the scheduling control of network encoding perceived by a transmission control protocol (TCP) in a wireless network, which comprises the following steps of: establishing a wireless network encoding model, a wireless channel model and a TCP model; assessing the channel quality of a wireless network system and the dynamic performance of the TCP; allocating a channel rate encoding mode in real time; encoding a group of TCP data packets selected from an intermediate node; and responding to a sender of the group of TCP data packets and forwarding the encoded data packets. By adopting the method for realizing the scheduling control of the network encoding perceived by the TCP in the wireless network, the change of channels can be known correctly, and an acknowledgement message is further sent to the sender of the data packets quickly and effectively, so network congestion is reduced, the transmission performance is improved, band width can be utilized effectively to allow the network to have higher throughput, the utilization rate of the band width is improved, wireless resources can be better utilized, the working performance is stable and reliable, and the application range is wide.

Owner:SPREADTRUM COMM (SHANGHAI) CO LTD

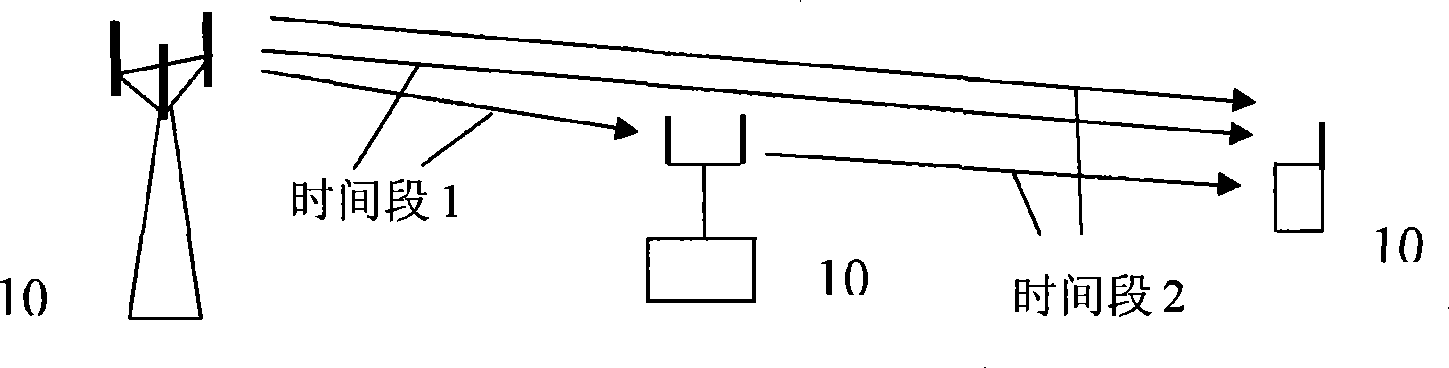

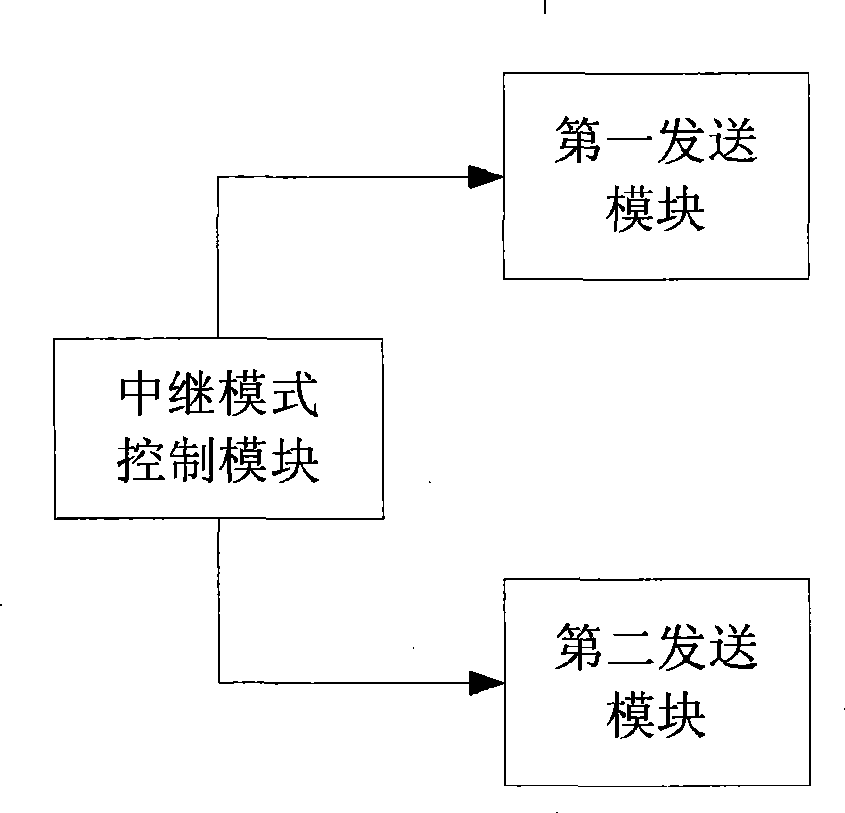

Switching method between semi-duplex and multicast collaboration relay scheme and corresponding based station

InactiveCN101389140AHigh gain performanceIncrease capacityNetwork topologiesRadio/inductive link selection arrangementsMode controlChannel rate

The invention discloses a switching method for semi-duplex and multicast collaborated relay mode and a corresponding base station, wherein the base station computes channel rate on three channel links according to channel quality information of three links of base station-relay station, relay station-mobile terminal and base station-mobile terminal, then computes effective channel rate on link of base station-relay station-mobile terminal under semi-duplex relay mode and multicast collaboration mode, executes mode switching judgment combining channel quality of base station-mobile terminal link and determined switching policy, switches between the semi-duplex relay mode and multicast collaborated relay mode. The corresponding base station comprises a first sending module, a second sending module and a relay mode control module. The invention can fully utilize relay system to reach the effect of improving network performance.

Owner:ZTE CORP

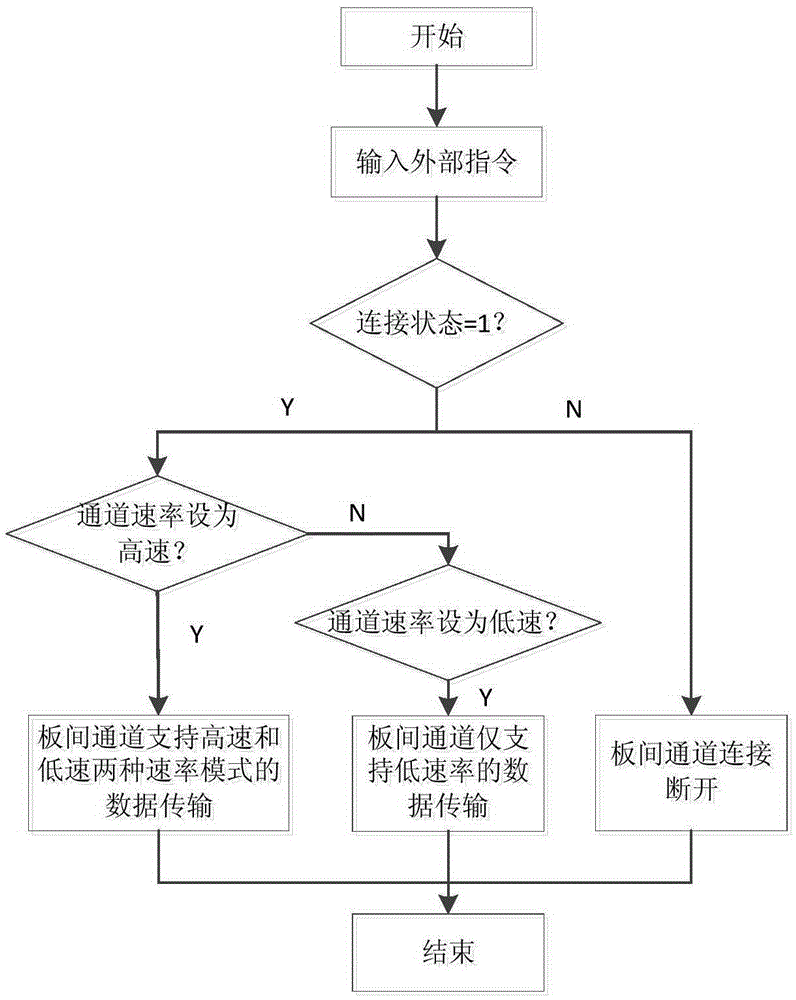

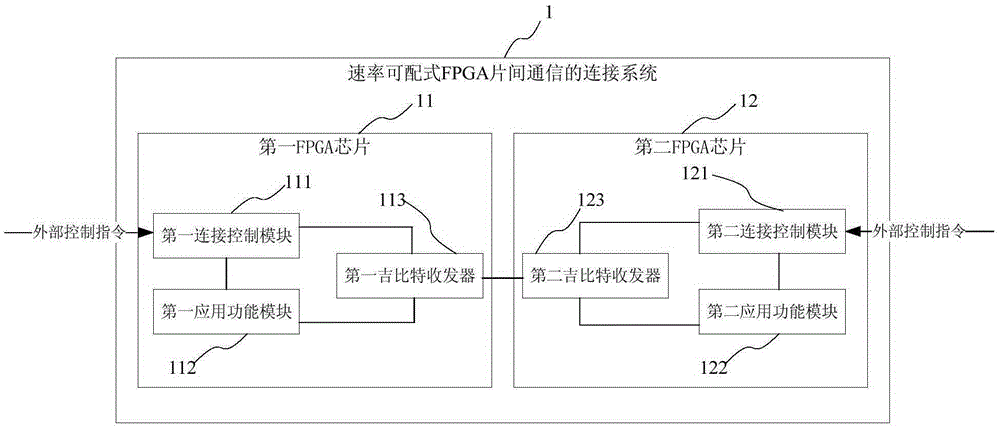

Connecting method and system for communication between rate configurable FPGA chips

ActiveCN105354160AShorten Design Verification CycleLow costElectric digital data processingTransceiverProcessor register

The present invention provides a connecting method and system for communication between rate configurable FPGA chips. The method comprises: connecting two FPGA chips through Gigabit transceivers respectively configured in the two FPGA chips. Each of the FPGA chips is configured with a connection state write register and a channel rate write register, which are respectively used for controlling channel connection states and channel rates in respective FPGA chips according to received external input instructions, while controlling the matching with data transmission rates of the respective FPGA chips receiving and transmitting data, thereby finally realizing switching control of inter-board data links. According to the connecting method and system, high and low-rate data transmission modes are compatible, and different rate modes are independent of each other and non-interfering; and a design verification mode compatible with high and low rates can set up a plurality of test environments at the same time to perform verification, cause no influence on transmission performance for change of a rate mode, effectively shorten a design verification period and reduce costs.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI +1

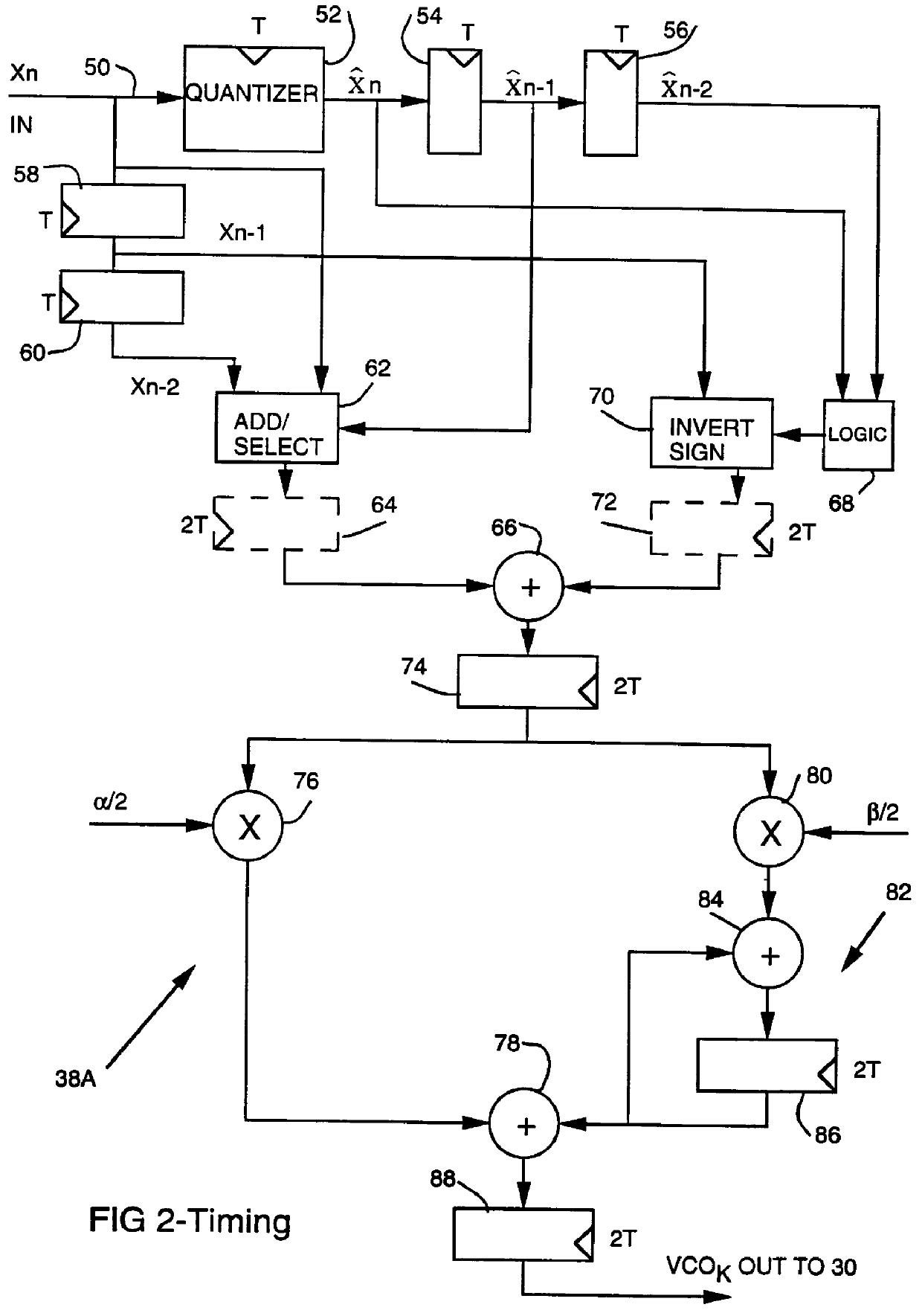

Control loops for low power, high speed PRML sampling data detection channel

InactiveUS6025965AReduce power consumptionReduce in quantityModification of read/write signalsRecord information storageHard disc driveClock rate

A power-reduced digital control within a feedback control loop of a sampling data detection channel controls a predetermined operating parameter of the channel in which an analog to digital converter provides digital samples of information in the channel at a predetermined channel clock rate. The digital control comprises a parameter error extraction circuit clocked at the predetermined channel rate which is connected to receive digital samples from the analog to digital converter, and which extracts parameter error values from the digital samples; an averaging circuit for averaging the extracted parameter error values over an integral submultiple of the predetermined channel clock rate; and a parameter error processing circuit which is connected to the parameter error extraction circuit and clocked at the integral submultiple of the predetermined channel rate for generating and putting out digital control values within the feedback control loop for controlling the predetermined operating parameter. The parameter may be timing, gain or DC offset, and the sampling data detection channel may be a PRML channel of a magnetic hard disk drive. A power-reduced control method is also described.

Owner:MAXTOR

Method and apparatus for dynamically changing a maximum access channel rate

ActiveUS20100020781A1Error preventionFrequency-division multiplex detailsCommunications systemChannel rate

A method, device and computer-readable storage element for dynamically changing a maximum access channel rate at a site in a communication system. The method includes setting a maximum access channel rate for an access channel at a site, which comprises a coverage area for a base station. The method further includes determining a first access probe success rate that measures a rate at which first attempt access probes sent from the terminals on the access channel are received, and changing the maximum access channel rate based on the first access probe success rate.

Owner:GOOGLE TECH HLDG LLC

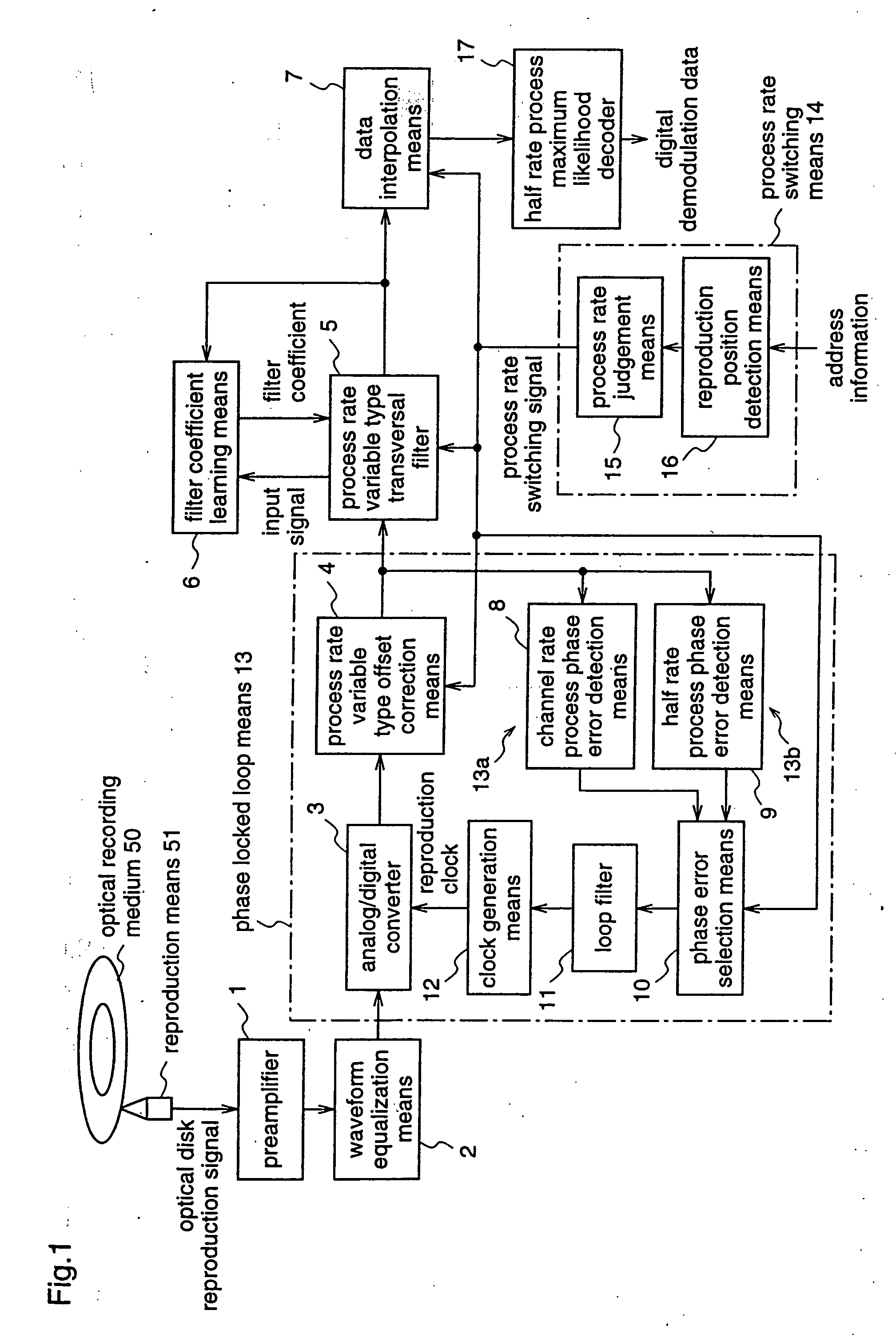

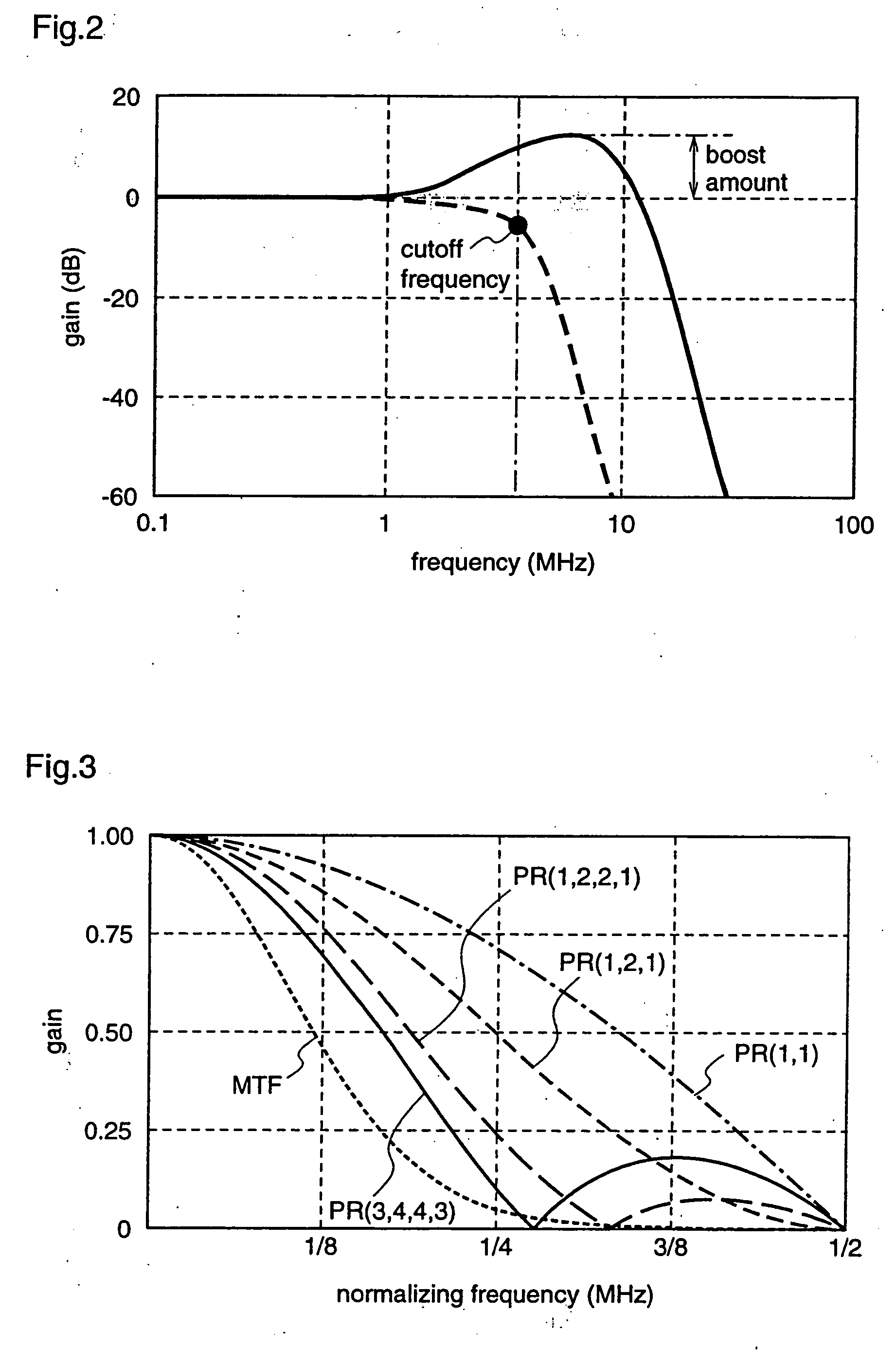

Optical disk reproducing device selectively using a channel bit frequency or a frequency that is half of the channel bit frequency

InactiveUS20060187800A1Reduce the number of timesReduce power consumptionTelevision system detailsModification of read/write signalsDigital dataHalf Rate

A data demodulation process rate is varied according to a reproduction state, thereby reducing power consumption while maintaining a reading performance in a favorable state. A channel rate process data demodulation device performs a data demodulation process by employing channel bit frequency. Further, a half rate process data demodulation device performs a data demodulation process by employing frequency half as high as the channel bit frequency. These devices demodulate digital data from an optical recording medium. A process rate switching device switches a process rate at data demodulation, whereby demodulation is performed by switching between the data demodulation devices according to a quality of a reproduction signal, so as to reproduce the digital data recorded on the optical recording medium.

Owner:PANASONIC HEALTHCARE HLDG CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com