Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

149results about How to "Small depth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

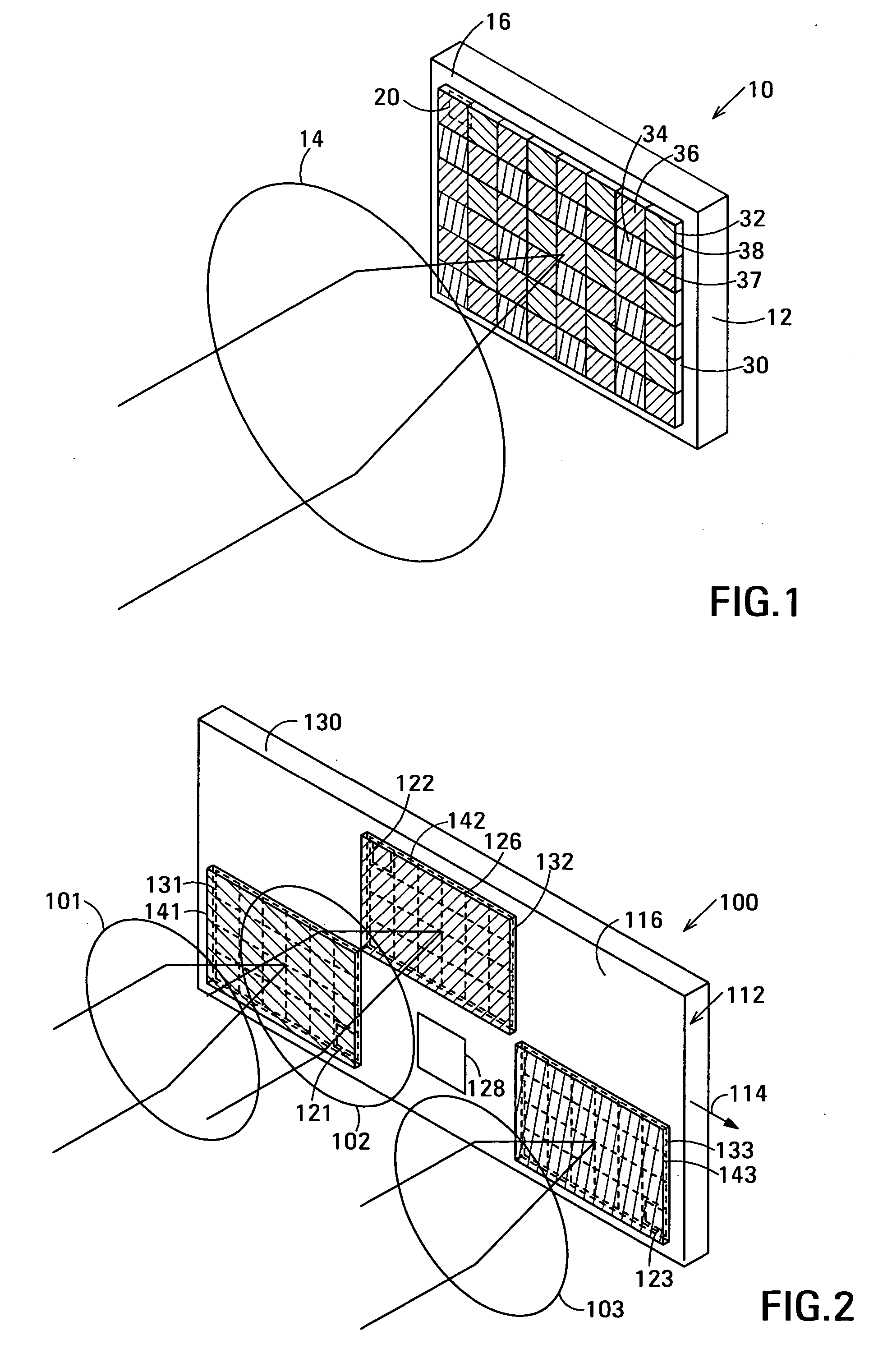

Color image sensor having imaging element array forming images on respective regions of sensor elements

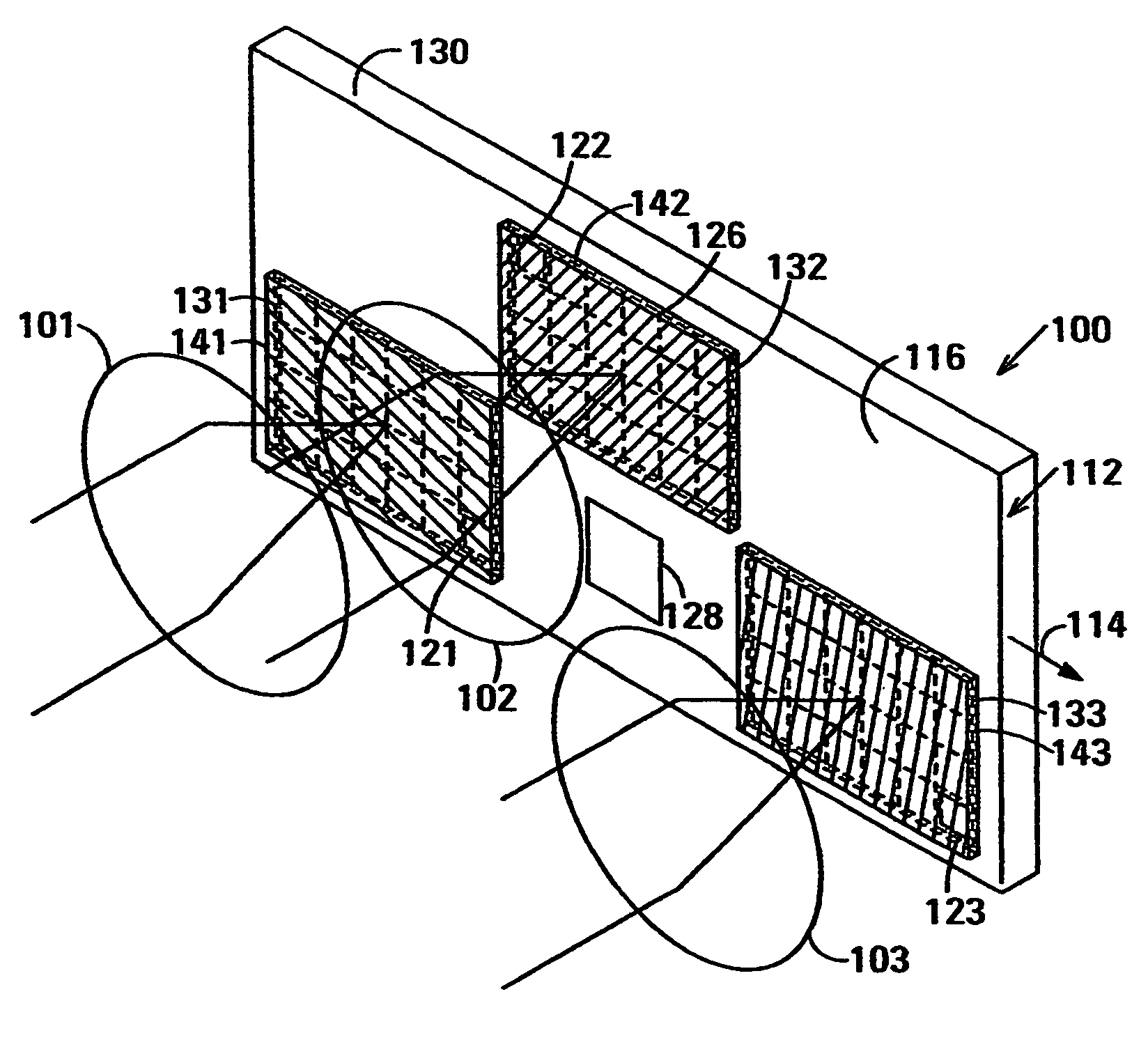

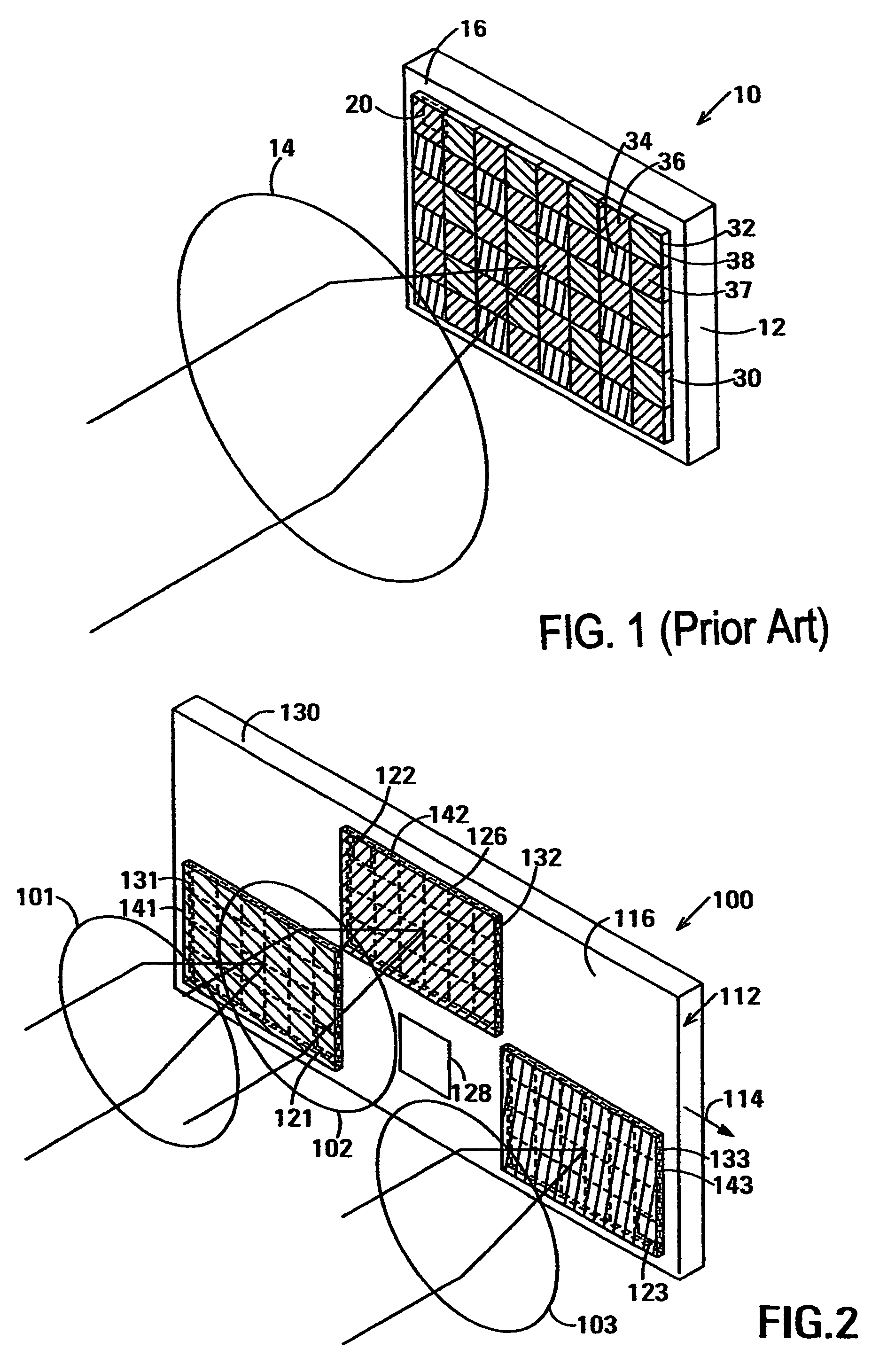

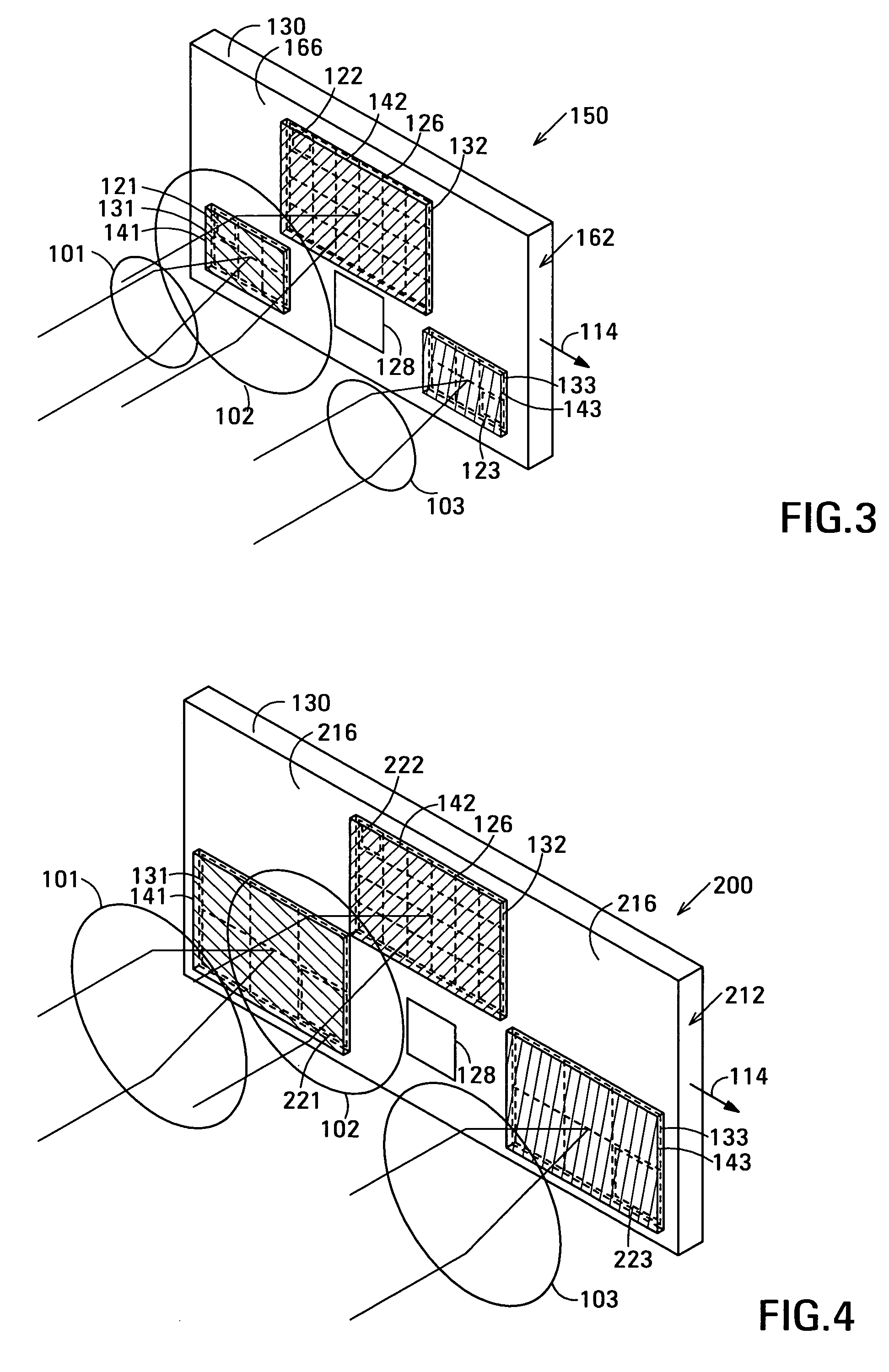

The color image sensor generates a color image signal representing a subject and includes an optical substrate and a light sensor. The optical substrate includes spatially-separated imaging elements. Each of the imaging elements is configured to image light of a respective color. The light sensor includes regions of sensor elements disposed opposite respective ones of the imaging elements. The sensor elements in each of the regions are operable to generate a component of the color image signal in response to the light of the respective color incident on them.

Owner:APTINA IMAGING CORP

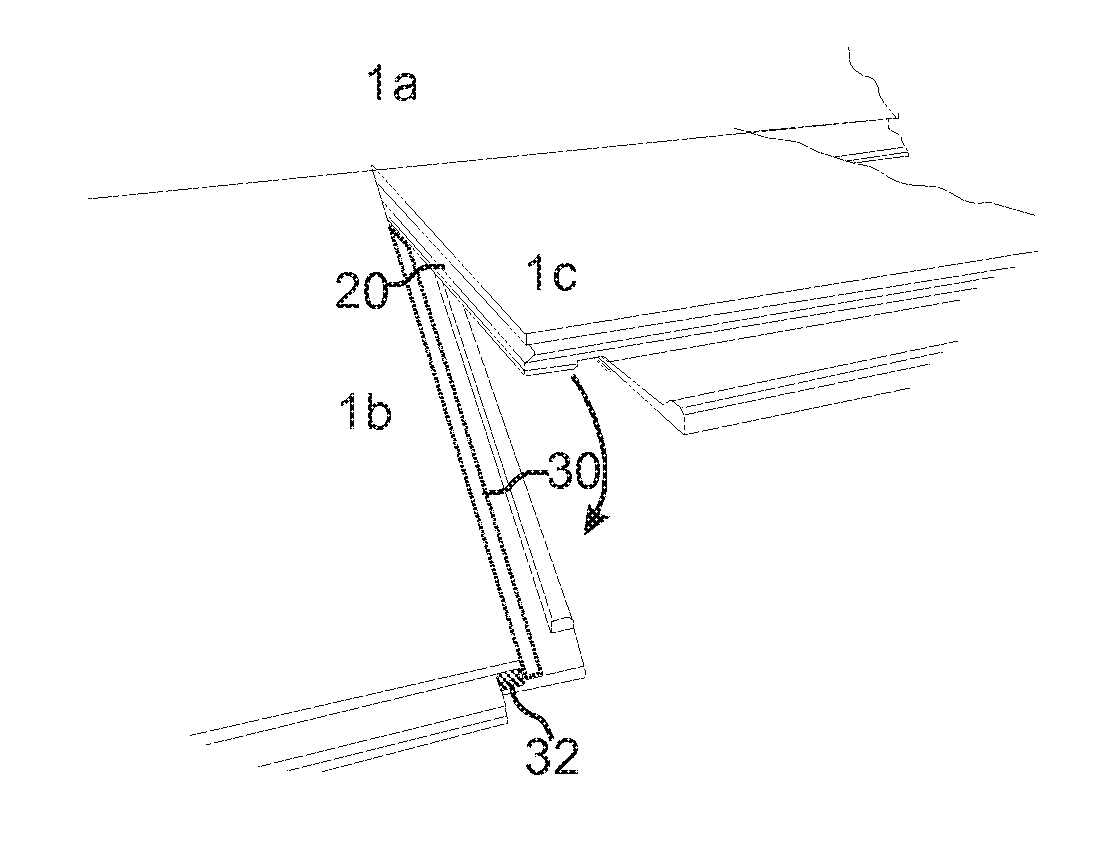

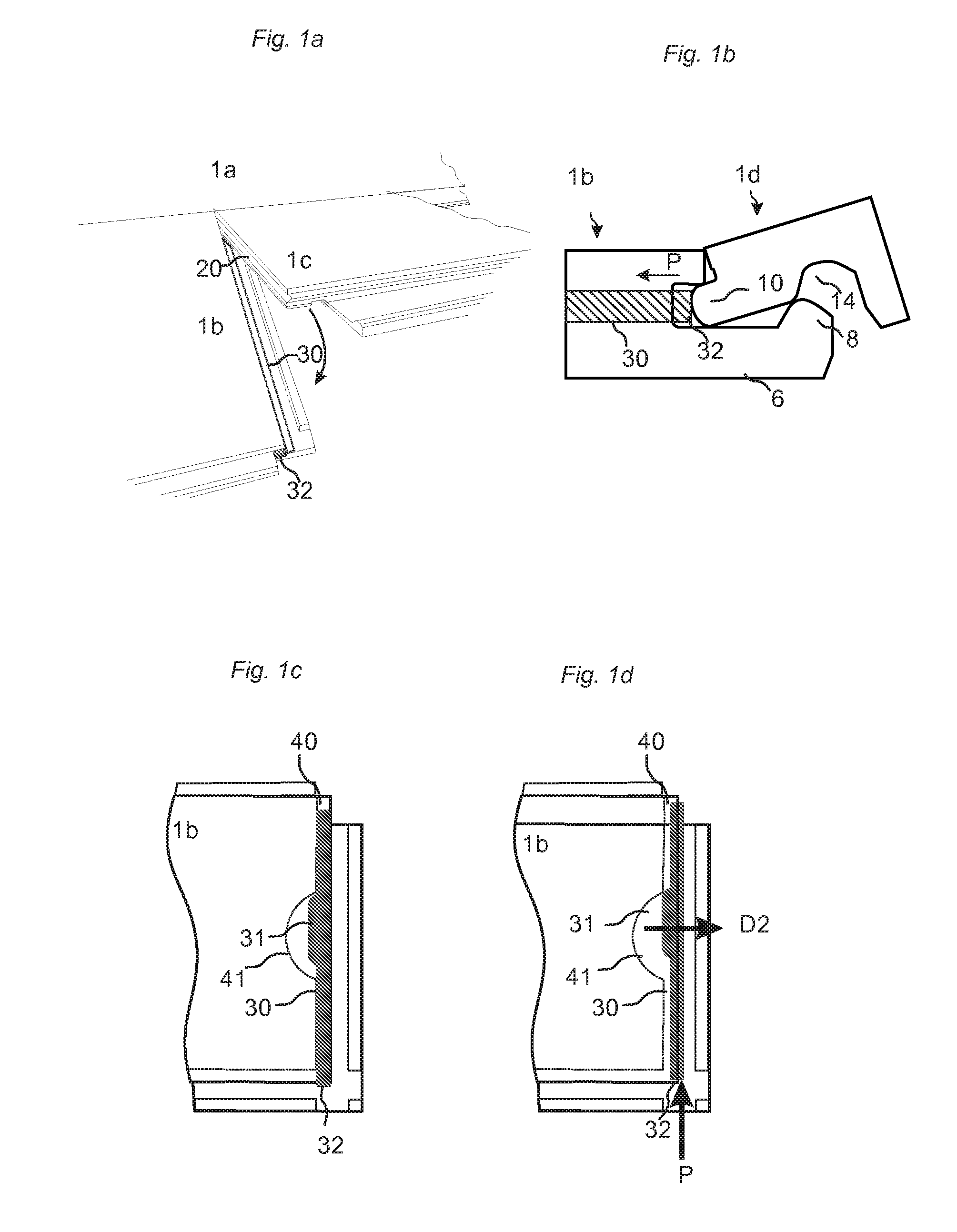

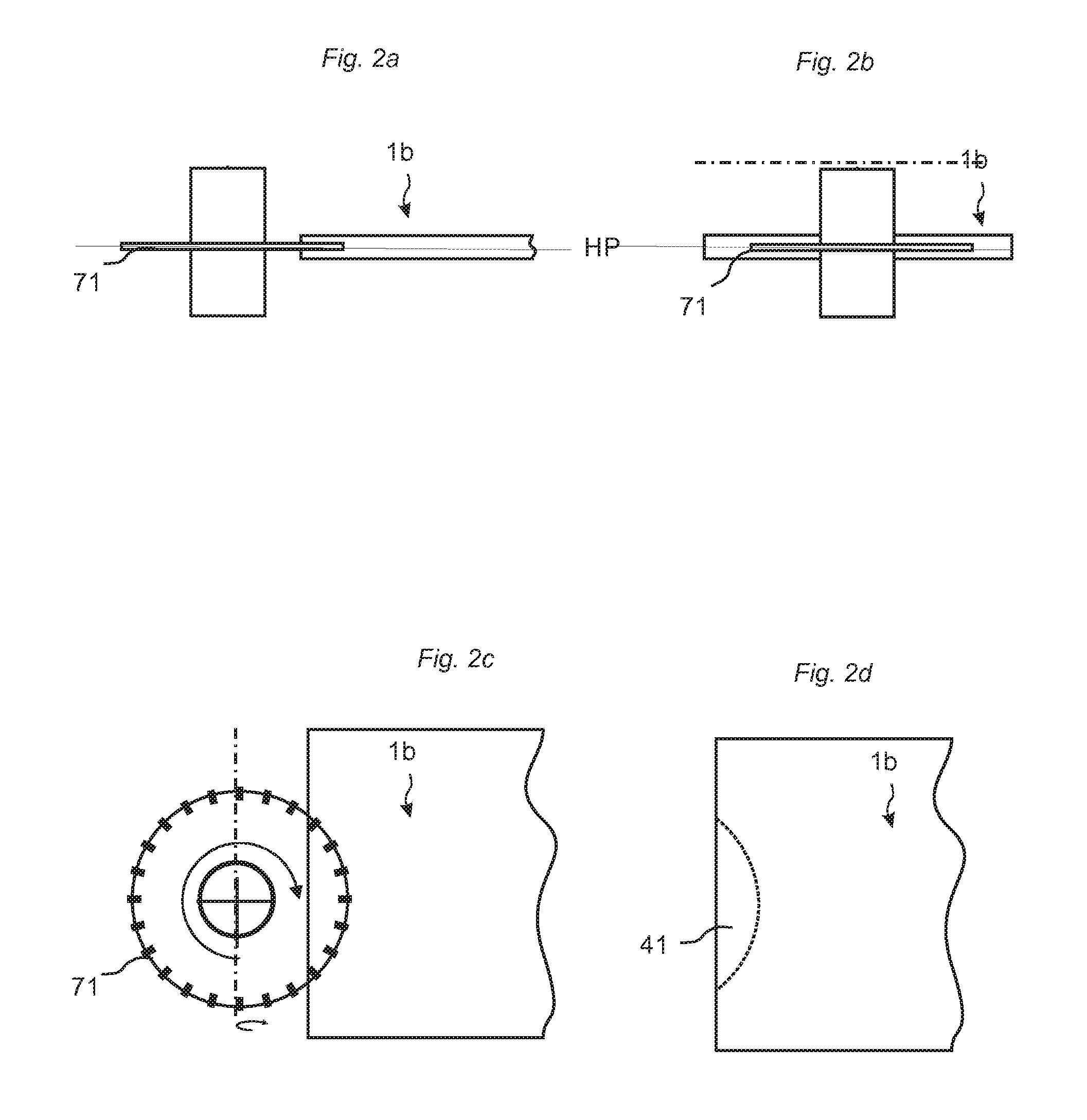

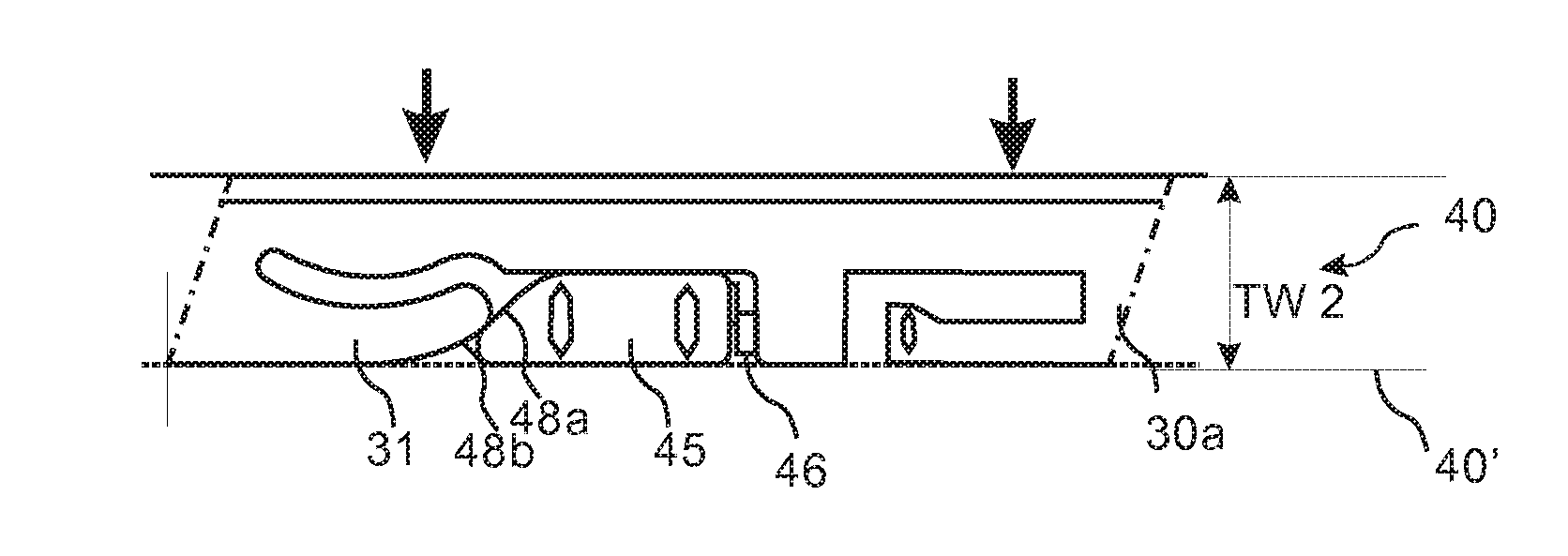

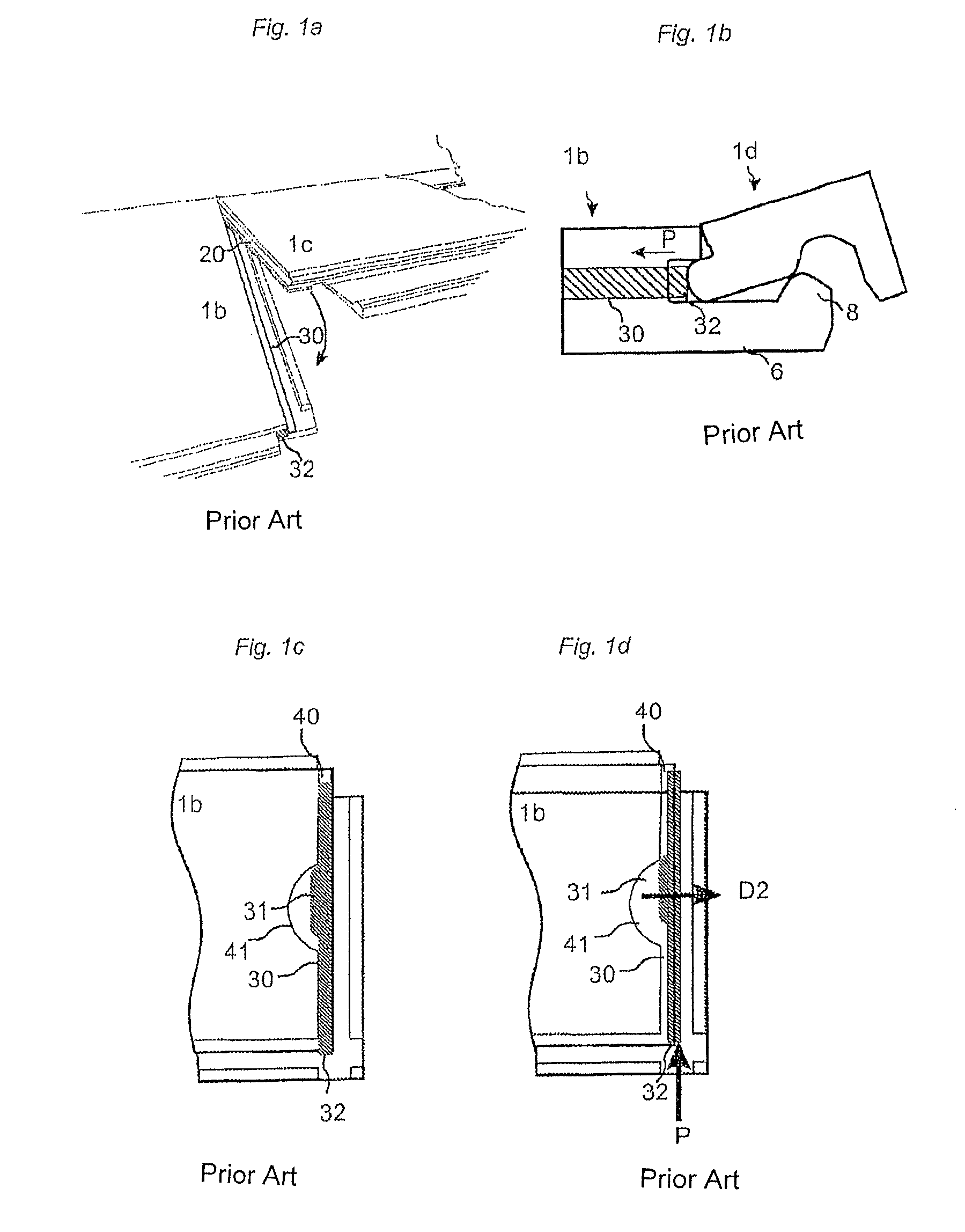

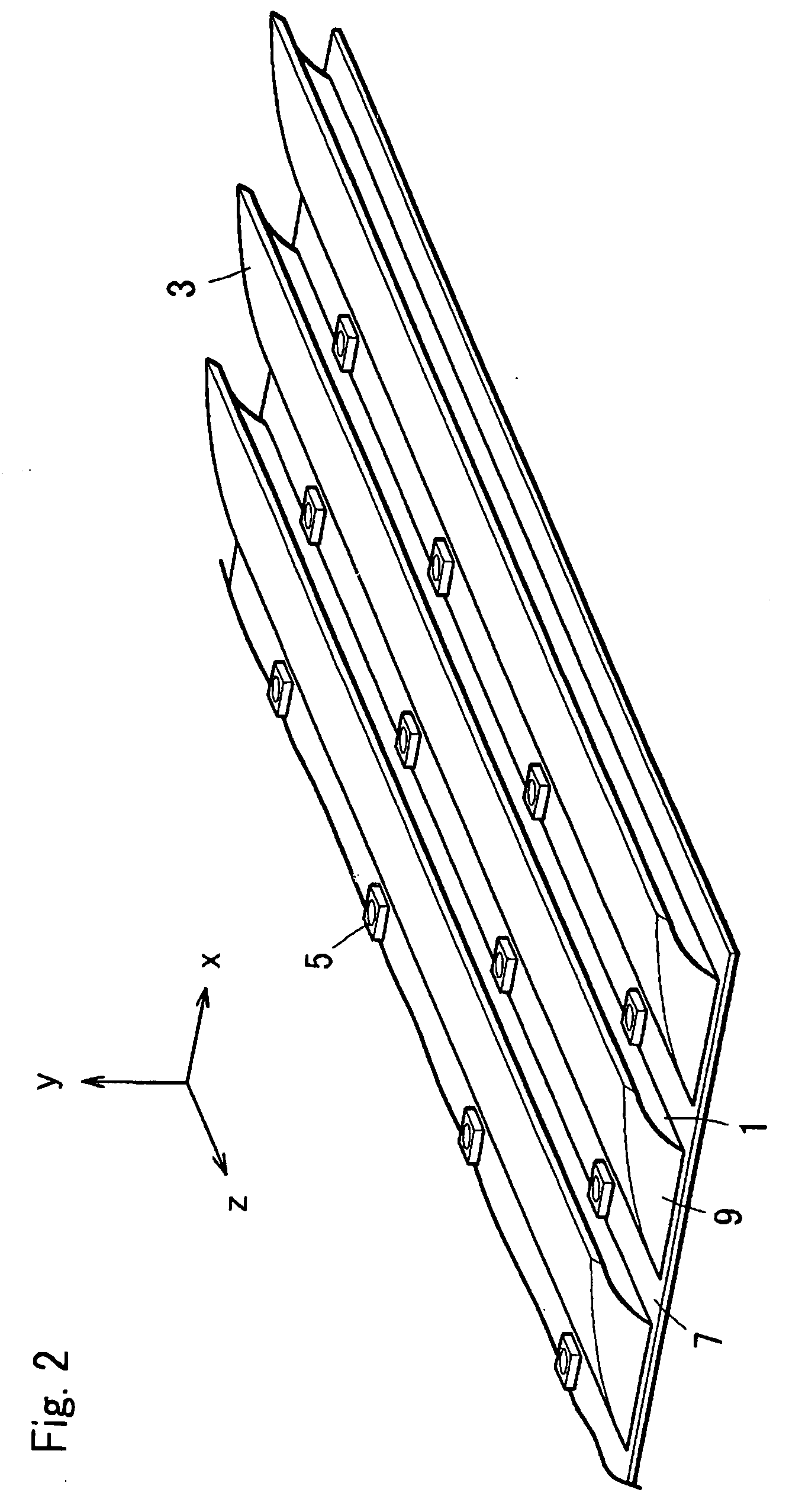

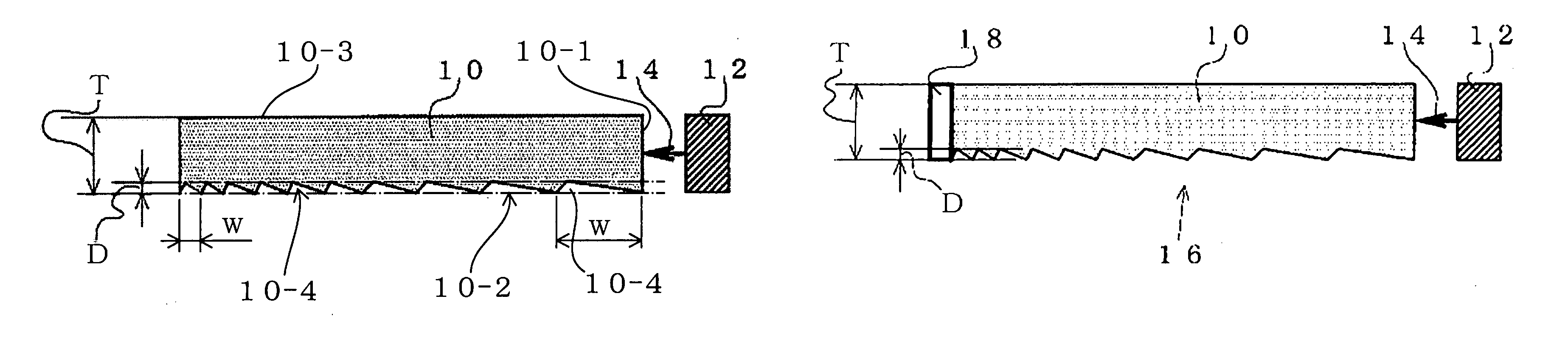

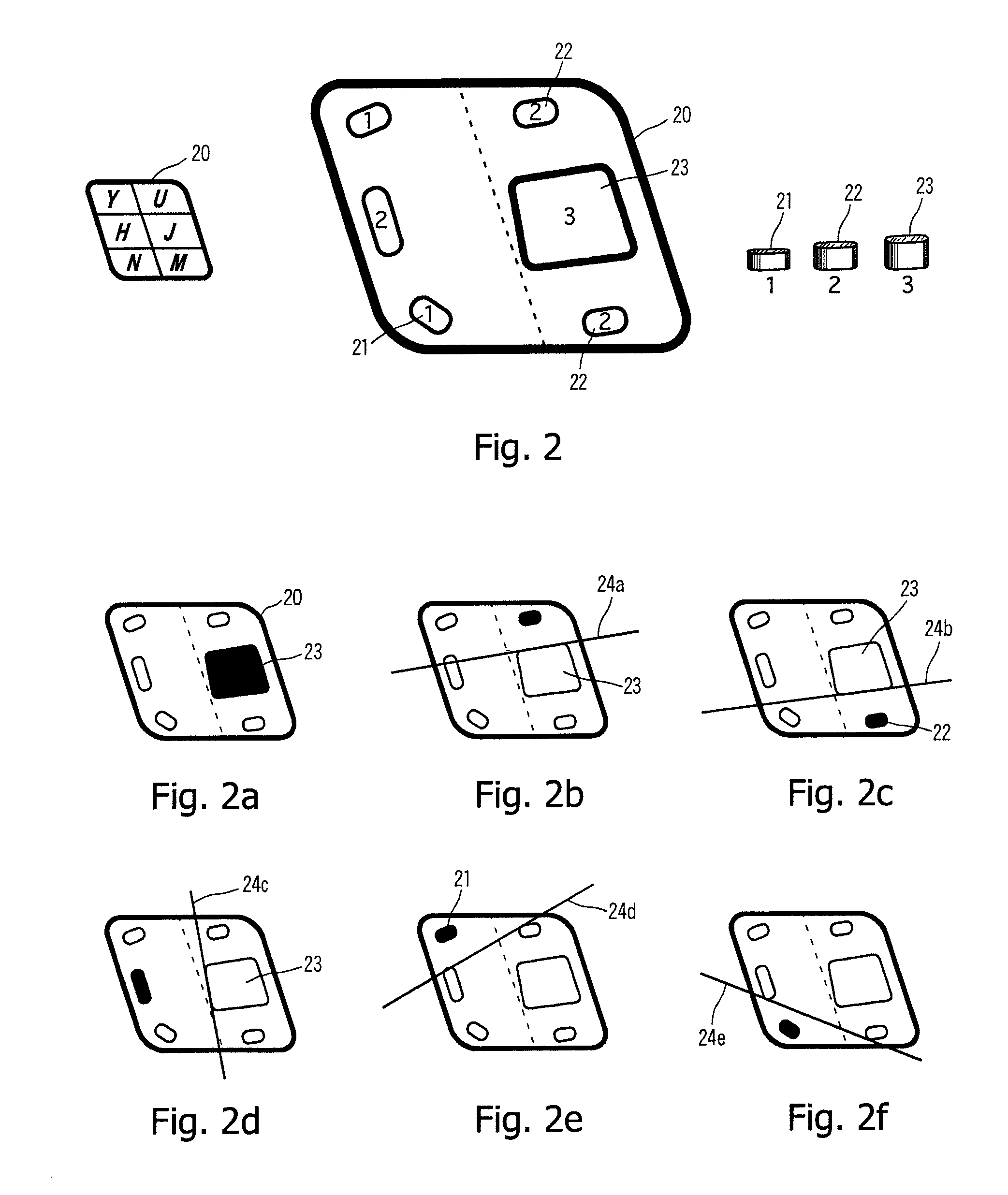

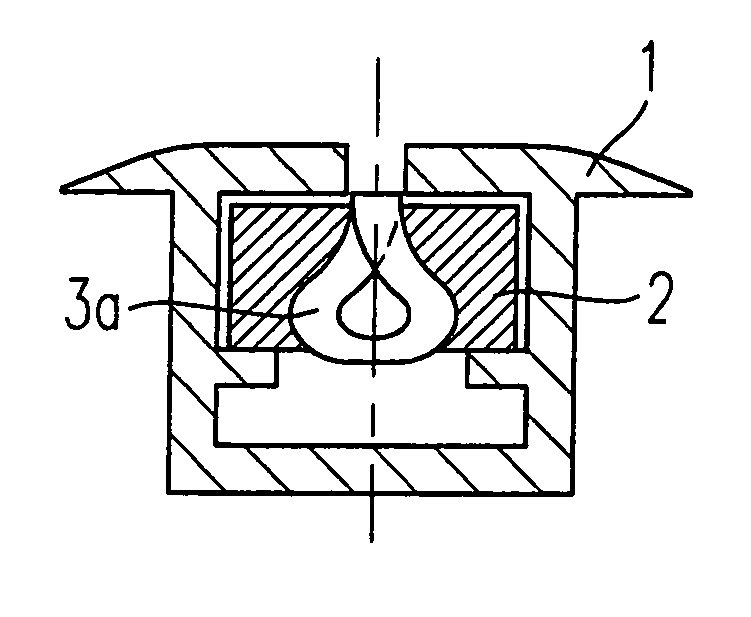

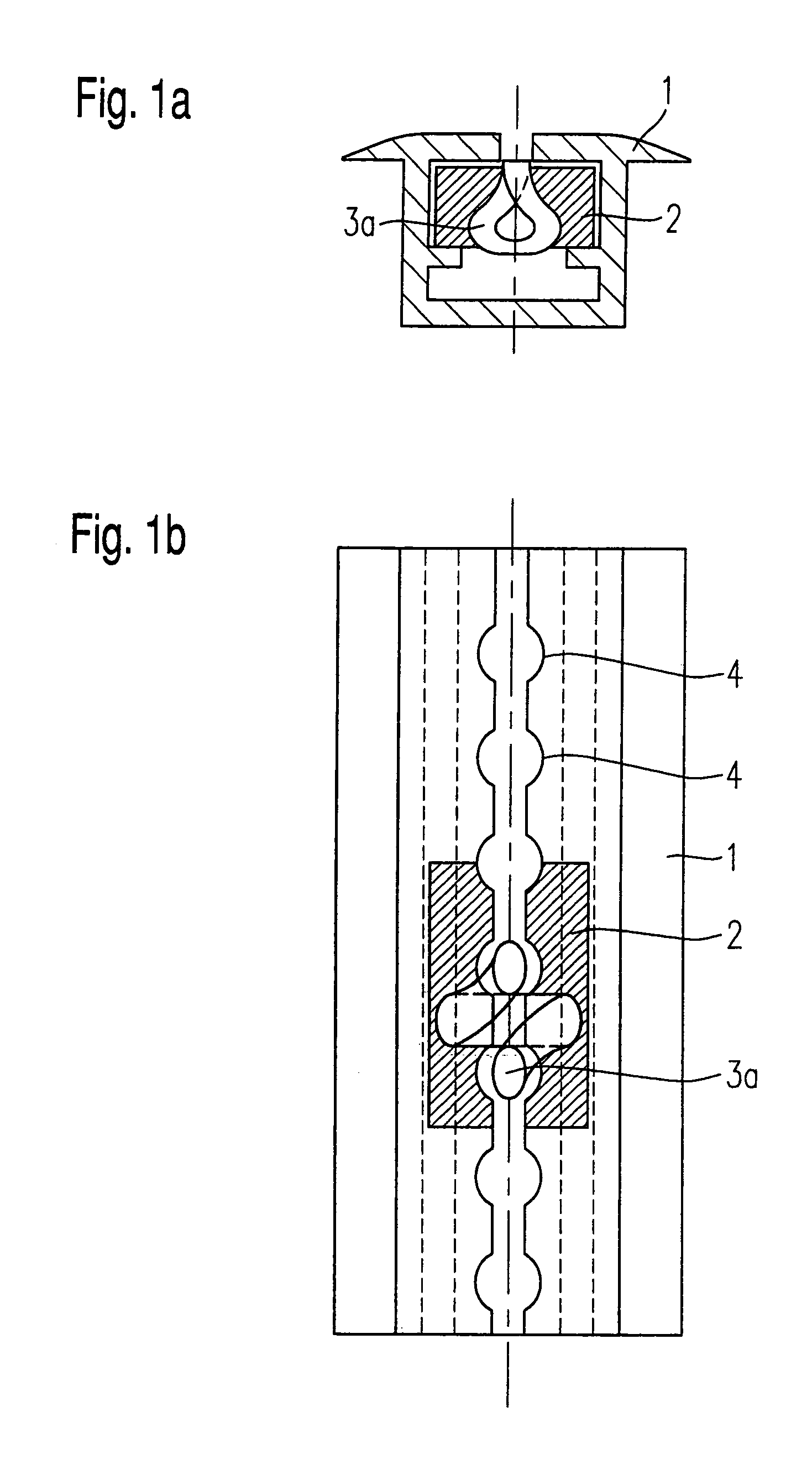

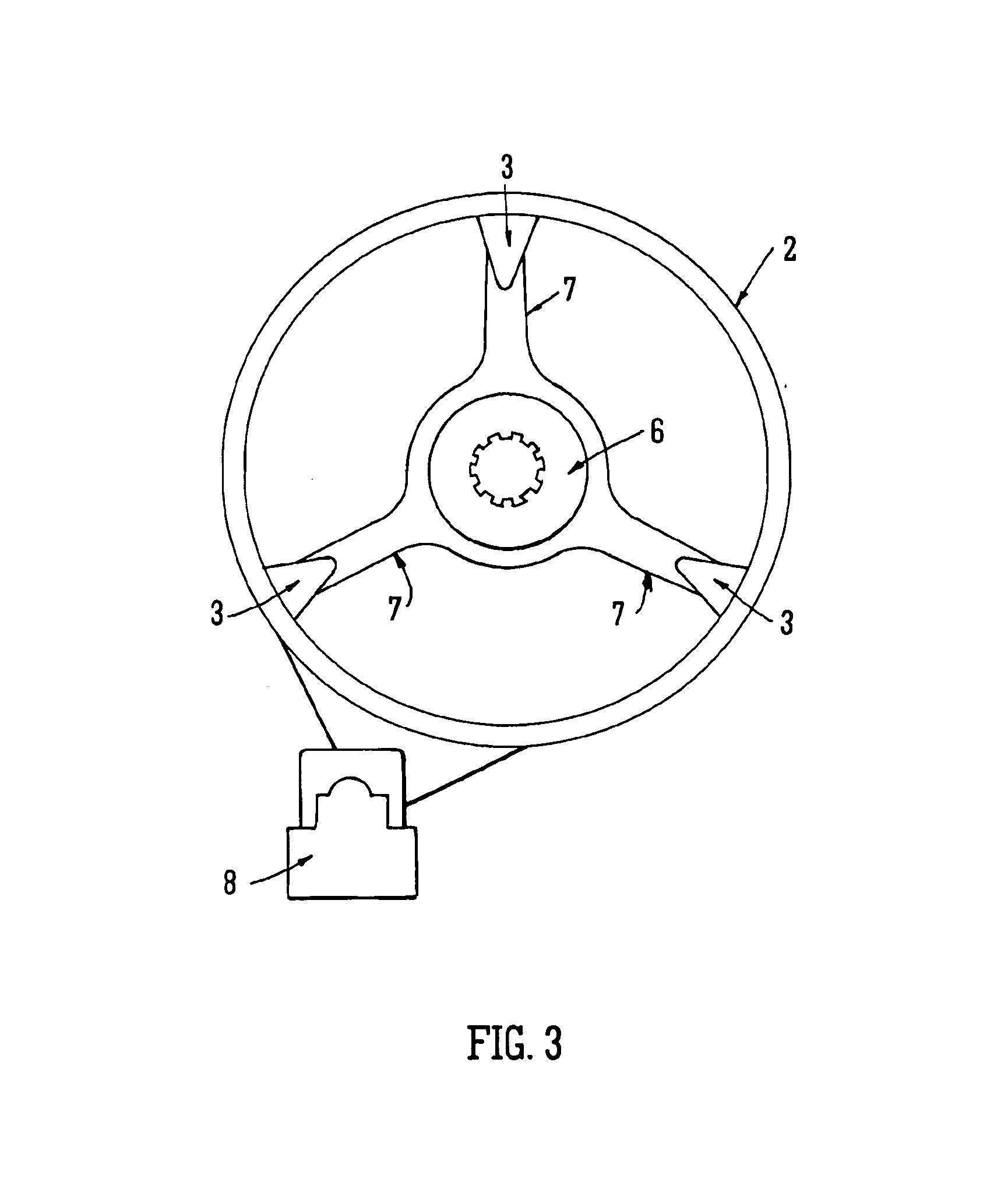

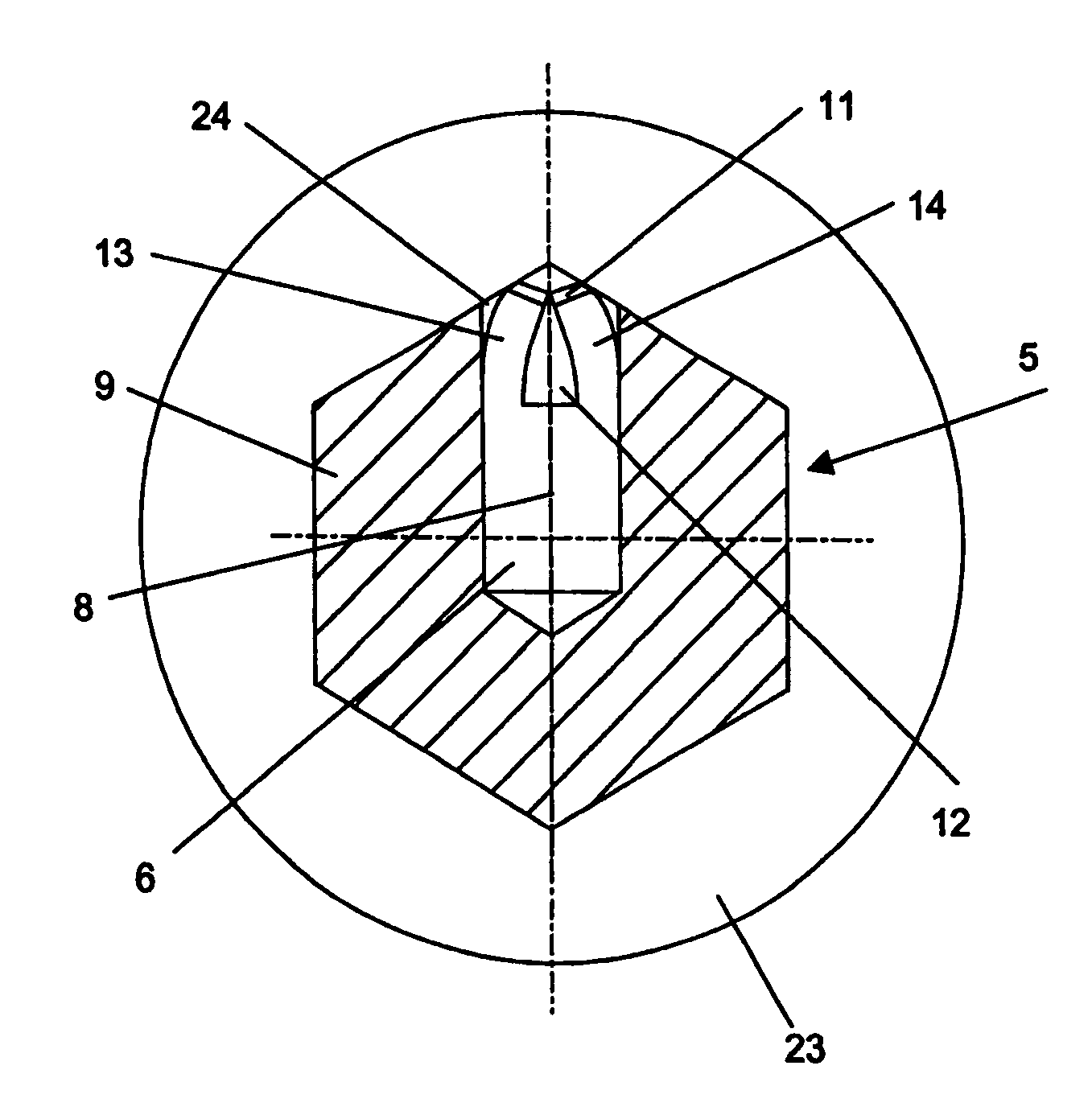

Mechanical lockings of floor panels and a tongue blank

ActiveUS20120017533A1Improve function and strengthFunction increaseFloorsFlooringTongue and grooveEngineering

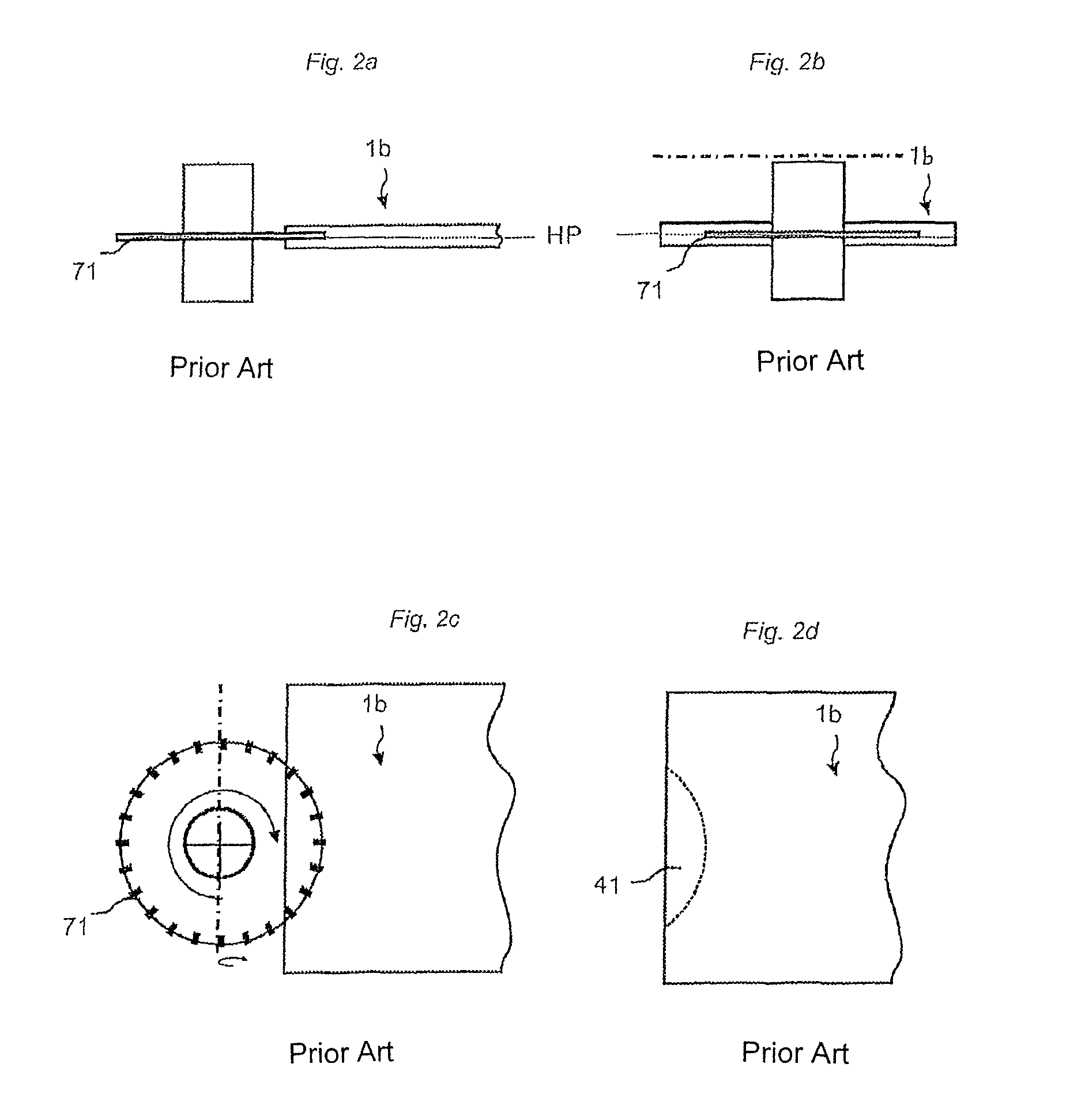

Floor panels (1, 1′) are shown, which are provided with a mechanical locking system comprising tongue and grooves provided with protrusions and cavities which are displaceable in relation to each other.

Owner:VÄLINGE INNOVATION AB

Mechanical lockings of floor panels and a tongue blank

Floor panels which are provided with a mechanical locking system comprising tongue and grooves provided with protrusions and cavities which are displaceable in relation to each other.

Owner:VÄLINGE INNOVATION AB

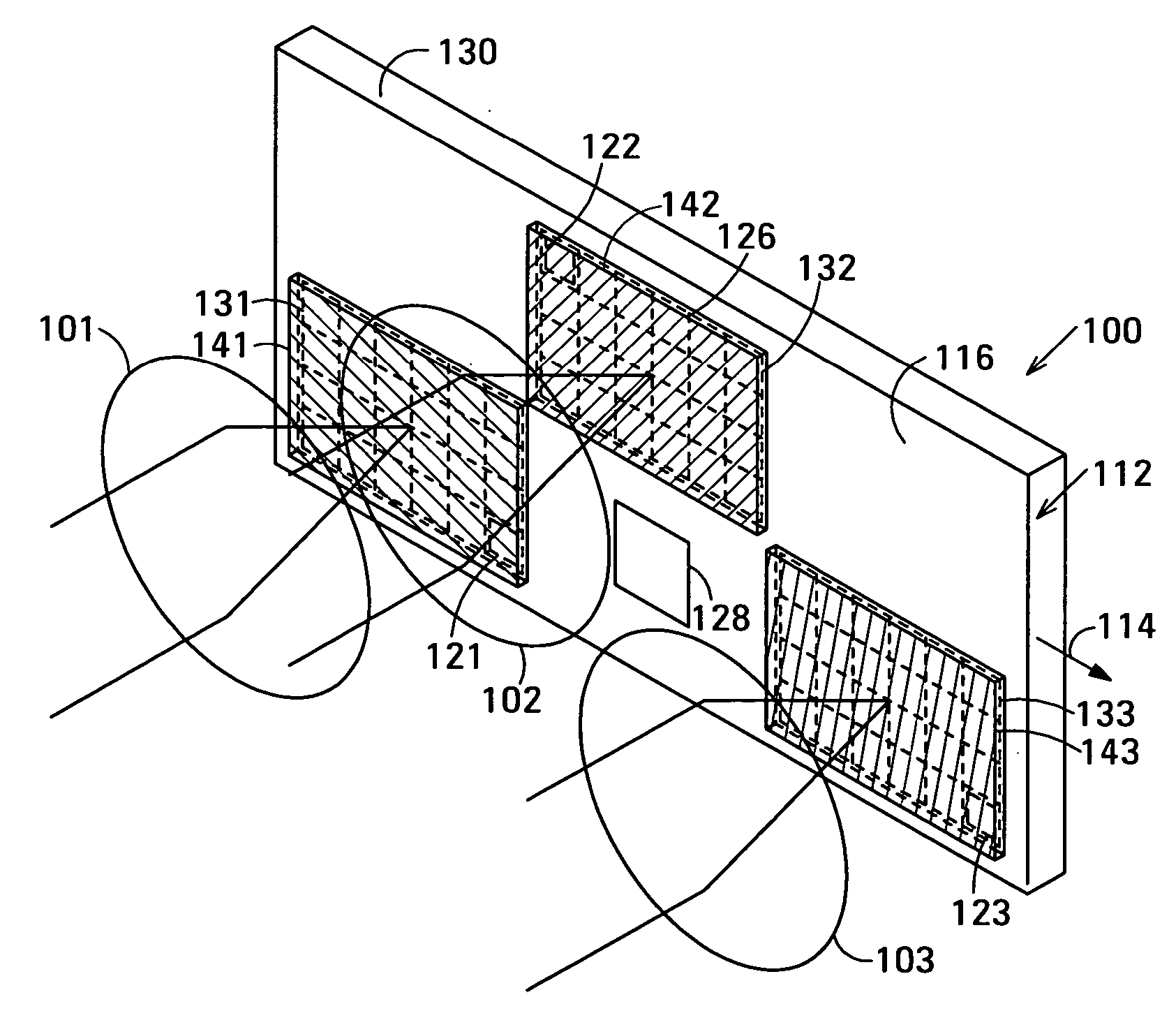

Color image sensor with imaging elements imaging on respective regions of sensor elements

ActiveUS7123298B2Reduce areaIntuitive imageTelevision system detailsTelevision system scanning detailsColor imageImage signal

The color image sensor generates an image signal representing a subject. The color image sensor has a light sensor and imaging elements arranged to form images of the subject in light of different colors on respective regions of the light sensor. The light sensor includes sensor elements and is operable to generate the image signal in response to light incident on it.

Owner:MICRON TECH INC

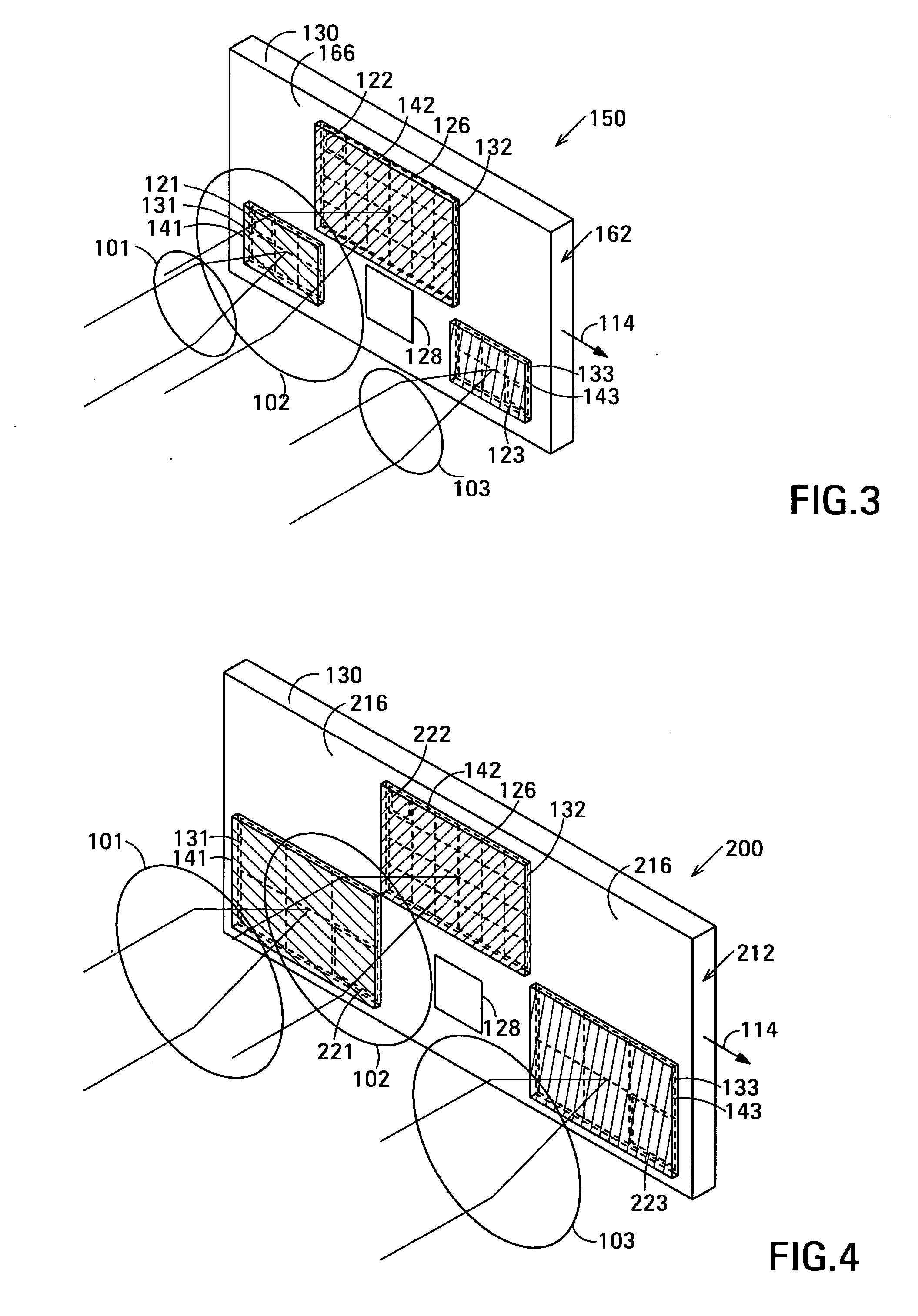

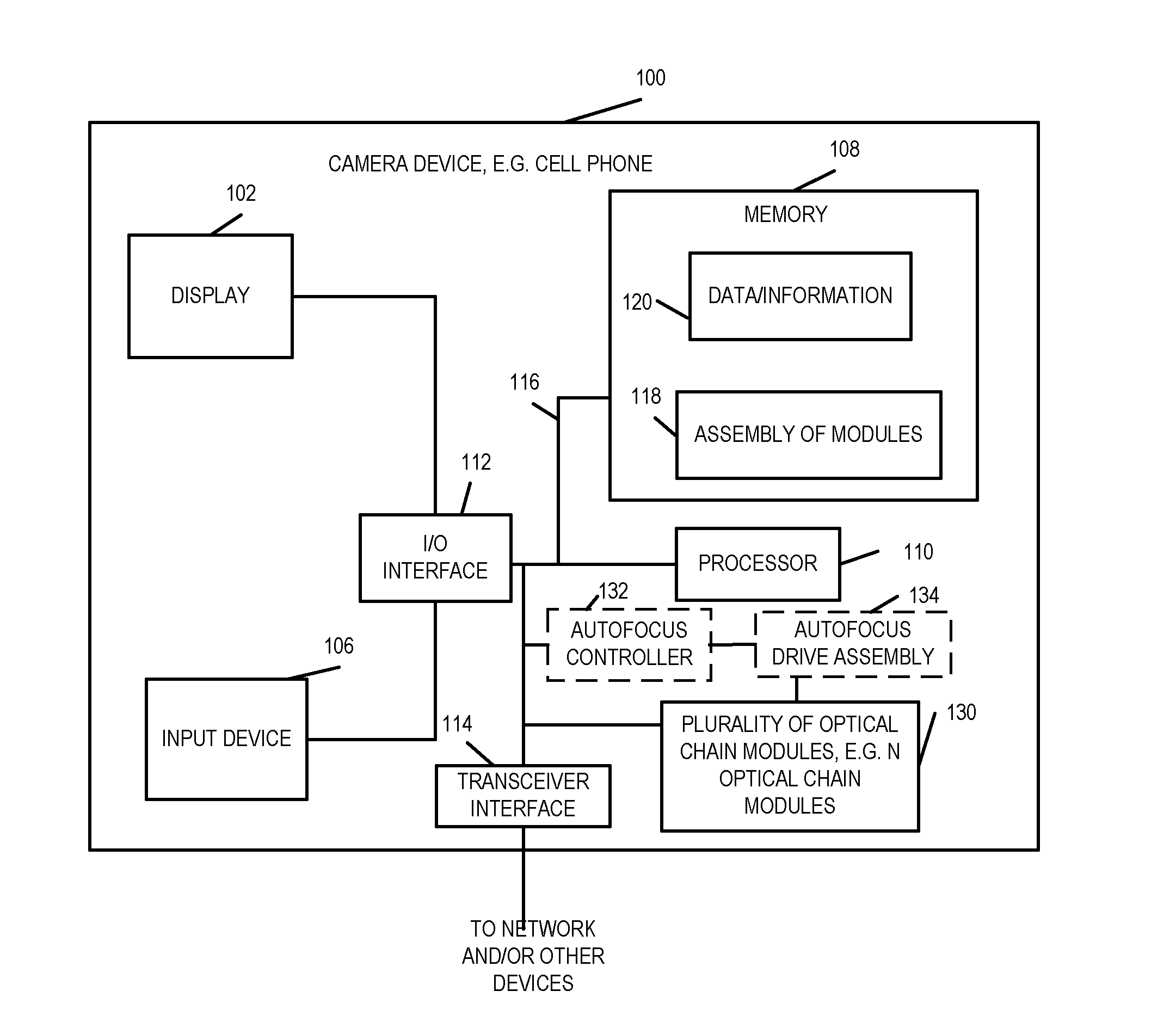

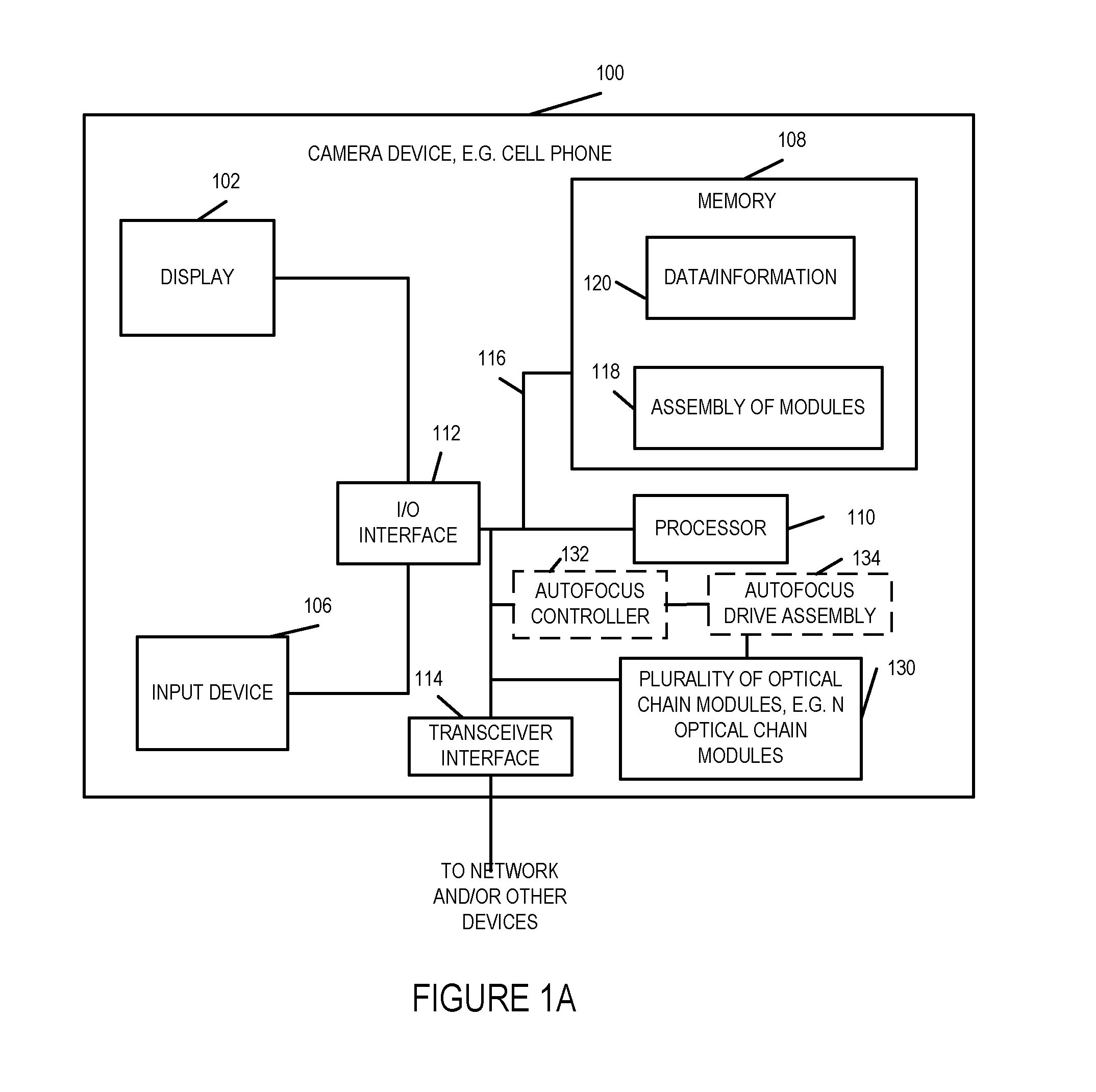

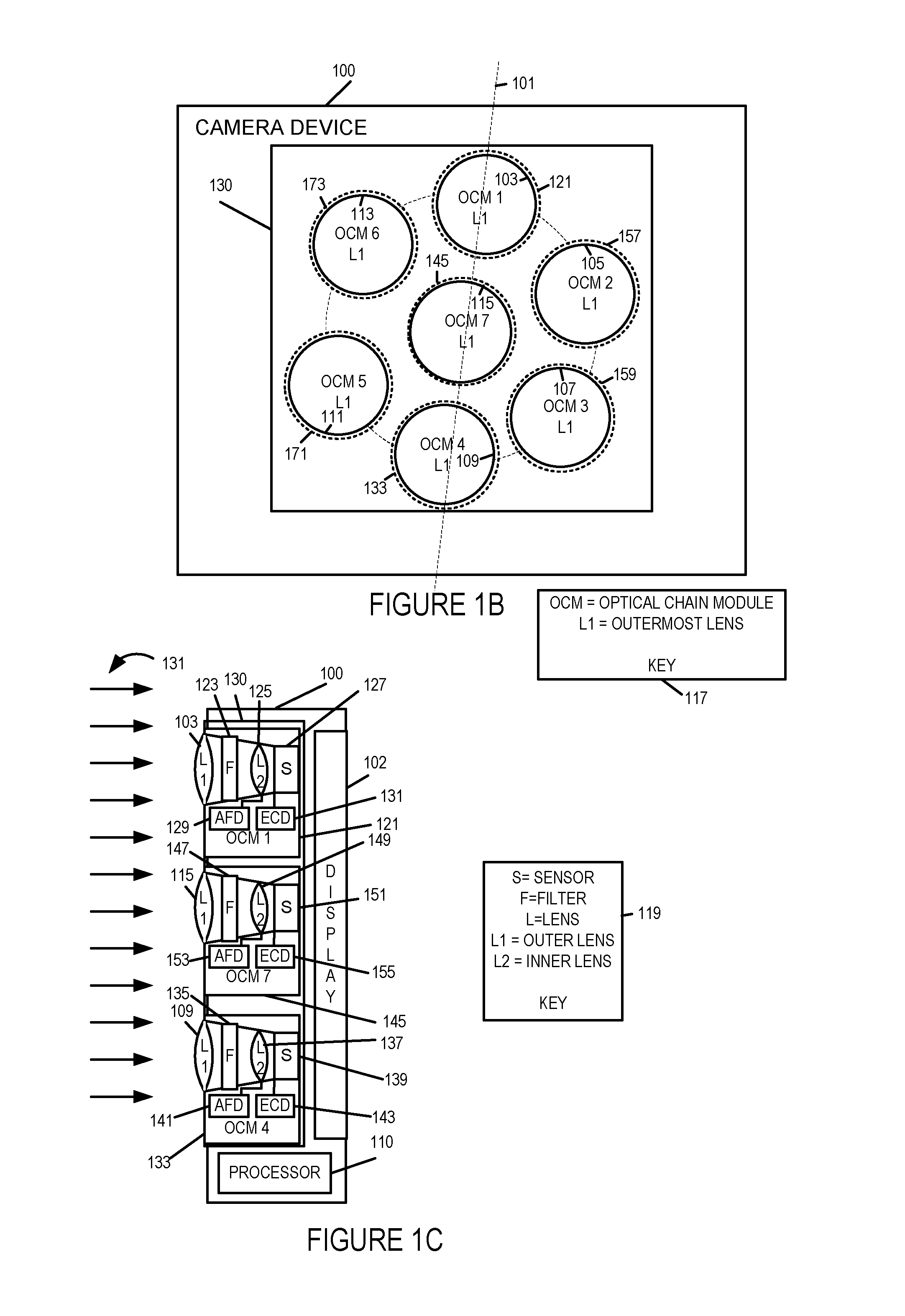

Methods and apparatus for using multiple optical chains in paralell

ActiveUS20140192214A1Enhance the imageImproved video generation resultTelevision system detailsColor television detailsCamera lensMultiple sensor

Methods and apparatus for capturing or generating images using multiple optical chains operating in parallel are described. Pixel values captured by individual optical chains corresponding to the same scene area are combined to provide an image with at least some of the benefits which would have been provided by capturing an image of the scene using a larger lens than that of the individual lenses of the optical chain modules. By using multiple optical chains in parallel at least some benefits normally obtained from using a large lens can be obtained without the need for a large lens. Furthermore in at least some embodiments, a wide dynamic range can be supported through the use of multiple sensors with the overall supported dynamic range being potentially larger than that of the individual sensors. Some lens and / or optical chain configurations are designed for use in small handheld devices, e.g., cell phones.

Owner:BLUE RIVER TECH

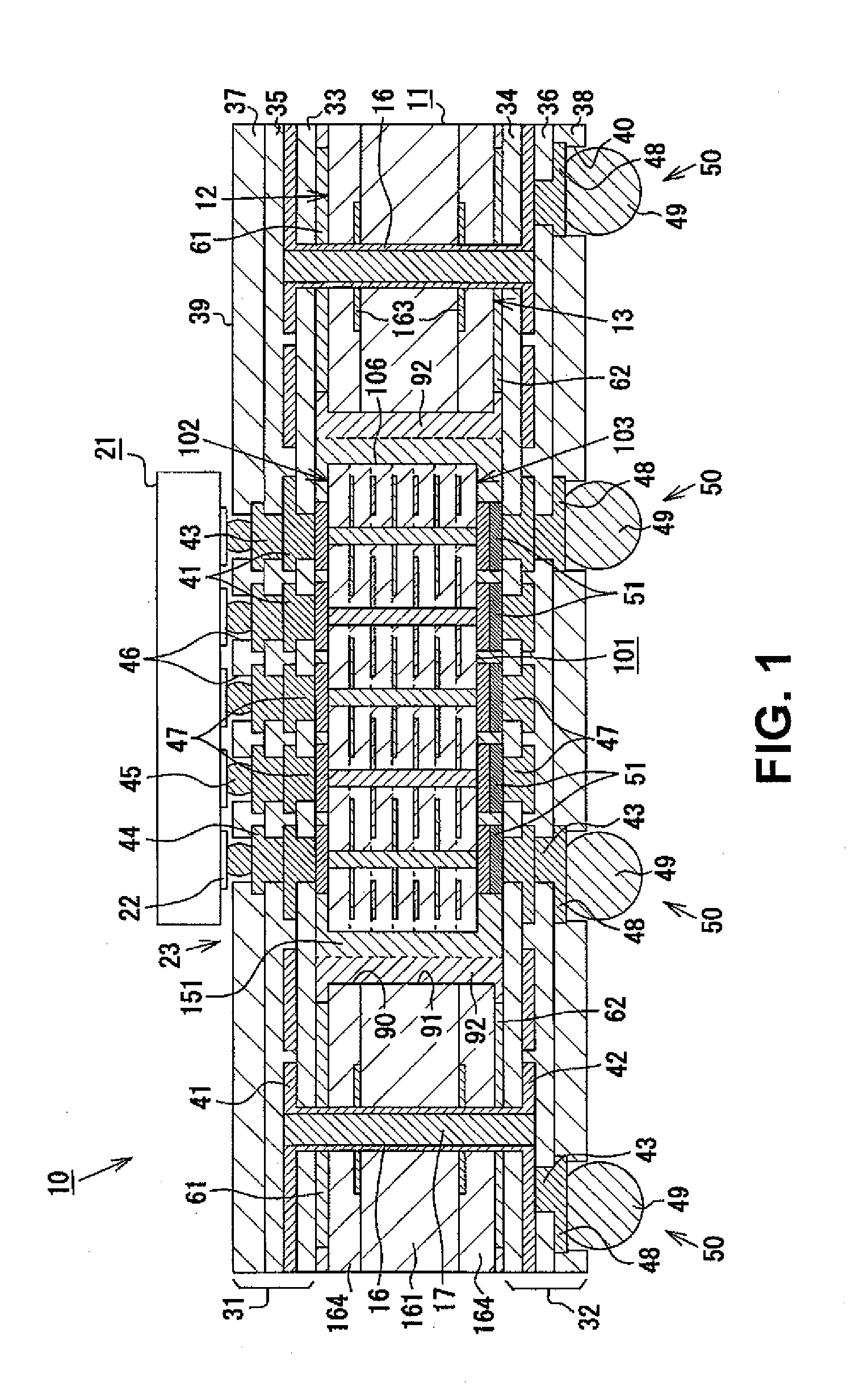

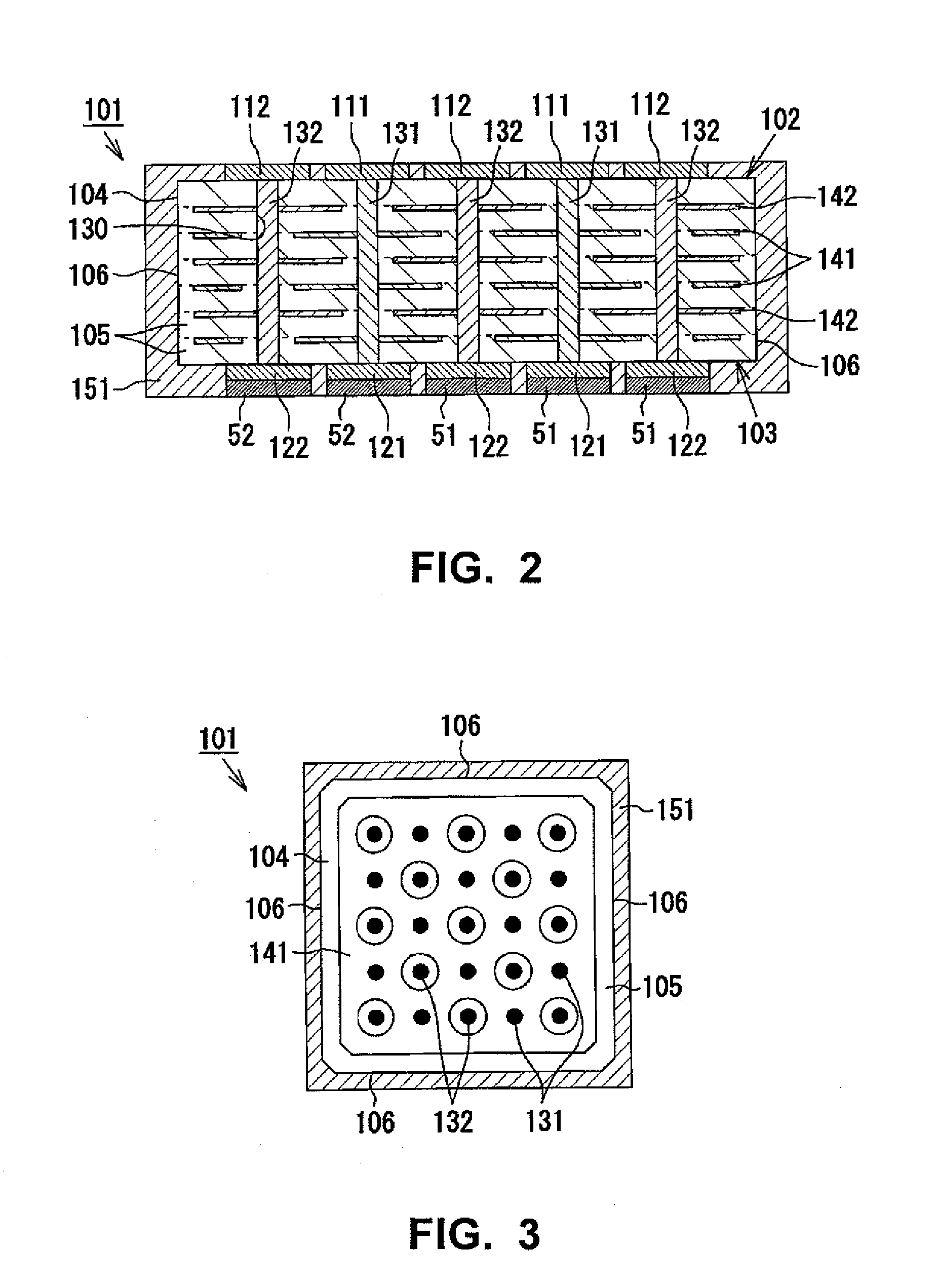

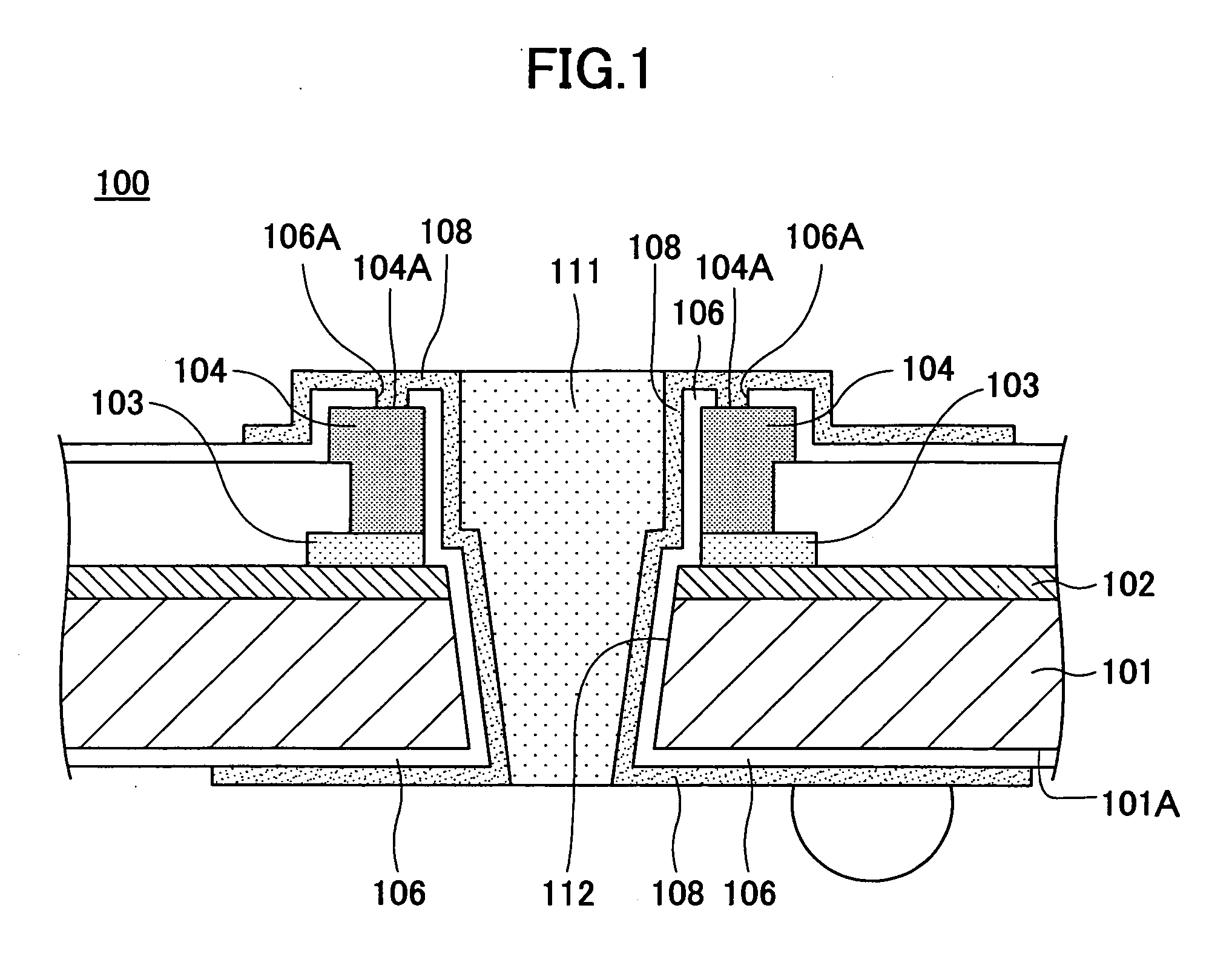

Wiring board with built-in component and method for manufacturing the same

InactiveUS20080277150A1Avoid defectsImprove reliabilityPrinted circuit assemblingSemiconductor/solid-state device detailsElectrical conductorCeramic capacitor

A method for manufacturing a wiring board with built-in component. The method provides a secure connection between a component and interlayer insulating layers so that the wiring board with built-in component has excellent reliability. The wiring board is manufactured through a core board preparation step, a component preparation step, an accommodation step and a height alignment step. In the core board preparation step, a core board having an accommodation hole therein is prepared. In the component preparation step, a ceramic capacitor having therein a plurality of protruding conductors which protrudes from a capacitor rear surface is prepared. In the accommodation step, the ceramic capacitor is accommodated in the accommodation hole with the core rear surface facing the same side as the capacitor rear surface. In the height alignment step, a surface of a top portion of the protruding conductor and a surface of a conductor layer formed on the core rear surface are aligned to the same height.

Owner:NGK SPARK PLUG CO LTD

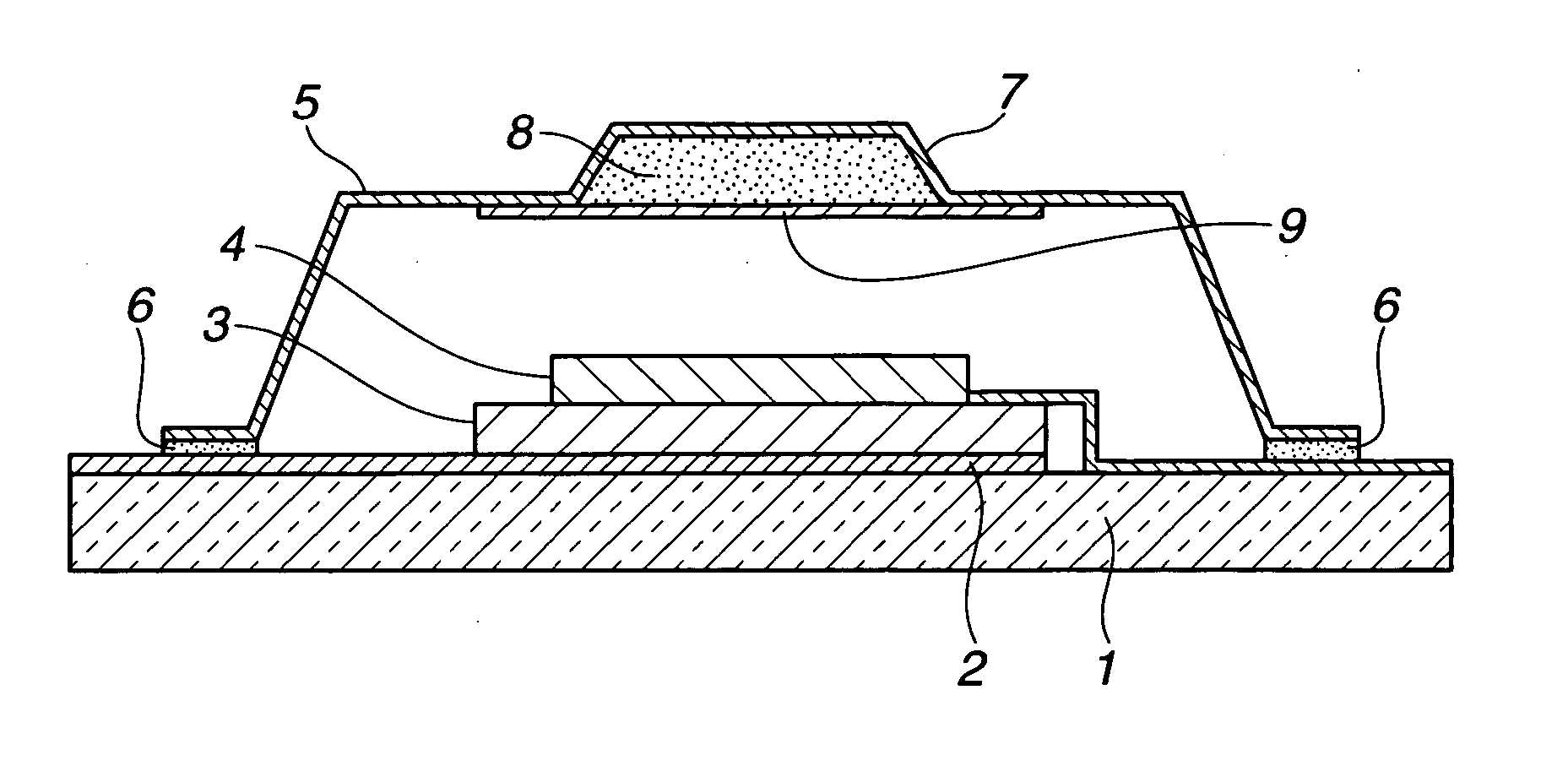

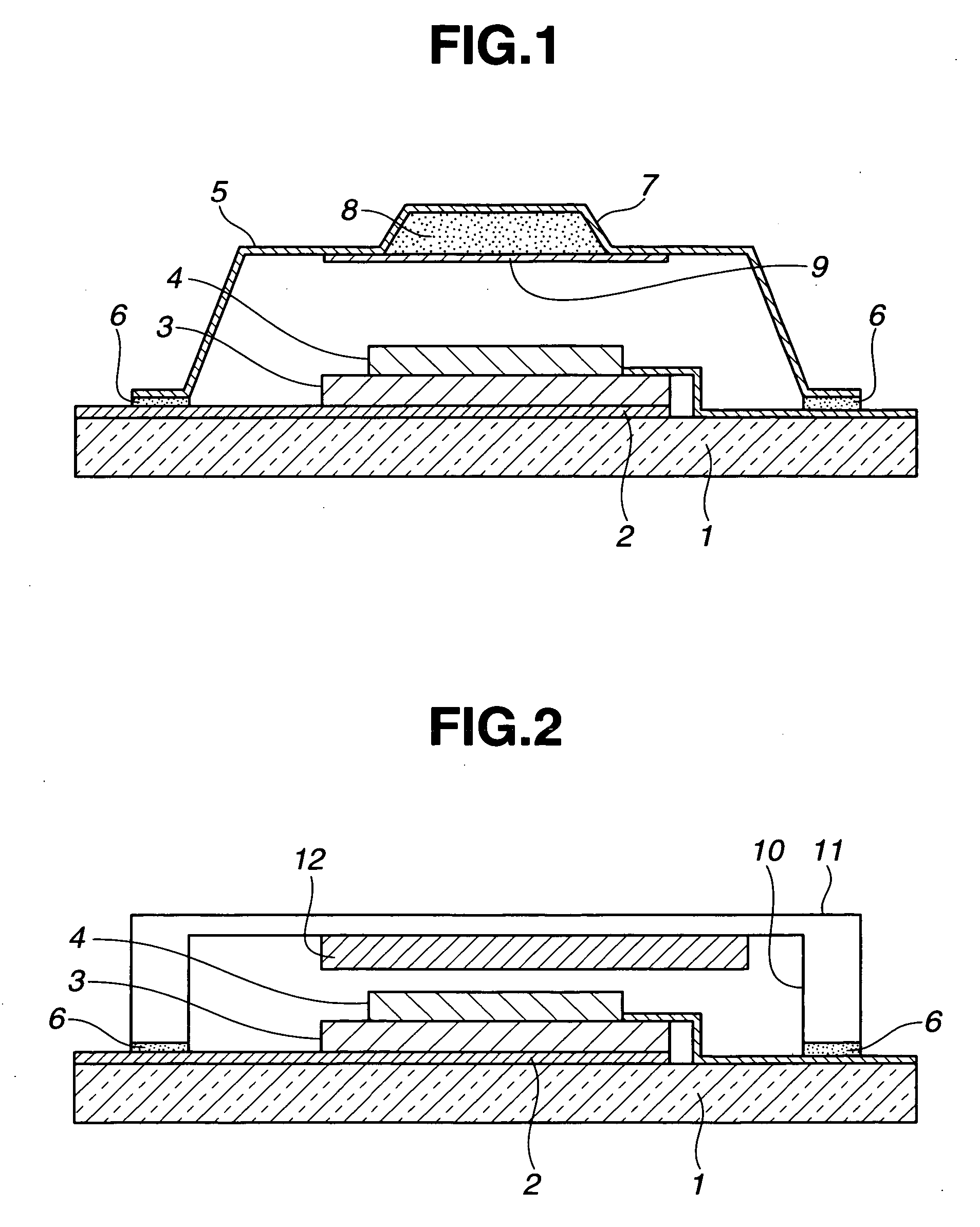

Surface light emitting apparatus

ActiveUS20060158080A1Reduce weightReduce depthIncadescent screens/filtersElectric discharge tubesLight emitting deviceLight source

A surface light emitting apparatus that can be made smaller in depth and lighter in weight and has high uniformity in luminance over the light emitting surface is disclosed. The surface light emitting apparatus of the present invention comprising a substrate, a plurality of light sources on the substrate, and a plurality of reflectors on the substrate, each of the reflectors having a first surface that covers the light sources and a second surface that reflects or scatters the irradiated light, wherein the reflectors are disposed so that the second surface is irradiated with a light emitted by the light source by the first surface of the adjacent reflector, and the light reflected or scattered by the second surface is emitted to outside.

Owner:NICHIA CORP

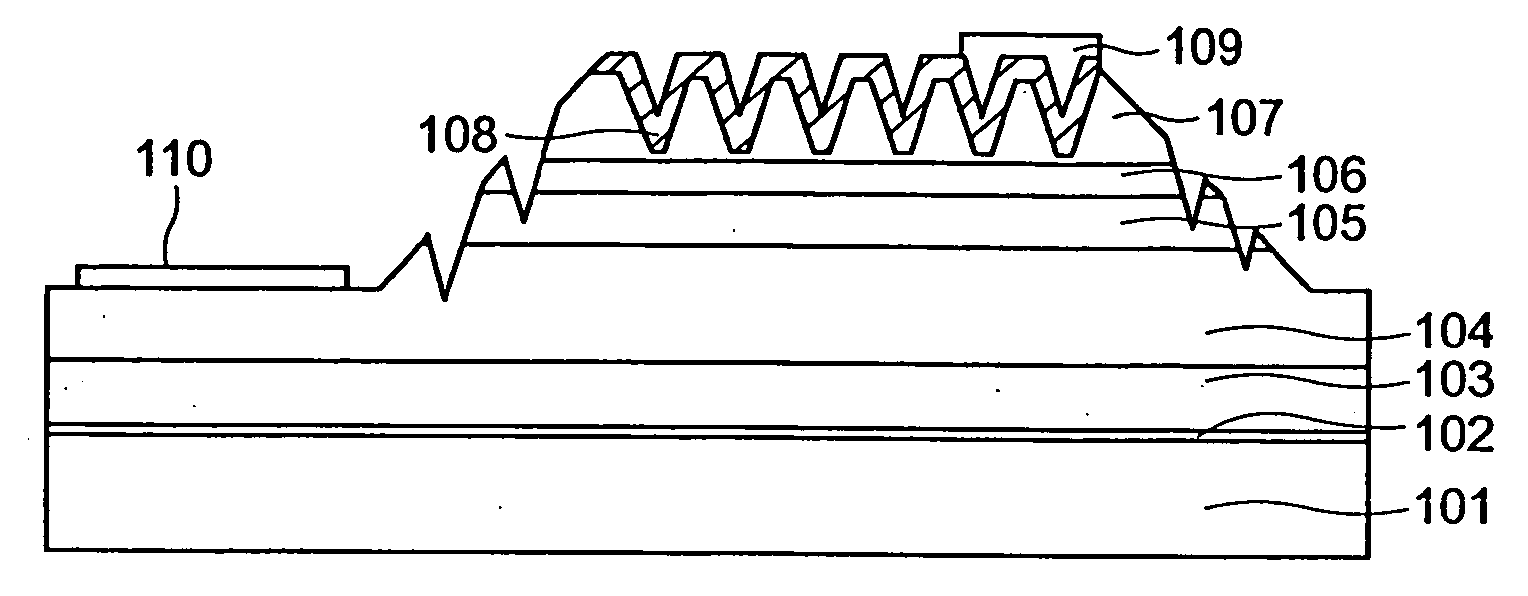

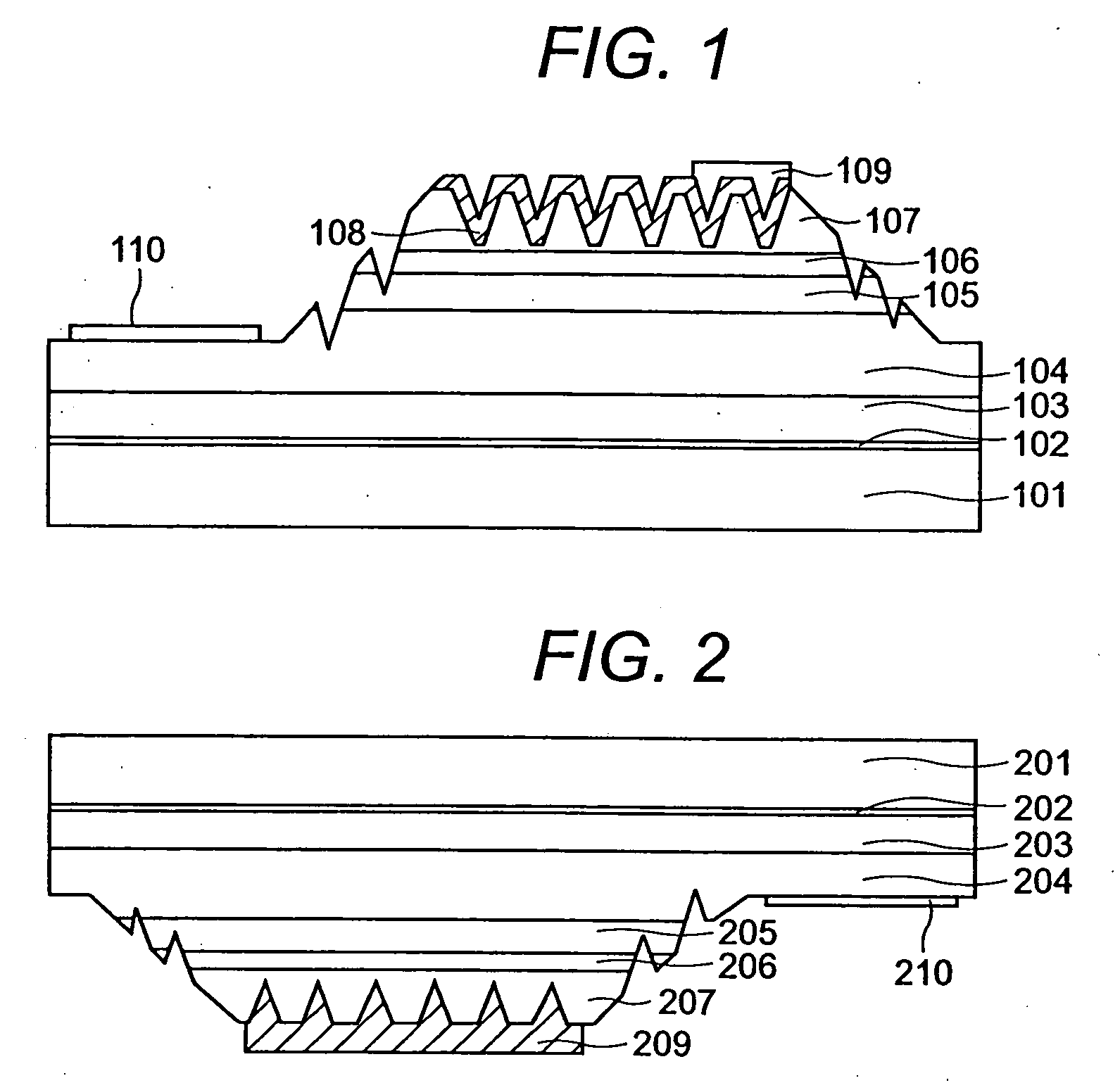

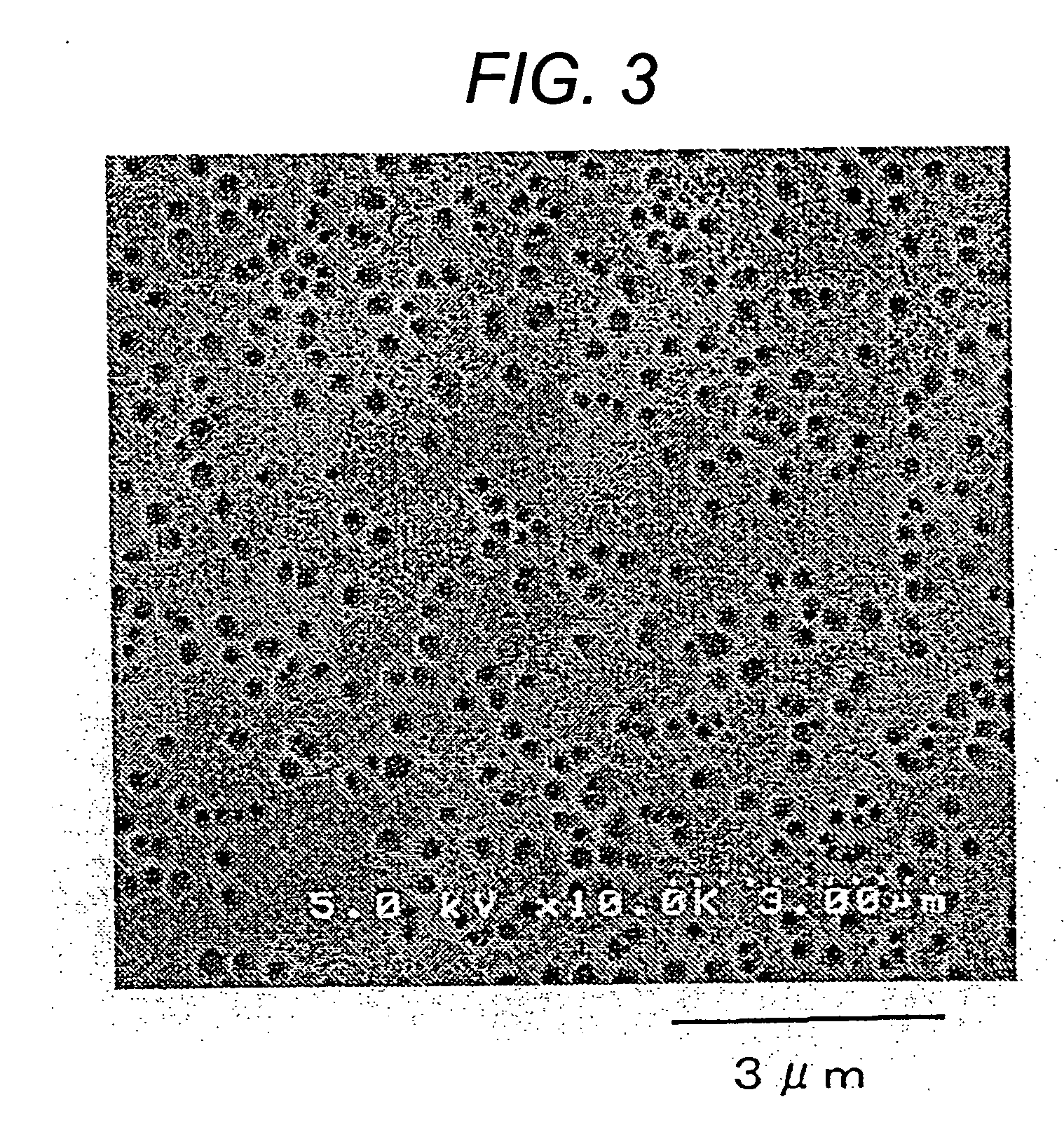

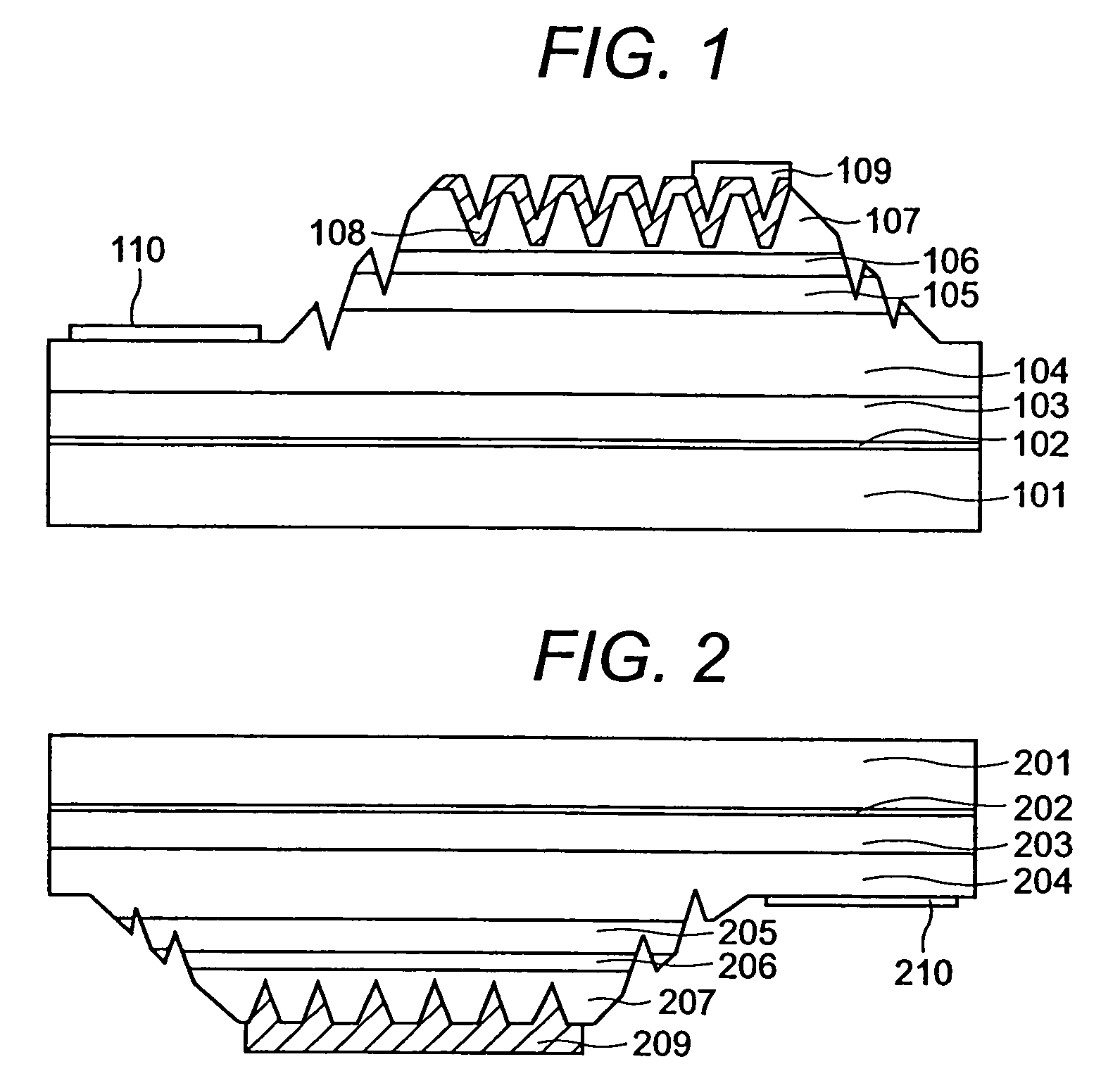

Light emitting diode and manufacturing method thereof

InactiveUS20060273336A1Light extraction efficiencyReduce contact resistanceSemiconductor devicesIn planeVolumetric Mass Density

A technique of ensuring compatibility between the method of improving the light extraction efficiency by roughening the surface of a LED structure, and the method of avoiding the adverse effect of a low-cost electrode pad ((1) forming a current distribution layer by a transparent conductive film made of metal or metal oxide, and (2) forming a flip chip structure). A light emitting diode comprises at least an n-type semiconducting layer, an active layer composed of 30 or less quantum well layers, and a p-type semiconducting layer provided on a substrate, wherein the surface of the semiconductor lamination structure contains a flat portion and a plurality of bores. In this case, the in-plane coverage rate ((the area of the bore opening / surface area)×100) of the plurality of the bores is 10% or more without exceeding 85%; the opening of the bore has a diameter of 100 nm or more without exceeding 4000 nm; the depth of the bore is smaller than the distance between the active layer and the flat portion; and the density of the plurality of the bores expressed in terms of number of bores is 8×105 per / cm2 or more without exceeding 1.08×1010 per / cm2.

Owner:SUMITOMO CHEM CO LTD

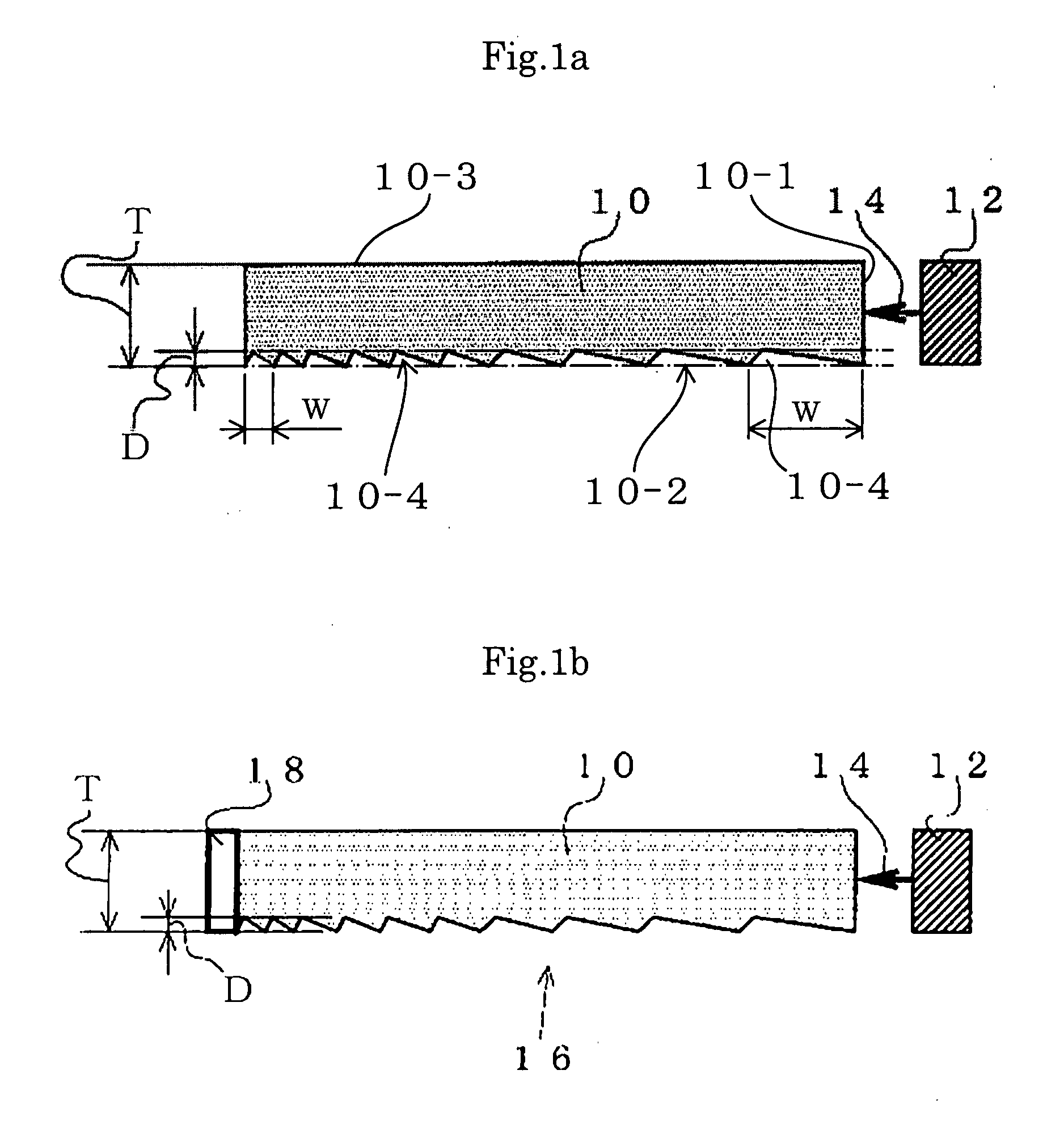

Light guide plate

InactiveUS20070189033A1Made lighterIncrease productionOptical light guidesRefractorsLight guideOptoelectronics

A light guide plate has a light emitting surface and a prism surface opposite to the light emitting surface. The prism surface includes a plurality of grooves extending parallel to each. The grooves have a constant depth, and widths of the grooves are varied, thereby adjusting the apex angles of the grooves. The depth of the grooves can be set to be not more than 20 microns.

Owner:CITIZEN ELECTRONICS CO LTD

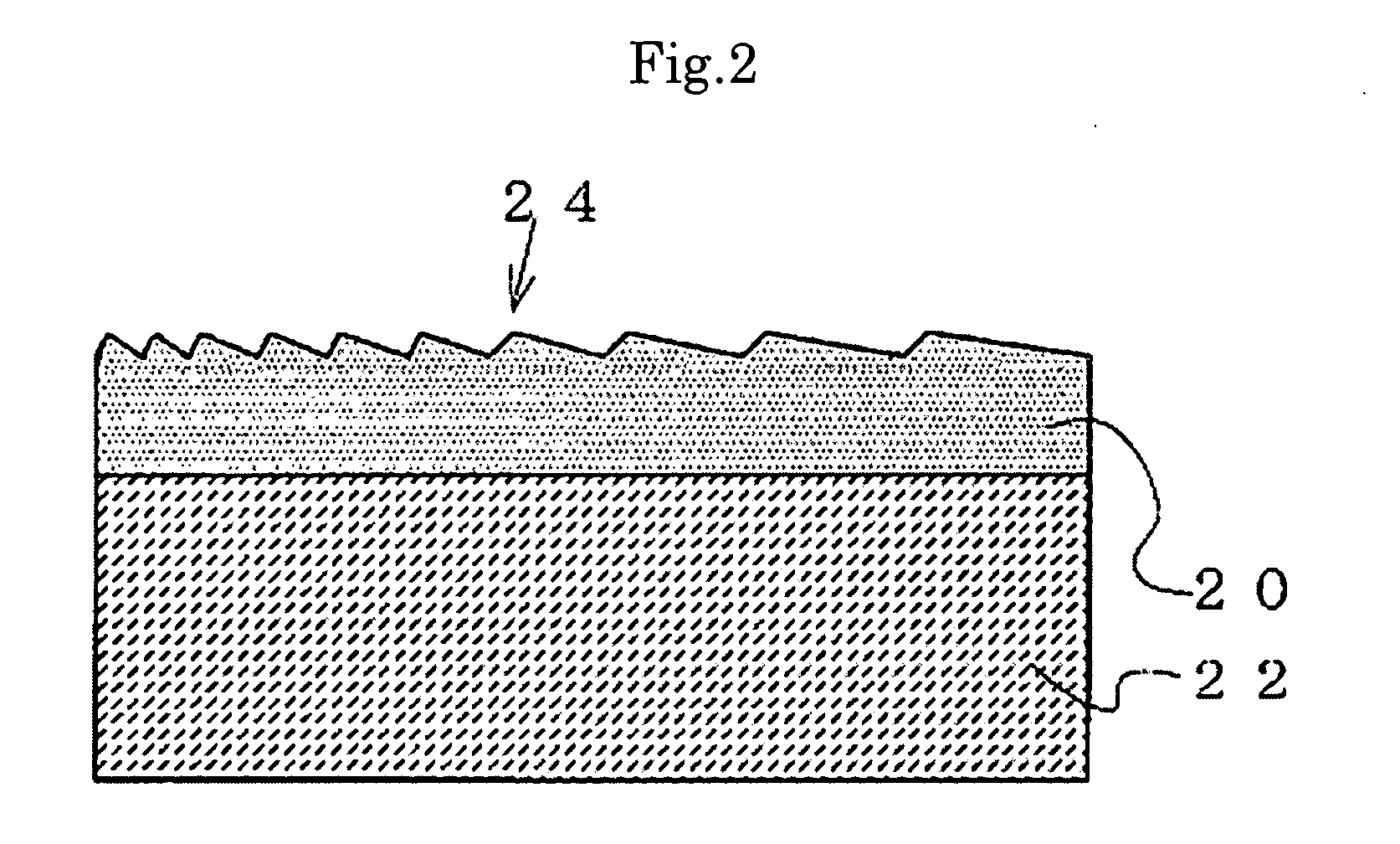

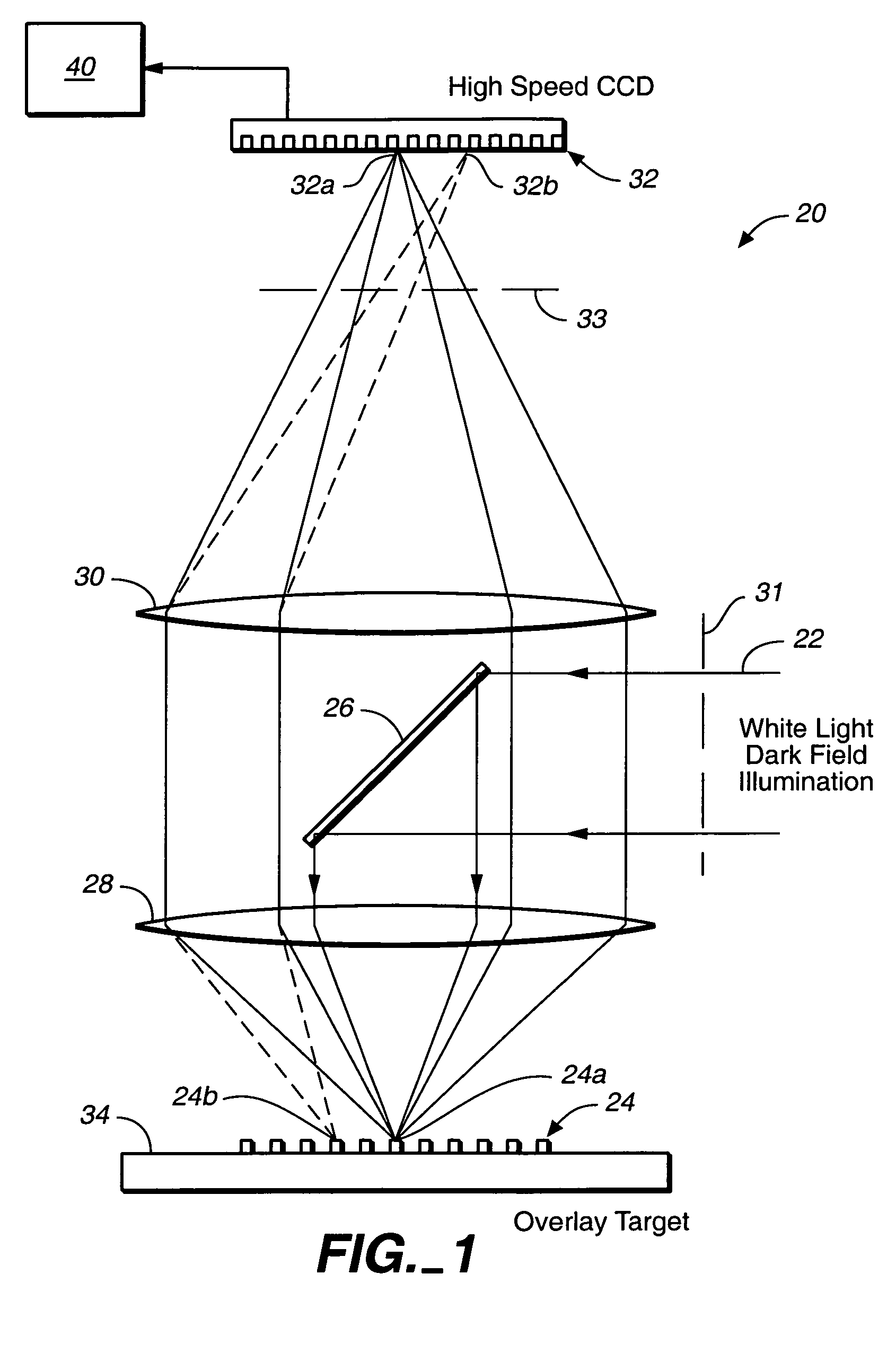

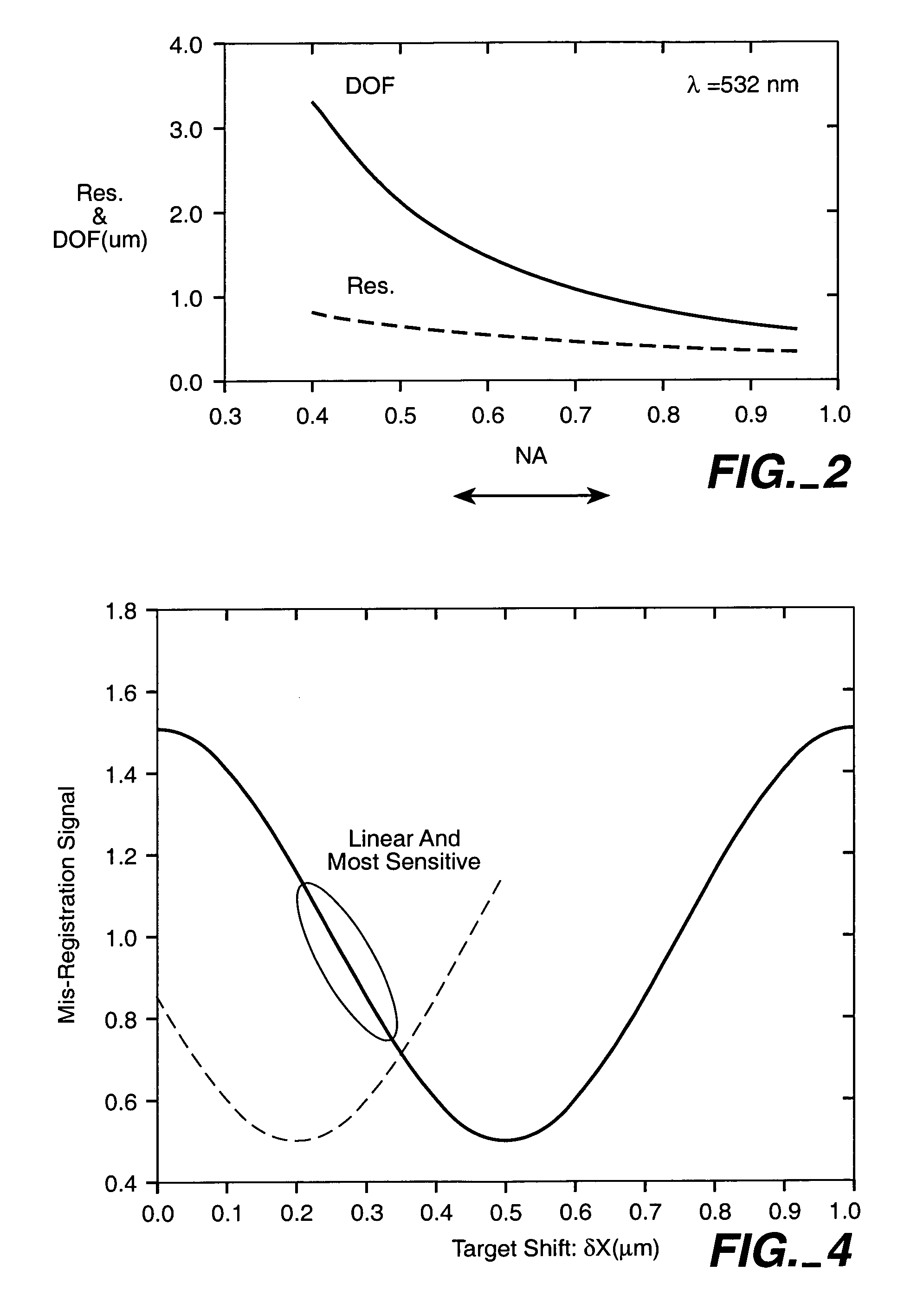

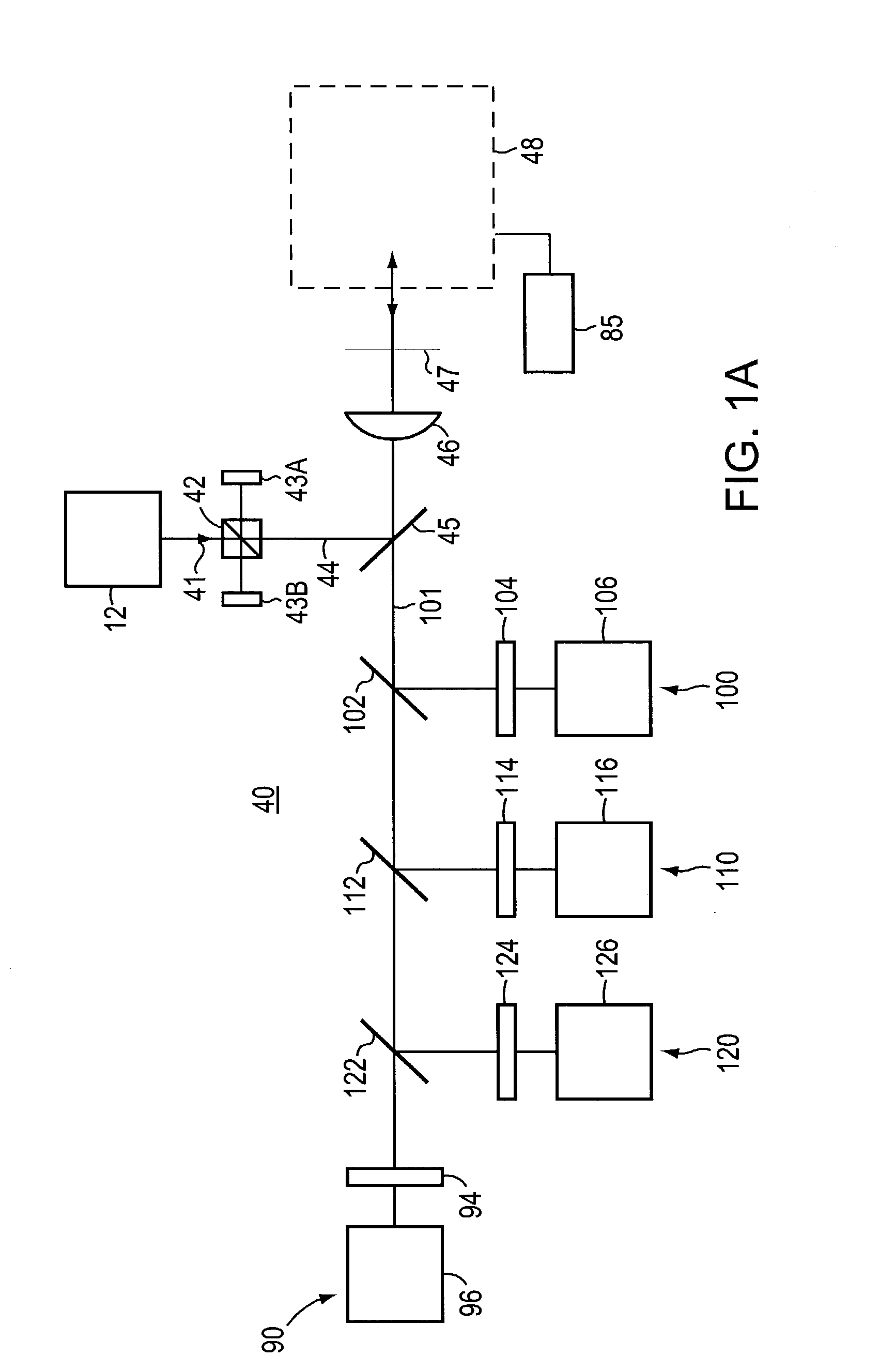

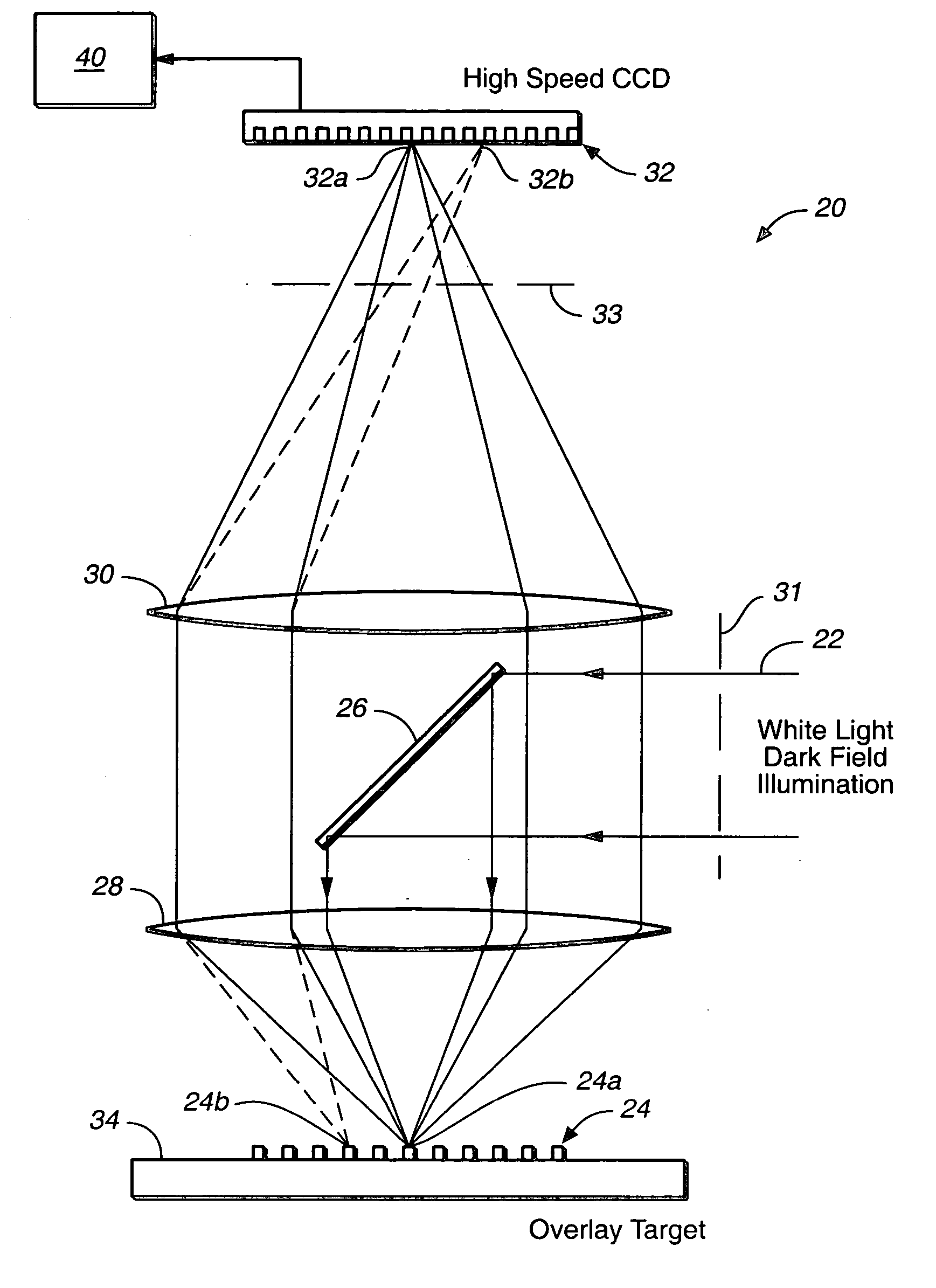

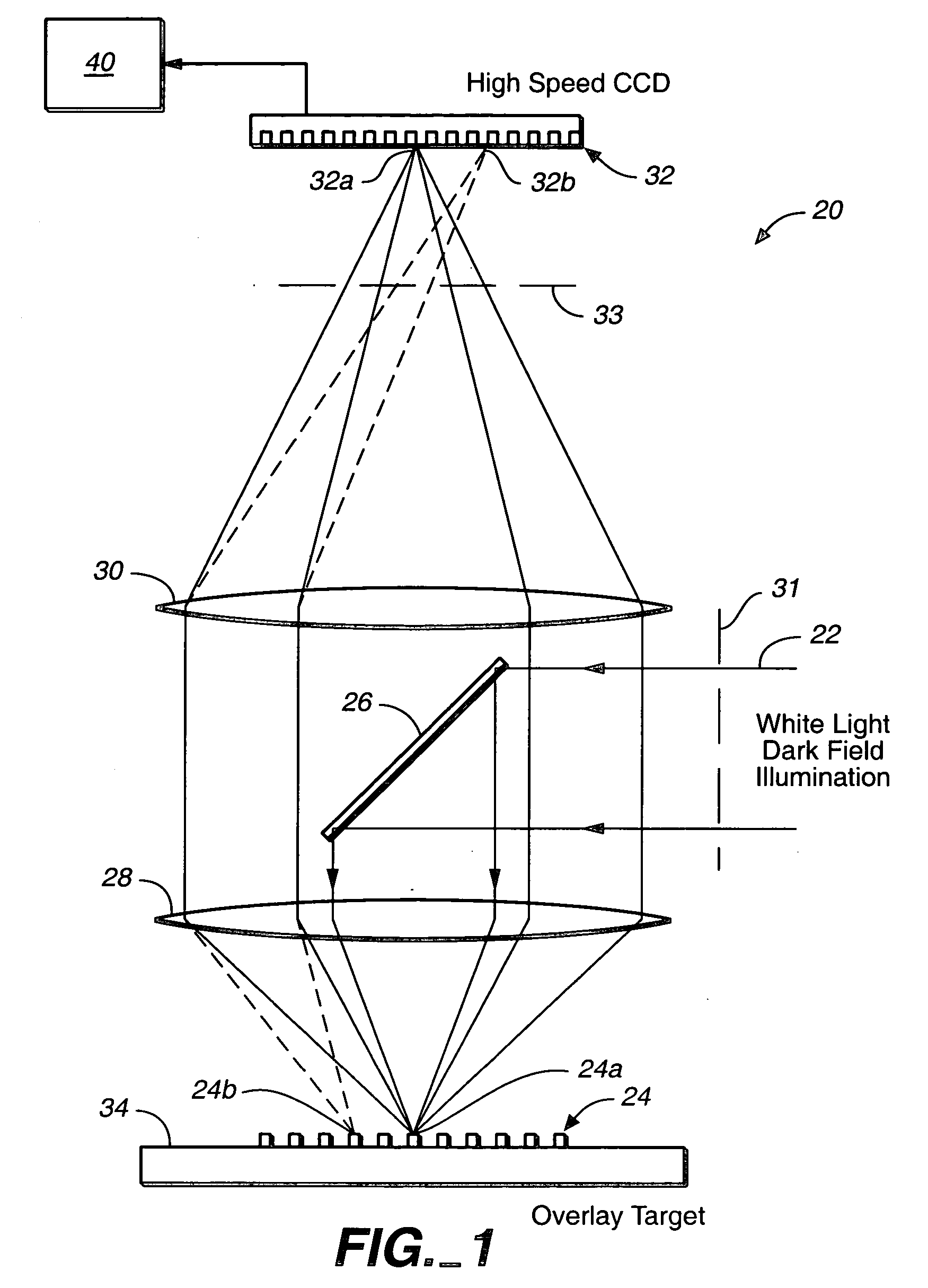

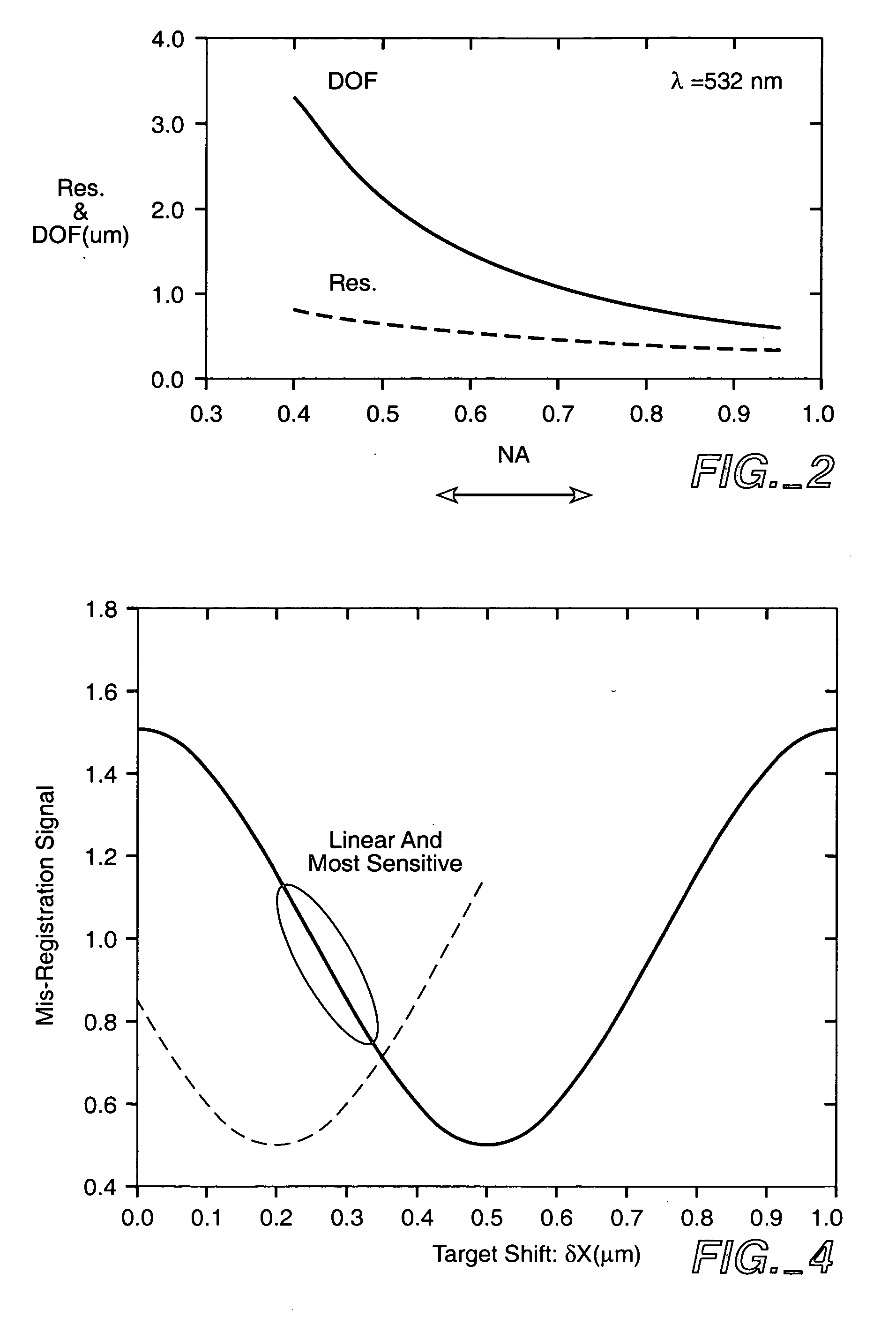

Overlay error detection

InactiveUS7009704B1Improve signal-to-noise ratioReduce contrastPhotomechanical apparatusSemiconductor/solid-state device manufacturingData pointSpecular reflection

An overlay target with gratings thereon is illuminated and radiation scattered by the target is imaged onto detectors. A phase difference is then detected between the outputs of the detectors to find the mis-alignment error. In another aspect, an overlay target with gratings or box-in-box structures is illuminated and radiation scattered by the target is imaged onto detectors located away from the specular reflection direction of the illumination in a dark field detection scheme. Medium numerical aperture optics may be employed for collecting the radiation from the overlay target in a bright or dark field configuration so that the system has a larger depth of focus and so that the two structures of the target at different elevations can be measured accurately at the same time. Analytical functions are constructed for the grating type targets. By finding the phase difference between the two gratings at different elevations, misalignment errors can be detected. Analytical functions are constructed as a model for box-in-box type targets where data points away from the edges of the box or bars can be used in the curve fitting. Symmetrical functions are employed to further reduce noise.

Owner:KLA TENCOR CORP

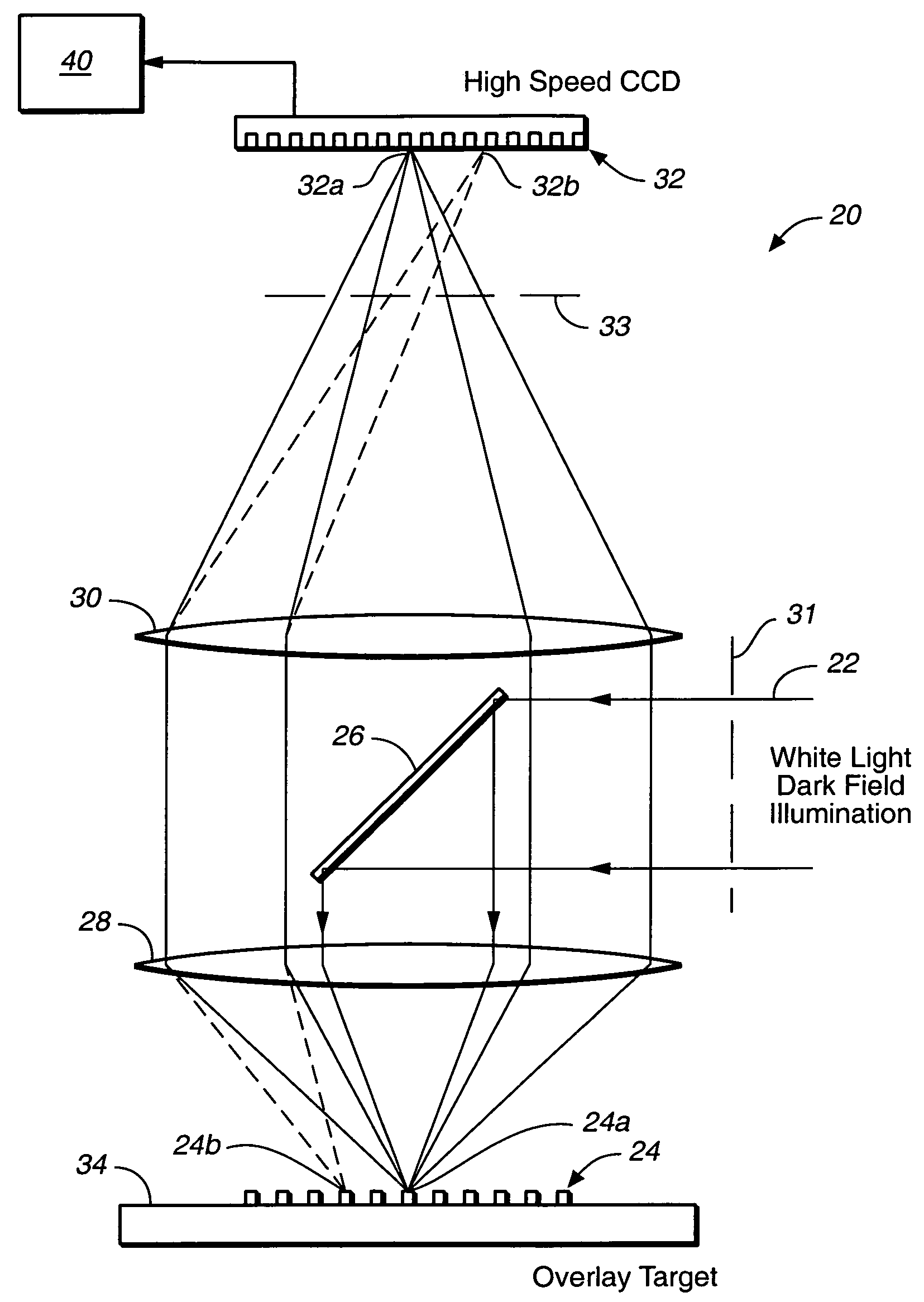

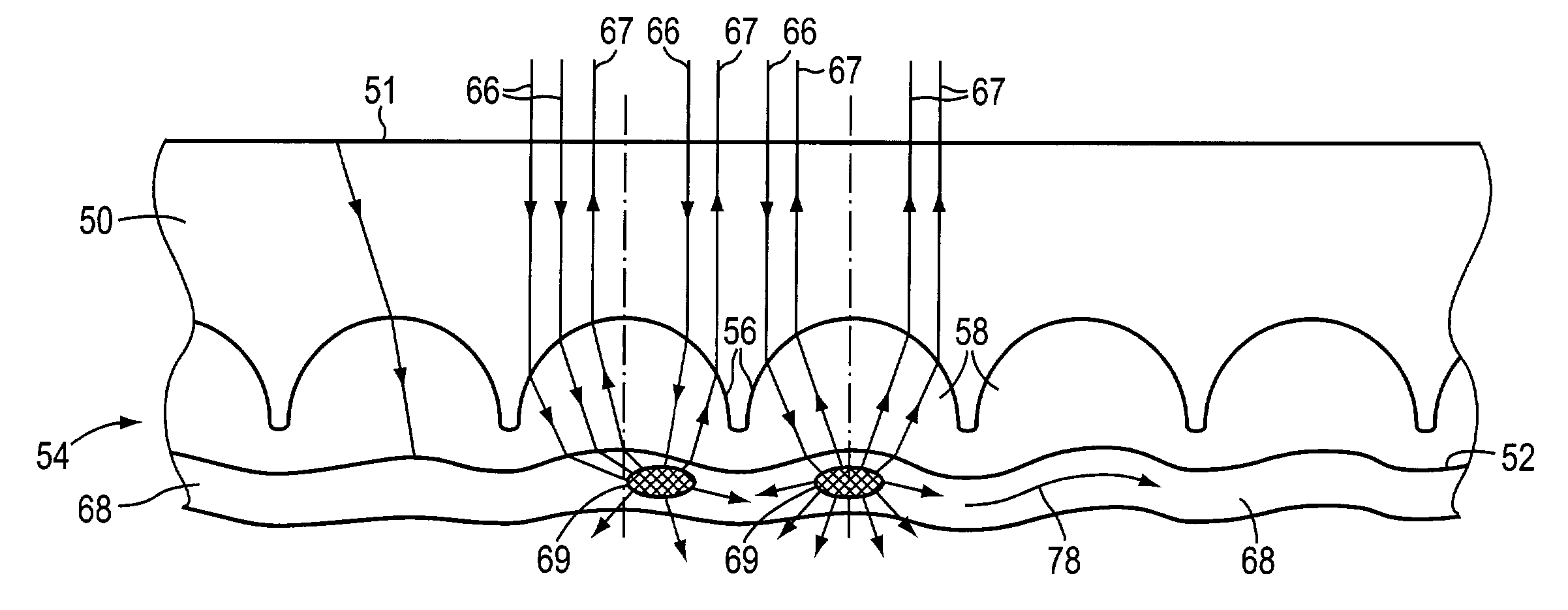

Optically active substrates

InactiveUS7158224B2High refractive indexExtension of timeChemiluminescene/bioluminescenceMicroscopesLength waveRadiation

A device for optical examination of biological materials using radiation of a selected wavelength includes a substrate having a first surface and a second surface opposite to the first surface. The first surface includes a dense array of micro-optical elements arranged to provide increased intensity radiation or evanescent radiation. The first surface is in close proximity to the biological material being examined.

Owner:AFFYMETRIX INC

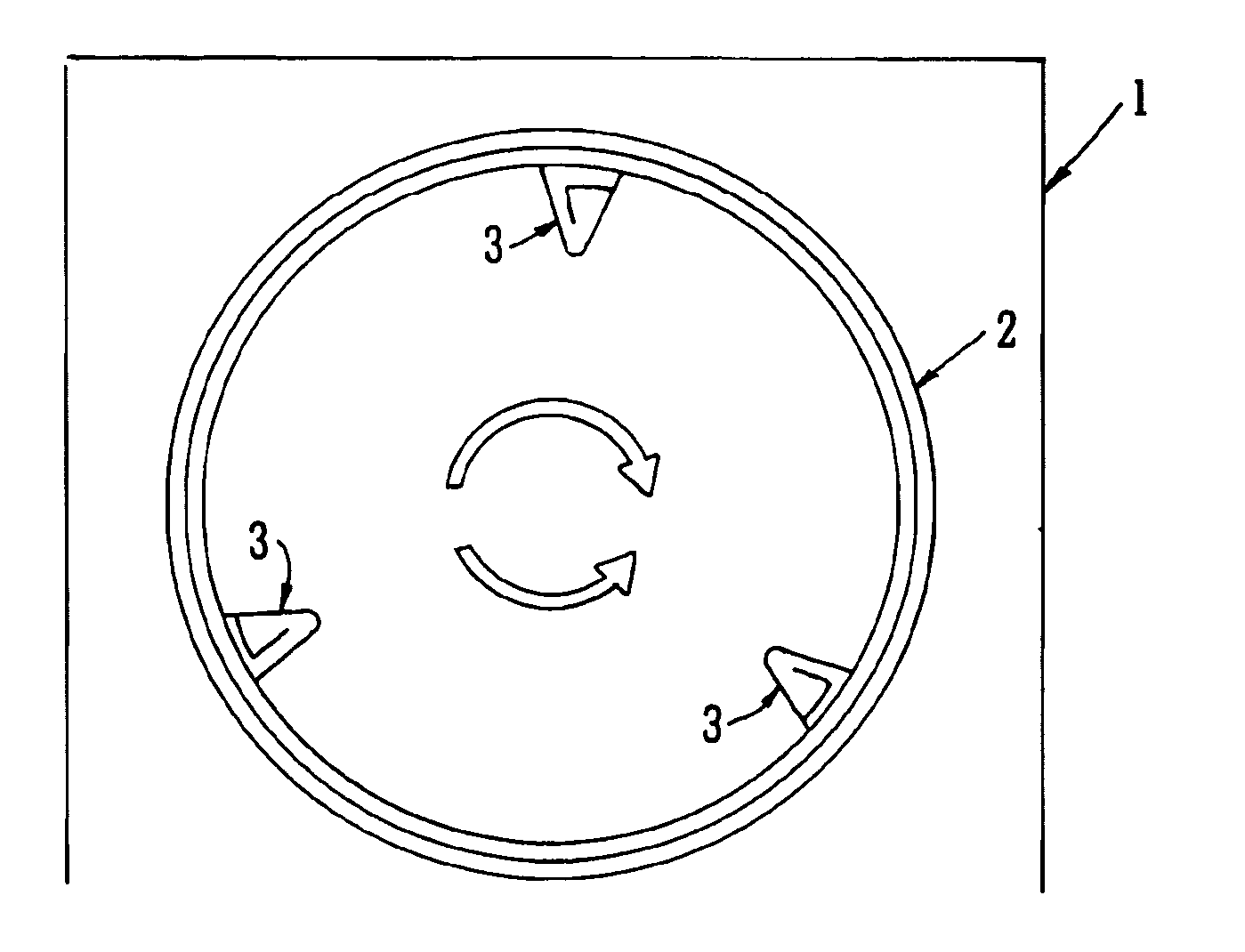

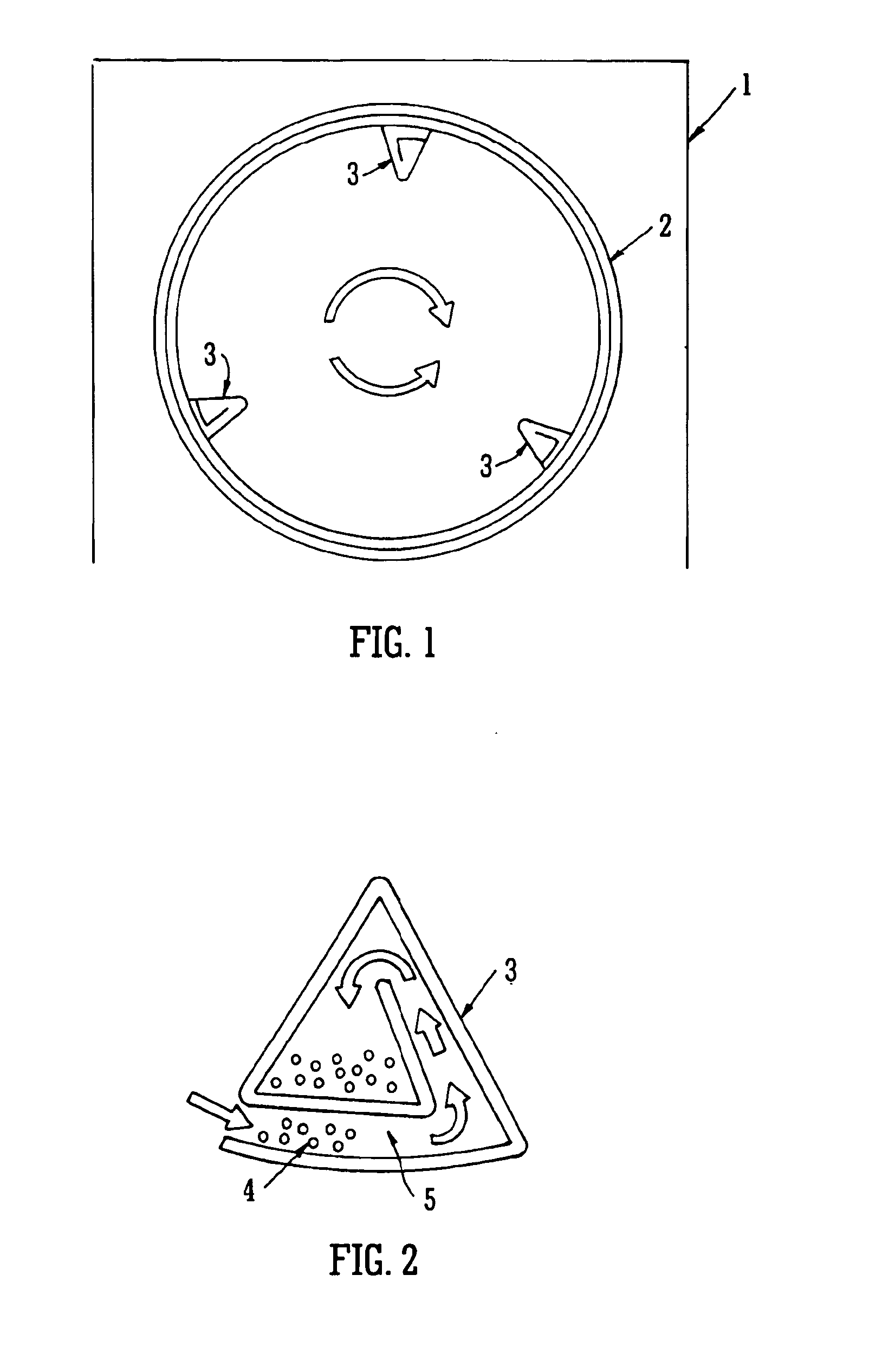

Water-absorbing agent for organic EL device and organic EL device

InactiveUS20050227114A1Luminous properties are stableImprove reliabilityDischarge tube luminescnet screensOther chemical processesOrganic layerUltraviolet

A thin-profile organic EL device with a high degree of reliability is provided. The anode, the organic layer and the light transmissible-type cathode are laminated on the substrate and the inorganic water-barrier layer are laminated thereon, and then a UV rays-curable type water-capturing agent comprising a UV rays-curing agent and a water-absorbing agent is cured to bond to the sealing substrate instead of an adhesive layer. The UV rays-curing agent comprises an acrylic monomer, initiator and accelerator. The UV rays-curable type sealing agent is placed to the outer peripheral portion of the UV rays-curable type water-capturing agent to be cured. The emission of the organic layer is transmitted upward via the cathode, UV rays-curable type water-capturing agent and the sealing substrate. The UV rays-curable type water-capturing agent can be formed in a desired thickness and pattern by applying it and irradiating with UV-rays, thereby making it possible to produce a low-profile organic EL device in large quantities with a high degree of reliability and without damaging the organic layer which is not resistant to water.

Owner:FUTABA CORPORATION

Semiconductor chip and method of manufacturing semiconductor chip

ActiveUS20070085189A1Simplify manufacturing stepsReduce manufacturing costSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor chip

A semiconductor chip includes a semiconductor substrate having a first principal surface, and having a device layer on the first principal surface in which a semiconductor device is formed, an electrode pad disposed on the first principal surface of the semiconductor substrate and electrically connected to the semiconductor device, a through via formed in a through hole penetrating through the semiconductor substrate and the electrode pad, and an Au bump deposited on the electrode pad and the through via such as to electrically connect between the electrode pad and the through via.

Owner:SHINKO ELECTRIC IND CO LTD

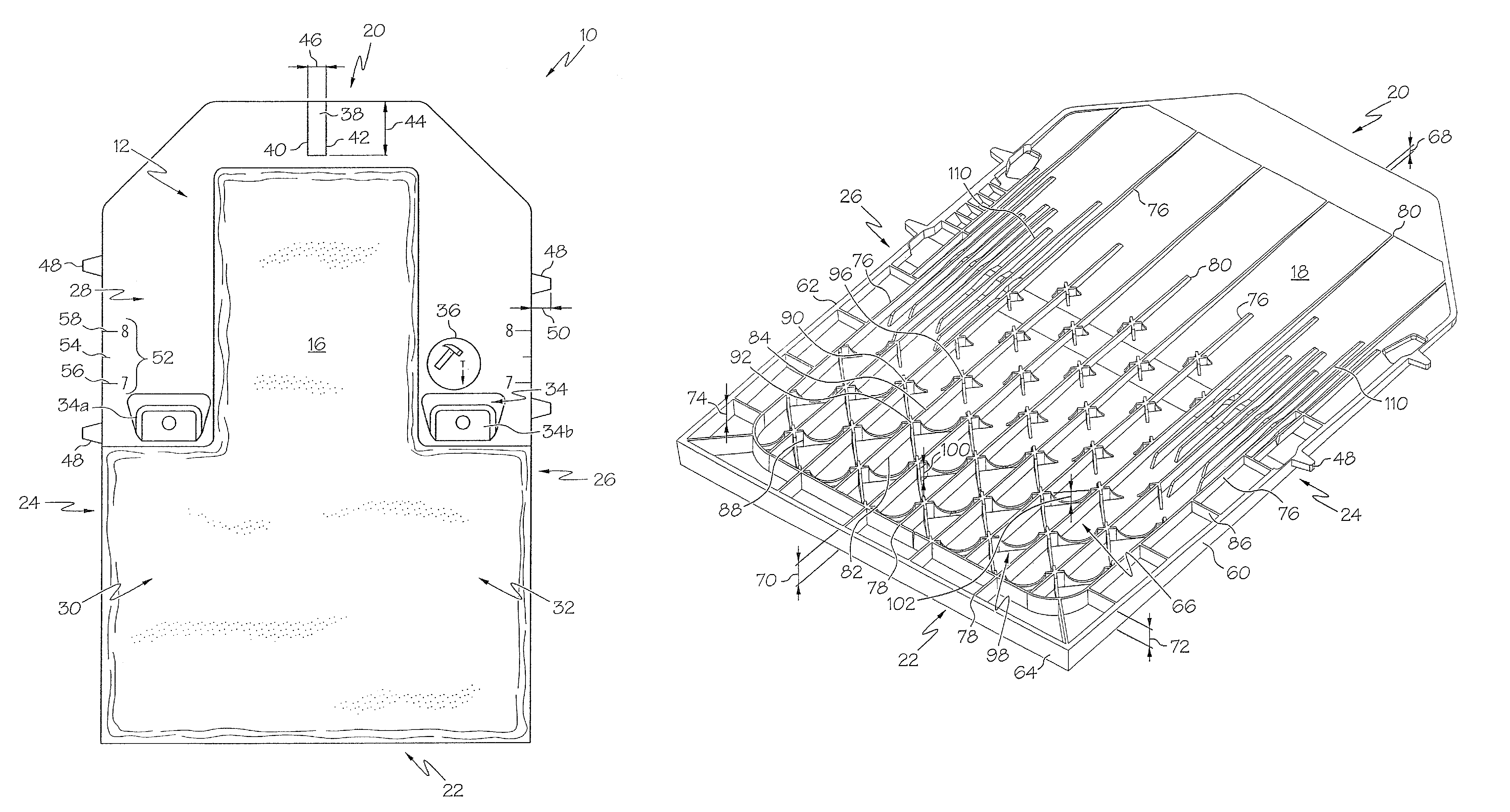

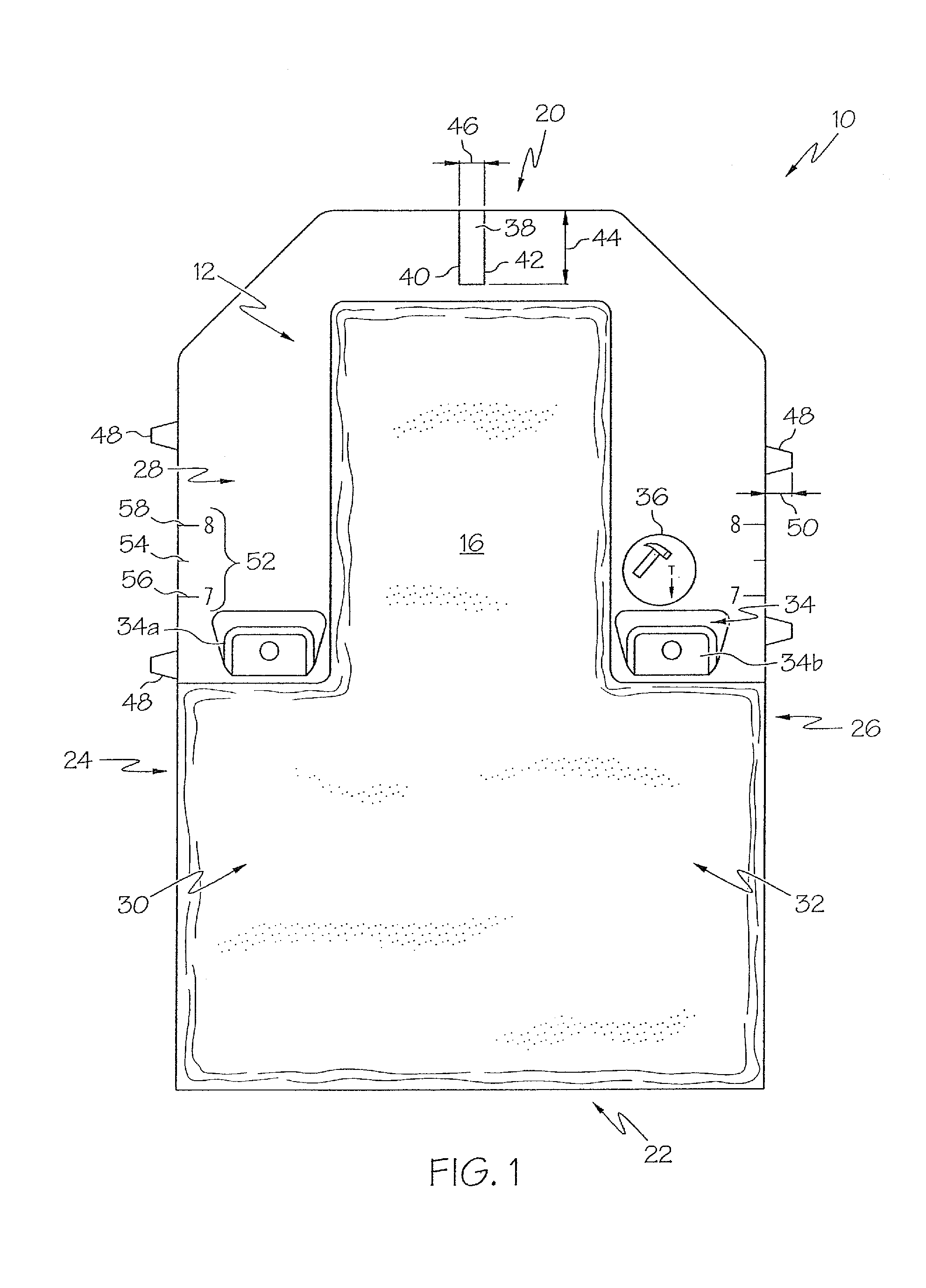

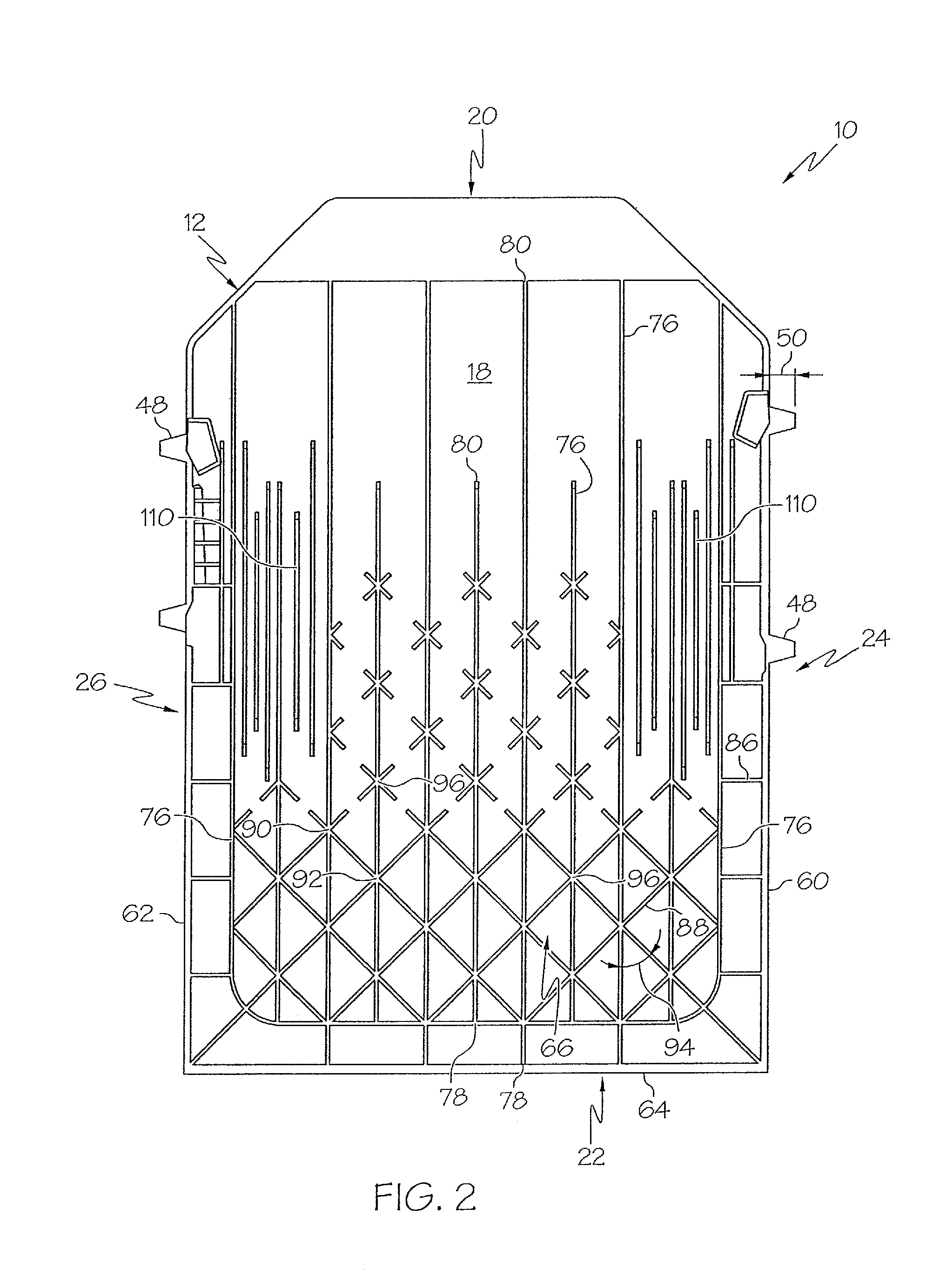

Composite shingle

InactiveUS8136322B2Reduce material usageSmall depthRoof covering using tiles/slatesBuilding repairsEngineeringBuilding construction

A composite shingle having unitary construction is presented that includes a body shell, a plurality of longitudinal ribs, and a plurality of rib stiffeners. The present composite shingle may also include transverse ribs, a depressed nailing zone, nailing zone ribs, and / or at least one alignment aid. The plurality of rib stiffeners may include a material saving profile. Further, the dimensions of the composite shingle more closely resemble true slate and shake shingles and at least a portion of the outside face of composite shingle may be textured to resemble slate or wood shake shingles.A plurality of assembled composite shingles of the present invention is also claimed as part of this invention. Finally, a method of applying multiple courses of shingles on a roof including the composite shingle of the present invention is presented.

Owner:TAMKO BUILDING PRODS

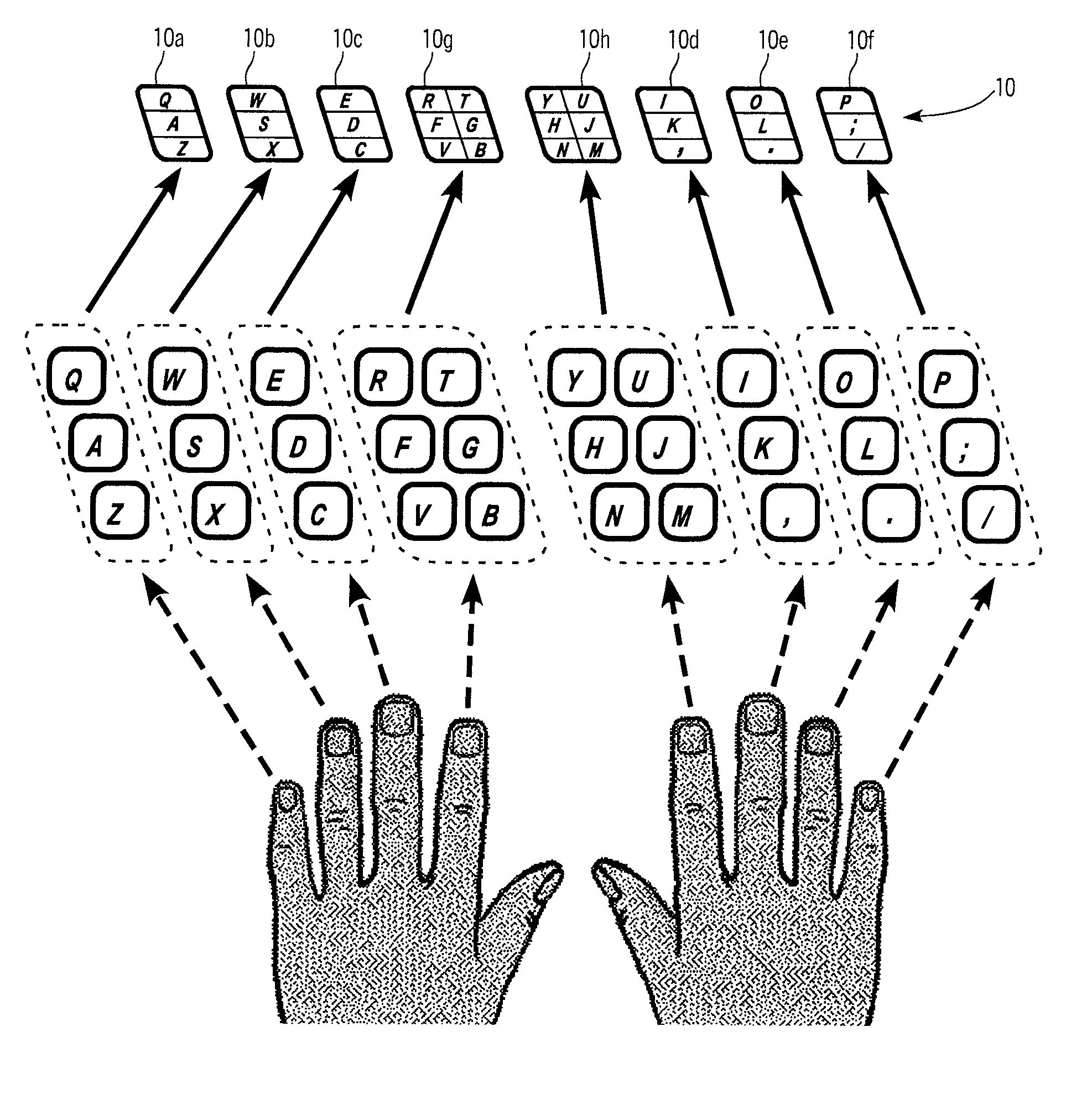

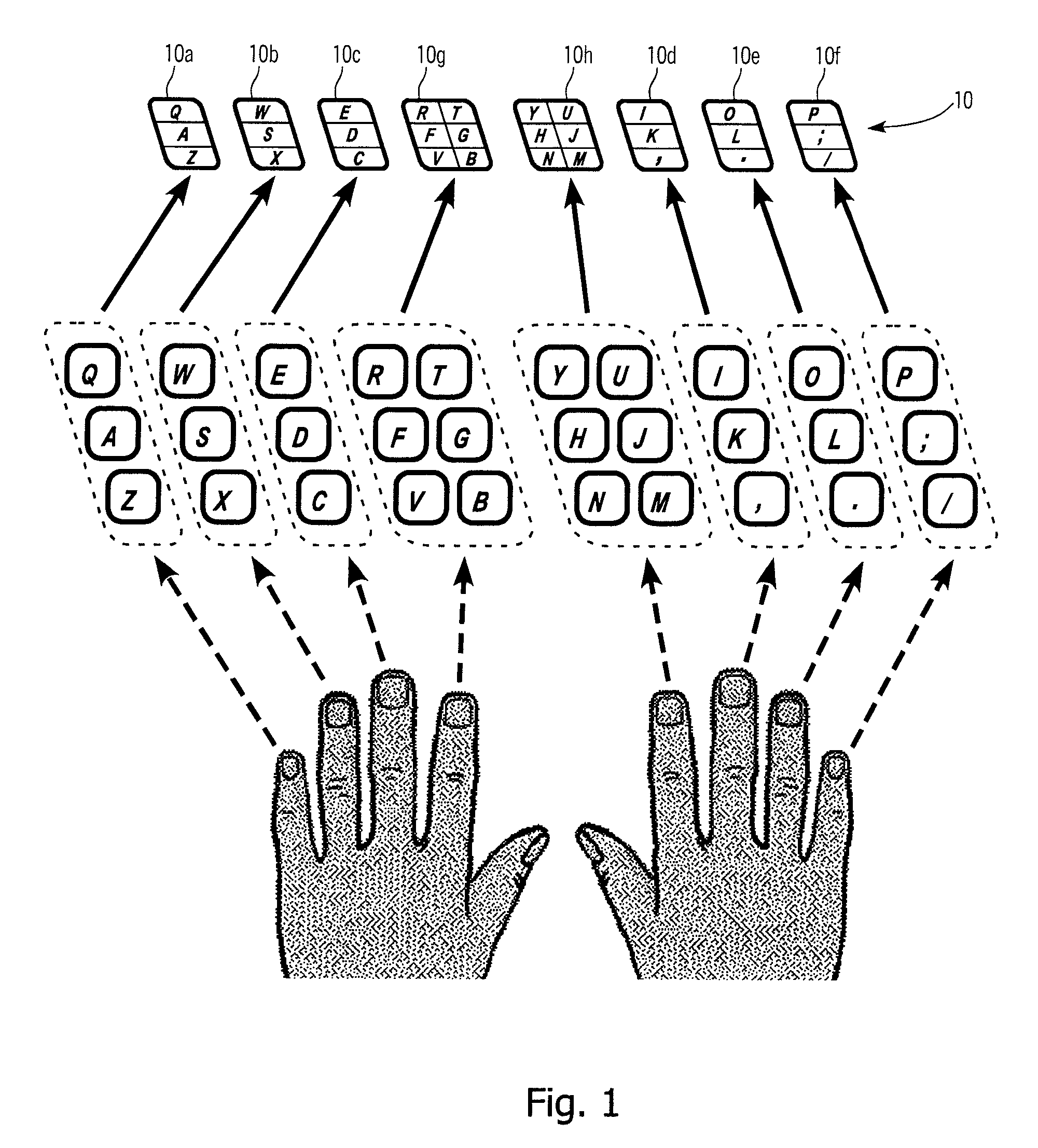

Keyboard and Keys

InactiveUS20070172287A1Avoids lateral slidingAvoid pushingOther printing apparatusComputer hardwareComputer science

In a preferred form, a keyboard has a single row of eight multi-position keys with the letters arranged in a standard QWERTY keyboard configuration. The eight keys correspond to the eight fingers used when touch typing; each finger operates one key, and that key contains all the letters that the finger normally accesses when touch typing on a standard QWERTY keyboard. With this design, no finger has to move to a different key while typing. When depressed at different locations on its key face, each key either moves straight down, or down while tilting slightly about one of a plurality of axes. Three-position keys have two tilt axes and six-position keys have five tilt axes. The switches utilize contacts located on the bottom of the switches which may be conductive or nonconductive.

Owner:HIRSCH

Light emitting diode having surface containing flat portion and plurality of bores

InactiveUS7504667B2Light extraction efficiencyReduce contact resistanceSemiconductor devicesIn planeLight-emitting diode

A technique of ensuring compatibility between the method of improving the light extraction efficiency by roughening the surface of a LED structure, and the method of avoiding the adverse effect of a low-cost electrode pad ((1) forming a current distribution layer by a transparent conductive film made of metal or metal oxide, and (2) forming a flip chip structure). A light emitting diode has at least an n-type semiconducting layer, an active layer composed of 30 or less quantum well layers, and a p-type semiconducting layer provided on a substrate, wherein the surface of the semiconductor lamination structure contains a flat portion and a plurality of bores. In this case, the in-plane coverage rate ((the area of the bore opening / surface area) ×100) of the plurality of the bores is 10% or more without exceeding 85%; the opening of the bore has a diameter of 100 nm or more without exceeding 4000 nm; the depth of the bore is smaller than the distance between the active layer and the flat portion; and the density of the plurality of the bores expressed in terms of number of bores is 8 ×105 per / cm2 or more without exceeding 1.08×1010 per / cm2.

Owner:SUMITOMO CHEM CO LTD

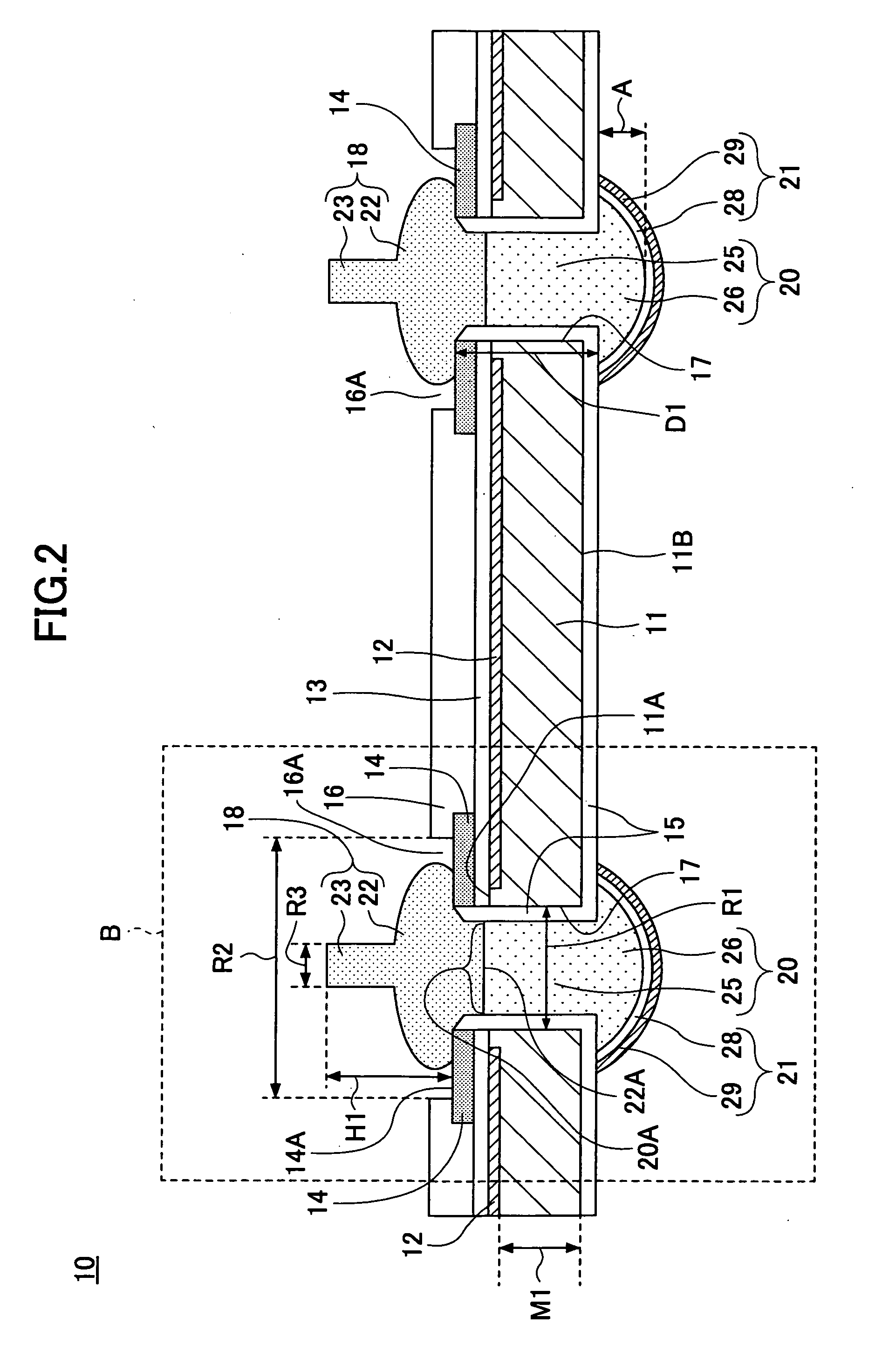

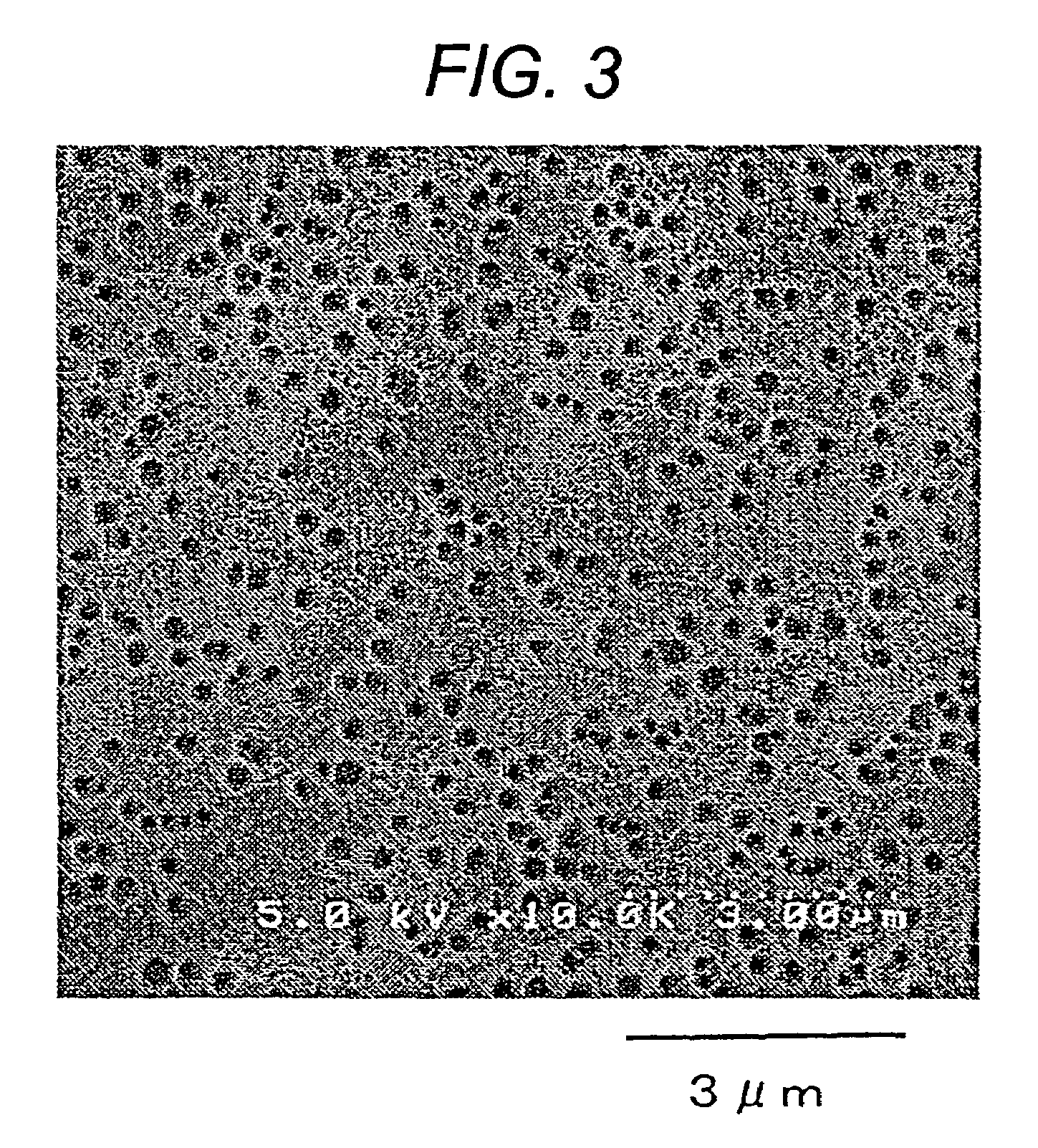

Fluid bearing device

ActiveUS7201516B2Small depthSufficient length dimensionShaftsRecord information storageEngineeringFluid bearing

A fluid bearing device capable of preventing a lubricant from scattering outward even during rotation thereof, while holding a relatively large amount of lubricant at a seal surface portion. A lubricant is filled between a sleeve and a shaft, a seal surface portion is formed on the sleeve in a location facing an open end thereof, the seal surface portion has a sectional shape defined by a plurality of inclined surfaces, and an inclination angle α of the inclined surface of the seal surface portion adjacent a radial bearing portion with respect to a shaft axis is formed to be larger than an inclination angle β of the inclined surface of the seal surface portion distant away from the radial bearing portion with respect to the shaft axis.

Owner:PHC HLDG CORP

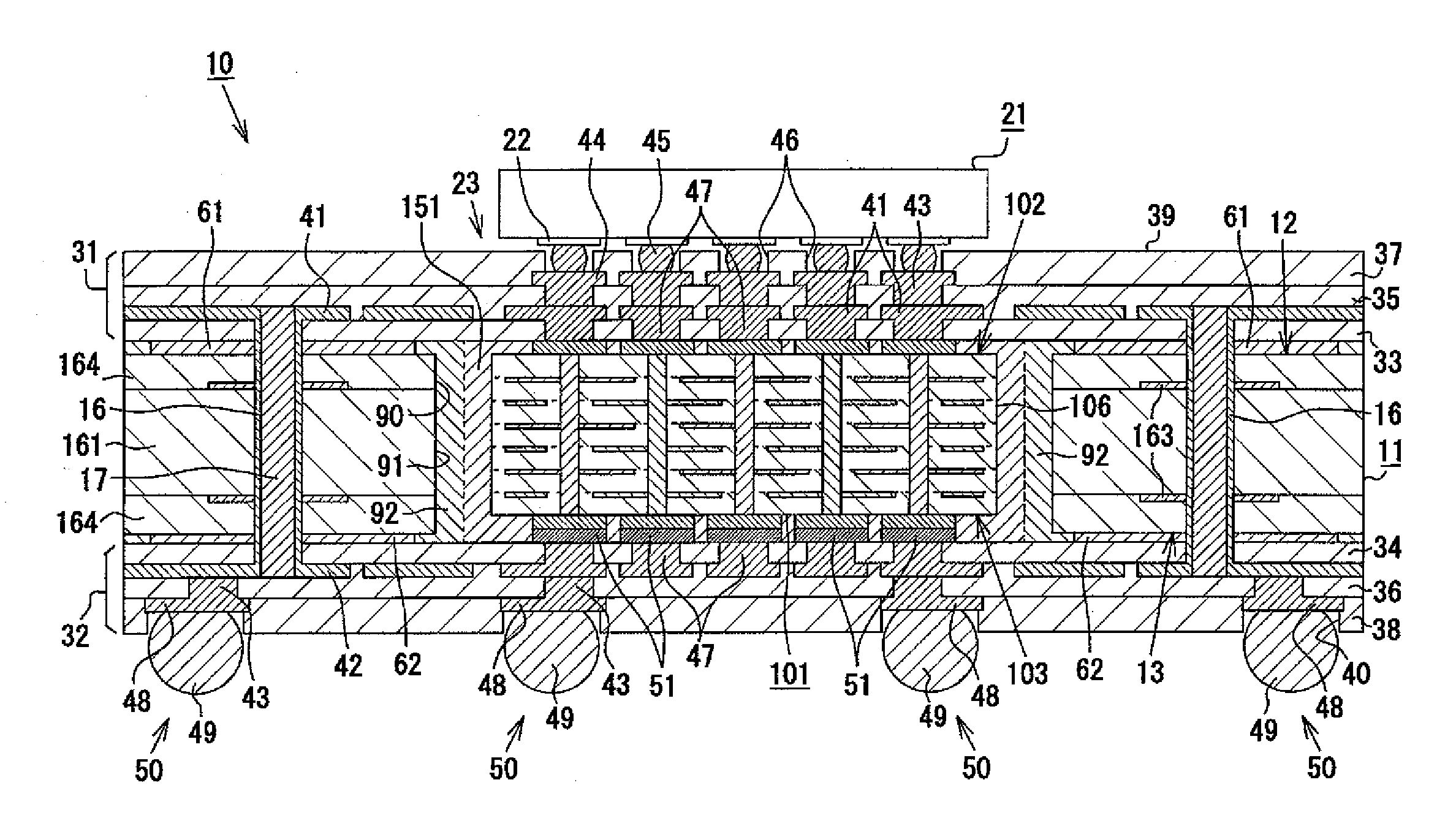

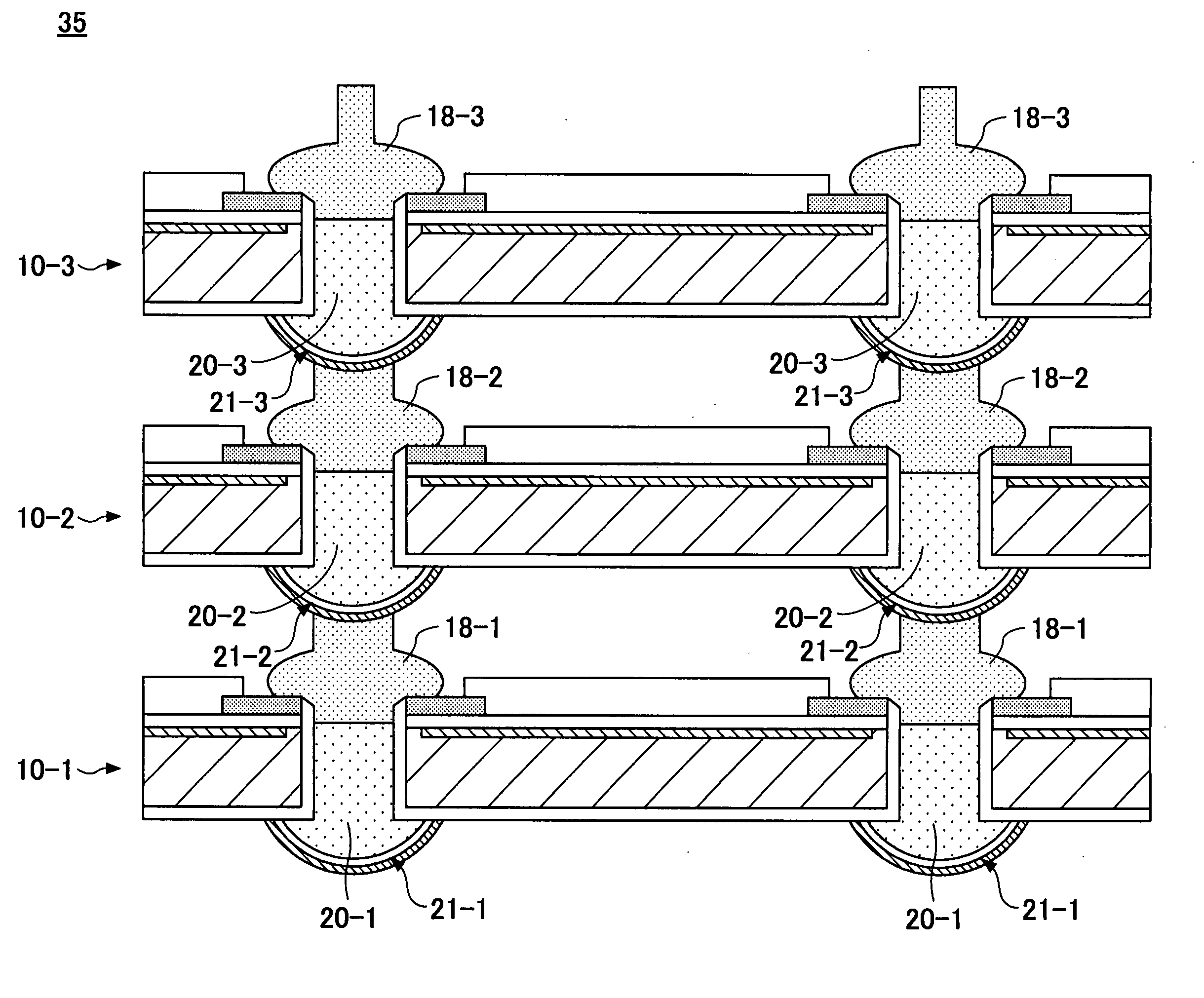

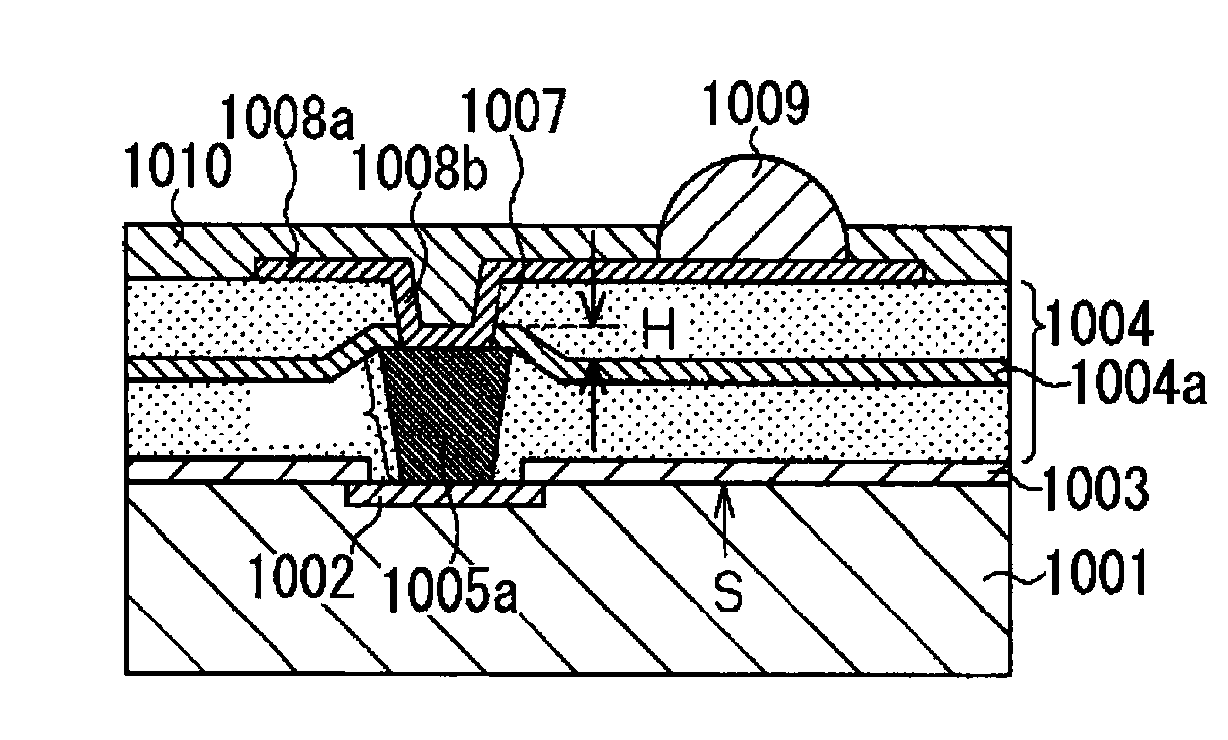

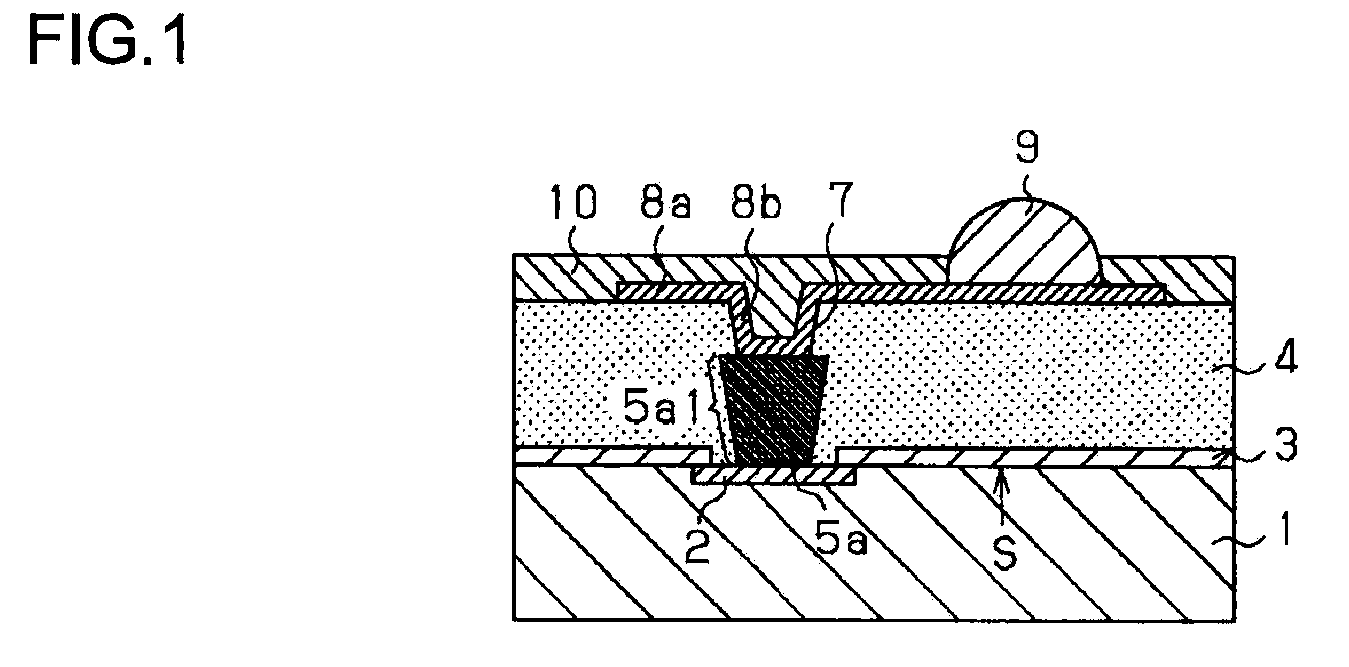

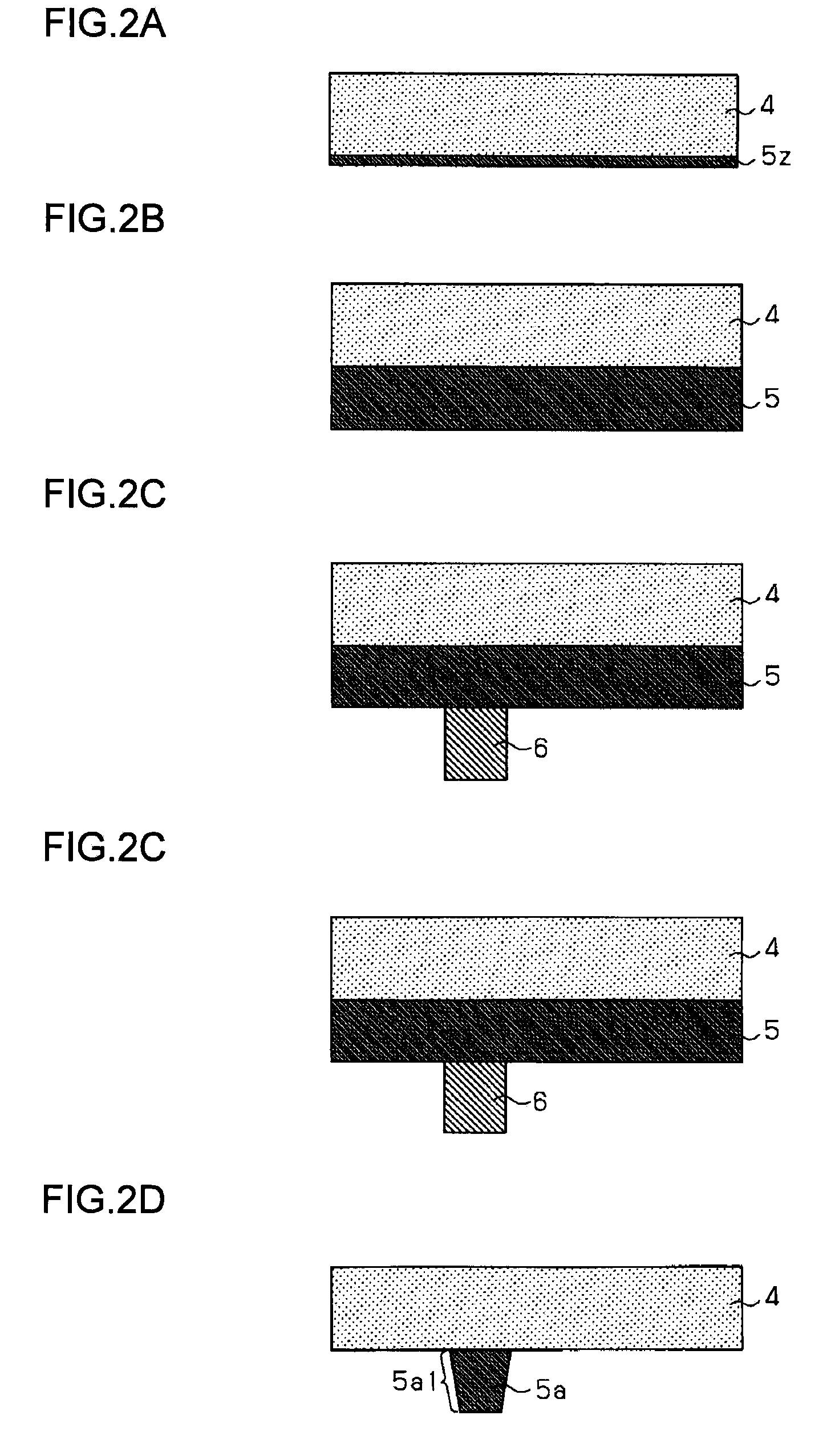

Packing board for electronic device, packing board manufacturing method, semiconductor module, semiconductor module manufacturing method, and mobile device

InactiveUS7915737B2Improve reliabilityImprove connection reliabilitySemiconductor/solid-state device detailsSolid-state devicesManufacturing technologyElectrical conductor

Owner:SANYO ELECTRIC CO LTD

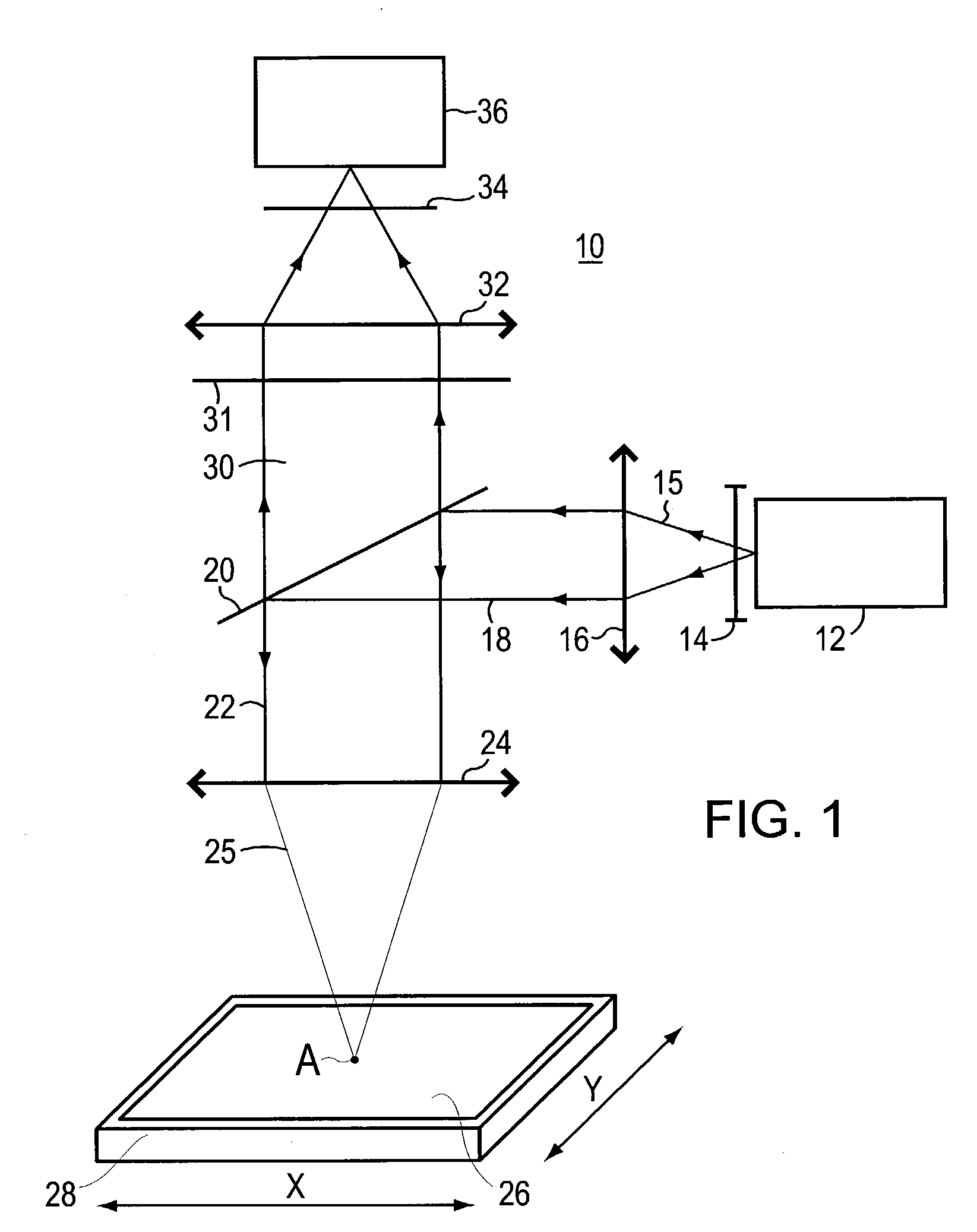

Overlay error detection

InactiveUS20060098199A1Accurate measurementLarge depth of fieldPhotomechanical apparatusSemiconductor/solid-state device manufacturingGratingPhase difference

An overlay target with gratings thereon is illuminated and radiation scattered by the target is imaged onto detectors. A phase difference is then detected between the outputs of the detectors to find the mis-alignment error. In another aspect, an overlay target with gratings or box-in-box structures is illuminated and radiation scattered by the target is imaged onto detectors located away from the specular reflection direction of the illumination in a dark field detection scheme. Medium numerical aperture optics may be employed for collecting the radiation from the overlay target in a bright or dark field configuration so that the system has a larger depth of focus and so that the two structures of the target at different elevations can be measured accurately at the same time. Analytical functions are constructed for the grating type targets. By finding the phase difference between the two gratings at different elevations, misalignment errors can be detected. Analytical functions are constructed as a model for box-in-box type targets where data points away from the edges of the box or bars can be used in the curve fitting. Symmetrical functions are employed to further reduce noise.

Owner:KLA CORP

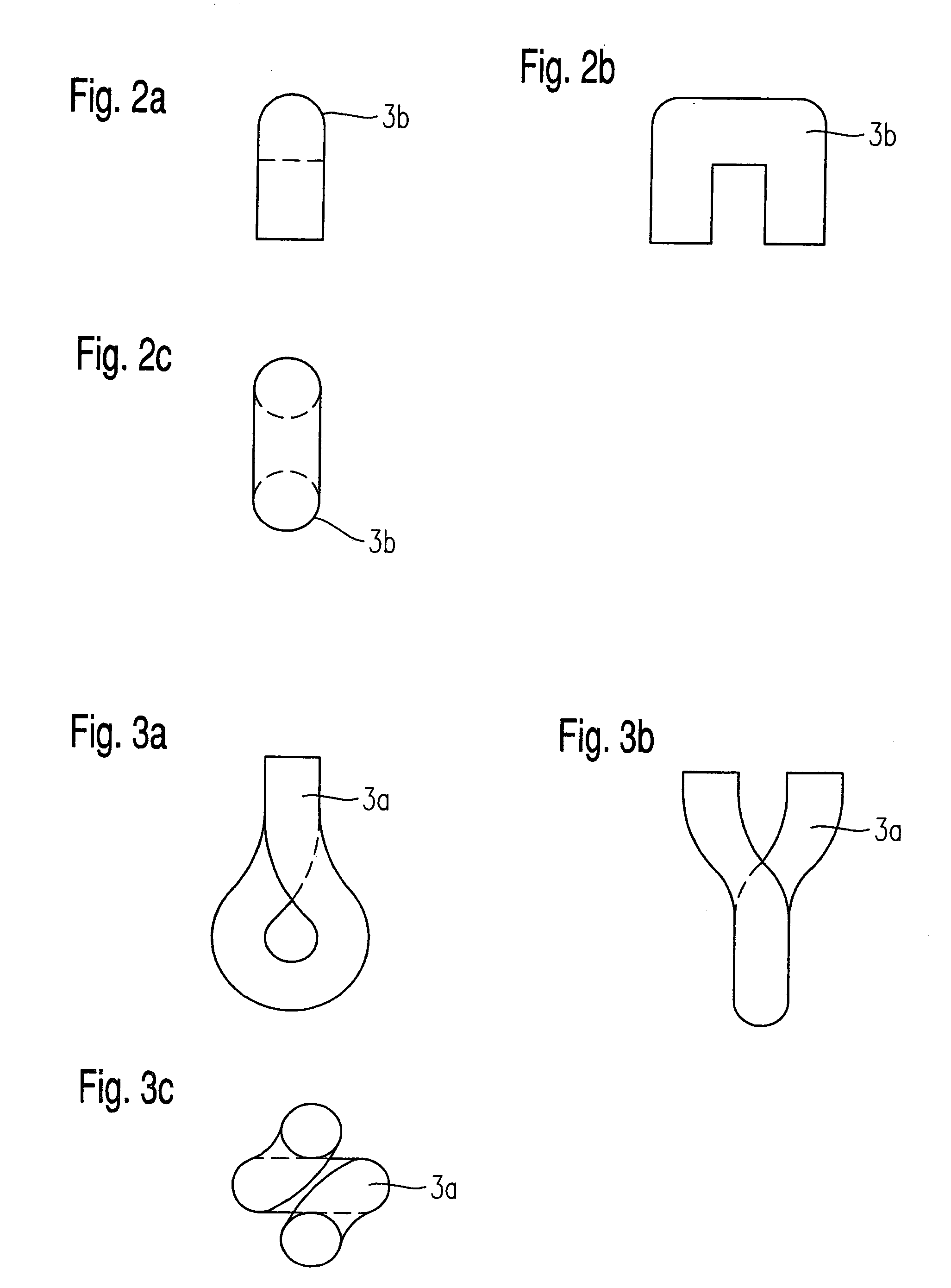

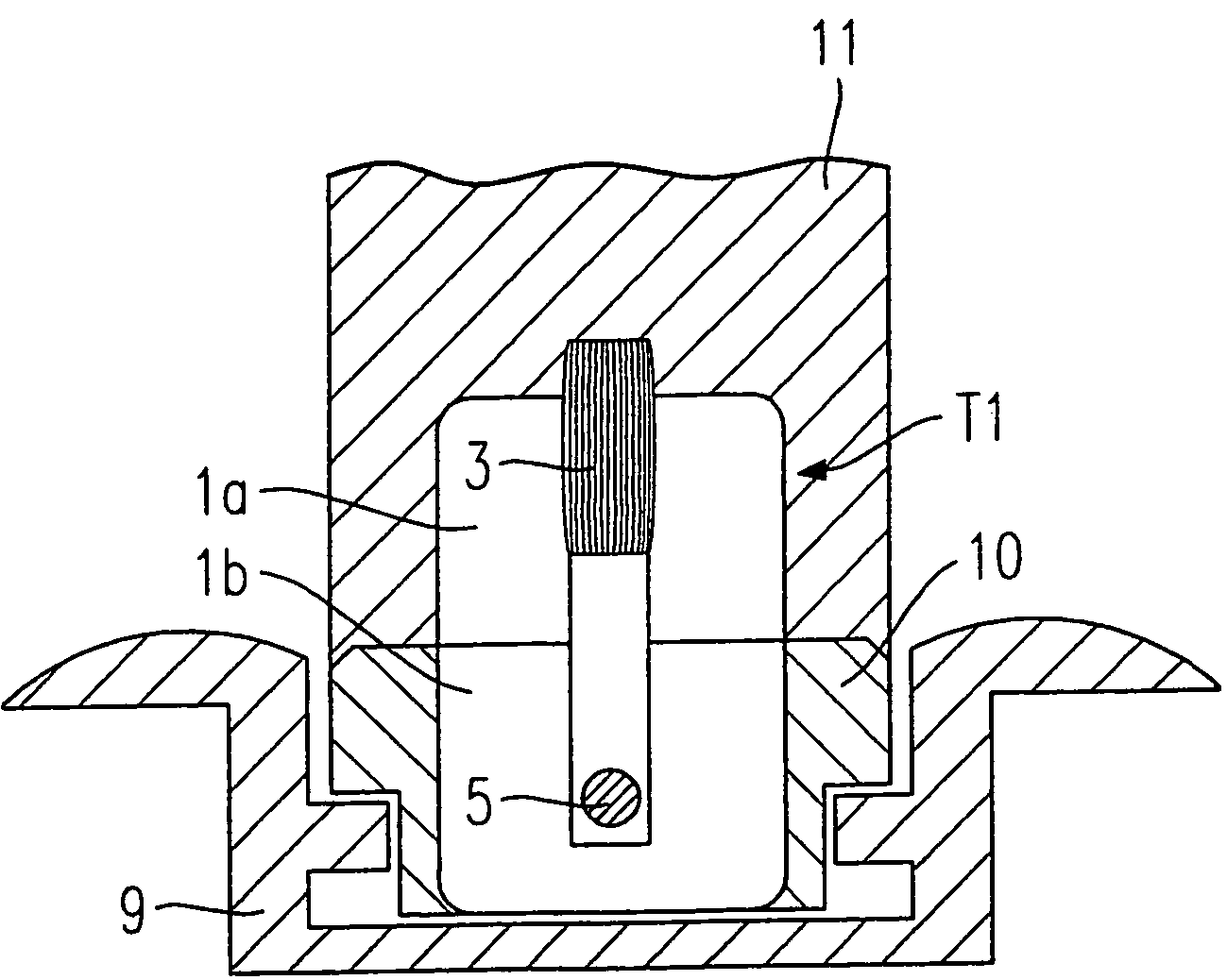

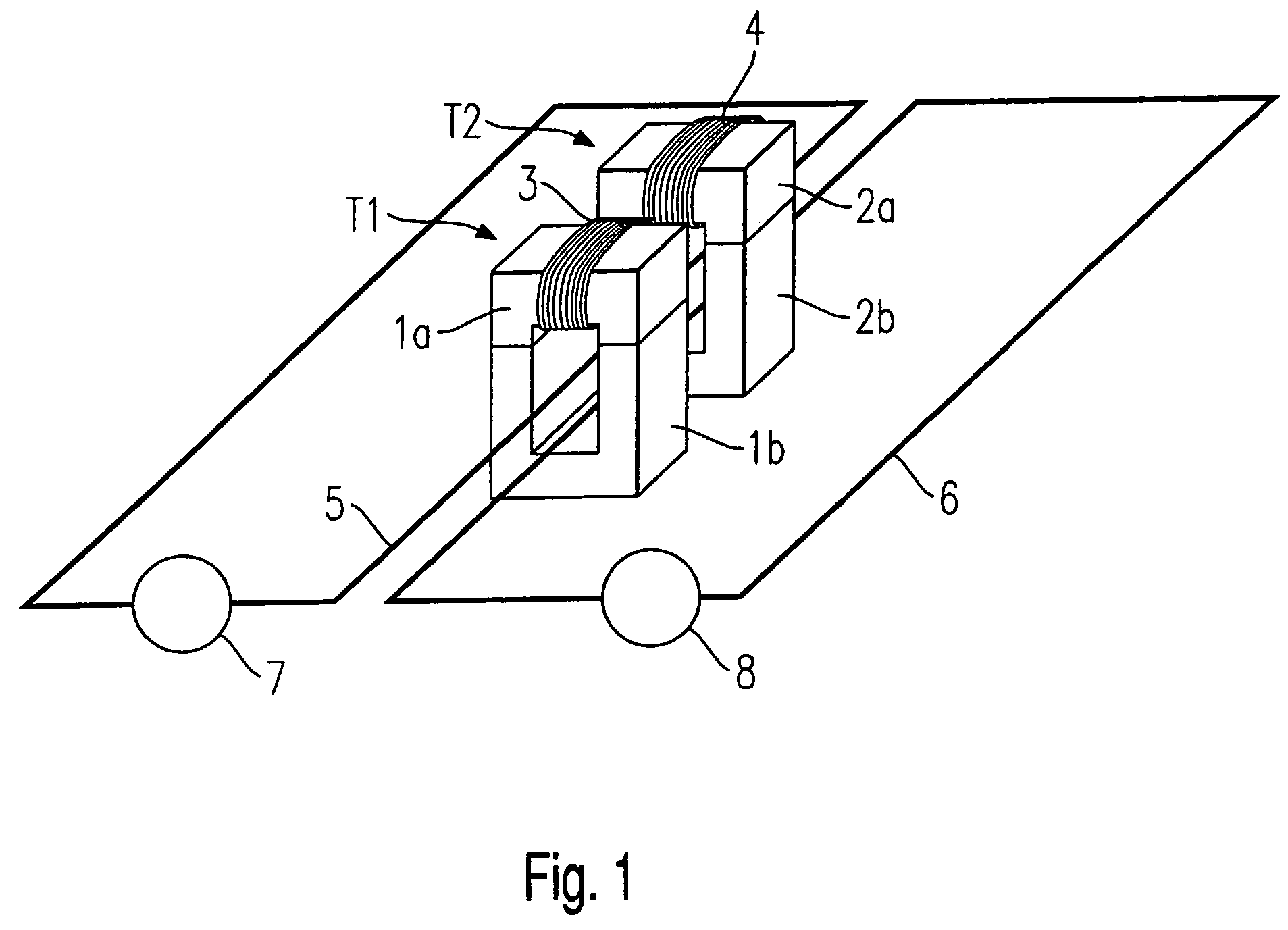

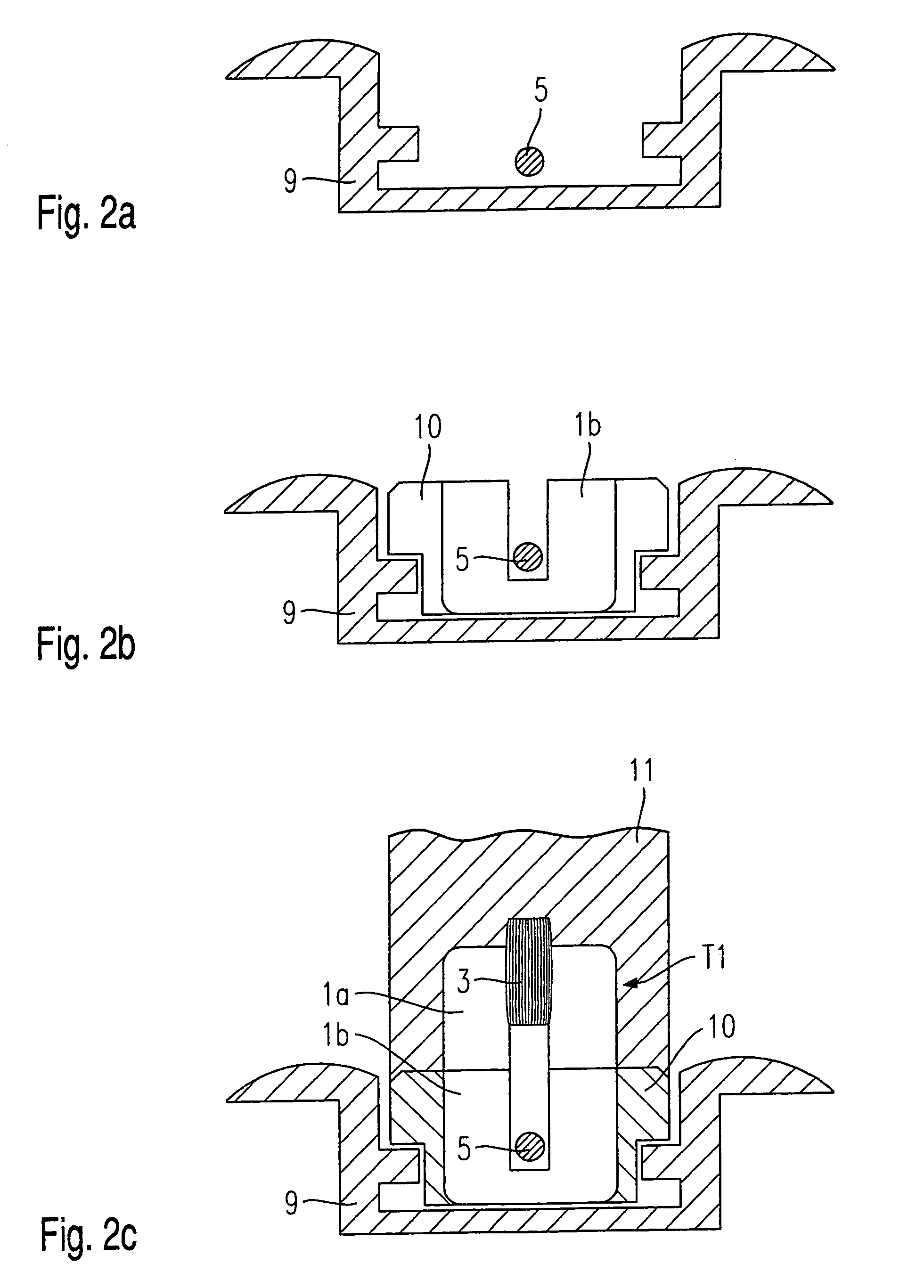

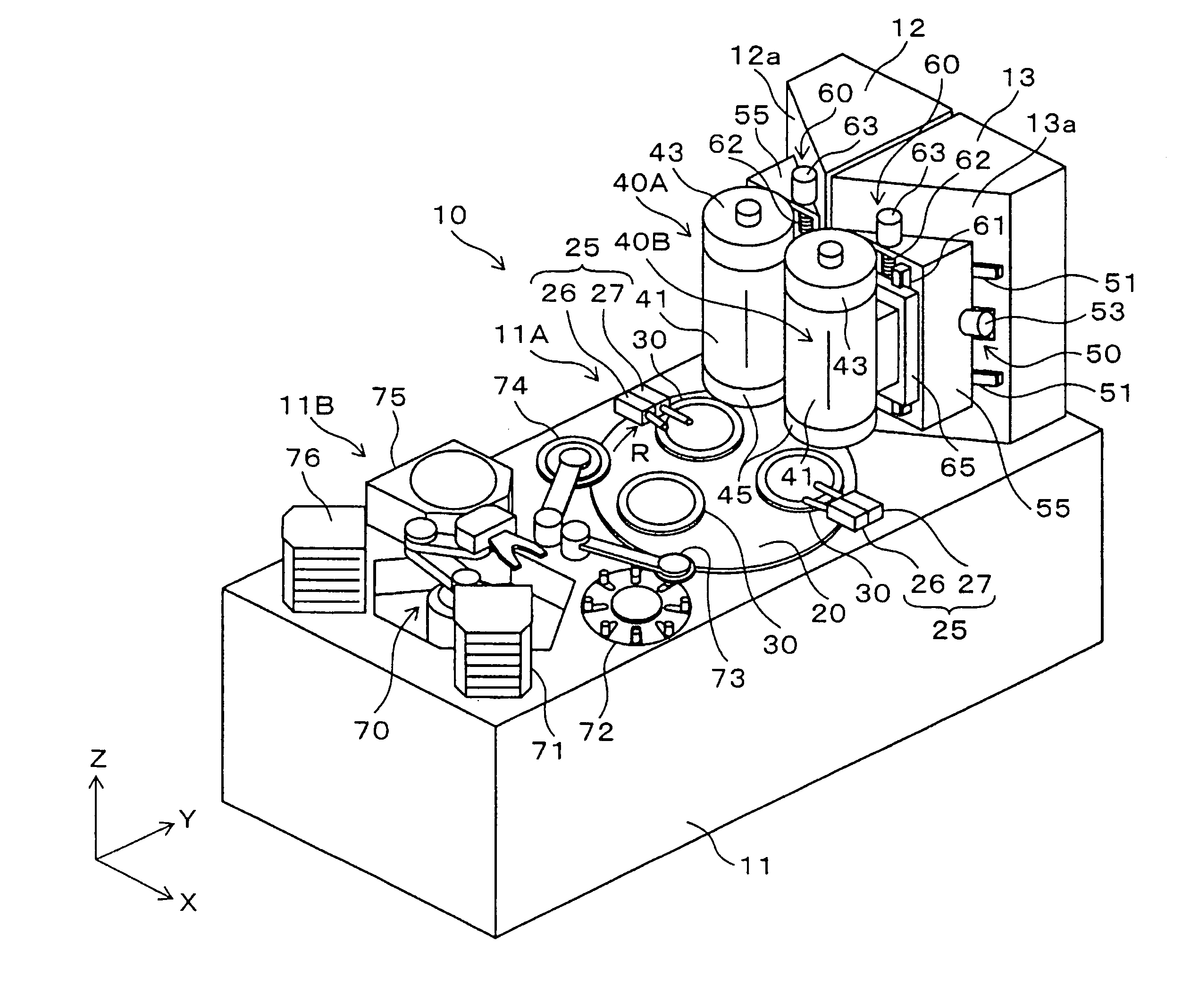

Data transmission between a chassis and a seat movably arranged on the chassis

InactiveUS7170192B2Small depthInexpensive and easy to assembleElectric signal transmission systemsElectric devicesTransformerEngineering

A system for transmitting data and / or energy between a chassis and a seat that is movably arranged on the chassis, the seat being able to glide with the aid of slides in guide rails attached to the chassis; one iron-core half of a transformer, the iron-core half bearing at least one primary winding is positioned on the slide gliding in the guide rail, the primary winding being a cable in the guide rail; and the other iron-core half of the transformer, having a secondary winding, is positioned on the seat, the two limbs of the other iron-core half being arranged in the longitudinal direction with respect to the guide rail, and both iron-core halves of the transformer being positioned relative to each other for the data and / or energy transmission.

Owner:ROBERT BOSCH GMBH

Data transmission between a chassis and a seat movably arranged on the chassis

InactiveUS7271501B2Easy to handleLow production costNear-field transmissionElectric signal transmission systemsTransformerEngineering

A system for transmitting data and / or energy between a chassis and a seat movably arranged on the chassis, the seat being able to glide in guide rails, attached to the chassis, with the aid of slides; one iron-core half of a transformer—the iron-core half bearing at least one primary winding—is disposed on the slide gliding in the guide rail, the primary winding being a cable lying in the guide rail; and the other iron-core half of the transformer having a secondary winding is arranged on the seat, the two iron-core halves of the transformer being positioned relative to each other for the data and / or energy transmission when the seat is mounted.

Owner:ROBERT BOSCH GMBH

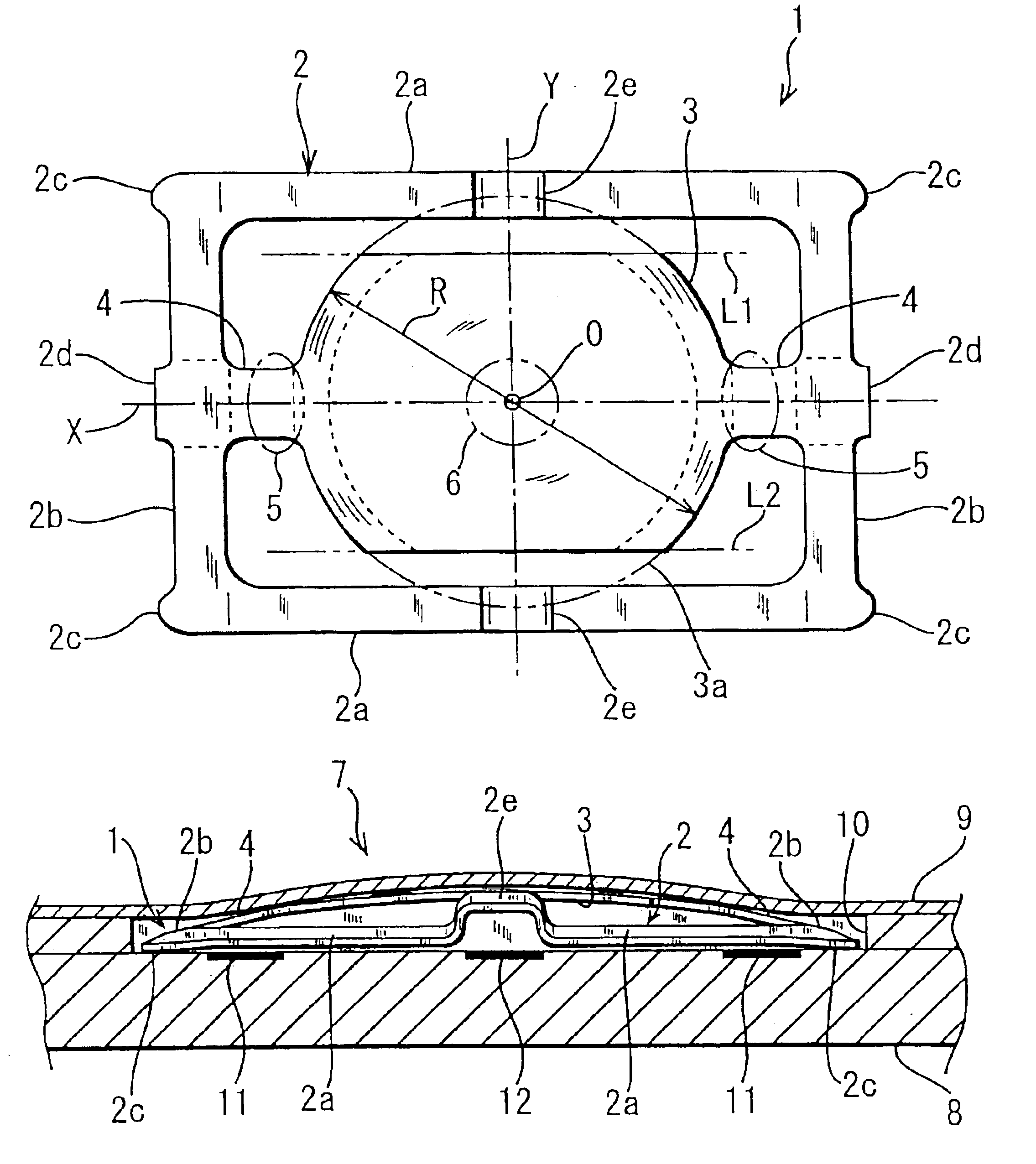

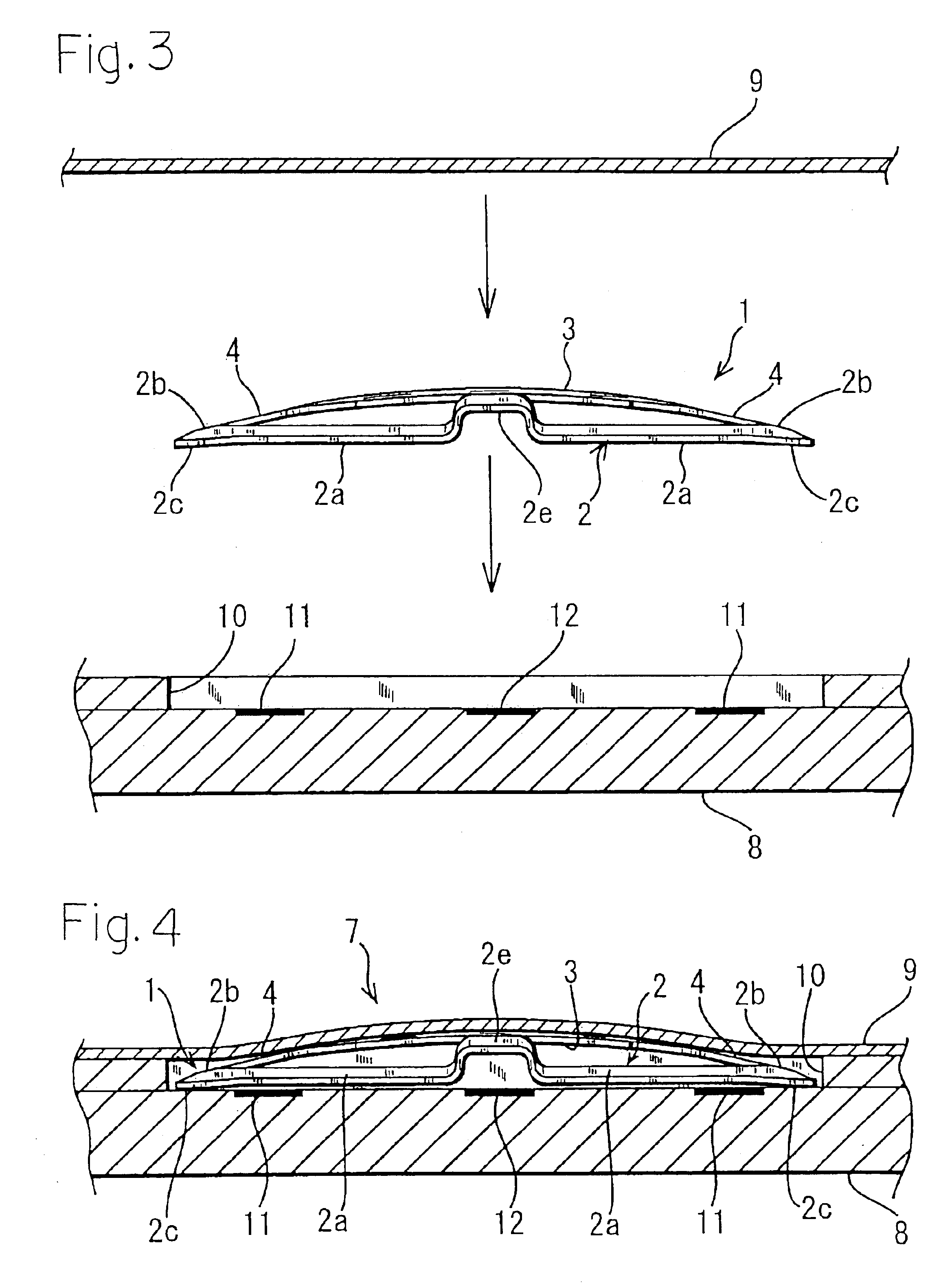

Movable contact for a push-on switch, and push-on switch

ActiveUS6951991B2Reduce widthFeel goodContact surface shape/structureSnap-action arrangementsFlexible electronicsPush switch

Owner:HOSIDEN CORP

Improved drying apparatus and method

ActiveUS20160122936A1Keep dryExtended drying timeDrying solid materials with heatDrying solid materials without heatSolid particleMaterial transfer

Owner:XEROS LTD

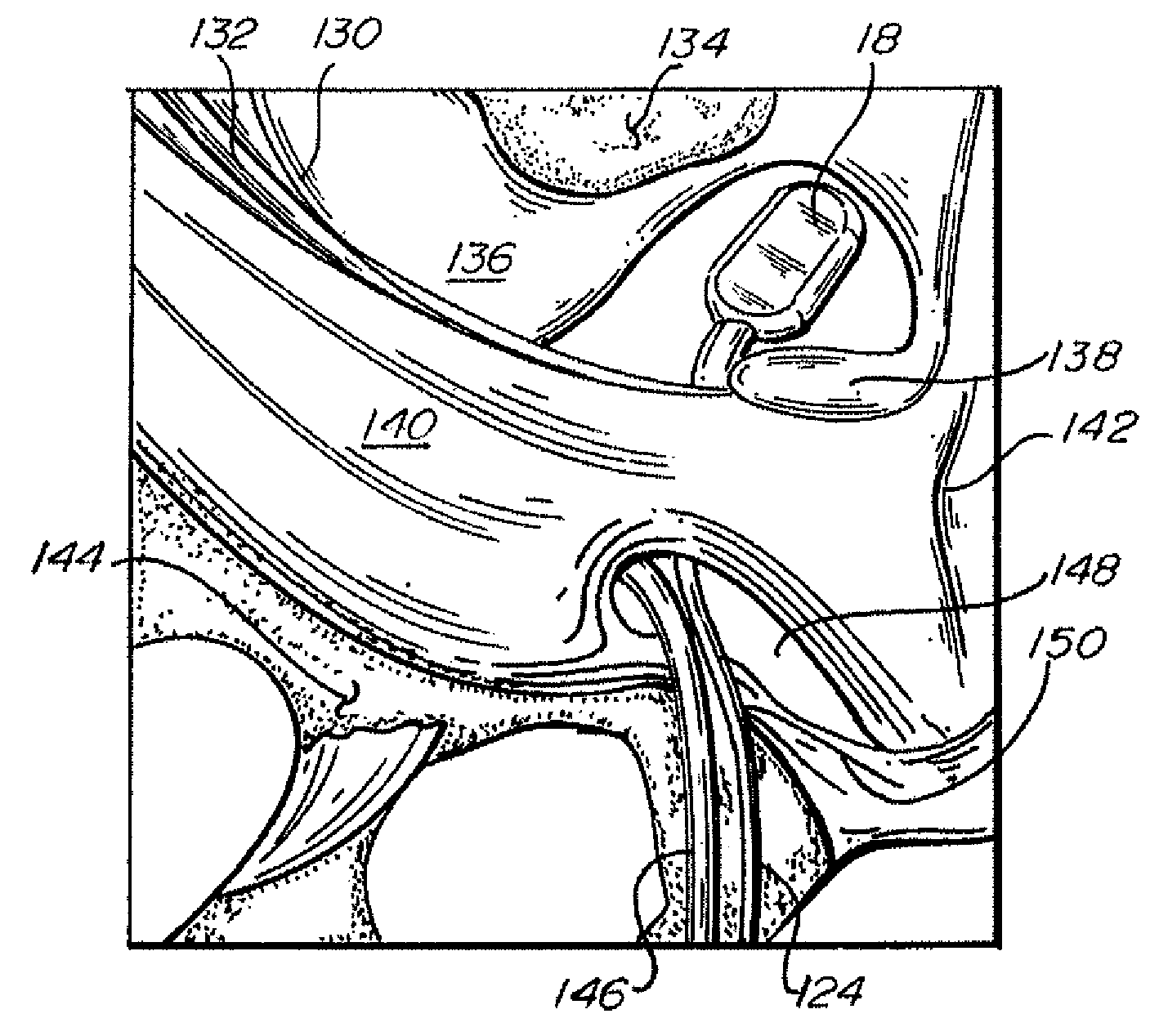

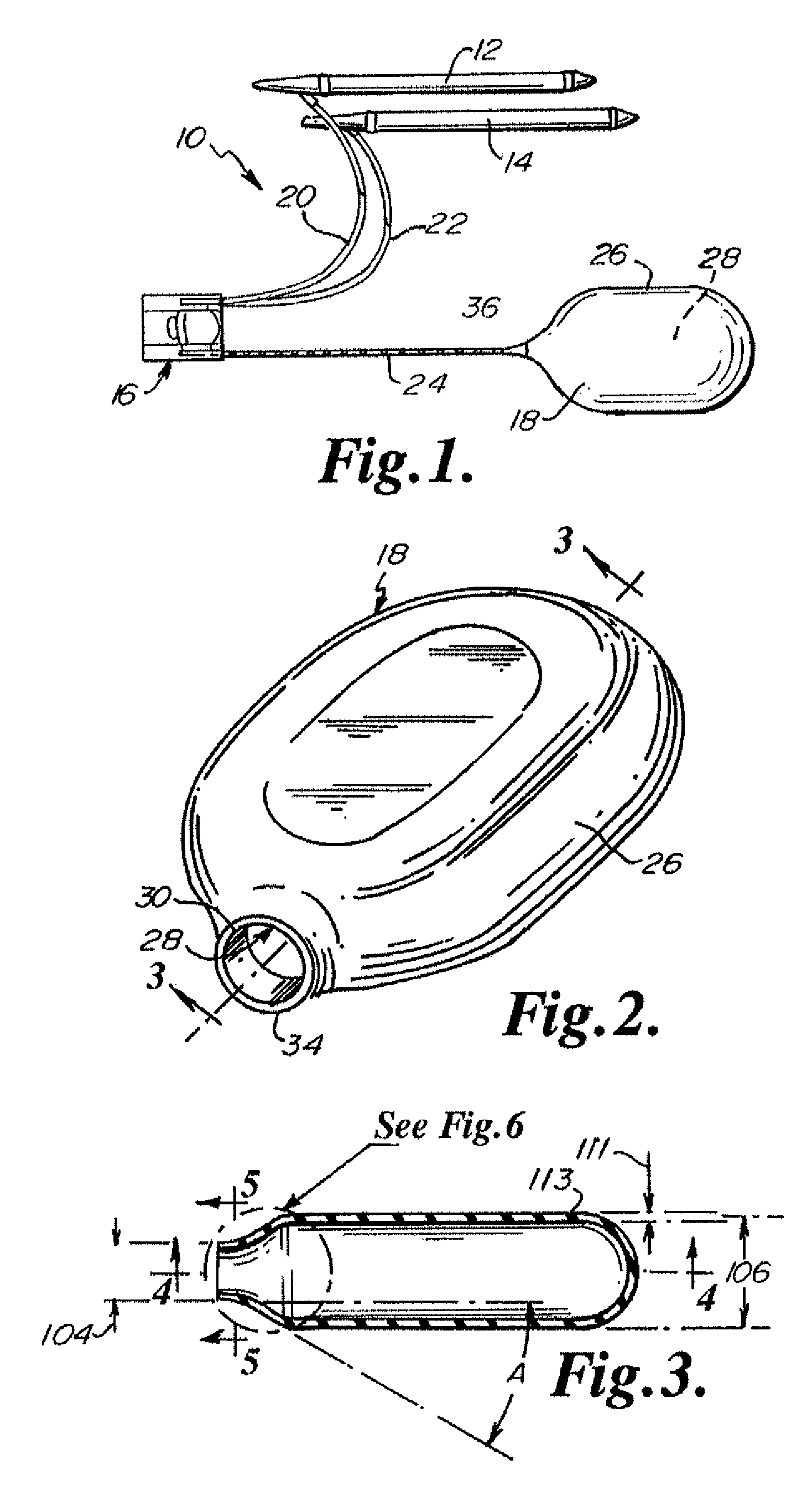

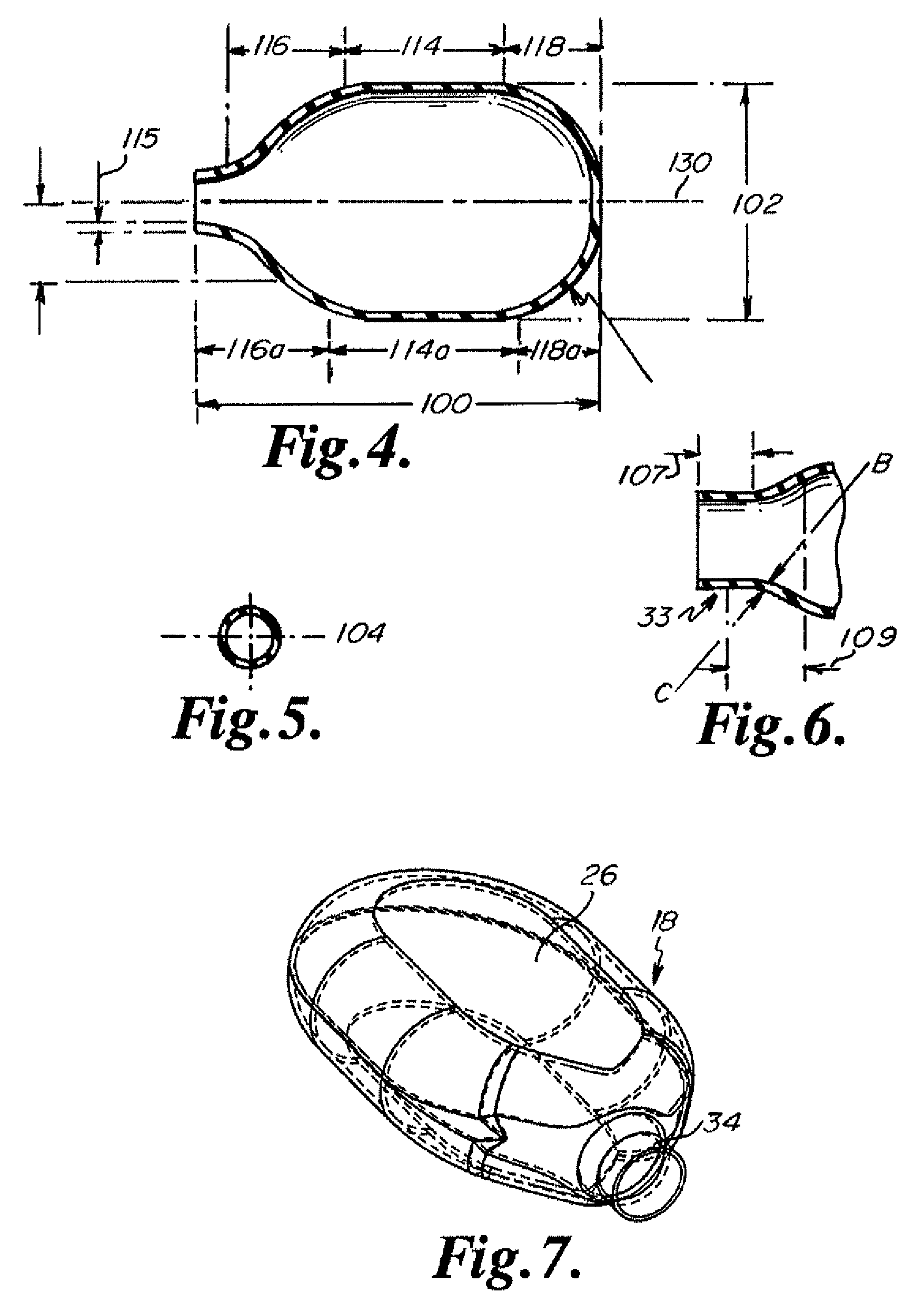

Fluid reservoir for penile implant devices

ActiveUS7946975B2Eliminate requirementsSmall depthNon-surgical orthopedic devicesPenis implantsPuborectalis musclePenile implant

Owner:BOSTON SCI SCIMED INC

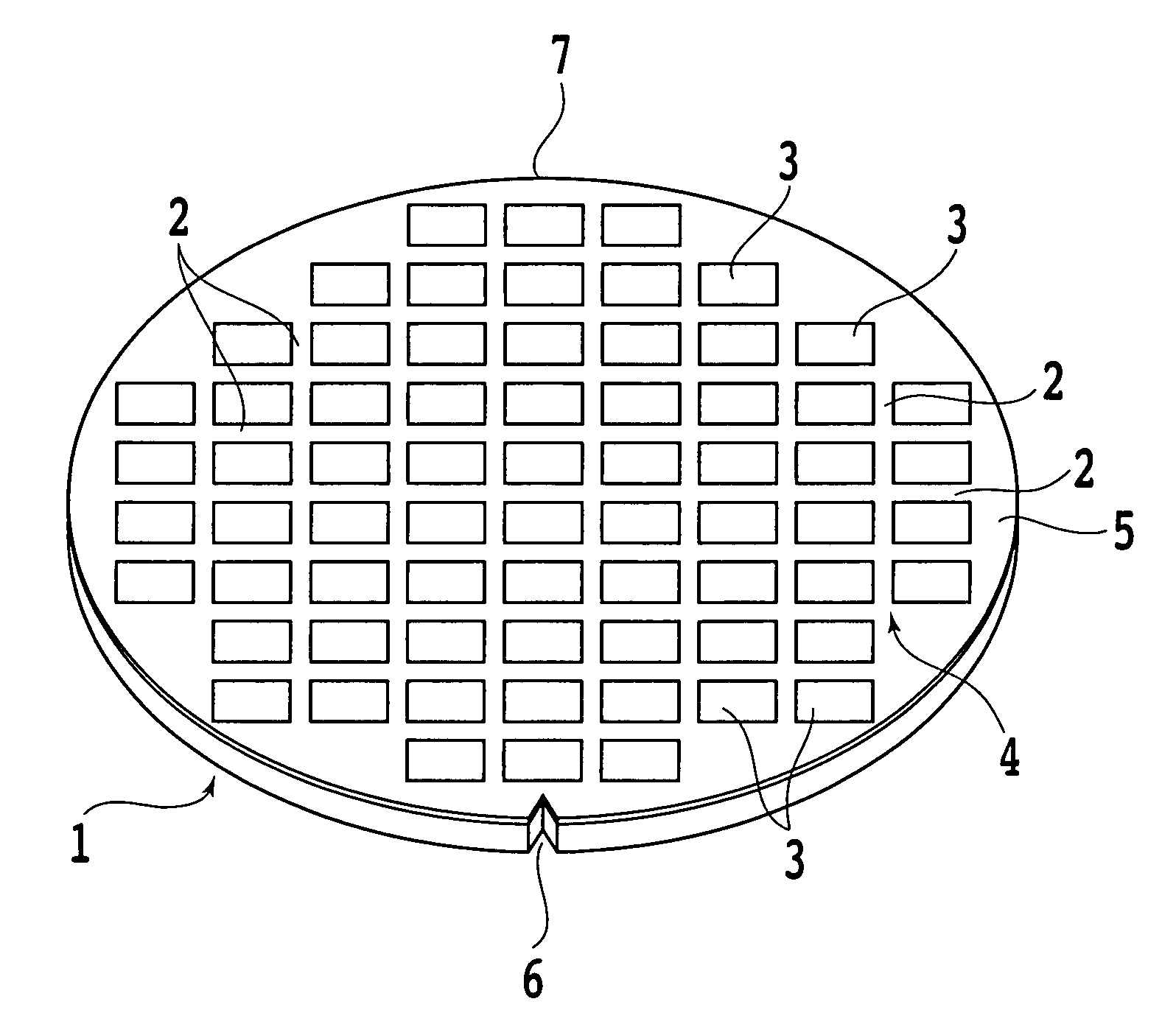

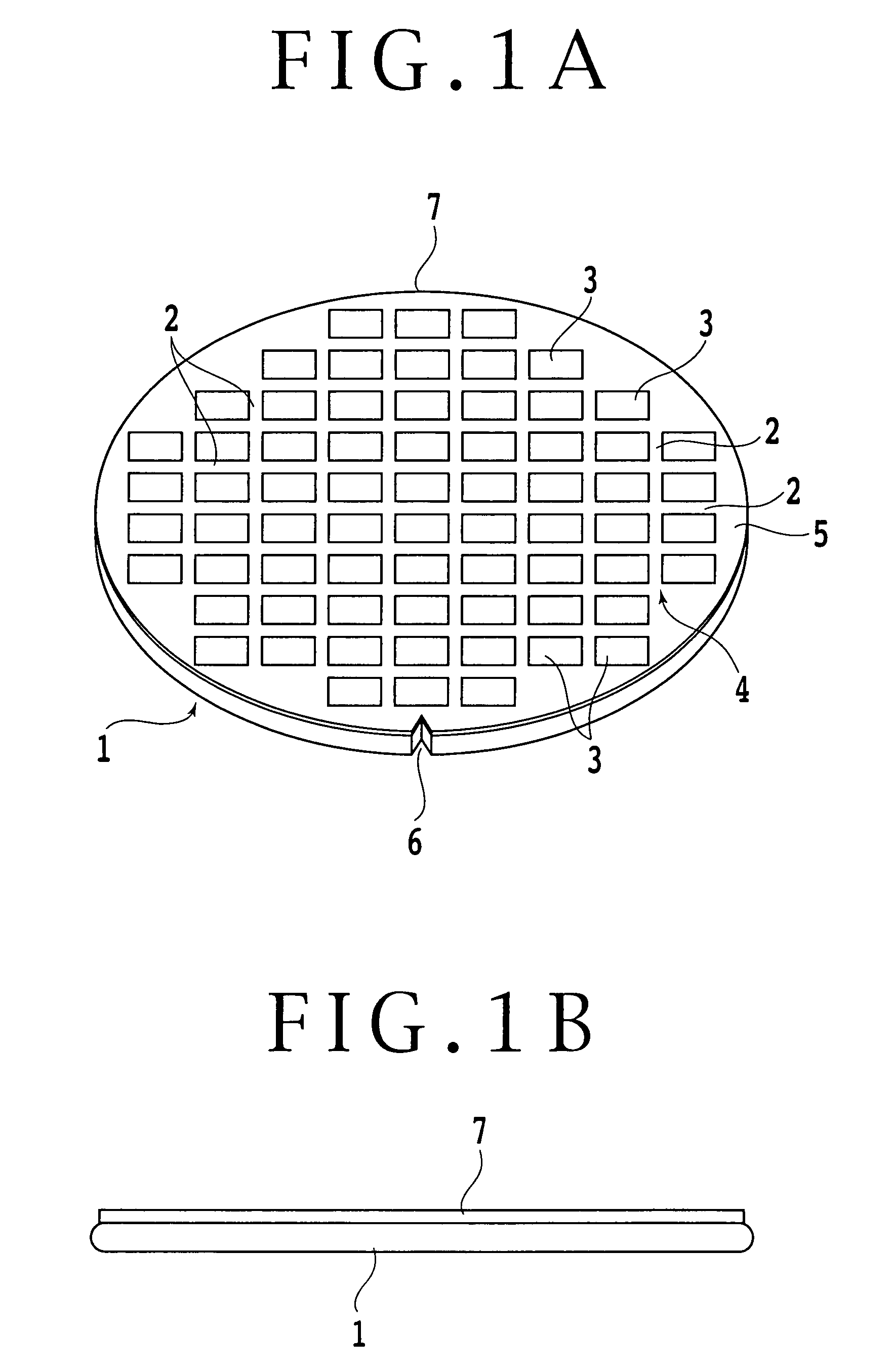

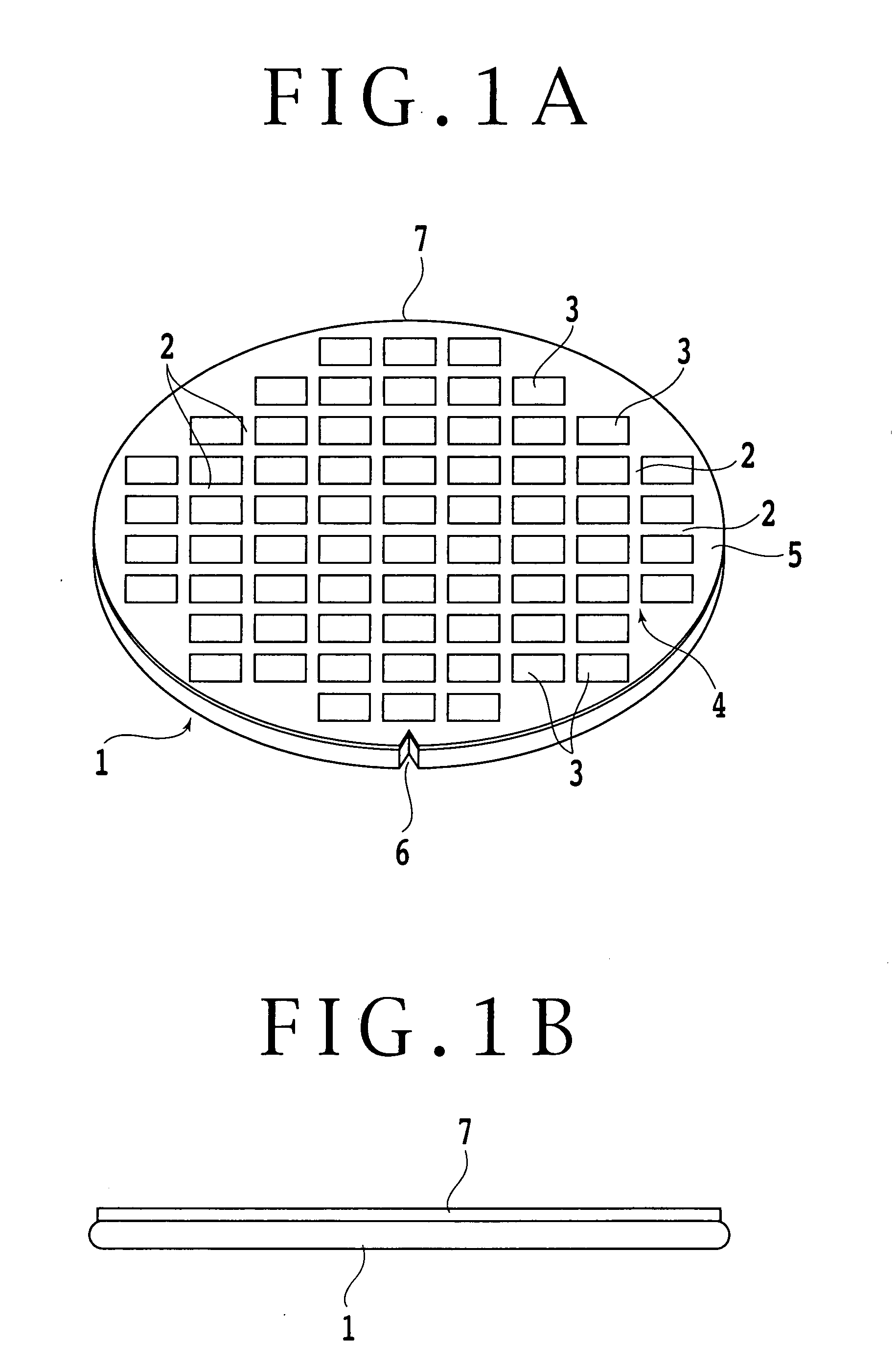

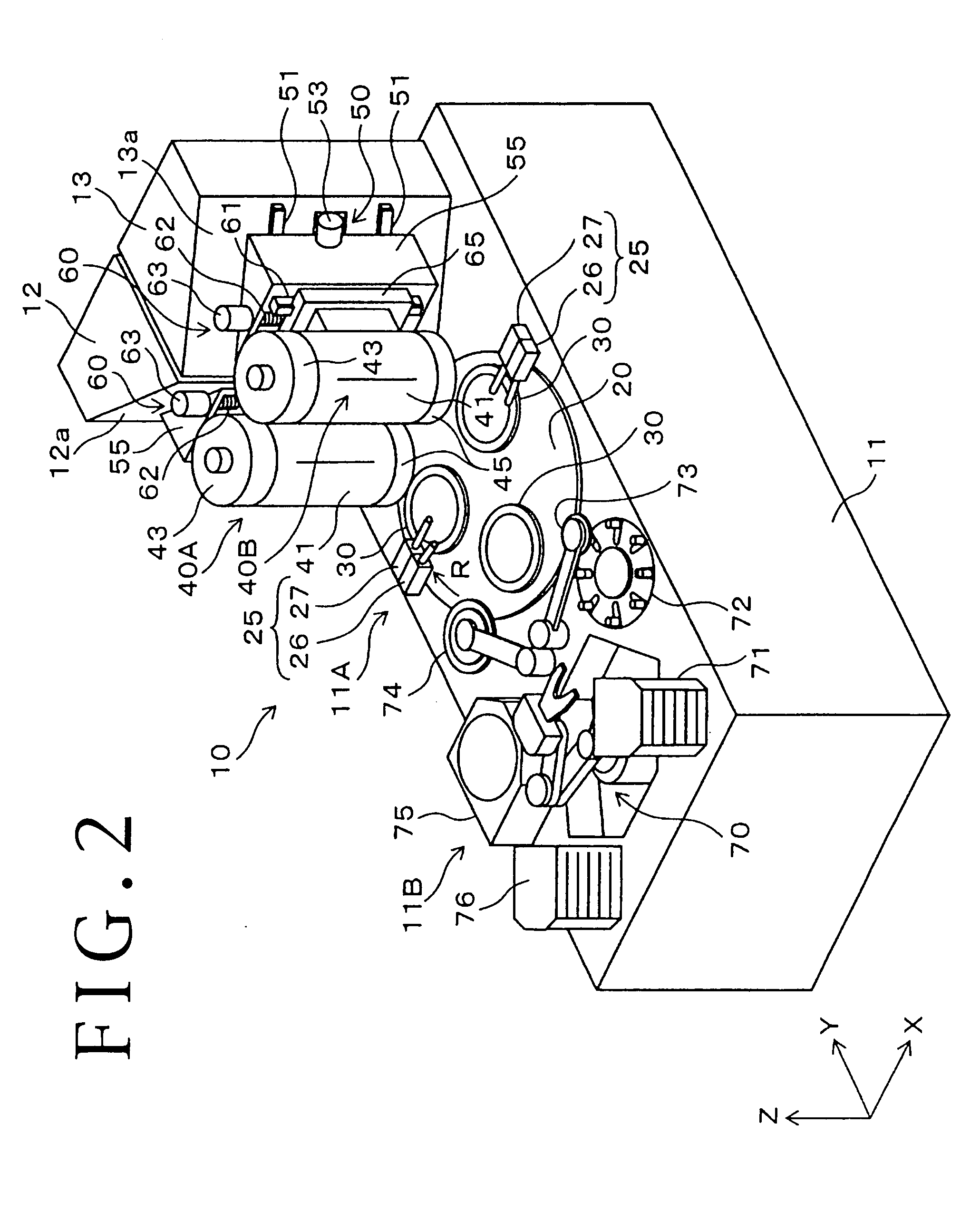

Wafer grinding method

ActiveUS7462094B2Lowering in productivityIncrease productionEdge grinding machinesPolishing machinesEngineeringElectrical and Electronics engineering

A wafer grinding method is disclosed, in which only a region, corresponding to a device formation region, of the back side of a wafer is ground in rough grinding conducted first, while the part surrounding the region thus ground is left unground as an annular projected part, to prevent the outer peripheral edge of the wafer from becoming knife edge-like in shape. In the subsequent finish grinding, the annular projected part is ground and, further, the whole area of the back side of the wafer is ground to be flat. Chippings of the outer peripheral edge may be generated only during the finish grinding, whereby the chippings are prevented from occurring or limited to minute ones.

Owner:DISCO CORP

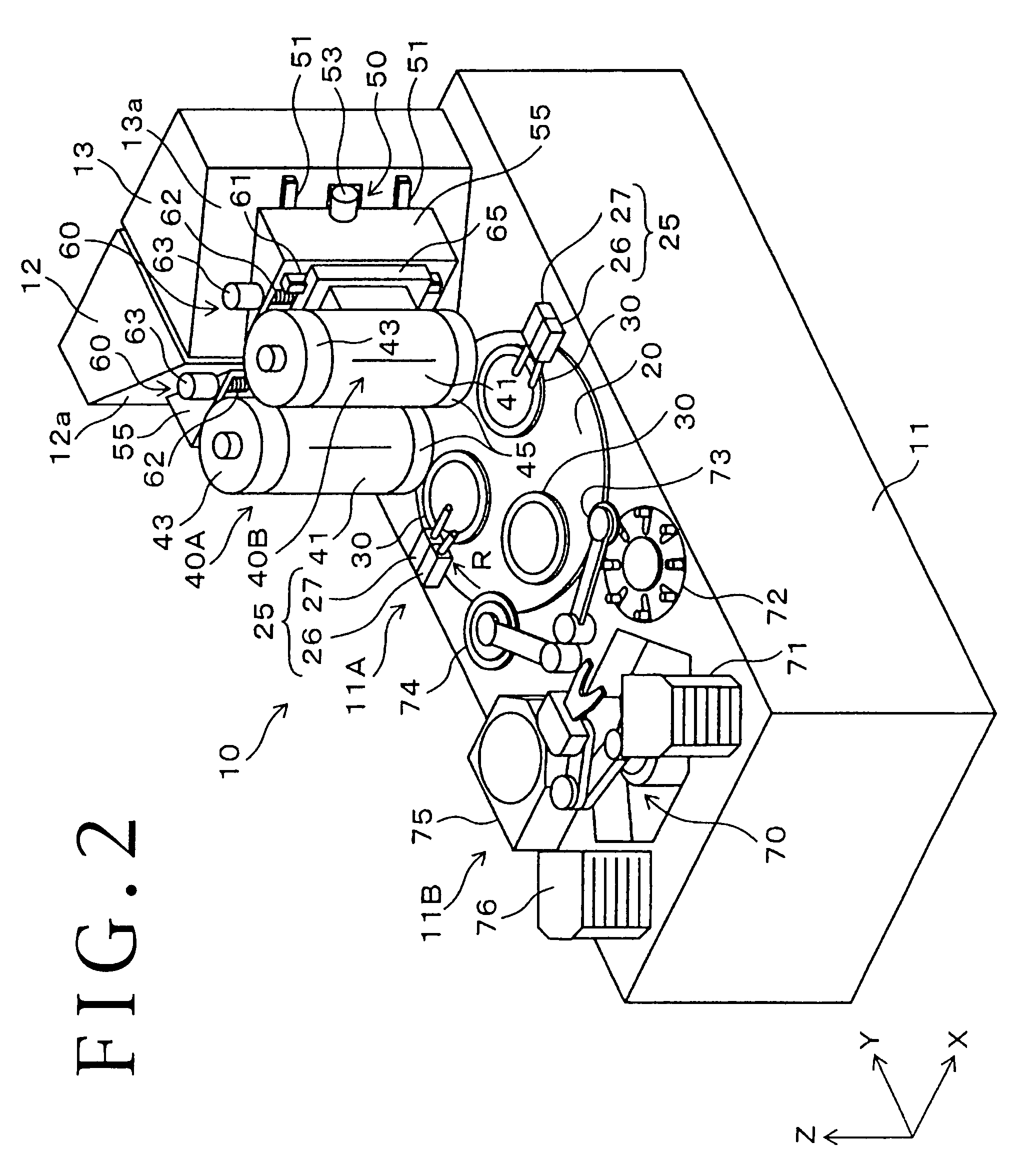

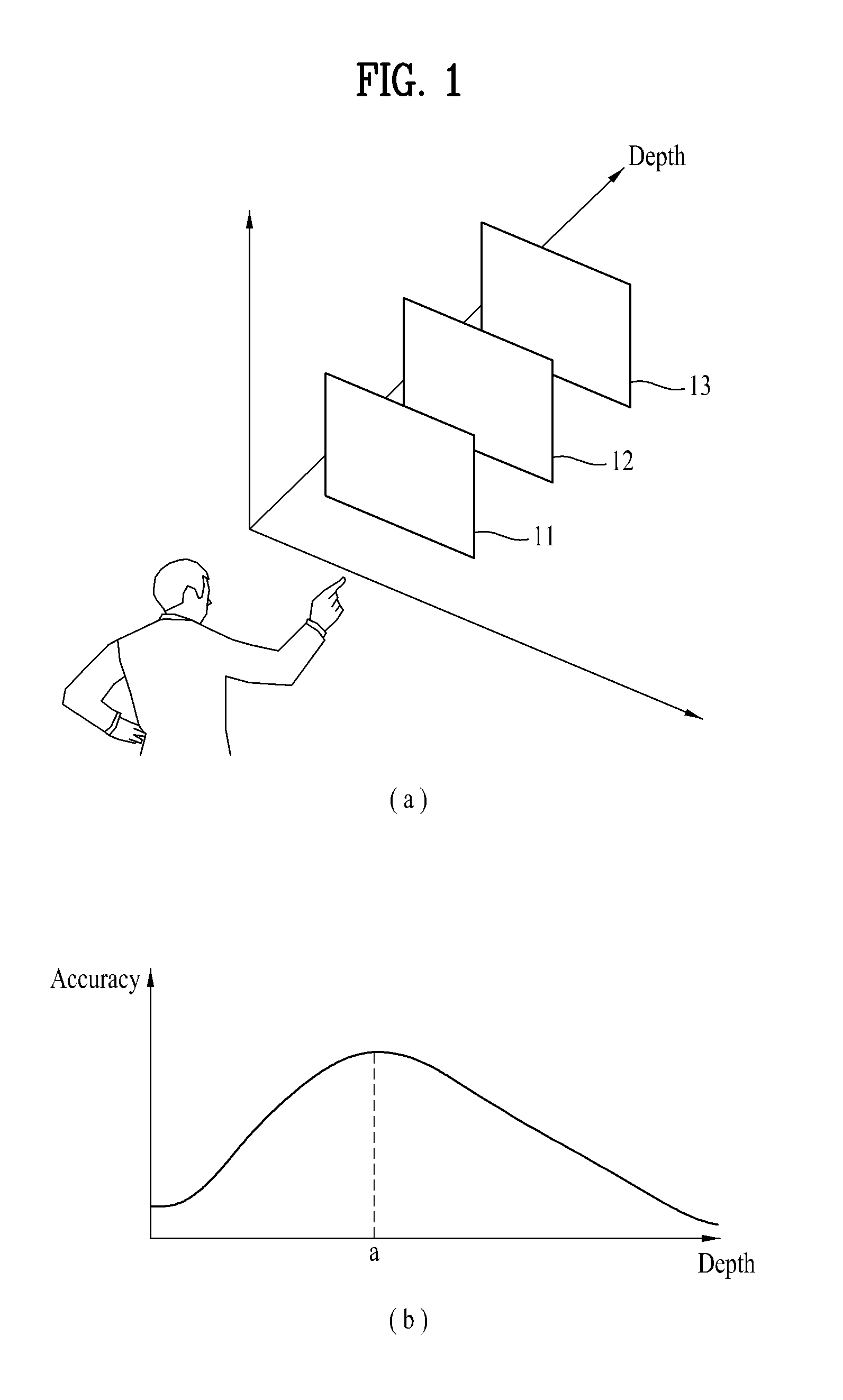

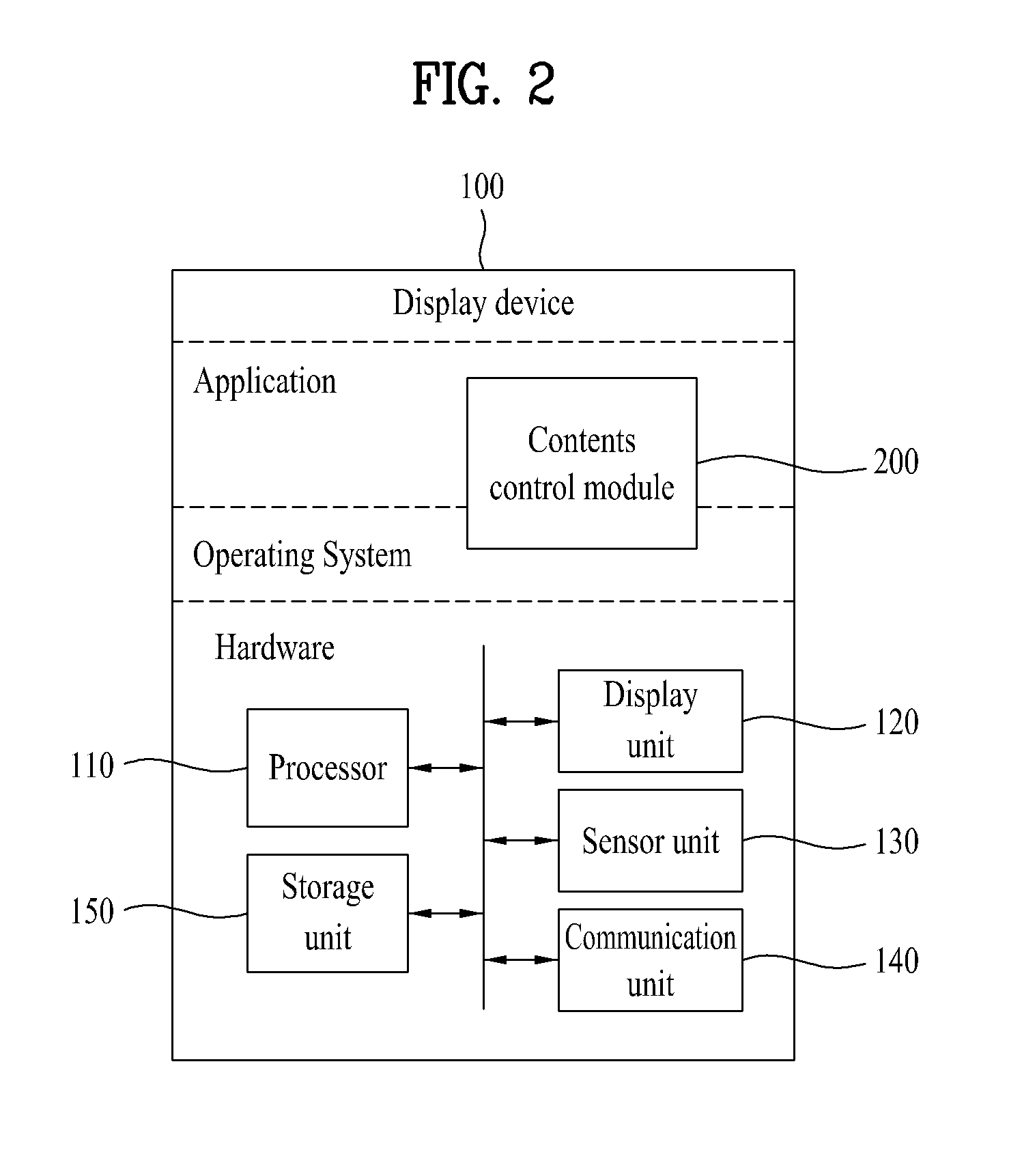

Display device having scope of accreditation in cooperation with depth of virtual object and controlling method thereof

InactiveUS20160012631A1Small depthCathode-ray tube indicatorsSteroscopic systems3d imageDisplay device

A display device having a scope of accreditation in cooperation with a depth of a virtual object and a controlling method thereof are disclosed in this specification. The display device according to this specification outputs a three-dimensional (3D) image including virtual objects. And a scope of accreditation accrediting (or recognizing) that a virtual object has been selected is configured in the virtual object. At this point, an area of a scope of accreditation may be configured to be in cooperation with a depth of a virtual object along an increasing or decreasing direction of the depth of the virtual object, wherein the depth of the virtual object indicates a distance level between the virtual object and a user's perspective within the 3D image.

Owner:LG ELECTRONICS INC

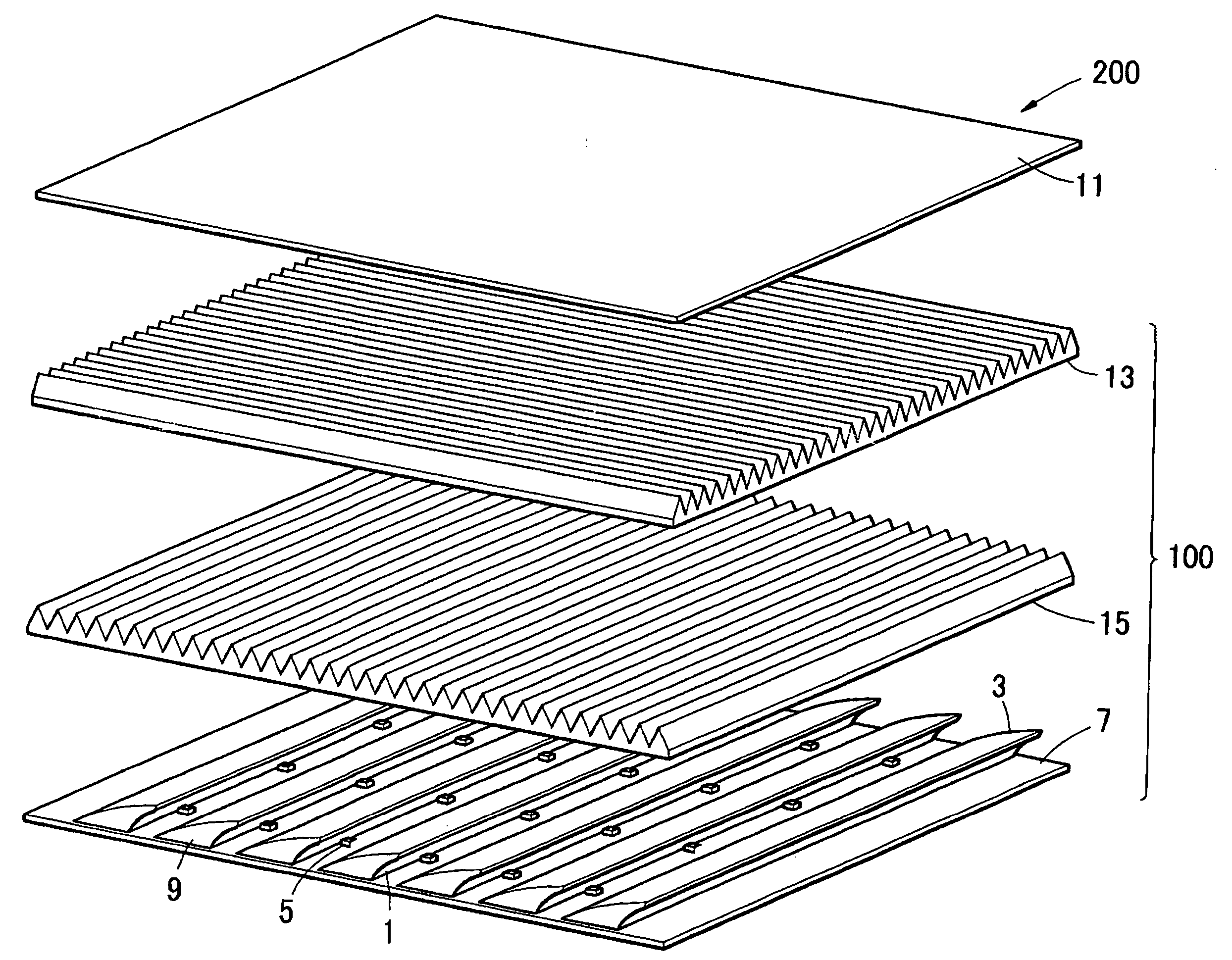

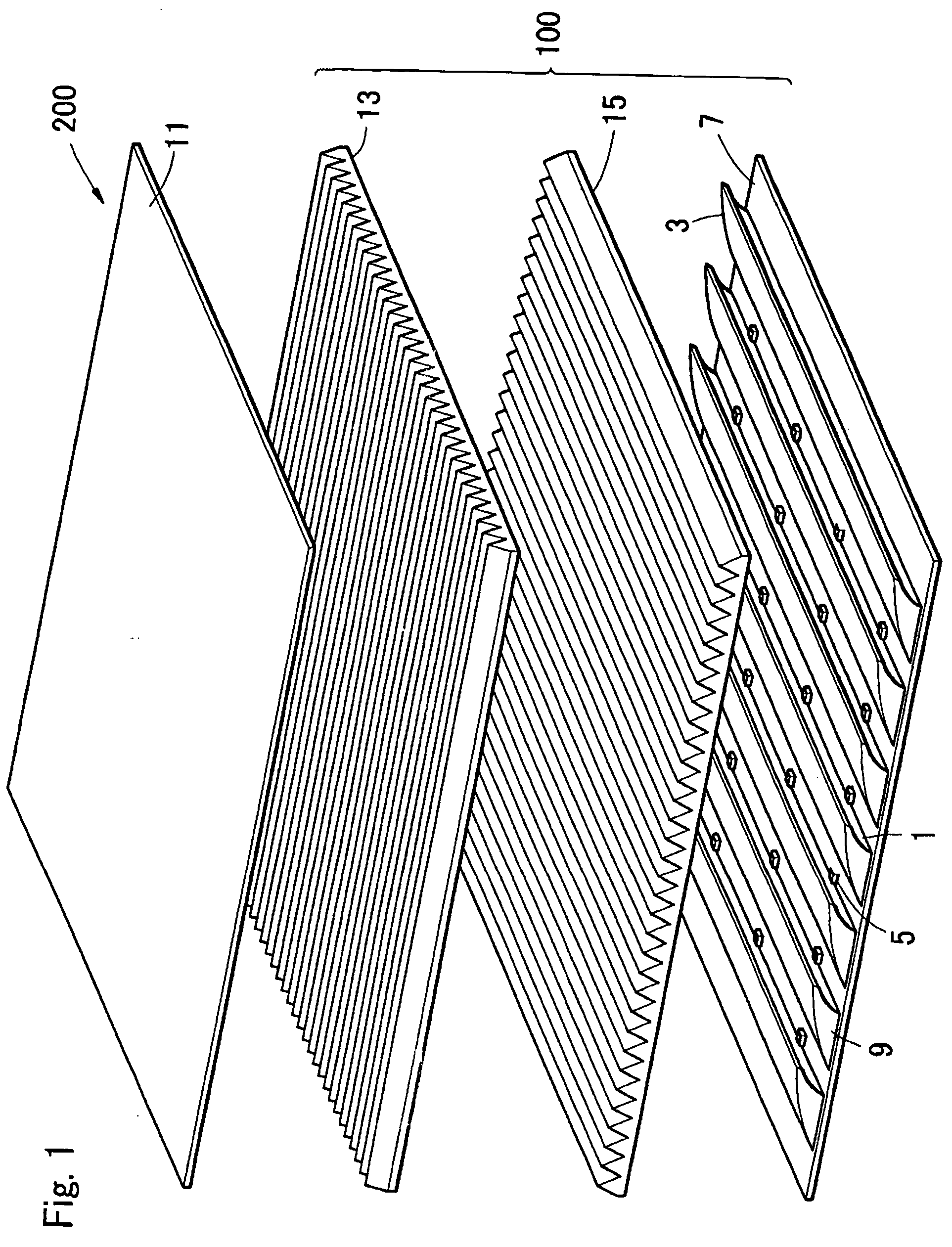

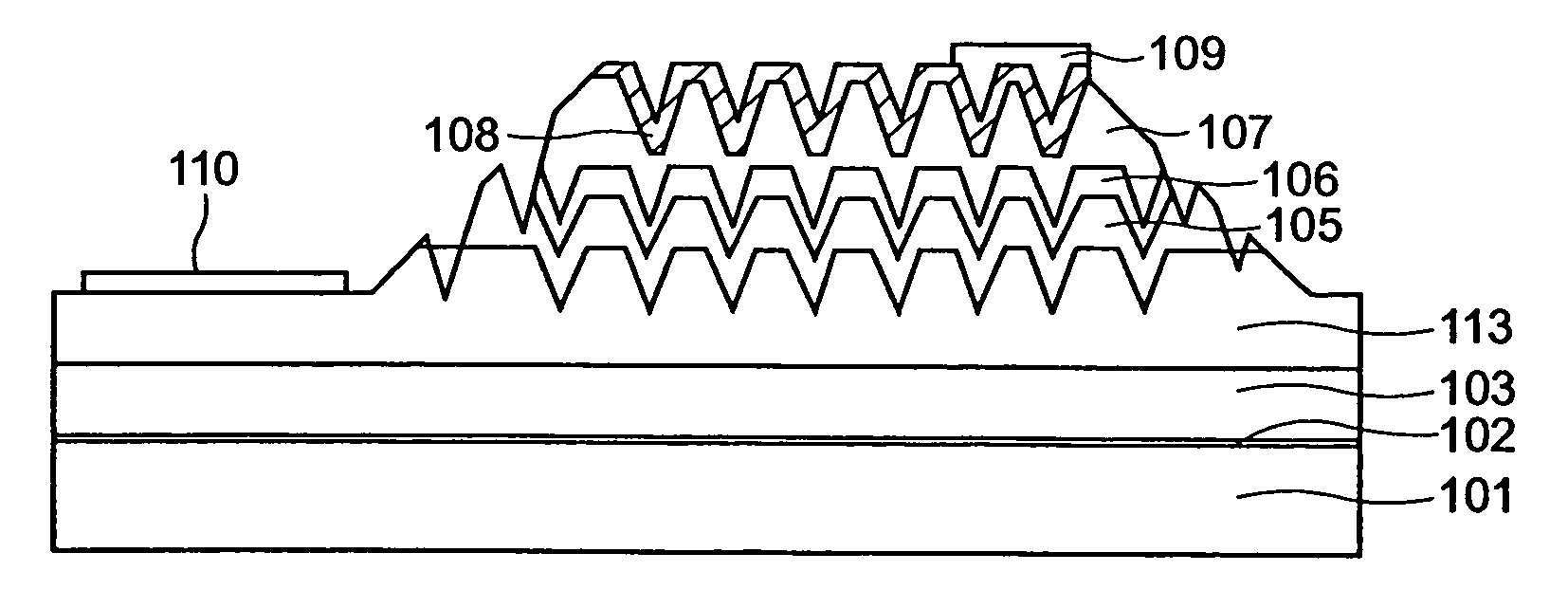

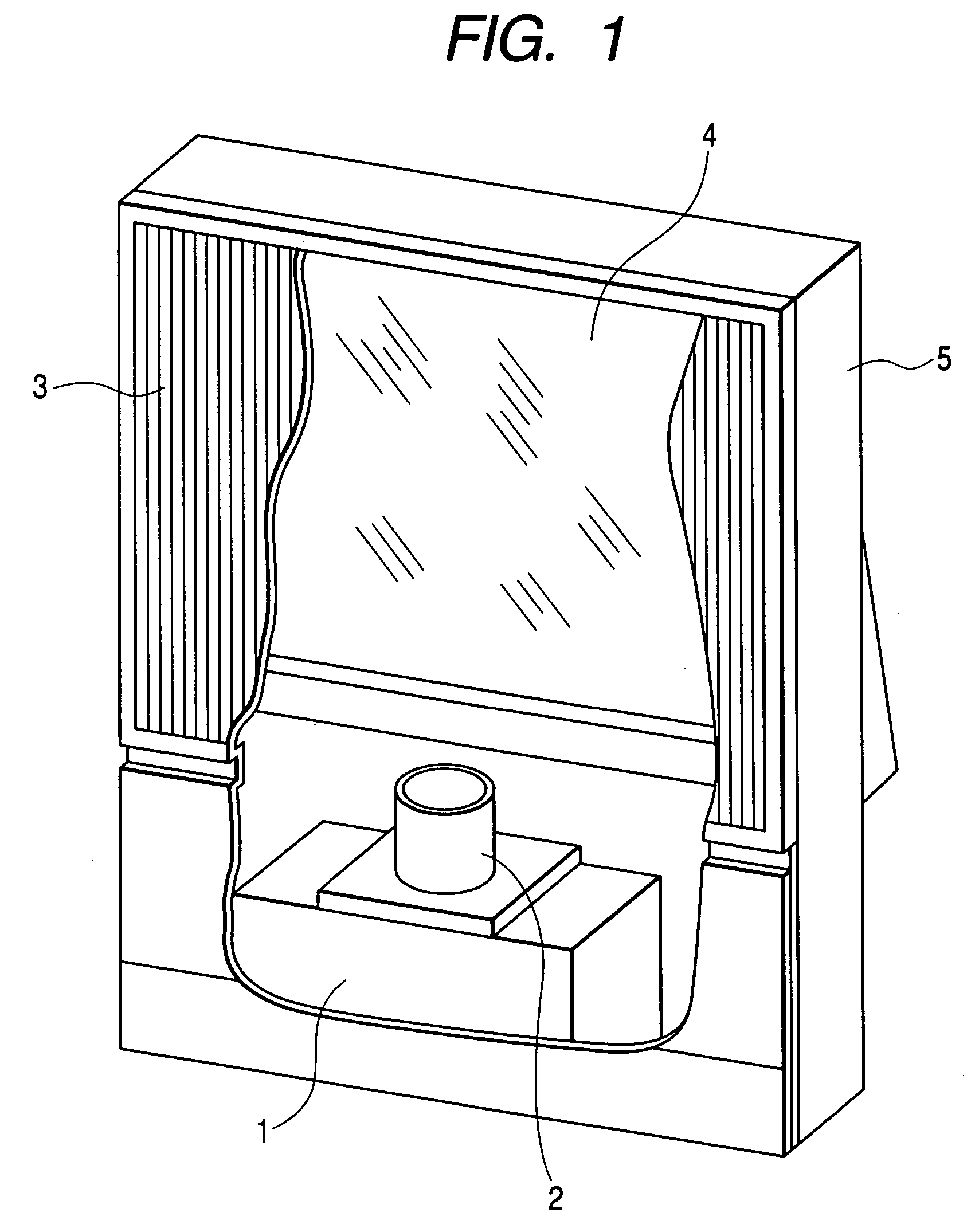

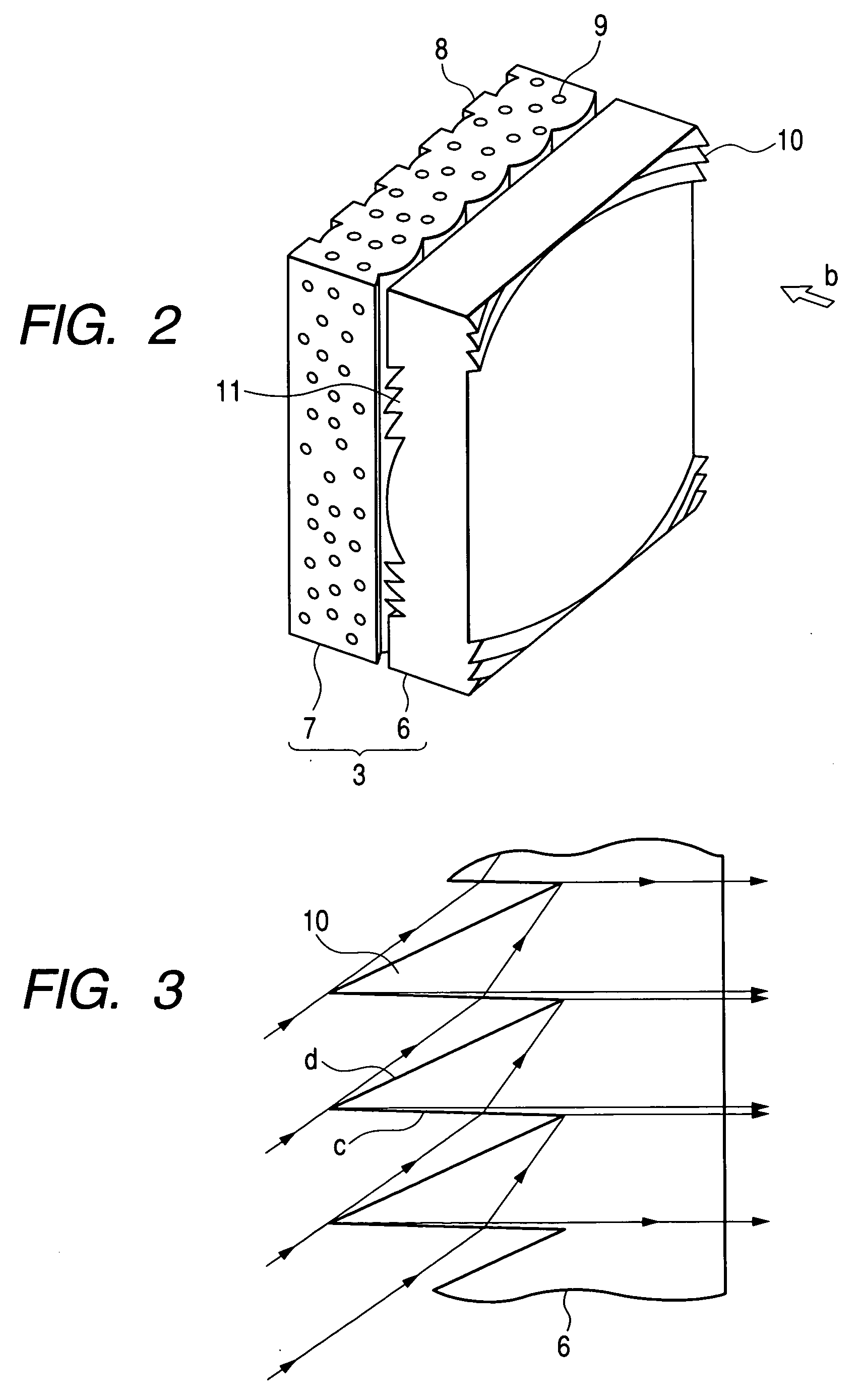

Image display device, rear projection type screen used in image display device, fresnel lens sheet, and method of making fresnel lens sheet

A total reflecting prism portion is formed on an image generation source side of a Fresnel lens sheet which constitutes a rear projection type screen. The total reflecting prism portion is formed in an area in which the angle of incidence of a projection image projected from an optical part on the Fresnel lens sheet is at least about 40°. The total reflecting prism portion causes incident light to be outputted as output light at a predetermined output angle by a total reflection phenomenon after a first refraction phenomenon. A refracting prism portion is formed on an image monitoring side of the Fresnel lens sheet. The refracting prism portion is formed in an area opposed to the portion where the total reflecting prism portion is not formed. The refracting prism portion causes incident light to be outputted as output light at a predetermined output angle by a second refraction phenomenon.

Owner:MAXELL HLDG LTD

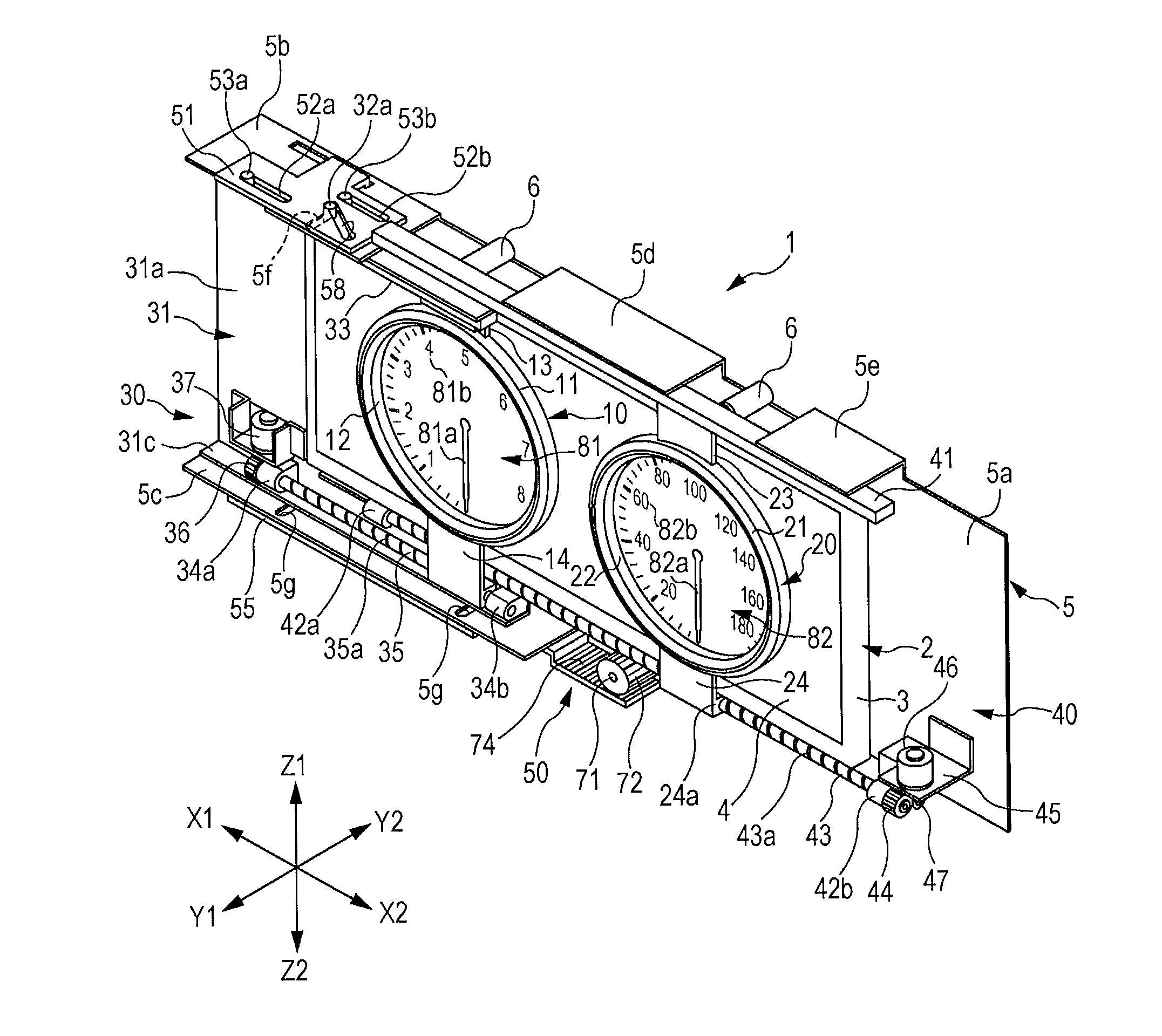

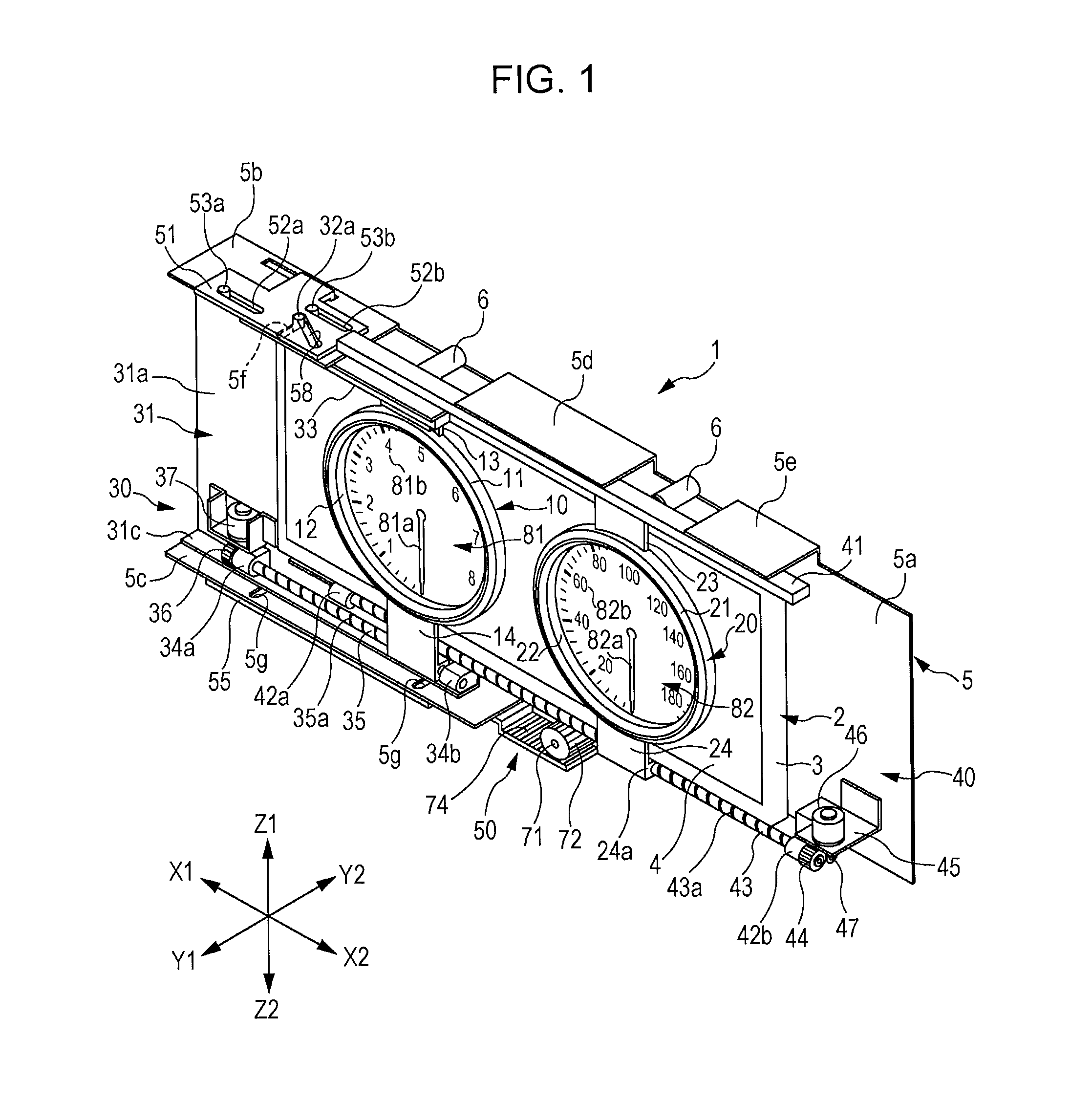

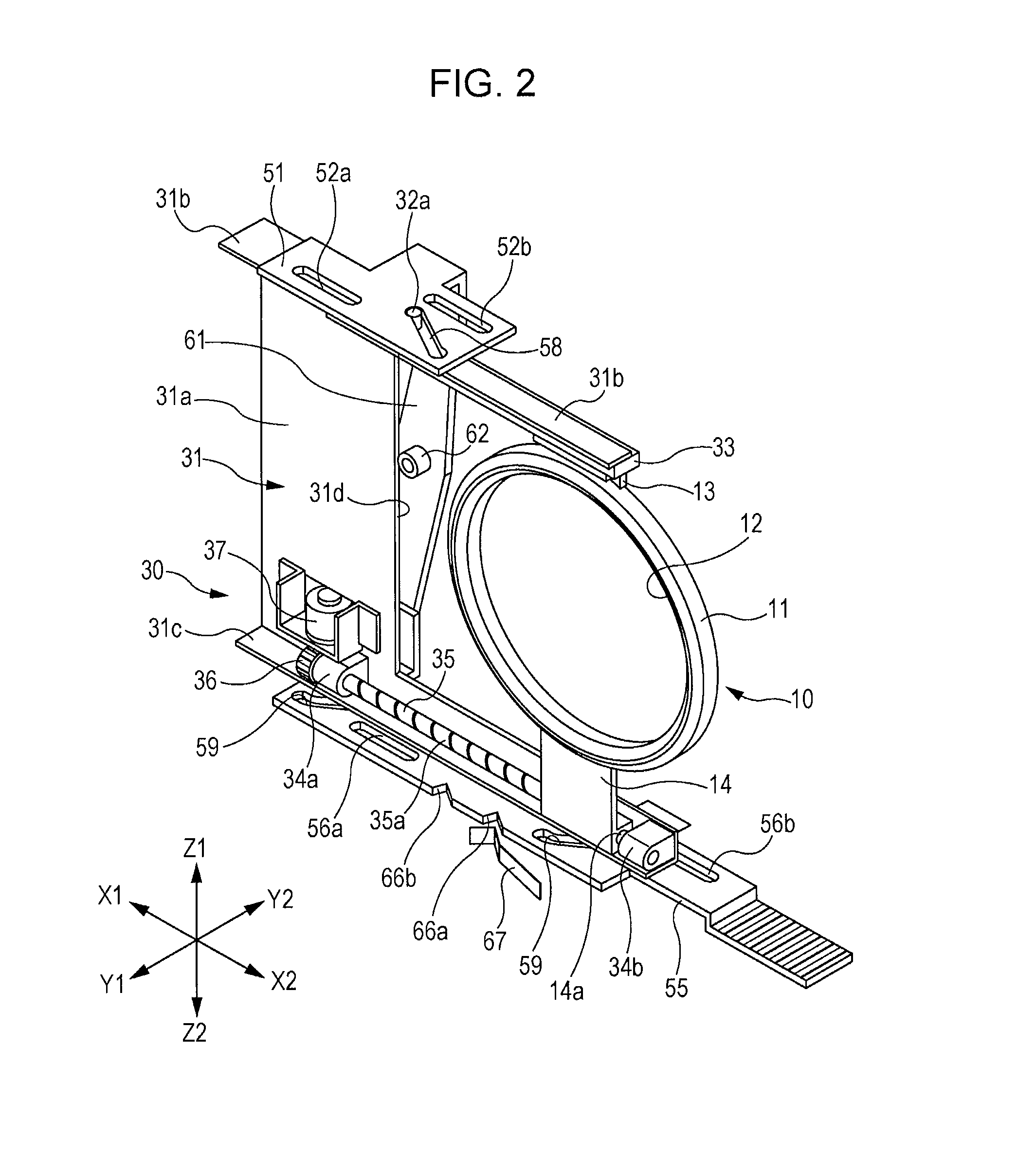

Vehicle display apparatus

InactiveUS20130186324A1Small depthSimple drive structureIndication apparatusInstrument arrangements/adaptationsElectrical and Electronics engineeringComputer hardware

Owner:ALPINE ELECTRONICS INC

Wafer grinding method

ActiveUS20080076334A1Enhanced yieldProductivity be lowerEdge grinding machinesPolishing machinesEngineeringElectrical and Electronics engineering

A wafer grinding method is disclosed, in which only a region, corresponding to a device formation region, of the back side of a wafer is ground in rough grinding conducted first, while the part surrounding the region thus ground is left unground as an annular projected part, to prevent the outer peripheral edge of the wafer from becoming knife edge-like in shape. In the subsequent finish grinding, the annular projected part is ground and, further, the whole area of the back side of the wafer is ground to be flat. Chippings of the outer peripheral edge may be generated only during the finish grinding, whereby the chippings are prevented from occurring or limited to minute ones.

Owner:DISCO CORP

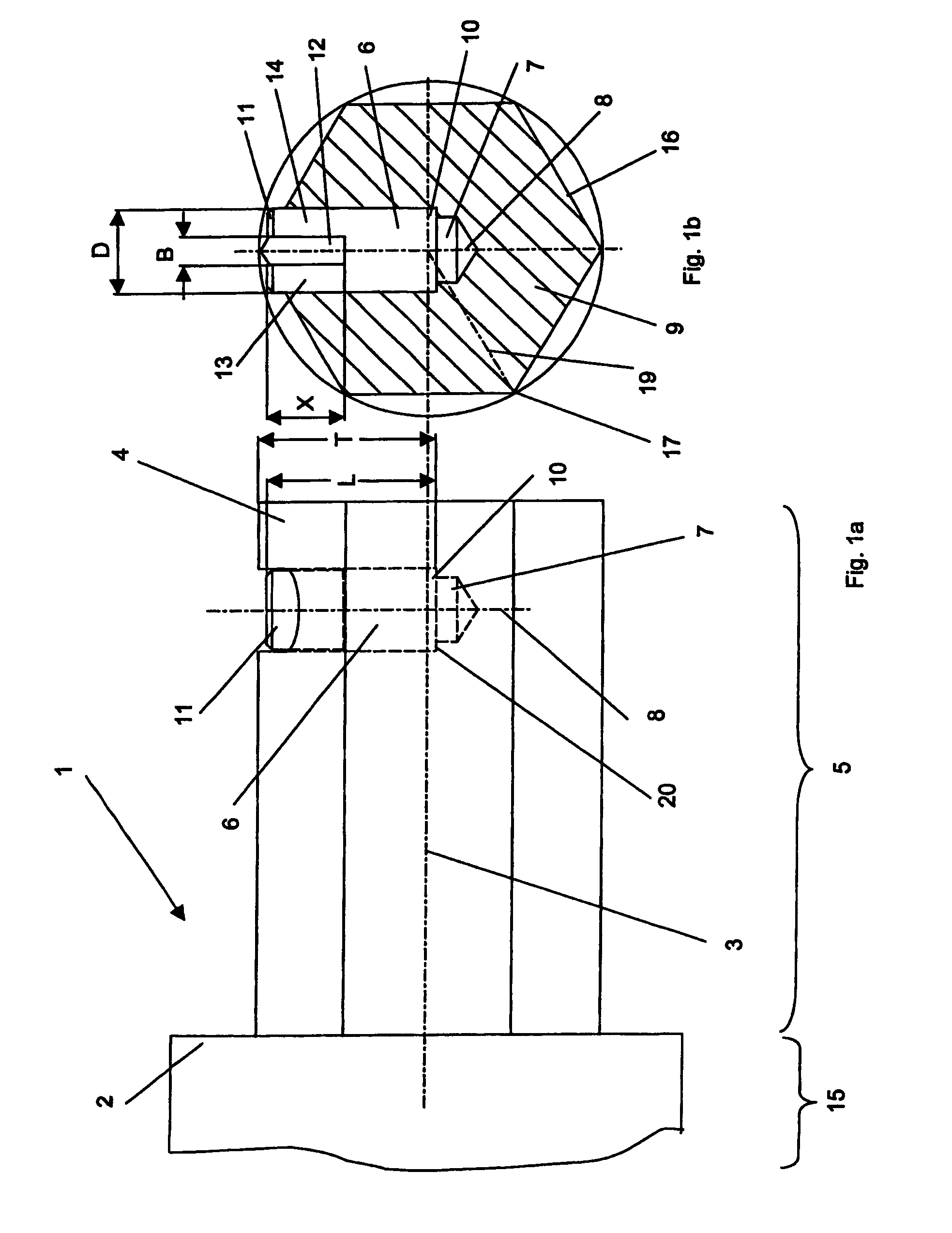

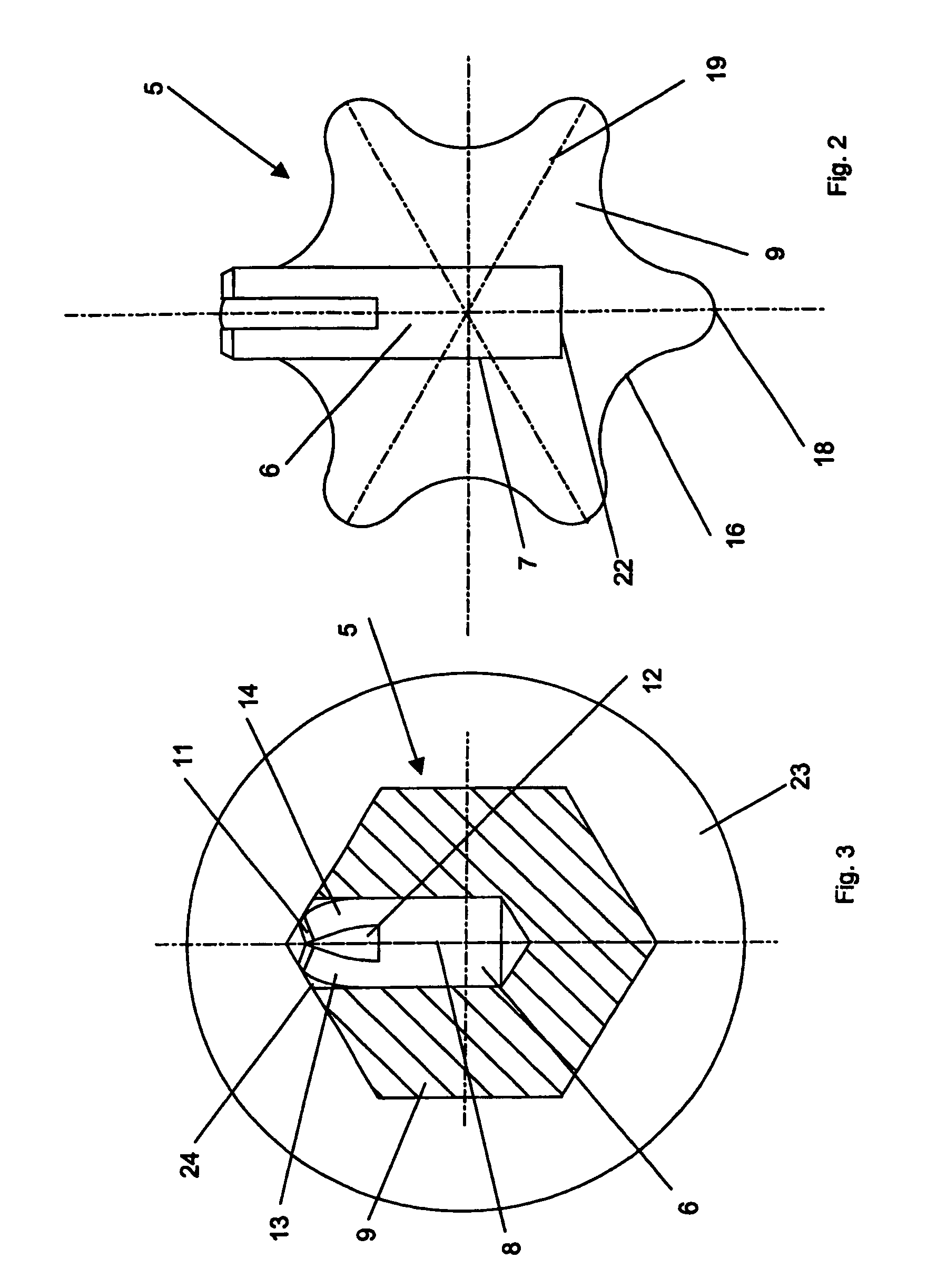

Screwdriver with screw holder

A tool is described comprising a shaft having a first longitudinal axis and a front segment, wherein the front segment has a cross-sectional area, wherein the front segment is configured to engage at least a portion of a screw head, and wherein the front segment has at least a first recess having a second longitudinal axis substantially transverse to the first longitudinal axis; at least one spring element housed in the first recess, wherein a first portion of the spring element at least partially protrudes transversely across the first longitudinal axis; wherein the cross-sectional area is substantially polygonal, having a least one radii; wherein the second longitudinal axis is substantially aligned with at least one radii; and wherein the portion of the spring element protruding transversely across the first longitudinal axis is elastically deformable.

Owner:SYNTHES USA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com