Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

114results about How to "Simple possibility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

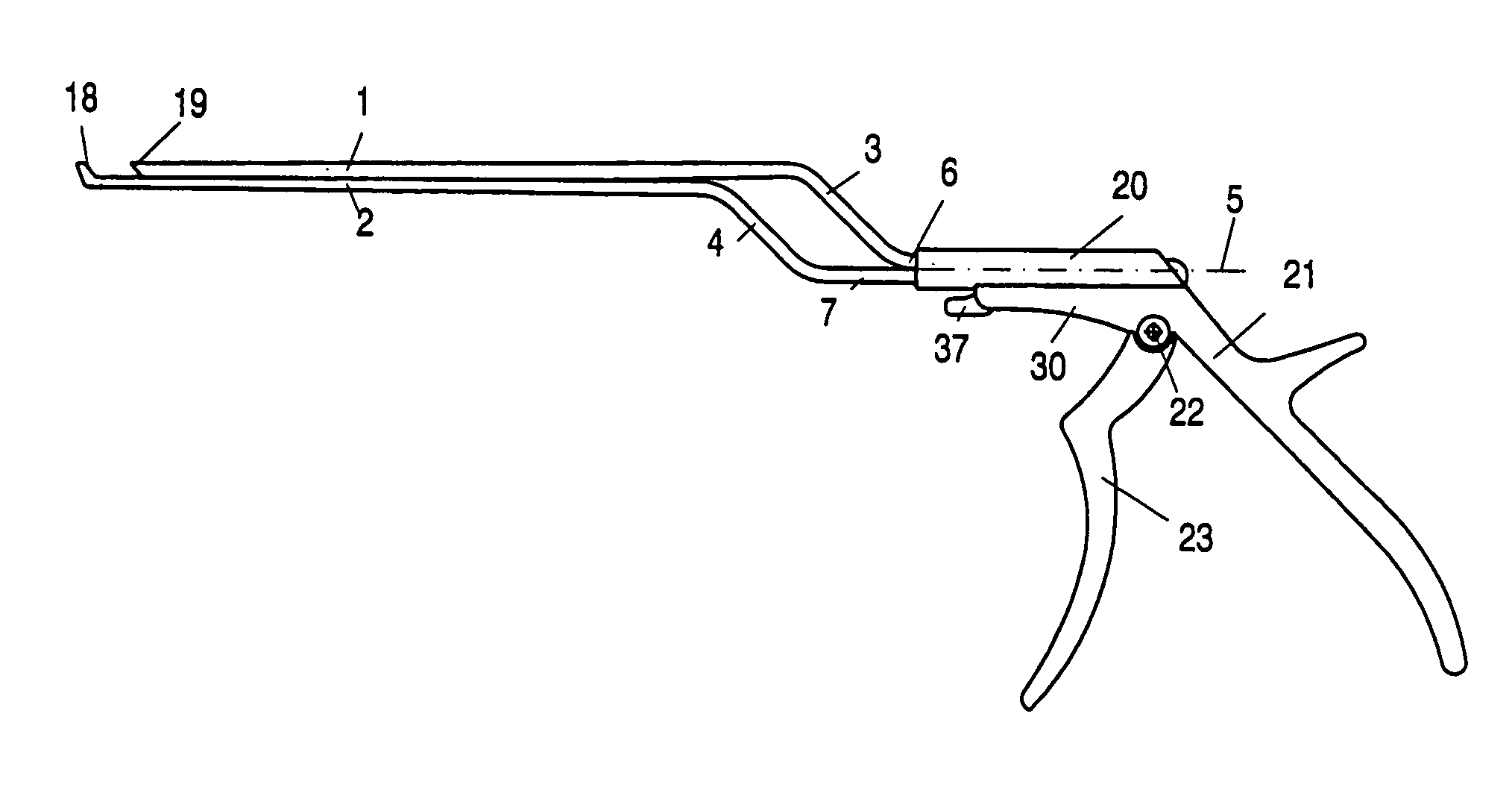

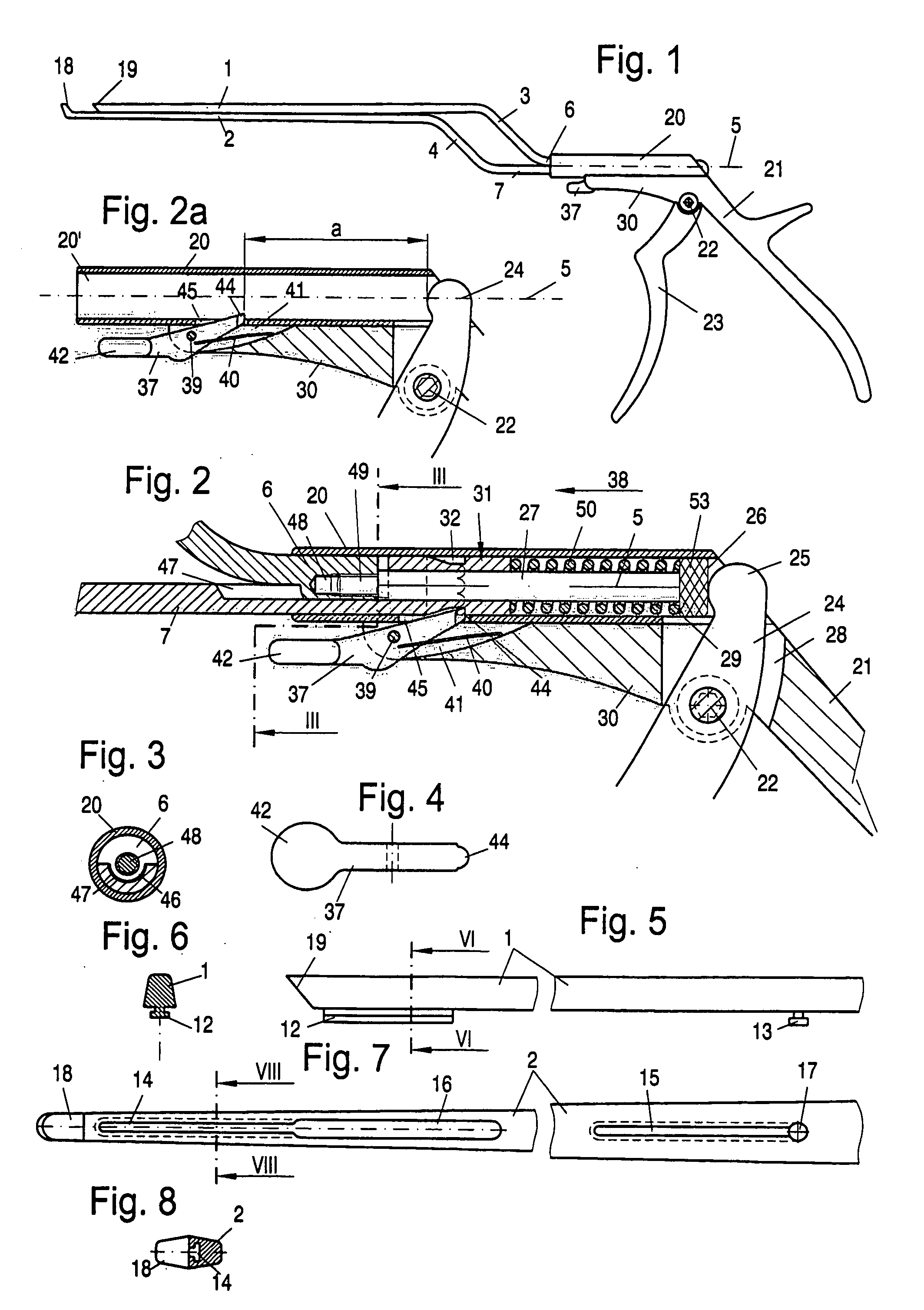

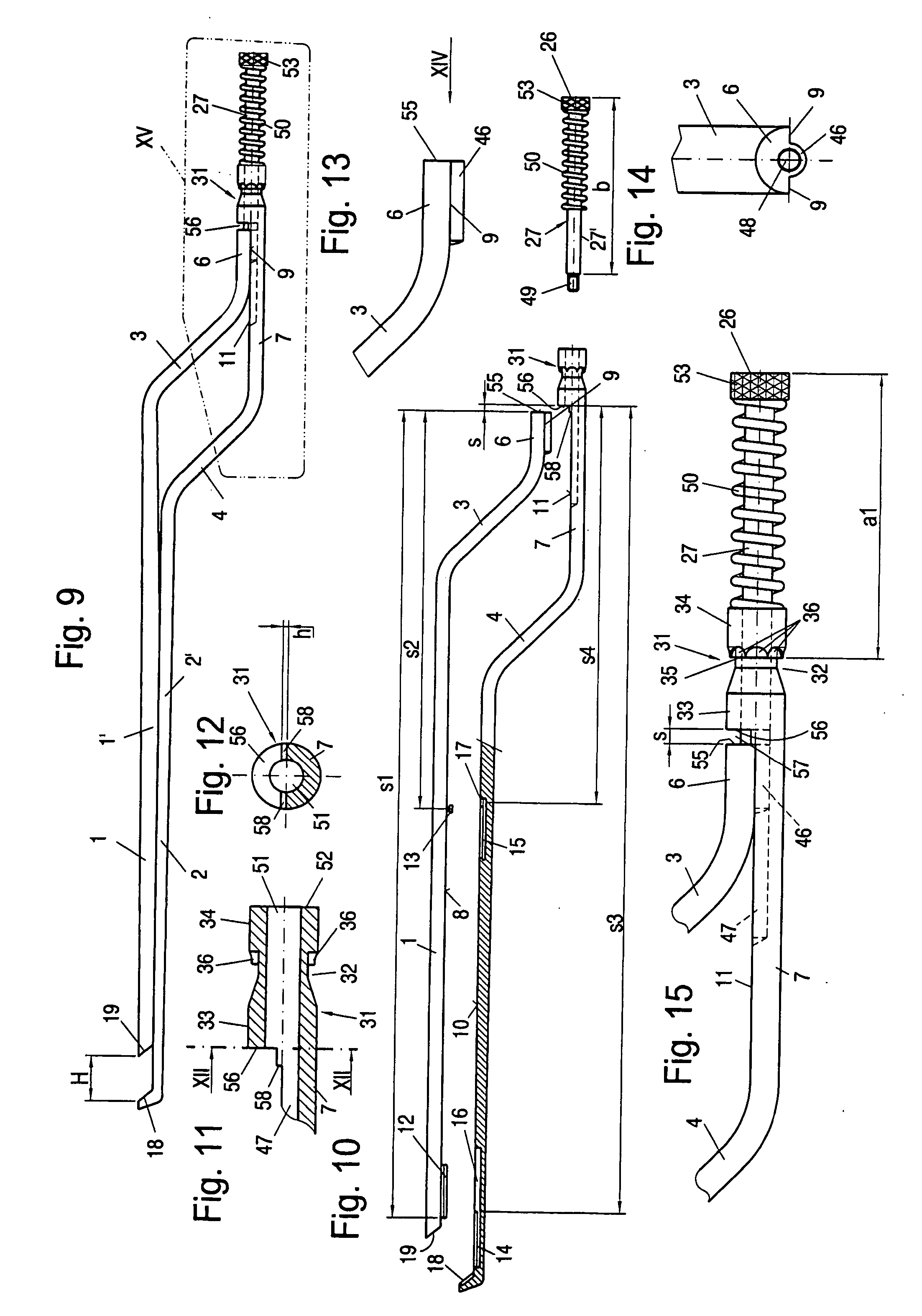

Surgical punching instrument

A surgical punching instrument with a fixed handle (21) is attached to a tubular guide part (20). An actuating lever (23) is mounted on the fixed handle (21) in a pivotingly movable manner and is in connection with a plunger (27) via a short lever arm (24). This plunger is in turn connected to a punching slide (1) and is mounted for actuating same against the action of a compression spring in an axially movable manner in a rearward mounting part (31) of a punching bar (2), which is guided rotatably by an at least partially cylindrical guide section (33, 34) and lockably in different rotated positions in the guide part (20). The punching bar is in contact in the guide part (20) with an axial stop acting in the direction of actuation with a ring shoulder (35) and it is locked in an axially detachable manner. The axial stop, with which the ring shoulder (35) is in contact, comprises a spring-loaded locking lever (37), which passes through a guide slot (45) of the guide part (20) radially into a cylindrical cavity (20′) of the guide part (20), in which the guide section (33, 34) of the mounting part (31) of the punching bar (2) is guided.

Owner:JORG WENZLER MEDIZINTECHN

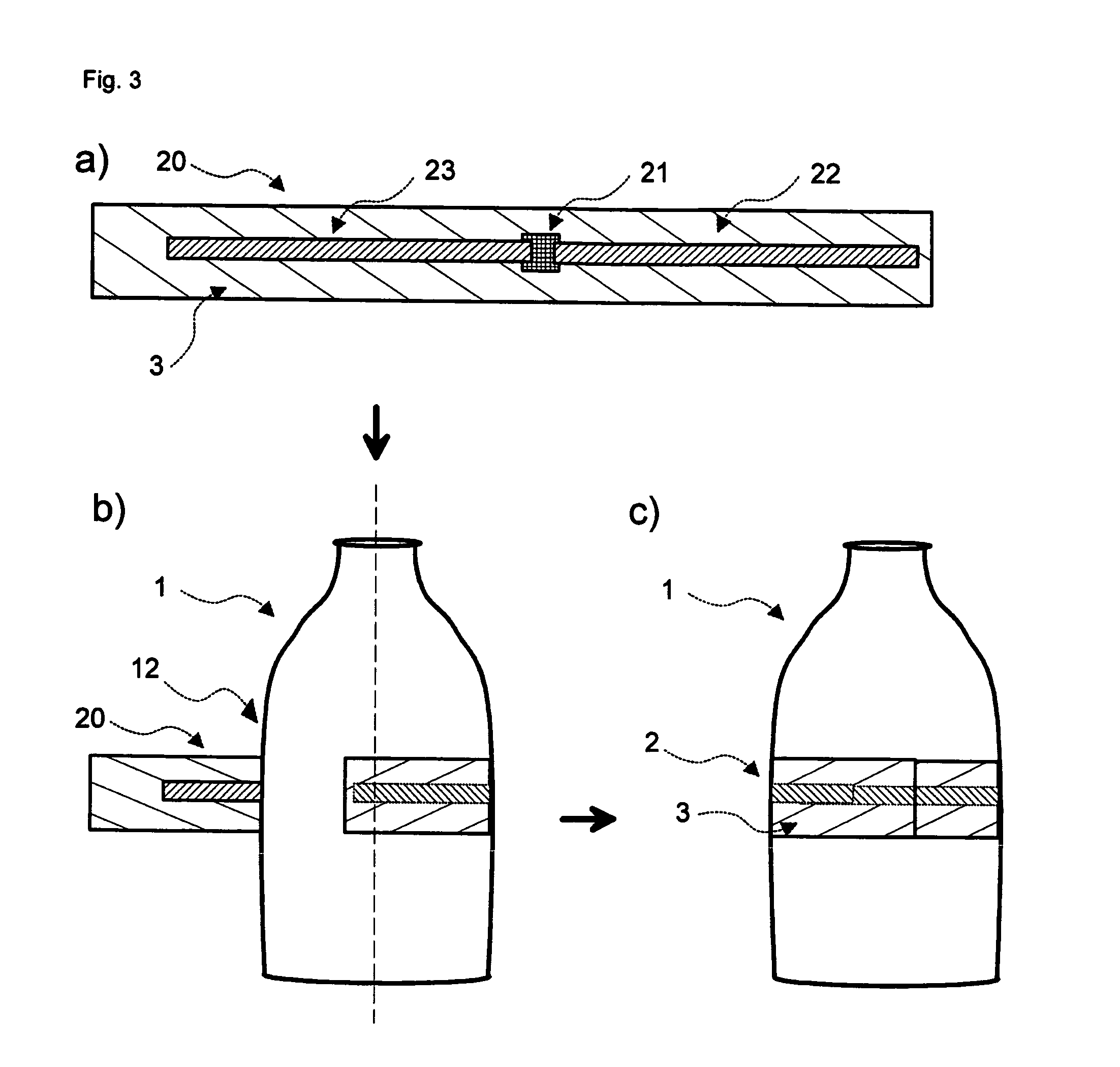

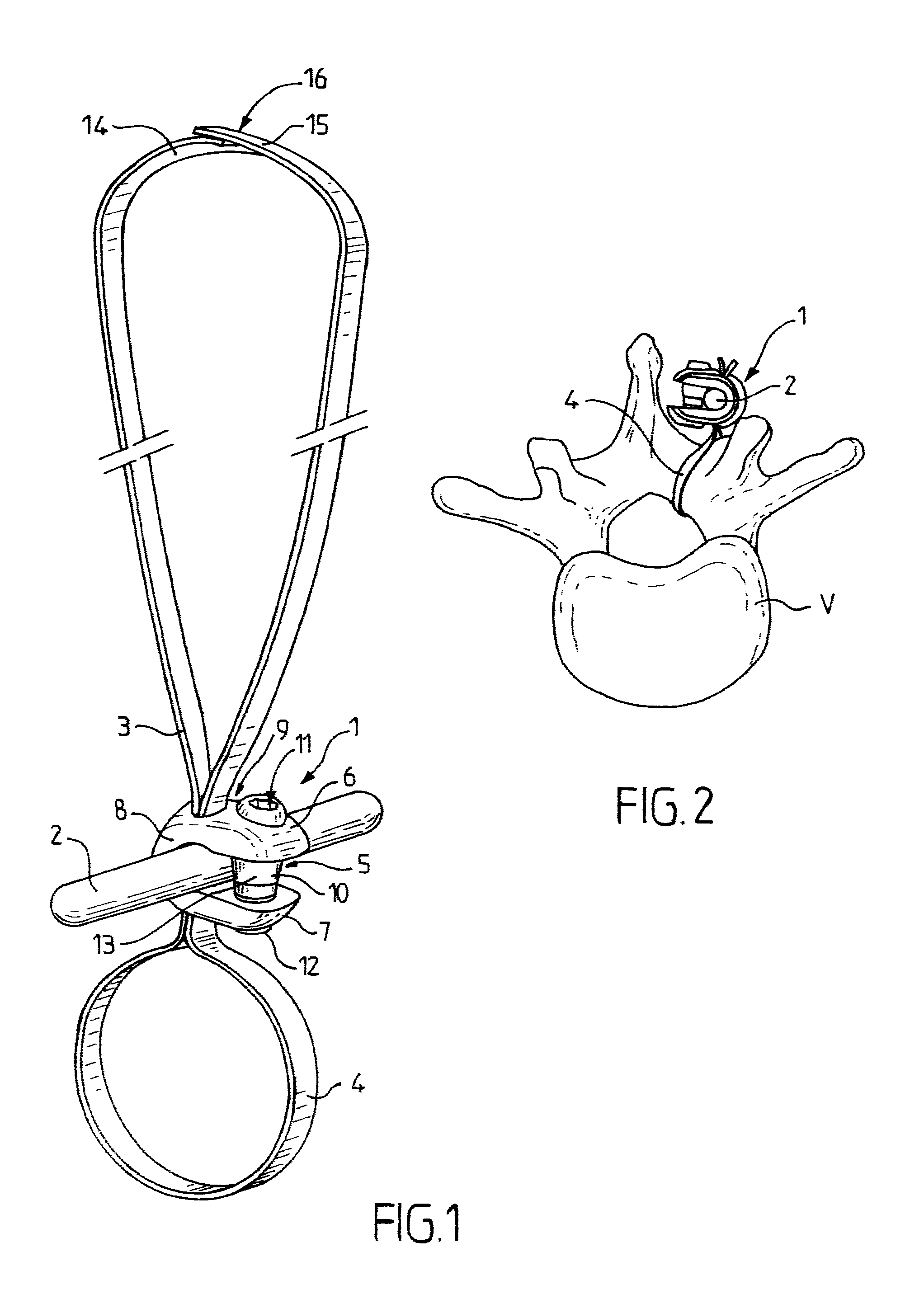

Transponder Comprising an Electronic Memory Chip and Magnetic Circular Antenna

InactiveUS20100052859A1Optimization rangeProduced economicallyRadiating elements structural formsLoop antennasCapacitorMagnetic loop

In a transponder having an electronic memory chip and a magnetic ring antenna is provided that the ring antenna comprises an electrically conductive coil having at least one turn, and a capacitor, wherein the capacitor exhibits, as a dielectric, a thin insulator foil that simultaneously serves as a substrate foil for the coil and / or the chip.

Owner:DYNAMIC SYST INC

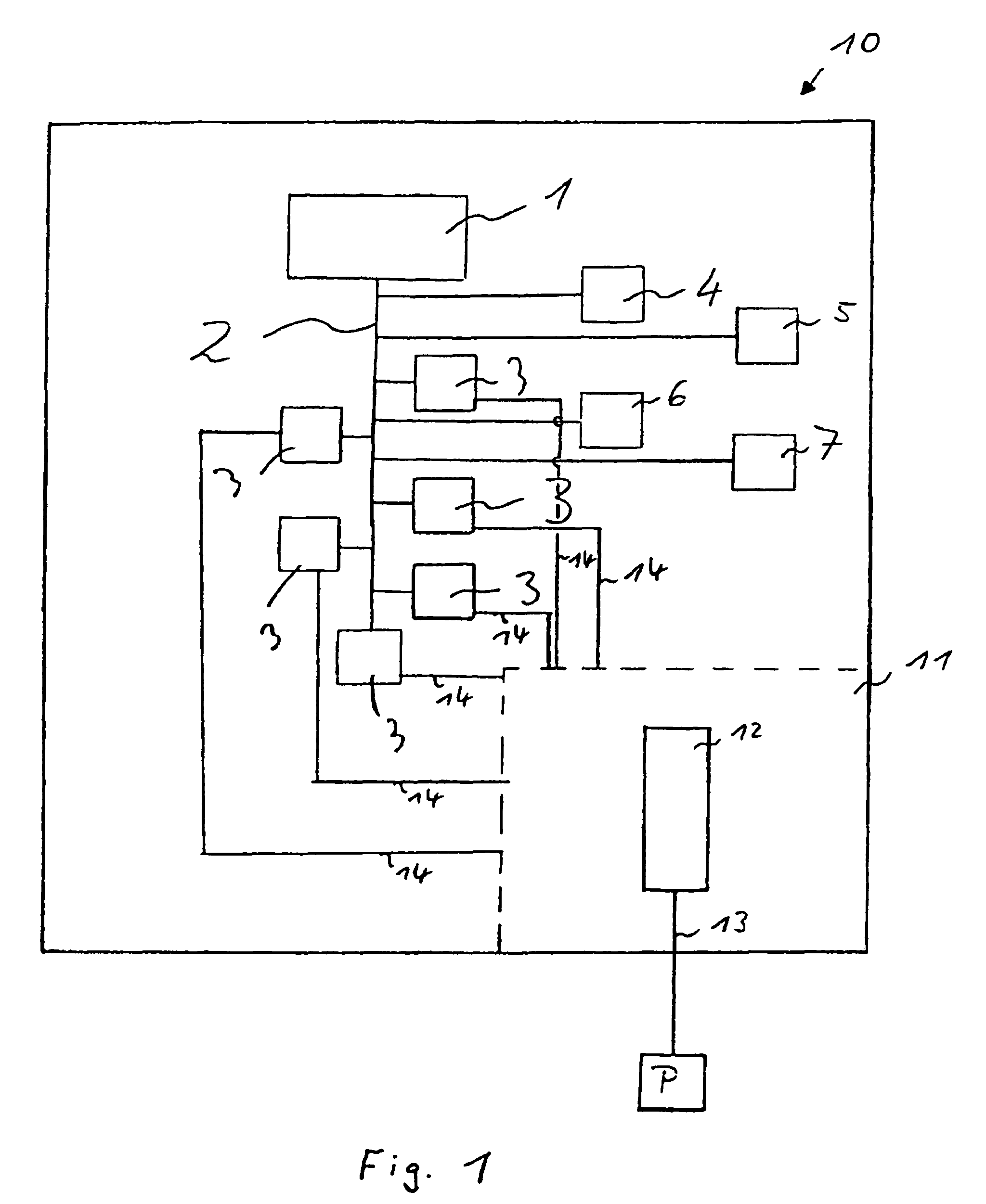

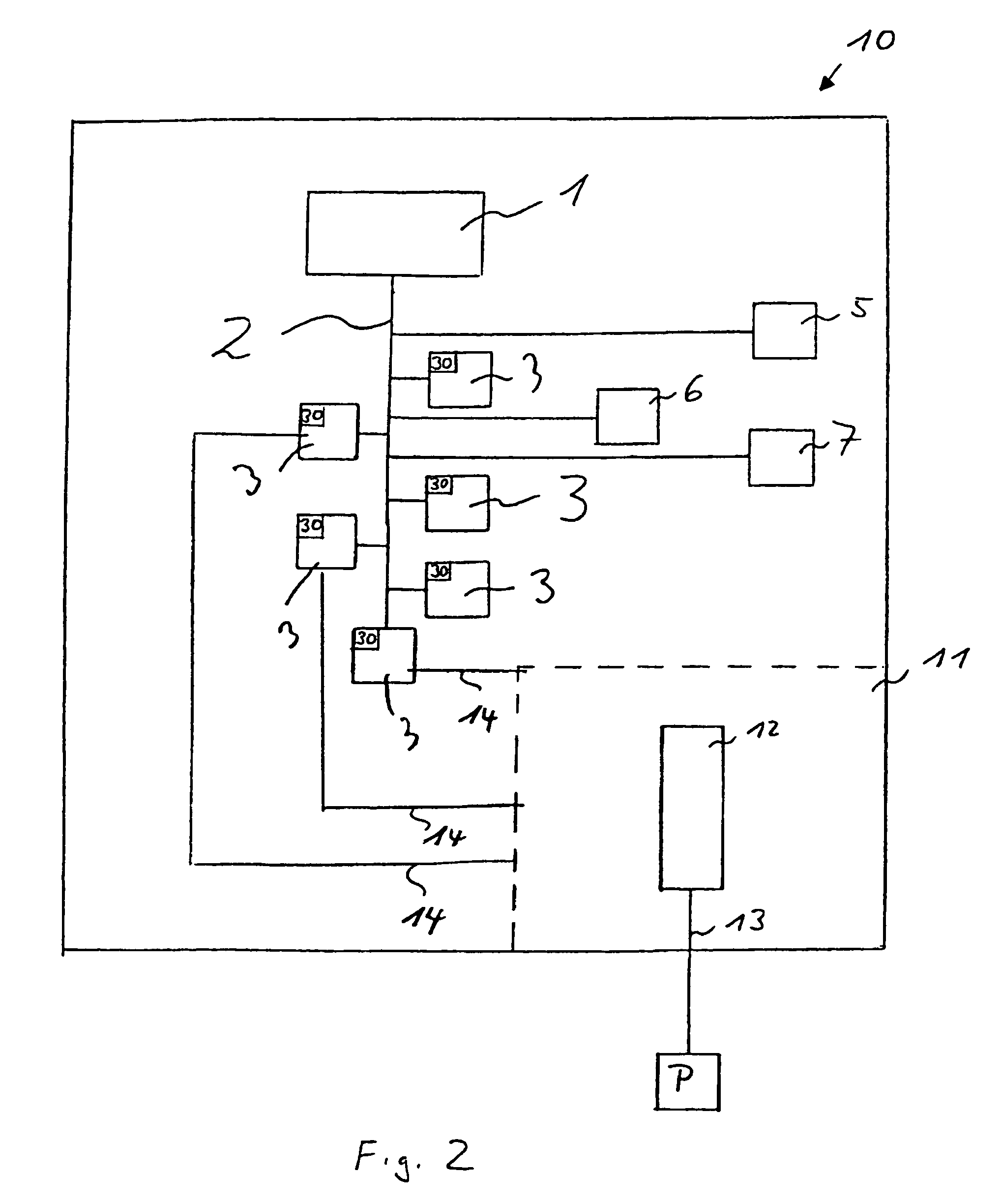

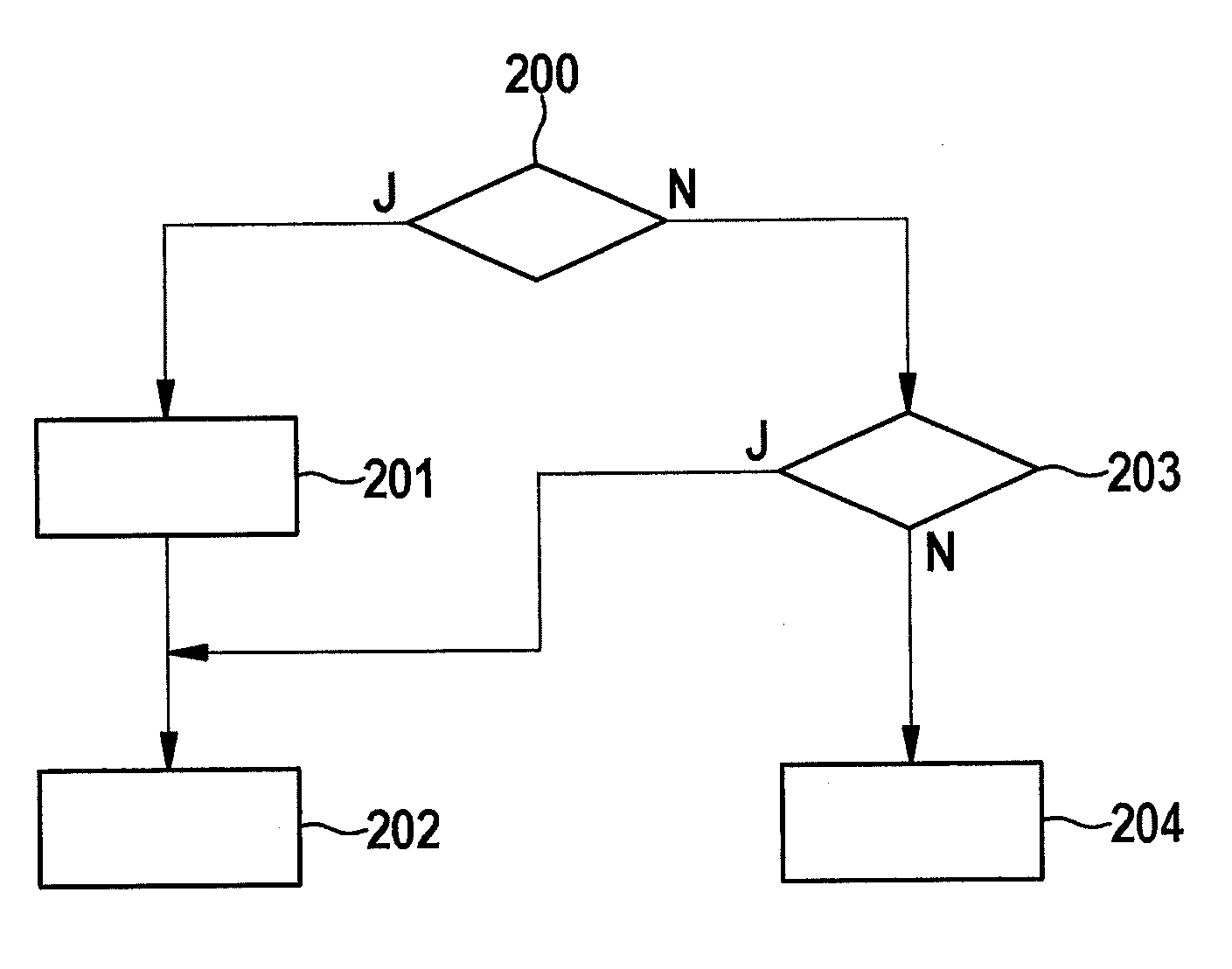

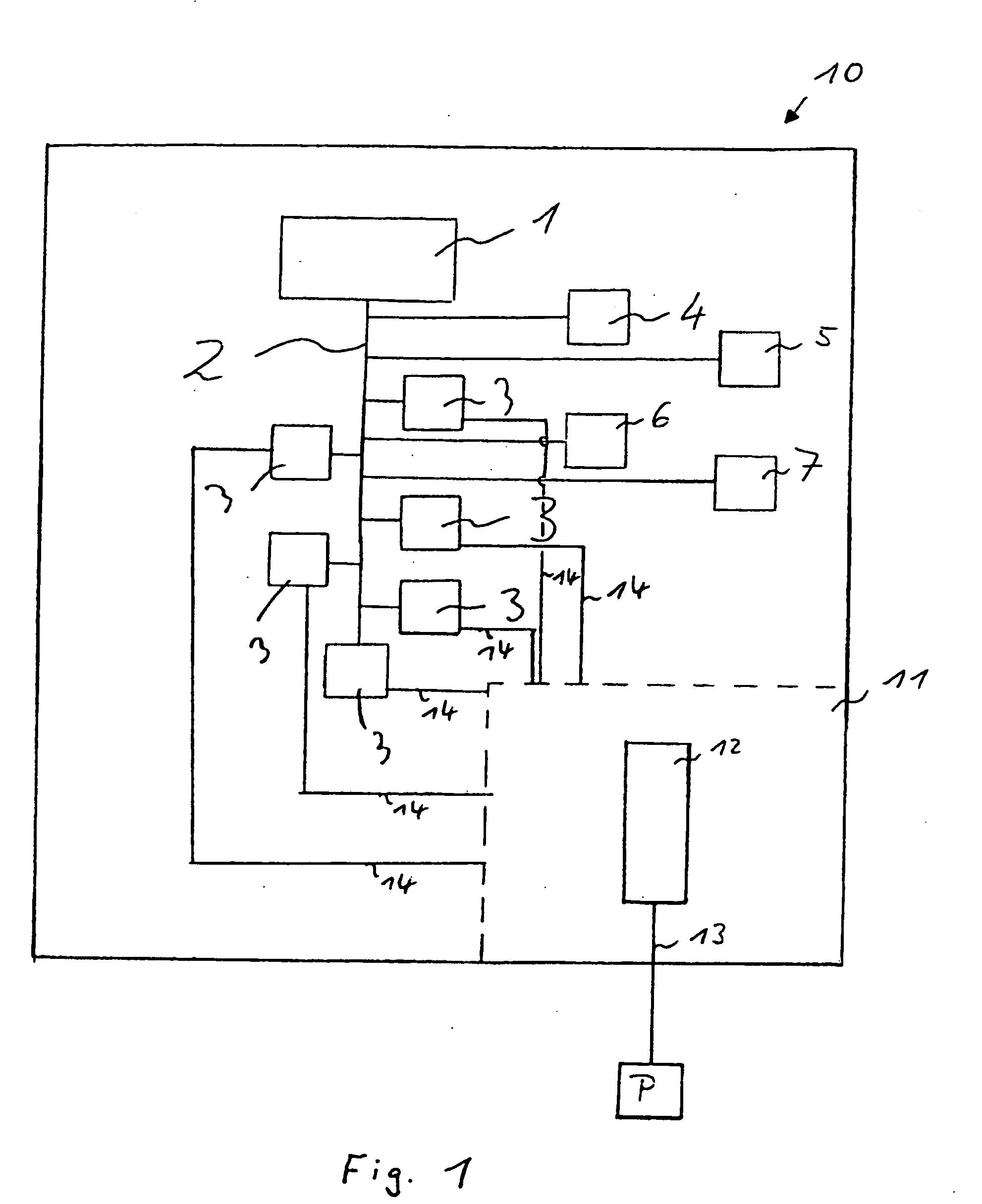

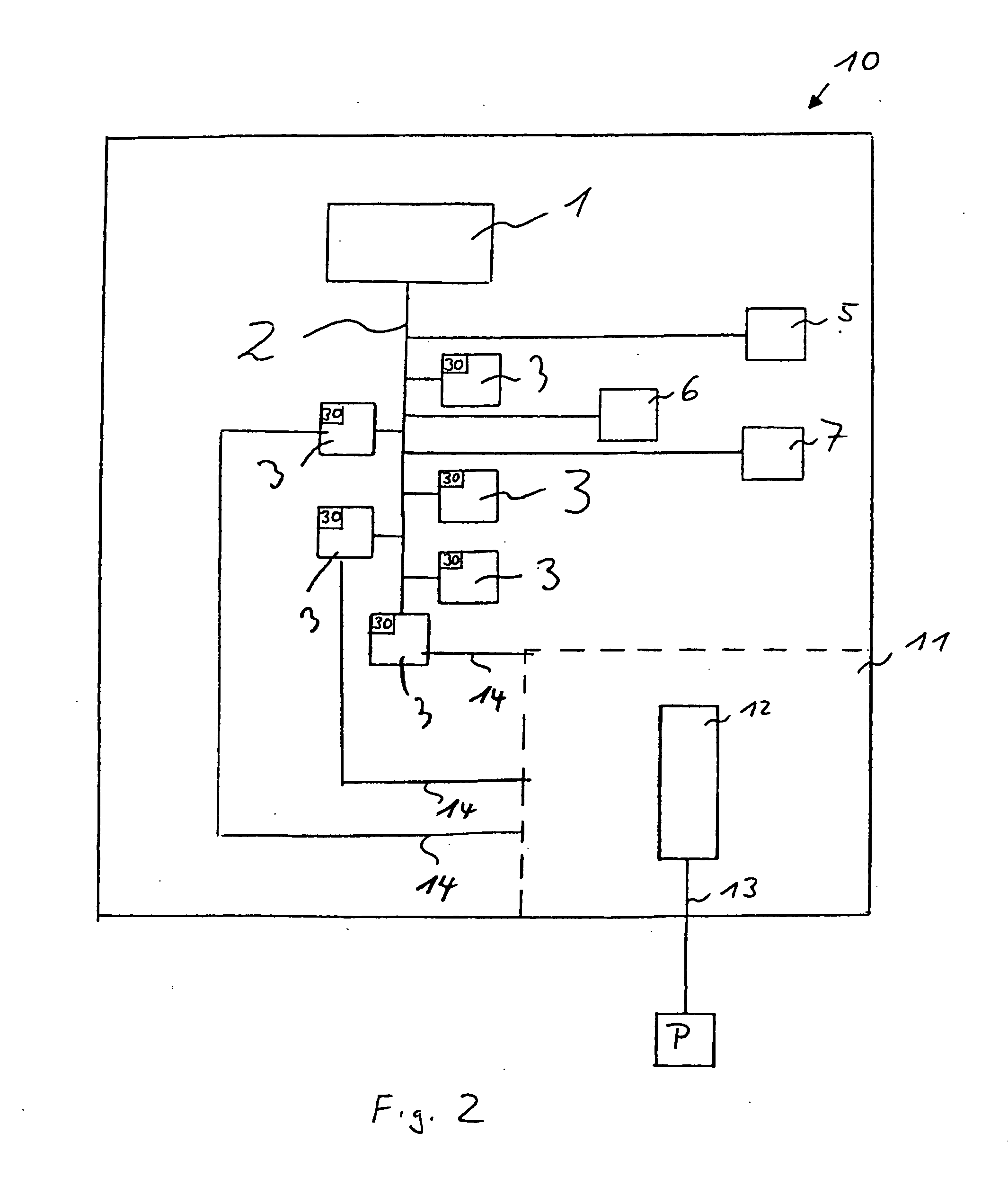

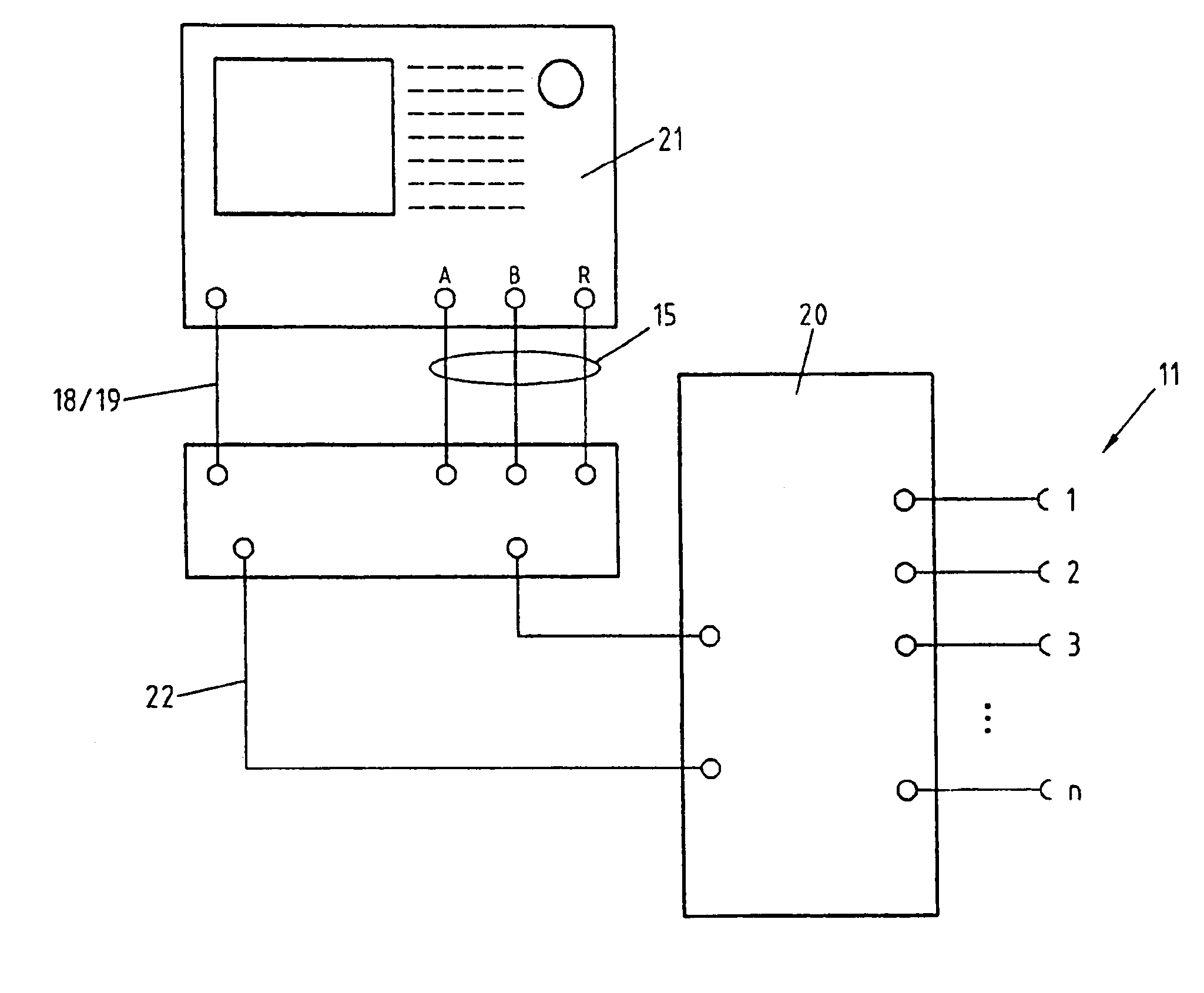

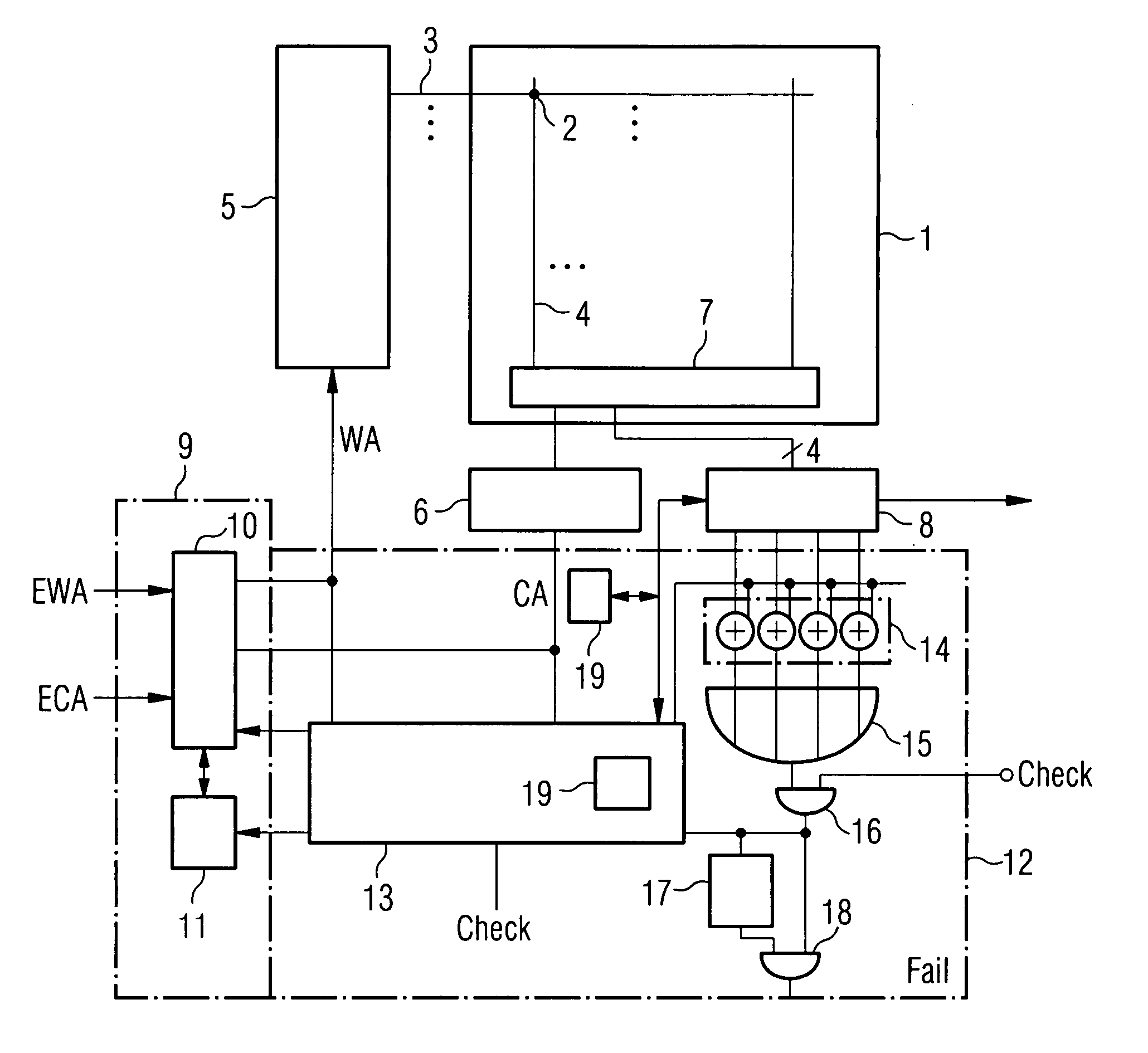

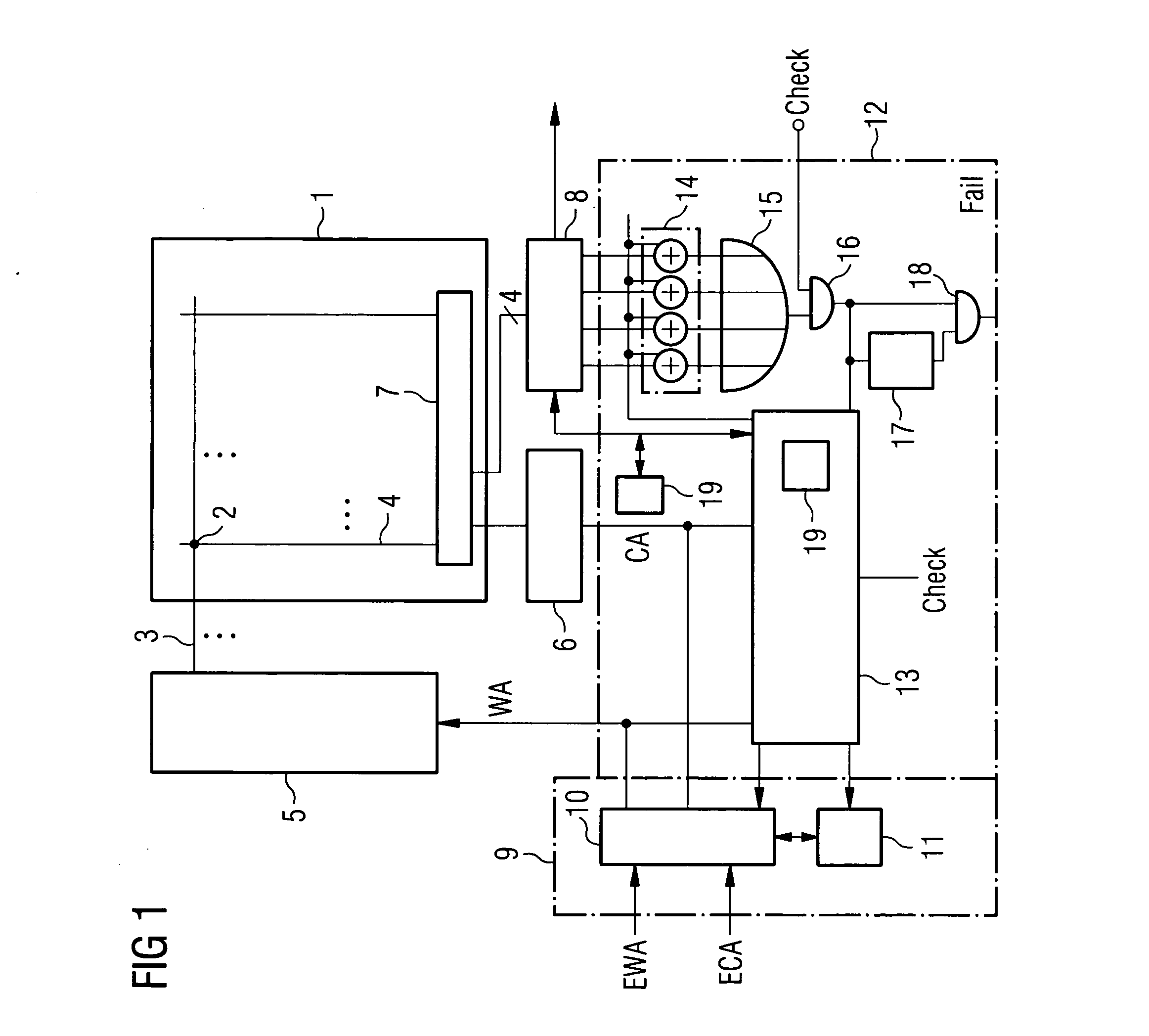

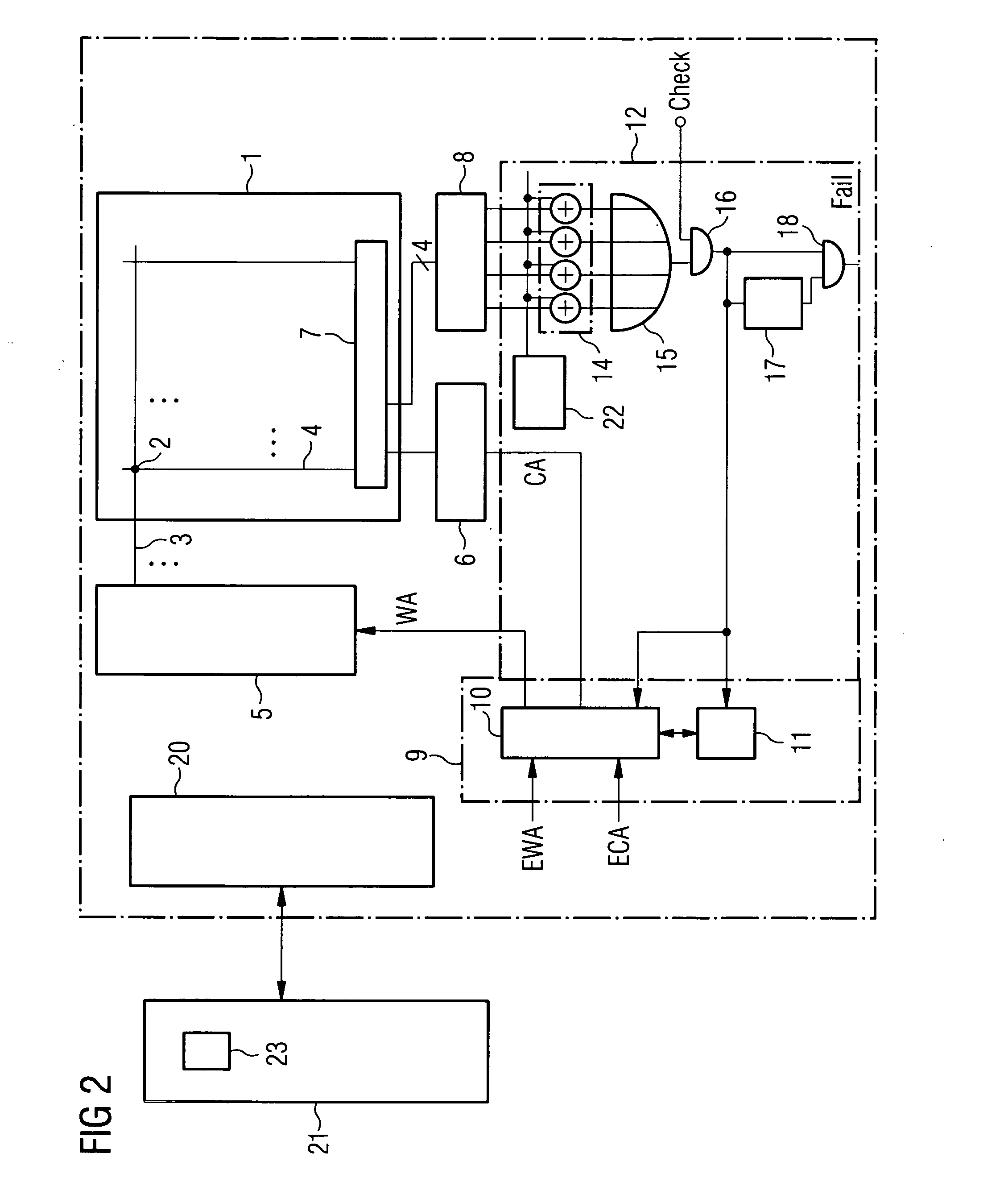

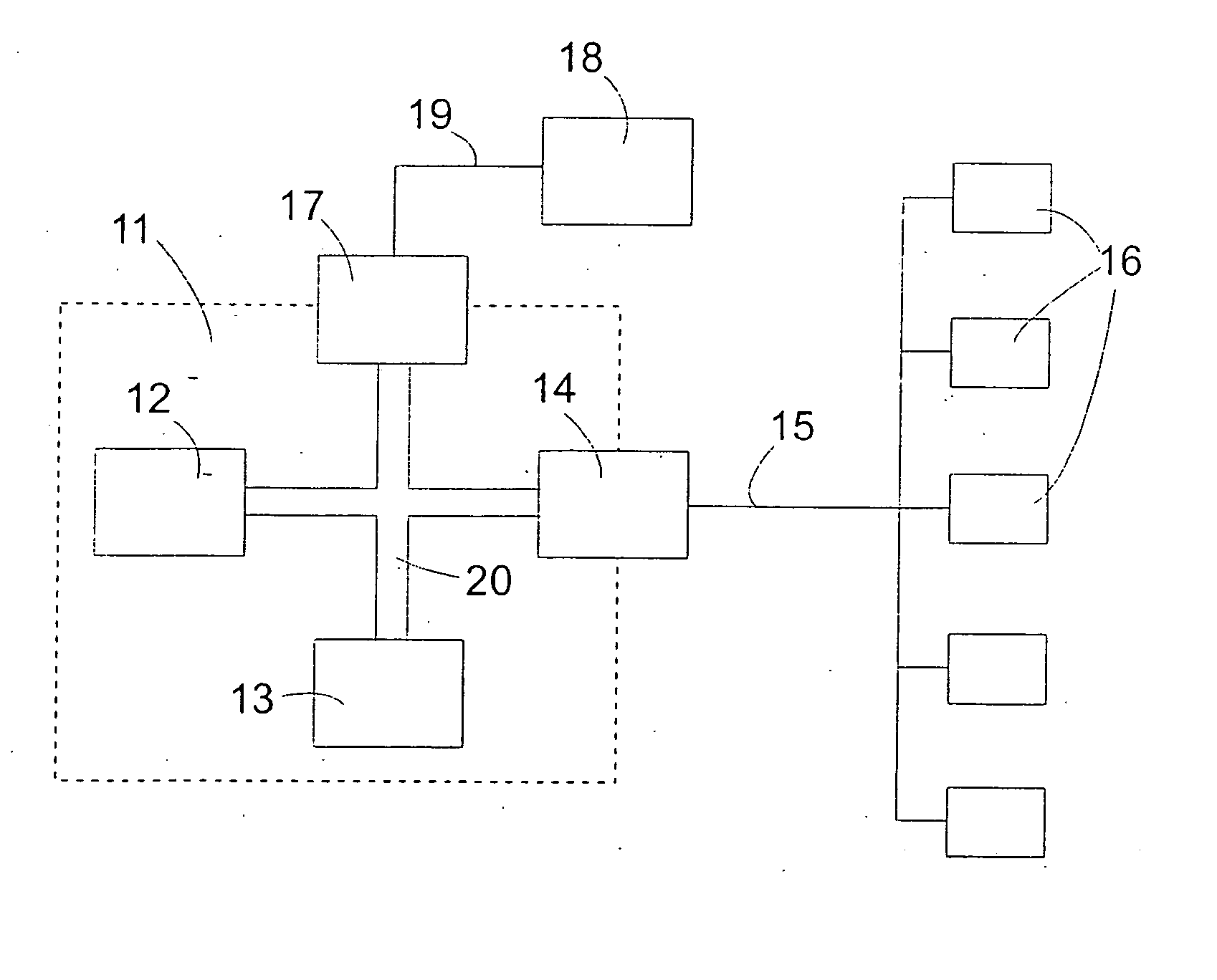

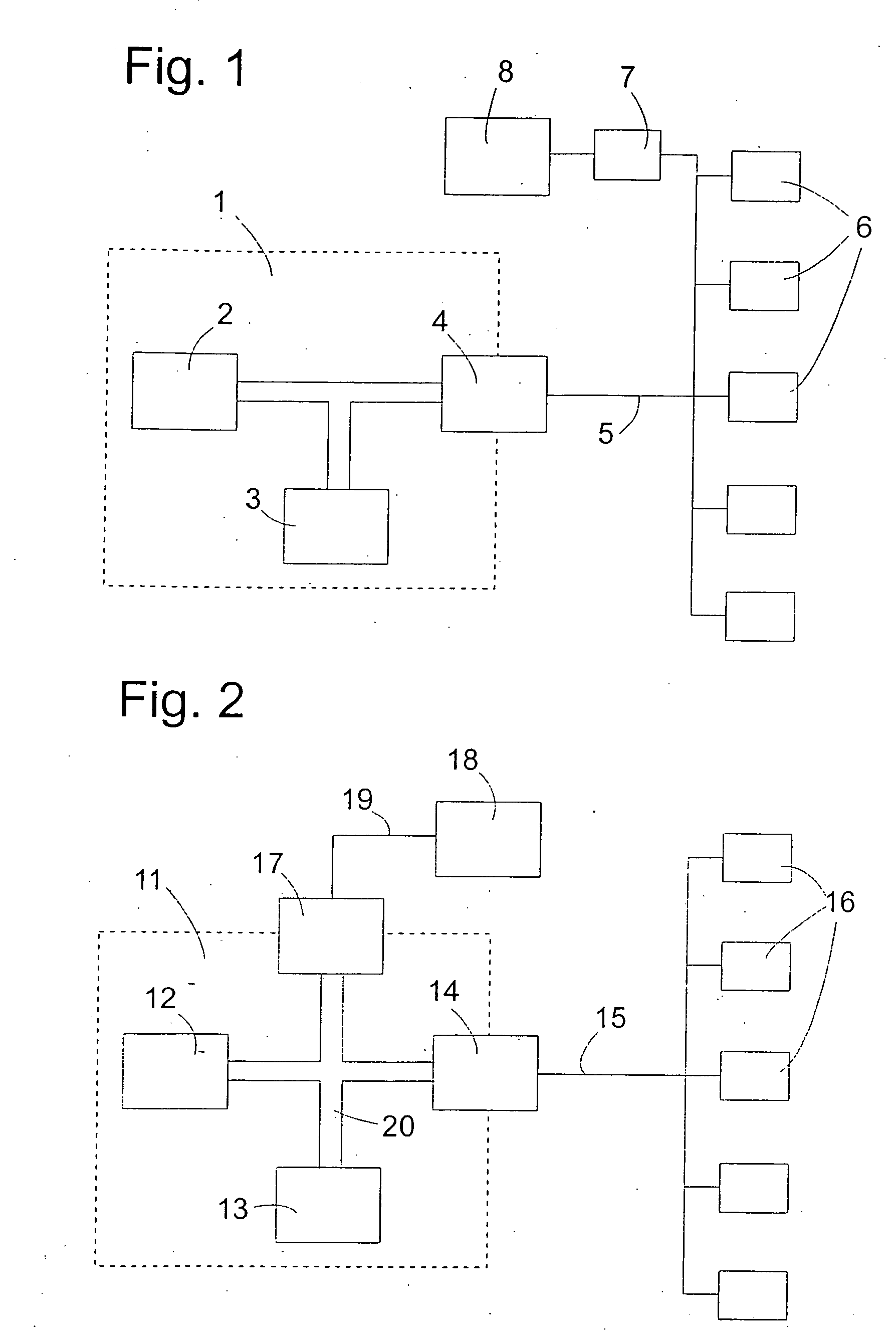

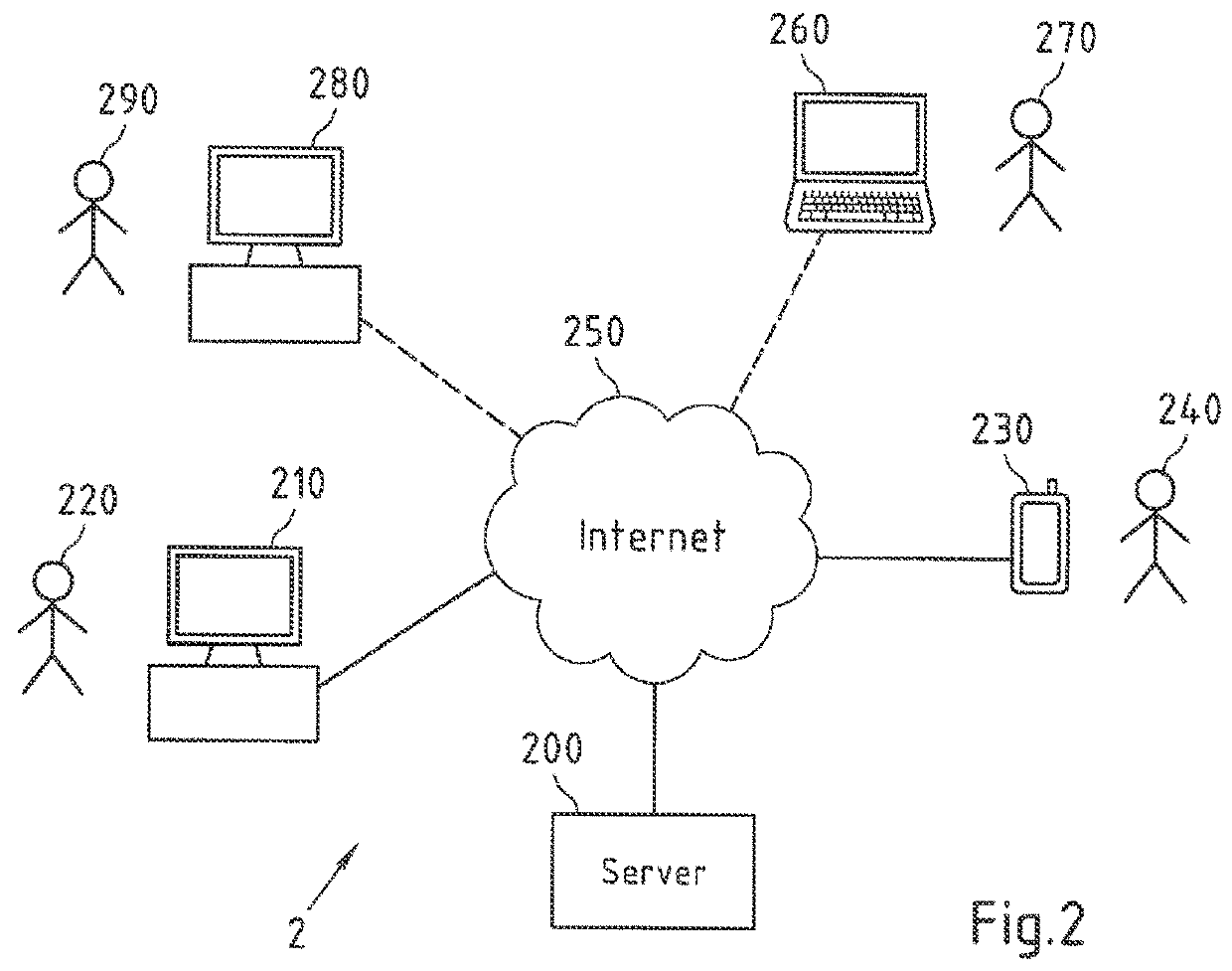

Software update for a medical fluid management device

InactiveUS8178040B2Simple priceEffectively and simply avoidedMechanical/radiation/invasive therapiesDialysis systemsSoftware updateTransfer system

A medical fluid management apparatus which includes a plurality of processor systems with respectively associated software programs. The fluid management apparatus has a fluid treatment component and / or a fluid source which can be connected to a patient via a fluid line. The processor systems are connected via a data transfer system to a data input apparatus via which an updating of the software programs belonging to the respective processor systems can take place. After actuation of an operating mode switch, a detection system, while taking into account the existing version of the software programs and / or the existing processor systems, determines which software programs have to be loaded via the data input apparatus. The medical fluid management apparatus allows a simple and user-friendly updating of the operating software even with a complex design of the apparatus.

Owner:FRESENIUS MEDICAL CARE DEUTSCHLAND GMBH

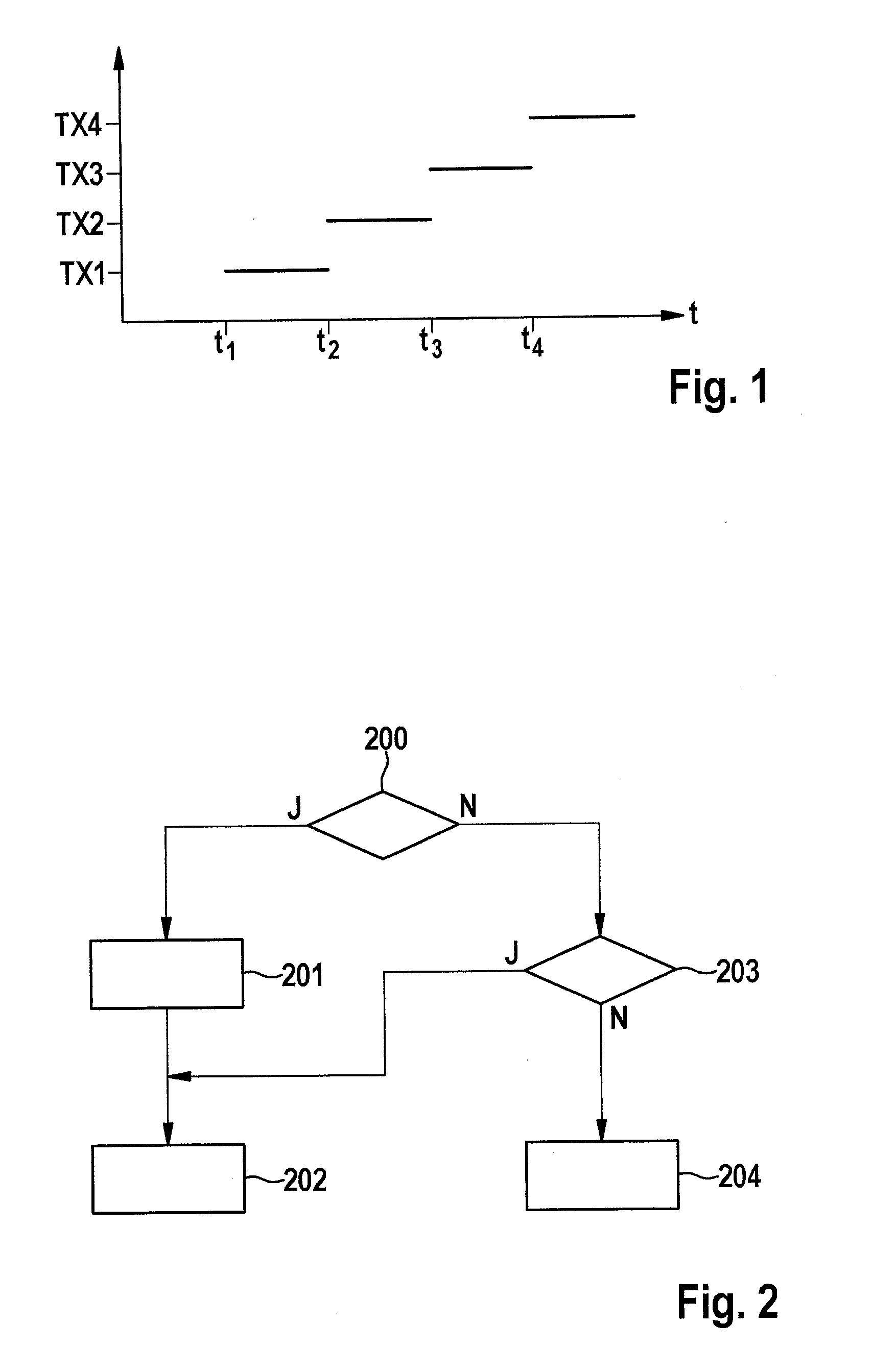

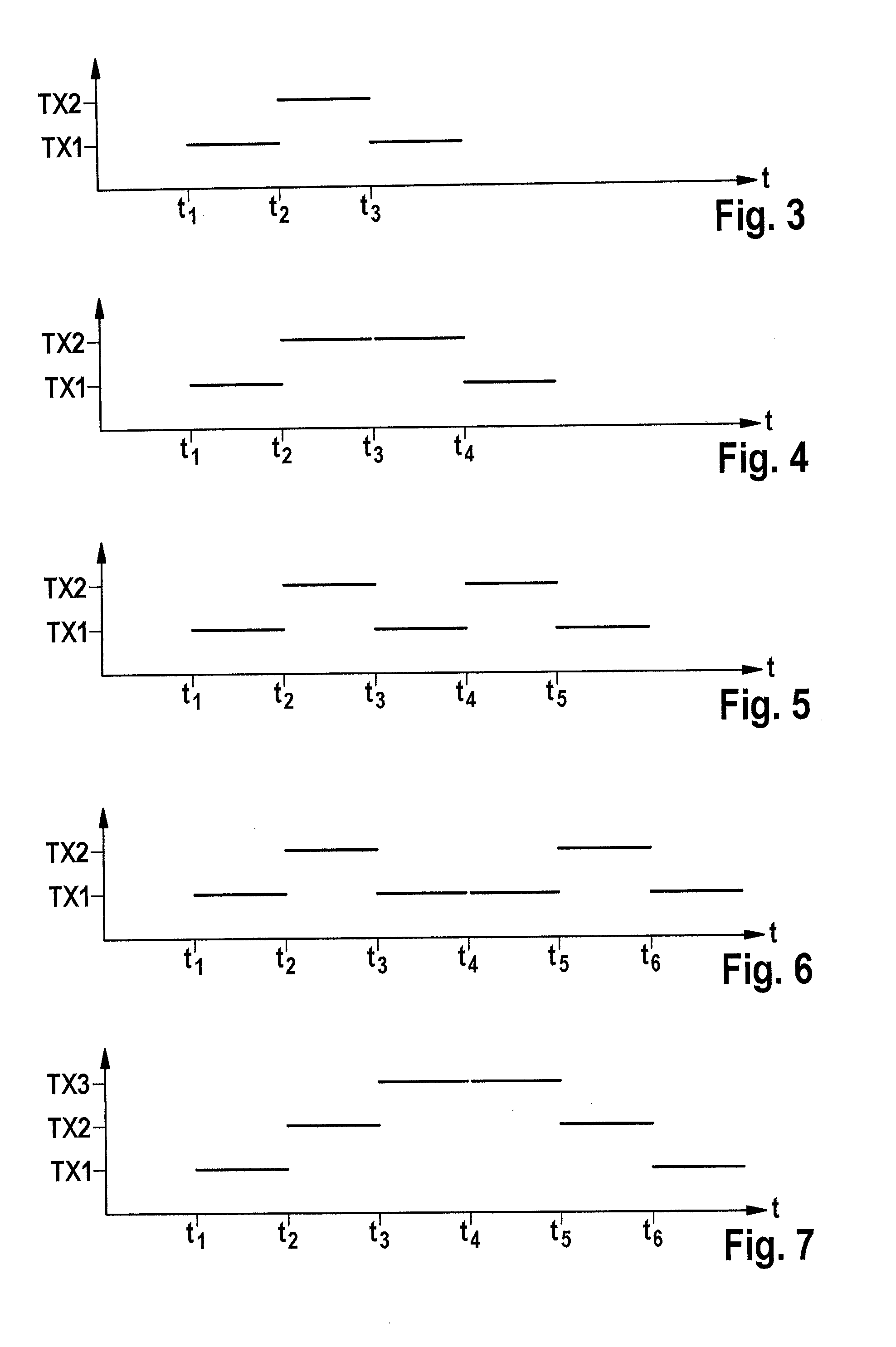

Method for operating a MIMO radar

ActiveUS20140347211A1Easy to operateExclude influenceRadio wave reradiation/reflectionObject motionCovariance

In a method for operating a MIMO radar, an influence of an object motion on an angle estimate is substantially eliminated, and a time multiplex schema having a transmission sequence and transmission instants of transmitters of the MIMO radar is identified by optimizing the following mathematical relationship: d _ pulses , opt = arg max d _ pulses [ Var S ( d _ pulses ) - ( Cov S ( d _ pulses , t ) ) 2 / Var S ( t _ ) ] in which: dpulses,opt is optimized positions of the transmitters in the sequence in which they transmit; dpulses is positions of the transmitters in the sequence in which they transmit; t is transmission instants; VarS is sample variance; and CovS is sample covariance.

Owner:ROBERT BOSCH GMBH

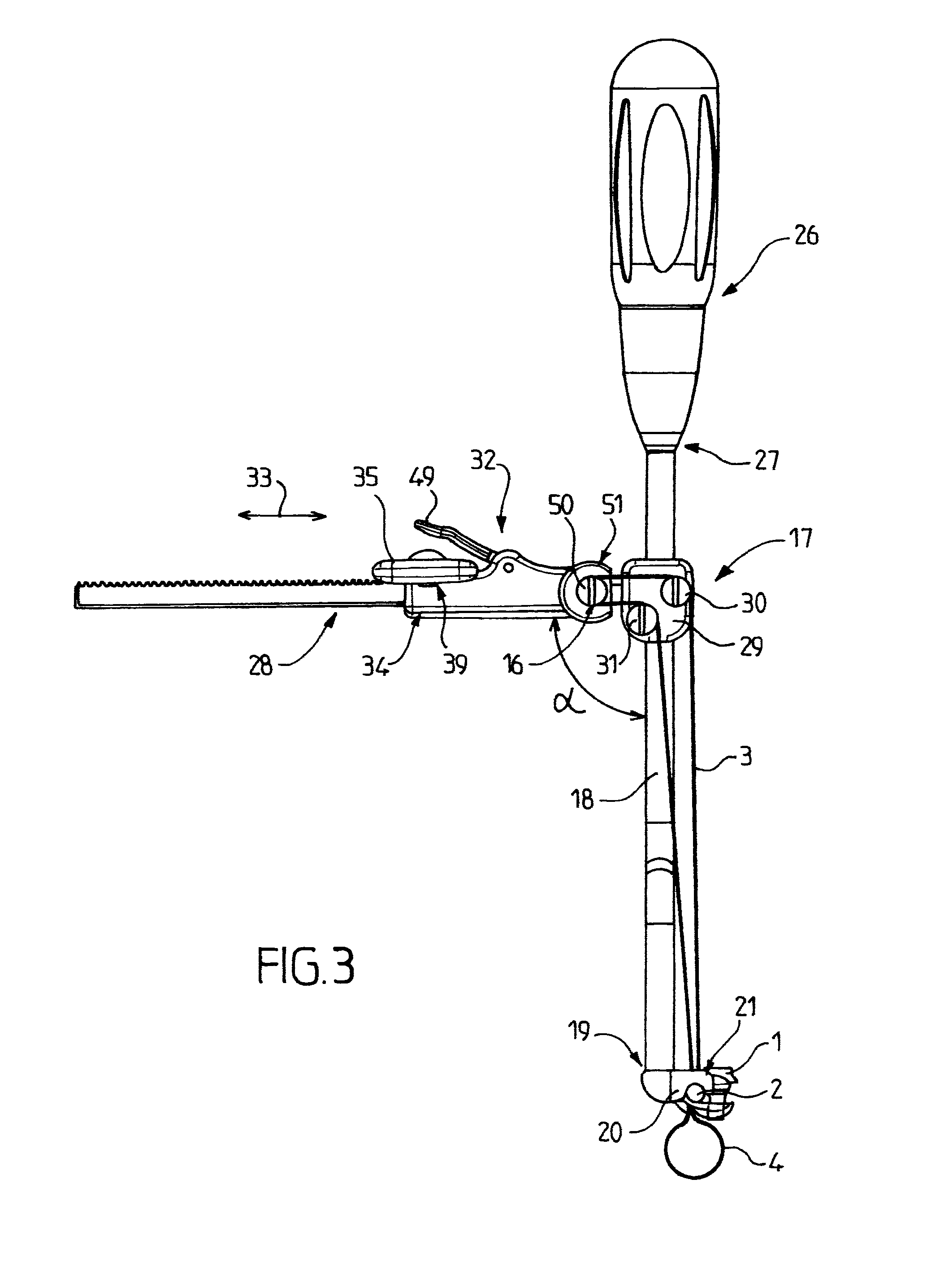

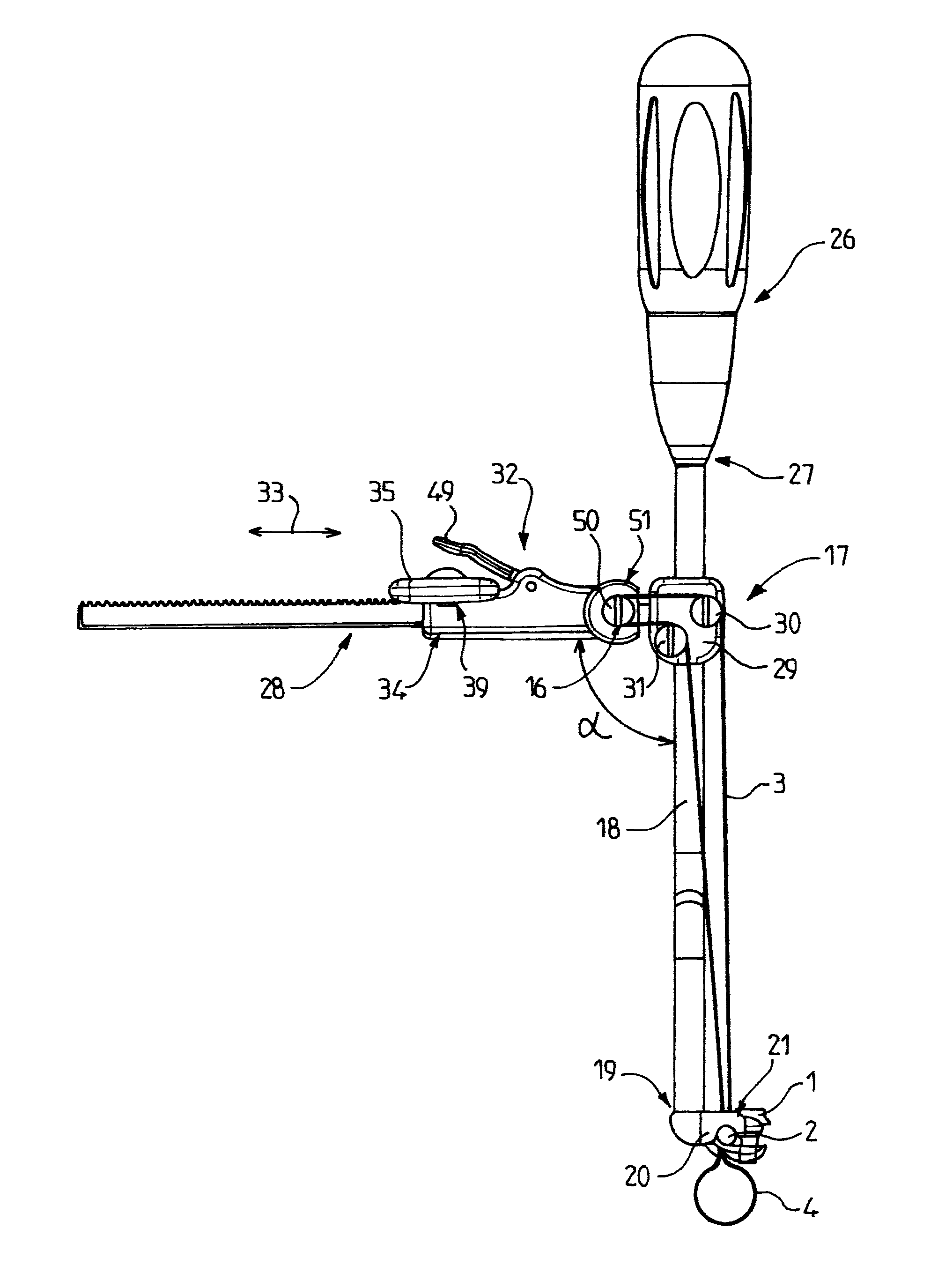

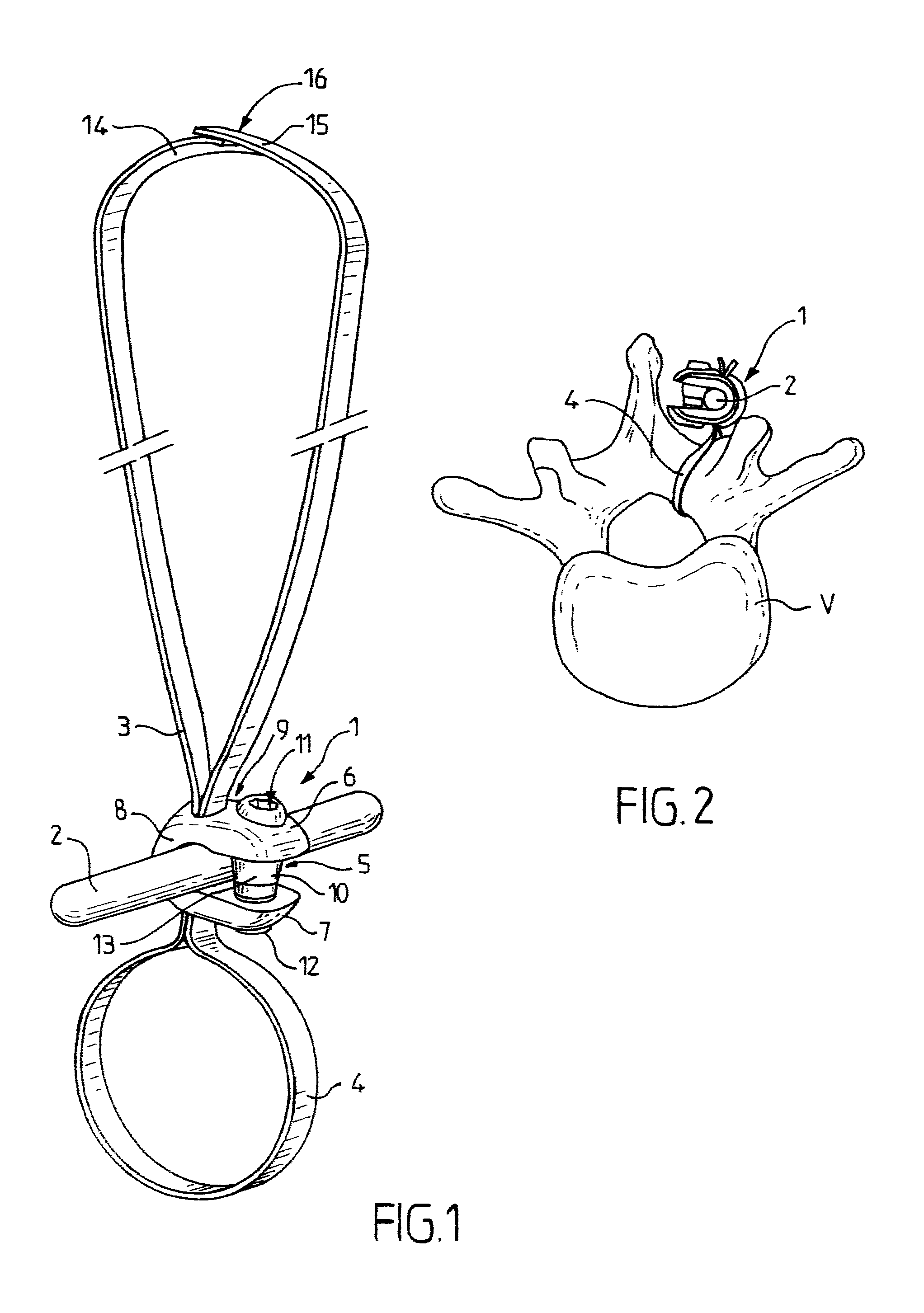

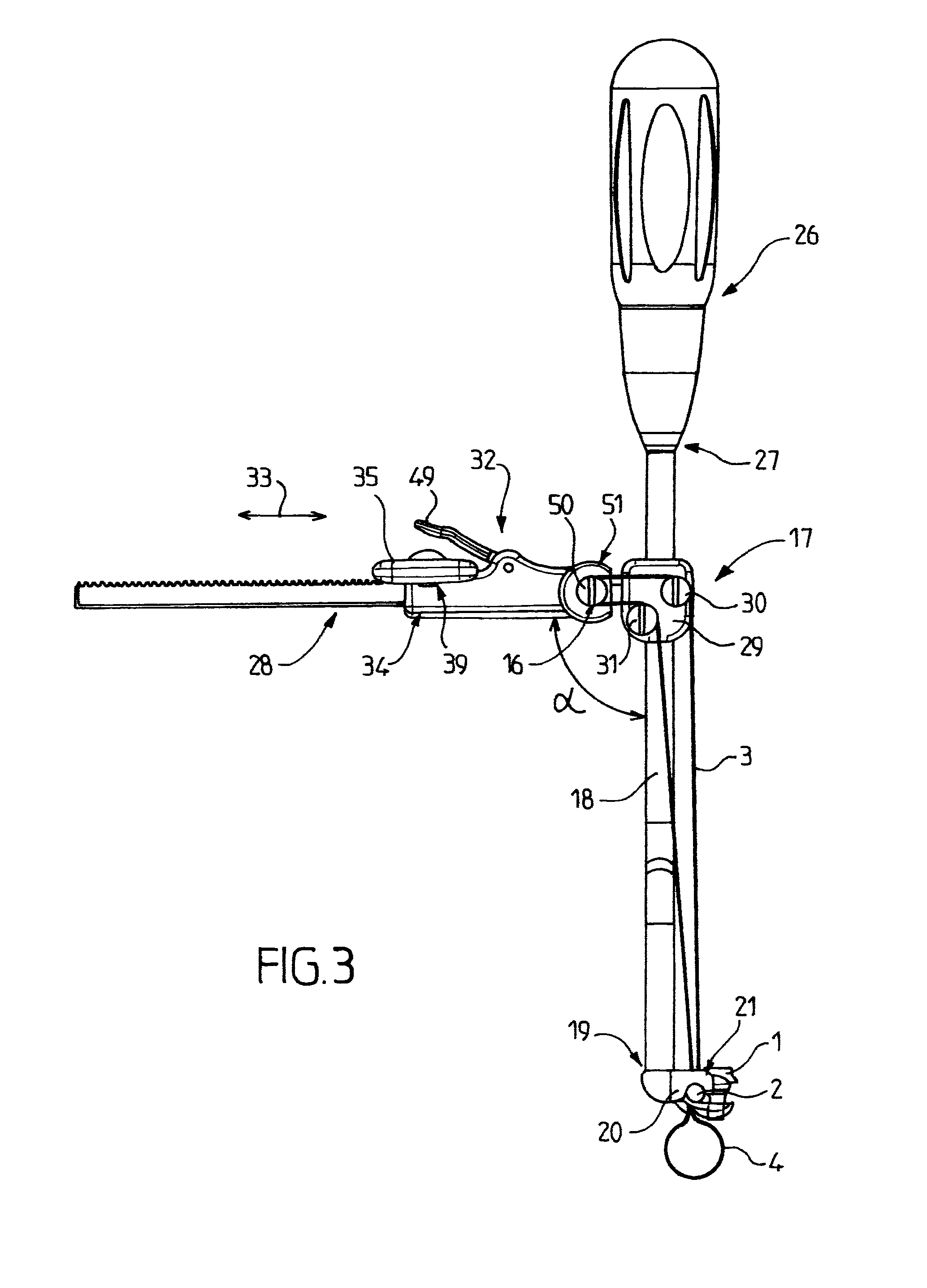

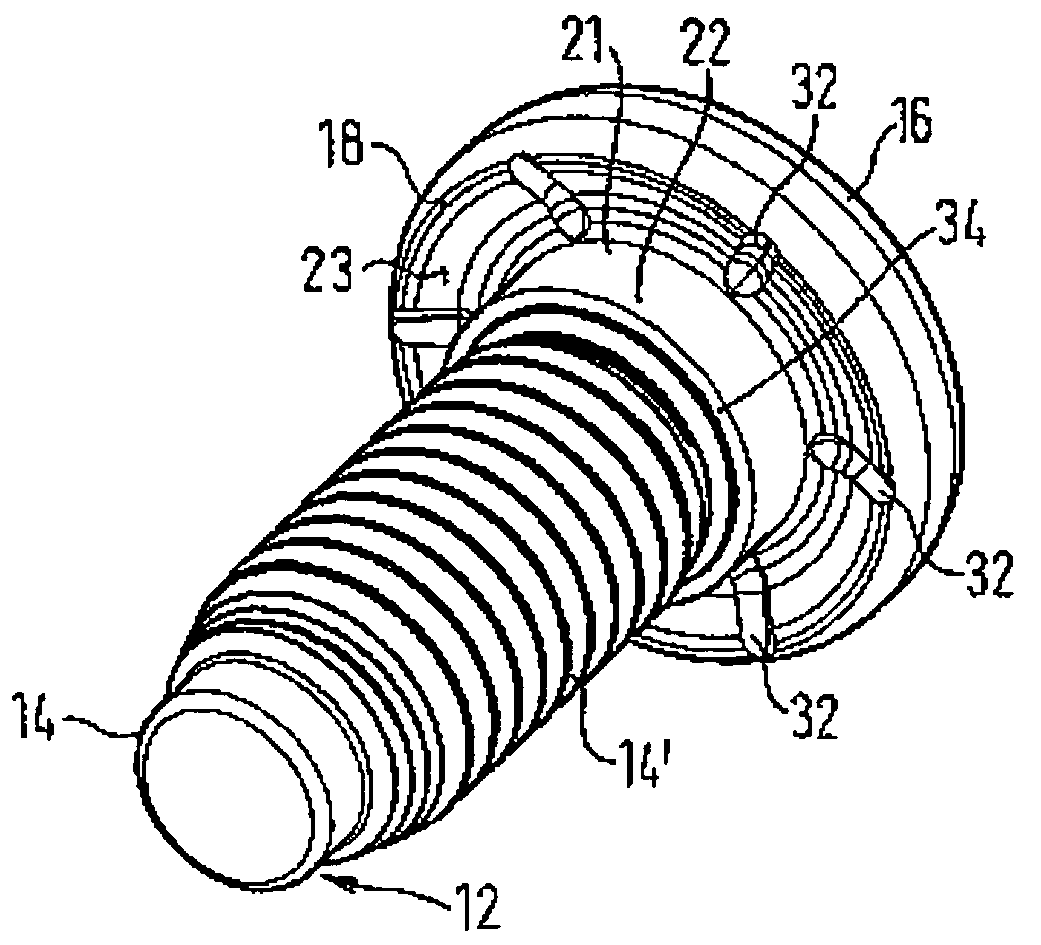

Device for tensioning a flexible band

ActiveUS20130261680A1Great flexibilityGood sensitivityInternal osteosythesisWire toolsBiomedical engineeringDevice form

A device (17) is provided for tensioning a flexible band (3) used to maintain a bone element on an implant. The device includes a rod (18) having a first end (19) provided with means (20) for bearing on the implant, a movable part (32) for hooking the flexible band onto a portion (28) of the device, and means (34) for adjustably locking the movable part in translation in relation to the portion of the device. The rod (18) includes a gripping handle (26) at the second end (27) thereof. The aforementioned portion of the device forms an angle α with the rod (18) to which it is rigidly connected at an intermediary point, the direction of the band being altered at an angle, and the aforementioned adjustable locking means (34) includes manual screwing means (35) for actuating the movable part.

Owner:IMPLANET SA

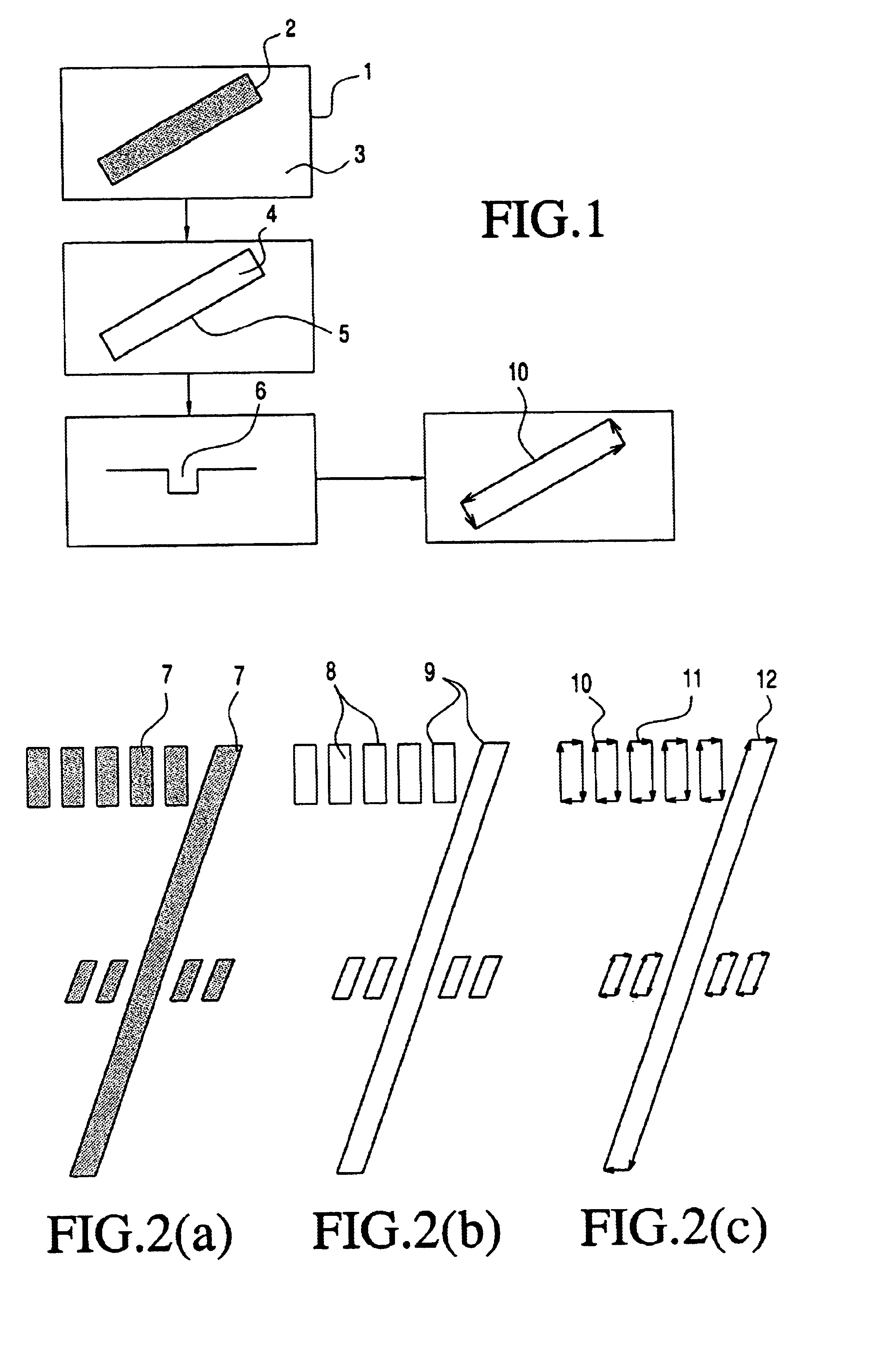

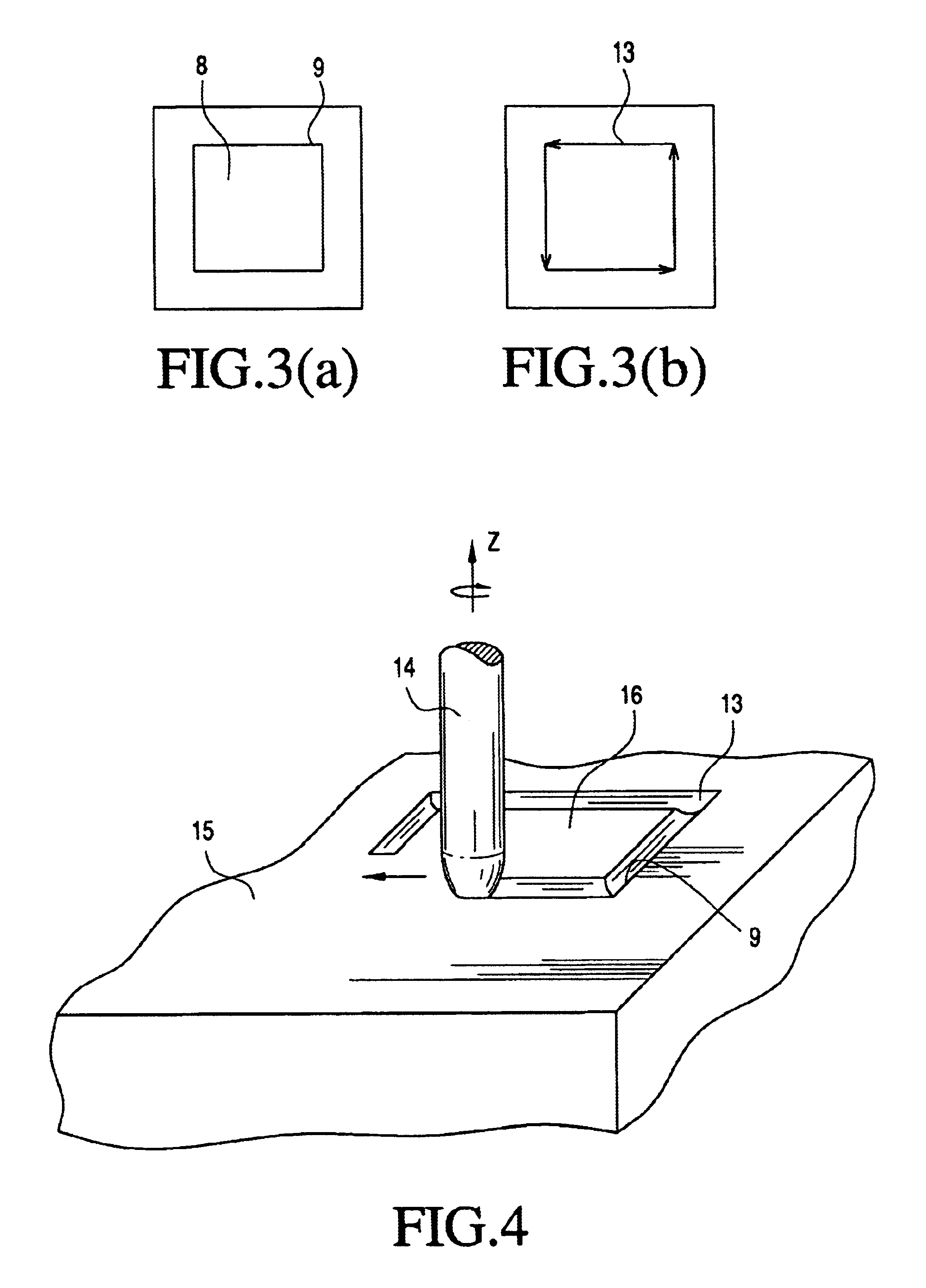

Process for producing dies

InactiveUS6840721B2Increase speedSimple possibilityPlaten pressesMilling machinesEngineeringMechanical engineering

In a method for producing embossing plates, in particular steel intaglio printing plates, a plane element is determined from a line drawing, the edge of the plane element defining a desired contour. A tool track is then calculated from the desired contour and a desired depth associated with the plane element, to be used for guiding an engraving tool such that the partial area is removed.

Owner:GIESECKE & DEVRIENT GMBH

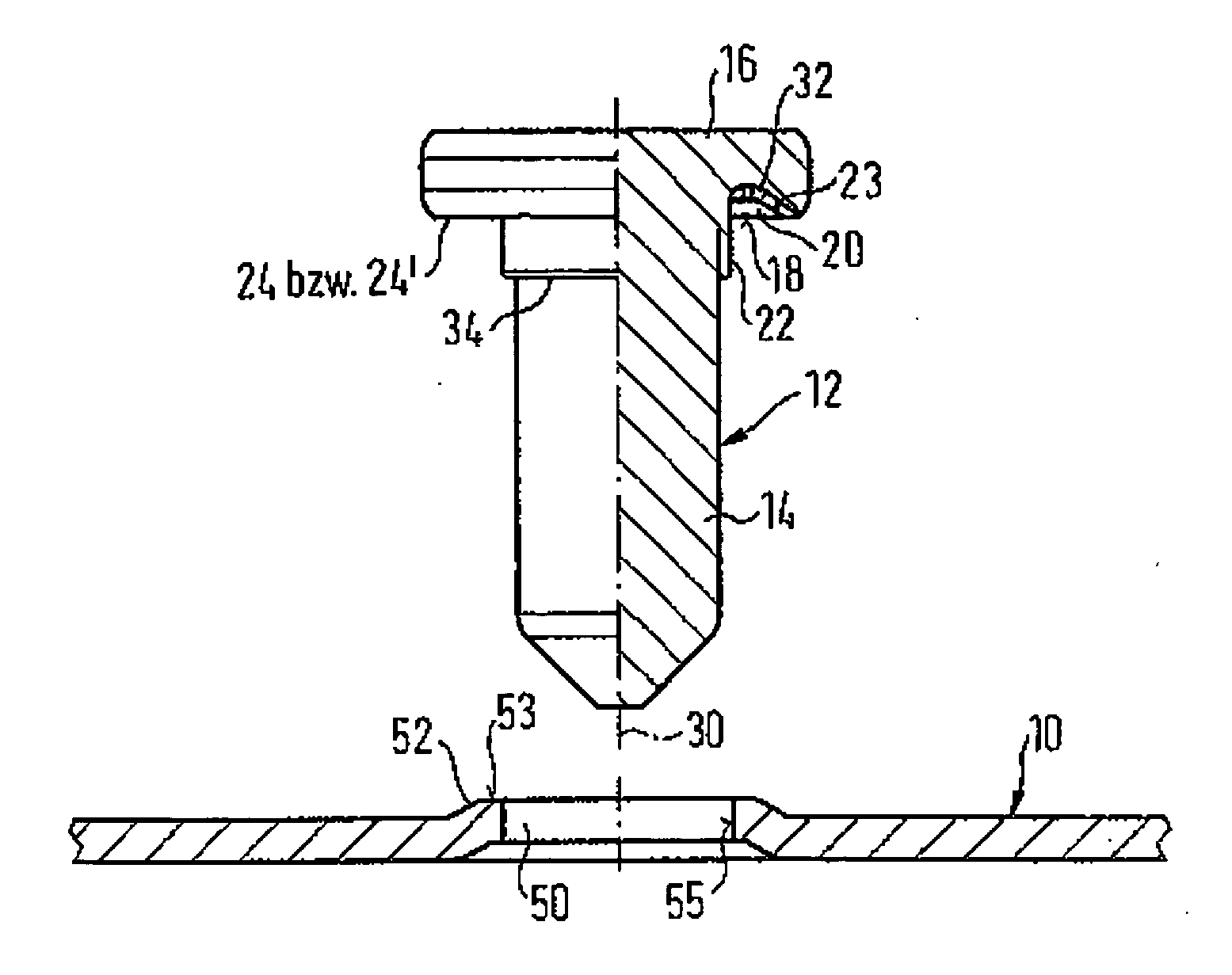

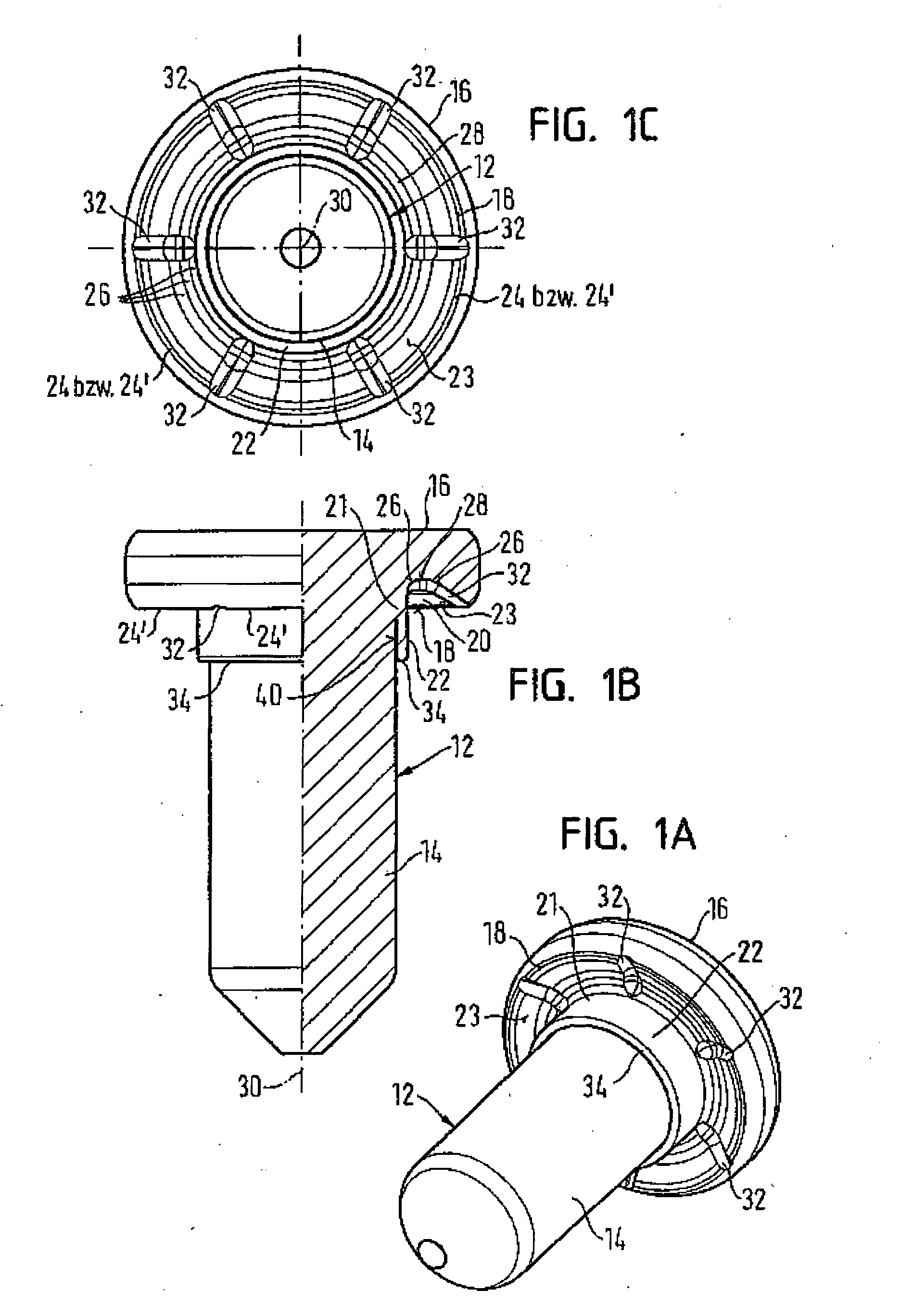

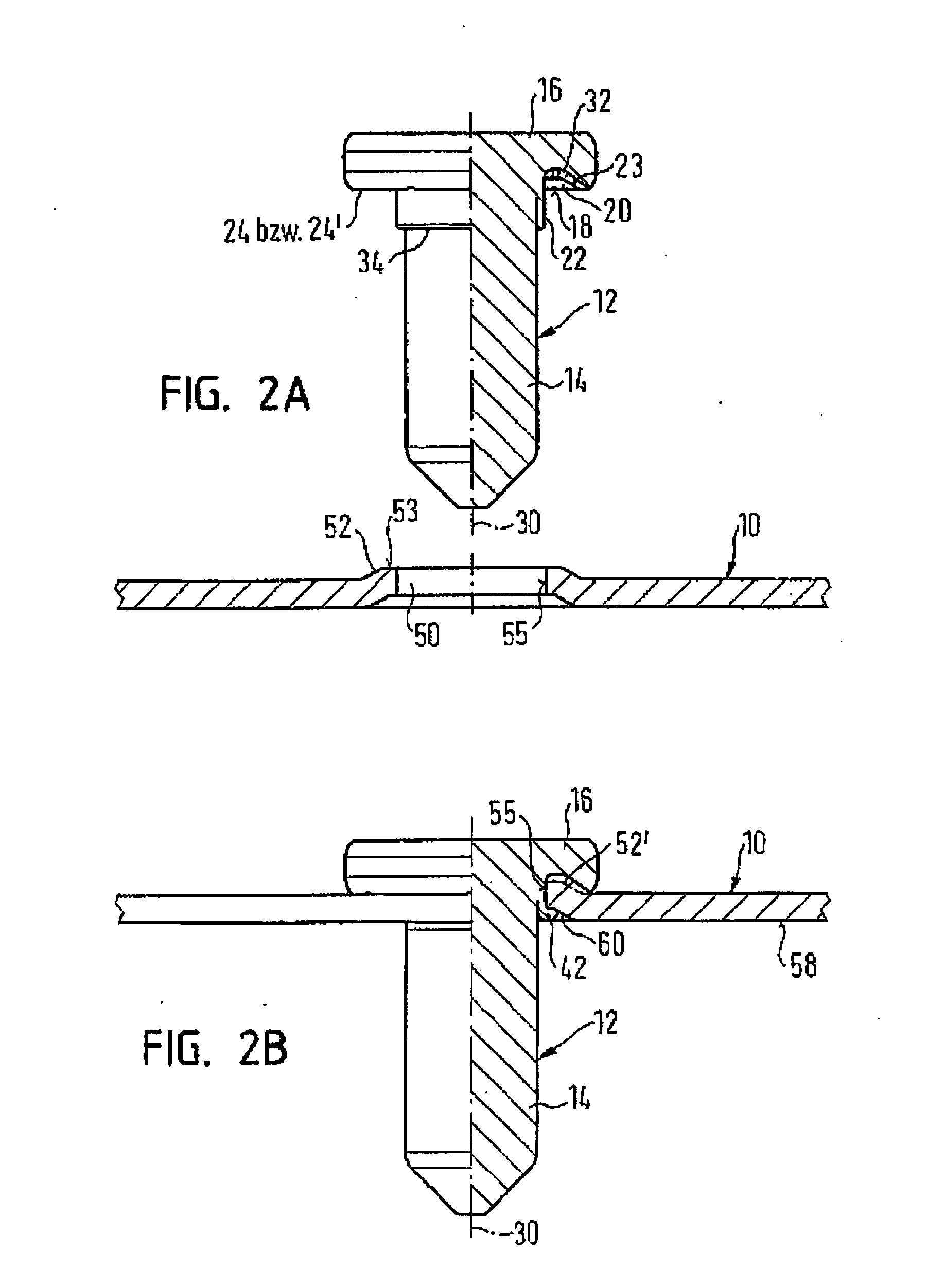

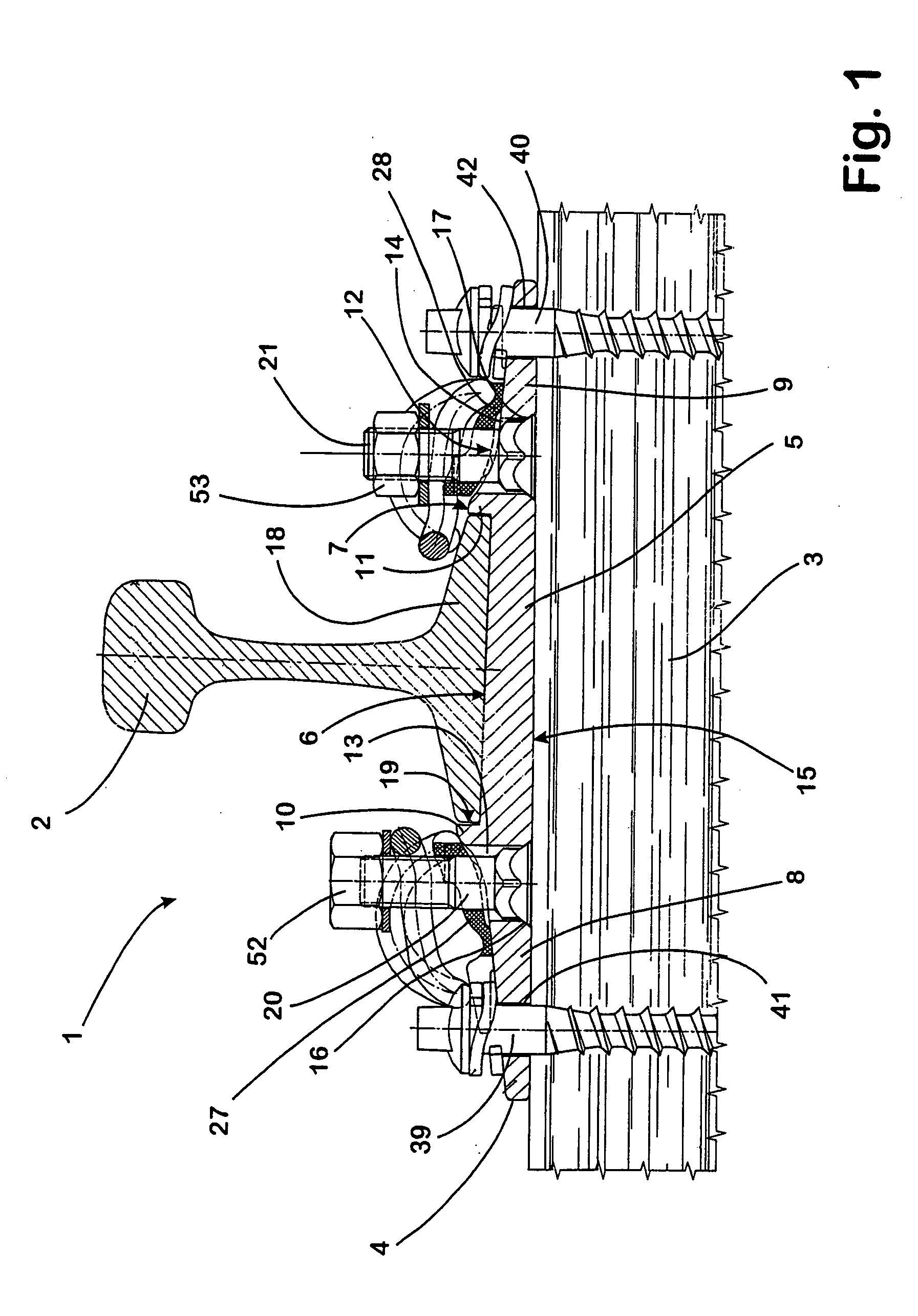

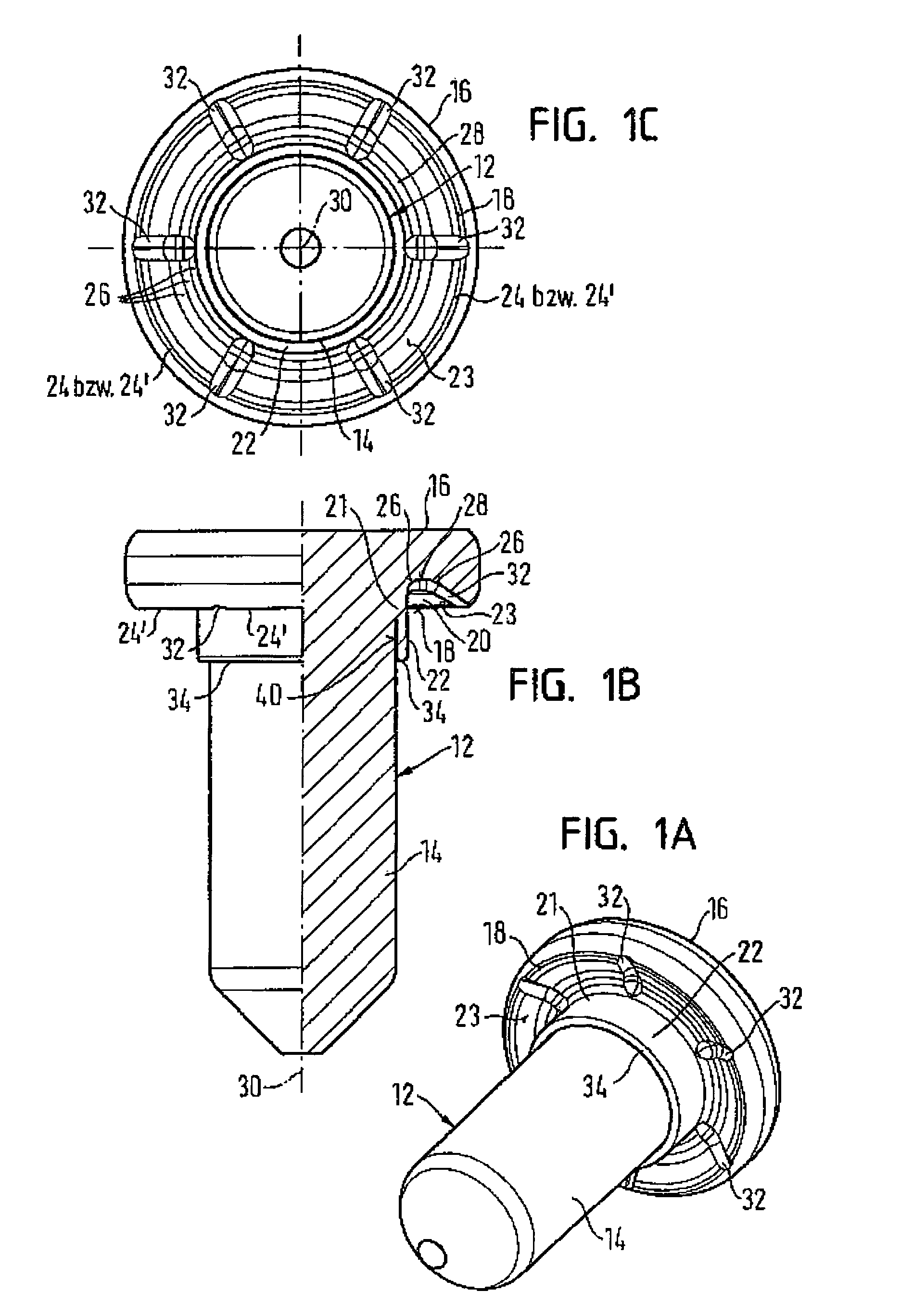

Element attachable by riveting to a sheet metal part and also a component assembly and a method for the production of the component assembly

ActiveUS20060137166A1Excellent resistanceImprove the immunityNutsBoltsManufacturing engineeringRivet

An element attachable to a sheet metal part by riveting, in particular an element in the form of a centering bolt, having a shaft part and a head part, wherein the head part has at its side confronting the sheet metal part an at least approximately ring-like ring recess which merges at the radially inner side into a cylinder section of the head part which in turn merges into the shaft part and into a tubular rivet section which surrounds the shaft part in the region of the head part, is disposed within a ring-like contact surface arranged radially outside of the ring recess and merges at the radially outer side via an at least approximately conical wall into the ring-like contact surface, is characterized in that at least one local recess and preferably a plurality of in particular uniformly distributed local recesses is or are provided in the conical wall of the ring recess and / or in an optionally present ring-like base surface of the ring recess. A component assembly comprising the element and a sheet metal part and also a method for the manufacture of such a component assembly are also described.

Owner:HVB BANQUE LUXEMBOURG

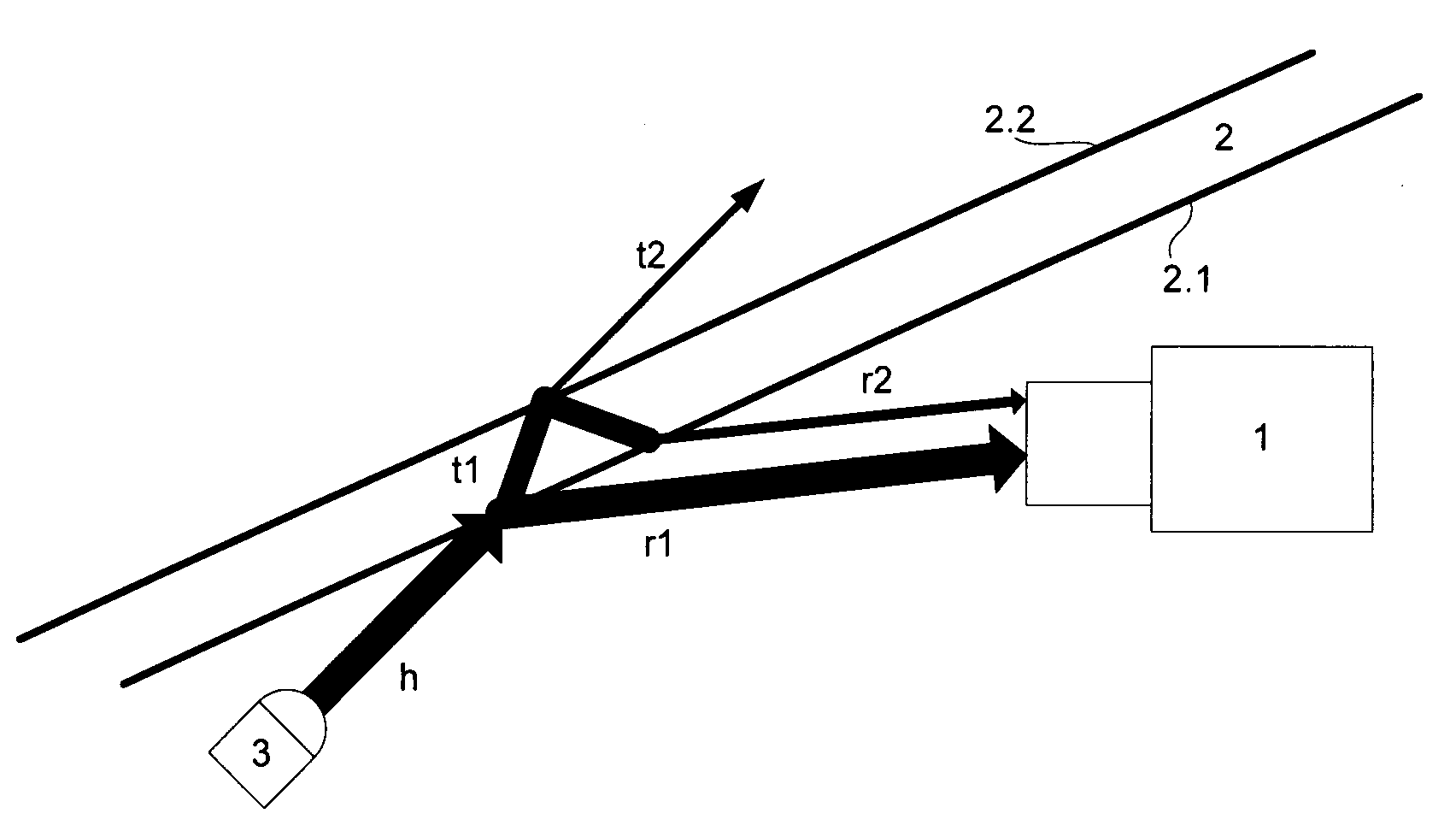

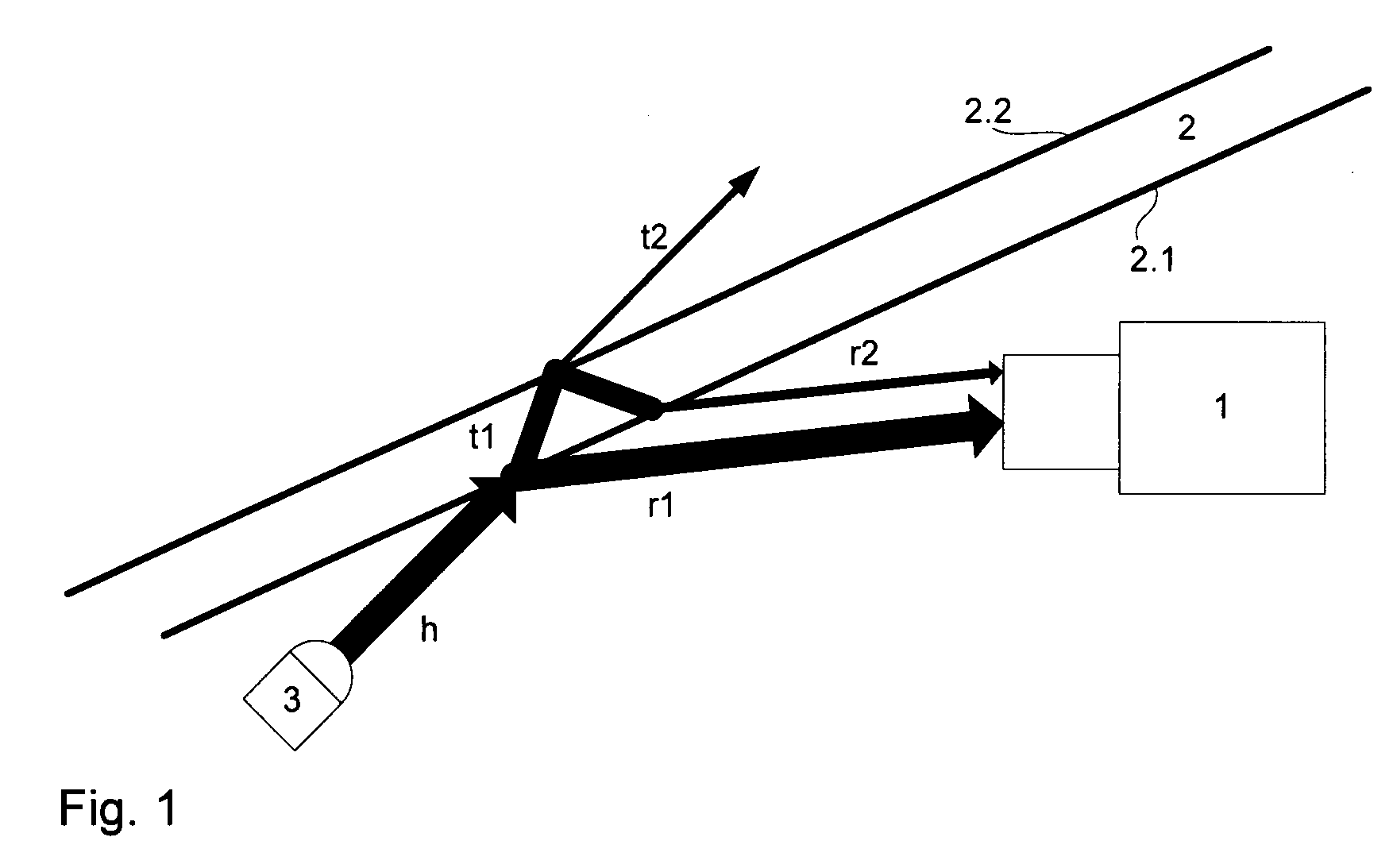

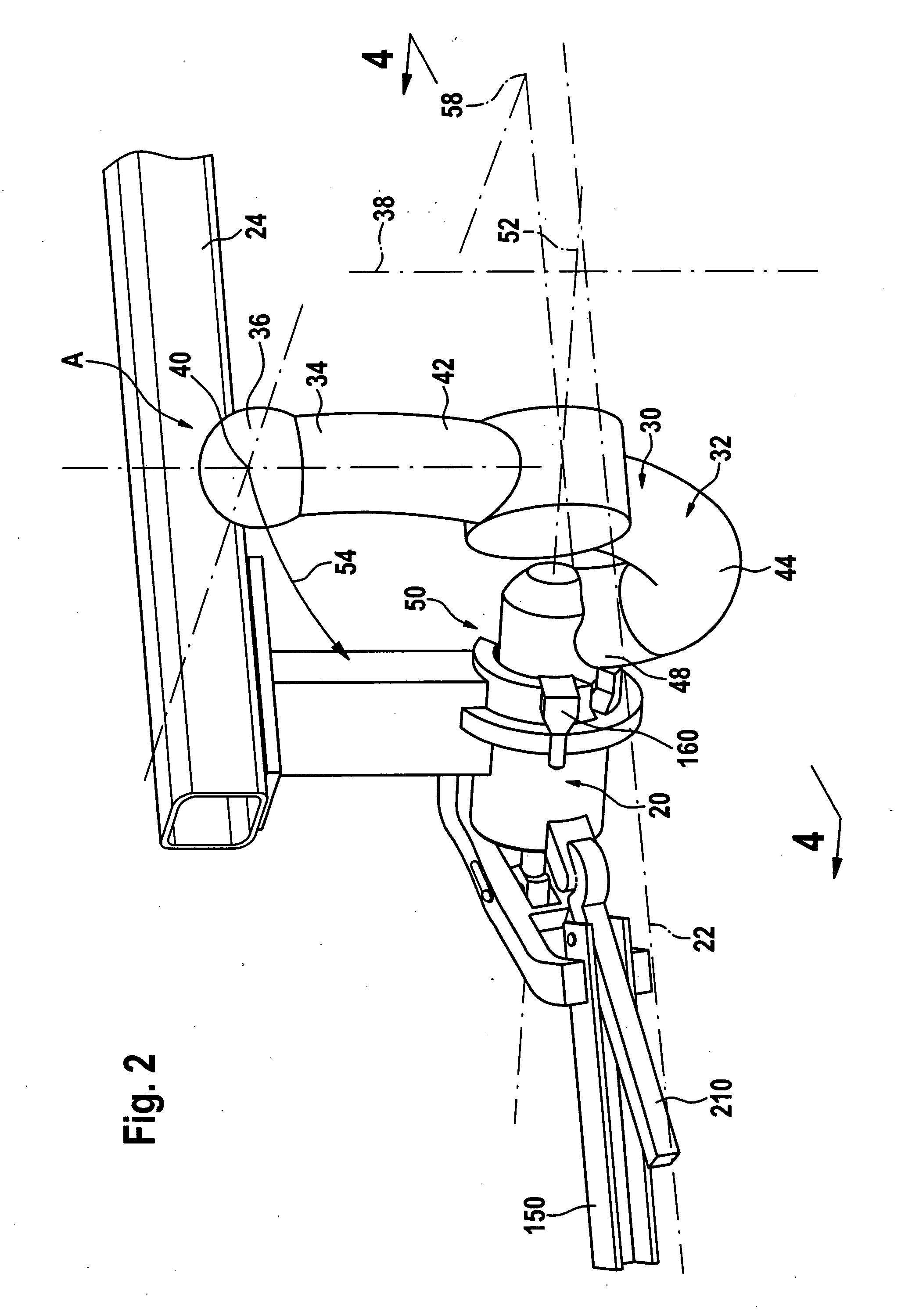

Detection of Raindrops on a Pane by Means of a Camera and Lighting

ActiveUS20130235381A1Simple possibilityLess susceptible to interferenceScattering properties measurementsCharacter and pattern recognitionEngineeringLight source

The invention relates to a device or a method for detecting rain (4), said device or method comprising a camera (1) and a lighting source (3). The camera (1) is disposed behind a pane (2), in particular in the interior of a vehicle behind a windscreen, and focused onto a far range that lies in front of the pane (2). The lighting source (3) for generating at least one light beam (h; n) that is directed at the pane (2) directs the at least one light beam (h; n) towards the pane (2) such that at least one beam (r2; r2′) that is reflected from the outer face (2.2) of the pane impinges on the camera (1).The light quantity of the at least one beam (r2; r2′) that impinges on the camera (1) can be measured by the camera (1).

Owner:CONTI TEMIC MICROELECTRONIC GMBH

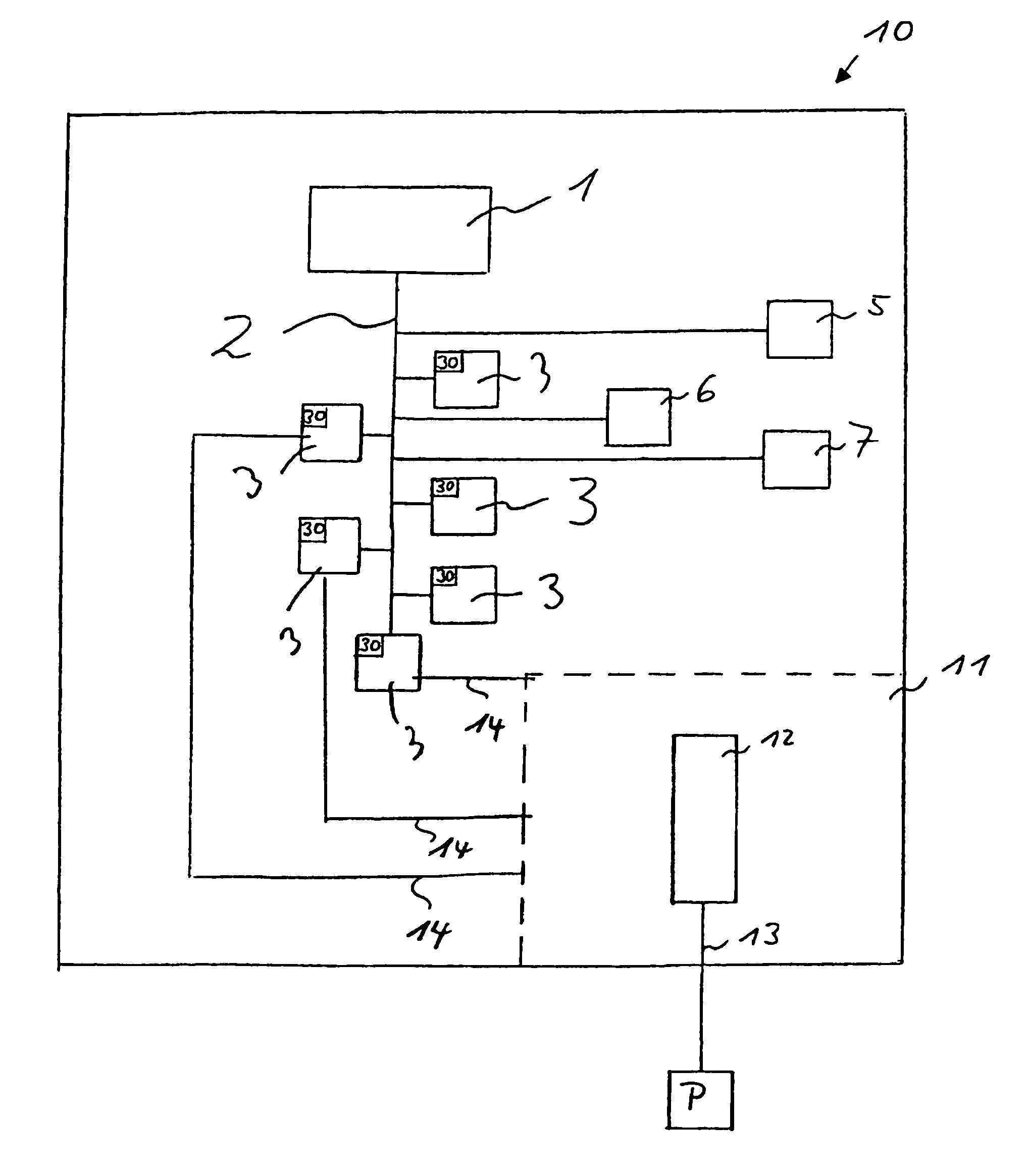

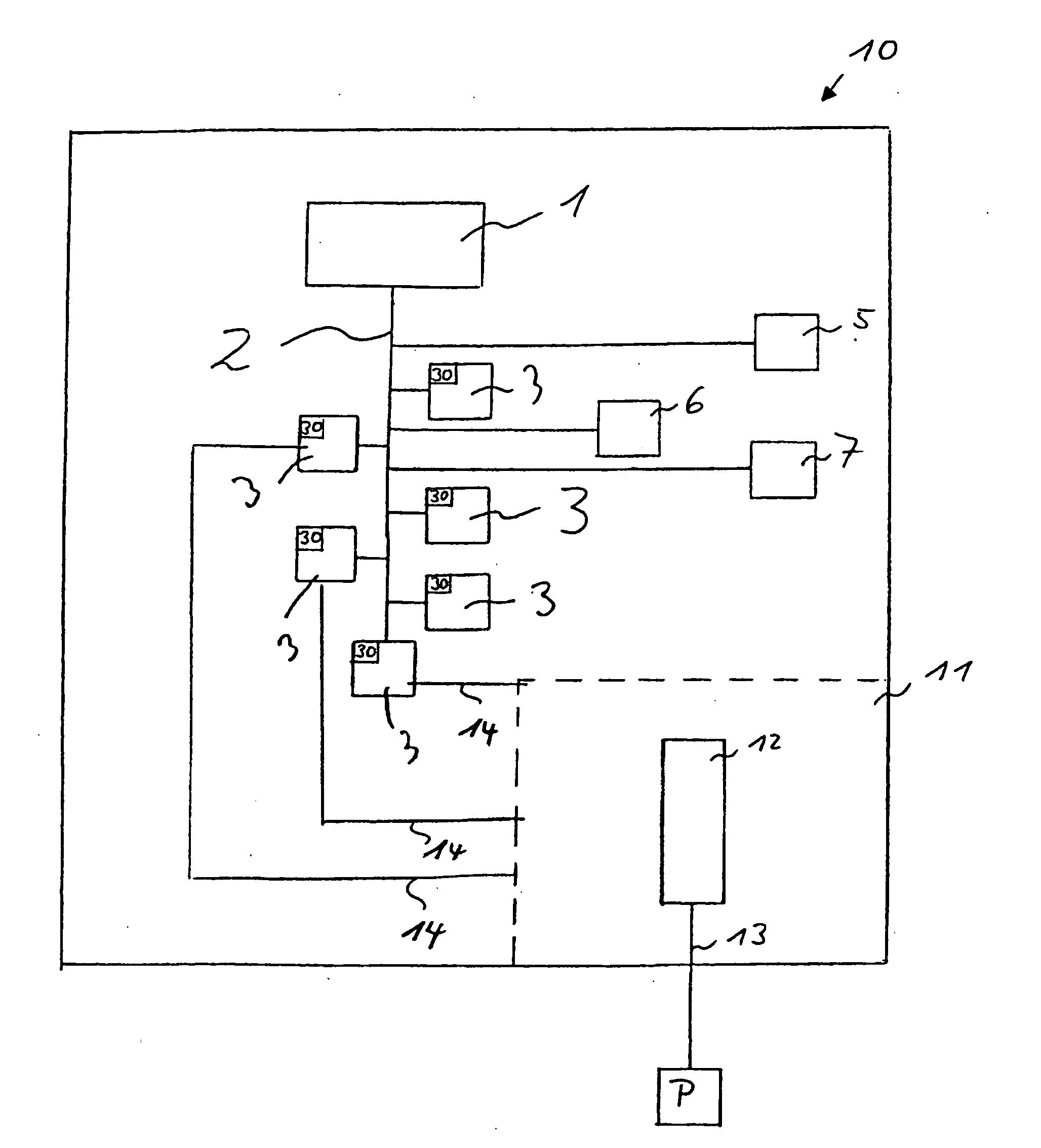

Software update for a medical fluid management device

InactiveUS20110072422A1Simple priceEffectively and simply avoidedMechanical/radiation/invasive therapiesDialysis systemsSoftware updateTransfer system

A medical fluid management apparatus which includes a plurality of processor systems with respectively associated software programs. The fluid management apparatus has a fluid treatment component and / or a fluid source which can be connected to a patient via a fluid line. The processor systems are connected via a data transfer system to a data input apparatus via which an updating of the software programs belonging to the respective processor systems can take place. After actuation of an operating mode switch, a detection system, while taking into account the existing version of the software programs and / or the existing processor systems, determines which software programs have to be loaded via the data input apparatus. The medical fluid management apparatus allows a simple and user-friendly updating of the operating software even with a complex design of the apparatus.

Owner:FRESENIUS MEDICAL CARE DEUTSCHLAND GMBH

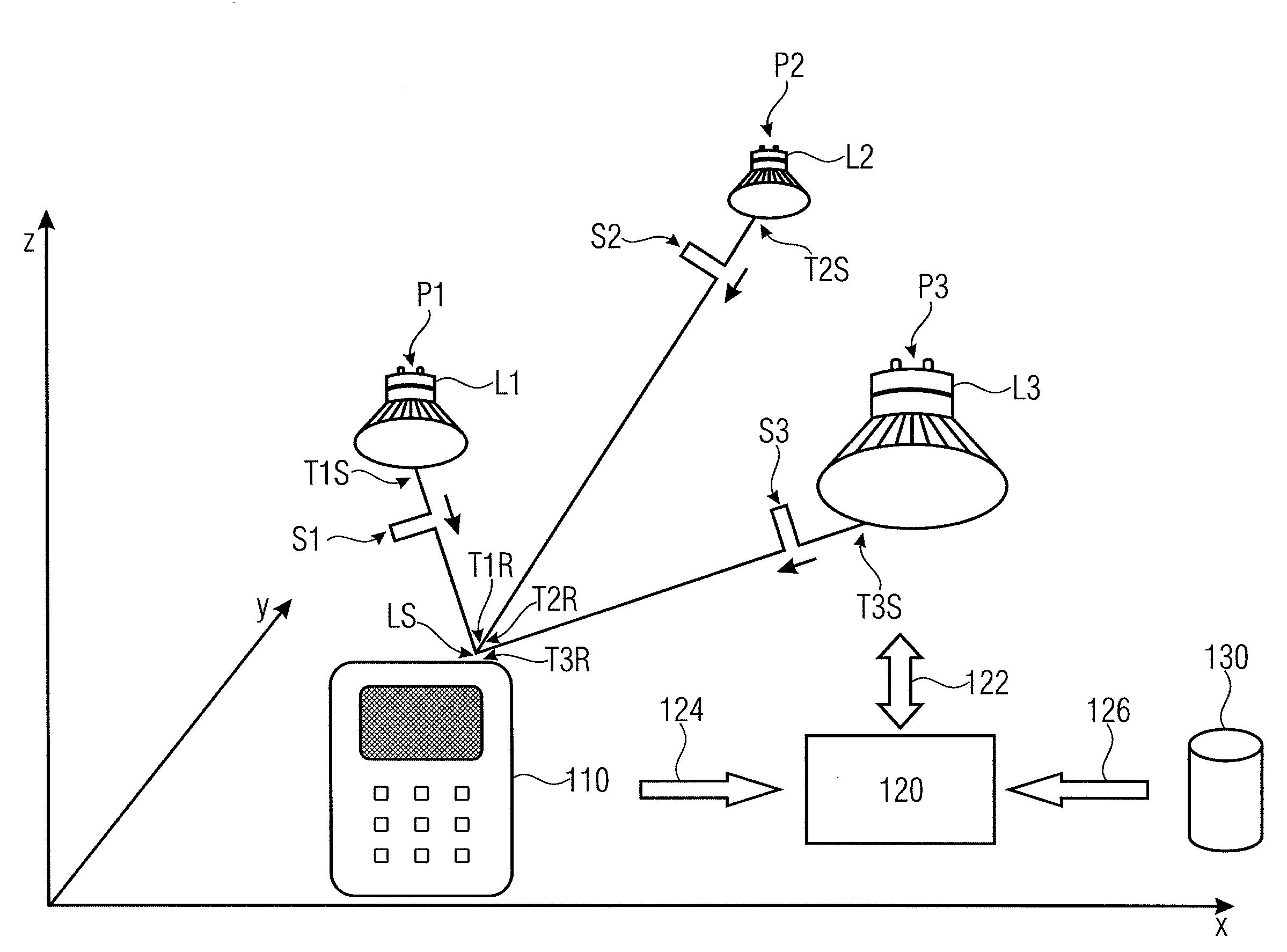

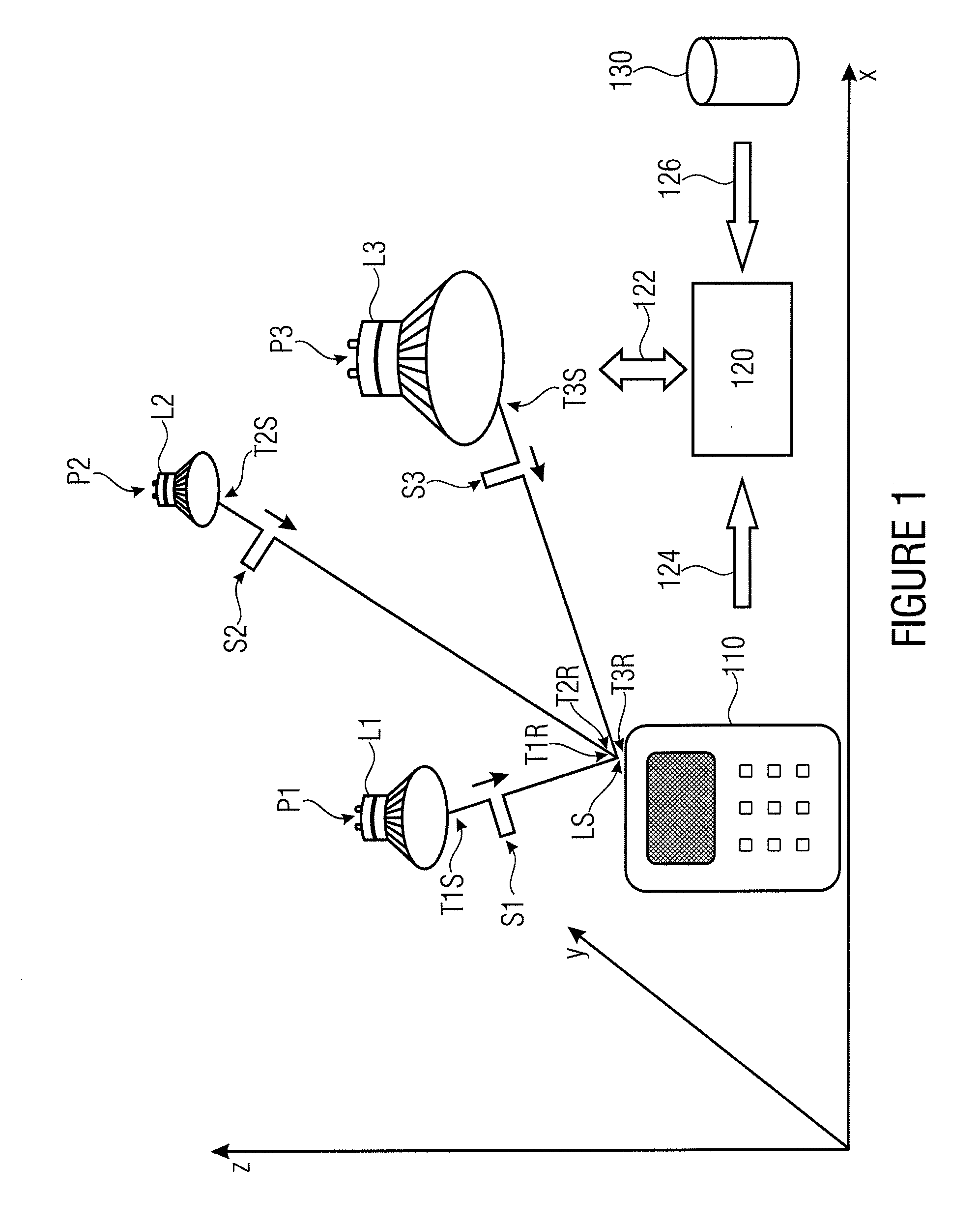

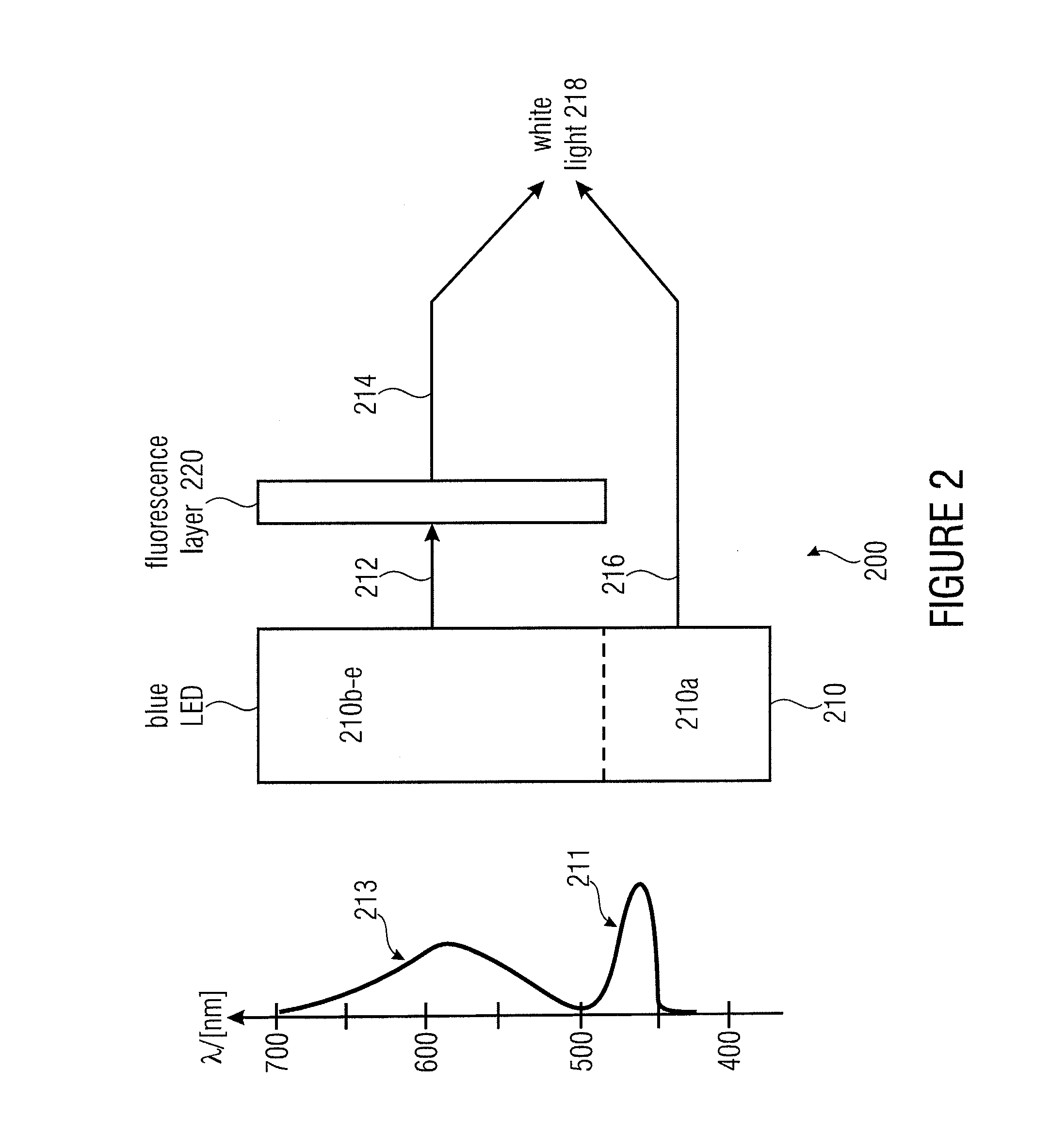

System and method for determining a position of a movable object, arrangement of general lighting LED and light sensor for a position determination of a movable object

ActiveUS20120022826A1Low costPrecise positioningBeacon systems using electromagnetic wavesDigital computer detailsTime informationObject based

A system for determining a position of a moving object is described, having: an arrangement having at least three general lighting LEDs, wherein each of the general lighting LEDs is implemented to transmit one light signal each with a transmission time information and a transmitter information, wherein the wavelength ranges of the general lighting LEDs for the signal transmission overlap, wherein the transmitter information enables at least a determination of a position of the respective general lighting LEDs and the transmission time information is information on a point in time when the respective signal was transmitted; a light sensor mounted to the moving object and implemented to receive the light signals and allocate one signal receive time each; and an evaluation unit which is implemented to determine the position of the object based on the transmitter information, the transmission time information and the receive time information.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

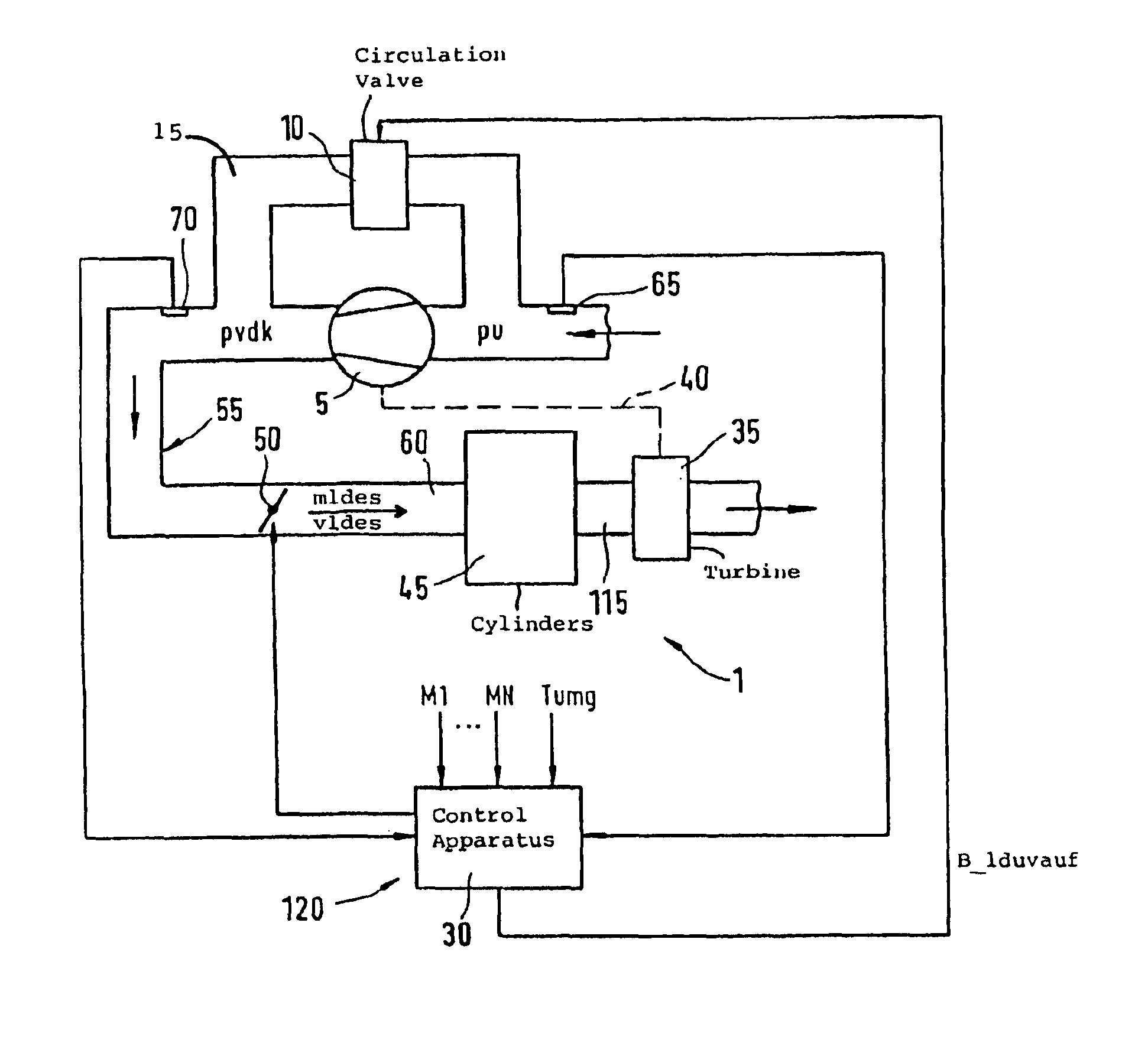

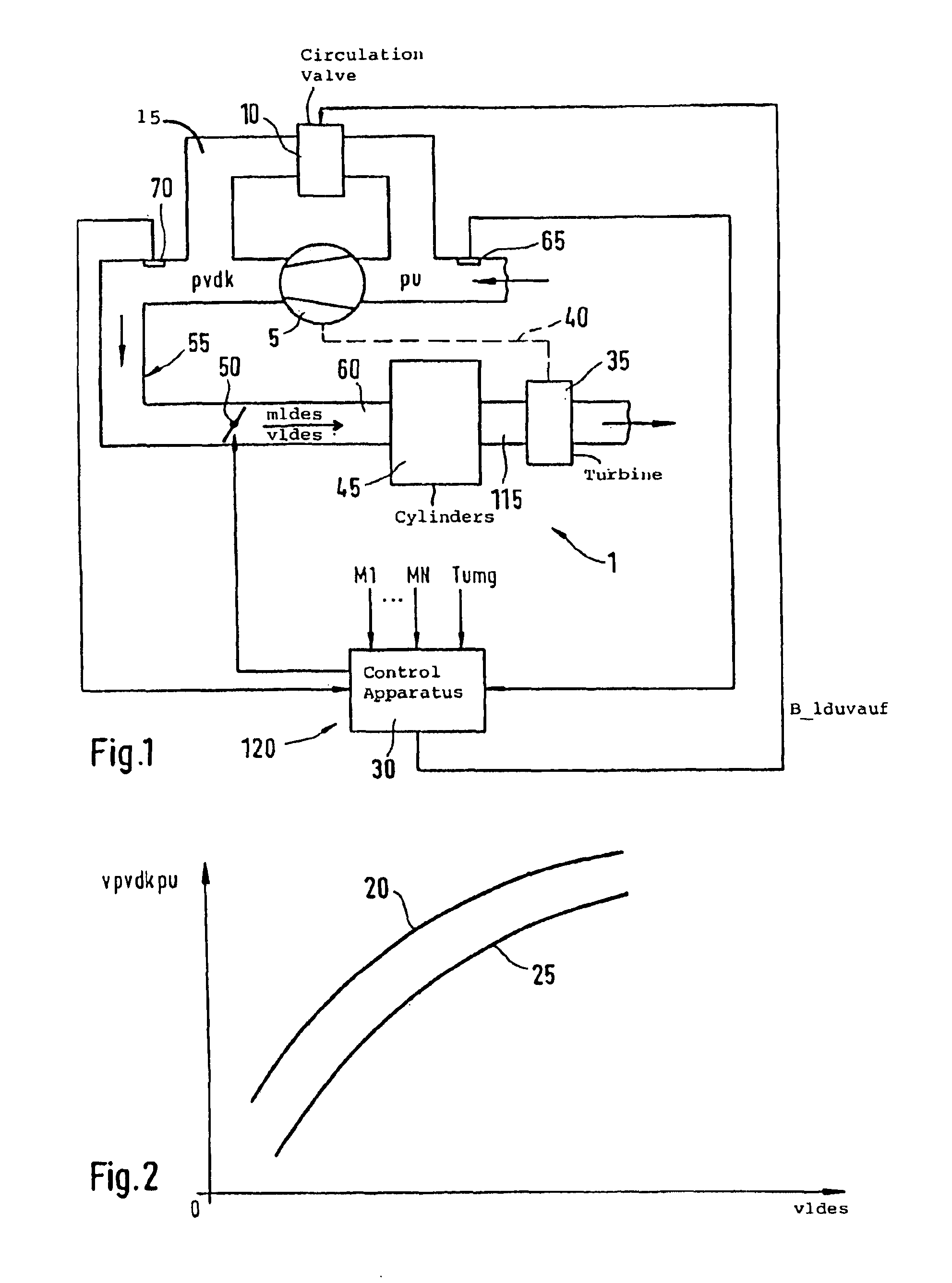

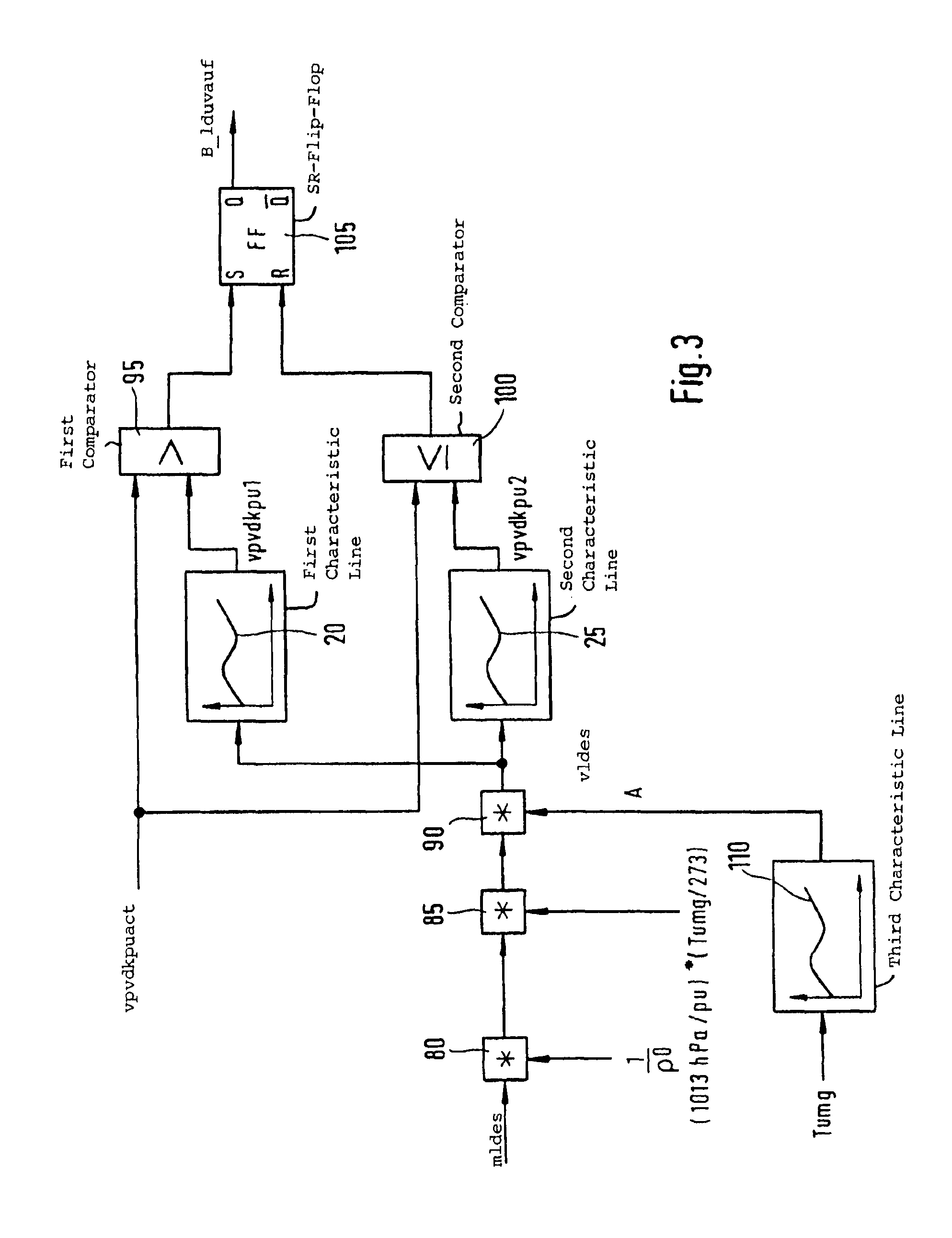

Method and arrangement for controlling an internal combustion engine

InactiveUS6983597B2Prevent unnecessary noiseSimple driveInternal combustion piston enginesLow pressure fuel injectionTurbochargerEngineering

The invention is directed to a method and an arrangement for controlling an internal combustion engine (1) having a compressor (5) for compressing the air drawn in by suction by the engine (1). The compressor is especially an exhaust-gas turbocharger. With the method and arrangement, a requirement-proper and timely opening of a valve (10) of an air path (15) is ensured for avoiding compressor pumping. The air path (15) bypasses the compressor (5). The valve (10) of the air path (15), which bypasses the compressor (5), is controlled in dependence upon at least one pregiven characteristic line (20, 25) of a compressor characteristic field.

Owner:ROBERT BOSCH GMBH

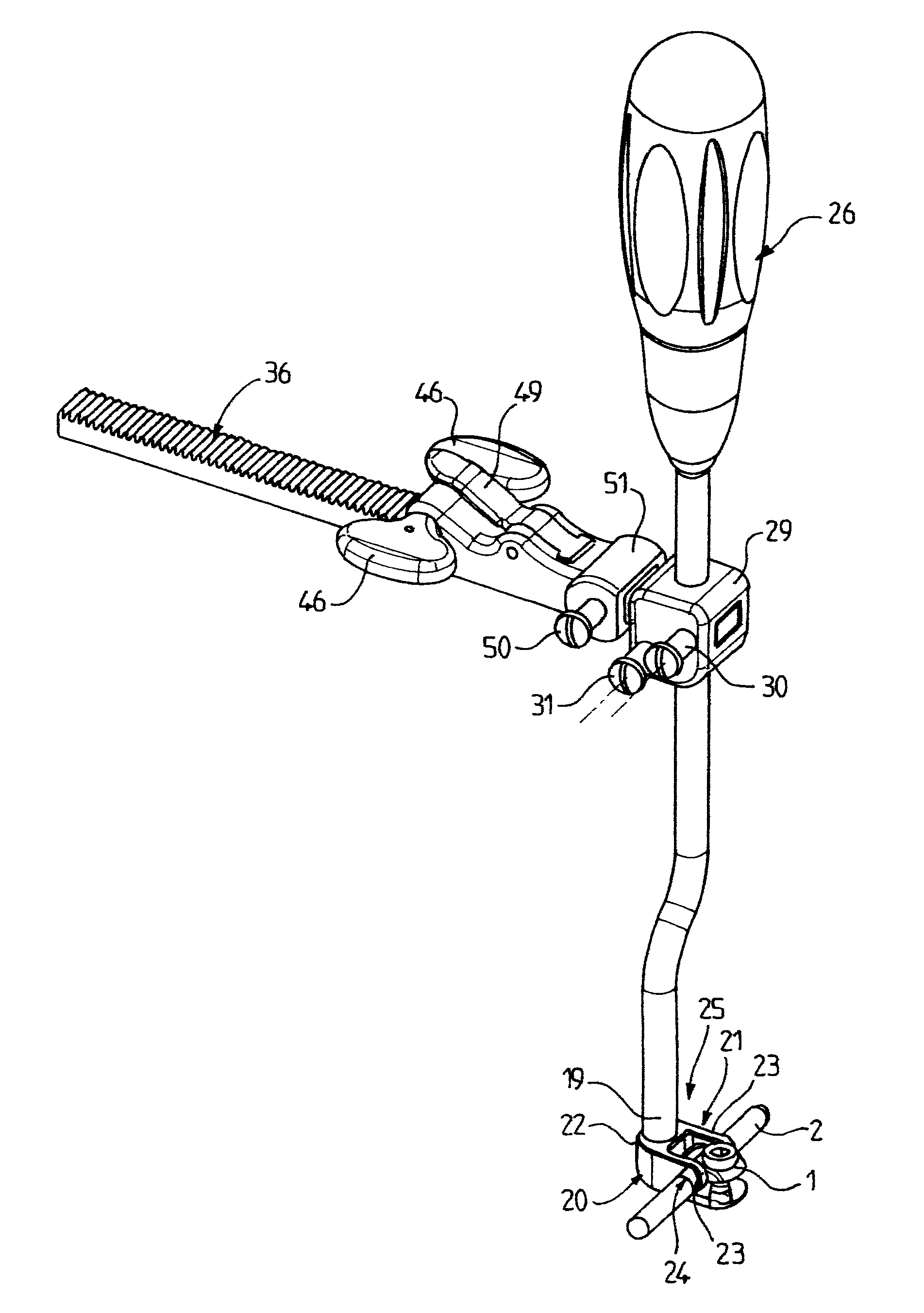

Device for tensioning a flexible band

ActiveUS8728083B2Good flexibilityHigh sensitivityInternal osteosythesisWire toolsDevice formBiomedical engineering

A device (17) is provided for tensioning a flexible band (3) used to maintain a bone element on an implant. The device includes a rod (18) having a first end (19) provided with means (20) for bearing on the implant, a movable part (32) for hooking the flexible band onto a portion (28) of the device, and means (34) for adjustably locking the movable part in translation in relation to the portion of the device. The rod (18) includes a gripping handle (26) at the second end (27) thereof. The aforementioned portion of the device forms an angle α with the rod (18) to which it is rigidly connected at an intermediary point, the direction of the band being altered at an angle, and the aforementioned adjustable locking means (34) includes manual screwing means (35) for actuating the movable part.

Owner:IMPLANET SA

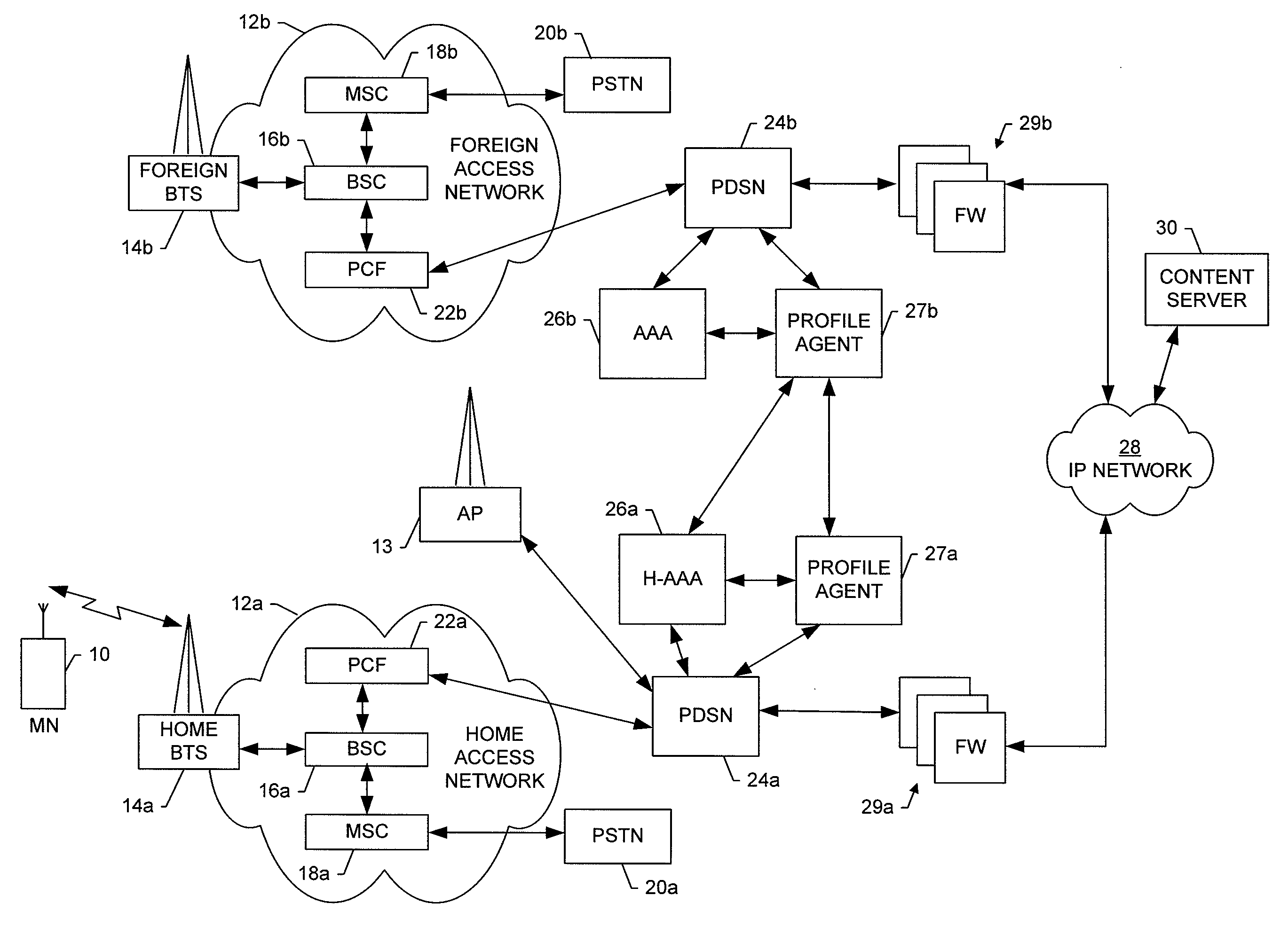

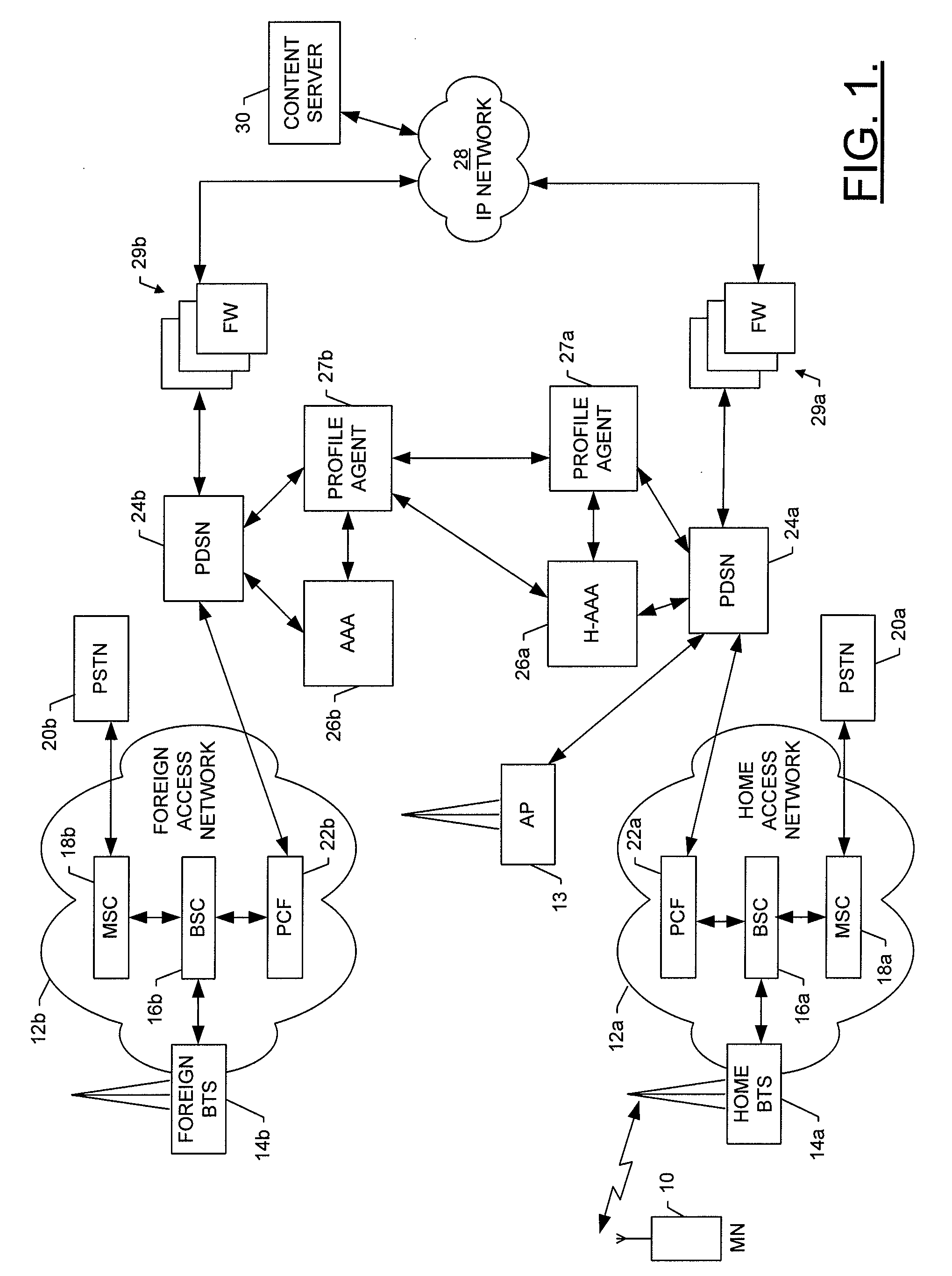

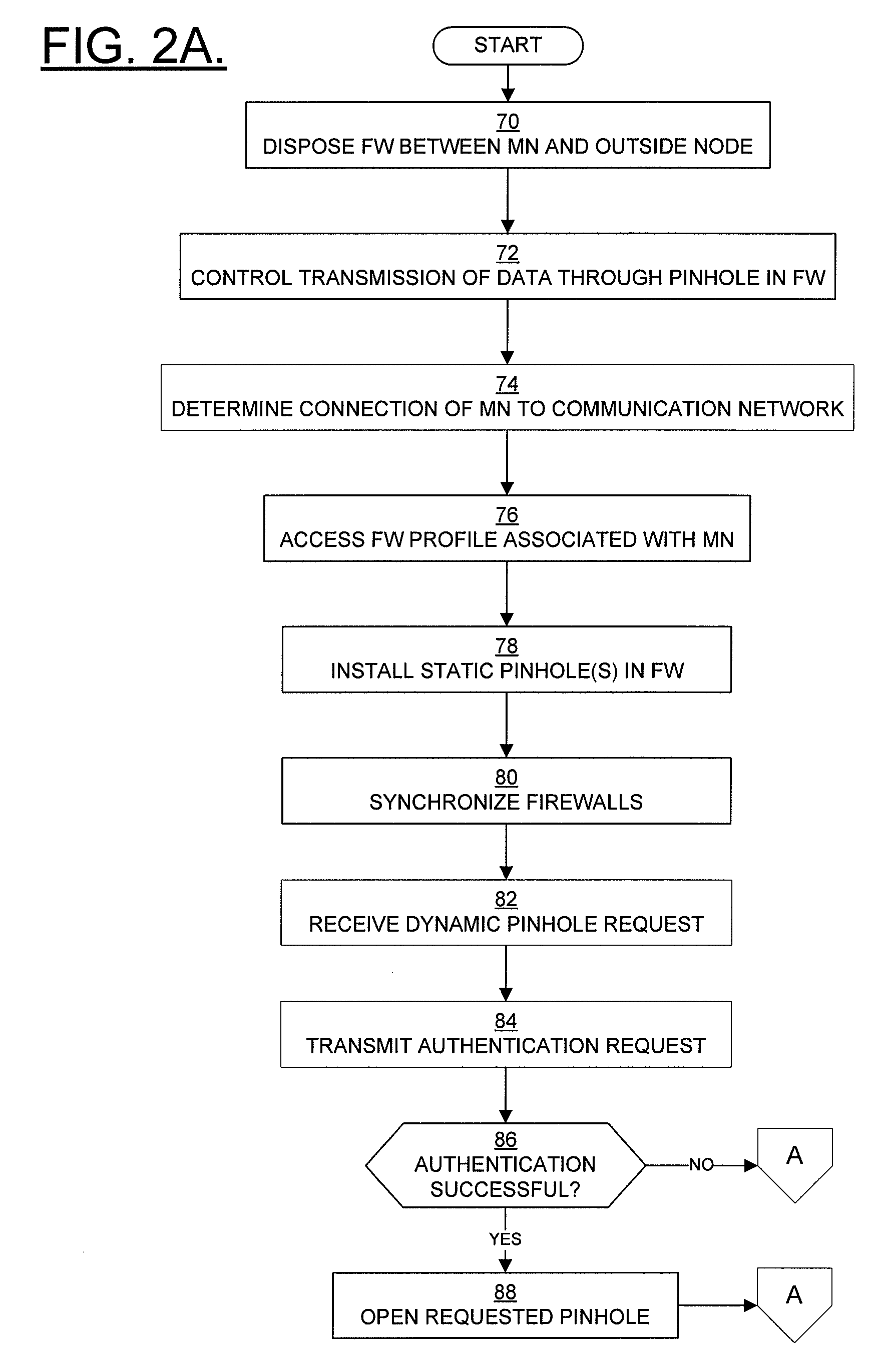

System, mobile node, network entity, method, and computer program product for network firewall configuration and control in a mobile communication system

InactiveUS20070067838A1Simple possibilitySimple structureMultiple digital computer combinationsProgram controlFirewall pinholeMobile communication systems

A system, mobile node, network entity, method and computer program product for providing firewall protection for a wireless communication network are provided in which a firewall profile is accessed by the network entity when a mobile node connects to the network. The firewall profile defines a list of static firewall pinholes which are opened in a firewall by the network entity. The mobile node may open additional pinholes dynamically. The opened pinholes are closed by the network entity when the mobile node disconnects from the network.

Owner:NOKIA CORP

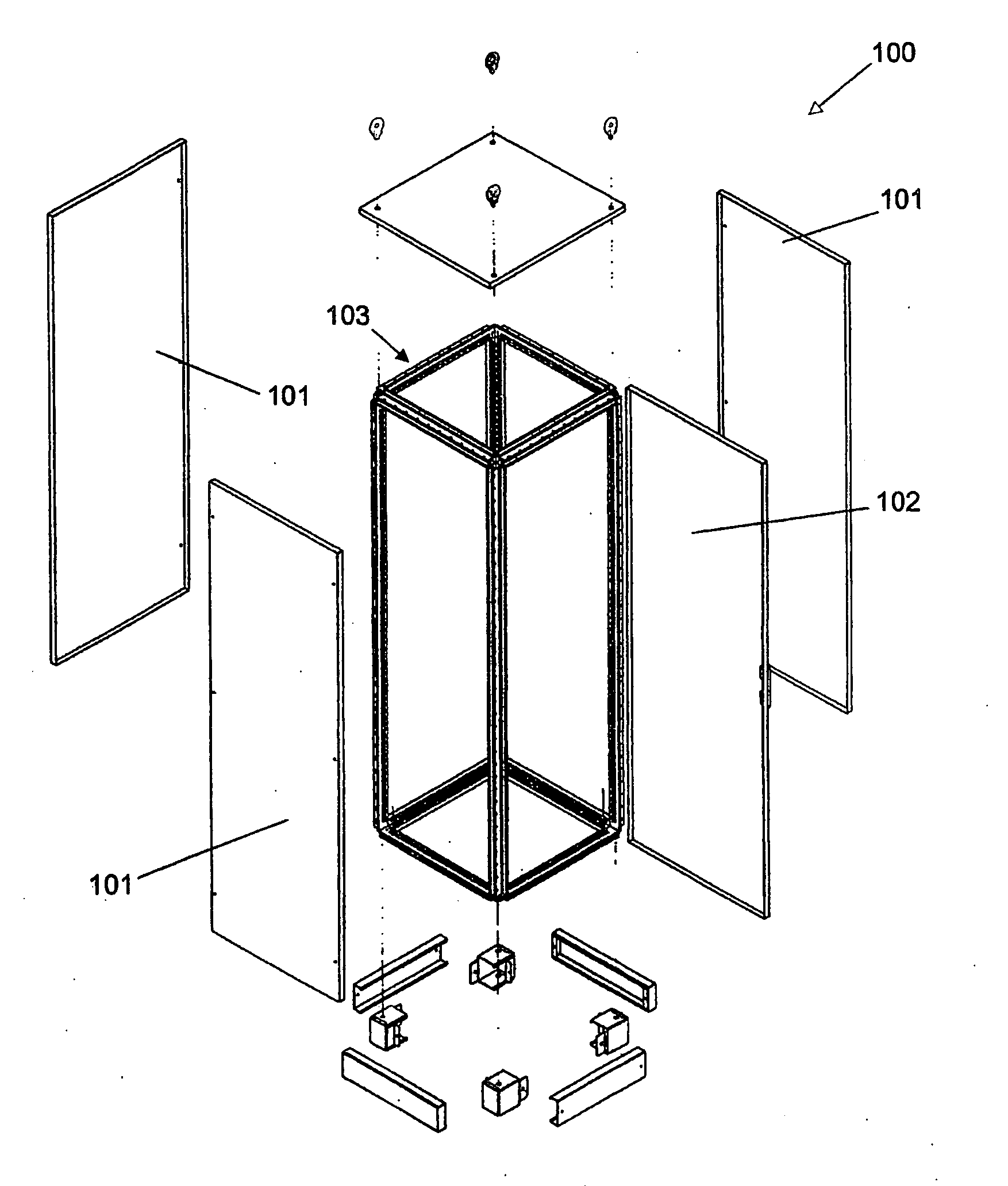

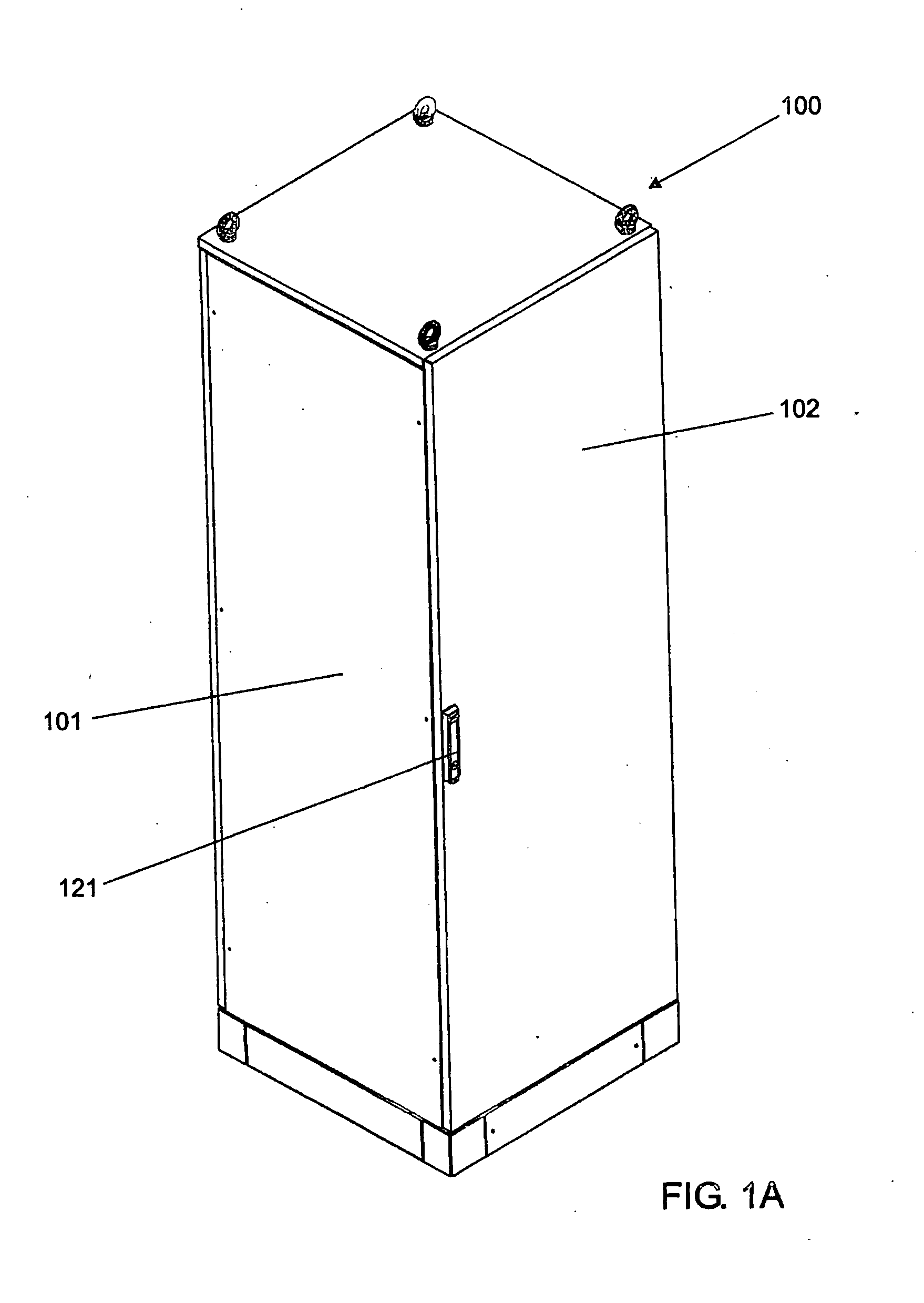

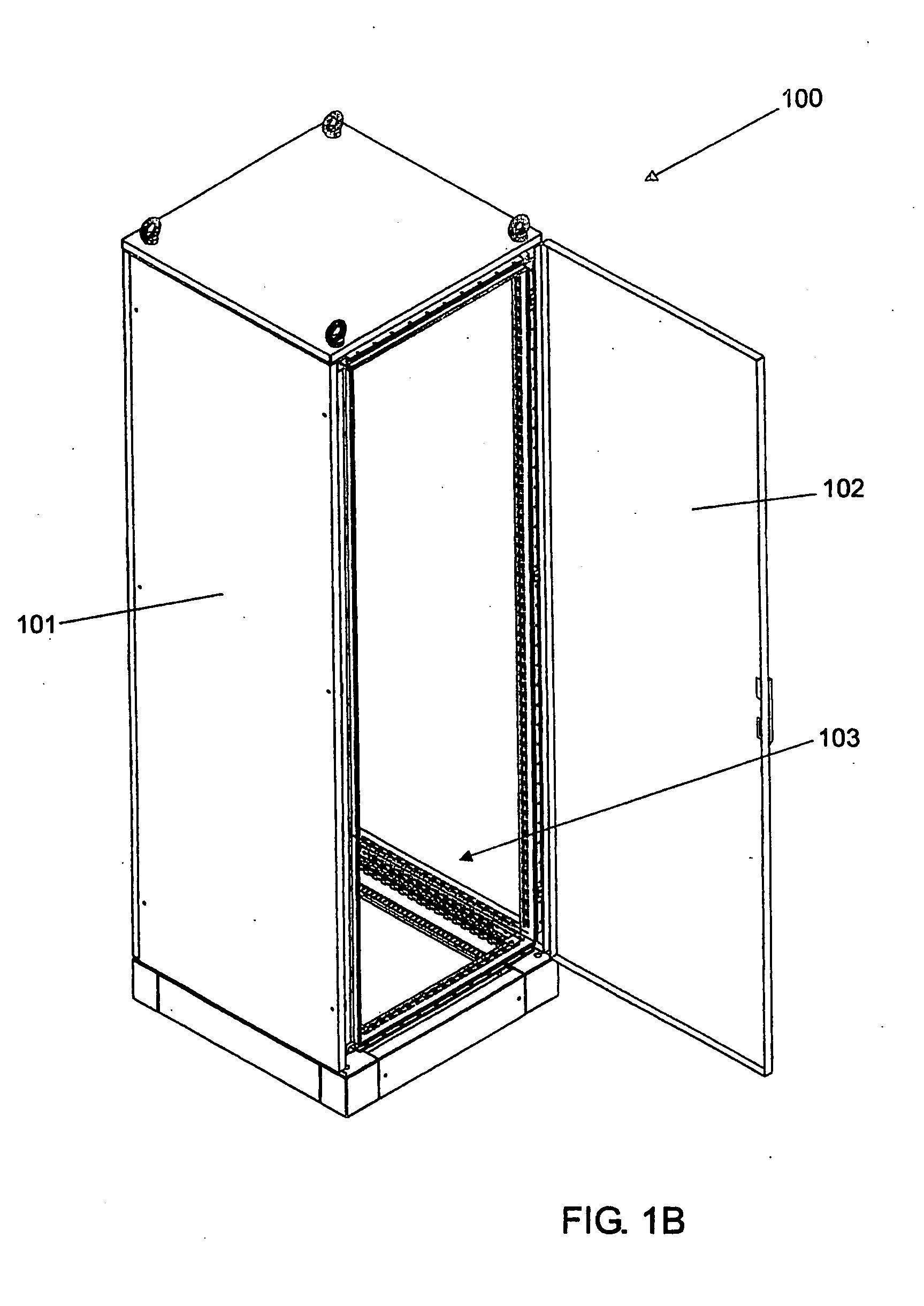

Improvement to metallic cross sections for the manufacture of housing for electrical panels

InactiveUS20070175648A1Good mechanical resistanceImprove stabilitySubstation/switching arrangement casingsGaseous cathodesElectronic componentMetal

Especially developed for the assembly of structures which are normally used in the most varied of cabinet types, these are also known as electrical panels, which in reality are cabinets with side closing doors to house a very large variety of electrical and electronic components and devices, encompassing a cross section (104) which on its exterior constitutes the means of support for the enclosures and accessories, whilst that on the inside, the same structure configures the uprights for the assembly of the electrical and electronic devices.

Owner:FRANCISQUINI MELQUISEDEC

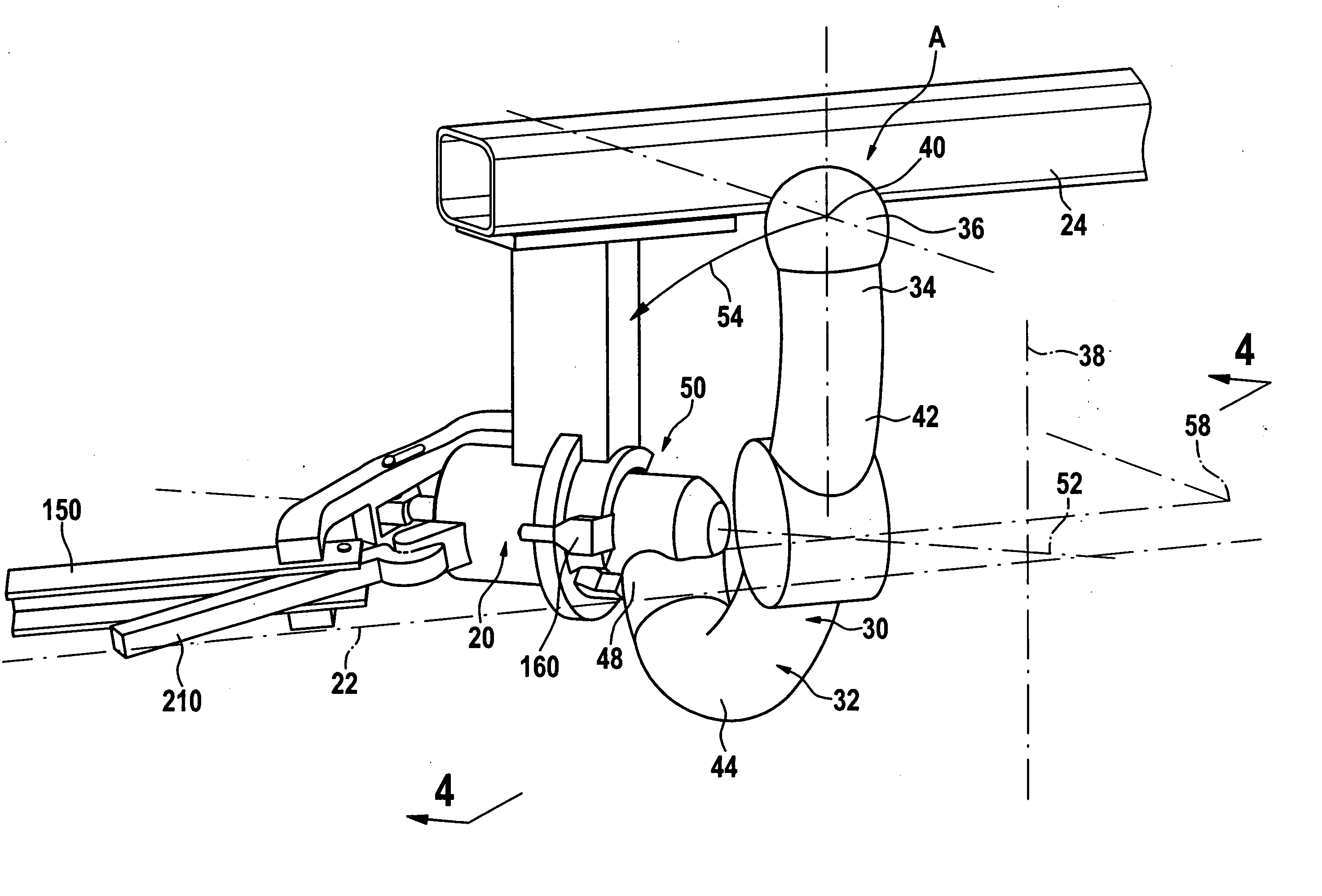

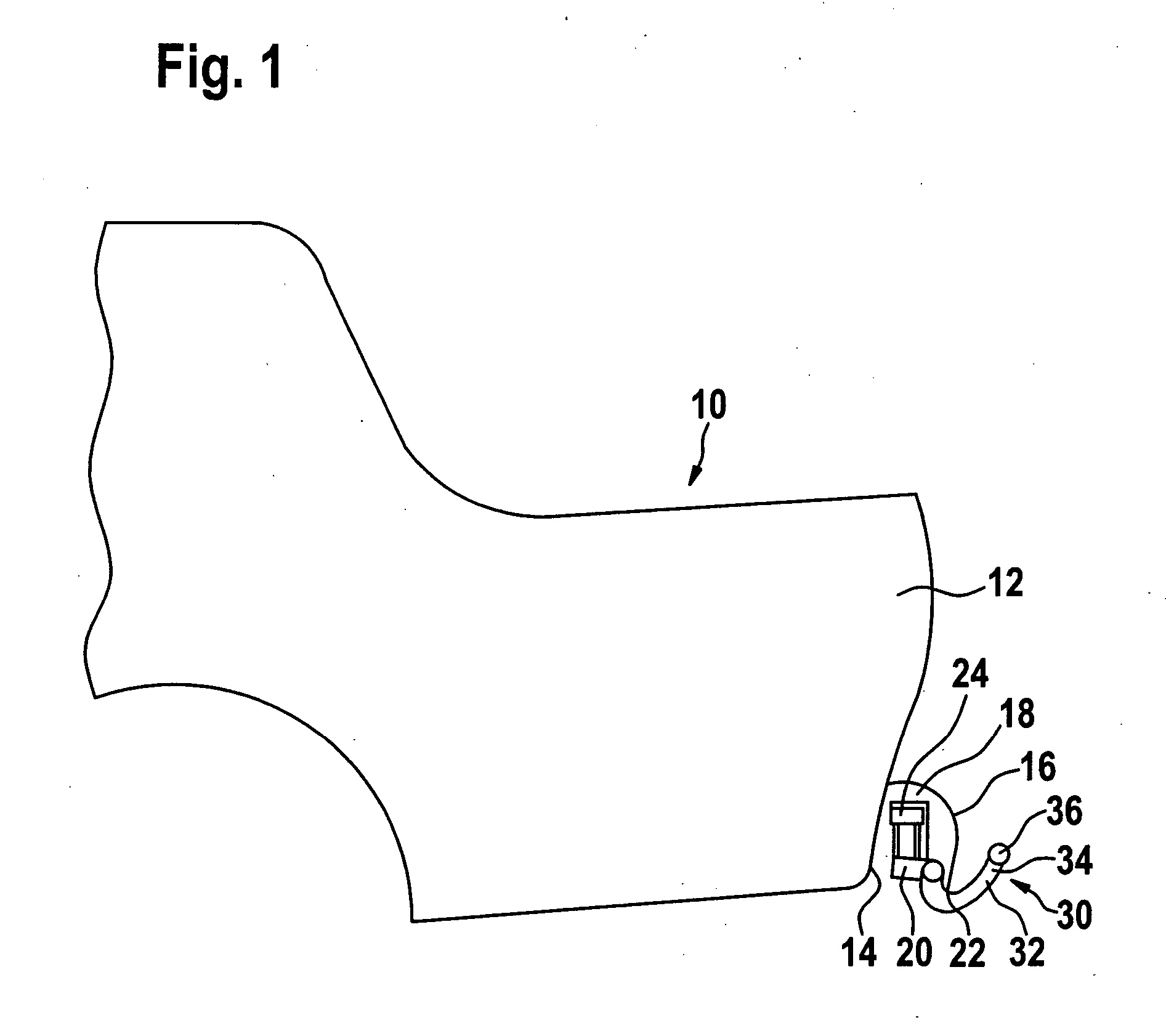

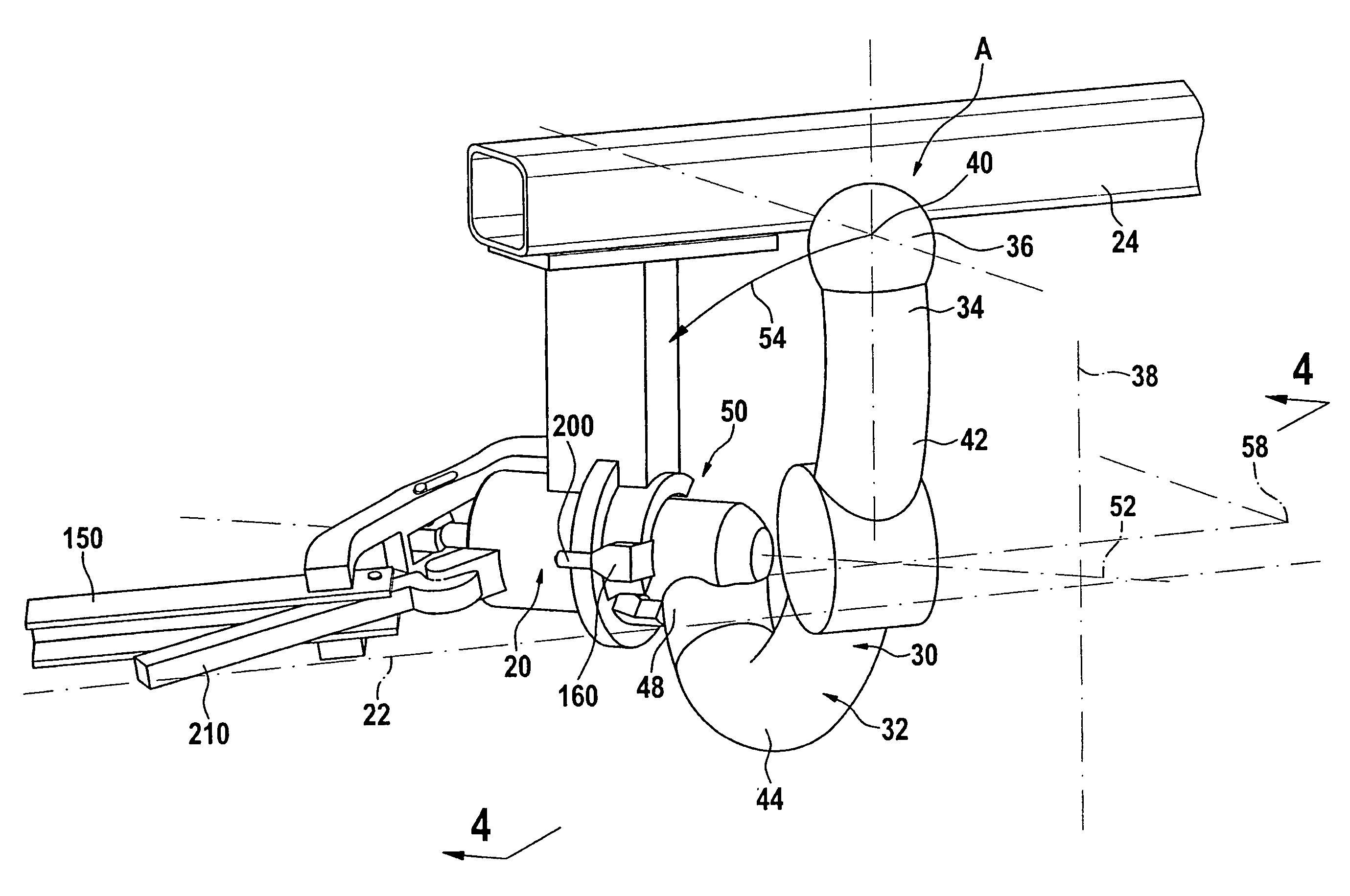

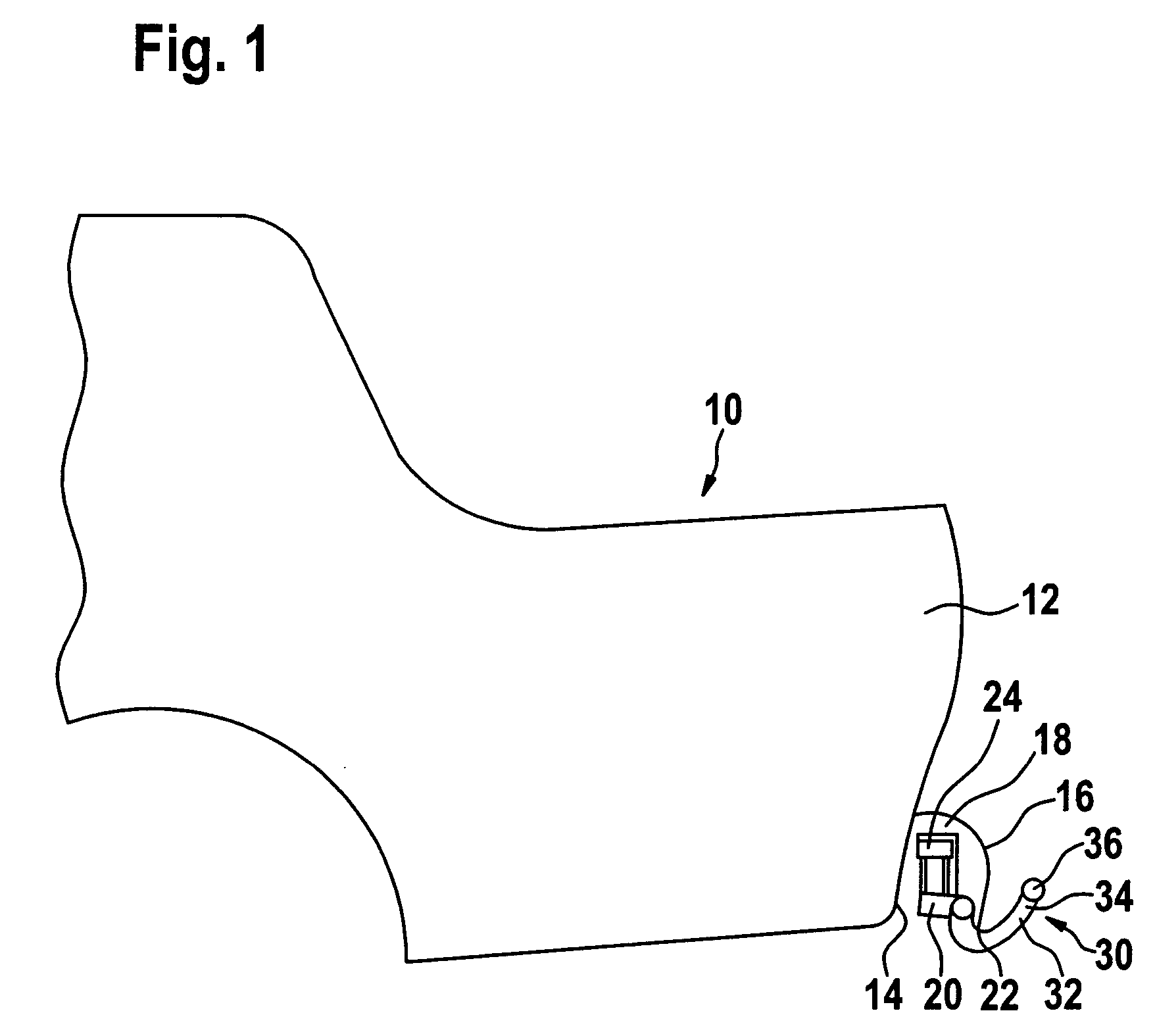

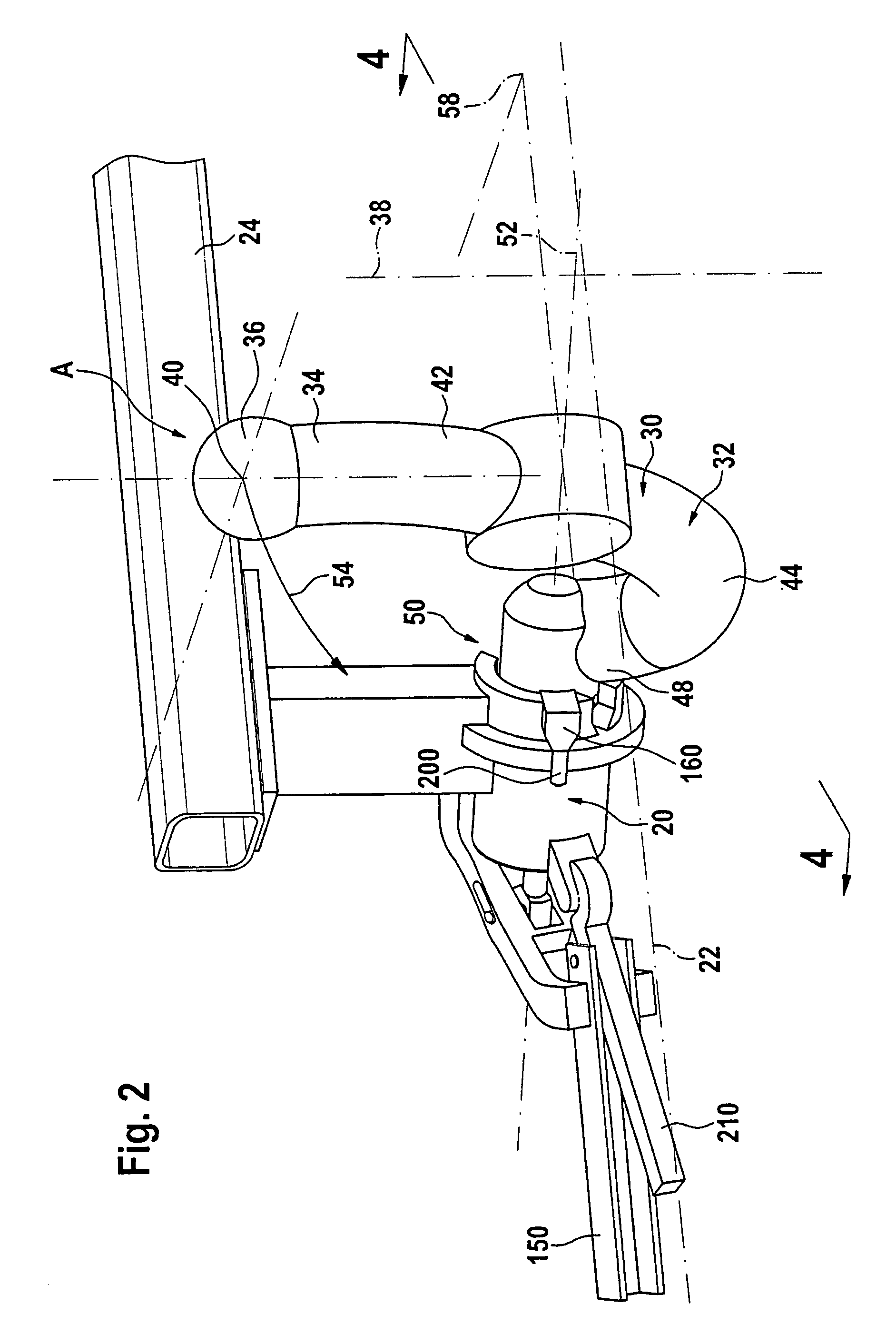

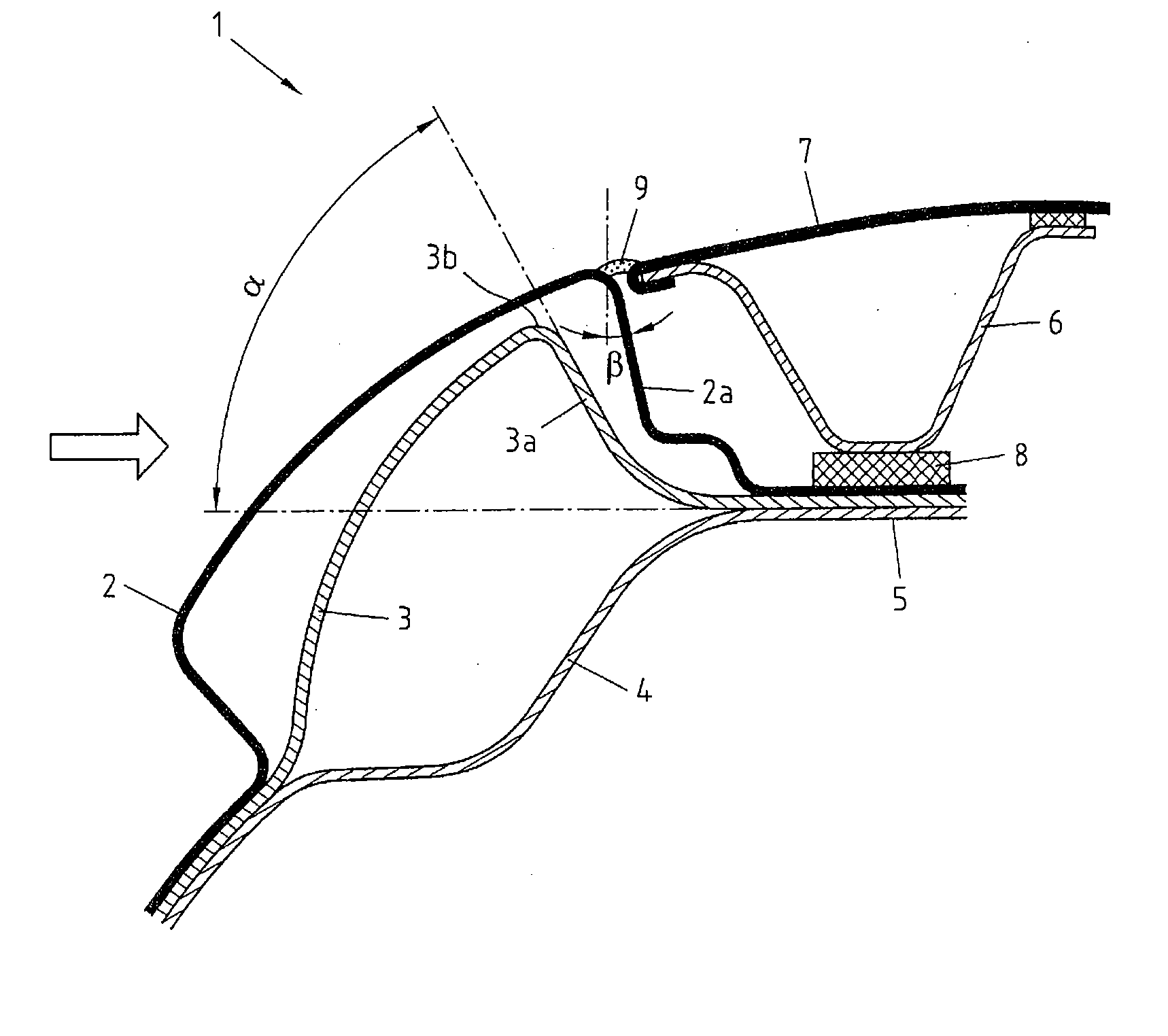

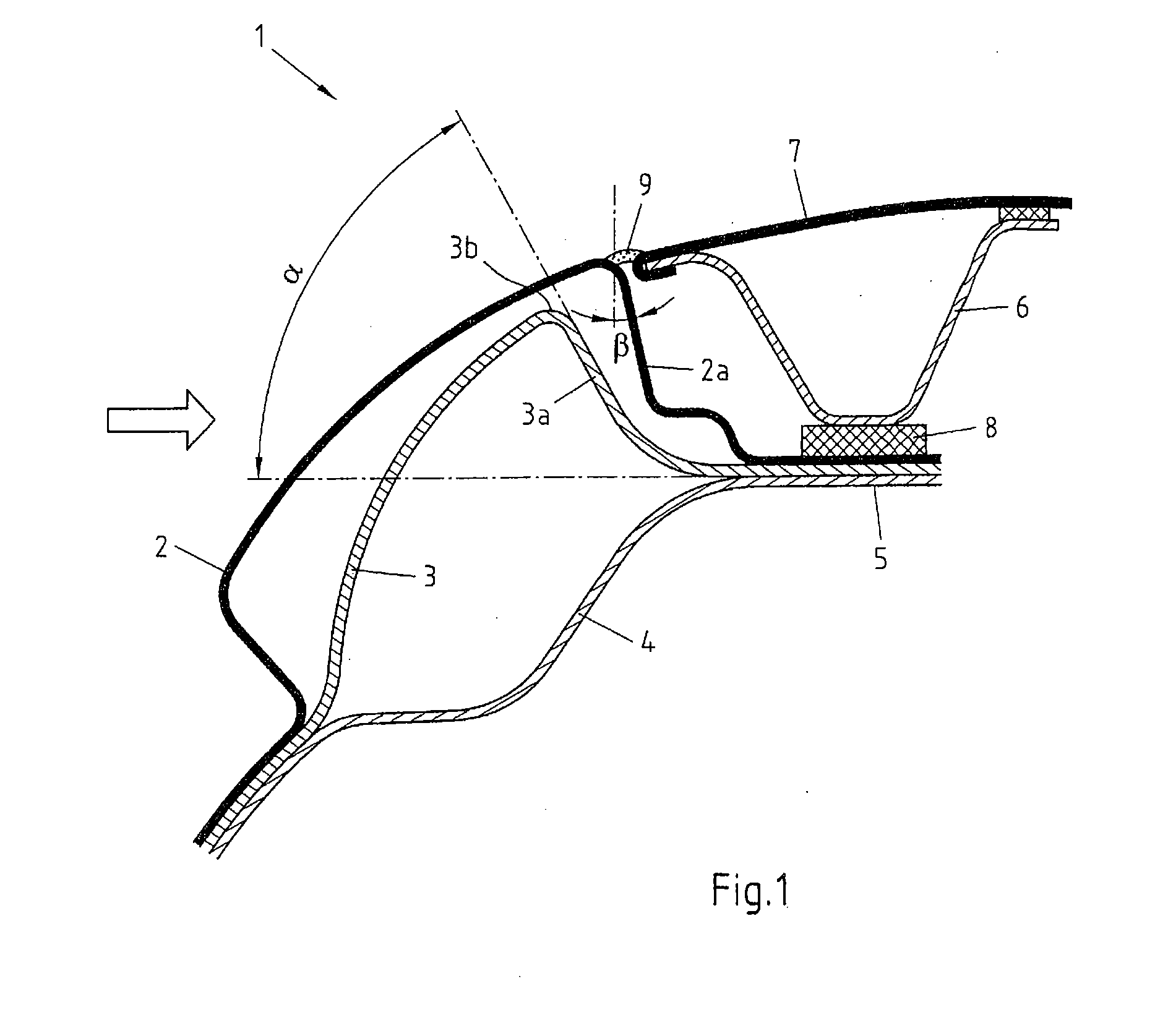

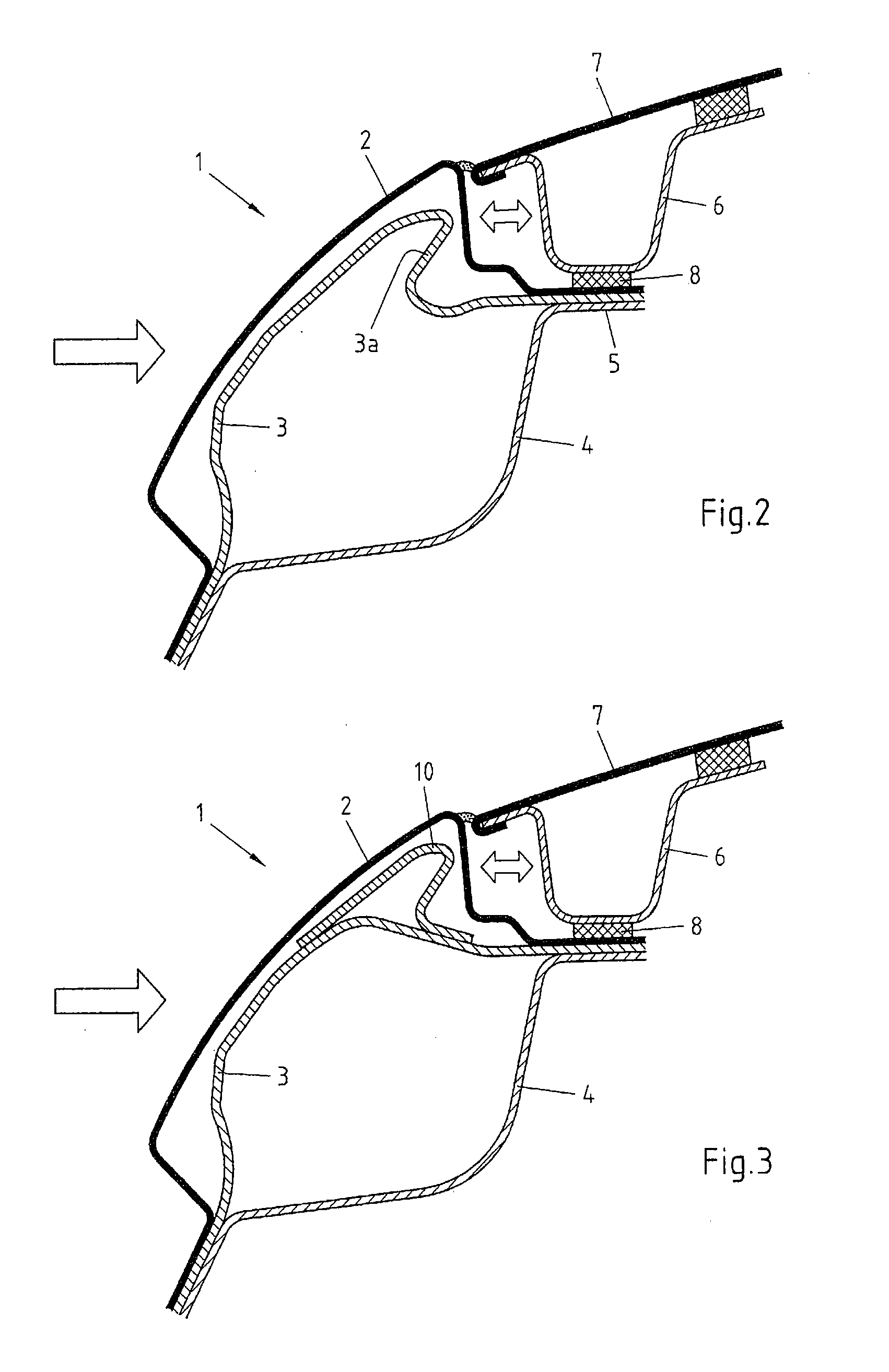

Trailer coupling

ActiveUS20050167945A1Sufficient operationSimple possibilityCamerasTowing devicesMobile vehicleRest position

In order to provide a trailer coupling for motor vehicles comprising a bearing element, a towing element which can be pivoted in relation to the bearing element between an operative position and a rest position and displaced in the direction of the pivot axis between a pivoting position and a fixing position and a fixing device, with which the towing element can be fixed in position on the bearing element, with a simplified fixing of the towing element on the bearing element it is suggested that the towing element have a bearing member, that the bearing element have a receiving member, in which the bearing member engages at least in the fixing position and in relation to which the bearing member can be moved between the pivoting position and the fixing position in a direction of displacement and vice versa, and that the fixing device have a blocking device which blocks the bearing member with respect to any movement in the direction of displacement relative to the receiving member and has at least one blocking member arranged in one of the elements and movable from a release position in the direction of a blocking position acted upon by a force and at least one blocking surface which is arranged on the other one of the elements and behind which the blocking member engages in the blocking position.

Owner:ACPS AUTOMOTIVE GMBH

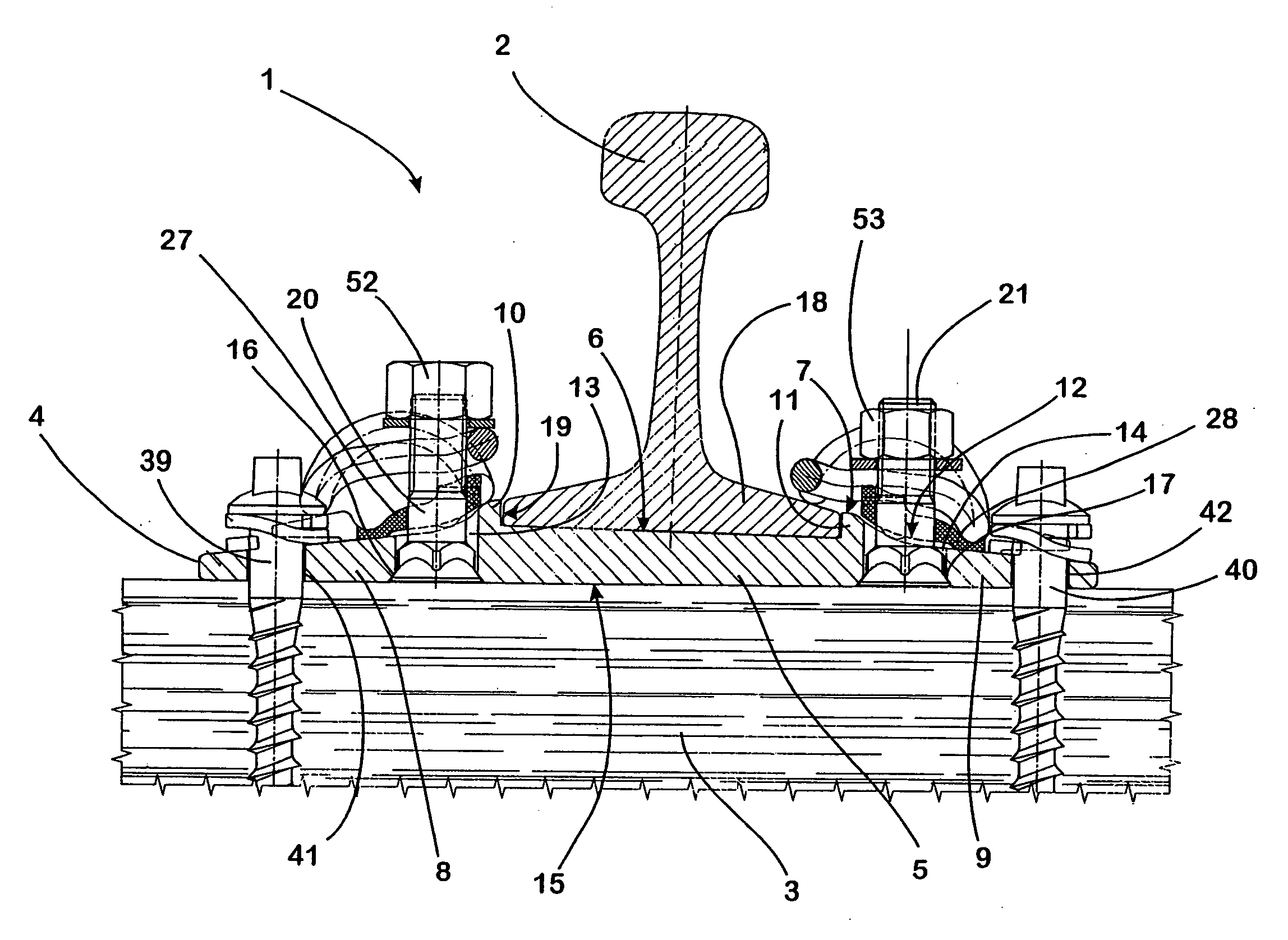

System for fastening a rail

ActiveUS20090084864A1Beneficial production costSimple assemblyRail fastenersTrack superstructureEngineeringMechanical engineering

Owner:VOSSLOH WERKE GMBH

Element attachable by riveting to a sheet metal part and also a component assembly and a method for the production of the component assembly

An element attachable to a sheet metal part by riveting, in particular an element in the form of a centering bolt, having a shaft part and a head part, wherein the head part has at its side confronting the sheet metal part an at least approximately ring-like ring recess which merges at the radially inner side into a cylinder section of the head part which in turn merges into the shaft part and into a tubular rivet section which surrounds the shaft part in the region of the head part, is disposed within a ring-like contact surface arranged radially outside of the ring recess and merges at the radially outer side via an at least approximately conical wall into the ring-like contact surface, is characterized in that at least one local recess and preferably a plurality of in particular uniformly distributed local recesses is or are provided in the conical wall of the ring recess and / or in an optionally present ring-like base surface of the ring recess. A component assembly comprising the element and a sheet metal part and also a method for the manufacture of such a component assembly are also described.

Owner:HVB BANQUE LUXEMBOURG

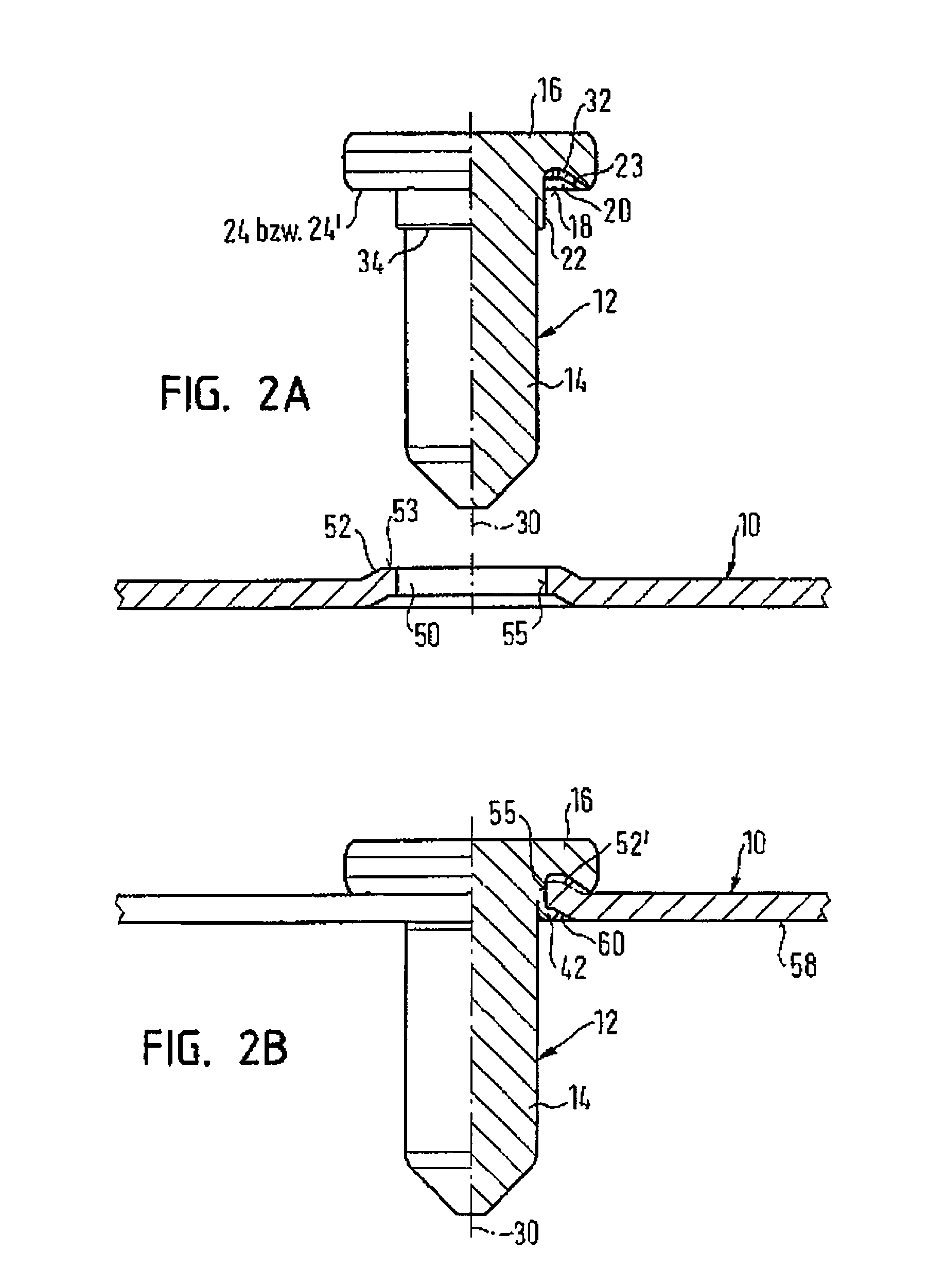

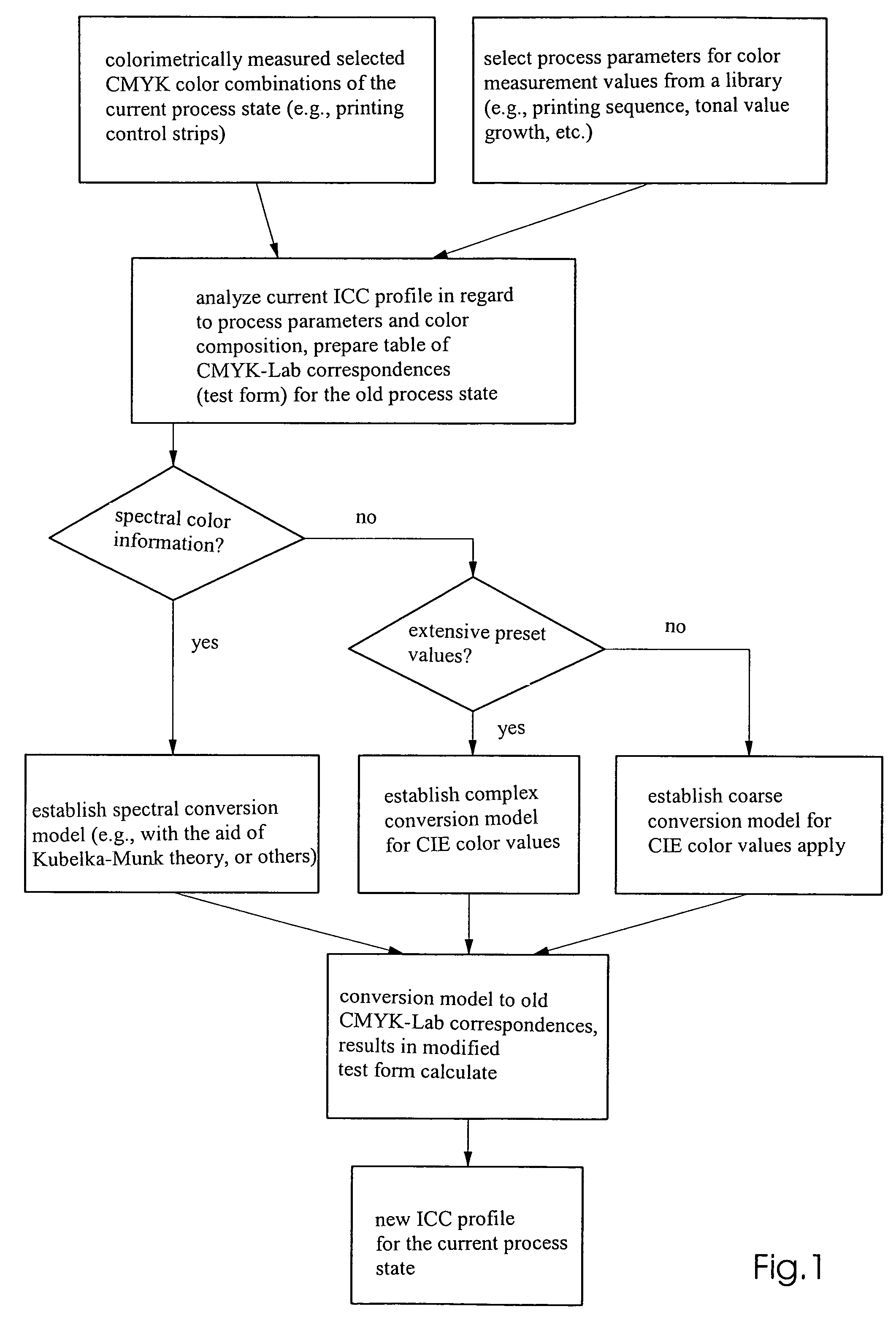

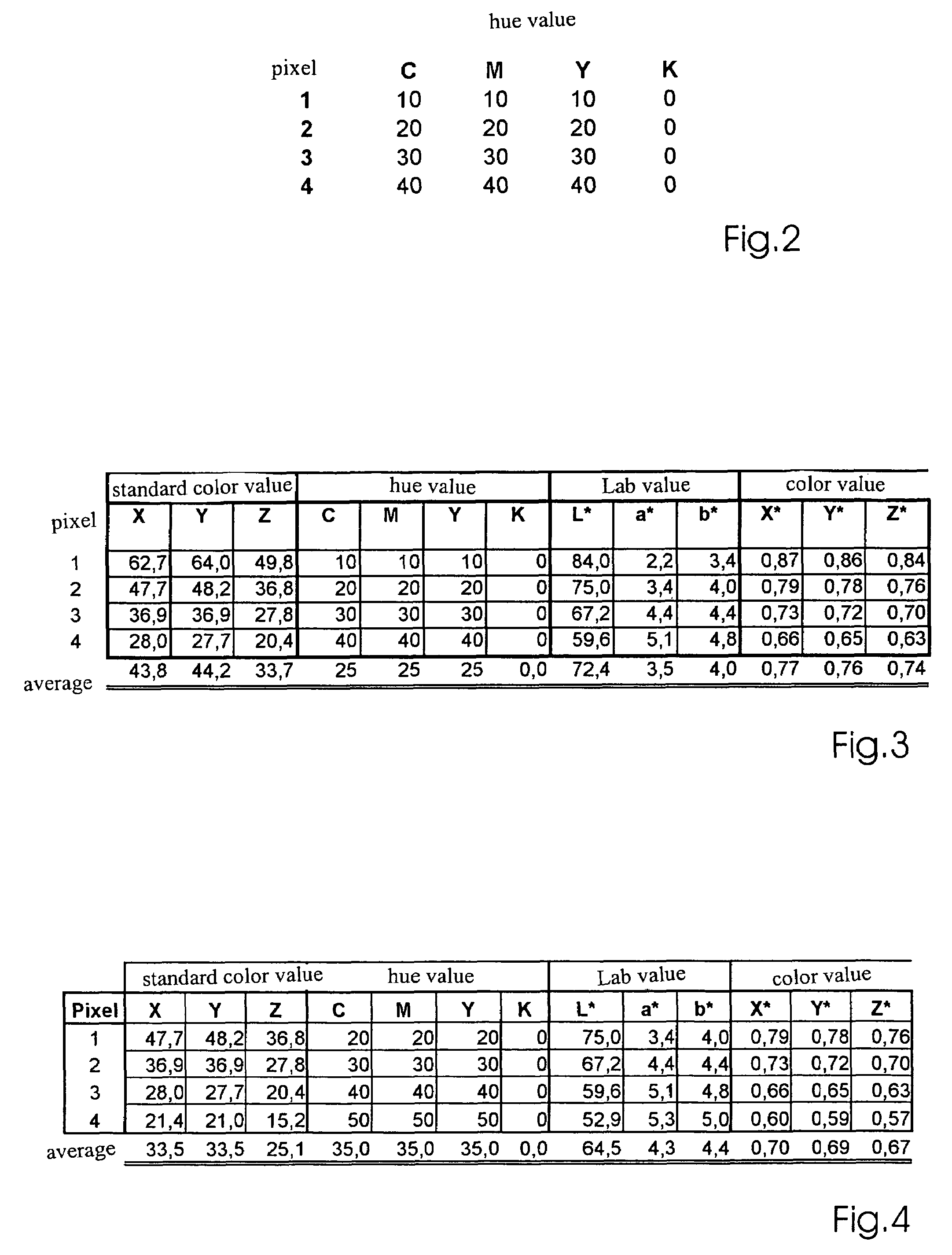

Method for correcting unadjusted printing data on the basis of colormetrically measured reference sheet

InactiveUS7307755B2Avoid unnecessary wasteGuaranteed predictive effectDigitally marking record carriersDigital computer detailsTolerance limitPrinting press

A method for correcting digitized image data in the prepress stage when using printing presses having a device-independent color profile in the main printing stage, having the following method steps:colorimetric measurement of a reference sheet and production of an image file in a device-independent color space,conversion of an image file belonging to the reference sheet in a device-dependent color space into a further image file in a device-independent color space using the device-independent color profile belonging to the printing press to be used,comparison of the two device-independent image files.performing alterations on the device-dependent image file associated with the reference sheet or alteration of the printing process in the selected printing press if tolerance limits are exceeded.

Owner:HEIDELBERGER DRUCKMASCHINEN AG

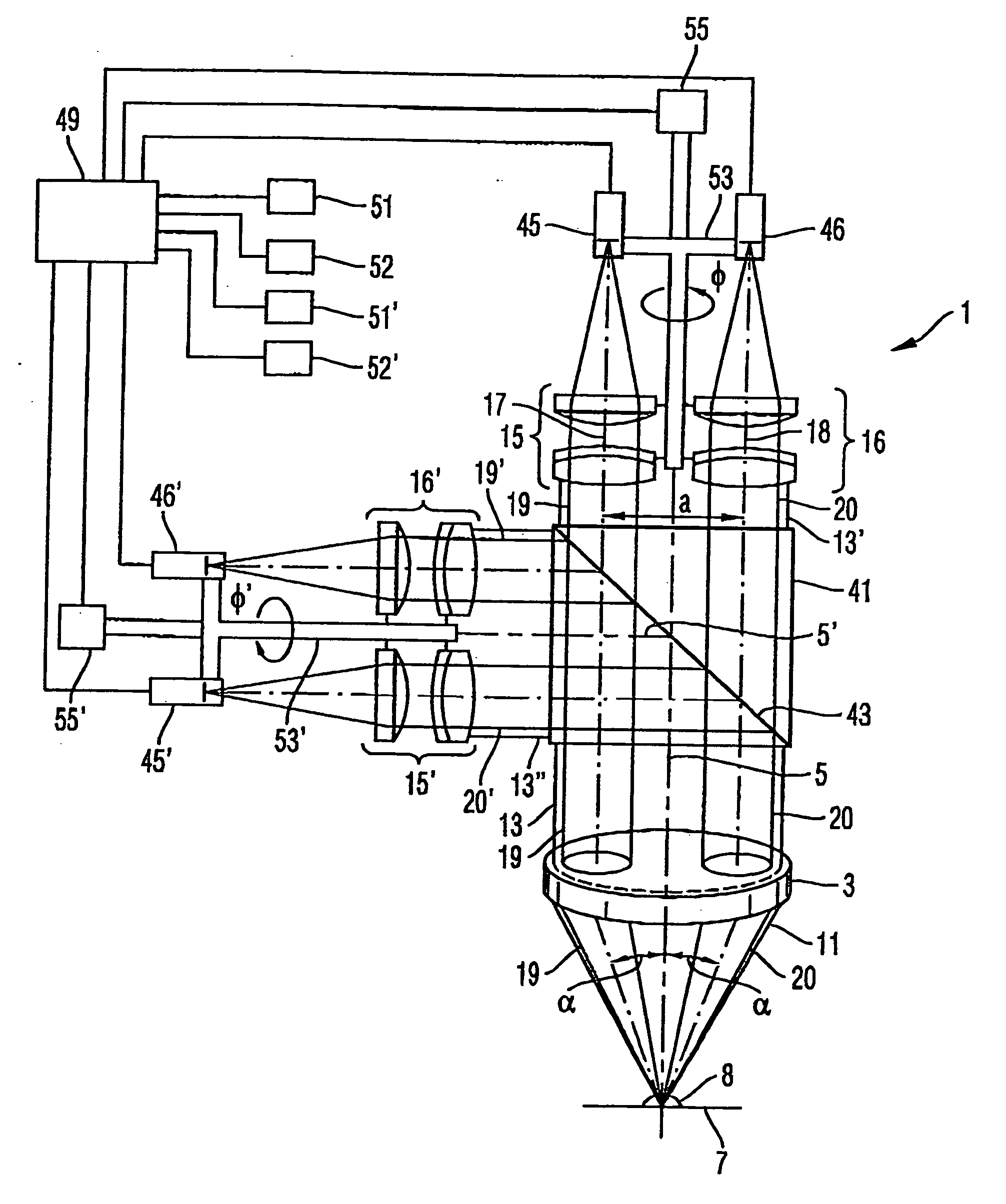

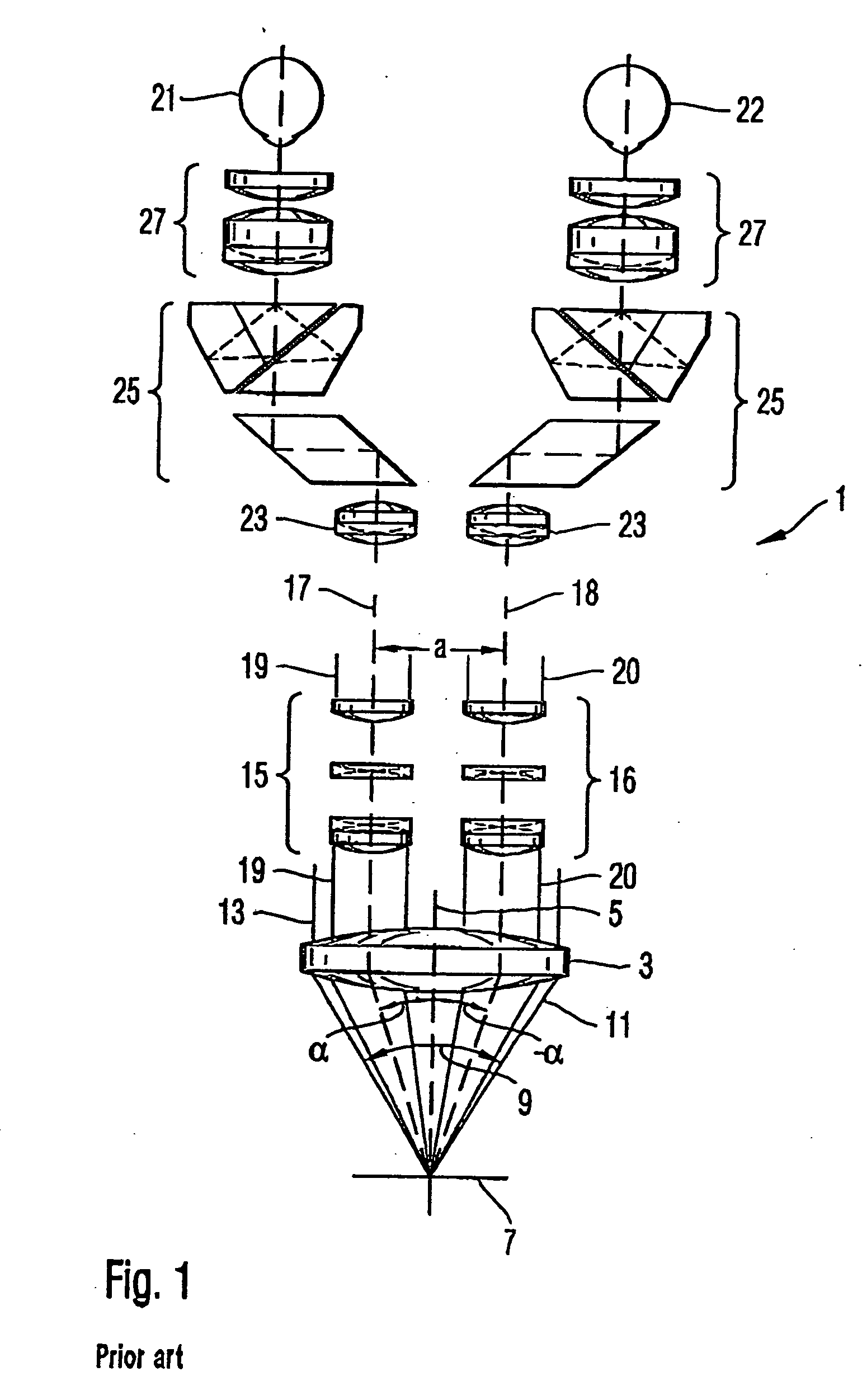

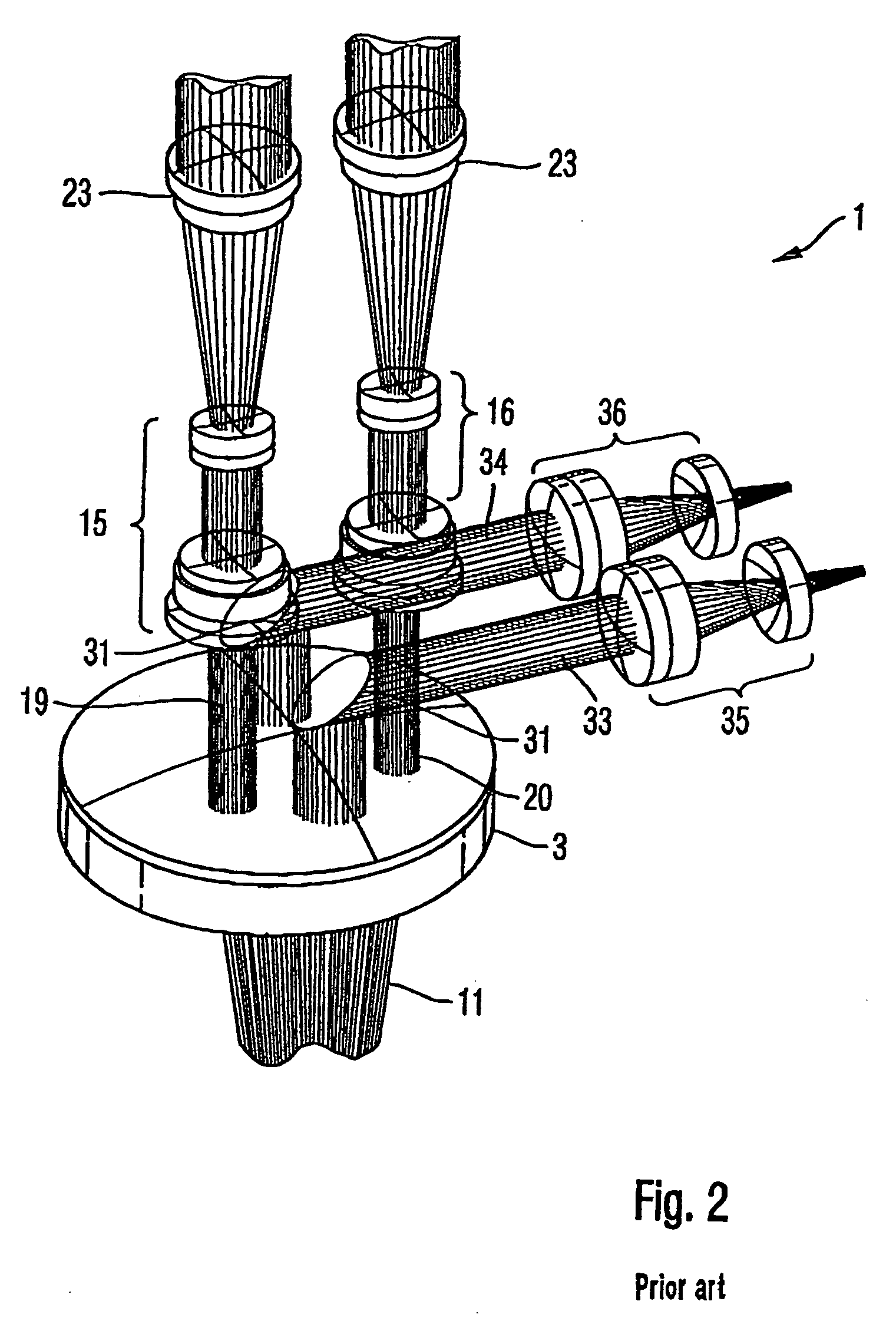

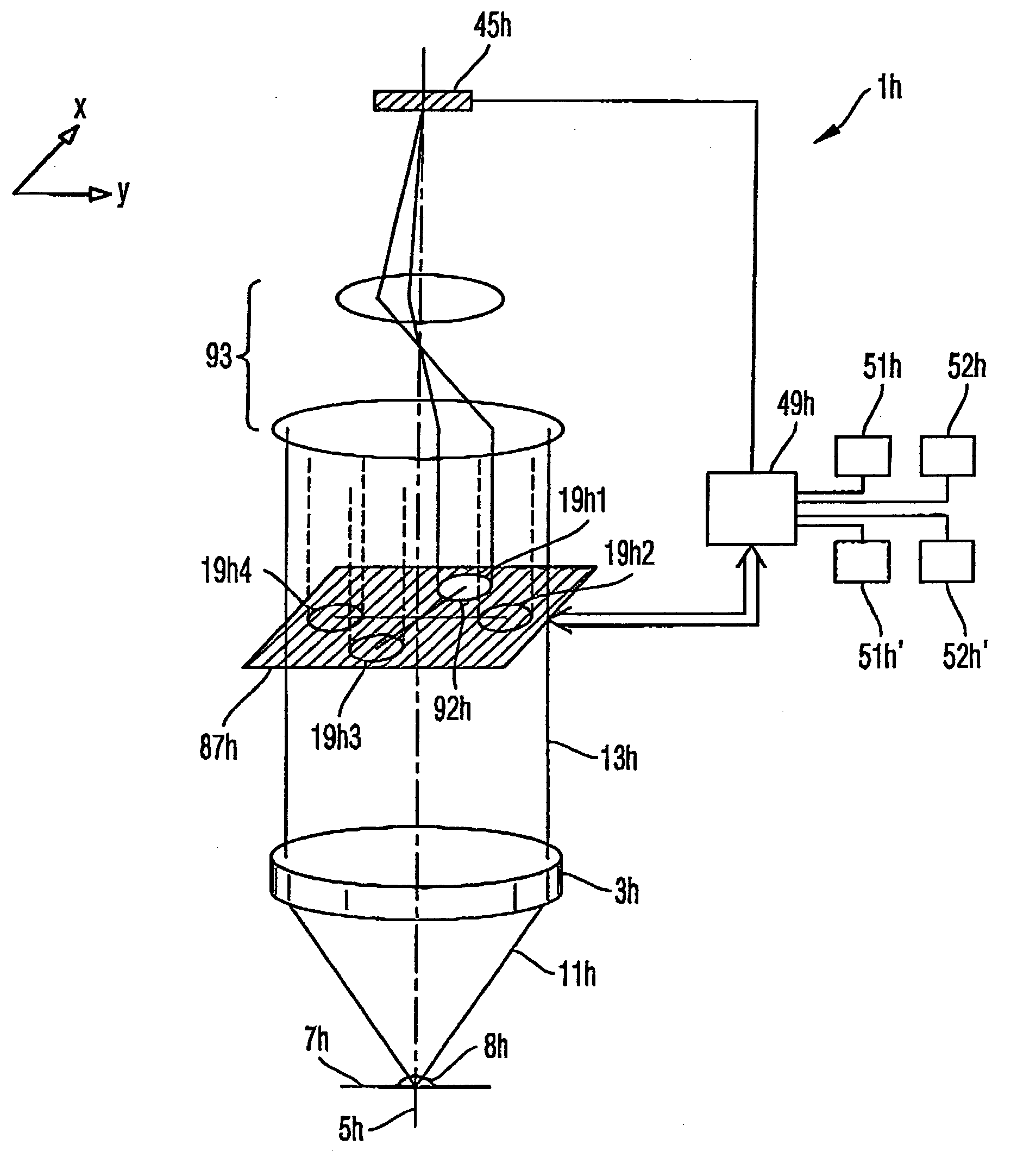

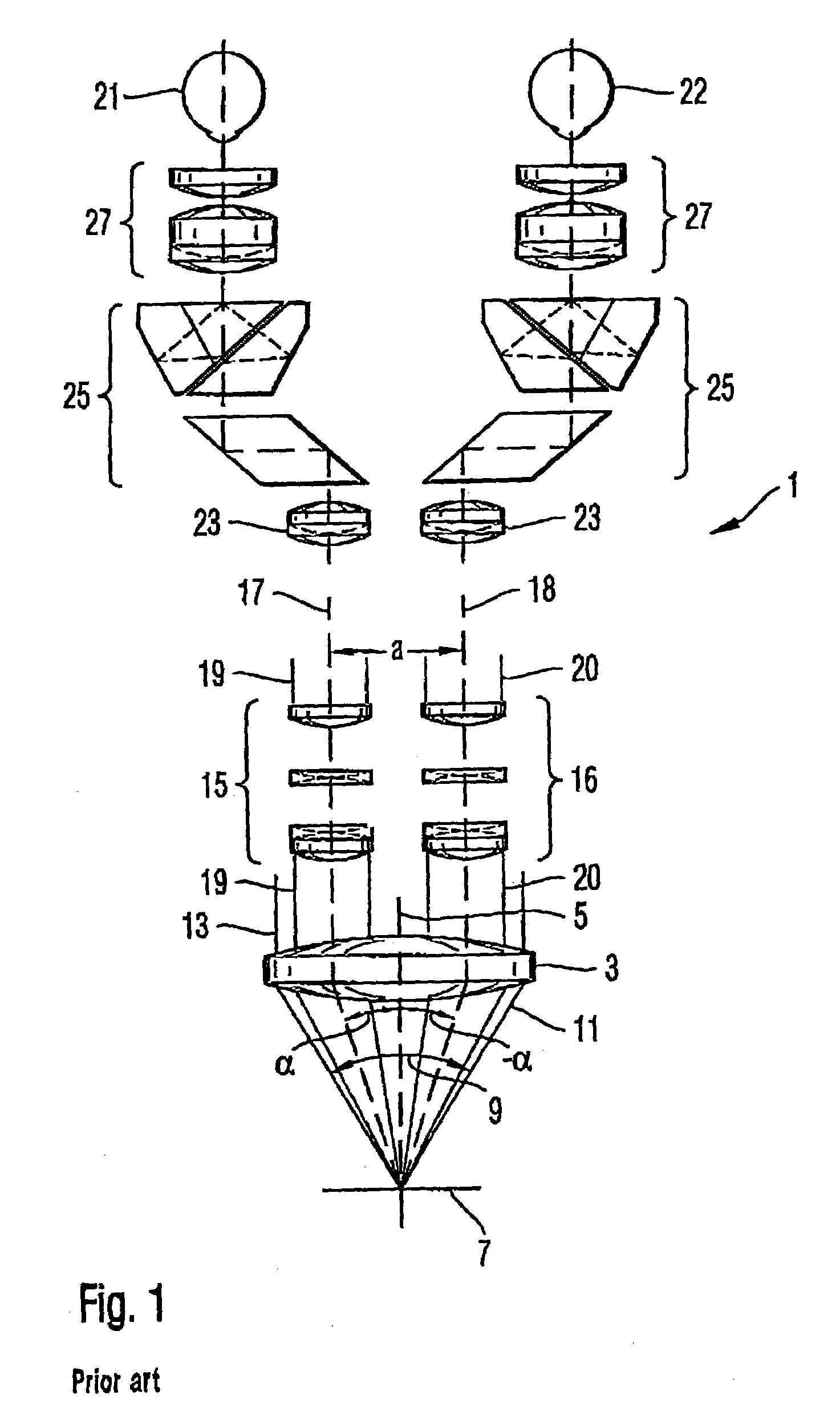

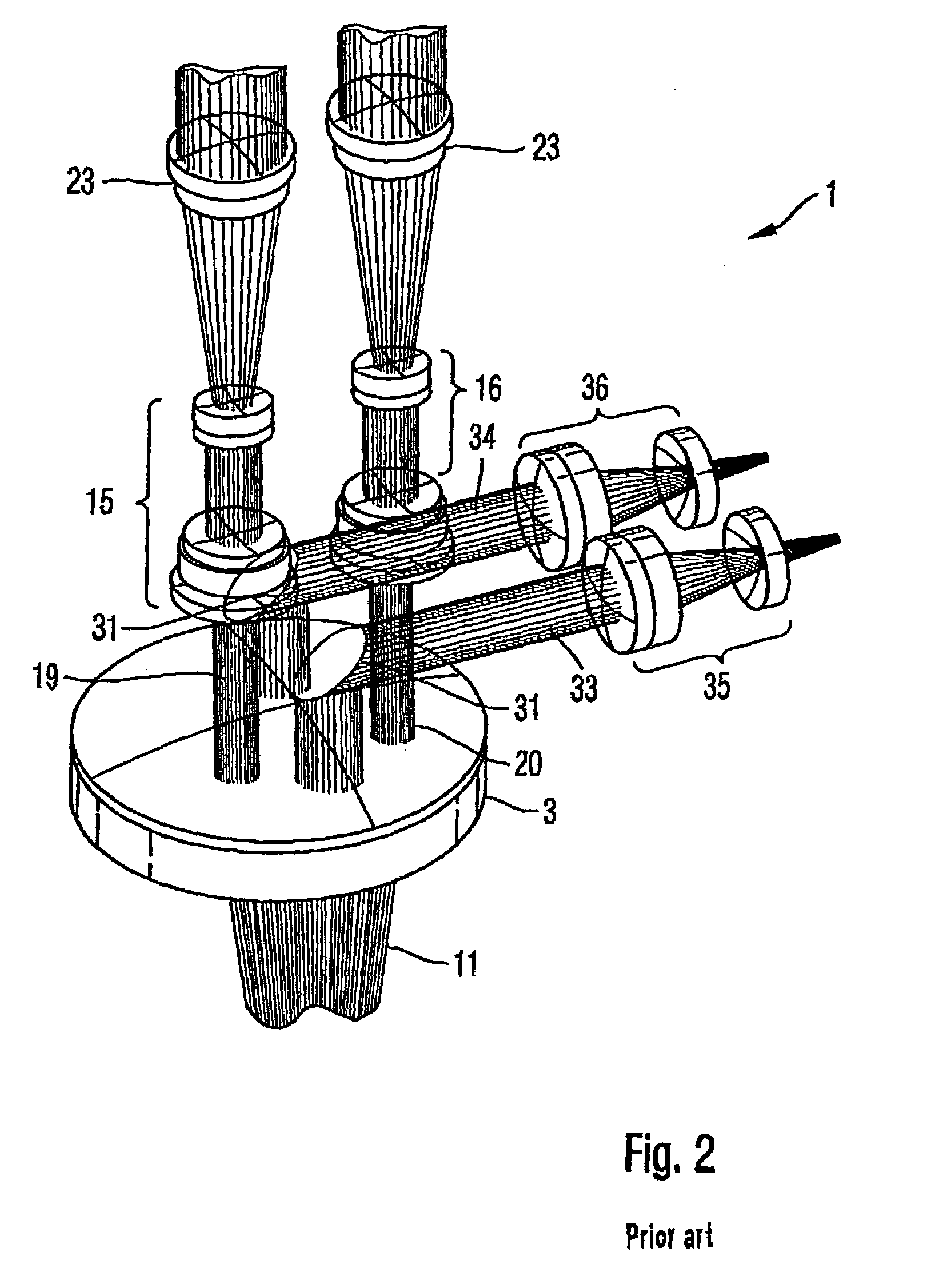

Stereo-examination systems and stereo-image generation apparatus as well as a method for operating the same

InactiveUS20070127115A1Easy to separateSimple possibilityUsing optical meansMicroscopesOptical axisLight beam

A stereo-examination system for imaging an object 8 is proposed, comprising an objective arrangement 3 having an optical axis 5 and an object plane 7 for positioning the object 8 to be imaged, wherein the objective arrangement 3 receives an object-side beam bundle 11 emanating from the object plane 7 into a solid angle region 9 and converts the same into an image-side beam bundle 13, a selection arrangement for selecting at least a pair of partial beam bundles 19, 20 from the image-side beam bundle 13, and an image transmission apparatus 51, 52 for generating a representation of images of the object 8 provided by the partial beam bundles 19, 20. The stereo-examination system is distinguished in that the selection arrangement is provided for displacing a beam cross-section of at least one of the two partial beam bundles 19, 20 relative to a beam cross-section of the image-side beam bundle 13, a controller 49 being provided for controlling the selection arrangement to displace the beam cross-section of the at least one partial beam bundle 19, 20 in circumferential direction about the optical axis 5.

Owner:CARL ZEISS SURGICAL

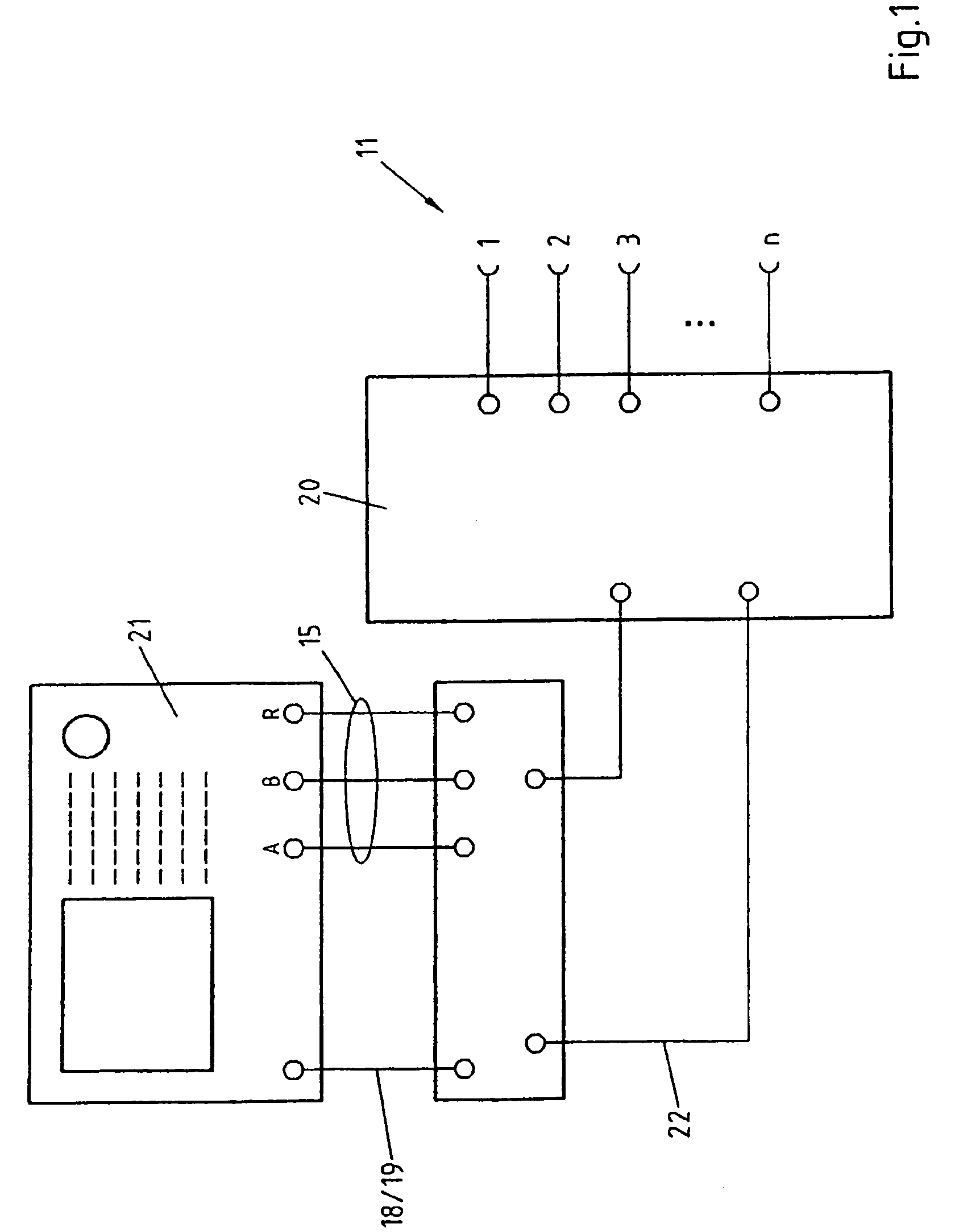

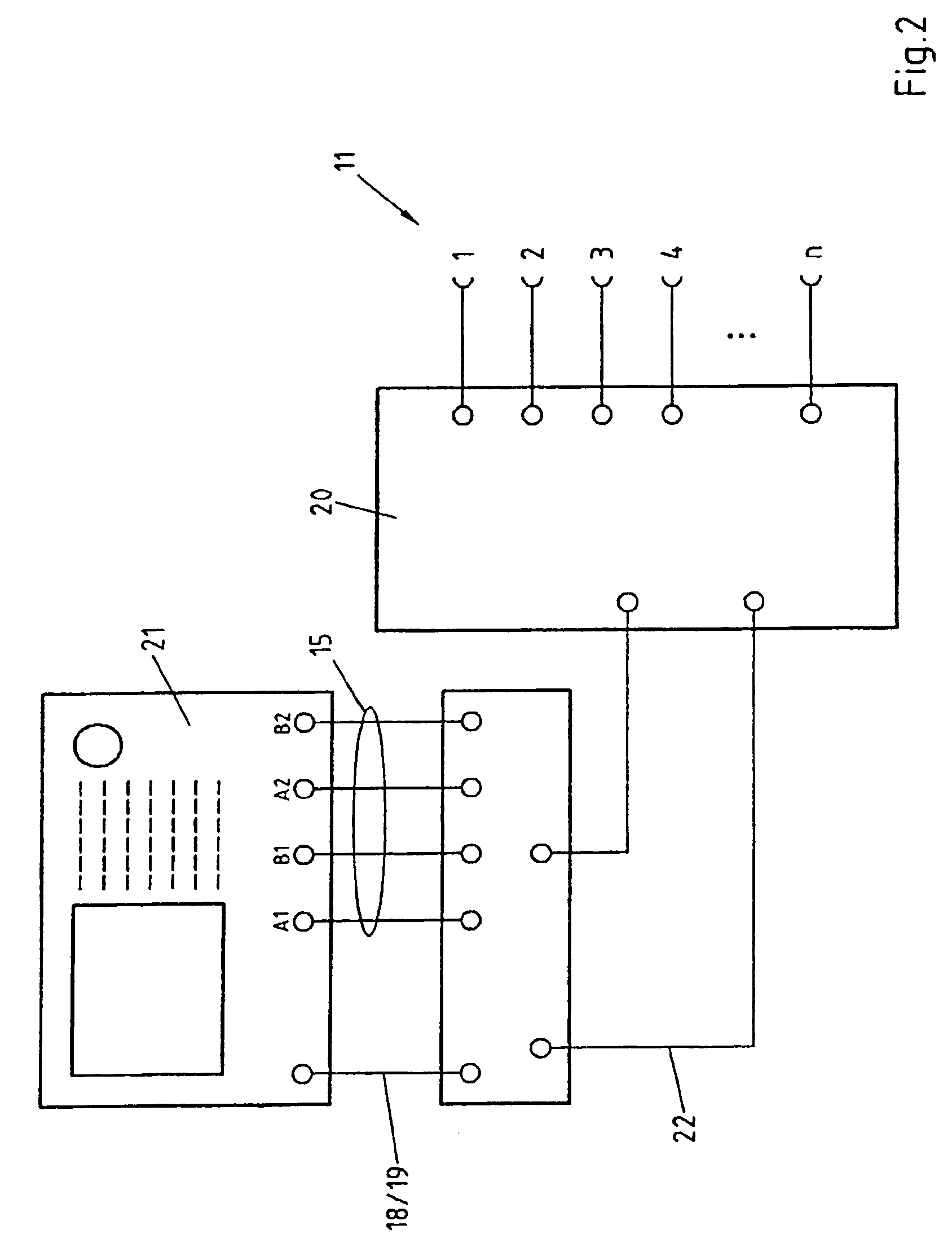

Method for correcting errors by de-embedding dispersion parameters network analyst and switching module

InactiveUS7075312B2Quick conversionLoss of timeElectronic circuit testingError detection/correctionComputer moduleFast methods

The invention relates to a method for correcting errors by de-embedding scattering parameters of a device under test associated with measuring ports (11), the parameters being measured by a vector network analyzer including n measuring ports. The aim of the invention is to create a universal, precise and fast method of correcting errors of scattering parameters. To this end, the method includes the following steps: formula (1) two-port calibrations are carried out on different calibrating standards in any order in the active state between the measuring ports (11), as a basis for a first error correction; the reflection parameters of at least one part of the n measuring ports (11) are determined in the inactive state, by way of the results of two-port measurements carried out on at least one calibrating standard switched in the active and / or inactive state on measuring ports (11), as a basis for a second error correction. The invention also relates to a network analyzer and to a switching module for a network analyzer.

Owner:ROHDE & SCHWARZ GMBH & CO KG

Integrated memory circuit and method for repairing a single bit error

The invention relates to an integrated memory circuit having a memory cell array comprising memory cells arranged on word lines and bit lines, and having a repair circuit for repairing a single bit error in one of the memory cells, the repair circuit comprising: an error memory for storing an item of repair information, an assignment unit in order, when accessing an address of the memory cell array, depending on the repair information, to access either a memory area of the memory cell array or a redundancy memory area, and a test unit for determining the repair information. The test unit comprises a write unit, which successively writes first test data and second test data to a plurality of memory cells of a memory area of the memory cell array, a read-out unit which reads out data stored in the memory area, a modification unit in order to modify the bits of the read-out data in such a way that the position of each bit changes and each of the bits is inverted in order to provide the second test data, which are subsequently written to the memory area with the aid of the write unit, and a comparator unit in order to compare the data read out after the writing of the second test data with expected data and to provide the repair information depending on the comparison result.

Owner:POLARIS INNOVATIONS

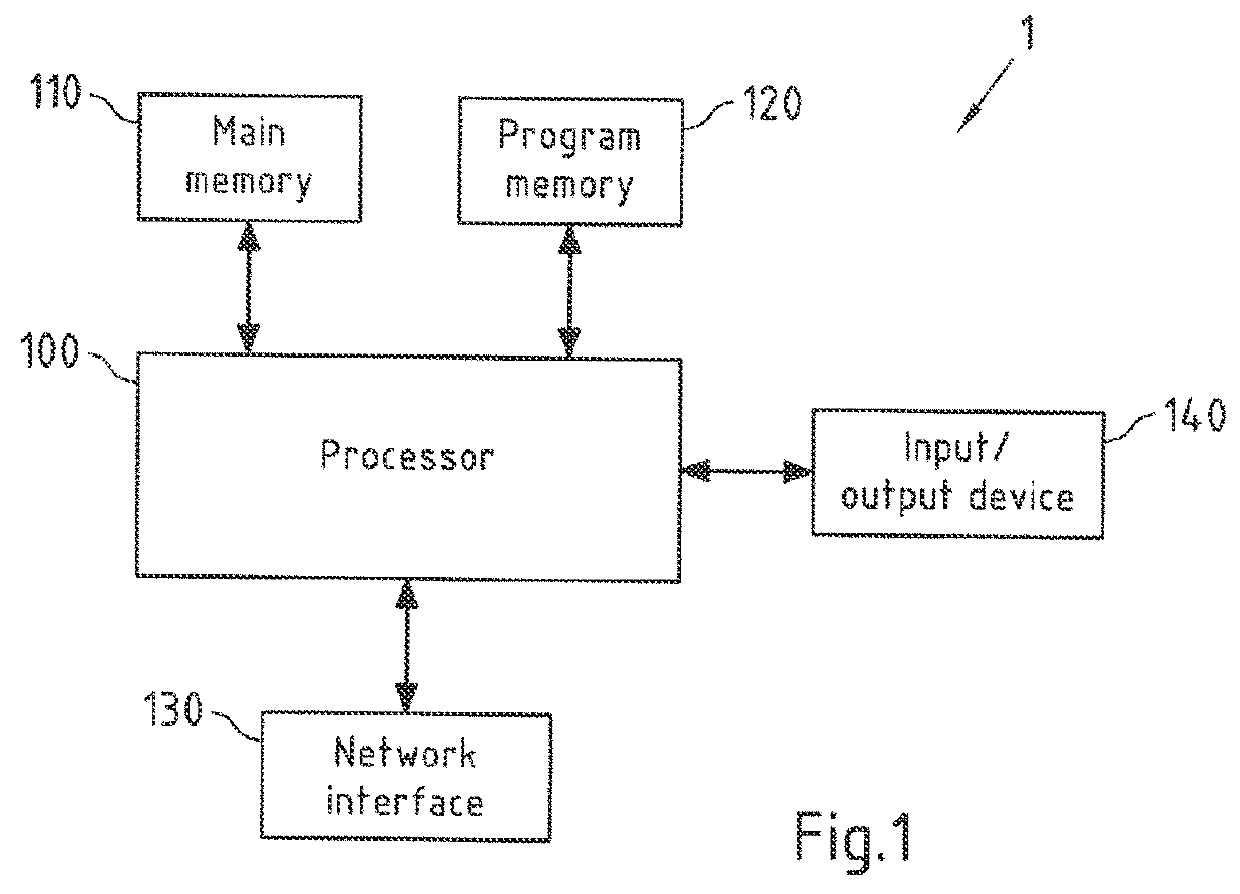

Control device for a motor vehicle and communication method therefor

InactiveUS20060178804A1Simple and cost-effectiveSimple possibilityAnalogue computers for vehiclesElectrical controlEngine control unitMotorized vehicle

A motor vehicle control unit, in particular an engine control unit, includes a processor, a first interface for the communication with functional units of the motor vehicle and at least one second interface, which is combined with the processor in a sub-assembly.

Owner:ROBERT BOSCH GMBH

Stereo-examination systems and stereo-image generation apparatus as well as a method for operating the same

InactiveUS7180660B2Easy to separateSimple possibilityUsing optical meansMicroscopesOptical axisLight beam

A stereo-examination system for imaging an object 8 is proposed, comprising an objective arrangement 3 having an optical axis 5 and an object plane 7 for positioning the object 8 to be imaged, wherein the objective arrangement 3 receives an object-side beam bundle 11 emanating from the object plane 7 into a solid angle region 9 and converts the same into an image-side beam bundle 13, a selection arrangement for selecting at least a pair of partial beam bundles 19, 20 from the image-side beam bundle 13, and an image transmission apparatus 51, 52 for generating a representation of images of the object 8 provided by the partial beam bundles 19, 20. The stereo-examination system is distinguished in that the selection arrangement is provided for displacing a beam cross-section of at least one of the two partial beam bundles 19, 20 relative to a beam cross-section of the image-side beam bundle 13, a controller 49 being provided for controlling the selection arrangement to displace the beam cross-section of the at least one partial beam bundle 19, 20 in circumferential direction about the optical axis 5.

Owner:CARL ZEISS SURGICAL

Trailer coupling

In order to provide a trailer coupling for motor vehicles comprising a bearing element, a towing element which can be pivoted in relation to the bearing element between an operative position and a rest position and displaced in the direction of the pivot axis between a pivoting position and a fixing position and a fixing device, with which the towing element can be fixed in position on the bearing element, with a simplified fixing of the towing element on the bearing element it is suggested that the towing element have a bearing member, that the bearing element have a receiving member, in which the bearing member engages at least in the fixing position and in relation to which the bearing member can be moved between the pivoting position and the fixing position in a direction of displacement and vice versa, and that the fixing device have a blocking device which blocks the bearing member with respect to any movement in the direction of displacement relative to the receiving member and has at least one blocking member arranged in one of the elements and movable from a release position in the direction of a blocking position acted upon by a force and at least one blocking surface which is arranged on the other one of the elements and behind which the blocking member engages in the blocking position.

Owner:ACPS AUTOMOTIVE GMBH

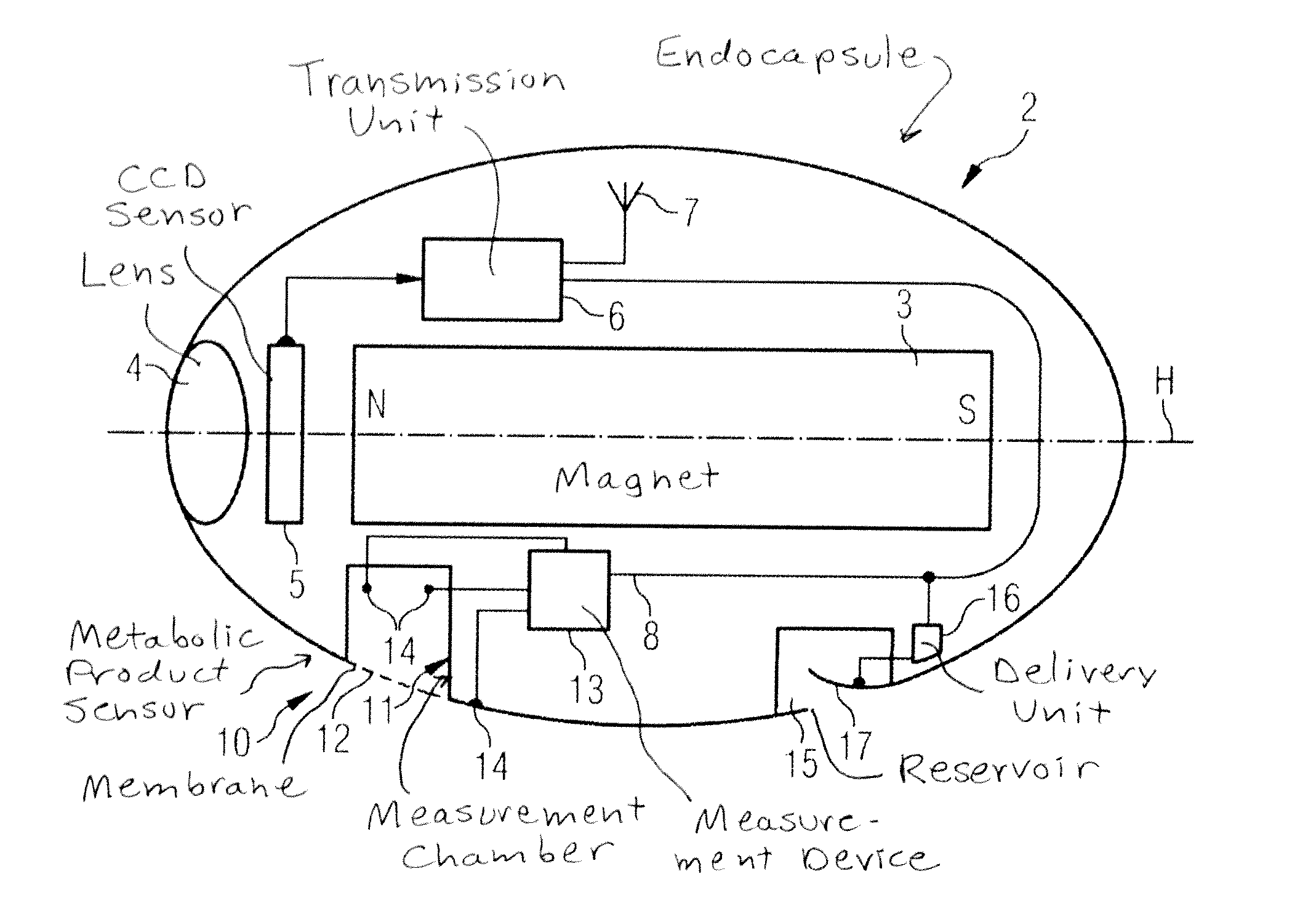

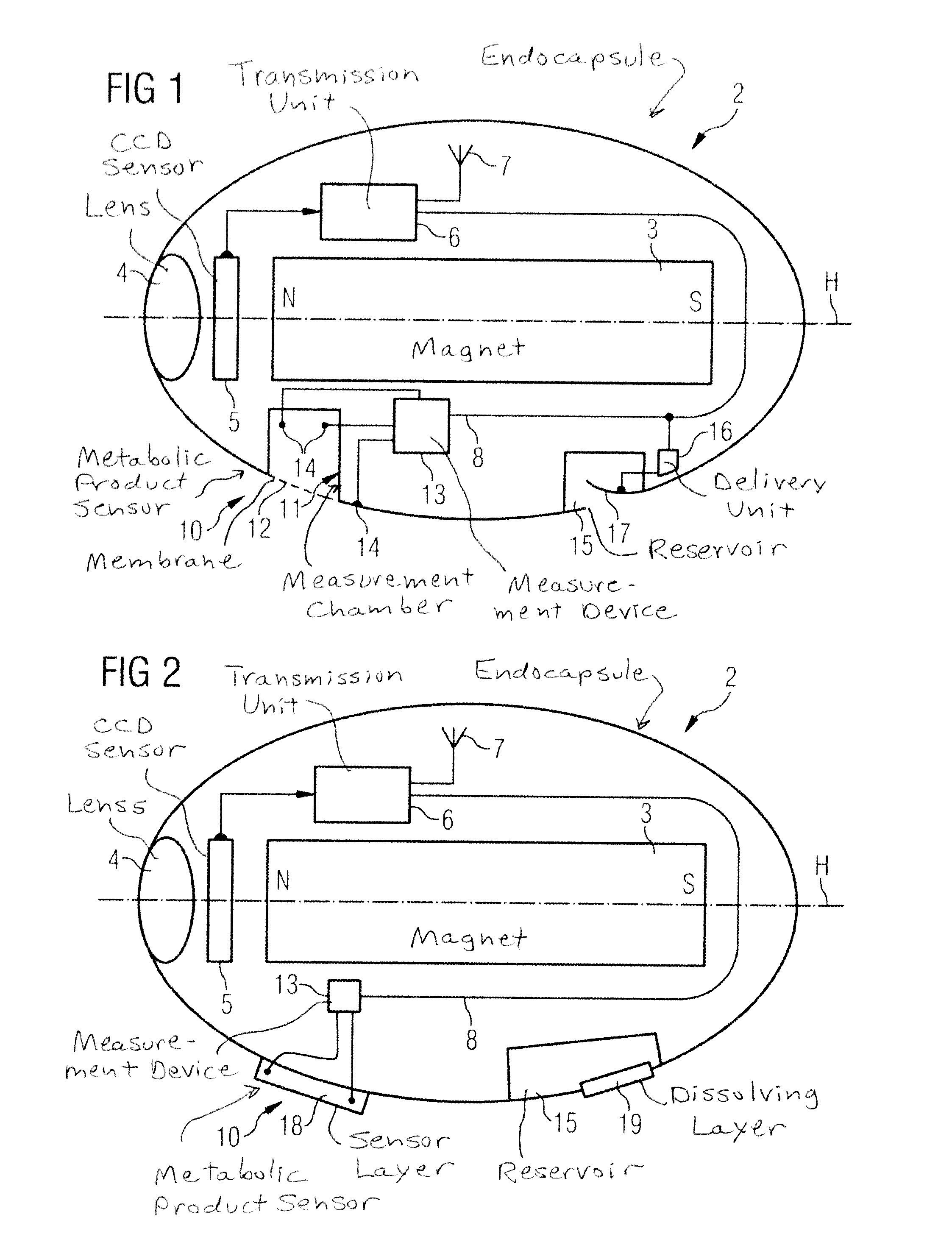

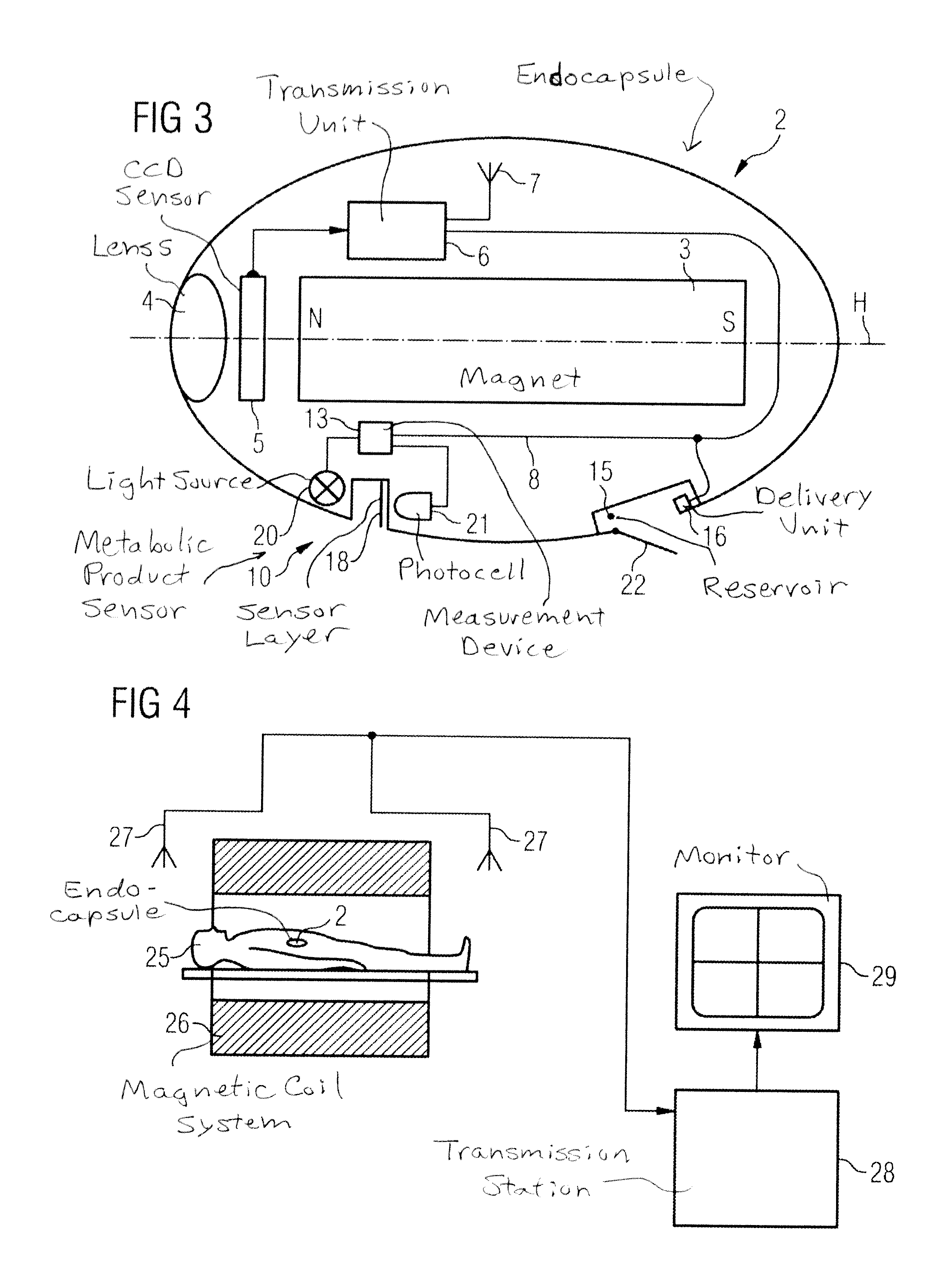

Endocapsule

InactiveUS20110092787A1Simple possibilitySimple and certain detectionEndoscopesEndoradiosondesBiologyGastrointestinal tract

An endocapsule has a measurement chamber therein containing a sensor that detects at least one metabolic product of a specific bacterium in a hollow organ of a human or animal gastrointestinal tract. The endocapsule is introduced into the hollow organ wherein detection of the at least one metabolic product takes place.

Owner:SIEMENS AG

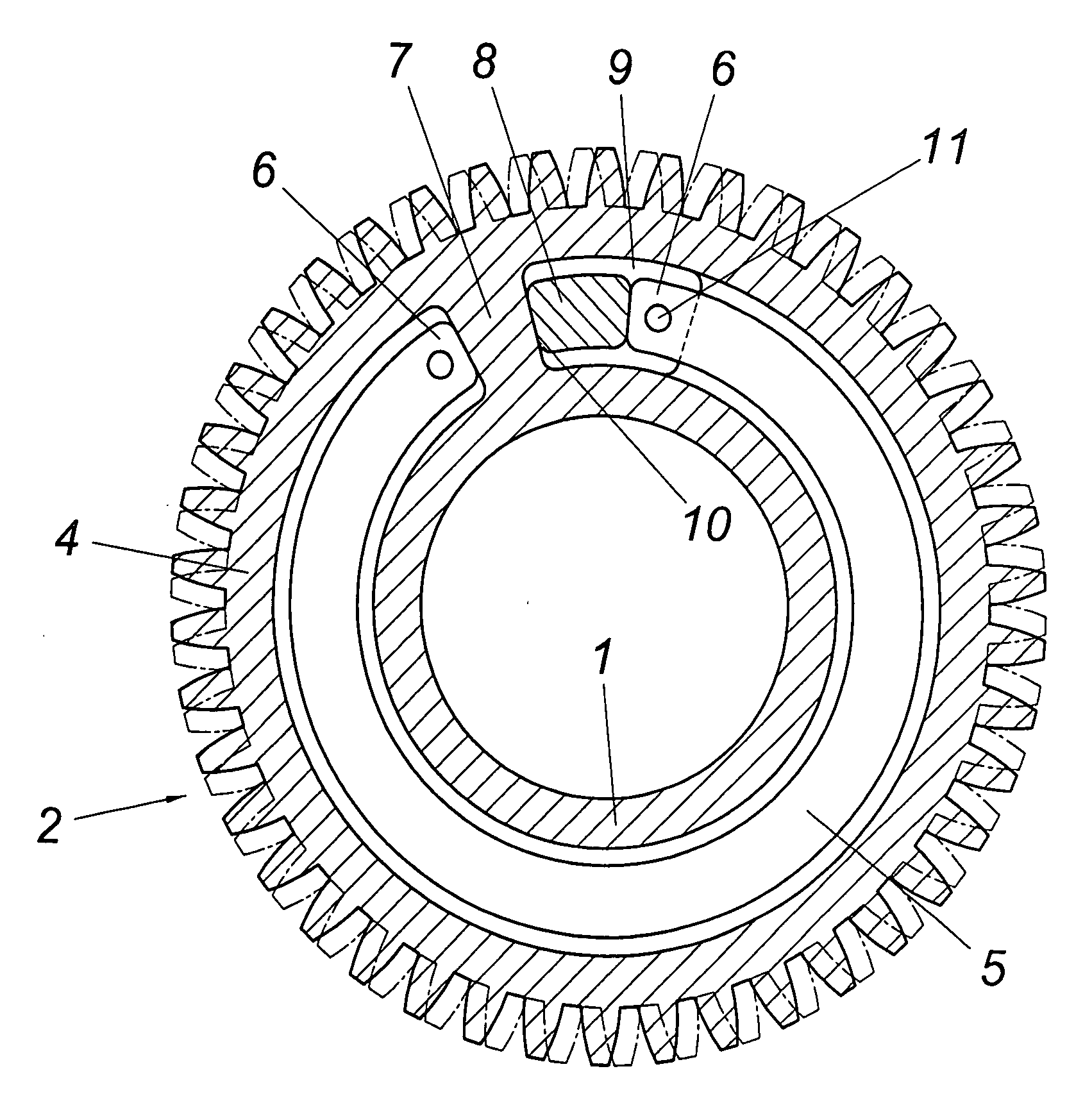

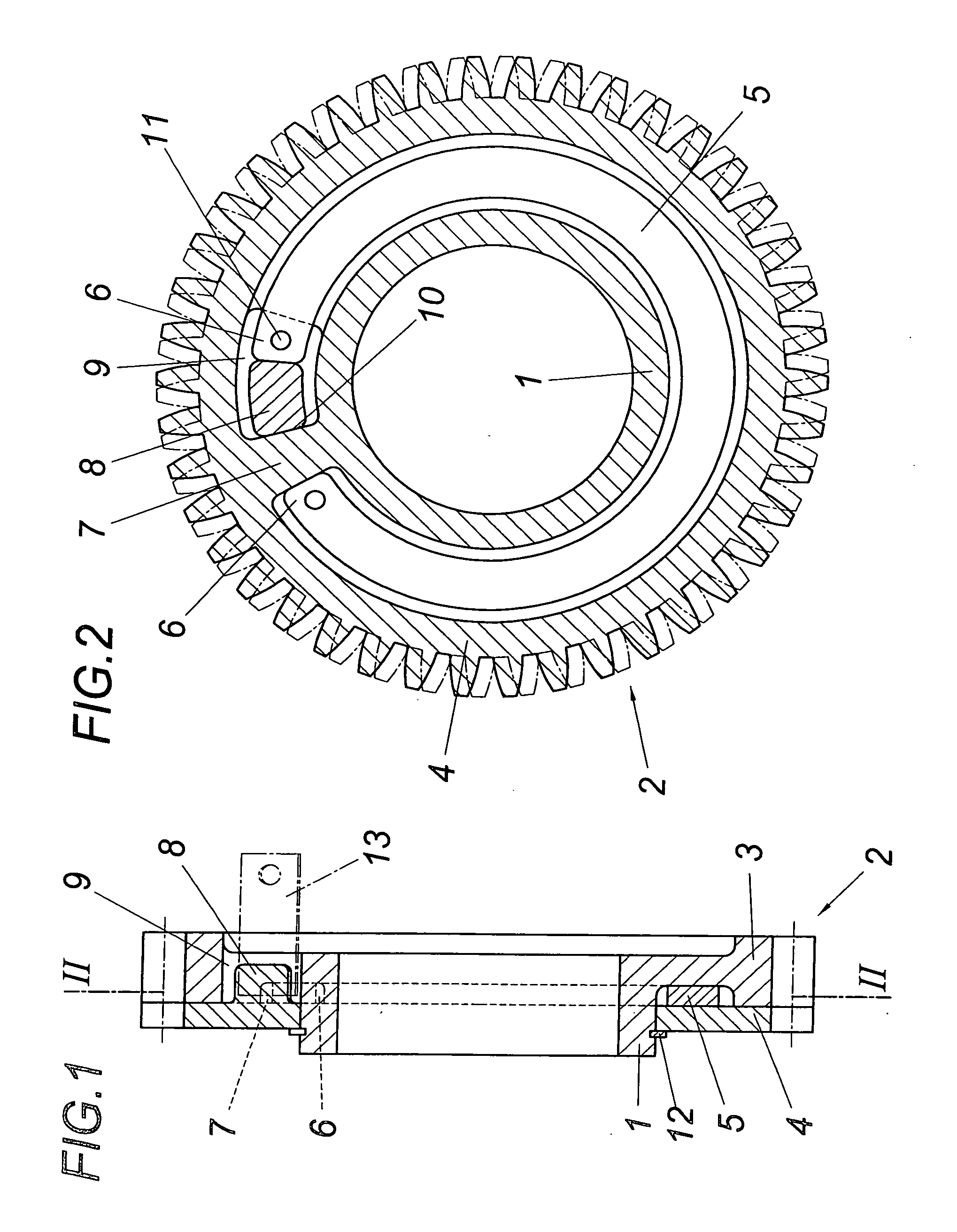

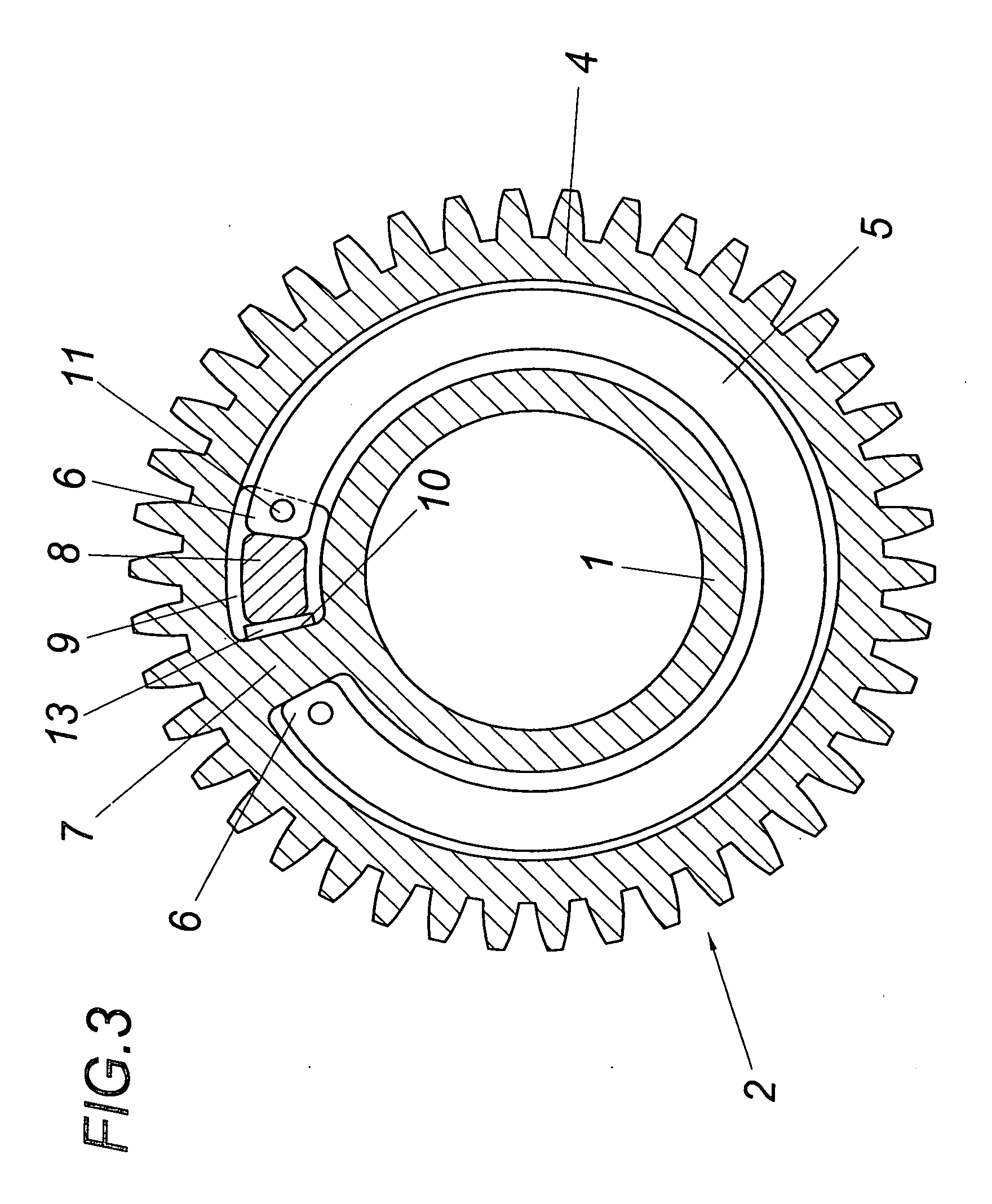

Toothed Wheel For a Play-Free Gear Spur Set

InactiveUS20080141811A1Simple possibilityEasy to assemblePortable liftingGearing elementsEngineeringSpur gear

A toothed wheel is described for a play-free spur gear set, comprising a hub (1), with a toothed ring (2) supported by the hub (1), which ring is split into two partial rings along a dividing plane normal to an axis, namely into a ring piece (3) fixed to the hub and a ring crown (4) mounted to rotate coaxially relative to the above, and an annular spring (5) enclosing the hub (1) with the circumferentially-opposed ends (6) resting on support webs (7, 8) embodied integrally with both partial rings, overlapping each other in the axial direction and arranged behind each other in the circumferential direction of the toothed ring. In order to avoid any overload of the partial rings produced by way of powder metallurgy and to ensure simple constructional conditions it is proposed that the support web (8) of one partial ring extends through the other partial ring in a through opening (9) with circumferential play and the support web (7) of the partial ring with the through opening (9) forms an assembly stop (10) defining the through opening (9) for the other support web (8).

Owner:MIBA SINTER AUSTRIA

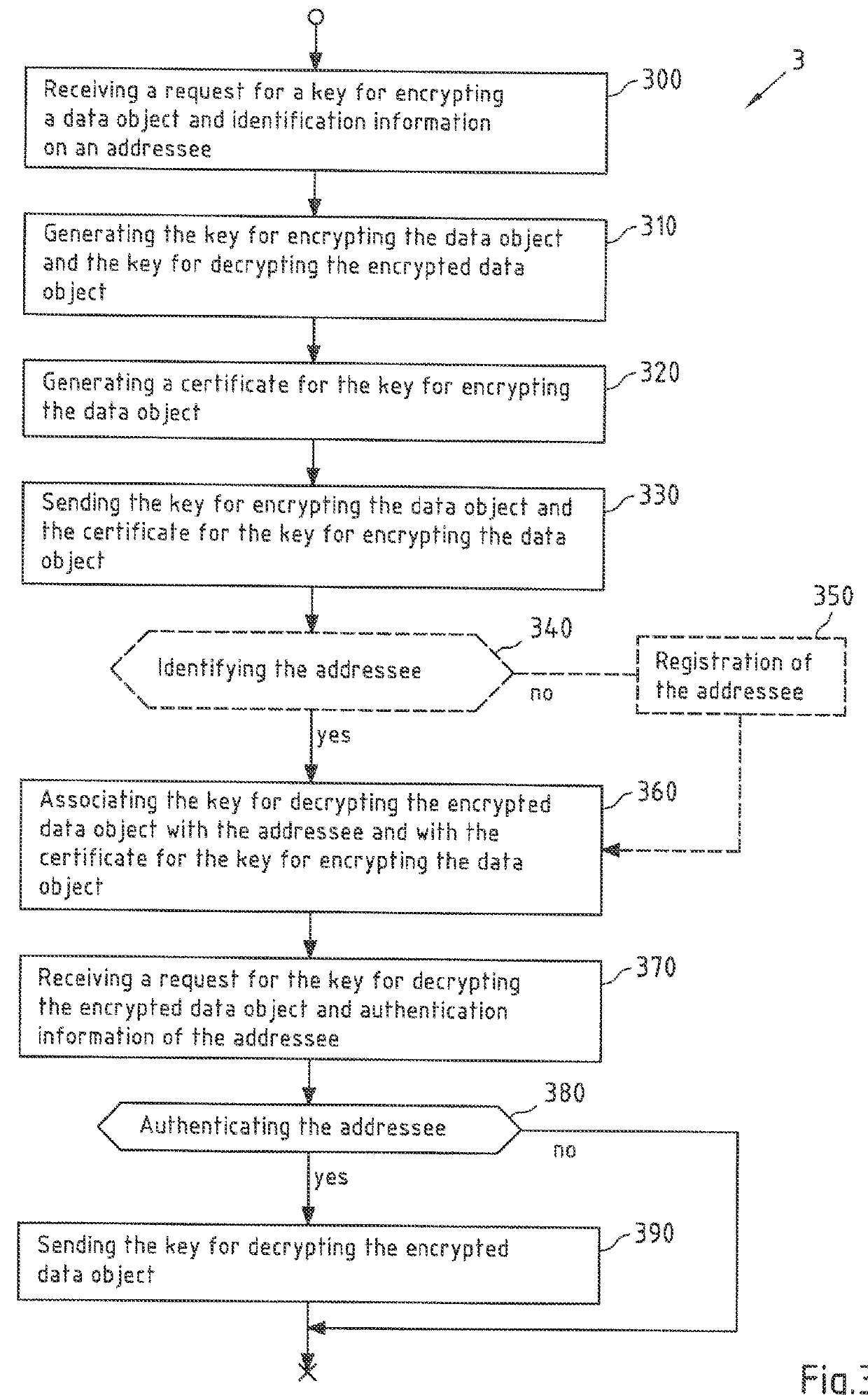

Method for secured transmission of a data object

ActiveUS20180183608A1Overcome disadvantagesSimple possibilityKey distribution for secure communicationUser identity/authority verificationComputer networkSecure transmission

A method is disclosed comprising receiving identification information on an addressee, to whom an encrypted data object is sent by a transmission device or for whom the encrypted data object is to be provided by the transmission device for retrieval , from the transmission device to a server, associating the identification information with a key for decrypting the encrypted data object by the server, sending the key for decrypting the encrypted data object to the addressee by the server, or providing by the server the key for decrypting the encrypted data object for retrieval by the addressee.

Owner:KOBIL SYST

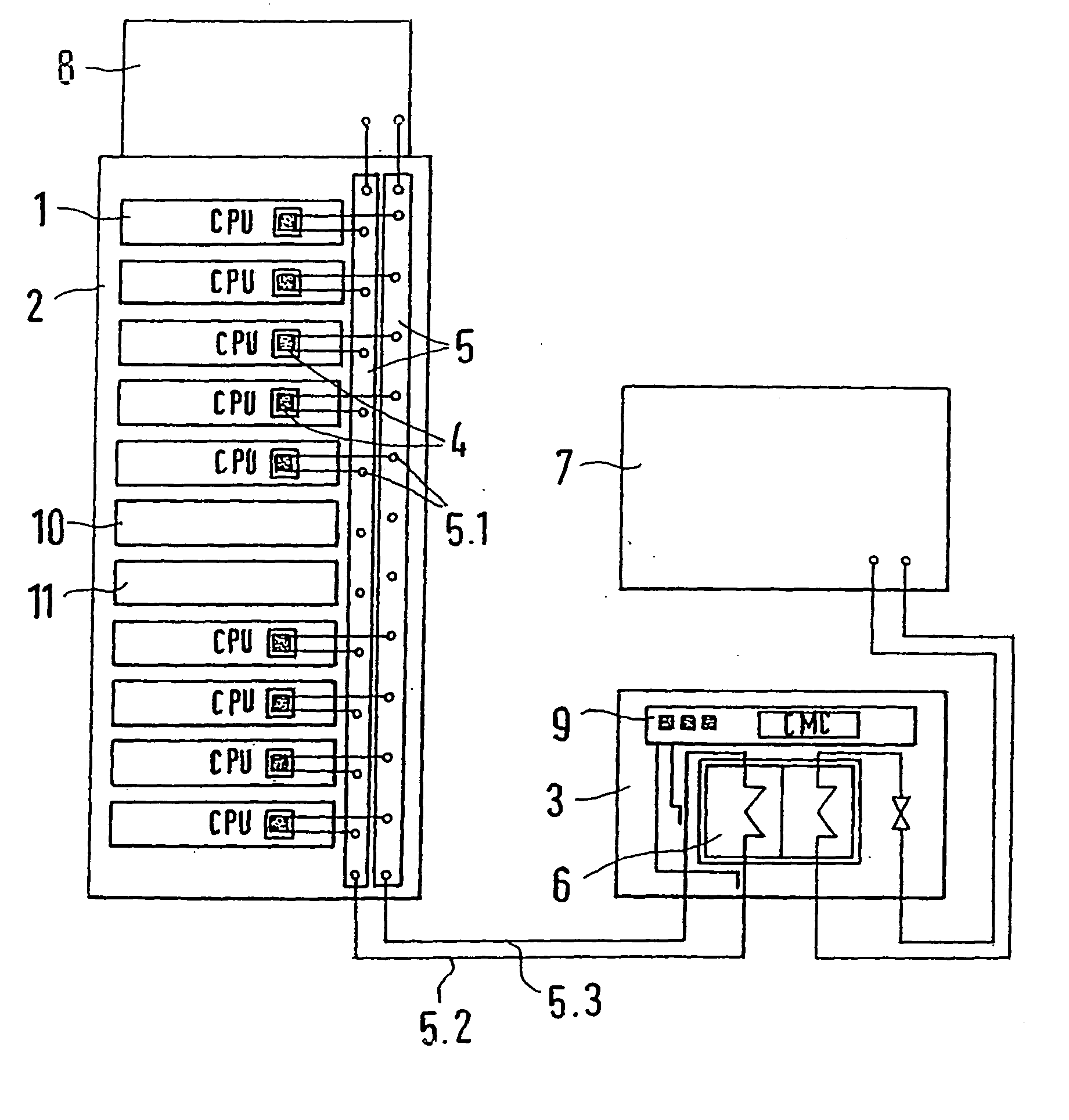

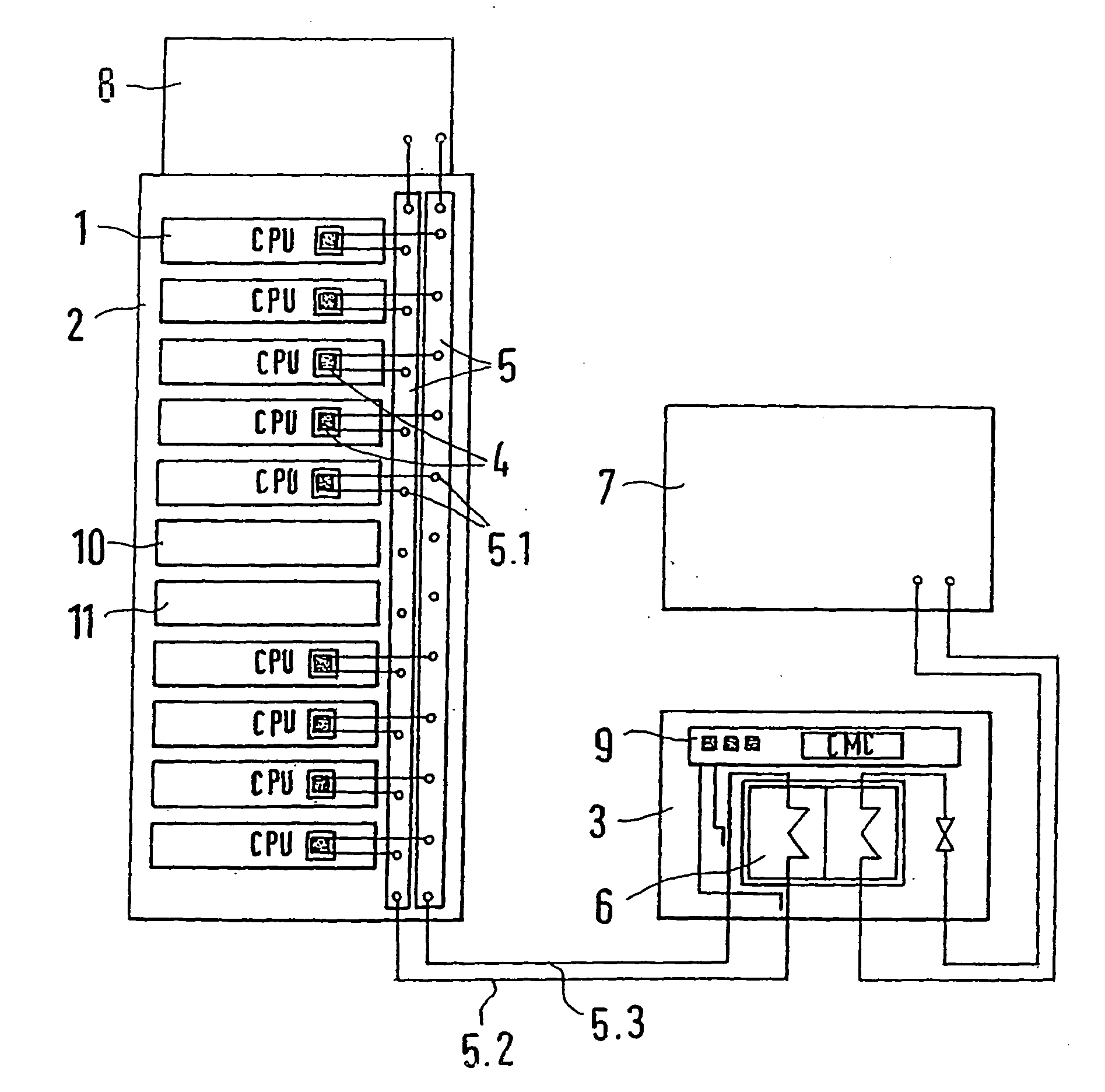

Liquid cooling system

ActiveUS20060037331A1Avoid heat damageSimple possibilityLighting and heating apparatusThermometer applicationsEngineeringSwitchgear

A liquid cooling system having cooling units individually assigned to electronic component groups housed in a rack or a switchgear cabinet, which are to be cooled, and having a monitoring and control arrangement for monitoring a cooling temperature. Effective cooling and temperature monitoring is obtained because the cooling units are liquid cooling units and are connected via branch points to a common central liquid line system integrated into the rack or the switchgear cabinet. The control and monitoring arrangement is for monitoring the cooling temperature in the central liquid line system and for emitting an error signal when a predetermined or a predeterminable threshold temperature in a liquid return branch is exceeded, or when a predetermined or predeterminable threshold temperature difference between a temperature in an inlet branch and a temperature in the return branch is exceeded, or when the liquid flow falls below a predetermined or predeterminable threshold value.

Owner:RITTALWERK RUDOLF LOH GMBH & CO KG

Roof construction of a vehicle body

ActiveUS20100259073A1Little costLittle effortVehicle seatsSuperstructure subunitsMobile vehicleEngineering

A body of a motor vehicle includes a lateral roof region that has an outer skin, an outer roof frame, and an inner roof frame, wherein the outer roof frame is arranged under the outer skin and the inner roof frame is arranged under the outer roof frame, and the outer skin, the outer roof frame, and the inner roof frame have a common welded flange, by means of which the outer skin and the outer and inner roof frames are connected to one another, and which is configured to receive an adhesive layer for a roof module having a roof module frame. An aspect of the invention is to provide an accident-optimized vehicle body at little expense that prevents a tearing off of the roof module, and is achieved in that the outer roof frame of the body is configured as a locking element for the roof module frame.

Owner:THYSSENKRUPP STEEL EURO AG

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com