Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

41results about How to "Prevent the diffusion of impurities" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

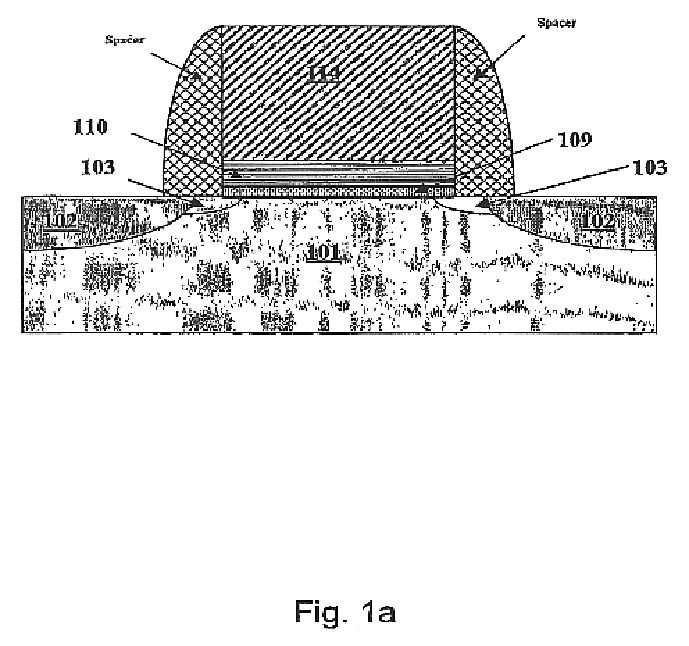

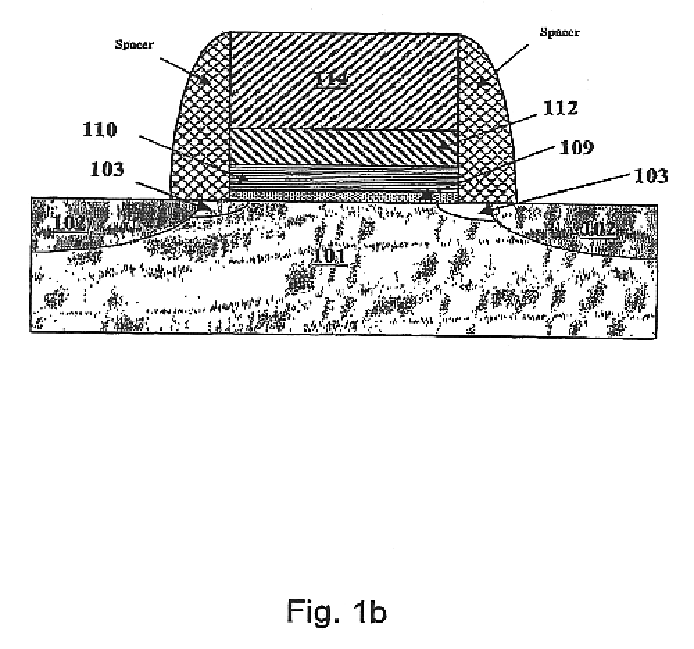

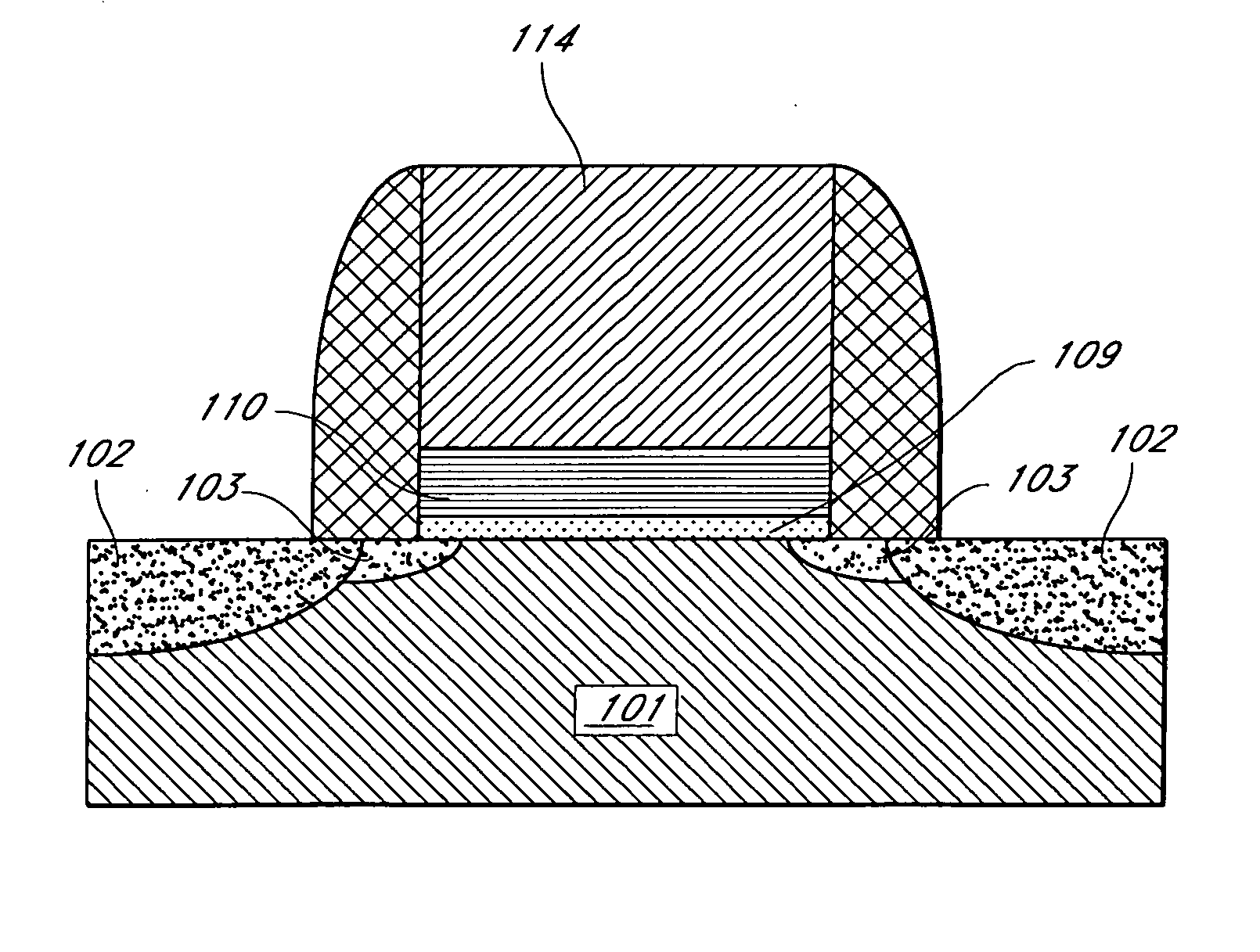

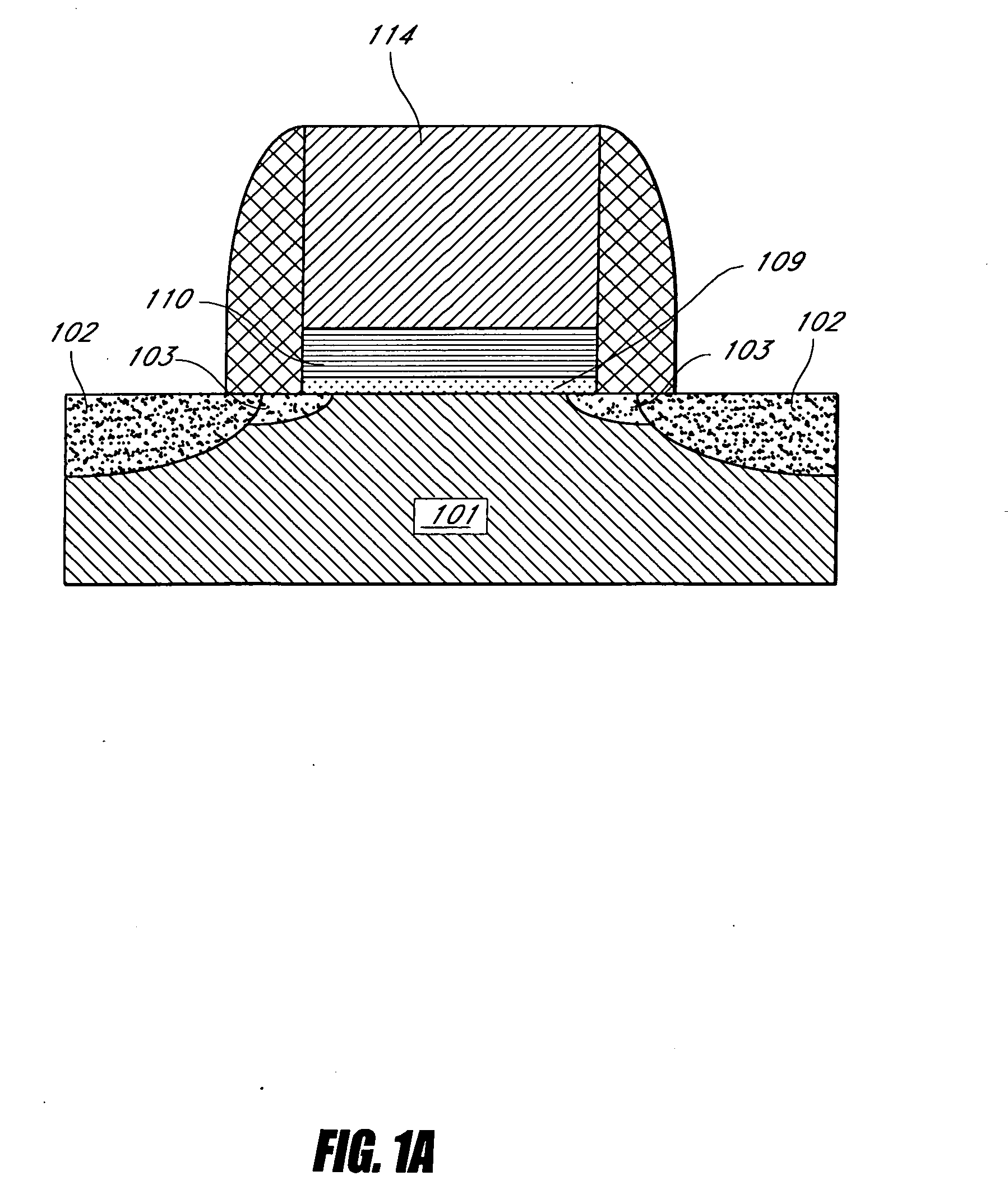

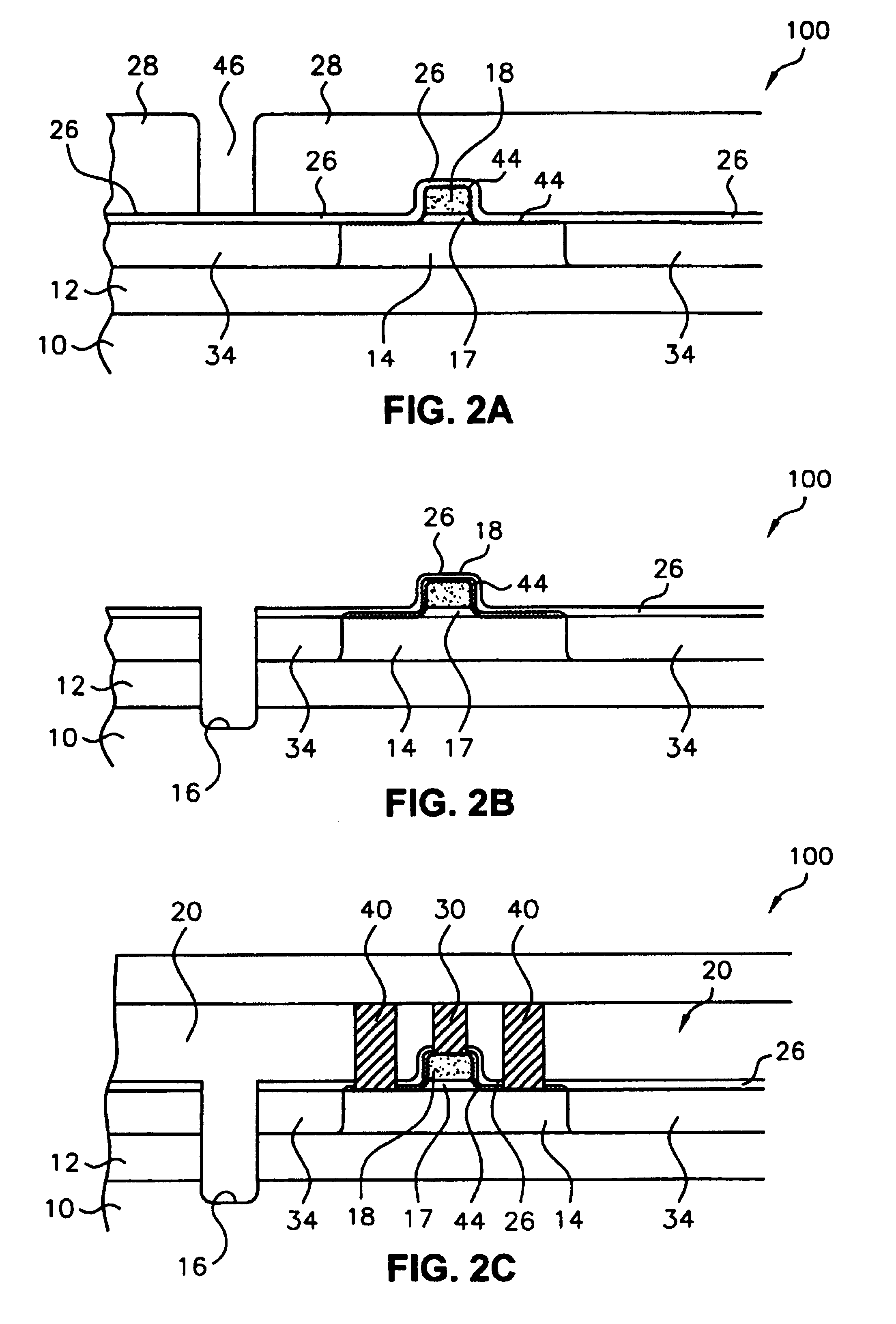

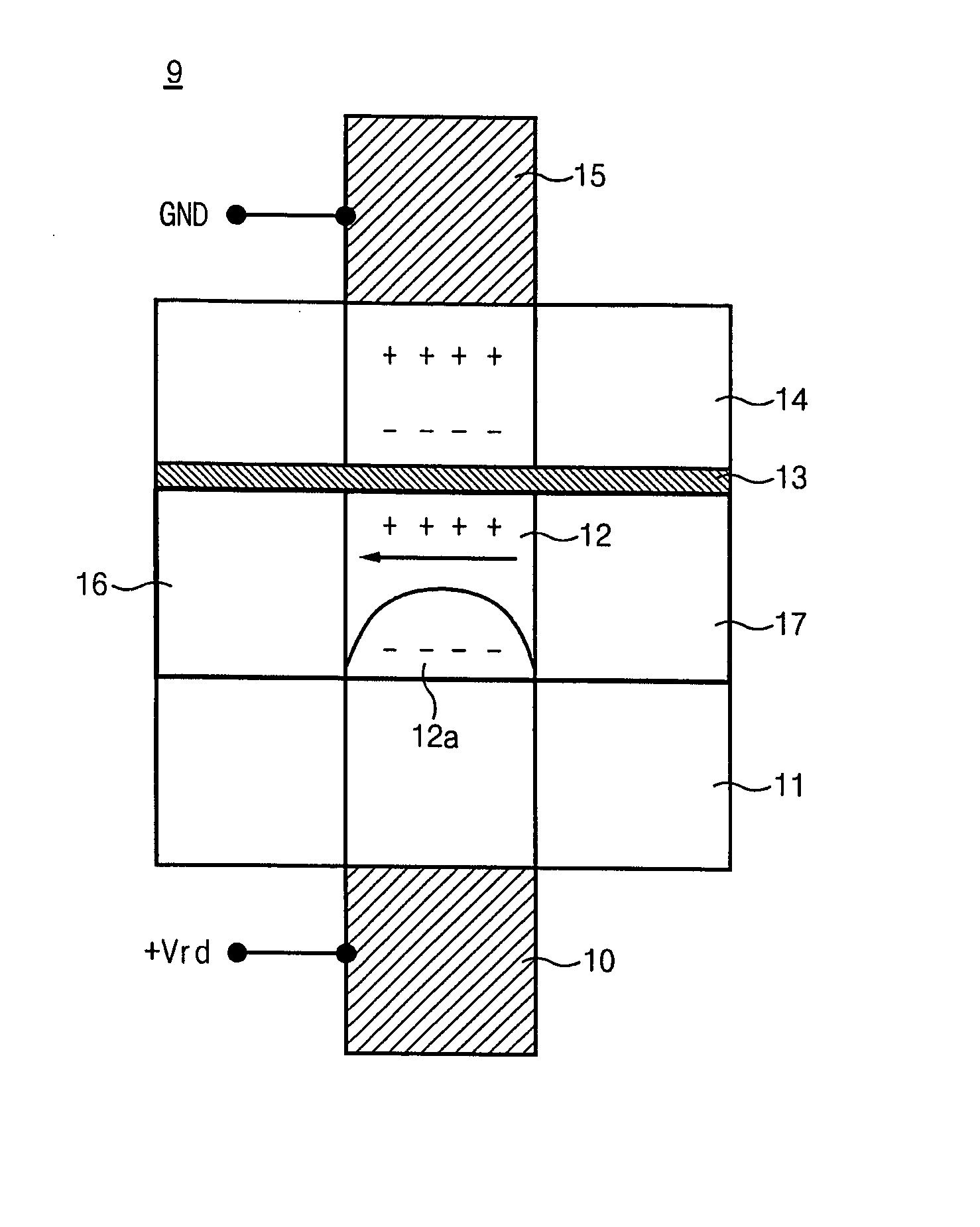

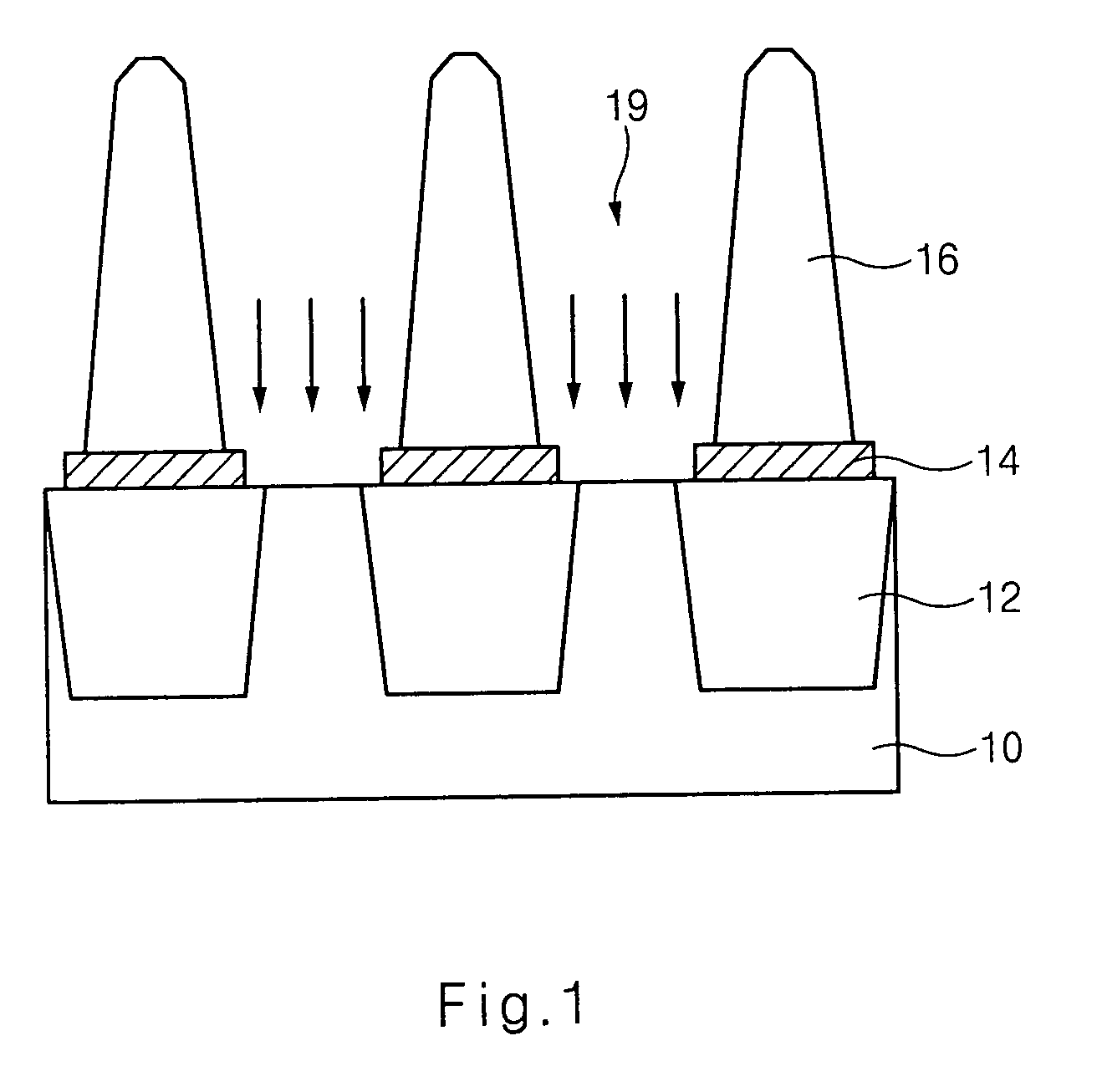

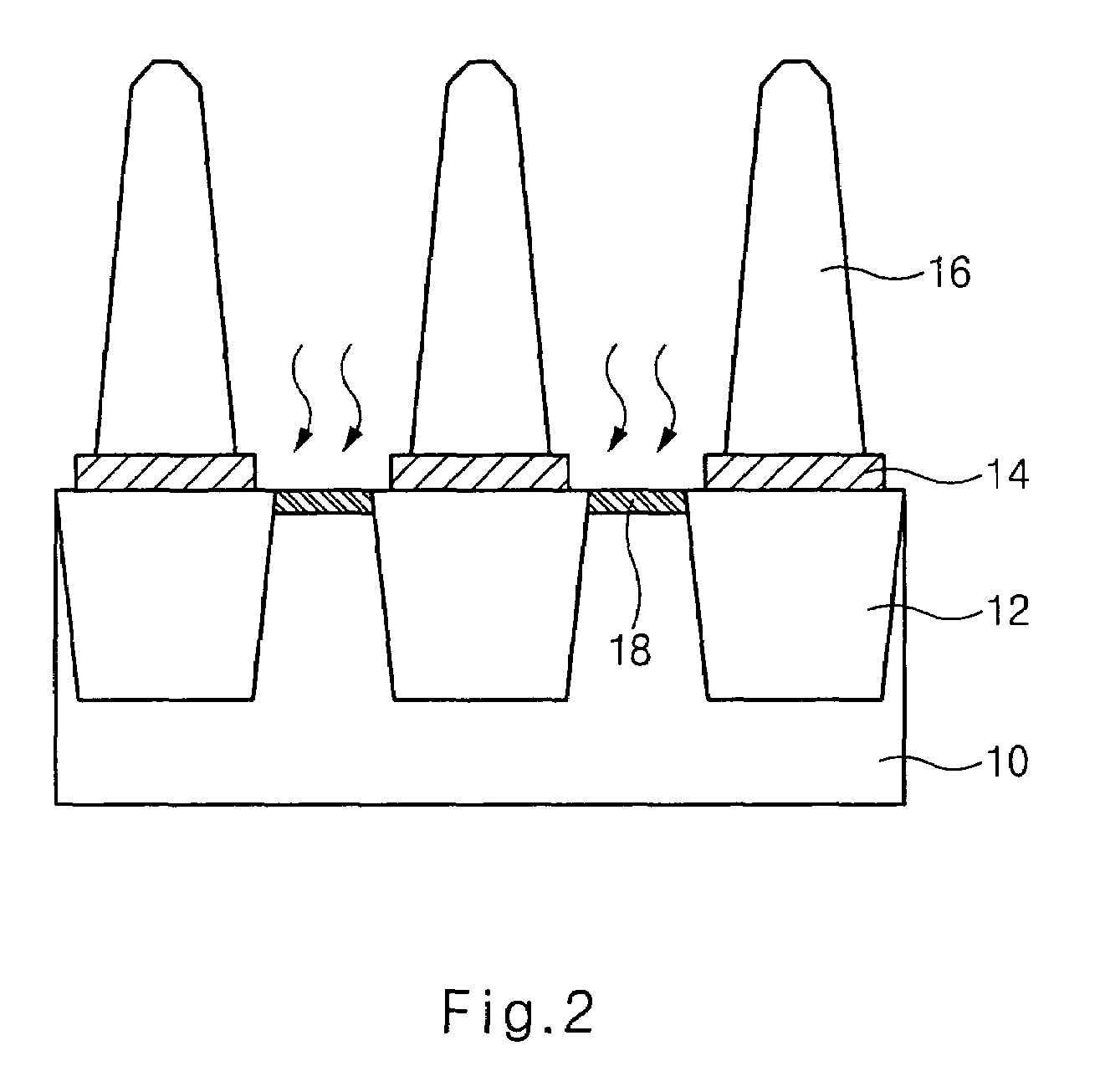

Method of depositing barrier layer for metal gates

InactiveUS6858524B2Eliminate the problemEasy to controlSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricRemote plasma

A method of manufacturing a high performance MOS device and transistor gate stacks comprises forming a gate dielectric layer over a semiconductor substrate; forming a barrier layer over the gate dielectric layer by an ALD type process; and forming a gate electrode layer over the barrier layer. The method enables the use of hydrogen plasma, high energy hydrogen radicals and ions, other reactive radicals, reactive oxygen and oxygen containing precursors in the processing steps subsequent to the deposition of the gate dielectric layer of the device. The ALD process for forming the barrier layer is performed essentially in the absence of plasma and reactive hydrogen radials and ions. This invention makes it possible to use oxygen as a precursor in the deposition of the metal gates. The barrier film also allows the use of hydrogen plasma in the form of either direct or remote plasma in the deposition of the gate electrode. Furthermore, the barrier film prevents the electrode material from reacting with the gate dielectric material. The barrier layer is ultra thin and, at the same time, it forms a uniform cover over the entire surface of the gate dielectric.

Owner:ASM INTERNATIONAL

Method of depositing barrier layer from metal gates

InactiveUS20050104112A1Improve performanceEasy to useTransistorSolid-state devicesGate dielectricRemote plasma

A method of manufacturing a high performance MOS device and transistor gate stacks comprises forming a gate dielectric layer over a semiconductor substrate; forming a barrier layer over the gate dielectric layer by an ALD type process; and forming a gate electrode layer over the barrier layer. The method enables the use of hydrogen plasma, high energy hydrogen radicals and ions, other reactive radicals, reactive oxygen and oxygen containing precursors in the processing steps subsequent to the deposition of the gate dielectric layer of the device. The ALD process for forming the barrier layer is performed essentially in the absence of plasma and reactive hydrogen radials and ions. This invention makes it possible to use oxygen as a precursor in the deposition of the metal gates. The barrier film also allows the use of hydrogen plasma in the form of either direct or remote plasma in the deposition of the gate electrode. Furthermore, the barrier film prevents the electrode material from reacting with the gate dielectric material. The barrier layer is ultra thin and, at the same time, it forms a uniform cover over the entire surface of the gate dielectric.

Owner:HAUKKA SUVI +1

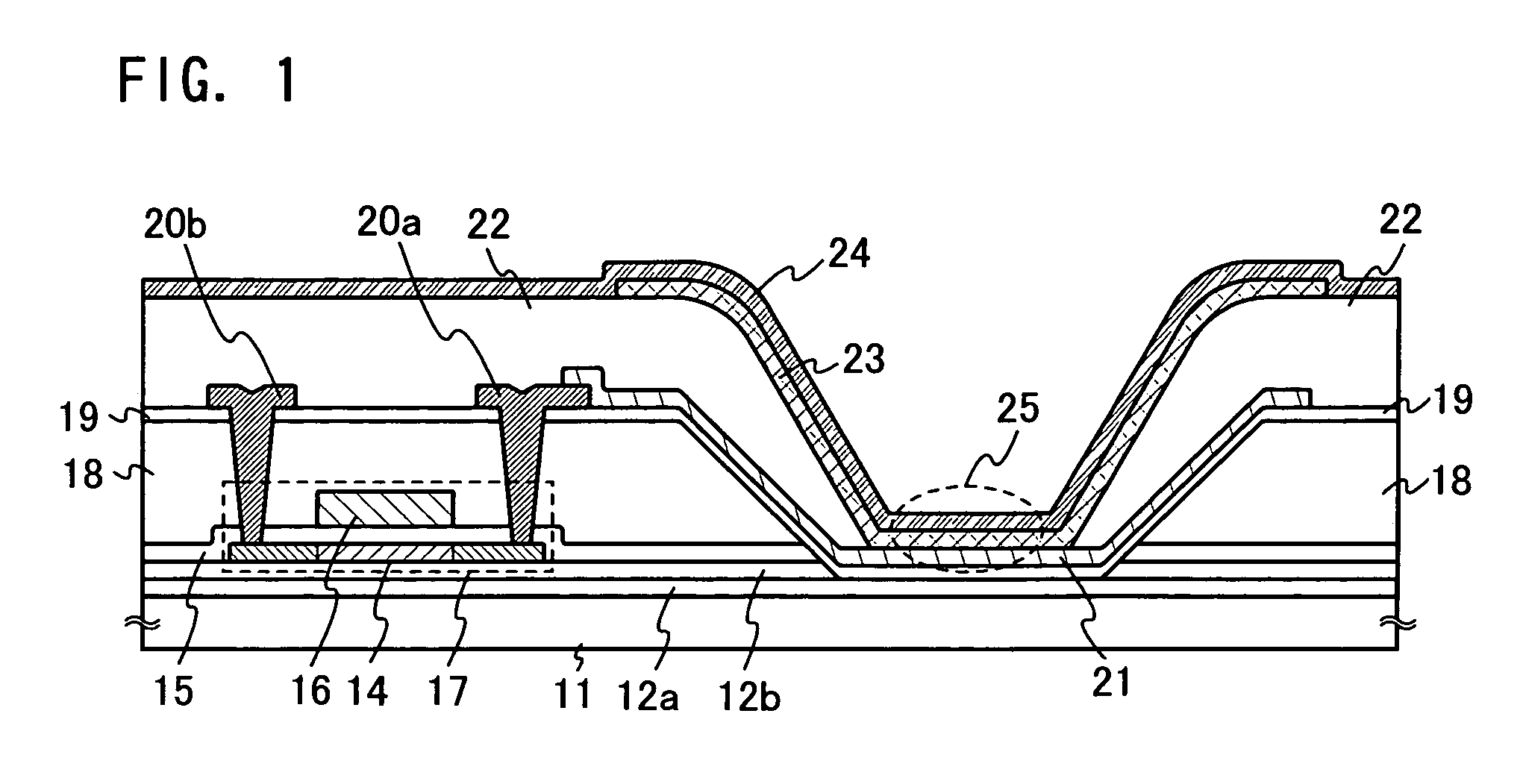

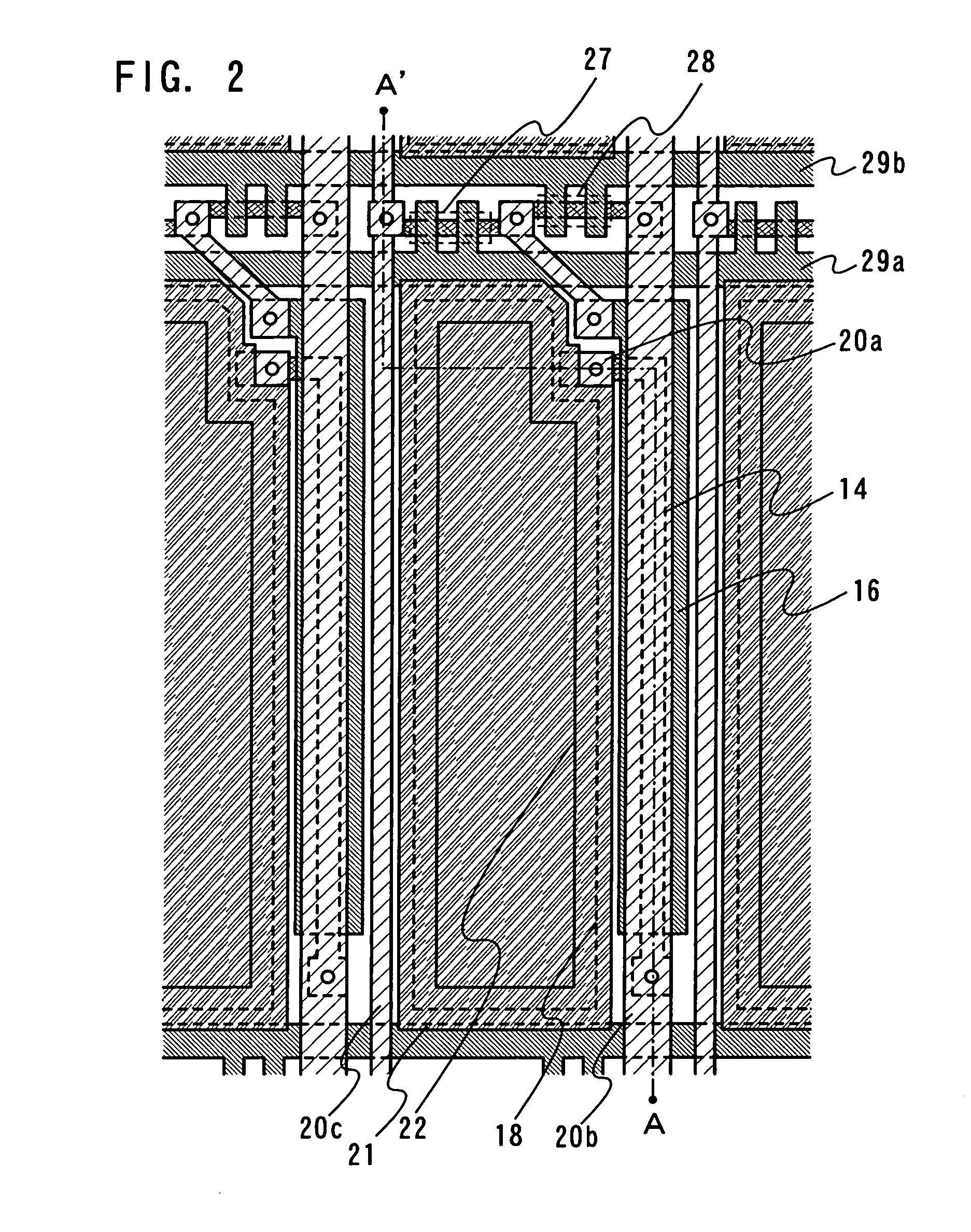

Display device

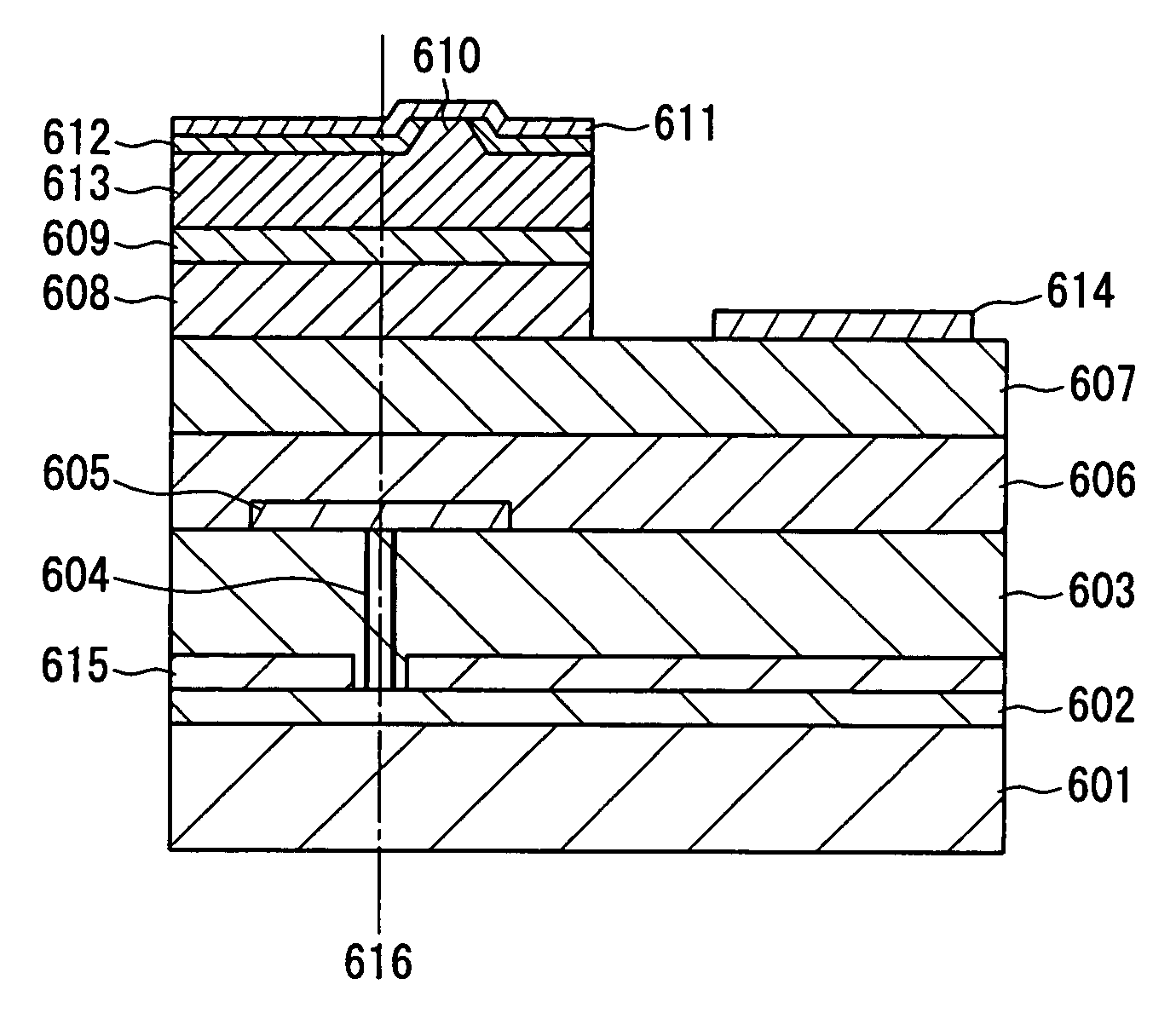

InactiveUS6960786B2Reduce impactSuppress mutationTransistorElectroluminescent light sourcesDisplay deviceOptoelectronics

Owner:SEMICON ENERGY LAB CO LTD

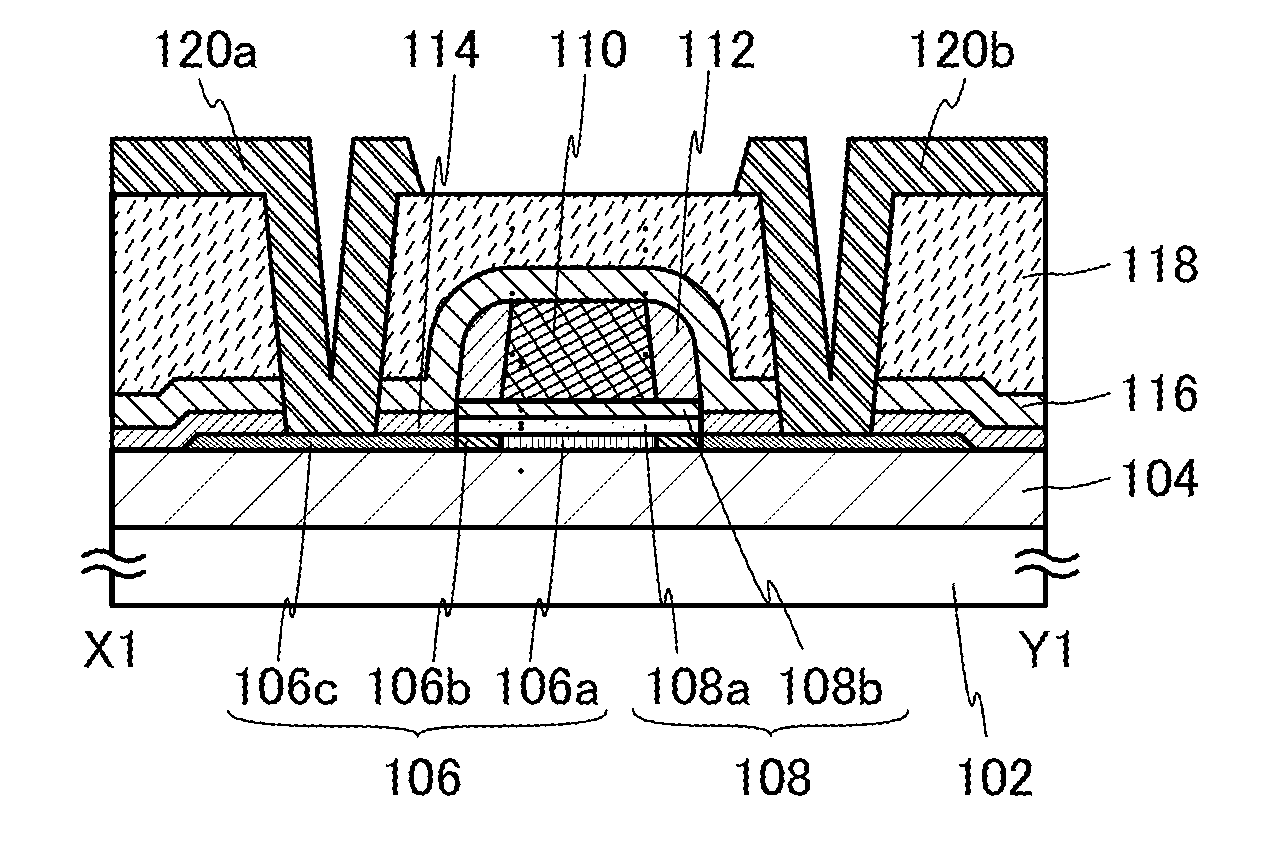

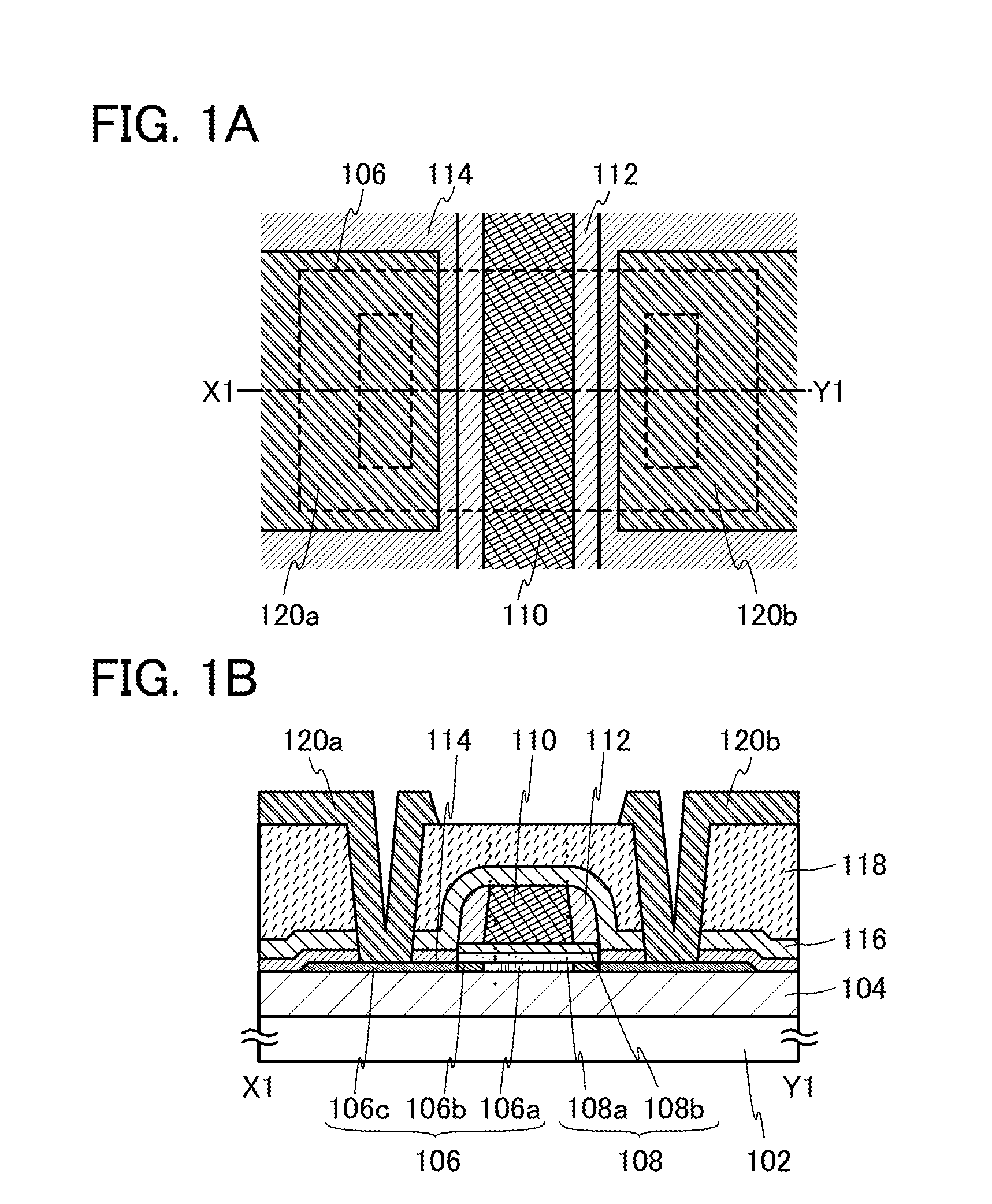

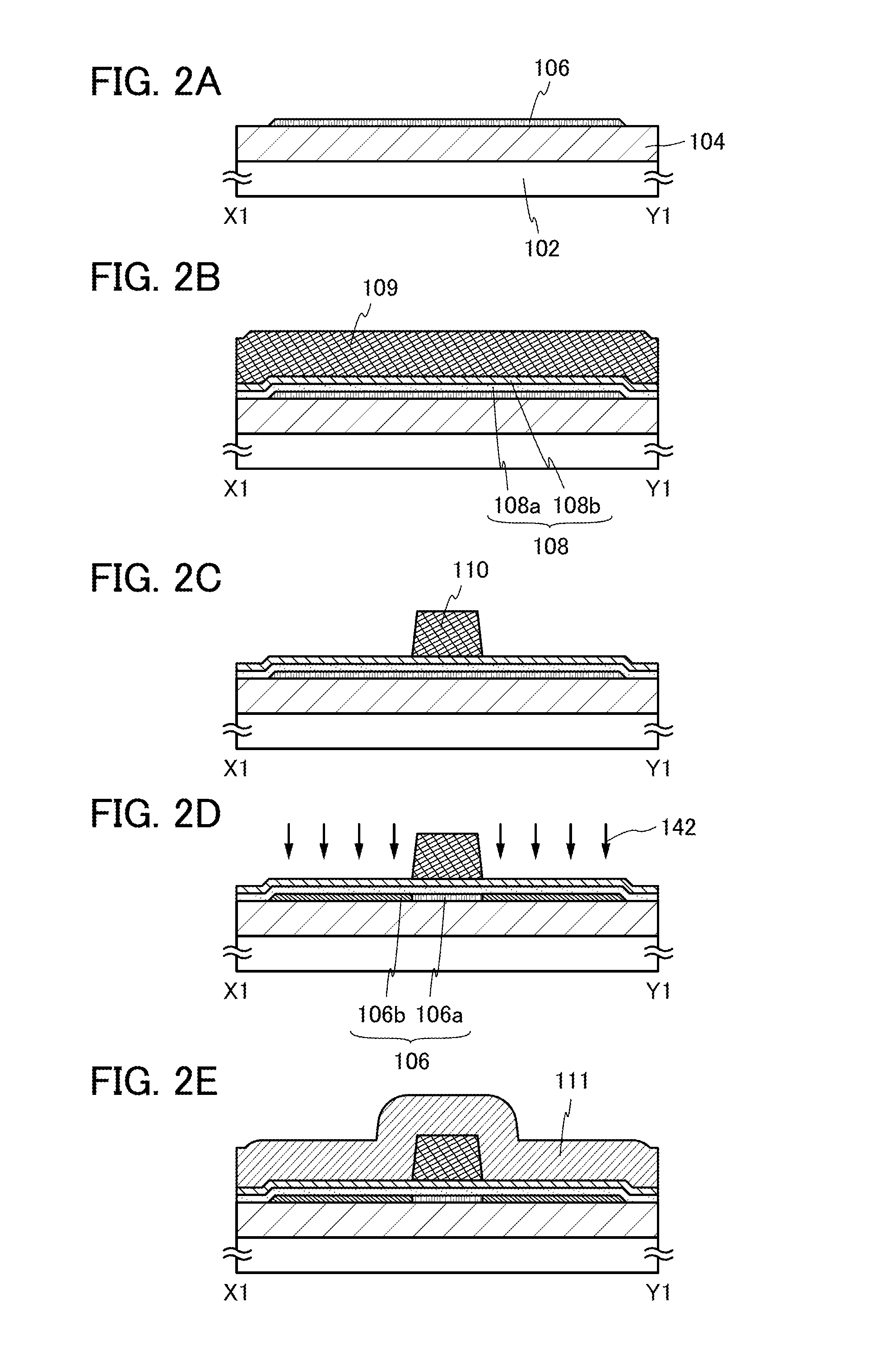

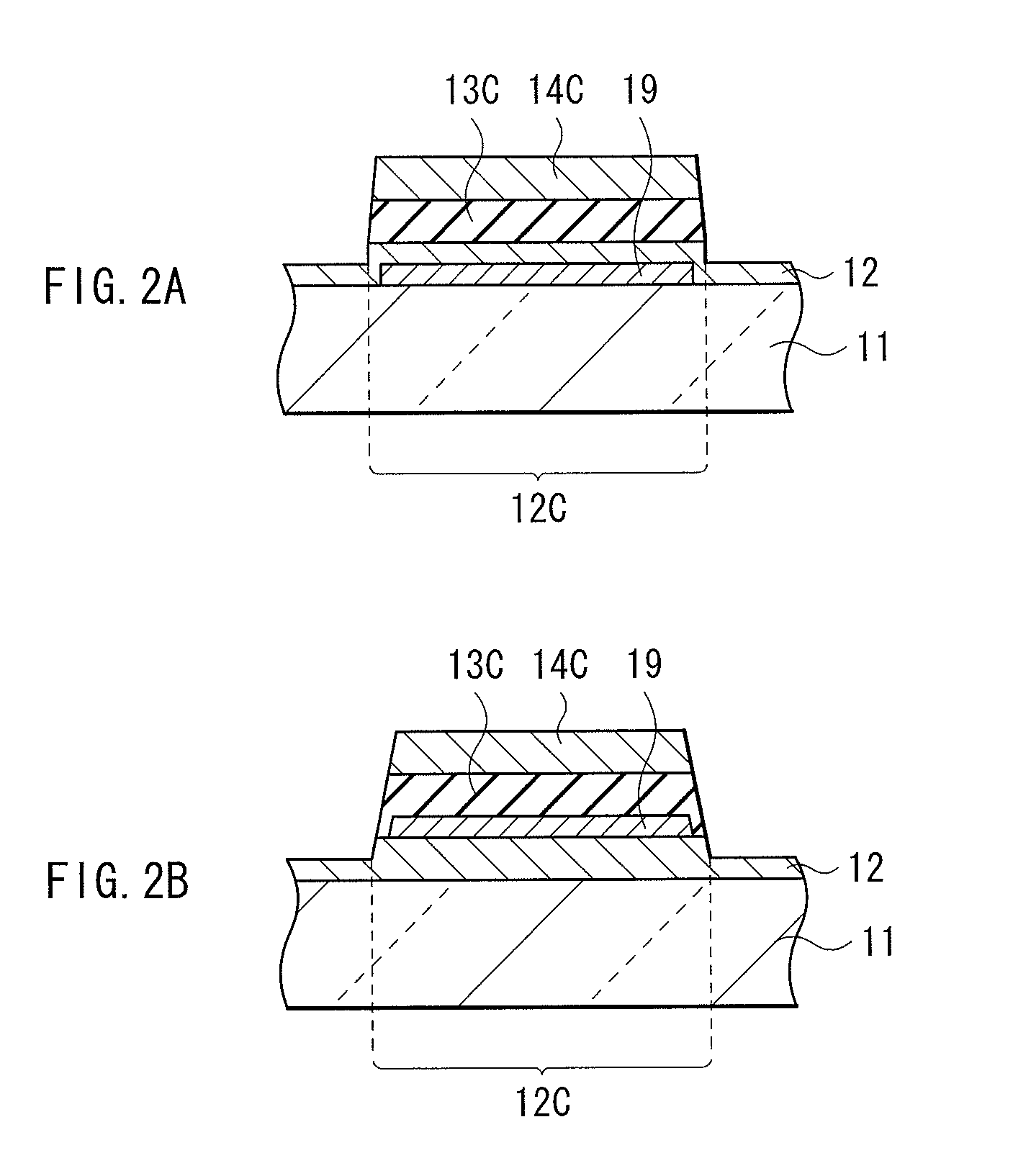

Semiconductor device and method for manufacturing the same

ActiveUS20130187152A1Excellent and stable electric characteristicPrevent the diffusion of impuritiesTransistorSolid-state devicesSemiconductorMetal

A metal element of a metal film is introduced into the oxide semiconductor film by performing heat treatment in the state where the oxide semiconductor film is in contact with the metal film, so that a low-resistance region having resistance lower than that of a channel formation region is formed. A region of the metal film, which is in contact with the oxide semiconductor film, becomes a metal oxide insulating film by the heat treatment. After that, an unnecessary metal film is removed. Thus, the metal oxide insulating film can be formed over the low-resistance region.

Owner:SEMICON ENERGY LAB CO LTD

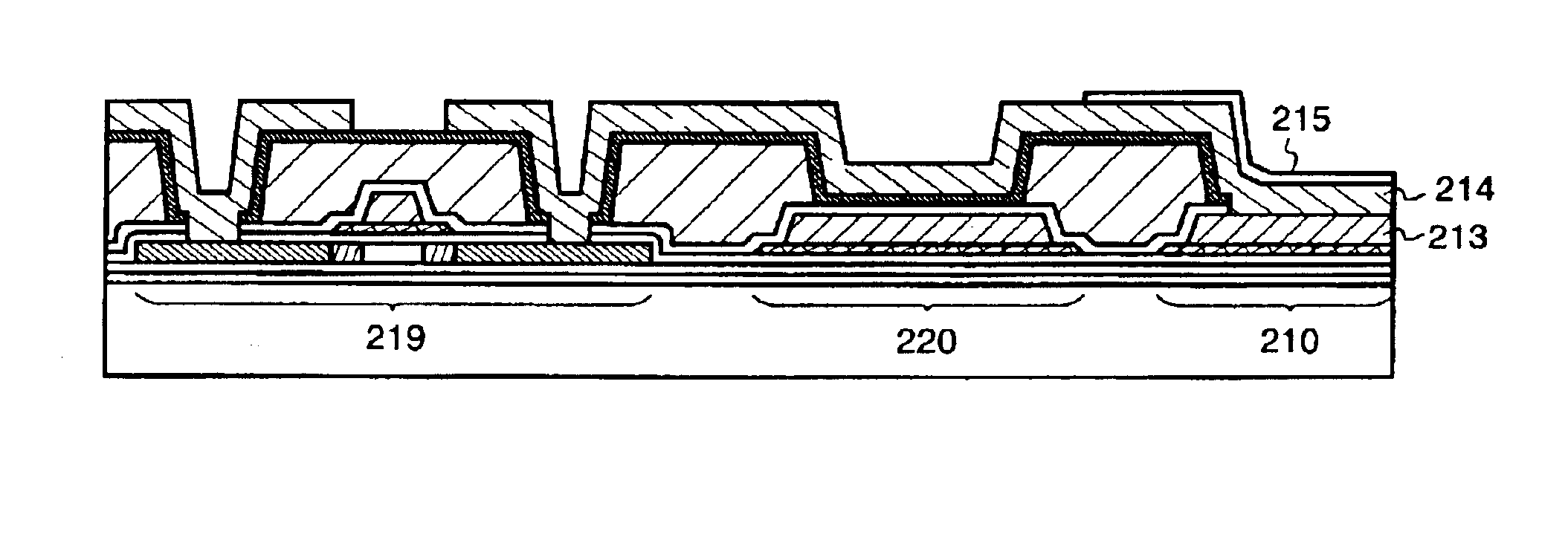

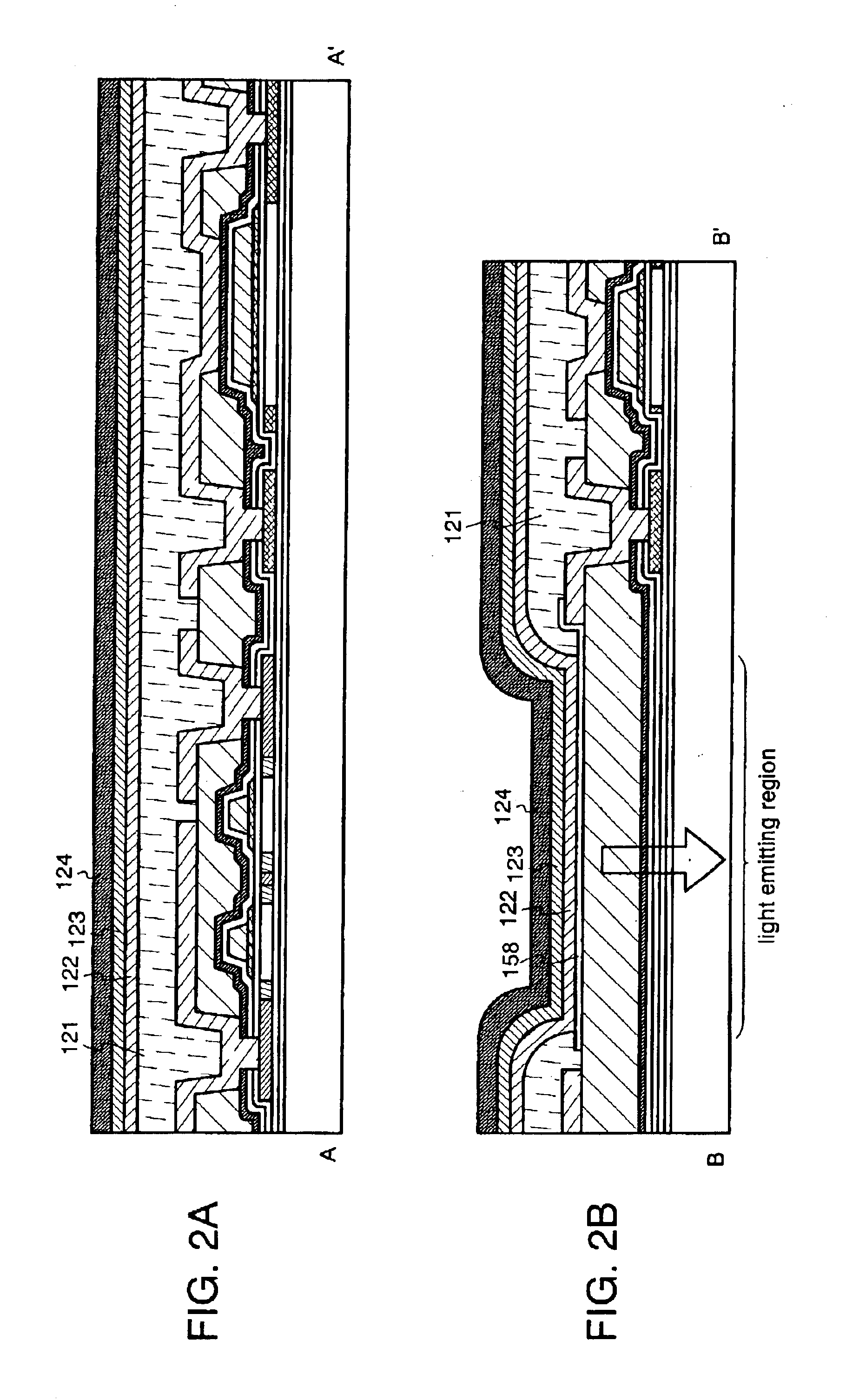

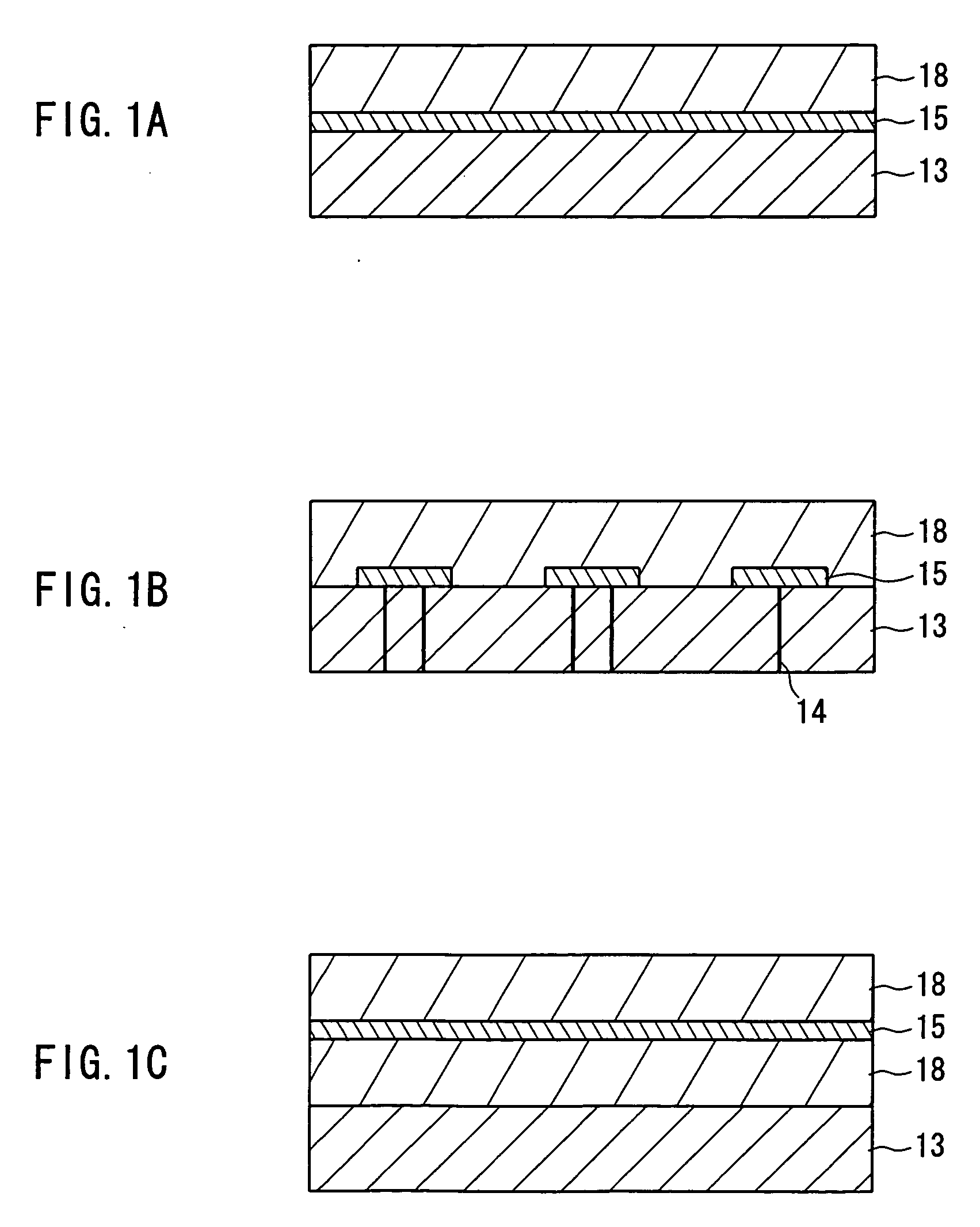

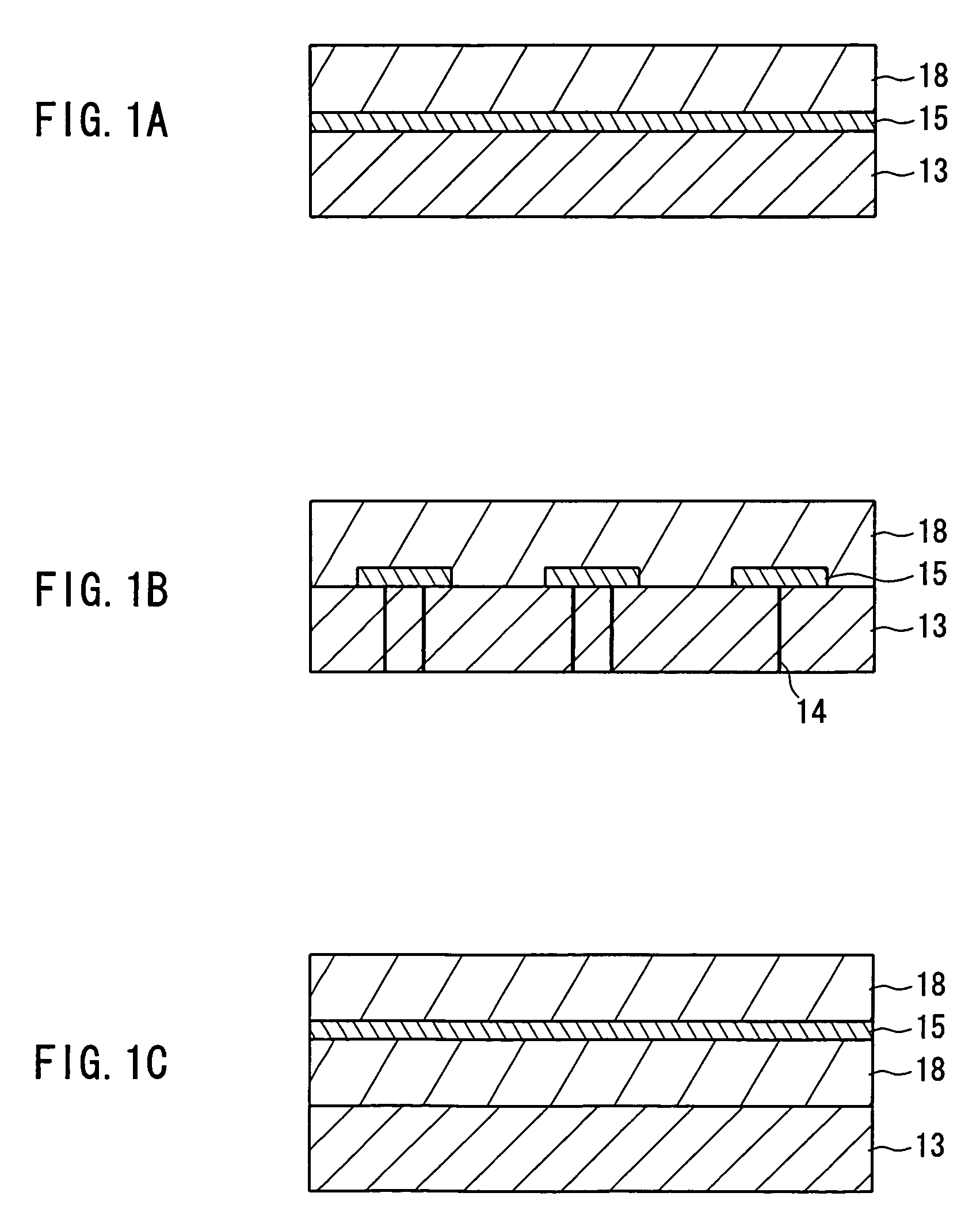

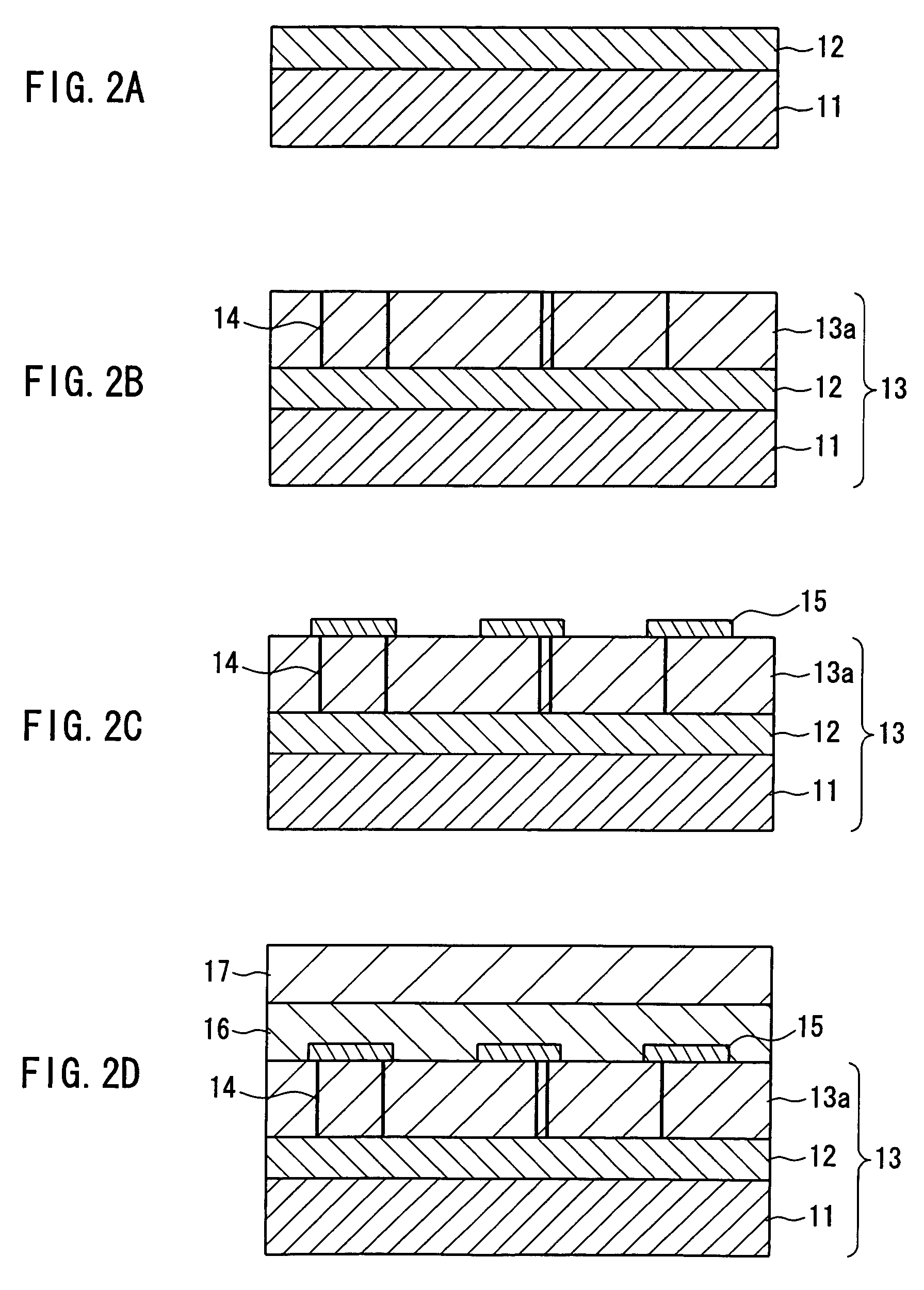

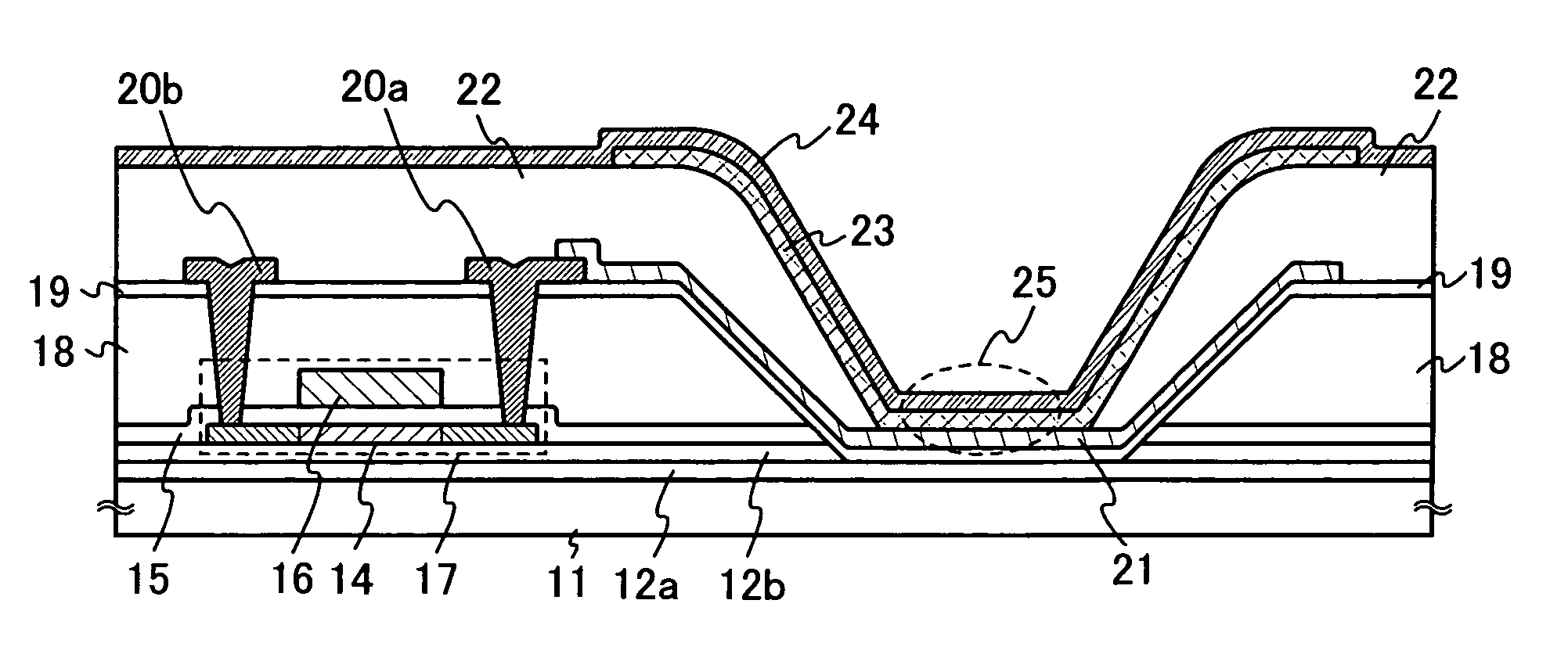

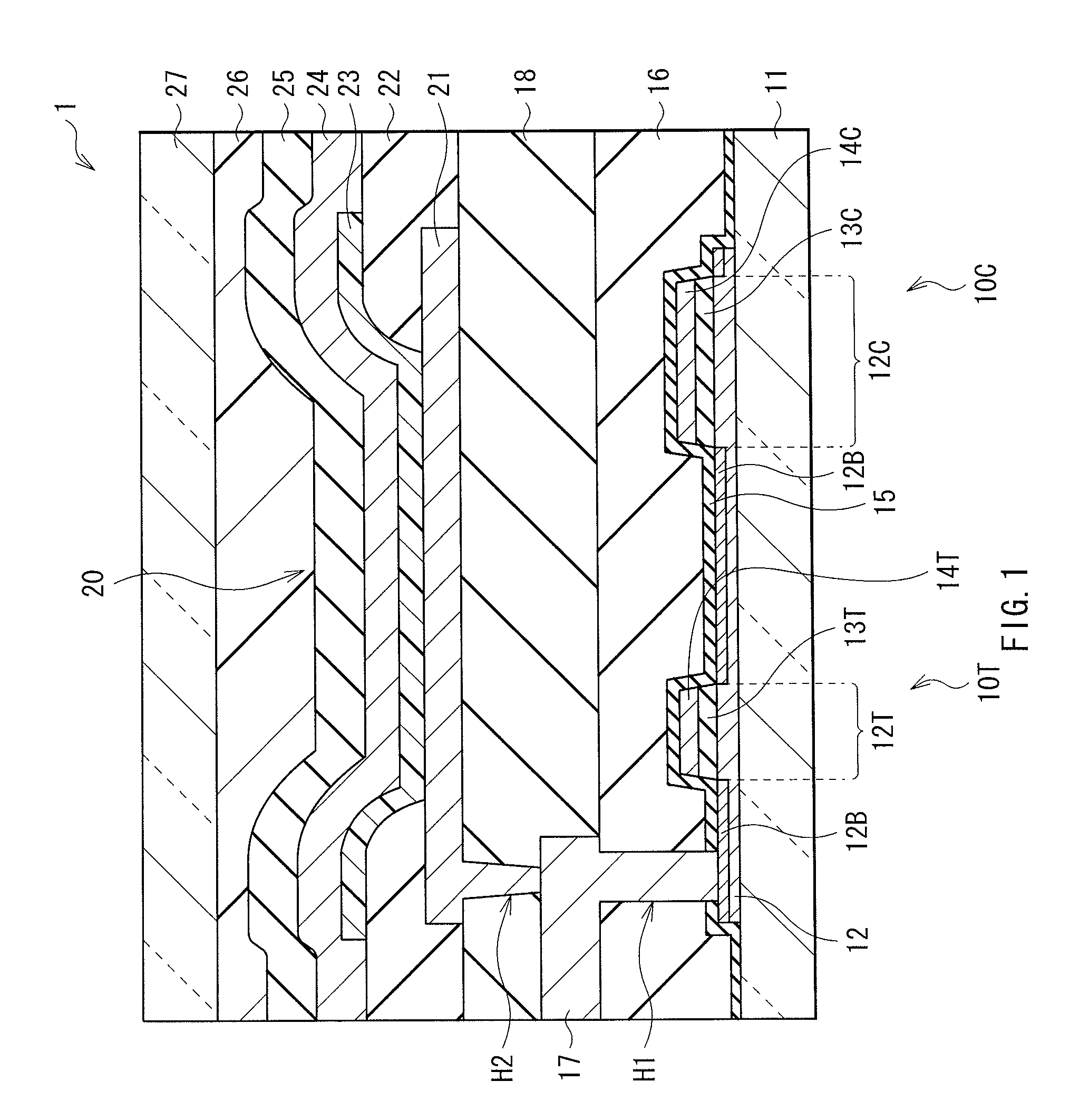

Light emitting device

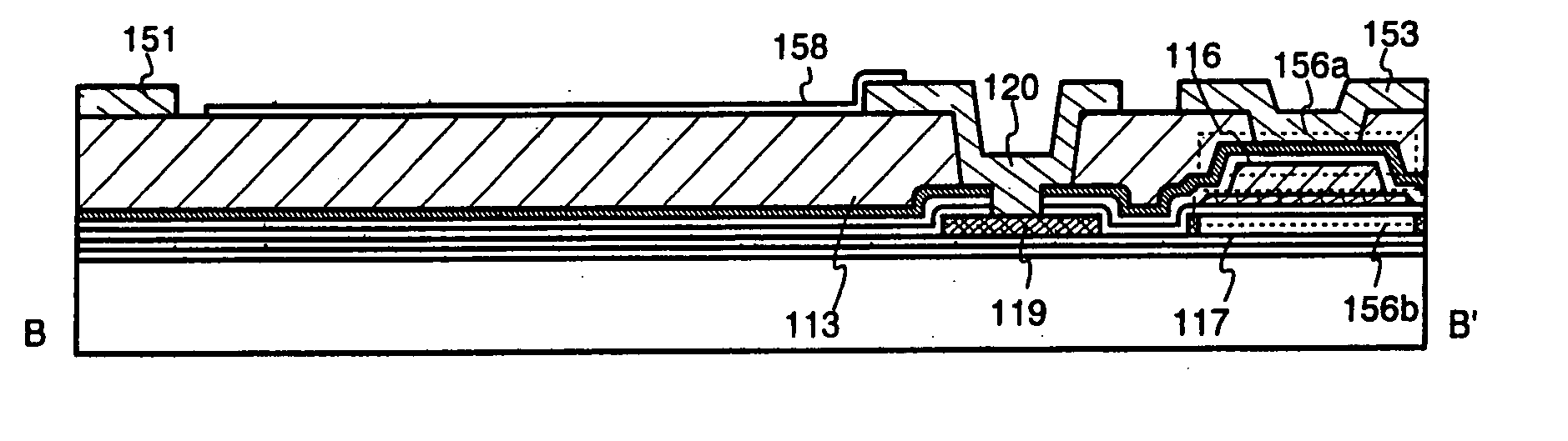

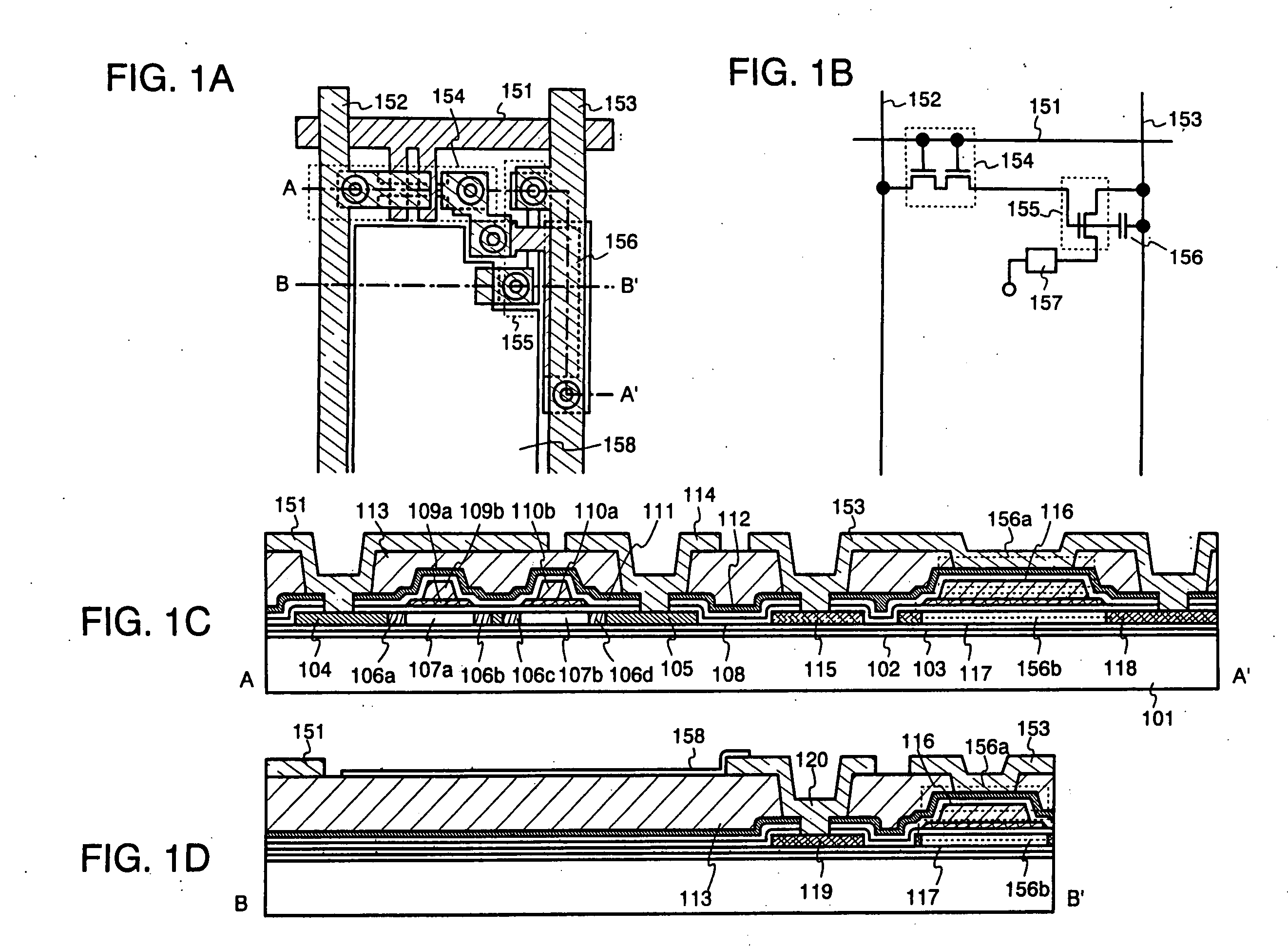

ActiveUS20050179372A1Prevent the diffusion of impuritiesReduce reflectionDischarge tube luminescnet screensElectroluminescent light sourcesActive matrixLight emitting device

It is an object of the present invention to provide an active matrix light emitting device which can efficiently prevent a diffusion of impurities from a substrate to a transistor, as well as reducing a reflection of light in a process of extracting light toward the outside of the light emitting device. One feature of the present invention is a light emitting device including a substrate, a first insulating layer provided over the substrate, a transistor provided over the first insulating layer, and a second insulating layer having a first opening portion which is provided to expose the substrate as well as covering the transistor, wherein a light emitting element is provided inside the first opening portion.

Owner:SEMICON ENERGY LAB CO LTD

Group-III-element nitride crystal semiconductor device

InactiveUS20050082564A1Prevent the diffusion of impuritiesReduce diffusion coefficientLaser detailsSemiconductor/solid-state device manufacturingAlkaline earth metalNitrogen

In a Group-III-element nitride semiconductor device including a Group-III-element nitride crystal layer stacked on a Group-III-element nitride crystal substrate, the substrate is produced by allowing nitrogen of nitrogen-containing gas and a Group III element to react with each other to crystallize in a melt (a flux) containing at least one of alkali metal and alkaline-earth metal, and a thin film layer is formed on the substrate and the thin film has a lower diffusion coefficient than that of the substrate with respect to impurities contained in the substrate. The present invention provides a semiconductor device in which alkali metal is prevented from diffusing.

Owner:PANASONIC CORP

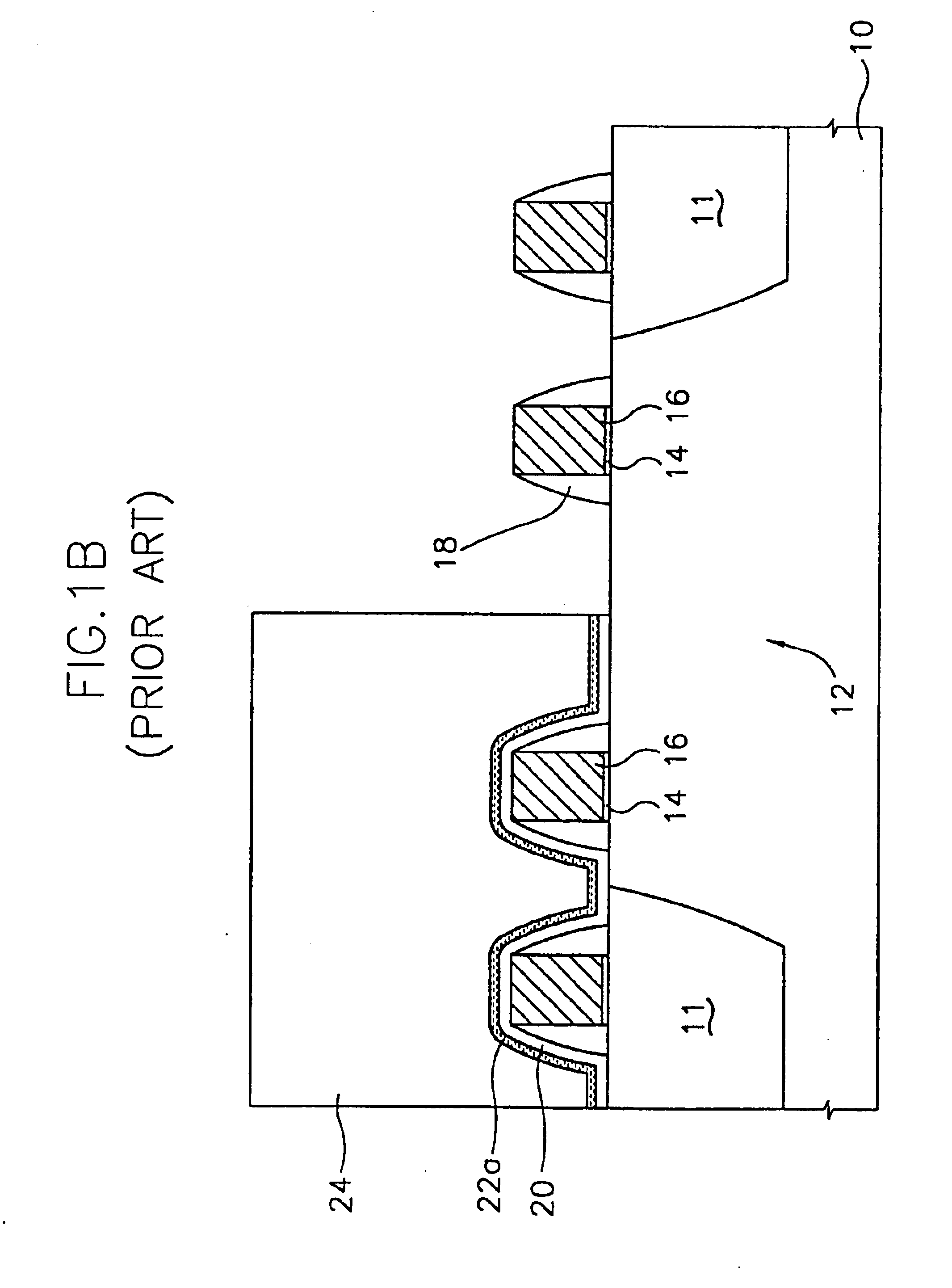

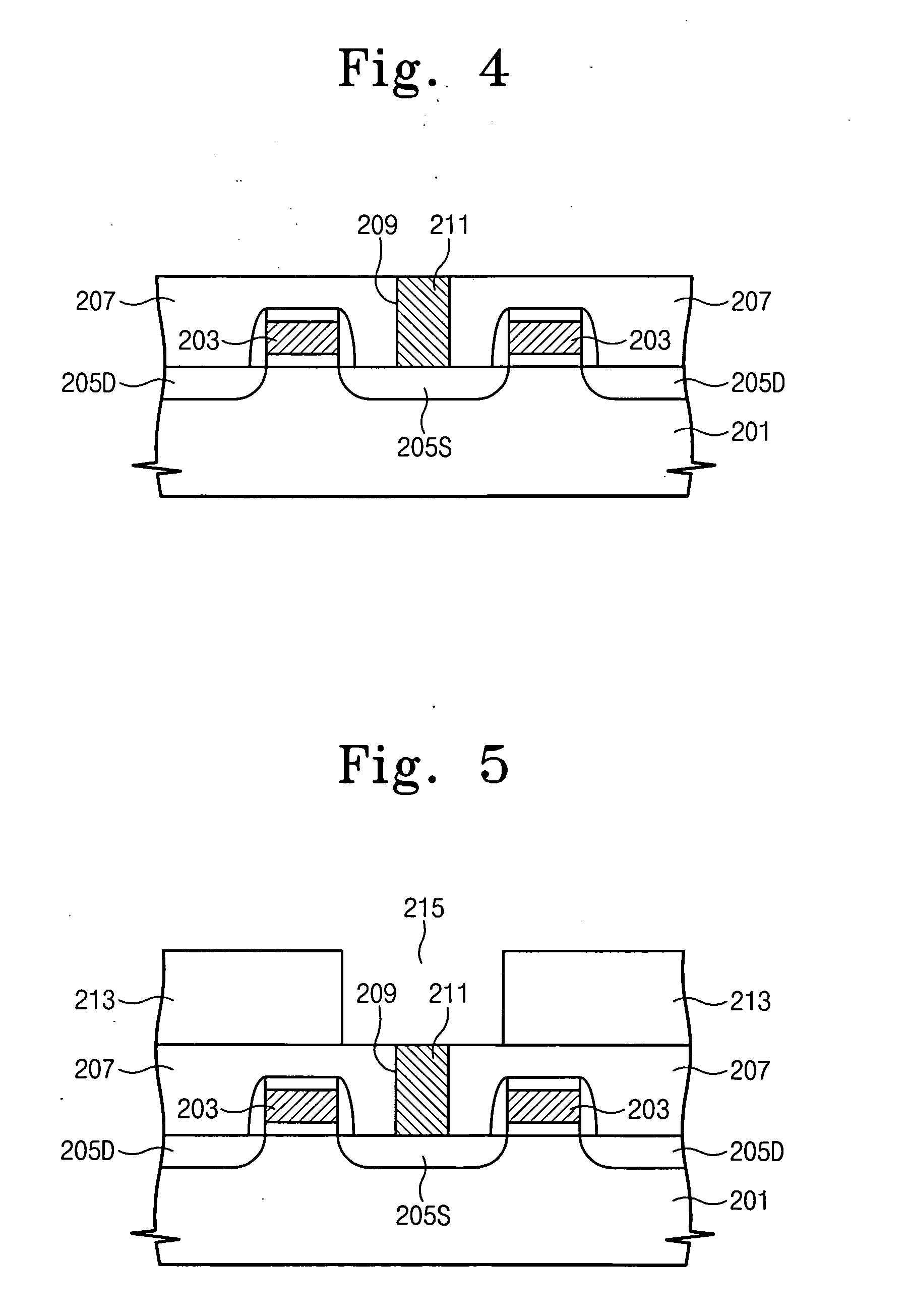

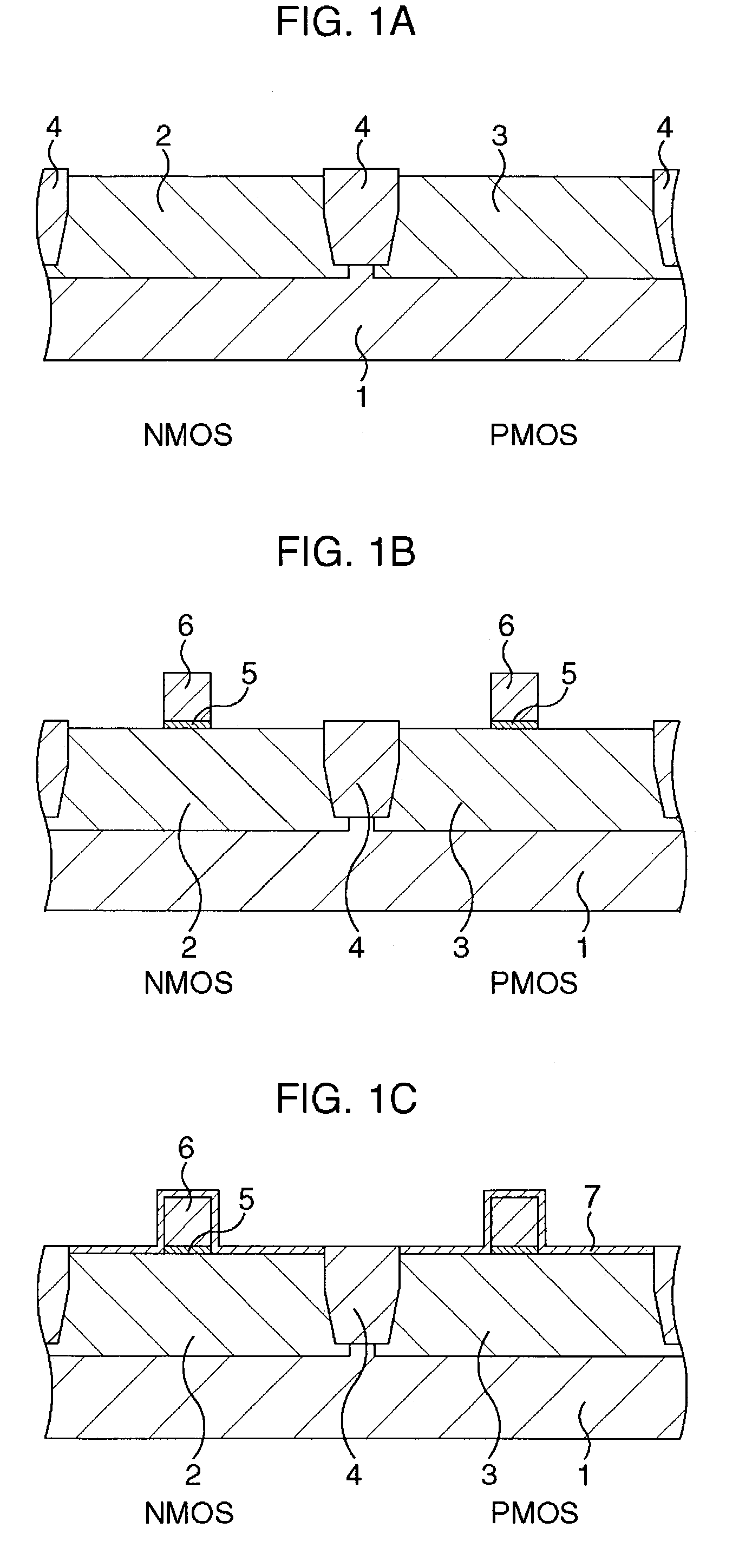

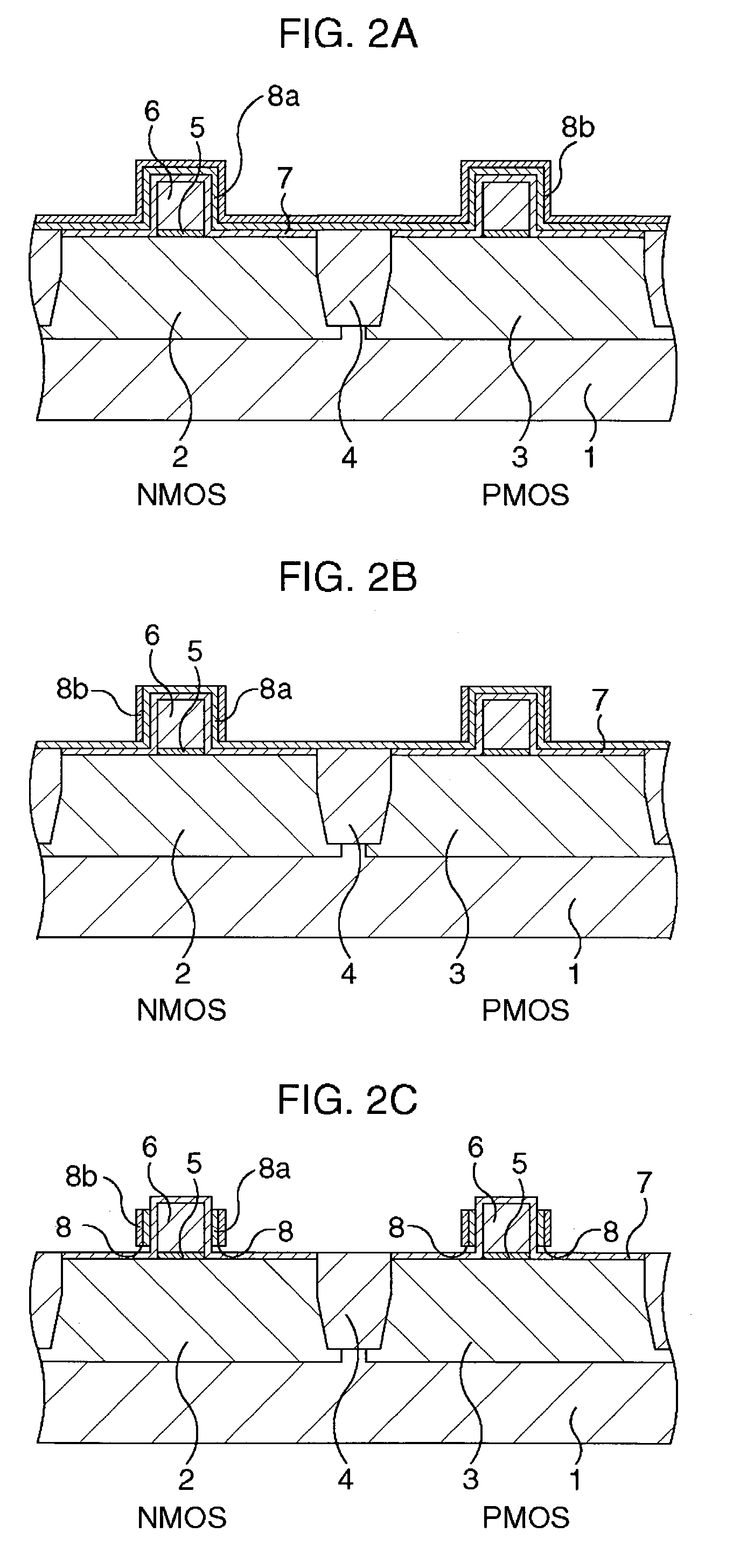

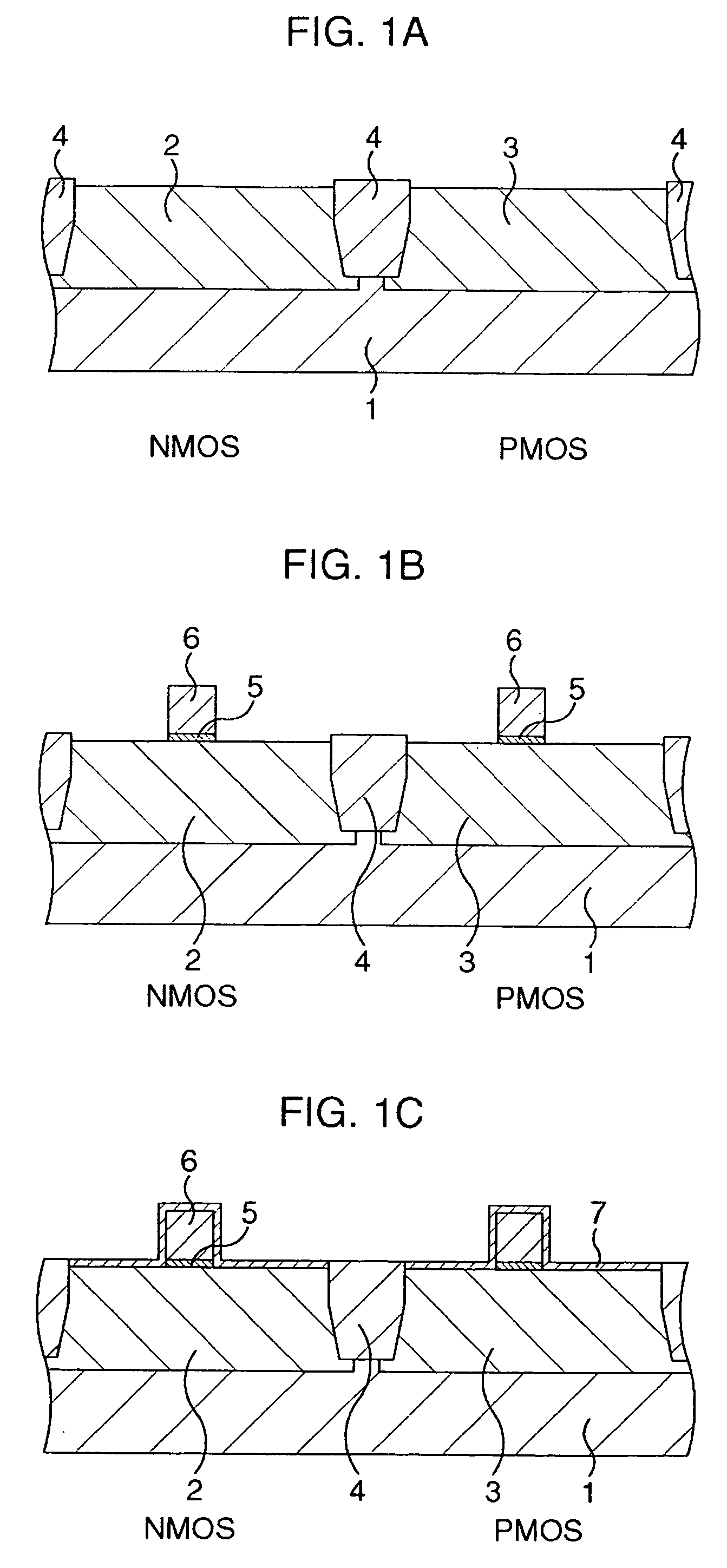

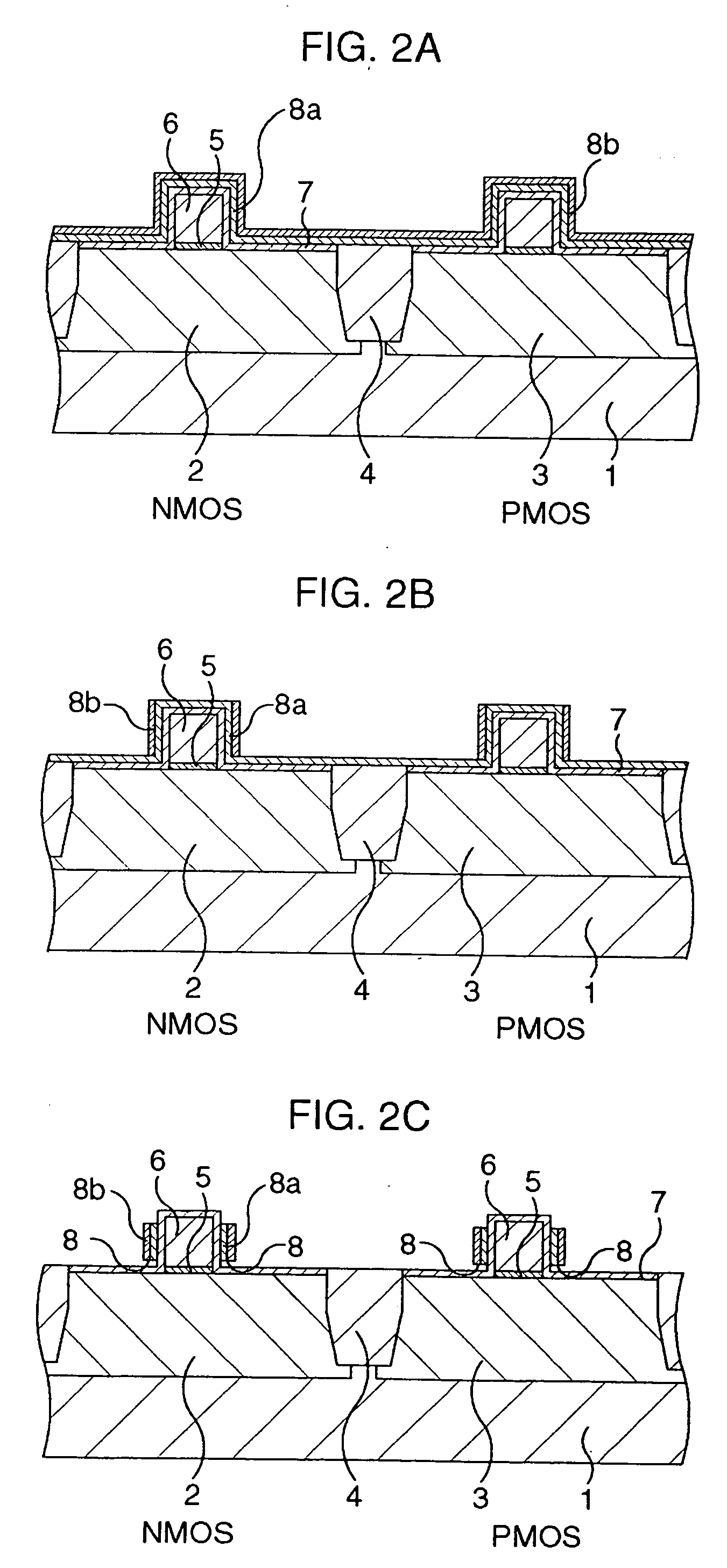

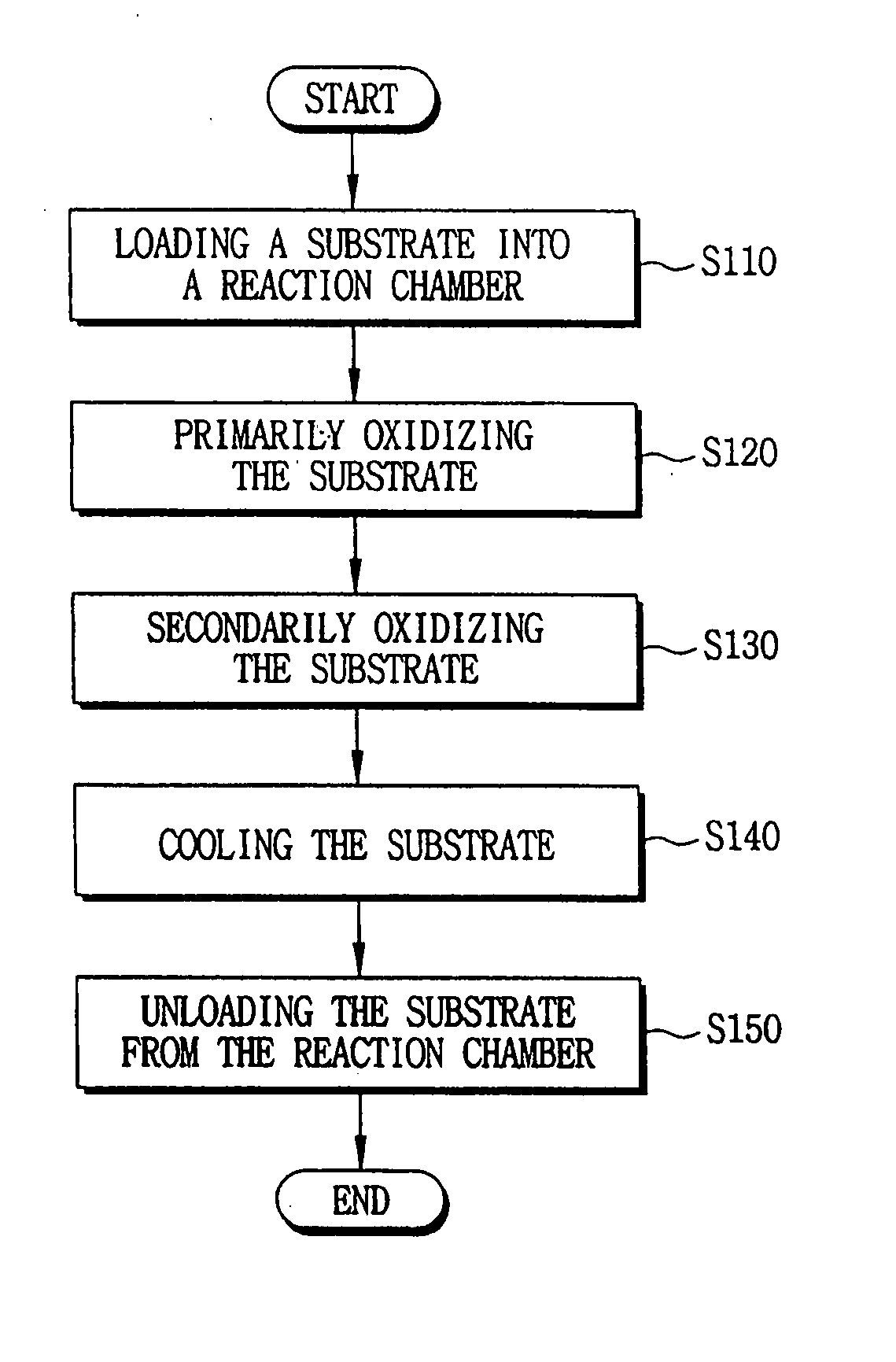

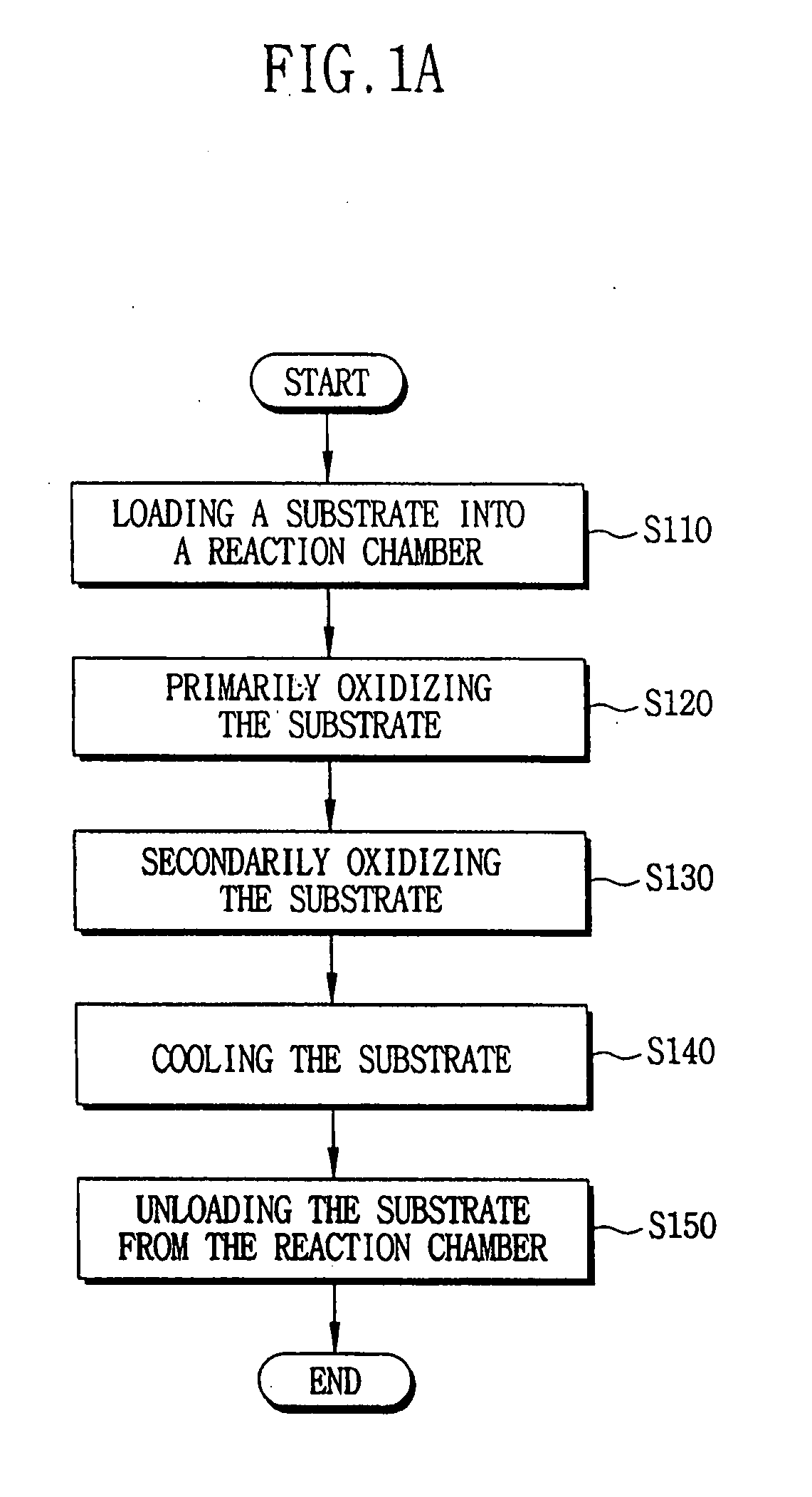

Method of forming silicidation blocking layer

InactiveUS6861369B2Prevent the diffusion of impuritiesPrevent diffusion and redistributionDecorative surface effectsSemiconductor/solid-state device manufacturingEtchingCelsius Degree

Disclosed is a method of manufacturing a semiconductor device. First, a silicidation blocking layer is formed on a semiconductor substrate by a plasma enhanced chemical vapor deposition process. Next, the silicidation blocking layer in a region in which a metal silicide contact is to be formed is removed by a wet etching process. Next, after a metal layer is formed on the resultant, the silicon in the region and the metal of the metal layer are reacted to form the metal silicide. Since the silicidation blocking layer consisting of PE-SiON is formed at a low temperature of less than 400 Celsius Degrees, it is possible to prevent diffusion and redistribution of impurities in gate and source / drain regions of a transistor during the deposition of the silicidation blocking layer.

Owner:SAMSUNG ELECTRONICS CO LTD

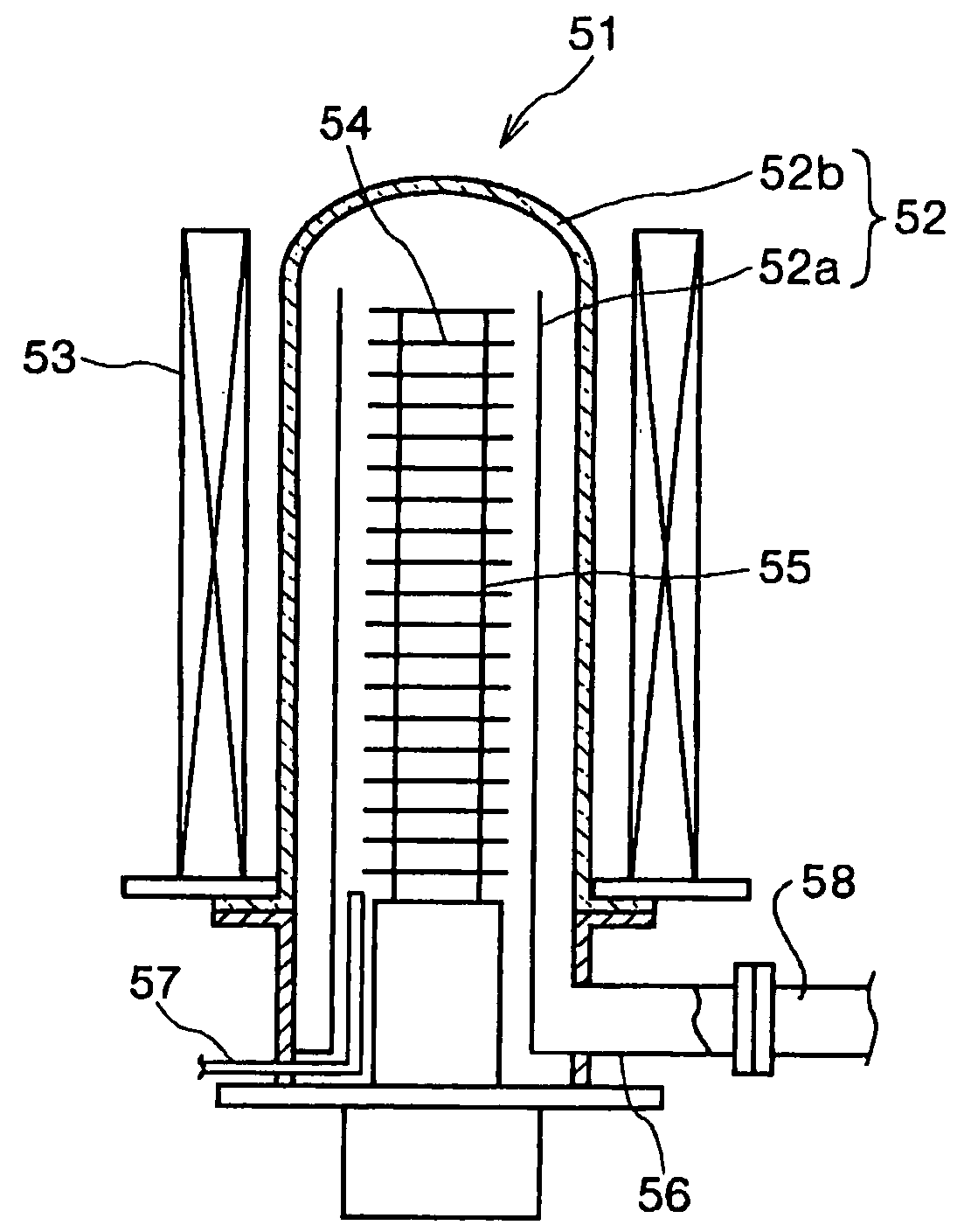

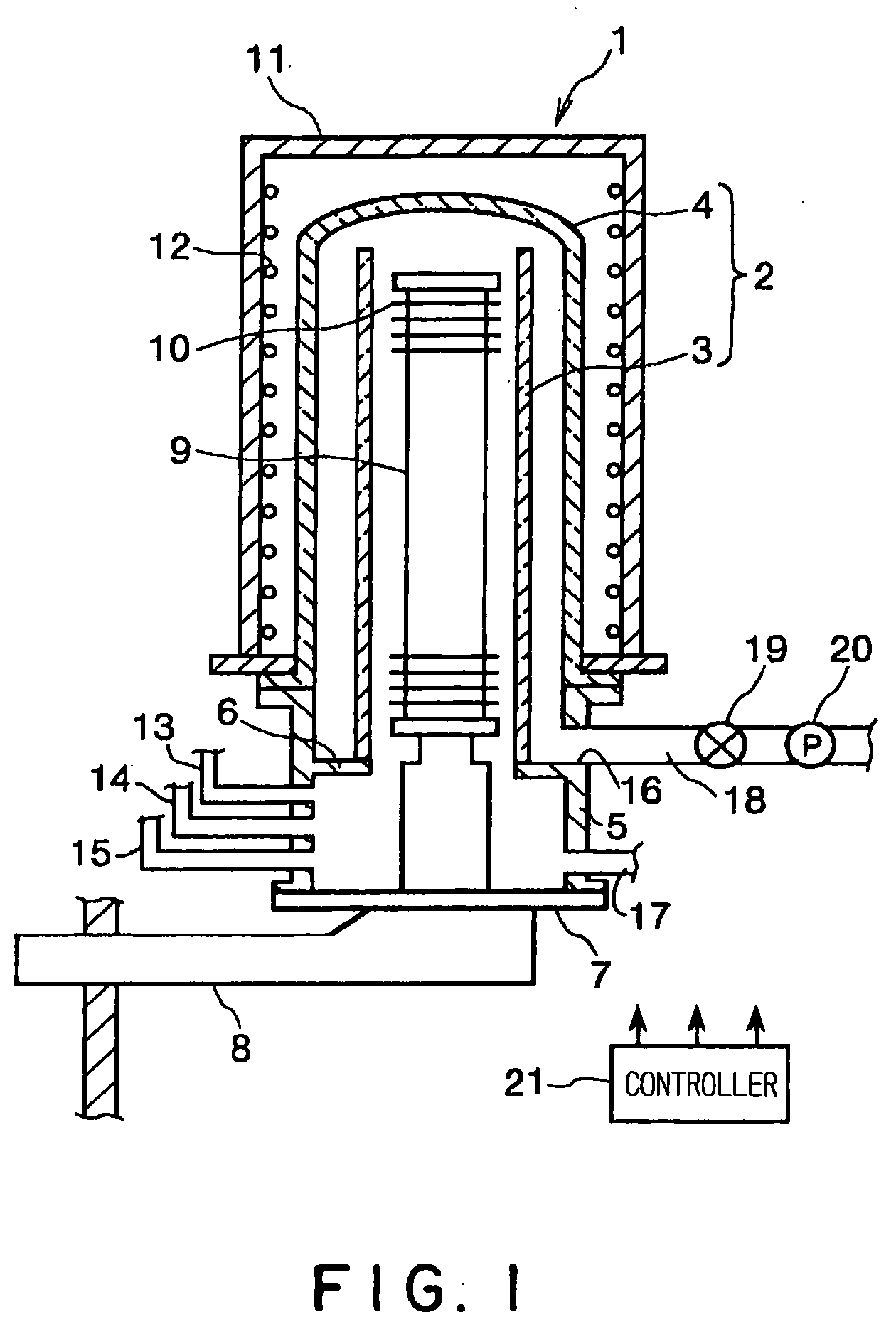

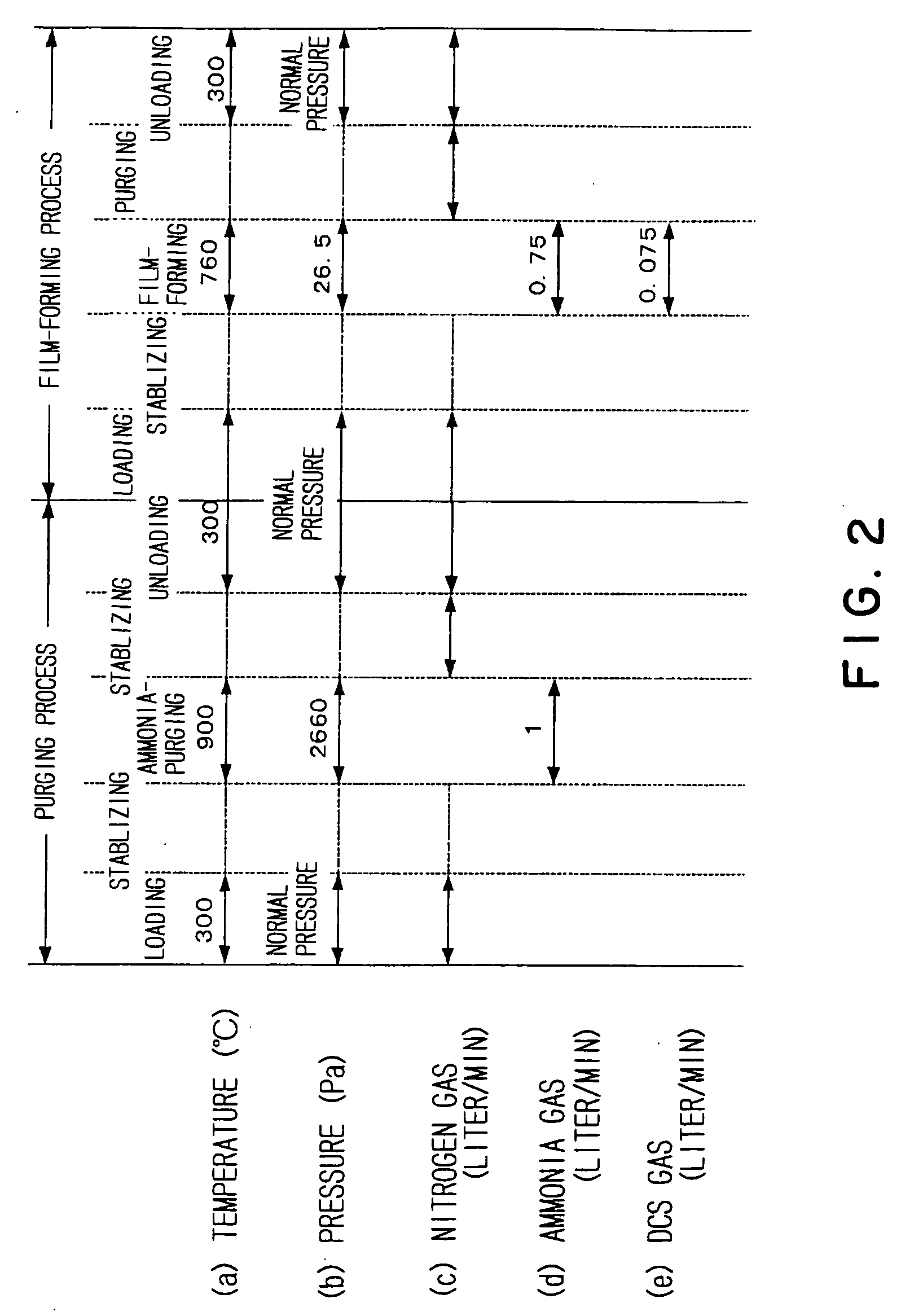

Method for cleaning thin-film forming apparatus

InactiveUS20060213539A1Efficient solutionPrevent the diffusion of impuritiesHollow article cleaningSemiconductor/solid-state device manufacturingNitrogenAnalytical chemistry

This invention is a cleaning method of a film-forming unit that forms a thin film on an object to be processed by supplying a process gas into a reaction chamber containing the object to be processed, the method comprising a purging step of purging an inside of the reaction chamber by supplying into the reaction chamber a nitrogen-including gas that includes nitrogen and that is capable of being activated. The purging step has a step of nitriding a surface of a member in the reaction chamber by activating the nitrogen-including gas.

Owner:TOKYO ELECTRON LTD

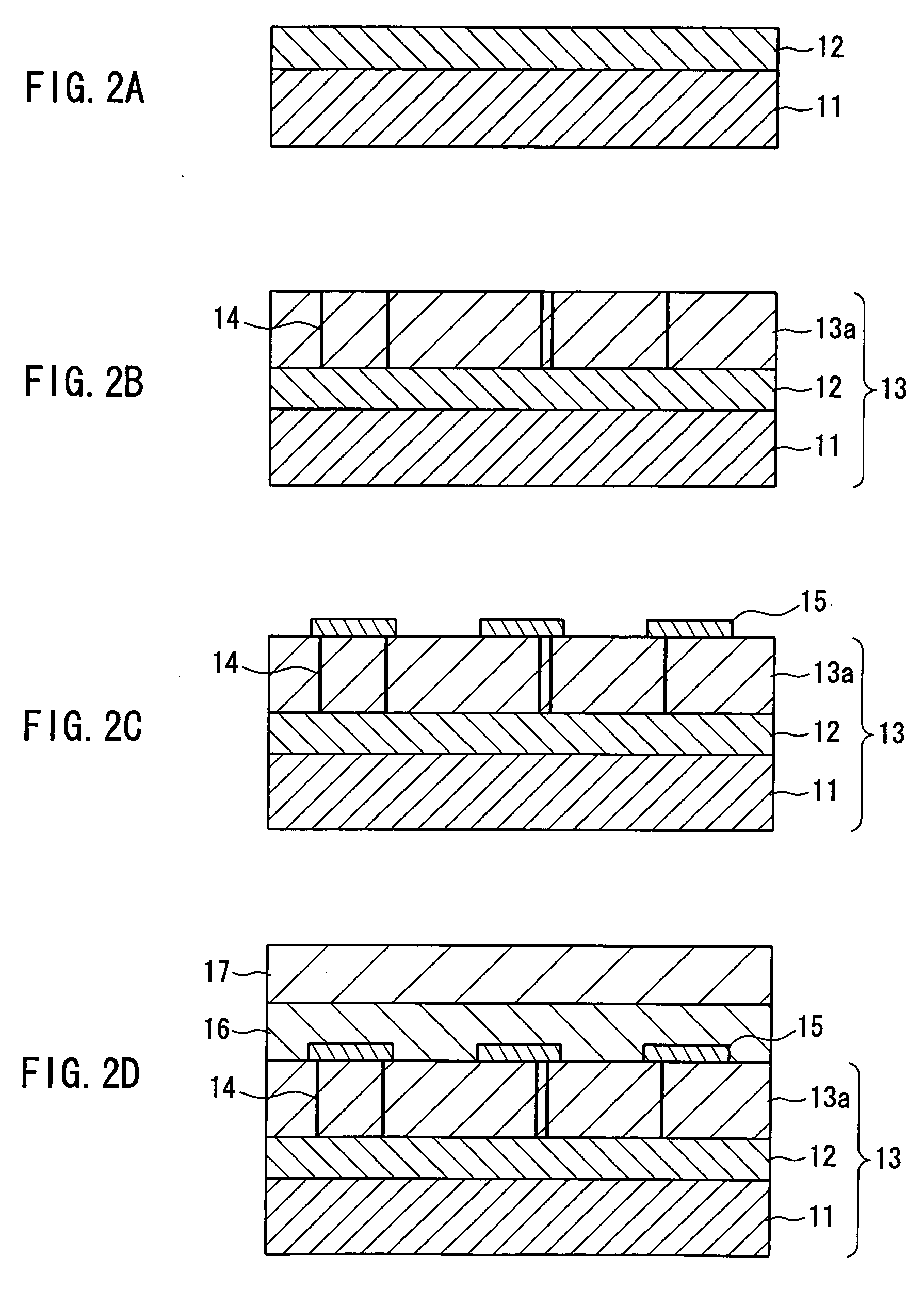

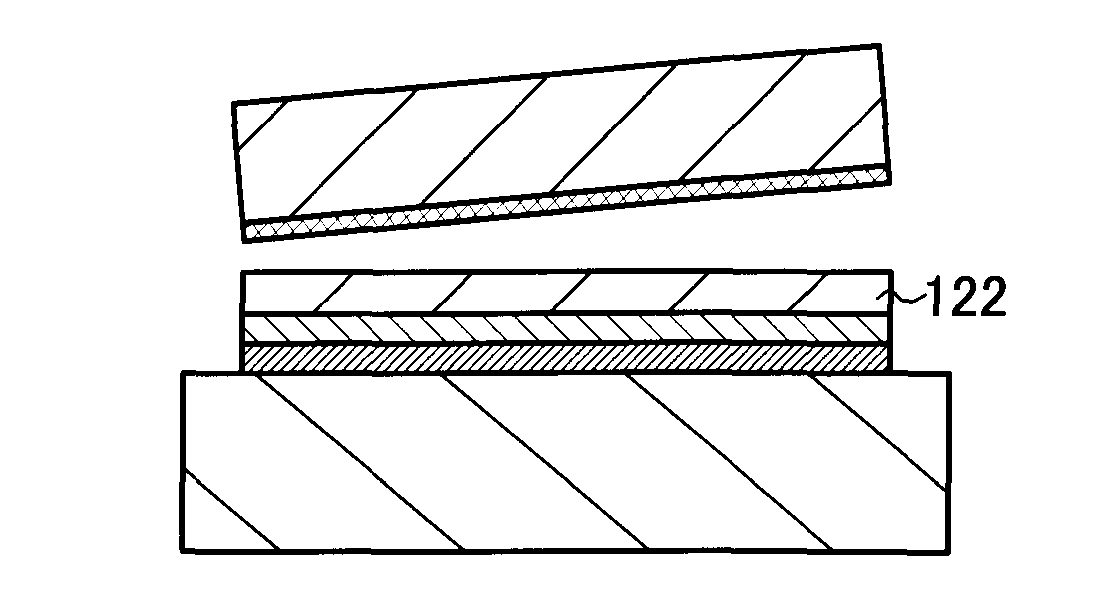

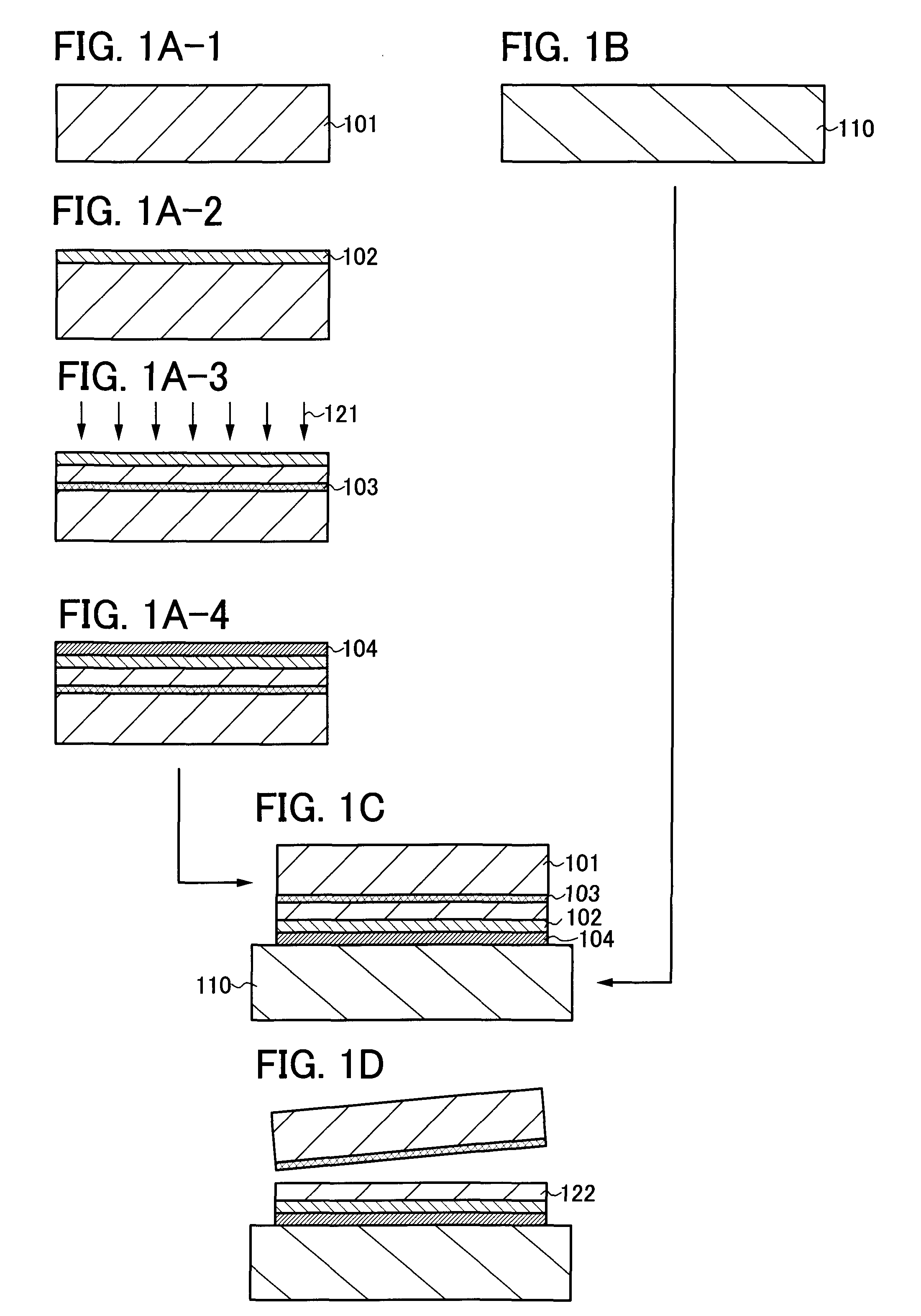

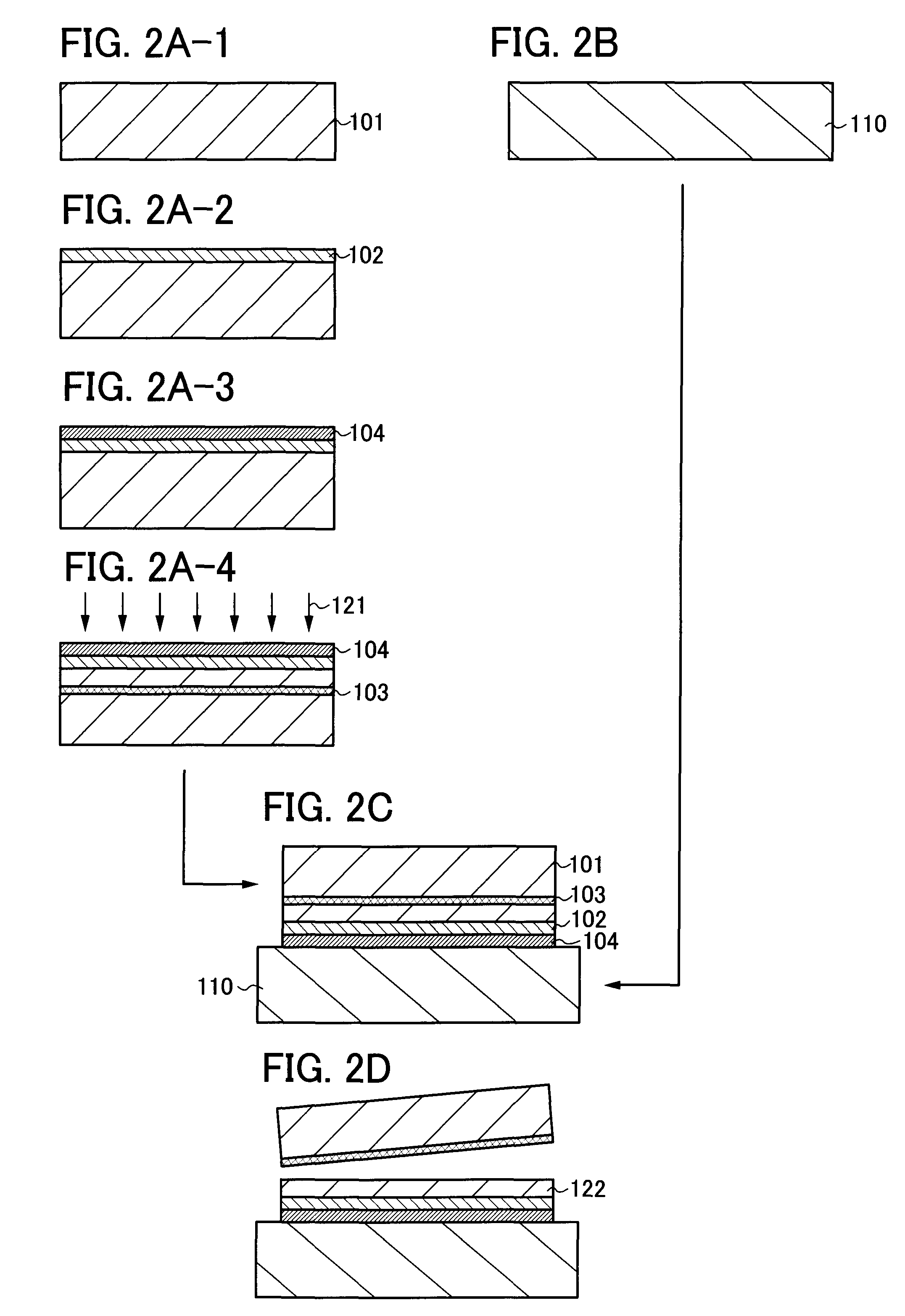

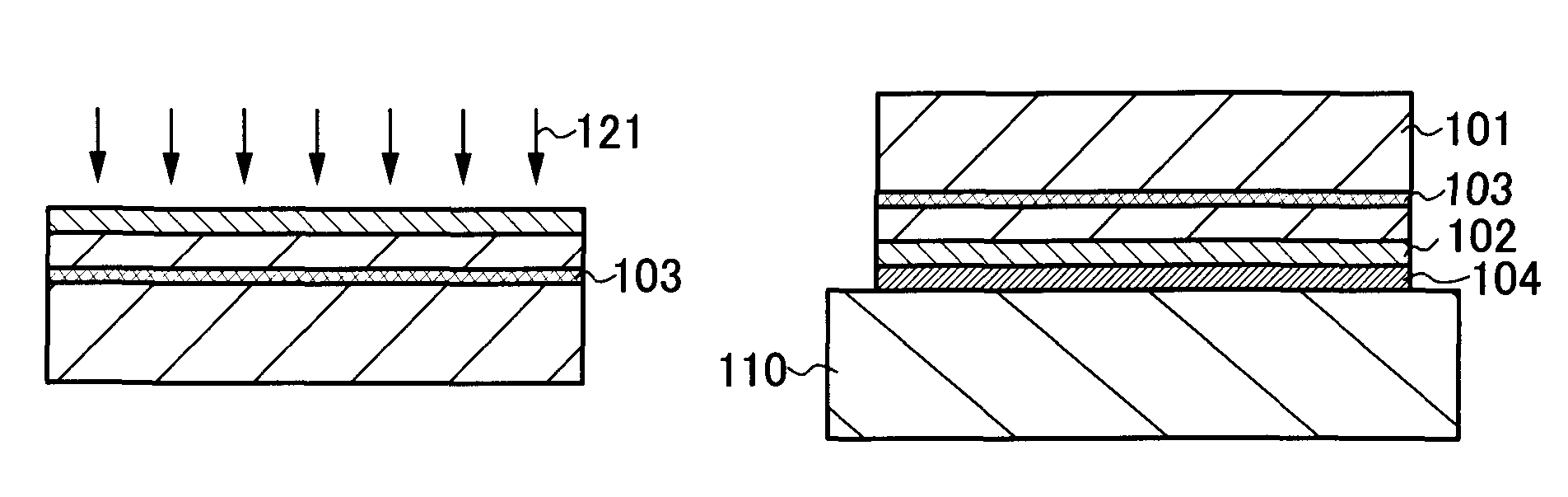

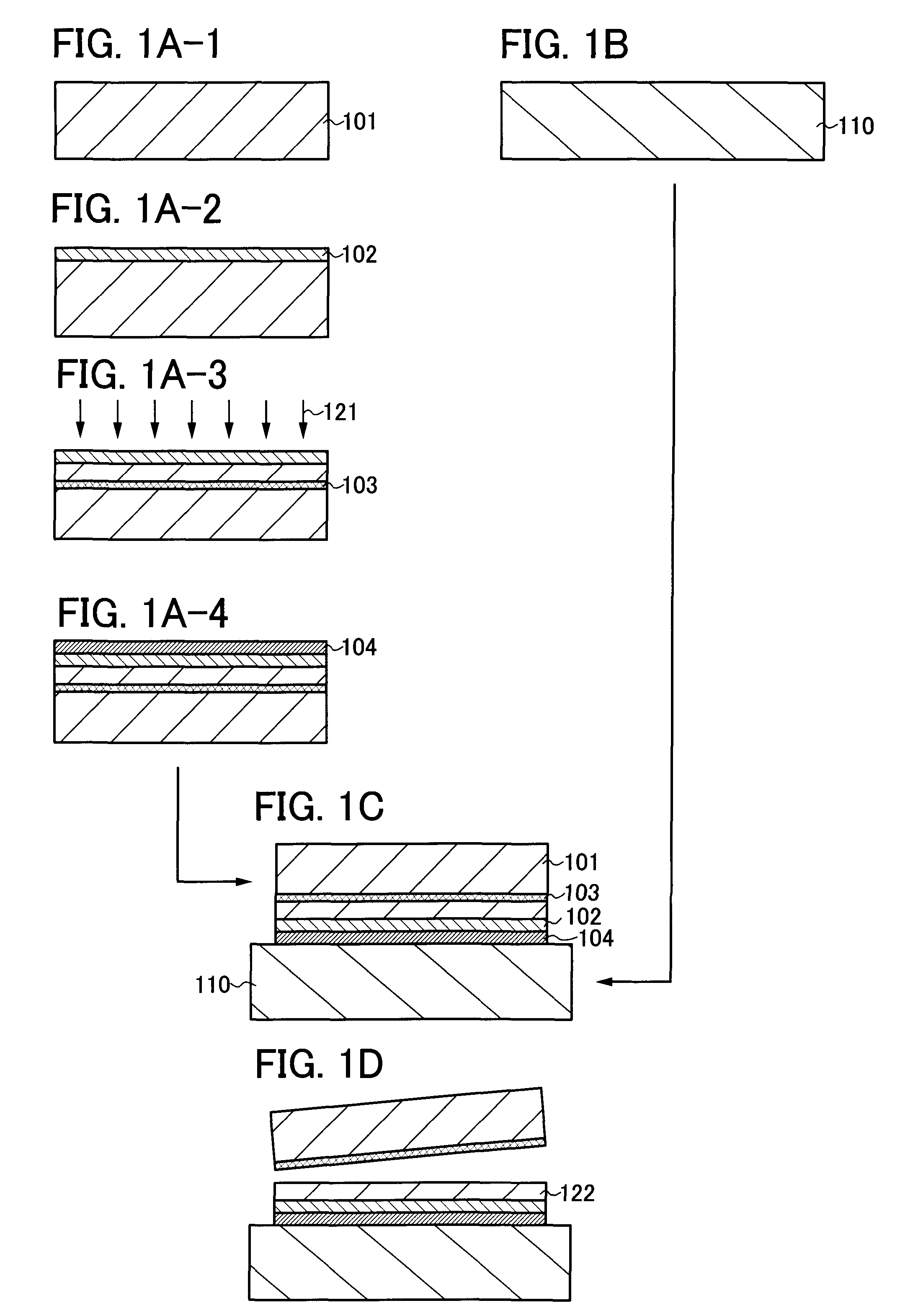

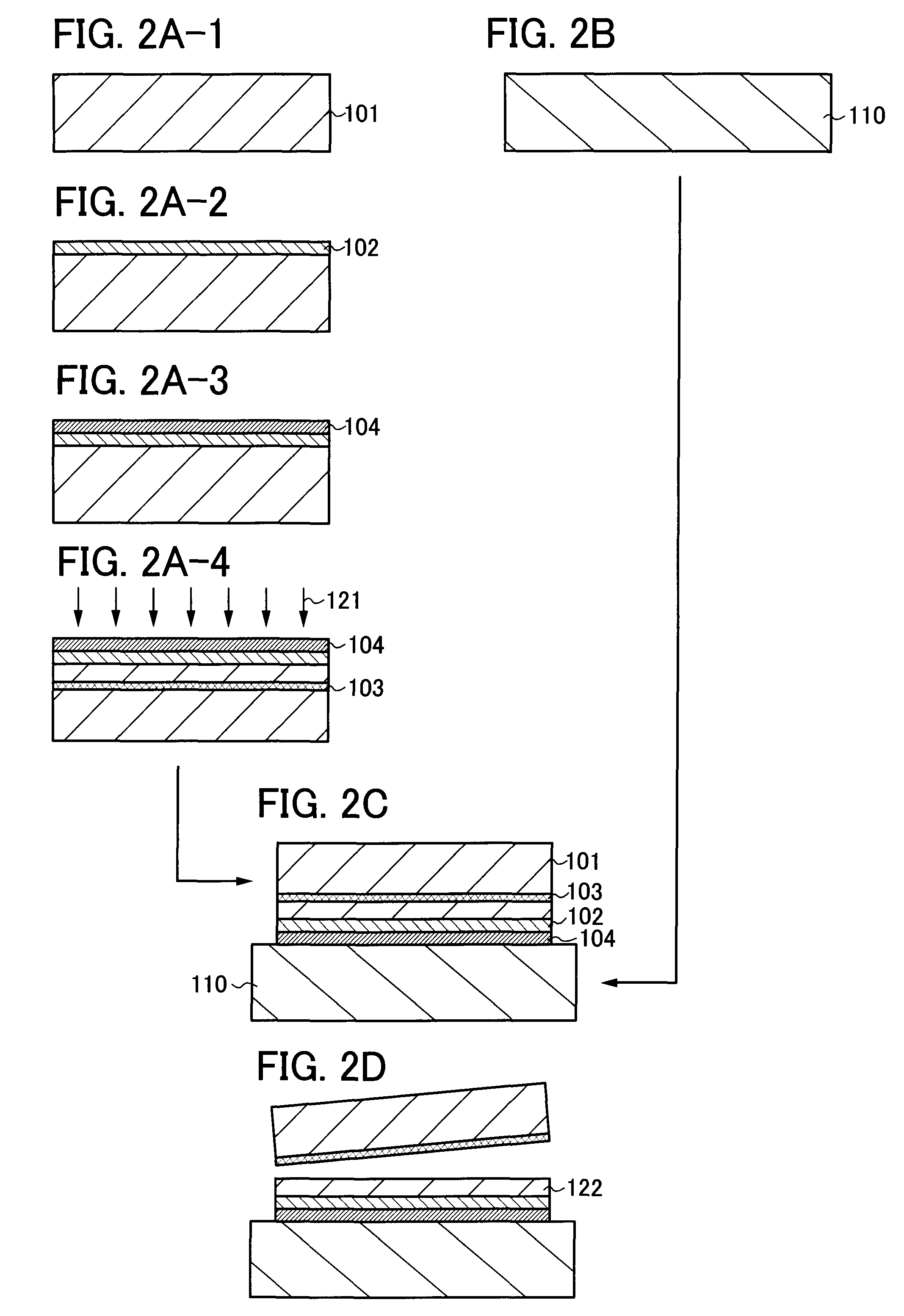

Method for manufacturing soi substrate

InactiveUS20090111236A1Occurrence of defectSimplification of processSolid-state devicesSemiconductor/solid-state device manufacturingNitrogenSingle crystal

An object is to reduce occurrence of defective bonding between a base substrate and a semiconductor substrate even when a silicon nitride film or the like is used as a bonding layer. Another object is to provide a method for manufacturing an SOI substrate by which an increase in the number of steps can be suppressed. A semiconductor substrate and a base substrate are prepared; an oxide film is formed over the semiconductor substrate; the semiconductor substrate is irradiated with accelerated ions through the oxide film to form a separation layer at a predetermined depth from a surface of the semiconductor substrate; a nitrogen-containing layer is formed over the oxide film after the ion irradiation; the semiconductor substrate and the base substrate are disposed opposite to each other to bond a surface of the nitrogen-containing layer and a surface of the base substrate to each other; and the semiconductor substrate is heated to cause separation along the separation layer, thereby forming a single crystal semiconductor layer over the base substrate with the oxide film and the nitrogen-containing layer interposed therebetween.

Owner:SEMICON ENERGY LAB CO LTD

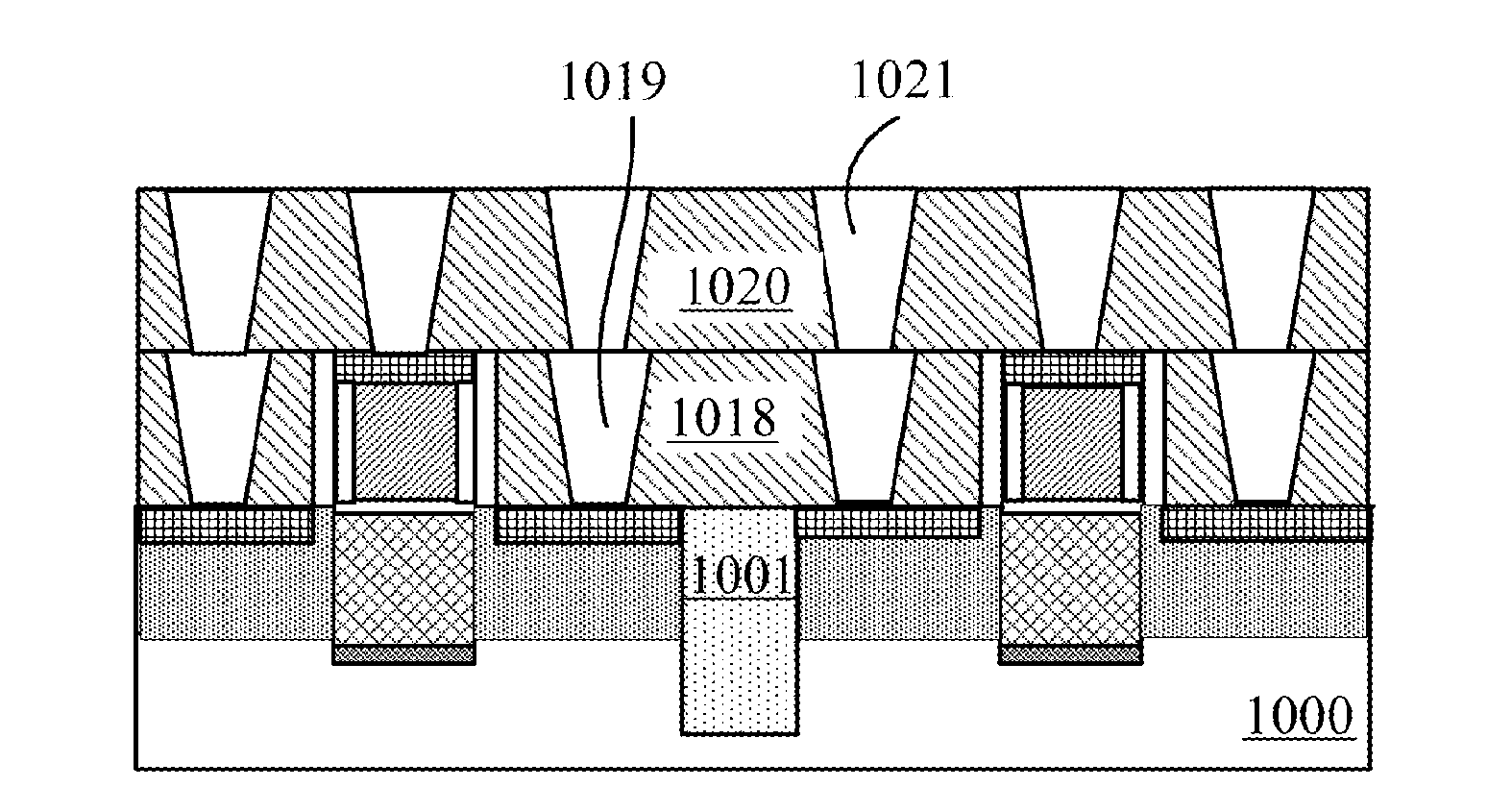

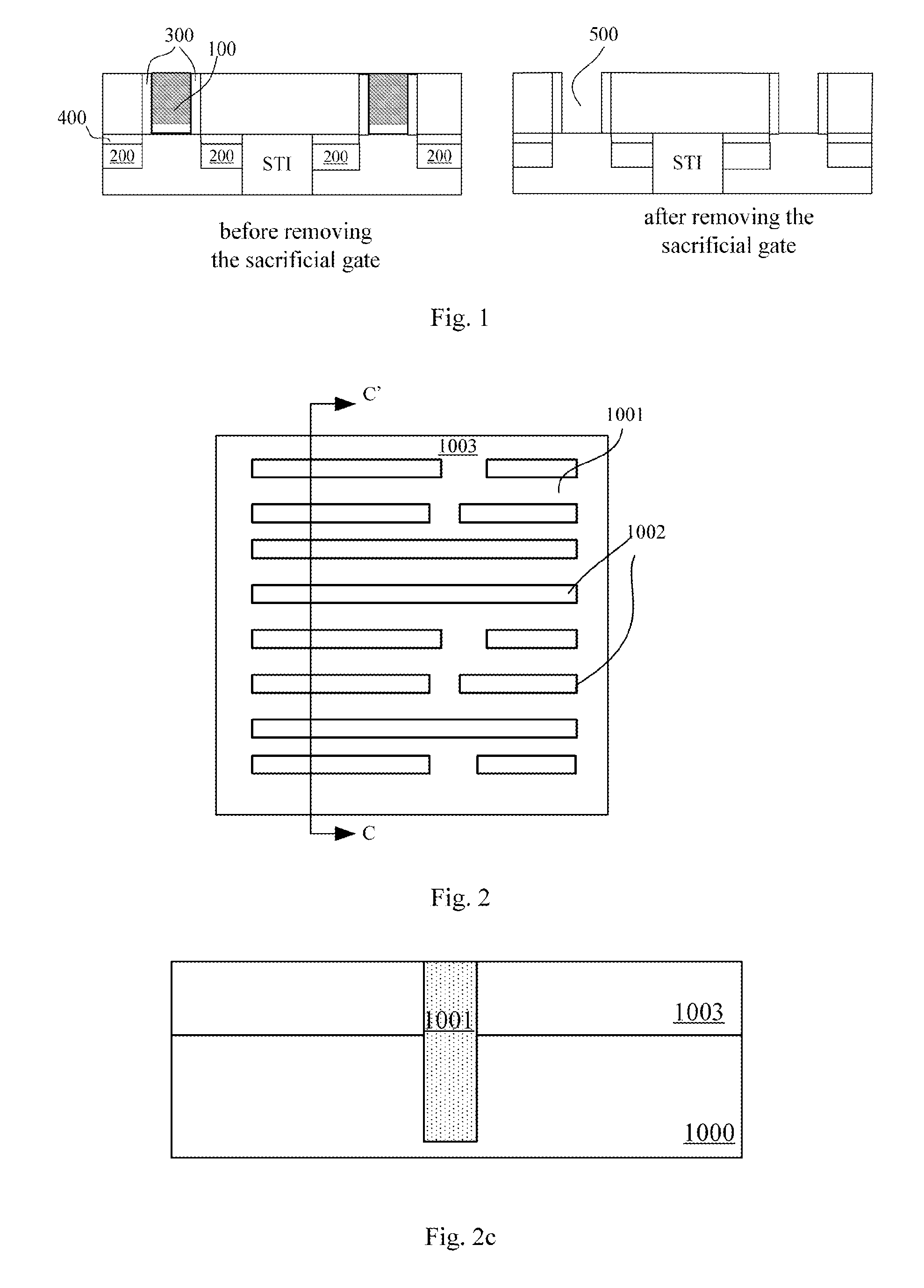

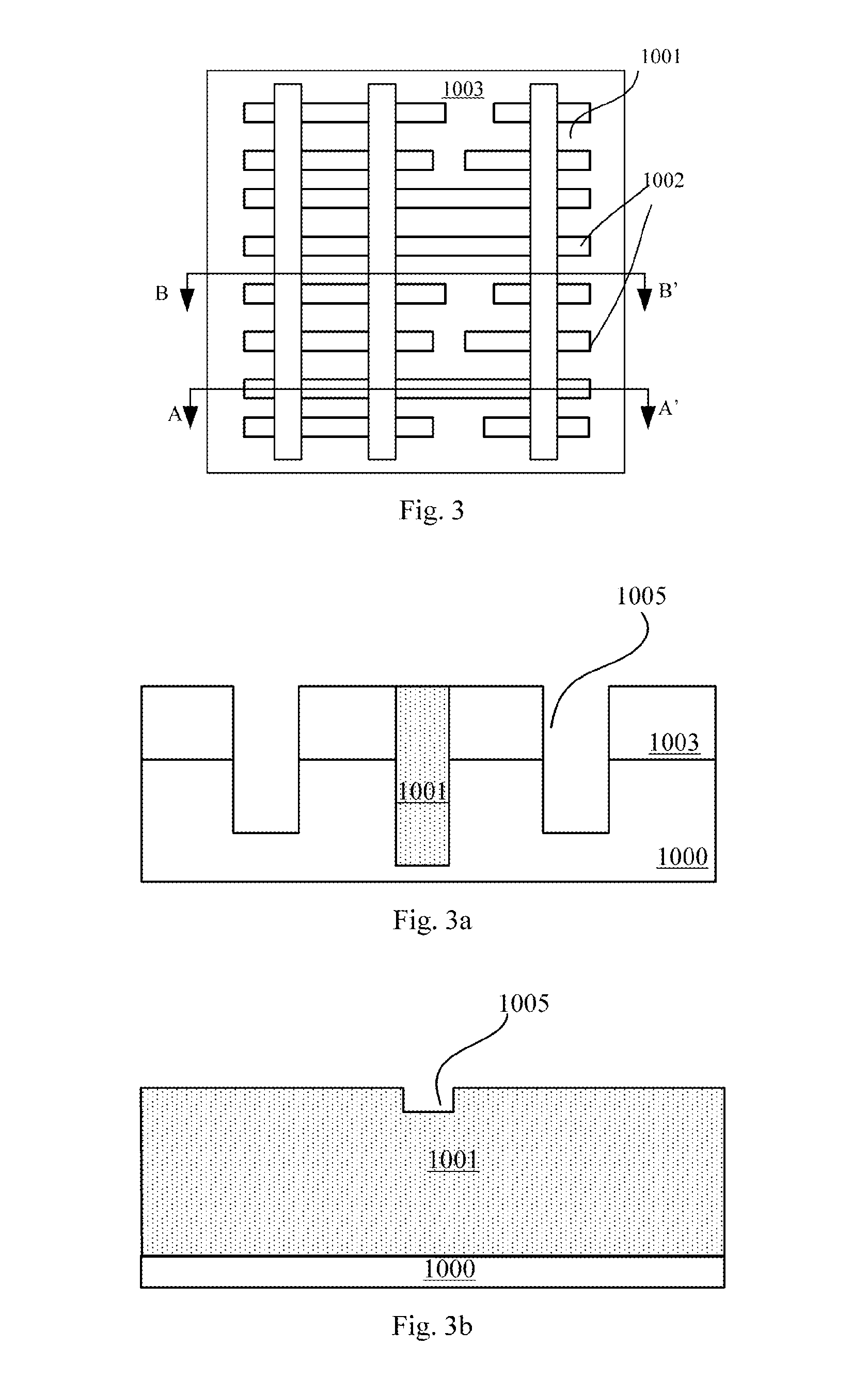

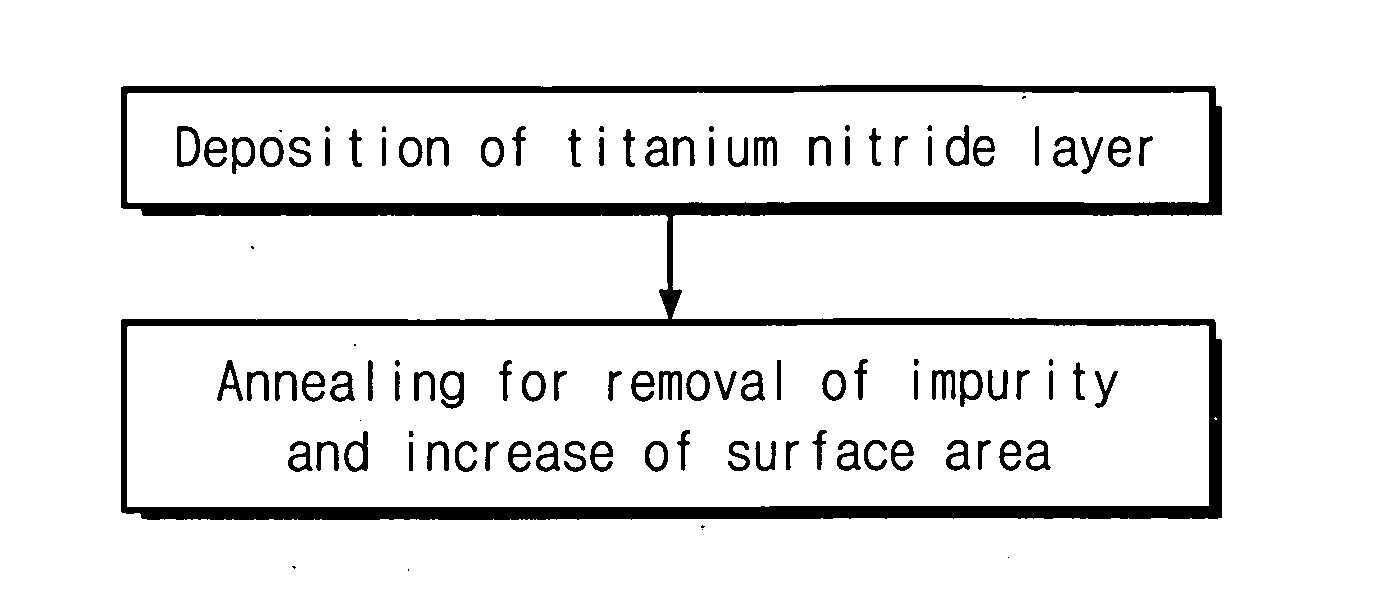

Semiconductor Device Structure and Method for Manufacturing the same

ActiveUS20120043593A1Prevent the diffusion of impuritiesImprove isolationSolid-state devicesSemiconductor/solid-state device manufacturingGate stackSemiconductor

The present invention presents a method for manufacturing a semiconductor device structure as well as the semiconductor device structure. Said method comprises: providing a semiconductor substrate; forming a first insulating layer on the semiconductor substrate; forming a shallow trench isolation embedded in the first insulating layer and the semiconductor substrate; forming a channel region embedded in the semiconductor substrate; and forming a gate stack stripe on the channel region. Said method further comprises, before forming the channel region, performing a source / drain implantation on the semiconductor substrate. By means of forming the source / drain regions in a self-aligned manner before forming the channel region and the gate stack, said method achieves the advantageous effects of the replacement gate process without using a dummy gate, thereby simplifying the process and reducing the cost.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

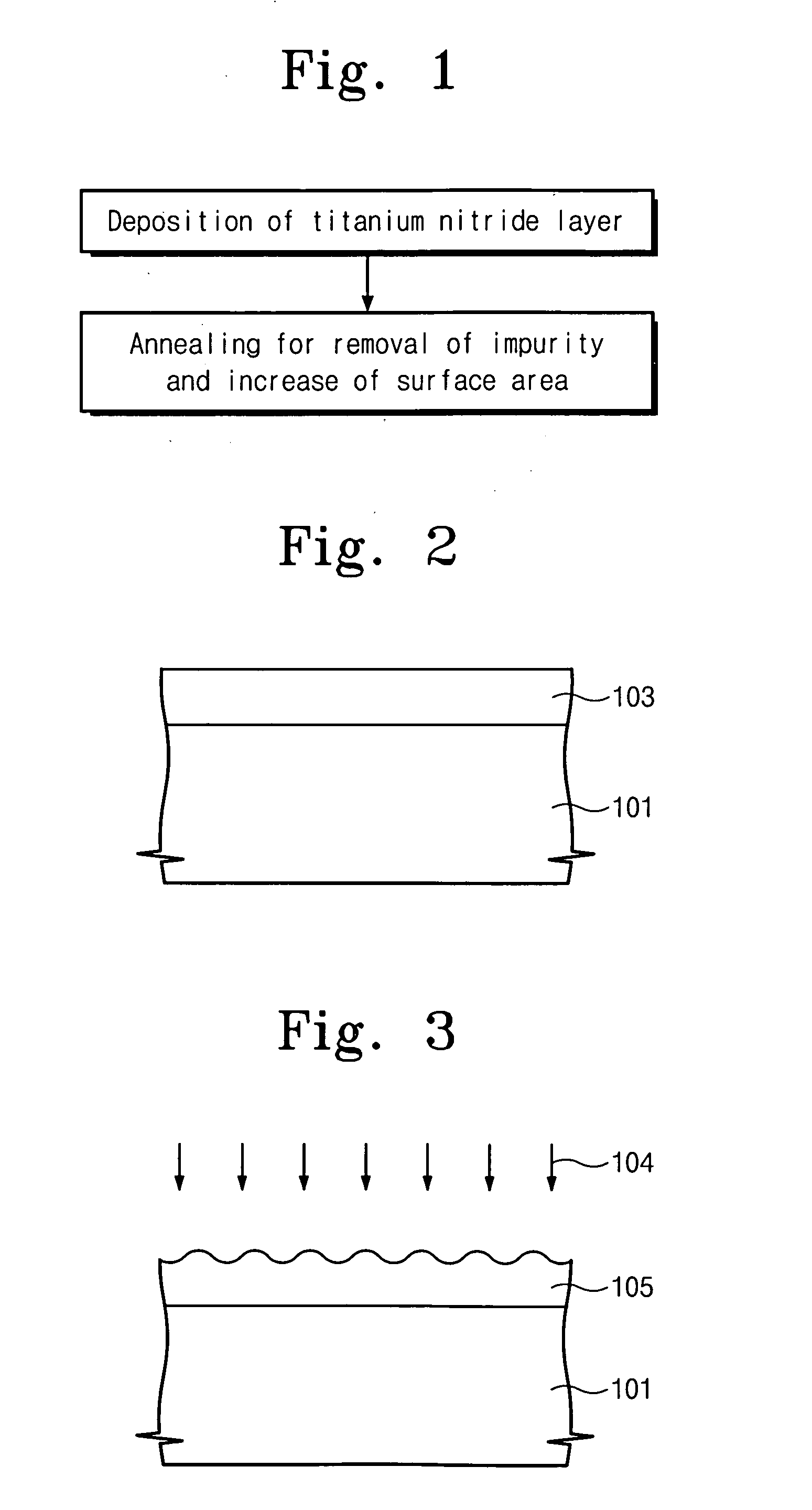

Method for forming a titanium nitride layer and method for forming a lower electrode of a MIM capacitor using the titanium nitride layer

InactiveUS20060128108A1Quality improvementIncrease surface areaSolid-state devicesSemiconductor/solid-state device manufacturingMetal-insulator-metalTitanium nitride

A method is provided for forming a titanium nitride layer in a metal-insulator-metal (MIM) capacitor. The deposition of a titanium nitride layer is carried out by means of an MOCVD method using a metallo-organic material as a source gas, followed by a rapid thermal process (RTP) at a high temperature. Through the RTP, impurities in the titanium nitride layer are removed and a surface area of the titanium nitride layer is increased in comparison with the titanium nitride layer before the RTP. The titanium nitride layer with increased surface area is useful for a lower electrode of a MIM capacitor.

Owner:SAMSUNG ELECTRONICS CO LTD

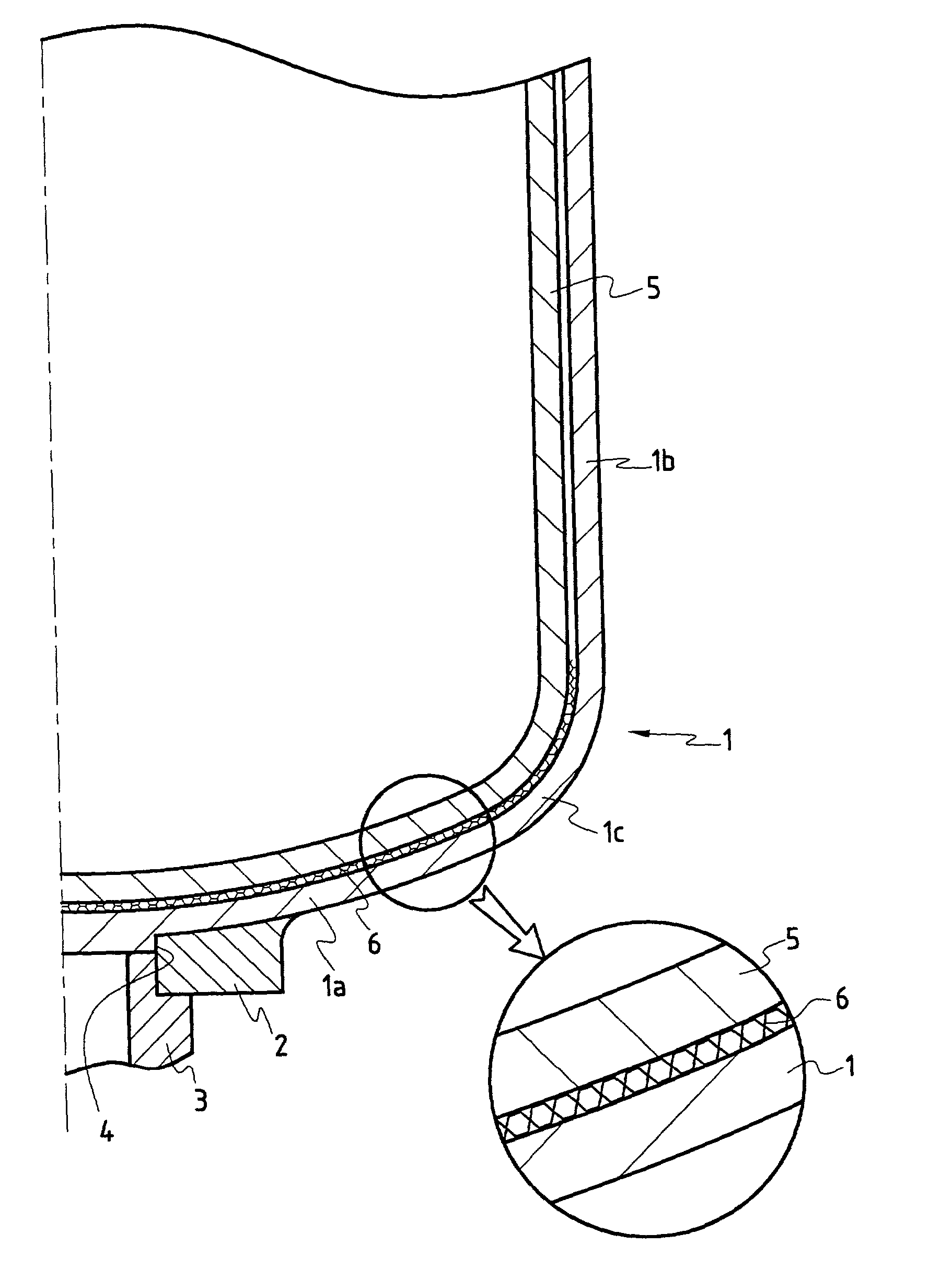

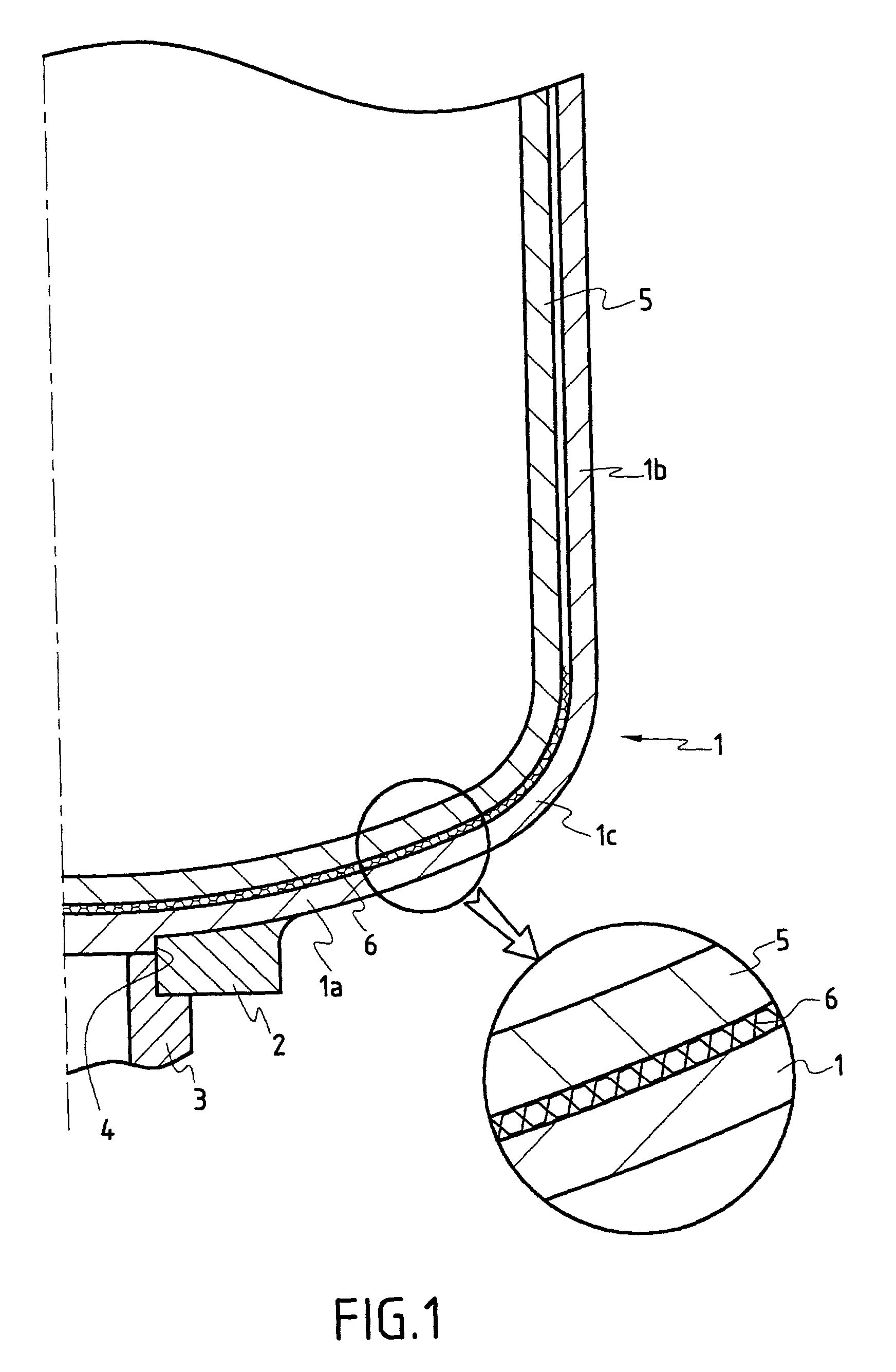

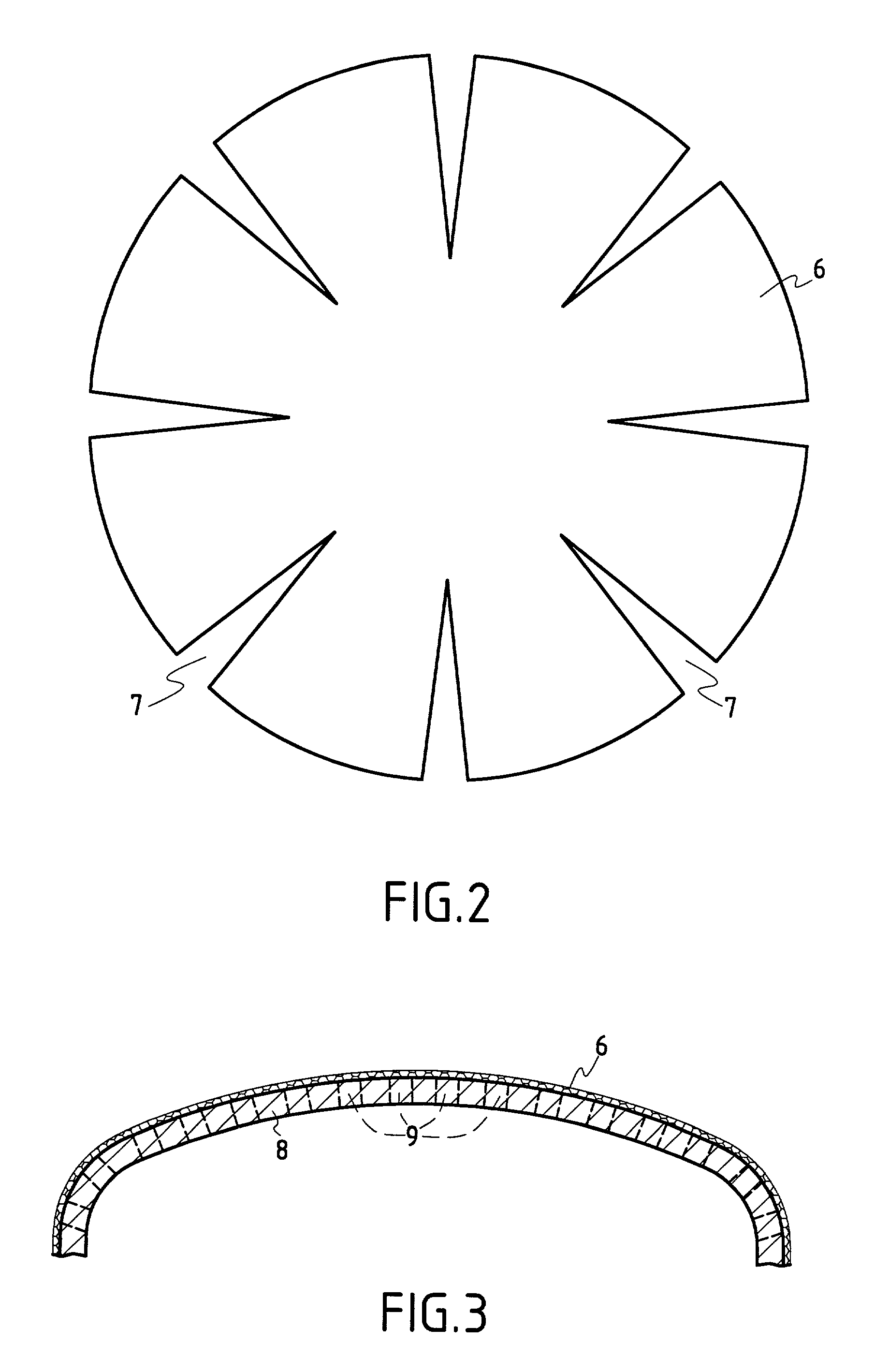

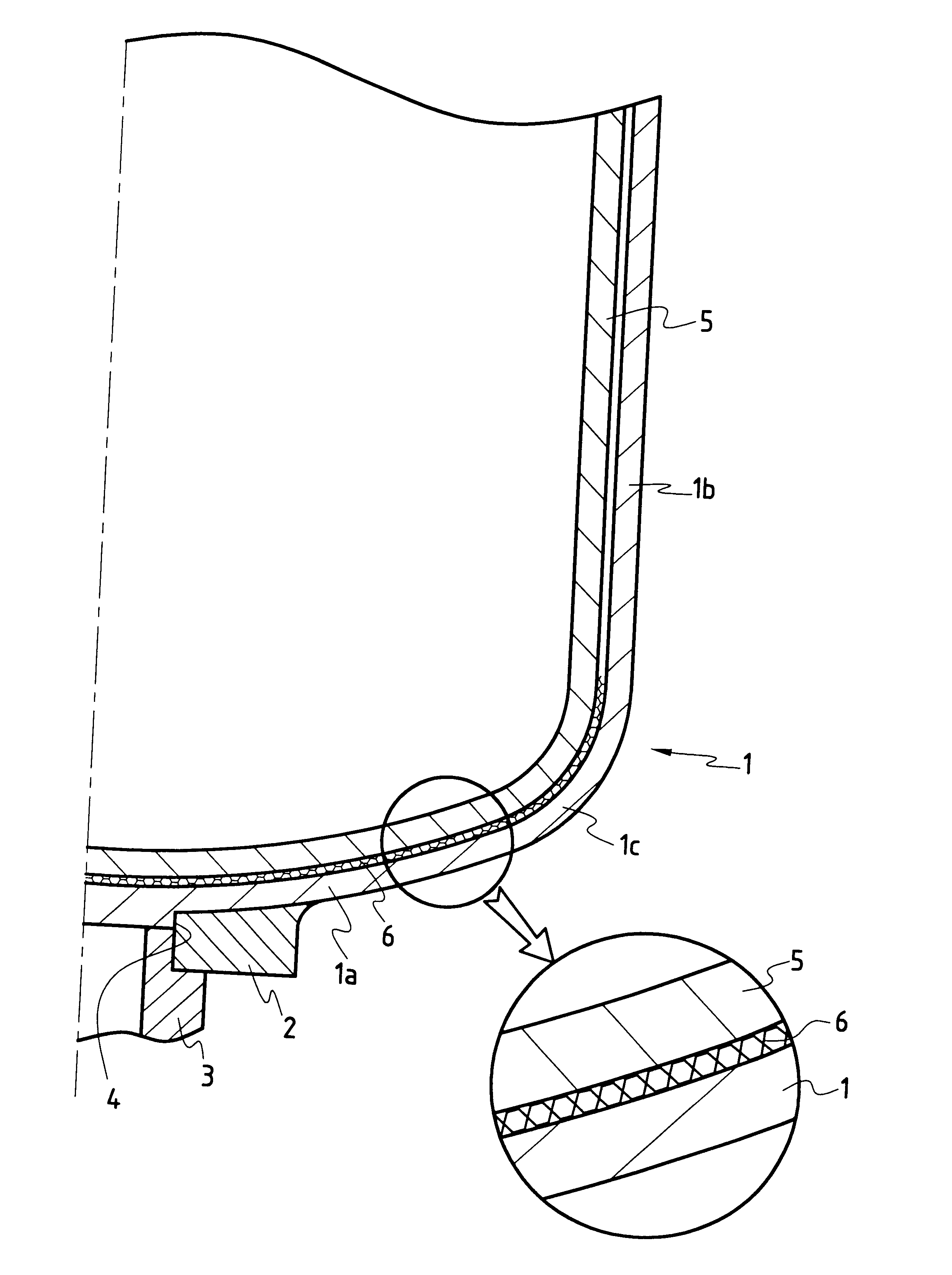

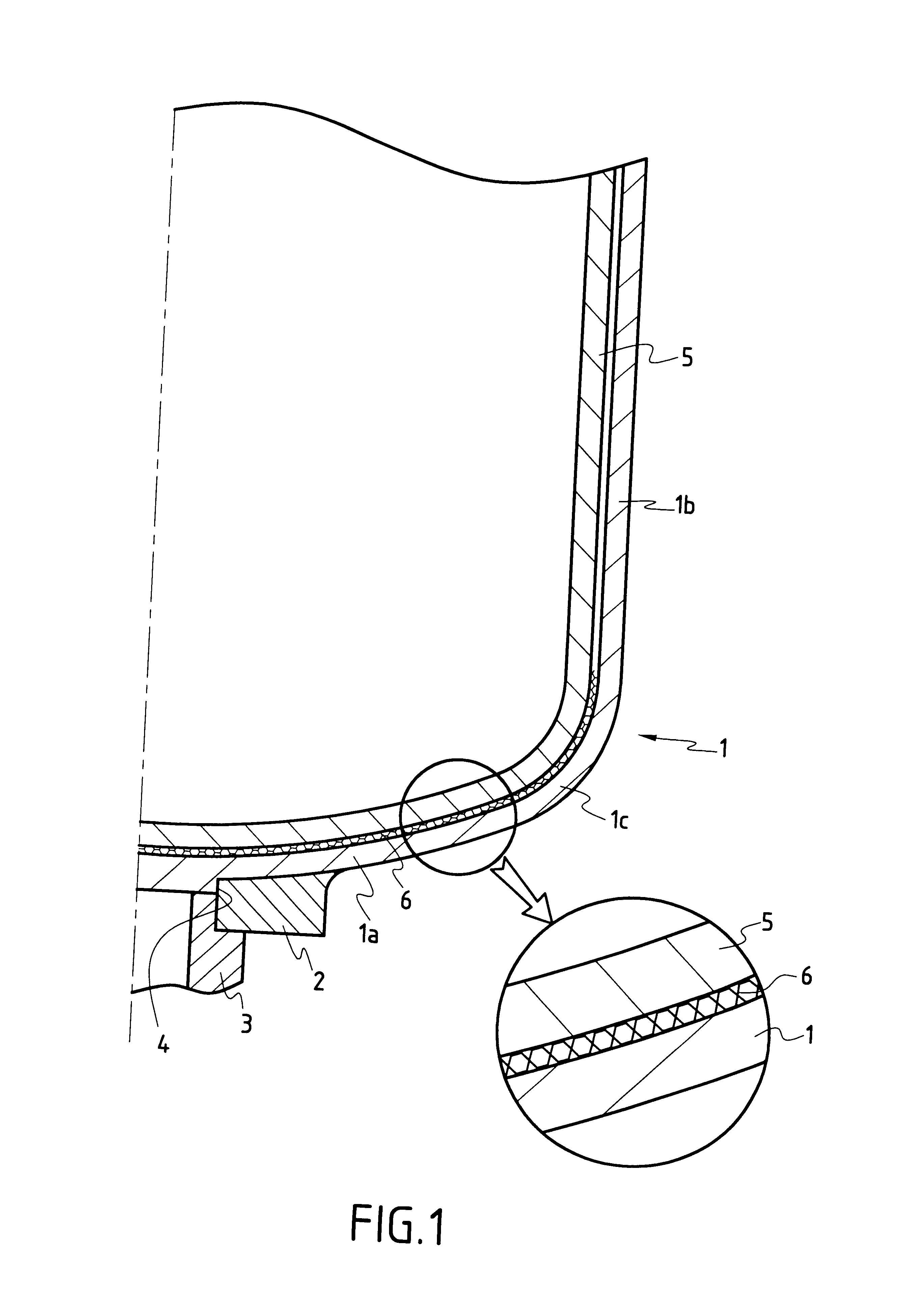

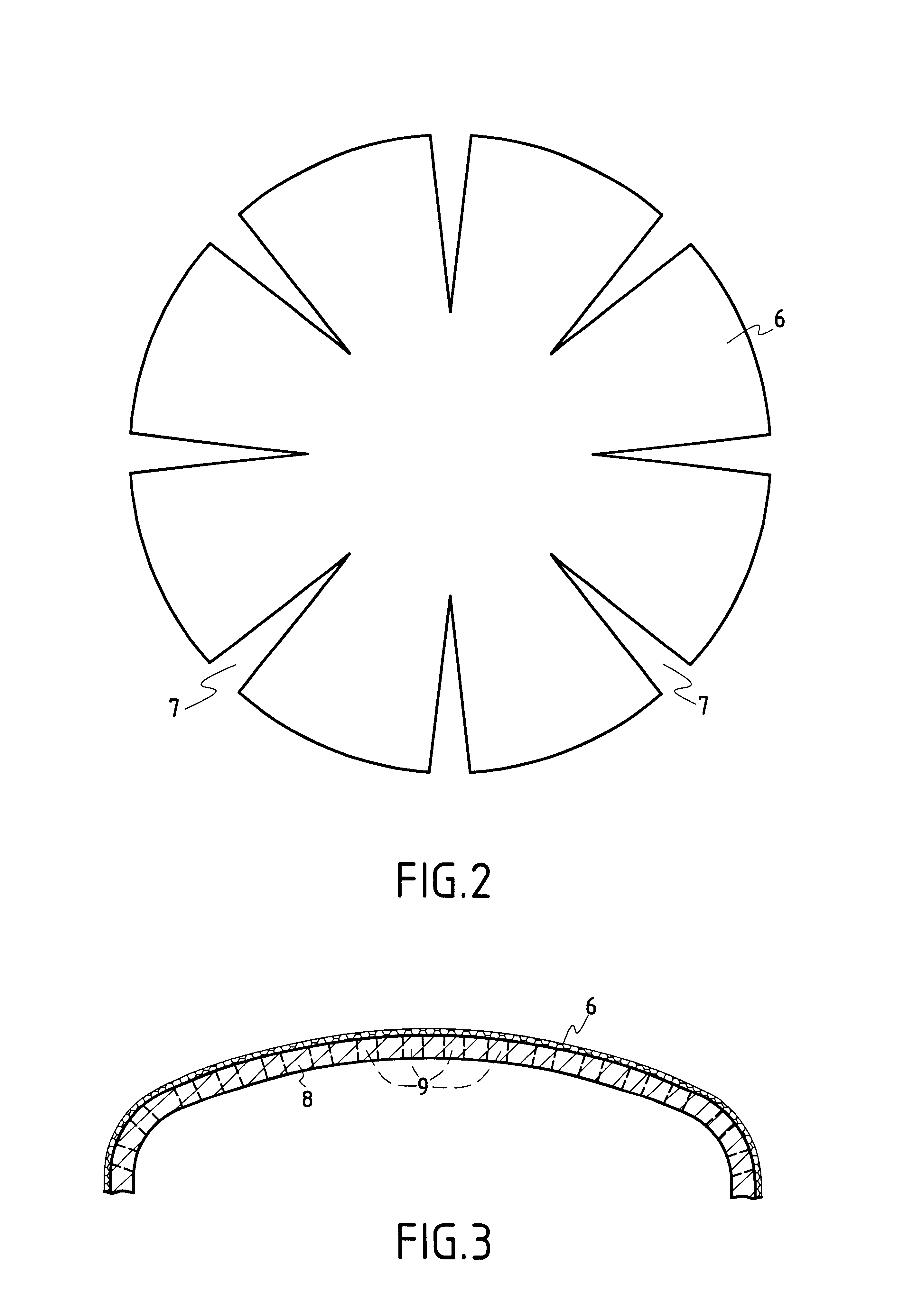

Protection for a carbon material, in particular C/C composite, bowl that is to receive a crucible, such as a silica crucible for drawing silicon

InactiveUS20020088390A1Limit mechanical stressExtended service lifeFurnace componentsFrom solid stateFiberCrucible

Prior to housing the crucible in the bowl, a consumable buffer ply is applied over at least a portion of the inside face of the bowl, the ply being constituted essentially by a non-rigid carbon fiber fabric for protecting the bowl from both physical and chemical interactions with the crucible. The buffer ply is essentially constituted by a flexible fabric selected from: a woven cloth, a knit, a multidirectional sheet, and a thin felt. Prior to putting the ply into place in the bowl, it is possible to form a thin deposit of pyrolytic carbon on the fibers of the fabric.

Owner:SNECMA MOTEURS SA

Group-III-element nitride crystal semiconductor device

InactiveUS7227172B2Prevent the diffusion of impuritiesReduce diffusion coefficientLaser detailsFrom solid stateAlkaline earth metalNitrogen

In a Group-III-element nitride semiconductor device including a Group-III-element nitride crystal layer stacked on a Group-III-element nitride crystal substrate, the substrate is produced by allowing nitrogen of nitrogen-containing gas and a Group III element to react with each other to crystallize in a melt (a flux) containing at least one of alkali metal and alkaline-earth metal, and a thin film layer is formed on the substrate and the thin film has a lower diffusion coefficient than that of the substrate with respect to impurities contained in the substrate. The present invention provides a semiconductor device in which alkali metal is prevented from diffusing.

Owner:PANASONIC CORP

Light emitting device

ActiveUS7274044B2Reduce light reflectionPrevent the diffusion of impuritiesElectroluminescent light sourcesSolid-state devicesActive matrixLight emitting device

It is an object of the present invention to provide an active matrix light emitting device which can efficiently prevent a diffusion of impurities from a substrate to a transistor, as well as reducing a reflection of light in a process of extracting light toward the outside of the light emitting device. One feature of the present invention is a light emitting device including a substrate, a first insulating layer provided over the substrate, a transistor provided over the first insulating layer, and a second insulating layer having a first opening portion which is provided to expose the substrate as well as covering the transistor, wherein a light emitting element is provided inside the first opening portion.

Owner:SEMICON ENERGY LAB CO LTD

Method for manufacturing SOI substrate

InactiveUS7696058B2Small sizePrevent the diffusion of impuritiesSolid-state devicesSemiconductor/solid-state device manufacturingNitrogenSingle crystal

An object is to reduce occurrence of defective bonding between a base substrate and a semiconductor substrate even when a silicon nitride film or the like is used as a bonding layer. Another object is to provide a method for manufacturing an SOI substrate by which an increase in the number of steps can be suppressed. A semiconductor substrate and a base substrate are prepared; an oxide film is formed over the semiconductor substrate; the semiconductor substrate is irradiated with accelerated ions through the oxide film to form a separation layer at a predetermined depth from a surface of the semiconductor substrate; a nitrogen-containing layer is formed over the oxide film after the ion irradiation; the semiconductor substrate and the base substrate are disposed opposite to each other to bond a surface of the nitrogen-containing layer and a surface of the base substrate to each other; and the semiconductor substrate is heated to cause separation along the separation layer, thereby forming a single crystal semiconductor layer over the base substrate with the oxide film and the nitrogen-containing layer interposed therebetween.

Owner:SEMICON ENERGY LAB CO LTD

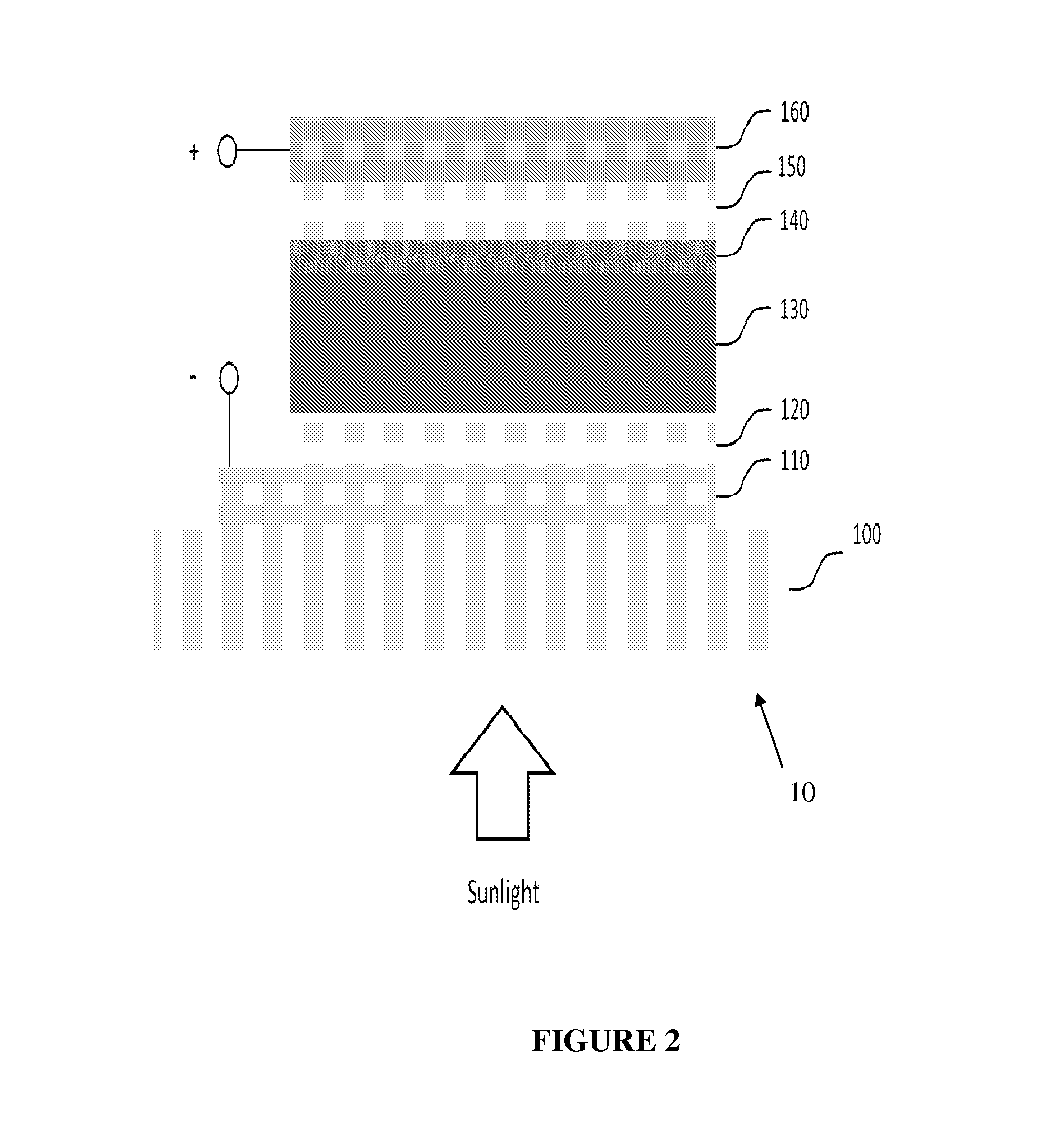

Solar cell substrate, method for manufacturing same, and solar cell using same

InactiveUS20140124028A1Superior diffusion prevent effectPreventive effectElectrolytic coatingsFinal product manufactureSolar cellMetal

One aspect of the present invention is a solar cell substrate, comprising: a lower substrate; and a lower electrode that is formed on the upper part of said lower substrate, wherein a metal diffusion-preventing film having at least one or two or more metal layers is included between said lower substrate and said lower electrode, and if two or more metal layers are formed, the metal layers adjoining each other can be different metals. Additionally, a solar cell, which is another aspect of the present invention, comprises: a lower substrate; and a lower electrode that is formed on the upper part of said lower substrate, wherein a metal diffusion-preventing film having at least one or two or more metal layers is included between said lower substrate and said lower electrode, and if two or more metal layers are formed, the metal layers adjoining each other comprise solar cell substrates which are of different metals; p-type light absorption layers formed on said solar cell substrates; n-type buffer layers formed on said light absorption layers; transparent windows formed on said buffer layers; and upper electrodes formed on said transparent windows.

Owner:POSCO

Display device

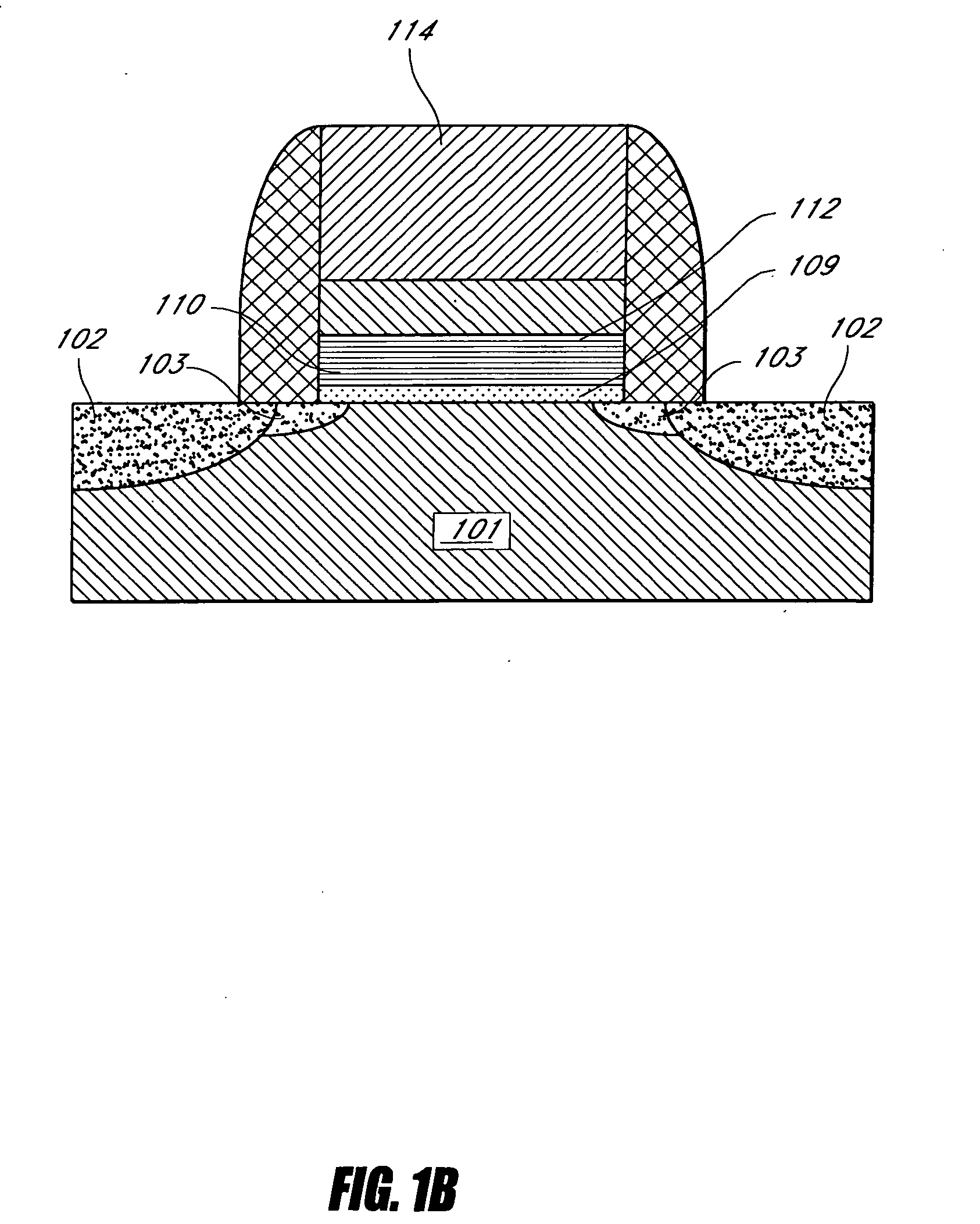

ActiveUS20050218452A1Reduce impactSuppress mutationTransistorElectroluminescent light sourcesDisplay deviceOptoelectronics

A display device according to the present invention includes: a planarization layer for insulating between a gate electrode etc. and a data wiring, a drain electrode, or the like of the transistor; and a barrier layer that is formed on an upper surface or lower surface of the planarization layer and at the same time, adapted to suppress diffusion of moisture or degassing components from the planarization layer. The display device adopts a device structure effective in reducing the plasma damage on the planarization layer by devising a positional relationship between the planarization layer and the barrier layer. Also, in combination with a novel structure as a structure for a pixel electrode, effects such as an increase in luminance can be provided as well.

Owner:SEMICON ENERGY LAB CO LTD

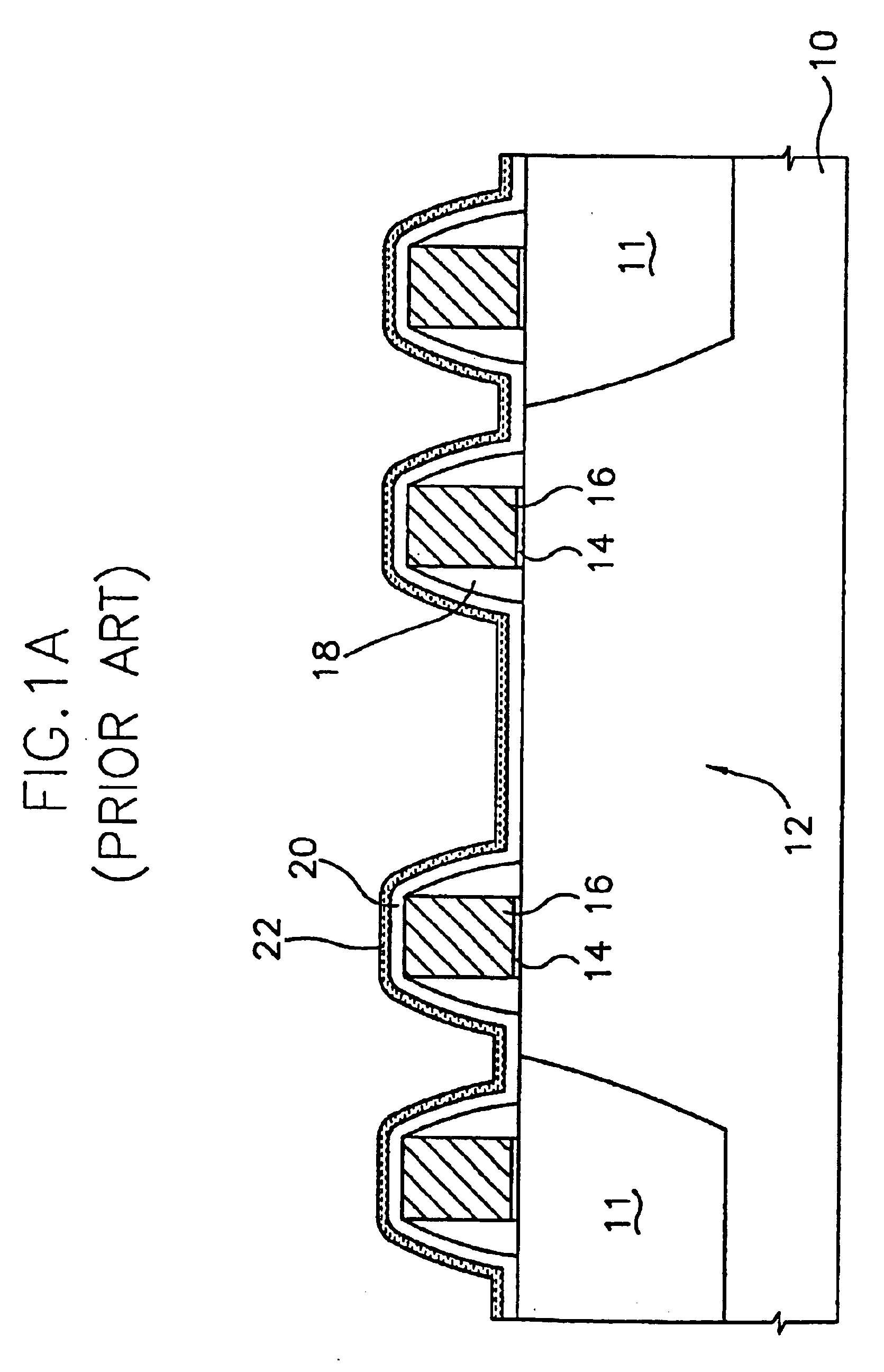

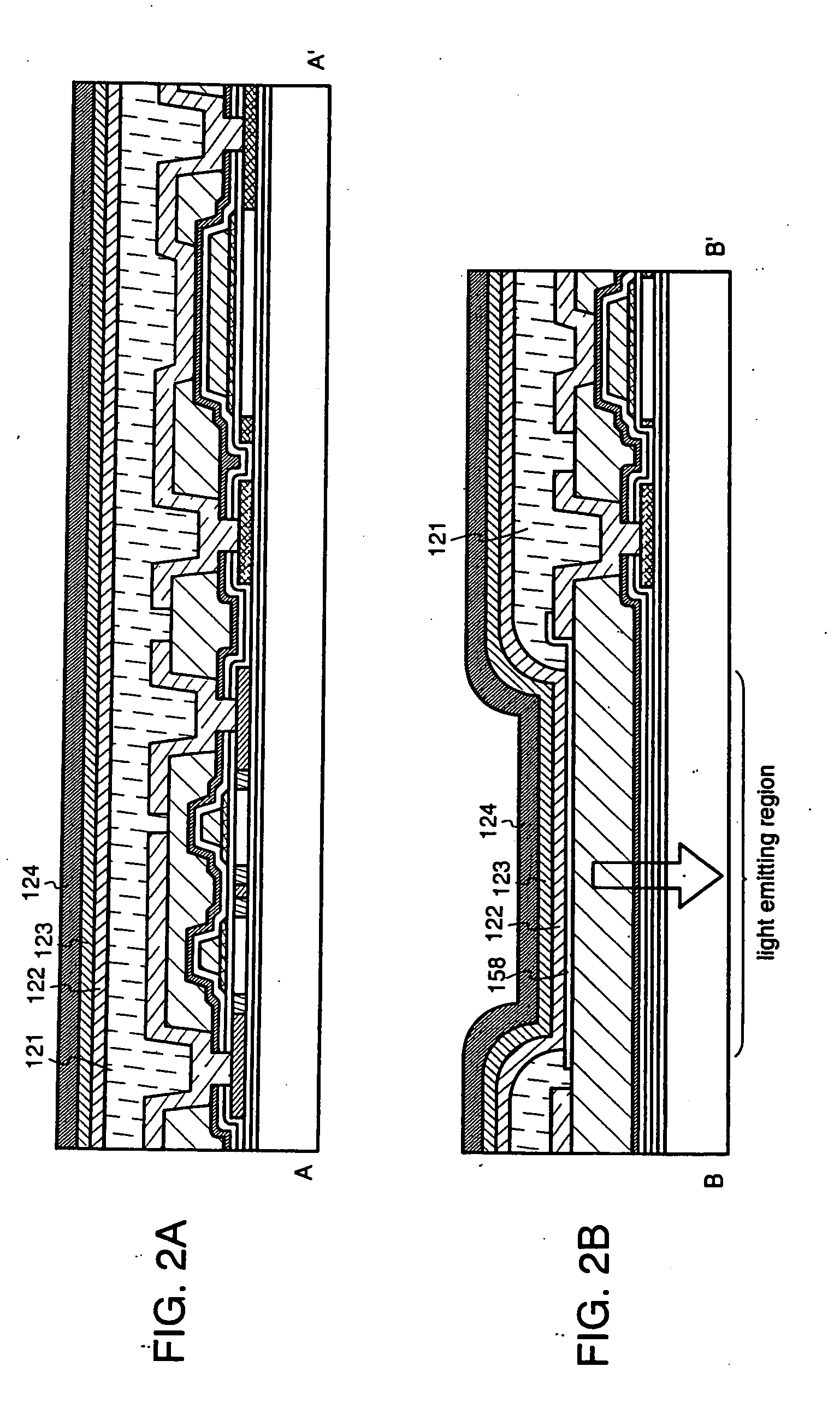

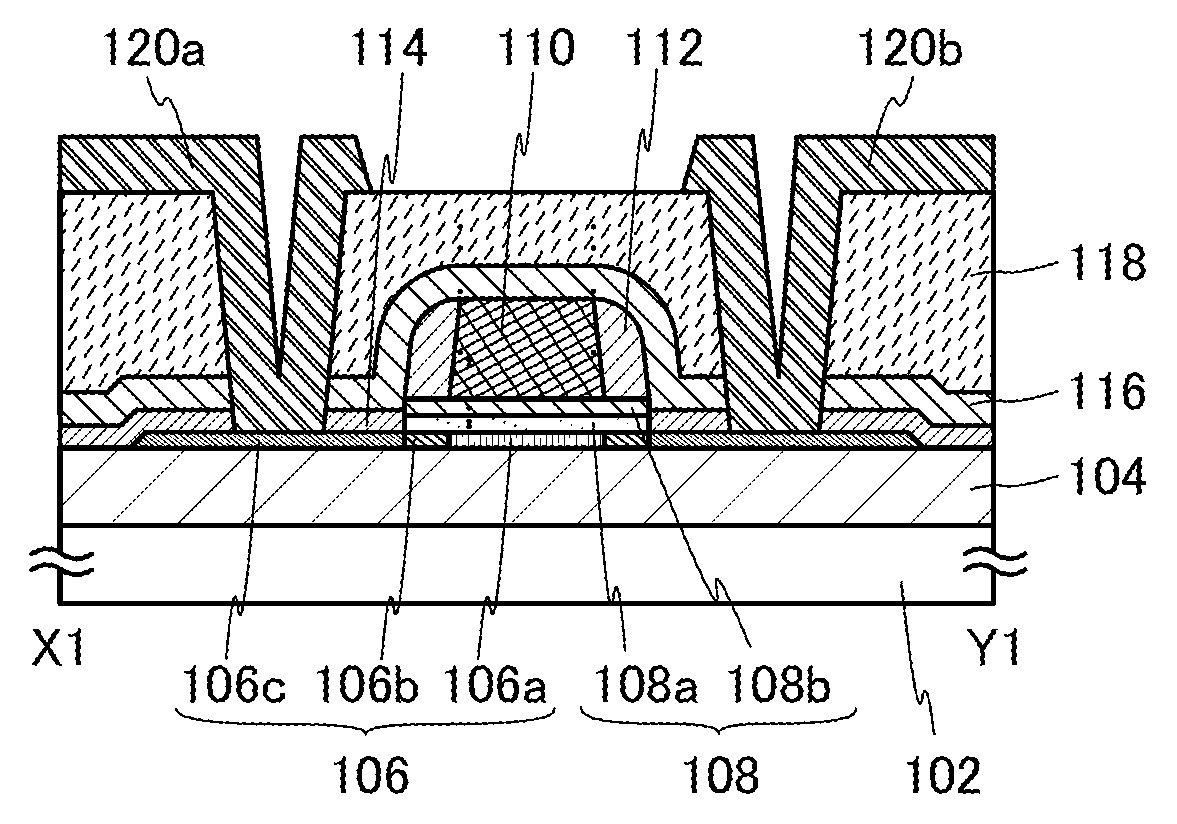

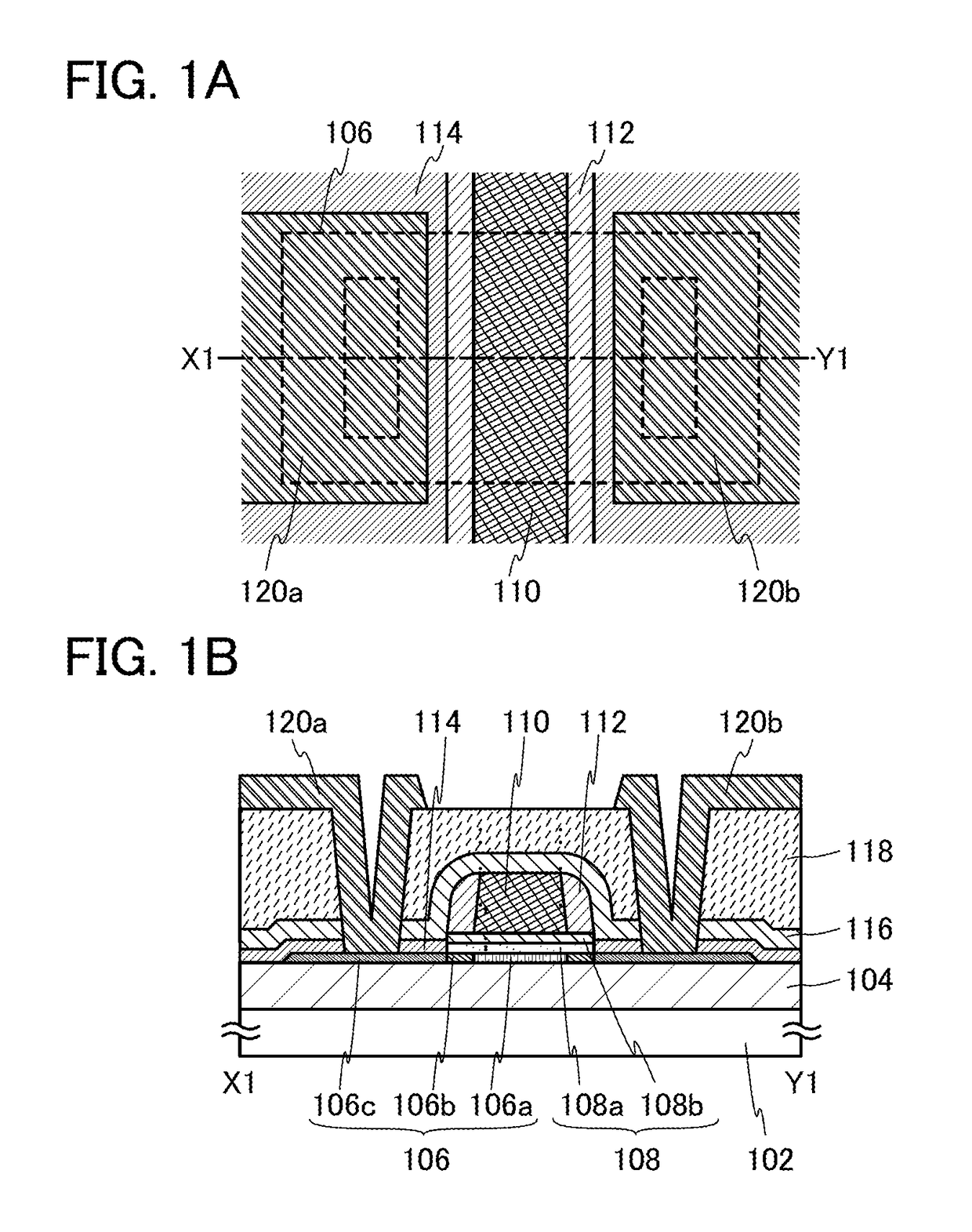

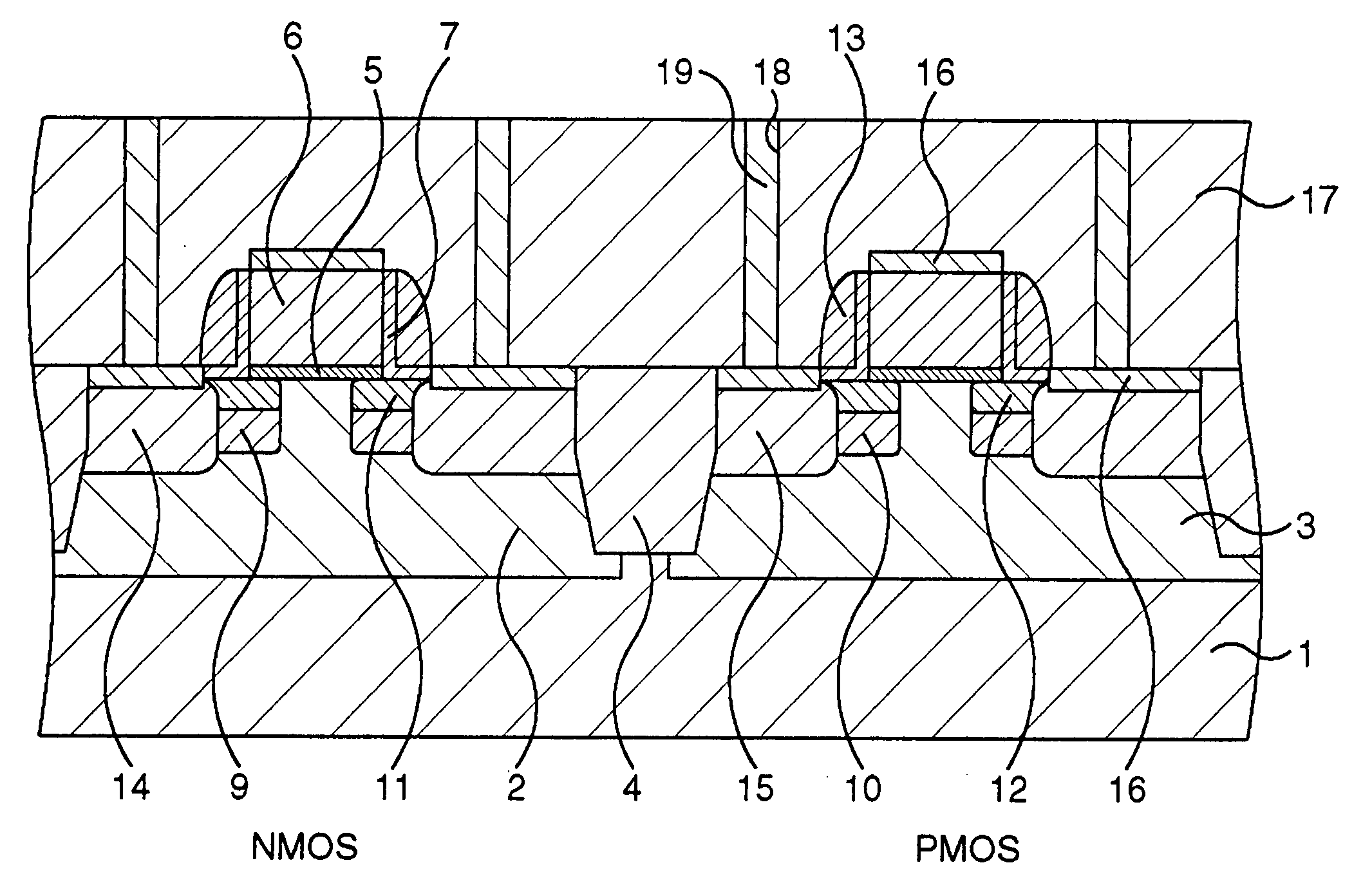

Semiconductor device and method of manufacturing thereof

InactiveUS7098110B2Prevents outward diffusion of impurityPrevent oxidationTransistorSemiconductor/solid-state device manufacturingNitrogen gasSemiconductor

A silicon nitride film having a thickness of 3 nm or less is formed on the surfaces of a P-well and N-well, as well as on the upper and side surfaces of a gate electrode, in which the silicon nitride film can be formed, for example, by exposing the surface of the P-well and N-well, and the upper and side surfaces of the gate electrode to a nitrogen-gas-containing plasma using a magnetron RIE apparatus. Then, pocket layers, extension layers and source / drain layers are formed while leaving the silicon nitride film unremoved.

Owner:FUJITSU SEMICON LTD

Semiconductor device and method for manufacturing the same

ActiveUS9653614B2Prevent the diffusion of impuritiesUnnecessary capacitanceTransistorSolid-state devicesPower semiconductor deviceSemiconductor

Owner:SEMICON ENERGY LAB CO LTD

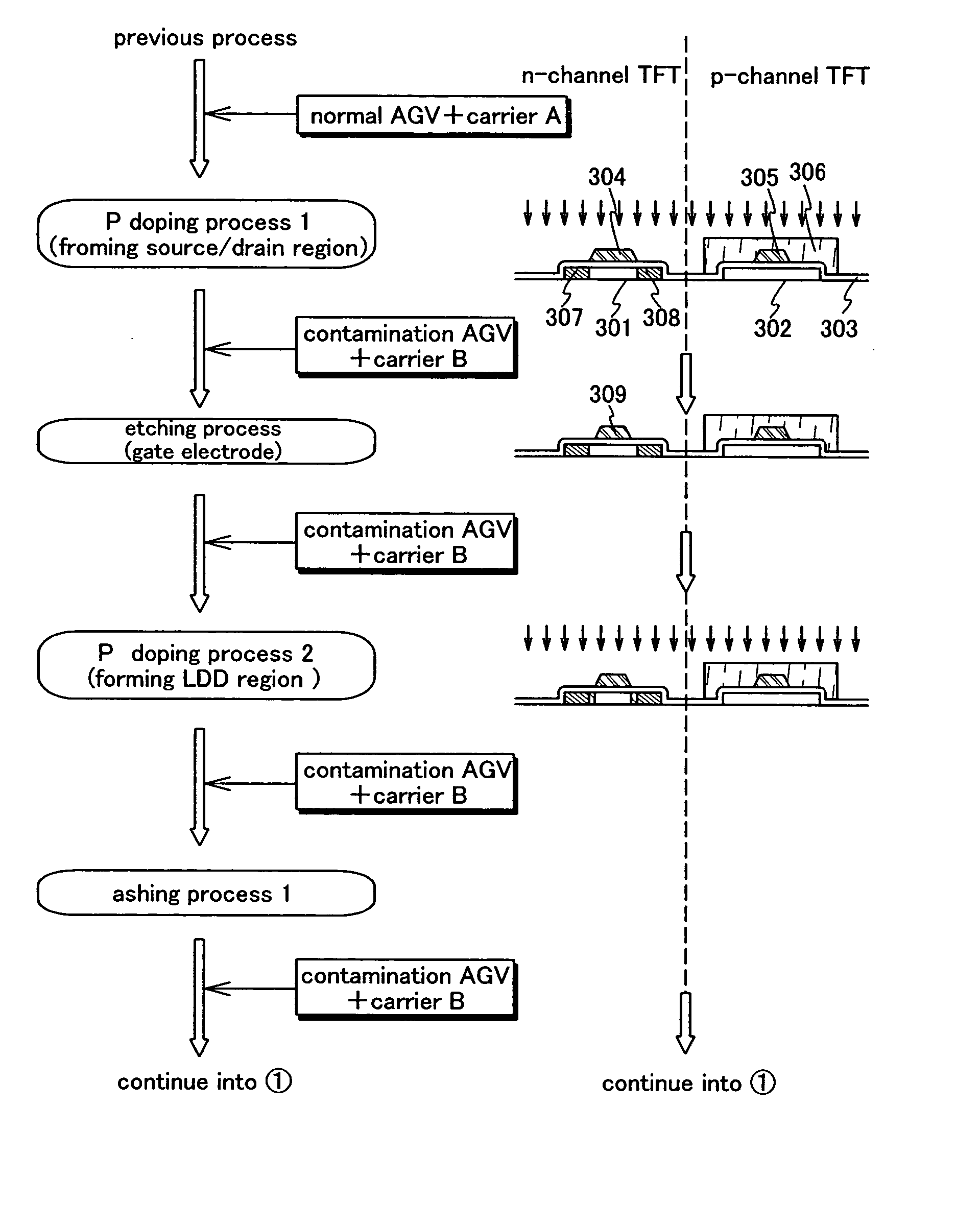

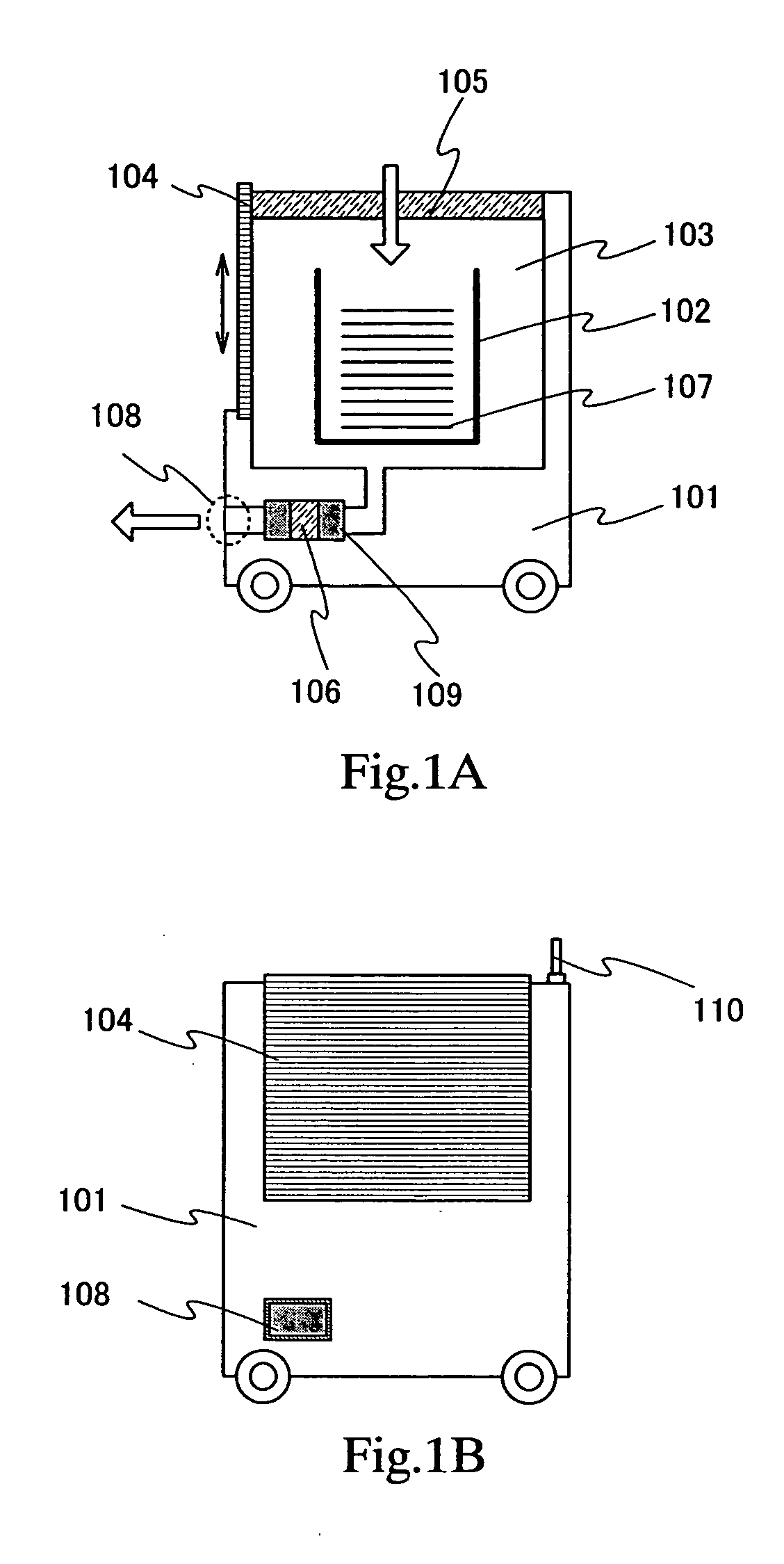

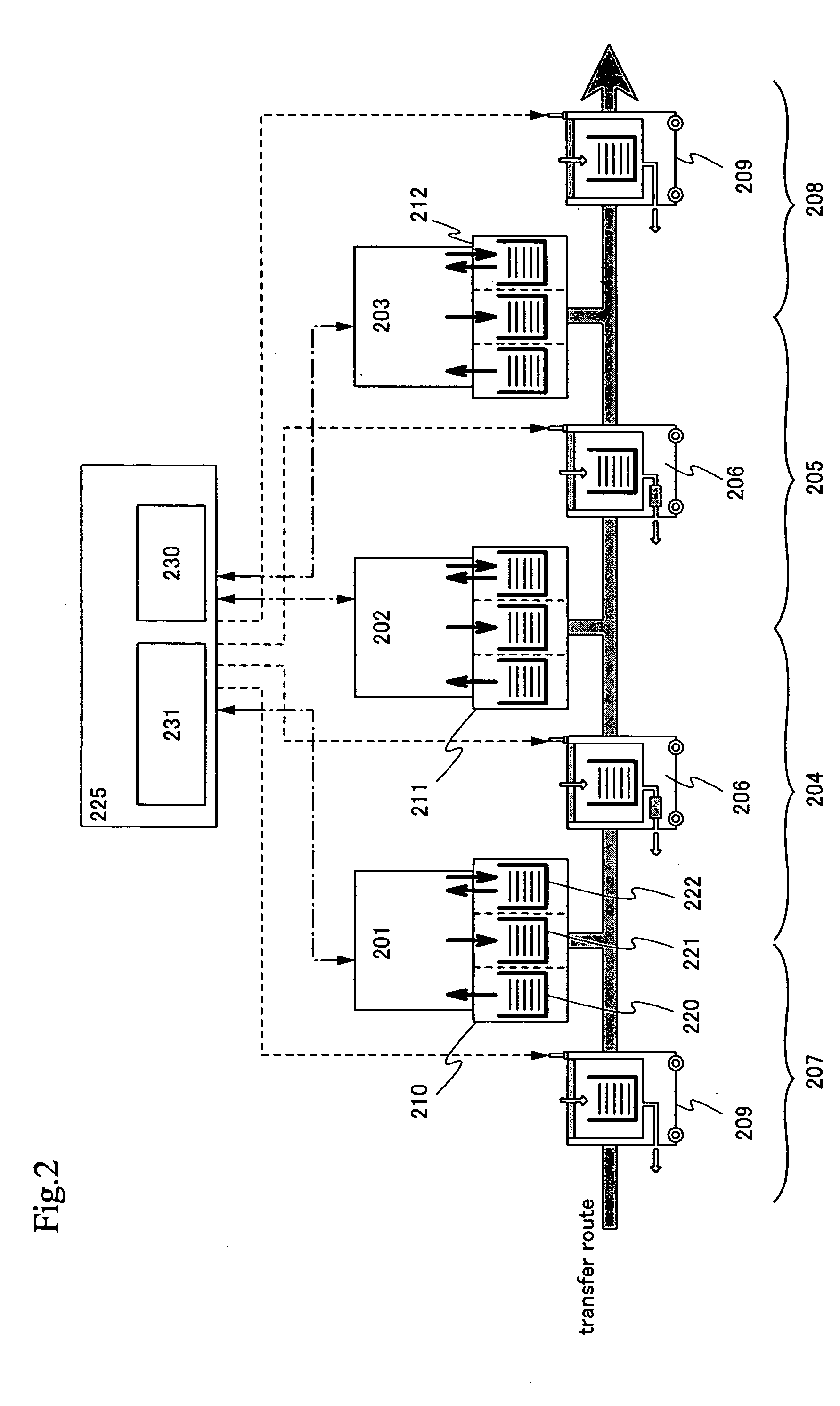

Automatic material handling system, production system for semiconductor device, and production management method for semiconductor device

InactiveUS20040093108A1Reduce the amount requiredPrevent the diffusion of impuritiesSemiconductor/solid-state device manufacturingCharge manipulationCharge carrierProduction control

It is an object to provide an AGV that enables preventing a substrate and a manufacturing system from being contaminated due to another substrate with an adhering contaminant generated in a manufacturing process, and also a production system for a semiconductor device and a production management method for a semiconductor device, which use the AGV. In the present invention, air filtered through a filter is introduced into a containing portion of an AGV, and air in the containing portion containing a carrier is exhausted after filtering the air in the containing portion through another filter. As the filter used before discharging the air, a filter that enables filtering an impurity on the order of a submicron level is used. In addition, a carrier used before doping is changed to another carrier after doping, and CIM system is used to control driving of the AGV and selection of the carrier.

Owner:SEMICON ENERGY LAB CO LTD

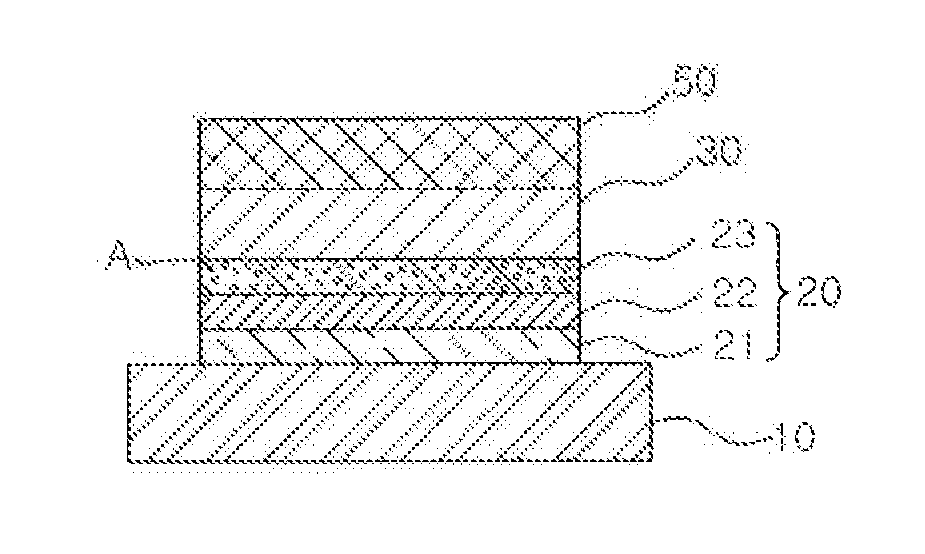

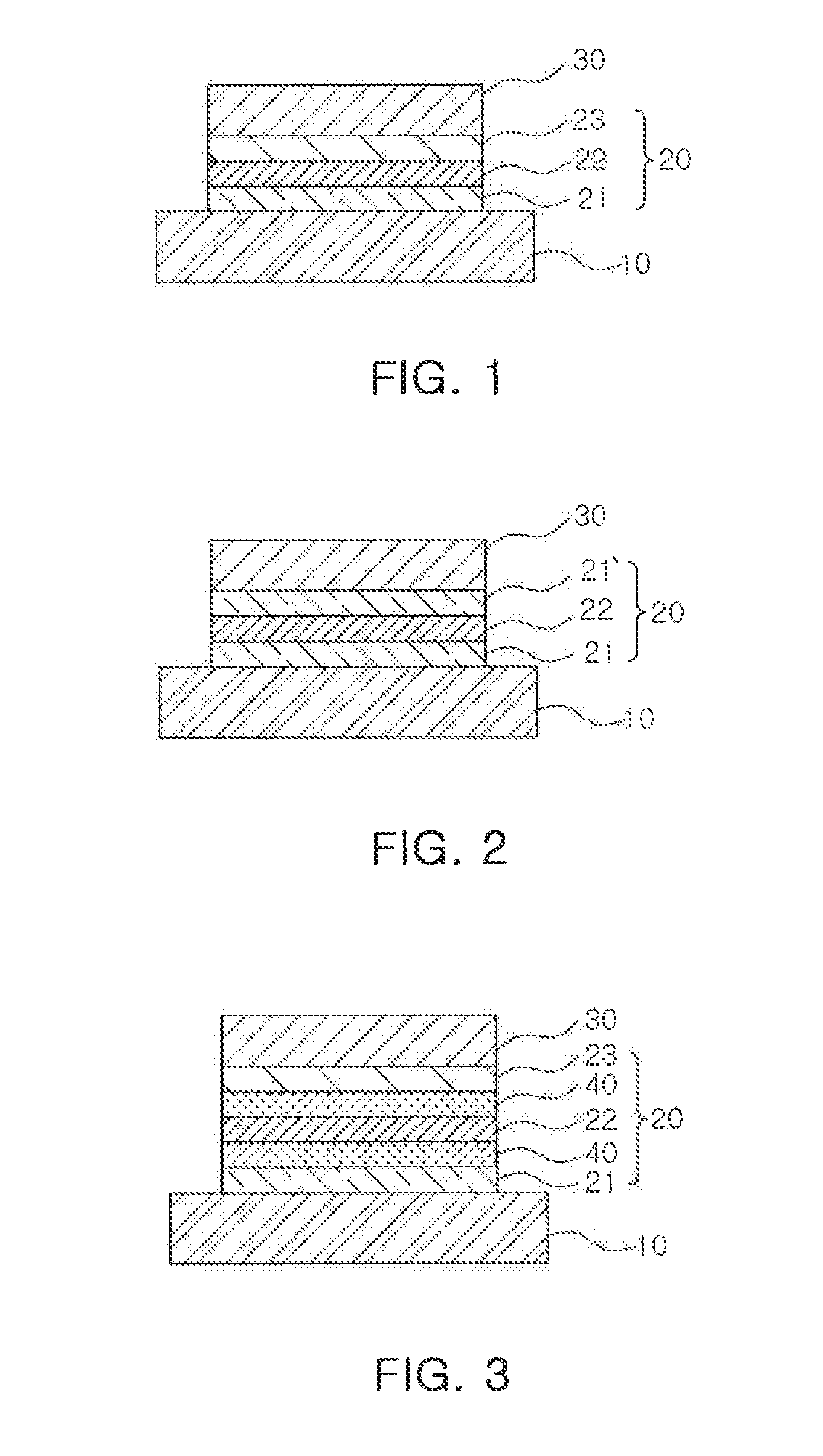

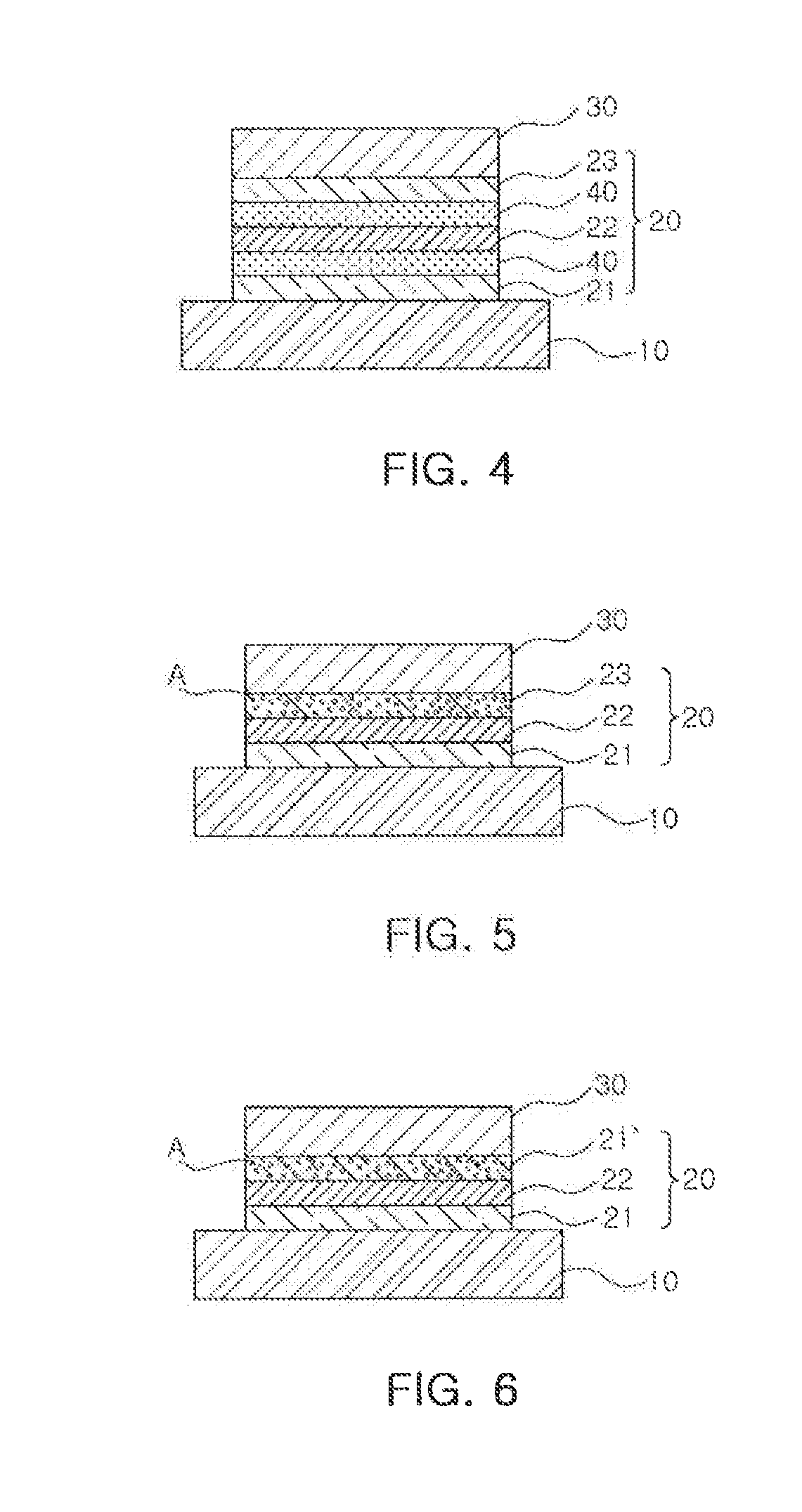

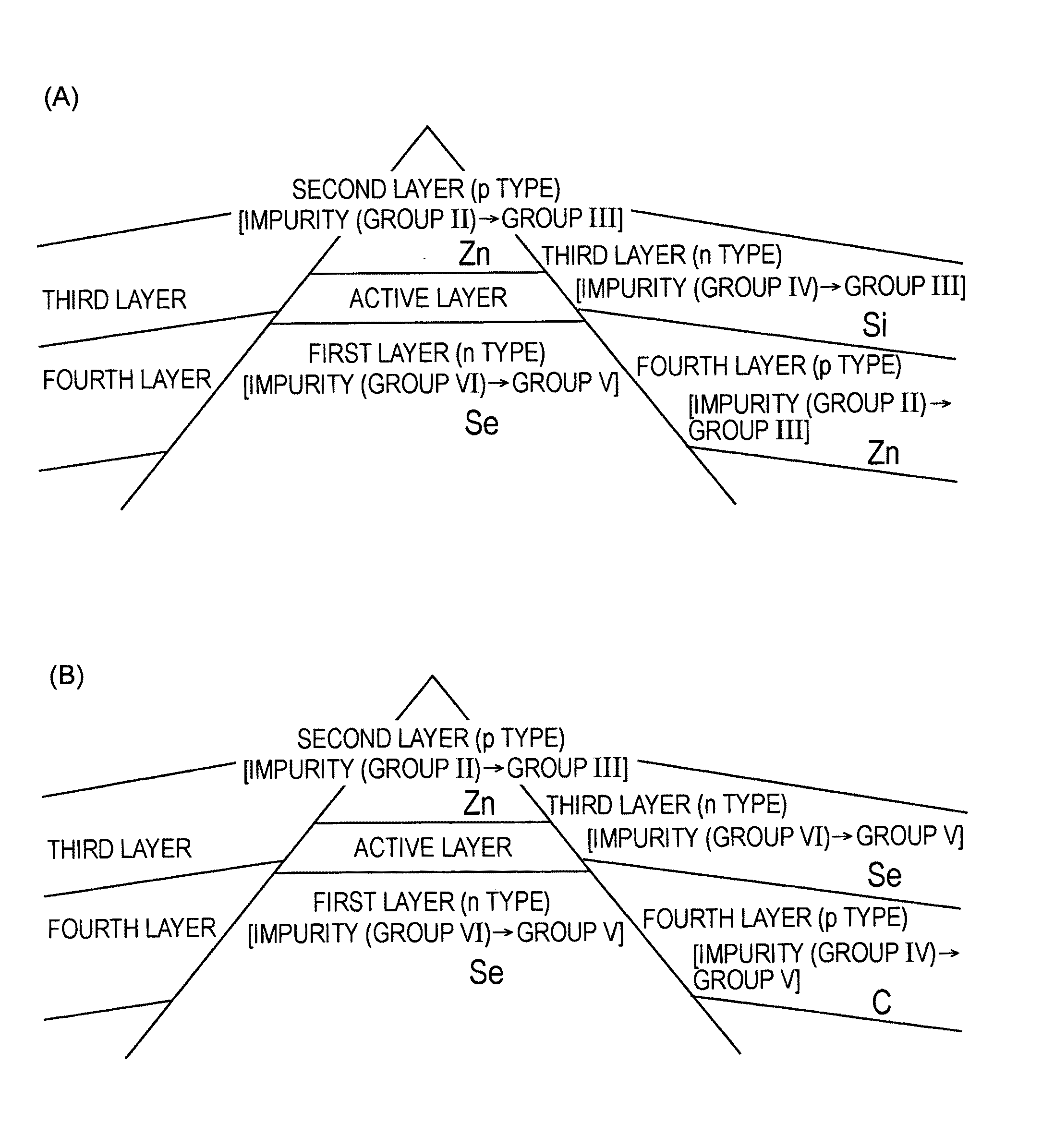

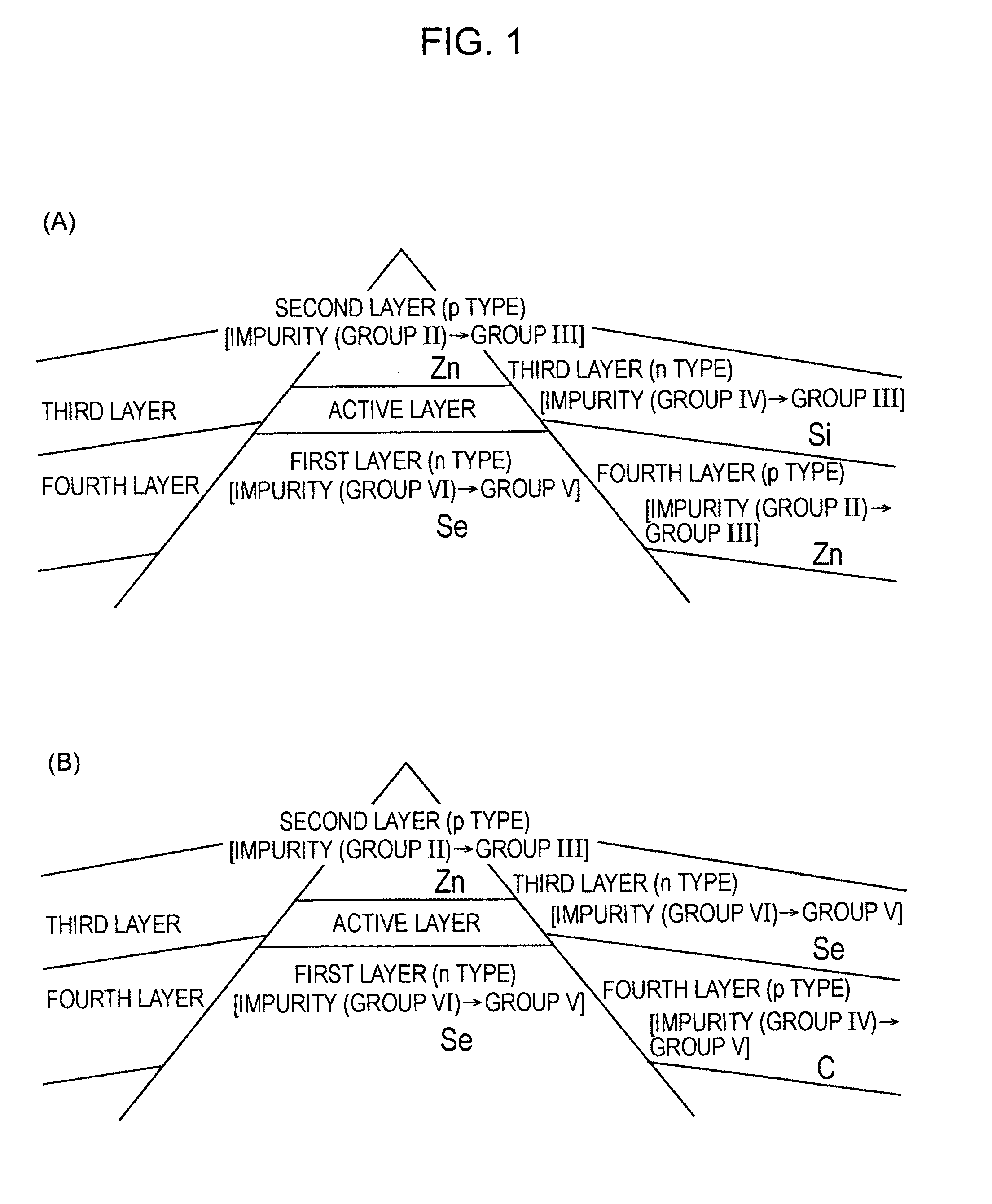

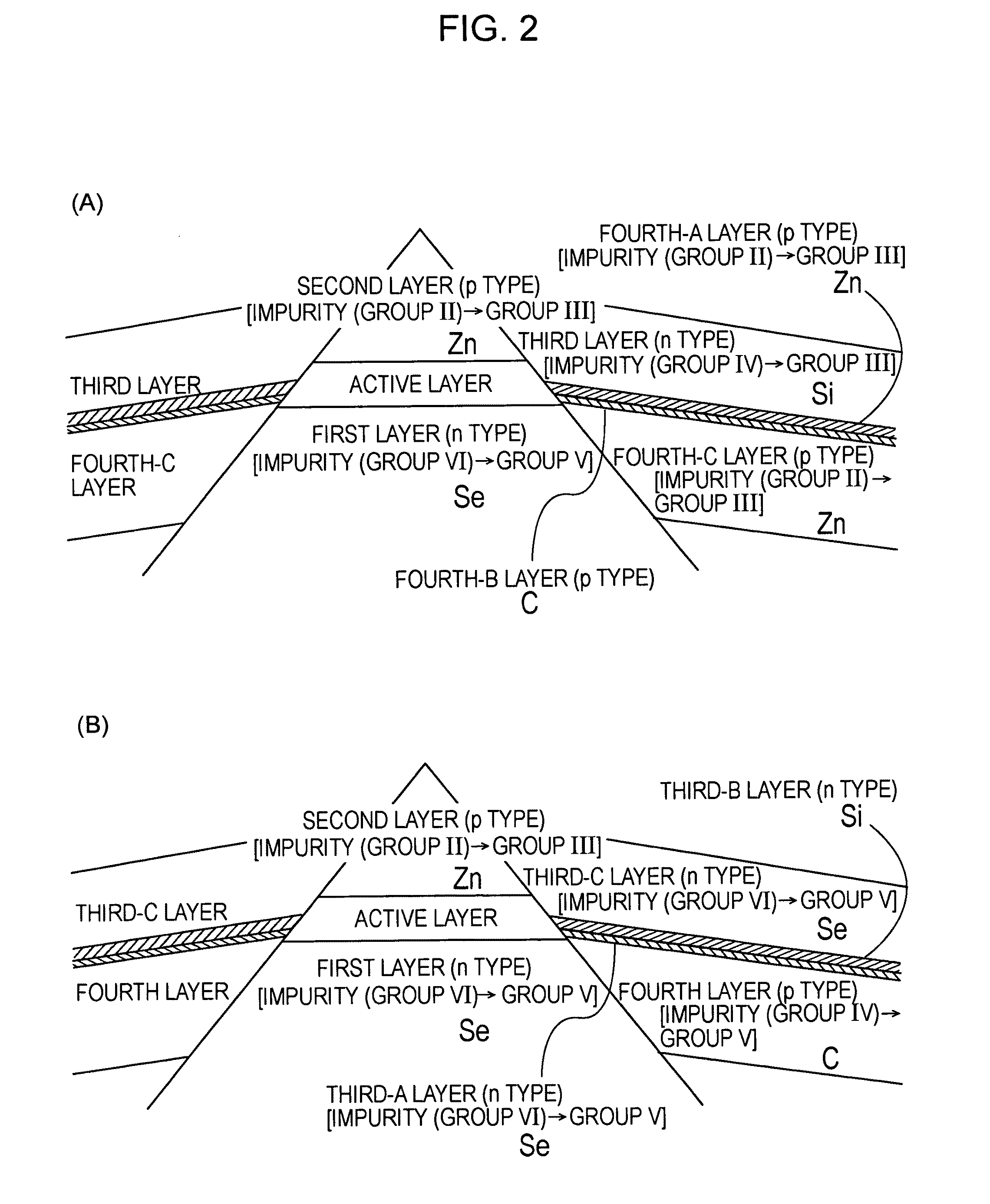

Semiconductor light-emitting device

ActiveUS20100019255A1Prevent the diffusion of impuritiesLow in diffusibilityLaser detailsNanoopticsEngineeringActive layer

There is provided a semiconductor light-emitting device capable of an attempt to further decrease a leakage current in a current-blocking layer and including (A) a light-emitting portion (20) composed of a first compound semiconductor layer (abbreviated as a layer hereinafter) (21) having a first conductivity type, an active layer (23), and a second layer (22) having a second conductivity type, and (B) a current-blocking layer (40) in contact with the side of the light-emitting portion and composed of a third layer (43) having the first conductivity type and a fourth layer (44) having the second conductivity type, wherein the impurity for imparting the first conductivity type to the first layer (21) includes an impurity in the first layer (21) at a substitution site which is uncompetitive with a substitution site of the impurity in the second layer (22), for imparting the second conductivity type to the second layer (22), and the impurity for imparting the first conductivity type to the third layer (43) includes an impurity in the third layer (43) at a substitution site which is competitive with a substitution site of the impurity in the fourth layer (44), for imparting the second conductivity type to the fourth layer (44).

Owner:SONY CORP

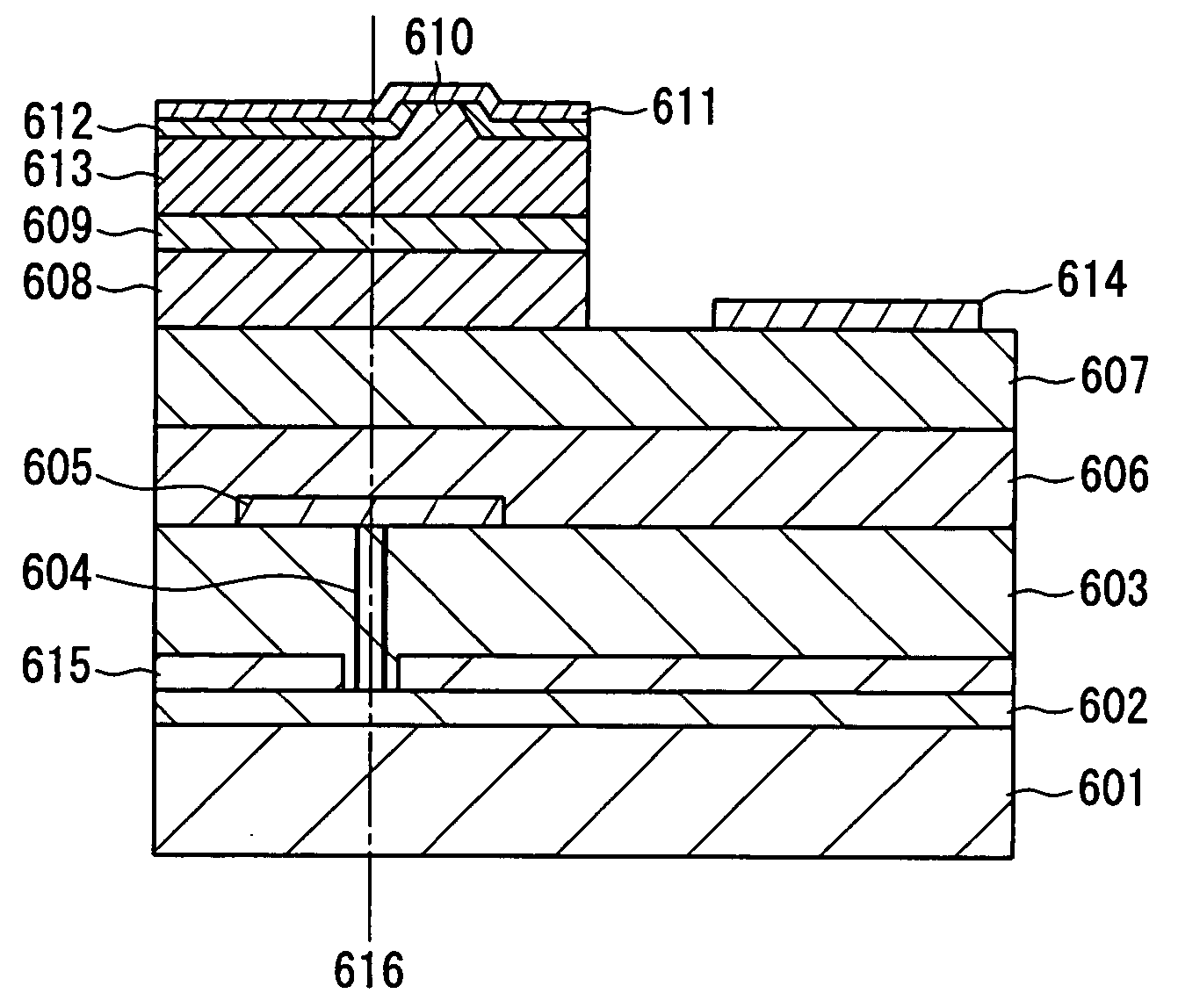

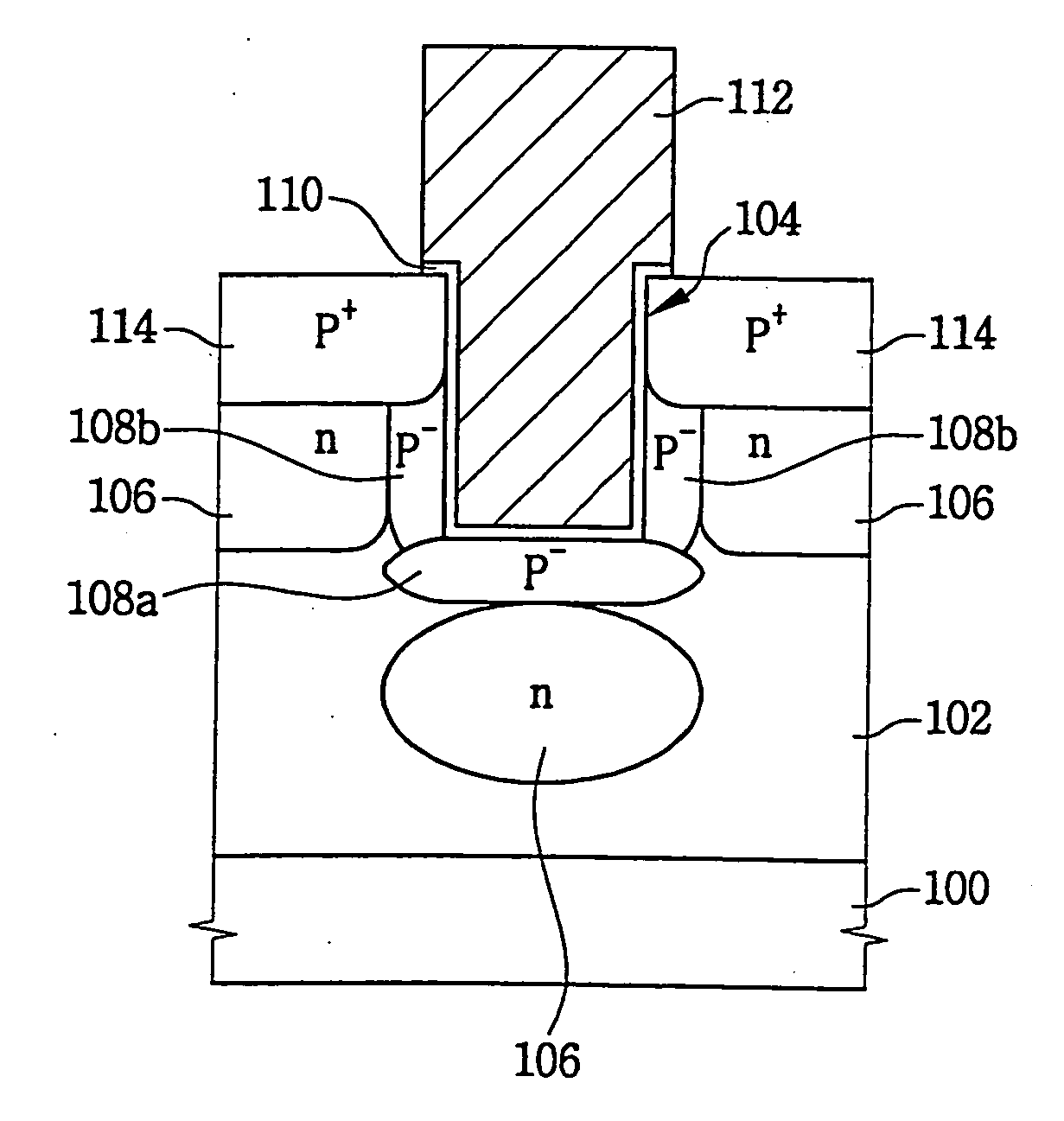

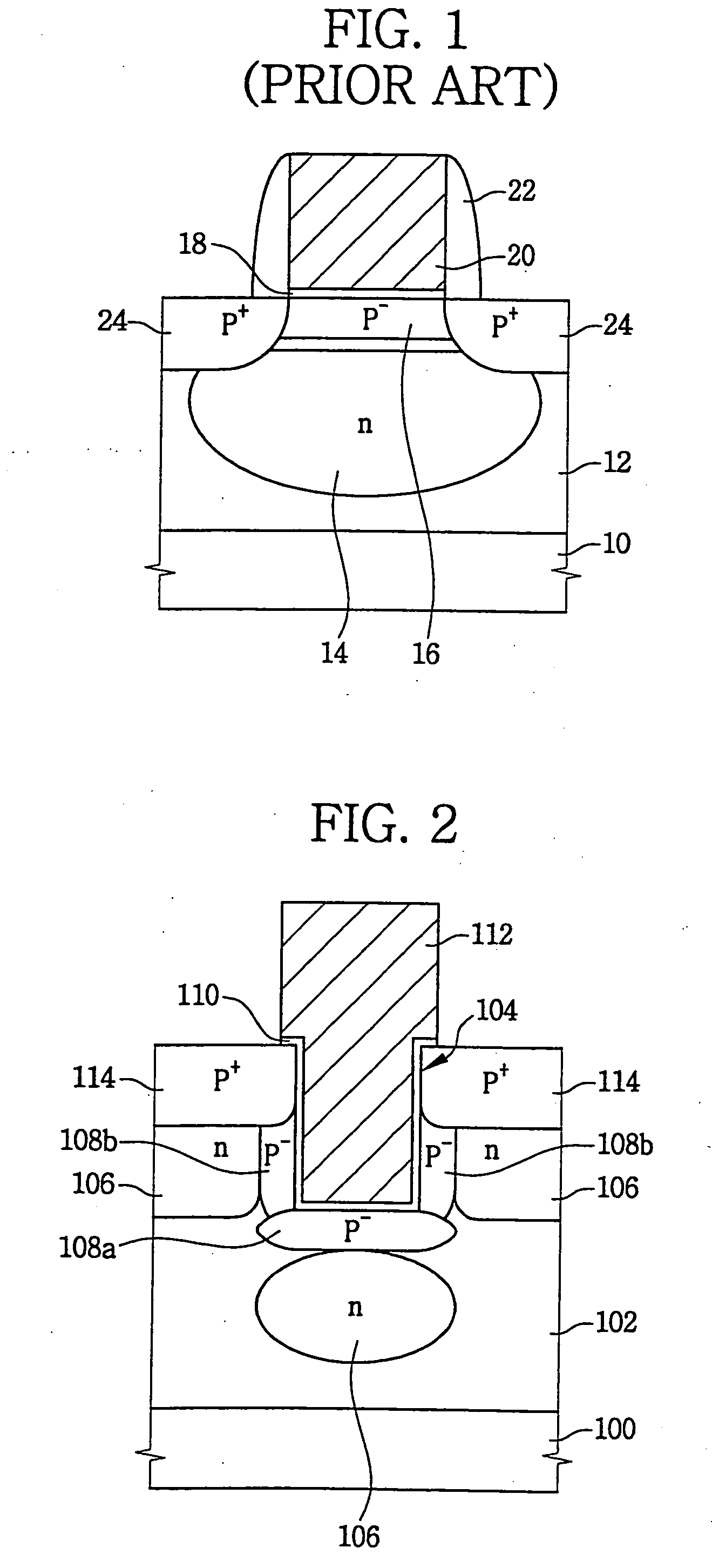

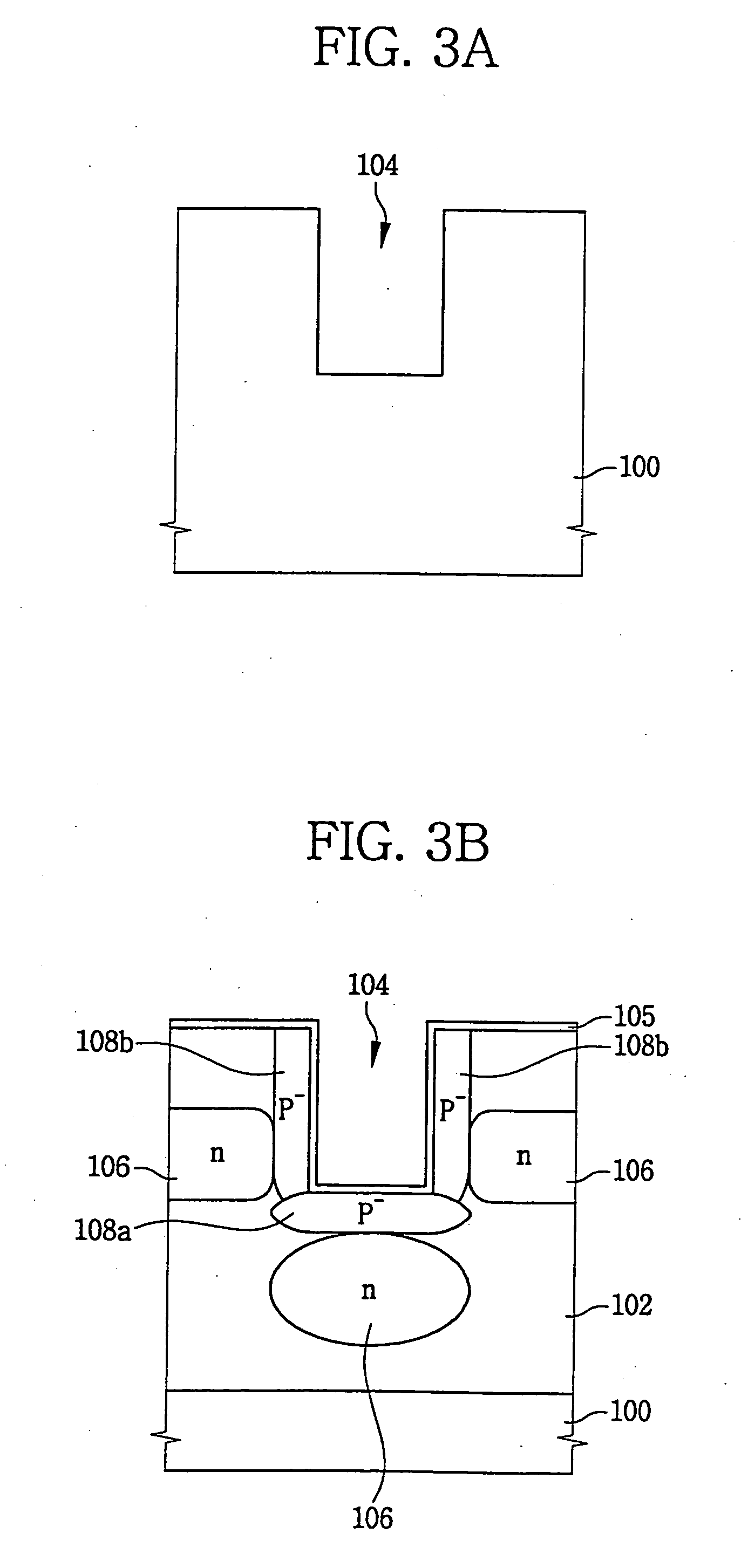

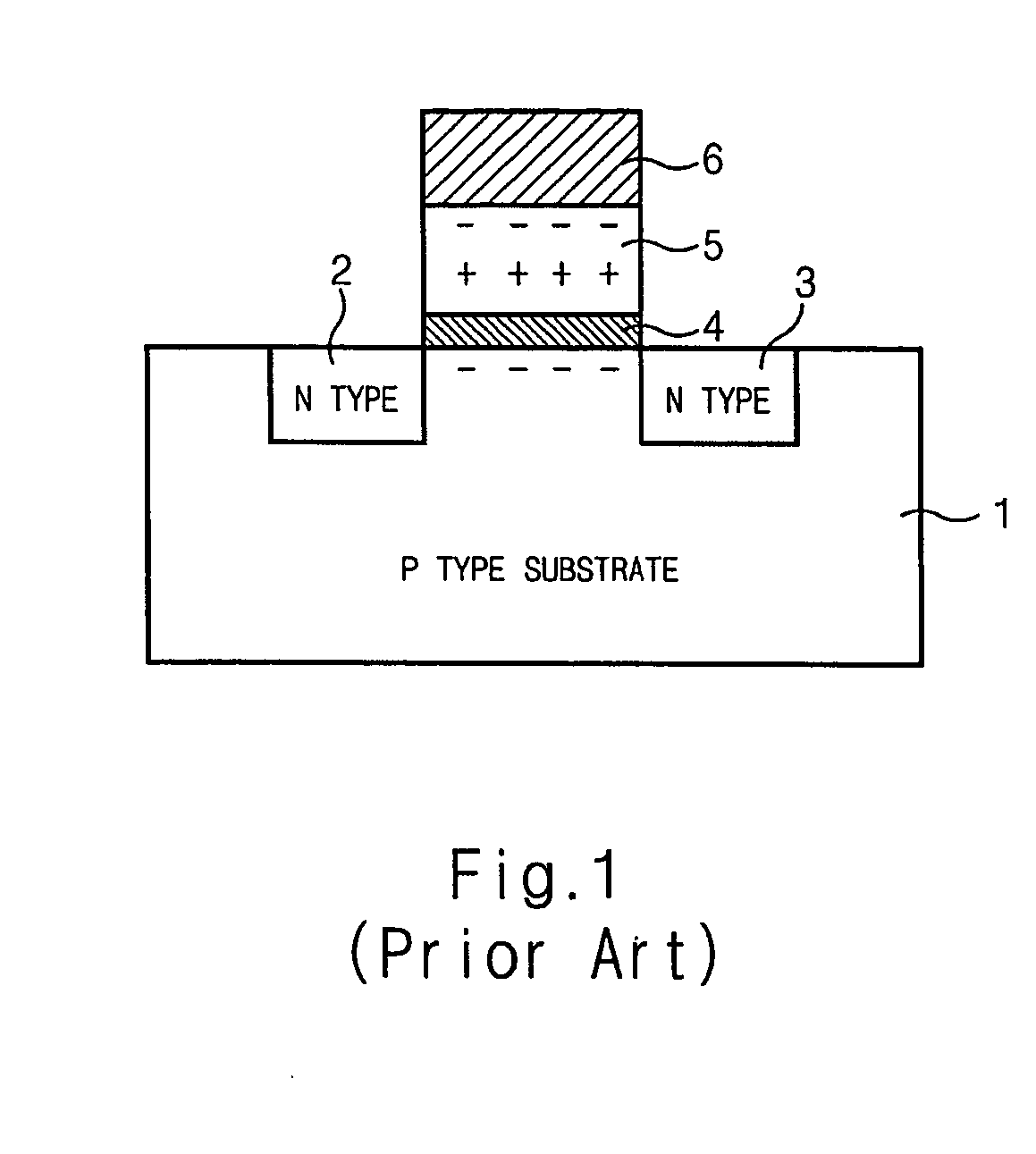

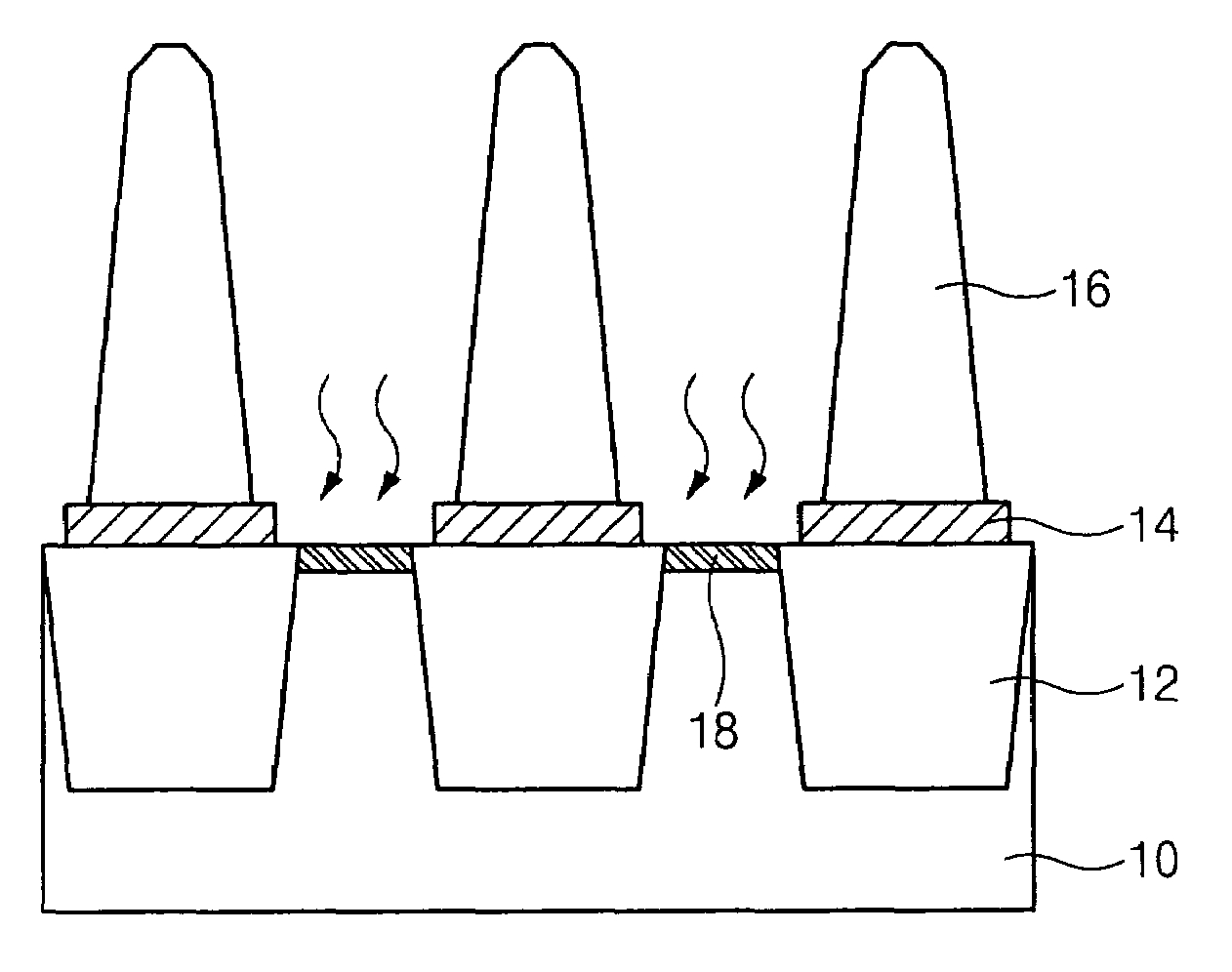

Buried channel type transistor having a trench gate and method of manufacturing the same

ActiveUS20060170039A1Prevent the diffusion of impuritiesEasy to manufactureTransistorSolid-state devicesEngineeringTrench gate

In a method of manufacturing a buried channel type transistor, a trench is formed at a surface portion of a substrate. A first and a second threshold voltage control regions are formed at portions of the substrate beneath a bottom face of the trench and adjacent to a sidewall of the trench, respectively. A gate electrode filling the trench is formed. Source / drain regions are formed at portions of the substrate adjacent to the sidewall of the gate electrode. Stopper regions are formed at portions of the substrate beneath the source / drain regions and beneath the first and second threshold voltage control regions, respectively. The buried channel type transistor has a high breakdown voltage between the source / drain regions although a threshold voltage thereof is low.

Owner:SAMSUNG ELECTRONICS CO LTD

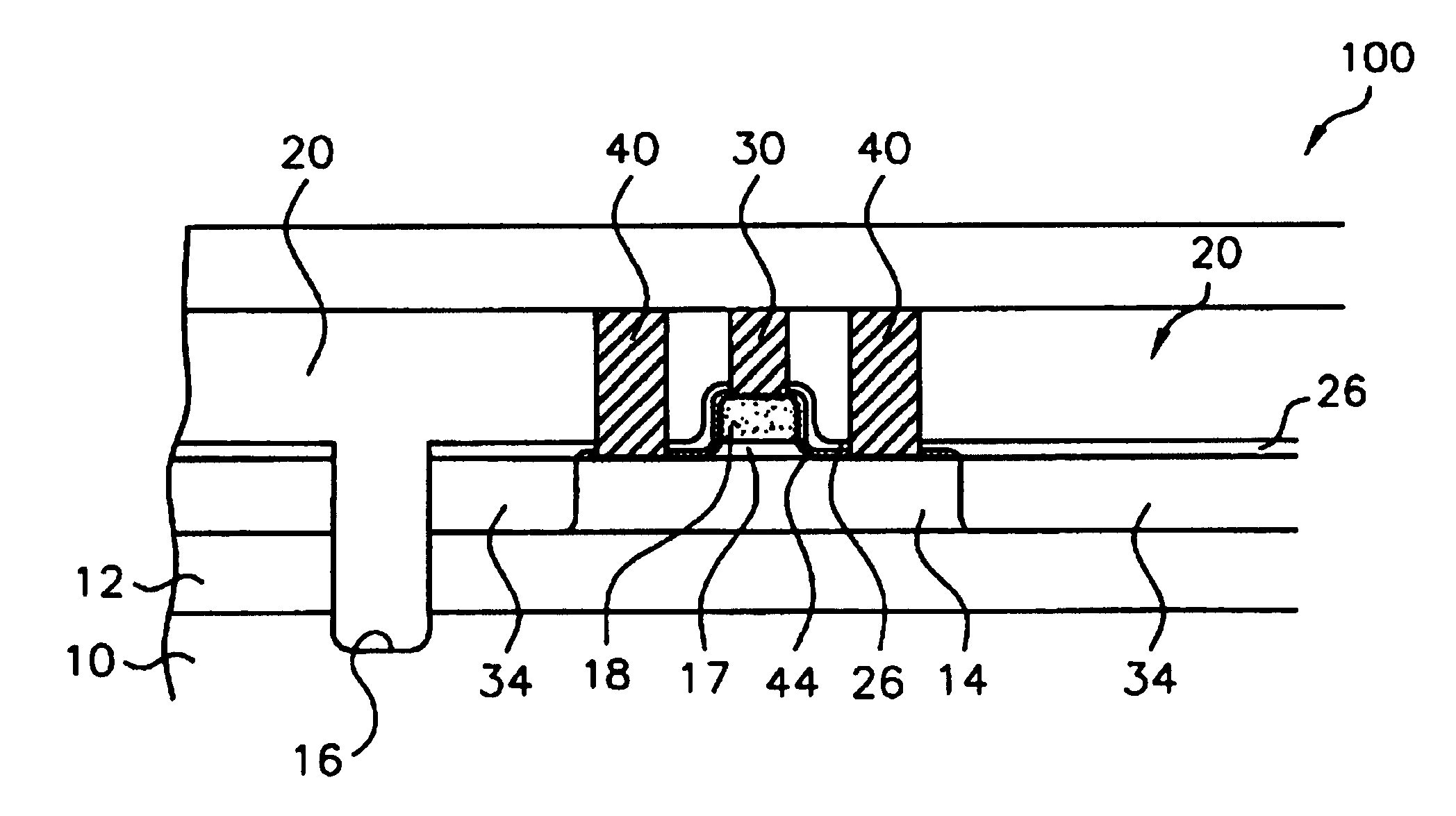

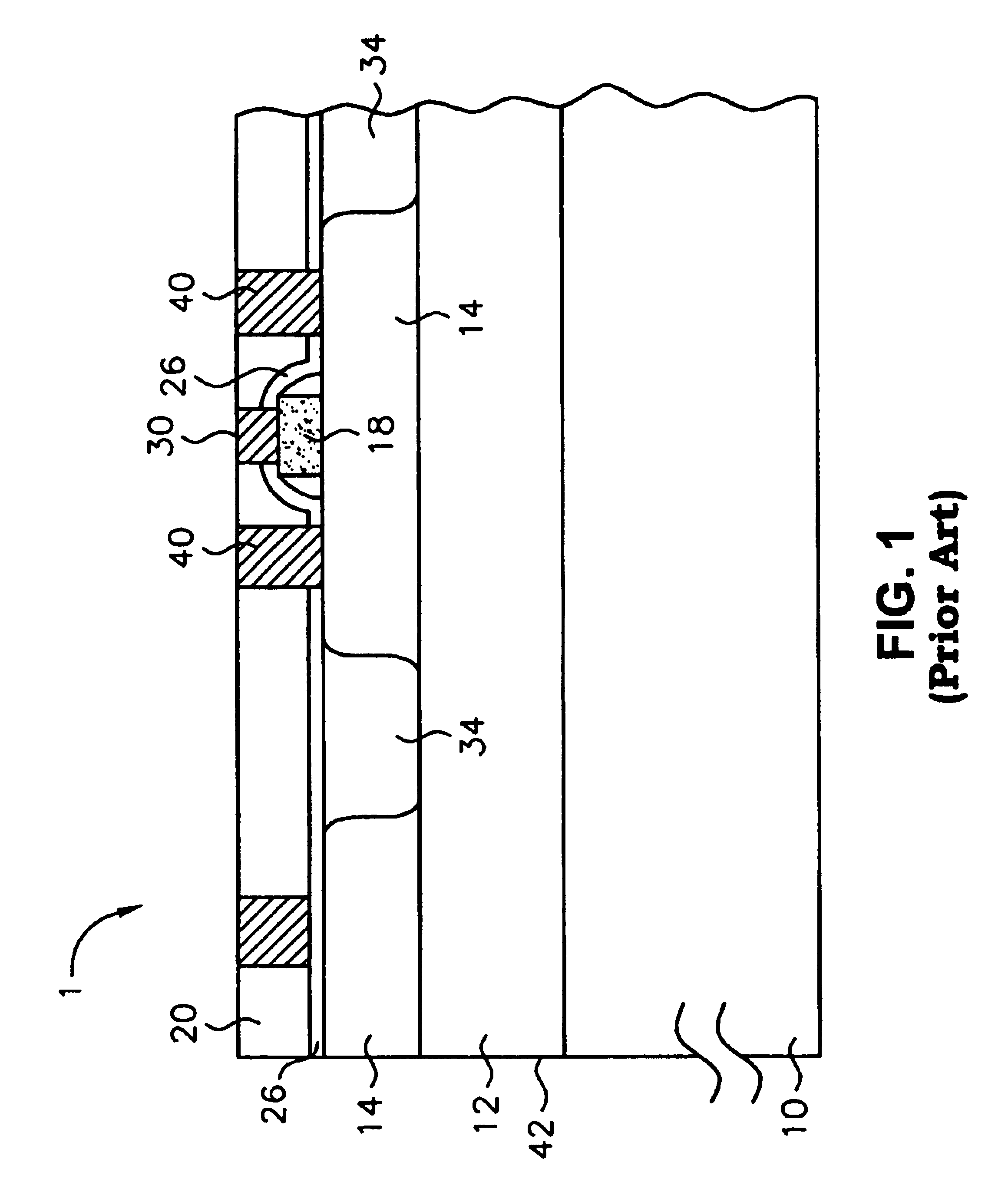

Silicon-on-insulator chip having an isolation barrier for reliability

InactiveUSRE40339E1Reduce processing stepsLess chargeTransistorSemiconductor/solid-state device detailsSilicon on insulatorImpurity

An SOI chip having an isolation barrier. The SOI chip includes a substrate, an oxide layer deposited on the substrate, and a silicon layer deposited on the oxide layer. A gate is deposited above the silicon layer. A first metal contact is deposited above the gate to form an electrical contact with the gate. Second and third metal contacts are deposited to form electrical contacts with the silicon layer. The isolation barrier extends through the silicon layer and the oxide layer, and partially into the substrate, to block impurities in the oxide layer outside the isolation barrier from diffusing into the oxide layer inside the isolation barrier. The isolation barrier surrounds the gate, the first metal contact, the second metal contact, and the third metal contact—which define an active chip area inside the isolation barrier. A method of manufacturing the SOI chip is also disclosed.

Owner:GLOBALFOUNDRIES INC

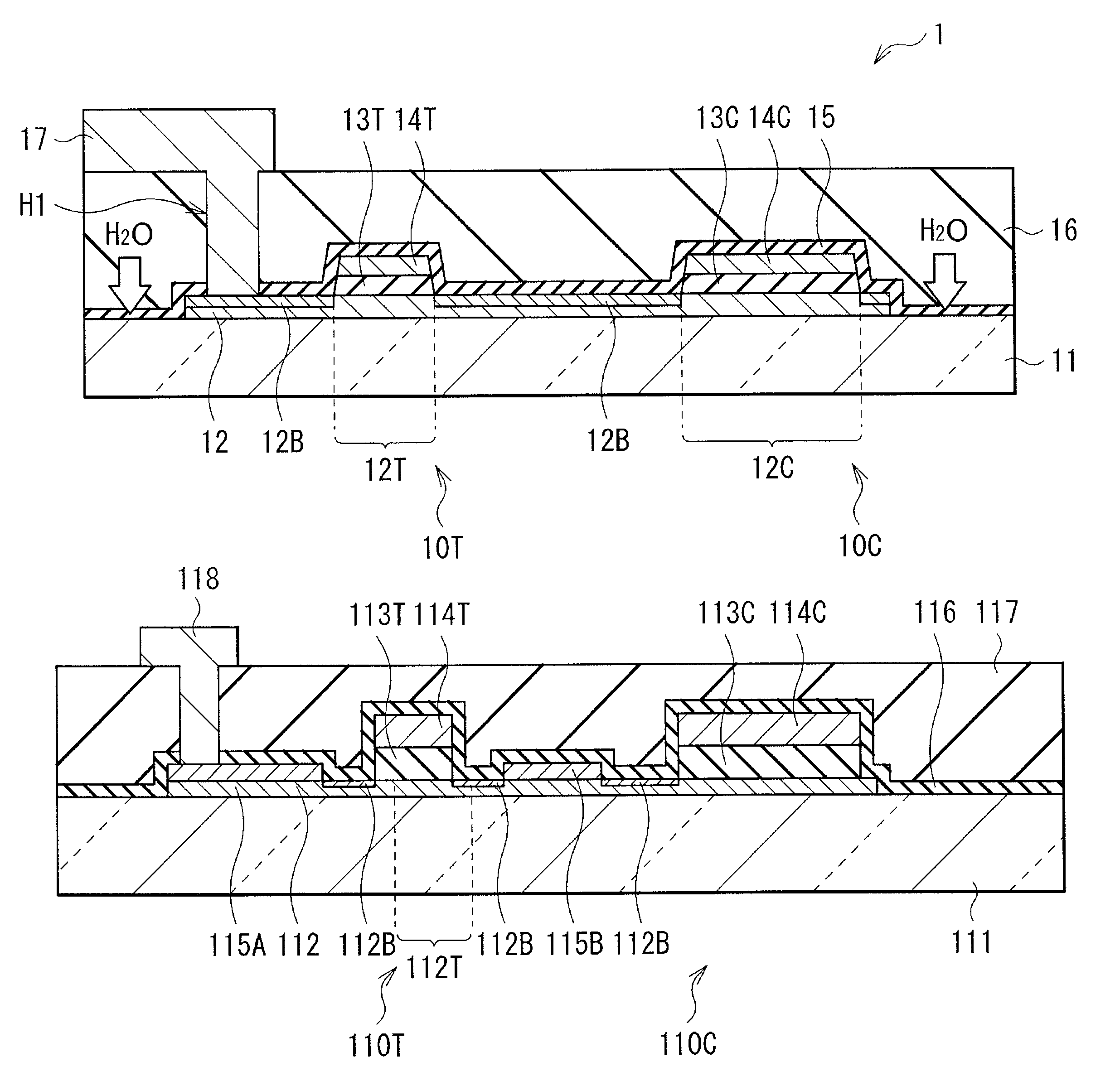

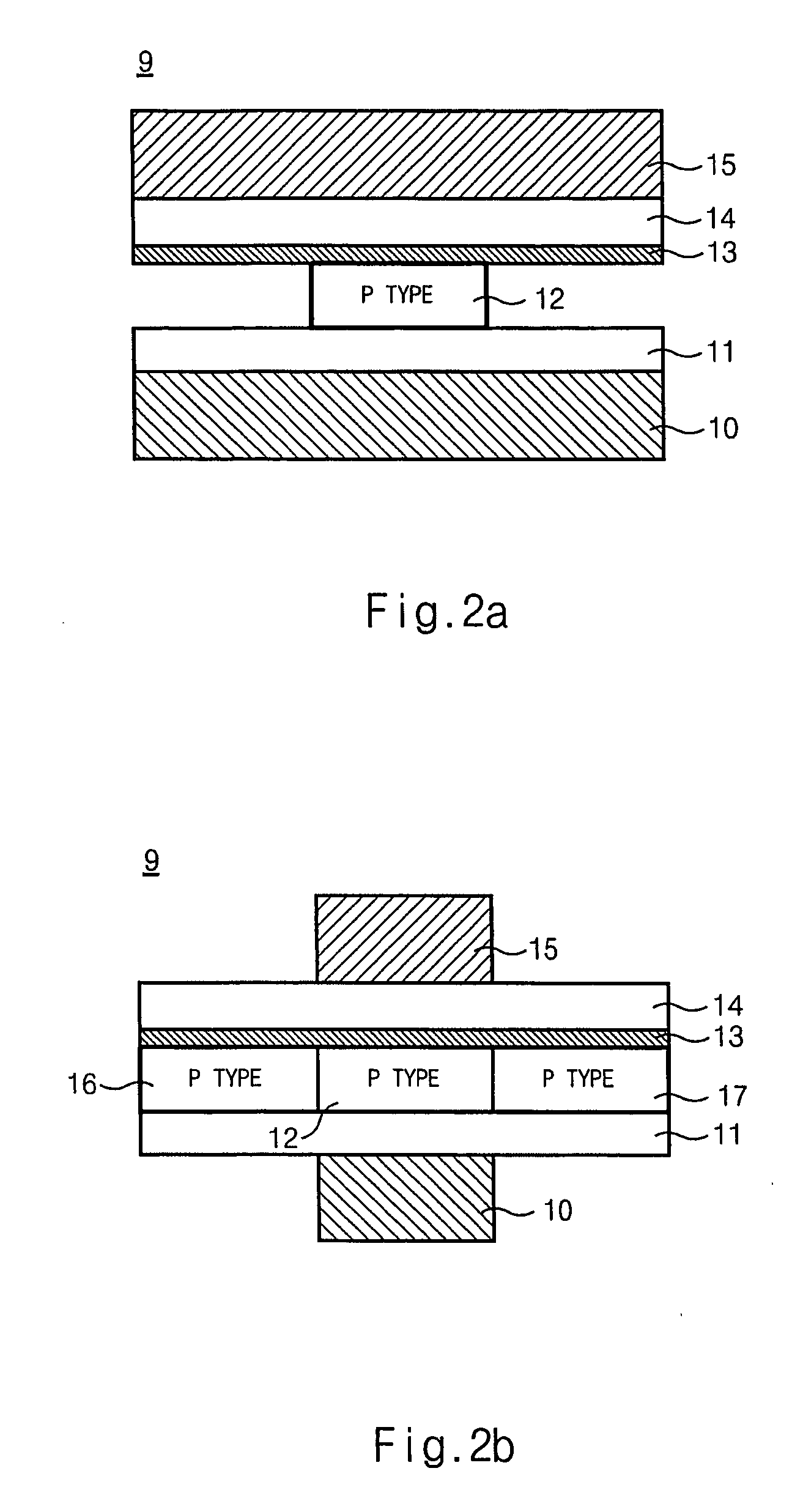

Transistor, method of manufacturing the transistor, semiconductor unit, method of manufacturing the semiconductor unit, display, and electronic apparatus

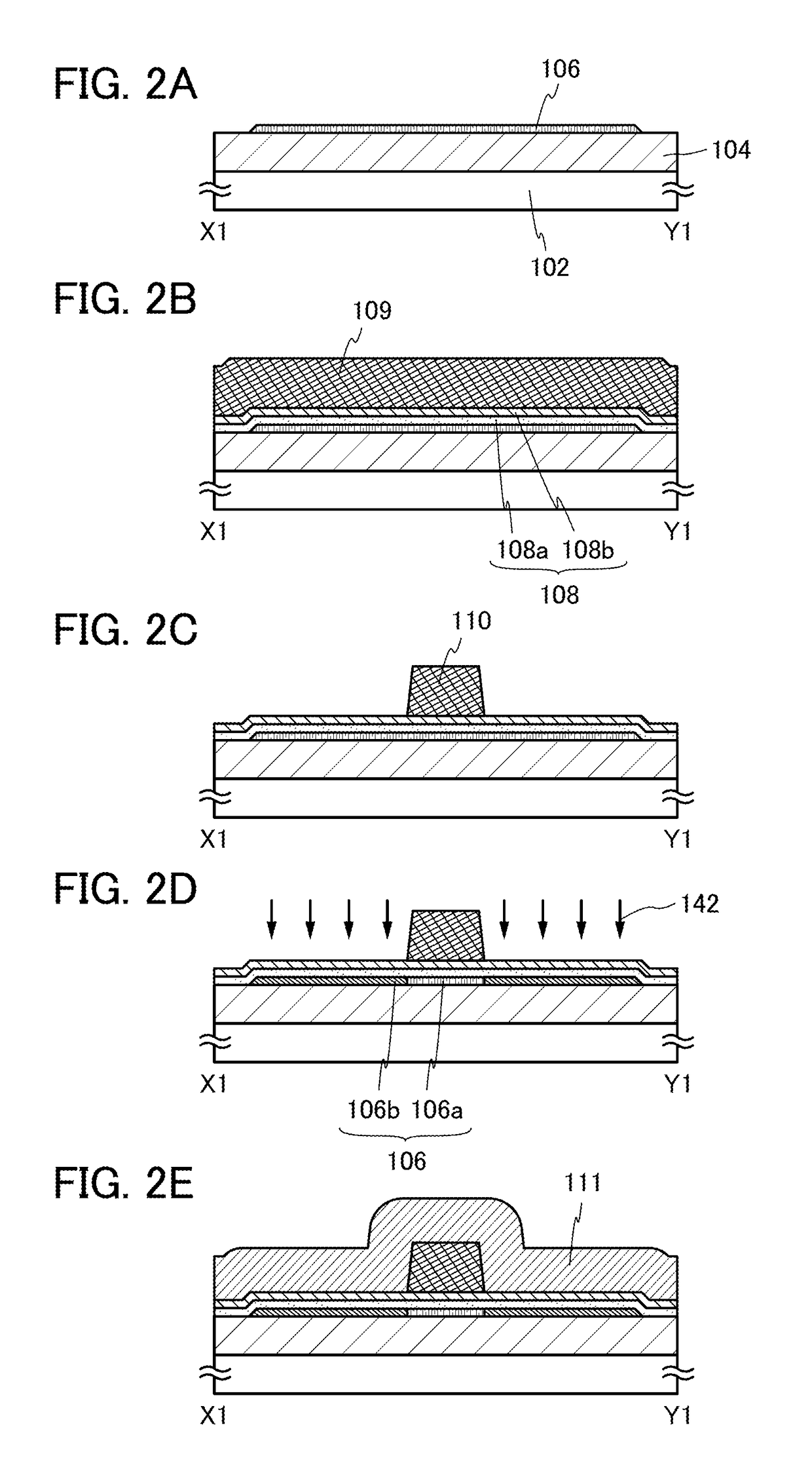

ActiveUS8883571B2Improve featuresPrevent the diffusion of impuritiesTransistorSolid-state devicesDisplay deviceEngineering

A method of manufacturing a transistor includes: forming an oxide semiconductor film and a gate electrode on a substrate, the oxide semiconductor film having a channel region, and the gate electrode facing the channel region; and forming an insulating film covering the gate electrode and the oxide semiconductor film. Infiltration of moisture from the insulating film into the oxide semiconductor film is suppressed by the substrate.

Owner:JOLED INC

Protection for a carbon material, in particular C/C composite, bowl that is to receive a crucible, such as a silica crucible for drawing silicon

InactiveUS6616756B2Reduce considerably the extentExtended service lifeAfter-treatment apparatusPolycrystalline material growthFiberCrucible

Prior to housing the crucible in the bowl, a consumable buffer ply is applied over at least a portion of the inside face of the bowl, the ply being constituted essentially by a non-rigid carbon fiber fabric for protecting the bowl from both physical and chemical interactions with the crucible. The buffer ply is essentially constituted by a flexible fabric selected from: a woven cloth, a knit, a multidirectional sheet, and a thin felt. Prior to putting the ply into place in the bowl, it is possible to form a thin deposit of pyrolytic carbon on the fibers of the fabric.

Owner:SNECMA MOTEURS SA

Nonvolatile latch circuit and system on chip with the same

InactiveUS20070086230A1Improve reliabilityPrevent the diffusion of impuritiesDigital storageBit lineElectrical polarity

A nonvolatile ferroelectric memory device includes a bottom word line, an insulating layer formed on the bottom word line, a bit line including a floating channel region formed on the insulating layer, a tunnel oxide film formed on the floating channel region, a ferroelectric layer formed on the tunnel oxide film, wherein a change in a polarity of the ferroelectric layer induces a change in a resistance of the floating channel region, and a top word line formed on the ferroelectric layer in parallel with the bottom word line.

Owner:SK HYNIX INC

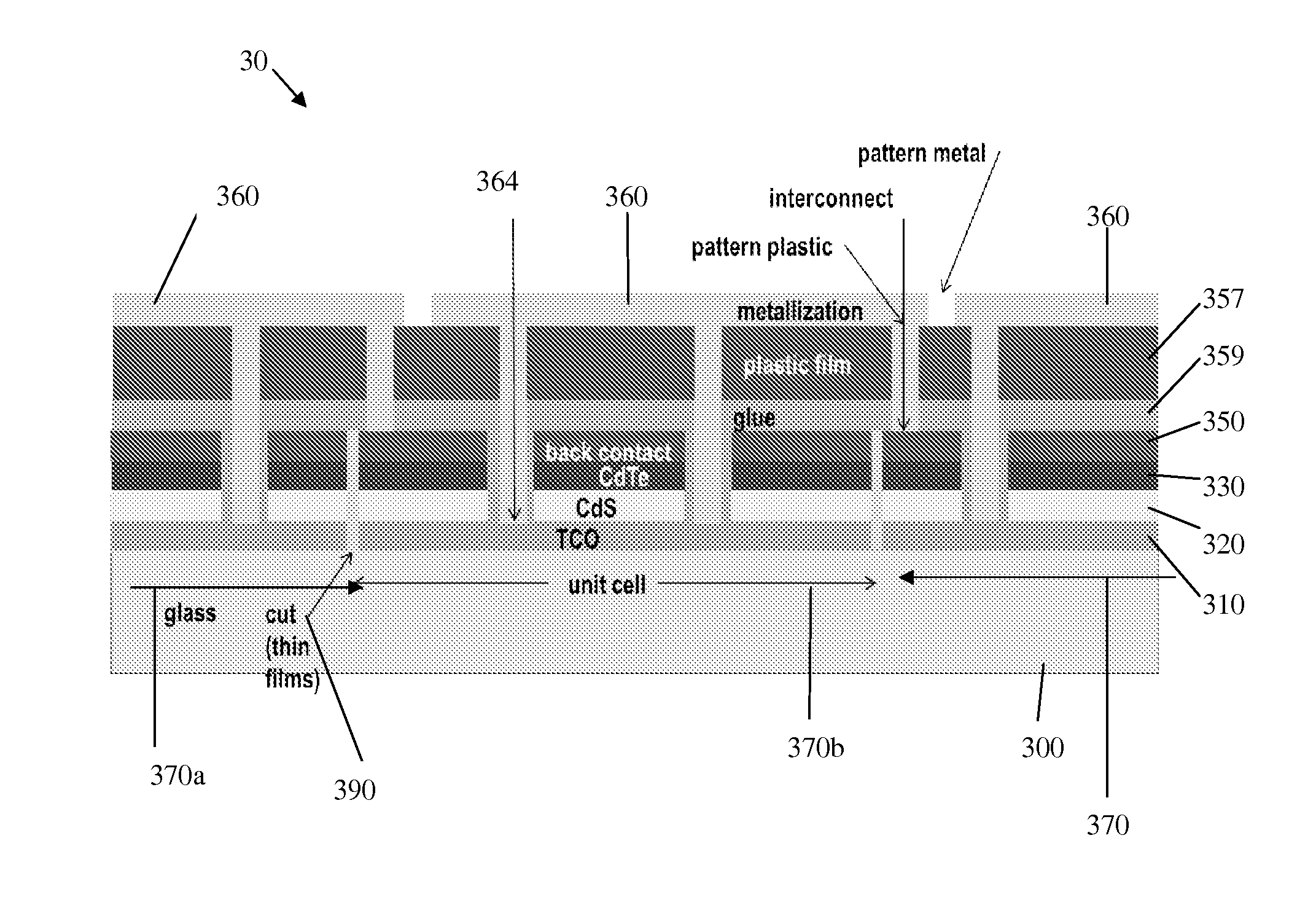

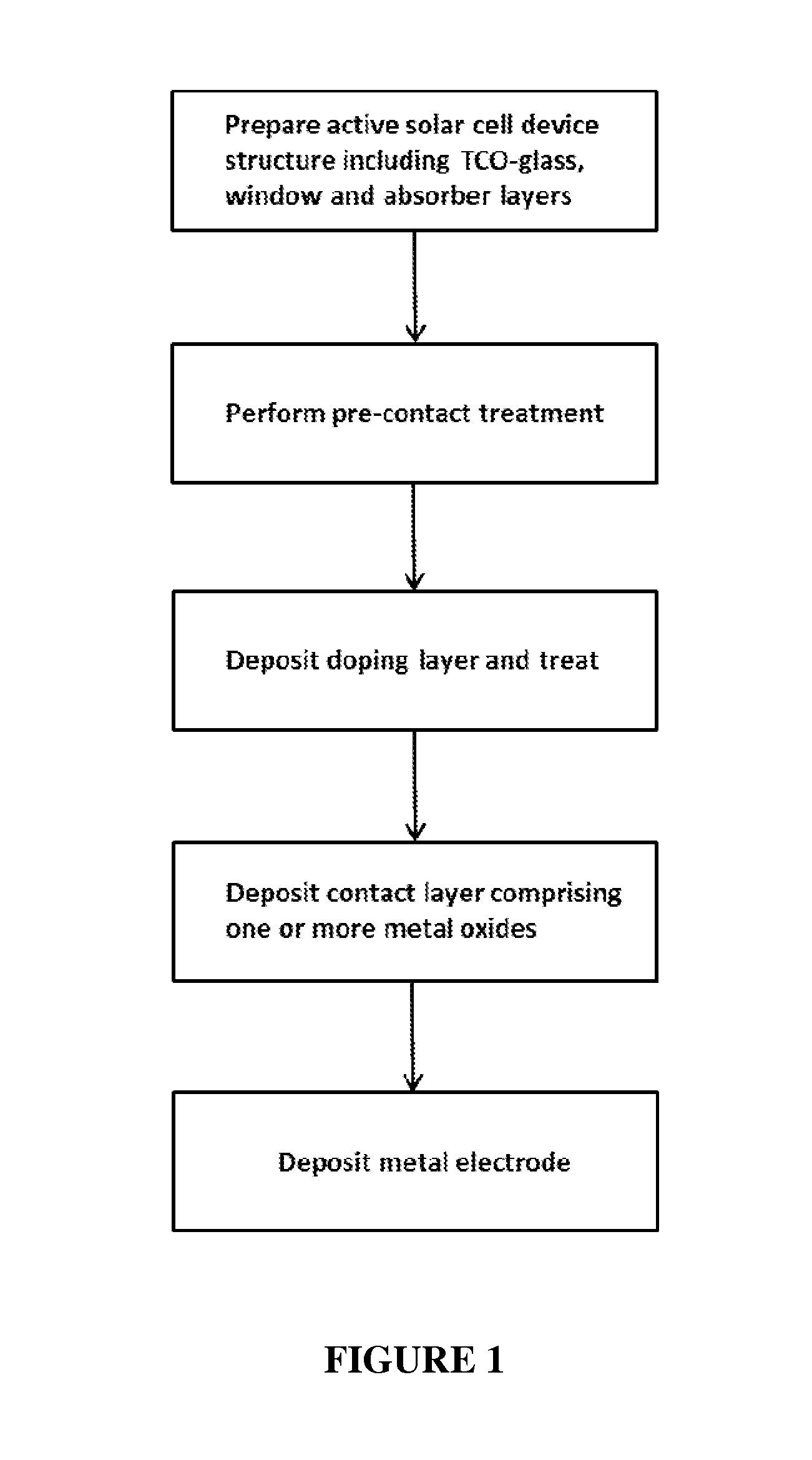

System and Method for Thin Film Photovoltaic Modules and Back Contact for Thin Solar Cells

ActiveUS20160027954A1Improved photovoltaicImproved CdTe photovoltaic devices/modulesSemiconductor/solid-state device manufacturingPhotovoltaic energy generationOhmic contactEngineering

The present disclosure provides improved thin film photovoltaic devices and related methods of fabrication. More particularly, the present disclosure provides improved CdTe photovoltaic devices and related fabrication methods. Disclosed is a novel thin film photovoltaic device and means for its fabrication. An exemplary device includes a metal oxide layer between the absorber layer and the rear electrode, resulting in an ohmic back contact and having improved device stability. The metal oxide layer can include at least one of silver oxide or copper oxide, and may additionally contain nickel oxide, molybdenum oxide, and / or vanadium oxide. The present disclosure is directed towards formation of a ohmic back contact for solar cells, the back contact having improved stability. In certain embodiments, the present disclosure provides for an ohmic contact to p-type II-VI semiconductors, and to the fabrication of solar cells having improved stability, and to solar panels incorporating such back contact schemes.

Owner:NEW JERSEY INSTITUTE OF TECHNOLOGY

Semiconductor device and method of manufacturing thereof

InactiveUS20060261420A1Improve featuresHigh resistivityTransistorSemiconductor/solid-state device manufacturingDevice materialNitrogen gas

A silicon nitride film having a thickness of 3 nm or less is formed on the surfaces of a P-well and N-well, as well as on the upper and side surfaces of a gate electrode, in which the silicon nitride film can be formed, for example, by exposing the surface of the P-well and N-well, and the upper and side surfaces of the gate electrode to a nitrogen-gas-containing plasma using a magnetron RIE apparatus. Then, pocket layers, extension layers and source / drain layers are formed while leaving the silicon nitride film unremoved.

Owner:FUJITSU SEMICON LTD

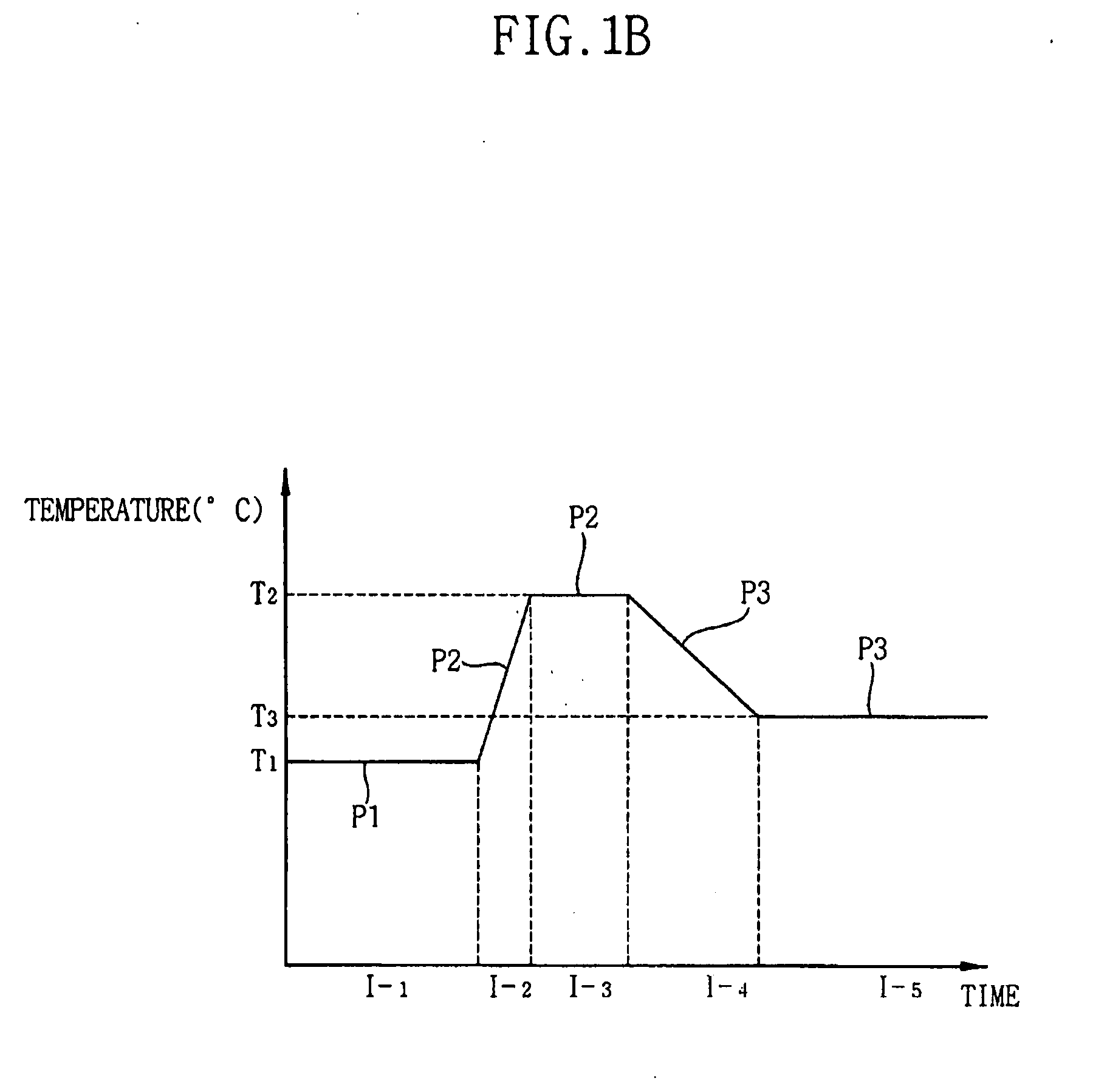

Method of forming an oxinitride layer

InactiveUS20080090424A1Accurate thicknessImprove reliabilitySemiconductor/solid-state device manufacturingDevice materialOxygen

In methods of forming an oxide layer and an oxynitride layer, a substrate is loaded into a reaction chamber having a first pressure and a first temperature. The oxide layer is formed on the substrate using a reaction gas while increasing a temperature of the reaction chamber from the first temperature to a second temperature under a second pressure. Additionally, the oxide layer is nitrified in the reaction chamber to form the oxynitride layer on the substrate. When the oxide layer and / or the oxynitride layer are formed on the substrate, minute patterns of a semiconductor device, for example a DRAM device, an SRAM device or an LOGIC device may be easily formed on the oxide layer or the oxynitride layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for reducing contact resistance of a semiconductor device

InactiveUS7026250B2Improve featuresReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringContact resistance

A method for fabricating a semiconductor device wherein the lower portion of a contact hole is cleaned, and doped with an impurity for reducing contact resistance is disclosed. The method comprises: sequentially forming a buffer layer and an interlayer insulating film on a semiconductor substrate; etching the interlayer insulating film and the buffer layer to form a contact hole exposing the semiconductor substrate; performing a cleaning process of a lower portion of the contact hole; doping an impurity into the surface of the semiconductor substrate exposed by the contact hole; and forming a conductive layer filling the contact hole on the entire surface of the resulting structure.

Owner:SK HYNIX INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com