Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

43results about How to "Large film thickness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

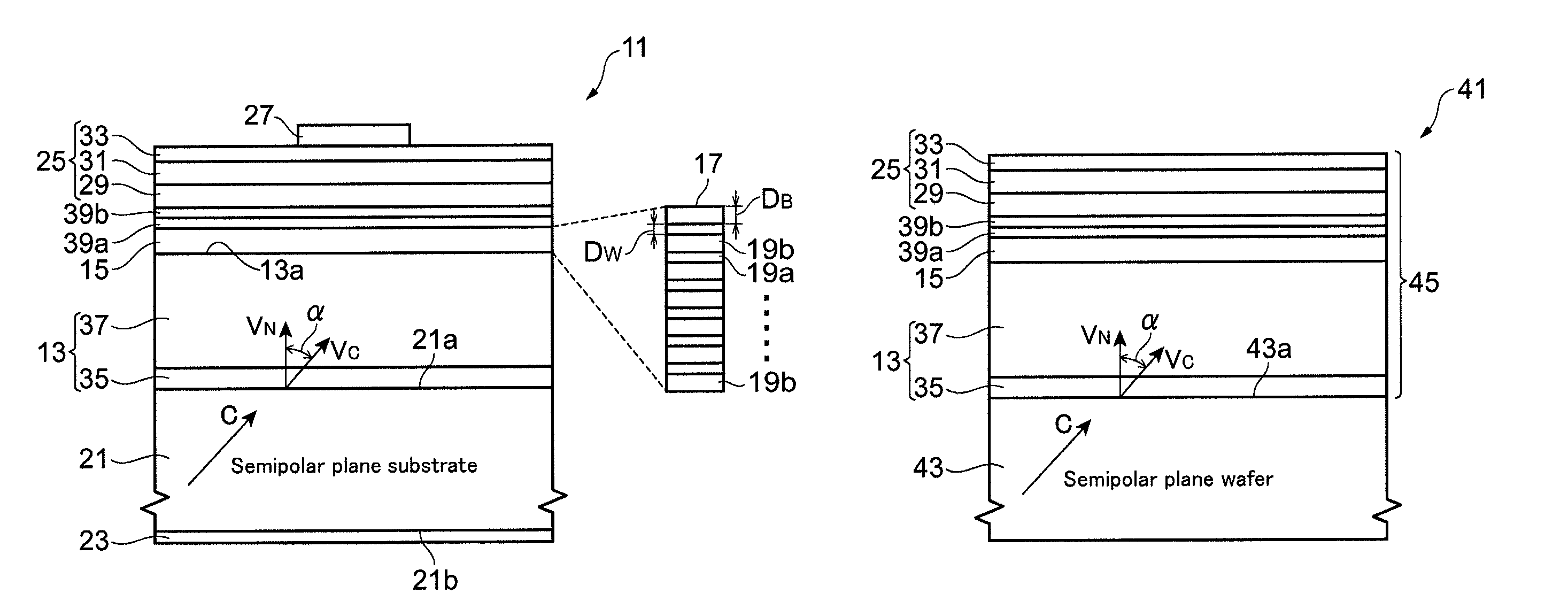

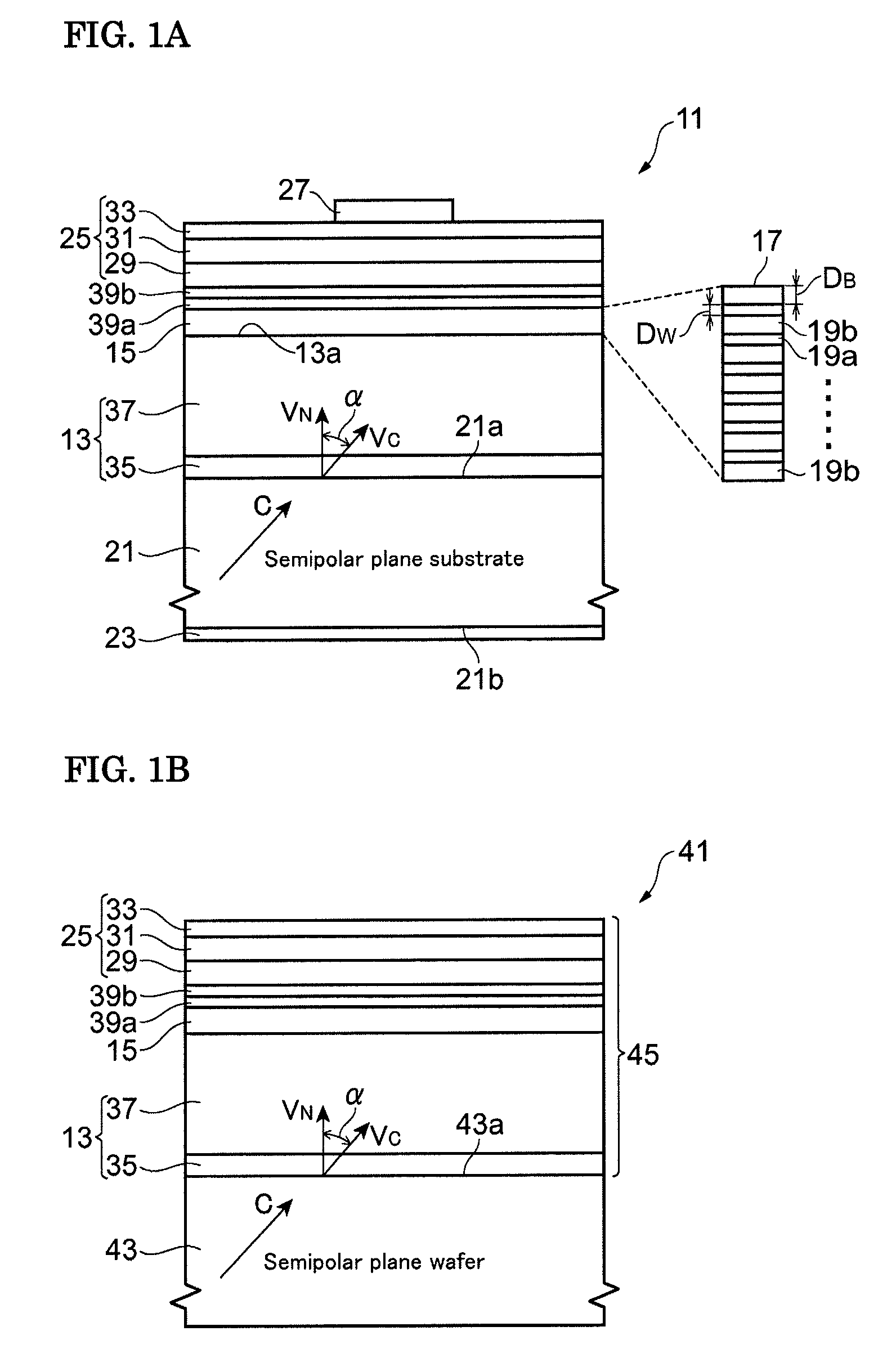

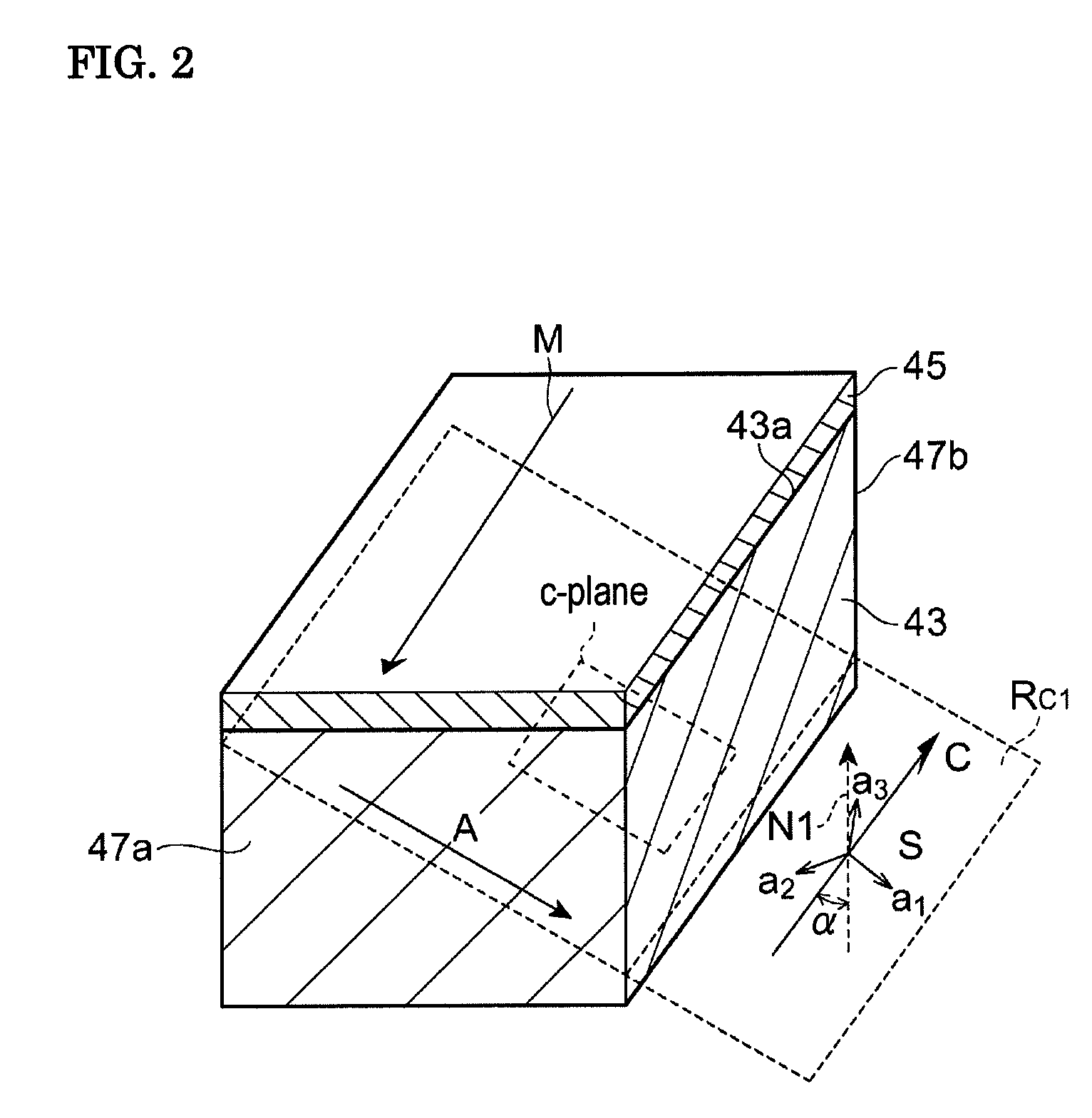

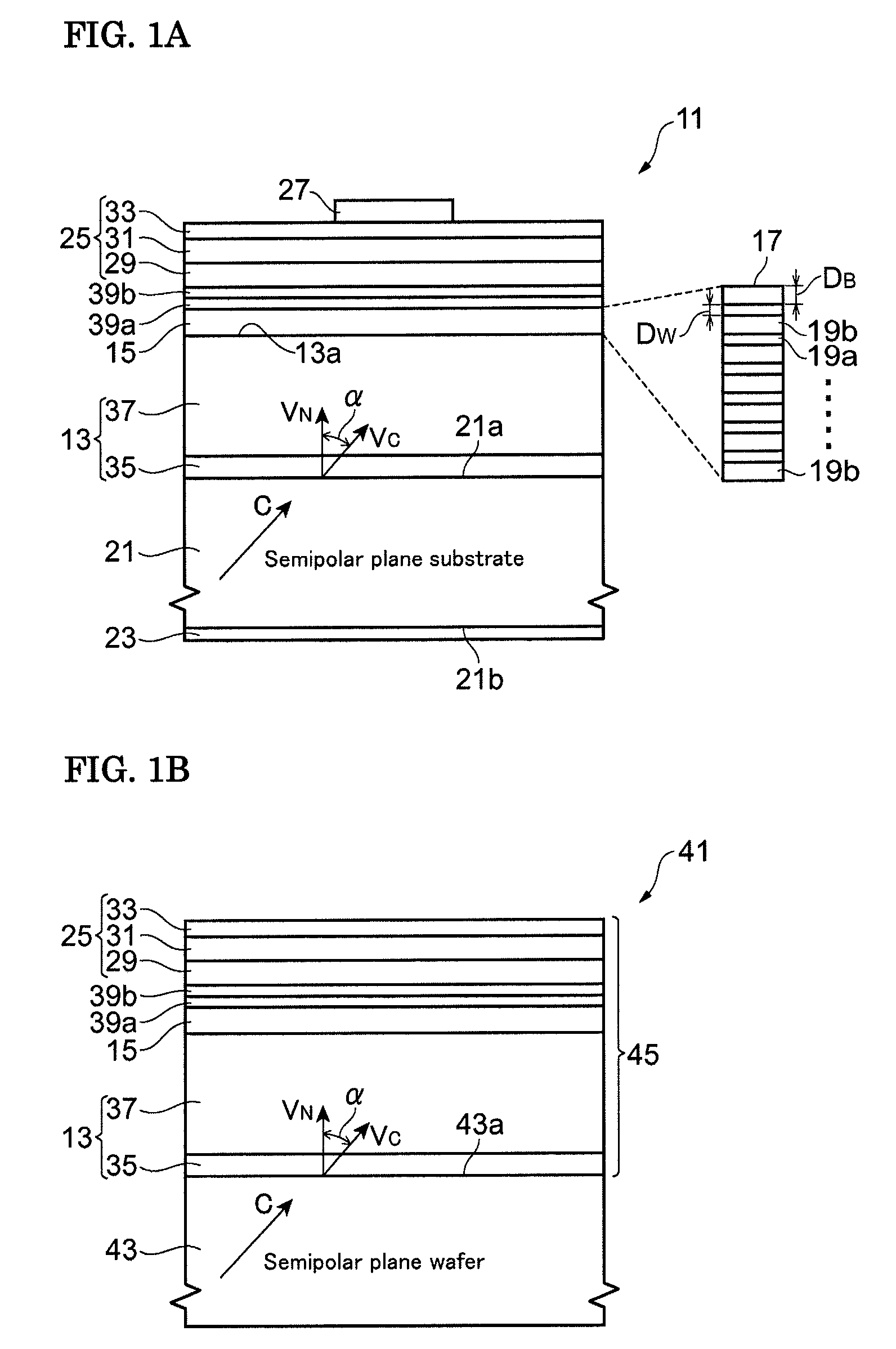

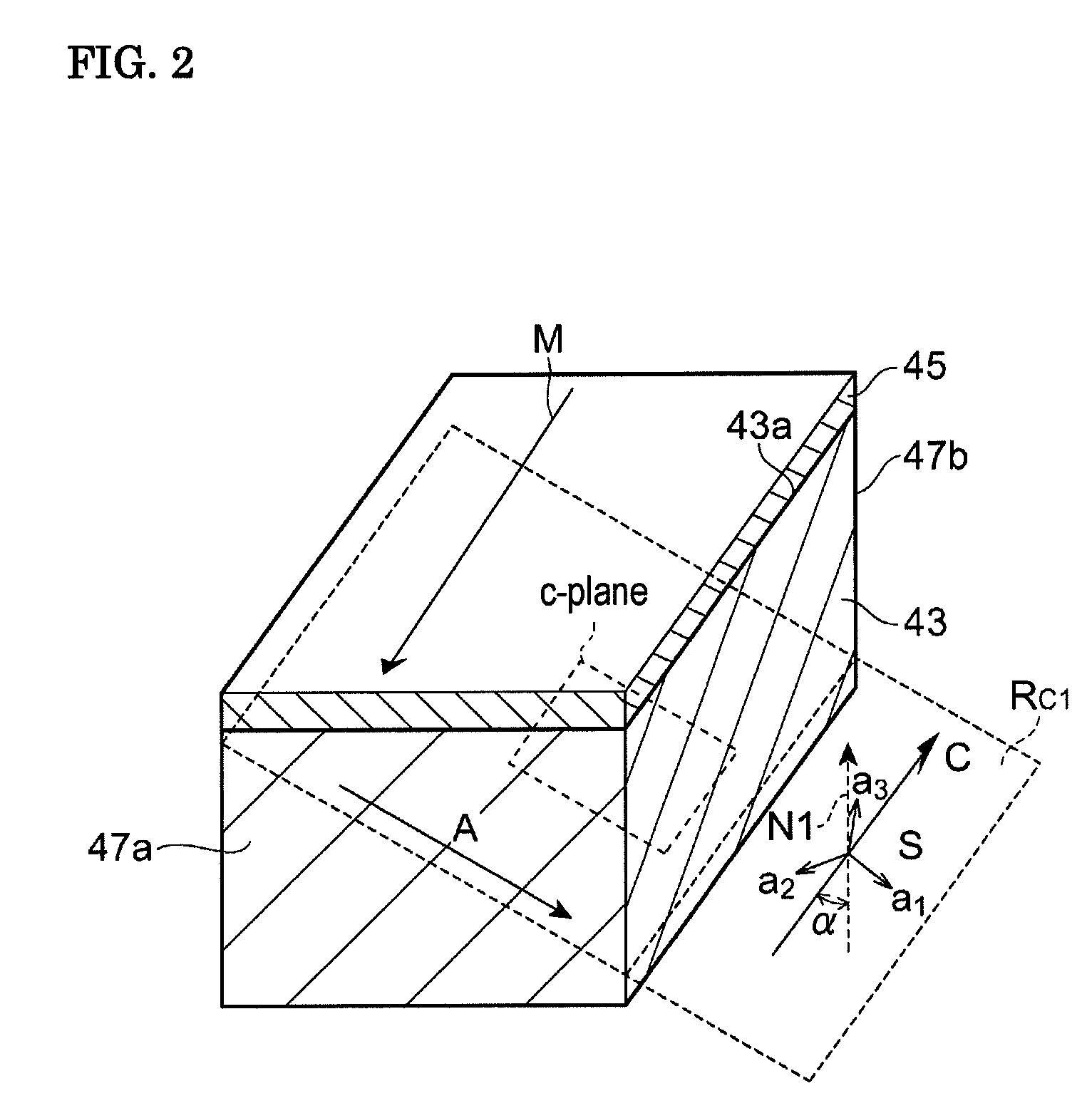

Group-III nitride light-emitting device

ActiveUS7968864B2Piezoelectric field is reducedLow efficiencyThyristorSolid-state devicesQuantum wellLength wave

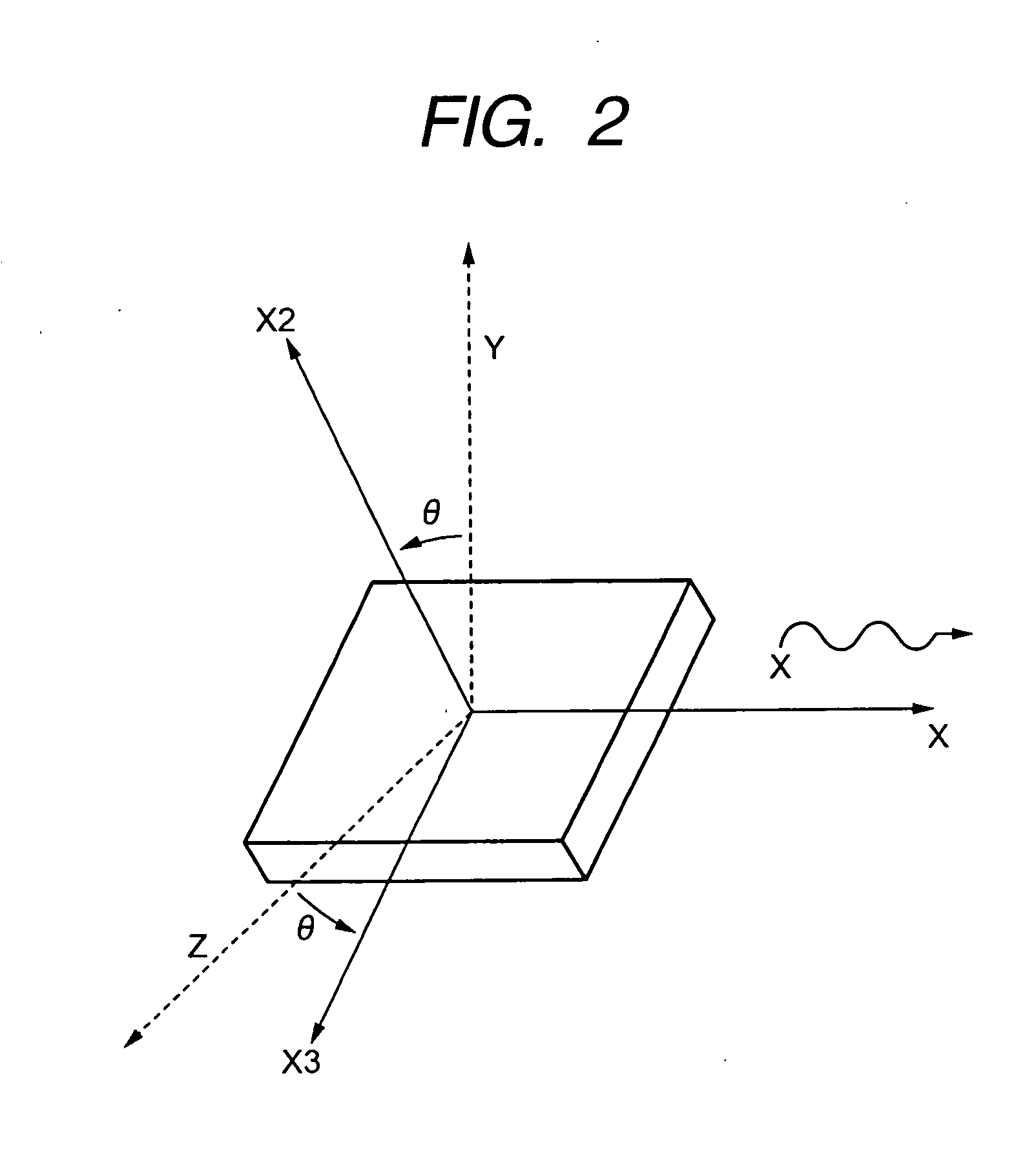

A group-III nitride light-emitting device is provided. An active layer having a quantum well structure is grown on a basal plane of a gallium nitride based semiconductor region. The quantum well structure is formed in such a way as to have an emission peak wavelength of 410 nm or more. The thickness of a well layer is 4 nm or more, and 10 nm or less. The well layer is composed of InXGa1-XN (0.15≦X<1, where X is a strained composition). The basal plane of the gallium nitride based semiconductor region is inclined at an inclination angle within the range of 15 degrees or more, and 85 degrees or less with reference to a {0001} plane or a {000-1} plane of a hexagonal system group III nitride. The basal plane in this range is a semipolar plane.

Owner:SUMITOMO ELECTRIC IND LTD

Group-iii nitride light-emitting device and method for manufacturing group-iii nitride based semiconductor light-emitting device

ActiveUS20090212277A1StructuredImprove crystal qualitySolid-state devicesSemiconductor/solid-state device manufacturingQuantum wellLength wave

A group-III nitride light-emitting device is provided. An active layer having a quantum well structure is grown on a basal plane of a gallium nitride based semiconductor region. The quantum well structure is formed in such a way as to have an emission peak wavelength of 410 nm or more. The thickness of a well layer is 4 nm or more, and 10 nm or less. The well layer is composed of InXGa1-XN (0.15≦X<1, where X is a strained composition). The basal plane of the gallium nitride based semiconductor region is inclined at an inclination angle within the range of 15 degrees or more, and 85 degrees or less with reference to a {0001} plane or a {000-1} plane of a hexagonal system group III nitride. The basal plane in this range is a semipolar plane.

Owner:SUMITOMO ELECTRIC IND LTD

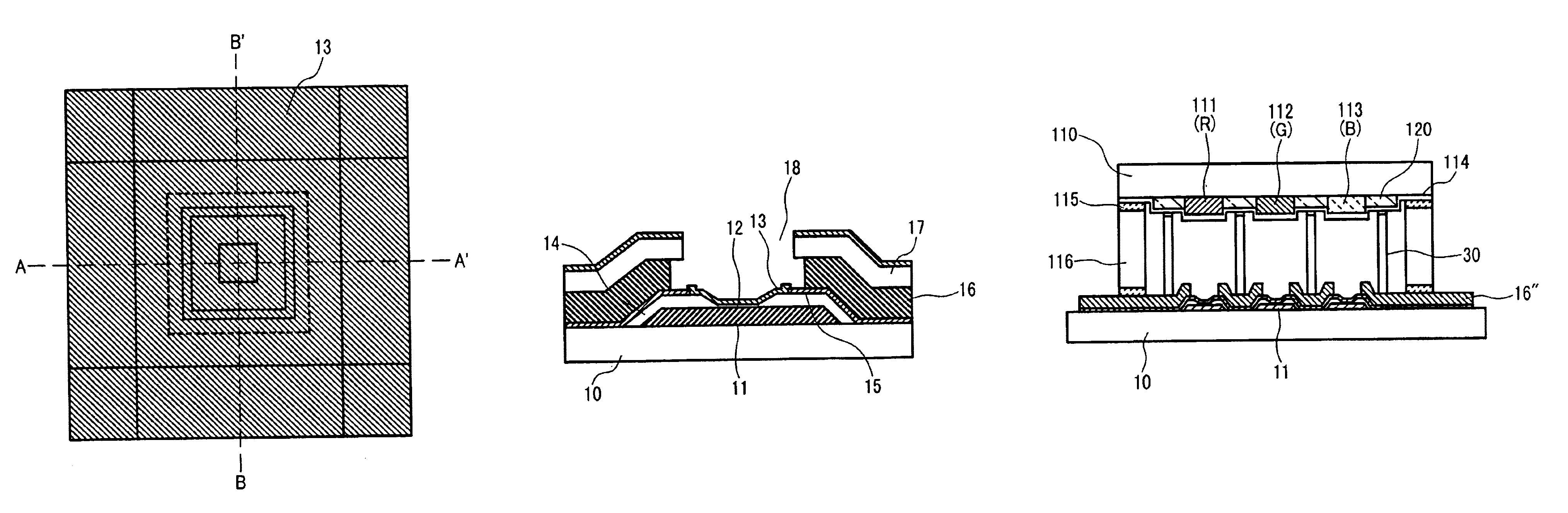

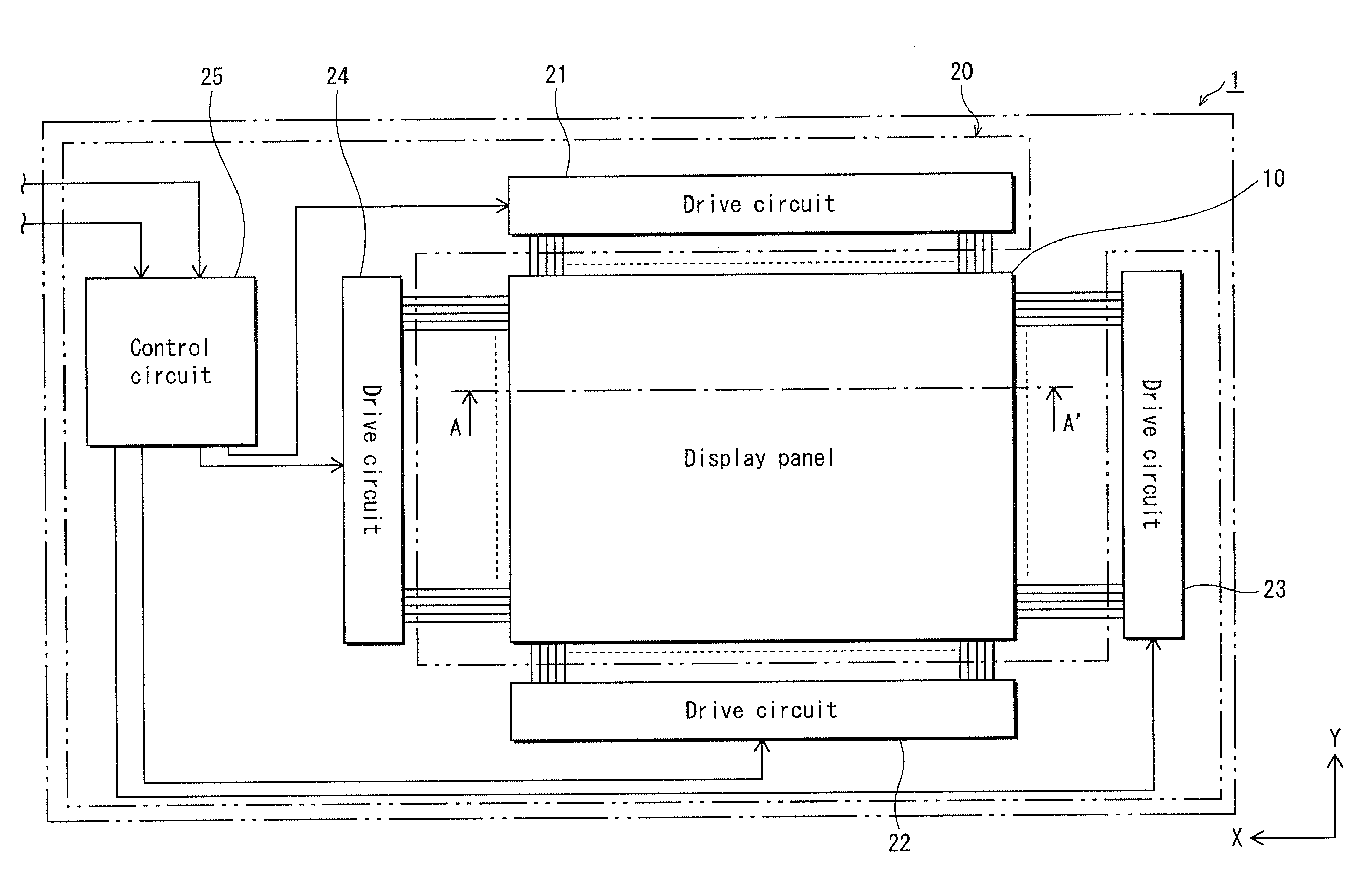

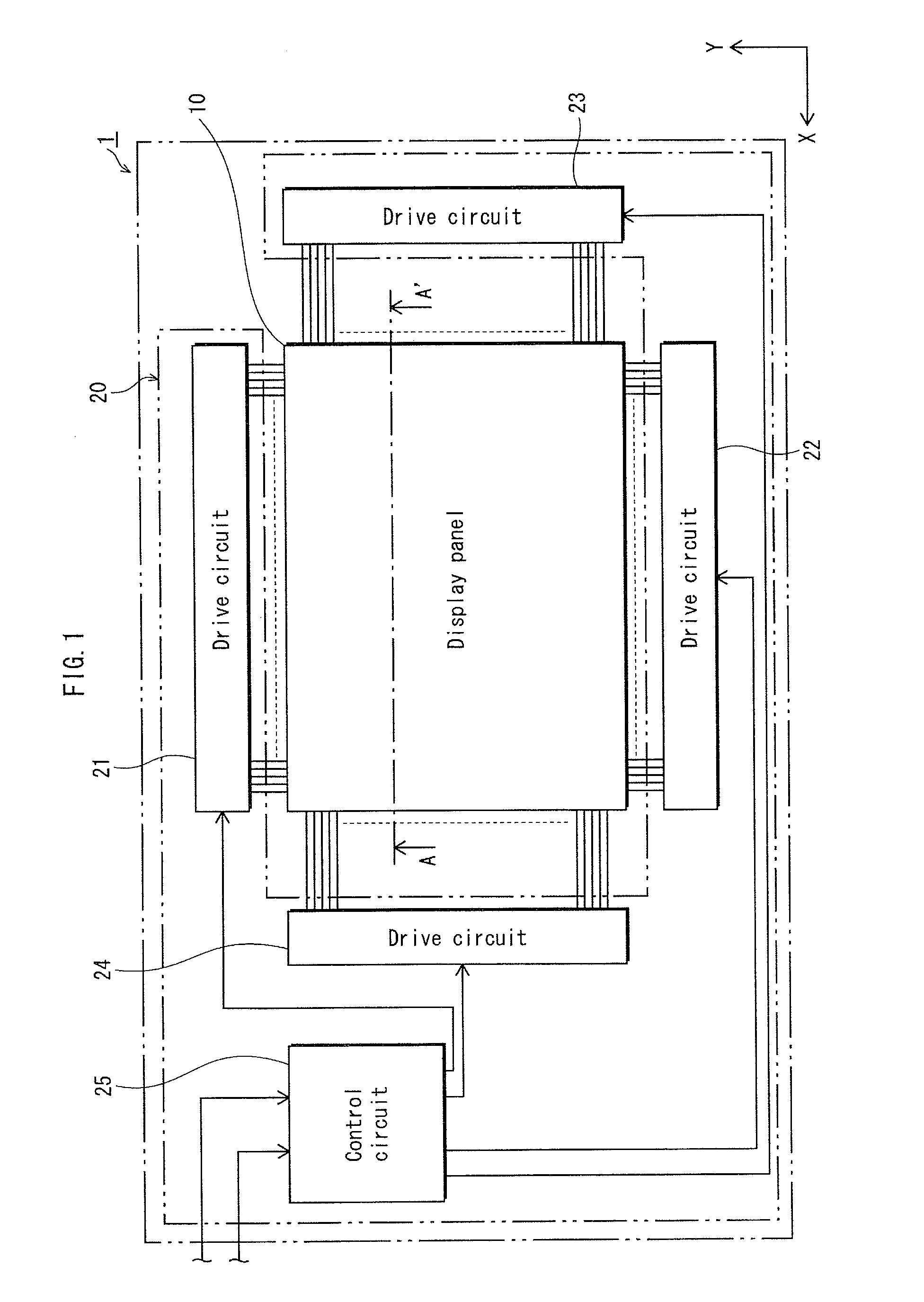

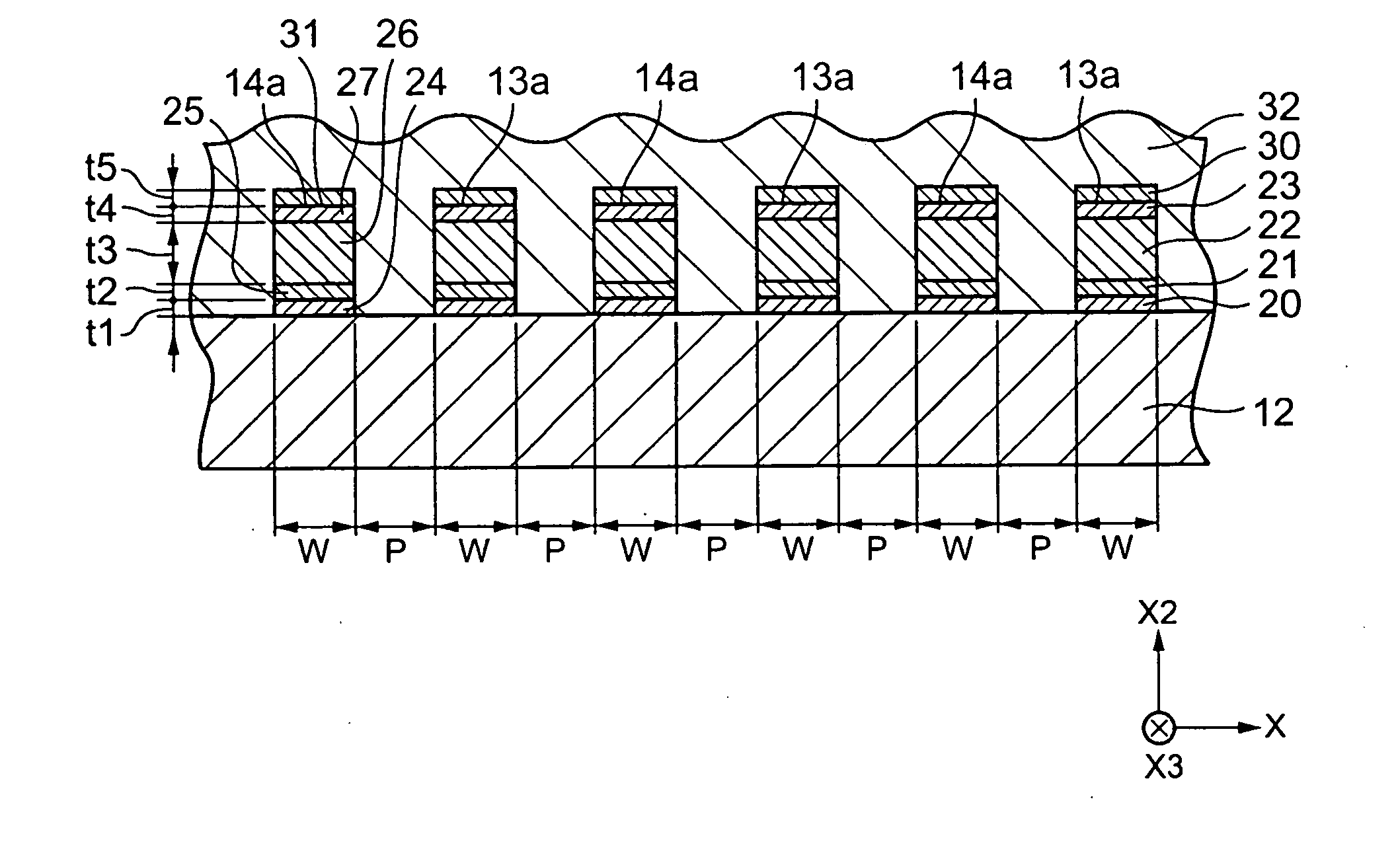

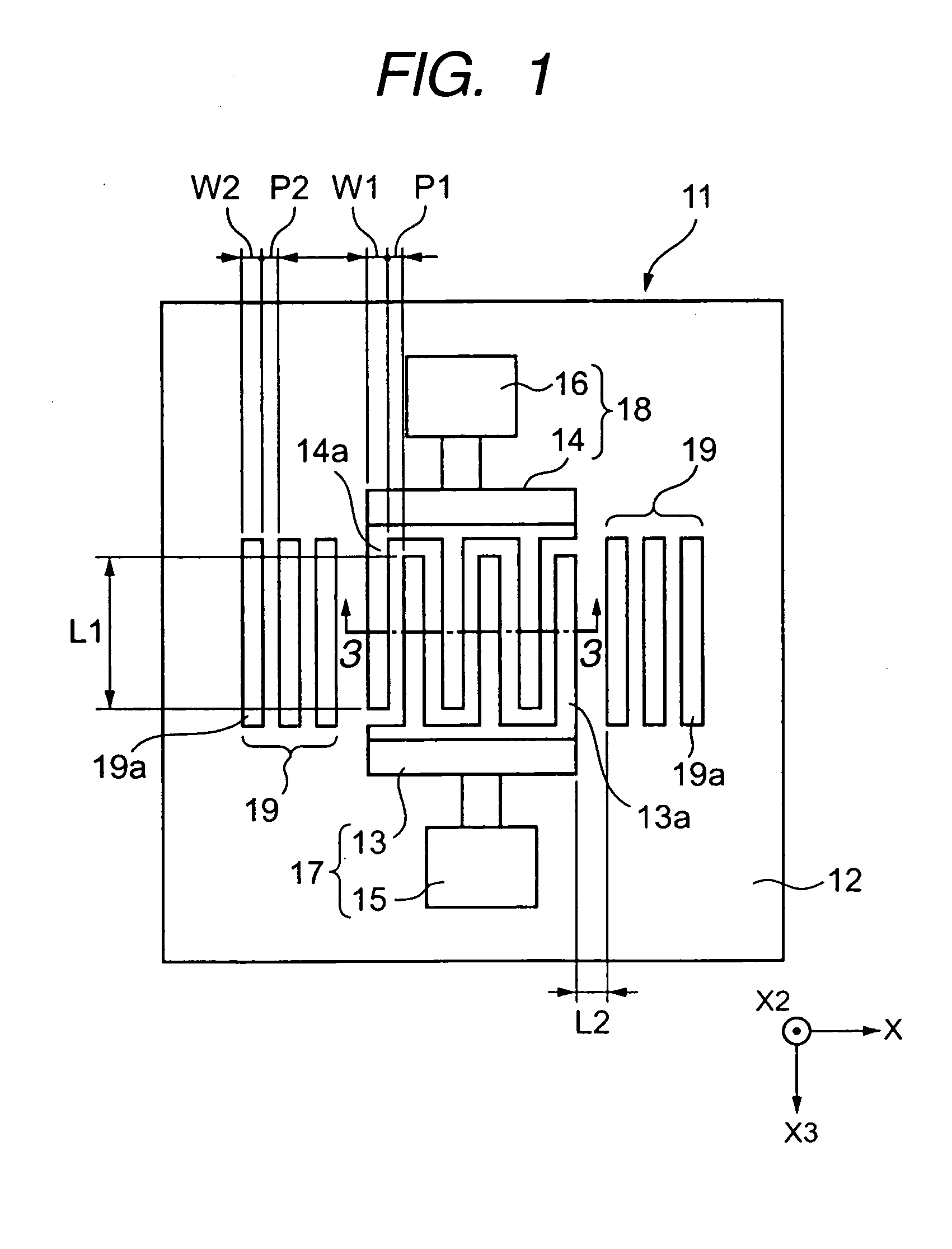

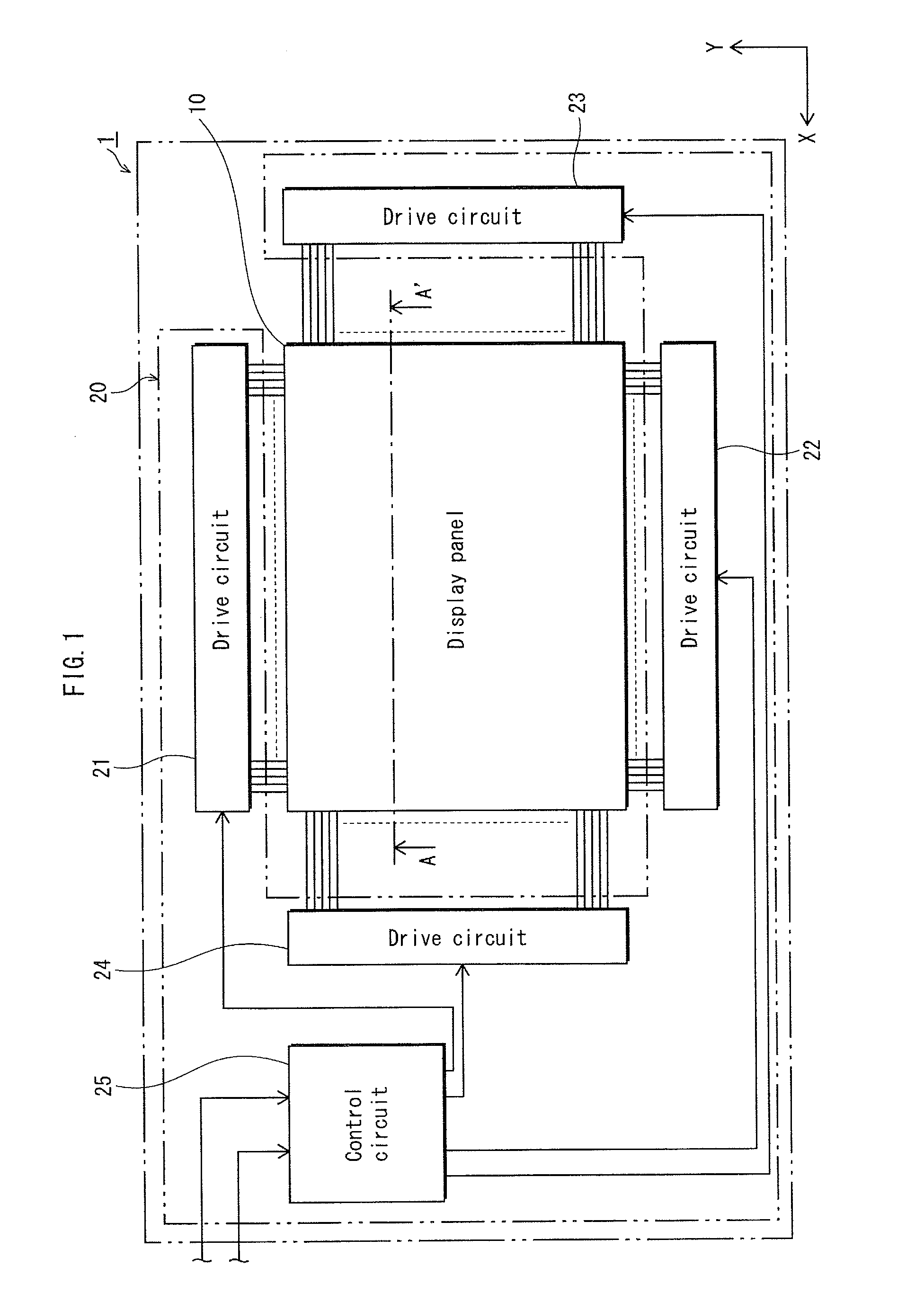

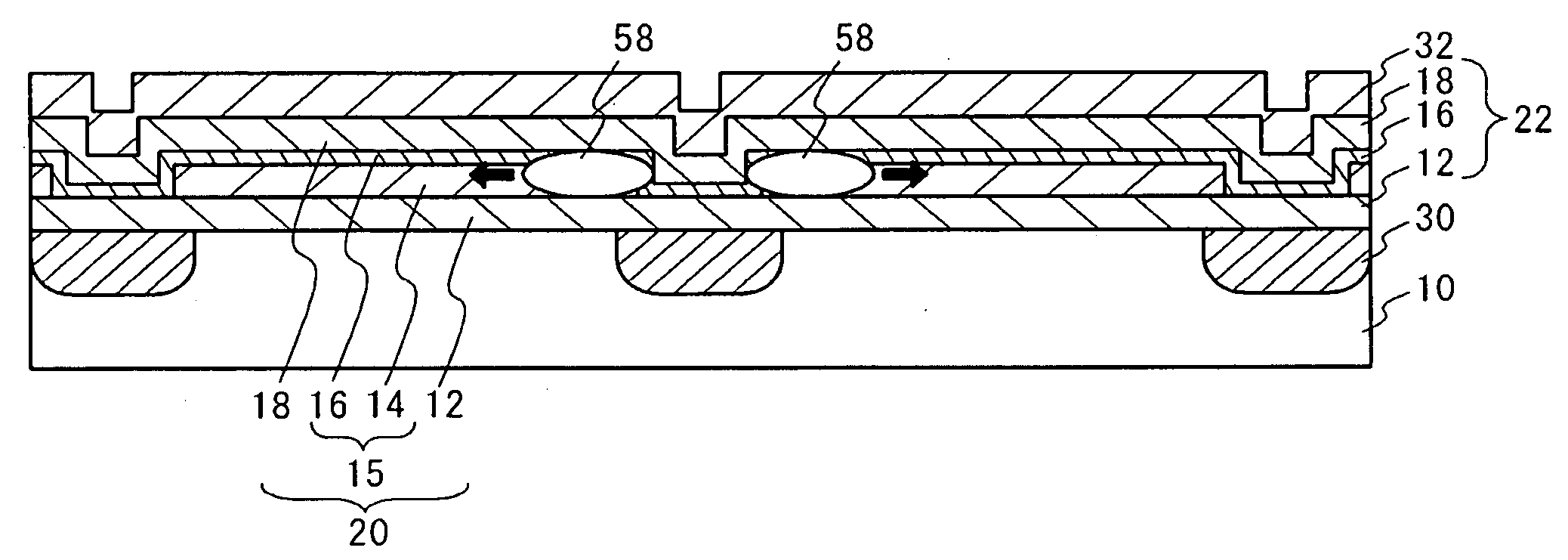

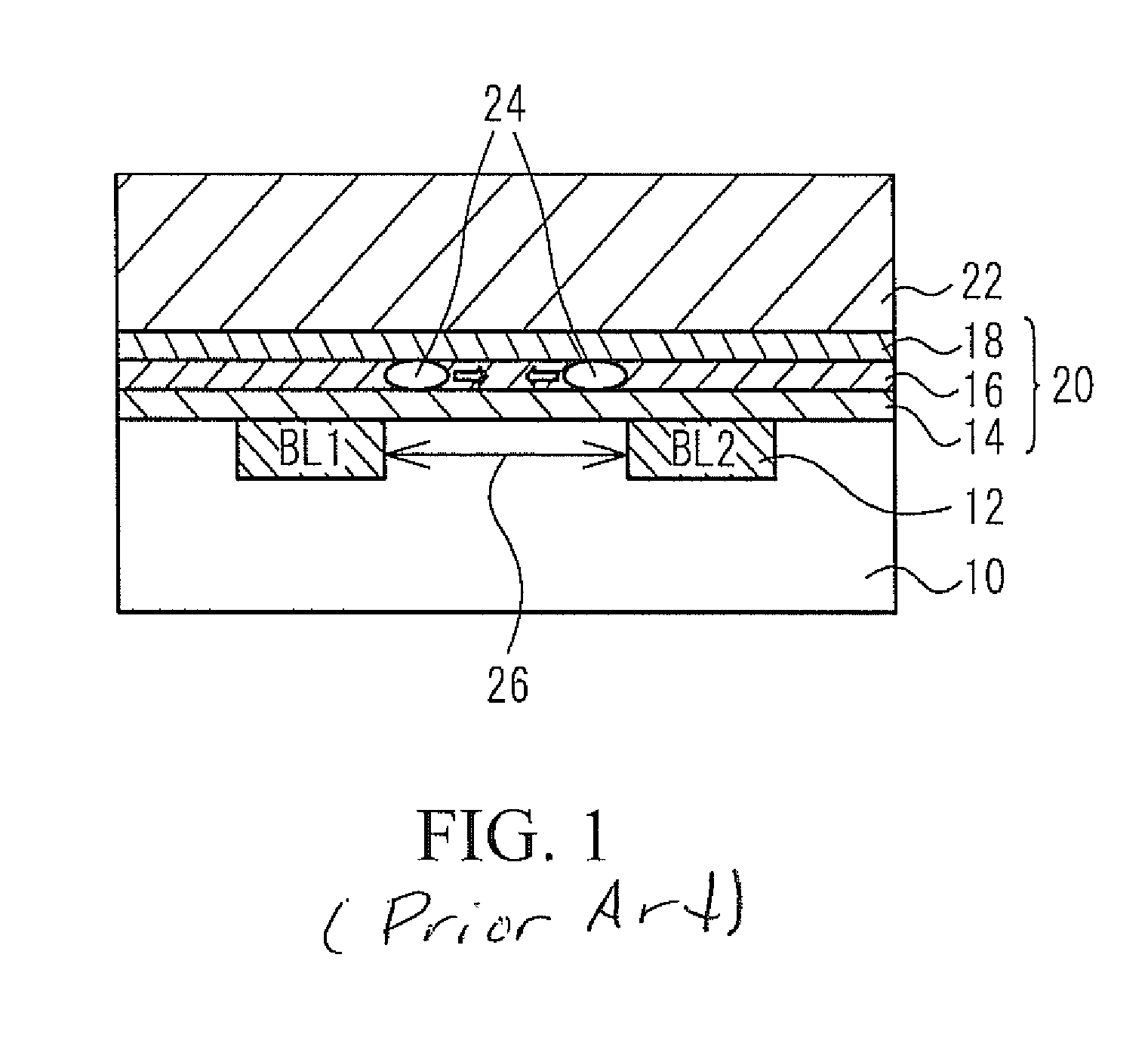

Field emission display

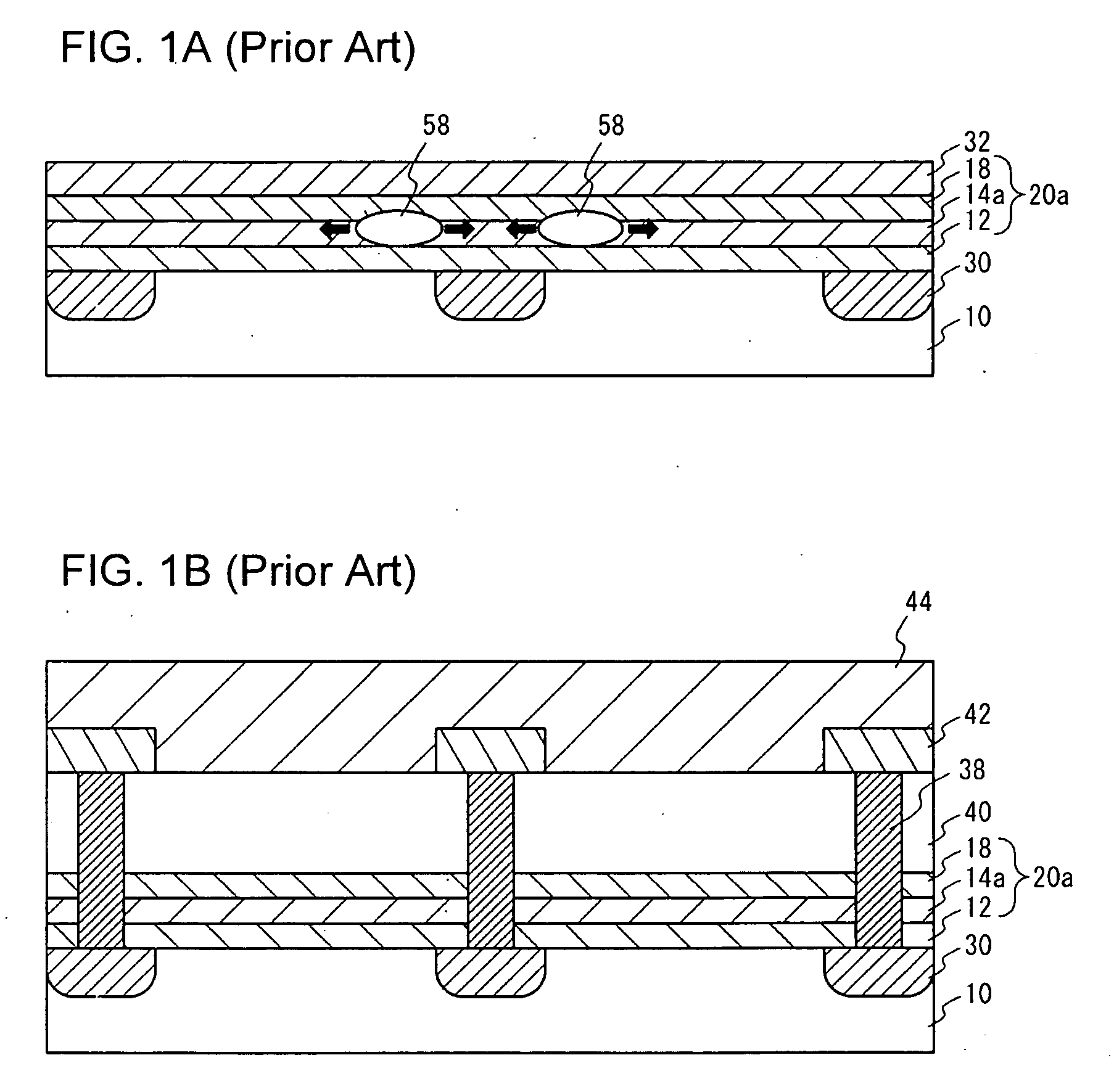

InactiveUS6873115B2Reduce sheet resistanceLarge film thicknessControl electrodesDischarge tube luminescnet screensElectron sourceScan line

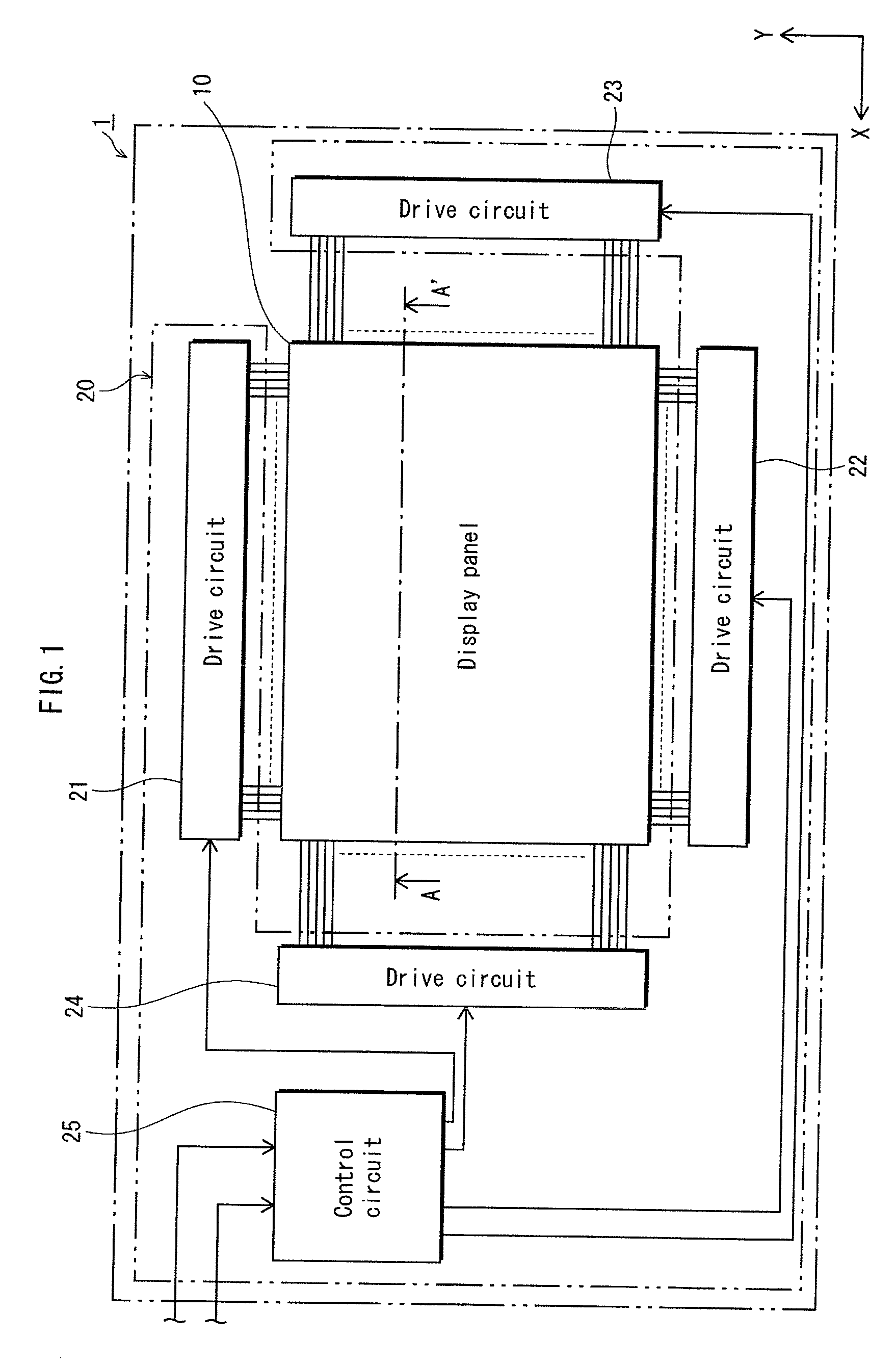

A display having hot electron type electron sources displaying an image by a line sequential scanning scheme is provided to prevent poor brightness uniformity along scan lines. The hot electron type electron source is provided with a top electrode bus line serving as a scan line and a bottom electrode bus line serving as a data line. The top electrode bus line has a sheet resistance lower than that of the bottom electrode. The wire sheet resistance of the scam line can be reduced to several m / square. When forming a 40 inch large screen FED using the hot electron type electron sources, a voltage drop amount produced in the scan line can be suppressed below an allowable range. As a result, high quality image without poor brightness uniformity can be obtained.

Owner:HITACHI LTD

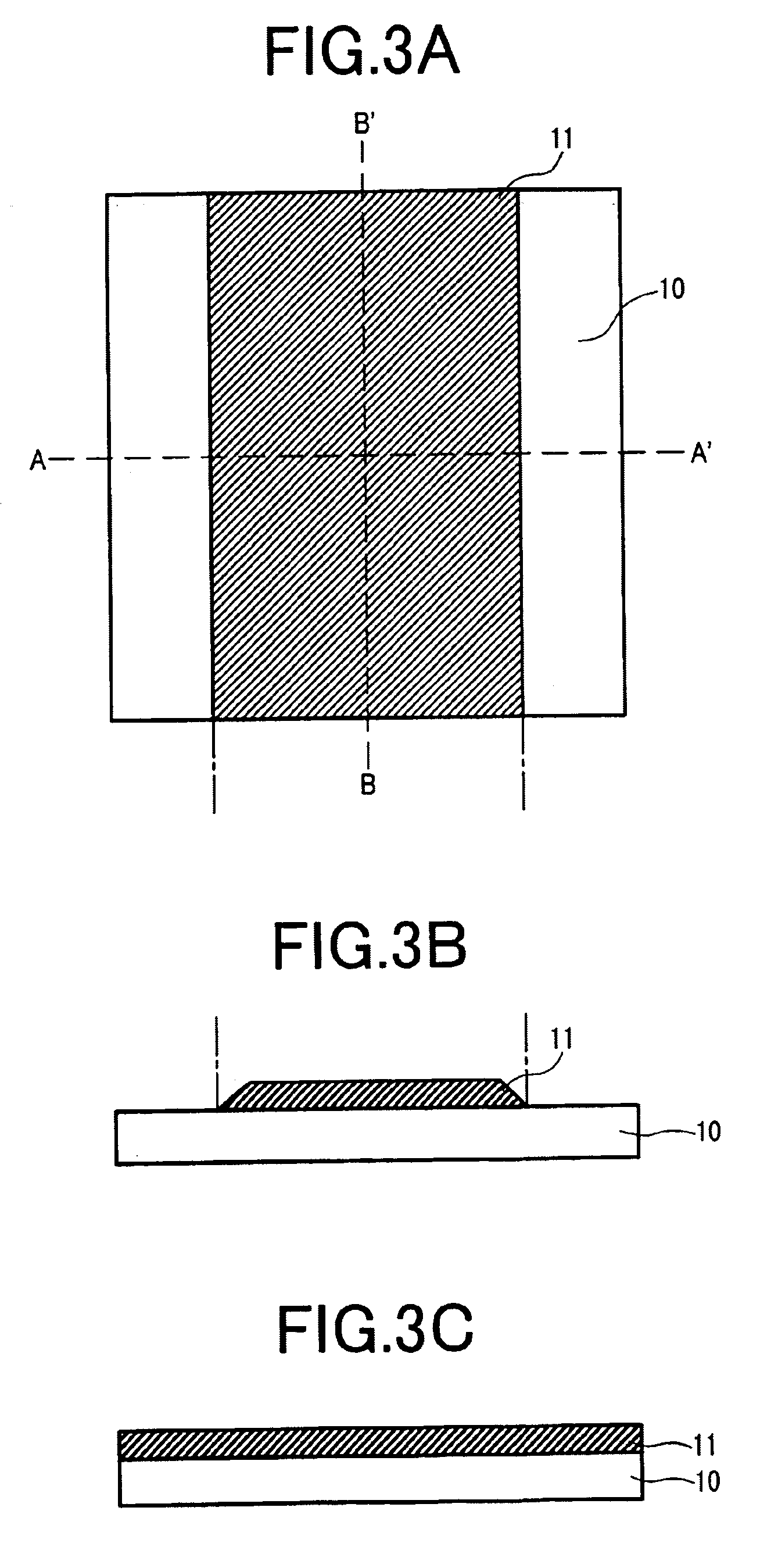

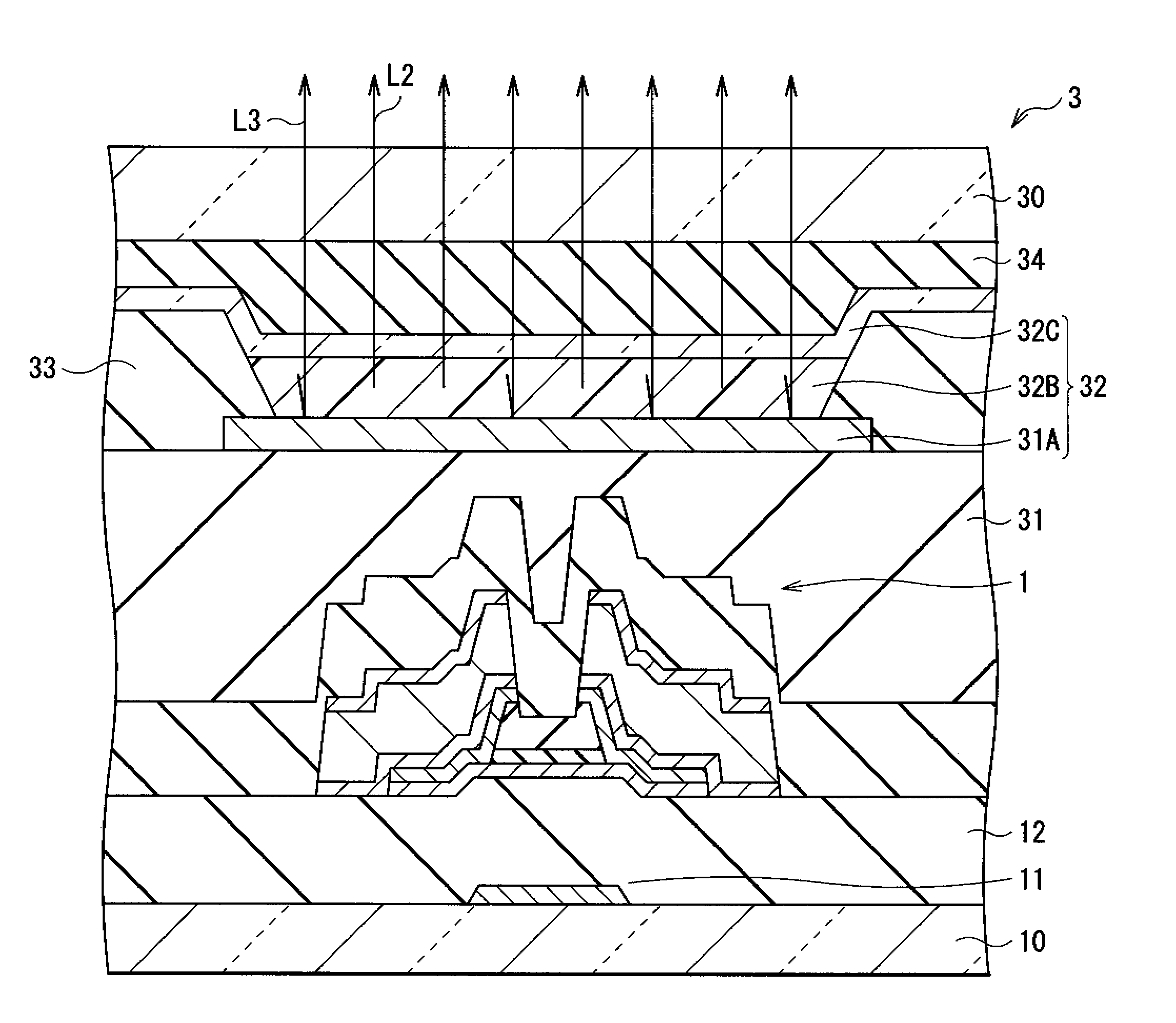

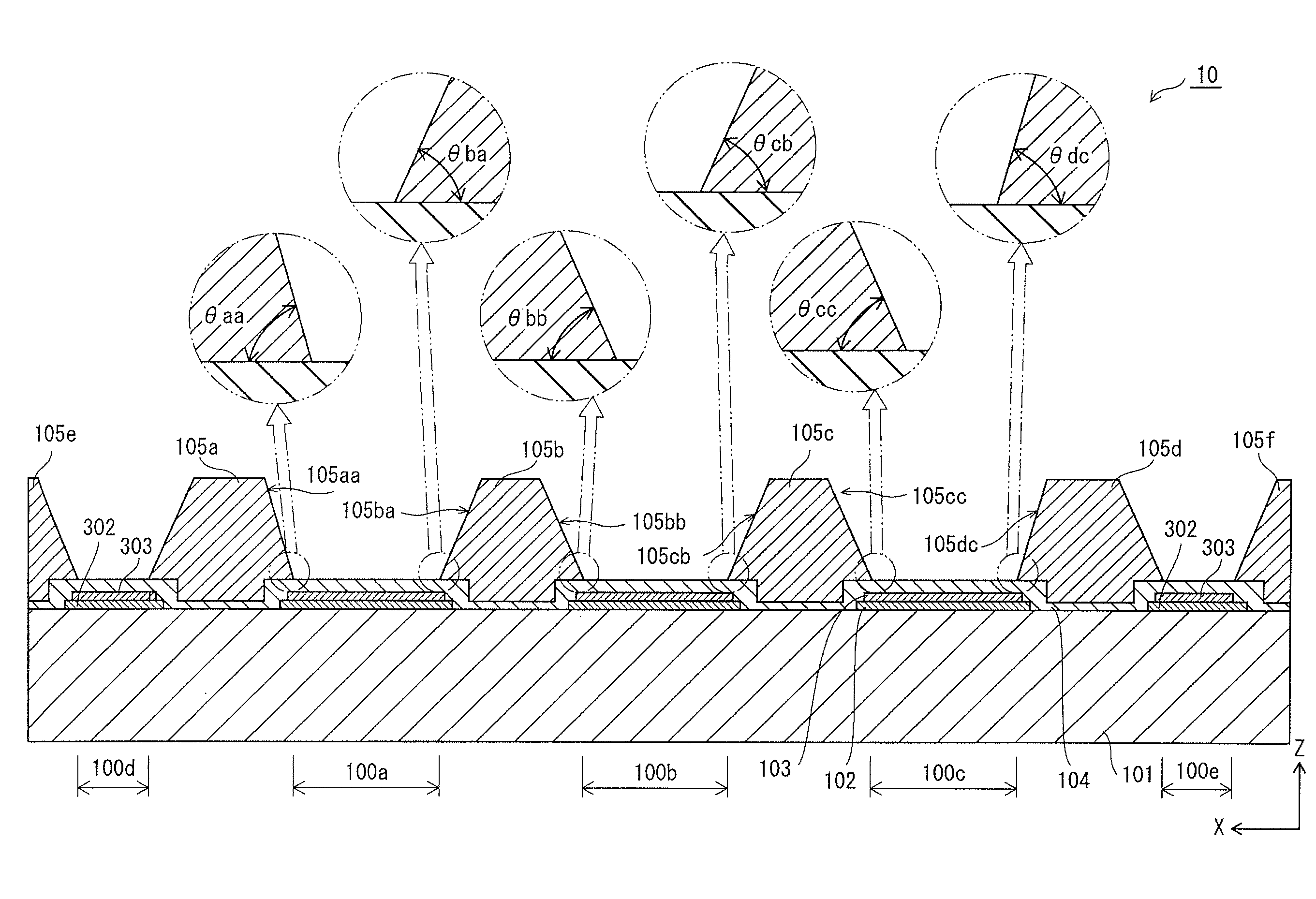

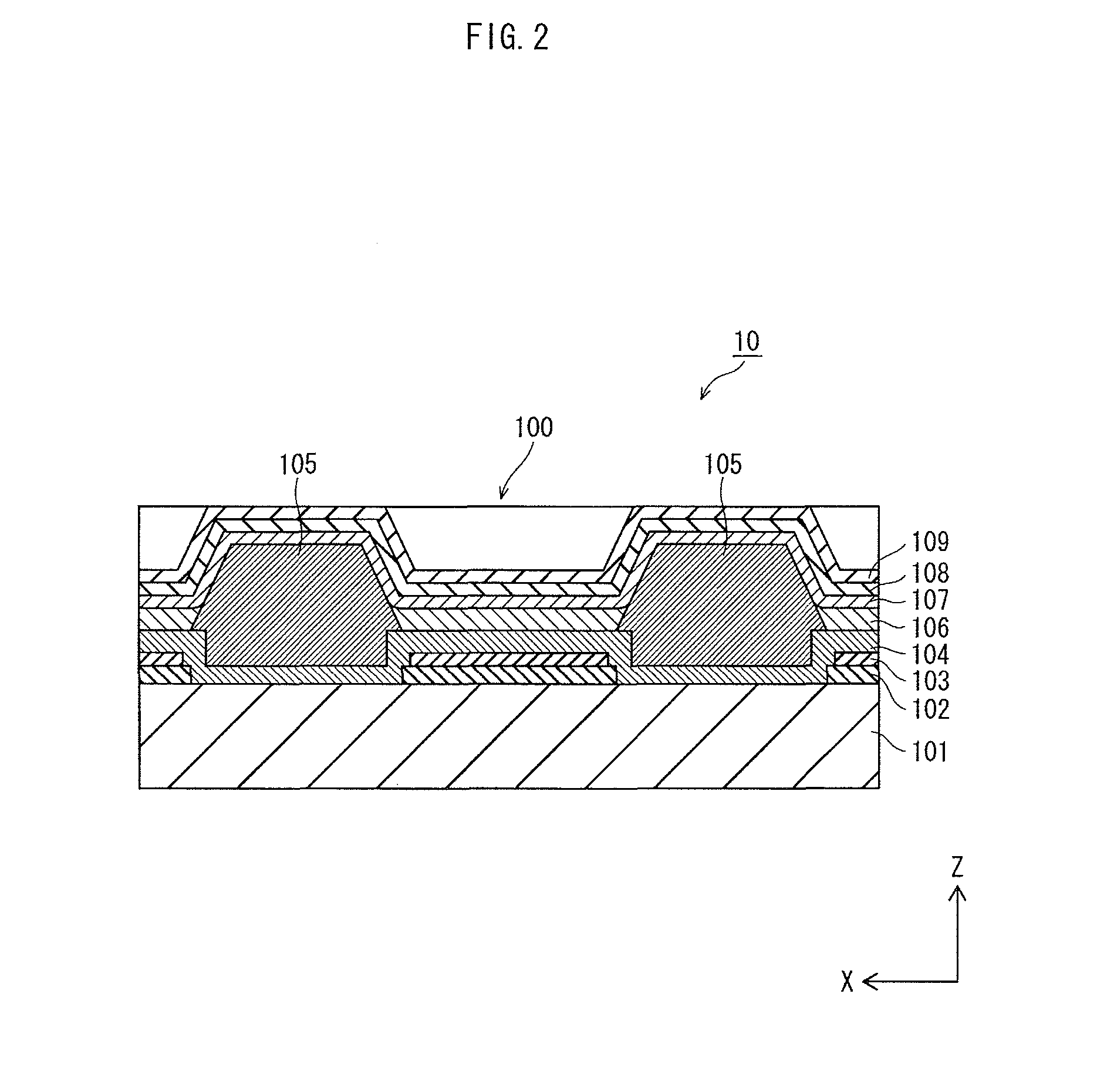

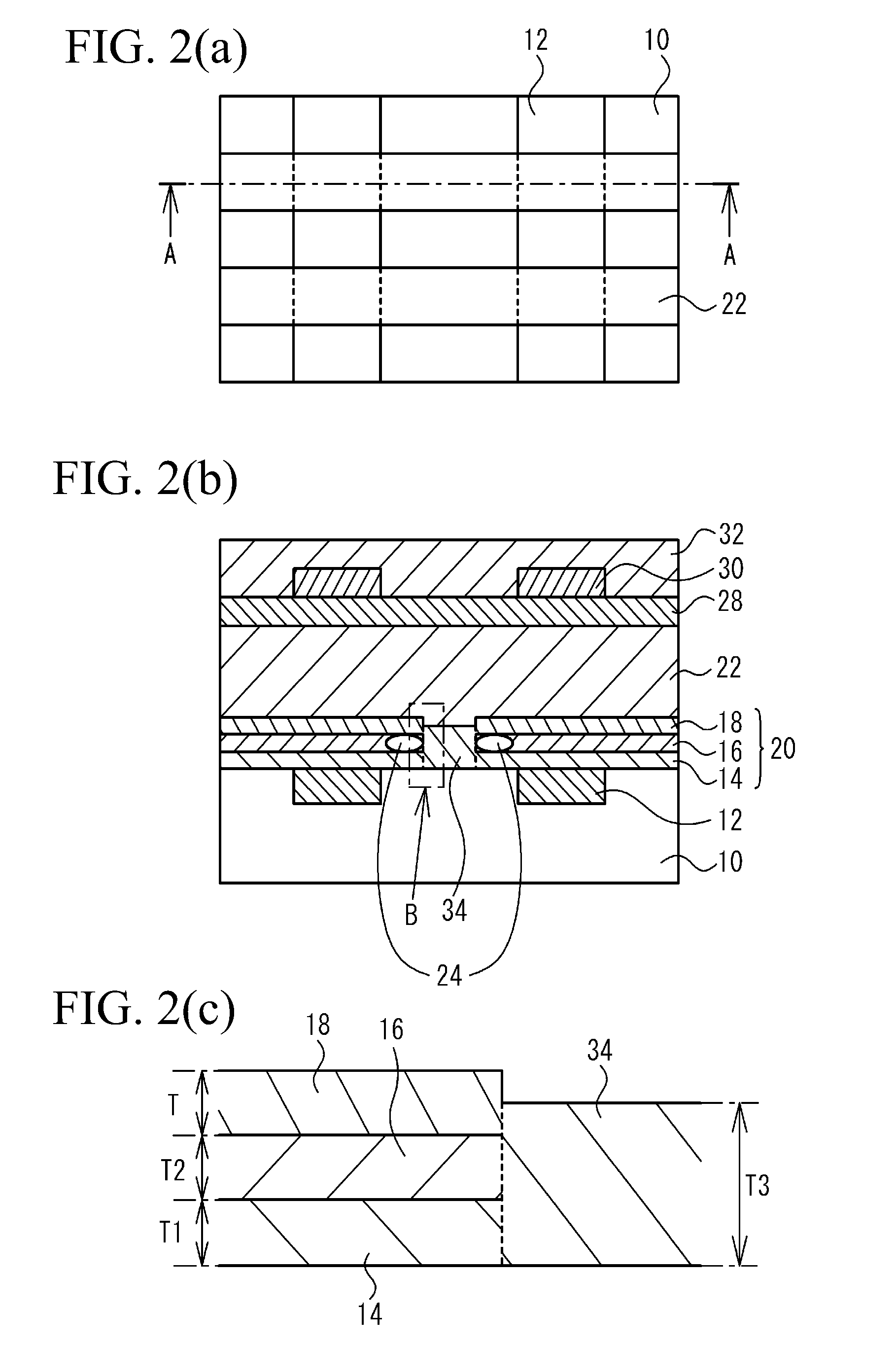

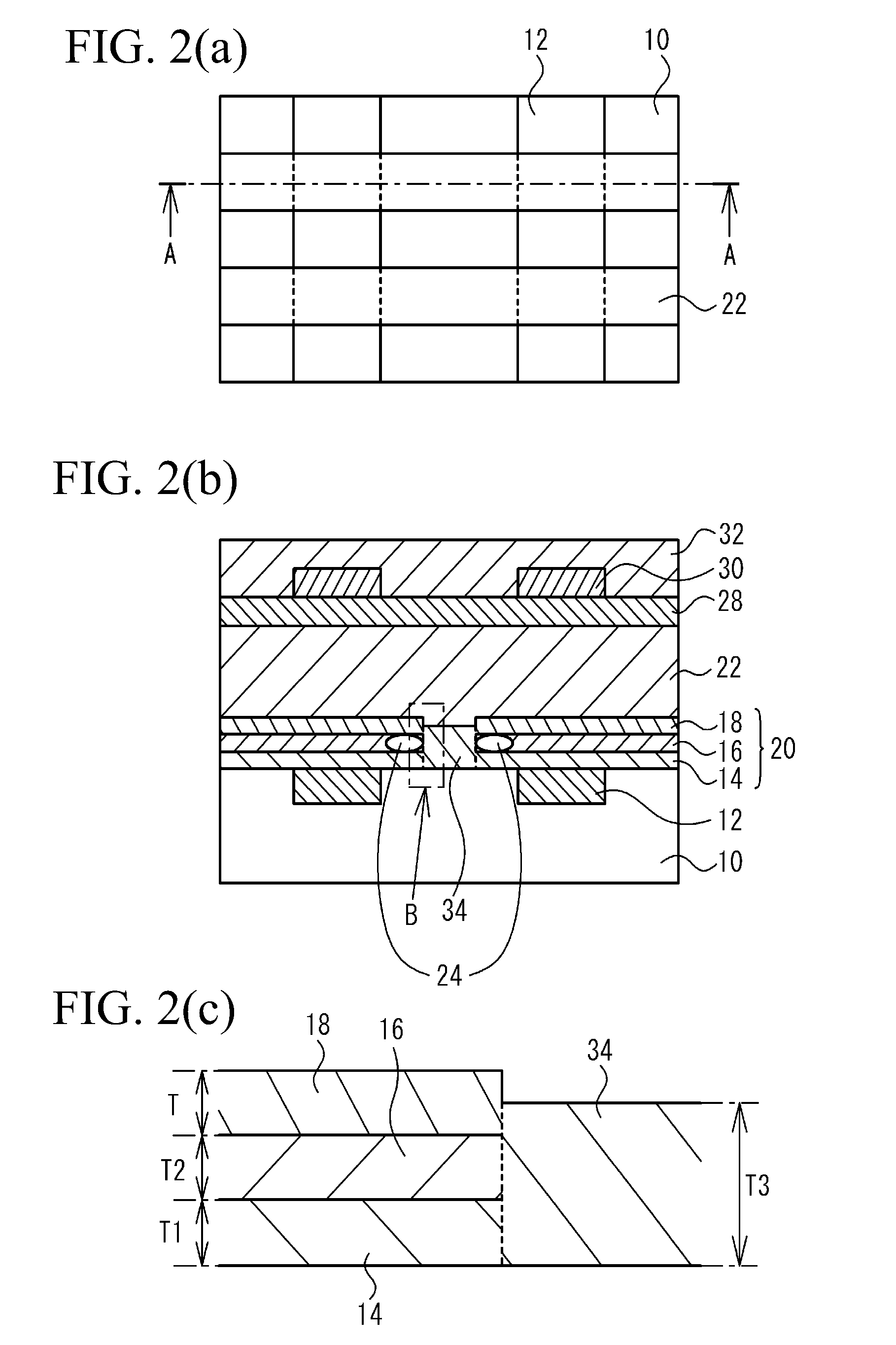

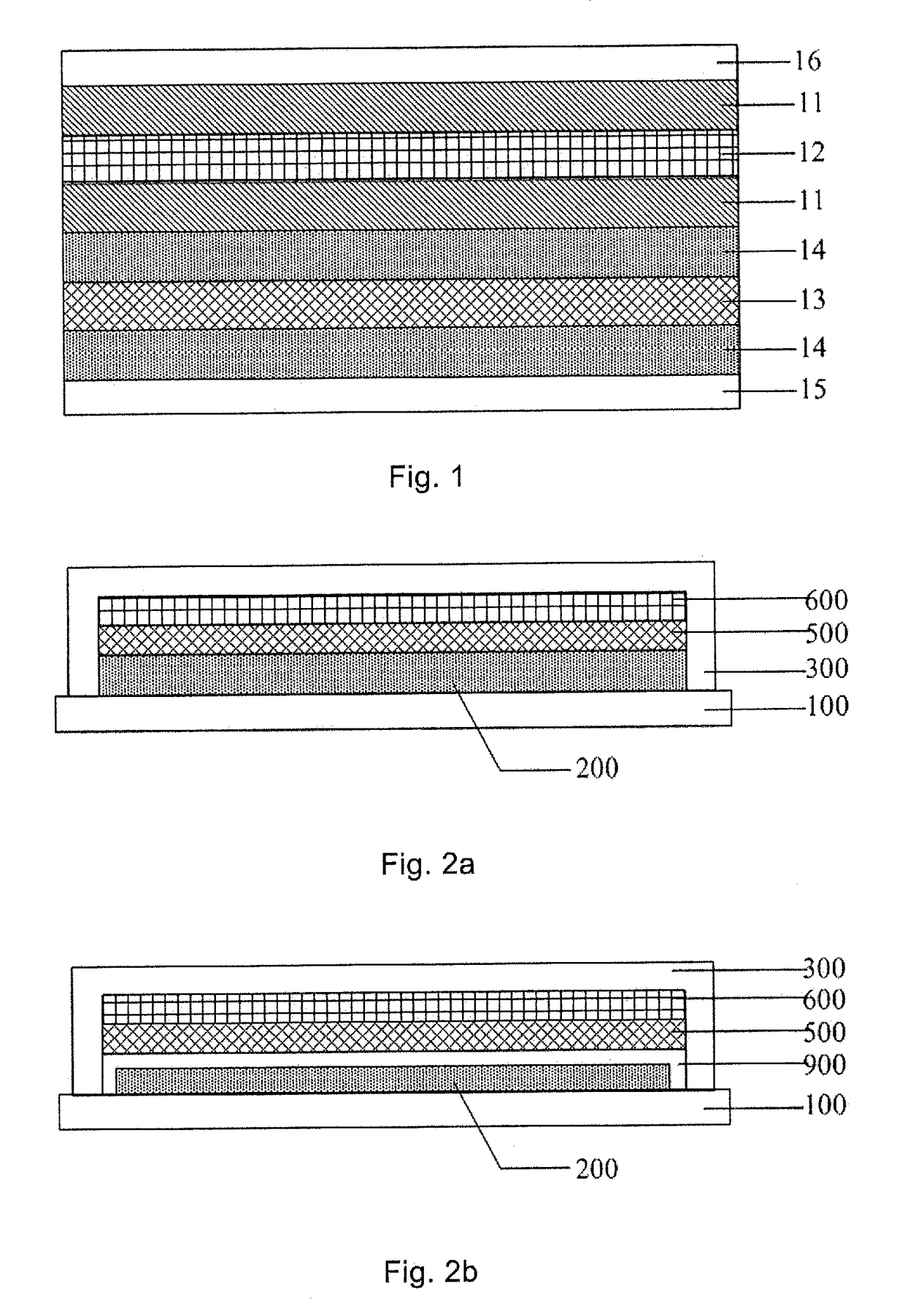

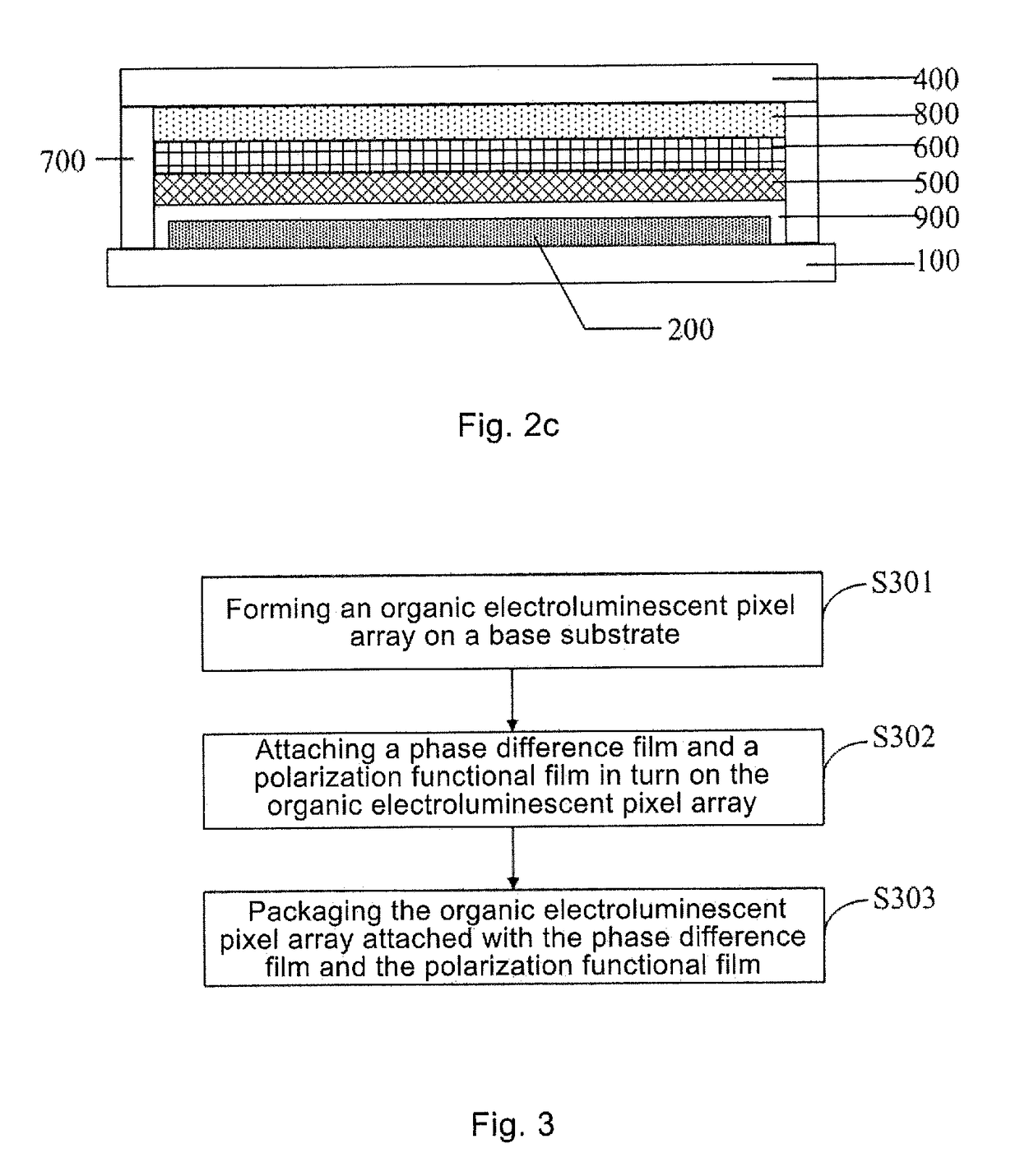

Organic light-emitting panel, manufacturing method thereof, and organic display device

ActiveUS20120193658A1High vapor concentrationLarge film thicknessElectroluminescent light sourcesSolid-state devicesDisplay deviceEngineering

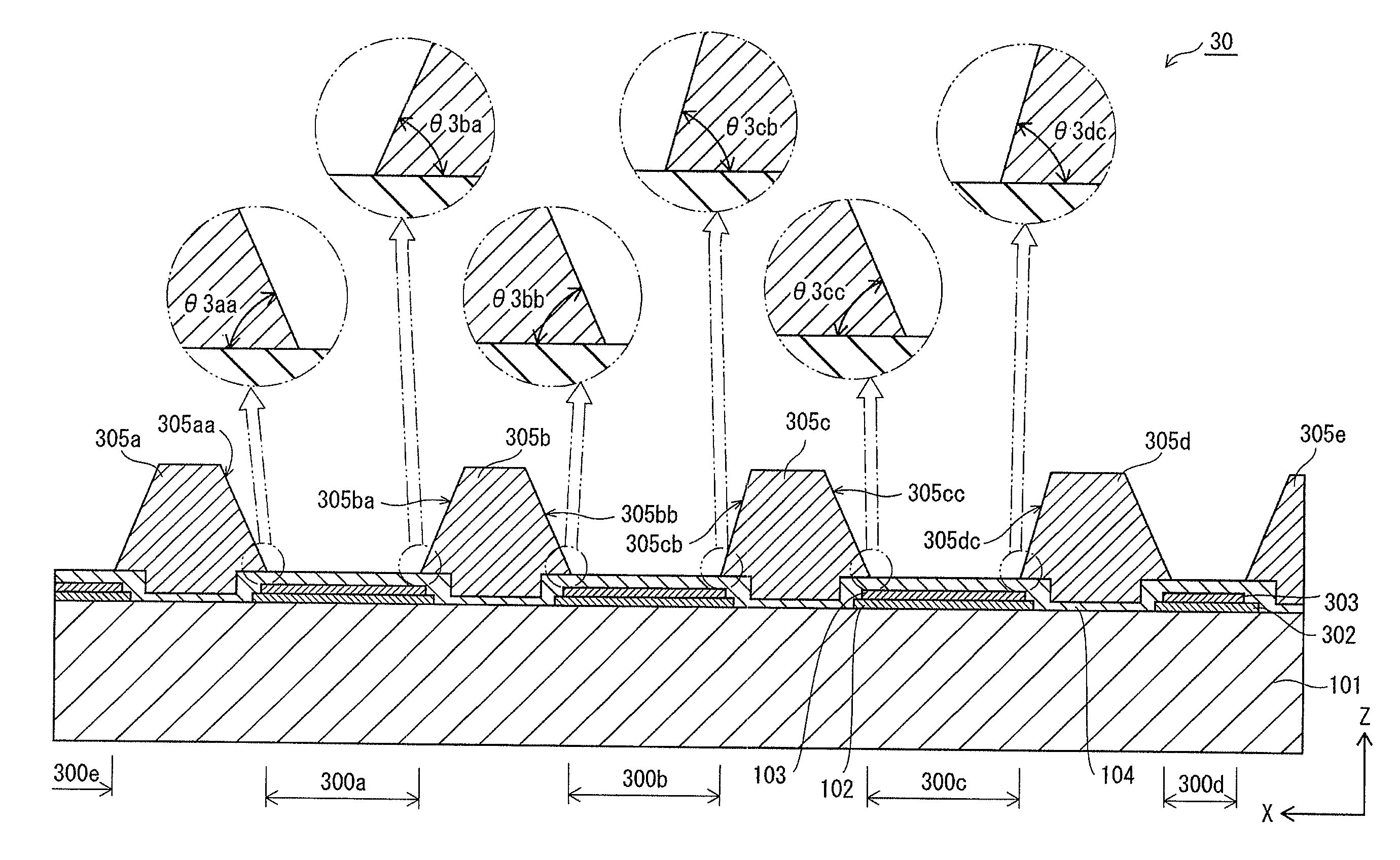

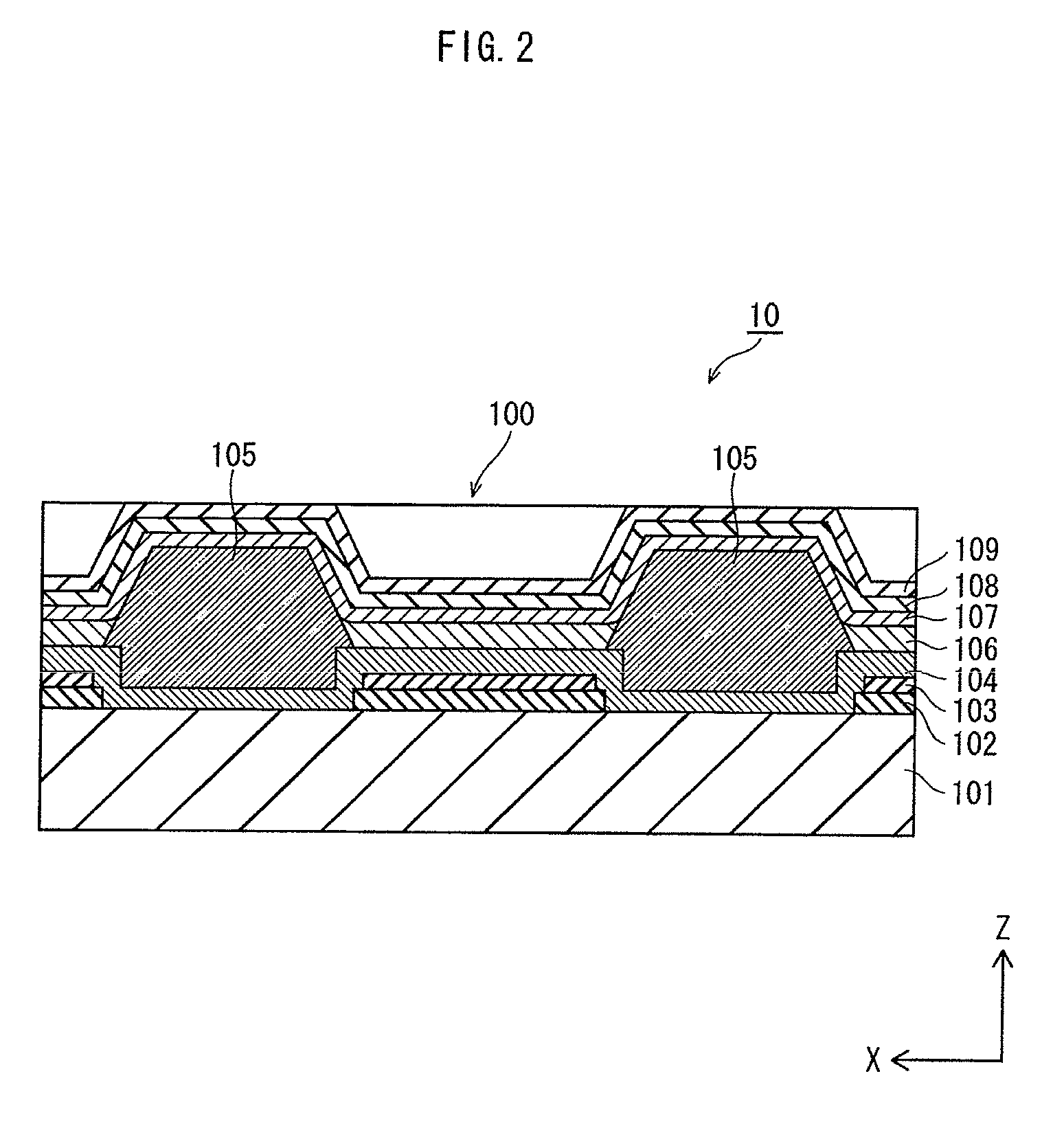

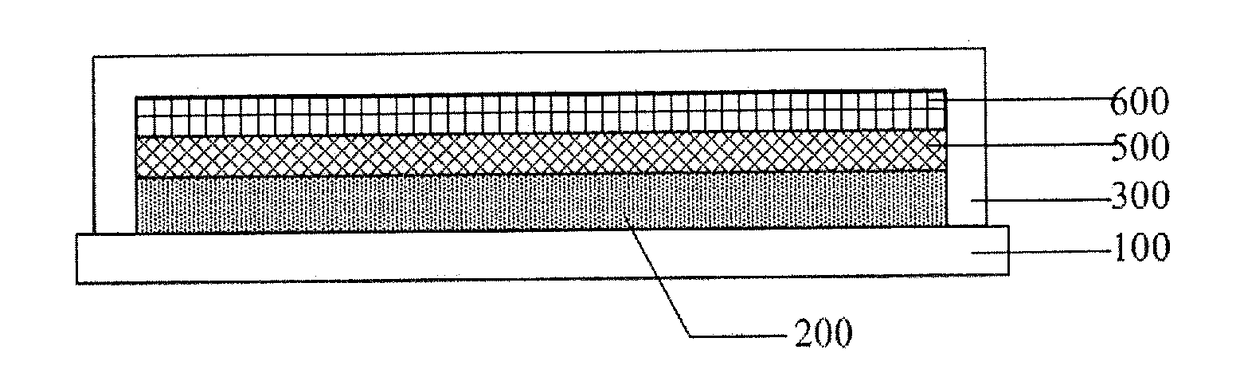

A pixel in the panel includes sub-pixels 100a, 100b, and 100c. Non-light-emitting cells 100d and 100e are provided between the pixel and adjacent pixels on both sides thereof, respectively. The organic light-emitting layer of sub-pixel 100a and non-light-emitting cell 100d are separated by bank 105a. Similarly, the organic light-emitting layer of sub-pixel 100c and non-light-emitting cell 100e are separated by bank 105d; the organic light-emitting layers of sub-pixels 100a and 100b are separated by bank 105b; and the organic light-emitting layers of sub-pixels 100b and 100c are separated by bank 105c. Inclination angle θaa of sidewall 105aa of bank 105a adjacent to sib-pixel 100a and inclination angle θdc of sidewall 105dc of bank 105d adjacent to sib-pixel 100c are larger than other inclination angles θba, θbb, θcb, and θcc.

Owner:JOLED INC

Manufacturing method for strained silicon wafer

InactiveUS20060057856A1Large thicknessLarge film thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesStrained siliconSingle crystal silicon

Owner:COVALENT MATERIALS CORP

Surface acoustic wave device and method of manufacturing the same

ActiveUS20060273687A1Suppress electromigrationSuppress stress migrationPiezoelectric/electrostriction/magnetostriction machinesImpedence networksResonanceParallel resonance

First base layers made of TiN or TiOxNy (where, 0<x<0.2, x+y=1) and second base layers made of Cr are provided between interdigital transducer portions and a piezoelectric substrate, and accordingly, it is possible to prevent voids from being generated in the interdigital transducer portions, which improves a power resistance of the surface acoustic wave device. In addition, since it is possible to prevent the voids from being generated in the interdigital transducer portions, it is possible to suppress the resistance of the interdigital transducer portions from increasing, which can reduce the loss of power. In addition, it is also possible to reduce the variations in a serial resonance frequency and a parallel resonance frequency.

Owner:QORVO US INC

Metal Oxide Particle-Containing Polysiloxane Composition and Method for Producing Same

InactiveUS20090050852A1Good flexibilityGood dispersionOther chemical processesSemiconductor/solid-state device detailsHydrogen atomOrganic solvent

The metal oxide fine particle-containing polysiloxane composition of the present invention is obtained by mixing (A) metal oxide fine particles with (B1) polyfunctional polysiloxane obtained by allowing alkoxy-terminated polyfunctional polysiloxane (b1) represented by the following average compositional formula (1): R1aSiOb(OR2)c (1) (wherein R1 is a hydrogen atom or a monovalent hydrocarbon group having no oxyalkylene group, R2 is an alkyl group, a is more than 0 but less than 2, b is more than 0 but less than 2, c is more than 0 but less than 4, and a+b×2+c=4) and having a weight-average molecular weight of not less than 3,000 but not more than 100,000 and hydroxy-terminated hydroxy-terminated polydimethylsiloxane (b2) having a weight-average molecular weight of not less than 2,000 but not more than 100,000 to undergo dealcoholization reaction in a specific ratio, in an organic solvent in the presence of a basic compound, an acidic compound or a metal chelate compound and thereby dispersing the metal oxide fine particles (A) in the organic solvent.

Owner:JSR CORPORATIOON

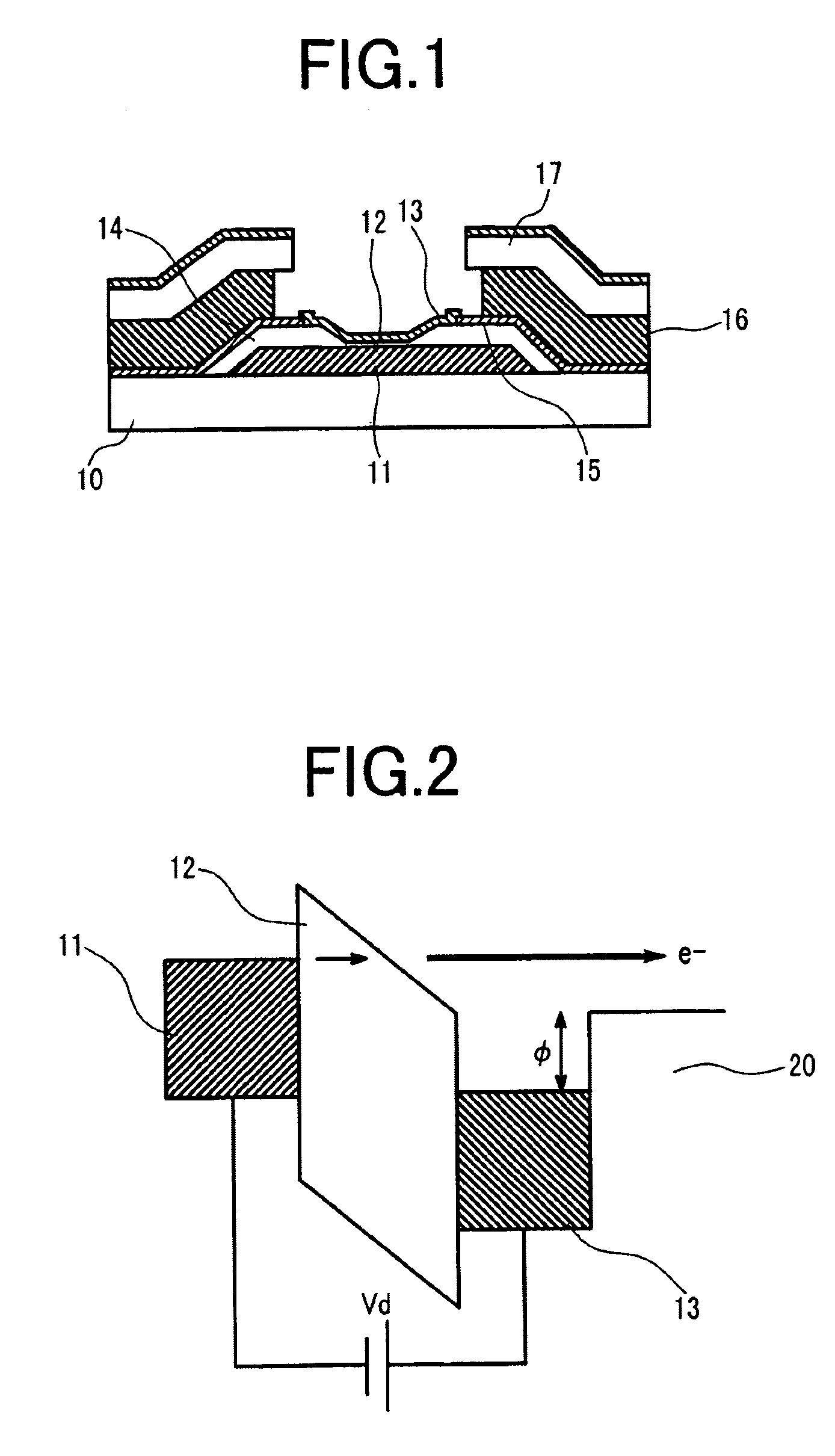

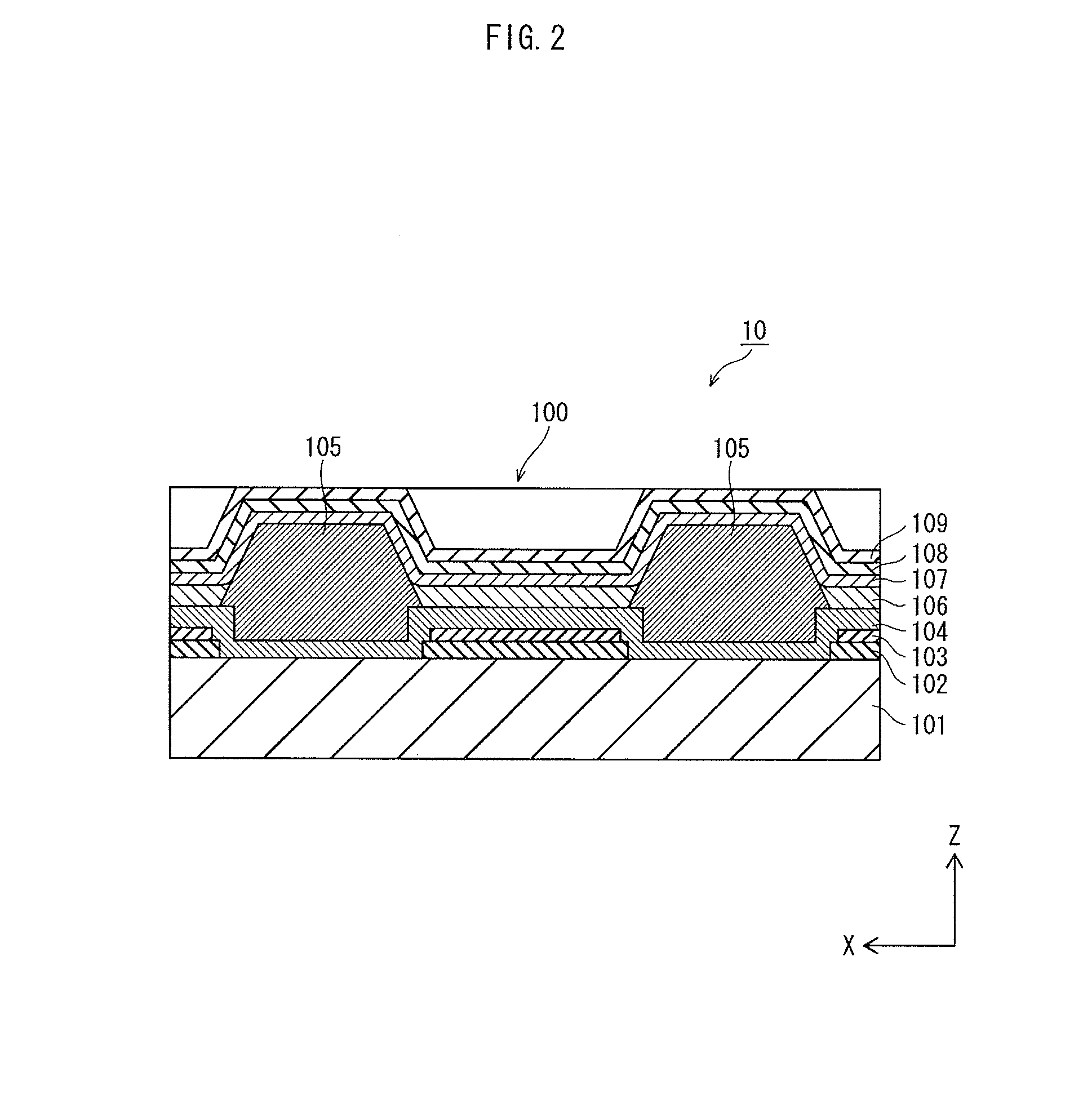

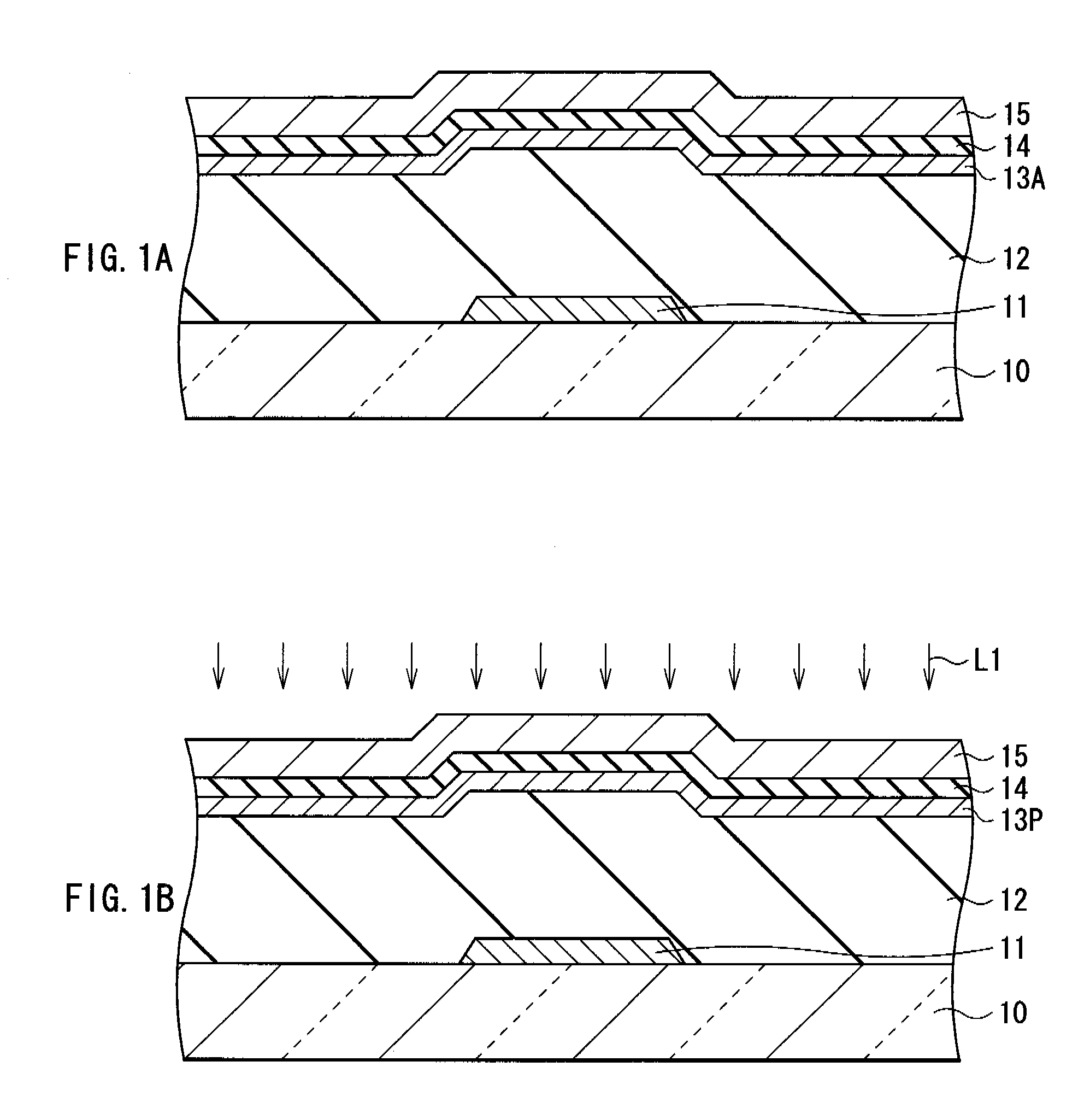

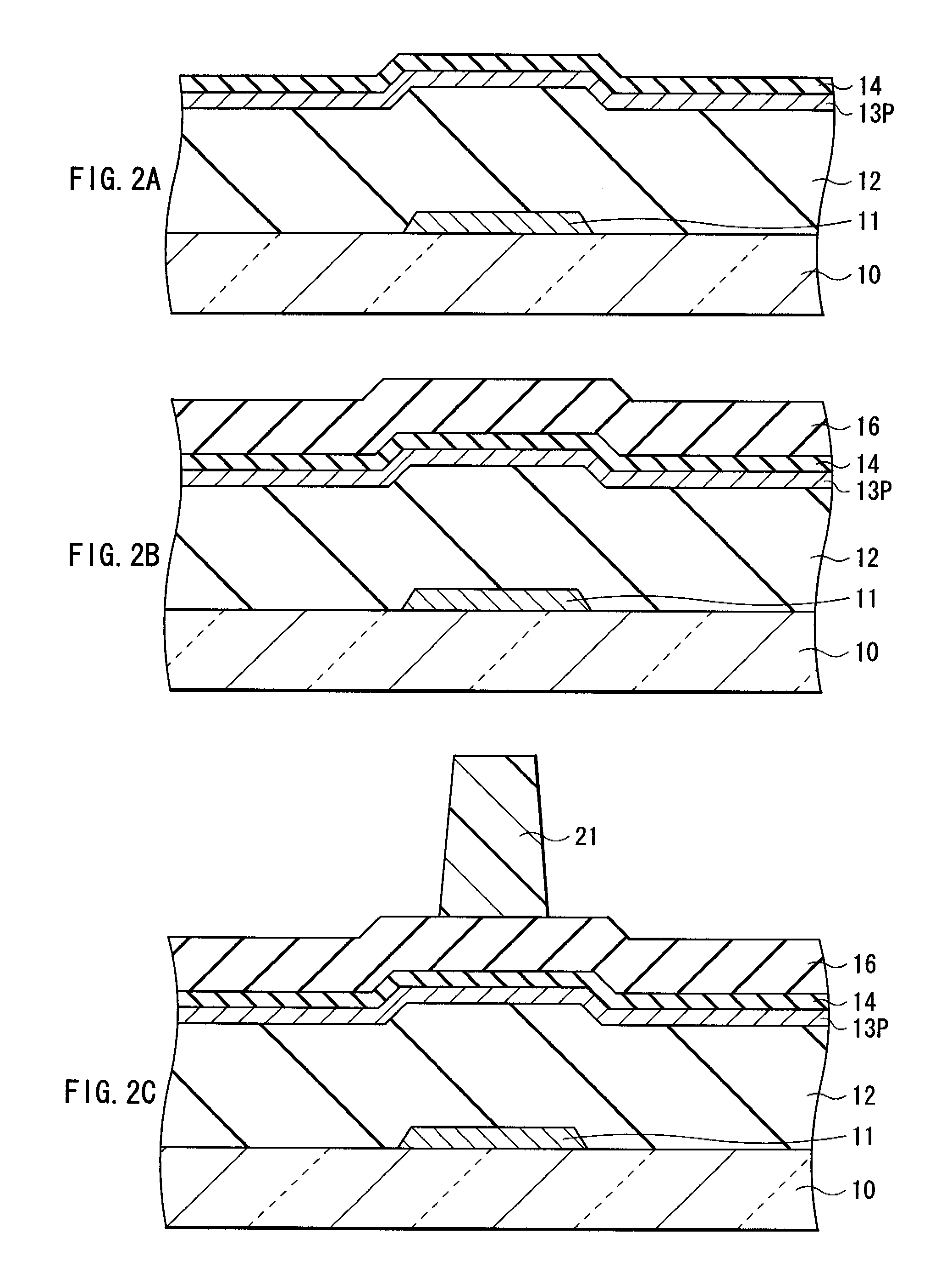

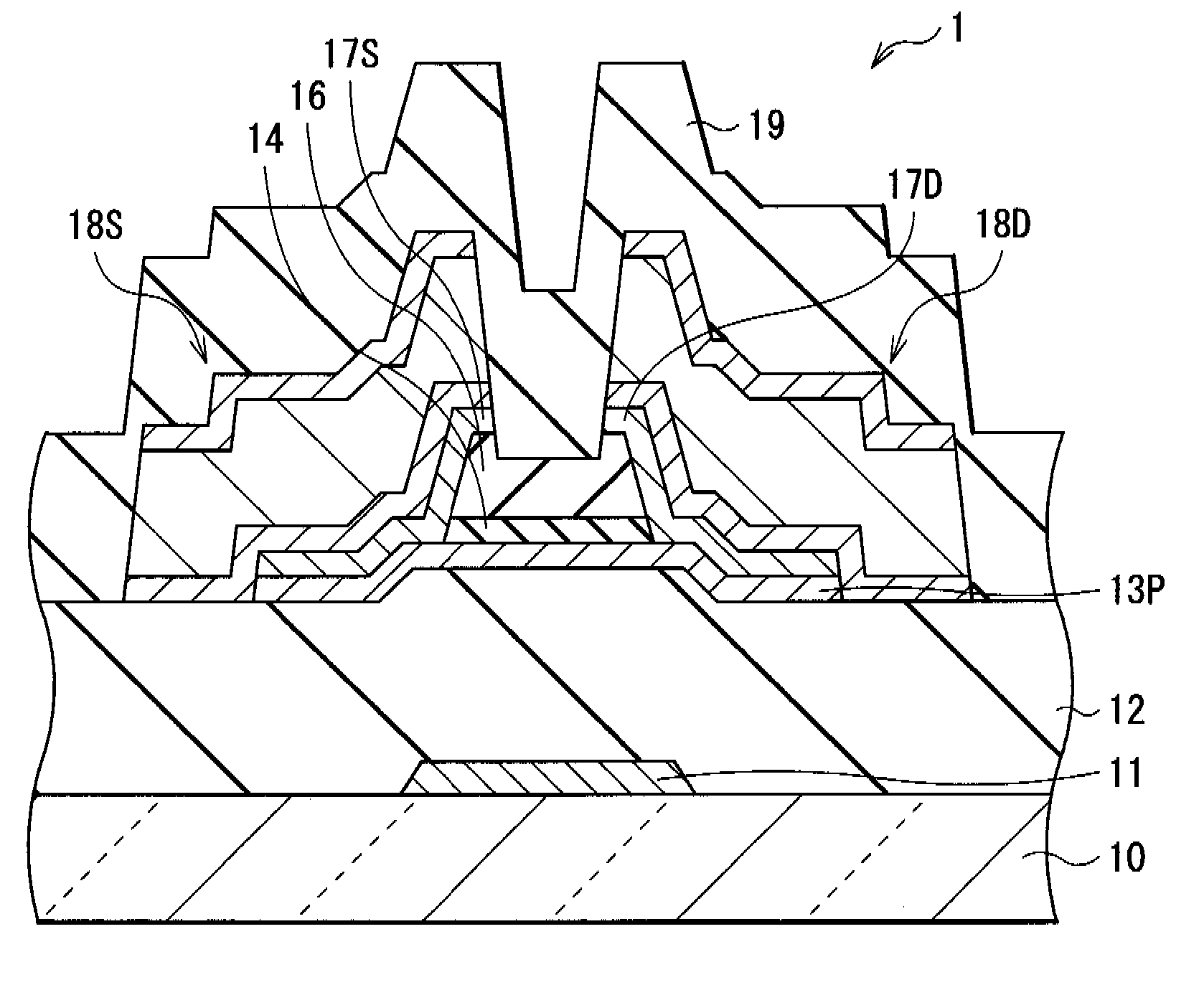

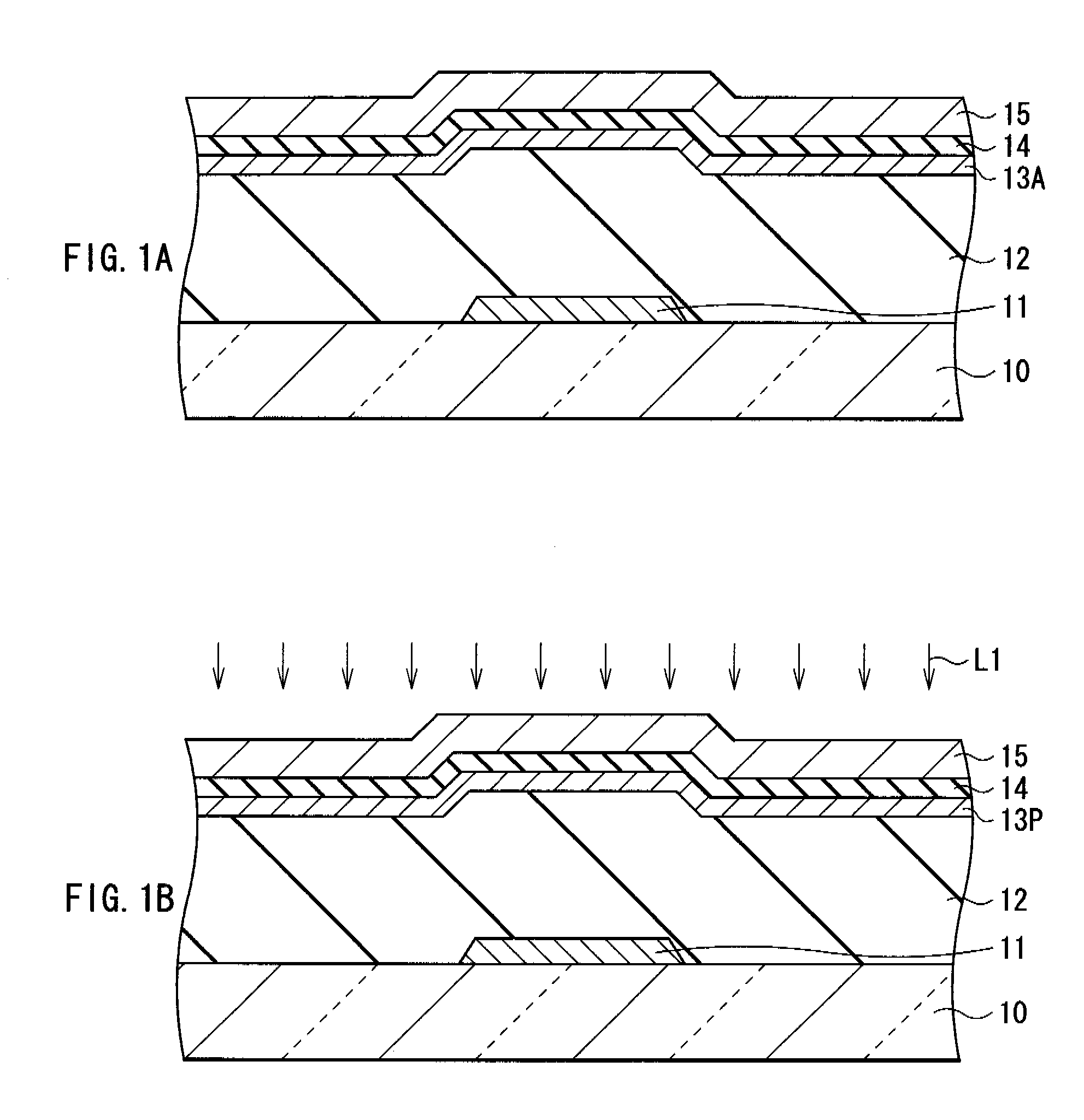

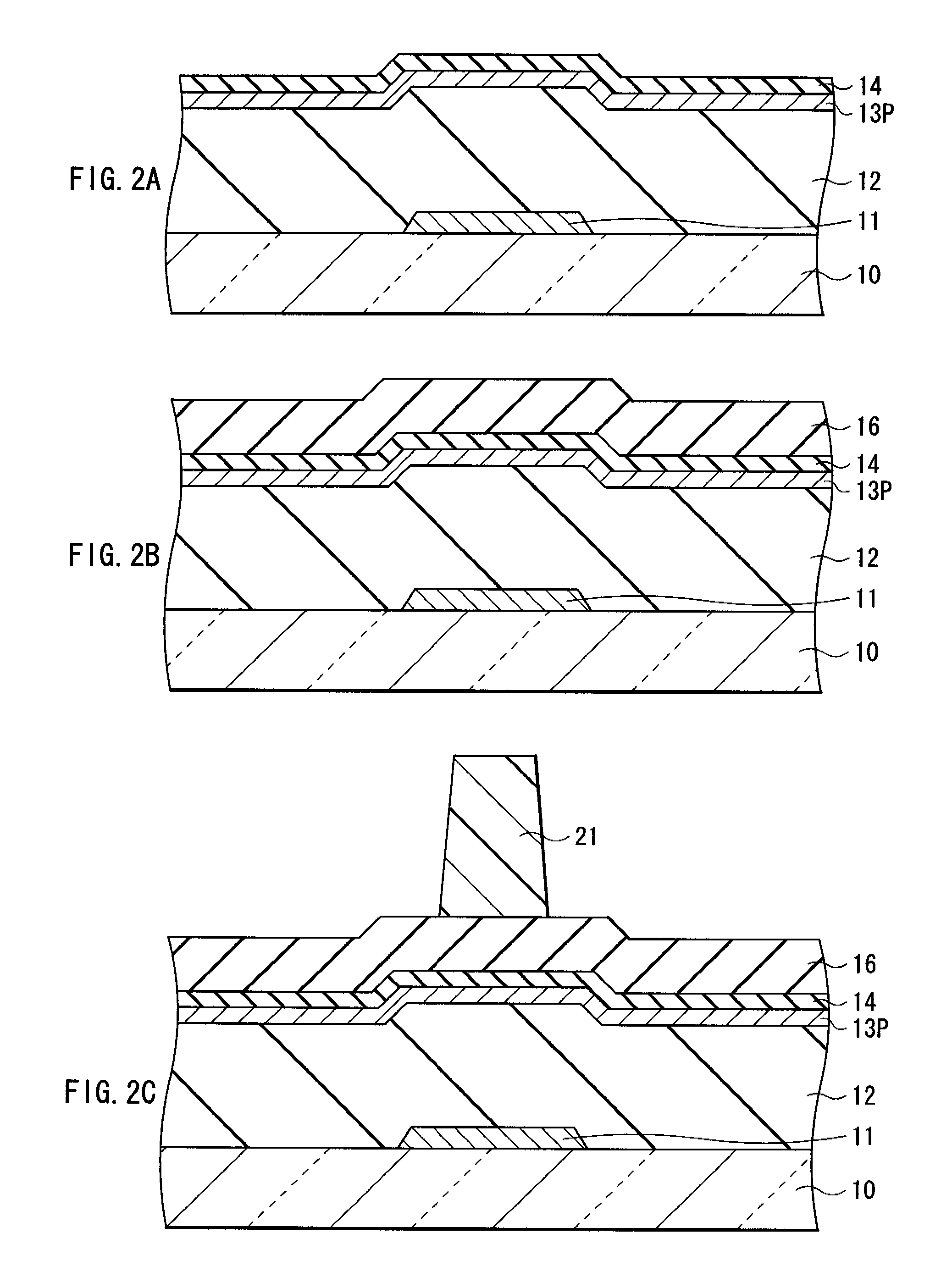

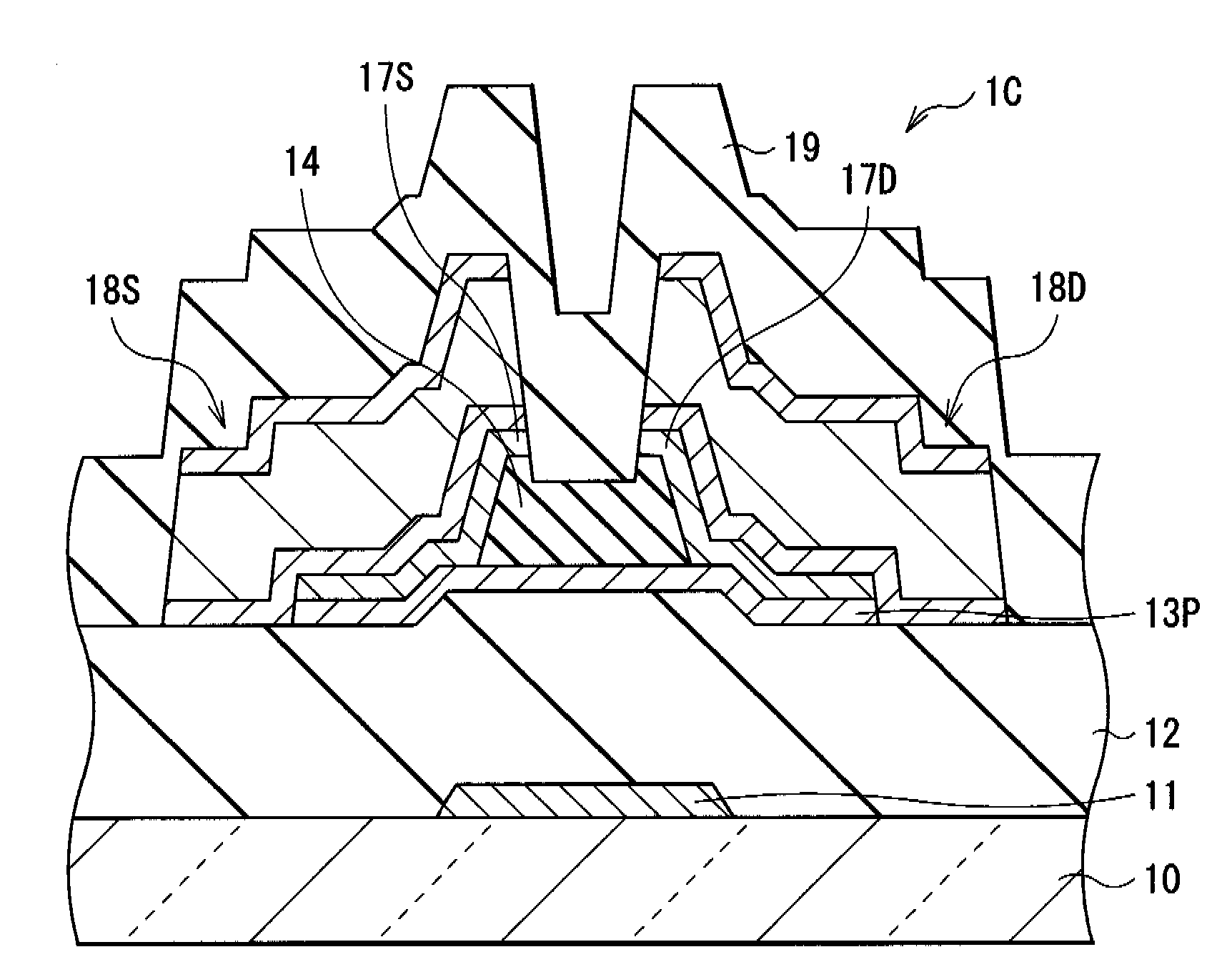

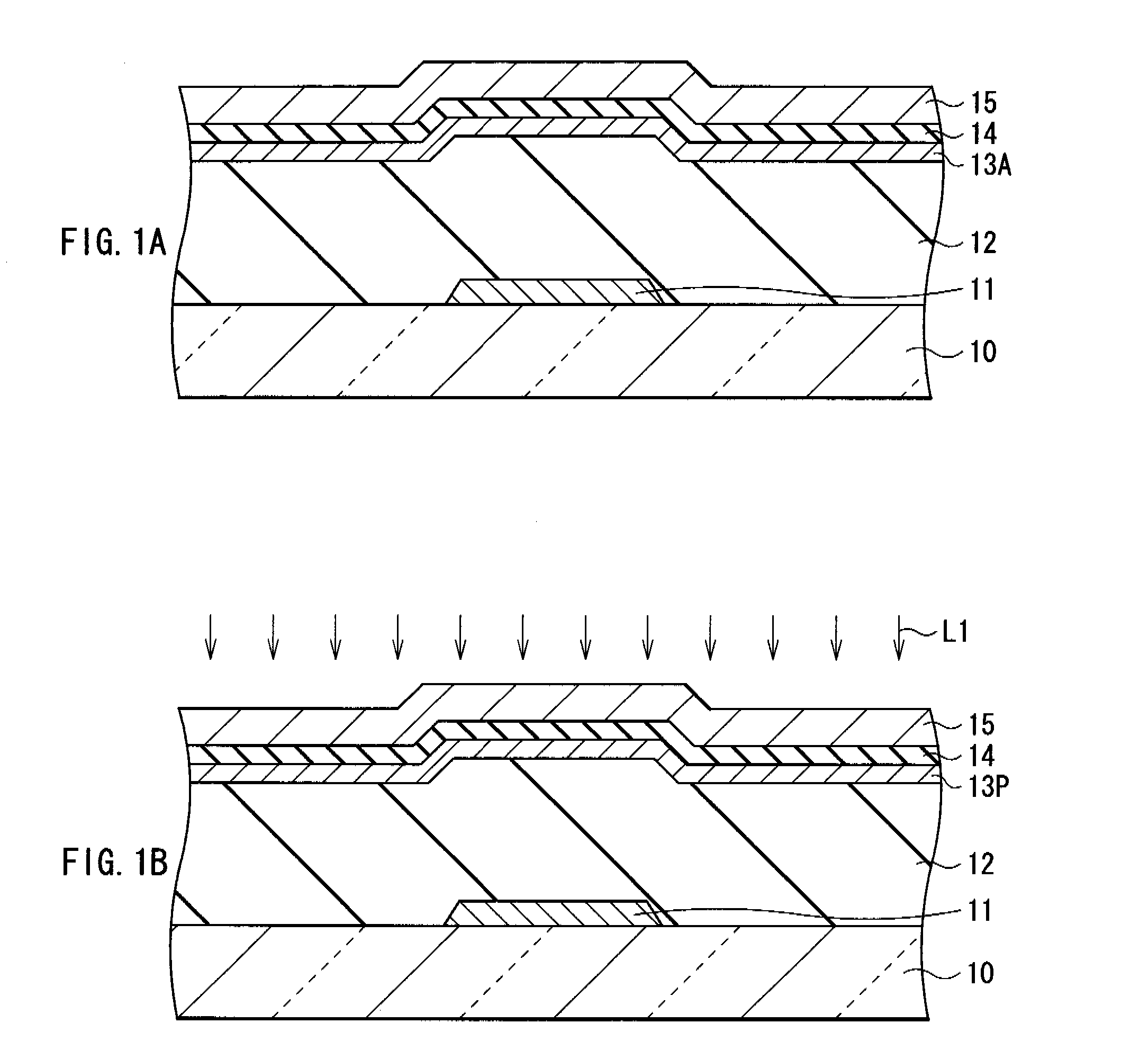

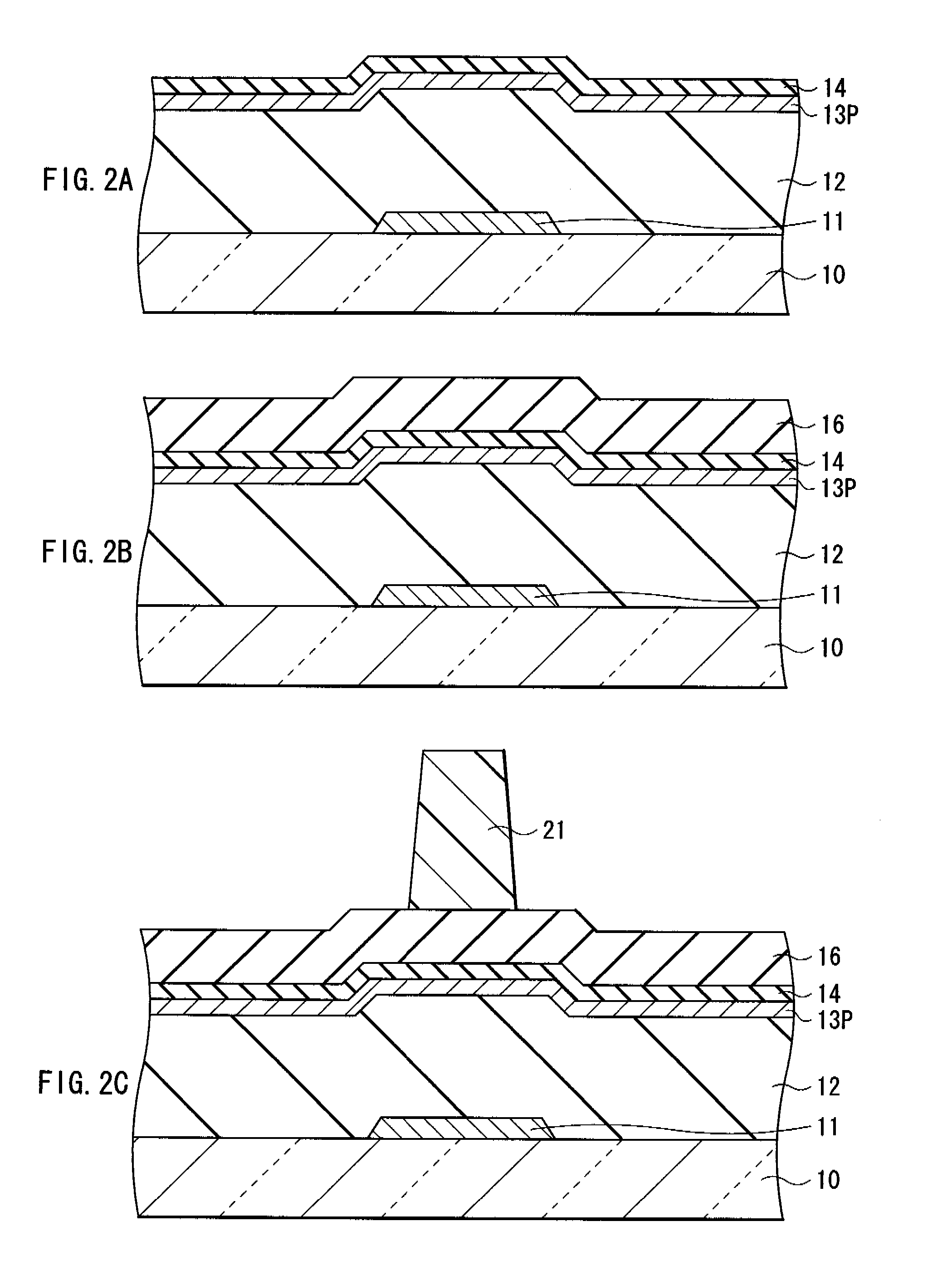

Method of manufacturing thin film transistor, thin film transistor, and display unit

InactiveUS20080142800A1Reduce etching residueOn-current is loweredTransistorSolid-state devicesPhotothermal conversionCrystalline silicon

A method of manufacturing a thin film transistor capable of inhibiting the characteristics variation of the thin film transistor without deteriorating the characteristics thereof is provided. A crystalline silicon film is formed by indirect heat treatment through a photothermal conversion layer and a buffer layer. By patterning the buffer layer and an insulating film, a channel protective film is selectively formed in a region corresponding to a channel region on the crystalline silicon film. Further, when an n+ silicon film and a metal layer are selectively removed, the channel protective film functions as an etching stopper. When the crystalline silicon film is formed, heat is uniformly supplied. Further, in etching, the channel region of the crystalline silicon film is protected.

Owner:SONY CORP

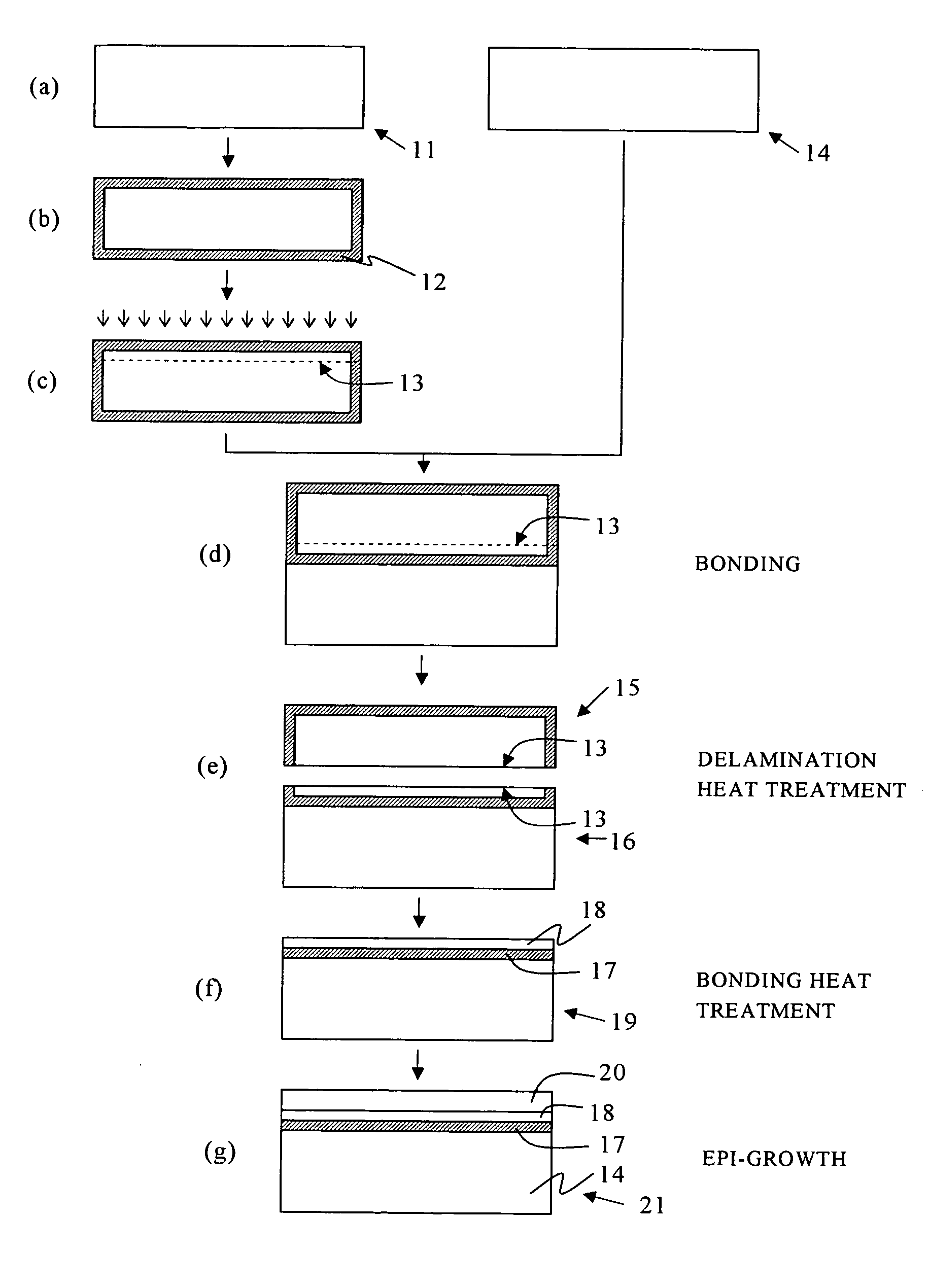

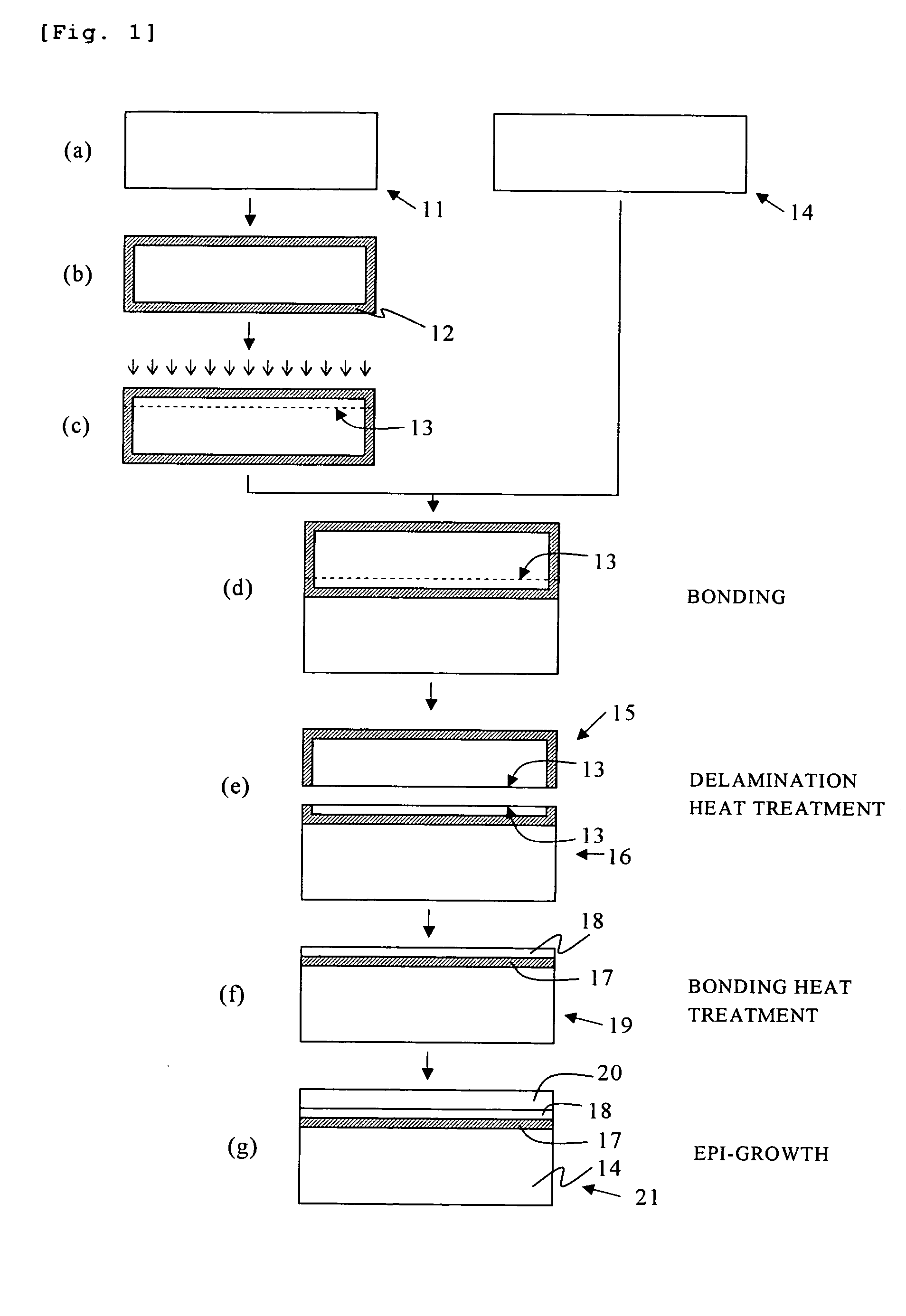

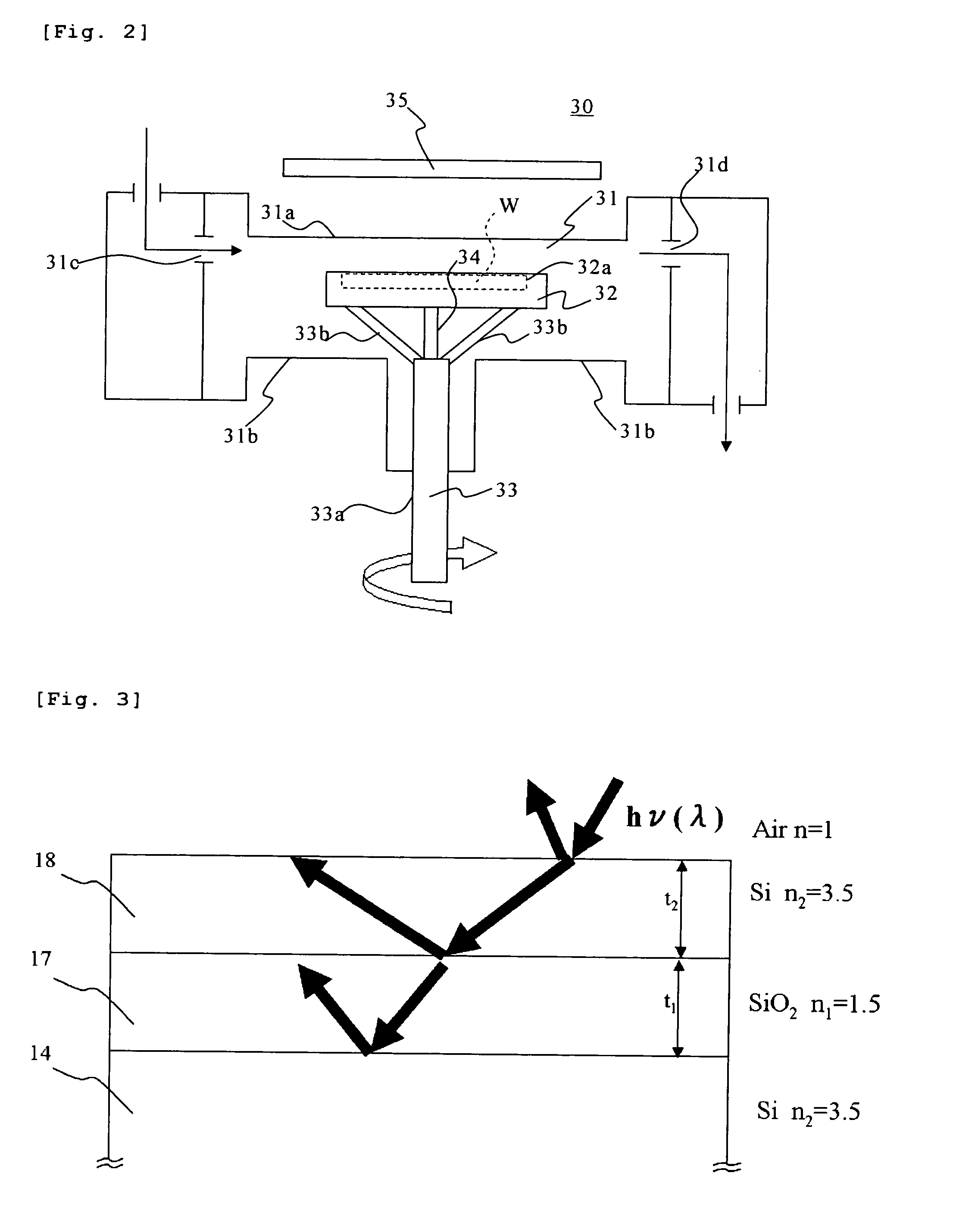

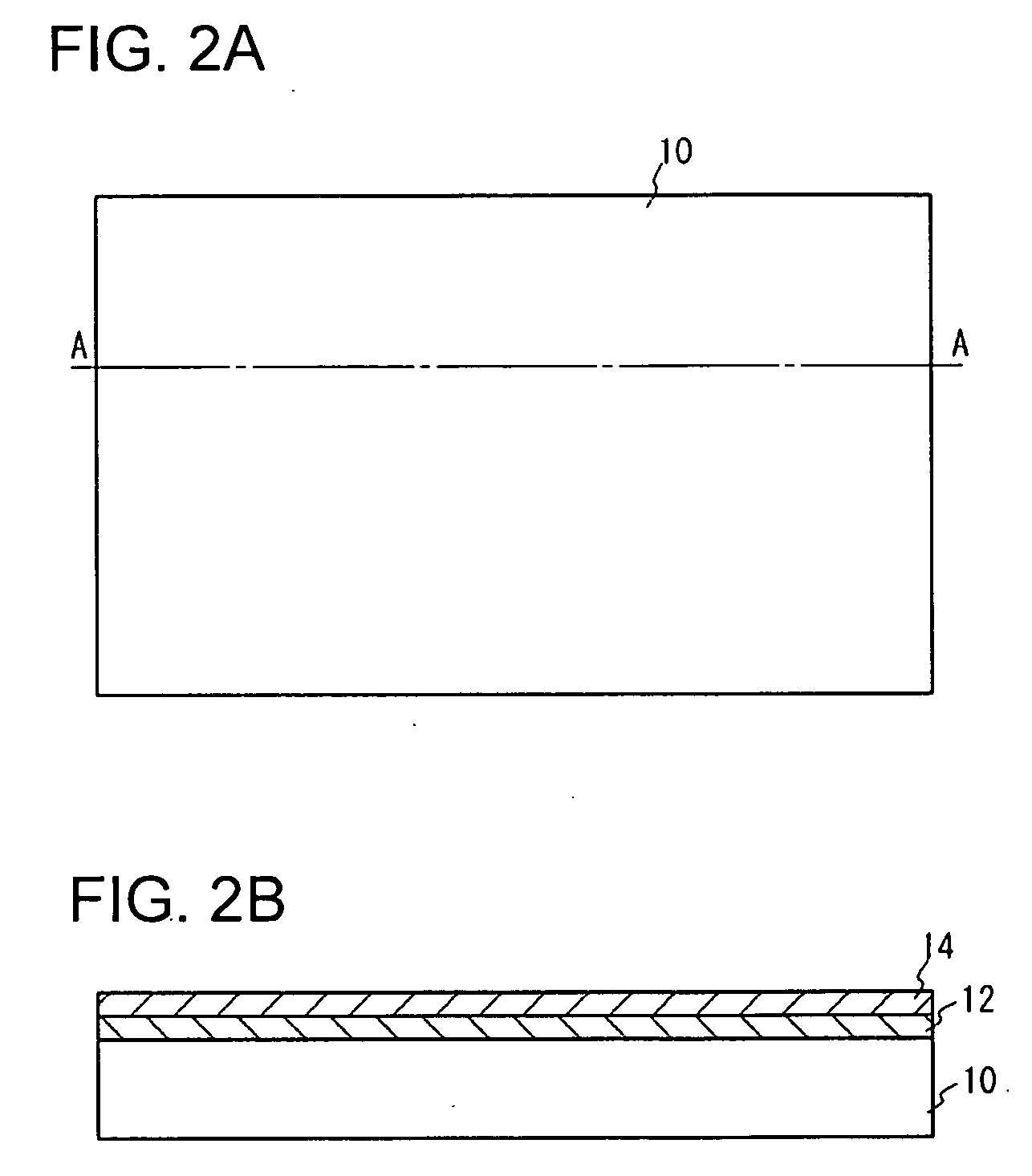

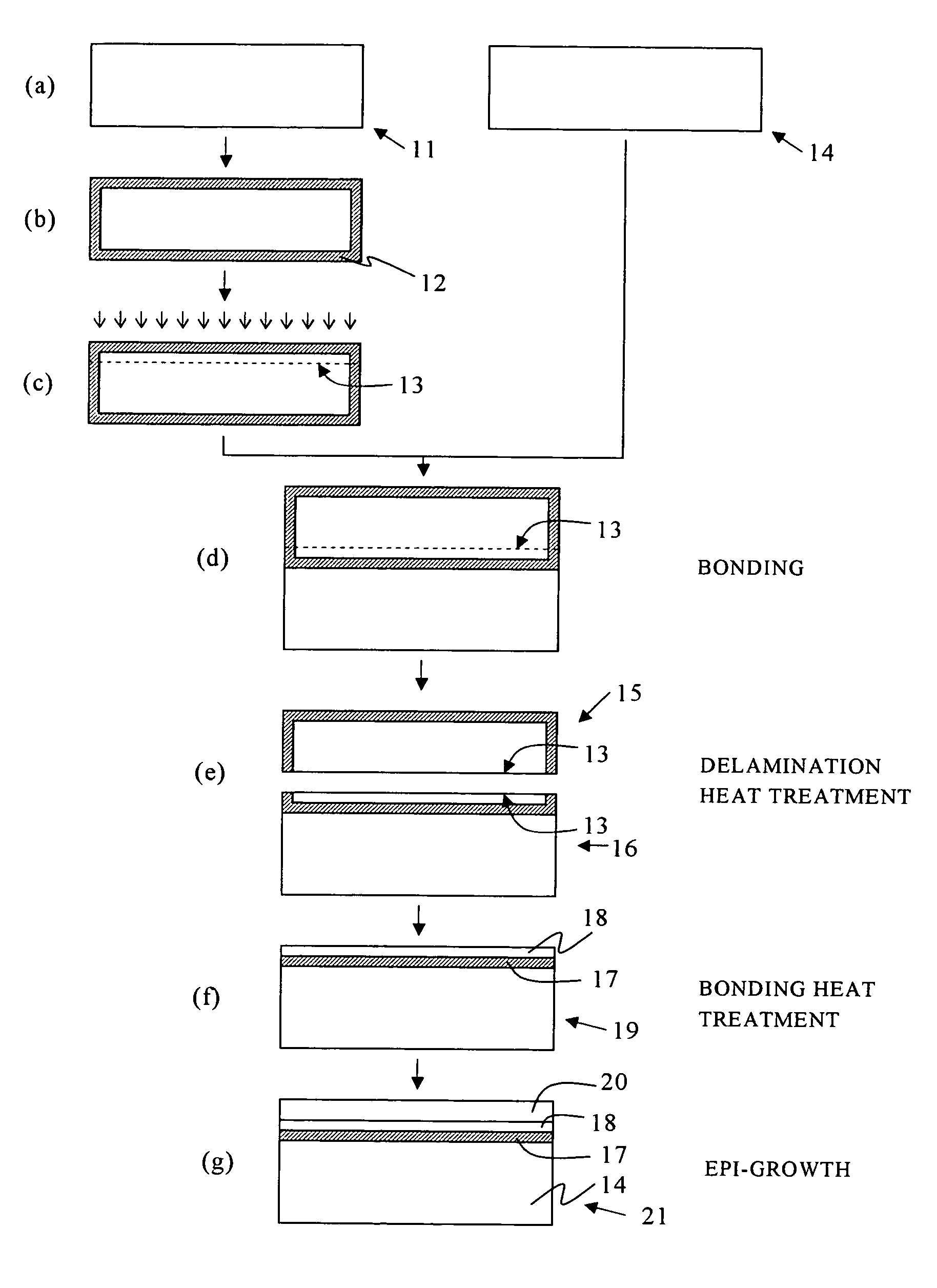

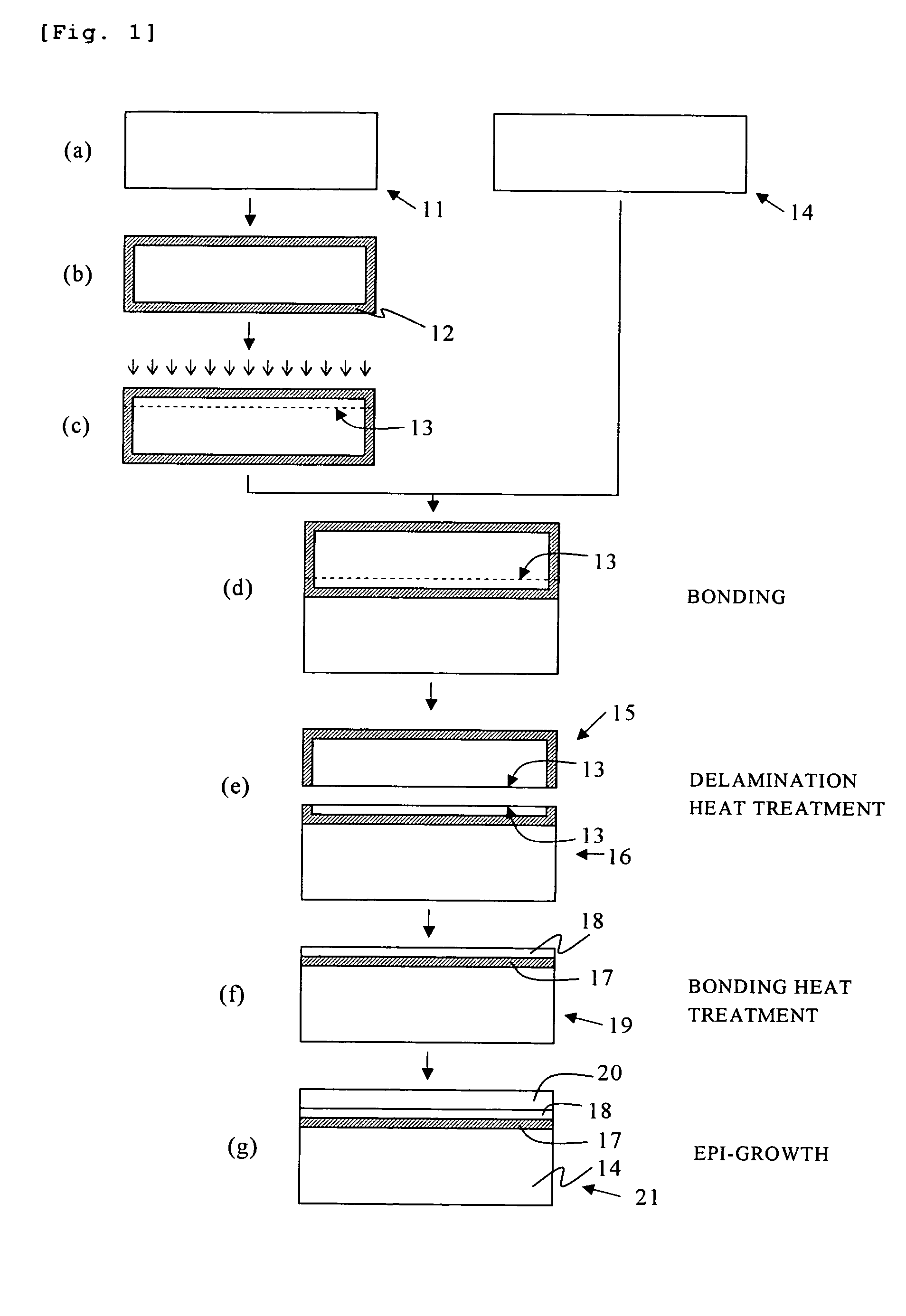

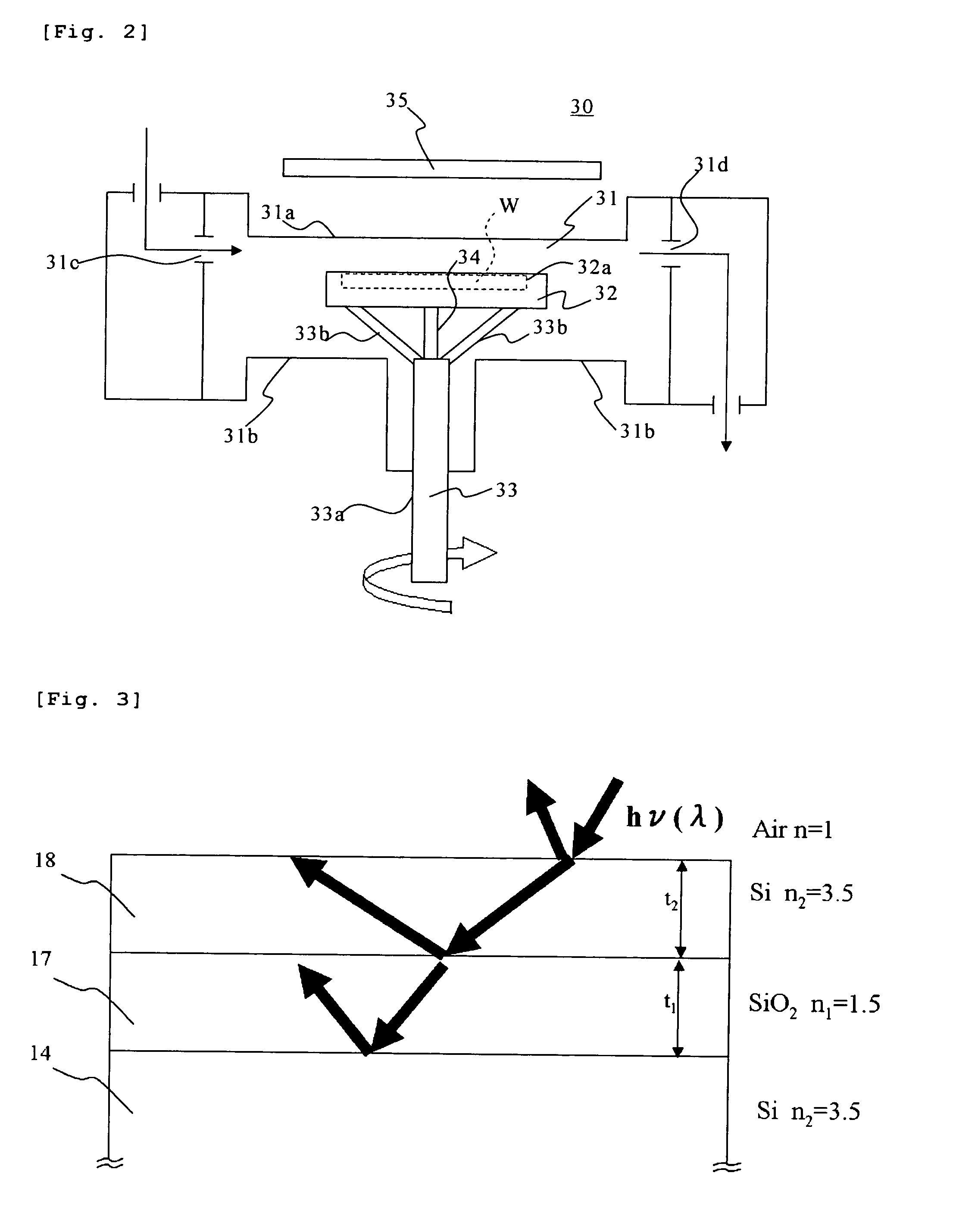

Method For Manufacturing Soi Wafer and Soi Wafer

ActiveUS20090042364A1Less slip dislocationIncreasing the thicknessSemiconductor/solid-state device manufacturingWaferingLength wave

The present invention provides a method for manufacturing an SOI wafer in which a thickness of an SOI layer is increased by growing an epitaxial layer on the SOI layer of the SOI wafer having an oxide film and the SOI layer formed on a base wafer, wherein the epitaxial growth is performed in such a manner that a reflectivity of a surface of the SOI wafer on which the epitaxial layer is grown in a wavelength region of a heating light at the start of the epitaxial growth falls within the range of 30% to 80%. As a result, in the method for manufacturing the SOI wafer in which a thickness of the SOI layer is increased by growing the epitaxial layer on the SOI layer of the SOI wafer having the oxide film and the SOI layer formed on the base wafer, a method for manufacturing a high-quality SOI wafer with less slip dislocation and others is provided.

Owner:SHIN-ETSU HANDOTAI CO LTD

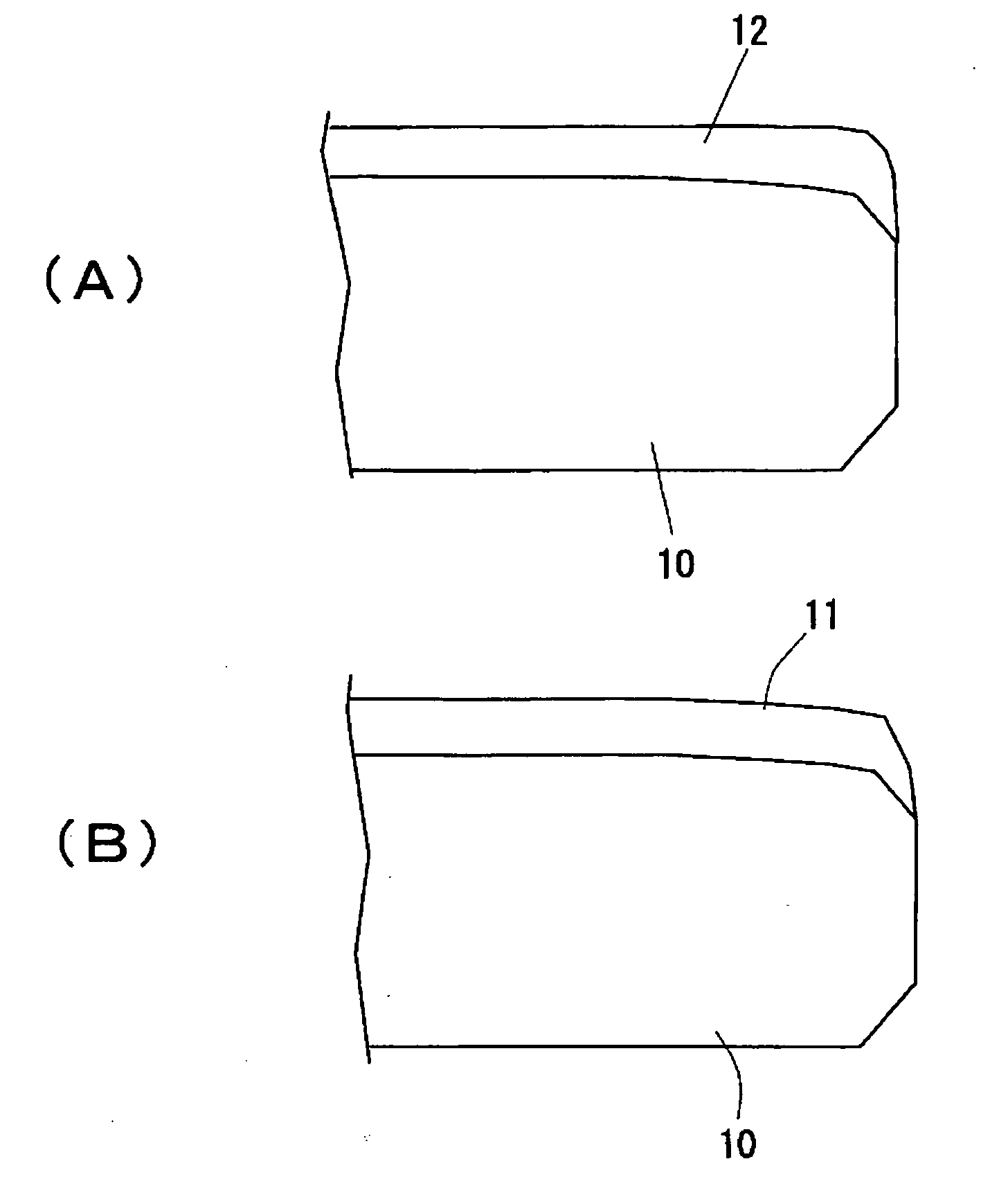

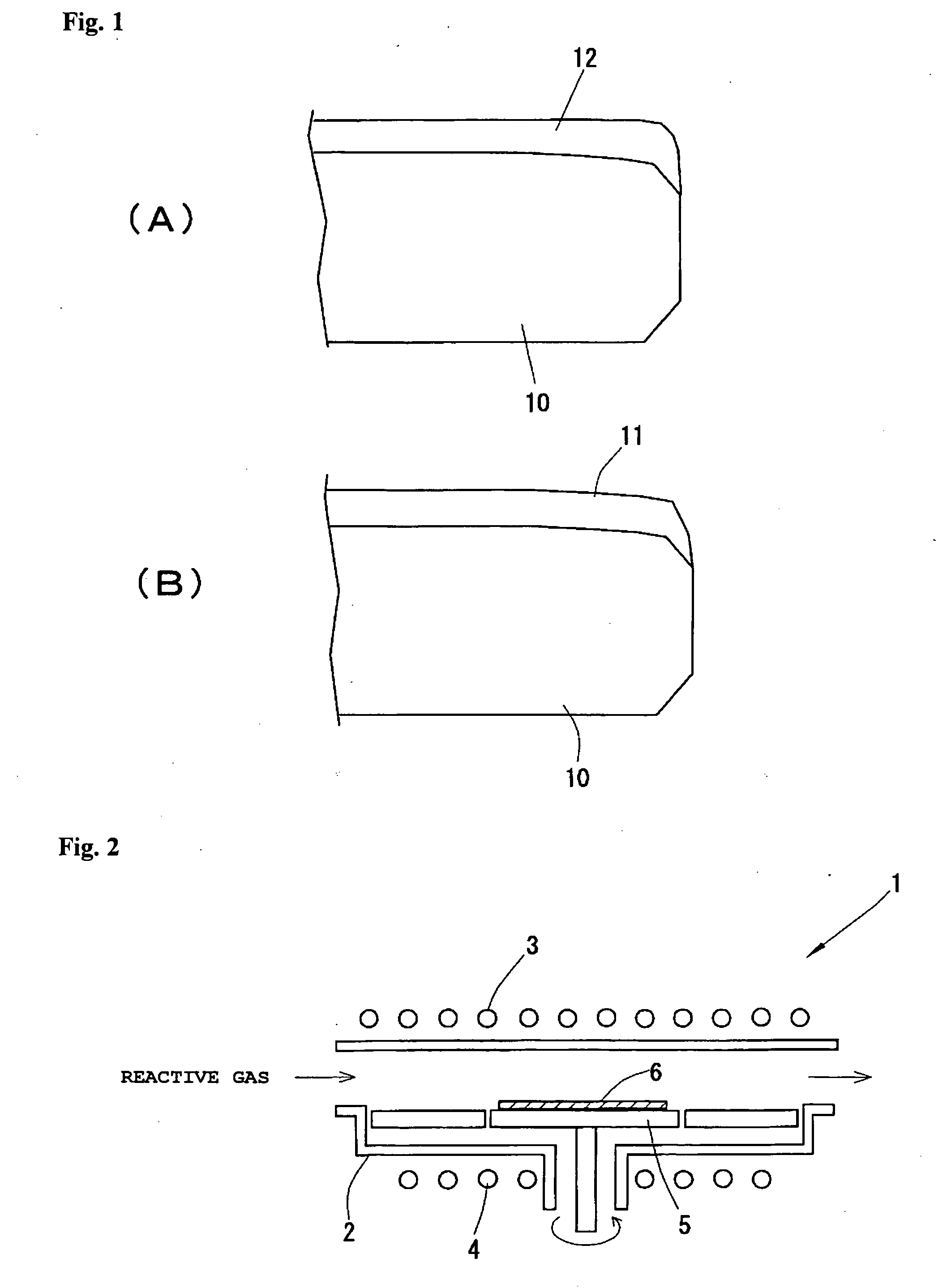

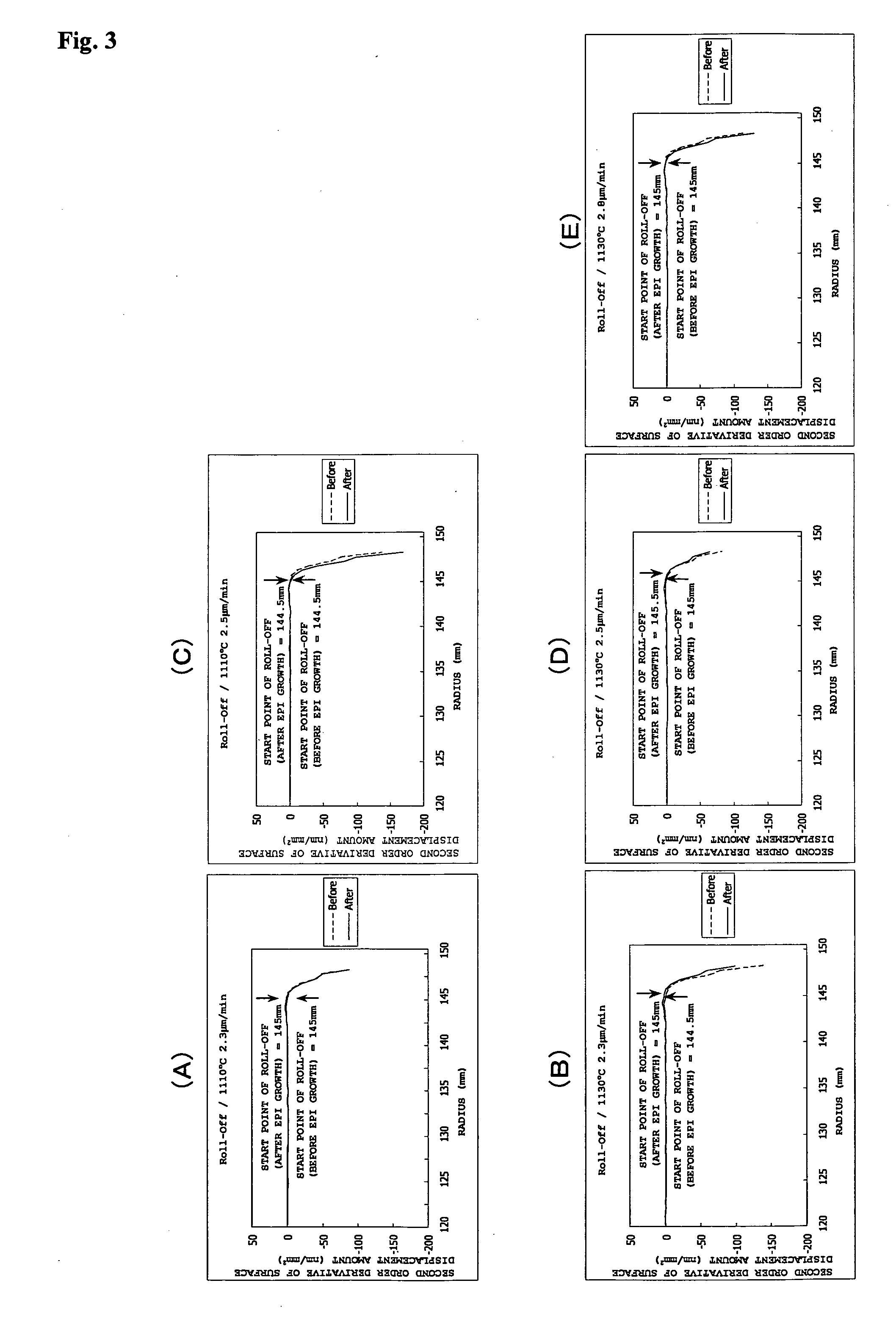

Method for Manufacturing Epitaxial Wafer and Epitaxial Wafer

InactiveUS20090252942A1Reduce the overall diameterLittle roll-offPolycrystalline material growthSiliconWaferingVapor phase

The present invention provides a method for manufacturing an epitaxial wafer by supplying a raw material gas onto a silicon wafer to perform vapor-phase growth of an epitaxial layer, wherein a thickness of the epitaxial layer that is formed at a peripheral portion of the silicon wafer is controlled by controlling a growth rate and / or a growth temperature of the epitaxial layer that is subjected to vapor-phase growth. As a result, there is provided the method that enables manufacturing an epitaxial wafer having a small roll-off value by controlling a thickness of an epitaxial layer near the outermost periphery at the time of epitaxial growth.

Owner:SHIN-ETSU HANDOTAI CO LTD

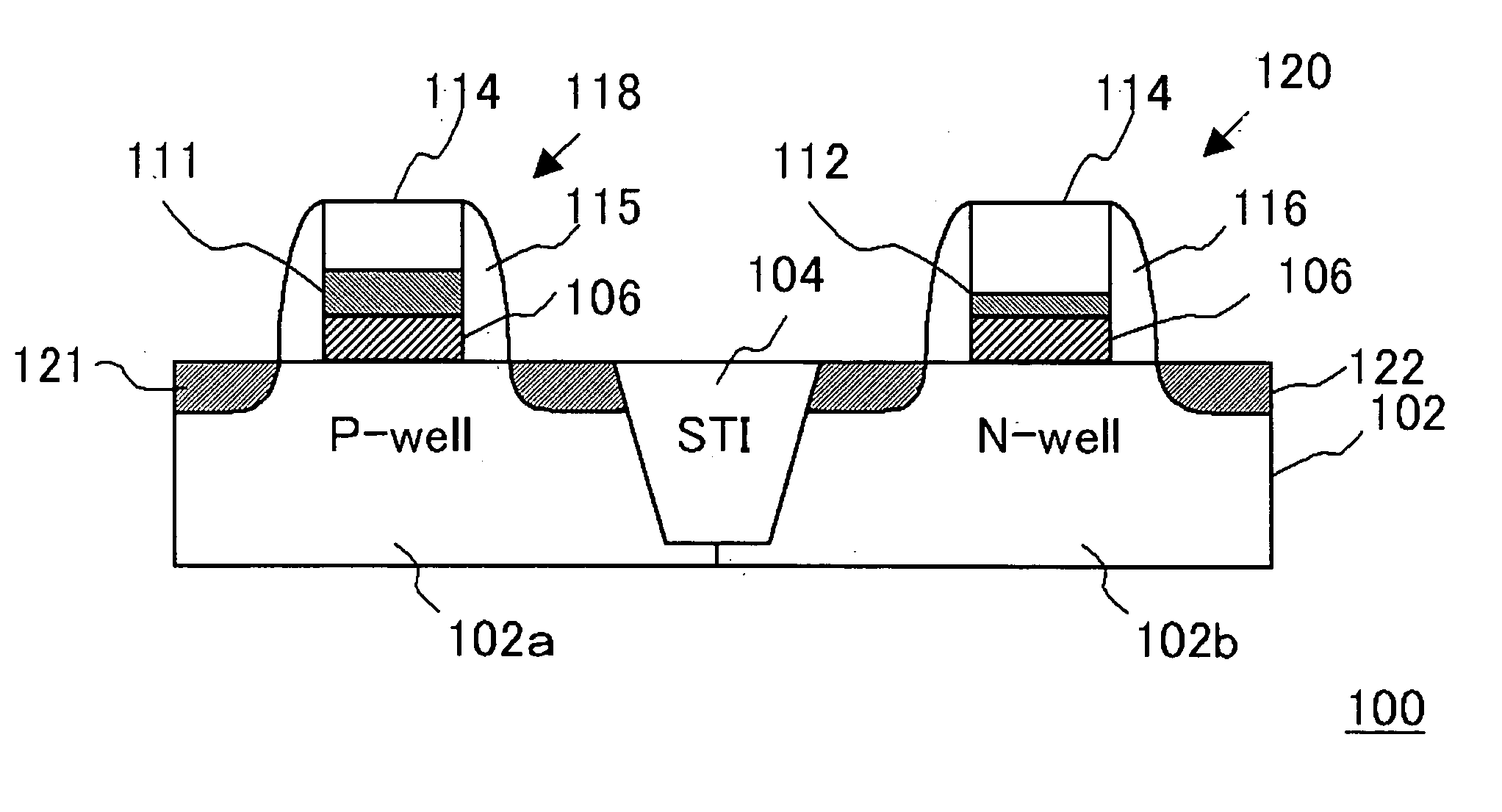

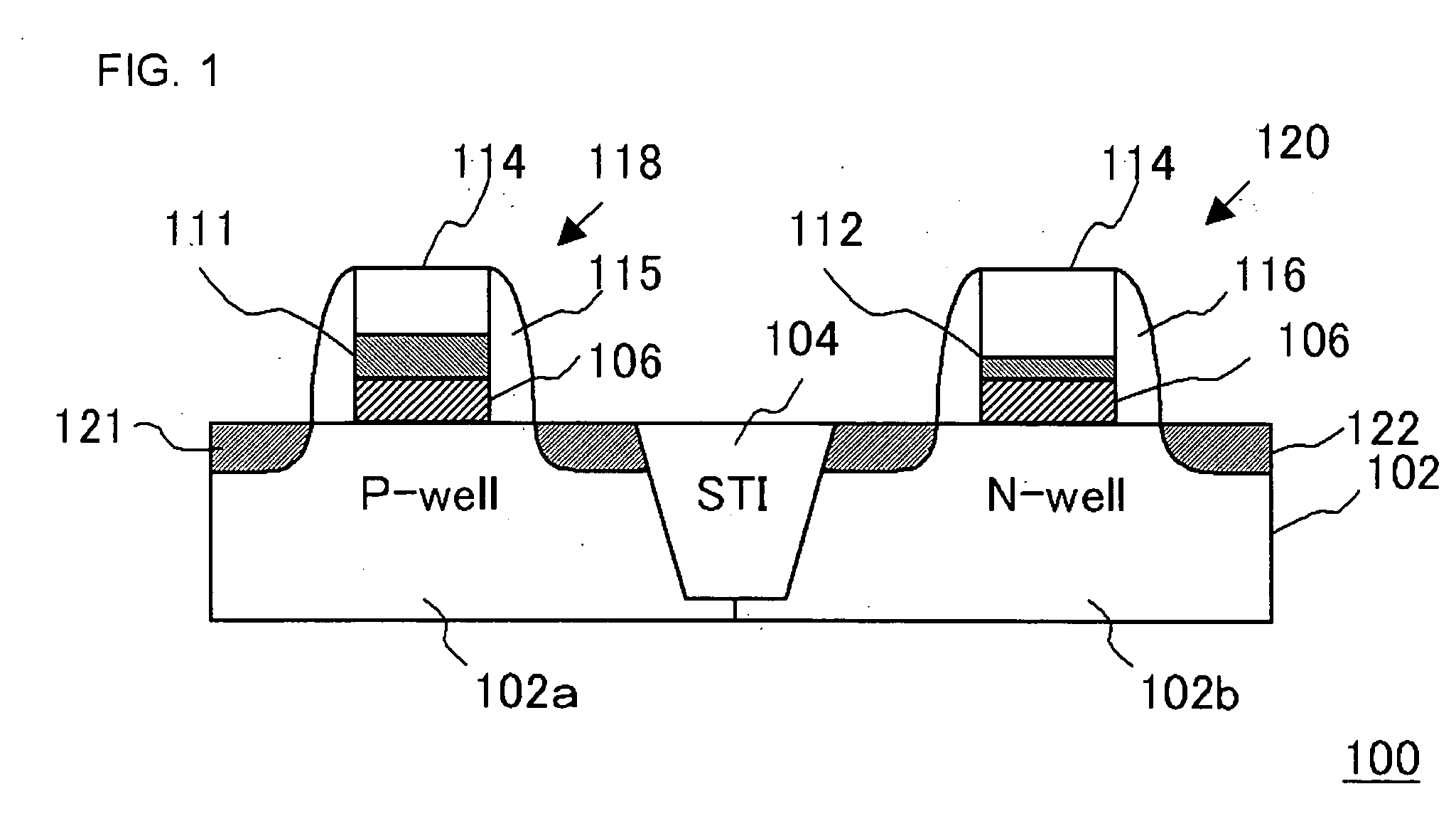

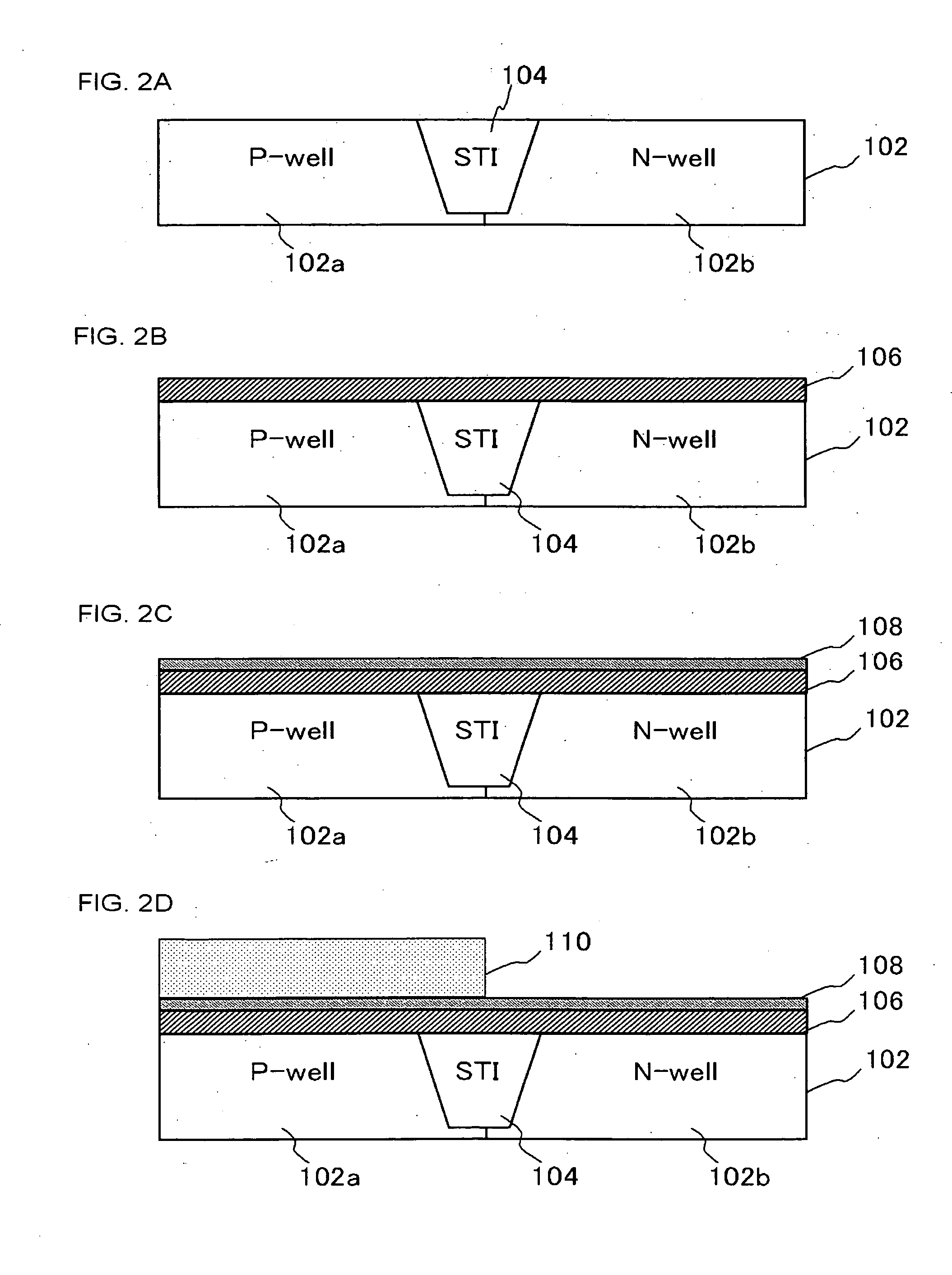

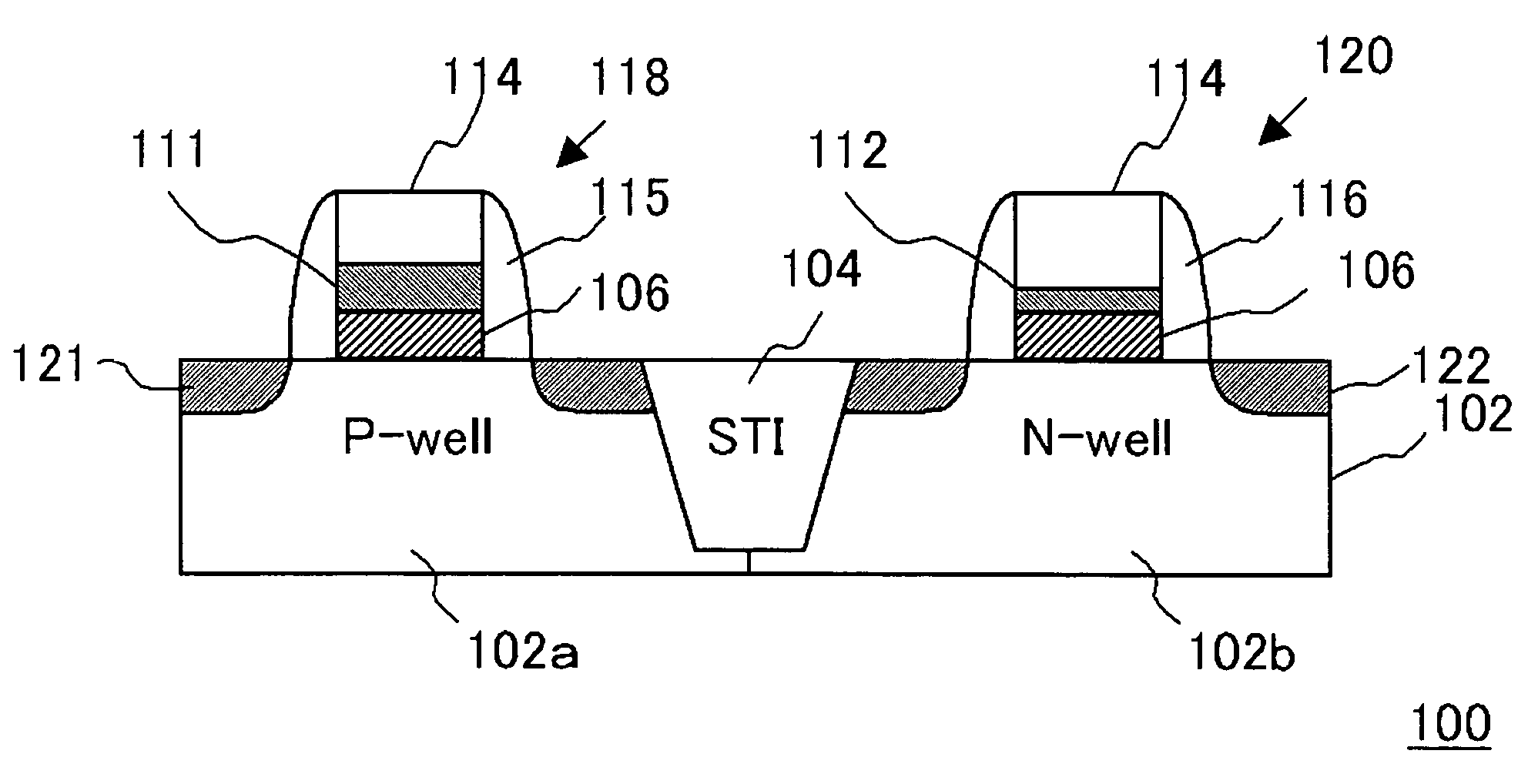

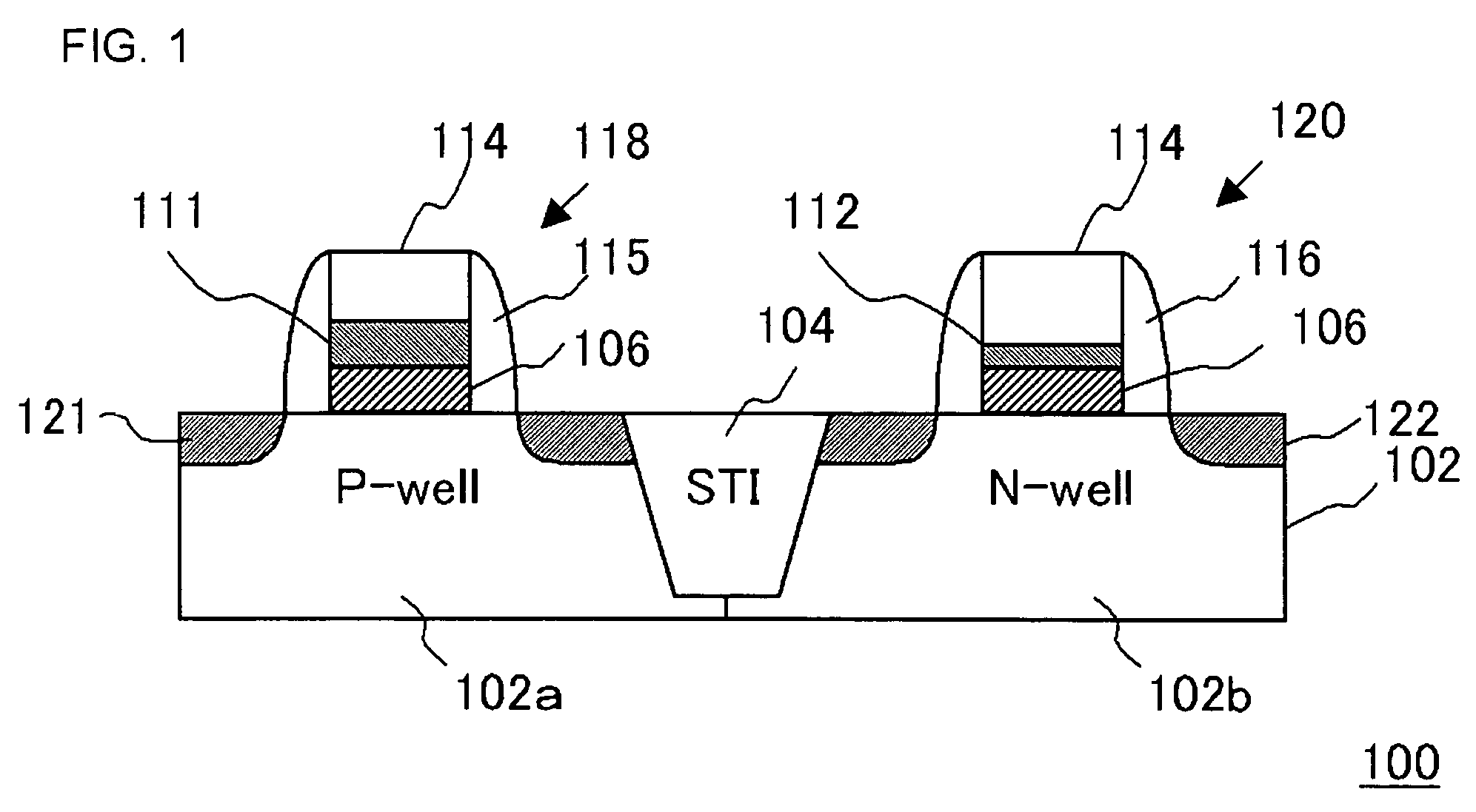

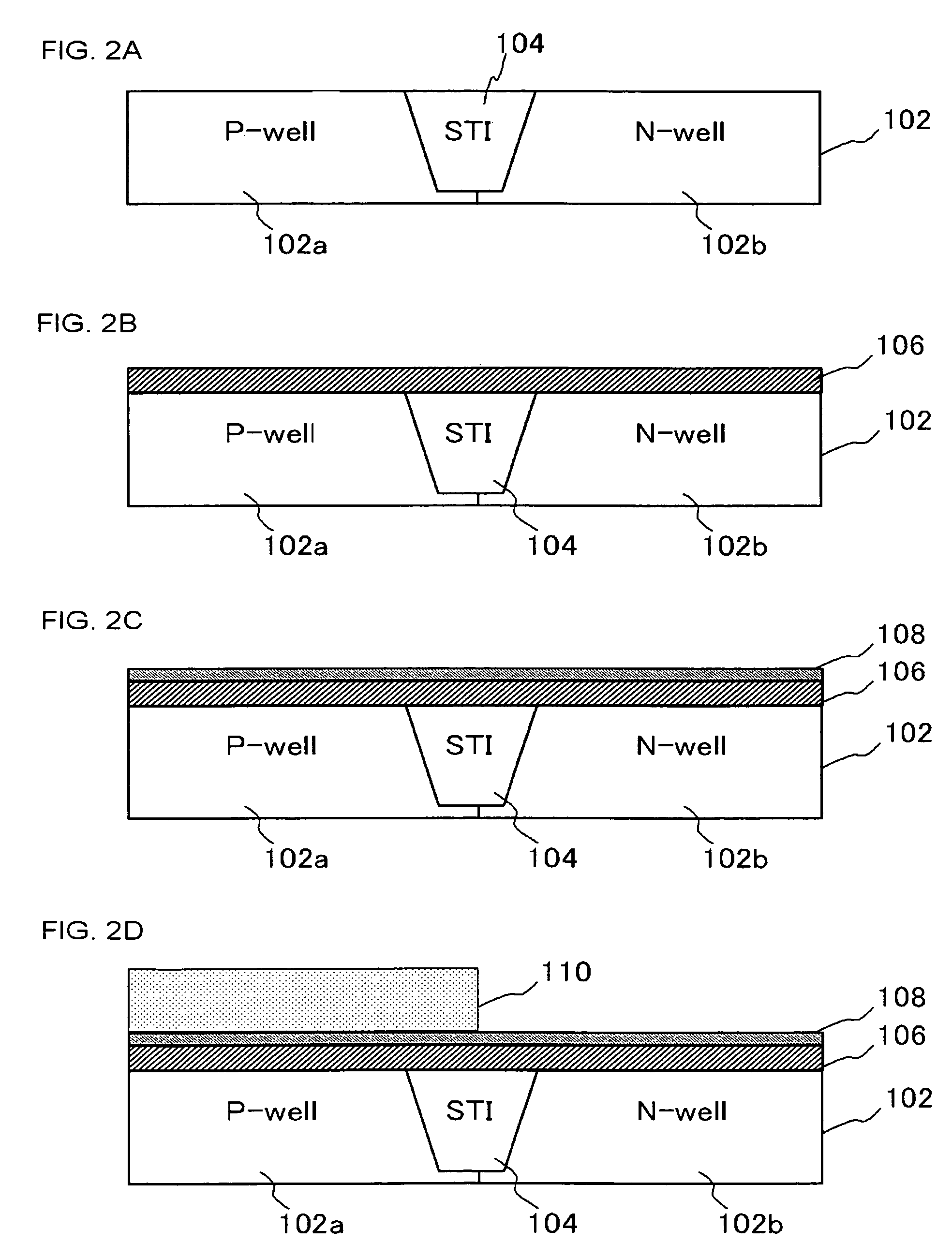

Semiconductor device

ActiveUS20050253181A1Lower threshold voltageRaise the threshold voltageTransistorSemiconductor/solid-state device detailsDielectricMOSFET

The semiconductor device 100 comprises a silicon substrate 102, an N-type MOSFET 118 including a first high dielectric constant film 111 and a polycrystalline silicon film 114 formed on the silicon substrate 102, and a P-type MOSFET 120 including a second high dielectric constant film 112 and a polycrystalline silicon film 114 juxtaposed to N-type MOSFET 118 on the silicon substrate 102. The second high dielectric constant film 112 is formed to have the film thickness thinner than the film thickness of the first high dielectric constant film 111. The first high dielectric constant film 111 and the second high dielectric constant film 112 contains one or more element(s) selected from a group consisting of Hf and Zr.

Owner:RENESAS ELECTRONICS CORP

Method of manufacturing thin film transistor, thin film transistor, and display unit

InactiveUS7629208B2Reduce etching residueOn-current is loweredTransistorSolid-state devicesPhotothermal conversionCrystalline silicon

A method of manufacturing a thin film transistor capable of inhibiting the characteristics variation of the thin film transistor without deteriorating the characteristics thereof is provided. A crystalline silicon film is formed by indirect heat treatment through a photothermal conversion layer and a buffer layer. By patterning the buffer layer and an insulating film, a channel protective film is selectively formed in a region corresponding to a channel region on the crystalline silicon film. Further, when an n+ silicon film and a metal layer are selectively removed, the channel protective film functions as an etching stopper. When the crystalline silicon film is formed, heat is uniformly supplied. Further, in etching, the channel region of the crystalline silicon film is protected.

Owner:SONY CORP

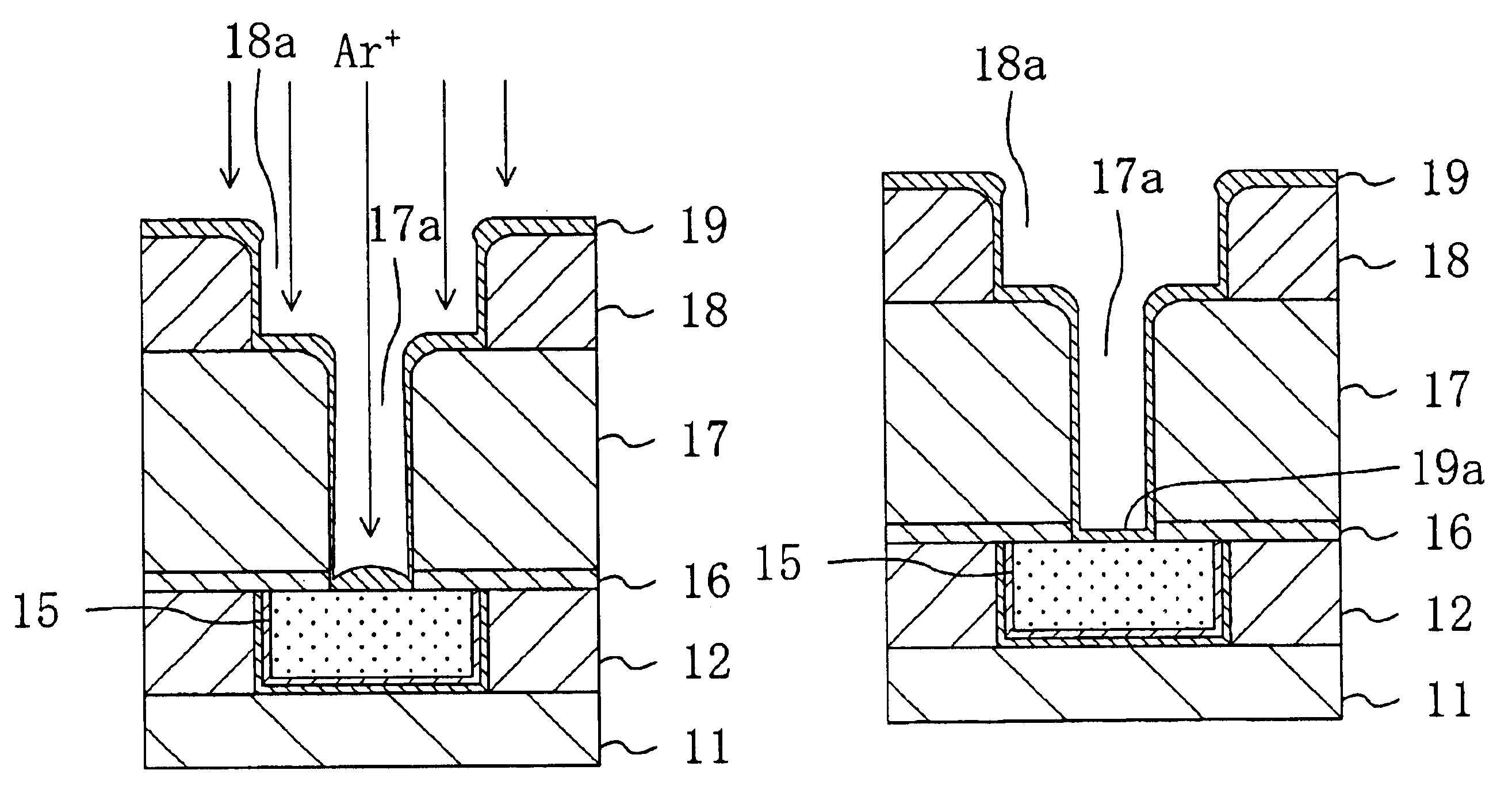

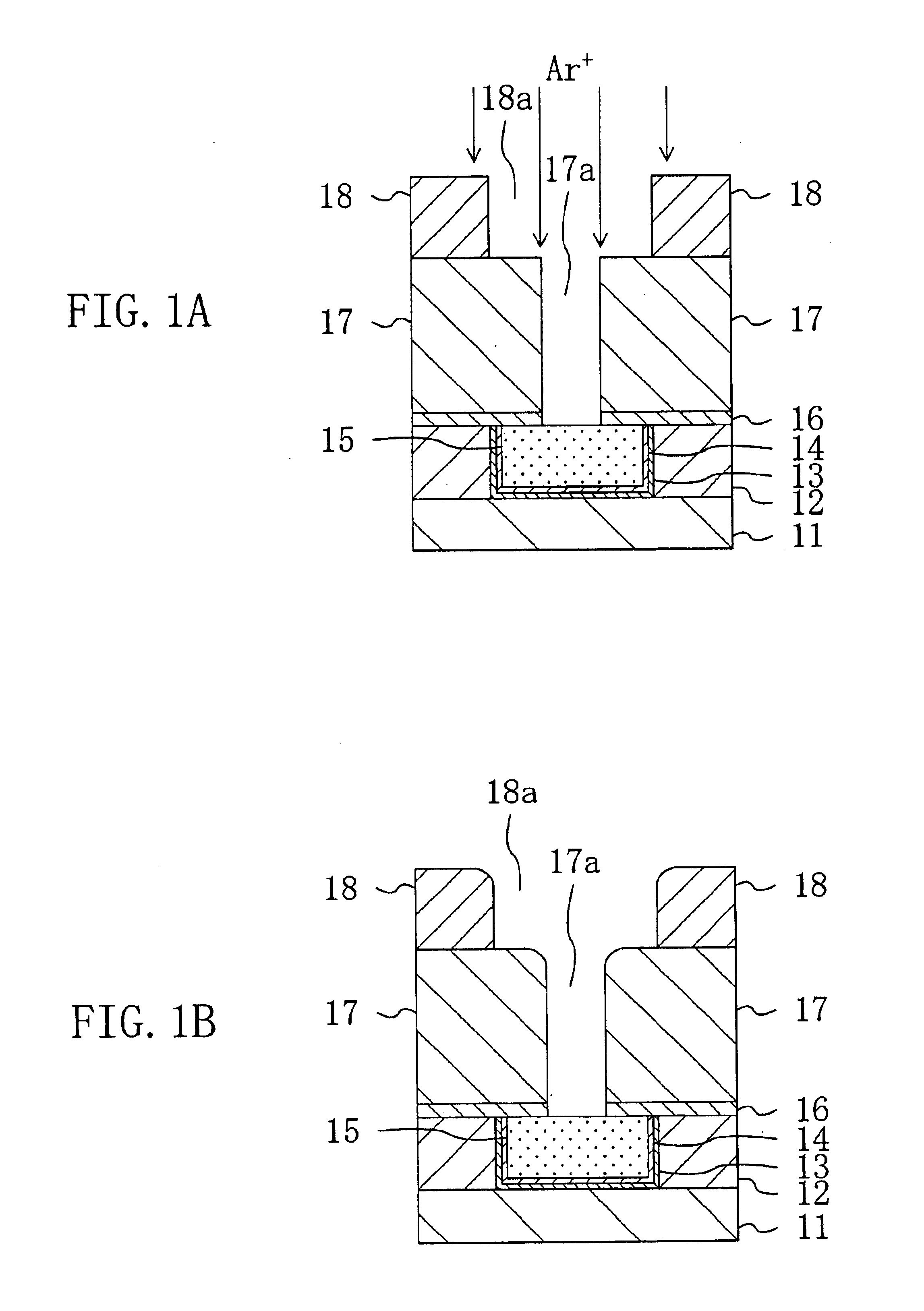

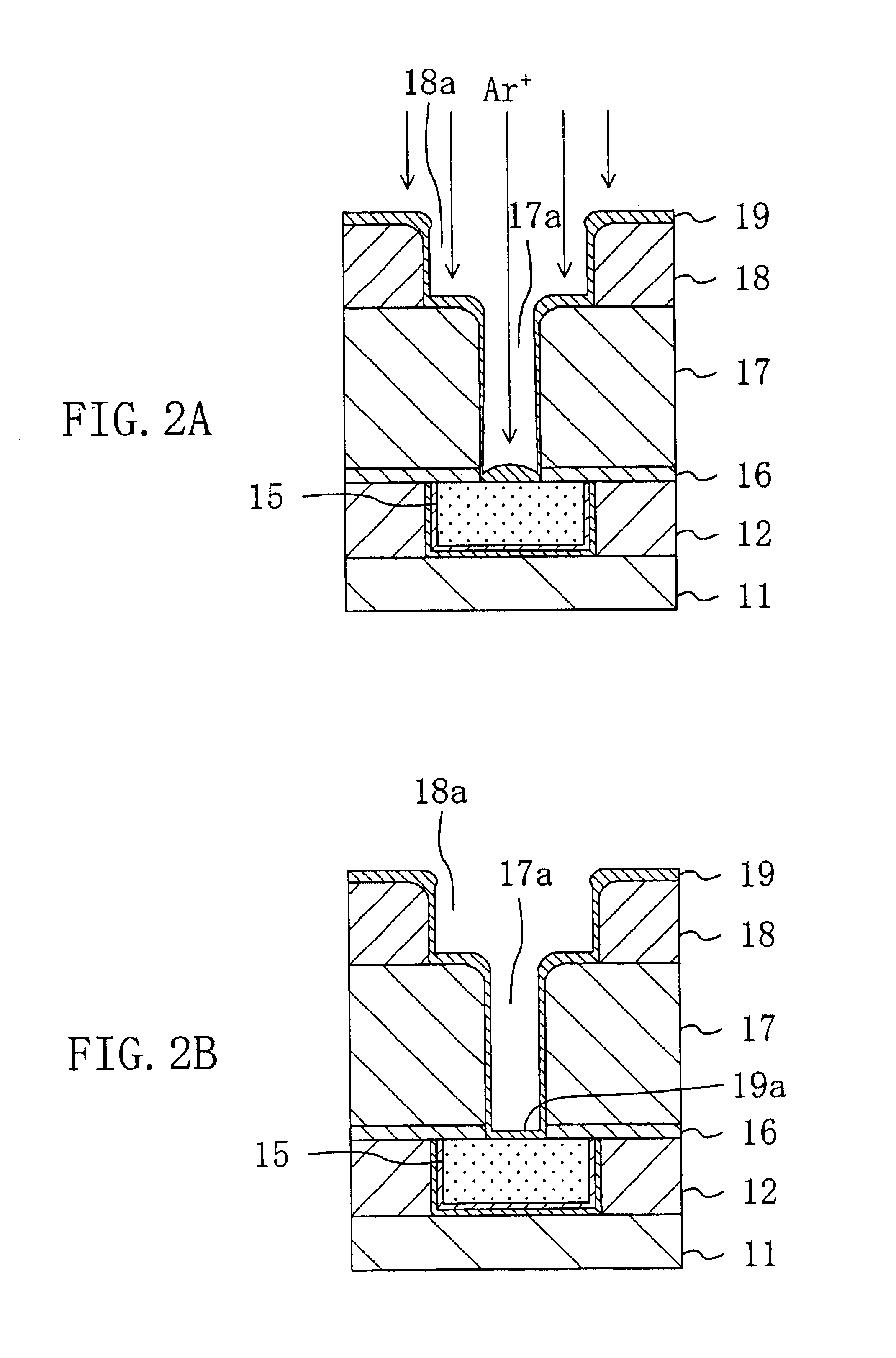

Method for manufacturing semiconductor device

ActiveUS6951809B2Good filling characteristicEasy to fillSemiconductor/solid-state device manufacturingTantalum nitrideSemiconductor

A lower barrier layer made of tantalum nitride having a thickness of approximately 25 nm is deposited by sputtering on a fourth insulating film inclusive of the sidewall surfaces and the bottom surfaces of a via hole and an upper-interconnect-forming groove. The sputtering is performed under the conditions where approximately 10 kW of DC source power is applied to a target. Thereafter, the DC source power is reduced to approximately 2 kW, and approximately 200 W of RF power is applied to a semiconductor substrate. Here, the lower barrier layer is subjected to a sputter-etching process employing argon gas at an etching amount of approximately 5 nm, so that a part of the lower barrier layer deposited on the bottom surface of the via hole is at least partially deposited on the lower part of the sidewall surface of the via hole.

Owner:PANNOVA SEMIC

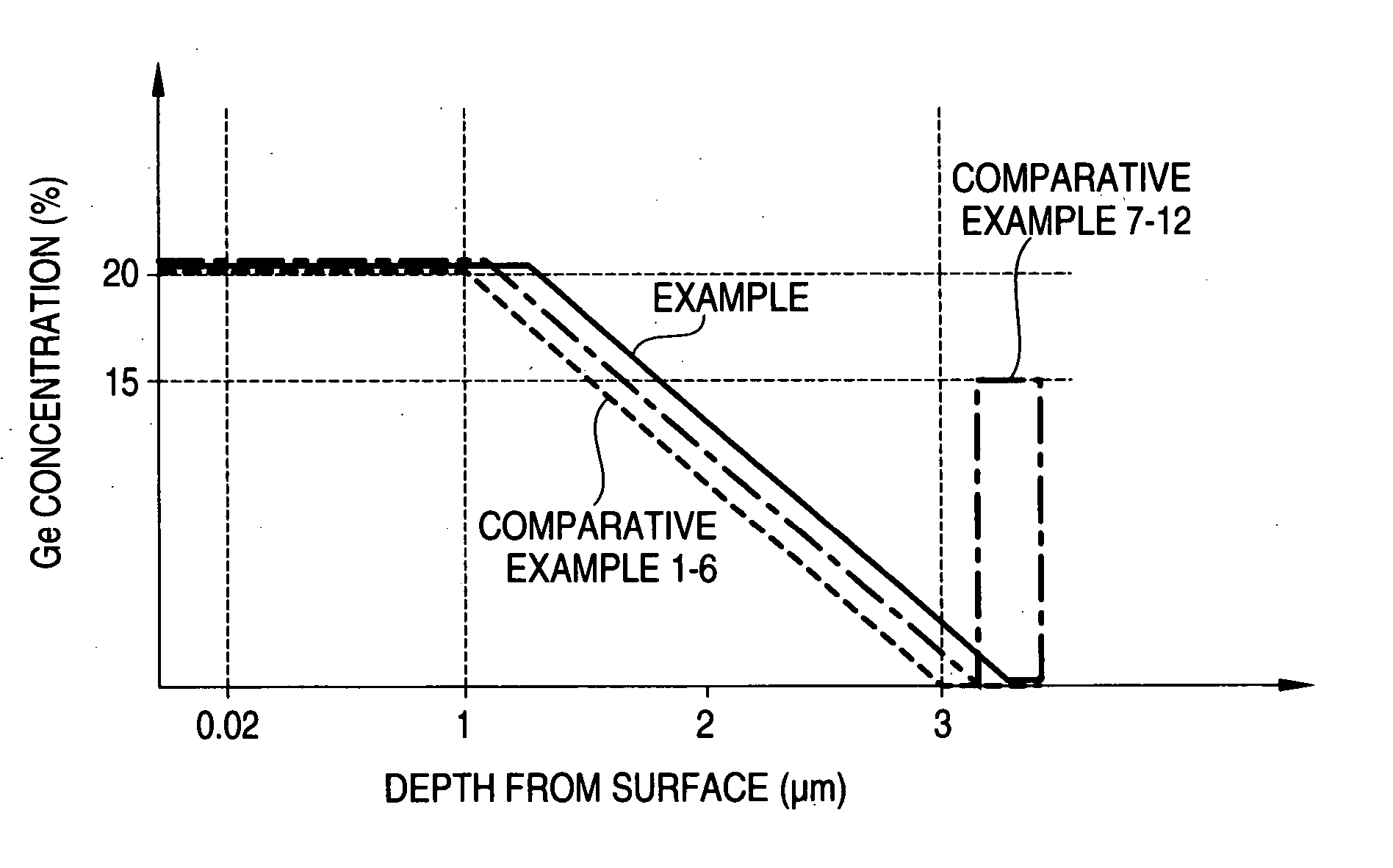

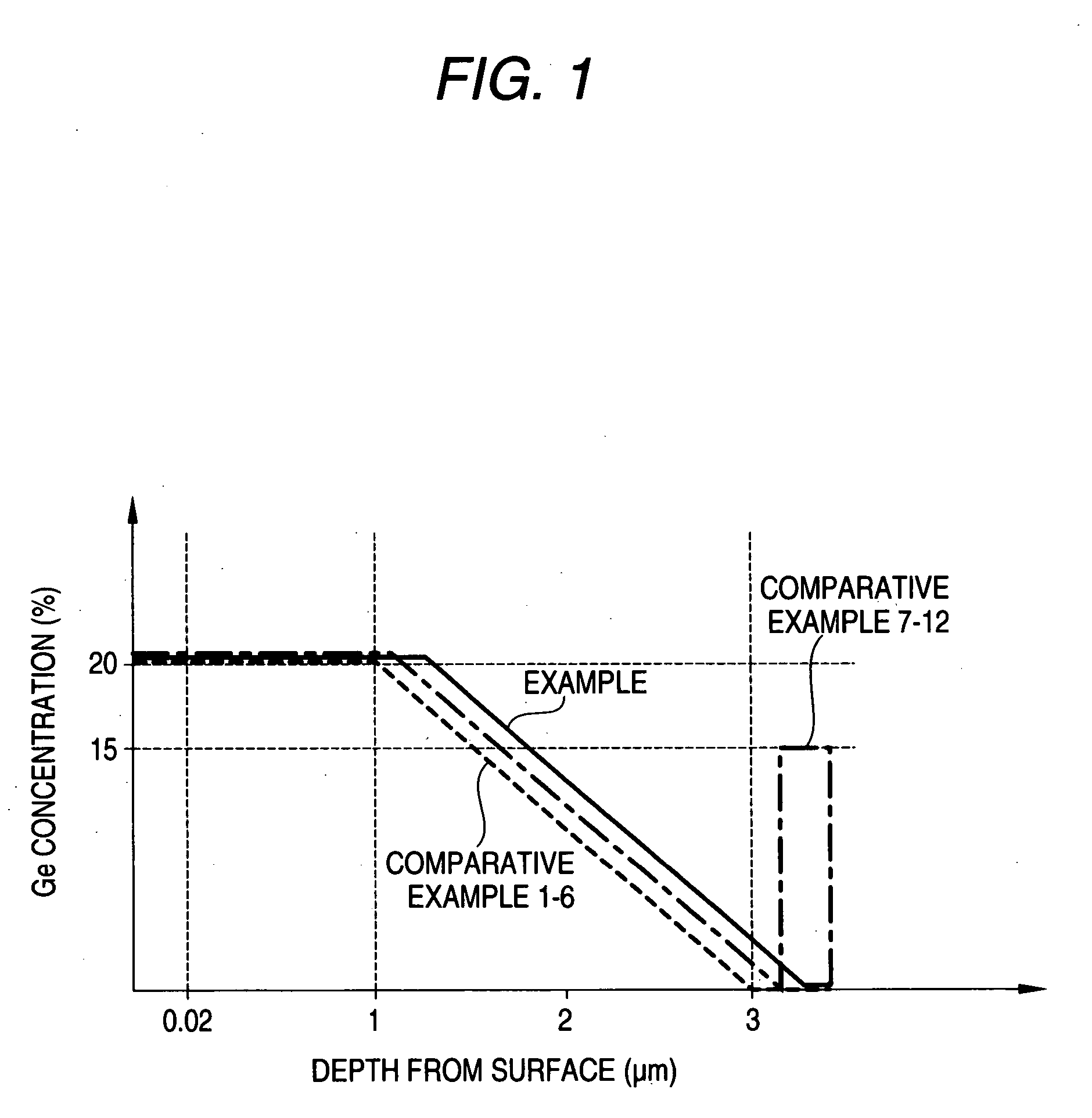

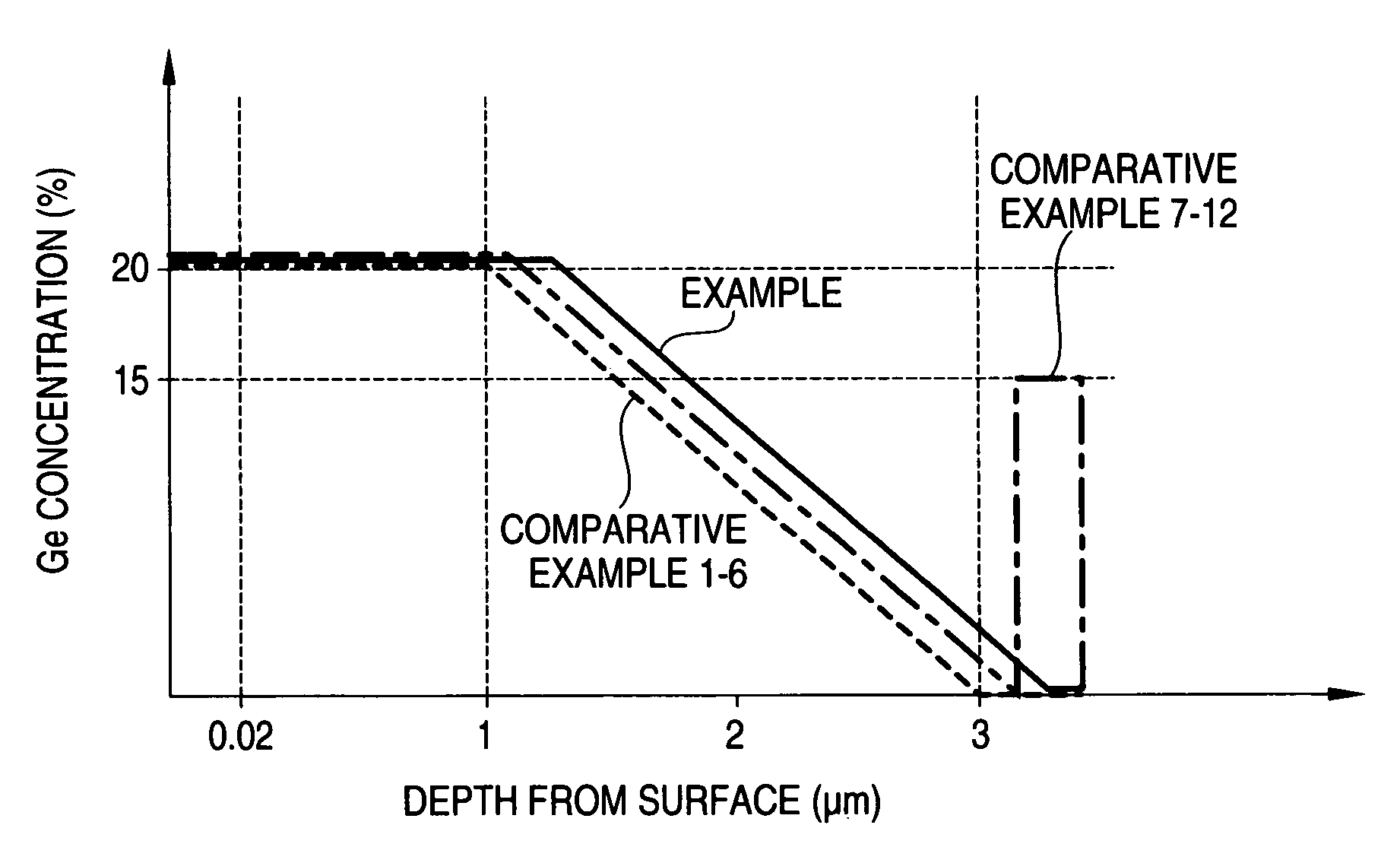

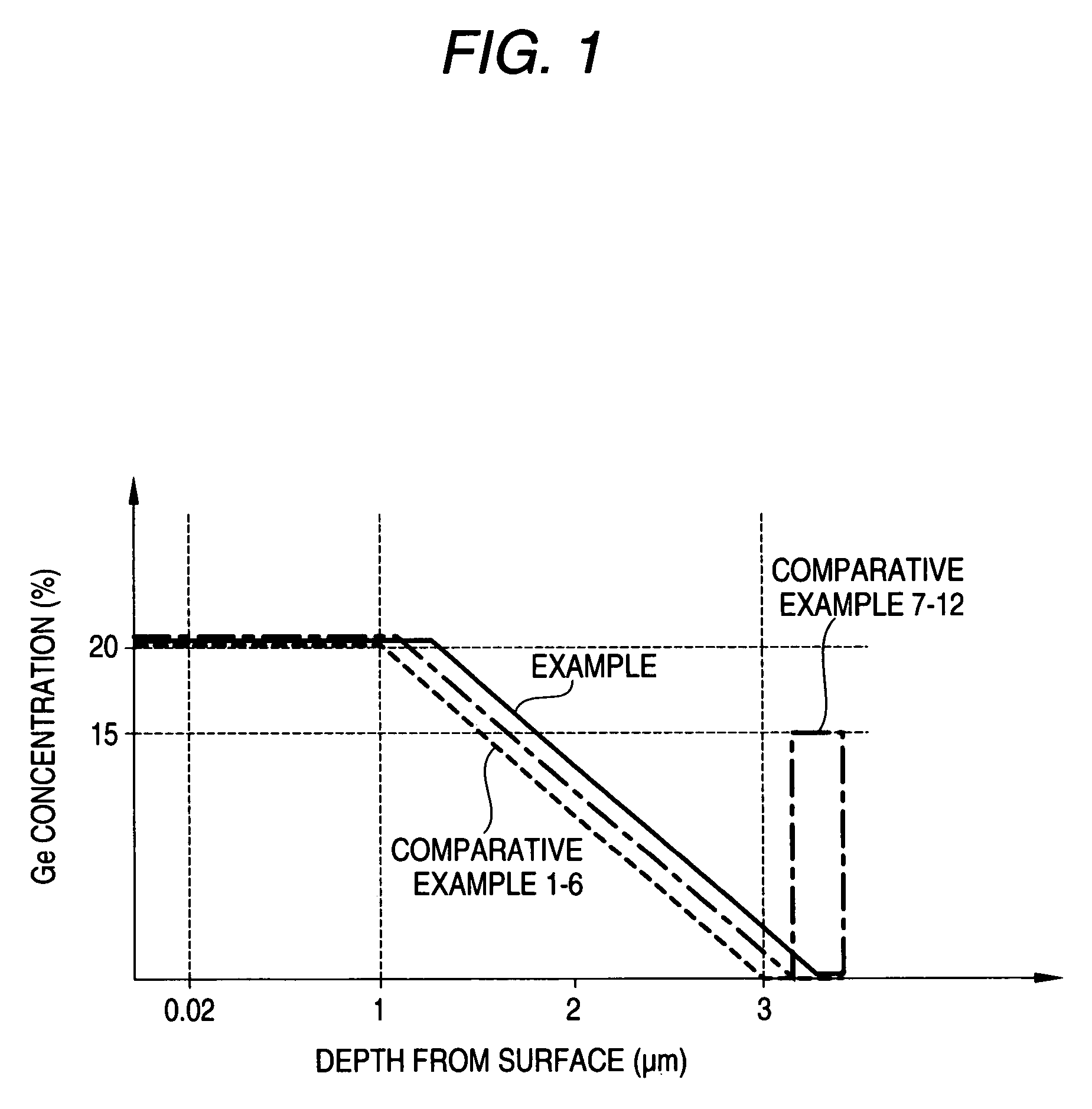

Manufacturing method for strained silicon wafer

InactiveUS7250357B2Penetrating dislocation density in the strained Si layer can be more reducedLarge thicknessSemiconductor/solid-state device manufacturingSemiconductor devicesMaterials scienceStrained silicon

A manufacturing method for producing a stained silicon wafer has the steps of forming an Si1-xGex composition-graded layer of which Ge concentration is stepwisely increased on a single crystal silicon substrate, forming an Si1-xGex uniform composition layer of which Ge concentration is constant on the Si1-xGex composition-graded layer, forming a stain-relaxed Si1-yGey layer of which Ge concentration y is constant while y satisfies relationship of 0.5x≦y<x on the Si1-xGex uniform composition layer and epitaxially growing a strained Si layer on the strain-relaxed Si1-yGey layer.

Owner:COVALENT MATERIALS CORP

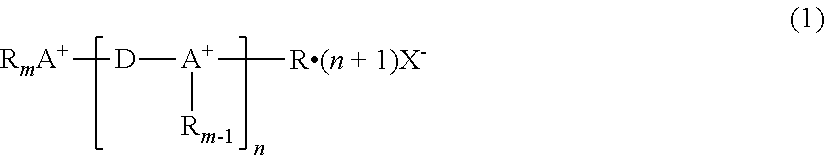

Photosensitive resin composition, and pattern formation method using the same

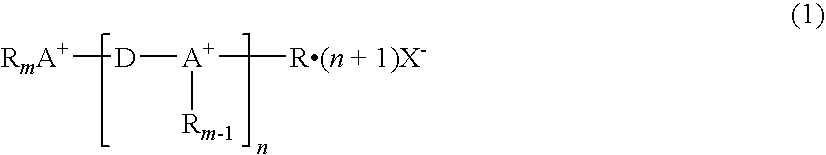

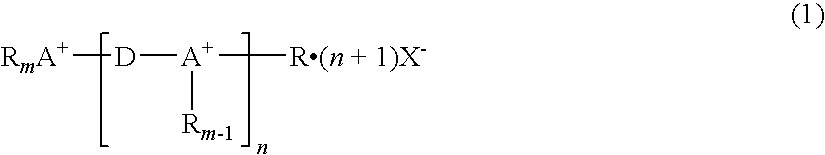

ActiveUS20100068649A1Large film thicknessIncrease heightPhotosensitive materialsPhotomechanical exposure apparatusPolymer scienceIonic polymerization

A photosensitive resin composition is provided that is highly safe, provides a coating film having superior uniformity, can improve the curing density of the cured resin pattern, and is capable of forming a micro resist pattern having a large film thickness and a high aspect ratio with high sensitivity and high resolving ability. According to a photosensitive resin composition including, in addition to an onium fluorinated alkyl fluorophosphate based cation polymerization initiator having a specific structure, a specified solvent or a specified sensitizing agent as essential components, a coating film having superior uniformity, can improve the curing density of the cured resin pattern, and also is capable of forming a micro resist pattern having a large film thickness and a high aspect ratio with high sensitivity and high resolving ability.

Owner:TOKYO OHKA KOGYO CO LTD

Organic light-emitting panel for controlling an organic light emitting layer thickness and organic display device

ActiveUS8624275B2High concentrationLarge film thicknessElectroluminescent light sourcesSolid-state devicesDisplay deviceEngineering

Owner:JOLED INC

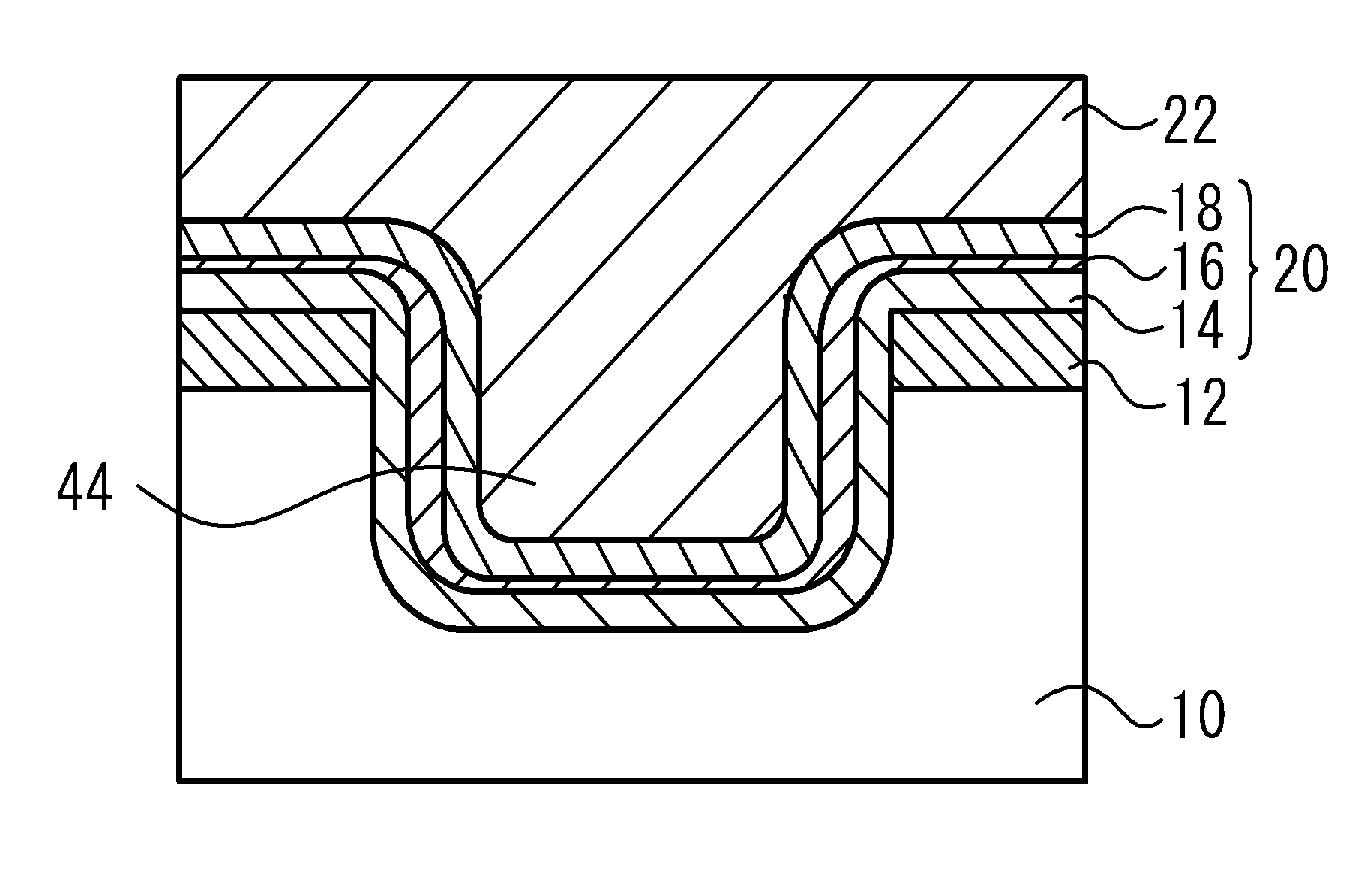

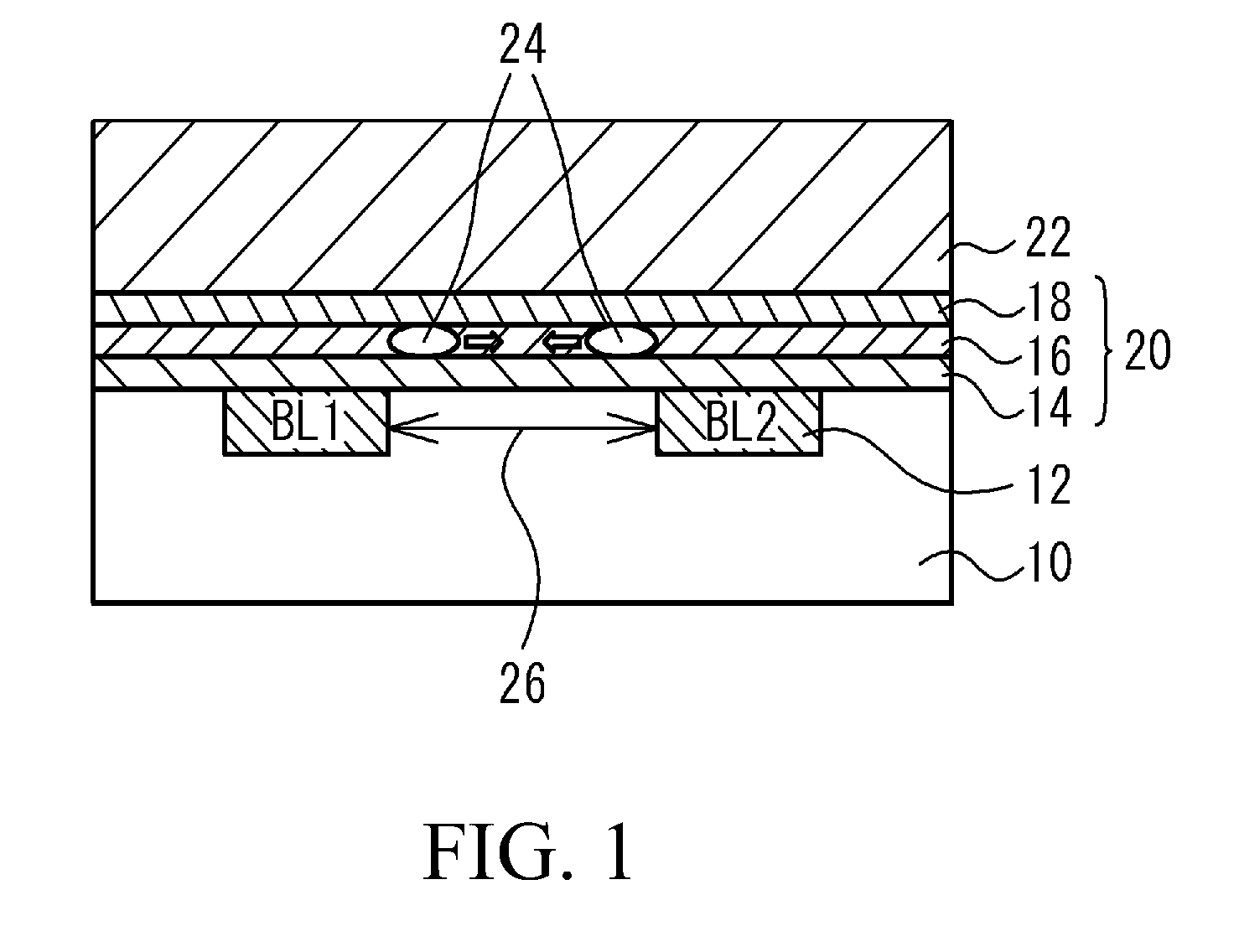

Semiconductor device and method for manufacturing thereof

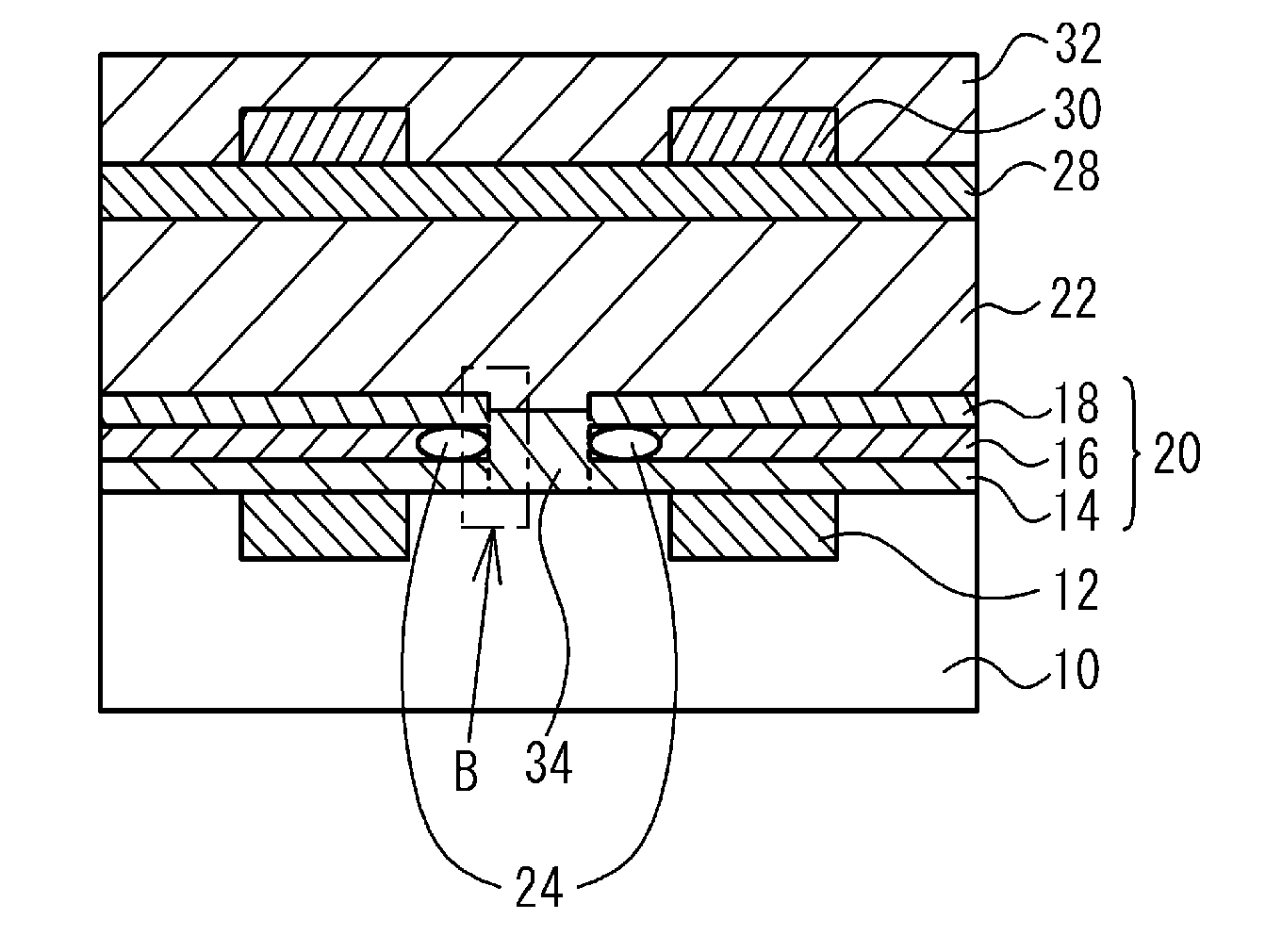

ActiveUS20080224275A1Highly integratedHighly miniaturizedSemiconductor/solid-state device detailsSolid-state devicesBit lineEngineering

A semiconductor device includes bit lines provided in a semiconductor substrate; an ONO film that is provided along the surface of the semiconductor substrate and is made of a tunnel oxide film, a trap layer, and a top oxide film; and an oxide film that is provided on the surface of the semiconductor substrate in the middle between the bit lines and contacts the side face of the ONO film, in which the film thickness of the oxide film is larger than the sum of the thicknesses of the tunnel oxide film and the top oxide film, and smaller than the thickness of the ONO film.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

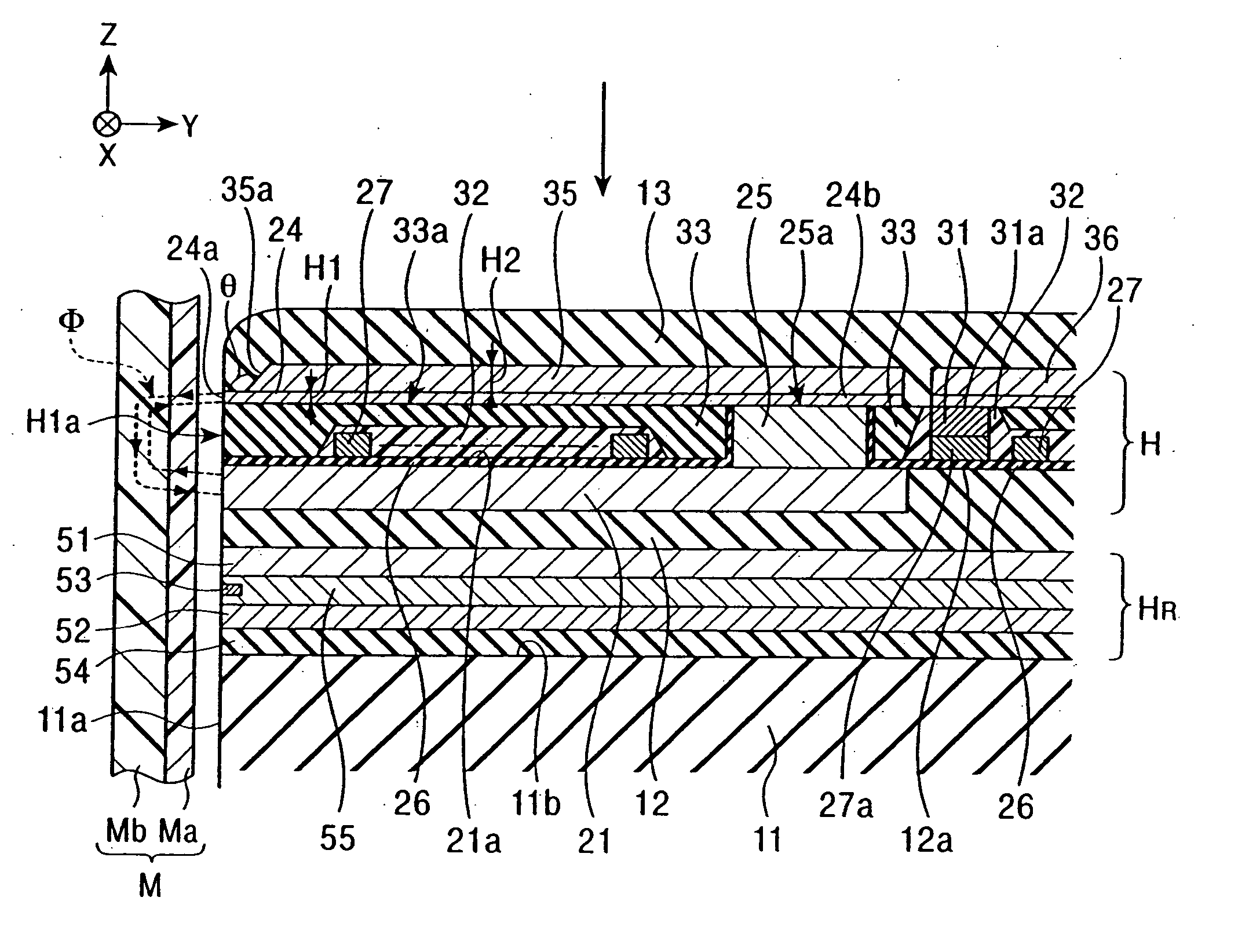

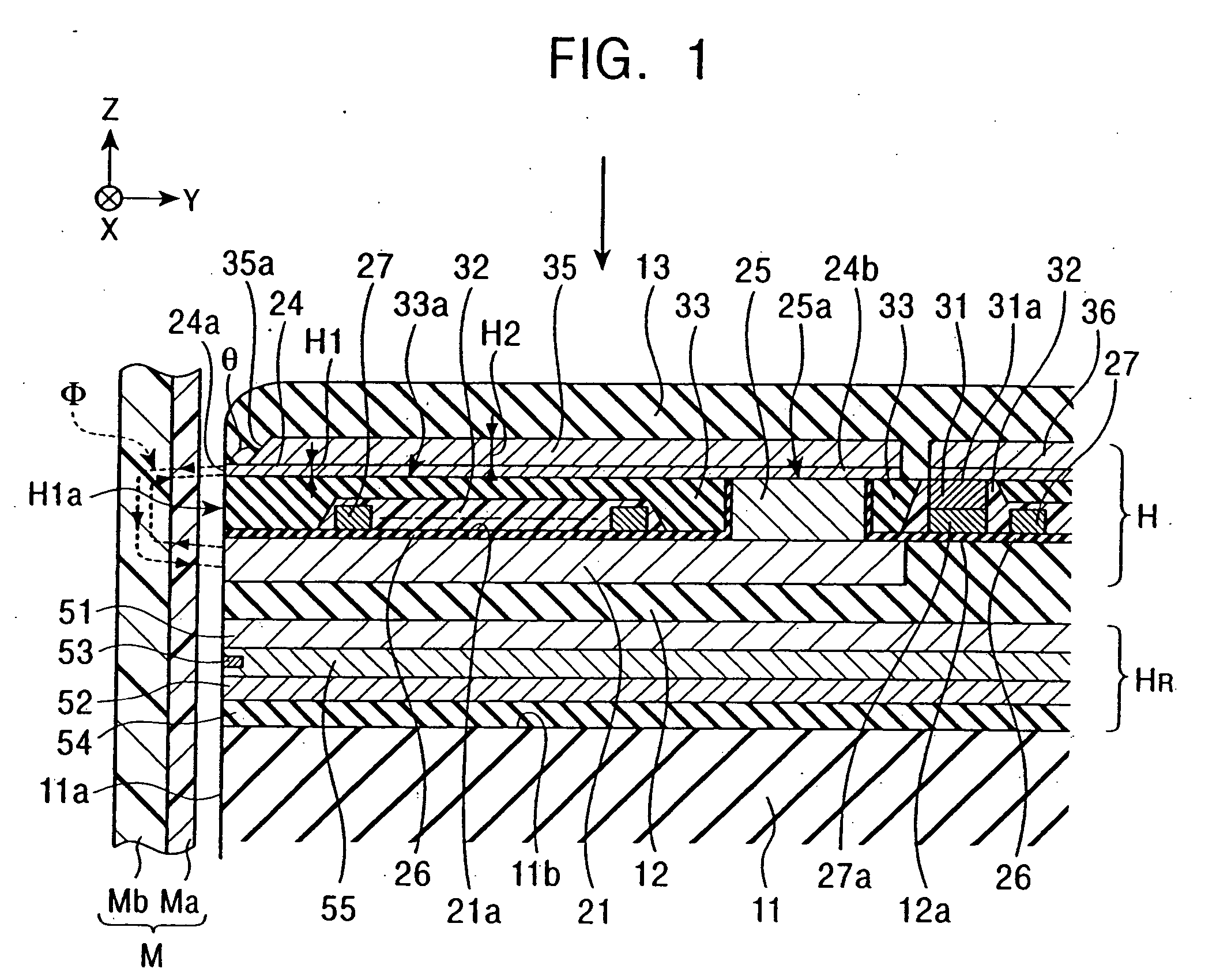

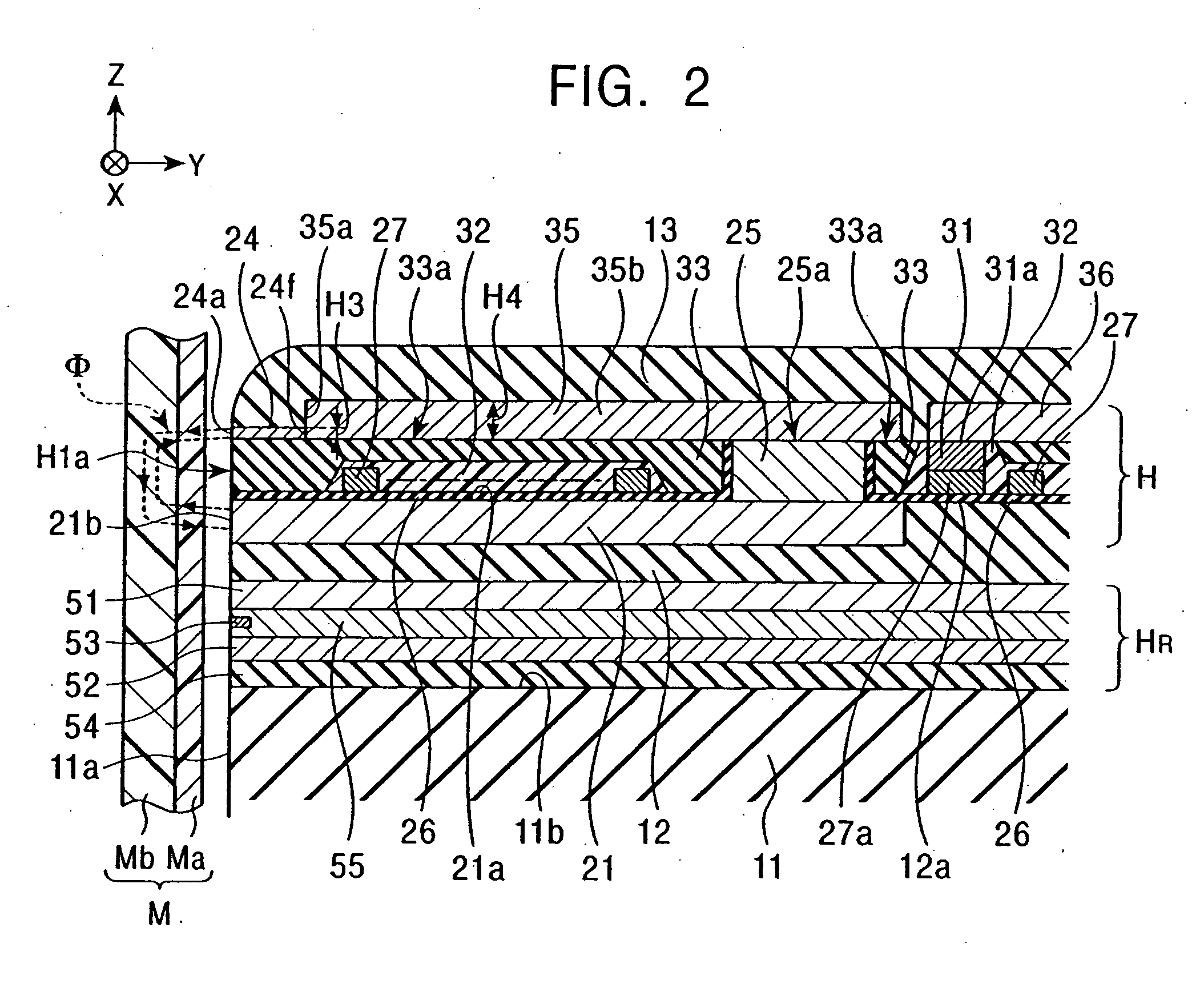

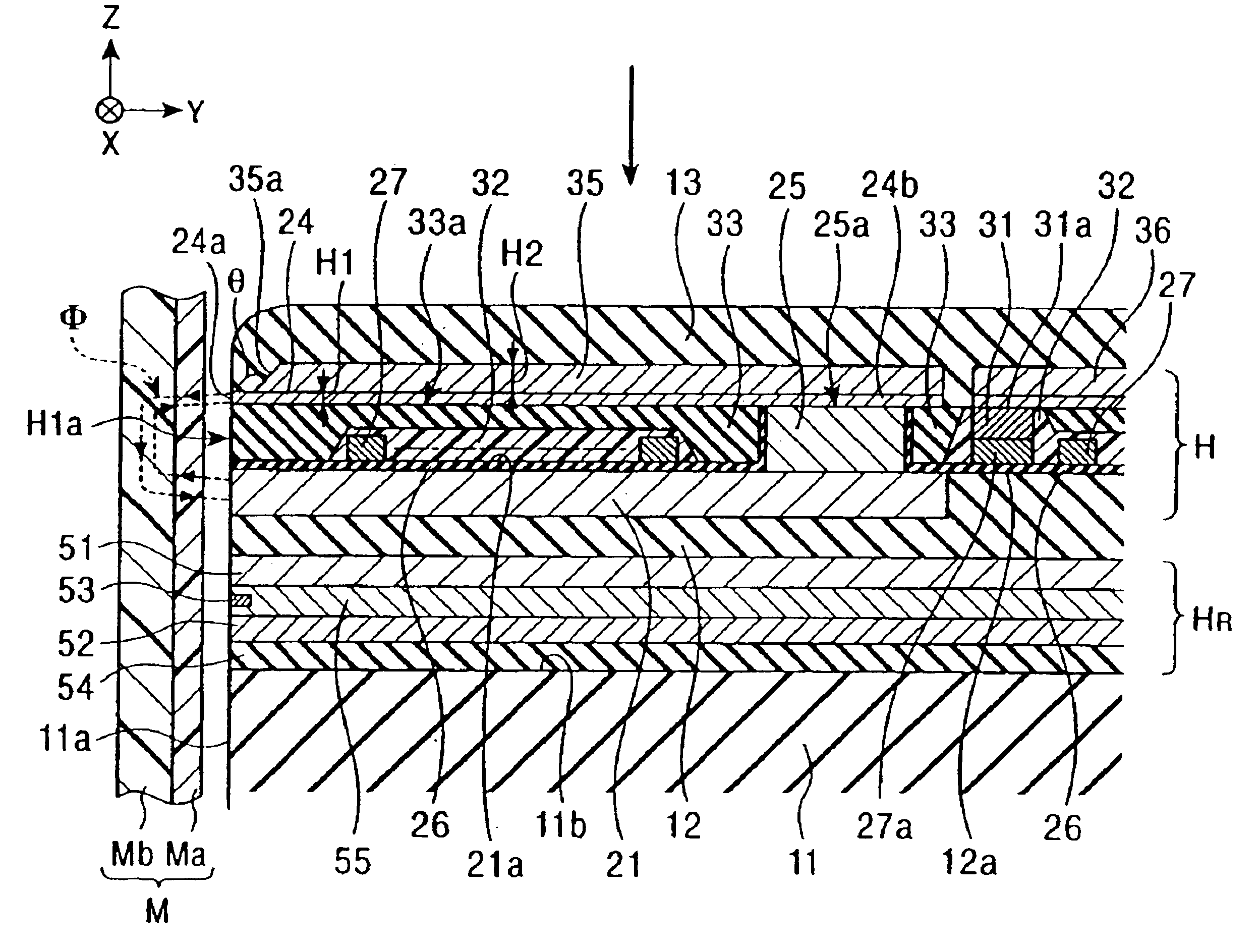

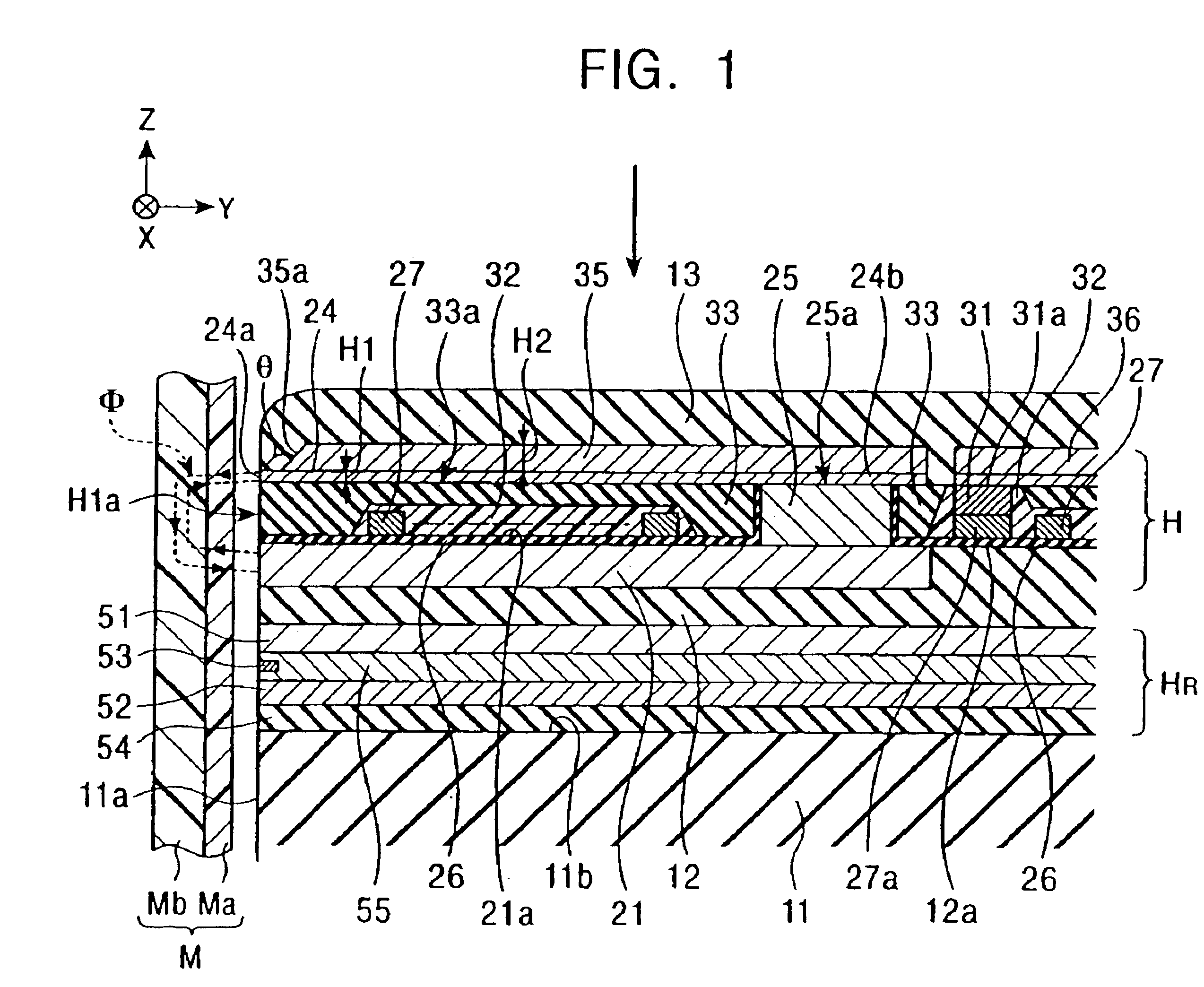

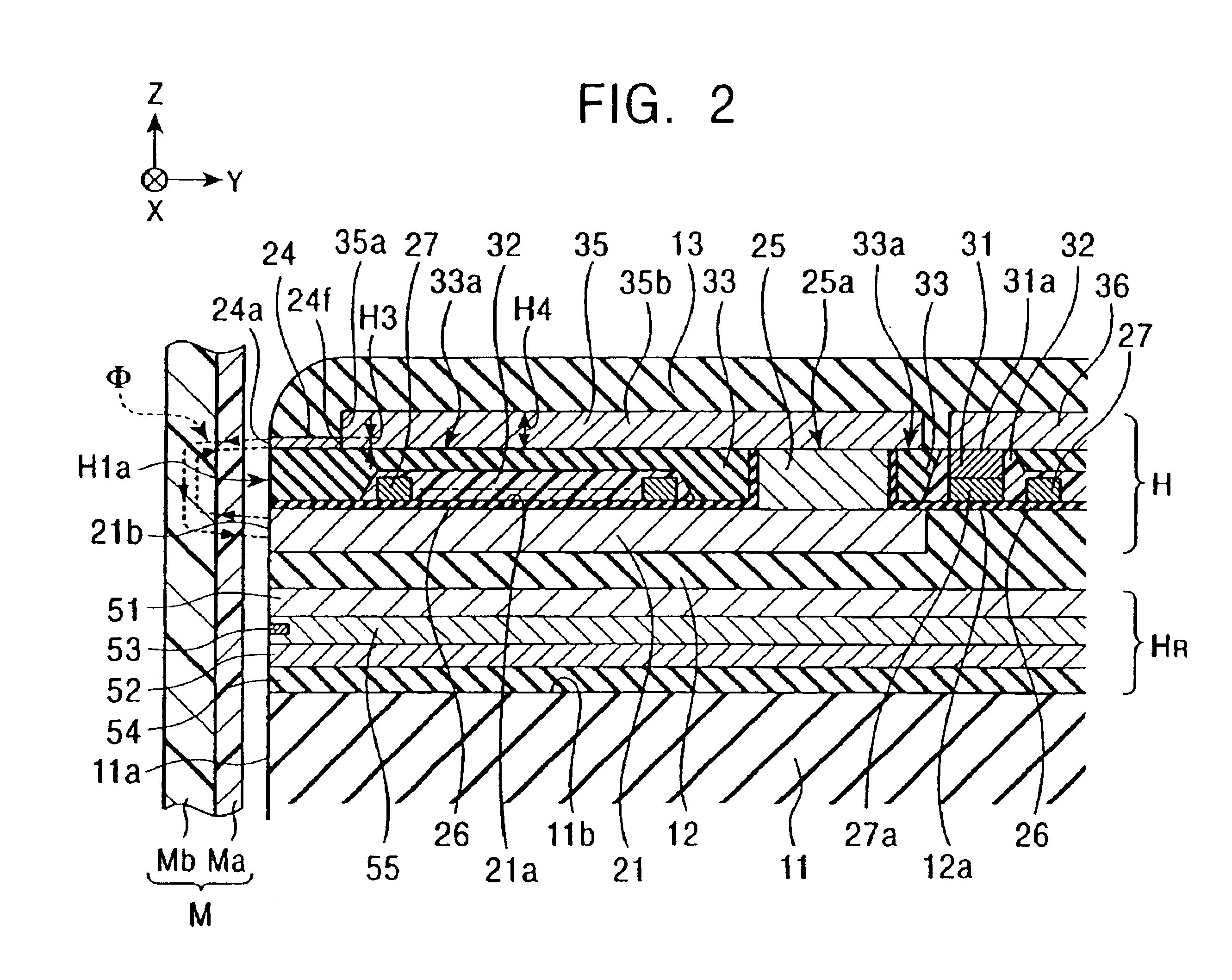

Perpendicular magnetic recording head having main magnetic pole layer formed on high-flatness surface, and method of manufacturing the head

InactiveUS20060002025A1High pattern accuracyNarrow trackManufacture head surfaceElectrical transducersMagnetic polesEngineering

Owner:TDK CORPARATION

Method of manufacturing thin film transistor, thin film transistor, and display unit

InactiveUS20100038646A1Reduce etching residueOn-current is loweredTransistorSolid-state devicesCrystalline siliconMetal

A thin film transistor having a crystalline silicon film that is formed over an insulating substrate with a gate electrode and a gate insulating film in between, and has a channel region in a region corresponding to the gate electrode; an insulating channel protective film that is selectively formed in a region corresponding to the channel region on the crystalline silicon film; an n+ silicon film having a source region and a drain region that sandwich a region corresponding to the channel region on the channel protective film and the crystalline silicon film; and a metal film having a source electrode and a drain electrode that respectively correspond to the source region and the drain region.

Owner:SONY GRP CORP

Sonos device with insulating storage layer and p-n junction isolation

ActiveUS20090237990A1Avoid formingReduce contact resistanceSolid-state devicesRead-only memoriesEngineeringP–n junction isolation

The present invention provides a semiconductor device and a method for manufacturing thereof. The semiconductor device includes bit lines disposed in a semiconductor substrate, a first ONO disposed between the bit lines on the semiconductor substrate, and a second ONO film disposed on each of the bit lines. The film thickness of a first silicon nitride film in the first ONO film is larger than the film thickness of a second silicon nitride film in the second ONO film.

Owner:MONTEREY RES LLC

Semiconductor device having high dielectric constant layers of different thicknesses

ActiveUS7759744B2Raise the threshold voltageAvoid layeringTransistorSemiconductor/solid-state device detailsMOSFETDielectric

A semiconductor device 100 includes a silicon substrate 102, an N-type MOSFET 118 including a first high dielectric constant film 111 and a polycrystalline silicon film 114 on the silicon substrate 102, and a P-type MOSFET 120 including a second high dielectric constant film 12 and a polycrystalline silicon film 114 juxtaposed to N-type MOSFET 118 on the silicon substrate 102. The second high dielectric constant film 112 is formed to have the film thickness thinner than the film thickness of the first high dielectric constant film 111. The first high dielectric constant film 111 and the second high dielectric constant film 112 contains one or more element(s) selected from Hf and Zr.

Owner:RENESAS ELECTRONICS CORP

Perpendicular magnetic recording head having main magnetic pole layer formed on high-flatness surface, and method of manufacturing the head

InactiveUS6958886B2High pattern accuracyNarrow trackManufacture head surfaceHeads using thin filmsRecording headEngineering

A main magnetic pole layer is formed on an insulating layer flattened into a high-flatness surface, and a yoke layer having a large film thickness is formed on the main magnetic pole layer independently of the main magnetic pole. The main magnetic pole layer has a front end surface formed in a shape with a width size gradually increasing in a direction of track width as the front end surface departs farther away from an auxiliary magnetic pole layer. A perpendicular magnetic recording head can be provided which can suppress the occurrence of fringing in a recording pattern, and can form the main magnetic pole layer with high pattern accuracy, and can satisfactorily introduce a recording magnetic field to a fore end of the main magnetic pole layer.

Owner:TDK CORPARATION

Method for manufacturing SOI wafer and SOI wafer

ActiveUS7892948B2Less slip dislocationIncreasing the thicknessSemiconductor/solid-state device manufacturingOptoelectronicsDislocation

The present invention provides a method for manufacturing an SOI wafer in which a thickness of an SOI layer is increased by growing an epitaxial layer on the SOI layer of the SOI wafer having an oxide film and the SOI layer formed on a base wafer, wherein the epitaxial growth is performed in such a manner that a reflectivity of a surface of the SOI wafer on which the epitaxial layer is grown in a wavelength region of a heating light at the start of the epitaxial growth falls within the range of 30% to 80%. As a result, in the method for manufacturing the SOI wafer in which a thickness of the SOI layer is increased by growing the epitaxial layer on the SOI layer of the SOI wafer having the oxide film and the SOI layer formed on the base wafer, a method for manufacturing a high-quality SOI wafer with less slip dislocation and others is provided.

Owner:SHIN-ETSU HANDOTAI CO LTD

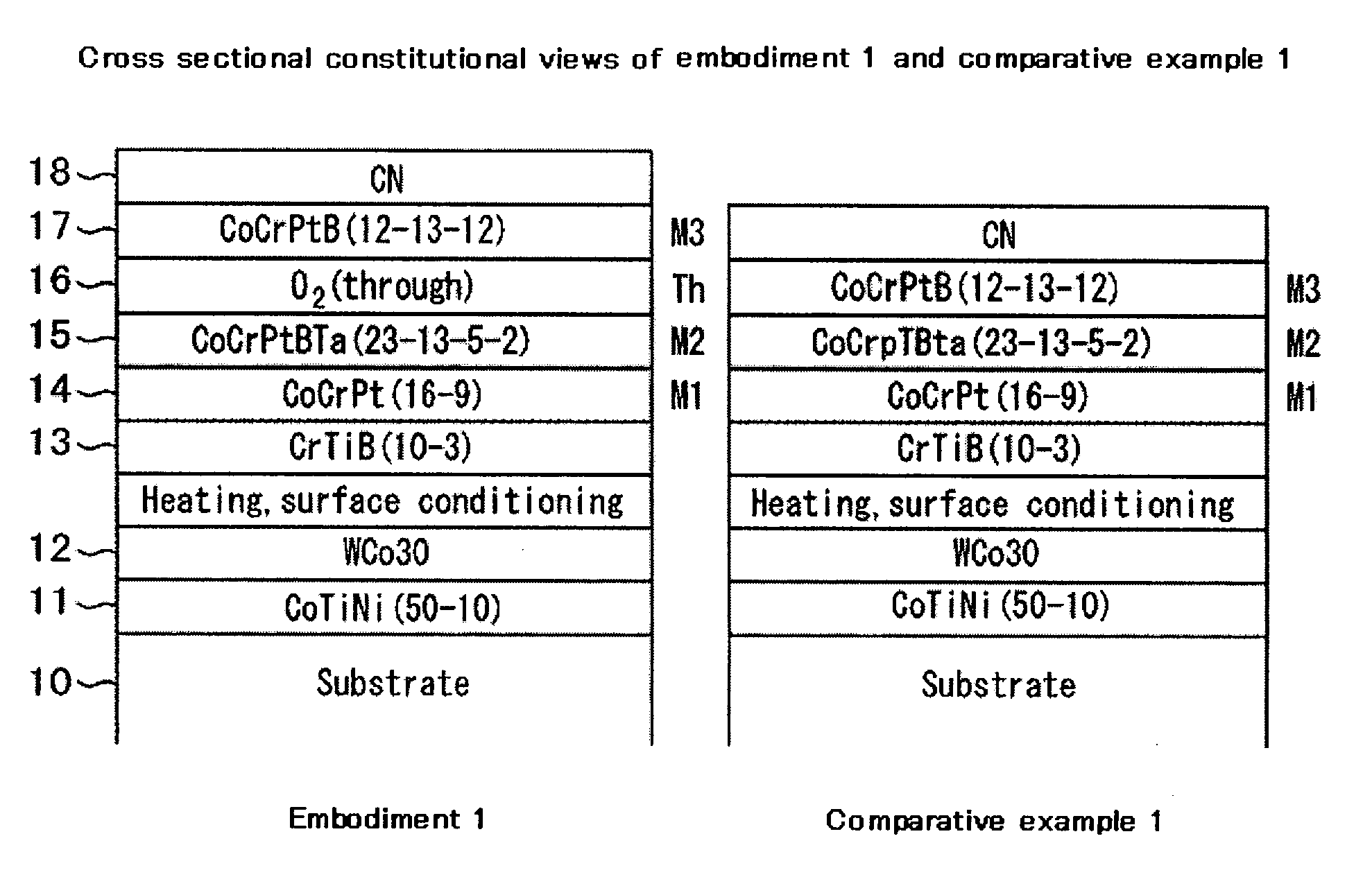

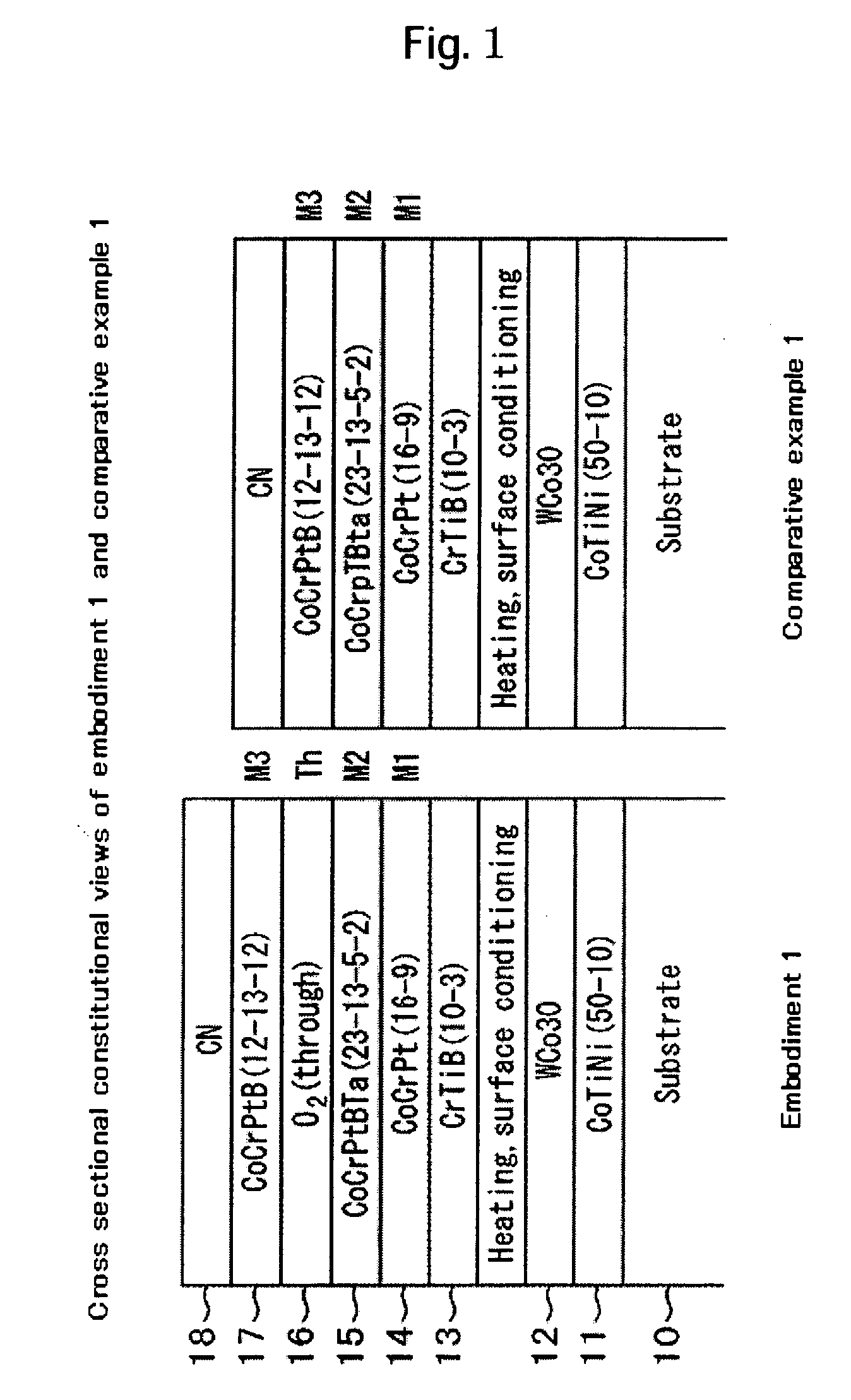

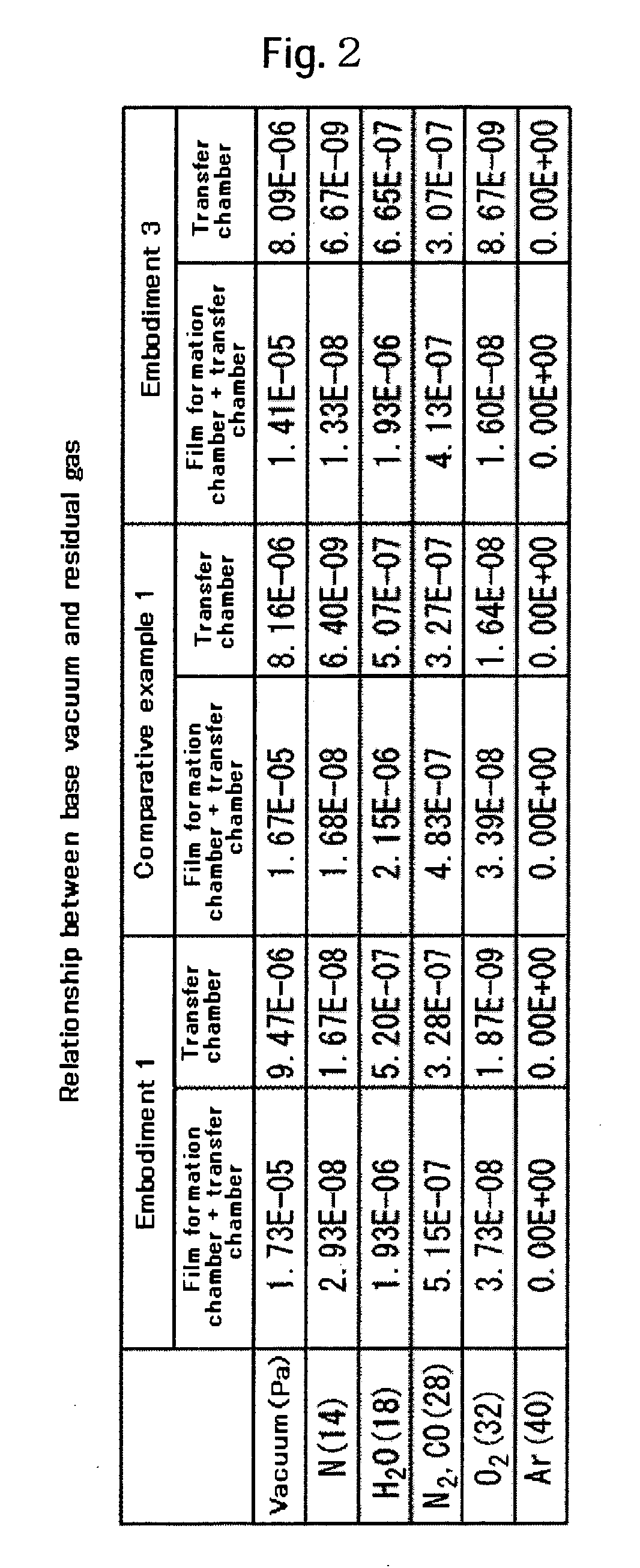

Magnetic recording medium

InactiveUS20060228588A1High medium S/NImprove featuresRecord information storageMagnetic recordingAlloyHigh oxygen

A magnetic recording material is provided which has high medium S / N, and provides excellent overwriting characteristic, excellent thermal fluctuation and sufficient stability against thermal fluctuation. In one embodiment, a first underlayer comprising one of alloys of a Ti—Co alloy, a Ti—Co—Ni alloy, and an Ni—Ta alloy, a second underlayer comprising a W—Co alloy or Ta, and a third underlayer of a body-centered cubic structure comprising a Cr—Ti—B alloy or a Cr—Ti alloy are disposed over a substrate. A first magnetic layer comprising a Co—Cr—B alloy or a Co—Cr—Ta alloy, a second magnetic layer comprising a Co—Cr—Pt—B—Ta alloy, a third magnetic layer comprising a Co—Cr—Pt—B alloy, and a protective film are disposed further thereover. An intermediate region (Th) is disposed between the second magnetic layer and the third magnetic layer, the intermediate region having a higher oxygen concentration than those of the magnetic layers.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

Semiconductor device with ONO film

ActiveUS8994093B2High integration and miniaturizationSuppress interferenceSemiconductor/solid-state device detailsSolid-state devicesEngineeringSemiconductor

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

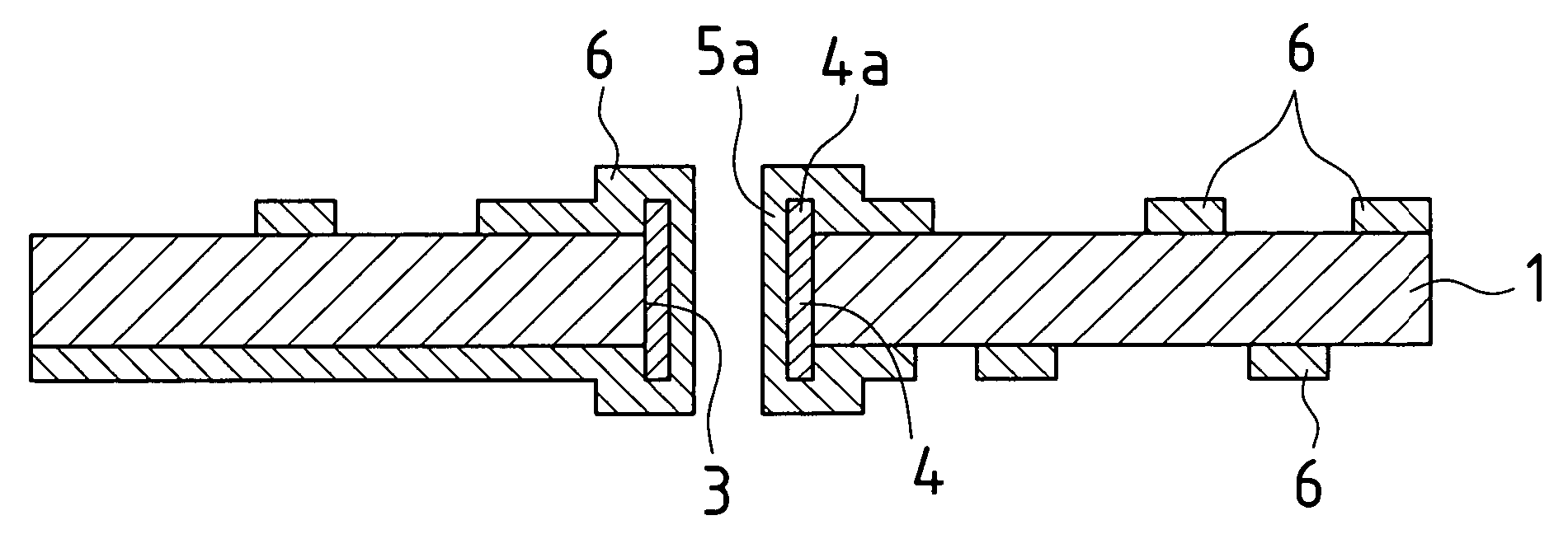

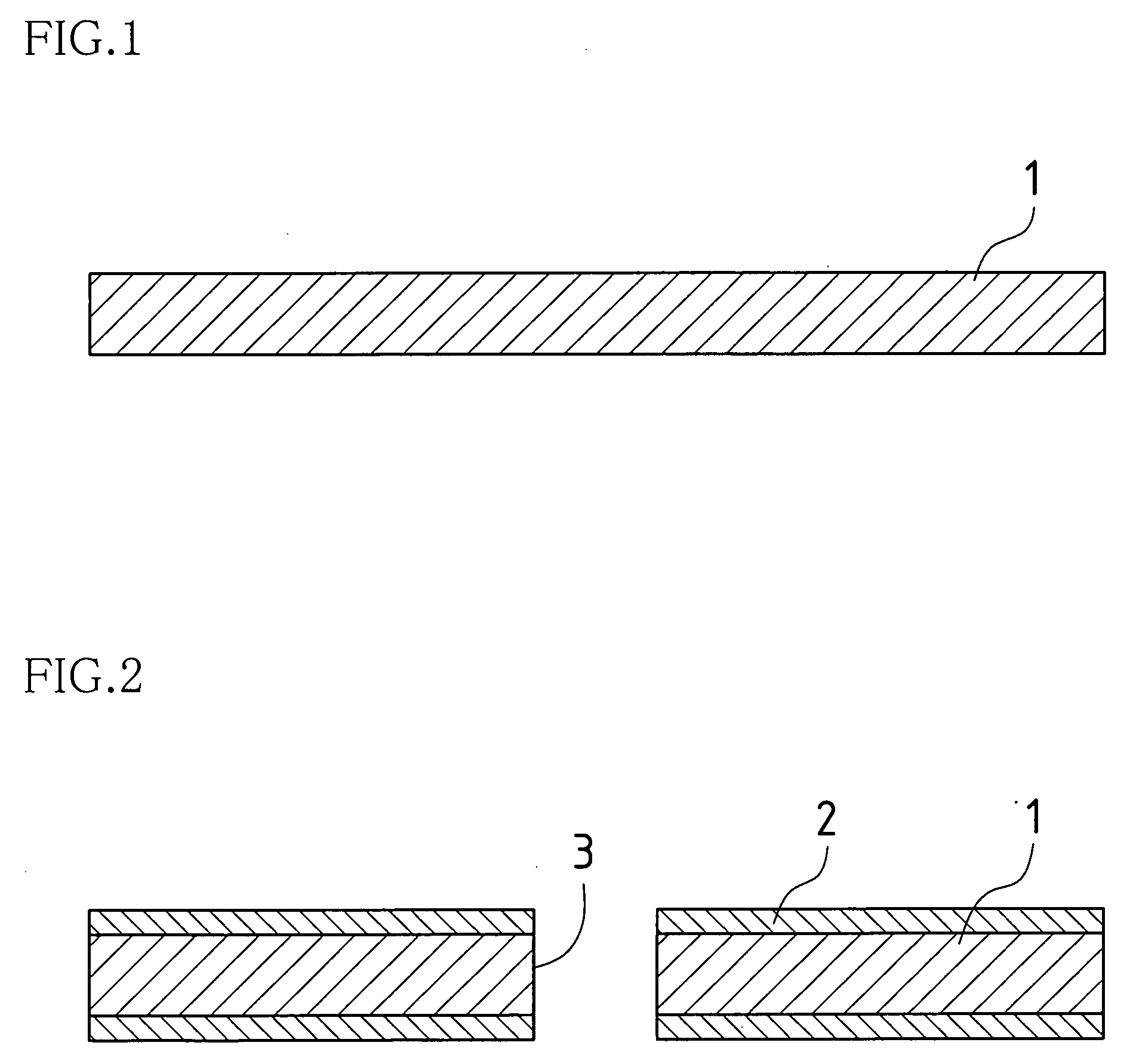

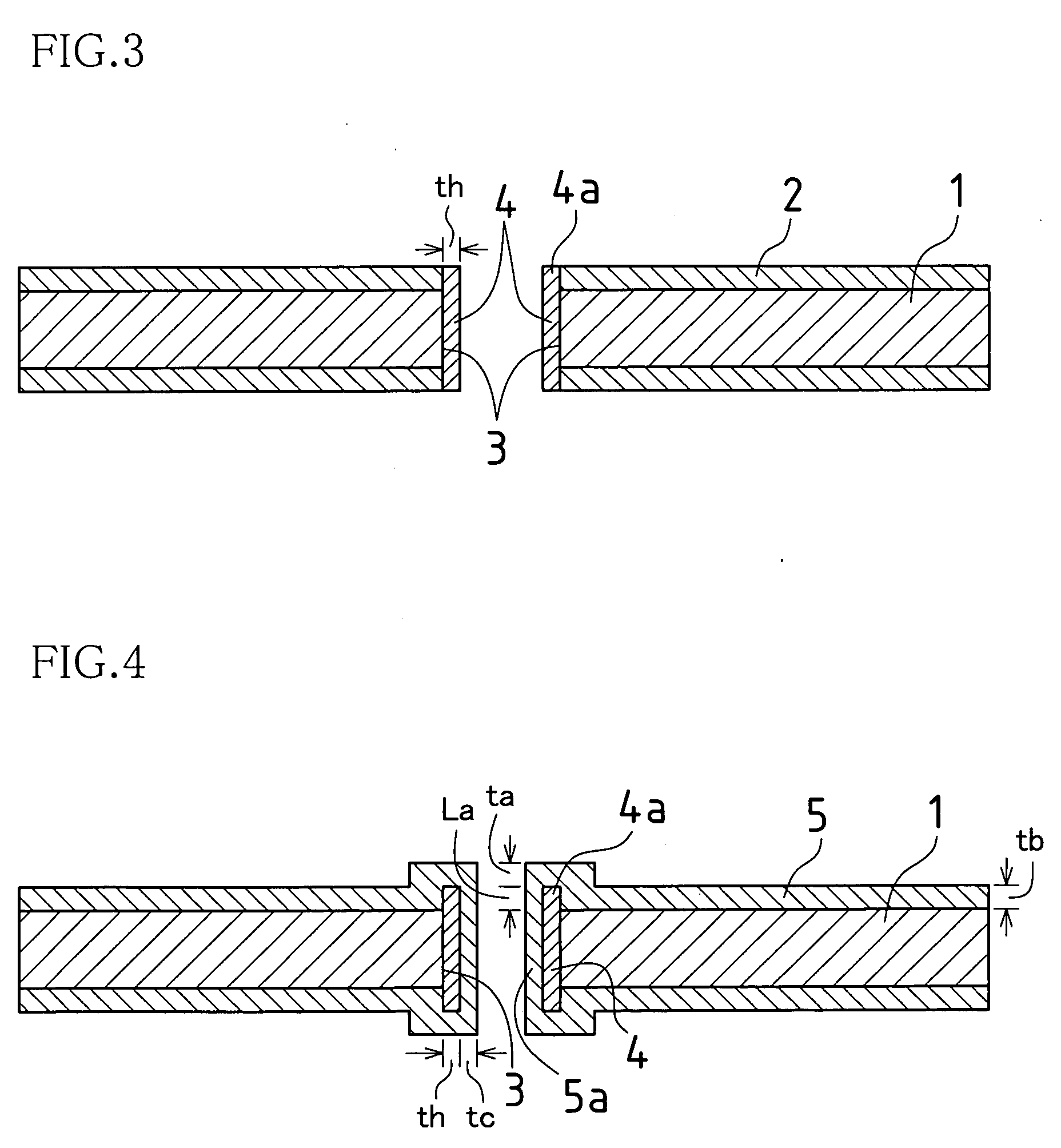

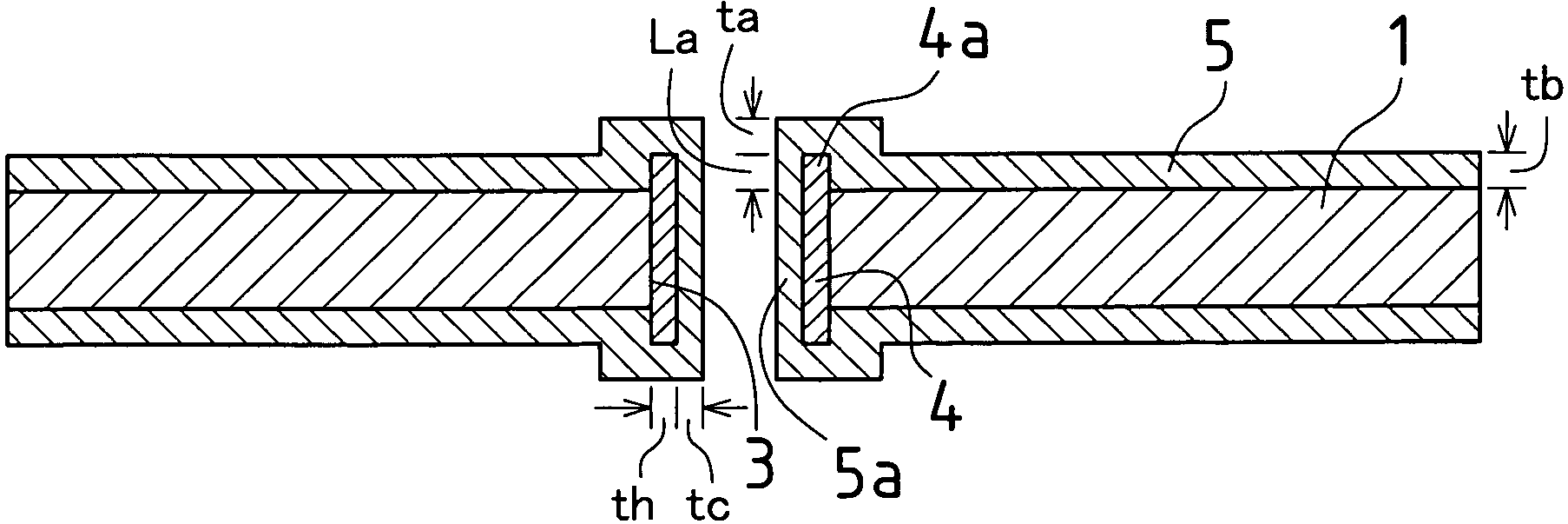

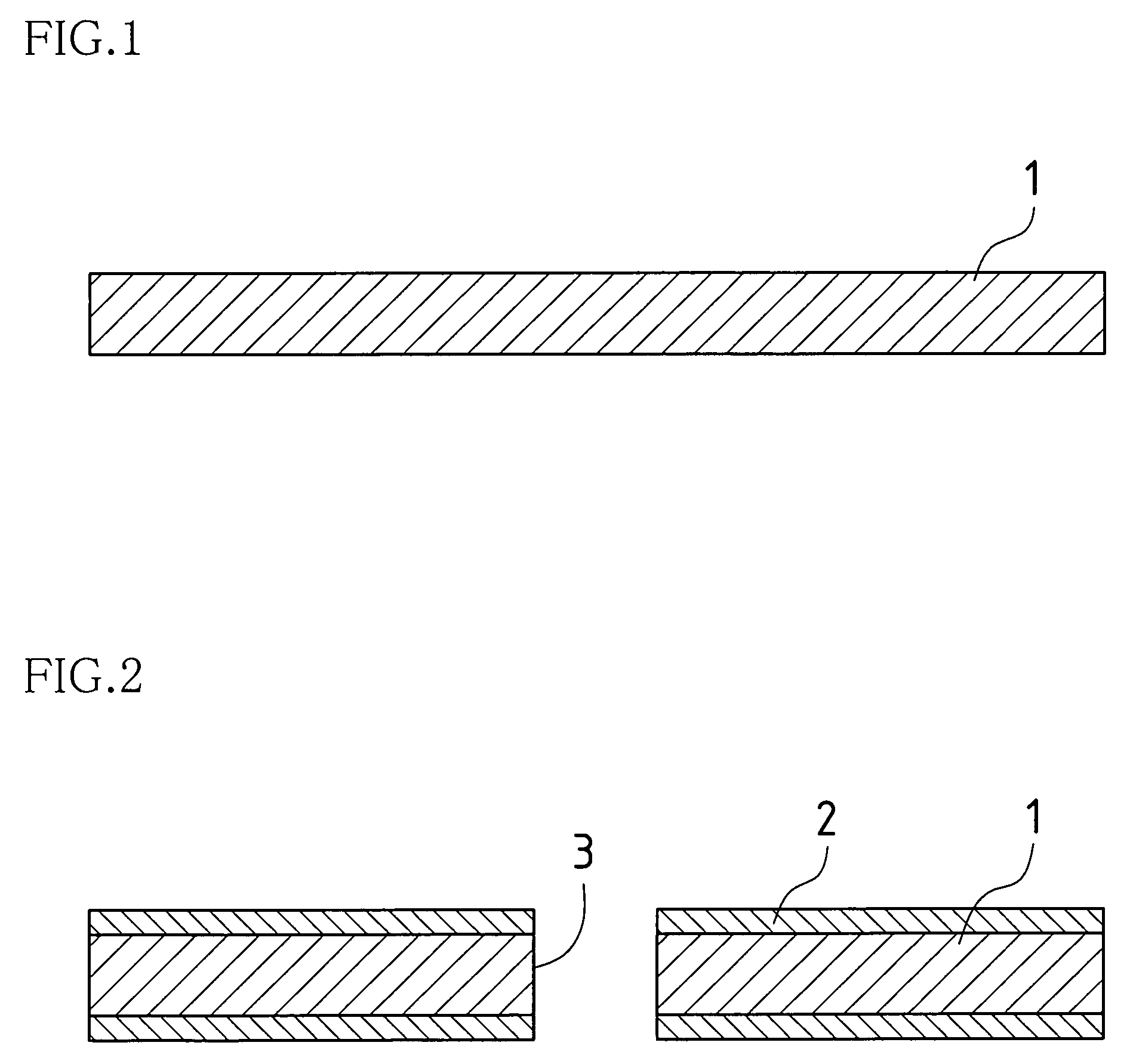

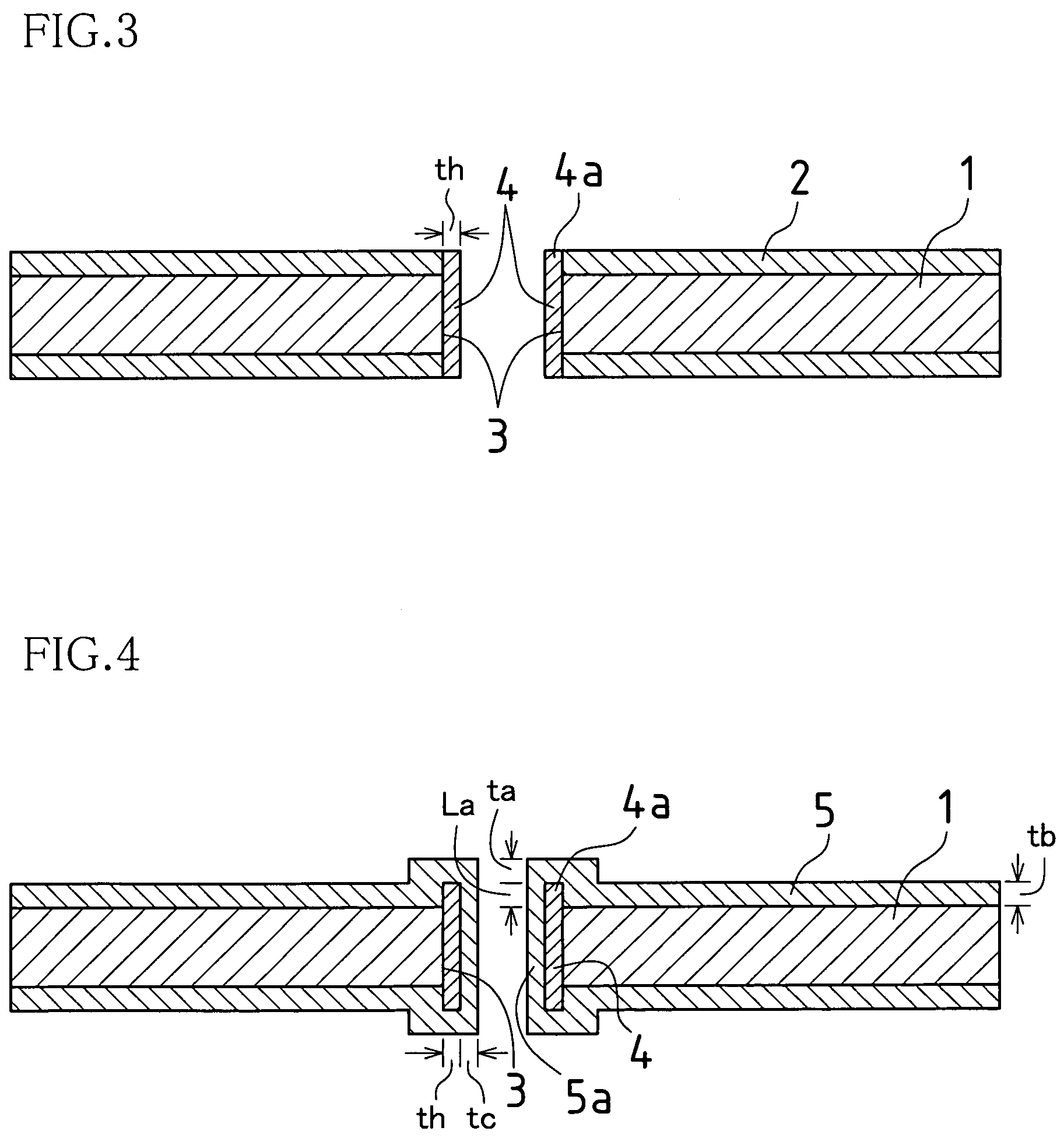

Method for producing multilayer printed wiring board, multilayer printed wiring board, and electronic device

InactiveUS20060086535A1Improve reliabilityReliable through-hole conductorPrinted circuit assemblingPrinted circuit aspectsResistElectrical conductor

A plating resist film 2 is formed on a wiring board substrate 1 as a core material of a multilayer printed wiring board, then a through-hole 3 is formed, and through-hole conductor 4 is formed along the wall surface of the through-hole 3 and the through-hole surface of the plating resist film 2, so that protrusion portion 4a is formed in the through-hole conductor 4. The plating resist film 2 is then stripped off and a panel plating layer 5 is formed on the surface of the wiring board substrate 1 and the through-hole conductor 4 so that the through-hole 4 and the panel plating layer 5 are connected with the protrusion 4a coated, and thus the connection area can be increased.

Owner:SHARP KK

Organic light-emitting panel, manufacturing method thereof, and organic display device

ActiveUS8901546B2Improve featuresHigh concentrationAfter-treatment detailsDischarge tube luminescnet screensDisplay deviceEngineering

Owner:JOLED INC

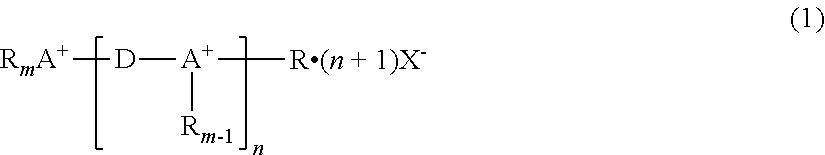

Organic electroluminiscent display and method for preparing the same, and display device

ActiveUS9614189B2Difficult can be rolledReduce transmittanceSolid-state devicesSemiconductor/solid-state device manufacturingPhase differenceTransmittance

Owner:BOE TECH GRP CO LTD

Photosensitive resin composition, and pattern formation method using the same

ActiveUS8288078B2Large film thicknessIncrease heightPhotosensitive materialsPhotosensitive material processingResistImage resolution

A photosensitive resin composition is provided that is highly safe, provides a coating film having superior uniformity, can improve the curing density of the cured resin pattern, and is capable of forming a micro resist pattern having a large film thickness and a high aspect ratio with high sensitivity and high resolving ability. According to a photosensitive resin composition including, in addition to an onium fluorinated alkyl fluorophosphate based cation polymerization initiator having a specific structure, a specified solvent or a specified sensitizing agent as essential components, a coating film having superior uniformity, can improve the curing density of the cured resin pattern, and also is capable of forming a micro resist pattern having a large film thickness and a high aspect ratio with high sensitivity and high resolving ability.

Owner:TOKYO OHKA KOGYO CO LTD

Method for producing multilayer printed wiring board, multilayer printed wiring board, and electronic device

InactiveUS7240431B2Reliable through-hole conductorSmall line widthPrinted circuit assemblingPrinted circuit aspectsResistElectrical conductor

A plating resist film 2 is formed on a wiring board substrate 1 as a core material of a multilayer printed wiring board, then a through-hole 3 is formed, and through-hole conductor 4 is formed along the wall surface of the through-hole 3 and the through-hole surface of the plating resist film 2, so that protrusion portion 4a is formed in the through-hole conductor 4. The plating resist film 2 is then stripped off and a panel plating layer 5 is formed on the surface of the wiring board substrate 1 and the through-hole conductor 4 so that the through-hole 4 and the panel plating layer 5 are connected with the protrusion 4a coated, and thus the connection area can be increased.

Owner:SHARP KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com