Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

73results about How to "Improve operating profit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

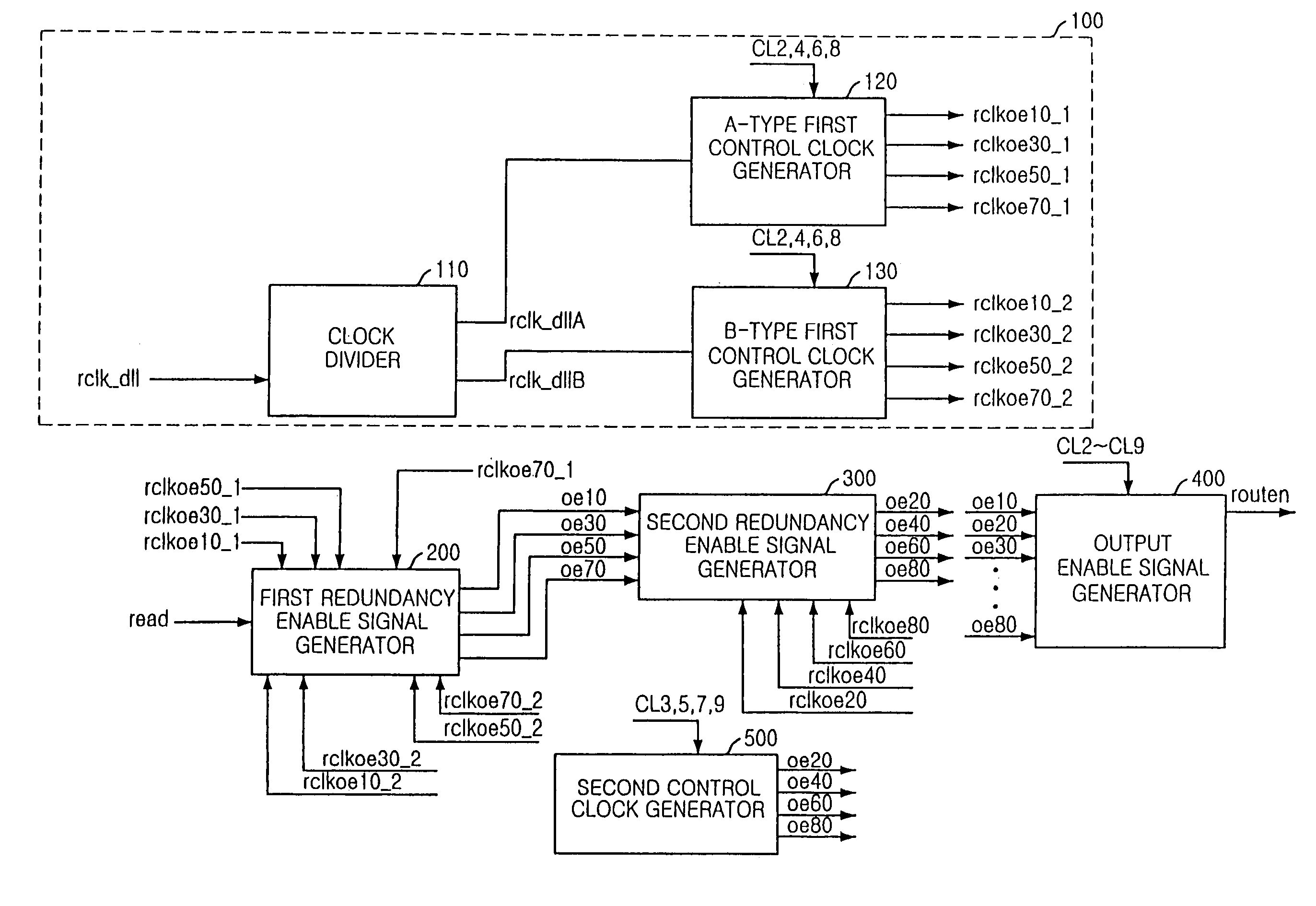

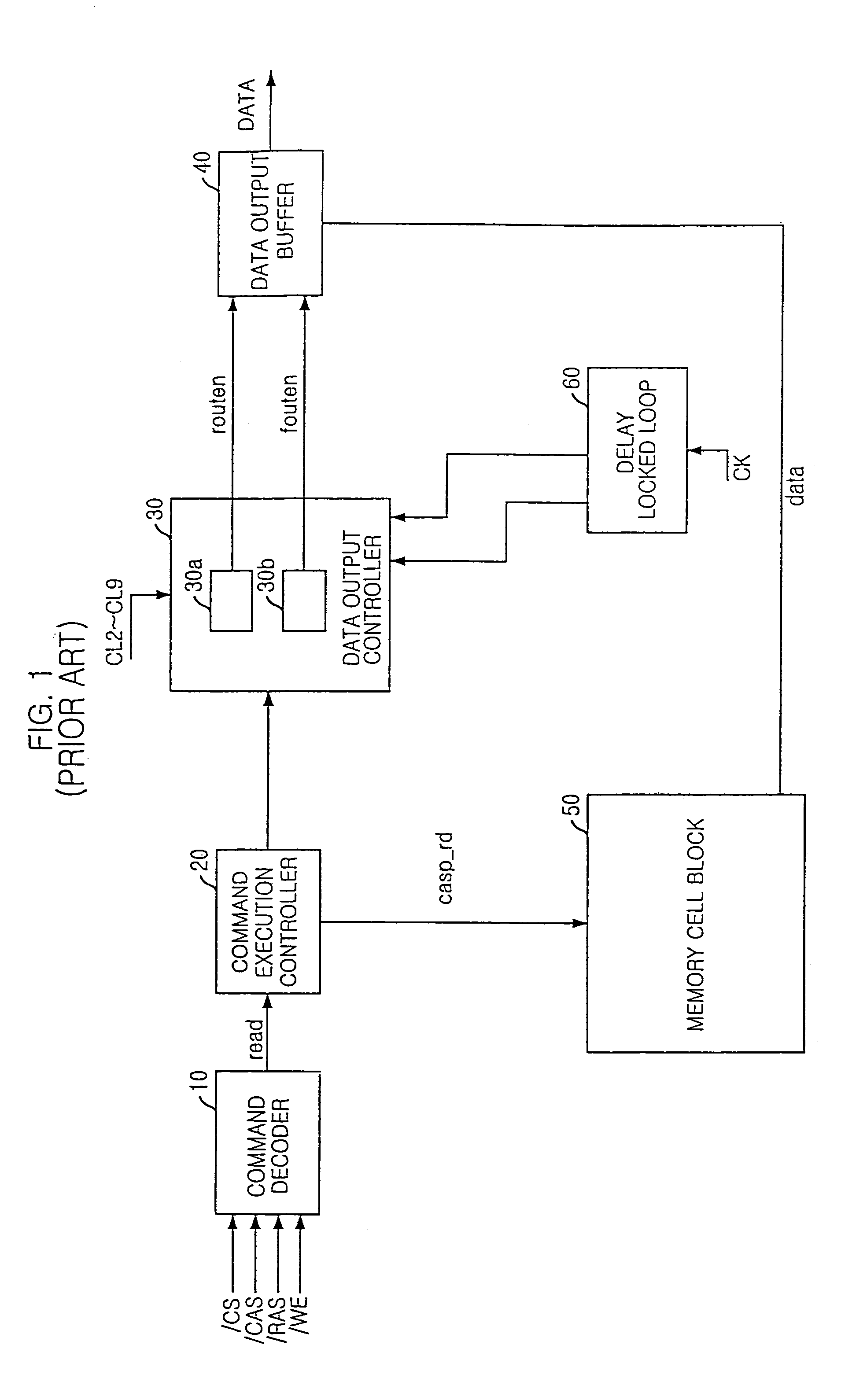

Memory device with improved output operation margin

InactiveUS6987705B2Wide-ranging CAS latency modeGuaranteed uptimeDigital storageSignal generatorClock generator

A synchronous memory device which generates a data output enable signal corresponding to a set CAS latency mode including: a control clock generator for generating an A-type first control clock and a B-type first control clock; a first redundancy enable signal generator for shifting an internal read signal by a predetermined interval in synchronization with one of the A-type first control clock and the B-type first control clock and generating a plurality of first redundancy enable signals; a second redundancy enable signal generator for synchronizing the plurality of first redundancy enable signals with a DLL clock and generating a plurality of second redundancy enable signals; and an output enable signal generator for selecting one redundancy enable signal corresponding to the set CAS latency mode among the first redundancy enable signals and the second redundancy enable signals and generating the selected redundancy enable signal as the data output enable signal.

Owner:SK HYNIX INC

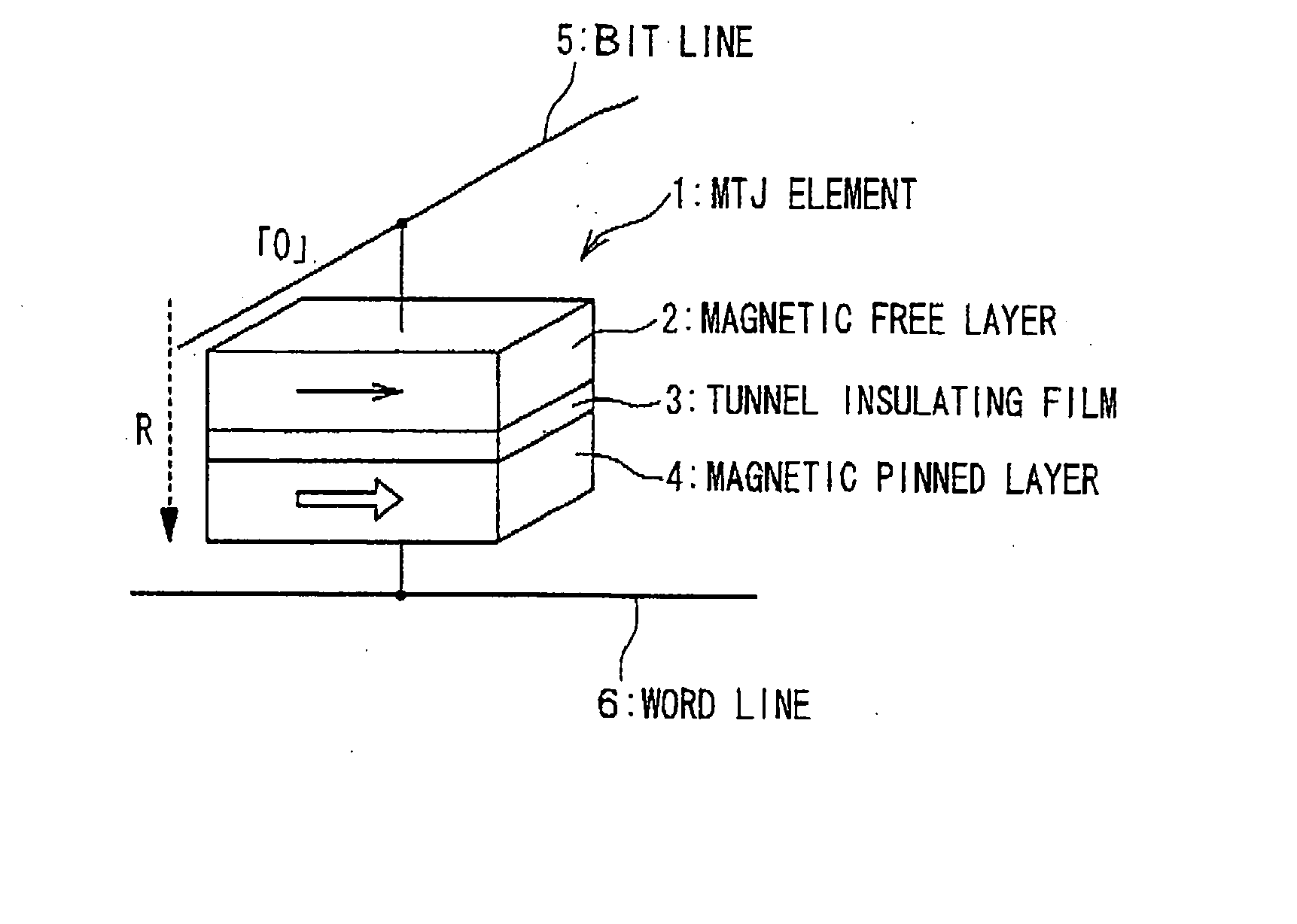

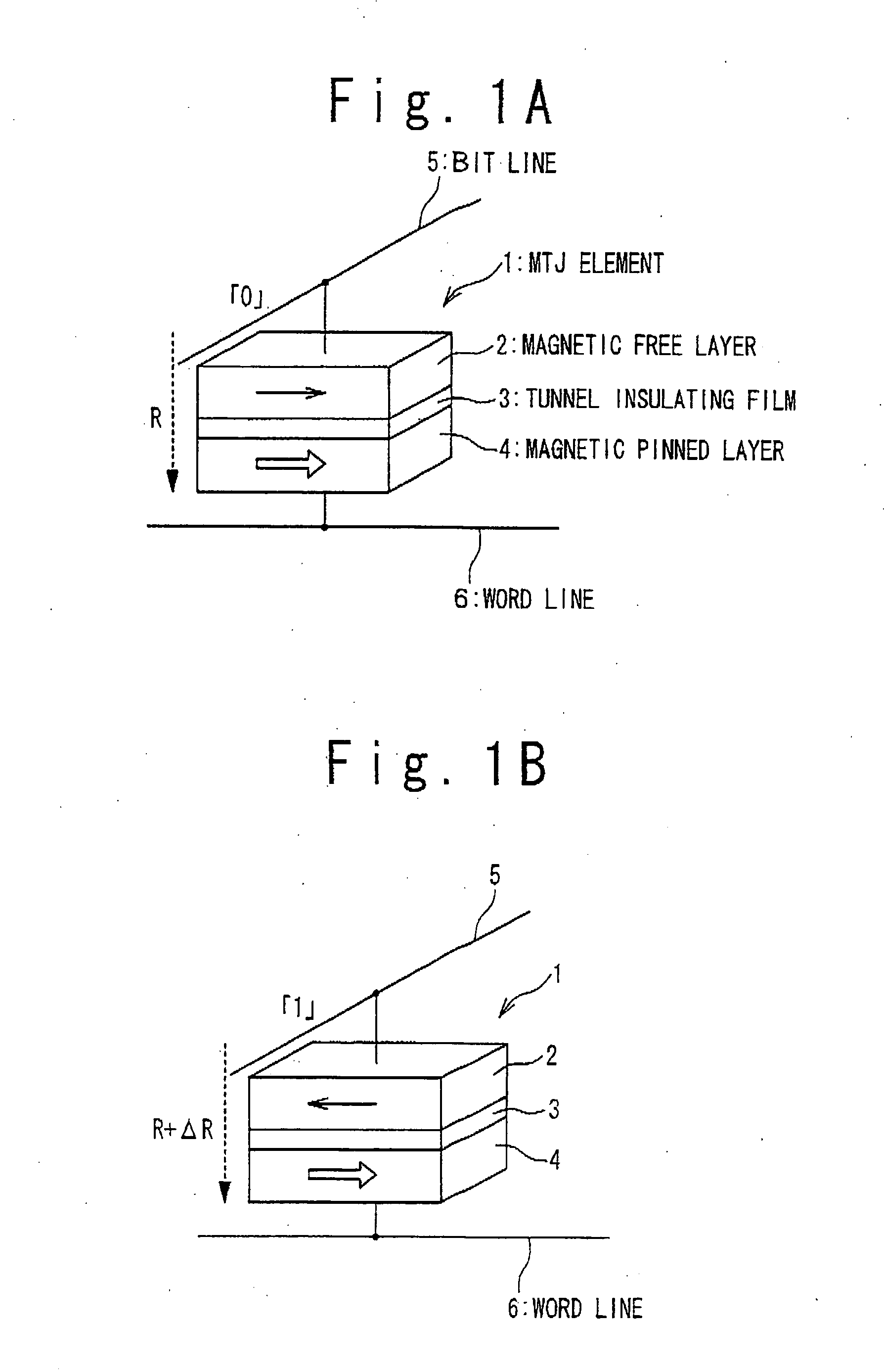

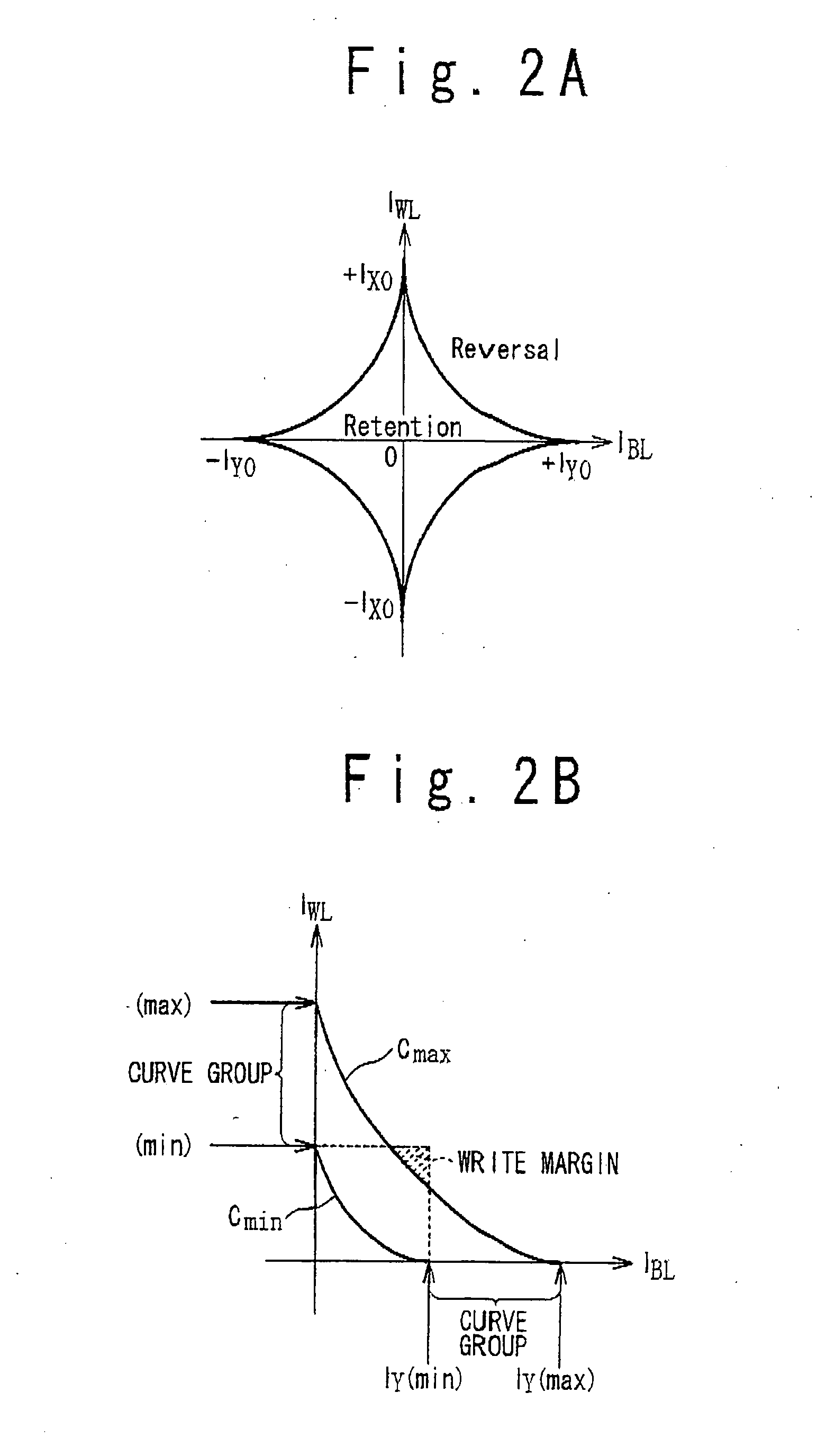

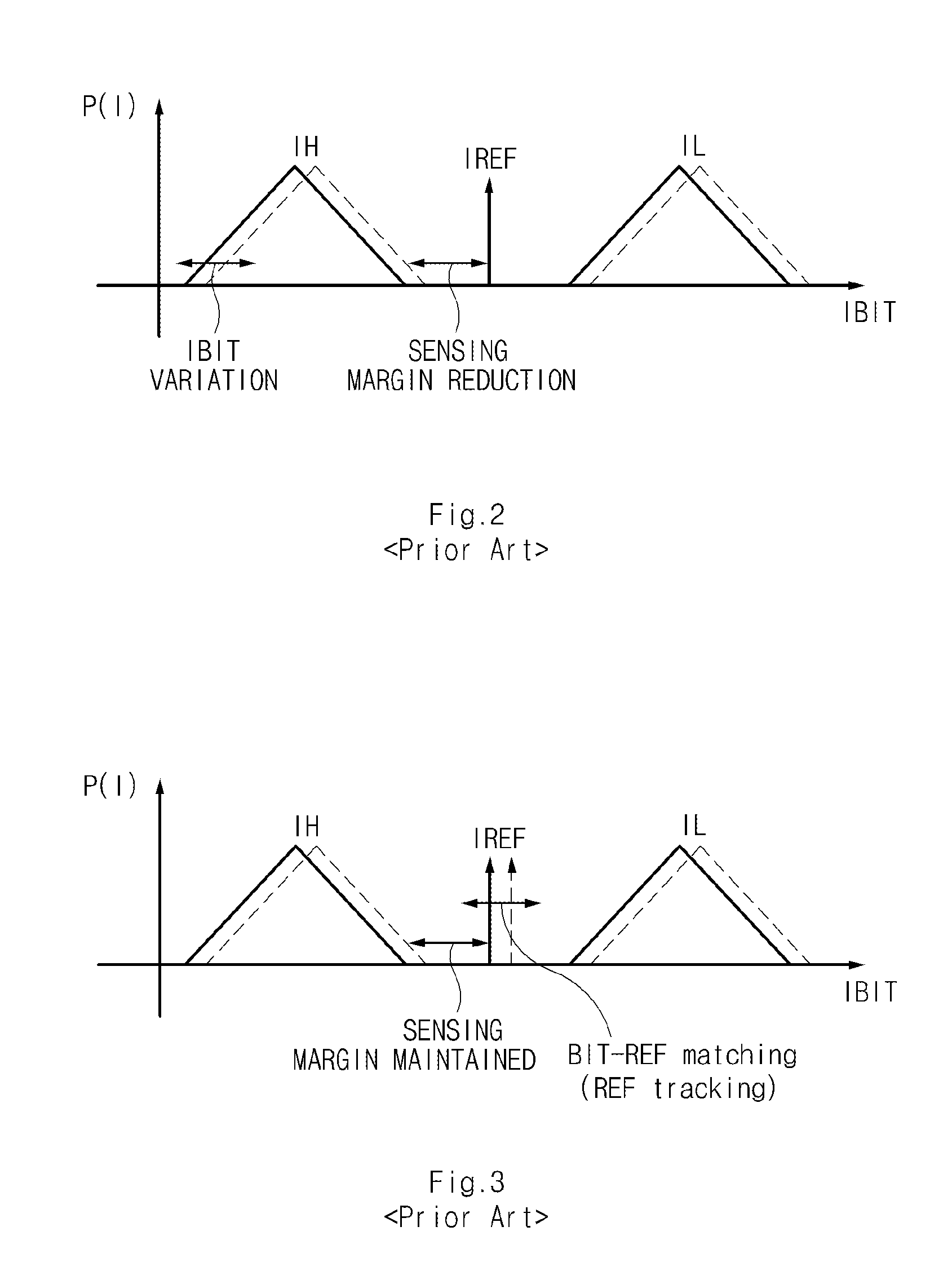

Ferromagnetic Film, Magneto-Resistance Element And Magnetic Random Access Memory

InactiveUS20080008908A1Reduce variationImprove operating profitNanomagnetismSynthetic resin layered productsElectrical resistance and conductanceRandom access memory

A ferromagnetic film according to the present invention includes ferromagnetic element and nonmagnetic element and has a first portion and a second portion. Concentration of the nonmagnetic element in the first portion is lower than an average concentration of the nonmagnetic element in the ferromagnetic film. On the other hand, concentration of the nonmagnetic element in the second portion is higher than the average concentration of the nonmagnetic element in the ferromagnetic film. The nonmagnetic element includes at least one element selected from the group consisting of Zr, Ti, Nb, Ta, Hf, Mo and W. The ferromagnetic film is applied to a magnetic free layer of a magneto-resistance element in an MRAM.

Owner:NEC CORP +1

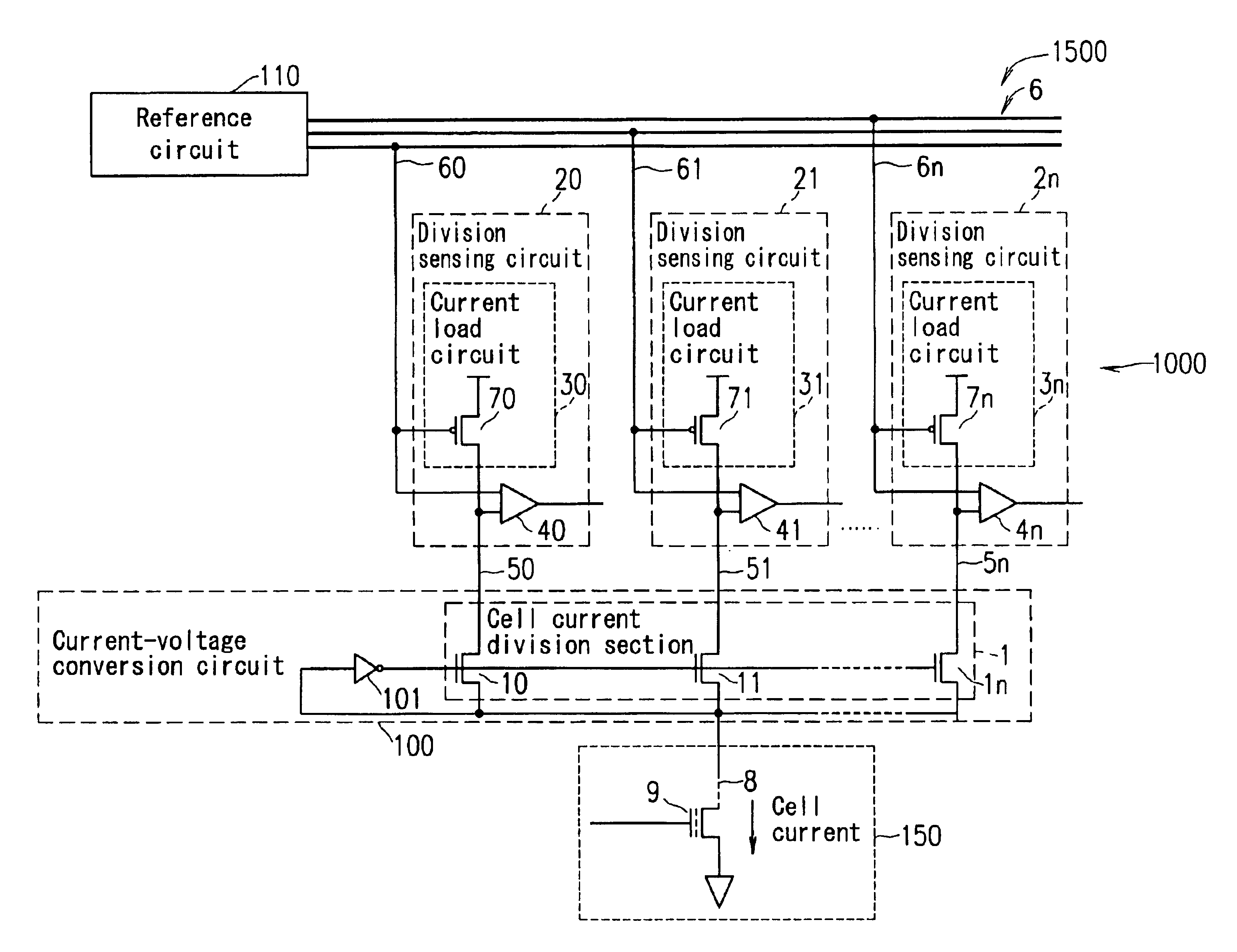

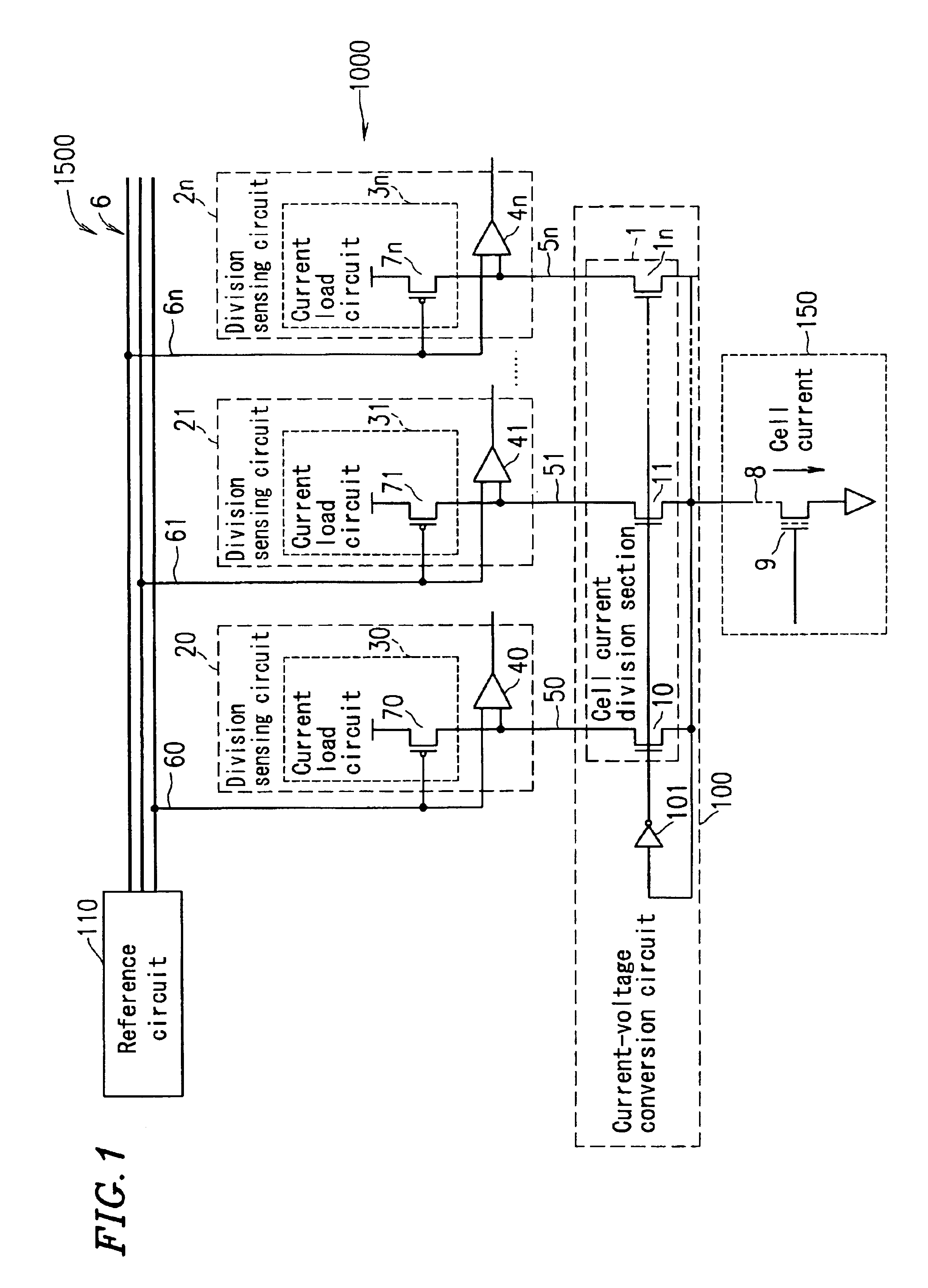

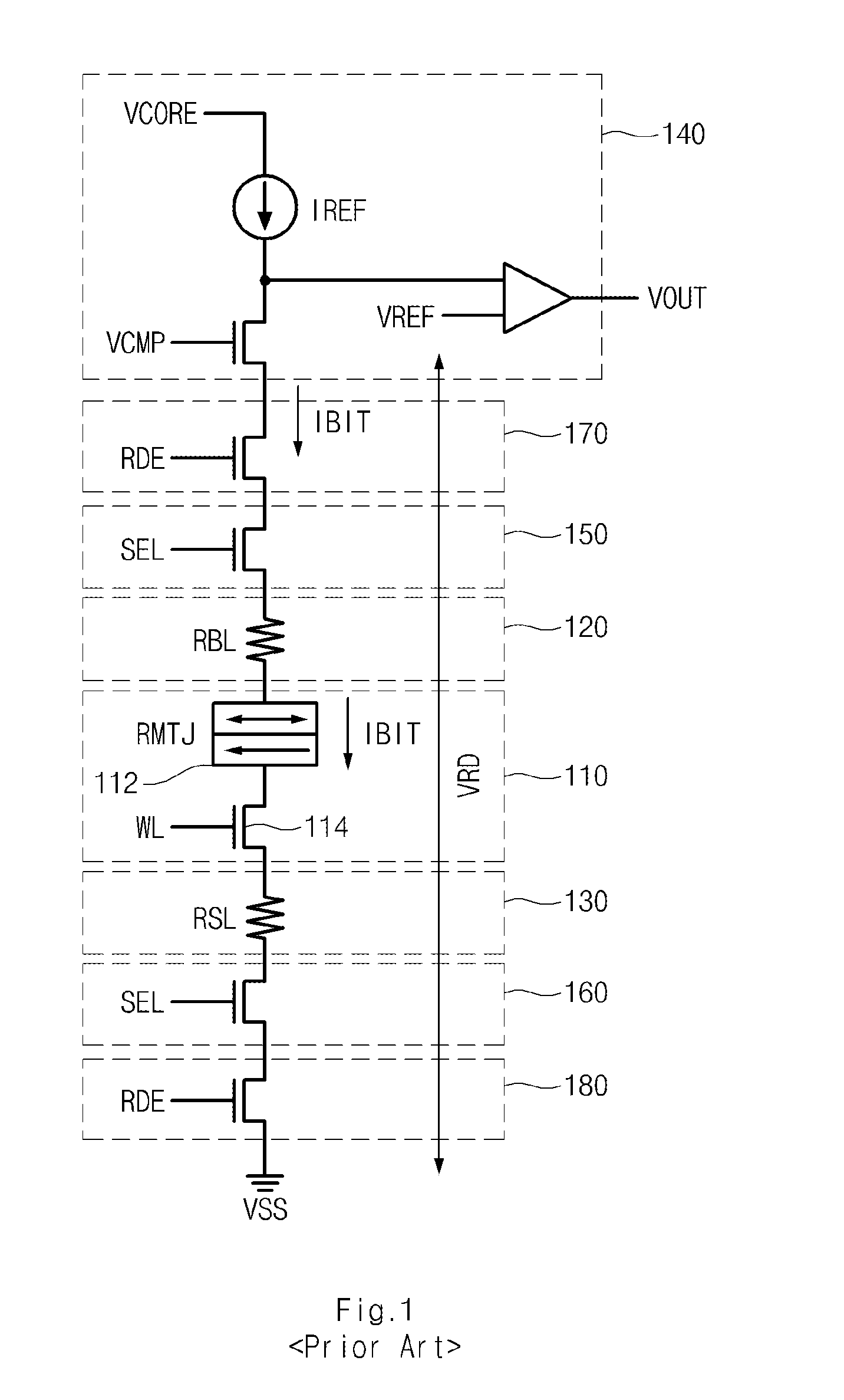

Reading circuit, reference circuit, and semiconductor memory device

ActiveUS6930922B2Easy to getEnlarging reading operation marginRead-only memoriesDigital storageCurrent loadPotential difference

A reading circuit, for reading data from one memory cell of a plurality of memory cells, includes a plurality of division sensing circuits each connected to the one memory cell via a sensing line corresponding thereto among a plurality of sensing lines; and a current-voltage conversion circuit for converting a current flowing through each sensing line into a sensing voltage representing a potential of the corresponding sensing line. Each division sensing circuit includes a current load circuit for supplying a current to the one memory cell via a corresponding sensing line, and a sense amplifier for sensing a potential difference between the corresponding sensing line and a corresponding reference line of a plurality of reference lines. The current load circuit included in at least one division sensing circuit has a current supply capability different from that of the current load circuit included in another division sensing circuits.

Owner:SAMSUNG ELECTRONICS CO LTD

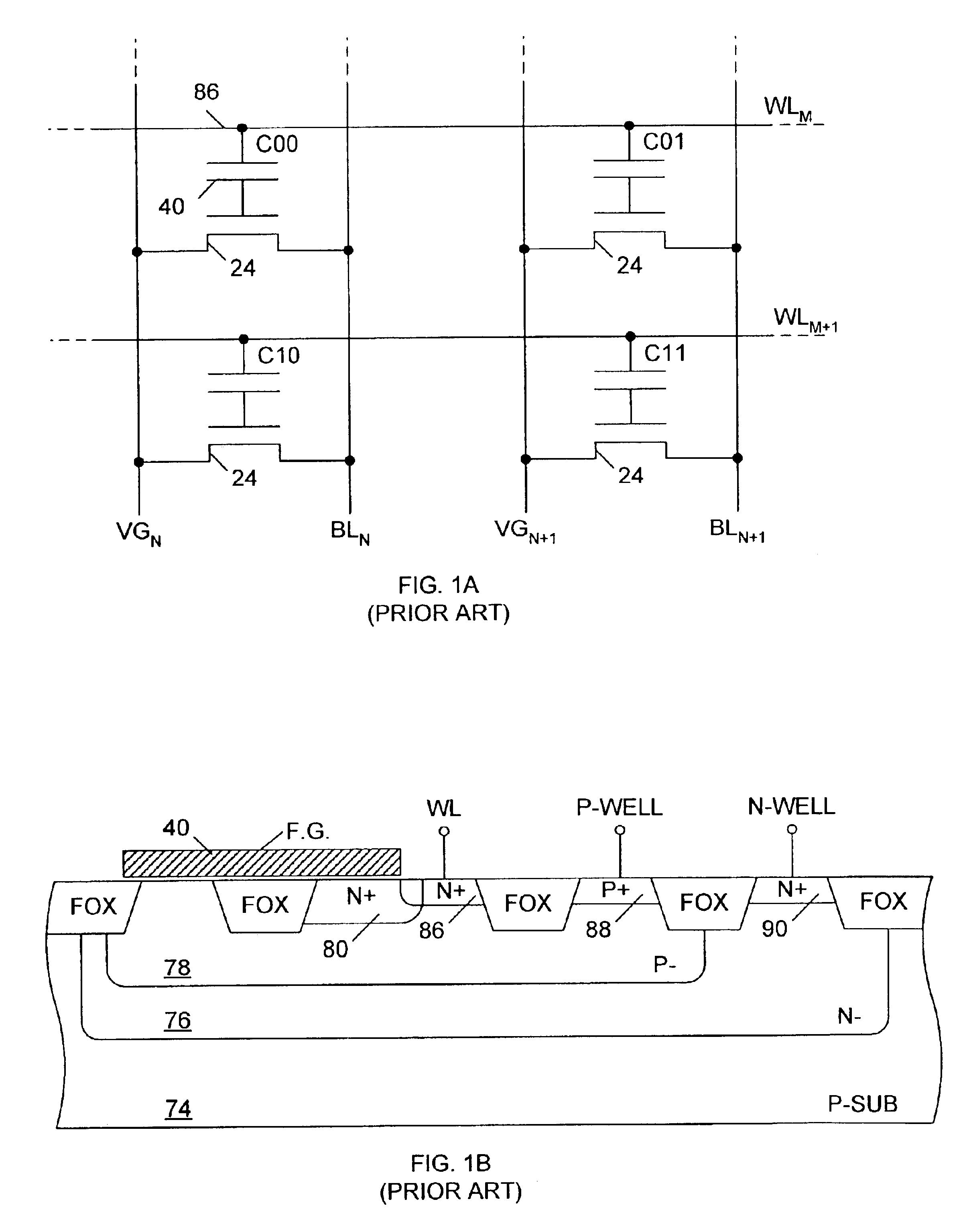

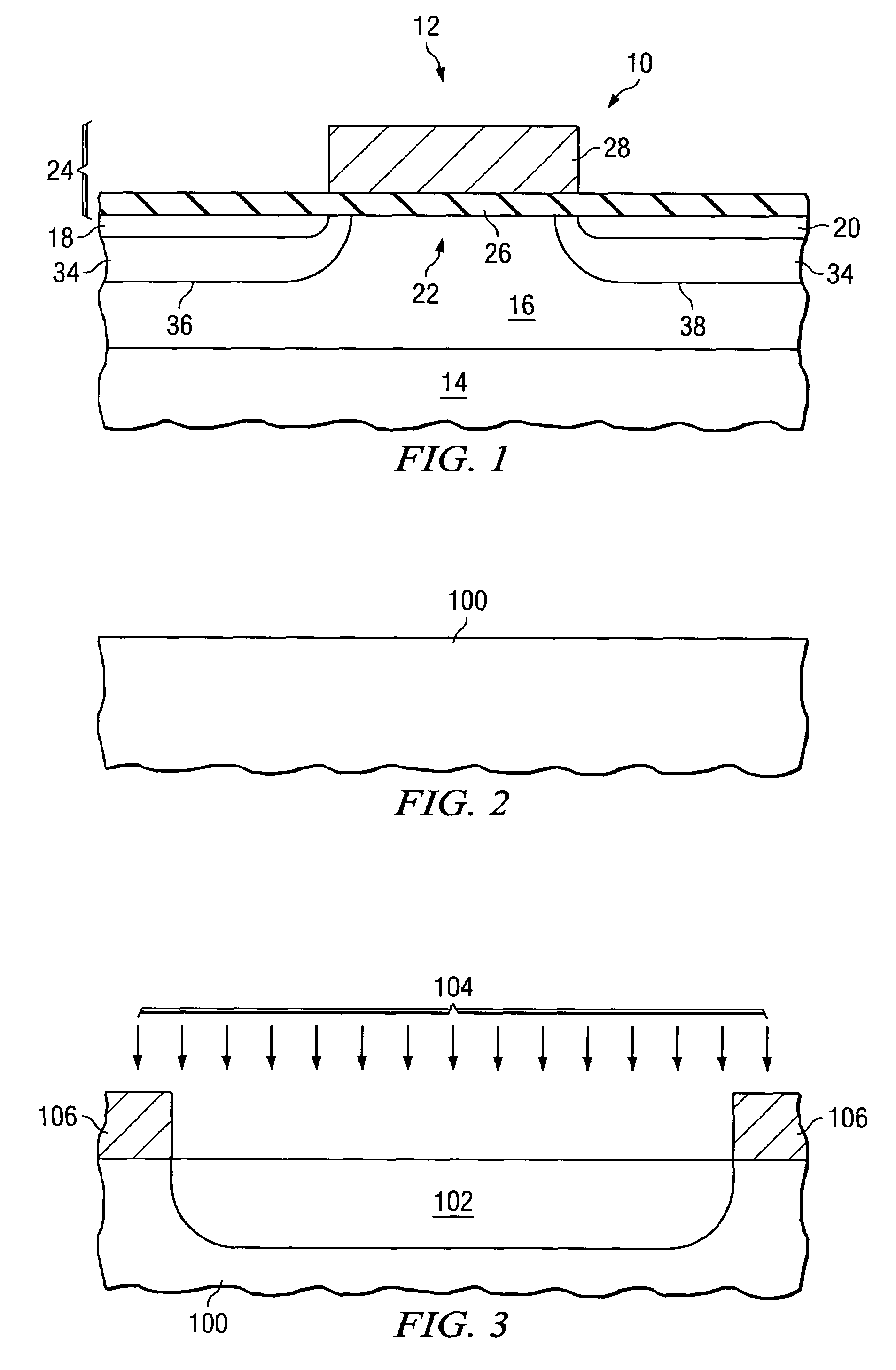

Non-volatile memory cell fabricated with slight modification to a conventional logic process and methods of operating same

InactiveUS6841821B2Enhance electron removal operationEnhance operation normal readTransistorSolid-state devicesEngineeringDielectric layer

A non-volatile memory cell is fabricated using a conventional logic process, with minor modifications. The cell is fabricated by forming a shallow trench isolation (STI) region in a well region of a semiconductor substrate. A recessed region is formed in the STI region, wherein the recessed region extends into the STI region and exposes a sidewall region in the well region. A capacitor region is formed in the sidewall region. A dielectric layer is formed over the well region, including the sidewall region. A gate electrode is then formed over the dielectric layer, wherein a portion of the gate electrode extends into the recessed region. An access transistor of the cell is then formed in a self-aligned manner with respect to the gate electrode. A capacitor structure is formed by the gate electrode (in the recessed region), the dielectric layer on the sidewall region, and the capacitor region.

Owner:MOSYS INC

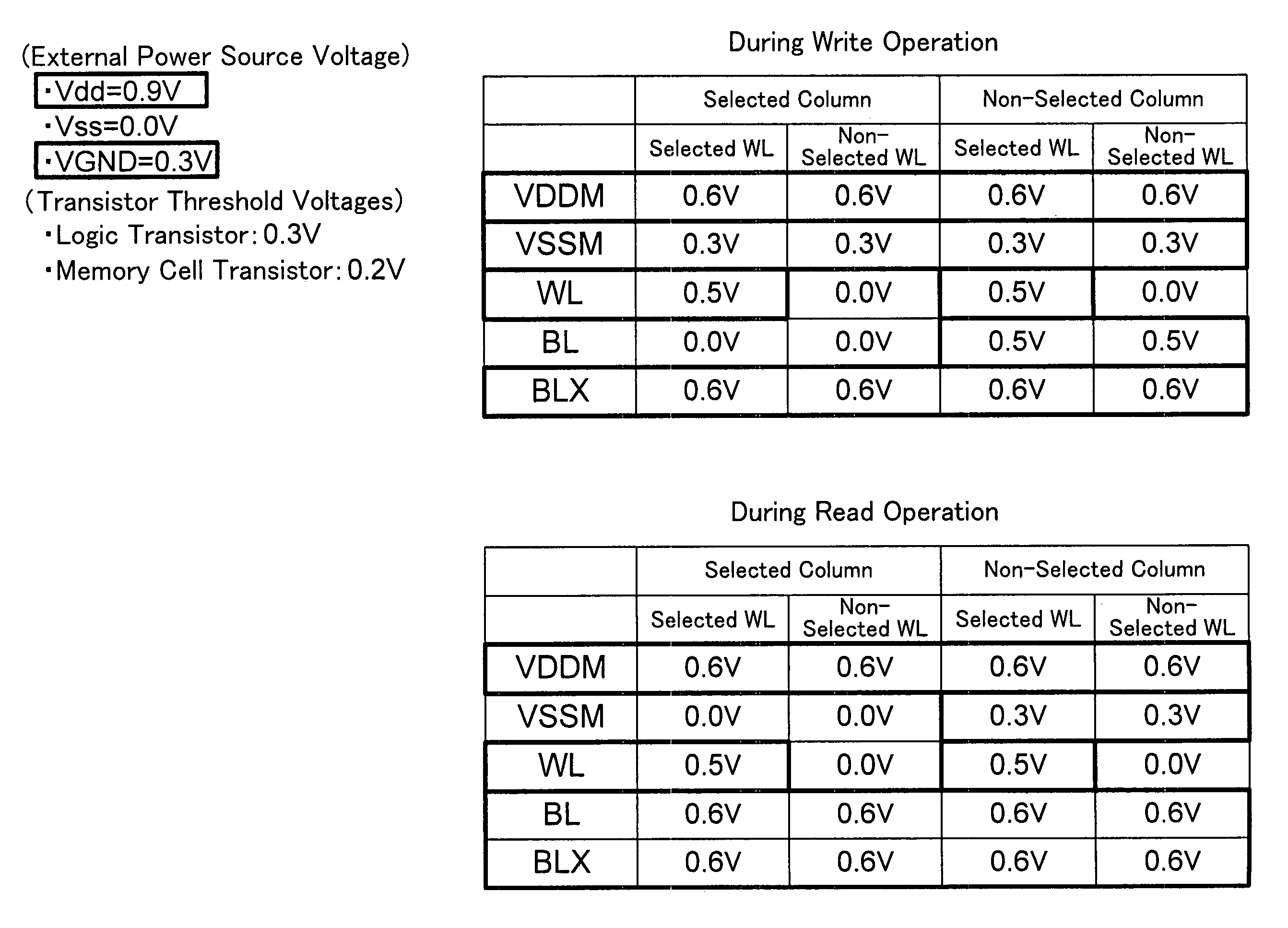

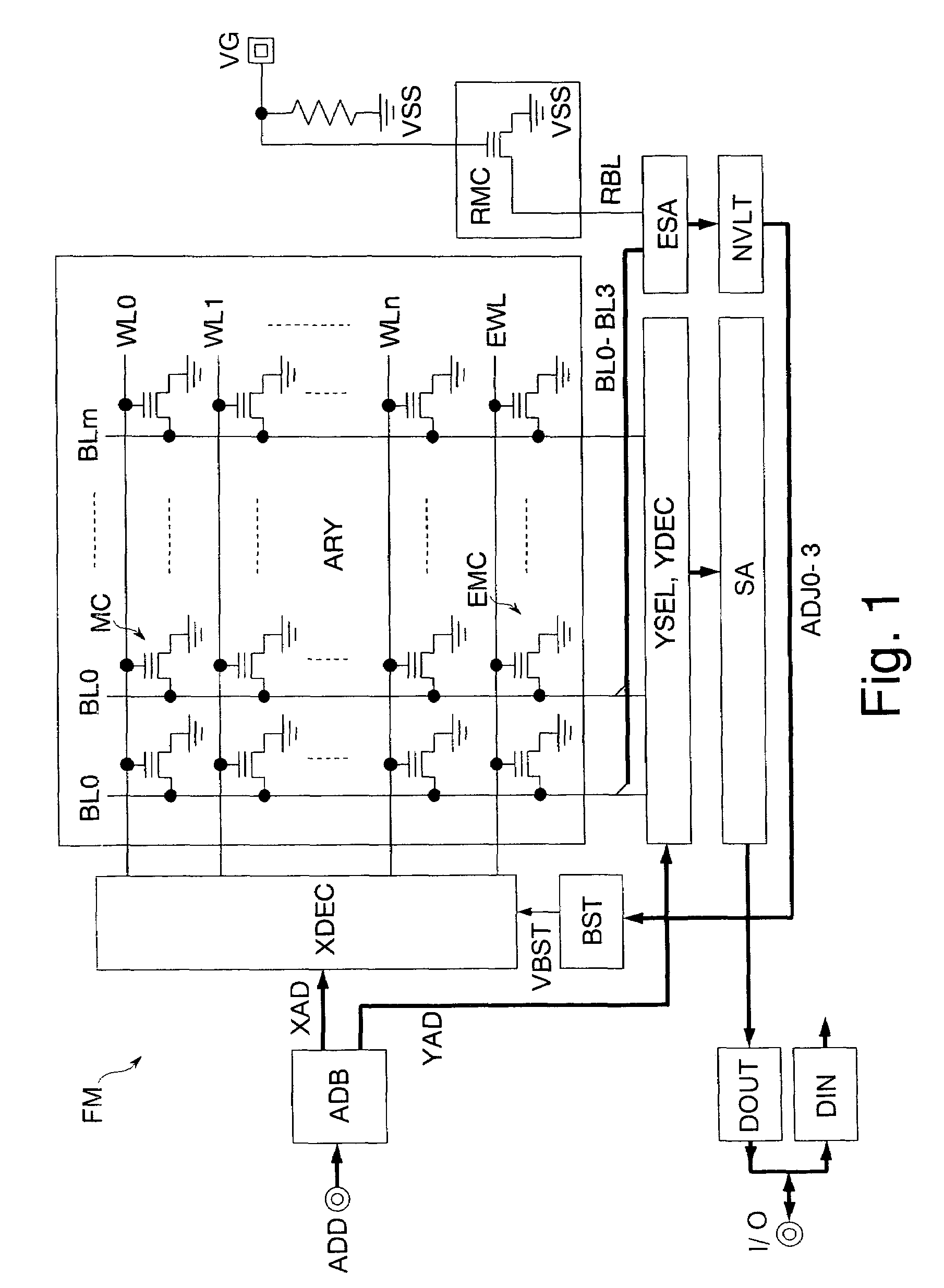

Semiconductor memory device

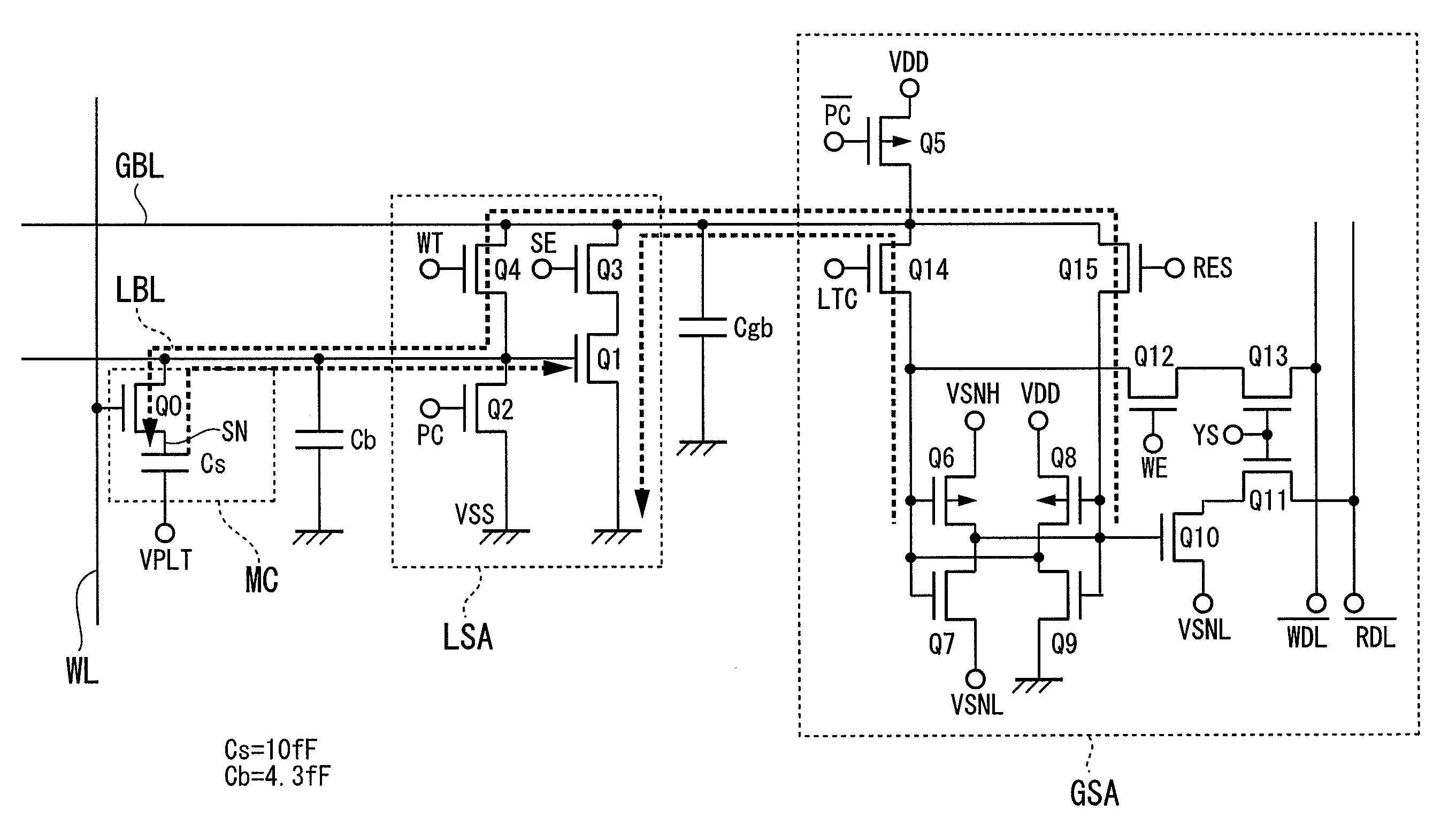

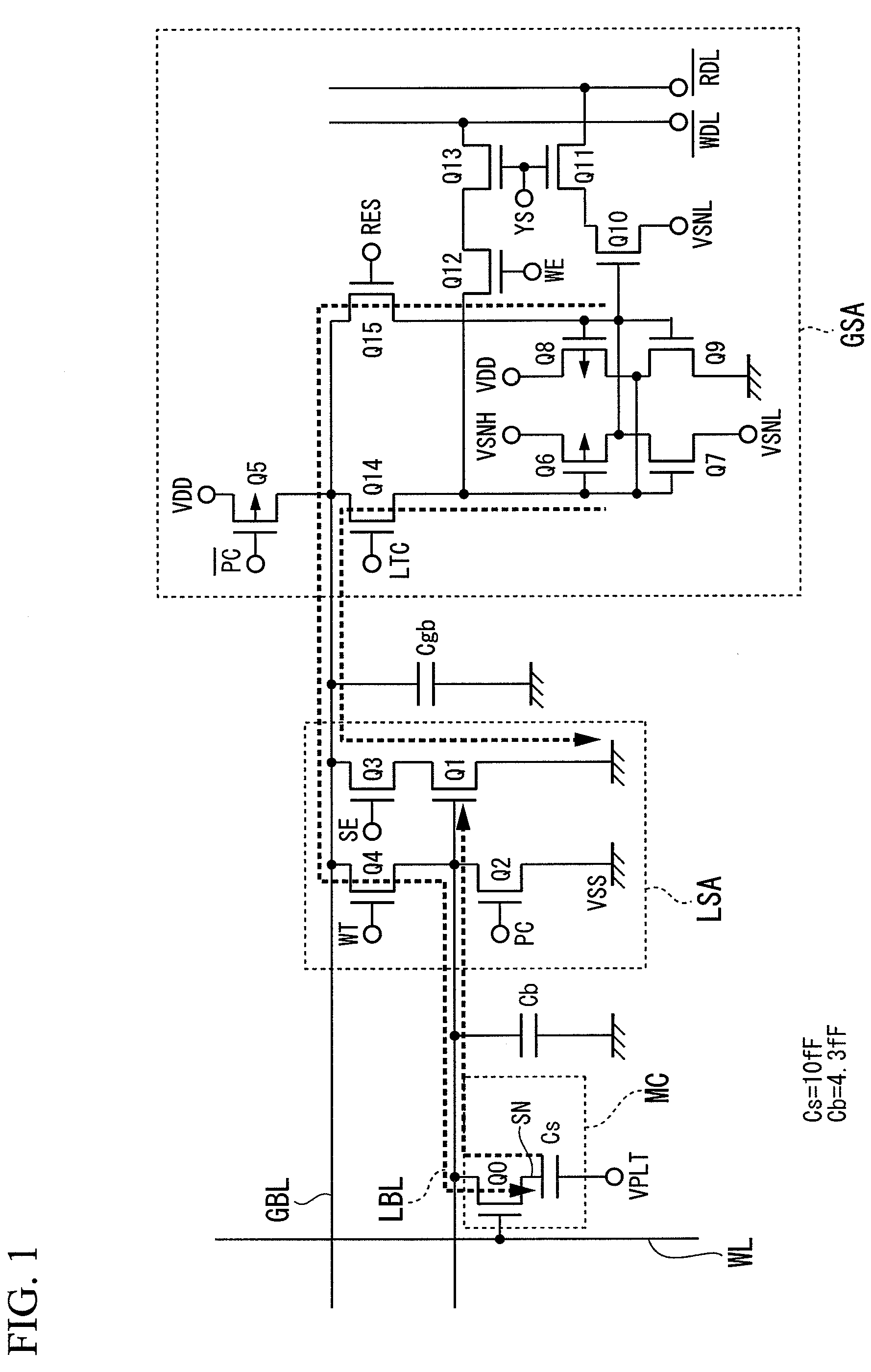

InactiveUS20090251948A1Improve operating profitStabilizing sense amplification.Digital storageBit lineAudio power amplifier

In a semiconductor memory device, a memory cell is connected with a local sense amplifier and a global sense amplifier via a local bit line and a global bit line. The local sense amplifier is a single-ended sense amplifier including a single MOS transistor, which detects a potential of the local bit line which varies when reading and writing data with the memory cell. The threshold voltage of the MOS transistor is monitored so as to produce a high-level write voltage and a low-level write voltage, which are corrected and shifted based on the monitoring result so as to properly perform a reload operation on the memory cell by the global local sense amplifier. Thus, it is possible to cancel out temperature-dependent variations of the threshold voltage and shifting of the threshold voltage due to dispersions of manufacturing processes.

Owner:LONGITUDE LICENSING LTD

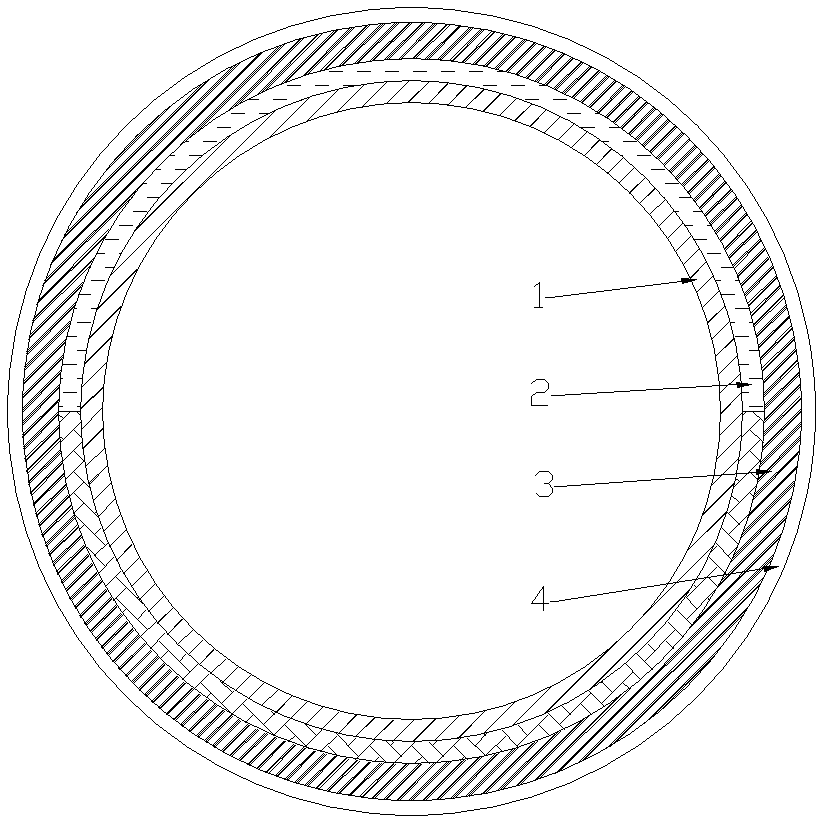

Carbon fiber composite, preparation method thereof and tank

ActiveCN103009716ALose weightHigh mechanical strengthSynthetic resin layered productsLarge containersProtection layerFilament winding

The invention discloses a carbon fiber composite. The carbon fiber composite comprises a metal inner layer, a local reinforcement layer, a reinforcement layer and an outer protection layer in sequence, wherein the reinforcement layer is formed by preferably winding large-tow carbon fibers. The invention also discloses a preparation method of the carbon fiber composite. The invention further discloses a tank prepared from the carbon fiber composite. The tank can be used for carrying liquid, powder, gases, pulp and other substances. The carbon fiber composite and the tank have the beneficial effects that compared with the traditional metal tanks, the tank prepared from the carbon fiber composite is lightened by more than 50%; the carrying capacity of a tank car can be obviously improved, and fuel consumption and carbon dioxide emission can be reduced; and the tank has the double effects of increasing the operating profits and reducing the environmental pollution.

Owner:北京蓝星清洗有限公司

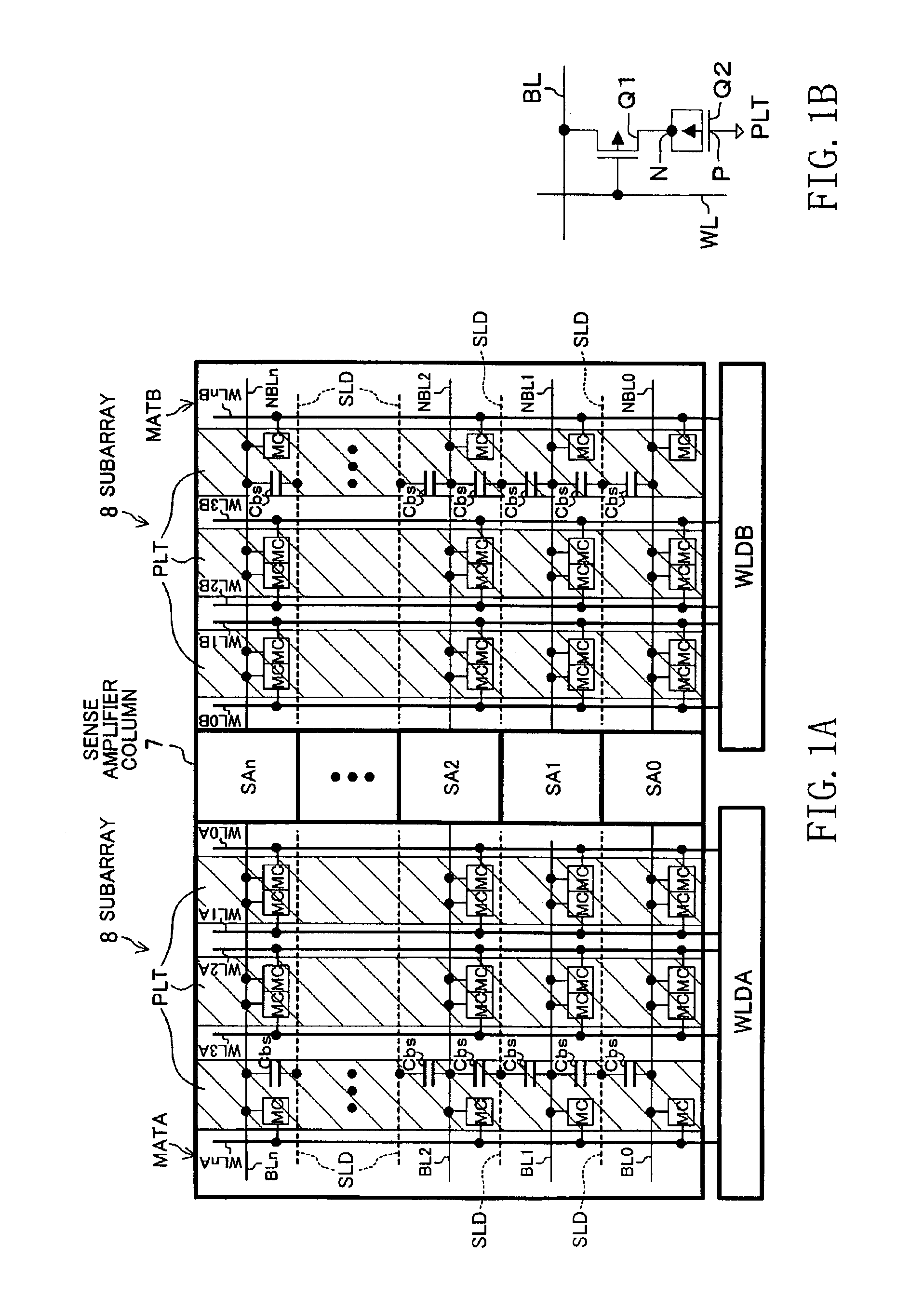

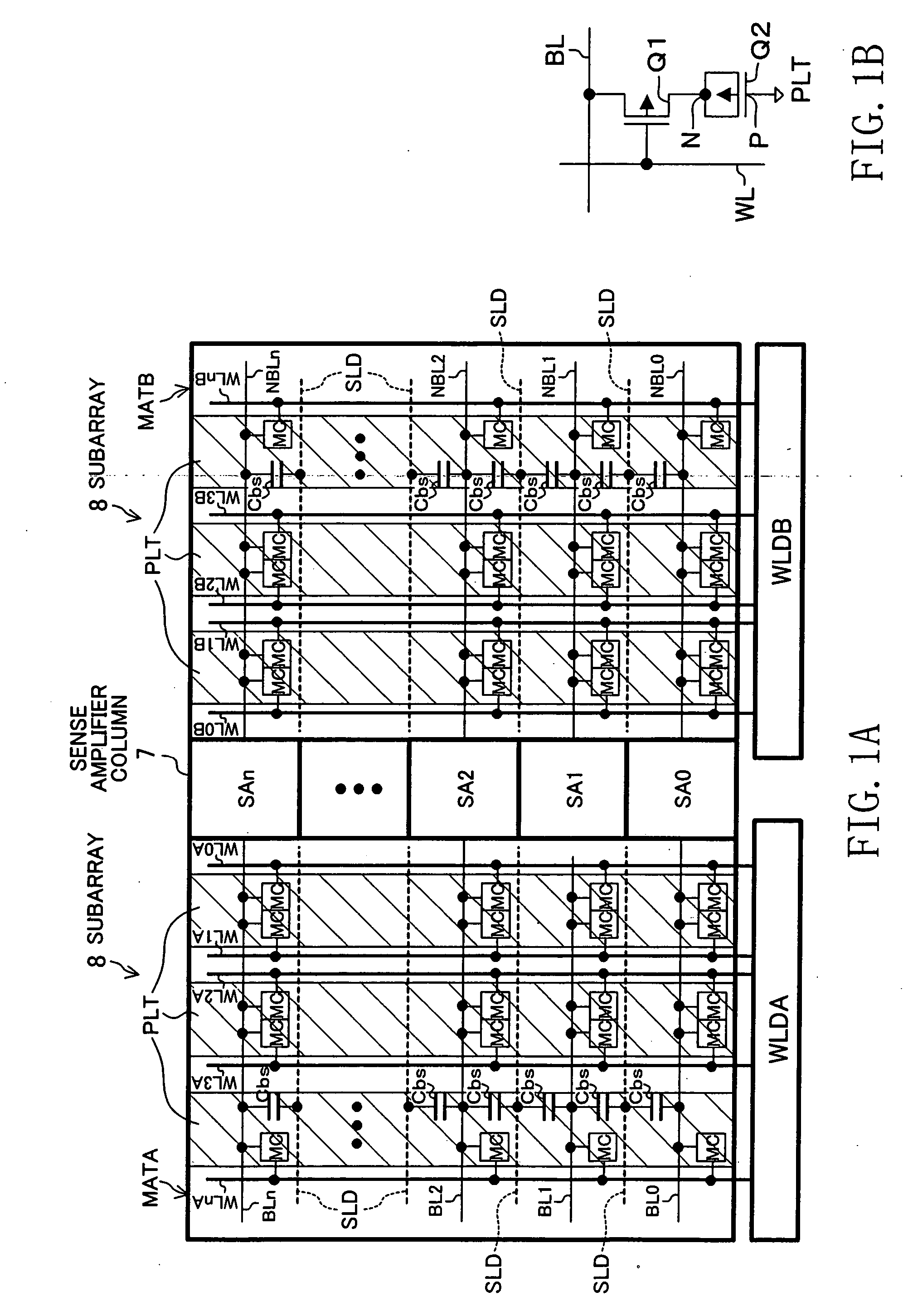

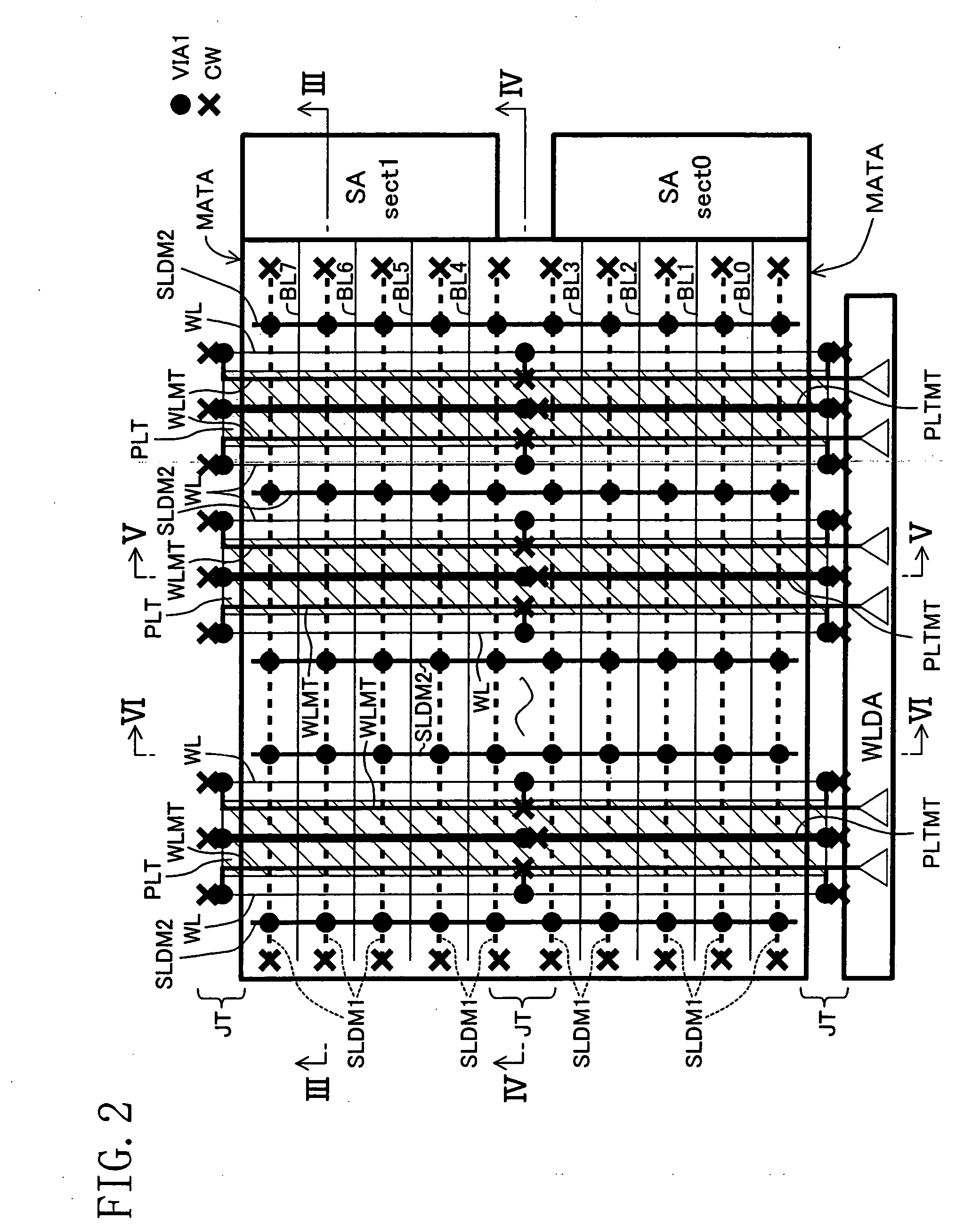

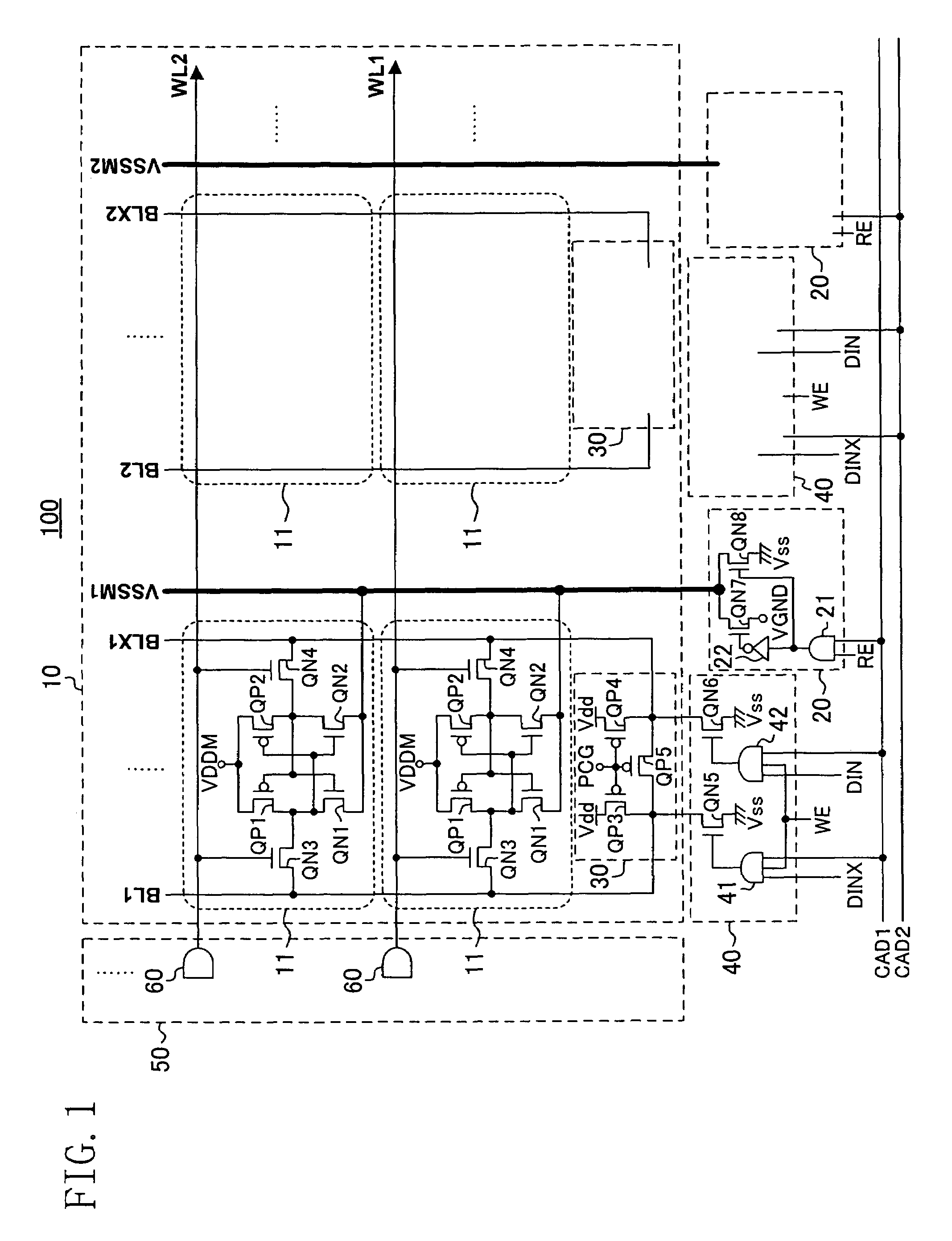

Semiconductor memory device in which bit lines connected to dynamic memory cells extend left and right of sense amplifier column

InactiveUS6898109B2VariationEasy to operateTransistorSemiconductor/solid-state device detailsBit lineEngineering

In a single intersection type (open bit line type) dynamic RAM, sub-arrays are disposed to the left and right sides of a sense amplifier column placed at the center. Each sub-array has a multiplicity of dynamic memory cells. In the subarrays located to the left and right of the sense amplifier column, bit lines in the same row constitute a complementary bit line pair. In each subarray, shielding wiring patterns that are formed parallel to, and in the same wiring layer of, these bit lines are disposed between the bit lines. All of these wiring patterns are set at a fixed potential, such as a power supply potential. Thus, interference noise between adjacent bit lines is effectively reduced.

Owner:CETUS TECH INC

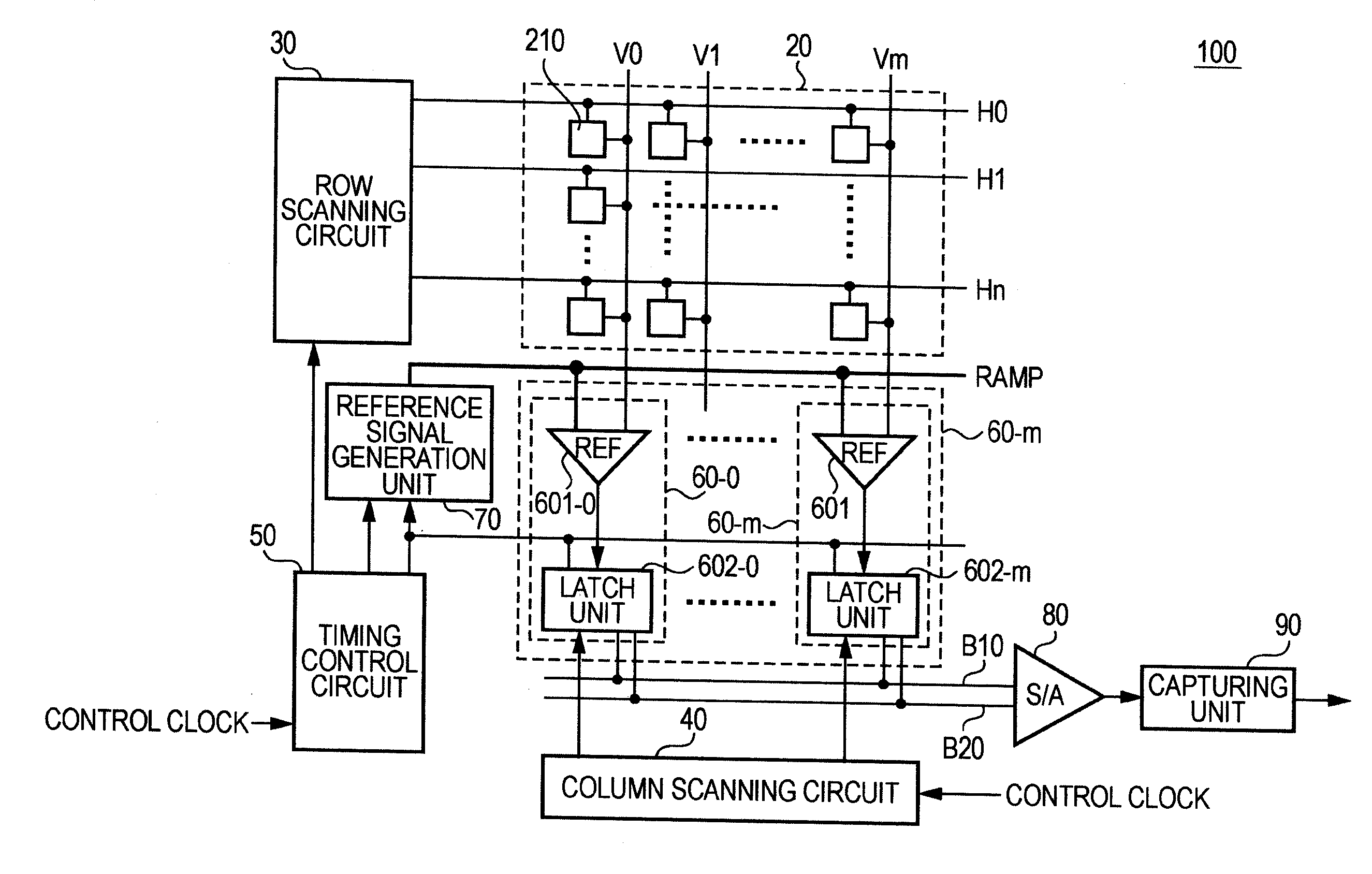

Solid-state imaging device, data transfer circuit, and camera system

InactiveUS20110037871A1Increase operation marginImprove operating profitTelevision system detailsTelevision system scanning detailsSynchronismData transmission circuit

To make it possible to appropriately set a capturing timing for a pixel value.For this, the present invention includes a pixel array unit 2 composed of pixels 21 arranged in a row direction and a column direction in a matrix manner and a latch unit 62 provided for each column constituting the pixel array unit 2 and configured to convert a pixel value of the pixel 21 into a digital pixel value to hold the pixel value. Also, the present invention includes a column scanning unit 4 for selecting the latch unit 62, a capturing unit 9 for sequentially capturing the pixel value held by the latch unit selected by the column scanning unit 4 in synchronism with a predetermined clock, and a delay unit 10 for delaying a clock for driving the capturing unit 9 in a plurality of stages. With the configuration described above, first dummy data is set in the latch unit 62-m at the near end, and second dummy data is set in the latch unit 62-0 at the far end. Then, a delay amount in the delay unit 10 is set as a delay amount at which both the first dummy data and the second dummy data can be captured by the capturing unit 9.

Owner:SONY CORP

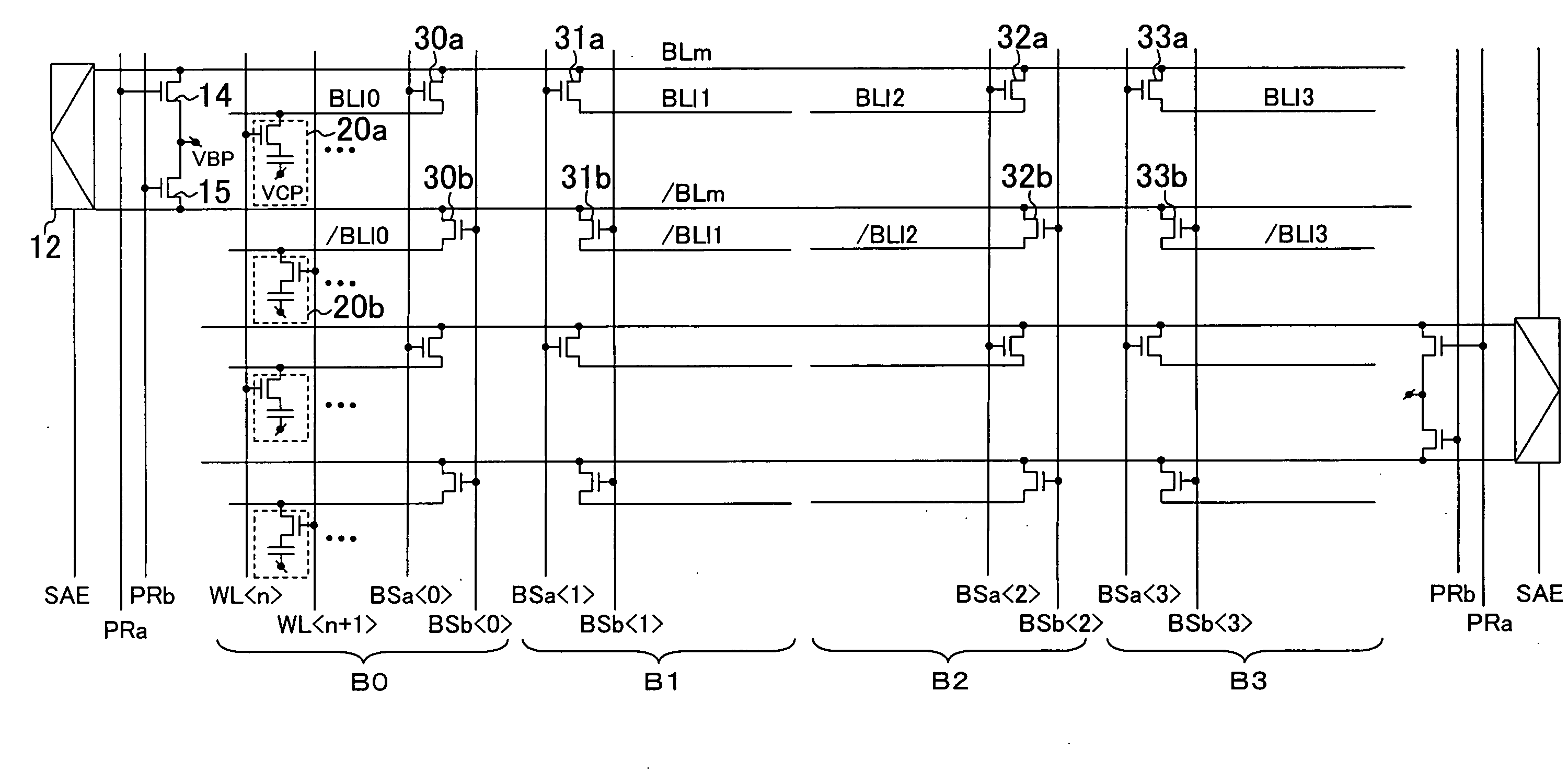

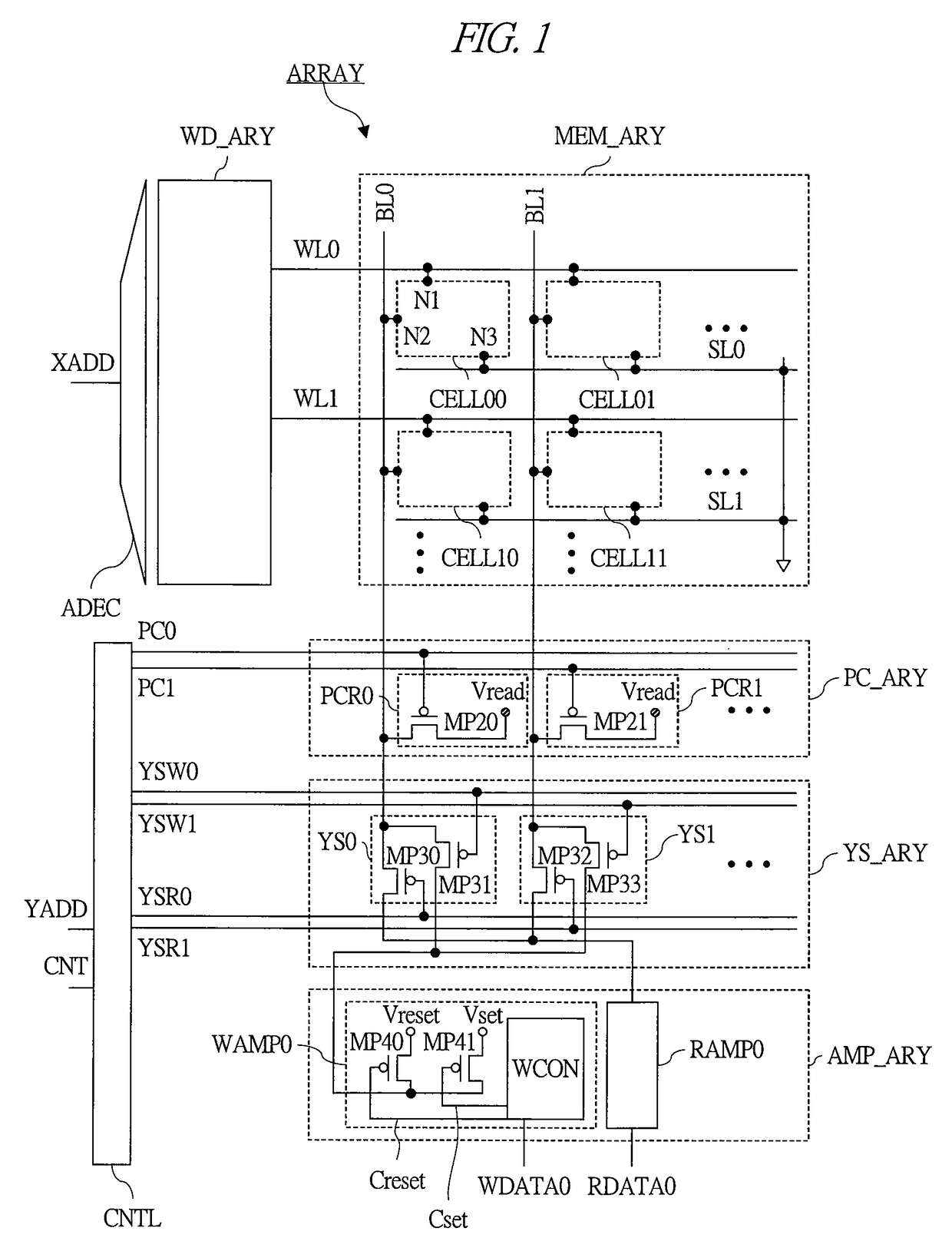

Semiconductor memory device

ActiveUS20070242539A1Improve charge transferring speedHigh voltageDigital storageBit lineComputer architecture

A semiconductor memory device includes first and second global bit lines; first, second, third and fourth local bit lines; first, second, third and fourth hierarchical switches for respectively connecting the first global bit line and the first local bit line to each other, the second global bit line and the second local bit line to each other, the first global bit line and the third local bit line to each other, and the second global bit line and the fourth local bit line to each other; and first and second precharge circuits for respectively precharging the first and second global bit lines. When a memory cell connected to the first local bit line is read, the third hierarchical switch is turned off, and the first precharge circuit terminates its precharge operation after the third hierarchical switch is turned off and before a selected word line connected to the memory cell to be read is activated.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

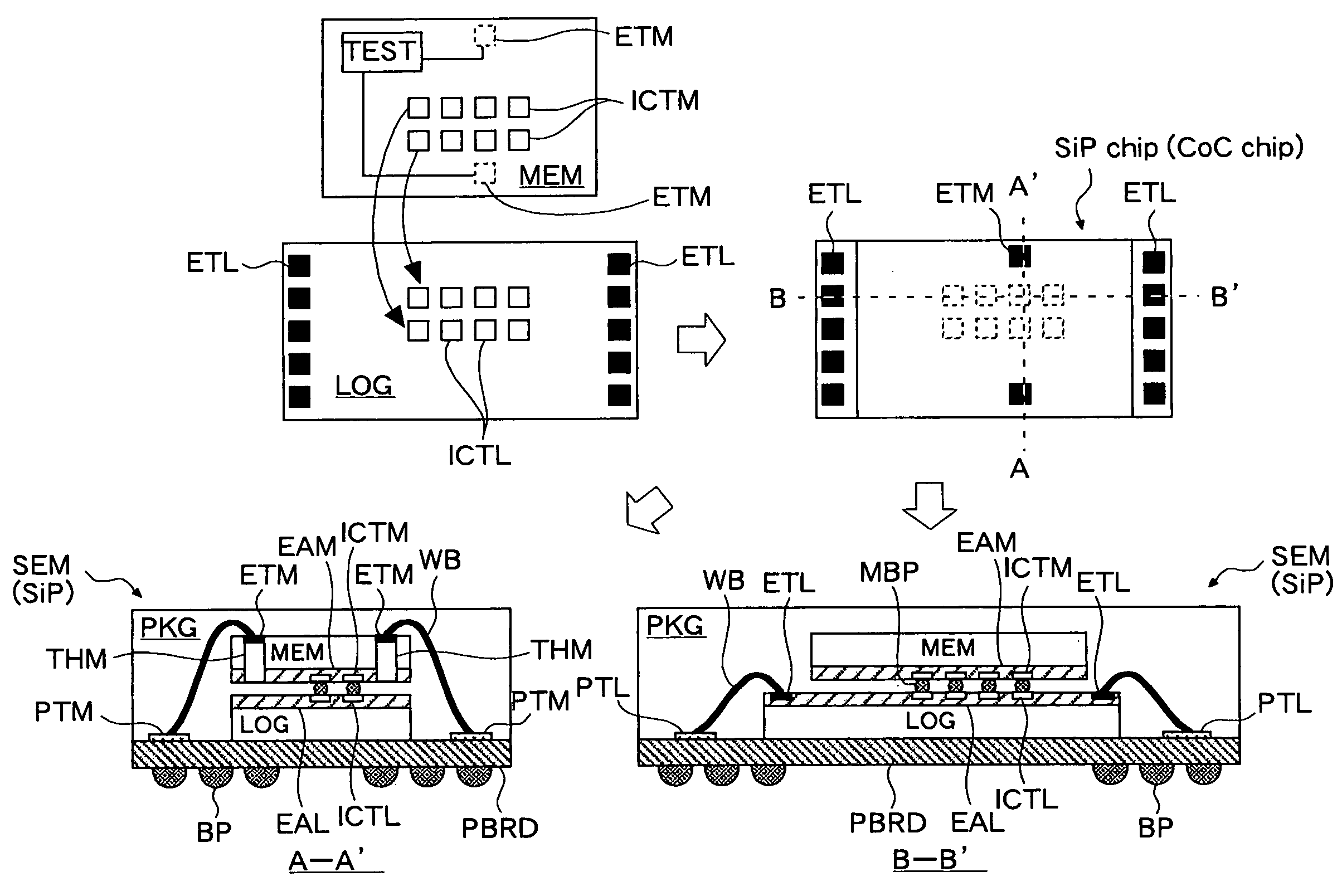

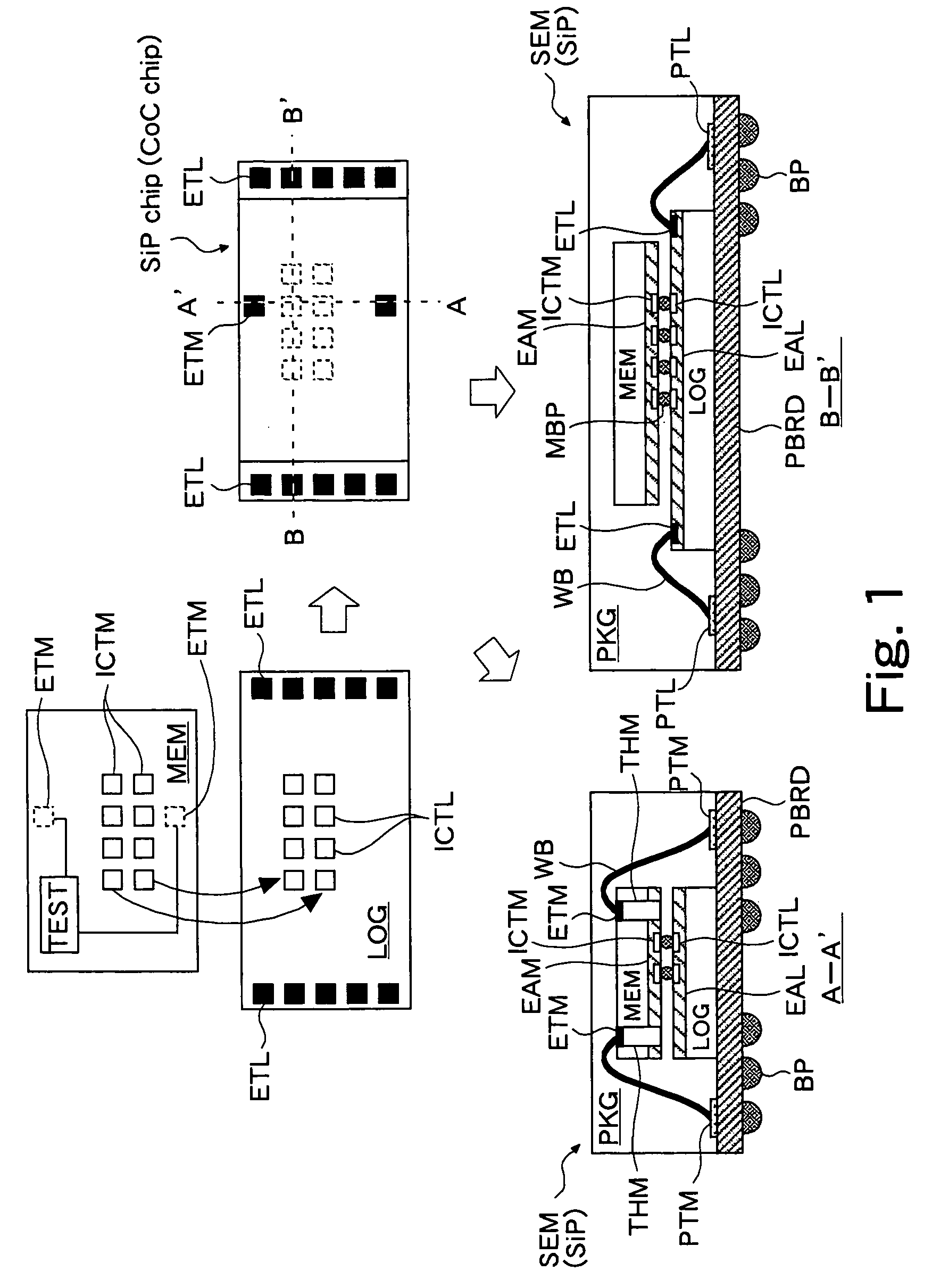

Semiconductor device comprising chip on chip structure

ActiveUS7741723B2Improve operating profitSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsChIP-on-chipSemiconductor chip

In a semiconductor device constituted of stacked semiconductor chips, in order to independently test each of the chips, a second chip is disposed to face a first chip, with a second interconnection terminal thereof connected to a first interconnection terminal of the first chip. First and second external terminals of the first and second chips are formed on surfaces of the first and second chips, the surface being on a same side of the first and second chips. Therefore, even after the first chip and the second chip are pasted together, it is possible to test the first chip and the second chip while operating them independently. Further, since test probes or the like can be brought into contact with the external terminals of the first chip and the second chip from the same side, it is possible to simultaneously test the first chip and the second chip.

Owner:SOCIONEXT INC

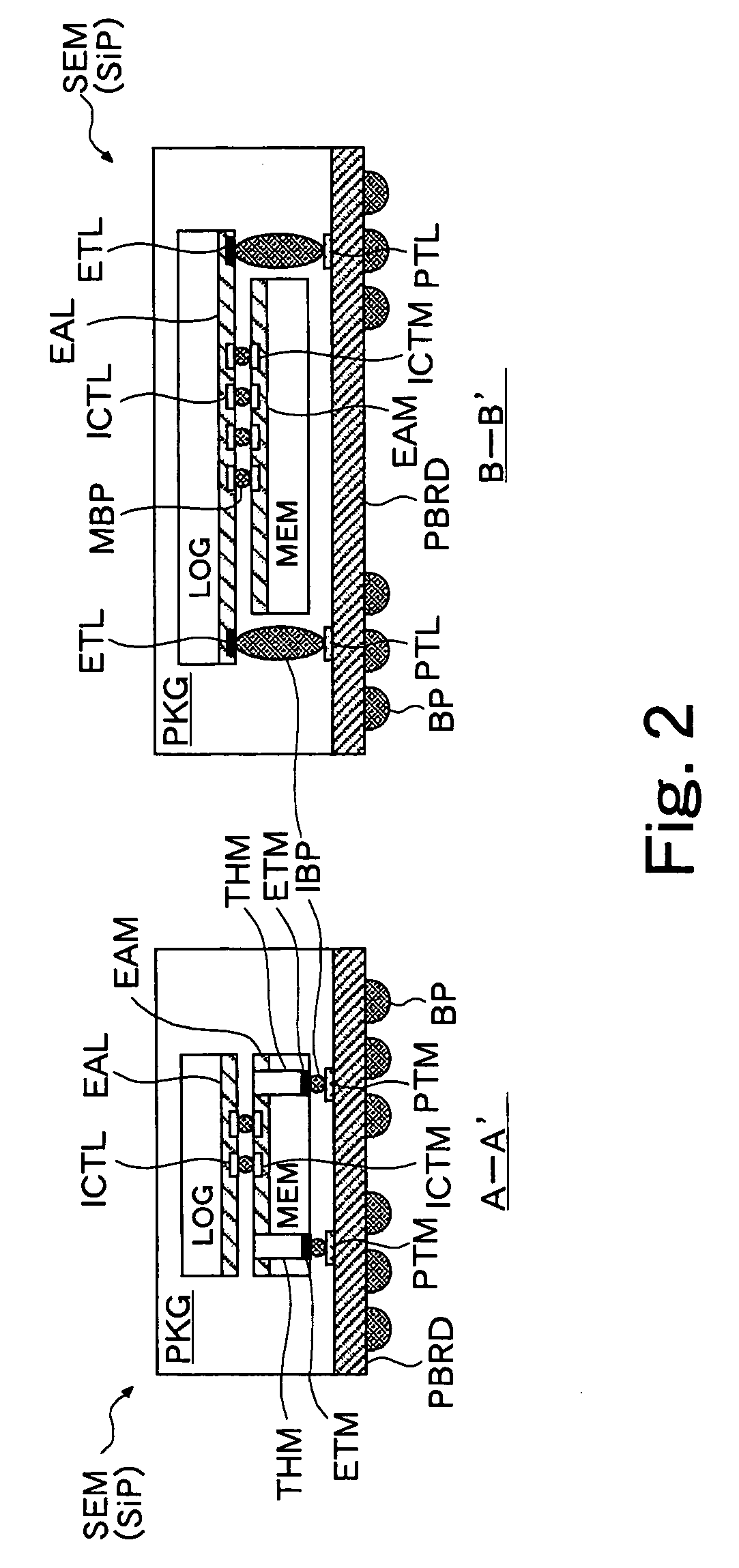

Synthetic Jet Actuator System and Related Methods

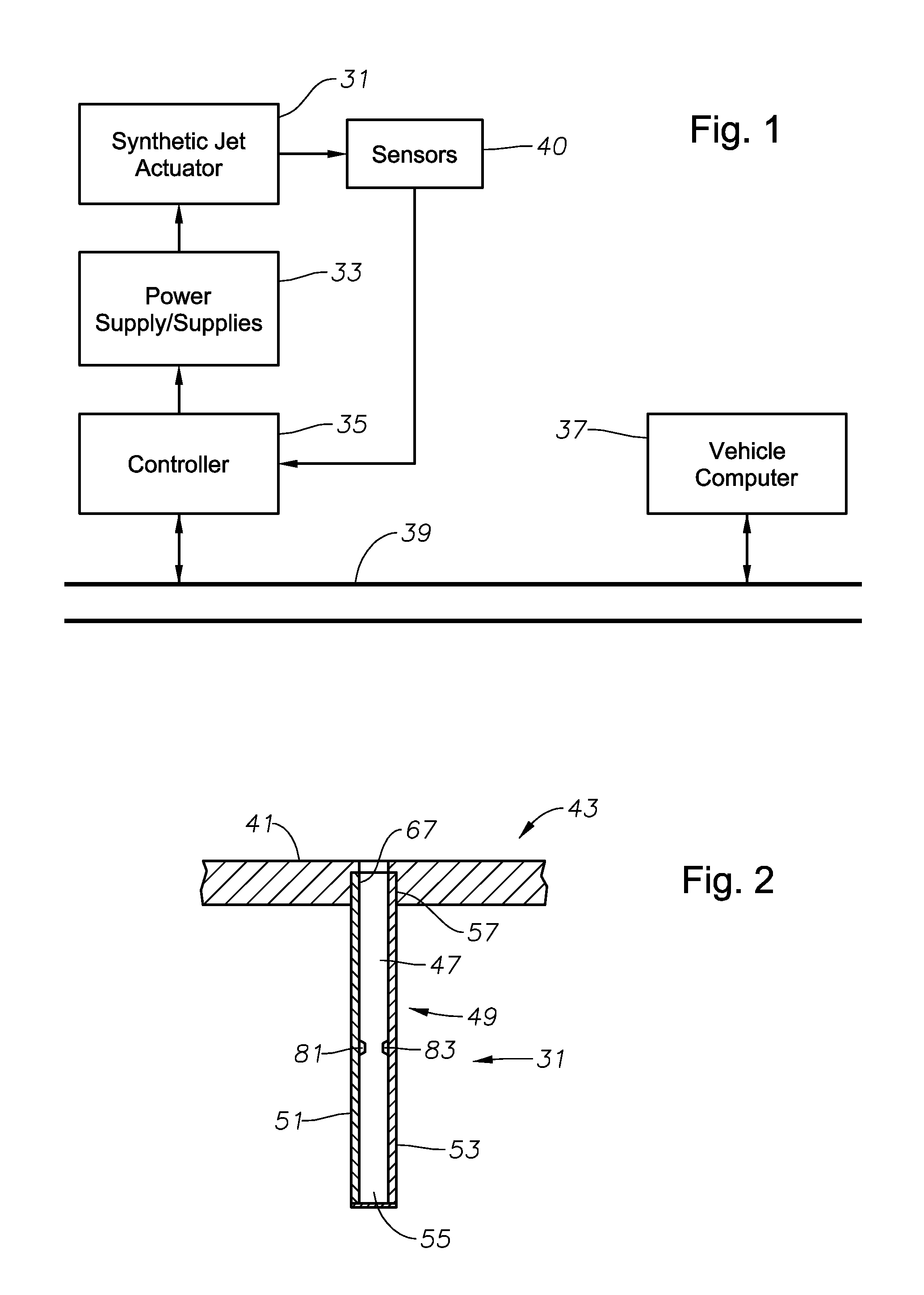

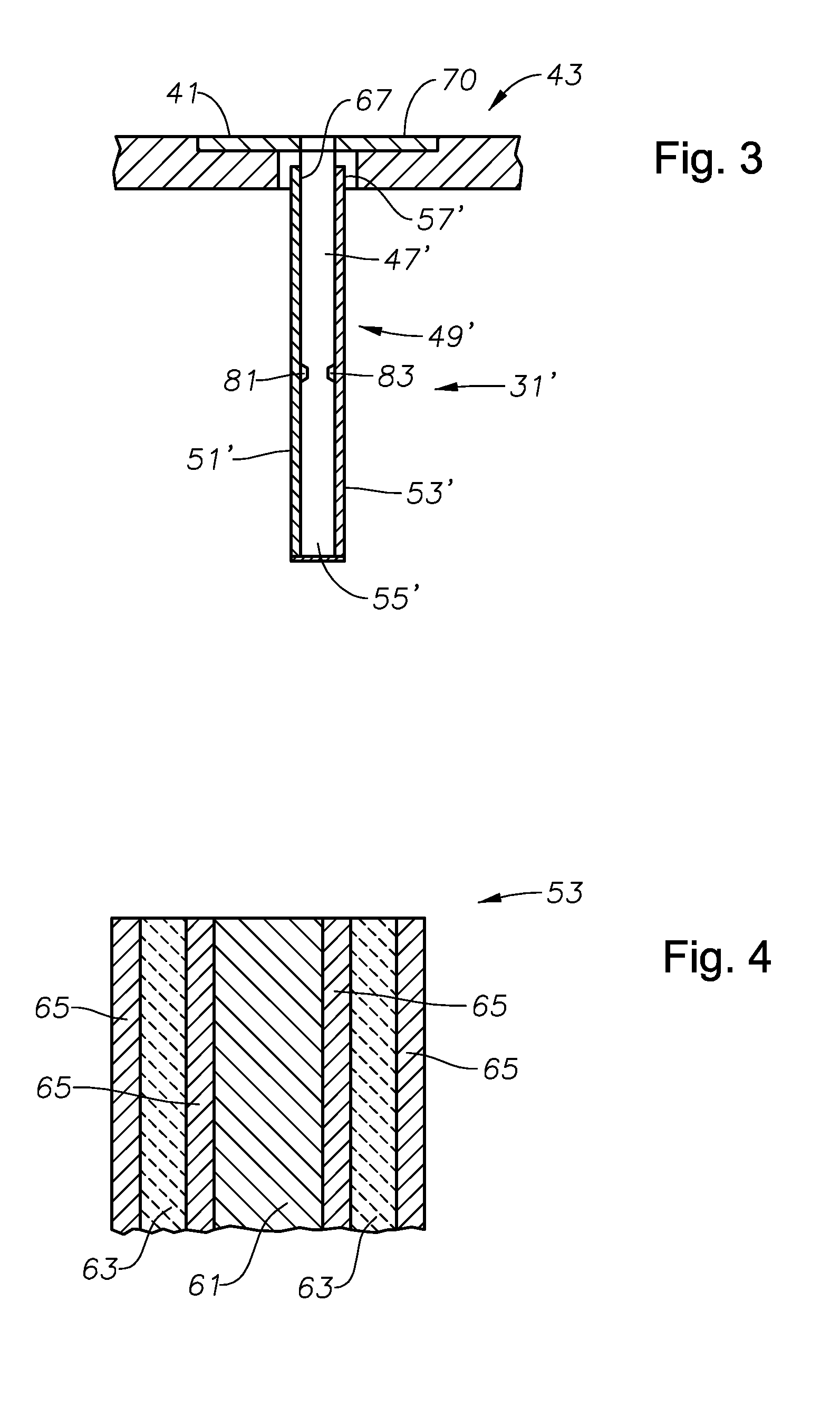

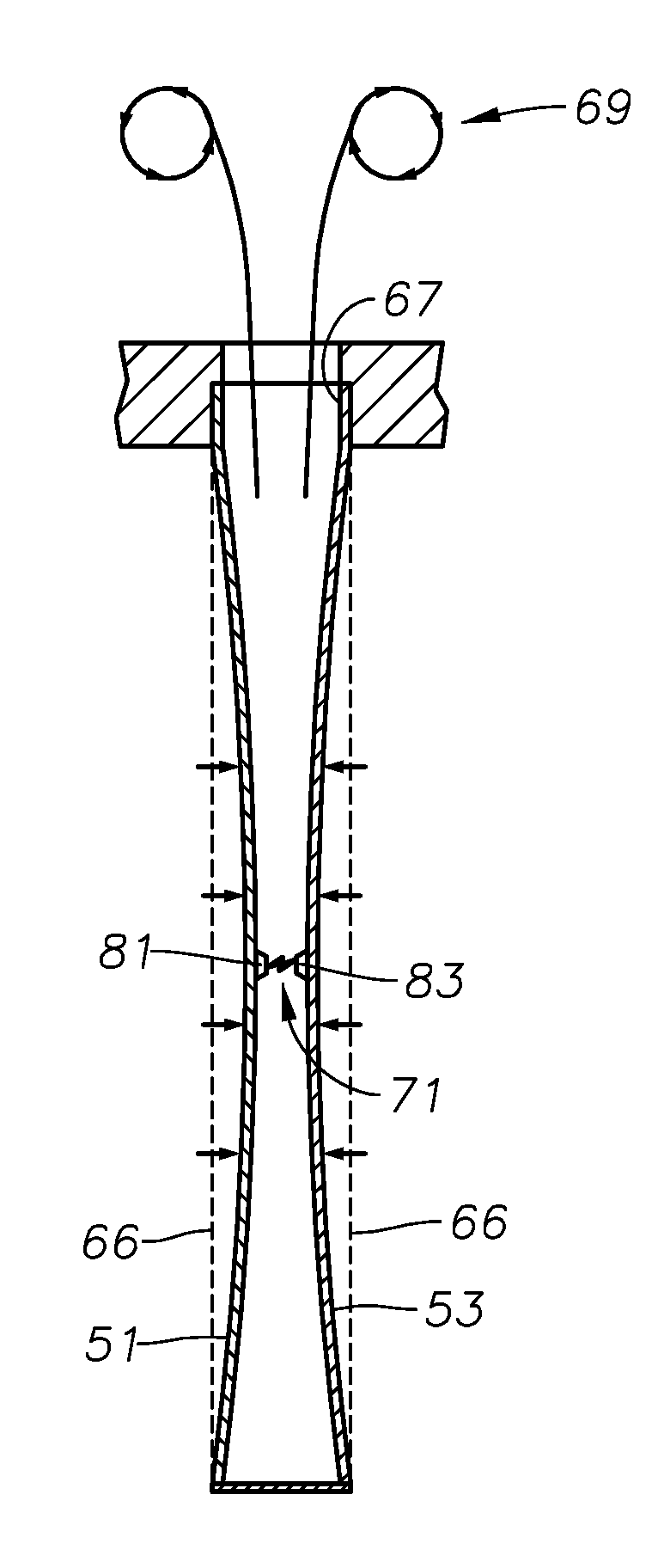

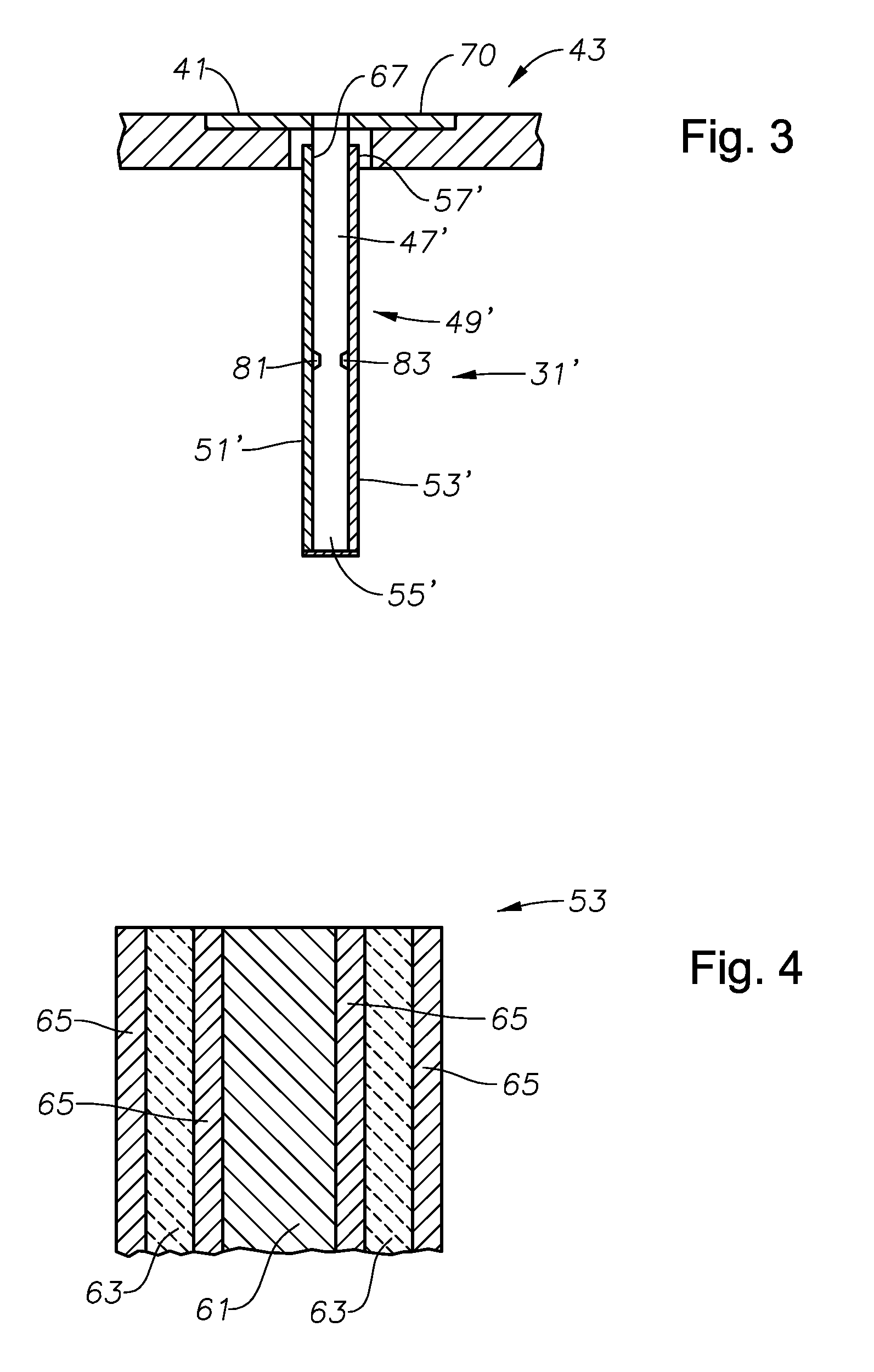

ActiveUS20110147476A1Improve performanceExtending operating marginBurnersWingsEngineeringElectrode interface

Systems and methods for controlling fluid flow utilizing a synthetic jet actuator, are provided. An example of a synthetic jet actuator system includes a synthetic jet actuator including a dual bimorph subsystem to provide low, medium, and high synthetic jet velocities and / or fine flow control response, and an arc-forming subsystem to provide enhanced pressure, velocity, and mass flow performance, enhanced flow control response, and / or heating of the fluid within the bimorph chamber to extend the performance or operating margin of the dual bimorph subsystem of the synthetic jet actuator. The arc-forming subsystem includes a pair of electrodes interfaced with inner surface walls of the dual bimorph subsystem. Various configurations of power supplies can be utilized to provide simultaneous function to both the subsystem and the arc-forming subsystem to allow selective activation.

Owner:LOCKHEED MARTIN CORP

Synthetic jet actuator system and related methods

ActiveUS8348200B2Improve operating profitImprove performanceBurnersWingsEngineeringBiological activation

Systems and methods for controlling fluid flow utilizing a synthetic jet actuator, are provided. An example of a synthetic jet actuator system includes a synthetic jet actuator including a dual bimorph subsystem to provide low, medium, and high synthetic jet velocities and / or fine flow control response, and an arc-forming subsystem to provide enhanced pressure, velocity, and mass flow performance, enhanced flow control response, and / or heating of the fluid within the bimorph chamber to extend the performance or operating margin of the dual bimorph subsystem of the synthetic jet actuator. The arc-forming subsystem includes a pair of electrodes interfaced with inner surface walls of the dual bimorph subsystem. Various configurations of power supplies can be utilized to provide simultaneous function to both the subsystem and the arc-forming subsystem to allow selective activation.

Owner:LOCKHEED MARTIN CORP

Semiconductor memory device

InactiveUS7933141B2Improve operating profitStabilizing sense amplification.Digital storageBit lineAudio power amplifier

In a semiconductor memory device, a memory cell is connected with a local sense amplifier and a global sense amplifier via a local bit line and a global bit line. The local sense amplifier is a single-ended sense amplifier including a single MOS transistor, which detects a potential of the local bit line which varies when reading and writing data with the memory cell. The threshold voltage of the MOS transistor is monitored so as to produce a high-level write voltage and a low-level write voltage, which are corrected and shifted based on the monitoring result so as to properly perform a reload operation on the memory cell by the global local sense amplifier. Thus, it is possible to cancel out temperature-dependent variations of the threshold voltage and shifting of the threshold voltage due to dispersions of manufacturing processes.

Owner:LONGITUDE LICENSING LTD

Semiconductor memory device

InactiveUS20050157527A1Improve operating profitSuppress noiseTransistorSemiconductor/solid-state device detailsBit lineEngineering

In a single intersection type (open bit line type) dynamic RAM, sub-arrays are disposed to the left and right sides of a sense amplifier column placed at the center. Each sub-array has a multiplicity of dynamic memory cells. In the subarrays located to the left and right of the sense amplifier column, bit lines in the same row constitute a complementary bit line pair. In each subarray, shielding wiring patterns that are formed parallel to, and in the same wiring layer of, these bit lines are disposed between the bit lines. All of these wiring patterns are set at a fixed potential, such as a power supply potential. Thus, interference noise between adjacent bit lines is effectively reduced.

Owner:CETUS TECH INC

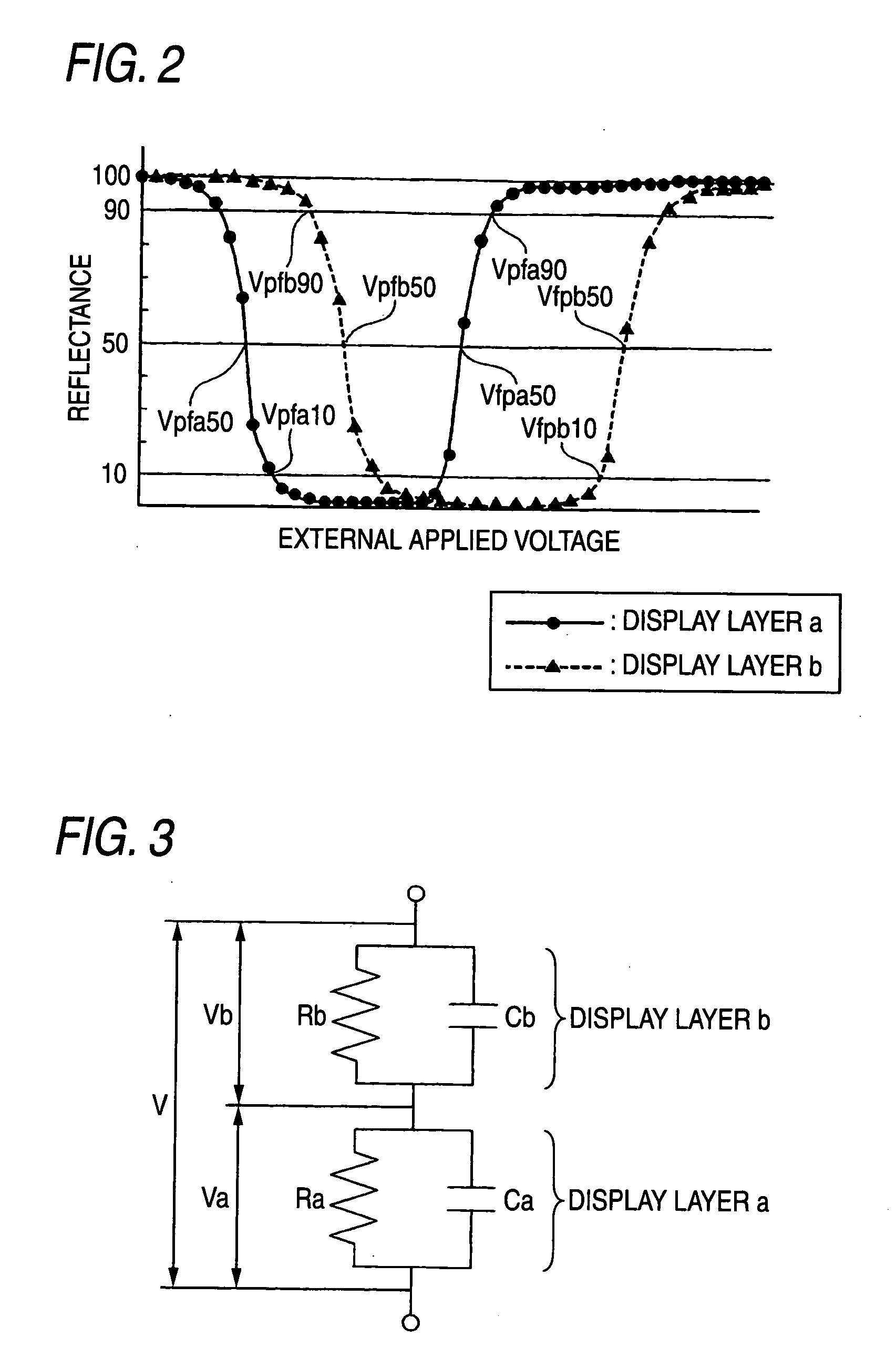

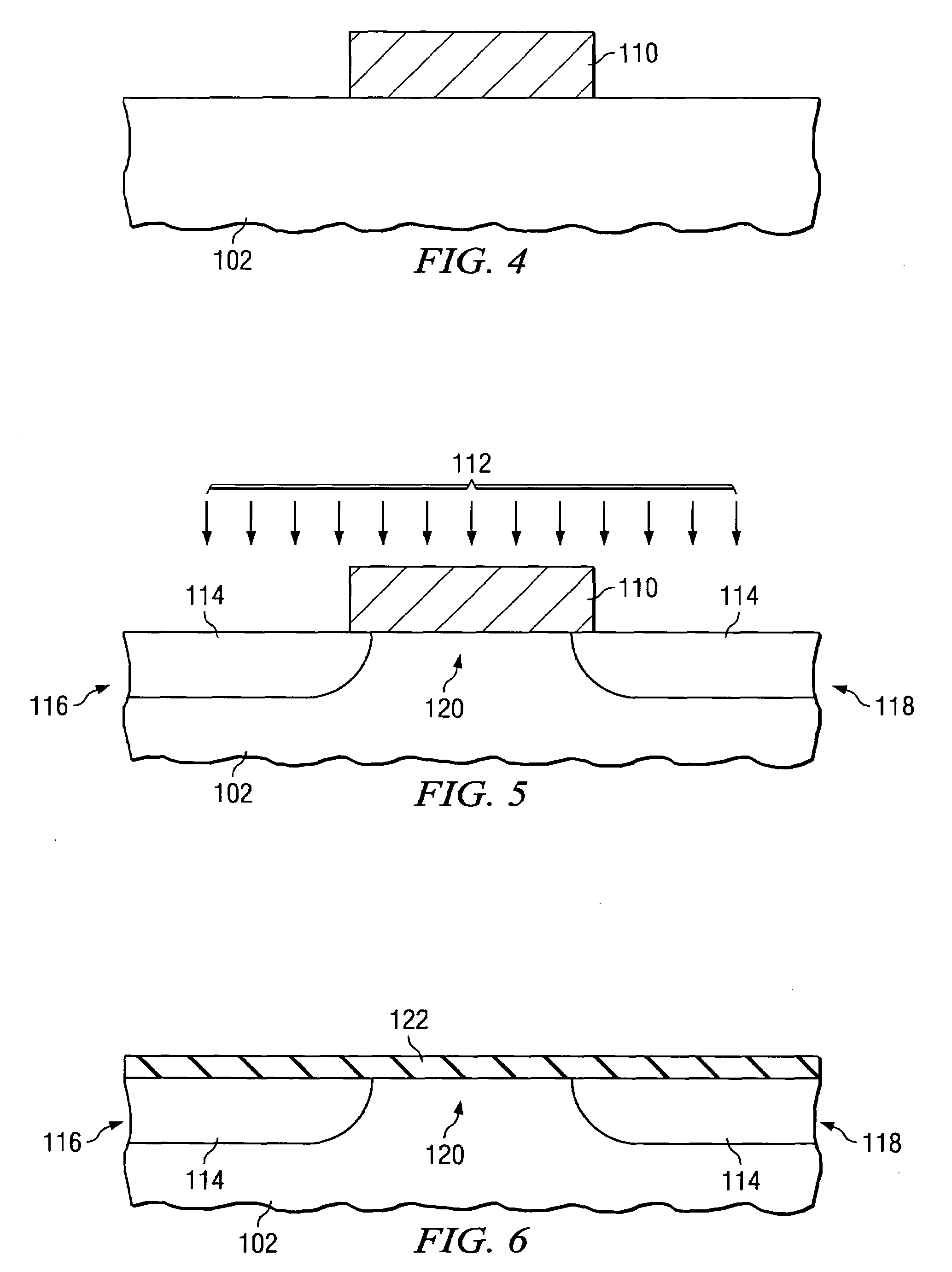

Driving method of stacked light modulating device, and driving device of stacked light modulating device

InactiveUS20070046595A1Improve operating profitStable threshold value shifting operationStatic indicating devicesNon-linear opticsSelective reflectionCircular cone

A driving method of a stacked light modulating device for recording an image therein, which includes selective reflection layers each having a cholesteric liquid crystal, reflecting light with different wavelengths within a visible range, and being different in a lower threshold value of texture change from a planar to a focal conic texture with respect to an externally applied voltage and an upper threshold value of texture change from the focal conic to a homeotropic texture, and a pair of electrodes disposed outside, includes applying between the pair of electrodes voltages including a voltage V1 and have a same frequency, to select an area exceeding or not exceeding the upper threshold value in each of the selective reflection layers, and applying voltages including a voltage V2 and have a same frequency different from the voltage V1, to select an area exceeding or not exceeding the lower threshold value.

Owner:FUJIFILM BUSINESS INNOVATION CORP

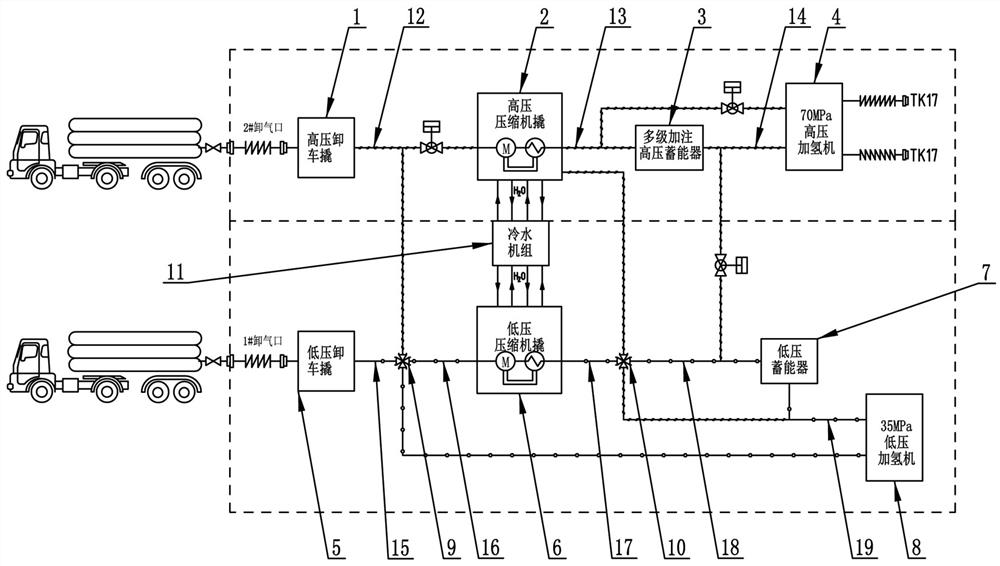

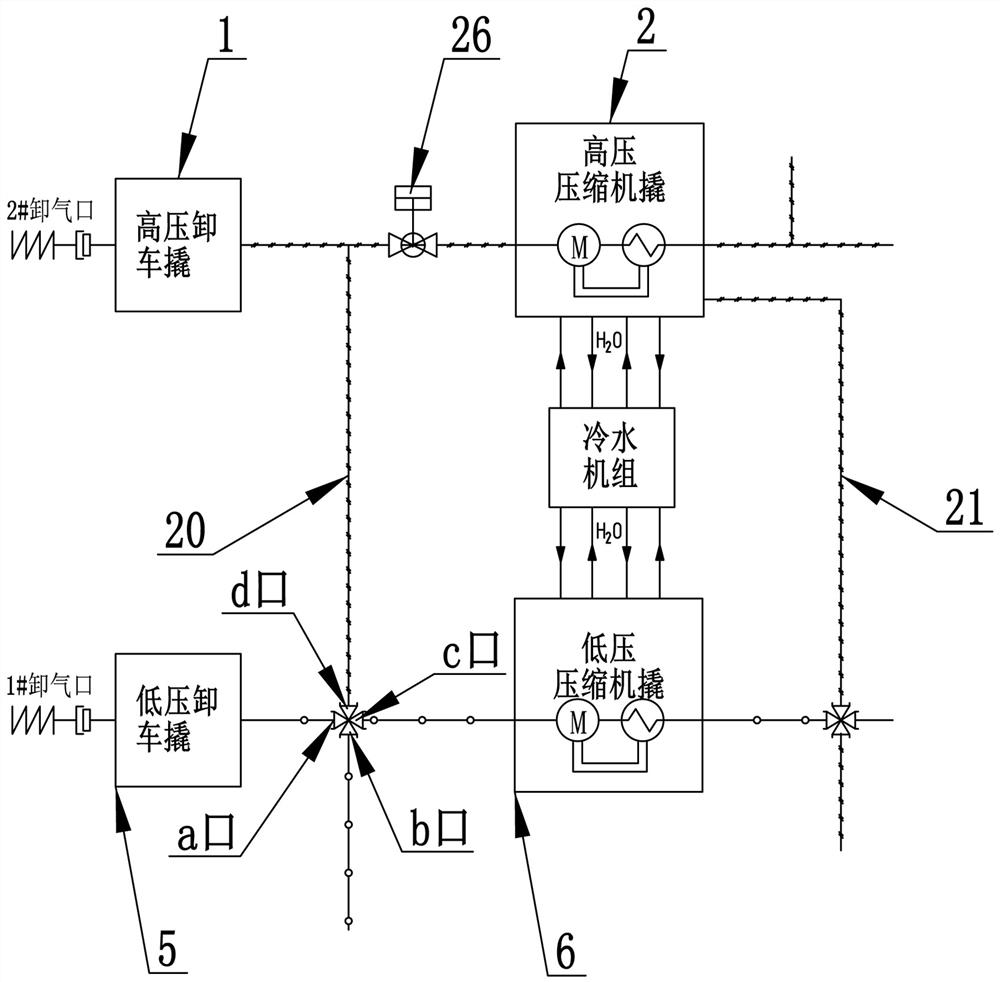

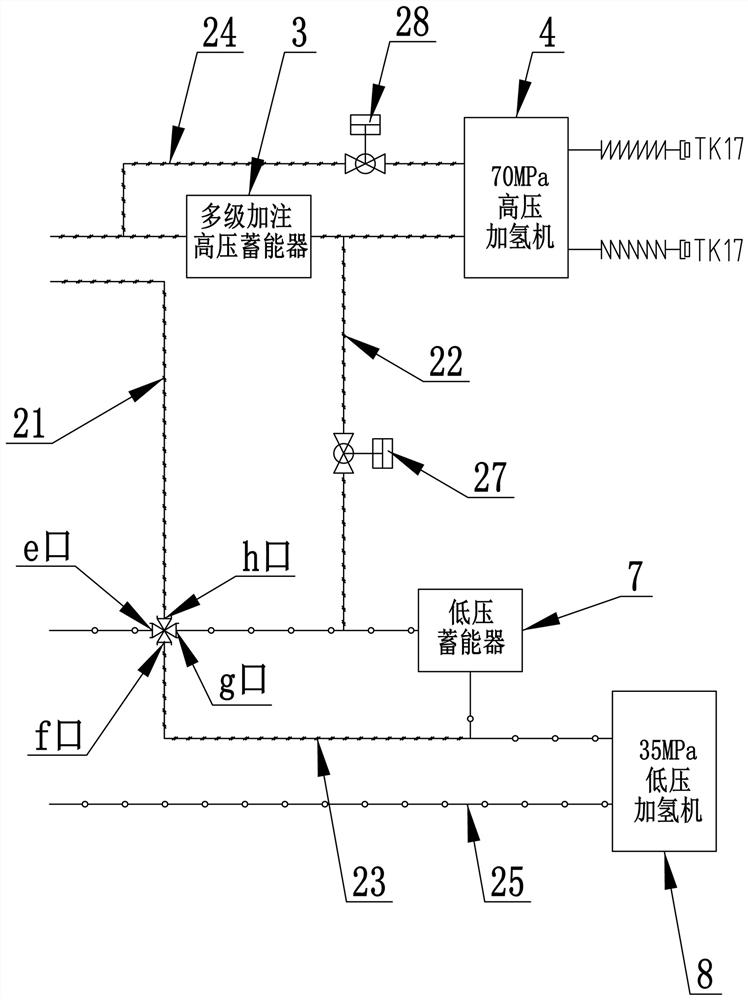

Hybrid pressurized multi-stage filling and hydrogenation device

PendingCN112483888ARetrofitting workload is smallLow costGas handling/storage effectsPipeline systemsThermodynamicsFour-way valve

The invention discloses a hybrid pressurized multi-stage filling and hydrogenation device which comprises the following composition units: a high-pressure unloading pry, a high-pressure compressor pry, a multi-stage filling high-pressure energy accumulator, a 70MPa high-pressure hydrogenation machine, a low-pressure unloading pry, a low-pressure compressor pry, a low-pressure energy accumulator, a35MPa low-pressure hydrogenation machine, a first four-way valve provided with a port a, a port b, a port c and a port d, a second four-way valve provided with a port e, a port f, a port g and a porth, and a water chilling unit used for cooling the high-pressure compressor pry and the low-pressure compressor pry. All the composition units are connected through a pipeline system, so that the purposes of 35MPa / 70MPa hybrid filling, low-pressure hydrogen multi-stage hybrid pressurization, and enabling the high-pressure energy accumulator and the low-pressure energy accumulator as mutual standbyhydrogen sources are achieved. On the basis of not influencing an original 35MPa skid-mounted hydrogenation device, pressurization and capacity expansion are carried out, wherein the hydrogenation pressure is increased from 35MPa to 70MPa / 35MPa for hybrid pressurization, and the daily hydrogenation scale is increased from not more than 500kg / d to 1000kg / d and above; and a pressurization and capacity expansion structure provided by the scheme has the advantages of being simple in structure, convenient to install, small in modification workload, low in cost and the like.

Owner:ZHANGJIAGANG FURUI HYDROGEN ENERGY EQUIP CO LTD +1

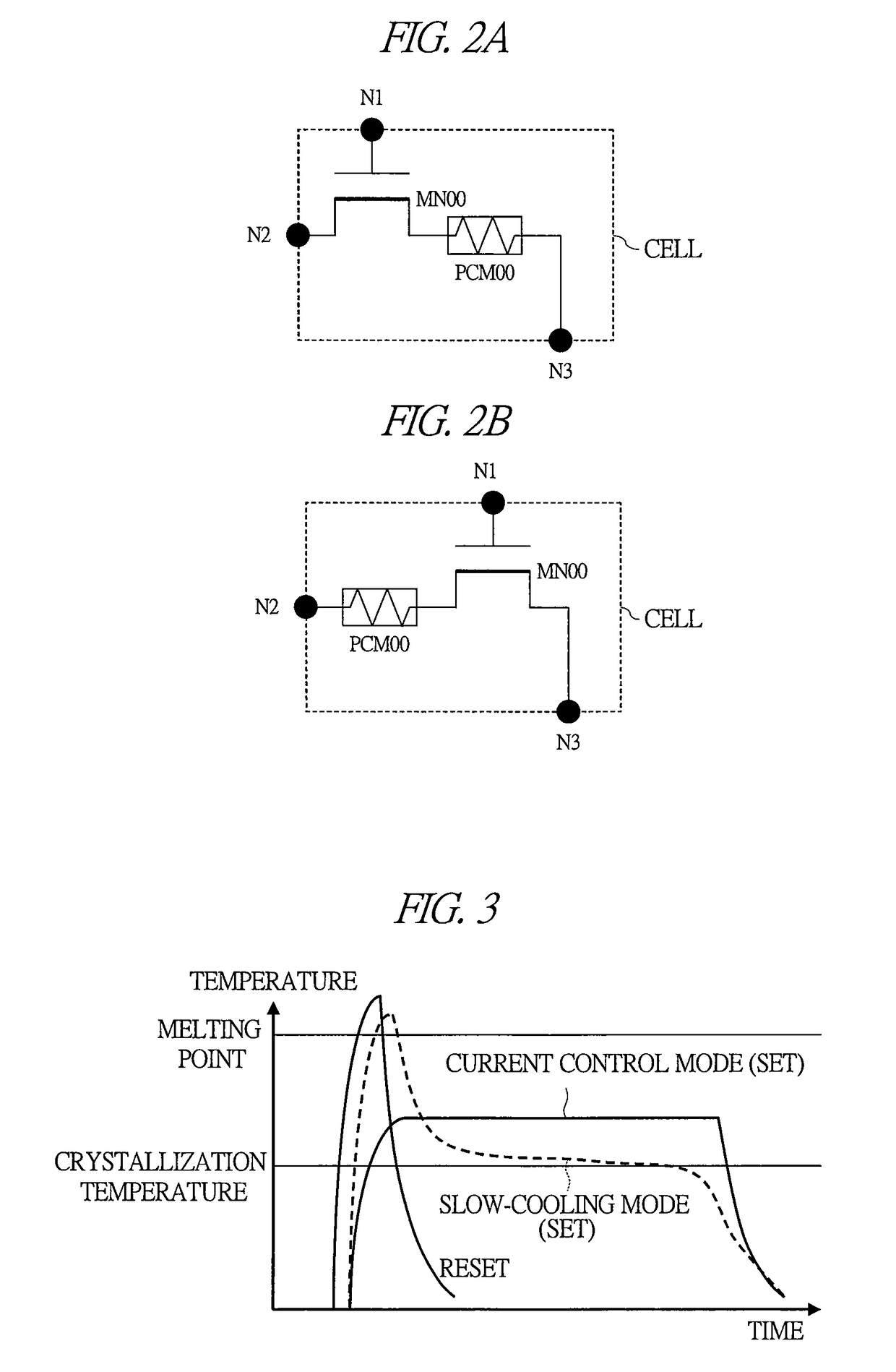

Semiconductor device

At the time of, for example, a set operation (SET) for making a phase-change element in a crystalline state, a pulse of a voltage Vreset required for melting the element is applied to the phase-change element, and subsequently a pulse of a voltage Vset that is lower than Vreset and is required for crystallizing the element is applied thereto. And, the magnitude of this voltage Vset is then changed depending on the ambient temperature so that the magnitude of the voltage Vset is small as the temperature becomes high (TH). In this manner, a margin of a write operation between the set operation and a reset operation (RESET) for making the element to be in amorphous state is improved.

Owner:RENESAS ELECTRONICS CORP

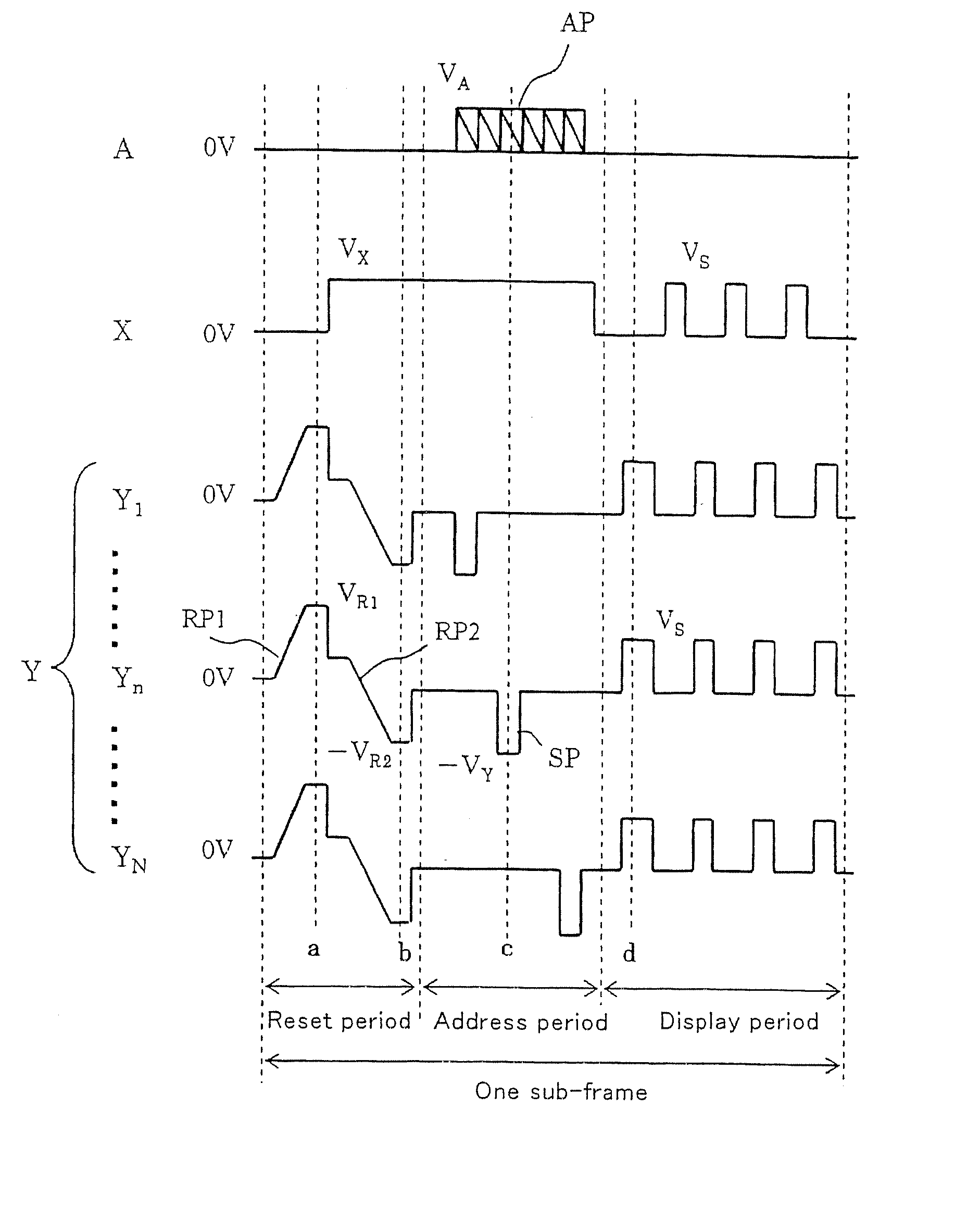

Plasma display apparatus and method of driving a plasma display panel

InactiveUS7170471B2Large operation marginHigh resolutionStatic indicating devicesImage resolutionEngineering

An interlace-type PDP is driven by an improved driving method so as to achieve a greater operating margin, higher resolution, and higher brightness. The interlace-type PDP is driven using odd and even frames in such a manner that the cells are grouped into cell groups such that each cell group includes two or three cells which are adjacent in a direction crossing the electrode pairs, and the cells are driven in units of cell groups. The grouping of cells is performed differently for even and odd frames such that, in one type of frame, locations of two or three cells grouped into each group are shifted by one cell, in the direction crossing the electrode pairs, from the locations of cells grouped together in the other type of frame.

Owner:MAXELL HLDG LTD

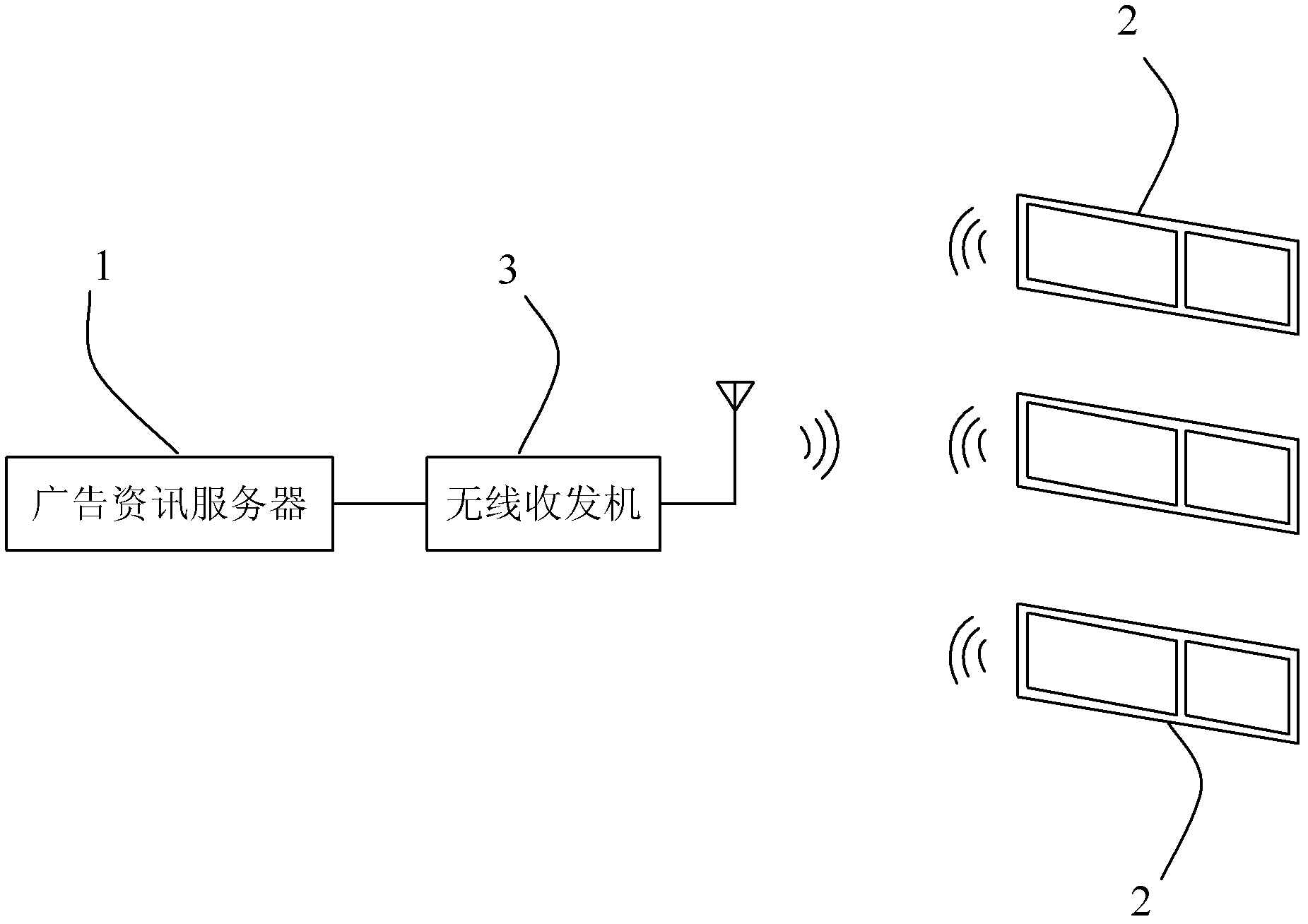

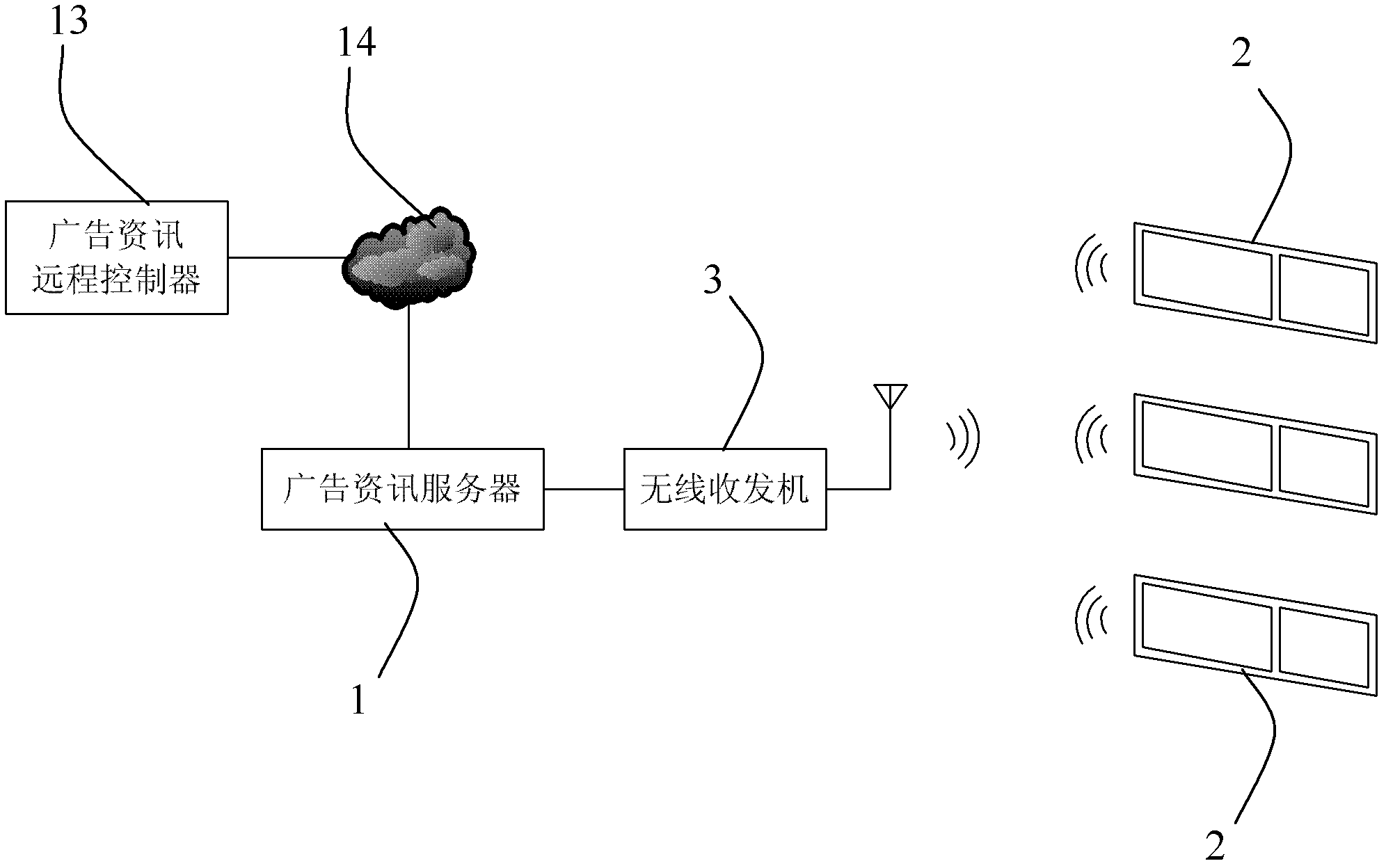

Electronic shelf advertising system capable of being controlled wirelessly and timely

InactiveCN102622945AImprove sales performanceEasy to understandAdvertisingDisplay meansWireless transceiverTransceiver

The invention provides an electronic shelf advertising system capable of being controlled wirelessly and timely. The system comprises an advertising information server and more than one electronic shelf advertising device, wherein the advertising information server is connected with wireless transceivers, and is used for carrying out unified management on the advertisement information and promotion of commodities; and the electronic shelf advertising devices are respectively arranged on each shelf or in stores, and are used for receiving and broadcasting commodity advertising information and promotion information sent by the advertising information server, each electronic shelf advertising device comprises a display screen and a wireless transceiver, and the display screen is connected with the wireless transceiver. According to the invention, static or dynamic advertisements can be made at commodity display parts or in stores, thereby increasing the purchasing desire of consumers, and increasing the revenues and profits of merchants.

Owner:TCHIPS TECH

Intelligent equipment management cloud service system

The invention discloses an intelligent equipment management cloud service system which comprises a data acquisition module, a data aggregation and transmission module, a database module, an application center management service module, a cloud service business application module, a network module, a user access module and a firewall module. The data acquisition module and the data aggregation and transmission module are connected via the network module, and the cloud service business application module and the user access module are connected via the network module; the data aggregation and transmission module, the database module, the application center management service module and the cloud service business application module are in data connection with each other; the firewall module is in through connection with the data aggregation and transmission module, the database module, the application center management service module, the cloud service business application module, the network module and the user access module. The intelligent equipment management cloud service system is characterized by capability of allowing enterprises to choose leases according to demand of service items, convenience of use, reduction of expenditure and cost of the enterprises, and improvement of business operation profits.

Owner:QUANGONG MACHINERY

Semiconductor memory device

In a semiconductor memory device including memory cells each having two inverters connected in a cross-coupled configuration to hold High data and Low data as a pair and two access transistors, a plurality of word lines, and a plurality of bit lines, the potential of the selected one of the plurality of word lines is controlled to be lower than a potential obtained by adding up the potential of one of Low-data-holding power sources each for holding the Low data at any time other than during a read operation and the threshold voltage of each of the access transistors.

Owner:SOCIONEXT INC

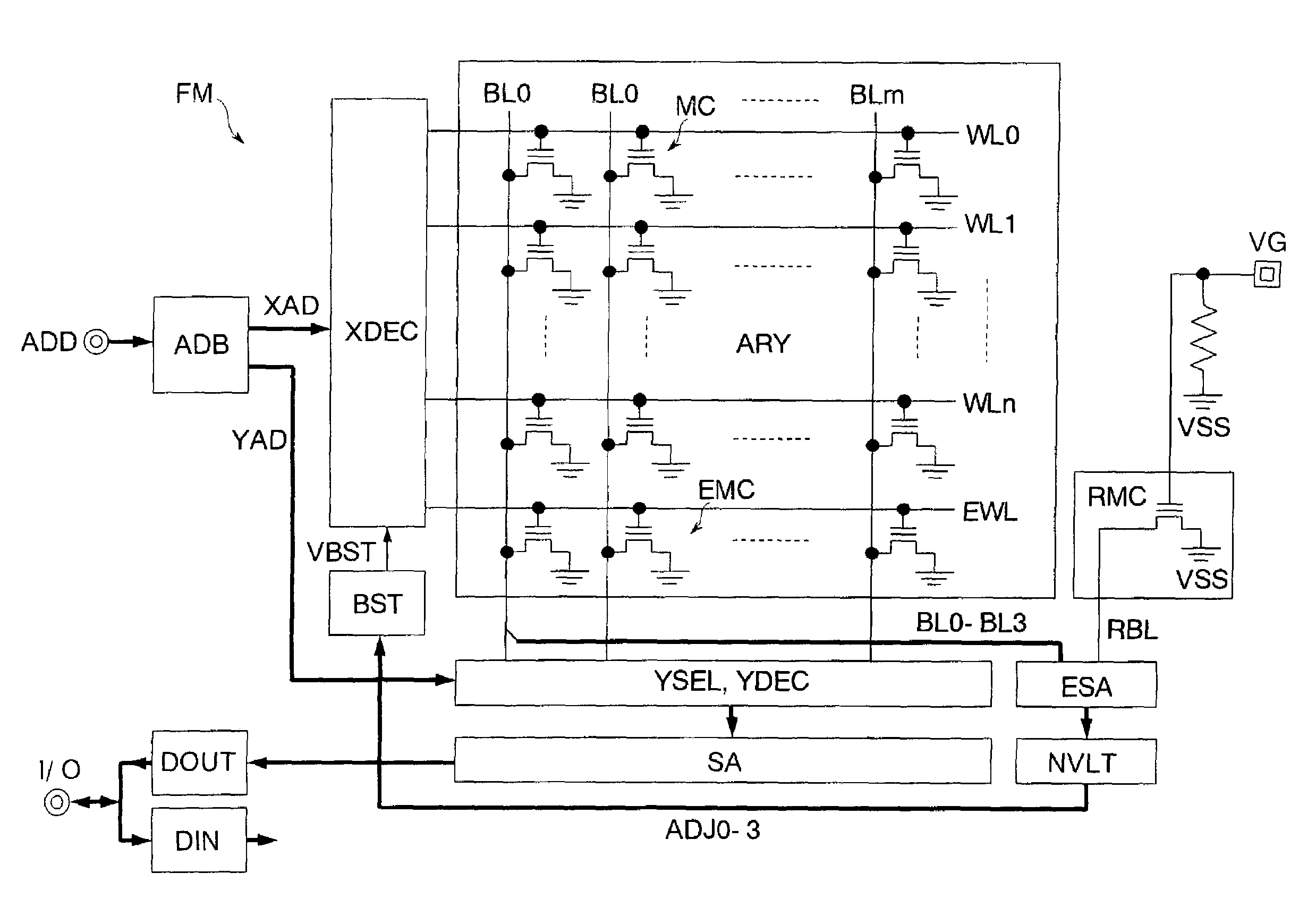

Nonvolatile semiconductor memory having voltage adjusting circuit

ActiveUS7586788B2Improve operating profitIncrease productionRead-only memoriesDigital storageHemt circuitsVoltage regulation

Nonvolatile evaluation memory cells are programmed to be a plurality of different values in advance, respectively. An internal voltage generating circuit can change the value of an internal voltage according to adjusting signals. To make the internal voltage close to its expected value, a voltage adjusting circuit outputs adjusting signals in accordance with cell currents that flow through the evaluation memory cells, respectively, in a read operation on the evaluation memory cells. As a result, the interval voltage that is shifted from its expected value due to variations in manufacturing conditions can automatically be set to the expected value by using the adjusting signals. Since an internal circuit operates on a correct internal voltage, operation margins can be increased. The yield of a nonvolatile semiconductor memory can thus be increased.

Owner:LONGITUDE FLASH MEMORY SOLUTIONS LTD

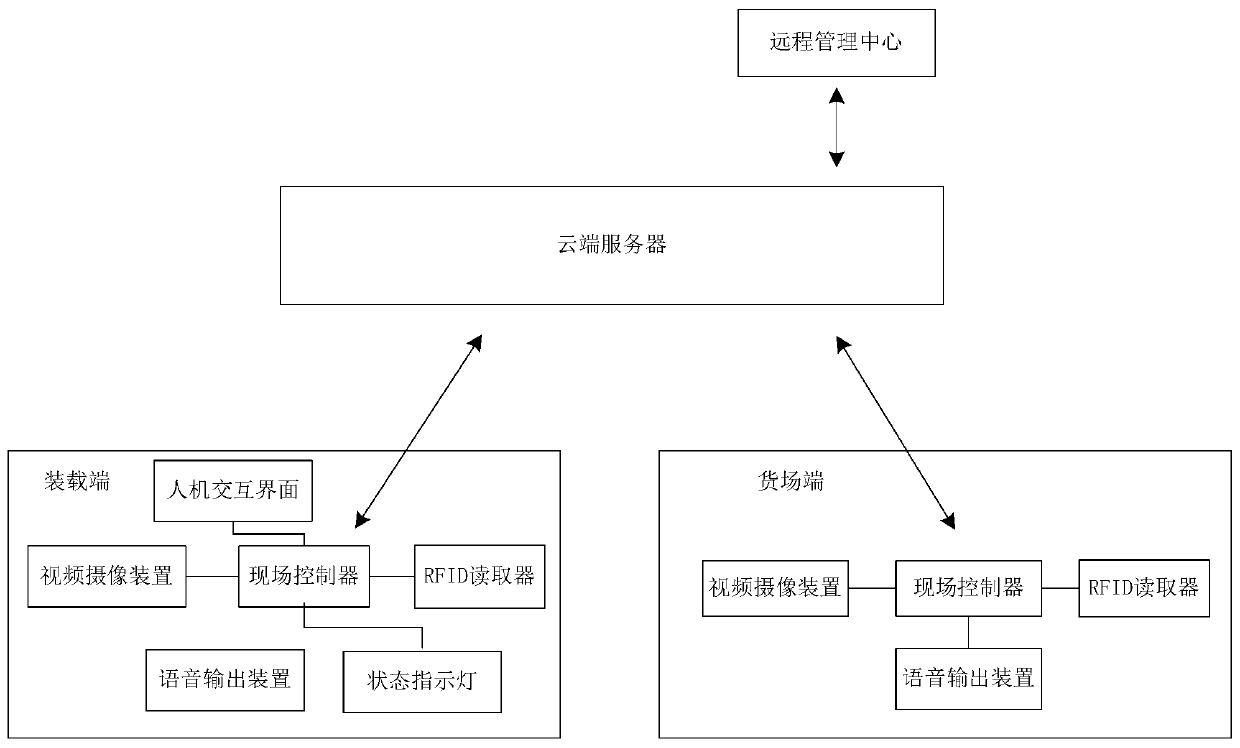

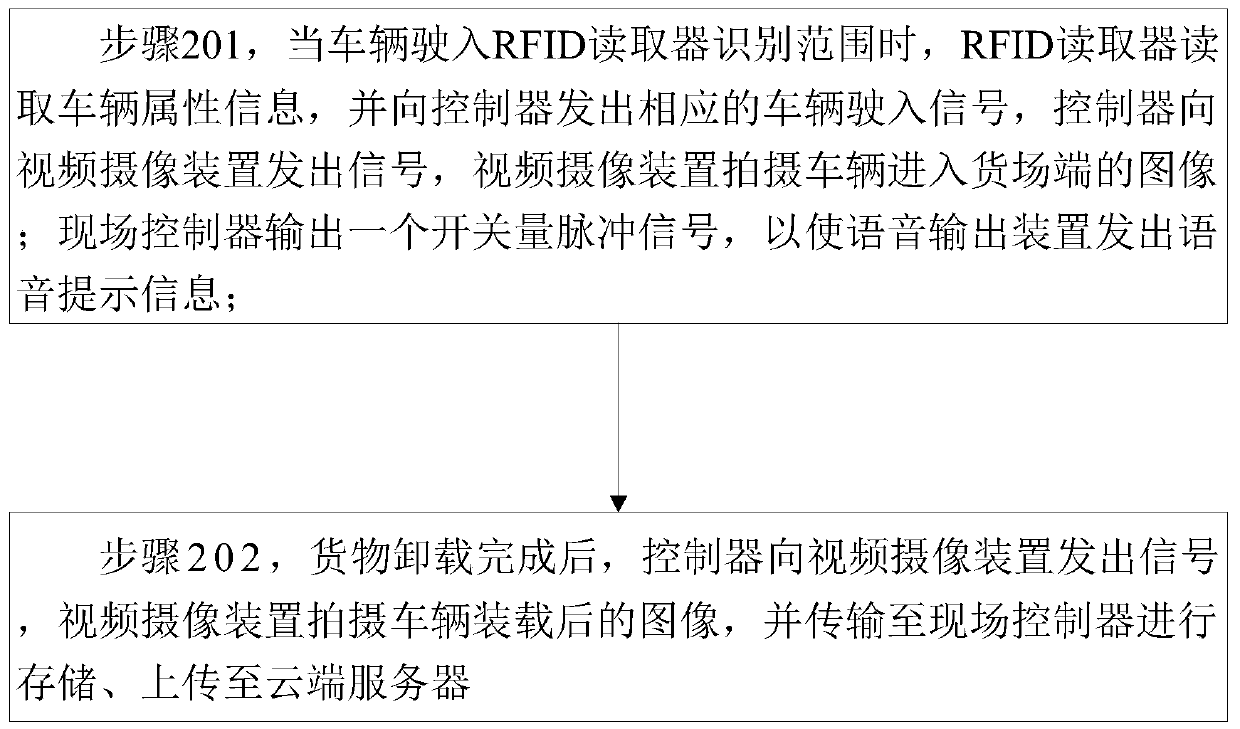

System and method for supervising and counting loading and transporting vehicle linkage operation

PendingCN109754196AReduce personal safety risksReduce laborCo-operative working arrangementsResourcesAnalysis dataInteraction interface

The invention discloses a system and a method for supervising and counting loading and transporting vehicle linkage operation. The system comprises a loading end monitoring device, a goods yard end monitoring device, a cloud server and a remote management center. The loading end monitoring device is arranged in a cargo loading field and comprises a data acquisition device, an on-site controller, ahuman-computer interaction interface and a voice output device. The goods yard end monitoring device is arranged on a goods unloading yard. The field controller is in communication connection with the cloud server through a wireless communication network, and the cloud server is further in communication connection with the remote management center so as to achieve real-time sharing of field datainformation. According to the system, a monitoring mechanism is generated from the source in a mode of respectively acquiring information and uploading, storing by a server and analyzing data to generate a report form in a mine field and a freight yard, and multi-post manpower is replaced by equipment, so that the personal safety risk and the labor amount in a high-risk environment during operation monitoring of mine enterprises are reduced to the maximum extent.

Owner:雷嗣制

Multifunctional buckle assembly automatic system

ActiveCN108044894AConducive to lean production managementLean manufacturing noveltyDual mechanismEngineering

The invention discloses a multifunctional buckle assembly automatic system which comprises a first rack and a conveying sliding table mechanism. A buckle mechanical arm and a buckle feeding mechanismare mounted in the first rack. A first conveying belt is arranged on the upper end face of the first rack. A vertical conveying mechanism is arranged beside the first conveying belt. One end of the conveying sliding table mechanism stretches into the first rack, and the other end of the conveying sliding table mechanism is located outside the first rack. At least one rotary disc is arranged at theaction tail end of the buckle mechanical arm, and multiple buckle clamps are arranged on the surface of the outer circle of the rotary disc. According to the multifunctional buckle assembly automaticsystem, through the arrangement of the conveying sliding table mechanism, the buckle mechanical arm, the buckle feeding mechanism, the first conveying belt and the vertical conveying mechanism, the functions of automatic product feeding, buckle assembly and the like are combined, and lean production novelty is achieved; and by means of the multifunctional buckle assembly automatic system, the efficiency is improved, the cost is reduced, enterprise lean production management is facilitated, intelligent factories are achieved, and earned profits are improved.

Owner:清远敏实汽车零部件有限公司

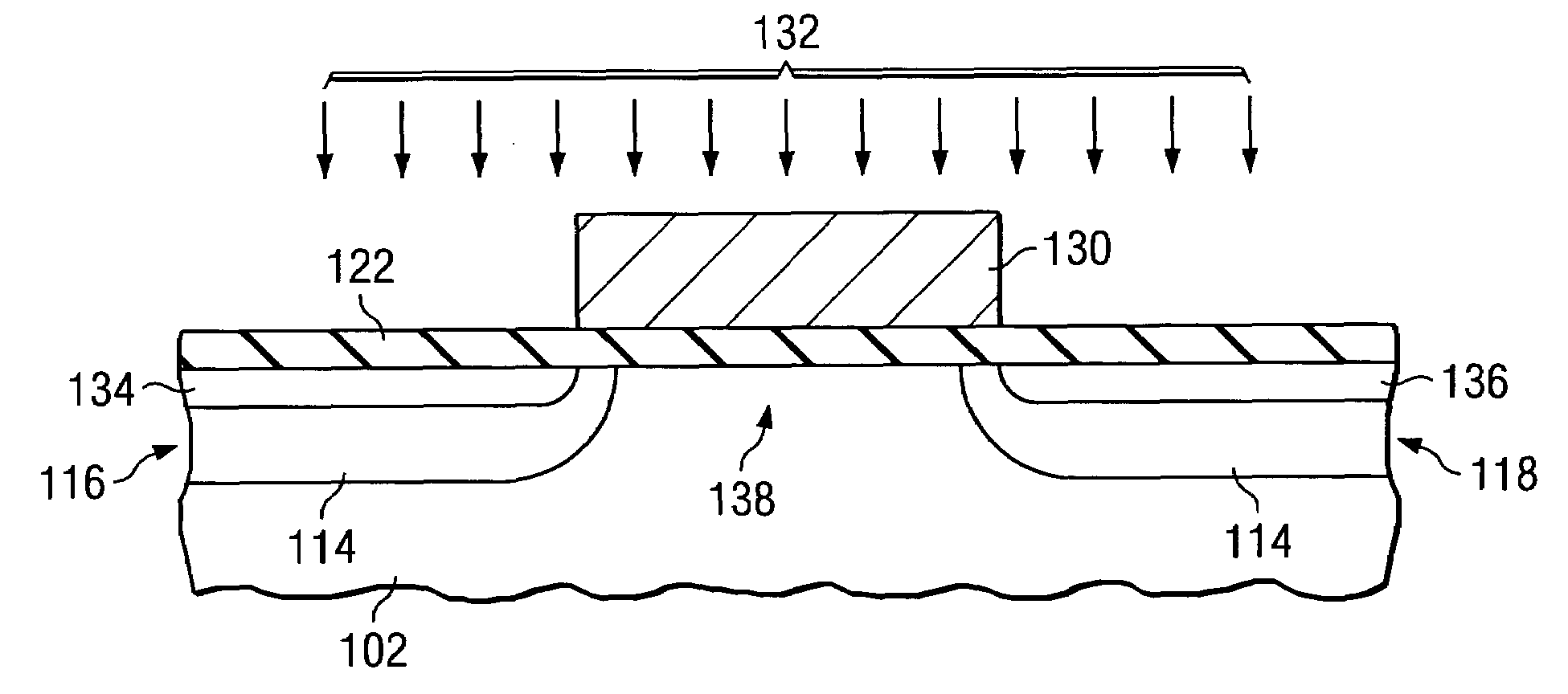

Fabrication of an OTP-EPROM having reduced leakage current

ActiveUS7244651B2Improve operating profitReduce leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingEPROMBiomedical engineering

The leakage current of an OTP-EPROM cell formed using buried channel PMOS technology can be reduced. The reduction in leakage current of the OTP-EPROM can be achieved by blocking implantation of the Vtp implant into a channel region of an n-well that substantially underlies a floating gate structure. The Vtp implant can be blocked by providing a mask overlying the surface of the channel region of the n-well during implantation of the Vtp implant.

Owner:TEXAS INSTR INC

Semiconductor device, memory system and electronic apparatus

InactiveUS6664603B2Easy to makeImprove operating profitTransistorSemiconductor/solid-state device detailsEngineeringSemiconductor

Owner:SEIKO EPSON CORP

Plasma display apparatus and method of driving a plasma display panel

InactiveUS20070120771A1Improve operating profitHigh resolutionStatic indicating devicesImage resolutionEngineering

An interlace-type PDP is driven by an improved driving method so as to achieve a greater operating margin, higher resolution, and higher brightness. The interlace-type PDP is driven using odd and even frames in such a manner that the cells are grouped into cell groups such that each cell group includes two or three cells which are adjacent in a direction crossing the electrode pairs, and the cells are driven in units of cell groups. The grouping of cells is performed differently for even and odd frames such that, in one type of frame, locations of two or three cells grouped into each group are shifted by one cell, in the direction crossing the electrode pairs, from the locations of cells grouped together in the other type of frame.

Owner:MAXELL HLDG LTD

Non-volatile memory device and method for controlling the same

ActiveUS8400824B2Improve operating profitAvoid misuseRead-only memoriesDigital storageSensing dataAudio power amplifier

A non-volatile memory and method for controlling the same prevents a faulty operation from being generated in a read operation, resulting in increase in operation reliability. The non-volatile memory device includes a cell array configured to include a plurality of unit cells in which a read or write operation of data is achieved in a unit cell in response to a variation of resistance, a reference cell array configured to include a plurality of reference cells, each of which has the same structure as that of the unit cell, a global reference current generation circuit configured to generate a global reference current corresponding to a position of the reference cell so as to verify data stored in the reference cell array, and a sense-amplifier configured to compare a current flowing in the reference cell array with the global reference current during a write verification operation of the reference cell array, and thus sense data.

Owner:SK HYNIX INC

Static random access memory and riving method thereof

ActiveUS20150364184A1Improve operating profitReduce power consumptionRead-only memoriesDigital storageMultiplexingStatic random-access memory

A static random access memory comprises a pre-charge unit that supplies a pre-charge voltage to first and second bit lines connected to a bit cell; a capacitor, of which one or the other terminal is selectively connected to a ground terminal; a clamping unit that selectively connects the bit lines with the capacitor to adjust a voltage level of the bit lines; and a mux unit that is included in a unit memory cell including the bit cell, the pre-charge unit, the capacitor and the clamping unit, and activates the bit lines of the unit memory cell in response to reception of a selection signal; wherein the clamping unit connects the first and second bit lines with the capacitor in response to a charge sharing control signal, to induce charge sharing between the first and second bit lines and the capacitor.

Owner:KOREA UNIV RES & BUSINESS FOUND

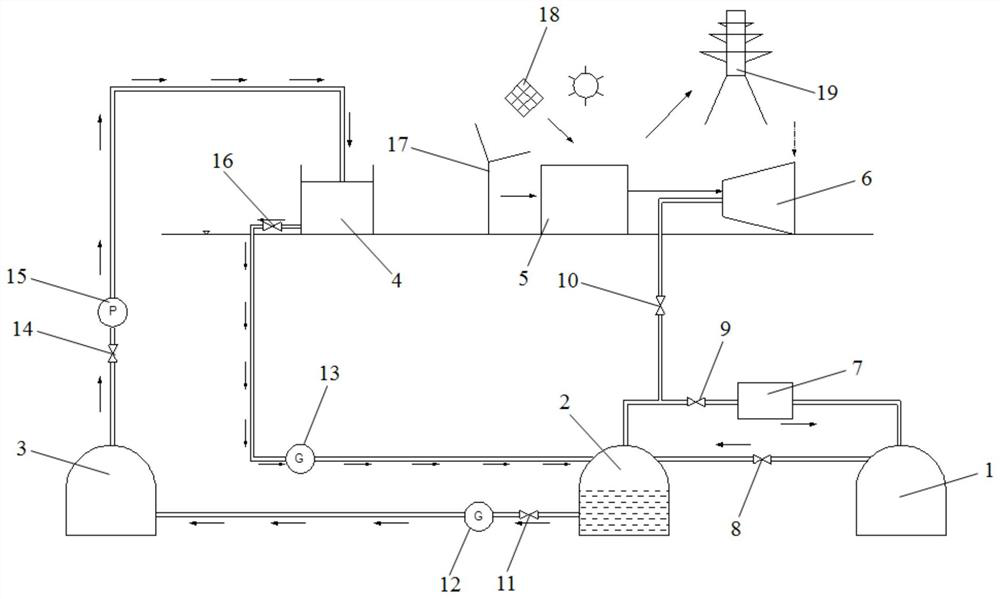

Water pumping and air compressing integrated energy storage system utilizing abandoned mine underground roadway

InactiveCN113464345AImprove operating profitRealize the second energy storagePressure pumpsHydro energy generationAir pumpAir compressor

The invention relates to a water pumping and air compressing integrated energy storage system utilizing an abandoned mine underground roadway. The water pumping and air compressing integrated energy storage system comprises an earth surface center power supply unit, a compressed air energy storage unit, a water pumping energy storage unit, a first turbine generator and a second turbine generator, wherein an air compressor and a high-pressure air pump in the compressed air energy storage unit are driven by the earth surface center power supply unit to store high-pressure air in a high-pressure air storage roadway, so that renewable energy absorbed by the earth surface center power supply unit is converted into compressed air stored energy; a water pumping electric motor in the water pumping energy storage unit is driven by the earth surface center power supply unit to extract water in an underground water storage reservoir to an earth surface reservoir, so that the renewable energy absorbed by the earth surface center power supply unit is converted into gravitational potential energy; and finally, the compressed air stored energy and the gravitational potential energy are converted into electric energy so as to be output through the turbine generators. Compared with the prior art, the water pumping and air compressing integrated energy storage system utilizing the abandoned mine underground roadway provided by the invention has high economical efficiency and energy storage efficiency, and a new way is provided for recycling of an abandoned mine.

Owner:TONGJI UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com