Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1190 results about "Data transmission circuit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In telecommunication, a data transmission circuit is the transmission media and the intervening equipment used for the data transfer between data terminal equipment (DTEs). A data transmission circuit includes any required signal conversion equipment.

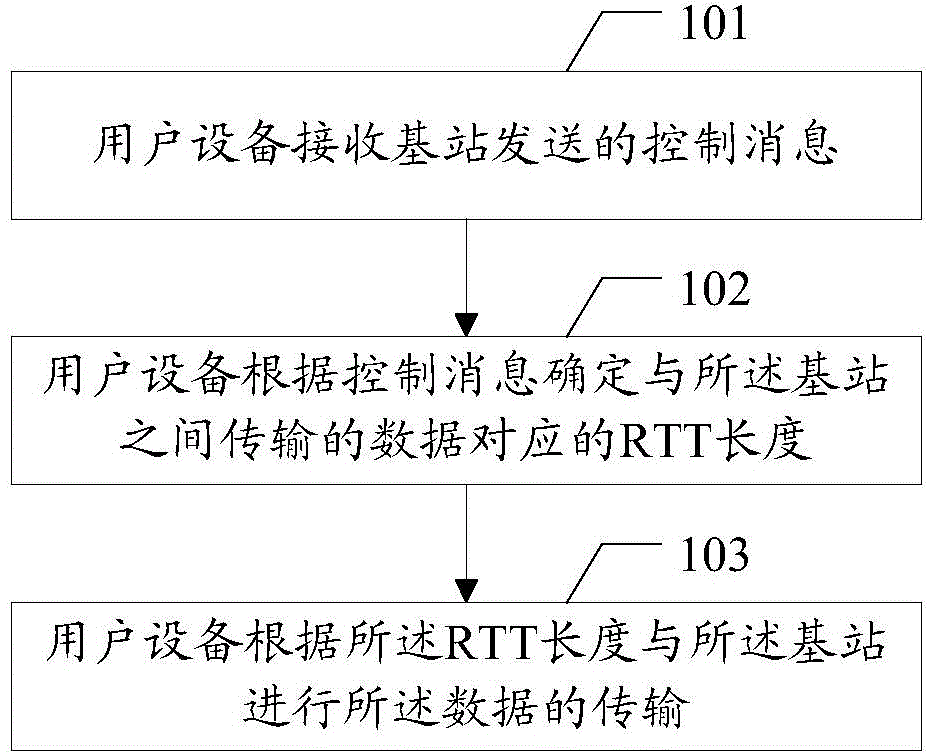

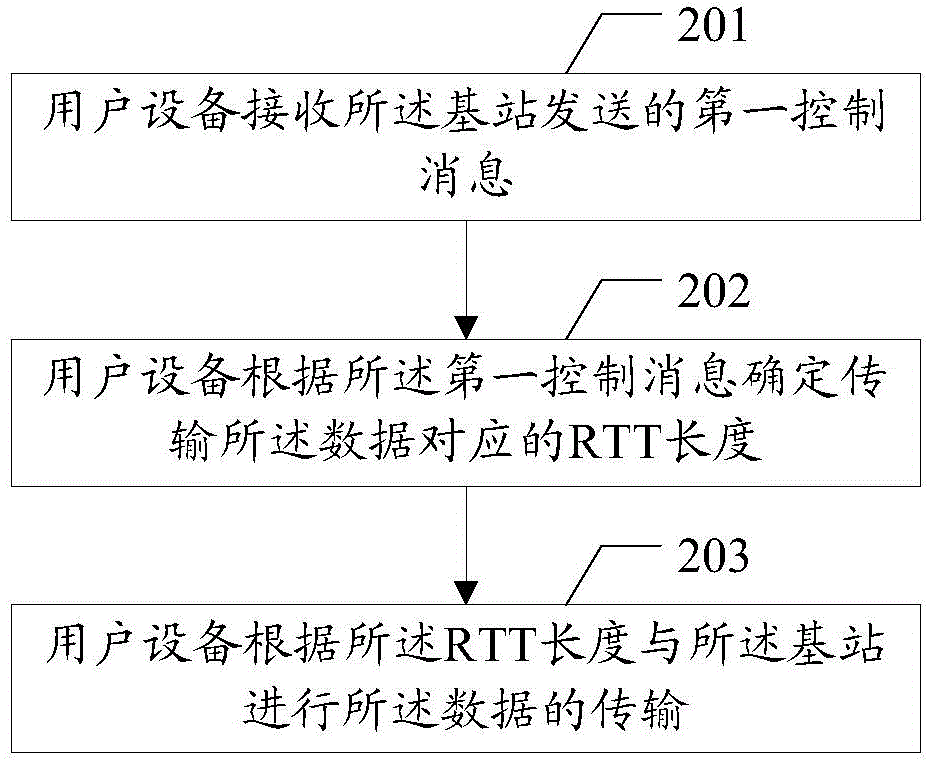

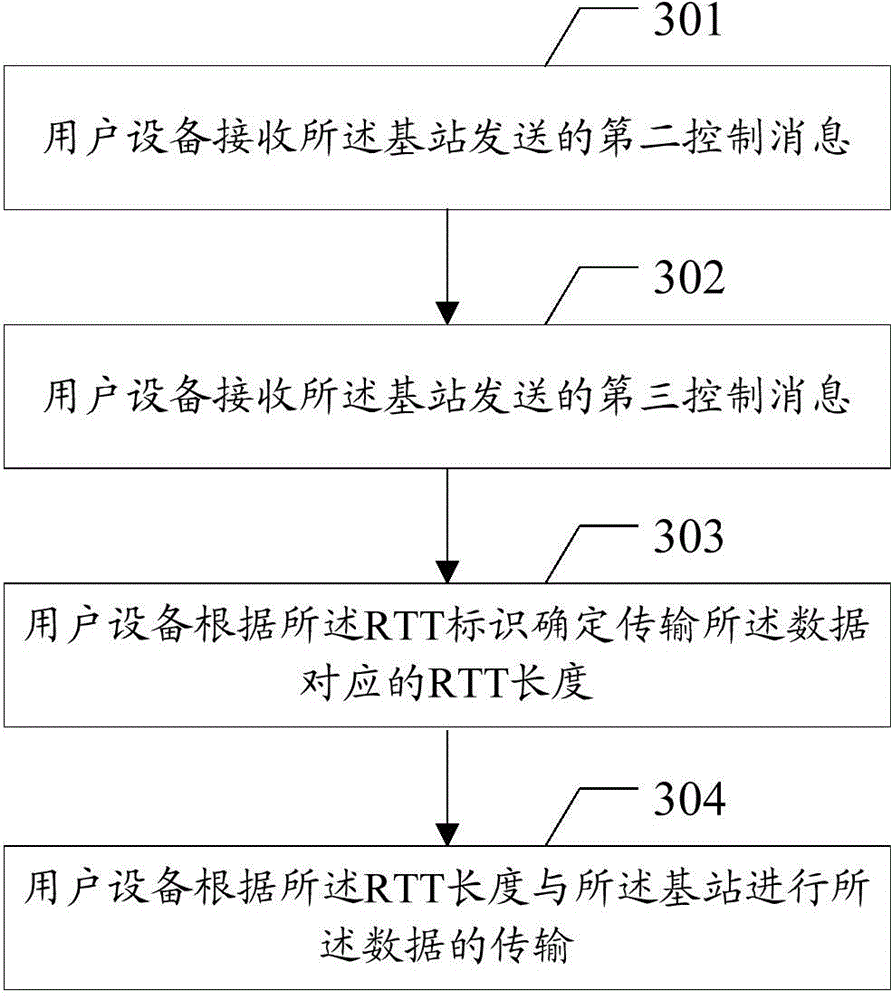

Data transmission method, user equipment and base station

InactiveCN104468030ASolve conflictsError preventionSignal allocationData transmission circuitUser equipment

The embodiment of the invention discloses a data transmission method, user equipment and a base station. The data transmission method, the user equipment and the base station are used for solving the problem about conflicts in the data transmission process under the condition of scene coexistence of different kinds of processing delay. The method includes the steps that the user equipment receives a control message sent by the base station, the control message is used for determining RTT length corresponding to data transmitted between the user equipment and the base station; the user equipment determines the RTT length corresponding to the data transmitted between the user equipment and the base station according to the control message; data transmission between the user equipment and the base station is achieved according to the RTT length.

Owner:SHANGHAI HUAWEI TECH CO LTD

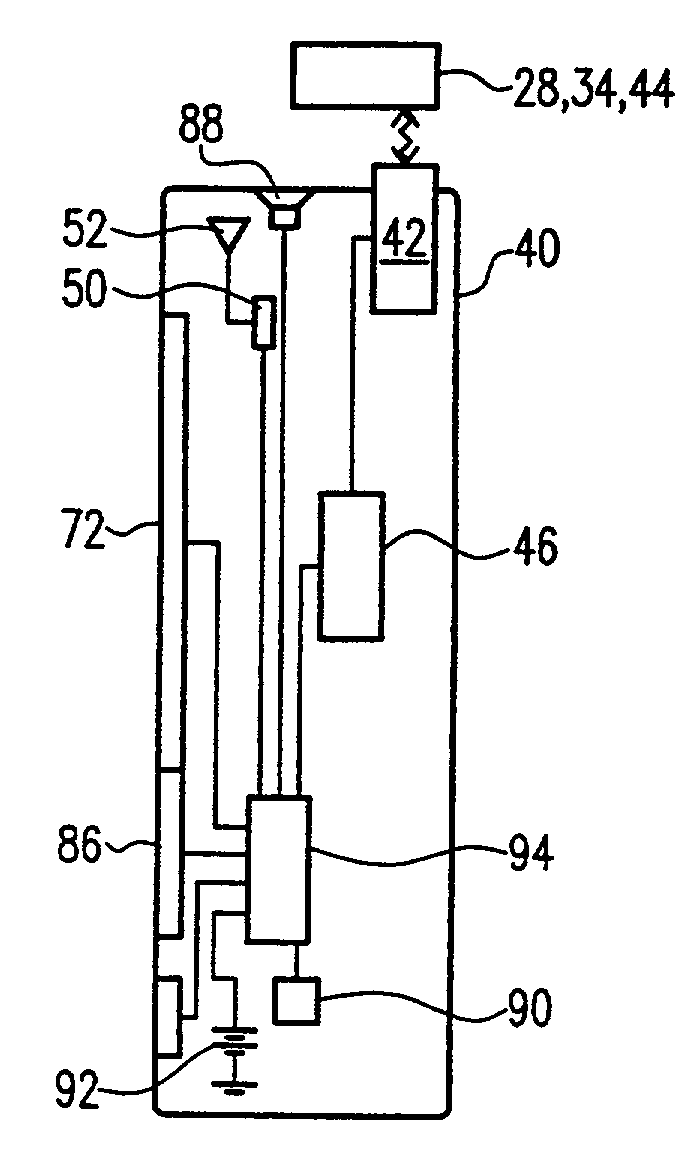

Portable electronic terminal and data processing system

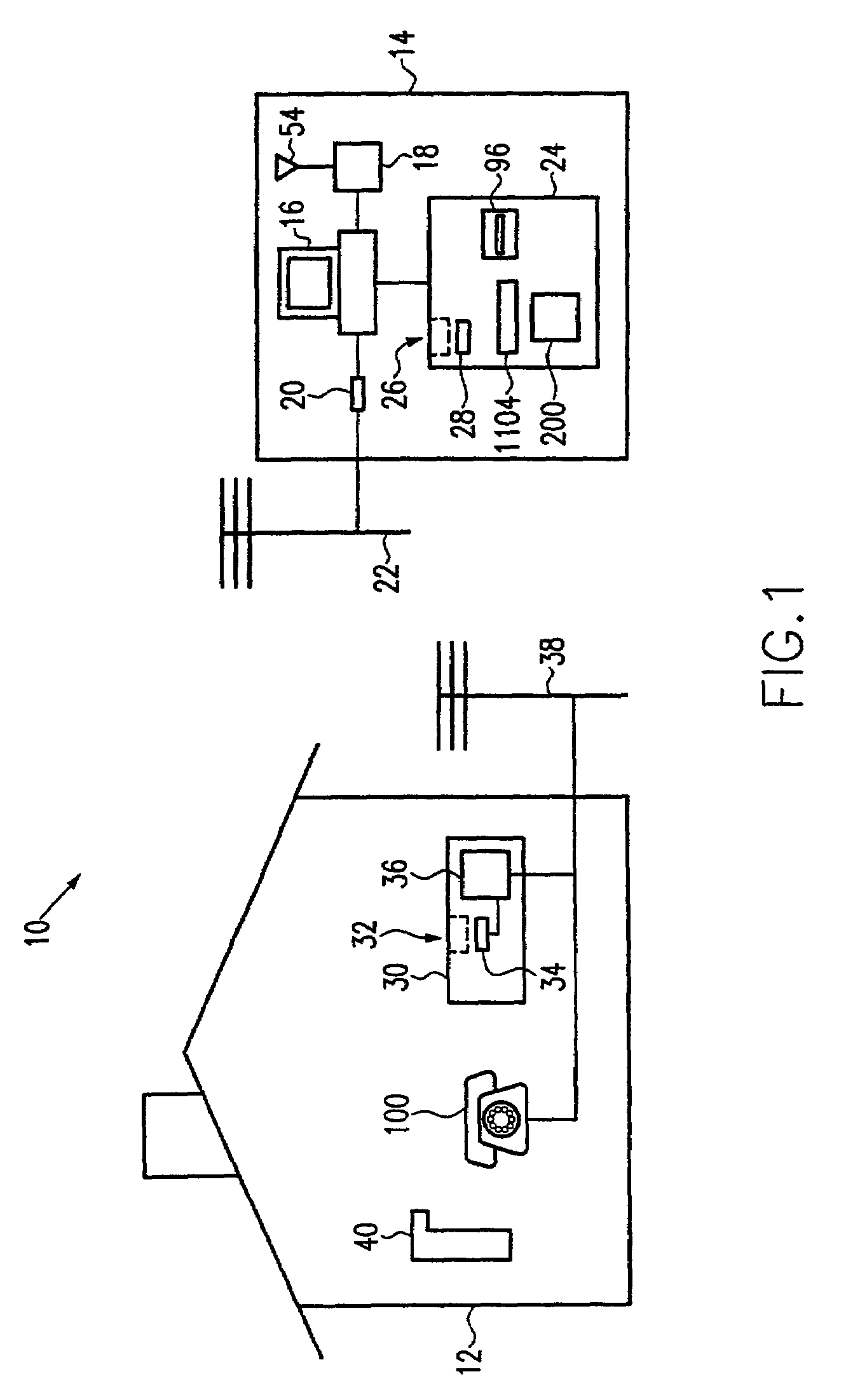

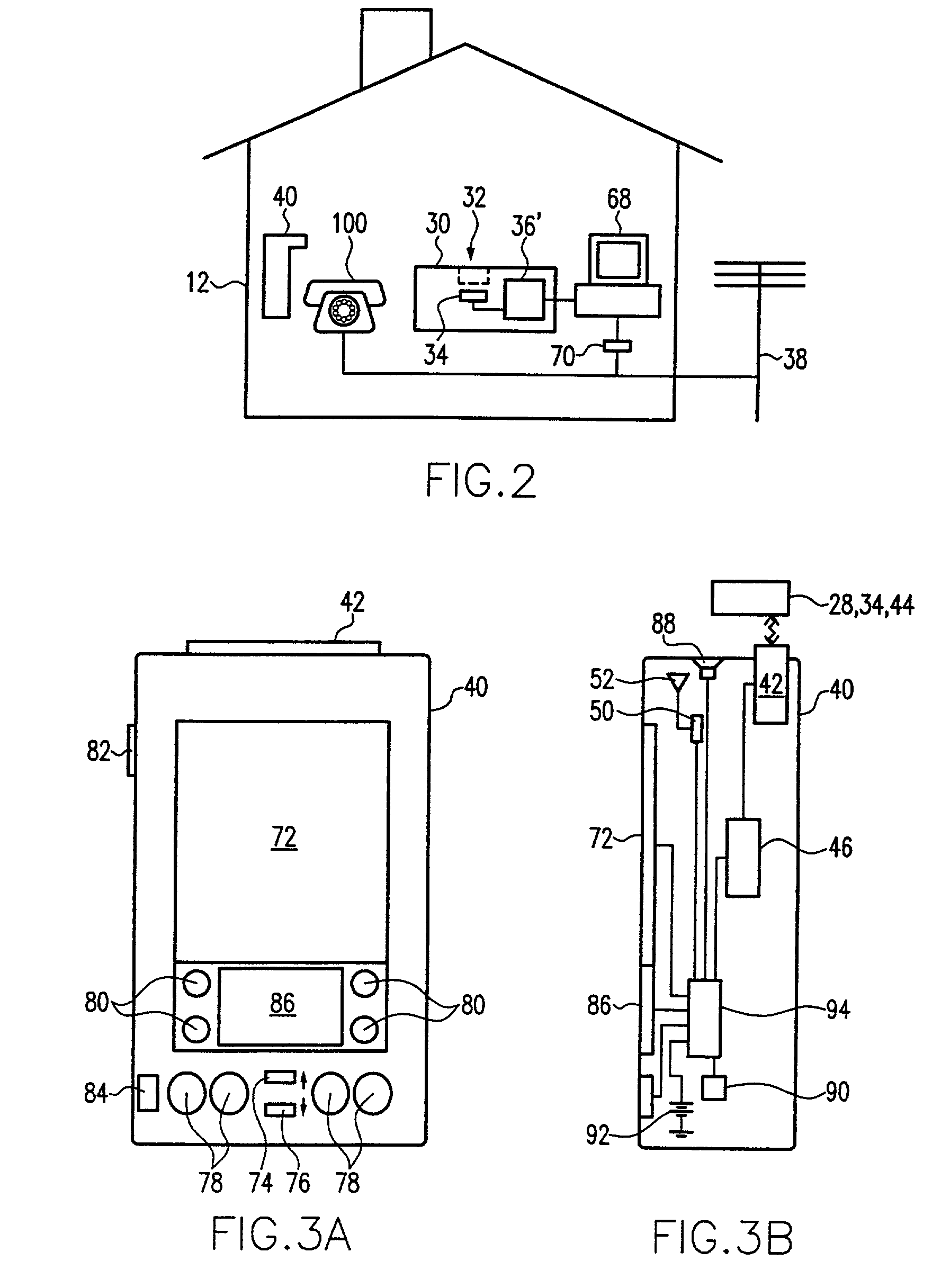

InactiveUS7171378B2Improve securityImprove programmabilityCredit registering devices actuationBuying/selling/leasing transactionsWireless transceiverModem device

The present invention relates to a personal shopping system for combined use in both the home of a user and a shopping establishment. The system includes a host computer which is coupled to a host modem and, optionally, to at least one wireless multi-access point. At least one shopping establishment kiosk cradle is employed to interface with a portable terminal which is also part of the system. The portable terminal can be used in both the shopping establishment and the home of the user. It is configured to read bar codes associated with items related to shopping, and includes a memory, a bar code reader, a wireless transceiver, and a data interface. The data interface of the terminal communicates with a data interface of the shopping establishment kiosk cradle. A home cradle for the portable terminal is also provided and is adapted to remain in the home of the user. It includes a home portable terminal-receiving station and a home data interface to communicate with the data interface of the portable terminal. A home data transfer circuit is also included to permit data exchange between the home data interface and the modem coupled to the host computer.

Owner:SYMBOL TECH INC

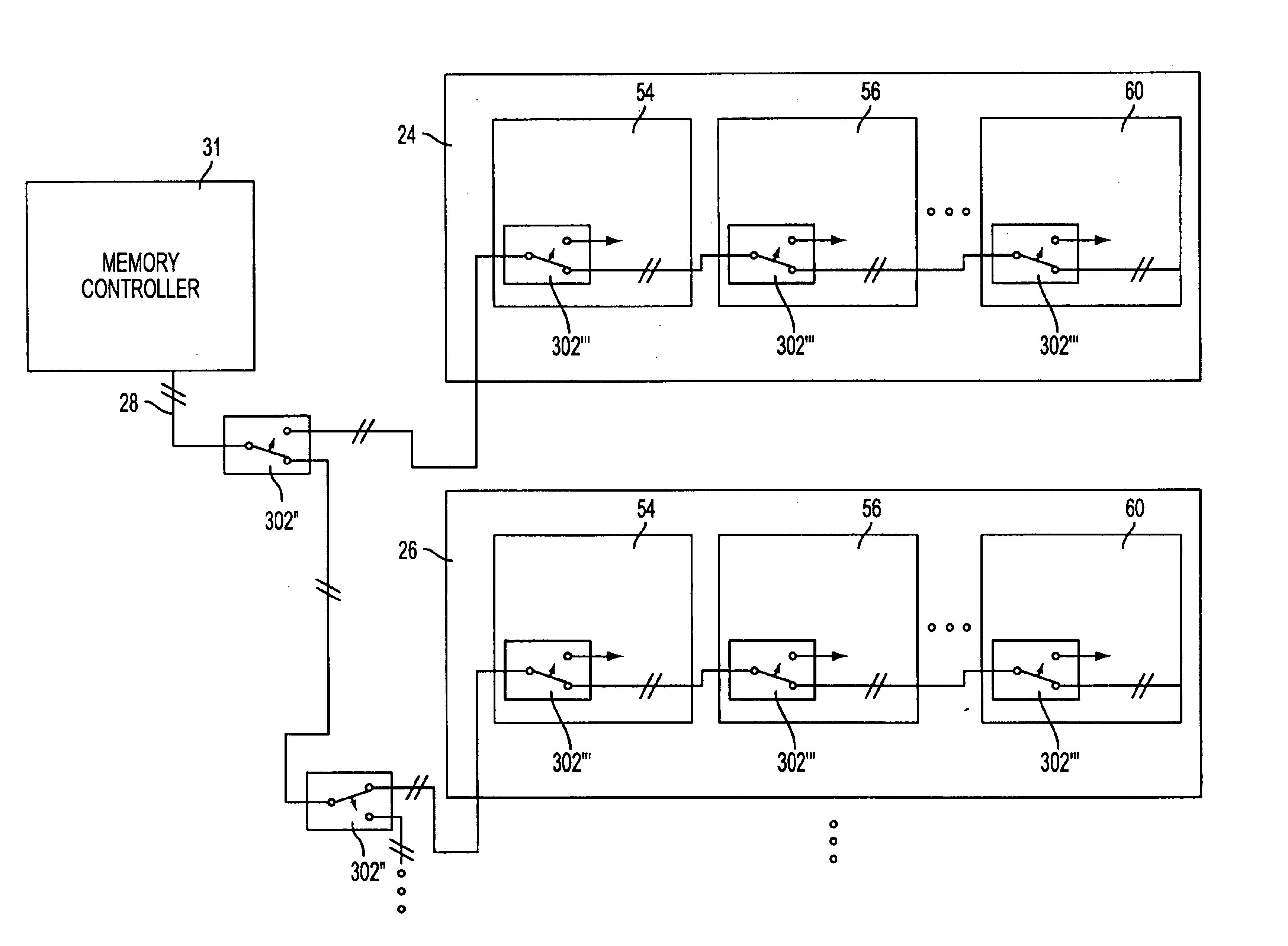

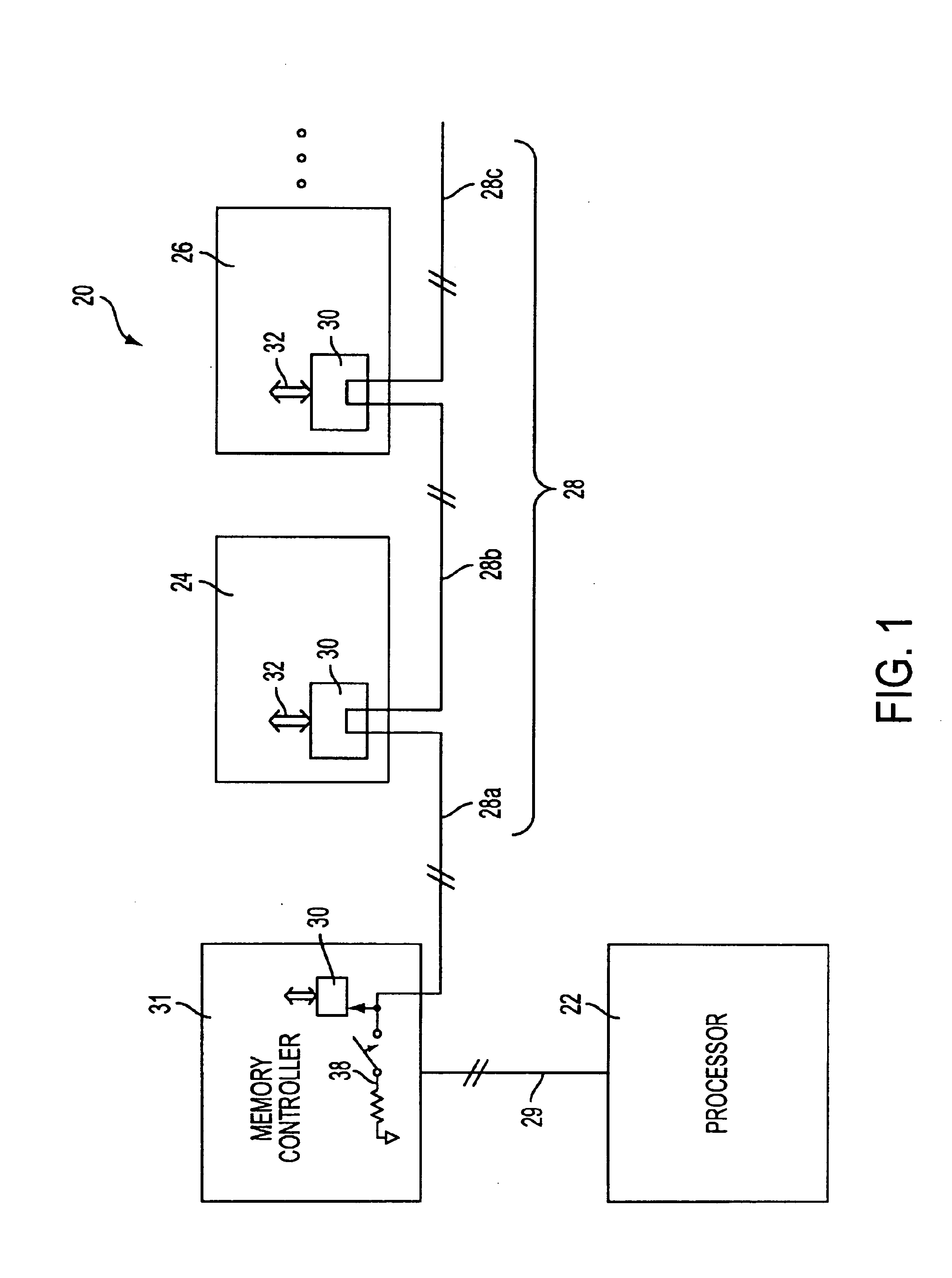

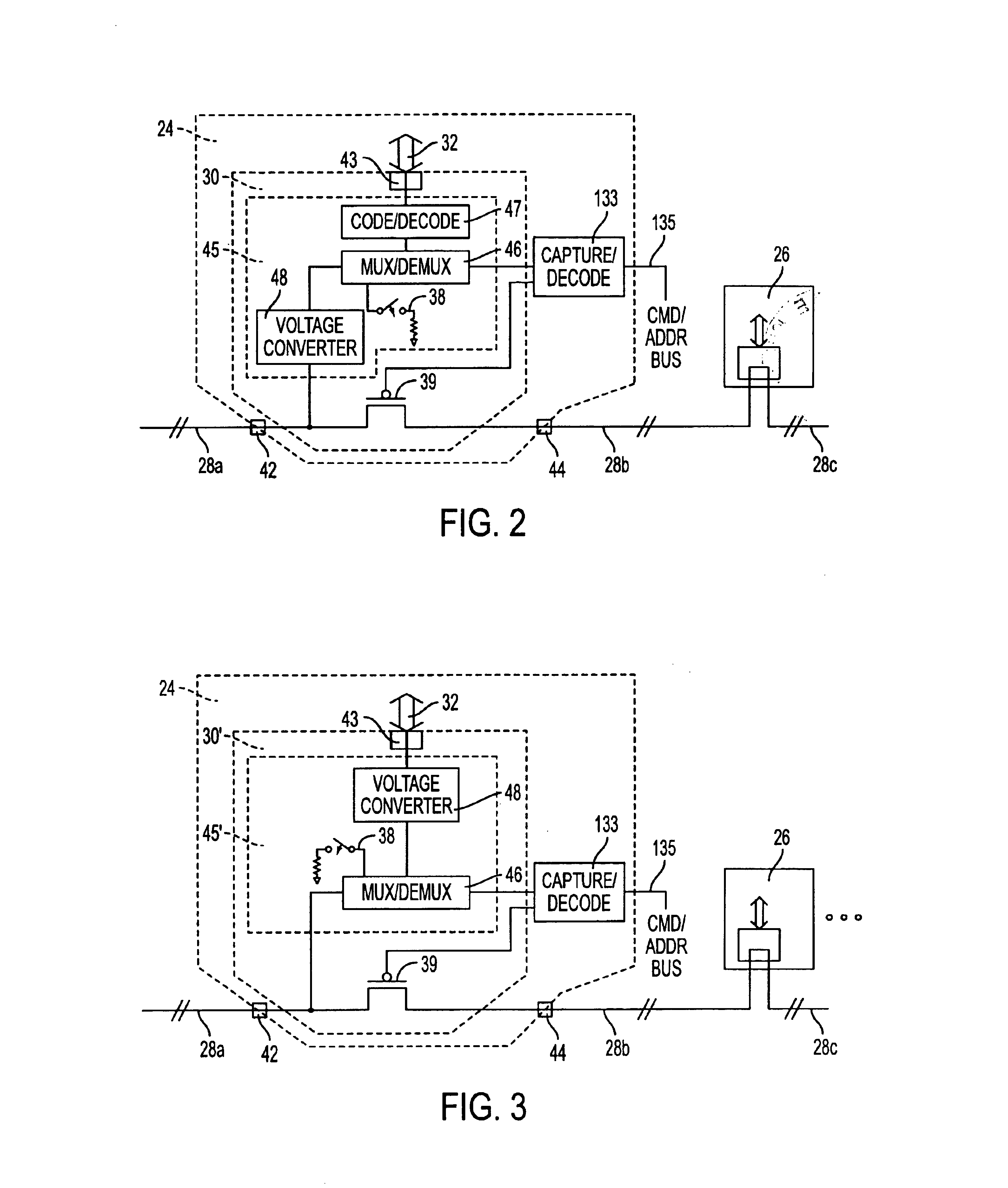

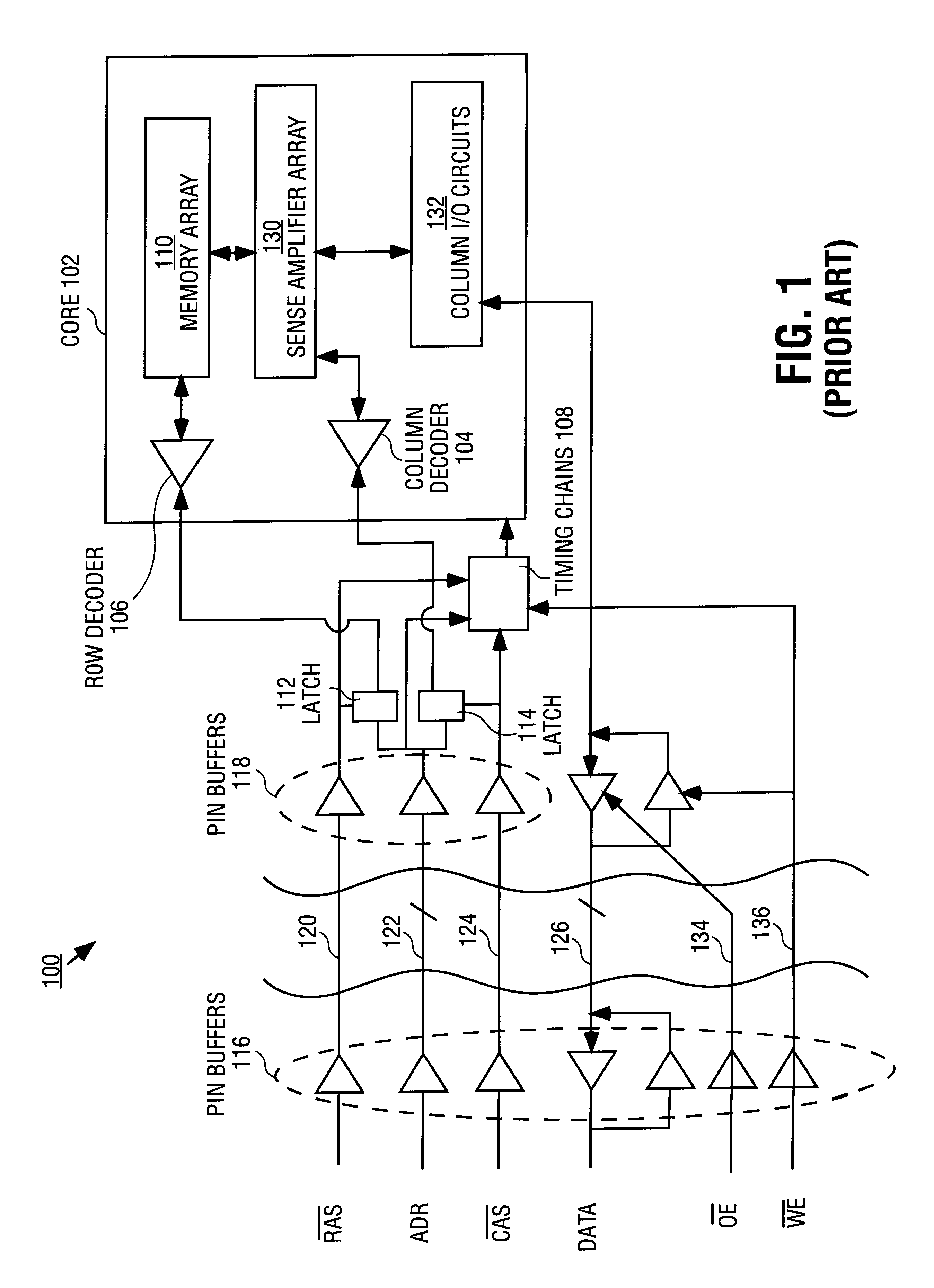

Data transmission circuit for memory subsystem, has switching circuit that selectively connects or disconnects two data bus segments to respectively enable data transmission or I/O circuit connection

InactiveUS6871253B2Improve acceleration performanceReduce reflectionEnergy efficient ICTDigital data processing detailsElectricityHigh speed memory

A method and associated apparatus is provided for improving the performance of a high speed memory bus using switches. Bus reflections caused by electrical stubs are substantially eliminated by connecting system components in a substantially stubless configuration using a segmented bus wherein bus segments are connected through switches. The switches disconnect unused bus segments during operations so that communicating devices are connected in an substantially point-to-point communication path.

Owner:MICRON TECH INC

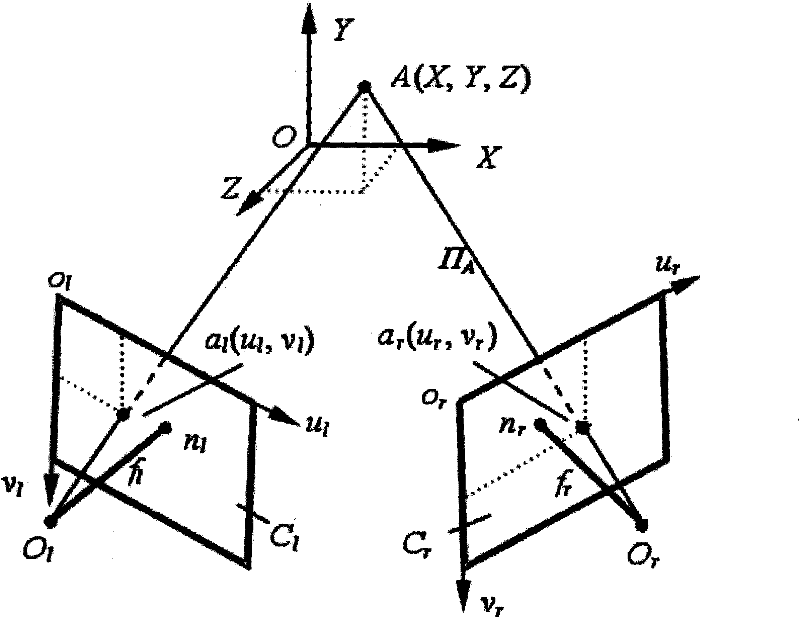

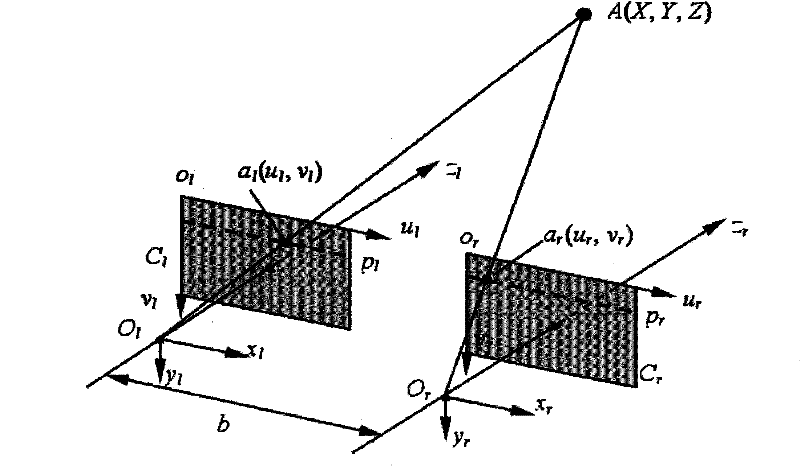

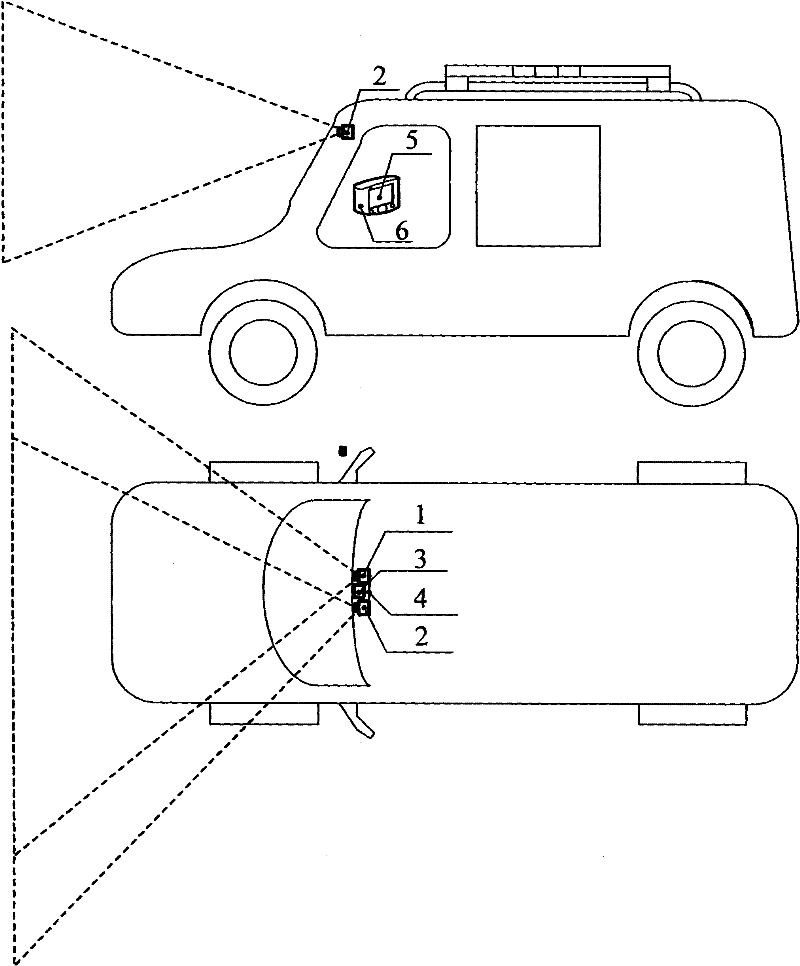

Active safety type assistant driving method based on stereoscopic vision

InactiveCN102685516AAvoid tailgatingPreventing accidents such as frontal collisionsImage enhancementImage analysisActive safetyDriver/operator

The invention discloses an active safety type assistant driving method based on stereoscopic vision. An active safety type assistant driving system comprehensively utilizes an OME information technology, consists of a stereoscopic vision subsystem, an image immediate processing subsystem and a safety assistant driving subsystem and comprises two sets of high resolution CCD (charge-coupled device) cameras, an ambient light sensor, a two-channel video collecting card, a synchronous controller, a data transmission circuit, a power supply circuit, an image immediate processing algorithms library, a voice reminding module, a screen display module and an active safety type driving control module. According to the active safety type assistant driving method, separation lines and parameters such as relative distance, relative speed, the relative acceleration and the like of dangerous objects such as front vehicles, front bicycles, front pedestrians and the like can be accurately identified in real time in sunny days, cloudy days, at nigh and under the severe weather conditions such as rain with snow, dense fog and the like, so that the system can prompt a driver to adopt countermeasure through voice and can realize automatic deceleration and emergency brake at emergency situation, thereby ensuring safe travel in a whole day.

Owner:李慧盈 +2

Fragment storage for data alignment and merger

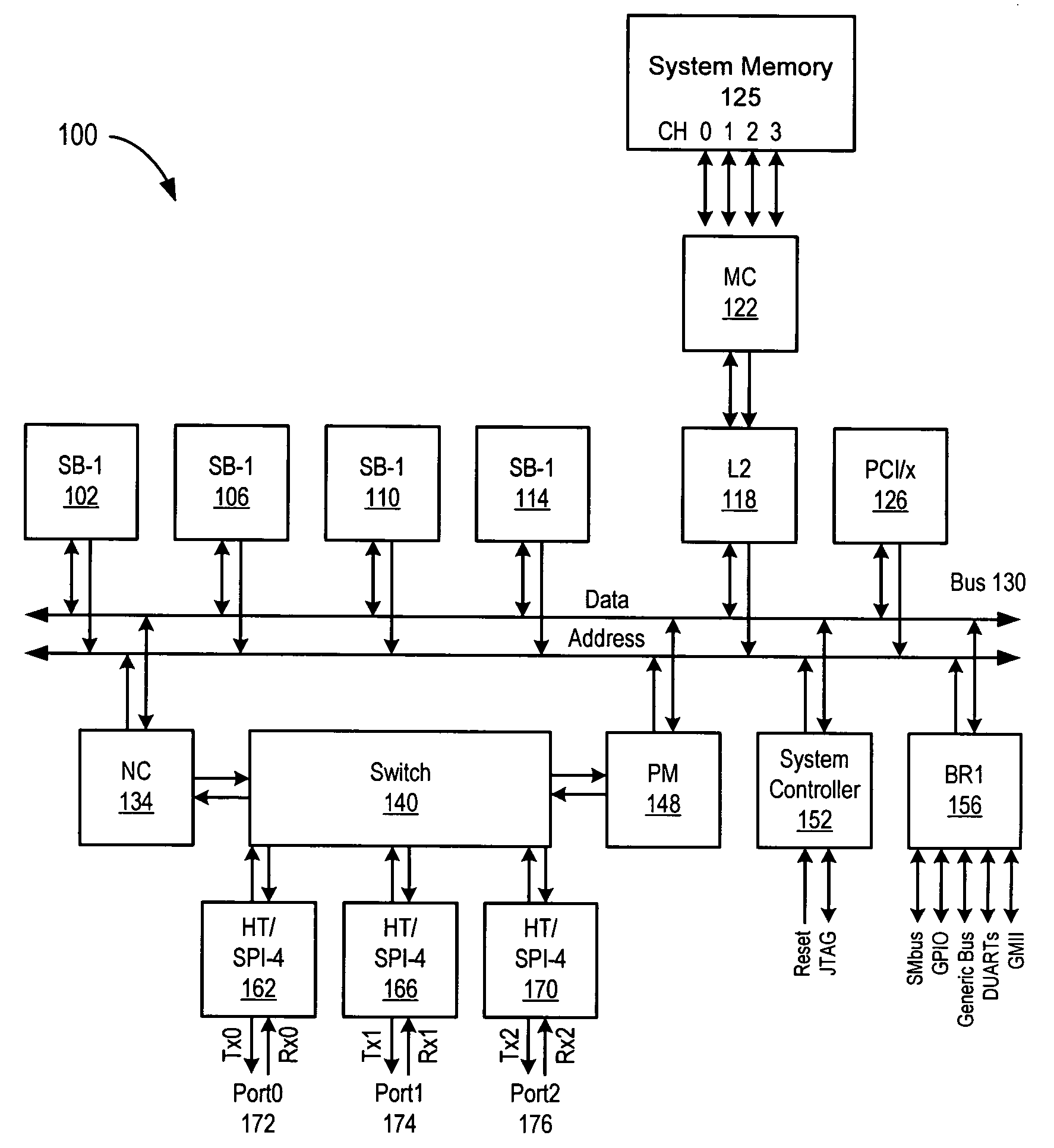

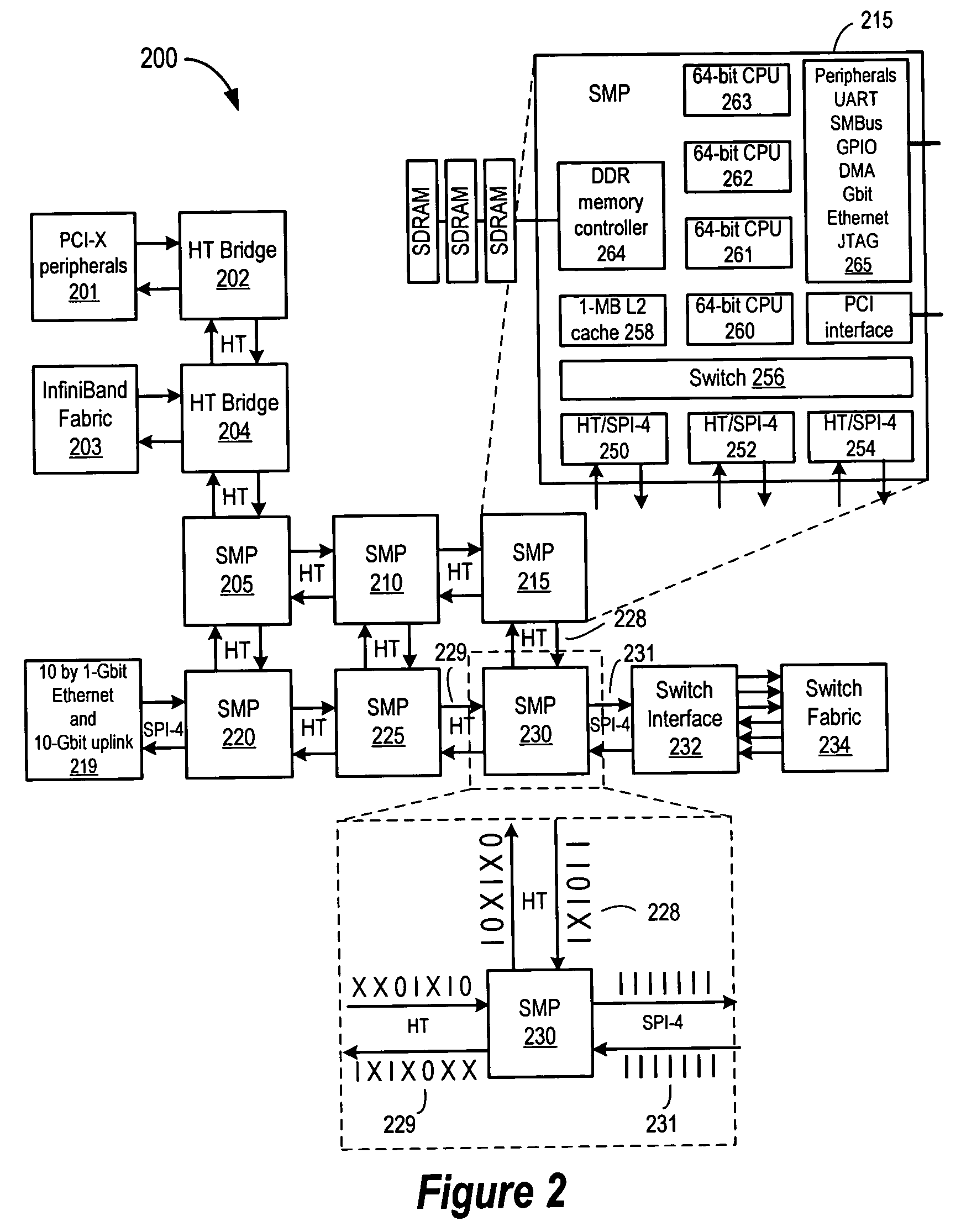

InactiveUS20050080953A1Input/output processes for data processingData conversionCMOSData transmission circuit

A multiprocessor switching device substantially implemented on a single CMOS integrated circuit is described in connection with a packet data transfer circuit that uses a fragment storage buffer to align and / or merge data being transferred to or from memory on a plurality of channels. In a packet reception embodiment, a data shifter and fragment store buffer are used to align received packet data to any required offset. The aligned data may and then be written to the system bus or combined with data fragments from prior data cycles before being written to the system bus. When packet data is being transferred to memory on a plurality of channels, the fragment storage may be channelized using register files or flip-flops to store intermediate values of packets and states for each channel.

Owner:AVAGO TECH INT SALES PTE LTD

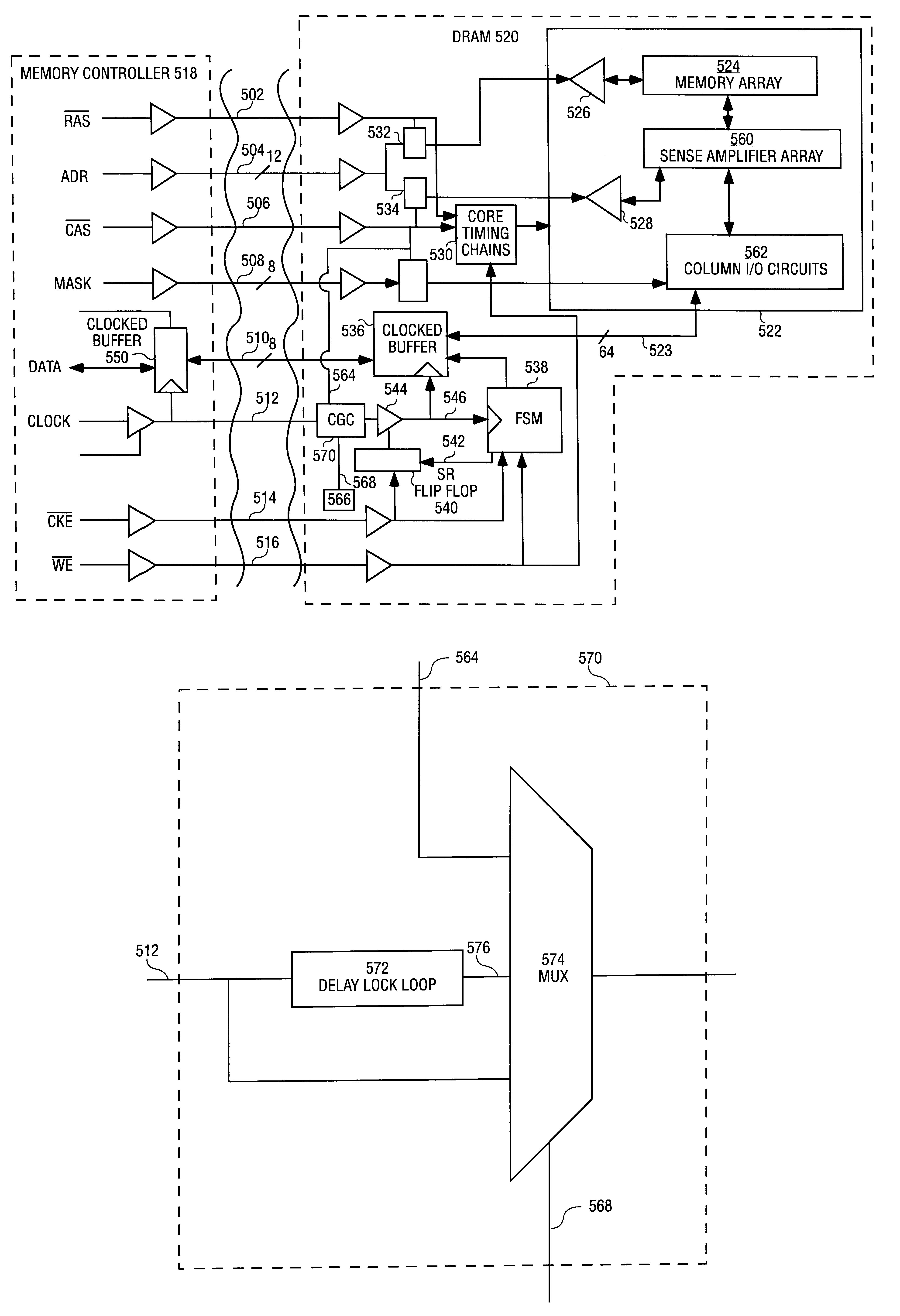

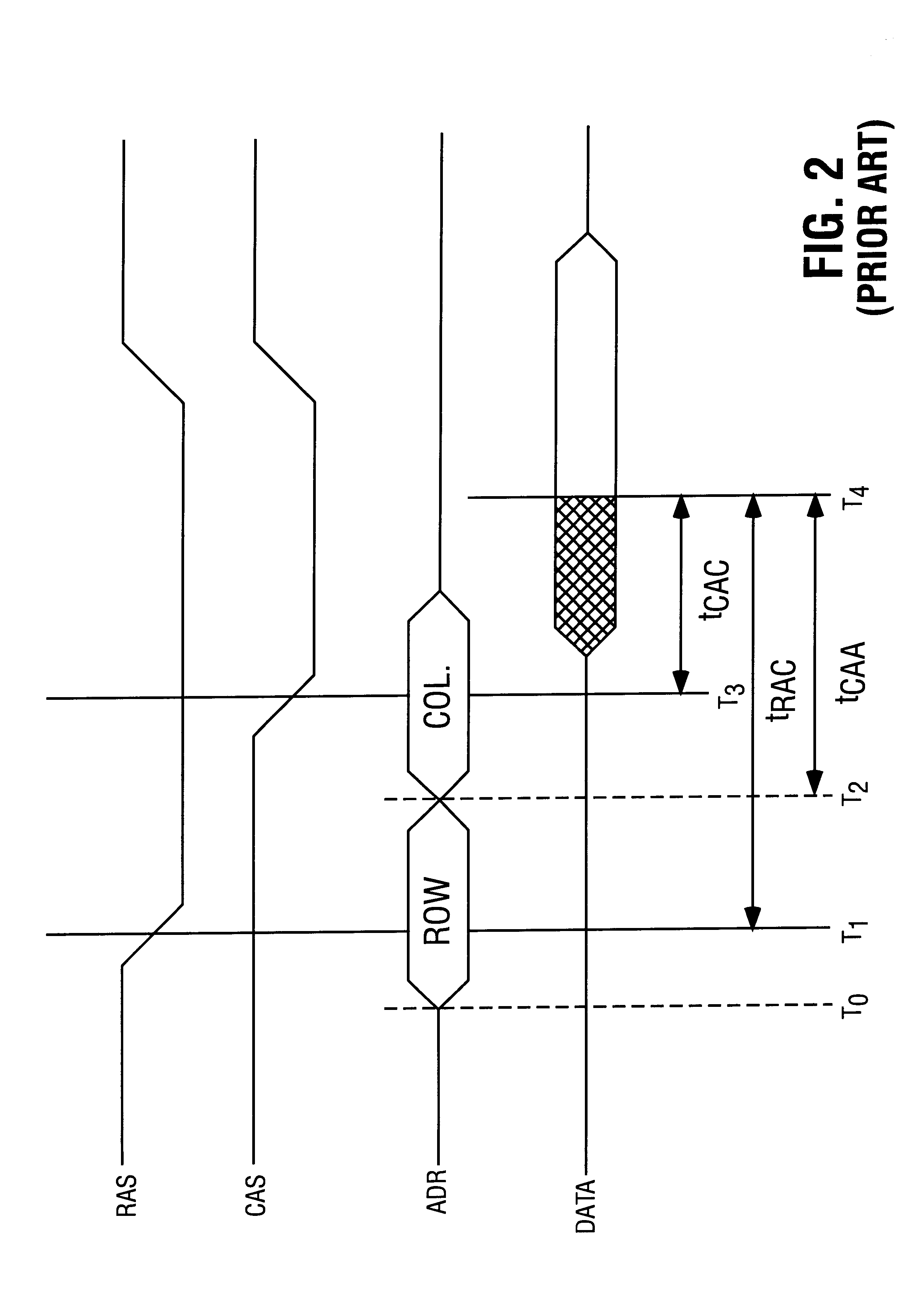

Asynchronous request/synchronous data dynamic random access memory

InactiveUS6209071B1Improve balanceReducing latency and power requirementEnergy efficient ICTDigital storagePower modeAsynchronous circuit

A method and system for transferring information within a computer system is provided. The system includes a memory device that has a lower power mode in which data transfer circuitry is not driven by a clock signal, and a higher power mode in which data transfer circuitry is driven by a clock signal. The system further includes a memory controller that sends control signals to the memory device to initiate a data transfer transaction. The memory device receives the control signals asynchronously, and assumes the second mode in response to one of the control signals. While the memory device is in the second mode, the memory controller sends a control signal to identify a particular clock cycle. The memory device synchronously transfers the data. The memory device determines when to begin the data transfer based on the identified clock cycle and the type of data transfer that has been specified.

Owner:RAMBUS INC

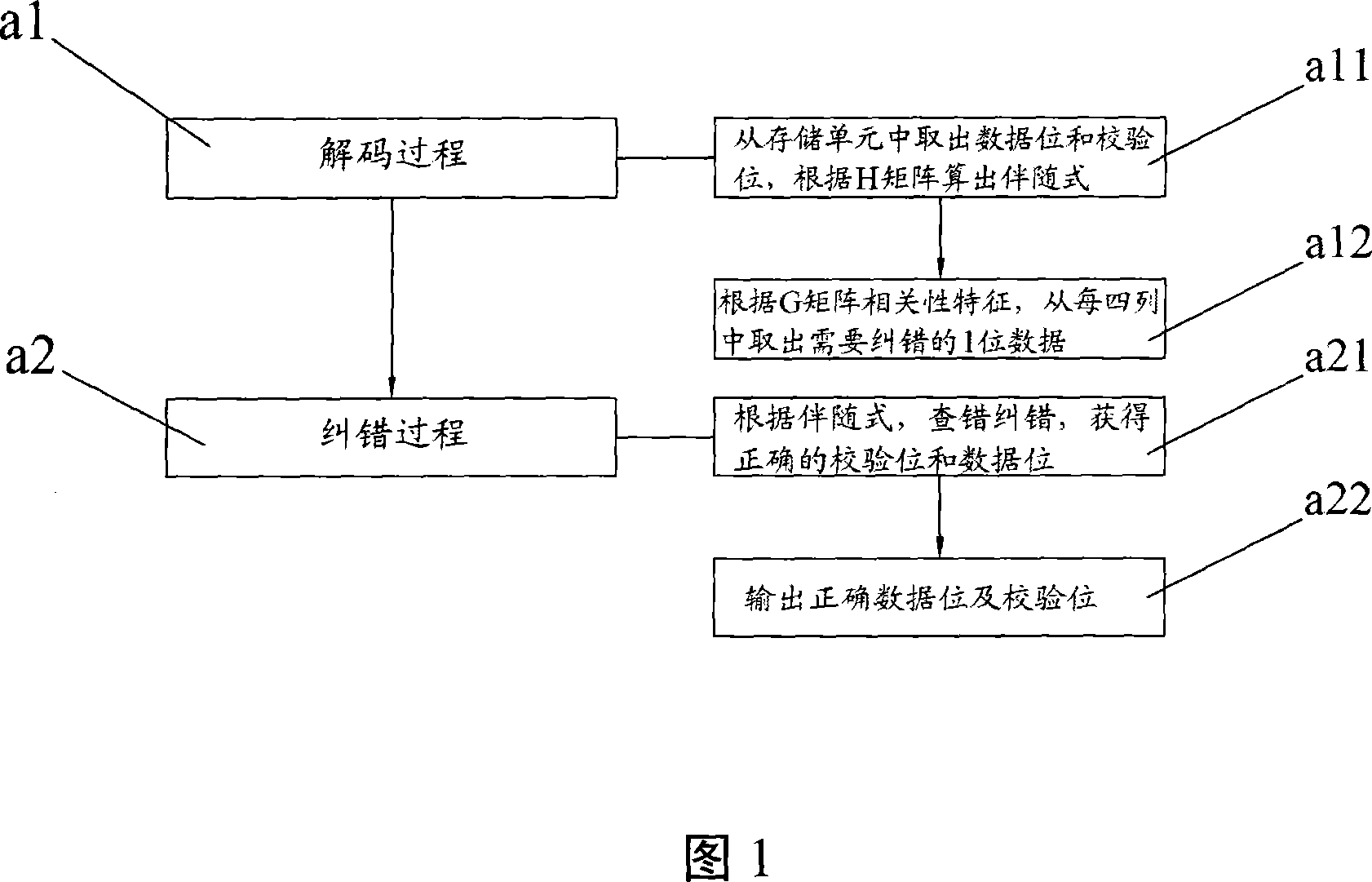

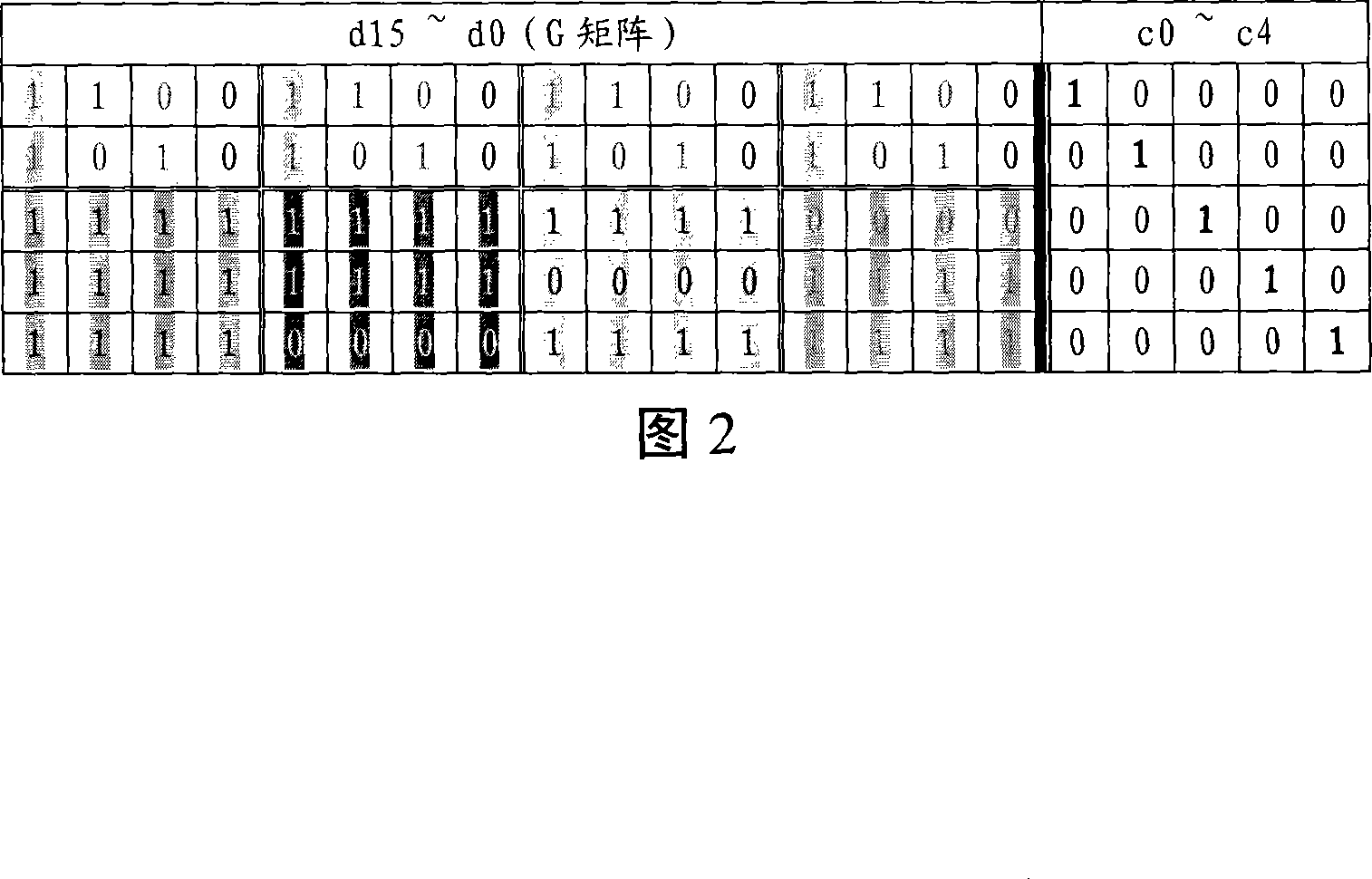

Memory error-detecting and error-correcting coding circuit and method for reading and writing data utilizing the same

ActiveCN101067972ASignificant simplificationImprove encoding rateStatic storageError checkComputer architecture

This invention relates to an error-check and error-correction code circuit for storages and a method for reading and writing data by it taking matrix G as a logic core including: a decoding process and a coding process and a method for writing in data by this method. Apart from a decoding process and an error correction process, it also includes a coding process, and finally puts forward an error check and correction and coding circuit for realizing said two methods including a decoder, an error-correction circuit, a coding circuit, an interface circuit and related data transmission circuit so as to simplify layout of bottom circuit and speed up operation speed of circuits.

Owner:GIGADEVICE SEMICON (BEIJING) INC

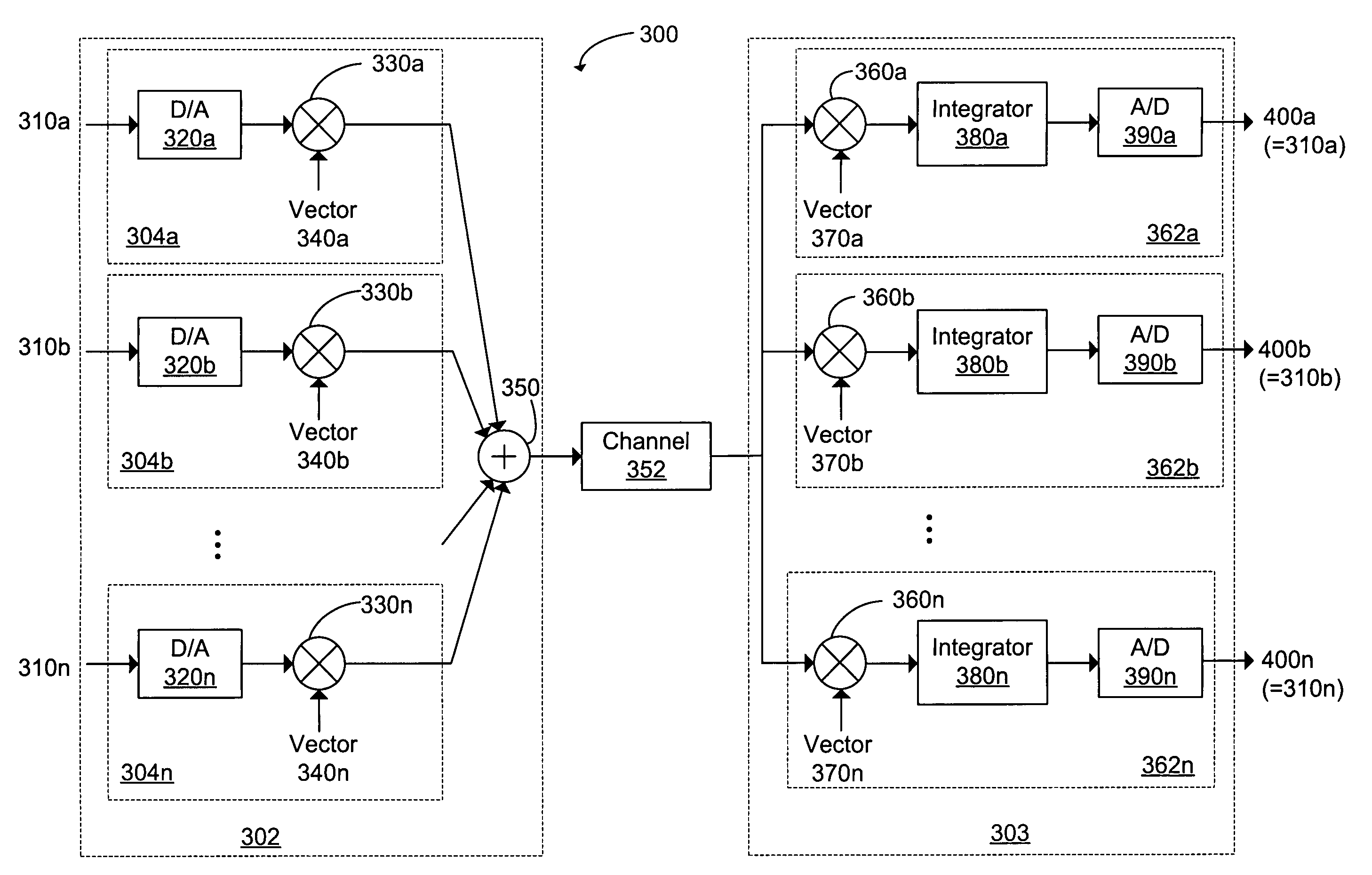

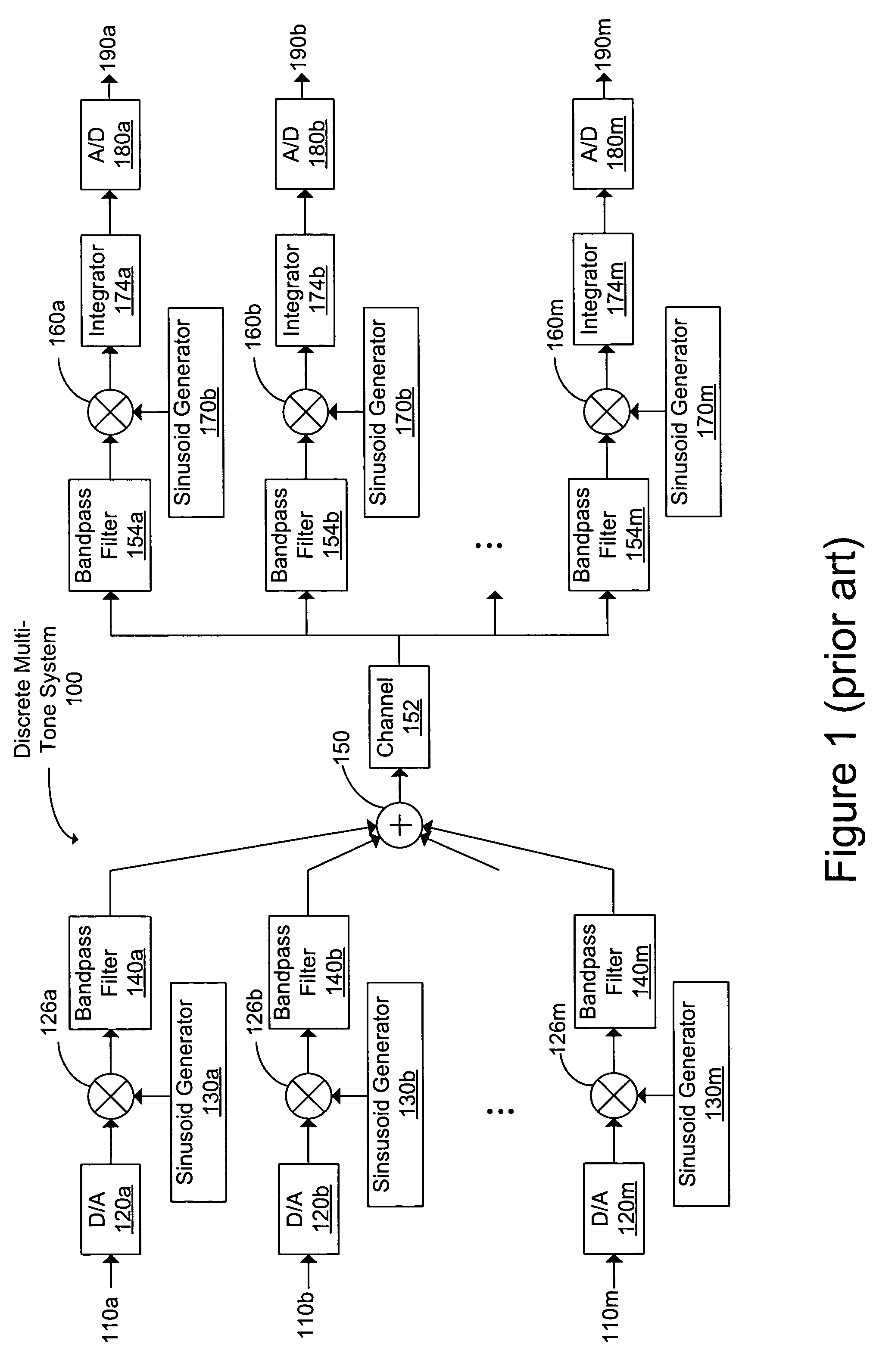

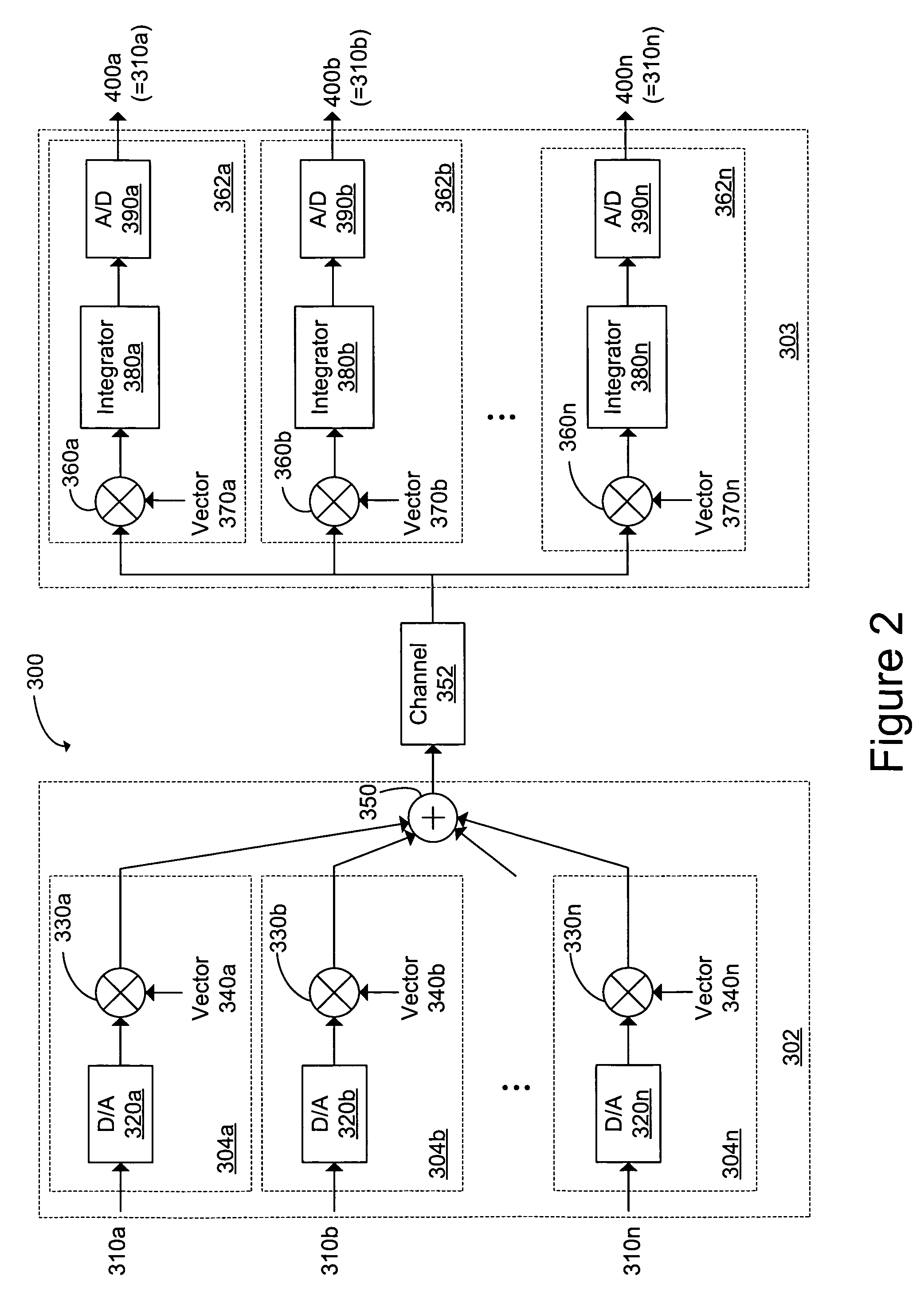

Approximate bit-loading for data transmission over frequency-selective channels

InactiveUS7599390B2Multiplex system selection arrangementsTime-division multiplexFrequency spectrumBinary multiplier

A high-speed communications system utilizes approximate bit-loading during data transmission in a channel. In one embodiment, a plurality of parallel data preparation circuits in a data transmission circuit receive respective subsets of a data stream, each of the respective subsets of the data stream having a data rate that is less than a data rate of the data stream. Converters in the data preparation circuits convert the respective subsets of the data stream into respective analog signals. Multipliers in the data preparation circuits multiply the respective analog signals by respective vectors to produce respective sub-channel signals. At least a frequency band in the spectrum corresponding to one of the respective sub-channel signals partially overlaps at least a frequency band for at least one other of the respective sub-channel signals. The respective sub-channel signals are combined prior to transmission.

Owner:RAMBUS INC

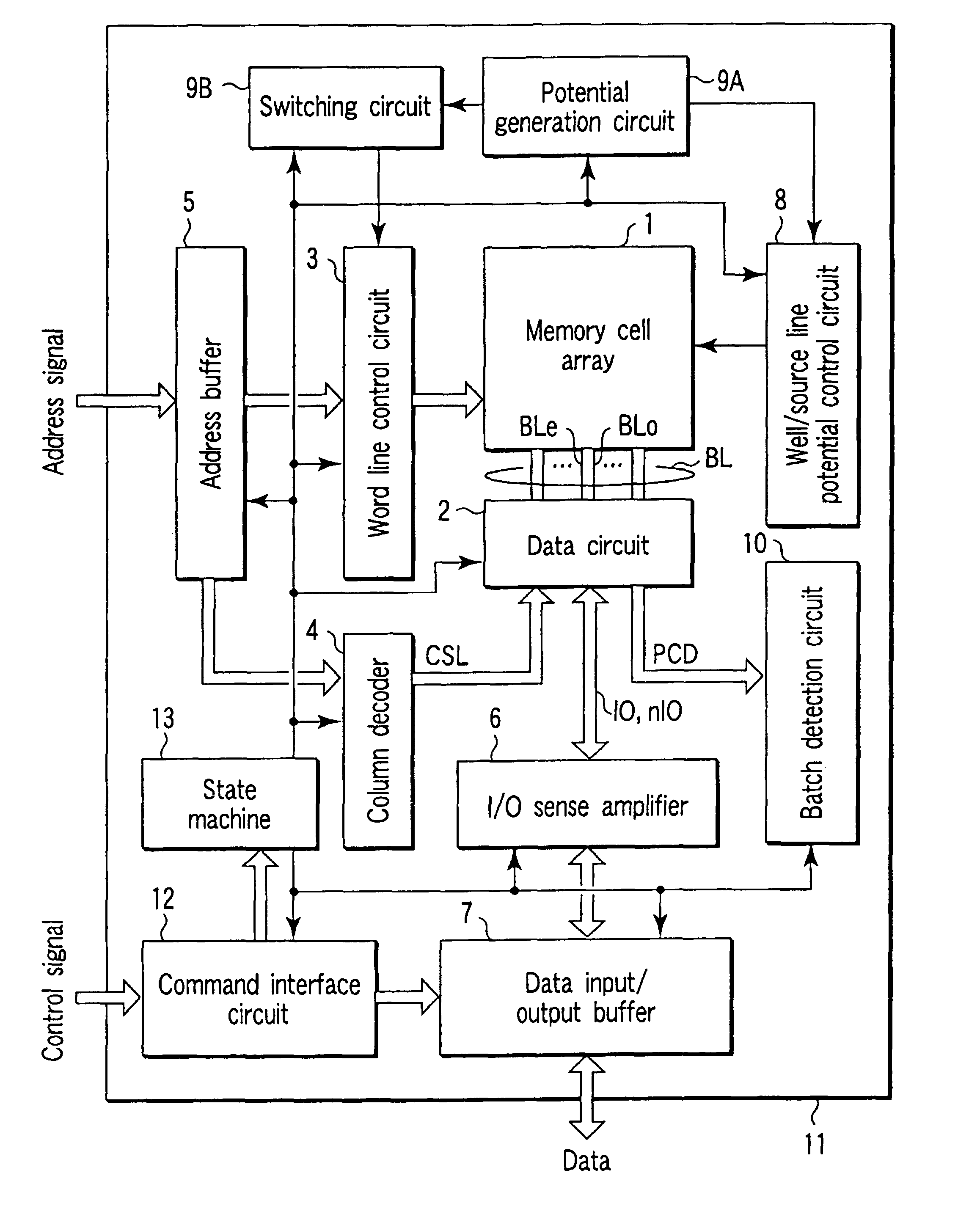

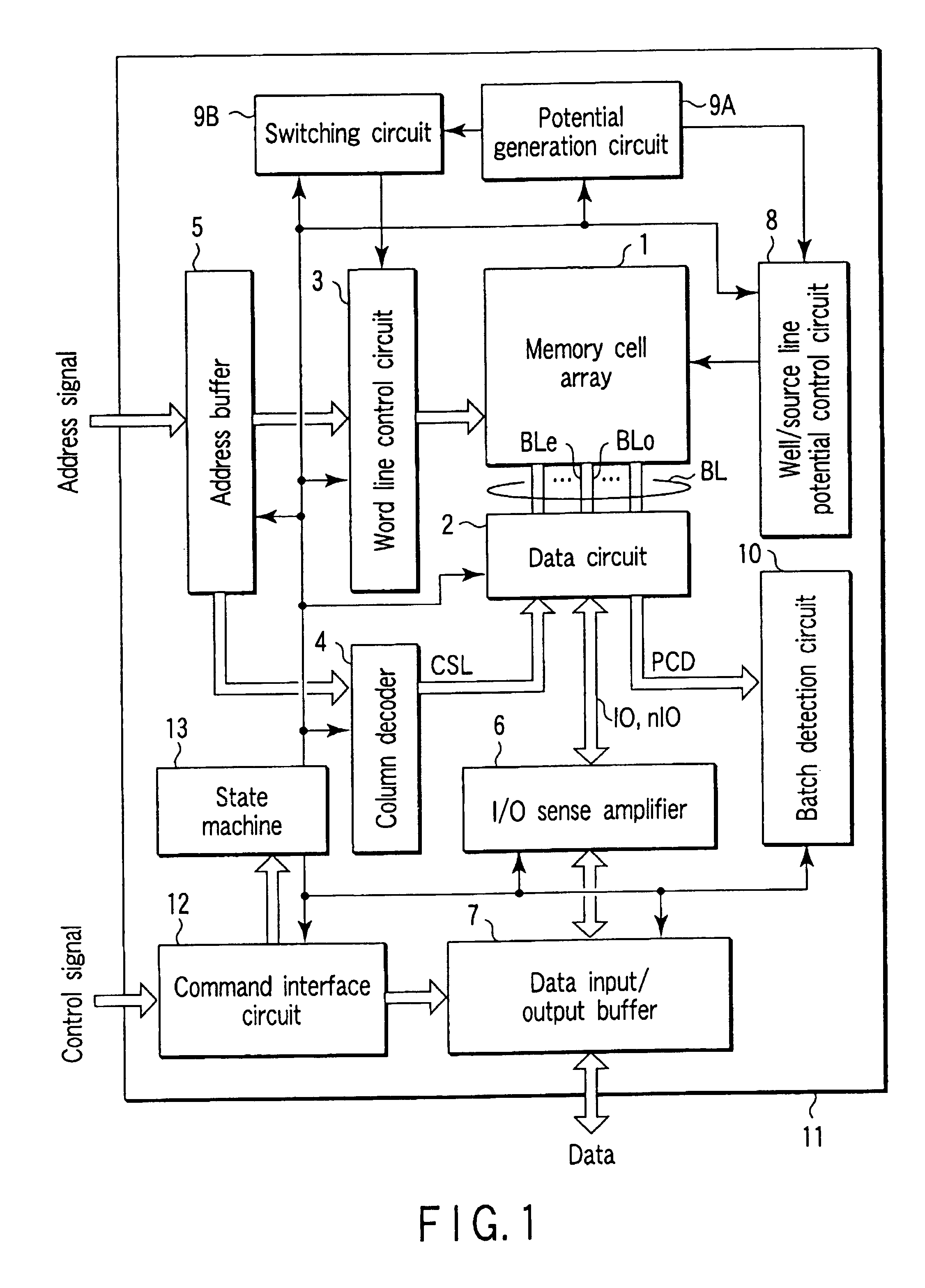

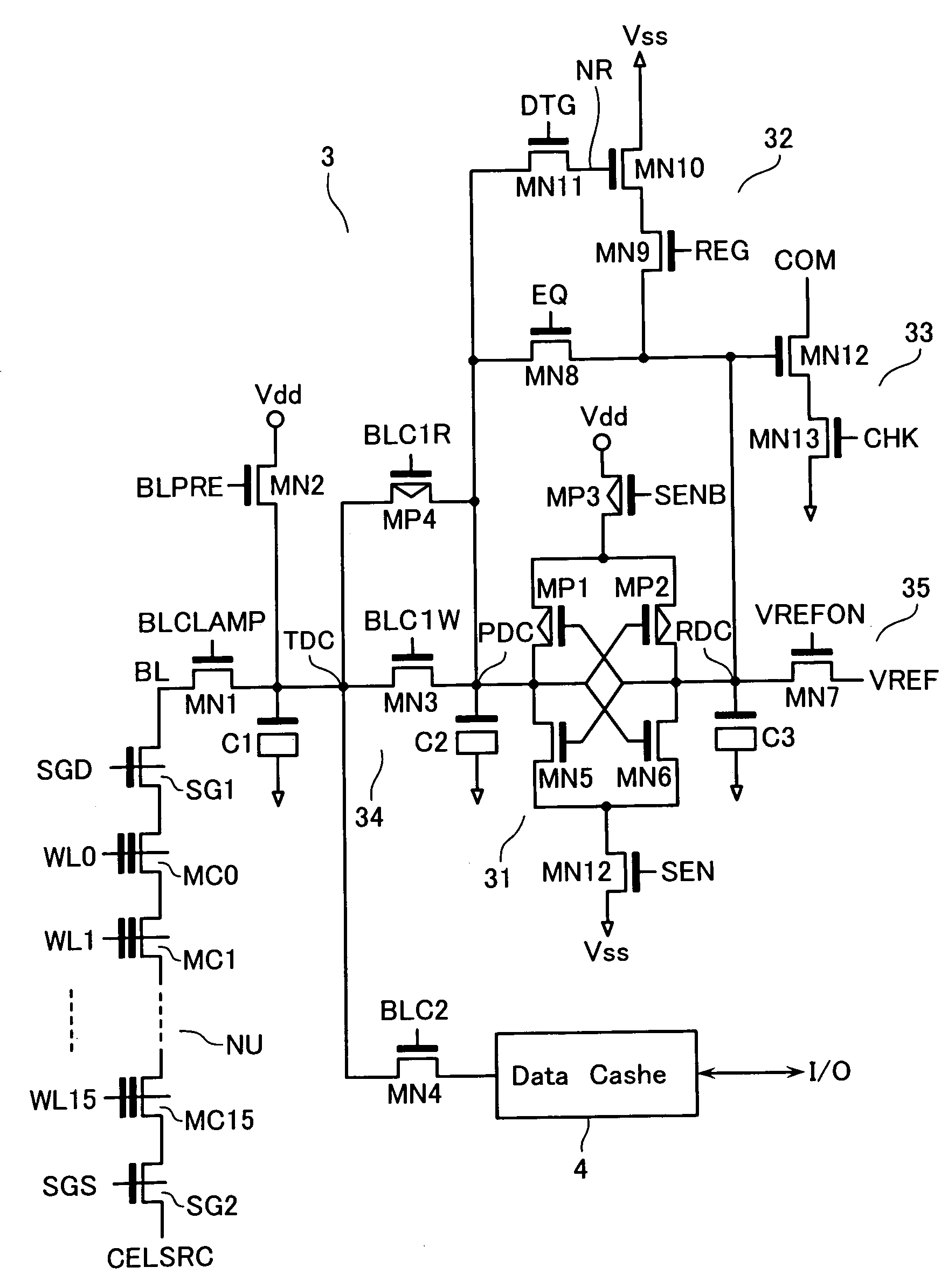

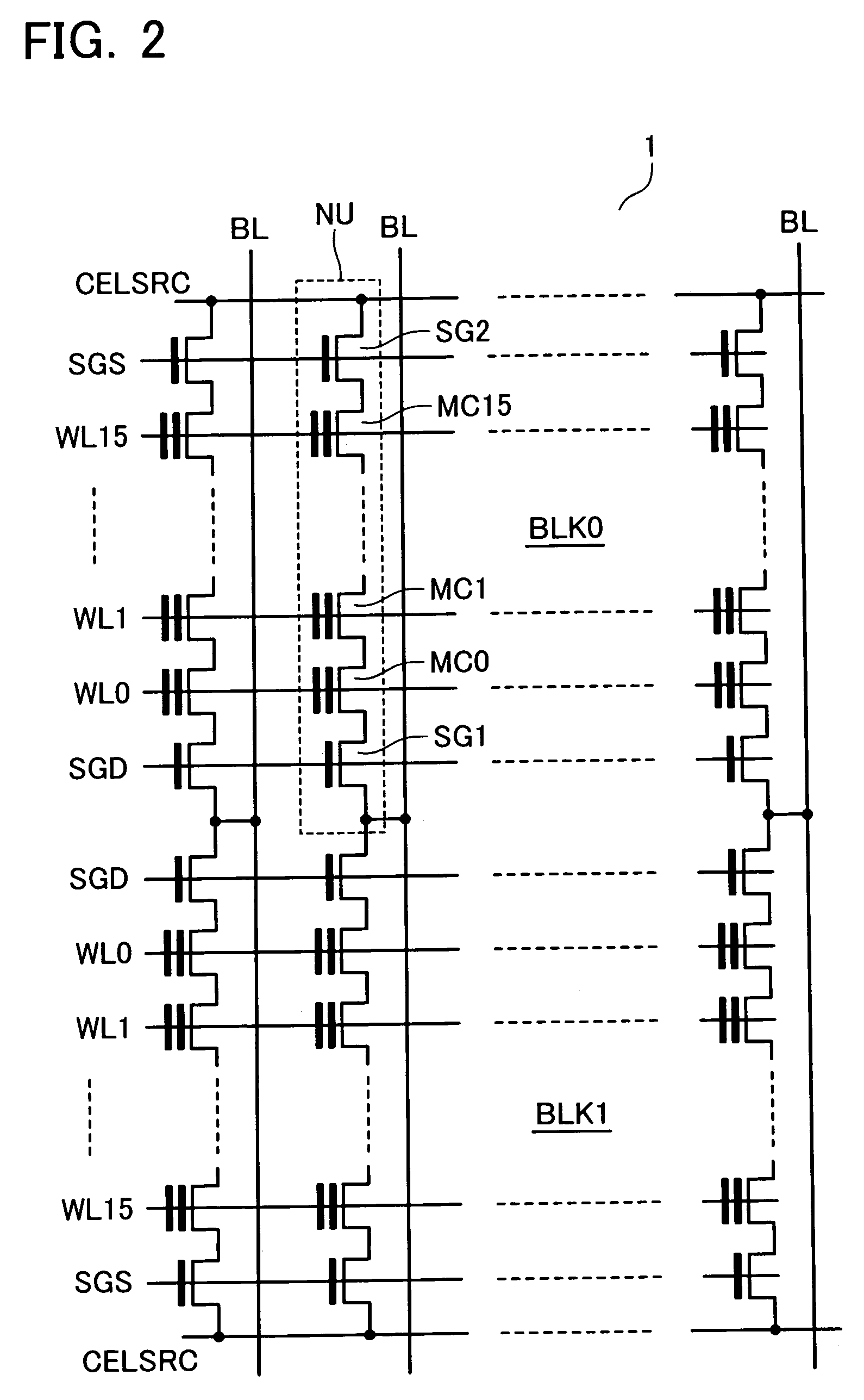

Nonvolatile semiconductor memory

A bit line is connected to a data circuit for use in a program / read time. The data circuit includes first, second, and third data storage units. The first data storage unit is connected to the bit line. A first data transfer circuit is connected between the first and third data storage units. A second data transfer circuit is connected between the second and third data storage units. The second data storage unit has a function of forcibly changing a value of data of the first data storage unit based on the data stored in the second data storage unit.

Owner:KIOXIA CORP

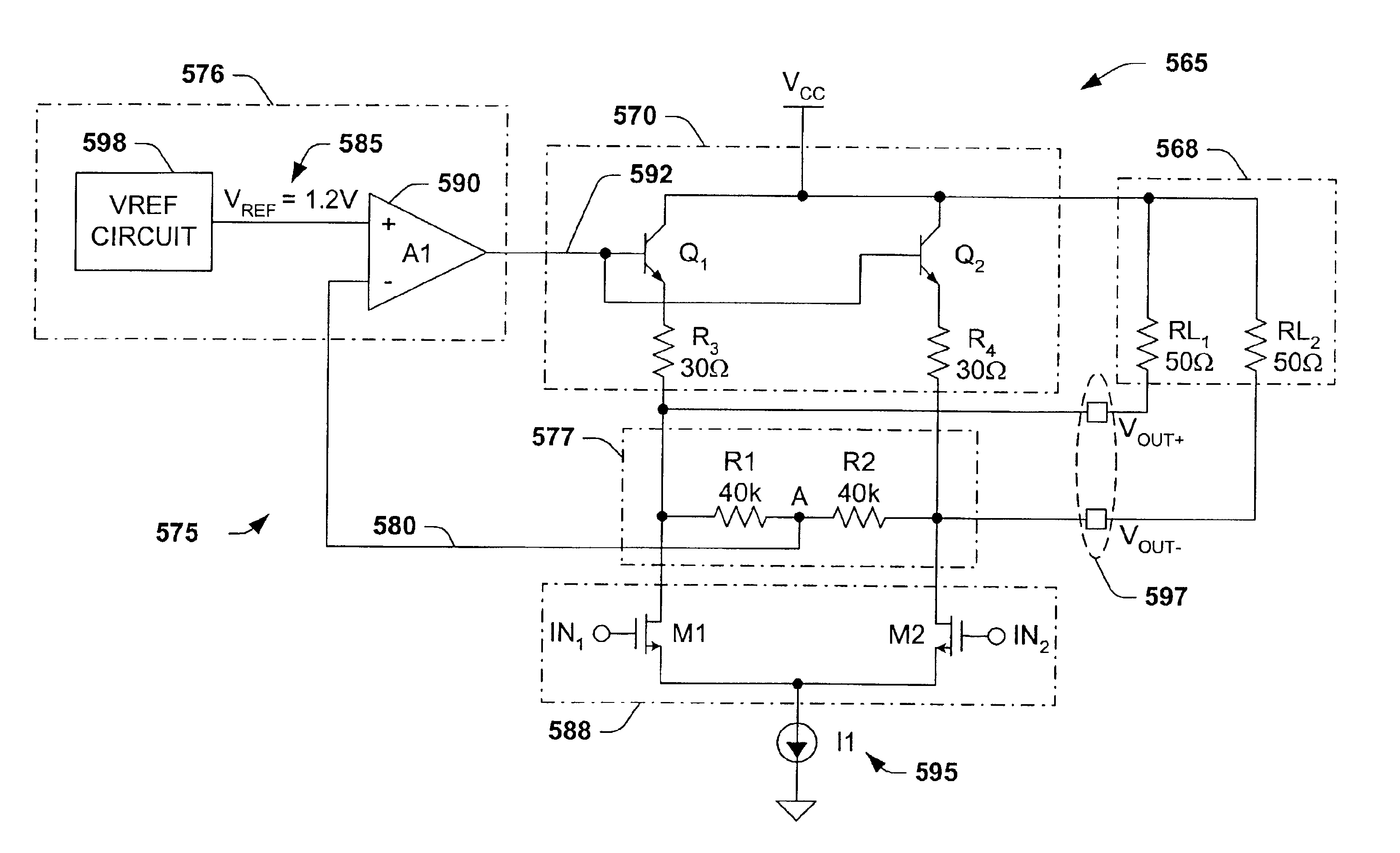

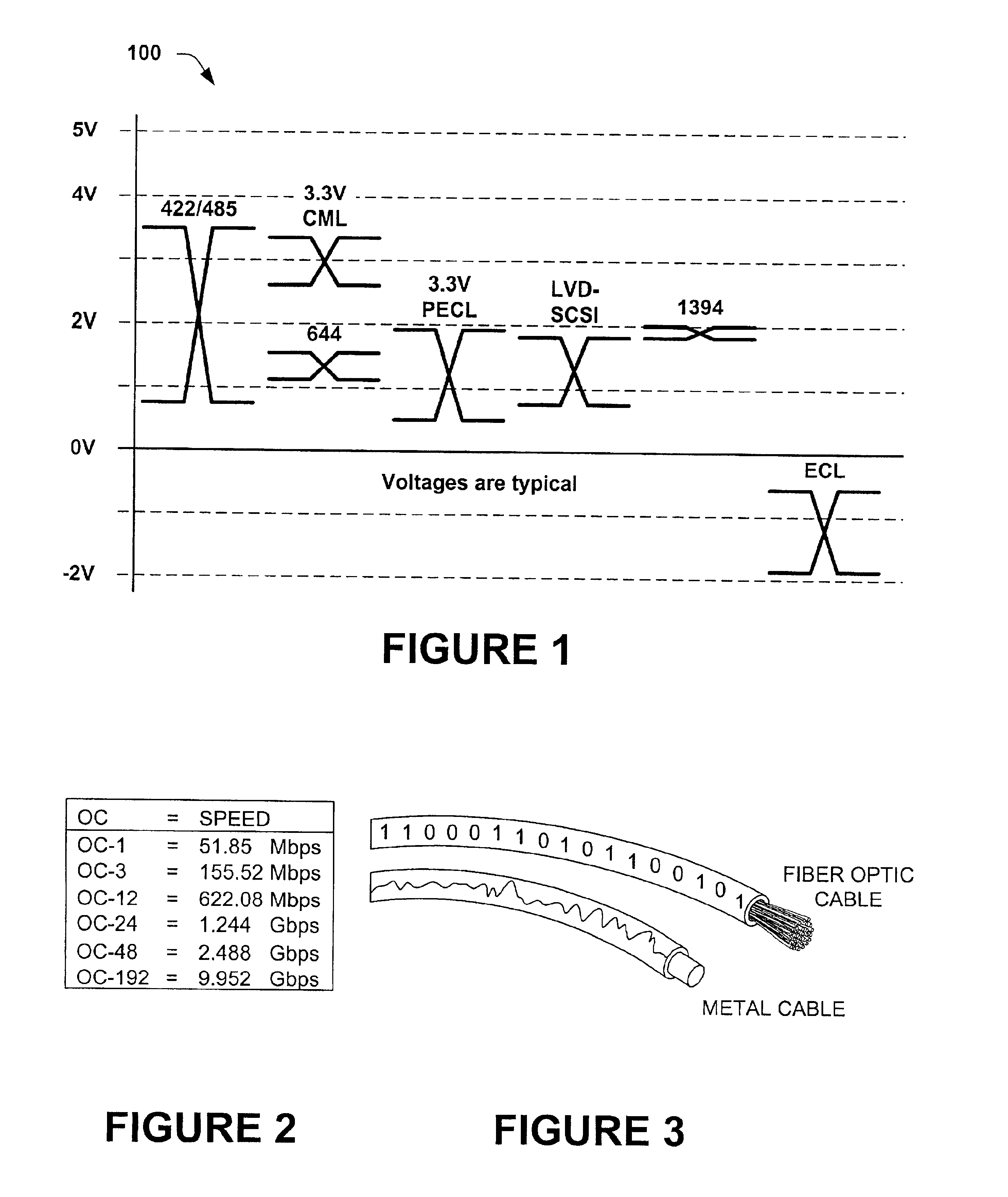

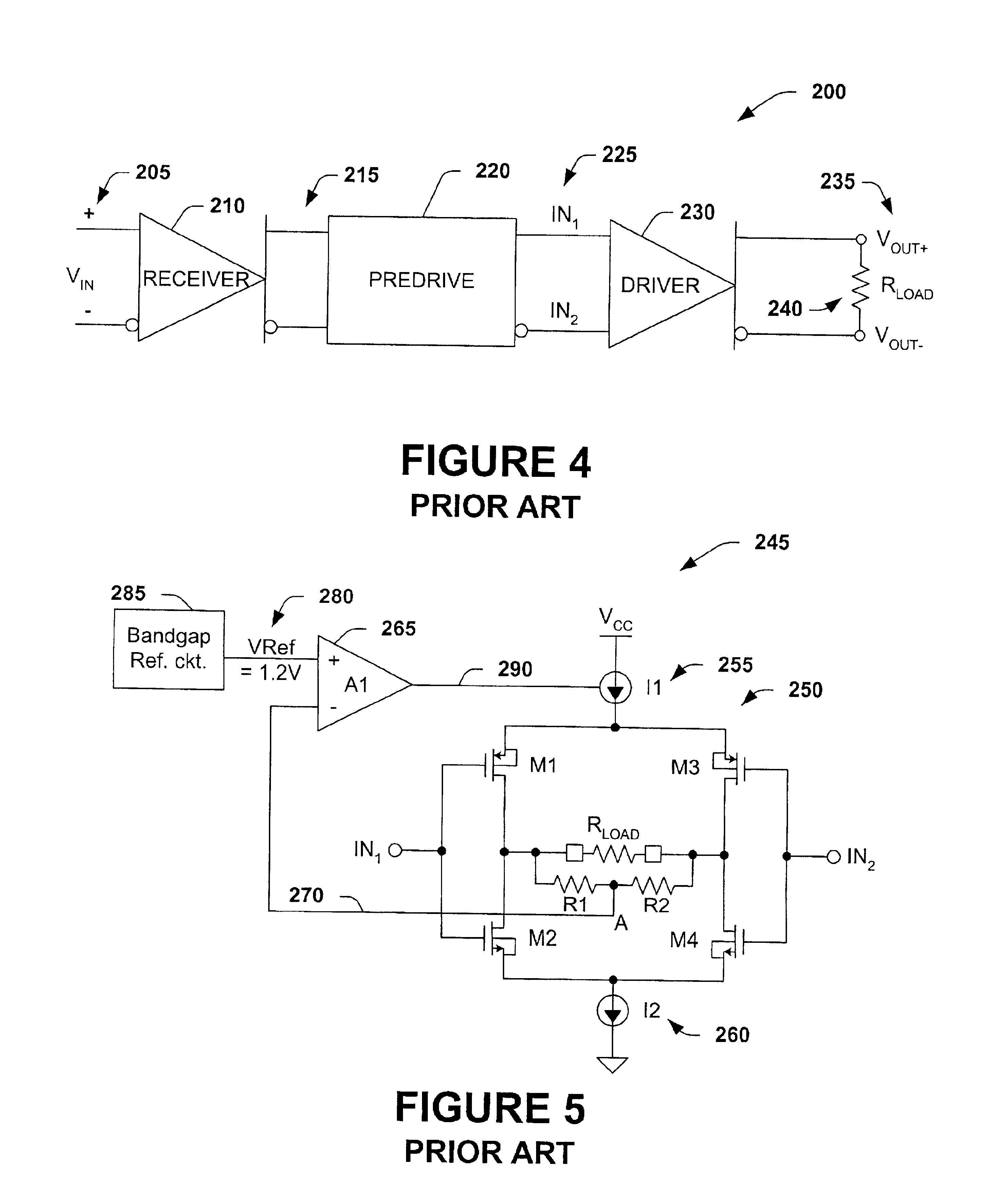

Interchangeable CML/LVDS data transmission circuit

InactiveUS6847232B2Easy to operateReduce input voltageLogic circuits coupling/interface using field-effect transistorsAmplifier with semiconductor-devices/discharge-tubesDriver circuitTransceiver

A system and method is described for a driver circuit used for high speed data transmission in LVDS and CML transceiver device applications. The transceivers are intended to receive a low voltage differential input signal and interchangeably drive a standard LVDS load with a TIA / EIA-644 compliant LVDS signal, and a standard CML load with a standard CML compatible signal. The driver circuit operates at speeds up to 1.36 Gbps, making it compatible with the OC-24 signaling rate for optical transmission. To accomplish this, the driver uses a mixed combination of voltage and current mode drive sections in the output circuit when coupled to LVDS loads, and when the driver is coupled to CML loads, operates purely in a current mode using only the current mode drive section. MOS transistors and a current source are used in the current mode switch portion to switch the drive with a constant current at the high speeds, and NPN transistors in the voltage mode output portion provide variable impedance for the output circuit. A common mode compensation circuit using a feedback voltage from the load generates a compensation signal for variable impedance control of the NPN transistors to yield a regulated voltage for the common mode dc voltage.

Owner:TEXAS INSTR INC

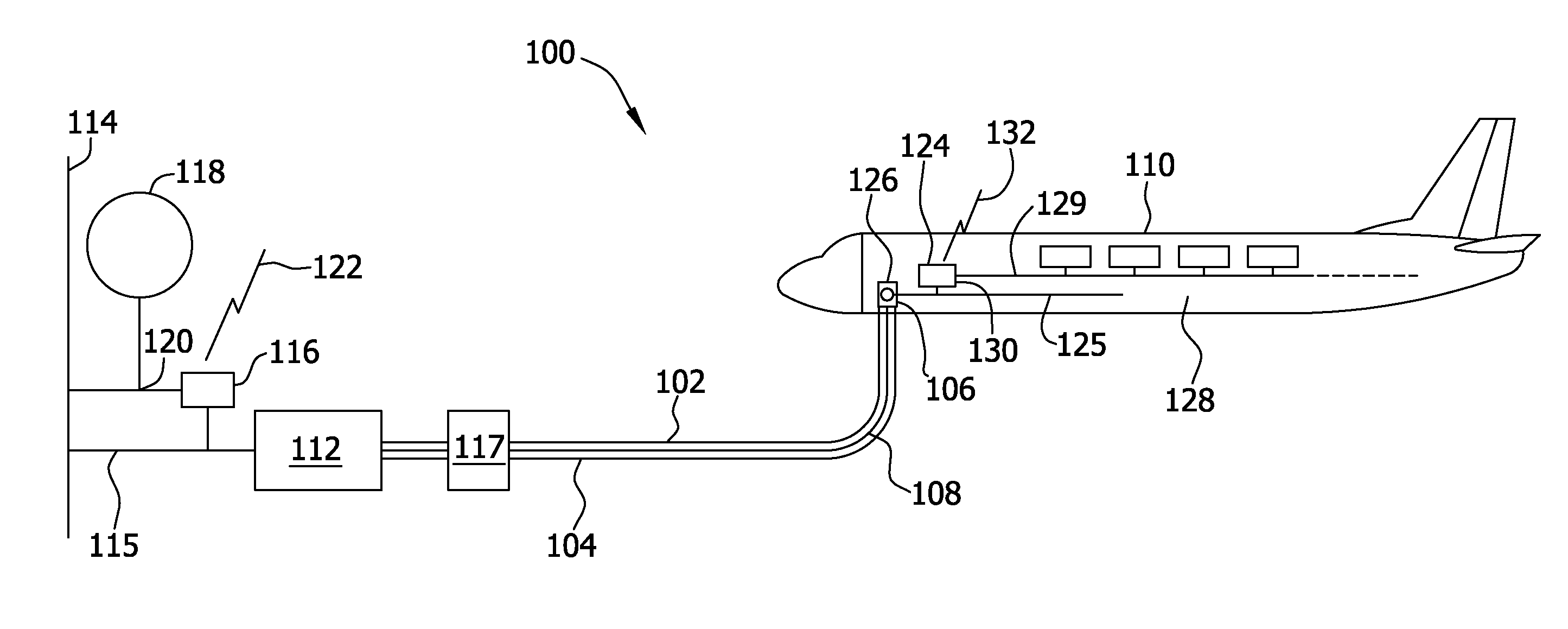

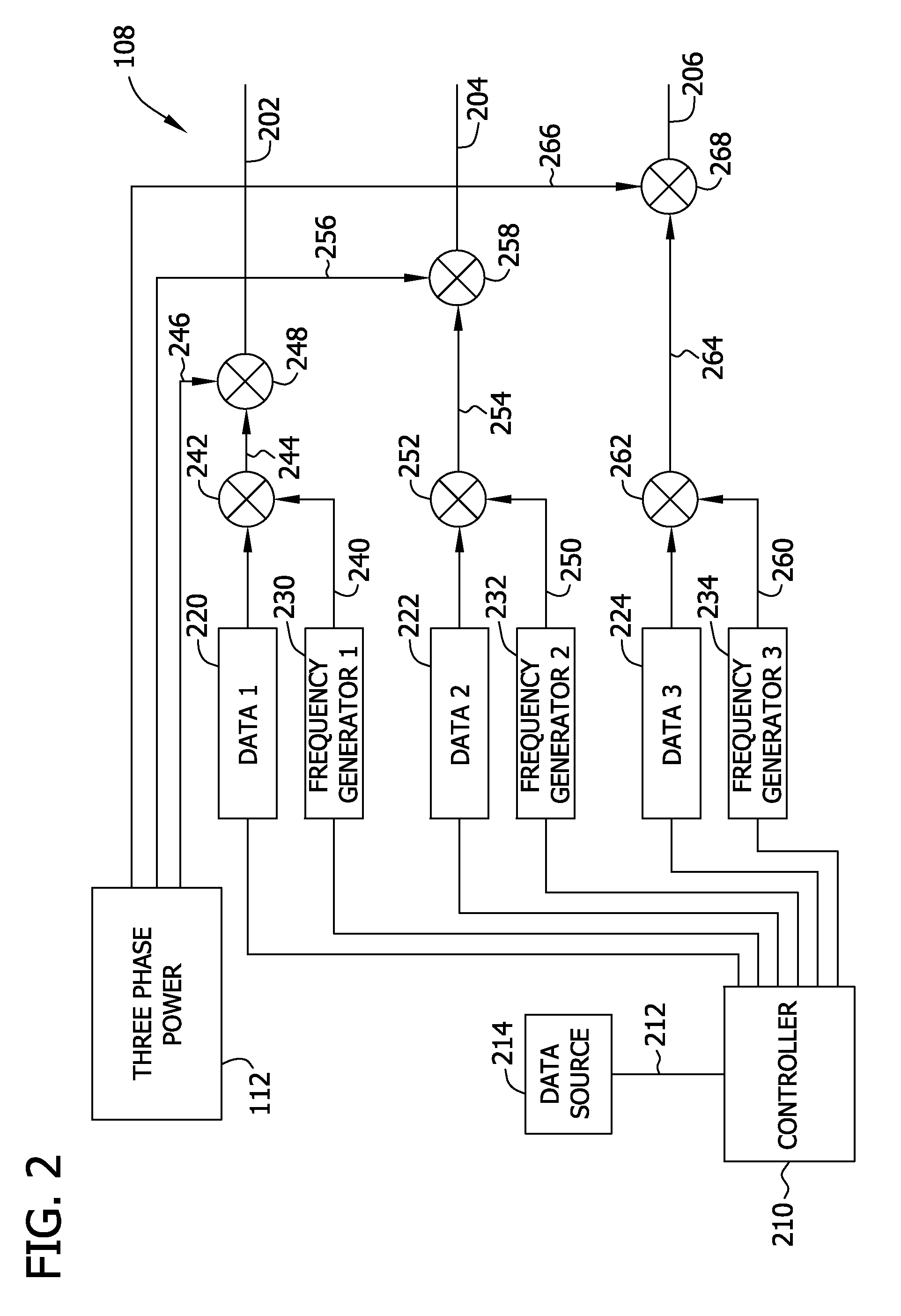

Methods and system for increasing data transmission rates across a three-phase power system

ActiveUS20130003756A1Power distribution line transmissionTime-division multiplexElectrical conductorData rate

A method for providing information by optimizing the data rate to a vehicle over a three-phase power line utilized to provide power to the vehicle is described. The method includes generating carrier signals in three separate frequency bands, modulating various data onto the three carrier signals to generate three transmission signals, switching the three transmission signals onto respective conductors of the three-phase power line, demodulating the various data within the vehicle, and providing the various data to one or more vehicle systems. The three transmission signals are dynamically monitored such that the three frequency bands are controlled to optimize a data rate of the transmission.

Owner:THE BOEING CO

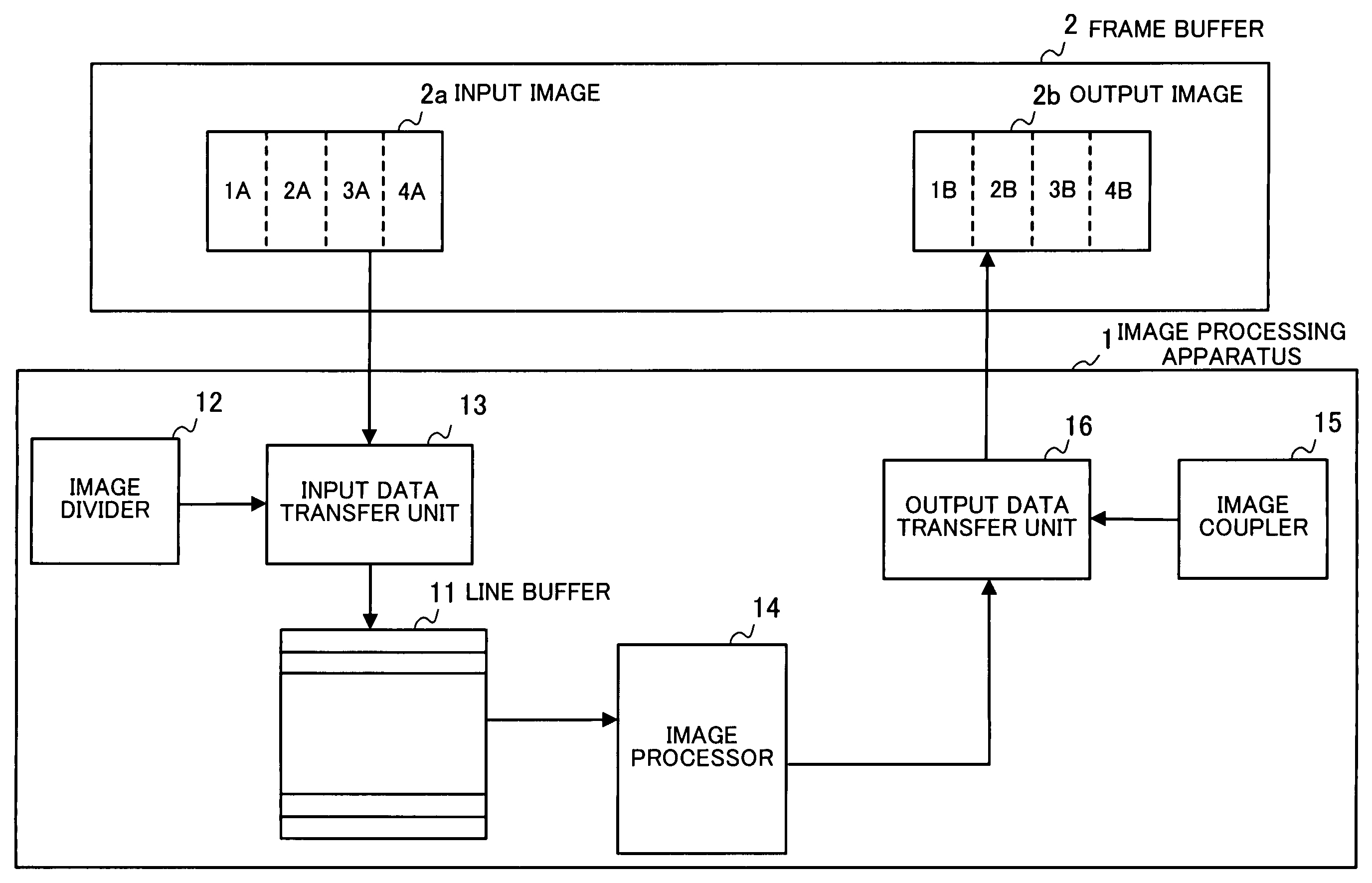

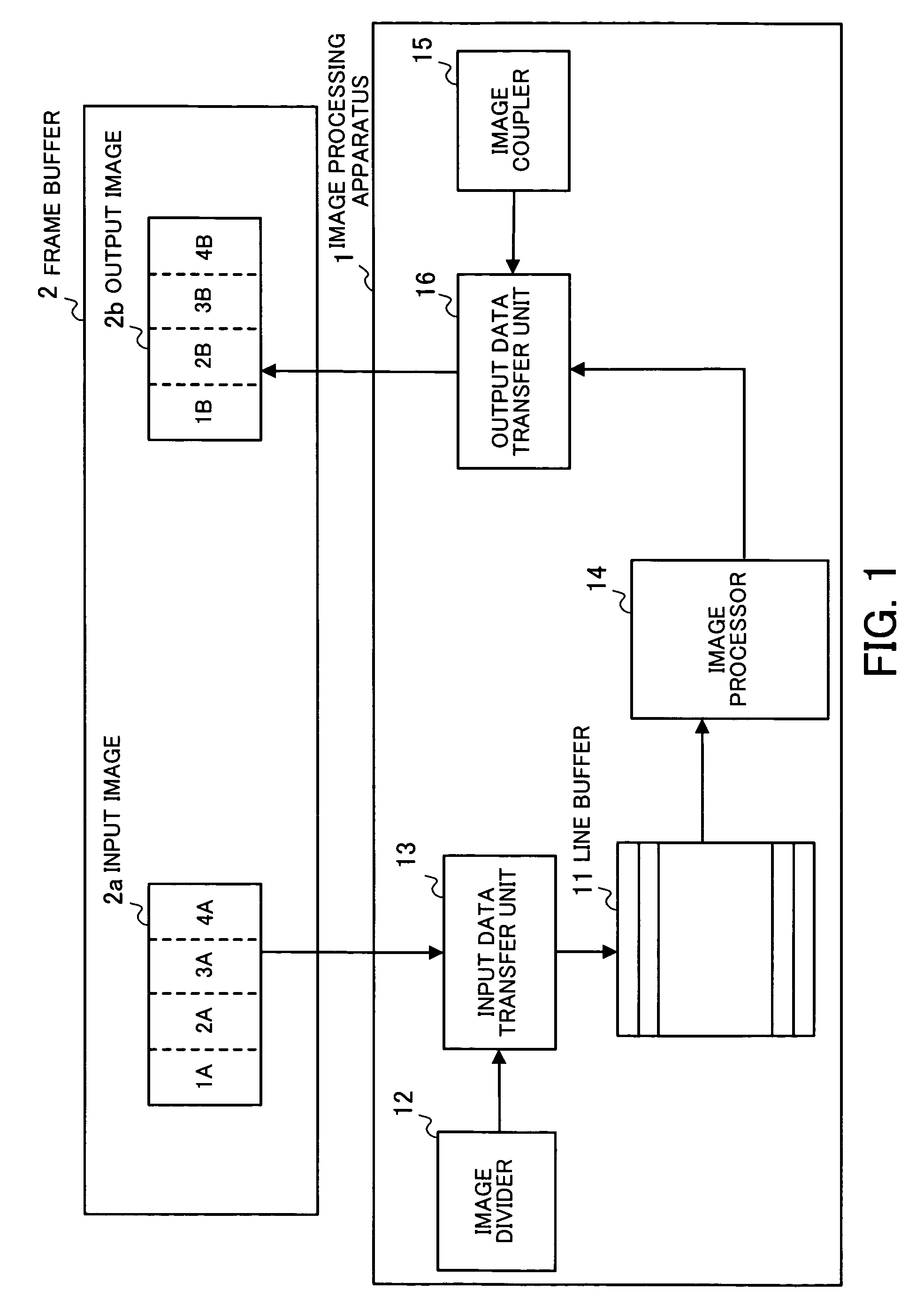

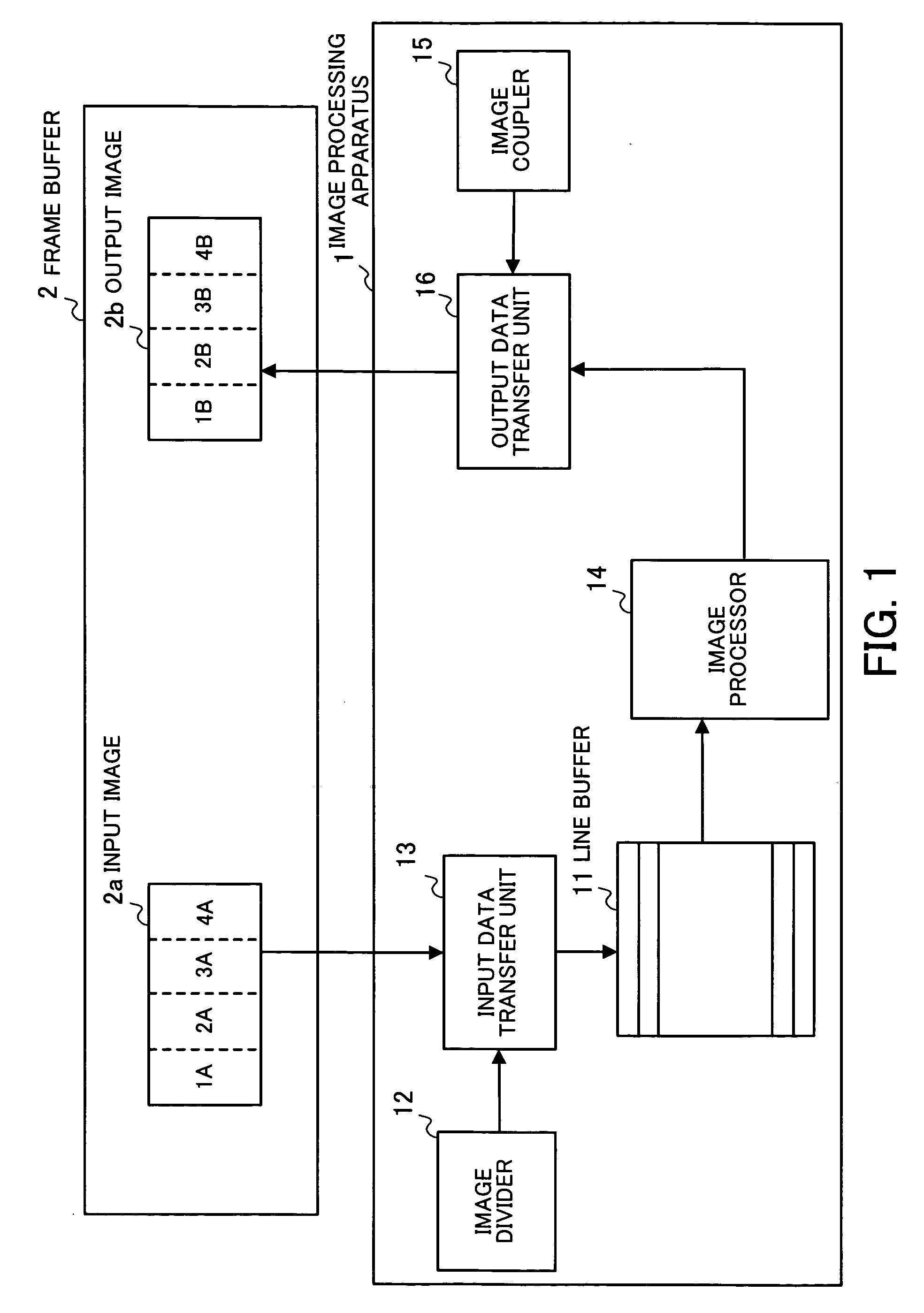

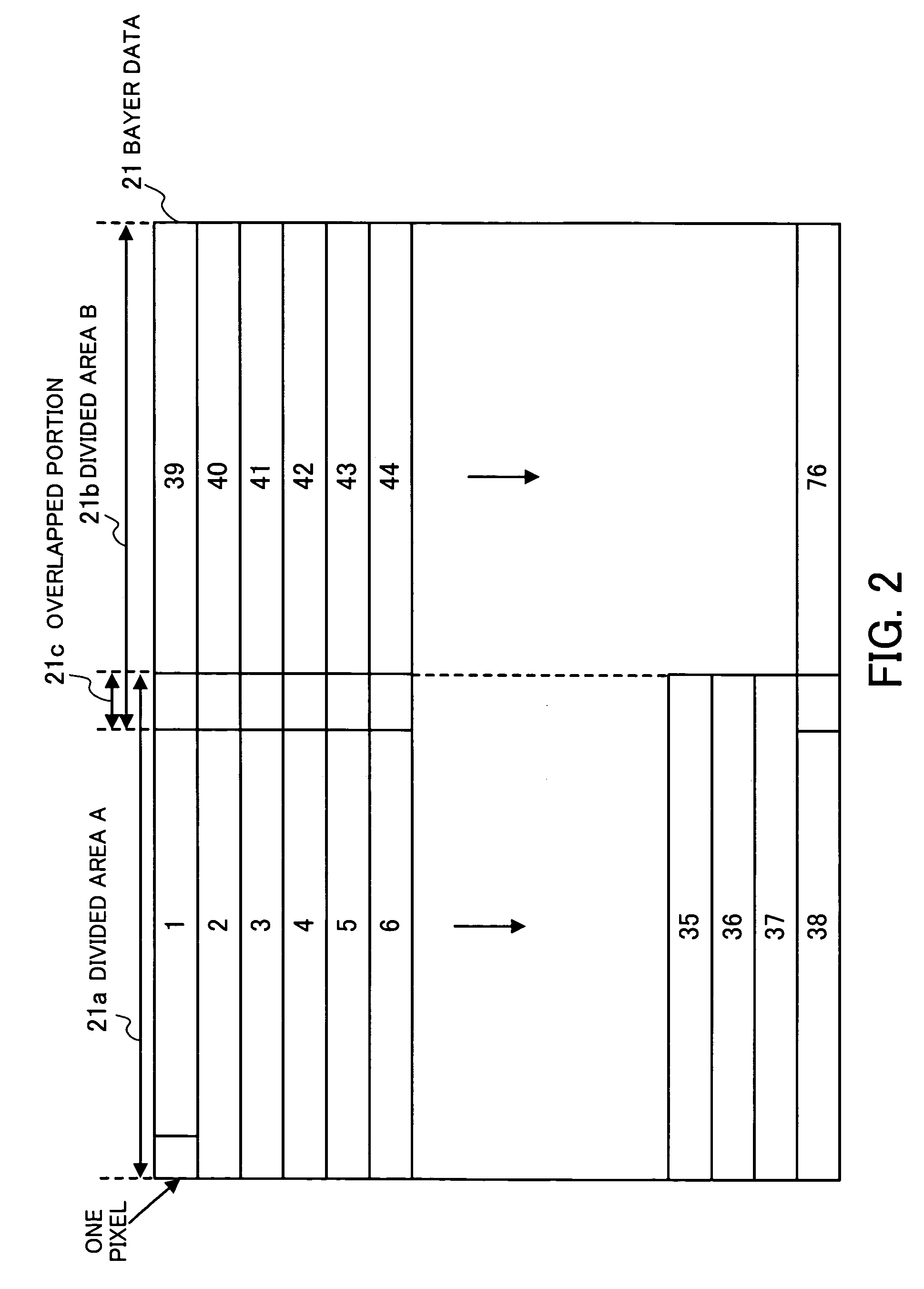

Apparatus and method for processing an image

InactiveUS7583851B2Increase in circuit sizeIncrease processing functionImage memory managementCharacter and pattern recognitionImaging processingComputer graphics (images)

An image processing apparatus is provided for enhancing the image processing function without having to increase the circuit scale. The image processing apparatus includes an image divider, a pixel processor, and an image coupler. If the number of horizontal pixels on the width of an input image is larger than a size of a line buffer, the image divider equally divides the input image in the vertical direction so that the resulting divided area is smaller than the number of horizontal pixels on the width of the line buffer. Then, the image divider controls an input data transfer circuit so that the pixel data of the input image may be sequentially transferred to the line buffer for each of the equally divided areas. The image processor sequentially processes the pixel data of the input image temporarily stored in the line buffer and then sends out the output pixel data. The image coupler controls the output data transfer circuit so that the output pixel data sequentially outputted for one divided area may be coupled with the output pixel for another divided area, for generating the output image.

Owner:SOCIONEXT INC

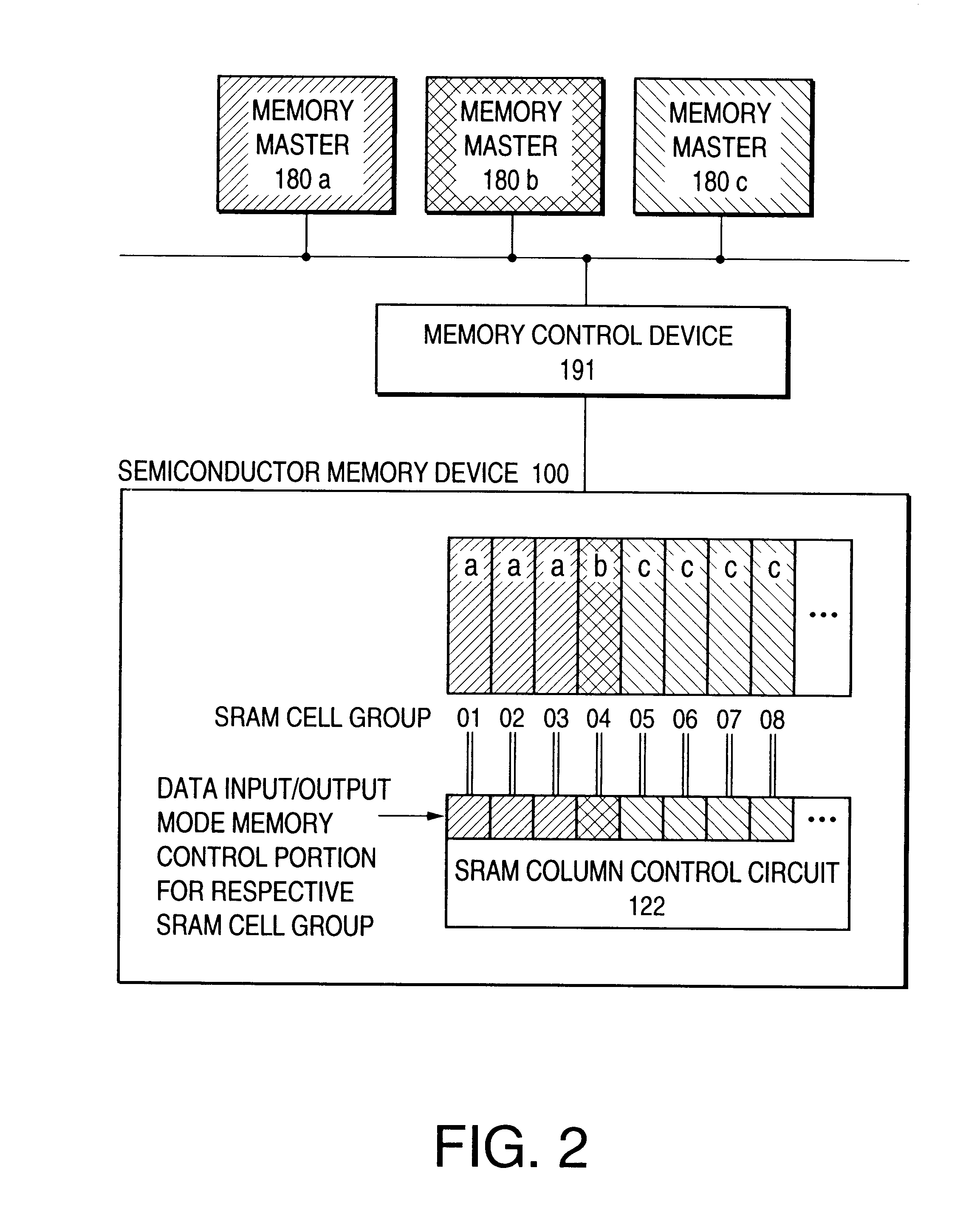

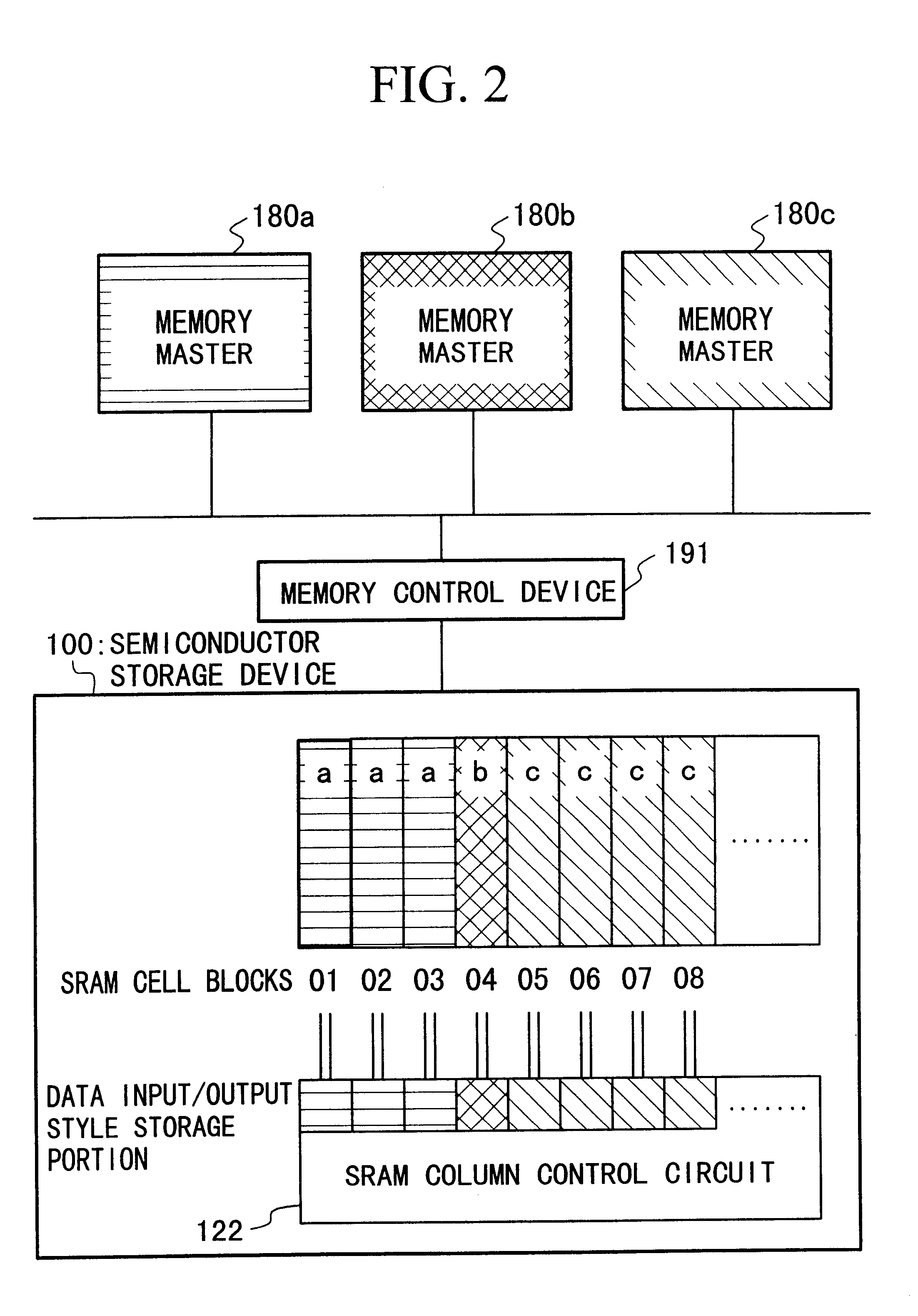

Semiconductor memory including main and sub memory portions having plural memory cell groups and a bidirectional data transfer circuit

InactiveUS6339817B1Guaranteed high speed operationOptimize the numberMemory adressing/allocation/relocationDigital storageComputer architectureData transmission circuit

A semiconductor integrated circuit device includes a main memory portion, a sub memory portion including a plurality of memory cell groups and a bidirectional data transfer circuit provided between the main memory portion and the sub memory portion. A bi-directional data transfer between an arbitrary area of the main memory portion and the plurality of the memory cell groups, and a read or write operation are performed simultaneously. Therefore, the semiconductor integrated circuit device has a main memory suitable for being accessed from a plurality of memory masters or data processors.

Owner:RENESAS ELECTRONICS CORP

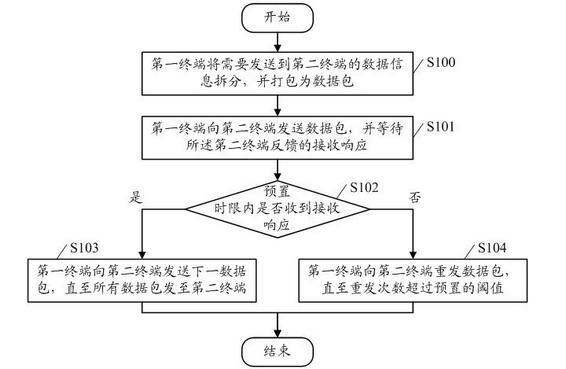

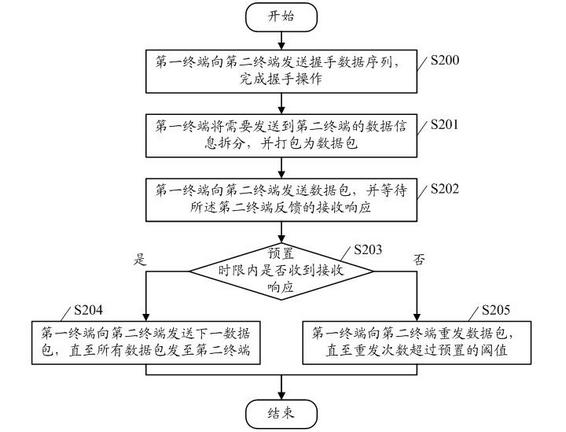

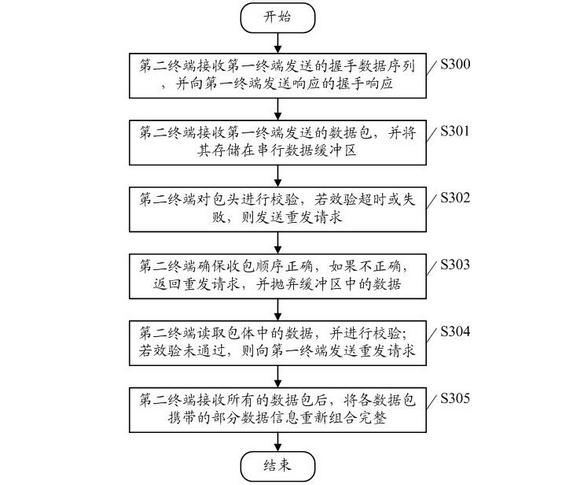

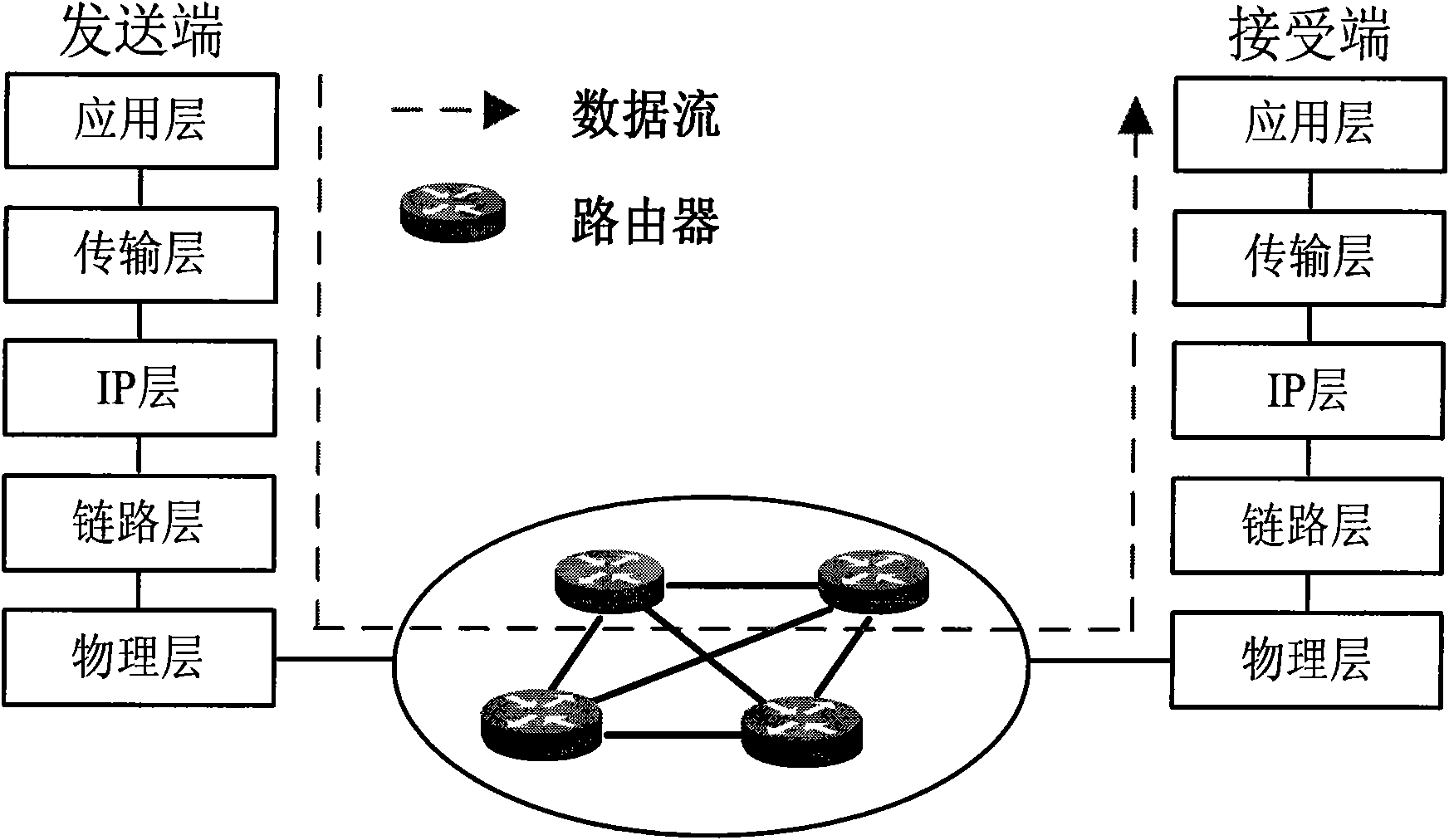

Data transmission method and system

InactiveCN102143073AQuality improvementQuick and effective remedial treatmentError prevention/detection by using return channelData switching networksNetwork packetData information

The embodiment of the invention discloses a data transmission method and a data transmission system. The method comprises that: a first terminal splits data information to be transmitted to a second terminal, and packs the data information into data packets, wherein the data packet comprises a packet header and a packet body; the first terminal transmits the data packet to the second terminal, and waits for a receiving response fed back by the second terminal; if receiving the receiving response fed back by the second terminal in a preset time limit, the first terminal transmits the next data packet to the second terminal until all the data packets are transmitted to the second terminal; and if not receiving the receiving response or a retransmission request fed back by the second terminal in the preset time limit, the first terminal retransmits the latest transmitted data packet to the second terminal until the number of retransmission times exceeds a preset threshold. By the data transmission method and the data transmission system provided by the invention, errors can be rapidly and effectively corrected and remedied in a serial communication process so as to improve the quality of serial communication.

Owner:SHENZHEN SKYWORTH DIGITAL TECH CO LTD

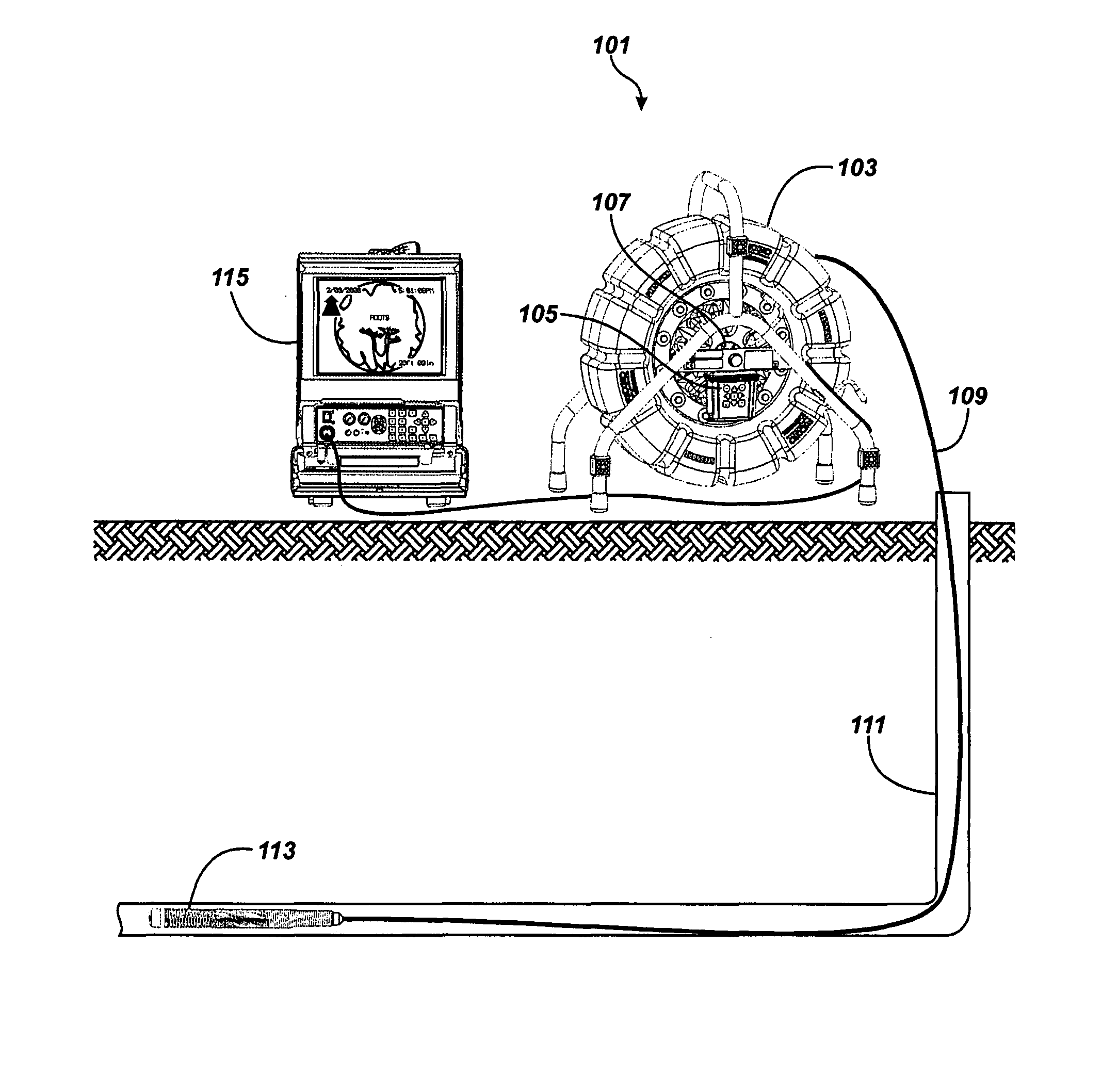

Pipe inspection system with selective image capture

ActiveUS8395661B1Additional imaging capabilityFacilitate communicationImage analysisEndoscopesVideo transmissionData transmission circuit

Owner:SEEKTECH

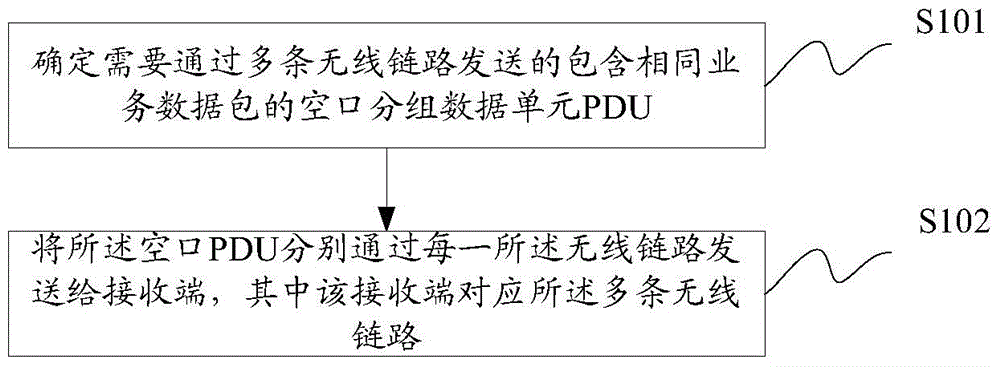

Data transmission method and system

The invention discloses a data transmission method and system, which are used to reduce the time delay of data transmission and improve the reliability of data transmission. A data sending method provided by the present invention includes: determining the air interface packet data unit PDU containing the same service data packet that needs to be sent through multiple wireless links; sending the air interface PDU through each of the wireless links to A receiving end, wherein the receiving end corresponds to the plurality of wireless links.

Owner:DATANG MOBILE COMM EQUIP CO LTD

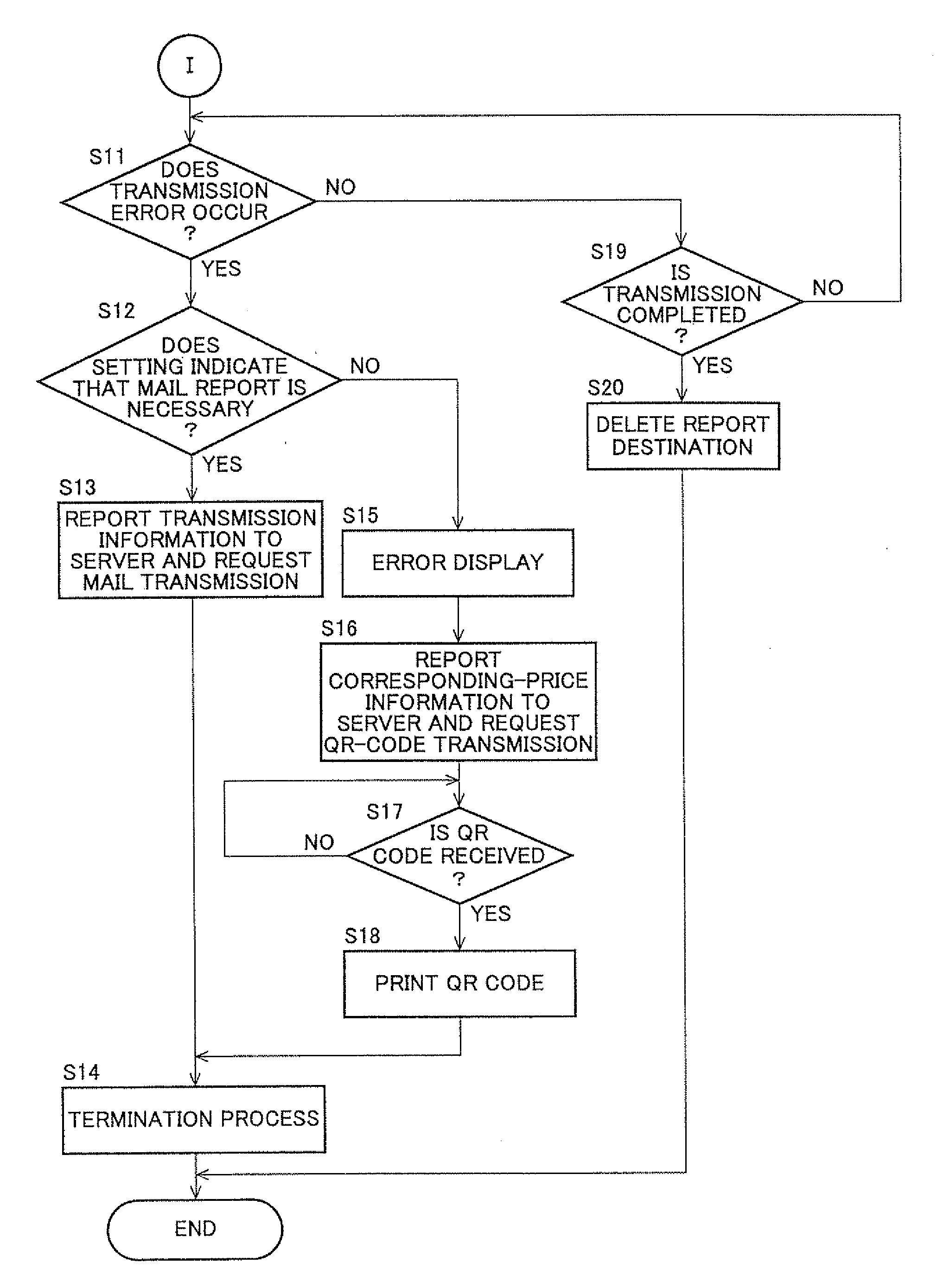

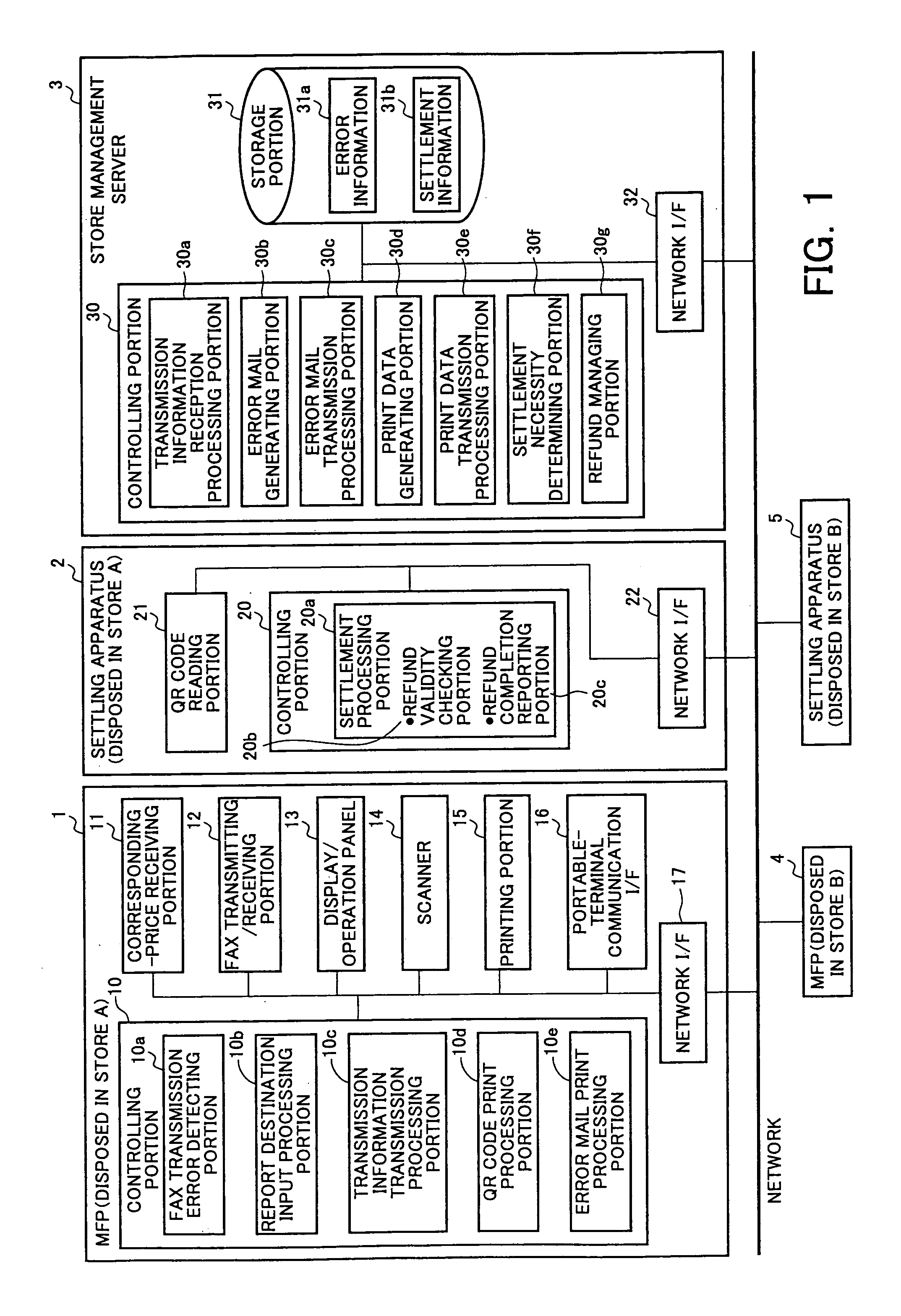

Data transmission system and data transmitting method

A data transmission system is provided that enables a user to move away before the completion of data transmission regardless of whether a refund is made in association with occurrence of a communication error when a data transmitting apparatus performs data transmission and collects a consideration. The data transmitting apparatus includes a consideration receiving portion that receives a consideration of FAX data transmission, a report destination input portion that inputs a report destination of a user, and a FAX transmission error detecting portion that detects a communication error at the time of the FAX data transmission. In case the FAX transmission error detecting portion detects a communication error, the system including the data transmitting apparatus transmits refund information for refunding the consideration of the FAX data transmission with the communication error to the report destination input through the report destination input portion.

Owner:SHARP KK

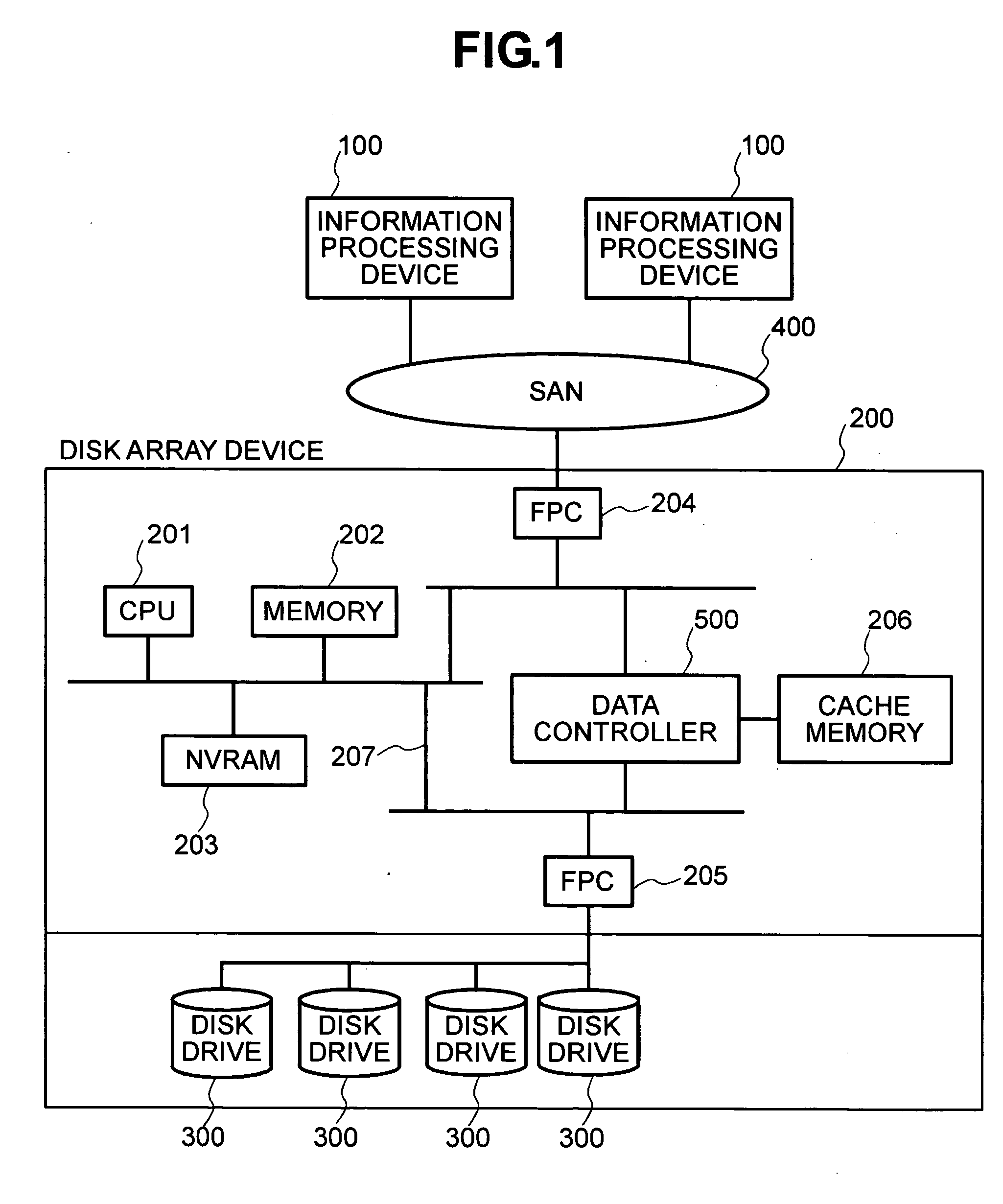

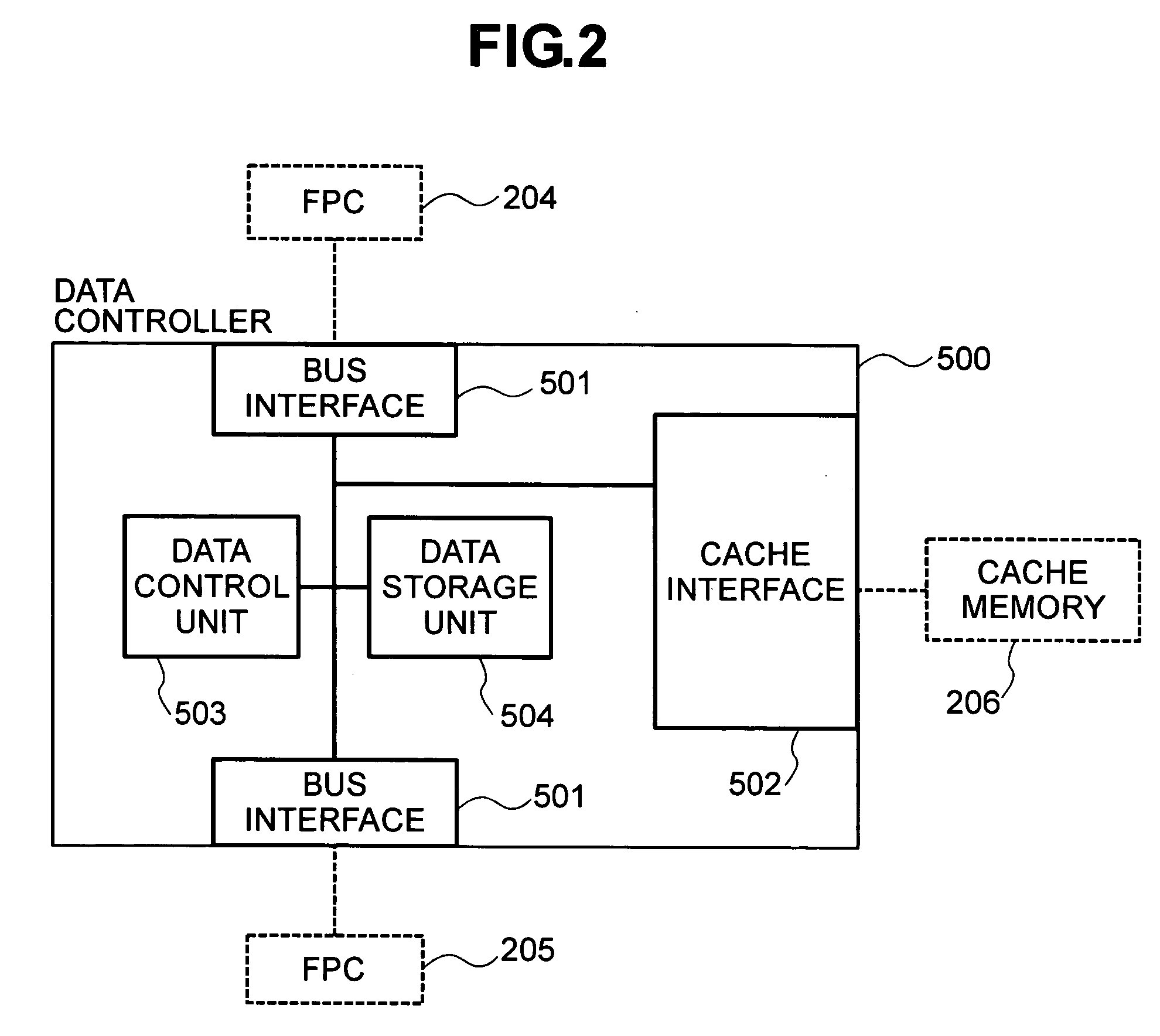

Control method for data transfer device, data transfer circuit, and disk array device

ActiveUS20050055522A1Input/output to record carriersUnauthorized memory use protectionData controlDisk array

A data transfer device has a data receiver, a data control unit, and a data storage unit. In a control method for the data transfer device, the data control unit reads serial data from the storage device in block units and stores this serial data in the data storage unit. When a block constituting the write destination of the write data and a block stored in the data storage unit differ, the data control unit generates a security code, based on the serial data stored in the data storage unit, and adds the generated security code to the serial data before transferring this serial data to the storage device. The data control unit reads the serial data in the block constituting the write destination of the write data, before storing this serial data in the data storage unit, and updates the stored serial data by means of the write data.

Owner:GOOGLE LLC

Joint layer 3 signalling coding for multicarrier operation

ActiveUS20110110441A1Ease of evaluationTransmission path divisionAssess restrictionCarrier signalData transmission circuit

Systems and methodologies are described that facilitate encoding layer 3 control information in a multicarrier wireless communication environment. The layer 3 control information can be jointly encoded for a plurality of component carriers. Further, the jointly encoded layer 3 control information for the plurality of component carriers can be included in a data transmission (e.g., PDSCH, PUSCH, . . . ) sent on a component carrier from the plurality of component carriers. Moreover, an allocation for the data transmission on the component carrier can be indicated by a control transmission (e.g., PDCCH, . . . ). For example, the control transmission and the data transmission, which can be scheduled by the control transmission, can be sent on a common component carrier or different component carriers from the plurality of component carriers (e.g., same carrier signalling or cross-carrier signalling can be implemented, . . . ).

Owner:QUALCOMM INC

Non-volatile semiconductor memory device and electric device with the same

A non-volatile semiconductor memory device includes a cell array in which electrically rewritable and non-volatile memory cells are arranged, and a sense amplifier circuit configured to read and write data in association with the cell array, wherein the sense amplifier circuit includes: differential amplifier having first and second input nodes and configured to amplify a difference voltage between the first and second input nodes; a data transfer circuit configured to selectively connect the first input node to a bit line in the cell array; a reference voltage setting circuit configured to apply a reference voltage to the second input node of the differential amplifier; and a data storing circuit configured to temporarily hold a loaded write data at the first input node of the differential amplifier, and control the reference voltage at the second input node of the differential amplifier in correspondence with the write data held therein.

Owner:KIOXIA CORP

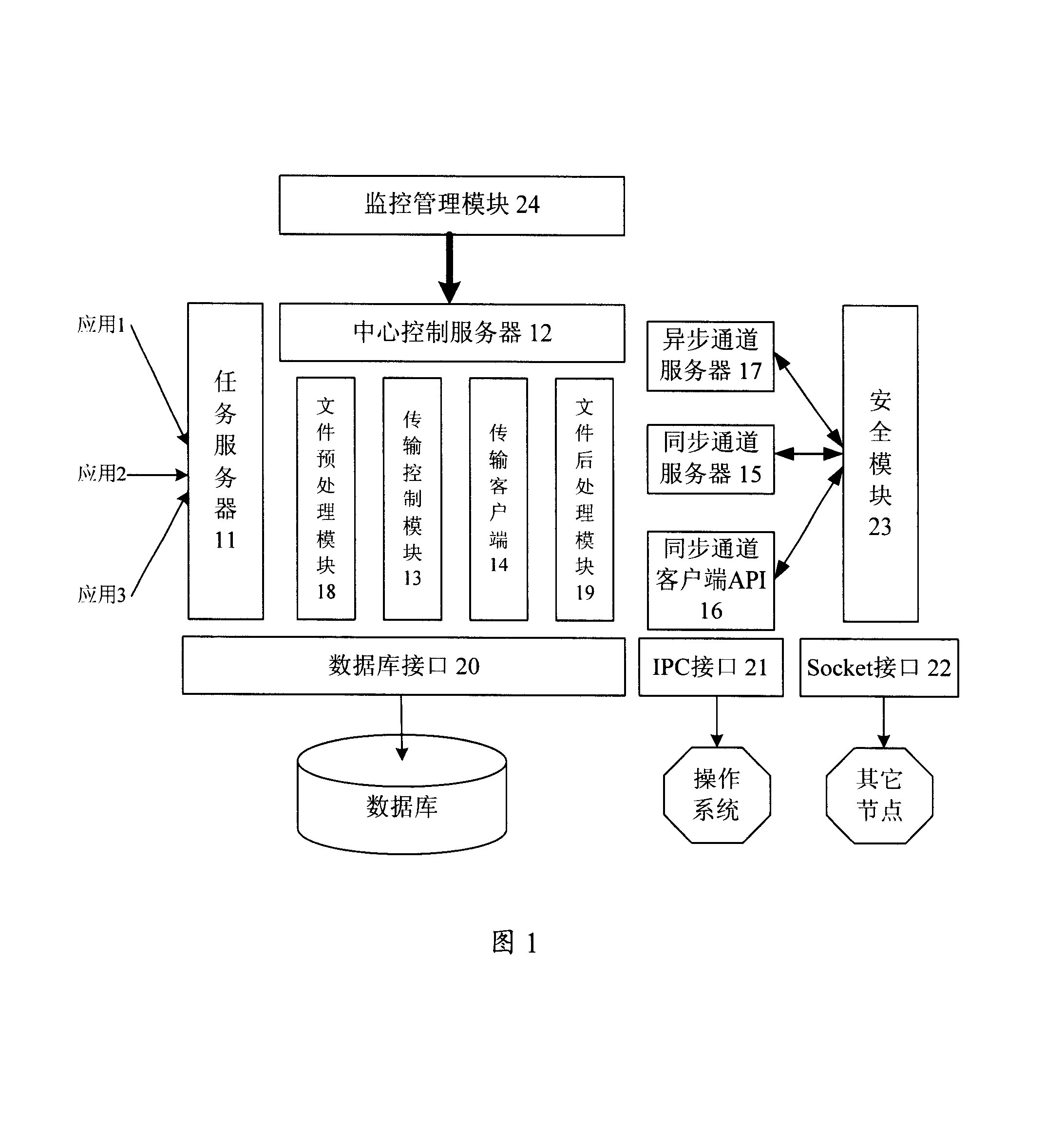

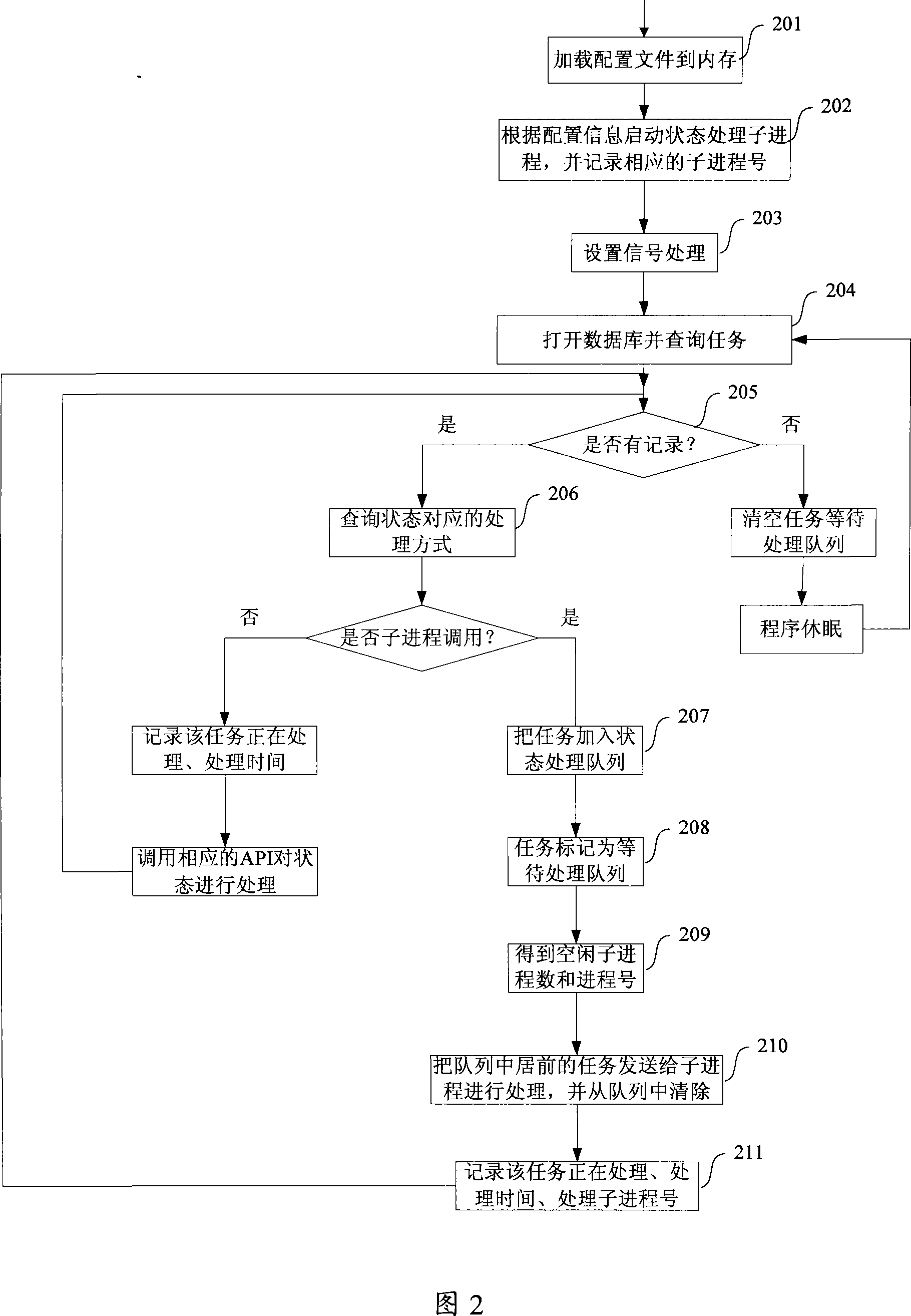

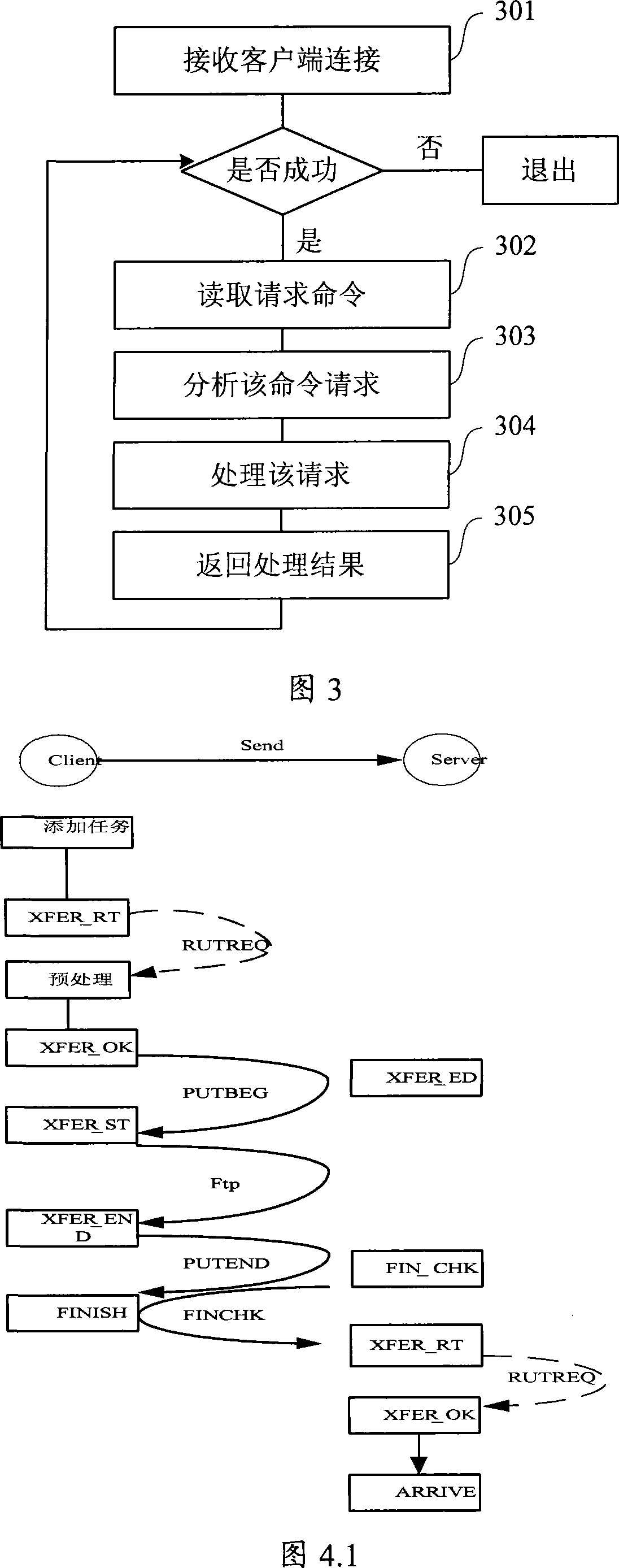

Data transmission system

ActiveCN101252506AReduce correlationImplement direct transfer functionSpecial service provision for substationStore and forwardTransmission channel

The invention discloses a data transmitting system, which solves the problem of the prior data transmitting method that only direct transmission between nodes in an upper and a lower grades and cross-grade storage and forwarding instead of point-to-point transmission can be realized. The system comprises a mission server in charge of monitoring and obtaining requests of source nodes; a central control server in charge of managing and adjusting the working progress which is composed of a transmission controlling module and a transmission client side; the transmission controlling module in charge of communicating with target nodes through a synchronous transmission channel and performing adjustment and control to the mission; the transmission client side is in charge of data transmission, and transmits the data transmission to the target nodes through an asynchronous transmission channel; the synchronous transmission channel is realized by a synchronous channel server and a synchronous channel client side API, and the asynchronous transmission channel is realized by an asynchronous channel server and a transmission client side. The system can realize the direct point-to-point transmission, and is provided with a mission priority managing and flow rate controlling mechanism as well as assemblage and load balancing of application layers.

Owner:CHINA CONSTRUCTION BANK

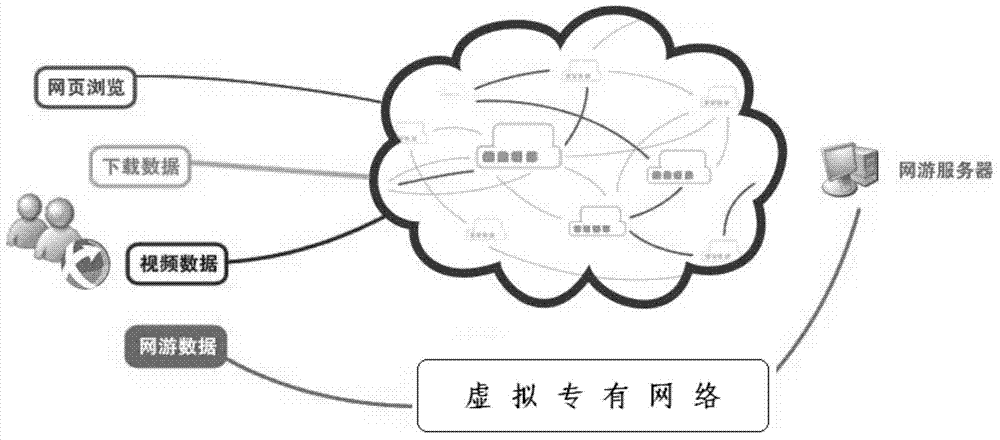

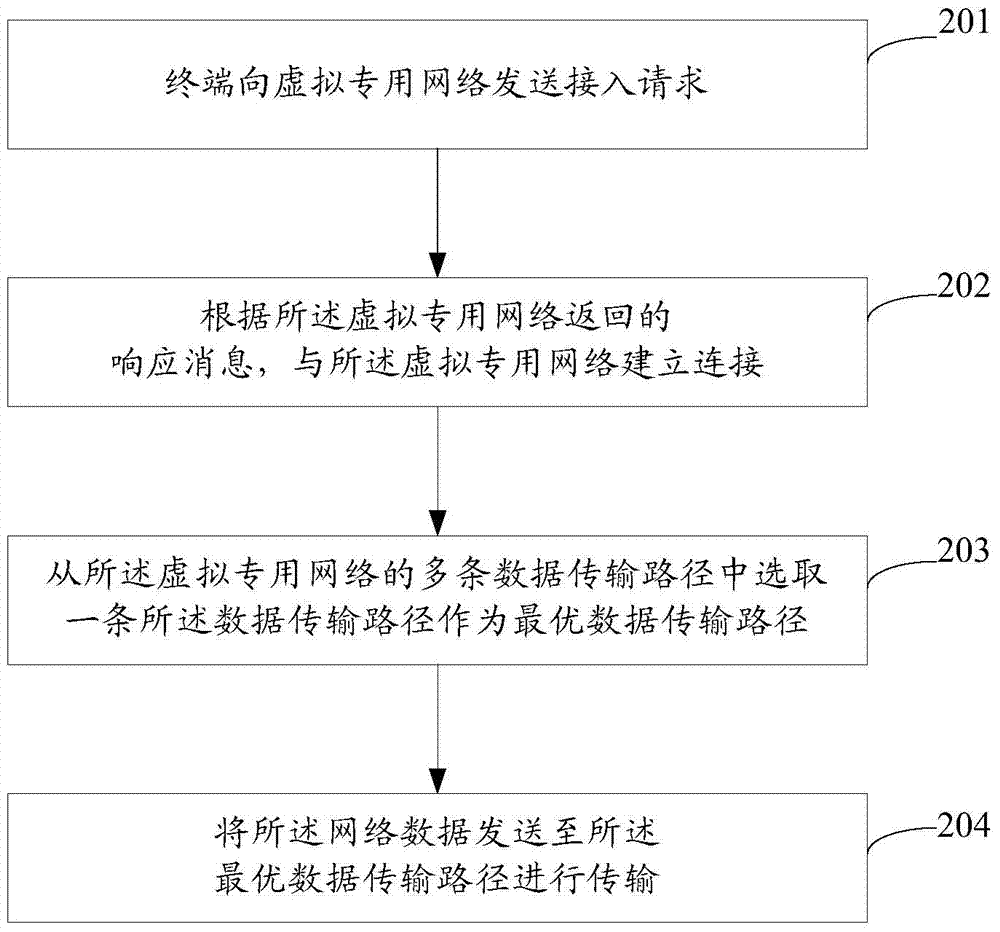

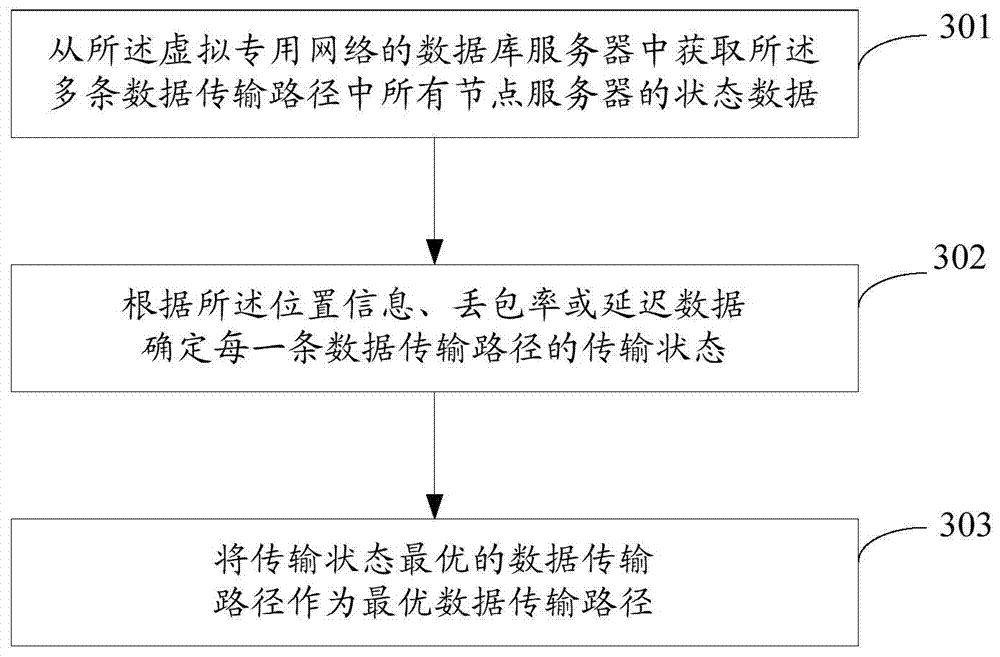

Acceleration transmission method and system for network data

The invention discloses an acceleration transmission method and acceleration transmission system for network data. According to the acceleration transmission method and the acceleration transmission system, a terminal is connected with a virtual special network which is independent from a public internet, and network data attended by a user and requiring separation transmission are transmitted through the virtual special network, so that the problems of network data blocking and long time delay in the public internet due to the fact that the data transmission route is too complex and the network is busy in the transmission process of the network data which need separation transmission, are avoided; network data which need separation and acceleration transmission are transmitted a special network which is different from other types of data transmission channels, and interference of other types of data to data to be accelerated in the transmission process is avoided, therefore, the network transmission speed of the data to which the user attends is greatly improved, and the network experience of the user is optimized.

Owner:SICHUAN XUNYOU NETWORK TECH

Apparatus and method for processing an image

InactiveUS20060140498A1Improve image processing capabilitiesIncrease in circuit sizeImage memory managementElectric controllersImaging processingComputer graphics (images)

An image processing apparatus is provided for enhancing the image processing function without having to increase the circuit scale. The image processing apparatus includes an image divider, a pixel processor, and an image coupler. If the number of horizontal pixels on the width of an input image is larger than a size of a line buffer, the image divider equally divides the input image in the vertical direction so that the resulting divided area is smaller than the number of horizontal pixels on the width of the line buffer. Then, the image divider controls an input data transfer circuit so that the pixel data of the input image may be sequentially transferred to the line buffer for each of the equally divided areas. The image processor sequentially processes the pixel data of the input image temporarily stored in the line buffer and then sends out the output pixel data. The image coupler controls the output data transfer circuit so that the output pixel data sequentially outputted for one divided area may be coupled with the output pixel for another divided area, for generating the output image.

Owner:SOCIONEXT INC

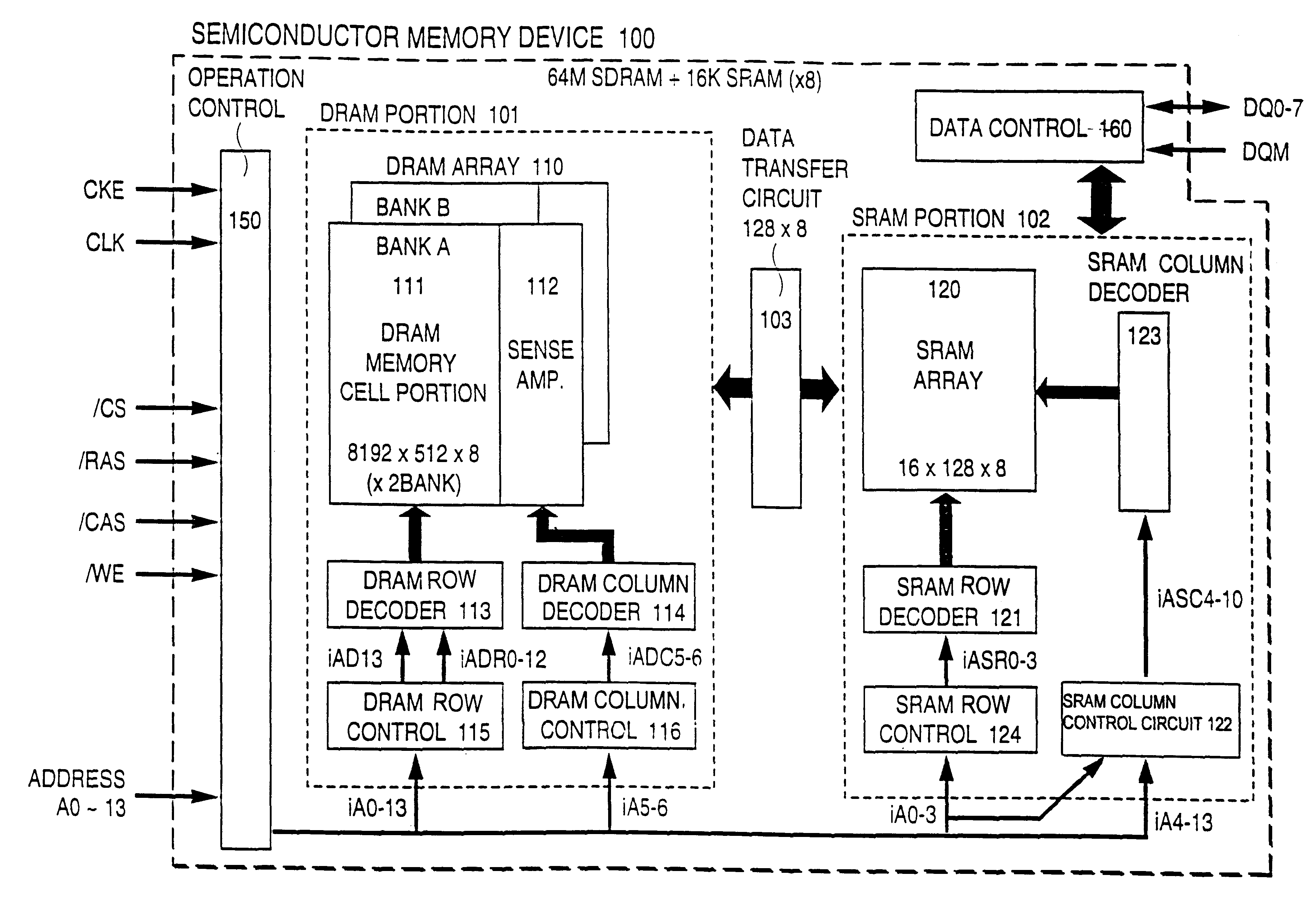

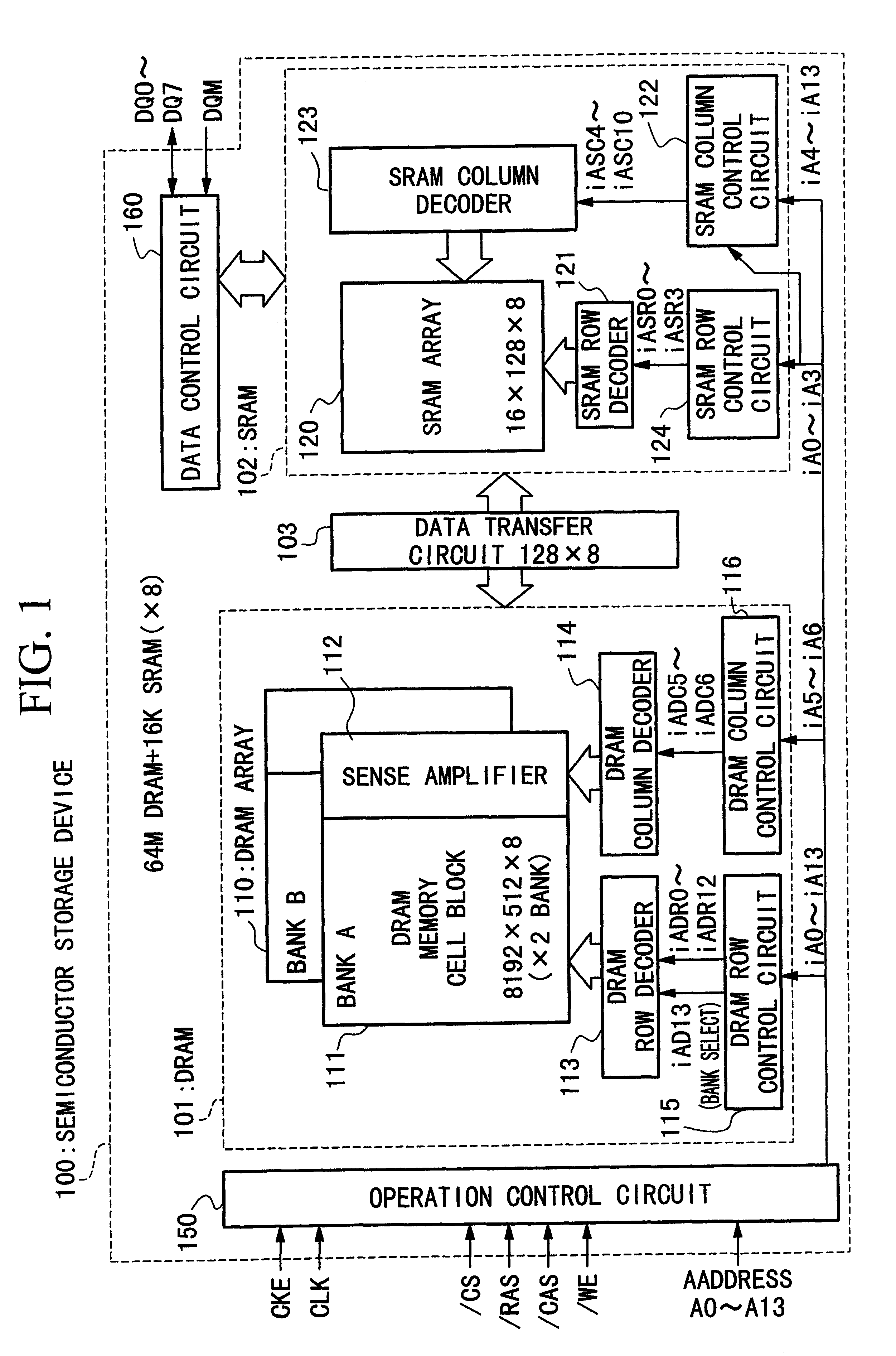

Semiconductor integrated circuit device

InactiveUS6335873B1TransistorMemory adressing/allocation/relocationComputer architectureData transmission circuit

A semiconductor integrated circuit device is configured using a DRAM and an SRAM between which data transfer is performed by way of a data transfer circuit using data transfer bus lines. Herein, the DRAM is divided into at least two DRAM arrays, each of which contains a number of columns each consisting of memory cells. In addition, the columns are arranged in mixture in connection with external I / O terminals respectively in such a way that columns respectively containing memory cells which are simultaneously subjected to read operations within a same cycle are arranged not to adjoin each other. Thus, it is possible to reduce a probability in which multiple memory cells which are simultaneously subjected to read operations within the same cycle exist within a range of an area under influence of charged particles, which are produced locally due to neutrons. Even if data of memory cells which are concentrated at a certain region are simultaneously placed under influence of the charged particles, it is possible to remarkably reduce a number of chances in that multiple bits of data being read out to the external I / O terminals go defective simultaneously.

Owner:RENESAS ELECTRONICS CORP

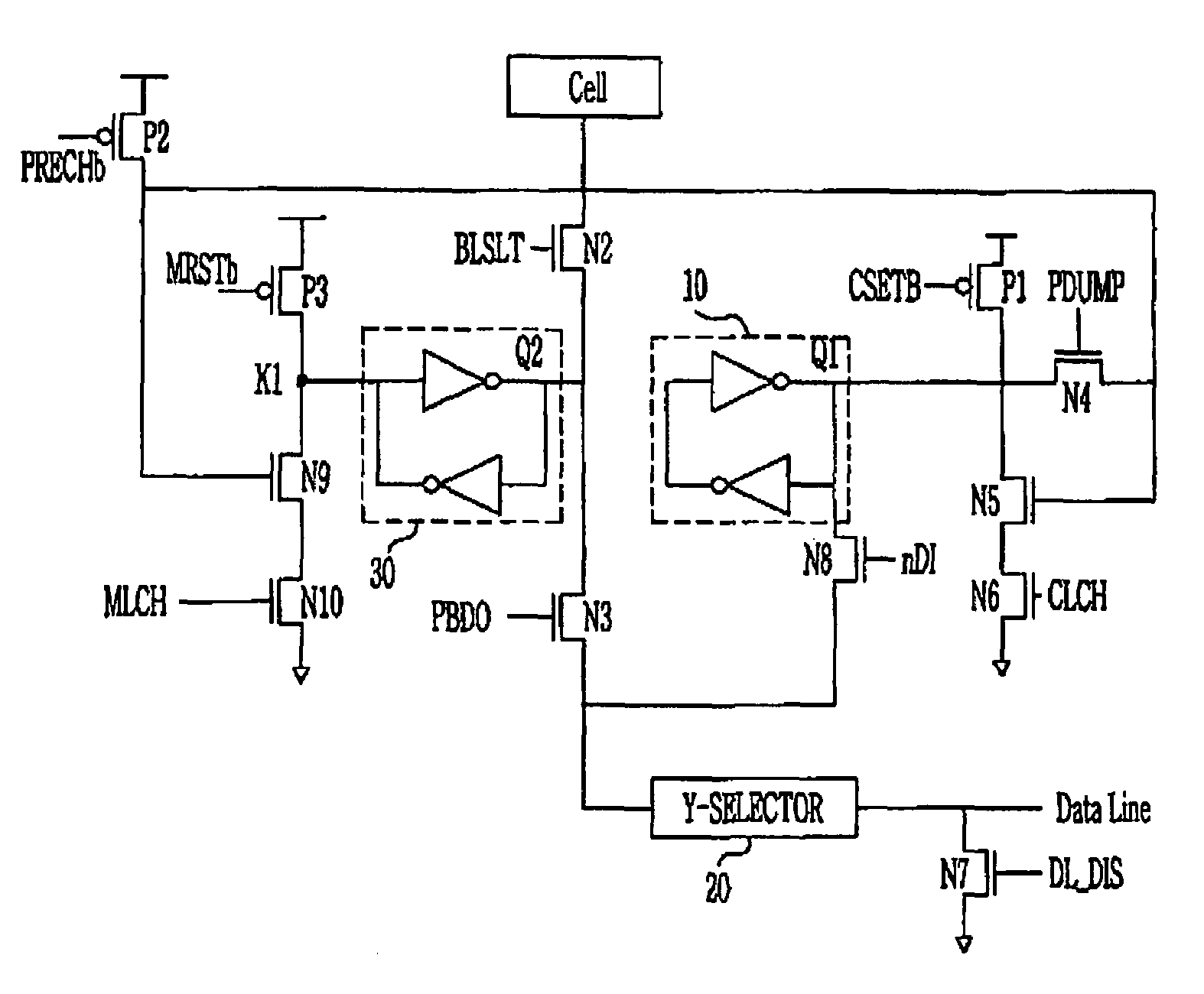

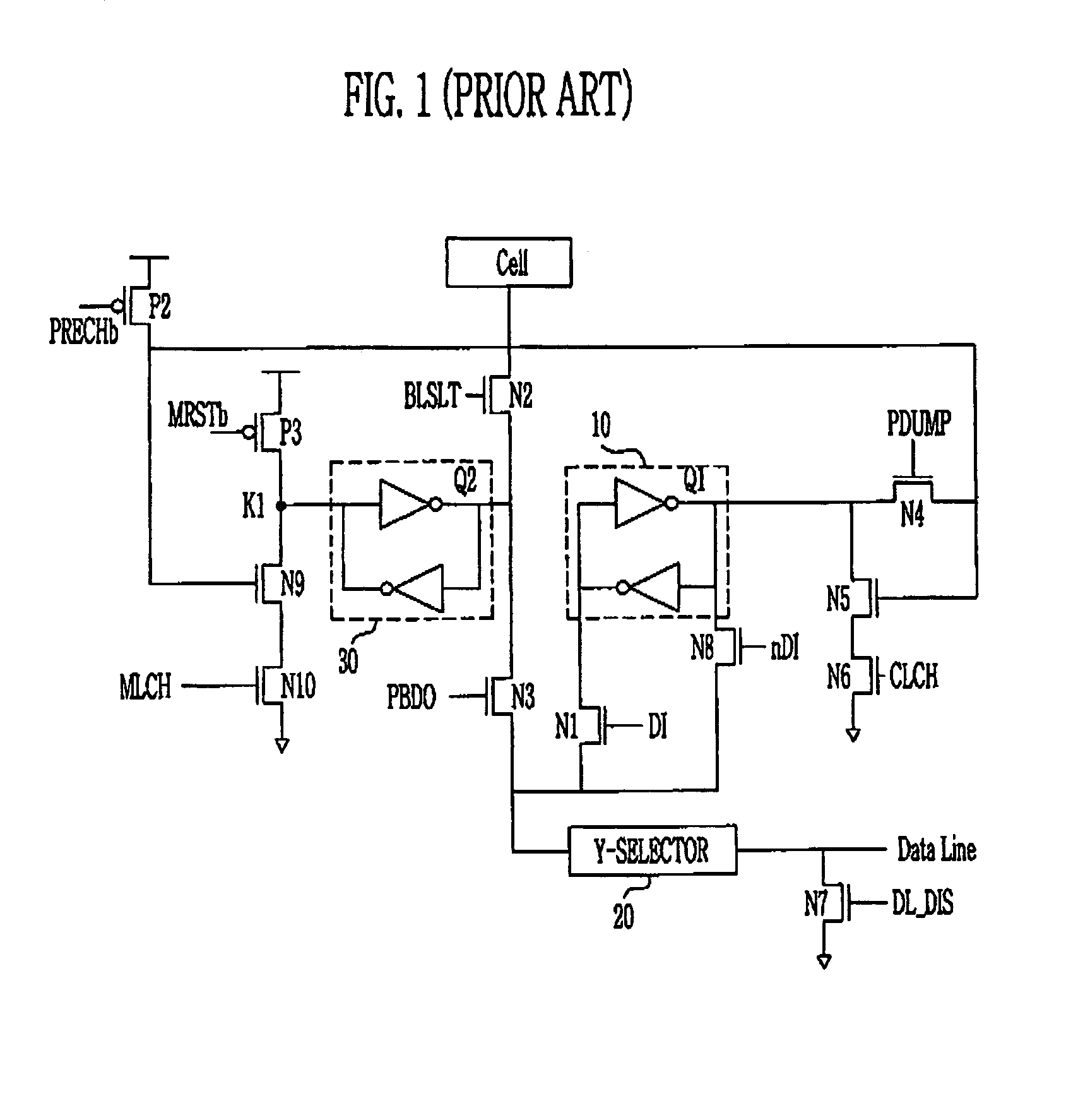

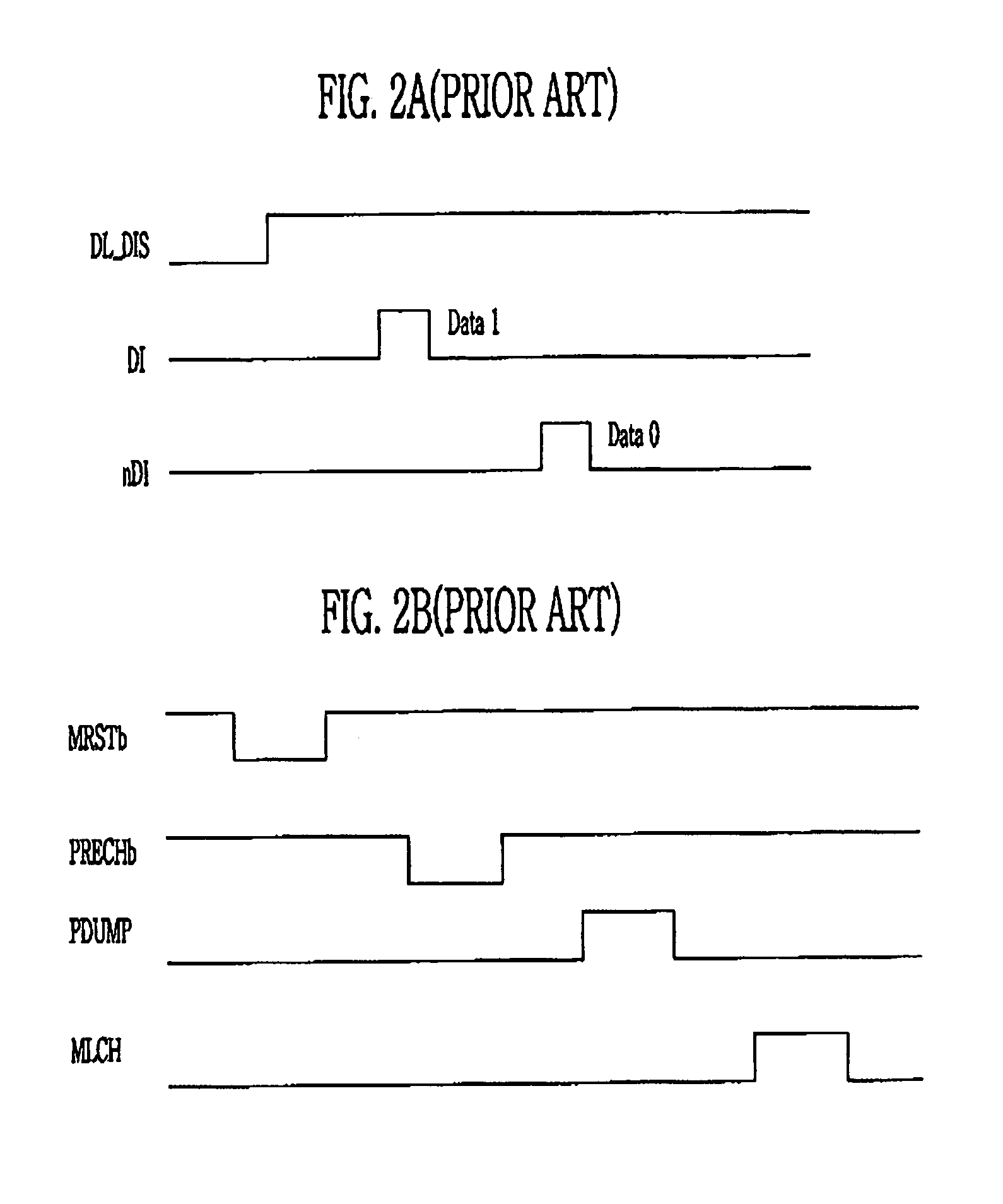

Page buffer for NAND flash memory

InactiveUS7016229B2Reduce decreaseImprove data loading speedRead-only memoriesDigital storageData controlControl signal

A page buffer for an NAND flash memory, including: a first latch for loading data; a second latch for storing data stored on a cell depending on a bit line selection signal; a setting circuit for setting the first latch to a high level to load data in a high level; a first switching circuit for transferring the data stored on the second latch depending on a data output signal of a page buffer; a discharging circuit for discharging charges on a data line; a second switching circuit for connecting the data line discharged by the discharging circuit to the first latch depending on a data control signal to load the data in a low level to the first latch; and a data transferring circuit for transferring the data of the first latch to the second latch.

Owner:SK HYNIX INC

Data transmission method and data transmission device

InactiveCN105764079AMeet speed requirementsReduce trafficPower managementHigh level techniquesTraffic capacitySignal quality

The invention discloses a data transmission method and a data transmission device. The data transmission method comprises the following steps: accessing a WIFI network, and establishing a first data channel; transmitting data through the first data channel; and in the process of data transmission, when a first preset condition is met, accessing an LTE network, establishing a second data channel, and transmitting data through the first data channel and the second data channel. The beneficial effects are as follows: data is transmitted only through WIFI when the WIFI signal quality is excellent, data is transmitted through both WIFI and LTE in order to meet the transmission rate when the WIFI signal quality is weak, and data is transmitted through LTE when the WIFI signal quality is poor; the rate demand of users is met; the power consumption of terminals is reduced effectively and the service life of terminals is improved on the basis of meeting the rate demand; and data is transmitted through LTE only when the WIFI signal quality is not optimal, the LTE traffic is saved for users, and the user experience is enhanced.

Owner:NUBIA TECHNOLOGY CO LTD

Clockless transmission system and clockless transmission method

ActiveUS20100039156A1Improve noise marginSignal transmission is convenientPulse automatic controlCathode-ray tube indicatorsControl signalControl data

A clockless transmission system includes display controller 101 and display driver 106. Display controller 101 includes data transmission circuit 102 configured to output general data obtained by multiplexing a clock by coding serialized pixel data for each pixel data during a data communication interval and also to output a predetermined control signal during a blanking interval. Display driver 106 includes clock and data recovery circuit 107 configured to output the pixel data from the general data transferred from the display controller and to increase a loop gain of a feedback loop in clock recovery such that the loop gain is larger than that when the general data is received, according to control data of the control signal, to recover and output a clock, and display driving circuit 109 configured to output a signal for driving a display based on the pixel data and the recovered clock.

Owner:NEC CORP

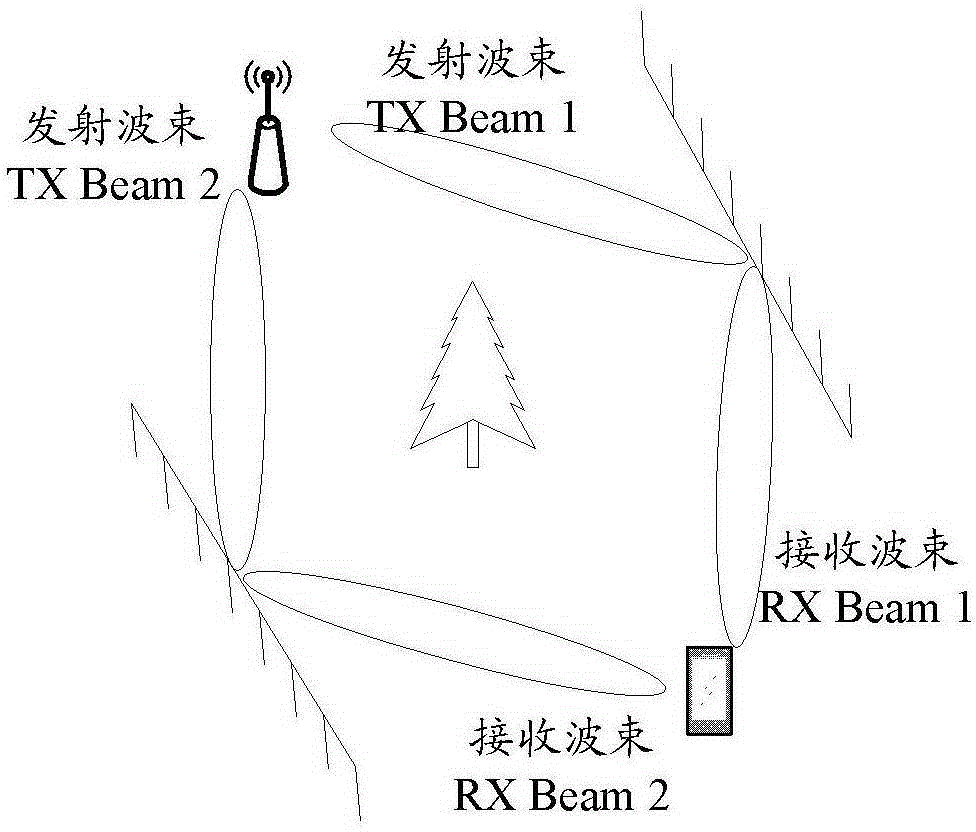

Data transmission method and system

ActiveCN106470062AImprove reliabilityImprove access speedSpatial transmit diversityChannel state informationData transmission circuit

The invention discloses a data transmission method and system. The method includes the steps of a base station informing the beam transmitting capability of a terminal base station and obtaining the beam receiving capability of a terminal, the base station determining the independent transmission and reception beam pairs for transmitting data according to the channel state information of the different transmission and reception beam pairs reported by the terminal, and the base station transmitting data to the terminal on each of the determined independent transmission and reception pairs and informing the terminal of the data transmission form of the determined independent transmission and reception beam pairs, when the number of determined independent transmission and reception beam pairs is at least two. The data transmission method and system disclosed in the invention solve the problem that in the conventional 3GPP or 802.11 technology, data transmission can not be realized by bi-beams or multi-beams.

Owner:ZTE CORP

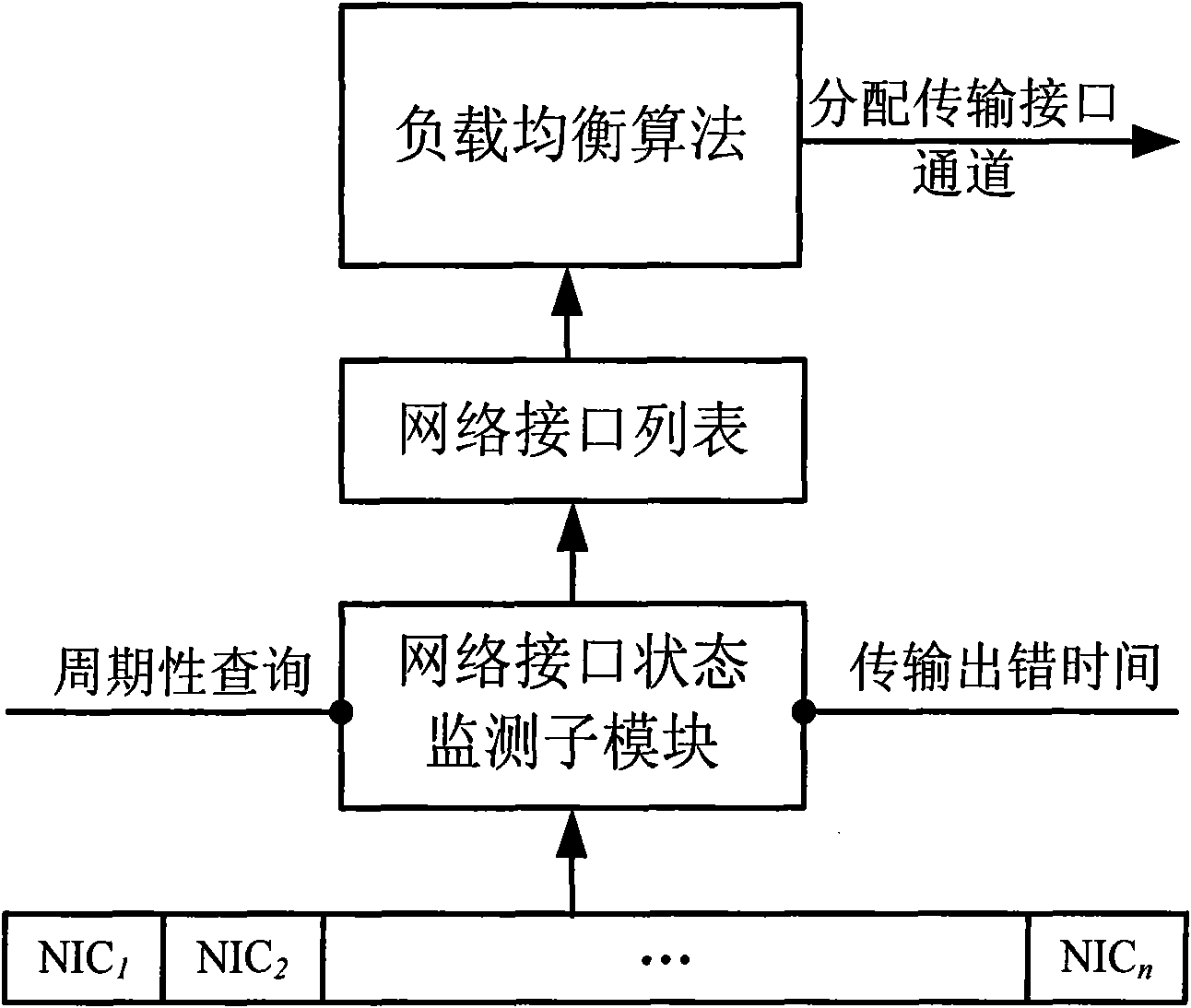

Data transmission accelerating engine method based on multiple access passages of transmitting end

InactiveCN101668005ALoad balancingTake advantage ofTransmissionOperational systemNetwork interface device

The invention relates to a data transmission accelerating engine method based on multiple access passages of a transmitting end, which comprises the following steps: after a transmitting end host machine downloads a data packet from an application layer, carrying out TCP multiplexing encapsulation; then delivering the data packet to a TCP / IP protocol stack of a host machine operation system to process; transmitting an encapsulated IP datagram formed by an IP layer to a link layer and then to a physical layer; arriving at a data receiving party by an intermediate routing and demultiplexing by the receiving party. The method is characterized by comprising the following steps: arranging a data transmission accelerating engine between the IP layer and the link layer; grouping the data to be transmitted of the IP datagram according to a mark bit in an IP masthead; then detecting the flow load condition of all transmission passages of the grouped datagram groups by a load balancing module; carrying out predistribution calculation by a corresponding flow distribution algorithm and distributing a data flow to be transmitted to all available transmission passages to transmit in parallel; and finally appointing the predistributed datagram groups to different network interface devices by a data dispatching module.

Owner:SOUTHEAST UNIV

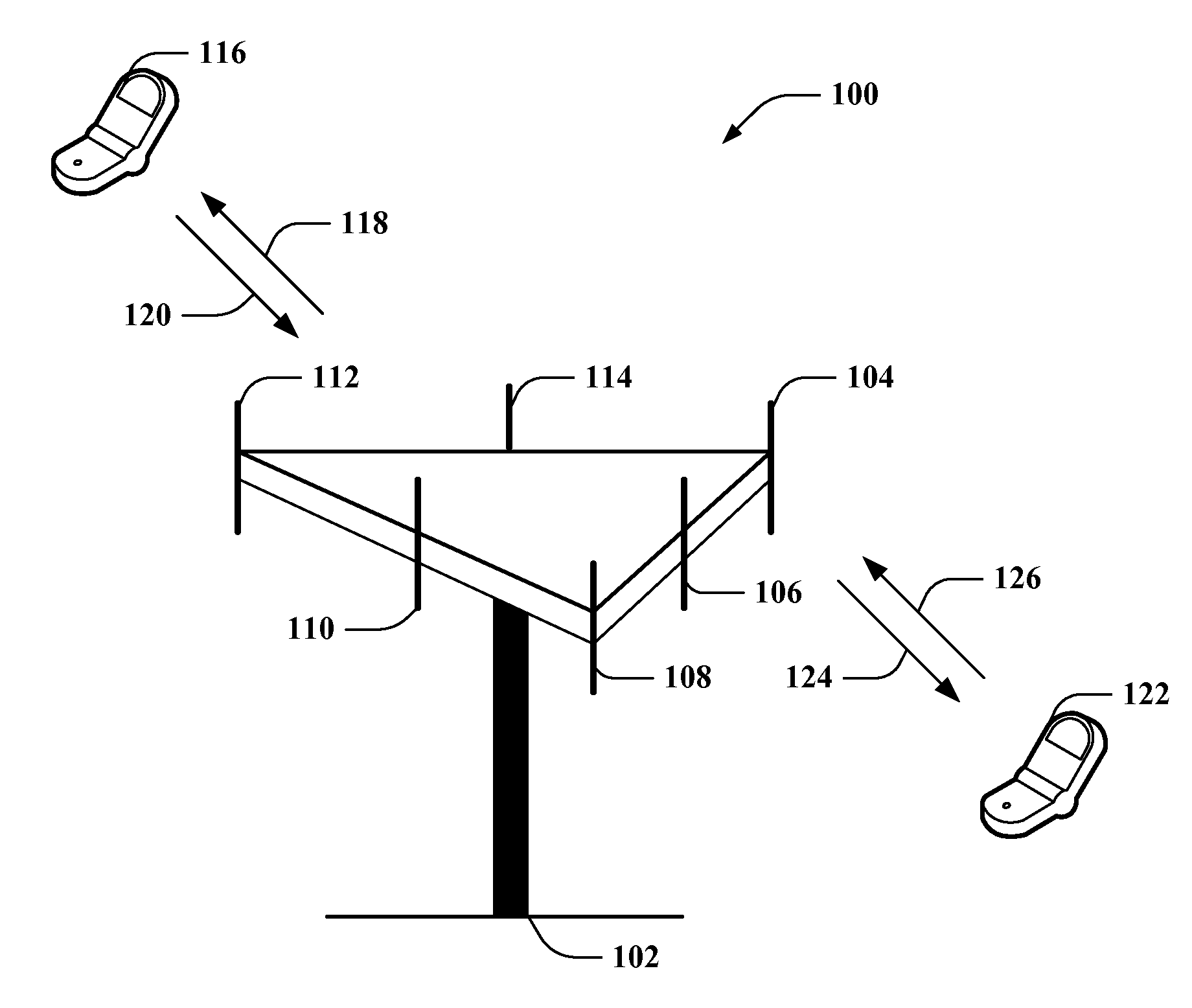

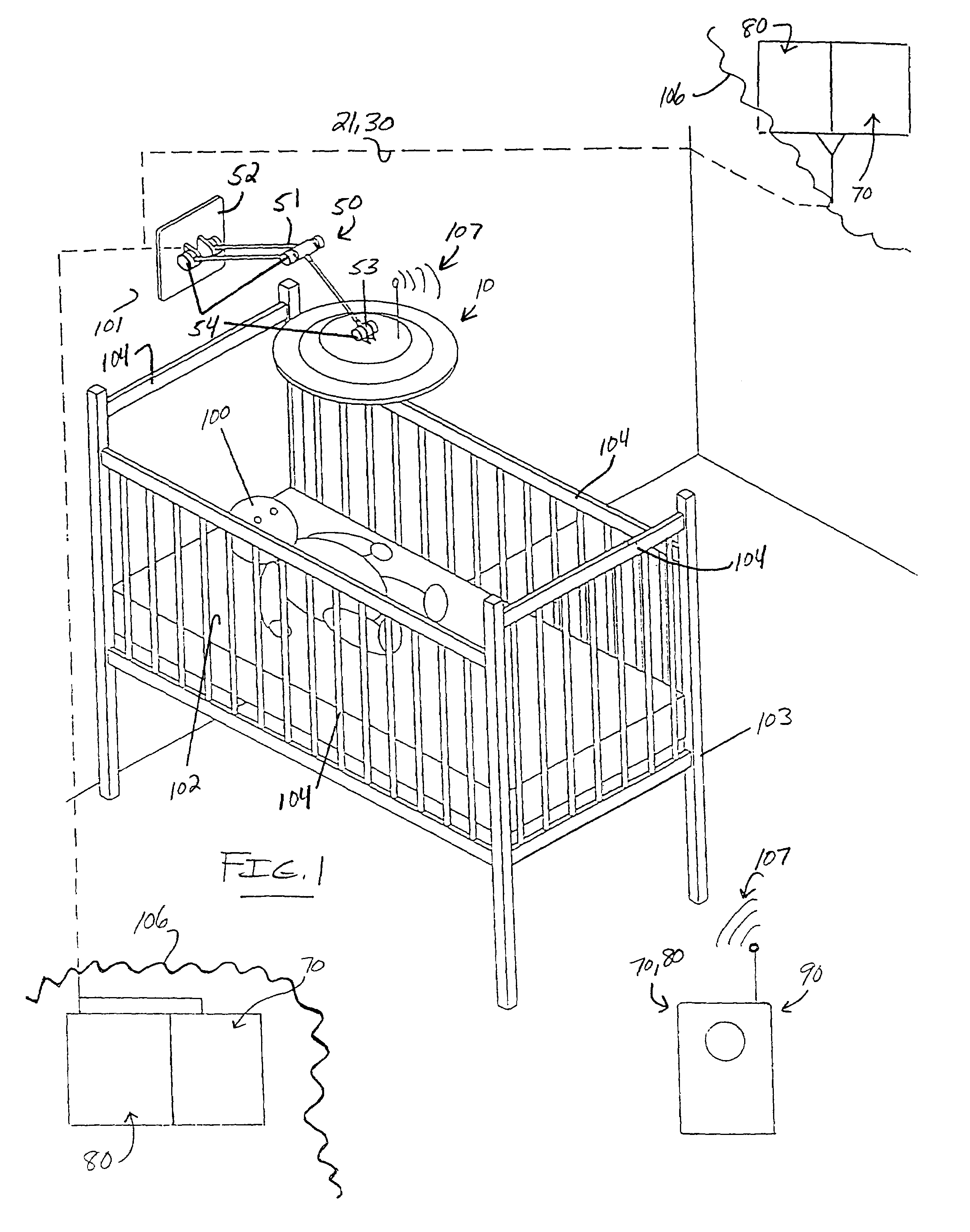

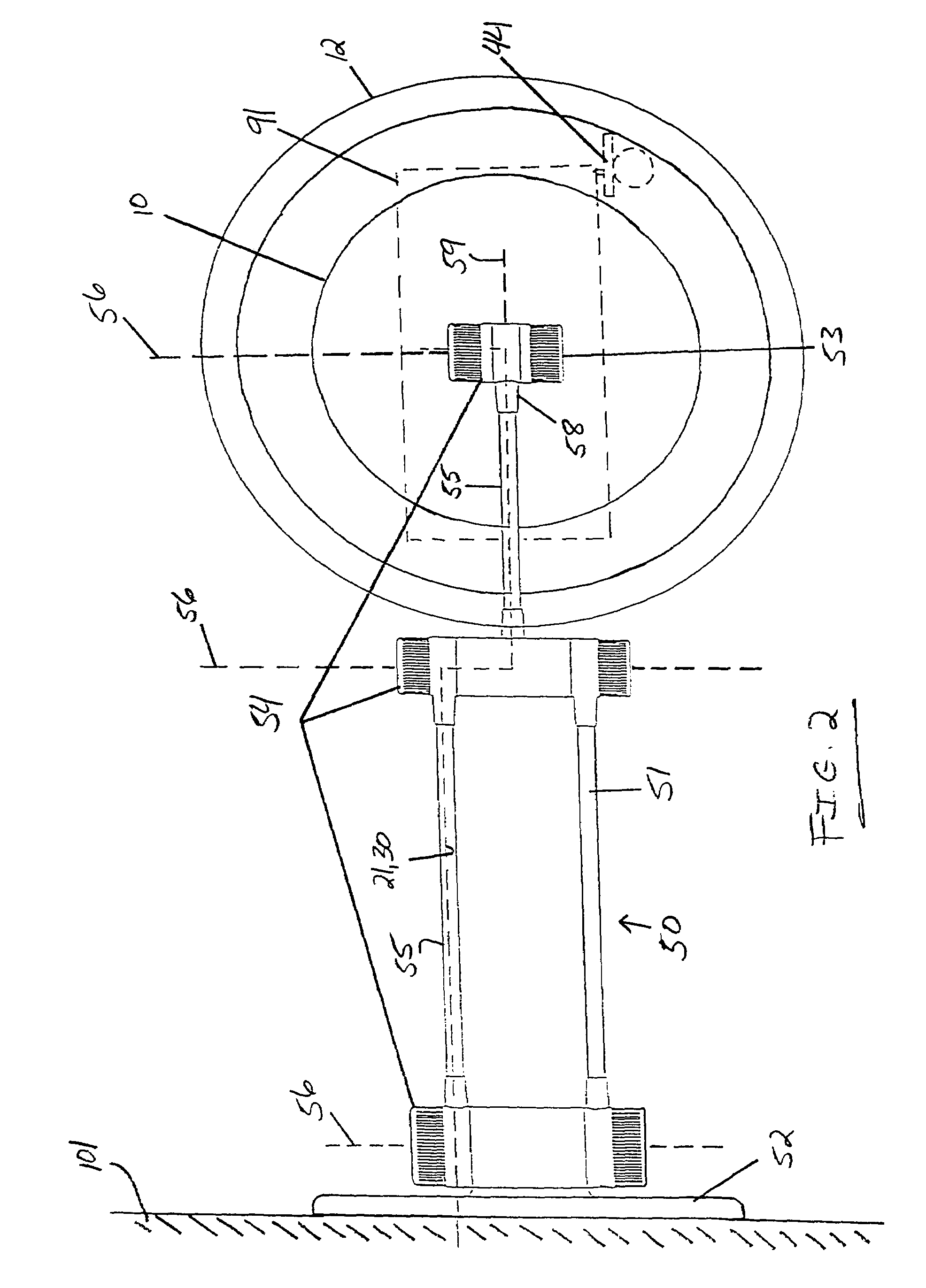

Combination monitoring and entertainment system for children

A dual functioning system for enabling a user to selectively monitor and entertain a subject comprises an entertainment system and a surveillance system. The entertainment system comprises a visual display, signal-delivering circuitry, signal-inputting hardware, and an extendable arm assembly. The arm assembly selectively positions the visual display for viewing by a target subject. The signal-inputting hardware enables the user to output stimuli upon the visual display via the signal-delivering circuitry. The visual display comprises at least one energy-passing aperture. The surveillance system comprises a camera assembly, data-transmitting circuitry, and monitoring hardware. The camera assembly is positioned adjacent a select energy-passing aperture for receiving and transmitting monitorial data input to the monitoring hardware via the select energy-passing aperture and the data-transmitting circuitry and, having a selectively colored lens light filter, also provides a color-camouflaged display to the subject.

Owner:CLARK CYNTHIA C

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com