Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

224results about How to "Avoid many problems" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

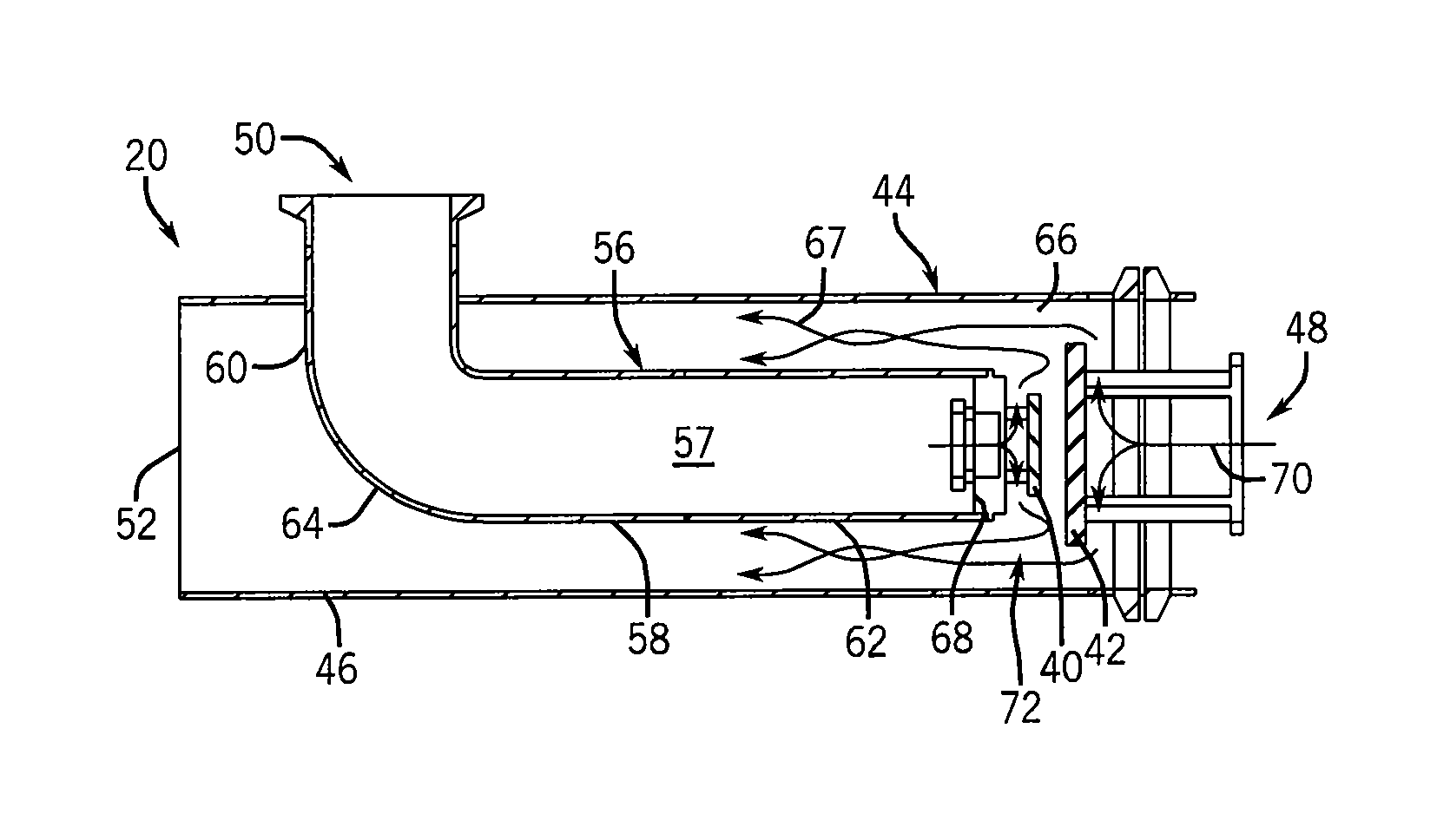

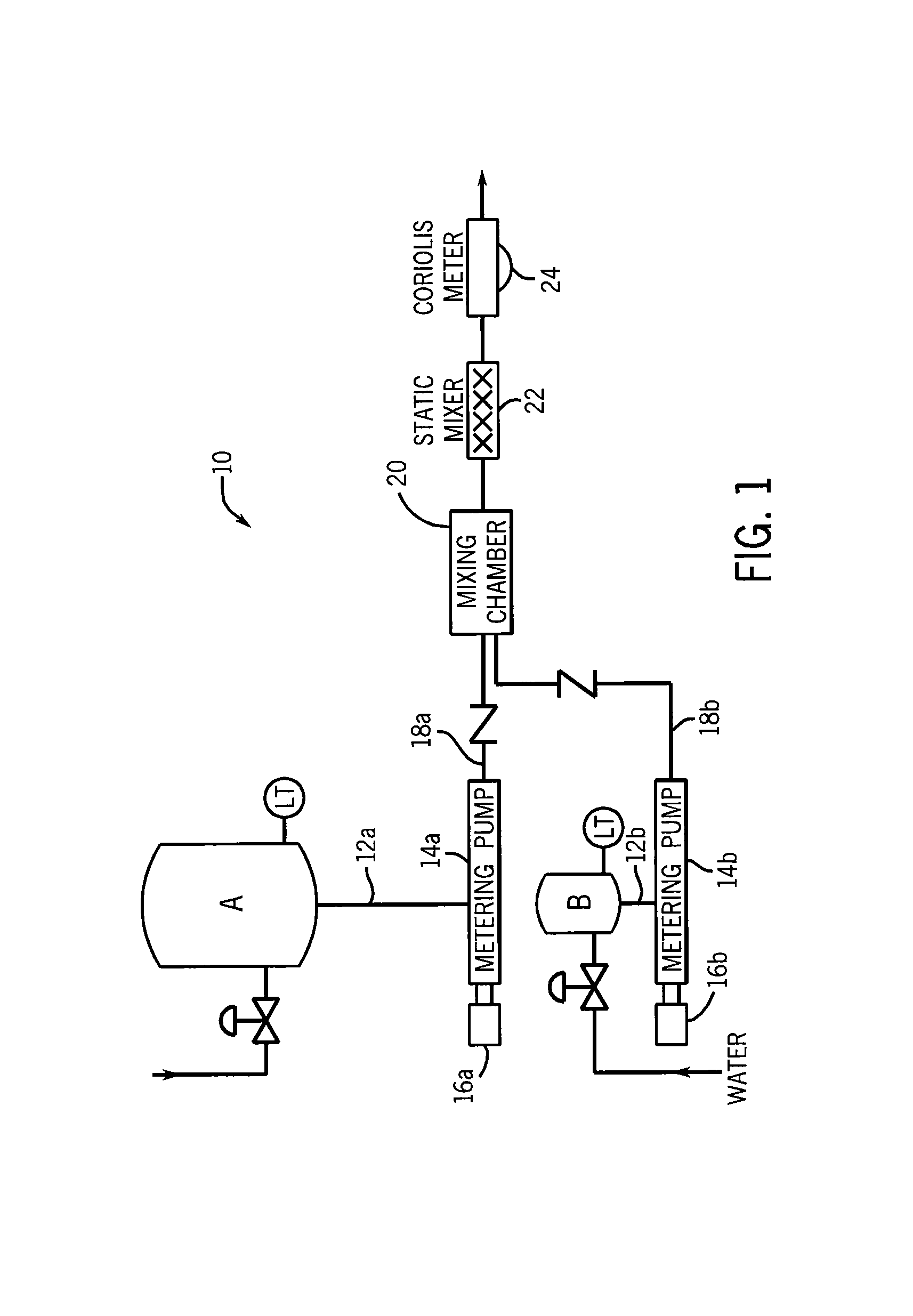

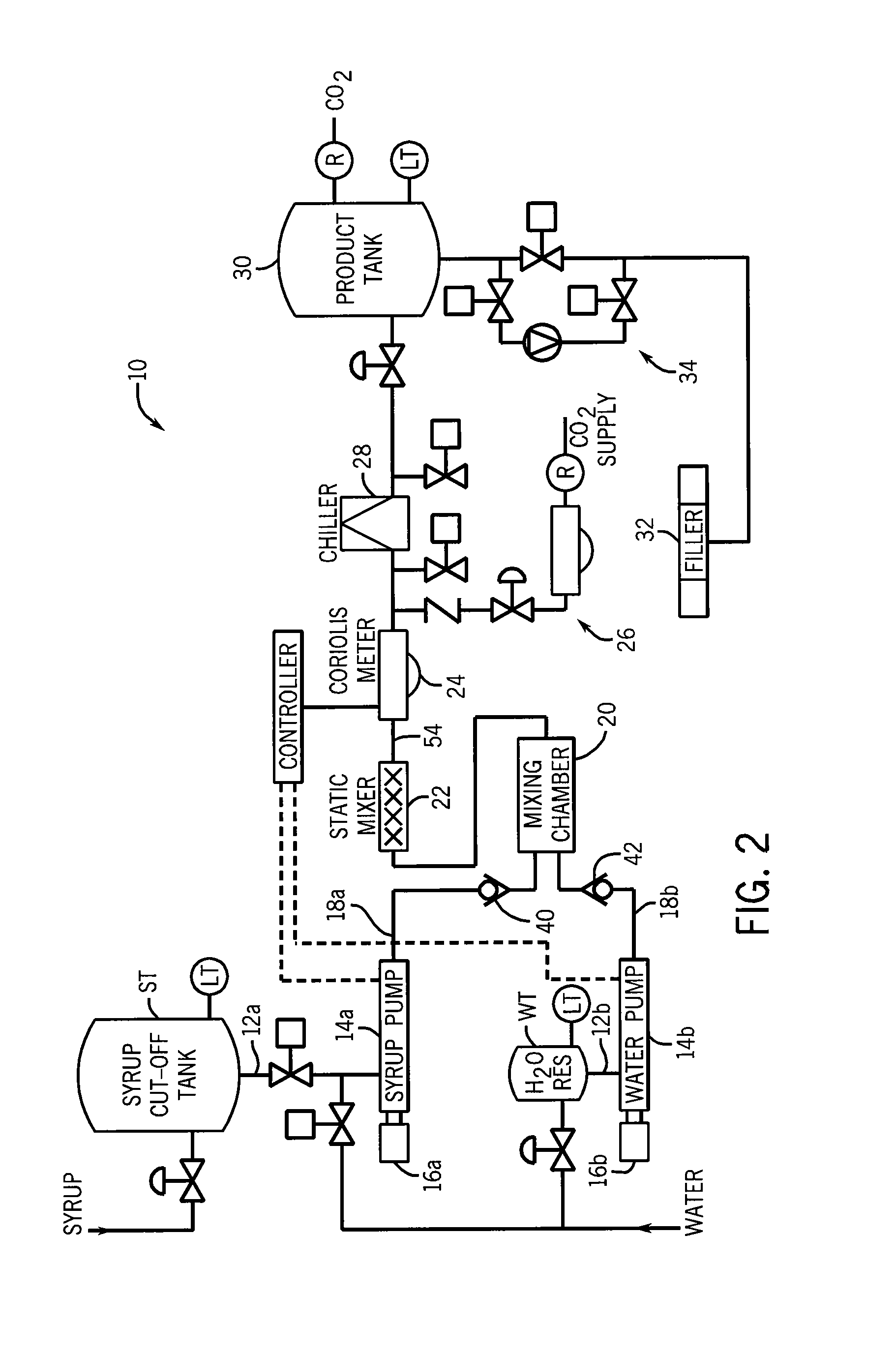

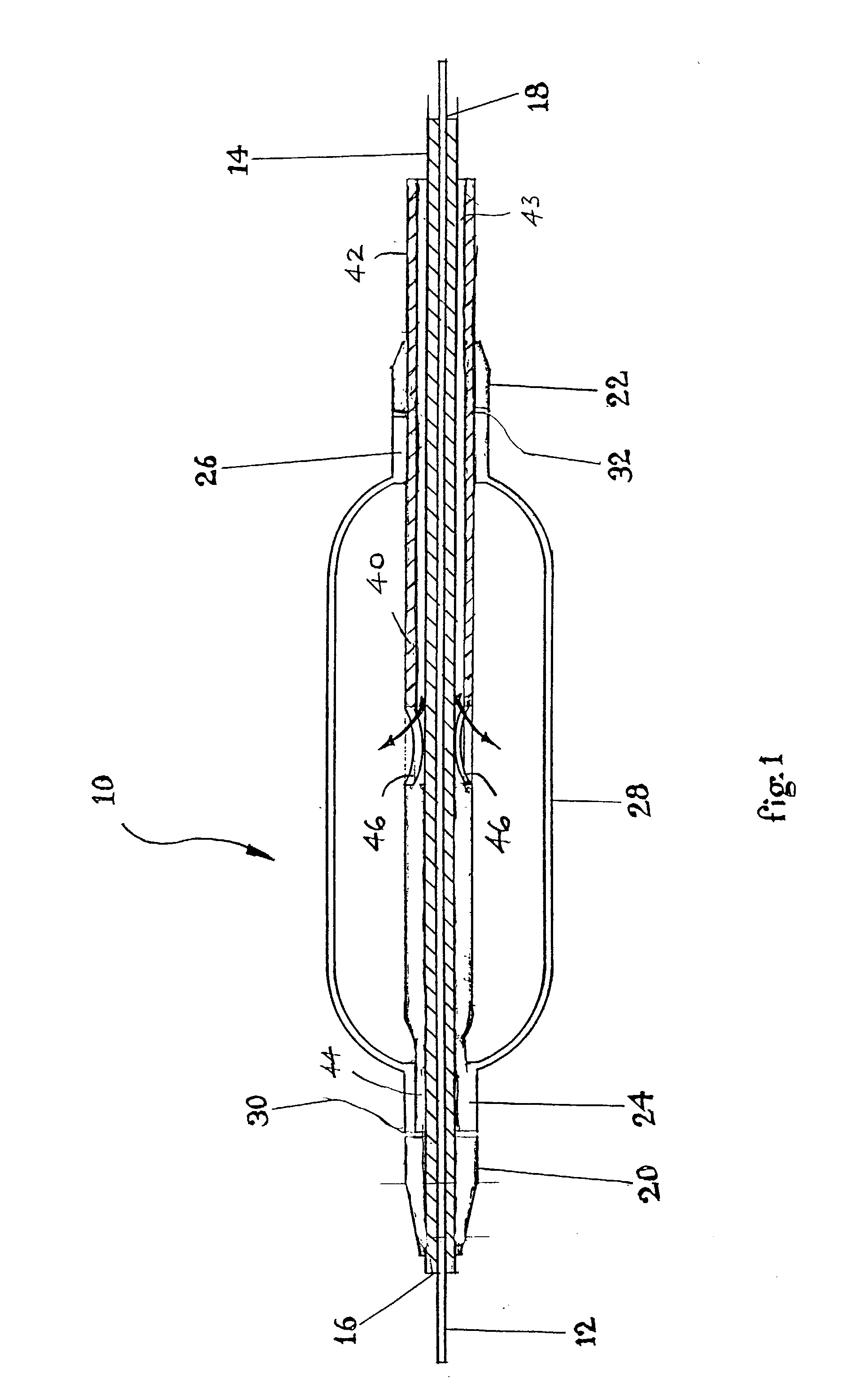

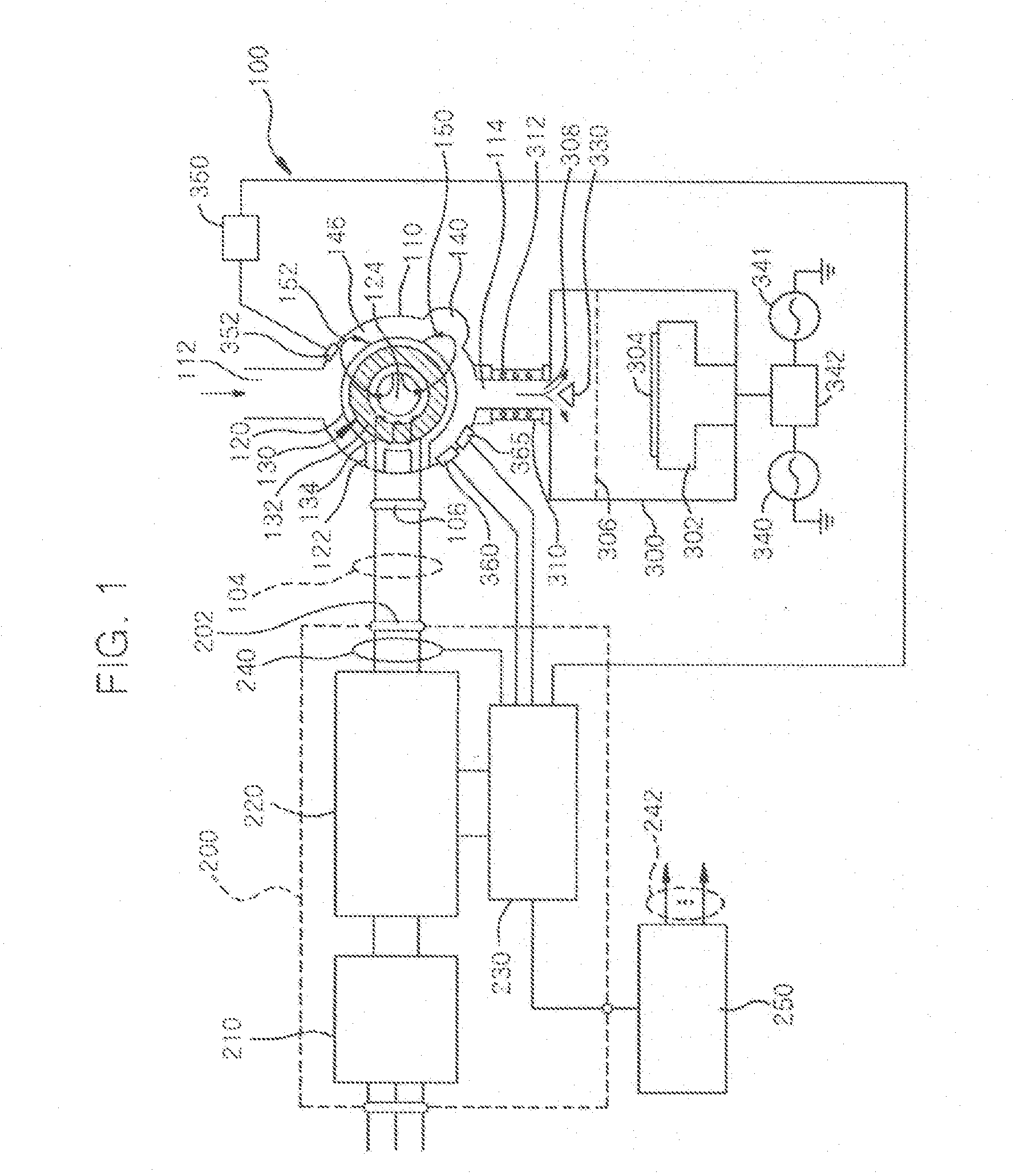

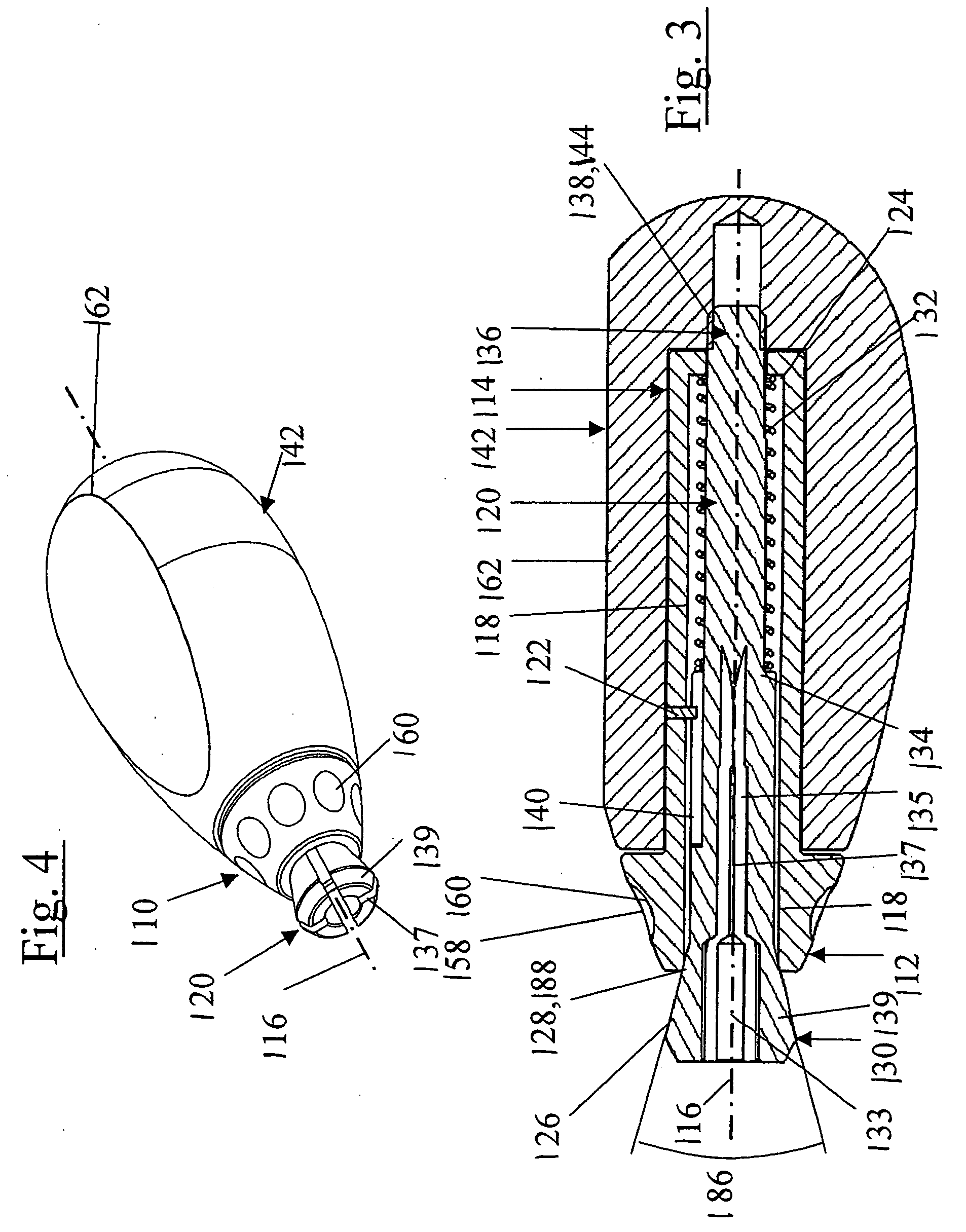

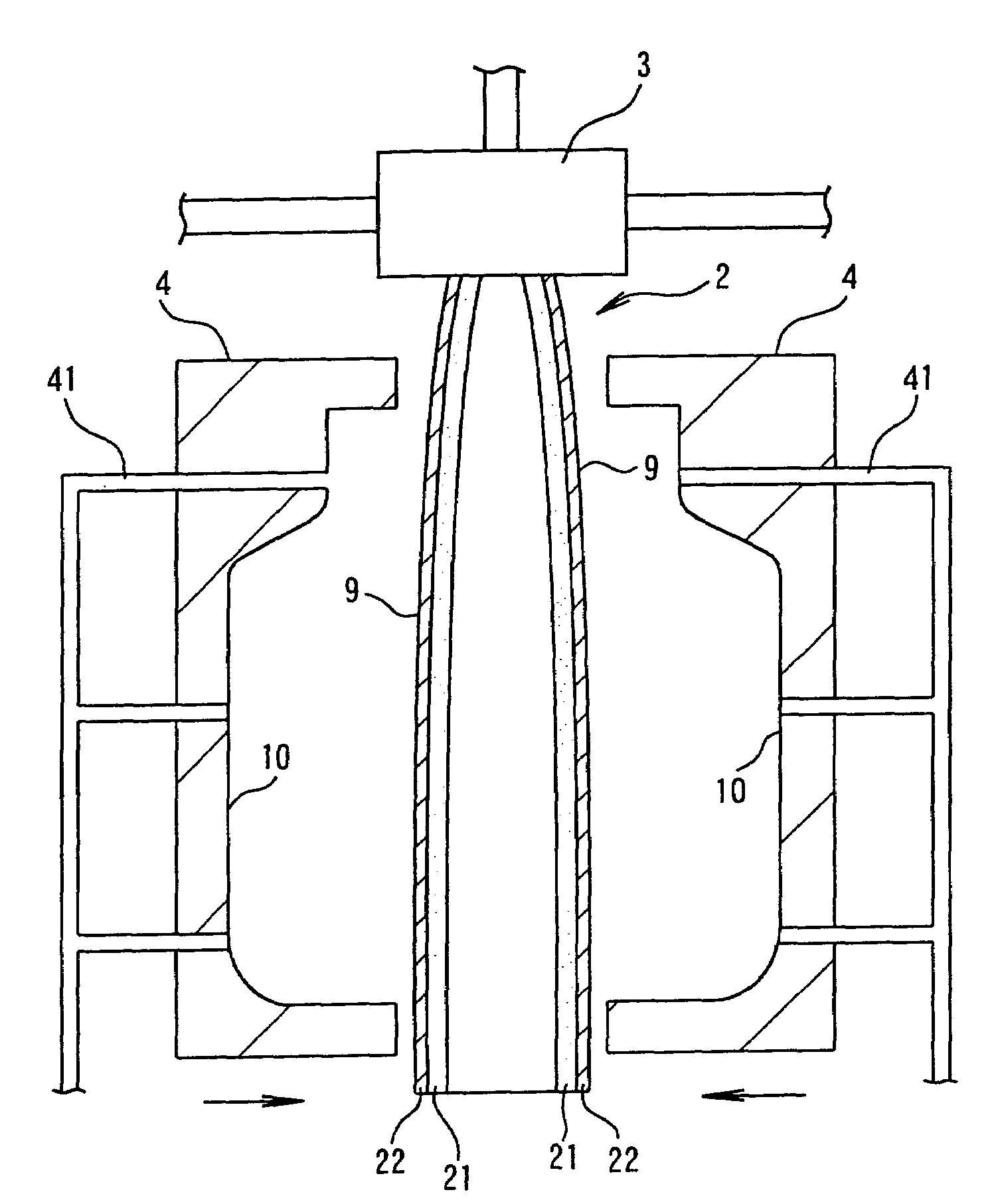

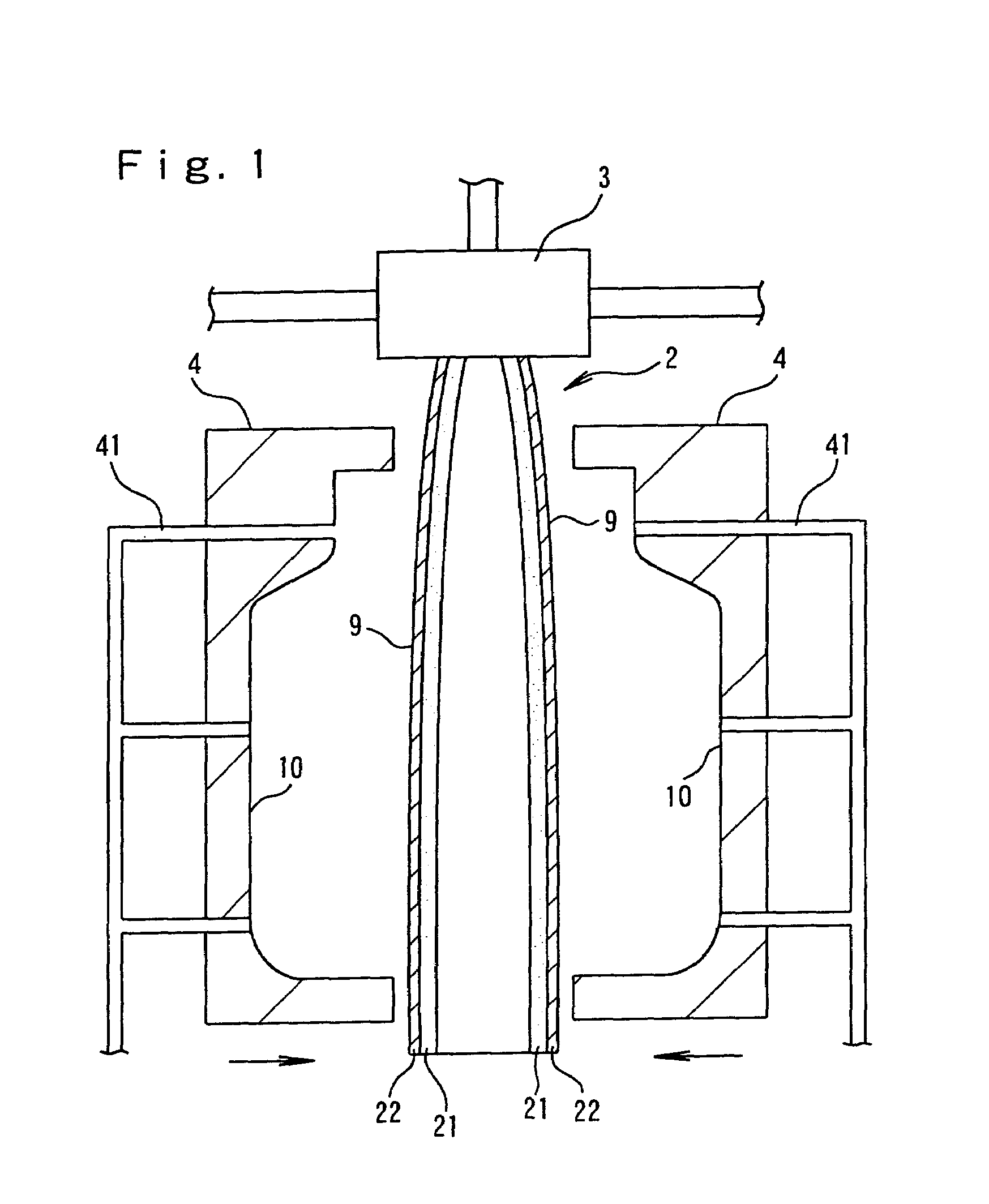

Fluid mixer using countercurrent injection

ActiveUS9004744B1Avoid many problemsEasy to controlFlow mixersTransportation and packagingEngineeringCheck valve

A method and apparatus for mixing fluids, such as beverage syrup and water, uses countercurrent injection to improve blending of the fluids. A mixing chamber has a first inlet through which a first fluid is fed to the mixing chamber, and a second inlet through which a countercurrent injection nozzle extends and is operative to inject a second fluid into a stream of the first fluid. The countercurrent injection nozzle is equipped with a check valve to control the flow of fluid into the mixing chamber. The mixing chamber may include additional inlets that may be fitted with countercurrent injection nozzles to permit the countercurrent injection of other fluid, such as flavorings, into the stream of the first fluid.

Owner:TECHNIBLEND LLC

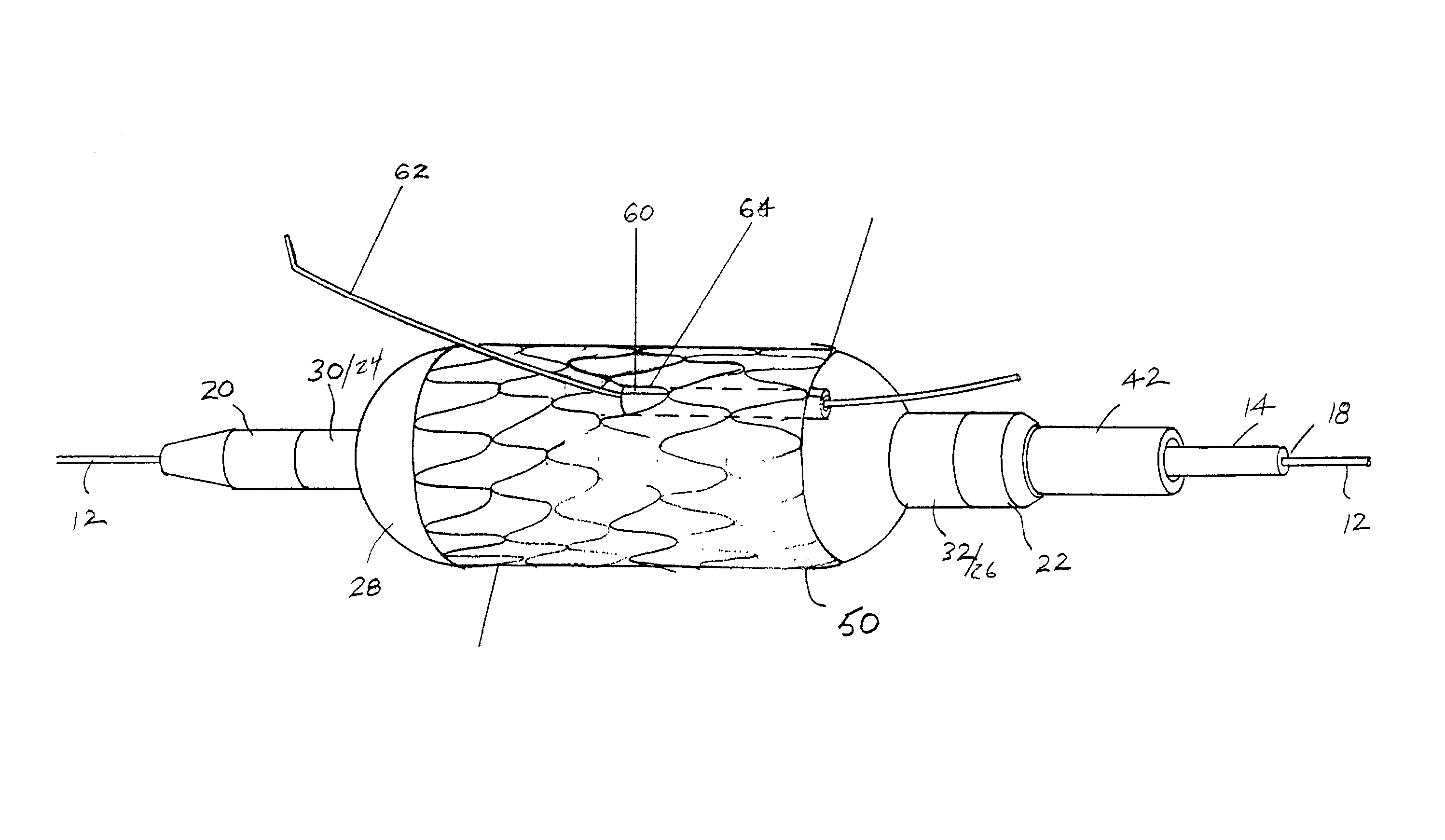

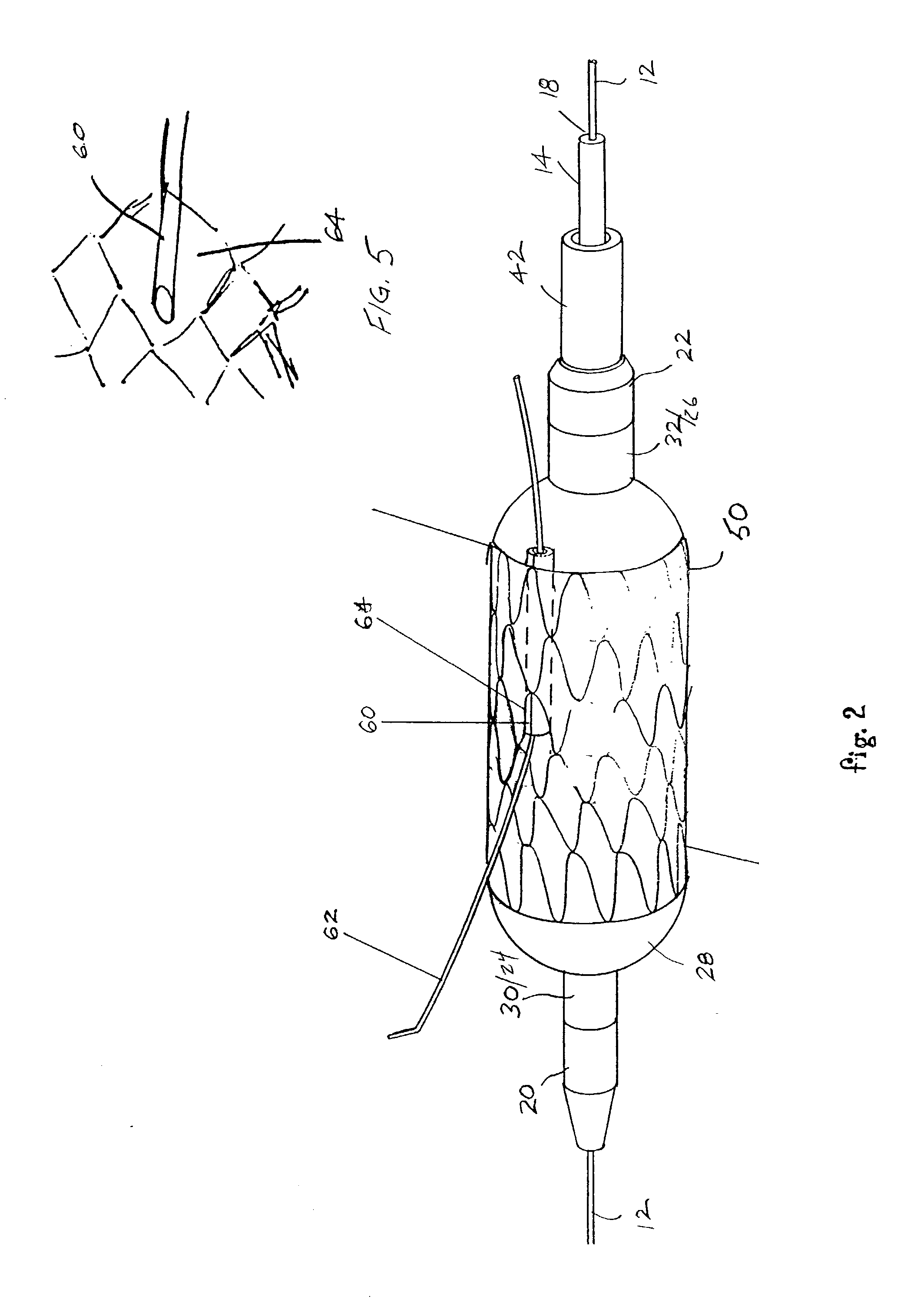

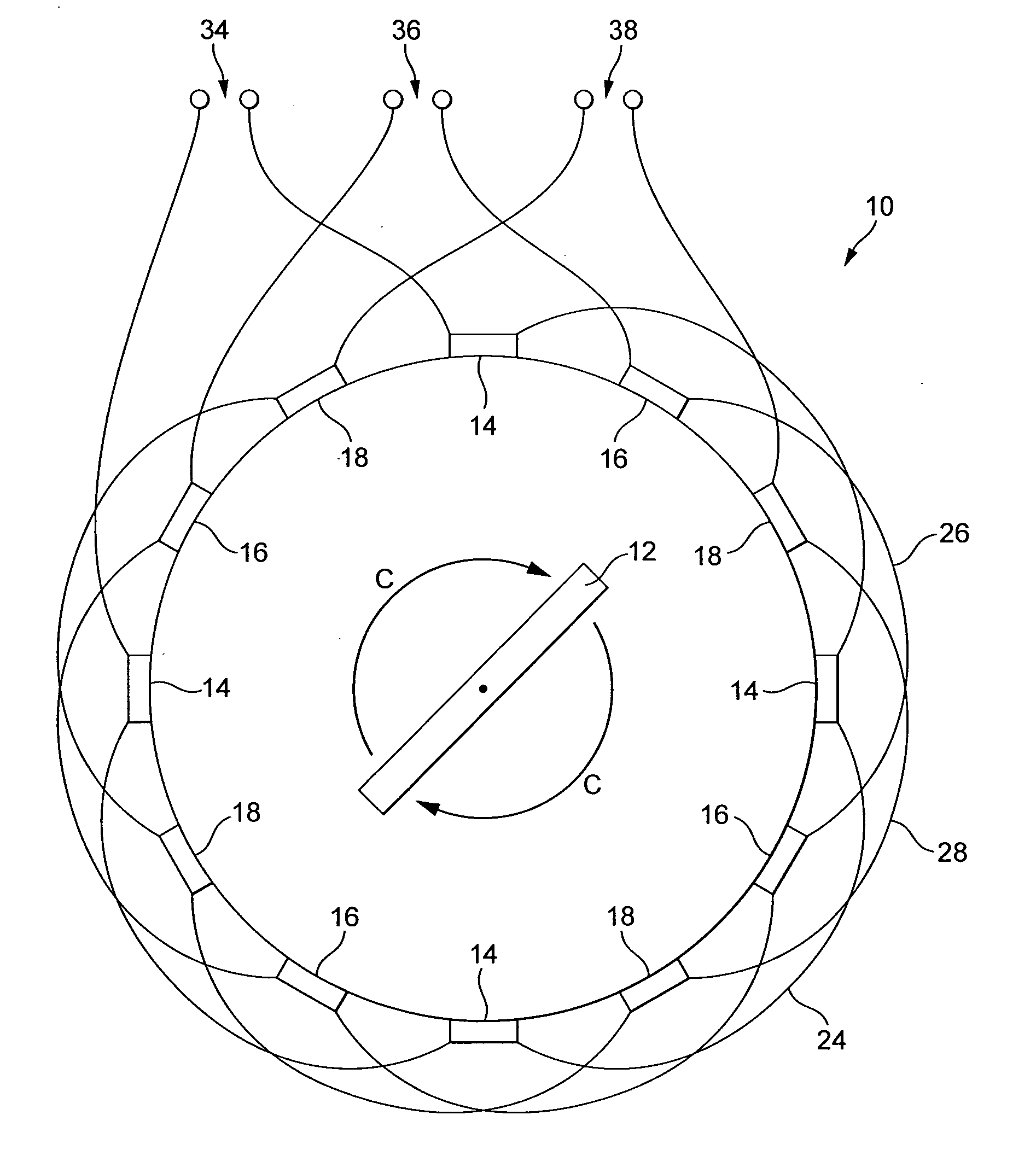

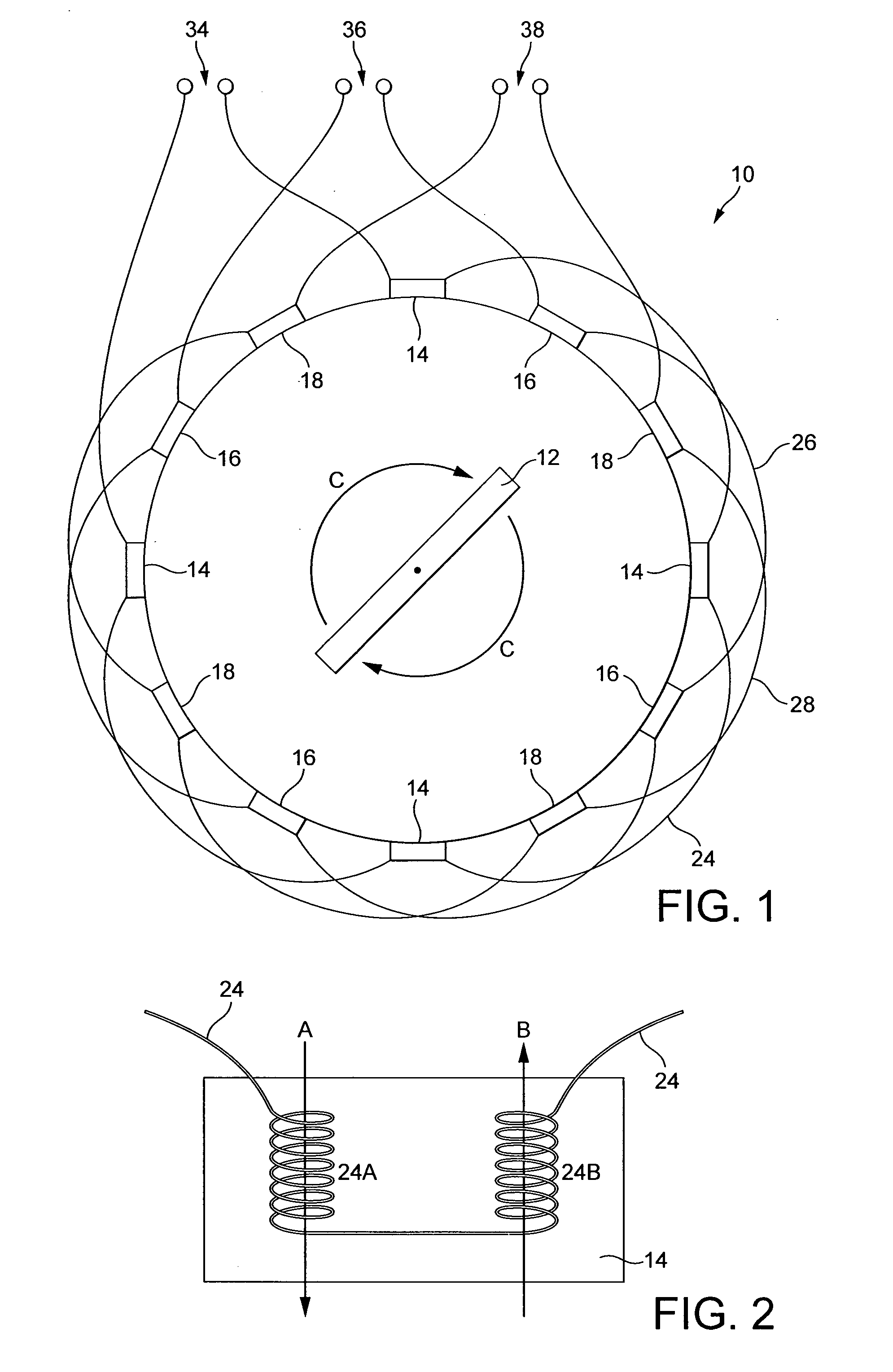

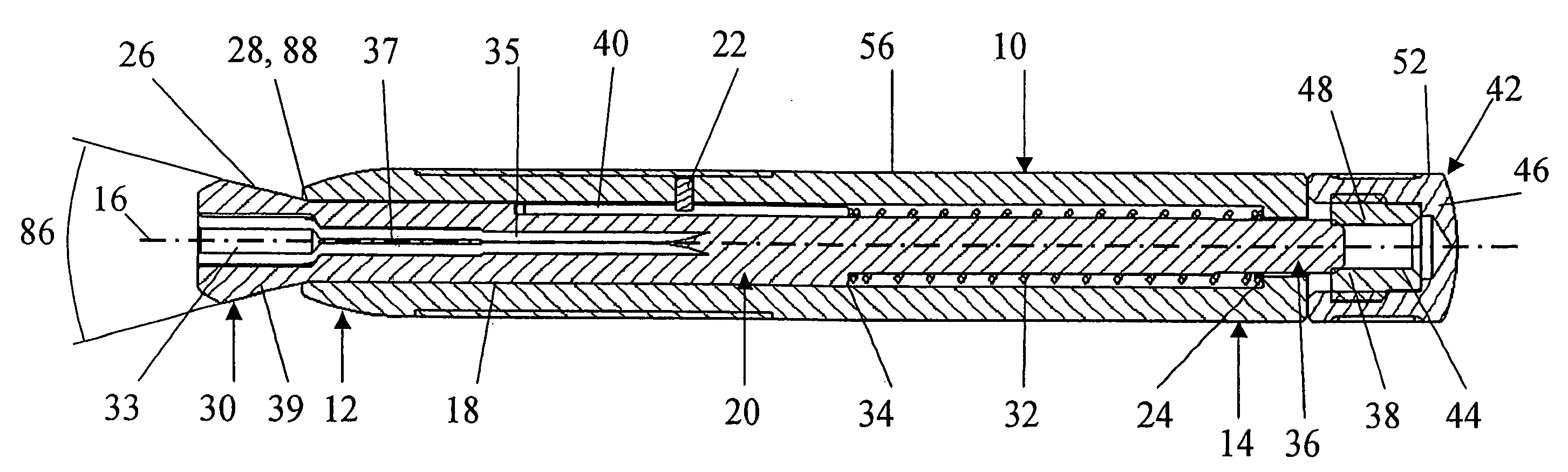

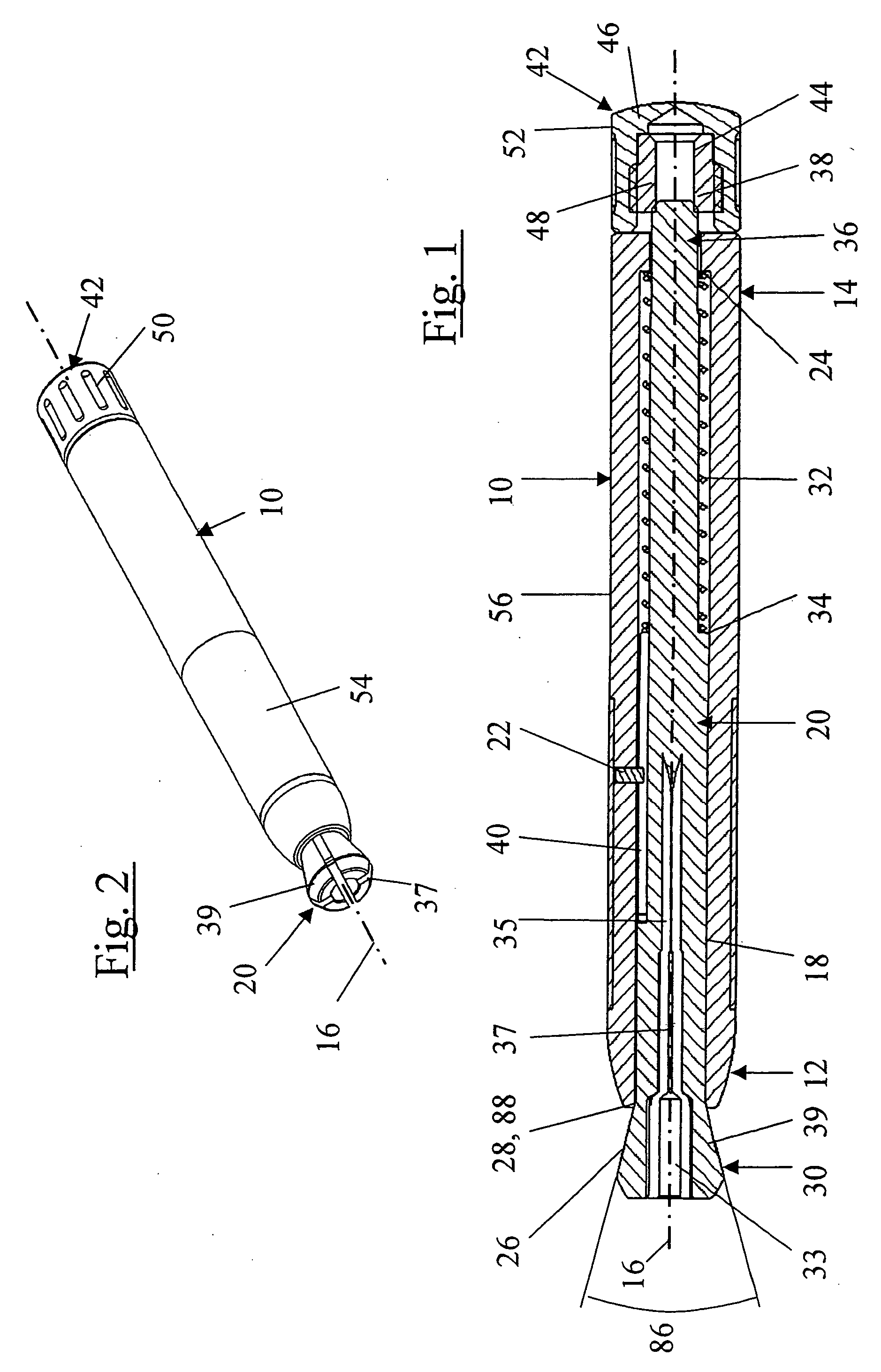

Rotating stent delivery system for side branch access and protection and method of using same

InactiveUS20030055483A1Improve directionImprove protectionStentsBalloon catheterGuide wiresCatheter device

A catheter assembly and method of use comprises advancing a catheter having a rotatably mounted balloon relative to the primary guide wire to a vessel bifurcation along first and second guide wires.

Owner:GUMM DARREL C

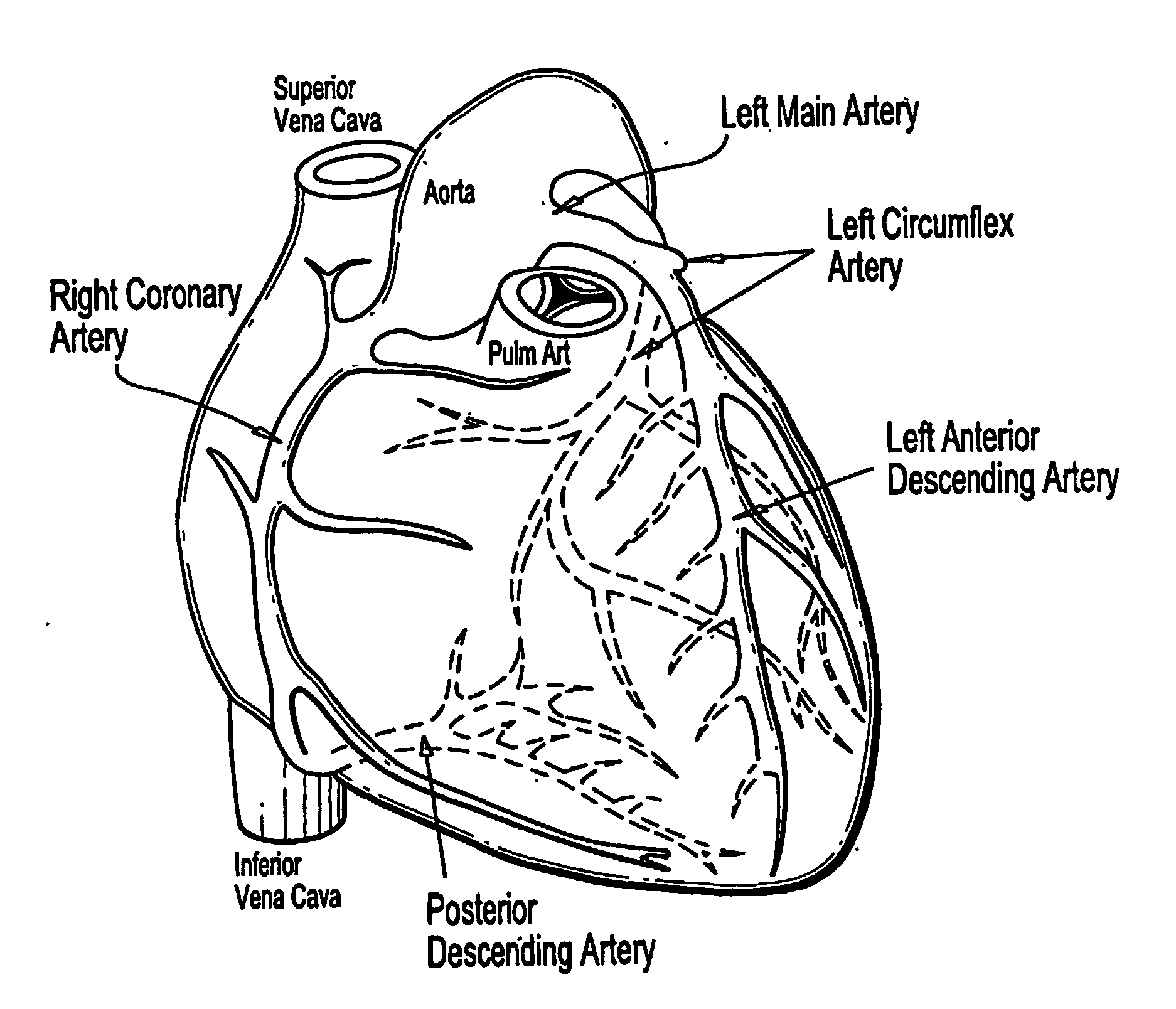

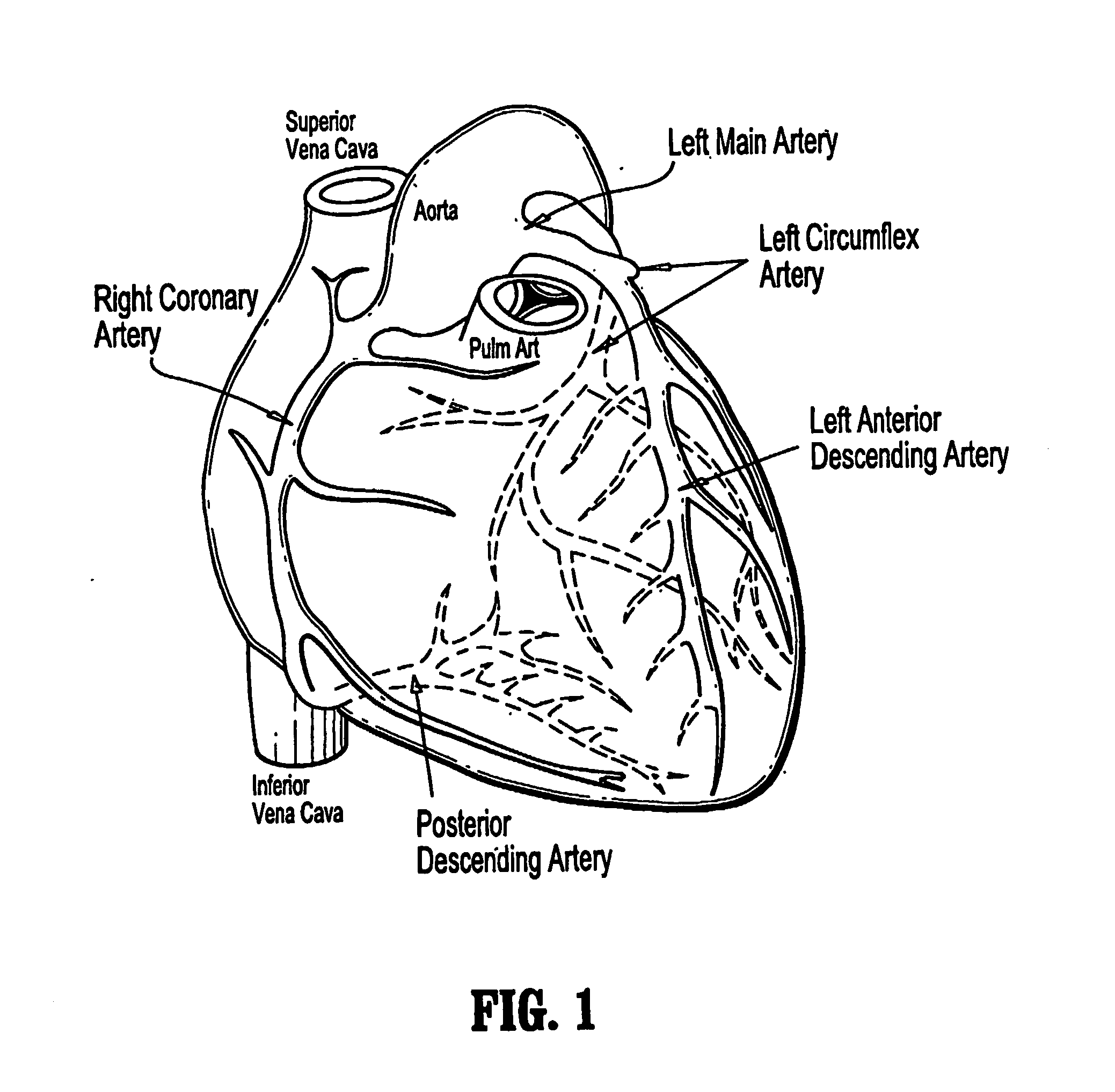

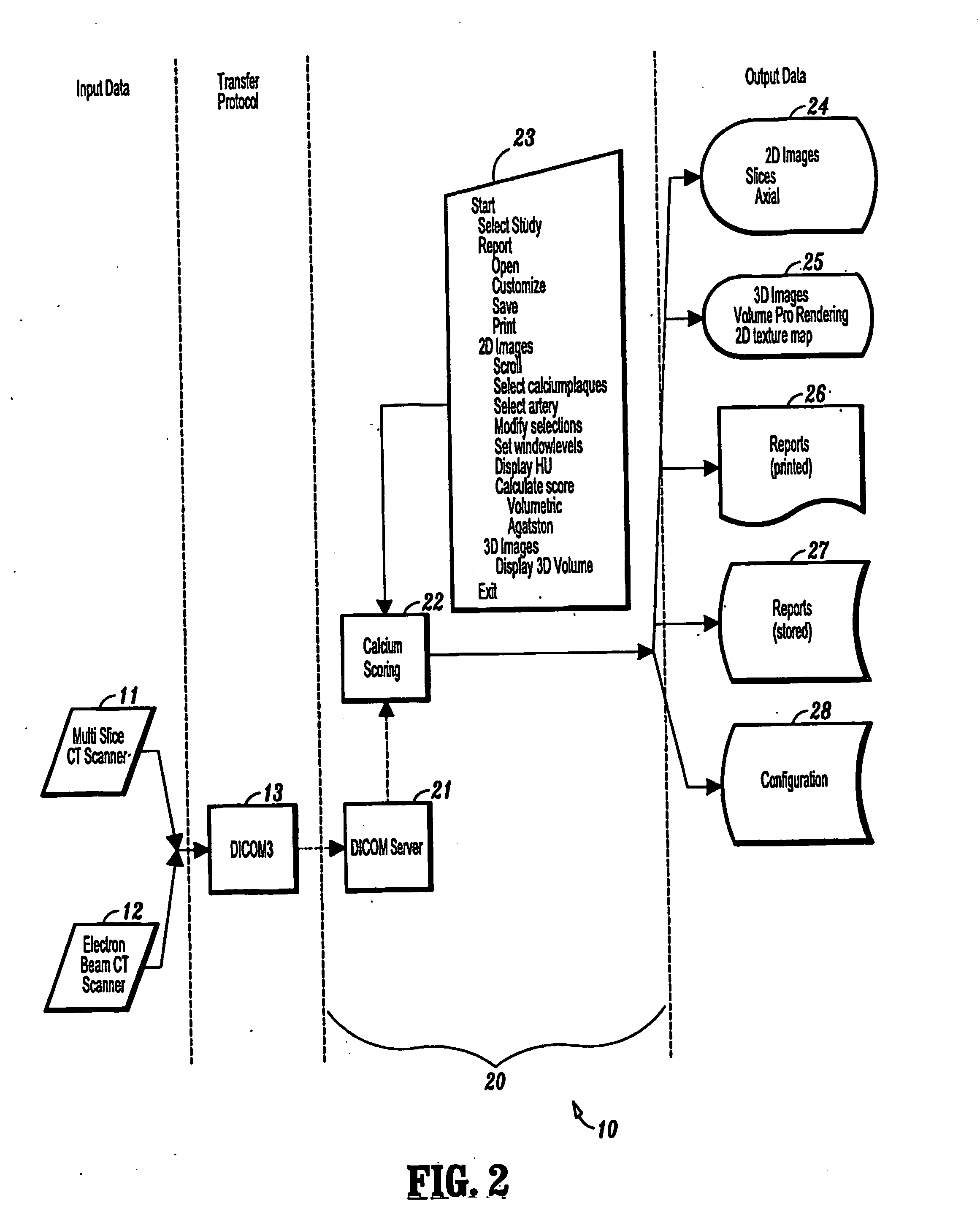

Imaging system and methods for cardiac analysis

InactiveUS20110206247A1Efficiently and accurately detect and viewLess tediousImage enhancementImage analysisGraphicsHuman anatomy

Imaging systems and methods for viewing medical images of human anatomy and, in particular, to a 3-dimensional imaging system that allows a user to efficiently and accurately detect and view coronary artery calcification as displayed graphically on a computer screen. In one aspect, a method for displaying medical images comprises obtaining an image dataset comprising anatomical image data (step 50), automatically grouping connected components in the image data to form groups of connected components (steps 50-57), and displaying the groups of connected components are distinguishable in the displayed image (58-59). The image dataset may comprise a volume data set and the groups of connected components comprise regions of neighboring voxels that share a similar property. The image dataset may comprise a 2-dimensional data set and the groups of connected components comprise regions of neighboring pixels that share a similar property. Different groups of connected components may be displayed in different colors and / or different opacities or certain groups may not be displayed at all.

Owner:VIATRONIX

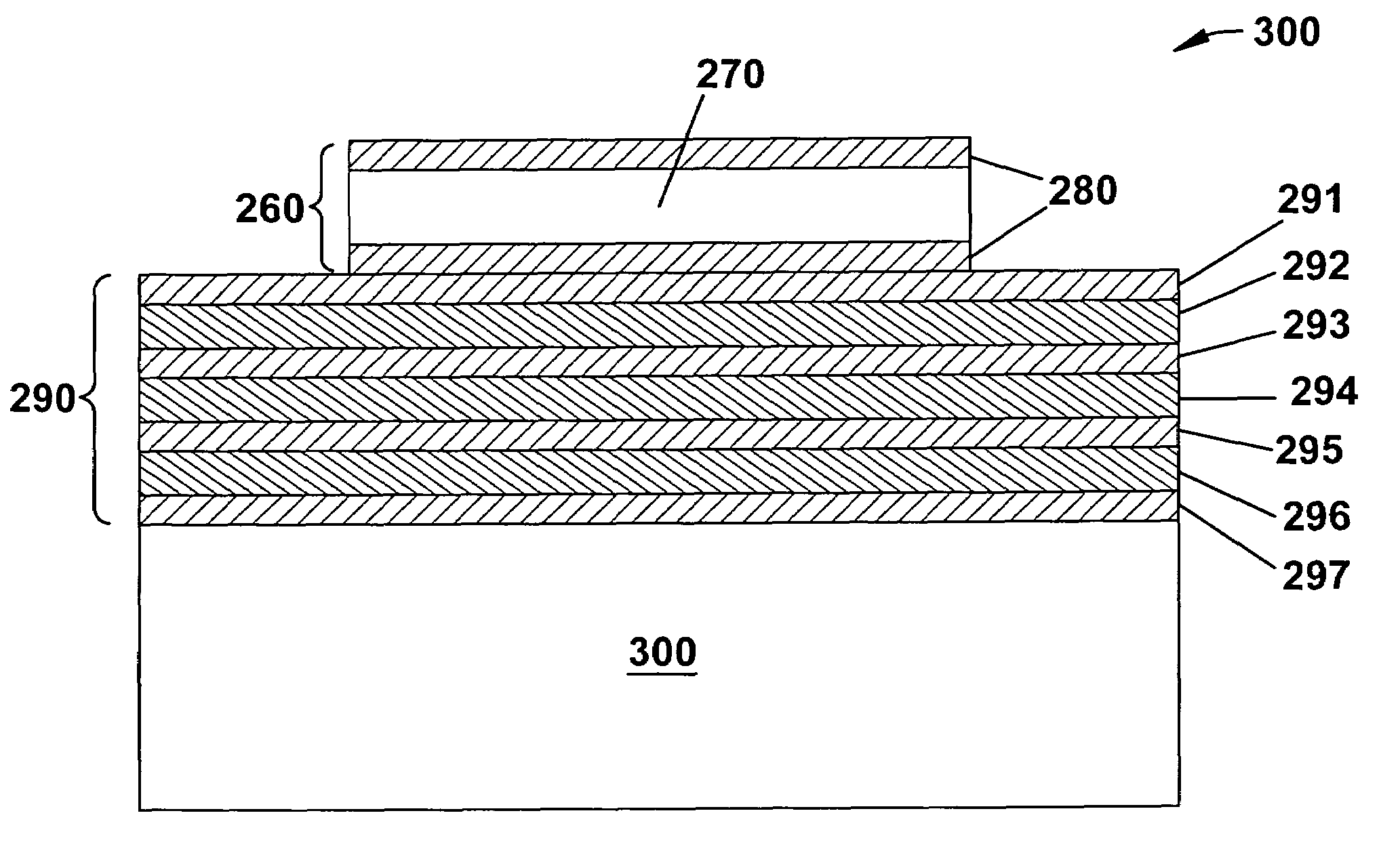

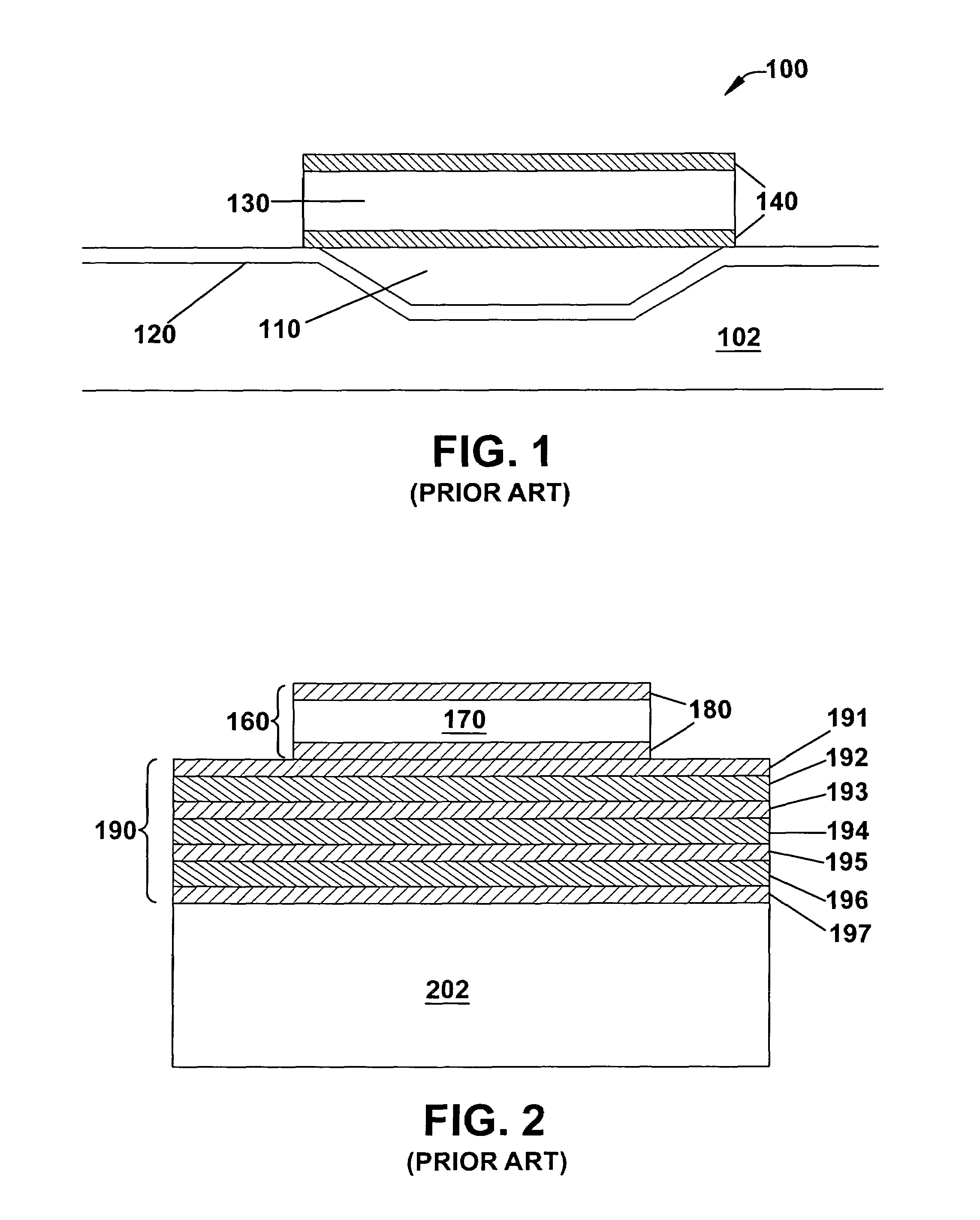

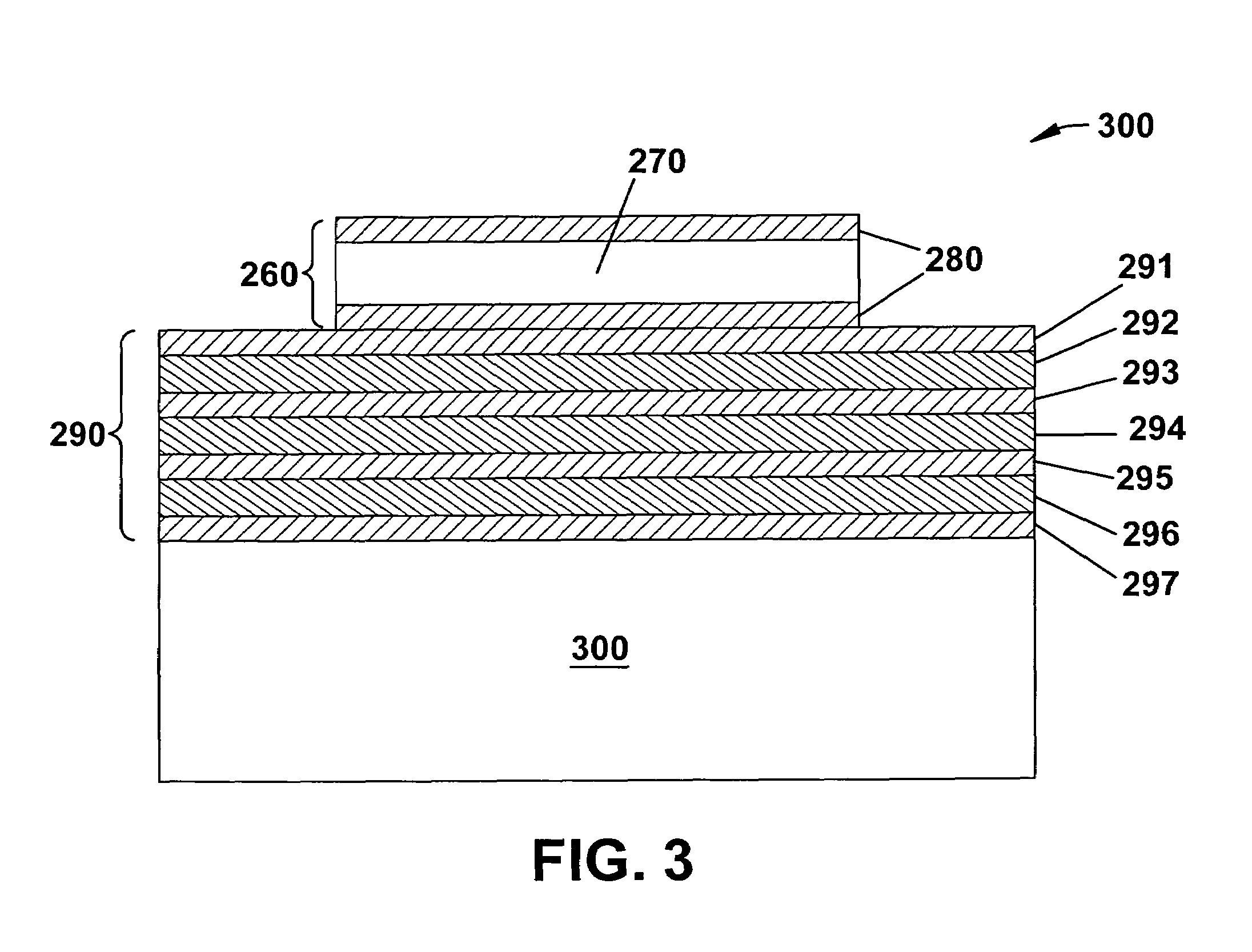

Piezoelectric resonator with an efficient all-dielectric Bragg reflector

ActiveUS7463118B2Increased acoustic impedanceImprove efficiencyImpedence networksPiezoelectric/electrostriction/magnetostriction machinesAcousticsAcoustic impedance

Owner:TEXAS INSTR INC

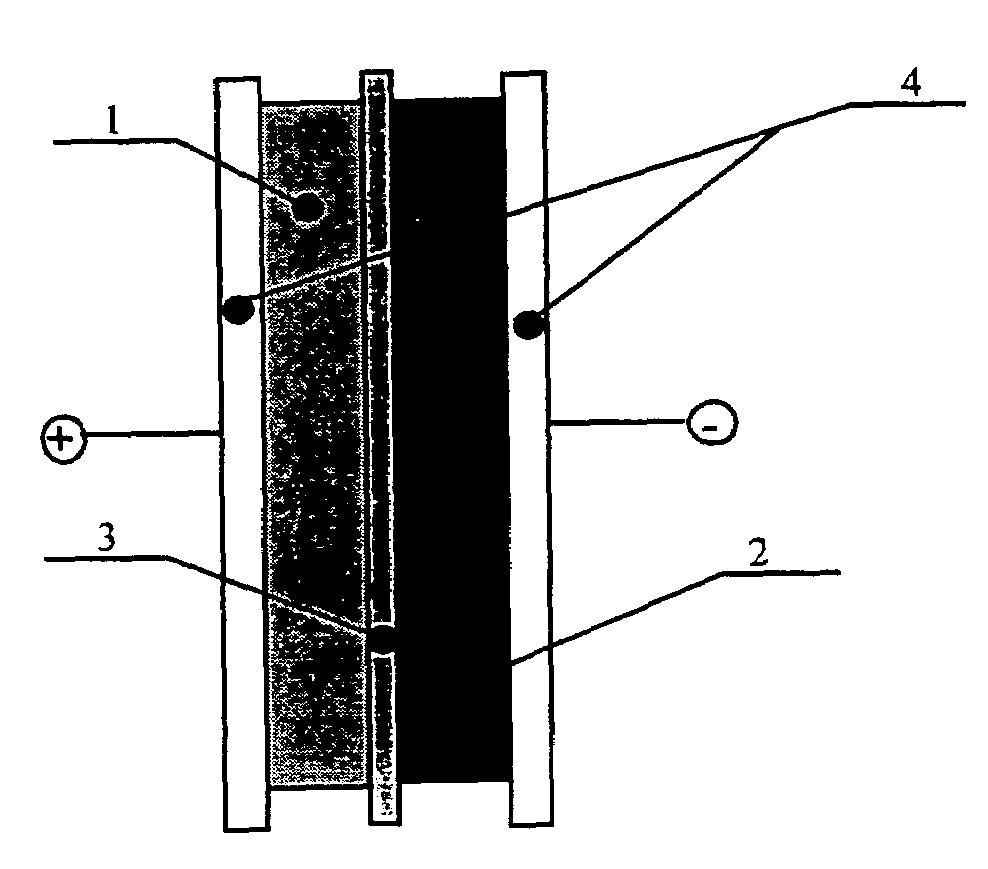

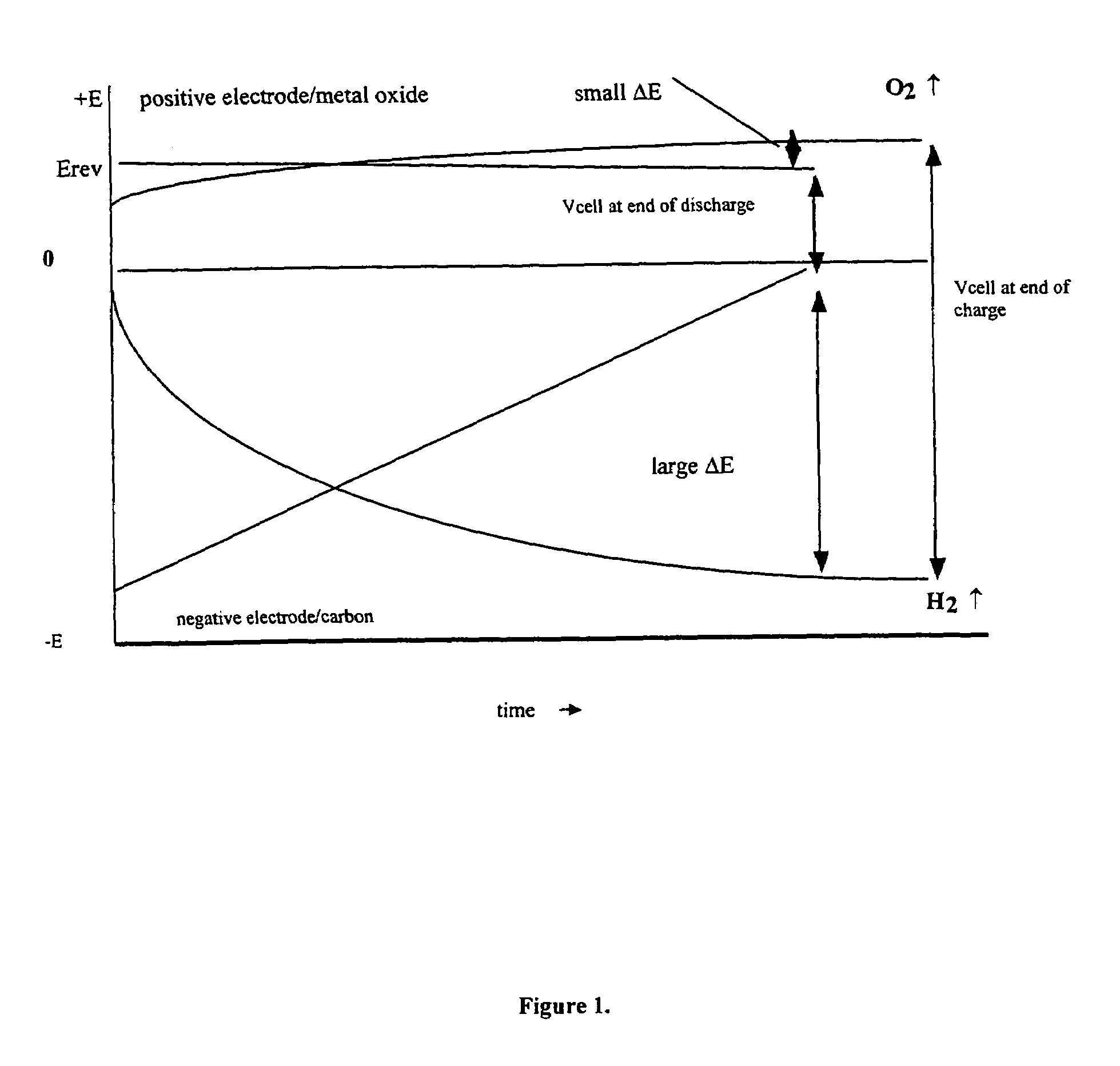

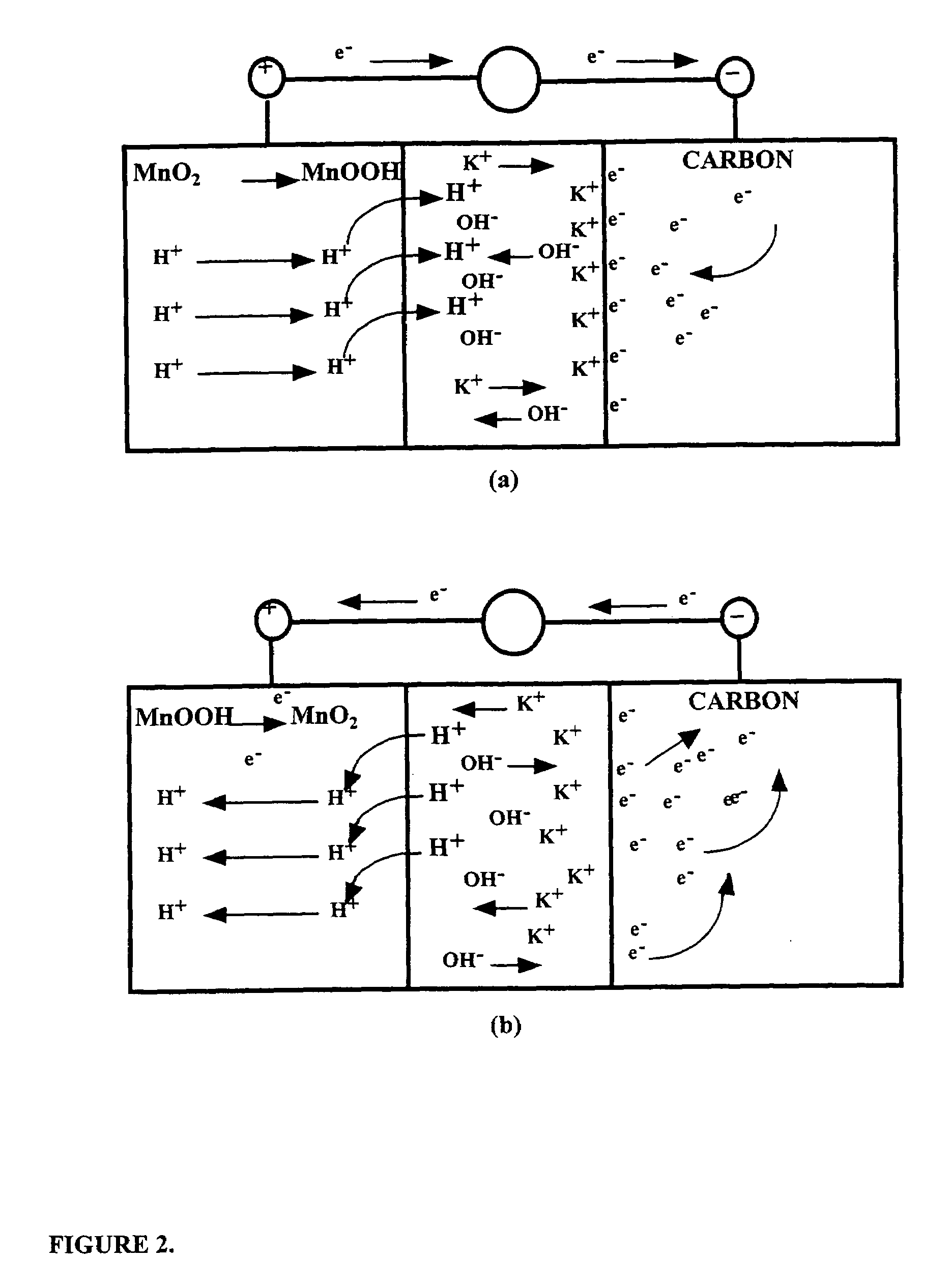

Asymmetric electrochemical supercapacitor and method of manufacture thereof

InactiveUS7199997B1Increase energy densityImprove power densityHybrid capacitor electrodesLiquid electrolytic capacitorsFiberCharge separation

An asymmetric supercapacitor has a positive electrode having a current collector an active material selected from the group consisting of manganese dioxide, silver oxide, iron sulfide and mixtures thereof, a negative electrode having a carbonaceous active material carbon and optional current collector, an electrolyte, and a separator plate. In a preferred embodiment at least one of the electrodes has nanostructured / nanofibrous material and in a more preferred embodiment, both electrodes have nanostructured / nanfibrous material. The electrolyte can be liquid or solid although liquid electrolytes are preferred.The asymmetric supercapacitor has improved energy density by electrically coupling an electrode of high faradaic capacity such as one having manganese oxide (MnO2) with an electrode such as carbon that stores charge through charge separation at the electric double-layer. The asymmetric supercapacitor also improves power density by using high surface area nanostructured / nanofibrous electrode materials.

Owner:U S NANOCORP +1

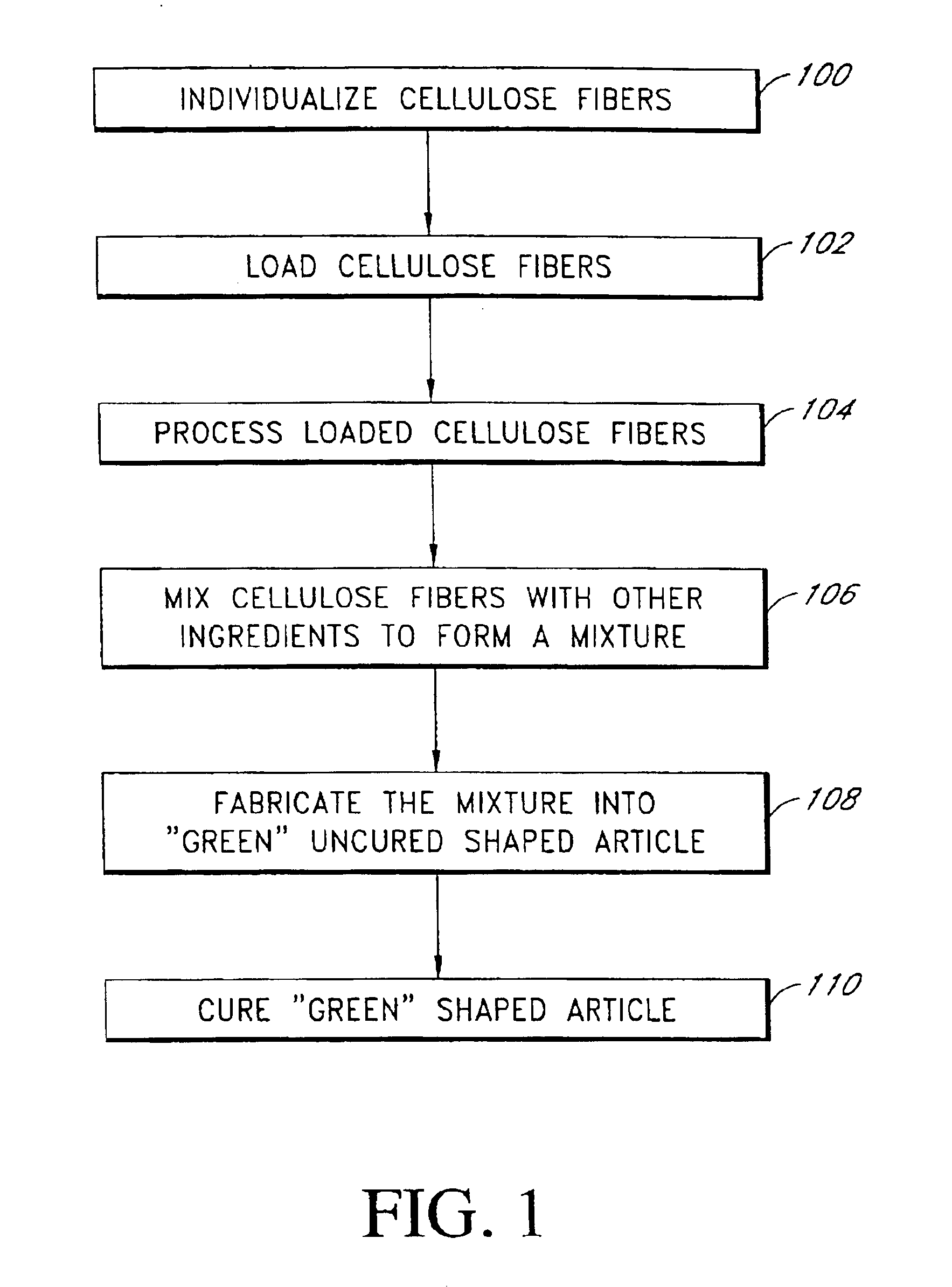

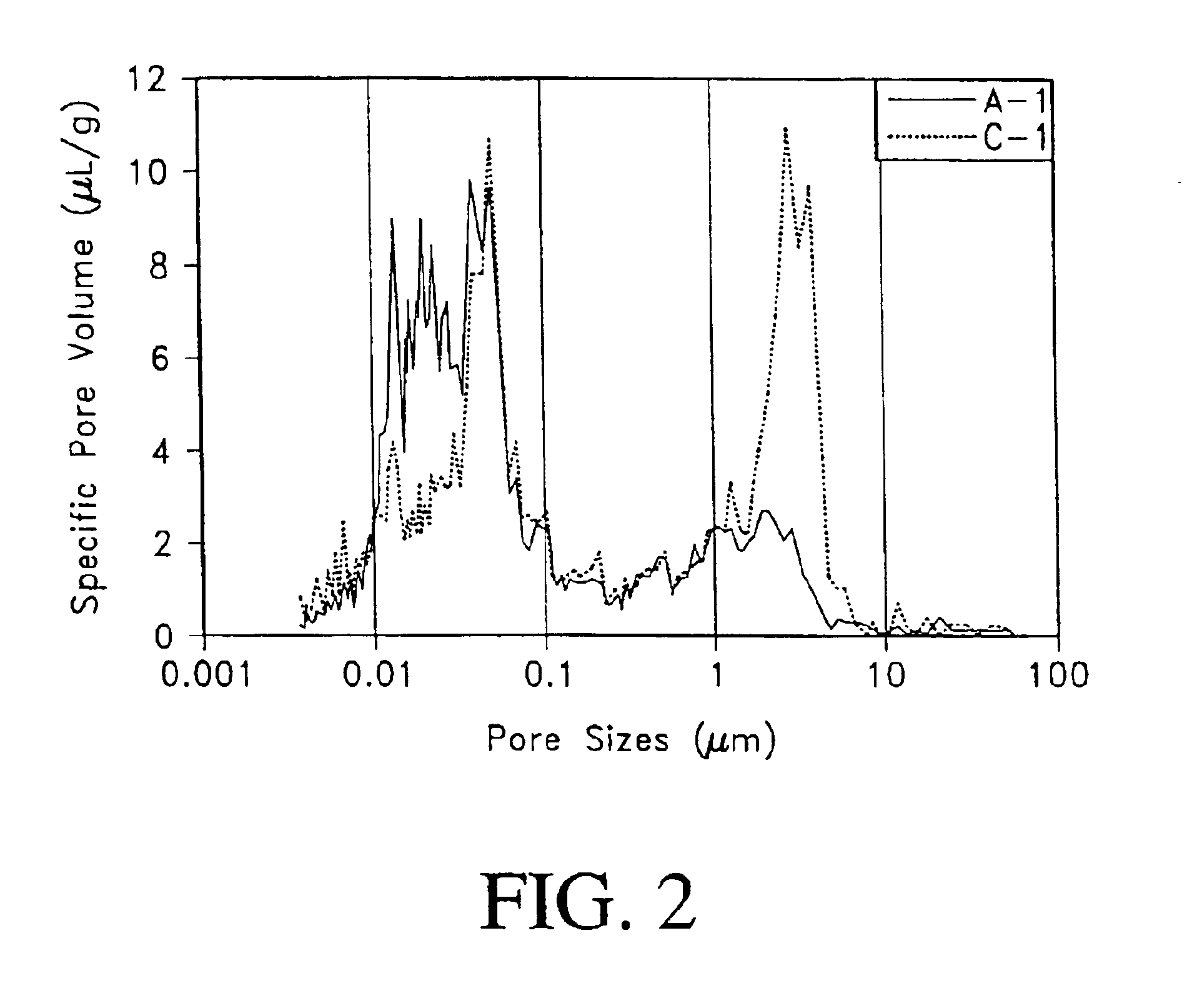

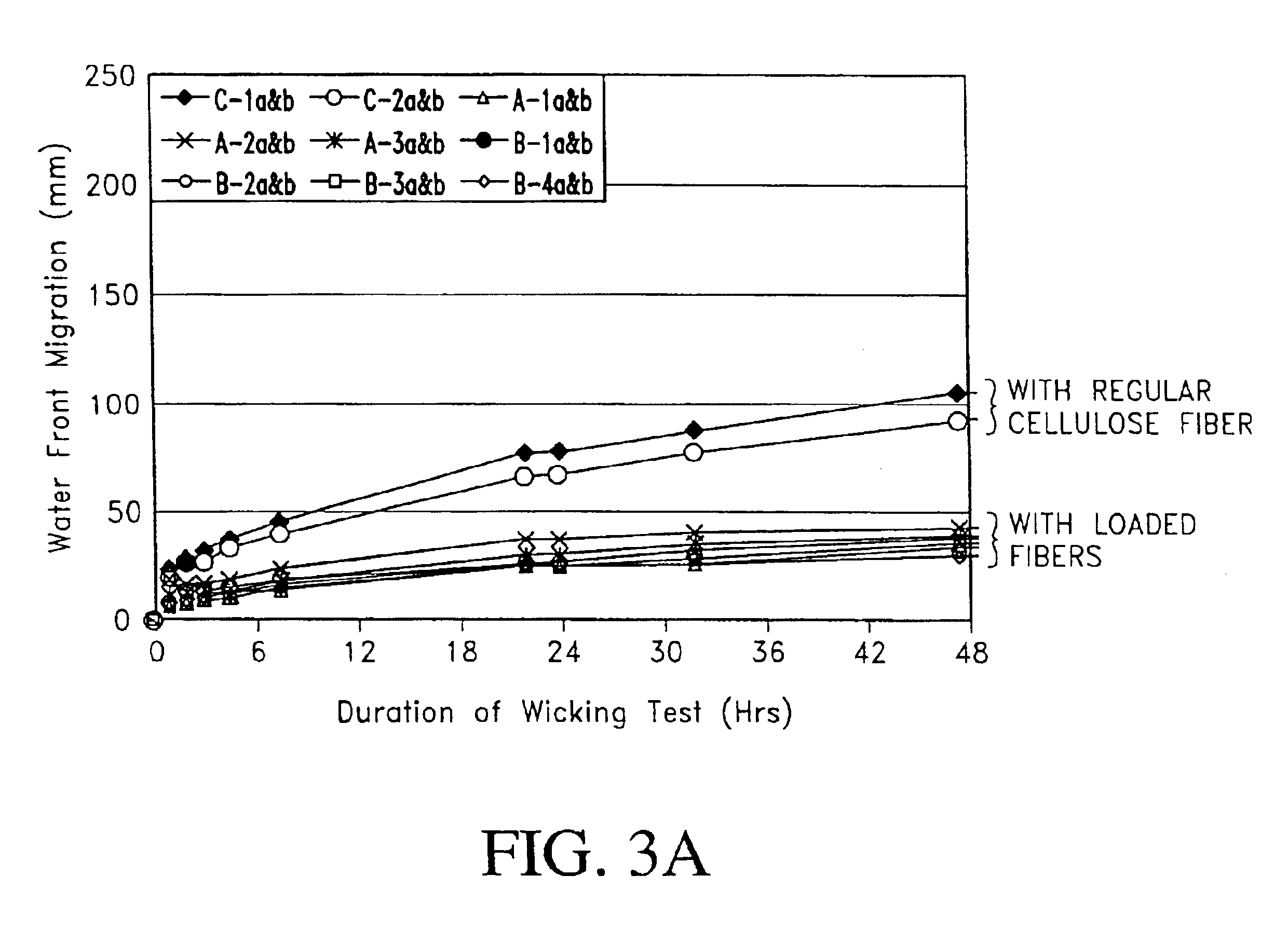

Fiber cement composite materials using cellulose fibers loaded with inorganic and/or organic substances

InactiveUS6872246B2Reduction of it pore volumeIncrease toughnessNatural cellulose pulp/paperSpecial paperFreeze thaw resistanceChemical dissolution

This invention discloses a new technology related to cellulose fiber reinforced cement composite materials using the loaded cellulose fibers. This invention discloses four aspects of the technology: fiber treatment, formulation, method and final product. This technology advantageously provides fiber cement building materials with the desirable characteristics of reduced water absorption, reduced rate of water absorption, lower water migration, and lower water permeability. This invention also impart the final products improved freeze-thaw resistance, reduced efflorescence, reduced chemical dissolution and re-deposition, and improved rot and fire resistances, compared to conventional fiber cement products. These improved attributes are gained without loss in dimensional stability, strength, strain or toughness.

Owner:JAMES HARDIE TECH

Method of treating peripheral bronchopleural fistulas

InactiveUS6358269B1ClosureEasy to implementSuture equipmentsDiagnosticsBronchopleural fistulaMedicine

A method of treating peripheral bronchopleural fistula using a collagen matrix hemostatic pad. The method includes the following steps: (1) selecting a peripheral bronchopleural fistula; (2) selecting a collagen matrix hemostatic pad having sufficient size to cover the fistula; (3) aligning the collagen matrix hemostatic pad completely over the fistula; and (4) securing the collagen matrix hemostatic pad to the tissue sorrounding the fistula.

Owner:AYE RALPH

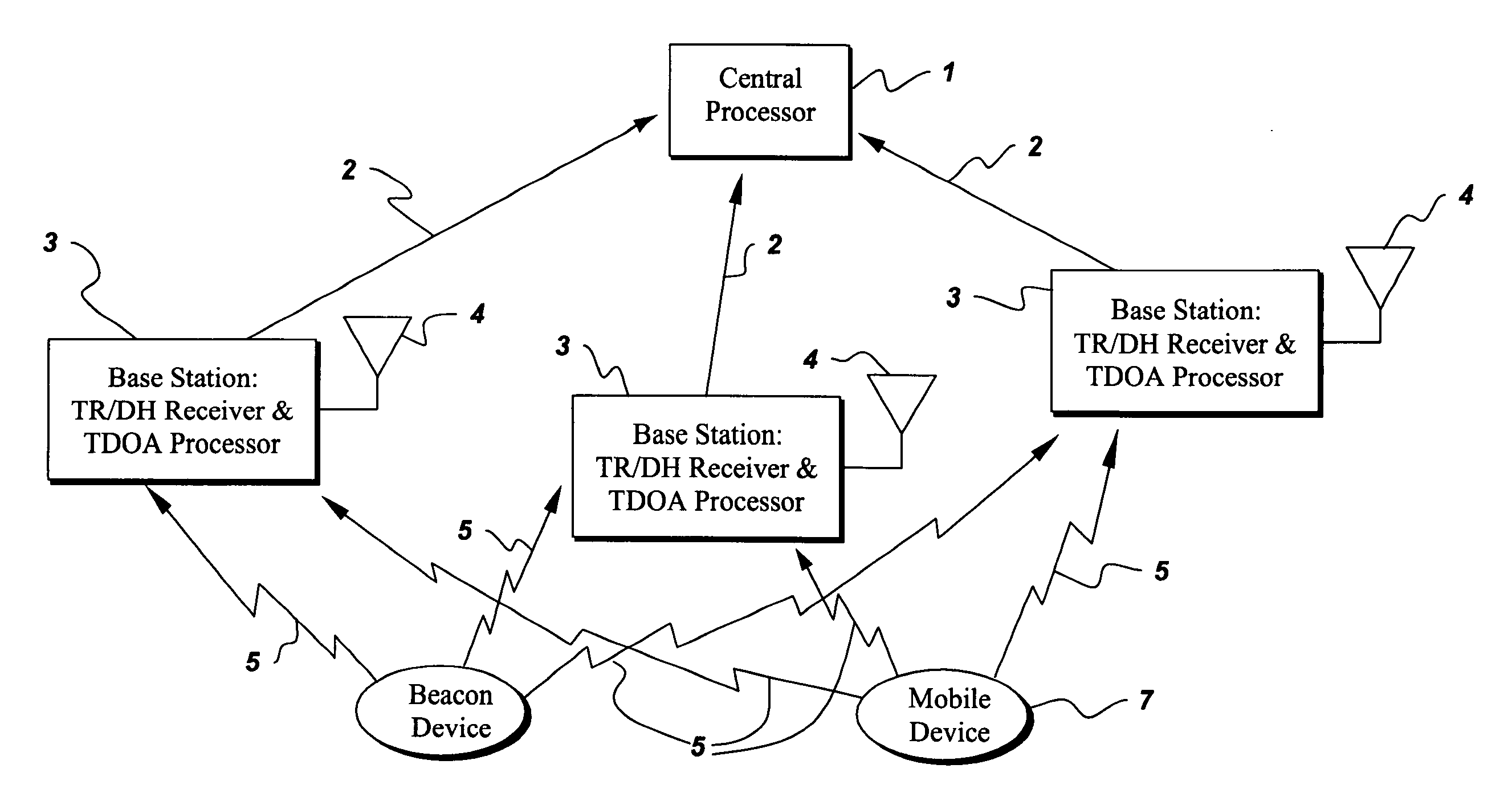

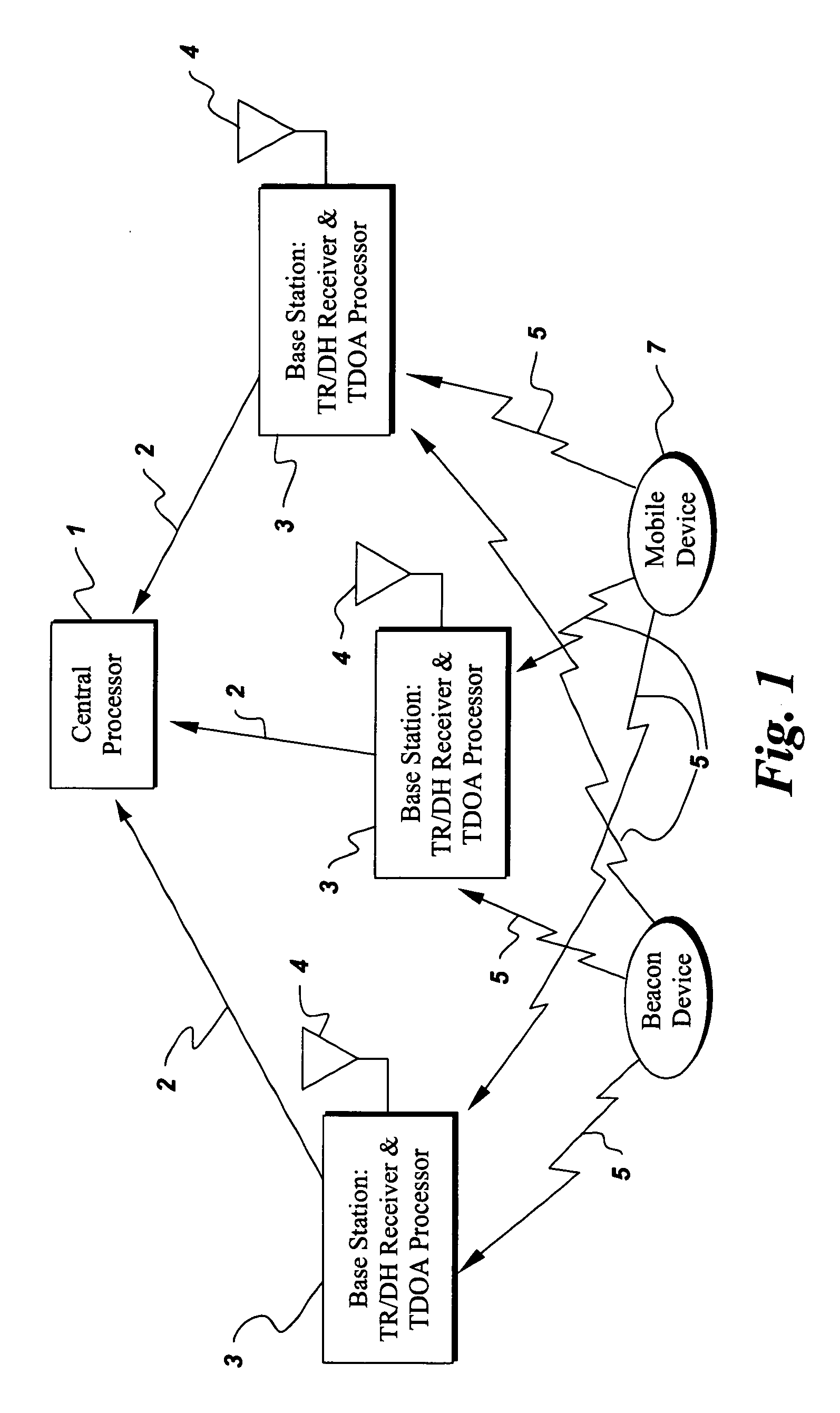

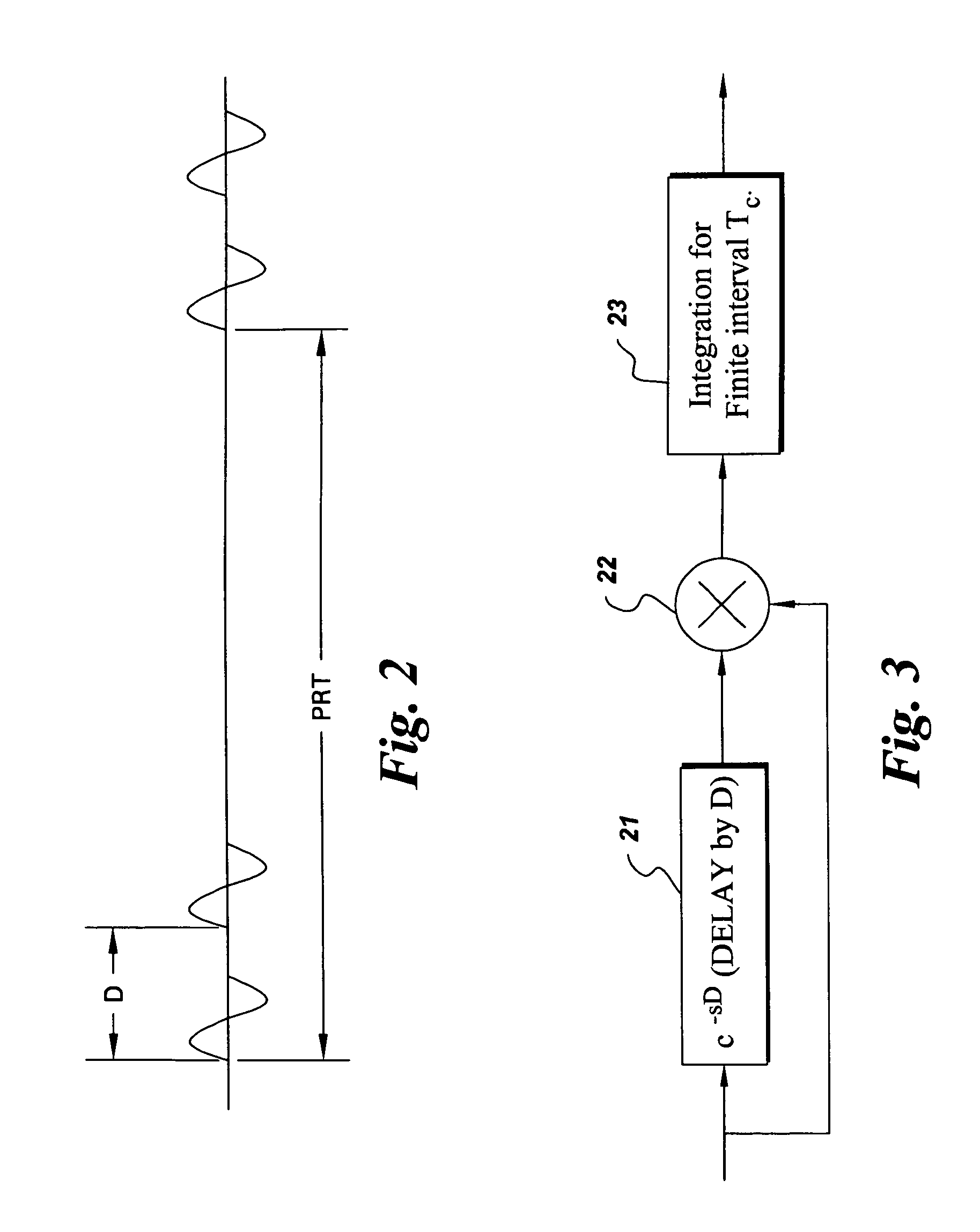

Transmitter location for ultra-wideband, transmitted-reference CDMA communication system

InactiveUS7269427B2Low costFew RF interference problemSpatial transmit diversityPosition fixationUltra-widebandTransmitter

A system and method involve tracking the location of objects within an area of interest using transmitted-reference ultra-wideband (TR-UWB) signals. The system includes at least three base stations communicating with a central processor, at least one mobile device and at least one fixed beacon transmitter of known location. The mobile device is equipped with a transmitter for transmitting a TR-UWB signal to a base station, which then determines a location of the mobile device based on time difference of arrival information between the beacon transmitters and mobile devices measured at all the base stations. Preferably, the area of interest includes a plurality of mobile devices each transmitting a delay-hopped TR-UWB signal according to a code-division multiple access scheme. The mobile devices may be attached to a patient and / or a medical asset within the hospital for tracking purposes. Additionally, patient medical information may be transmitted with the TR-UWB signals to allow patient monitoring to occur simultaneously with asset / patient tracking.

Owner:GENERAL ELECTRIC CO

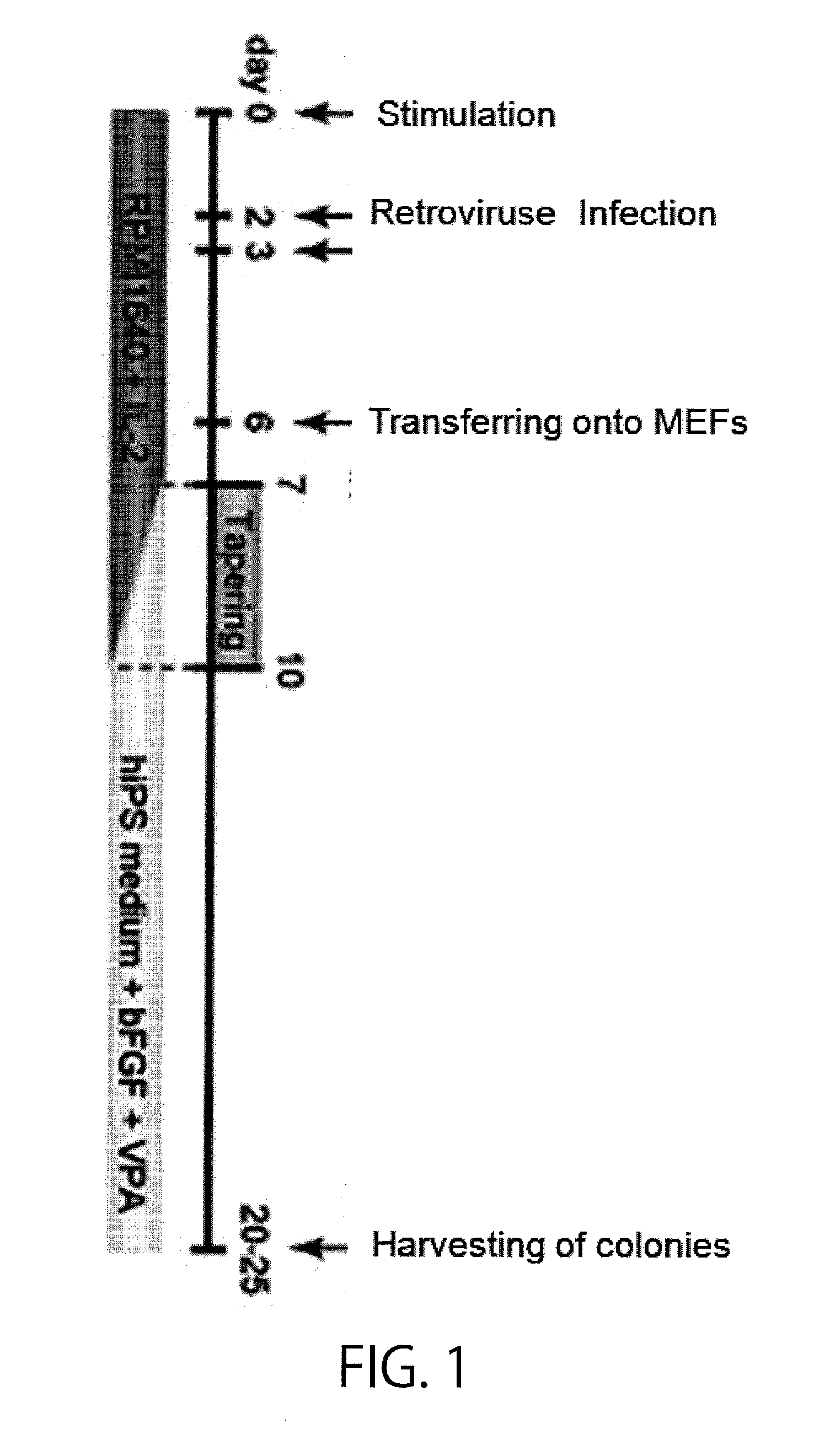

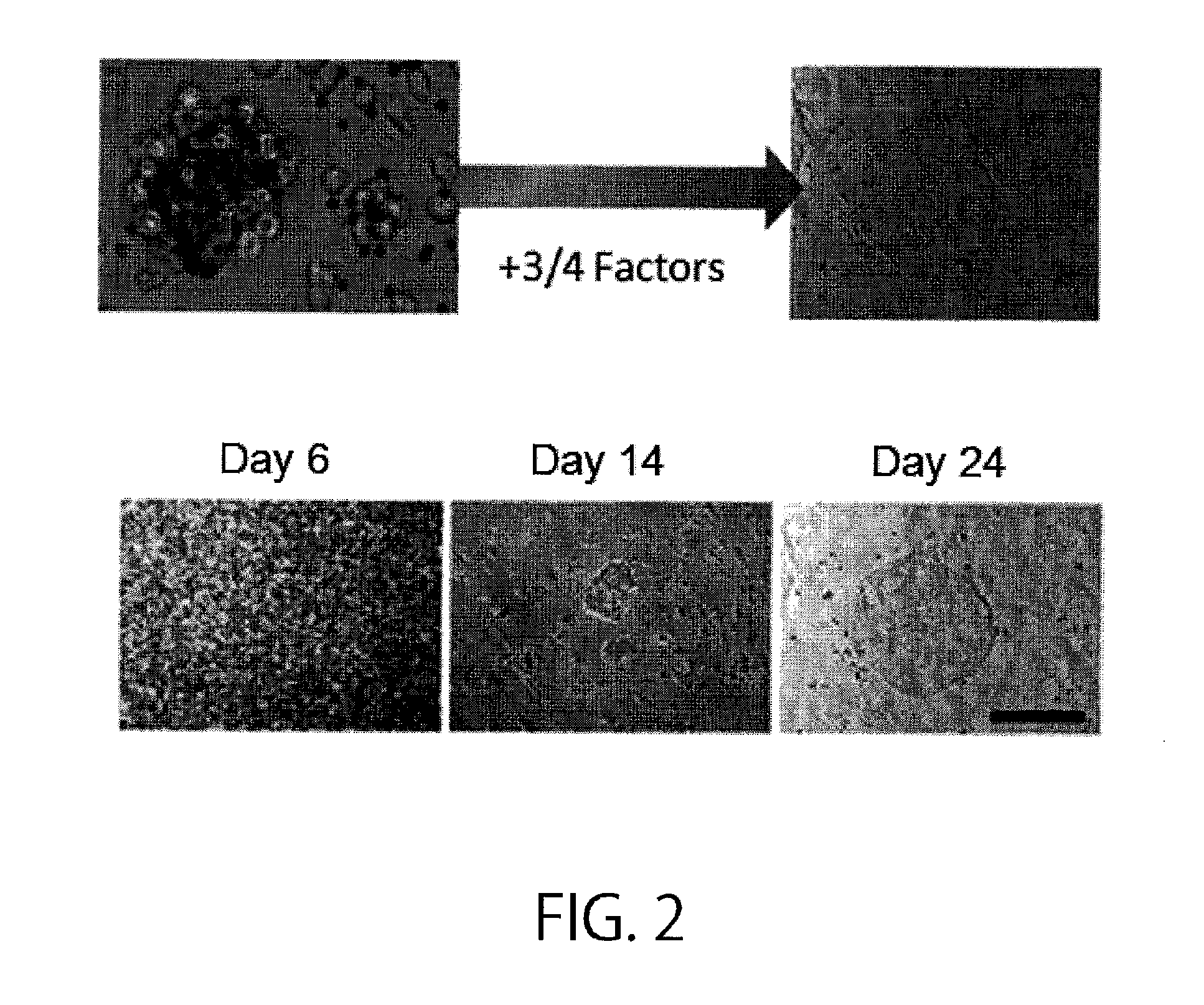

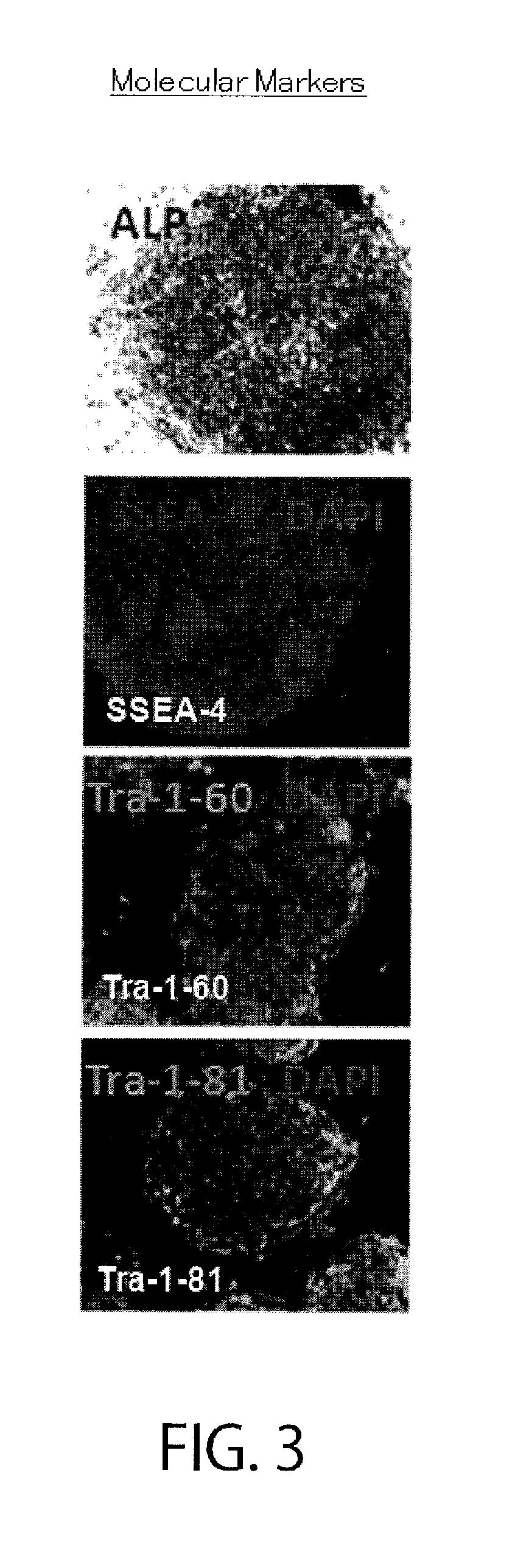

Method for reconstructing immune function using pluripotent stem cells

ActiveUS20130078226A1Efficient productionAvoid many problemsBiocideGenetically modified cellsInduced pluripotent stem cellT cell

According to the present invention, there are provided a method for producing a human T cell, which comprises the steps of inducing an iPS cell from a human T cell, and differentiating the iPS cell into a T cell; a pharmaceutical composition comprising the T cell produced by the method; and a method for cell-based immunotherapy using the method.

Owner:THE UNIV OF TOKYO

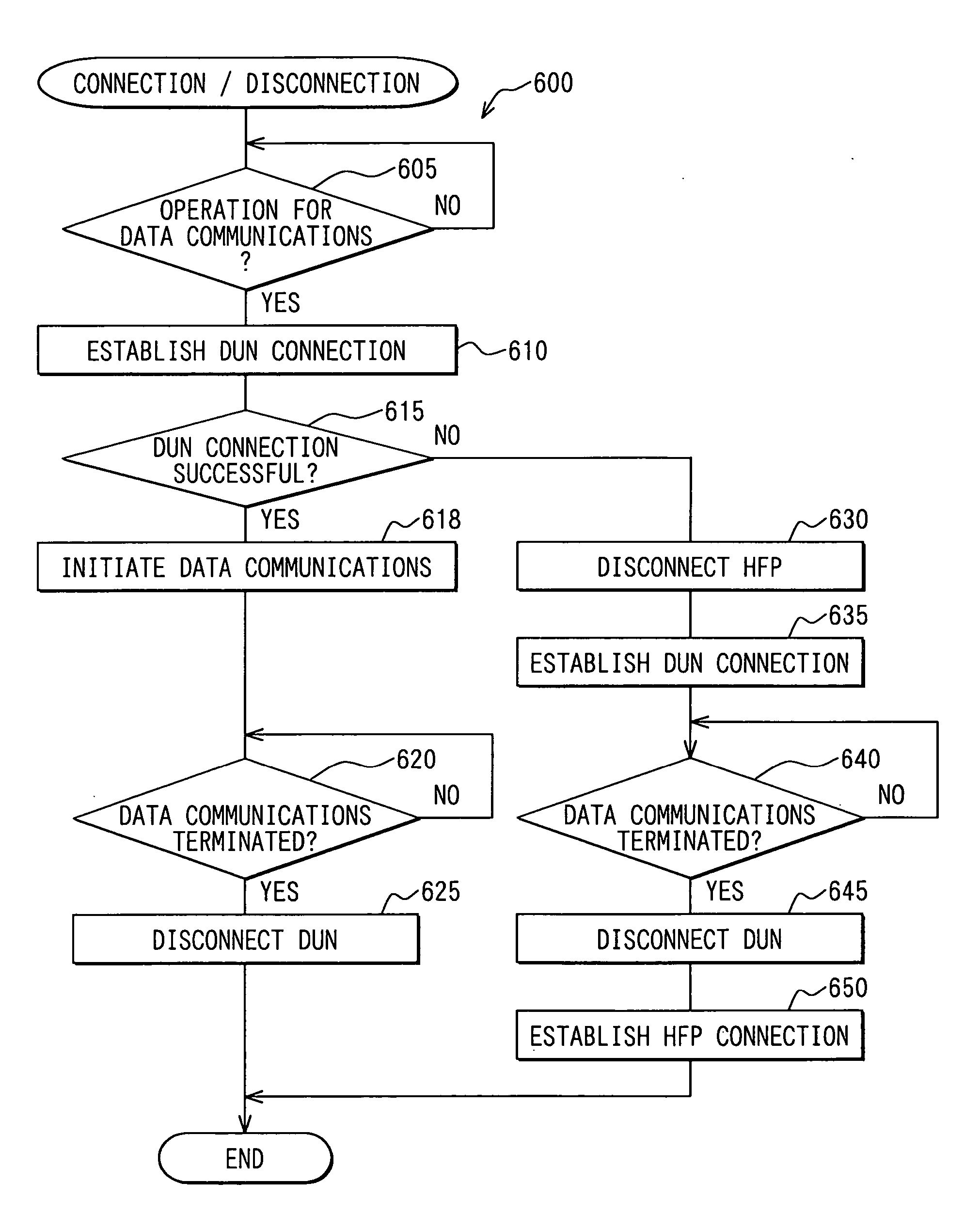

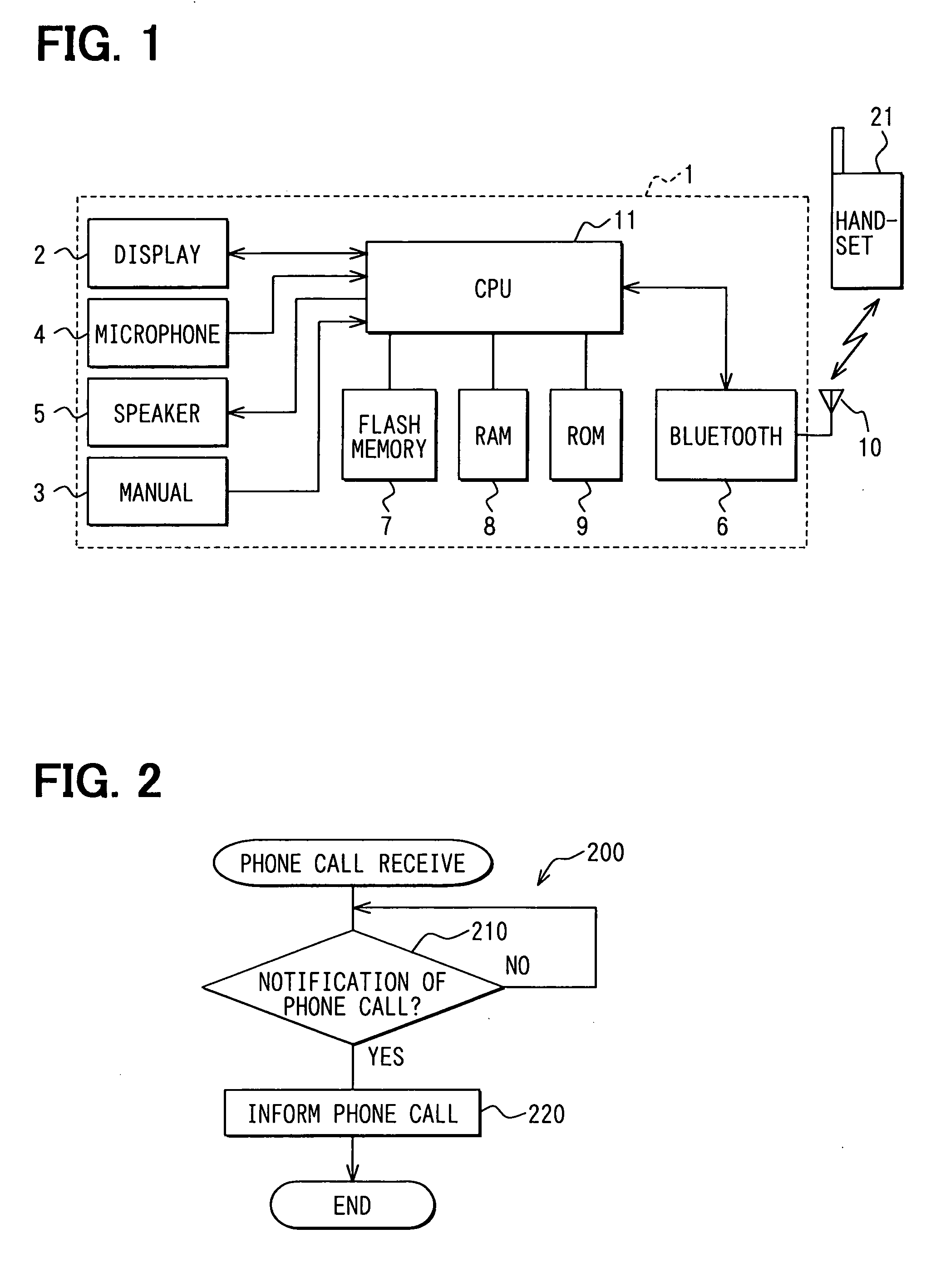

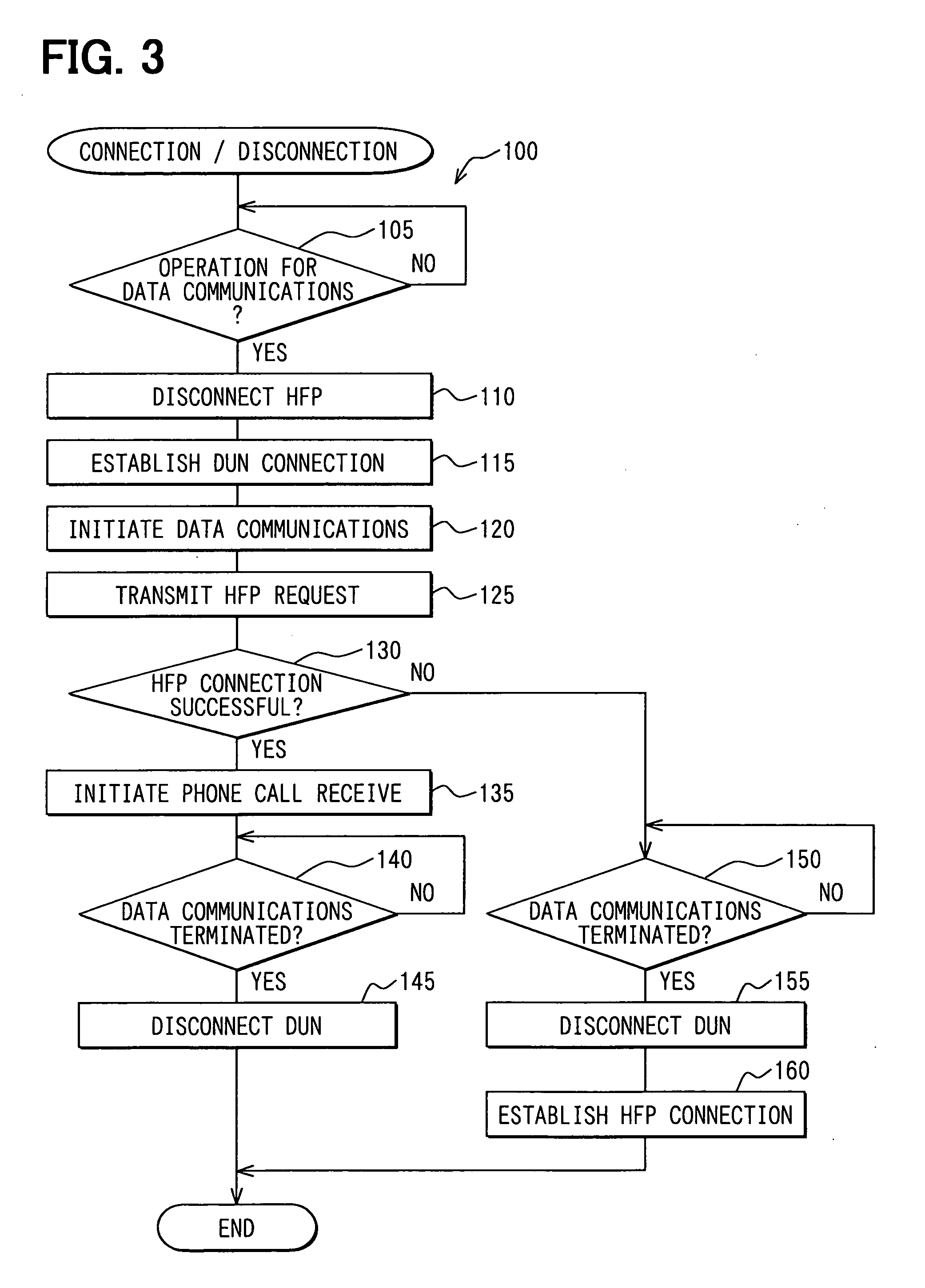

Bluetooth communicator, short range wireless communicator and program

InactiveUS20060079182A1Avoid many problemsCommunication problemNetwork topologiesConnection managementBluetoothHandsfree

While a handsfree device being multi-profile compatible is maintaining a connection for a handsfree profile (HFP) with a mobile phone handset, the handsfree device cuts off the connection for the HFP based on a user's operation. After cutting off, the handsfree device establishes a connection for a dial-up network profile (DUN), and subsequently transmits a request for a connection for the HFP while maintaining the connection for the DUN. Subsequently, the handsfree device determines whether the handset is multi-profile compatible according to the response to the request from the handset. Based on the determination that the handset is multi-profile compatible, the handsfree device executes the processes for the HFP while maintaining the connection for the DUN.

Owner:DENSO CORP

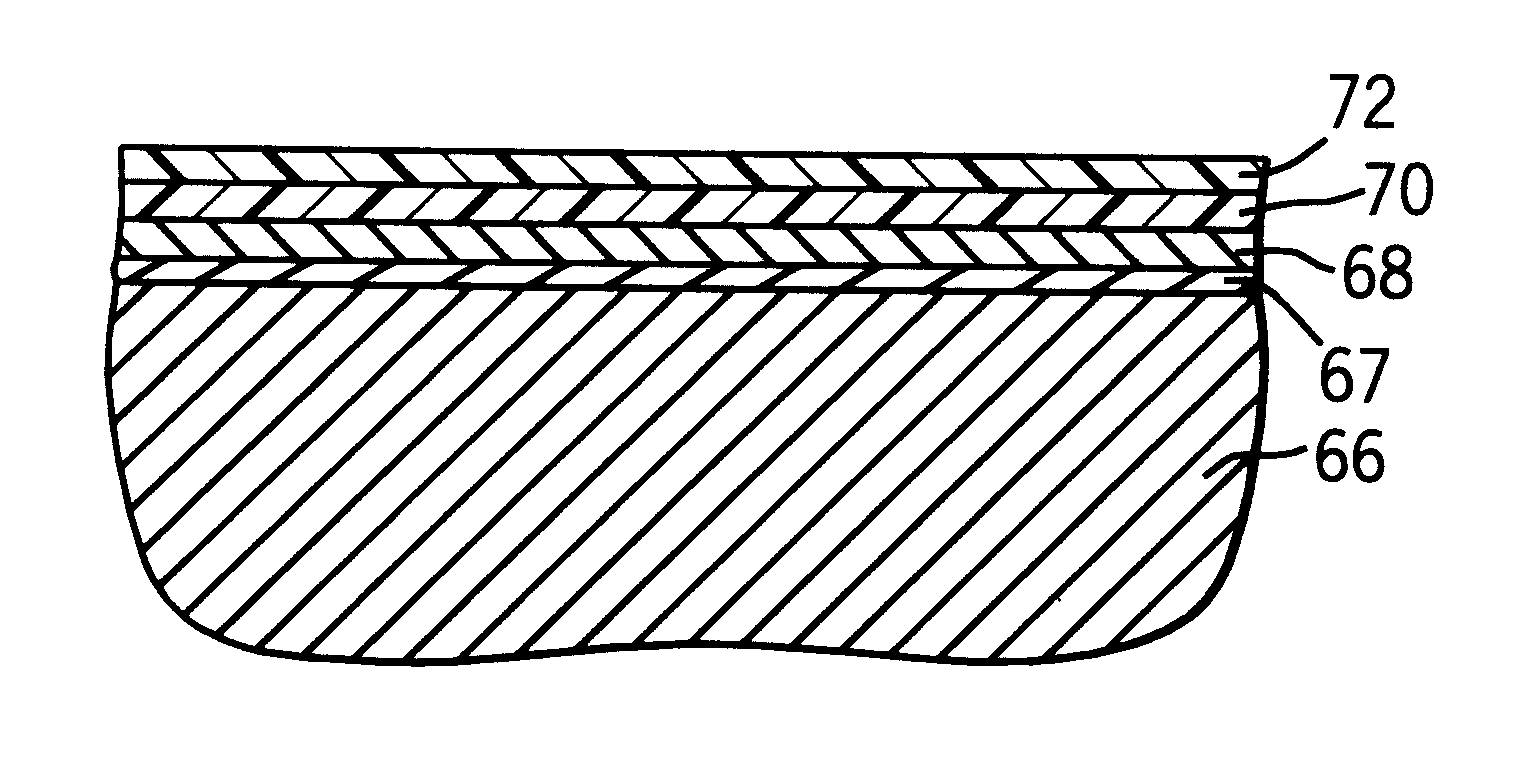

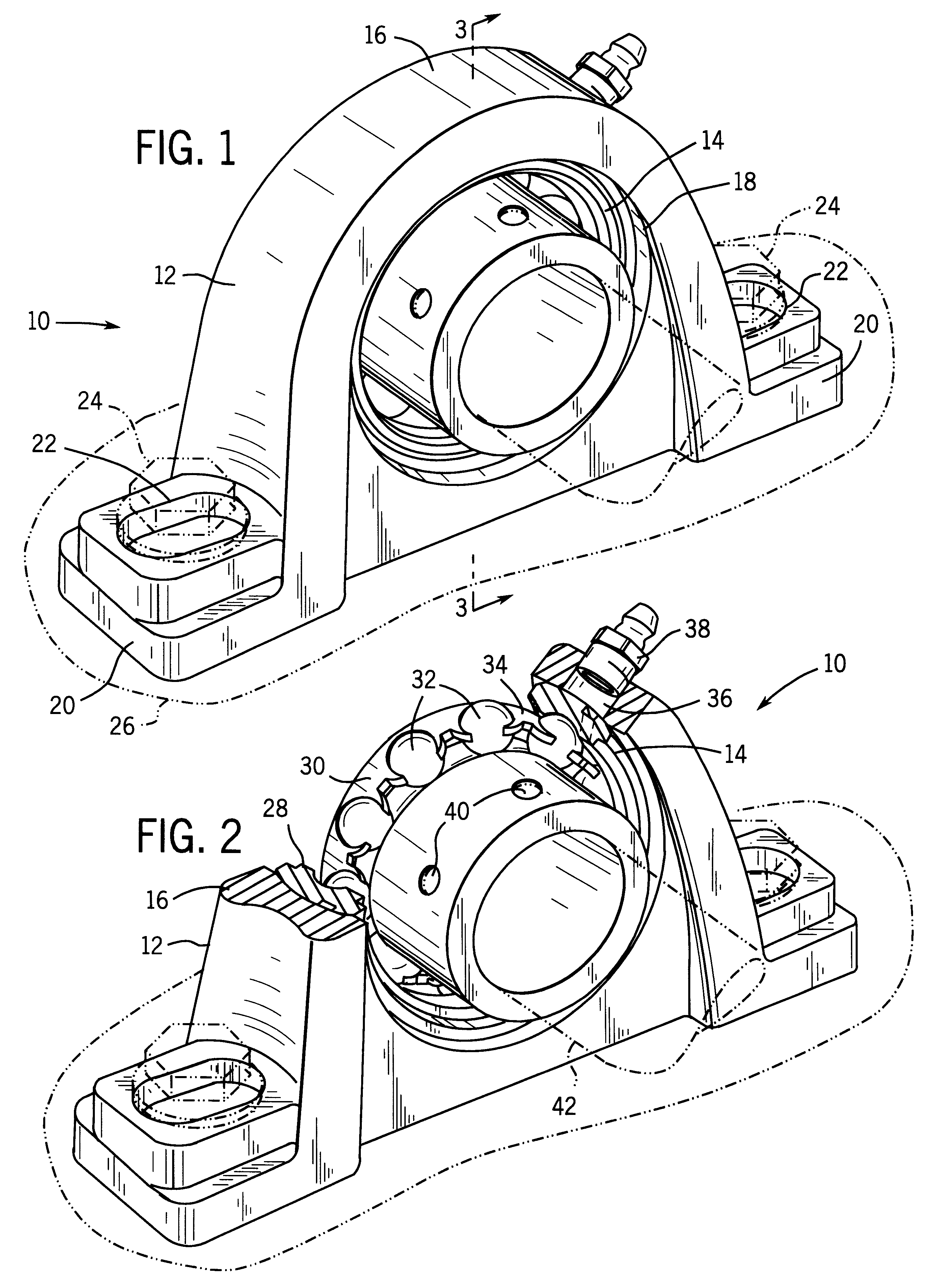

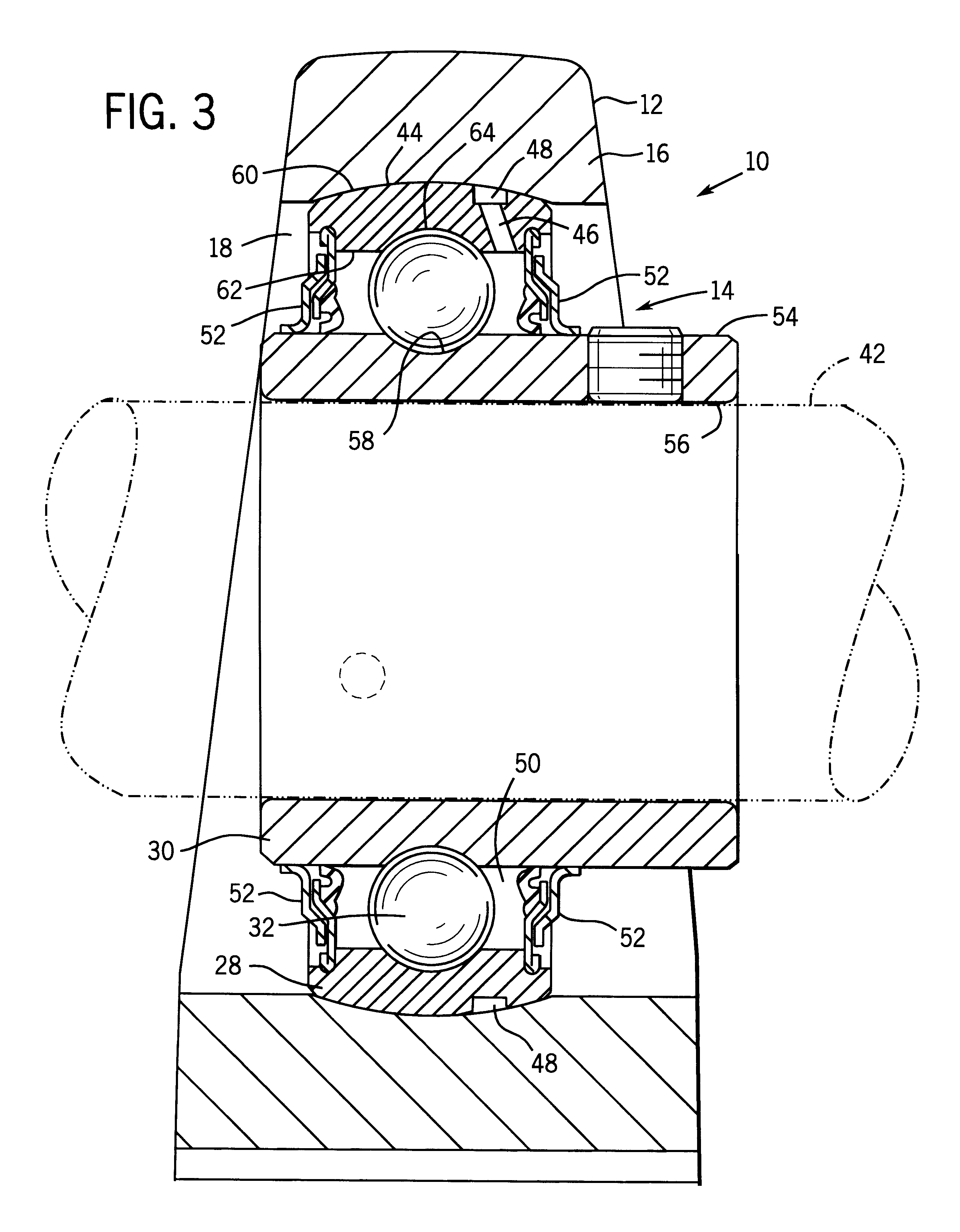

Corrosion-resistant bearing and method for making same

InactiveUS6318898B1Improve corrosion resistanceMore cost-effectiveBall bearingsBearing componentsAlloyProtection system

A corrosion-resistant antifriction bearing is disclosed that includes a multi-layer corrosion protection system over a metallic substrate. The corrosion-resistant system may be applied to a single or multiple components of the bearing, including inner and outer rings, bearing elements, collars, and so forth. The system includes a nickel-phosphorous alloy plating layer applied by an autocatalytic process after surface preparation of the protected component. The surface preparation aids in adherence of the nickel-phosphorous alloy plating layer to the substrate. The preparation may include the application of rust inhibitors, liquid vapor honing, acid neutralizing, and so forth. Additional topcoat layers may be applied to the nickel-phosphorous alloy plating layer. These may include a chromate conversion coating and a polymeric topcoat layer. The polymeric topcoat layer, such as polytetrafluoroethylene, may include a UV marker to enable identification of the bearing when placed in service and throughout its useful life.

Owner:BALDOR ELECTRIC COMPANY

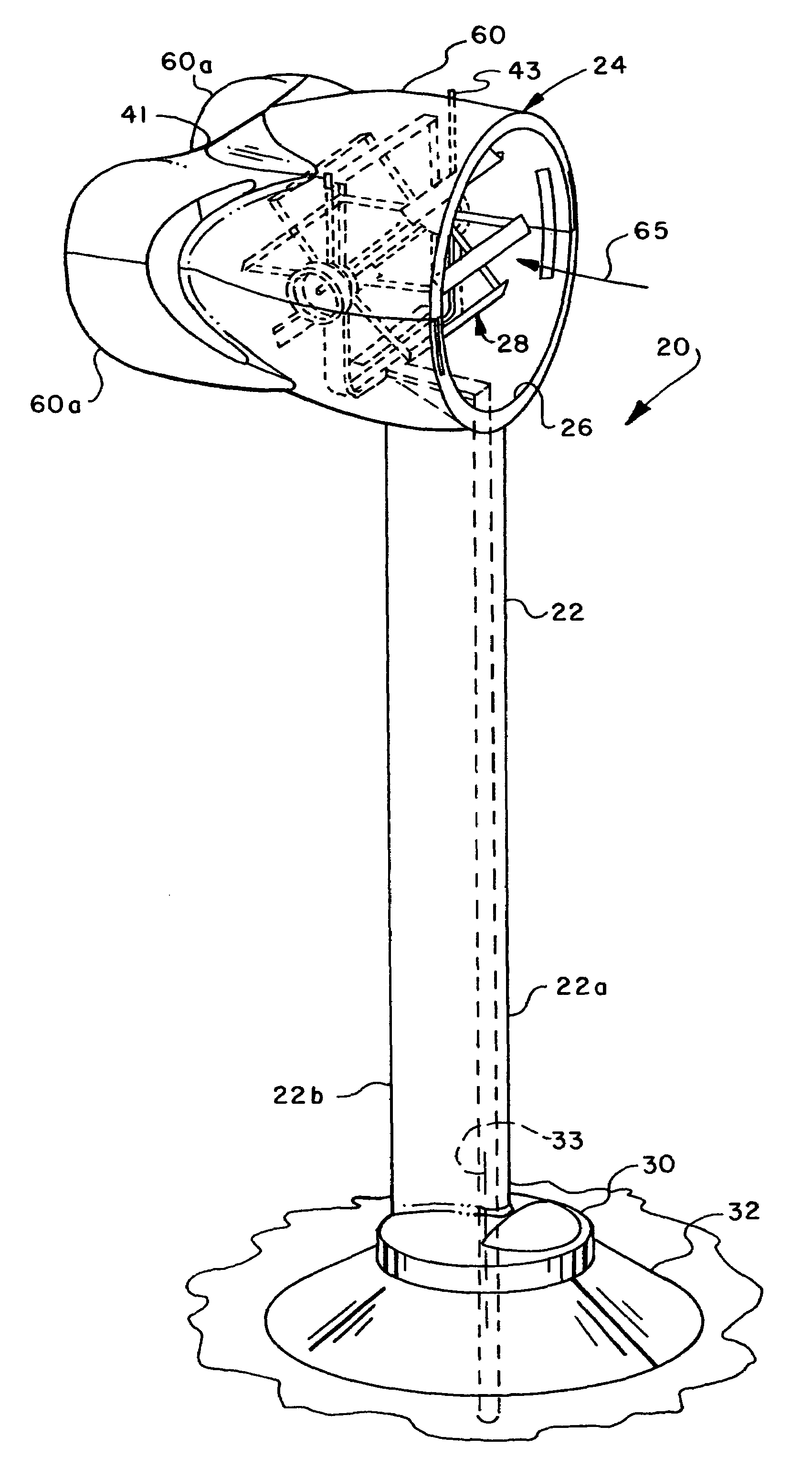

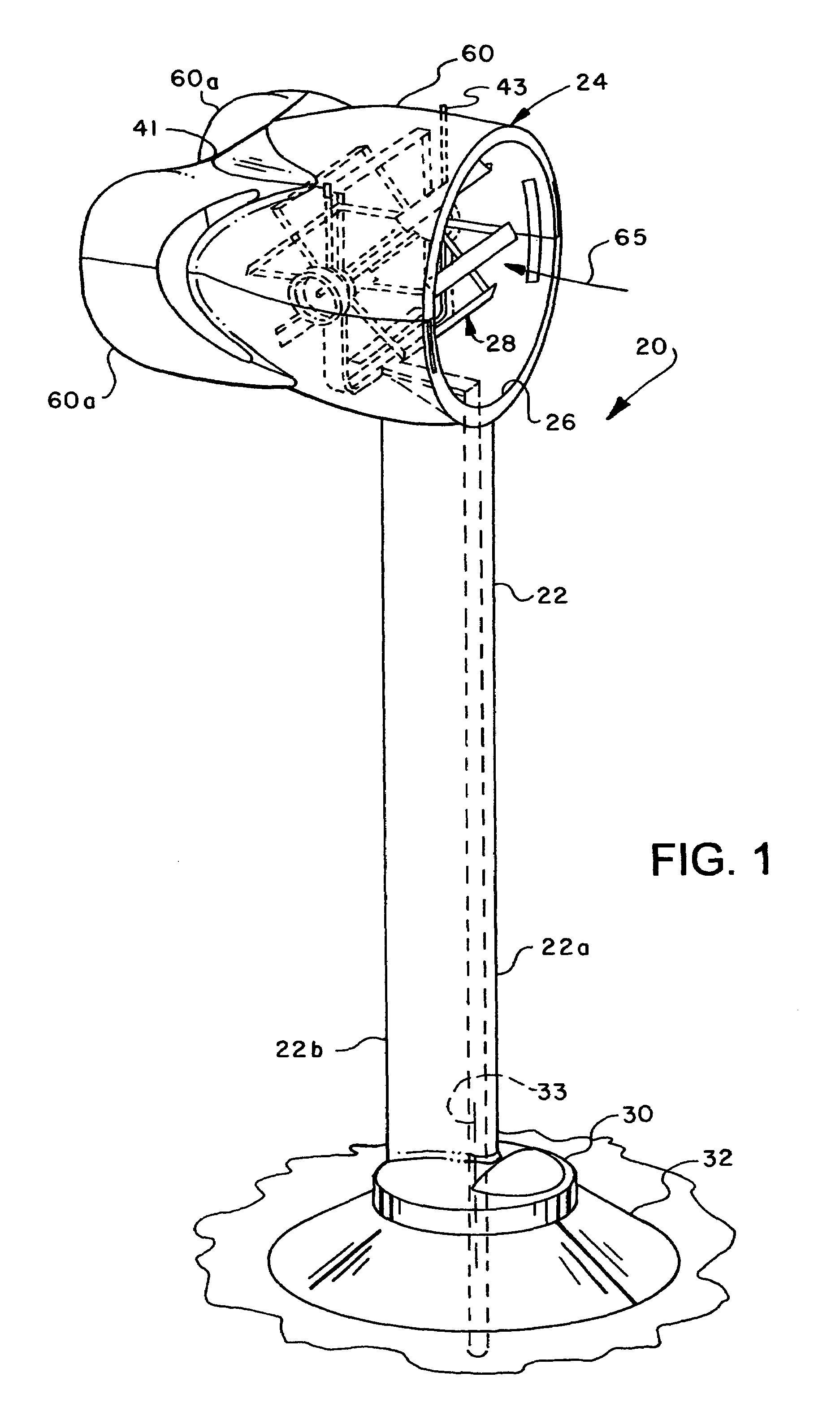

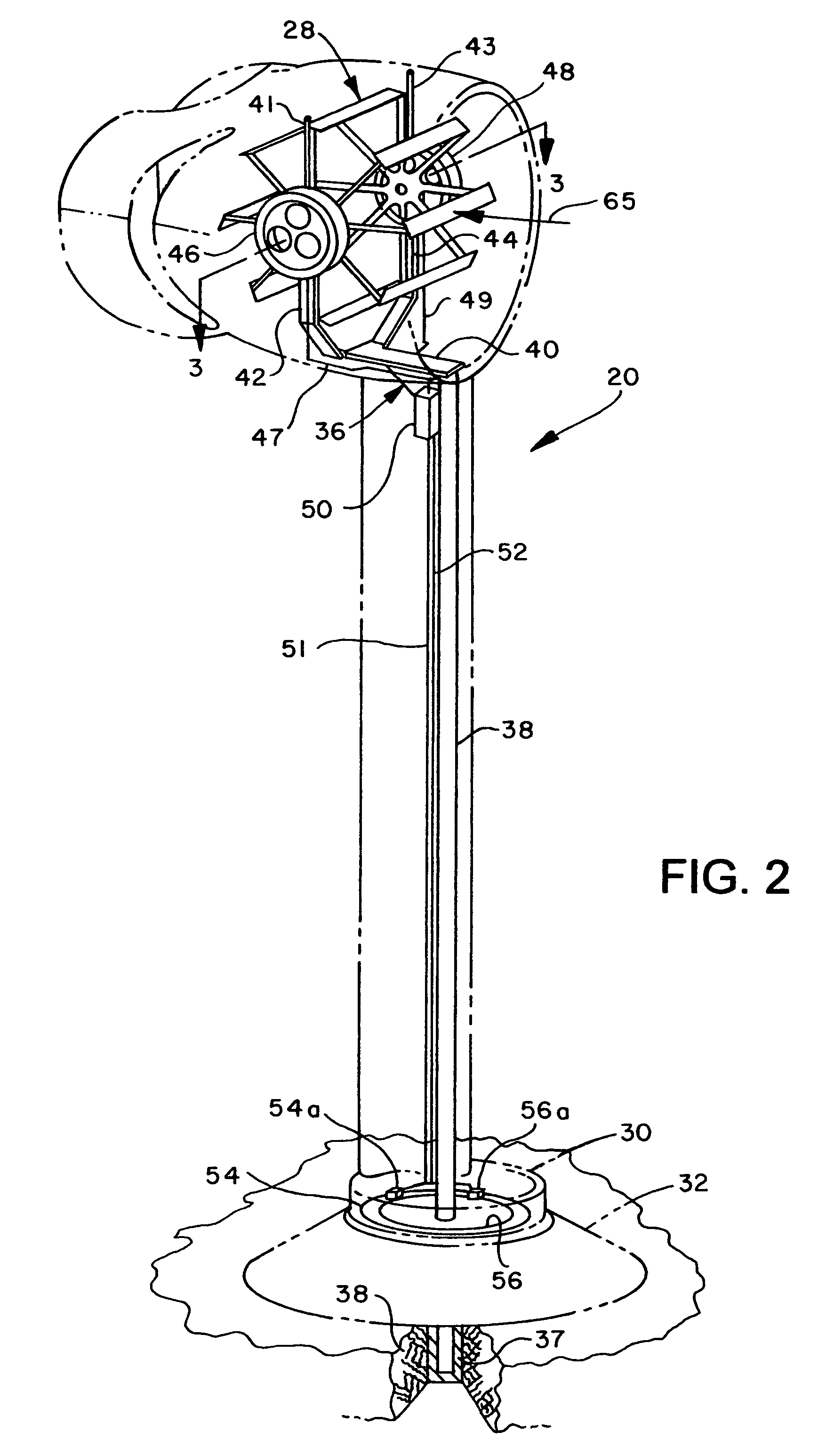

Wind driven power generator

InactiveUS7365448B2Less obtrusiveMinimizing to bird lifeEngine fuctionsWind motor supports/mountsWind drivenHorizontal axis

A wind driven generator includes a rotor disposed in a cylindrical duct and supported by a frame for rotation in response to wind flowing through the duct. The rotor includes plural circumferentially spaced paralleled rotor blades supported for rotation about a generally horizontal axis. Each blade is supported for pivotal movement to change blade pitch, angle of attack or camber as the rotor rotates. A pitch or camber control motor or self-governing wind vane mechanism is operable to move a circular cam to vary blade pitch or camber to control rotor speed. The duct is mounted on a mast having a base supported on a foundation for pivotal movement to face the wind for maximizing air flow through the duct. Electric power generators are connected to opposite ends of the rotor at respective power output or drive shafts.

Owner:BROADSTAR INVESTMENT COMPANY

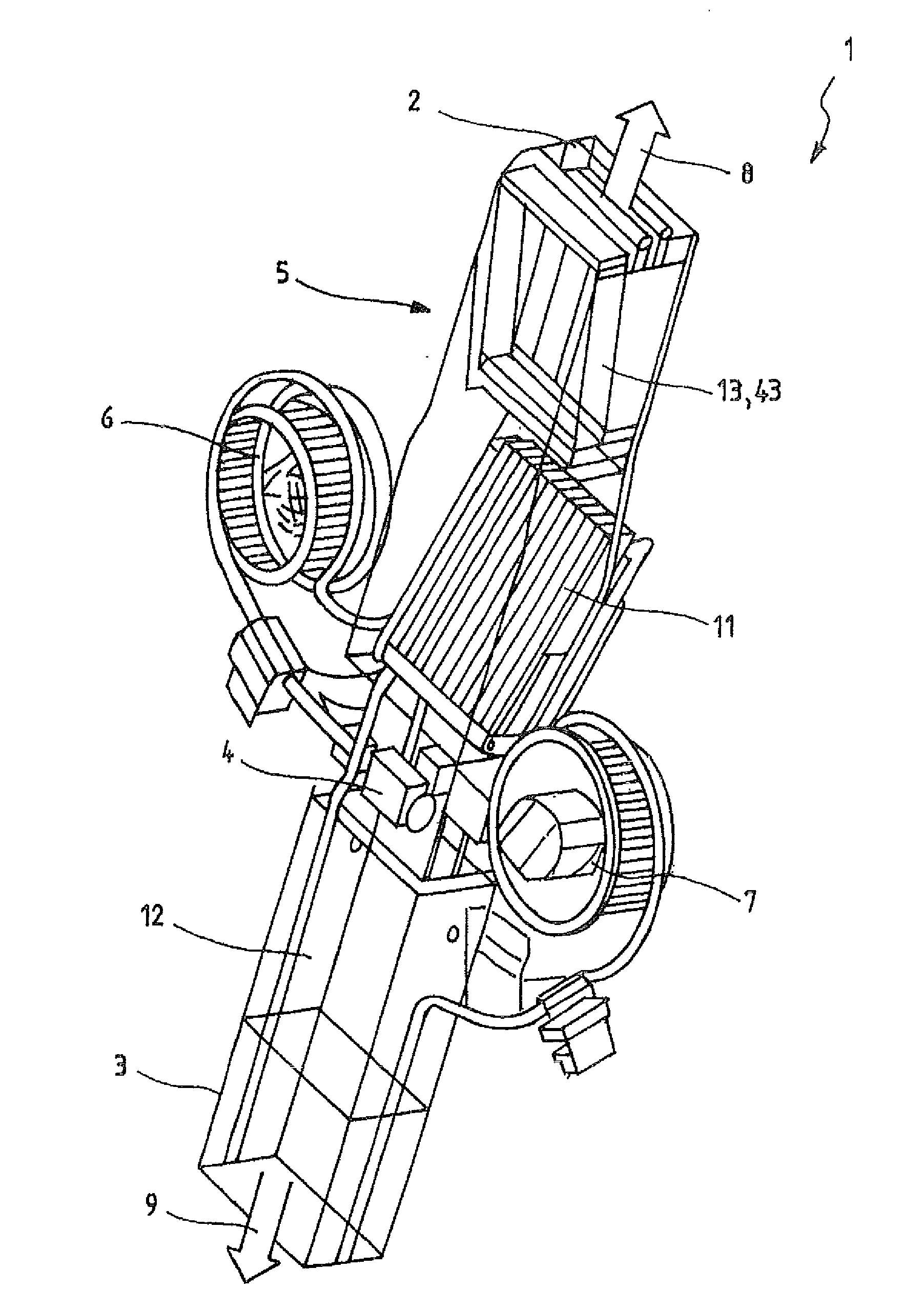

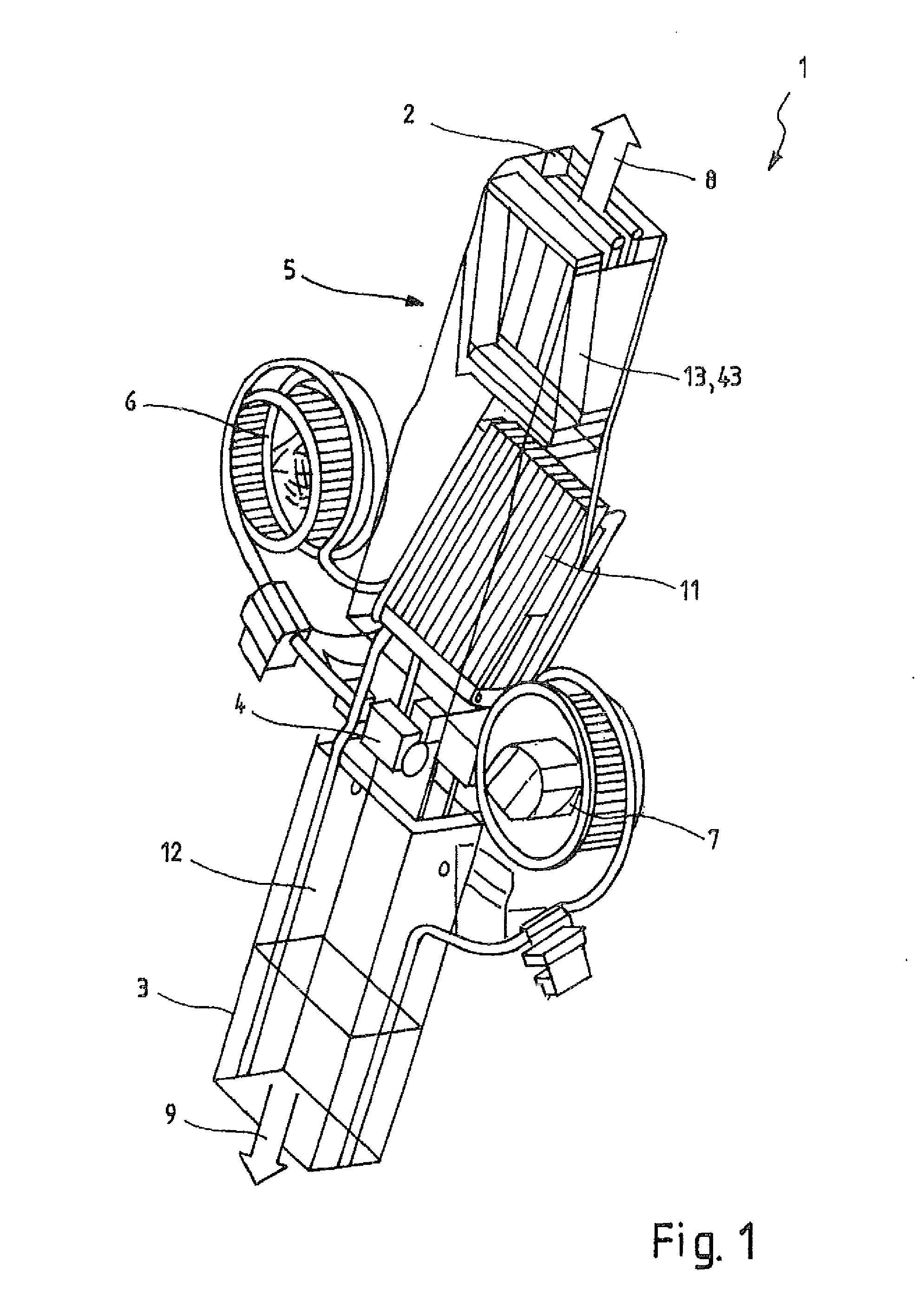

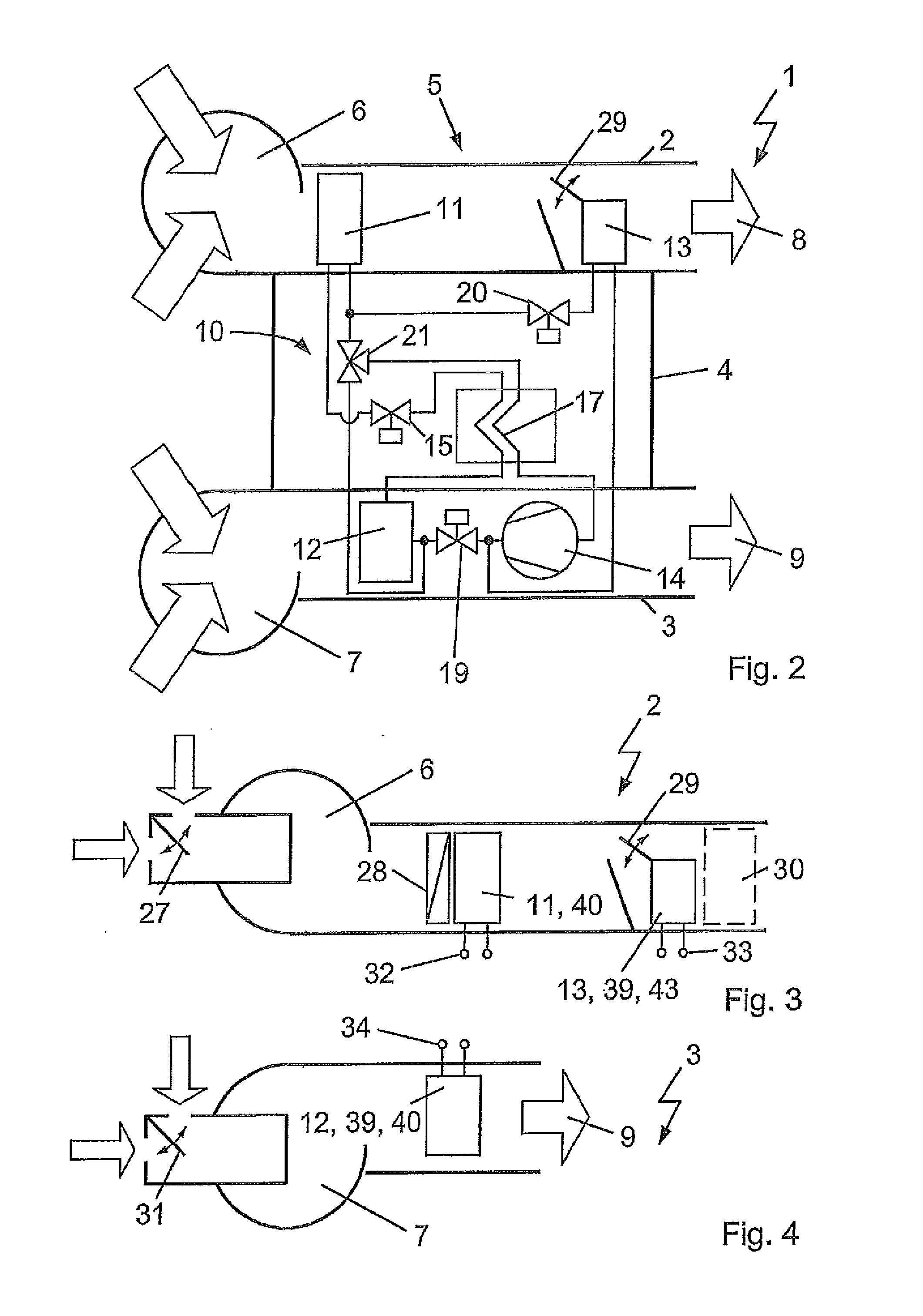

Compact HVAC system for a motor vehicle

InactiveUS20110036117A1Improve controllabilityReduce capacityEvaporators/condensersVehicle heating/cooling devicesGas coolerEngineering

The invention relates to a compact vehicle HVAC system including an evaporator unit, a condenser unit, and a component unit, as well as a refrigerant circuit. The evaporator unit and the condenser unit each are provided with air-passed heat exchangers and a fan in a casing. Further circuit components are displaced within the component unit. The casings of the evaporator unit, the condenser unit, and the component unit advantageously establish a connected compact casing arrangement. The heat exchangers are displaced within the compact casing arrangement. The refrigerant circuit is established for a combined refrigeration plant and heat pump operation as well as an afterheating operation, whereby in the afterheating operational mode the heating power of the afterheater established as condenser / gas cooler and the cooling power of the evaporator are controllable independently of each other.

Owner:HANON SYST

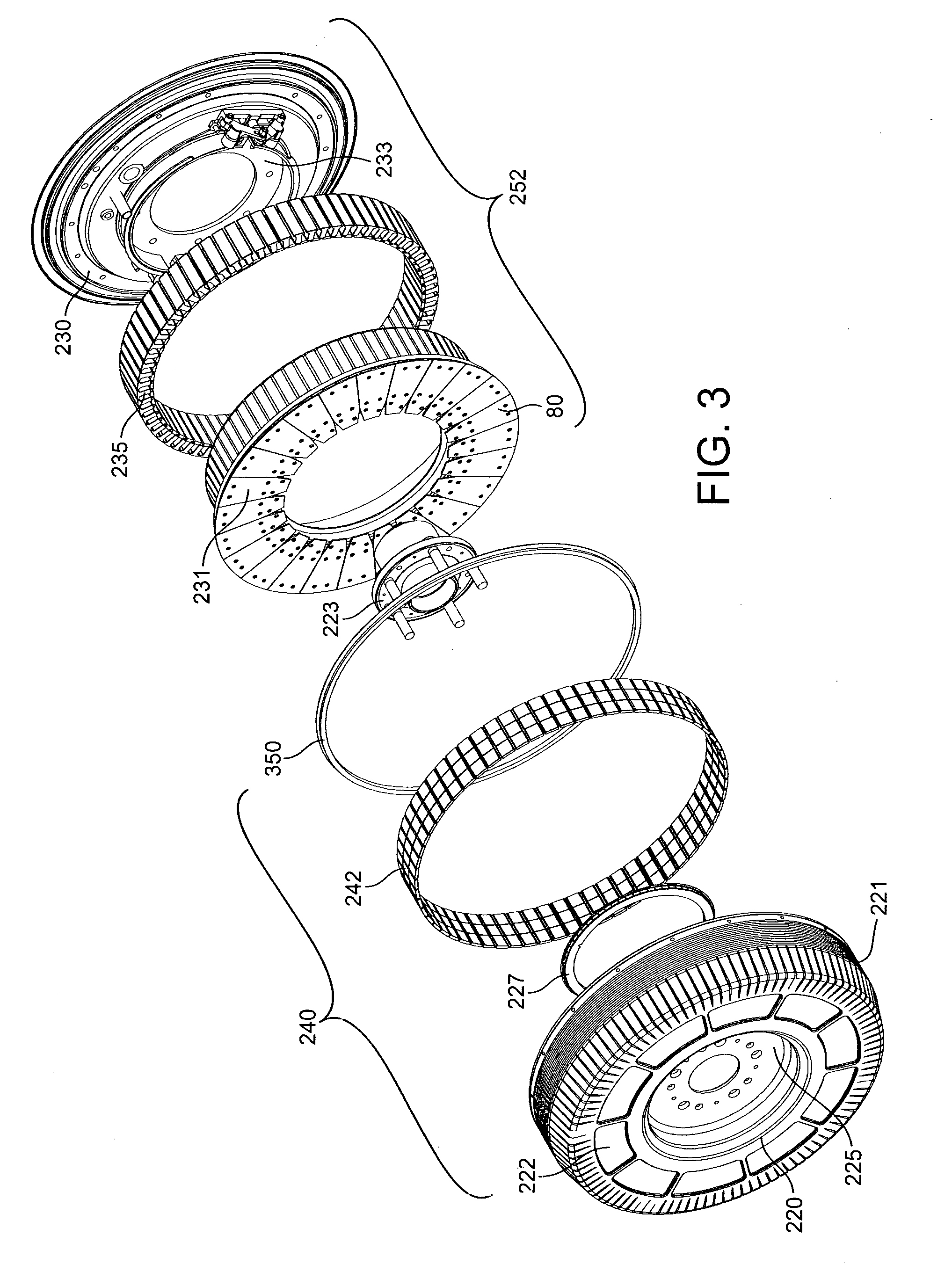

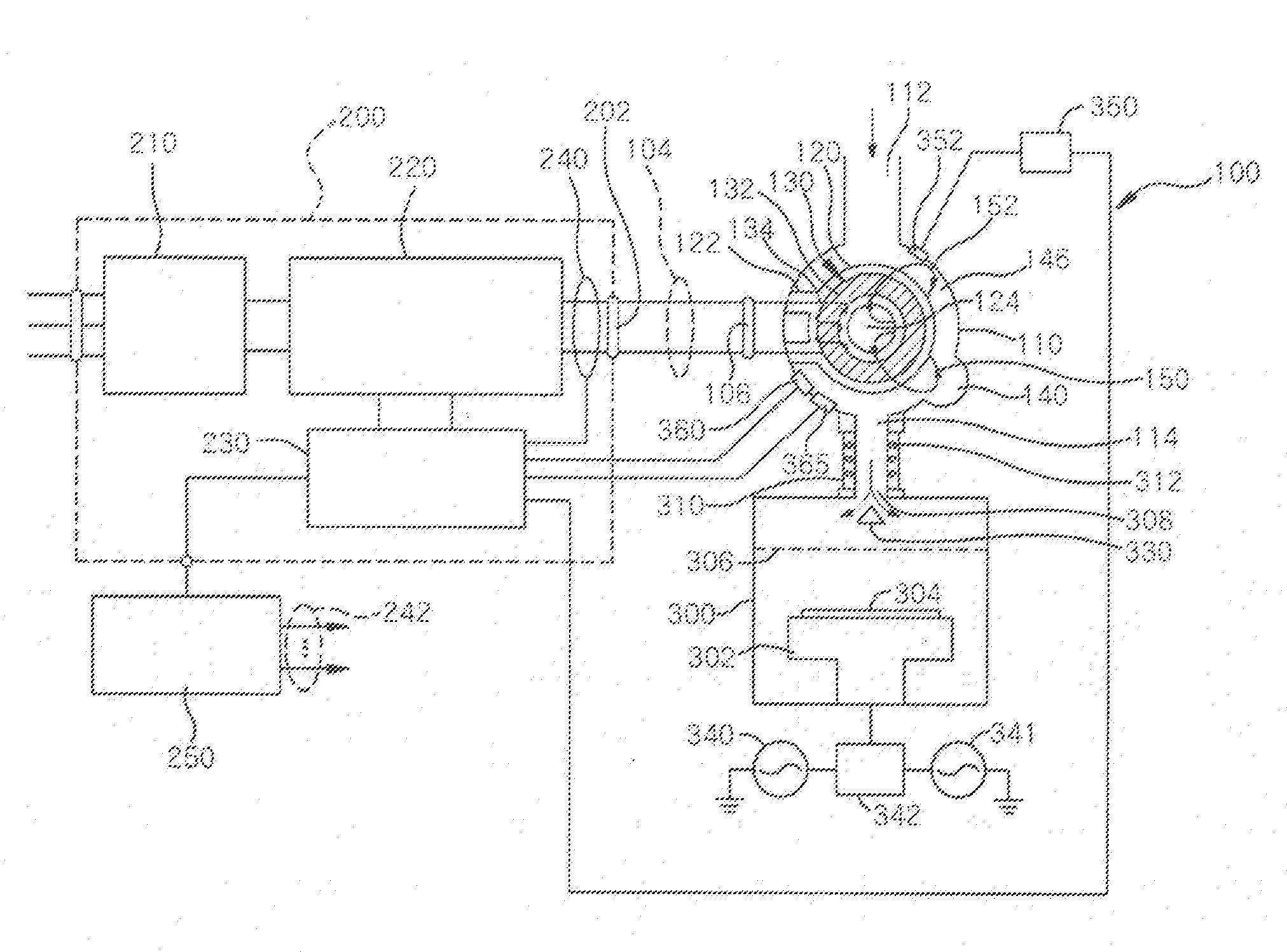

Electric motors

ActiveUS20100138127A1Increase inductanceEasy to controlSingle motor speed/torque controlMagnetic circuitControl systemTraction control system

An electric motor includes one or more separate coil sets arranged to produce a magnetic field of the motor. The electric motor also includes a plurality of control devices coupled to respective sub-sets of coils for current control. A similar arrangement is proposed for a generator. A coil mounting system for an electric motor or generator includes one or more coil teeth for windably receiving a coil for the motor and a back portion for attachably receiving a plurality of the coil teeth. A traction control system and method for a vehicle having a plurality of wheels independently powered by a respective motor. A suspension control system and method for a vehicle having a plurality of wheels, each wheel being mounted on a suspension arm of the vehicle and being independently powered by a respective motor.

Owner:PROTEAN ELECTRIC LIMITED

Plasma reactor with internal transformer

InactiveUS20090291027A1Easy to makeAvoid many problemsExhaust apparatusElement comparisonEnergy transferTransformer

There is provided a plasma reactor with an internal transformer. The plasma reactor comprises: a plasma chamber with a gas inlet and a gas outlet, for providing a plasma discharging space; one or more core cylinder jackets for providing a core storage space in the plasma discharging space and forming a plasma centralized channel and a plasma decentralized channel by including one or more through-apertures; and one or more transformers each including a magnetic core with primary winding surrounding the through-aperture and installed in the core storage space, wherein the plasma discharging space comprises one or more first spatial regions to form the plasma centralized channel and one or more second spatial regions to form the plasma decentralized channel. In the plasma reactor, since the transformer is installed in the plasma chamber, energy is transferred with almost no loss from the transformer to the plasma discharging space and therefore the energy transfer efficiency is very high. Then, since most of gases flow through the first spatial region and the through-aperture inside the plasma chamber, most of active gases are generated in the plasma centralized channel. Consequently, the plasma reactor is very suitable for generating large amount of active gases. Further, even though the plasma chamber is composed of a conductive material, since no special insulating region needs to be formed, it is very easy to constitute the plasma chamber. Further, since the plasma chamber itself is sufficiently capable of forming an outer case, the plasma reactor is very simply manufactured.

Owner:NEW POWER PLASMA CO LTD

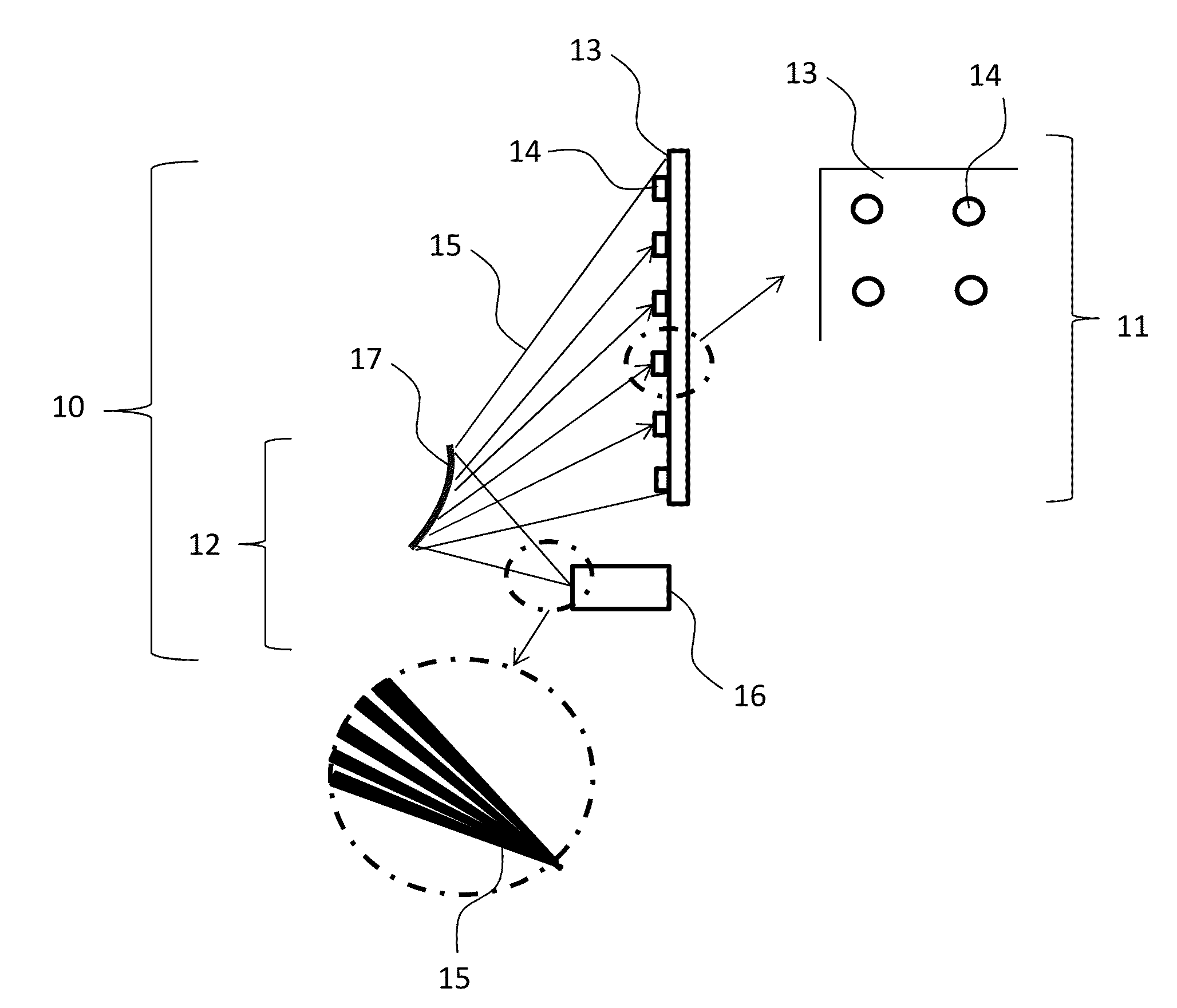

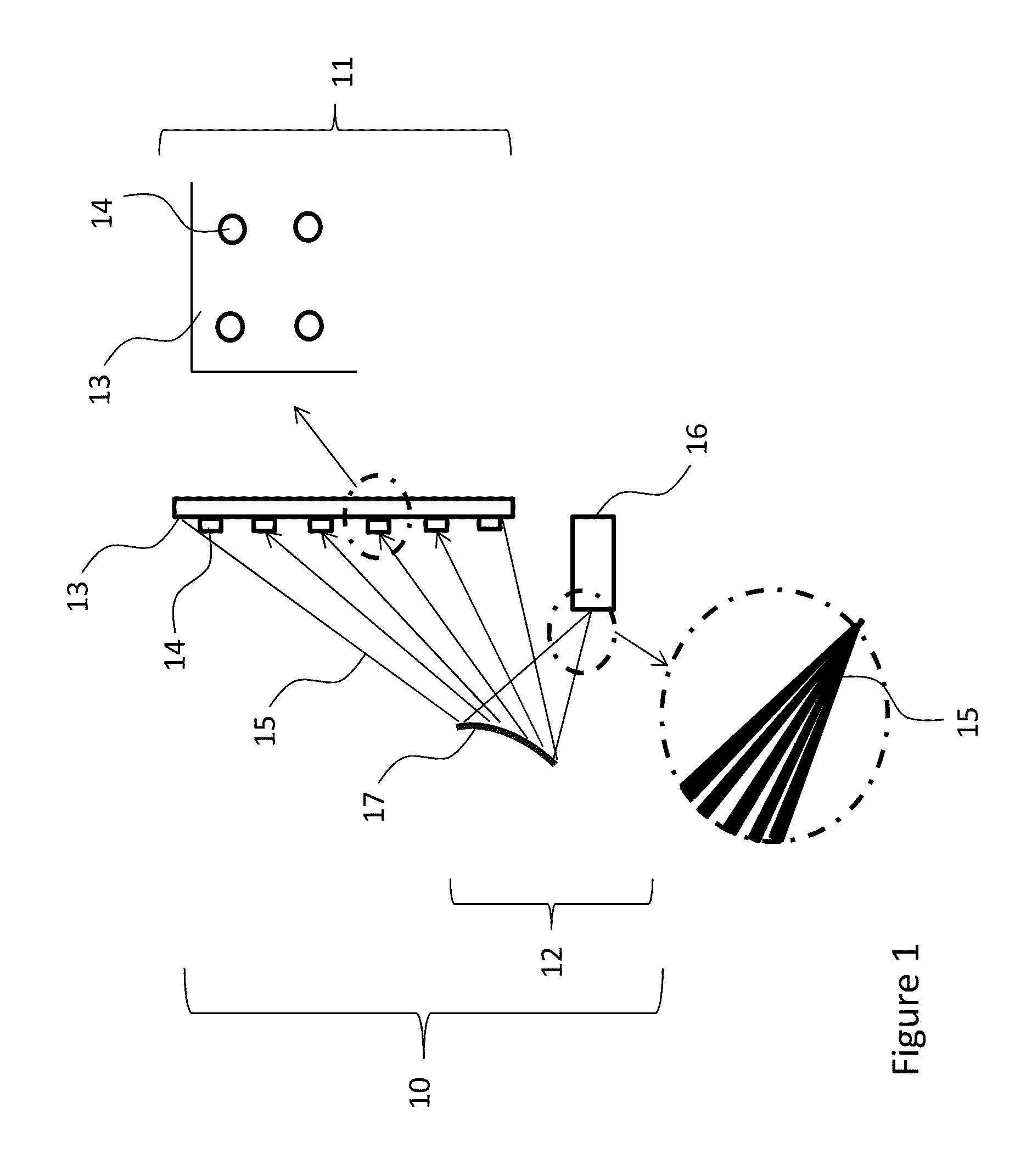

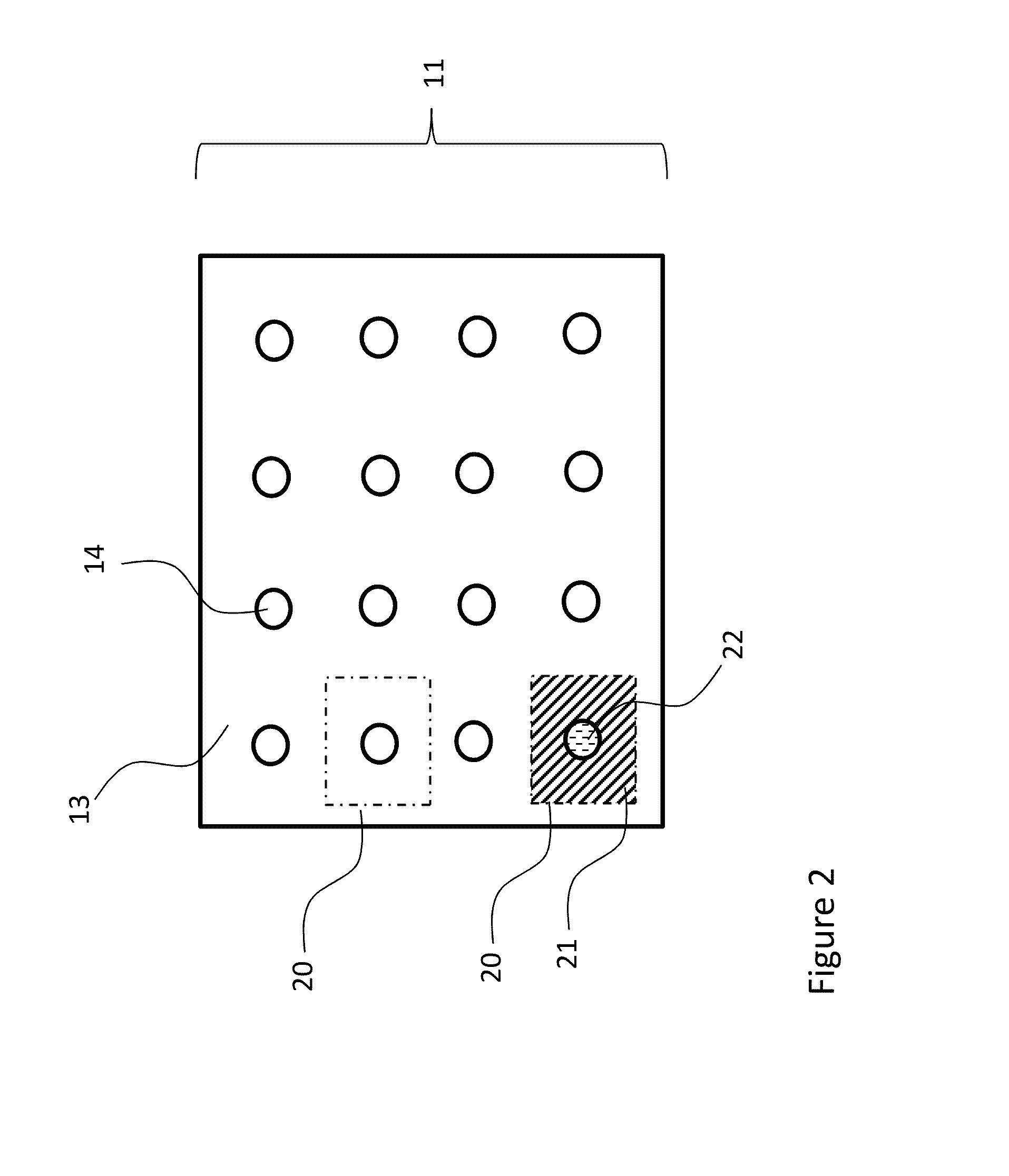

Transparent display including a screen with patterned light deflective elements

ActiveUS20160124295A1Limit reliability and lifetimeEasy to scaleBuilt-on/built-in screen projectorsAdvertisingOptical powerDisplay device

A transparent display device includes a screen that has a plurality of light deflecting elements that are separated by transparent areas, and a projector device. The projector device is configured to direct light onto the light deflecting elements and not onto the transparent areas. The display device may include a first screen and a second screen separated longitudinally relative to the projector, wherein each screen respectively has a plurality of light deflecting elements. The projector is configured to direct light onto the light deflecting elements and not onto the transparent areas of the two screens such that light from the first and second light deflecting elements appear in different virtual depth planes. Alternatively, a single screen may have first and second pluralities of light deflecting elements of different optical powers, such that light from the first and second light deflecting elements appear in different virtual depth planes.

Owner:SHARP KK

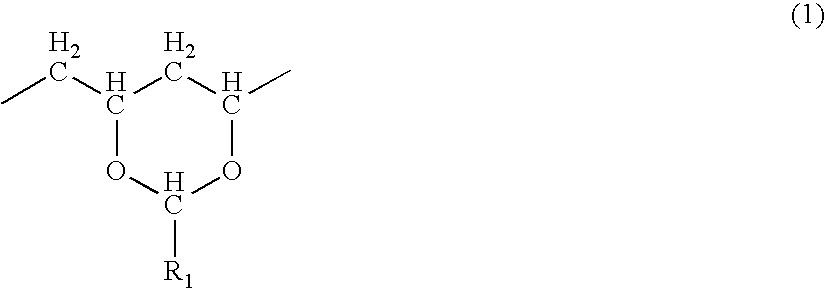

Polyvinyl Acetal Resin Varnish Gelling Agent, Nonaqueous Electrolyte Solution, And Electrochemical Device

ActiveUS20080090145A1Improve securityLow viscosityFinal product manufactureConductive materialOrganic solventPolyvinyl alcohol

A polyvinyl acetal resin varnish which is so low in stimulus property, toxicity, environment-polluting property, offensive odor, and inflammability that no problem is caused in practical use, and which is high in safety, low in viscosity, and thus favorable in workability, and an application of the polyvinyl acetal resin varnish are provided. As an organic solvent for dissolving the polyvinyl acetal resin, there is used a nonaqueous solvent, preferably carbonate ester, and more preferably a mixed solvent composed of cyclic carbonate ester and chain carbonate ester, into which the polyvinyl acetal resin is evenly dissolved regardless of its type, resulting in varnish which is high in safety and low in viscosity. Since the varnish has an action of gelling the organic solvent, the varnish can be used as a gelling agent in various applications.

Owner:MITSUI CHEM INC

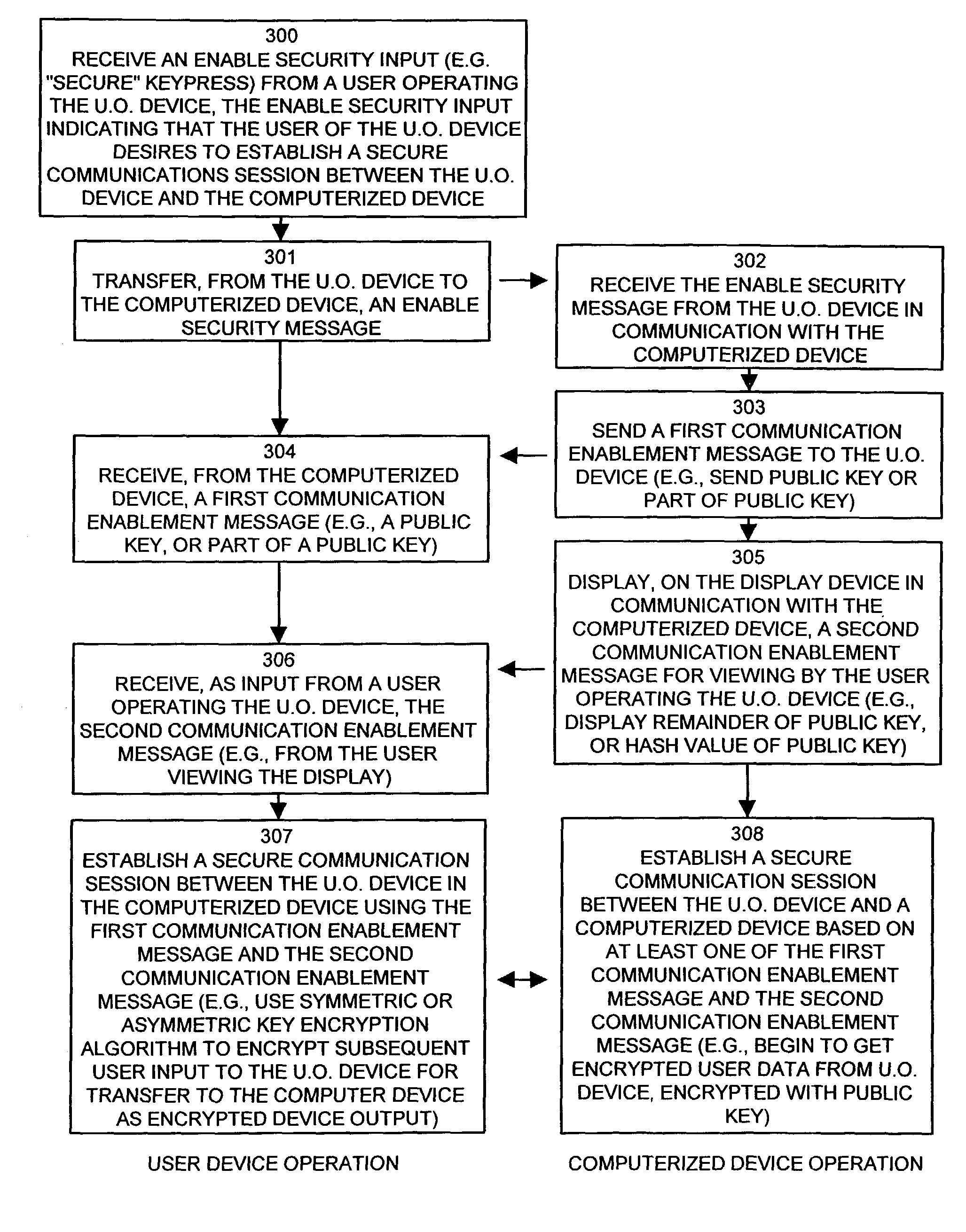

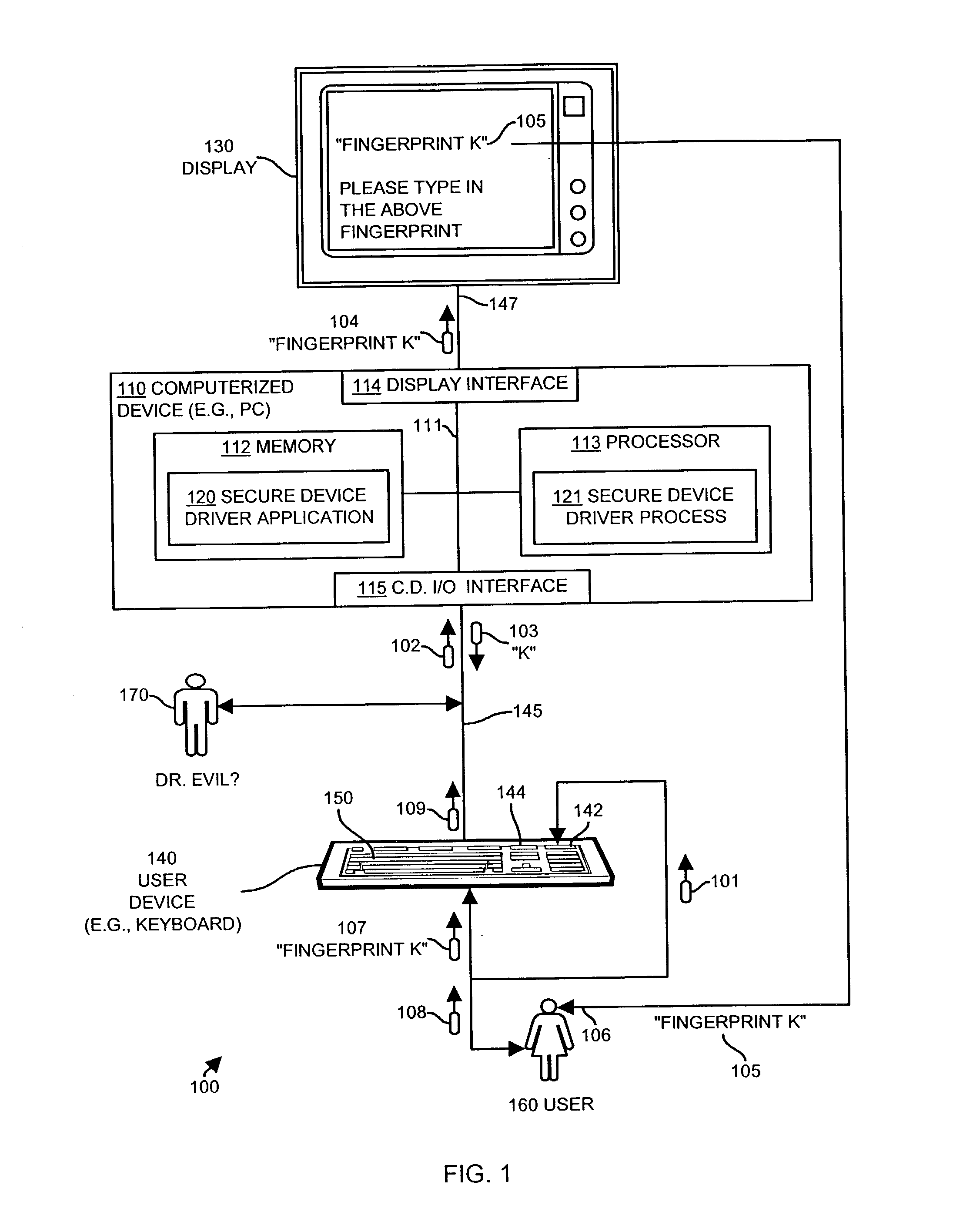

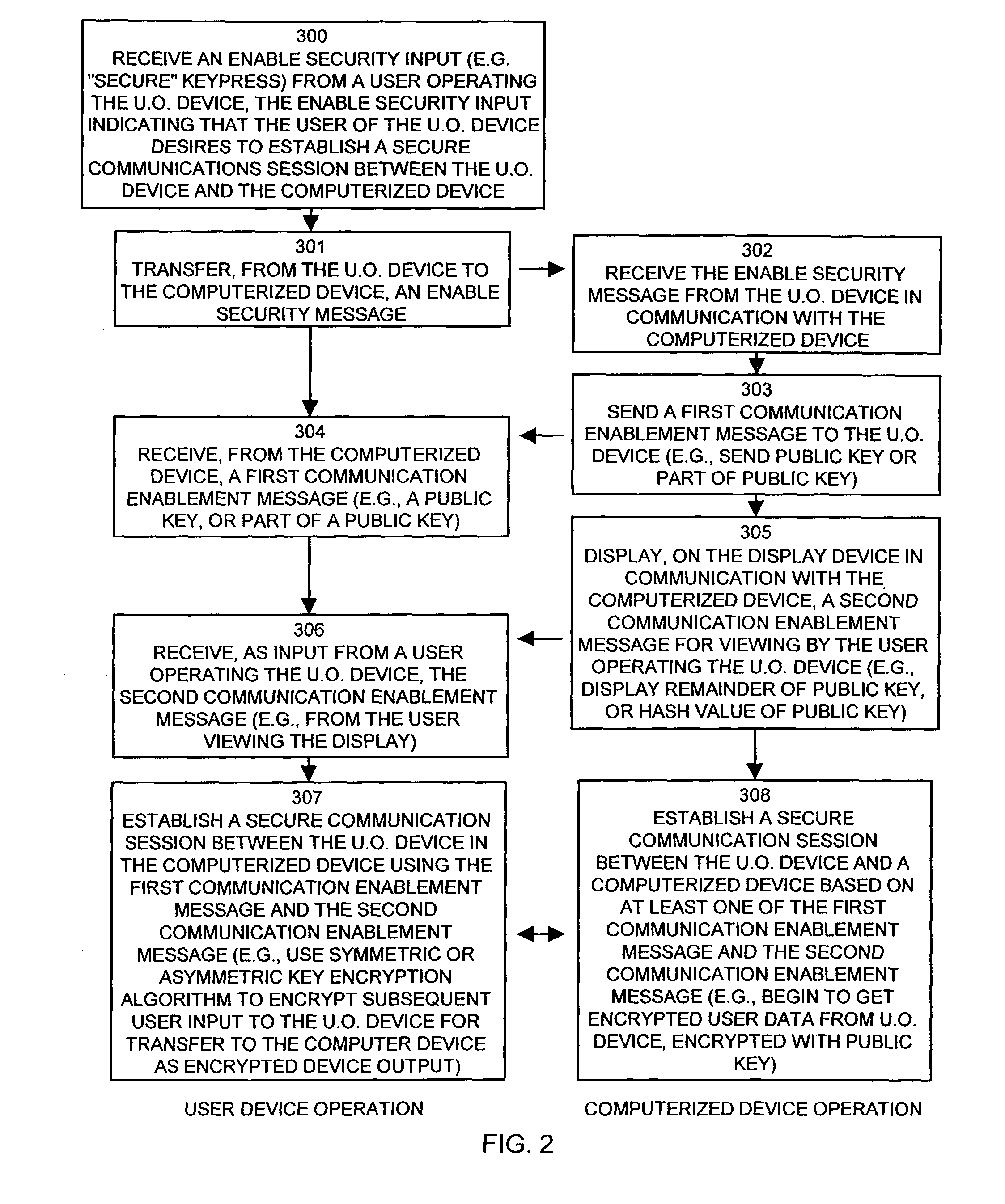

Methods and apparatus for securing communications of a user operated device

ActiveUS8180051B1Further level of securityFaster communication sessionKey distribution for secure communicationMultiple keys/algorithms usageSecure communicationComputer hardware

A system provides secure communications between a user operated device and a computerized device. The user operated device transfers an enable security message to the computerized device, and in response, the computerized device sends a first communications enablement message to the user operated device and displays a second communications enablement message on a display of the computerized device for viewing by a user operating the user operated device. The user operated device receives the first communications enablement message from the computerized device and receives the second communications enablement message from the user and establishes a secure communications session between the user operated device and the computerized device using the first communications enablement message and the second communications enablement message. The communications enablement messages can contain key material that enable encryption between the user operated device and the computerized device.

Owner:CISCO TECH INC

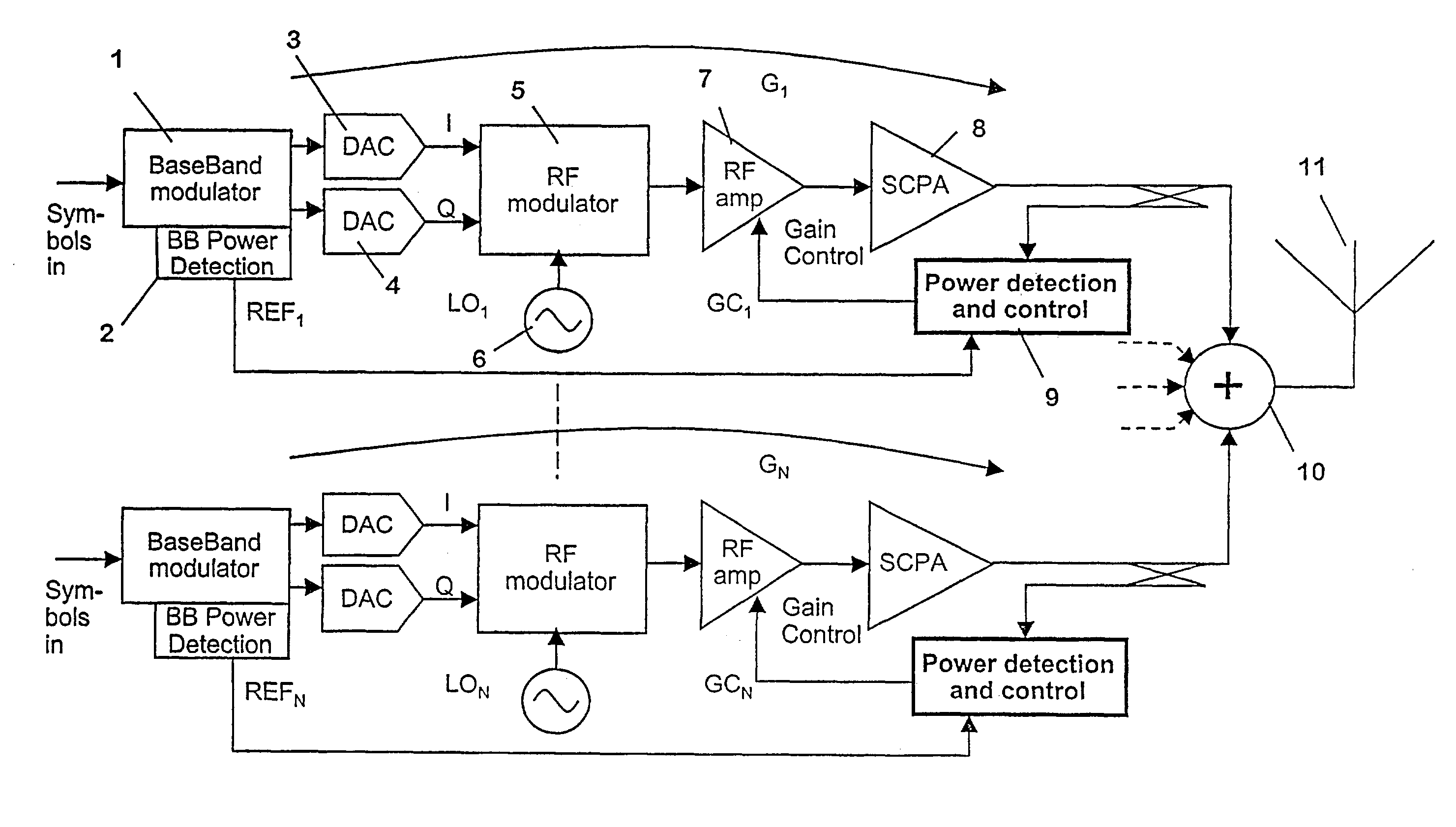

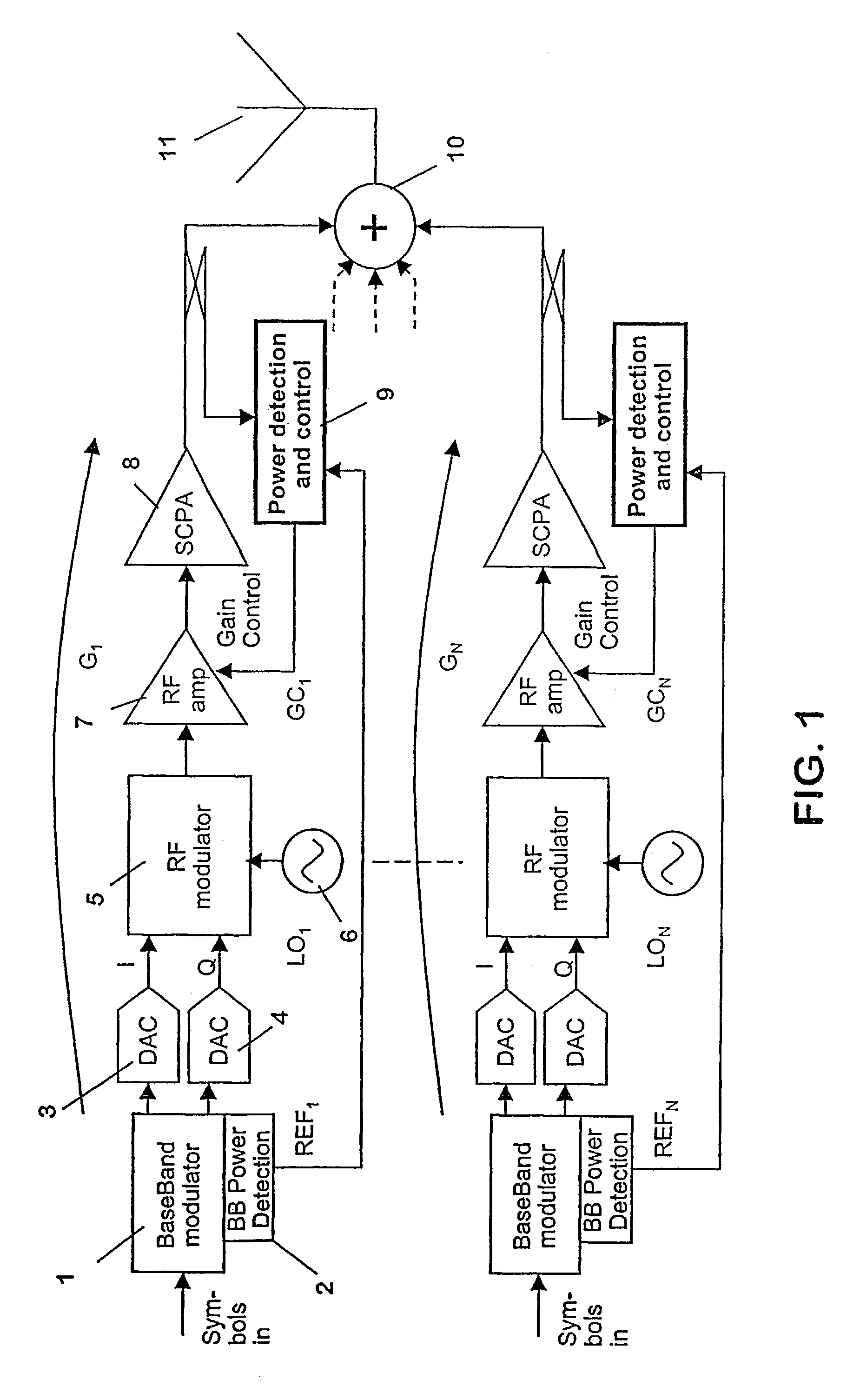

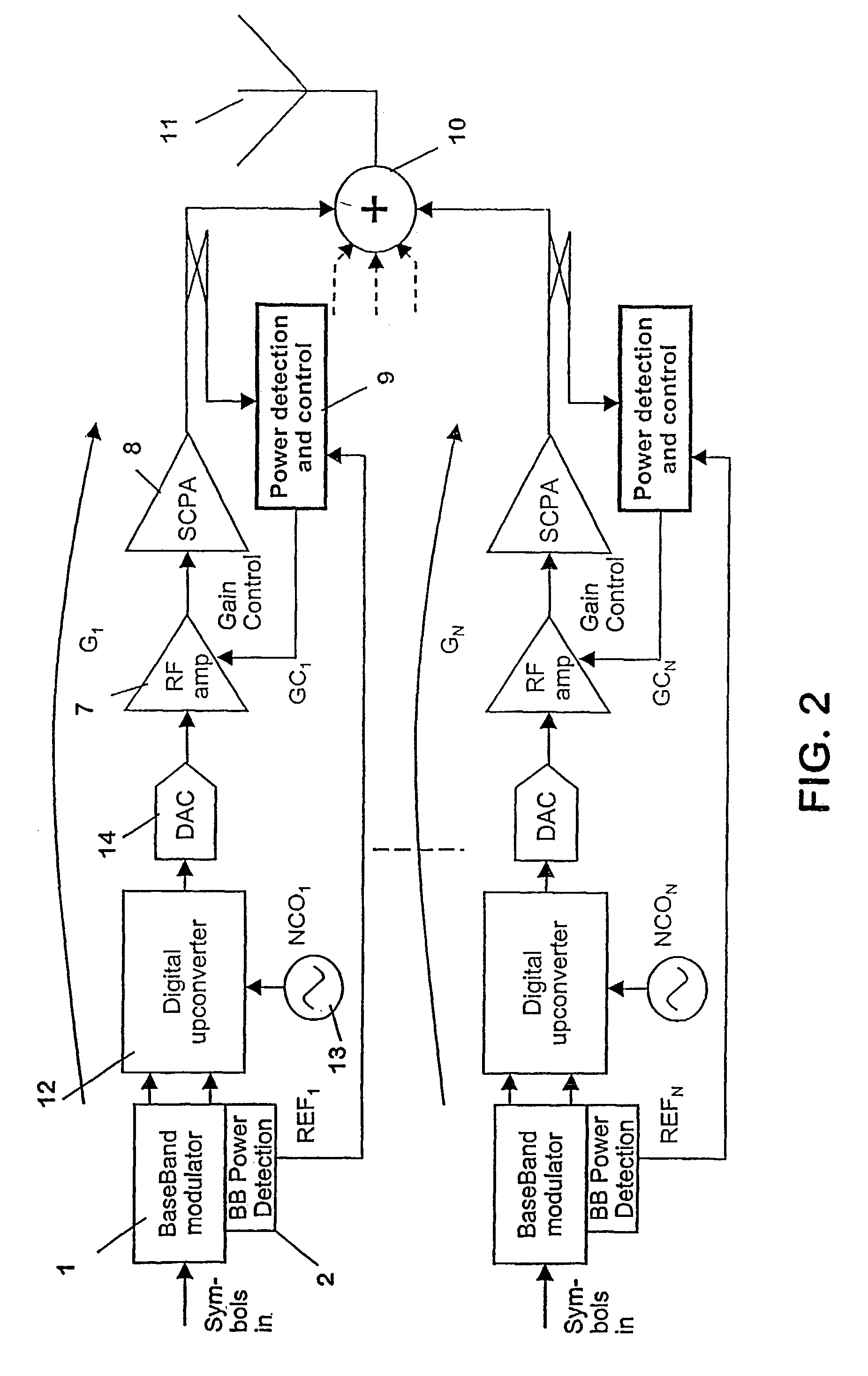

Methods for determining the gains of different carriers, radio transmission units and modules for such units

InactiveUS7110727B2Simplified determinationAvoid many problemsPower managementResonant long antennasCommunications systemCarrier signal

The invention relates to methods for determining the separate radio frequency gains for carriers in a multi-carrier transmitter of a radio transmission unit of a radio communications system. In order to enable a simple and accurate estimation of the gains, it is proposed to determine the individual gains (G1–GN) of the different carriers mathematically from different sets of powers (REF1–REFN) at some point in each single carrier unit and the corresponding total output powers of the transmitter. Alternatively, the relation of the powers of the different carriers to each other is determined just before the carriers are combined to a single multi-carrier signal. This relation is used for determining the contribution of the different carriers to the transmission power of the multi-carrier signal and for therefrom determining the radio frequency gains for the different carriers. The invention equally relates to corresponding radio transmission units and modules of such radio transmission units.

Owner:NOKIA CORP

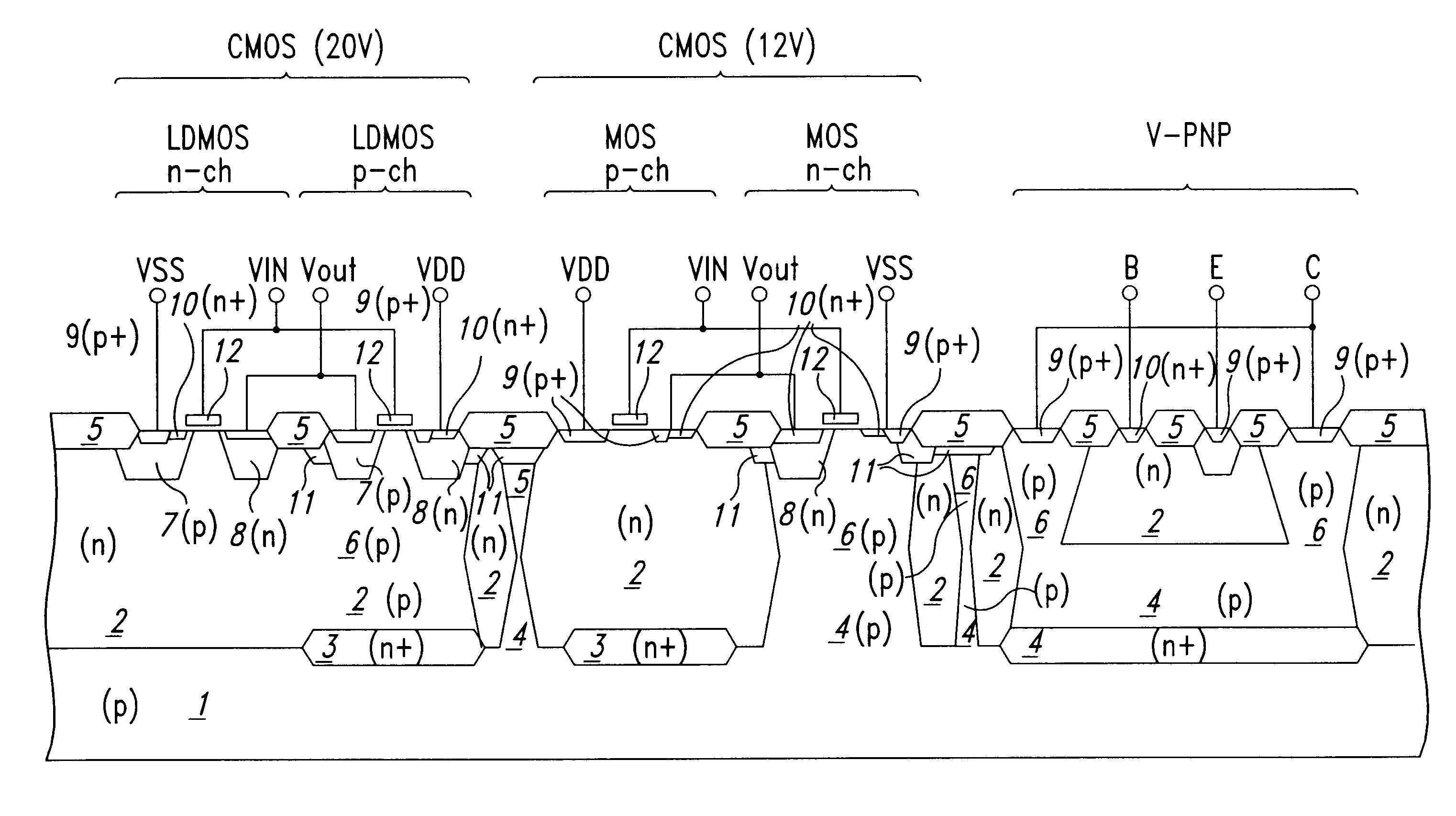

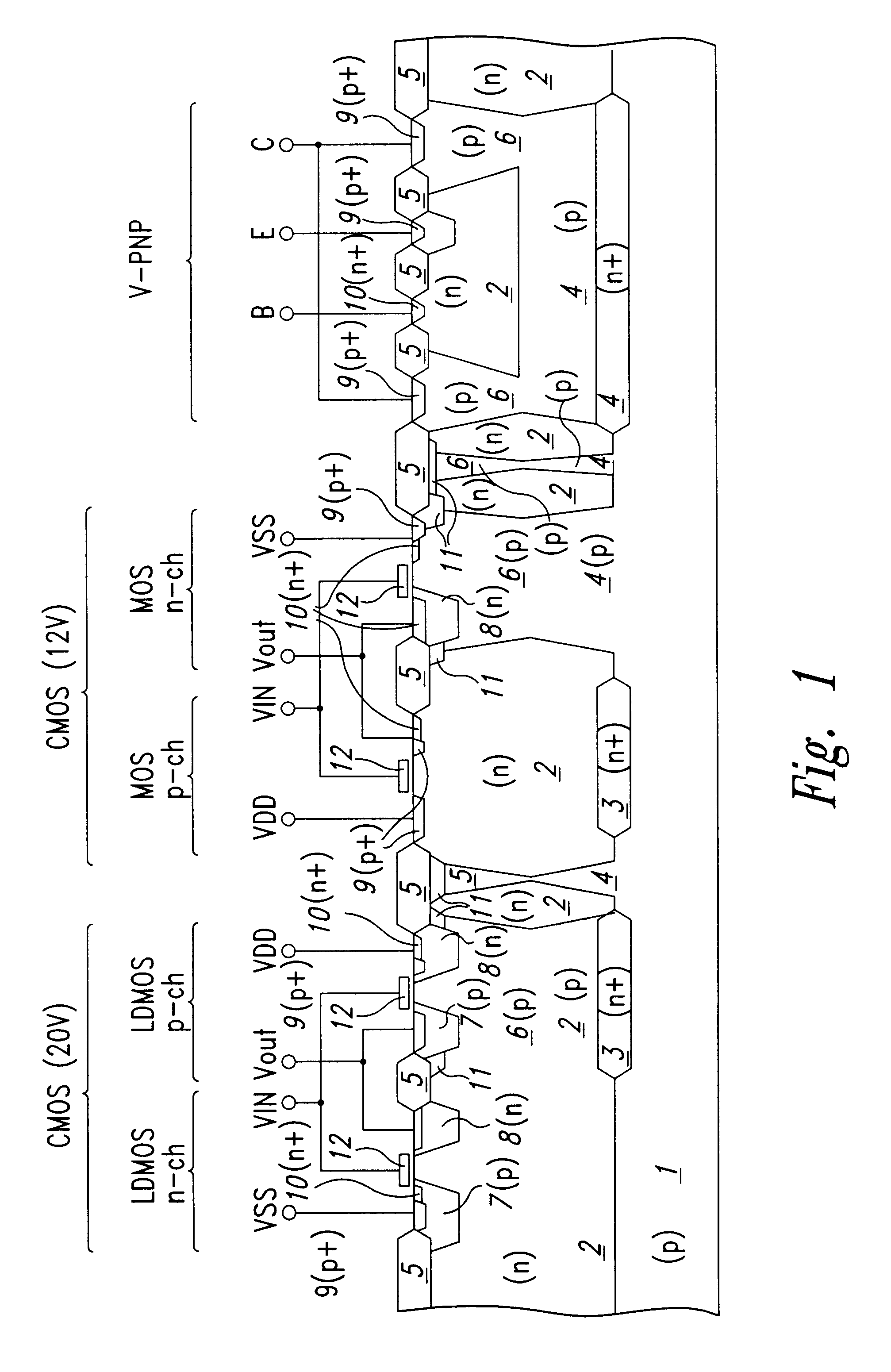

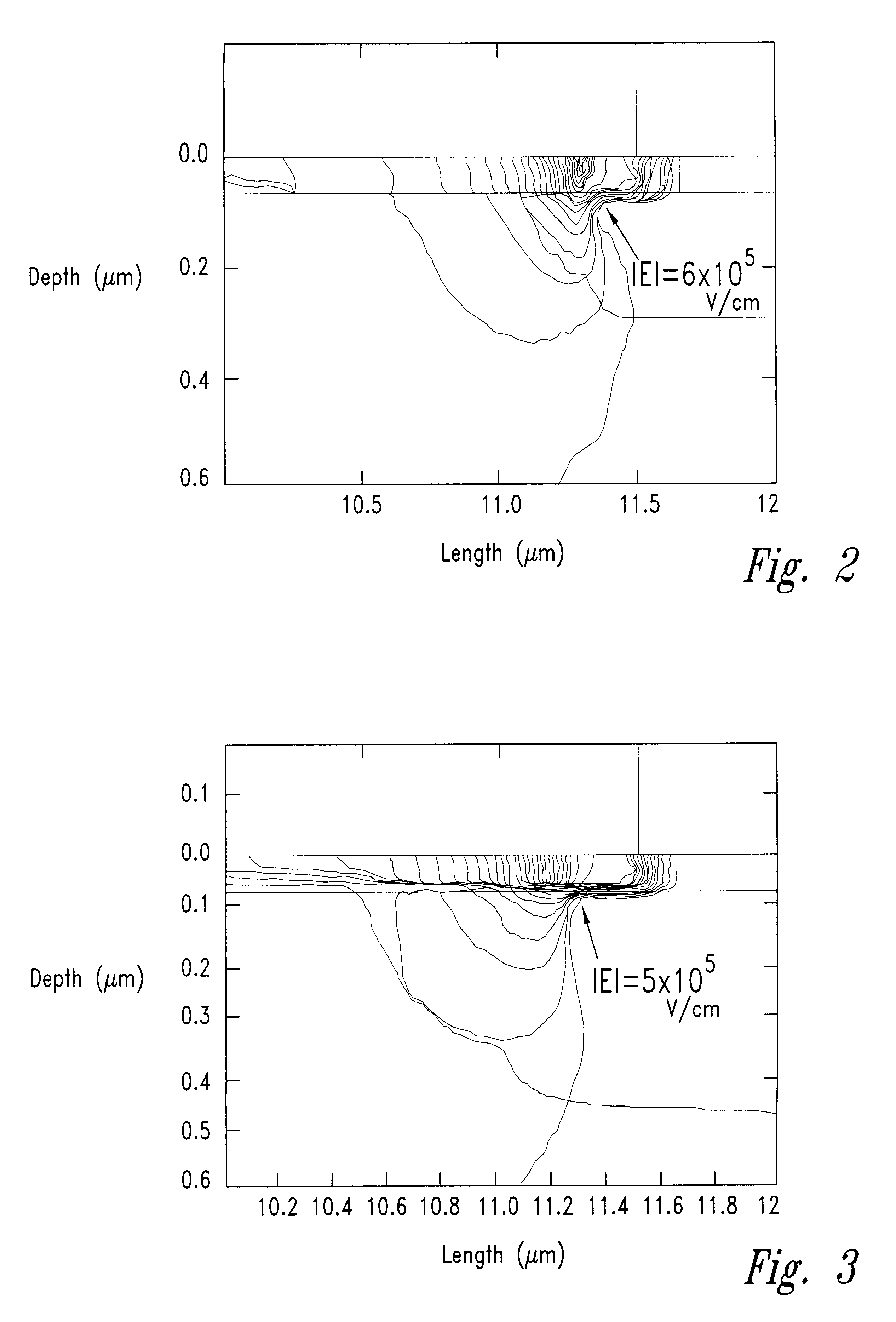

Mixed technology integrated device comprising complementary LDMOS power transistors, CMOS and vertical PNP integrated structures having an enhanced ability to withstand a relatively high supply voltage

InactiveUSRE37424E1Reduce sensitivityImprove performanceTransistorSolid-state devicesCMOSIntegrated circuit

Complementary LDMOS and MOS structures and vertical PNP transistors capable of withstanding a relatively high voltage may be realized in a mixed-technology integrated circuit of the so-called "smart power" type, by forming a phosphorus doped n-region of a similar diffusion profile, respectively in: The drain zone of the n-channel LDMOS transistors, in the body zone of the p-channel LDMOS transistors forming first CMOS structures; in the drain zone of n-channel MOS transistors belonging to second CMOS structures and in a base region near the emitter region of isolated collector, vertical PNP transistors, thus simultaneously achieving the result of increasing the voltage withstanding ability of all these monolithically integrated structures. The complementary LDMOS structures may be used either as power structures having a reduced conduction resistance or may be used for realizing CMOS stages capable of operating at a relatively high voltage (of about 20V) thus permitting a direct interfacing with VDMOS power devices without requiring any "level shifting" stages. The whole integrated circuit has less interfacing problems and improved electrical and reliability characteristics.

Owner:STMICROELECTRONICS SRL

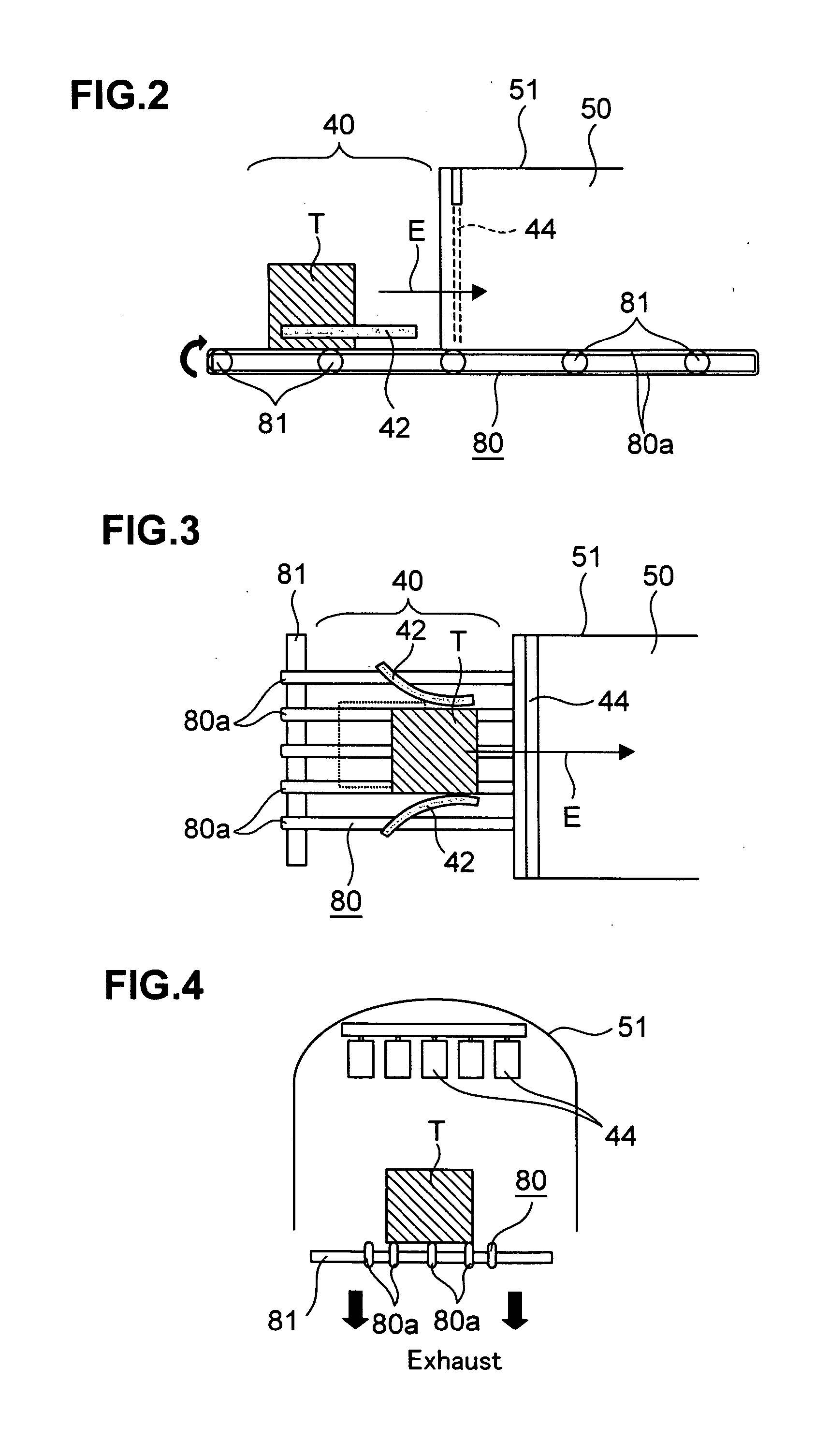

Washing apparatus, washing stystem, and washing method

InactiveUS20060281326A1Easy to disassembleLow costSemiconductor/solid-state device manufacturingCleaning using liquidsEngineeringHigh pressure

The present invention provides a cleaning apparatus, a cleaning system and a cleaning method for a member used in the semiconductor field, excellent in cleaning capability and good in operation efficiency. The present invention is directed to a cleaning apparatus for cleaning the member used in the semiconductor field, which comprises: one nozzle or plural nozzles; and a jet mechanism for jetting a mist-like cleaning liquid (L1) with a high pressure from the one nozzle or the plural nozzles (52a) to the member (T) to be cleaned. The present invention is also directed to a cleaning system (30) for cleaning members used in the semiconductor field, which comprises: a loader section (40) for setting a member to be cleaned; an unloader section (70) for collecting the members; and a transport stage (80) for continuously transporting the member from the loader section to the unloader section, wherein a cleaning section (50) for cleaning the member with a mist-like cleaning liquid is provided on the transport stage, and the member is transported by the transport stage and is also cleaned in the cleaning section.

Owner:SHIN-ETSU HANDOTAI CO LTD

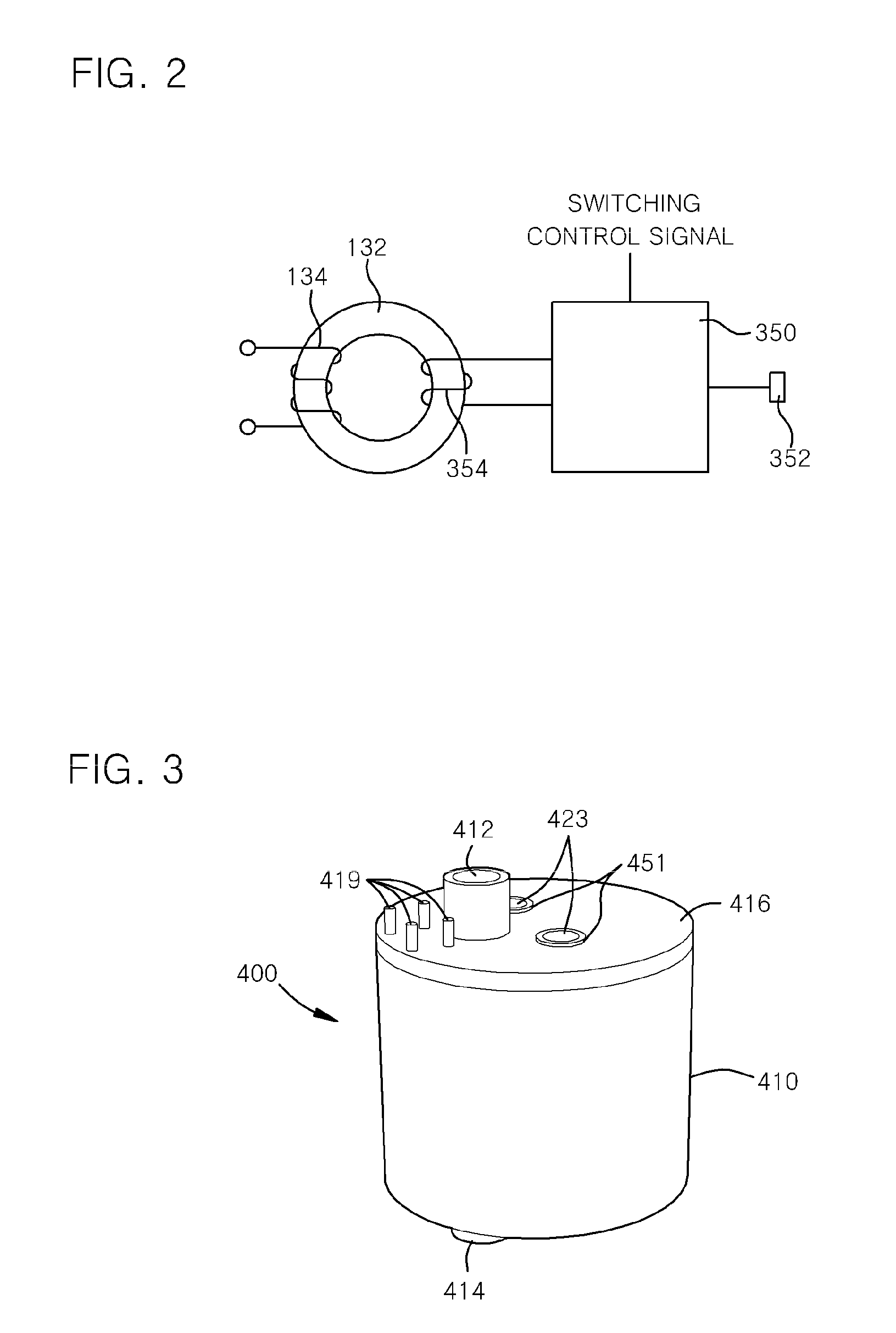

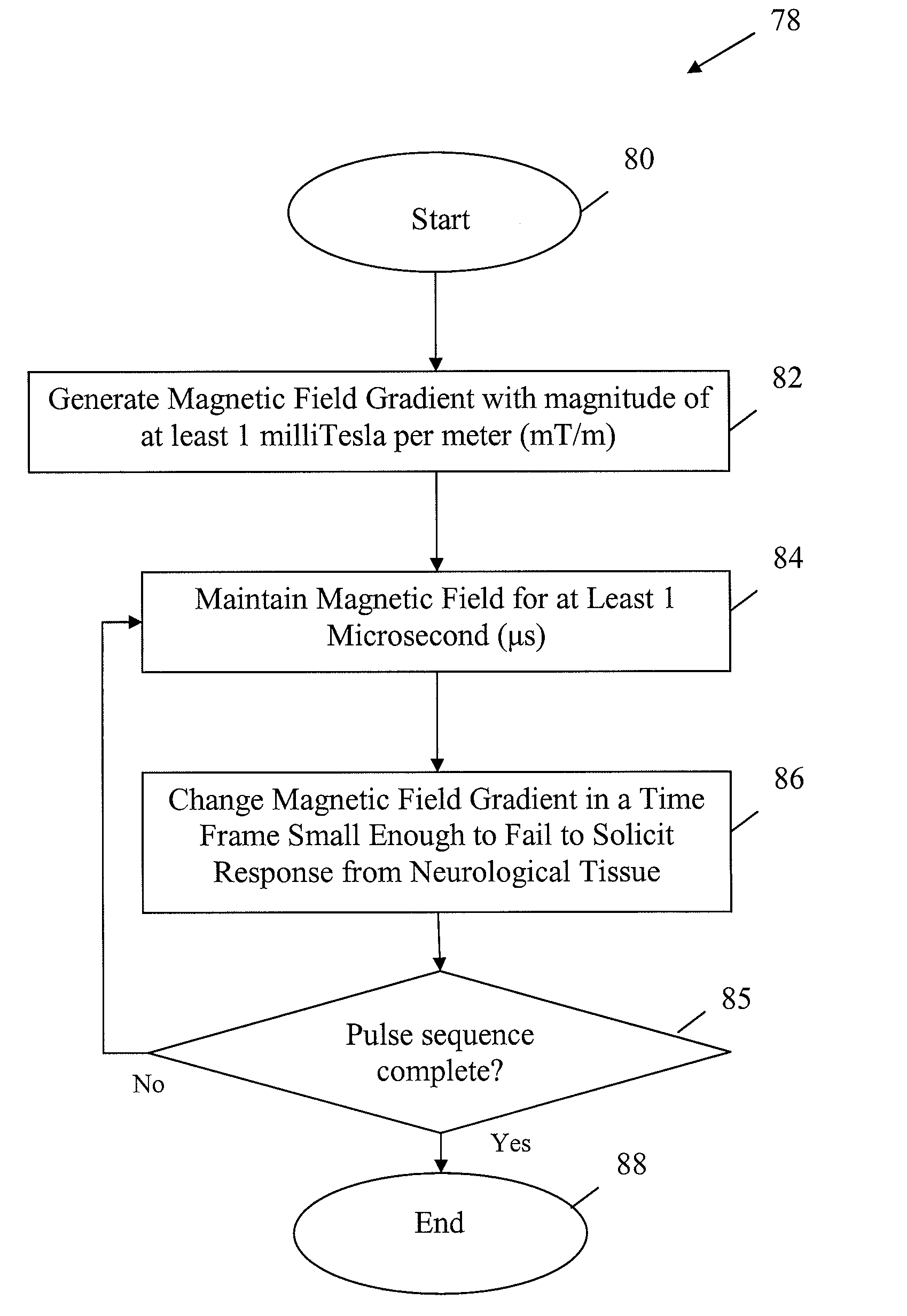

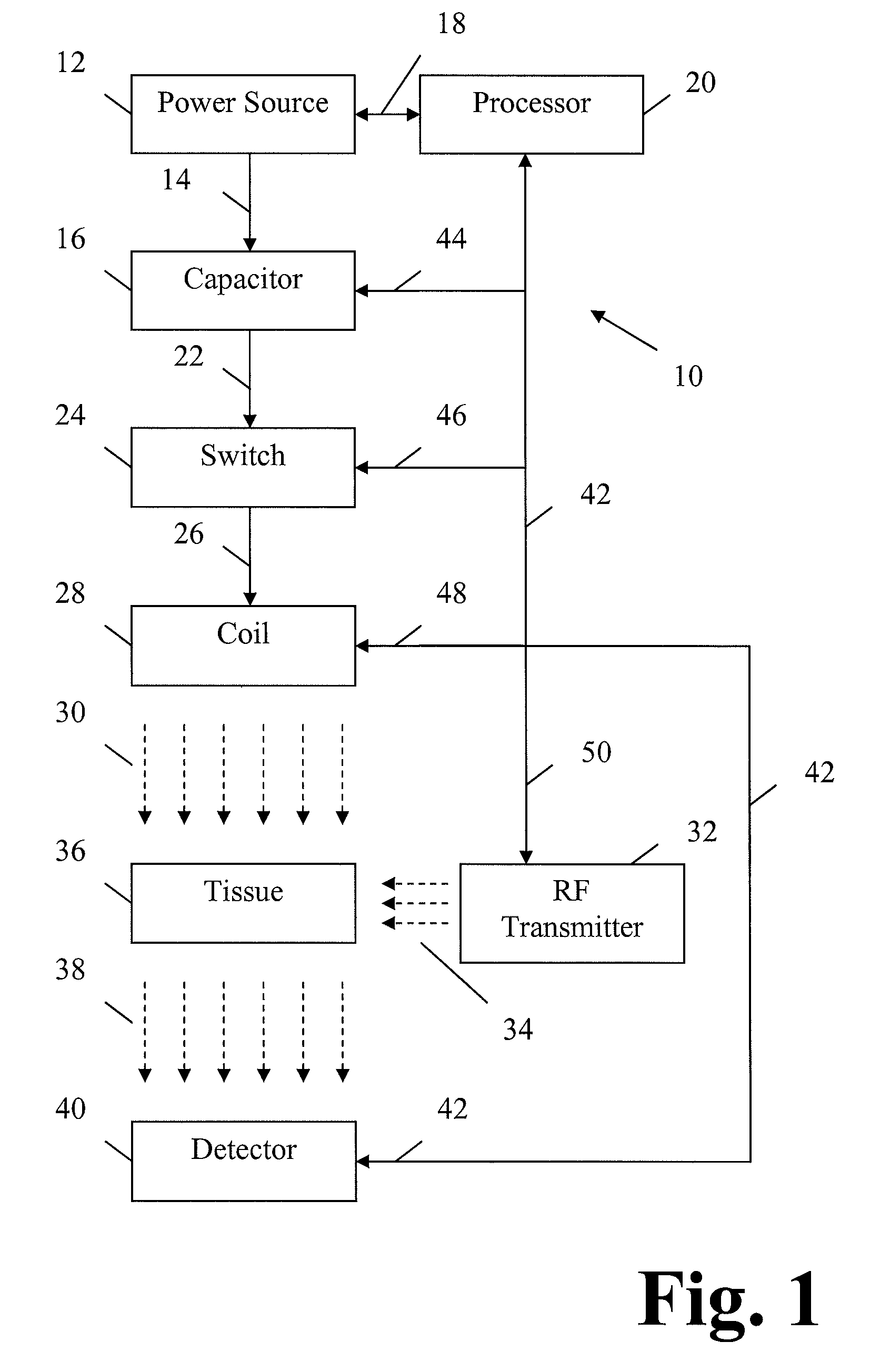

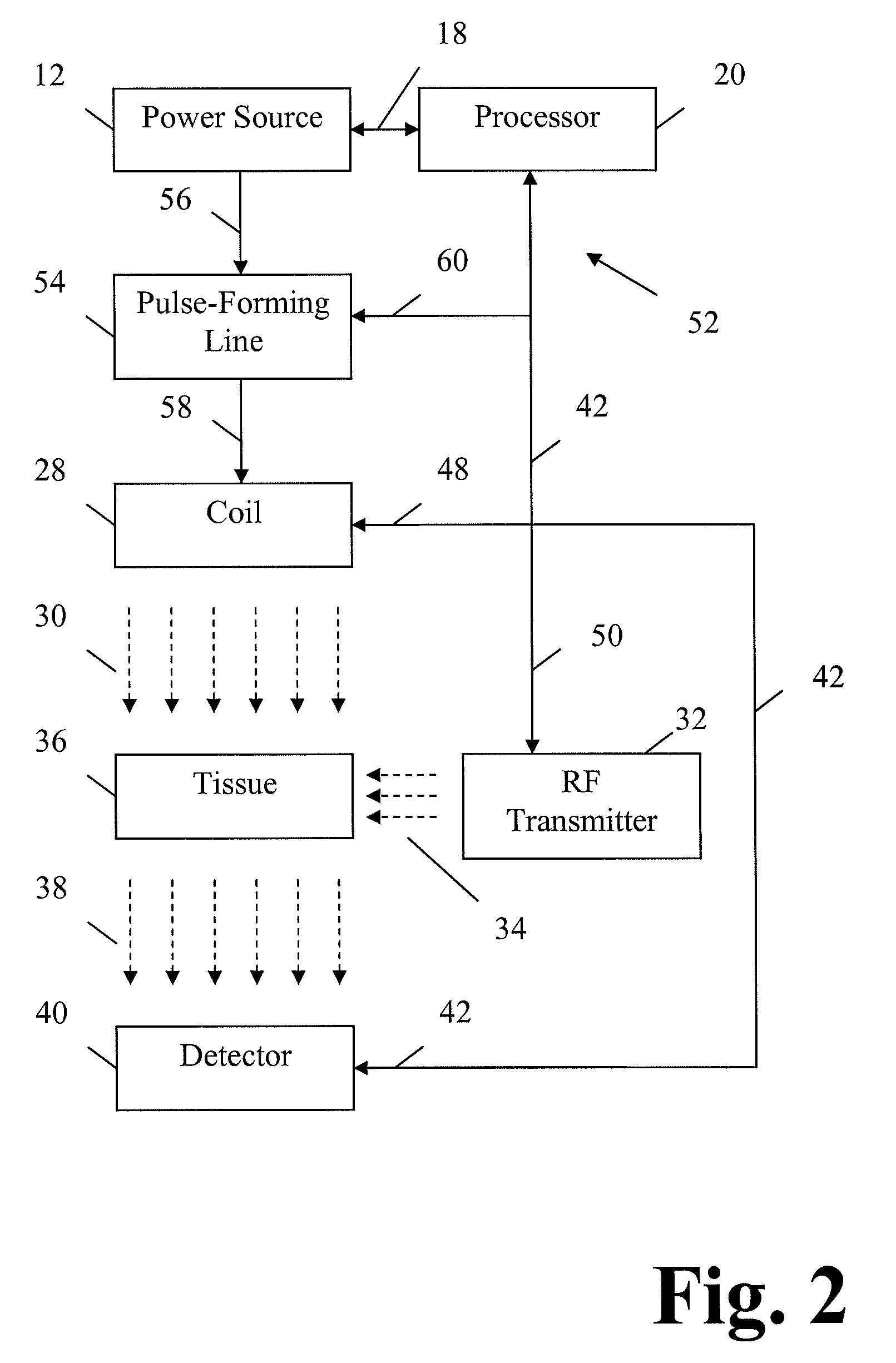

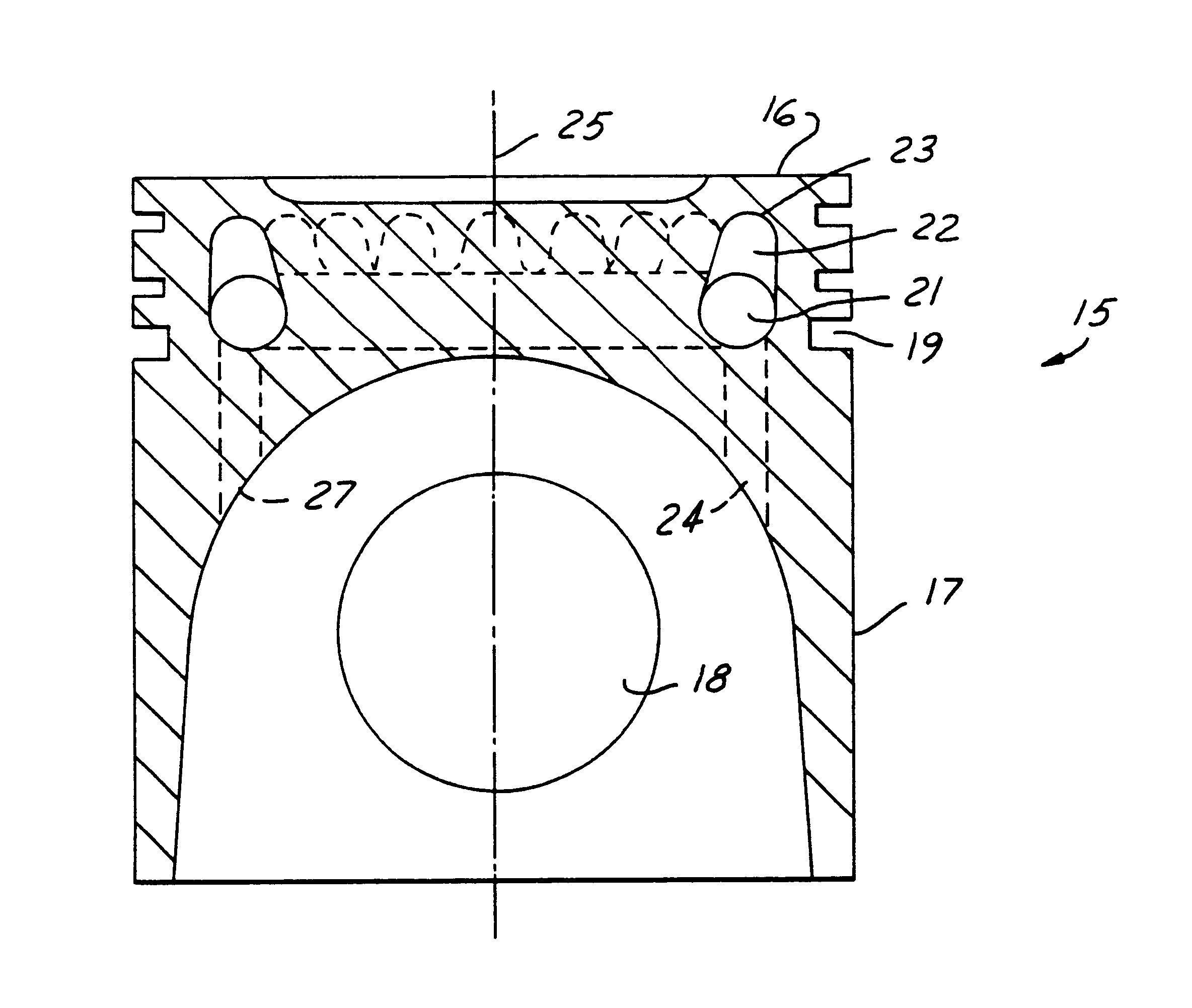

Apparatus and method for decreasing bio-effects of magnetic fields

ActiveUS8154286B2Shorten the construction periodReduce gradientMagnetic measurementsElectric/magnetic detectionPulse forming networkMagnetic field gradient

A magnetic field generator includes a power source and a coil connected to the power source to generate a time-varying magnetic field. Energy is applied to the coil so that the coil generates a time-varying magnetic field gradient with a magnitude of at least 1 milliTesla per meter and a rise-time of less than 10 microseconds. One or more of a capacitor, a multi-stage high-voltage switch, and / or a pulse-forming network may assist with the generation of the magnetic field gradient.

Owner:WEINBERG MEDICAL PHYSICS

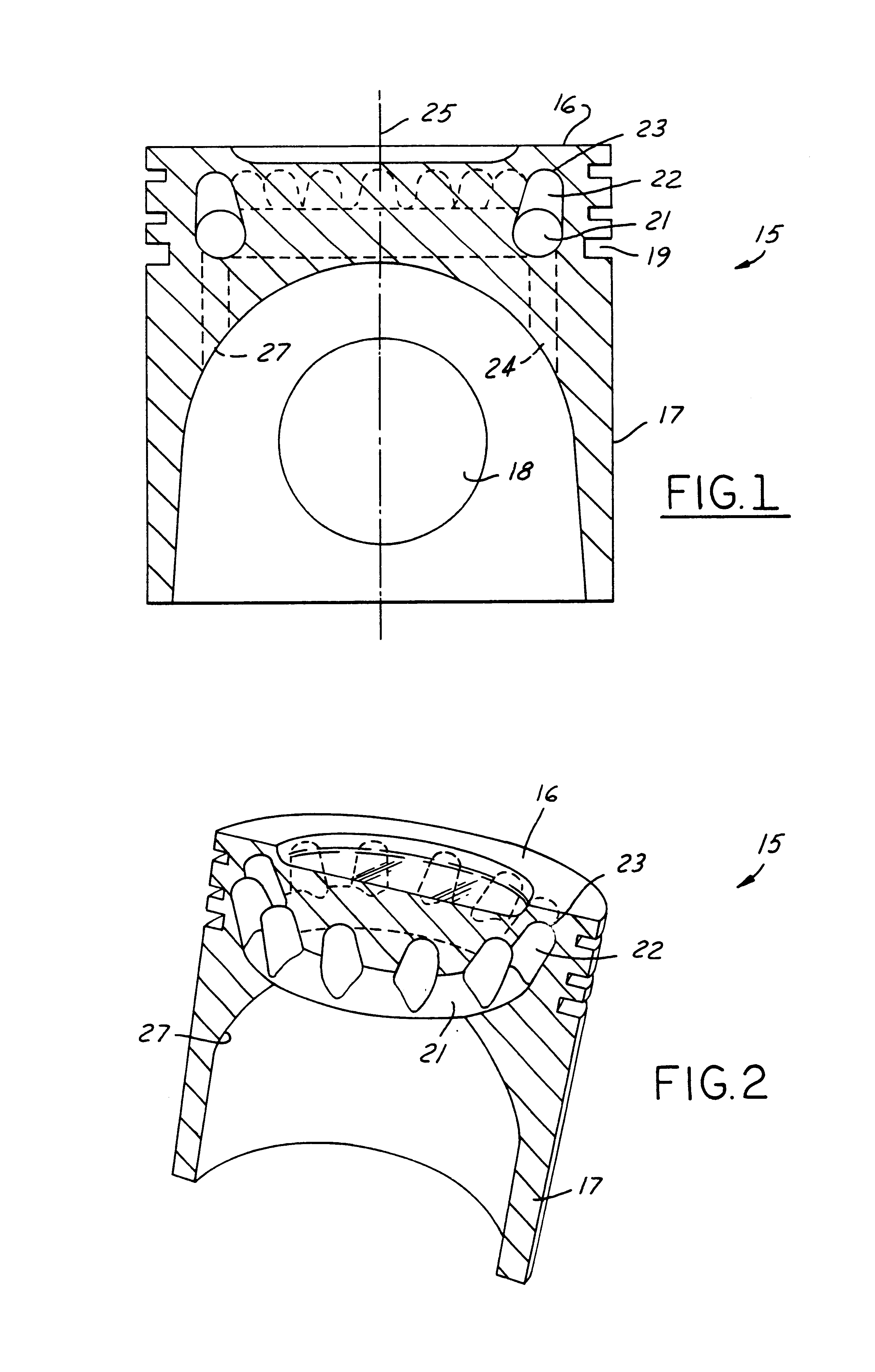

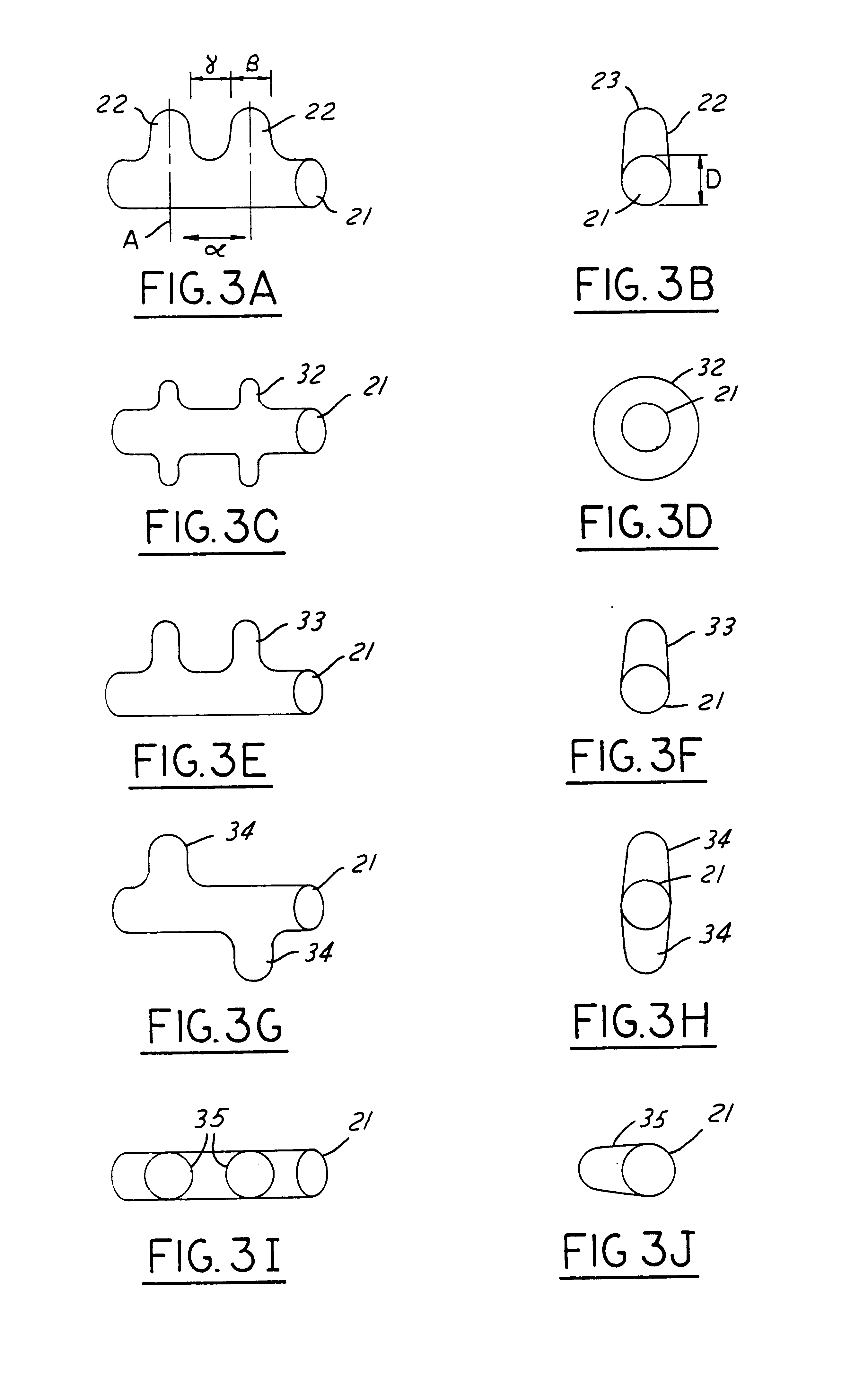

Piston coolant gallery

InactiveUS7281466B1Low sectionAvoid many problemsFoundry mouldsMachines/enginesWorking fluidHeat flow

A cast piston, for an internal combustion engine or pump has an integral coolant ring gallery, with localized extensions, to achieve a coolant interchange with the gallery upon piston reciprocation. At least a portion of an extension lies generally parallel to the longitudinal piston axis and towards an upper end of the piston adjacent the working fluid. This provides an attendant increase in surface area exposed to coolant allowing either a decrease in operational piston temperature or an increase in allowable heat flow into the piston from a working fluid.

Owner:SENECA TECH

Hand tool for dentistry and dental prosthetics

InactiveUS20060131906A1Quick changeQuick releaseTooth pincettesMetal-working hand toolsEngineeringDental treatments

A hand tool for dentistry and / or dental prosthetics, having a grip part which defines a main axis and, in the direction of the main axis, comprises a front end area and a rear end area. The grip part has, in the front end area, an open receiving recess in which the collet element is arranged with an adjustable receiving diameter for receiving an object. The receiving diameter of the collet element can be modified by way of an actuating device. The collet element can be secured against rotation in the grip part.

Owner:STRAUMANN HLDG AG

Effervescent compositions containing dried fruit juices

InactiveUS6838092B2Less violentFew contactsDispersion deliveryUnknown materialsFruit juiceFreeze-drying

The present invention relates to effervescent compositions containing active ingredients, in particular dry plant extracts, wherein the acid donor of the effervescent couple is constituted by a dried fruit juice with a natural acid pH, such as freeze-dried citrus fruit juice.

Owner:ABOCA

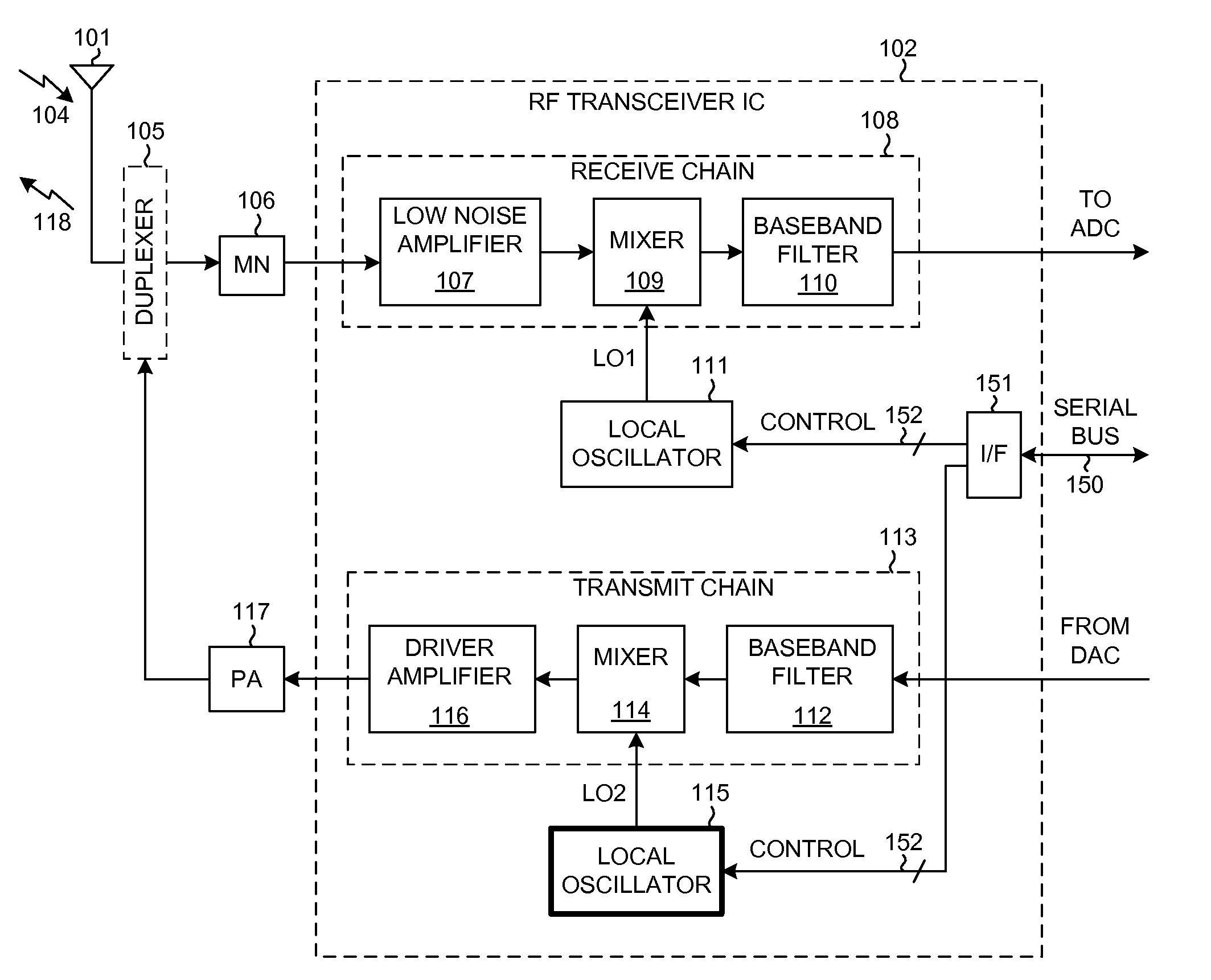

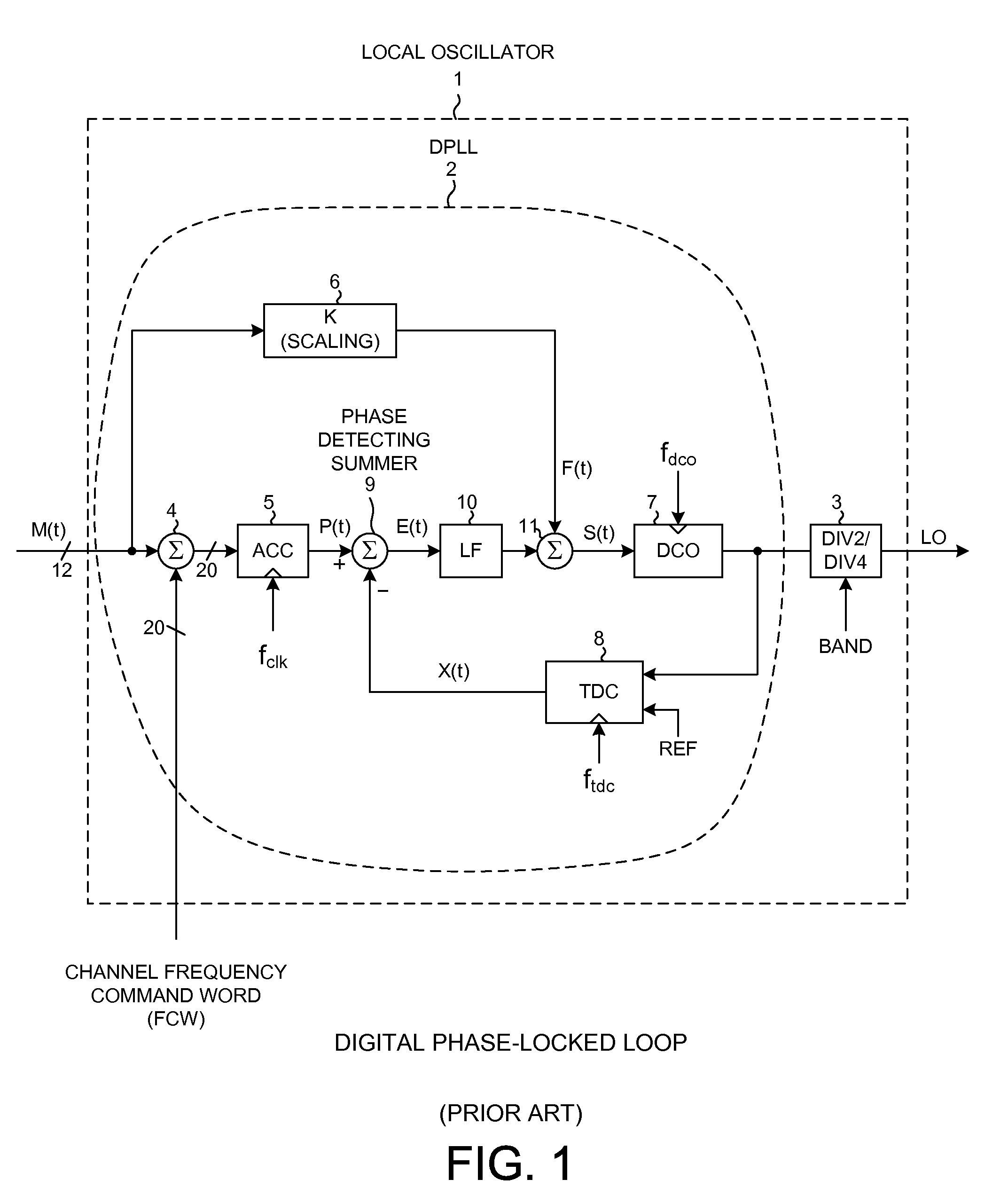

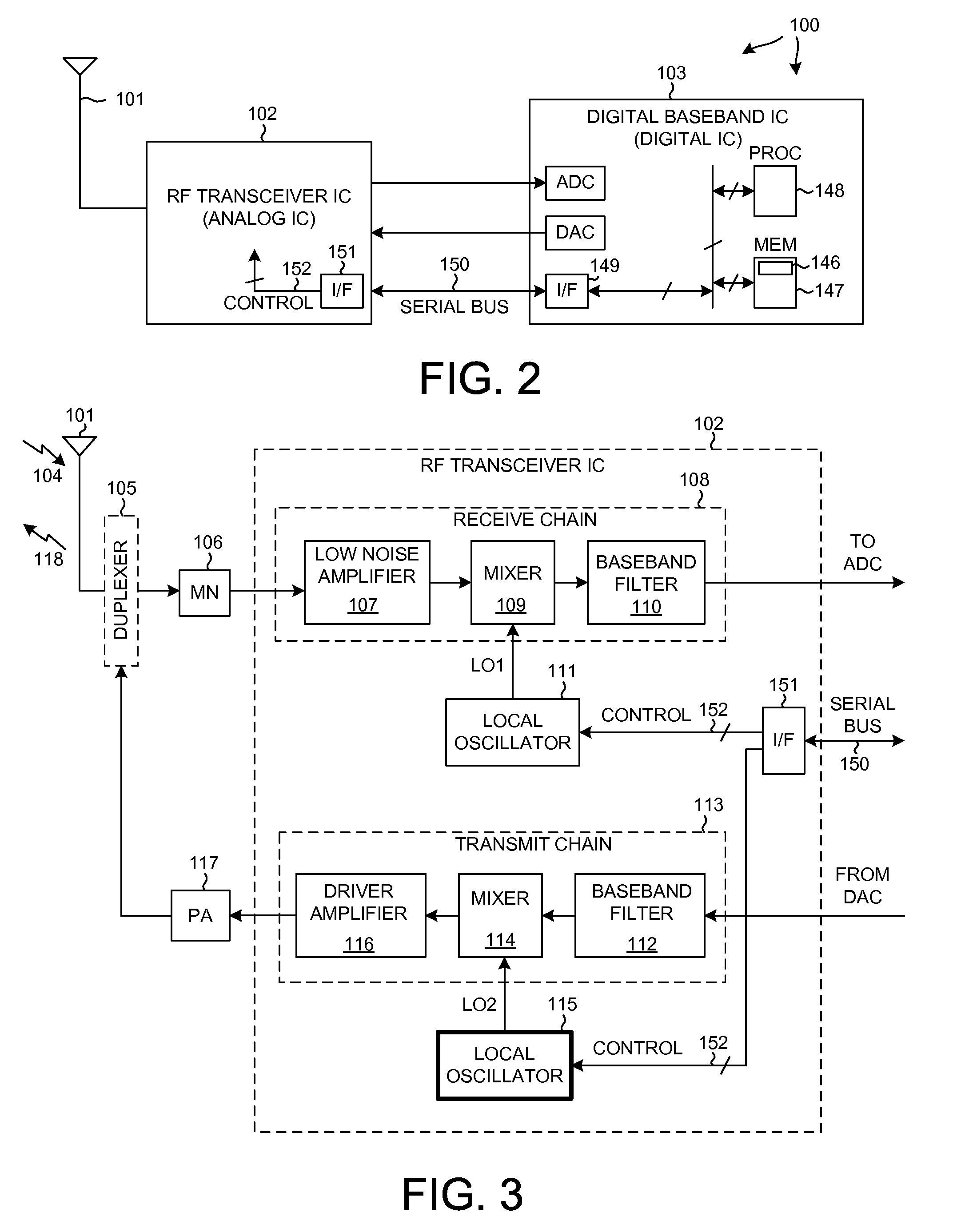

Multi-rate digital phase locked loop

InactiveUS20100310031A1Reduce power consumptionReduce digital imagePulse transformerPulse automatic controlDigital tuningHigh rate

A Digital Phase-Locked Loop (DPLL) involves a Time-to-Digital Converter (TDC) that receives a DCO output signal and a reference clock and outputs a first stream of digital values. Quantization noise is reduced by clocking the TDC at a high rate. Downsampling circuitry converts the first stream into a second stream. The second stream is supplied to a phase detecting summer of the DPLL such that a control portion of the DPLL can switch at a lower rate to reduce power consumption. The DPLL is therefore referred to as a multi-rate DPLL. A third stream of digital tuning words output by the control portion is upsampled before being supplied to the DCO so that the DCO can be clocked at the higher rate, thereby reducing digital images. In a receiver application, no upsampling is performed and the DCO is clocked at the lower rate, thereby further reducing power consumption.

Owner:QUALCOMM INC

Reusable electrophotographic recording medium and method for producing the same, image forming method, and method for repeatedly using electrophotographic recording medium

InactiveUS20060062997A1Reduce environmental loadEfficient reuseDuplicating/marking methodsSynthetic resin layered productsEngineeringMaleic anhydride

Disclosed is an electrophotographic recording medium that contains a support and an olefin-maleic anhydride copolymer, wherein the olefin-maleic anhydride copolymer exists at least near the surface of the electrophotographic recording medium on which an image is recorded, and the electrophotographic recording medium is reusable; and a method for producing an electrophotographic recording medium, an image forming method, a method for repeatedly using an electrophotographic recording medium, and a method for repeatedly using an electrophotographic recording medium.

Owner:RICOH KK

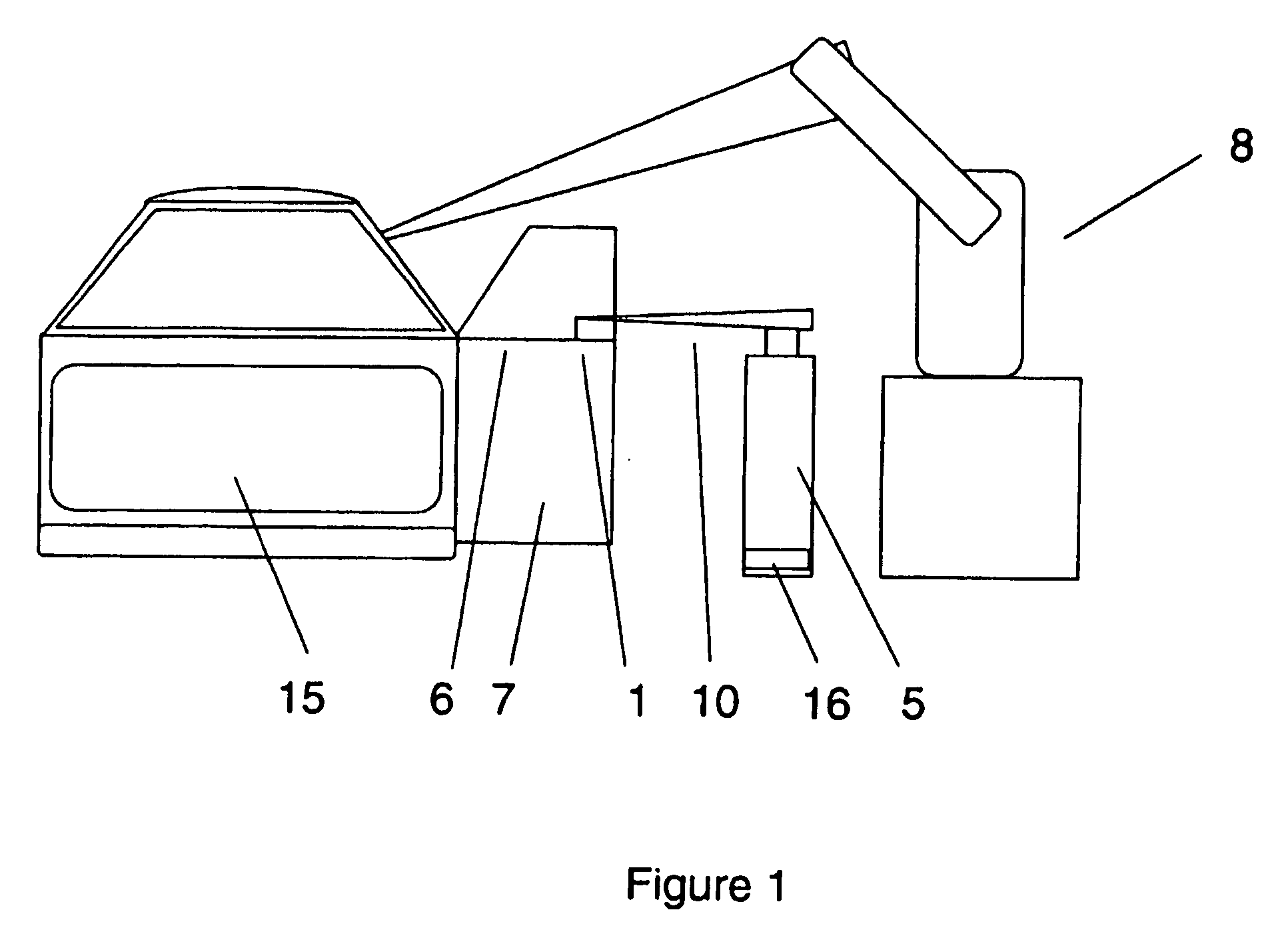

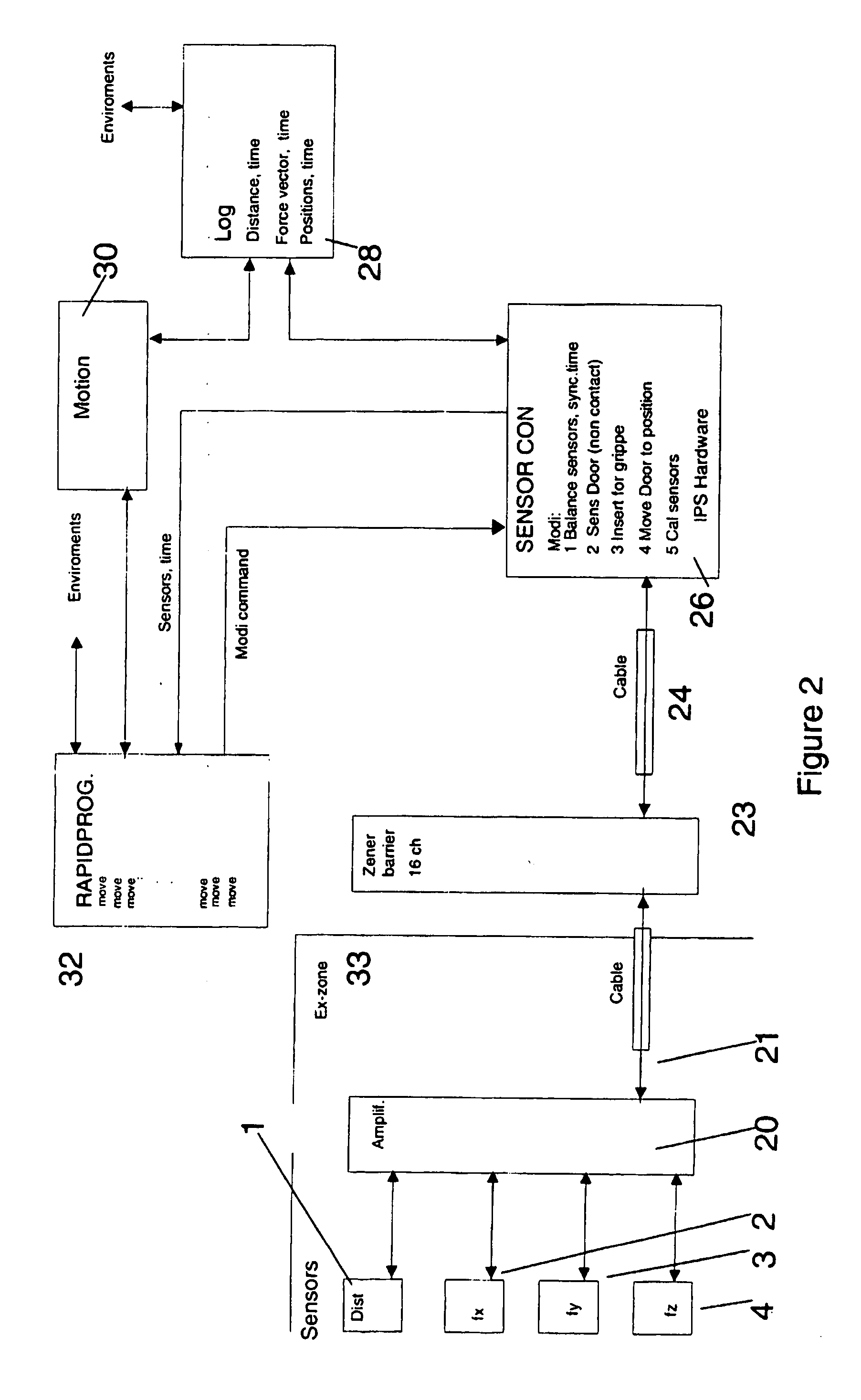

Door Opener Arrangement for Use with an Industrial Robot

InactiveUS20090204260A1Simple but accurateNon-destructive grippingProgramme controlComputer controlEngineeringElectromagnetic field

A door opener arrangement for a robot coating device, used for detecting a position of a part (6) of a door (7) so that the door can be opened and / or closed for interior painting. The door opener is arranged with at least one non-contact sensor member (1), preferably for detecting changes in a field strength of a magnetic or electromagnetic field in a Z and vertical direction, and may be arranged with a plurality of sensors to detect a collision etc. A method, system and computer program are also described.

Owner:ABB AS

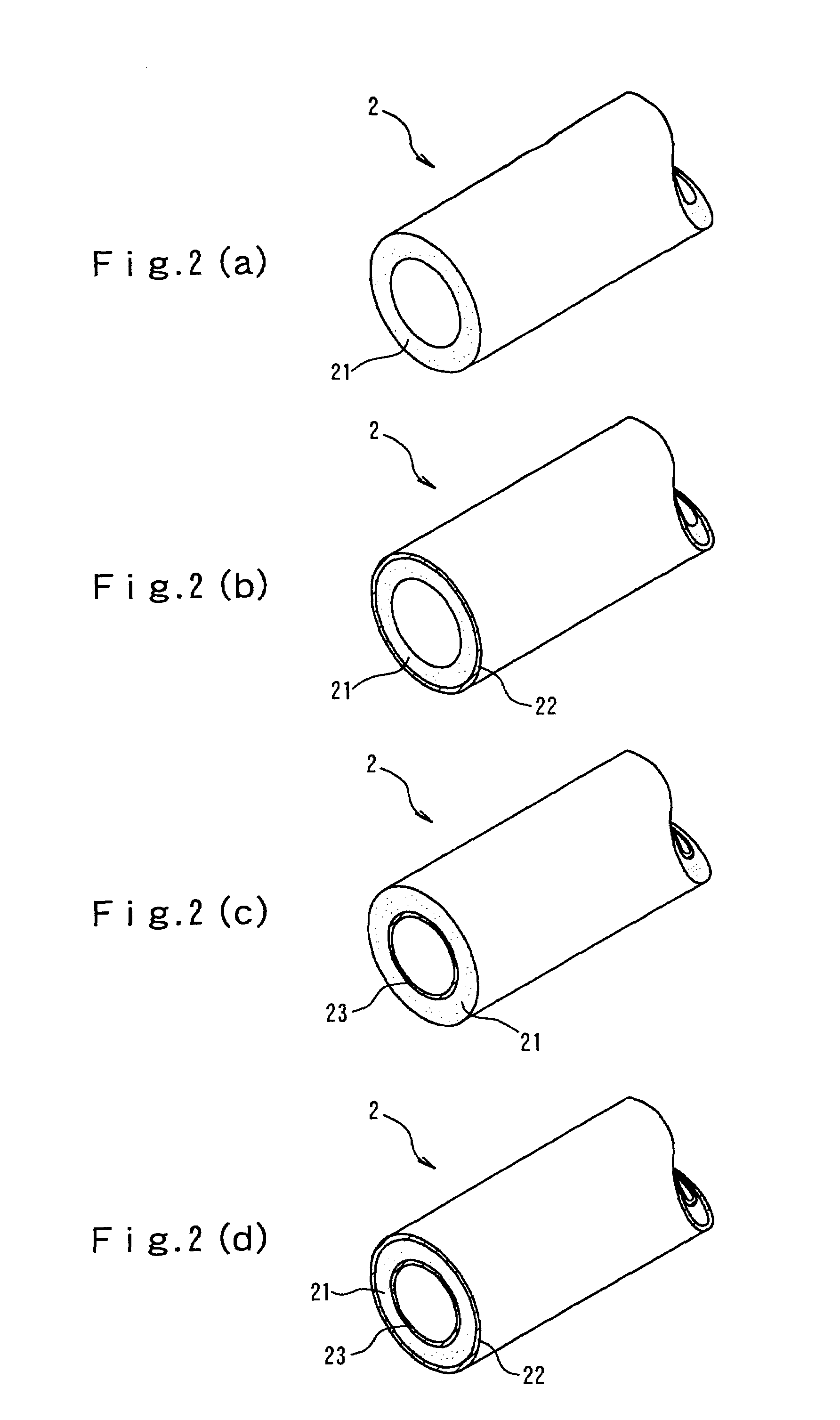

Polypropylene resin hollow molded foam article and a process for the production thereof

ActiveUS7014801B2Low production costHigh expansion rateDomestic articlesFlat articlesApparent densityPolymer science

The present invention relates to a hollow molded foam article in which a plurality of polypropylene resins are used as the base resin, and to a process for the production of this hollow molded foam article. More particularly, the present invention relates to a polypropylene resin hollow molded foam article having a foam layer, in which the base resin comprises (a) a polypropylene resin with a melt tension of at least 98 mN and a melt flow rate of 0.5 to 15 g / 10 minutes, (b) a polypropylene resin with a melt tension of less than 30 mN (excluding O) and a melt flow rate of 2 to 30 g / 10 minutes, and (c) a polypropylene resin with a melt tension of at least 30 mN and less than 98 mN and a melt flow rate of 2 to 15 g / 10 minutes, formed by positioning in a mold a softened cylindrical foam having a foam layer obtained by extruding from the die of an extruder a foamable molten resin composition containing a foaming agent, wherein the melt tension at 230° C. of the polypropylene resin that forms the foam layer is at least 10 mN and less than 49 mN, and the apparent density of the foam layer is no more than 0.3 g / cm3.

Owner:JSP CORP

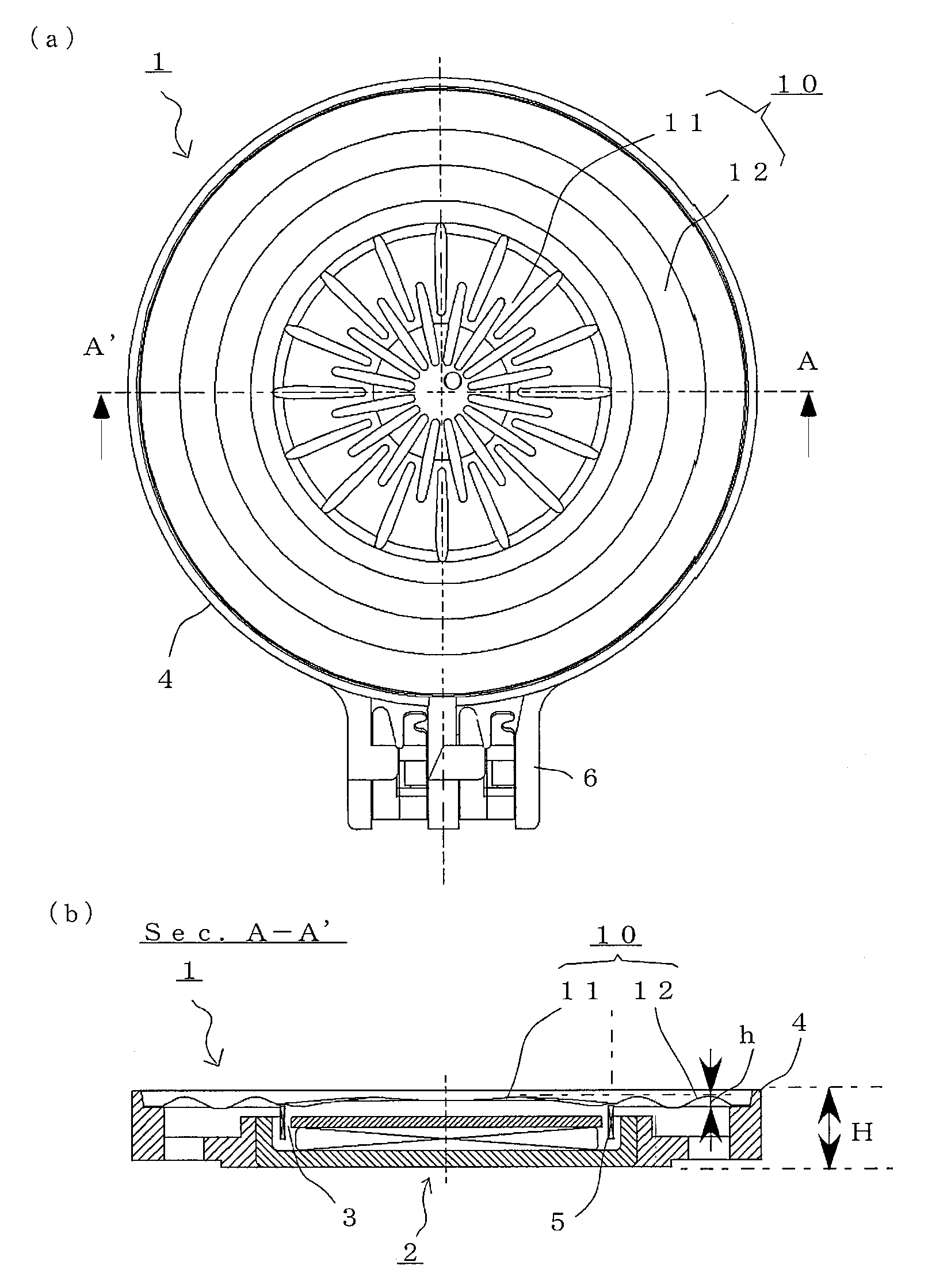

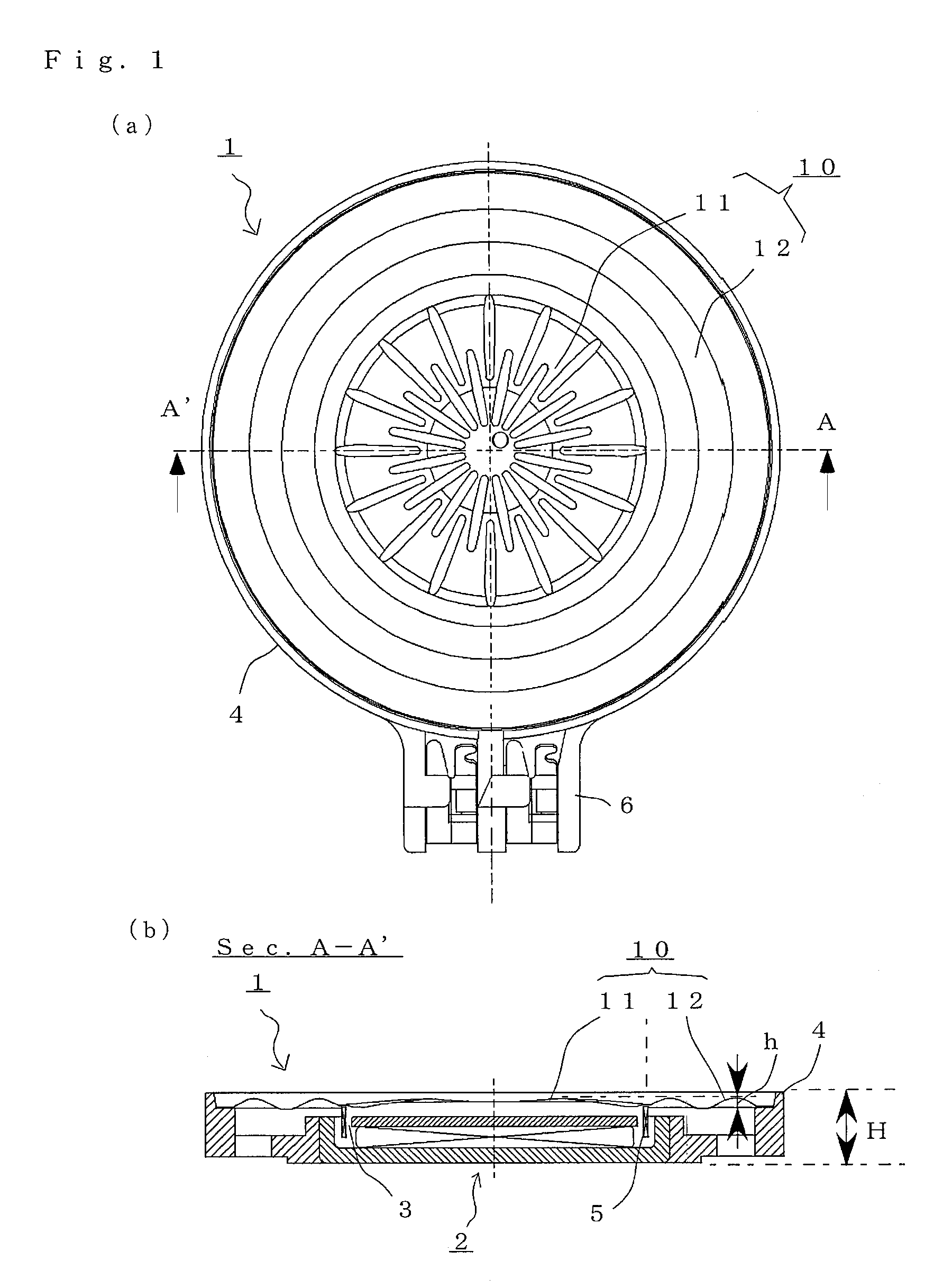

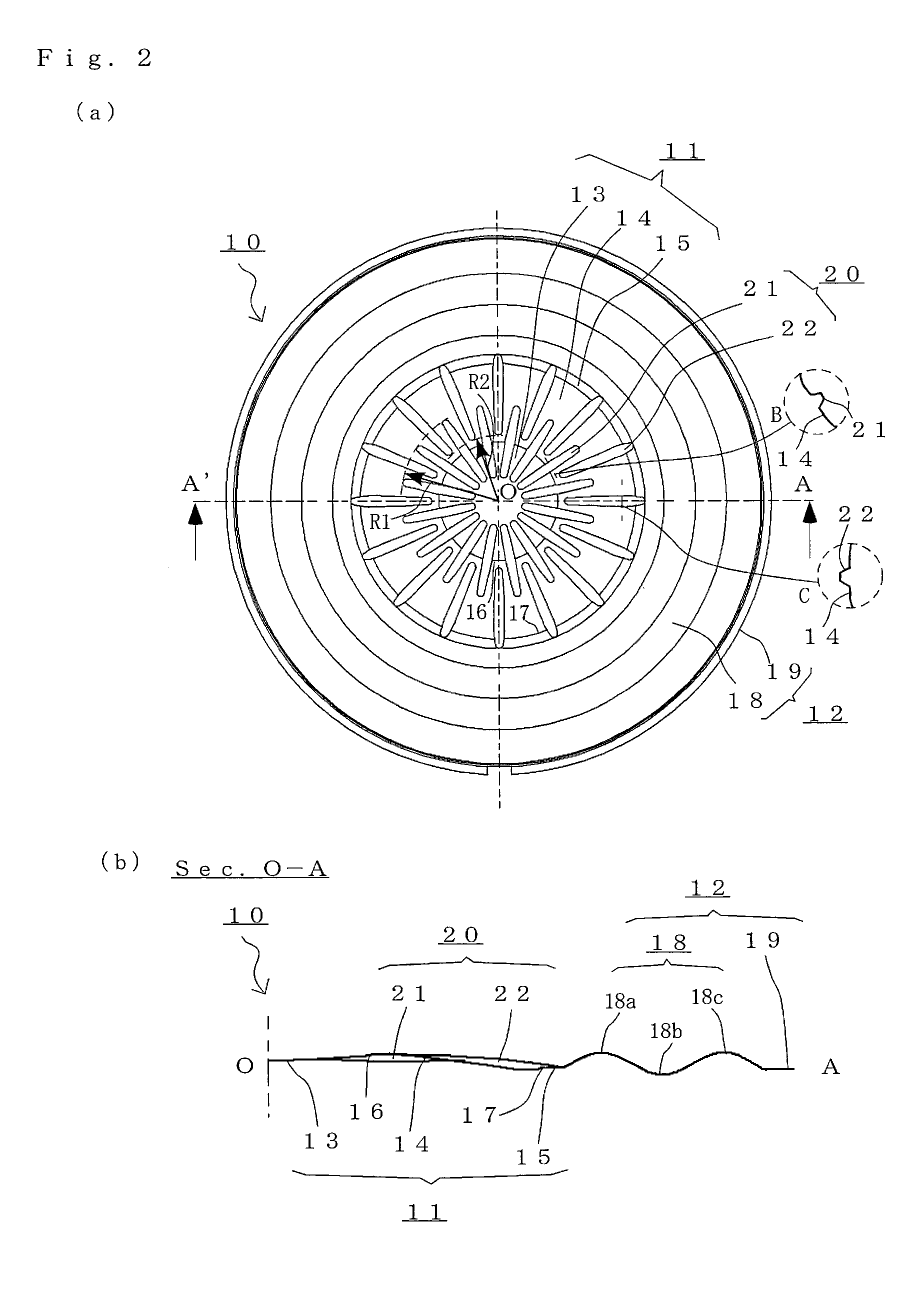

Loudspeaker diaphragm and loudspeaker using the same

InactiveUS20090060251A1Rigid enoughInhibition heightTransducer detailsSound producing devicesEngineeringDepressed rib

A loudspeaker diaphragm having a small overall height dimension, in which a dome portion has a sufficient rigidity and which is capable of realizing a stable loudspeaker operation, wherein the loudspeaker diaphragm can realize a desirable sound reproduction without noise, or the like, with a frequency response that is flat over a wide range. In the loudspeaker diaphragm of the present invention, the dome portion includes a concave dome portion formed at a center thereof, a convex dome portion along an outer periphery of the concave dome portion, a plurality of depressed ribs each extending in a radial direction across a boundary between the concave dome portion and the convex dome portion, a voice coil attachment portion along an outer periphery of the convex dome portion, and a plurality of protruding ribs extending in the radial direction across a boundary between the convex dome portion and the voice coil attachment portion, wherein each protruding rib is spaced apart in a circumferential direction from two adjacent depressed ribs.

Owner:ONKYO KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com