Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

825results about How to "Avoid disorder" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

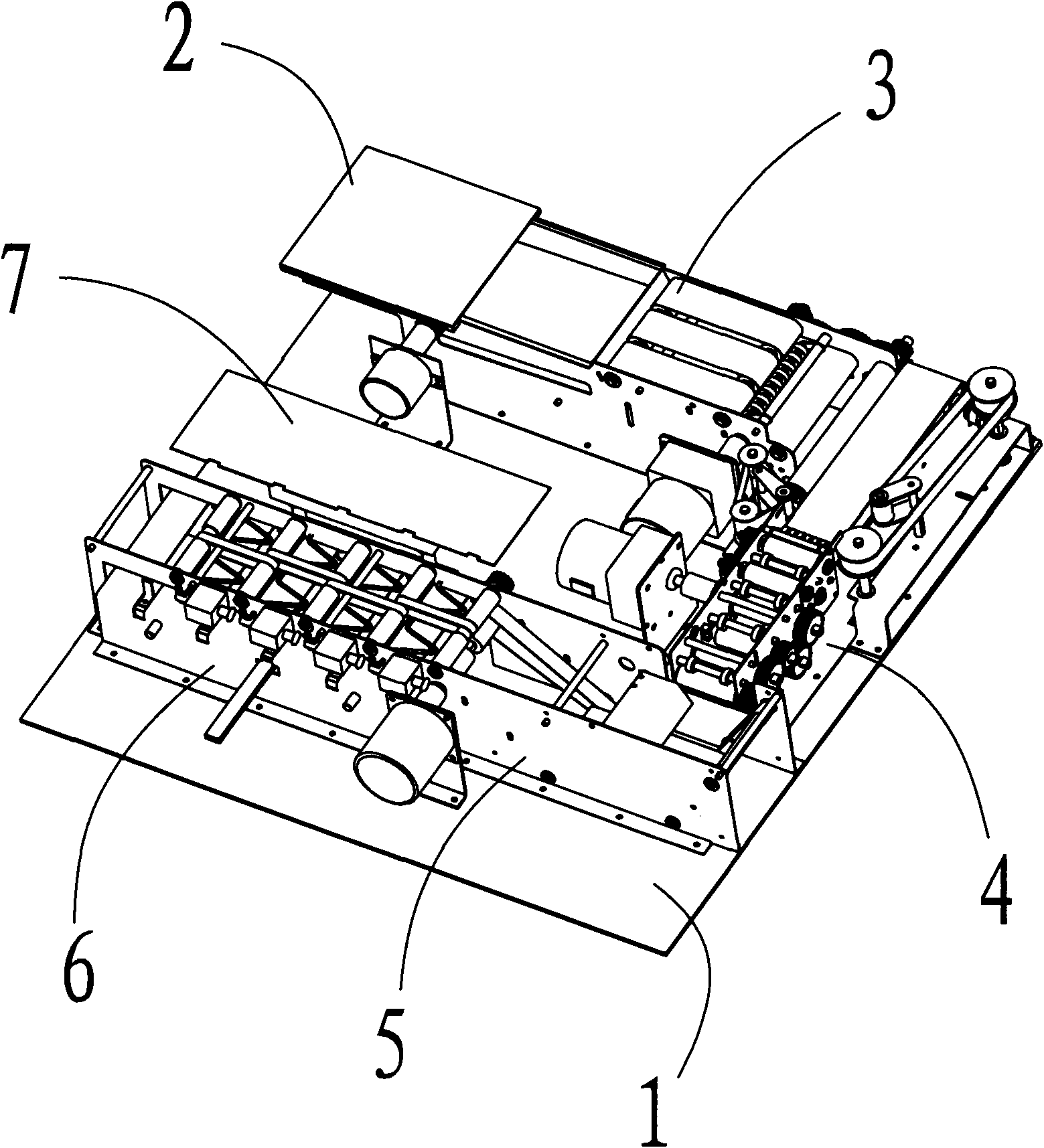

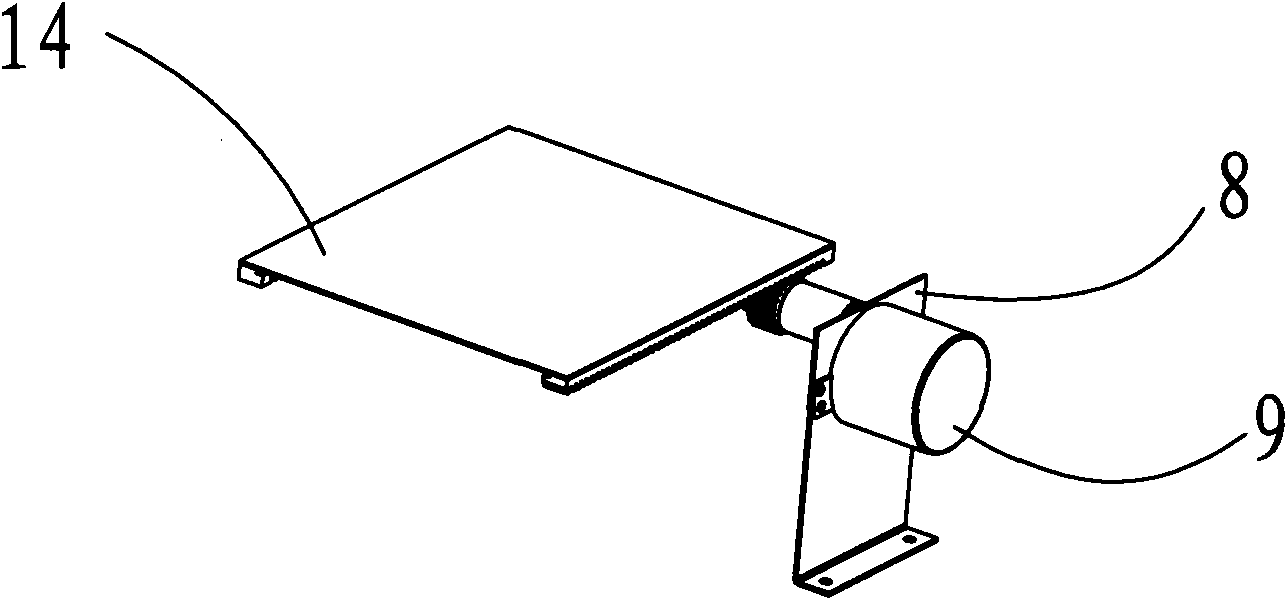

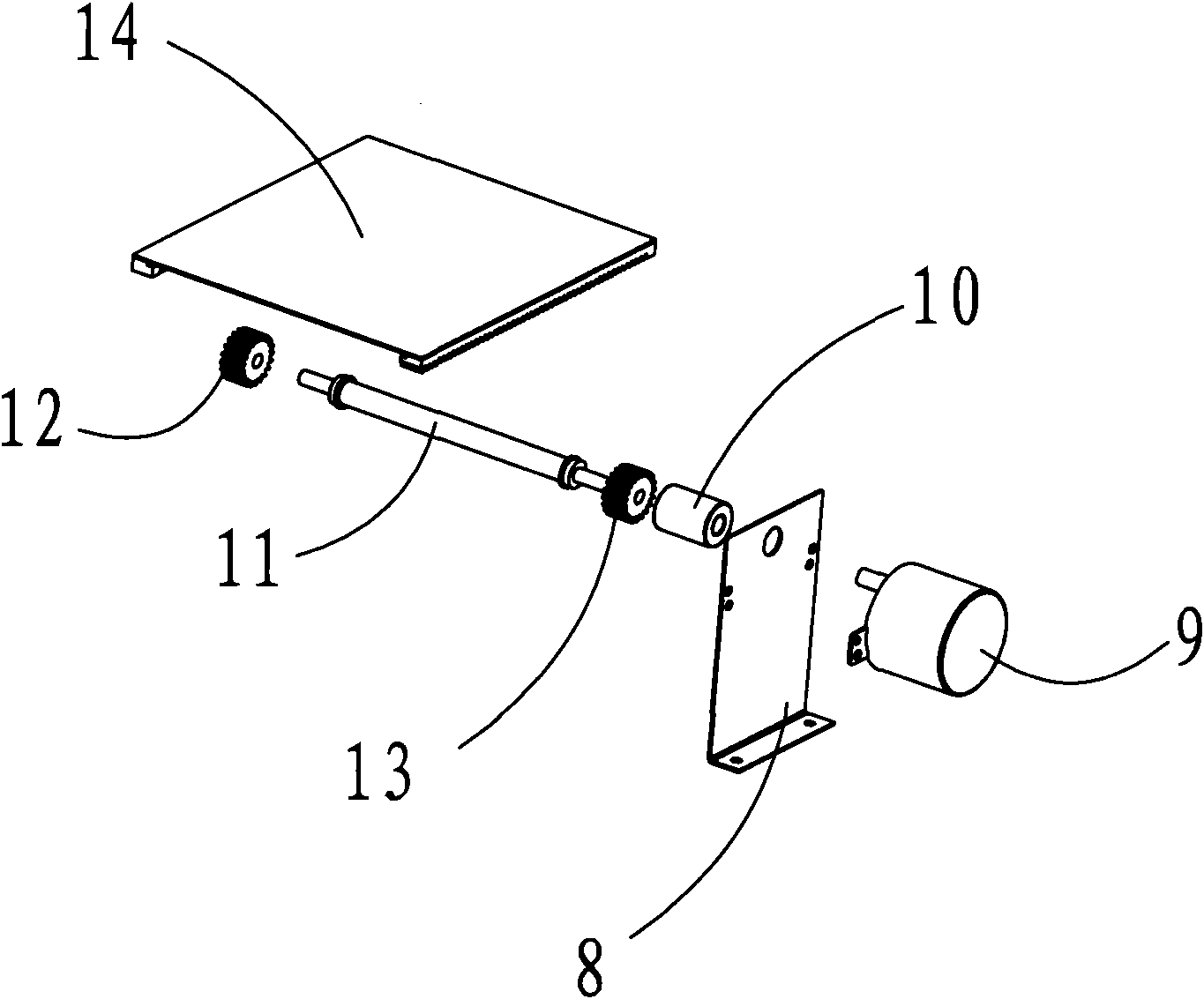

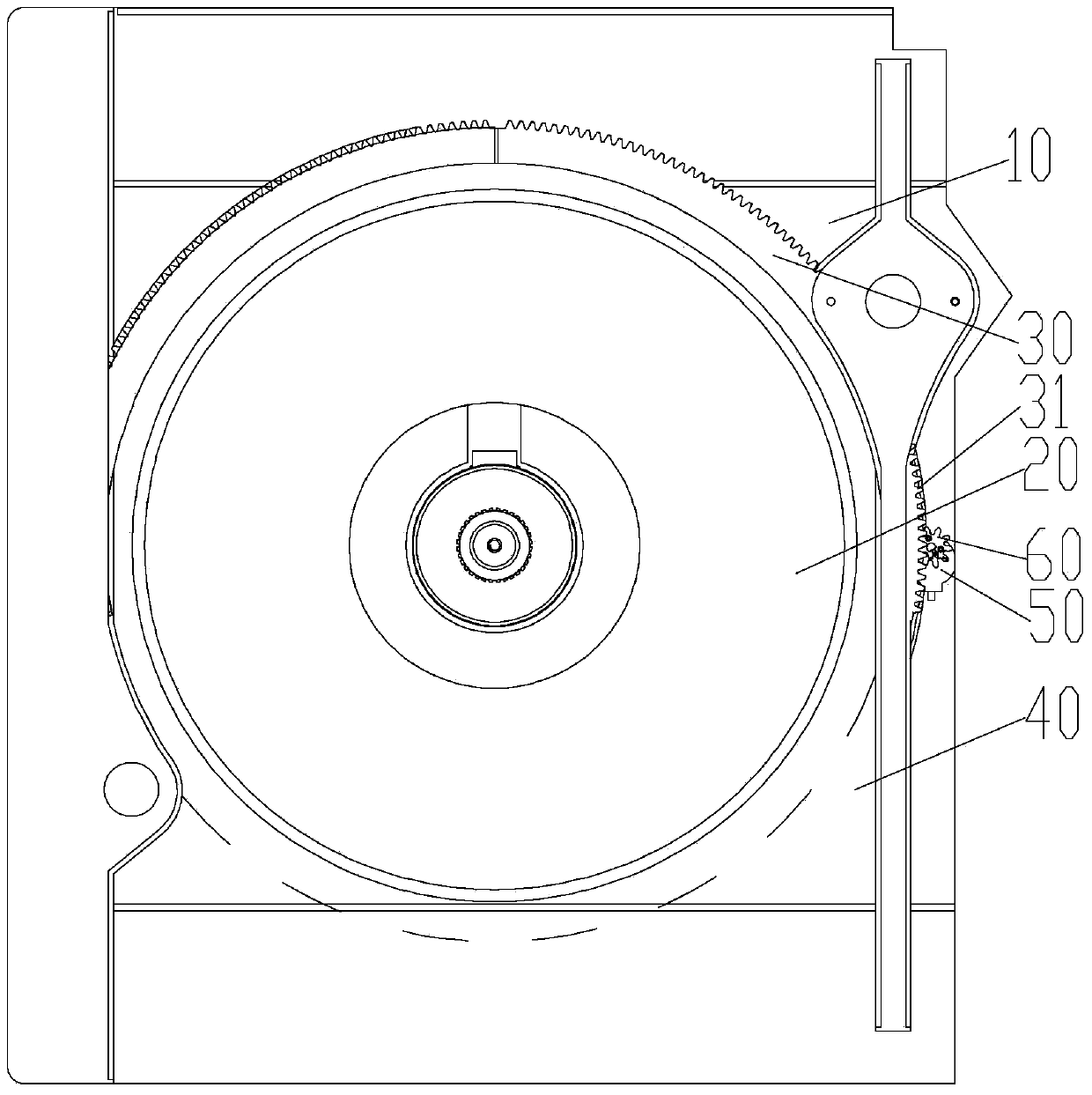

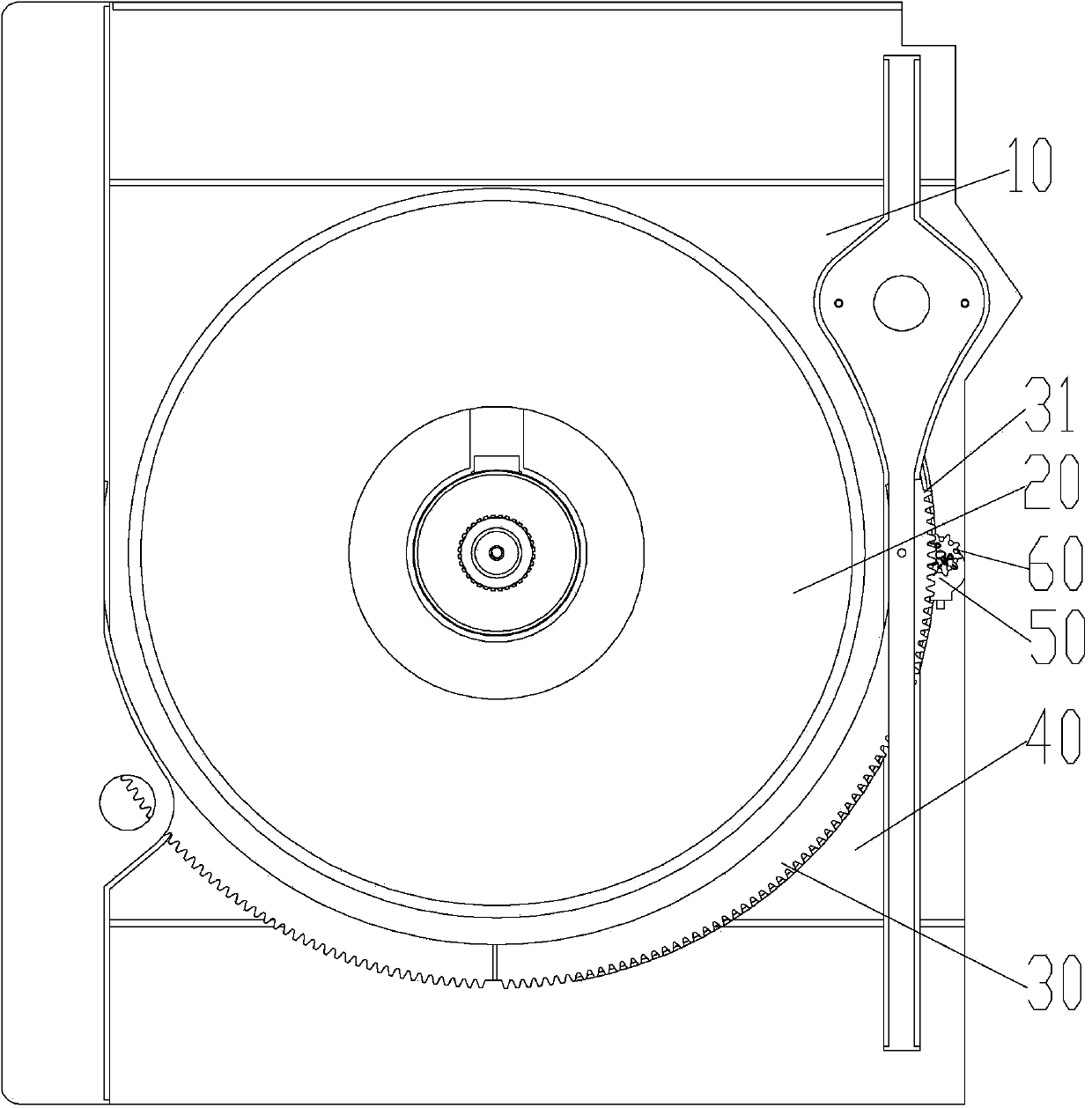

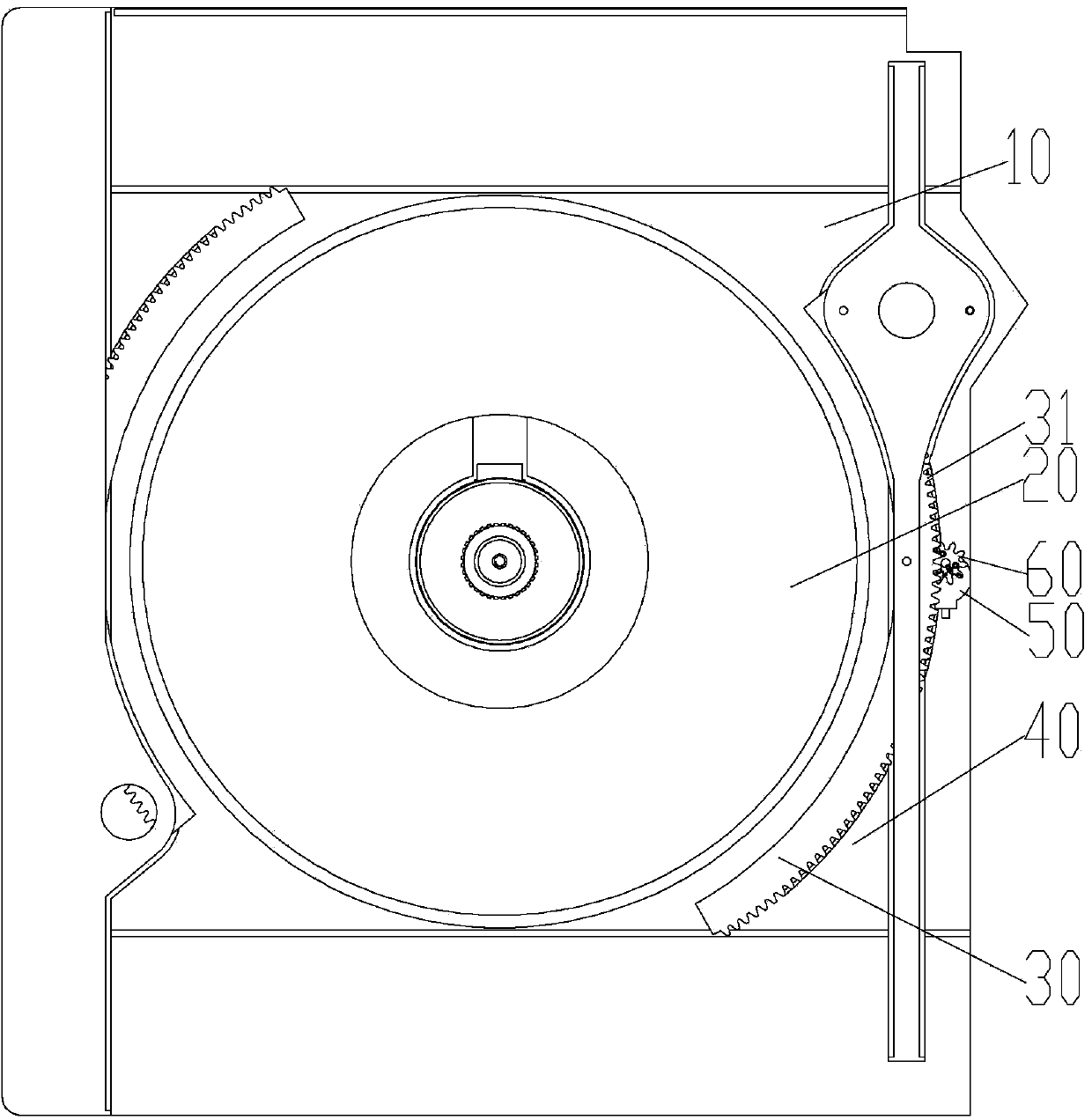

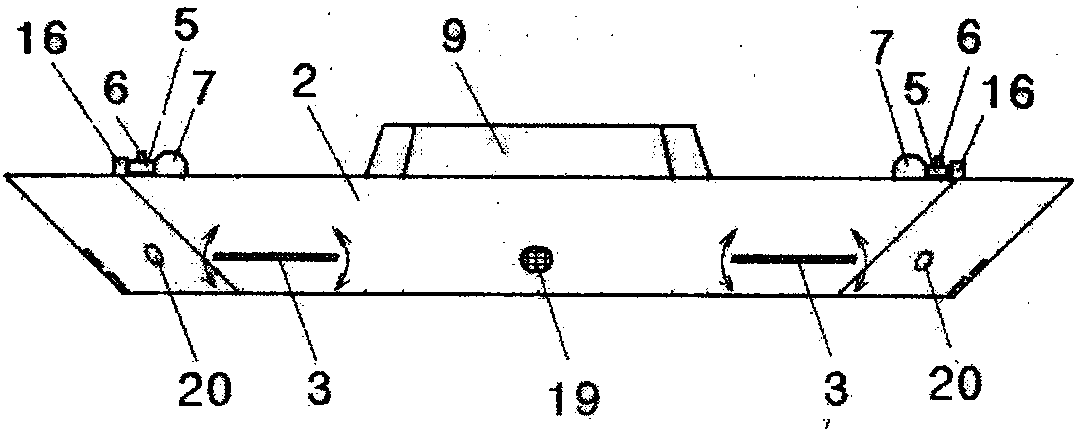

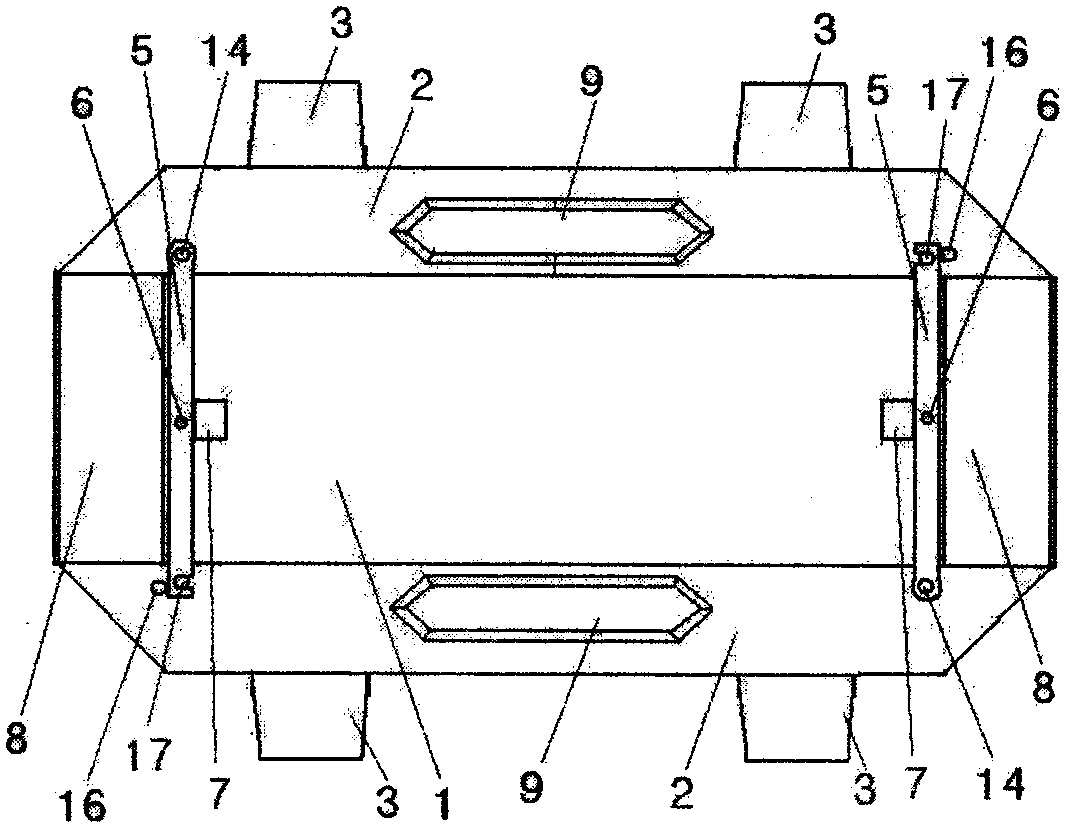

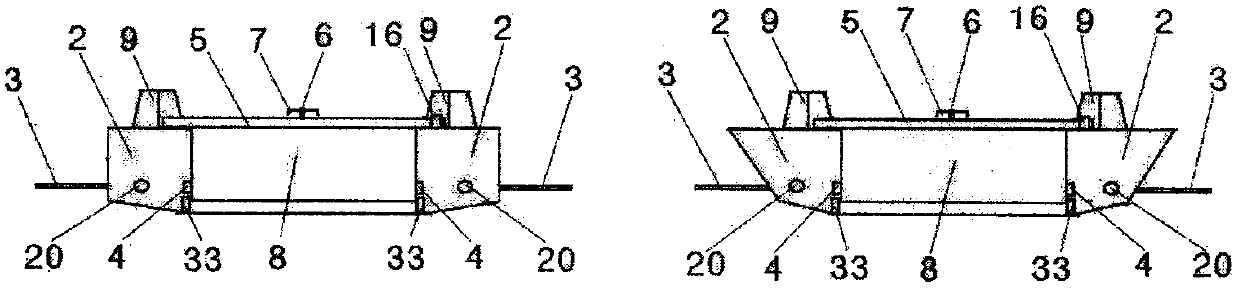

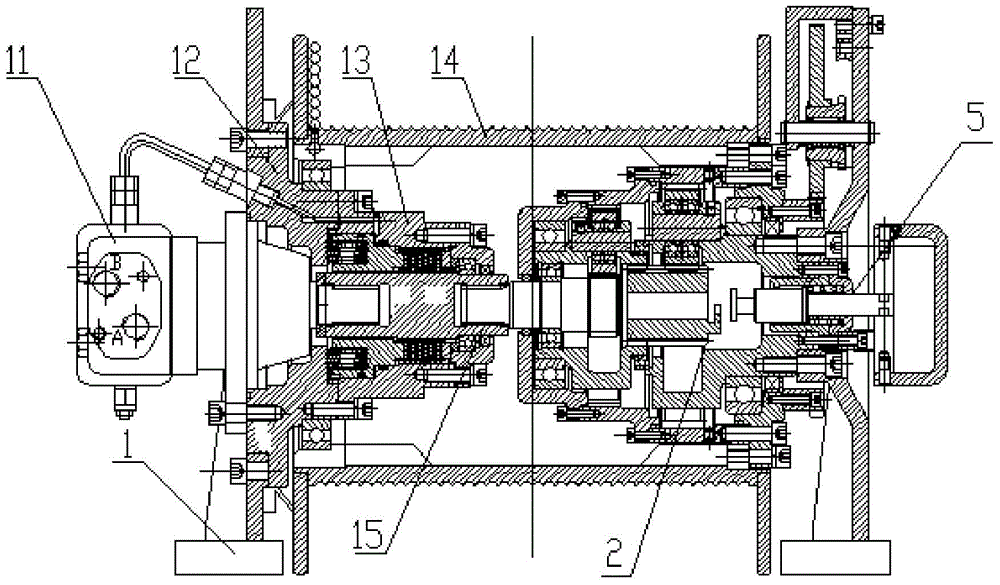

Full-automatic poker machine

InactiveCN102580307AAvoid misidentificationHigh degree of full automationCard gamesEngineeringWaiting time

The invention relates to a full-automatic poker machine, which comprises a mounting bottom plate and a plurality of support legs. A card inlet is disposed on the mounting bottom plate, card cutting and primary card distributing equipment is arranged at one end of the card inlet, card sorting and secondary card distributing equipment is arranged at the other end of the card cutting and primary card distributing equipment, card flopping and dealing equipment is disposed at the other end of the card sorting and secondary card distributing equipment, card pushing equipment is arranged at the other end of the card flopping and dealing equipment, and card lifting equipment is disposed on one side of the card pushing equipment. When the full-automatic poker machine works, disorder poker cards are primarily separated by the aid of the card cutting and primary card distributing equipment, then are adjusted to face the same direction and separated from each other by the card sorting and secondary card distributing equipment, then by the aid of the card flopping and dealing equipment, the single poker cards with front surfaces facing upwards and downwards are adjusted so that the front surfaces of the single poker cards face upwards or downwards in a unified manner and the single poker cards are dealt, the poker cards are pushed to specified positions by the card pushing equipment, and finally are lifted to a tabletop by the card lifting equipment, and card cutting and dealing actions are completed. The full-automatic poker machine brings convenience for reducing labor intensity of game, waiting time is shortened, and simultaneously, automation degree of the machine is improved.

Owner:陈雄兵

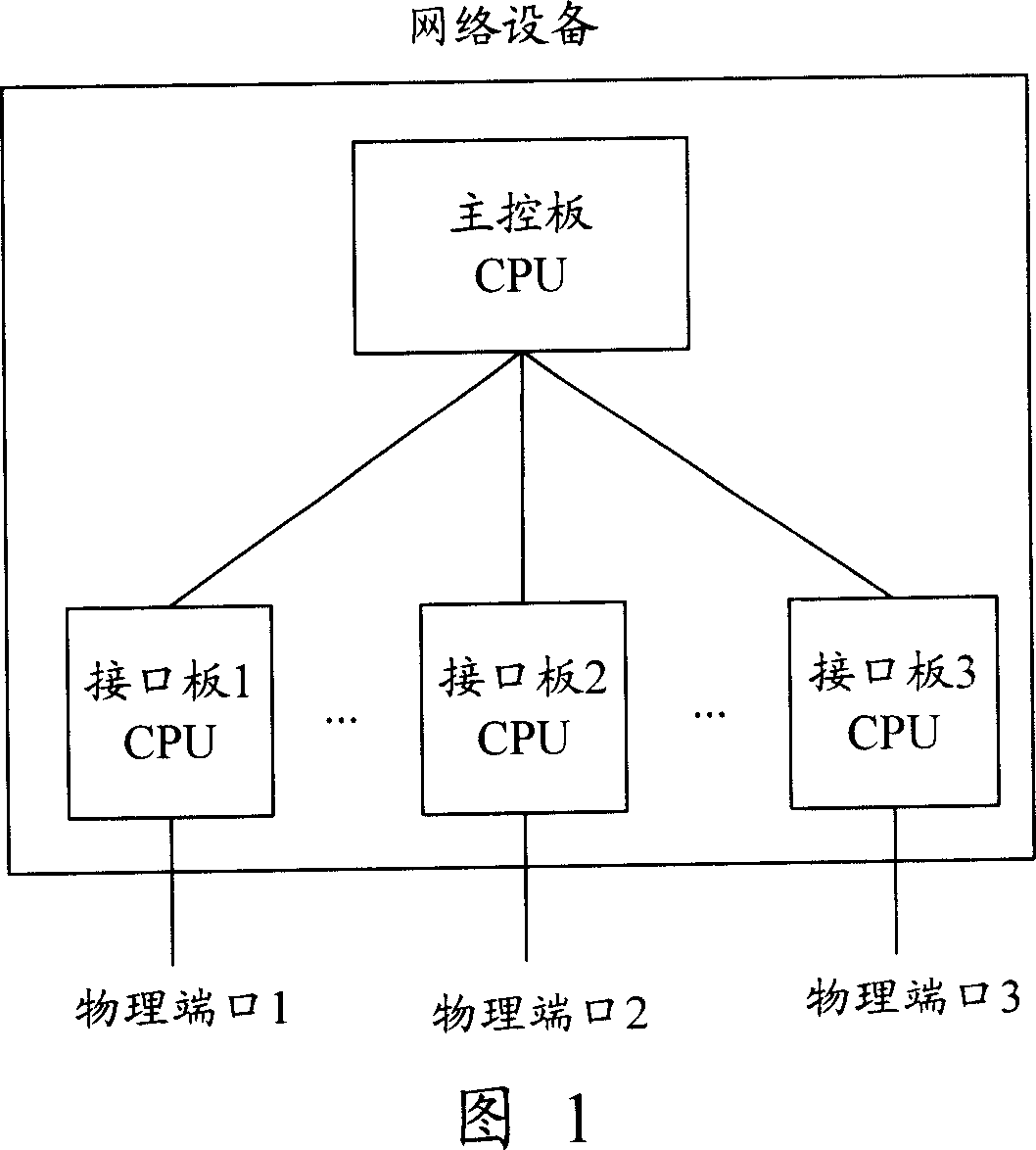

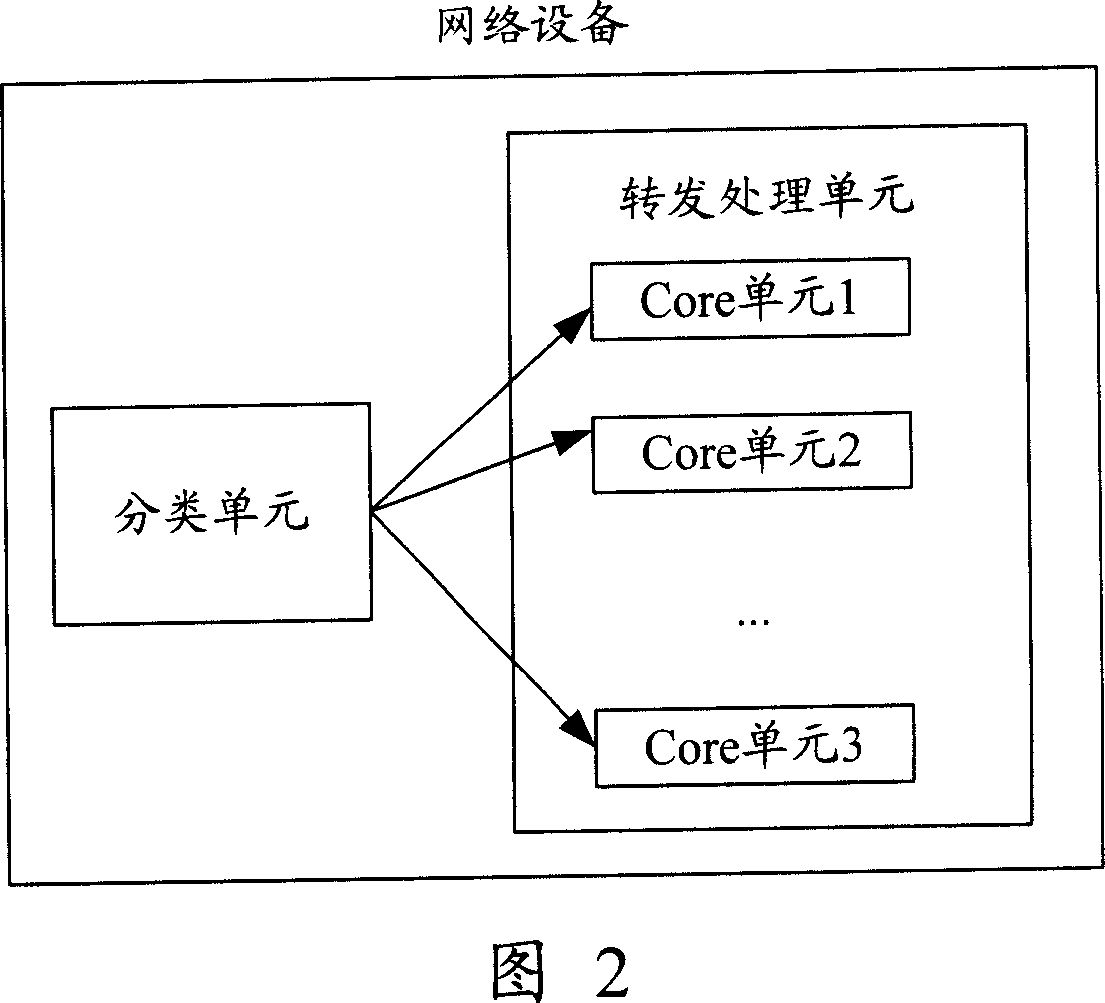

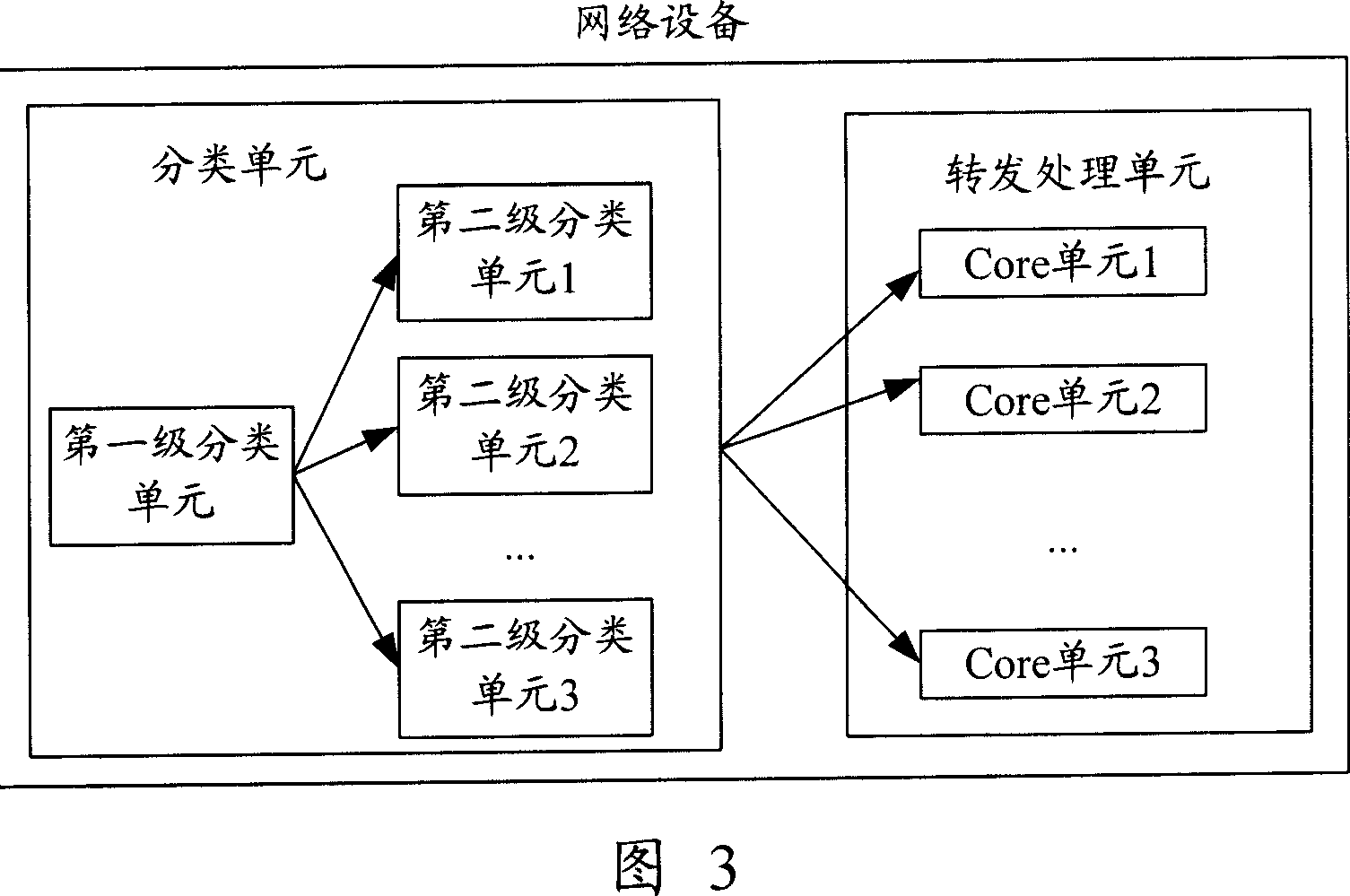

Network equipment and message transferring method based on multiple-core processor

ActiveCN1921457AForwarding Processing GuaranteesImprove packet forwarding and processing capabilitiesPulse modulation television signal transmissionError preventionMulti-core processorTransfer Ability

The invention relates to a network device, and a report transfer method based on multi-core processor. Wherein, said network device comprises: classifying unit and transfer processor with multi-core unit; the classifying unit receives report at any port of network device, selects core unit from the transfer processor, and sends received report to selected core unit; one core unit of transfer processor transfers report when receives report. The invention can use classifying unit to select core unit to balance the load between core units, to make them parallel transfer reports, to improve the report transfer ability of network device.

Owner:NEW H3C TECH CO LTD

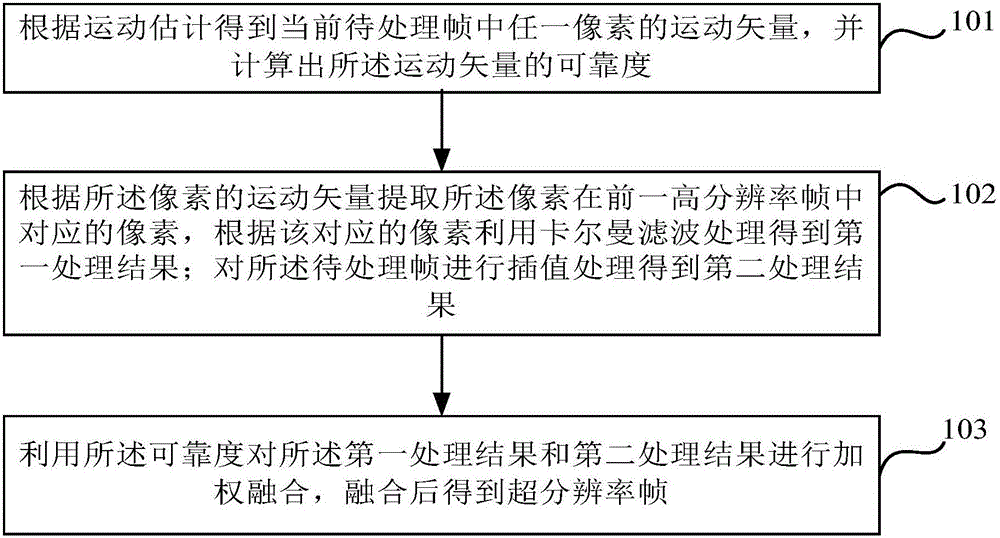

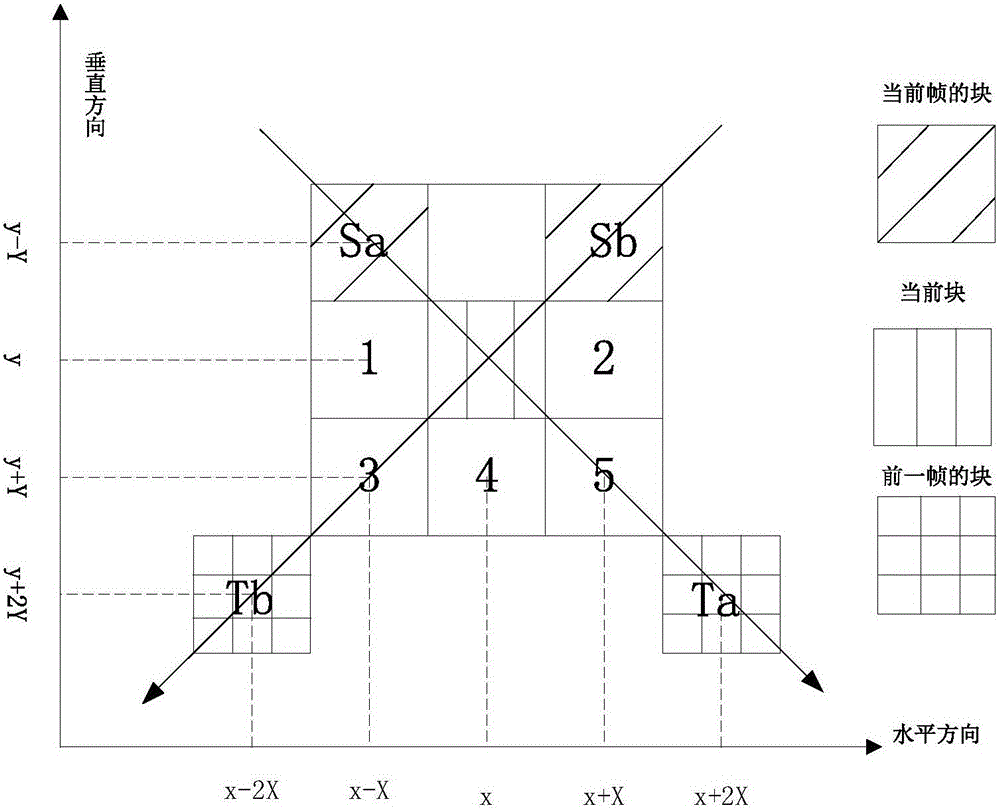

Video dynamic super-resolution processing method and system

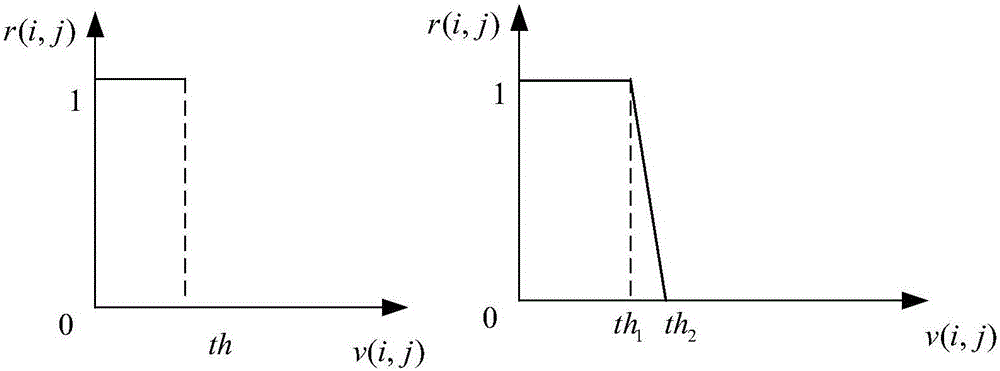

InactiveCN106851046AImprove protectionImprove edge aliasing and other issuesTelevision system detailsColor television detailsMotion vectorTime cost

The invention relates to a video dynamic super-resolution processing method and system. The processing method comprises the steps of obtaining a motion vector of any pixel in a current to-be-processed frame according to motion estimation and calculating reliability degree of the motion vector; extracting the corresponding pixel of the pixel in a former high-resolution frame according to the motion vector of the pixel and carrying out Kalman filtering processing according to the corresponding pixel, thereby obtaining a first processing result; carrying out interpolation processing on the to-be-processed frame to obtain a second processing result; and carrying out weight fusion on the first processing result and the second processing result through utilization of the reliability degree, thereby obtaining a super-resolution frame after fusion. According to the method and the system, the problems of protecting edge information well and improving image edge sawteeth are realized; more image details are restored effectively on the condition of not increasing excessive extra time cost; moreover, relatively high robustness is achieved; and disorder of a super-resolution result or motion blurring resulting from inaccurate motion estimation is avoided.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

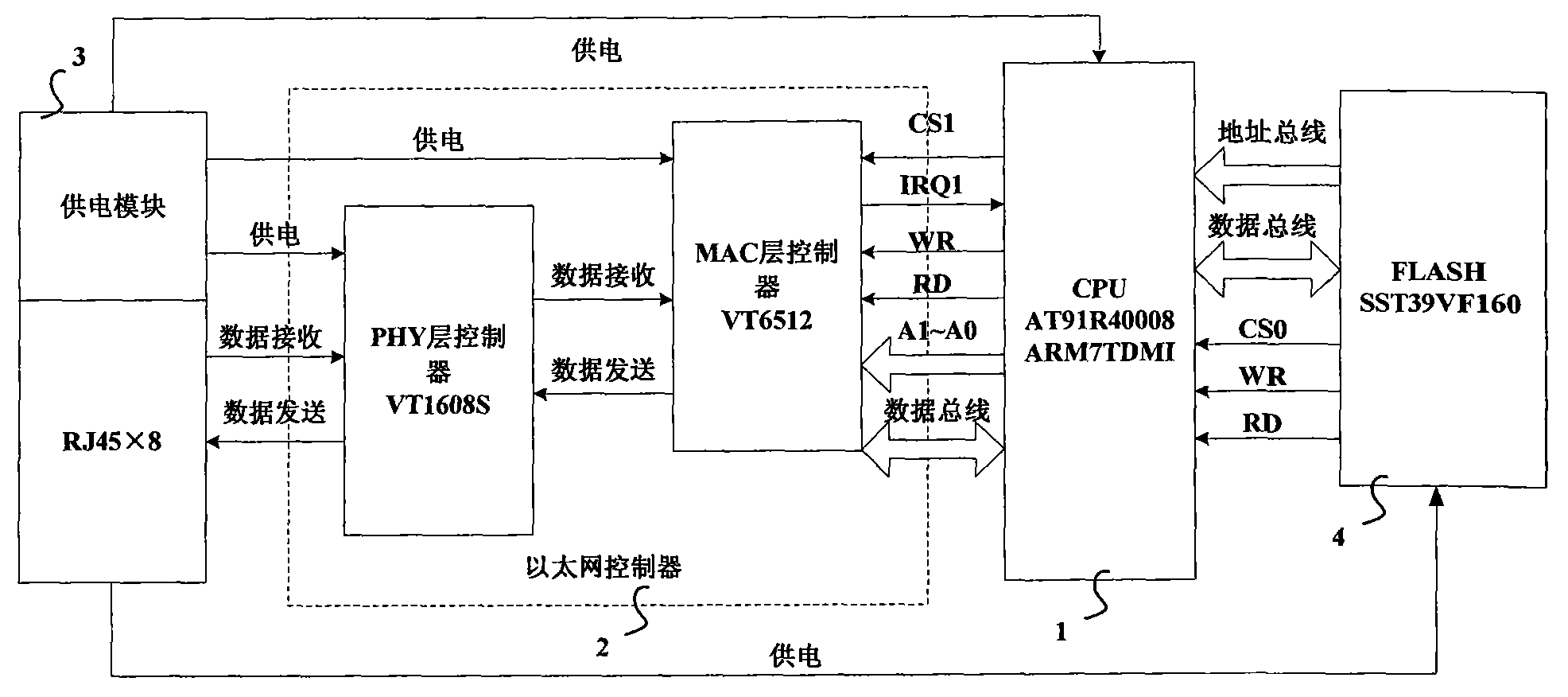

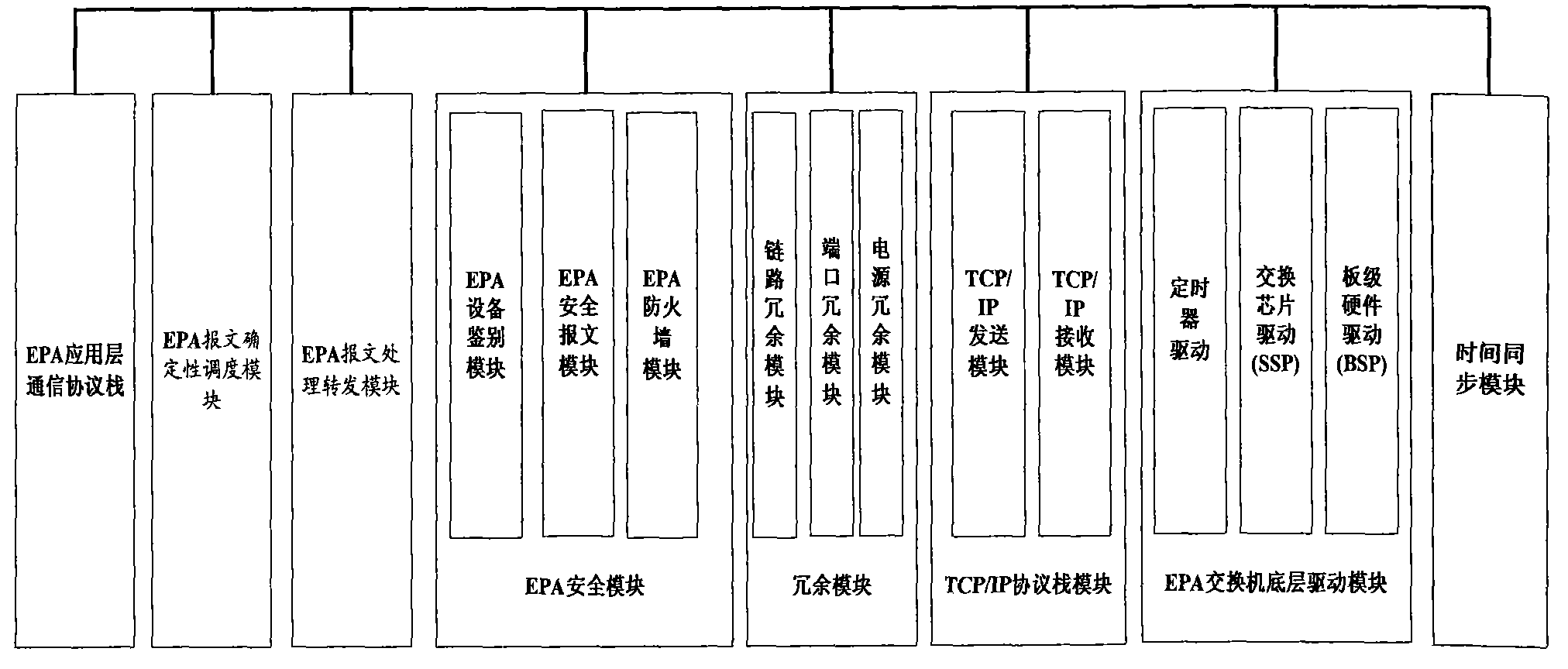

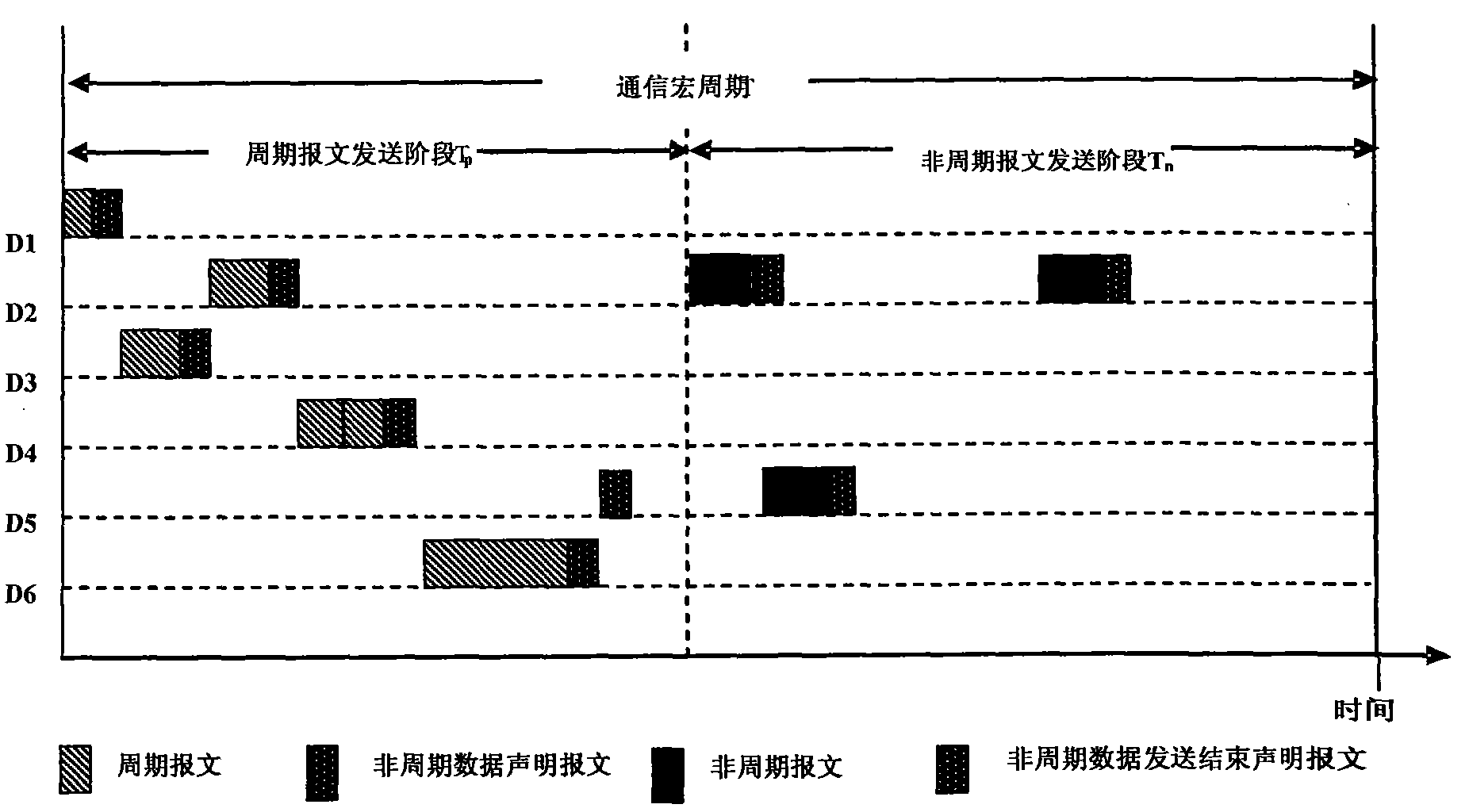

Industrial Ethernet exchanger and message forwarding method based on EPA protocol

ActiveCN101631080AEnsure safetyGuaranteed real-timeData switching networksSynchronising arrangementIndustrial EthernetMessage processing

The invention provides an industrial Ethernet exchanger based on an EPA protocol, comprising an EPA message processing and forwarding module and an EPA message deterministic scheduling module, wherein the EPA message processing and forwarding module directly forwards the EPA network data messages of communication between EPA site equipment in the same subfield; the EPA message deterministic scheduling module divides the EPA network data messages of the communication between the EPA site equipment in different subfields into periodic EPA network data messages and nonperiodic EPA network data messages; and in one macro period, the periodic EPA network data messages and the nonperiodic EPA network data messages are respectively scheduled and forwarded, wherein the periodic EPA network data messages are transmitted in a fixed time slice, and the nonperiodic EPA network data messages are sequentially transmitted according to the priority in a nonperiodic time section. The invention also provides a message forwarding method of an industrial Ethernet based on an EPA protocol.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

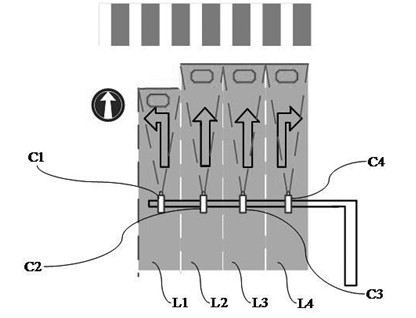

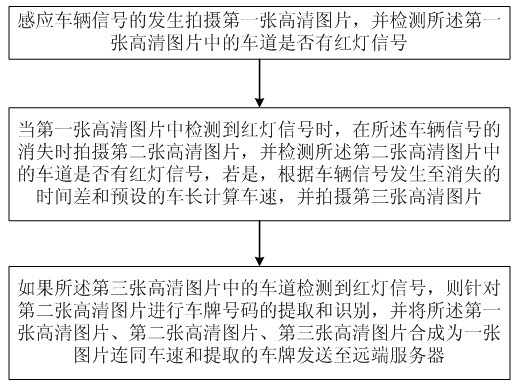

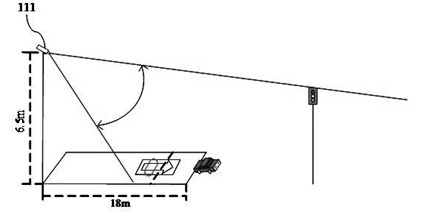

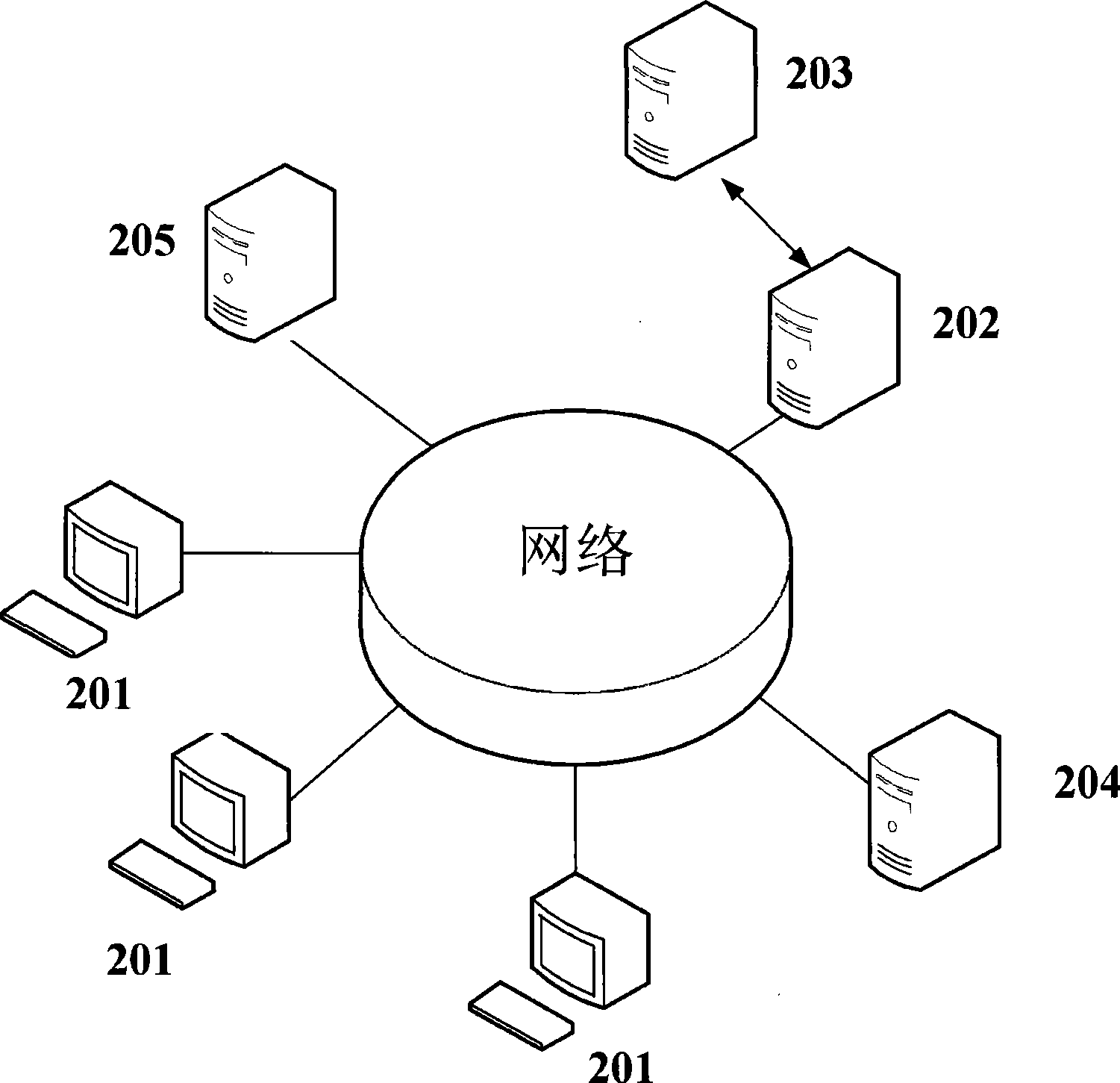

Jaywalking snapshot method and device

ActiveCN102110369AReduce the burden onAvoid disorderTelevision system detailsRoad vehicles traffic controlVideo monitoringJaywalking

The invention belongs to the field of video monitoring, and discloses a jaywalking snapshot method and a jaywalking snapshot device. The method comprises the following steps of: sequentially shooting high-definition pictures, performing jaywalking identification on the contents of the high-definition pictures and computing the speed of a vehicle through a high-definition camera and an embedded digital signal processor; when an effective jaywalking event is determined, combining three high-definition pictures into one jaywalking picture; and transmitting the picture to a remote-end server through a network. Due to the adoption of the method and the device, false shooting and leaked shooting can be effectively prevented; particularly, a number plate and the states of traffic lights can be clearly distinguished; and the load of the network can be further reduced obviously, and remote-end servers and database resources can be saved.

Owner:北京数字智通科技有限公司

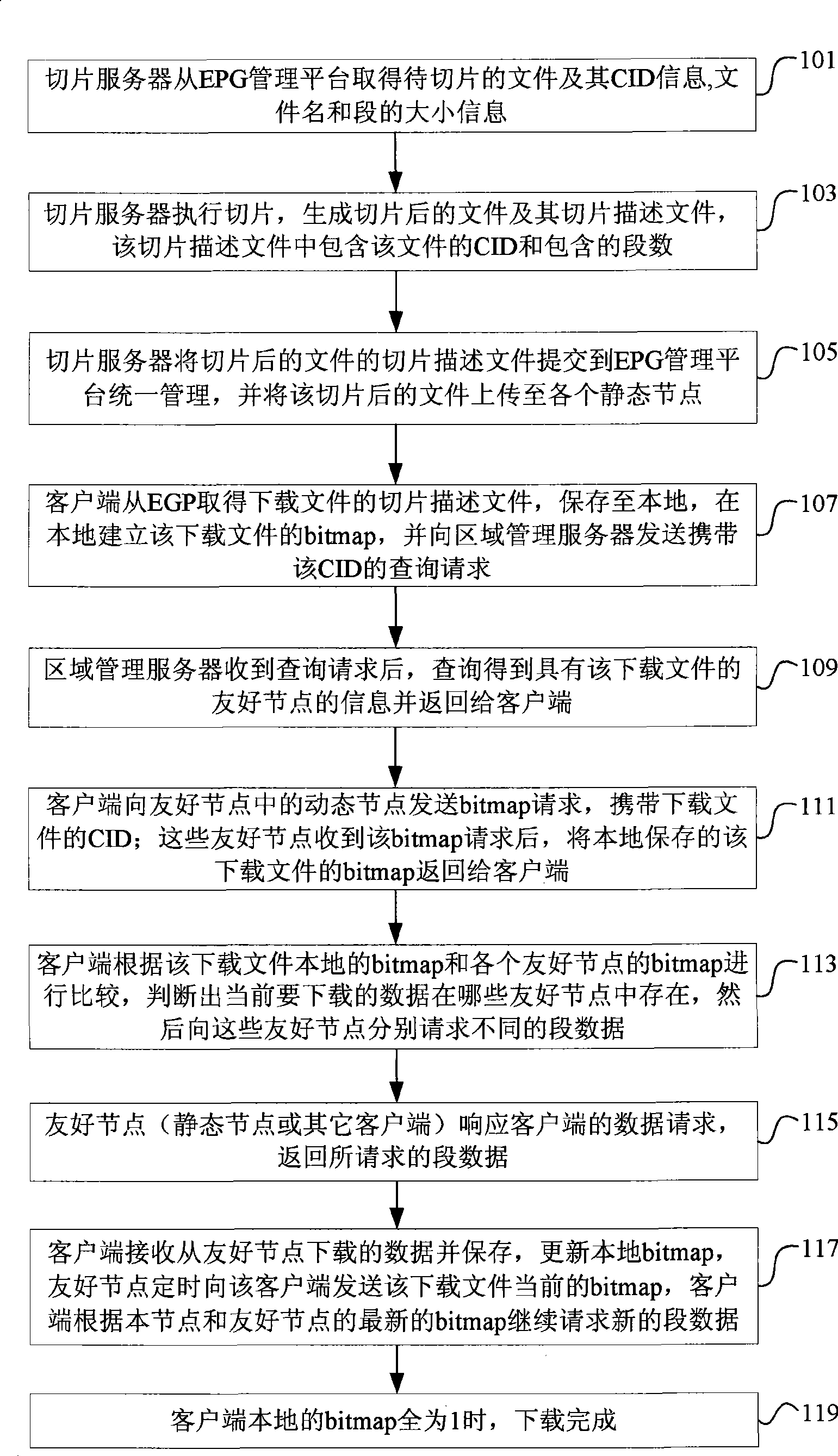

Method and system for downloading file by point-to-point network technique based on sliced sheet

InactiveCN101437044AReduce overheadReduce the burden onSpecific information broadcast systemsTransmissionBroadbandClient-side

The invention discloses a slice-based file download method for point-to-point network technology and a system thereof. The method comprises: when a client carries out point-to-point download, creating and maintaining local record information indicating whether slice contents of a file to be downloaded exist at the current node or not; acquiring record information maintained by dynamic nodes from friendly nodes, wherein the record information indicates whether the slice contents of the file to be downloaded exist in the dynamic nodes or not; in the download process, carrying out real time updating of record information of the current node and the dynamic nodes in the download process; comparing the record information of the current node with the record information of the dynamic nodes, determining friendly nodes containing the slice contents which are not downloaded and sending requests for downloading the data to be downloaded to the friendly nodes; dividing the downloaded file by the slice contents according to the set slice length to obtain parts which represent a slice content each. The invention can use a broadband resource to the maximum degree.

Owner:ZTE CORP

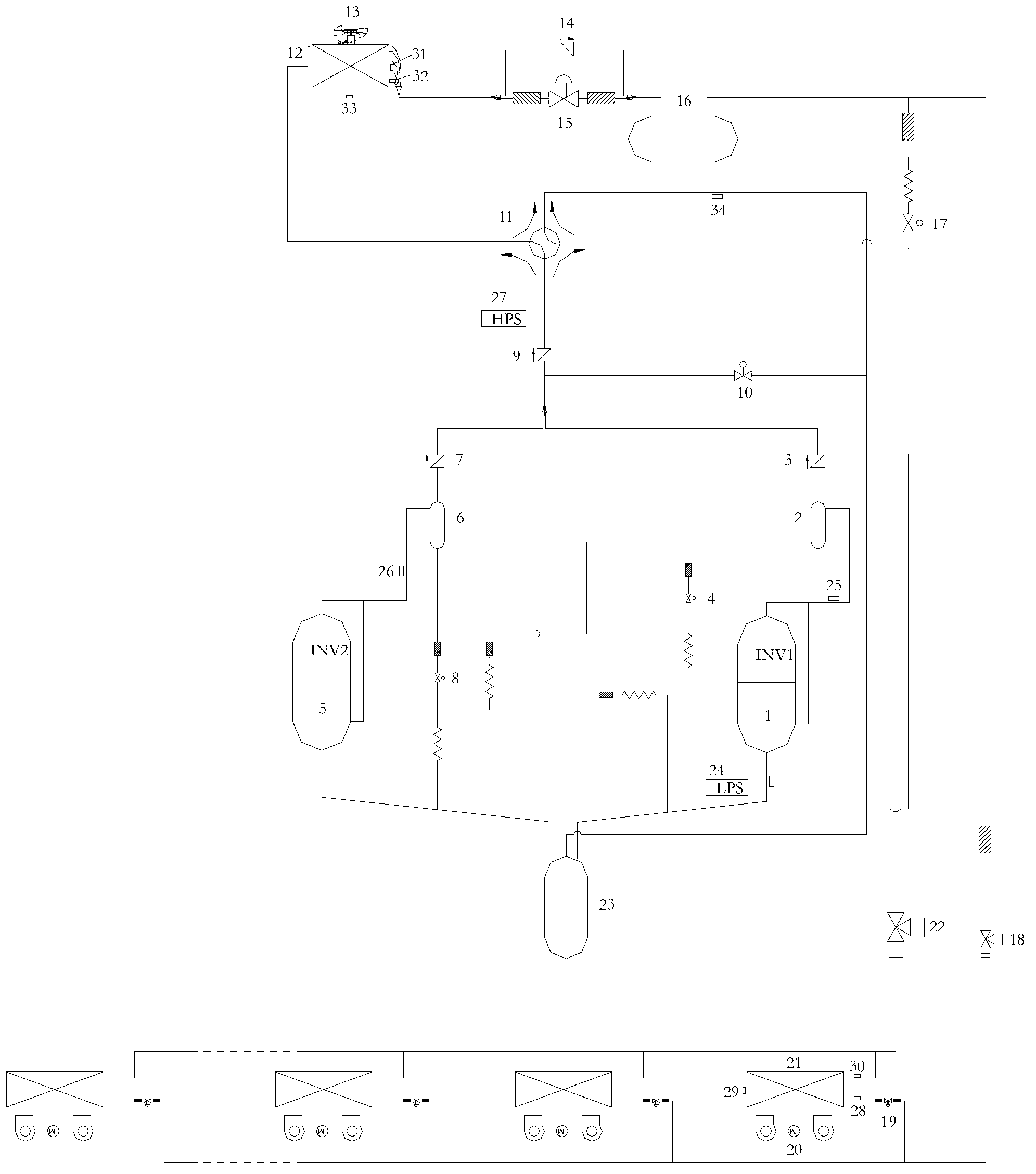

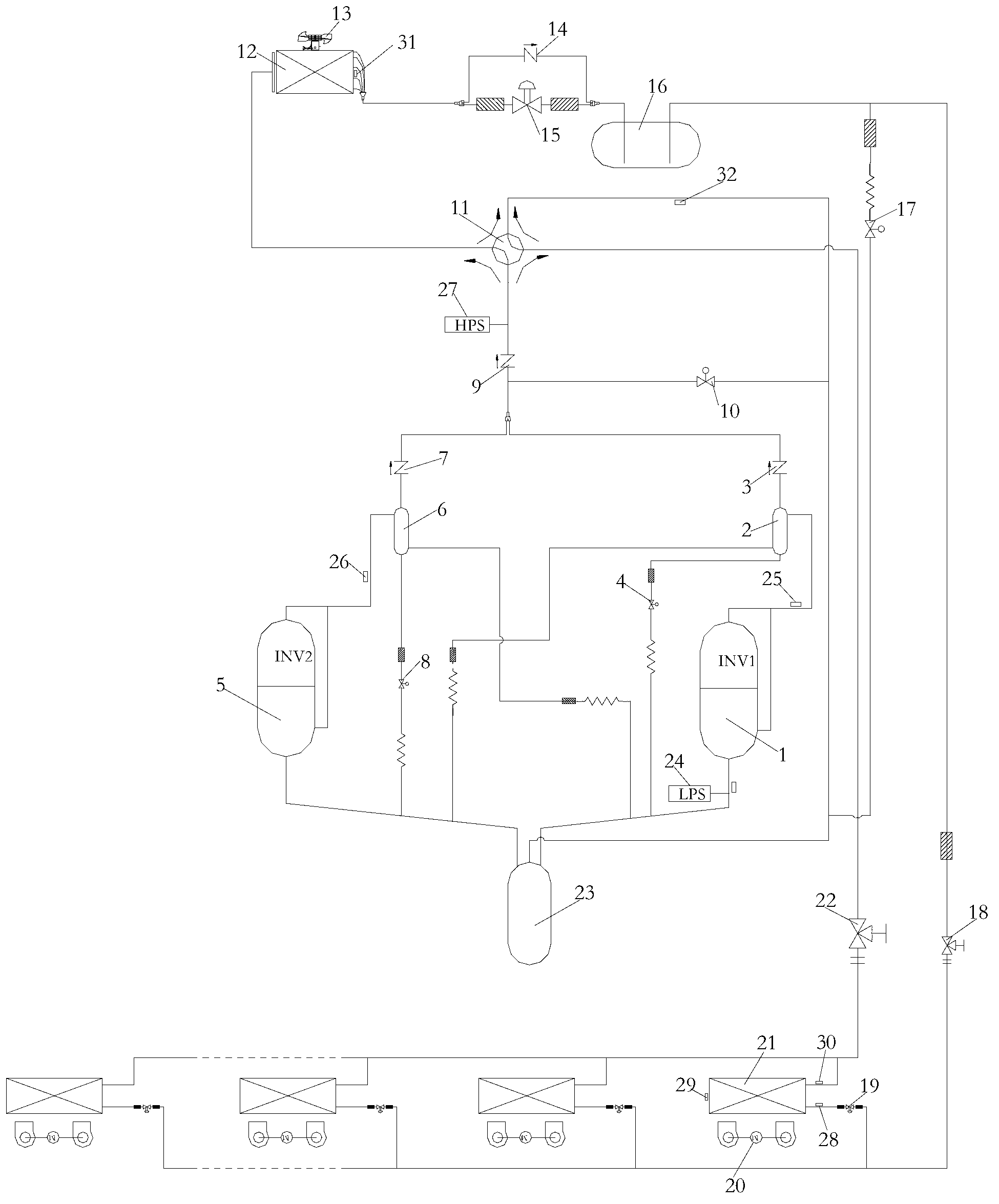

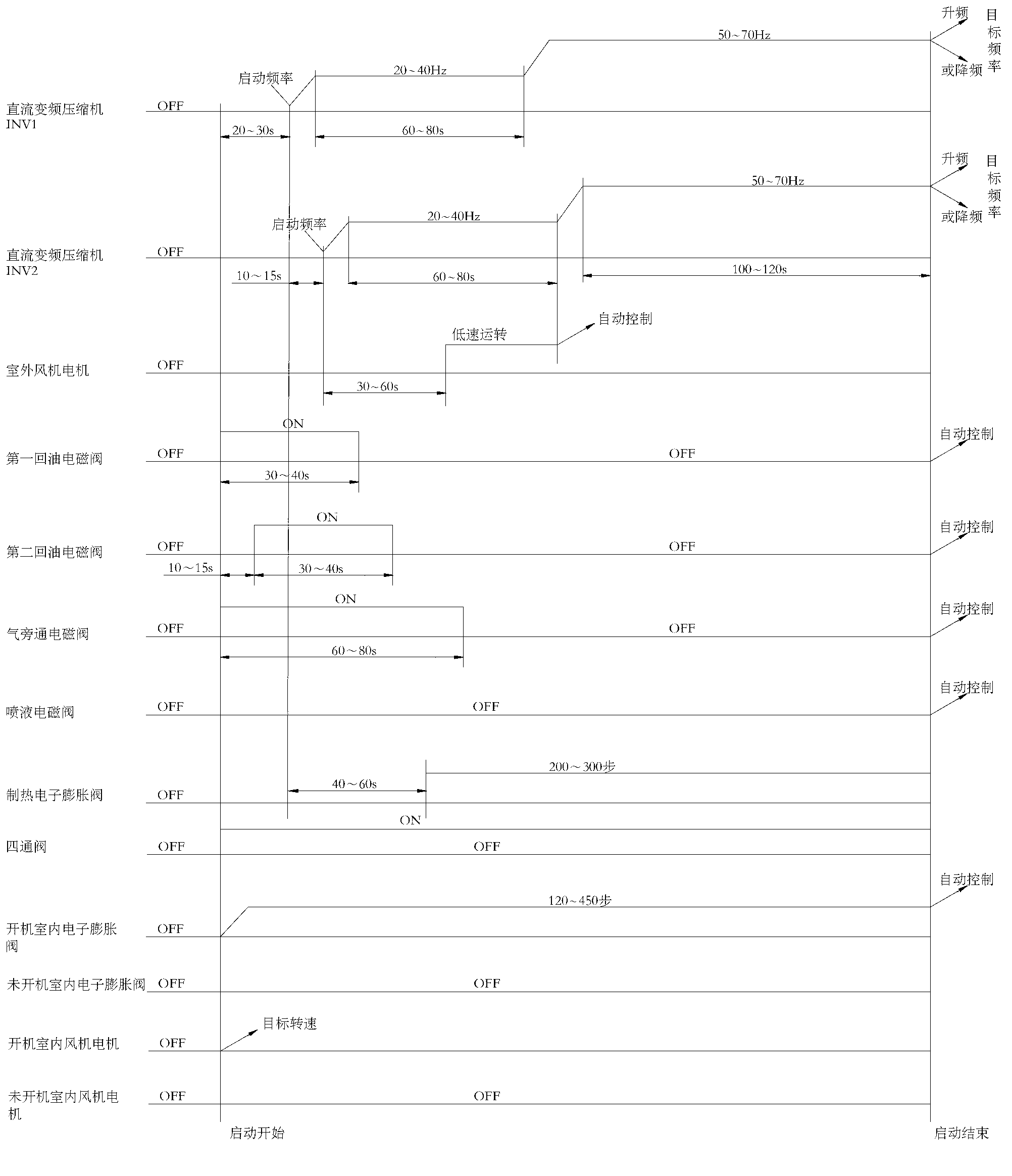

Refrigeration-to-heating mode starting method of multi-split air conditioner

ActiveCN103017295AAvoid disorderGuaranteed successful commutationSpace heating and ventilation safety systemsLighting and heating apparatusStart timeFour-way valve

The invention discloses a refrigeration-to-heating mode starting method of a multi-split air conditioner. Coordinate control is performed according to different time intervals during which each part in an air-conditioning system runs at different times. Action time sequence of each part is sequentially and reasonably coordinated according to respective start time and start time interval of each part in the multi-split air conditioning system, so that a four-way valve is enabled to be successfully switched, the multi-split air conditioning system can be controlled in a normal and reliable running way, the disorder of running of the whole multi-split air conditioning system is avoided, a direct-current inverter compressor is enabled to normally run, and the service life of the direct-current inverter compressor is prolonged.

Owner:NINGBO AUX ELECTRIC

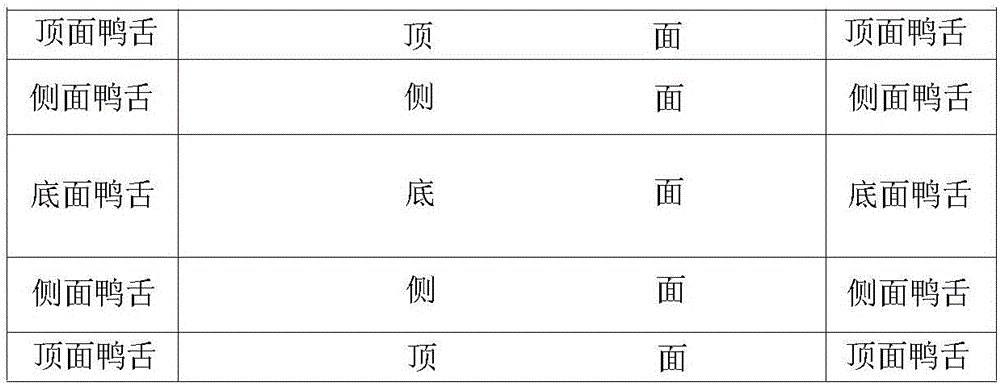

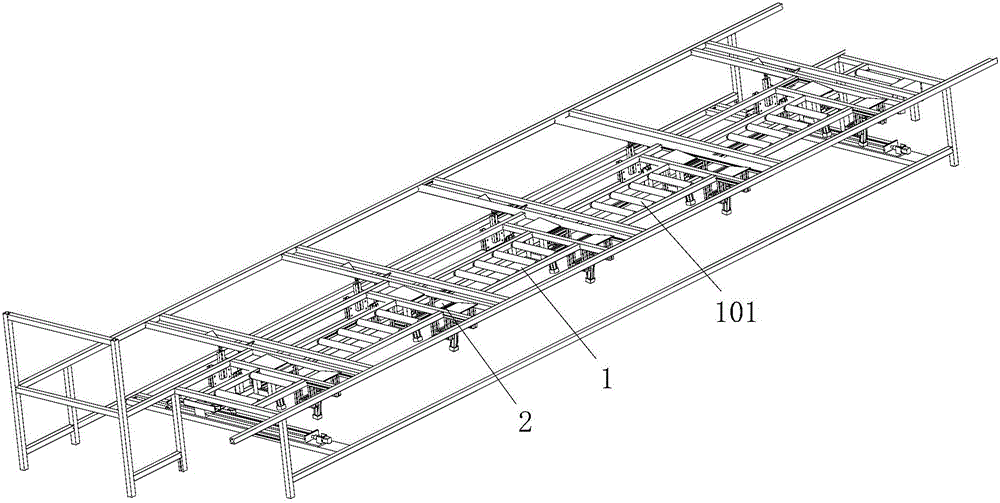

Automatic package machine for corrugated cartons with different lengths

InactiveCN105730772AHigh conveying precisionModerate delivery speedWrapper twisting/gatheringCartonEngineering

The invention discloses an automatic package machine for corrugated cartons with different lengths. The automatic package machine comprises a rack. An initial material position containing area, a wrapping forming area and a carton sealing area are sequentially arranged on the rack in the carton conveying direction. A material conveying device is arranged below the initial material position containing area. A carton containing area is arranged in the wrapping forming area. A top face folding mechanism, a front end folding system and a tail end folding system are arranged in the carton containing area. A side face folding mechanism is arranged below the carton containing area. Each of the front end folding mechanism and the tail end folding mechanism comprises a side face duck tongue folding mechanism, a top face duck tongue folding mechanism and a bottom face duck tongue folding mechanism. A plurality of powerless transmission rollers are arranged in the carton sealing area in the length direction of the carton sealing area. A two-end carton sealing mechanism, a length direction carton sealing system and a width direction carton sealing system are arranged in the carton sealing area in the carton conveying direction. By means of the automatic package machine, packaging of carton type products of different specifications and different sizes can be achieved, and the application range is wide.

Owner:SHANDONG UNIV OF SCI & TECH

Heating start method of multi-split air conditioner

ActiveCN103017294AAvoid disorderExtended service lifeSpace heating and ventilation safety systemsLighting and heating apparatusStart timeFour-way valve

The invention discloses a heating start method of a multi-split air conditioner. Coordinate control is performed according to different time intervals during which each part in an air-conditioning system runs at different times. Action time sequence of each part is sequentially and reasonably coordinated according to respective start time and start time interval of each part in the multi-split air conditioning system, so that a four-way valve is enabled to be successfully switched, the multi-split air conditioning system can be controlled in a normal and reliable running way, the disorder of running of the whole multi-split air conditioning system is avoided, a direct-current inverter compressor is enabled to normally run, and the service life of the direct-current inverter compressor is prolonged.

Owner:NINGBO AUX ELECTRIC

Fully-mixed daily feed for dairy cow

InactiveCN101791063AAddress nutritional imbalancesImprove nutritional statusAnimal feeding stuffMilk cow'sRumen

The invention relates to a fully-mixed daily feed for dairy cows, comprising concentrate supplement, silage, weed, alfalfa and carrots, wherein the concentrate supplement comprises grain seeds, cakes, by-products of agriculture product processing and premix feeds. In the invention, the raw materials are smashed and mixed respectively and uniformly, the moisture content of the feed is controlled to be less than 15%, and then the mixture is pressed into finished feed. The invention solves the problem of nutrient unbalance of dairy cows caused by feed intake difference in traditional feeding methods, decreases feed waste, helps relatively stabilize the pH value of dairy cow rumens, avoids digestive system disorder of dairy cows effectively, and improves nutrition condition of dairy cows. By using the feed in the invention and coordinating with the matched management technology, dairy cow eliminating amount can be decreased by about 8% every year and the average milk yield can be increased by 2.5kg per dairy cow, thereby improving economic benefits.

Owner:CHANGZHI SUBURB YUCHANG ANIMAL HUSBANDRY

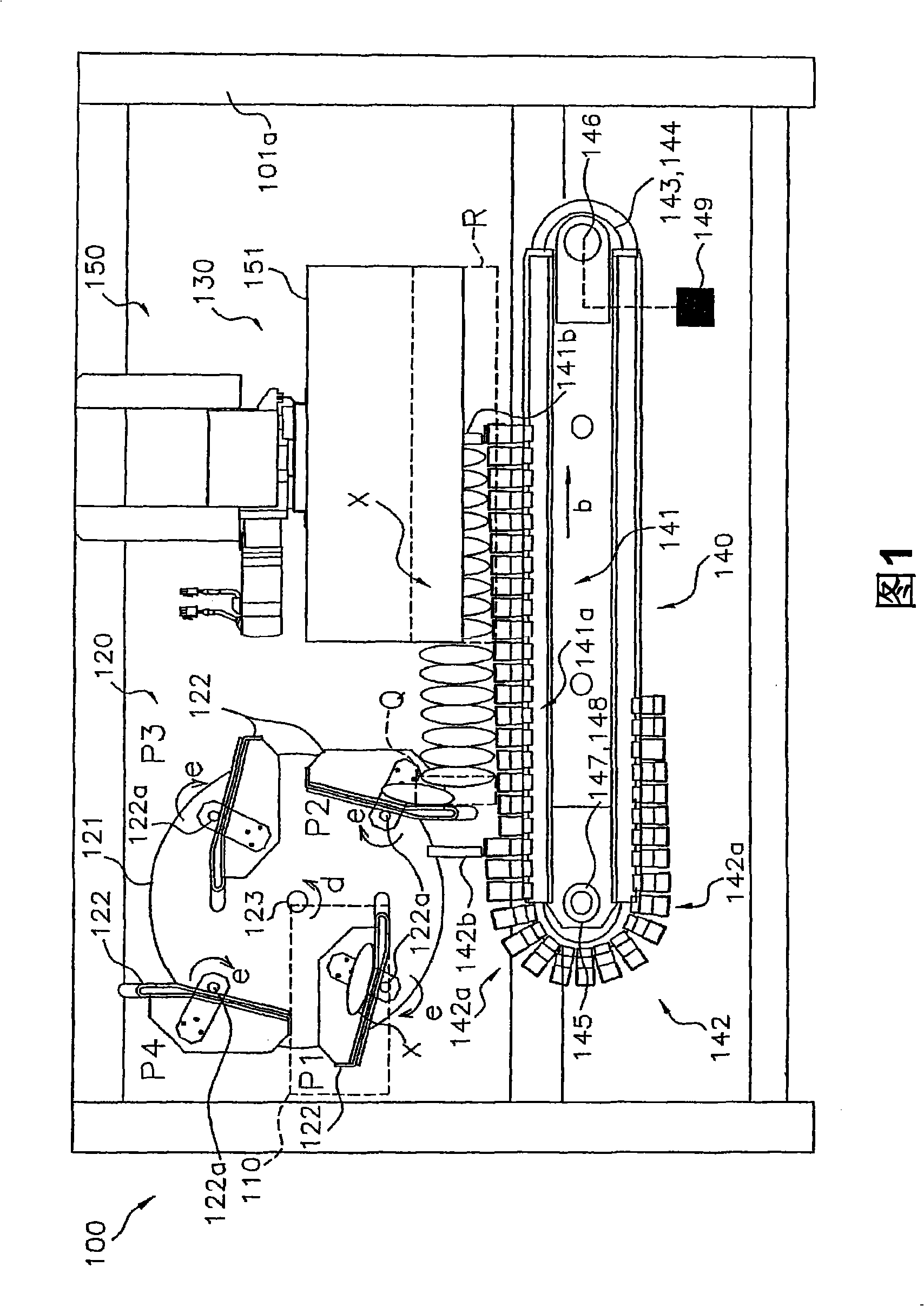

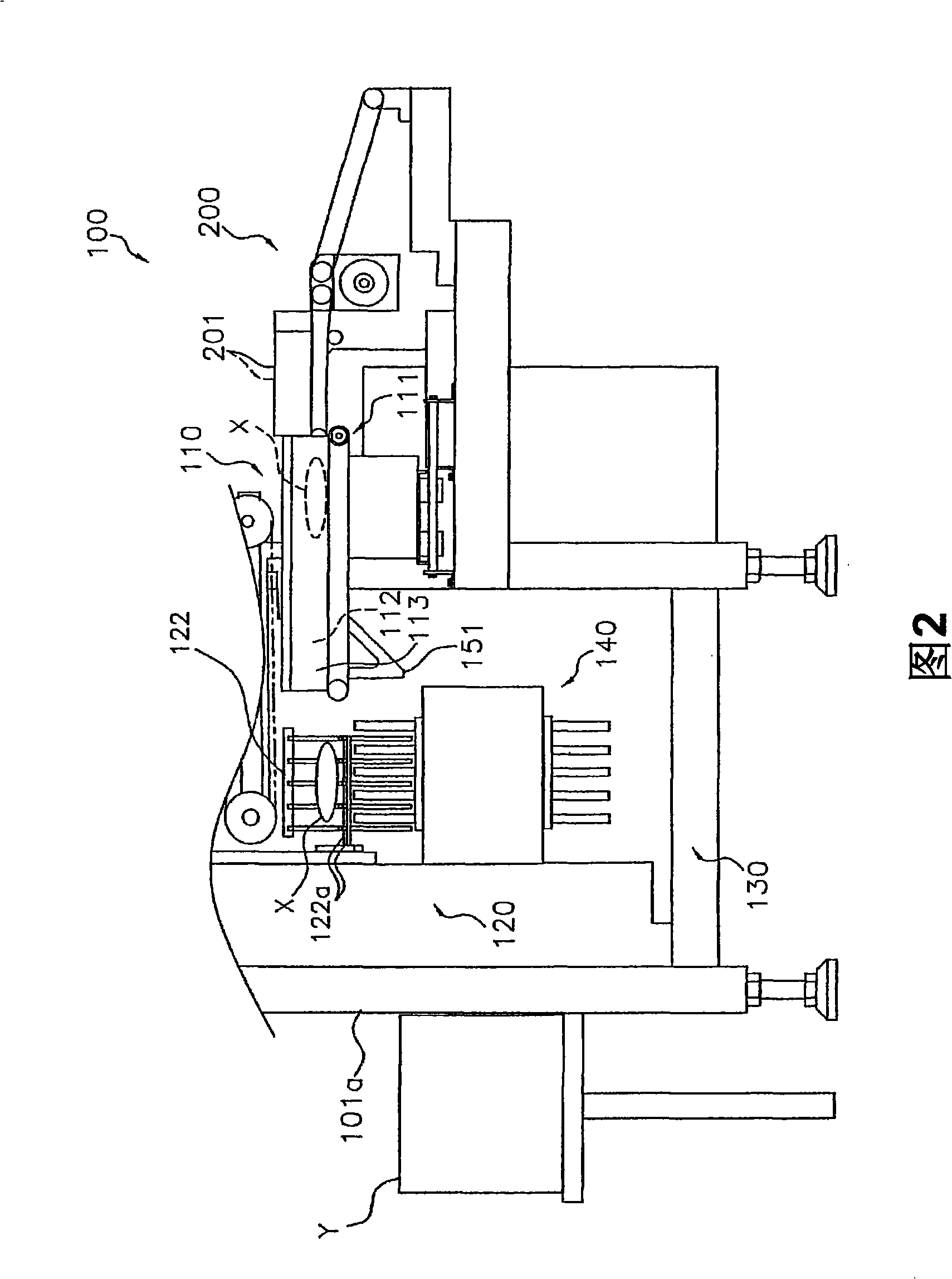

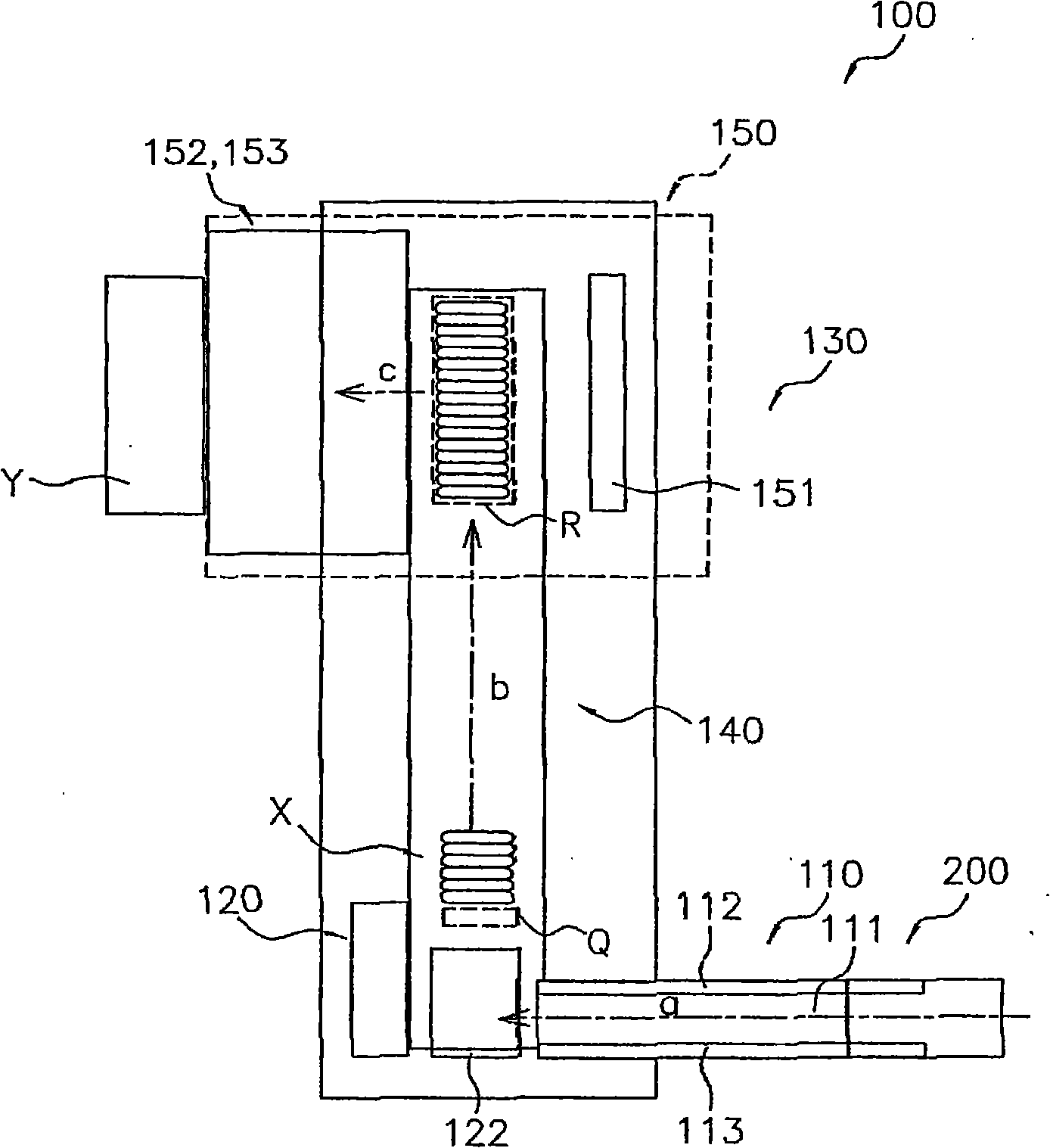

Conveyance device, and box packing device and box packing system with the same

InactiveCN101516734AThe queuing state is not easily disorderedQueuing disorderIndividual articlesConveyor partsCartonEngineering

The present invention provides a conveyance device capable of changing, relative to the opening of a corrugated cardboard box, the orientation of an article to be packed in the box. Depending on a desired accumulation condition [horizontal mode, oblique mode, and vertical mode], the box packing device (100) switches between delivery / reception intervals (CL) in delivery and reception of an article (X) between a paddle (122) and buckets (141, 142).

Owner:ISHIDA CO LTD

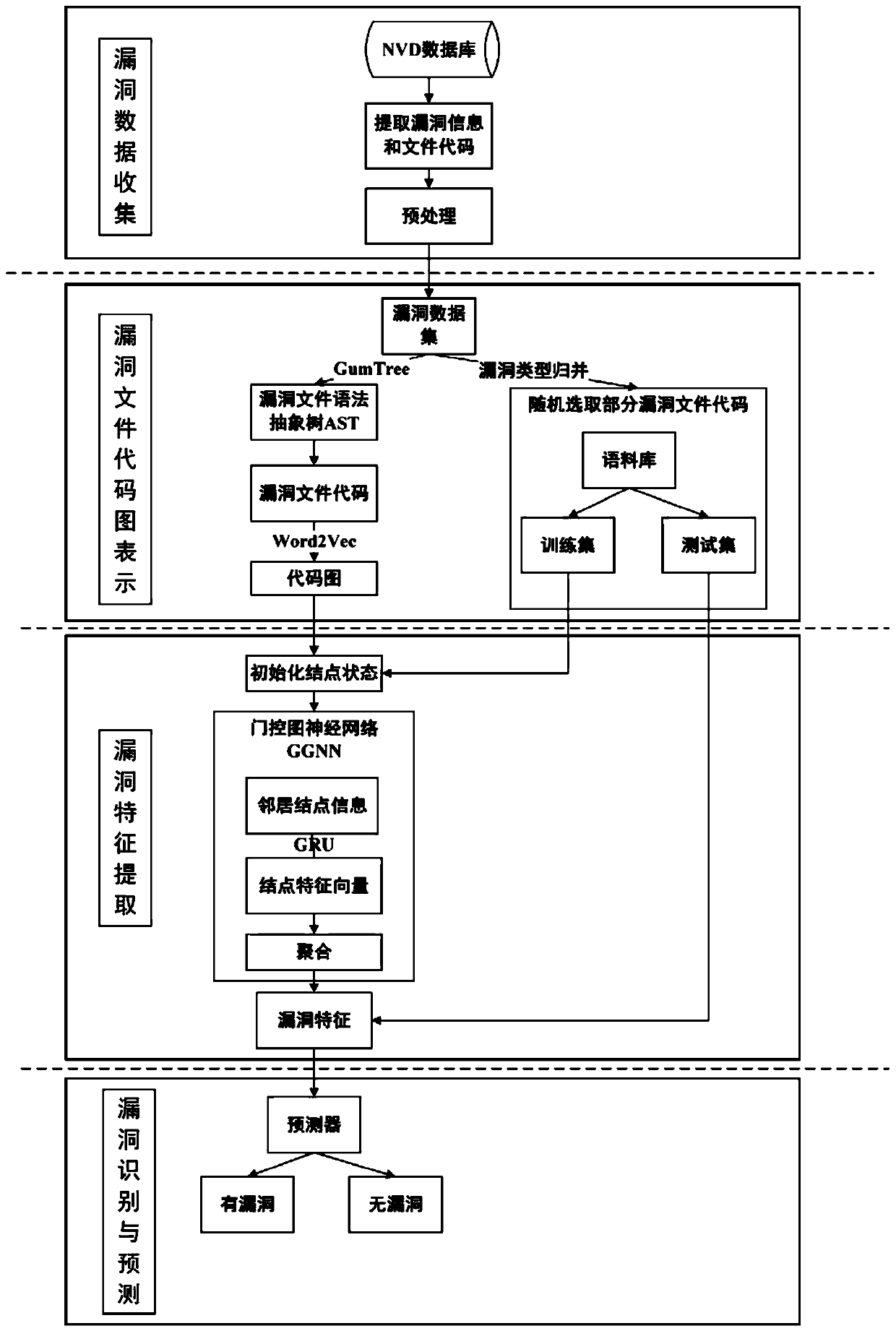

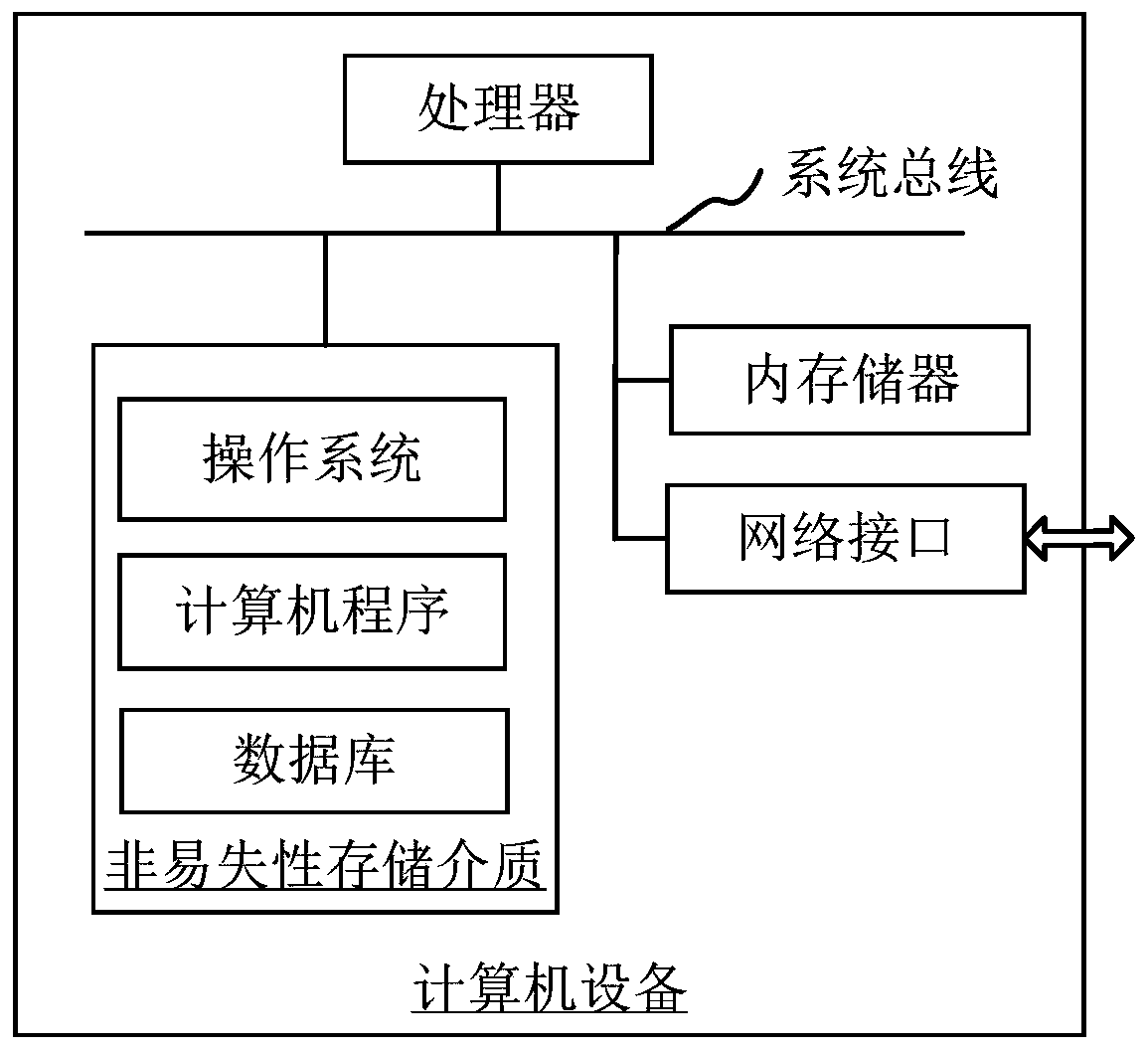

Graph neural network-based vulnerability identification and prediction method and system, computer equipment and storage medium

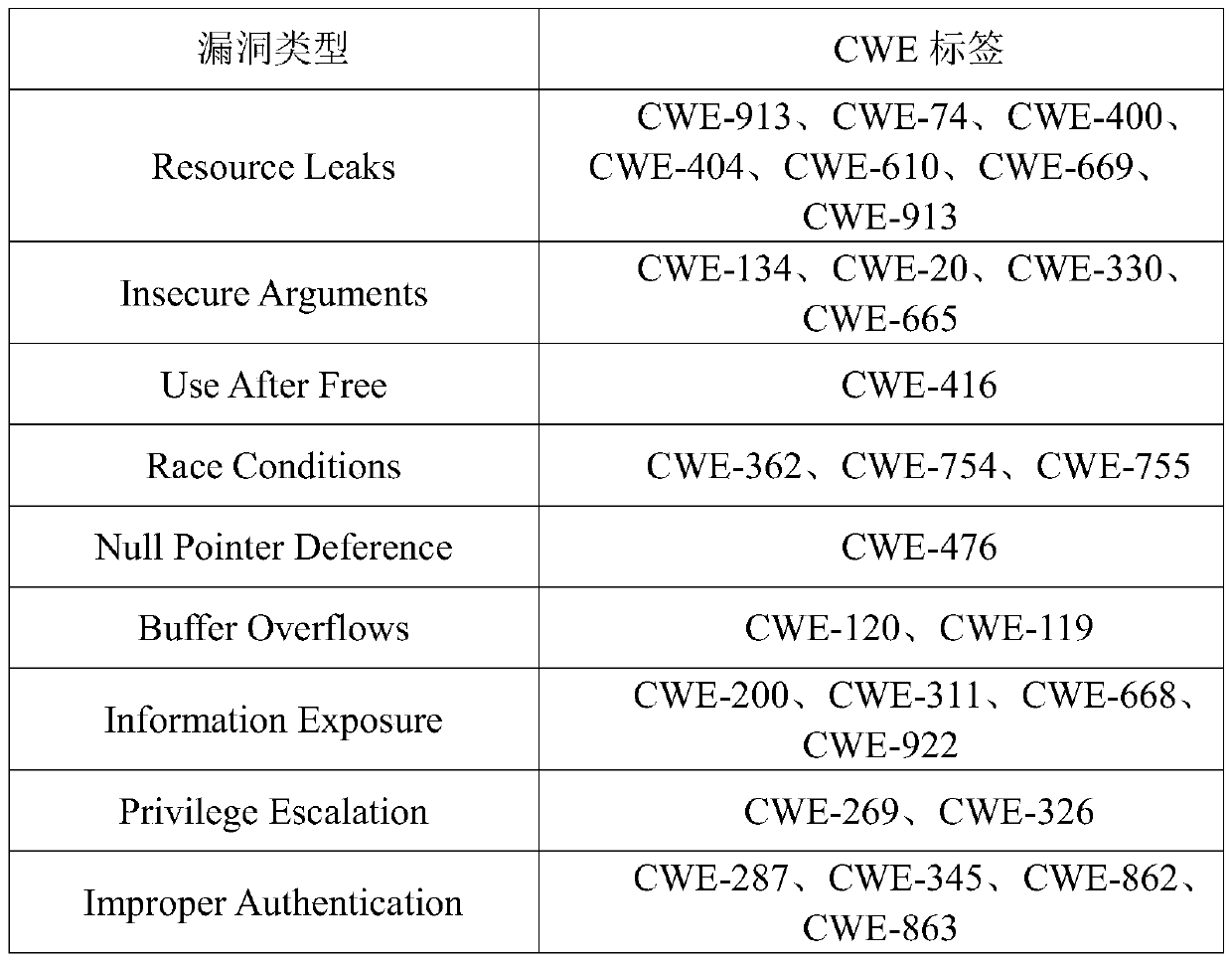

ActiveCN111274134AFully excavatedAvoid disorderSoftware testing/debuggingPlatform integrity maintainanceData setTheoretical computer science

The invention discloses a graph neural network-based vulnerability identification and prediction method and system, computer equipment and a storage medium. The method comprises the following steps: constructing a vulnerability data set; dividing the vulnerability data set into a training set and a test set; expressing a vulnerability file code graph; vulnerability feature extraction; and constructing a predictor, and predicting vulnerabilities in the code file by utilizing the predictor. The system is used for realizing the process of the method, and the computer equipment and the storage medium can realize the process of the method by executing computer programs. According to the method, the grammar and semantic information of the vulnerability codes can be better utilized, the relationship between the vulnerability codes and the context is fully mined, one type of vulnerability is effectively identified, the universality and universality are higher, the link of manually formulatingvulnerability indexes in actual code auditing can be replaced, the actual use cost is lower, the application field is wider, and the precision is higher.

Owner:YANGZHOU UNIV

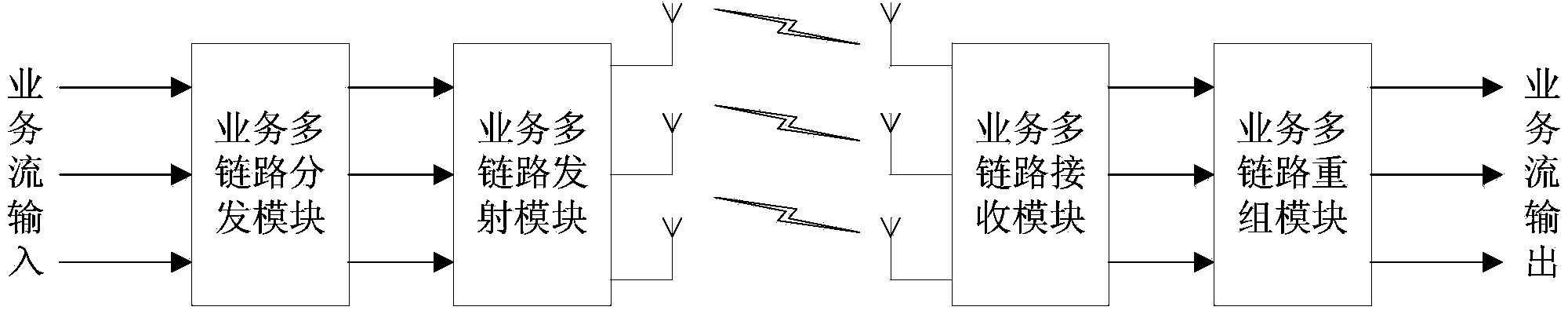

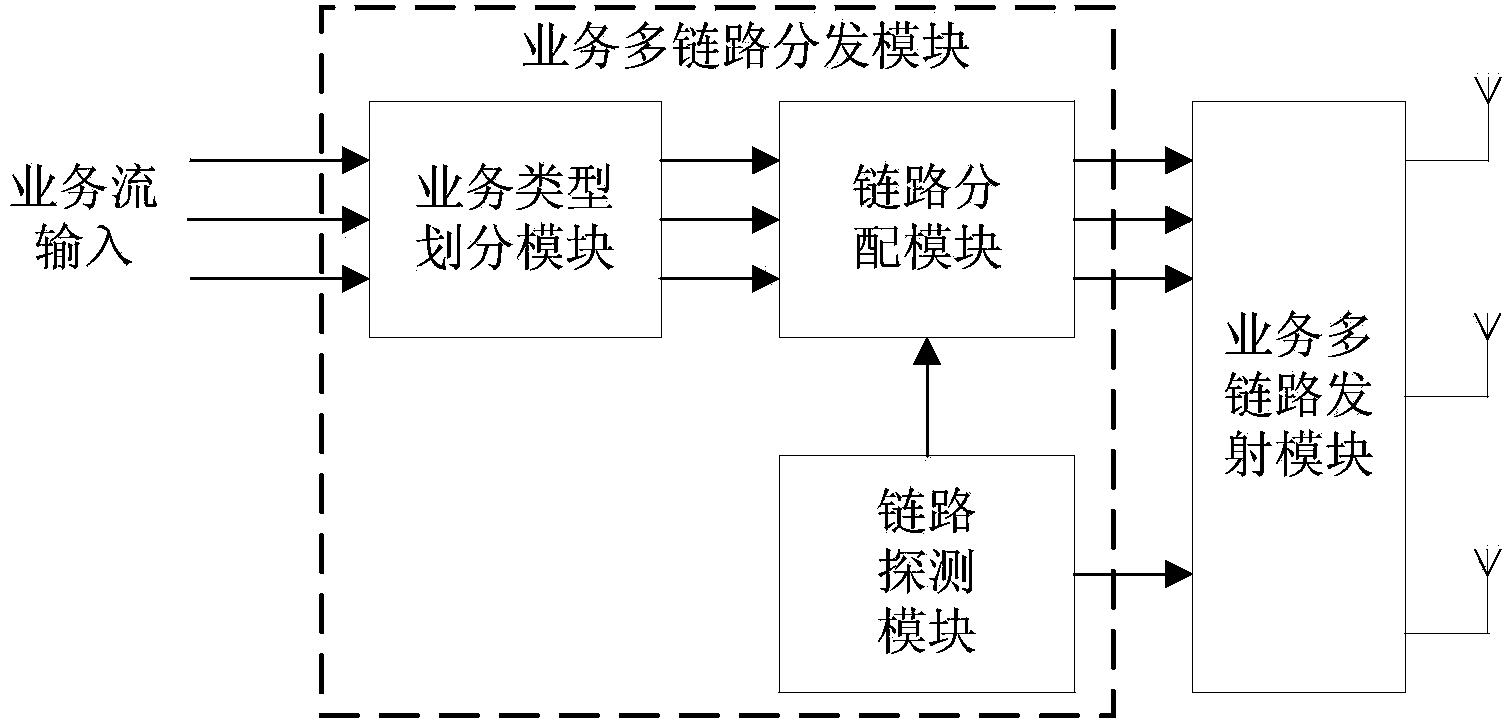

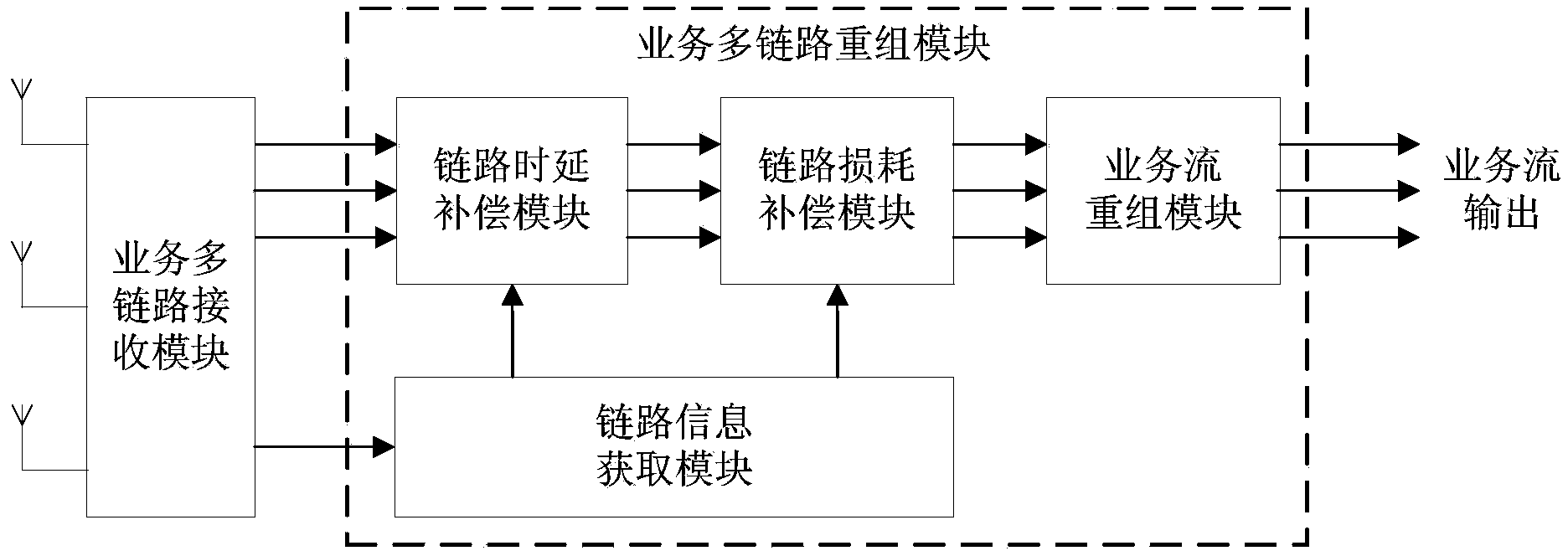

Multi-service link distribution and reorganization device and method

ActiveCN103561472AMeet needsImprove channel utilizationError preventionWireless communicationQuality of serviceTime delays

The invention provides a multi-service link distribution and reorganization device and method. The device comprises a service multi-link distribution module and a service multi-link reorganization module, wherein the service multi-link distribution module can classify services of different input service streams according to service quality requirements, detect available links, and then distribute the classified service streams to different links, and the classified service streams are sent out through a service multi-link transmission module; the service multi-link reorganization module is used for compensating for the time delay of the different links of the services which are received by a service multi-link receiving module so as to balance link loss, reorganize the service streams and restore original service streams. According to the scheme of the multi-service link distribution and reorganization device and method, link resources are distributed to the different services at the sending end according to link states and the service quality requirements, as a result, service transmission demands are met, and the utilization rate of system channel resources also can be increased; time delay and loss compensation can be conducted on data at the receiving end, and meanwhile, the out-of-order problem in parallel transmission is solved due to the fact that the same service is reorganized according to the type and package number of the service.

Owner:PLA UNIV OF SCI & TECH

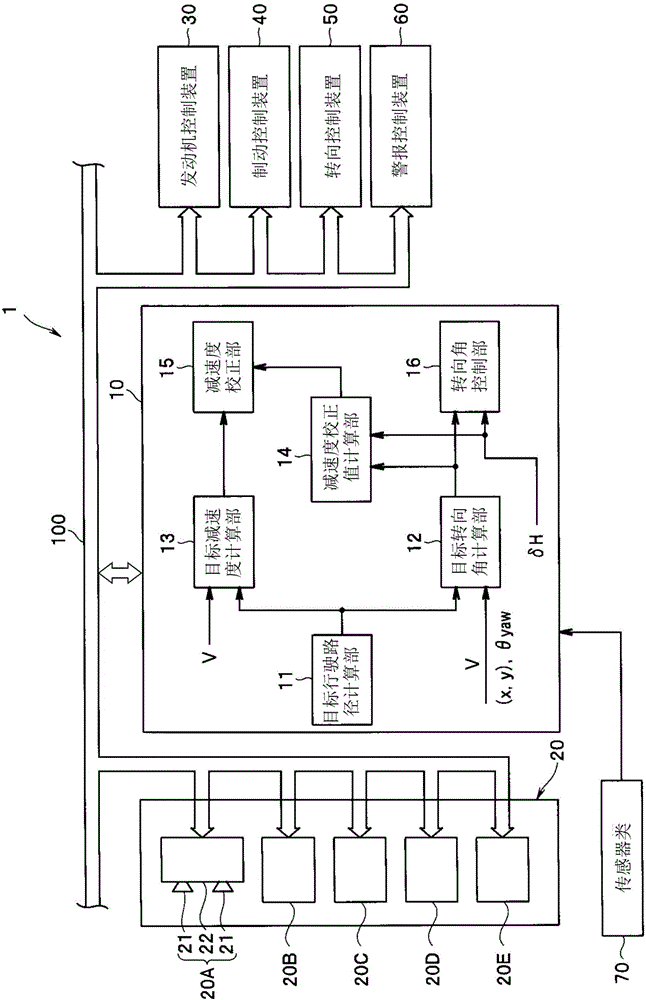

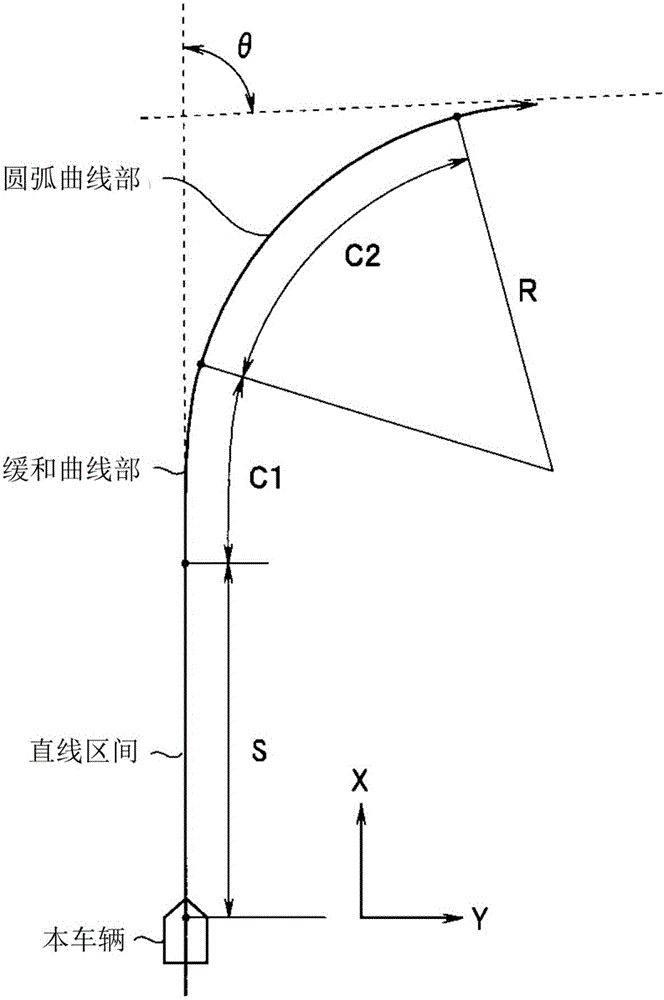

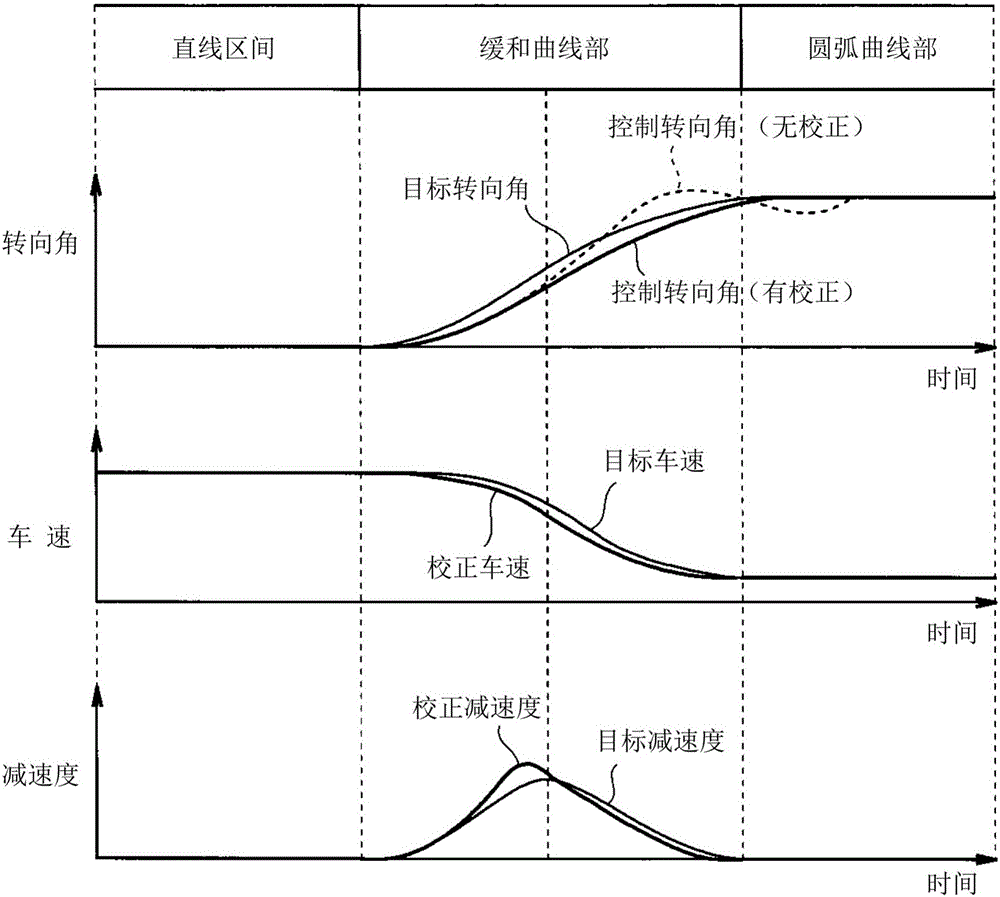

Driving support system for vehicle

InactiveCN106004857AAvoid disorderEnsure follow accuracyExternal condition input parametersSteering angleSteering control

A driving support system optimizes cooperative control of steering and deceleration control, ensures following precision of a travel route of a trate and inhibits disorder of an elastic system in the vehicle. A deceleration control part 14 includes: a target steering angle calculation unit 12 that calculates a target steering angle at the time of passing through a curved section of the target travel route; a target deceleration calculation unit 13 that calculates a target deceleration in the curved section; a deceleration correction value calculation unit that calculates, on the basis of the target steering angle and an actual steering angle, a corrected vehicle speed for correcting a target vehicle speed determined by the target deceleration; and a deceleration correction unit 15 that corrects the target deceleration such that the target vehicle speed becomes the corrected vehicle speed. The system reduces the feedback correction value on the basis of steering angle control of deflection of target steering angle and actual steering angle without inversion of steering, thereby ensuring following precision of a travel route of a trate and inhibiting disorder of an elastic system in the vehicle.

Owner:SUBARU CORP

Turf protection utilization method

ActiveCN106416652AImprove targetingHigh feasibilityAgriculture tools and machinesHops/wine cultivationRoad engineeringEngineering

A turf protection utilization method is provided for turf protection utilization programming and planning, and comprises the following steps: delimiting a turf protection level according to nature vegetation types and coverage; delimiting a vegetation retrieval level according to rainfall, temperature and soil factors; carrying out field investigation to check two said levels; superposing and delimiting a plurality of ecology control sections; determining the turf excavating technology according to the vegetation types and coverage in each ecology control section; selecting three protection technologies according to road engineering construction progress and turf utilization time intervals, wherein the three technologies include piled stacking, layered stacking, and skeleton layered temporary planting; determining three planting modes according to wind erosion and water erosion characteristics and propagation coefficients, wherein the three planting modes include a chessboard type, a tic-tac-toe mode and a bar stripped mode. The method can scientifically unify turf protection and utilization planning, storage and utilization, thus providing best ecology benefits; the turf protection utilization method is practical in applications.

Owner:CHINA ACAD OF TRANSPORTATION SCI

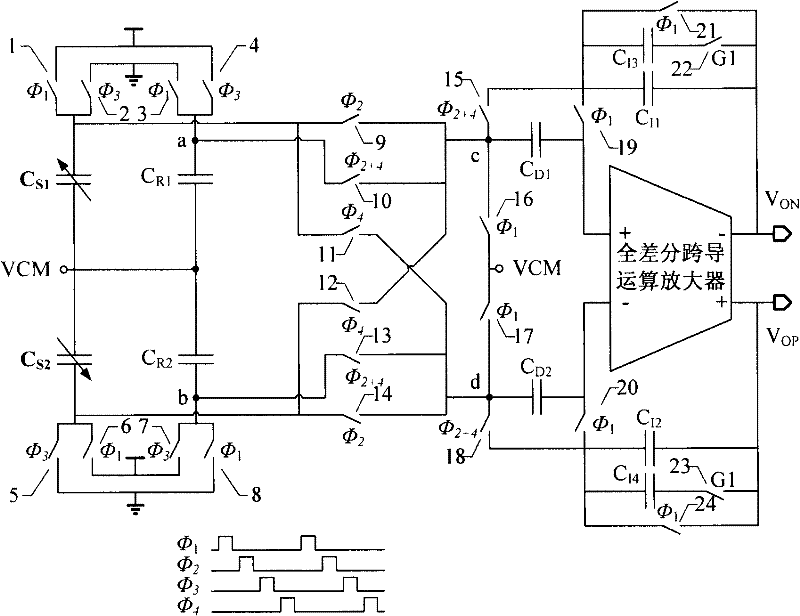

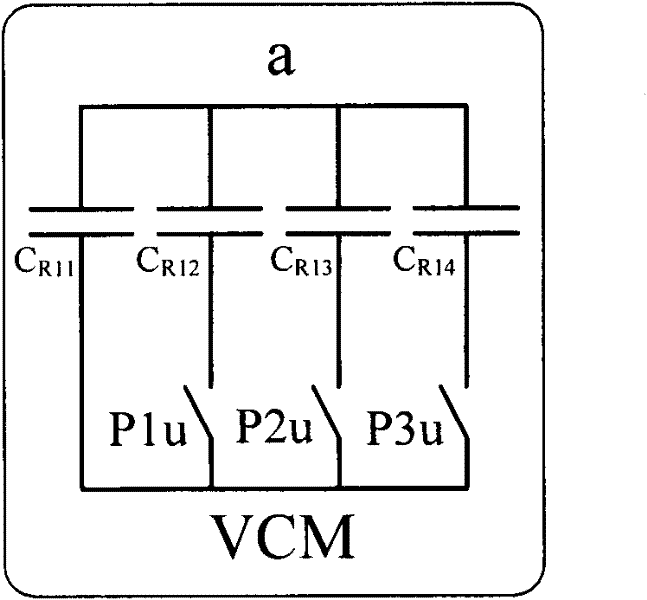

A Fully Differential Capacitance Readout Circuit with Cross Sampling and Double Summing of Charges

InactiveCN102297688AAvoid disorderSuppress noiseAcceleration measurementTurn-sensitive devicesCapacitanceOperating point

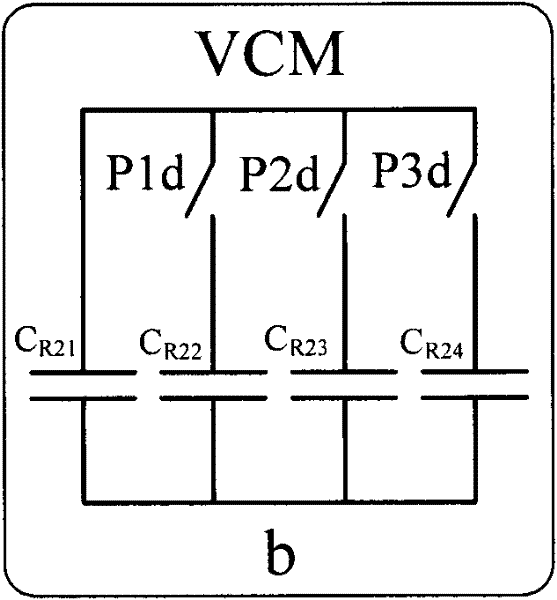

A capacitance readout circuit for secondary summation of cross-sampling charge, which is a symmetrical circuit structure, including switches 1, 2, 5, 6 for charging the sensor capacitance, reference capacitor arrays CR1 and CR2, and for charging the reference Switches 3, 4, 7, 8 for charging the capacitor array, switches 9, 10, 11, 12, 13, 14, 15, 18 for charge transfer, capacitors CD1 and CD2 for offset cancellation and low frequency noise suppression, and The switches 16 and 17 that provide the DC operating point for the circuit, the fully differential transconductance operational amplifier, the integrating capacitors CI1 and CI2 for storing the transferred charges, the integrating capacitors CI3, CI4 and switches 22 and 23 for adjusting the circuit gain, and the For the switches 19, 20, 21, 24 that provide DC bias for the fully differential transconductance inputs, the entire readout circuit is controlled by a 4-phase non-overlapping clock circuit.

Owner:INST OF ELECTRONICS CHINESE ACAD OF SCI

Air conditioner air outlet structure and air conditioner

ActiveCN104214920AAvoid disorderAvoid it happening againAir-flow control membersFan bladeEnergy loss

The invention provides an air conditioner air outlet structure and an air conditioner. The air conditioner air outlet structure comprises an air channel provided with at least two air outlets, a fan blade arranged in the air coming direction of the air channel, and at least two air baffles; the at least two air baffles are used for blocking coming air from passing through, movably arranged in the air channel and positioned between the fan blade and the air outlets. As the air baffles are arranged in the air channel between the fan blade and the air outlets, the air baffles can be used for blocking air outputting of at least one air outlet through the movement of the air baffles, the coming air is blown out through other air outlets, the air outlet condition of each air outlet is independently controlled, energy loss, airflow turbulence in the air channel and airflow vortex are effectively avoided, the noise and the vibration of the air conditioner air outlet structure are reduced and the integral performance and the heat exchange effect of the air conditioner are guaranteed.

Owner:GREE ELECTRIC APPLIANCES INC

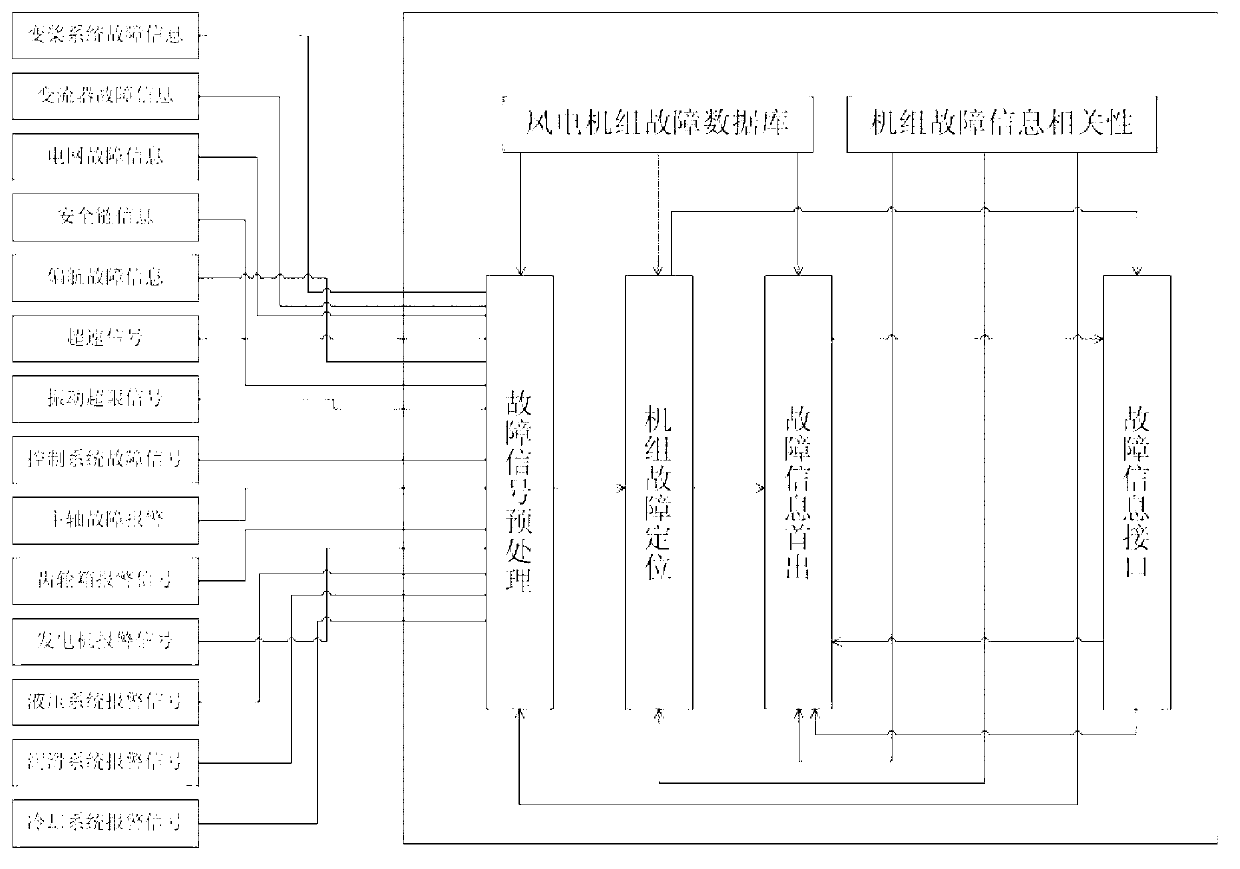

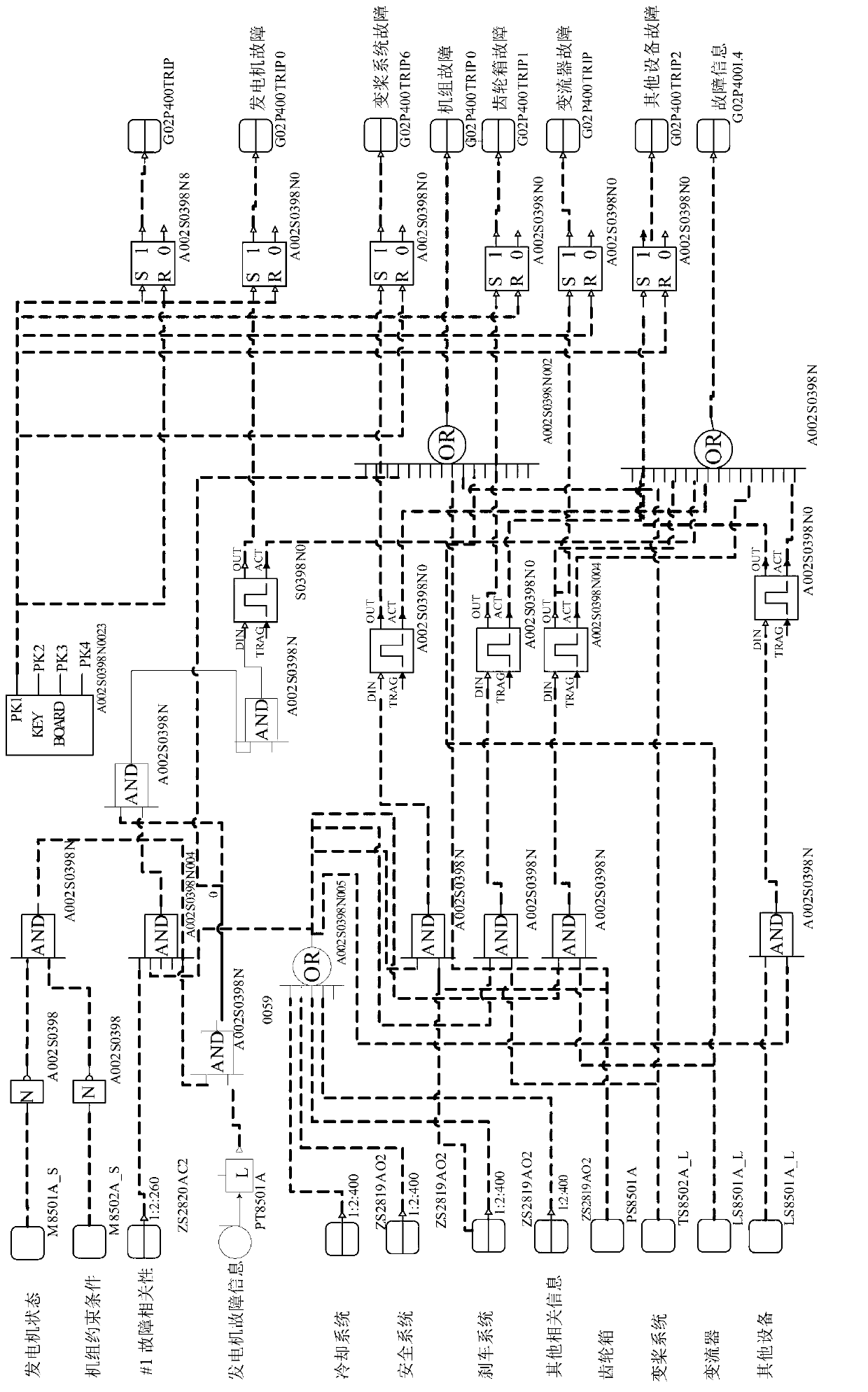

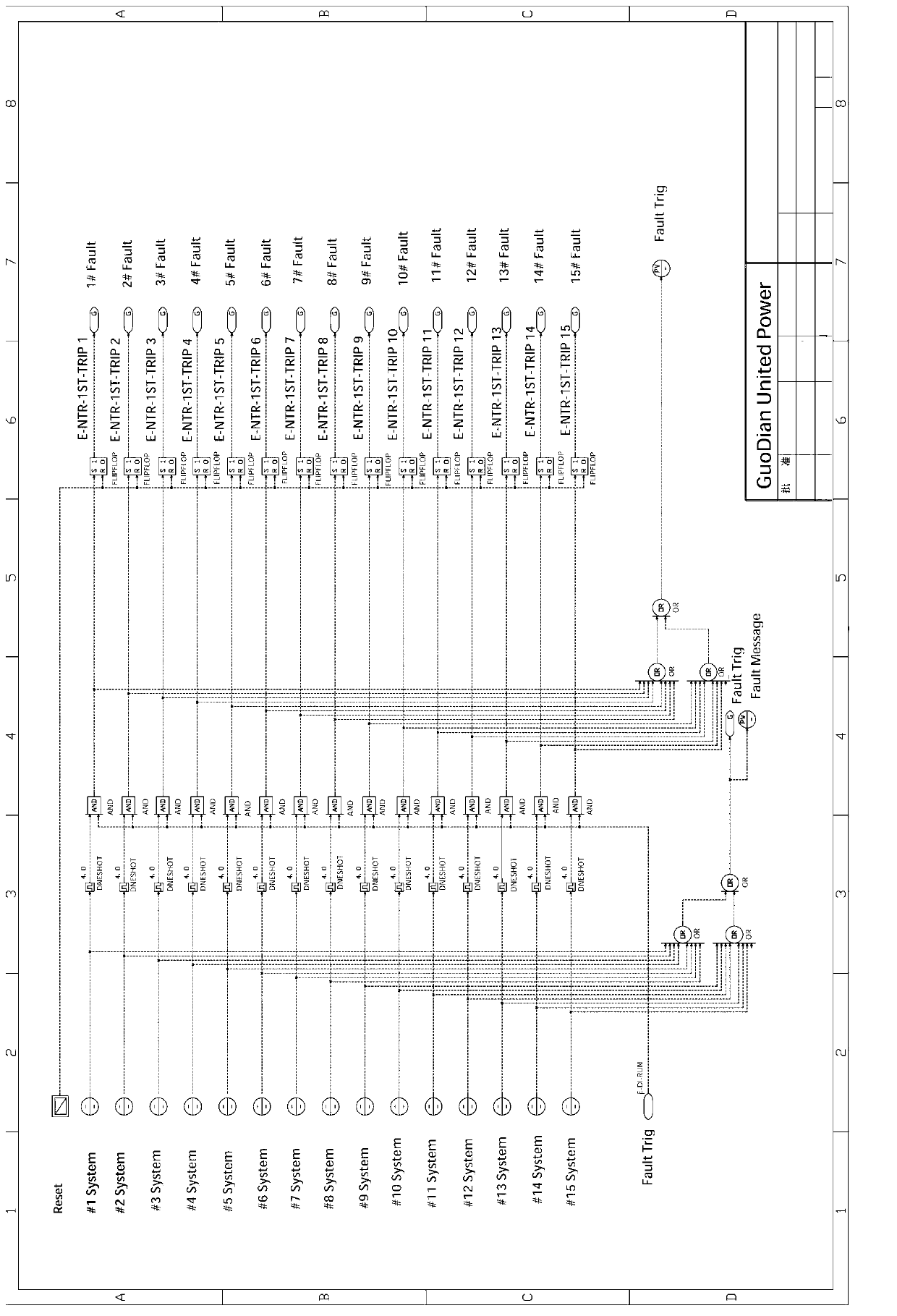

Wind generating set fault diagnosis method and system

ActiveCN103217291AIncrease profitIncrease power generationEngine testingSpecial data processing applicationsElectricityWind field

The invention relates to a wind generating set fault diagnosis method and a wind generating set fault diagnosis system. The method includes the steps of building a wind generating set fault database according to wind generating set fault statistic data, collecting set fault information and building logic relationships between independent faults, judging generation of fault signals, carrying out filtering processing on the fault signals and converting pulse signals to logic variables, locating the fault signals and shielding secondary fault signals with the logic relationships according to the logic relationships of the step B, and judging a fault which happens to a wind generating set firstly from the primary fault signals. The system comprises a wind generating set fault database, a set fault information relativity processing module, a fault signal pre-processing module, a set fault locating module and a fault information first judge module. The method and the system solve the problem that the wind generating set needs manual trouble shooting and fault source diagnosis after the fault happens, improve the utilization rate of the wind generating set and wind field generating capacity, and are reliable in logic, low in equipment cost and beneficial to popularize.

Owner:GUODIAN UNITED POWER TECH

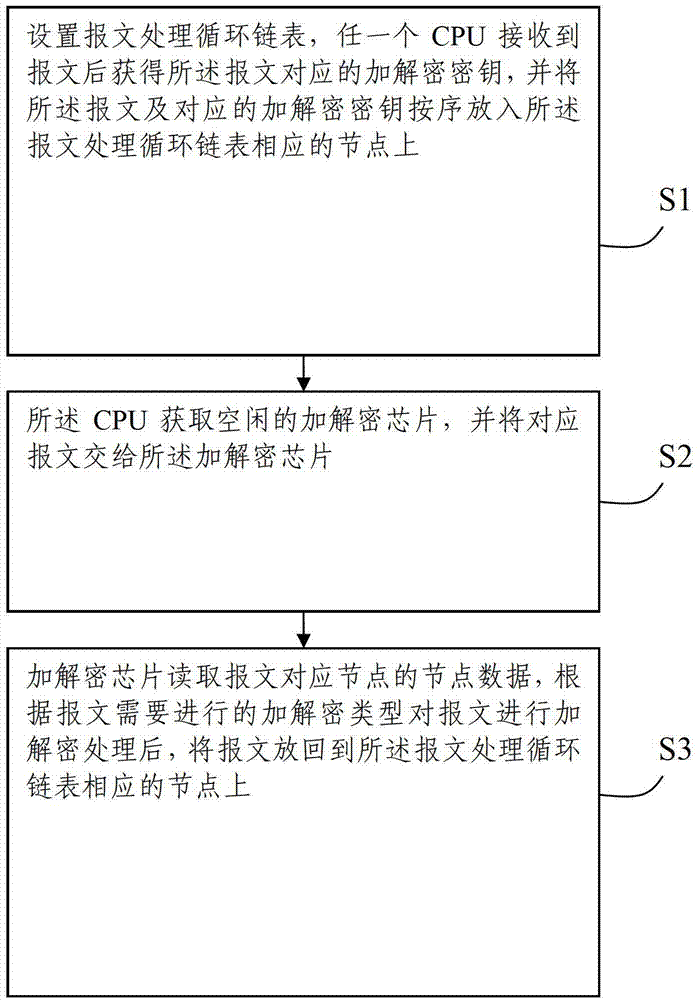

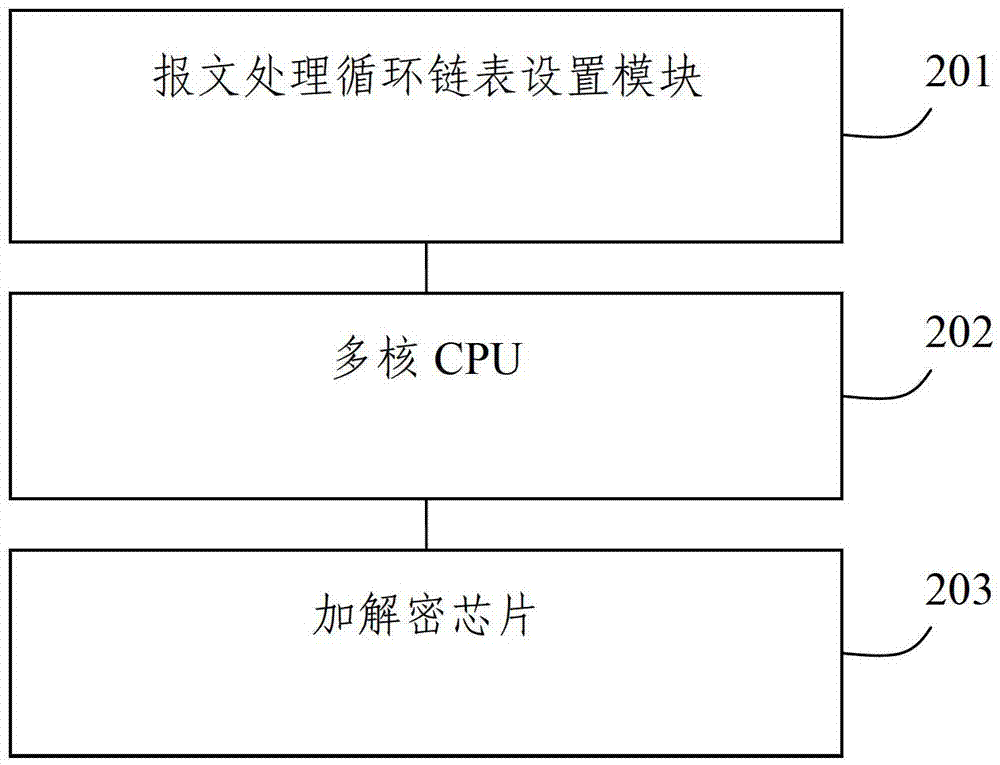

Order-preserving method and system for encrypting and decrypting messages by multiple encryption and decryption chips in parallel

The invention discloses an order-preserving method for encrypting and decrypting messages by multiple encryption and decryption chips in parallel. The order-preserving method comprises the following steps of: S1, setting a message processing cyclic chain table, after any central processing unit (CPU) receives a message, acquiring an encryption and decryption key corresponding to the message, and putting the messages and the corresponding encryption and decryption keys to corresponding nodes of the message processing cyclic chain table; S2, acquiring idling encryption and decryption chips by the CPU, and sending the corresponding messages to the encryption and decryption chips; and S3, reading node data of the nodes corresponding to the messages, encrypting and decrypting the messages according to encryption and decryption types of the messages, and putting the messages back to the corresponding nodes of the message processing cyclic chain table. The invention also discloses an order-preserving system implementing the order-preserving method. By the method and the system, the order of the messages can be guaranteed when multiple encryption and decryption chips encrypt and decrypt the messages at the same time, and a disorder phenomenon during sending of the messages is avoided.

Owner:OPZOON TECH

Method for managing complex spacecraft three-dimensional model

InactiveCN104217048ARealize managementRealize synergistic integrationSpecial data processing applicationsEngineeringSerialization

The invention relates to a method for managing a complex spacecraft three-dimensional model. Framework models of the complex spacecraft three-dimensional model are divided into a configuration-layer framework model and a layout-layer framework model from top to bottom. The configuration-layer framework model is a first-layer framework model and is composed of top layer coordinate systems for expressing a spacecraft, large system interfaces, complete machine configuration and cabin interfaces. The layout-layer framework model is a second-layer framework model and is used for expressing layout information of single equipment, loads and structural mechanisms of all subsystems in the spacecraft on the basis of receiving configuration layer information, a single equipment coordinate system is built, transmission from top to bottom is carried out through the uniform coordinate system of the whole spacecraft three-dimensional model, the uniform data transmission and assembling standard is built, three-dimensional model information is managed, the changeability and accuracy of the spacecraft three-dimensional model are improved, cooperation and integration between designers are achieved, and therefore fast derivation and deformation of serialization products are achieved.

Owner:BEIJING SPACE TECH RES & TEST CENT

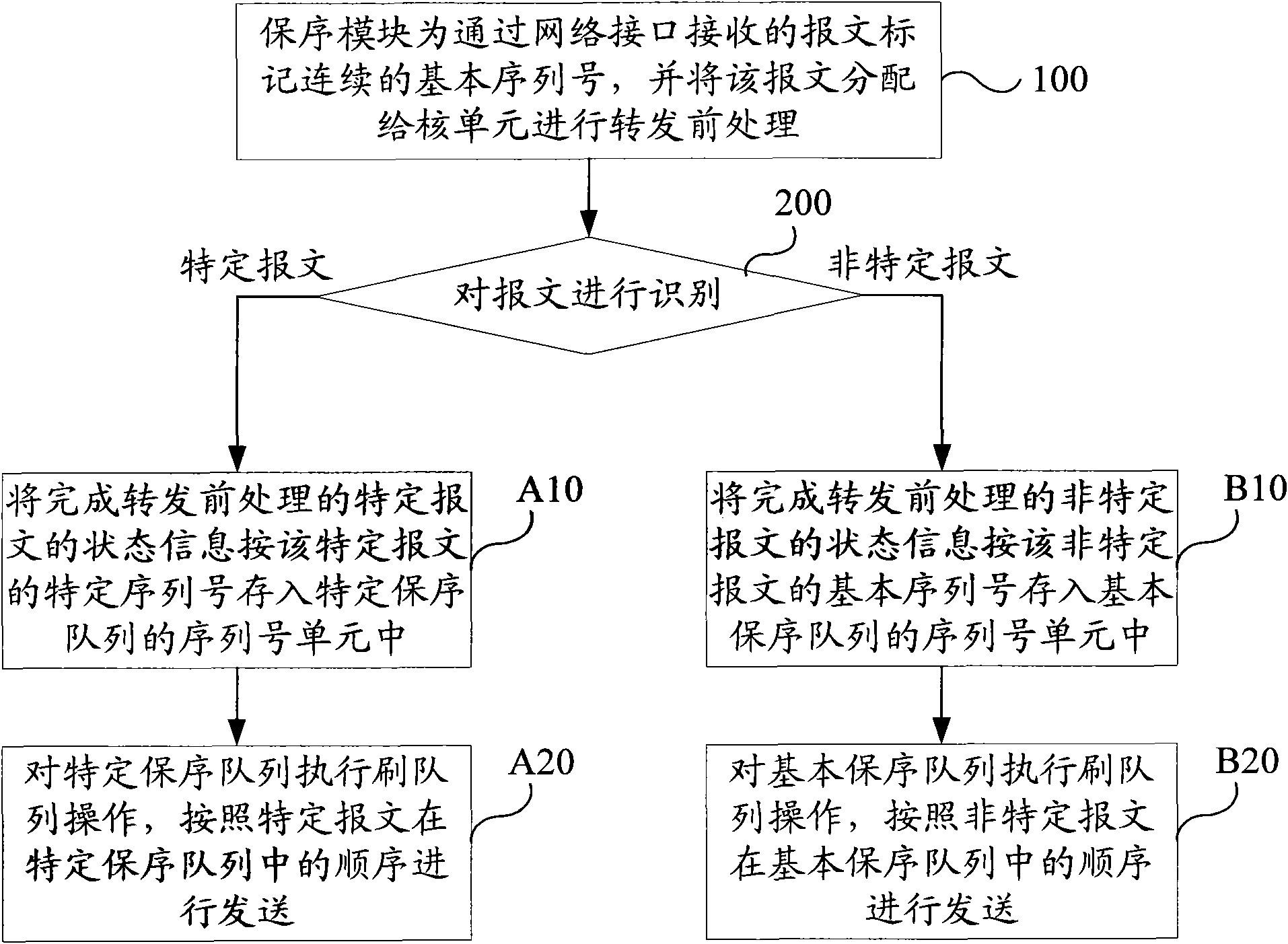

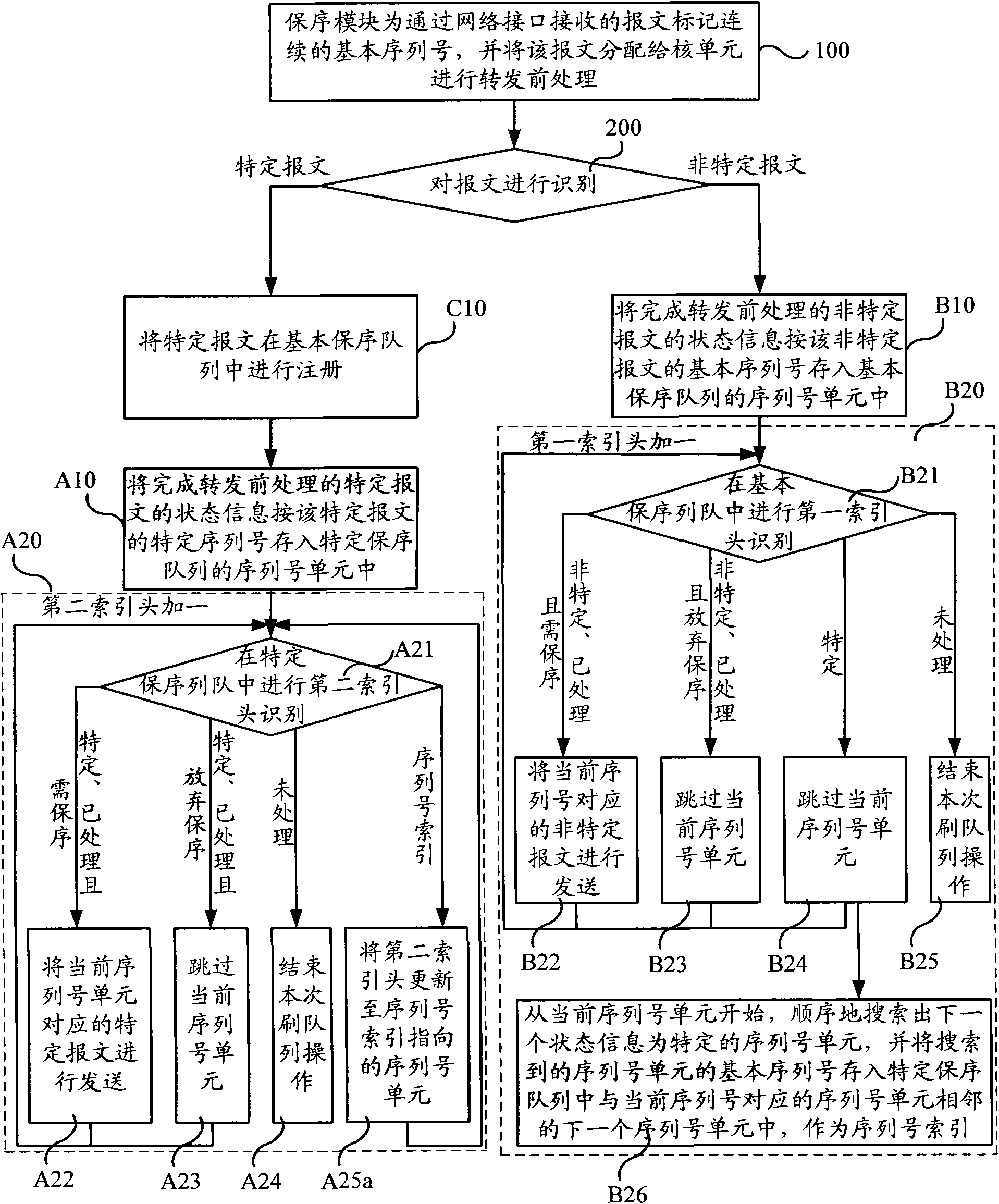

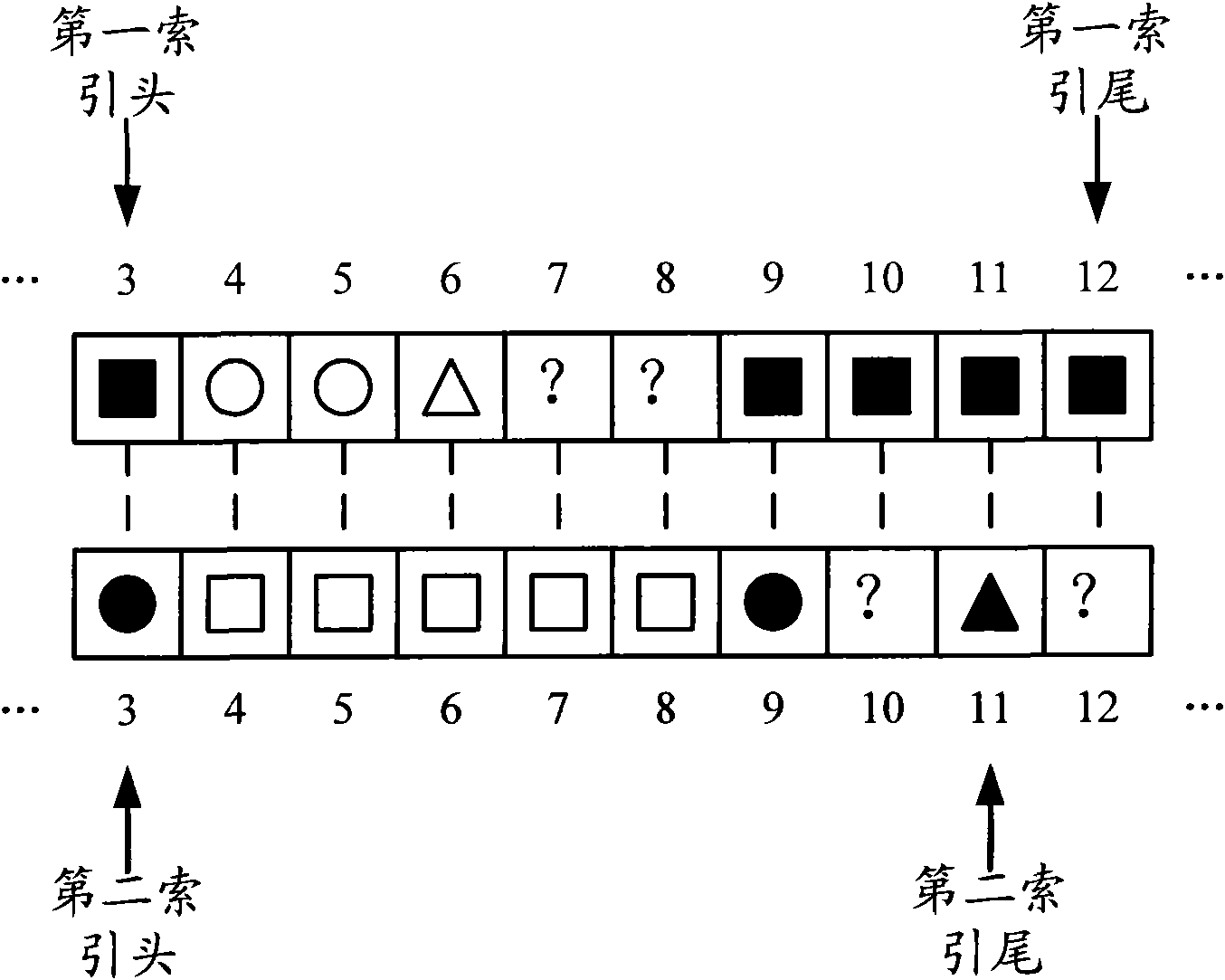

Method, device and system for treating messages of multi-core system

InactiveCN102055649ARealize the order preservation functionAvoid disorderData switching networksReal-time computingNetwork interface

The embodiment of the invention relates to a method, a device, and a system for processing messages of a multi-core system. The method comprises the following steps that the messages received through a network interface are marked with continuous basic serial numbers, and the messages are distributed to a core unit for processing prior to transmission; the messages are identified; when the messages are identified as specific messages, the state information of the specific messages of which the processing prior to transmission is finished is stored in the serial number unit in a specific order-preserving queue as per the specific serial number of the specific messages; and the specific order-preserving queen is subjected to the queue brushing operation, and the messages are transmitted as per the sequence of the specific messages in the specific order-preserving queue. The embodiment of the invention adopts the technical means of the specific order-preserving queue independent of a basic order-preserving queue, thereby avoiding the disorder of the specific messages and improving the message processing performance of the multi-core system.

Owner:HUAWEI DIGITAL TECH (CHENGDU) CO LTD

Household video monitoring system

InactiveCN109889795AImprove reliabilityEnsure consistencyClosed circuit television systemsVideo monitoringCapacitance

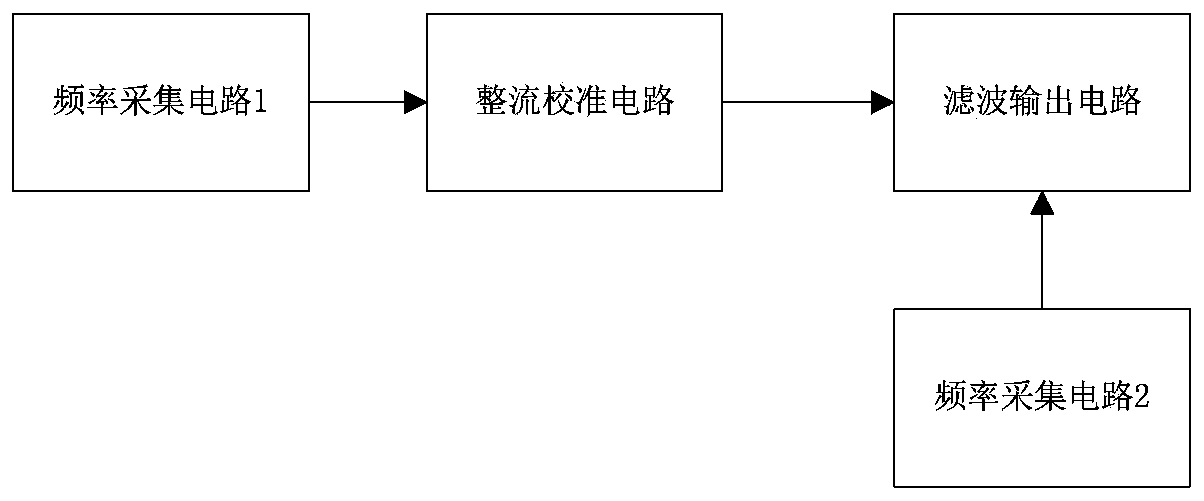

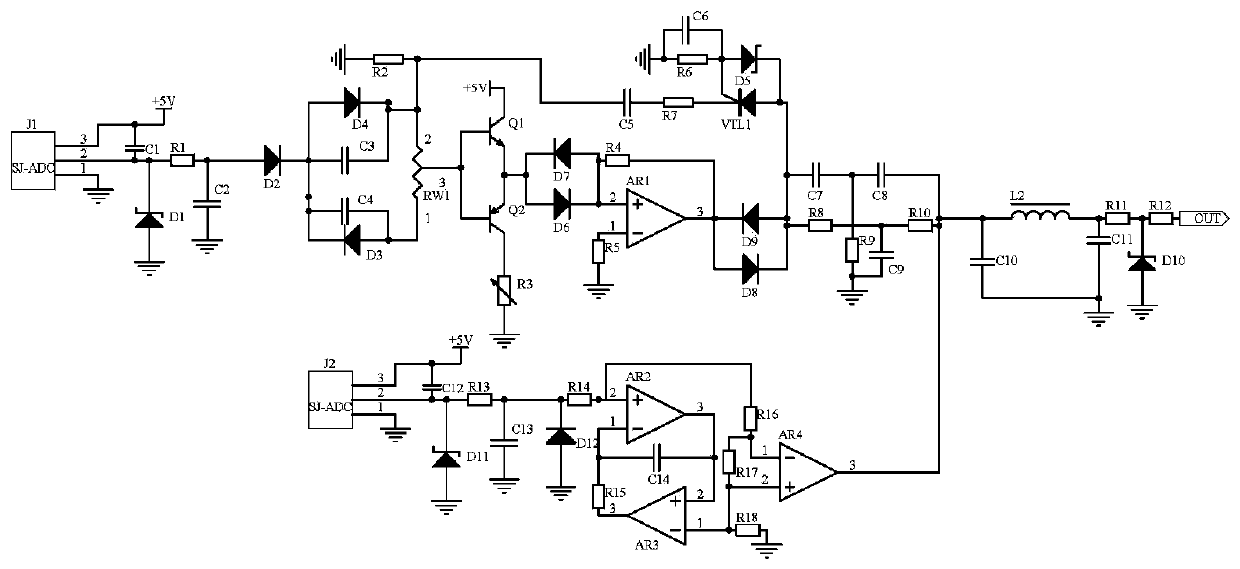

The invention discloses a household video monitoring system. The system comprises a frequency acquisition circuit 1, a frequency acquisition circuit 2, a rectification calibration circuit and a filtering output circuit. The frequency acquisition circuit 1 and the frequency acquisition circuit 2 respectively acquire analog signals at the input end and the output end of a signal transmission channelin a control terminal of the household video monitoring system. The rectification calibration circuit uses a variable resistor RW1, a capacitor C4, and a capacitor C3 to form a rectifying circuit torectify the signal, and uses a diode D6-diode D9 and an amplifier AR1 to form a composite circuit for signal limiting, amplification, and limiting processing. The frequency acquisition circuit 2 usesthe op amp AR2-AR4 and the capacitor C14 to form a loss compensation circuit to compensate the output signal of the rectification and calibration circuit. Finally, the filter output circuit uses the inductor L2, the capacitor C10, and the capacitor C11 to form a [pi]-type filter circuit. The filtered output can convert the signal frequency into a compensation signal of the signal at the output endof the signal transmission channel in the control terminal of the home video monitoring system.

Owner:冯芊雅

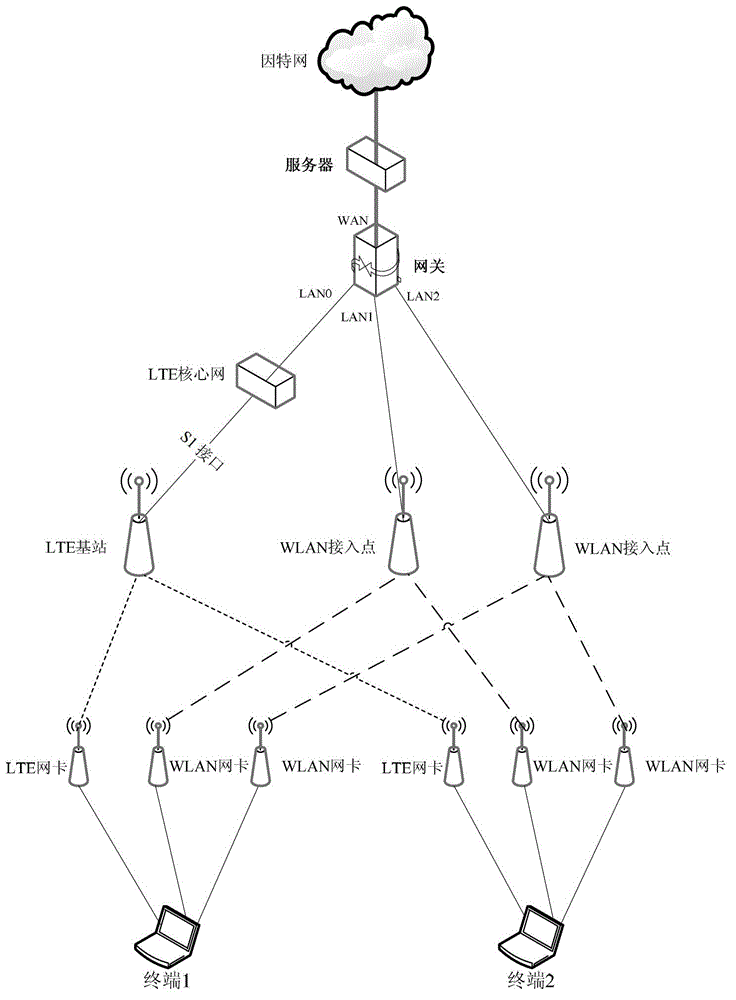

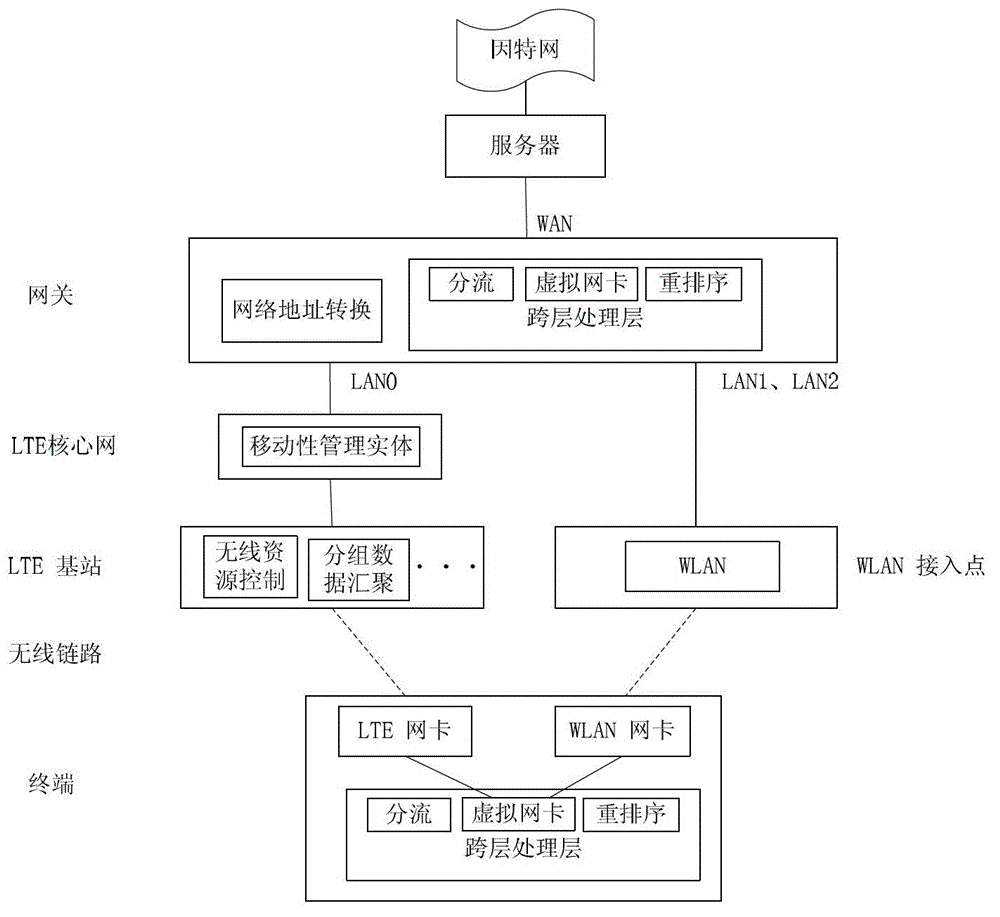

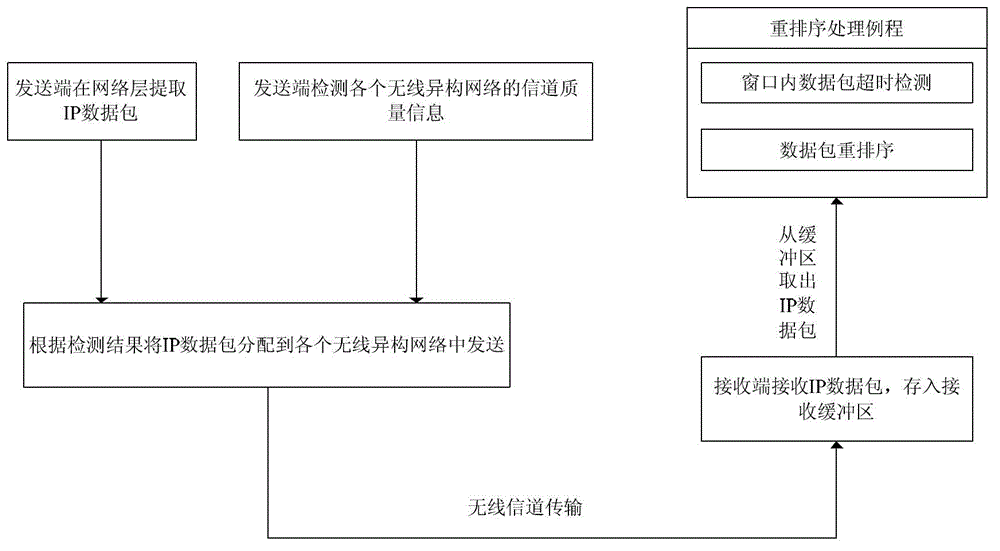

Data concurrence transmission method based on cross-layer optimization in wireless heterogeneous network system

InactiveCN103067977AImprove end-to-end throughputReduce latencyNetwork traffic/resource managementData packNetworked system

The invention relates to a data concurrence transmission method based on cross-layer optimization in a wireless heterogeneous network system. The data concurrence transmission method based on cross-layer optimization in the wireless heterogeneous network system comprises the following steps: a gateway is defined as an assembling point of a plurality of wireless heterogeneous networks which are assembled between a server and a terminal; a new protocol layer, namely a cross-layer processing layer, is built between a network layer and a data link layer of the gateway, and meanwhile, a visual interface card is built on the cross-layer processing layer; when data transmitted from the server arrives at the gateway, an internet protocol (IP) data package is abstracted from the network layer of the gateway, and meanwhile, information channel quality information of each wireless heterogeneous network is detected by the gateway; and the IP data package to be sent is allocated to the each wireless heterogeneous network by the cross-layer processing layer according to detection results and is sent to terminal equipment; the terminal receives the data, puts the received IP data package into a receiving buffering area, and conducts reordering and processing routines on the IP data package in the buffering area. The data concurrence transmission method based on cross-layer optimization in the wireless heterogeneous network system can increase end-to-end transmission speed of the network, reduce service end-to-end transmission delay, and achieve equalization transmission of concurrence data in the wireless heterogeneous network system.

Owner:HUAZHONG UNIV OF SCI & TECH

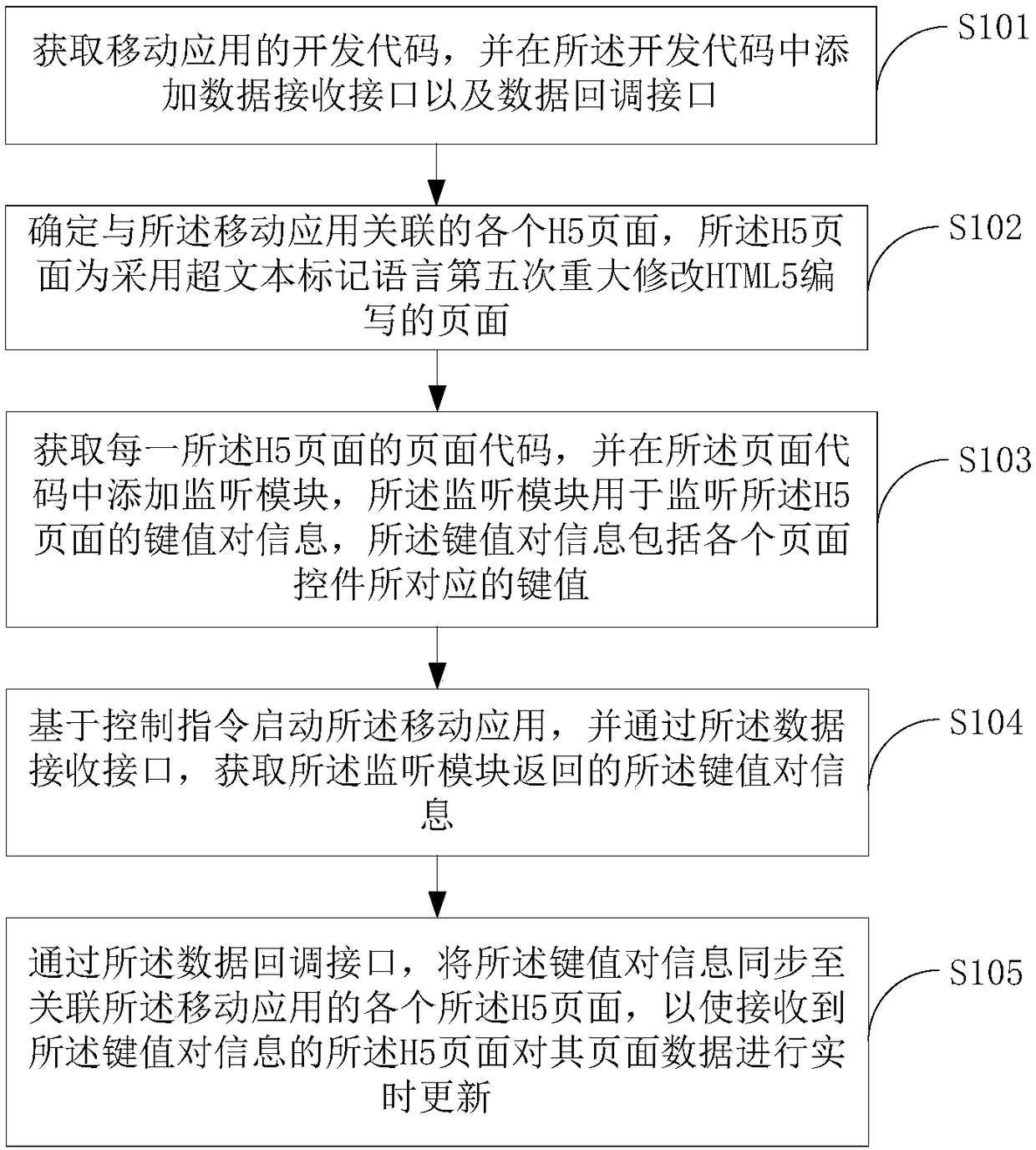

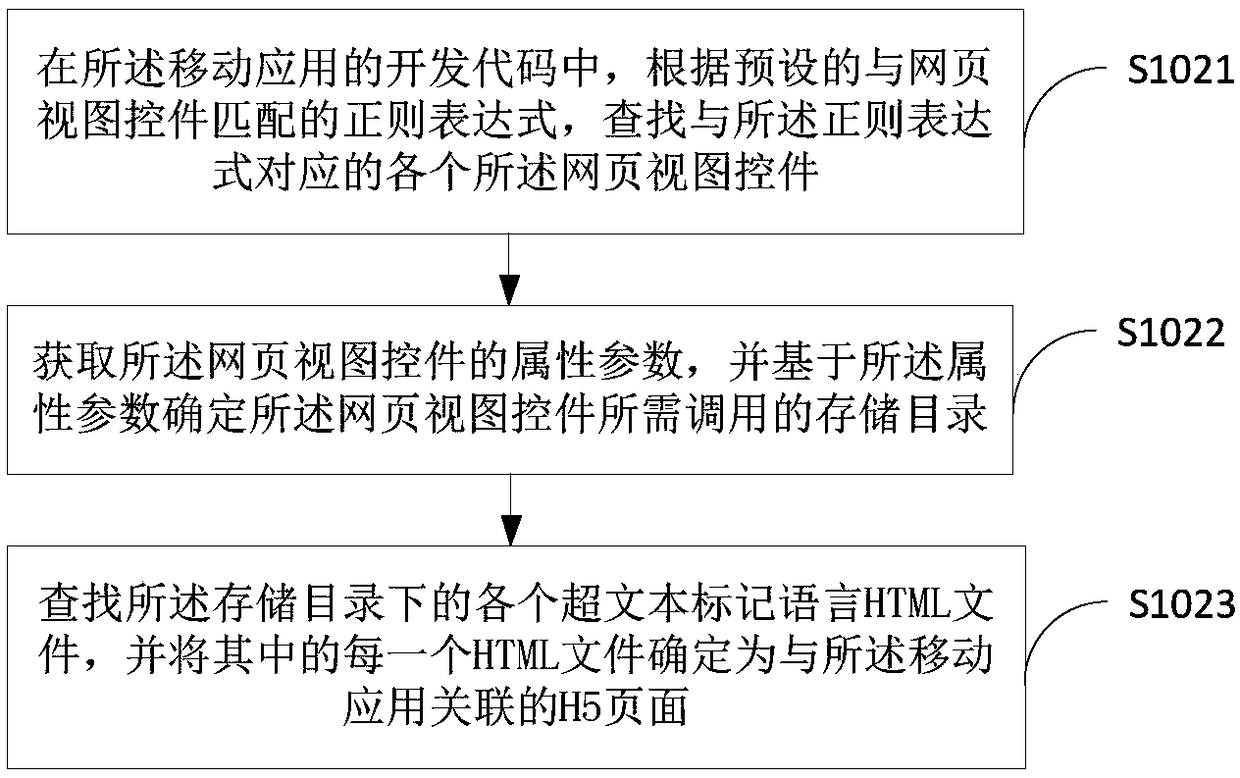

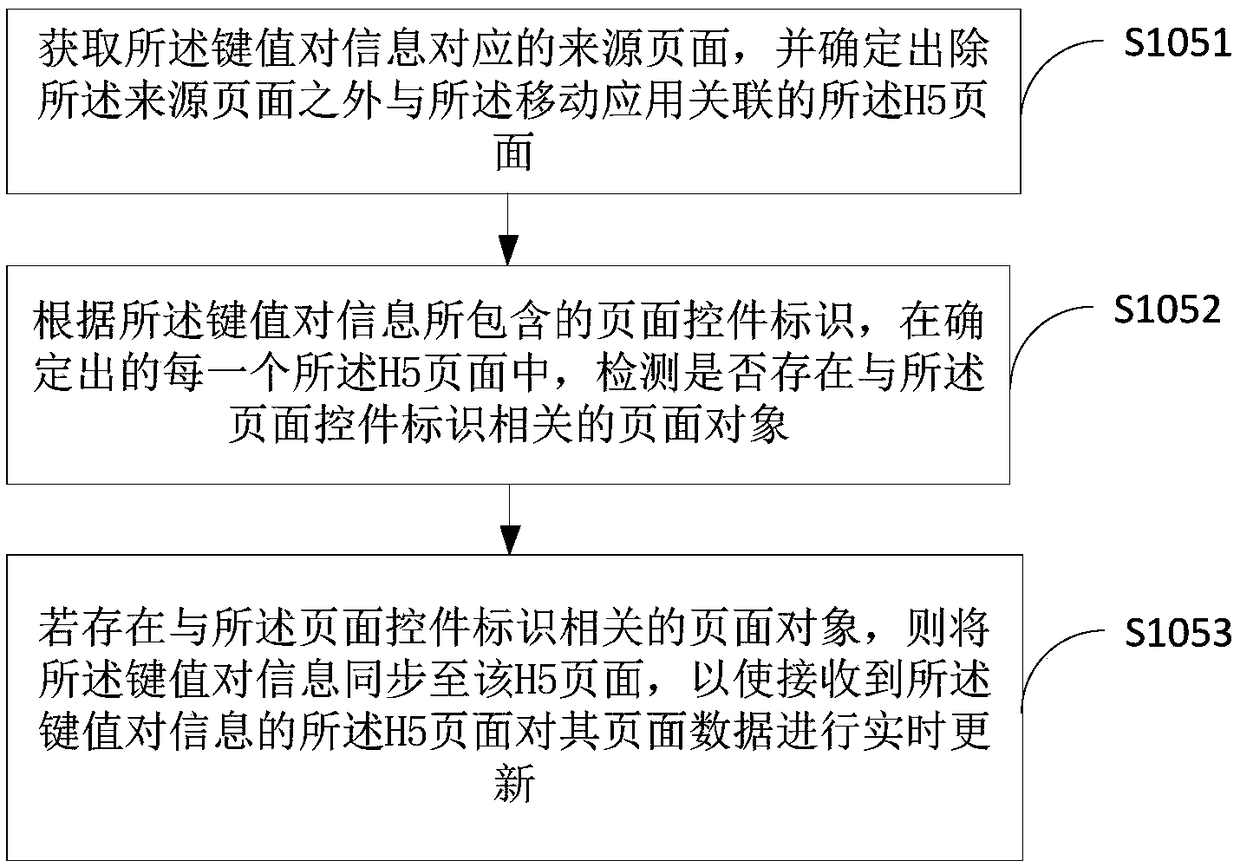

Method for updating page data, terminal device and medium

PendingCN109446457AImprove data refresh effectImplement synchronous updatesWebsite content managementWeb data browsing optimisationData synchronizationThe Internet

The invention is applicable to the technical field of the Internet, and provides a method for updating page data, a terminal device and a medium. The method comprises the following steps of obtaininga development code of a mobile application; adding a data receiving interface and a data callback interface into the development code; determining respective H5 pages associated with the mobile application; obtaining the page code of each H5 page, and adding a listening module into the page code, wherein the listening module is used for listening to the key value pair information of the H5 page, and the key value pair information comprises the key values corresponding to each page control; starting the mobile application based on the control instruction, and obtaining the key-value pair information returned by the monitoring module through the data receiving interface; through the data callback interface, synchronizing the key-value pair information to each associated H5 page, so that theH5 page receiving the key-value pair information updates its page data. The invention realizes the data synchronous updating among a plurality of H5 pages, greatly improves the data refreshing effectof the H5 pages, and maintains the consistency of the page data.

Owner:PINGAN PUHUI ENTERPRISE MANAGEMENT CO LTD

Submergible carrier

InactiveCN107867372AHigh security concealed survival performanceEnsure safetyWaterborne vesselsSpecial purpose vesselsEngineeringHeavy equipment

The invention relates to a submergible carrier carrying main battle tanks and other land battle heavy equipment to submerge and sail across a sea for beach landing and invasion. The submergible carrier is mainly used for carrying closed waterproof tanks and other equipment or goods and materials on a simple and open carrying platform, performs shallow and deep submerging relying on downstream wings under the assistance of an external power in an under-water distribution and dispersion state and a serial traction way and can be self-powered to sail for beach landing and invasion. Therefore, theconcealing performance of the submergible carrier and the equipment carried by the submergible carrier are strong during sailing, the submergible carrier can be really prevented from being attacked by various guided weapons and cluster munitions, and the phenomenon is also avoided that the individual carrier or equipment is damaged of breaks down and accordingly battle of other carrier equipmentis affected.

Owner:王宜

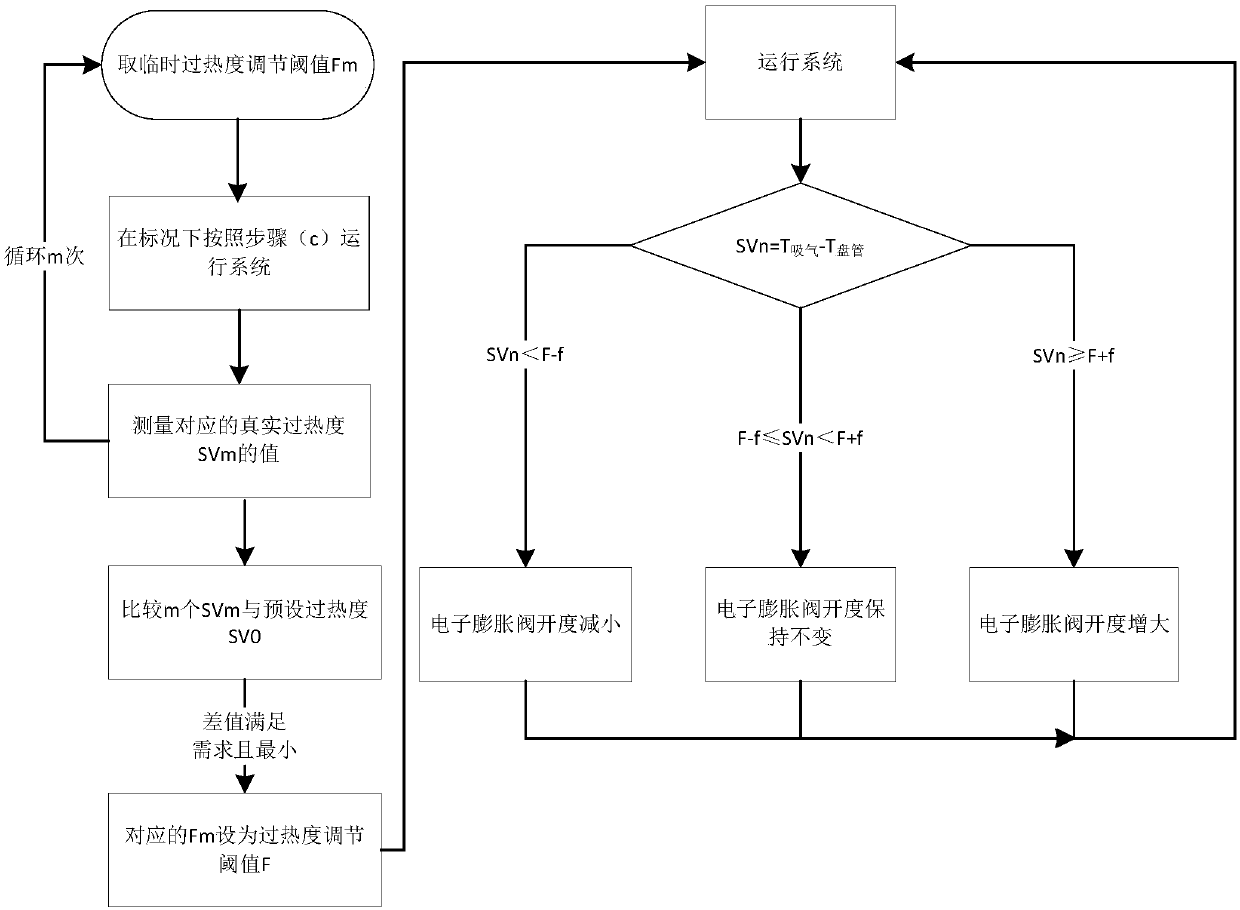

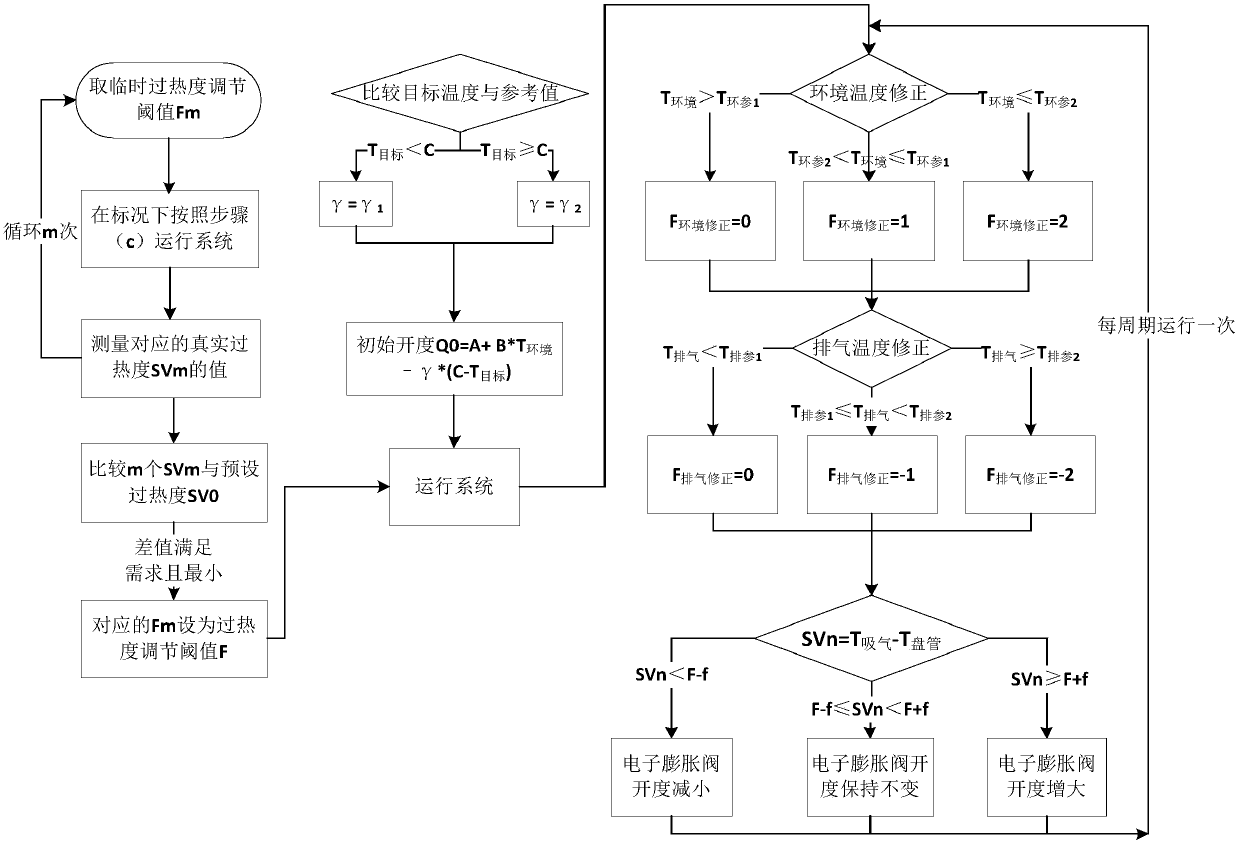

Method for adjusting electronic expansion valve

ActiveCN107606830AImprove operating economyAvoid disorderMechanical apparatusEfficient regulation technologiesSystem stabilityElectronic expansion valve

The invention provides a method for adjusting an electronic expansion valve. The method comprises the following steps: (a) acquiring superheat degree adjusting threshold F of a refrigerating system; (b) measuring the value of superheat degree SVn, wherein n is a natural number; and (c) determining the running mode of the electronic expansion valve according to the value of the superheat degree SVnmeasured in step (b); keeping the electronic expansion valve in current opening degree in case of SVn is not less than F-f and is less than F+f; decreasing the opening degree of the electronic expansion valve if the SVn is less than F-f; increasing the opening degree of the electronic expansion valve if the SVn is not less than F+f, wherein f is deviation value. According to the method, the system data can be detected through the control method when the system runs, and the opening degree is changed in real time so as to improve the system stability. Therefore, the system can be kept within asafe and reasonable working condition range all the time under the variation of the load and outer conditions, and meanwhile, the operation economy of the system under various working condition changing conditions can be improved; and the defect that the control method of an electronic expansion in the prior art is incomplete in case of the change of outside environment and the system cannot be kept in the optimal state all the time can be overcome.

Owner:ZHEJIANG AMA & HIEN TECH

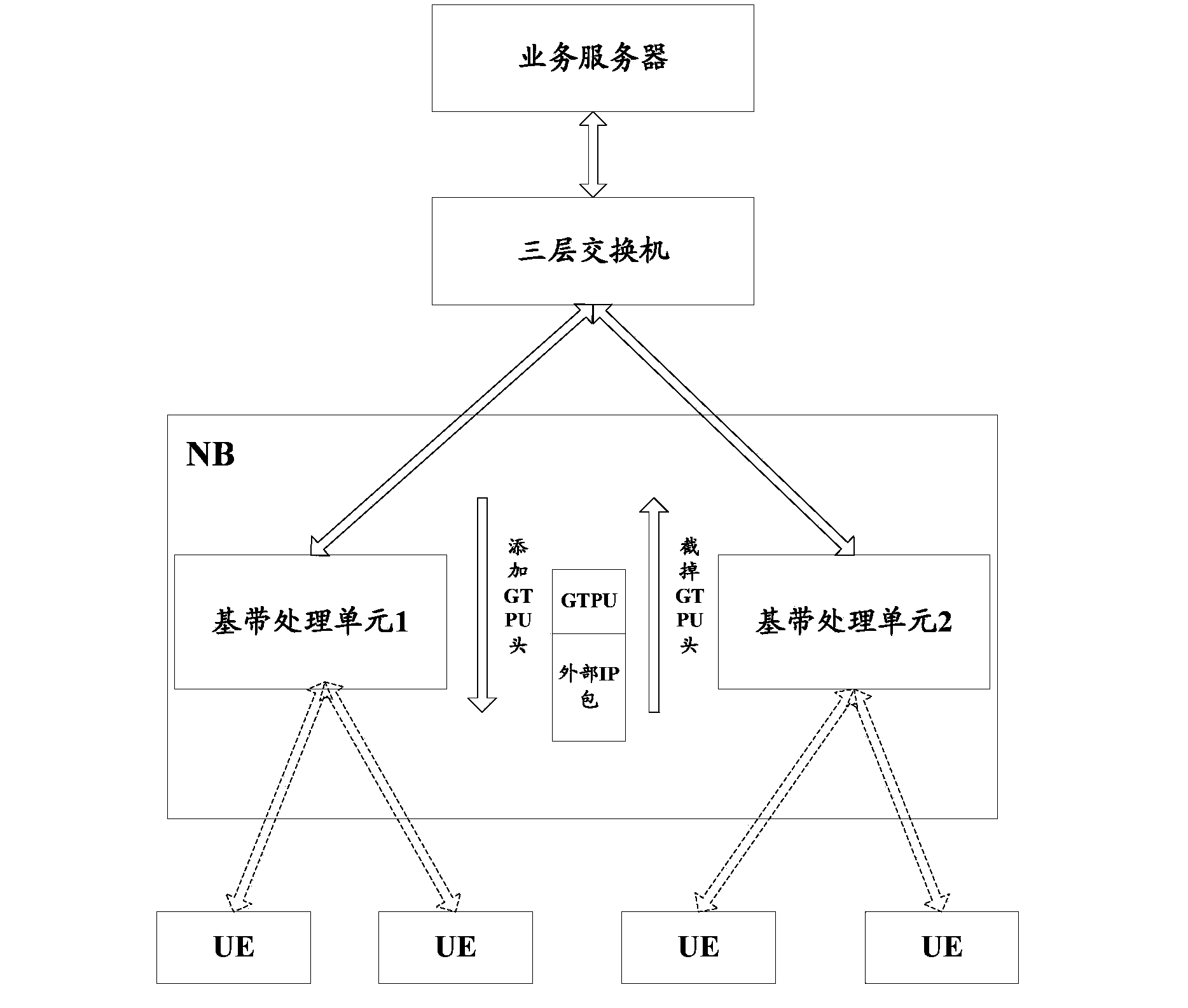

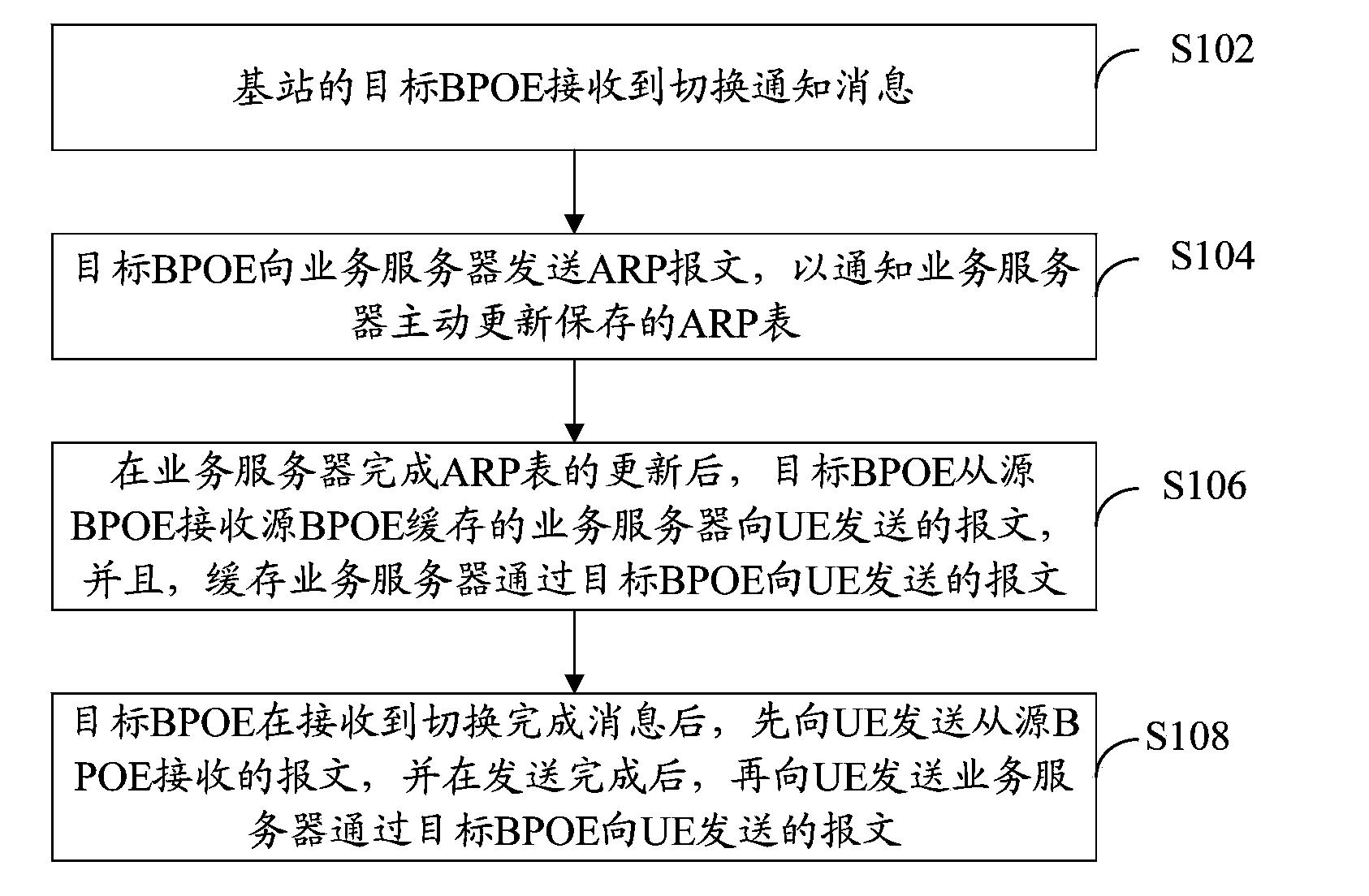

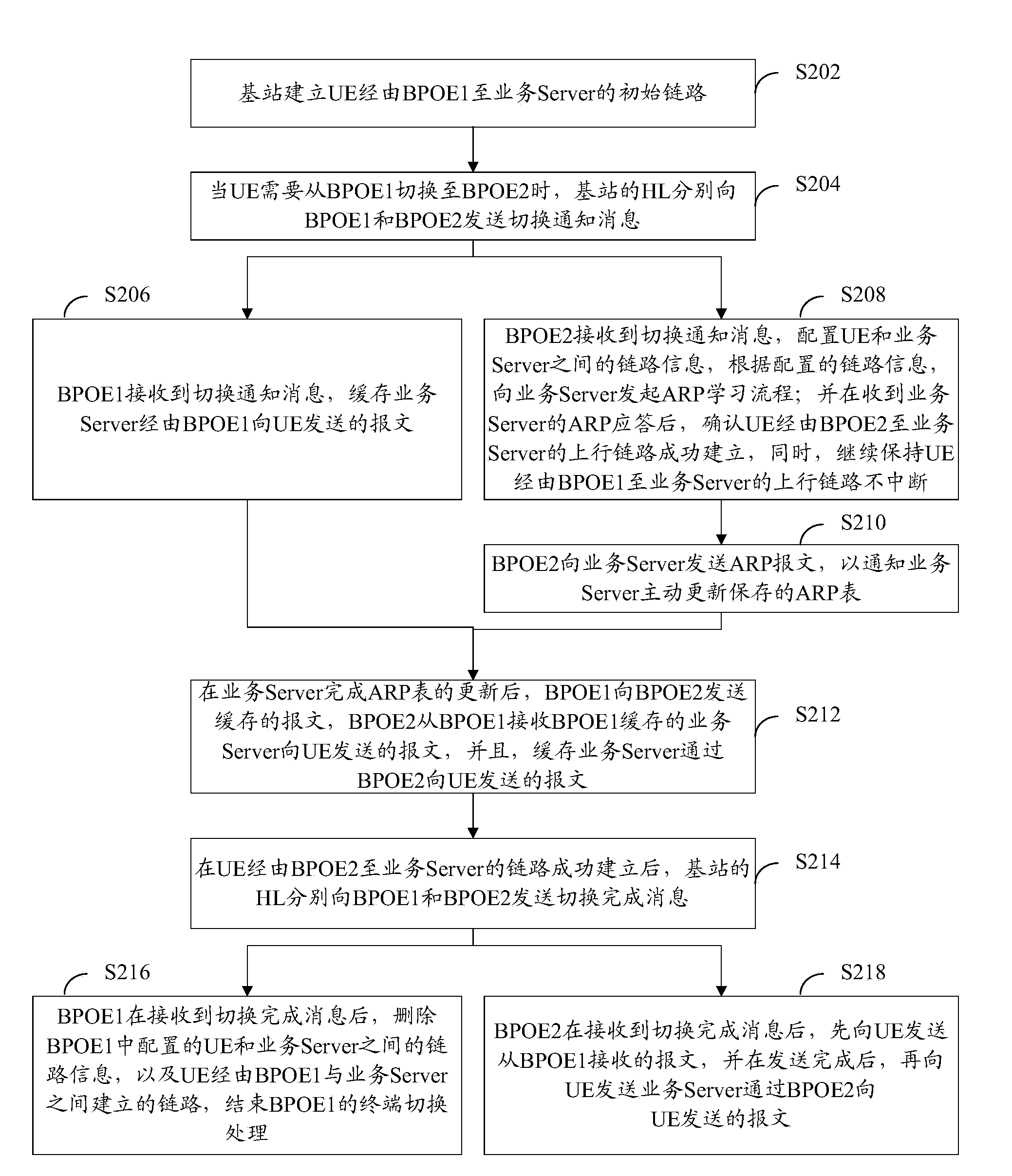

Terminal switching method and base station

ActiveCN103686888AUninterrupted and maintain transfer rateEfficient perceptionWireless communicationTransmission channelComputer terminal

The invention provides a terminal switching method and a base station. The terminal switching method is used for intra-base-station terminal switching in an MME mode and comprises the steps that a BPOE of the base station receives a switching notification message; a target BPOE sends an ARP message to a service server to inform the service server of active updating of a saved ARP table; after the updating of the ARP table is accomplished by the service server, the target BPOE receives a message, sent to UE by the service server and cached in a source BPOE, from the source BPOE, and a message sent to the UE by the service server through the target BPOE is cached; the target BPOE sends the message received from the source BPOE to the UE firstly after receiving a switching completion message and then sends the message sent to the UE by the service server through the target BPOE to the UE. According to the terminal switching method and the base station, a transmission channel for switching can be provided fast, interruption of service during switching is avoided, and certain transmission rate is maintained.

Owner:DATANG MOBILE COMM EQUIP CO LTD

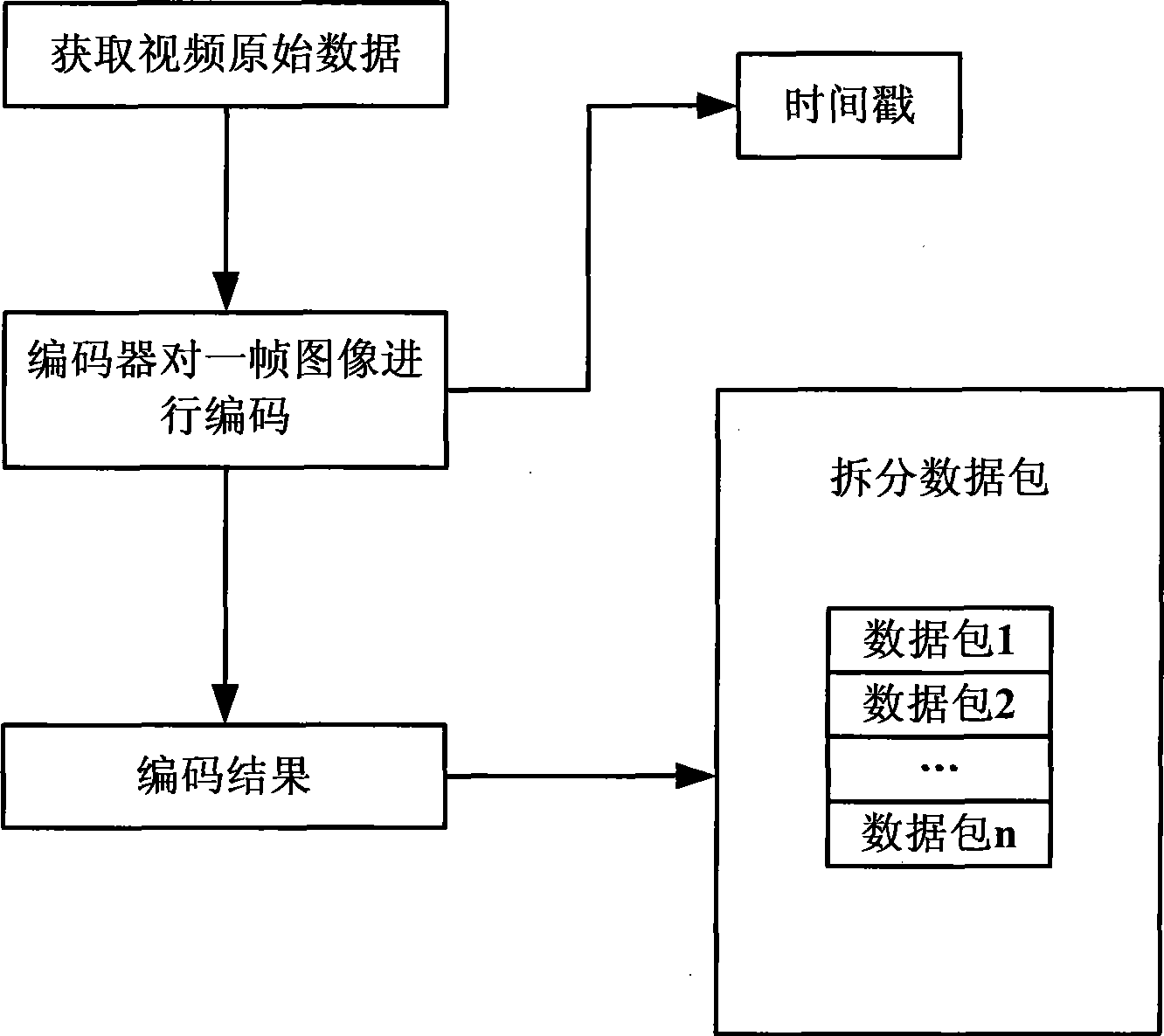

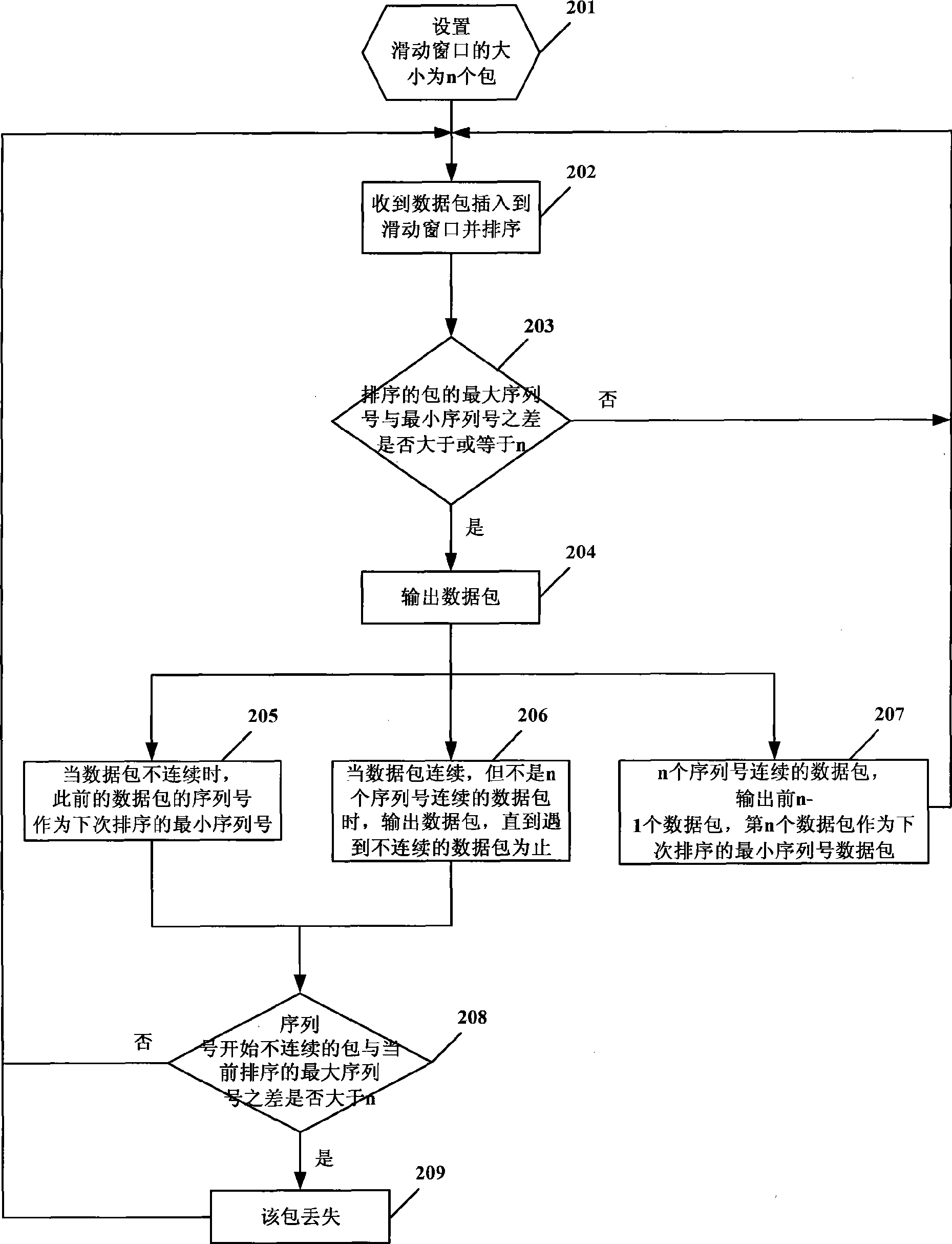

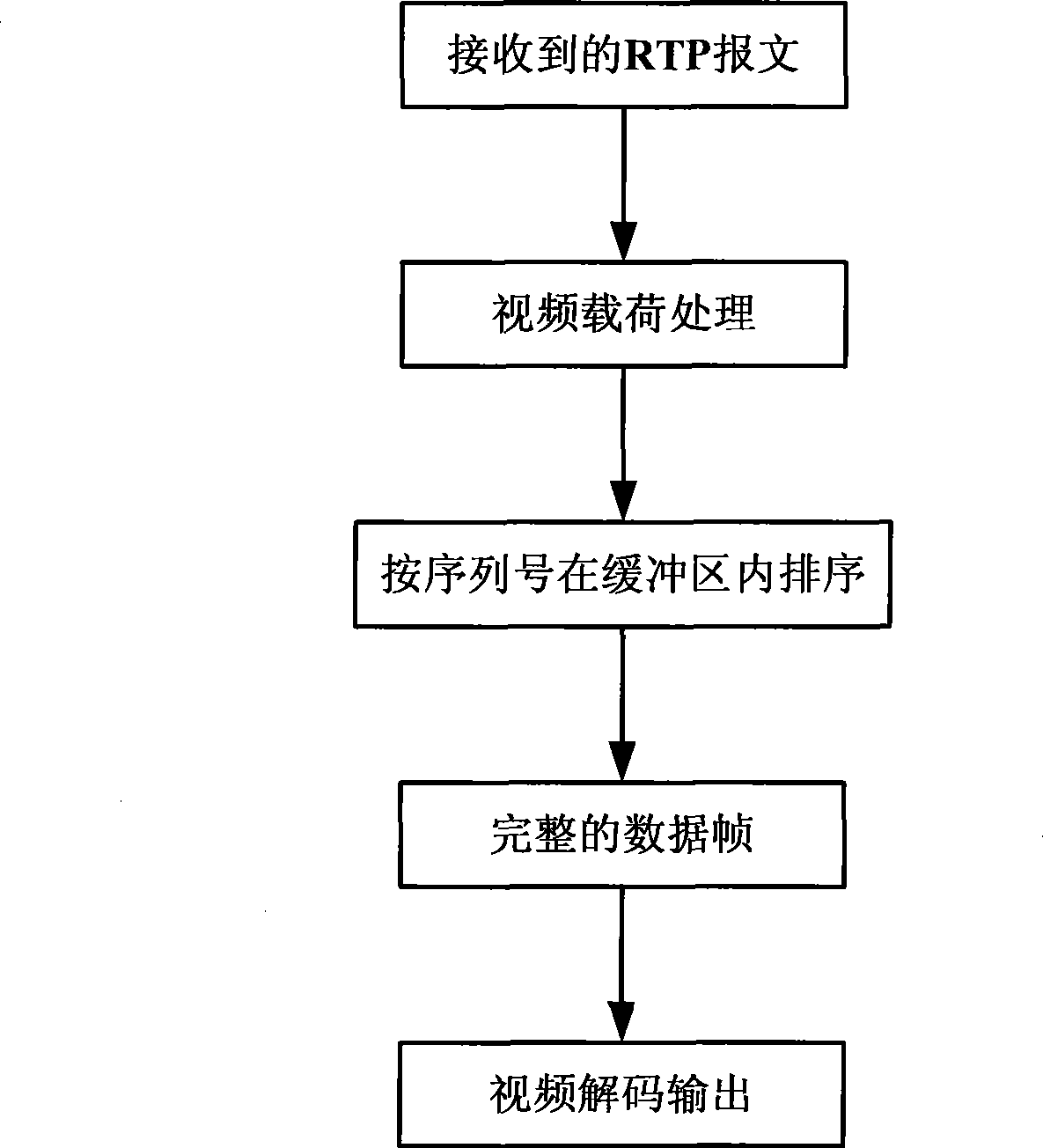

Data transmission method based on RTP

InactiveCN101394252AAvoid disorderImprove transmission efficiencyError preventionData transmissionSlide window

The invention discloses an RTP-based data transmitting method in the technical field of computer network multimedia communication. The technical scheme is as follows: assuming that the size of the sliding window is data packets numbering n; inserting the received data packets into the sliding window and sorting; when the difference between the maximum serial number and the minimum serial number of the sorted data packets is larger than or equal to n, starting to output the sorted data packet from the minimum serial number, wherein if the serial number is continuous, the data packets can be outputted, and if the serial number is not continuous, the previous data packet is taken as the minimum serial number of the next sorting; if the difference between the maximum serial number of the data packet, the serial number of which is not continuous at the start, and the maximum serial number of the current sorted data packet is larger than n, confirming that the data packet is missing; and if the serial number of the data packets numbering n is continuous, the previous data packets numbering n-1 are outputted, and the data packets numbering n is taken as the minimum serial number of the data packet in the next sorting. The invention avoids the problem of the disorder during the process of data packet transmitting.

Owner:BEIJING JIAXUN FEIHONG ELECTRIC CO LTD

Method and system to control quality in cold rolling system

InactiveCN102179413AQuality improvementEasy transferMeasurement devicesMeasuring devicesSheet steelCurrent sensor

The invention discloses a method and a system to control quality in a cold rolling system capable of preventing frequent chatter masks and hot cracks in the continuous cold rolling process. Meanwhile, the distortion and cutting of steel plates due to the roughness difference between the upper and lower surfaces of steel plates is also prevented. More specifically, the invention discloses a system and a method for detecting the quality abnormality in a cold rolling system, wherein a vibration sensor, a torque sensor, a temperature sensor and a current sensor are arranged inside a rolling mill. The information measured by the above sensors are used for detecting signals which cause defects, which are also used for minimize the defect ratio of the steel plates being rolled.

Owner:POHANG IRON & STEEL CO LTD

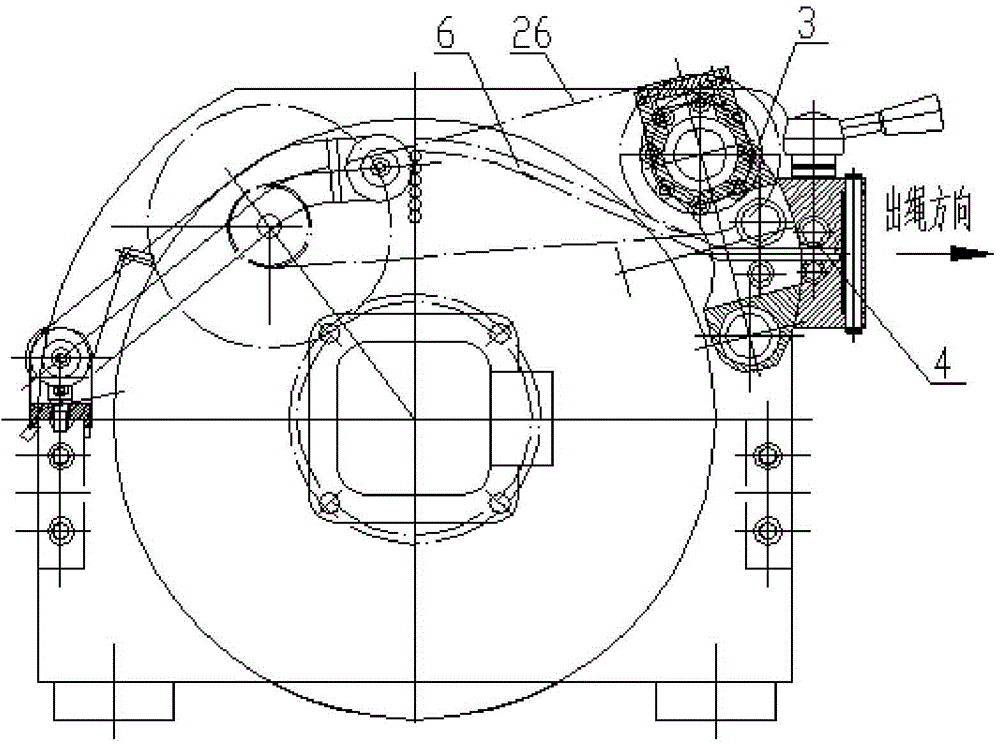

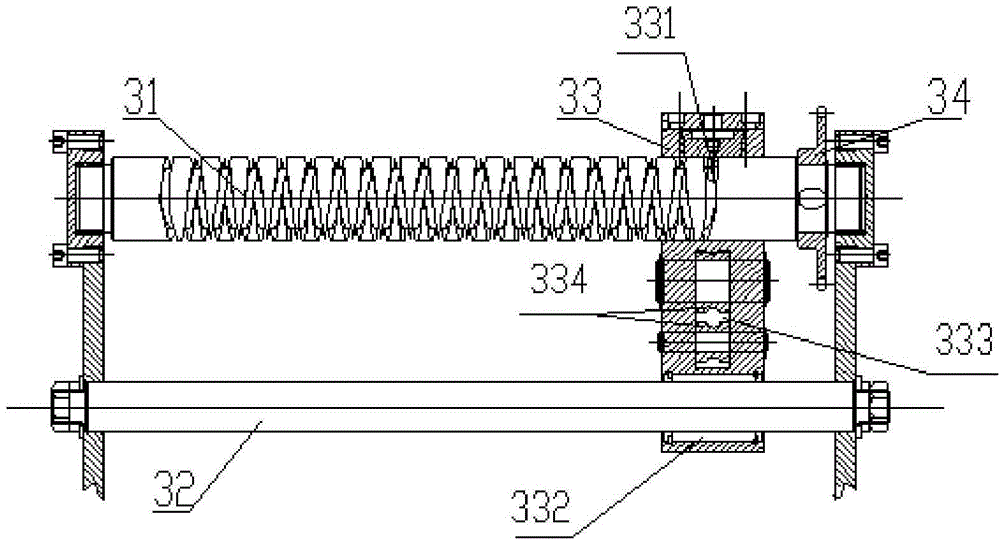

Rope-guiding hydraulic winch

The invention discloses a rope-guiding hydraulic winch. The rope-guiding hydraulic winch comprises an automatic rope aligning device. The automatic rope aligning device comprises a reciprocating shaft, a guide shaft and a rope aligning base. The reciprocating shaft and the guide shaft are arranged on the circumferential outer side of a winding drum and are parallel to the axial direction of the winding drum. A bidirectional spiral groove is formed in the reciprocating shaft. A meshed tooth is arranged on the rope aligning base and meshed with the bidirectional spiral groove. A rope aligning hole for a steel wire rope to penetrate through is formed in the rope aligning base. A guide hole is formed in the rope aligning base and is in sliding fit with the guide shaft. While the reciprocating shaft synchronously rotates along with the winding drum, the rope aligning base moves in the axial direction of the reciprocating shaft and drives the steel wire rope on the rope aligning base to move together. A rope pressing device for tightly pressing the steel wire rope is arranged on the rope aligning base. By means of the rope-guiding hydraulic winch, the steel wire rope is tidily and orderly arranged on the winding drum, disorderly arranging of the steel wire rope and pressing and abrasion, which are caused by disorderly rope arranging, of the steel wire rope are avoided, the workloads generated when the rope is manually wound can be greatly reduced, and the service life of the steel wire rope can be prolonged.

Owner:ZHEJIANG NOWVOW MECHANICAL & ELECTRICAL

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com