Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

91results about How to "Accurate time delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

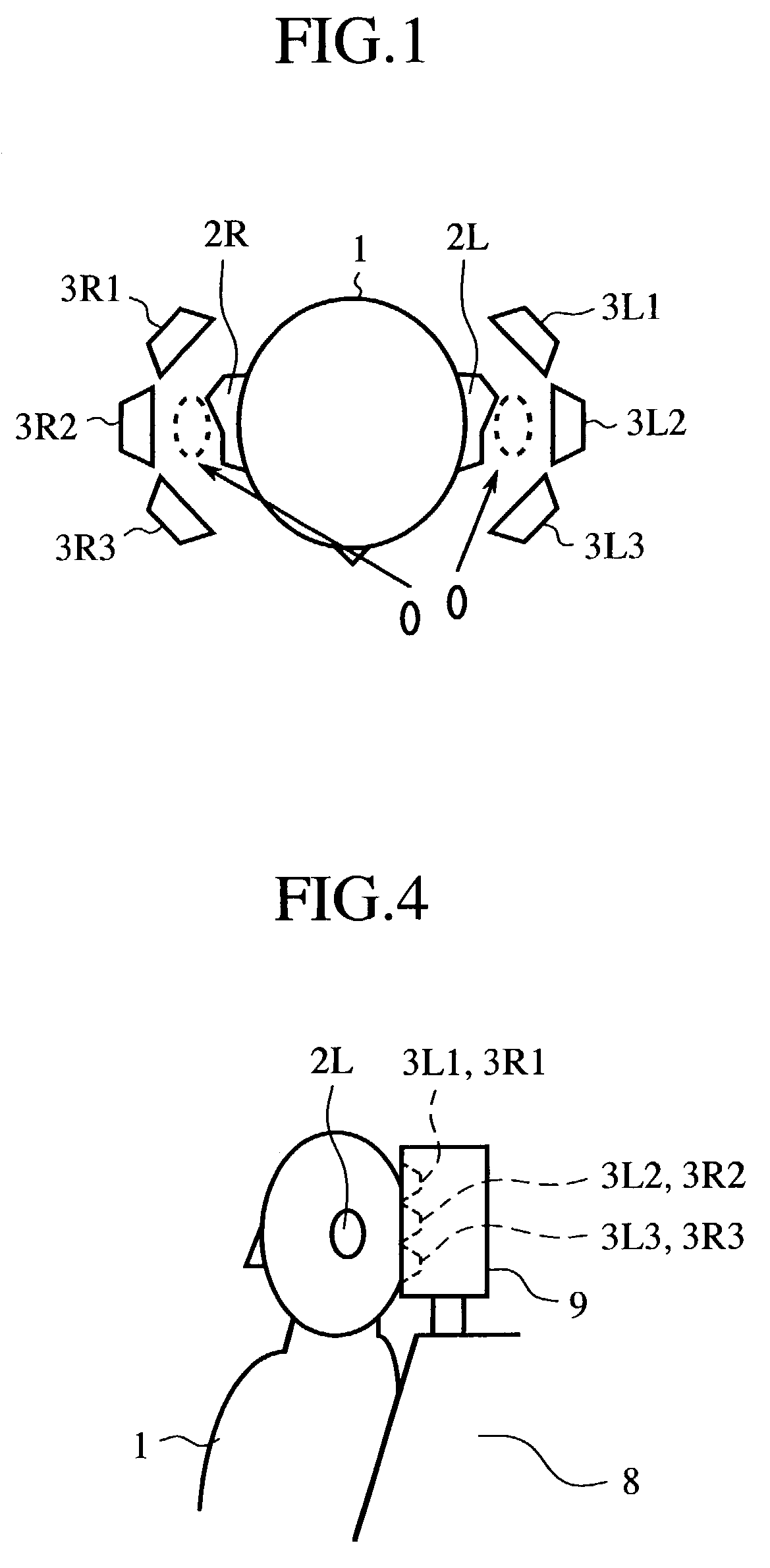

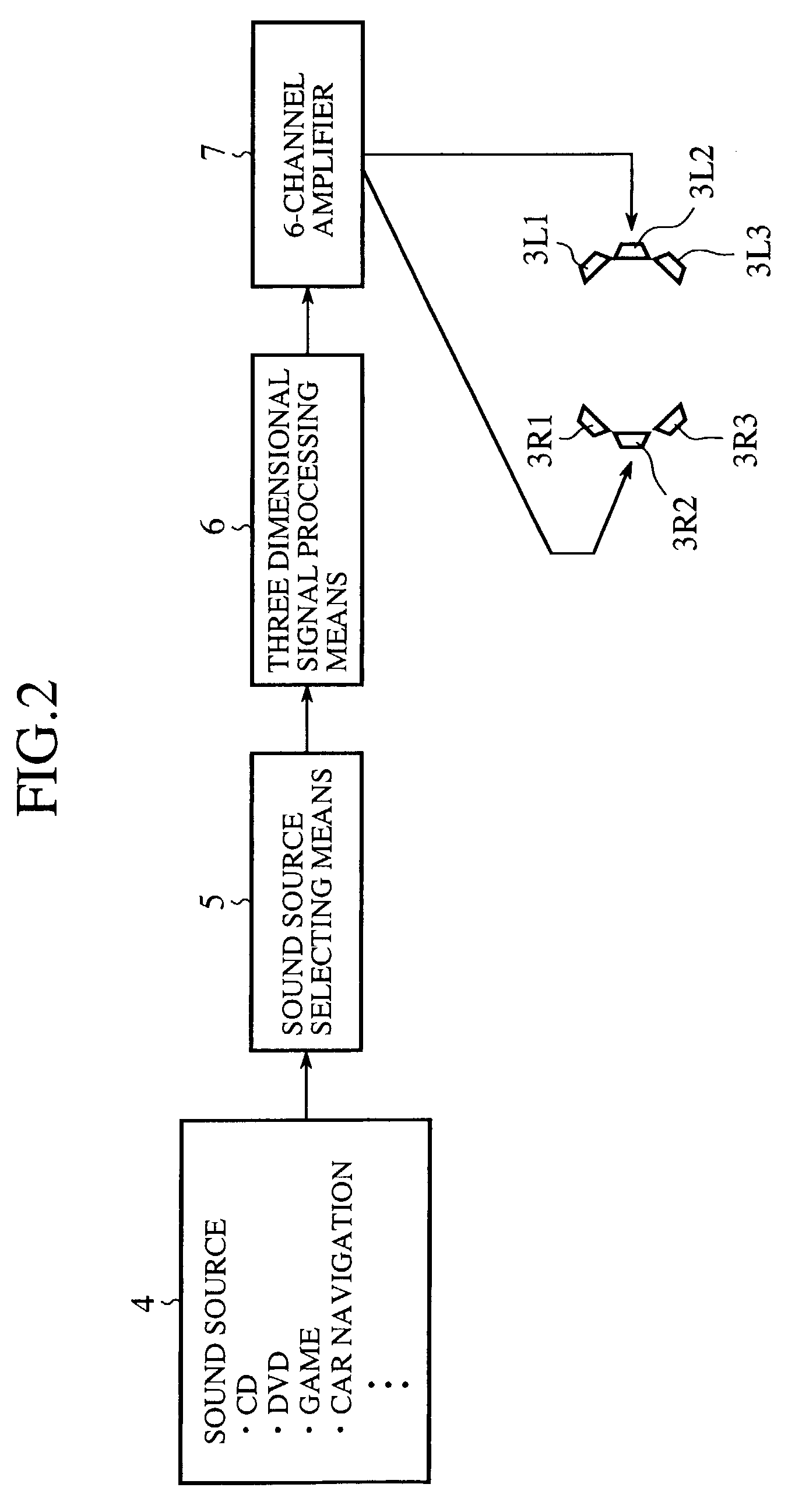

Vehicle-mounted stereophonic sound field reproducer

ActiveUS7684577B2Reduce crosstalkSmall distanceVehicle seatsEarpiece/earphone attachmentsSound sourcesRight external ear

In correspondence with the left and right external ears of a listener occupying a seat, a three dimensional sound field reproducing unit includes at least more than two speakers disposed on a headrest on the top of a backrest of the seat, and three dimensional signal processing means which converts an output signal from a sound source into a three dimensional sound field signal for supplying it to each of the speakers. Three dimensional sound field with high accuracy and fidelity is reproduced near the external ears of the listener.

Owner:AUTO TECH GRP LLC

Time-delay circuit

InactiveCN102130668AImprove performanceImprove reading speedSingle output arrangementsCapacitanceTime delays

The invention discloses a time-delay circuit. In the invention, a first PMOS (P-channel Metal Oxide Semiconductor) tube, a second NMOS (N-channel metal oxide semiconductor) tube, a first current source circuit, a second power supply circuit and a first capacitor form a first capacitance charge and discharge switching circuit; a third PMOS tube, a fourth NMOS tube, a third current source circuit, a fourth current source circuit and a second capacitor form a second capacitance charge and discharge switching circuit; and an input signal is output sequentially through the first capacitance charge and discharge switching circuit, a first buffer, the second capacitance charge and discharge switching circuit and a second buffer or a phase inverter. The time-delay circuit eliminates the influence of process offsets by utilizing the time delay of the two capacitance charge and discharge switching circuits to mutually compensate so as to ensure that the time delay is more precise.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

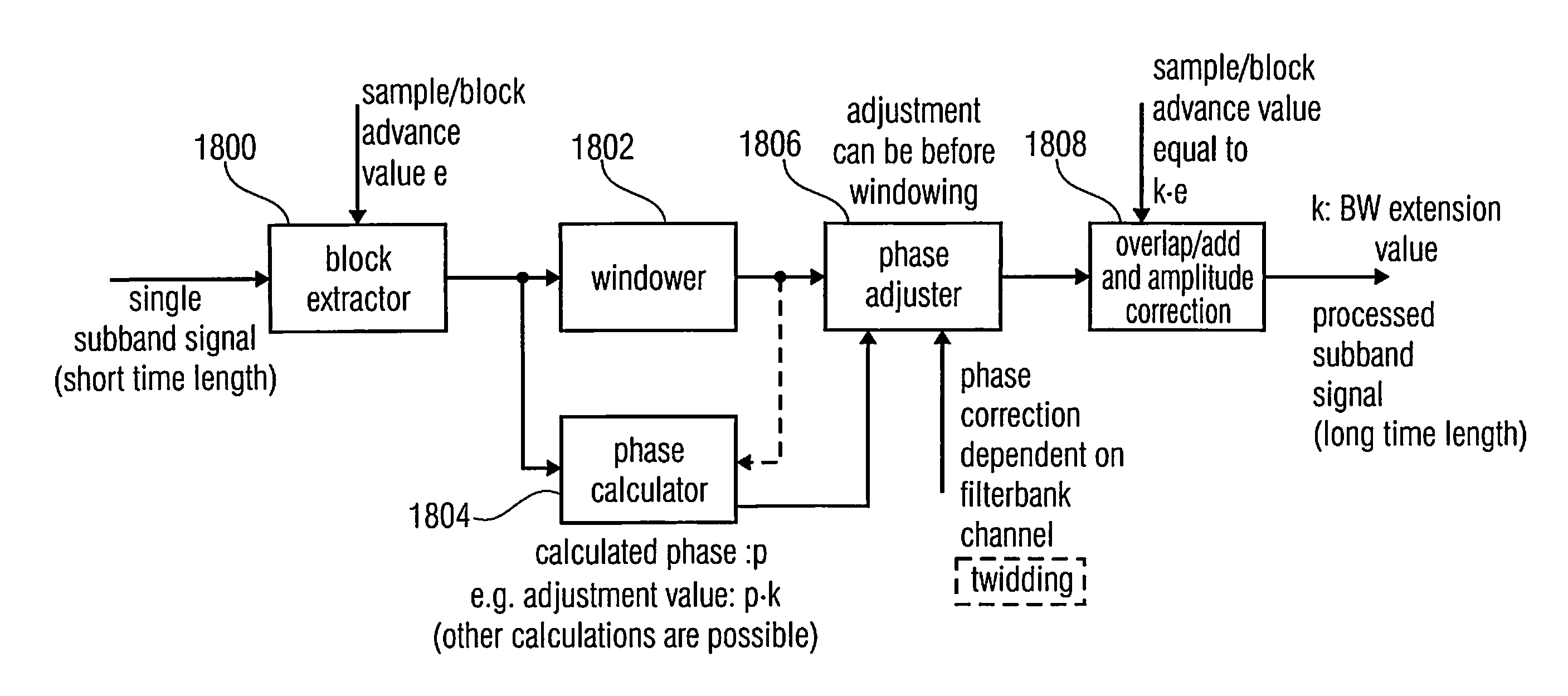

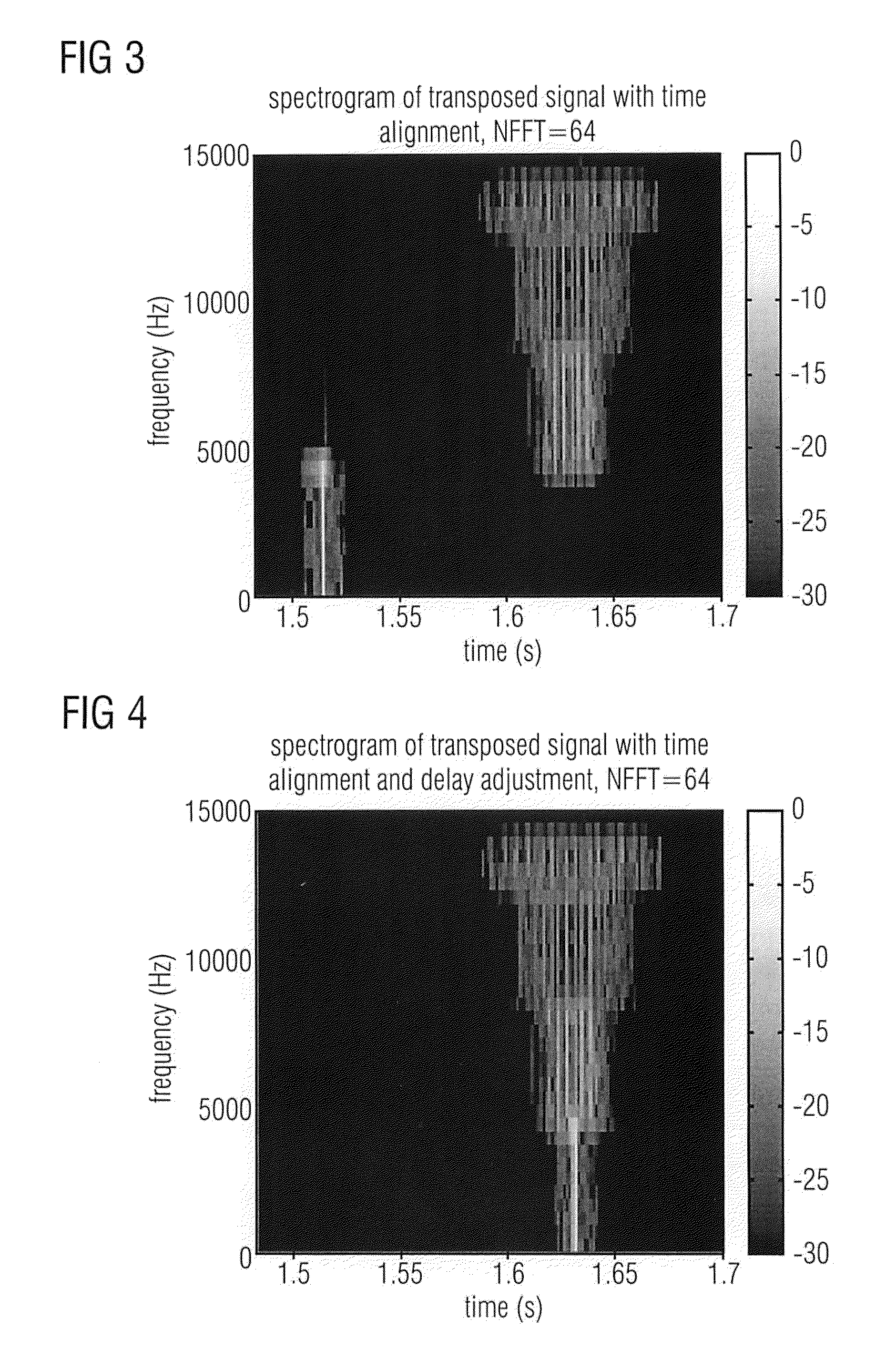

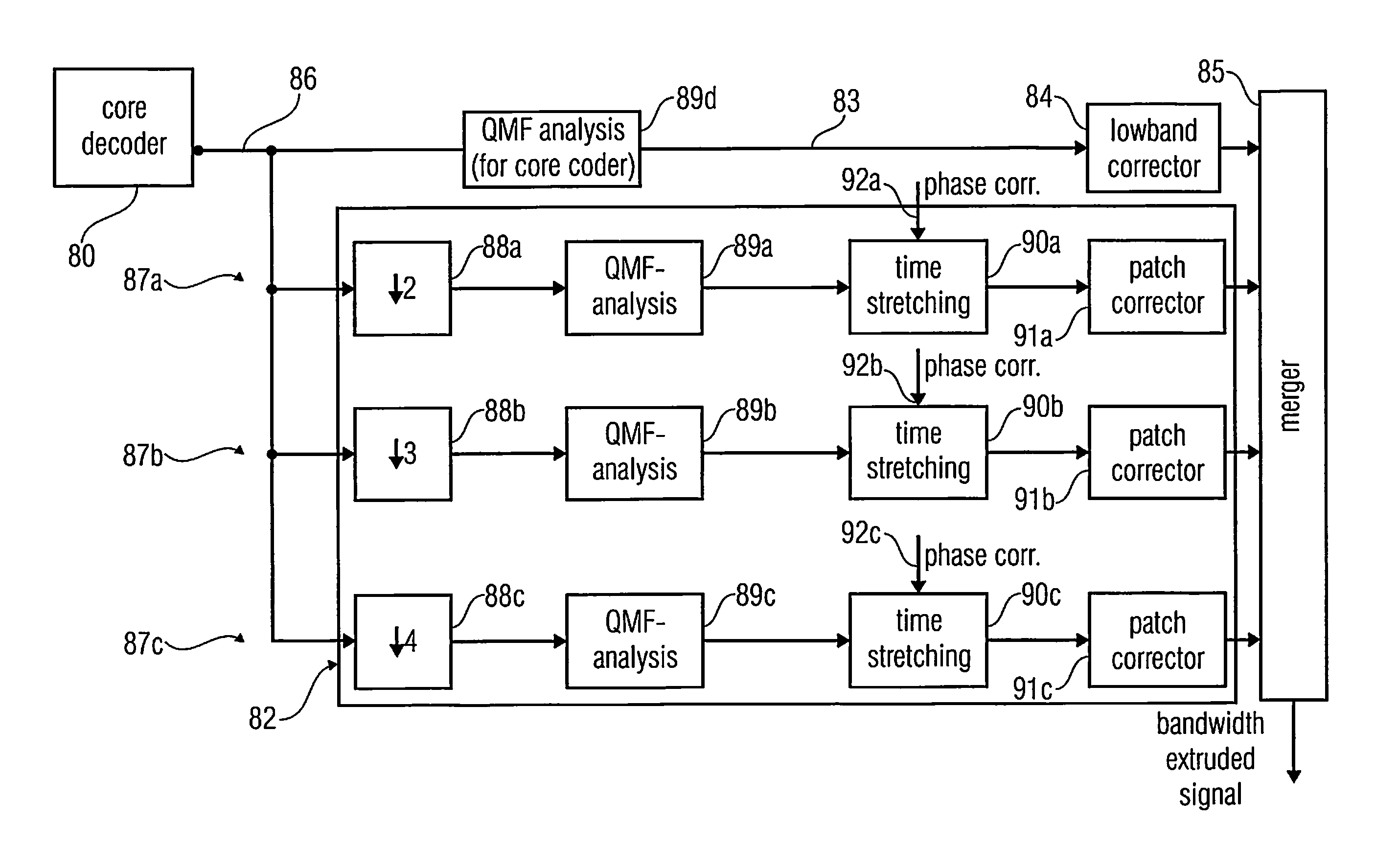

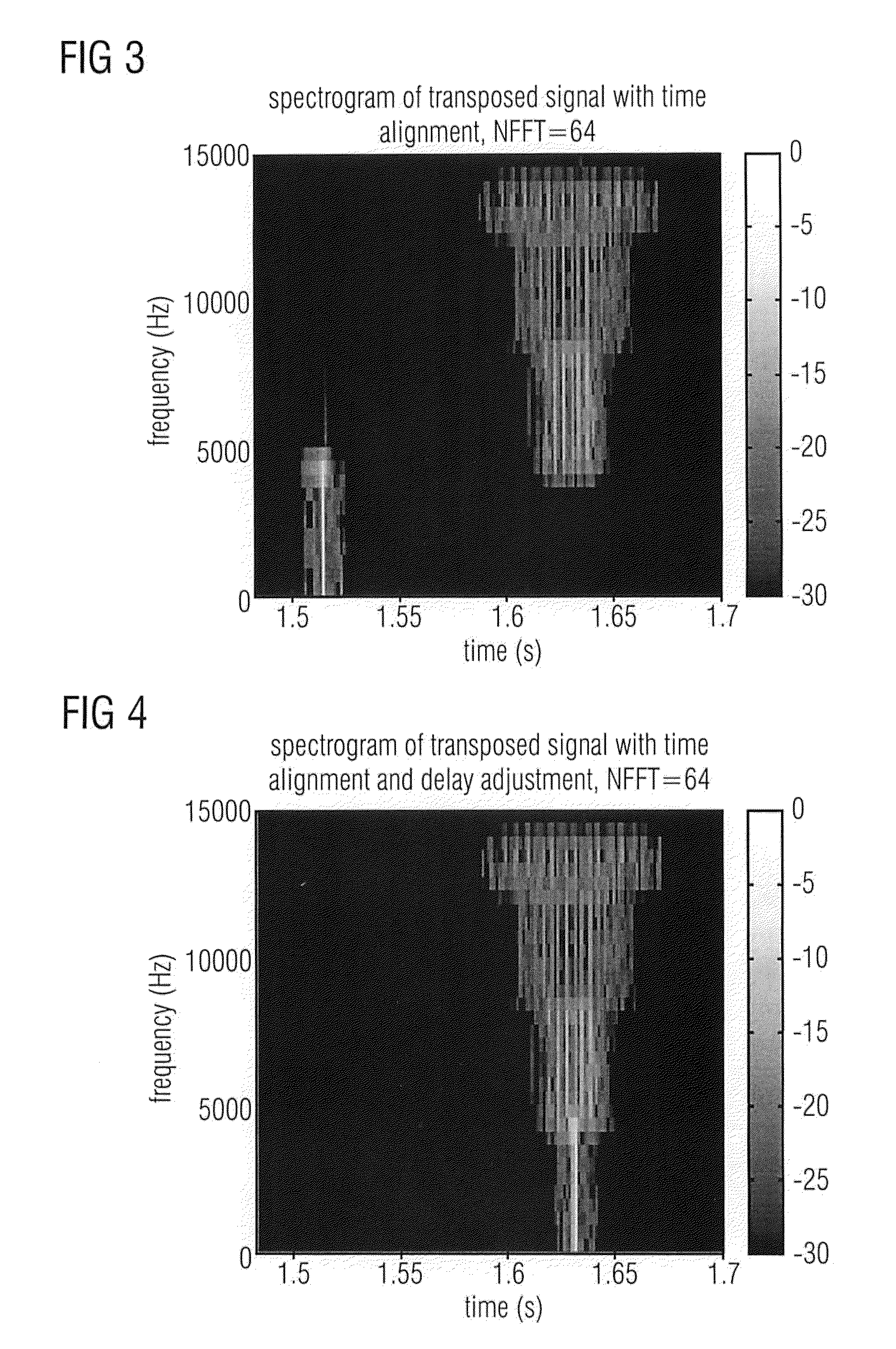

Device and method for improved magnitude response and temporal alignment in a phase vocoder based bandwidth extension method for audio signals

ActiveUS20130058498A1Impact magnitude responseAvoid negative effectsSpeech analysisFrequency/directions obtaining arrangementsPhase correctionBandwidth extension

An apparatus for generating a bandwidth extended audio signal from an input signal, includes a patch generator for generating one or more patch signals from the input signal, wherein the patch generator is configured for performing a time stretching of subband signals from an analysis filterbank, and wherein the patch generator further includes a phase adjuster for adjusting phases of the subband signals using a filterbank-channel dependent phase correction.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV +1

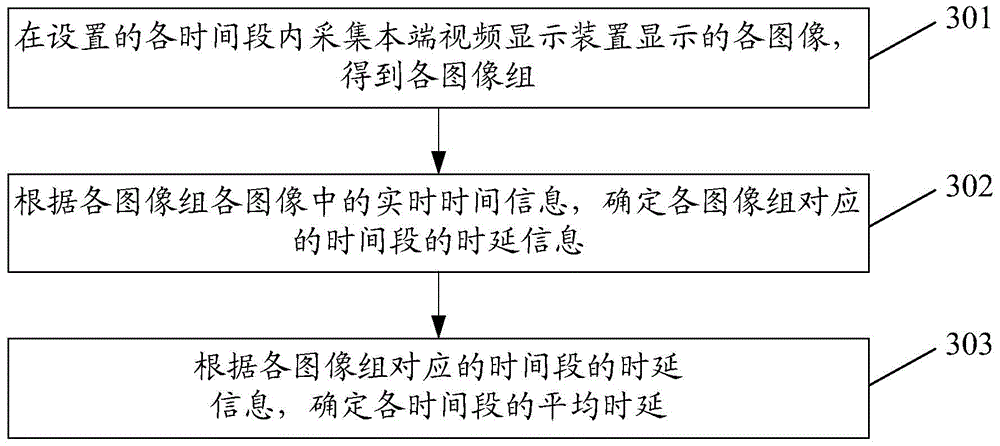

Video time delay detection method and device

ActiveCN105791986AEasy to measureQuick measurementTelevision conference systemsTwo-way working systemsTime informationTime delays

The invention discloses a video time delay detection method. The method comprises following steps of obtaining current first real time information of a local end image collection device and a first image displayed by a local end video display device at the same time, wherein the first image is the image containing the second real time information corresponding to the first image collected by the local end image collection device; and determining time delay information according to the first real time information and second real time information. The invention also discloses a video time delay detection device.

Owner:CHINA MOBILE COMM GRP CO LTD

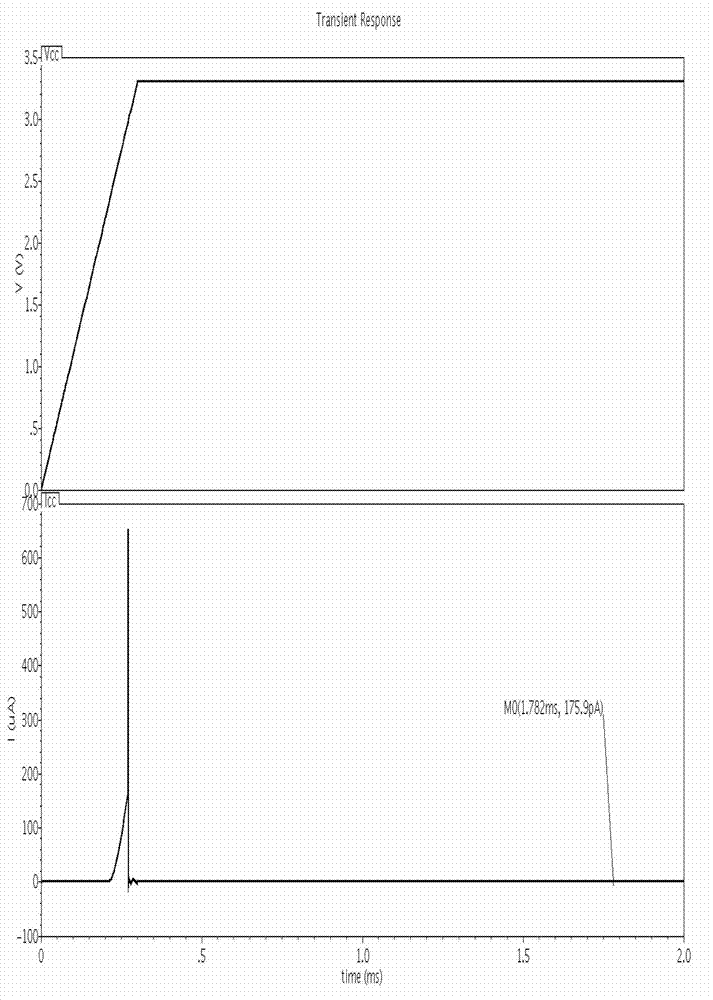

Power-on resetting circuit

ActiveCN102891670AReduce power consumptionAccurate time delayElectronic switchingCapacitanceLevel trigger

The invention discloses a power-on resetting circuit which comprises a power-on circuit, a level triggering circuit and a discharging circuit, wherein the power-on circuit comprises a current mirror, a first capacitor and a second capacitor; when power-on voltage is supplied to the power-on resetting circuit, the current mirror respectively charges the first capacitor and the second capacitor; the level triggering circuit is connected to a voltage reference node of a power-on circuit and is used for detecting the voltage of the voltage reference node and outputting a power-on resetting signal when the voltage of the voltage reference node is greater than a triggering value; and the discharging circuit is connected between the power-on circuit and the level triggering circuit and is used for discharging the first capacitor and the second capacitor after the power-on voltage disappears. By the power-on resetting circuit, when power voltage is powered on for many times, the power-on resetting signal can still be correctly generated; and after the resetting signal is generated, a static working current dose not exist, so that the power consumption is reduced.

Owner:广州润芯信息技术有限公司

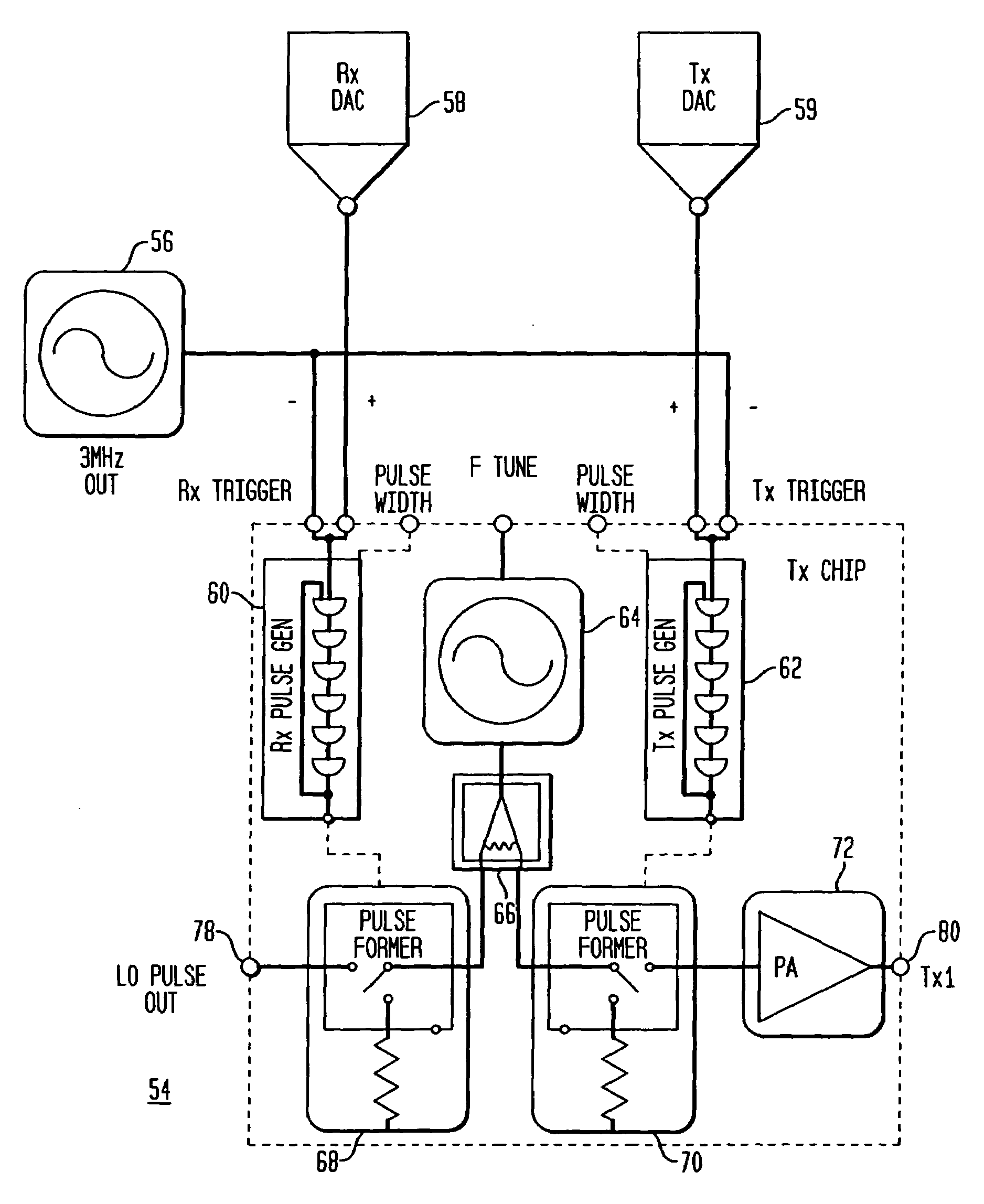

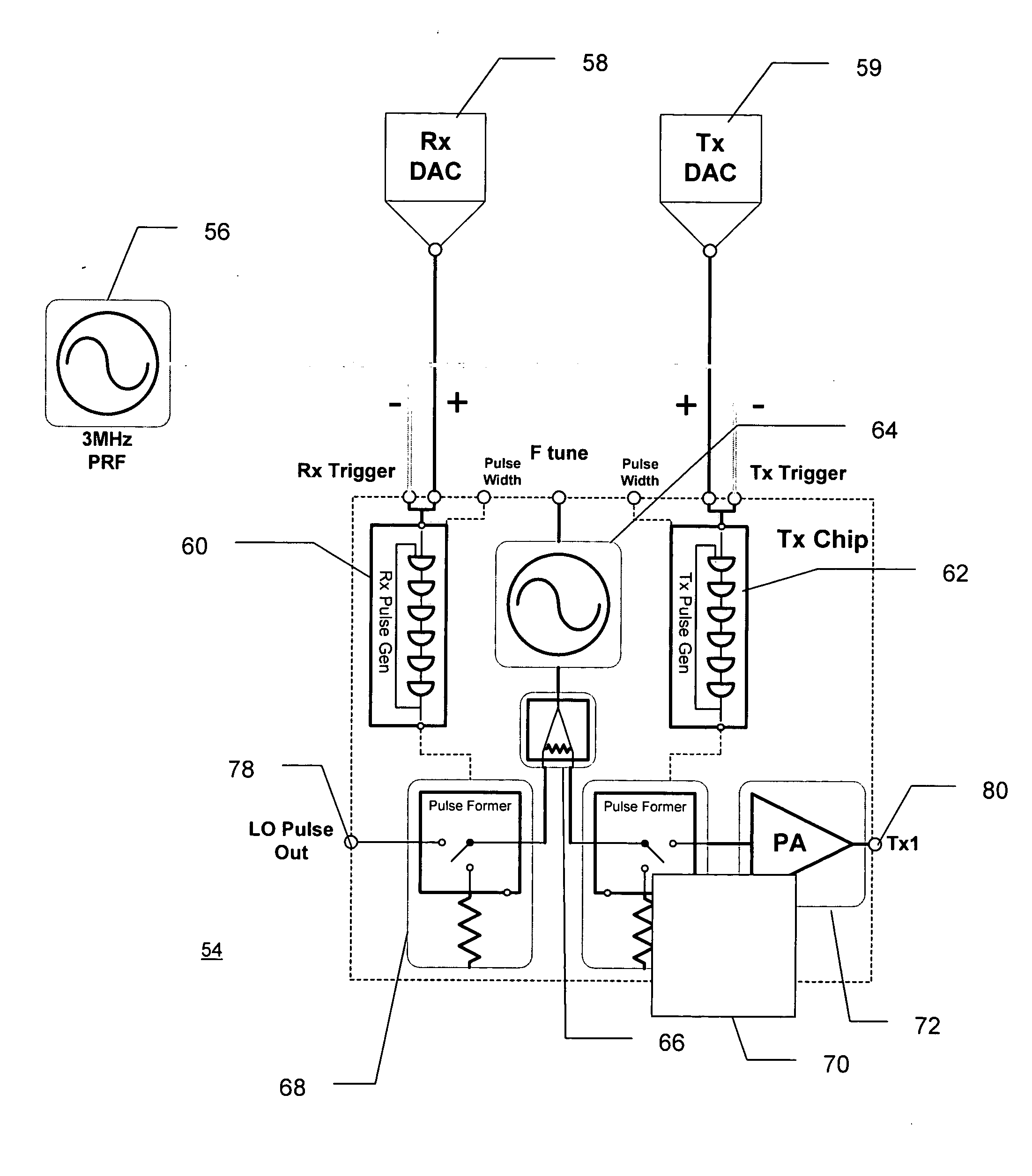

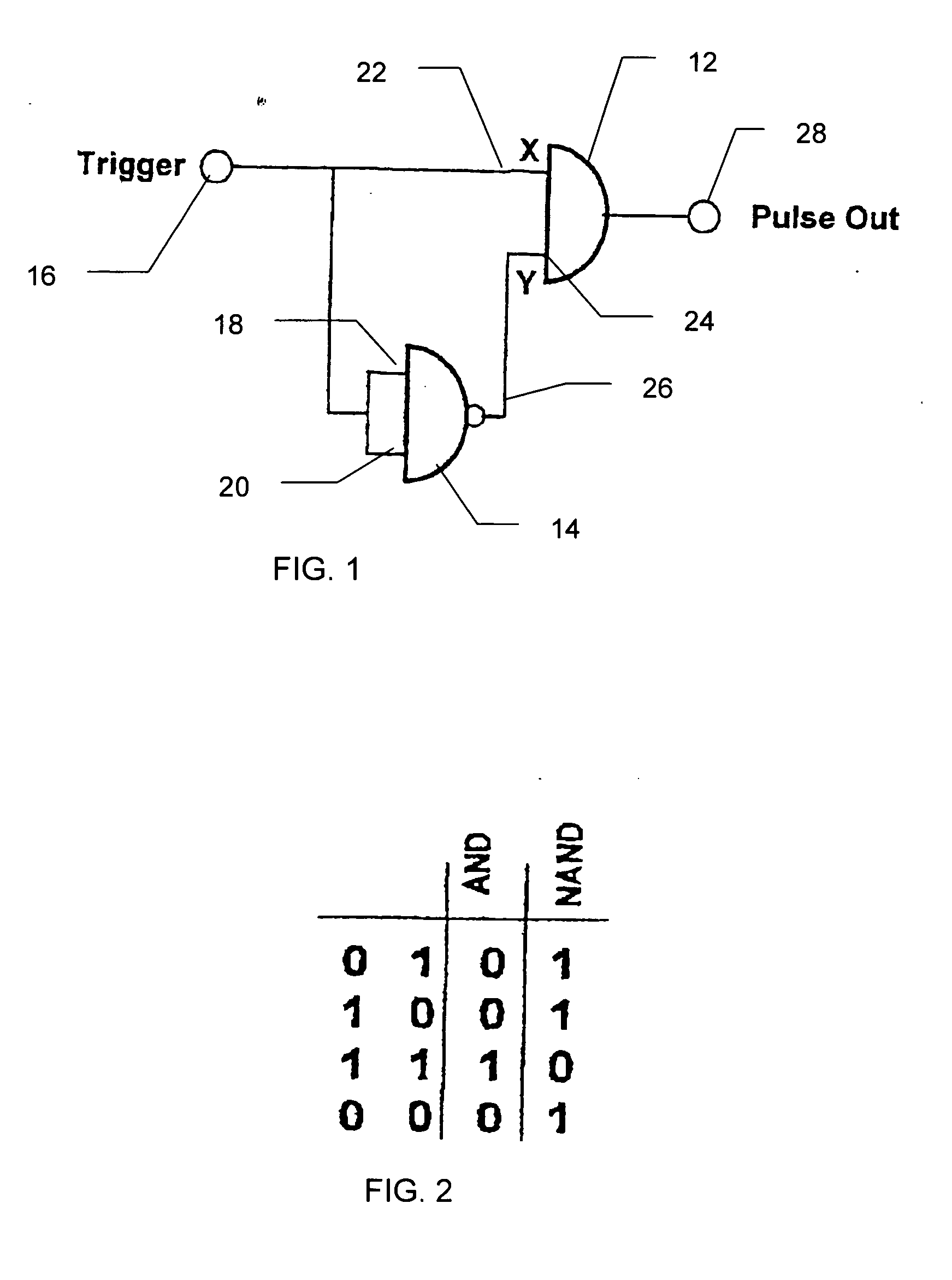

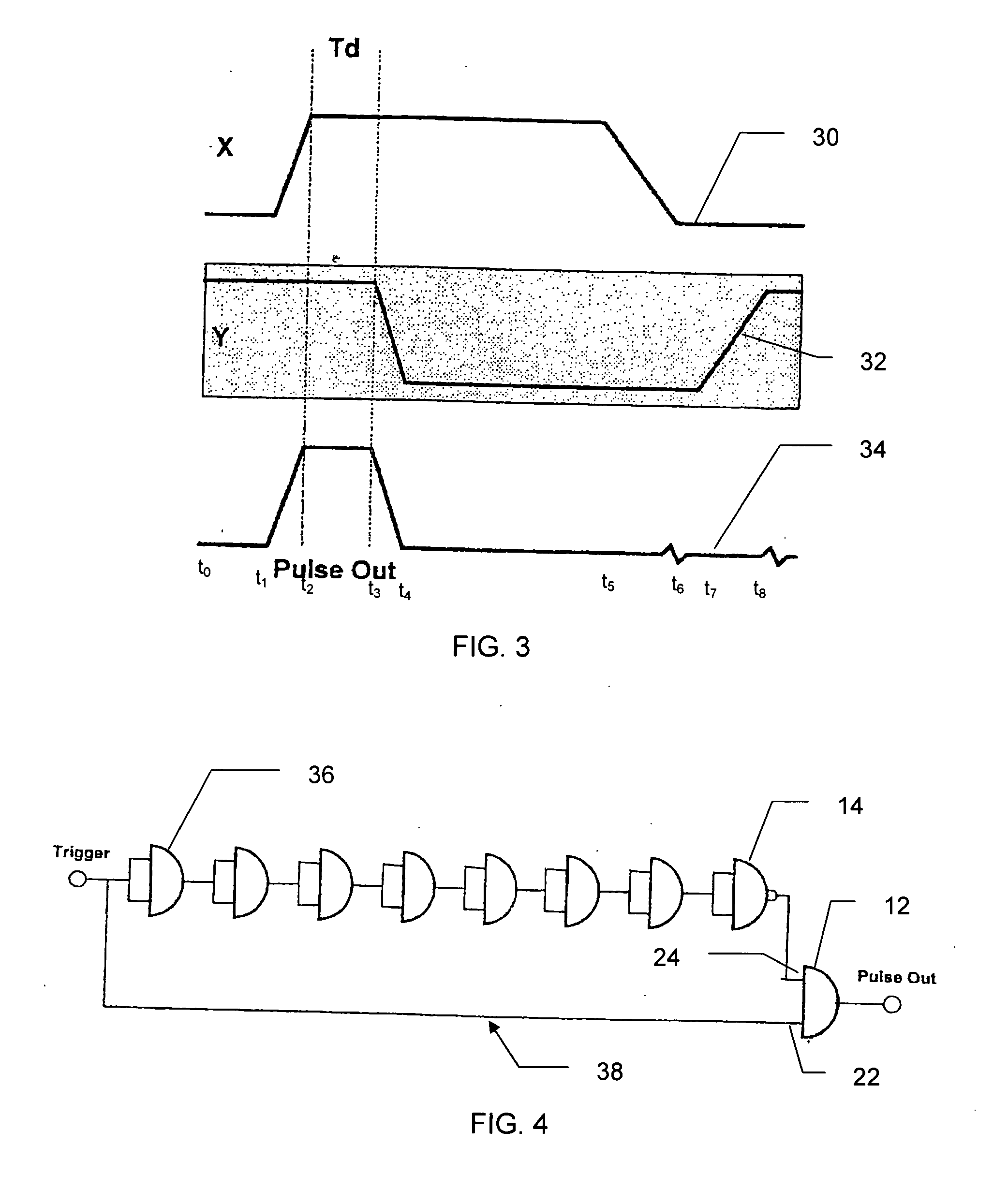

Generating a fine time offset using a SiGe pulse generator

InactiveUS7199747B2Precise changeLow costInstant pulse delivery arrangementsPulse shapingNAND gateEngineering

A method and apparatus for generating short electronic pulses using a modified differential trigger that is partly an analogue sinusoidal voltage and partly a selectable, DC voltage. The differential trigger is applied to a differential base band pulse generator having a NAND gate and AND gate. The trigger is applied to both NAND inputs and to one AND input. The NAND output is applied the other AND input. Such a circuit is an OFF state for all input states. However, as the input switches state, the NAND gate delay causes the AND gate to be ON briefly, generating a short pulse. The timing of this pulse can be controlled by varying the constant DC voltage. By using fast switching SiGe CML gates, short pulses with a controllable time off-set can be generated that are suitable for use in automotive radar applications, using only sub-GHz clocks.

Owner:AUTOLIV ASP INC

Method for accurately measuring wide-area power grid PMU (Phasor Measurement Unit) data time delay

ActiveCN104618087AAccurate time delayData switching networksSynchronising arrangementWide areaTime information

The invention discloses a method for accurately measuring wide-area power grid PMU (Phasor Measurement Unit) data time delay, and relates to the field of real-time dynamic monitoring of electric power systems. At present, the wide-area power grid PMU data time delay cannot be accurately measured. The method includes the following steps of: arranging a simulated front-end system at a WAMS master station terminal; transmitting-receiving mirror images by a port on the PMU data communication side of an interchanger between the PMU and the simulated front-end system or between the PMU and the WAMS interchanger to an idle port; access the mirror image port into a collection internet access of a network recorder which records moment of data passing through the interchanger; analyzing to obtain the time information of a required data interaction process according to the original communication data collected by the network recorder; calculating the wide-area power grid PMU data time delay according to the time information of the data interaction process. The technical scheme does not influence the existing data interaction of WAMS and PMU, and can obtain the accurate PMU data time delay.

Owner:STATE GRID CORP OF CHINA +2

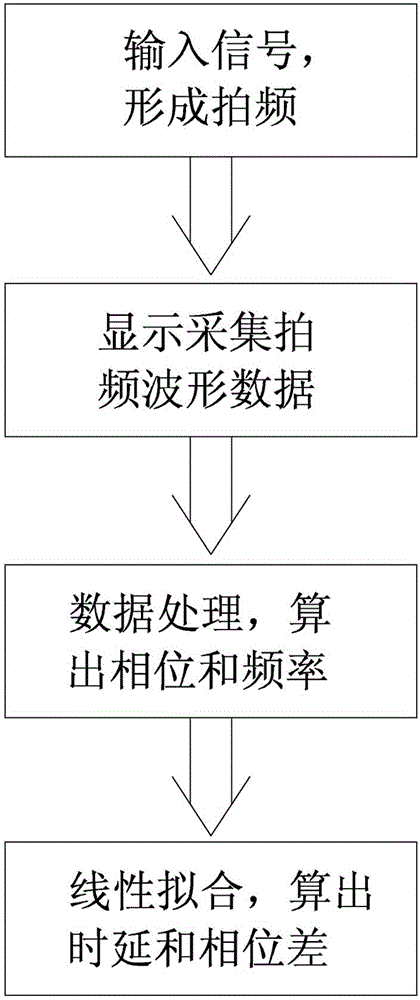

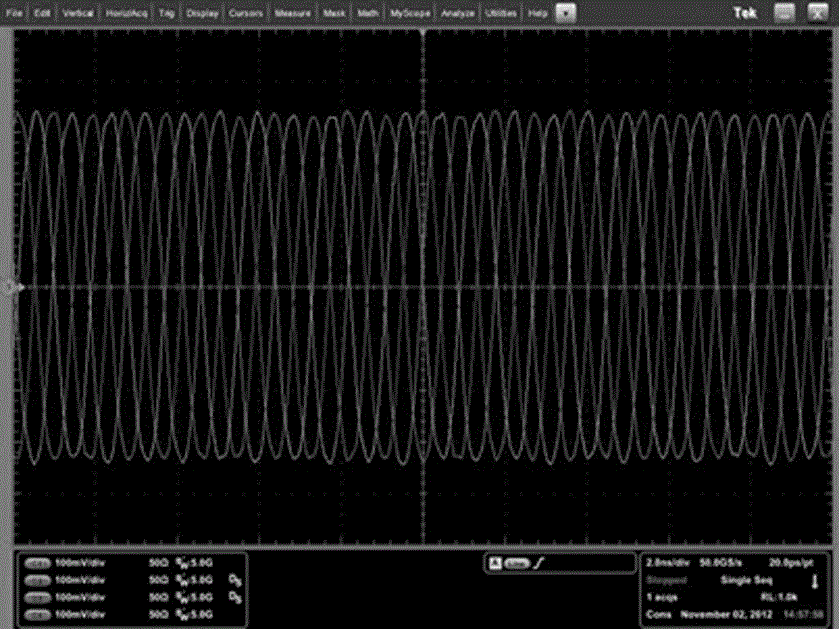

Optical coherent receiver time delay and phase difference test method and test system

ActiveCN104426606AOvercoming the inability to directly test the phase difference between 25GHz high-speed signal channelsOvercoming delayElectromagnetic transmissionLocal oscillator signalTime delays

The invention discloses an optical coherent receiver time delay and phase difference test method which comprises the following steps: generating beat frequency through inputting scanning signals, of which the frequency is similar to that of local oscillator signals, to an optical coherent receiver to be tested; collecting beat frequency information output by each radio frequency of the optical coherent receiver to be tested by utilizing an oscilloscope; carrying out noise elimination through the FFT operation and calculating the phase and frequency of the beat frequency; and finally, carrying out linear fitting to obtain relation curve of the phase and frequency, and calculating the time delay and phase difference between channels of the optical coherent receiver to be tested according to the curve. The invention also discloses a test system for the method. The test system comprises a local oscillator signal source, a tunable scanning signal source, the optical coherent receiver to be tested, the oscilloscope and a data processing unit. The beat frequency method is utilized to test the time delay and phase difference between the channels of the optical coherent receiver to be tested, so that simple and practicable effects are achieved, time delay and phase difference between the channels can be accurately measured, the difficulty that a conventional instrument cannot directly measure the phase difference and time delay between 25 GHz high-speed signal channels is overcome, and the repeatability of test data is good.

Owner:SHANGHAI BRANCH FUZHOU GAOYI COMM CO LTD

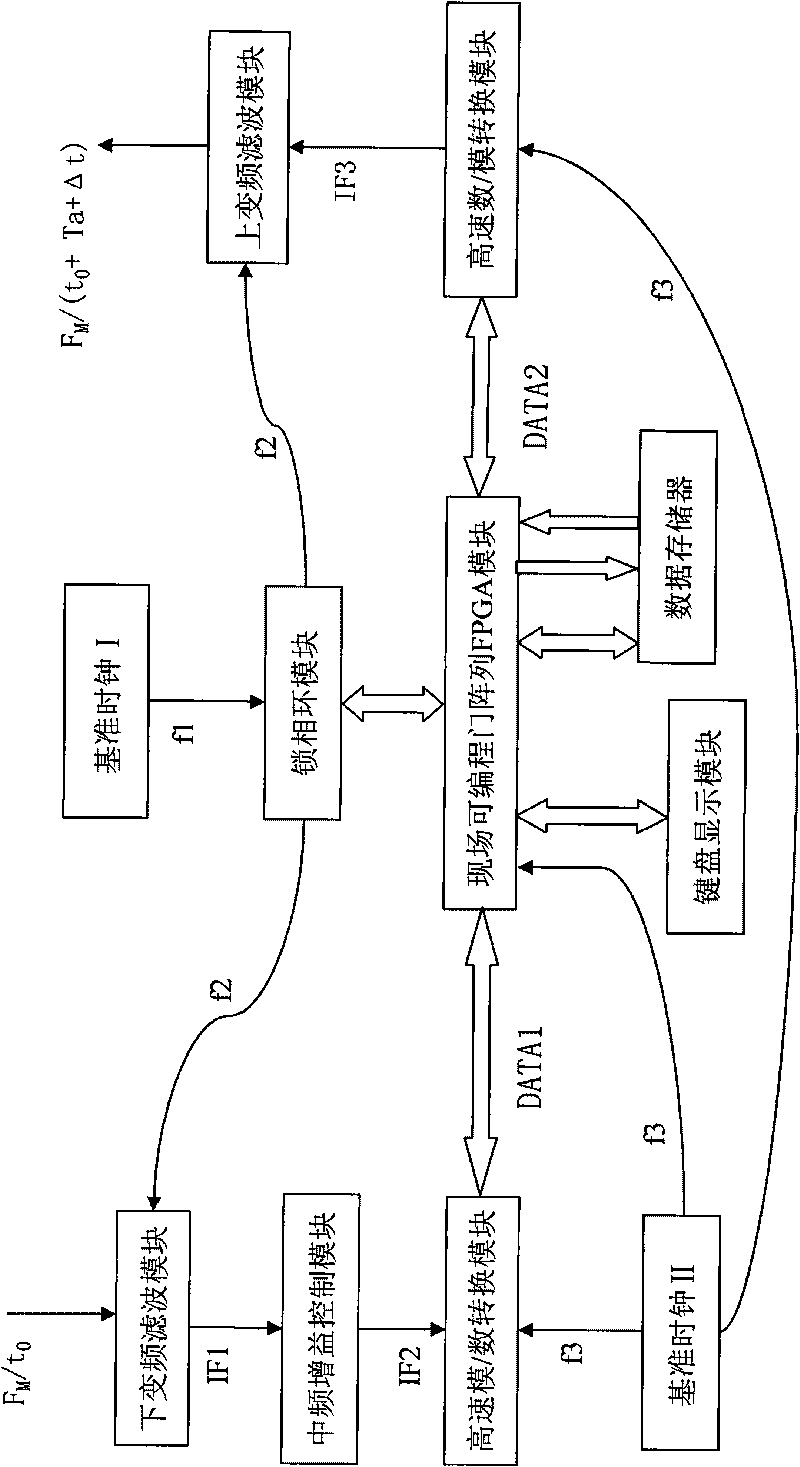

Digital television single frequency network radio frequency adapter and broadband network system thereof

InactiveCN101742133AImprove reception performanceAccurate time delayTelevision system detailsPulse modulation television signal transmissionIntermediate frequencyDelayed time

The invention provides a digital television single frequency network radio frequency adapter and a broadband network system thereof. The adapter comprises a programmable module, and a broadband radio-frequency signal FM is subjected to down-conversion filtering to acquire a broadband intermediate frequency signal IF1. IF1 is switched in an intermediate frequency gain control module to acquire a broadband intermediate frequency signal IF2 with constant signal power. A / D conversion is performed to acquire a digital signal DATA1, which is switched in the programmable module to form DATA2=DATA1+delta t according to set time delay. The IF2 is subjected to D / A conversion to become a broadband intermediate frequency signal IF3 having accordant frequency domain with the IF2 and delayed time domain, and then the IF3 is subjected to up-conversion filtering to acquire a delayed broadband radio-frequency signal. The broadband network system is provided with the single frequency network radio frequency adapter. A multipath audio / video program source is processed by a front-end information source processing module, a channel processing module and a small signal broadband synthesizer into a small signal broadband radio-frequency signal FM. A signal chain transmits to each node, the single frequency network radio frequency adapter of each node adjusts the signal time delay and each broadband transmitter amplifies and transmits the signal FM, so the stability and covering effect of the system are improved and the cost is lowered.

Owner:桂林市思奇通信设备有限公司 +1

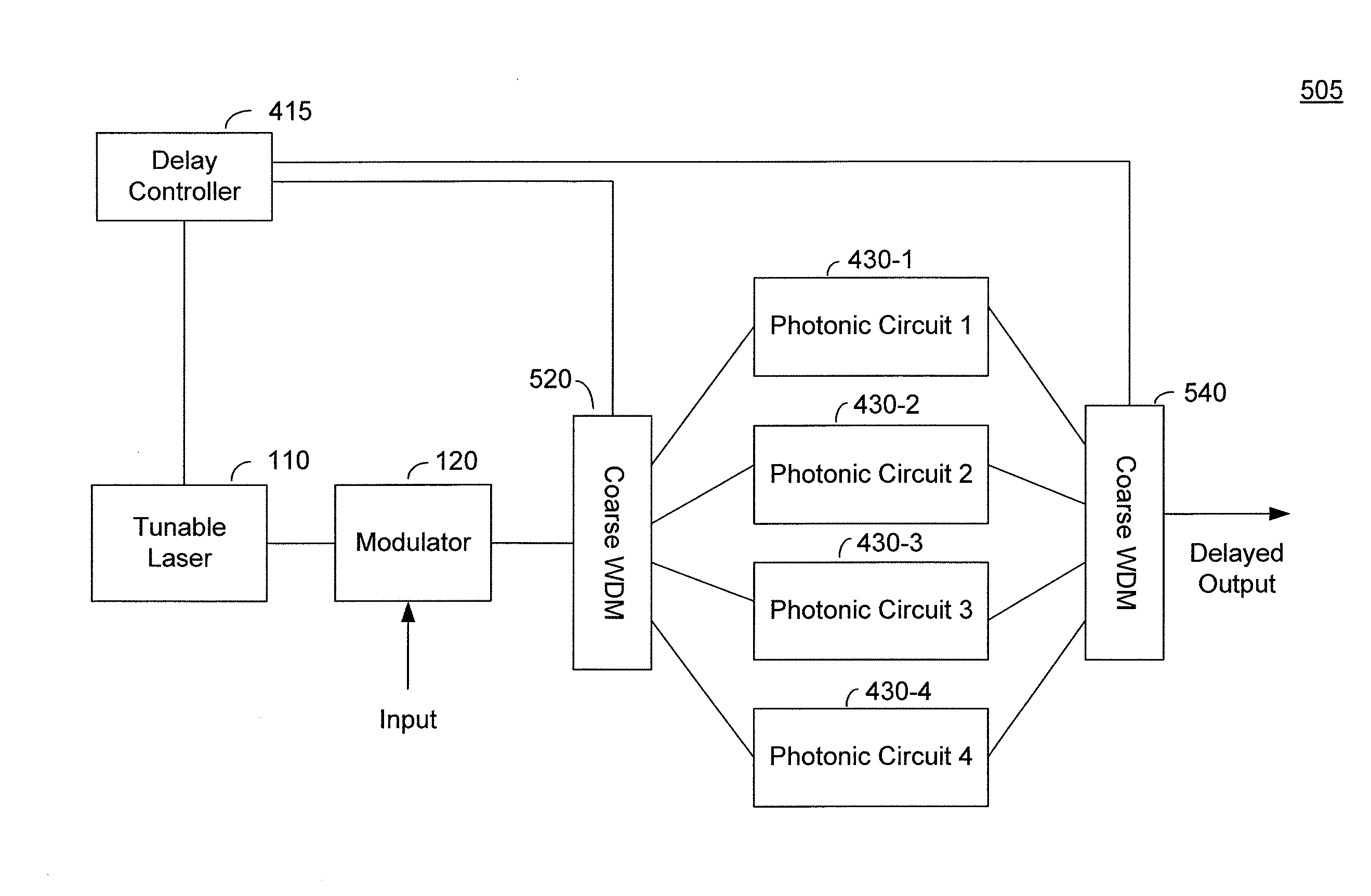

True time delay photonic circuit

ActiveUS8200047B1Accurate time delayTime-division optical multiplex systemsCoupling light guidesTunable laserTime delays

Described are systems and methods that provide tunable true time delay of a signal using a compact photonic circuit. The photonic circuit comprises a plurality of waveguides, in which each waveguide corresponds to a different time delay. A particular one of the waveguides corresponding to a desired time delay is selected by tuning the wavelength of a tunable laser. Additional photonic circuits can be used to provide additional selectable time delays.

Owner:LOCKHEED MARTIN CORP

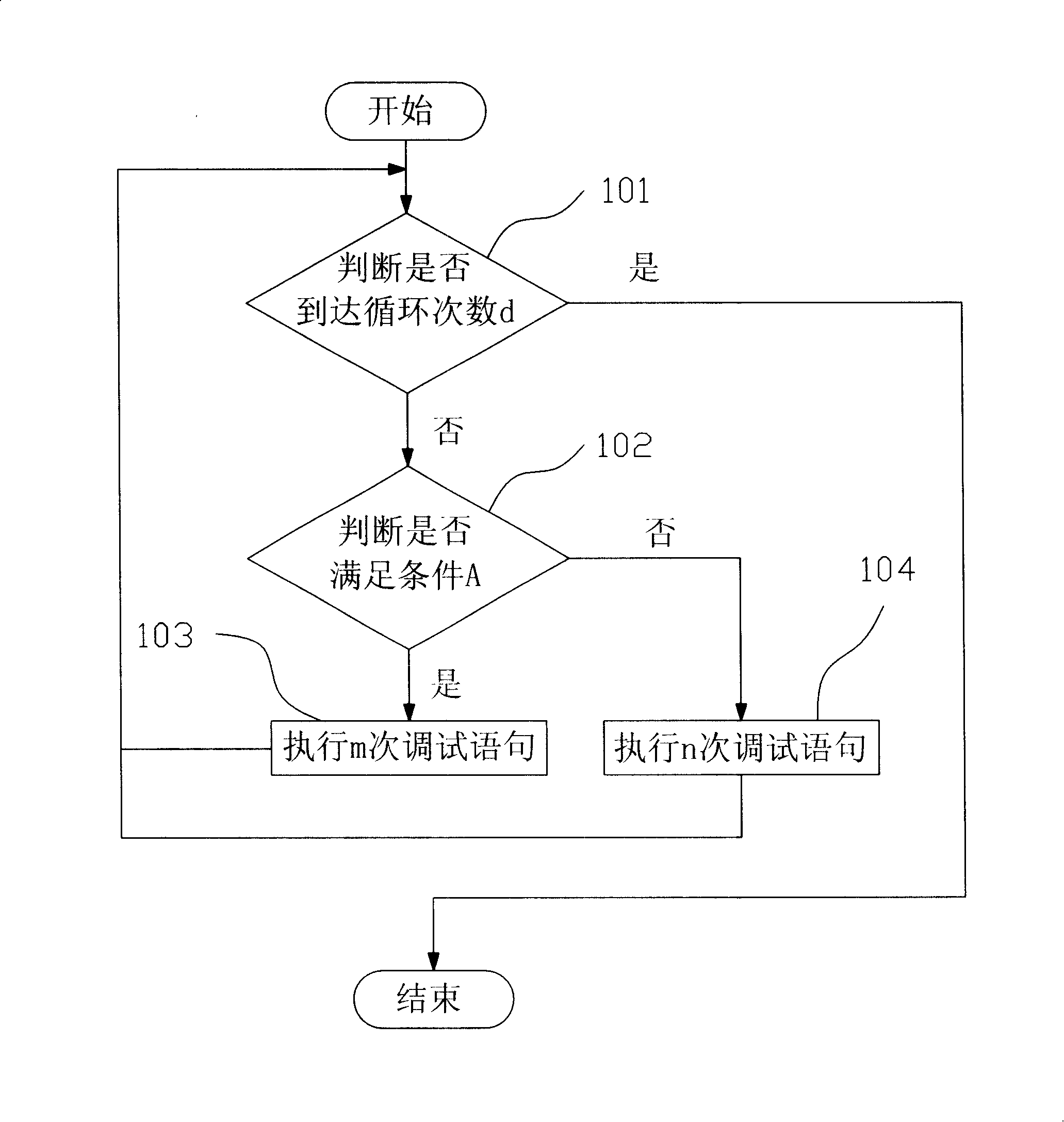

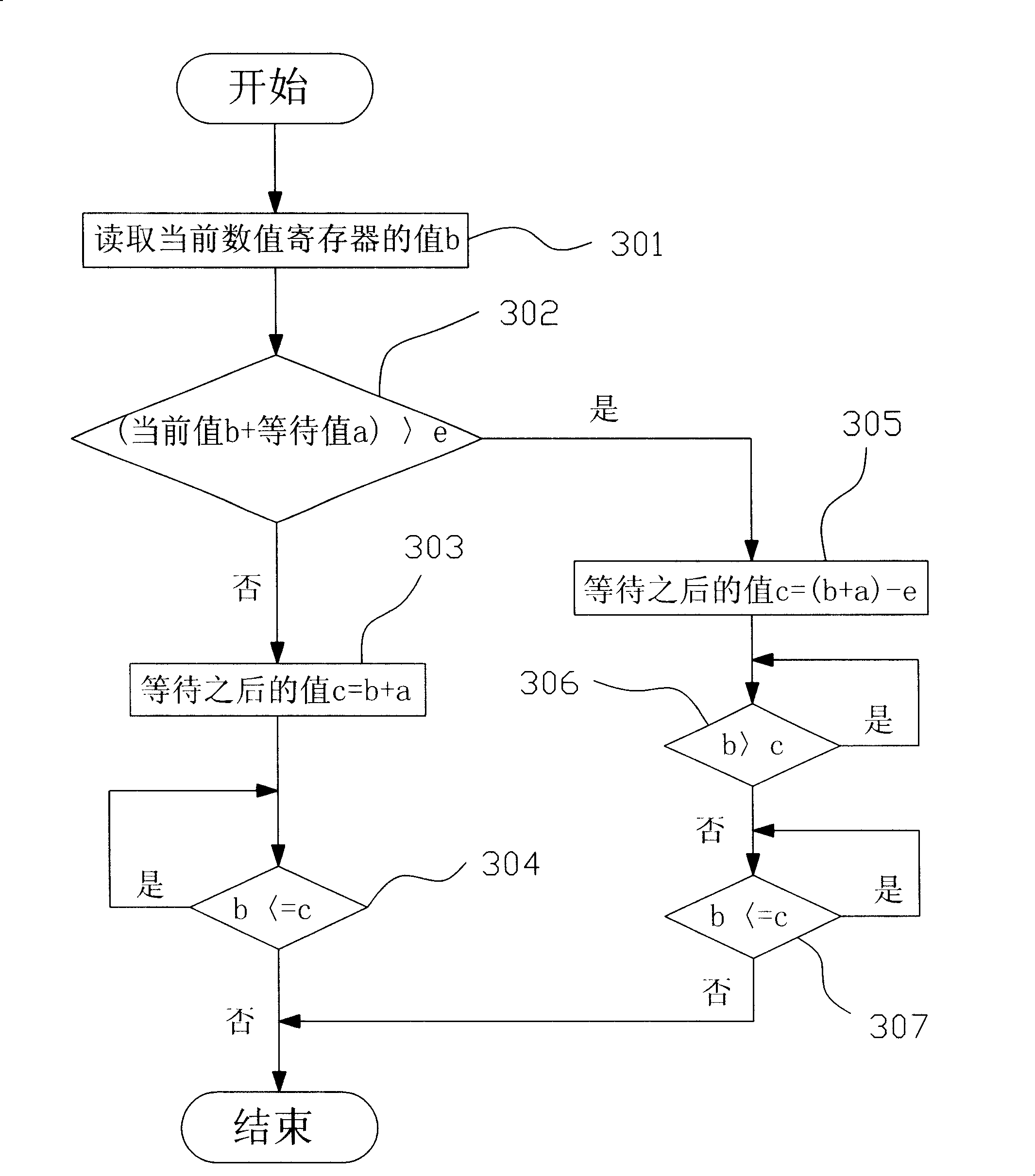

Hardware timer based time-delay method

InactiveCN101236514AWill not affect delay accuracyAccurate time delayError detection/correctionSpecific program execution arrangementsTime delaysTimer

The present invention relates to a time delay method based on a hardware timer. The method combines the hardware timer with a program stored in a computer to realize time delay, and the timer is a numerical decreasing type timer or a numerical increasing type timer. The time delay method reads a current timer value through the program and judges whether the current timer value reaches latency time so as to achieve the objective of time delay. The time delay method adopts the mode of combining software control with hardware timing, depends on the accuracy of timing and the flexibility of software control to realize accurate time delay. Moreover, when the hardware or software environment changes, the time delay precision of the time delay method cannot be affected too much, thereby the time delay method has high adaptability.

Owner:HUANDA COMPUTER (SHANGHAI) CO LTD

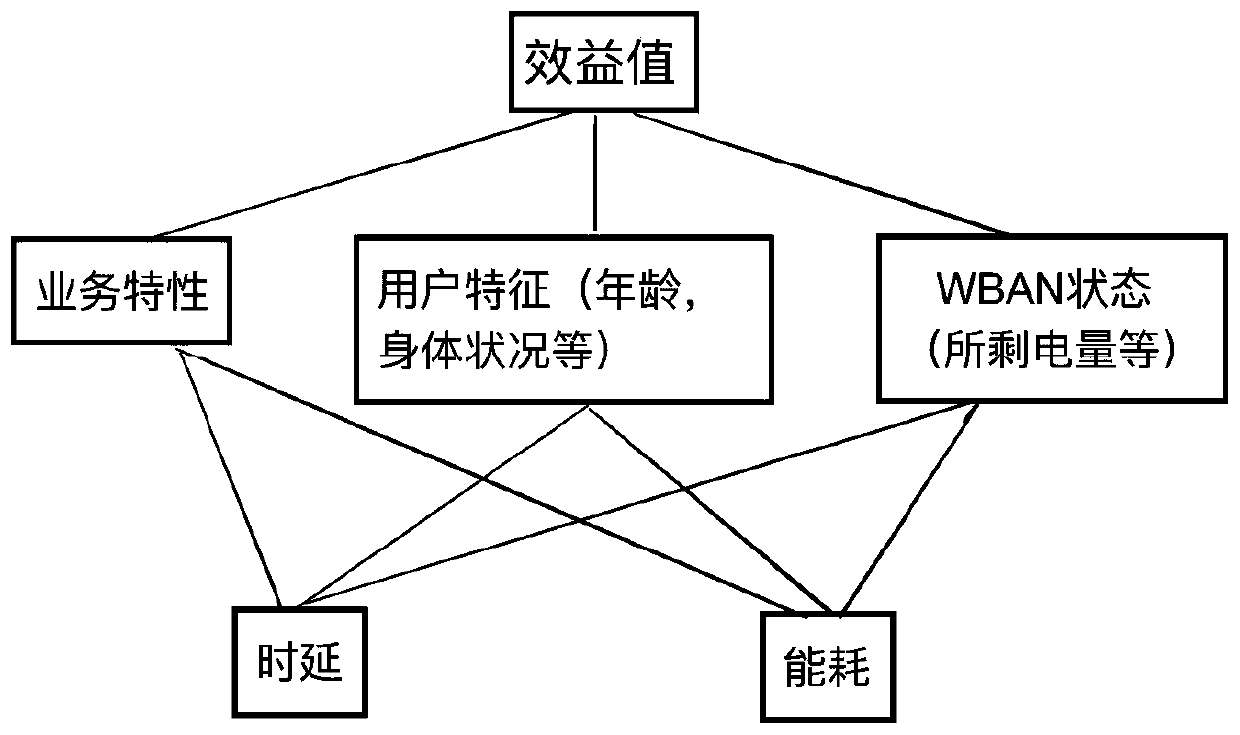

Mobile unloading migration algorithm based on improved HRRN algorithm and multi-attribute decision

ActiveCN111132235ARelieve computing pressureImprove processing speedNetwork traffic/resource managementEdge serverBody area network

The invention relates to a mobile unloading migration algorithm based on an improved HRRN (High Resolution Response Next) algorithm and a multi-attribute decision. The method comprises the following steps: step 1, a single wireless body area network generates a plurality of tasks with different priorities at a certain moment, if the tasks can be locally processed, the tasks are directly locally processed, otherwise, the tasks are uploaded to an edge server; 2, establishing a benefit function of an edge server, and taking the edge server with a high benefit value as an initial edge server of the current task; 3, judging whether the current edge server is suitable or not; 4, judging whether the edge server meets two criteria or not, wherein one of the criteria can be used as a candidate edgeserver; and step 5, according to the benefit function of the edge server established in the step 2, calculating the benefit values of all candidate edge servers, and selecting the edge server with the highest benefit value to migrate.

Owner:东北大学秦皇岛分校

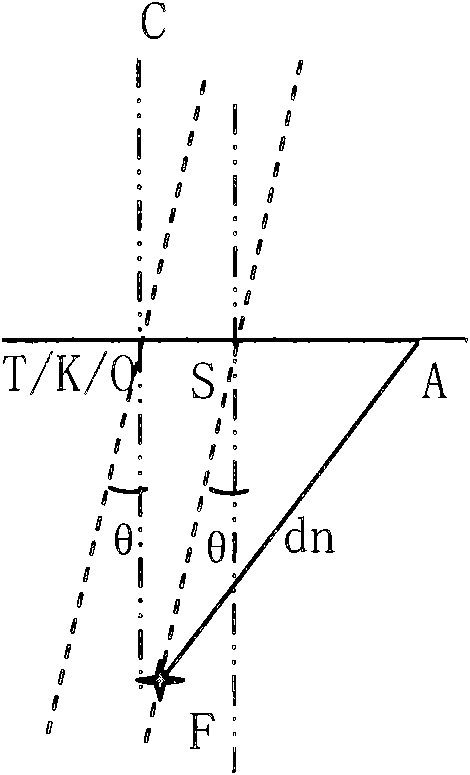

Delay parameter computation method for multi-channel scanning and device thereof

InactiveCN101900808AReduce the amount of stored dataAccurate time delayUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsArray elementPhased array

The invention provides a delay parameter computation method for a multi-channel scanning, which unifies delay computational formulas of three probes such as a linear array, a convex array and a phased array, and the formulas are applicable to non-deflection scanning and deflection scanning; and scanning lines with different densities can be calculated only by changing location variables of the scanning lines. In the invention, only an array element position, a scanning starting point position and relative focus parameters need to be stored, thus having small quantity of stored data; real-timecomputation can realize accurate delay without a large quantity of the stored data; delay in various situations for the probes, the density and deflection is calculated using a unified circuit to greatly simplify a circuit structure; and delay of each scanning line is independently controlled to conveniently realize arbitrary density scanning, for if no integral multiple relationship exists between spacing among the scanning lines and spacing among array elements of the probes, different scanning lines have different delay data. In the invention, the scanning lines are independently controlled, thus achieving arbitrary density scanning.

Owner:SHENZHEN LANDWIND IND

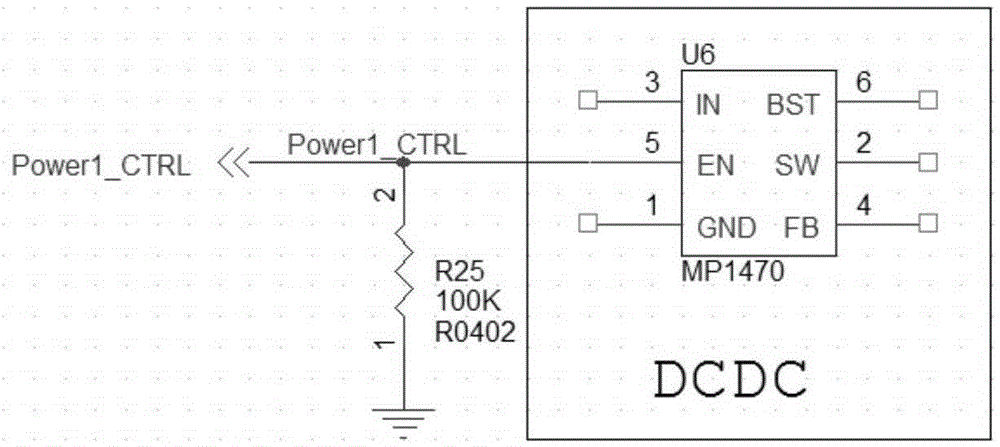

Power-on sequence control circuit, power-on sequence control method, control device and electronic terminal

ActiveCN105320040AAccurate time delayAccurate securityProgramme controlComputer controlSequence controlElectricity

The invention provides a power-on sequence control circuit, a power-on sequence control method, a control device and an electronic terminal. The circuit comprises a trigger unit comprising a first trigger and a second trigger. Two input ends of each trigger are each connected with a time delay circuit, so that the time delay of an output power source control signal is the sum of the time delay of two input end signals. Power source drive signals are output through the output signals of the two triggers to drive power source units. The time delay differences between the power source drive signals form power-on sequences of the power source units, and accurate power-on time delay control and safe power-on sequences are realized.

Owner:恩平市赢力电子科技有限公司

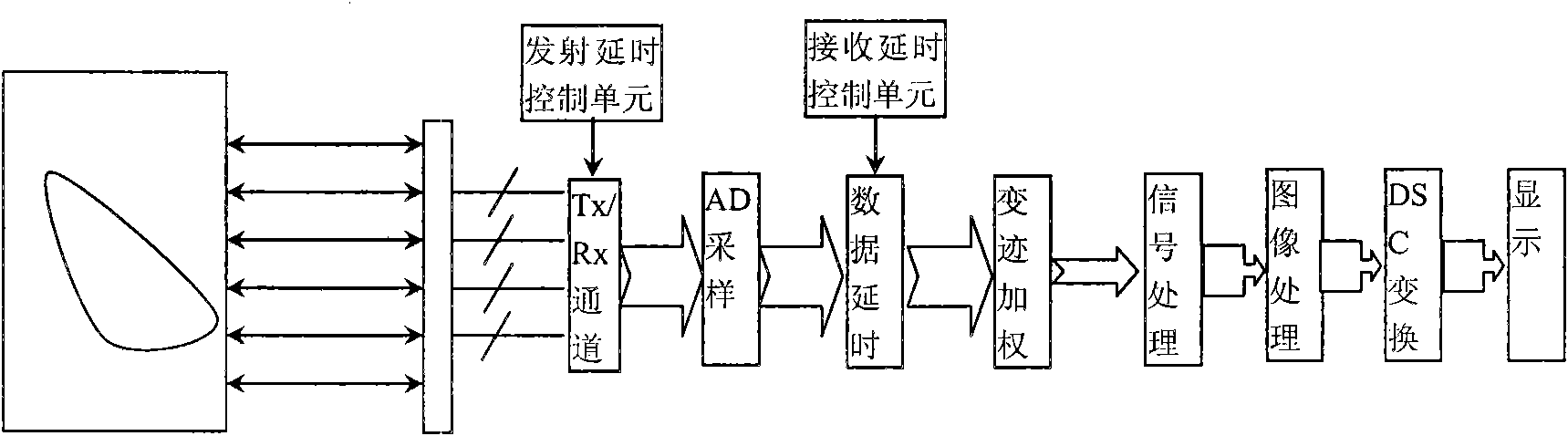

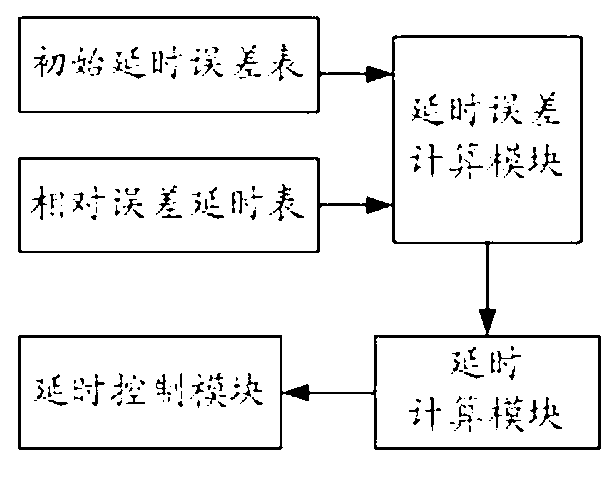

Method and device of delay control for ultrasonic imaging

ActiveCN102846336AQuality improvementAvoid delay errorsUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsPhase correctionSonification

The invention discloses a method and a device of delay control for ultrasonic imaging. The method includes steps of calculating an initial delay error generated if an ultrasonic wave in each channel arrives at an initial focus point of a corresponding scanning line in advance and calculating a relative value of a delay error between each focus point and a previous adjacent focus point on the same scanning line corresponding to each channel; accumulating to obtain the delay error of the focus point corresponding to each channel according to the initial delay errors calculated in advance and the relative delay errors calculated in advance of all focus points; adding each delay error and delay which is calculated according to sound velocity of a scanned object together to obtain real delay of the corresponding focus point corresponding to the corresponding channel; or respectively calculating delays in a probe matching layer and the scanned object, adding the delays together to obtain real delay, and then performing delay control to transmission and receiving of the ultrasonic wave by the aid of the real delay. Phase correction is realized by the delay control, delay of the ultrasonic wave of different channels arriving at the same focus point is more accurate, and imaging quality of an ultrasonic system is improved.

Owner:深圳蓝影医学科技股份有限公司

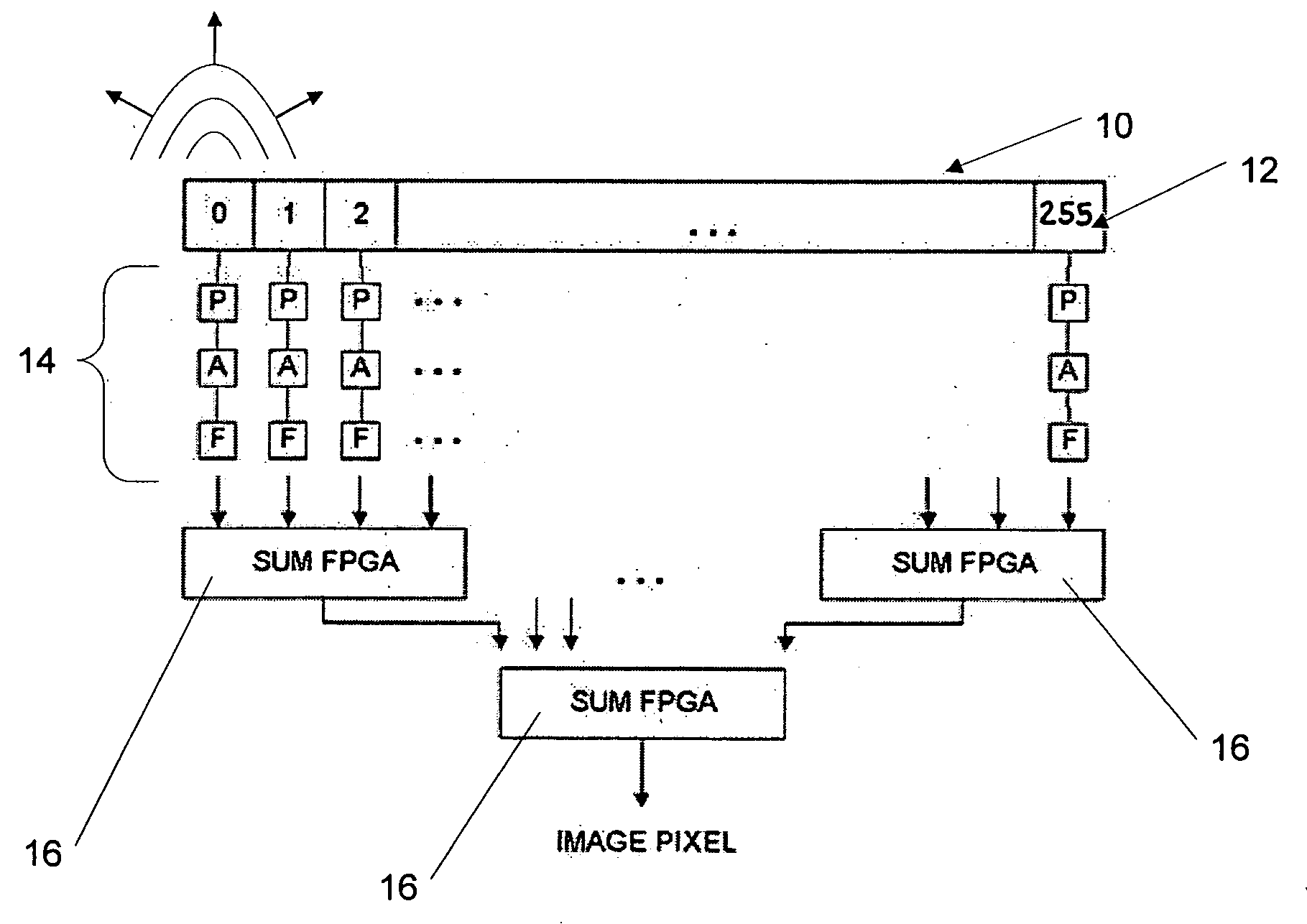

Apparatus and method for synthetic focus ultrasonic imaging

InactiveUS20050148872A1Improve developmentAccurate sound speedWave based measurement systemsOrgan movement/changes detectionFocus ultrasoundUltrasonic imaging

An ultrasonic imaging apparatus configured to generate synthetic focus ultrasonic images in real-time in a first operation mode, and which is configured to pulse multiple transducers with accurate time delays between each pulse to form images using conventional sum beam-forming and / or focus-and-steer techniques in a second mode, providing a “dual-use” system capable of forming both synthetic focus images and beam-formed images using the same transducer array.

Owner:BECS TECH

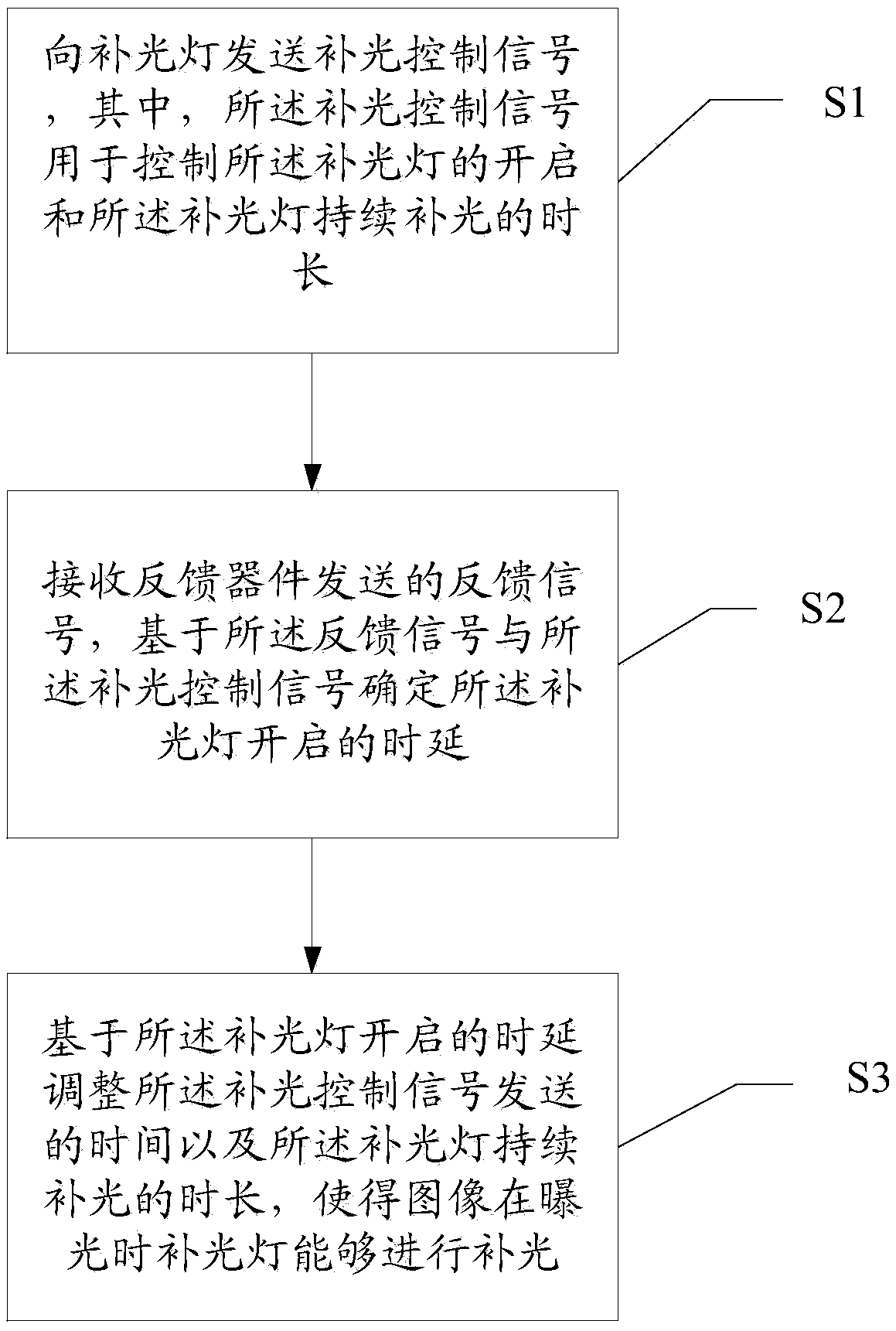

A method and a device for controlling the turning-on of a light supplemental lamp

ActiveCN109005365AAvoid Poor Image QualityAccurate determination of time delayTelevision system detailsColor television detailsContinuous lightTime delays

The invention discloses a method and a device for controlling the turn-on of a light supplemental lamp. The method comprises the following steps: sending a light supplemental control signal to the light supplemental lamp, wherein, the light supplemental control signal is used for controlling the turn-on of the light supplemental lamp and the duration of the continuous light supplemental of the light supplemental lamp; receiving a feedback signal sent by a feedback device, and determining a time delay of turning on the light compensation lamp based on the feedback signal and the light compensation control signal; based on the time delay of turning on the light supplemental lamp, adjusting the transmission time of the light supplemental control signal and the time length of continuous lightsupplemental of the light supplemental lamp, so that the light supplemental lamp can perform light supplementing when the image is exposed. The invention solves the technical problem that the image quality is not high due to the incomplete exposure of the image in the prior art.

Owner:ZHEJIANG DAHUA TECH CO LTD

Self-adaptive smooth treatment method of input time delay based on time delay gradient information

The invention discloses a self-adaptive smooth treatment method of input time delay based on time delay gradient information, which is characterized by comprising the following steps of firstly, storing each node in an IP (Internet Protocol) network locating system in a recent period of time and obtaining a time delay value record by directly measuring each node with other nodes; secondly, inputting the record in a self-adaptive smooth treatment wave filter based on time delay gradient information with a tries limited window; and thirdly, realizing indirect measurement of a time delay value by using an output value processed by the wave filter as input time delay of the IP network locating system. The treatment method can solve the problems that the directly measured time delay value is usually polluted by random delay to enable the IP network locating system to be instable and the locating accuracy to be lowered in an IP network, thereby reducing random delay pollution caused by queuing delay and the like, enabling input time delay data to keep stable and maintaining the stability of the system and the accuracy of distance prediction.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

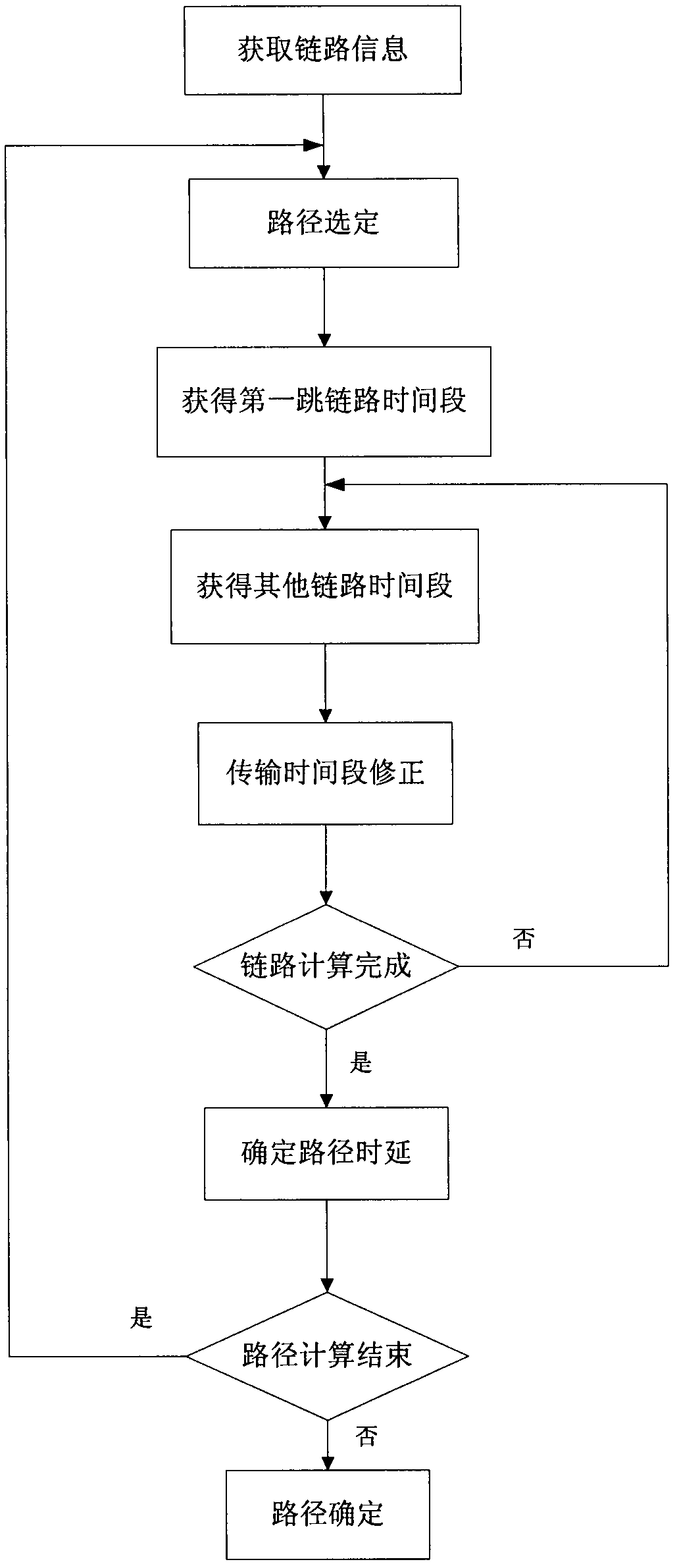

Deep-space network routing method with QoS assurance

ActiveCN102387086AMeet QoS requirementsOvercoming the problem of large delayData switching networksTime delaysTransmission time delay

The invention discloses a deep-space network routing method with a QoS (Quality of Service) assurance, and solves the problem in the prior art that deep-space network service requirements can not be satisfied. The method particularly comprises the following steps: acquiring all link information in the network at first, correcting the communication time slots, then bringing link transmission time delay and link transmission rate into consideration to calculate the transmission time slots, and finally, calculating the path time delay according to the path transmission time to select the minimal path as the optimal path. By adopting the method, the calculated and acquired path time delay is more accurate, the selected optimal path has the shortest time delay, and the QoS requirement for the time delay of the service can be satisfied while the service throughput is guaranteed; and the service transmission time can be set more reasonably, the data transmission blindness is small, the probability of false transmission due to disconnection of links when data is transmitted on the links is low, and the network performance is improved.

Owner:XIDIAN UNIV

Software phase locked loop improving method

ActiveCN104467823AAccurate time delaySuppress fluctuationsPulse automatic controlClosed loop feedbackEngineering

The invention relates to a software phase locked loop improving method. The software phase locked loop improving method is characterized by comprising the following steps that sampling is carried out on power grid voltage, and voltage components ualpha and ubeta under a two-phase coordinate system are obtained through Clarke conversion; accurate delayed signals ualpha-D and ubeta-D of the voltage components ualpha and ubeta are calculated through a weighted average method; power grid voltage positive-sequence components u and u are extracted according to a delayed signal cancellation principle; rotation axis conversion is carried out on the power grid voltage positive-sequence components u and u so as to obtain u (n) and u (n), wherein n represents the current nth control period; the frequency of the power grid voltage is calculated; digital integration is carried out on the frequency of the power grid voltage so as to obtain a power grid voltage phase angle used for calculation of rotation axis conversion, and closed loop feedback is formed. The weighted average method of two sets of delayed signals is adopted to approach the expected delayed signals, and therefore signal delaying is more accurate, direct current offset and fluctuation in the phase locked angle and amplitude are effectively restrained, accuracy of power grid fundamental wave voltage phase locking is improved, and the method can be widely applied on the occasions high in requirement for the PLL response speed.

Owner:TIANJIN RES INST OF ELECTRIC SCI

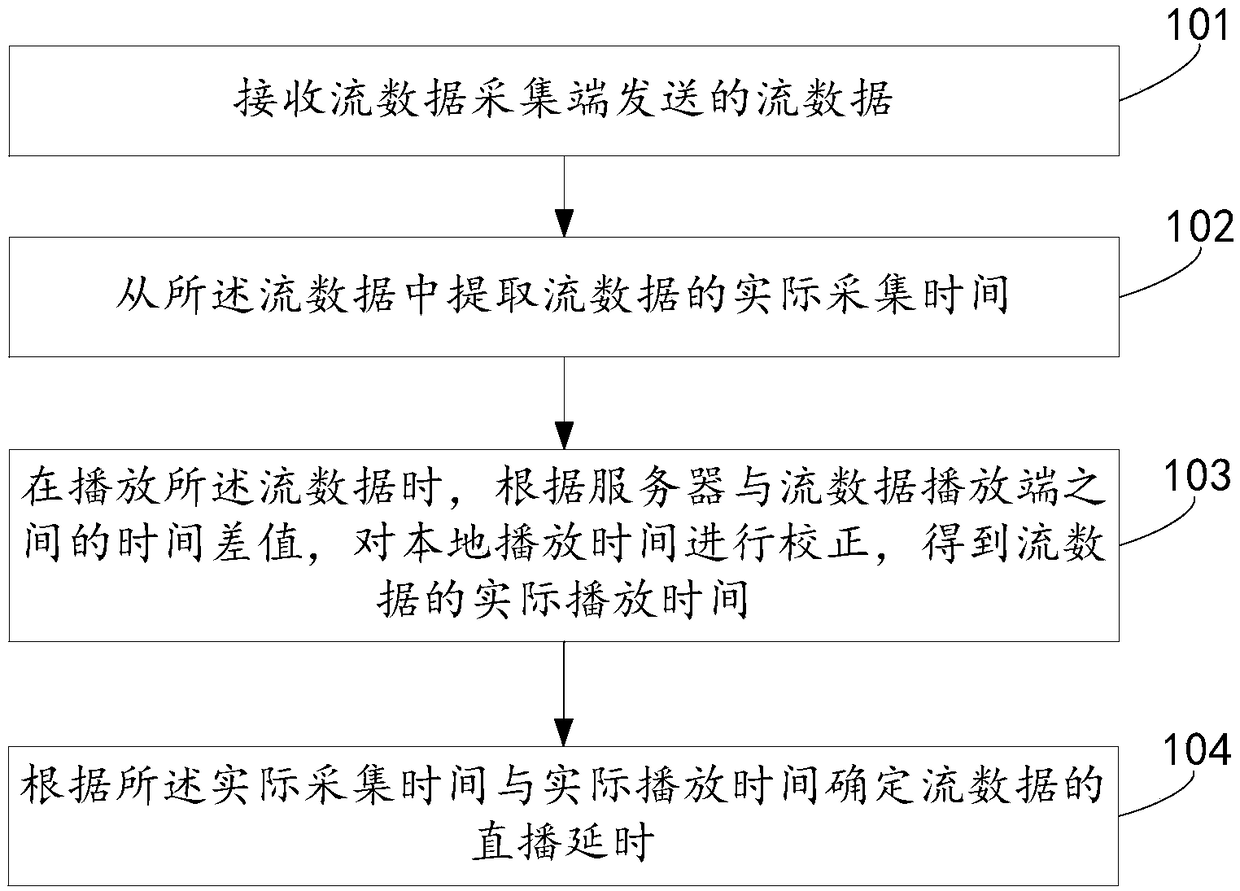

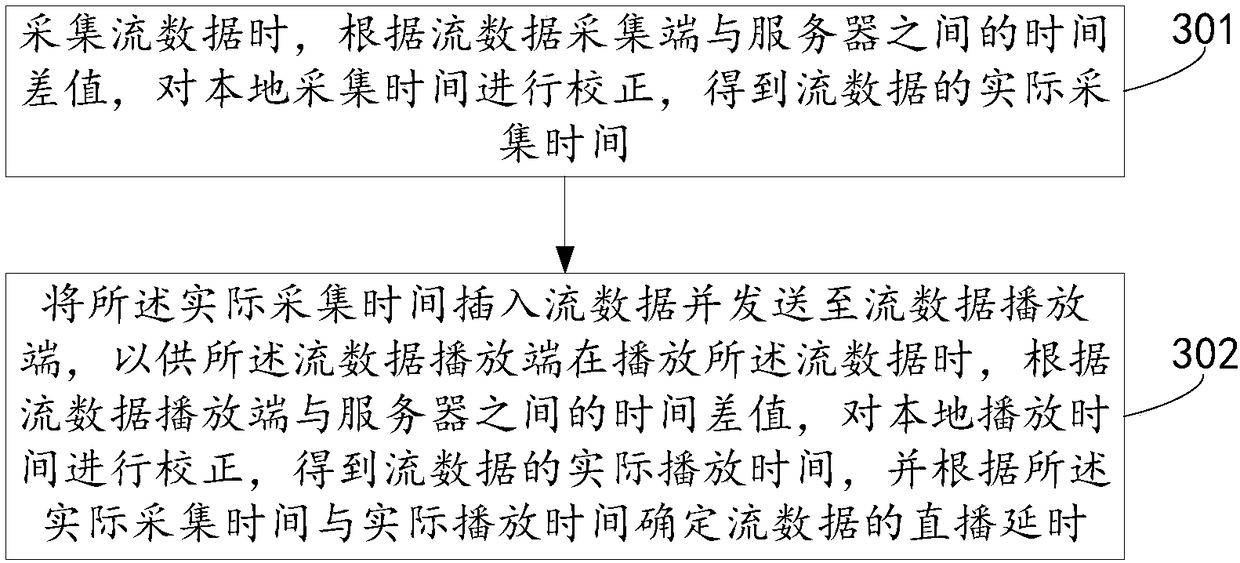

Method and device for determining live broadcasting delay

ActiveCN108174229AOvercome the problem that the end-to-end delay cannot be measuredAccurate time delaySelective content distributionAcquisition timeStream data

The invention discloses a method and a device for determining live broadcasting delay. The method comprises the following steps: receiving streaming data sent by a streaming data acquisition end, extracting actual acquisition time of the streaming data, while broadcasting the streaming data, correcting local broadcasting time according to a value of time difference between a server and the streaming data broadcasting end, obtaining actual broadcasting time of the streaming data, and determining live broadcasting delay according to the actual acquisition time and the actual broadcasting time. In the method, the actual acquisition time inserted into the streaming data is the time corrected with the server, and then the live broadcasting delay is obtained through the actual acquisition time corrected by the server and the actual broadcasting time, thus, a problem of failure in measurement and calculation of end-to-end delay caused by inaccuracy of equipment time of different client sides,such as the acquisition end and each broadcasting end, and accurate measurement and calculation of delay from the acquisition end to the broadcasting end during video live broadcasting is realized.

Owner:BEIJING QIHOO TECH CO LTD

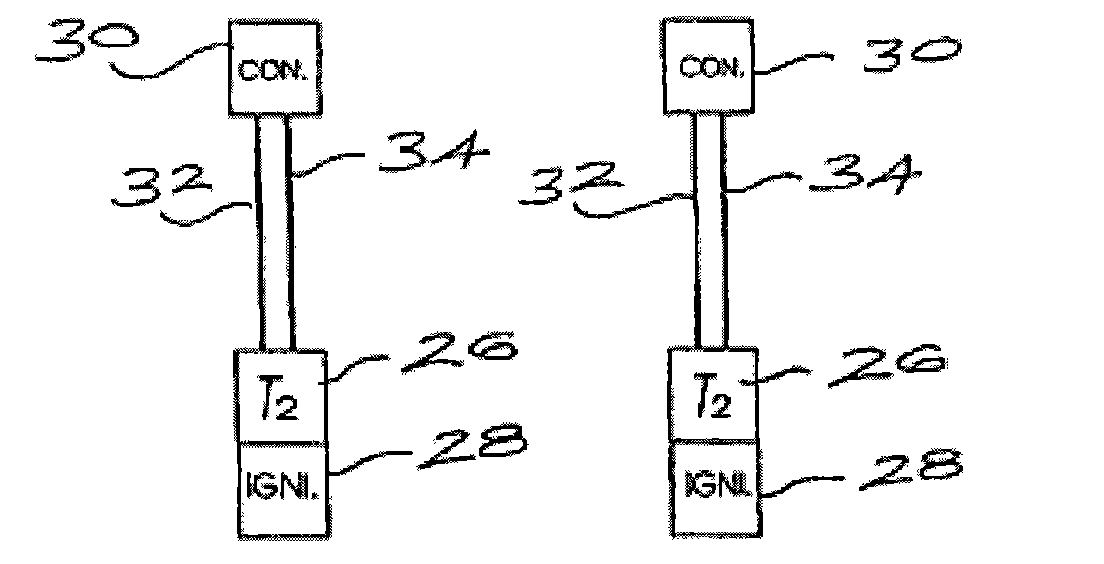

Detonator system

The invention discloses a detonator system. The system comprises an array and a plurality of detonators, wherein the array is formed by connecting a plurality of time delay relays which are in series connection with each other; and the plurality of detonators are connected to the array according to a predetermined interval respectively. The invention also discloses another detonator system. The system comprises a plurality of detonators and a plurality of connecting parts which comprise time delay relays, wherein the detonators are connected with the connecting parts by adopting lead wires; and a first connecting part connected with a first detonator is connected to a lead wire between an adjacent second detonator and a corresponding second connecting part. The invention also provides corresponding time delay relays. By using the system, a precise time delay length between any two detonators can be determined, and the continuity and the effectiveness of the conversion of energy and signal from one end of a time delay line to the other end are ensured.

Owner:北京维深数码科技有限公司

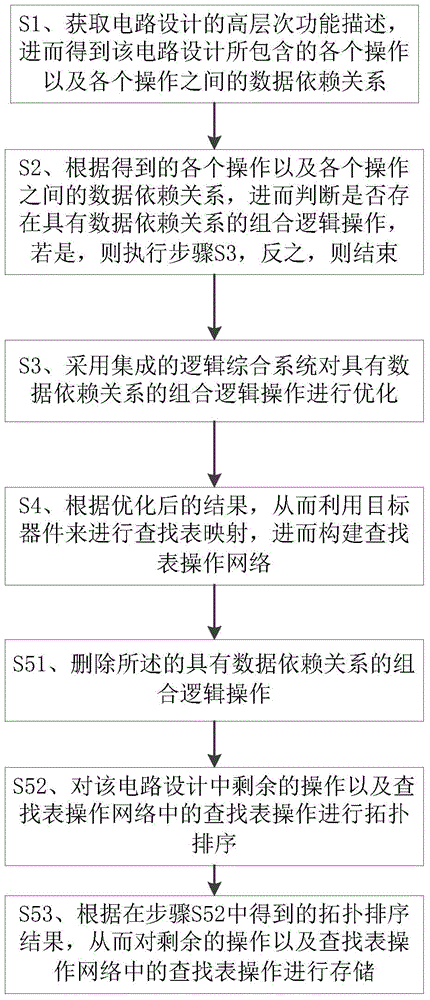

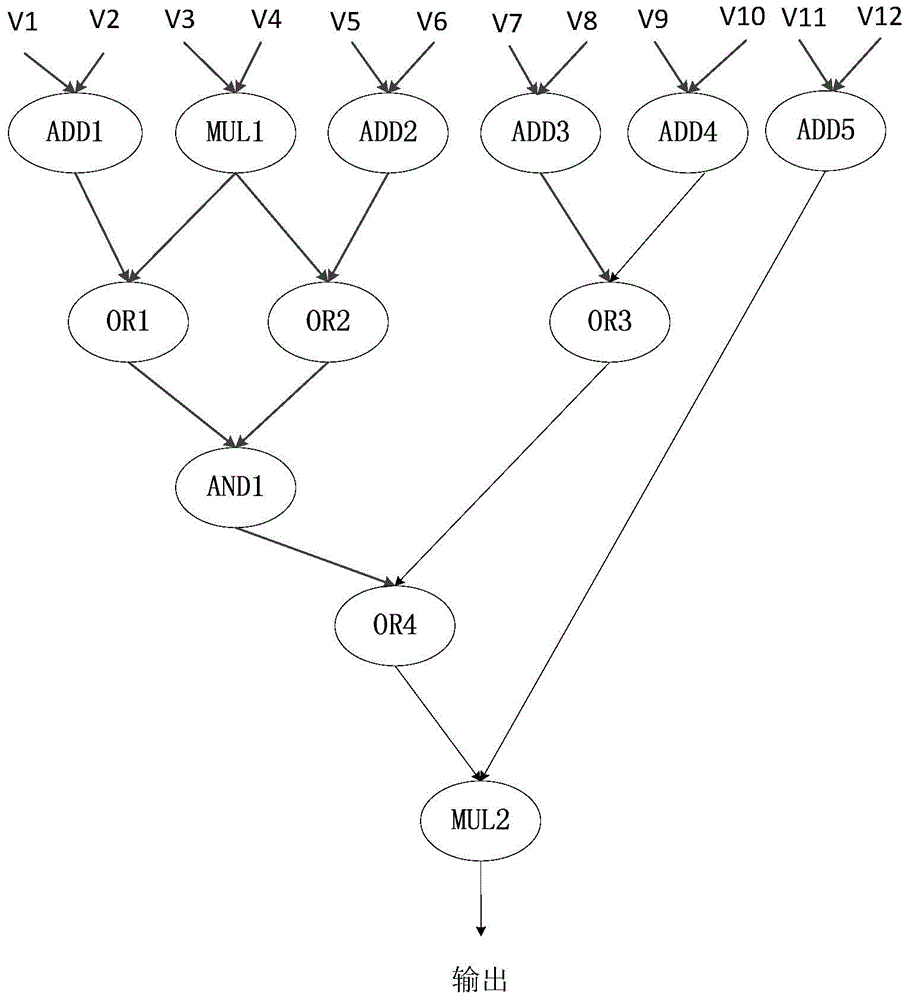

Combinational logic optimization method and system in high-level synthesis

ActiveCN104408232AExcellent build performanceReduce redundancySpecial data processing applicationsLogic optimizationTheoretical computer science

The invention discloses a combinational logic optimization method and system in high-level synthesis. The combinational logic optimization system in the high-level synthesis comprises an obtaining unit, a combinational logic optimization mapping unit and a reconstruction unit. The combinational logic optimization method in the high-level synthesis comprises the following steps of obtaining operations designed in a circuit and a data dependence relationship between the operations; optimizing the combinational logic operations having the data dependence relationship, performing lookup table mapping according to an optimized result, and accordingly constructing a lookup table operation network; replacing the combinational logic operations having the data dependence relationship with the lookup table operation network. The combinational logic optimization method and system in the high-level synthesis can optimize the designing combinational logic in a high-level synthesis stage, remove redundant combinational logic calculations, introduce bottom layer hardware information to the high-level synthesis by adding the lookup table operation, provide more accurate combinational logic time delay and resource expenditure information for a follow-up high-level synthesis step, are beneficial to improvement of performance of each high-level synthesis tool, and can be widely applied to the hardware design field.

Owner:SUN YAT SEN UNIV

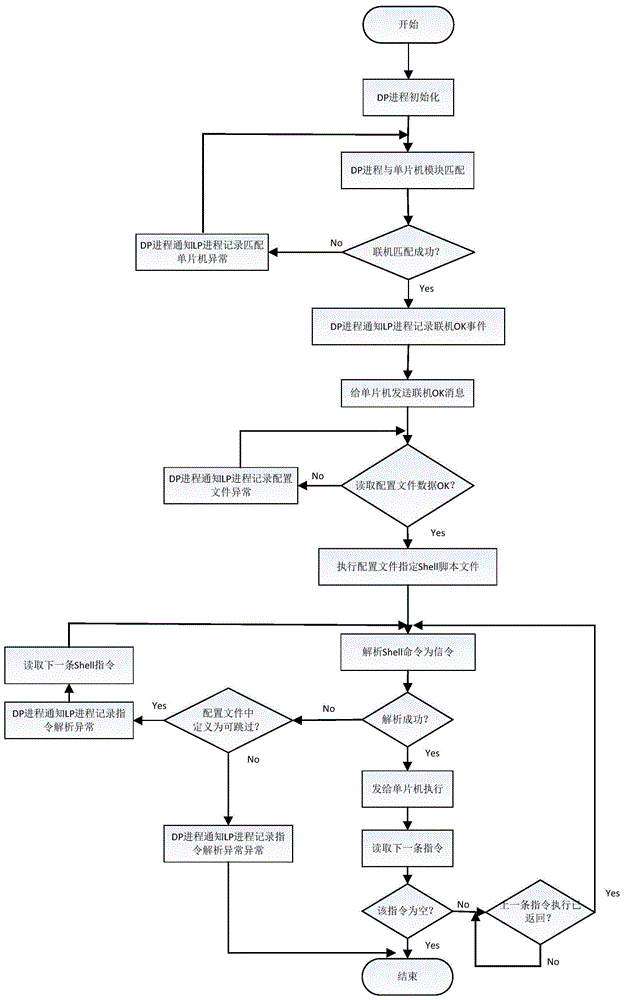

Abnormal power failure simulation test device

ActiveCN104635722AEasy to controlPrecise power-on timingElectric testing/monitoringMicrocontrollerMicrocomputer

The invention relates to an abnormal power failure simulation test device comprising a control processing module and a power control module and a tested electric equipment on-off control module connected with the control processing module. The control processing module is used for operating a preset test script and respectively sending a power control command and a tested electric equipment on-off command in the script to the power control module and the tested electric equipment on-off control module in a wireless communication mode; the power control module is used for receiving and executing the power control command; the tested electric equipment on-off control module is used for receiving and executing the tested electric equipment on-off command. Compared with the prior art, the abnormal power failure simulation test device has the advantages that service scenarios such as abnormal power failure, power-on and power hopping can be subjected to simulation test, and logging trace is provided; an event trigger command of a script synchronization service system is converted into signaling to control a single-chip microcomputer to operate the power supply state of a power source, and reality and effectiveness in simulation are achieved.

Owner:EISOO SOFTWARE

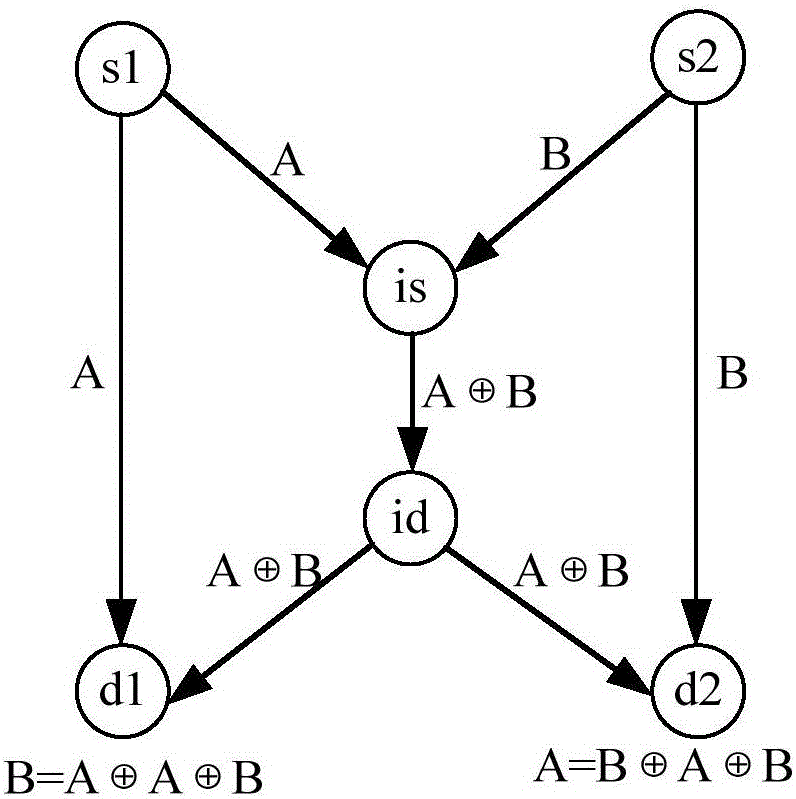

Novel compact, efficient and fast on-chip network router based on network coding

ActiveCN105871730ASolve alignmentSolve real-timeForward error control useData switching networksNetwork codeTransfer mode

The invention discloses a novel compact, efficient and fast on-chip network router based on network coding. The router comprises P ways of input and output channels, wherein each input channel is provided with v virtual channels; each input channel is provided with one routing logic and a virtual channel allocator which are respectively responsible for a routing direction of data transmission and allocation of the virtual channels; the virtual channel allocator is also connected to a switch allocator; the switch allocator is responsible for allocating crossbars to the P ways of input channels, so that arbitration of one output channel is simultaneously requested by multiple input channels; network coding modules NCU are also arranged between the P ways of input channels and the cross switches; the output of flits of the virtual channel passes through a simple coding selection circuit, the NCU carries out coding operations on the input which conforms to the conditions, after the coded flits are arbitrated by the switch allocator, the flits are sent to the crossbars. The on-chip network router supports a transmission mode with the flits as a unit, the real-time coding is realized and the additional hardware and power consumption can be effectively reduced.

Owner:GUANGDONG UNIV OF TECH

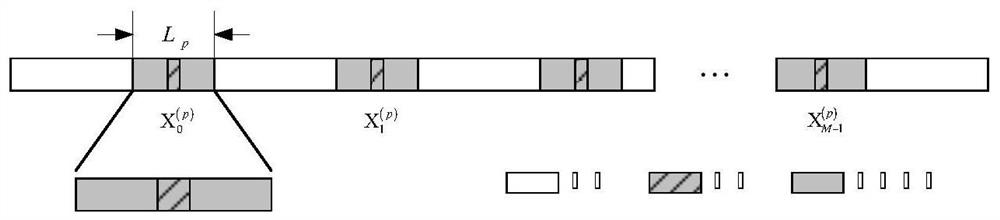

Computing method for accurate time delay based on long term evolution (LTE) locating and reference signal characteristic

InactiveCN103200677AAccurate time delayReduce computationPosition fixationWireless communicationTime domainTime delays

The invention discloses a computing method for accurate time delay based on a long term evolution (LTE) locating and reference signal characteristic. Firstly, a corresponding correlation chart between a time difference and a phase difference from a source node to two anchor nodes respectively is built, then an integral value of a receiving signal between the source node and each pair of anchor nodes is calculated, and finally the calculated integral value of each receiving signal between the source node and each pair of anchor nodes serves as the phase difference. In the corresponding correlation chart between the time difference and the phase difference, the time difference is inquired and obtained. Through utilization of the LTE locating and reference signal characteristic, corresponding correlations between the time difference and the phase difference from the source node to an aim node are built. On the basic of constructing the corresponding correlation chart between the time difference and the phase difference, and through product and integral operation on the receiving signals in a time domain, the accurate time delay can be obtained through looking up on the chart according to a computing result.

Owner:SOUTHEAST UNIV

Device and method for improved magnitude response and temporal alignment in a phase vocoder based bandwidth extension method for audio signals

ActiveUS9318127B2Impact magnitude responseAvoid negative effectsSpeech analysisFrequency/directions obtaining arrangementsPhase correctionBandwidth extension

An apparatus for generating a bandwidth extended audio signal from an input signal, includes a patch generator for generating one or more patch signals from the input signal, wherein the patch generator is configured for performing a time stretching of subband signals from an analysis filterbank, and wherein the patch generator further includes a phase adjuster for adjusting phases of the subband signals using a filterbank-channel dependent phase correction.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV +1

Generating a fine time offset using a SiGe pulse generator

InactiveUS20060250293A1Precise changeLow costInstant pulse delivery arrangementsPulse shapingNAND gateDc voltage

A method and apparatus for generating short electronic pulses using a modified differential trigger that is partly an analogue sinusoidal voltage and partly a selectable, DC voltage. The differential trigger is applied to a differential base band pulse generator having a NAND gate and AND gate. The trigger is applied to both NAND inputs and to one AND input. The NAND output is applied the other AND input. Such a circuit is an OFF state for all input states. However, as the input switches state, the NAND gate delay causes the AND gate to be ON briefly, generating a short pulse. The timing of this pulse can be controlled by varying the constant DC voltage. By using fast switching SiGe CML gates, short pulses with a controllable time off-set can be generated that are suitable for use in automotive radar applications, using only sub-GHz clocks.

Owner:AUTOLIV ASP INC

Aviation communication system base extension channel estimation method based on prior time delay information

ActiveCN111786921AAccurate time delayImprove estimation accuracyTransmission monitoringRadio transmissionTime domainCommunications system

The invention discloses an aviation communication system base extension channel estimation method based on prior time delay information, and the method comprises the following steps: expressing a to-be-estimated channel impulse response as a product of a base function and a base coefficient through a time-varying channel estimation model based on base extension, and carrying out the vectorizationoperation; performing Fourier transform to obtain a frequency domain channel impulse response matrix H, and substituting the frequency domain channel impulse response matrix H into a formula for performing Fourier transform on a time domain receiving signal to obtain a new receiving signal; decomposing the new receiving signal into a pilot frequency part and a data part, and simplifying the same;obtaining a pilot frequency data matrix according to simplification; synthesizing all the observation intervals to obtain a received signal; estimating the received signal to obtain channel estimation; estimating channel time delay by utilizing prior time delay information according to the received signal to obtain a distinguishable multipath number of the channel, further obtaining a pilot frequency data matrix, and then obtaining a primary function coefficient matrix; substituting the primary function coefficient matrix into the estimation module subjected to the vectorization operation, andperforming de-vectorization to obtain a channel impulse response matrix; and finally obtaining a channel impulse response matrix. According to the invention, huge Doppler frequency shift caused by ultra-high-speed flight can be overcome, and high-speed data transmission is realized.

Owner:CHINA ELECTRONICS TECH GRP NO 7 RES INST +1

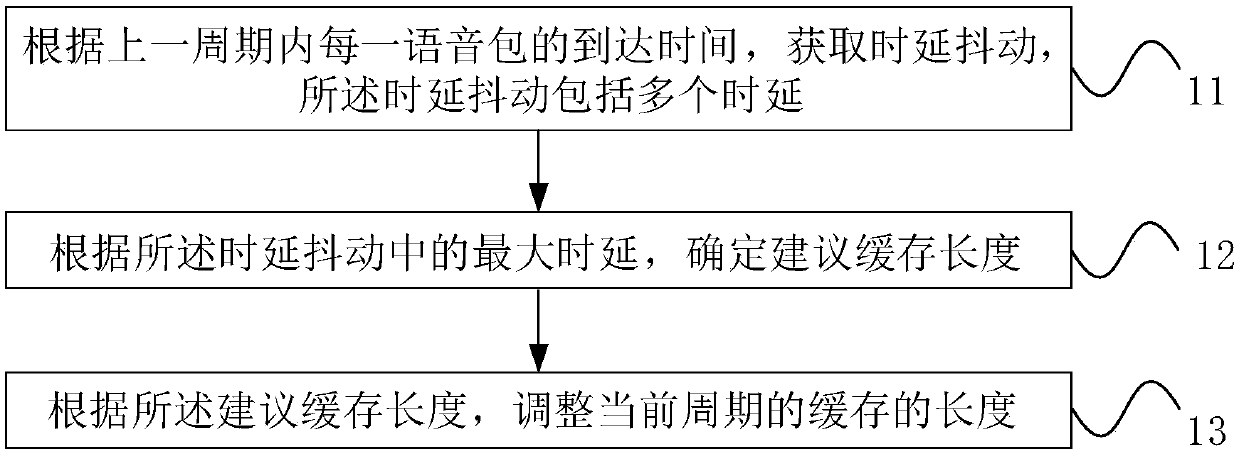

Method and device for adjusting cache length, electronic equipment and storage medium

PendingCN110300429AAccurate time delayAccurate calculationNetwork traffic/resource managementArrival timeSelf adaptive

The embodiment of the invention provides a cache length adjusting method and device, electronic equipment and a storage medium. The method comprises the steps of acquiring delay jitter according to the arrival time of each voice packet in a previous period, wherein the delay jitter comprises a plurality of delays; determining a suggested cache length according to the maximum time delay in the timedelay jitter; and adjusting the length of the cache in the current period according to the suggested cache length. According to the method, the accurate time delay is obtained through the arrival time of the voice packet in the previous period, and the suggested cache length can be accurately calculated, so that the cache length of the current period is adaptively adjusted, the time delay jitteris eliminated, and the voice quality is improved.

Owner:CHINA MOBILE GRP GUANGDONG CO LTD +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com