Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

273 results about "Non linear response" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Reactive sensor modules using pade' approximant based compensation and providing module-sourced excitation

ActiveUS20050283330A1High precision measurementLow costSpeed measurement using gyroscopic effectsApparatus with stored calibration coefficientsEngineeringIntegrated circuit

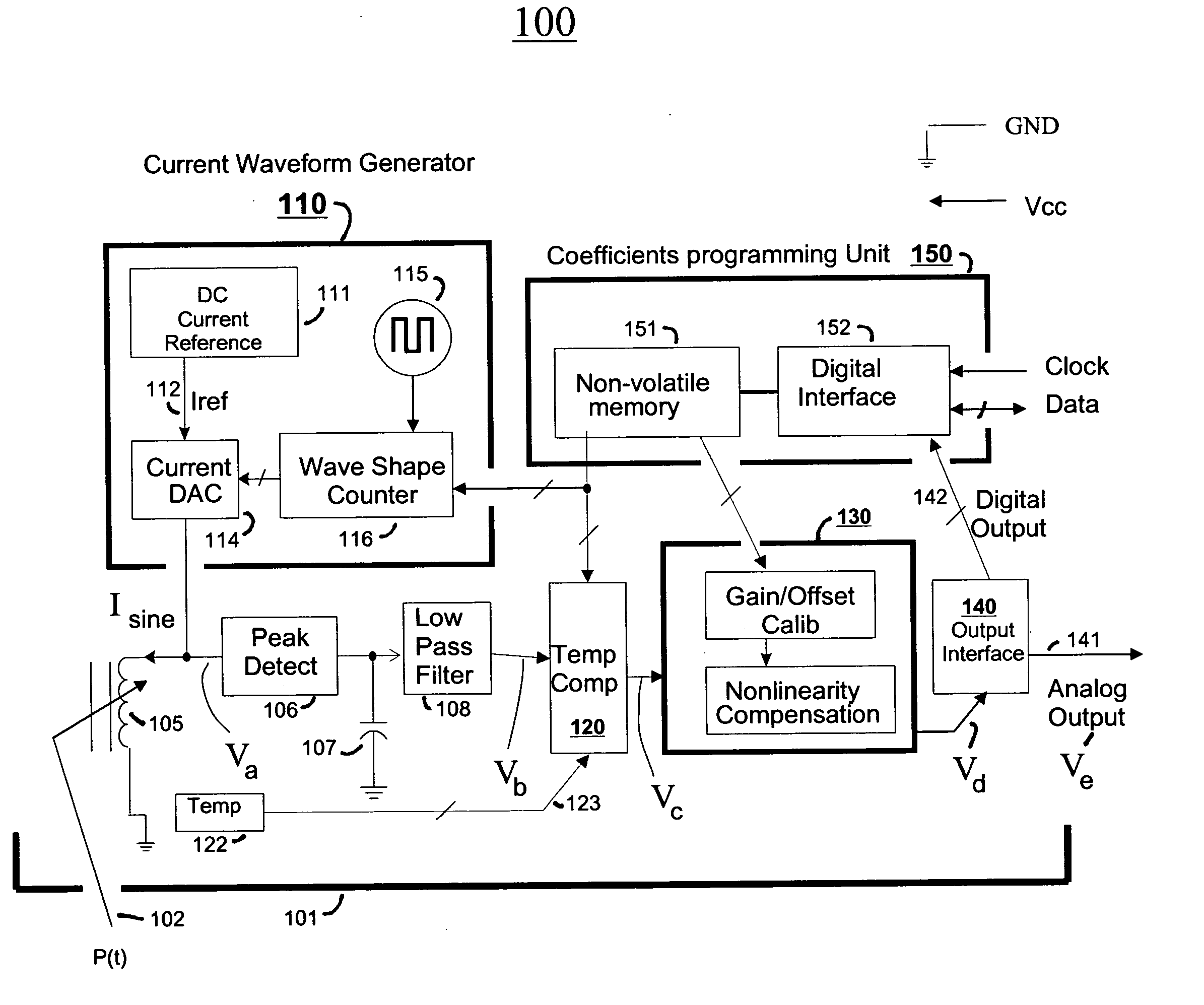

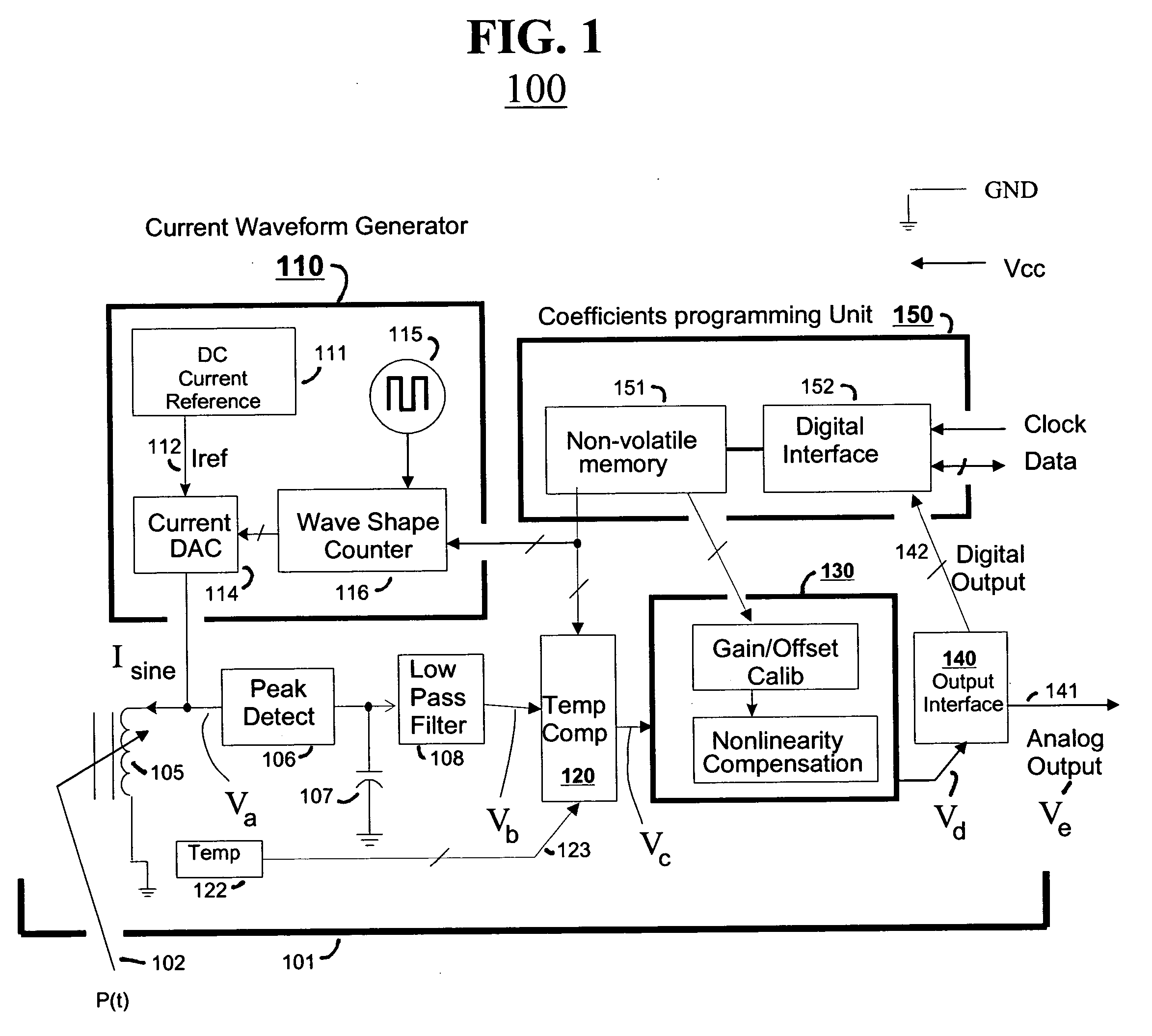

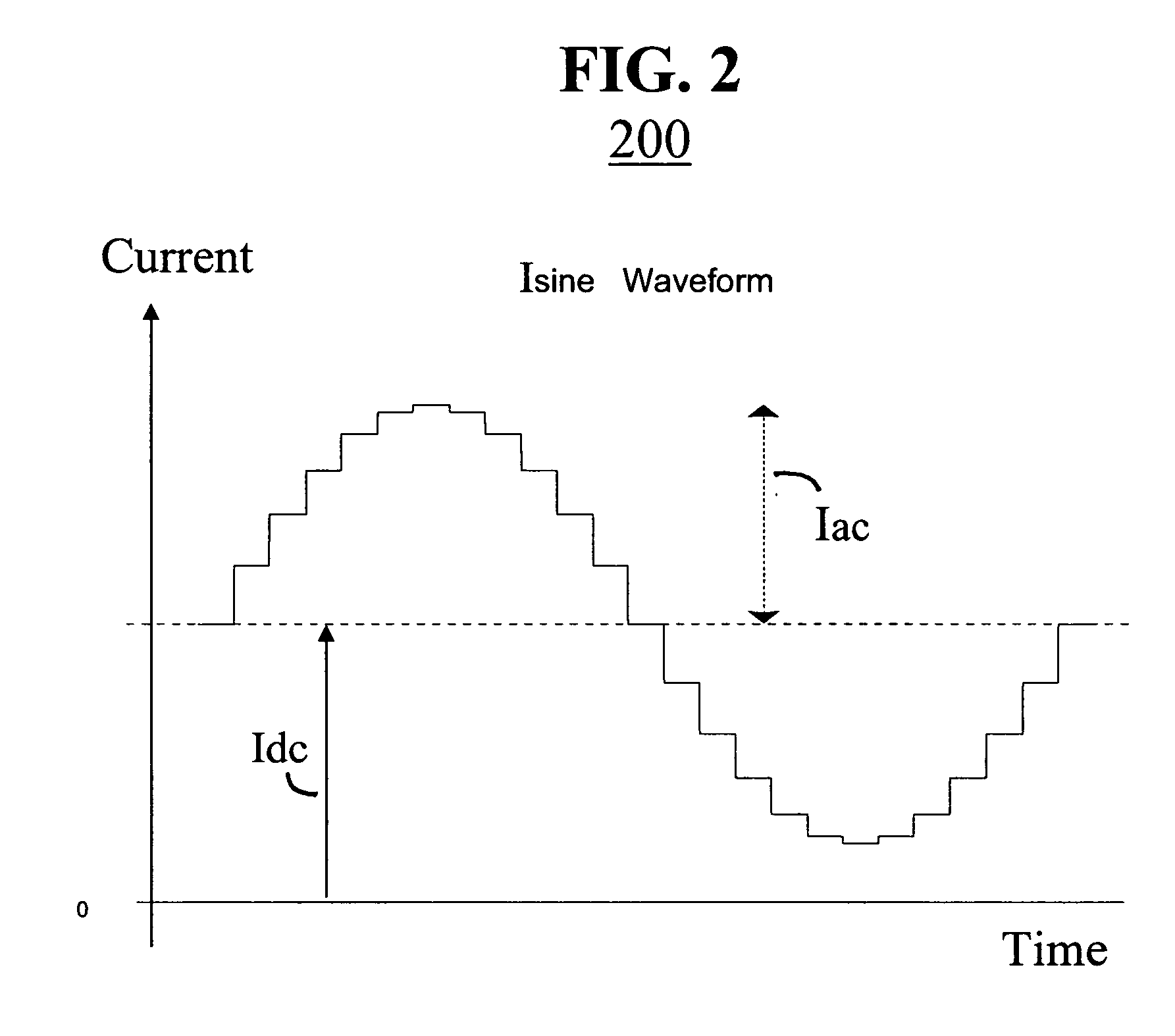

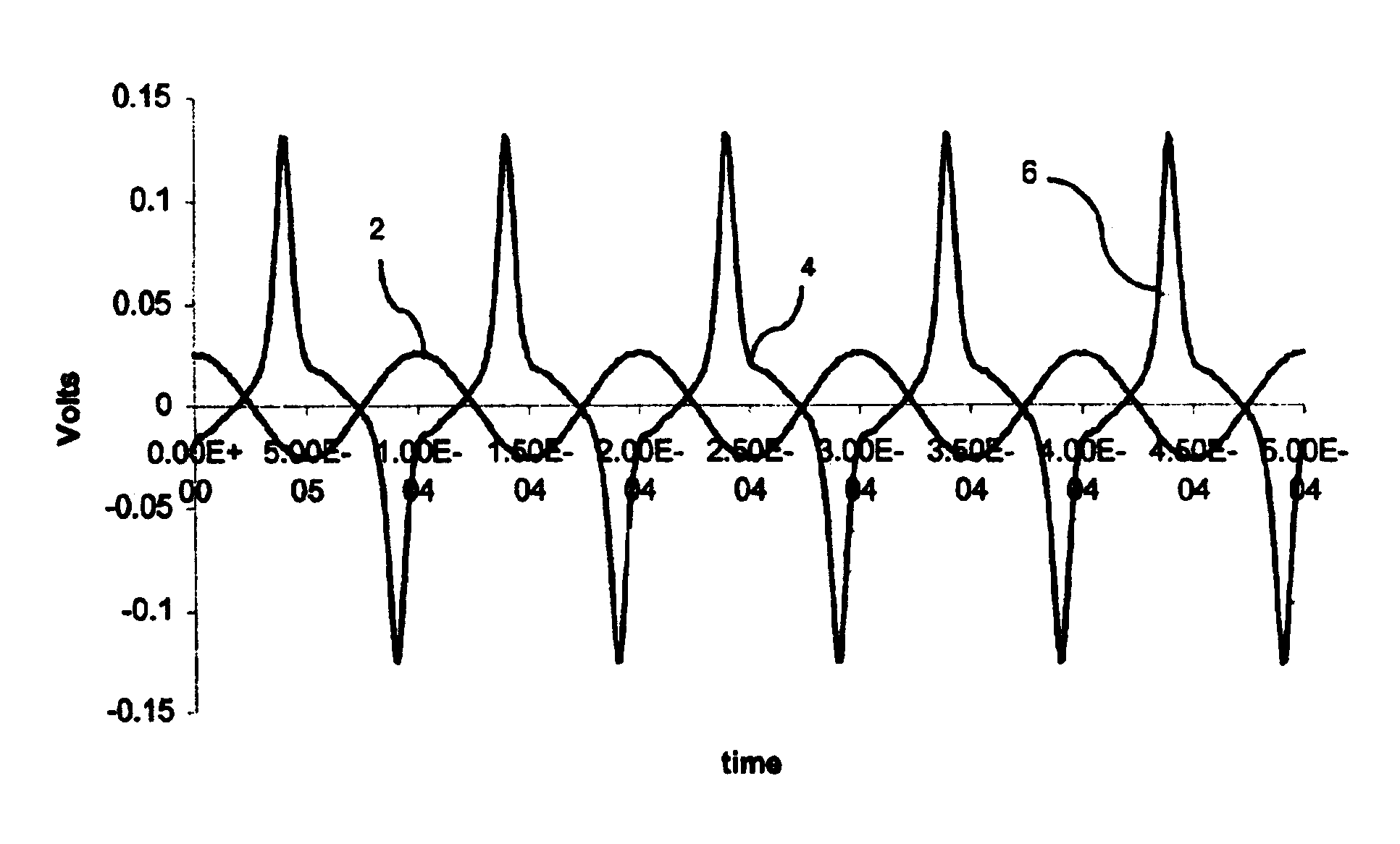

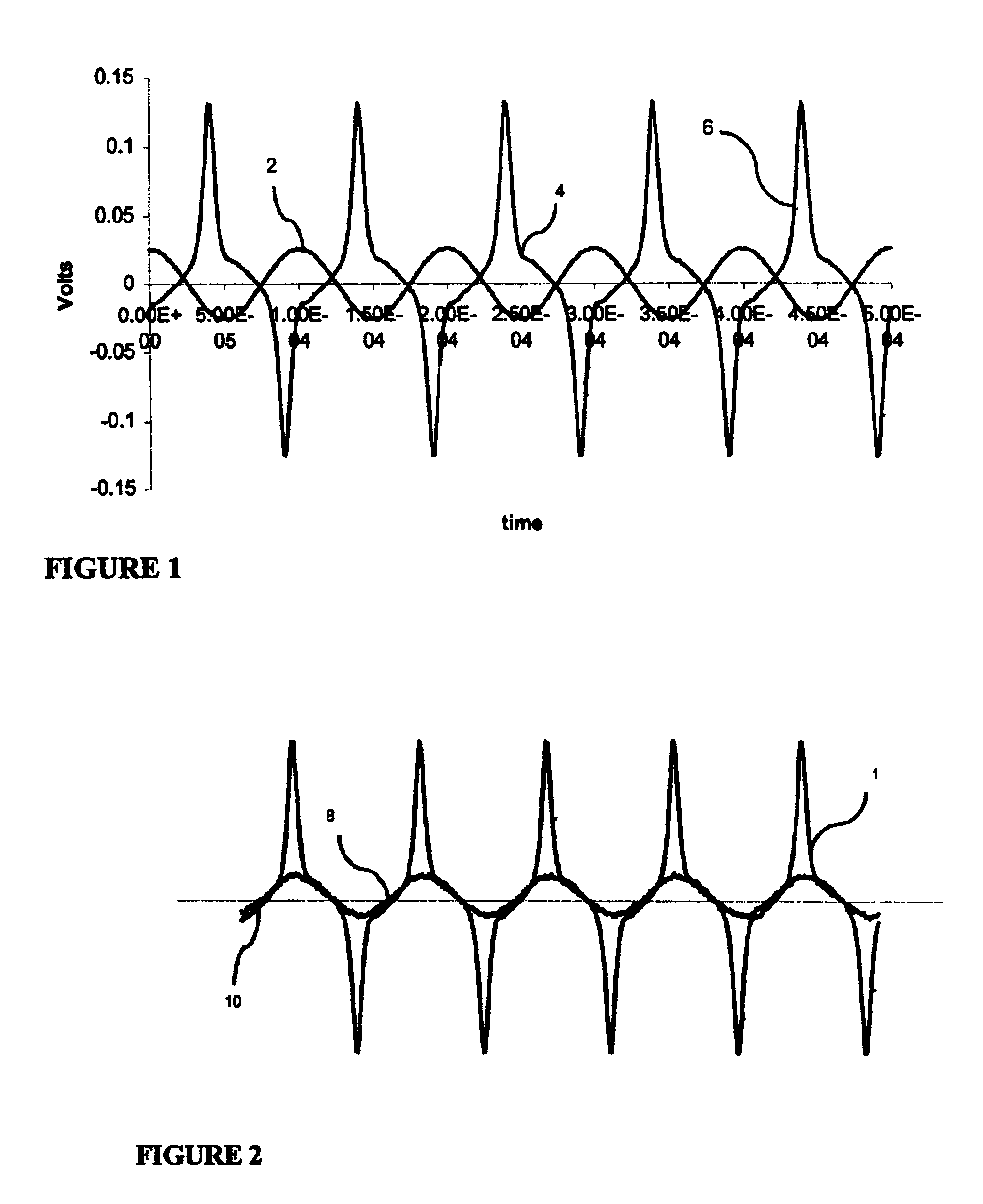

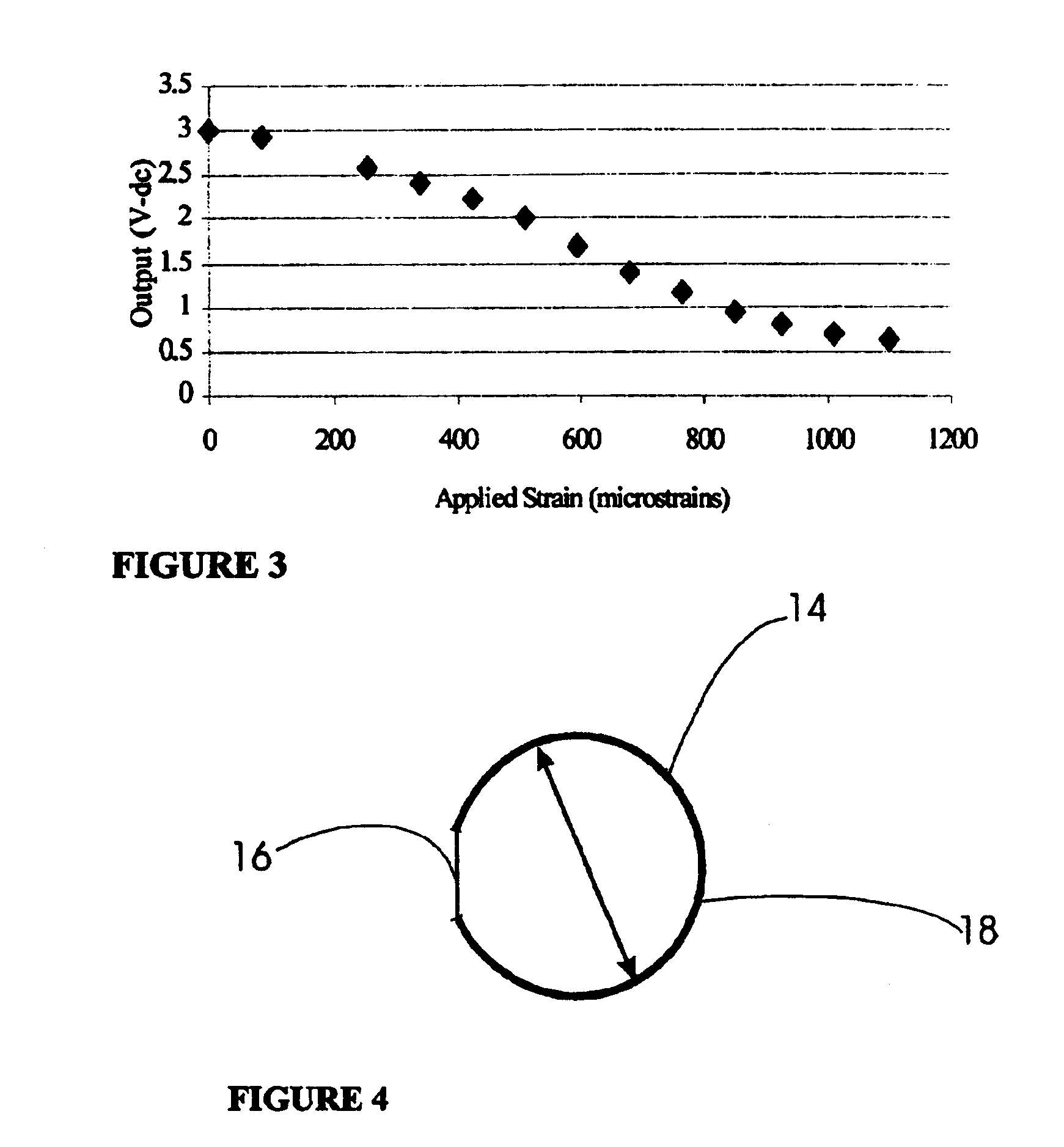

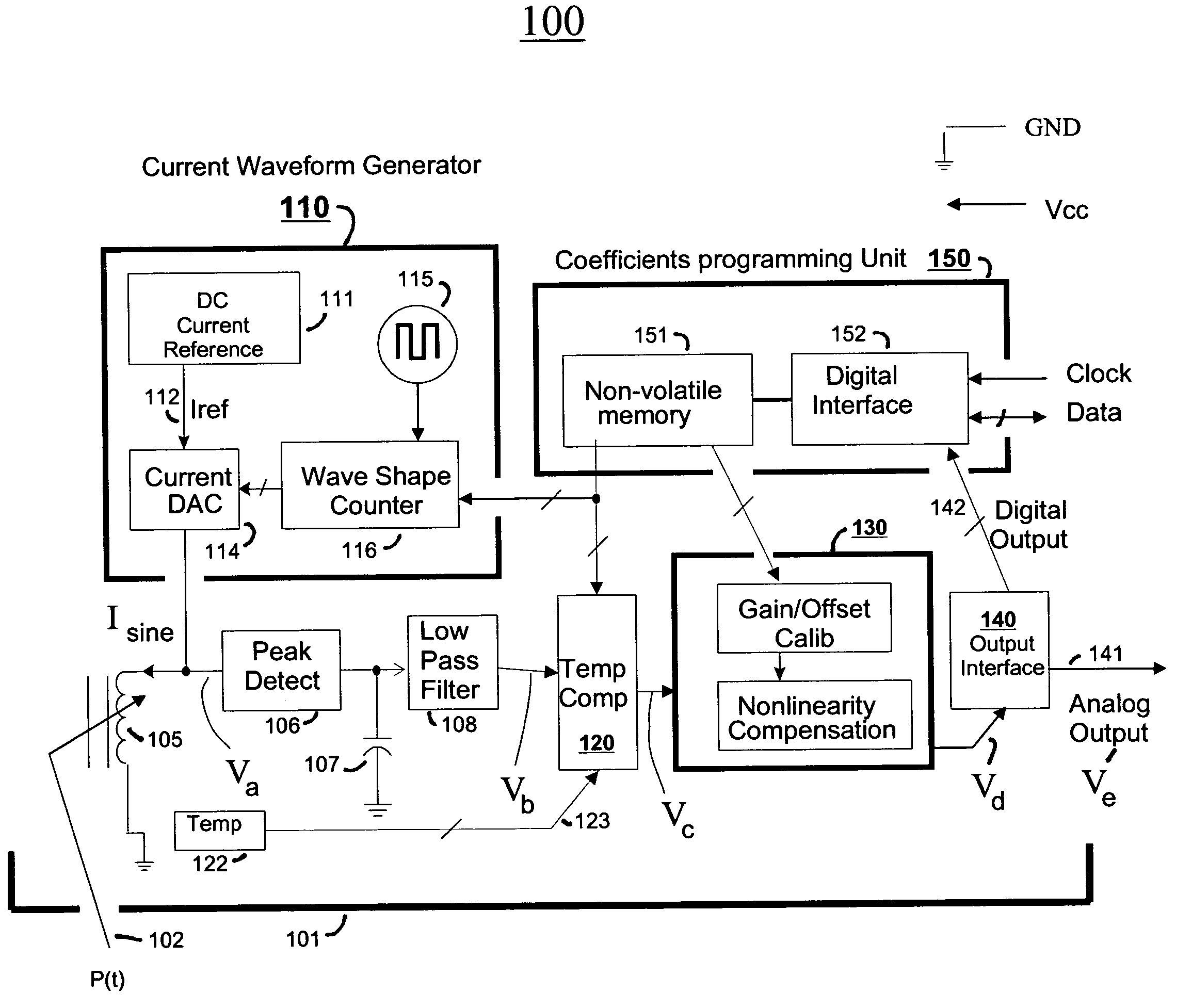

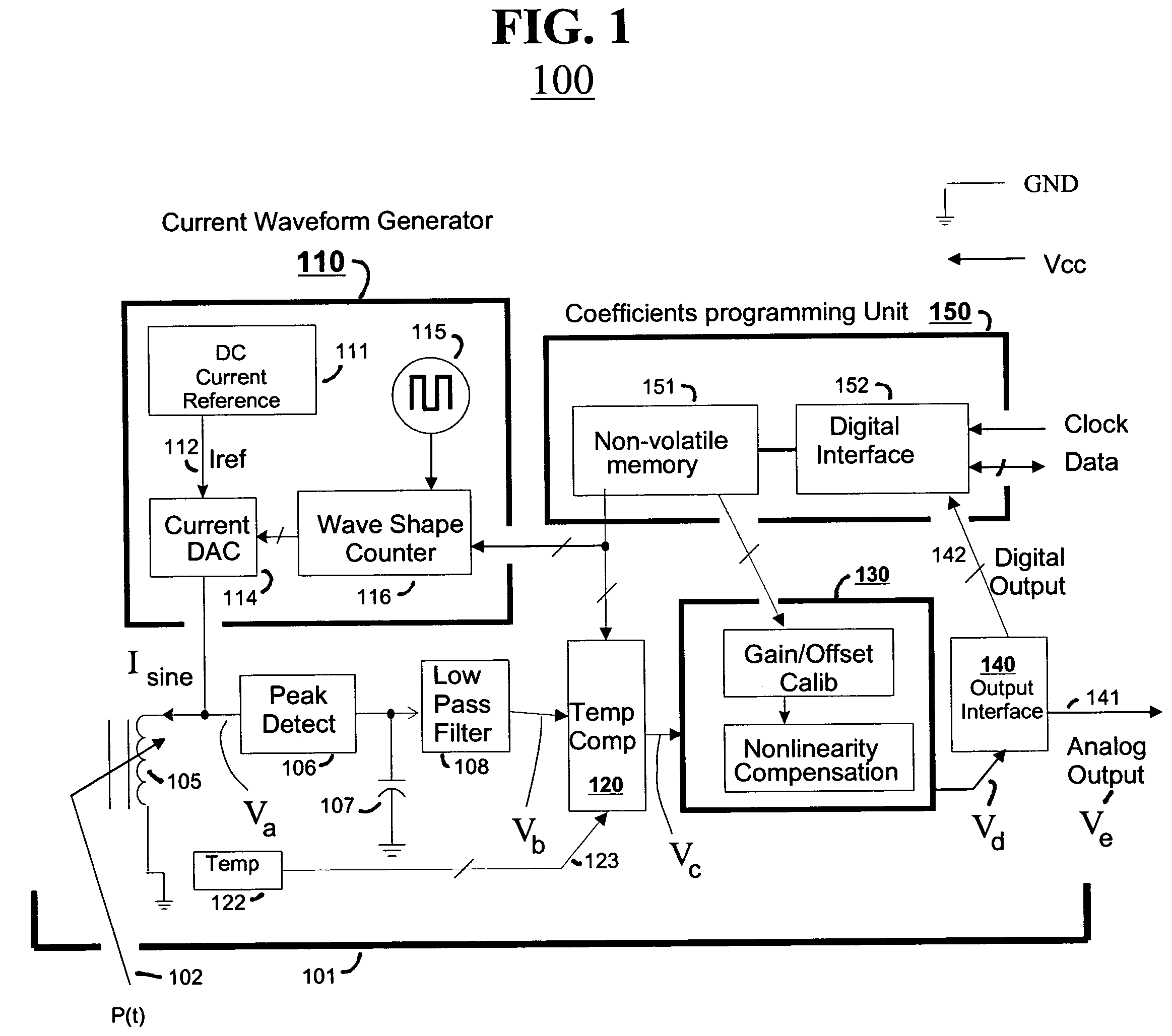

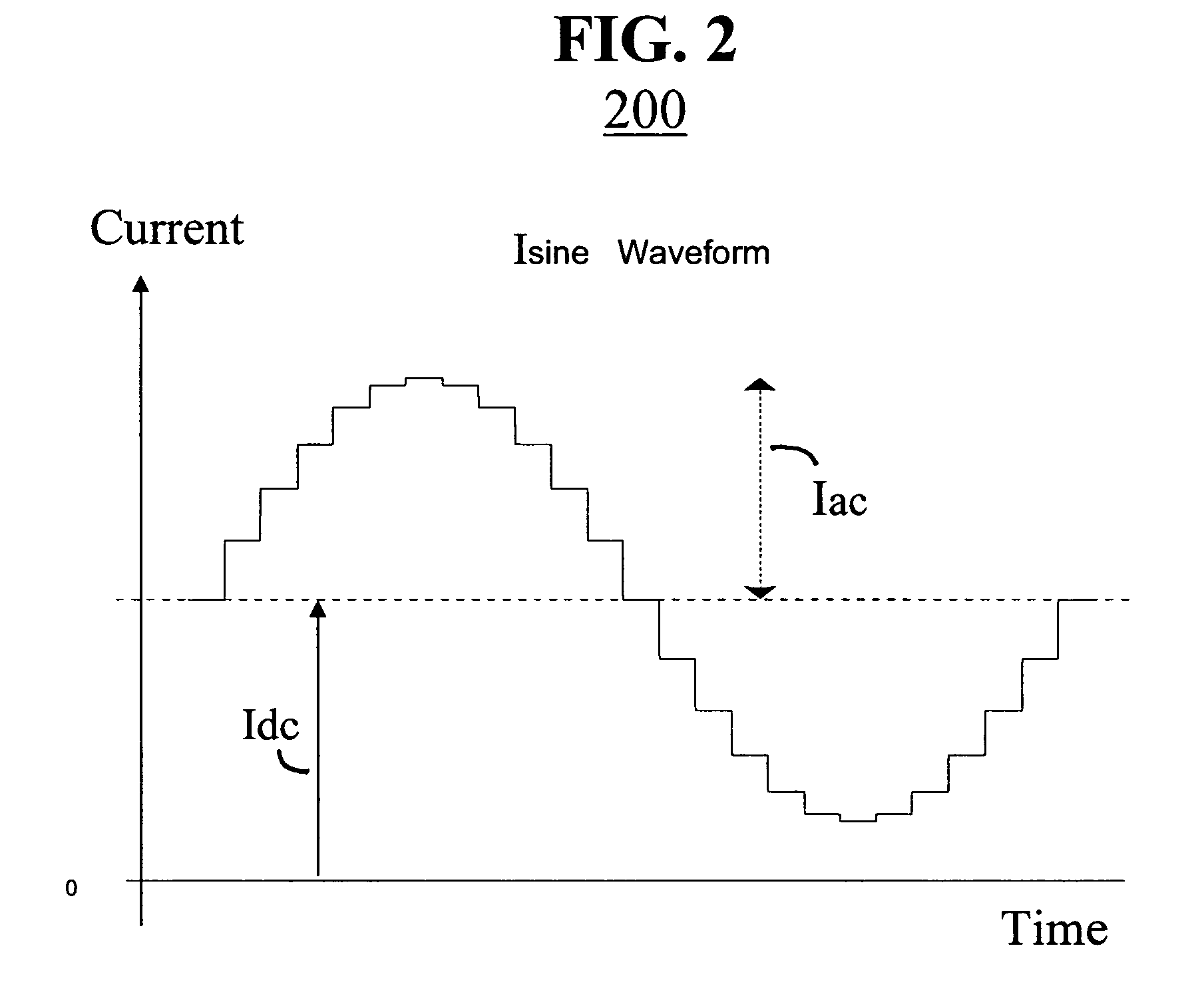

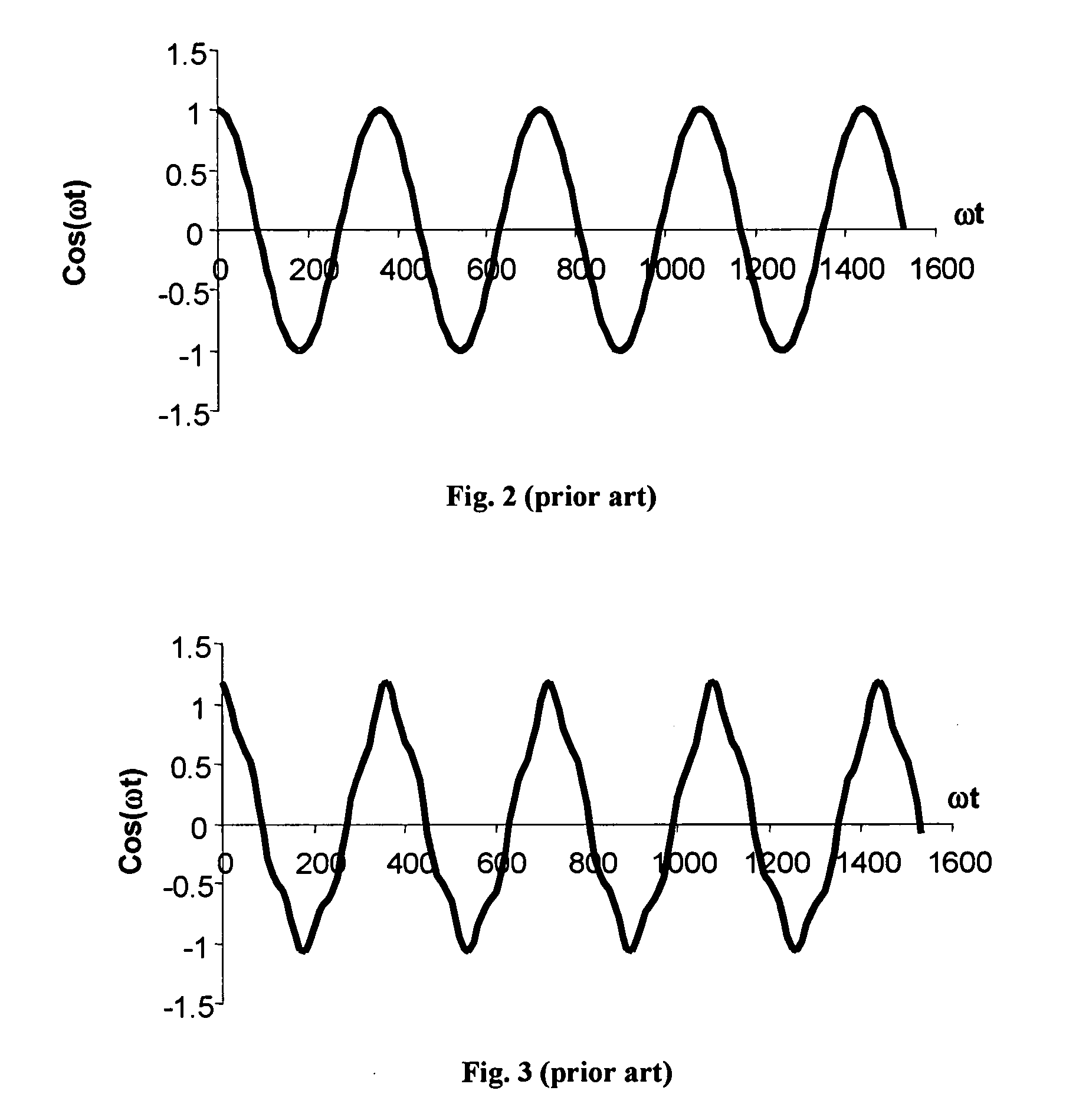

Reactive sensors typically exhibit nonlinear response to the combination of an excitational signal (e.g., sinusoidally oscillating signal) and a physical parameter under measure (e.g., position of magnetic core member). Such sensors are typically sensitive to temperature variation. Systems and methods are disclosed for compensating for the nonlinear and / or temperature dependant behavior of reactive sensors and for calibrating the post-compensation output signals relative to known samples of the physical parameter under measure (e.g., position). One class of embodiments comprises a housing containing at least part of a reactive sensor, a monolithic integrated circuit and a timing reference (e.g., an oscillator crystal). The integrated circuit includes a waveform generator for generating a sensor exciting signal, a detector for detecting the response of the sensor to the combination of the exciting signal and the under-measure physical parameter, a temperature compensating unit and a Pade' Approximant based, nonlinearity compensating unit. The temperature compensating unit and the Pade' Approximant nonlinearity compensating unit are tuned by use of digitally programmed coefficients. The coefficients calibrate the final output as well as compensating for nonlinearity and temperature sensitivity. A highly accurate measurement of the under-measure physical parameter is made possible even though each of the sensor and compensating circuitry may be relatively simple, compact, and low in cost.

Owner:SEMICON COMPONENTS IND LLC +1

Systems and methods to determine elastic properties of materials

InactiveUS20050267695A1Elastic properties can be determinedInherent in massVibration measurement in solidsAnalysing solids using sonic/ultrasonic/infrasonic wavesTime domainHarmonic

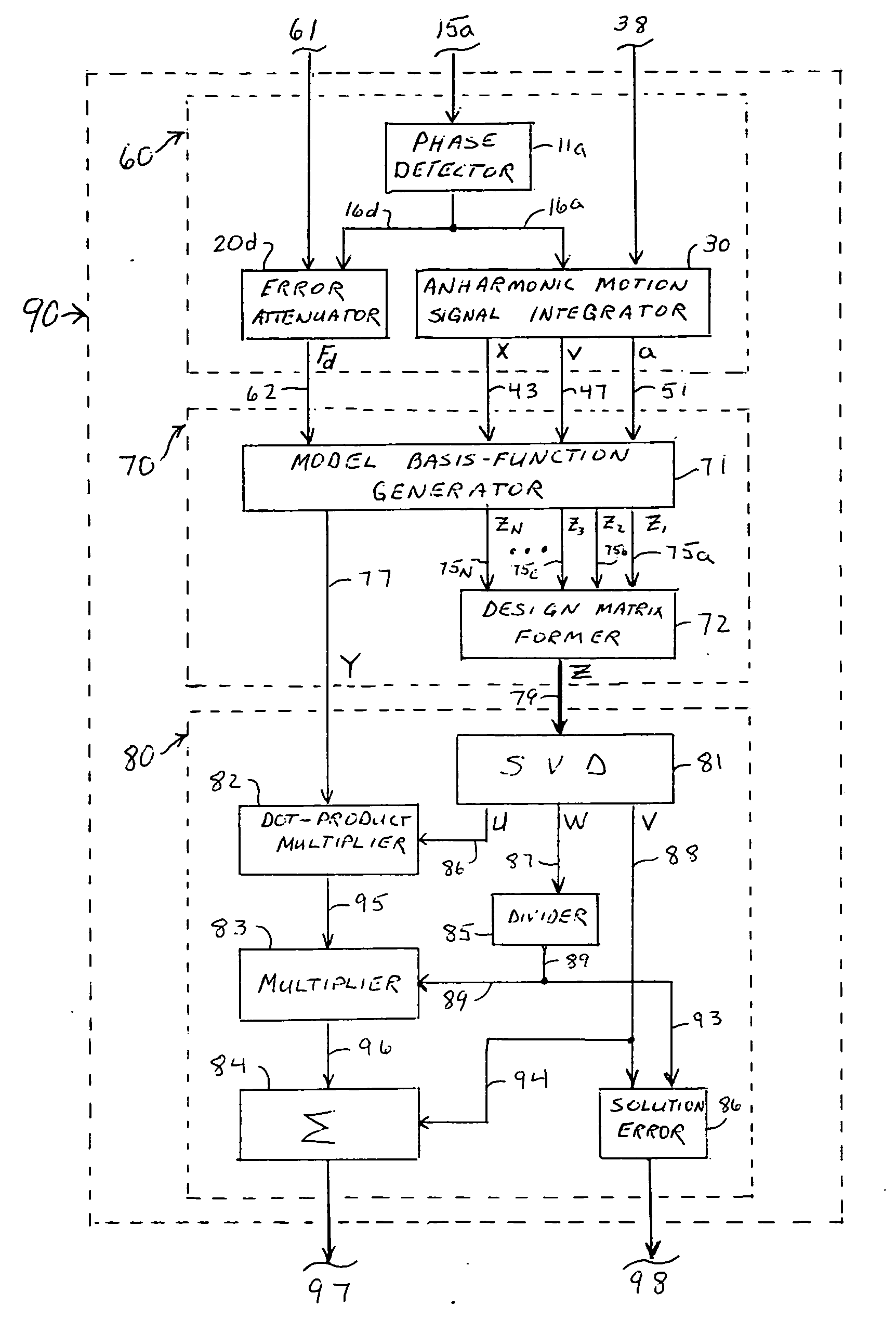

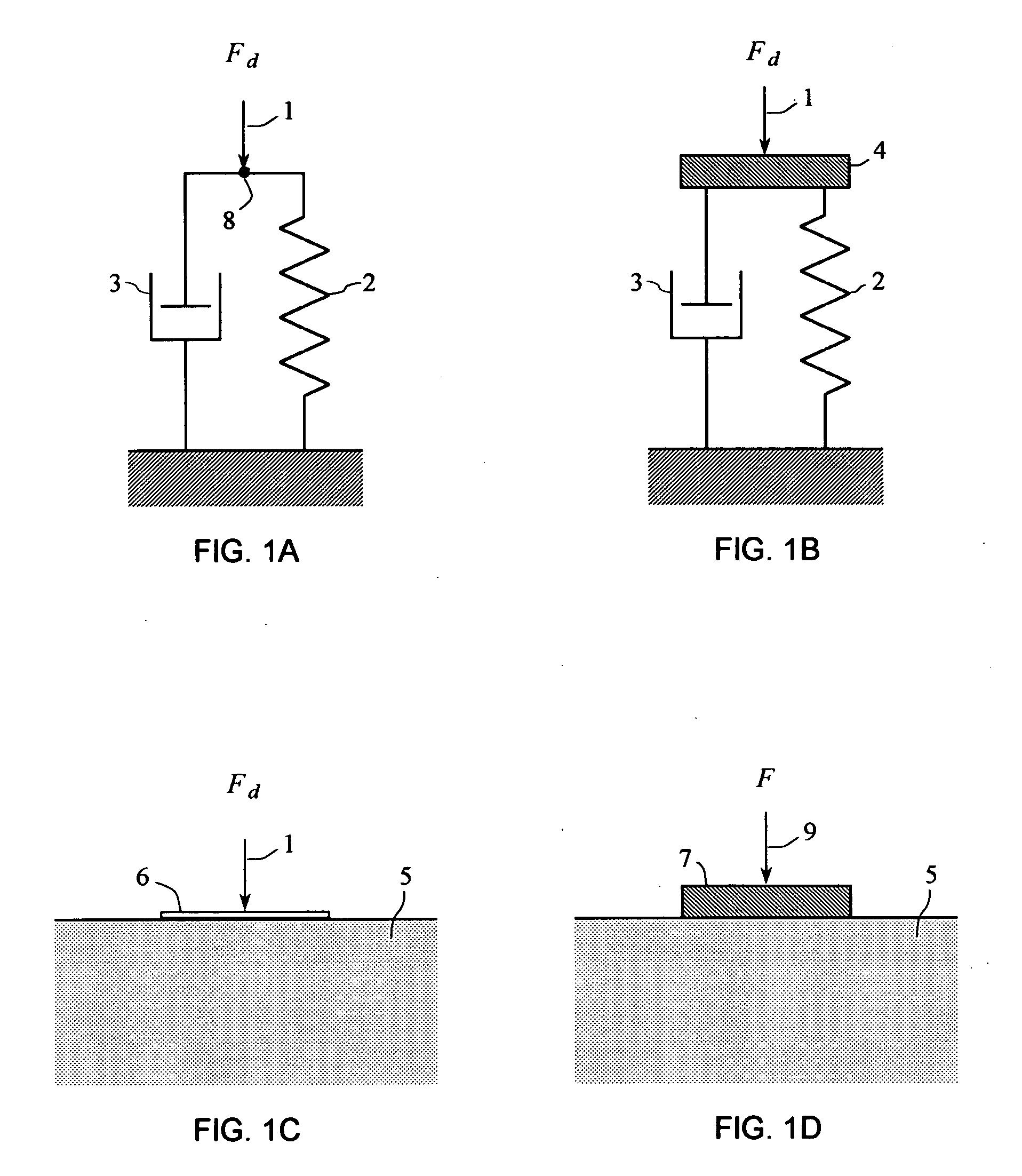

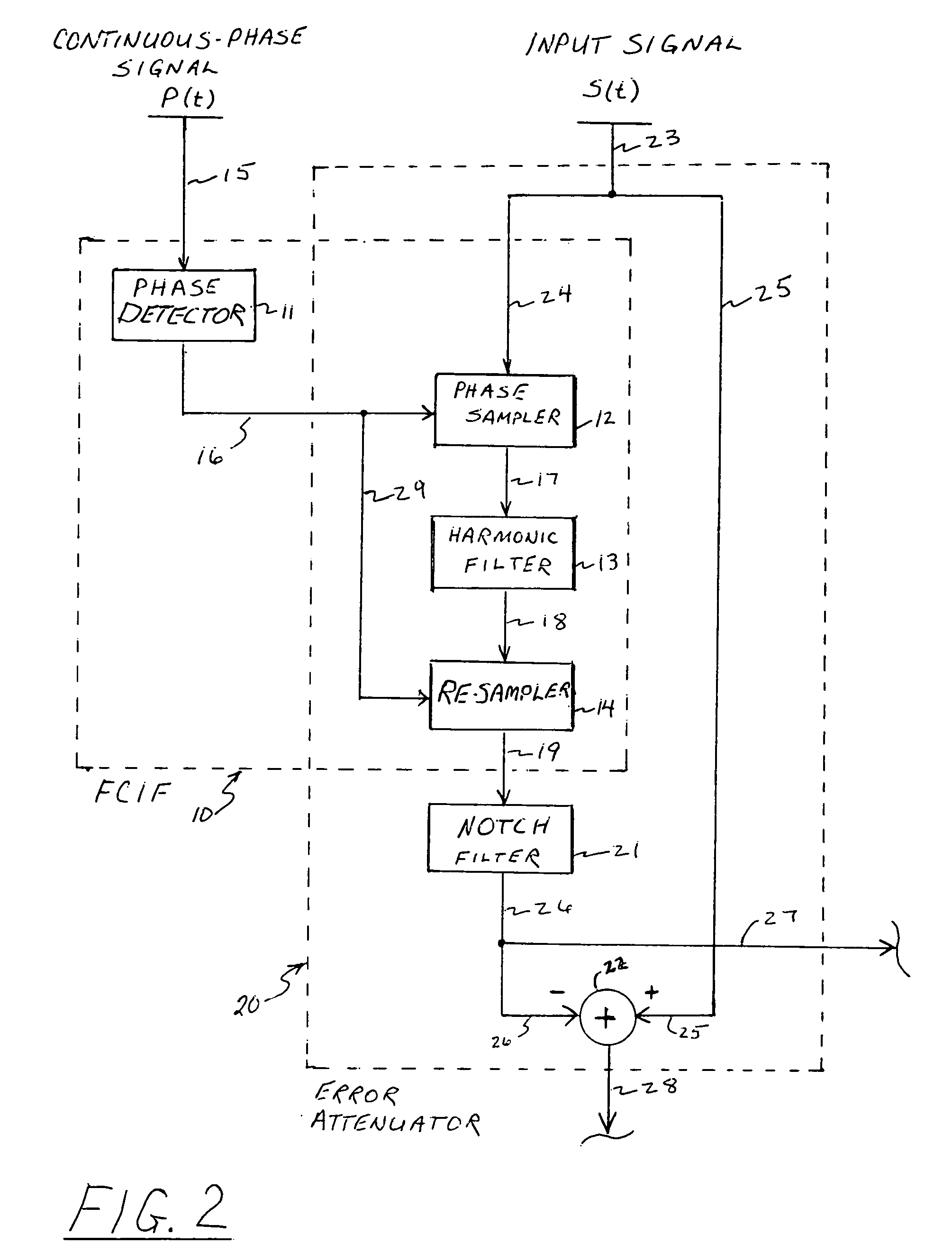

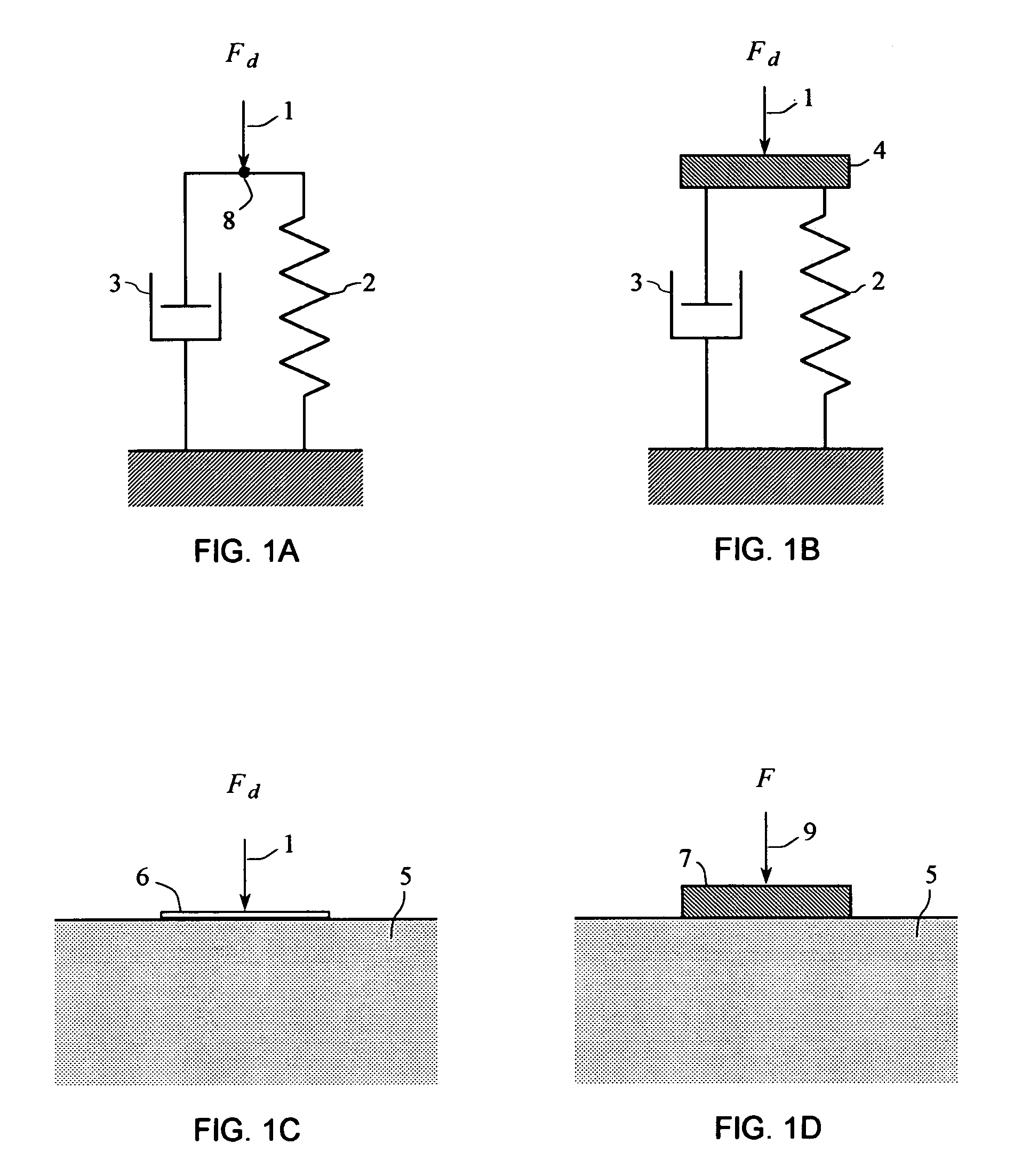

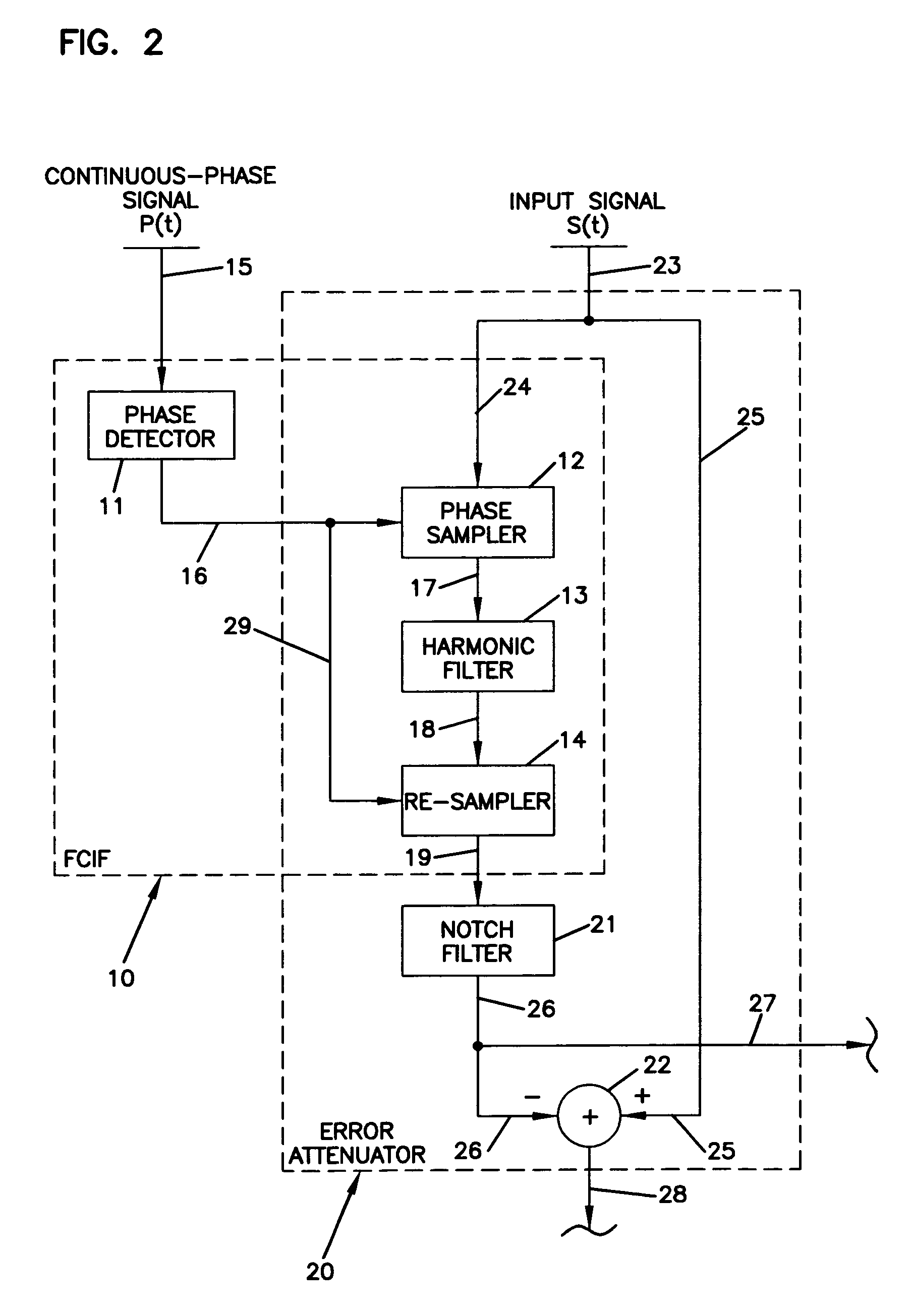

The present invention provides systems and methods to use a measured driving-point response of a nonlinear material to determine one or more elastic properties of the material. The present invention takes advantage of the full information represented by the transient component, the steady-state component, the anharmonic components, and the nonlinear response components of a measured driving-point response of a real nonlinear material, without limitation in the use of large-amplitude forces. The elastic properties are determined by forming and solving a time-domain system of linear equations representing a differential equation model of the driving-point motions of the material. Based on a single, short duration, large-amplitude driving point measurement, both linear and nonlinear properties can be determined; both large-amplitude and near-zero amplitude properties can be determined; and elastic-wave speed and elastic moduli and their variation with depth can be determined. The present invention also provides a system and a method to filter an input signal to either attenuate or preserve each of one or more selected harmonic components that are harmonics of a phase reference signal.

Owner:GERMAN PETER THOMAS

Sampled amplitude read channel employing an adaptive non-linear correction circuit for correcting non-linear distortions in a read signal

InactiveUS7012772B1Minimize complexityLow costMultiple-port networksModification of read/write signalsNonlinear distortionAsymmetric head

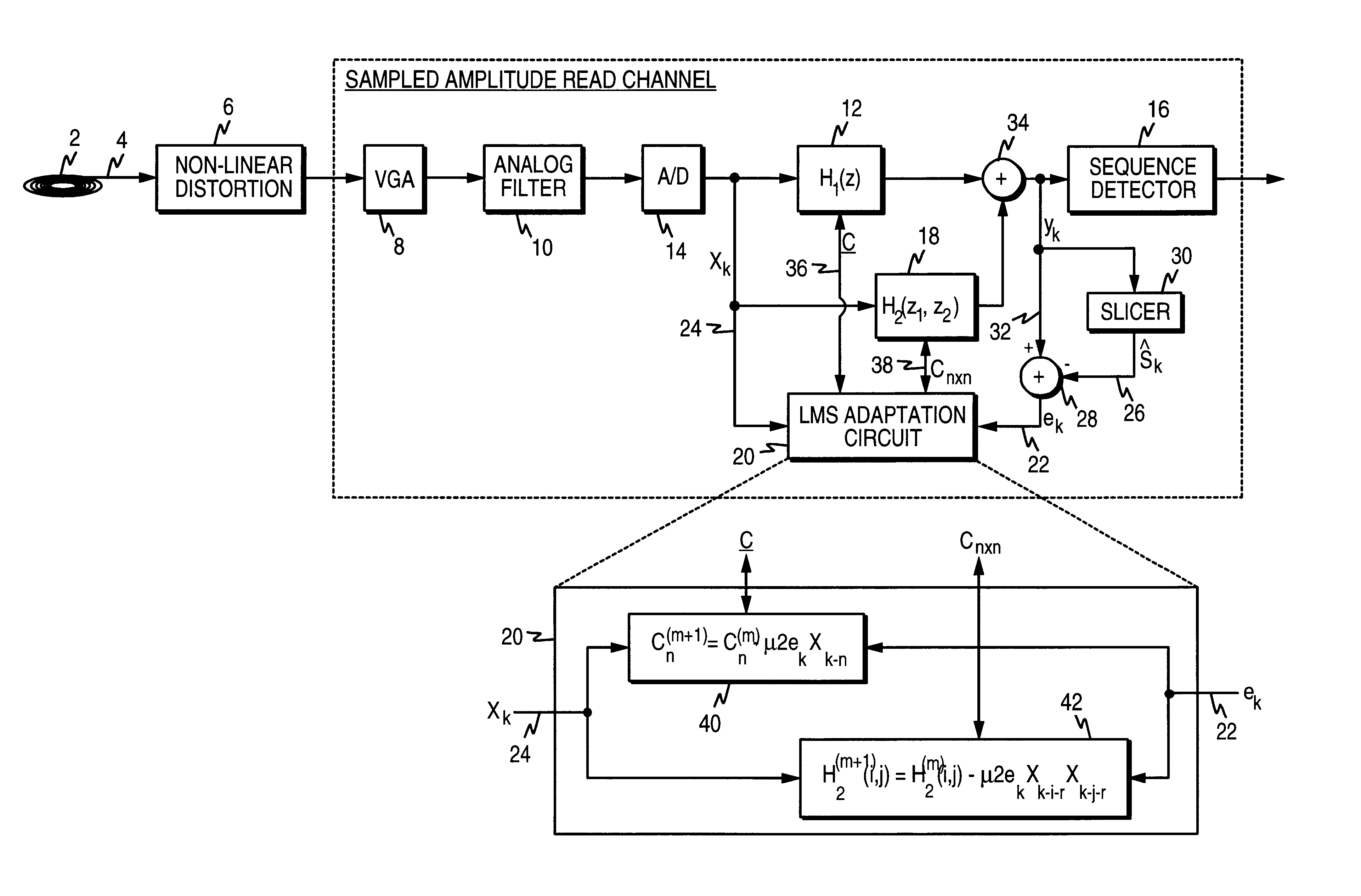

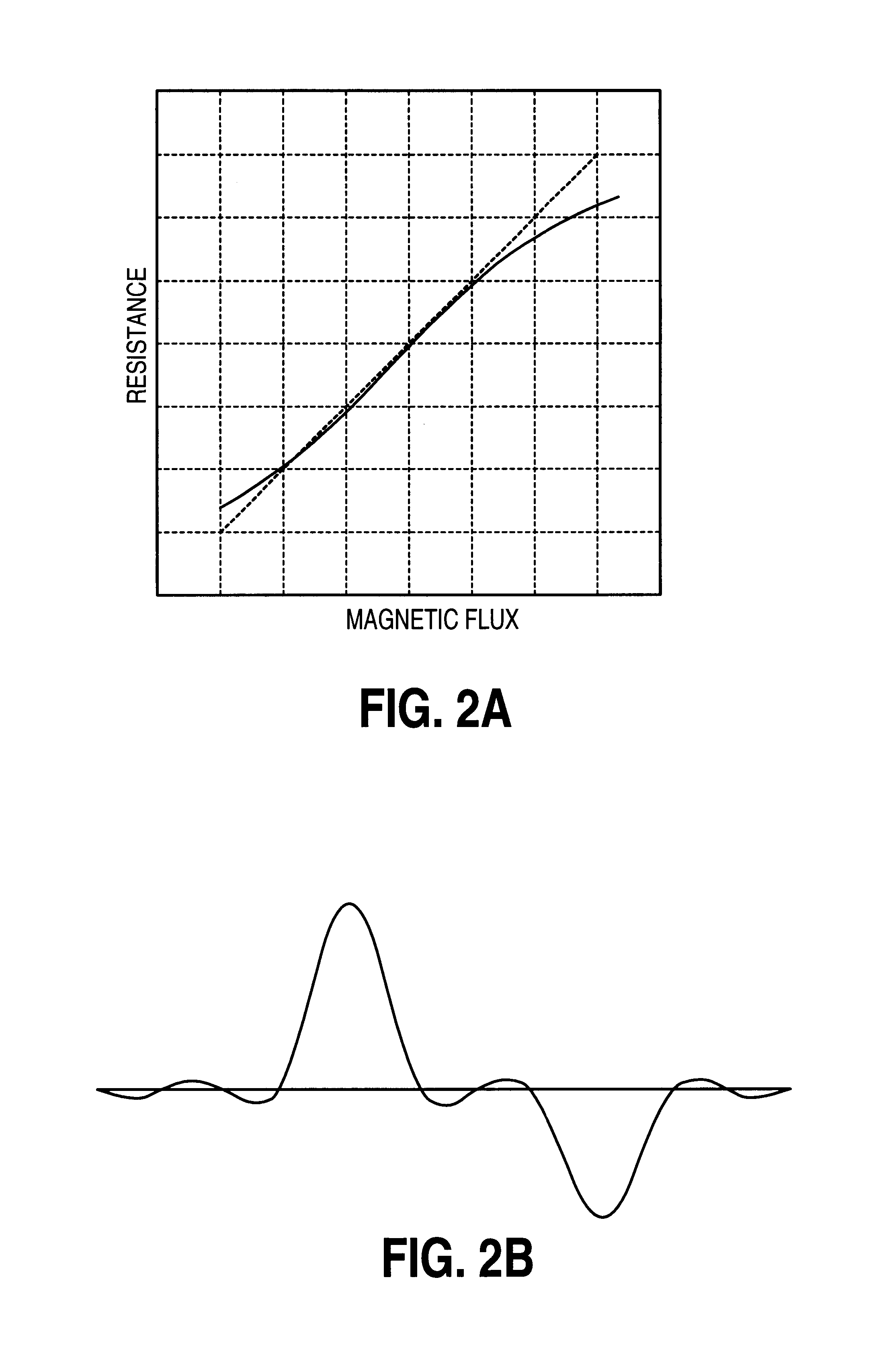

A sampled amplitude read channel is disclosed for magnetic disk storage systems comprising an adaptive non-linear correction circuit for correcting non-linear distortions in the read signal, such as asymmetry caused by the non-linear response of a magneto-resistive (MR) read head. The analog read signal is sampled and the discrete time sample values equalized into a desired partial response prior to sequence detection. The non-linear correction circuit is inserted into the read path prior to the sequence detector and adaptively tuned by a least-mean-square (LMS) adaptation circuit. In one embodiment, the non-linear correction circuit is a discrete-time Volterra filter comprising a linear response for implementing an equalizing filter, and a non-linear response for attenuating non-linear distortions in the read signal. The filter coefficients of both the linear and non-linear sections of the Volterra filter are adaptively adjusted by the LMS adaptation circuit. In an alternative embodiment, the non-linear correction circuit operates in the analog domain, prior to the sampling device, where the cost and complexity can be minimized. The analog correction circuit implements an inverse response to that of the non-linearity in the read signal, and the response is adaptively tuned using an LMS update value computed in discrete-time for a Volterra filter, without actually implementing a Volterra filter. Further, the LMS update value for the analog correction circuit can be implemented using a simple squaring circuit.

Owner:CIRRUS LOGIC INC

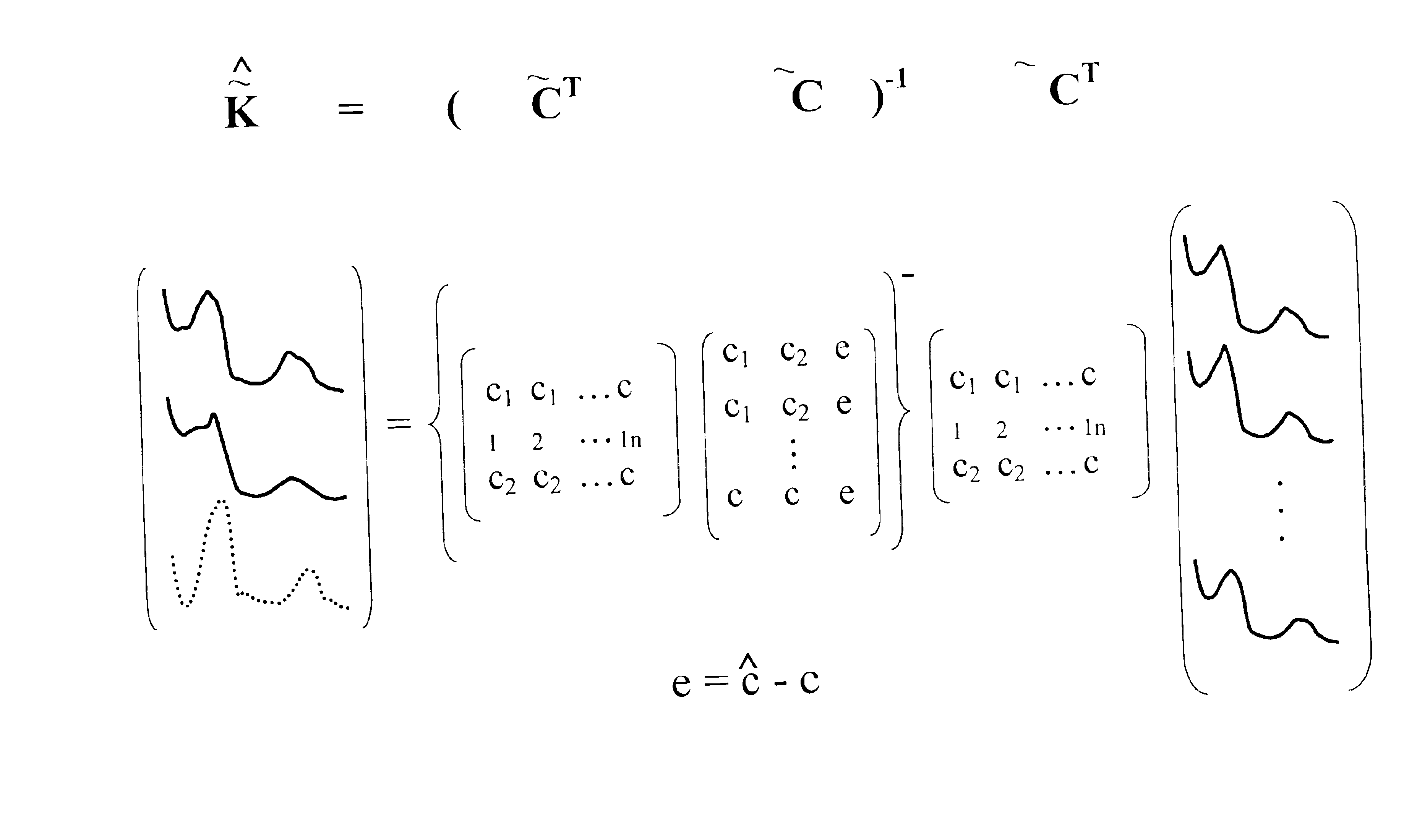

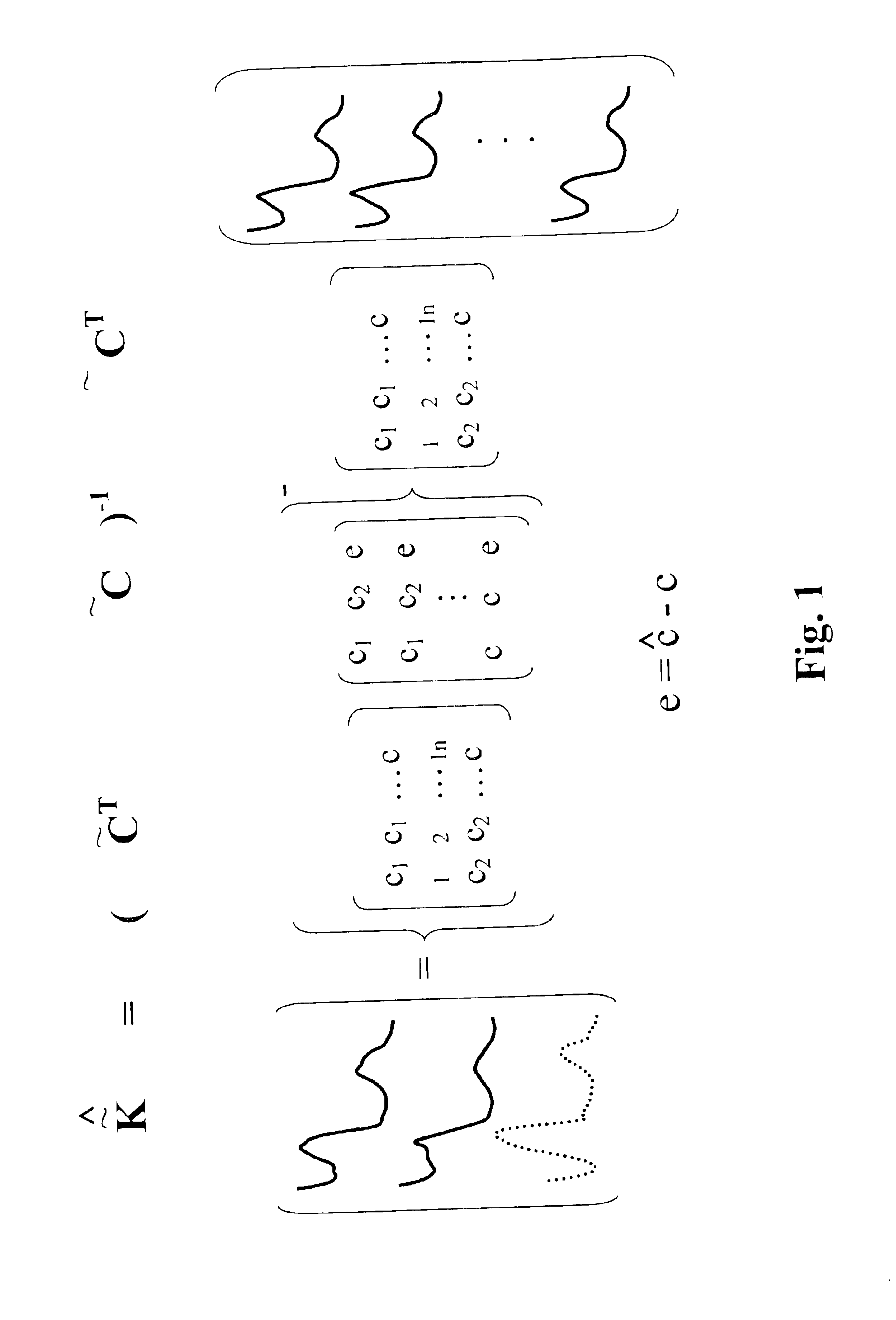

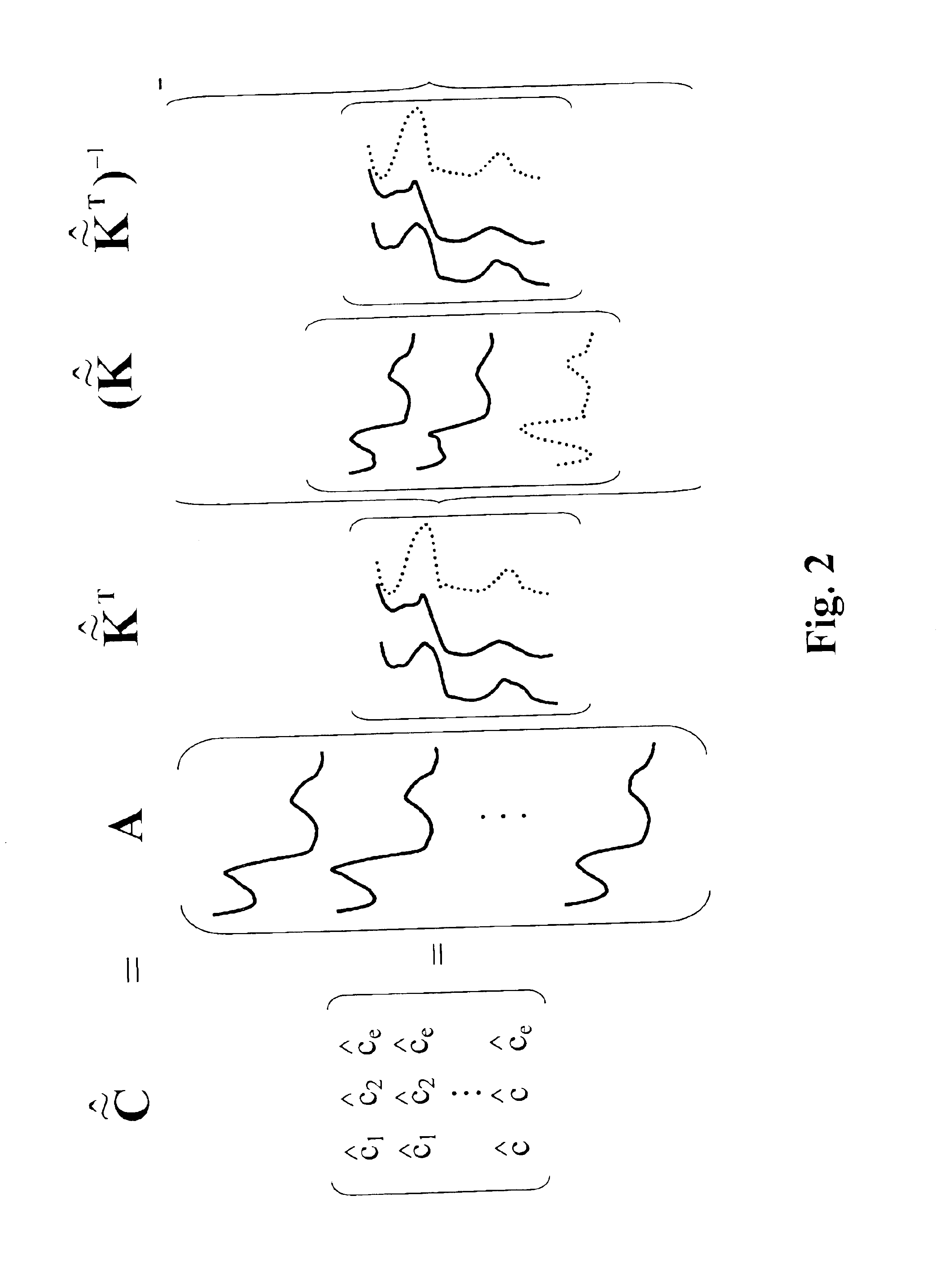

Augmented classical least squares multivariate spectral analysis

InactiveUS6842702B2Accurate and precise prediction modelAccurate and precise predictionInvestigating moving fluids/granular solidsScattering properties measurementsAlternating least squaresSpectral analysis

A method of multivariate spectral analysis, termed augmented classical least squares (ACLS), provides an improved CLS calibration model when unmodeled sources of spectral variation are contained in a calibration sample set. The ACLS methods use information derived from component or spectral residuals during the CLS calibration to provide an improved calibration-augmented CLS model. The ACLS methods are based on CLS so that they retain the qualitative benefits of CLS, yet they have the flexibility of PLS and other hybrid techniques in that they can define a prediction model even with unmodeled sources of spectral variation that are not explicitly included in the calibration model. The unmodeled sources of spectral variation may be unknown constituents, constituents with unknown concentrations, nonlinear responses, non-uniform and correlated errors, or other sources of spectral variation that are present in the calibration sample spectra. Also, since the various ACLS methods are based on CLS, they can incorporate the new prediction-augmented CLS (PACLS) method of updating the prediction model for new sources of spectral variation contained in the prediction sample set without having to return to the calibration process. The ACLS methods can also be applied to alternating least squares models. The ACLS methods can be applied to all types of multivariate data.

Owner:NAT TECH & ENG SOLUTIONS OF SANDIA LLC

Systems and methods to determine elastic properties of materials

InactiveUS7107159B2Elastic propertyInherent ambiguityVibration measurement in solidsAnalysing solids using sonic/ultrasonic/infrasonic wavesTime domainHarmonic

The present invention provides systems and methods to used a measured driving-point response of a nonlinear material to determined one or more elastic properties of the material. The present invention takes advantage of the full information represented by the transient component, the steady-state component, the anharmonic components, and the nonlinear response components of a measured driving-point response of a real nonlinear material, without limitation in the use of large-amplitude forces. The elastic properties are determined by forming and solving a time-domain system of linear equations representing a differential equation model of the driving-point motions of the material. Based on a single, short duration, large-amplitude driving point measurement, both linear and nonlinear properties can be determined; both large-amplitude and near-zero amplitude properties can be determined; and elastic-wave speed and elastic moduli and their variation with depth can be determined.

Owner:GERMAN PETER THOMAS

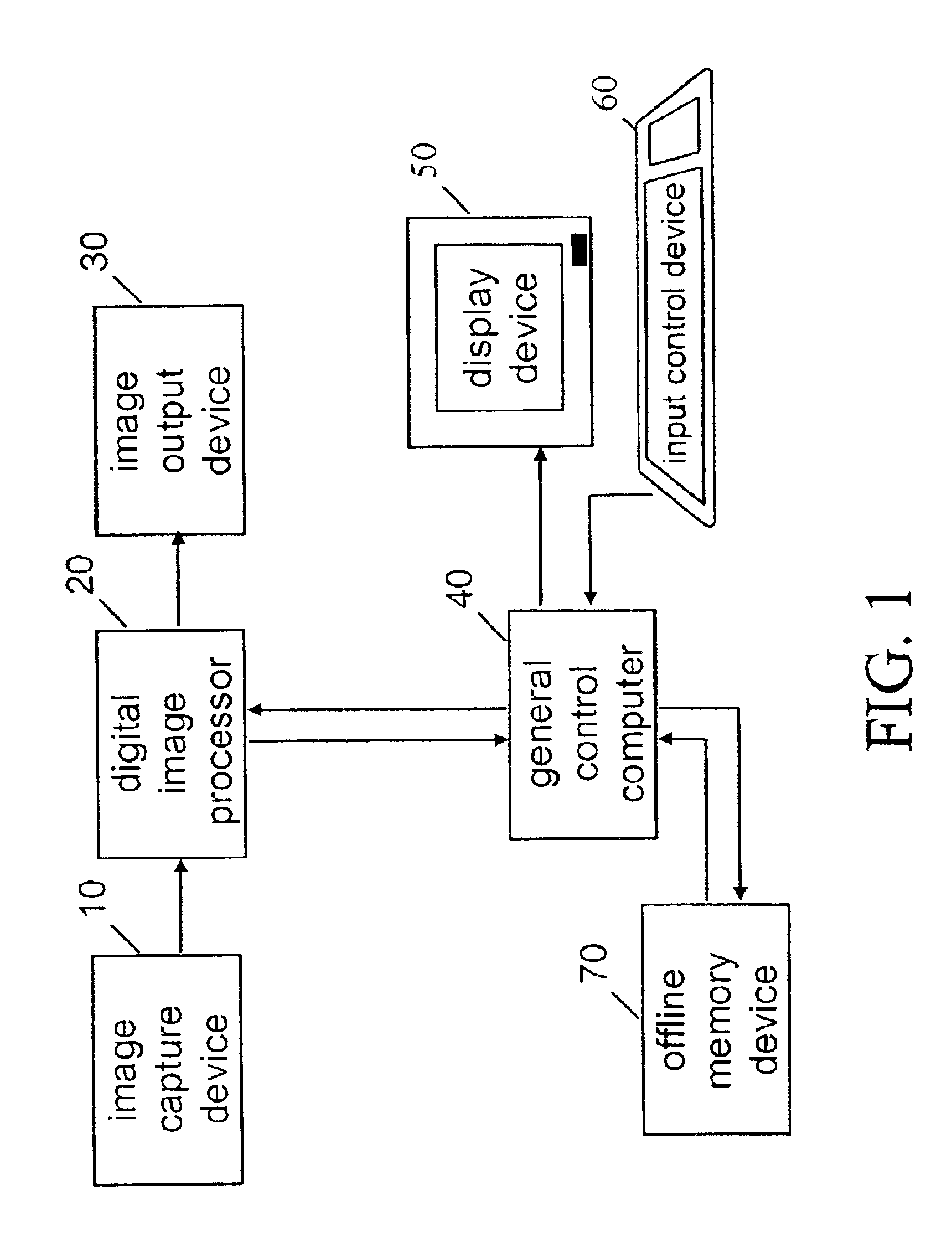

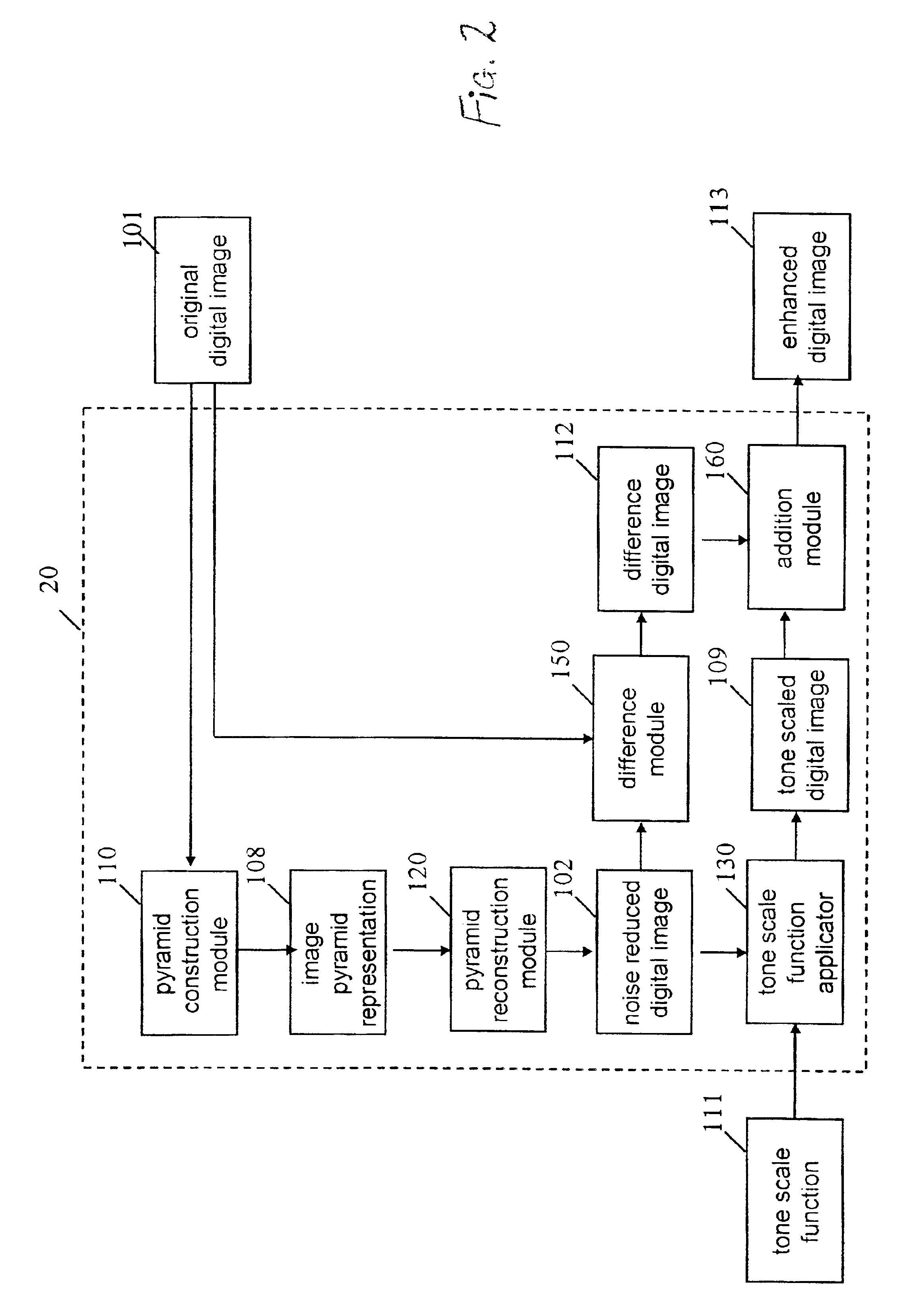

Method of enhancing the tone scale of a digital image to extend the linear response range without amplifying noise

A method of processing a digital image to improve contrast, the digital image being derived from an image captured by a recording medium having a nonlinear response to light, includes the steps of: applying a spatial filter to the digital image to produce a noise reduced digital image; subtracting the noise reduced digital image from the digital image to produce a difference digital image; applying a tone scale function to the noise reduced digital image to produce a tone scale adjusted digital image having the appearance of being derived from an image captured by a recording medium having a linear response; and combining the difference digital image with the tone scale adjusted digital image to produce a processed digital image, whereby the contrast of the digital image is improved without amplifying noise.

Owner:MONUMENT PEAK VENTURES LLC

Inductively coupled stress/strain sensor

InactiveUS6912911B2Change relationshipForce measurement by measuring magnetic property varationWork measurementMagnetostrictionCouple stress

An improved method of sensing strain allows measurements of stress, torque, vibration and other loads imposed on a body without physical contact between the body / sensor and the monitoring equipment. An induction loop is at least partially comprised of a magnetostrictive material with a non-linear current-voltage relationship. An excitation device such as a coil is used to induce an AC response in the sensor. The non-linear response to the induced current is received by a sensing device such as a sensing coil, and the output thereof is filtered. The excitation device and sensing device are located in operative proximity to the sensor, but need not be in contact therewith, allowing easy measurement in small spaces, under harsh conditions, or of moving bodies such as drive shafts. The non-linear response of the sensor induces easily detectable harmonics of the base frequency of excitation. These harmonics may advantageously be measured as well.

Owner:SENSORTEX

Reactive sensor modules using Pade' Approximant based compensation and providing module-sourced excitation

ActiveUS7006938B2High precision measurementLow costSpeed measurement using gyroscopic effectsApparatus with stored calibration coefficientsIntegrated circuitNon linear response

Reactive sensors typically exhibit nonlinear response to temperature variation. Systems and methods are disclosed for compensating for the nonlinear and / or temperature dependent behavior of reactive sensors and for calibrating the post-compensation output signals relative to known samples of the physical parameter under measure. One call of embodiments includes a housing containing at least part of a reactive sensor, a monolithic integrated circuit and a timing reference. The integrated circuit includes a waveform generator for generating a sensor exciting signal, a detector for detecting the response of the sensor to the combination of the exciting signal and the under-measure physical parameter, a temperature compensating unit and the Pade Approximant nonlinearity compensating unit are tuned by use of digitally programmed coefficients. The coefficients calibrate the final output as well as compensating for nonlinearity and temperature sensitivity.

Owner:SEMICON COMPONENTS IND LLC +1

Method and system for detecting electrical arcing in a plasma process powered by an AC source

InactiveUS20050212450A1Electric discharge tubesStatic indicating devicesNon linear responseElectrical and Electronics engineering

A method for detecting electrical arcing in a plasma process powered by an AC source comprises the steps of sampling at least one Fourier component of the AC source waveform distorted by the non-linear response of the plasma, determining when a change in amplitude of the component, irrespective of the direction of the change, exceeds any one of a plurality of different threshold levels, and determining the duration that each such threshold is exceeded. Each threshold is a predetermined fraction of a running average of the amplitude of the component.

Owner:SCI SYST RES

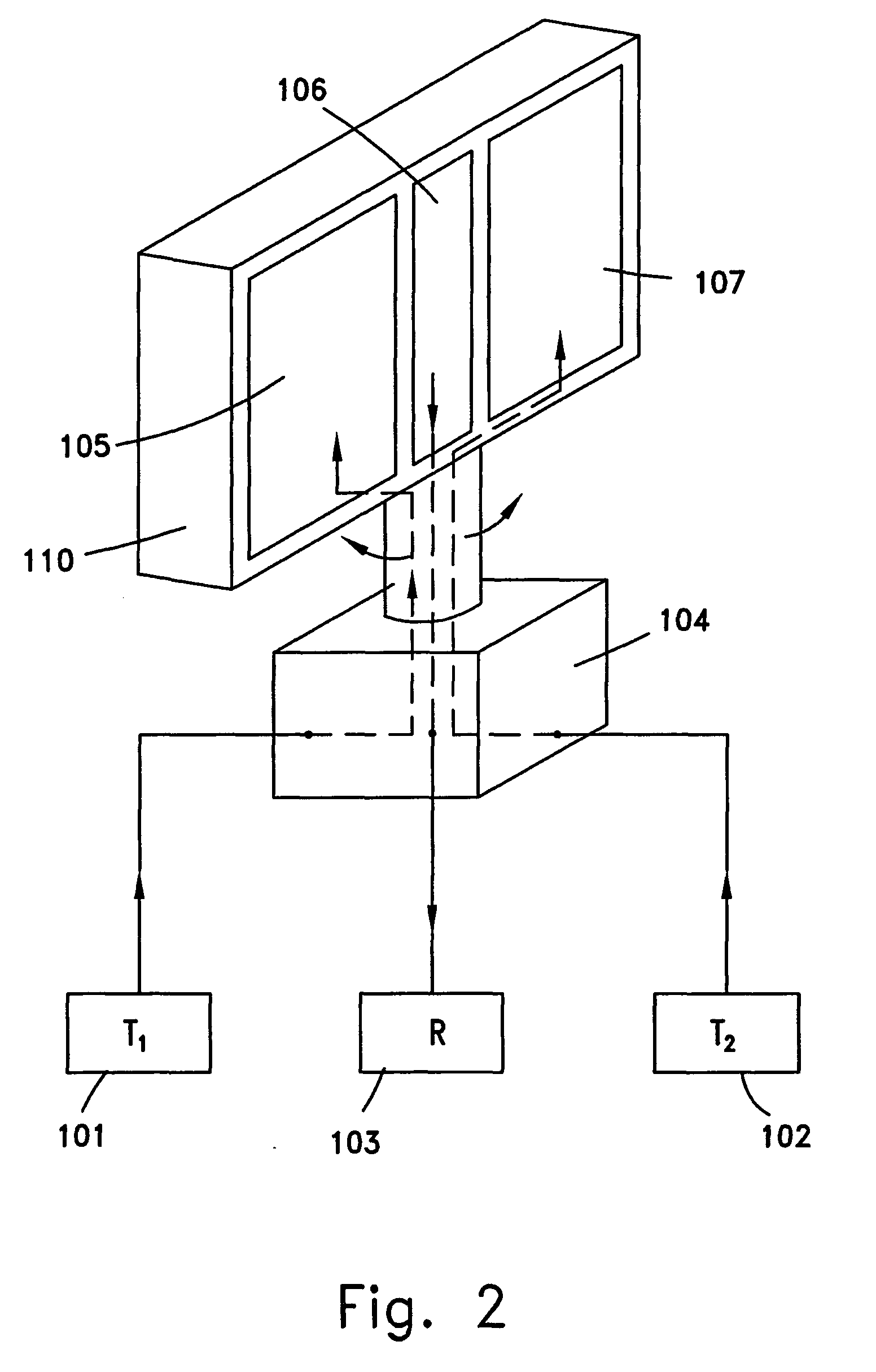

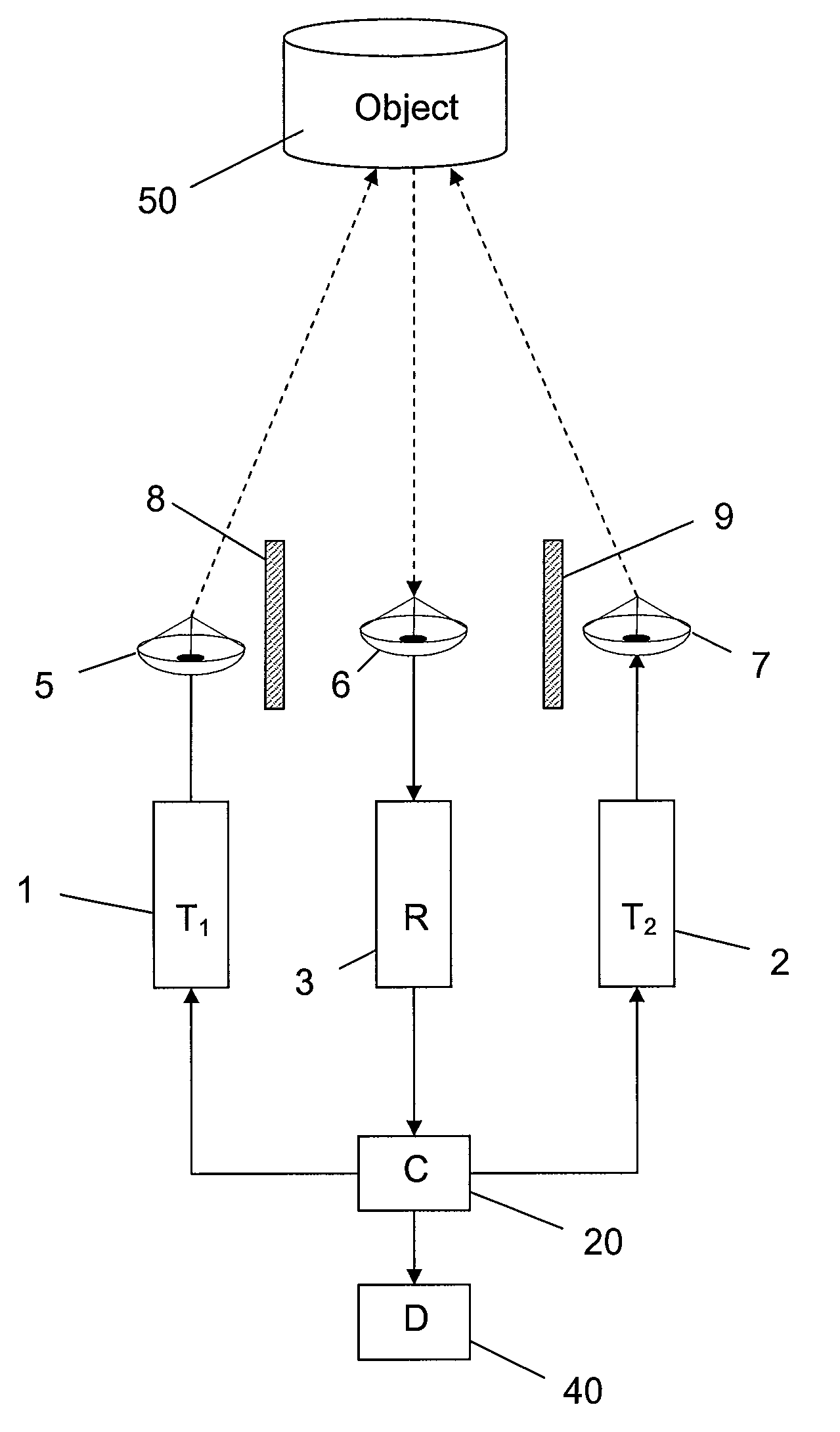

Radar system and method

InactiveUS7777671B2Eliminate productionEliminate transmissionRadio wave reradiation/reflectionRadar systemsElectromagnetic radiation

The invention relates to a radar system which comprises: (a) at least two transmitting units for simultaneously, and in synchronization transmitting electromagnetic radiation in distinct frequencies f1, f2, f3 . . . towards a space of interest; and (b) at least one receiving unit tuned to a frequency of nf1+mf2+qf3 . . . , wherein n, m, q . . . being integers not equal to zero, for receiving a non-linear response of said radiation from objects located within the said space of interest.

Owner:STATE OF ISRAEL MINIST OF AGRI & RURAL DEV AGRI RES ORG (A R O) (VOLCANI CENT)

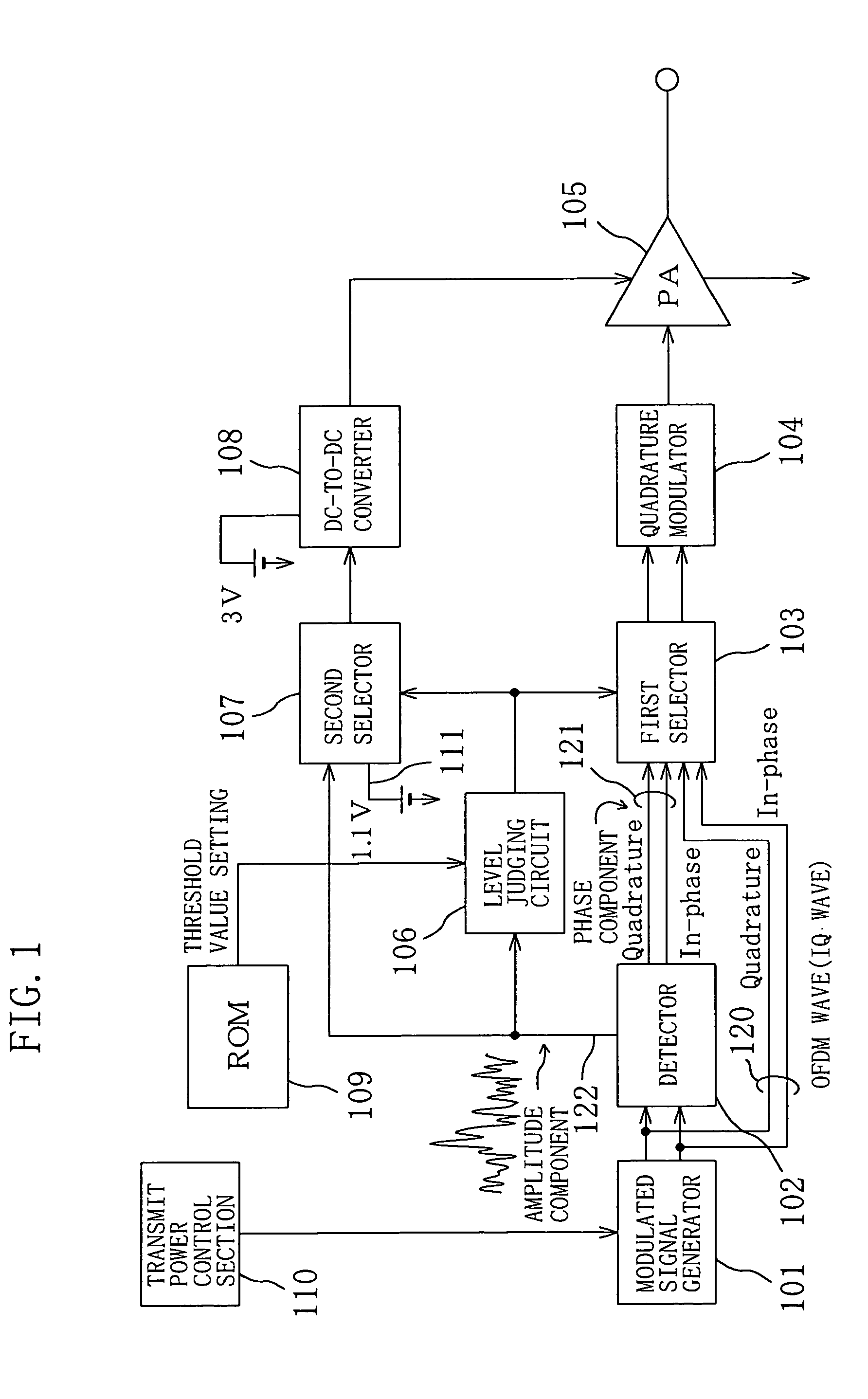

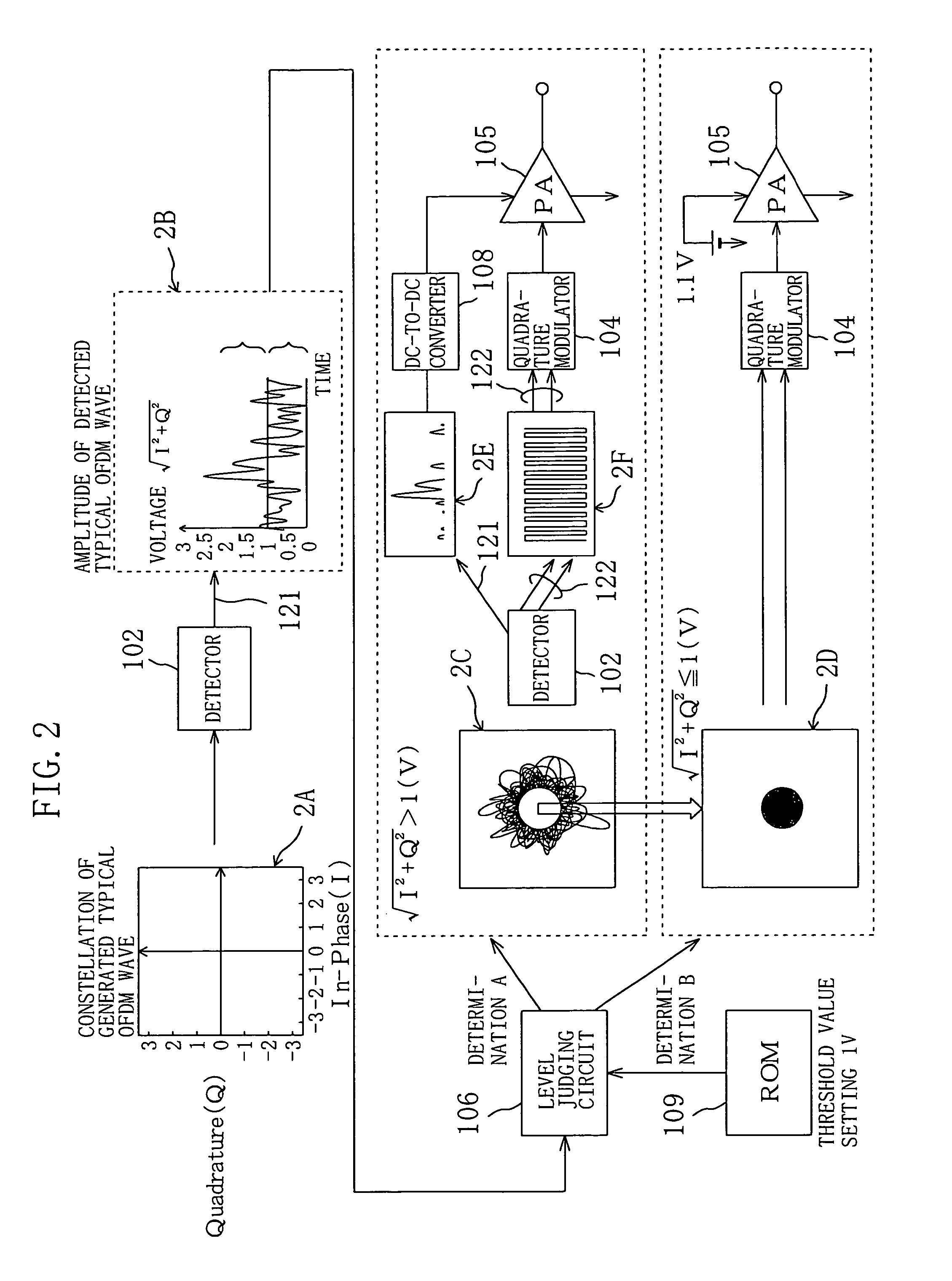

Transmission circuit

InactiveUS7139534B2Signal deterioration can be preventedImprove efficiencyResonant long antennasAmplifier modifications to raise efficiencyAudio power amplifierEngineering

A transmission circuit includes: a modulated signal generator; a modulated signal line where an OFDM modulated wave flows; a detector; a phase component line for transmitting a phase component; an amplitude component line for transmitting an amplitude component; a level judging circuit for judging the level of the amplitude component; a constant-voltage supply line; first and second selectors; a quadrature converter; and an RF power amplifier. An EER or pseudo-EER technique is performed in a region where the RF input-output characteristic of the RF power amplifier with an EER technique exhibits a linear response, whereas usual modulation is performed in a region where a nonlinear response is exhibited. The modulation method is switched using the level judging circuit and the selectors with reference to a threshold value which is the boundary between the region where the linear response is exhibited and the region where the nonlinear response is exhibited.

Owner:COLLABO INNOVATIONS INC

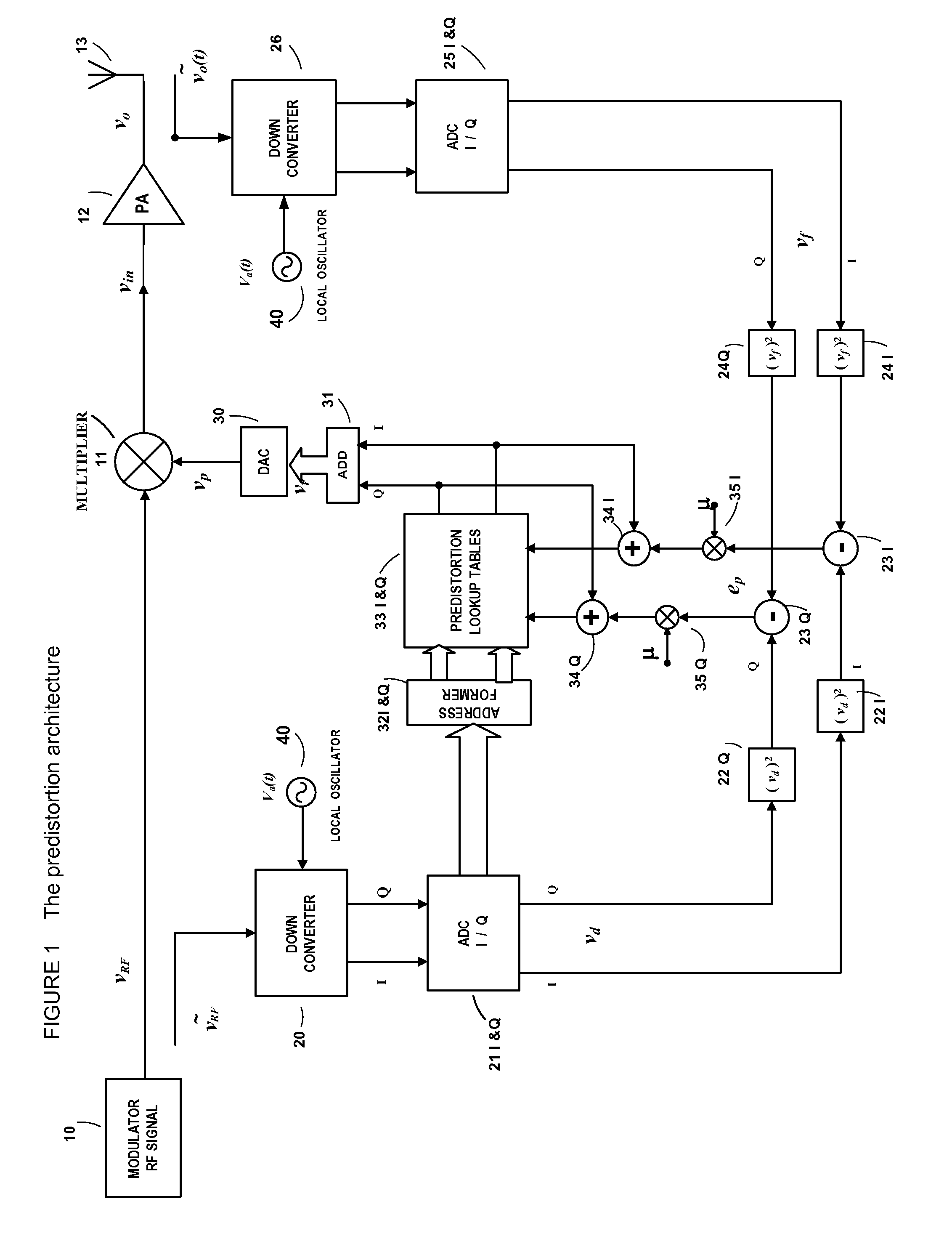

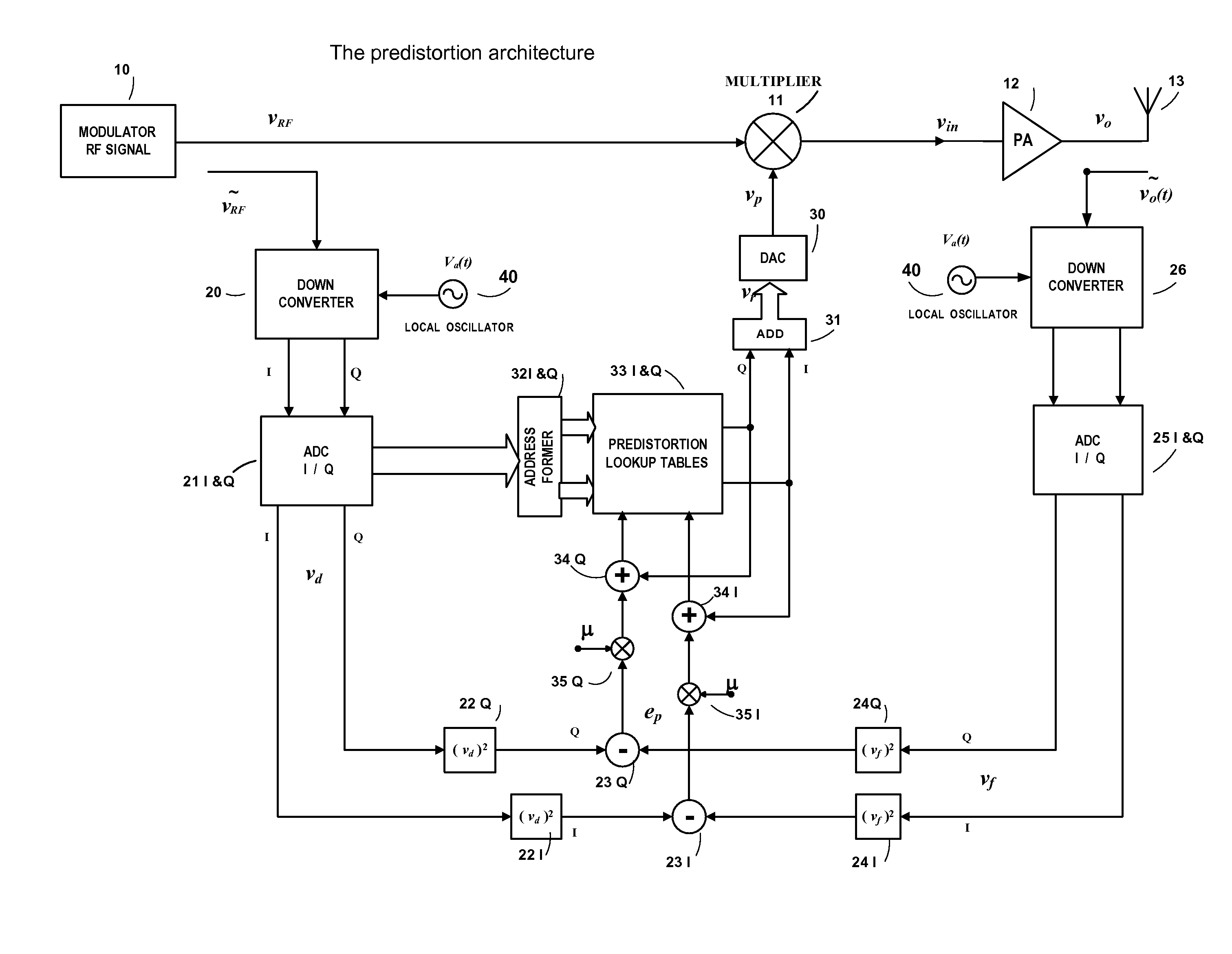

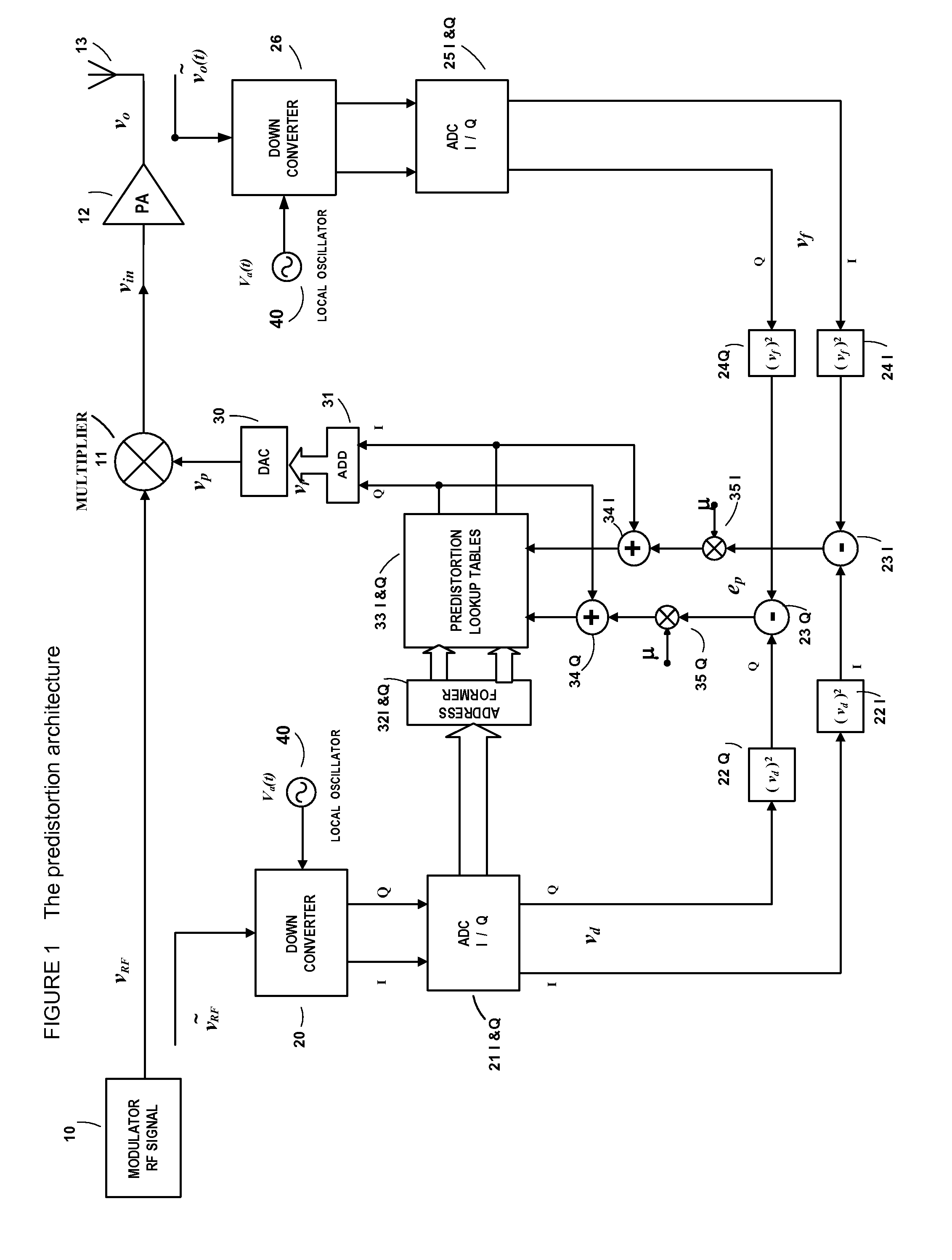

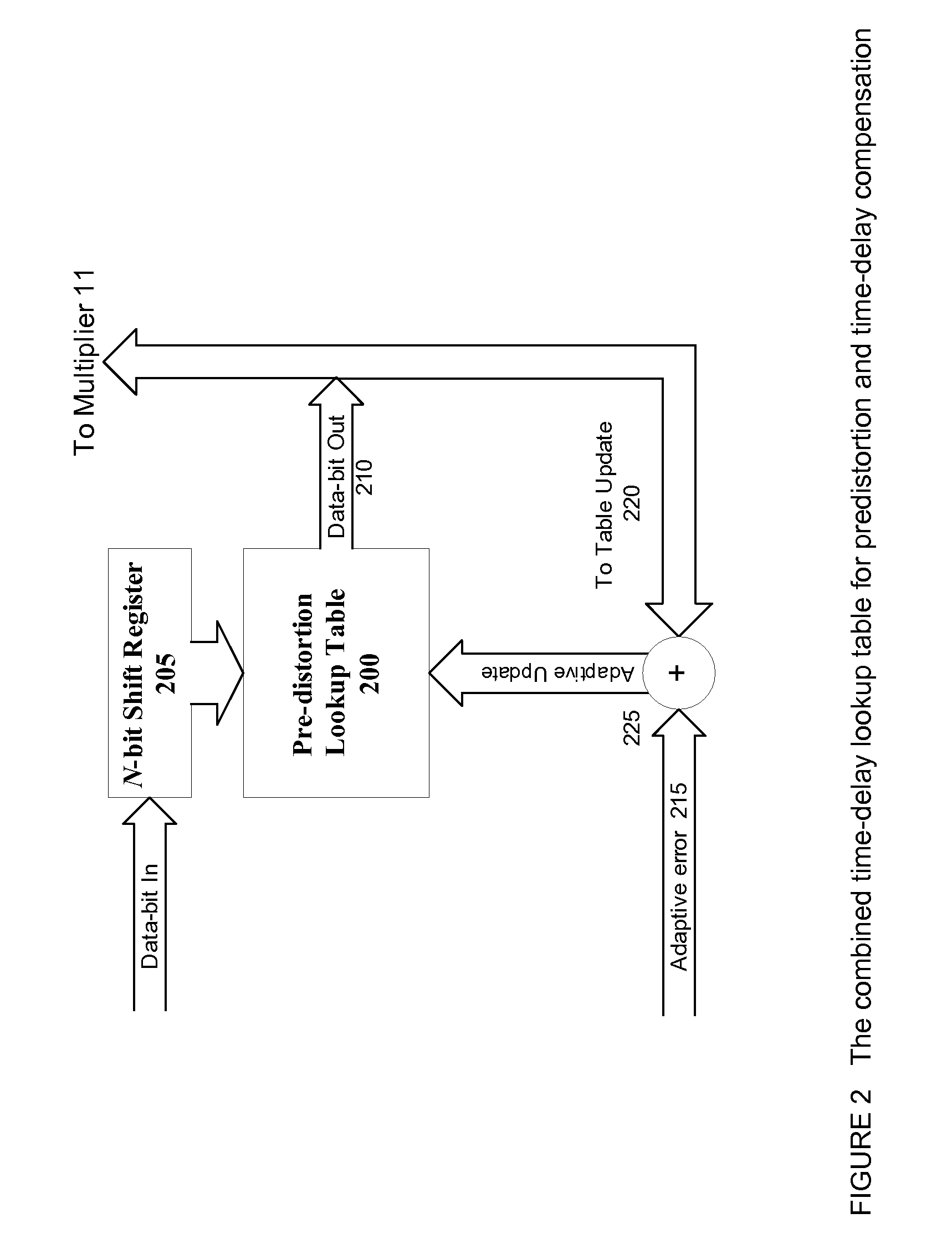

Power amplifier time-delay invariant predistortion methods and apparatus

InactiveUS8380143B2Easy to implementSimple circuit structureResonant long antennasError preventionEngineeringWide dynamic range

An embodiment of the invention is a time-delay invariant predistortion approach to linearize power amplifiers in wireless RF transmitters. The predistortion architecture is based on the stored-compensation or memory-compensation principle by using a combined time-delay addressing method, and therefore, the architecture has an intrinsic, self-calibrating time-delay compensation function. The predistortion architecture only uses a lookup table to conduct both the correction of non-linear responses of a power amplifier and the compensation of any time-delay effects presented in the same system. Due to the time-delay invariant characteristic, the predistortion design has a wider dynamic range processing advantage for wireless RF signals, and therefore can be implemented in multi-carrier and multi-channel wireless systems.

Owner:DALI WIRELESS

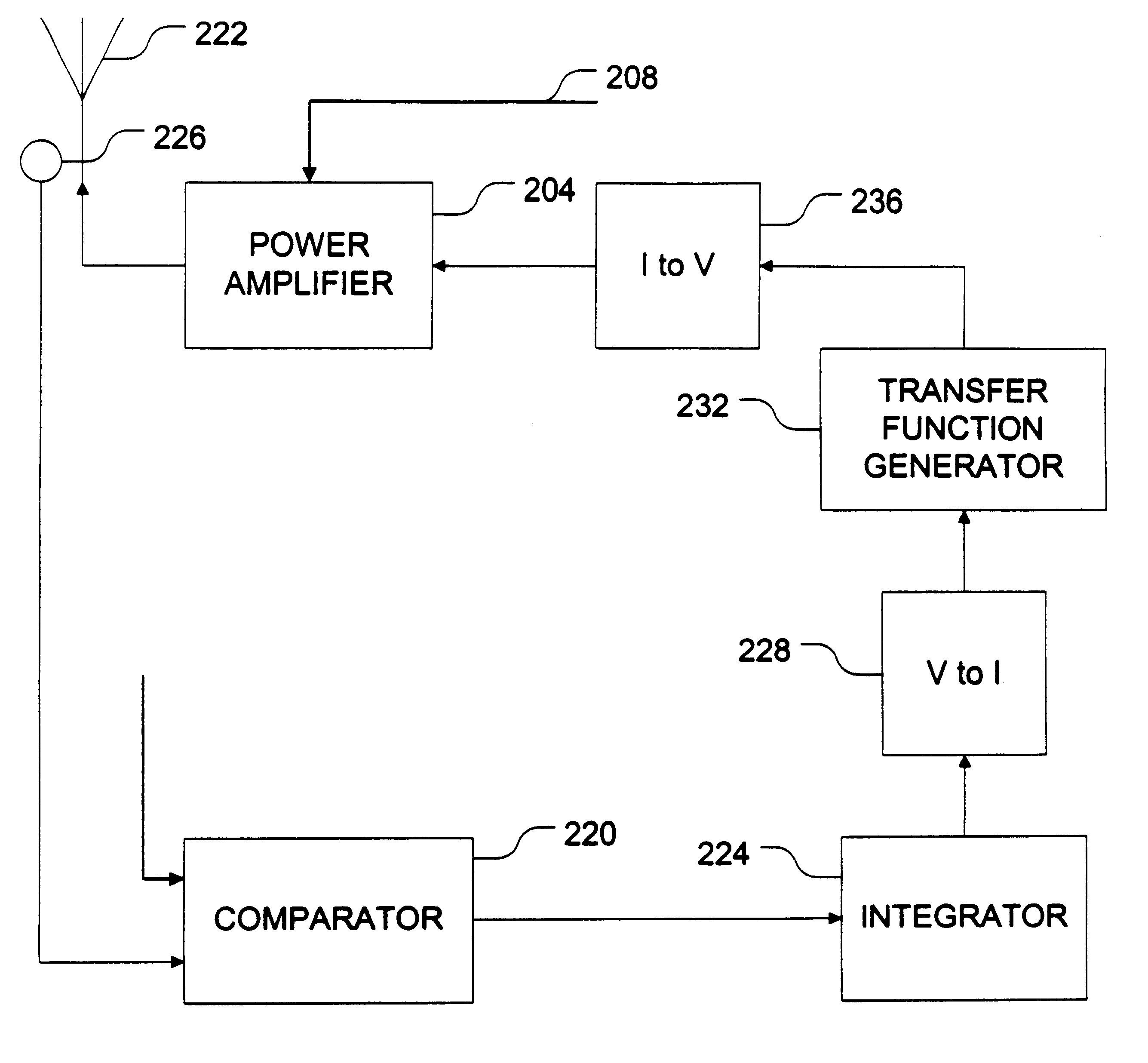

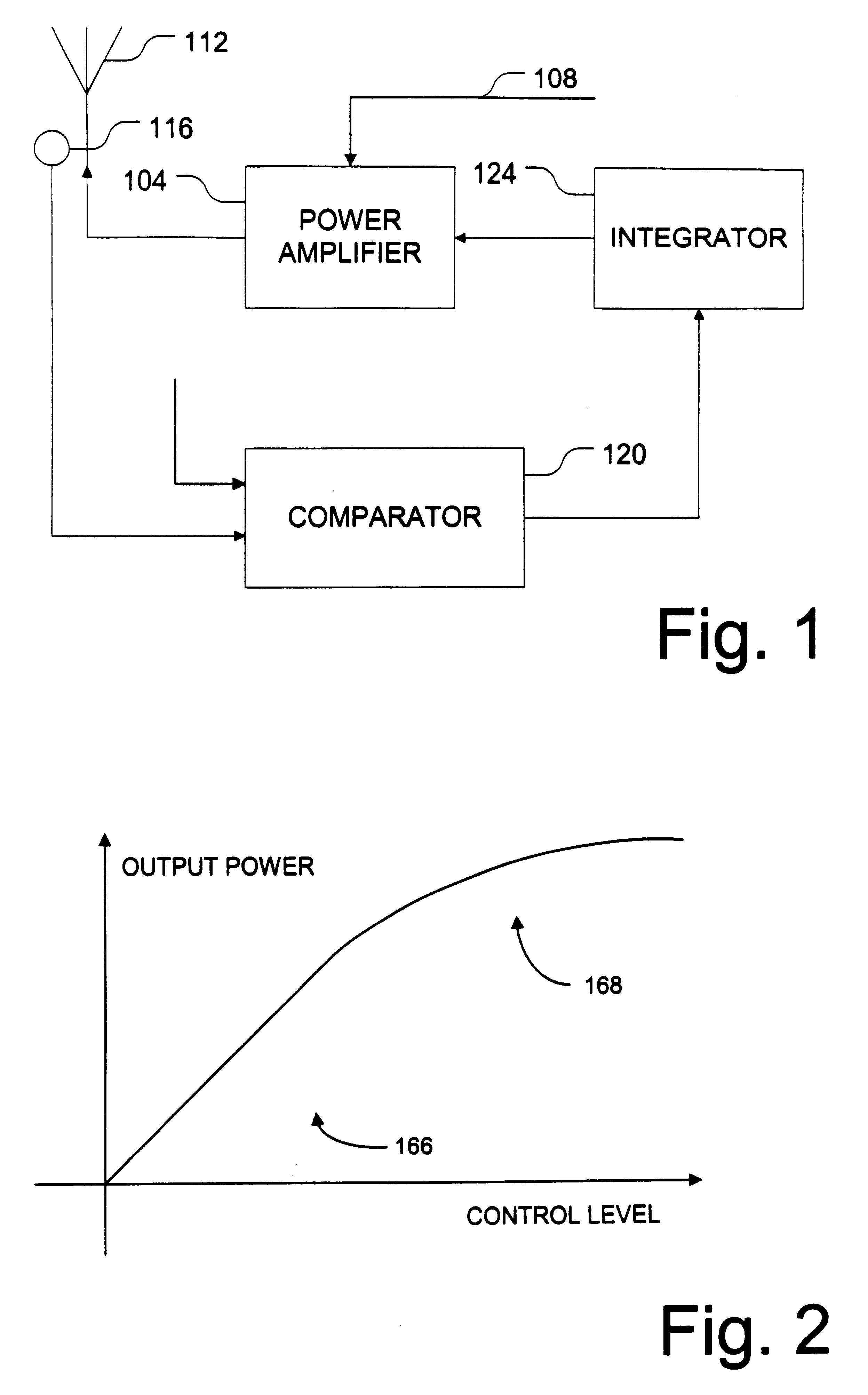

Distortion control feedback loop utilizing a non-linear transfer function generator to compensate for non-linearities in a transmitter circuit

InactiveUS6321072B1Adjustable outputLimiting output levelAmplifier modifications to reduce non-linear distortionResonant long antennasFunction generatorTransmitter

A transfer function generator provides the ability to provide a non-linear response in a feedback loop to compensate for non-linearities introduced elsewhere in the system. The transfer function generator includes a non-linear function generator configured to provide an output current that is a non-linear function of an input signal representing an error to be corrected. The transfer function generator can also include a linear function generator configure to provide a linear output current as a function of an input current representing the error corrected. Tuning devices can be provided to adjust the turn-on level of the non-linear function generator and the output level of the linear function generator to allow the transfer function generator flexibility in implementation.

Owner:SKYWORKS SOLUTIONS INC

Radar system and method

InactiveUS20070013577A1Eliminate productionEliminate transmissionRadio wave reradiation/reflectionRadar systemsElectromagnetic radiation

The invention relates to a radar system which comprises: (a) at least two transmitting units for simultaneously, and in synchronization transmitting electromagnetic radiation in distinct frequencies f1, f2, f3 . . . towards a space of interest; and (b) at least one receiving unit tuned to a frequency of nf1+mf2+qf3 . . . , wherein n, m, q . . . being integers not equal to zero, for receiving a non-linear response of said radiation from objects located within the said space of interest.

Owner:THE STATE OF ISRAEL MINIST OF AGRI & RURAL DEV AGRI RES ORG ARO VOLCANI CENT

Radar system and method

ActiveUS7777672B2Eliminate productionEliminate transmissionRadio wave reradiation/reflectionRadar systemsNanosecond

The invention relates to a radar system which comprises: (a) at least two transmitting units for simultaneously, and in synchronization transmitting electromagnetic radiation in distinct frequencies f1, f2, f3 . . . towards a space of interest; and (b) at least one receiving unit tuned to a frequency of nf1+mf2+qf3 . . . , wherein n, m, q . . . being integers not equal to zero, for receiving a non-linear response of said radiation from objects located within the said space of interest, and wherein the system is characterized in that said transmitted pulses are narrow pulses having duration in the range of between about 1 nanoseconds and about 100 nanoseconds.

Owner:STATE OF ISRAEL MINIST OF AGRI & RURAL DEV AGRI RES ORG (A R O) (VOLCANI CENT)

Acoustic effect apparatus and method and program recorded medium therefor

A high pass filter 32 having a cut-off frequency of 200 Hz and a cut-off response of +12 dB / OCT and a low pass filter 33 having a cut-off frequency of 400 Hz and a cut-off response steeper than −24 dB / OCT are used to pick out components in a double overtone region of 200˜400 Hz of a bass musical instrument such as a base or a bass drum from an input audio signal. The component which is picked out is input to distortion applying means 34 having an input-output response which is a non-linear response having no point symmetry with respect to 0 point, thus applying a distortion to cause even-numbered overtone components to be produced. An output from the distortion applying means 34 and the input audio signal are summed in a summer 18 to be delivered. Natural tones which have boosted bass tones and which are free from impurity are obtained.

Owner:KORG

Nonlinear optical and electro-optical devices and methods of use thereof for amplification of non-linear properties

InactiveUS20130134309A1Simple materialBeam/ray focussing/reflecting arrangementsSpectrum generation using diffraction elementsElectromagnetic fieldOptical nonlinearity

This invention provides devices and methods for broad-band amplification of non linear properties. This invention provides devices comprising optically non linear material that is in contact with a slit array. The slit array causes enhancement of the electromagnetic field within the non linear materials. The enhancement of the electromagnetic field within the optically non linear material results in an amplified non linear response exhibited by the optically non linear materials. This invention provides detectors and imaging systems based on devices and methods of this invention.

Owner:YISSUM RES DEV CO OF THE HEBREWUNIVERSITY OF JERUSALEM LTD

Power Amplifier Time-Delay Invariant Predistortion Methods and Apparatus

InactiveUS20080174365A1Improve performanceConveniently implementedResonant long antennasError preventionTime delaysMulti carrier

An embodiment of the invention is a time-delay invariant predistortion approach to linearize power amplifiers in wireless RF transmitters. The predistortion architecture is based on the stored-compensation or memory-compensation principle by using a combined time-delay addressing method, and therefore, the architecture has an intrinsic, self-calibrating time-delay compensation function. The predistortion architecture only uses a lookup table to conduct both the correction of non-linear responses of a power amplifier and the compensation of any time-delay effects presented in the same system. Due to the time-delay invariant characteristic, the predistortion design has a wider dynamic range processing advantage for wireless RF signals, and therefore can be implemented in multi-carrier and multi-channel wireless systems.

Owner:DALI WIRELESS

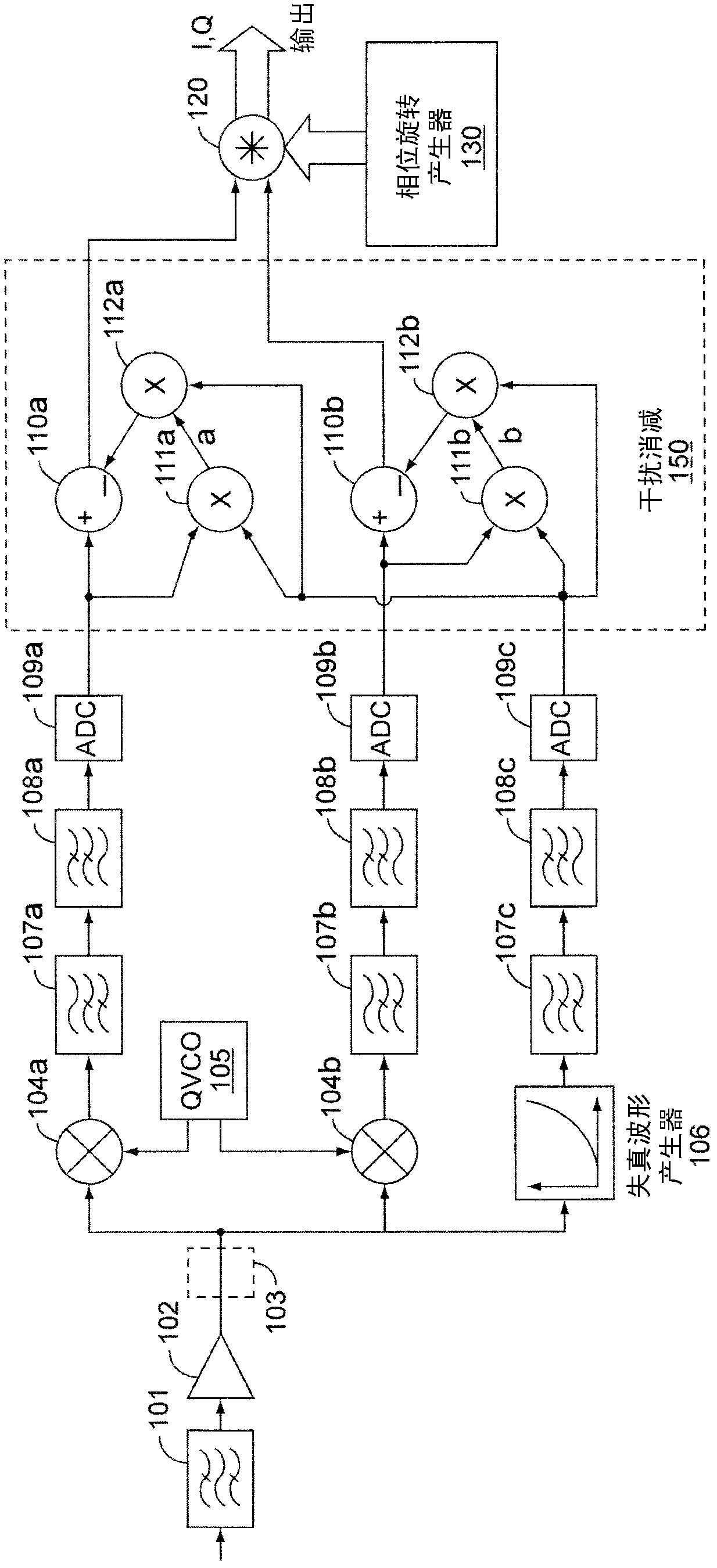

Interference cancellation in an OFDM receiver

Circuits and methods are disclosed for compensating for received signal distortion caused by non-linearittes in wideband receivers. An exemplary receiver includes a distortion waveform generator (106) configured to approximate non-linear response characteristics of a downconverter circuit (104a-b, 105) used to downconvert the received radio frequency signal. The resulting estimated distortion waveform is filtered, using filter(s) (107c) substantially similar to those used for filtering an intermediate frequency signal that includes the desired signal and non-linear distortion products caused by strong interfering signals. The filtered estimated distortion waveform and intermediate frequency signal are sampled, to obtain a sampled distortion signal and a sampled signal of interest. The sampled distortion signal and the sampled signal of interest are divided into a plurality of frequency channels. For a selected number of frequency channels, the sampled distortion signal for a frequency channel is scaled, and subtracted from the corresponding sampled signal of interest for the same frequency channel to obtain reduced-interference signal samples for the frequency channel.

Owner:TELEFON AB LM ERICSSON (PUBL)

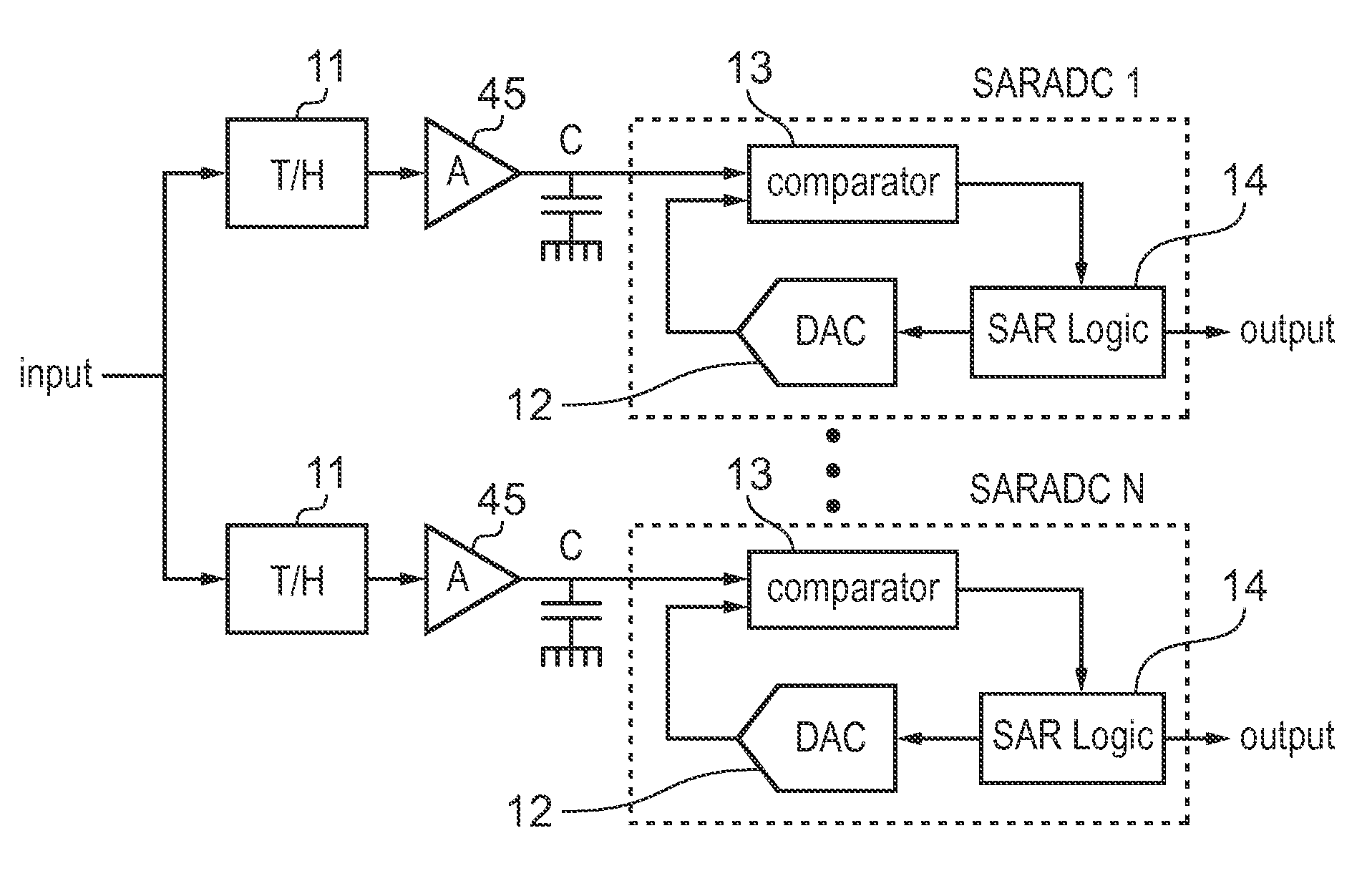

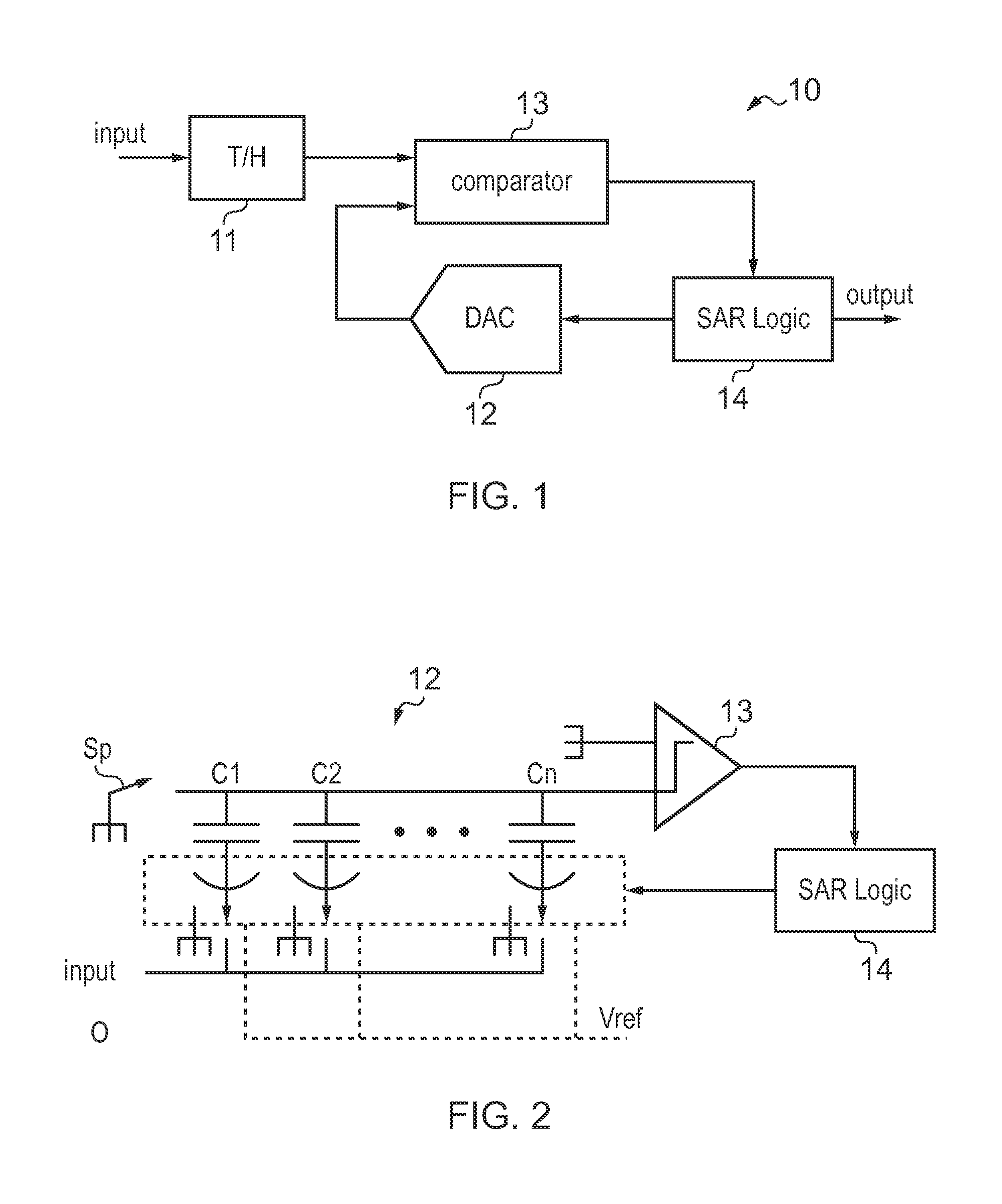

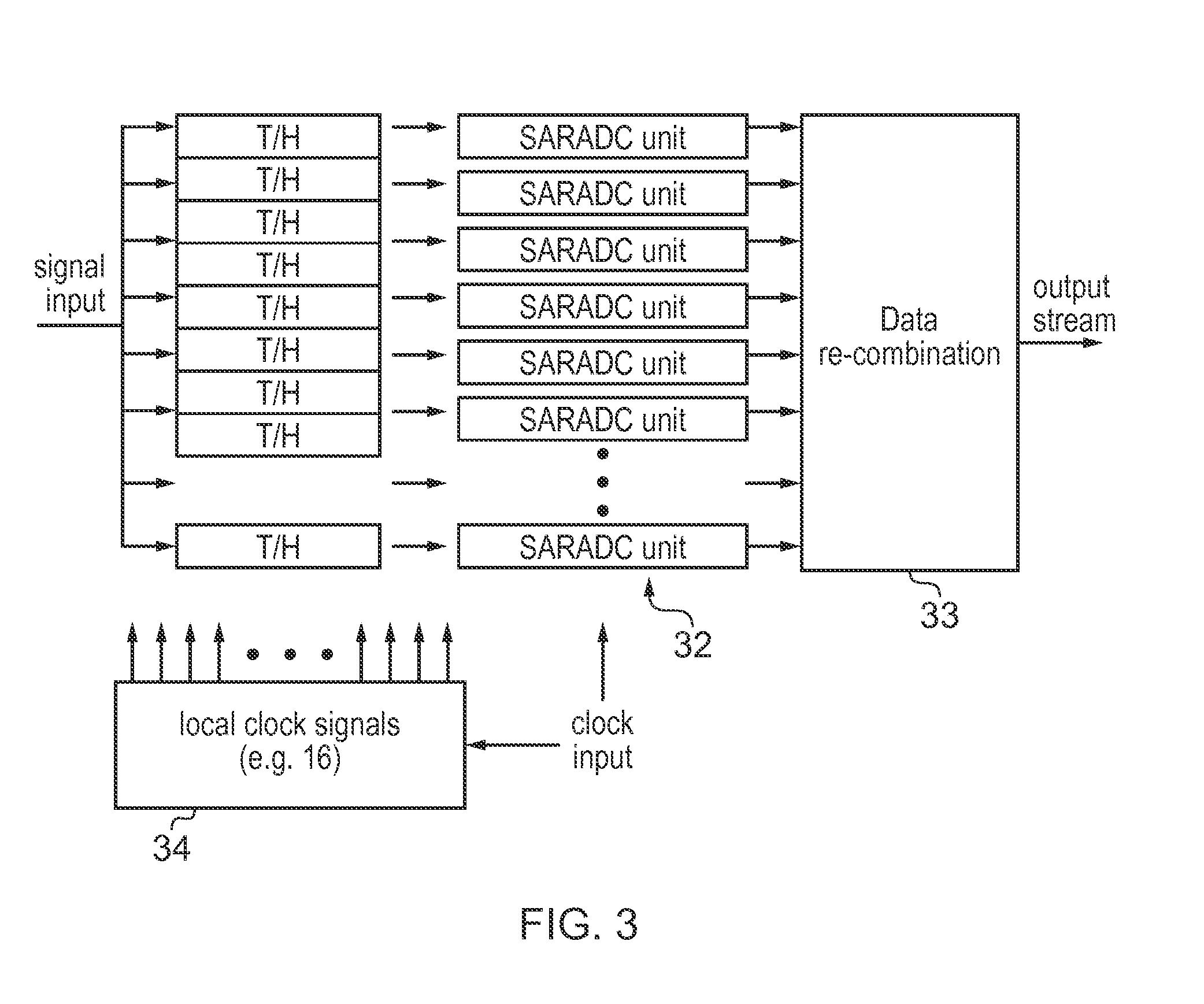

ADC

ActiveUS20110241912A1Run fastMore degree of design freedomElectric signal transmission systemsAnalogue-digital convertersCapacitanceAlternating current

This invention relates to Analog to Digital Converters (ADC) and, inter alia, to Time Interleaved ADCs and Successive Approximation Register (SAR) ADC's. In a conventional Time Interleaved ADC employing SAR ADC units, the input signal is processed through a track-and-hold circuit (T / H), and then through a buffer circuit, before the SAR ADC unit. There, by means of a comparator, the signal is compared with a Digital-to-Analog Converter (DAC) signal from the SAR logic. The buffer reduces the influence of capacitive loading and physical layout design on the SAR ADC input, but typically has a non-linear response and thus introduces distortion to the input signal. This can limit the ADC linearity, particularly for high-speed ADCs operating with low-supply voltages. An objective of the invention is to reduce or eliminate the effect of the buffer non-linearity. This is done in some embodiments by routing both the signals to the comparator through the same buffer circuit. In another embodiment the DAC signal is routed through a separate second buffer circuit. By use of a single buffer circuit, or where there is ideal matching of the buffer circuits in the latter embodiment, the distortion effects are completely eliminated; however, for practical imperfectly matched buffer circuits according to the latter embodiment, the gain and off-set mismatches can be accommodated through calibration of the buffers or, in suitable applications, through the DAC calibration.

Owner:NXP BV

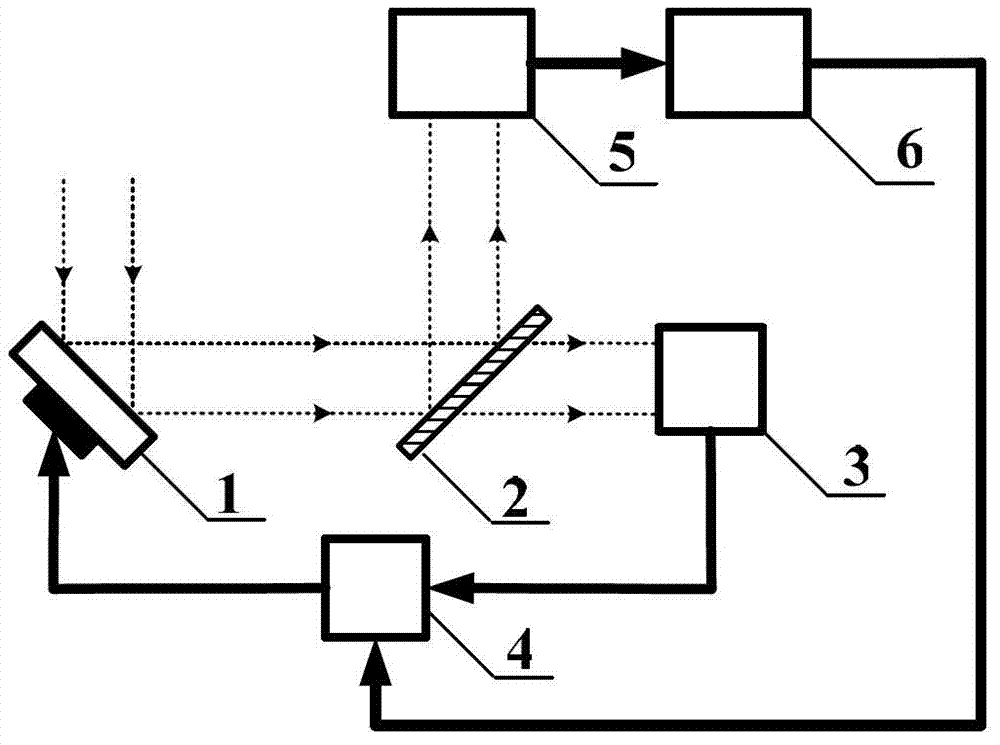

Frequency modulated continuous wave laser radar frequency modulation nonlinear response coefficient measuring method and device

The invention provides a frequency modulated continuous wave laser radar frequency modulation nonlinear response coefficient measuring method. According to the method, a signal generator generates sawtooth wave frequency-modulated signals, inputs the sawtooth wave frequency-modulated signals into a driving circuit and drives a laser to work, modulation signal light output by the laser is divided into two paths through a first coupler, one path of light is emitted to a measured object through a circulator, return light returned by the measured object is received by the circulator, the return light and the other path of light are coupled through a second coupler, light output by the second coupler is received by a photoelectric detector, obtained beat frequency signals are processed through a signal processing circuit, difference frequency is obtained through processing of computer software and a nonlinear frequency modulation coefficient is worked out. The frequency modulated continuous wave laser radar frequency modulation nonlinear response coefficient measuring method can be used for accurately measuring the nonlinear coefficient, provides key parameters for frequency modulation nonlinear rectification for a system, and has great significance for improving the frequency modulation linearity of frequency modulated continuous wave laser radar range radar, and the accuracy of measurement of the speed and distance of the system .

Owner:HUAQIAO UNIVERSITY

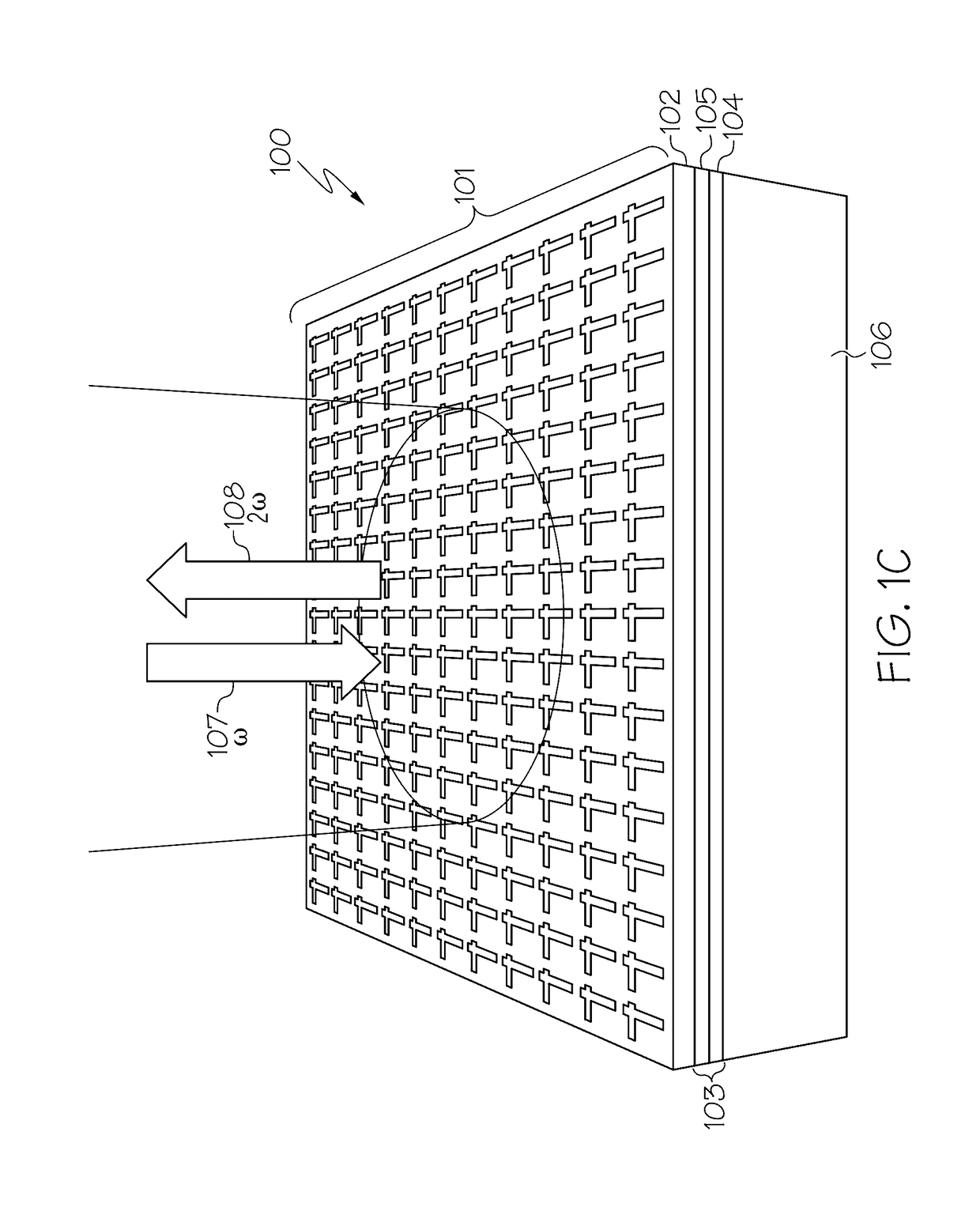

Nonlinear metasurfaces based on plasmonic resonators coupled to intersubband transitions

A nonlinear metasurface structure including a multi-quantum-well layer designed for a nonlinear response for a desired nonlinear optical process and an array of nanoantennas coupled to the intersubband transitions of the multi-quantum-well layer. Each nanoantenna in the array is designed to have electromagnetic resonances at or close to all input and output frequencies of a given nonlinear optical process. Nanoantennas allow efficient coupling of any incident and outgoing light polarizations to intersubband transitions. Nanoantennas may further provide significant field enhancement in the multi-quantum-well layer. As a result, the nonlinear metasurface structure can be designed to produce a highly nonlinear response for any polarization and angle of incidence of incoming and outgoing waves in a nonlinear optical process. Due to their very larger nonlinear response, efficient frequency conversion can be produced in these metasurfaces without the stringent phase-matching constraints of bulk nonlinear crystals.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

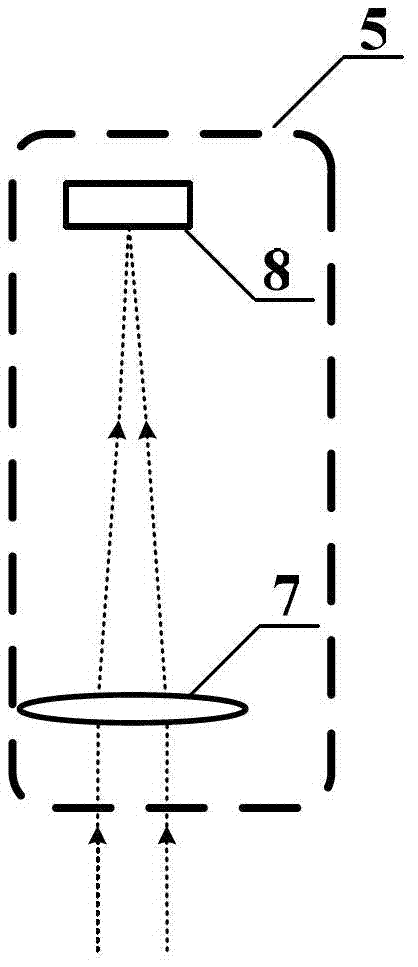

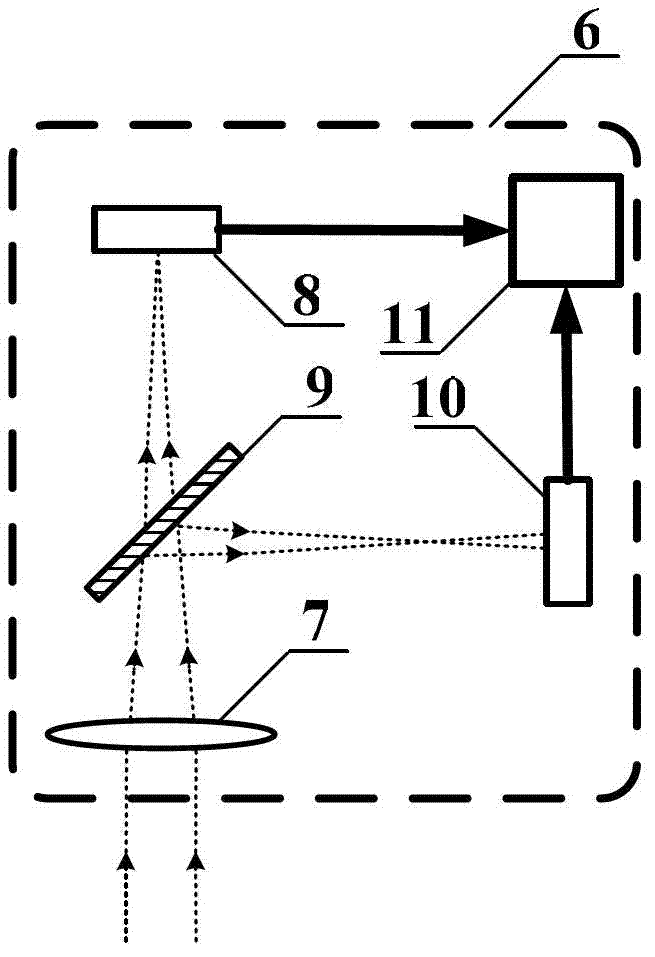

Self-adaptation optical system near-field wave-front sensor calibration device and calibration method based on phase-diversity method

InactiveCN102889935ARealize full optical path aberration correctionImproved wavefront controlOptical measurementsTesting optical propertiesWavefront sensorPupil

The invention discloses a self-adaptation optical system near-field wave-front sensor calibration device and a calibration method based on a phase-diversity method. The self-adaptation optical system near-field wave-front sensor calibration device consists of a wave-front corrector, a spectroscope, a near-field wave-front sensor, a wave-front controller, an imaging system and a phase-diversity wave-front sensor. According to the method, the phase-diversity wave-front sensor is used for measuring the static aberration of the whole system, and the wave-front controller is used for controlling the wave-front corrector to correct the static aberration; and after the static aberration is corrected, the zero point at the reference position of the near-field wave-front sensor at the pupil plane position is calibrated or the zero point of the absolute aberration is set, and the two zero points are used as the wave-front control objective of the self-adaptation optical system to effectively correct the static aberration of the whole optical path. According to the self-adaptation optical system near-field wave-front sensor calibration device and the calibration method, the static aberration of the whole optical path can be effectively corrected, the wave-front control error caused by the non-linear response of the corrector can be avoided, and the correction capability of the self-adaptation optical system can be improved obviously without obviously increasing the system complexity and the additional aberration.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

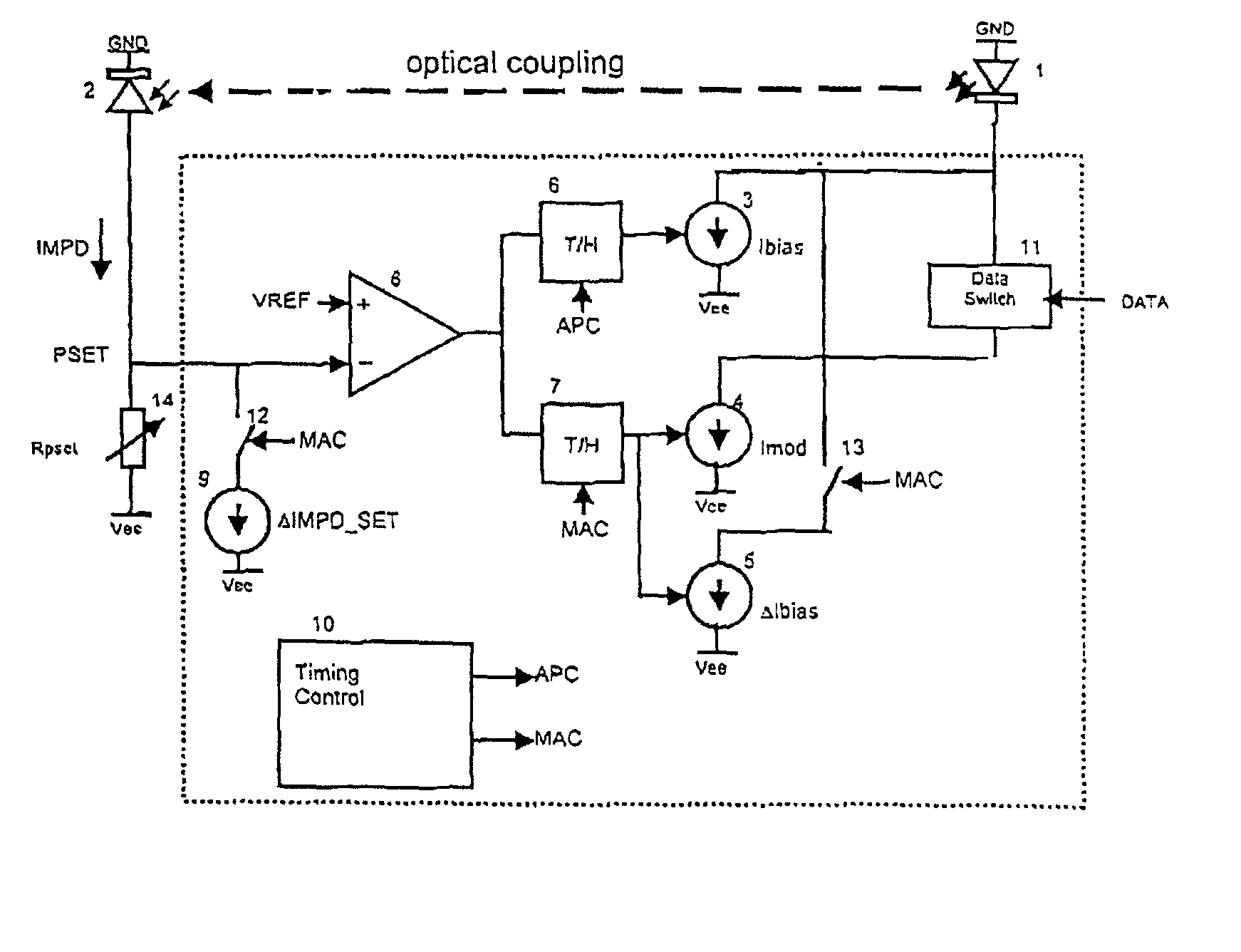

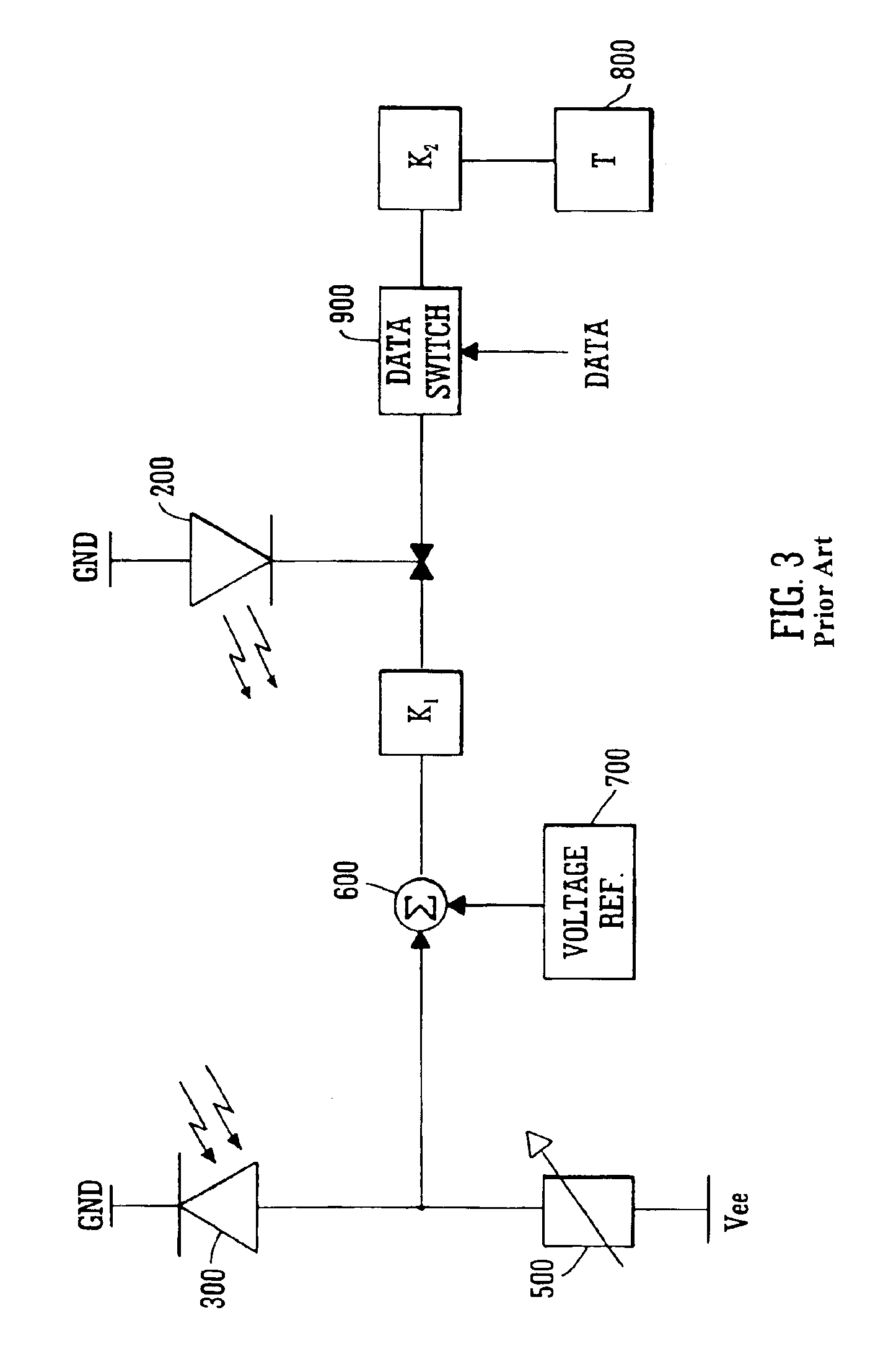

Method and circuit for measuring the optical modulation amplitude (OMA) in the operating region of a laser diode

InactiveUS20030090289A1Accurate measurementAccurate operationLaser detailsSemiconductor lasersOptoelectronicsOptical modulation amplitude

A method and circuit for measuring the optical modulation amplitude in the operating region of a laser diode is described. The method utilises two measurements of OMA, each measurement being related to the slope in a specific portion of the operating region of the power / current characteristic curve of the laser diode. By combining the two measurement values, the invention provides a 1 measurement for OMA in the operating region of the laser diode that allows for the presence of a non-linear response in the region.

Owner:ANALOG DEVICES INC

Method and device for achieving all-optical nonlinear activation function of optical neural network

ActiveCN111860822AAvoid high demandsFast operationNeural architecturesPhysical realisationActivation functionPhase shift module

The invention discloses a method and a device for achieving an all-optical nonlinear activation function of an optical neural network. The method comprises the following steps: acquiring a to-be-processed signal optical signal and a reference optical signal coherent with the to-be-processed signal optical signal; inputting the to-be-processed signal optical signal and the reference optical signalinto a first phase shift module, wherein the first phase shift module performs phase shift operation on the to-be-processed signal optical signal and the reference optical signal to obtain an opticalsignal of a first array; and inputting the optical signal of the first array into an optical interference module, performing nonlinear operation on the optical signal of the first array in the opticalinterference module to obtain an optical signal of a second array, and outputting the optical signal of the second array as a nonlinear response of the signal optical signal to be processed. According to the technical scheme, the problem that an existing optical nonlinear function calculation unit has high requirements for optical power and a transimpedance amplifier is solved, parameters are adjustable, and a provided nonlinear function is flexible and controllable.

Owner:UNITED MICROELECTRONICS CENT CO LTD

Method and circuit for measuring the optical modulation amplitude (OMA) in the operating region of a laser diode

A method and circuit for measuring the optical modulation amplitude in the operating region of a laser diode is described. The method utilises two measurements of OMA, each measurement being related to the slope in a specific portion of the operating region of the power / current characteristic curve of the laser diode. By combining the two measurement values, the invention provides a 1 measurement for OMA in the operating region of the laser diode that allows for the presence of a non-linear response in the region.

Owner:ANALOG DEVICES INC

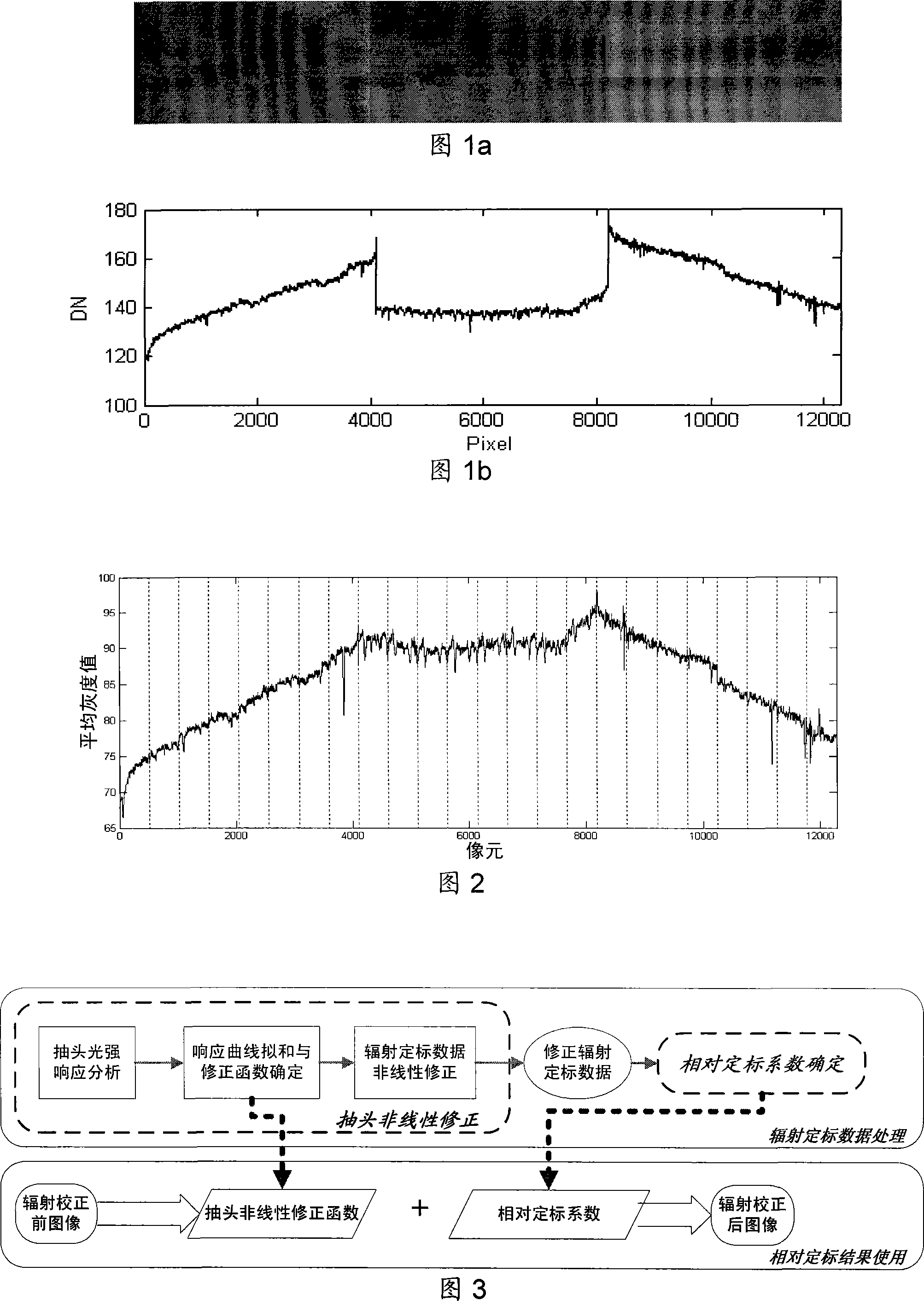

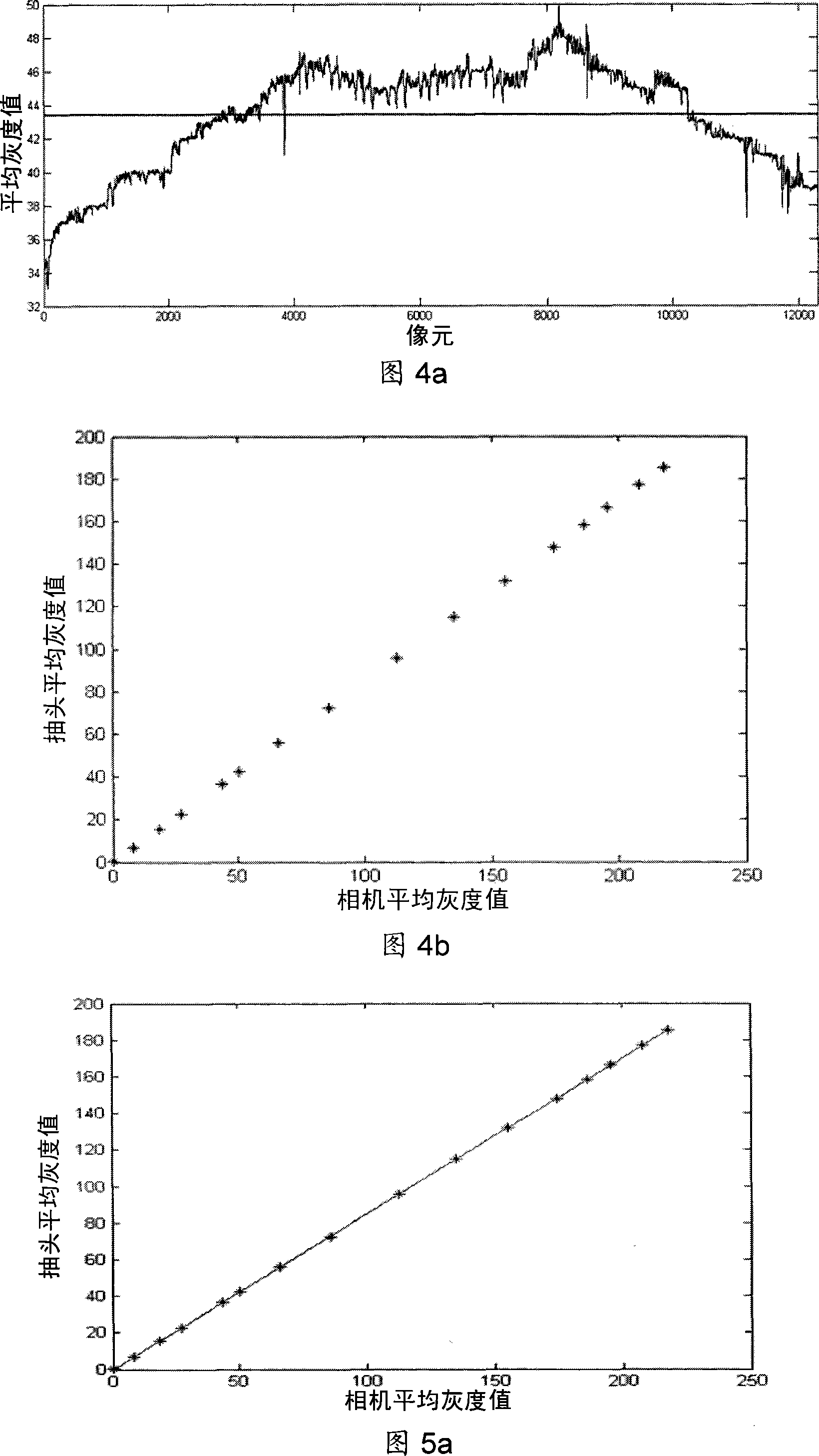

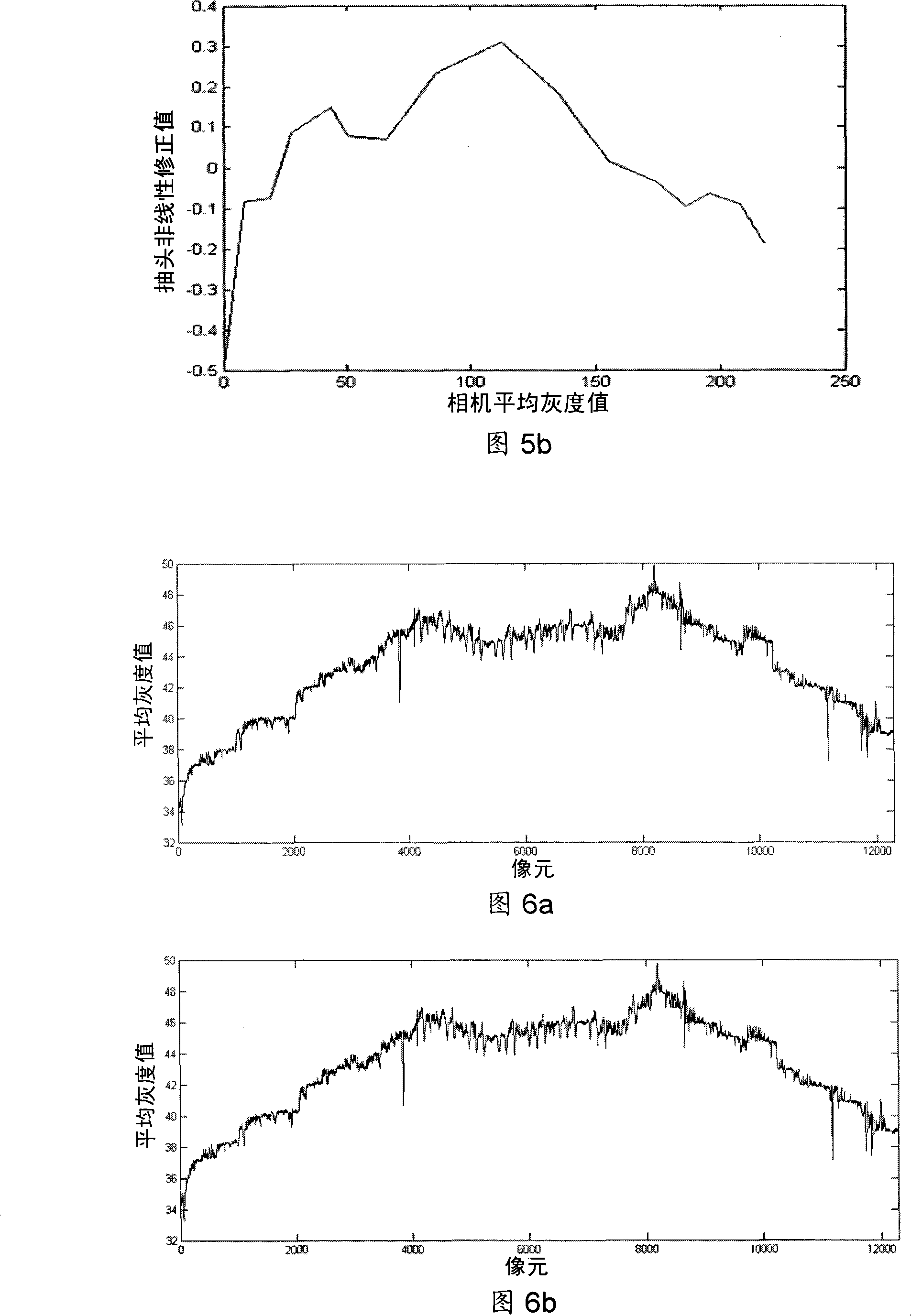

Relative radiometric correction method for star-load TDICCD camera

ActiveCN101226639ASolve the problem of different nonlinearity of light intensity responseSolve for uniformityImage analysisWave based measurement systemsCalibration coefficientLinear fitting

Disclosed is a relative radiometric correction method for the satellite-borne TDICCD camera. The steps comprises (1) analyzing the response output of a tapping under different light intensities and acquiring a scatter diagram of tapping light intensity response, (2) carrying out linear fitting to the scatter diagram of tapping light intensity response, then carrying out linear interpolation to the scatter diagram to obtain an interpolation curve, subtracting the interpolation curve of each tapping from respective fitting line to obtain a non-linear modified function of the tapping to light intensity, (3) using the non-linear modified function to carry out non-linear modification one after another to tapping of radiometric calibration data, and obtaining modified radiometric calibration data, (4) processing the modified radiometric calibration data and obtaining a modified inter- calibration coefficient, (5) carrying out radiation homogeneousness correction to arbitrary image produced by TDICCD via using the non-linear modified function and the modified inter- calibration coefficient. The invention resolves the problem that non-linear response to light intensity of the tapping can not be corrected in existing radiometric calibration method, and can increase relative radiometric calibration accuracy.

Owner:AEROSPACE DONGFANGHONG SATELLITE

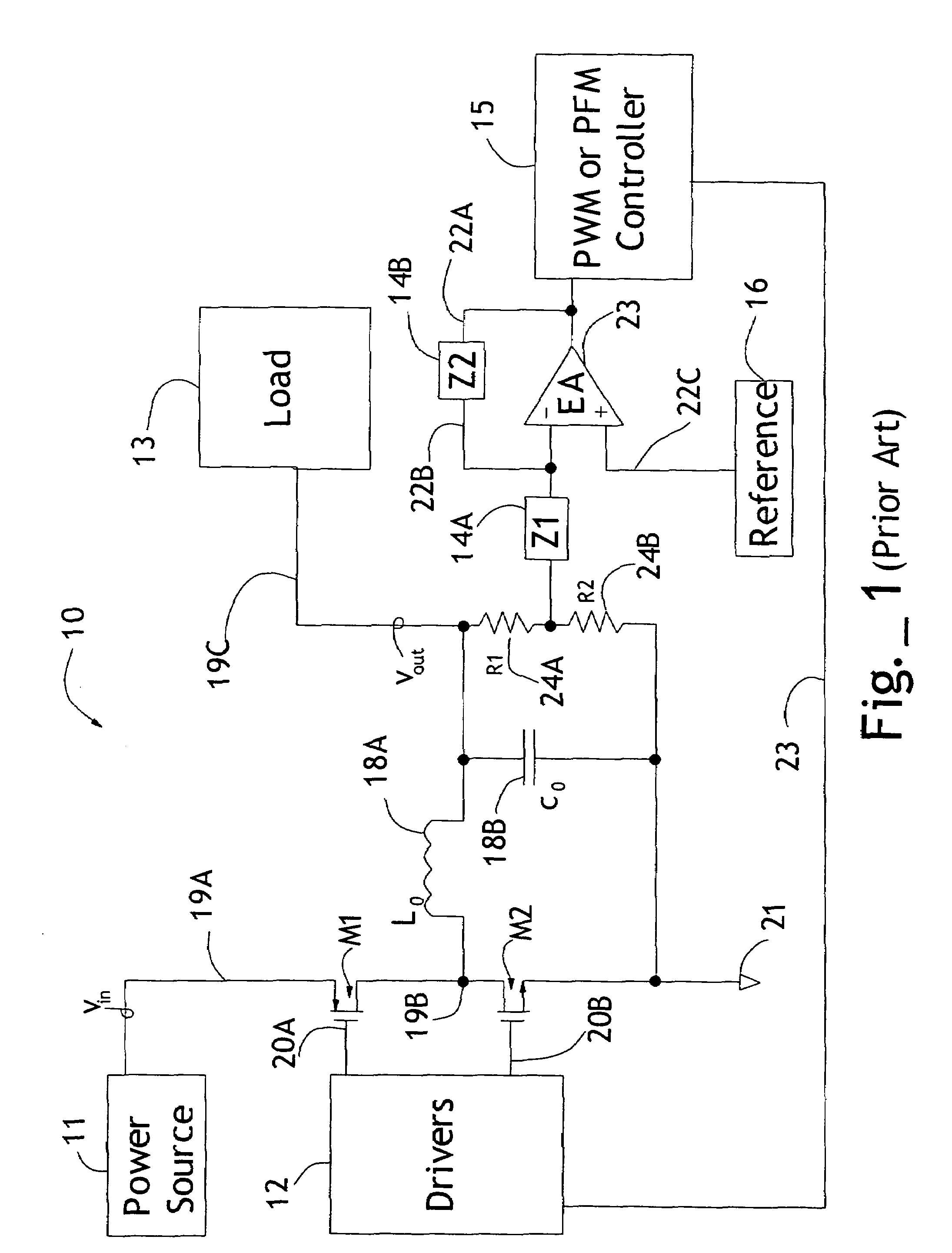

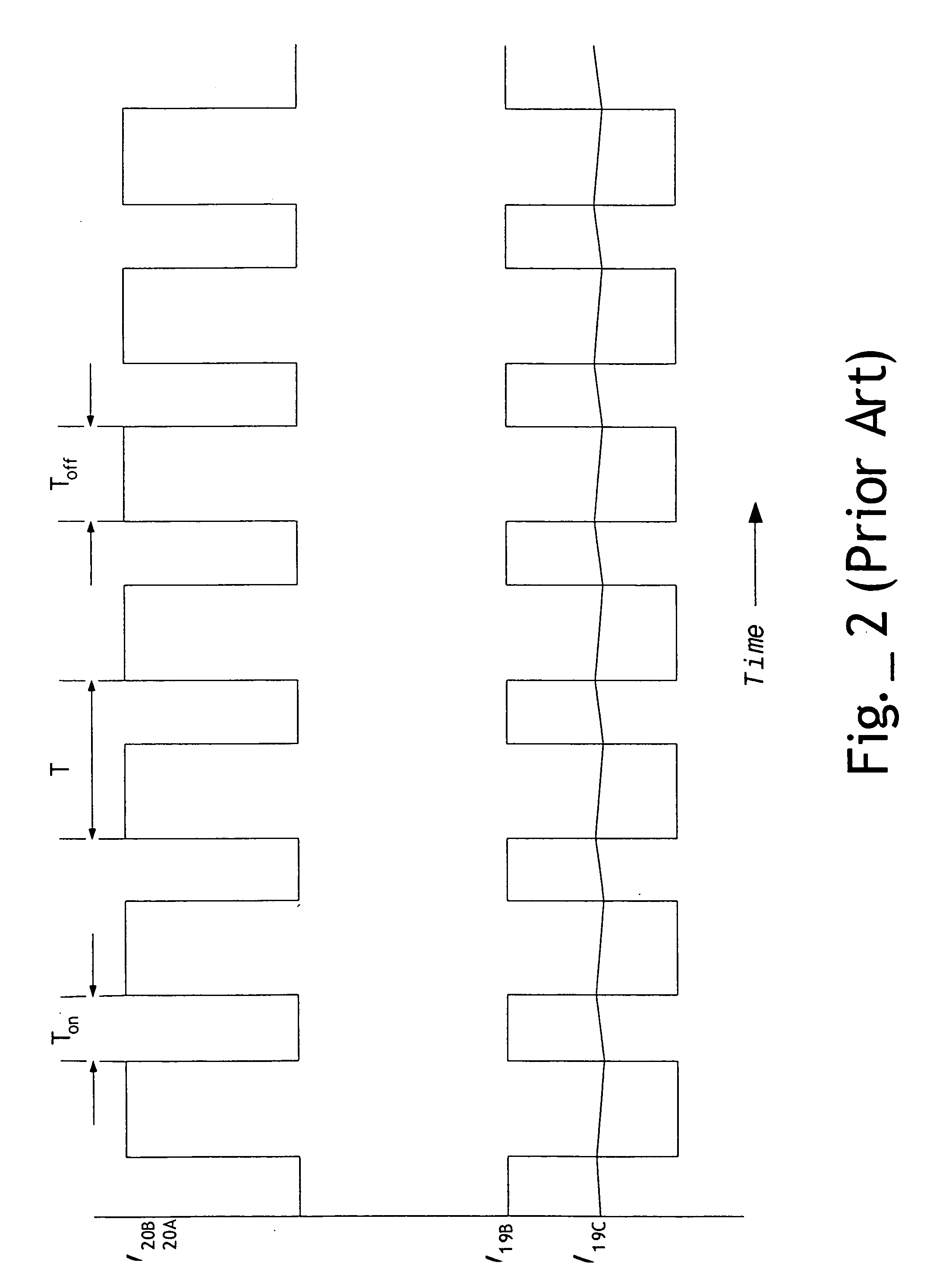

Control loop for switching power converters

InactiveUS7265523B2Linearize nonlinear responseImprove stabilityDc-dc conversionElectric variable regulationControl theoryComparator

A control loop for a clocked switching power converter where the loop features a comparator (44) and a filter (61) in series to linearize the nonlinear response of the comparator (44). The filter (61) has poles and zeros offsetting the poles and zeros of a bridge rectifier (M1 and M2).

Owner:AIVAKA

Method and apparatus to enhance ultrasound contrast imaging using stepped-chirp waveforms

InactiveUS6953434B2Increase heightBlood flow measurement devicesOrgan movement/changes detectionUltrasound imagingSonification

A method and apparatus in an ultrasound imaging system is disclosed that enhances the contrast-to-tissue ratio and signal-to-noise ratio of contrast imaging using stepped-chirp waveforms. The first waveform component is employed with a first frequency optimized to initiate the bubble dynamics and the second waveform component is employed with a second frequency optimized to produce an enhanced bubble nonlinear response. The first waveform component and the at least a second waveform component are transmitted as a single stepped-chirp transmit pulse. At least one of a center frequency, an amplitude, a starting phase, and a bandwidth of the waveform components are adjusted to generate the single stepped-chirp transmit pulse. A relative phase, a switch time, and a time delay between the waveform components are also adjusted for maximal enhancement of bubble nonlinear response.

Owner:GE MEDICAL SYST GLOBAL TECH CO LLC

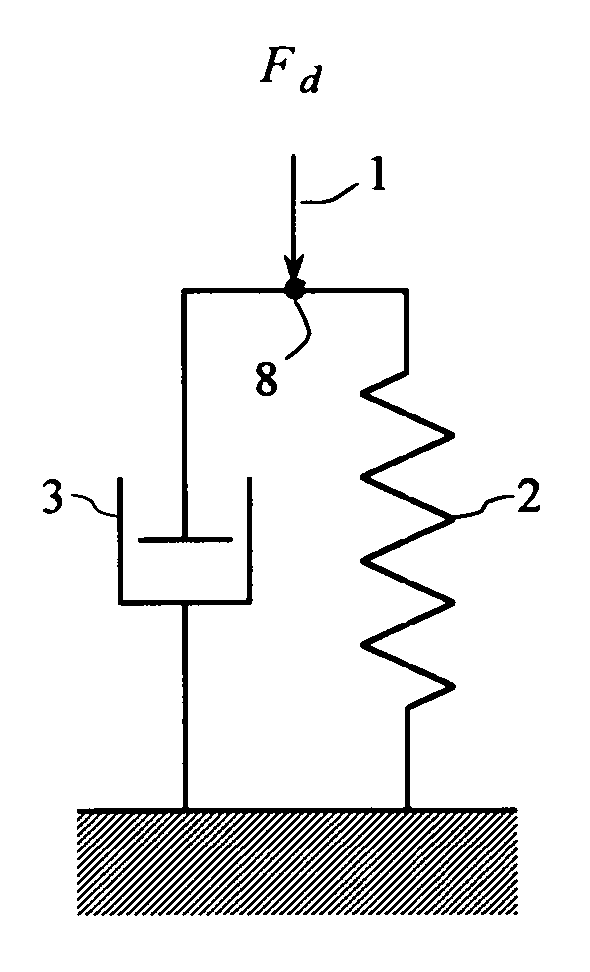

Method and apparatus for control of hydraulic systems

InactiveUS20050144936A1Easy to controlFluid-pressure actuator testingFluid couplingsGraphicsGraphical user interface

An apparatus and method for controlling hydraulic systems. The control apparatus (module) accepts a variety of input forms, and the output is user-configurable to control both sides of an attached coil. The master module is programmable via a graphical user interface defining states and conditions triggering transitions between states. The master module may be combined with slave modules on a connection bus to control many subsystems. Reprogramming of the master module may occur in the field by use of flash memory, and input / output characteristics may be adjusted during operation of the system, allowing adjustment of systems exhibiting nonlinear response characteristics.

Owner:HIGH COUNTRY TEK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com