Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

81 results about "Dislocation free" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

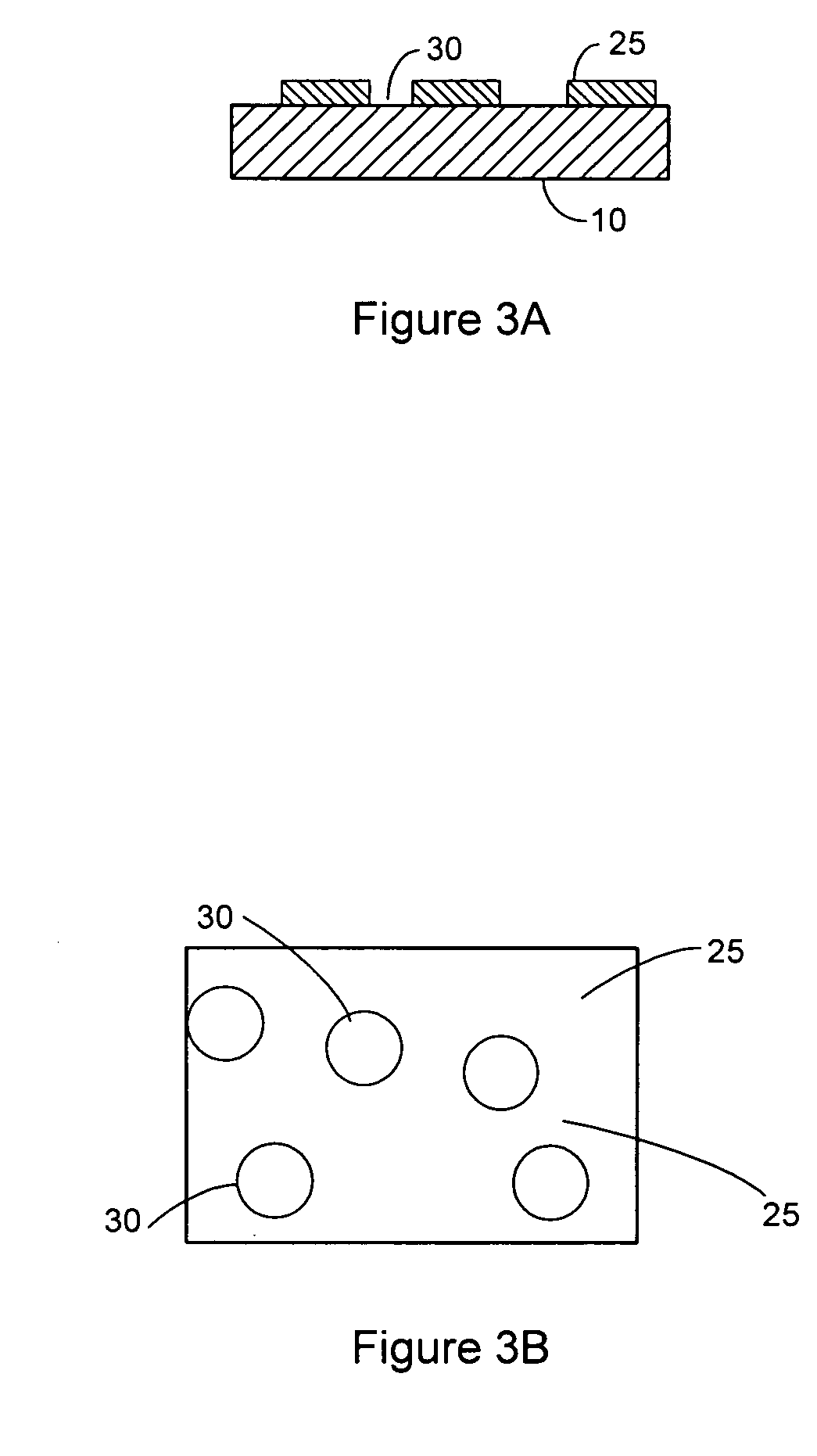

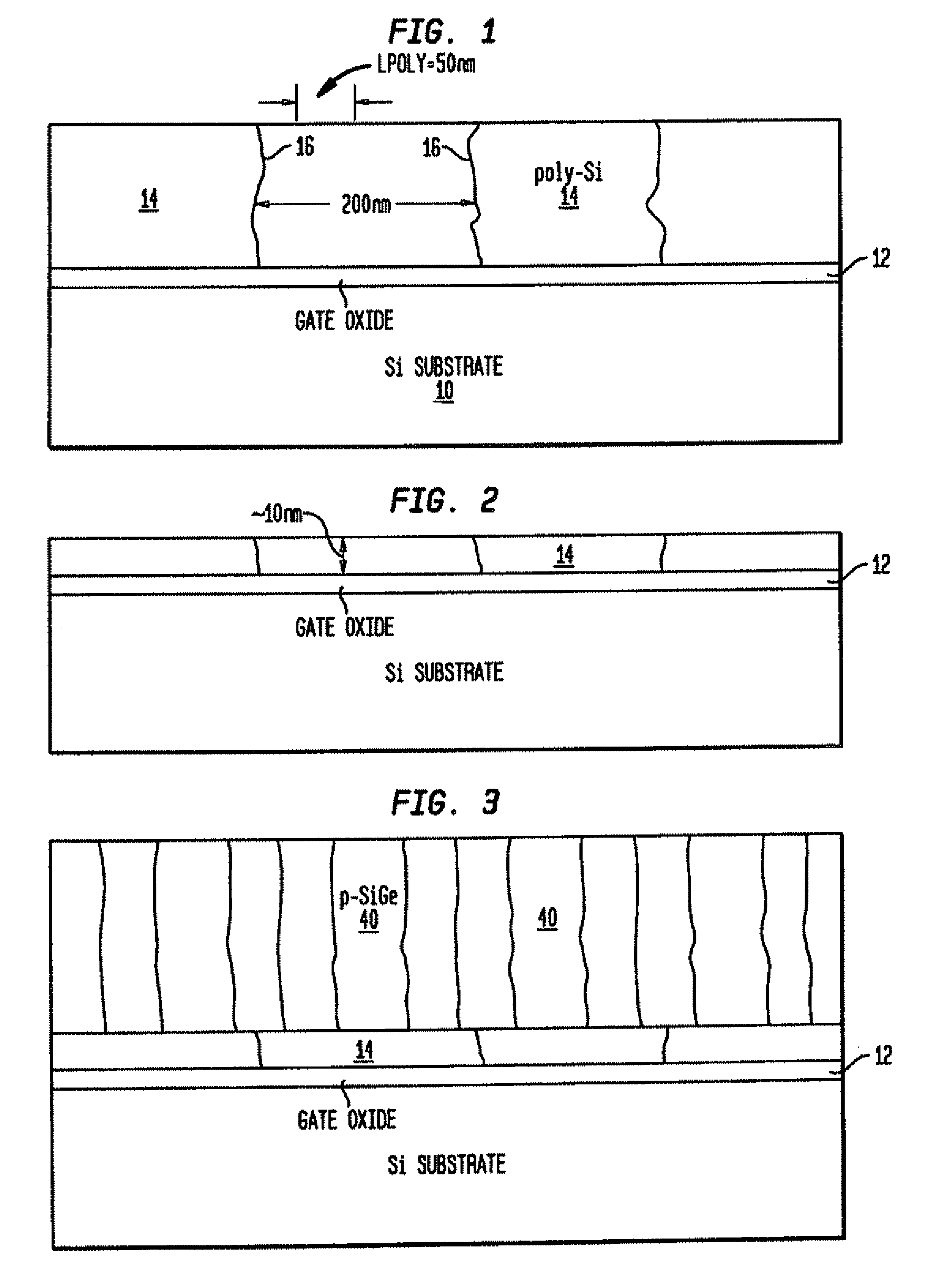

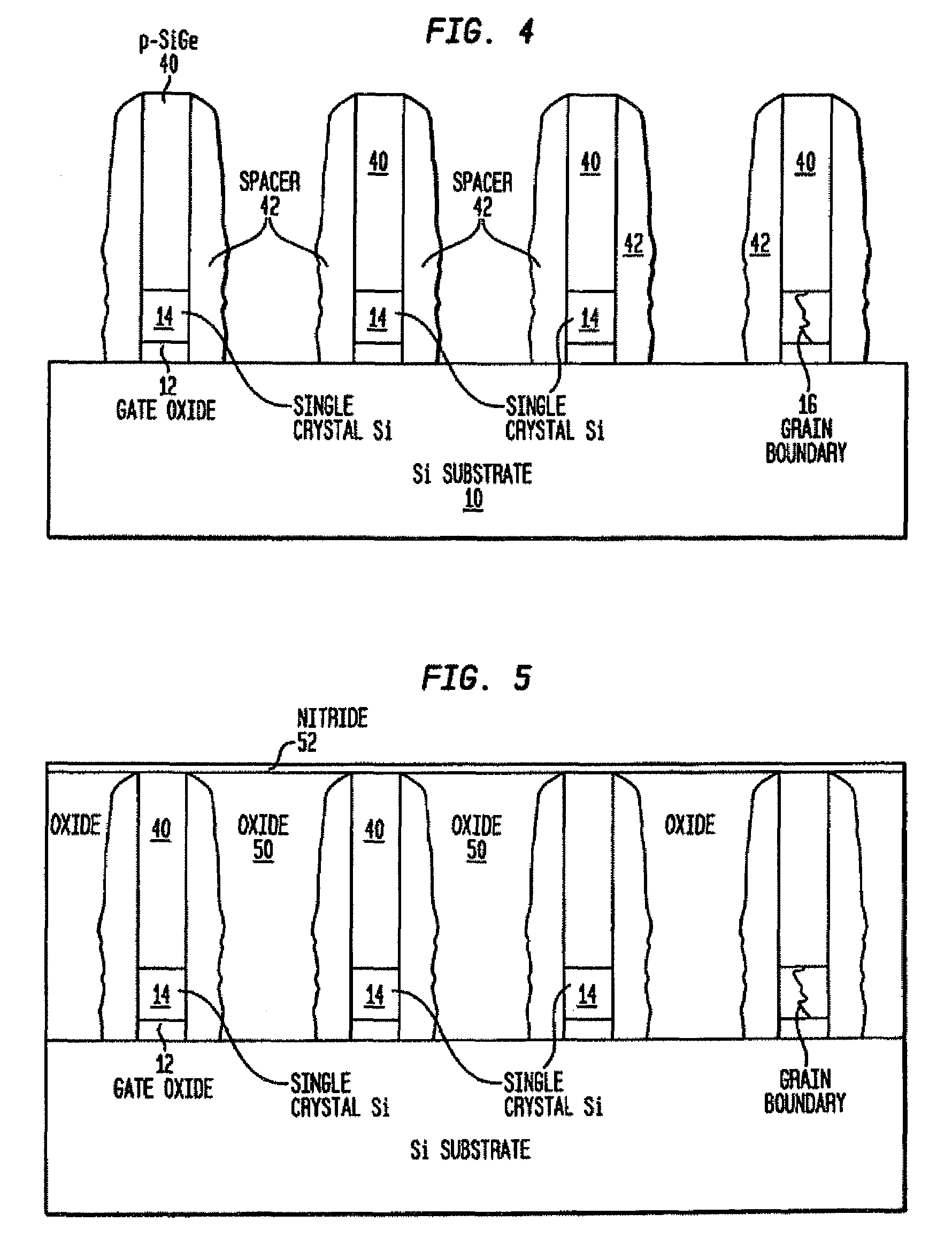

STRUCTURES AND METHODS FOR MANUFACTURING OF DISLOCATION FREE STRESSED CHANNELS IN BULK SILICON AND SOI CMOS DEVICES BY GATE STRESS ENGINEERING WITH SiGe AND/OR Si:C

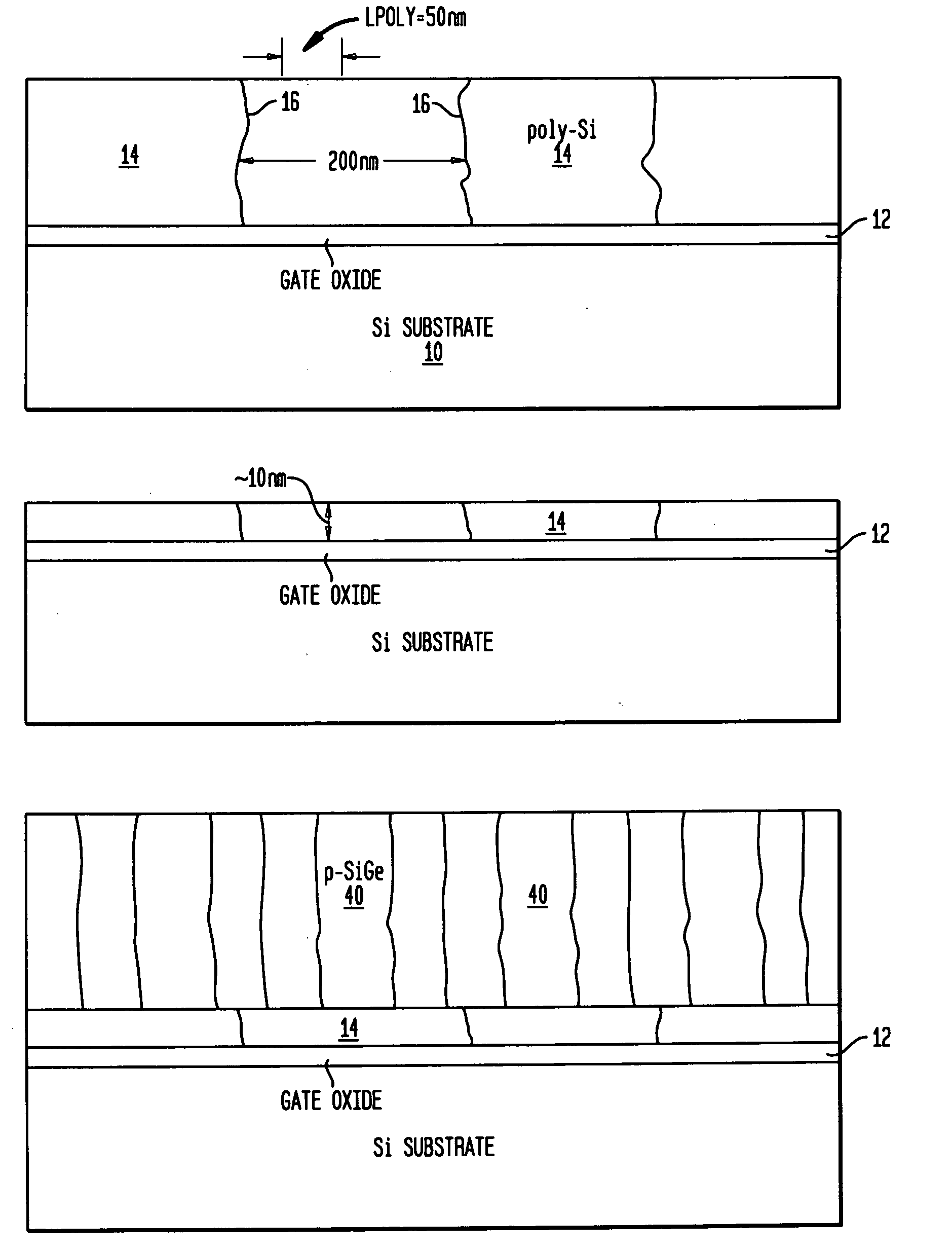

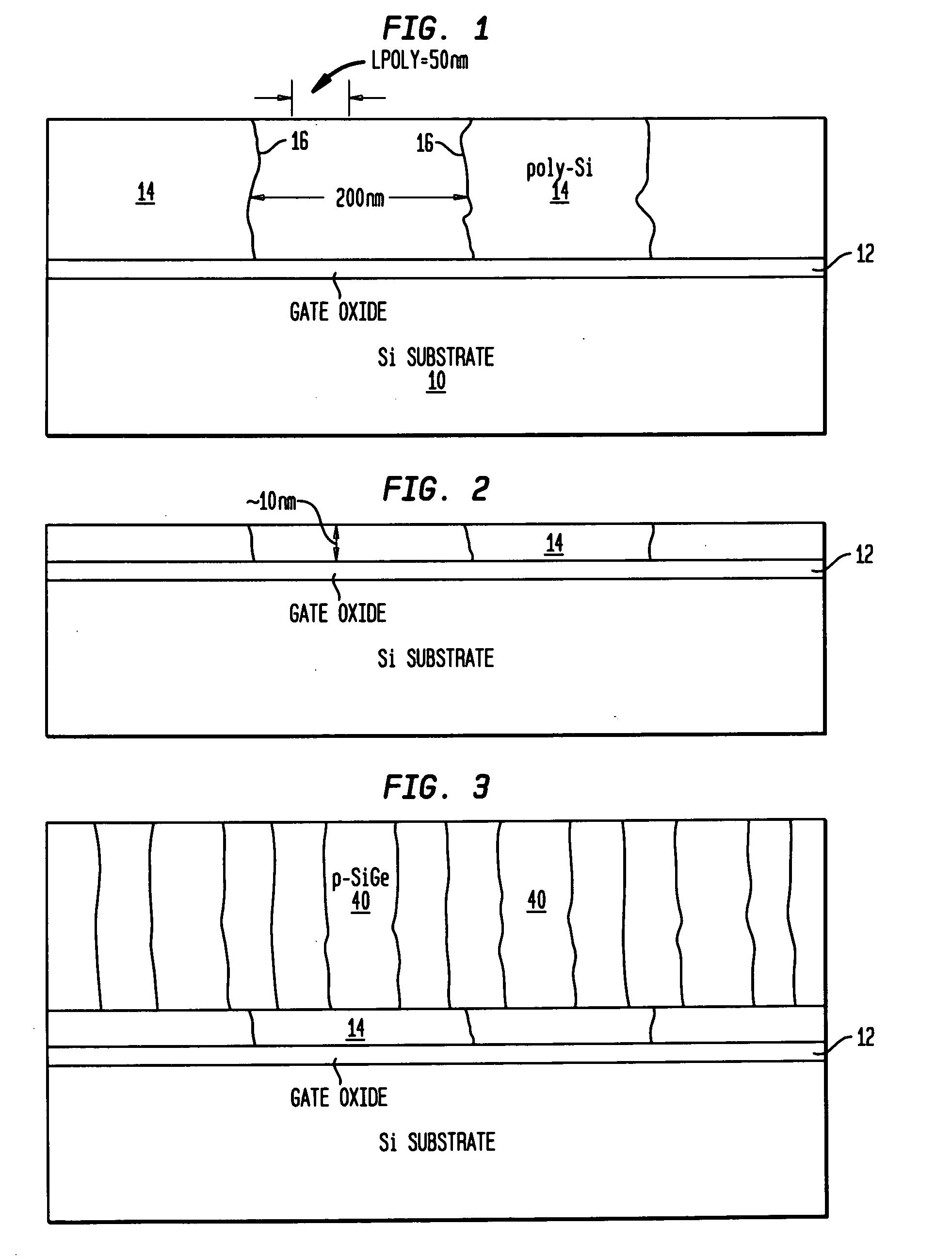

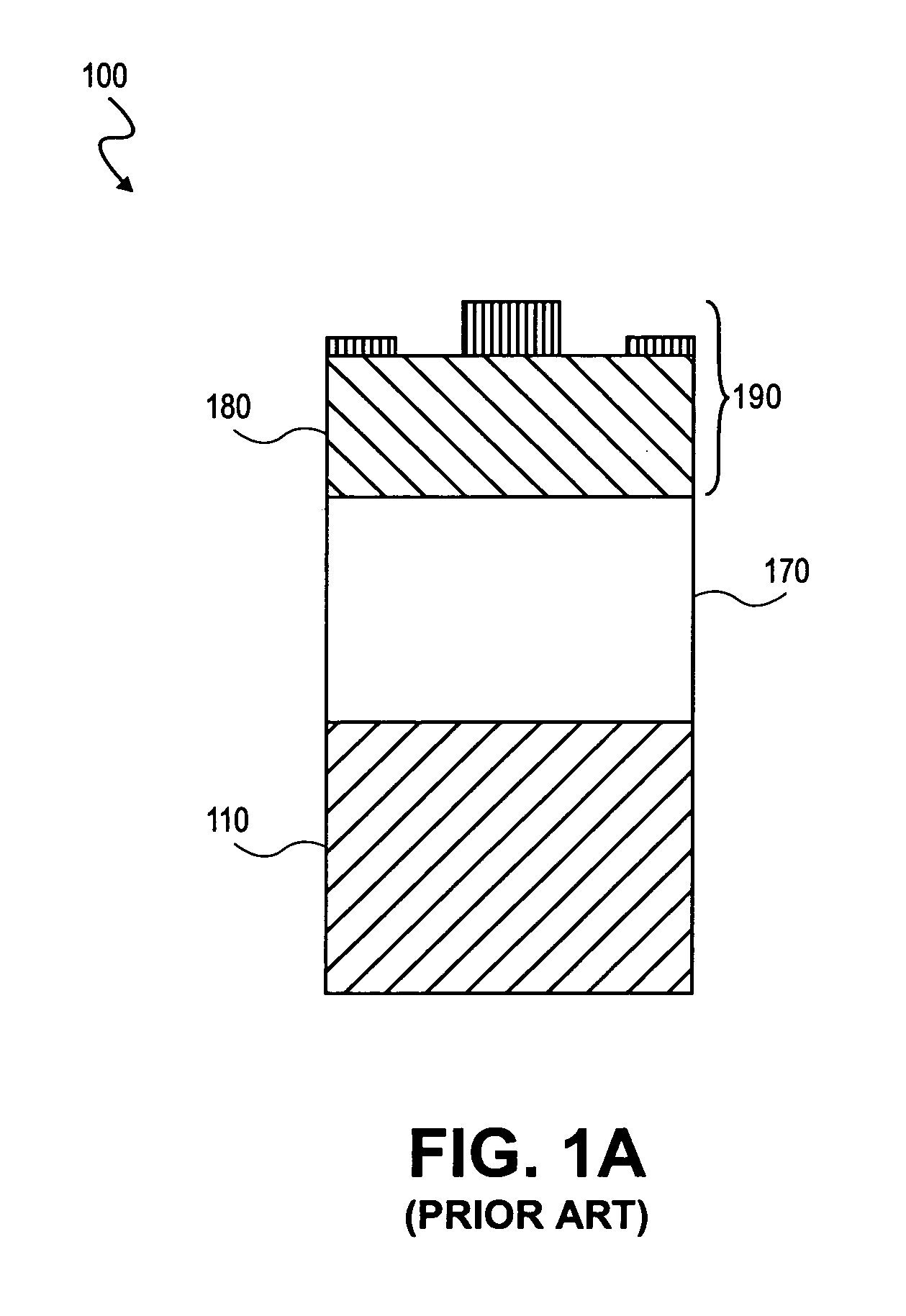

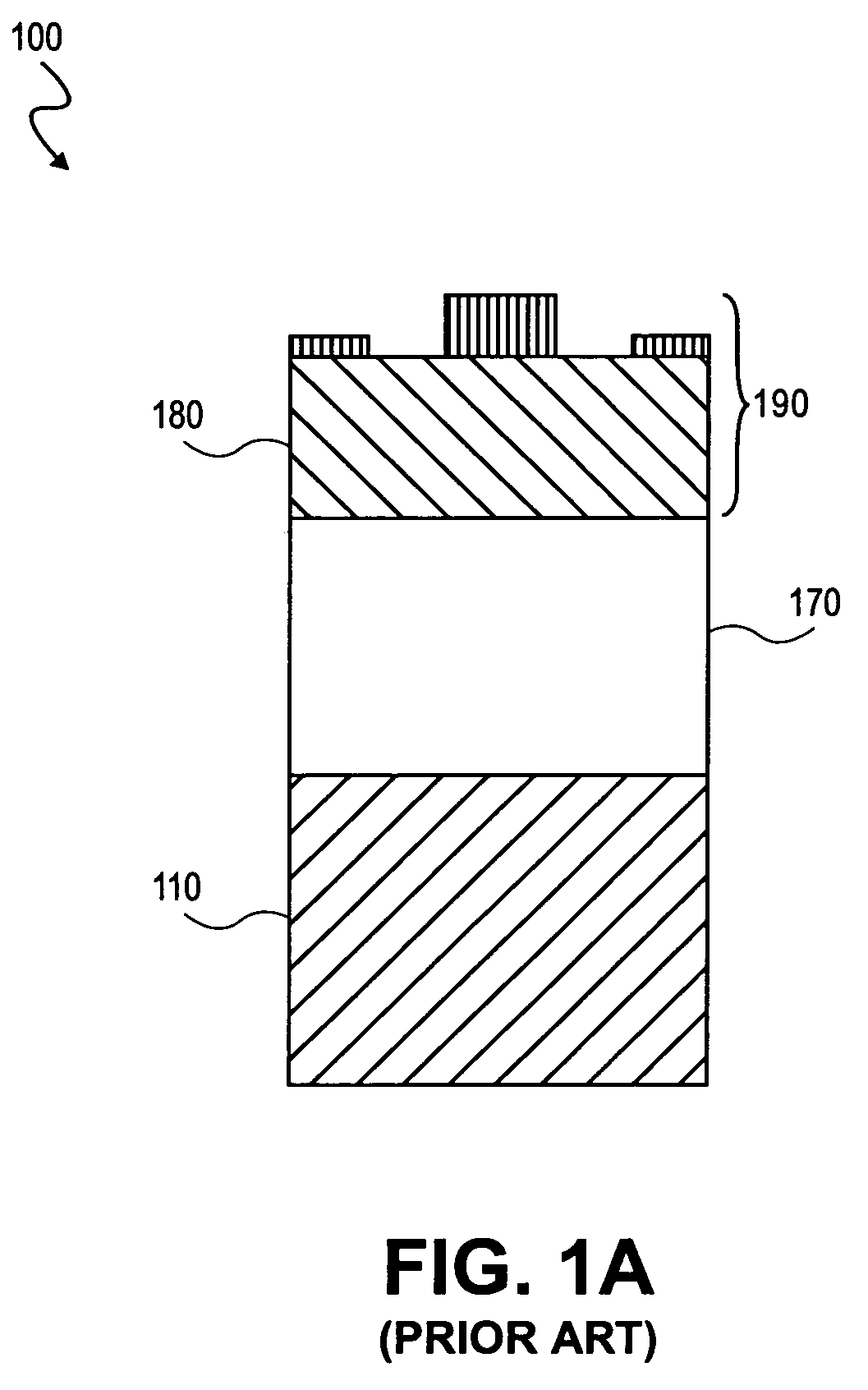

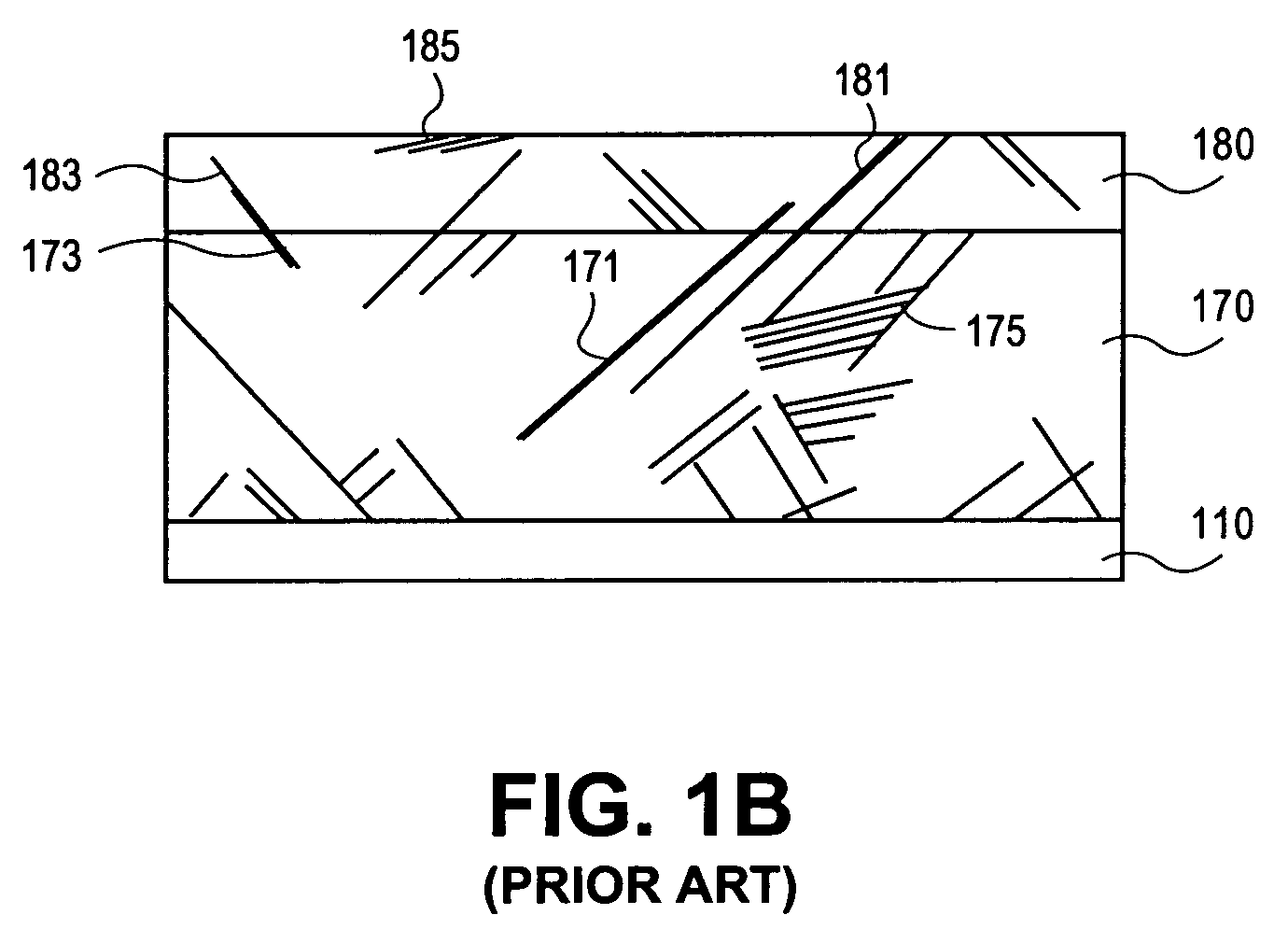

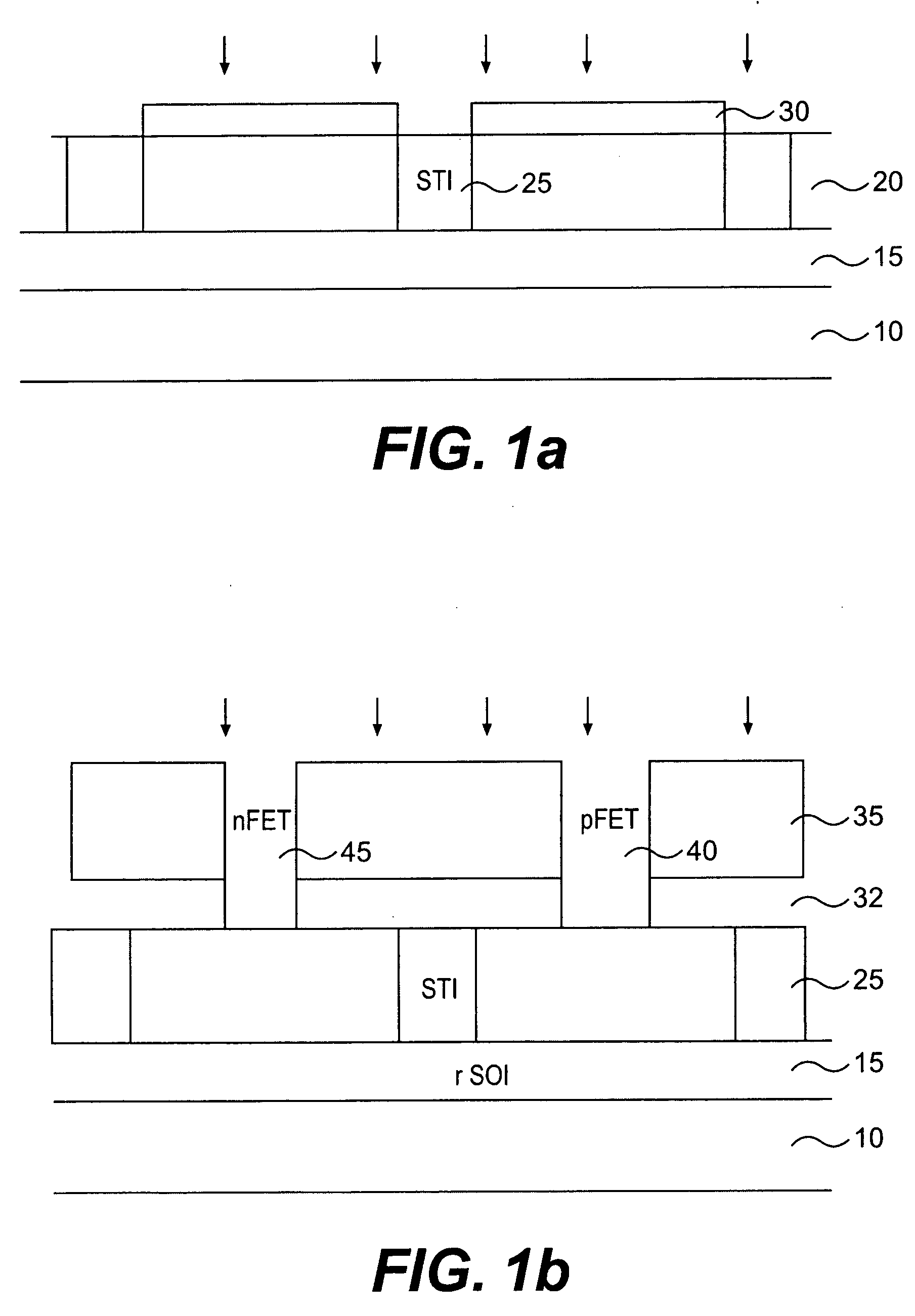

ActiveUS20050236668A1Avoid misalignmentReduce generationTransistorSemiconductor/solid-state device detailsSoi cmosCMOS

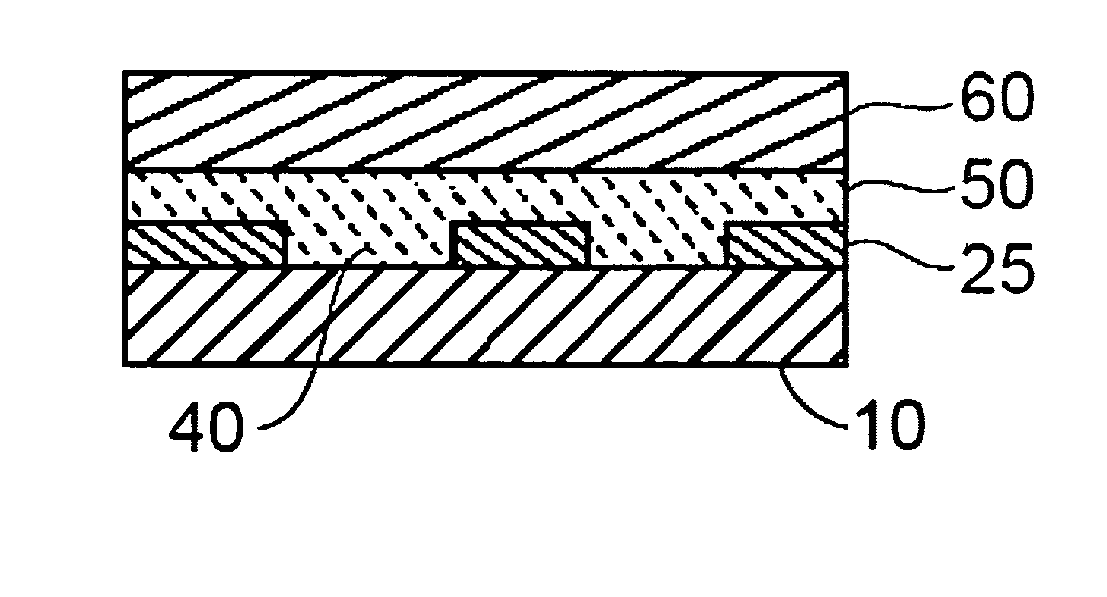

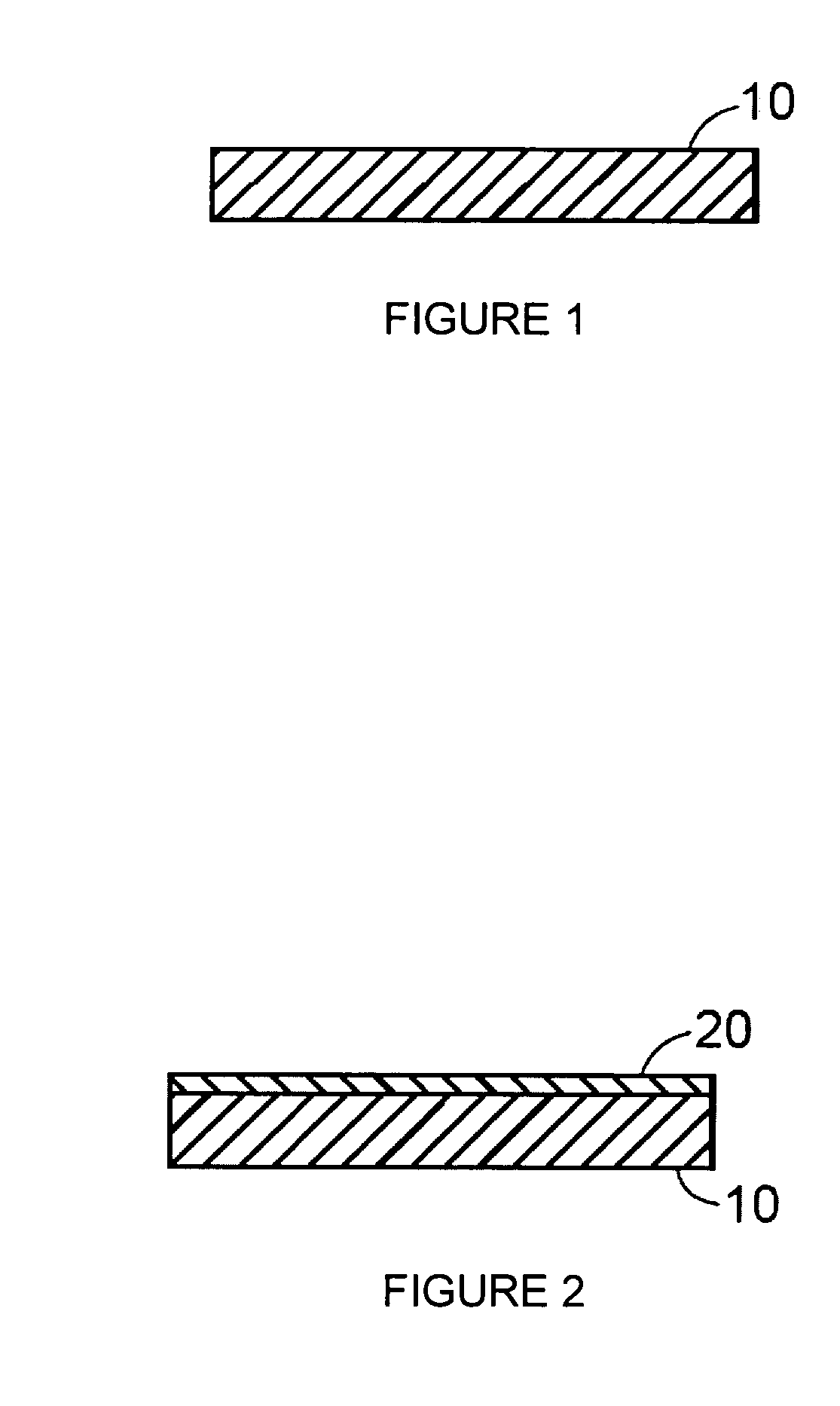

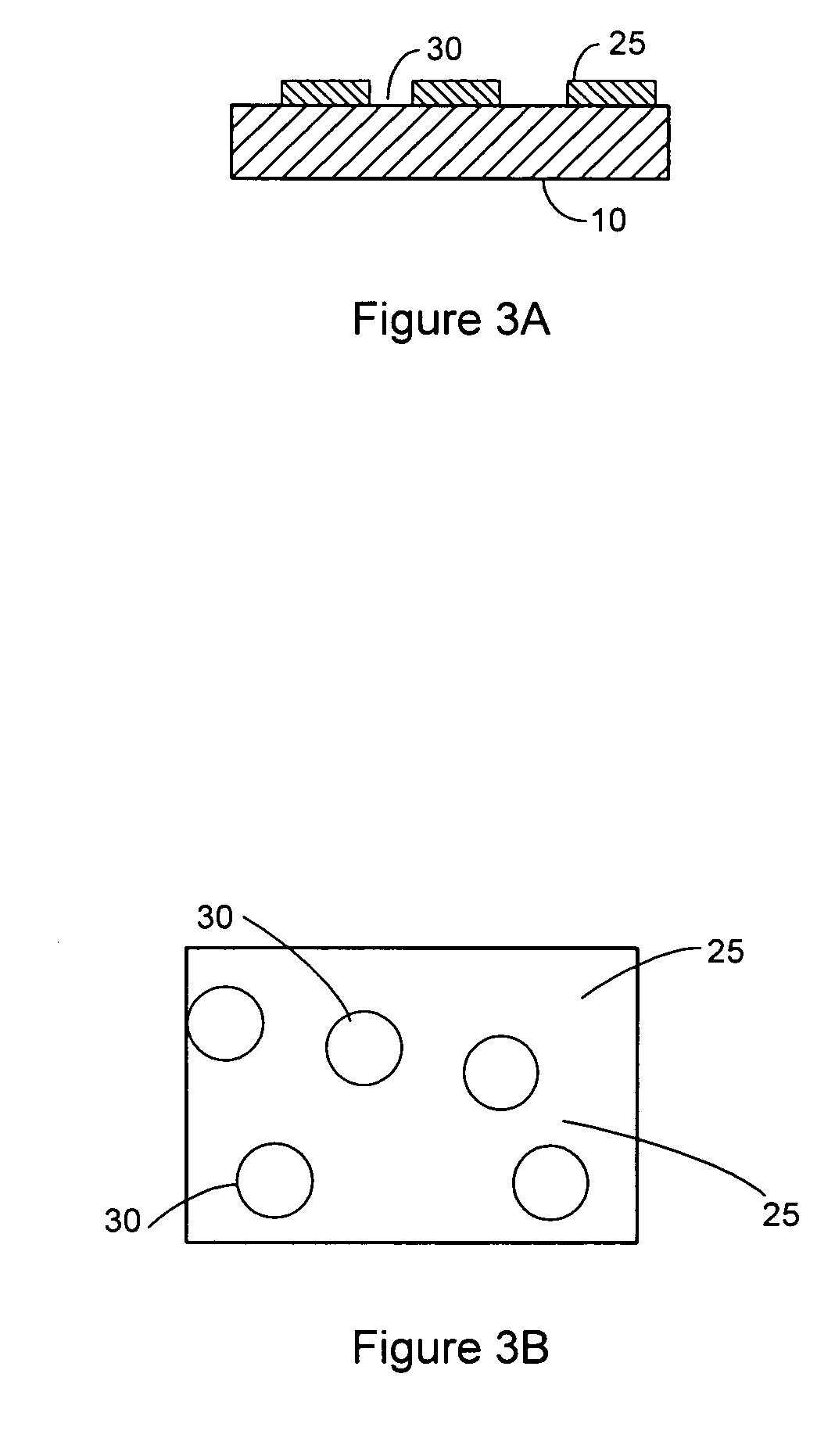

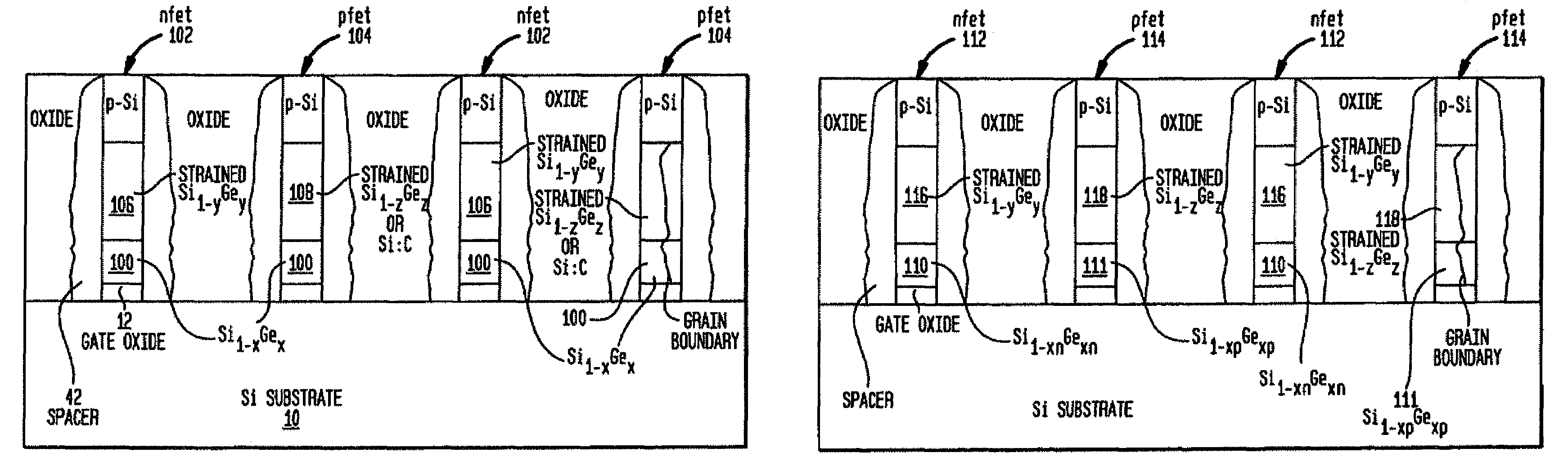

Structures and methods of manufacturing are disclosed of dislocation free stressed channels in bulk silicon and SOI (silicon on insulator) CMOS (complementary metal oxide semiconductor) devices by gate stress engineering with SiGe and / or Si:C. A CMOS device comprises a substrate of either bulk Si or SOI, a gate dielectric layer over the substrate, and a stacked gate structure of SiGe and / or Si:C having stresses produced at the interfaces of SSi(strained Si) / SiGe or SSi / Si:C in the stacked gate structure. The stacked gate structure has a first stressed film layer of large grain size Si or SiGe over the gate dielectric layer, a second stressed film layer of strained SiGe or strained Si:C over the first stressed film layer, and a semiconductor or conductor such as p(poly)-Si over the second stressed film layer.

Owner:GLOBALFOUNDRIES US INC

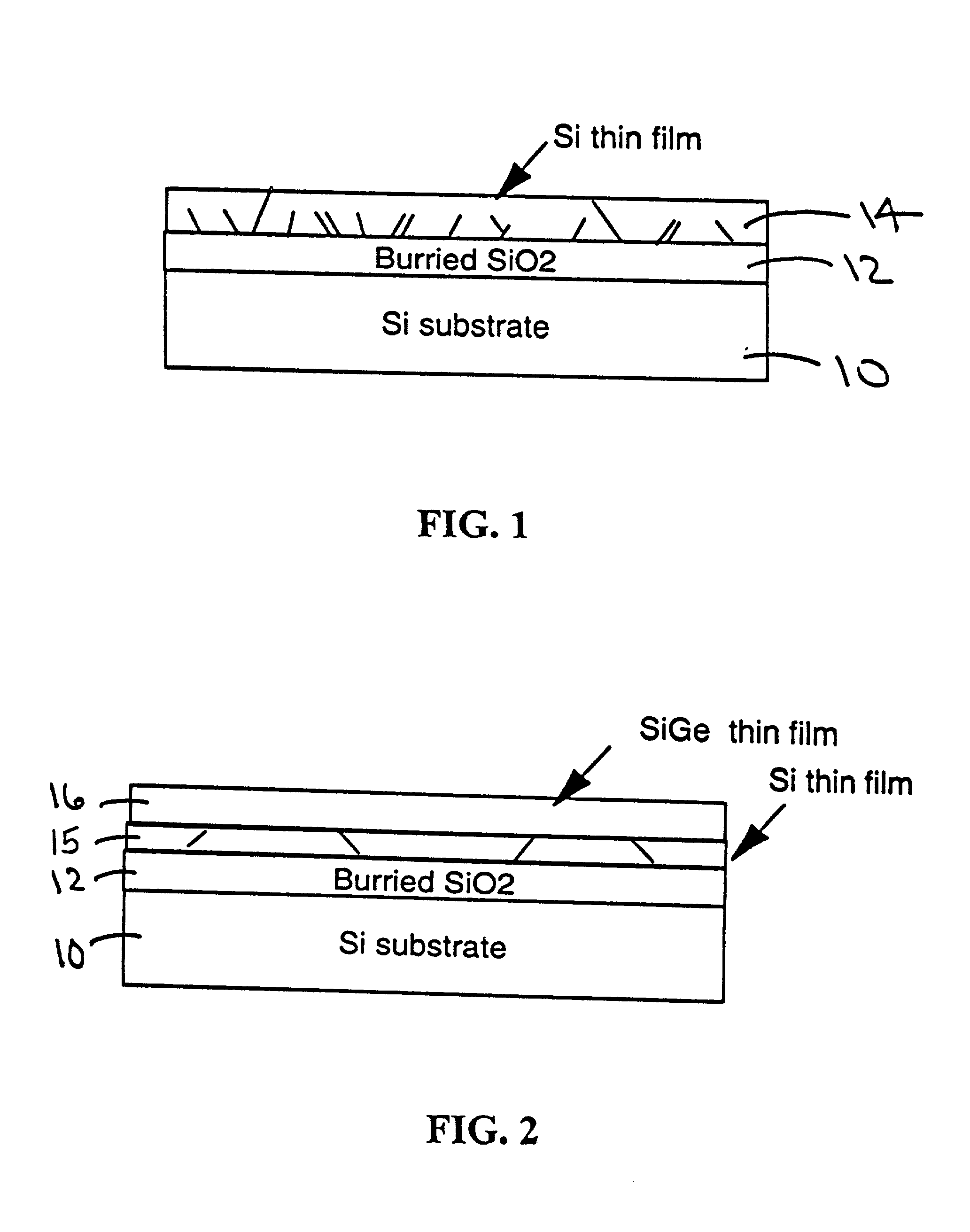

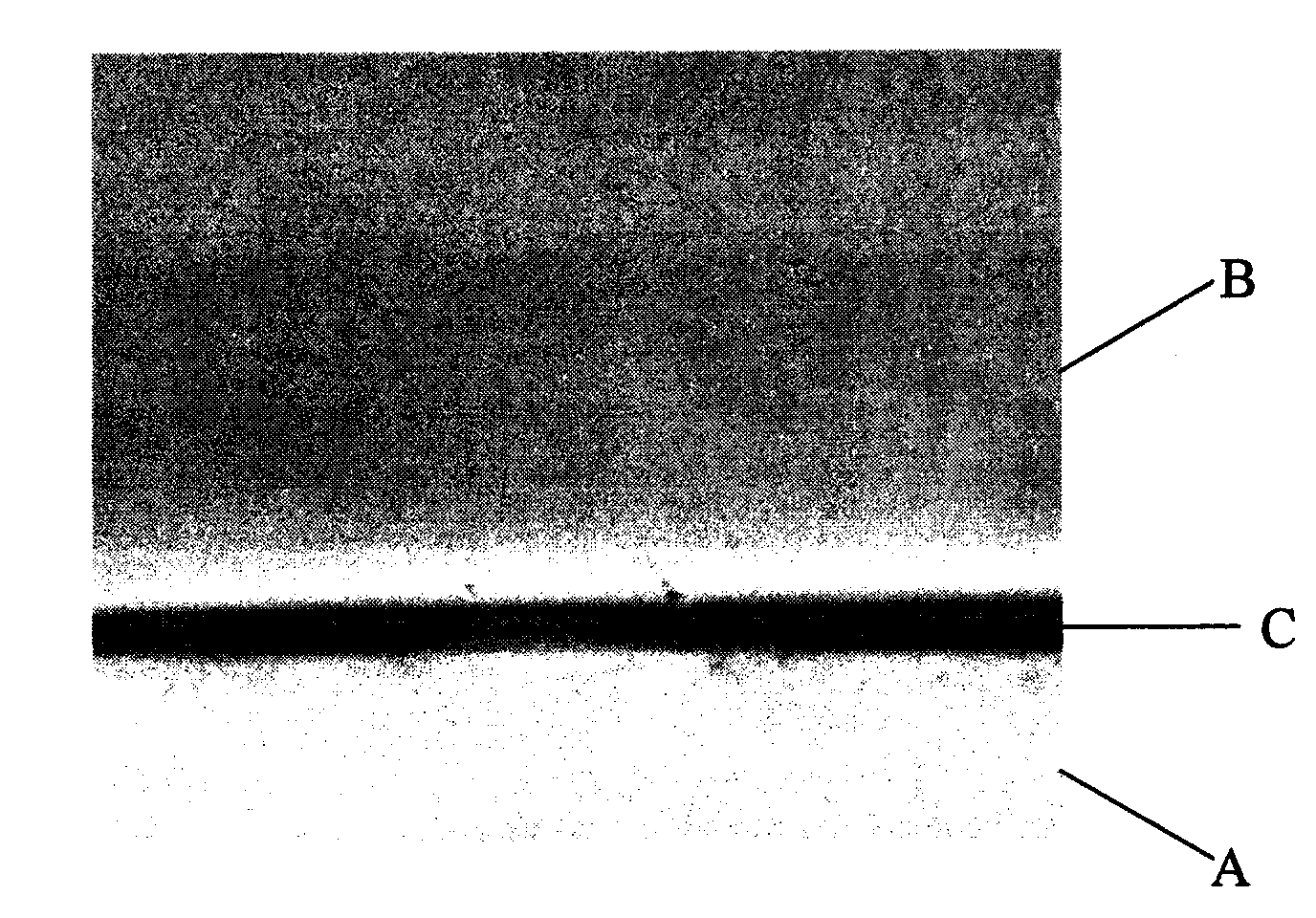

Method for producing dislocation-free strained crystalline films

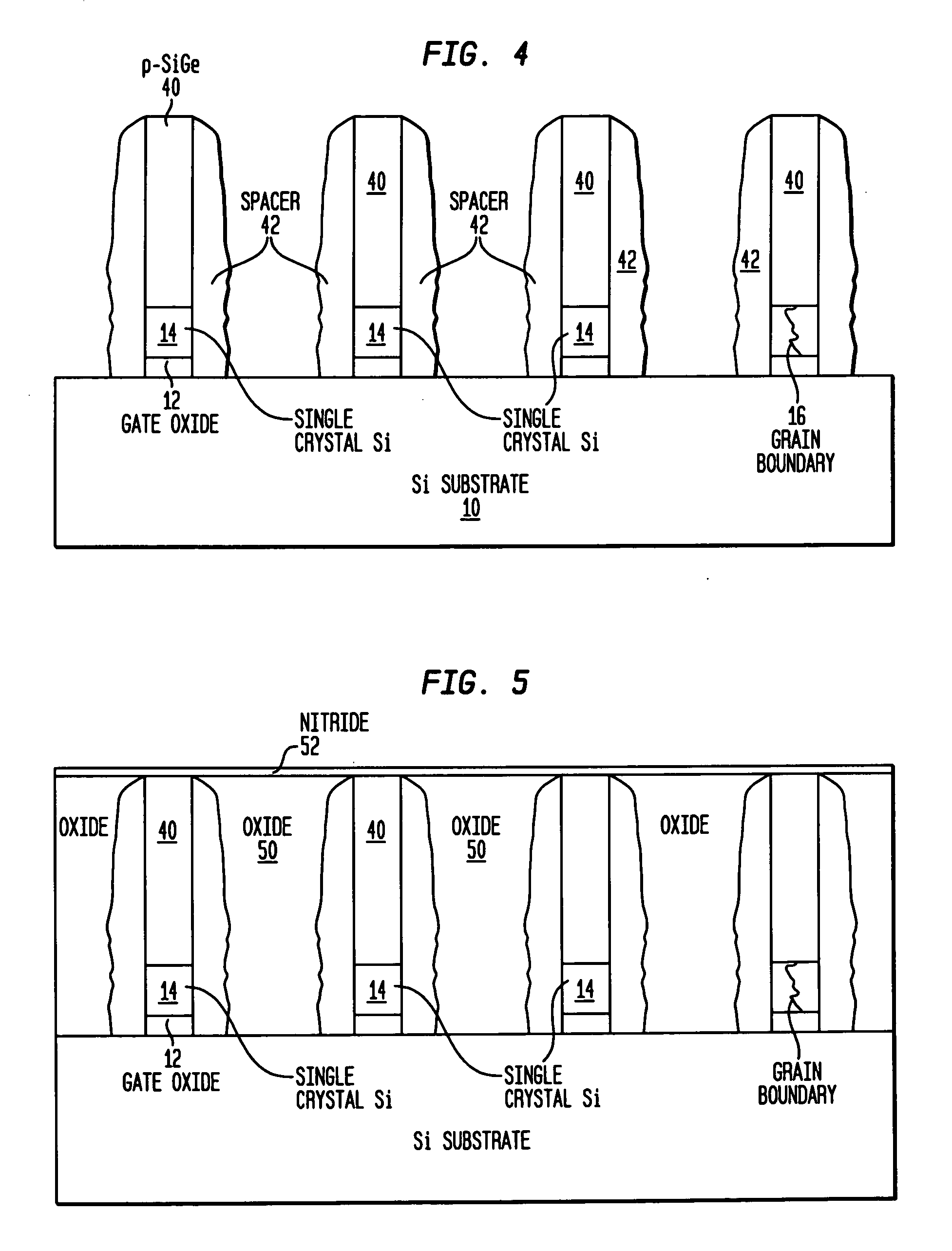

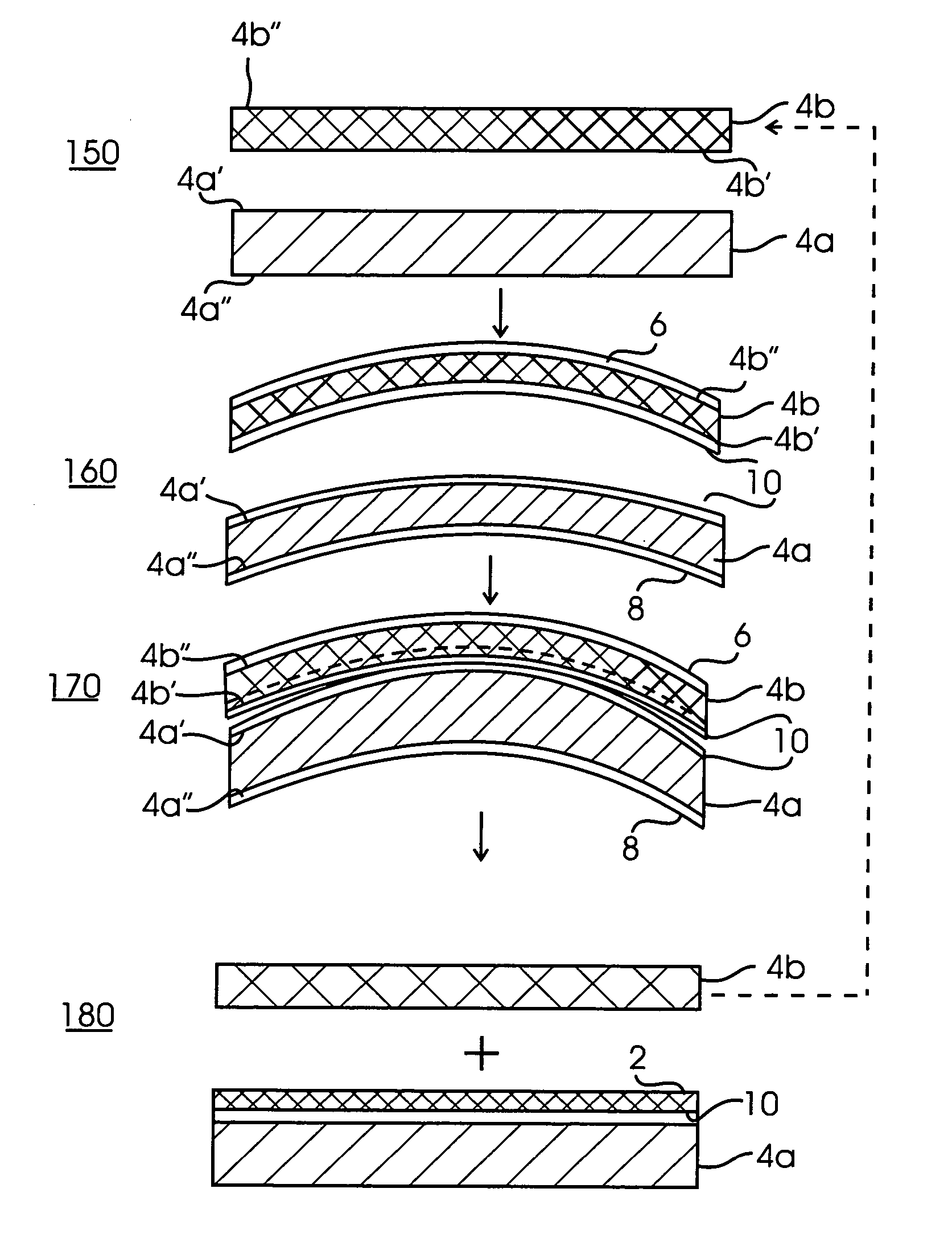

ActiveUS20060292822A1Small thicknessSemiconductor/solid-state device manufacturingHydrogenOptoelectronics

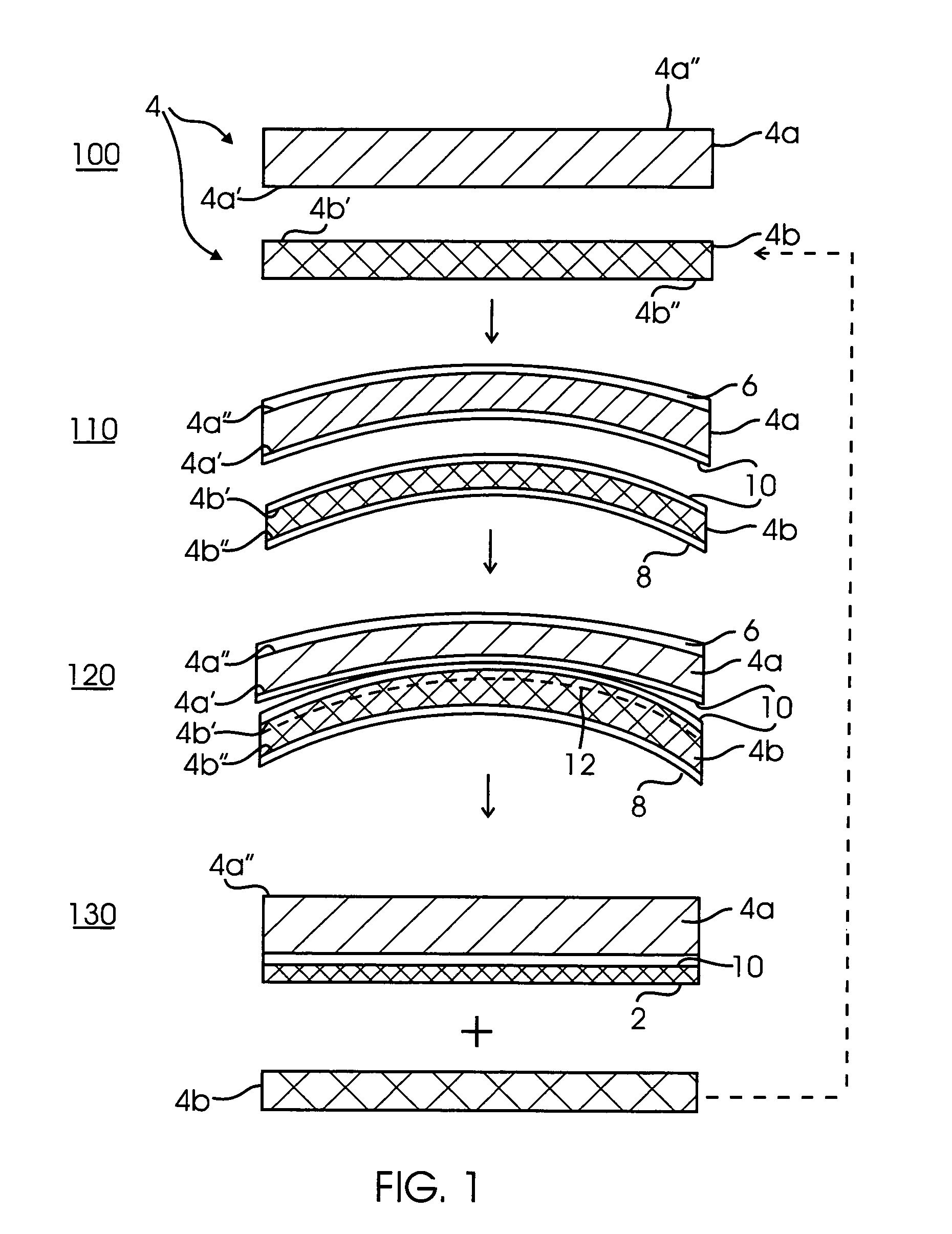

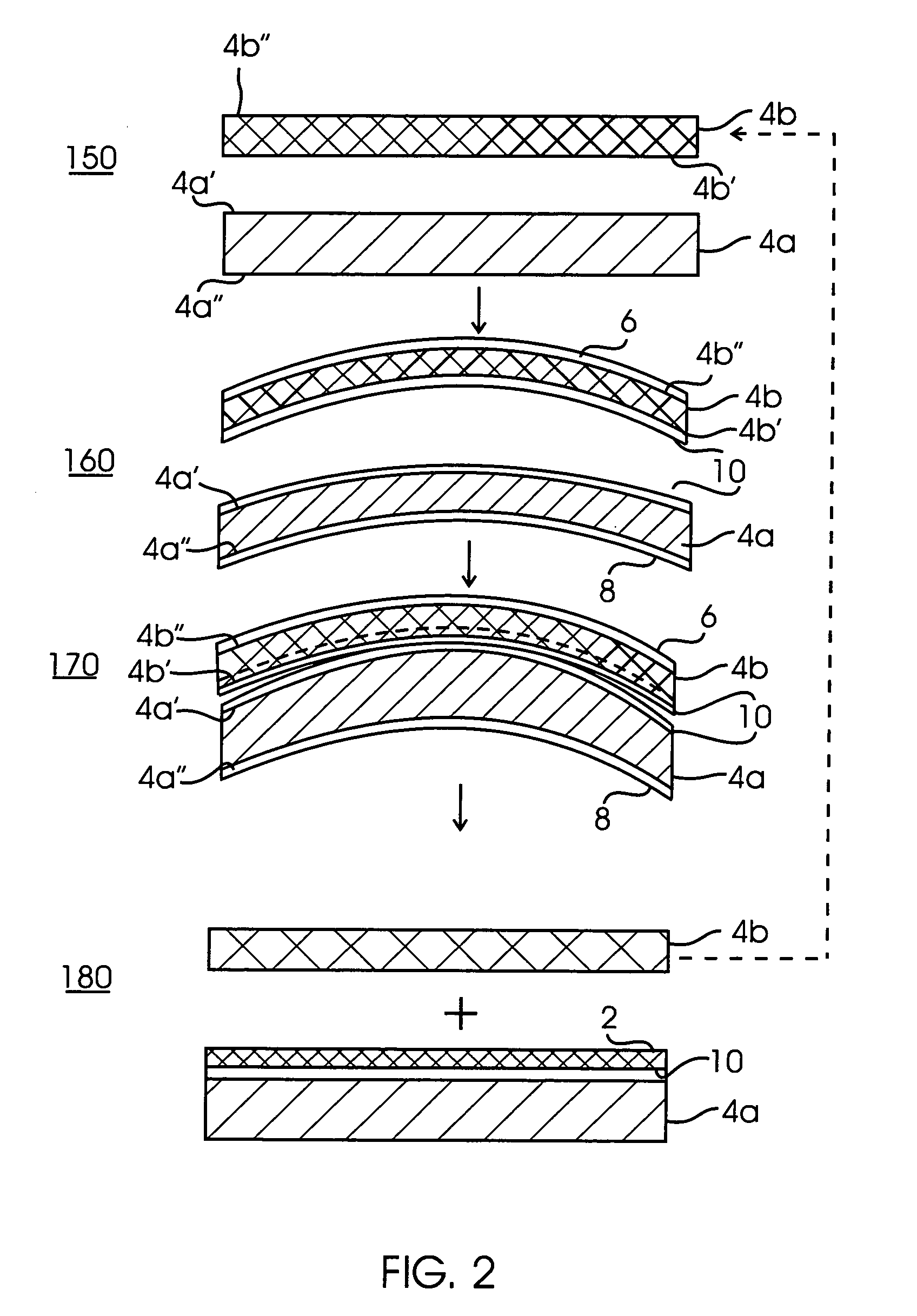

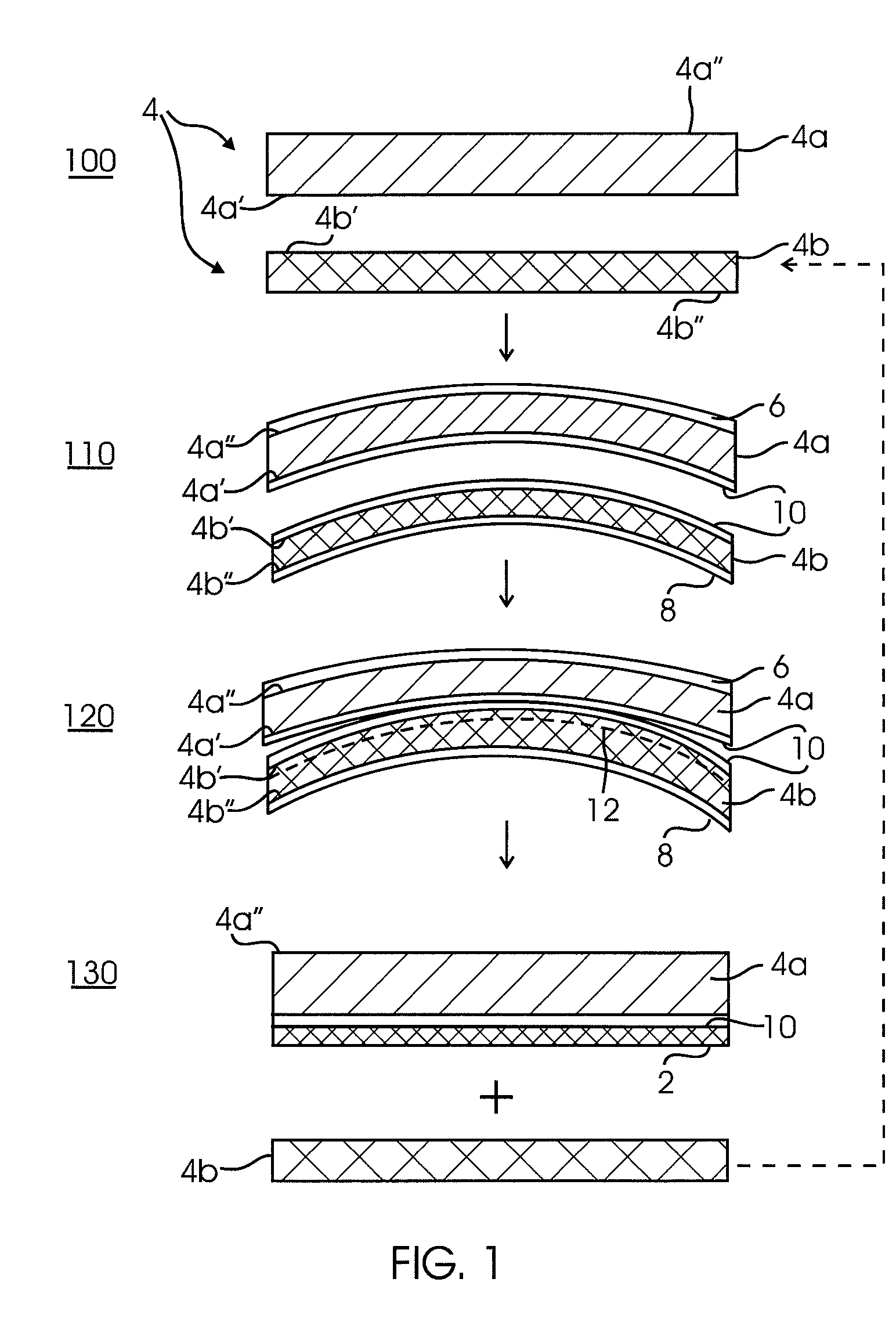

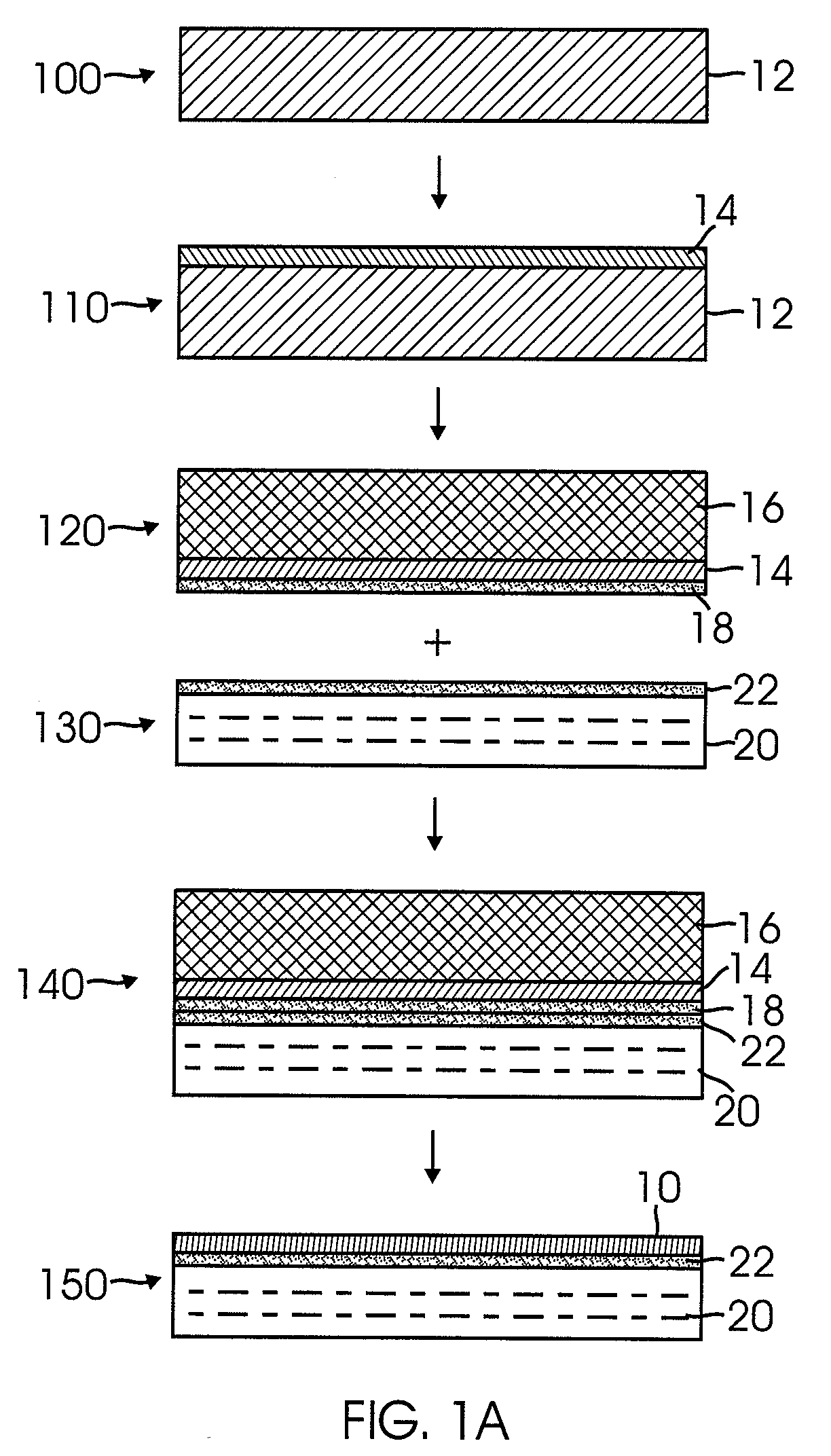

A method for forming dislocation-free strained silicon thin film includes the step of providing two curved silicon substrates. One substrate is curved by the presence of silicon dioxide on a back surface. The other substrate is curved by the presence of a silicon nitride layer. One of the substrates is subject to hydrogen implantation and the two substrates are bonded to one another in an annealing process. The two substrates are separated, thereby leaving a layer of strained silicon on a front side of one of the substrates. A back side layer of silicon dioxide or silicon nitride is then removed to restore the substrate to a substantially planar state. The method may be employed to form dislocation-free strained silicon thin films. The films may be under tensile or compressive strain.

Owner:RGT UNIV OF CALIFORNIA

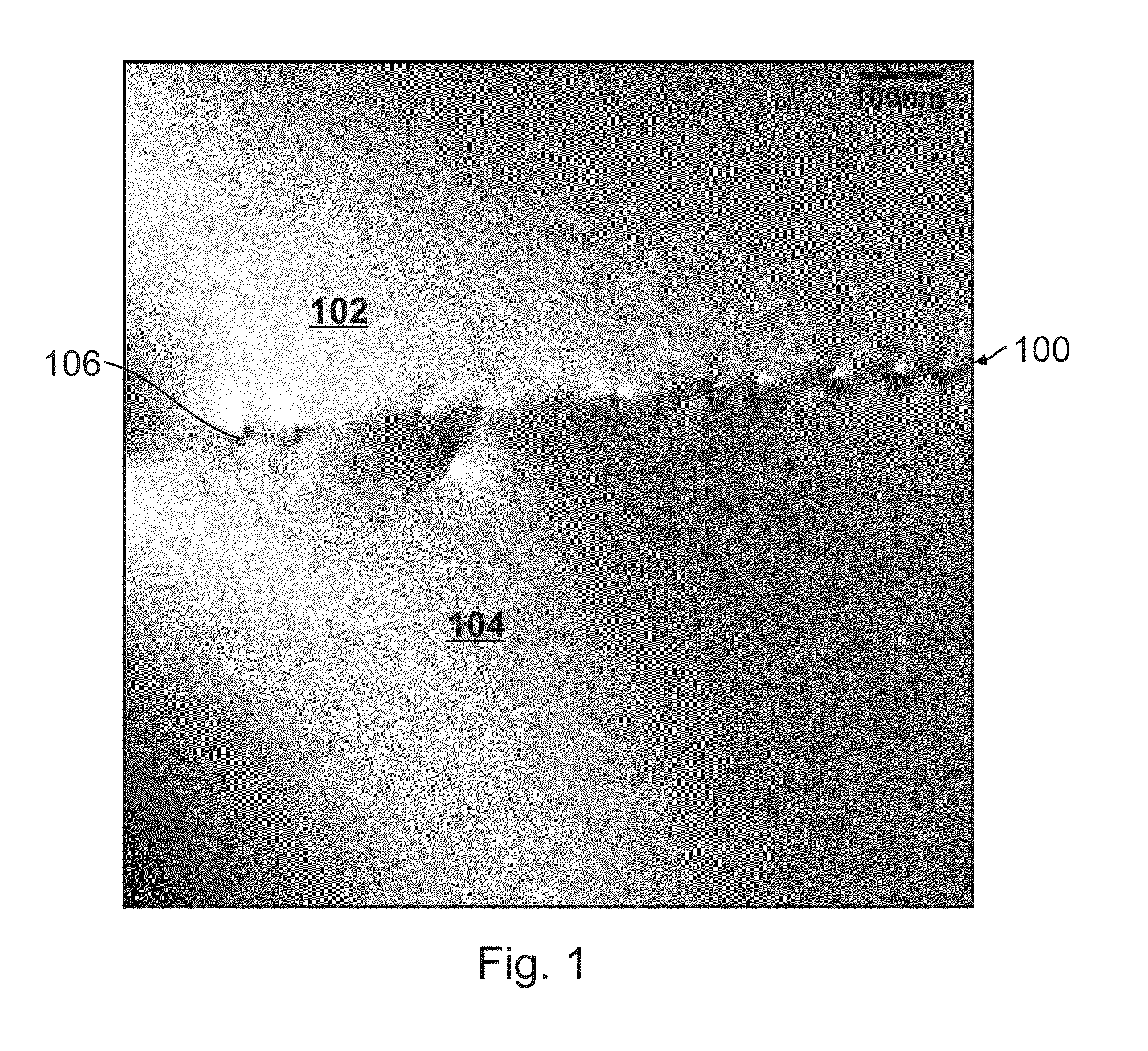

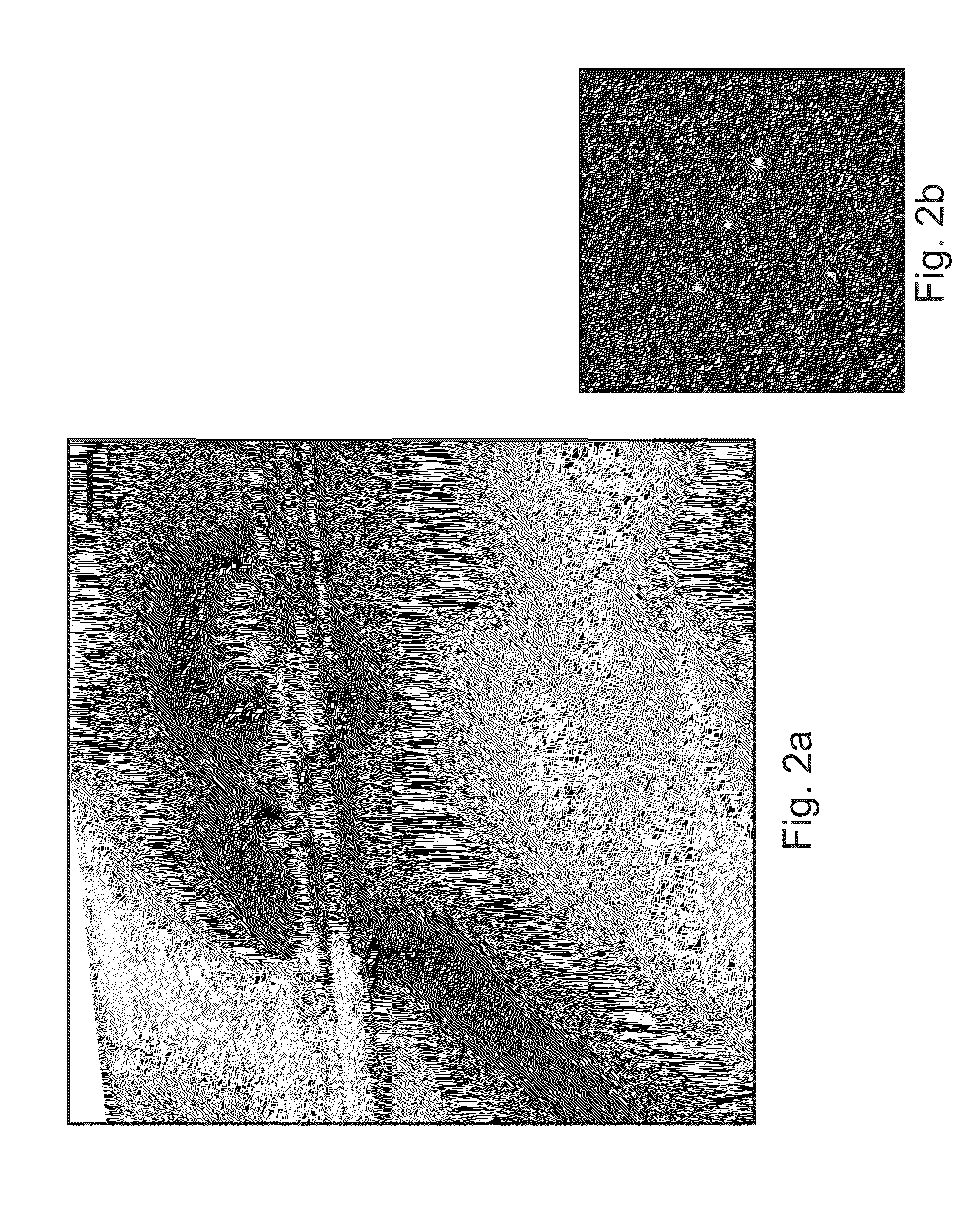

Threading-dislocation-free nanoheteroepitaxy of Ge on Si using self-directed touch-down of Ge through a thin SiO2 layer

ActiveUS20050054180A1Polycrystalline material growthSolid-state devicesThreading dislocationsDirect touch

A method of forming a virtually defect free lattice mismatched nanoheteroepitaxial layer is disclosed. The method includes forming an interface layer on a portion of a substrate. A plurality of seed pads are then formed by self-directed touchdown by exposing the interface layer to a material comprising a semiconductor material. The plurality of seed pads, having an average width of about 1 nm to 10 nm, are interspersed within the interface layer and contact the substrate. An epitaxial layer is then formed by lateral growth of the seed pads over the interface layer.

Owner:STC UNM

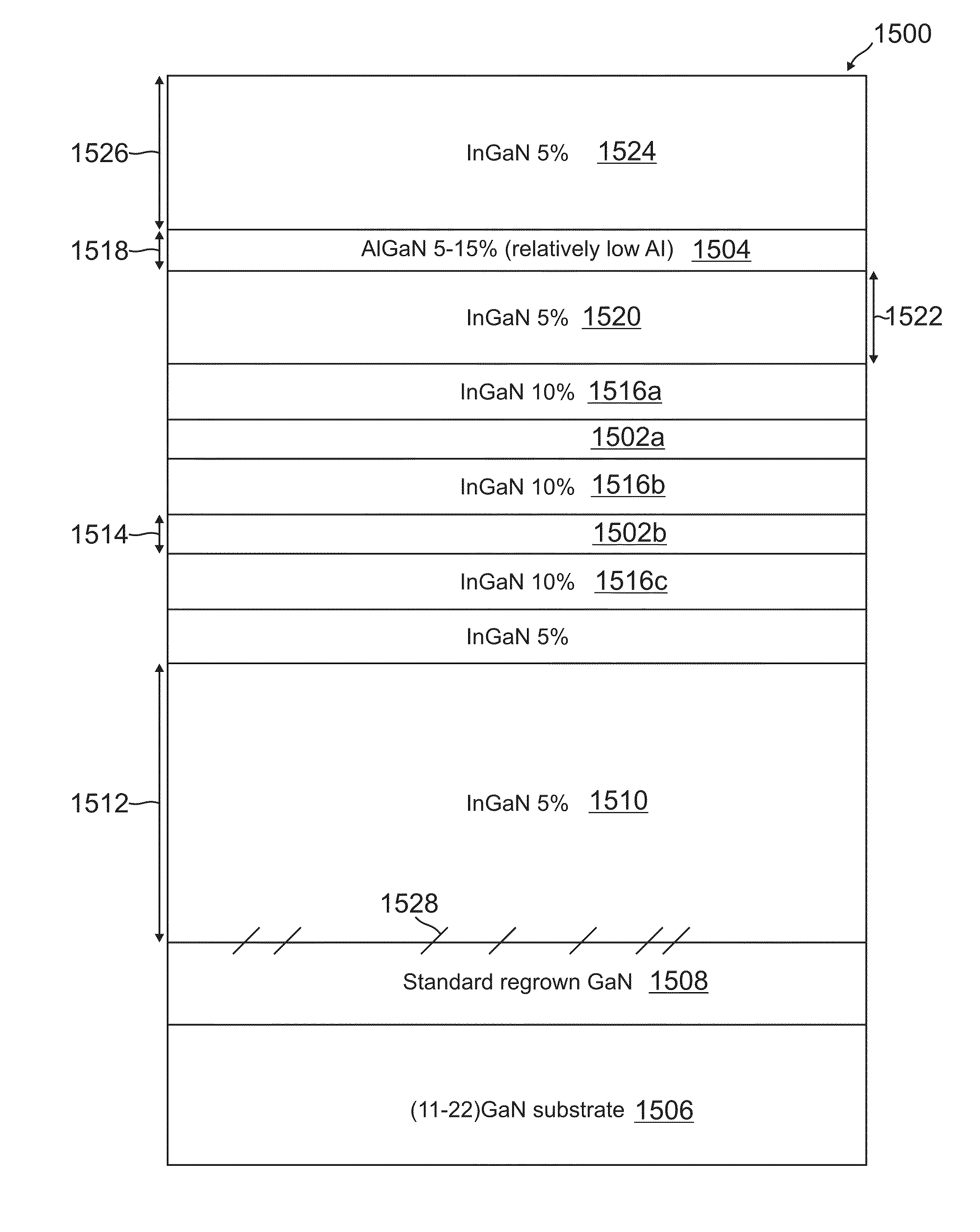

Semipolar nitride-based devices on partially or fully relaxed alloys with misfit dislocations at the heterointerface

ActiveUS20110064103A1Quality improvementImprovement ingredientsPolycrystalline material growthLaser detailsAlloyLattice constant

A dislocation-free high quality template with relaxed lattice constant, fabricated by spatially restricting misfit dislocation(s) around heterointerfaces. This can be used as a template layer for high In composition devices. Specifically, the present invention prepares high quality InGaN templates (In composition is around 5-10%), and can grow much higher In-composition InGaN quantum wells (QWs) (or multi quantum wells (MQWs)) on these templates than would otherwise be possible.

Owner:RGT UNIV OF CALIFORNIA

Dislocation-free InSb quantum well structure on Si using novel buffer architecture

InactiveUS20080073639A1Solid-state devicesSemiconductor/solid-state device manufacturingQuantum wellDislocation free

A device grade III-V quantum well structure formed on a silicon substrate using a composite buffer architechture and the method of manufacture is described. Embodiments of the present invention enable III-V InSb quantum well device layers with defect densities below 1×108 cm−2 to be formed on silicon substrates. In an embodiment of the present invention, an InSb quantum well layer is sandwiched between two larger band gap barrier layers. In an embodiment of the present invention, InSb quantum well layer is strained. In a specific embodiment, the two larger band gap barrier layers are graded.

Owner:INTEL CORP

Dislocation-free InSb quantum well structure on Si using novel buffer architecture

InactiveUS7573059B2Solid-state devicesSemiconductor/solid-state device manufacturingQuantum wellDislocation free

A device grade III-V quantum well structure formed on a silicon substrate using a composite buffer architecture and the method of manufacture is described. Embodiments of the present invention enable III-V InSb quantum well device layers with defect densities below 1×108 cm−2 to be formed on silicon substrates. In an embodiment of the present invention, an InSb quantum well layer is sandwiched between two larger band gap barrier layers. In an embodiment of the present invention, InSb quantum well layer is strained. In a specific embodiment, the two larger band gap barrier layers are graded.

Owner:INTEL CORP

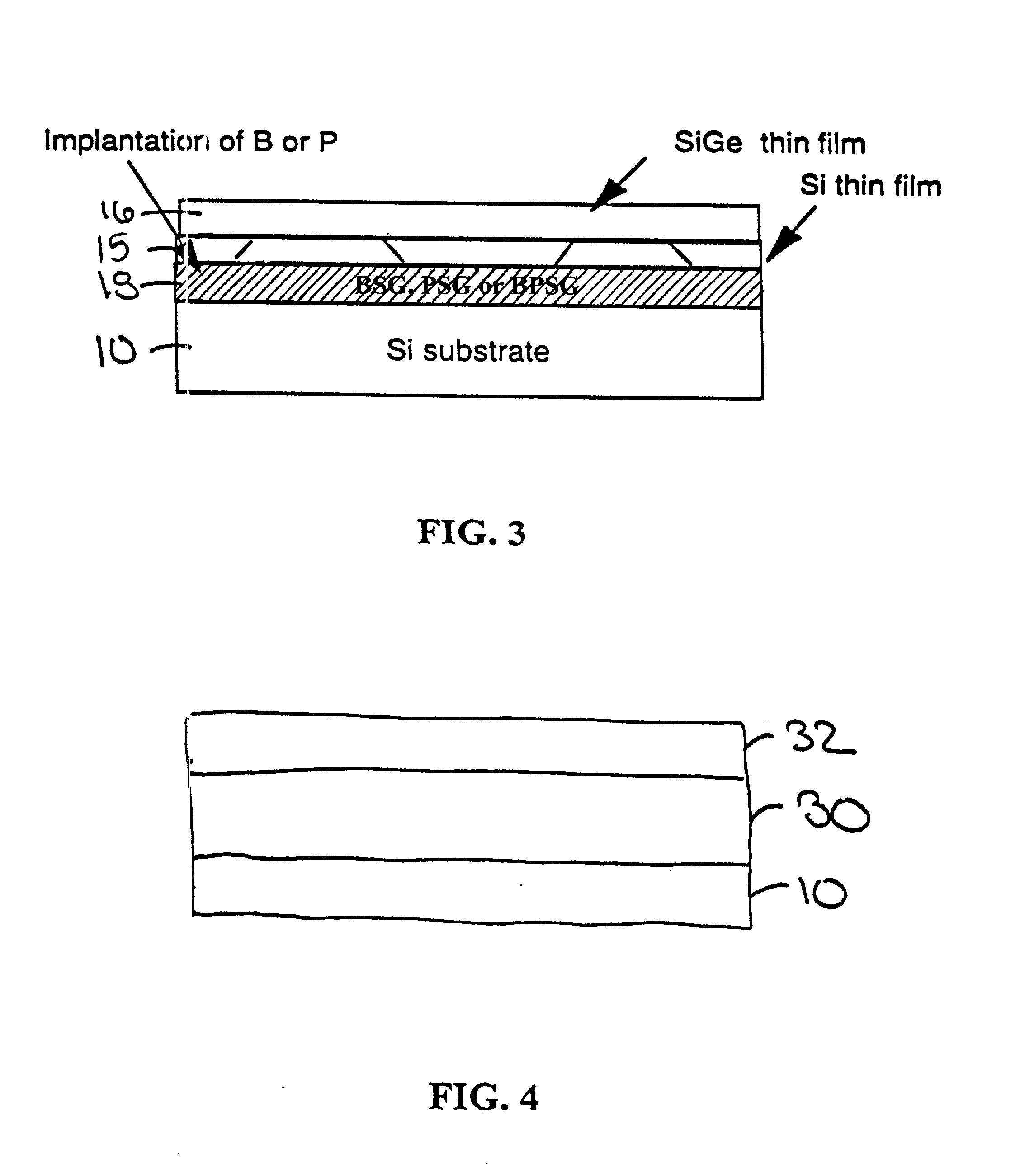

Processing method for forming dislocation-free silicon-on-insulator substrate prepared by implantation of oxygen

A SIMOX semiconductor structure is provided that may include a silicon substrate, a doped glass layer formed on the silicon substrate by ion implantation and a silicon layer formed on the silicon substrate. Ion implantation may form the doped glass layer to reduce the dislocation density of the silicon layer.

Owner:IBM CORP

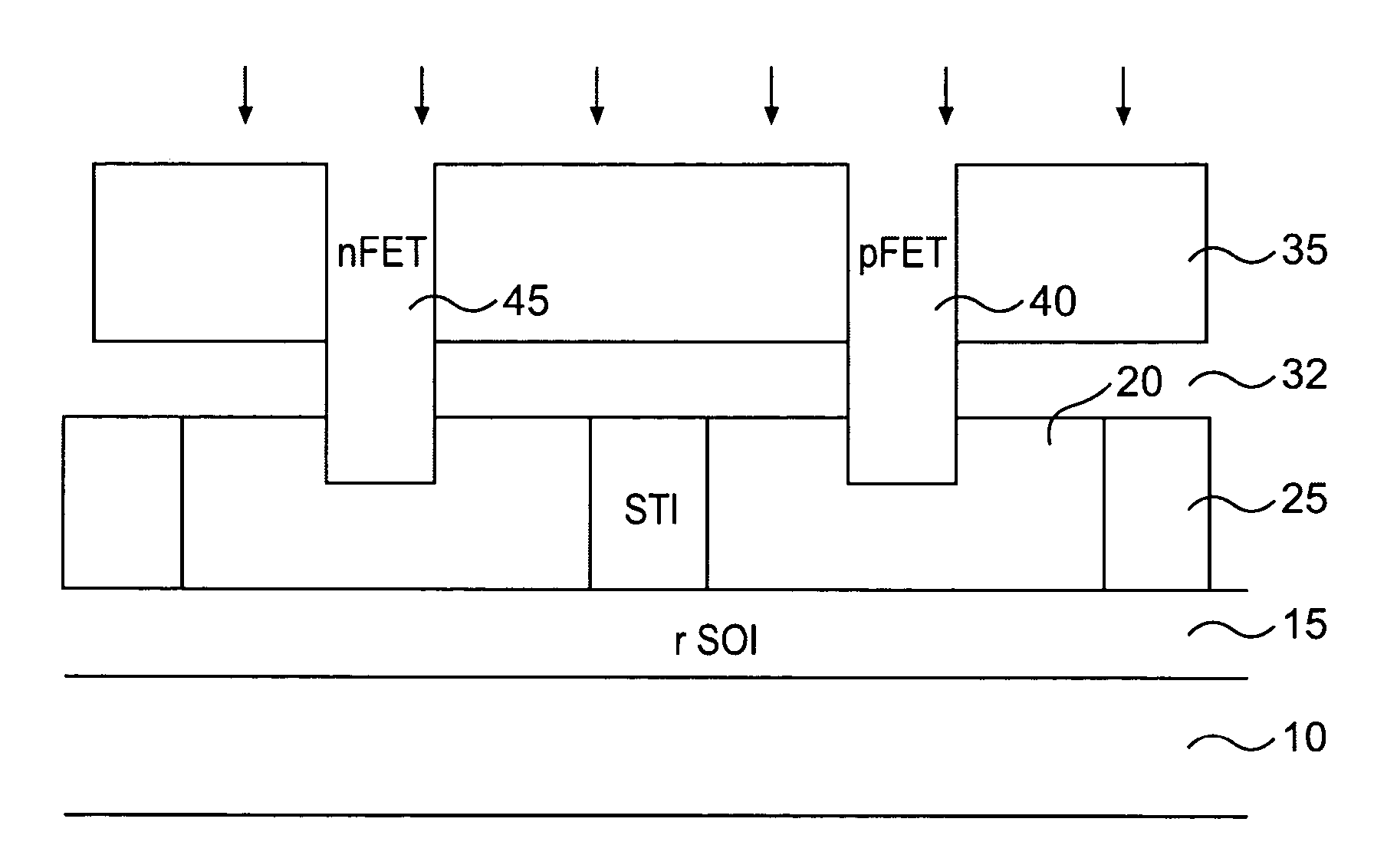

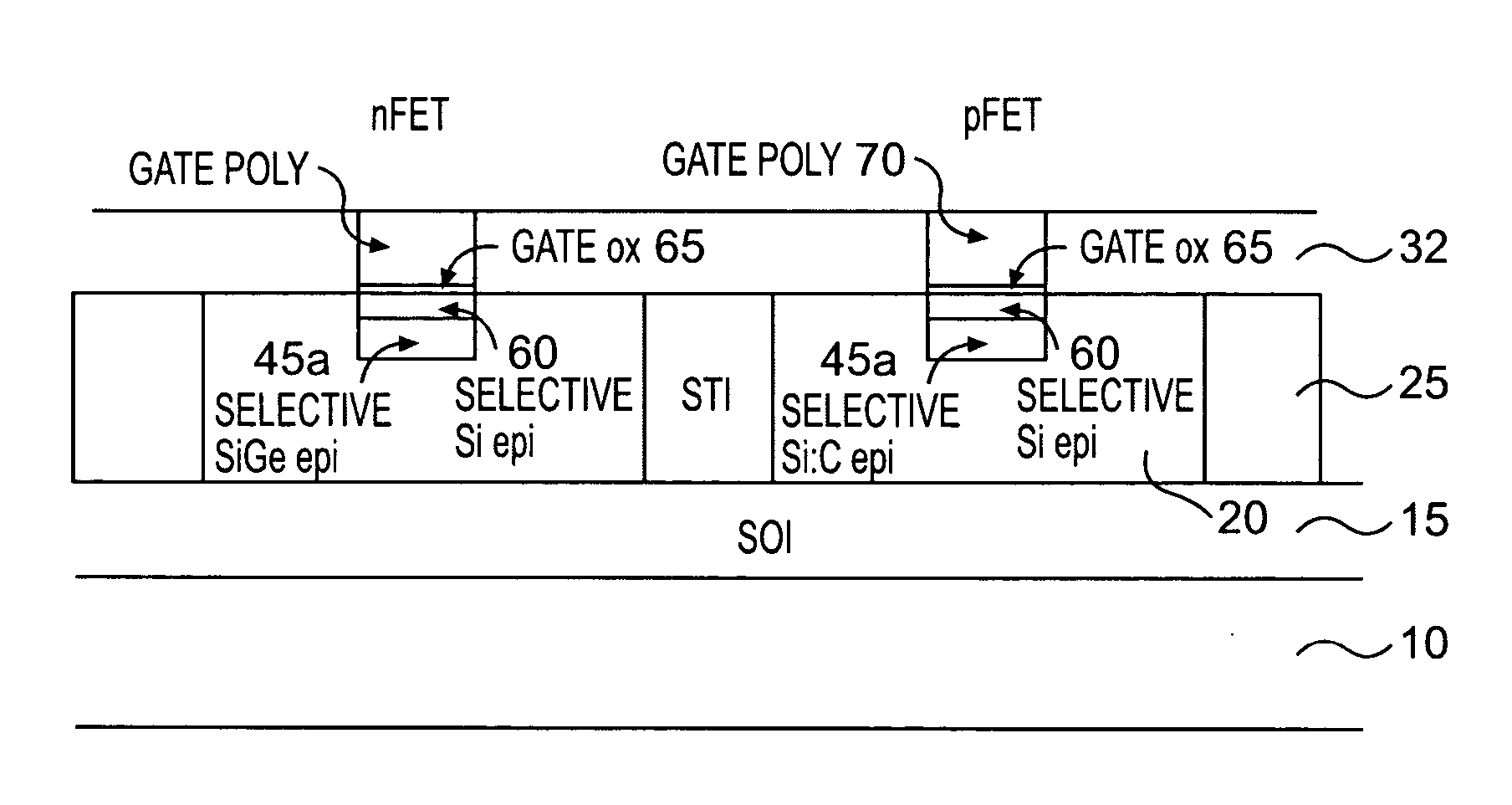

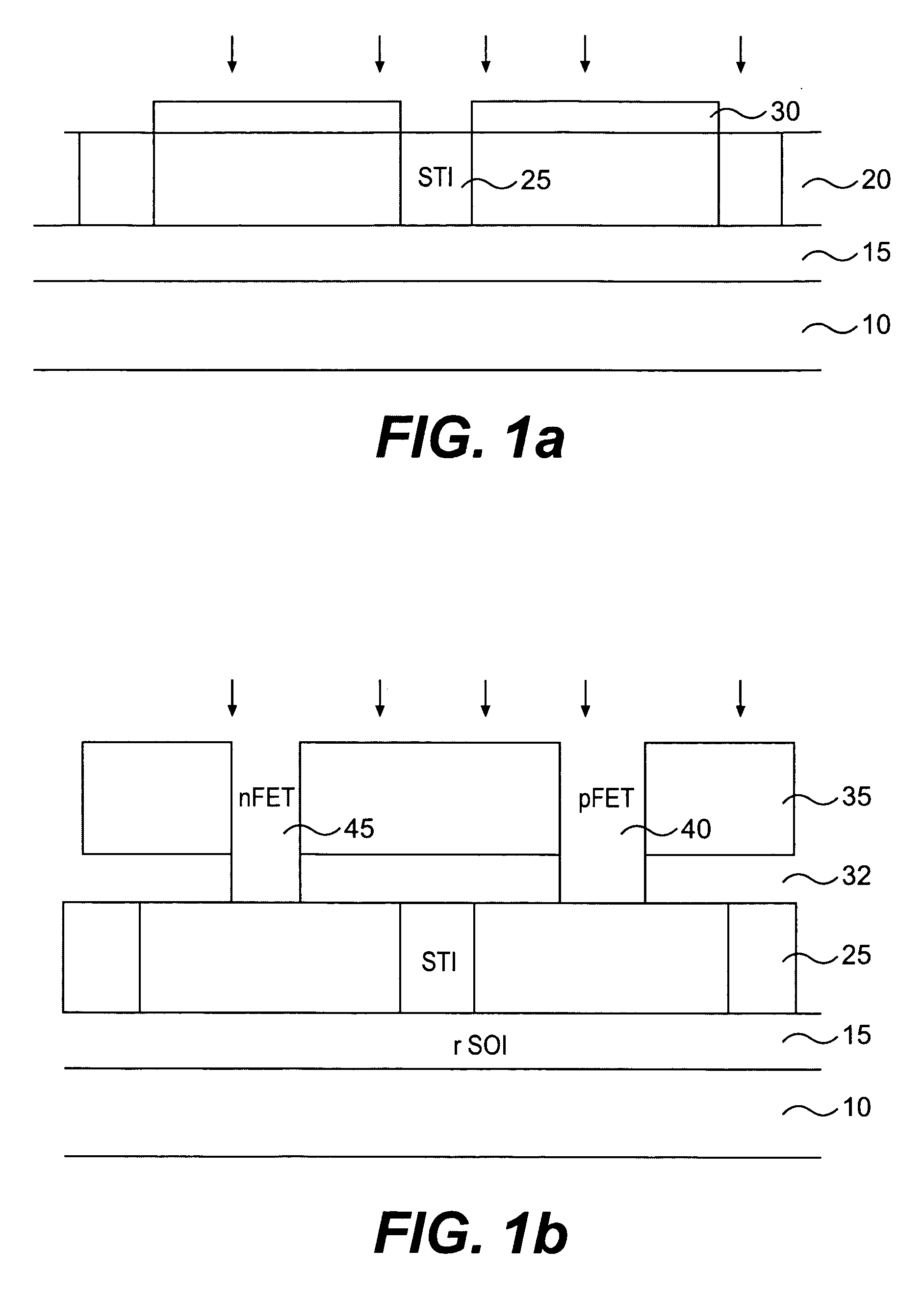

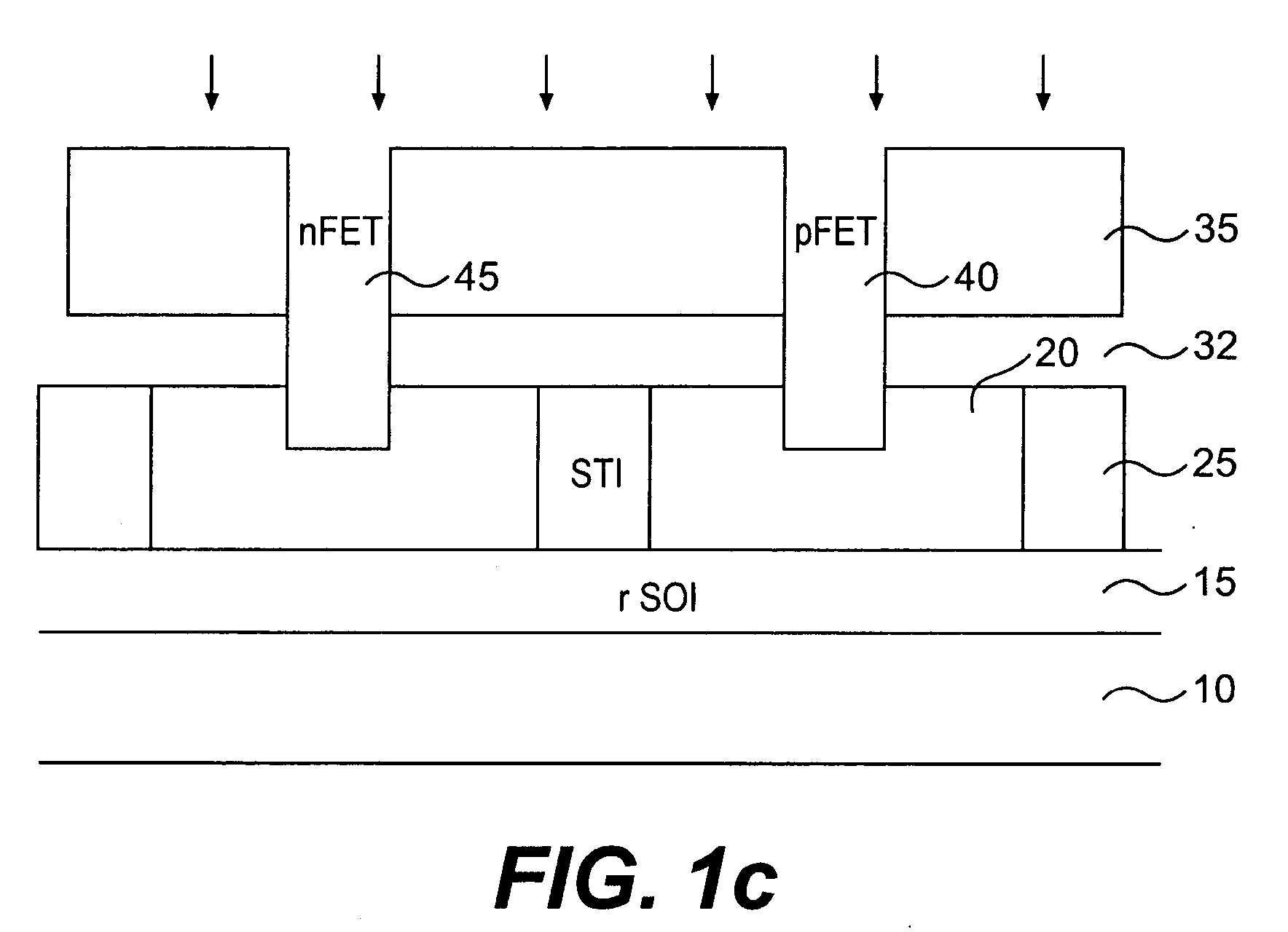

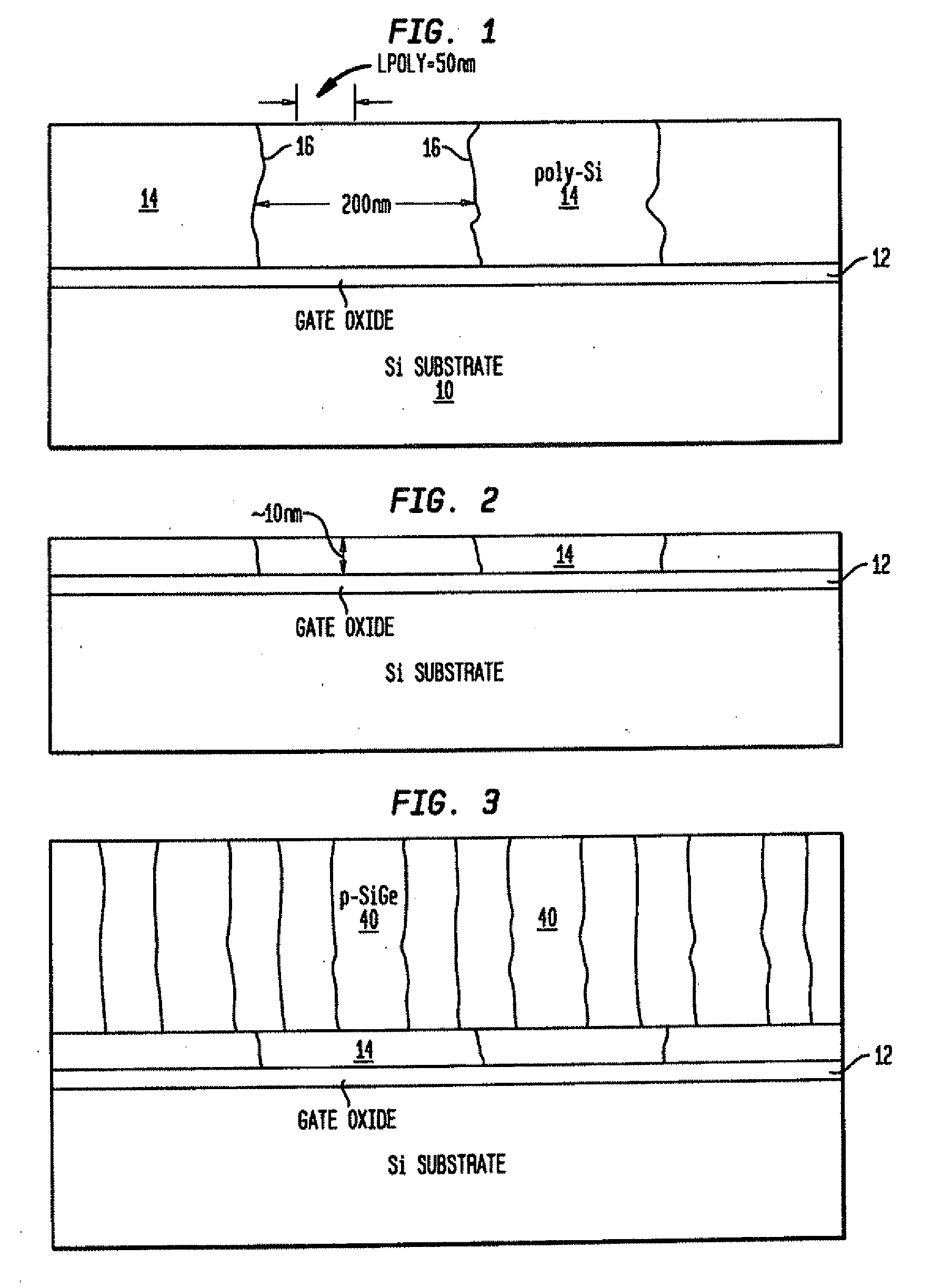

Method of manufacturing strained dislocation-free channels for CMOS

InactiveUS7037770B2Solid-state devicesSemiconductor/solid-state device manufacturingCMOSStress level

A semiconductor device and method of manufacturing a semiconductor device. The semiconductor device includes channels for a pFET and an nFET. An SiGe layer is grown in the channel of the nFET channel and a Si:C layer is grown in the pFET channel. The SiGe and Si:C layer match a lattice network of the underlying Si layer to create a stress component in an overlying grown epitaxial layer. In one implementation, this causes a compressive component in the pFET channel and a tensile component in the nFET channel. In a further implementation, the SiGe layer is grown in both the nFET and pFET channels. In this implementation, the stress level in the pFET channel should be greater than approximately 3 GPa.

Owner:INT BUSINESS MASCH CORP

Strained dislocation-free channels for CMOS and method of manufacture

InactiveUS20050085022A1Solid-state devicesSemiconductor/solid-state device manufacturingCMOSStress level

A semiconductor device and method of manufacturing a semiconductor device. The semiconductor device includes channels for a pFET and an NFET. An SiGe layer is grown in the channel of the NFET channel and a Si:C layer is grown in the pFET channel. The SiGe and Si:C layer match a lattice network of the underlying Si layer to create a stress component in an overlying grown epitaxial layer. In one implementation, this causes a compressive component in the pFET channel and a tensile component in the NFET channel. In a further implementation, the SiGe layer is grown in both the NFET and pFET channels. In this implementation, the stress level in the pFET channel should be greater than approximately 3 GPa.

Owner:IBM CORP

Strained dislocation-free channels for CMOS and method of manufacture

A semiconductor device and method of manufacturing a semiconductor device. The semiconductor device includes channels for a pFET and an nFET. An SiGe layer is grown in the channel of the nFET channel and a Si:C layer is grown in the pFET channel. The SiGe and Si:C layer match a lattice network of the underlying Si layer to create a stress component in an overlying grown epitaxial layer. In one implementation, this causes a compressive component in the pFET channel and a tensile component in the nFET channel. In a further implementation, the SiGe layer is grown in both the nFET and pFET channels. In this implementation, the stress level in the pFET channel should be greater than approximately 3 GPa.

Owner:IBM CORP

Germanium-doped directionally solidified casting monocrystalline silicon and preparation method thereof

InactiveCN101591808AHigh mechanical strengthReduce dislocation densityPolycrystalline material growthFrom frozen solutionsSolar cellDislocation free

The invention discloses germanium-doped directionally solidified casting monocrystalline silicon, which contains boron, gallium or phosphorus with the concentration of between 1*10 and 1*10 / cm and germanium with the concentration of between 1*10 and 5*10 / cm. The invention also discloses a preparation method for the germanium-doped directionally solidified casting monocrystalline silicon, which comprises the following steps: placing polycrystalline silicon, the germanium and an electroactive doping agent on a dislocation-free monocrystalline silicon block paved on the bottom of a crucible; completely melting the polycrystalline silicon, the germanium and the doping agent and partially melting the dislocation-free monocrystalline silicon block by thermal field regulation; and performing directional solidification by heat exchange, and using a part of unmelted dislocation-free momocrystalline silicon block as a seed crystal to induce to grow the germanium-doped casting monocrystalline silicon from bottom to top. The product has strong mechanical strength and long minority carrier lifetime, can be used for preparing a high efficiency wafer solar cell, and greatly reduces the production cost.

Owner:ZHEJIANG UNIV

Surface modified quartz glass crucible and its modification process

InactiveUS20030183161A1Raise the ratioHigh strengthAfter-treatment apparatusFrom gel stateCrucibleStrontium

A surface modified quartz glass crucible and a process for modifying the crucible includes a layer of a metal oxide on the whole or a part of the inside and / or outside of the crucible, and baking it. At least an inside surface of the crucible is coated with a said metal oxide of magnesium, calcium, strontium or barium. The coated layer of the crucible does not abrade easily and provides a high dislocation free ratio of silicon single crystals pulled by using the crucible.

Owner:JAPAN SUPER QUARTZ CORP

Method for preparing (110) float zone silicon crystal

ActiveCN101974779AMeet the requirements for preparing silicon materials for high-efficiency solar cellsMeeting Silicon Material Requirements for High Efficiency Solar CellsPolycrystalline material growthBy zone-melting liquidsSingle crystalEngineering

The invention discloses a method for preparing a (110) float zone silicon crystal. The key point of the technical scheme is that: 1, in the seeding technology, by controlling and adjusting the descending speed of a lower shaft and adjusting the power, the seeding neck diameter is controlled in a range from 2 to 6 mm, wherein the seeding neck diameter is more than or equal to 1.5 times the diameter of a single crystal; 2, in the shouldering technology, by controlling and adjusting the descending speed and rotating speed of the lower shaft and the descending speed and rotating speed of an upper shaft and adjusting the power, the shouldering angle is 50+ / -5 degrees; and 3, in the ending technology, the ending length is more than 1.2 times the diameter of the single crystal, and the minimum tail diameter is less than or equal to 5mm. The method overcomes the defects that the (110) silicon single crystal prepared by the conventional direct pulling method has high impurity content and cannot meet the requirement on the silicon single crystal of a high-efficiency solar cell, and successfully prepares a low-impurity content and long-service life (110) dislocation-free float zone silicon crystal by a floating zone method, wherein the (110) float zone silicon crystal has the dislocation density of less than or equal to 500 units / cm<2> and the minority carrier lifetime of more than or equal to 300us, and meets the requirement of a silicon material for preparing the high-efficiency solar cell.

Owner:ZHONGHUAN ADVANCED SEMICON MATERIALS CO LTD +1

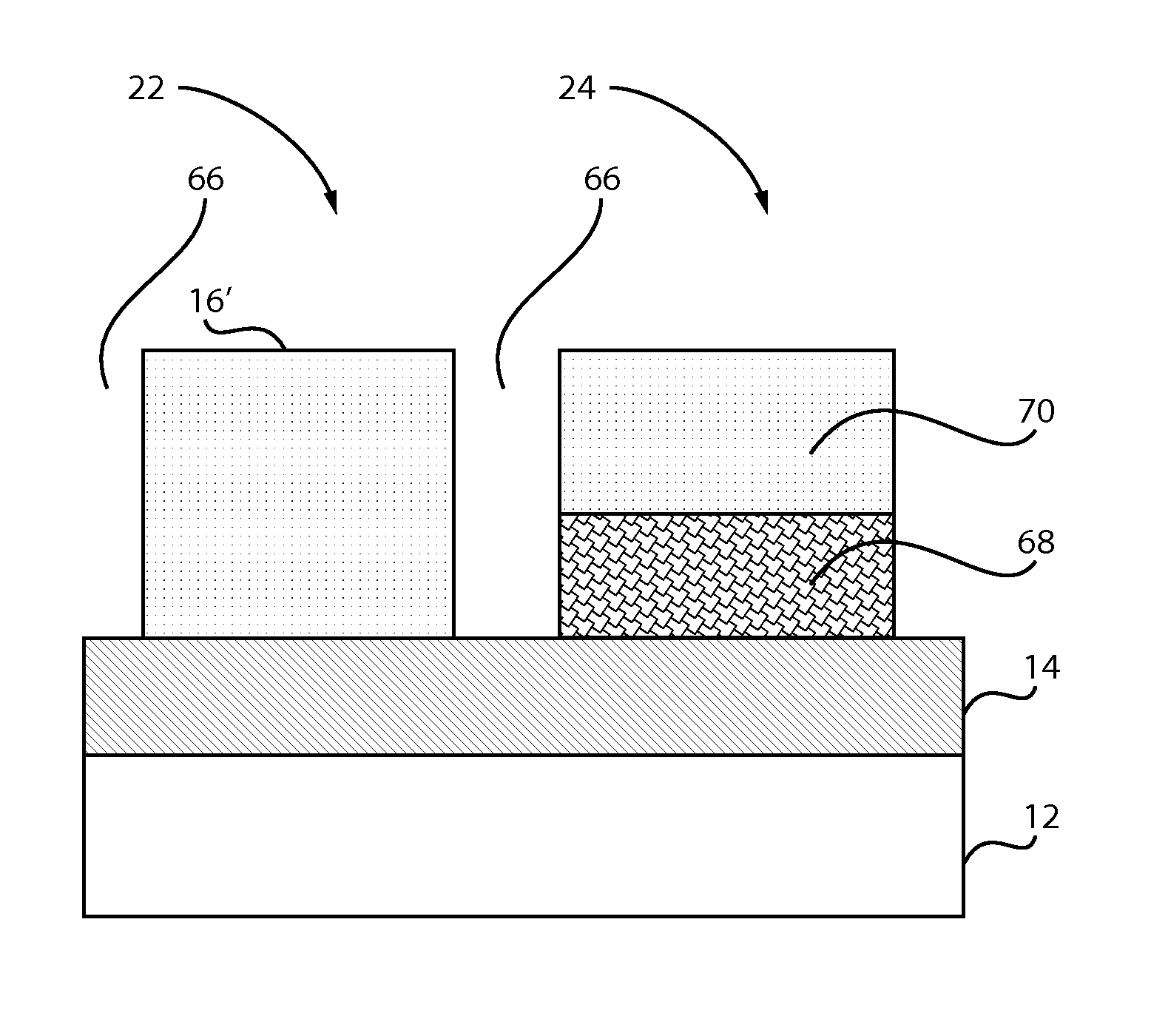

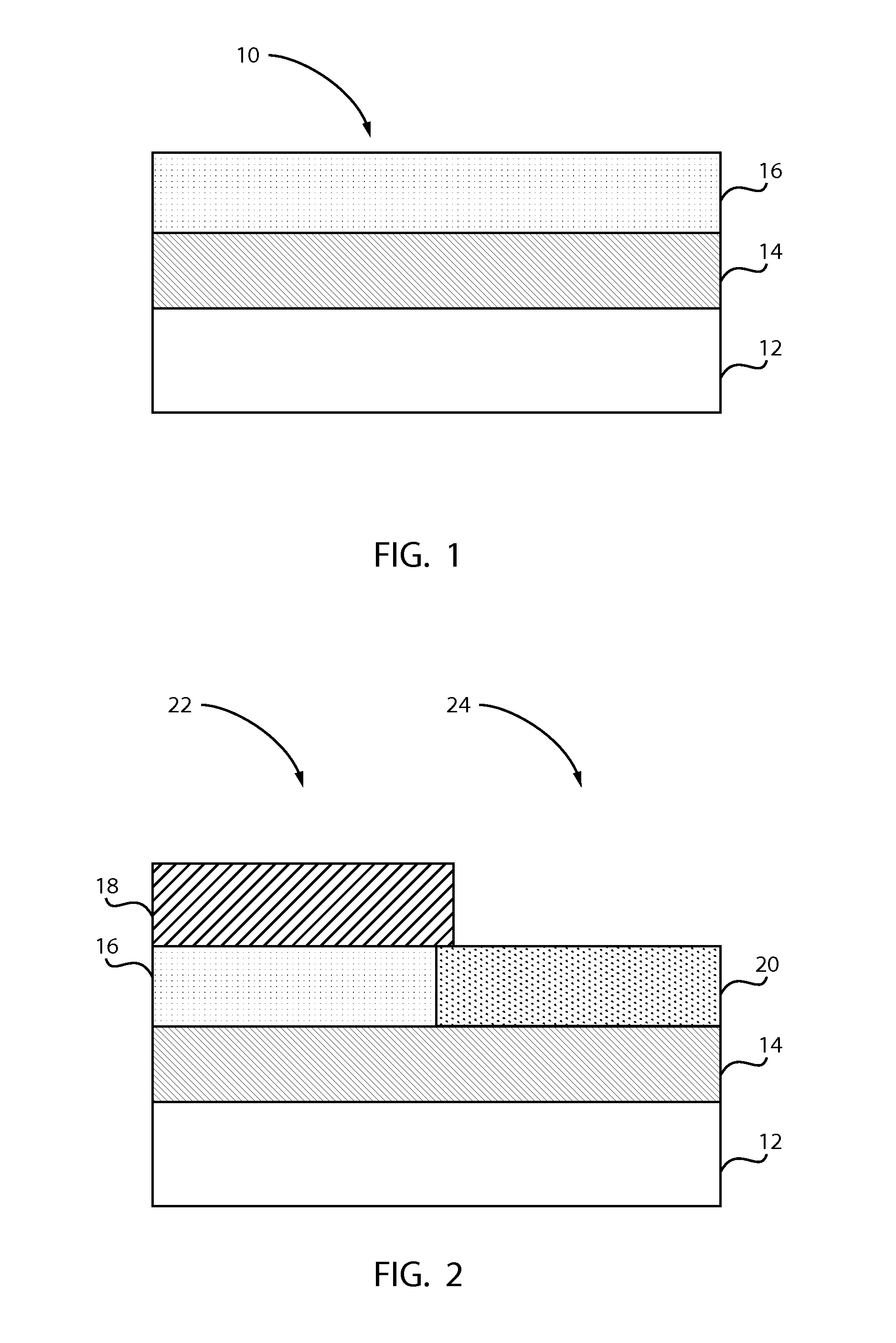

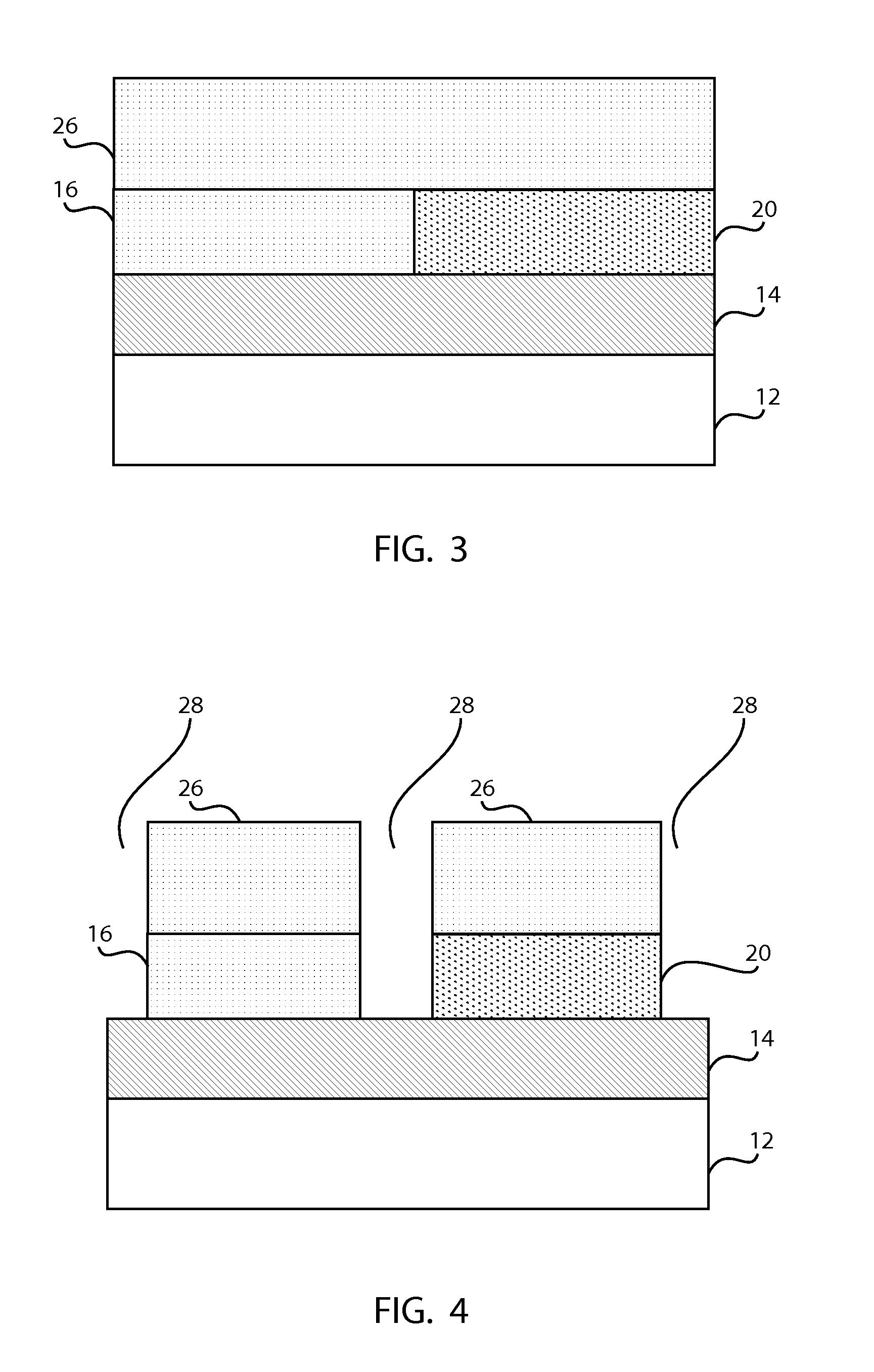

STRUCTURES AND METHODS FOR MANUFACTURING OF DISLOCATION FREE STRESSED CHANNELS IN BULK SILICON AND SOI MOS DEVICES BY GATE STRESS ENGINEERING WITH SiGe AND/OR Si:C

InactiveUS20080064197A1Avoid misalignmentReduce generationSolid-state devicesSemiconductor/solid-state device manufacturingCMOSGate dielectric

Structures and methods of manufacturing are disclosed of dislocation free stressed channels in bulk silicon and SOI (silicon on insulator) CMOS (complementary metal oxide semiconductor) devices by gate stress engineering with SiGe and / or Si:C. A CMOS device comprises a substrate of either bulk Si or SOI, a gate dielectric layer over the substrate, and a stacked gate structure of SiGe and / or Si:C having stresses produced at the interfaces of SSi(strained Si) / SiGe or SSi / Si:C in the stacked gate structure. The stacked gate structure has a first stressed film layer of large grain size Si or SiGe over the gate dielectric layer, a second stressed film layer of strained SiGe or strained Si:C over the first stressed film layer, and a semiconductor or conductor such as p(poly)-Si over the second stressed film layer.

Owner:GLOBALFOUNDRIES INC

Method for producing dislocation-free strained crystalline films

A method for forming dislocation-free strained silicon thin film includes the step of providing two curved silicon substrates. One substrate is curved by the presence of silicon dioxide on a back surface. The other substrate is curved by the presence of a silicon nitride layer. One of the substrates is subject to hydrogen implantation and the two substrates are bonded to one another in an annealing process. The two substrates are separated, thereby leaving a layer of strained silicon on a front side of one of the substrates. A back side layer of silicon dioxide or silicon nitride is then removed to restore the substrate to a substantially planar state. The method may be employed to form dislocation-free strained silicon thin films. The films may be under tensile or compressive strain.

Owner:RGT UNIV OF CALIFORNIA

Dislocation-free silicon monocrystal production method

ActiveCN1995485AMeet needsAchieve productionAfter-treatment apparatusPolycrystalline material growthGraphiteSingle crystal

The invention discloses a crystal drawing technique of silicon monocrystal in the semiconductor and solar photoelectric devices < and110> and making method of non-dislocation monocrystal and modification in the graphite heat system, which comprises the following steps: (1) introducing crystal with diameter not less than 5mm; setting the narrowing or widening rate at 100% and crystal drawing speed not less than 5mm / min and crystal drawing length at 150-300mm; (2) setting the shouldering speed at 0.2-1. 5mm / min; (3) making the heat drawing speed of monocrystal at 1. 0-3. 0mm / min and end drawing speed at 0.5-2. 0mm / min in the miter technique; (4) epilog.

Owner:内蒙古中环领先半导体材料有限公司 +1

Method for production of dislocation-free silicon single crystal

InactiveUS6080237APolycrystalline material growthSemiconductor/solid-state device manufacturingCzochralski methodDislocation free

This invention is directed to a method for the production of a dislocation-free silicon single crystal by the Czochralski method. This method attains growth of the main body part of the dislocation-free silicon single crystal by immersing a seed crystal in a melt of silicon and then pulling the seed crystal without recourse to the necking. The seed crystal thus used is a dislocation-free silicon single crystal. The horizontal maximum length of the part of the seed crystal being immersed in the melt at the time of completing the immersion of the seed crystal in the melt is not less than 5 mm. The immersing rate of the seed crystal in the melt is not more than 2.8 mm / min and the part of the seed crystal to be immersed in the melt is a crystal as grown.

Owner:WACKER NSCE CORP

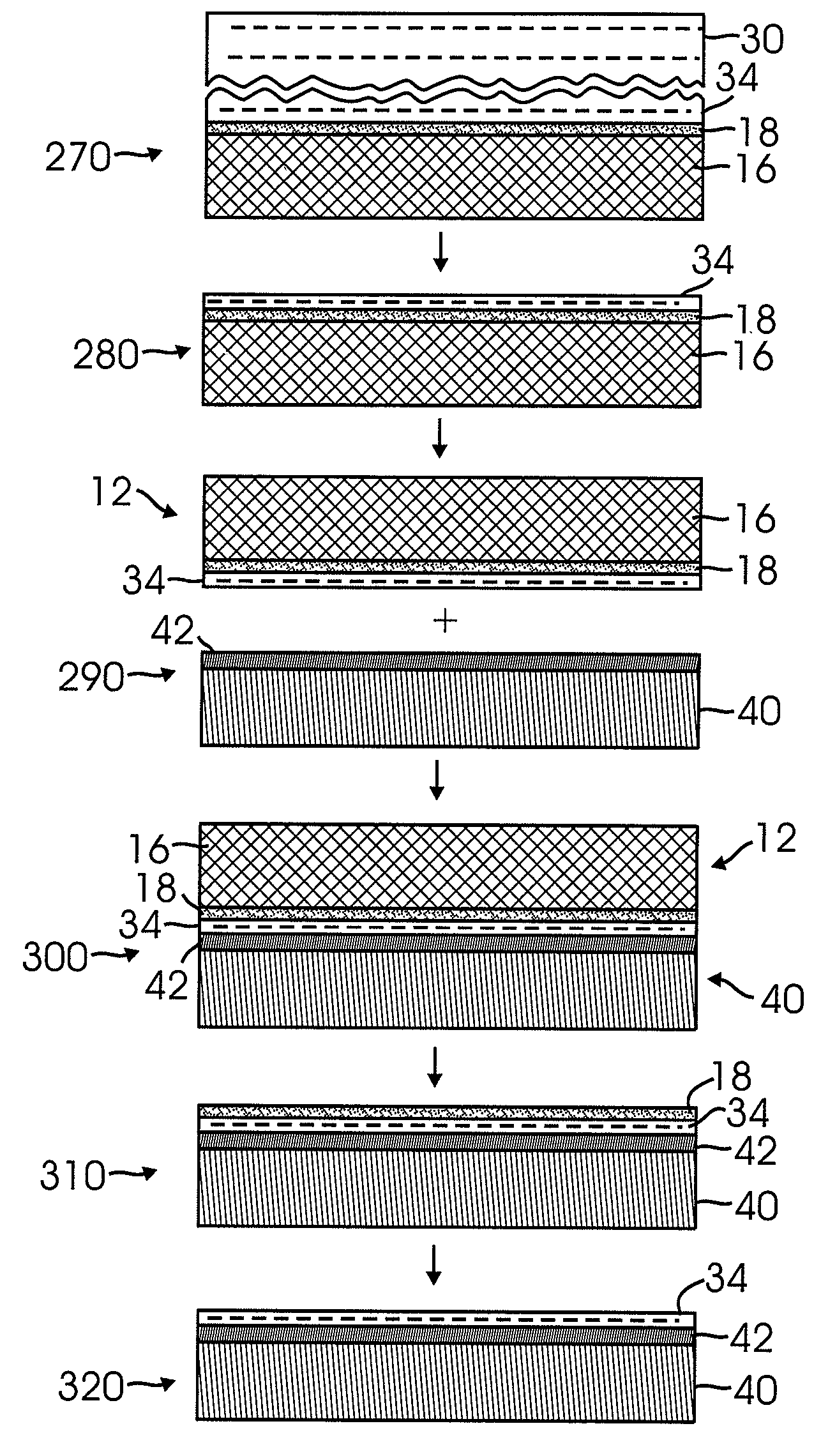

Method for fabricating dislocation-free stressed thin films

A method of forming a stressed thin film on a substrate includes the steps of depositing a thin film of silicon on a first substrate and transforming the first substrate into a porous substrate. The porous substrate containing the thin film of silicon is then transformed into a stressed state such that at least a portion of the stress is transferred to the thin film. The thin film may be under compressive stress or tensile stress. For example, volumetric expansion of the porous substrate imparts tensile stress to the thin film while volumetric contraction of the porous substrate imparts compressive stress to the thin film. The porous substrate containing the stressed thin film of silicon is then bonded to a second substrate. The porous substrate is removed so as to deposit the stressed thin film of silicon to the second substrate.

Owner:RGT UNIV OF CALIFORNIA

Porous silicon relaxation medium for dislocation free CMOS devices

A method for forming CMOS devices includes masking a first portion of a tensile-strained silicon layer of a SOI substrate, doping a second portion of the layer outside the first portion and growing an undoped silicon layer on the doped portion and the first portion. The undoped silicon layer becomes tensile-strained. Strain in the undoped silicon layer over the doped portion is relaxed by converting the doped portion to a porous silicon to form a relaxed silicon layer. The porous silicon is converted to an oxide. A SiGe layer is grown and oxidized to convert the relaxed silicon layer to a compressed SiGe layer. Fins are etched in the first portion from the tensile-strained silicon layer and the undoped silicon layer and in the second portion from the compressed SiGe layer.

Owner:ELPIS TECH INC

Threading-dislocation-free nanoheteroepitaxy of Ge on Si using self-directed touch-down of Ge through a thin SiO2 layer

ActiveUS7579263B2Polycrystalline material growthSolid-state devicesThreading dislocationsDirect touch

A method of forming a virtually defect free lattice mismatched nanoheteroepitaxial layer is disclosed. The method includes forming an interface layer on a portion of a substrate. A plurality of seed pads are then formed by self-directed touchdown by exposing the interface layer to a material comprising a semiconductor material. The plurality of seed pads, having an average width of about 1 nm to 10 nm, are interspersed within the interface layer and contact the substrate. An epitaxial layer is then formed by lateral growth of the seed pads over the interface layer.

Owner:STC UNM

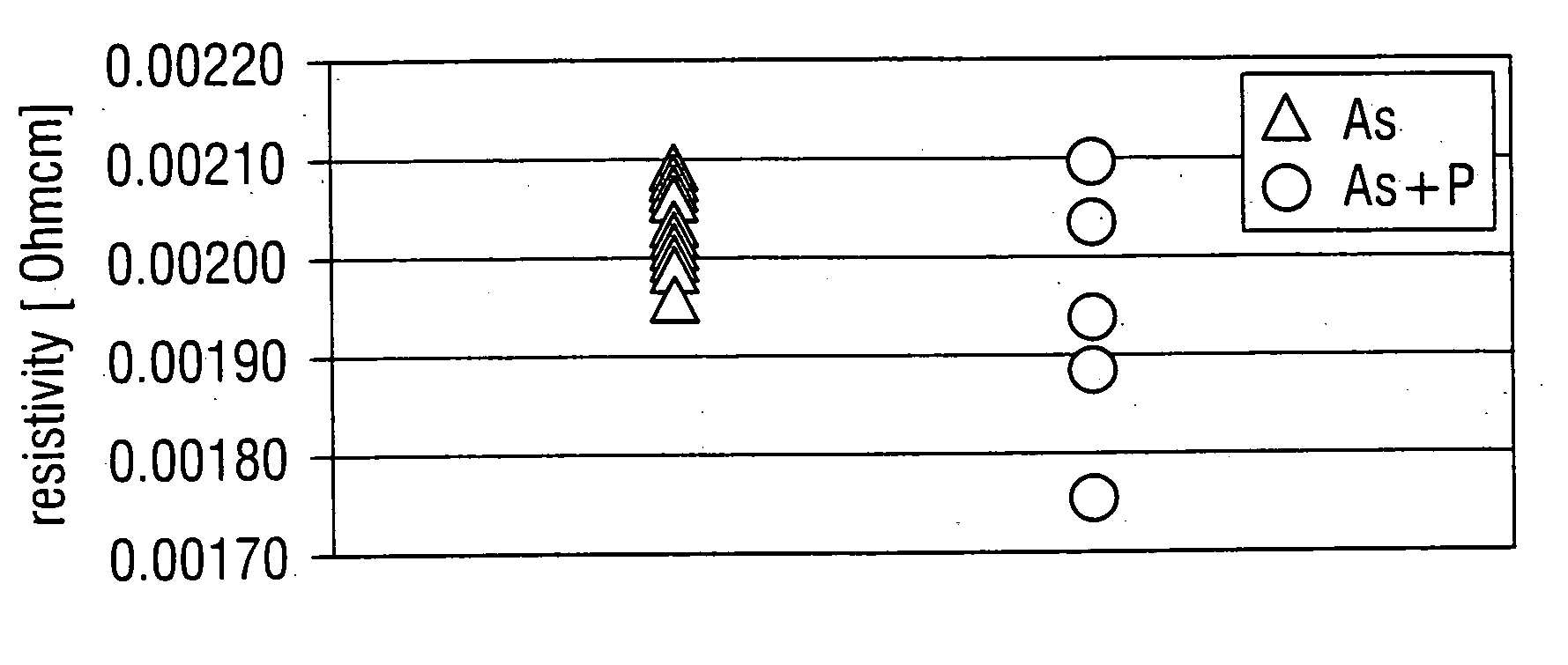

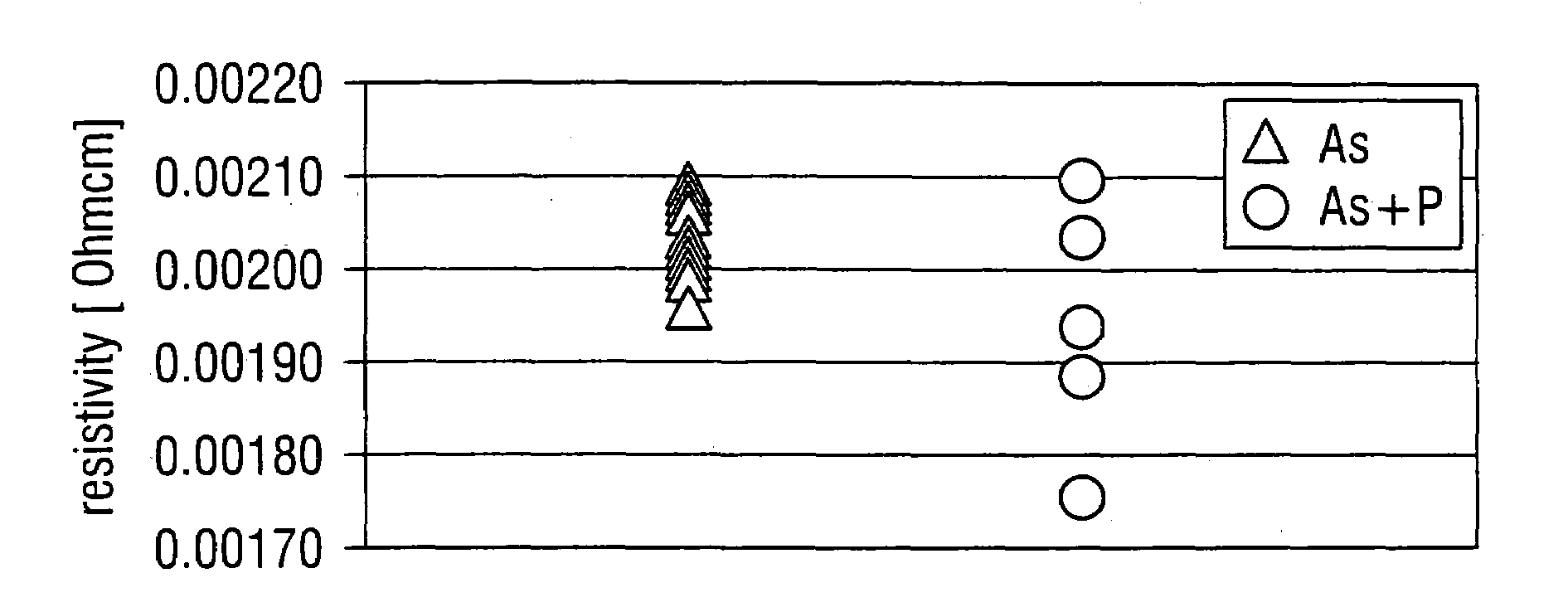

Process for producing highly doped semiconductor wafers, and dislocation-free highly doped semiconductor wafers

InactiveUS20050167001A1Easy to manufactureImprove propertiesPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantDislocation free

The invention relates to a process for producing highly doped semiconductor wafers, in which at least two dopants which are electrically active and belong to the same group of the periodic system of the elements are used for the doping. The invention also relates to a semiconductor wafer which is free of dislocations and is doped with at least two electrically active dopants which belong to the same group of the periodic system of the elements.

Owner:SILTRONIC AG

Nitrogen-doped directionally solidified casting monocrystalline silicon and preparation method thereof

InactiveCN101591807AOvercome the disadvantage of low mechanical strengthReduce manufacturing costPolycrystalline material growthFrom frozen solutionsNitrogen gasSolar cell

The invention discloses nitrogen-doped directionally solidified casting monocrystalline silicon, which contains boron, gallium and phosphorus with the concentration of between 1*10 and 1*10 / cm and nitrogen with the concentration of between 1*10 and 5*10 / cm. The invention also discloses a preparation method for the nitrogen-doped directionally solidified casting monocrystalline silicon, which comprises the following steps: using cheap nitrogen to replace expensive argon to be taken as protective gas; and taking partial unmelted dislocation-free monocrystalline silicon blocks as a seed crystal to perform directional solidification and casting on the monocrystalline silicon. The preparation method reduces the production cost of the monocrystalline silicon and improves the mechanical strength of the monocrystalline silicon. A casting monocrystalline silicon product obtained by the method has high mechanical strength, can be used for preparing a high-efficiency wafer solar cell, and greatly reduces the production cost.

Owner:ZHEJIANG UNIV

Structures and methods for manufacturing of dislocation free stressed channels in bulk silicon and SOI CMOS devices by gate stress engineering with SiGe and/or Si:C

InactiveUS7476580B2Low mobilityReduce generationSolid-state devicesSemiconductor/solid-state device manufacturingSoi cmosCMOS

Structures and methods of manufacturing are disclosed of dislocation free stressed channels in bulk silicon and SOI (silicon on insulator) CMOS (complementary metal oxide semiconductor) devices by gate stress engineering with SiGe and / or Si:C. A CMOS device comprises a substrate of either bulk Si or SOI, a gate dielectric layer over the substrate, and a stacked gate structure of SiGe and / or Si:C having stresses produced at the interfaces of SSi(strained Si) / SiGe or SSi / Si:C in the stacked gate structure. The stacked gate structure has a first stressed film layer of large grain size Si or SiGe over the gate dielectric layer, a second stressed film layer of strained SiGe or strained Si:C over the first stressed film layer, and a semiconductor or conductor such as p(poly)-Si over the second stressed film layer.

Owner:GLOBALFOUNDRIES INC

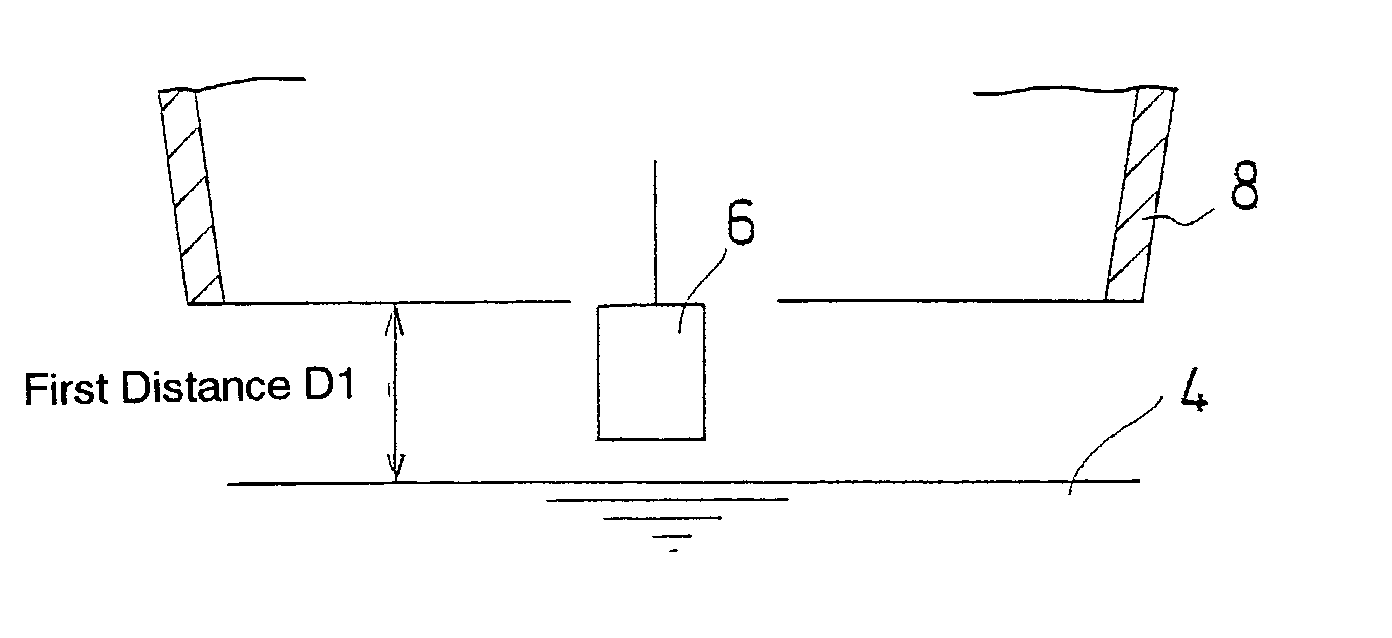

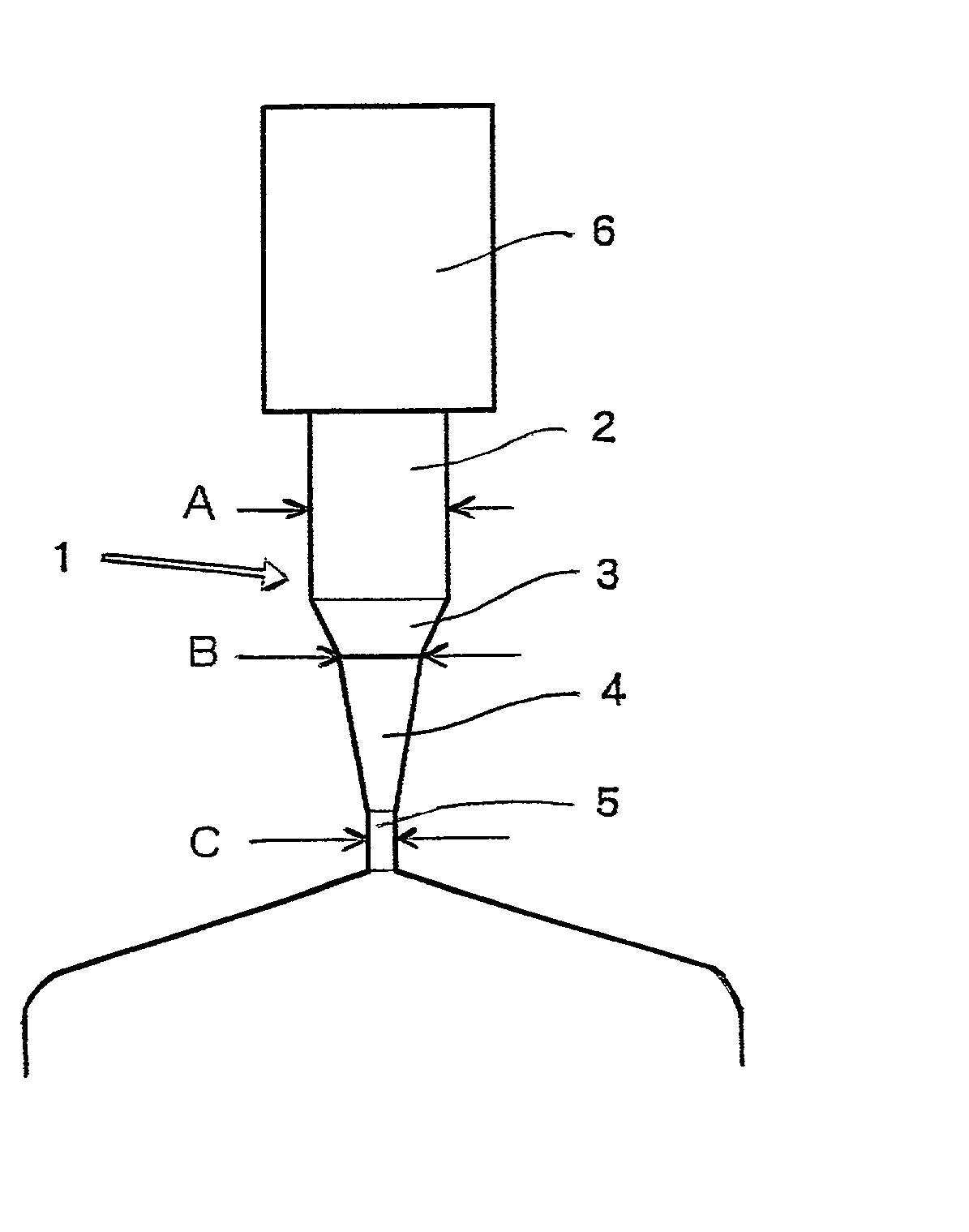

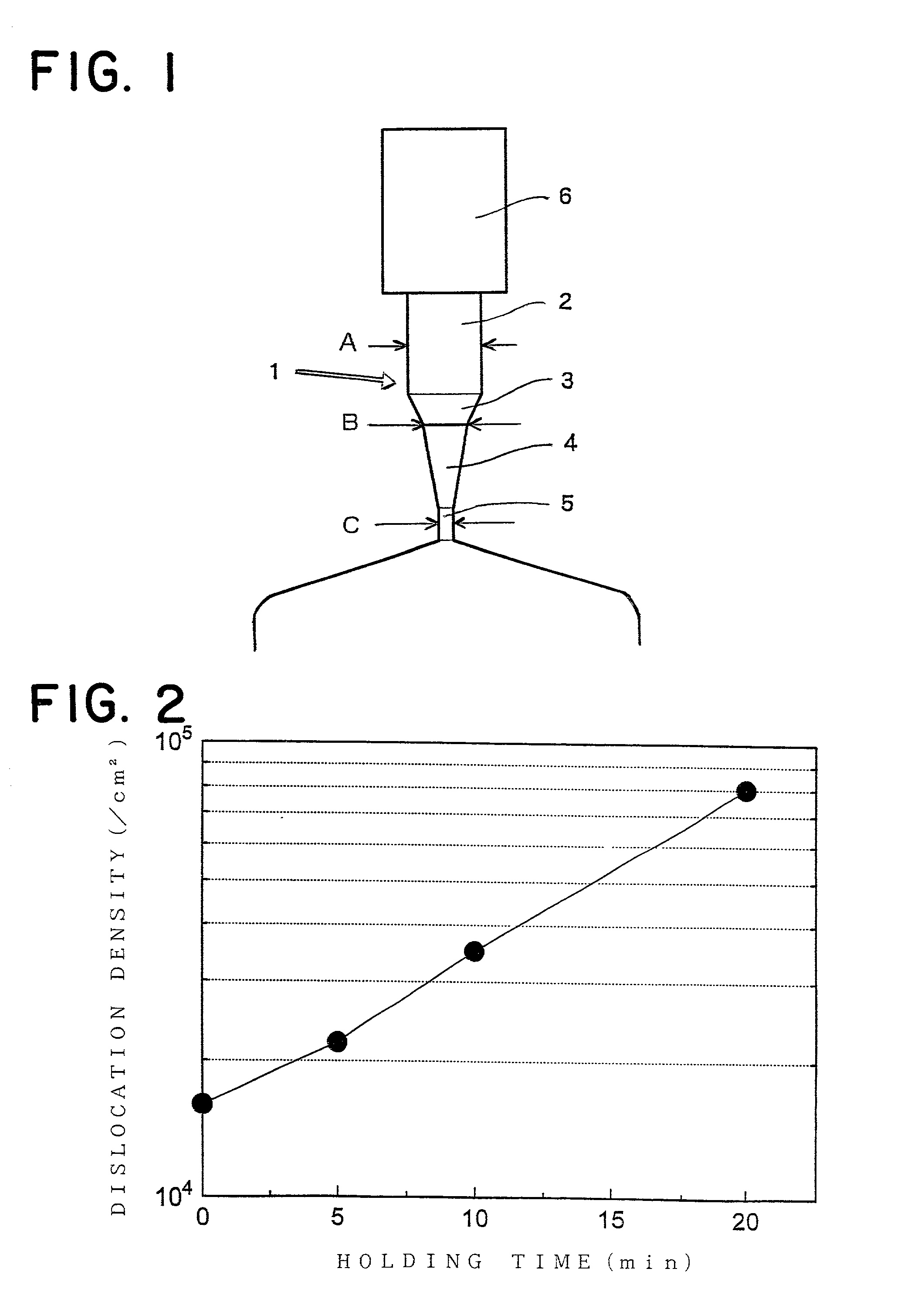

Method for pulling single crystal

A method capable of securely pulling up a heavy single crystal is described. Using an apparatus comprising a crucible for storing a molten material for a single crystal; a heater for heating the molten material; means for pulling up the single crystal to grow by bringing a seed crystal in contact with the surface of the molten material in the crucible; and a flow-regulating member surrounding the single crystal at the growth area for shielding the heat of radiation and for regulating inert gas flow, the method comprises the following steps of: setting the distance between the lower end of the flow-regulating member and the surface of the molten material to be a first distance D1 when the seed crystal comes into contact with the surface of the molten material in said crucible; forming the single crystal at the neck portion; thereafter setting the distance between the lower end of the flow-regulating member and the surface of the molten material to be a second distance D2 where D1 (mm)>D2 (mm); and forming the single crystal at the shoulder portion and subsequently forming the single crystal at the body portion. A dislocation-free single crystal having a heavy weight can be produced with a high crystal quality, and the method is applicable to various operation modes at which the apparatus is operated under various conditions of crystal growth.

Owner:SUMITOMO MITSUBISHI SILICON CORP

Method of producing a silicon monocrystal

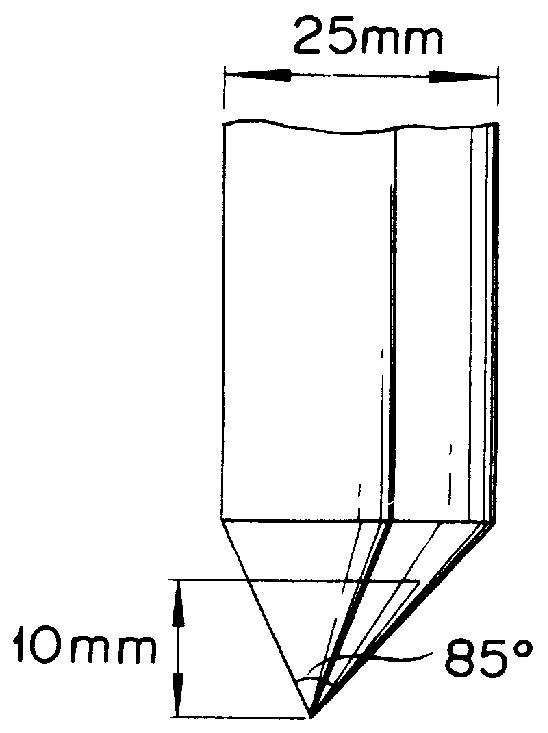

InactiveUS20020000187A1Thermal shock is decreasedImprove productivityPolycrystalline material growthBy pulling from meltNeck partsIngot

There is disclosed a method of producing a silicon monocrystal which comprises preparing a silicon seed crystal having a sharp tip end, and melting down a part of the silicon seed crystal from a tip end to a position having a predetermined thickness, followed by performing a necking operation to form a tapered necking part and a neck portion, and subsequently pulling a monocrystal ingot after increasing a diameter, wherein said part to be melted down is a part from a tip end to a position in which a thickness is twice as large as the diameter of the neck portion to be formed or more; said necking operation is performed in such a way that a tapered necking part is formed at an early stage by pulling a crystal with gradually decreasing the diameter to a minimum diameter of 5 mm or more, and then a neck portion is formed, subsequently the monocrystal ingot is pulled with increasing a diameter. There can be provided a method of producing a silicon monocrystal ingot which enables growing of monocrystal ingot without lowering rate of success in making a crystal dislocation free in the case that a thick neck is formed, and thereby improves productivity of a heavy silicon monocrystal having a large diameter.

Owner:SHIN-ETSU HANDOTAI CO LTD

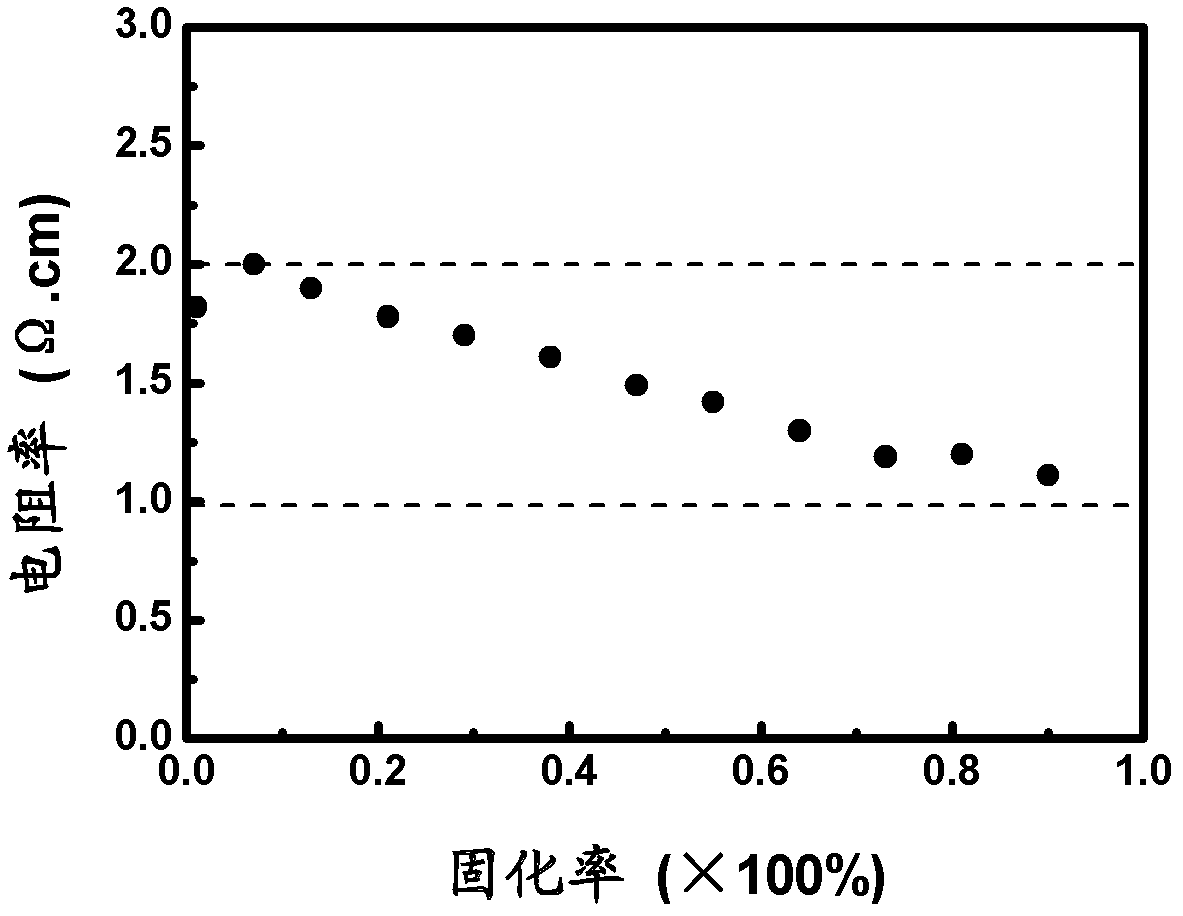

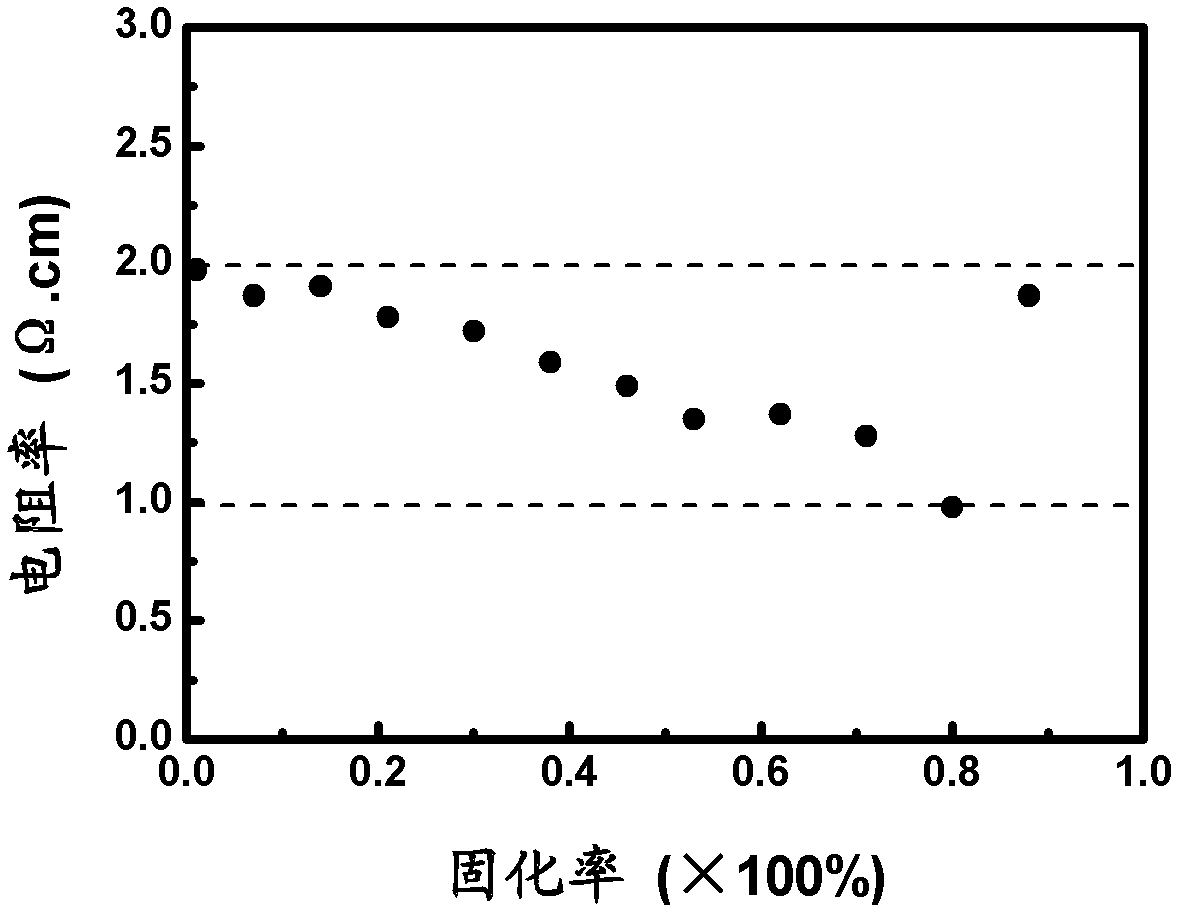

N-type casting monocrystalline silicon with uniform doping resistivity and preparation method thereof

ActiveCN102560646AIncrease profitReduce manufacturing costPolycrystalline material growthFrom frozen solutionsPhotovoltaic industrySingle crystal

The invention discloses an N-type casting monocrystalline silicon with a uniform doping resistivity and a preparation method thereof. The preparation method comprises the following steps of: paving dislocation-free materials of monocrystalline silicon blocks at the bottom of a crucible; then placing a polycrystalline silicon material, a phosphorus doping agent and gallium into the crucible; raising temperature and fusing the monocrystalline silicon material, the phosphorus doping agent, the gallium and a part of materials of monocrystalline silicon blocks close to the polycrystalline silicon; and growing a monocrystalline silicon body by using a casting method. According to the monocrystalline silicon with the uniform doping resistivity, the resistivity of about 90% N-type phosphorus doping phosphorus doping cast ingots can be controlled in the range of 1.0-2.0 omega.cm, therefore, the utilization rate of the N-type monocrystalline silicon in the process of manufacturing a solar cell is effectively improved, the manufacturing cost of the solar cell is remarkably lowered, the preparation method is simple to operate and easy to popularize and use in the photovoltaic industry.

Owner:ZHEJIANG UNIV

Process for producing highly doped semiconductor wafers, and dislocation-free highly doped semiconductor wafers

InactiveUS7341787B2Easy to manufactureImprove propertiesPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantDislocation free

The invention relates to a process for producing highly doped semiconductor wafers, in which at least two dopants which are electrically active and belong to the same group of the periodic system of the elements are used for the doping. The invention also relates to a semiconductor wafer which is free of dislocations and is doped with at least two electrically active dopants which belong to the same group of the periodic system of the elements.

Owner:SILTRONIC AG

Method for preparing crystallization rate of monocrystal silicon 110

InactiveCN102168303AGuaranteed normal growthGuaranteed YieldPolycrystalline material growthBy pulling from meltCrystal orientationDislocation free

The invention relates to a method for preparing the crystallization rate of crystal orientation monocrystal silicon (110), which is characterized in that: a seed crystal of which the crystal orientation deviates an angle of X from the (110) direction is cut by adopting a monocrystal (110) or (100); and the seed crystal is subjected to seeding, and the seeding length is kept by more than 12 centimeters, wherein the X is between 1 and 9 degrees. In the method, a crystal axis of the seed crystal (110) deviates an angle X from the growth direction, dislocation can be discharged completely in the seeding process, and the led crystal with the crystal orientation (110) can grow in a dislocation-free mode, so the crystallization rate can be improved, and the yield can be ensured.

Owner:浙江晨方光电科技有限公司

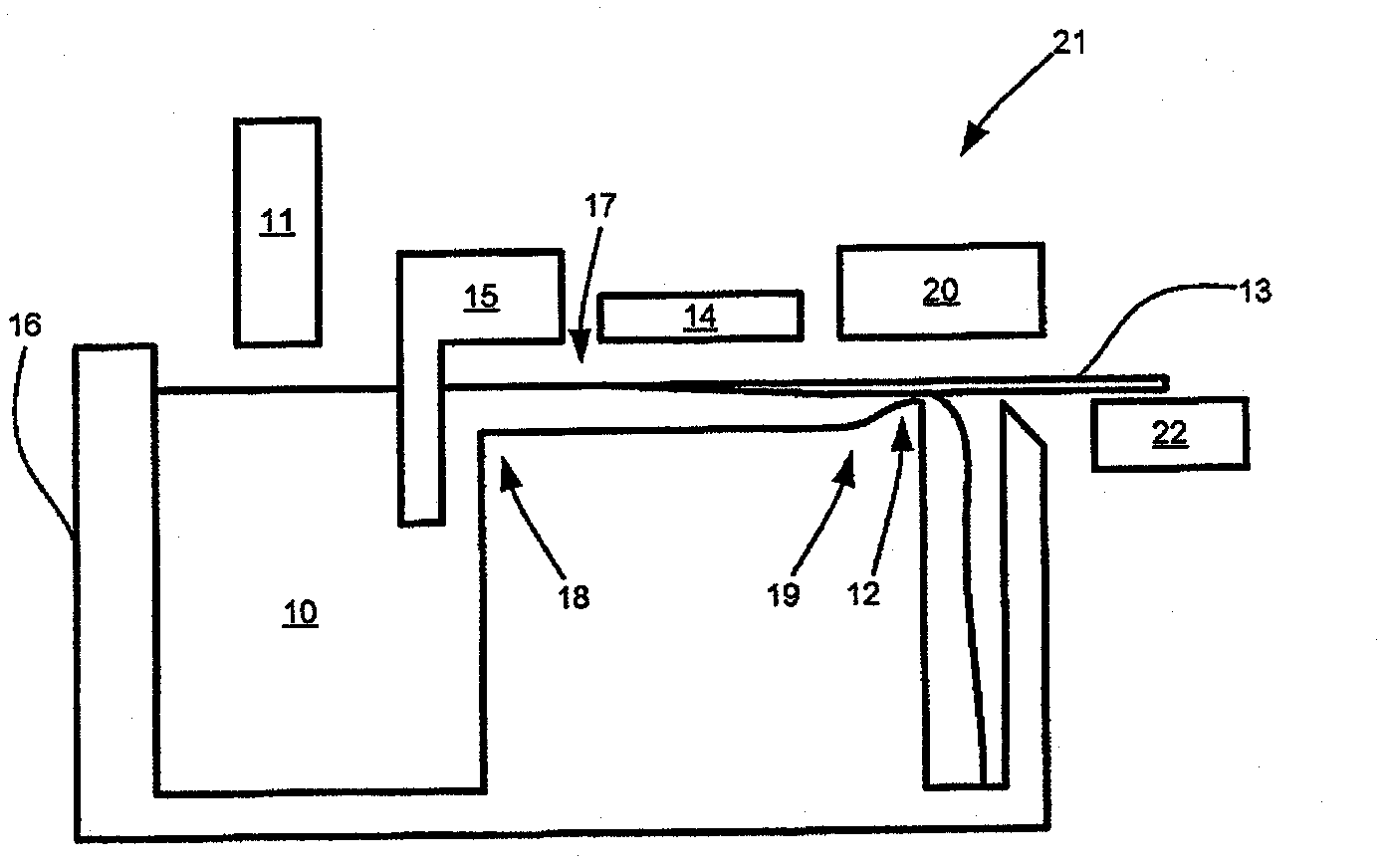

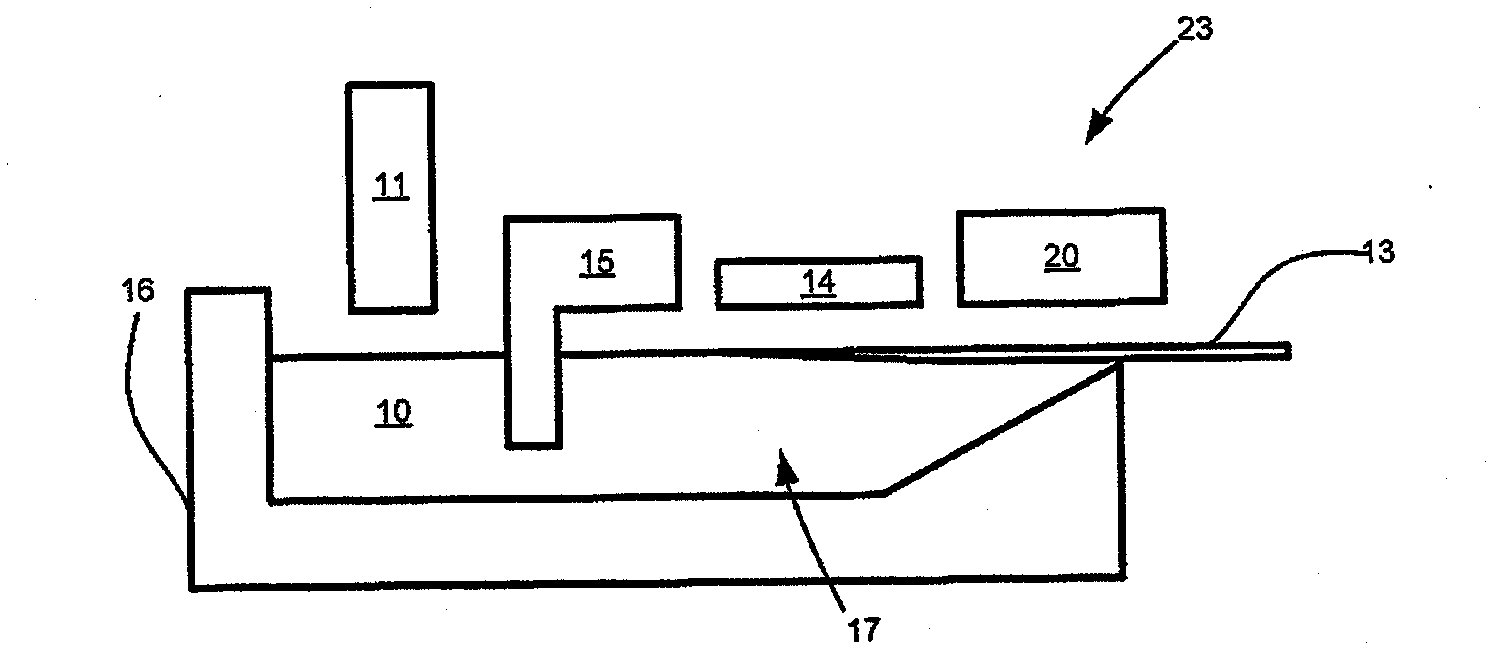

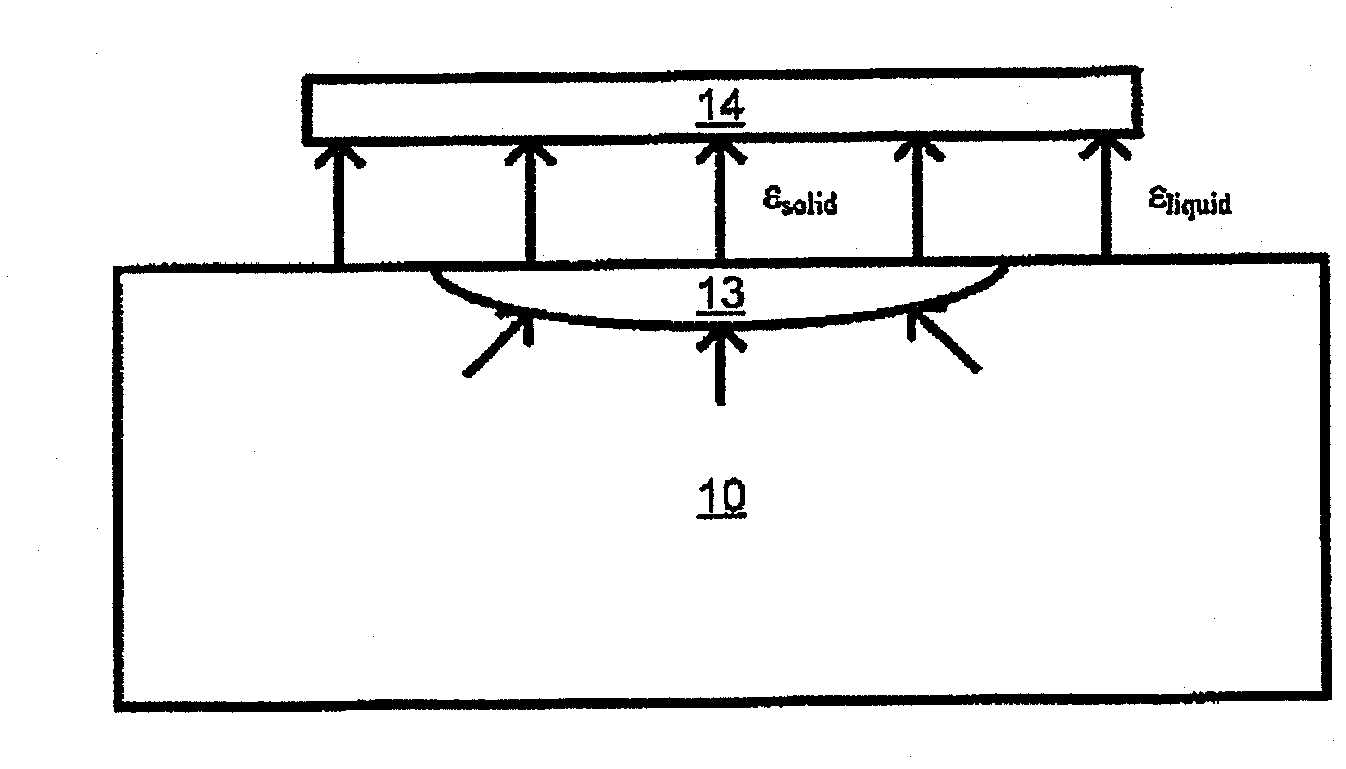

Method and apparatus for producing a dislocation-free crystalline sheet

ActiveCN102113095APolycrystalline material growthSemiconductor/solid-state device manufacturingEngineeringDislocation free

A dislocation-free sheet may be formed from a melt. A sheet of material with a first width is formed on a melt of the material using a cooling plate. This sheet has dislocations. The sheet is transported with respect to the cooling plate and the dislocations migrate to an edge of the sheet. The first width of the sheet is increased to a second width by the cooling plate. The sheet does not have dislocations at the second width. The cooling plate may have a shape with two different widths in one instance. The cooling plate may have segments that operate at different temperatures to increase the width of the sheet in another instance. The sheet may be pulled or flowed with respect to the cooling plate.

Owner:VARIAN SEMICON EQUIP ASSOC INC

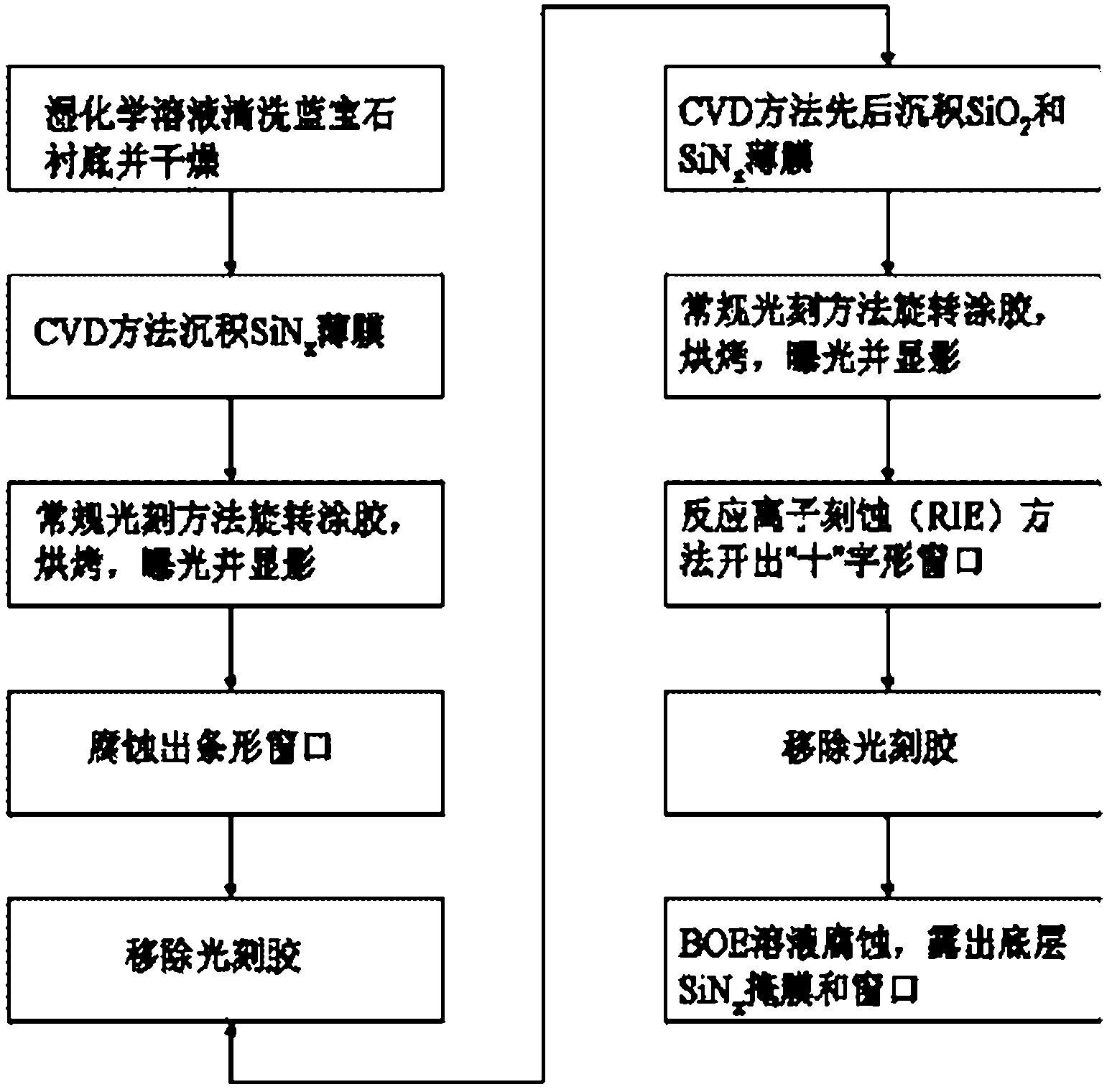

Selective area hetero-epitaxial substrate structure, preparation thereof and epitaxial layer growing method

ActiveCN102492986AIncrease effective widthSimple processPolycrystalline material growthSemiconductor/solid-state device manufacturingOptoelectronicsDislocation free

The invention discloses a selective area hetero-epitaxial substrate structure, a preparation thereof and an epitaxial layer growing method, which belong to the field of photoelectronic technique. The substrate structure comprises a substrate, wherein a bottom mask layer and a top mask layer are sequentially arranged on the substrate, the ground floor mask layer is provided with bar-type windows which are distributed in a periodical mode, the top floor mask layer is provided with cross type windows which are distributed in a periodical mode, and an I-shaped top floor mask area is arranged between the cross type windows. Two ends of the I-shaped top floor mask area at the top are connected with a bar-type mask area of the ground floor mask layer through a fragmented dielectric layer, and the cross type windows at the top and the bar-type windows on the ground floor are staggered. The invention further provides the preparation method of the substrate structure and the epitaxial layer growing method based on the substrate structure. Compared with the prior art, the selective area hetero-epitaxial substrate structure provides a one-step method hetero-epitaxial substrate structure, simplifies growing processes, improves effective width of a dislocation-free epitaxial film simultaneously, and has using value.

Owner:北京飓芯科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com