Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

43results about How to "Save wiring resources" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

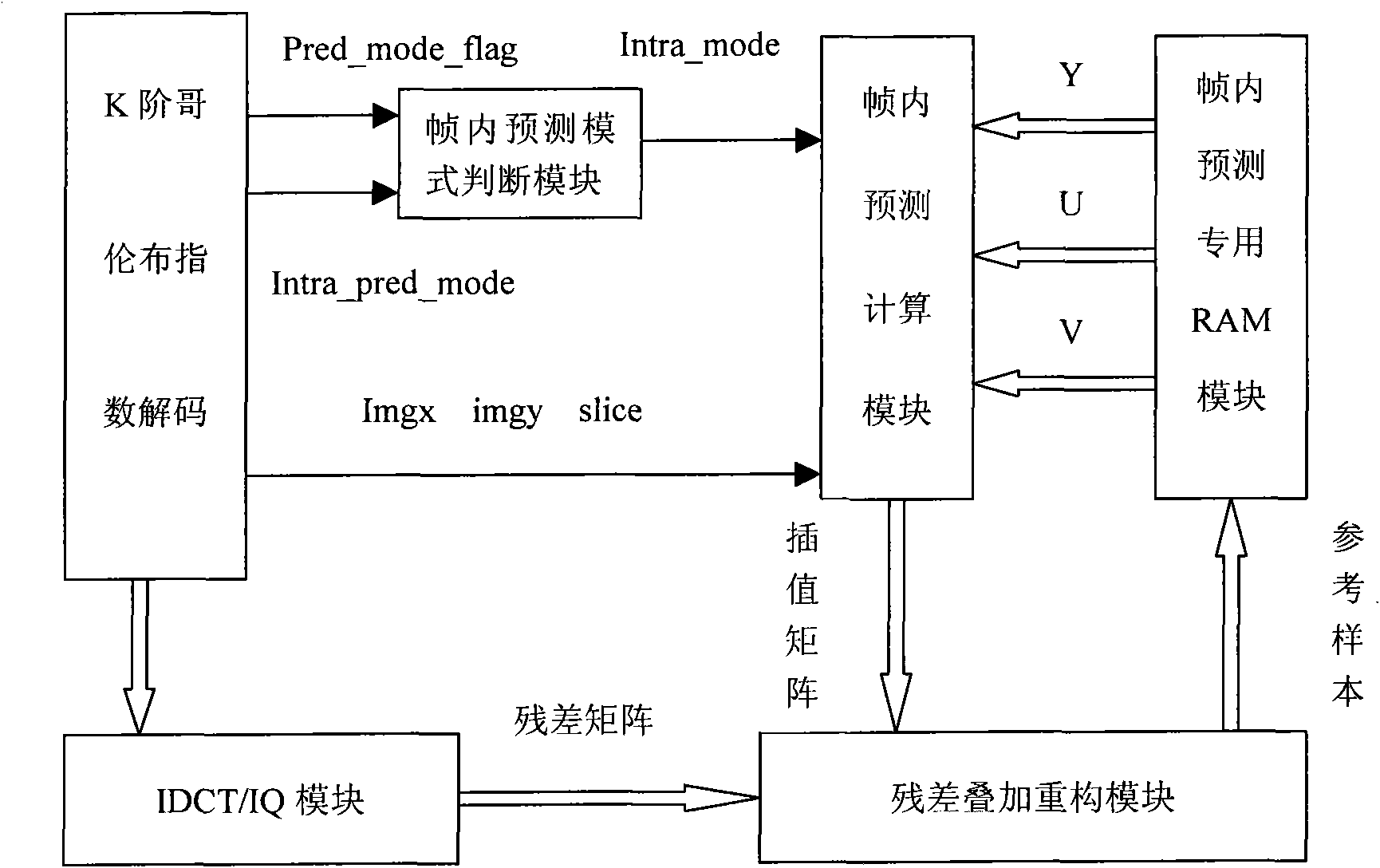

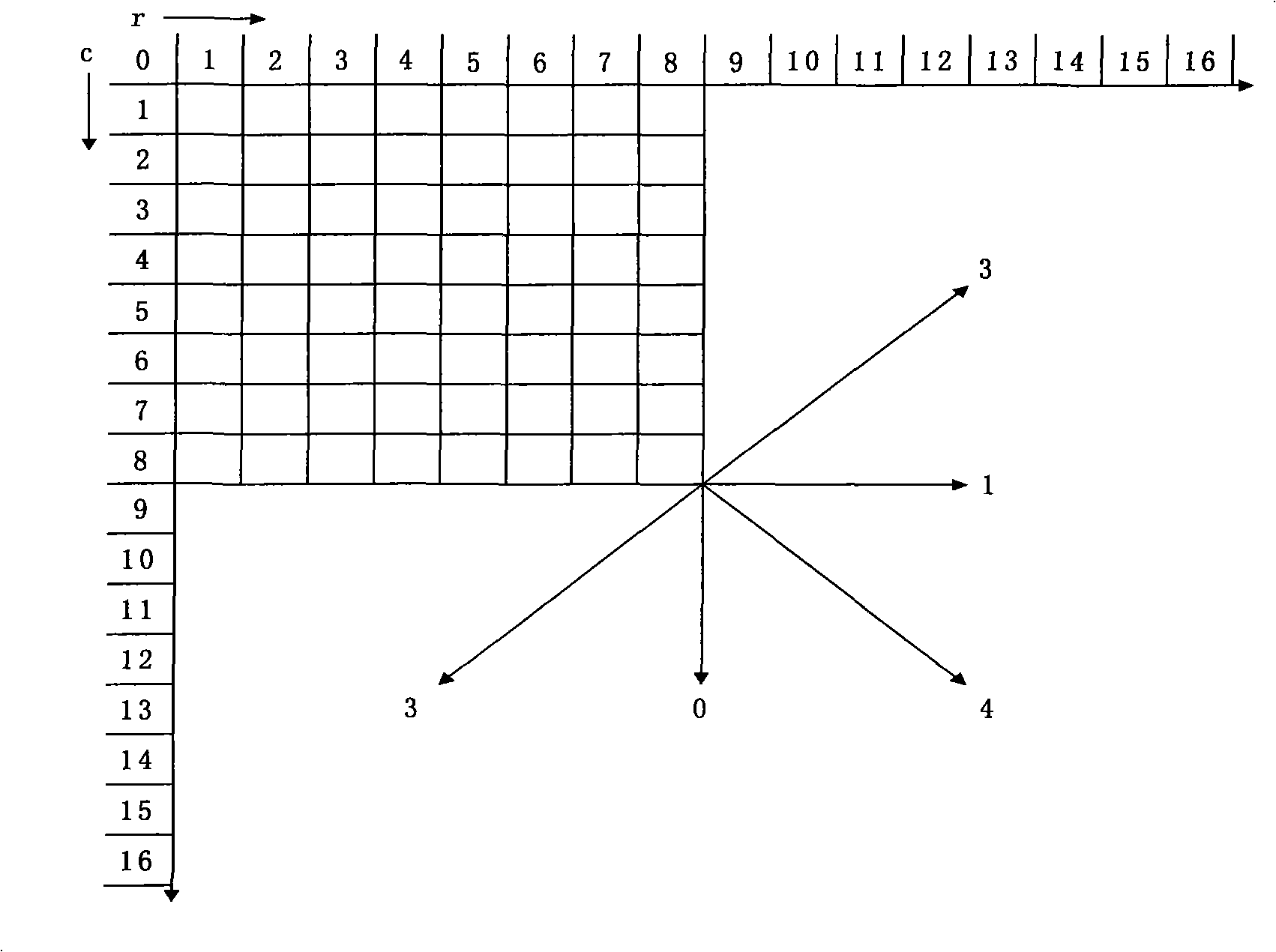

AVS fast intra-frame predicting method and device thereof

InactiveCN101646081AReduce areaFast operationTelevision systemsDigital video signal modificationMultiplexingData operations

The invention relates to an AVS fast intra-frame predicting method and a device thereof. The method is characterized by comprising the following steps: a decoding module recodes the current sub-blockframe code stream; an intra-frame predicting mode judging module obtains a current sub-block intra-frame code predicting mode according to decoded data operation; an intra-frame predicting computing module interpolates according to an intra-frame predicting mode and memorized adjoining one-row and one-line sample points; an IDCT / IQ module computes residual data; and a residual overlapping reconstructed module overlaps an interpolation matrix obtained by the interpolation and a residual matrix obtained by the IDCT / IQ module to obtain the final current frame image data and control the one-row and one-line sample points need for returning to the next interpolation. By adopting the design idea such as module multiplexing, the maximum parallel processing among the modules, and the like, the invention greatly improves computing speed and is very applicable to being realized by FPGA.

Owner:杭州高特信息技术有限公司

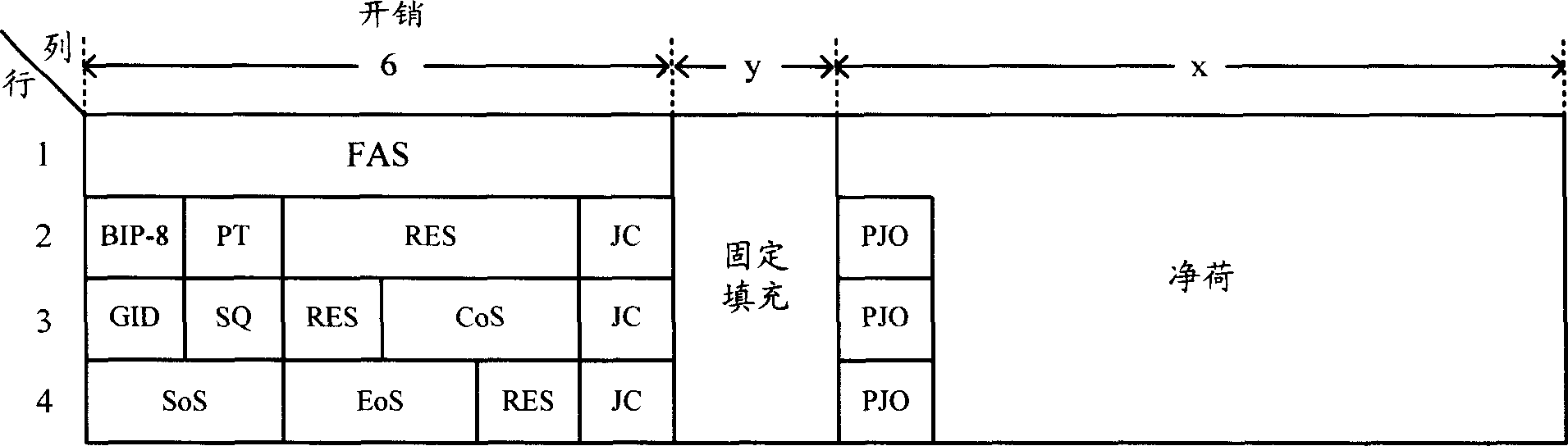

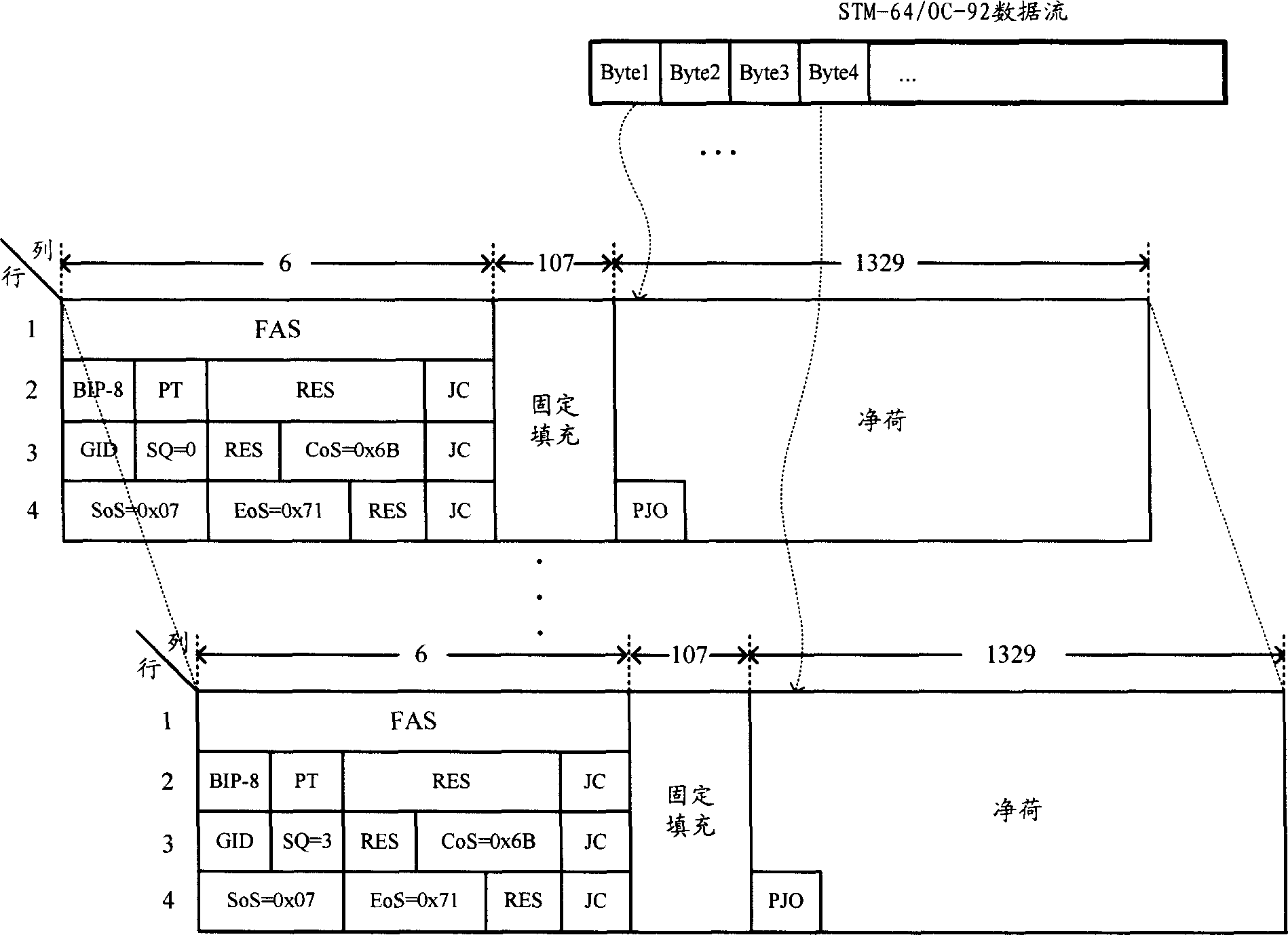

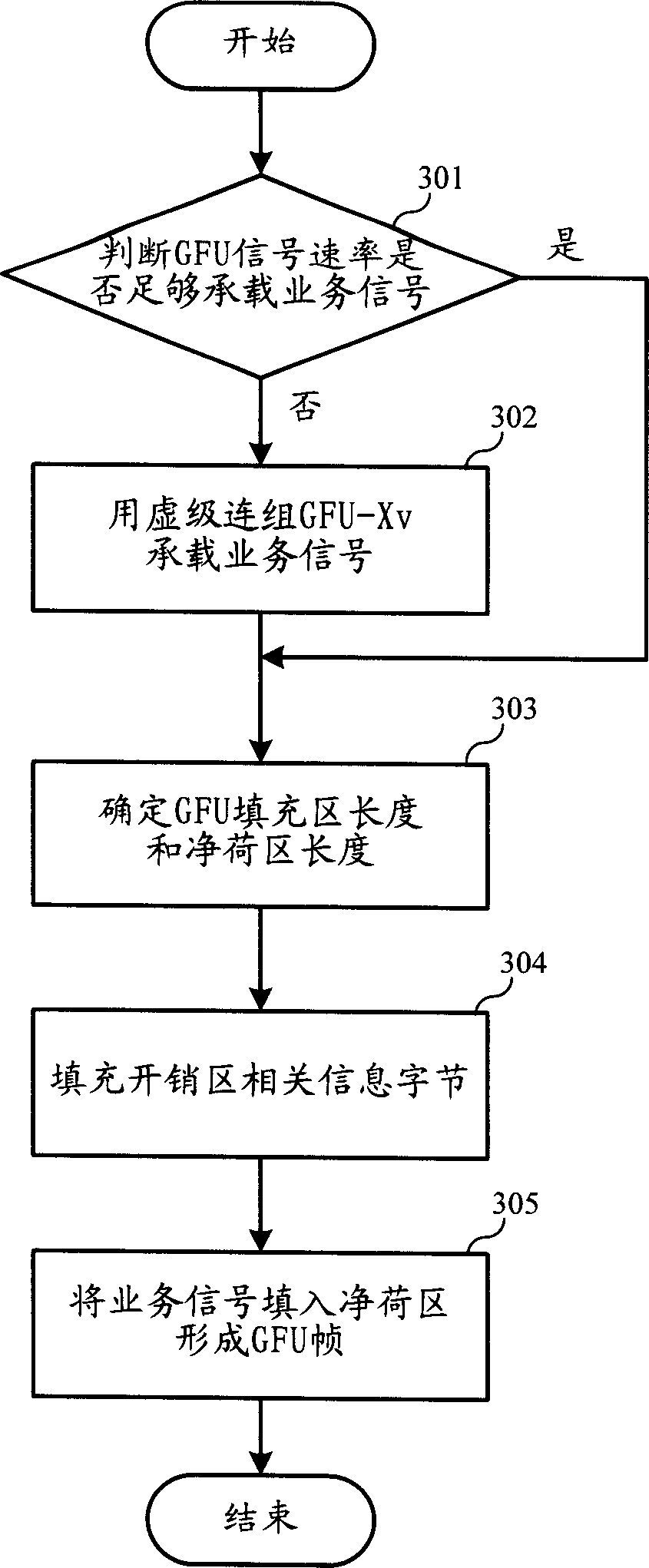

Service signal dispatching method and device in optical transport network

InactiveCN1842221AControl cross actionImplement schedulingElectromagnetic transmissionTime-division multiplexing selectionOptical Transport NetworkSignal processing

The invention discloses a light transmission network business signal dispatching method and its device in the field of light transmission network business signal processing technology. It defines the speed rate suit for the common sealed unit of the current cross dispatching hardware ability, uses the virtual degree connecting group and the multiplexer mode to map each type of business to the common sealed unit and dose cross dispatching to the sealed unit. It adopts local clock to generate the frame structure and the frame head note of the common sealed unit and controls the cross movement of the cross dispatching unit.

Owner:HUAWEI TECH CO LTD

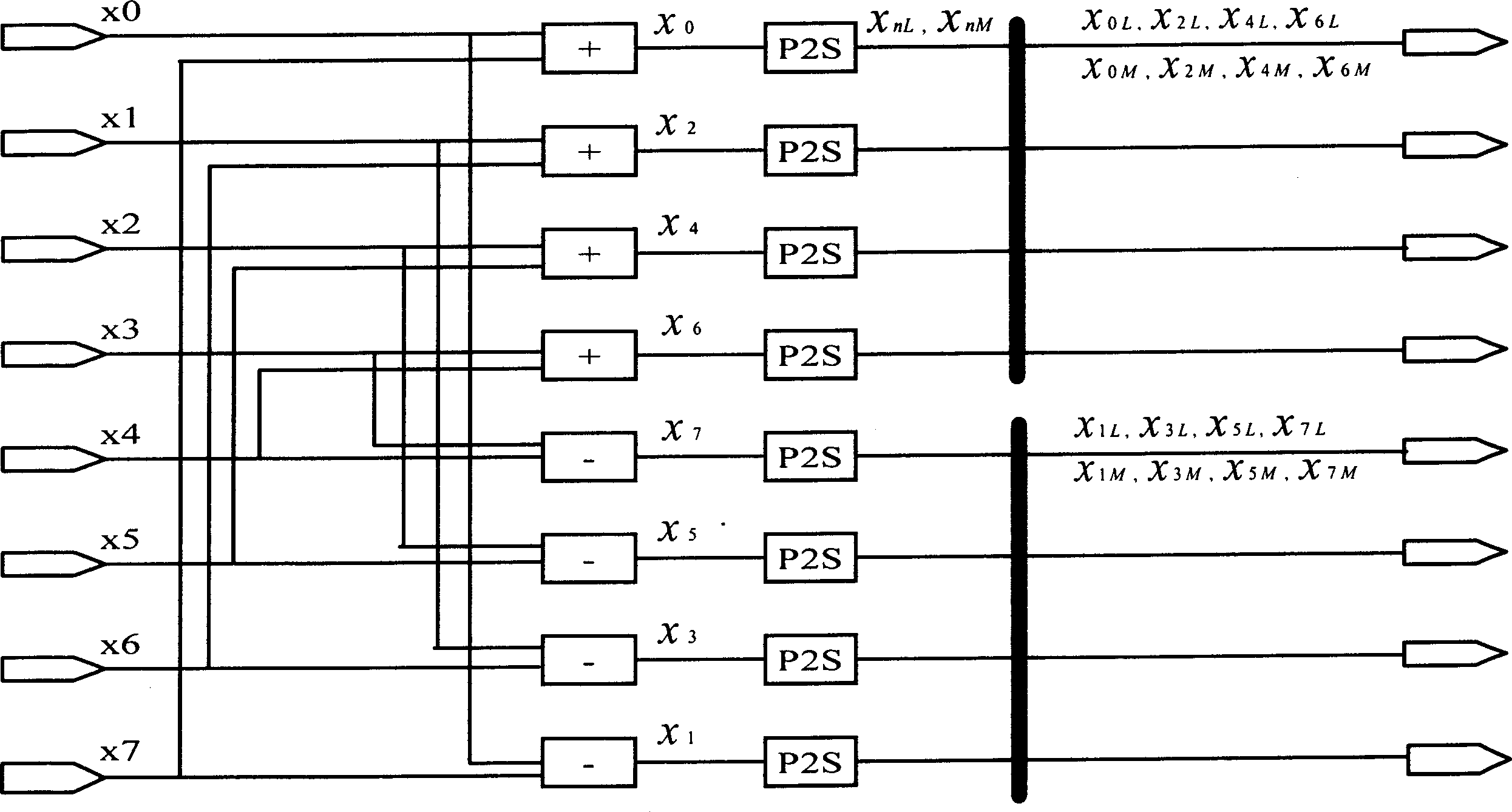

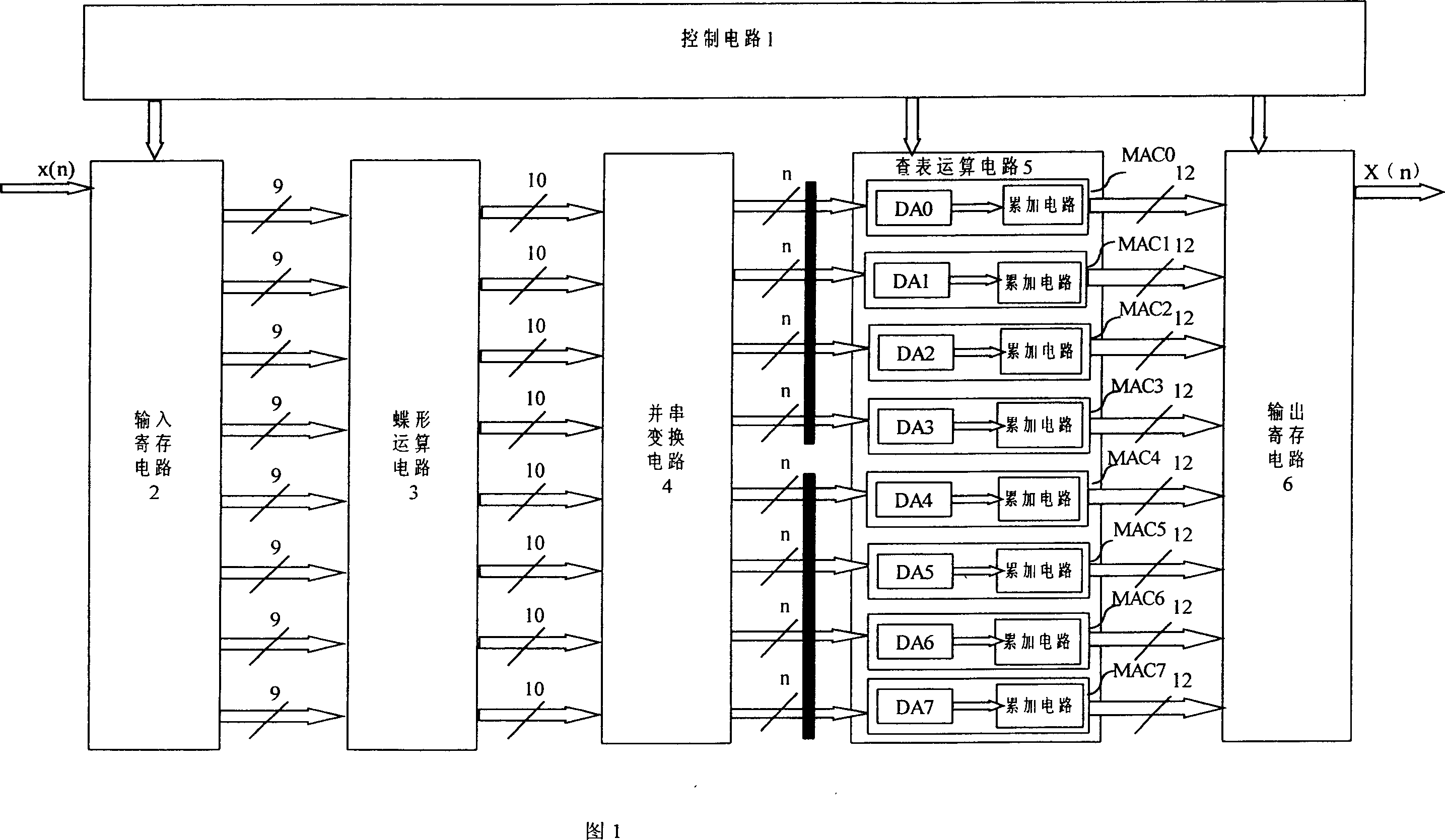

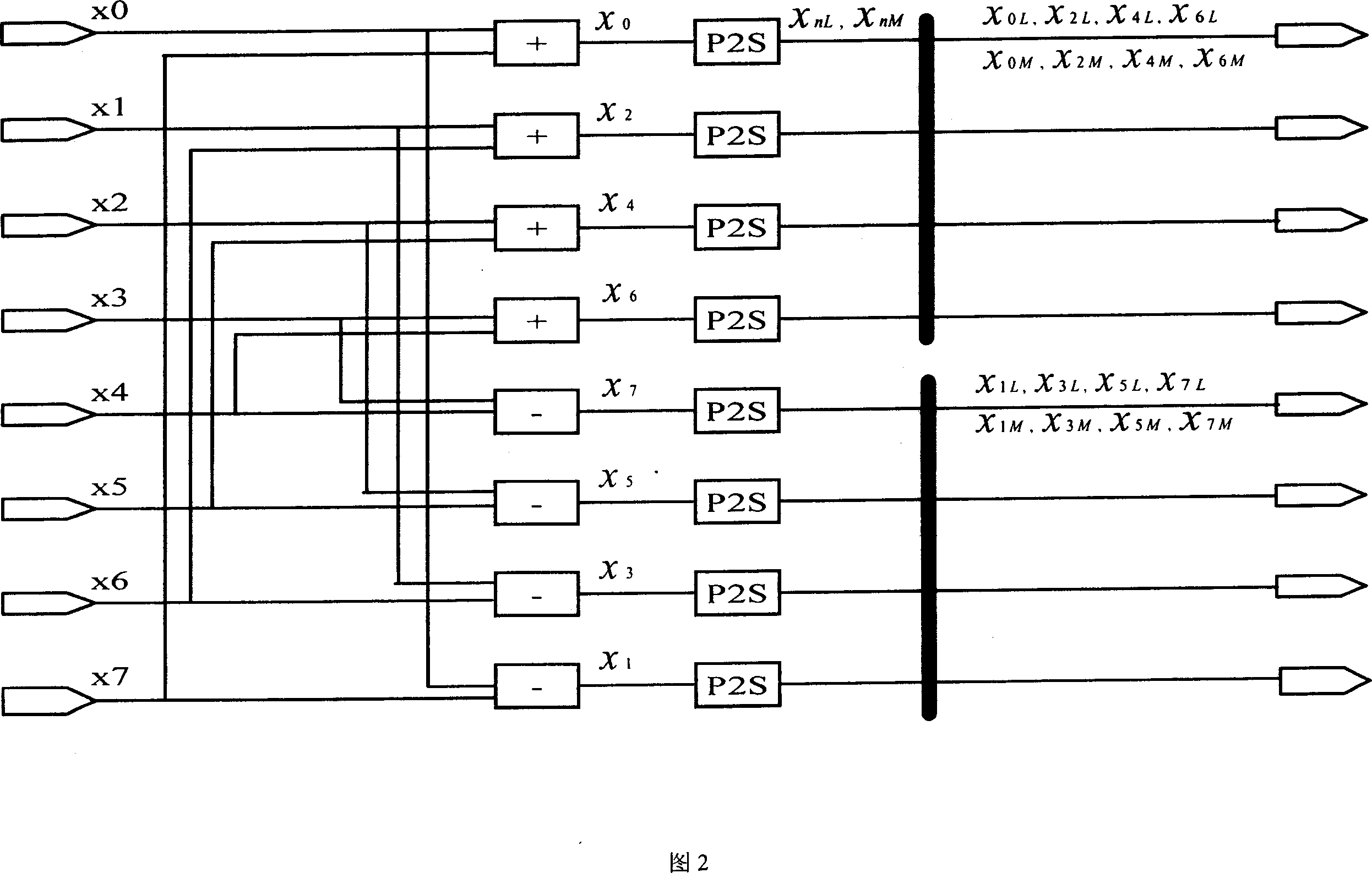

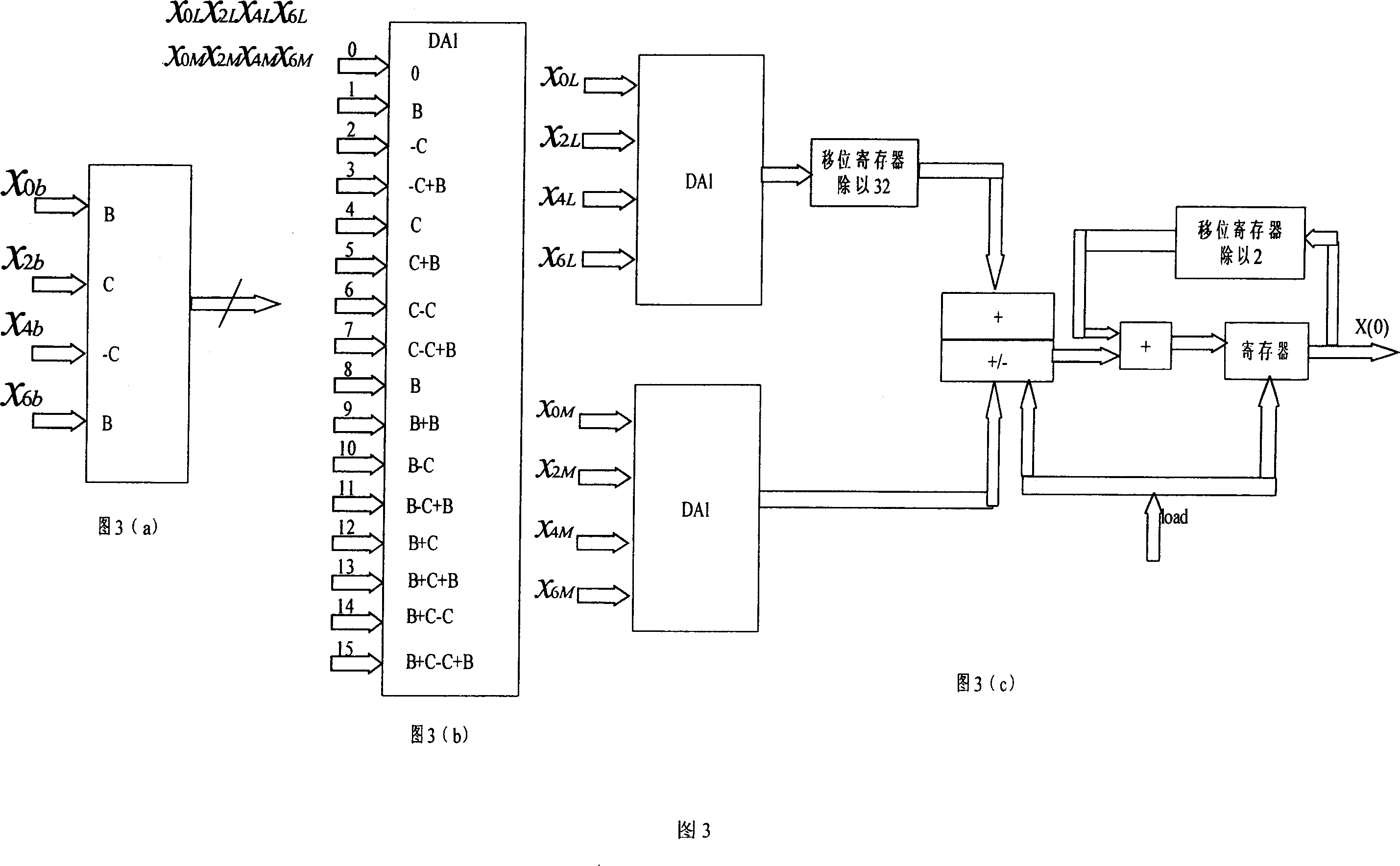

DCT rapid changing structure

InactiveCN1553707AReduce areaFast operationTelevision system detailsImage codingImage compressionDct transform

This invention provides a device for taking a two- dimensional fast DCT transform or a two -dimensional fast IDCT transform to the image data composed of 8X8 sub-block. Takes example for one dimensional DCT transform to 8X8 sub-block: the transform device comprises: the control circuit; the input deposit circuit; the butterfly operation circuit; the parallel / serial conversion circuit; table look up operation circuit; the output deposit circuit. The invention adopts the design philosophy that is to replace the multiply operation by look up table, so it need only once butterfly operation, 24 adder, 0 multiplying to complete once DCT. The design philosophy using the pipeline greatly increases the operating speed. The data can be inputted consecutively, the operation result can be gotten at each clock period. The invention is adapted to implement by using FPGA, the resource requirement saves above 30% than current structure. It can be applied in various image compression, especially in MPEG, H.26X format data that makes high requirement for the compression speed and quality.

Owner:杭州高特信息技术有限公司

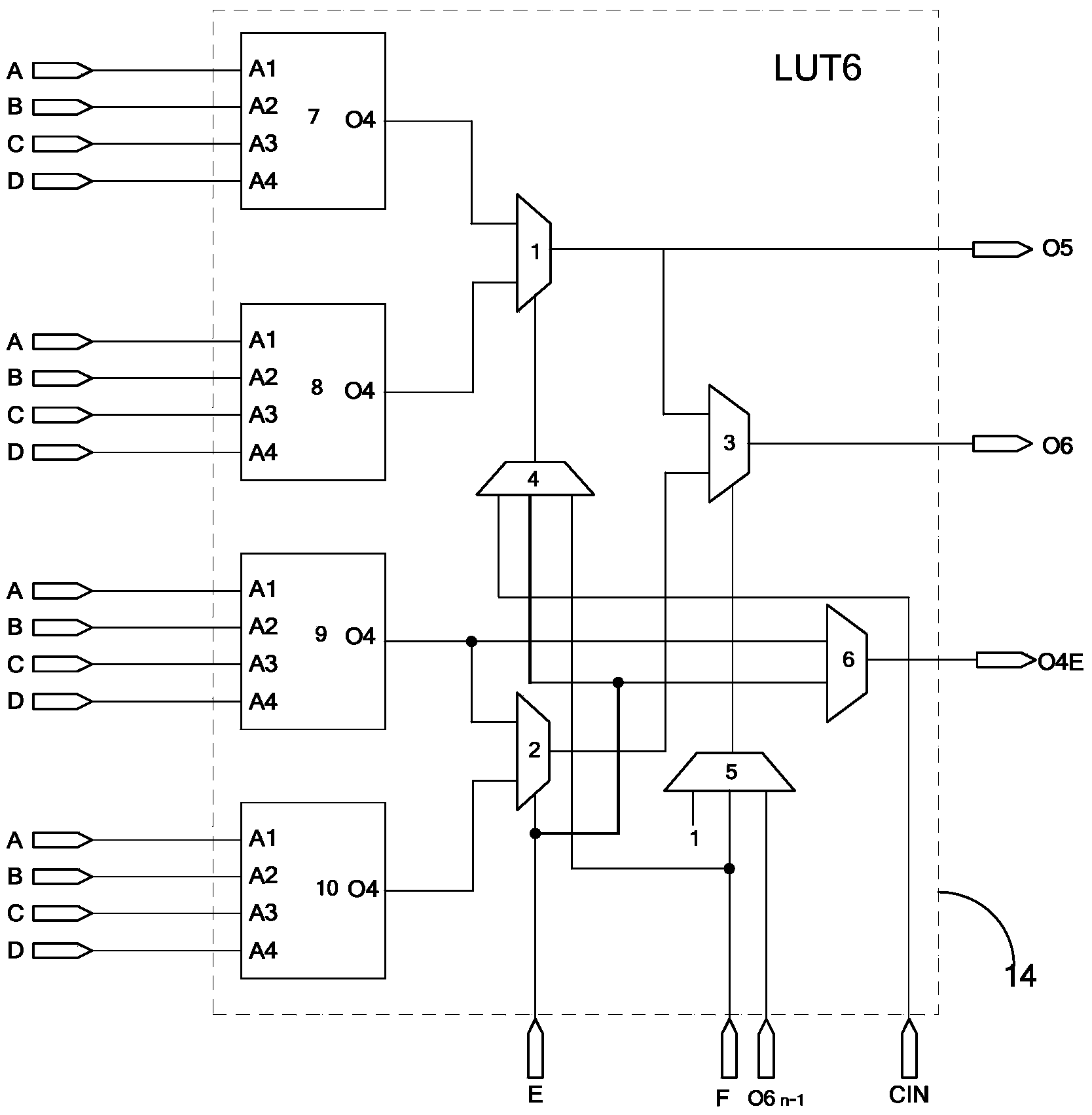

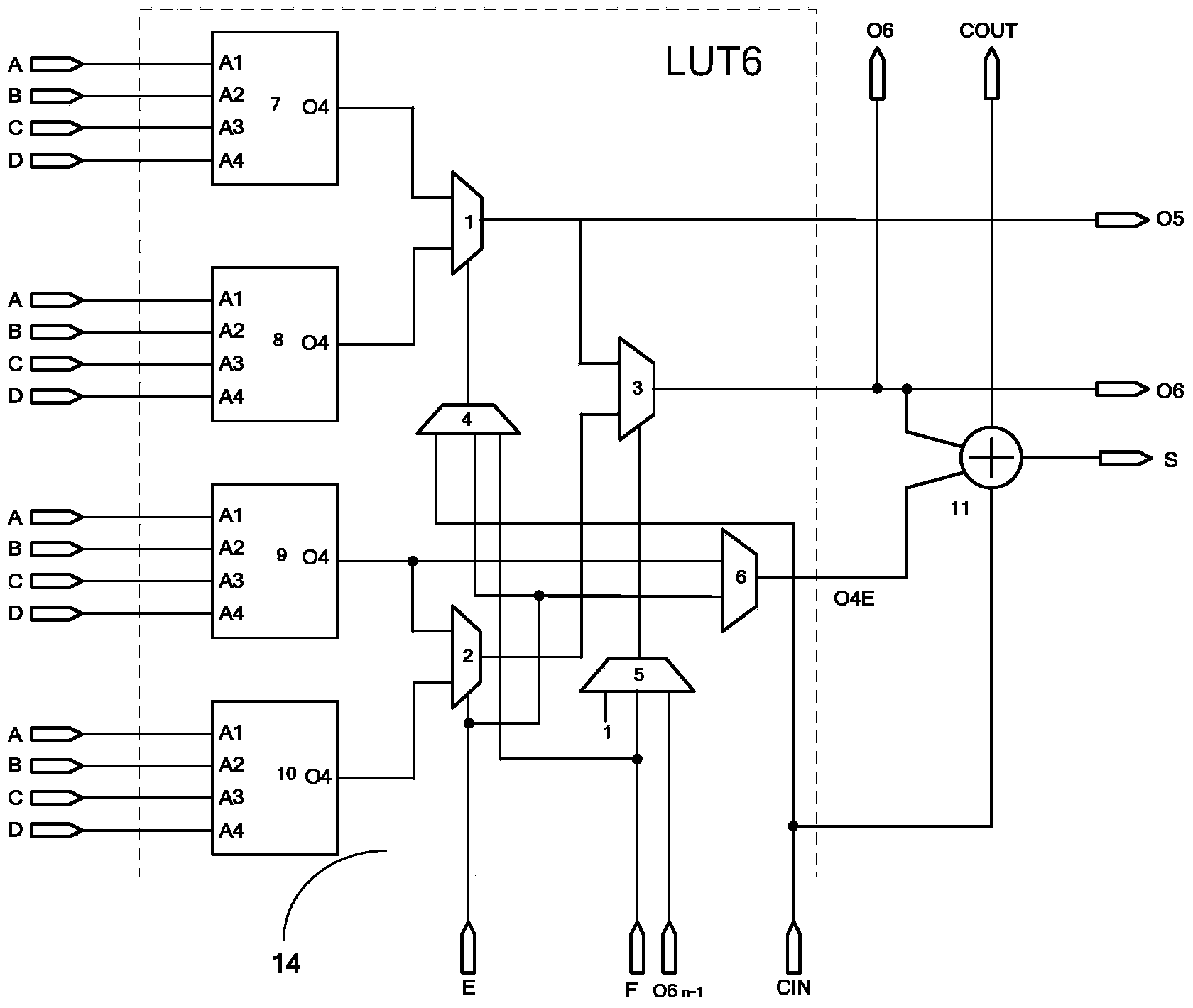

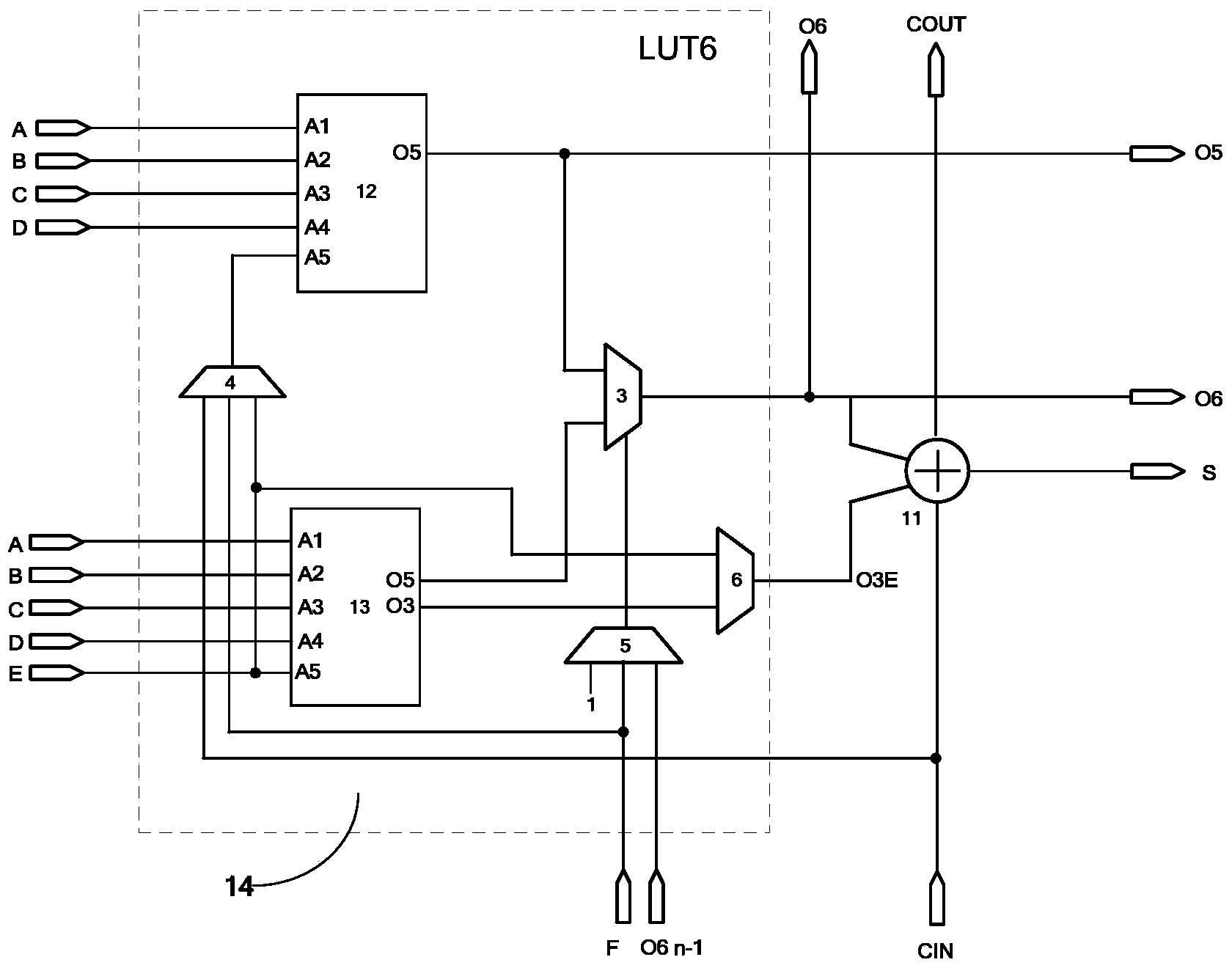

Multifunctional and configurable six-input lookup table structure

ActiveCN103762974AStrong configurabilityIncrease flexibilityLogic circuits using elementary logic circuit componentsOperandLookup table

The invention relates to a multifunctional and configurable six-input lookup table structure. The lookup table structure with different inputs and sharing with different signal numbers can be configured by flexibly selecting configuration signals, a function extension logic chain is designed, and a wide logic function can be achieved rapidly without external wiring. A special adder carry chain and an operand selection control end are designed, carry signals enter the lookup table through a four-input lookup table, and wide logic operation on a sum function of an adder and other operand can be achieved rapidly. Due to high flexibility and configuration capacity of the lookup table and the rapid carry of the carry chain, the wide logic function can be achieved through fewer logic resources, multiple functions are achieved, the utilization rate of wiring resources can be improved effectively, the occupied area of the resources is reduced, the working speed of a chip is improved, and more functions and applications can be achieved with limited gate counts.

Owner:WUXI ESIONTECH CO LTD

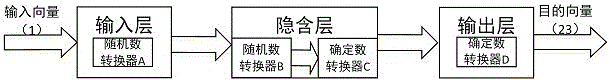

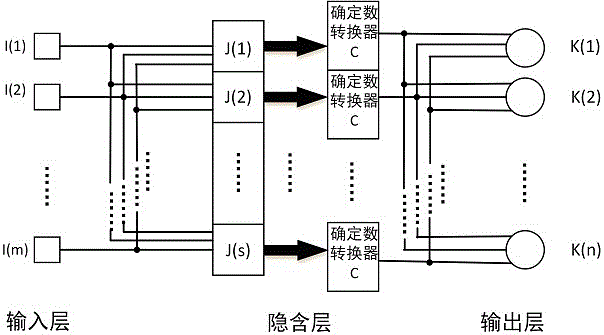

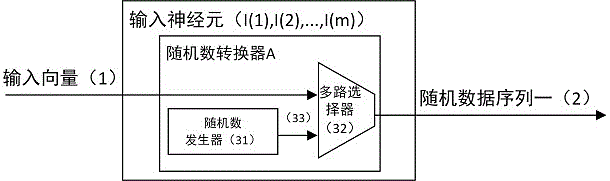

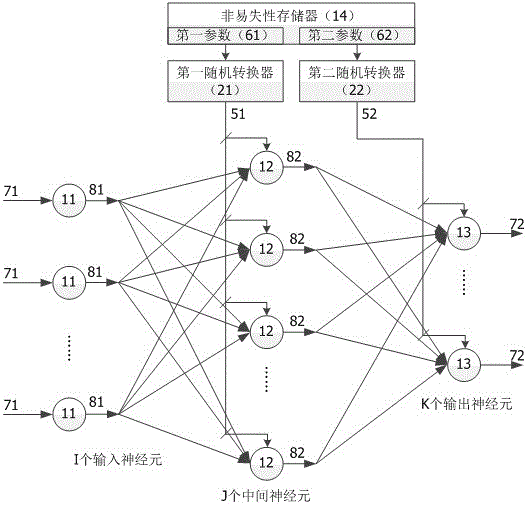

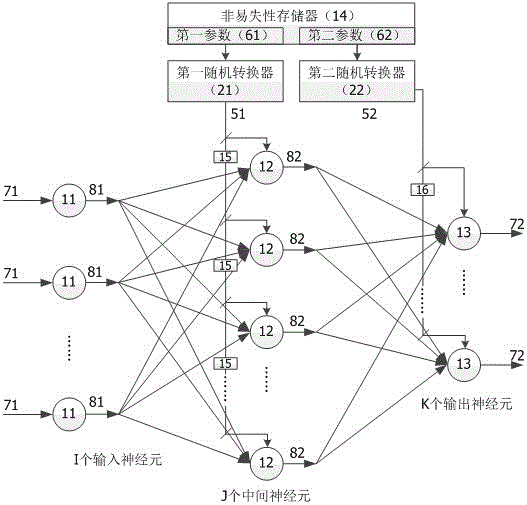

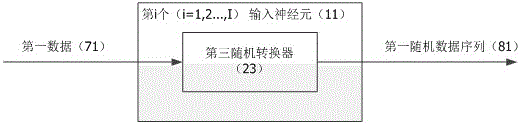

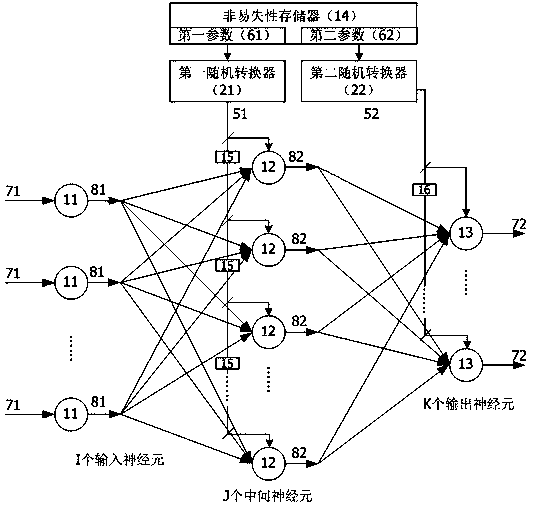

Random neural network hardware realization apparatus

ActiveCN106127301ASave hardware logic resourcesLower build costsPhysical realisationHidden layerNeuron

The invention relates to a random neural network hardware realization apparatus. The apparatus comprises an input layer, a hidden layer and an output layer, wherein the input layer consists of m input neurons I, each input neuron I comprises a random number converter A, and after an input vector passes through the random number converter A, a random data sequence I is output; the hidden layer consists of s hidden neurons J, each hidden neuron J comprises a random number converter B, a random function generator and a definite number converter C, a parameter code stream passes through the random number converter B, is aligned to the random data sequence and passes through the random function generator, so a random data sequence II is obtained, and the random number sequence II passes through the definite number converter C and a definite number I is output; the output layer consists of n output neurons K, each output neuron K comprises a definite number converter D and a linear function processor, and a parameter code stream II passes through the definite number converter D, is aligned to the definite number and passes through the linear function processor, so an object vector is output. According to the apparatus, hardware logic and wiring resources can be greatly reduced, circuit cost and power consumption can be reduced, the network operation precision is high, and the fitting capability of training samples is enhanced.

Owner:SHANGHAI UNIV

Artificial neural network hardware implementation device based on probability calculation

ActiveCN105913118ASave hardware logic resourcesLow costPhysical realisationRandom parametersArtificial neural network

Owner:SHANGHAI UNIV

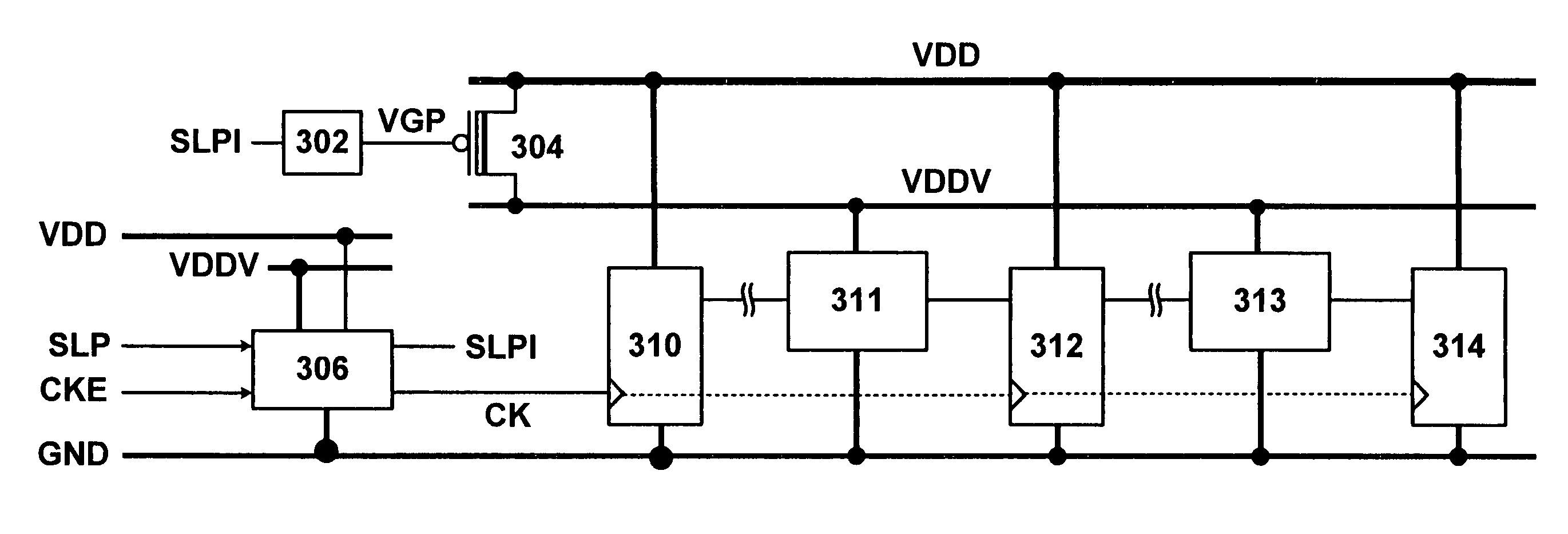

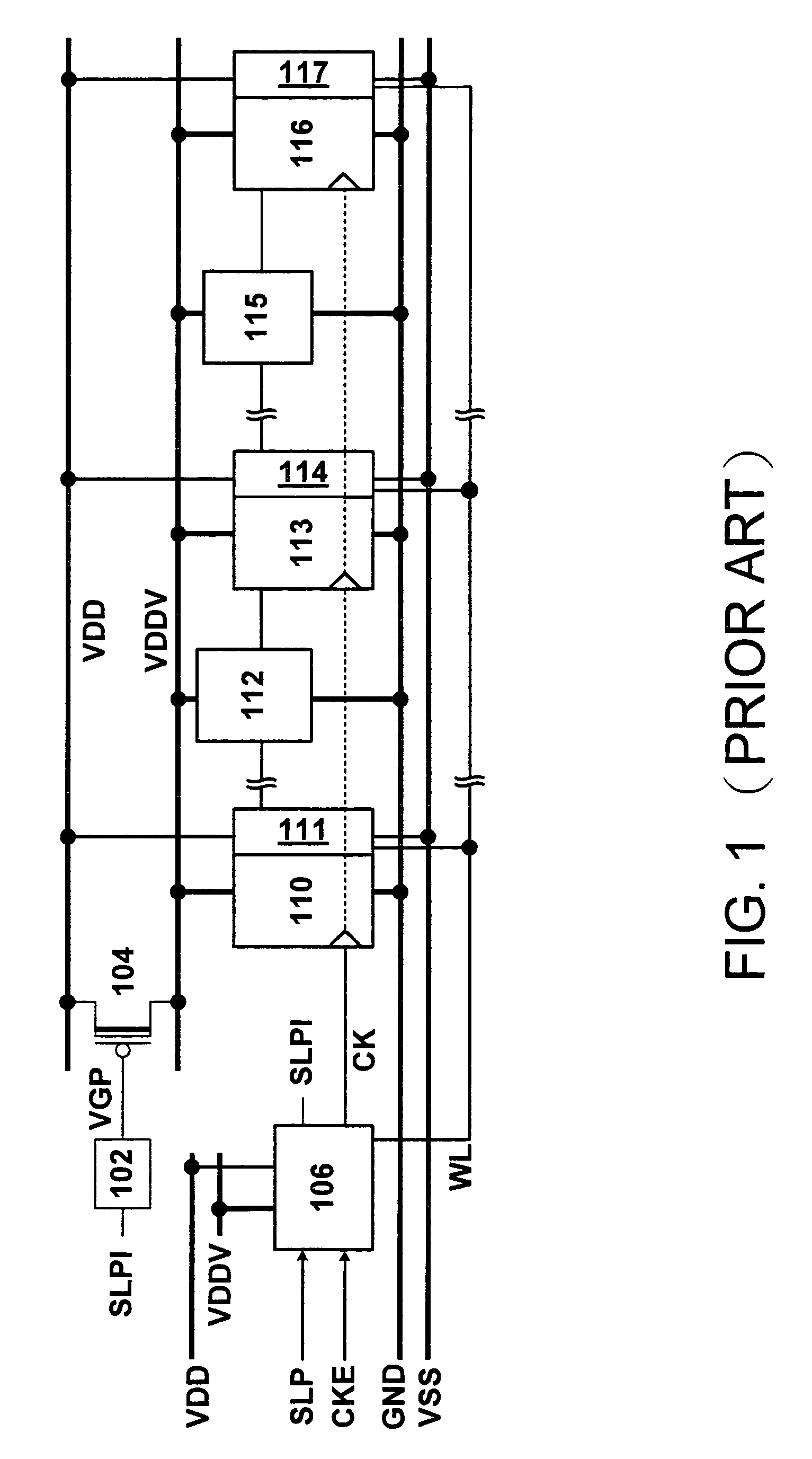

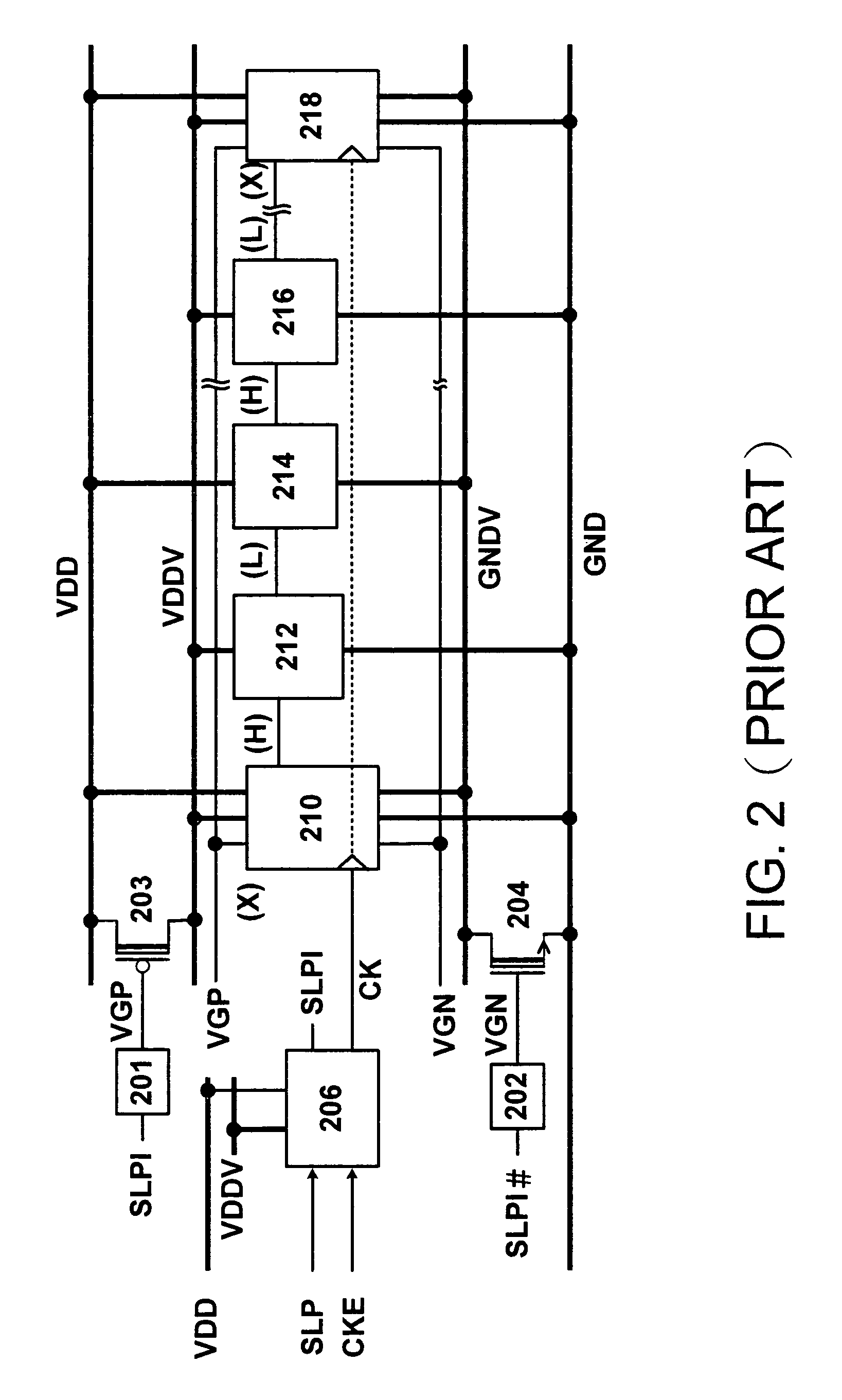

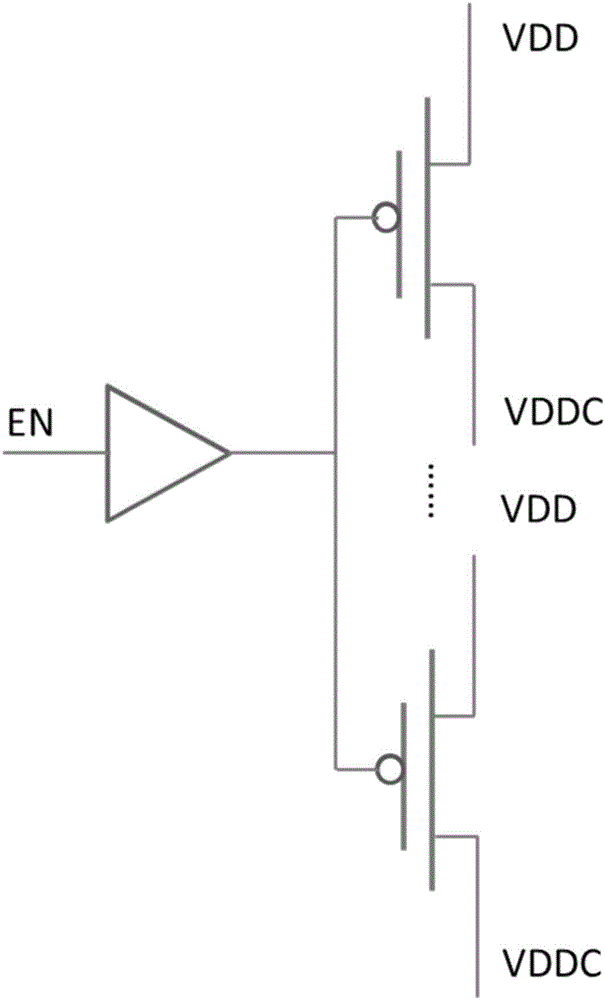

Leakage current control circuit with a single low voltage power supply and method thereof

InactiveUS7649405B2Avoid leakage currentSave wiring resourcesReliability increasing modificationsPower reduction by control/clock signalLow voltageEngineering

Owner:IND TECH RES INST

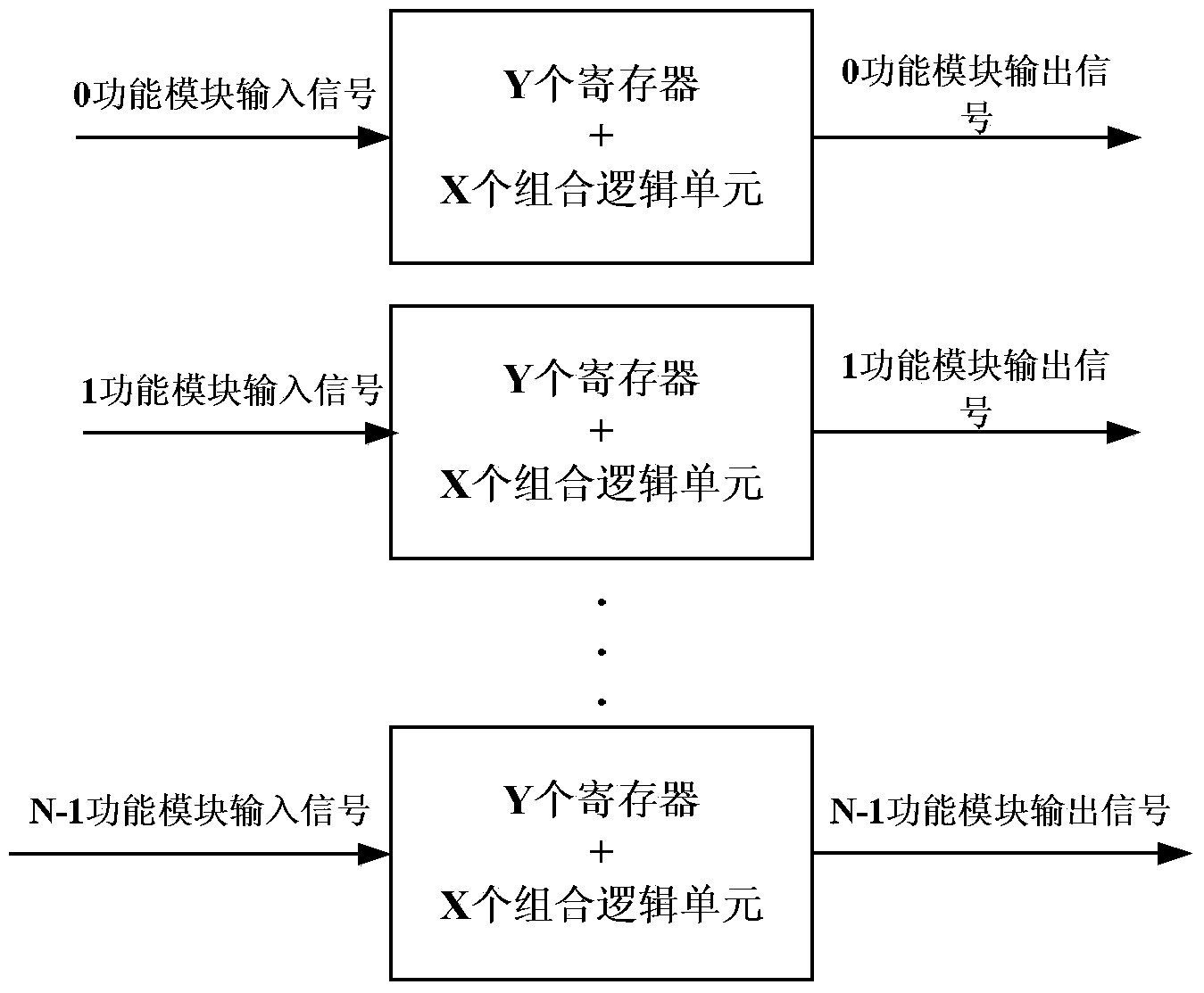

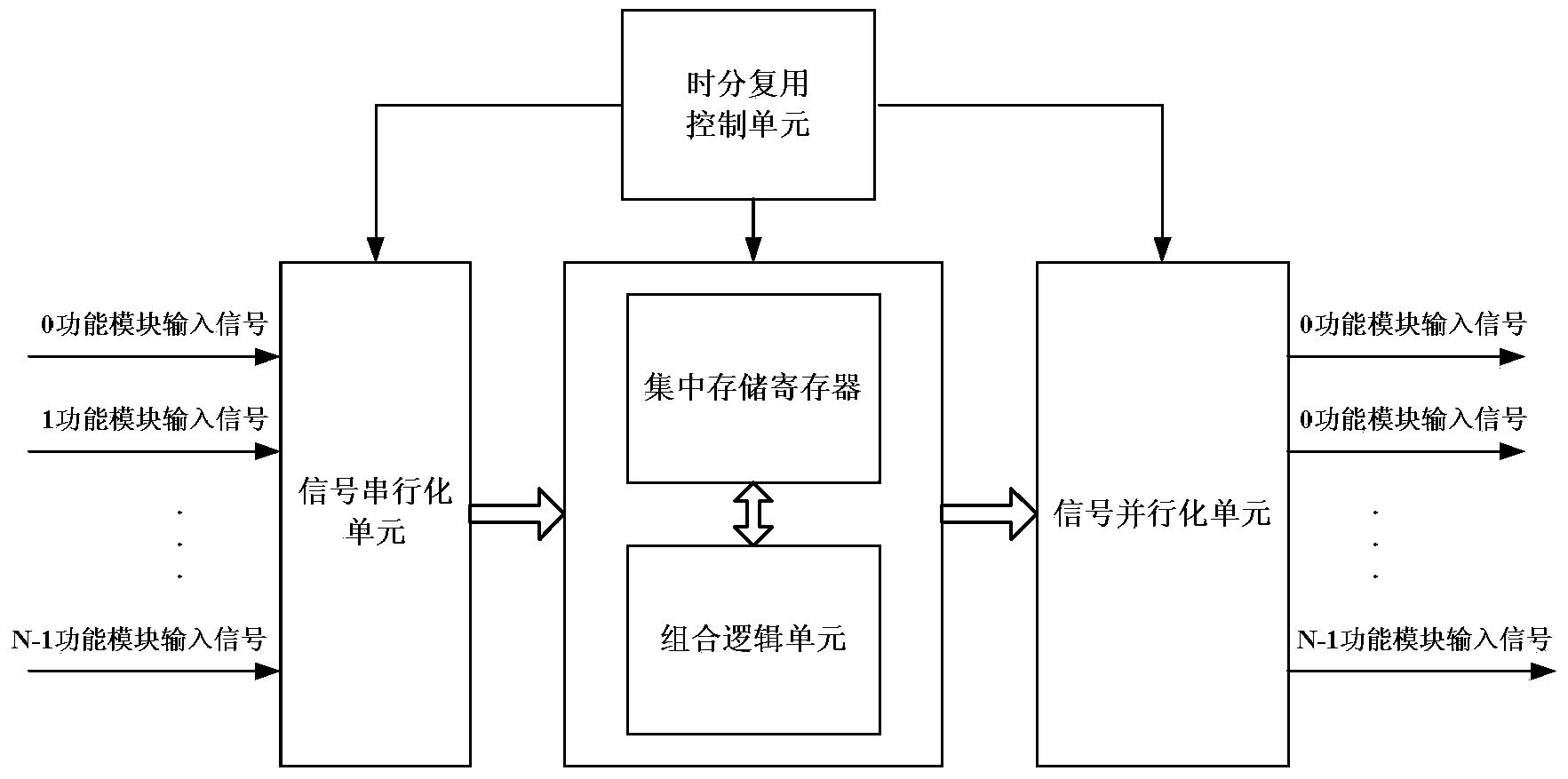

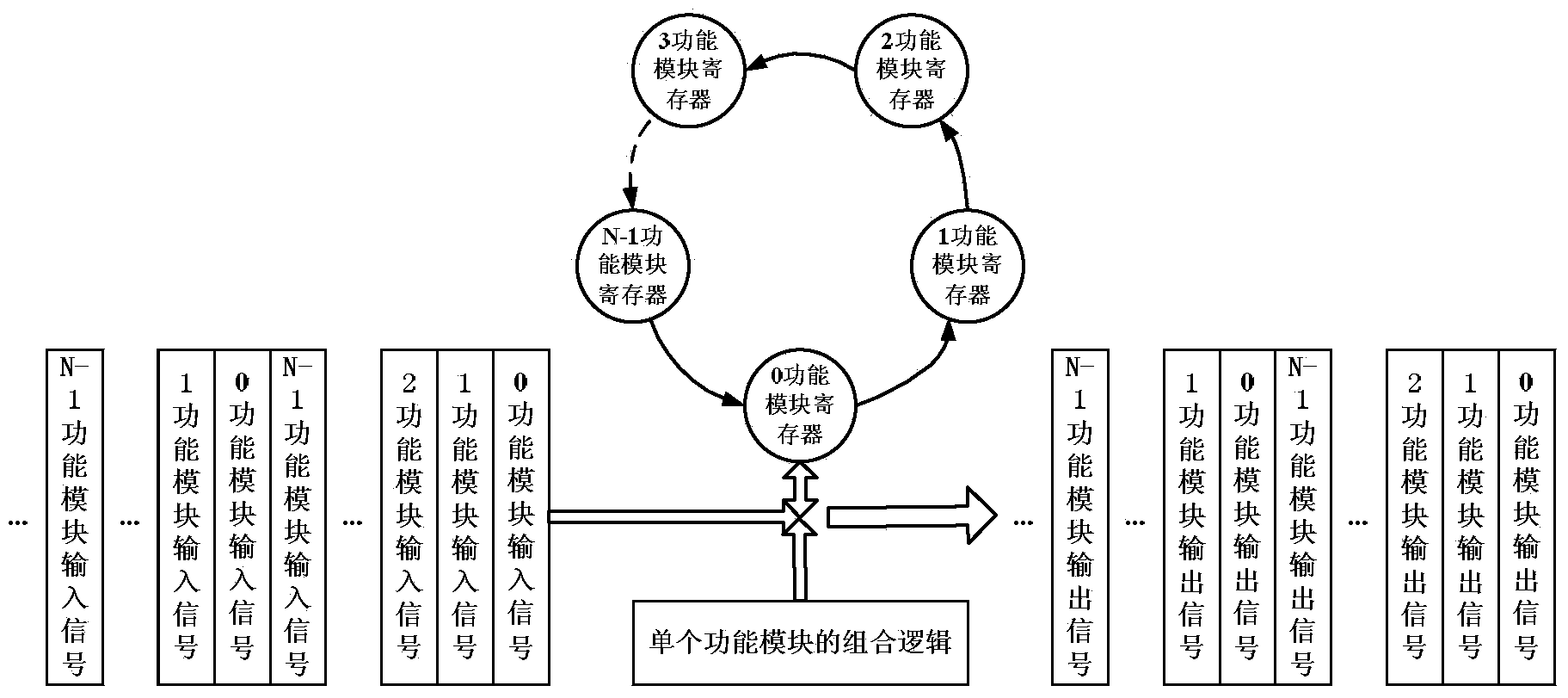

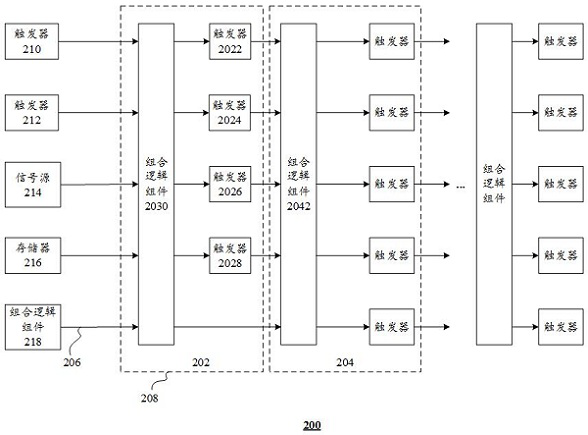

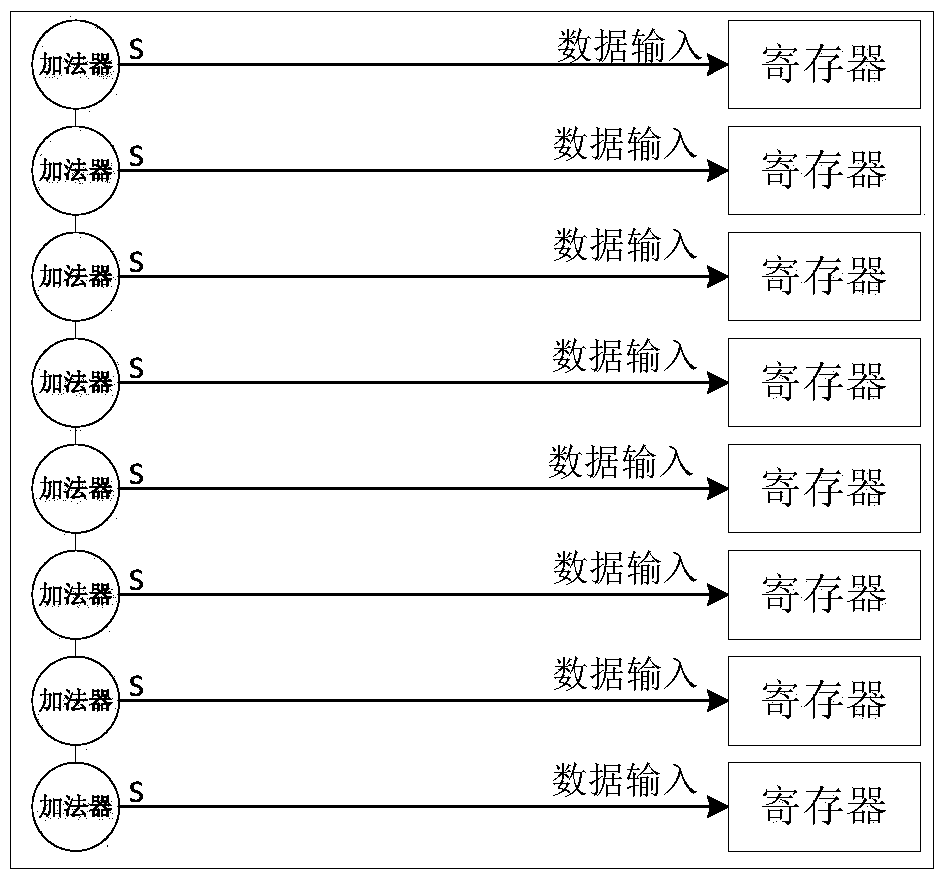

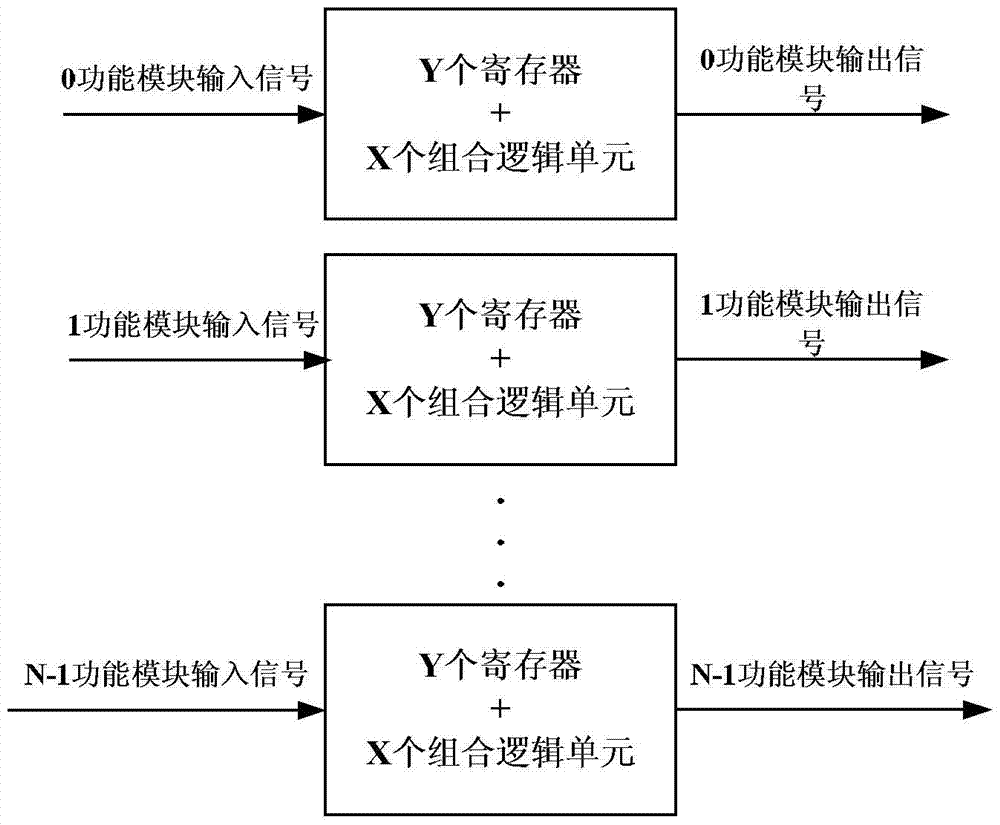

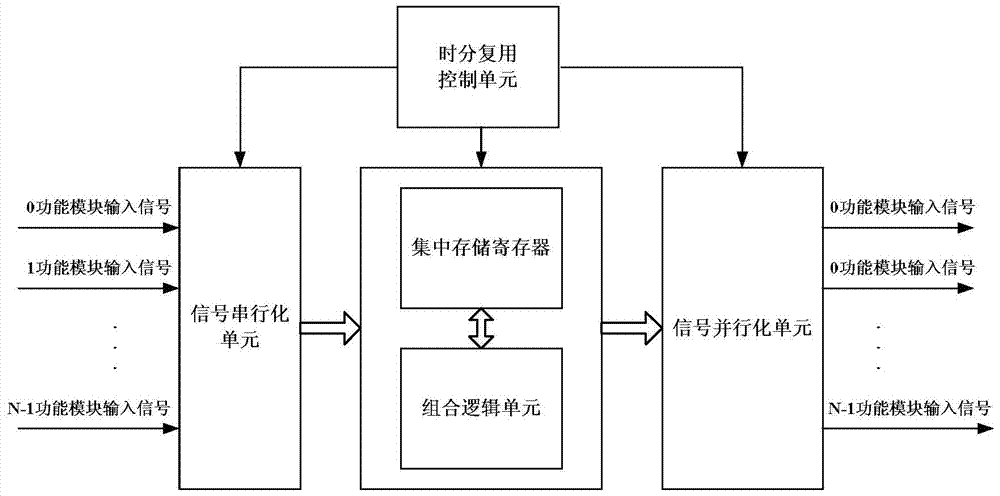

Centralized-cache device and design method based on field-programmable gate arrays

ActiveCN104252560AReduce occupancyIncrease the number ofSpecial data processing applicationsProcessor registerComputer module

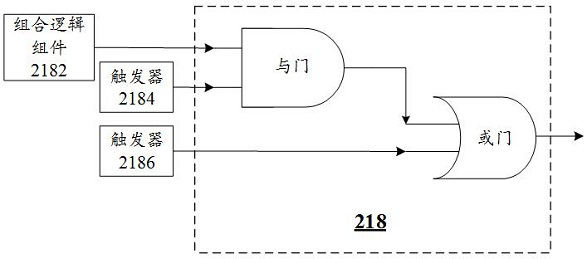

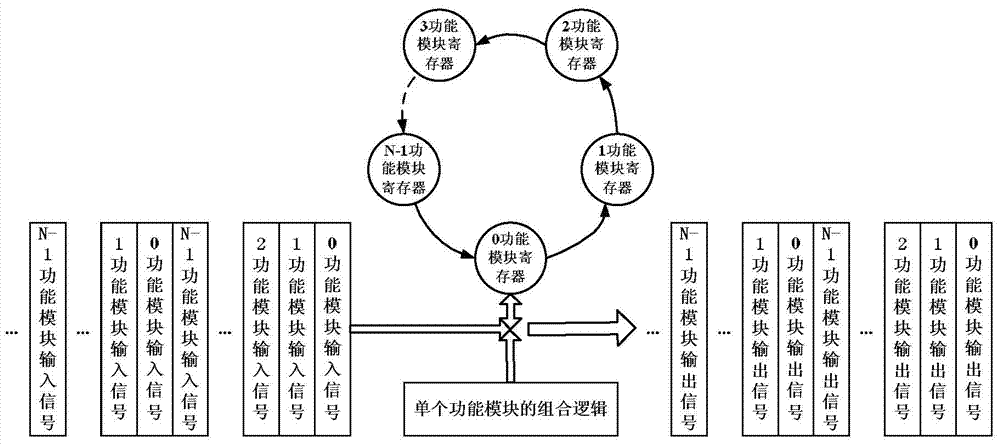

The invention relates to a centralized-cache device and design method based on field-programmable gate arrays and relates to the field of field-programmable gate array design, and the centralized-cache device and design method is adaptive to at least two same functional modules. The device comprises a time division multiplexing control unit, a signal serialization unit, a centralizing storage register, a combinational logic unit and a signal parallelization unit. The time division multiplexing control unit is used for dividing the period into two time slots with the same length of time, each time slot corresponds to one functional module sequentially, and each functional module performs input signal processing in the corresponded time slot. The signal serialization unit is used for converting the parallel input signals of each functional module into serial input signals. The centralizing storage register is used for storing the register of each functional module and reading and writing the register of the functional module in the time slot corresponding to the functional module. The combinational logic unit is used for combinational logic of input signal processing of single functional module. The signal parallelization unit is used for restoring serial output signals as parallel output signals after the input signals of each functional module are processed.

Owner:FENGHUO COMM SCI & TECH CO LTD

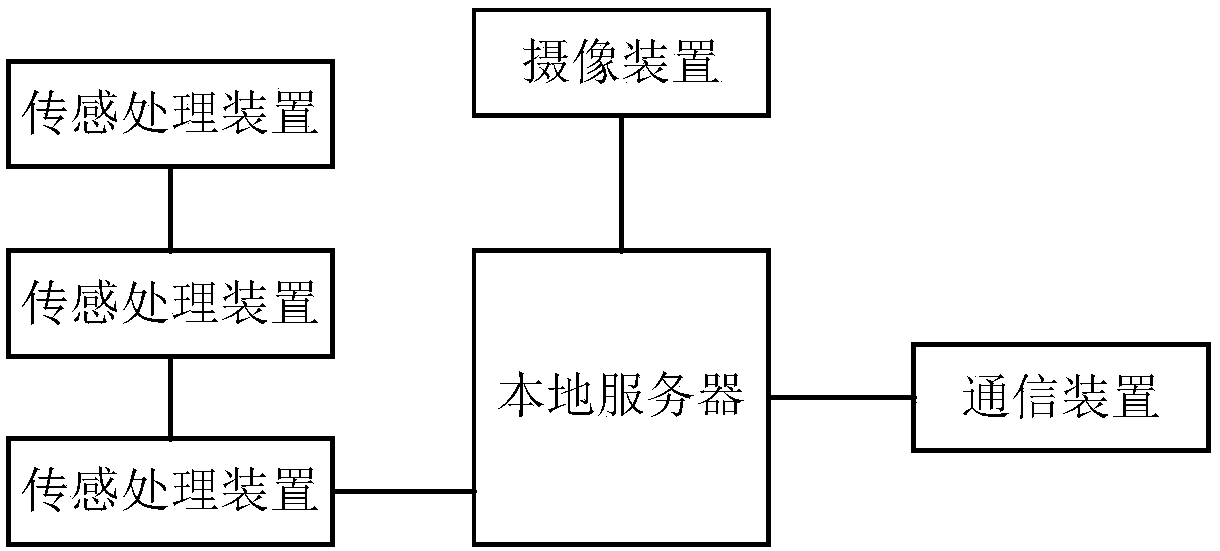

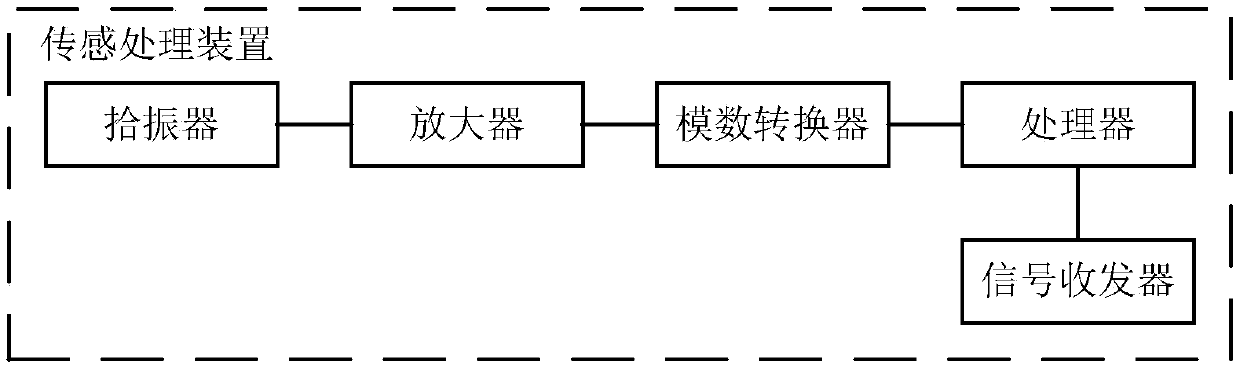

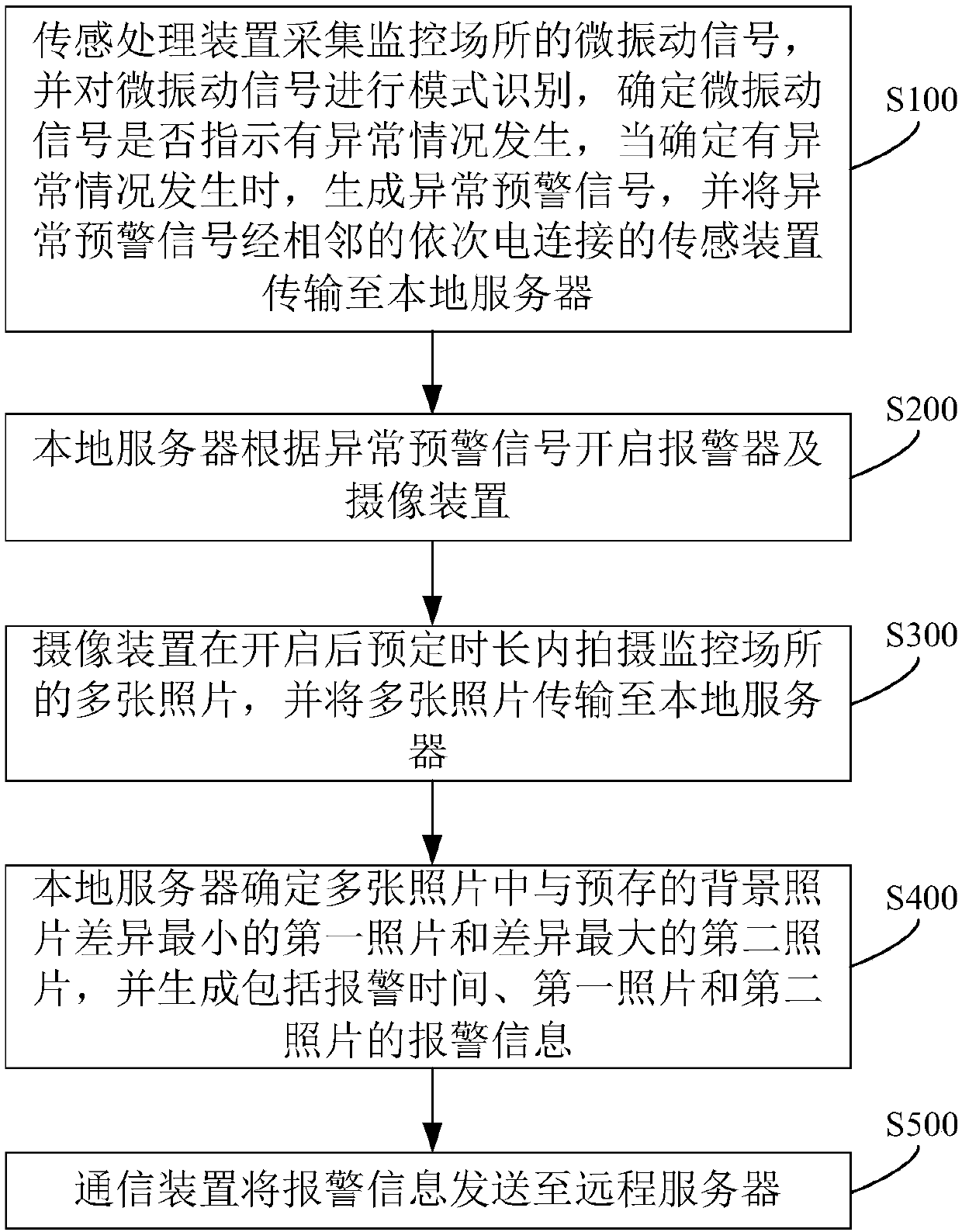

Perimeter security and protection system

ActiveCN107564215AImprove securitySave wiring resourcesBurglar alarm mechanical actuationElectricityProtection system

The invention relates to a perimeter security and protection system and method. The system includes a local server, a camera device, a communication device and a plurality of sensing processing devices located underground in a monitoring place, the plurality of sensing processing devices are electrically connected in sequence, the first one or the last one of the plurality of sensing processing devices electrically connected in sequence is electrically connected with the local server, and the local server is electrically connected with the camera device and the communication device. The technical scheme of the invention can expand a perimeter defense range, accurately judge whether a situation of an abnormal intrusion occurs in the monitoring place, and record related information when an abnormal situation occurs, so that staff can dispose in time, thereby improving safety of the monitoring place.

Owner:武汉安保通科技有限公司

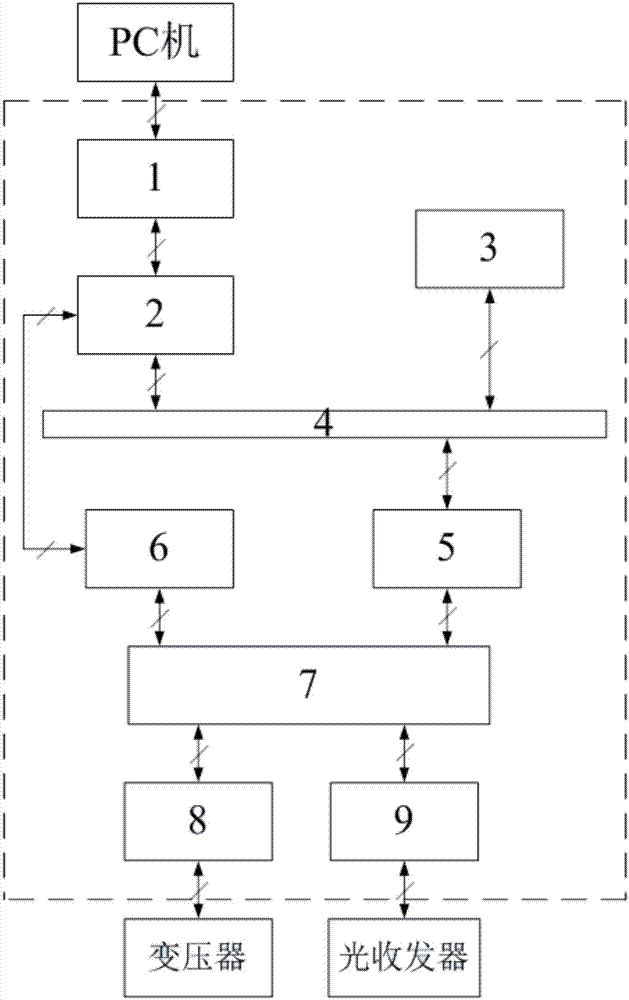

Gigabit network control circuit based on AMBA-AHB bus

InactiveCN107231319AImprove access efficiencySave wiring resourcesData switching networksHigh level techniquesEmbedded systemTransceiver

The invention discloses a Gigabit network control circuit based on an AMBA-AHB bus. The Gigabit network control circuit comprises a PC, an AMBA-AHB bus module, an MAC controller, a transformer and an optical transceiver. The PC is connected with the AMBA-AHB bus module through a DMA module. The AMBA-AHB bus module is divided into two ways through the MAC controller. The two ways are respectively connected with the transformer and the optical transceiver. The DMA module is also connected with the MAC controller through a storage management module. According to the gigabit network control circuit based on the AMBA-AHB bus, the performance indexes of a bus transmission rate 1Gbps and a host interface transmission rate 5GT / s are realized, layout resources are clearly saved, a chip area is reduced, and the chip power consumption is reduced.

Owner:XIAN MICROELECTRONICS TECH INST

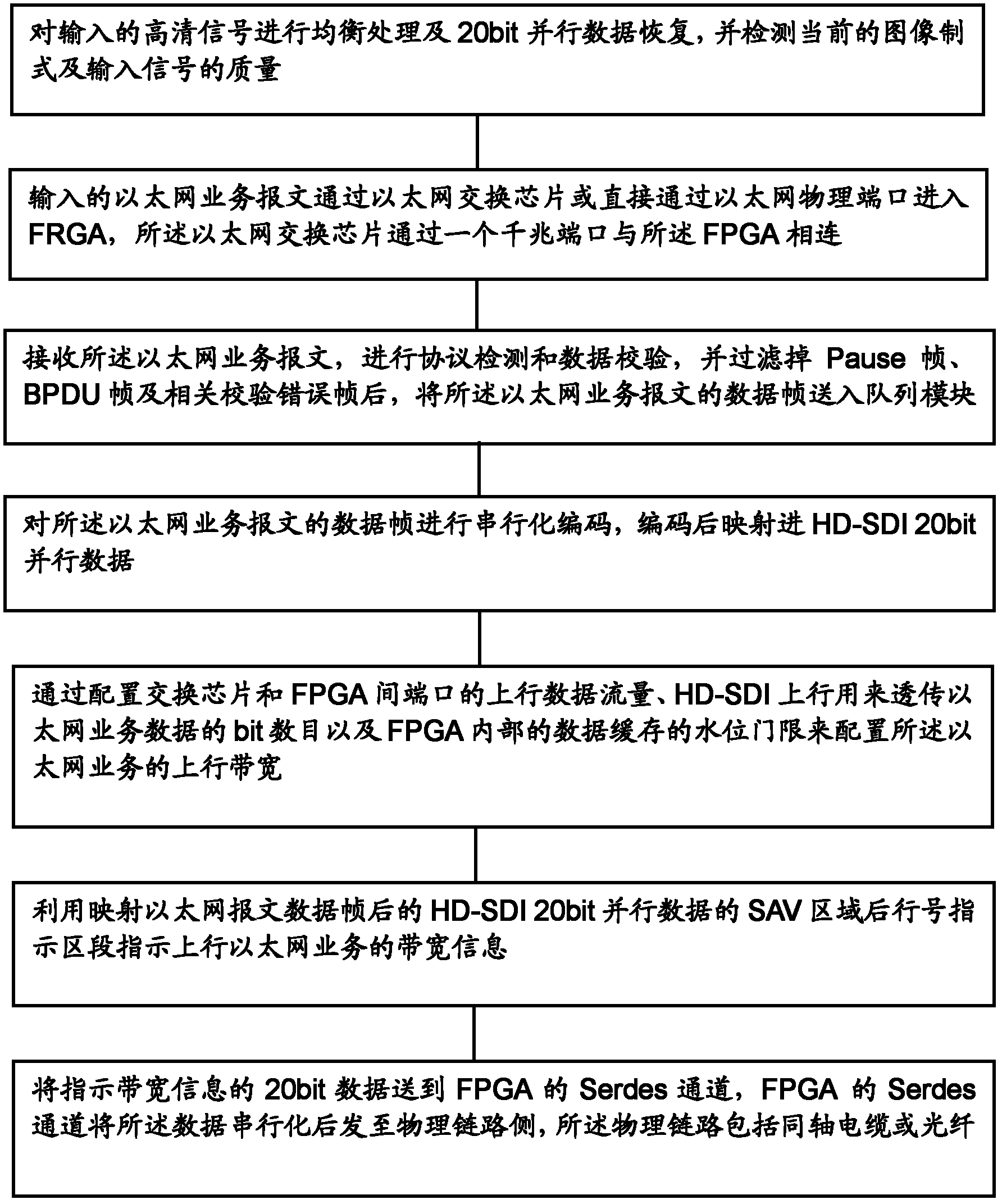

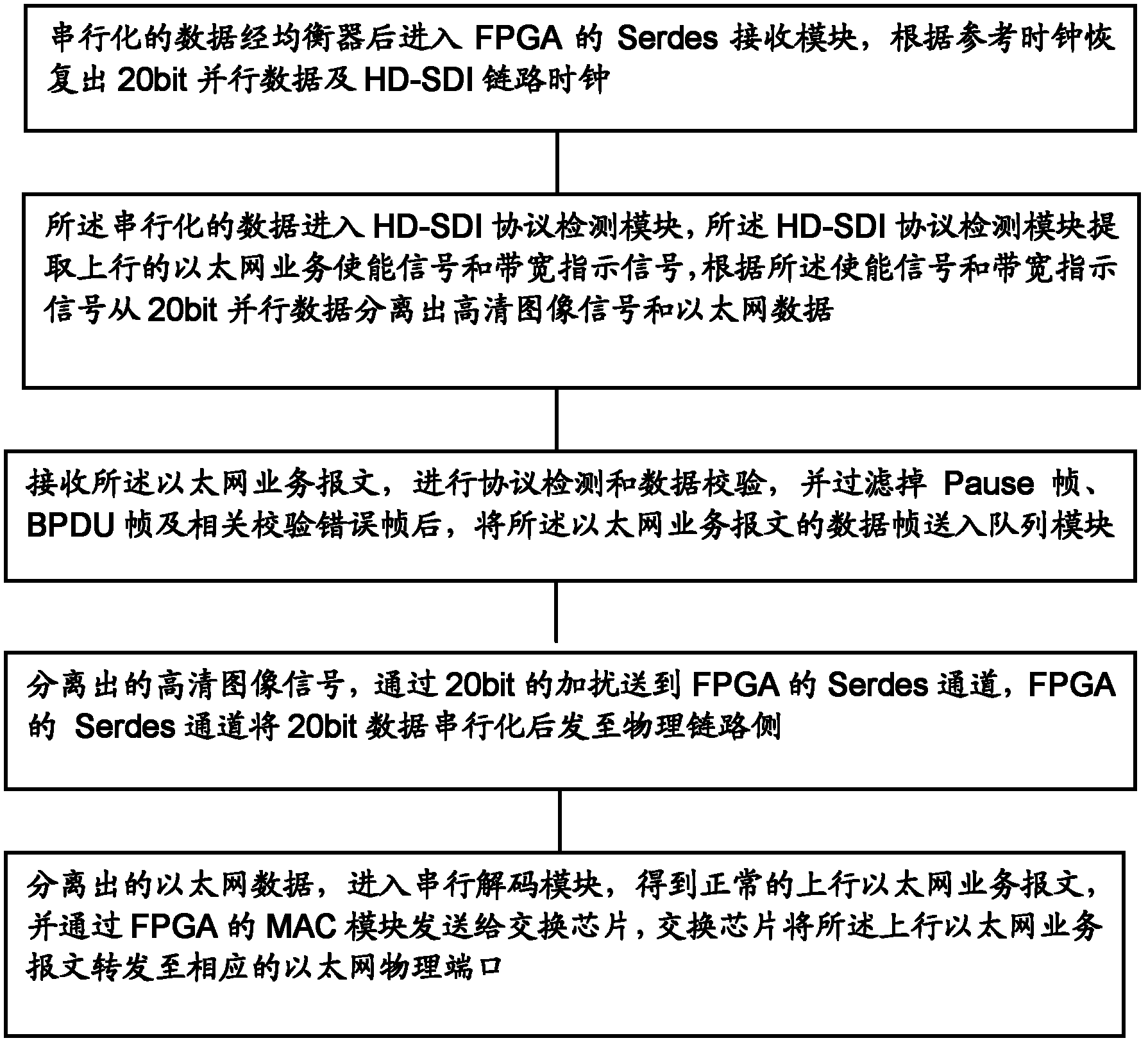

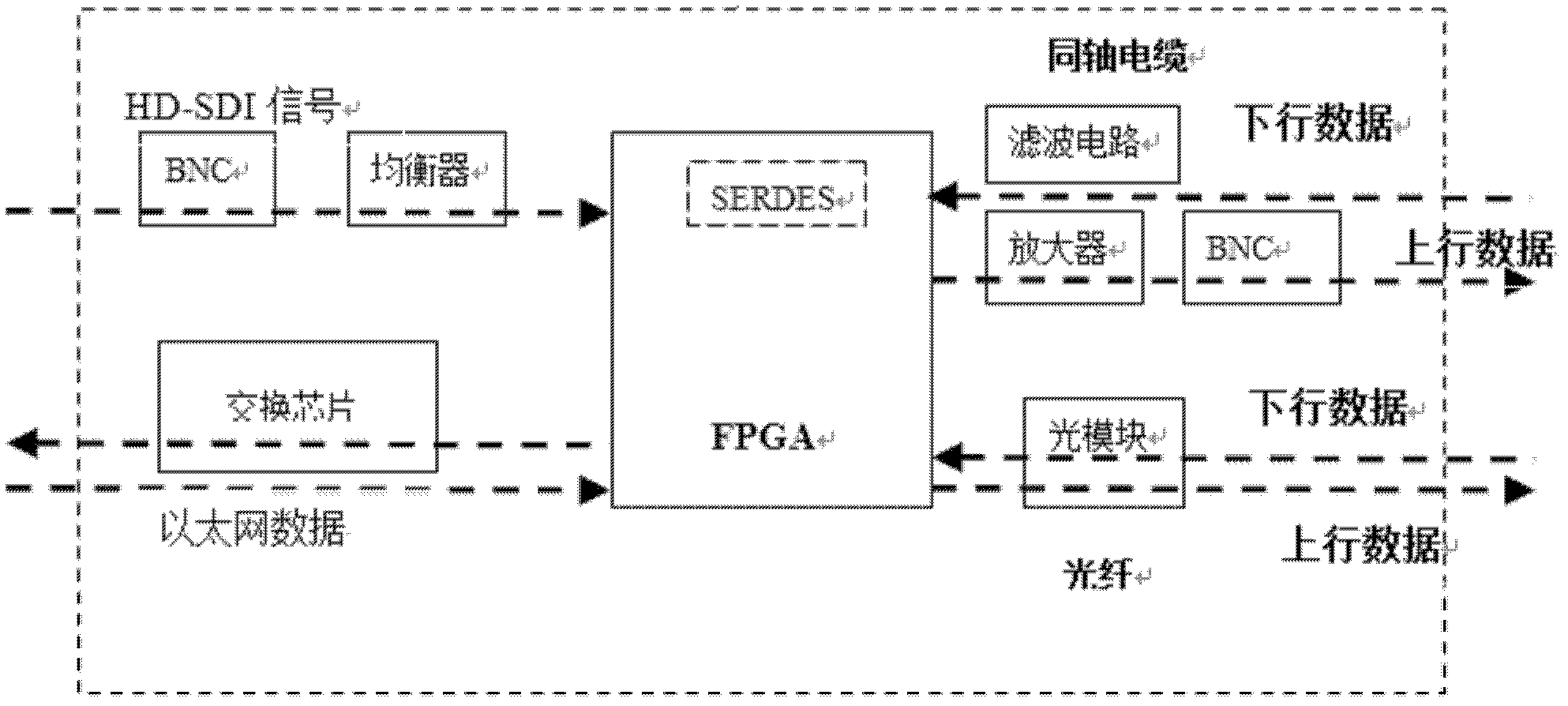

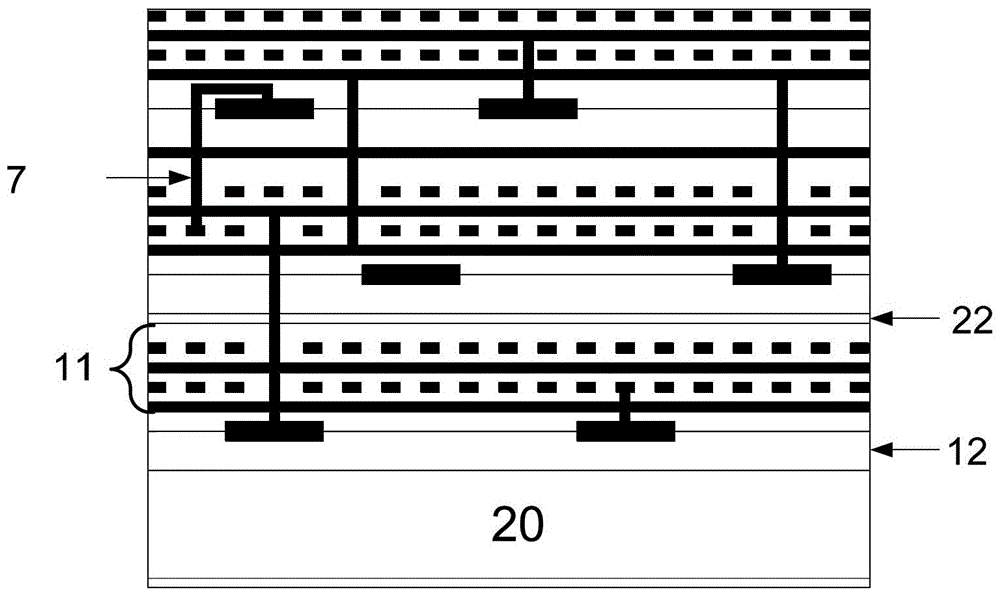

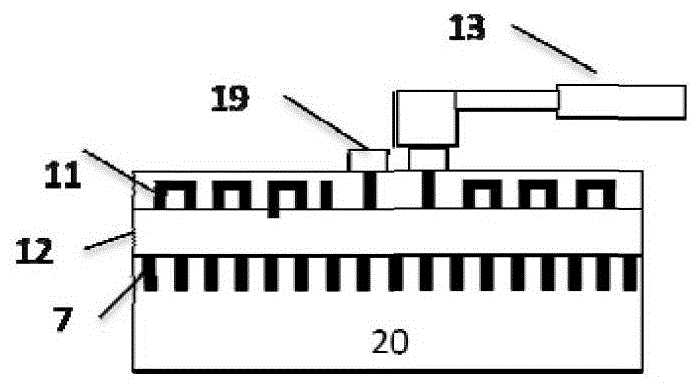

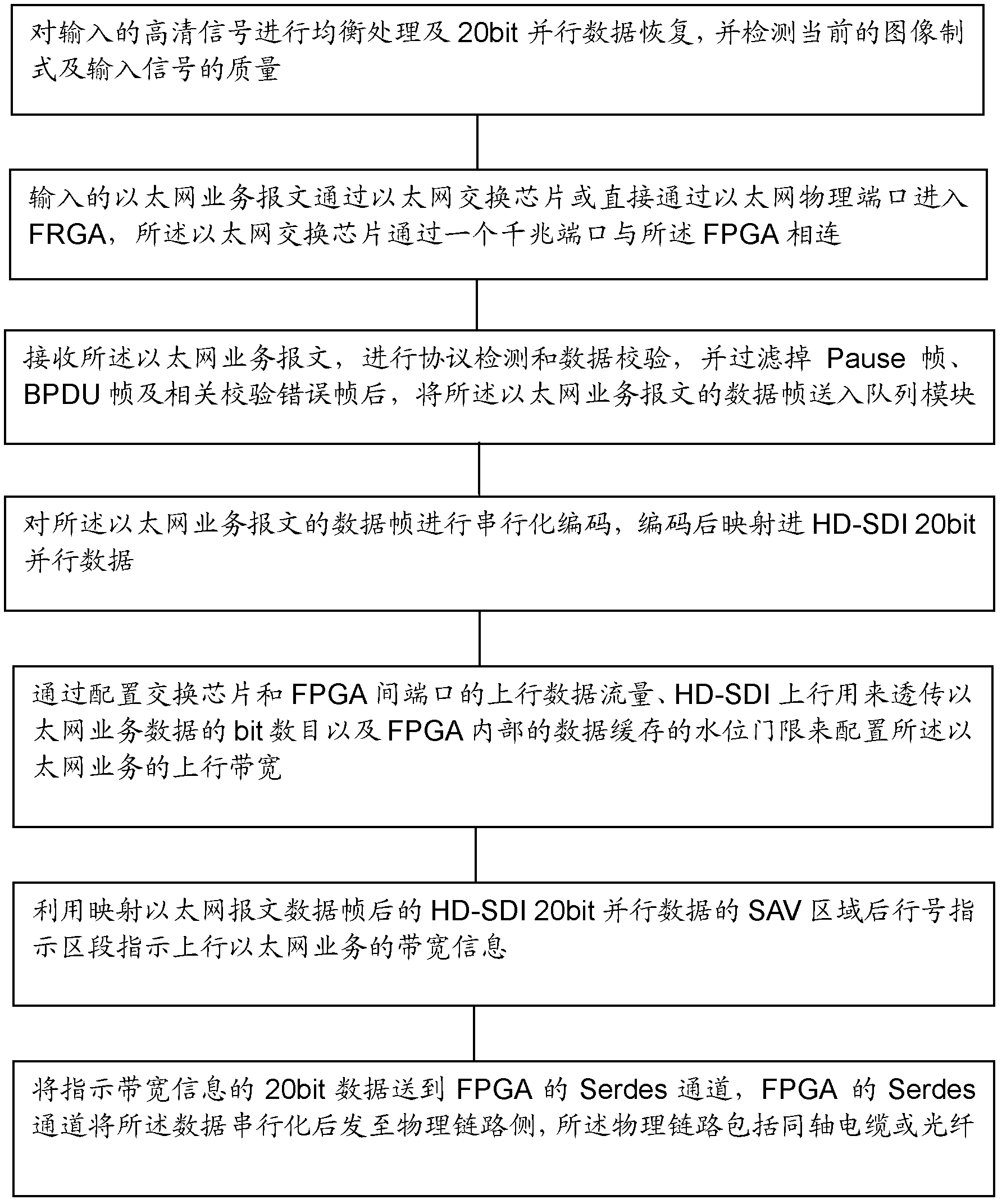

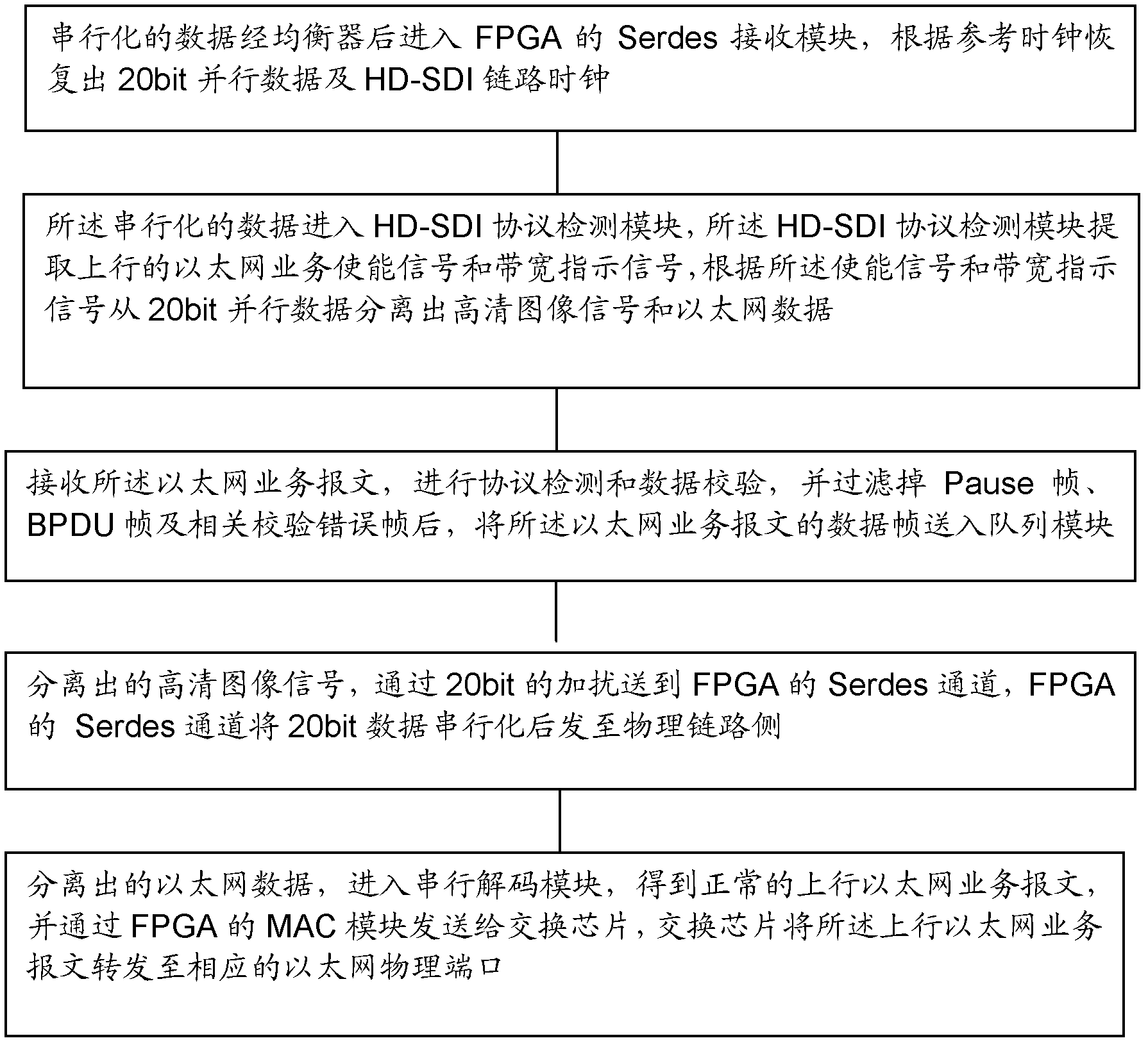

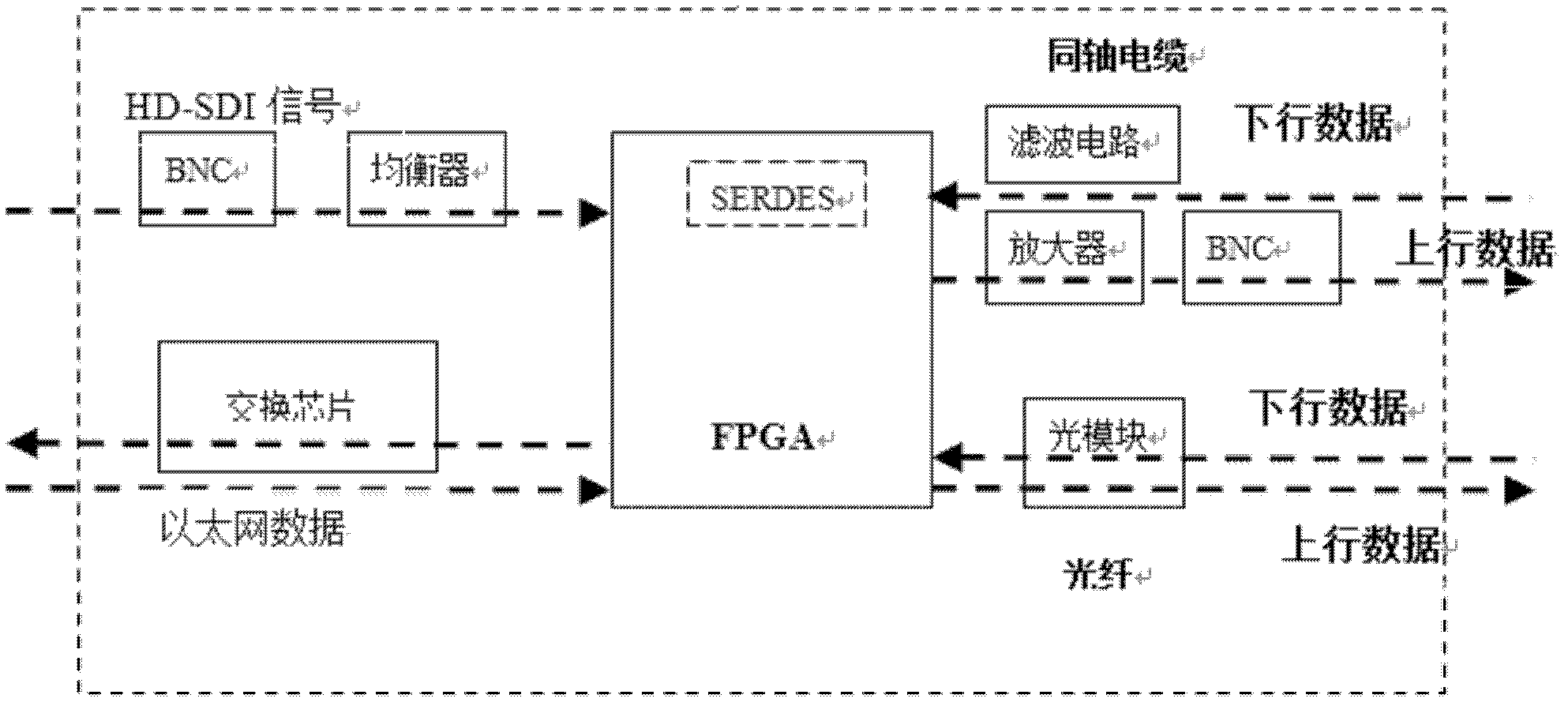

Ethernet service transmitting and receiving method and device capable of dynamically configuring bandwidth

ActiveCN102215173AAvoid interactionSave wiring resourcesTelevision systemsData switching networksSerial digital interfaceImaging quality

The embodiment of the invention discloses an Ethernet service transmitting and receiving method and device capable of dynamically configuring a bandwidth, which are used for the field of information transmission; an Ethernet data frame is scrambled into a high-definition image HD-SDI signal after being encoded; the Ethernet service is enabled and decoded to seamlessly fuse two service data of a HD-SDI (High-Definition Serial Digital Interface) image signal and Ethernet data on an HD-SDI; without substantially affecting the image quality, the bandwidth is dynamically configured to transmit the Ethernet service data while the HD-SDI image signal is transmitted; meanwhile, absolute isolation is assured at two levels of the high-definition image signal and the Ethernet service data so that the mutual influence during transmission is avoided. Therefore, a large quantity of wiring resources, huge time cost and human resources cost are saved for related projects in the fields like broadcast television, security monitoring and the like.

Owner:ENC DATA SERVICE CO LTD

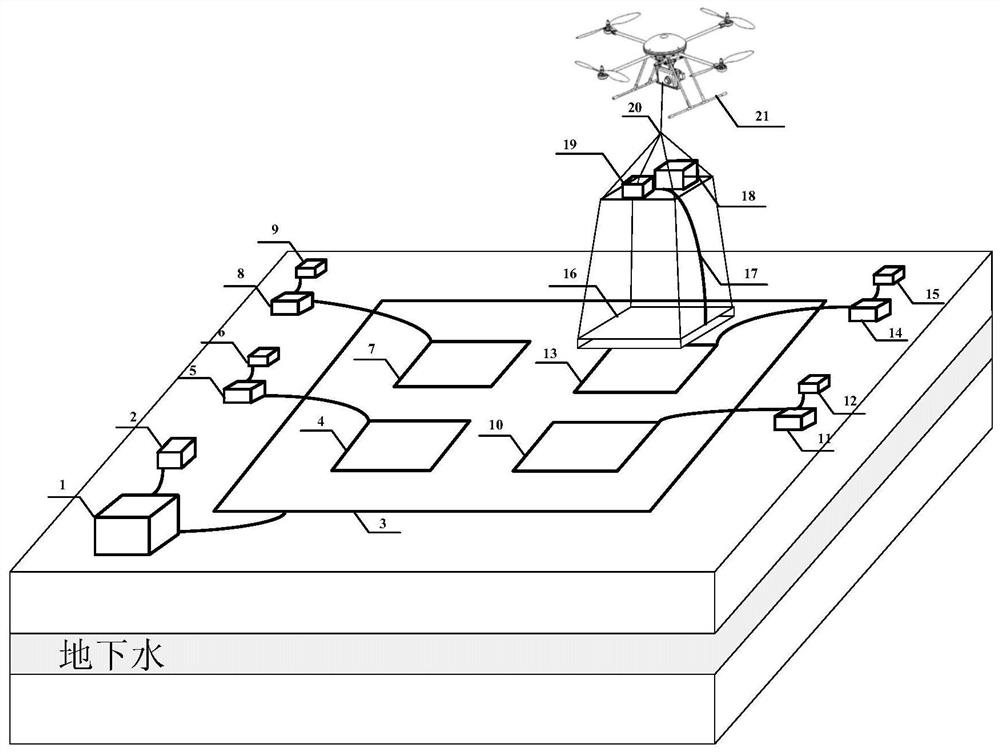

Distributed magnetic resonance underground water detection device and method

ActiveCN111856601AAvoid the trouble of frequently laying coilsFast detectionMagnetic measurementsWater resource assessmentWater sourceEngineering

The invention relates to a distributed magnetic resonance underground water detection device and method. The device comprises an excitation device, a polarization device, an air receiving structure carrying an array type cold coil sensor and a detection coil to which the air receiving structure belongs. A polarization transmitter determines the positions of the polarization transmitter and the airborne receiving structure through a position analysis module and determines whether the polarization transmitter outputs the signals or not. During detection, the polarization device polarizes a watersource to enhance the amplitude of a magnetic resonance signal; after the polarization current is quickly and stably turned off, the excitation device outputs instantaneous local Larmor frequency pulses to excite hydrogen protons in water; after excitation is stopped, the hydrogen protons return to the initial energy level, and an array type cold coil sensor is used for collecting magnetic resonance signals; and finally, the signal is transmitted to a handheld terminal through a wireless module to be displayed and stored. The distributed transmitting structure and the array type cold coil areused for detecting underground water, the advantages of being high in noise immunity, capable of achieving multi-dimensional fine imaging and high in efficiency are achieved, and the underground water exploration range is expanded.

Owner:JILIN UNIV

DCT rapid changing structure

InactiveCN1326397CReduce areaFast operationTelevision system detailsImage codingImage compressionDct transform

This invention provides a device for taking a two- dimensional fast DCT transform or a two -dimensional fast IDCT transform to the image data composed of 8X8 sub-block. Takes example for one dimensional DCT transform to 8X8 sub-block: the transform device comprises: the control circuit; the input deposit circuit; the butterfly operation circuit; the parallel / serial conversion circuit; table look up operation circuit; the output deposit circuit. The invention adopts the design philosophy that is to replace the multiply operation by look up table, so it need only once butterfly operation, 24 adder, 0 multiplying to complete once DCT. The design philosophy using the pipeline greatly increases the operating speed. The data can be inputted consecutively, the operation result can be gotten at each clock period. The invention is adapted to implement by using FPGA, the resource requirement saves above 30% than current structure. It can be applied in various image compression, especially in MPEG, H.26X format data that makes high requirement for the compression speed and quality.

Owner:杭州高特信息技术有限公司

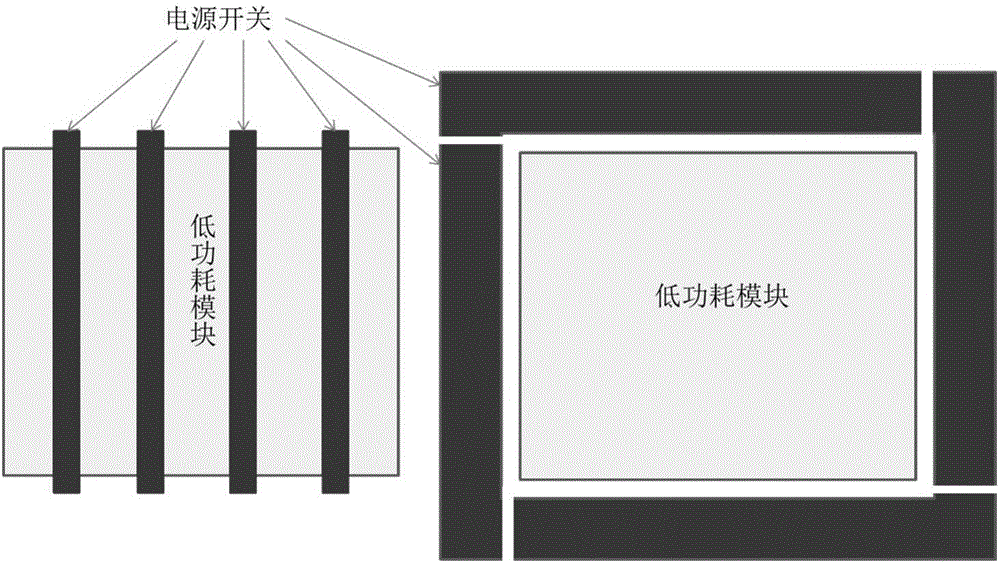

Surge current control module and method thereof

ActiveCN106849041AReduce sizeImprove reliabilityAc-dc conversionElectronic switchingPower switchingComputer module

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

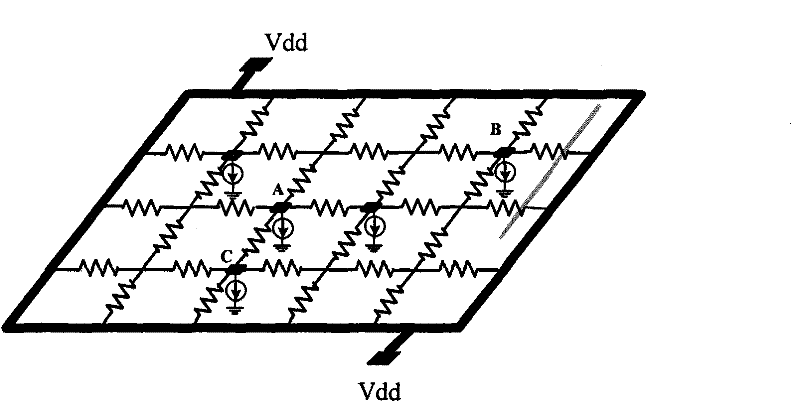

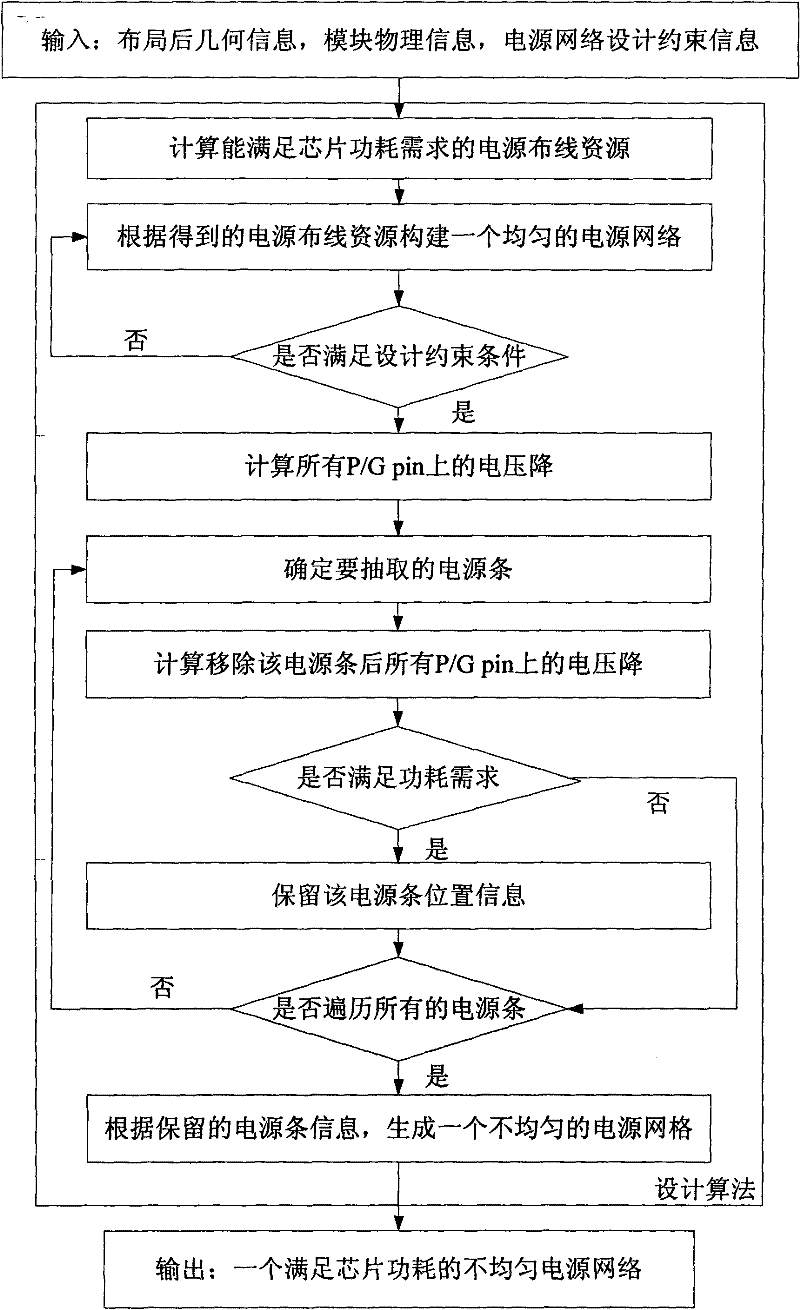

Method for designing power supply network quickly

InactiveCN101908080BGuaranteed performanceReduce the numberSpecial data processing applicationsElectrical currentSupply network

Owner:FUDAN UNIV

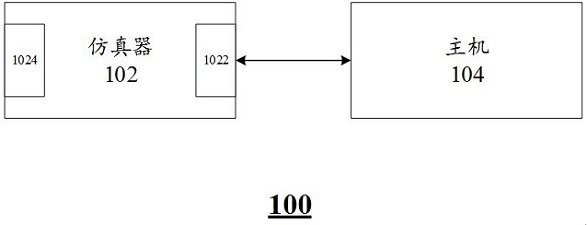

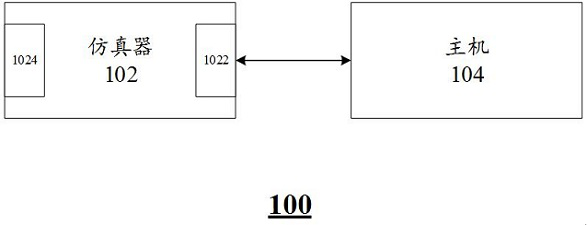

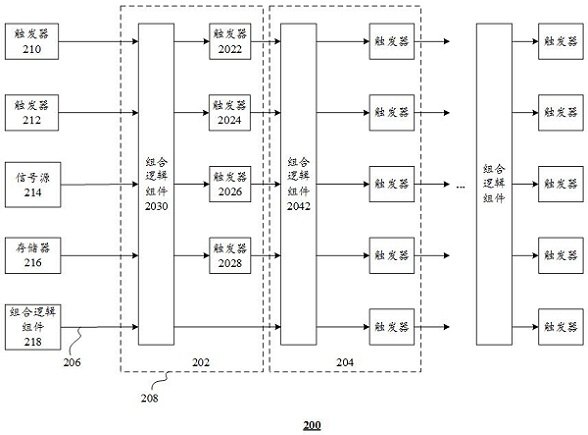

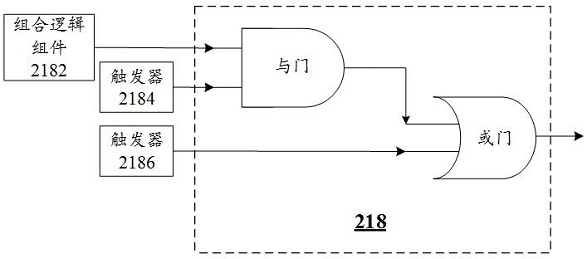

Method for debugging logic system design, simulator and storage medium

ActiveCN112100957ASave wiring resourcesShorten the detection timeComputer aided designSpecial data processing applicationsEmbedded systemSystems design

The invention provides a method for debugging logic system design, a simulator and a storage medium. The method comprises the following steps: cutting the logic system design into at least two blocks,wherein the at least two blocks comprise a target block; acquiring runtime information of a plurality of excitation signals of the target block; determining a circuit structure of the target block; and determining runtime information of output signals of a plurality of components of the target block according to the runtime information of the plurality of excitation signals of the target block and the circuit structure of the target block.

Owner:芯华章科技股份有限公司

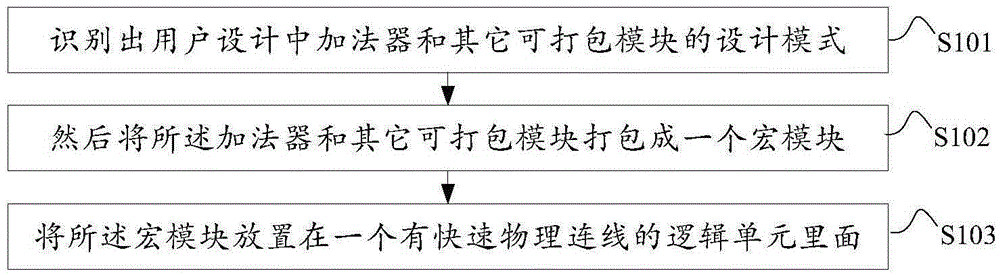

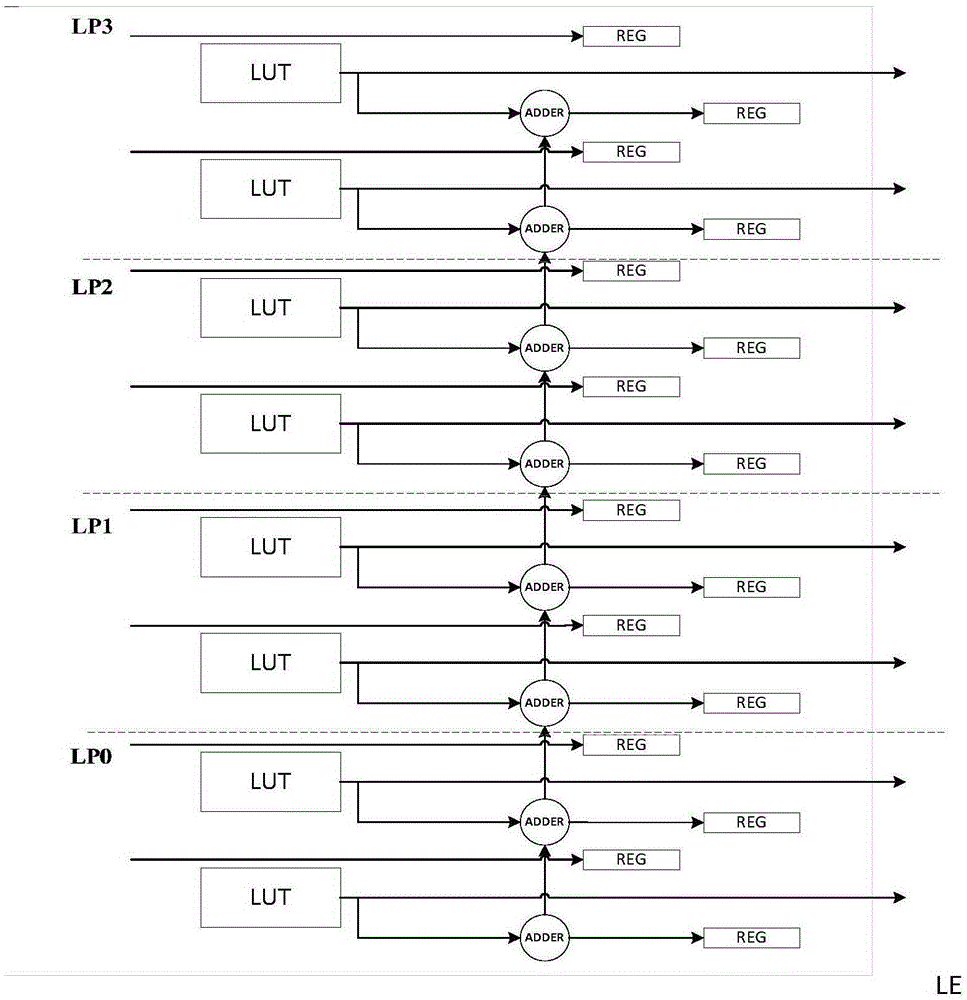

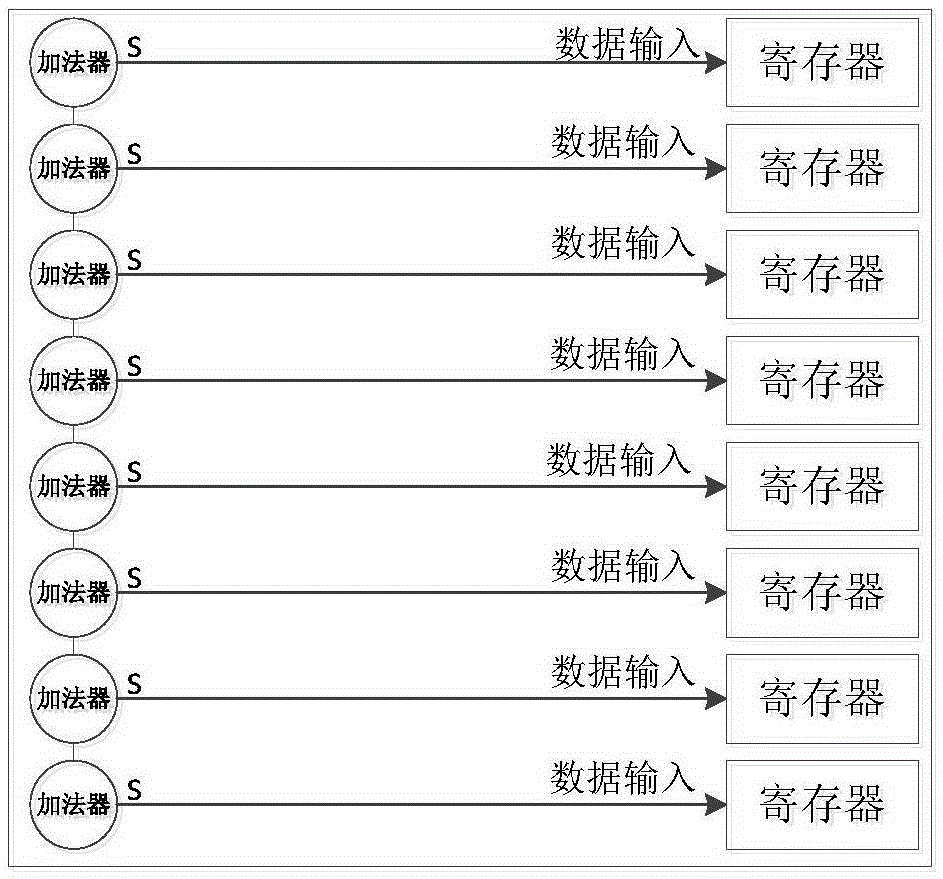

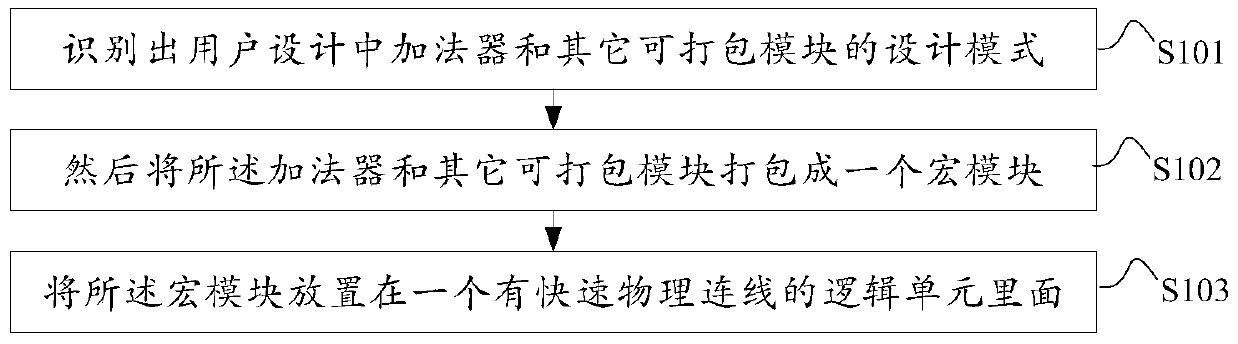

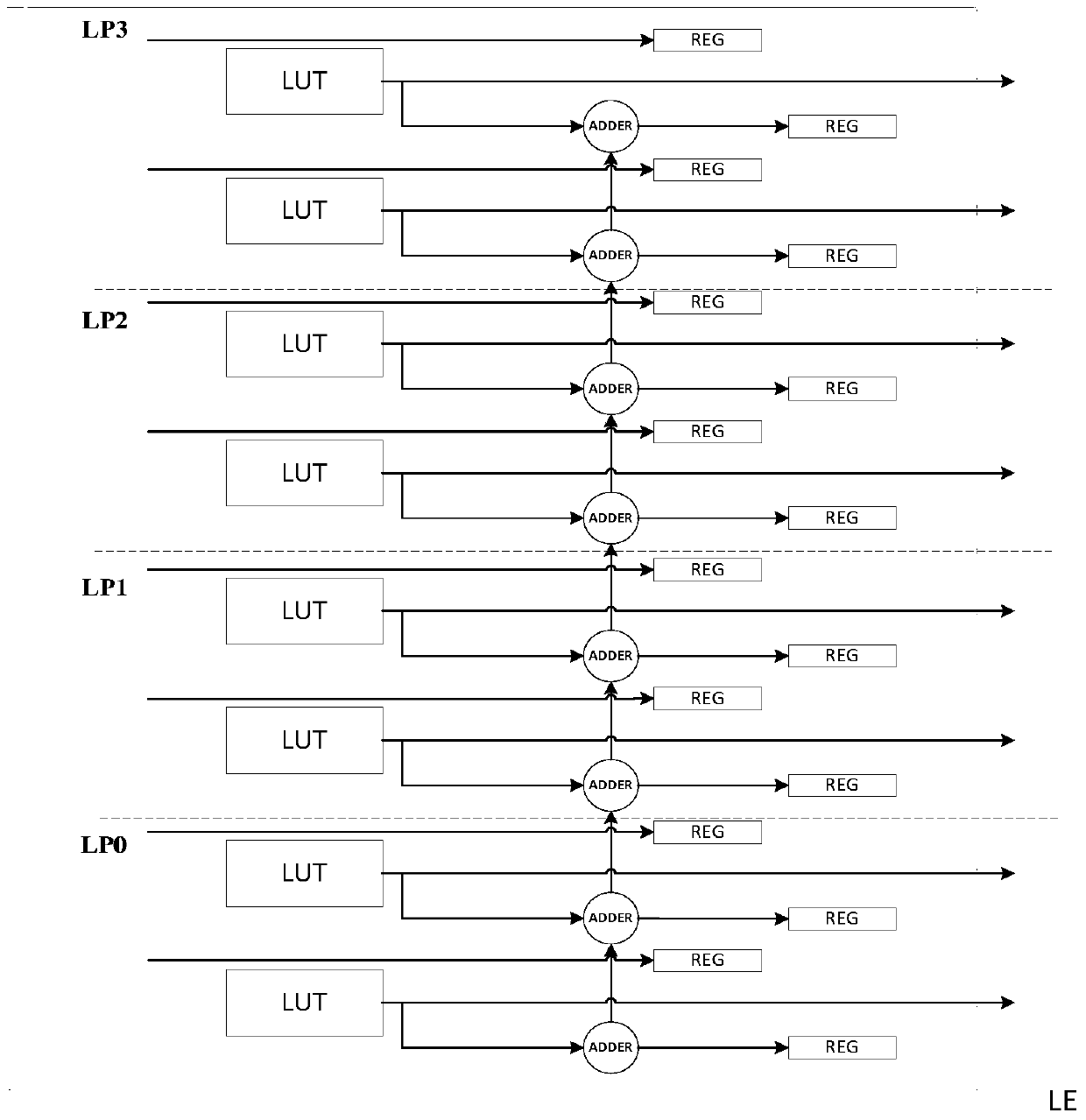

Method for packing and deploying adders

ActiveCN106649898AReduce usageSave wiring resourcesSpecial data processing applicationsTime delaysLogic cell

The invention relates to a method for packing and deploying adders. The method includes the steps of: identifying the design mode of the adders and other packageable modules in a design of a user; then packing the adders and other packageable modules into one macro block; and disposing the macro block in a logic unit with a fast physical connection line. According to the invention, the design mode of the user can be matched through a usage mode according to the inherent fast line resource of a chip; and after the design mode of the user is matched, the line routing resources used by the adders and other modules are reduced, thereby reducing usage of line routing resources and also reducing the time delay.

Owner:CAPITAL MICROELECTRONICS

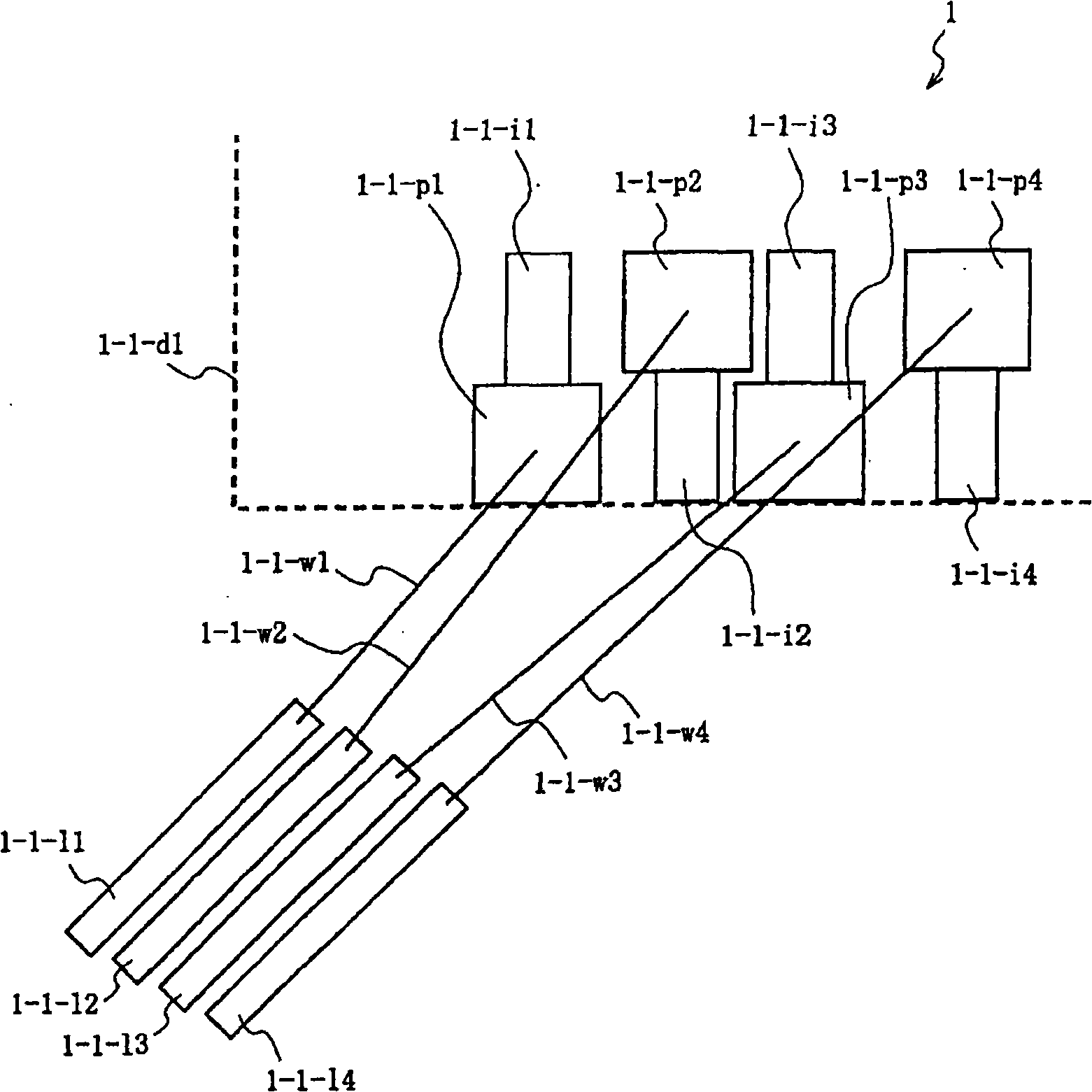

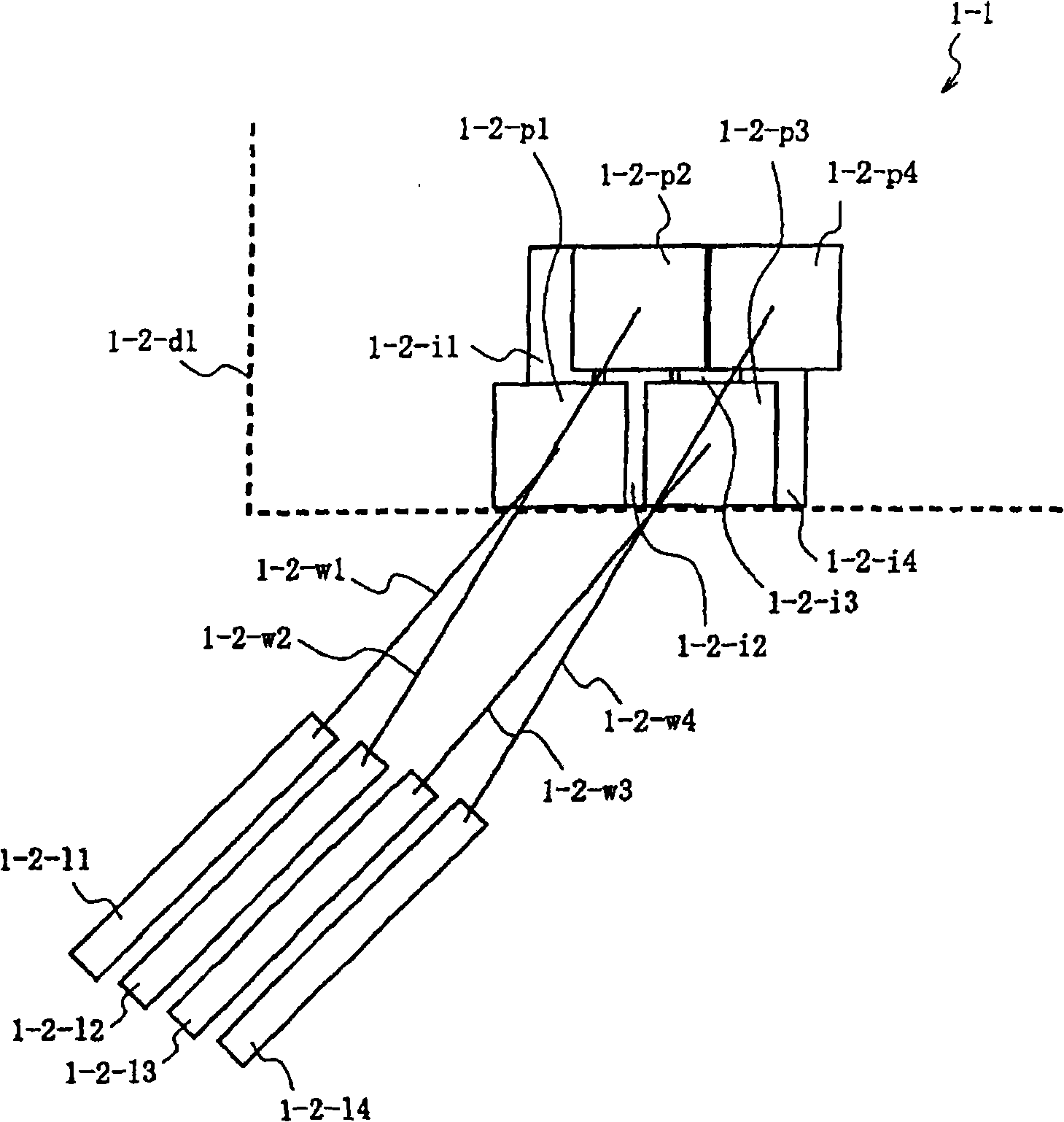

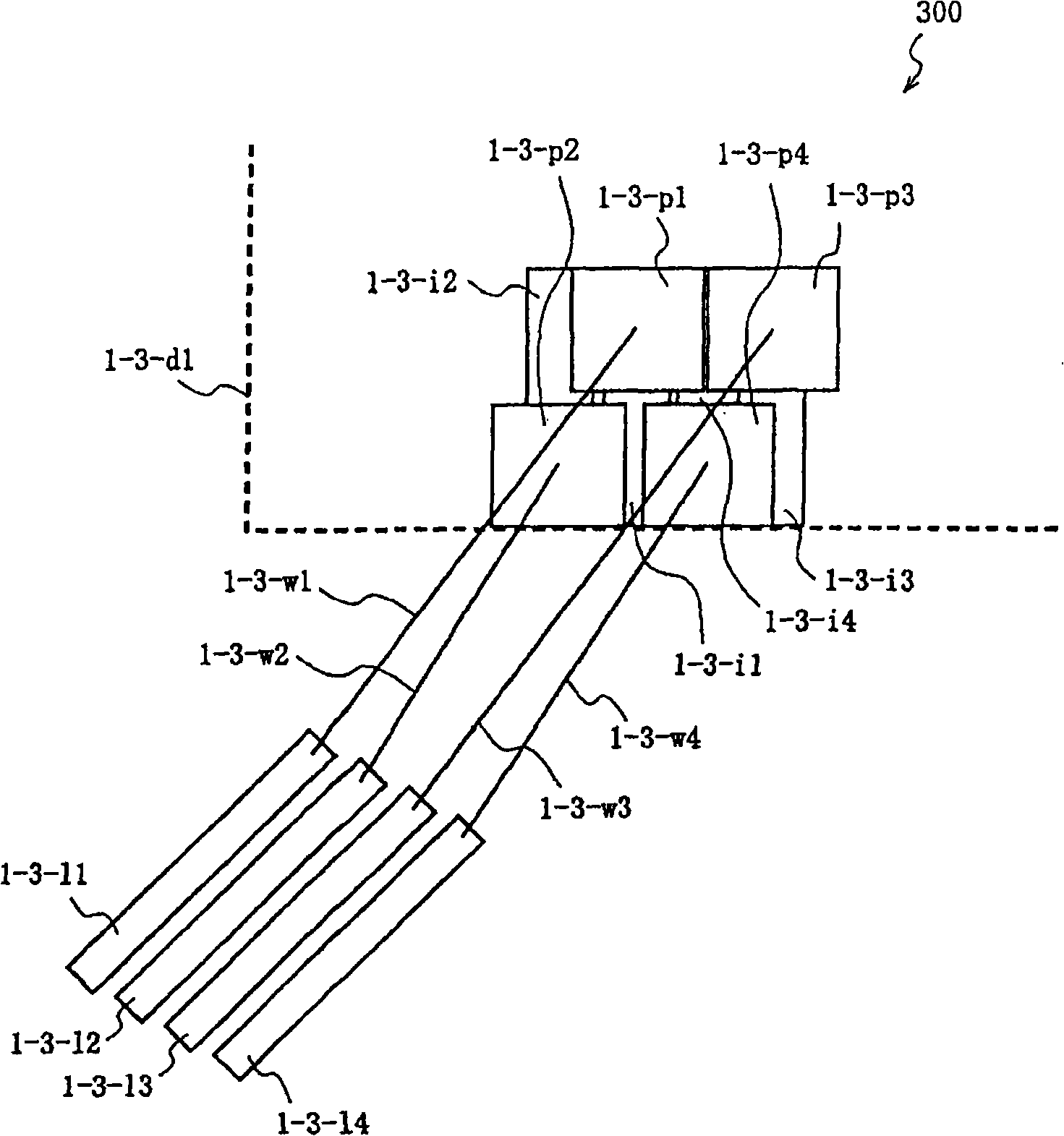

Semiconductor device

InactiveCN101263587ASmall sizeSituations to Avoid Causes of Bad WorkSemiconductor/solid-state device detailsSolid-state devicesChip sizePosition shift

Provided is a semiconductor device having staggered pad arrangement wherein pads are arranged by being alternately shifted, as a pad arrangement for connecting with an external package on an LSI. In the semiconductor device, wire short-circuit during assembly, chip size increase due to wire short-circuit prevention, propagation of power supply and GND noise due to reduction of an IO cell interval, signal transmission delay difference due to pad position shift, and the like can be eliminated. In the semiconductor device, a plurality of pads to be connected with functional terminals of the external package on the semiconductor element are arranged in two rows along the periphery of the semiconductor element. The arrangement order of the pads on the semiconductor element is different from that of the functional terminals of the external package.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

A noise processing method and a circuit after a noise processing process

ActiveCN103338007AImprove optimization efficiencyMeet trace noise voltage threshold requirementsNoise generationComputer science

The invention provides a noise processing method and a circuit after a noise processing process. The circuit after the noise processing process comprises at least two disturbed lines and at least one disturbing line. The number of parallel lines among the at least three line does not exceed two. Parallel portions exist between the disturbed lines and the disturbing line. Common parallel portions exist between the disturbed lines. The width of a gap between the common parallel portions is wider than or equal with a sum value of two times the width of a minimum line gap and the width of the line.

Owner:华力智芯(成都)集成电路有限公司

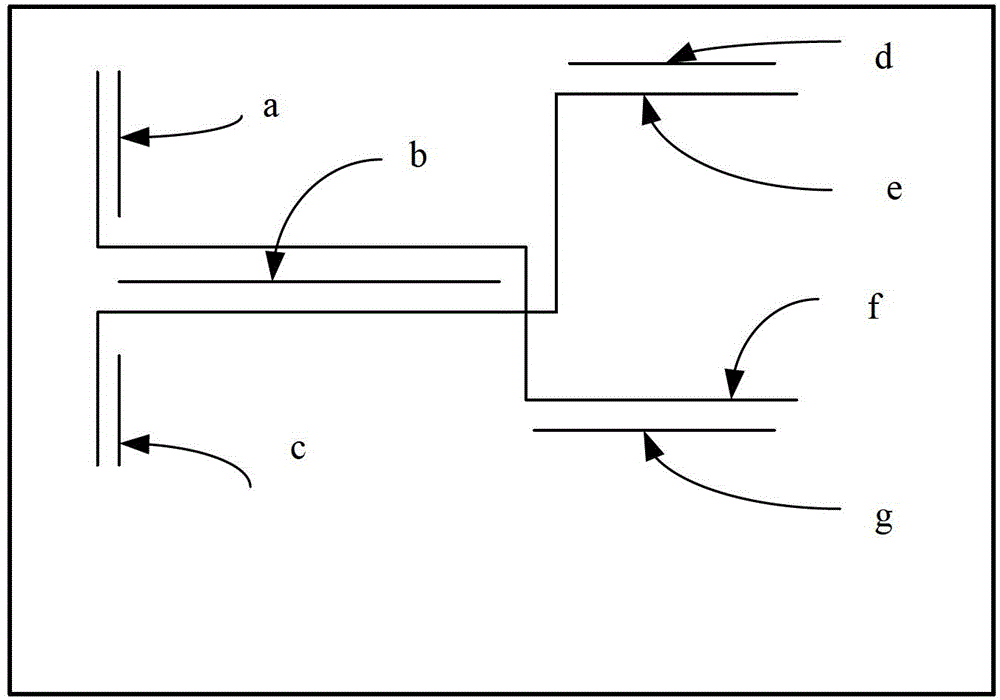

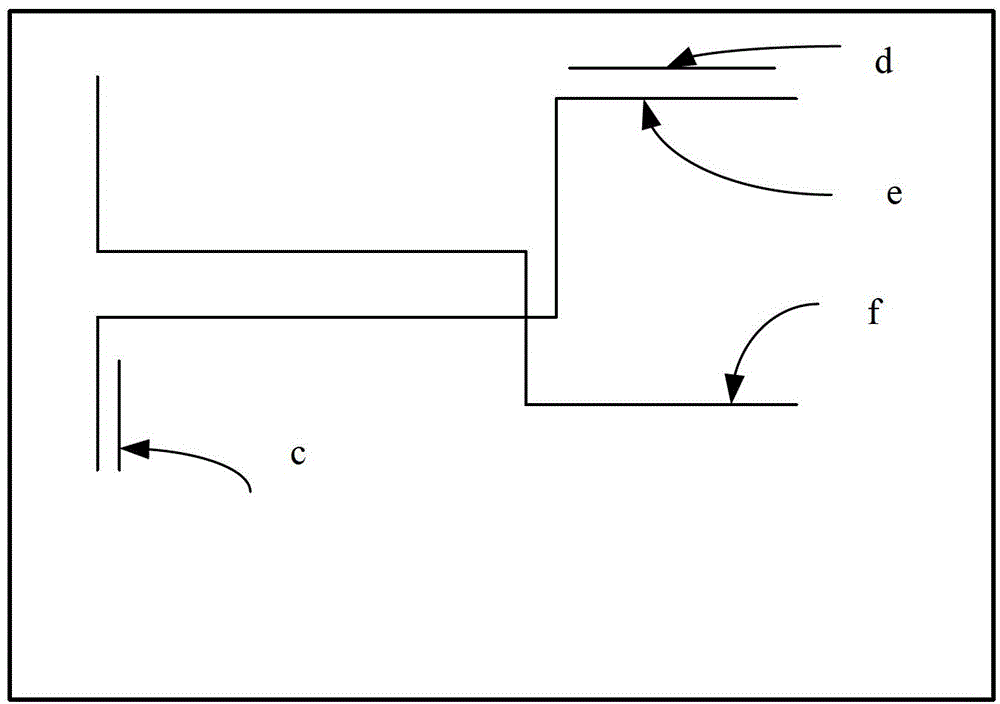

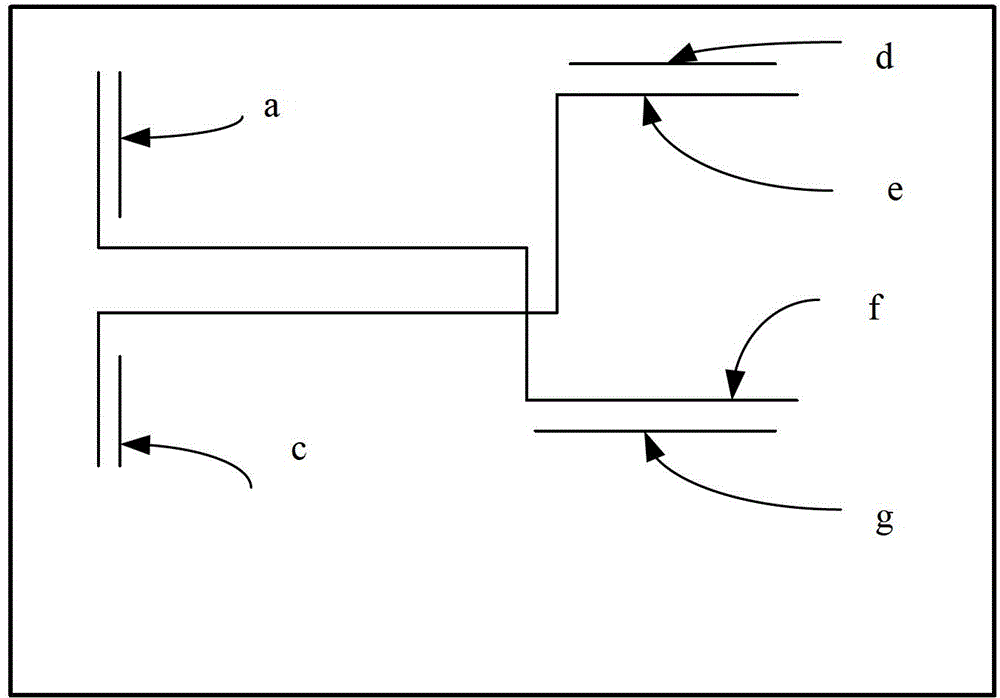

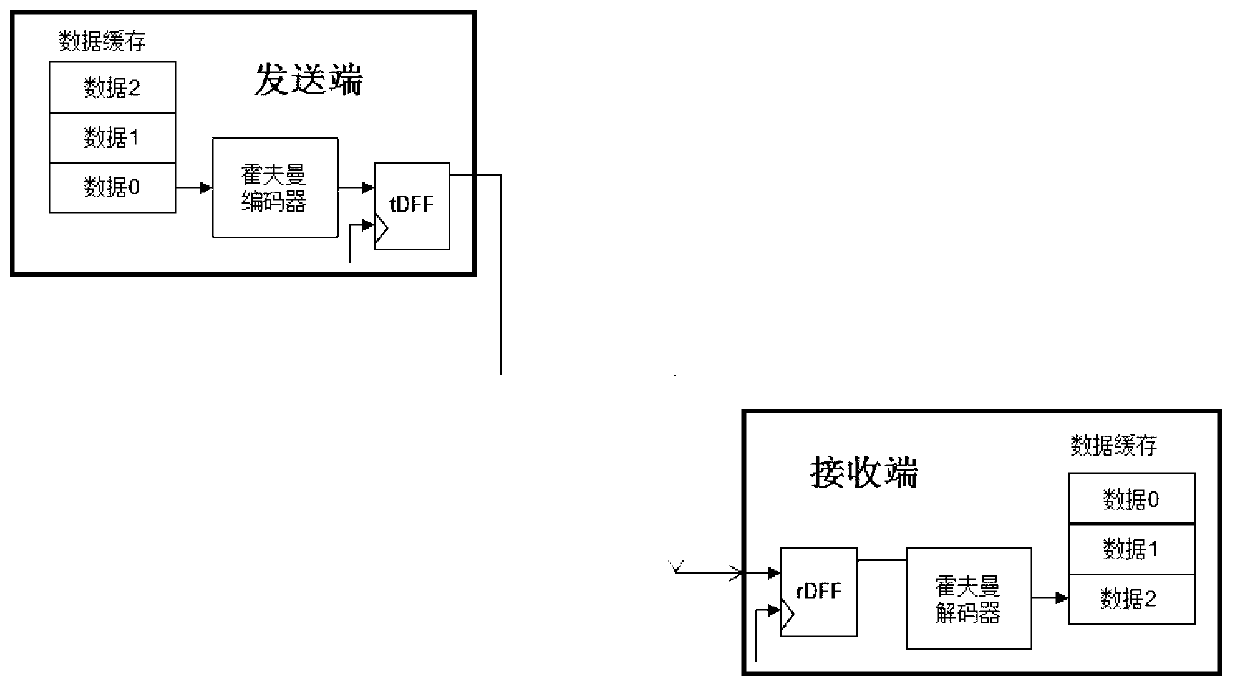

Method and circuit for transmitting data among modules in chip of integrated circuit by single-wire bus

ActiveCN103218476AReduce occupancySave wiring resourcesSpecial data processing applicationsTransmission protocolHuffman decoding

The invention relates to a method and a circuit for transmitting data among modules in a chip of an integrated circuit by a single-wire bus, and aims to solve the problems that the wiring resources are increased, the design flexibility is poor, and the manpower and material cost are increased because of transmitting the data among the modules in the chip of the conventional integrated circuit through a multi-wire bus. The method comprises the following steps of (1) performing Huffman coding on the data to be transmitted in the modules on the chip, and storing the coded data to a transmitting register; (2) transmitting the data in the transmitting register to an acquisition register through the single-wire bus; and (3) performing Huffman decoding on the data in the acquisition register, and extracting effective data for the module to receive data to use. The circuit mainly comprises a Huffman coder, the transmitting register, the acquisition register and a Huffman decoder. By the method and the circuit, least wiring resources are occupied; the transmission mode is flexible; the data can be transmitted and received at any time; a transmission protocol is simple; complex frame structure and packaging design are not required; and the circuit is simple in structure and easy to realize and has no special requirement on hardware.

Owner:XI AN UNIIC SEMICON CO LTD

A Packed Layout Method for Adders

ActiveCN106649898BReduce usageSave wiring resourcesSpecial data processing applicationsComputer architectureTime delays

Owner:CAPITAL MICROELECTRONICS

Centralized cache device and design method based on field programmable gate array

ActiveCN104252560BReduce occupancyIncrease the number ofSpecial data processing applicationsComputer architectureProcessor register

The invention relates to a centralized-cache device and design method based on field-programmable gate arrays and relates to the field of field-programmable gate array design, and the centralized-cache device and design method is adaptive to at least two same functional modules. The device comprises a time division multiplexing control unit, a signal serialization unit, a centralizing storage register, a combinational logic unit and a signal parallelization unit. The time division multiplexing control unit is used for dividing the period into two time slots with the same length of time, each time slot corresponds to one functional module sequentially, and each functional module performs input signal processing in the corresponded time slot. The signal serialization unit is used for converting the parallel input signals of each functional module into serial input signals. The centralizing storage register is used for storing the register of each functional module and reading and writing the register of the functional module in the time slot corresponding to the functional module. The combinational logic unit is used for combinational logic of input signal processing of single functional module. The signal parallelization unit is used for restoring serial output signals as parallel output signals after the input signals of each functional module are processed.

Owner:FENGHUO COMM SCI & TECH CO LTD

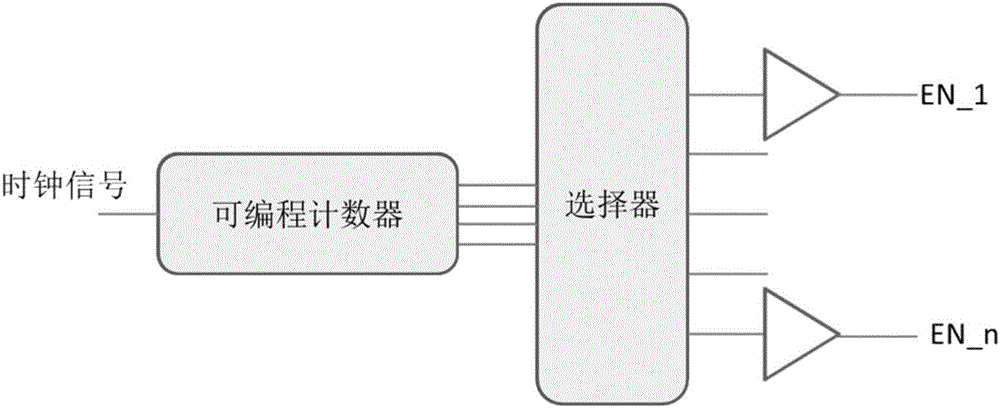

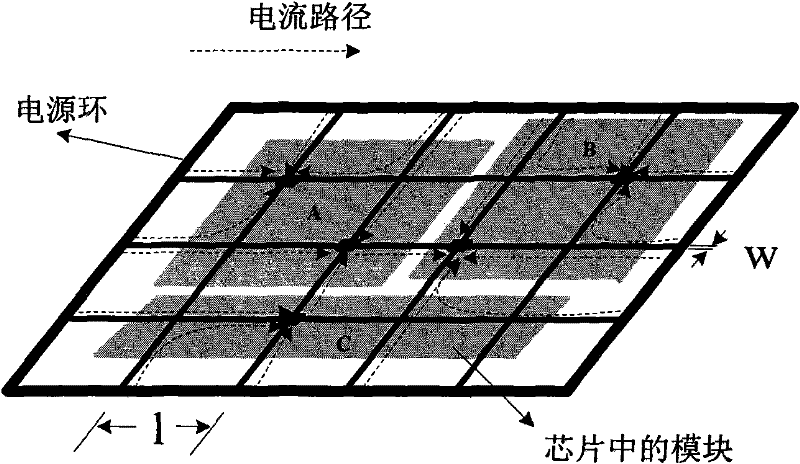

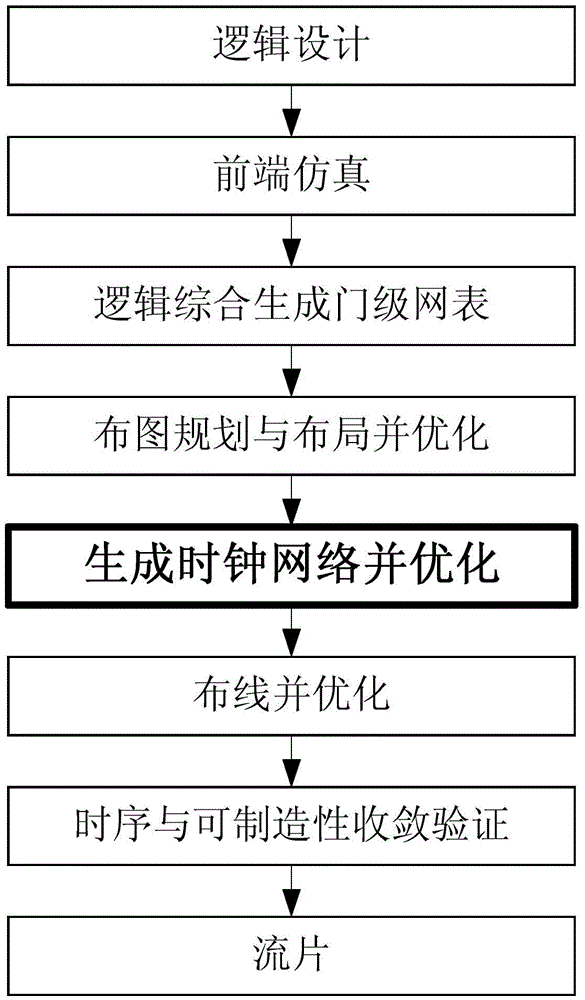

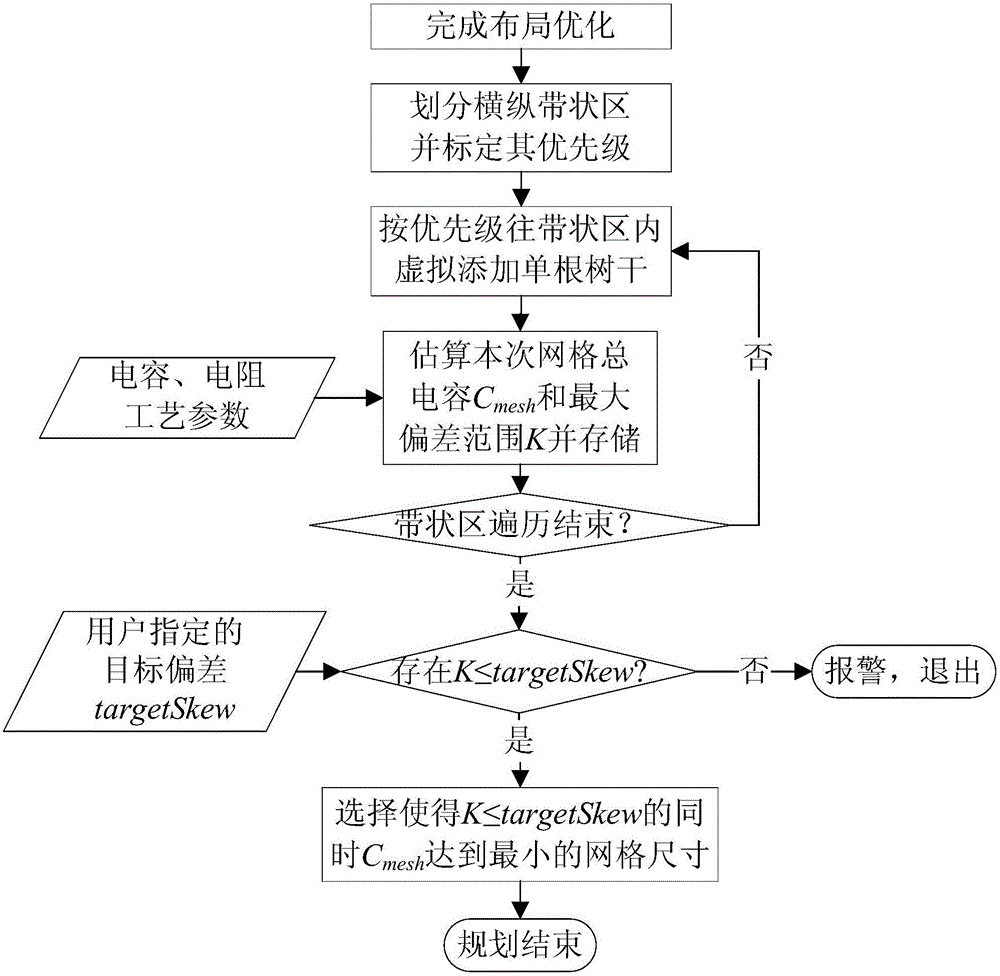

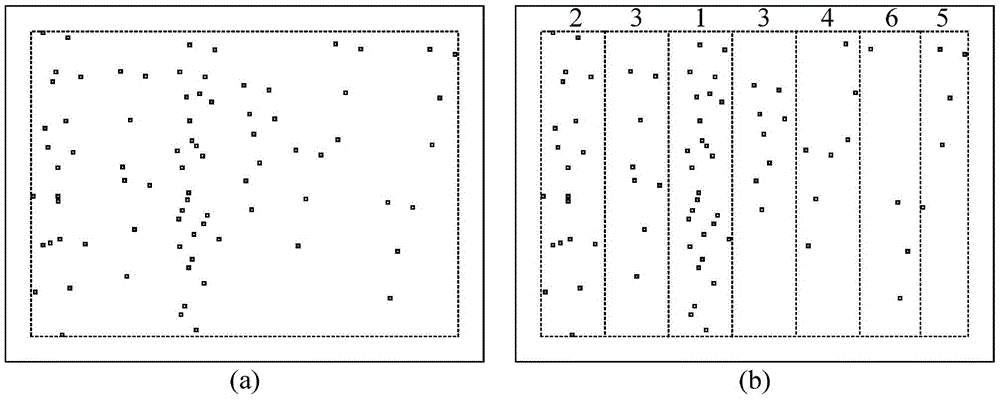

A Planning Method for Backbone Dimensions of Integrated Circuit Clock Grid

ActiveCN103605863BReduce power consumptionShorten connection lengthSpecial data processing applicationsCapacitanceClock offset

The invention discloses a method for planning the size of the trunk of clock meshes of an integrated circuit board. The method for planning the size of the trunk of the clock meshes of the integrated circuit board comprises the steps that (1) an arranged design is longitudinally and horizontally zoned evenly to obtain multiple strip-shaped areas; (2) the priorities of the strip-shaped areas are ranked according to the number of loads of the strip-shaped areas, wherein the larger the number of the loads of a strip-shaped area is, the higher the priority of the strip-shaped area is; (3) a single mesh trunk is virtually added to each longitudinal or horizontal strip-shaped area correspondingly in accordance with the order from the highest priority to the lowest priority, and the line capacitance and the clock offset range of the whole meshes are estimated every time one mesh trunk is virtually added until the mesh trunks are added to all the strip-shaped areas; (4) an overall mesh size which can guarantee that the estimated range clock offset range is within a clock offset value range which is assigned by a user and the line capacitance is the smallest serves as a final planning result. The method for planning the size of the trunk of the clock meshes of the integrated circuit board has the advantages that the clock wiring length is small, wiring resources are saved, the clock mesh power consumption caused by the line capacitance is low, the expansibility is good, and the clock line capacitance or the power consumption can be minimized on the premise that indexes of clock offset are obtained.

Owner:NAT UNIV OF DEFENSE TECH

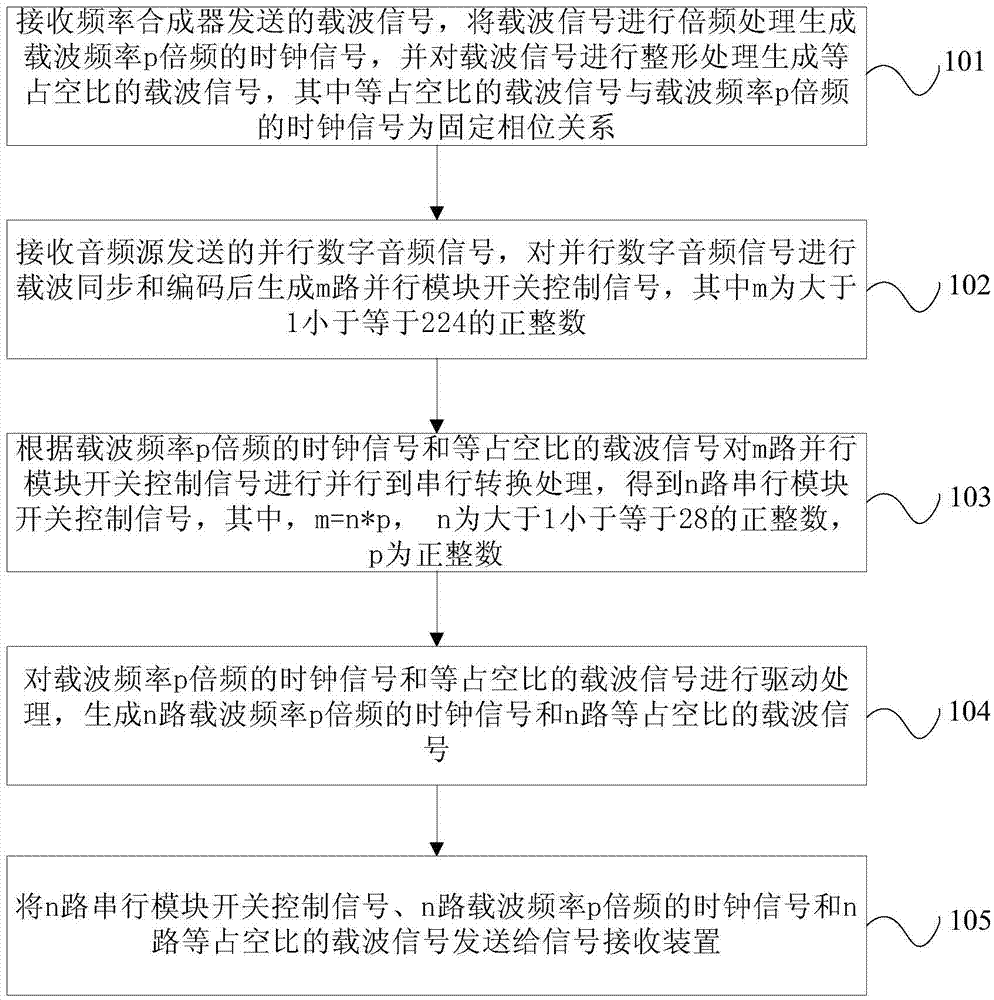

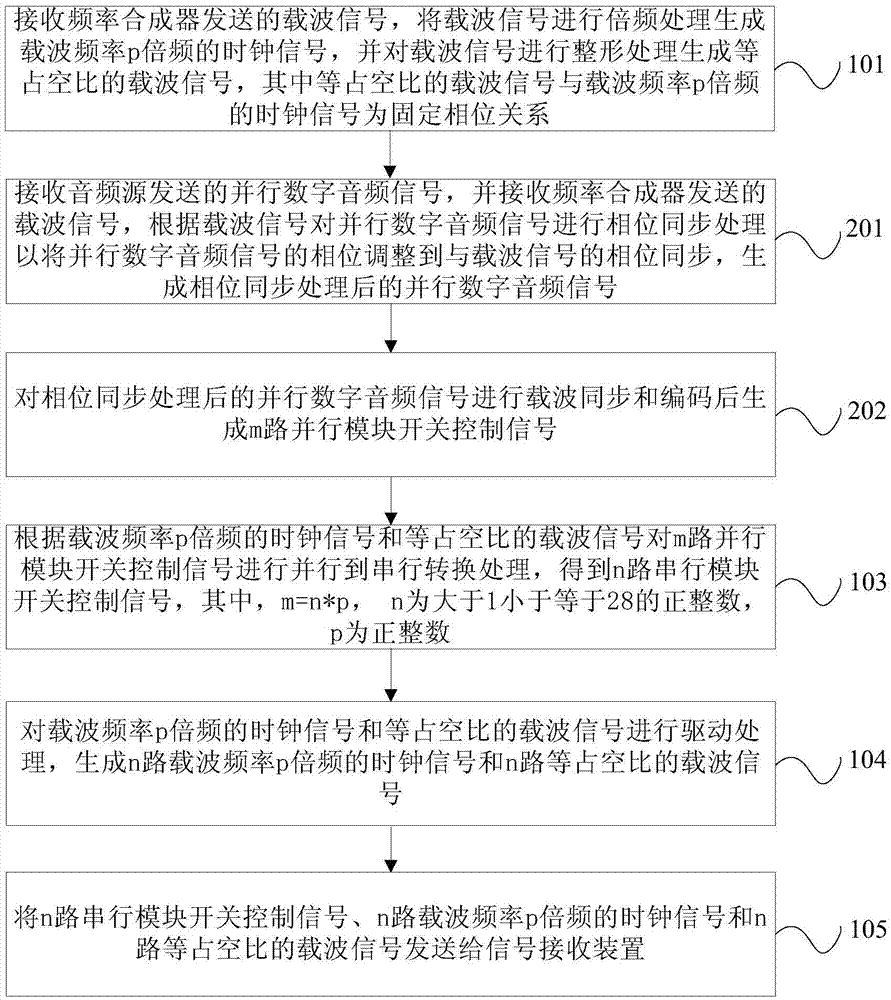

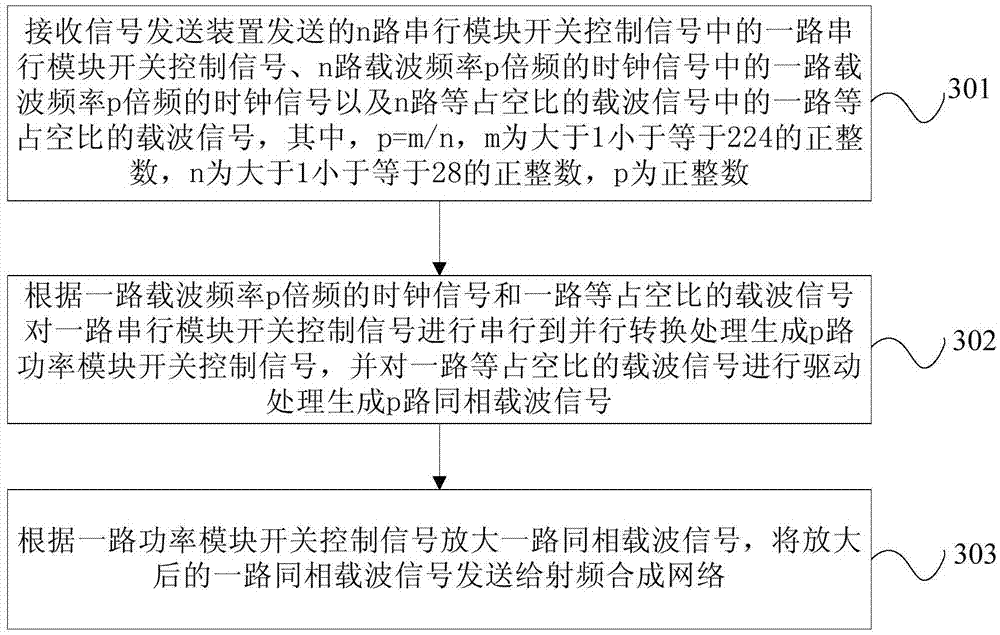

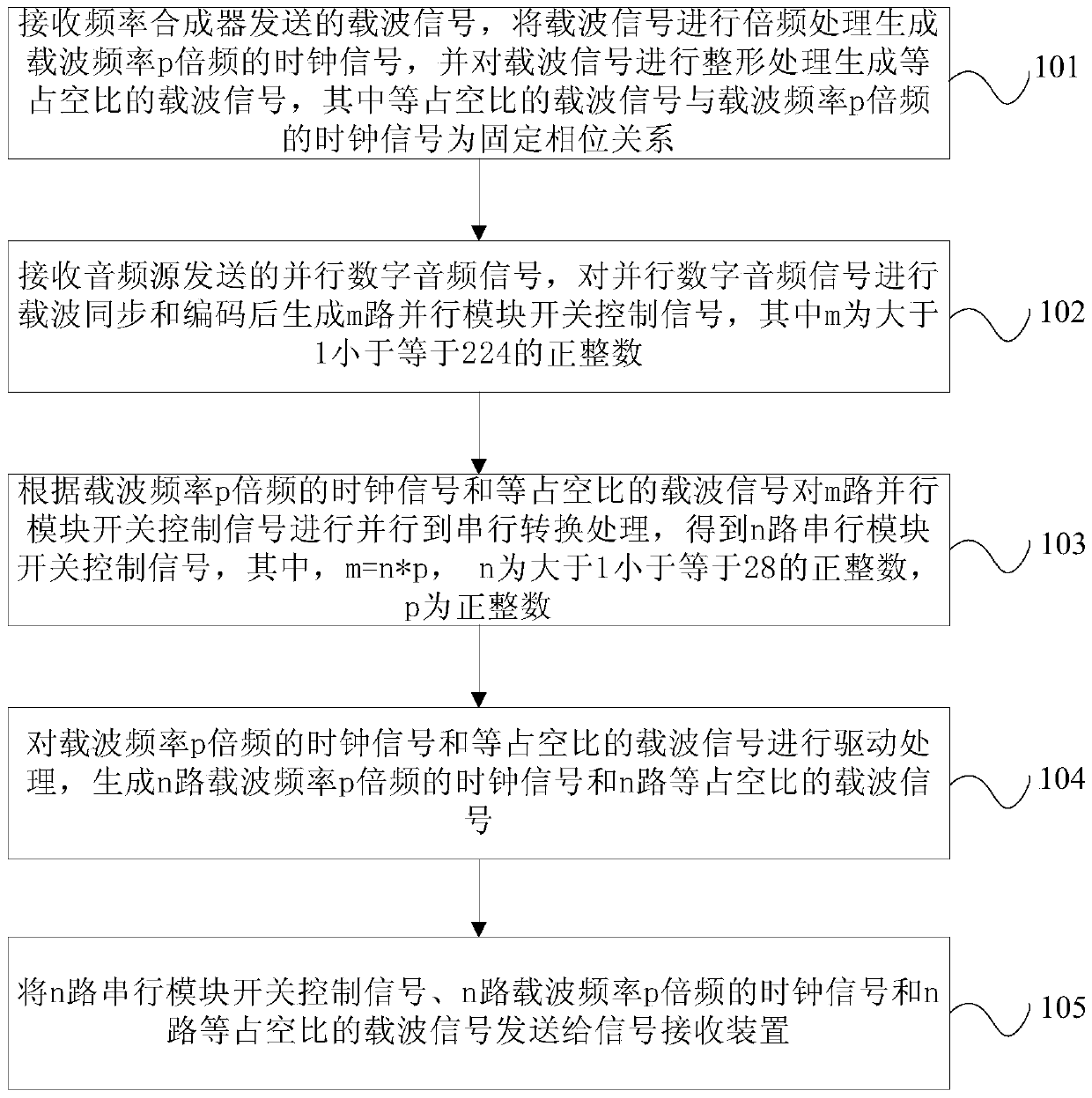

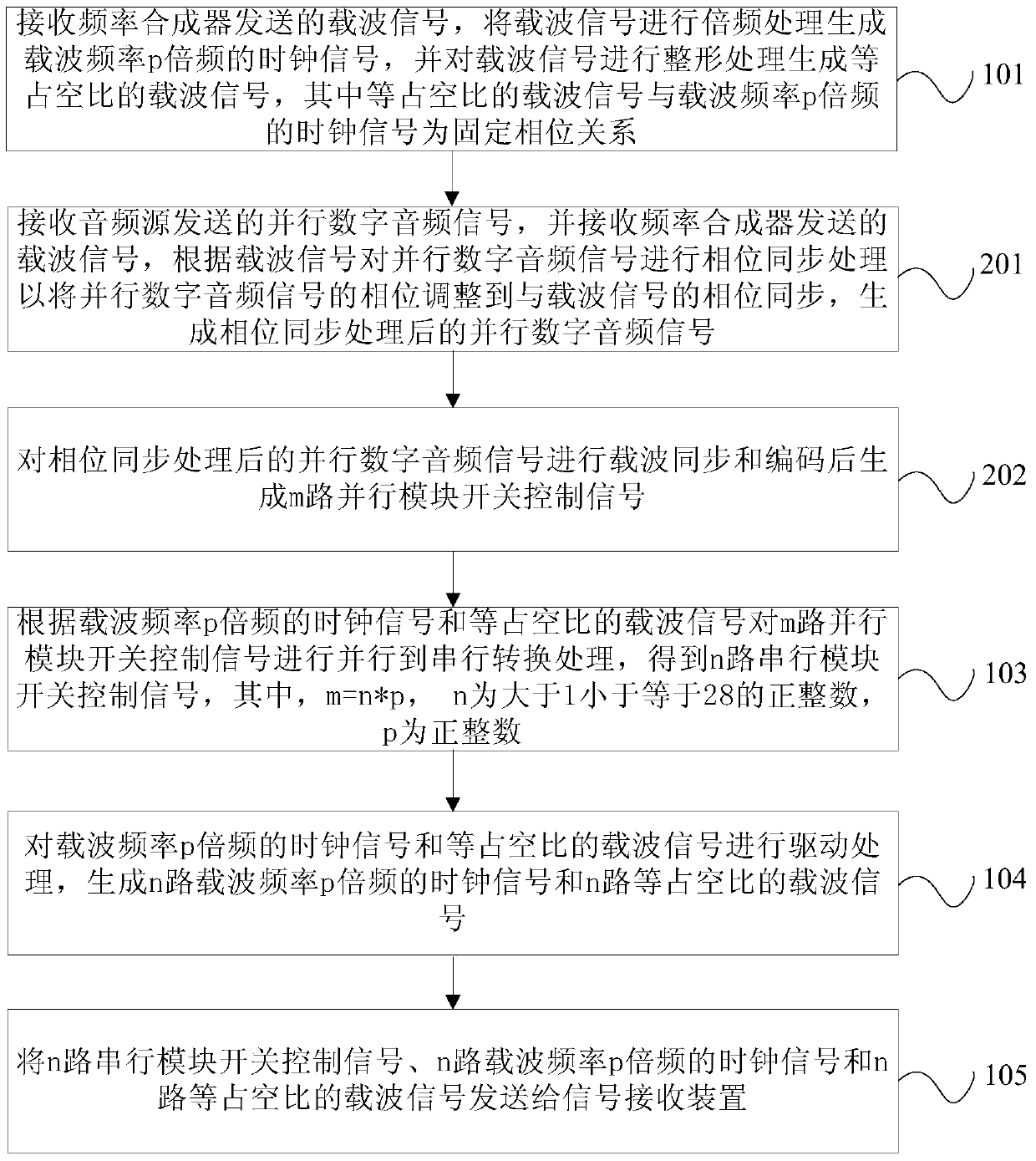

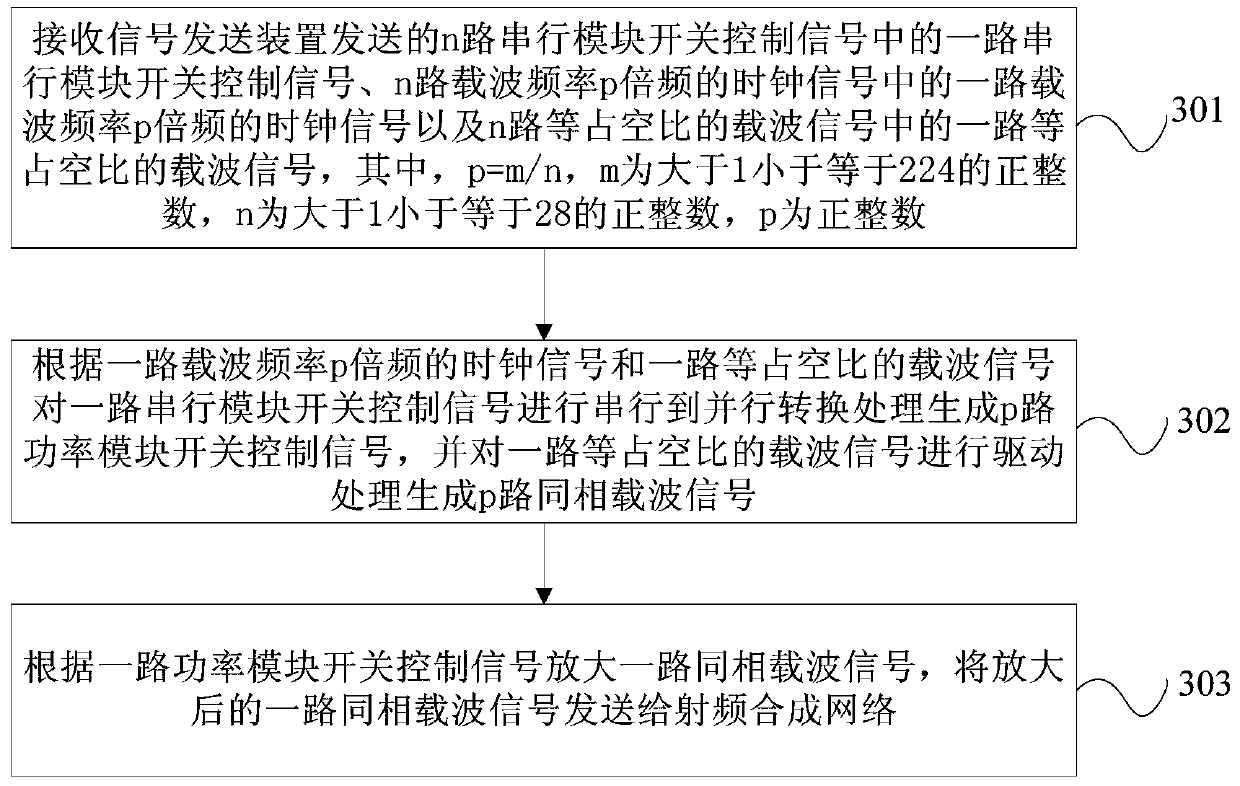

Signal transmission method, signal transmission device and signal receiving device

ActiveCN106911357AReduce connecting cablesGenerate fewer pathsSynchronisation information channelsPhase-modulated carrier systemsControl signalCarrier signal

The invention provides a signal transmission method, a signal transmission device and a signal receiving device. The method comprises the steps of carrying out parallel-to-serial conversion processing on m parallel module switching control signals according to clock signals of which carrier frequency is multiplied by p and carrier signals with equal duty cycles, thereby obtaining n serial module switching control signals; carrying out drive processing on the clock signals of which carrier frequency is multiplied by p and the carrier signals with the equal duty cycles, thereby generating n clock signals of which carrier frequency is multiplied by p and n carrier signals with the equal duty cycles; and sending the n serial module switching control signals, the n clock signals of which carrier frequency is multiplied by p and the n carrier signals with the equal duty cycles to a signal receiving device, wherein the m is equal to n*p, the m is greater than 1 and is smaller than or equal to 224 and the m is a positive integer, the n is greater than 1 and is smaller than or equal to 28 and the n is the positive integer, and the p is the positive integer. A great number of wiring resources are reduced, and the same frequency interference between the carrier signals and the module switching control signals is reduced.

Owner:ADMINISTATION OF RADIO STATIONS OF STATE ADMINISTATION OF PRESS PUBLICATION RADIO FILM & TELEVISION +2

A Probabilistic Calculation-Based Artificial Neural Network Hardware Realization Device

The invention relates to an artificial neural network hardware implementation device based on probability calculation. The artificial neural network hardware implementation device based on probability calculation comprises input, intermediate and output modules. The input module is formed by I input neurons, and the input neurons receive first data and output a first random data sequence; the intermediate module is formed by J intermediate neurons, and the intermediate neurons receive the first random data / parameter sequence and output a second random sequence; and the output module is formed by K output neurons, and the output neurons receive the second random data / parameter sequence and output the second data, wherein I, J and K are integers greater than or equal to 1. The output end of the input neurons is connected with the input end of the intermediate neurons, the output end of the intermediate neurons is connected with the input end of the output neurons, and a complete or partial connection mode is adopted. The first and second random data sequences and the first and second random parameter sequences are expressed by the probability values of 0 or 1 appearing in the data sequences within a period of time. According to the neural network device, hardware logic and wiring resources can be greatly reduced, and circuit cost and power consumption can be reduced so that implementation of a super-large-scale neural network through small and medium-sized circuits is enabled to be possible.

Owner:SHANGHAI UNIV

Signal transmission method, signal sending device and signal receiving device

ActiveCN106911357BReduce connecting cablesGenerate fewer pathsSynchronisation information channelsPhase-modulated carrier systemsTelecommunicationsControl signal

Owner:ADMINISTATION OF RADIO STATIONS OF STATE ADMINISTATION OF PRESS PUBLICATION RADIO FILM & TELEVISION +2

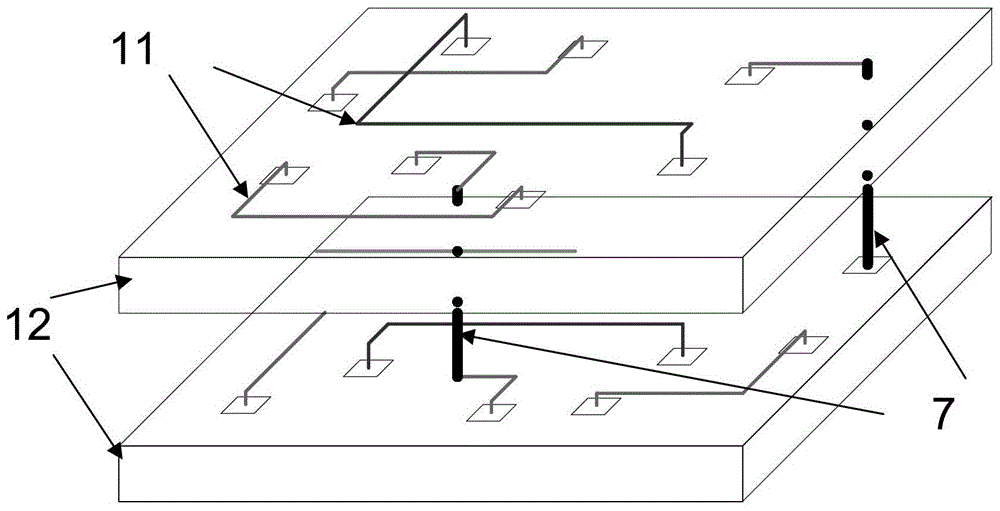

A test substrate and a probe card manufactured using the test substrate

ActiveCN103344791BImprove yield rateShorten detection timeElectrical measurement instrument detailsElectrical testingProbe cardEngineering

Provided are a test substrate and a probe card manufactured using the test substrate. Test-end micro bulges (2) on a top surface of the test substrate are arranged according to the layout of contacts (7) to be detected at the bottom of a wafer (10) to be detected, are correspondingly connected to through-substrate via holes (3) via top wirings (8) and are electrically conducted, the through-substrate via holes (3) are correspondingly connected to detection bulges (4) on the bottom surface of the test substrate and are electrically conducted, and the detection bulges (4) match test probes (13) in size, so that a one-to-one correspondence signal relationship between the test probes (13) and the test-end micro bulges (2) and the contacts (7) to be detected is established, and the problem that there is no way for the test probes (13) to directly detect each contact (7) to be detected due to the test probes (13) being too big and the contacts (7) to be detected being too small in the related art is solved. By overlaying an anisotropic conductive resin on the top surface of the test substrate, the test-end micro bulges (2) can be electrically conducted without the need for them to come into contact with the contacts (7) to be detected, thereby avoiding damage to the wafer (10) and improving the signal transmission property.

Owner:SHANDONG INST OF ADVANCED TECH CHINESE ACAD OF SCI CO LTD

Ethernet service transmitting and receiving method and device capable of dynamically configuring bandwidth

ActiveCN102215173BAvoid interactionSave wiring resourcesDigital video signal modificationData switching networksSerial digital interfaceImaging quality

The embodiment of the invention discloses an Ethernet service transmitting and receiving method and device capable of dynamically configuring a bandwidth, which are used for the field of information transmission; an Ethernet data frame is scrambled into a high-definition image HD-SDI signal after being encoded; the Ethernet service is enabled and decoded to seamlessly fuse two service data of a HD-SDI (High-Definition Serial Digital Interface) image signal and Ethernet data on an HD-SDI; without substantially affecting the image quality, the bandwidth is dynamically configured to transmit the Ethernet service data while the HD-SDI image signal is transmitted; meanwhile, absolute isolation is assured at two levels of the high-definition image signal and the Ethernet service data so that the mutual influence during transmission is avoided. Therefore, a large quantity of wiring resources, huge time cost and human resources cost are saved for related projects in the fields like broadcast television, security monitoring and the like.

Owner:ENC DATA SERVICE CO LTD

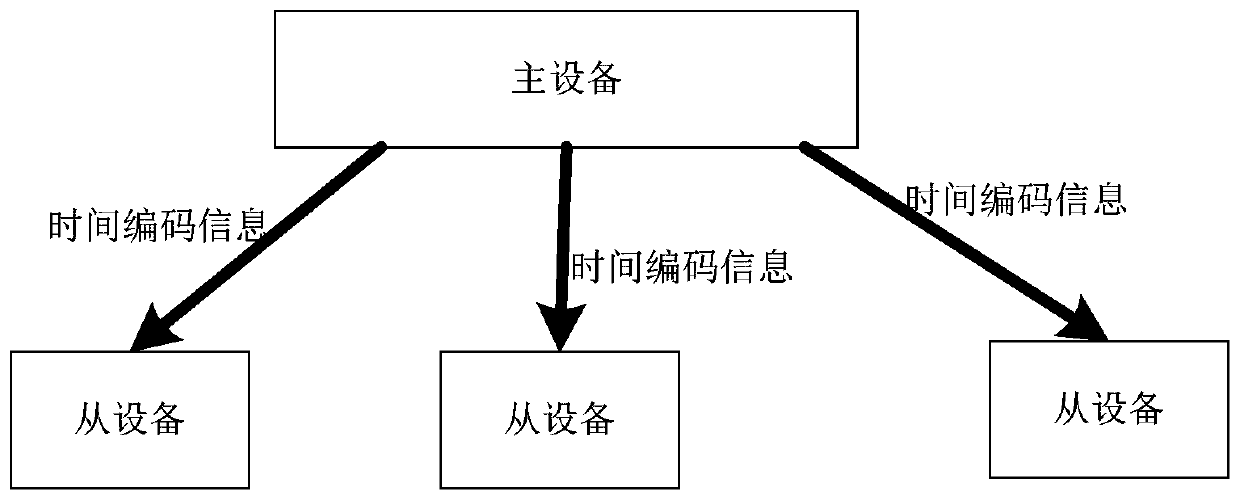

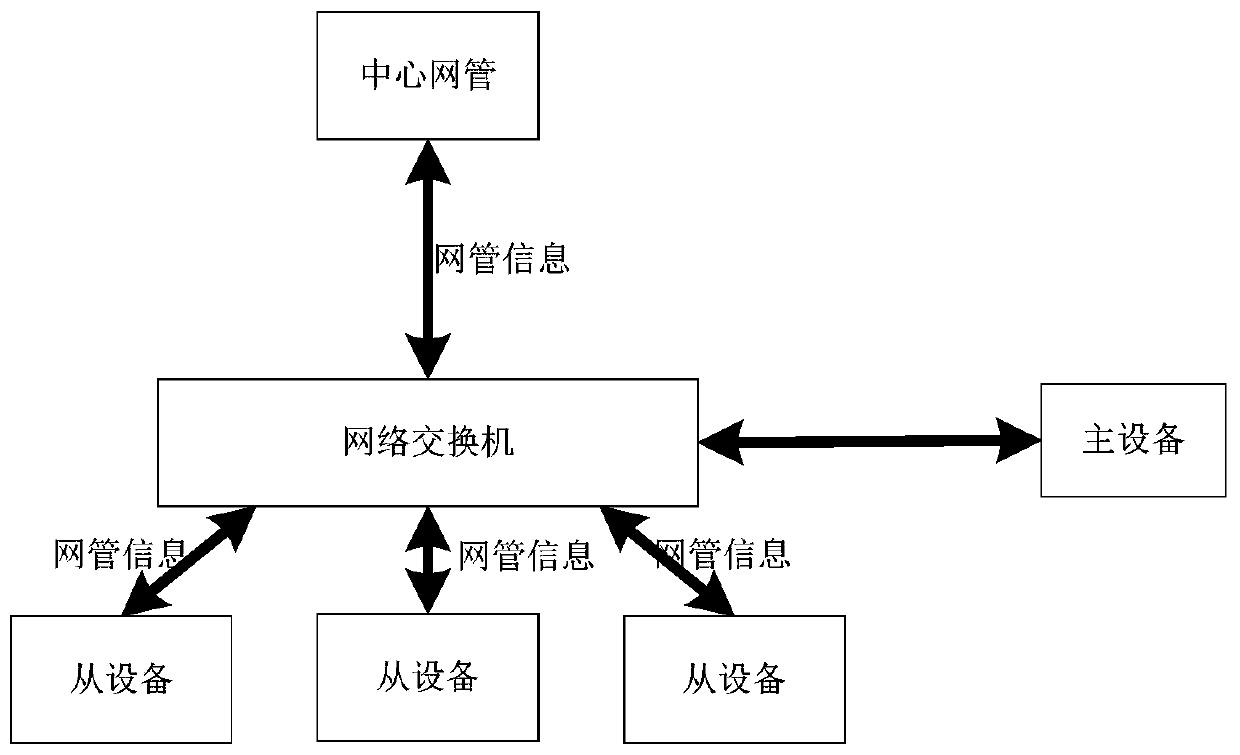

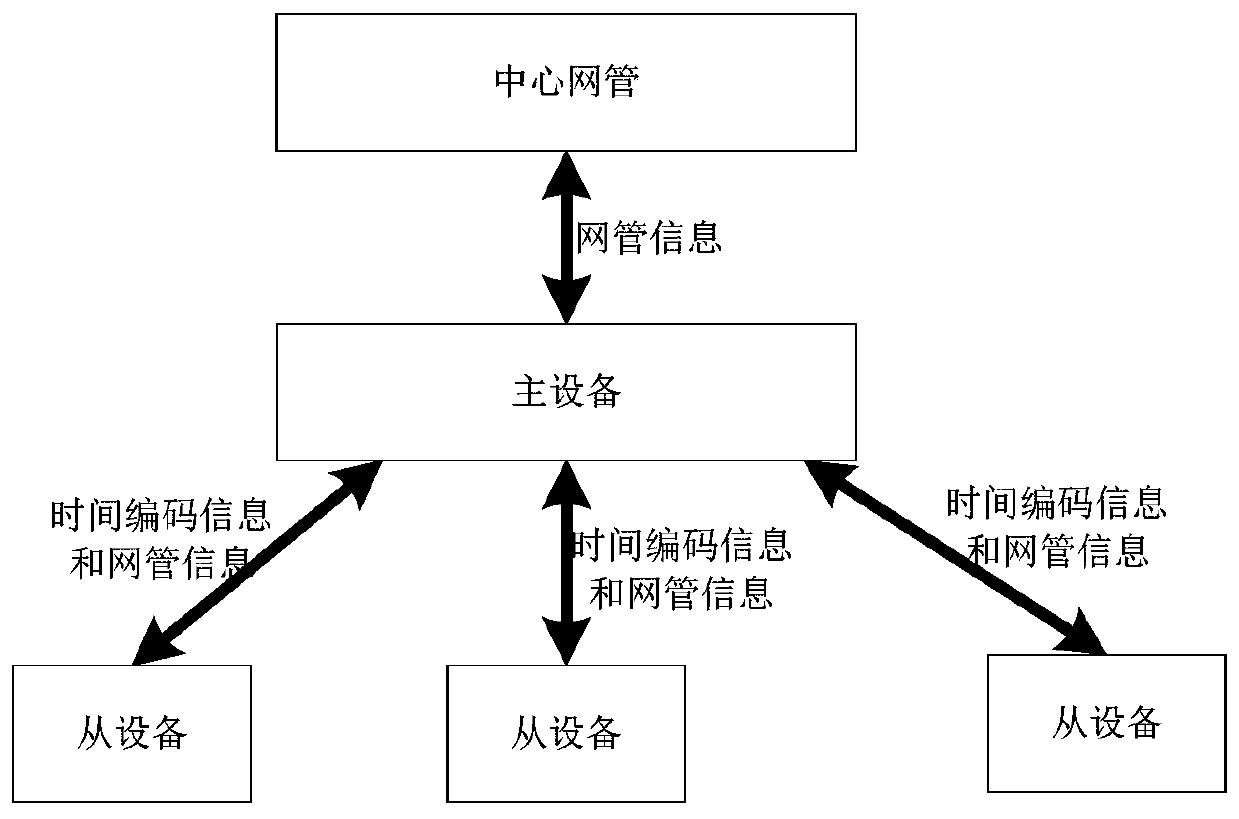

A method for implementing in-band management of a master-slave time synchronization system

ActiveCN106411462BSolve the delay automatic calculation problemReduce construction costsSynchronisation by photonic/optical meansSource coding adaptationComputational problemNetwork management application

The invention discloses an implementation method for in-band management of a master-slave time synchronization system. A central webmaster carries out management on slave devices through a master device; the master device sends network management information to the master device; after the master device encodes the network management information, the master device sends the network management information to the slave devices; the slave devices execute corresponding network management operation instructions, and meanwhile, the slave devices return device status information to the master device according to an encoding way. Through improvement of an IRIG-B code, a problem of automatic calculation of a delay of a physical link between the master device and the slave devices is solved, the construction cost is effectively reduced, and meanwhile, the central webmaster carries out network management on all slave devices through the master device, so that the wiring resources are effectively saved.

Owner:大唐电信(成都)信息技术有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com