A test substrate and a probe card manufactured using the test substrate

A technology for testing substrates and test terminals, which is applied in the field of probe cards, and can solve the problems of small TSVs, inability to detect TSVs, and inapplicable wafer detection for 3D chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

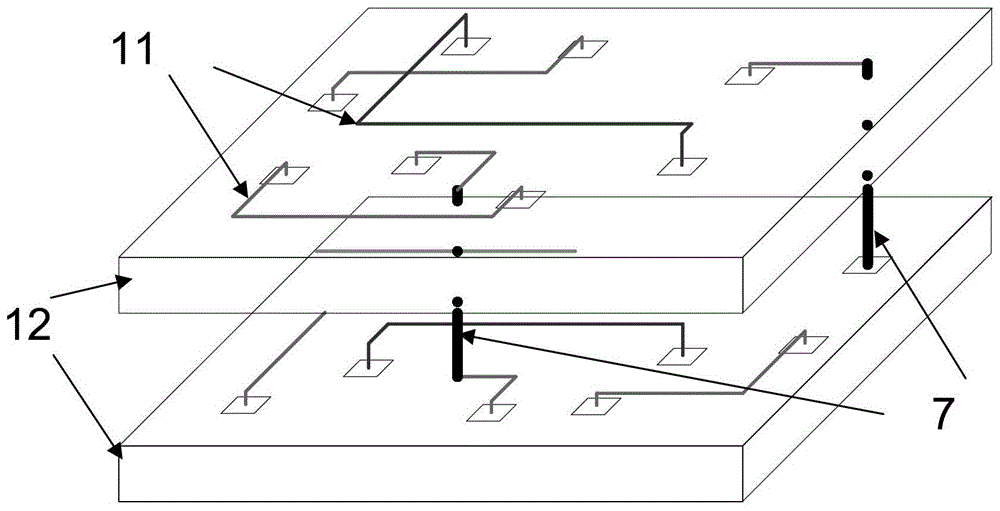

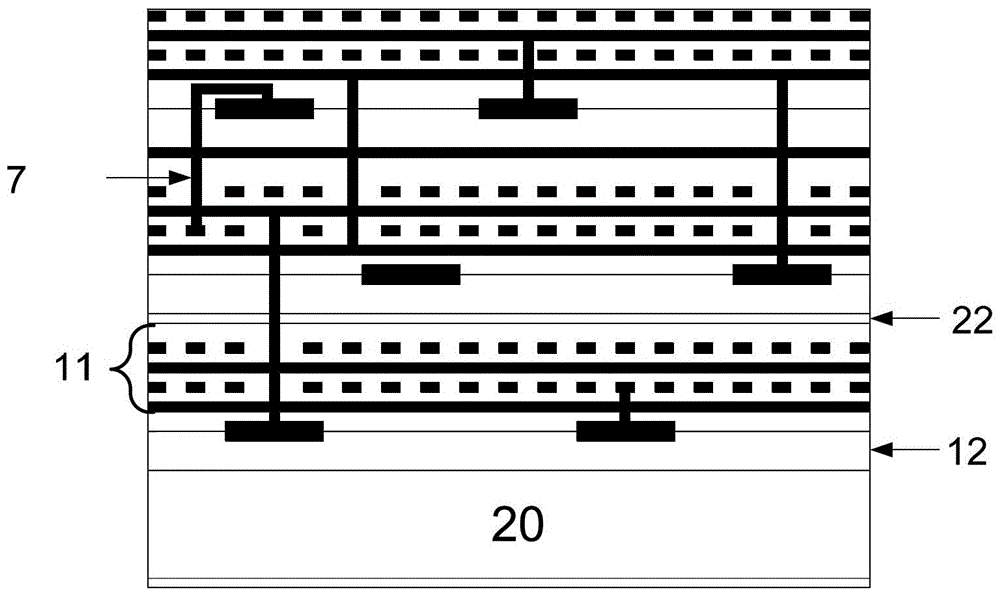

[0050] The test substrate of the present invention is used to test the wafer 10 before stacking, such as Figure 5 , Image 6 shown, including:

[0051] A plurality of test terminal micro-protrusions 2 are arranged on the top surface of the base 1 of the test substrate according to the same layout as the contact 7 to be tested at the bottom of the wafer 10, and each of the test terminal micro-protrusions 2 It matches the size of the contact 7 to be tested.

[0052] For the three-dimensional chip, the contact 7 to be tested is a through-silicon hole, and the manufacturing process of the through-silicon hole is an existing technology, so it will not be repeated here; The top surface of the base 1 of the test substrate, currently, the etching technology has reached the 20 nanometer level, therefore, the micro-protrusion 2 of the test end can be made small enough, such as 5-10 microns, so the micro-protrusion 2 of the test end The size of the through-silicon via can be made to ...

Embodiment 2

[0068] Because the chip 10 in the 2.5-dimensional chip has no TSV, the following changes can be made on the basis of Embodiment 1:

[0069] In order to perform a pre-stacking test on the wafer 10 constituting a 2.5-dimensional chip, as an optional implementation, micro-protrusions at the end to be tested may be formed on the bottom of the wafer 10 by etching technology as input and output ports for test signals. At present, the etching technology has reached the level of 20 nanometers. Therefore, the micro-protrusion at the terminal to be tested can be made small enough, such as 5-10 microns, to establish signal connection with each device on the wafer 10 through the wafer wiring layer 11 .

[0070] Because the test terminal micro-protrusions 2 on the top surface of the base 1 of the test substrate are arranged according to the same layout of the contact points 7 to be tested at the bottom of the wafer 10, that is, the micro-protrusions of the terminal to be tested, A one-to-o...

Embodiment approach

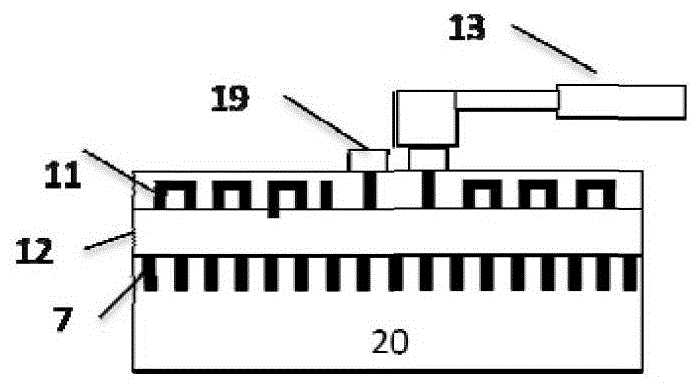

[0072] The test substrates described in Embodiment 1 and Embodiment 2 can also be used to manufacture probe cards, without additional use of test probes 13 to indirectly transmit test signals to the contacts 7 to be tested on the wafer 10 . The implementation is as follows:

[0073] For a test substrate that does not contain contact pads 5, it is only necessary to remove the detection bumps 4 located on the bottom surface of the base 1 of the test substrate, and add wiring to the bottom of the base 1 of the test substrate, and pass the new Adding wiring directly transmits the test signal from the automatic testing machine to each test terminal micro-protrusion 2 on the top surface of the base 1 of the test substrate, and passes through the test terminal micro-protrusion 2 to the test signal located on the test substrate. Each contact 7 to be tested on the bottom of the wafer 10, and the tested signal is output to an automatic testing machine through newly added wiring, so that...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com