DCT rapid changing structure

A fast, serial conversion technology, applied in image data processing, TV, color TV, etc., can solve the problems of large amount of computation, large circuit area, and consumption of wiring resources, and achieve the goals of reducing area, saving wiring resources, and improving computing speed Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

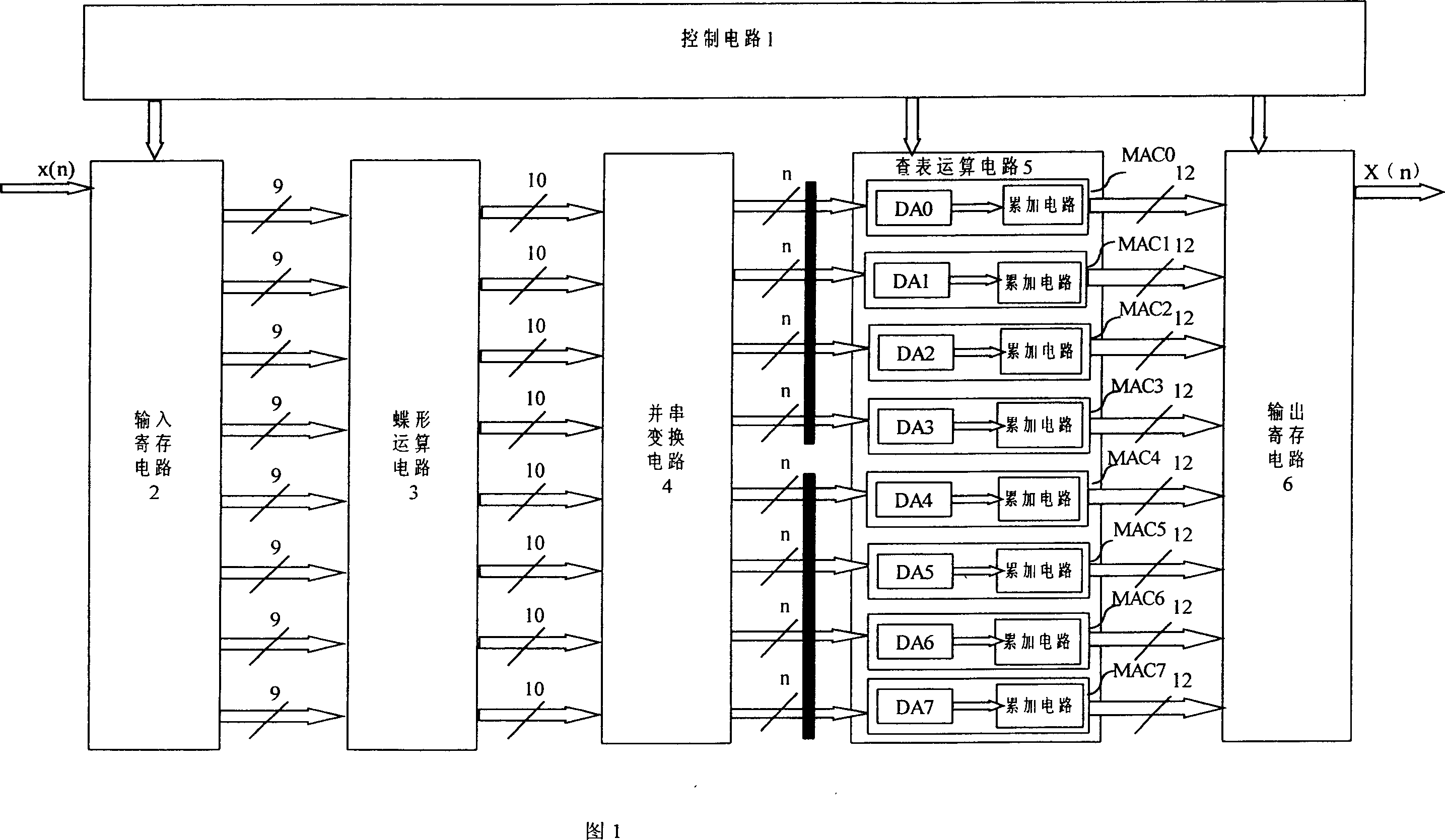

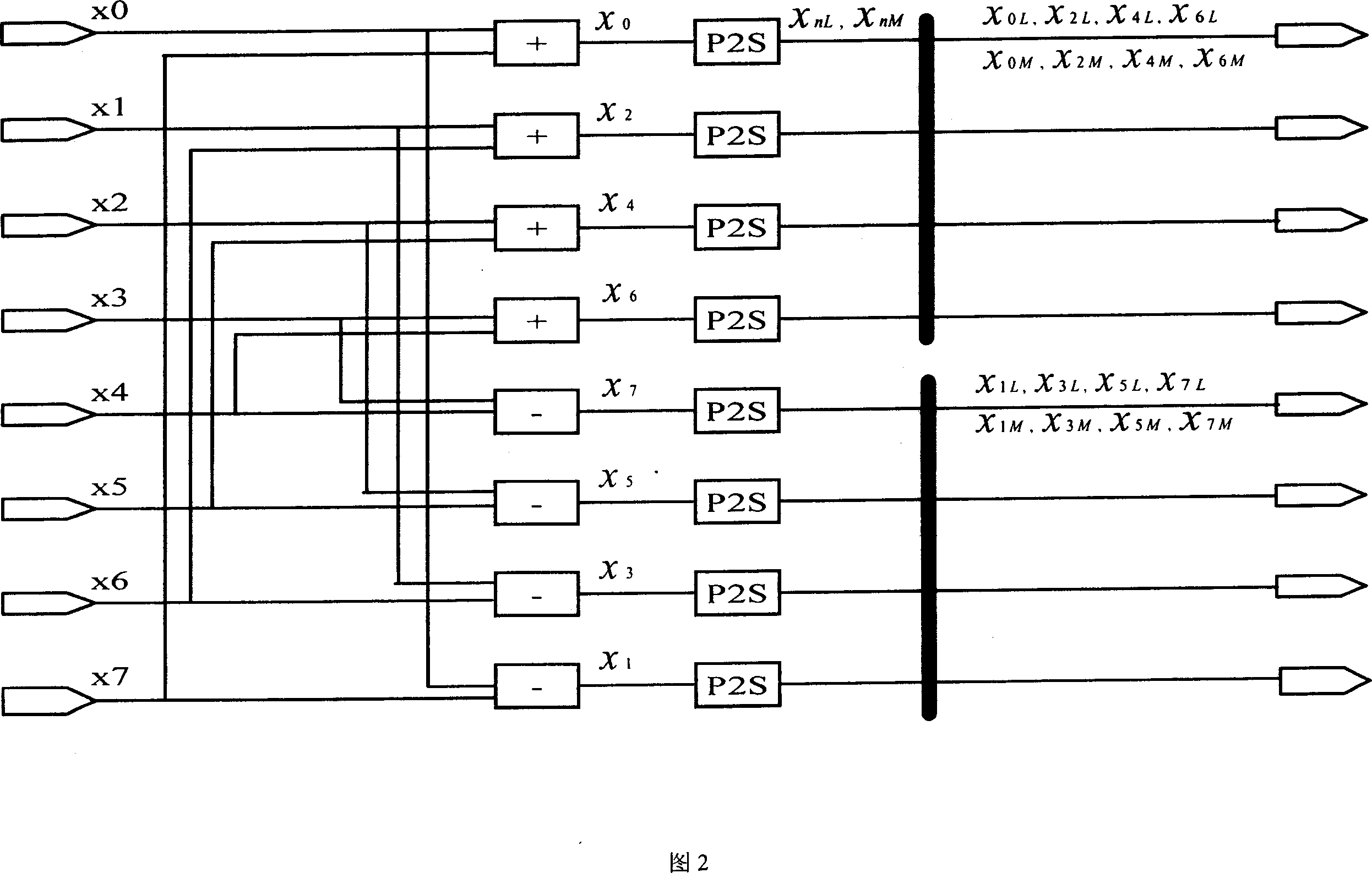

[0071] The DCT device of this embodiment takes 8×8 as a unit of image block, inputs one row or one column of image data at a time, uses table look-up operation instead of multiplication operation, and completes fast DCT transformation.

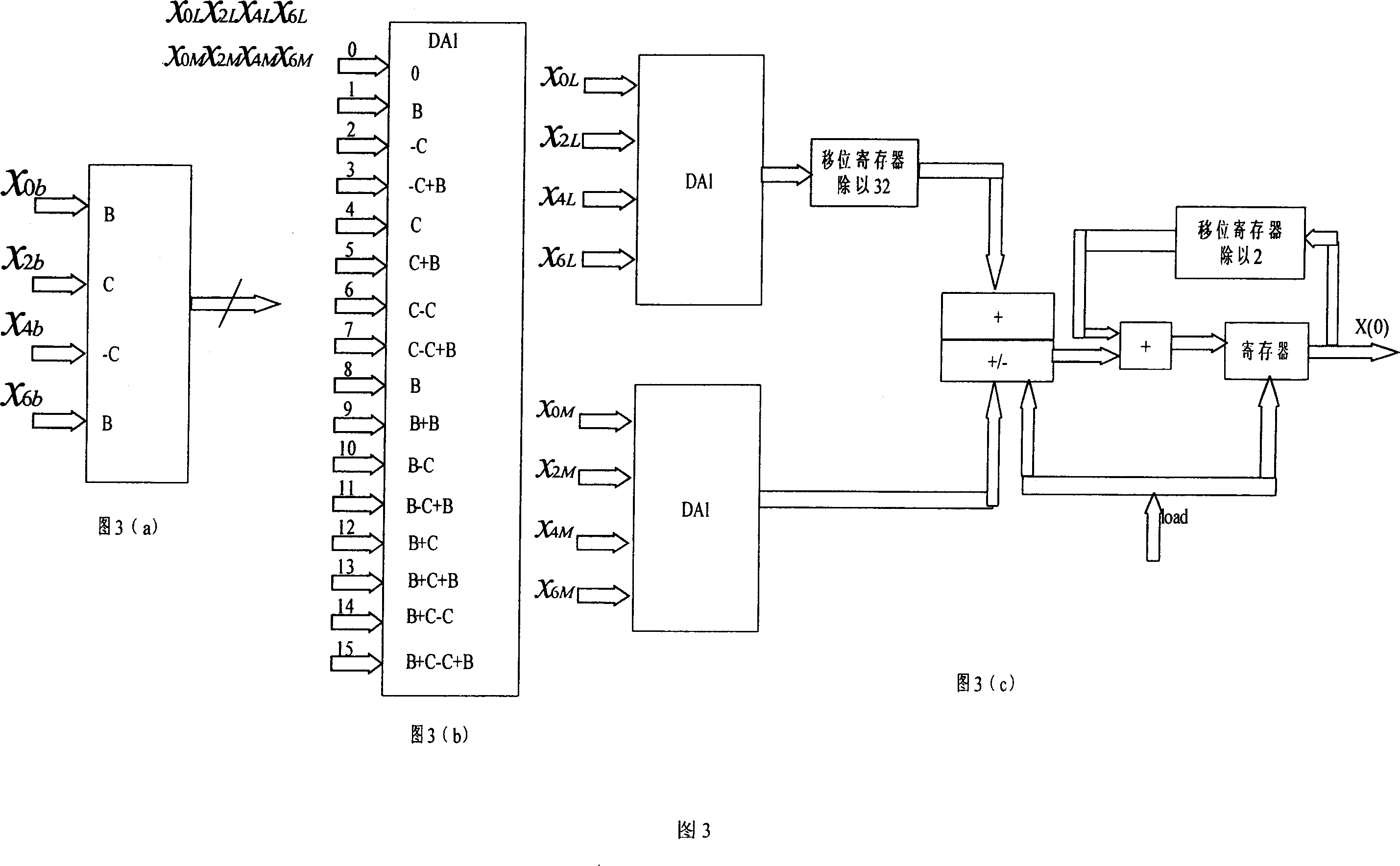

[0072] Suppose we want to implement the following formula:

[0073] y ( n ) Σ k = 1 K A k x k ( n ) - - - ( 10 )

[0074]where A k is a constant, and x k is a variable expressed in two's complement notation. For the convenience of derivation, the x k It is limited in the range of ±1 (the actual situation does not necessarily meet this condition, but the coefficient can be transformed into thi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com