Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

55results about How to "Reduce Power Noise" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

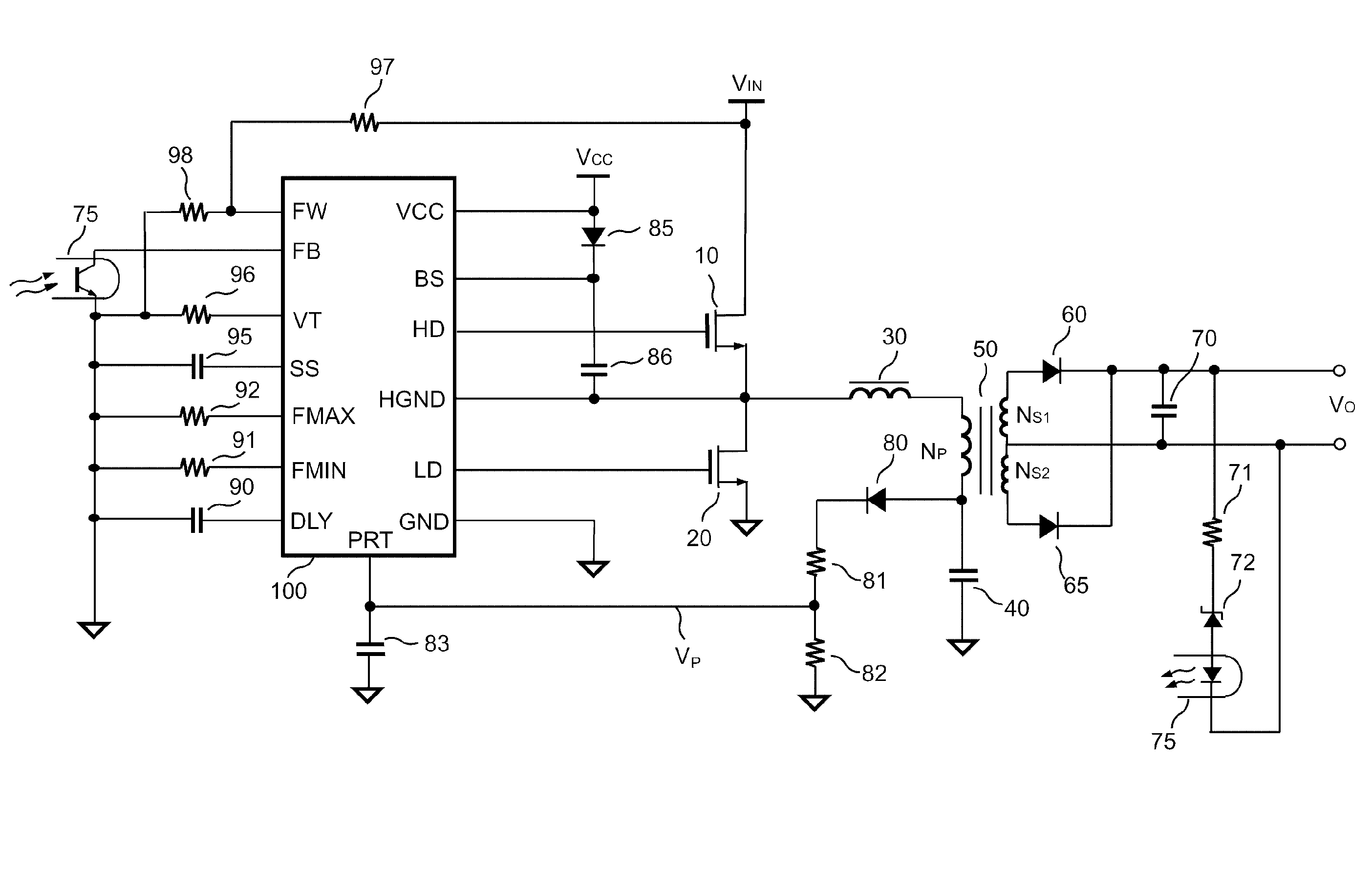

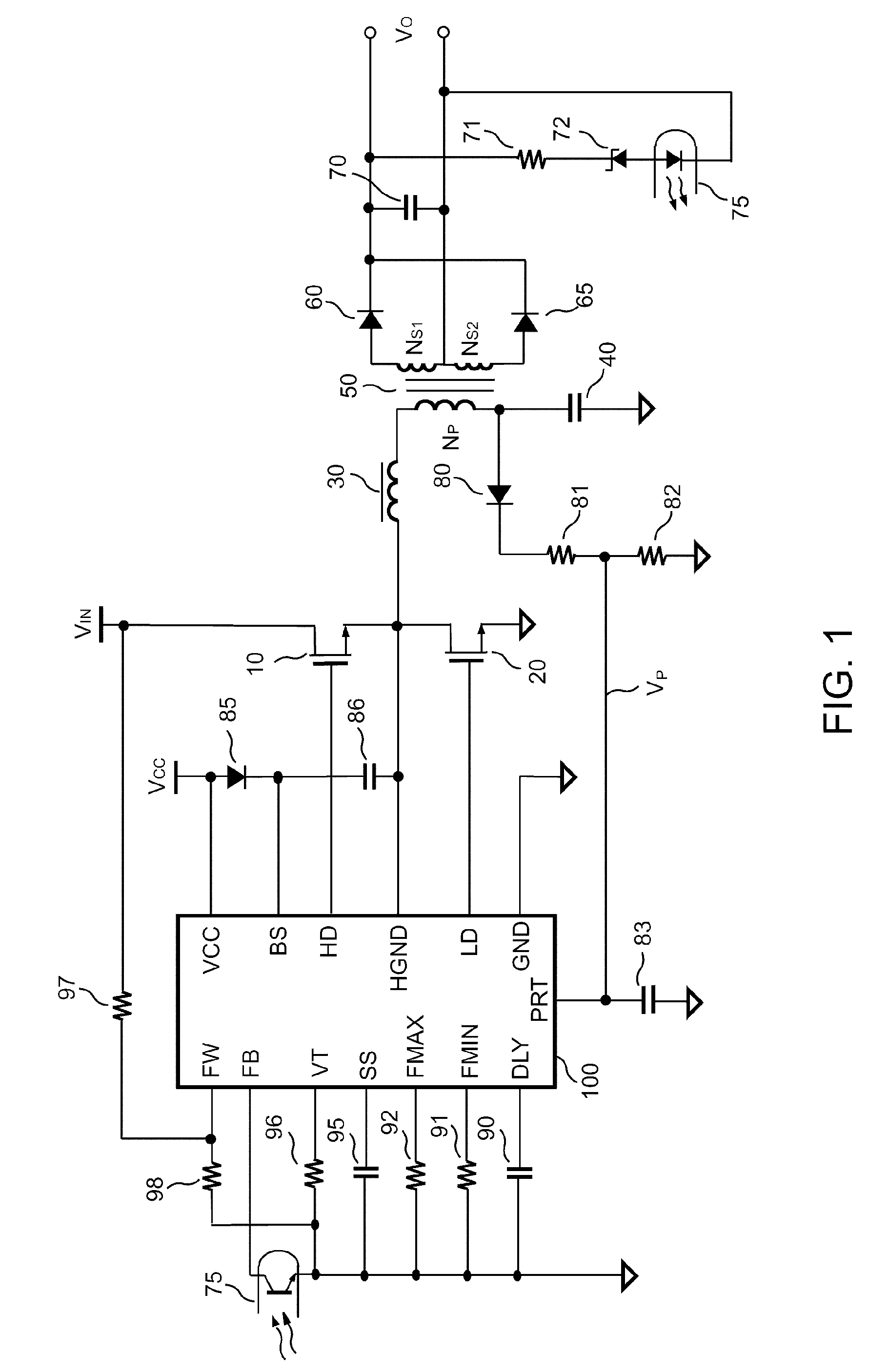

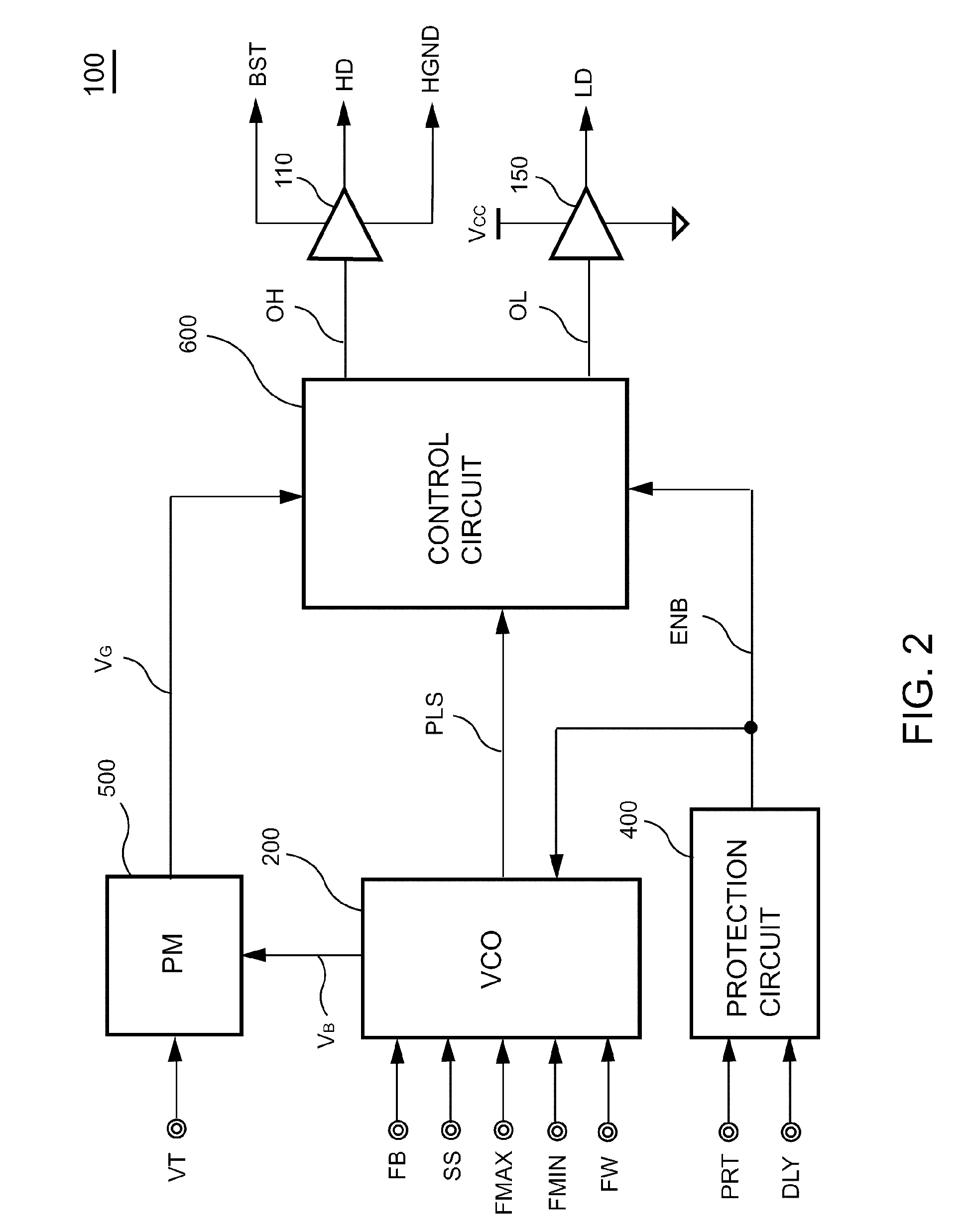

Switching controller for resonant power converter

ActiveUS7313004B1Reduce power noiseImprove audio-susceptibilityEfficient power electronics conversionConversion with intermediate conversion to dcResonant power convertersFeedback circuits

An integrated control circuit for a resonant power converter includes a minimum-frequency programming circuit connected a first resistor to program a minimum switching frequency of the power converter. A feedback circuit is coupled to a feedback terminal to receive a feedback signal for generating an adjustment signal. A maximum-frequency programming circuit connects a second resistor to determine a maximum switching frequency in response to the adjustment signal. An oscillator is coupled to the minimum-frequency programming circuit and the maximum-frequency programming circuit to generate an oscillation signal for determining the switching frequency of the power converter. A feed-forward circuit is connected to a feed-forward terminal to receive a feed-forward signal represents the input voltage of the power converter. The switching frequency is increased in response to decrease of the feedback signal, and the switching frequency is increased in response to the increase of the feed-forward signal.

Owner:SEMICON COMPONENTS IND LLC

Bit line setup and discharge circuit for programming non-volatile memory

InactiveUS7453729B2Reduce ground noiseReduce Power NoiseRead-only memoriesDigital storagePre-chargeHemt circuits

A NAND EEPROM having a shielded bit line architecture reduces supply voltage and ground noise resulting from charging or discharging bit lines. The EEPROM has a PMOS pull-up transistor and an NMOS pull down transistor connected to a virtual power node. A control circuit for charging or discharging bit lines controls the gate voltage of the PMOS or NMOS transistor to limit peak current when charging or discharging bit lines via the virtual power node. In particular, the control circuit operates the PMOS or NMOS transistor in a non-saturation mode to limit current. One such control circuit creates a current mirror or applies a reference voltage to control gate voltages. A programming method sets up bit lines by pre-charging unselected bit lines via the PMOS pull-up transistor having controlled gate voltage while latches in the programming circuitry charge or discharge selected bit lines according to respective data bits being stored. Another bit line setup includes two stages. A first stage pre-charges all bit lines via PMOS pull-up, and the second stage uses the latches to discharge or leave charged the selected bit lines depending on respective data bits being stored. The gate voltages of NMOS transistors in the programming circuitry can be controlled to reduce noise caused by discharging selected bit lines through the latches.

Owner:SAMSUNG ELECTRONICS CO LTD

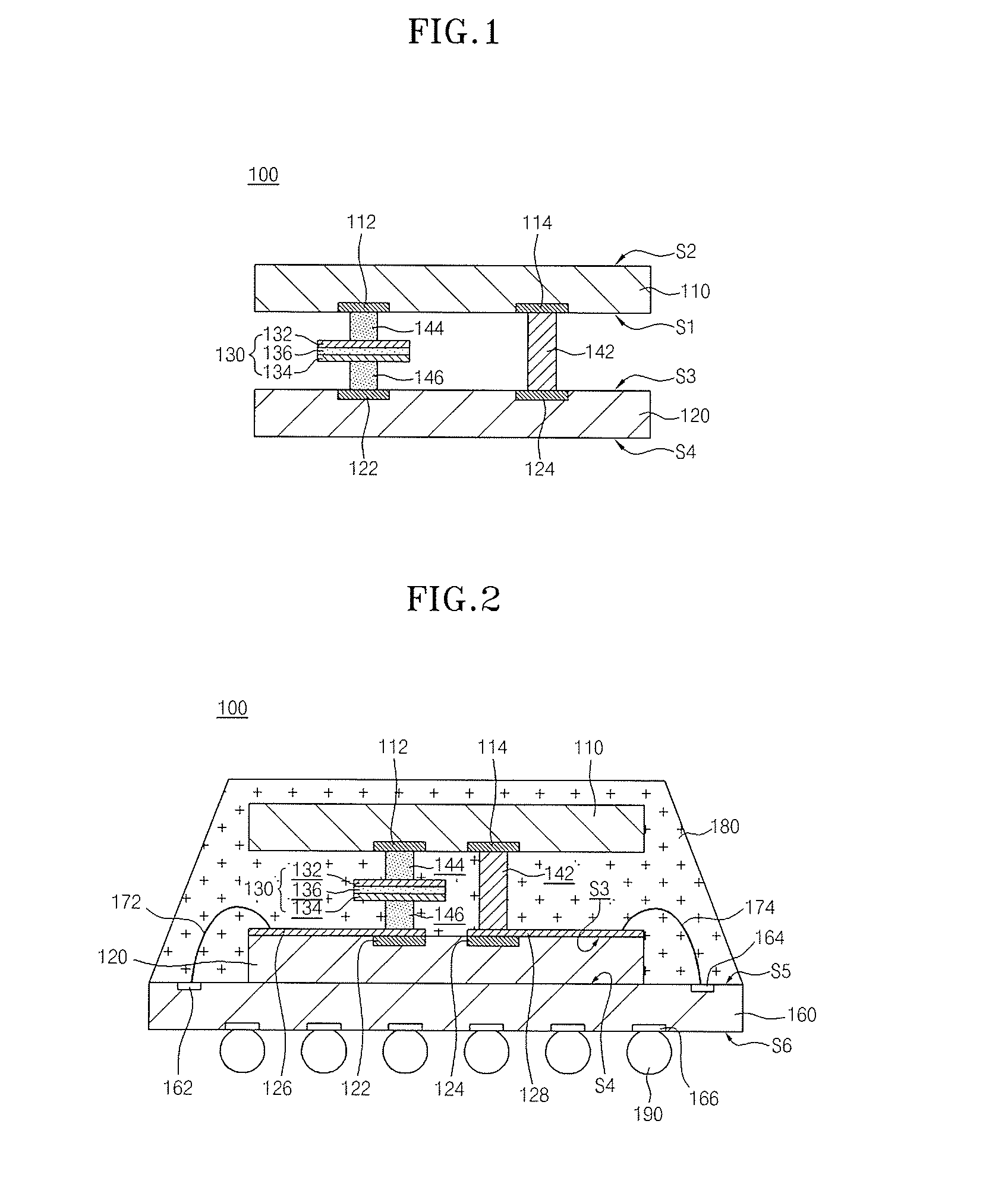

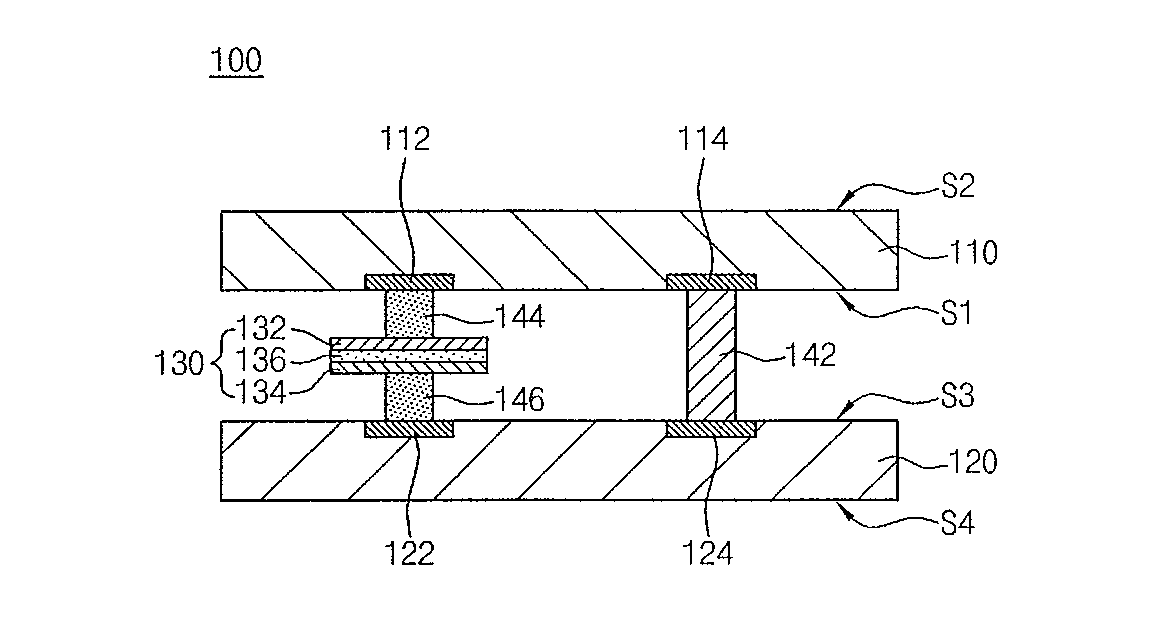

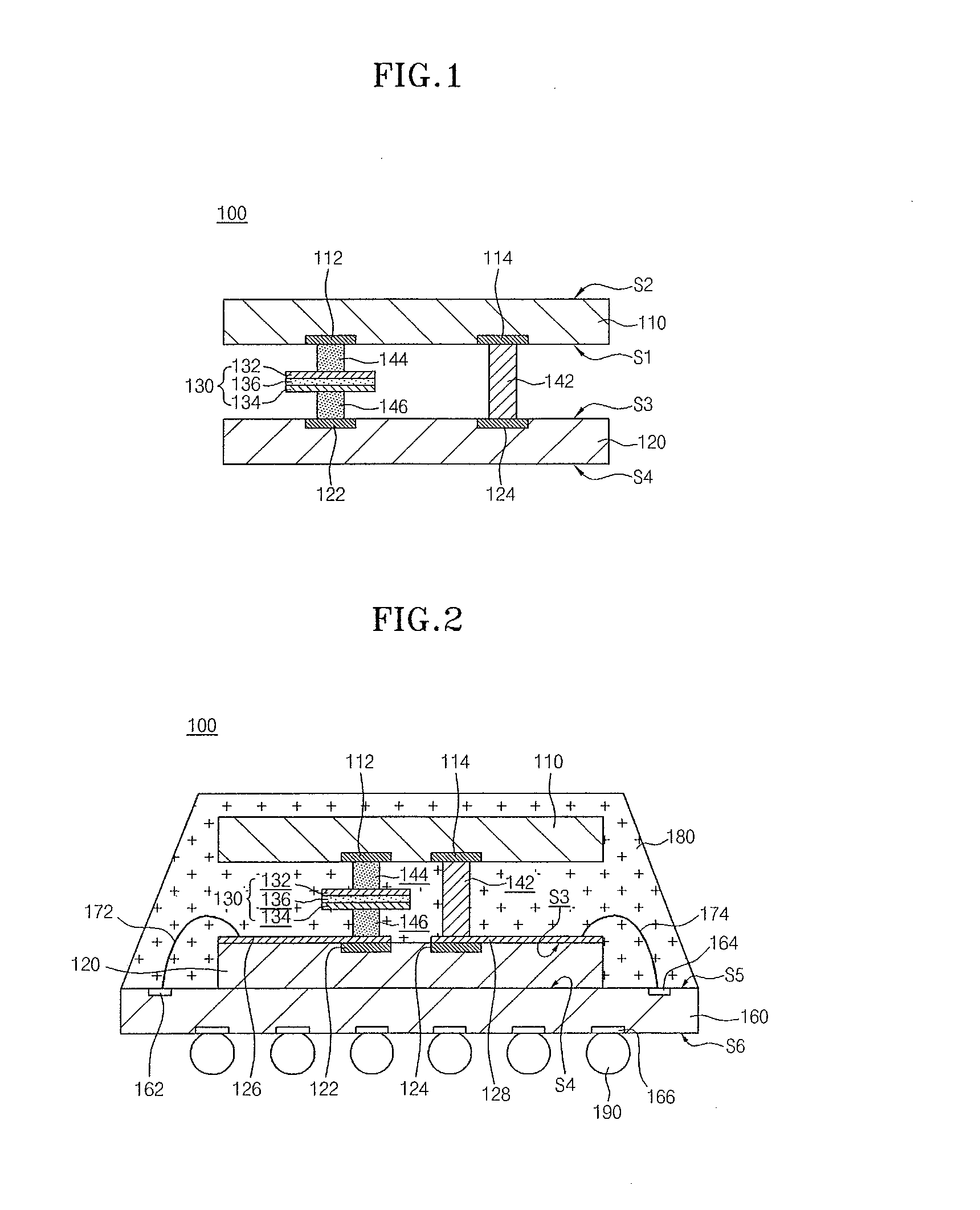

Stack package

InactiveUS20110186978A1Low costReduce Power NoiseSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor chip

A stack package includes a first semiconductor chip first pads and second pads disposed thereon and a second semiconductor chip having third pads and fourth pads electrically connected with the second pads disposed thereon. Capacitors are interposed between the first semiconductor chip and the second semiconductor chip, and include first electrodes electrically connected with the first pads to of the first semiconductor chip, second electrodes electrically connected with the third pads of the second semiconductor chip, and dielectrics interposed between the first electrodes and the second electrodes.

Owner:SK HYNIX INC

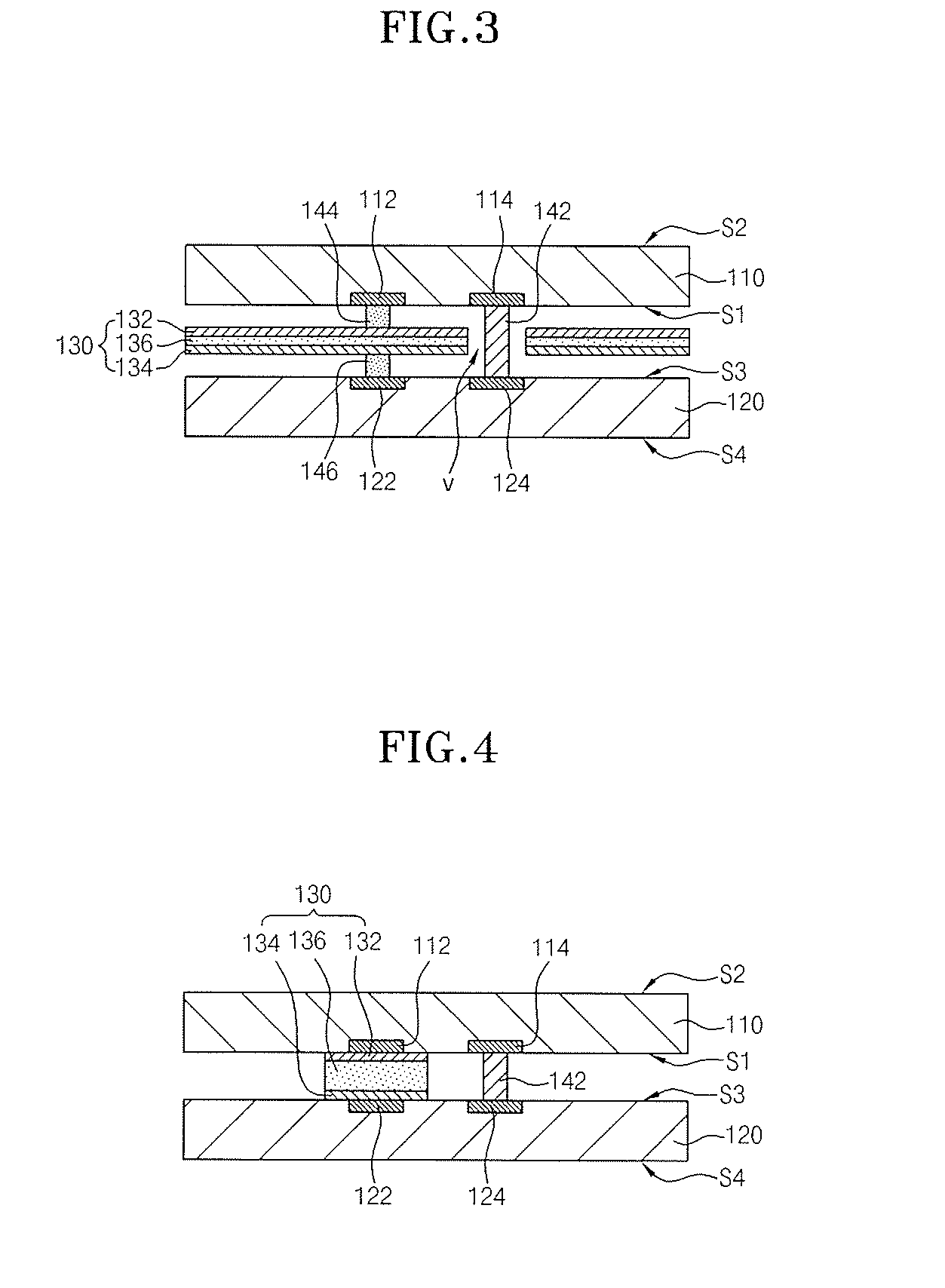

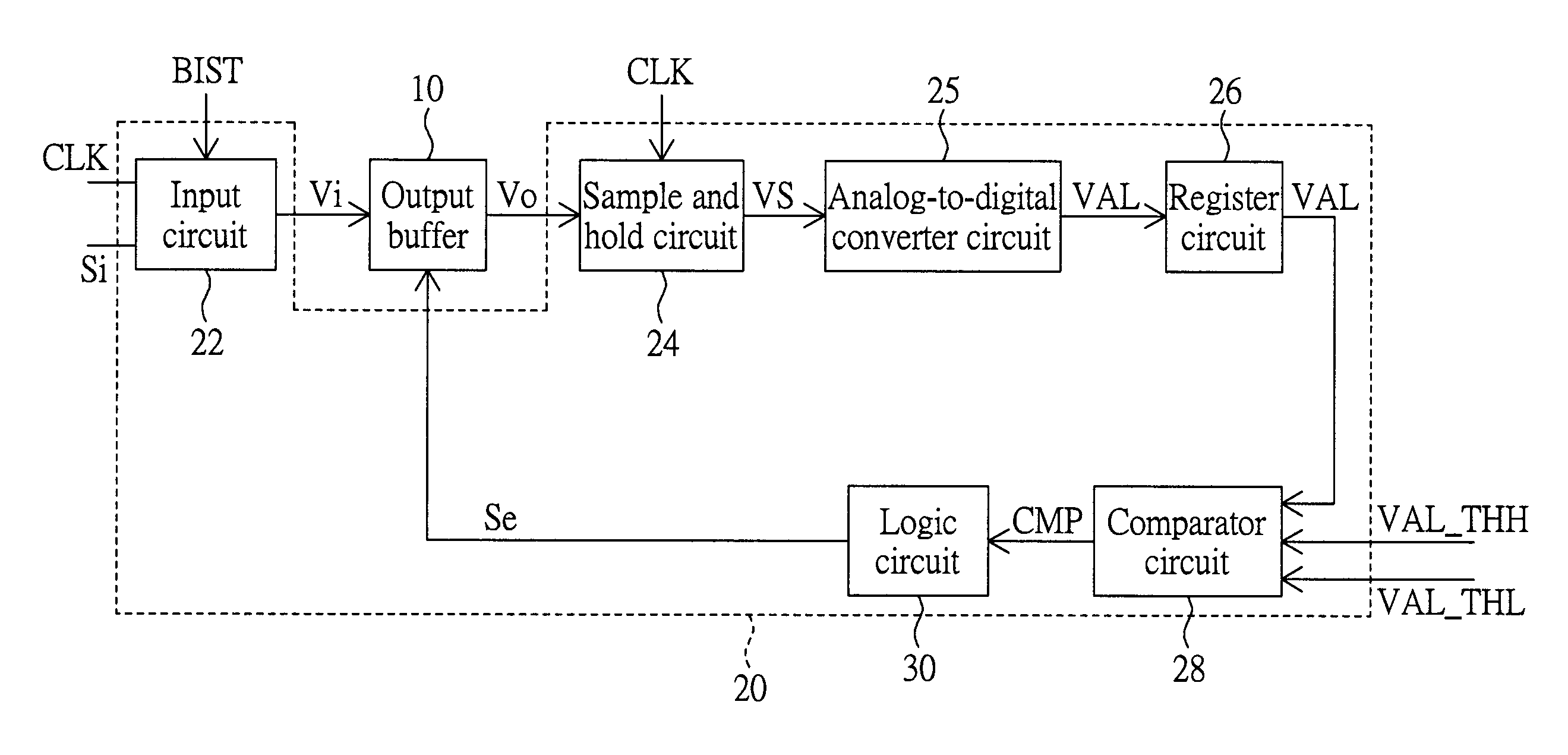

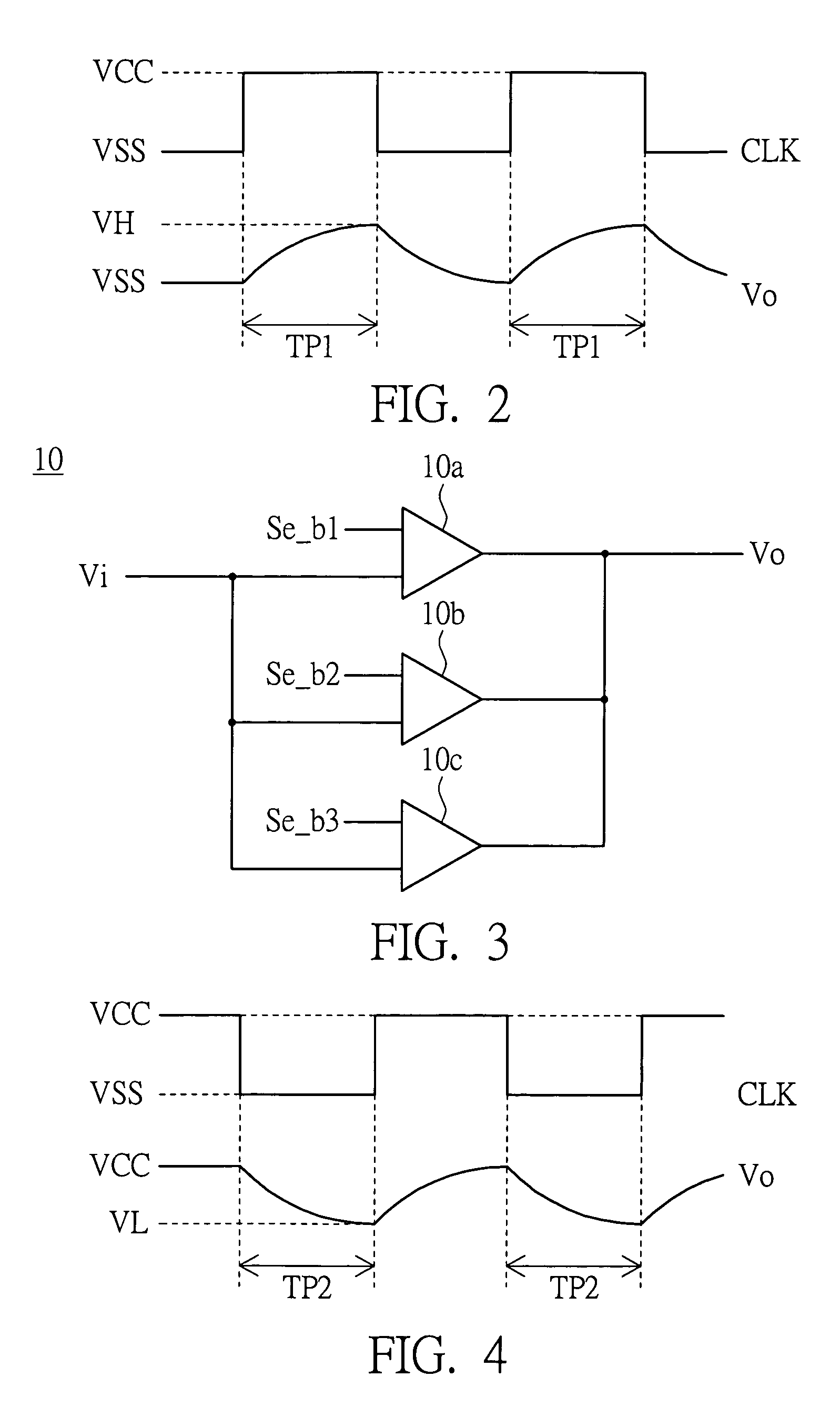

Adjusting method and circuit using the same

ActiveUS7863934B2Reduce Power NoiseReduce power consumptionAnalogue/digital conversionElectric signal transmission systemsEngineeringVoltage

A method adjusts driving ability of an output buffer. The output buffer has multiple driving ability classes. The method includes the following steps. First, the driving ability of the output buffer is initialized as an initial class among the driving ability classes. Next, a voltage at an output terminal of the output buffer is initialized to an initial voltage. Then, an input voltage is inputted via the input terminal at a first time instant. Next, an output voltage outputted from the output terminal is sampled to obtain a voltage value at a second time instant. Then, whether the voltage value satisfies a predetermined condition is judged. Next, if the voltage value satisfies the predetermined condition, the driving ability class of the output buffer is recorded and set.

Owner:MACRONIX INT CO LTD

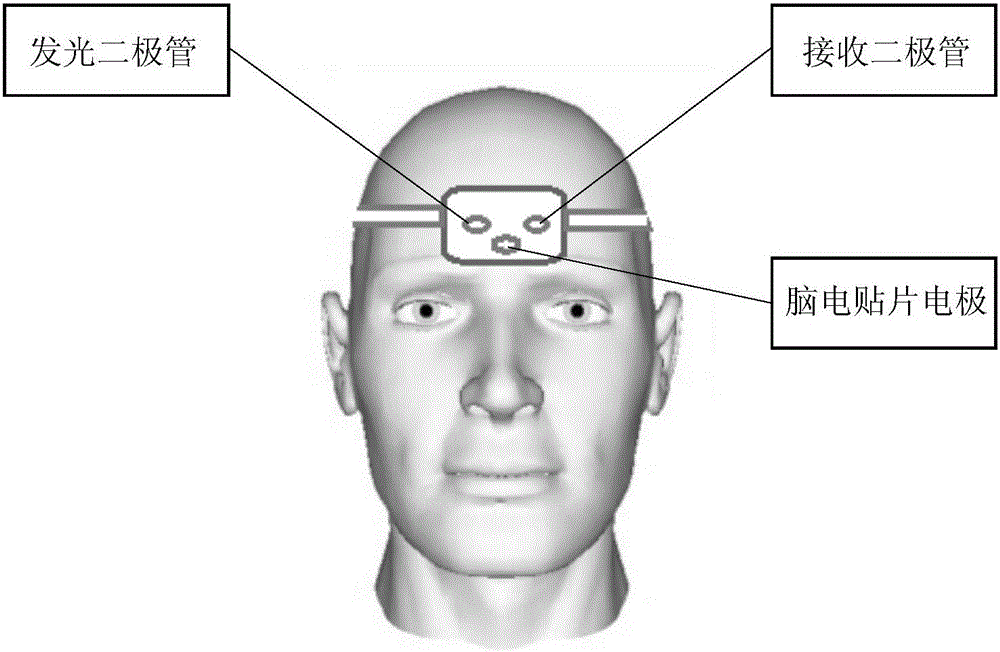

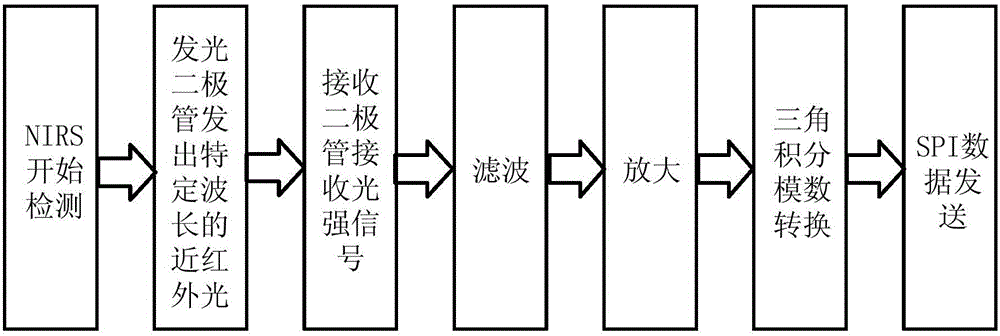

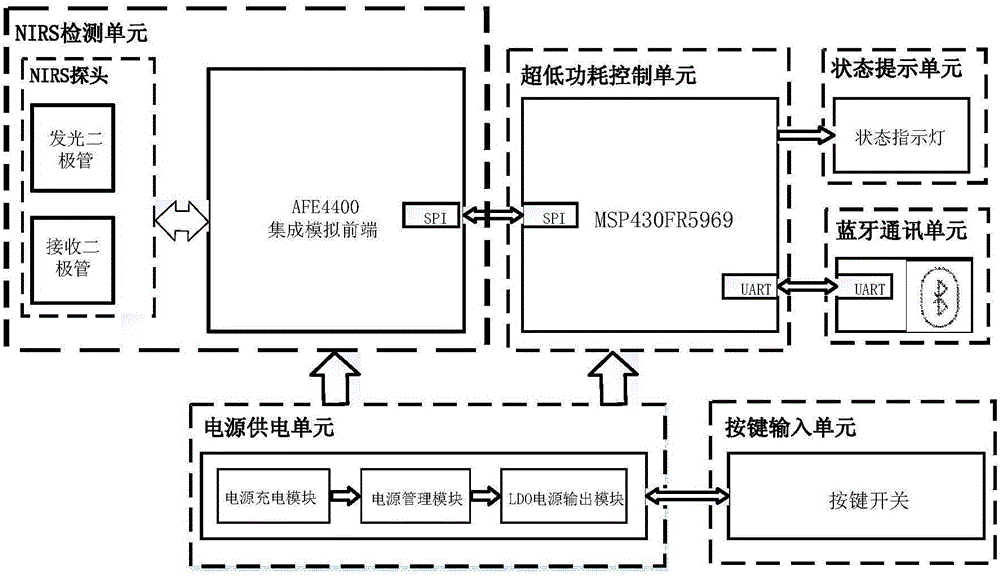

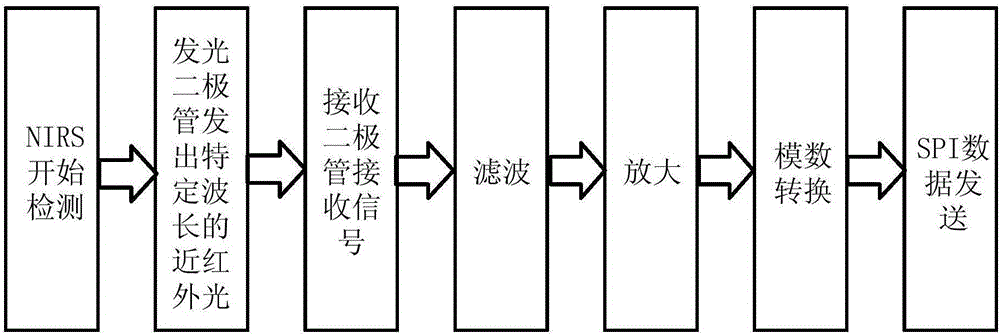

Wearable multimode brain function detection device based on NIRS-EEG

InactiveCN105852854AImprove medical experiencePortable and comfortableSensorsPsychotechnic devicesEngineeringUltra low power

The invention discloses a wearable multimode brain function detection device based on NIRS-EEG. The wearable multimode brain function detection device comprises an NIRS-EEG detection unit, an ultra-low power consumption control unit, a state prompt unit, a Bluetooth communication unit, a key input unit and a power supply unit; the ultra-low power consumption control unit is connected with the NIRS-EEG detection unit, the state prompt unit and the Bluetooth communication unit respectively, the ultra-low power consumption control unit conducts data instruction communication with the NIRS-EEG detection unit through SPI interfaces, the ultra-low power consumption control unit conducts data transmission communication with the Bluetooth communication unit through a UART serial port communication protocol, and the Bluetooth communication unit sends received data to a mobile terminal for subsequent processing; the key input unit is connected with the power supply unit, and the power supply unit is used for supplying power to the NIRS-EEG detection unit, the ultra-low power consumption control unit, the state prompt unit and the Bluetooth communication unit and conducting power supply protection and power management. The wearable multimode brain function detection device has good comfortability, and monitoring on occasions such as the brain cognitive function, neurological and psychiatric diseases and sleep and fatigue states can be conveniently conducted anytime and anywhere.

Owner:SOUTH CHINA UNIV OF TECH +1

Stack package

InactiveUS20130082352A1Low costReduce Power NoiseSemiconductor/solid-state device detailsSolid-state devicesDielectricSemiconductor chip

A stack package includes a first semiconductor chip first pads and second pads disposed thereon and a second semiconductor chip having third pads and fourth pads electrically connected with the second pads disposed thereon. Capacitors are interposed between the first semiconductor chip and the second semiconductor chip, and include first electrodes electrically connected with the first pads of the first semiconductor chip, second electrodes electrically connected with the third pads of the second semiconductor chip, and dielectrics interposed between the first electrodes and the second electrodes.

Owner:SK HYNIX INC

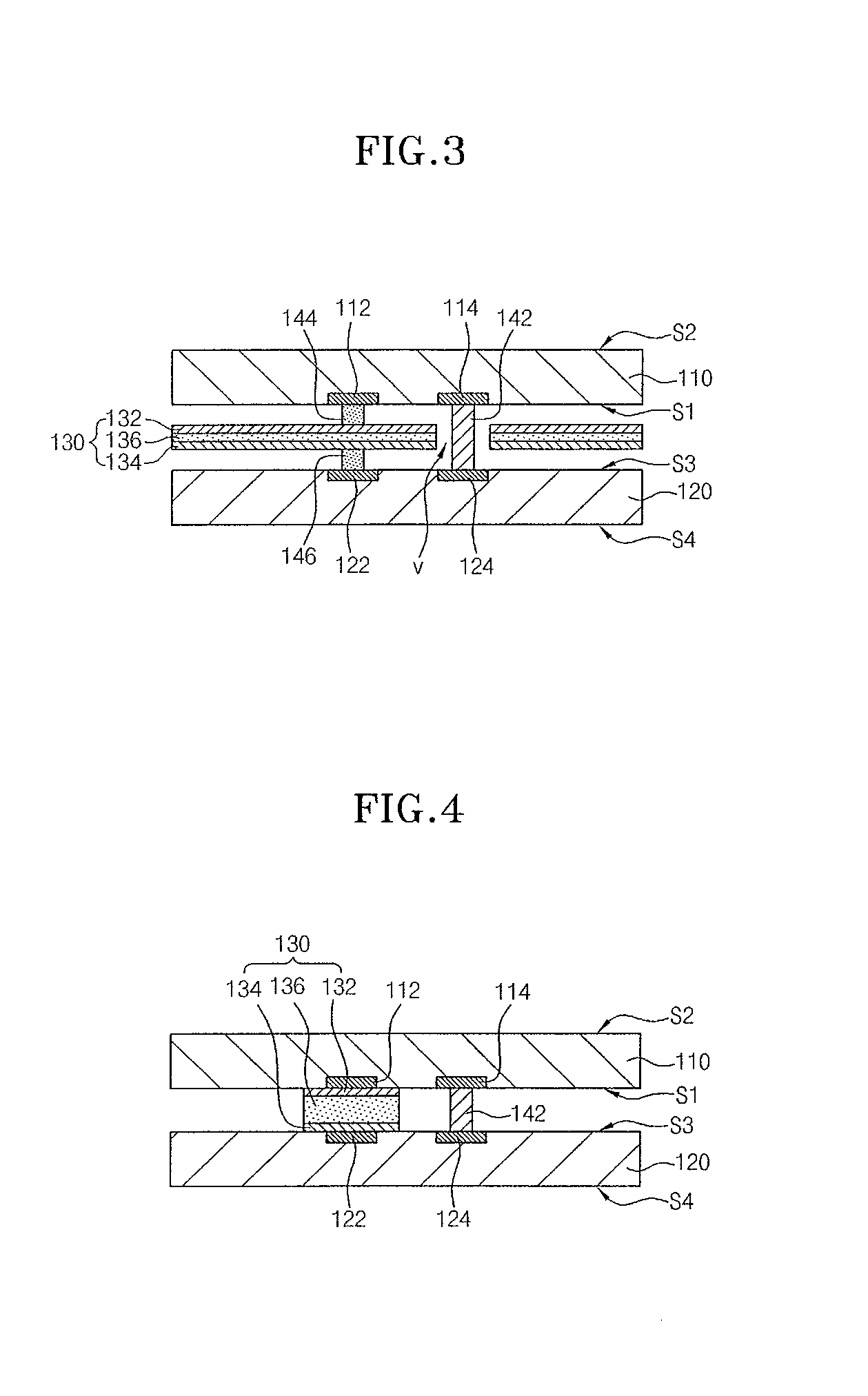

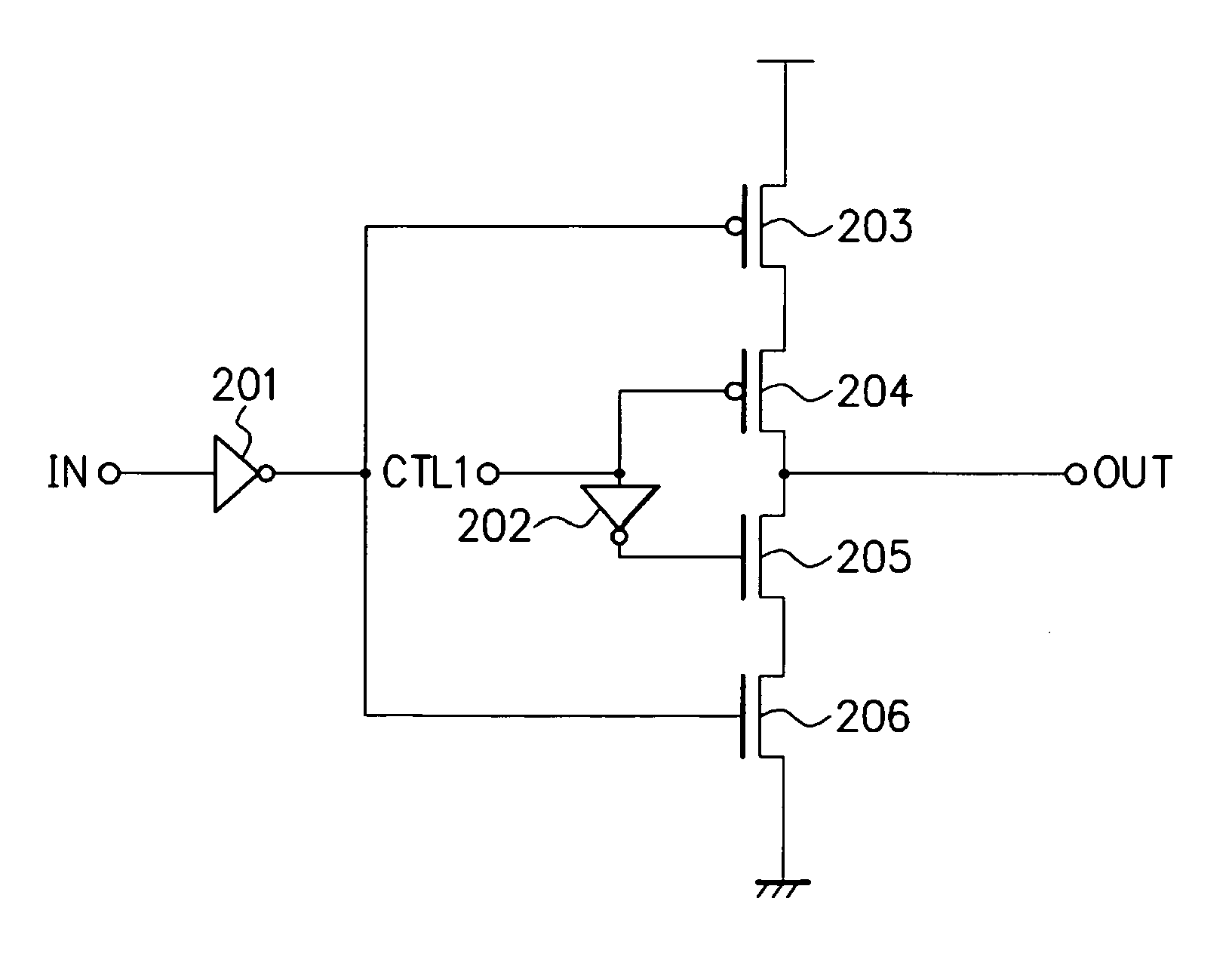

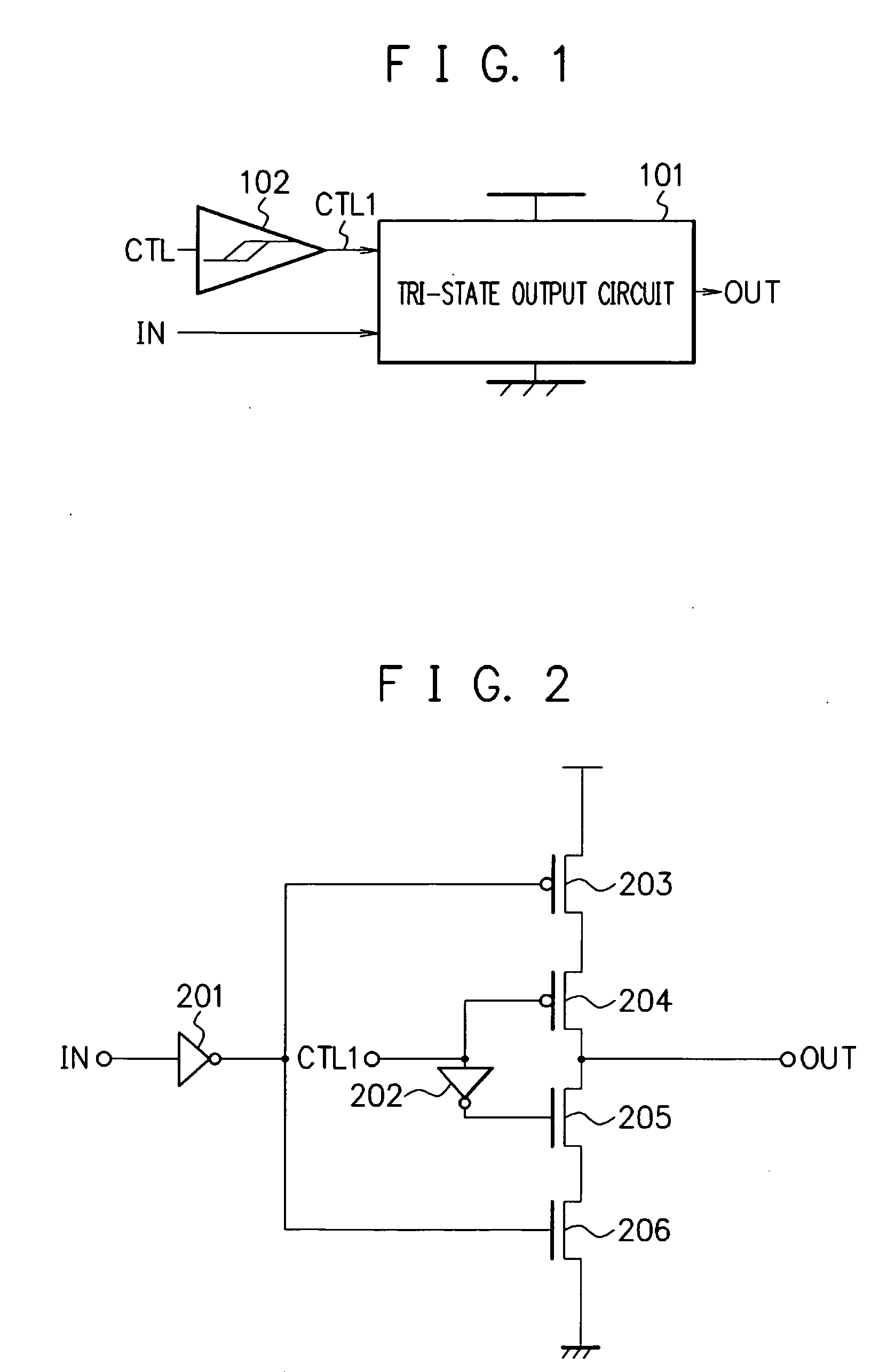

Output circuit

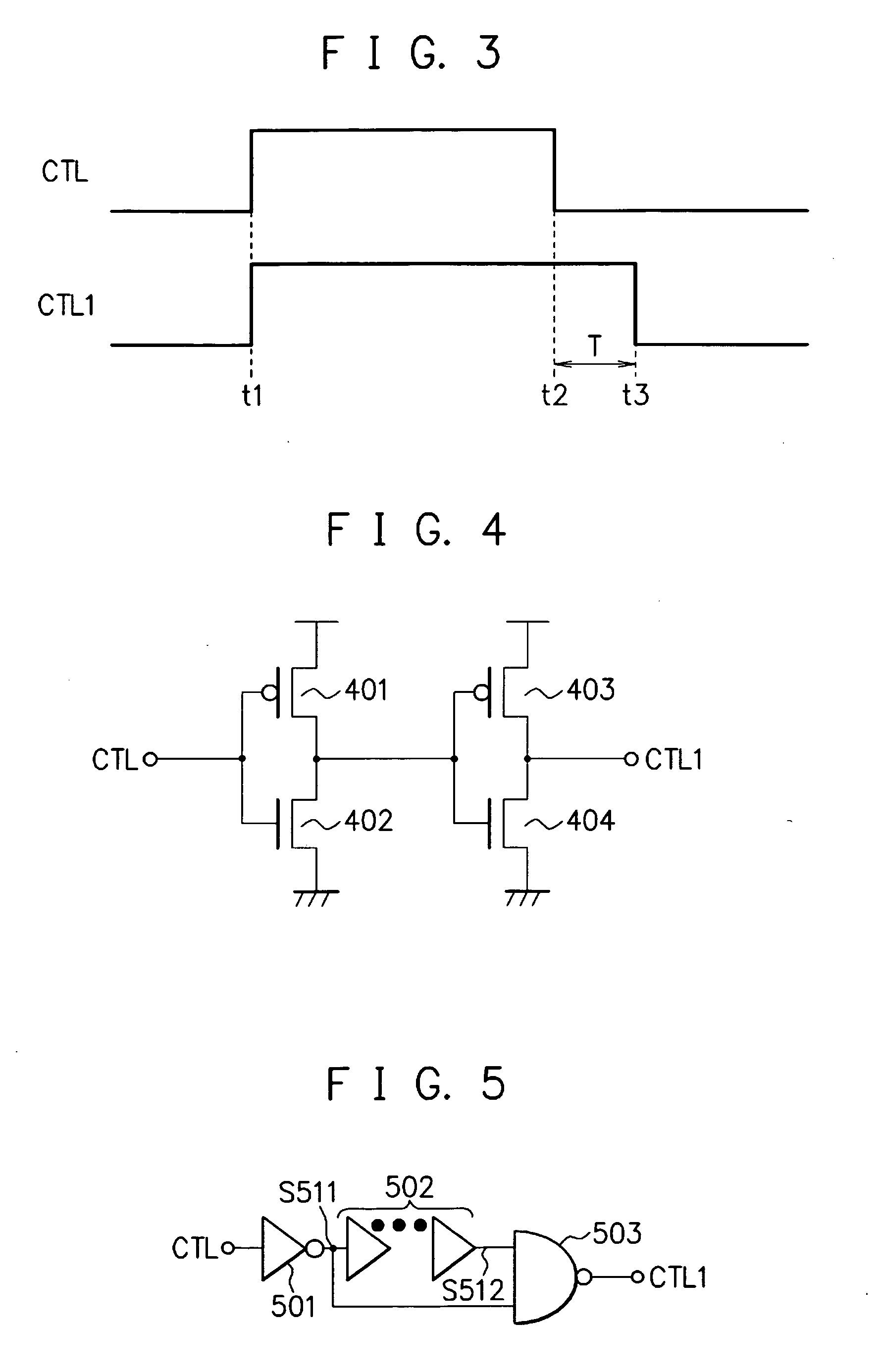

InactiveUS20070176633A1Prevent malfunctionReduce power noiseLogic circuits using specific componentsVoltage/current interference eliminationHigh impedanceEngineering

An output circuit including: a tri-state output circuit capable of outputting high-impedance state, high-level state, and low-level state, in which the high-level state and low-level state are low-impedance state, and switching the high-impedance state and the low-impedance state in accordance with a first control signal; and a delay circuit outputting the first control signal to the tri-state output circuit by inputting a second control signal and delaying the second control signal so that timing delay time of the second control signal switching the high-impedance state to the low-impedance state is longer than the timing delay time of the second control signal switching the low-impedance state to the high-impedance state, is provided.

Owner:FUJITSU LTD

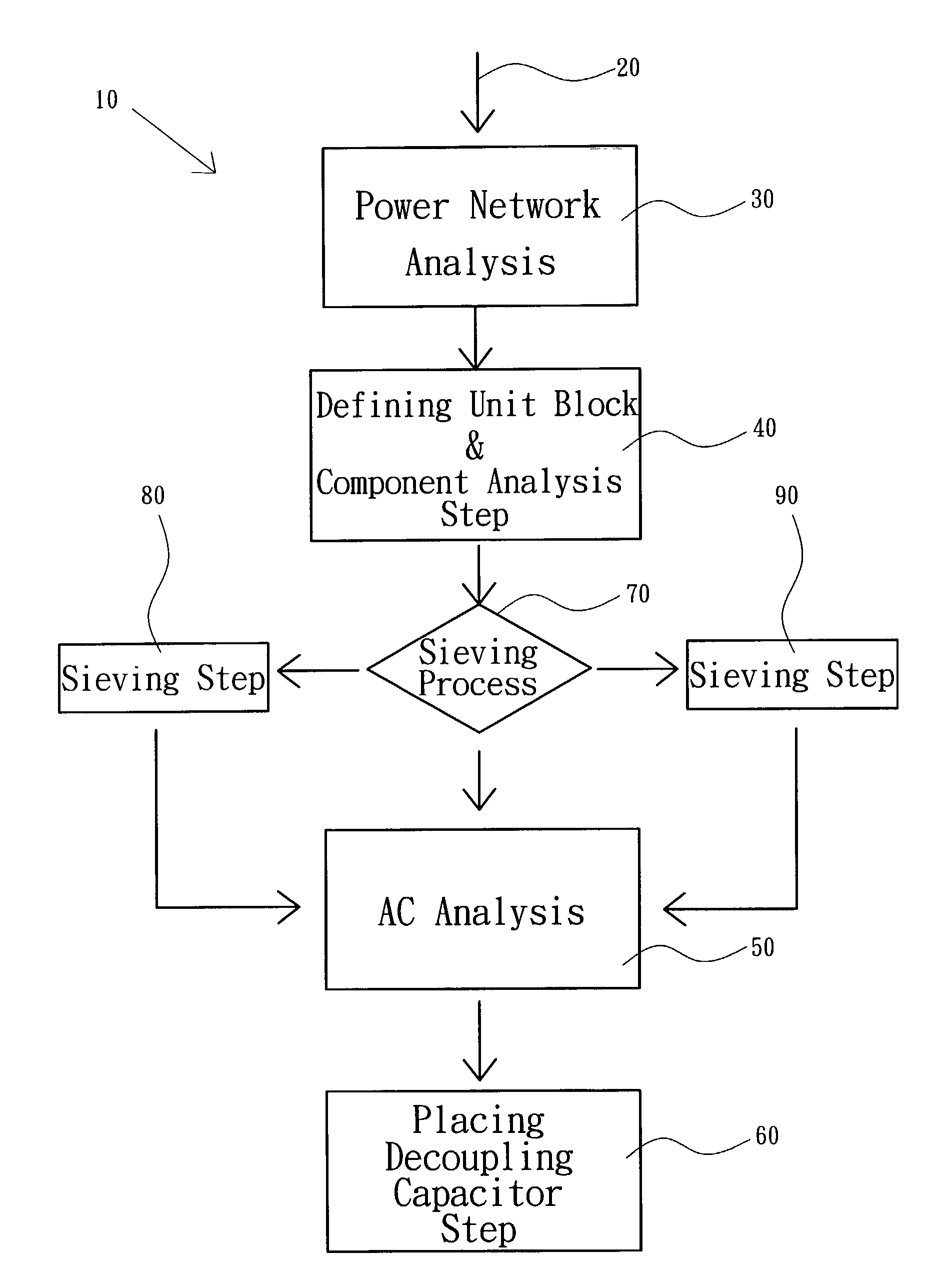

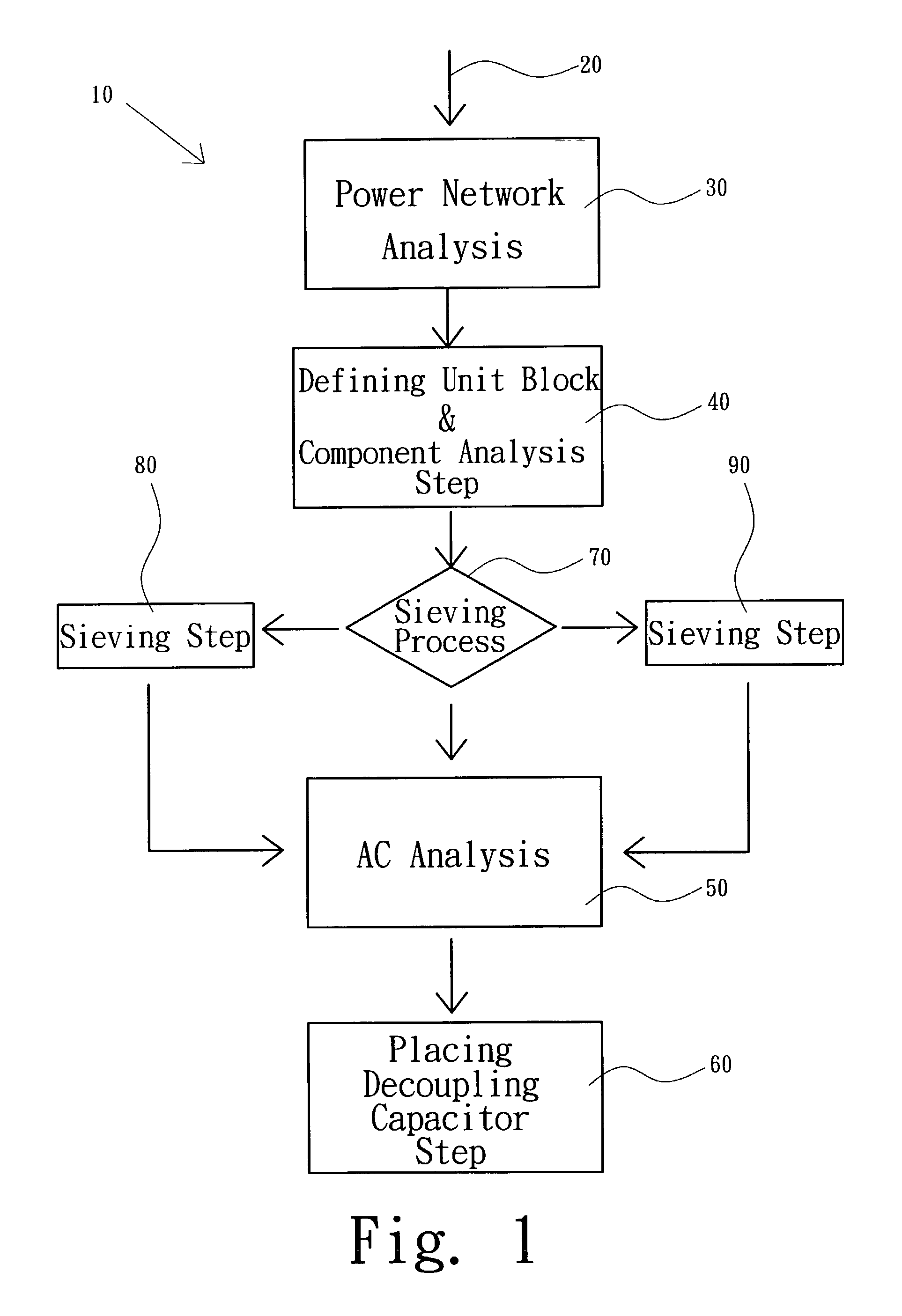

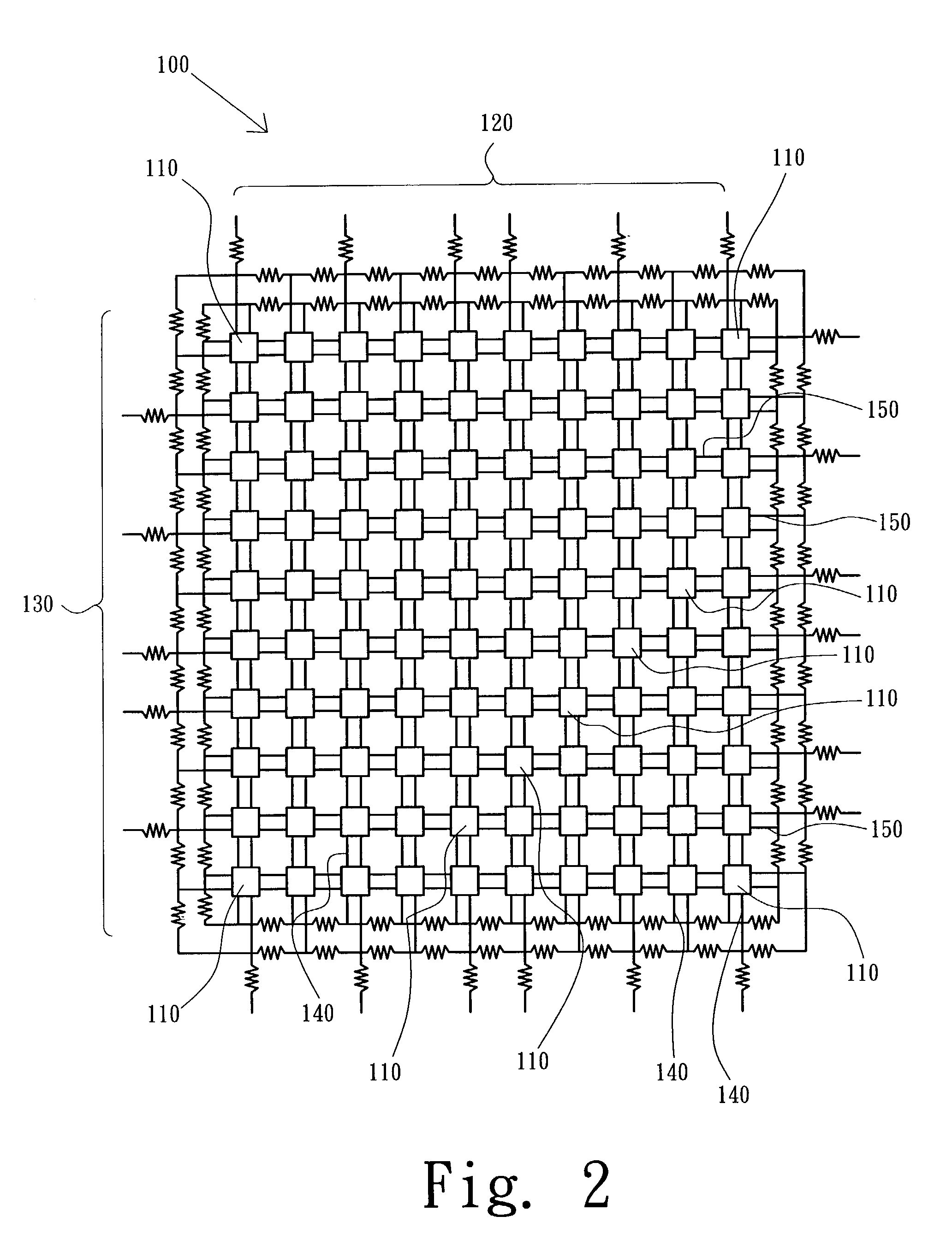

Method for analyzing power noise and method for reducing the same

InactiveUS7079998B2Reduce Power NoiseReduce total powerElectric devicesNoise figure or signal-to-noise ratio measurementElectricityComputer Aided Design

A method for analyzing power noise and method for reducing the same are disclosed, wherein the present invention is utilized in an IC design process. First, a DC analysis is performed with a related IC design by utilizing computer aided design (CAD) software and circuit simulation software for obtaining a power network model of the IC design. Then, the power network model is defined as being composed of a plurality of unit blocks. After analysis, the quantity and type, etc., of components connected electrically to each of the unit blocks are recognized and are regarded as component reference data of each of the unit blocks. Afterwards, according to the component reference data of each of the unit blocks, the voltage drop (IR drop) occurring in operation for each of the unit blocks is evaluated and obtained by utilizing an equivalent circuit constructed by components that are connected electrically to each of the unit blocks. Therefore, the voltage consumption and distribution in each region of the power network model are obtained, so that at least one appropriate capacitor can be placed on proper locations of the power network model, to compensate the voltage drop caused by the IC design components while in operation, and to decrease the power noise in the IC design.

Owner:SILICON INTEGRATED SYSTEMS

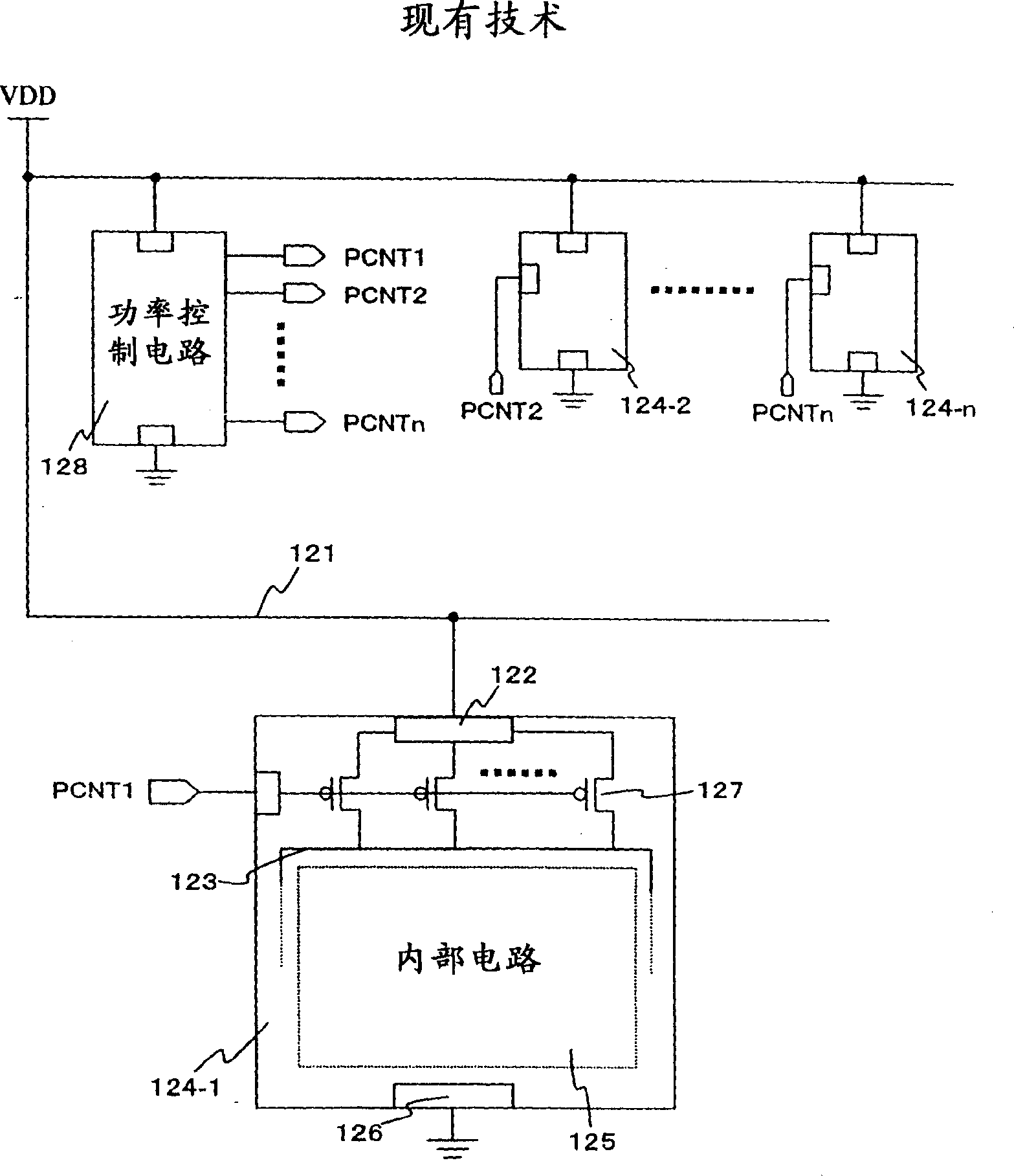

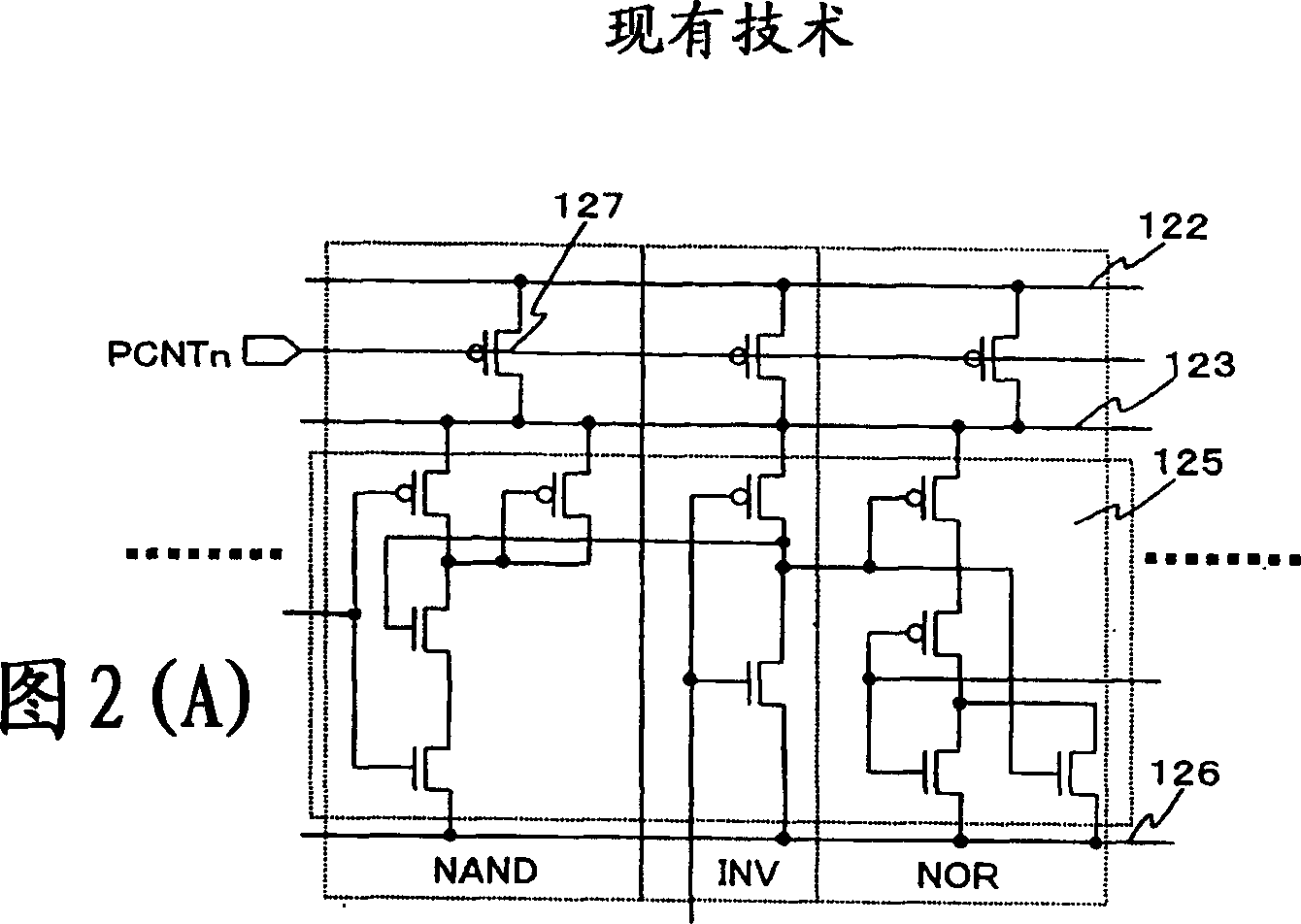

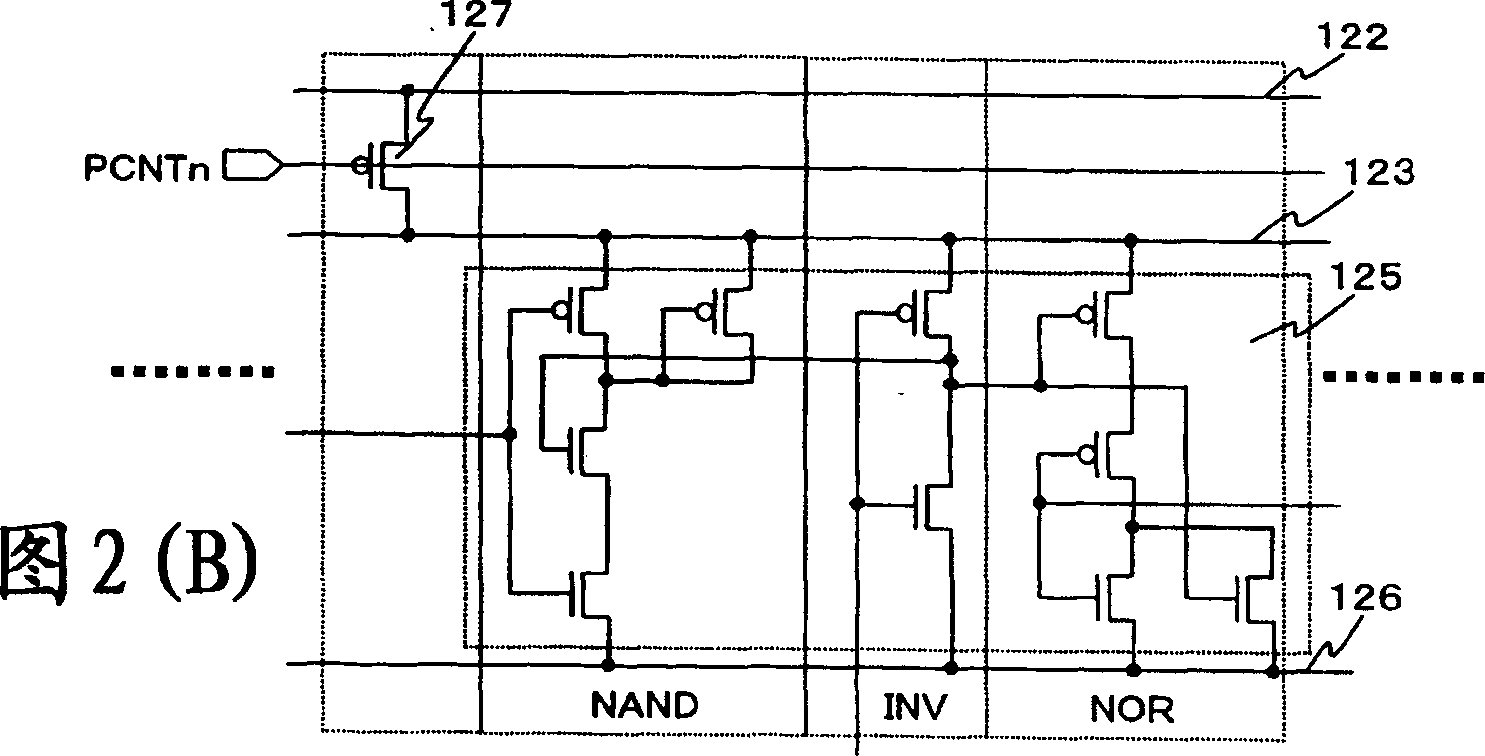

Semiconductor integrated circuit having leakage current cut-off circuit

InactiveCN1449112AReduce voltage dropReduce Power NoisePower reduction by control/clock signalSolid-state devicesTime delaysVoltage drop

In the disclosed semiconductor integrated circuit, a plurality of power supply terminals of the logic circuit block are connected to the actual power supply line via the leak current cut-off circuit. When the logic circuit block is to be activated, the delay control circuit controls the leak current cut-off circuit to electrically connect the power supply terminal to the actual power supply line with a delay of the predetermined time. Therefore, when the logic circuit block is activated, voltage drop of the actual power supply line can be lowered to a small value and erroneous operation of the other logic circuit block in the activated condition due to the power supply noise can be prevented.

Owner:SOCIONEXT INC

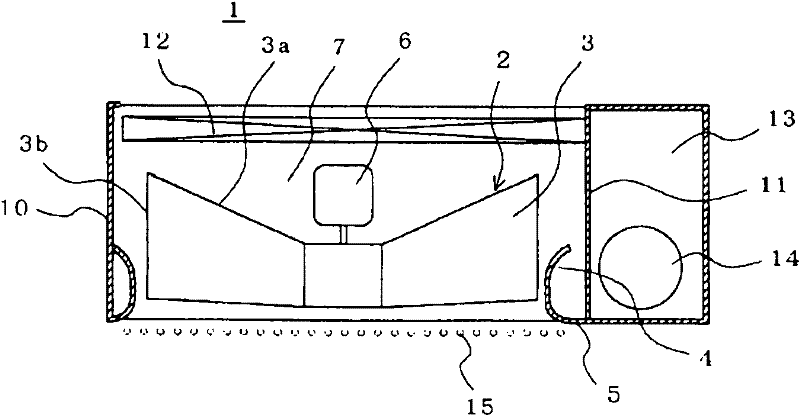

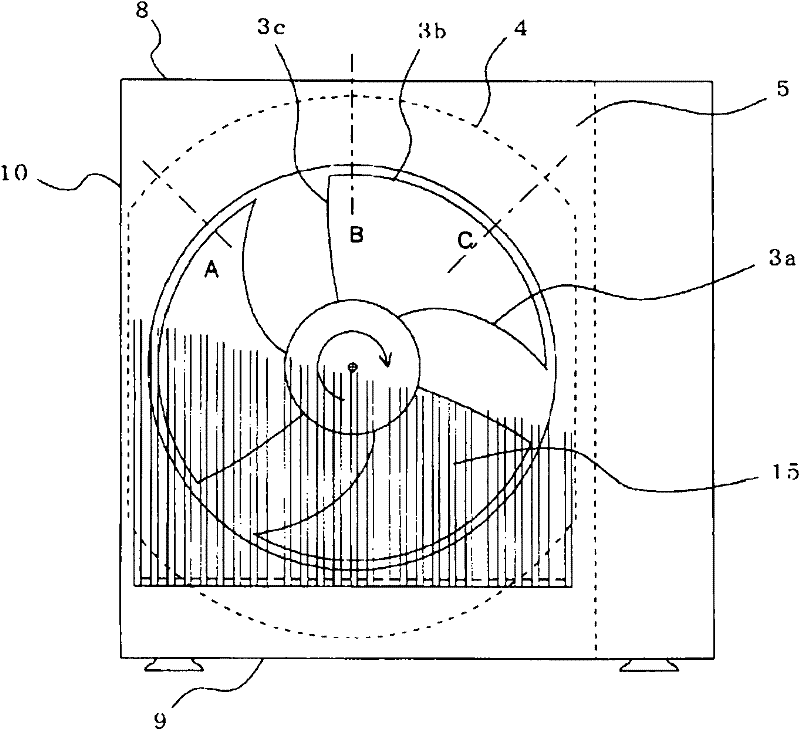

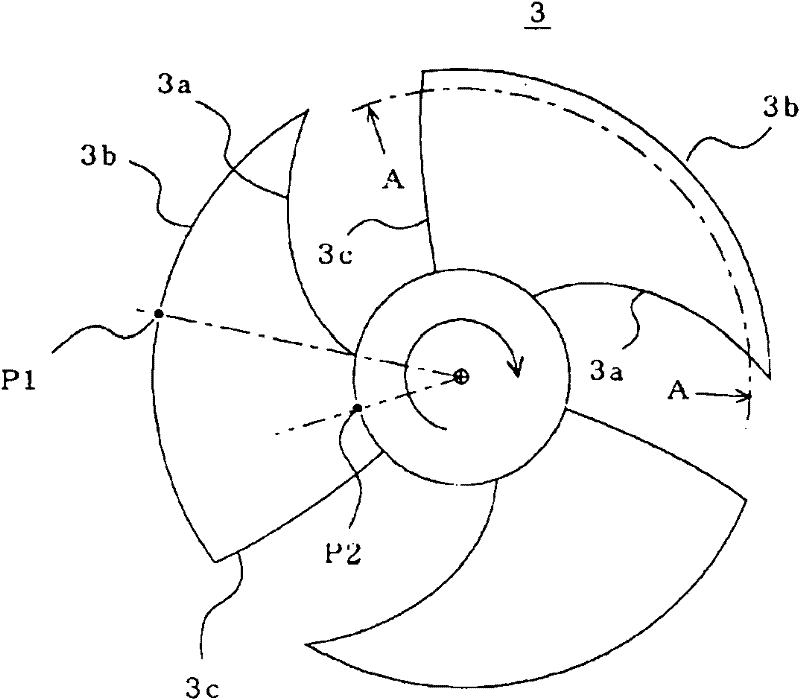

Blower and heat pump utilizing said blower

ActiveCN102203430ADecrease the expansion angleIncrease overlap heightPump componentsLighting and heating apparatusPropellerHeat pump

The peripheral edge at the rear edge of a propeller fan (3), which is driven by a motor (6) serving as a propeller fan driver, is covered with a bell-mouth (4). Multiple plates, namely, a top plate (8), a bottom plate (9), and side plates (10) which constitute an intake-side air duct on the outside of the propeller fan in the radial direction, and a machine room plate (11) are provided. In the cross-section of the bell-mouth at the position where the blades of the propeller fan are closest front to back at a position on the plates where the distance between the propeller fan and the plates that constitute the air duct on the outside in the radial direction is relatively small, the widening angle (?1) of the bell-mouth on the intake-side is set smaller, and the height (Hb) of overlap of the propeller fan and the bell-mouth is set higher, than those in the cross-section at the position where the distance between the propeller fan and the plates is relatively large, and the cross-sectional shape of the bell-mouth is changed gradually between the two positions.

Owner:MITSUBISHI ELECTRIC CORP

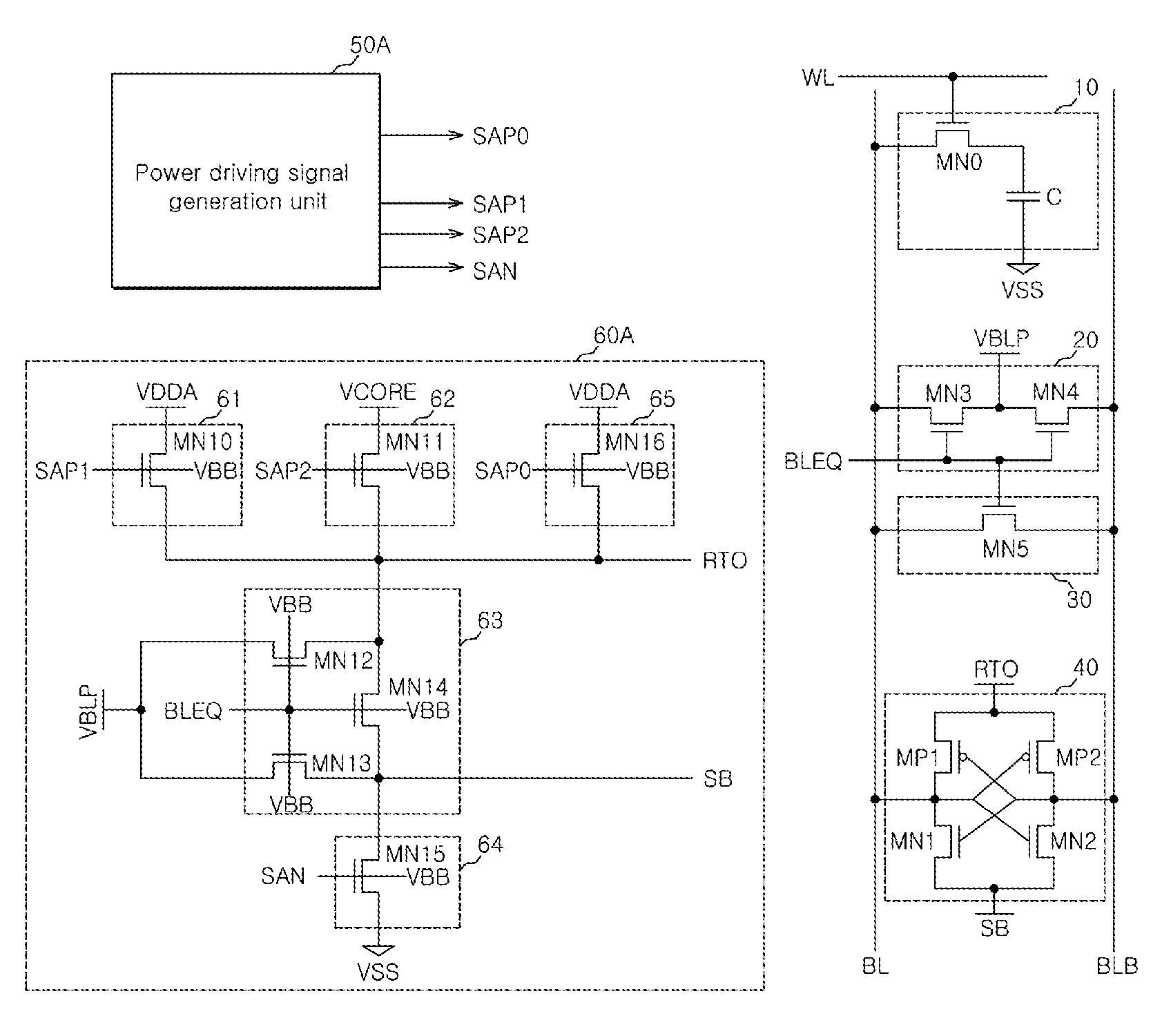

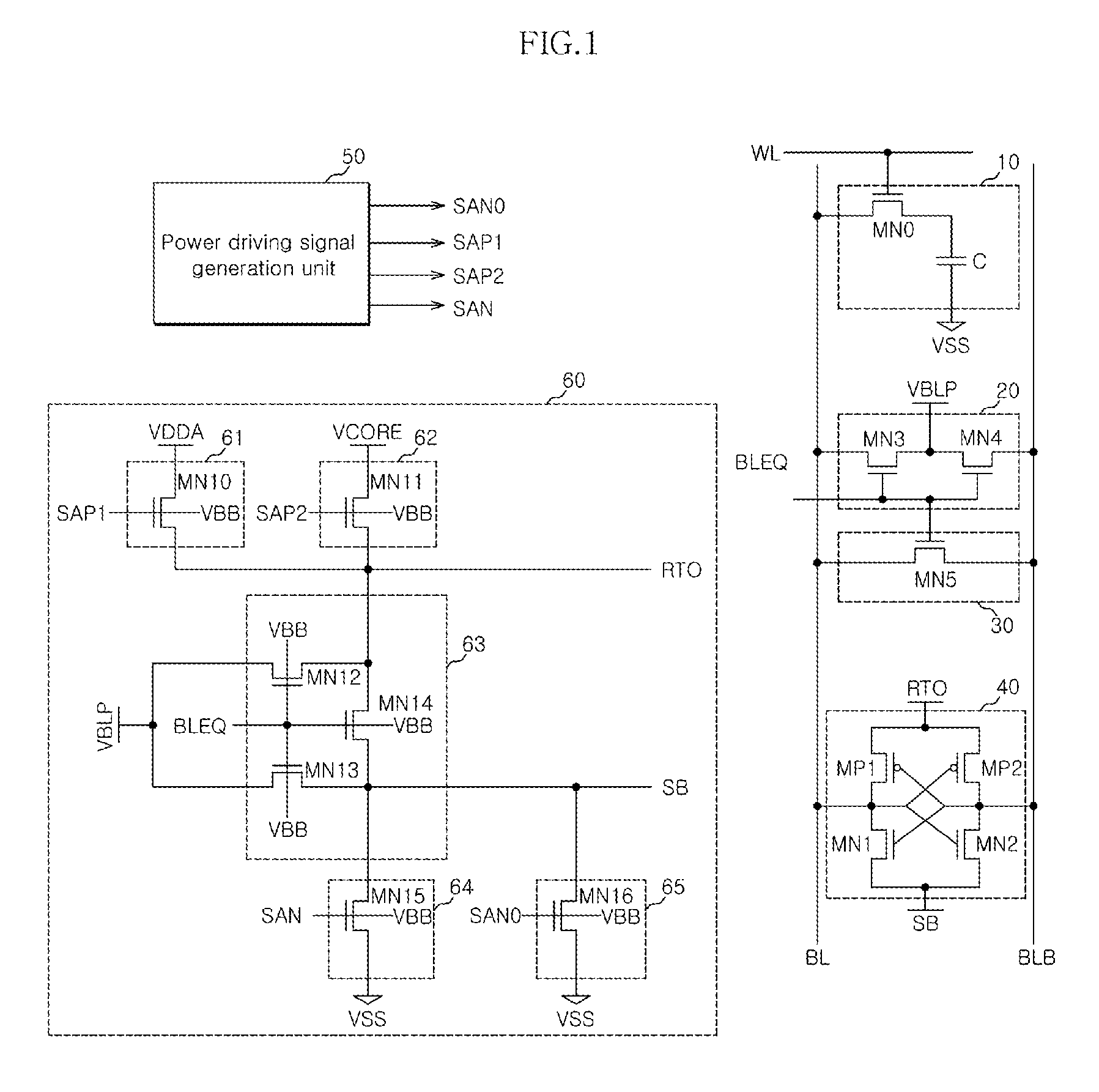

Semiconductor memory apparatus

A semiconductor memory apparatus includes a bit line sense amplifier unit and a driving voltage supply unit. The bit line sense amplifier unit senses and amplifies a signal provided from a memory cell using a pull-up driving voltage provided through a pull-up power line and a pull-down driving voltage provided through a pull-down power line. The driving voltage supply unit supplies the pull-down driving voltage having a first pull-down driving force during a first amplification period, and supplies the pull-down driving voltage having a second pull-down driving force greater than the first pull-down driving force during a second amplification period after the first amplification period.

Owner:SK HYNIX INC

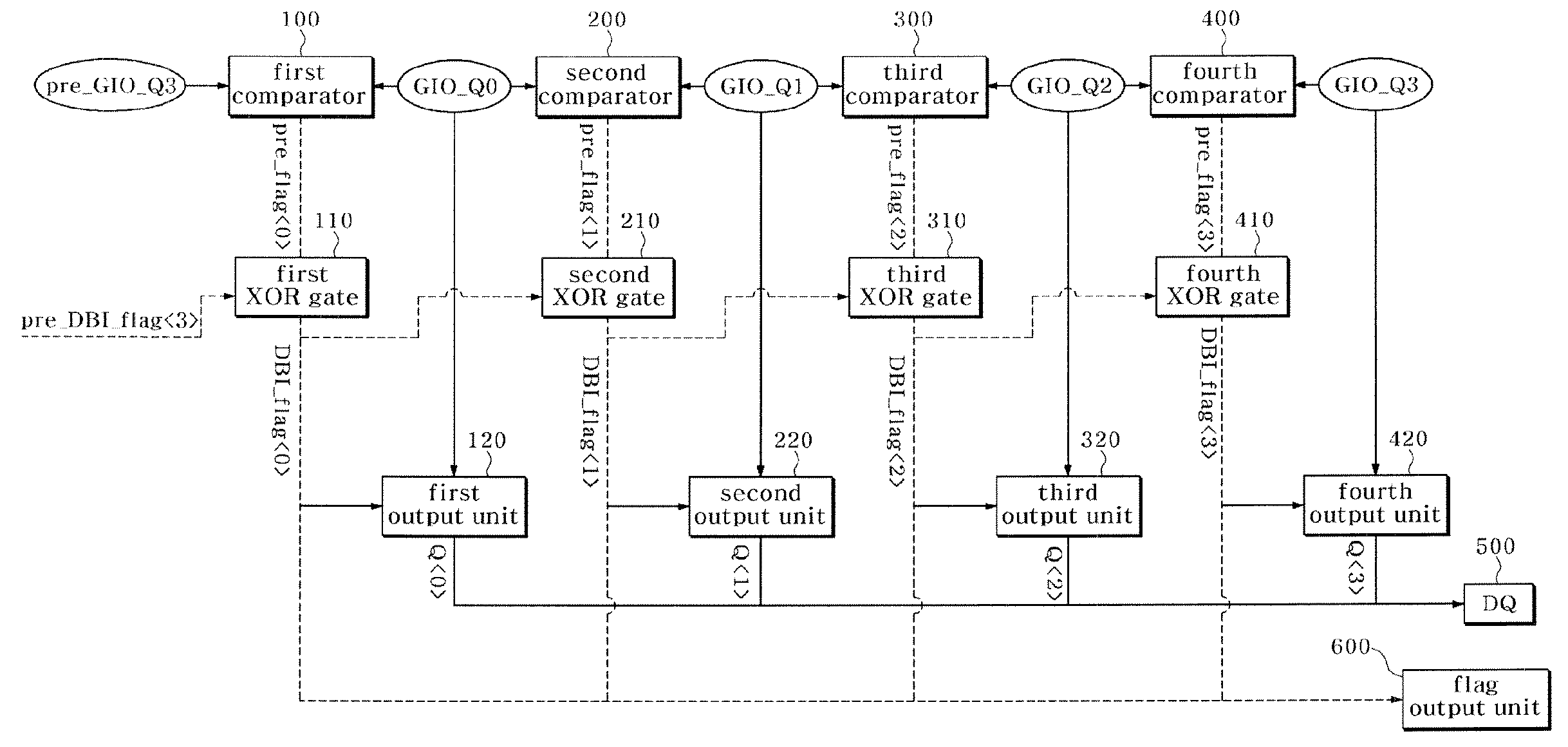

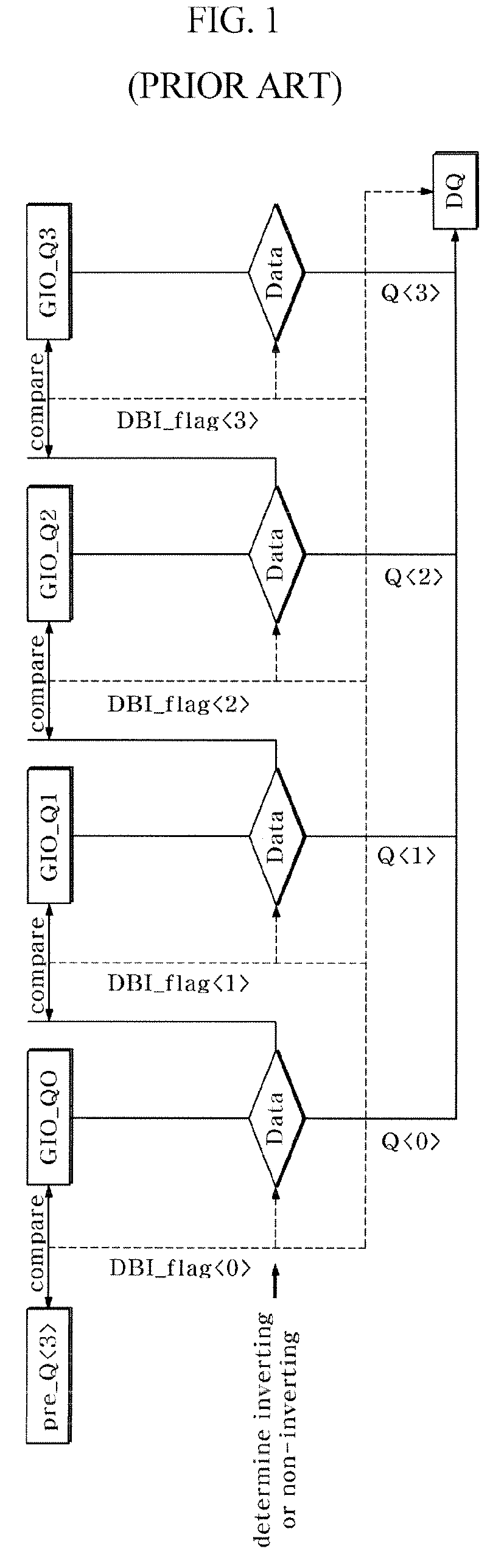

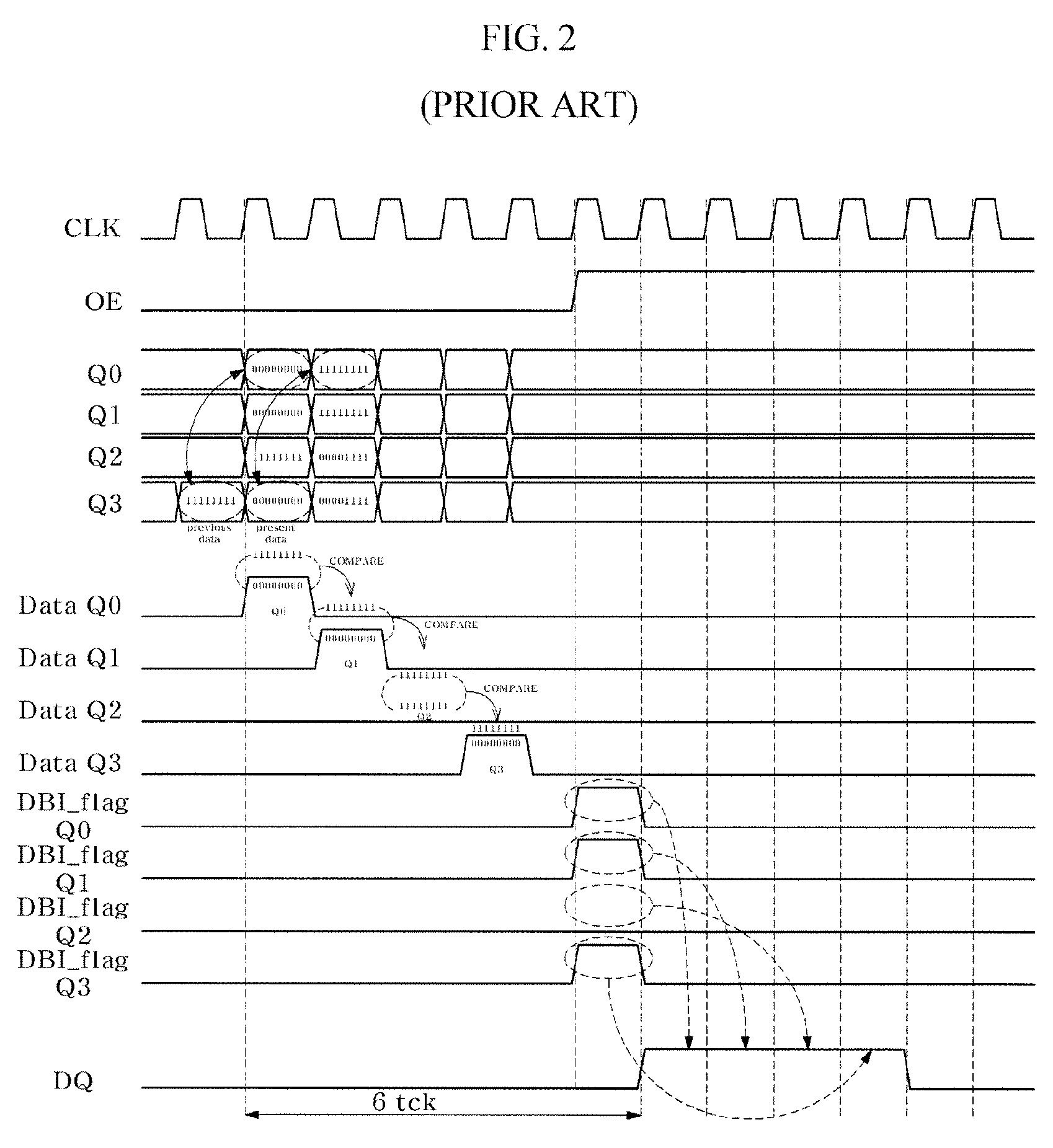

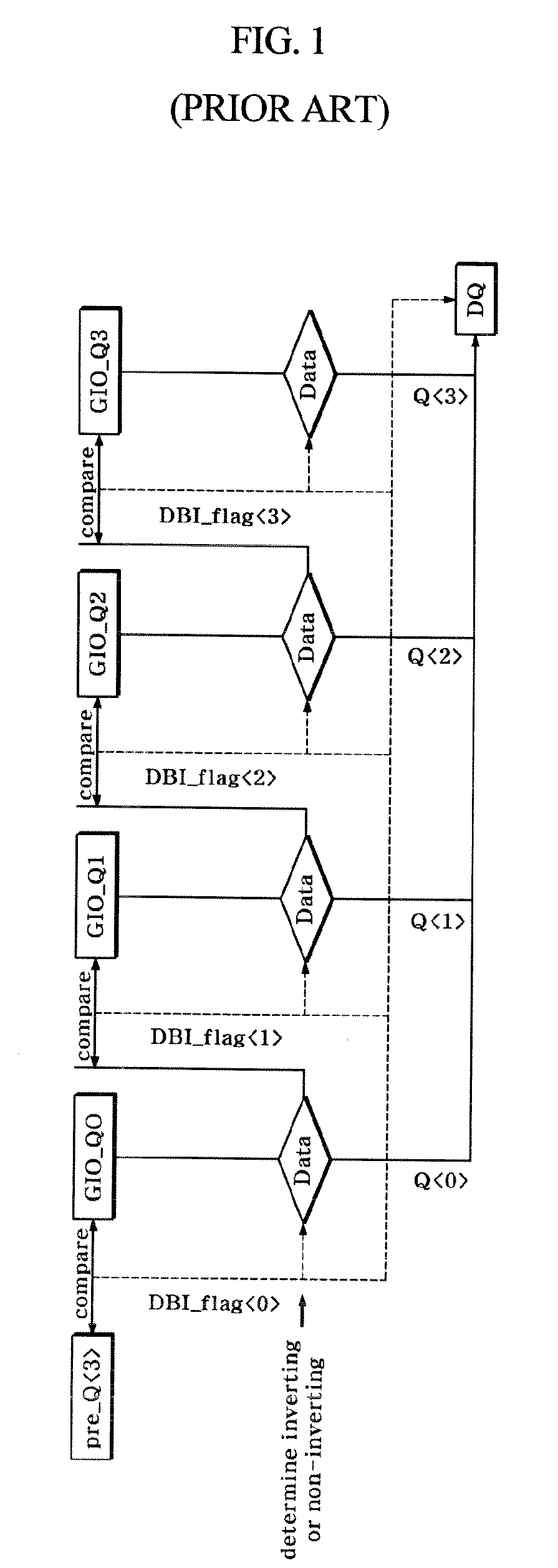

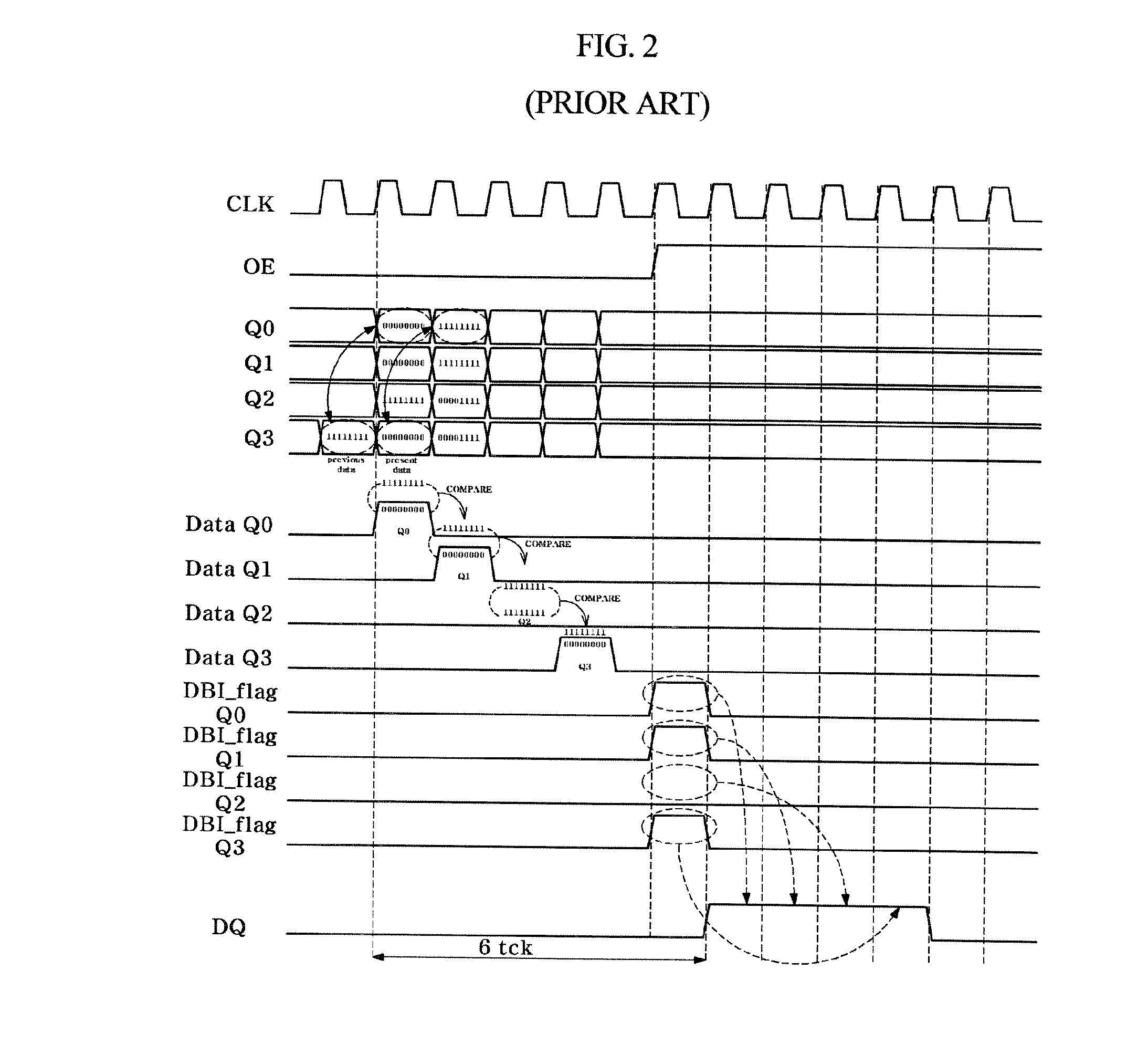

Data output device and method of semiconductor device

ActiveUS7228370B2Reduce Power NoiseAccurately and stably processParallel/series conversionDigital storageDevice materialLogical operations

A data output device is disclosed having a first comparator for comparing first output data with arbitrary output data on a bit-by-bit basis and outputting a first pre-flag signal, a second comparator for comparing second output data with the first output data on a bit-by-bit basis and outputting a second pre-flag signal, first and second logic units for performing logic operations with respect to pre-flag signals and data inversion flag signals, a first output unit for inverting or non-inverting and outputting a plurality of bits contained in the first output data in response to the first data inversion flag signal, a second output unit for inverting or non-inverting and outputting a plurality of bits contained in the second output data in response to the second data inversion flag signal, and an output data initializer for, when a no-operation period is generated in a series of data output operations, initializing the arbitrary output data and supplying the resulting data to the first comparator.

Owner:SK HYNIX INC

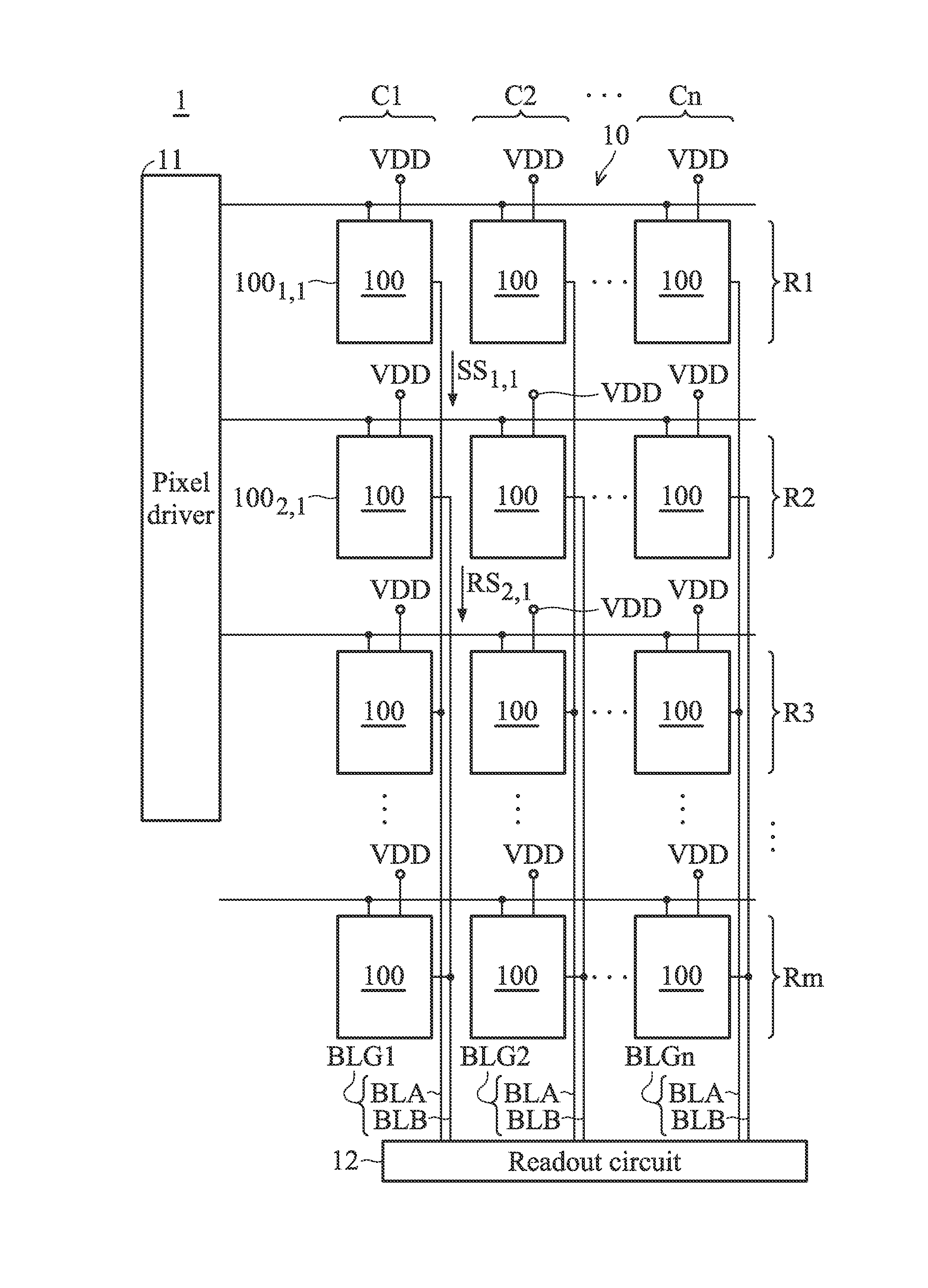

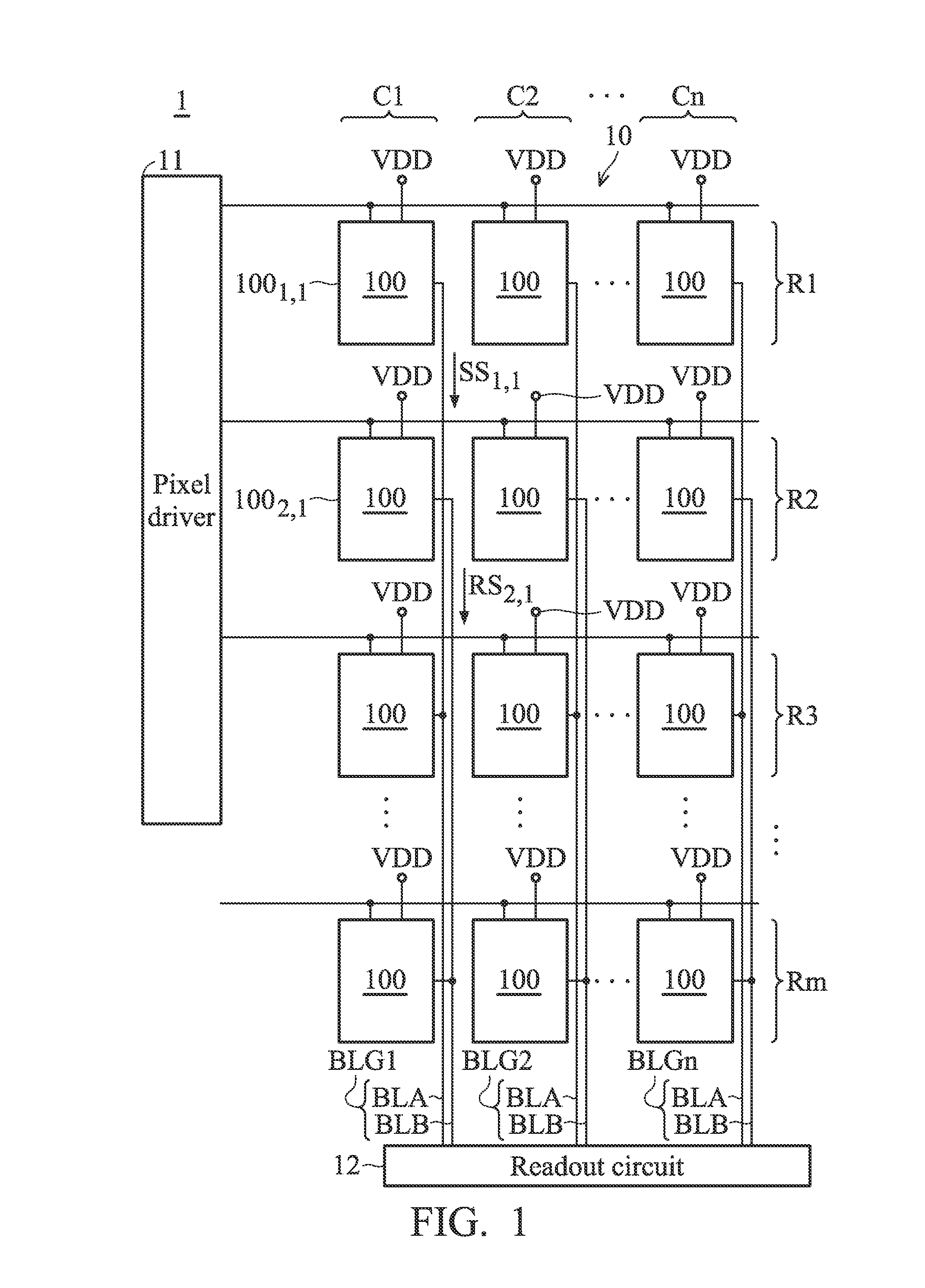

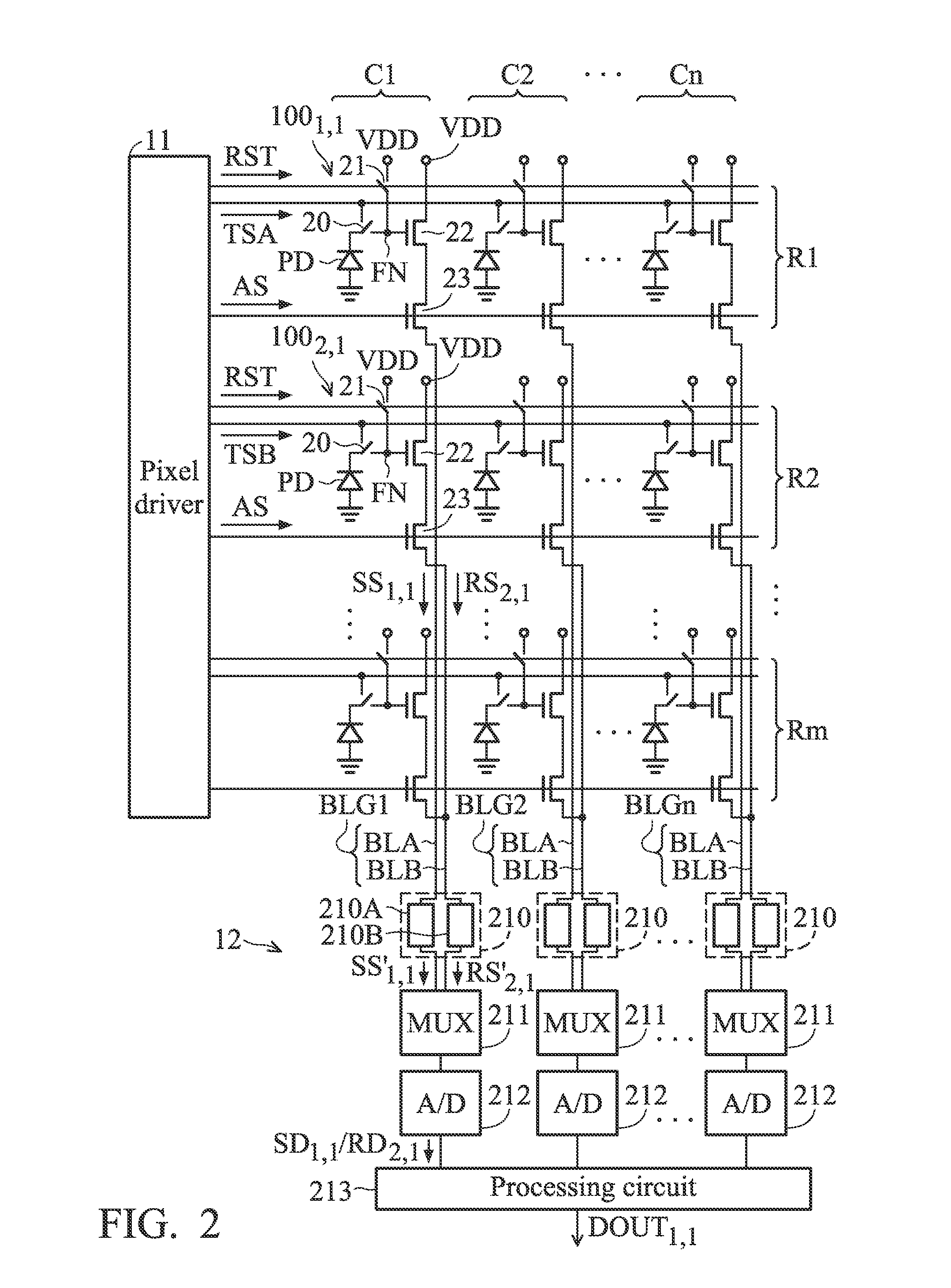

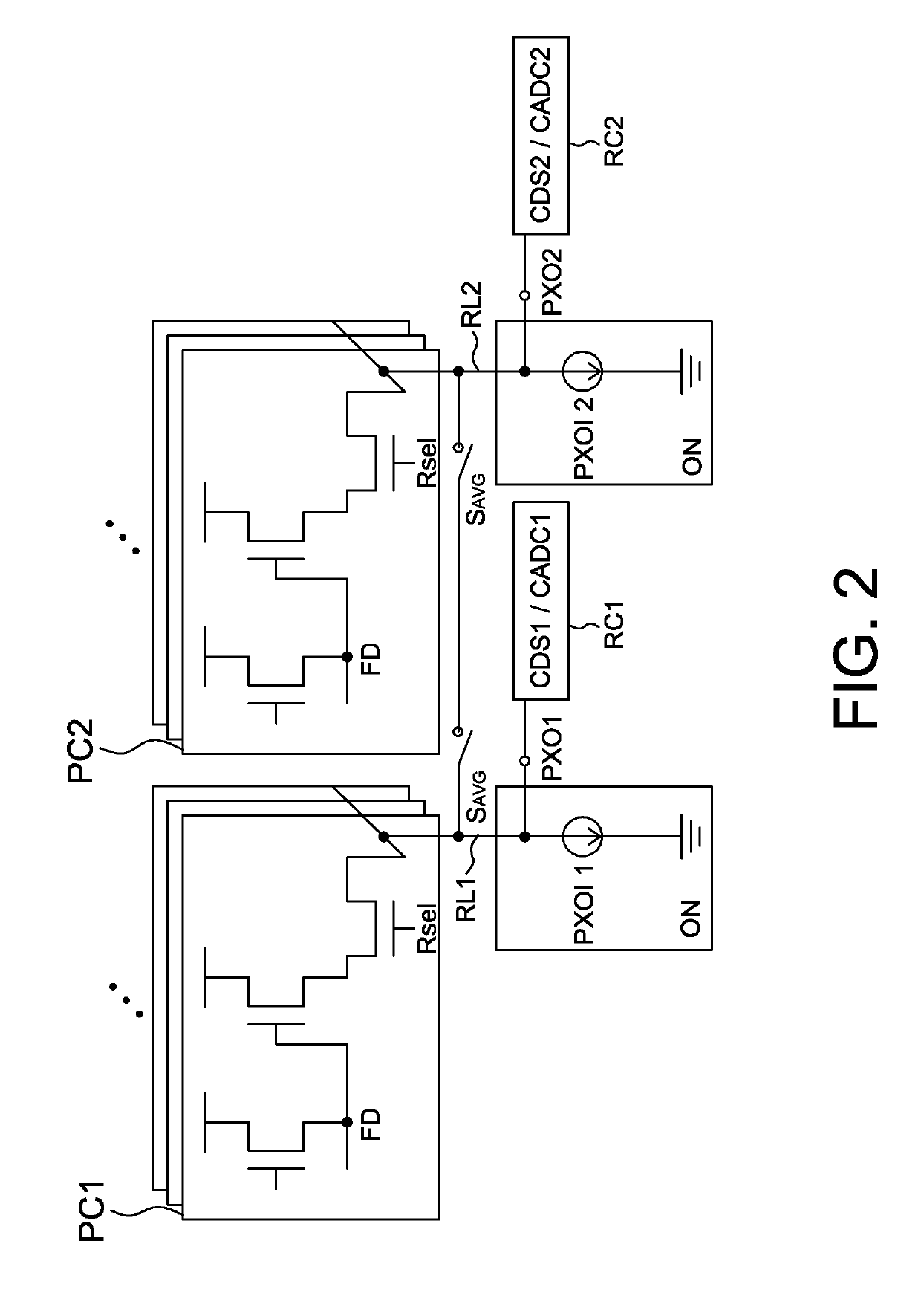

Sensing devices

ActiveUS20150304580A1Reduce Power NoiseImprove sensing qualityTelevision system detailsTelevision system scanning detailsComputer sciencePixel array

A sensing device is provided. The sensing device includes a plurality of pixel groups and a readout circuit. The pixel groups are arranged on a plurality of rows and a plurality of columns to form a pixel array. The pixel groups include a first pixel group and a second pixel group which are arranged on the different rows and the same column. The readout circuit is coupled to the pixel groups. When the first pixel group is triggered to perform a readout operation to generate a first sensing signal, the second pixel group performs a coupling operation to generate a reference signal. The readout circuit performs a subtraction operation based on the first sensing signal and the reference signal to generate a first readout data corresponding to the readout operation of the first pixel group.

Owner:HIMAX IMAGING LIMITED

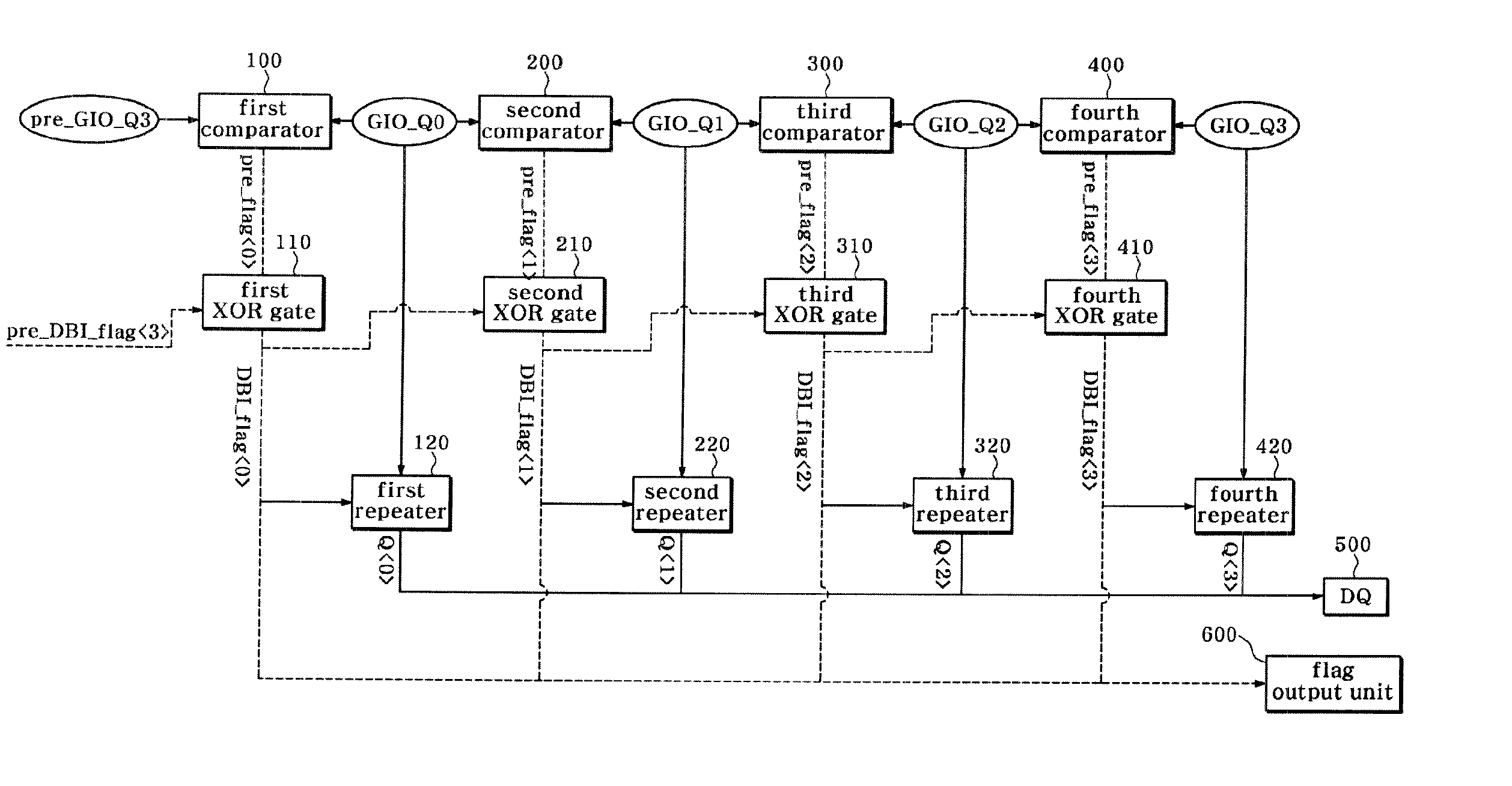

Data Output Device and Method of Semiconductor Device

ActiveUS20070011481A1Reduce Power NoiseAccurately and stably processDigital data processing detailsDigital storageLevel shiftingDevice material

A data output device and method is disclosed, the device having a first comparator for comparing first output data with arbitrary output data on a bit-by-bit basis and outputting a first pre-flag signal which is enabled or disabled according to the number of bits of the first output data having made level transitions, a second comparator for comparing second output data with the first output data on a bit-by-bit basis and outputting a second pre-flag signal which is enabled or disabled according to the number of bits of the second output data having made level transitions, first and second logic units for performing logic operations with respect to pre-flag signals and data inversion flag signals, a first repeater for inverting or non-inverting and outputting a plurality of bits contained in the first output data in response to the first data inversion flag signal, and a second repeater for inverting or non-inverting and outputting a plurality of bits contained in the second output data in response to the second data inversion flag signal.

Owner:SK HYNIX INC

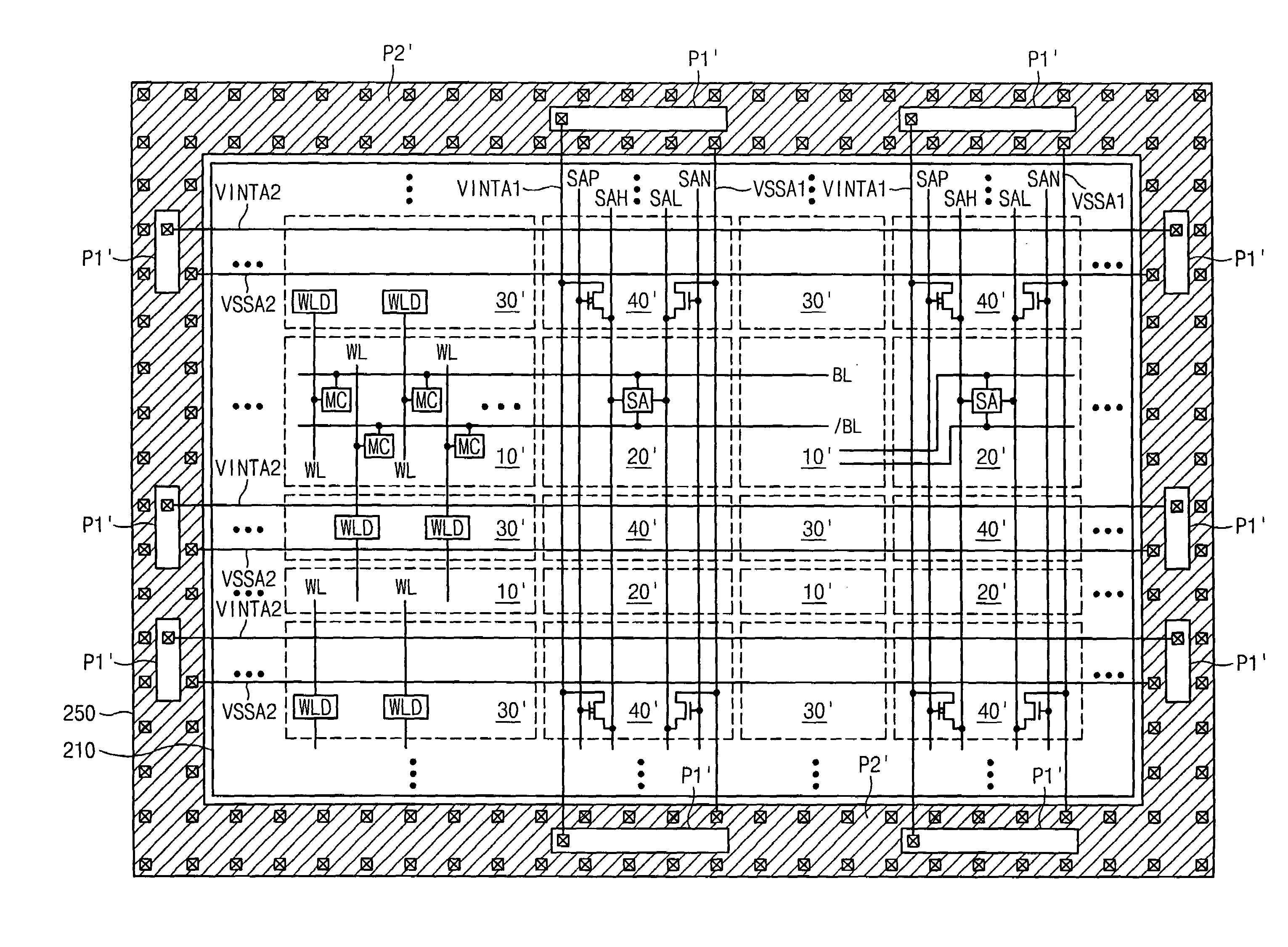

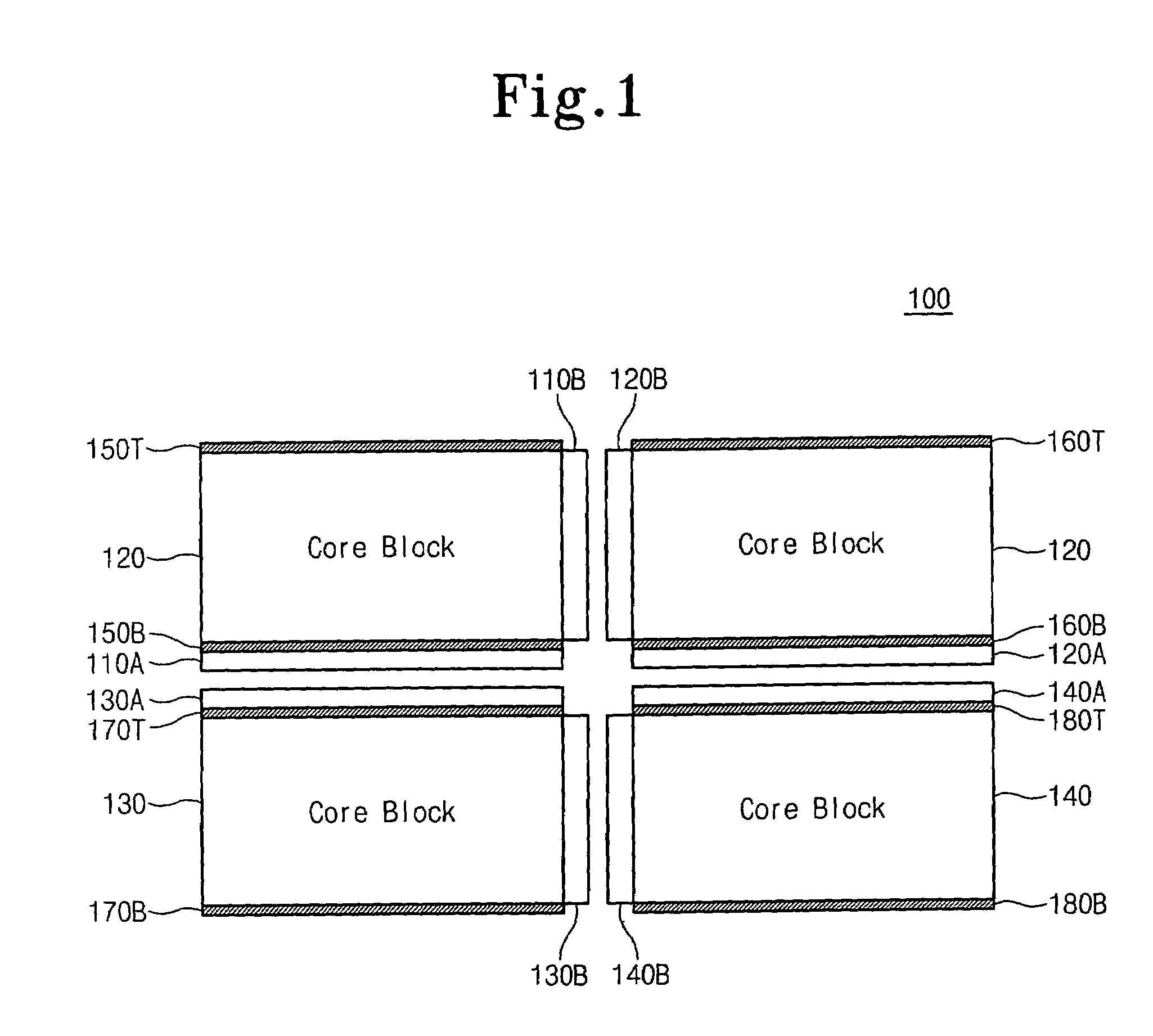

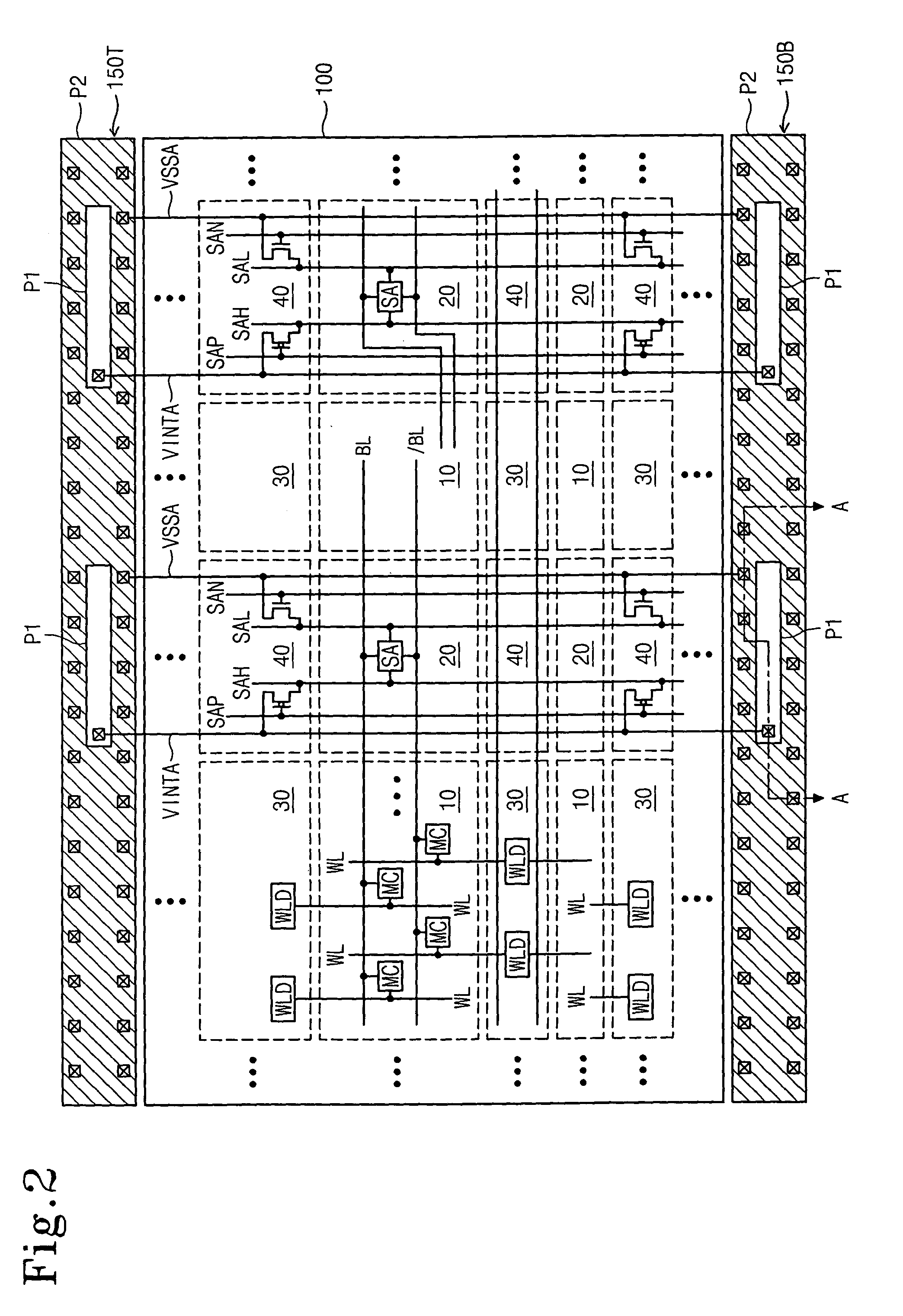

Semiconductor memory device with a decoupling capacitor

InactiveUS7002872B2Reduce Power NoiseHigh speedDigital storageAudio power amplifierDecoupling capacitor

A semiconductor memory device includes a core block having sub-arrays and sense amplifier regions. First and second charge storing regions are disposed at sides of the core block. First and second decoupling capacitors are formed at the first and second charge storing regions, respectively. A plurality of first voltage supply lines are disposed to supply a power supply voltage to the sense amplifier regions and are connected to one electrode of each of the first and second decoupling capacitors. A plurality of second voltage supply lines are disposed to supply a ground voltage to the sense amplifier regions and are connected to the other electrode of each of the first and second decoupling capacitors.

Owner:SAMSUNG ELECTRONICS CO LTD

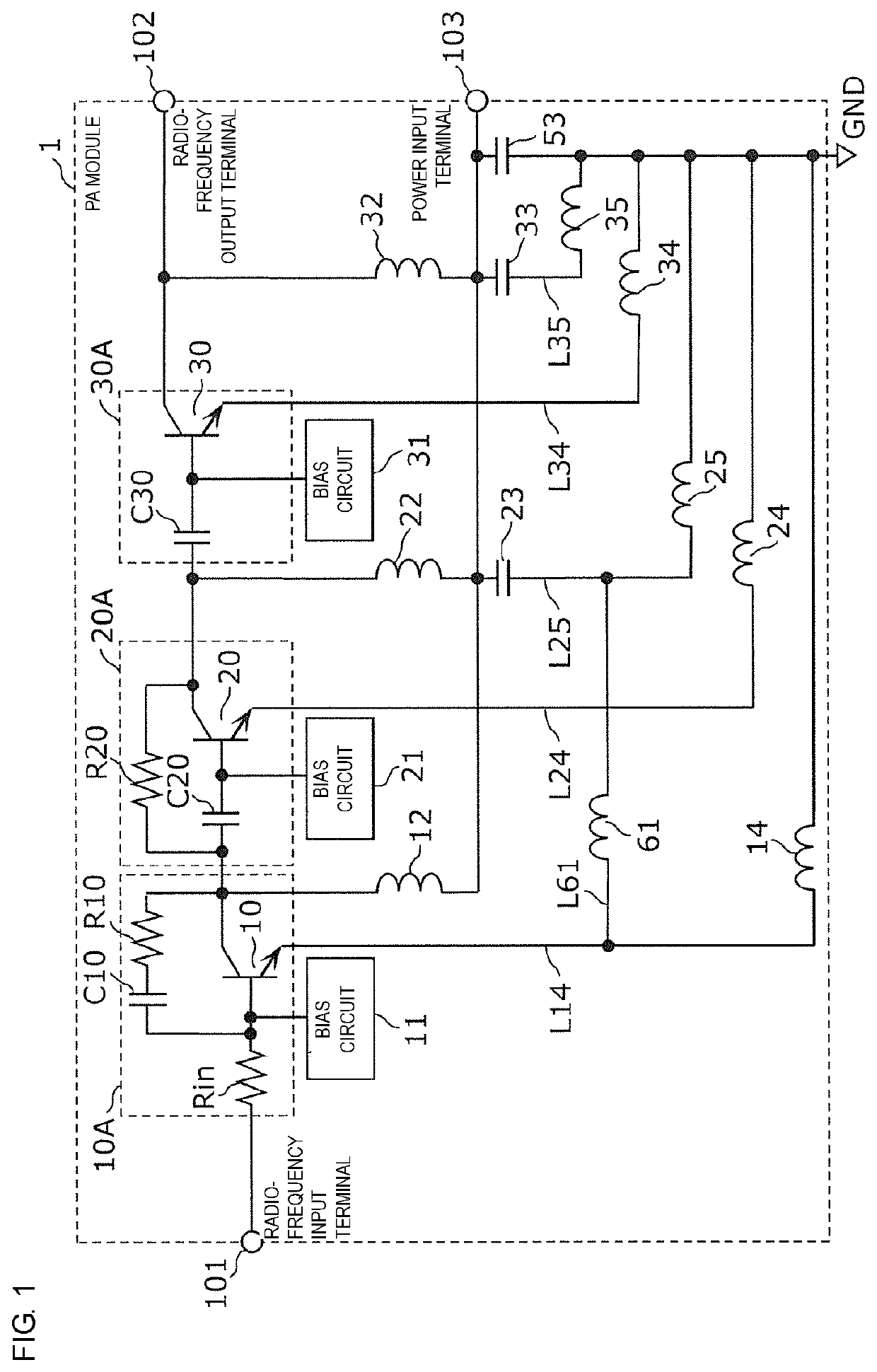

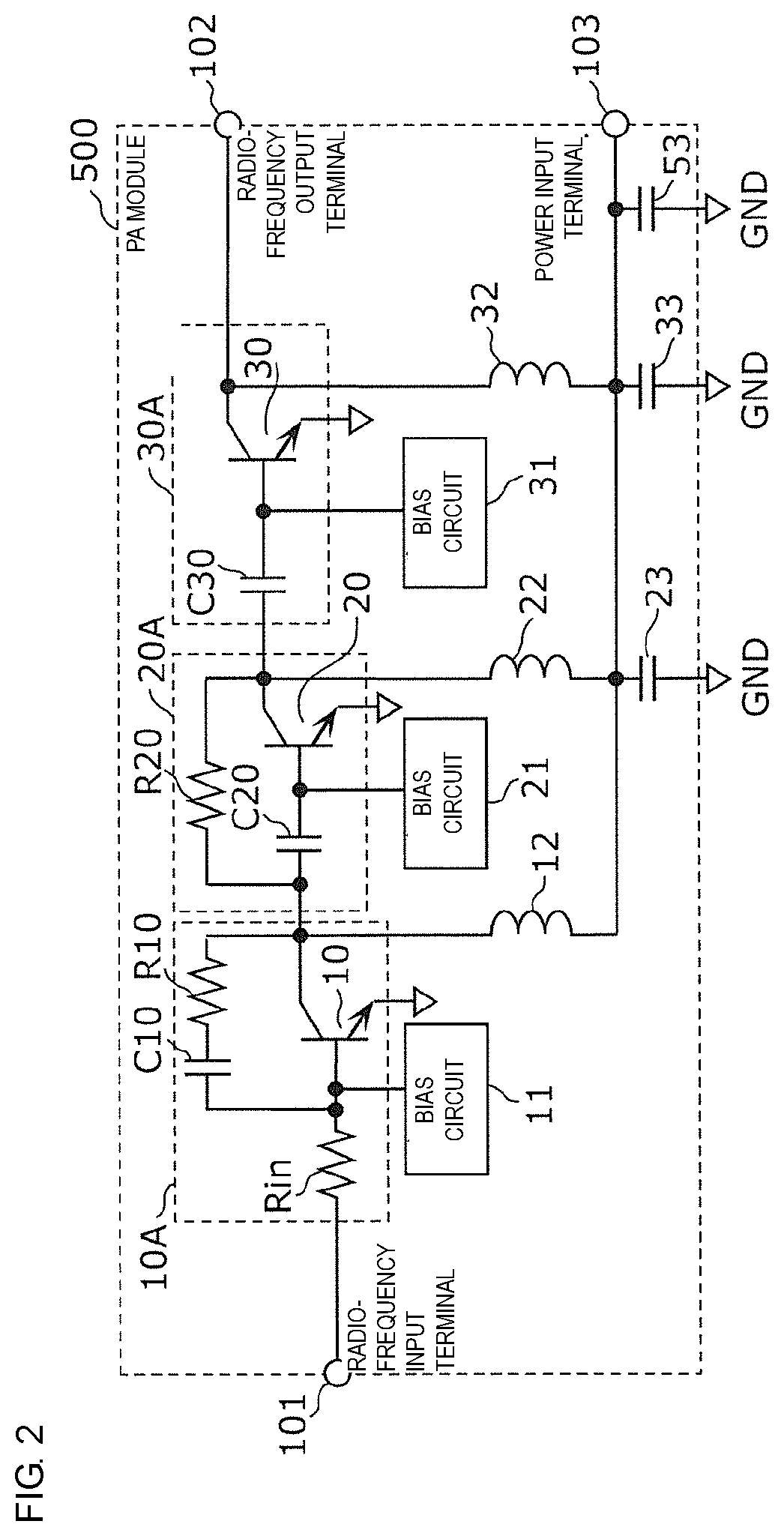

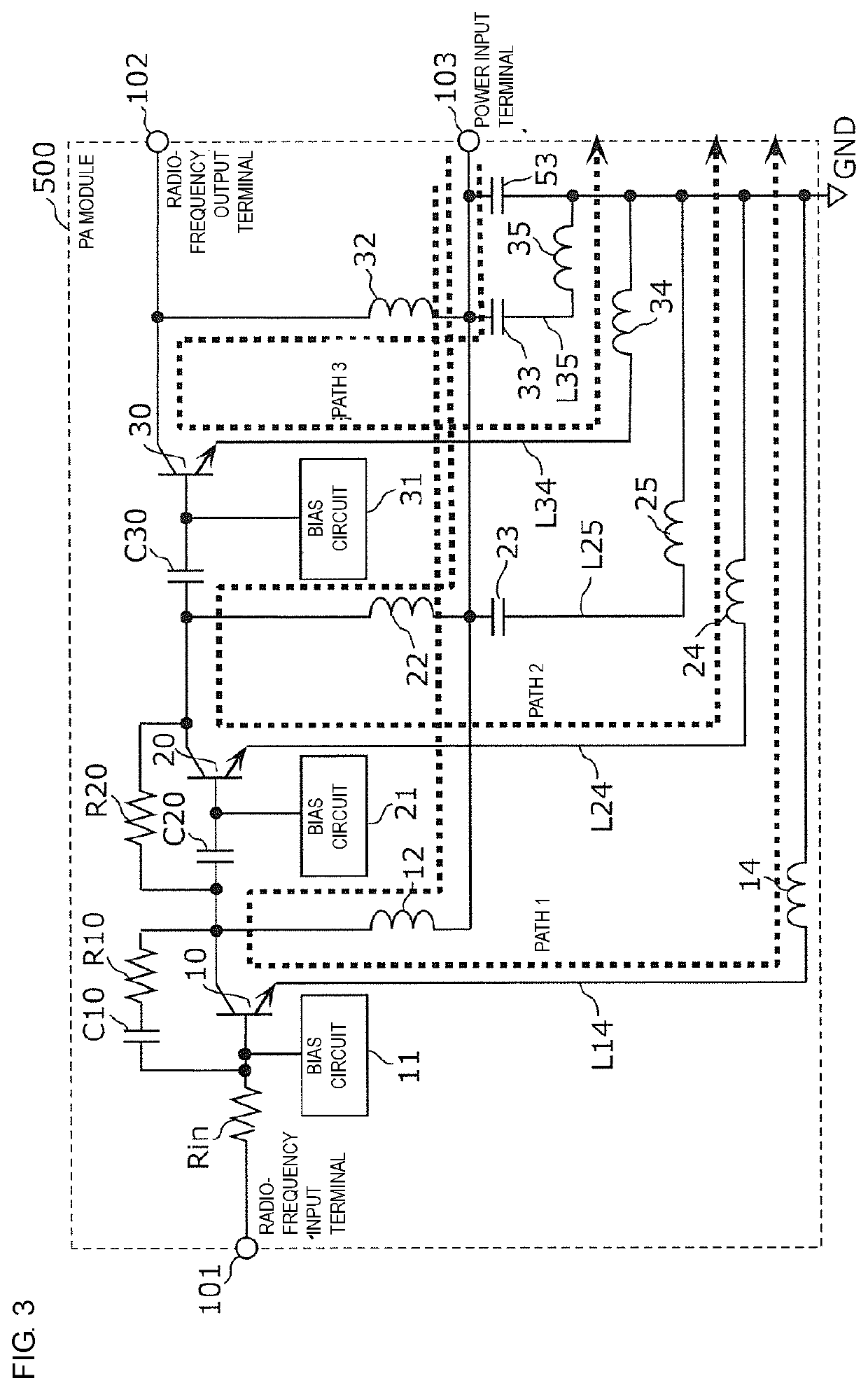

Power amplifier module, frontend circuit, and communication device

ActiveUS10554180B2Reduce Power NoiseAmplifier modifications to reduce noise influenceSemiconductor/solid-state device detailsCapacitanceTelecommunications

A PA module includes: a multilayer substrate having a ground pattern layer connected to a ground of a power source; amplifier transistors disposed on the multilayer substrate; a bypass capacitor having one end connected to the collector of the amplifier transistor; a first wiring line connecting the emitter of the amplifier transistor and the ground pattern layer to each other; a second wiring line connecting the emitter of the amplifier transistor and the ground pattern layer to each other; a third wiring line connecting the other end of the bypass capacitor and the ground pattern layer to each other; and a fourth wiring line formed between the amplifier transistor and the ground pattern layer and between the bypass capacitor and the ground pattern layer and connecting the first wiring line and the third wiring line to each other.

Owner:MURATA MFG CO LTD

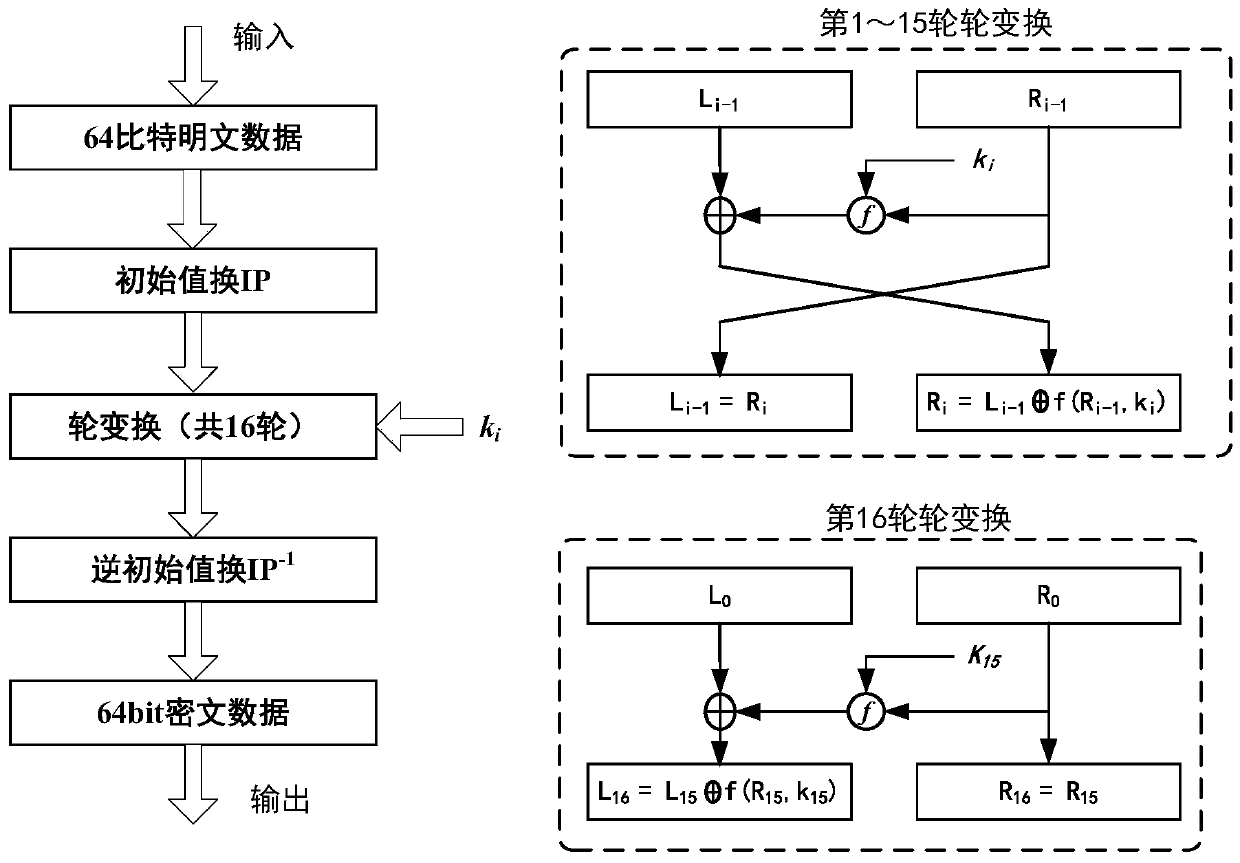

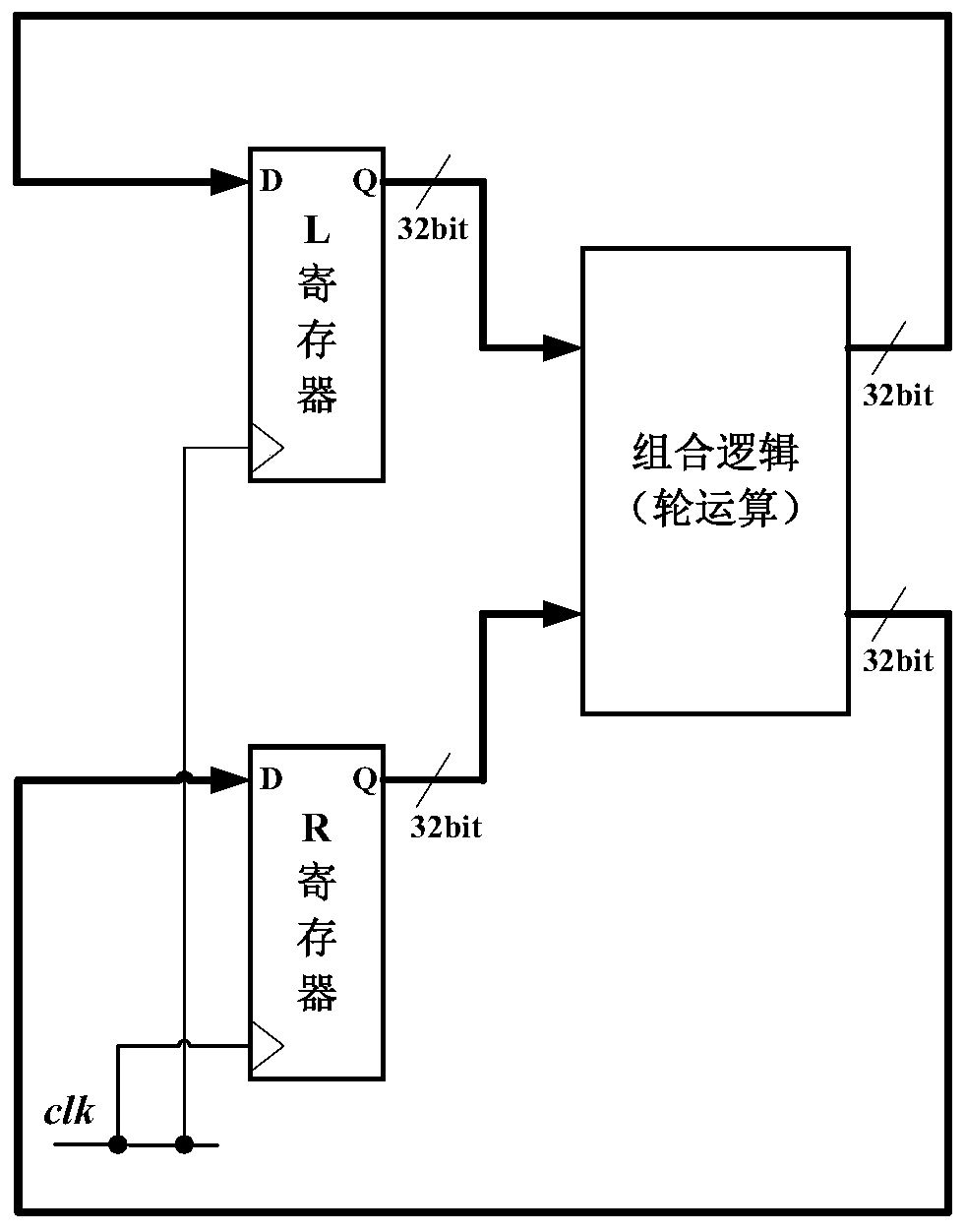

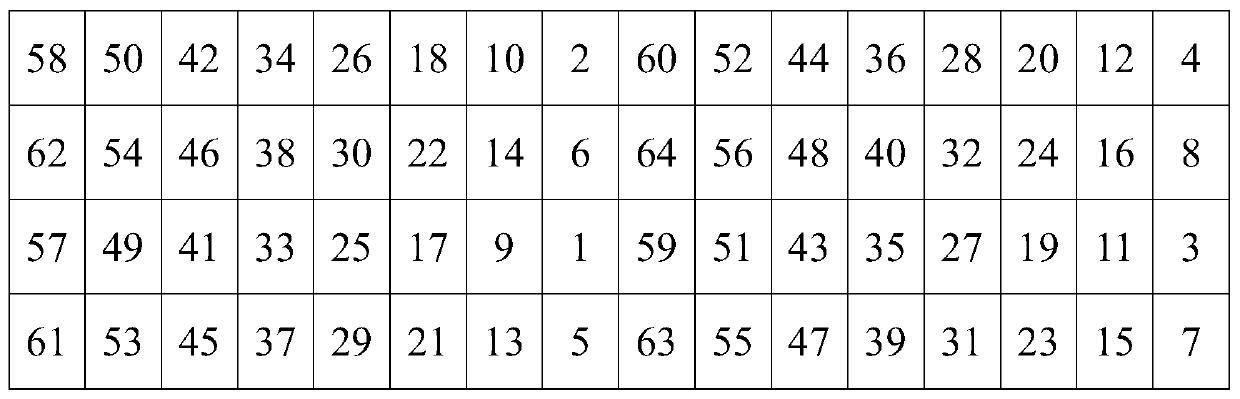

Power consumption attack method and system for DES algorithm L register flipping

ActiveCN110190951AIncrease aggressivenessImprove the accuracy of security assessmentEncryption apparatus with shift registers/memoriesCryptographic attack countermeasuresPlaintextArray data structure

The invention discloses a power consumption attack method and system for DES algorithm L register flipping, and relates to the technical field of DES hardware module safety evaluation, and the methodcomprises the following steps: generating a 32-bit random number R through RNG, and generating a corresponding plaintext; inputting the plaintext into a hardware module with a DES algorithm for operation, collecting power consumption information during operation, generating a power consumption curve, and repeatedly executing the operation until the collected power consumption curve meets the requirement of DPA attack; calculating by utilizing plaintext and guessing keys; selecting an intermediate value corresponding to the plaintext, wherein the intermediate values of the plaintext form an intermediate data array; repeatedly calculating to obtain a plurality of intermediate data arrays corresponding to the plurality of guessing keys; respectively calculating the relevance of the pluralityof intermediate data arrays and power consumption data to find the guessing key corresponding to the intermediate data arrays with the maximum relevance. According to the DES hardware module securityassessment method and device, the SNR can be effectively improved, the DPA attack effect can be enhanced, and the security assessment accuracy of the DES hardware module can be improved.

Owner:CHINA FINANCIAL CERTIFICATION AUTHORITY

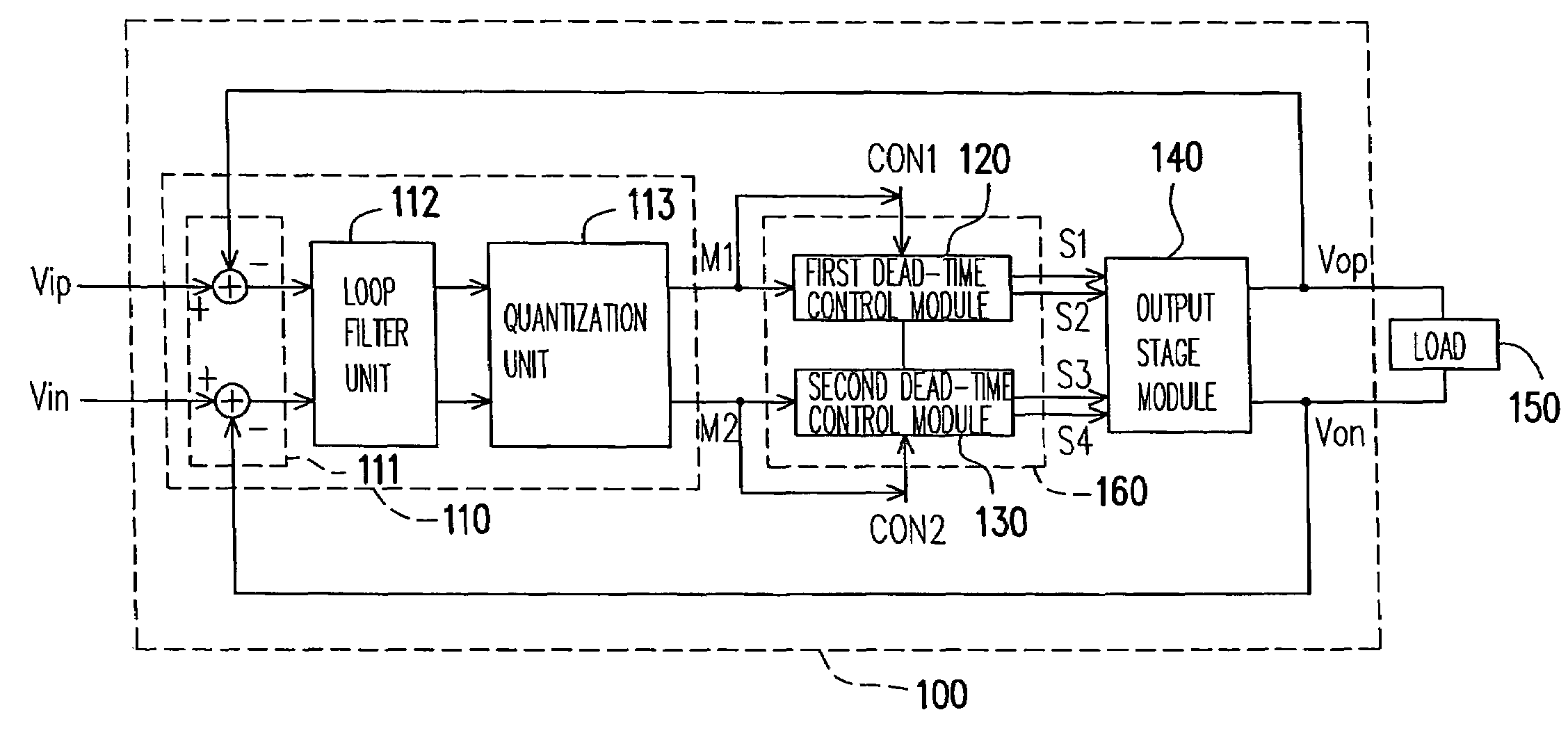

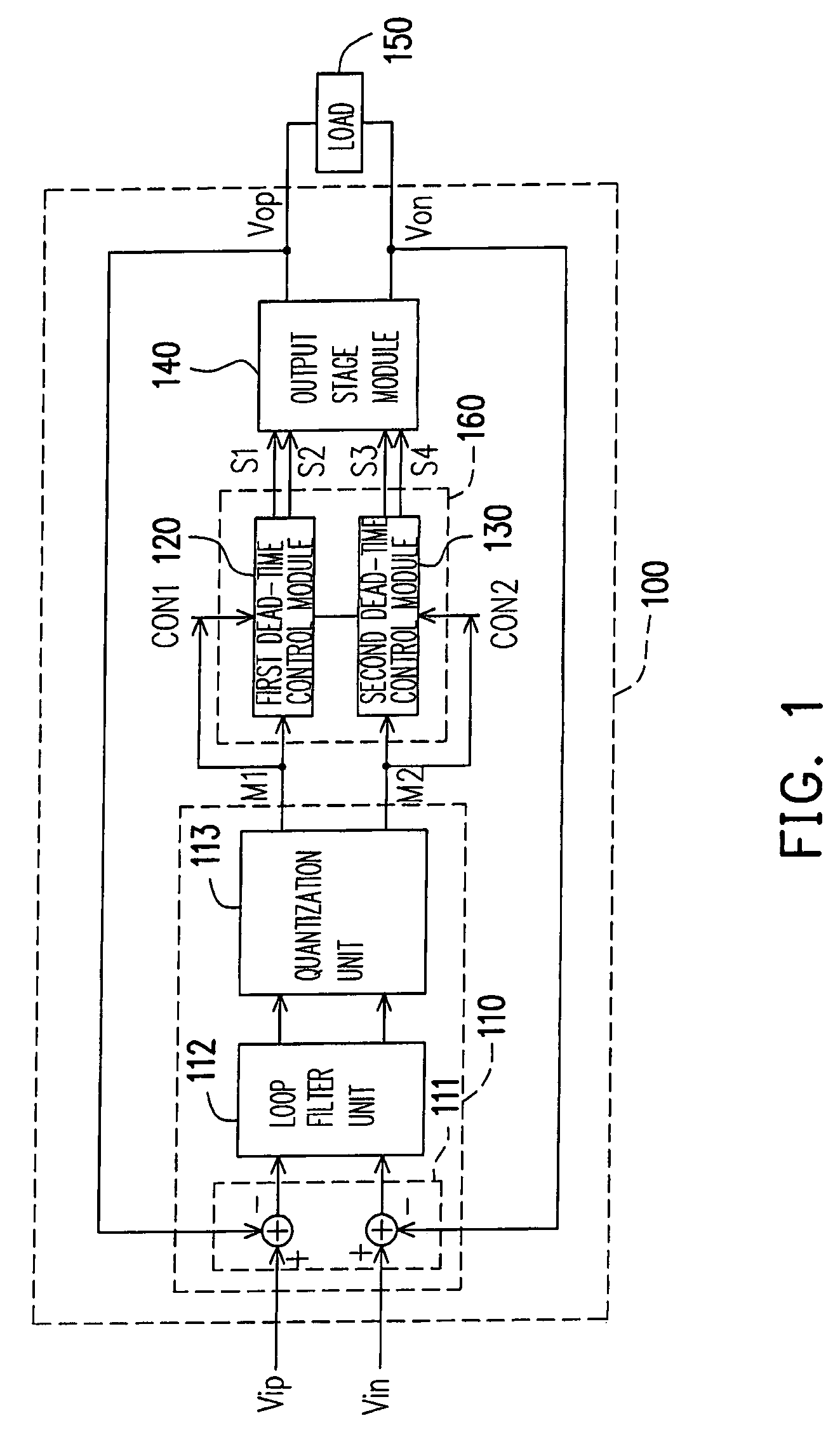

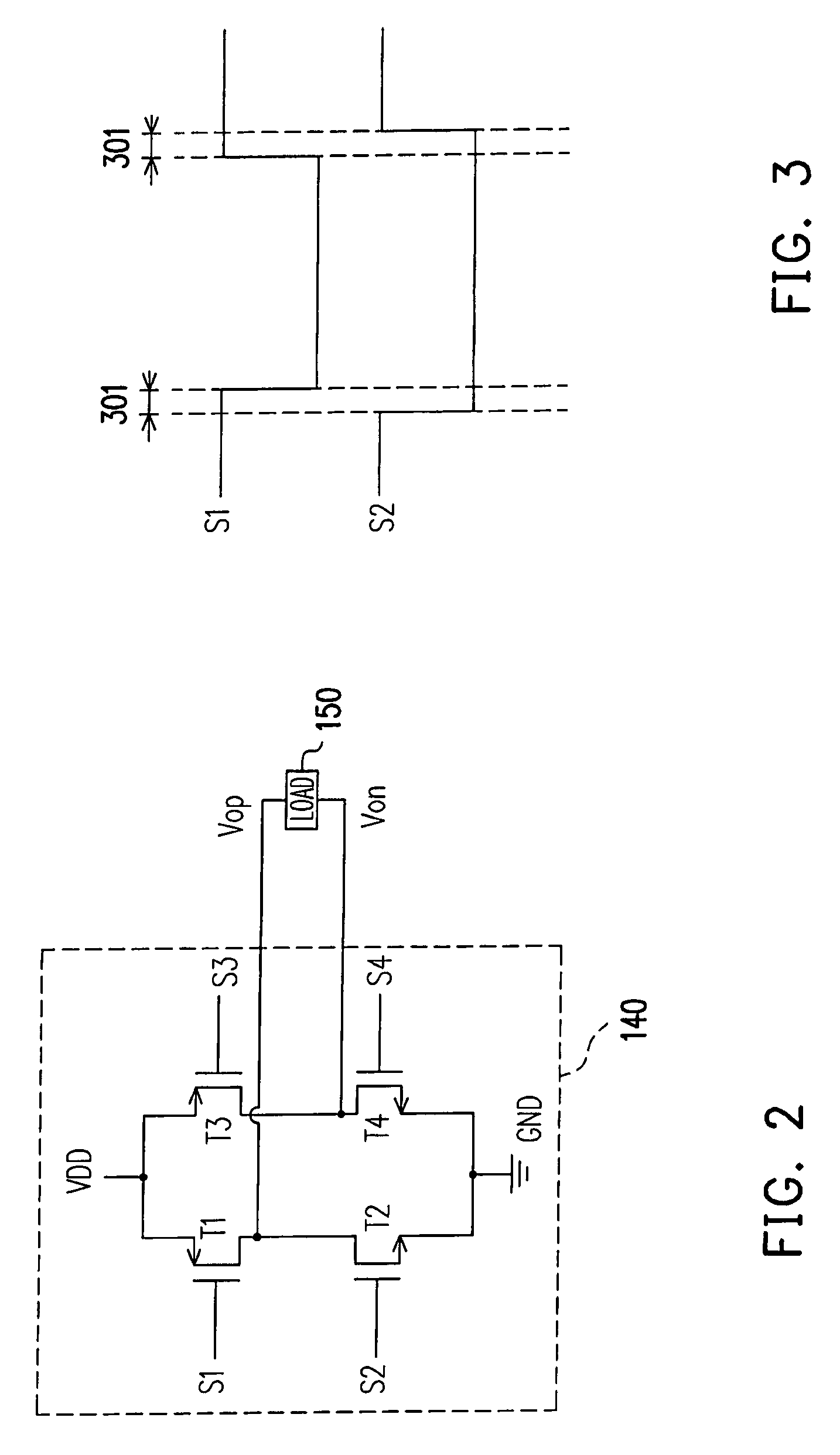

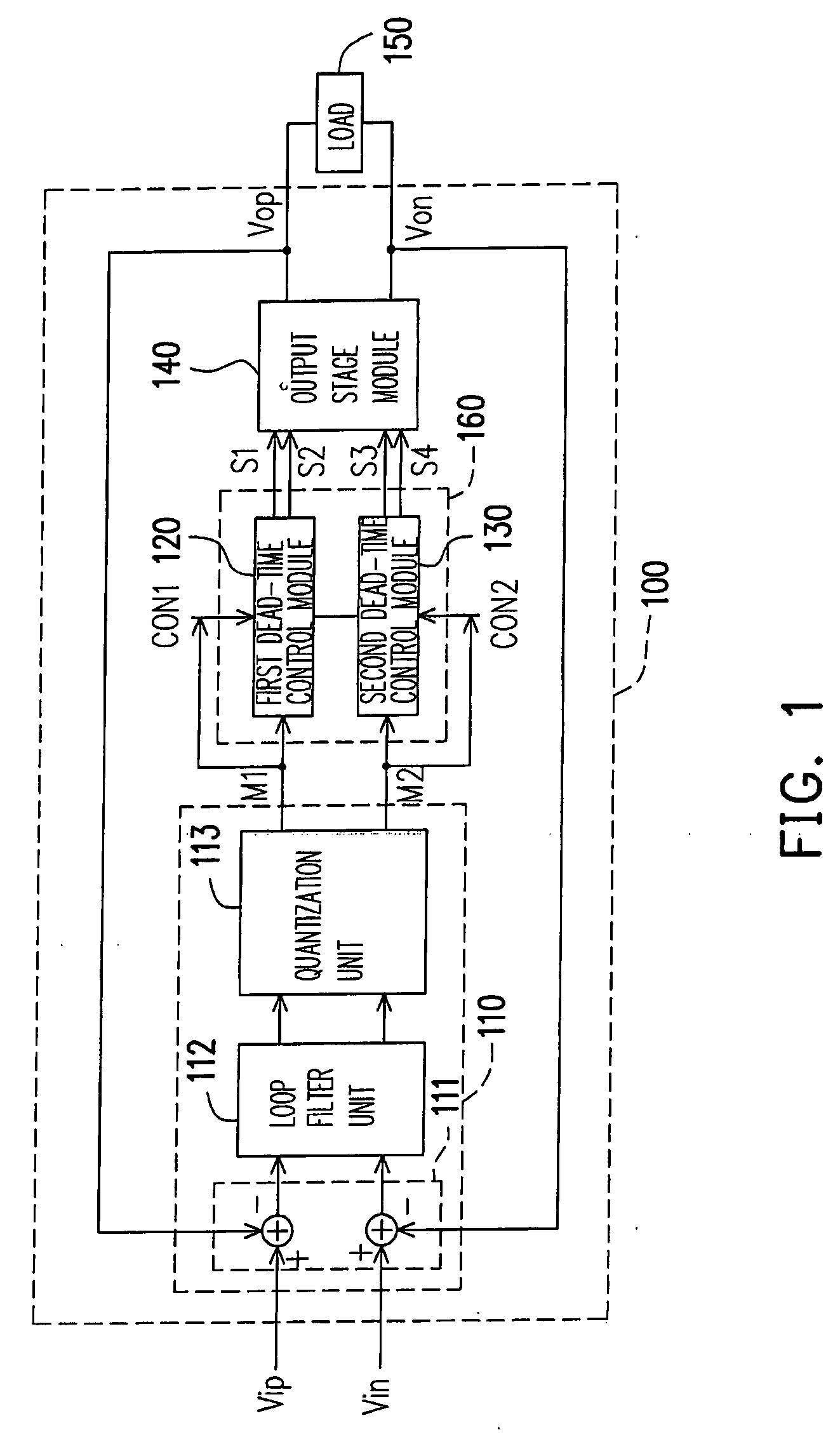

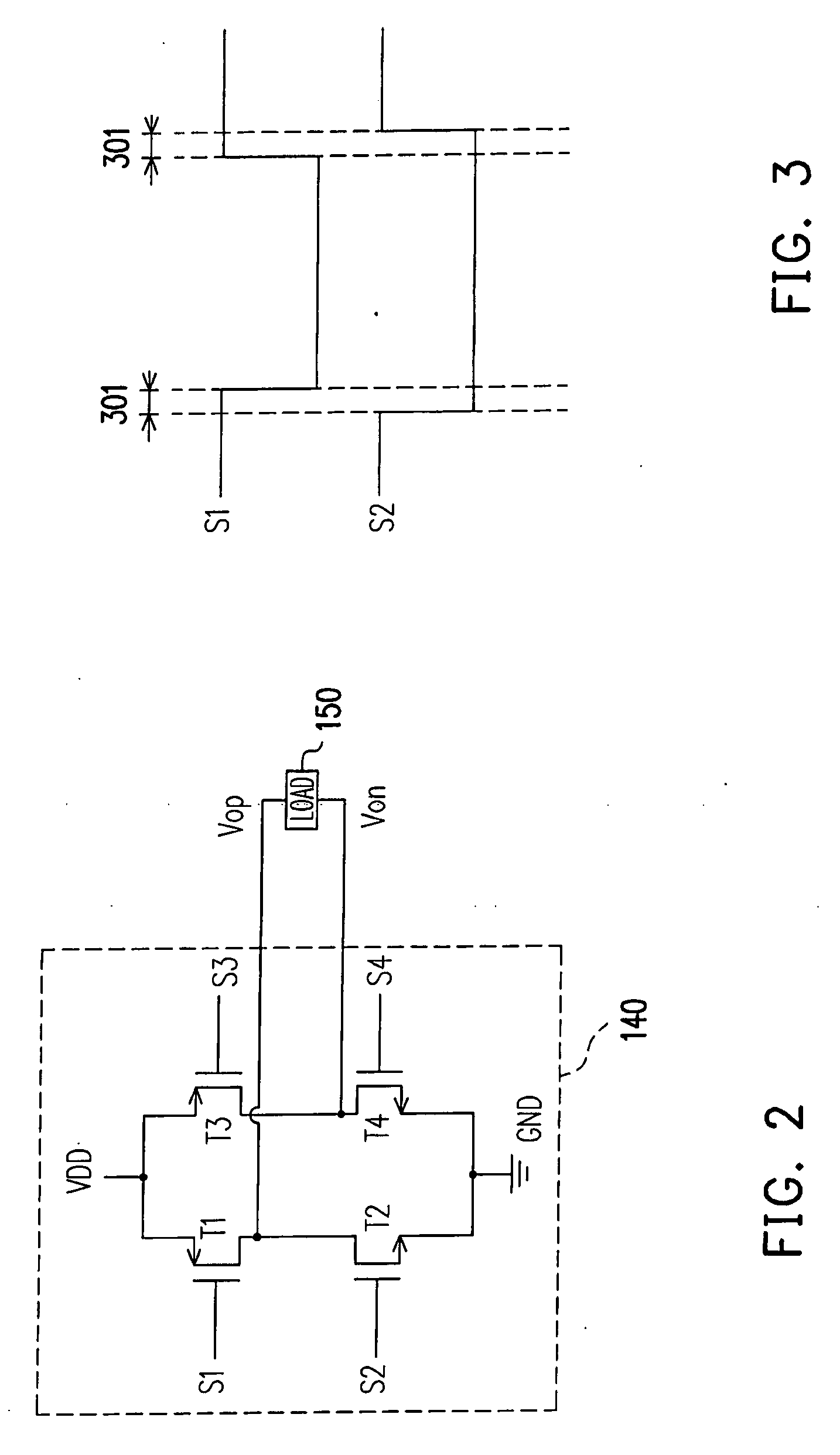

Power amplifier and method for reducing common noise of power amplifier

InactiveUS7548110B2Improve conversion efficiencyReduce signal distortionNegative-feedback-circuit arrangementsAmplifier modifications to reduce noise influenceAudio power amplifierControl signal

A power amplifier including a delta-sigma modulation module, a differential programmable dead-time-control module, and an output stage module is provided. The delta-sigma modulation module integrates and quantizes an error between a differential-mode input signal and an output signal to generate a first and a second mean signal. The differential programmable dead-time-control module includes a first and a second dead-time-control module which respectively generate a first and a second signal corresponding to the first mean signal and a third and a fourth signals corresponding to the second mean signal through logic calculations. The differential programmable dead-time-control module determines a dead time between the first signal and the second signal according to a first control signal and a dead time between the third signal and the fourth signal according to a second control signal. The output stage module generates the output signal according to the first, second, third, and fourth signal.

Owner:IND TECH RES INST

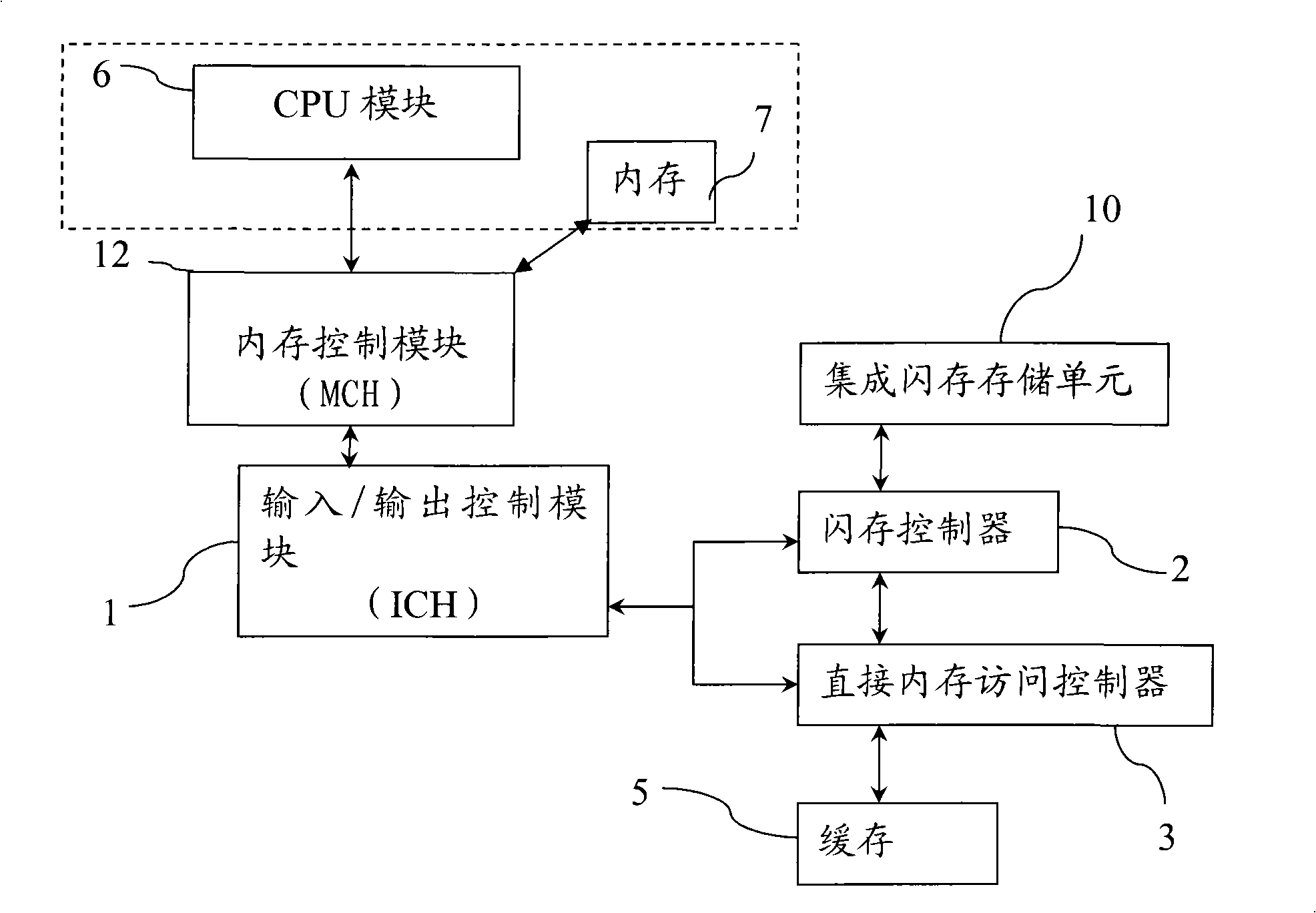

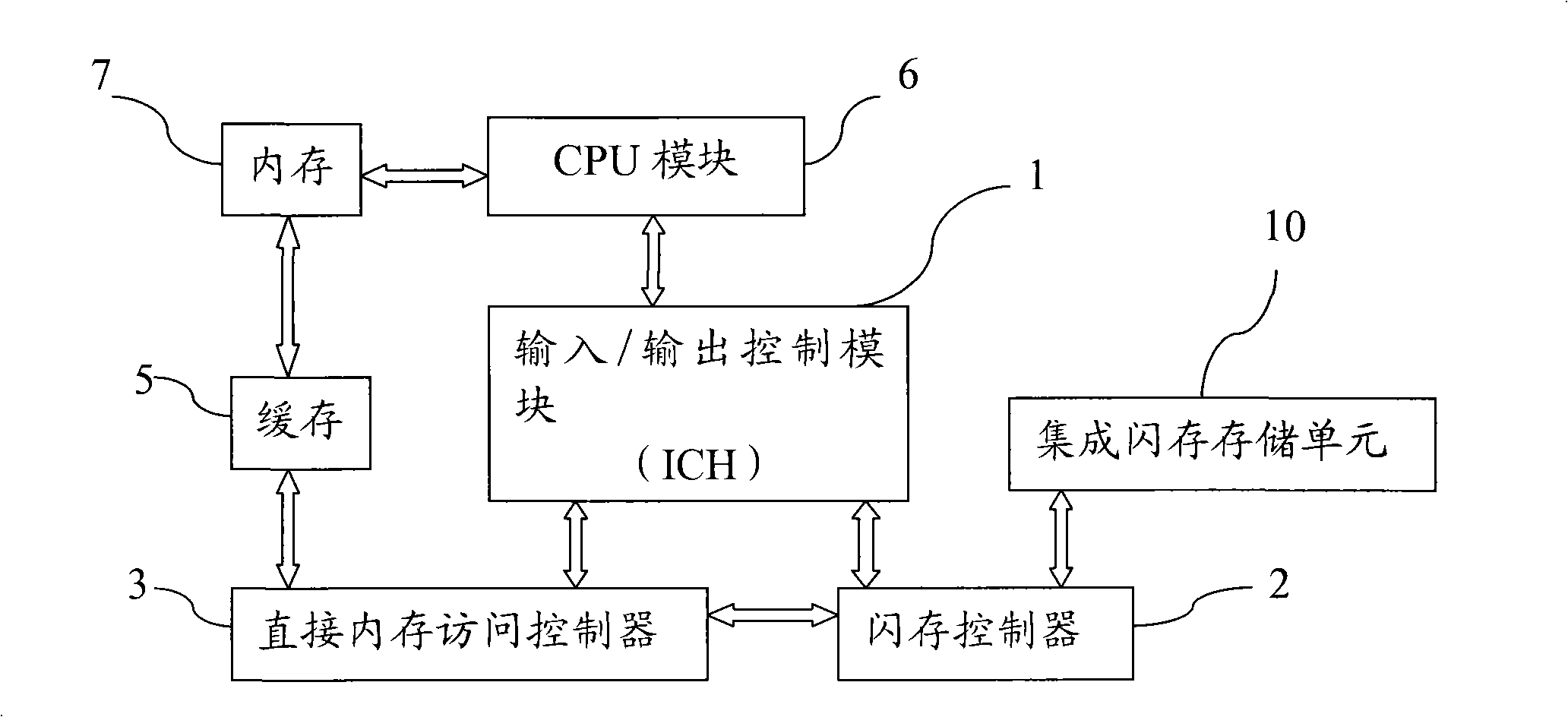

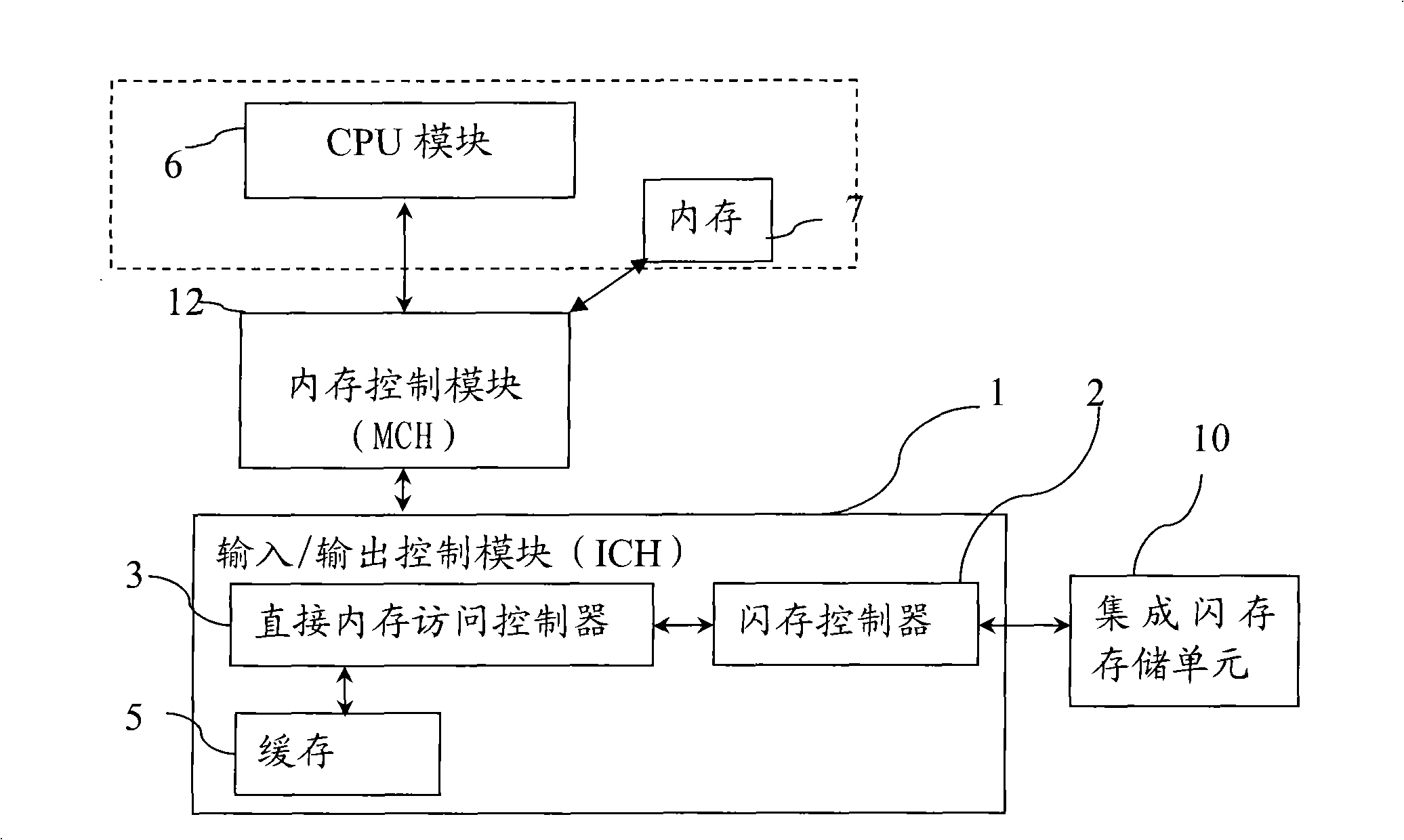

Mainboard with integrated flash memory storage unit

ActiveCN101539785AHigh speedImprove seismic performanceInput/output to record carriersDigital data processing detailsDirect memory accessComputer module

The invention provides a mainboard with an integrated flash memory storage unit. The mainboard comprises a memory control module, an input / output control module, and an integrated flash memory storage unit which is integrated on the mainboard for storing data, a flash memory controller which is connected with the integrated flash memory storage unit, receives commands of the input / output control module and controls the communication of the integrated flash memory storage unit, and a direct memory access controller which cooperates with the flash memory controller in the control of the communication of the integrated flash memory storage unit. The mainboard with flash memory storage provided by the invention makes use of the advantages of quick reading and writing speed, good shock resistance and low power consumption of flash memory and uses the flash memory as a storage medium to form a storage unit of a computer, and the direct integration of the flash memory on the mainboard simplifies a circuit and reduces the volume and weight of the mainboard. According to the characteristics of the flash memory, the flash memory storage unit has a higher speed, lower energy consumption and noise as well as better safety compared with hard disk.

Owner:NETAK TECH KO LTD

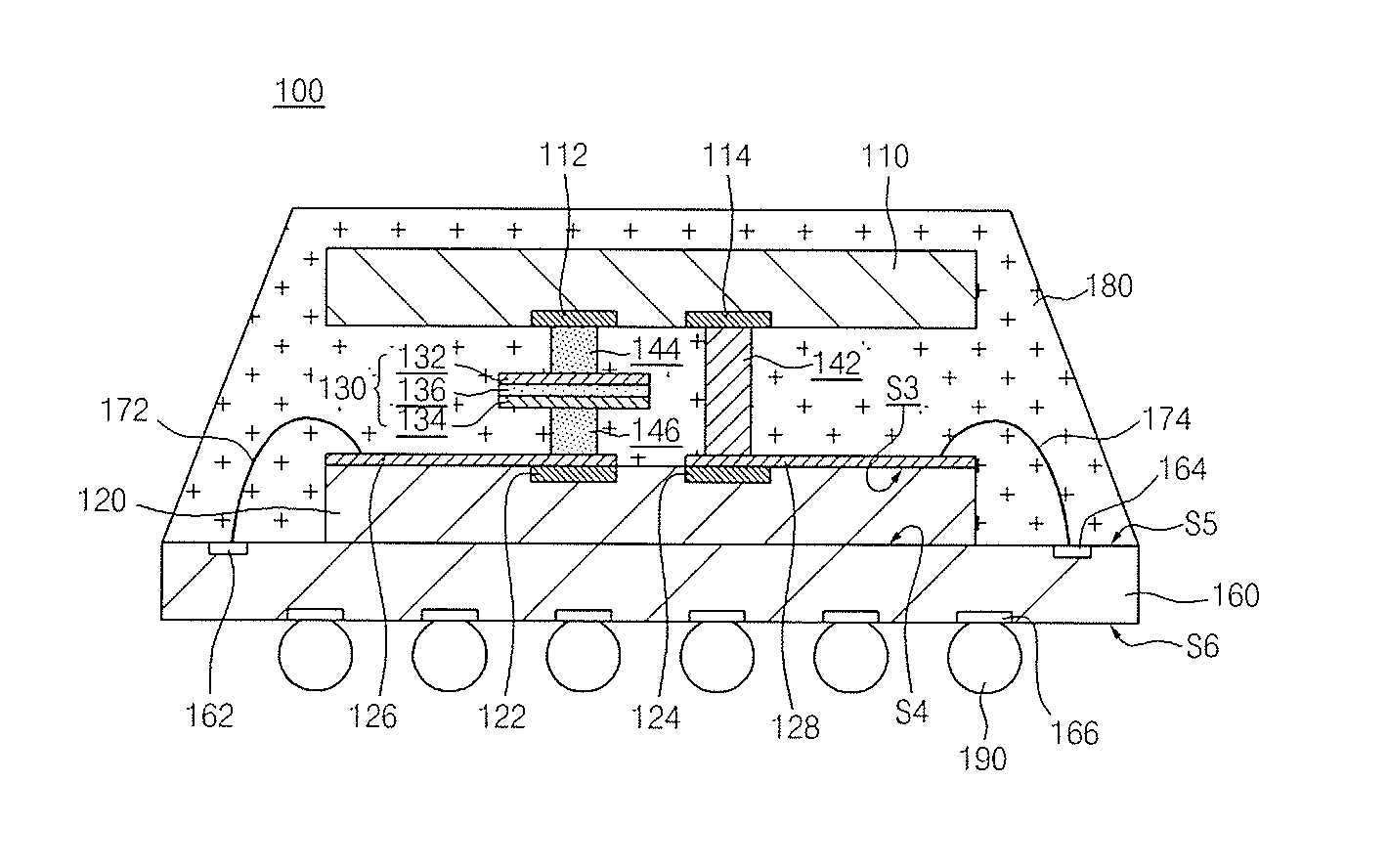

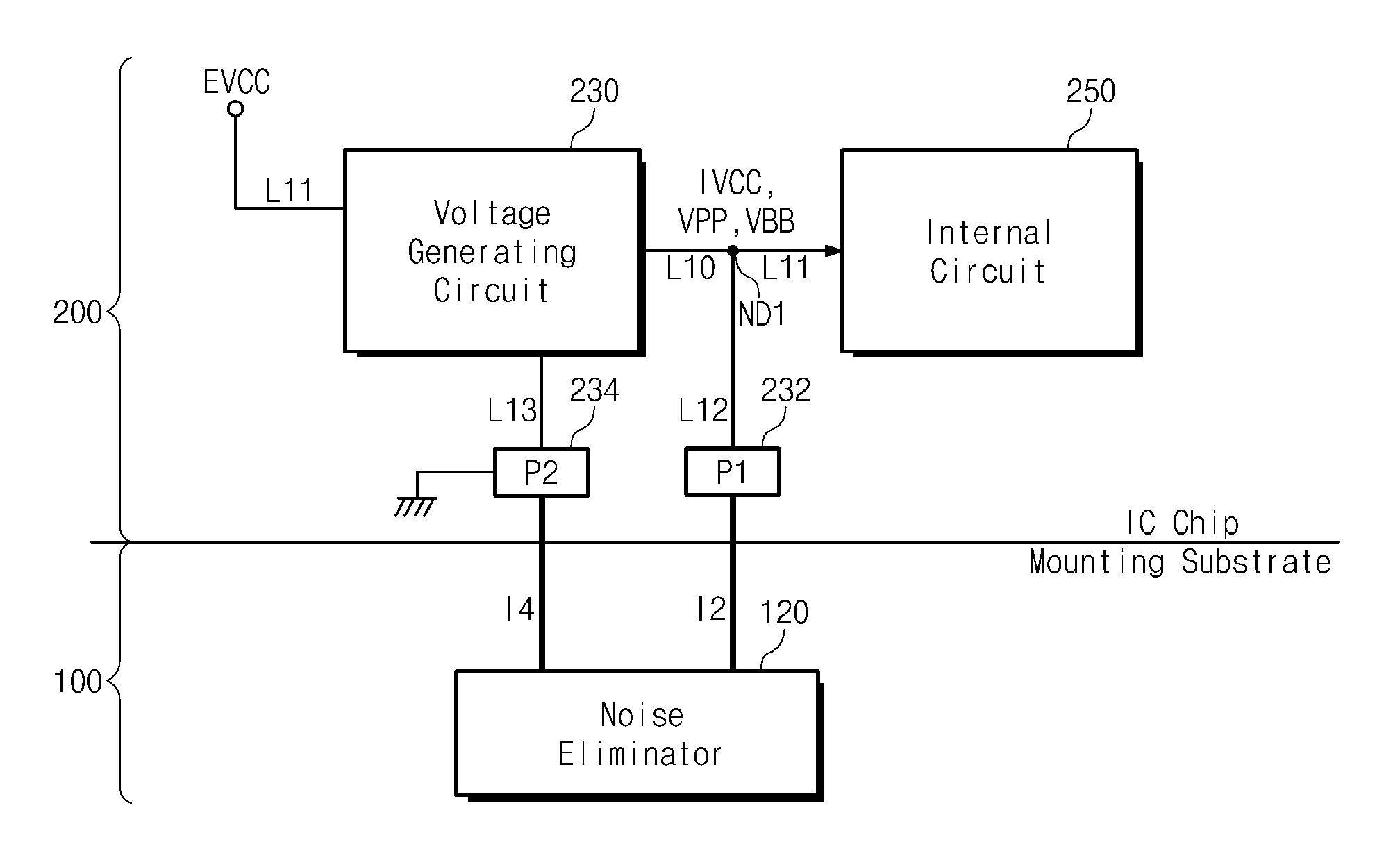

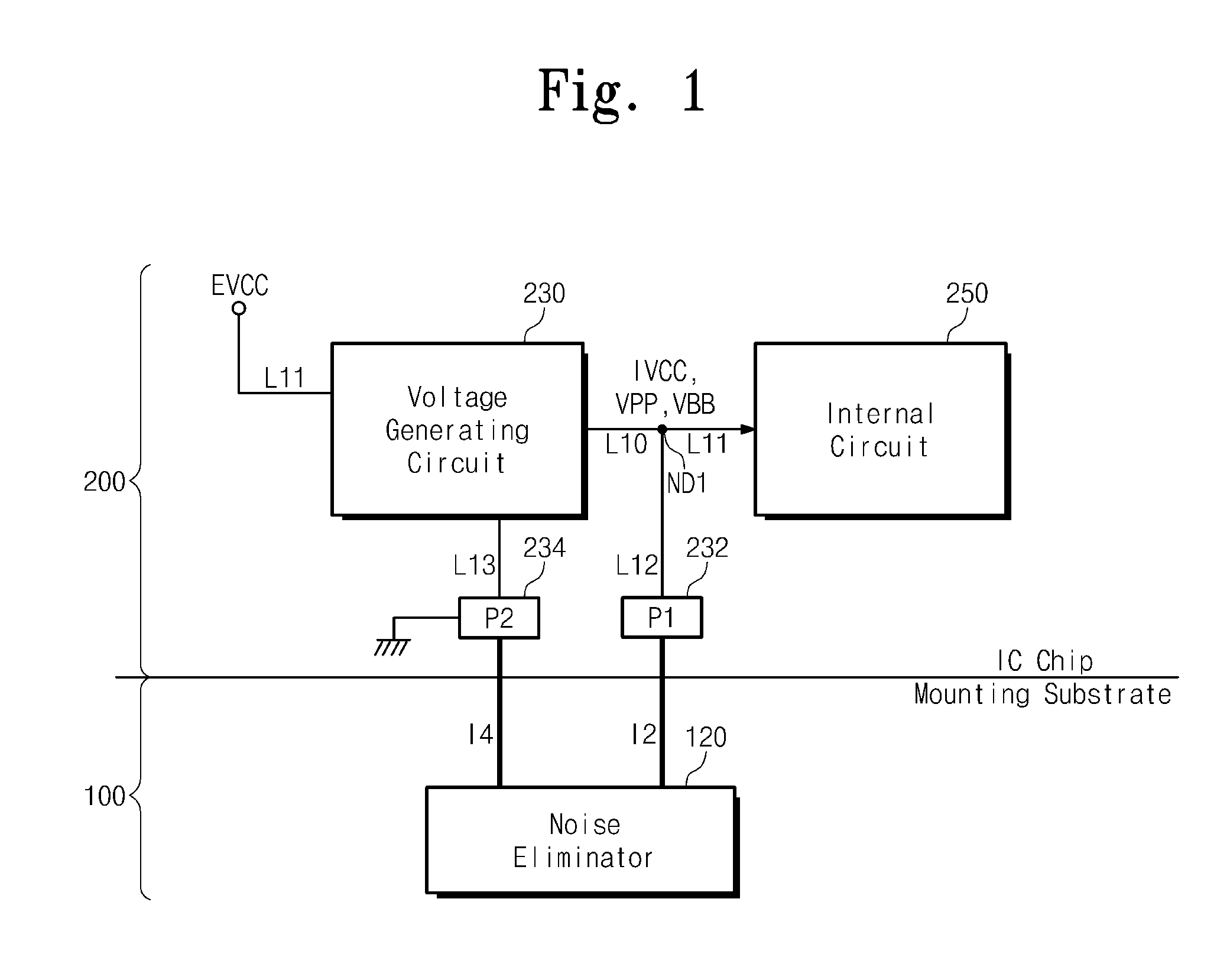

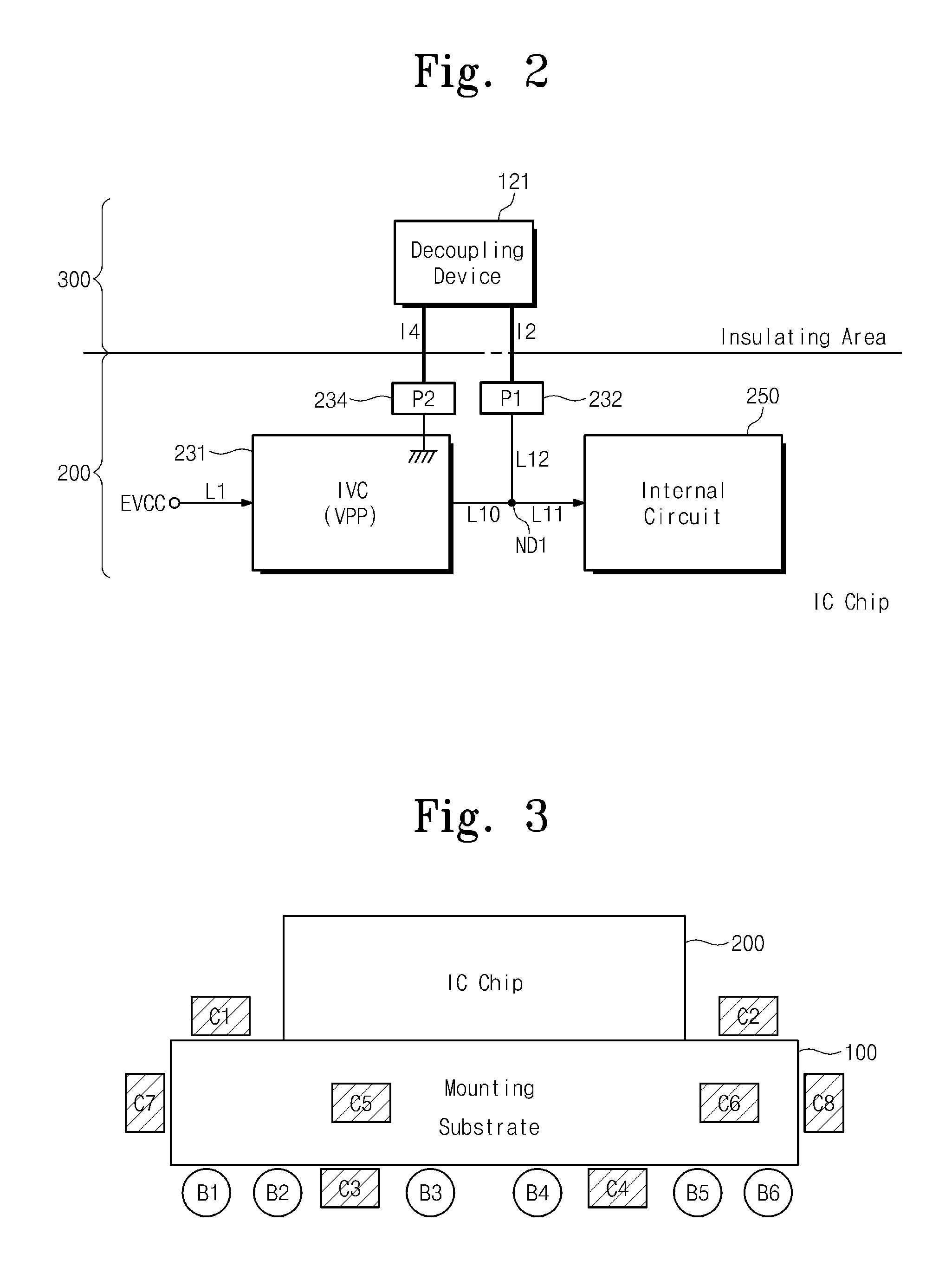

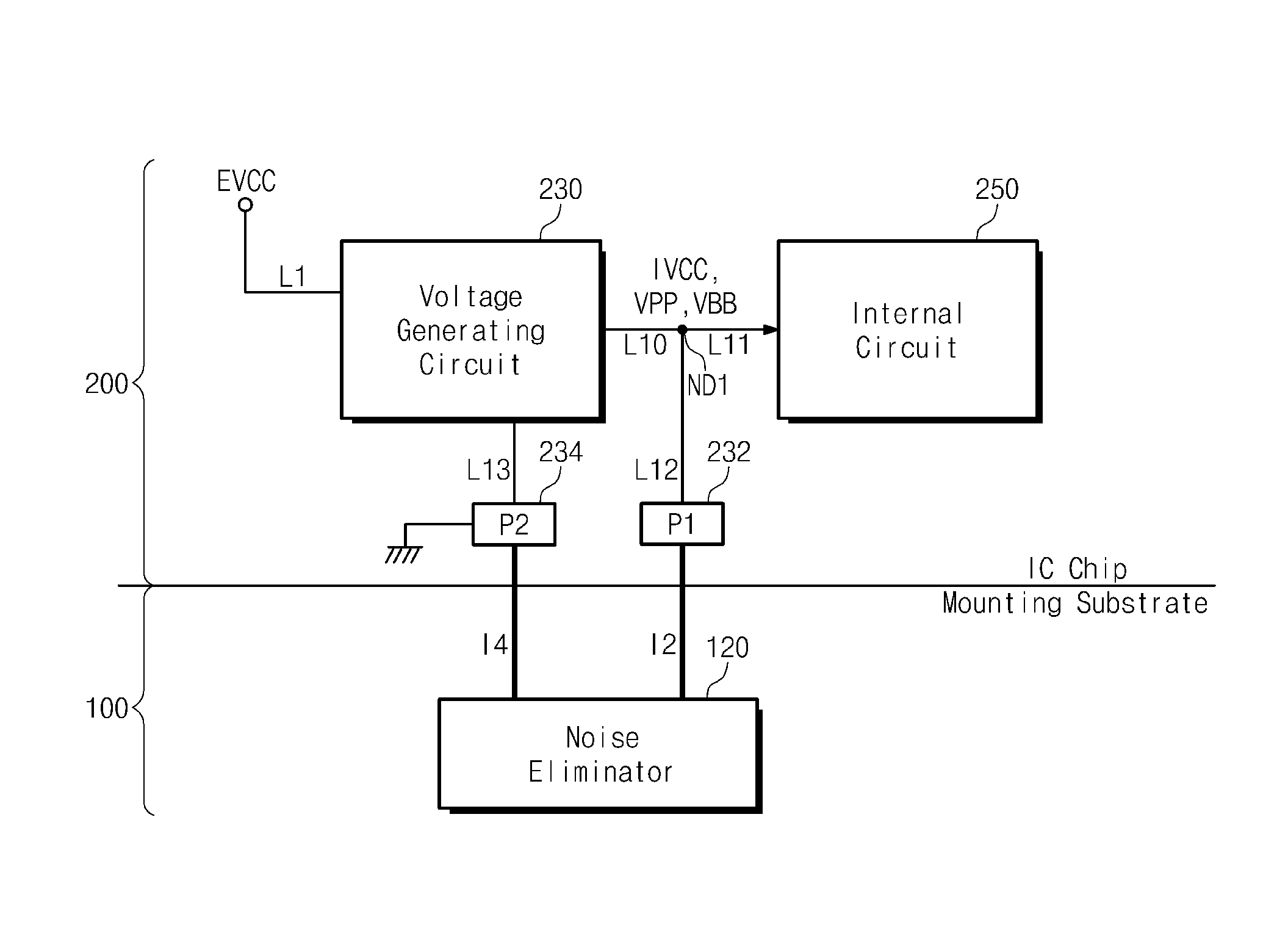

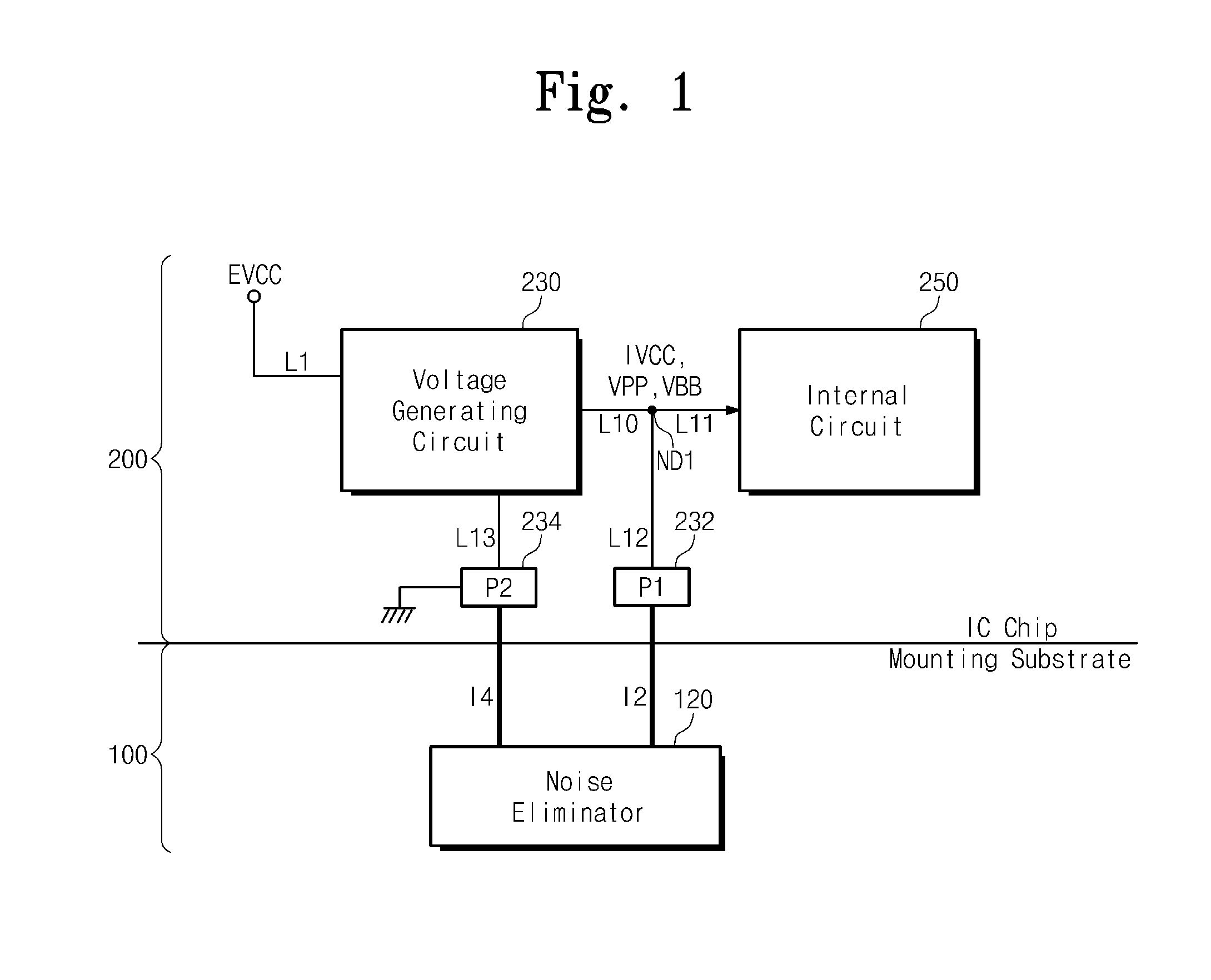

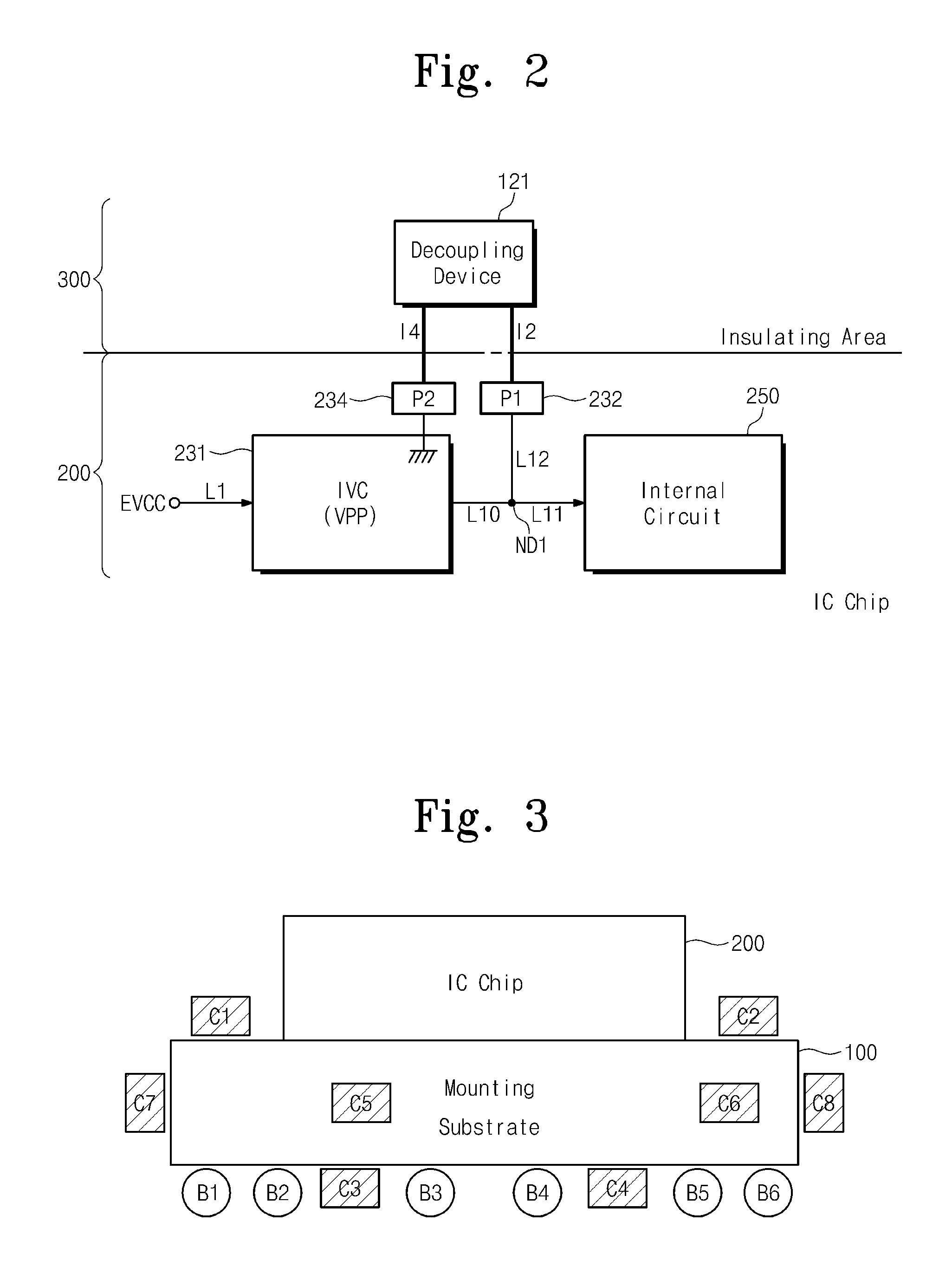

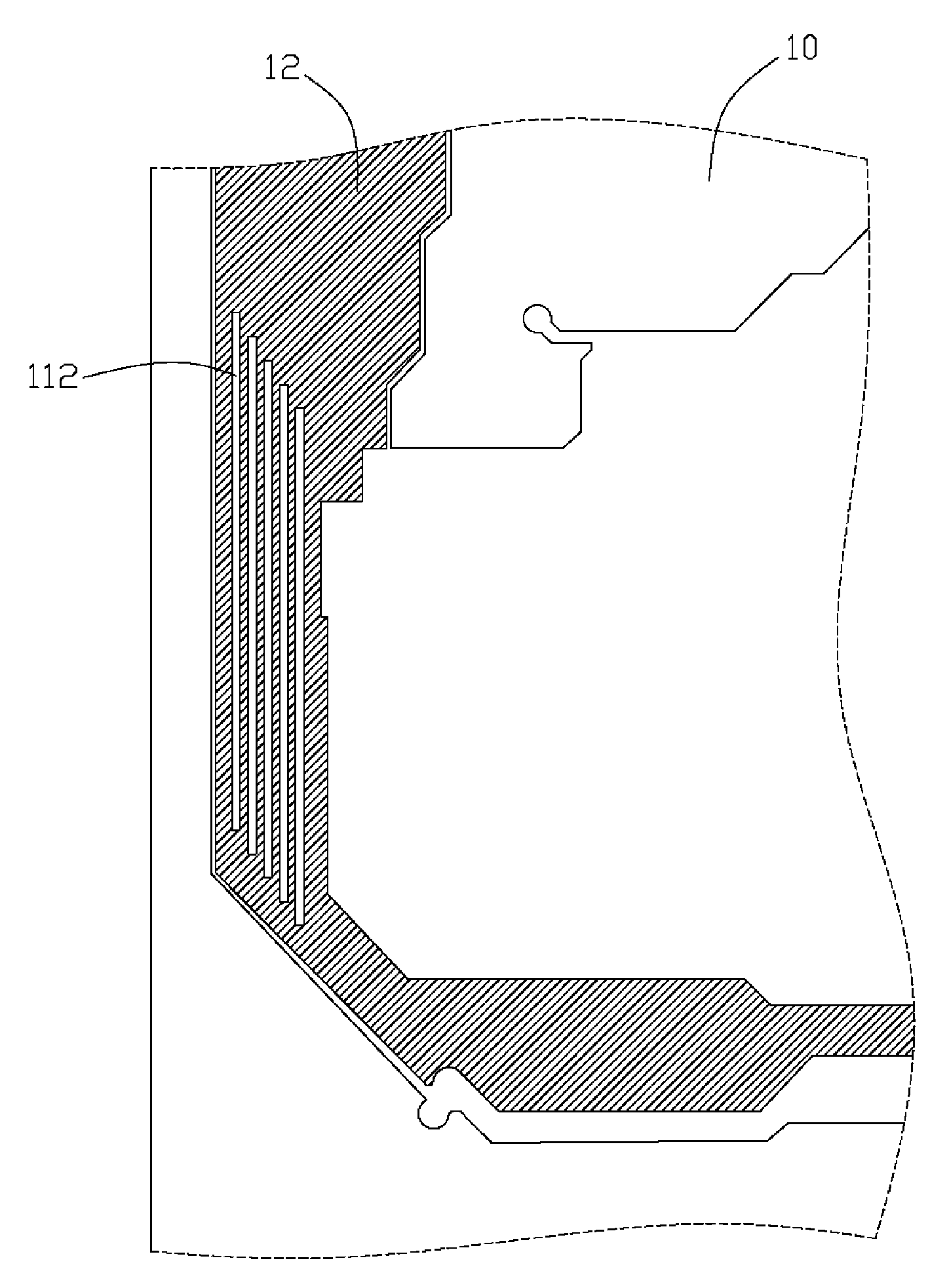

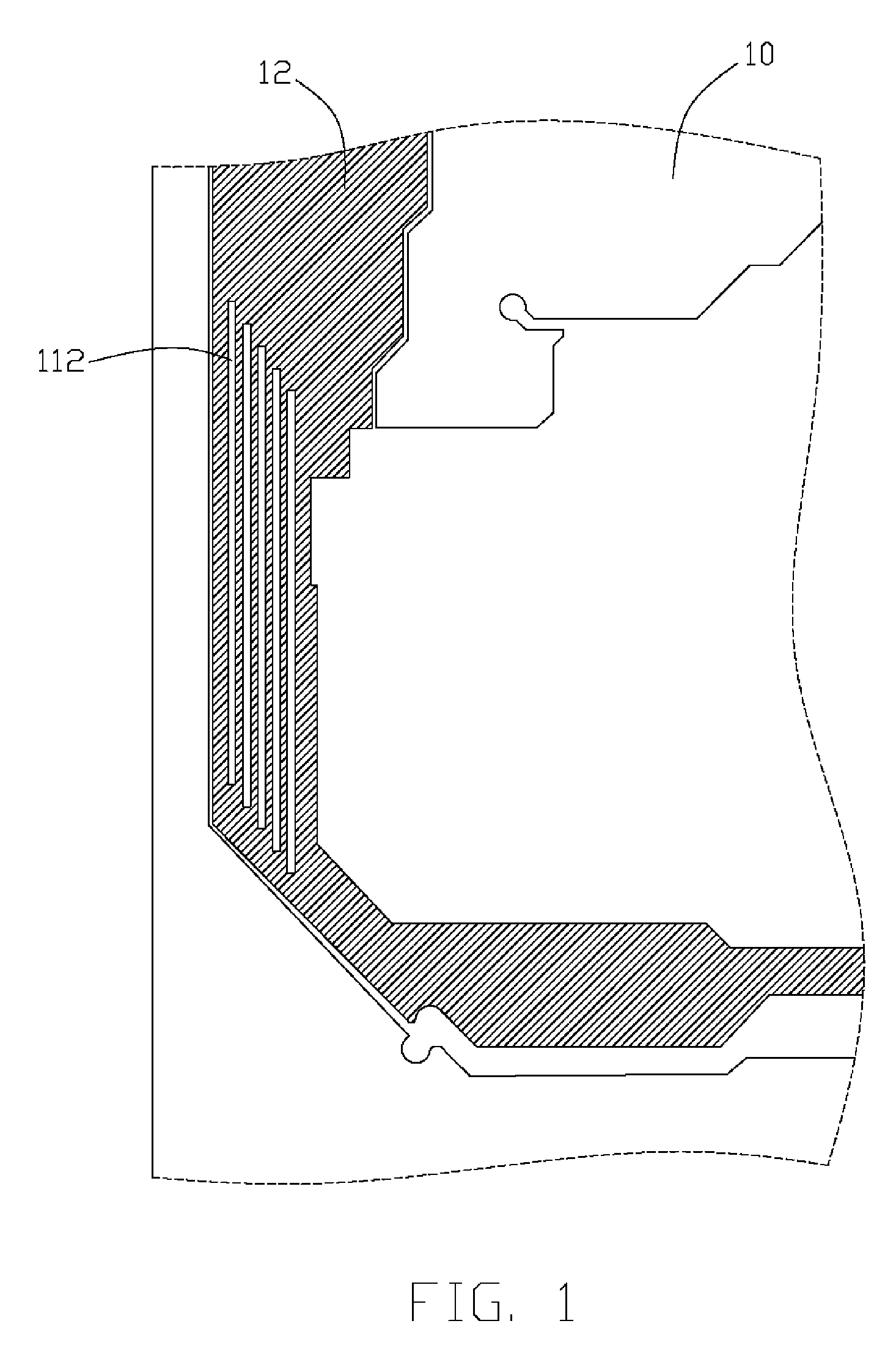

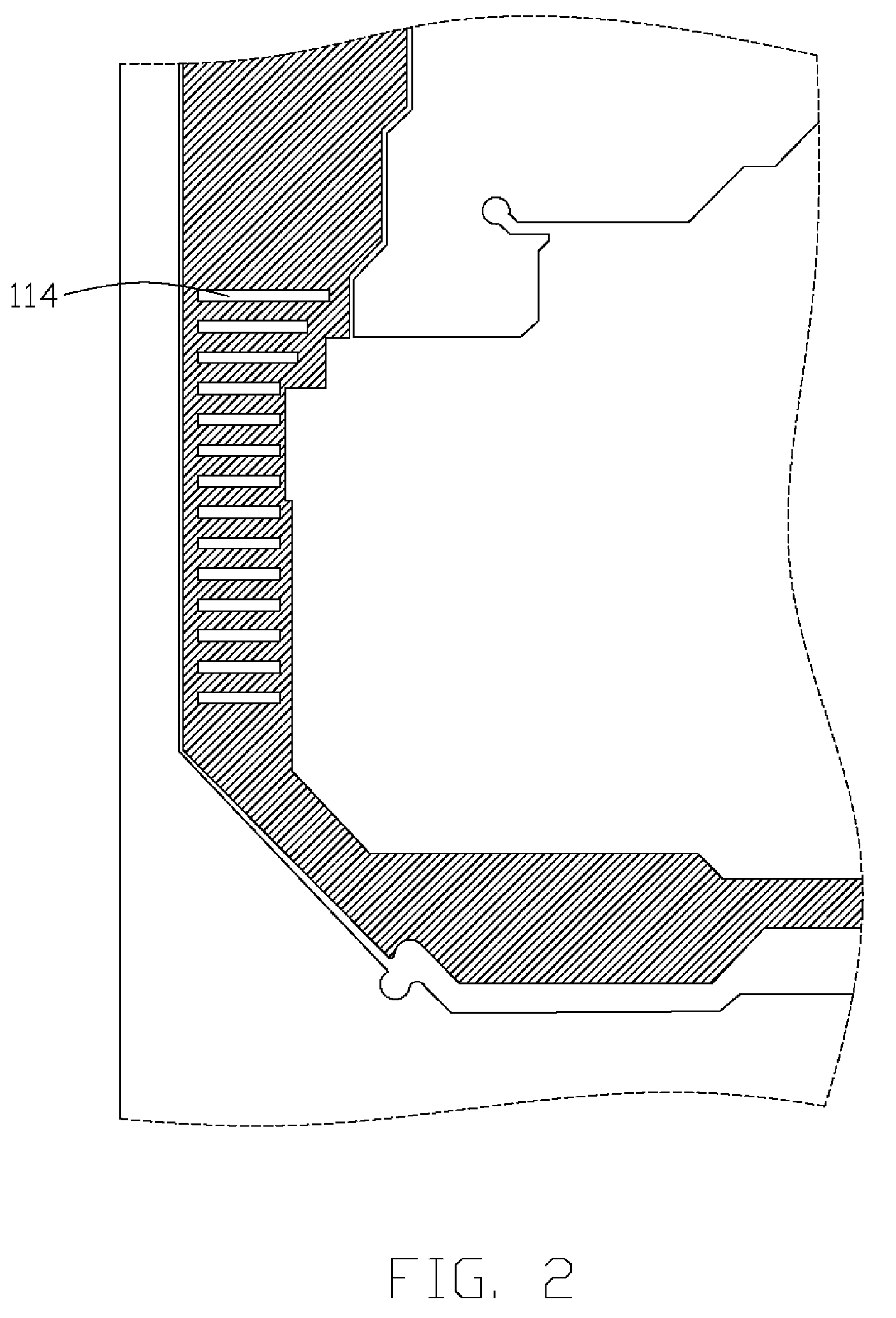

Semiconductor chip package including voltage generation circuit with reduced power noise

ActiveUS20130088289A1Reduce Power NoiseLower Level RequirementsSemiconductor/solid-state device detailsSolid-state devicesPower noiseSemiconductor chip

A semiconductor chip package illuminates and minimizes a power noise generated from a voltage generation circuit in the semiconductor chip package includes an integrated circuit chip with a voltage generation circuit that receives an external voltage to generate a supply voltage to be used in an internal circuit and a connection terminal connected to an output node of the voltage generation circuit, and a mounting substrate including a noise eliminator electrically connected to the connection terminal to reduce a power noise of the supply voltage and a mounting substrate to mount the integrated circuit chip to package the integrated circuit chip as the semiconductor chip package.

Owner:SAMSUNG ELECTRONICS CO LTD

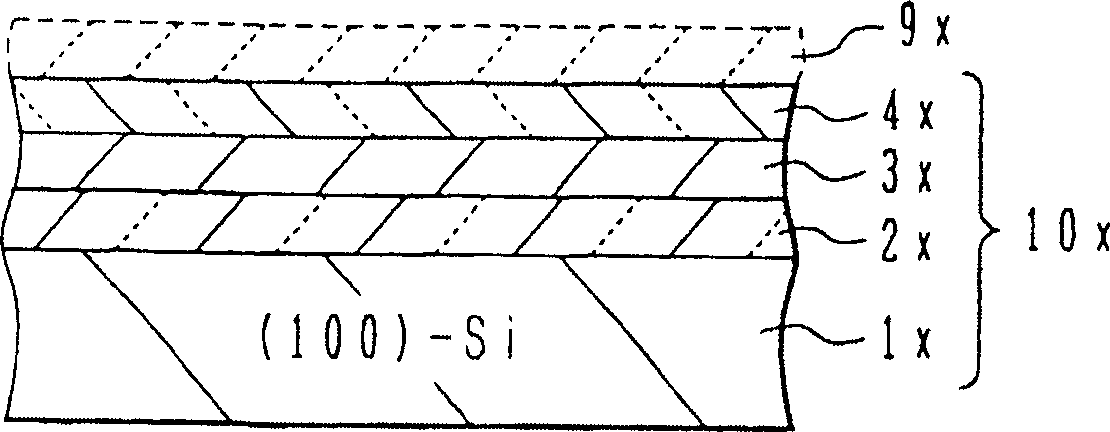

Thin film capacitor and method for manufacturing same

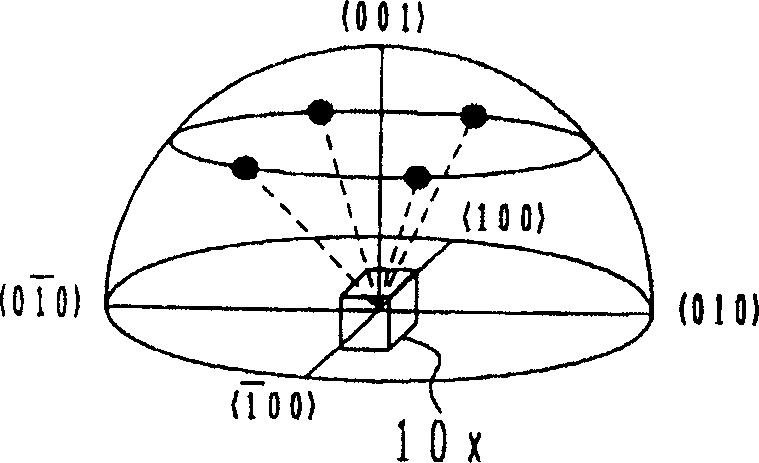

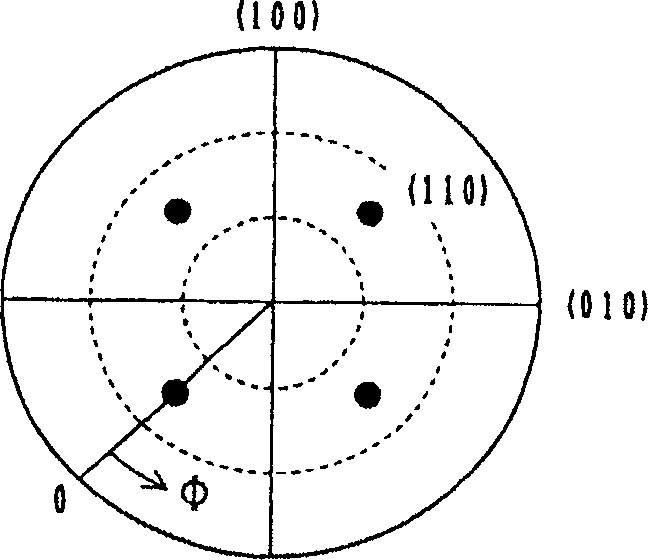

InactiveCN1679124AReduce Power NoiseTransistorThin/thick film capacitorSingle crystalDielectric layer

A thin film capacitor is provided which includes a single crystal high dielectric constant dielectric layer. The thin film capacitor has a single crystal silicon substrate, a single crystal intermediate layer epitaxially grown on the single crystal silicon substrate, a single crystal lower electrode epitaxially grown on the single crystal intermediate layer, a single crystal high dielectric constant dielectric layer epitaxially grown on the lower electrode layer, an upper electrode layer formed above the single crystal high dielectric constant dielectric layer, and a plurality of conductor terminals connected to the lower electrode layer and upper electrode layer at a plurality of positions.

Owner:FUJITSU LTD

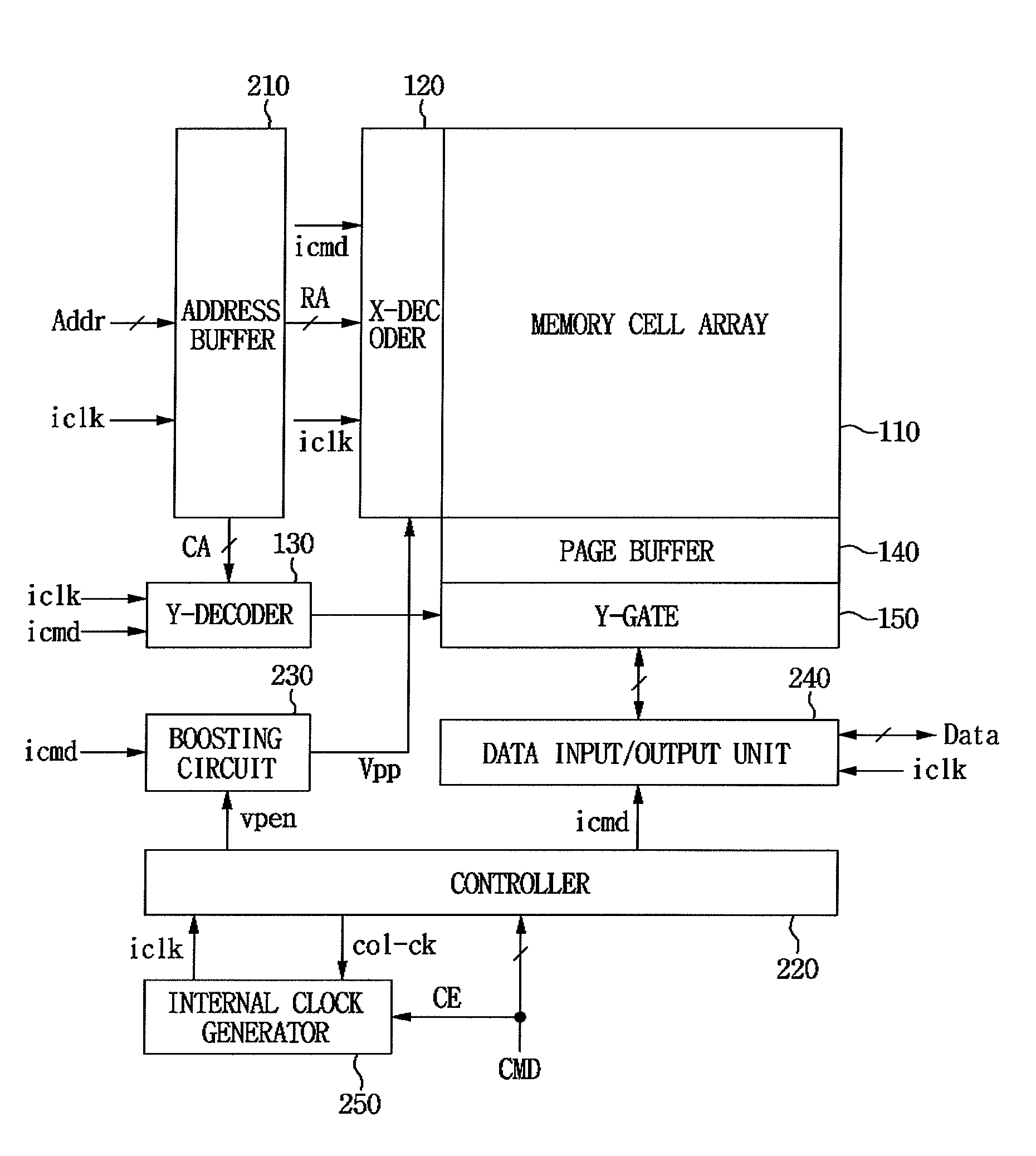

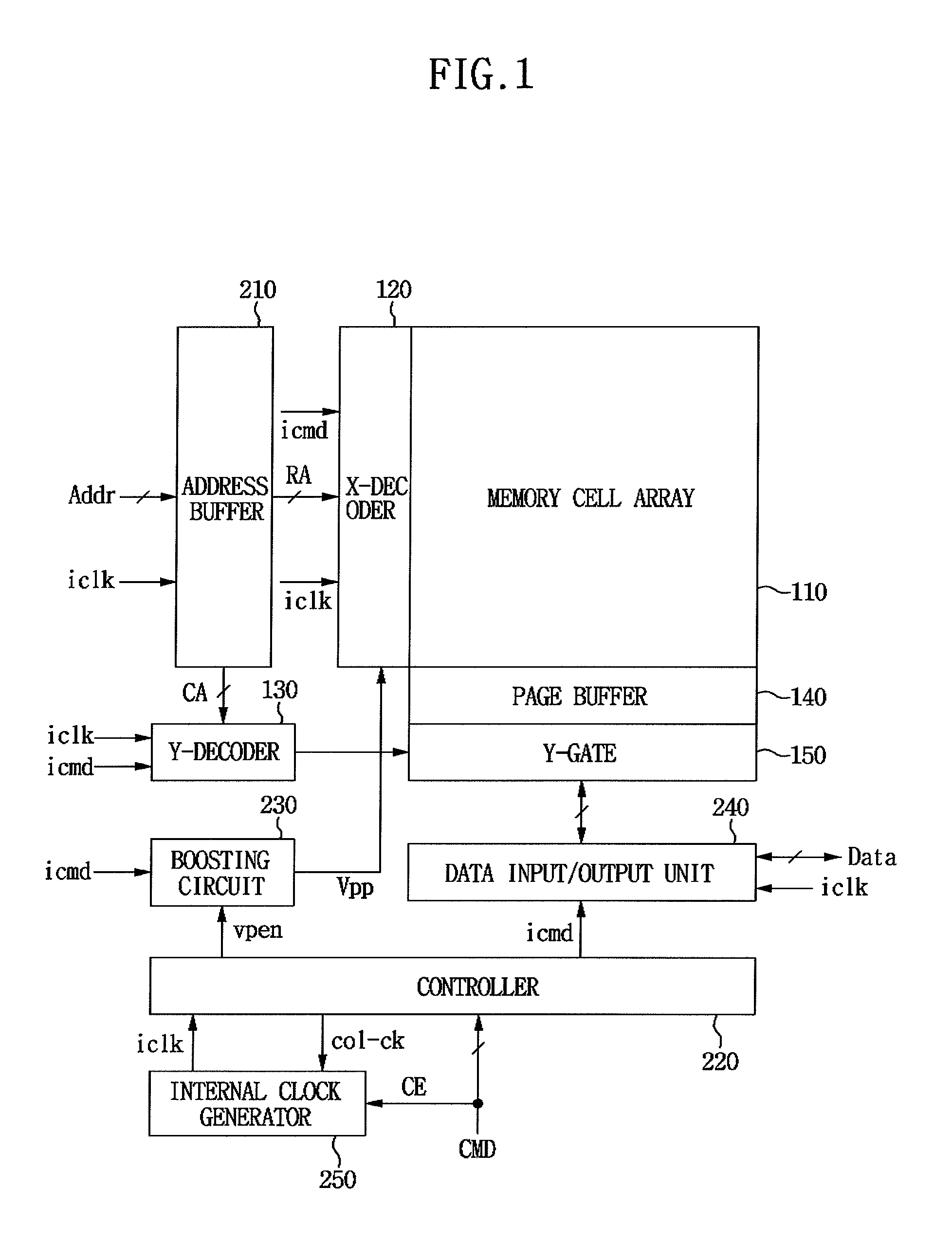

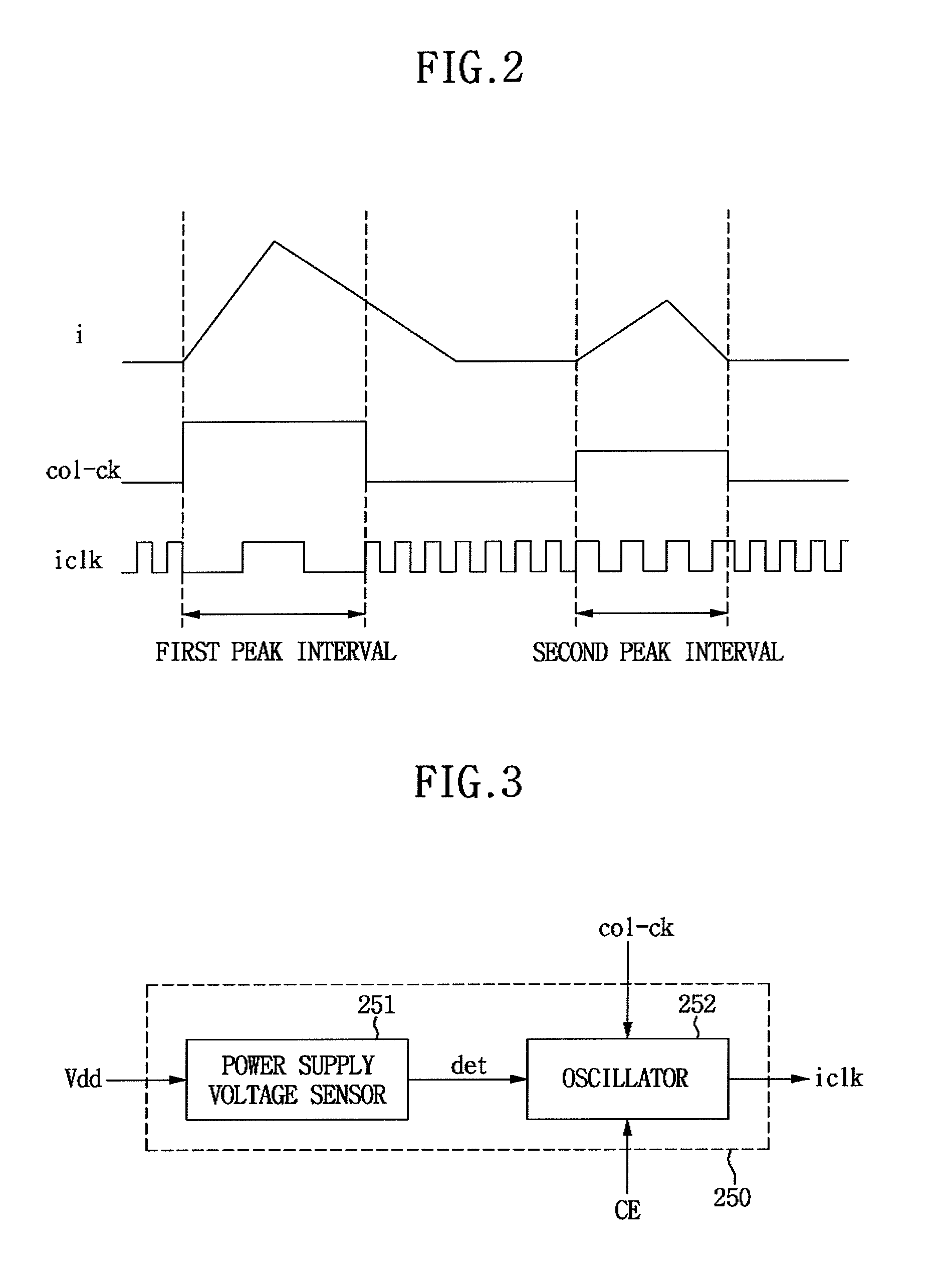

Semiconductor memory device with reduced power noise

A semiconductor memory device includes an internal clock generator configured to generate an internal clock signal having a first clock period in response to a chip enable signal and change the first clock period of the internal clock signal in response to a clock control signal, and a controller configured to receive external commands including the chip enable signal and generate the clock control signal corresponding to a first external command other than the chip enable signal. Here, the semiconductor memory device performs a data input / output operation in response to the internal clock signal with the changed clock period.

Owner:SAMSUNG ELECTRONICS CO LTD

Industrial intelligent motion control carrying robot

InactiveCN113071997AEasy to carryReasonable structural designLifting devicesLoad-engaging elementsControl systemControl engineering

The invention relates to the technical field of automatic carrying equipment, and particularly discloses an industrial intelligent motion control carrying robot. The robot comprises a motion chassis, a carrying plate is arranged on the motion chassis, an electric rotating disc is arranged between the motion chassis and the carrying plate, a carrying fork is arranged on one side of the upper portion of the carrying plate, automatic lifting of the carrying fork is achieved through a lifting power driving structure, an electric control box is arranged on the other side of the upper portion of the carrying plate and comprises a control system and a sensor system, a rotatable mechanical shaft arm structure is arranged between the carrying fork and the electric control box, a rotatable telescopic mechanical arm is arranged at the top end of the mechanical shaft arm structure, a rotatable mechanical gripper structure is arranged at the top end of the telescopic mechanical arm, and the mechanical gripper structure comprises a movable and turnable gripping plate. The high-low-position automatic carrying requirement is met, automatic loading and unloading are achieved in the whole process, and the overall automation degree is high.

Owner:ZHENGZHOU RAILWAY VOCATIONAL & TECH COLLEGE

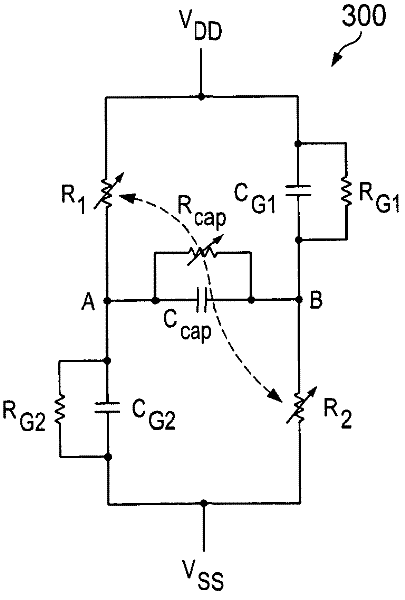

Defectivity-immune technique of implementing MIM-based decoupling capacitors

ActiveCN102339824AReduce Power NoiseLimit currentSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitEngineering

The invention relates to a defectivity-immune technique of implementing MIM-based decoupling capacitors. An integrated circuit power supply decoupling circuit includes a capacitor and a protection circuit. The capacitor has a first terminal and a second terminal. The protection circuit includes a first transistor having a first conduction path, and a second transistor having a second conduction path. One terminal of the first conduction path is connected to the first terminal of the capacitor, and another terminal of the first conduction path is connected to a first power supply rail. One terminal of the second conduction path is connected to the second terminal of the capacitor, and another terminal of the second conduction path is connected to a second power supply rail.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Semiconductor chip package including voltage generation circuit with reduced power noise

ActiveUS8933747B2Reduce Power NoiseLower Level RequirementsSemiconductor/solid-state device detailsSolid-state devicesElectricityPower noise

A semiconductor chip package eliminates and minimizes a power noise generated from a voltage generation circuit in the semiconductor chip package includes an integrated circuit chip with a voltage generation circuit that receives an external voltage to generate a supply voltage to be used in an internal circuit and a connection terminal connected to an output node of the voltage generation circuit, and a mounting substrate including a noise eliminator electrically connected to the connection terminal to reduce a power noise of the supply voltage and a mounting substrate to mount the integrated circuit chip to package the integrated circuit chip as the semiconductor chip package.

Owner:SAMSUNG ELECTRONICS CO LTD

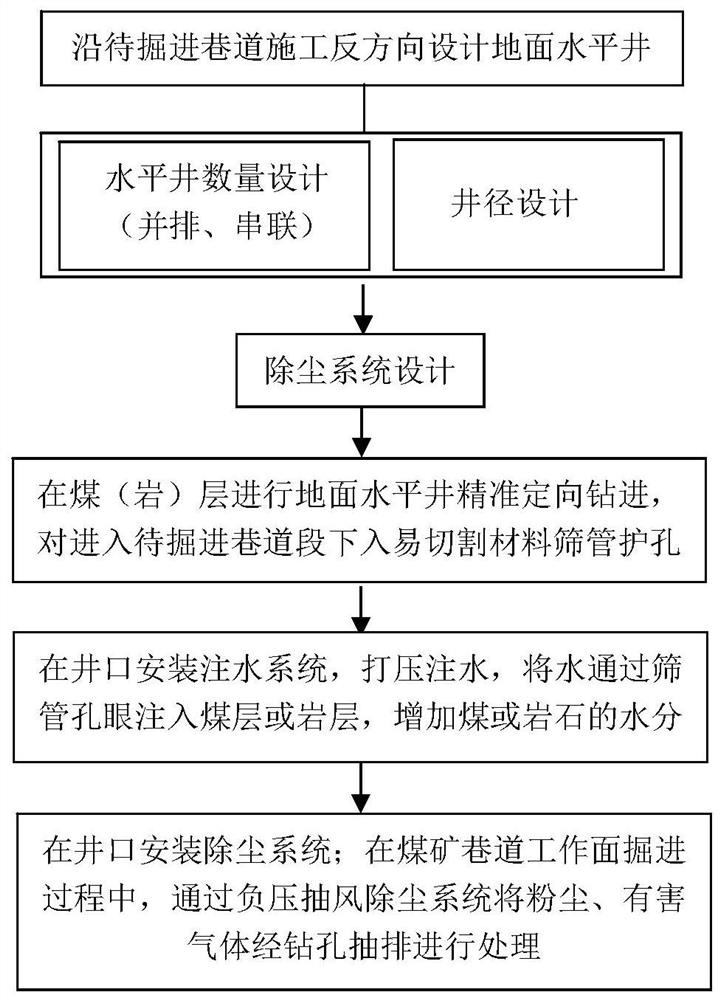

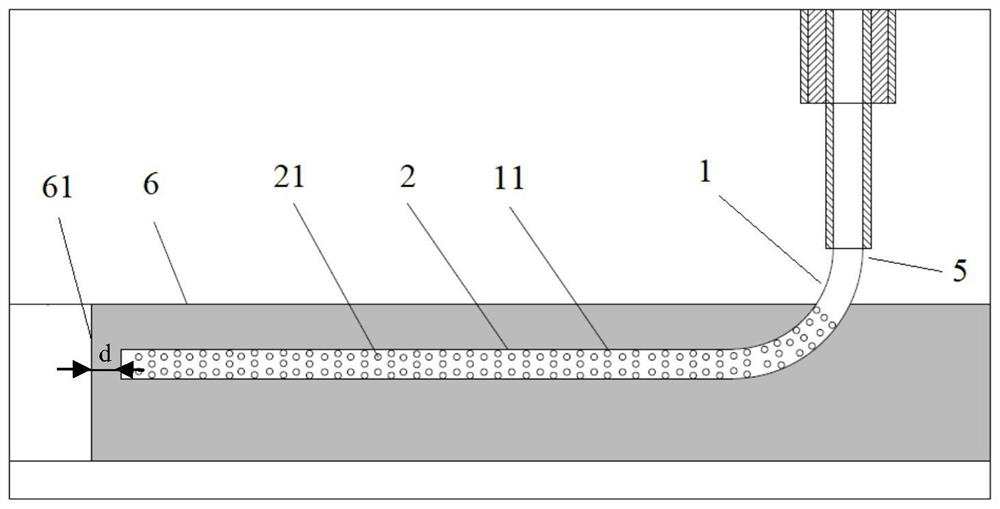

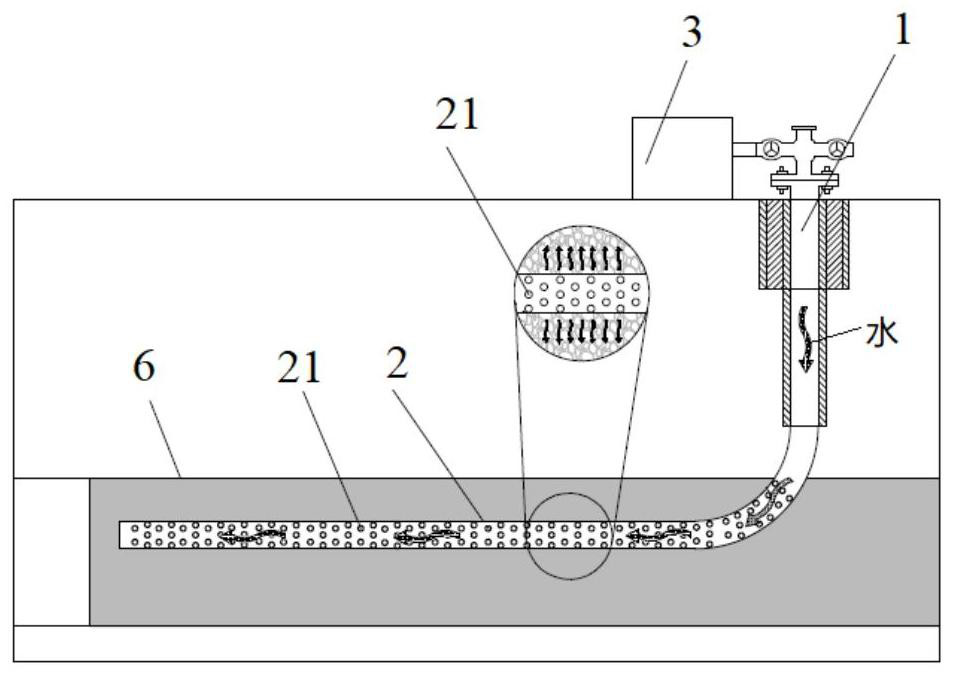

Dust removal method and device for ground horizontal well of coal mine roadway driving face

ActiveCN112761704AReduce in quantityReduce production capacityDust removalFire preventionMining engineeringHorizontal wells

The invention discloses a dust removal method and device for a ground horizontal well of a coal mine roadway driving face. The method comprises the steps that firstly, the ground horizontal well is reversely designed along a to-be-driven roadway; secondly, directional drilling of the ground horizontal well is conducted on a coal seam, and an easily-cut hole protection screen pipe is put into a horizontal section of the ground horizontal well and provided with holes; thirdly, water is injected into the ground horizontal well from the ground in a pressurized mode, and the water is injected into the coal seam through the holes of the hole protection screen pipe; and finally, coal mine roadway driving face driving is conducted, and when the driving face reaches the tail end of the horizontal section, a dust removal system arranged on the ground is started to pump and discharge dust generated by the driving face. According to the dust removal method and device for the ground horizontal well of the coal mine roadway driving face, the problems that the dust causes safety production of the driving face and worsens the working environment are solved, power noise is reduced, the construction efficiency of the driving face is improved, the health of underground constructors is protected, and the requirements for comprehensive dust prevention, safety, economy, energy conservation and environmental protection of the driving face are met.

Owner:XIAN RES INST OF CHINA COAL TECH& ENG GROUP CORP

Printed circuit board

InactiveUS20080000677A1Reduce power noiseCross-talk/noise/interference reductionPrinted circuit aspectsPrinted circuit boardEngineering

A printed circuit board (PCB) includes at least one power trace. A plurality of etched portions are defined in the at least one power trace, acting as electromagnetic bandgaps for transferring resonant frequencies produced around the at least one power trace to avoid working frequencies of the PCB, thereby reducing power noise around the at least one power trace.

Owner:HON HAI PRECISION IND CO LTD

Power amplifier and method for reducing common noise of power amplifier

InactiveUS20090039957A1Reduce Power NoiseImprove signal stabilityAmplifier modifications to reduce noise influenceGain controlAudio power amplifierControl signal

A power amplifier including a delta-sigma modulation module, a differential programmable dead-time-control module, and an output stage module is provided. The delta-sigma modulation module integrates and quantizes an error between a differential-mode input signal and an output signal to generate a first and a second mean signal. The differential programmable dead-time-control module includes a first and a second dead-time-control module which respectively generate a first and a second signal corresponding to the first mean signal and a third and a fourth signals corresponding to the second mean signal through logic calculations. The differential programmable dead-time-control module determines a dead time between the first signal and the second signal according to a first control signal and a dead time between the third signal and the fourth signal according to a second control signal. The output stage module generates the output signal according to the first, second, third, and fourth signal.

Owner:IND TECH RES INST

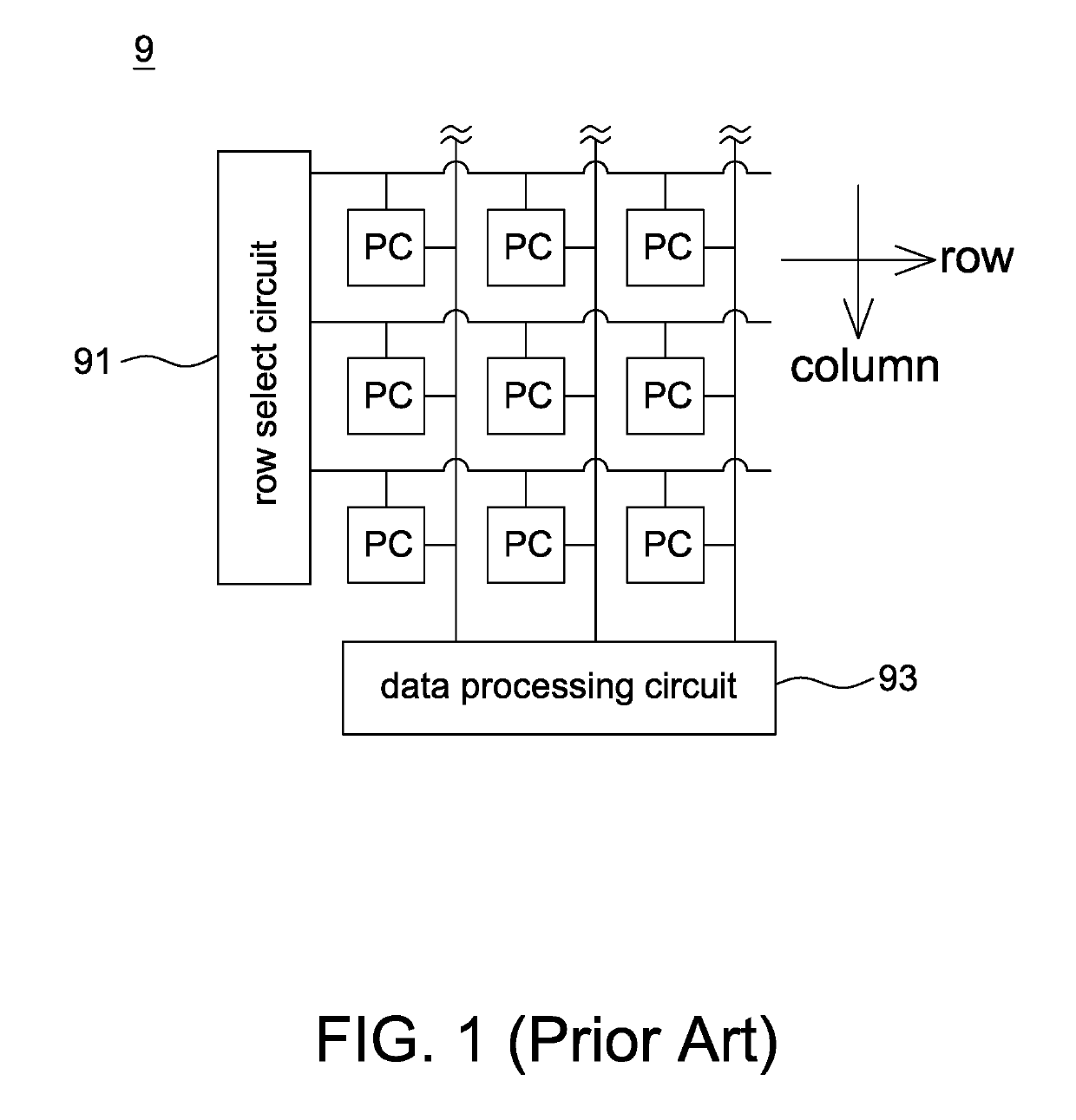

Image sensor capable of averaging pixel data

ActiveUS20190174084A1Improve signal-to-noise ratioLow power modeTelevision system detailsColor television detailsPixel arrayComputer science

An image sensor including a first pixel circuit, a second pixel circuit, a first readout line, a second readout line, a first readout circuit, a second readout circuit and an average switch is provided. The first and second pixel circuits are in two columns of a pixel array. The first readout line transmits pixel data of the first pixel circuit to the first readout circuit. The second readout line transmits pixel data of the second pixel circuit to the second readout circuit. The average switch is arranged between the first and second readout lines and used to electrically connect the first and second readout lines in an average mode to average the pixel data on the first and second readout lines.

Owner:PIXART IMAGING INC

Wearable brain function detection device based on NIRS

InactiveCN105997102AEasy to monitor in real timeImprove medical experienceMedical imagingDiagnostic recording/measuringElectricityE communication

The invention discloses a wearable brain function detection device based on NIRS. The wearable brain function detection device comprises an NIRS detection unit, an ultra-low power consumption control unit, a state prompt unit, a bluetooth communication unit, a key input unit and a power supply unit, wherein the ultra-low power consumption control unit is connected with the NIRS detection unit, the state prompt unit and the bluetooth communication unit respectively, is in data command communication with the NIRS detection unit through an SPI interface, controls the working mode of the NIRS detection unit, and is in data transmission communication with the bluetooth communication unit through a UART serial communication protocol, and the bluetooth communication unit sends the received data to a mobile terminal for follow-up processing; the key input unit is connected with the power supply unit, the power supply unit is used for providing electricity for the NIRS detection unit, the ultra-low power consumption control unit, the state prompt unit and the bluetooth communication unit, and carries out power supply protection and power management. The wearable brain function detection device is small in size, the detection result is accurate, the power consumption is extremely low, and the real-time monitoring on the brain blood-oxygen based on NIRS is convenient.

Owner:SOUTH CHINA UNIV OF TECH +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com