Defectivity-immune technique of implementing MIM-based decoupling capacitors

A capacitor and power supply decoupling technology, applied in the direction of electric solid-state devices, instruments, circuits, etc., can solve the problems of low defect rate, lower device output and/or reliability, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

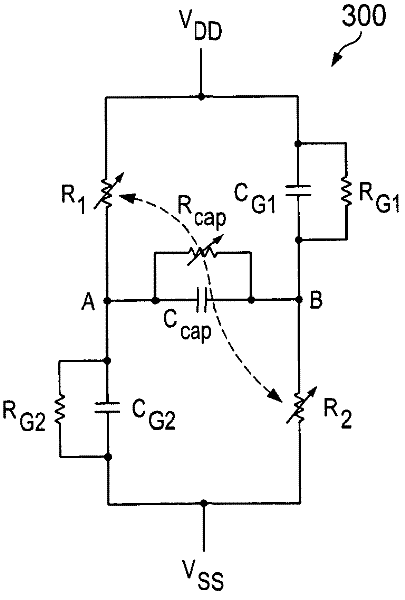

[0021] Using the gate dielectric layer as the capacitor dielectric, the defectivity of DECAP cells at the transistor layer is relatively low. This is because the decoupling capacitors are fabricated using the same processes used for standard CMOS transistors, which include high-quality gate dielectric layers. Therefore, the yield loss and / or current leakage of a design utilizing this DECAP is relatively low.

[0022] However, the interconnect layers used to form MiM-based DECAPs are generally more susceptible to processing defects that can lead to low-resistance paths (sometimes referred to herein as short circuits) between MiM DECAP levels. These deficiencies may reduce the overall yield and reliability of products utilizing the MiM DECAP. A short circuit through the MiM capacitor may cause a high current between the current source node and the ground node, thereby compromising the functionality of the entire device.

[0023] The present disclosure introduces a simple and n...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com