Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

48results about How to "Reduce hardware area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

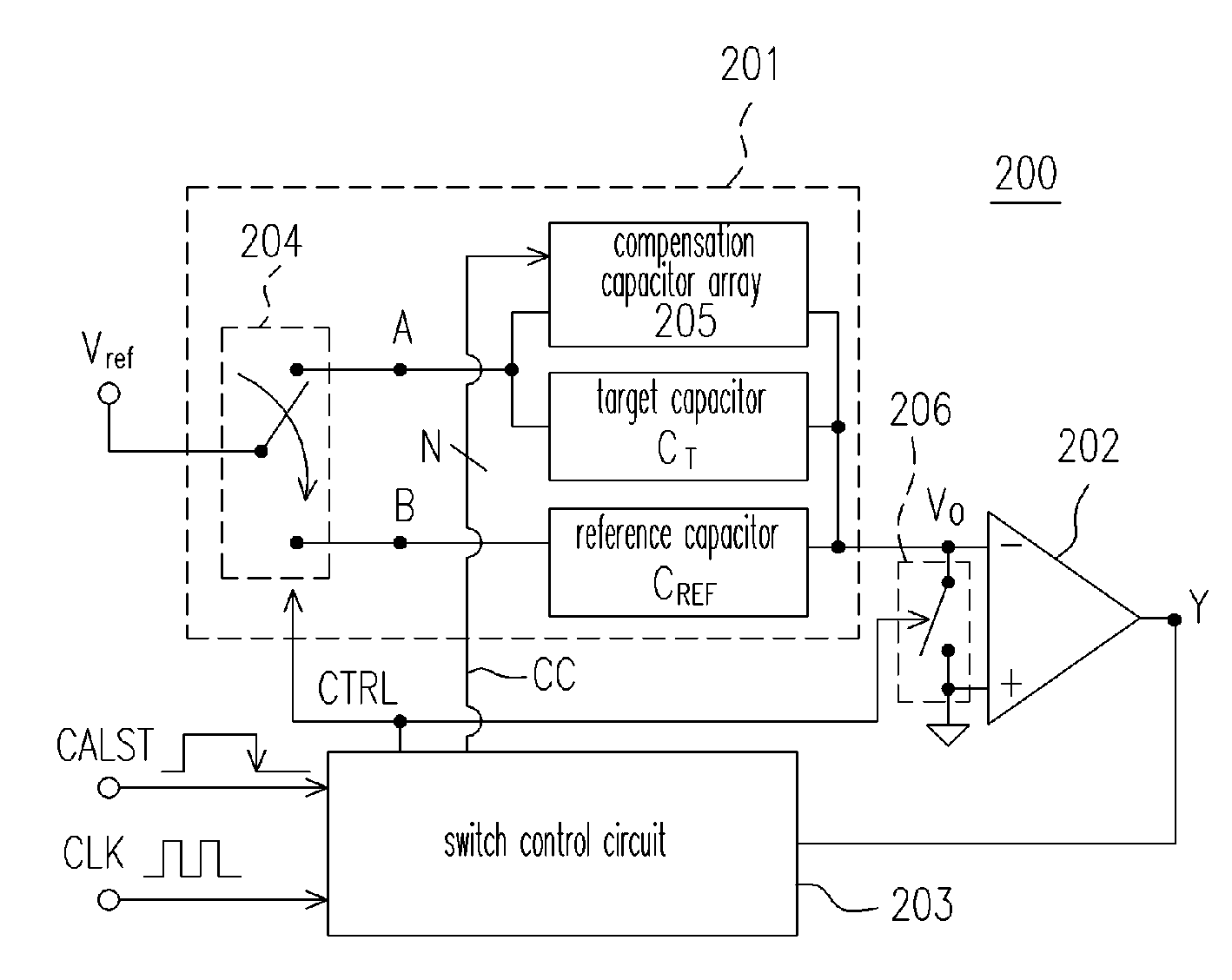

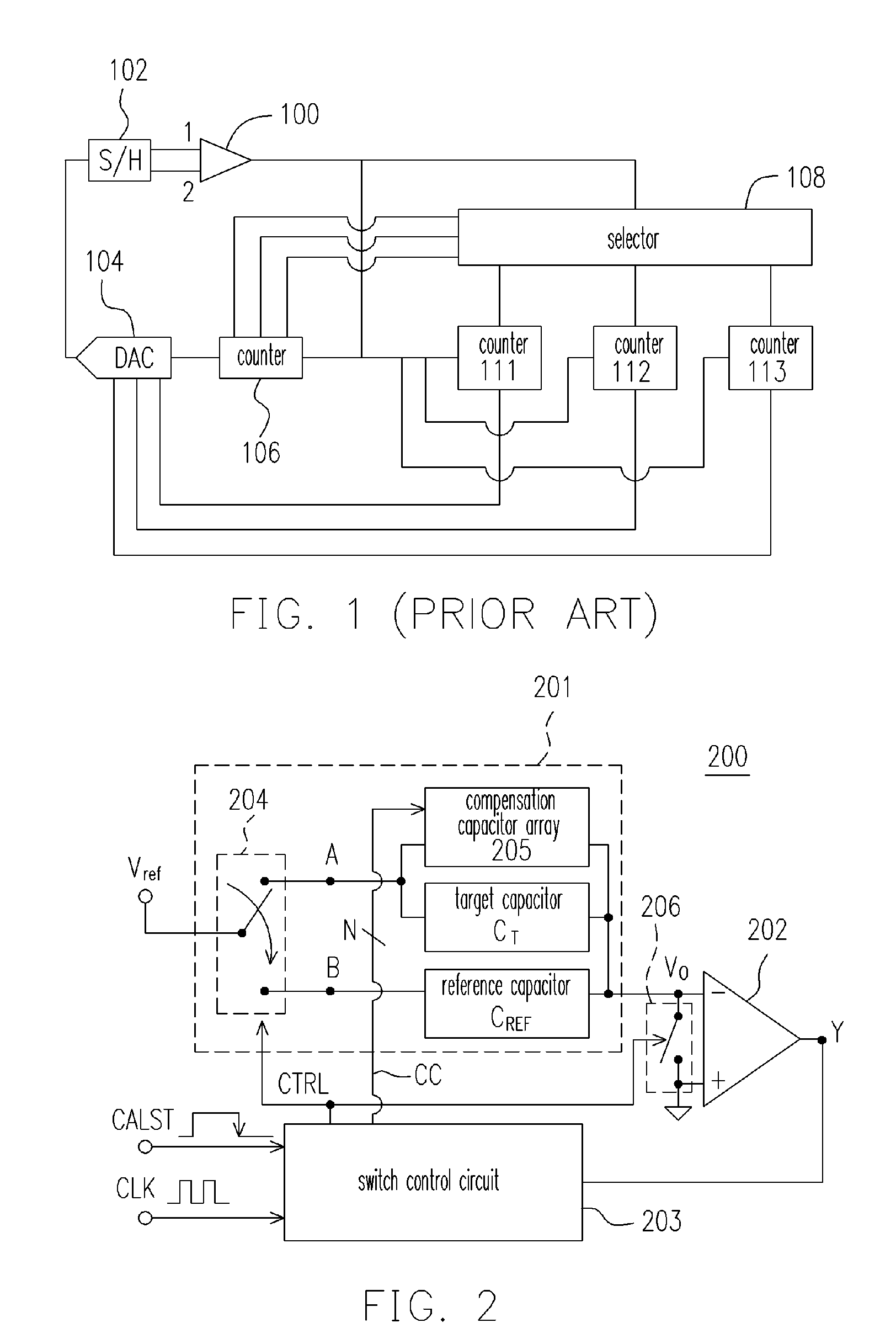

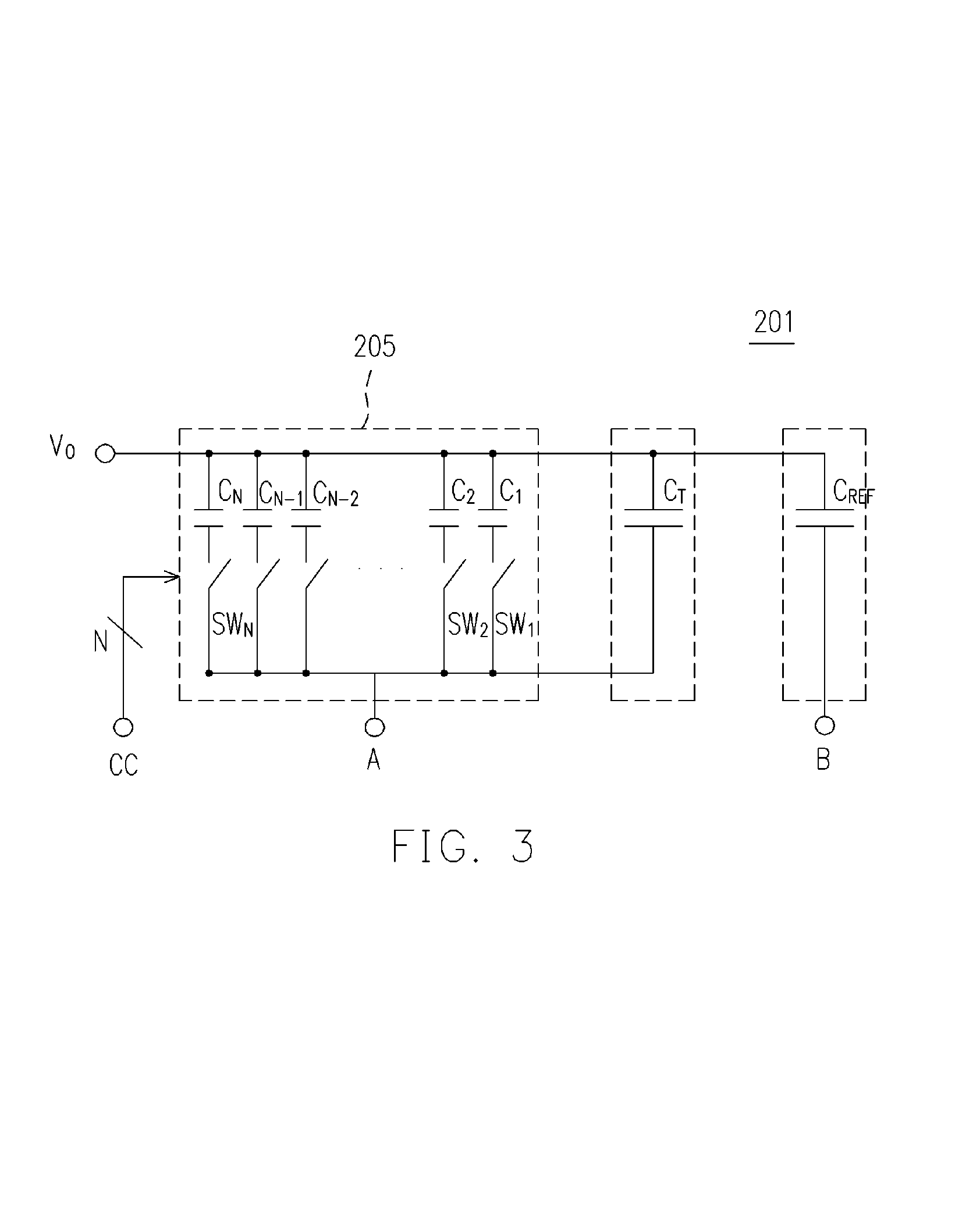

Self-calibration circuit for capacitance mismatch

InactiveUS7170439B1Simple circuit designSimple designElectric signal transmission systemsAnalogue-digital convertersCapacitanceControl circuit

A self-calibration circuit for capacitance mismatch is provided. The circuit comprises a sample-and-hold (S / H) circuit, a comparator, and a switch control circuit. The S / H circuit comprises a compensation capacitor array, a target capacitor, and a reference capacitor. The S / H circuit provides an output voltage, wherein the output voltage is an operation result based on the capacitance of the target capacitor and the reference capacitor, and the equivalent capacitance of the compensation capacitor array. The comparator provides a comparison signal according to whether the output voltage of the S / H circuit is positive or negative. The switch control circuit controls the equivalent capacitance of the array according to the comparison signal such that the result of the target capacitance added to the equivalent capacitance of the array gradually approximates the reference capacitance with each cycle of a clock signal.

Owner:PROLIFIC TECH INC

Image defective pixel detection method and apparatus

ActiveCN107016669AImprove detection efficiencyReduce hardware areaImage analysisPattern recognitionDefective pixel

The invention discloses an image defective pixel detection method and apparatus. The method includes: obtaining an N*M pixel block of an image, arranging all pixel points in the pixel block in sequence to obtain a pixel value sequence, calculating a median of the pixel value sequence, and obtaining a pixel median; determining a specified small pixel value and a specified large pixel value from the pixel value sequence, calculating a first difference, and determining the pixel type of a current pixel point and calculating a second difference according to the relation between the current pixel point and the pixel median; and determining whether the current pixel point is a suspected defective pixel by determining whether the quotient of the second difference and the first difference is greater than a first preset error. The defective pixel is checked based on the attribute of the defective pixel of the image, compared with the conventional defective pixel detection method, the hardware area is reduced, pixel points of the image are checked one by one, more suspected defective pixels can be discovered, and the detection efficiency of the defective pixels is improved.

Owner:FUZHOU ROCKCHIP SEMICON

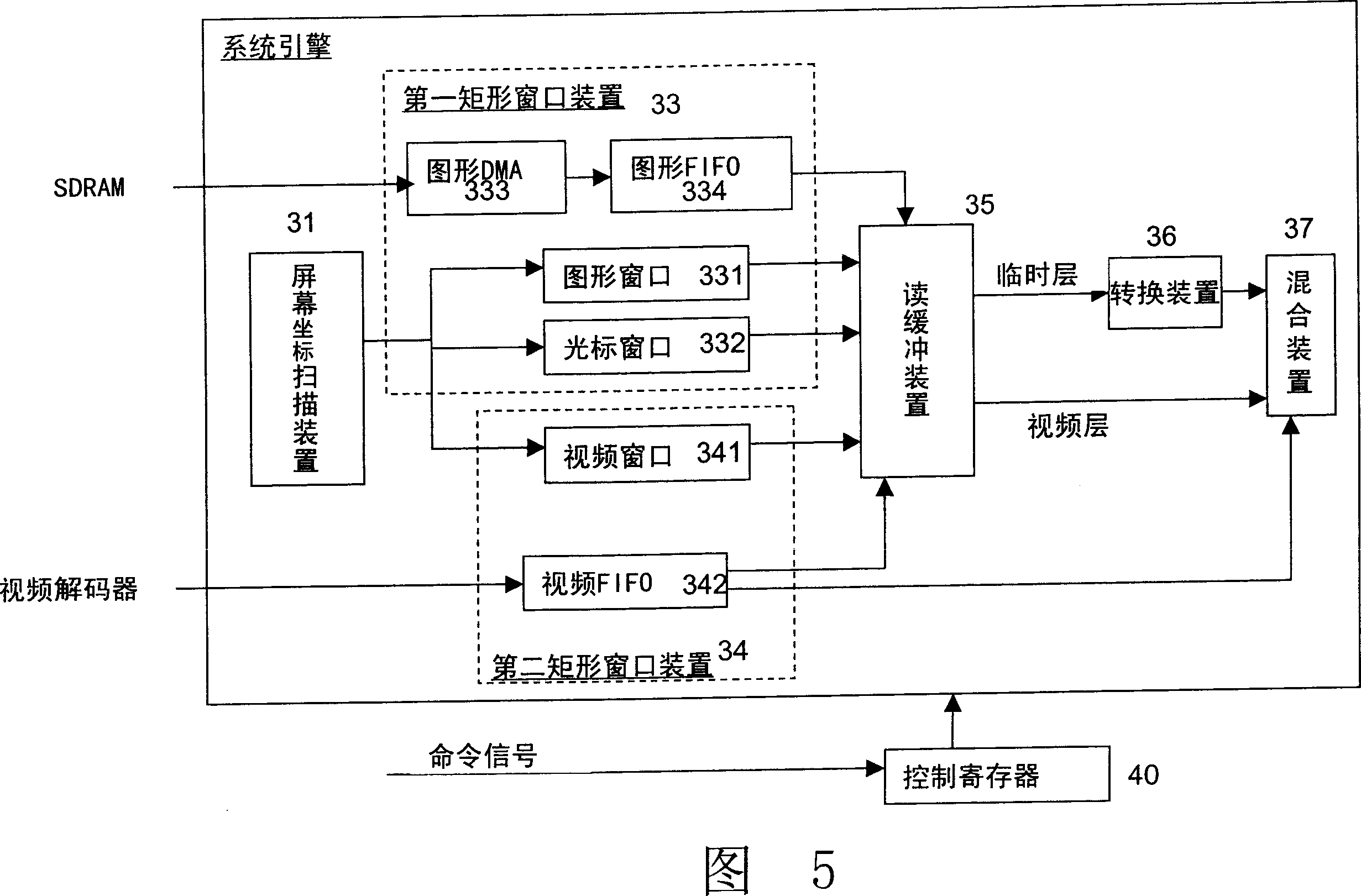

Screen display mixing system and method

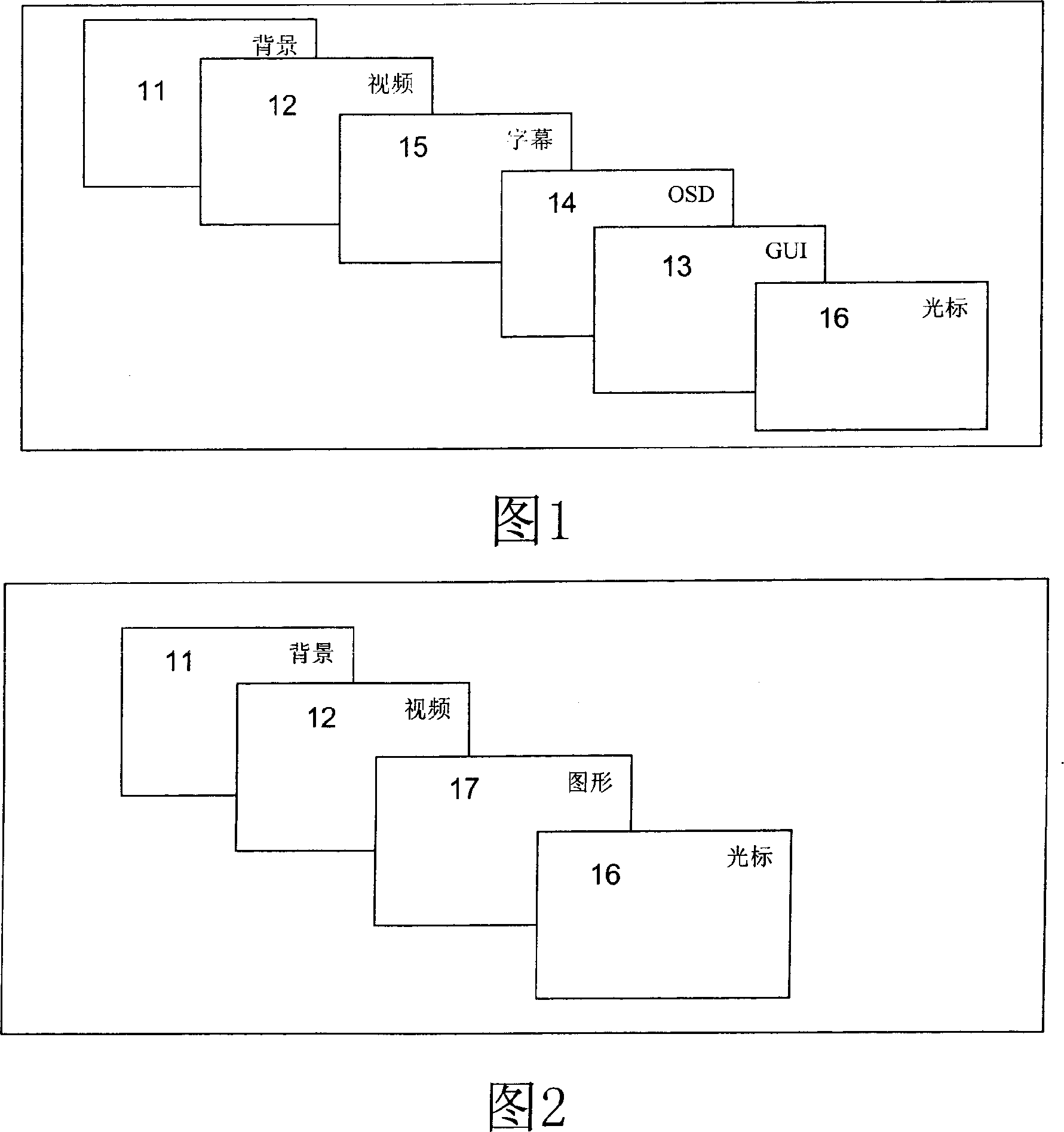

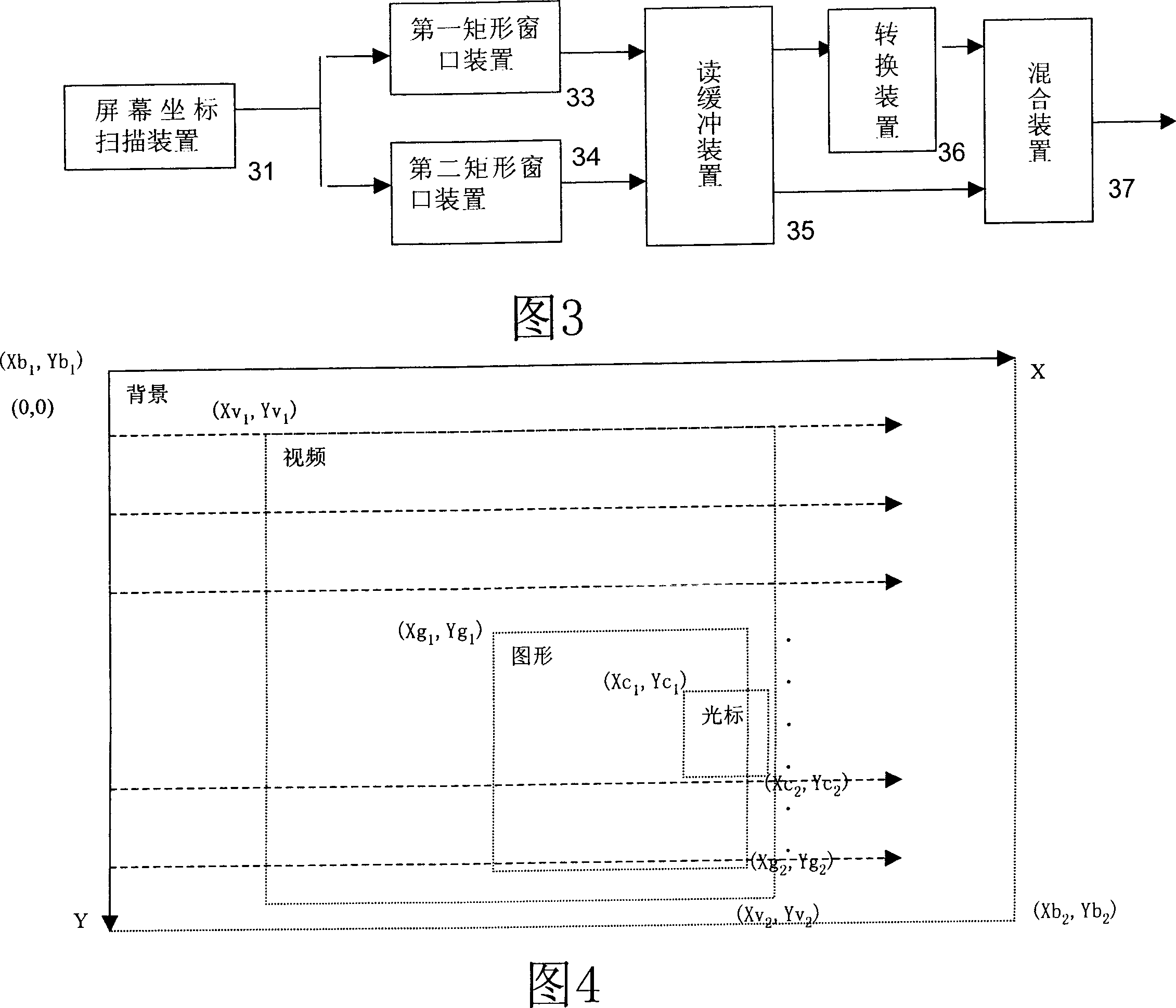

InactiveCN1964439AReduce hardware areaLow costTelevision system detailsTelevision system scanning detailsGraphicsOn-screen display

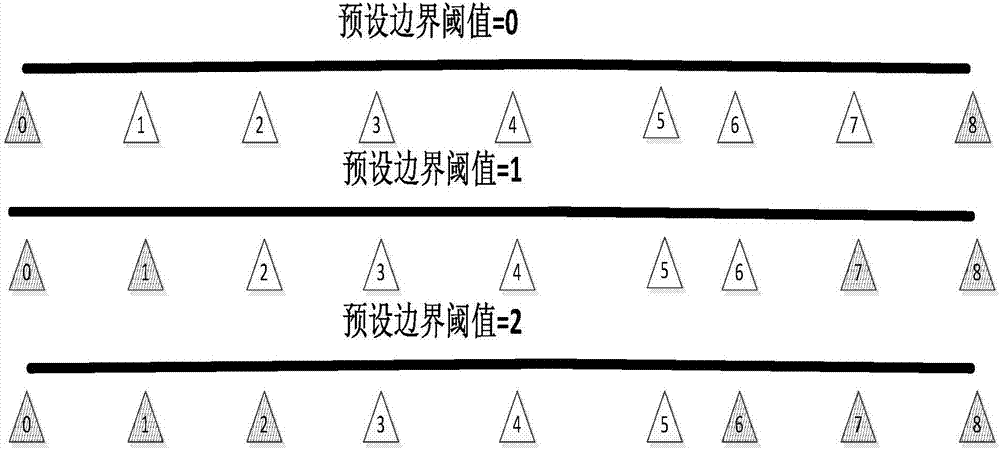

The mixed display screen system comprises: a coordinate scanning device to scan screen and generate current scanning pixel as coordinate flow; a first rectangular window device to decide the window contained current scanning pixel and select data to from a RGB domain temporary layer; a second rectangular window device to decide the video widow contained current pixel, a read buffer device to receive data from two rectangular windows, a conversion device to convert the temporary layer data from RGB domain into YUV domain; and an Alpha mixer to mix YUV domain data with video data.

Owner:SHANGHAI MAGIMA DIGITAL INFORMATION

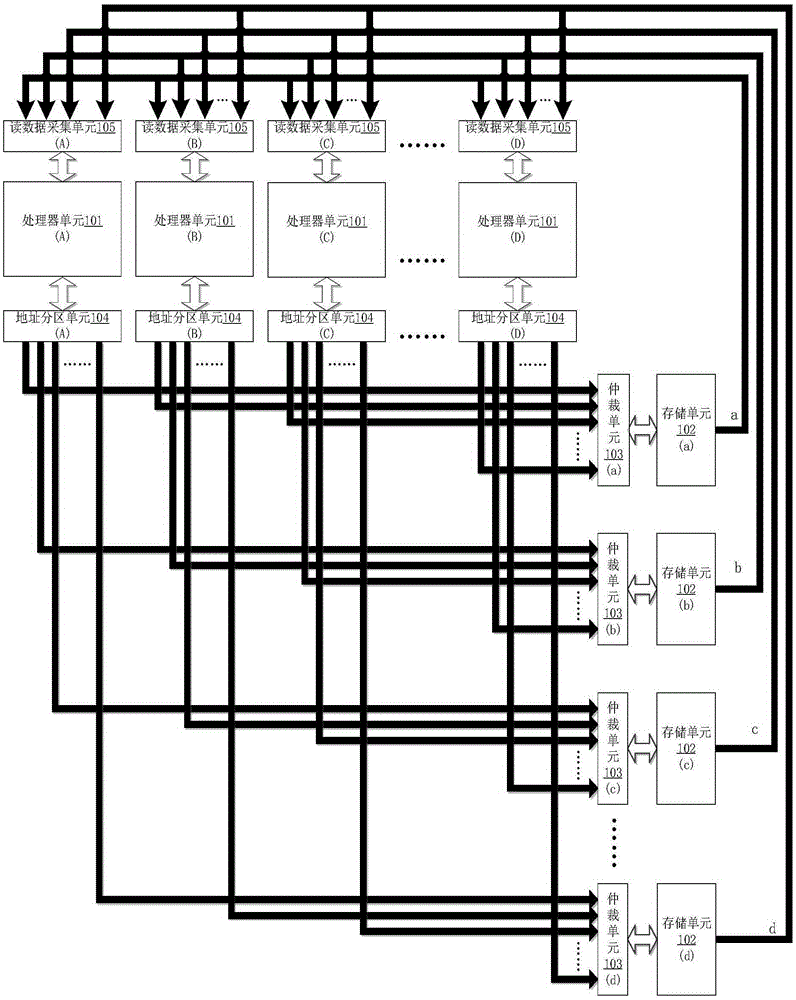

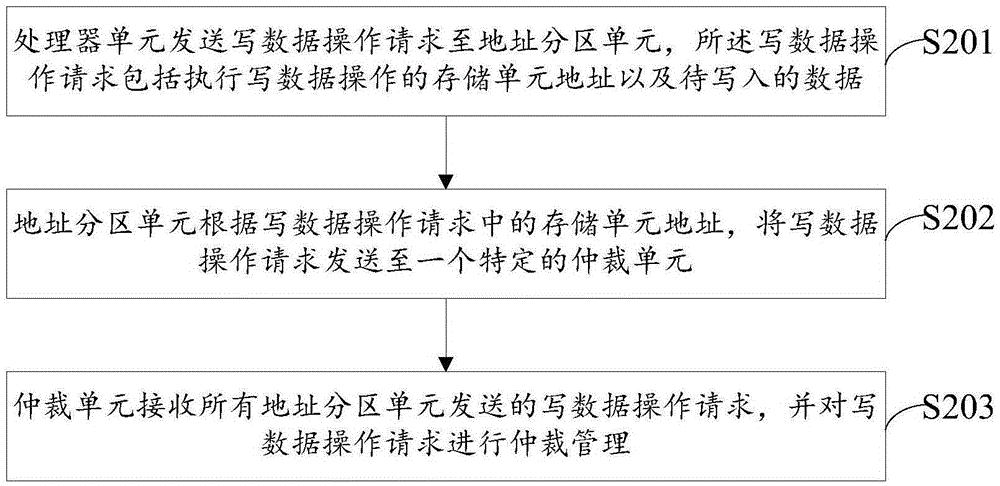

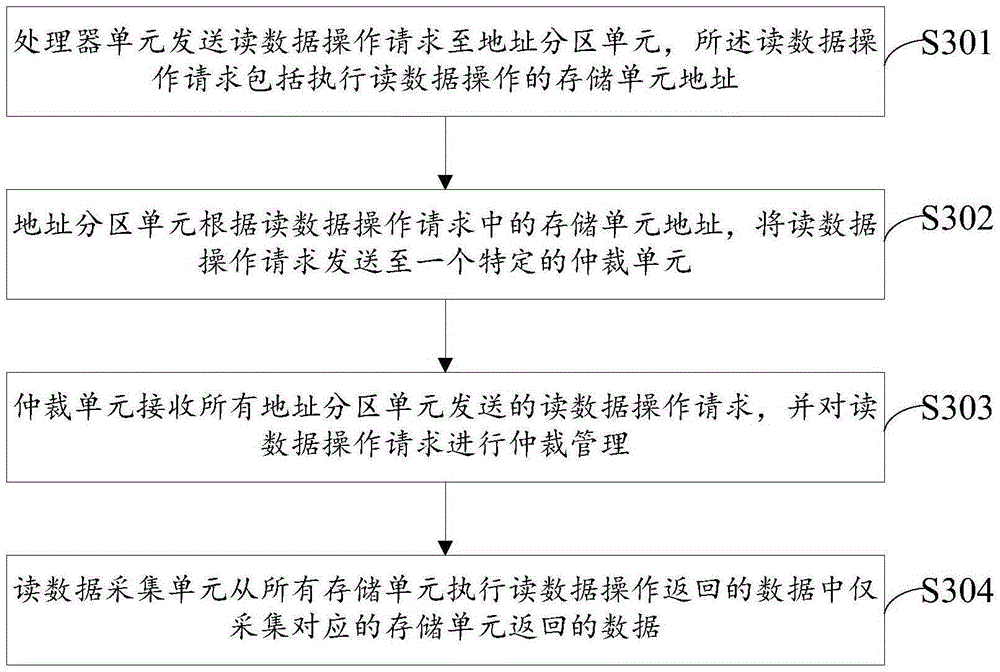

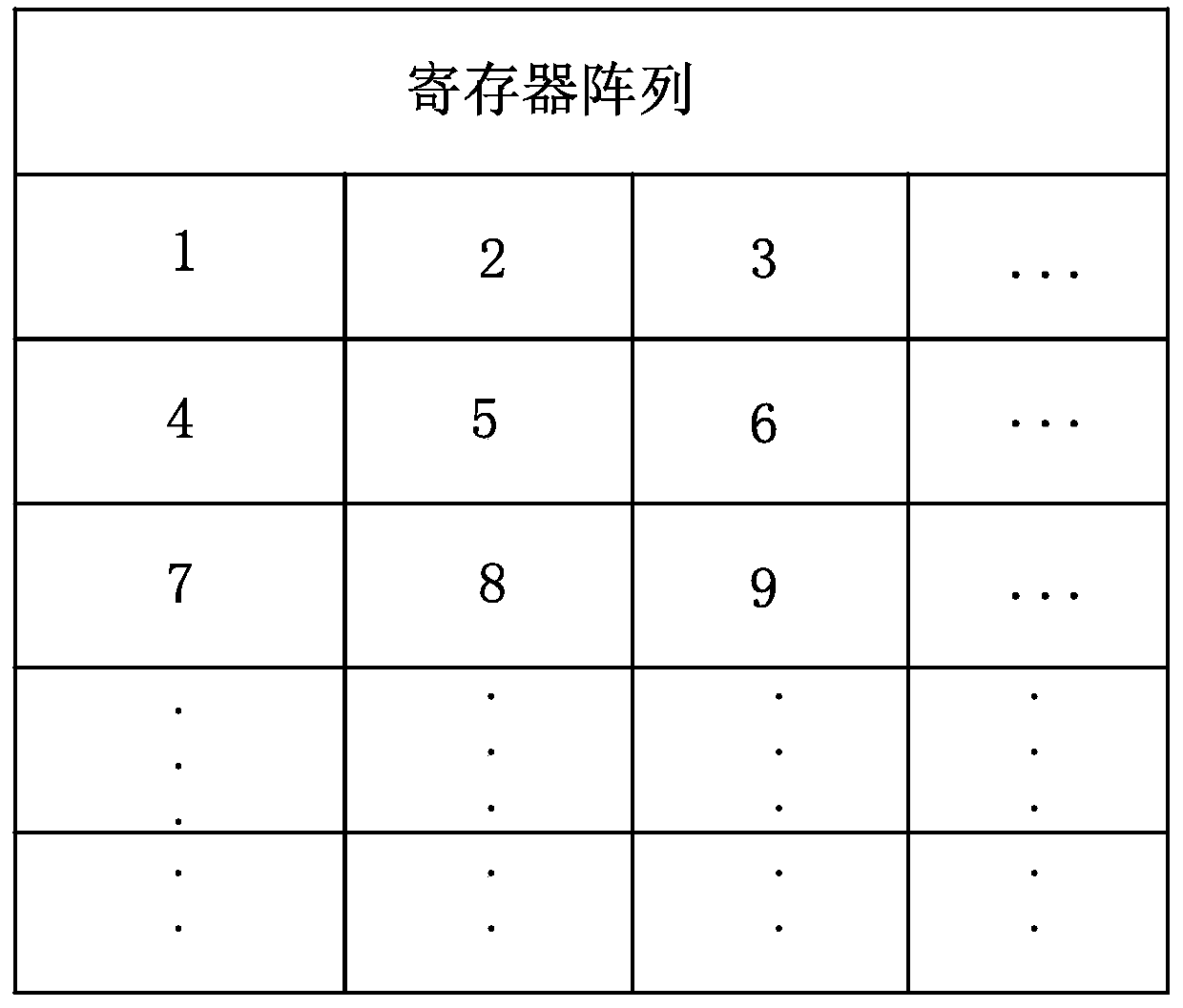

Shared parallel data reading-writing apparatus of multi memories among multi controllers, and reading-writing method of the same

ActiveCN106569727AReduce hardware areaSatisfy the computing performanceInput/output to record carriersHigh bandwidthData operations

The invention provides a shared parallel data reading-writing apparatus of multi memories among multi controllers, and a reading-writing method of the same. The shared parallel data reading-writing apparatus of multi memories among multi controllers includes a plurality of processor units and a plurality of storage units, wherein each storage unit is corresponding to each arbitration unit; each processor unit is corresponding to an address partition unit and a read data acquisition unit; aiming at the situation that the plurality of processor units access one storage unit at the same time, the arbitration unit can be used for carrying out arbitration management on a data operation request; and only the data operation request satisfying the preset conditions is selected; and the corresponding storage unit is used to execute data operation. As the processor units can directly access the storage units according to the addresses distributed by the address partition units, higher bandwidth can be provided; the operating performance of the processors can be satisfied; and the data access efficiency is greatly improved. Besides, the data exchange redundancy problem among the plurality of processors can be solved, so that the shared parallel data reading-writing apparatus of multi memories among multi controllers has wide market prospect in the integrated circuit field.

Owner:FUZHOU ROCKCHIP SEMICON

Motion vector prediction multiplex design method in multi-mode standard decoder

InactiveCN1801941ASimple logicImprove access speedTelevision systemsDigital video signal modificationMultiplexingData stream

Present invention relates to motion vector prediction multiplexing design method for in standard decoder, 1, firmware transmitting a avs_flag sign to MVP module, 2, adopting deblocking lower embedded subblock format, 3, taking adjacent block messages module pair frame field self adaptation sign poke, to make two different standard proceeding same processing, to realize multiplexing, 4, taking reference macroblock messages design all messages of parallel macroblock always taking from the first one reference picture in reference picture macroblock movement messages cache, in updating also saving to first reference picture, 5, the design to adjacent block data stream updating system, to make multiplexing required adjacent block information content down to the least, reducing times for reading external storage. The advantages are realizing compatibility of H,264 with AVS video coding standard MVP function, not only to ensure validity but also greatly to reduce decoder hard ware area. Said invention can reduce cache by 75 %, and realize real time decode to high resolution image.

Owner:宁波中科集成电路设计中心有限公司

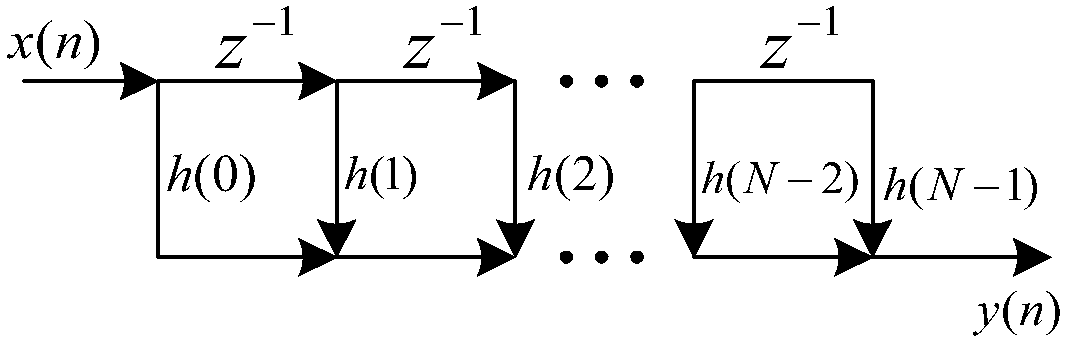

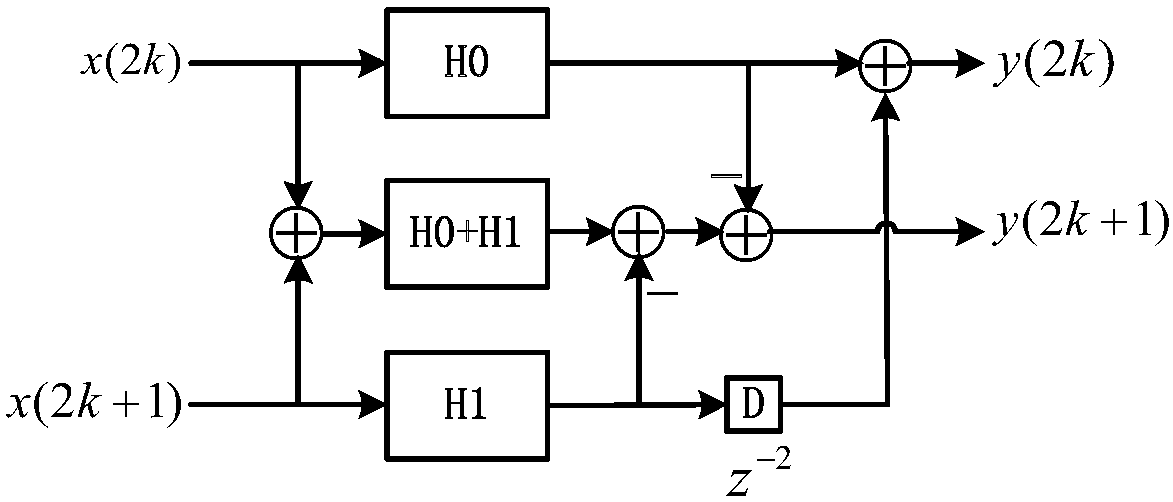

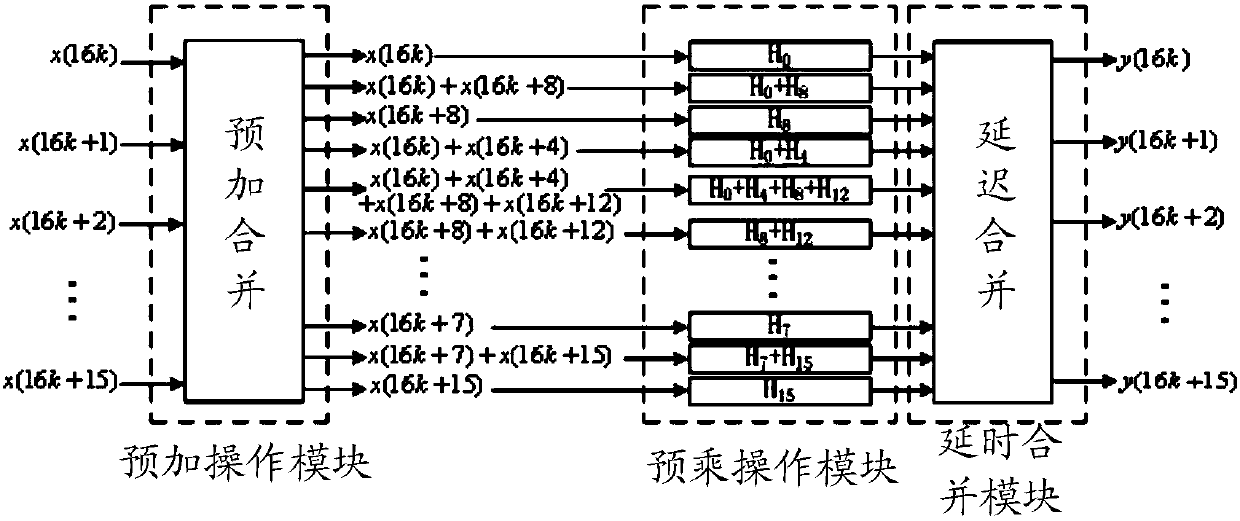

Parallel FIR filtering method and FIR filter

The embodiment of the invention discloses a parallel FIR filtering method and a FIR filter, and aims to effectively reduce hardware cost and improve computing speed; the method comprises the following steps: pre-adding and merging input signals so as to obtain first to-be-processed signals, wherein the numbers of the input signals and first to-be-processed signals are bigger than 1; pre-multiplying the first to-be-processed signals with an objective filter coefficient so as to obtain second to-be-processed signals, wherein the objective filter coefficient is matched with the first to-be-processed signals; delaying and merging the second to-be-processed signals so as to obtain an output signal.

Owner:SHANGHAI HUAWEI TECH CO LTD

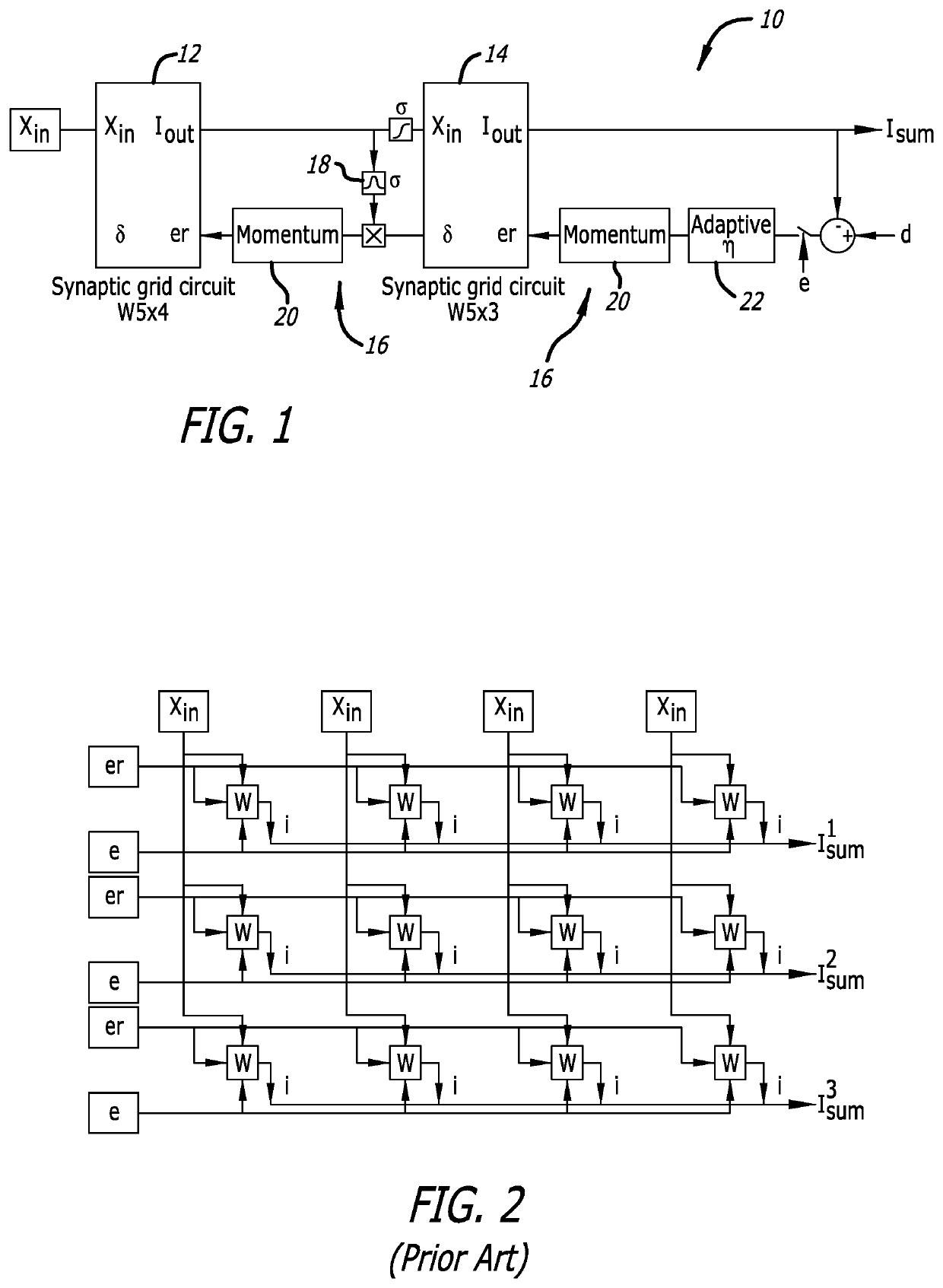

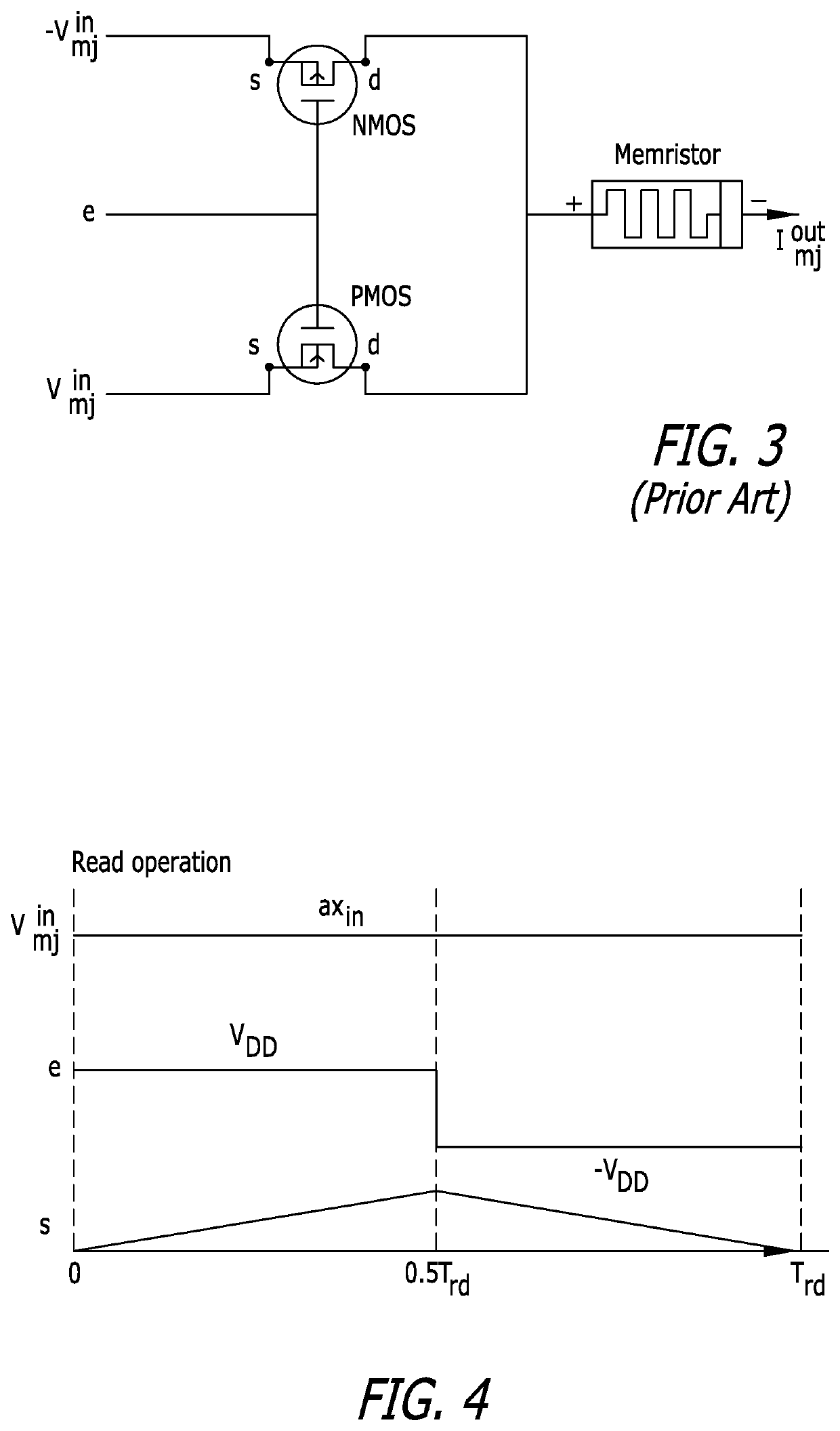

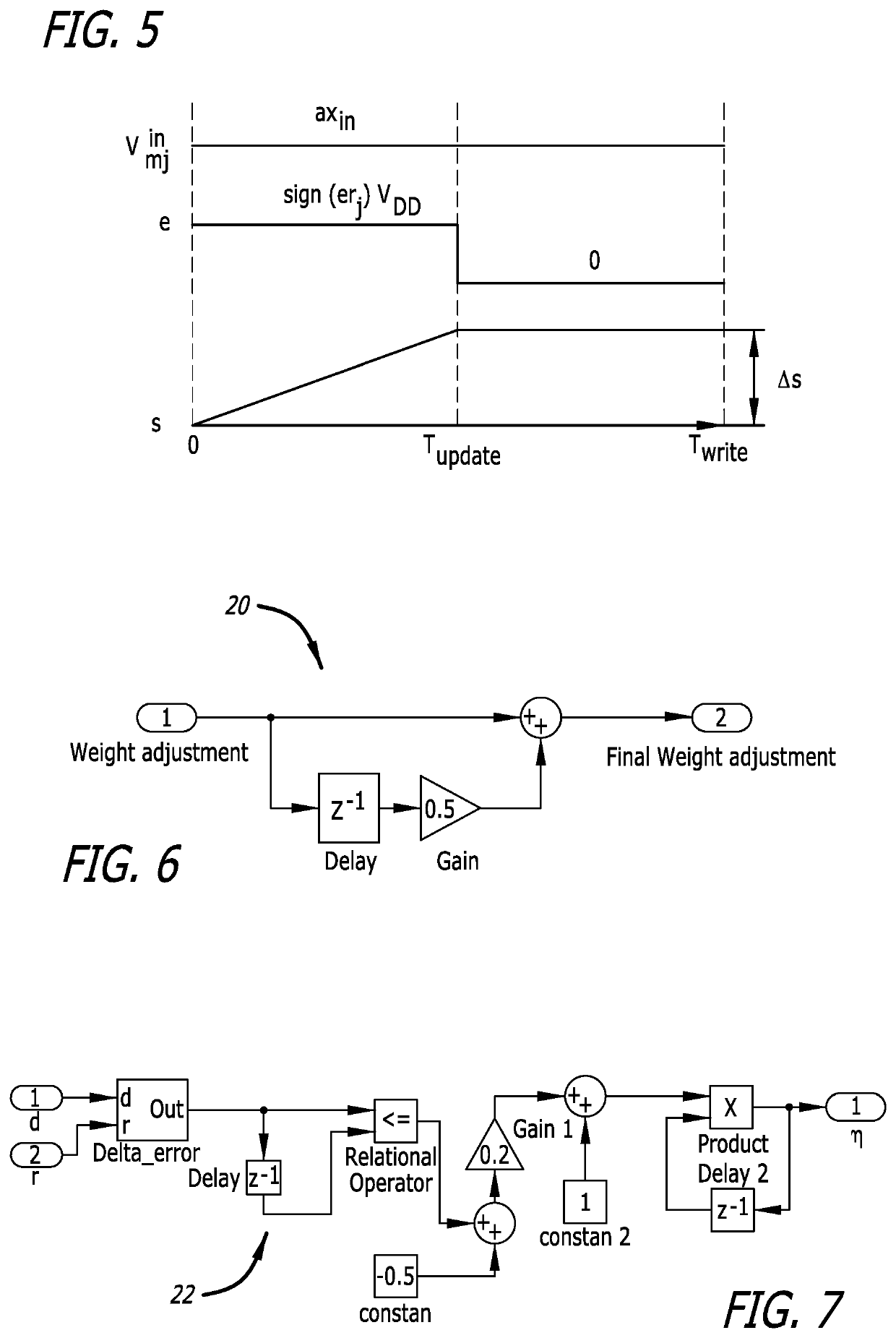

Circuit for calculating weight adjustments of an artificial neural network, and a module implementing a long short-term artificial neural network

PendingUS20210097379A1Reduce resistanceSimplify hardware circuit design processDigital storagePhysical realisationWeight adjustmentArtificial intelligence

A circuit structure for implementing a multilayer artificial neural network, the circuit comprising: a plurality of memristors implementing a synaptic grid array, the memristors storing weights of the network; and a calculation and control module configured to calculate the value of weight adjustments within the network.

Owner:QATOR FOUND FOR EDUCATION SCI & COMMUNITY DEV

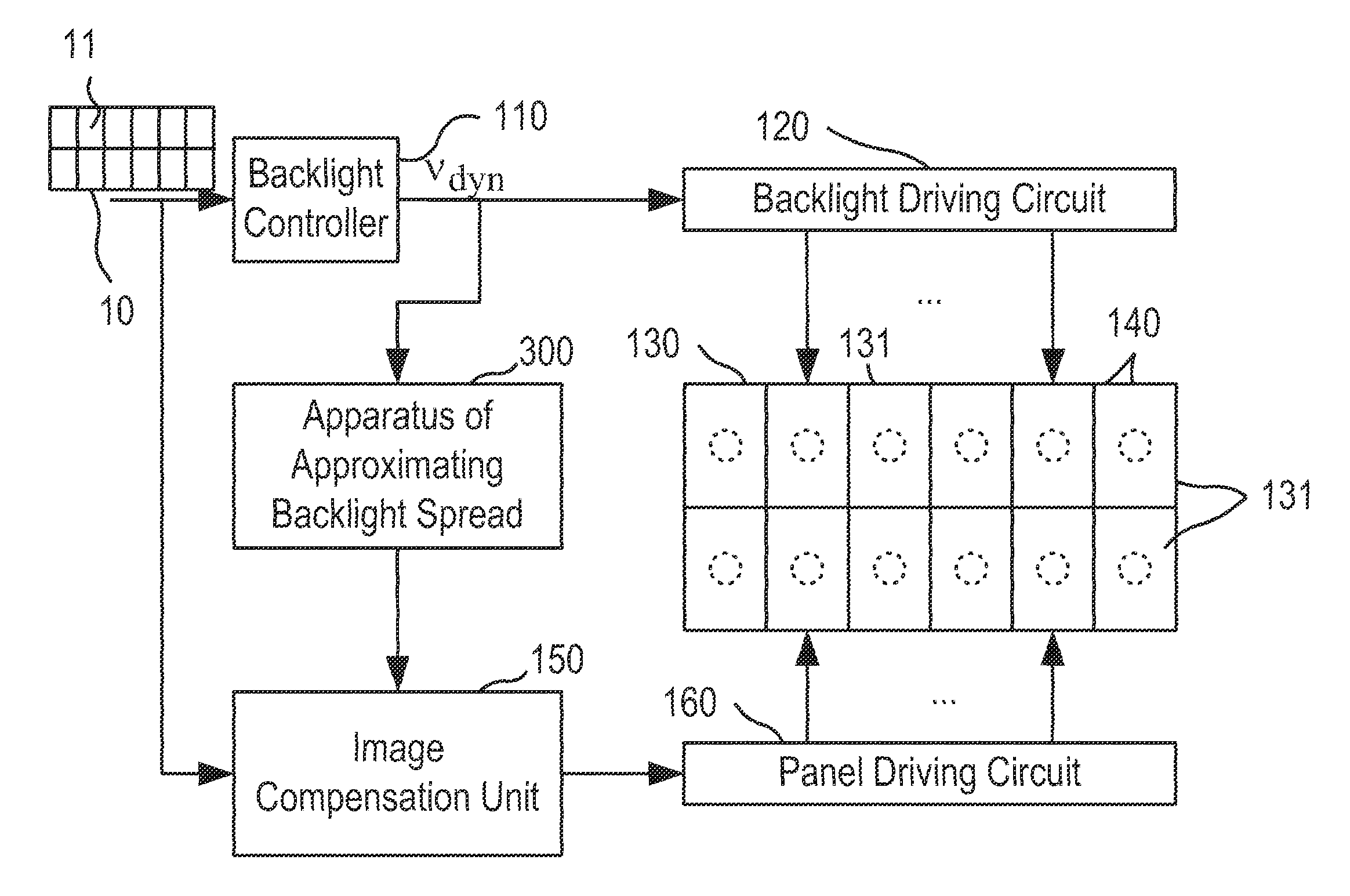

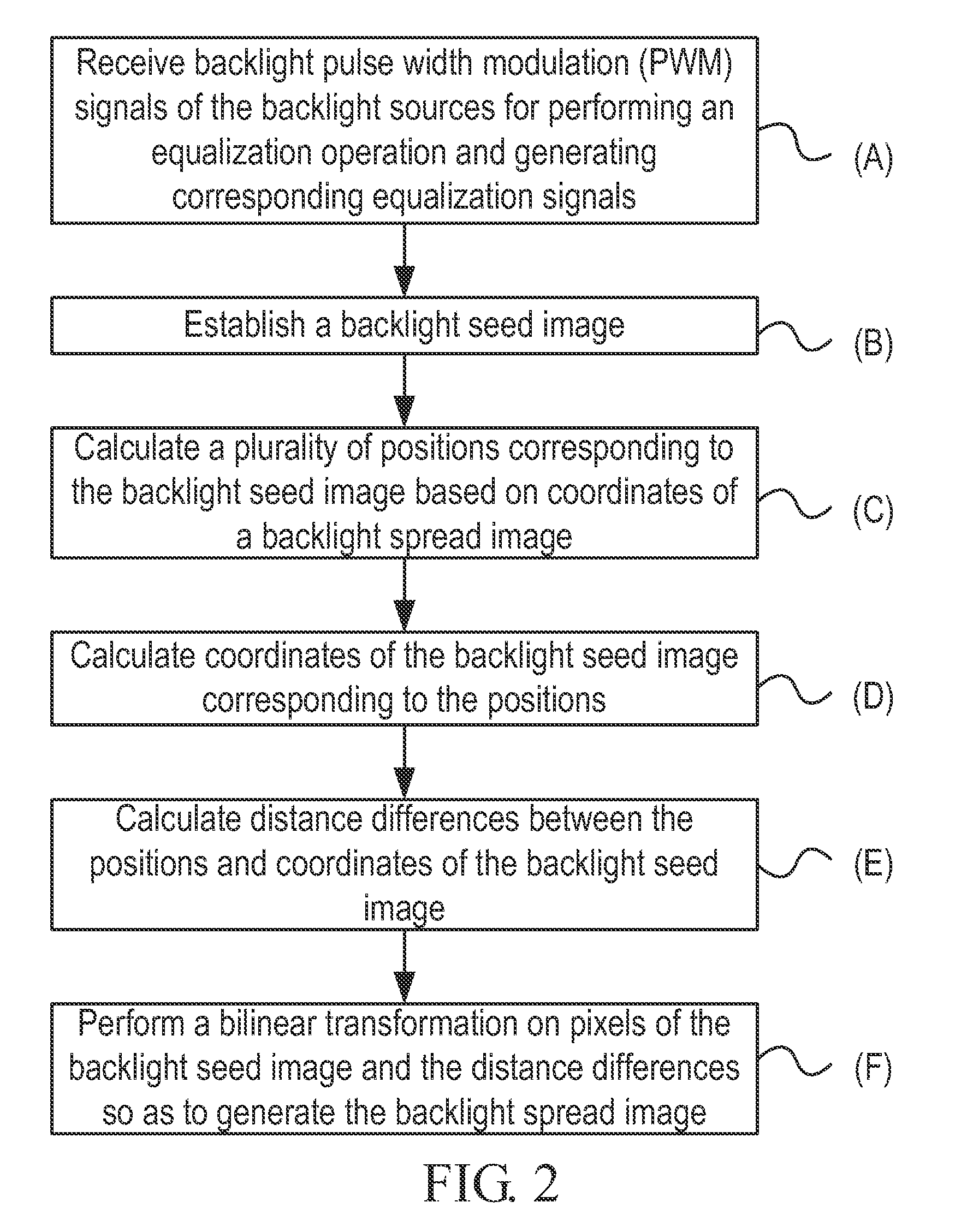

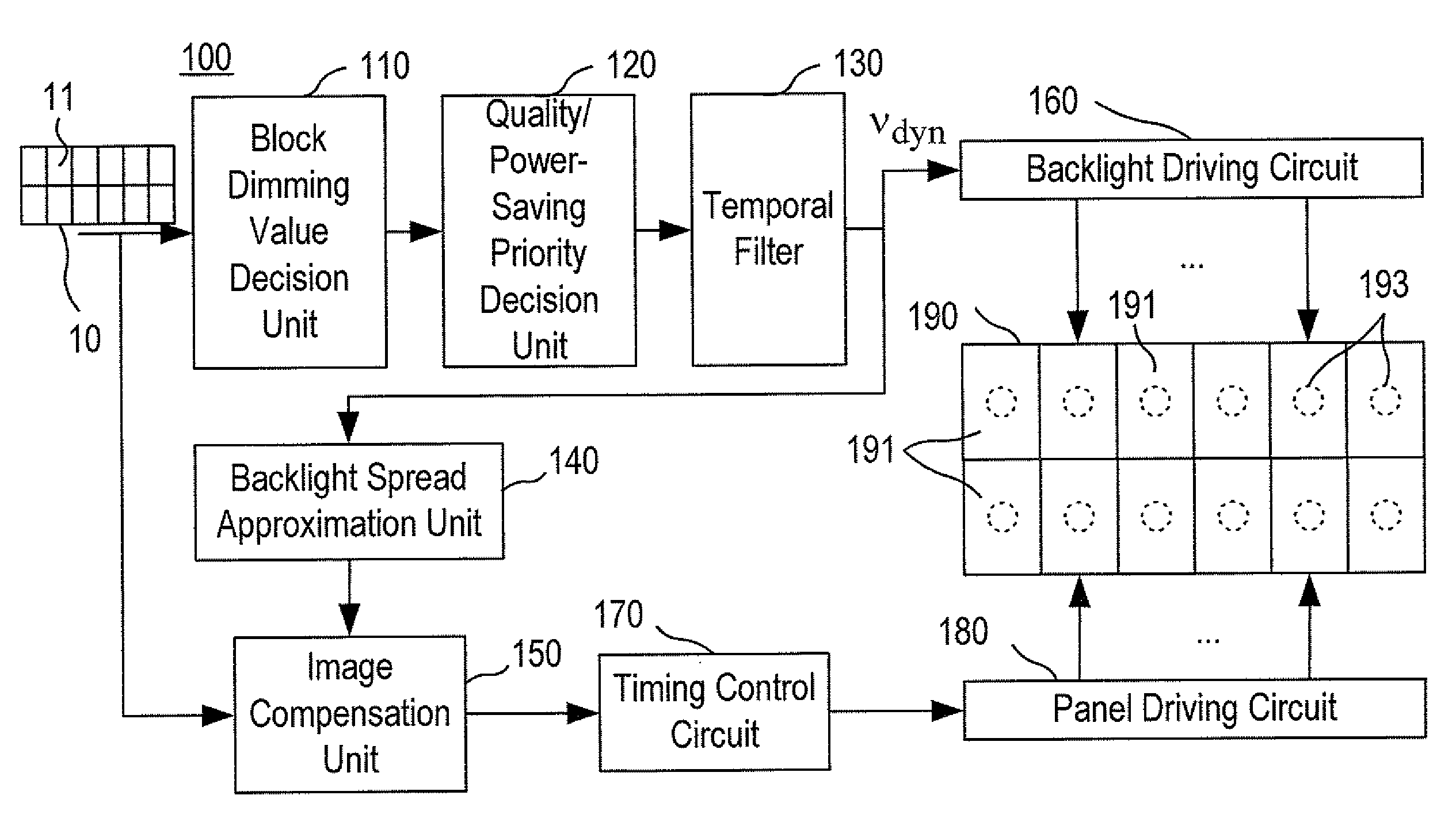

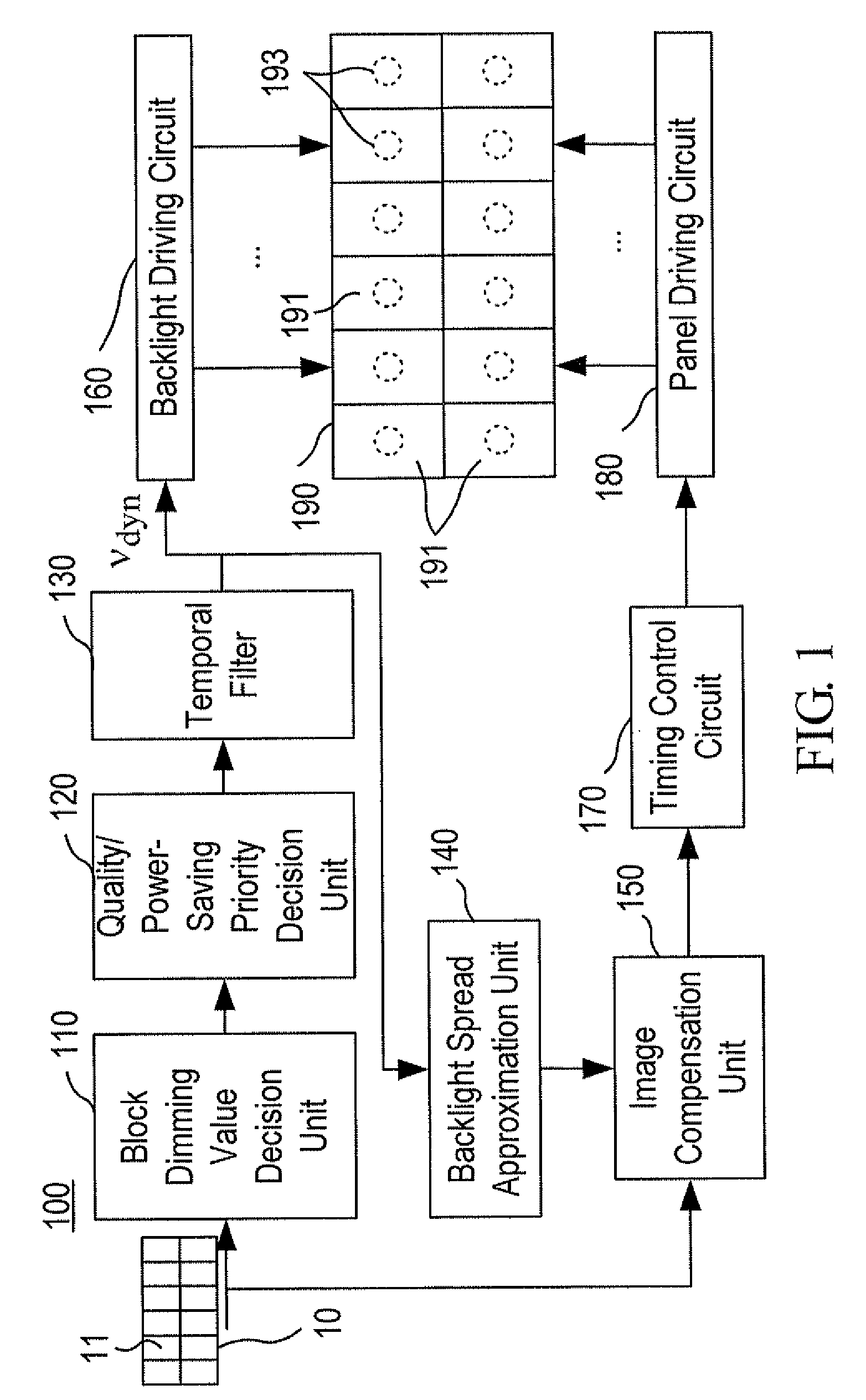

Method and apparatus of approximating backlight spread in a local dimming system

ActiveUS20130016036A1Increase power consumptionReduce the amount requiredStatic indicating devicesDisplay deviceTransformation unit

An apparatus of approximating backlight spread is used in a display to estimate a backlight spread image corresponding to an image after backlight spreading of a plurality of backlight sources arranged in a matrix form. An equalizer receives backlight pulse width modulation signals of the backlight sources for performing an equalization operation and generating corresponding equalization signals. A backlight seed image constructor receives the equalization signals to establish a backlight seed image. A first calculation unit calculates positions corresponding to the backlight seed image based on a backlight spread image. A second calculation unit calculates coordinates of the backlight seed image corresponding to the positions. A distance calculator calculates distance differences between the positions and coordinates of the backlight seed image. A bilinear transformation unit performs a bilinear transformation on pixels of the backlight seed image and the distance differences so as to generate the backlight spread image.

Owner:ORISE TECH CO LTD

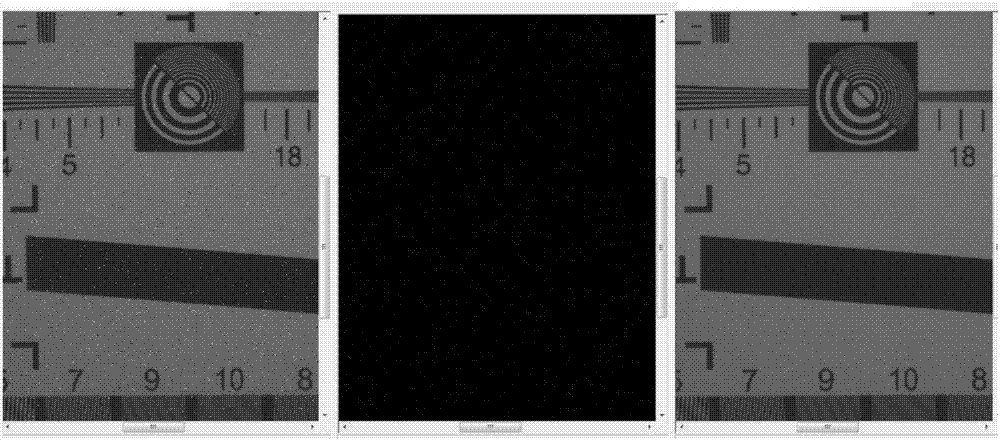

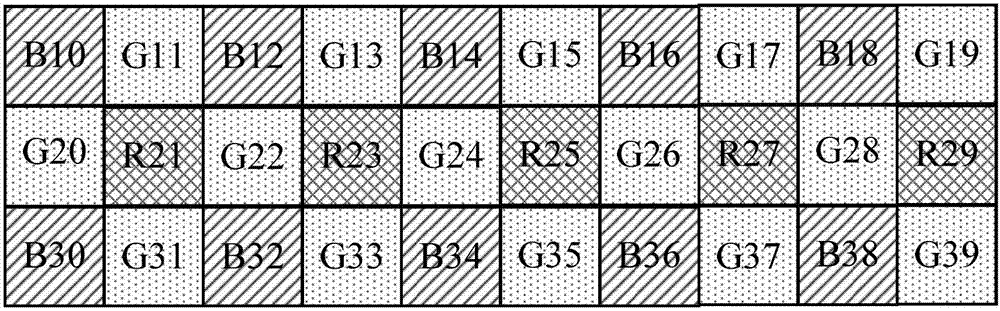

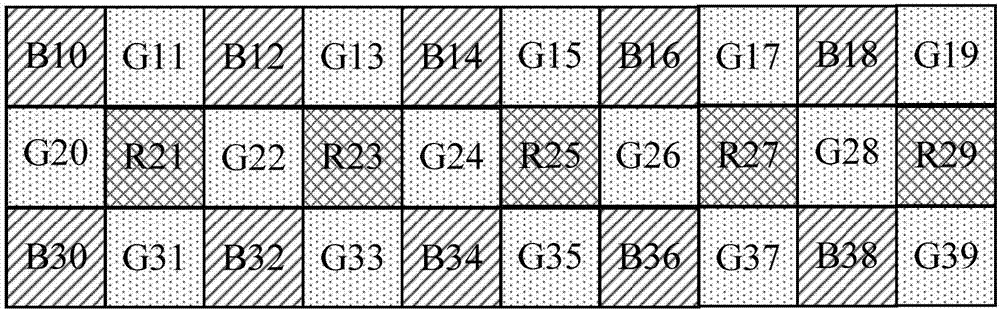

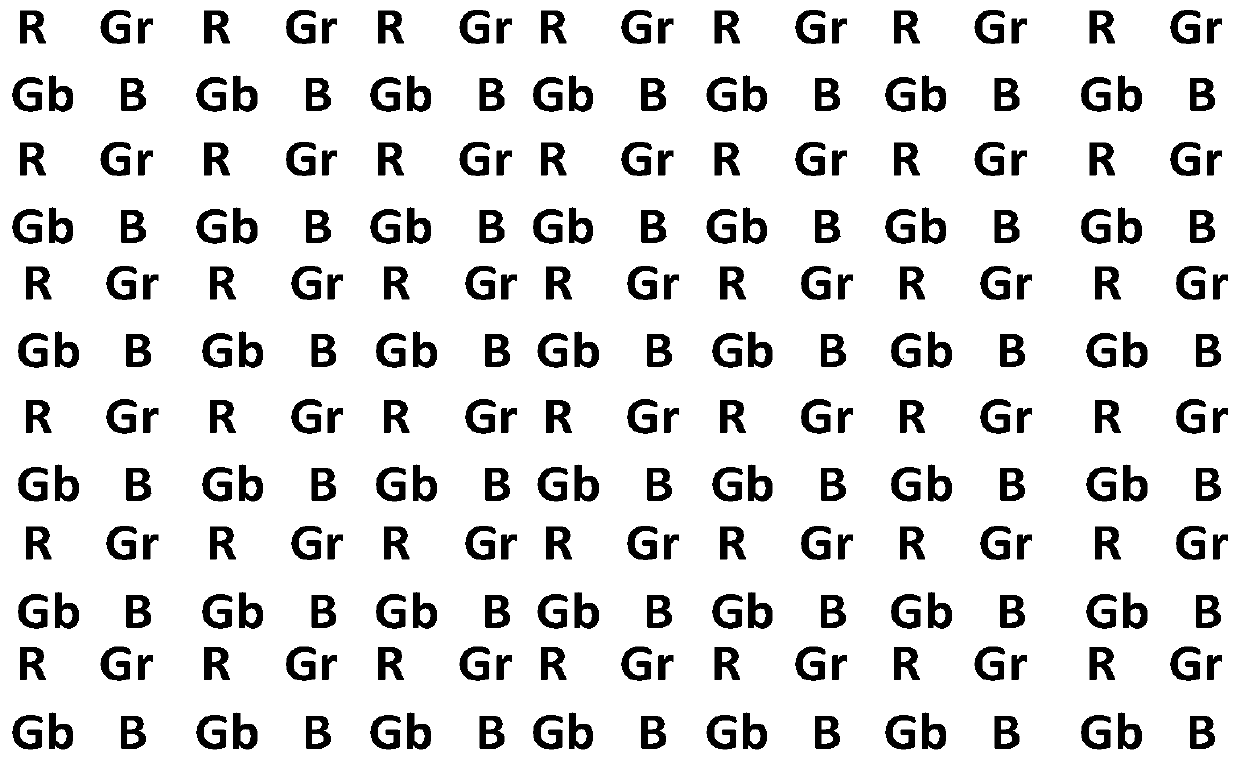

Image defective pixel detection method and apparatus

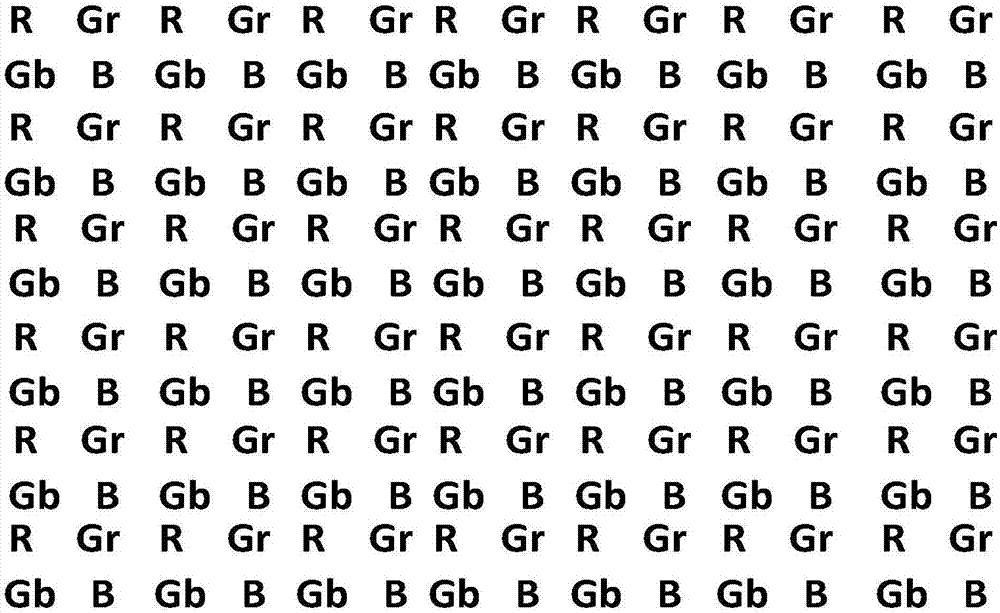

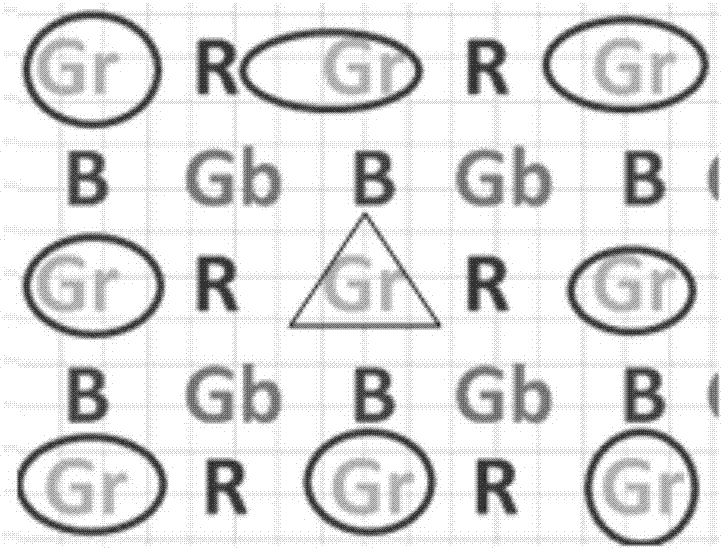

ActiveCN107016670AImprove detection efficiencyReduce hardware areaImage enhancementImage analysisDefective pixelImage based

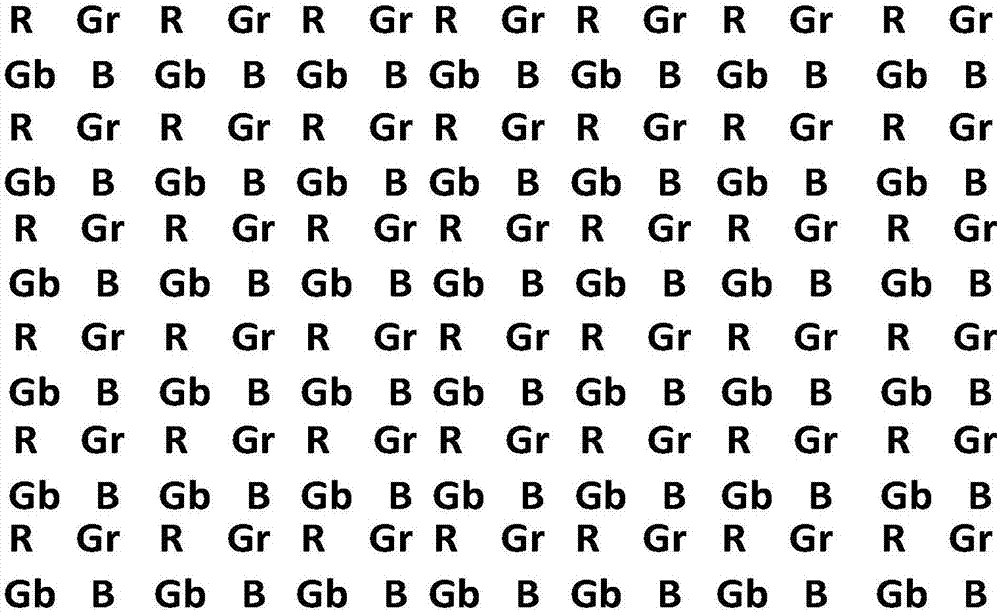

The invention discloses an image defective pixel detection method and apparatus. The method includes: defective pixel detection of an image with the bayer format is performed; a first gradient value, a second gradient value, and a third gradient value are calculated according to the position of a current pixel point and the corresponding relations between the current pixel point and surrounding pixel points; and whether the current pixel point is a suspected defective pixel is determined through comparison of the relations of the three gradient values. The defective pixels are searched based on the attribute of the defective pixels of the image, compared with the conventional defective pixel detection method, the hardware area is reduced, the pixel points of the image are checked one by one, more suspected defective pixels can be discovered, the suspected defective pixels are checked, and the efficiency of defective pixel detection is effectively improved.

Owner:FUZHOU ROCKCHIP SEMICON

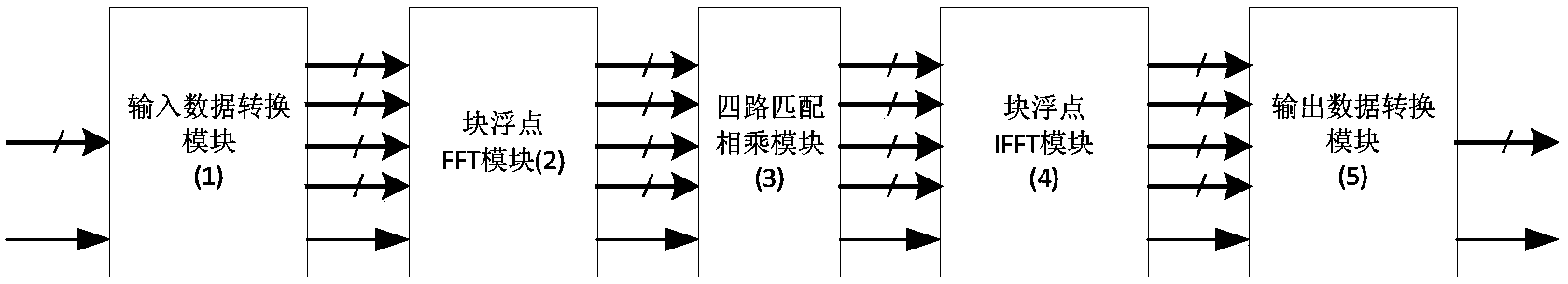

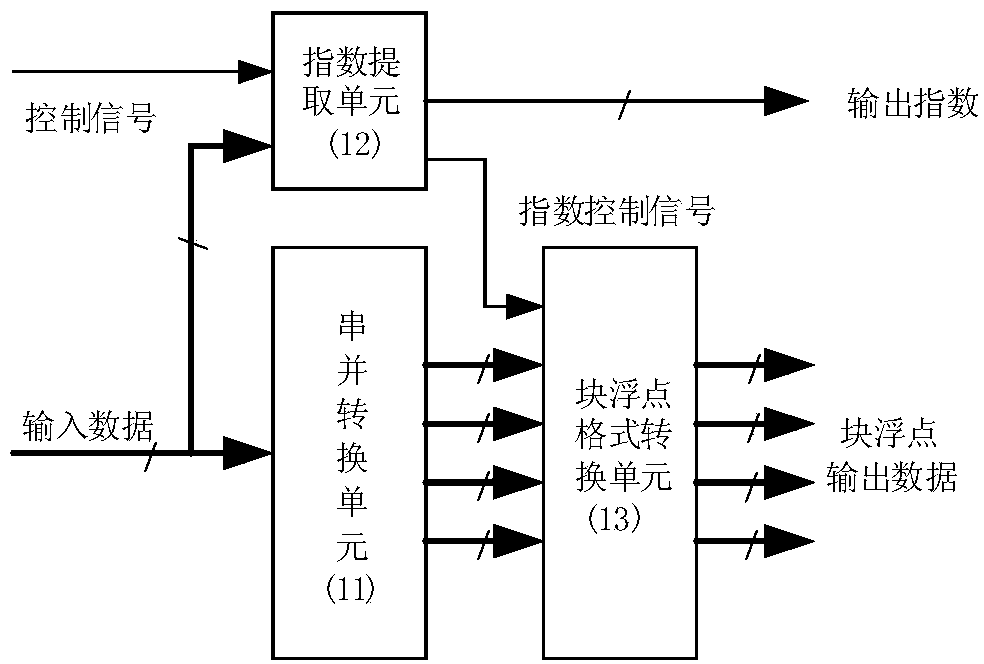

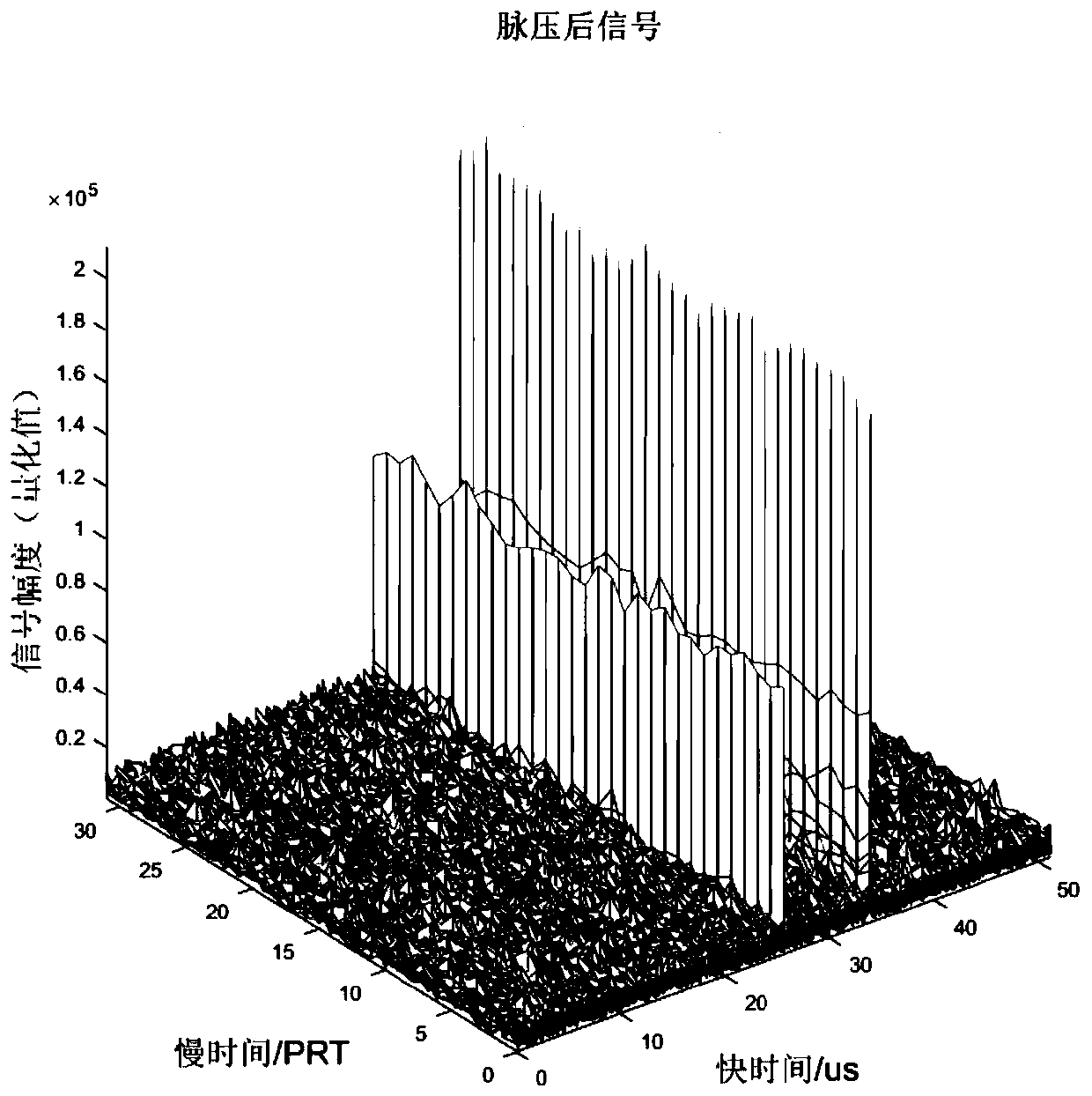

Real-time block floating point frequency domain four-route pulse compressor and pulse compression method thereof

InactiveCN103901405AGuaranteed dynamic rangeReduce hardware areaWave based measurement systemsData conversionTime delays

The invention discloses a real-time block floating point frequency domain four-route pulse compressor and a pulse compression method thereof, and the problems that the existing pulse compression technology is long in time delay and poor in reusability are solved. The pulse compressor comprises an input data conversion module (1), a block floating point FFT module (2), a four-route matching multiplying module (3), a block floating point IFFT module (4) and an output data conversion module (5). A route of input serial data are converted by the first module (1) to four-route parallel block floating point data which are supplied to the second module (2) for FFT, after FFT, the data are supplied to the third module (3) for four-route matching multiplication, multiplication results are subjected to IFFT by the fourth module (4), and after IFFT, the data are converted by the fifth module (5) to be a route of serial fixed-point data or a route of serial floating-point data which are used as output results of pulse compression. The real-time block floating point frequency domain four-route pulse compressor has the advantages of being short in time delay and high in real-time ability, and can be used for real-time processing of radar signals.

Owner:XIDIAN UNIV

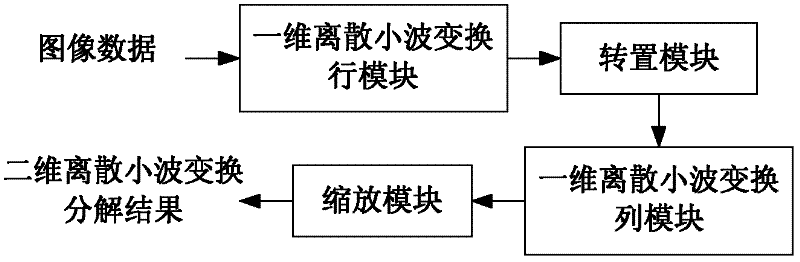

Hardware framework for two-dimensional discrete wavelet transformation

ActiveCN102572429AReduce the numberShorten the critical pathTelevision systemsDigital video signal modificationInternal memoryProduction line

The invention provides a hardware framework for two-dimensional discrete wavelet transformation, which comprises a one-dimensional discrete wavelet transformation row module, a transposition module, a one-dimensional discrete wavelet transformation column module and a zoom module which are respectively connected in serial, image data are connected with the input end of the one-dimensional discrete wavelet transformation row module, and the zoom module outputs two-dimensional discrete wavelet transformation decomposing results. The framework has the advantages of high performance and low storage, and is suitable for realization of discrete wavelet transformation in JPEG2000 static image coding standards. By adopting the folding technology and the production line technology, the hardware framework provided by the invention reduces the number of operation units, shortens a key path of a system, and improves system performances. The one-dimensional discrete wavelet transformation row module and the one-dimensional discrete wavelet transformation column module in the hardware framework are scheduled by adopting row-based data flow, so that required middle caches can be greatly reduced, and further the area of an internal memory and the hardware area of the two-dimensional discrete wavelet transformation framework are reduced.

Owner:SOUTHEAST UNIV

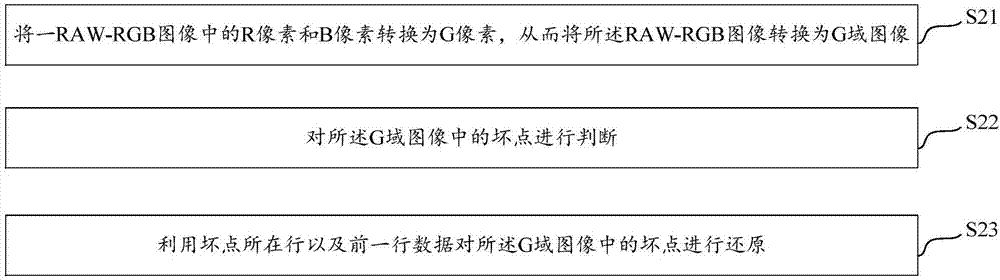

Method for eliminating dead pixels in RAW-RGB image

ActiveCN107248147AShorten the timeReduce hardware areaImage enhancementImage analysisRgb imageComputer vision

The invention provides a method for eliminating dead pixels in an RAW-RGB image, which comprises the steps of converting R-pixels and B-pixels in an RAW-RGB image into G-pixels so as to convert the RAW-RGB image into a G-domain image, performing dead pixel judgment in the G-domain image, and then carrying out dead pixel elimination and restoration in the G-domain image. In the above process, the method can be implemented by only utilizing data of the current line where a dead pixel is located and a previous line, so that the volume of data required in the current technical scheme is greatly reduced, the time of data processing is reduced, and the possibility of real-time processing is increased. Meanwhile, the required hardware area is reduced, and the consumption of resources is lowered.

Owner:思特威(上海)电子科技股份有限公司

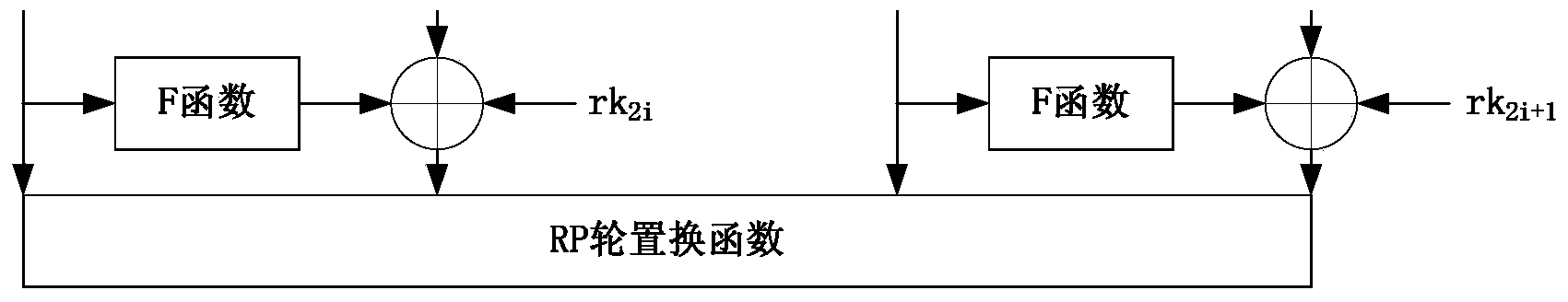

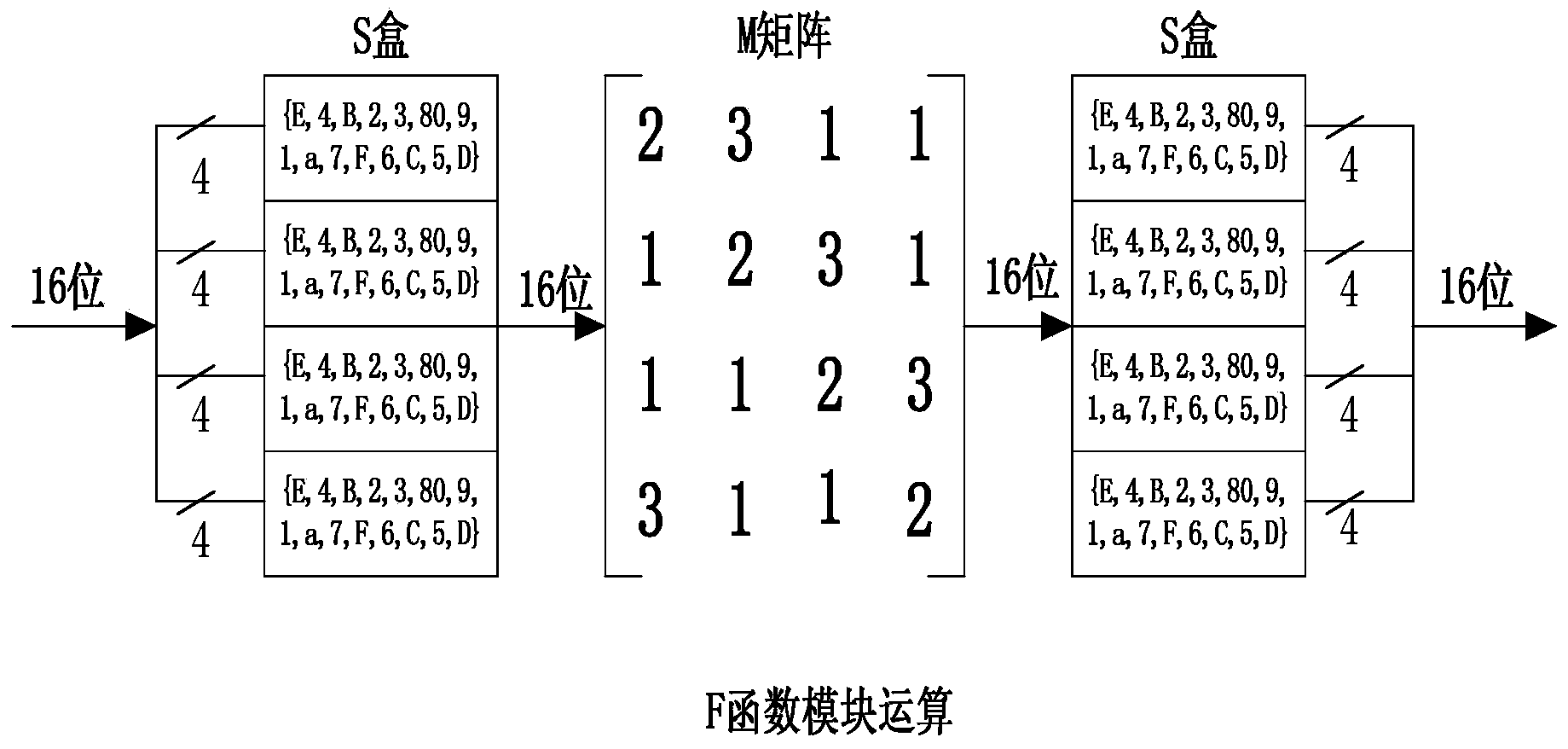

Piccolo encryption algorithm hardware achieving method

InactiveCN103731257AReduce hardware areaReduce the number of occupancyEncryption apparatus with shift registers/memoriesCiphertextRound function

The invention discloses a Piccolo encryption algorithm hardware achieving method. The Piccolo encryption algorithm hardware can be achieved once by utilizing identical round operation in a repeated calling mode. The original r-1 round repeated calling is directly converted into r wheel repeated calling. Meanwhile, an RP-1 round displacement function is added on the r round circulation operation, and operation is conducted once to enable an output cipher to be correct. By means of the method, an original algorithm is not required to achieve again in the last rth round, the former repeated round function module can be directly multiplexed, and users only need to add the relatively simple RP-1 in the end. By means of the method, modules in the Piccolo encryption algorithm to be highly multiplexed, hardware achieving area is effectively saved, and meanwhile the encryption speed is increased.

Owner:HENGYANG NORMAL UNIV

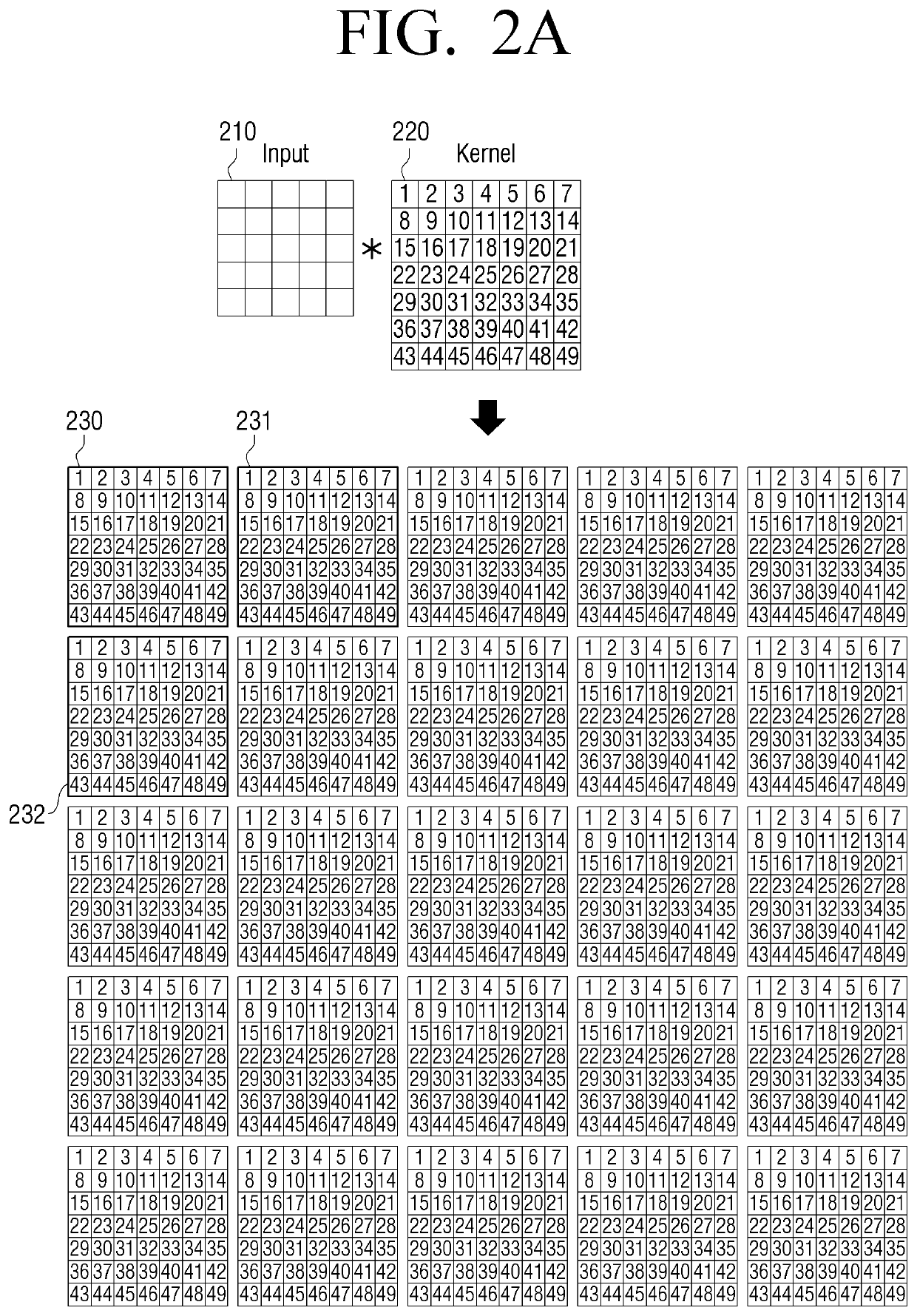

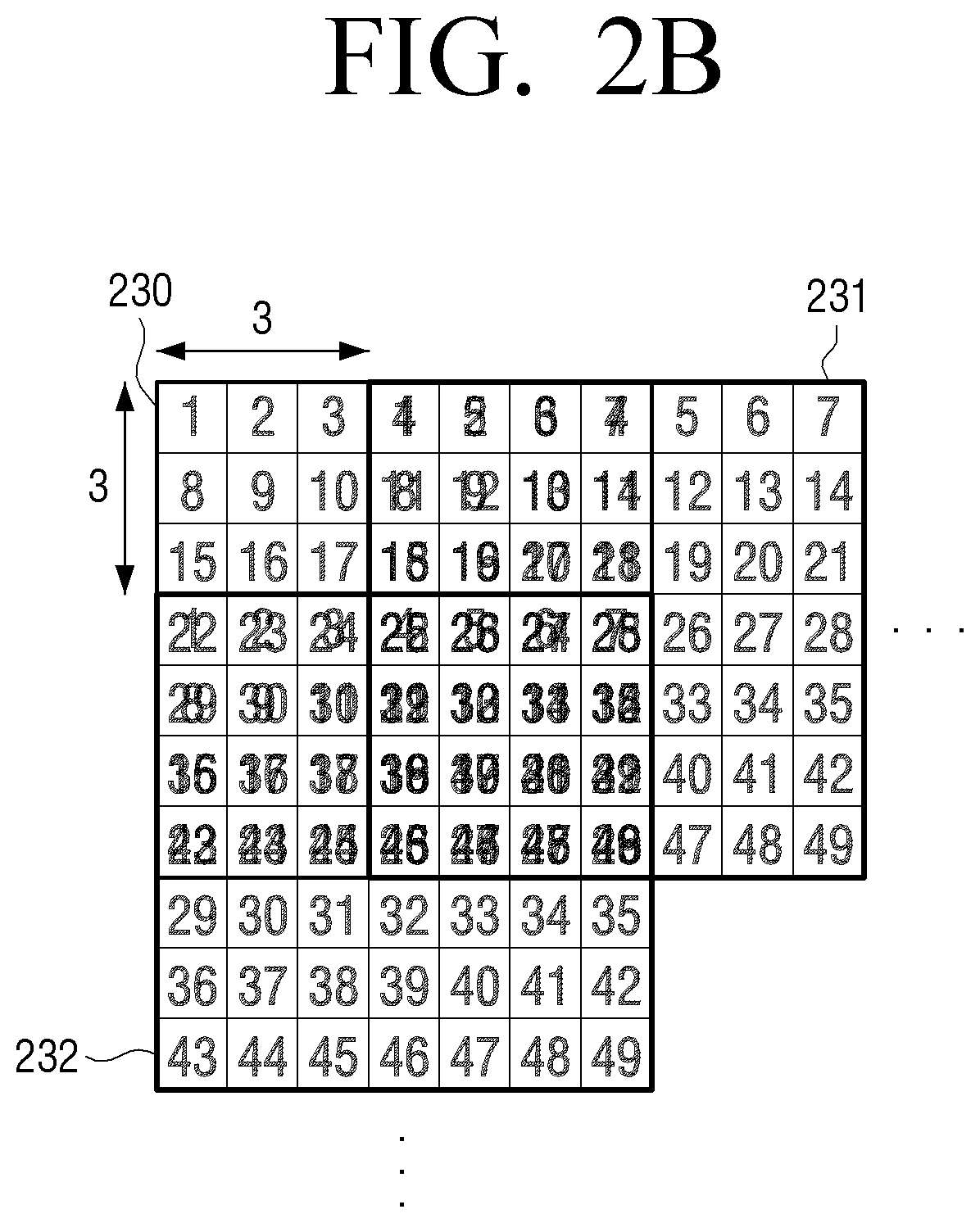

Electronic apparatus and control method thereof

PendingUS20190370692A1Eliminates additional hardwareReduce hardware areaKernel methodsPhysical realisationParallel computingConvolution

An electronic apparatus for executing artificial intelligence algorithm is provided. The electronic apparatus includes a memory which stores input data and a plurality of second kernel data obtained from first kernel data, and a processor which obtains upscaled data in which at least a portion of the input data is upscaled by the first kernel data. The data is upscaled by performing a convolution operation on each of the plurality of second kernel data with the input data. Each of the plurality of second kernel data includes a different first kernel element from among a plurality of first kernel elements in the first kernel data.

Owner:SAMSUNG ELECTRONICS CO LTD

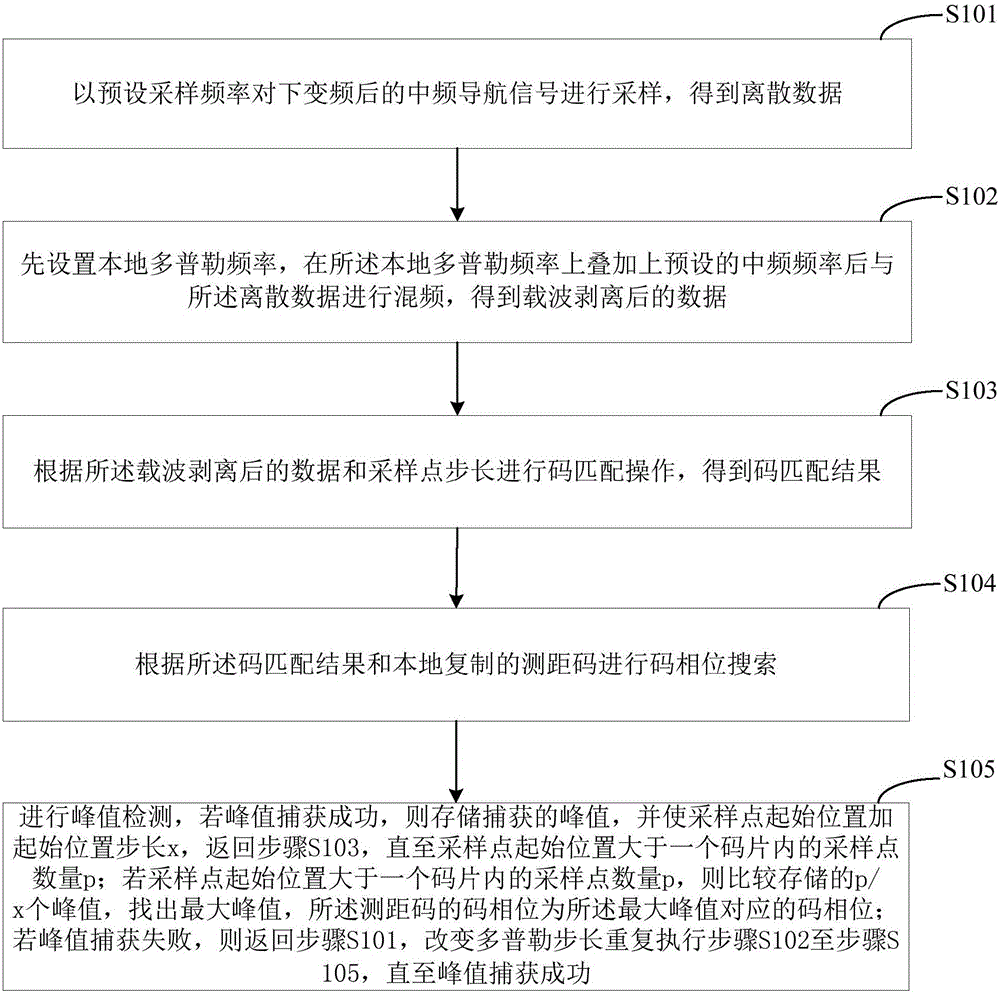

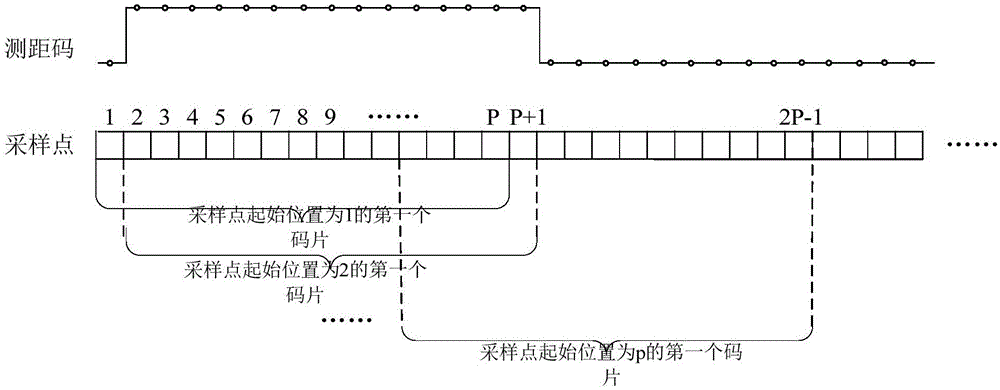

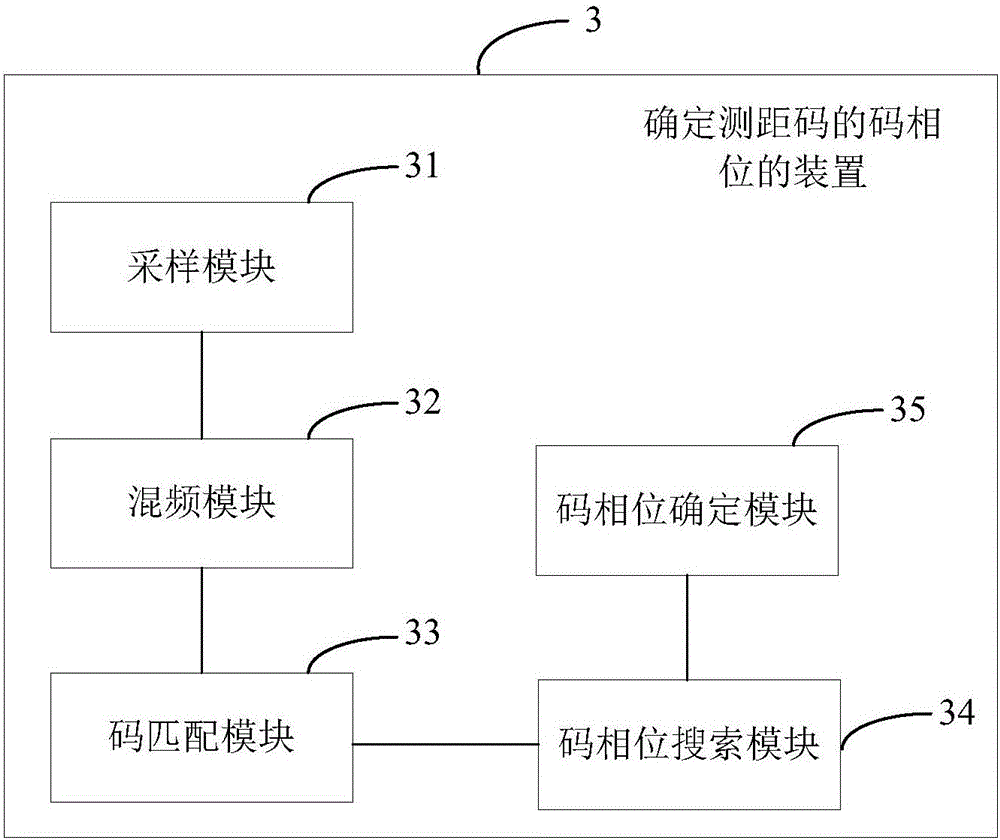

Method and device for determining code phase of ranging code, and user terminal

ActiveCN106656257AReduce hardware areaHigh precisionSatellite radio beaconingTransmissionCarrier signalPeak value

The invention belongs to the technical field of communication and provides a method and device for determining a code phase of a ranging code, and a user terminal. The method comprises the steps of SA, obtaining discrete data; SB, obtaining carrier stripped data; SC, carrying out code matching operation according to the carrier stripped data and an initial position of sampling points, thereby obtaining a code matching result; SD, carrying out code phase search according to the code matching result and the locally copied ranging code; and SE, carrying out peak detection, if peaks are captured successfully, storing the captured peaks, adding the initial position of the sampling points and the step size x of the initial position, returning to the SC until the initial position of the sampling points is greater than the number p of the sampling points in a chip, and if the initial position of the sampling points is greater than the p, comparing p / x stored peaks, and finding the maximum peak, wherein the code phase of the ranging code is the code phase corresponding to the maximum peak. Through application of the method, the device and the user terminal, the code phase precision of the ranging code can be increased, and an area of a correlator is not increased.

Owner:ARKMICRO TECH

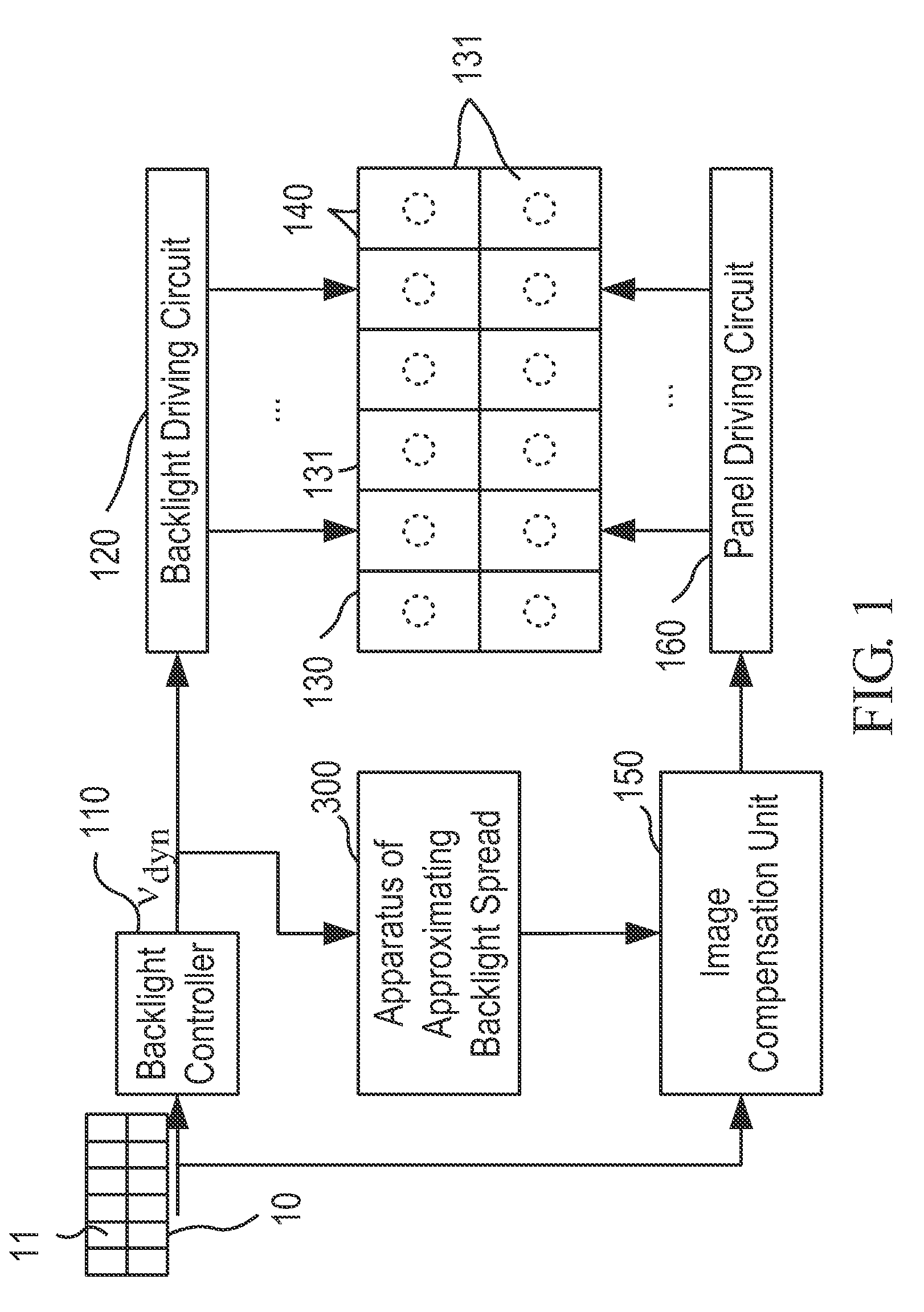

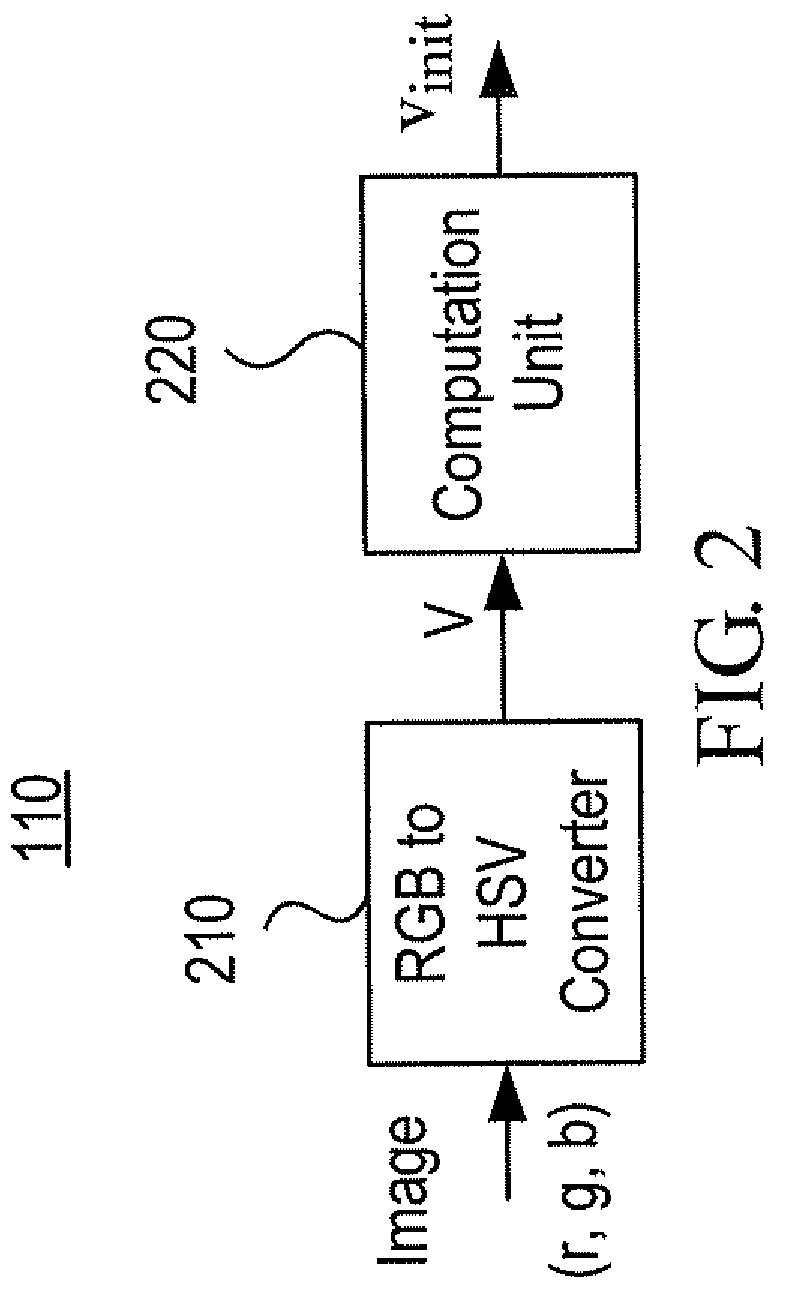

Method and apparatus of compensating image in a backlight local dimming system

ActiveUS8643593B2Reduce areaReduce hardware areaCathode-ray tube indicatorsIlluminated signsControl signalComputer science

An apparatus compensates image in a backlight local dimming system for estimating pixels of the image after backlight spreading of a plurality of backlight sources in the backlight local dimming system. The apparatus includes a block dimming value decision unit, a quality / power-saving priority decision unit, a temporal filter, a backlight spread approximation unit, and an image compensation unit. The block dimming value decision unit calculates an average value, a maximum value and a initial value for each image block. The quality / power-saving priority decision unit generates a backlight control signal based on the average value, the initial value, and two thresholds. The temporal filter adaptively generates a backlight pulse width modulation signal based on the backlight control signal. The backlight spread approximation unit generates a backlight spread image based on the backlight pulse width modulation signal. The image compensation unit compensates the image based on the backlight spread image.

Owner:ORISE TECH CO LTD

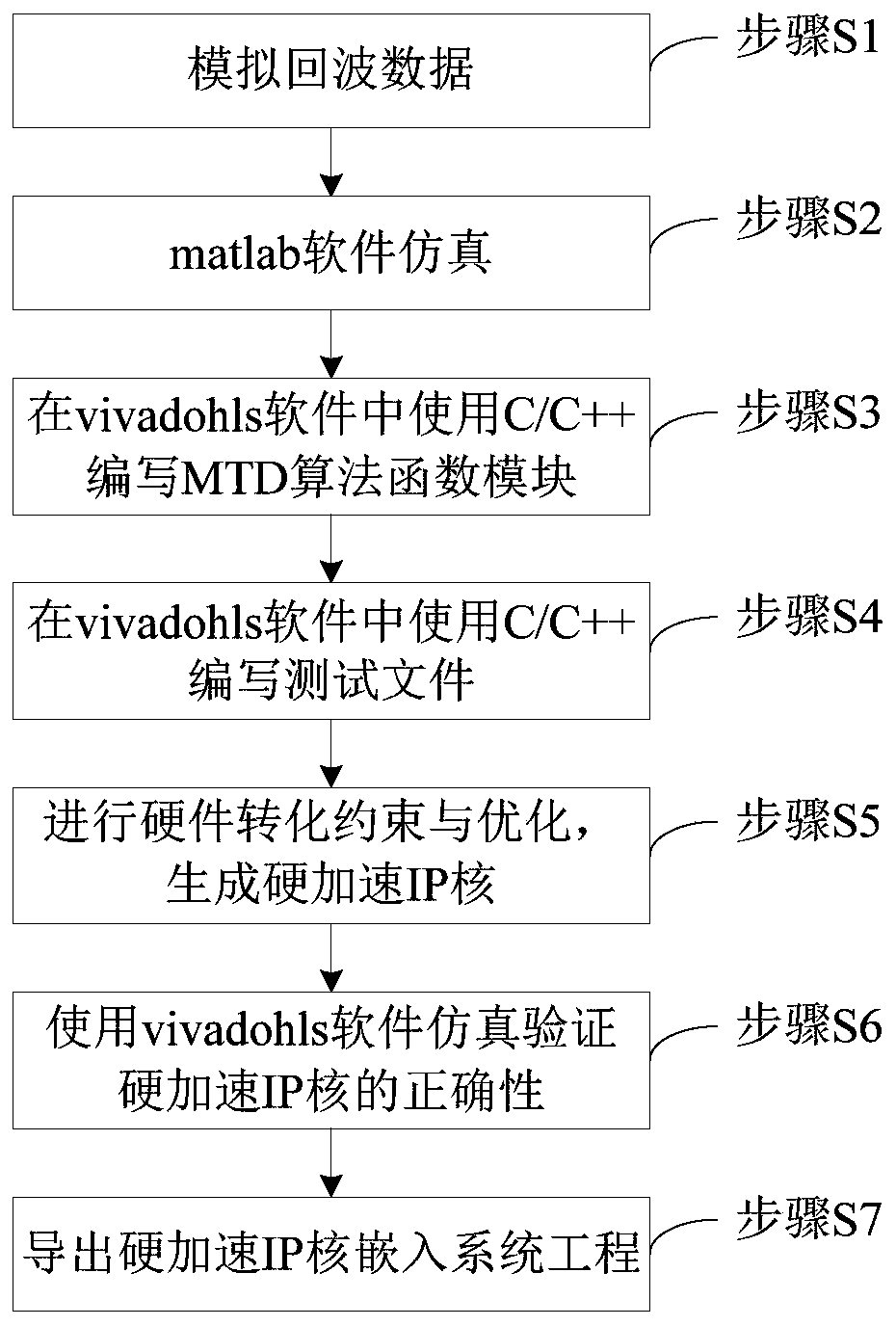

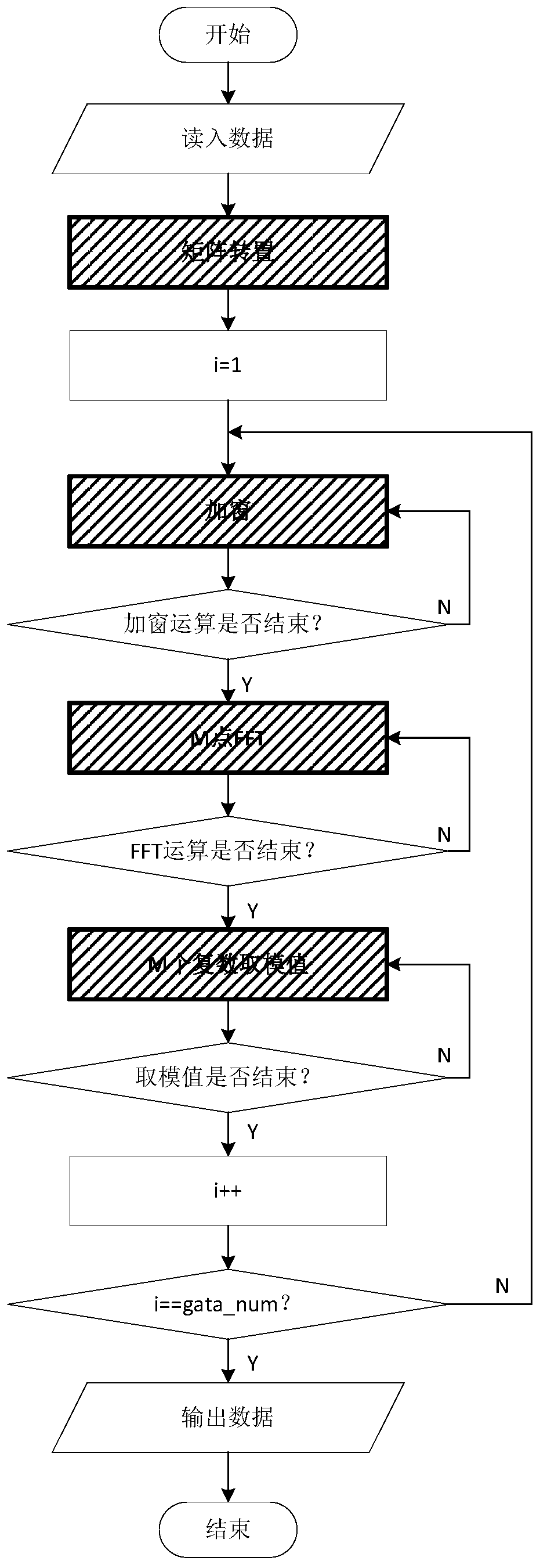

Method for realizing moving target detection acceleration

PendingCN111337896AReduce areaImprove development efficiencyWave based measurement systemsDesign optimisation/simulationComputer engineeringSoftware

The invention discloses a method for realizing moving target detection acceleration. The method comprises the steps of writing an MTD moving target detection algorithm by using C / C + + in vivalohls software; packaging the top layer into a function module; writing a test file by using C / C + + in vivalohls software; comparing the output data of the test file with the simulation output data of matlabsoftware; discriminating degree of matching, verifying correctness of a function module, aDDITION OF CONSTRAINTS AND OPTIMIZATION STRATEGY, hardware conversion is carried out to generate a hard acceleration IP core which can be synthesized by the FPGA; and automatically generating an excitation file according to the test file by using vivadohls software, automatically calling a waveform simulation tool to automatically start simulation, verifying the correctness of the hard acceleration IP core through a simulation waveform, and finally exporting a hard acceleration IP core embedded system project. According to the method, the development efficiency is improved, the project period is shortened, the hardware area is saved, and the calculation precision and the communication rate are improved.

Owner:SHANGHAI RADIO EQUIP RES INST

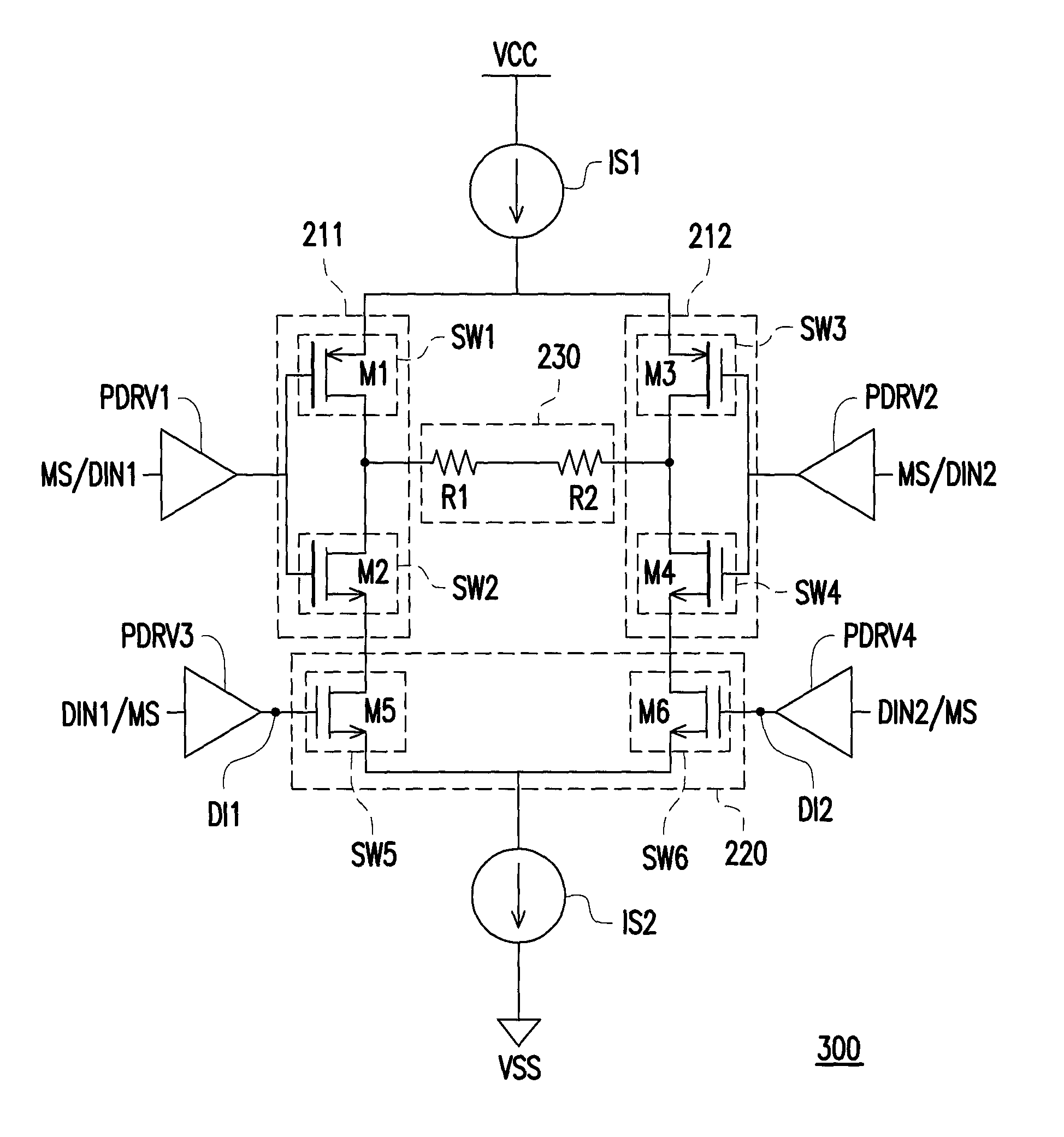

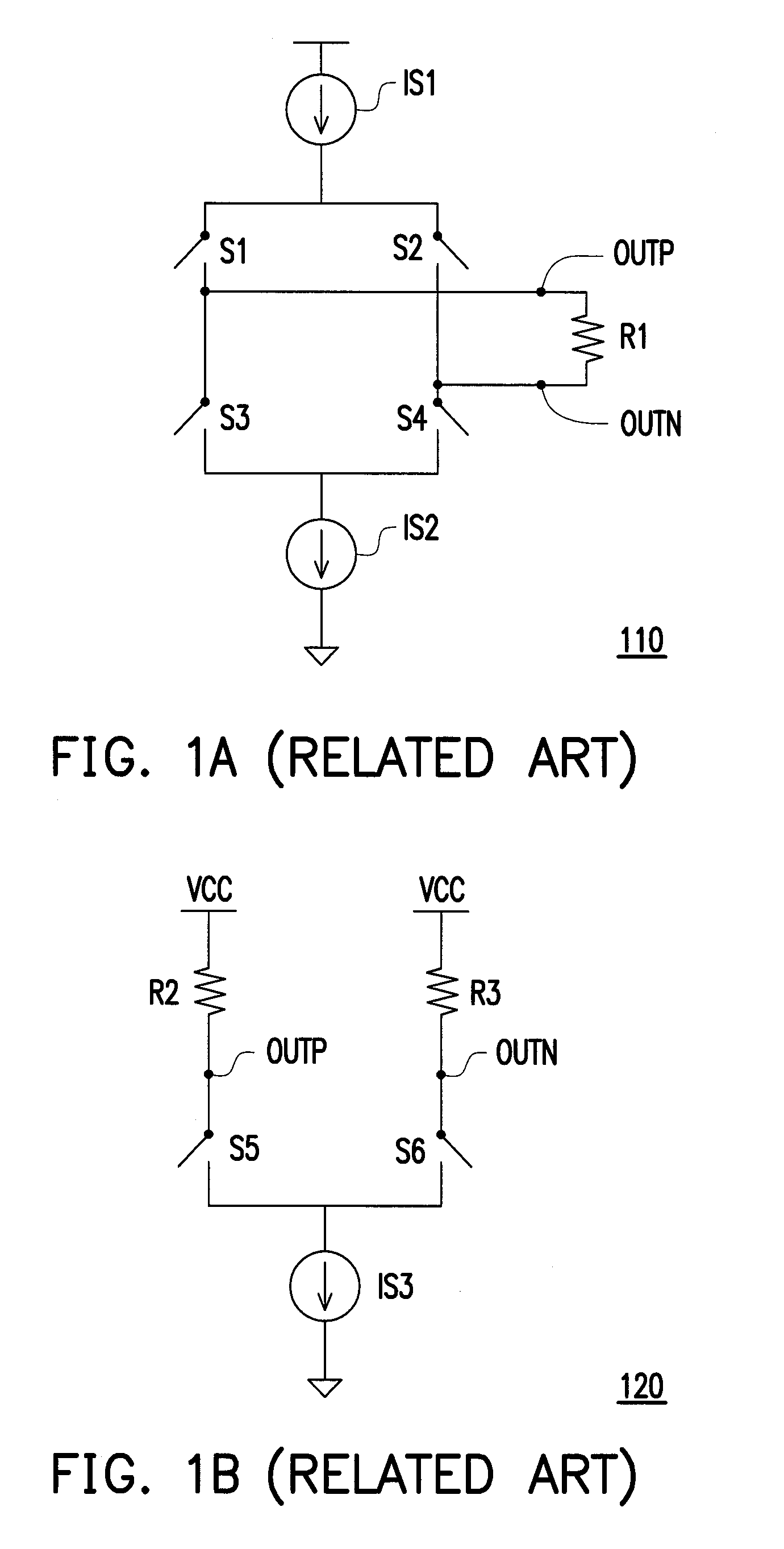

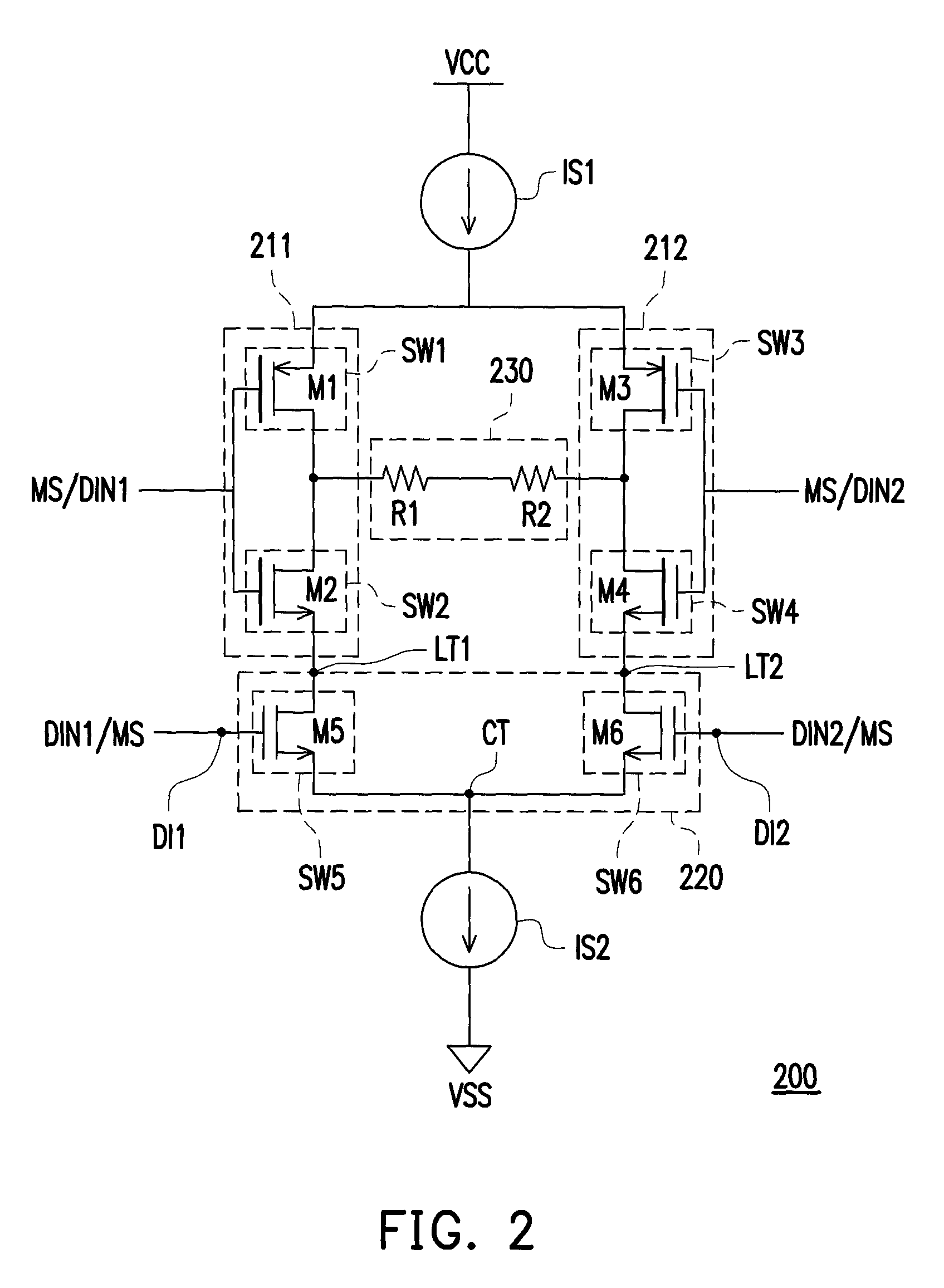

Dual mode serial transmission apparatus and method for switching mode thereof

ActiveUS9515699B2Reduce hardware areaWith balanceModulated-carrier systemsCross-talk reductionDual modeEngineering

A dual mode serial transmission apparatus and method for switching a mode thereof are provided. The dual mode serial transmission apparatus includes a first and second current sources, a first and second inverting circuits, a differential pair and a resistor string. The first inverting circuit receives a mode selecting signal or a first data transmission signal, the second inverting circuit receives the mode selecting signal or a second data transmission signal. First and second load terminals of the differential pair are respectively coupled to the first and second inverting circuits. A common terminal of the differential pair is coupled to the second current source. First and second differential input terminals receive the mode selecting signal or respectively receive the first and second data transmission signals. The resistor string is coupled in series between output terminals of the first and second inverting circuits.

Owner:NOVATEK MICROELECTRONICS CORP

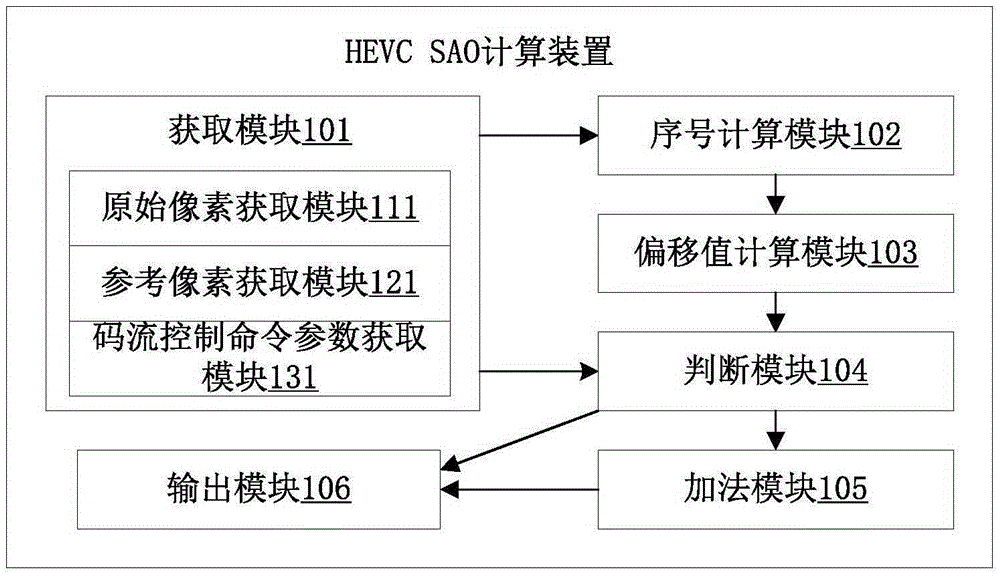

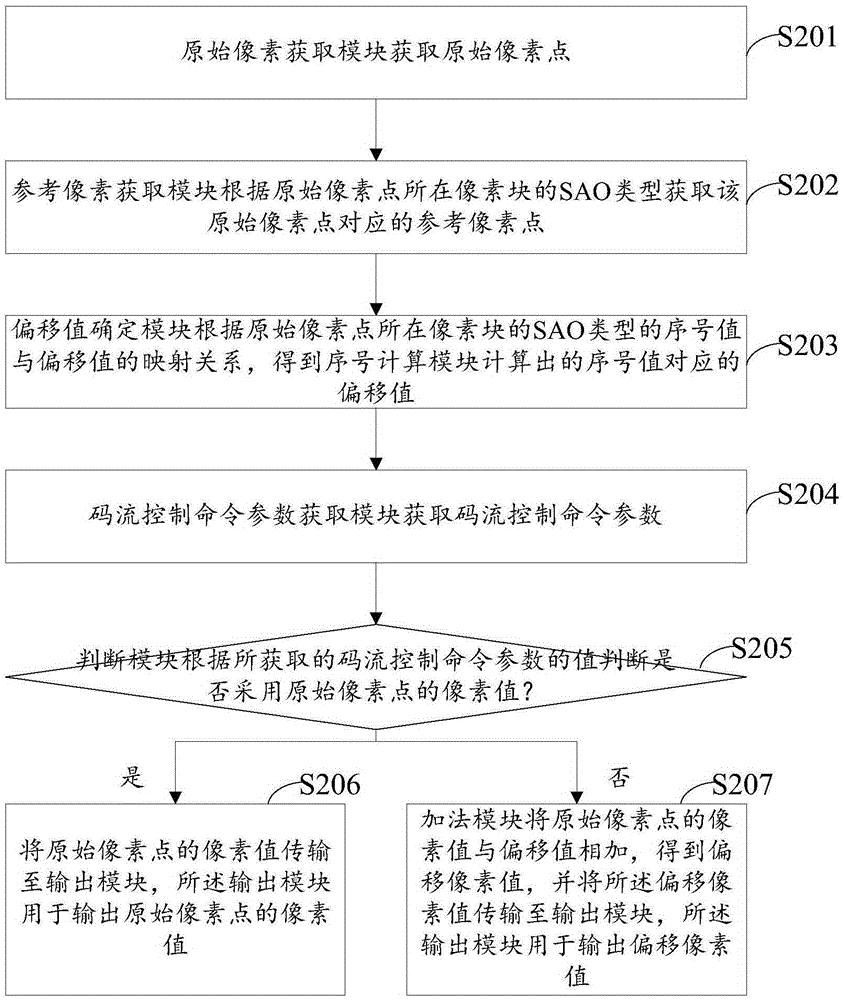

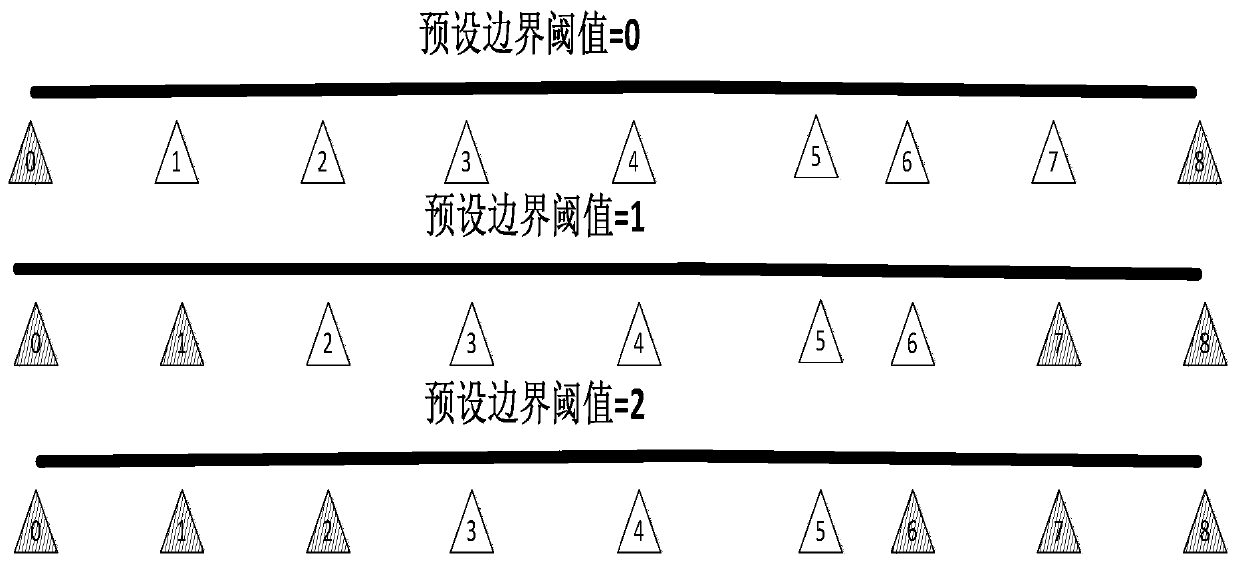

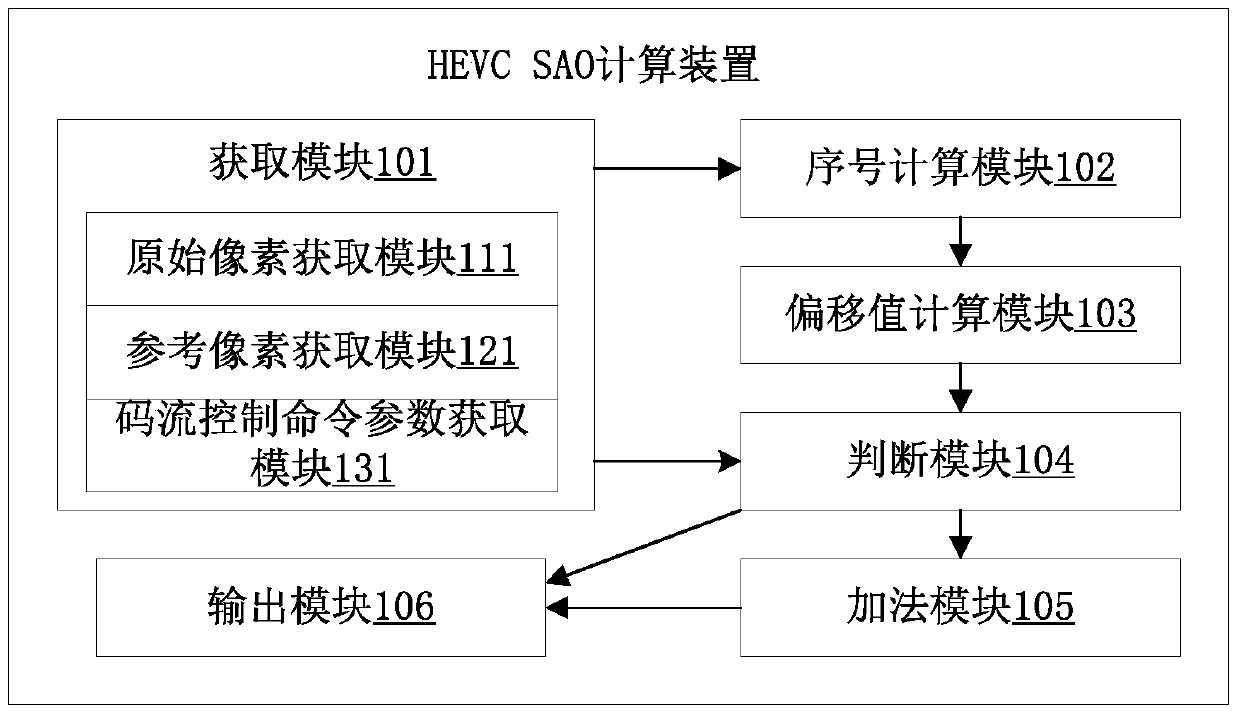

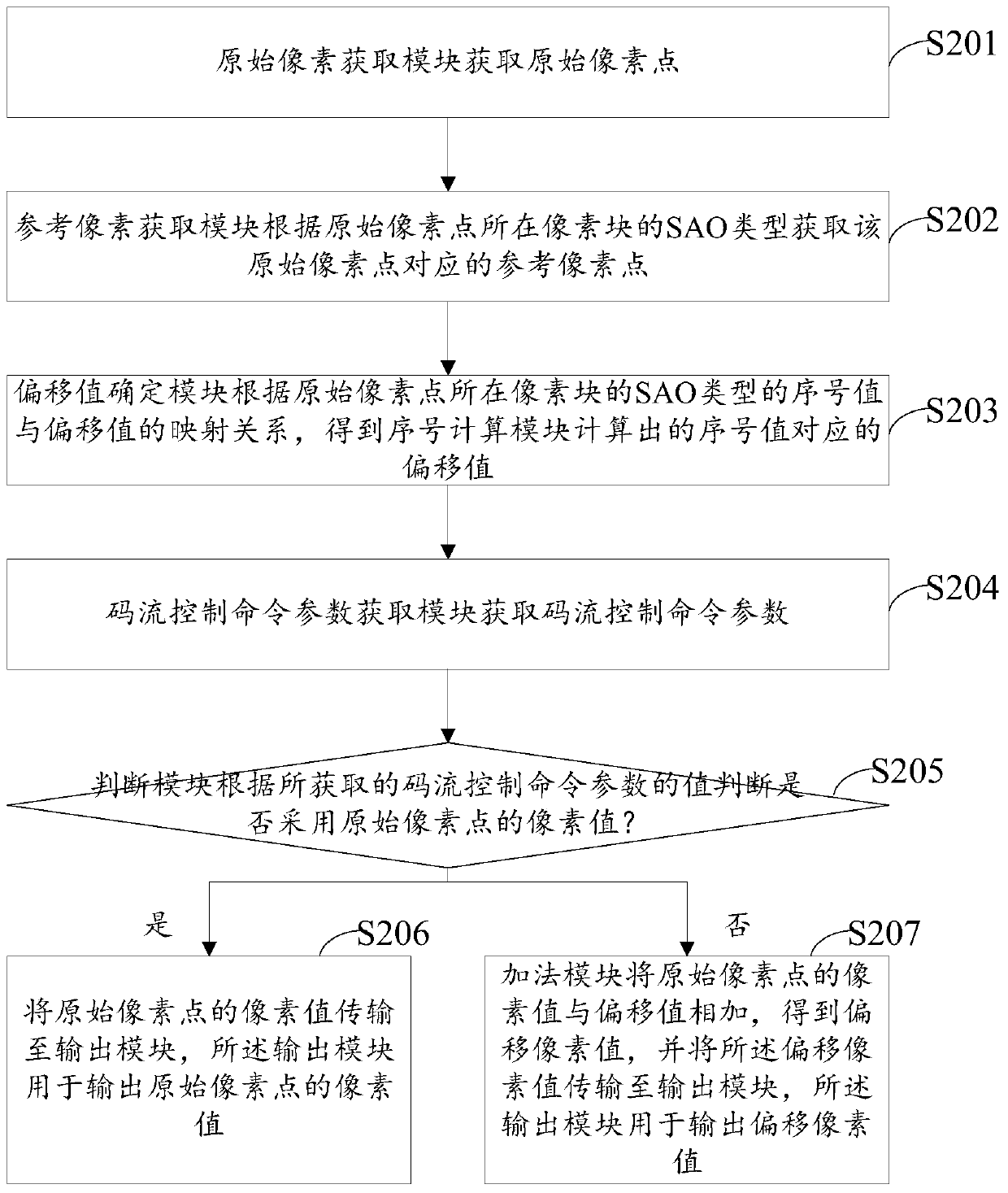

HEVC SAO calculation method and HEVC SAO calculation device

ActiveCN106817583ASimplify the decoding calculation process stepsReduce hardware areaDigital video signal modificationComputation processCalculation methods

The invention discloses an HEVC (High Efficiency Video Coding) SAO (Sample Adaptive Offset) calculation method and an HEVC SAO calculation device. The device comprises an acquisition module, a serial number calculation module, an offset value determination module, a judgment module, an addition module, and an output module. First, offset values are calculated according to original pixels acquired by the acquisition module and reference pixels corresponding to the original pixel values. Then, the judgment module judges the pixel values or offset pixel values of the original pixels output and adopted finally according to the values of code flow control command parameters acquired. Thus, SAO decoding is completed by means of two-level pipelining. The speed of SAO decoding computation is increased. The steps of the SAO decoding computation process are greatly simplified. The hardware area of an SAO computation device is reduced in hardware circuit design, and therefore, the hardware cost is lowered. Therefore, the method and the device have a broad market prospect in the field of computer chips.

Owner:FUZHOU ROCKCHIP SEMICON

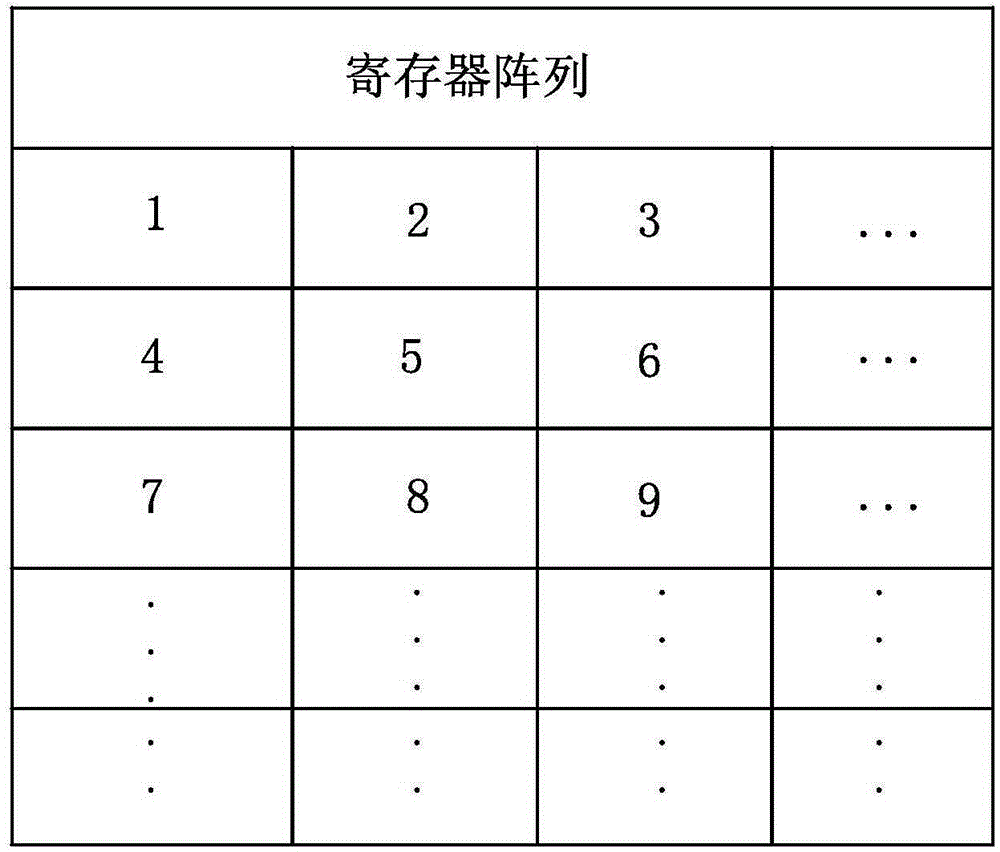

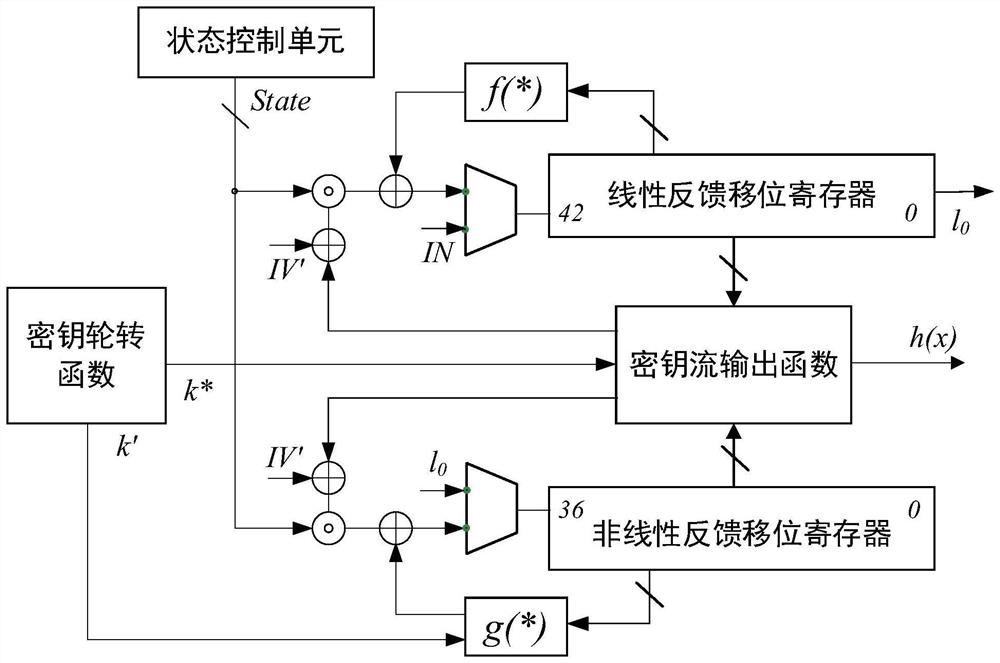

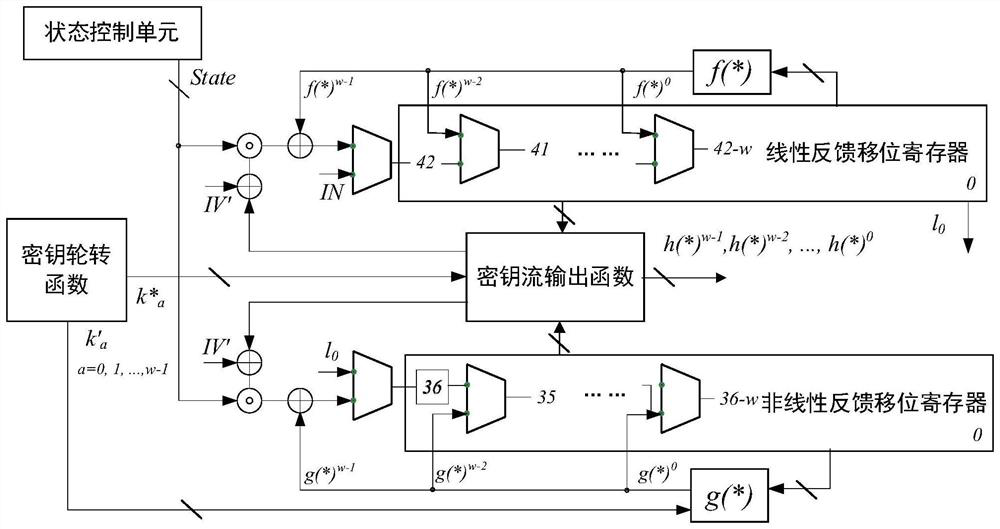

Hardware implementation device and method for Fruit-80 ultra-lightweight encryption algorithm

ActiveCN113612609AMeeting Compact Endpoint Security NeedsMeet security needsKey distribution for secure communicationAlgorithmNonlinear feedback shift register

The invention discloses a hardware implementation device and method for a Fruit-80 ultra-lightweight encryption algorithm. The hardware implementation device comprises a key rotation function, a nonlinear feedback shift register, a linear feedback shift register, a key stream output function and a state control unit. The key rotation function is used for providing two key correlation bits; each of the nonlinear feedback shift register and the linear feedback shift register comprises a nonlinear feedback function and a linear feedback function; the key stream output function extracts the internal states of the nonlinear feedback shift register and the linear feedback shift register in each round, and generates a key stream for encryption; and the state control unit is used for coordinating the state updating of the nonlinear feedback shift register and the linear feedback shift register in the password stage of the device. According to the hardware implementation device and method disclosed by the invention, the hardware resource occupation of the Fruit-80 ultra-lightweight sequence cipher can be reduced, and the throughput rate of the Fruit-80 ultra-lightweight sequence cipher can be improved to the greatest extent.

Owner:SHANDONG UNIV

Layered decoding architecture with reduced number of hardware buffers for LDPC codes

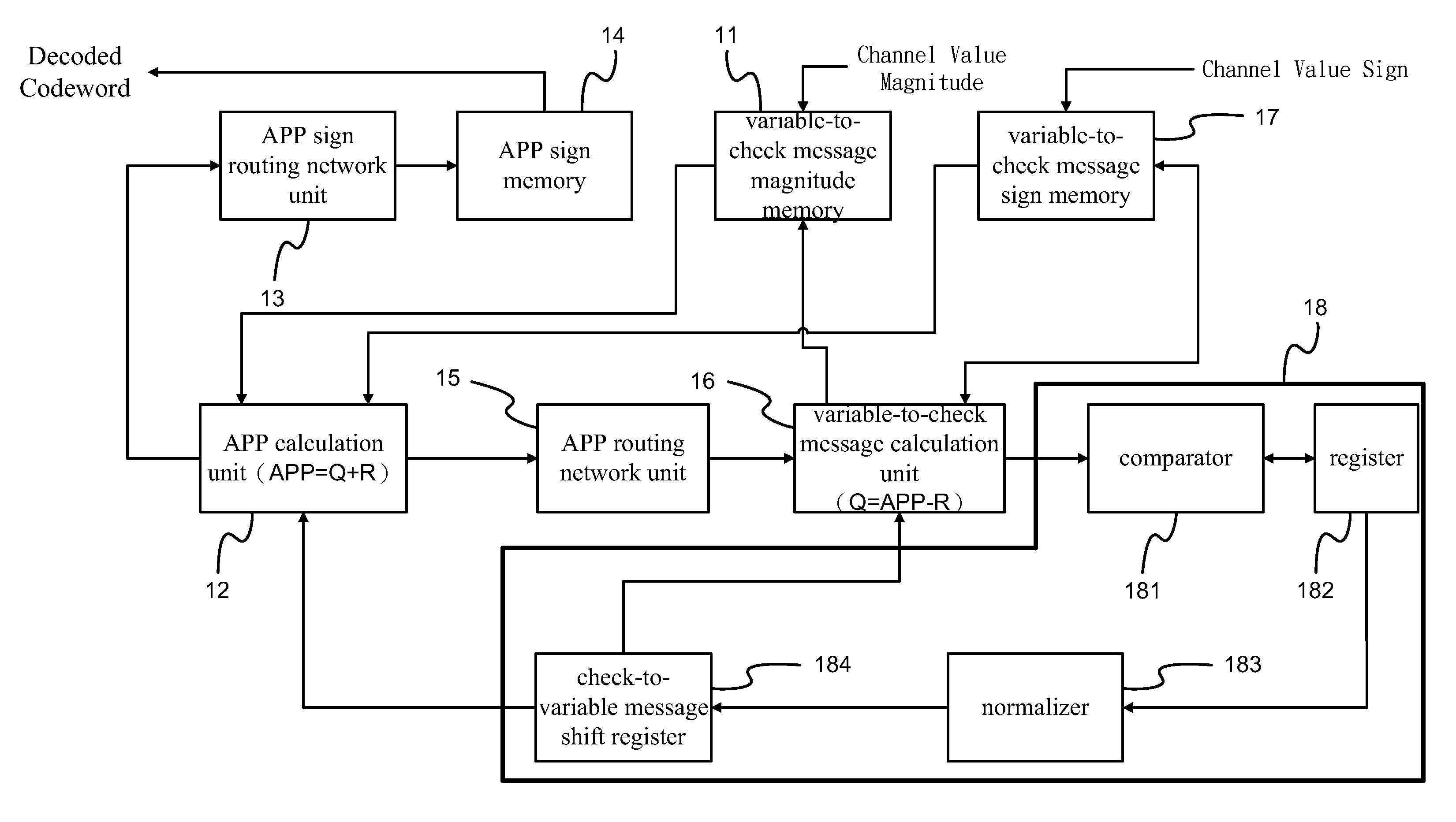

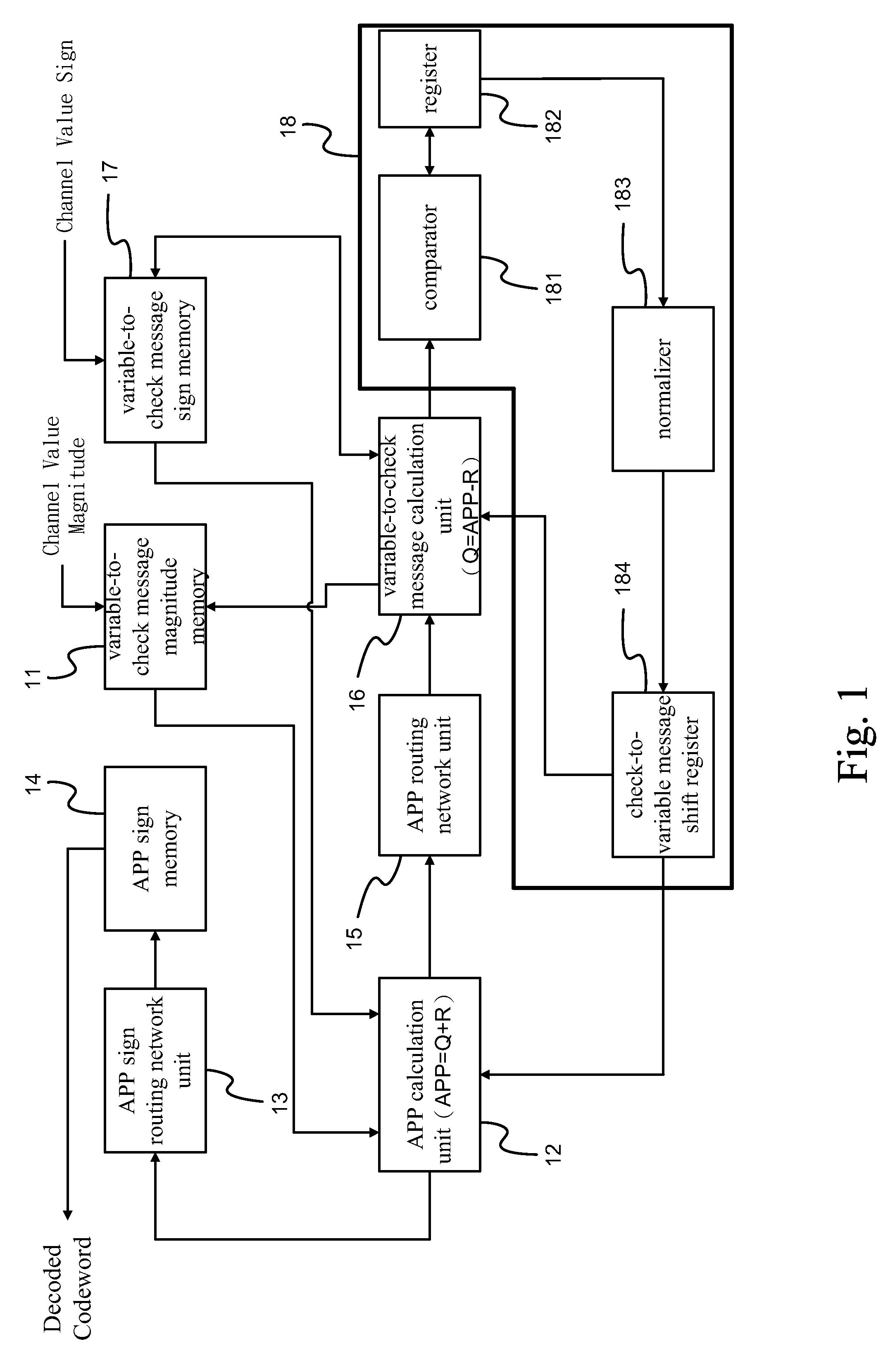

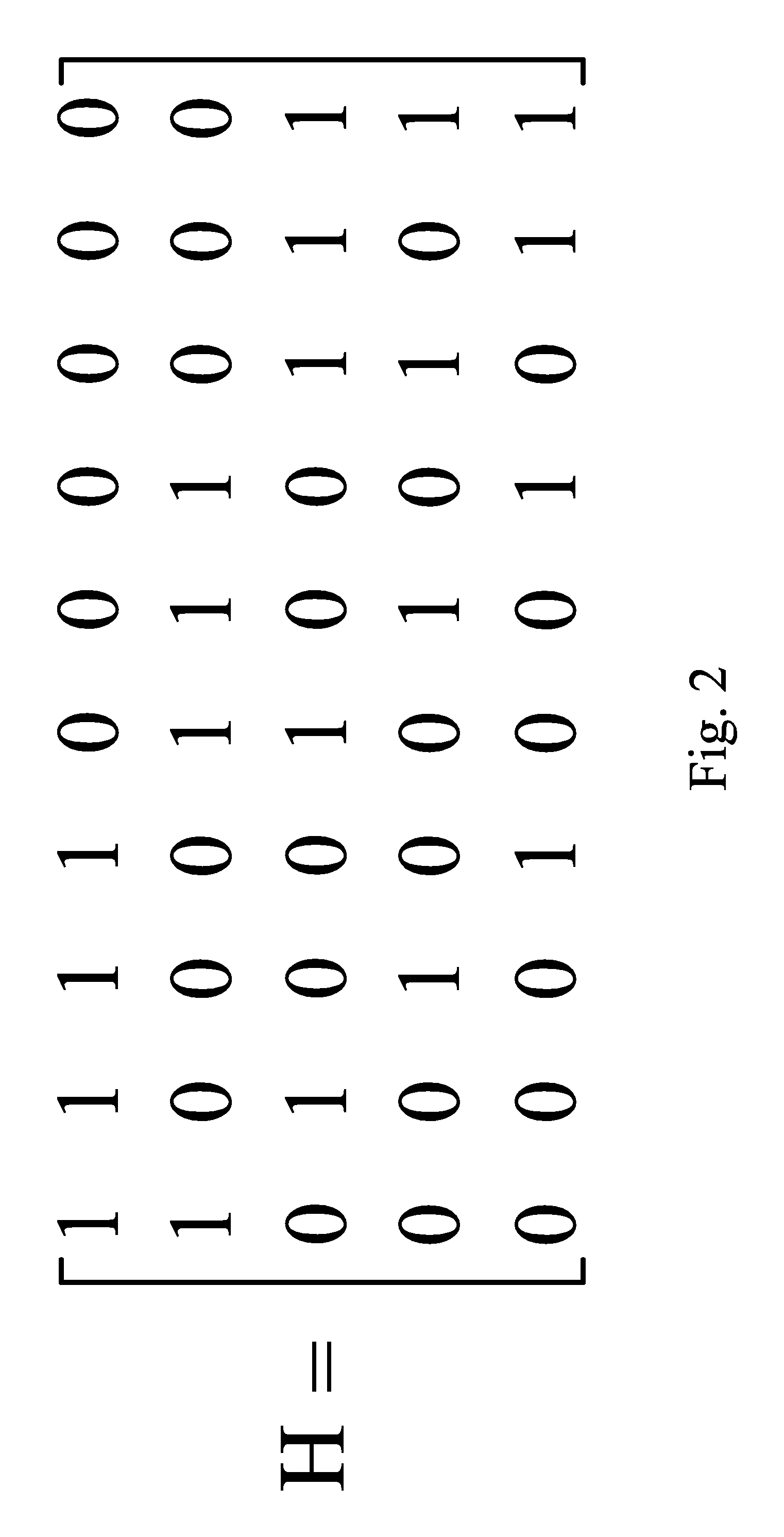

ActiveUS9048872B2Reduce hardware areaImprove hardware utilizationError correction/detection using multiple parity bitsCode conversionShift registerProcessor register

A layered decoding architecture with a reduced number of hardware buffers for low-density parity-check (LDPC) decoding by storing a variable-to-check message. When a check node begins a new operation, a variable-to-check message (Q) is added to a check-to-variable message (R) obtained in previous check-node operation to obtain an updated APP value. Then, the R value for the check node in the layer being processed is deducted from the APP value to obtain a variable-to-check message (Q). This variable-to-check message is stored in the memory and inserted into the check node equation to obtain a check-to-variable message. Finally the check-to-variable message obtained in this operation is stored to the check-to-variable message shift register to complete the updating operation for the check node and the variable node for the layer being processed. Improved hardware utilization and fewer buffers, thus achieving a smaller hardware area while retaining the converge speed, is obtained.

Owner:NATIONAL TSING HUA UNIVERSITY

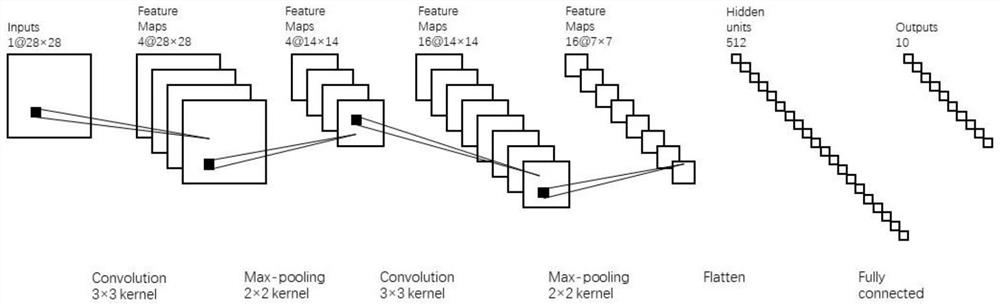

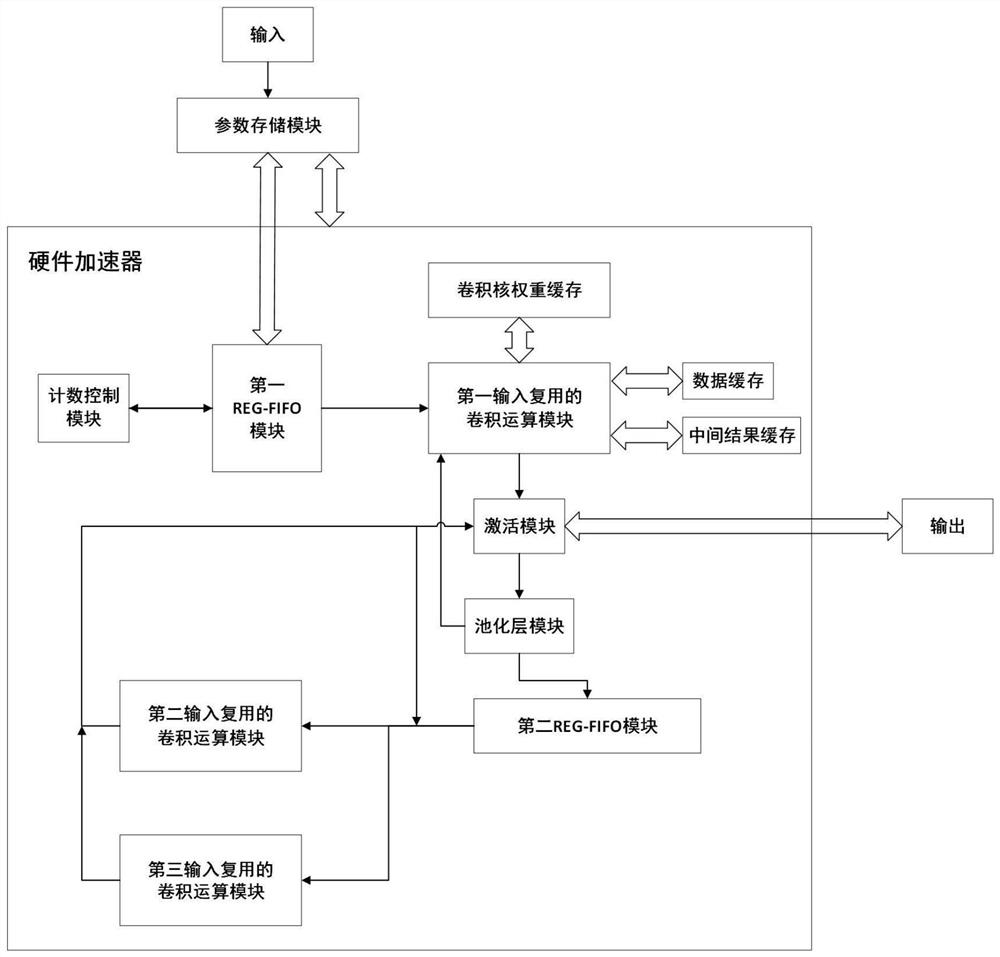

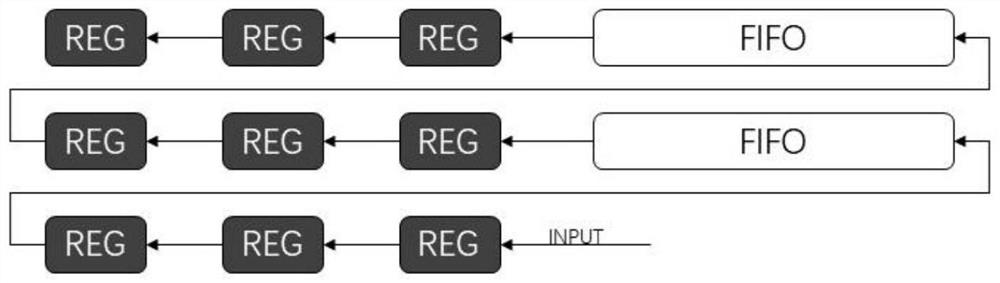

Hardware accelerator of convolutional neural network based on parallel multiplexing and parallel multiplexing method

PendingCN114781629AImprove reusabilityFast operationNeural architecturesPhysical realisationComputer hardwareMultiplexing

The invention discloses a hardware accelerator of a convolutional neural network based on parallel multiplexing and a parallel multiplexing method. The hardware accelerator comprises a parameter storage module, an REG-FIFO module, a counting control module, an input multiplexing convolution operation module, an activation module and a pooling layer module. Wherein the parameter storage module is responsible for pre-storing picture parameters and trained weight parameters; the REG-FIFO module is responsible for generating an input matrix matched with the convolution kernel and reading matrix data; the counting control module is responsible for clock cycle counting and controls input and output of the REG-FIFO module according to the clock cycle counting. The input multiplexing convolution operation module is responsible for convolution operation of a convolution layer and a full connection layer; the activation module is responsible for output activation operation of the convolution layer and the full connection layer; and the pooling layer module is responsible for pooling operation output by the activated convolutional layer. The invention aims to realize convolutional neural network calculation with high operation parallelism, high data multiplexing and low hardware complexity.

Owner:HEFEI UNIV OF TECH

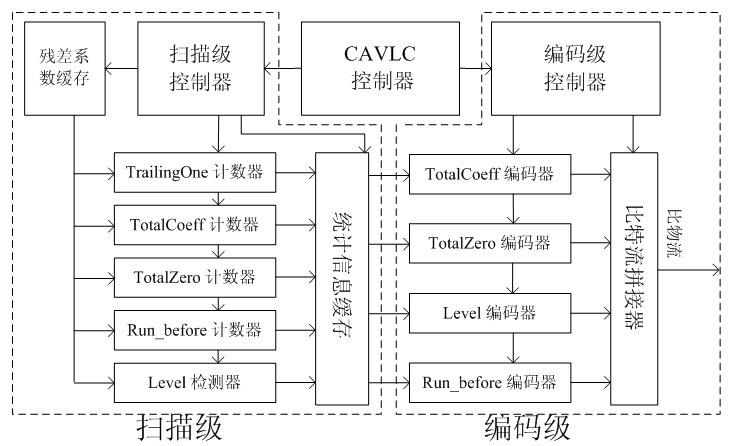

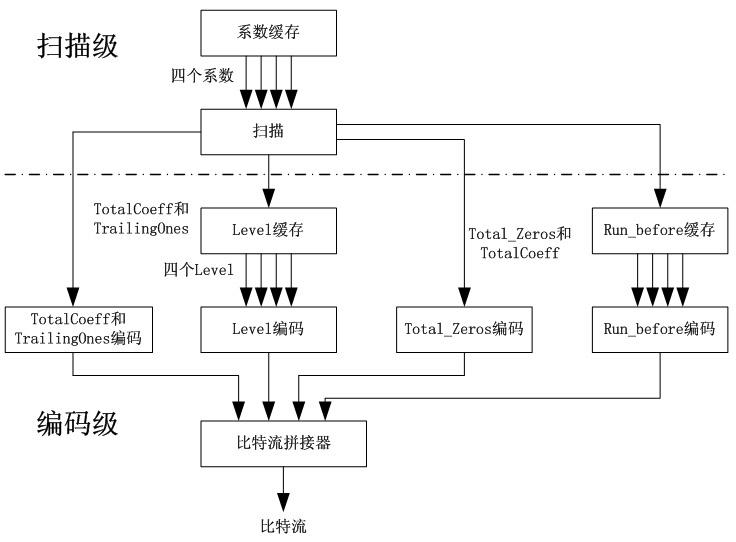

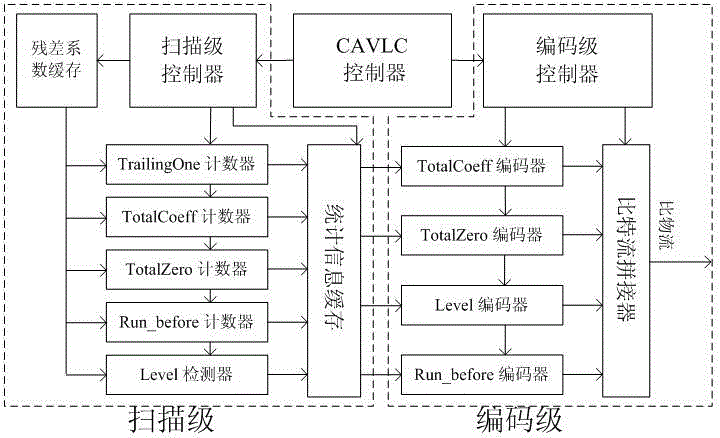

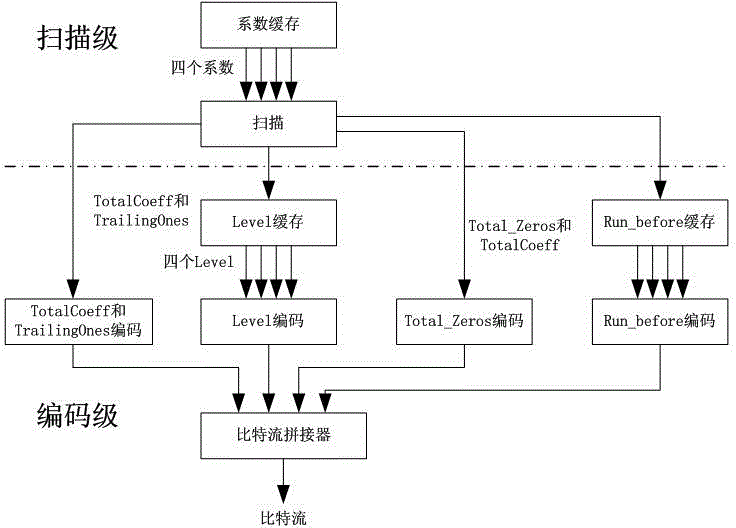

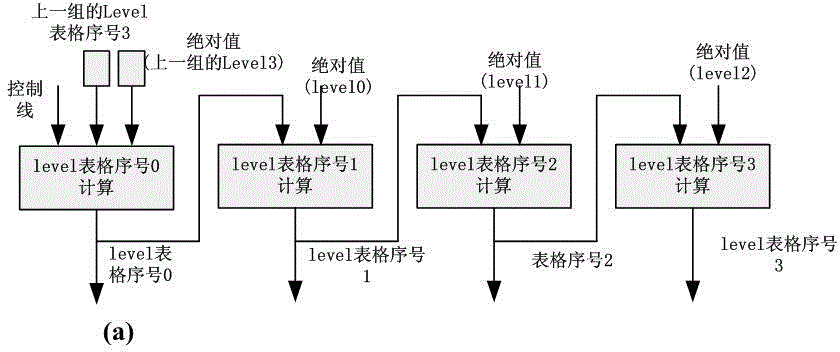

CAVLC (context-adaptive variable-length coding) coder for four-channel parallel coding

InactiveCN102325253AImprove throughputReduce hardware areaTelevision systemsDigital video signal modificationParallel encodingVideo encoding

The invention belongs to the technical field of video coding, in particular to a CAVLC (context-adaptive variable-length coding) coder for four-channel parallel coding. The CAVLC coder for four-channel parallel coding adopts a double-stage pipeline structure for scanning stage and coding stage parallel processing, and a scanning stage can scan four coefficients at a time, thus greatly shortening the time of scanning a 4 multiplied by 4 block. Likewise, a four-level and Run_before parallel coding mode is utilized to shorten the time needed by a coding stage. The time needed by the coding stageis carefully designed, so that the time consumed by the coding stage can be equal to the time consumed by the scanning stage. Consequently, the whole double-stage pipeline for CAVLC can obtain the maximum throughput rate, thus greatly reducing the clock number of finishing the coding of a macroblock.

Owner:FUDAN UNIV

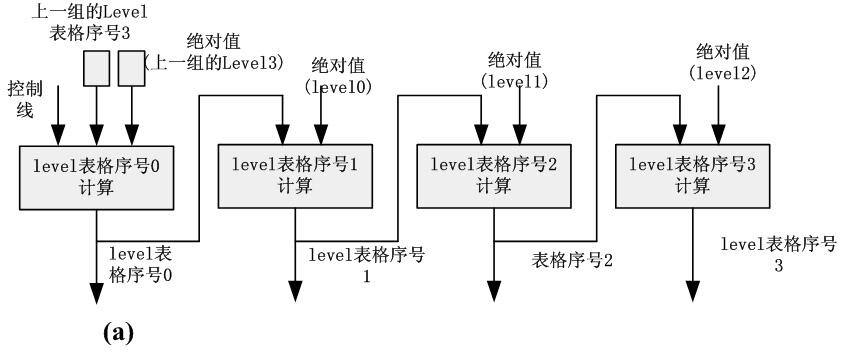

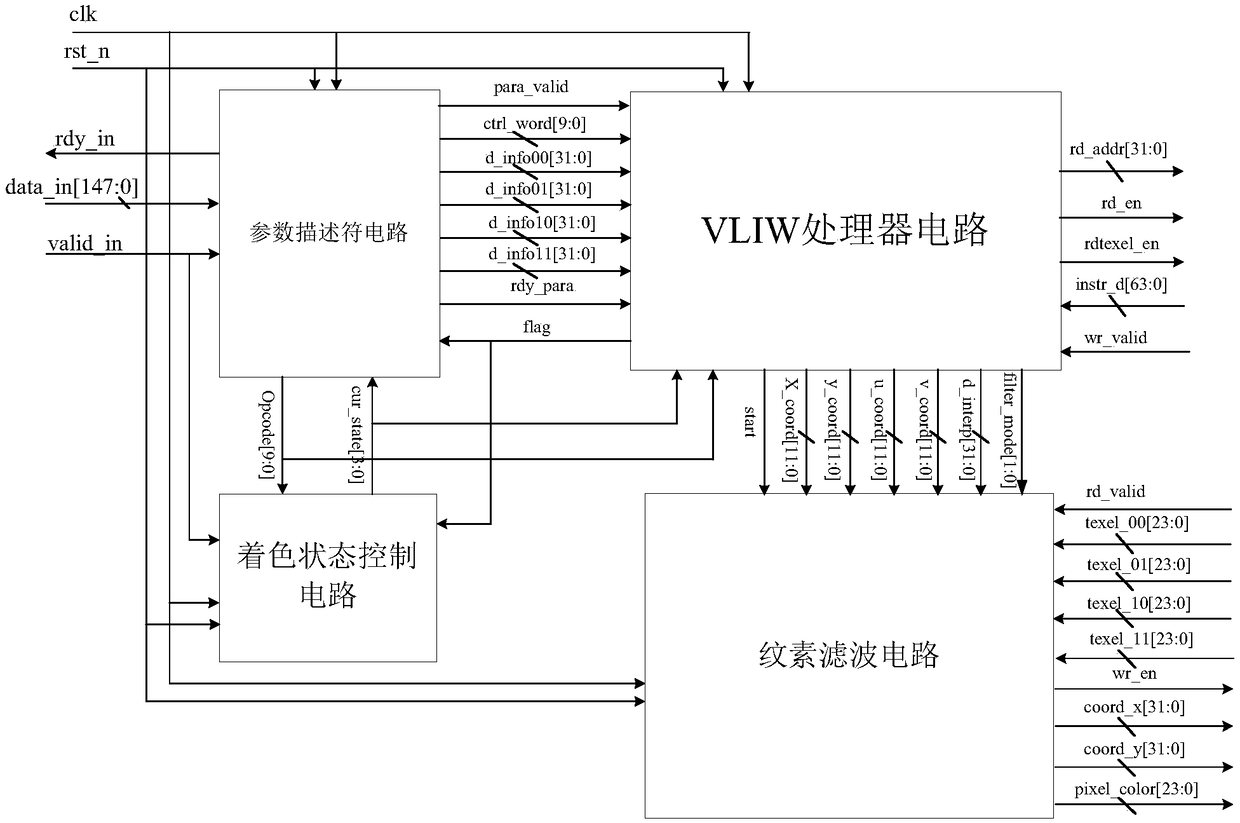

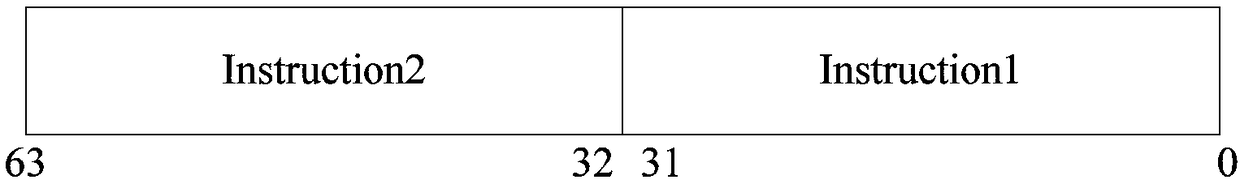

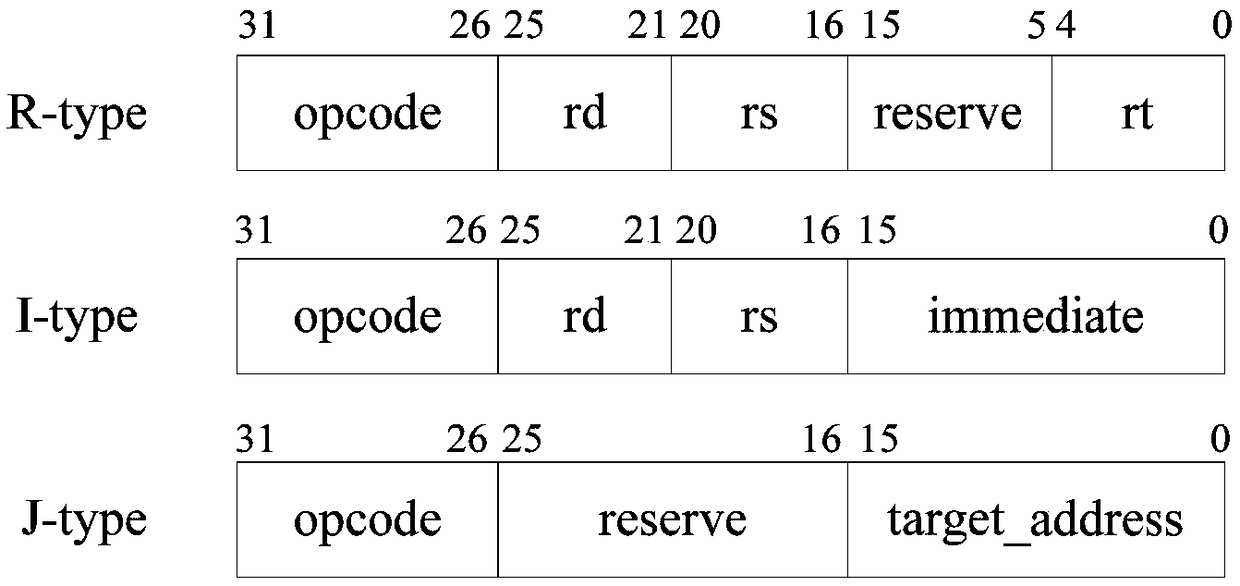

A unified architecture rendering shader based on dual-emitter VLIW

ActiveCN109087381AReduce Design ComplexityReduced conversion timeConcurrent instruction execution3D-image renderingGeneral purposeComputational science

The invention belongs to the technical field of graphics processing chip design, and discloses a unified structure rendering shader based on a double-emission VLIW. The shader is provided with a parameter descriptor circuit for analyzing and processing input command flow information; a shading state control circuit which determines the processing contents of different pipeline stages of the unified shader according to the rendering information of the polygon to be rendered; a dual-transmit VLIW processor circuit which performs corresponding graphics task processing or general-purpose computingprocessing according to the current state and configuration parameters; a texture filter circuit which performs bilinear interpolation or trilinear interpolation filtering on the texture texture texture values read from the texture memory under the configuration of the VLIW processor circuit. The invention can reduce the complexity of hardware design and the conversion time of the data between the vertex shader and the pixel shader in the traditional architecture. The unified shader has the advantages of simple structure, small hardware area and good real-time performance.

Owner:XIAN UNIV OF POSTS & TELECOMM

Method and device for detecting dead pixels in an image

ActiveCN107016669BImprove detection efficiencyReduce hardware areaImage analysisComputer visionComputer science

The invention discloses an image defective pixel detection method and apparatus. The method includes: obtaining an N*M pixel block of an image, arranging all pixel points in the pixel block in sequence to obtain a pixel value sequence, calculating a median of the pixel value sequence, and obtaining a pixel median; determining a specified small pixel value and a specified large pixel value from the pixel value sequence, calculating a first difference, and determining the pixel type of a current pixel point and calculating a second difference according to the relation between the current pixel point and the pixel median; and determining whether the current pixel point is a suspected defective pixel by determining whether the quotient of the second difference and the first difference is greater than a first preset error. The defective pixel is checked based on the attribute of the defective pixel of the image, compared with the conventional defective pixel detection method, the hardware area is reduced, pixel points of the image are checked one by one, more suspected defective pixels can be discovered, and the detection efficiency of the defective pixels is improved.

Owner:FUZHOU ROCKCHIP SEMICON

A method and device for calculating hevc SAO

ActiveCN106817583BSimplify the decoding calculation process stepsReduce hardware areaDigital video signal modificationAlgorithmComputation process

Owner:FUZHOU ROCKCHIP SEMICON

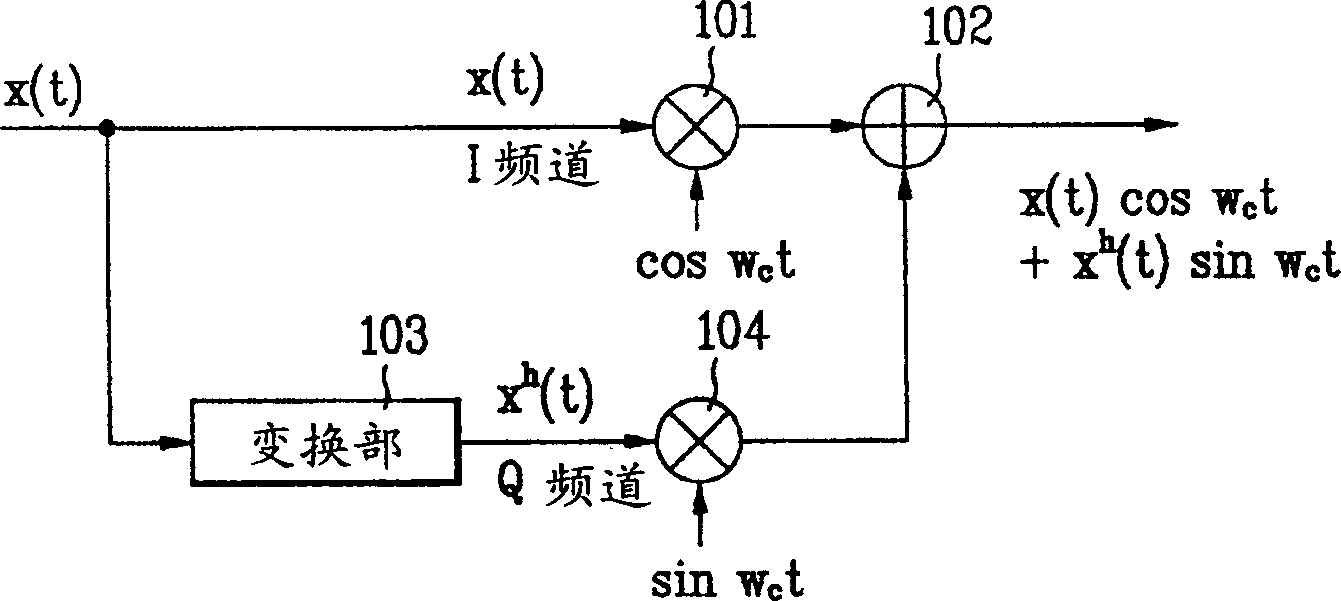

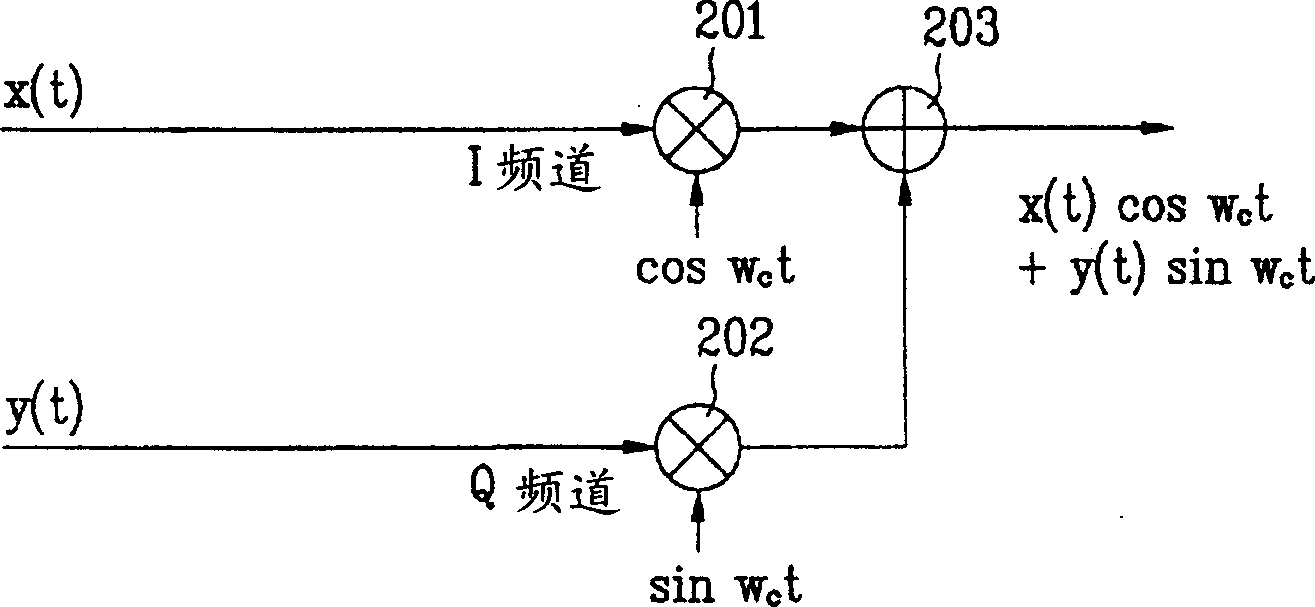

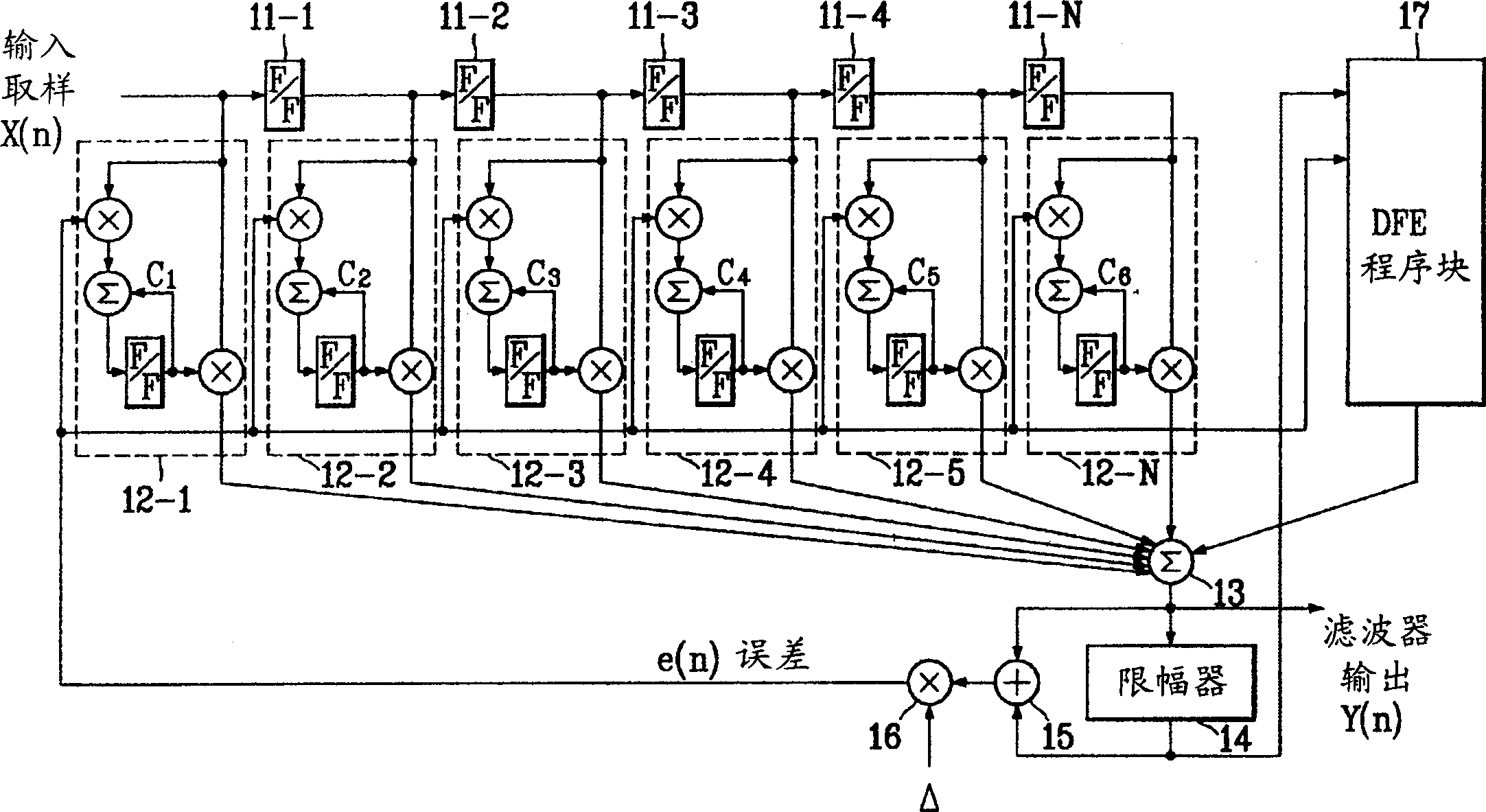

VSB/QAM compatible frequency balancer

InactiveCN1440139AReduce hardware areaLow powerTransmission control/equalisingLine-faulsts/interference reductionControl signalChannel equalizer

This invention discloses a multi-purposes channels equalizer compatible with VSB / QAM. This equalizer first makes it clear that whether the VSB signals or the QAM signals, whether the symbol spacing or the fine spacing, the signal channel equalization of whether the real number or the complex number and like are for the received signals for channel equalization of the received signals. Then the corresponding filtering coefficient will be generated according to these factors and the transmission of the signals is controlled according to the various conditions. Therefore an equalizing function equalizes the VSB signals and the QAM signals. Thus, the area of the hardware for realizing the equalization can be reduced by a big margin.

Owner:LEIJIN ELECTRONIC SHENYANG CO LTD

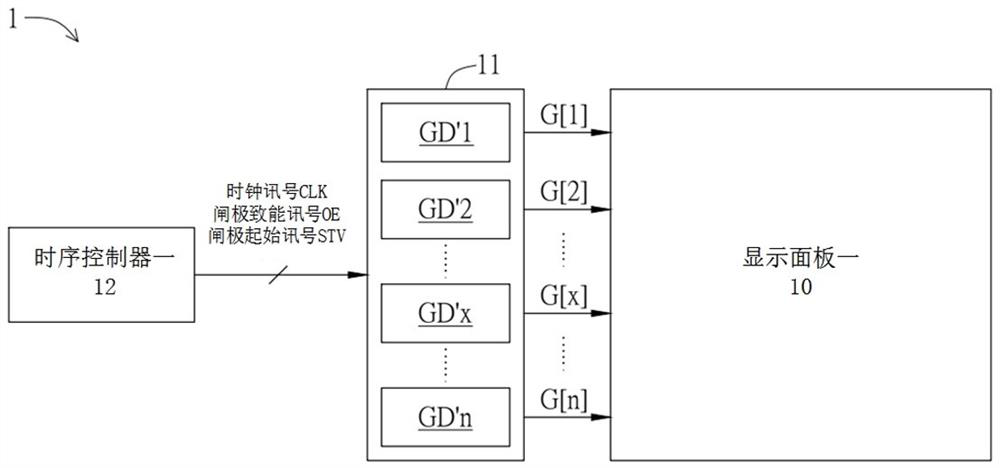

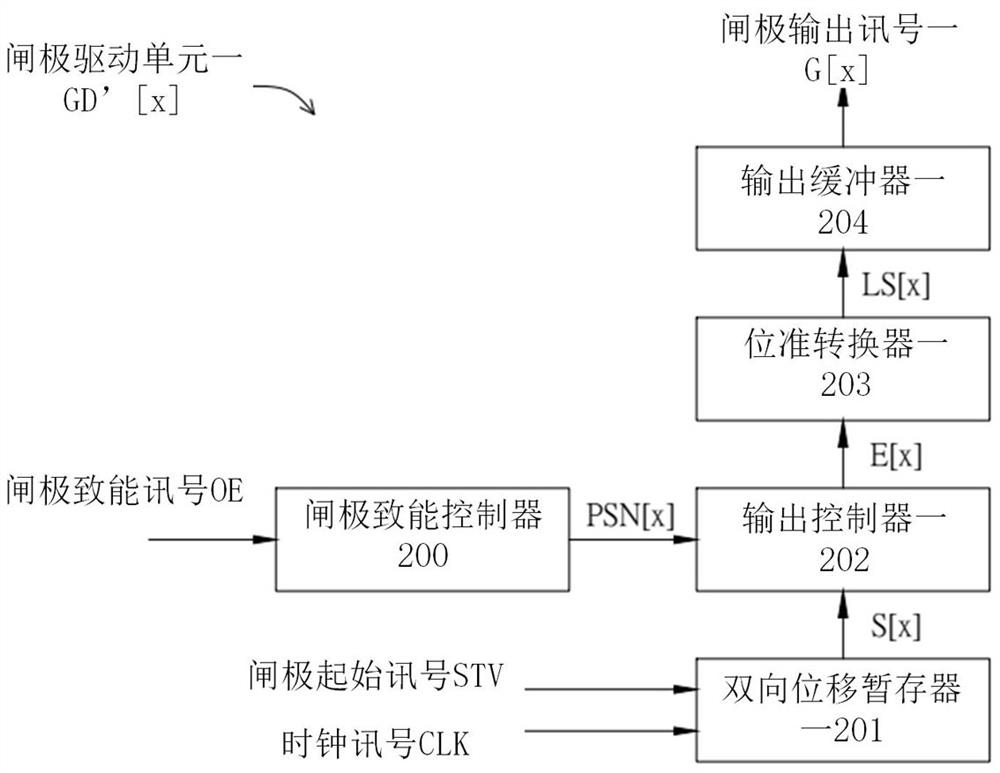

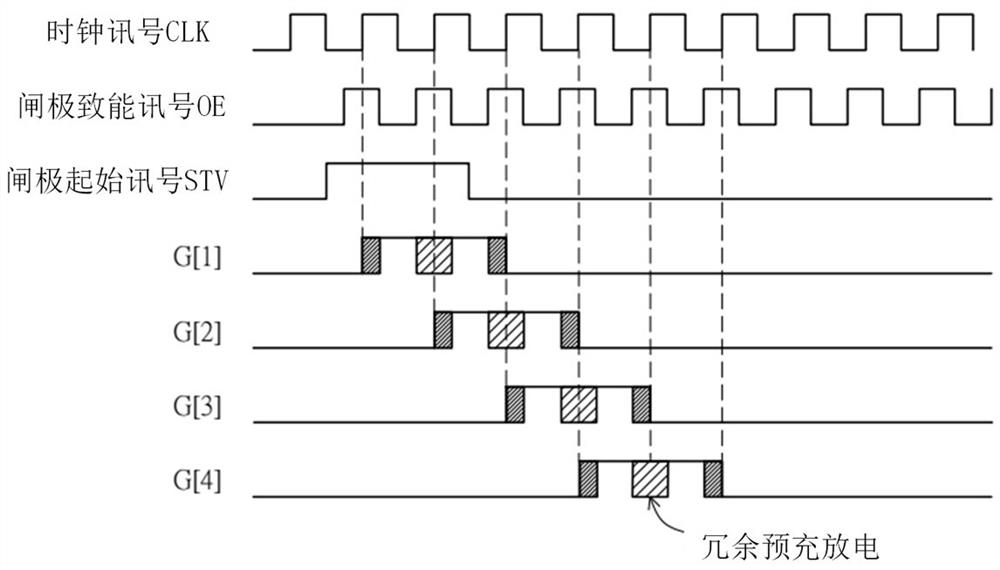

Display device and gate enabling method thereof

ActiveCN113674716AAvoid wasting electricityReduce hardware areaStatic indicating devicesStart signalGate driver

The invention discloses a display device. The display device comprises a display panel, a time schedule controller, a gate enabling frequency division controller and a gate driver, and the time schedule controller is used for generating a clock signal, a gate starting signal and a gate enabling signal. The gate enabling frequency division controller is coupled to the time schedule controller and is used for generating a plurality of frequency division gate enabling signals according to the clock signal, the gate starting signal and the gate enabling signal. The gate driver is coupled to the time schedule controller, the gate enabling frequency division controller and the display panel, and is used for generating a plurality of gate output signals to the display panel according to the clock signal, the gate starting signal and the plurality of frequency division gate enabling signals. According to the invention, the display device does not have a section of redundant pre-charging and discharging, so that waste of electricity can be avoided.

Owner:APLUS SEMICON TECH CO LTD

CAVLC (context-adaptive variable-length coding) coder for four-channel parallel coding

InactiveCN102325253BImprove throughputReduce hardware areaTelevision systemsDigital video signal modificationParallel encodingVideo encoding

The invention belongs to the technical field of video coding, in particular to a CAVLC (context-adaptive variable-length coding) coder for four-channel parallel coding. The CAVLC coder for four-channel parallel coding adopts a double-stage pipeline structure for scanning stage and coding stage parallel processing, and a scanning stage can scan four coefficients at a time, thus greatly shortening the time of scanning a 4 multiplied by 4 block. Likewise, a four-level and Run_before parallel coding mode is utilized to shorten the time needed by a coding stage. The time needed by the coding stage is carefully designed, so that the time consumed by the coding stage can be equal to the time consumed by the scanning stage. Consequently, the whole double-stage pipeline for CAVLC can obtain the maximum throughput rate, thus greatly reducing the clock number of finishing the coding of a macroblock.

Owner:FUDAN UNIV

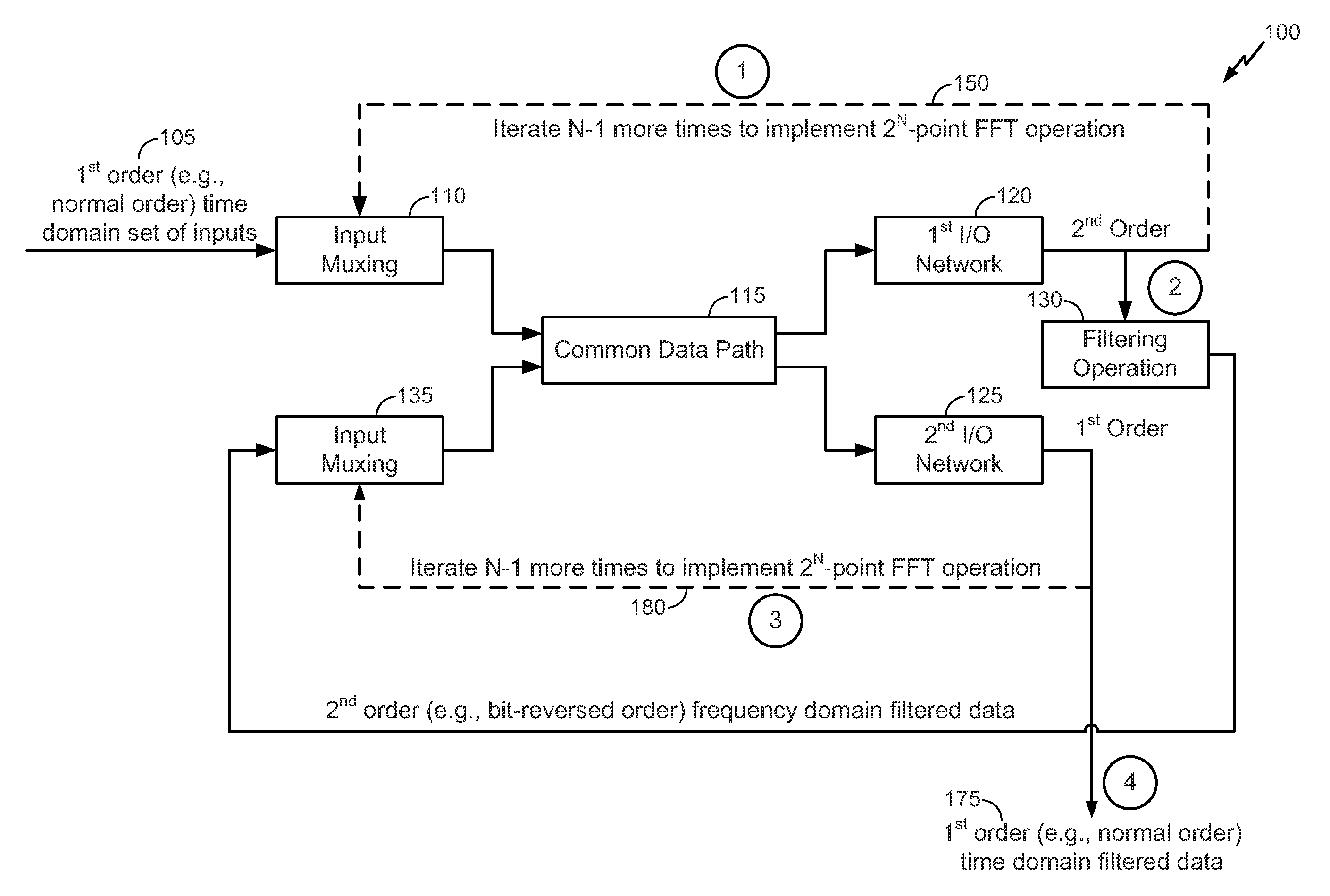

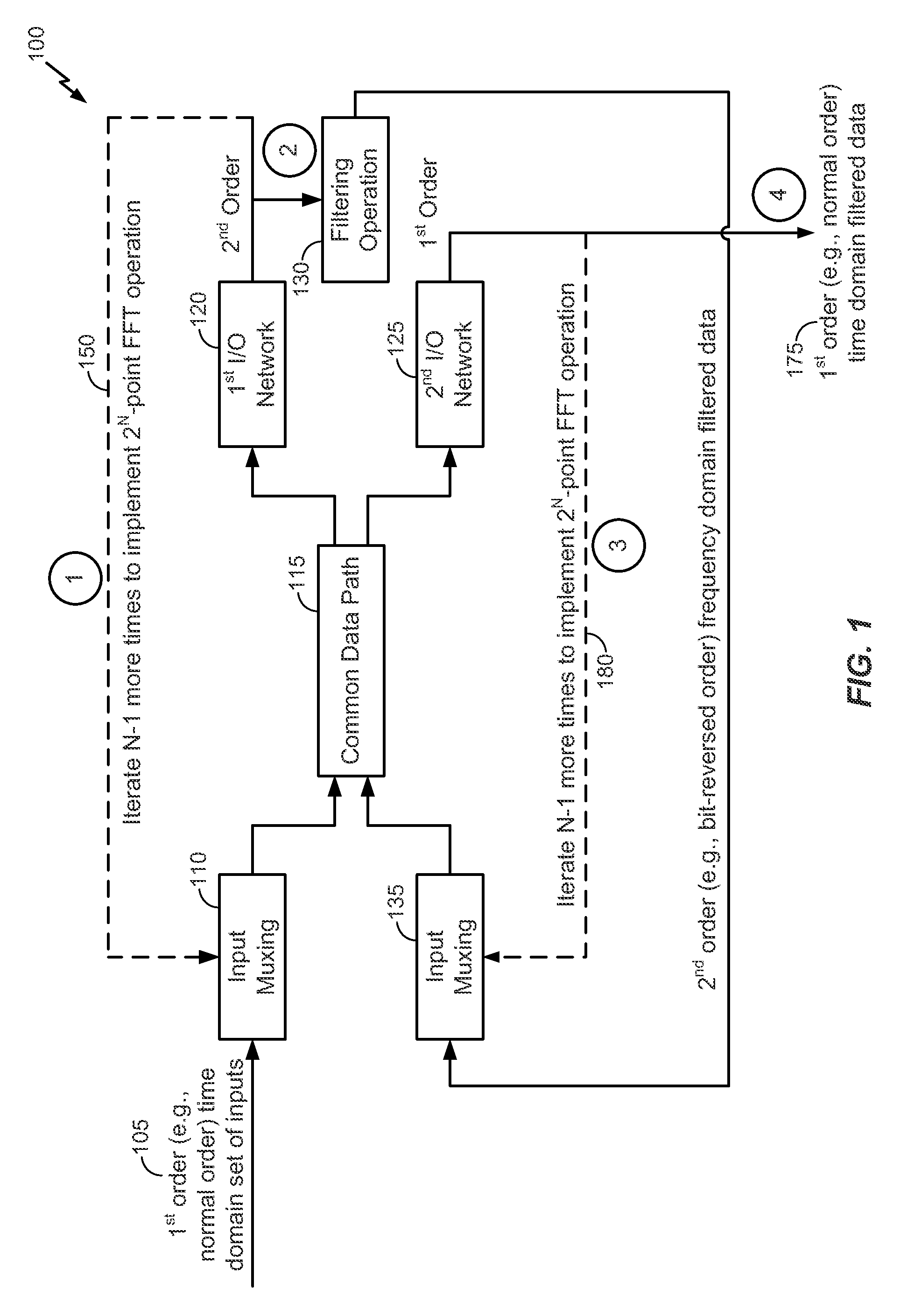

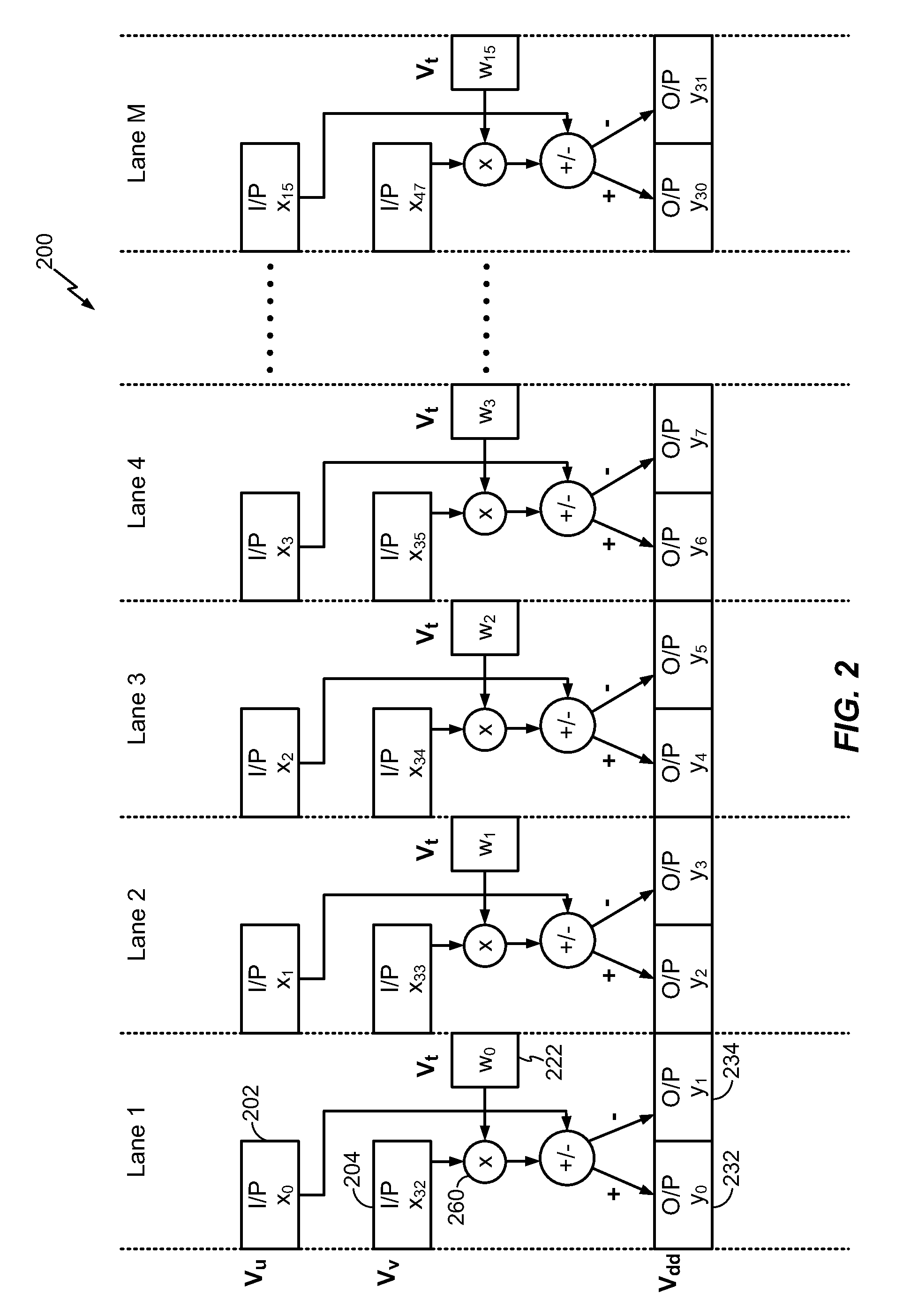

Dual fixed geometry fast fourier transform (FFT)

ActiveUS8787422B2Reduce complexityReduce power consumptionSecret communicationProgram controlTime domainFast Fourier transform

A method includes executing a first instruction at a processor to perform a first fast Fourier transform (FFT) operation on a set of inputs in a time domain to produce data in a frequency domain, where the set of inputs is in a first order and where the data in the frequency domain is in a second order. The method also includes performing an operation on the data in the frequency domain to produce data in the frequency domain, where the data in the frequency domain is in the second order. The method includes executing a second instruction at the processor to perform a second FFT operation on the data in the frequency domain to produce data in the time domain, where the data in the time domain is in the first order.

Owner:QUALCOMM INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com