A unified architecture rendering shader based on dual-emitter VLIW

A dual emission and shader technology, applied in the direction of instruments, concurrent instruction execution, machine execution devices, etc., can solve the problem of reducing hardware design complexity and data conversion time in processor cores, shader computing resources cannot be fully utilized at the same time, bandwidth consumption etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0053] In order to make the objectives, technical solutions and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0054] In the prior art, adopting a unified architecture to design a graphics processor of a mobile terminal cannot well reduce hardware design complexity and data conversion time between processor cores.

[0055] It is difficult to achieve high hardware resource utilization between vertex shader and pixel shader processing.

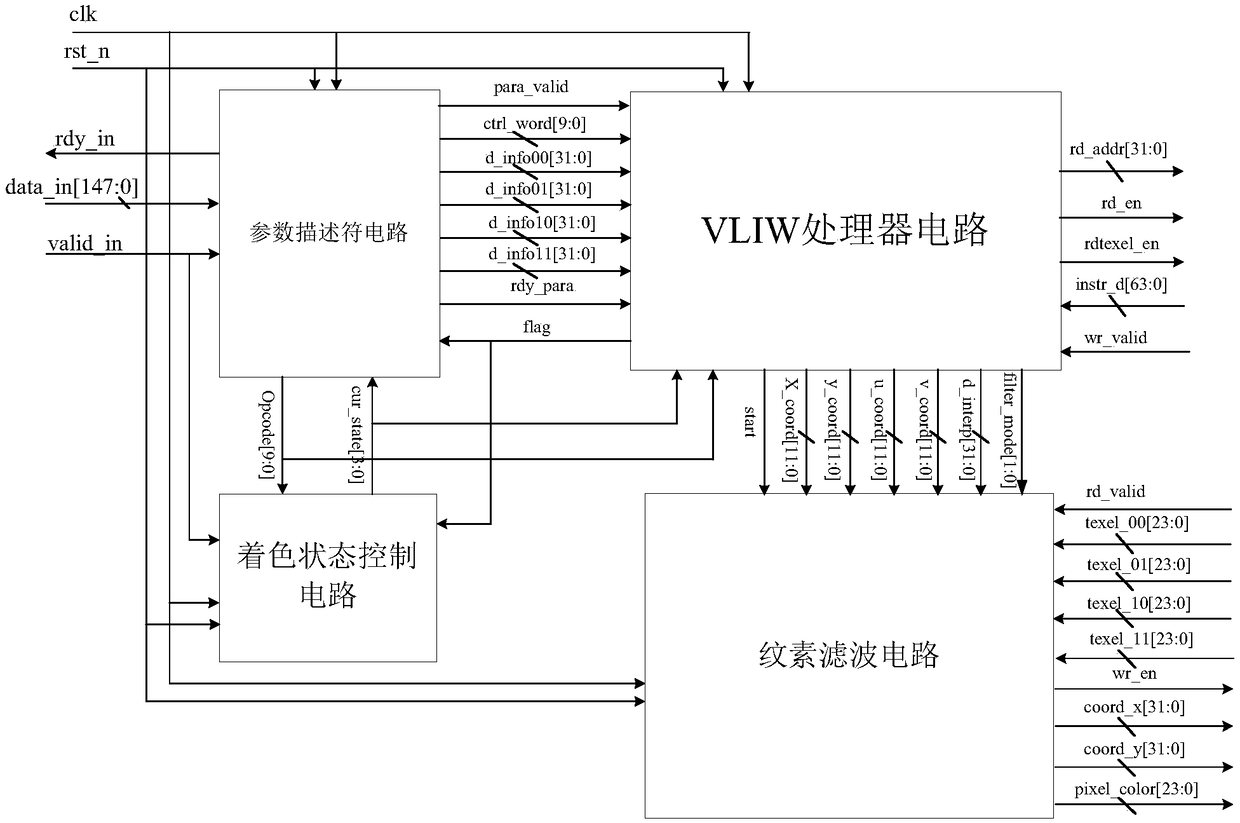

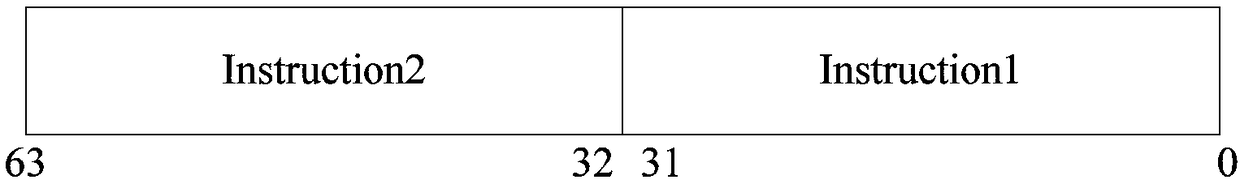

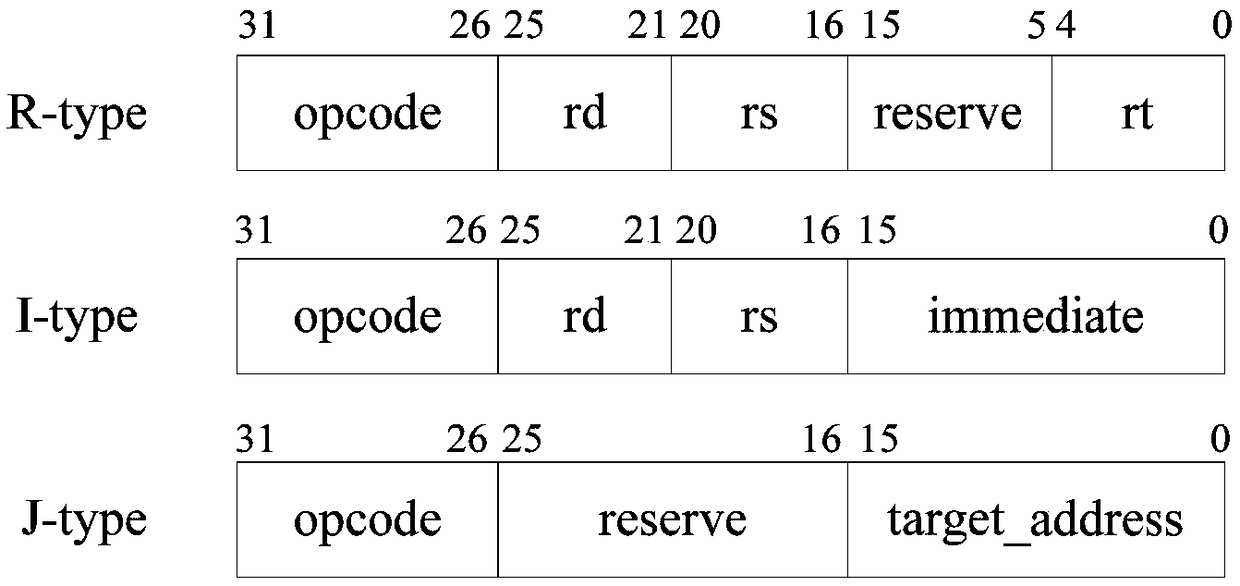

[0056] like figure 1 As shown, the dual-shot VLIW-based unified architecture rendering shader provided by the embodiment of the present invention is a unified mobile shader processor for basic graphics processing tasks such as vertex task processing and pixel task processing, and specifically rel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com