Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

42results about How to "Improve hardware utilization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

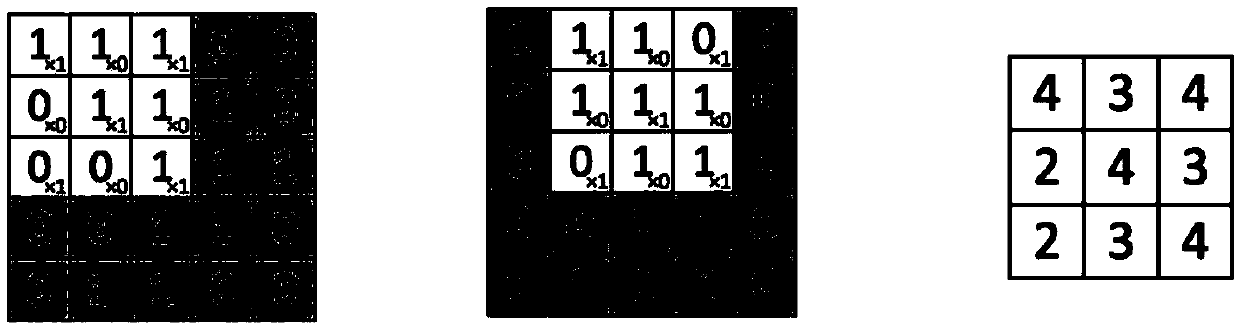

Image Processing with Highly Threaded Texture Fragment Generation

ActiveUS20090231348A1Minimizing any bottleneckImprove hardware utilizationCharacter and pattern recognitionCathode-ray tube indicatorsImaging processingComputer graphics (images)

A circuit arrangement and method support a multithreaded rendering architecture capable of dynamically routing pixel fragments from a pixel fragment generator to any pixel shader from among a pool of pixel shaders. The pixel fragment generator is therefore not tied to a specific pixel shader, but is instead able to utilize multiple pixel shaders in a pool of pixel shaders to minimize bottlenecks and improve overall hardware utilization and performance during image processing.

Owner:RAKUTEN GRP INC

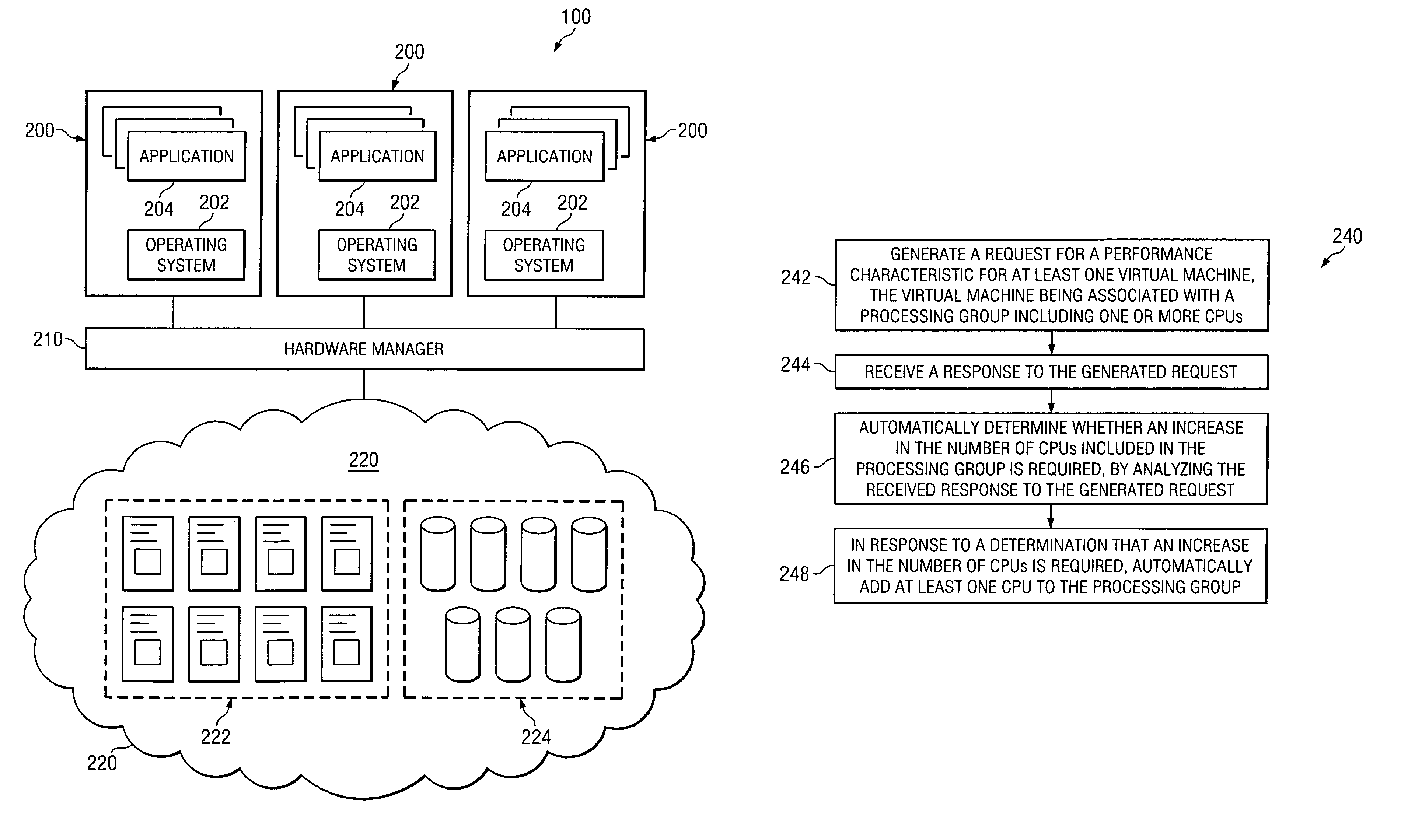

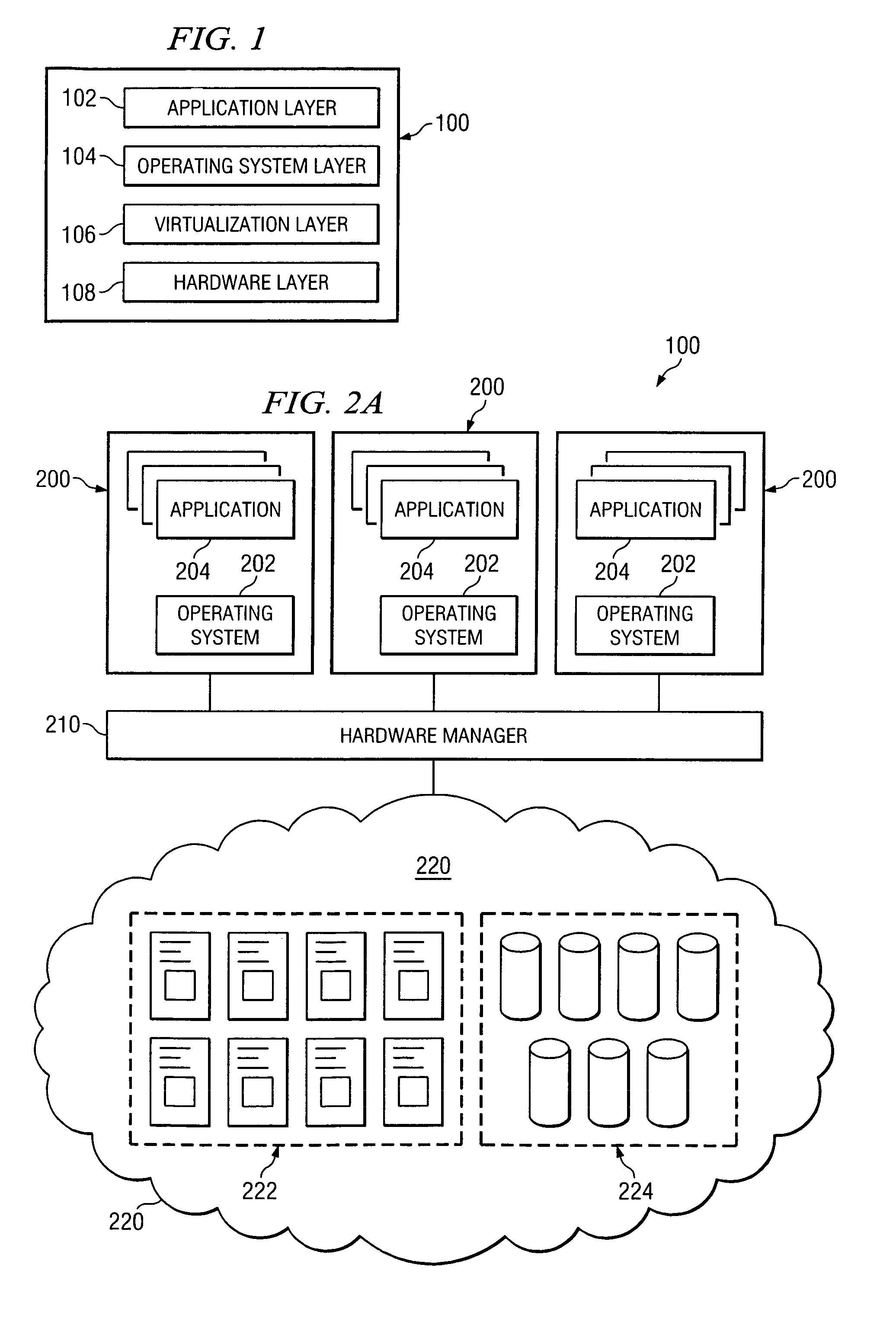

Managing virtual machines based on business priority

ActiveUS8104033B2Easy to controlImprove hardware utilizationMultiprogramming arrangementsSoftware simulation/interpretation/emulationBus priorityVirtual machine

Owner:COMP ASSOC THINK INC

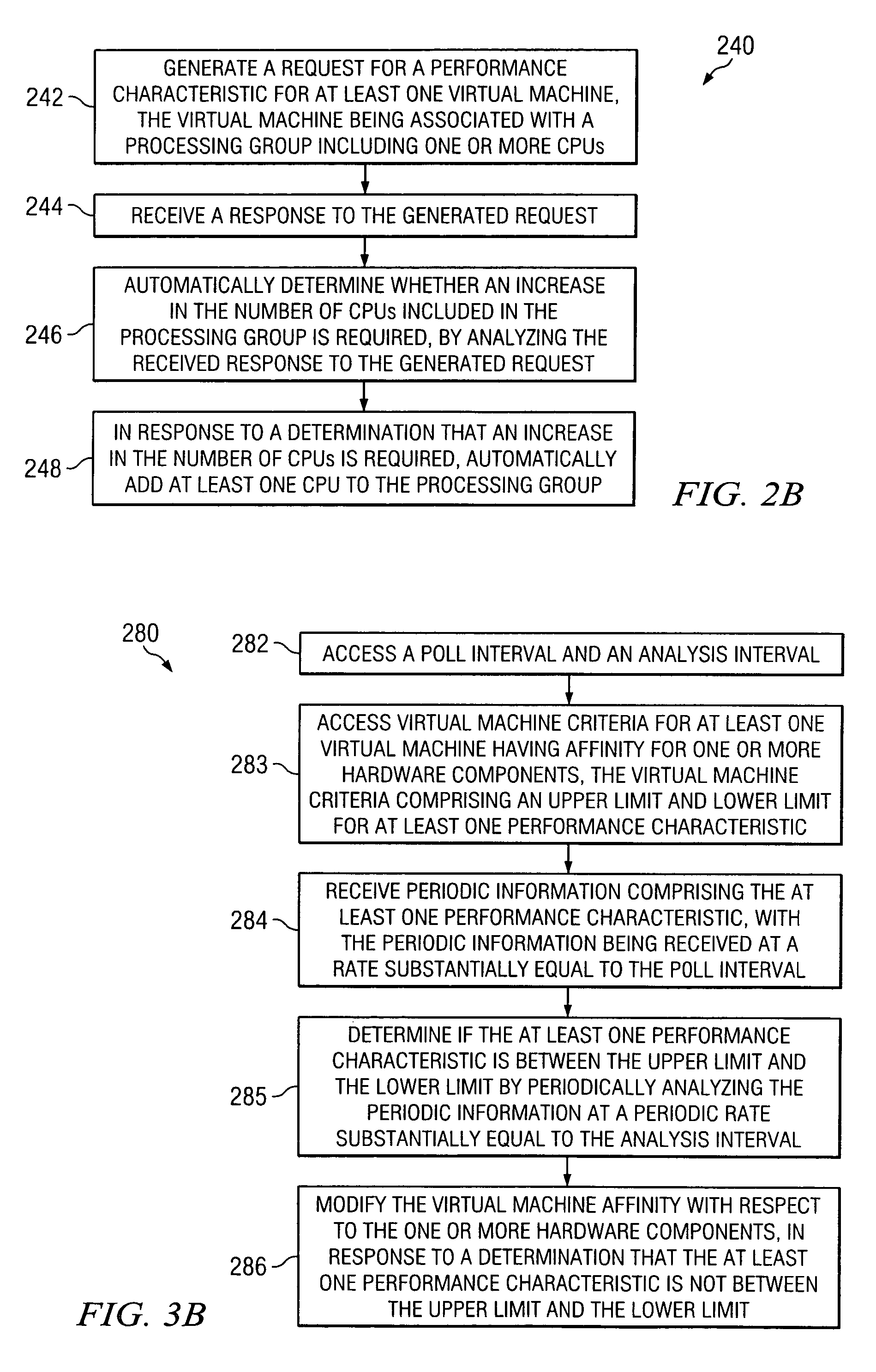

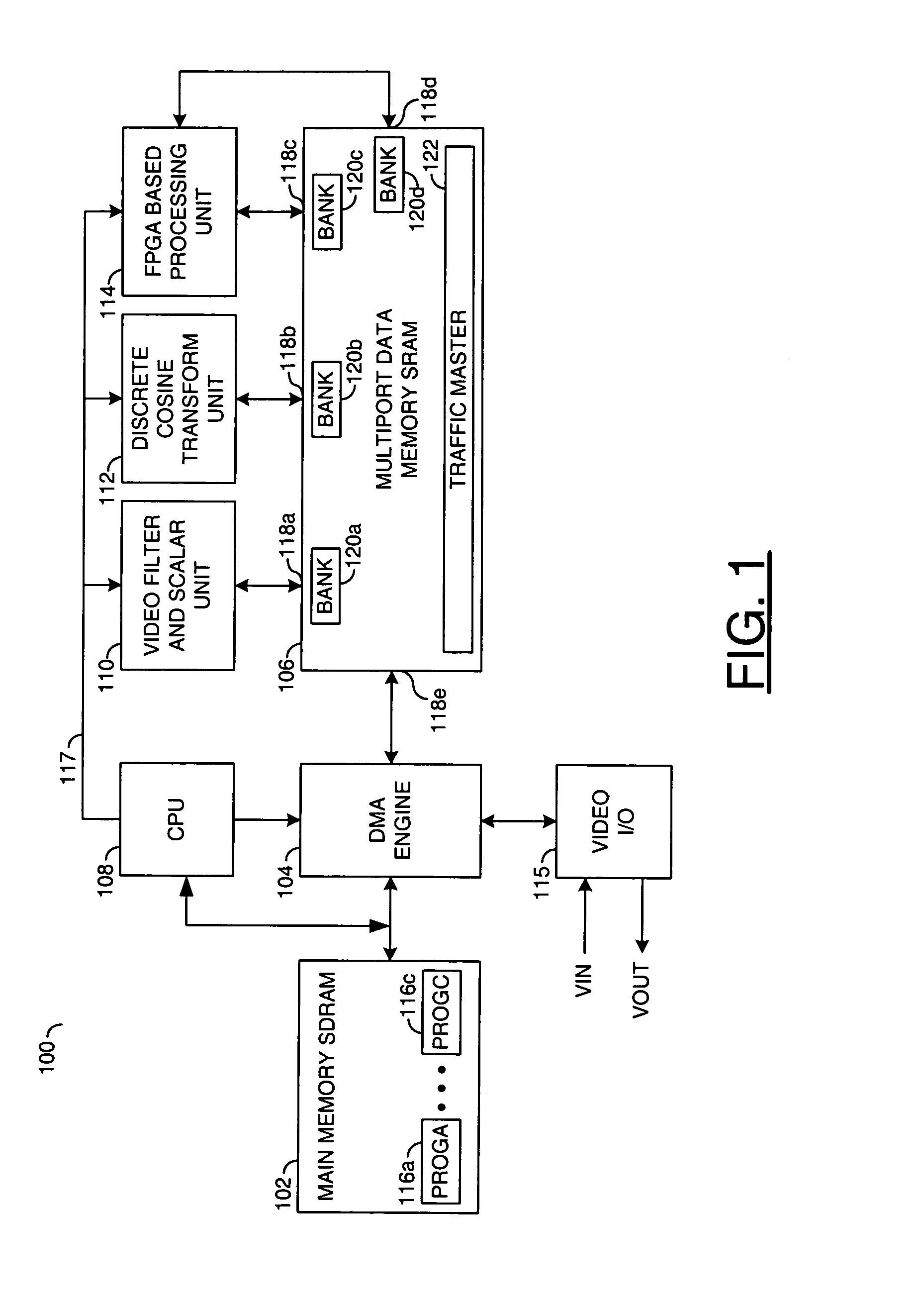

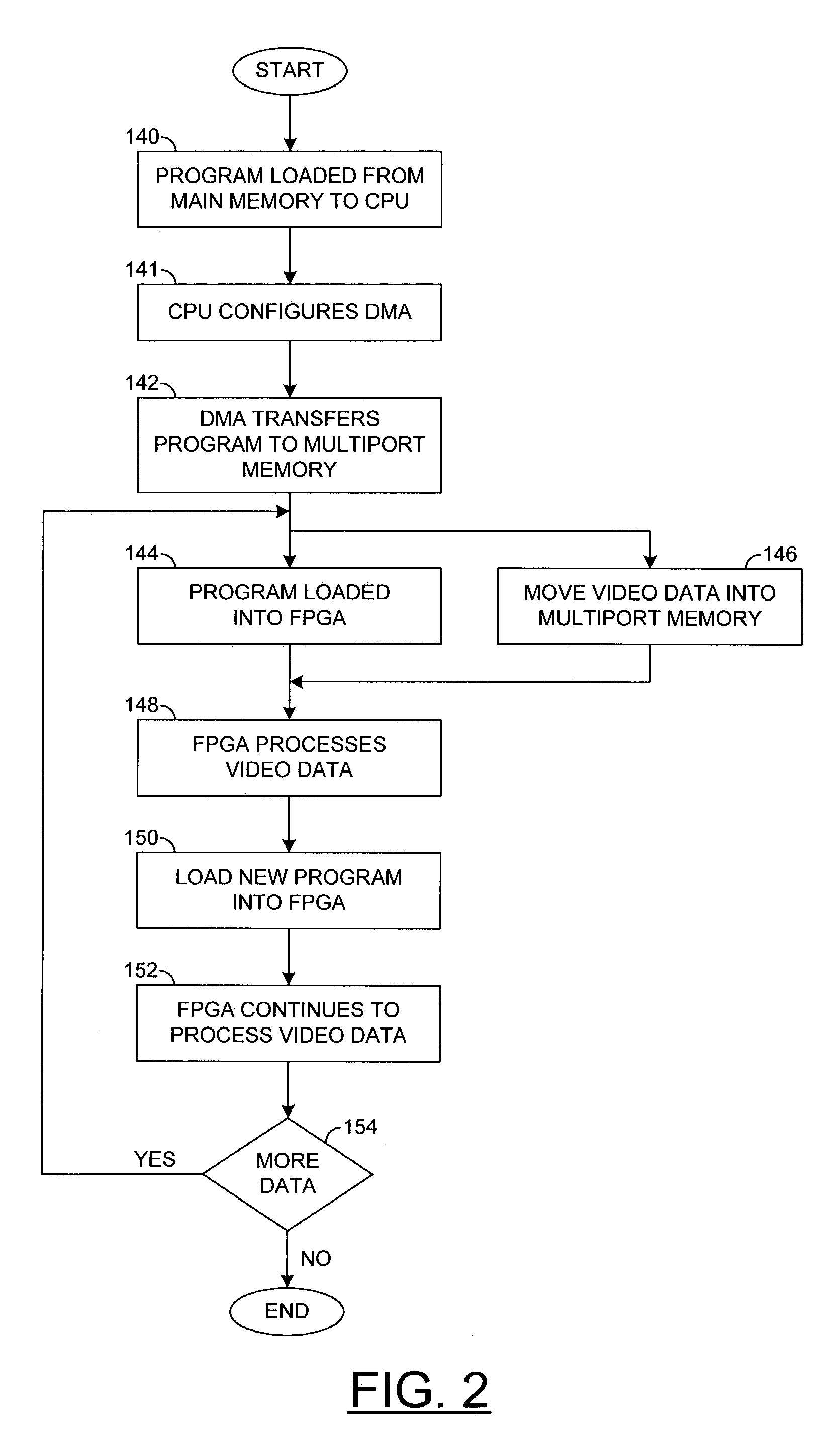

Reconfigurable computing based multi-standard video codec

InactiveUS7236525B2Reduce mold sizeImprove hardware utilizationColor television with pulse code modulationColor television with bandwidth reductionDirect memory accessGate array

A circuit generally comprising a multiport memory, a direct memory access engine and a programmable gate array is disclosed. The direct memory access engine may be configured to transfer a first program to the multiport memory. The programmable gate array may be configured to (i) load the first program directly from the multiported memory to program a codec function and (ii) generate a video output signal by performing the codec function on a video input signal using video data exchanged with the multiport memory.

Owner:AVAGO TECH INT SALES PTE LTD

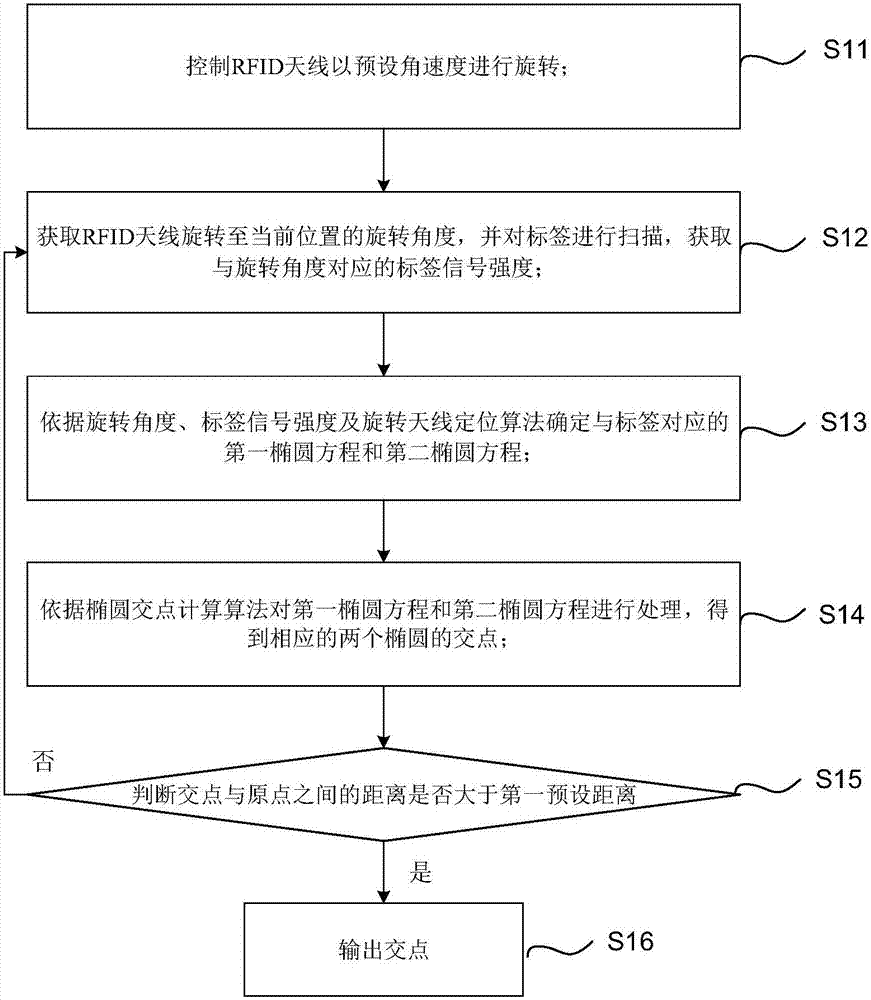

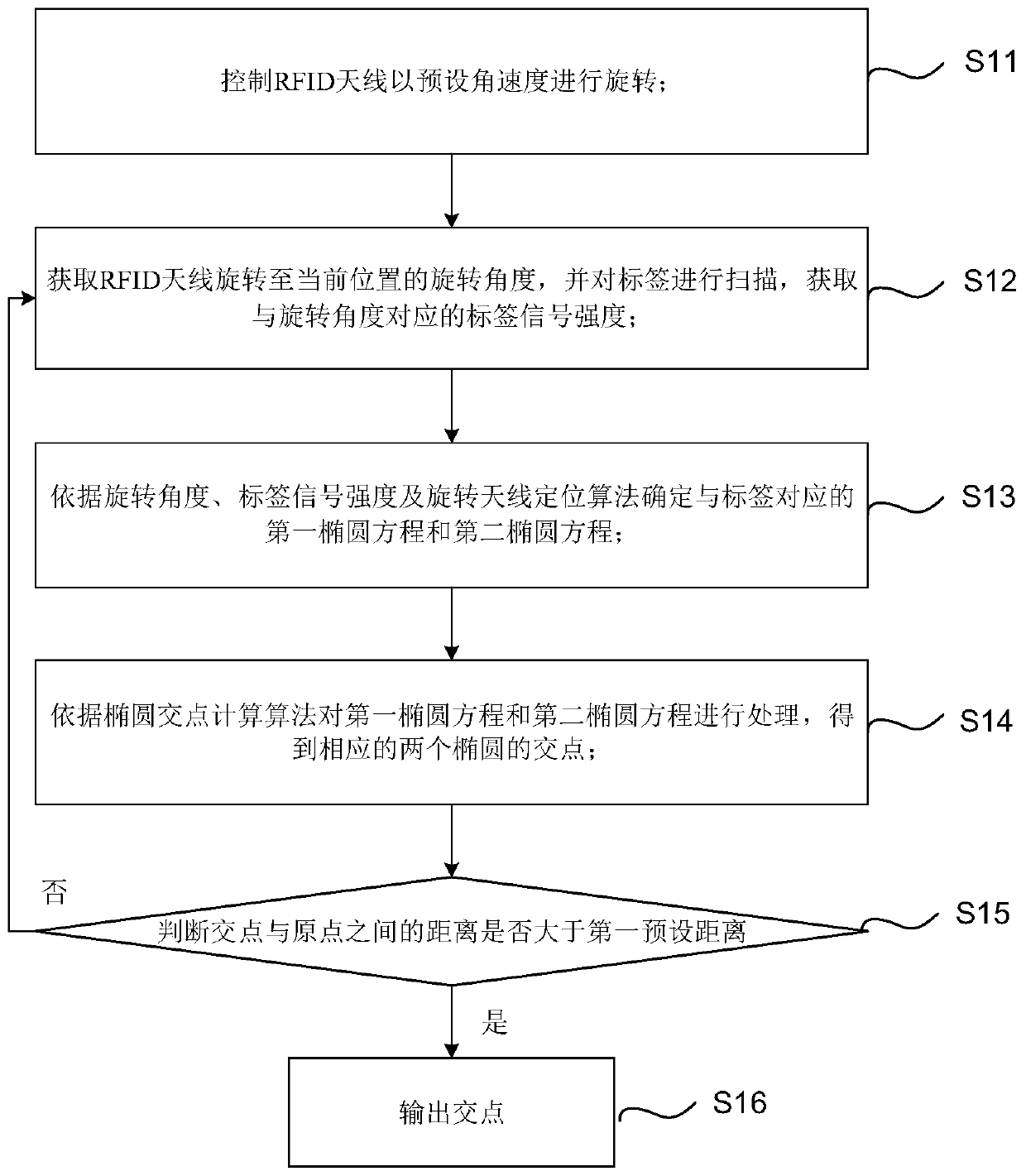

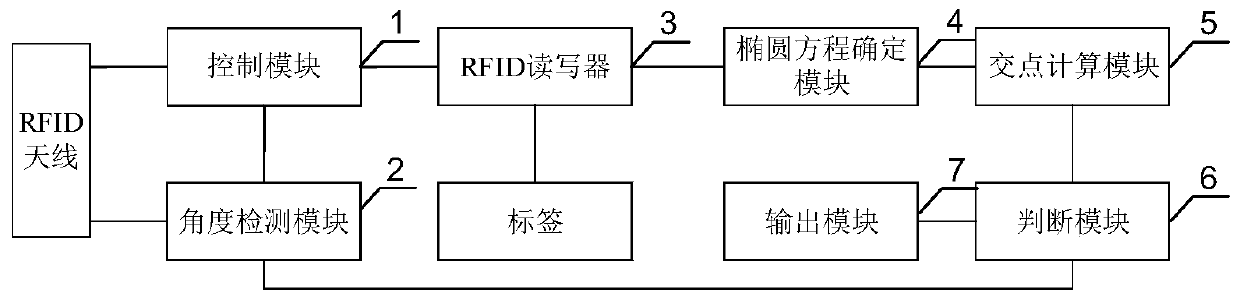

Indoor positioning method, device and system based on RFID (radio frequency identification)

ActiveCN107462249ASimple structureLow costNavigational calculation instrumentsPosition fixationSystem structureComputer science

The embodiment of the invention discloses an indoor positioning method, device and system based on RFID (radio frequency identification). The method comprises the following steps of controlling an RFID antenna to rotate at the preset angle; obtaining the rotating angle of the RFID antenna for rotating to the current position; scanning a label; obtaining the label signal intensity corresponding to the rotating angle; determining a first elliptic equation and a second elliptic equation corresponding to the label according to the rotating angle, the label signal intensity and the rotating antenna positioning algorithm; processing the first elliptic equation and the second elliptic equation according to the elliptic intersection point calculation algorithm to obtain the corresponding two elliptic intersection points; whether the distance between the intersection point and the origin is greater than the first preset distance or not; if so, the intersection point is output; otherwise, the rotating angle when the RFID antenna rotates to another position is continuously obtained, and the cyclic operation is performed until the final intersection point is obtained. The embodiment of the invention has the advantages that only one RFID antenna is used; the advantages of simple system structure, low cost, low deployment difficulty and high hardware utilization rate are realized.

Owner:GUANGDONG UNIV OF TECH

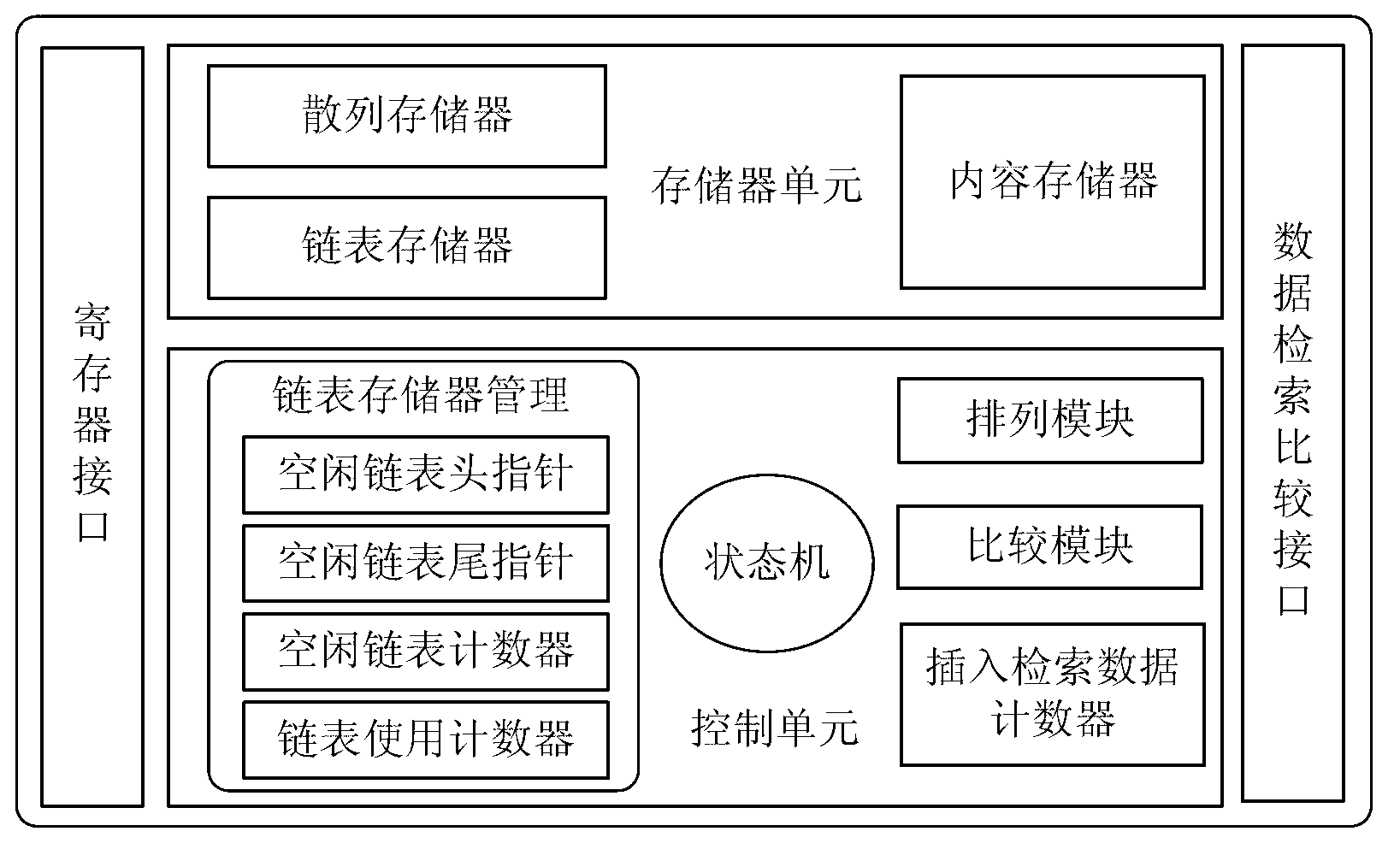

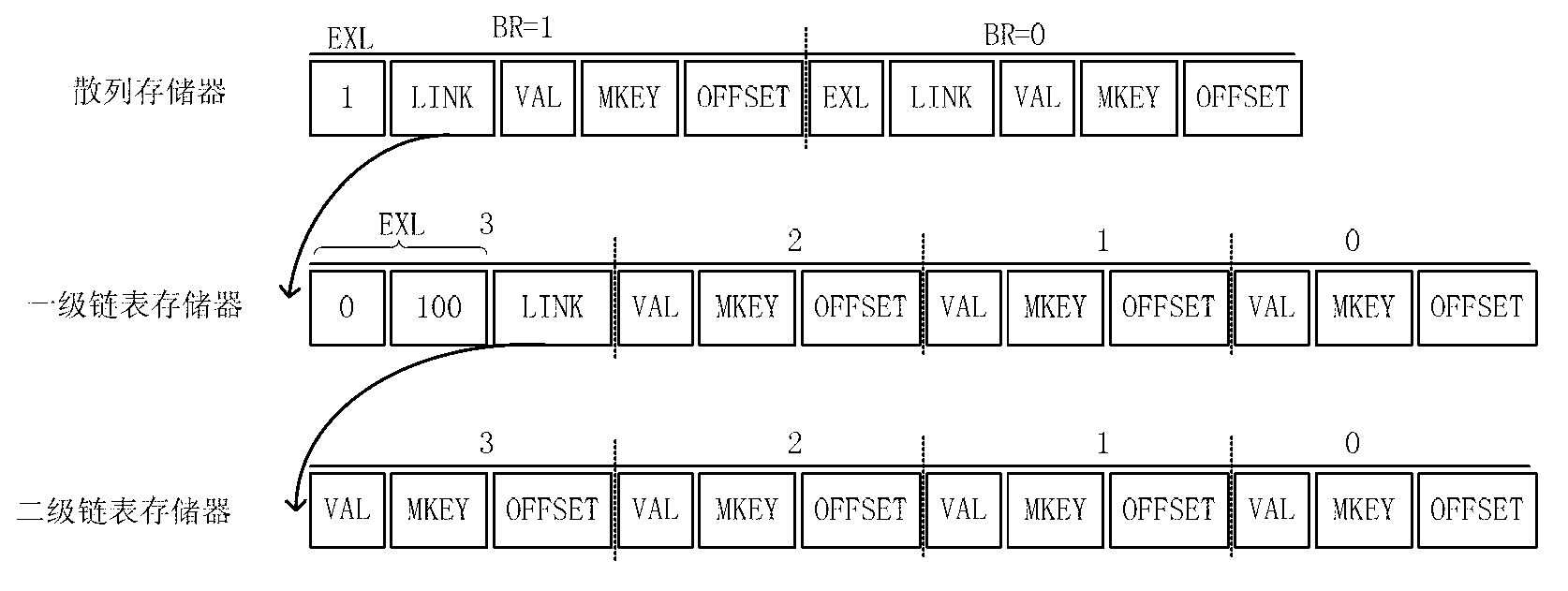

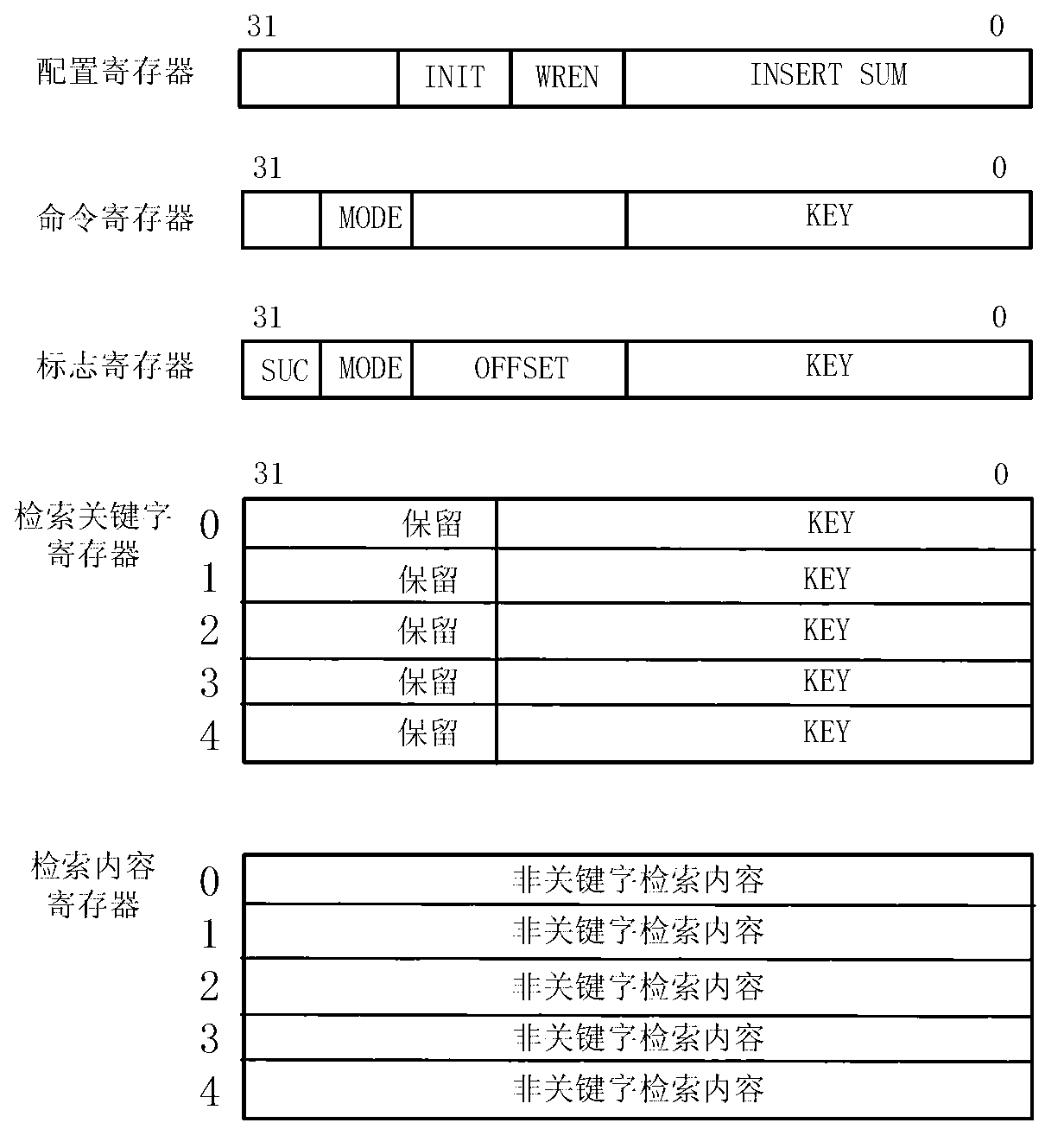

Content addressing method based on hash chain table and corresponding storage circuit

ActiveCN103064948AImprove general performanceEasy to useMemory adressing/allocation/relocationSpecial data processing applicationsHash chainMemory circuits

The invention relates to a content addressing method based on a hash chain table and a corresponding storage circuit. The storage circuit includes a storage unit, a control unit, a register interface and a data search comparison interface. The content addressing method adopts the methods of hash, chain, multi-character parallel storage, comparison and the like, resolves the problem in the prior art of use limit caused by the fact that a special process or a device is adopted to achieve the content addressing storage and the problems of small content addressing search speed, large consumption resources, difficulty in content addressing search depth and width expansion and the like in a traditional design method, has the advantages of being high in generality, high in search speed, high in hardware utilization rate, easy to expand and the like, and is not limited by the chip process or a field programmable gate array (FPGA) device.

Owner:西安翔腾微电子科技有限公司

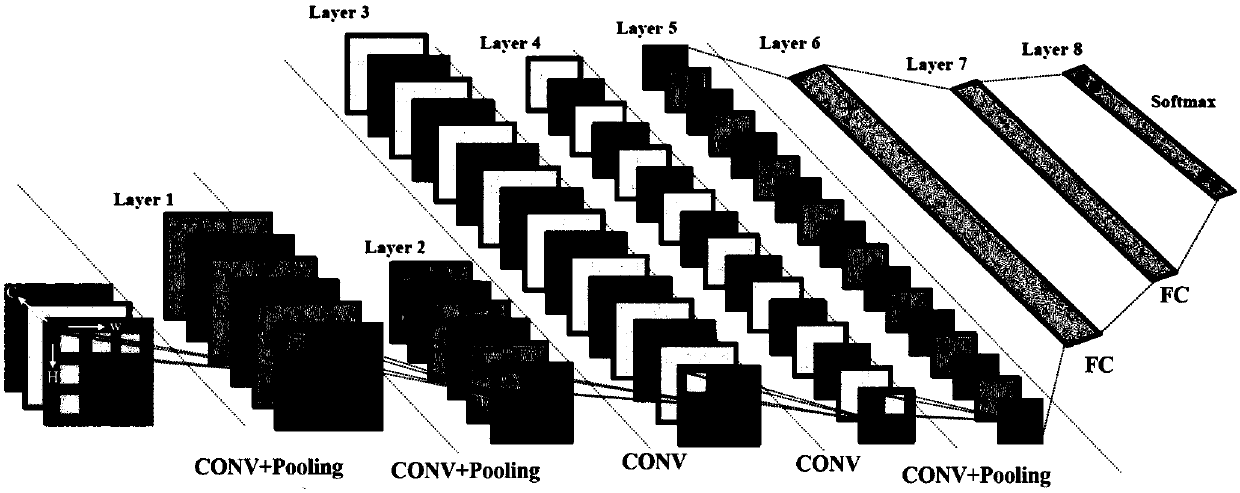

Neural network calculation special circuit and related calculation platform and implementation method thereof

ActiveCN110766127AImprove hardware utilizationSave hardware resourcesProcessor architectures/configurationNeural architecturesComputer hardwareMap reading

The invention discloses a special circuit for a neural network and a related computing platform and implementation method thereof. The special circuit comprises: a data reading module which comprisesa feature map reading sub-module and a weight reading sub-module which are respectively used for reading feature map data and weight data from an on-chip cache to a data calculation module when a depthwise convolution operation is executed, wherein the feature map reading sub-module is also used for reading the feature map data from the on-chip cache to the data calculation module when executing pooling operation; a data calculation module which comprises a dwconv module used for executing depthwise convolution calculation and a pooling module used for executing pooling calculation; and a datawrite-back module which is used for writing a calculation result of the data calculation module back to the on-chip cache. The use of hardware resources is reduced by multiplexing the read logic andthe write-back logic of the two types of operations. The special circuit provided by the invention adopts a high-concurrency pipeline design, so that the computing performance can be further improved.

Owner:XILINX TECH BEIJING LTD

Efficient collaborative multiplexing method for software and hardware resources in block chain distributed networking

ActiveCN111770130AImprove hardware utilizationUser identity/authority verificationSoftware simulation/interpretation/emulationComputer hardwareResource pool

The invention relates to the technical field of efficient multiplexing modes of hardware resources and software resources, and discloses a service node, a root node, an application node and an accessnode, data and hardware of each layer of the service node, the root node, the application node and the access node are abstracted into a data layer and a resource pool respectively, and particularly comprises a software resource multiplexing method and a hardware resource multiplexing method matched with software resources for cooperative use. Full utilization of resources is realized under efficient cooperation of software and hardware, and the cost of block chain distributed deployment is reduced.

Owner:贵阳信息技术研究院

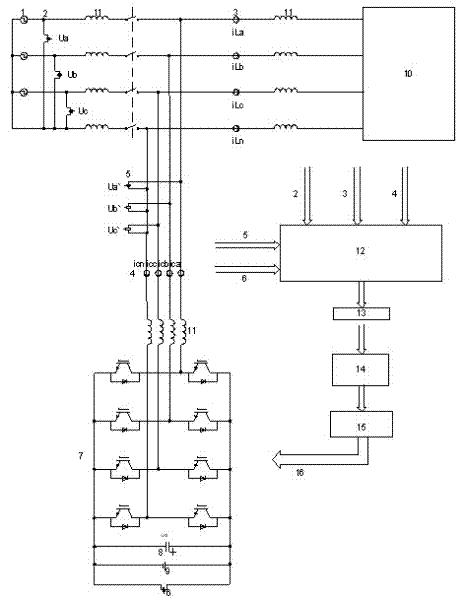

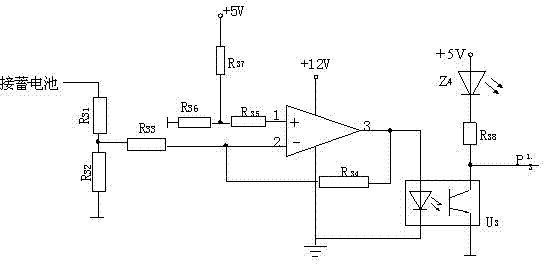

Power inverter with functions of UPS (uninterrupted power supply) and active power filter

InactiveCN102412609AQuality improvementLow costBatteries circuit arrangementsElectric powerPower inverterElectricity

The invention relates to a power inverter with functions of a UPS (uninterrupted power supply) and an active power filter, belonging to the technical fields of power inverters. The power inverter comprises an active power filter a digital control circuit and further comprises a storage battery, wherein the storage battery and the digital control circuit are respectively electrically connected with the active power filter. The power inverter has the beneficial effects that the storage battery is parallel connected to the direct-current side of the main circuit of the active power filter, and when harmonic current and reactive compensation are finished, energy is stored for the storage battery, thus when malfunctions of power supply through the power grid voltage occurs, power can be supplied for the load by the storage battery through the inverter; through the control of the inverter, the additional UPS device is saved for the system, thus the device cost is lowered; and when power is supplied normally for the power supply, after certain voltage stabilization and filtering is carried out on the power supply by the UPS, power is sent to the load, thus an alternating-current power supply with better quality can be obtained for the load.

Owner:CHAJNA MAJNING DRAJVS EHND AUTOMEHJSHN KO +1

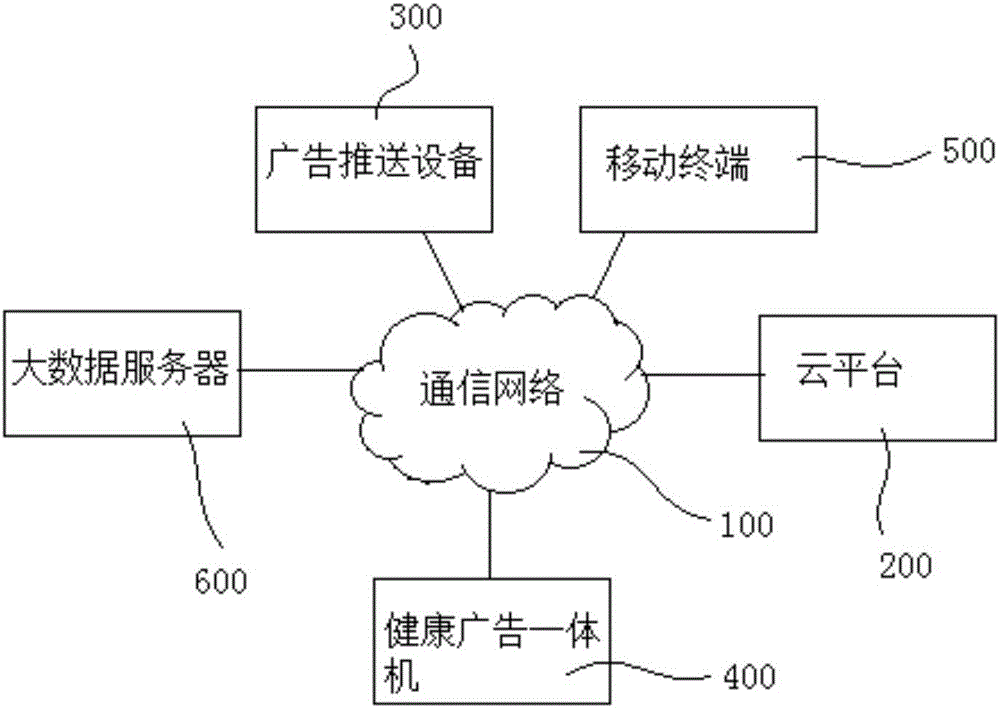

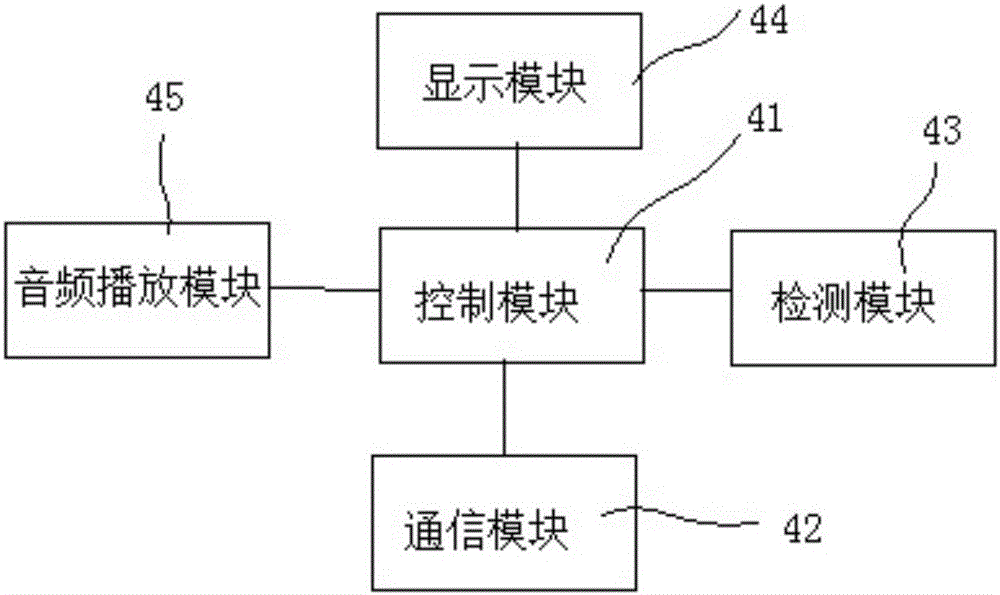

Internet health detection system with advertisement network function

InactiveCN106131005AImprove hardware utilizationBroaden data service capabilitiesAdvertisingTransmissionThe InternetCrowds

The present invention provides an internet health detection system with an advertisement network function. The system comprises a communication network, a cloud platform, an advertisement push device, a health advertisement all-in-one machine, a mobile terminal and a big data server that are all communicated with the communication network. The big data server acquires a physical sign database for detection by the health advertisement all-in-one machine from the cloud platform through the communication network, analyzes the physical sign database, determines health defects or lesion existing in the physical sign database, and sends an advertisement push advise related to the defects or lesion to the advertisement push device. The advertisement push device pushes advertisement information suitable for watching by corresponding users to the health advertisement all-in-one machine to play. The mobile terminal is used for identity logging by the user, authenticating or acquiring the physical sign database. Through adoption of the system, a hardware use ratio of a traditional advertisement system is improved, a function of checking detection data and advertisement information remotely at any time is realized, advertisement display attention is increased, and a crowd effect is improved.

Owner:ZHONGSHAN LAIKANG MEDICAL INFORMATION SOFTWARE TECH CO LTD

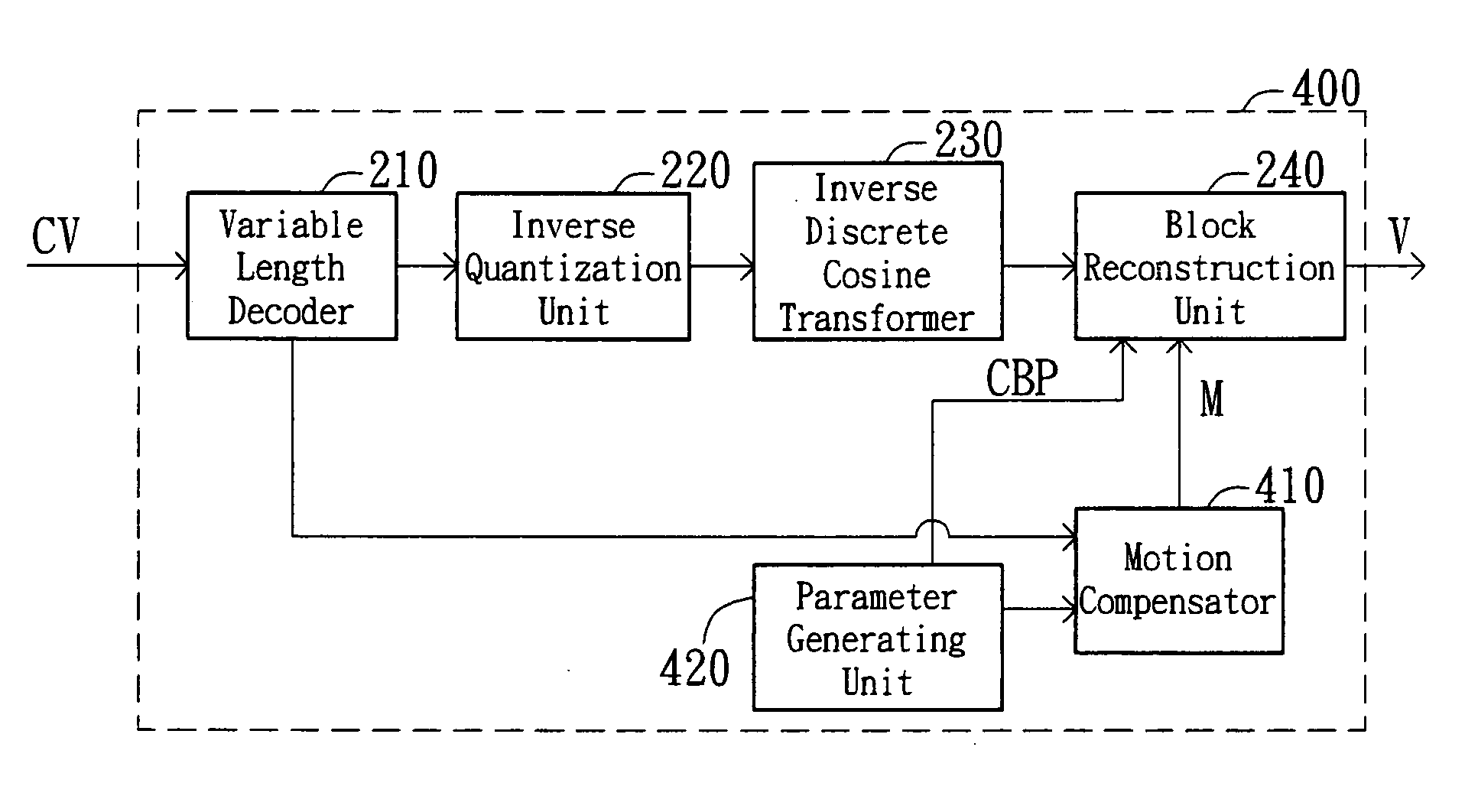

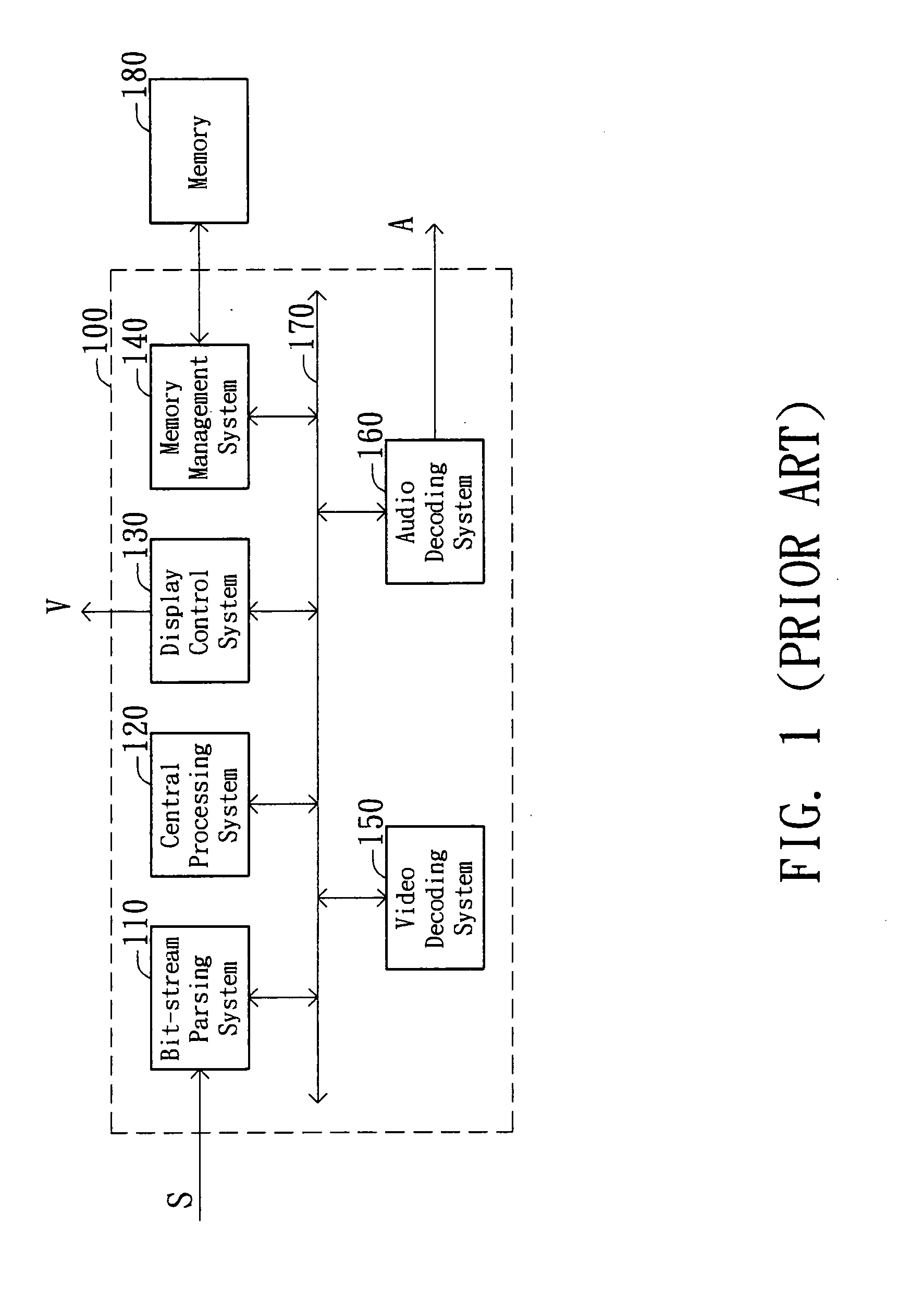

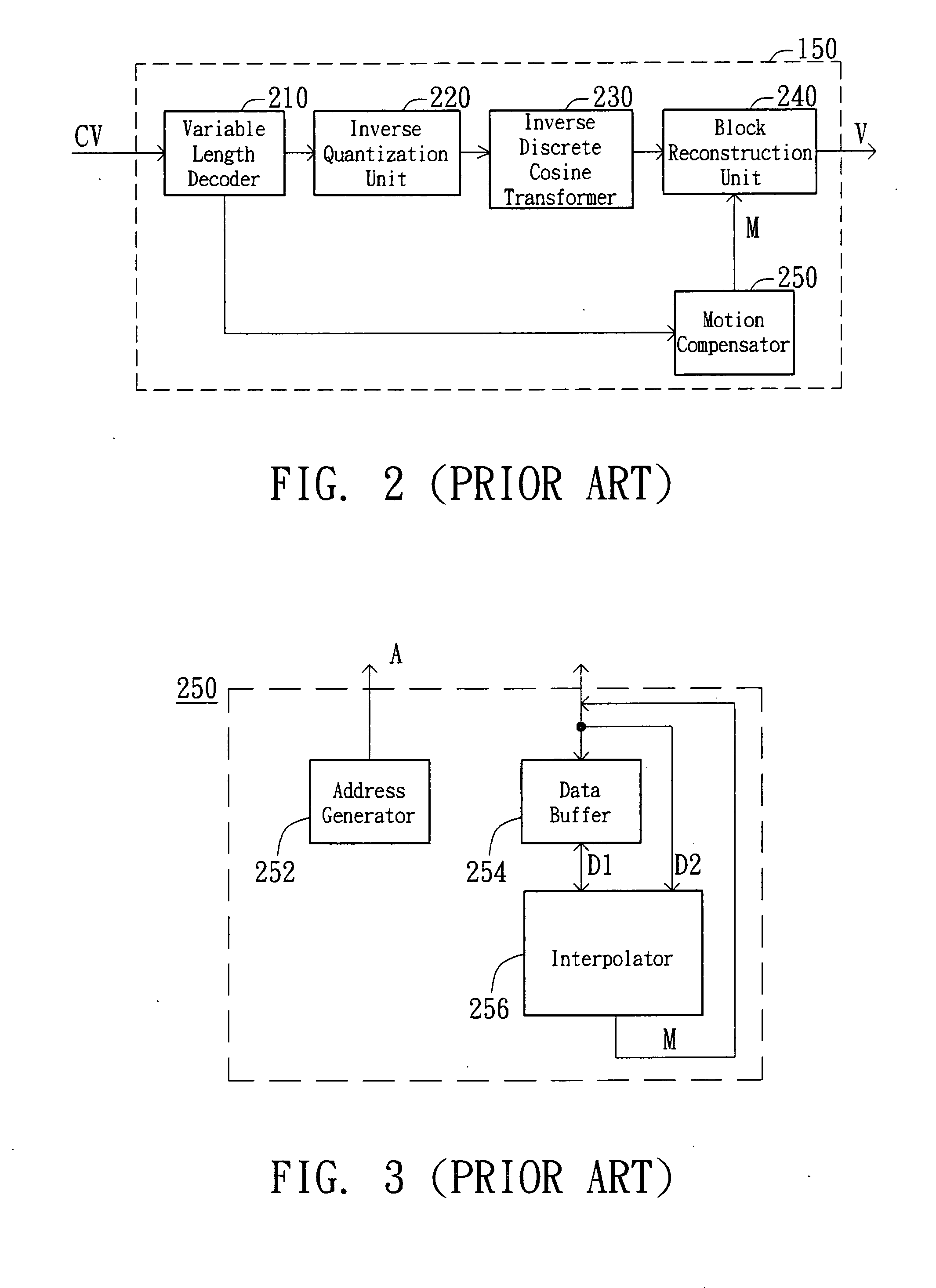

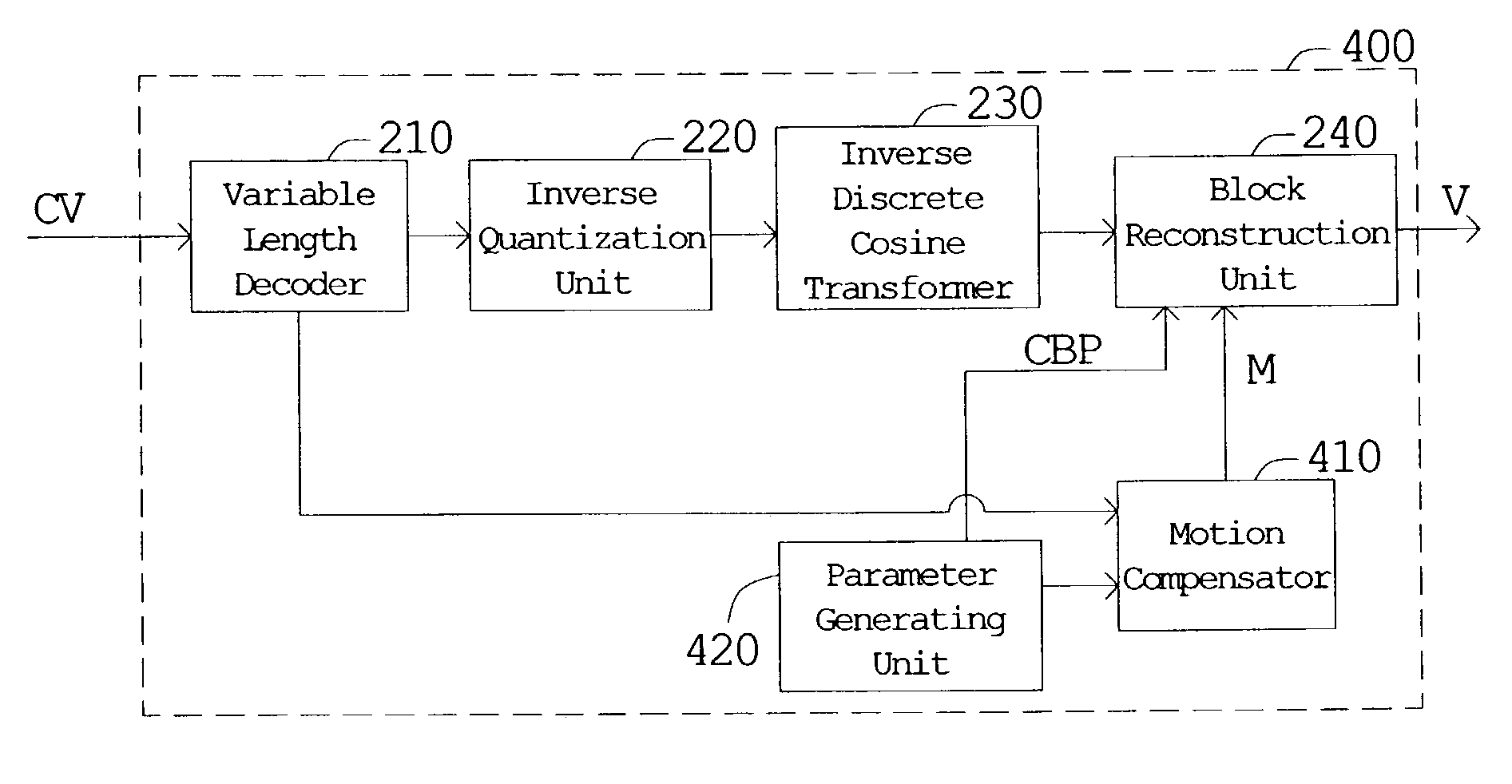

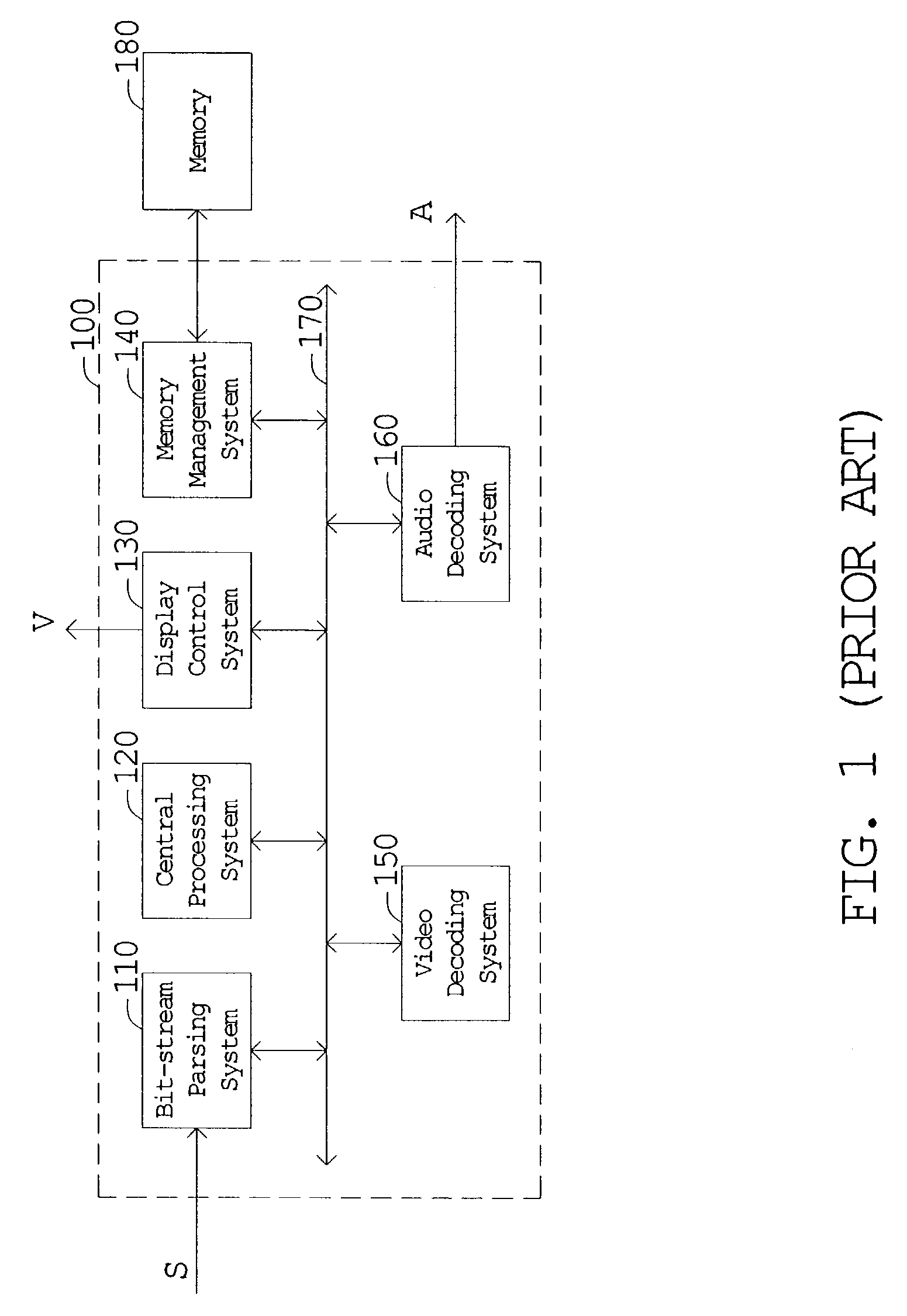

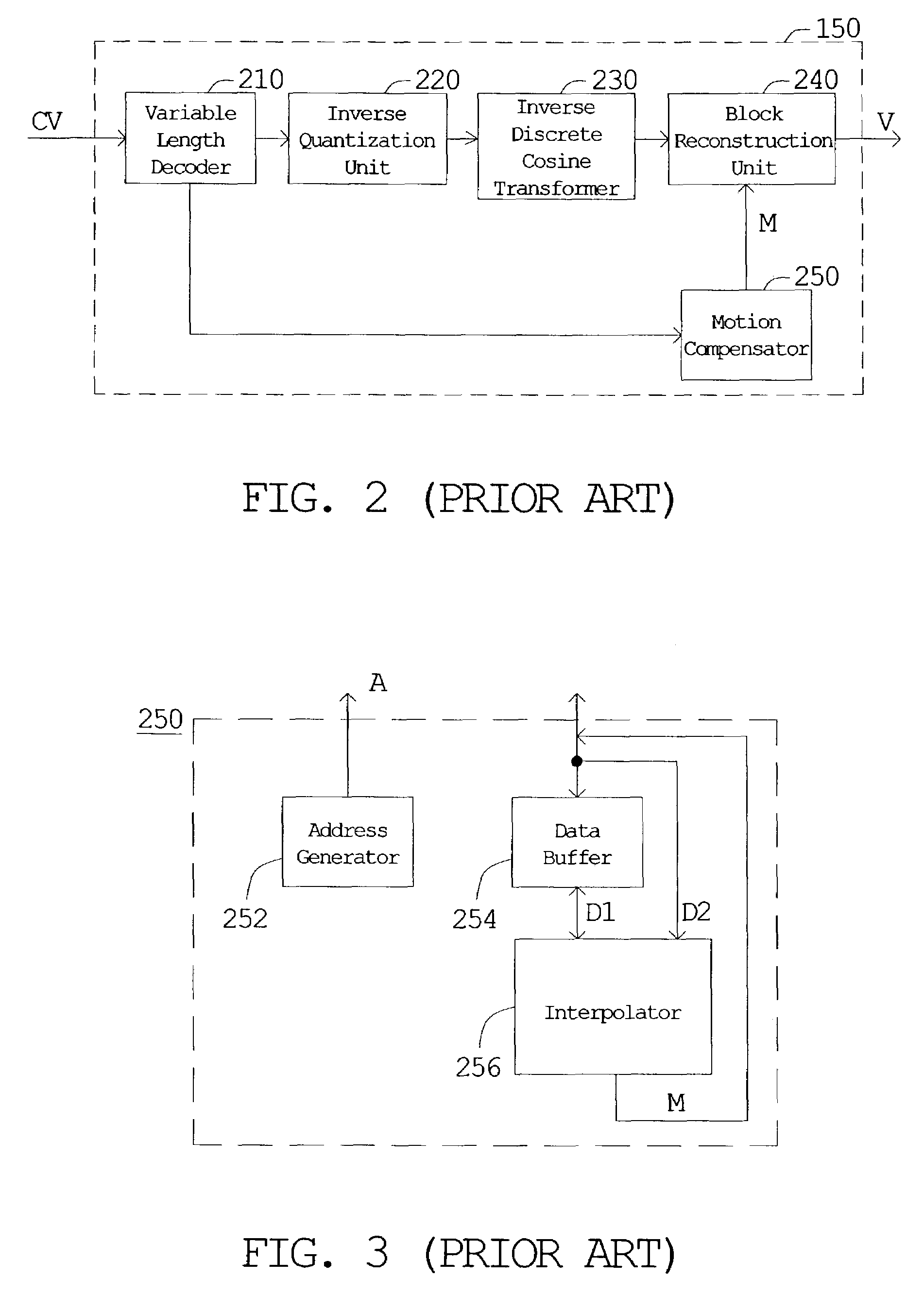

Method and apparatus of picture display

InactiveUS20070263729A1Simplification and improvement of processReduce hardware costsTelevision system detailsColor television with pulse code modulationComputer graphics (images)Image display

A method and an apparatus of picture display. The invention displays the first picture and the second picture and displaying at least one virtual picture in between the first and the second picture. The motion compensator is included in a DVD player. The method includes: decoding the first and the second pictures from the received bit-stream; creating the virtual picture parameter according to the transition effect; and generating the virtual picture according to the virtual picture parameter by the motion compensator.

Owner:XUESHAN TECH INC

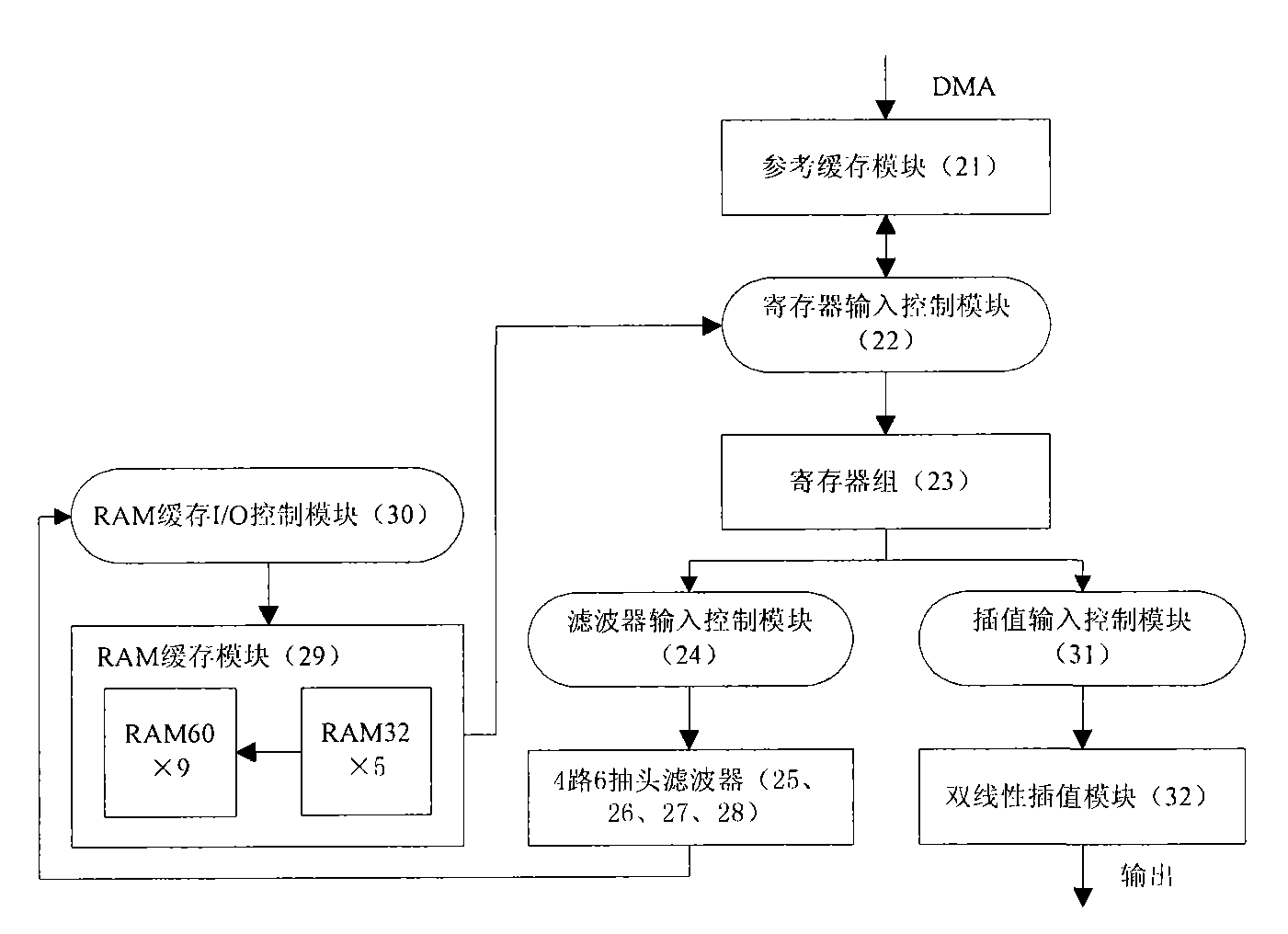

H.264 high-speed luminance interpolating device and method

InactiveCN101795405AImprove hardware utilizationReduce the number of clocksTelevision systemsDigital video signal modificationInput controlDigital video

The invention provides an H.264 high-speed luminance interpolating device comprising a reference caching module, a register input control module, a register set, a filter input control module, N paths of six-tap filters, an RAM (Random-Access Memory) caching I / O control module and an RAM caching module. The reference caching module reads reference pixel matrixes required for the interpolation of the current luminance block from the outside, the reference pixel matrixes are put in the register set after fully being read in the reference caching module, the N paths of six-tap filters simultaneously and respectively obtain six reference pixels as inputs from the register set through the filter input control module, and 1 / 2 pixel points are acquired and then are cached in the RAM caching module. The whole interpolating process of the device achieves a saturated state through the steam running of multiple parallel filters so that the device effectively reduces the luminance interpolating clock number, improves maximum calculating frequency and satisfies the demands of the real-time encoding and decoding of multiple high-definition digital video signals.

Owner:HANGZHOU SILAN MICROELECTRONICS

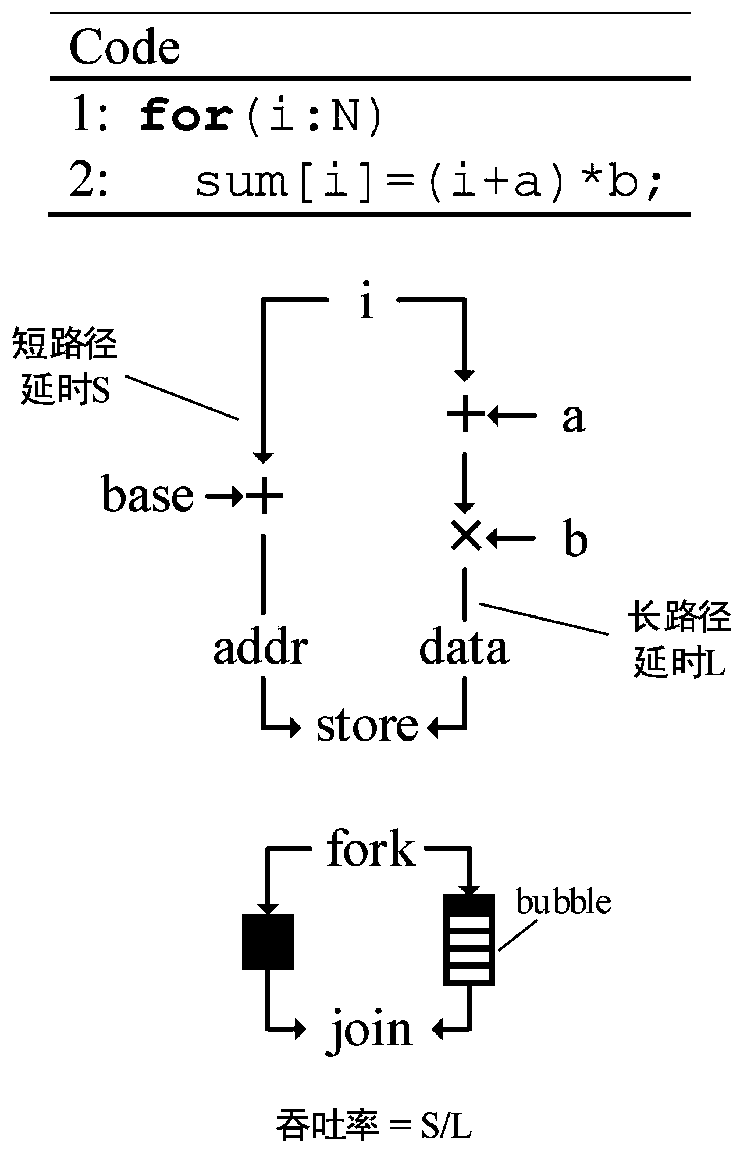

Coarse-grained reconfigurable array structure design method based on data flow decoupling

ActiveCN111475205AHas abstract consistencyImprove hardware utilizationConcurrent instruction executionEnergy efficient computingMutual influenceAssembly line

The invention discloses a coarse-grained reconfigurable array structure design method based on data flow decoupling and a decoupling unit. The invention relates to the field of computer coprocessor acceleration. A data flow coupling phenomenon causing pause of an assembly line in a static CGRA is concluded as mutual influence generated by different data flow rates caused by factors such as memoryaccess, control and the like; decoupling is carried out, the decoupling unit is designed and inserted into the coupling interaction position between different areas, the decoupling unit serves as a unified memory access interface, assembly line pause of different forms is optimized, and the CGRA performance and the resource utilization rate are improved.

Owner:SHANGHAI JIAO TONG UNIV +1

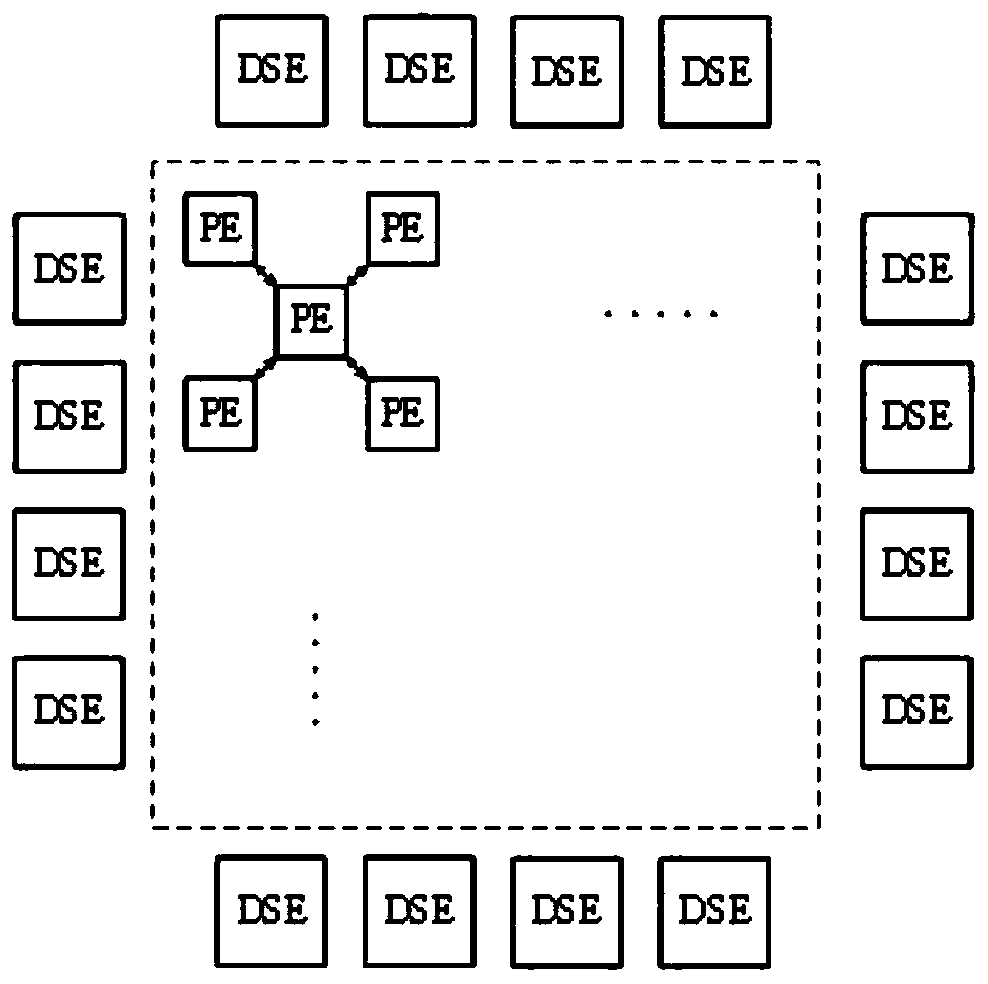

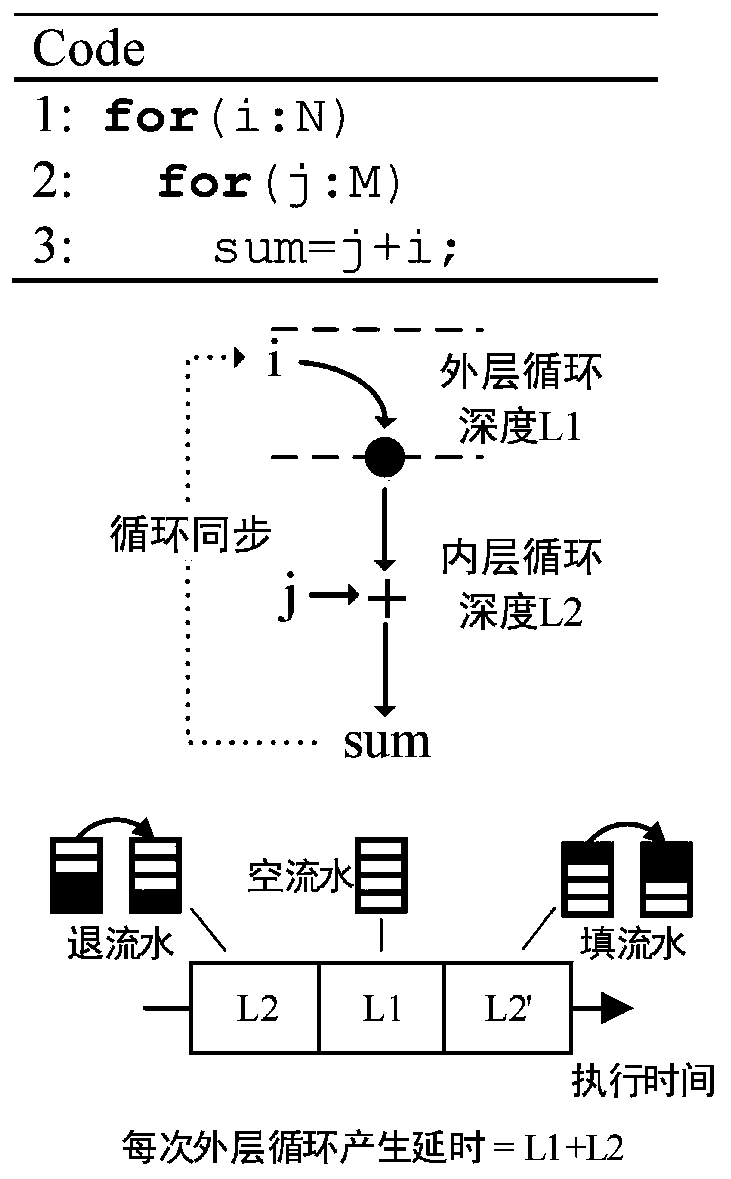

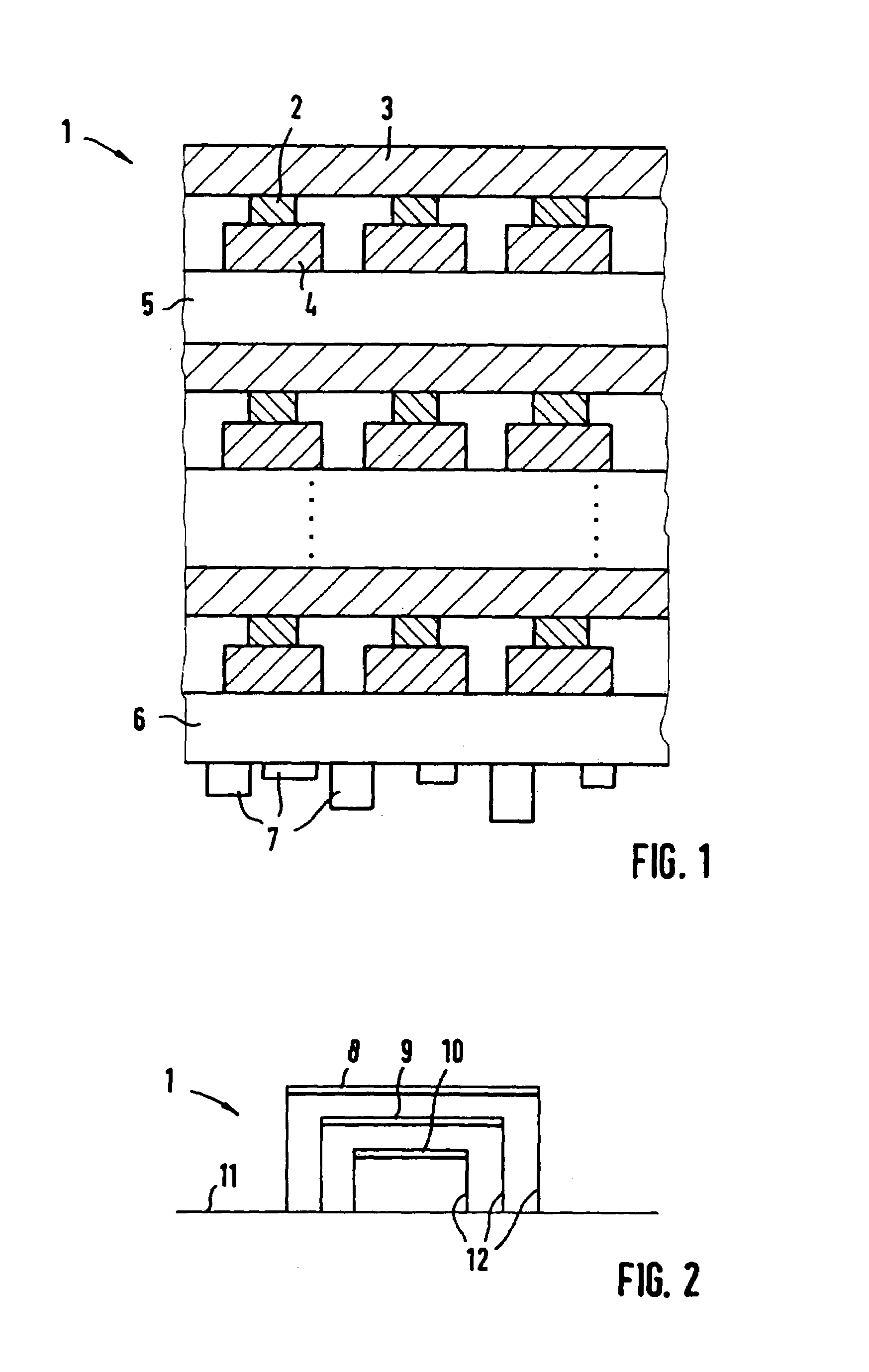

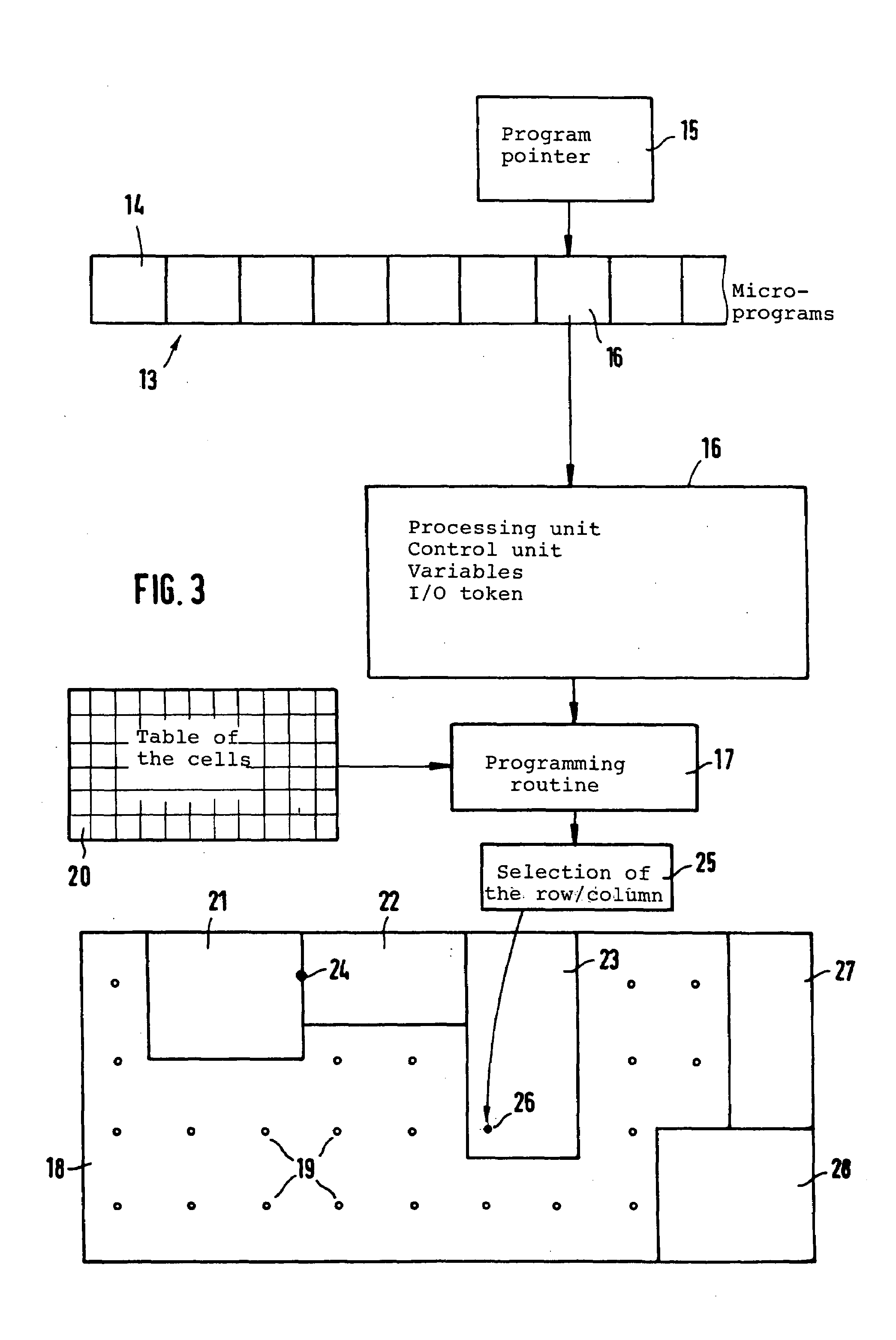

Reprogrammable microprogram based reconfigurable multi-cell logic concurrently processing configuration and data signals

InactiveUS7225321B2Improve hardware utilizationEnergy efficient ICTArchitecture with single central processing unitProcess configurationEmbedded system

Owner:SIEMENS AG

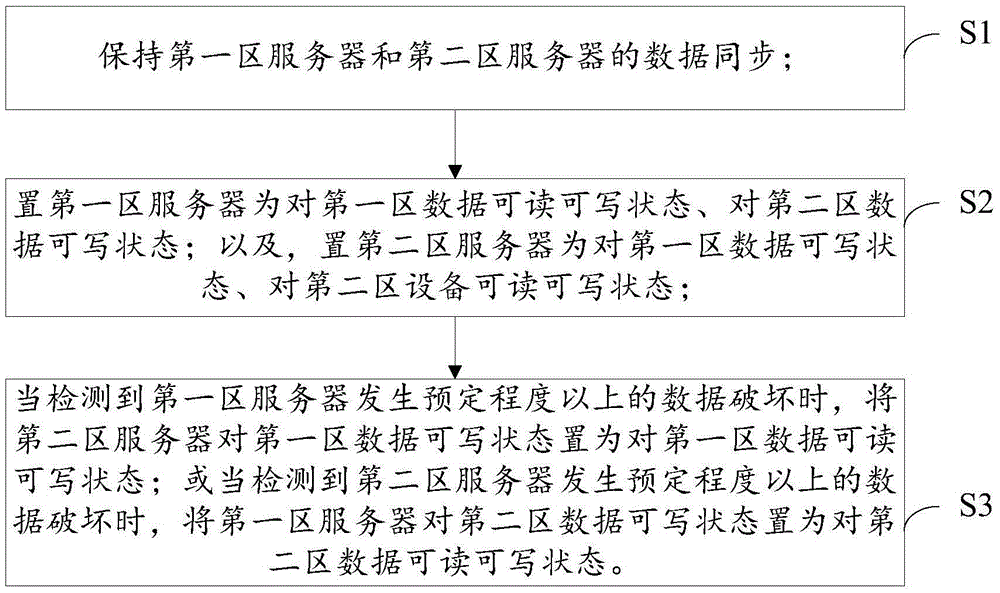

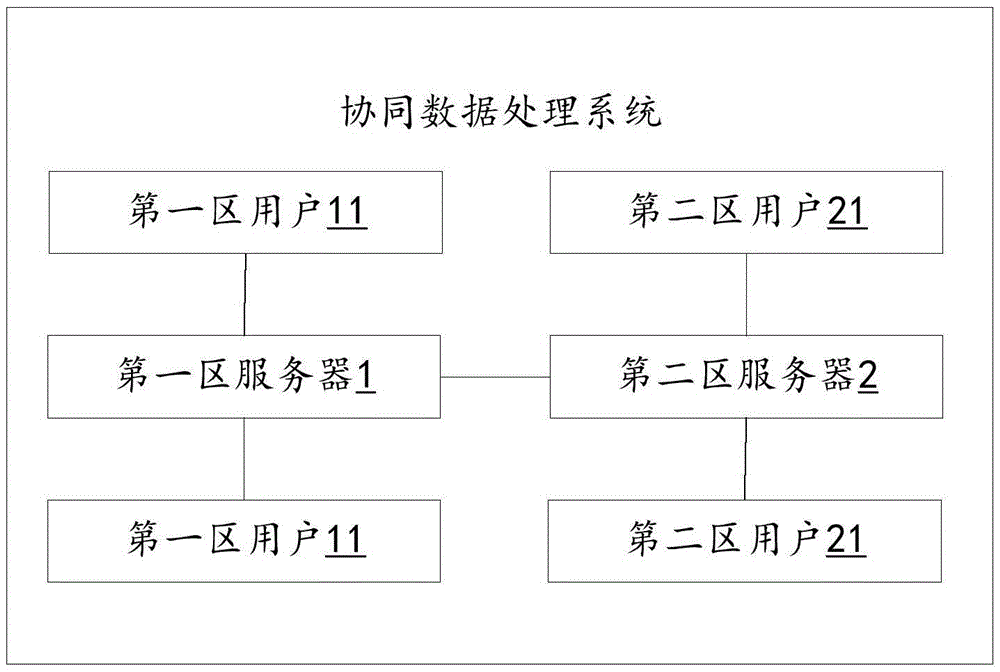

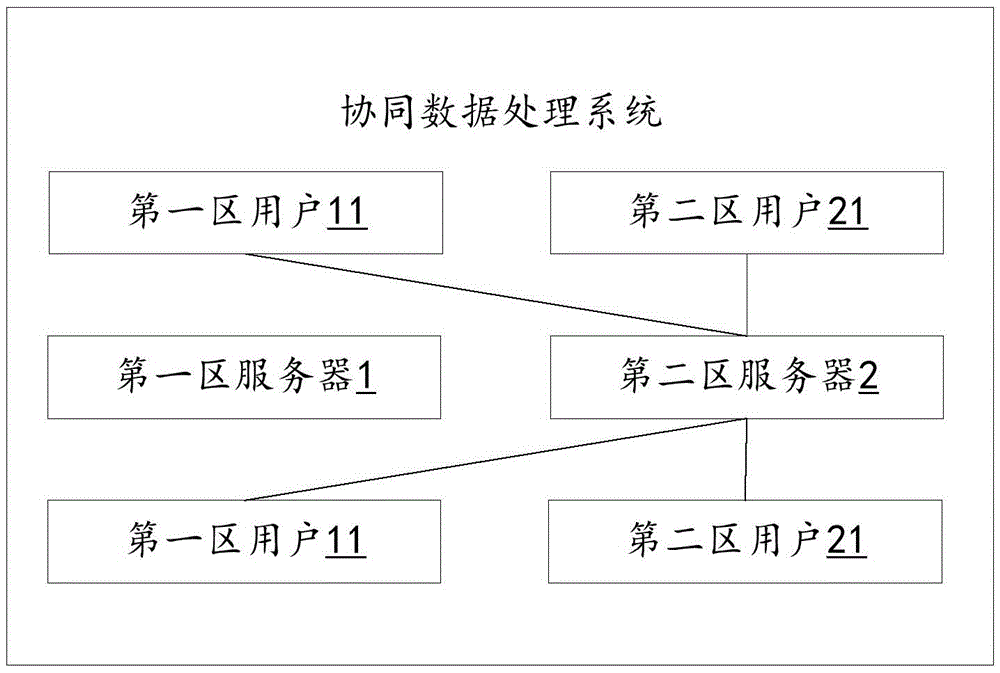

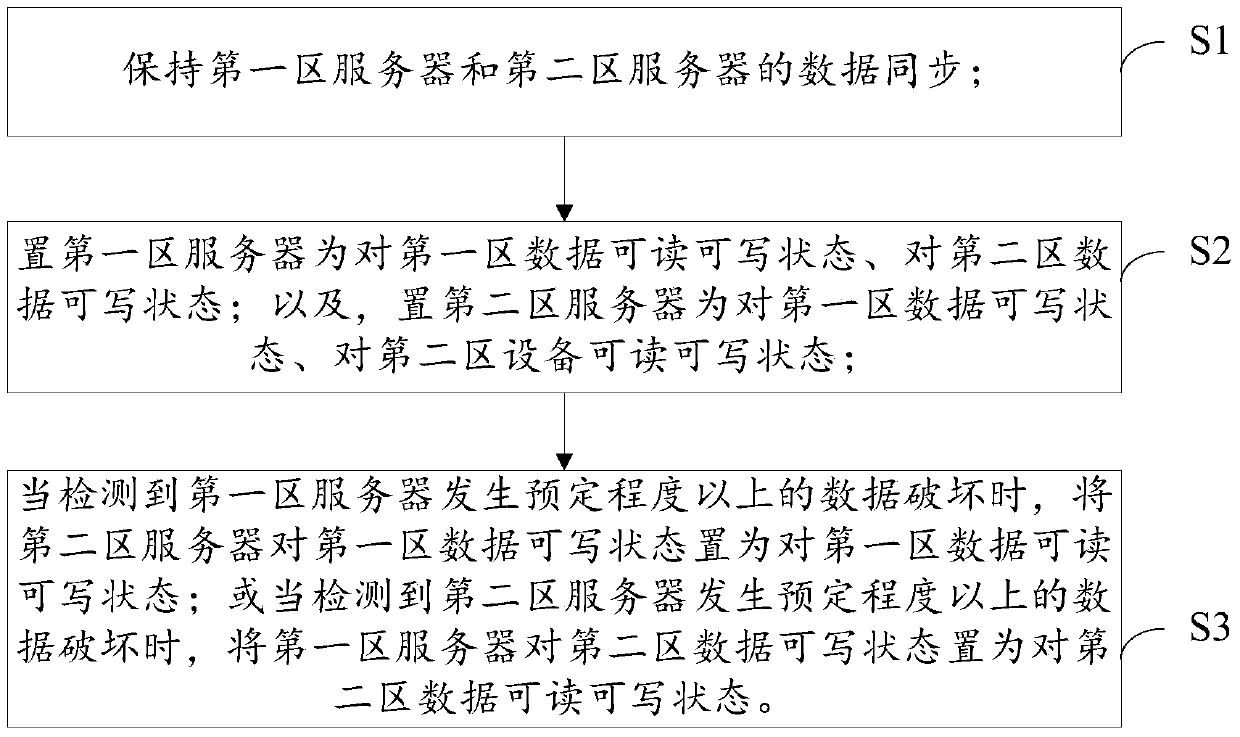

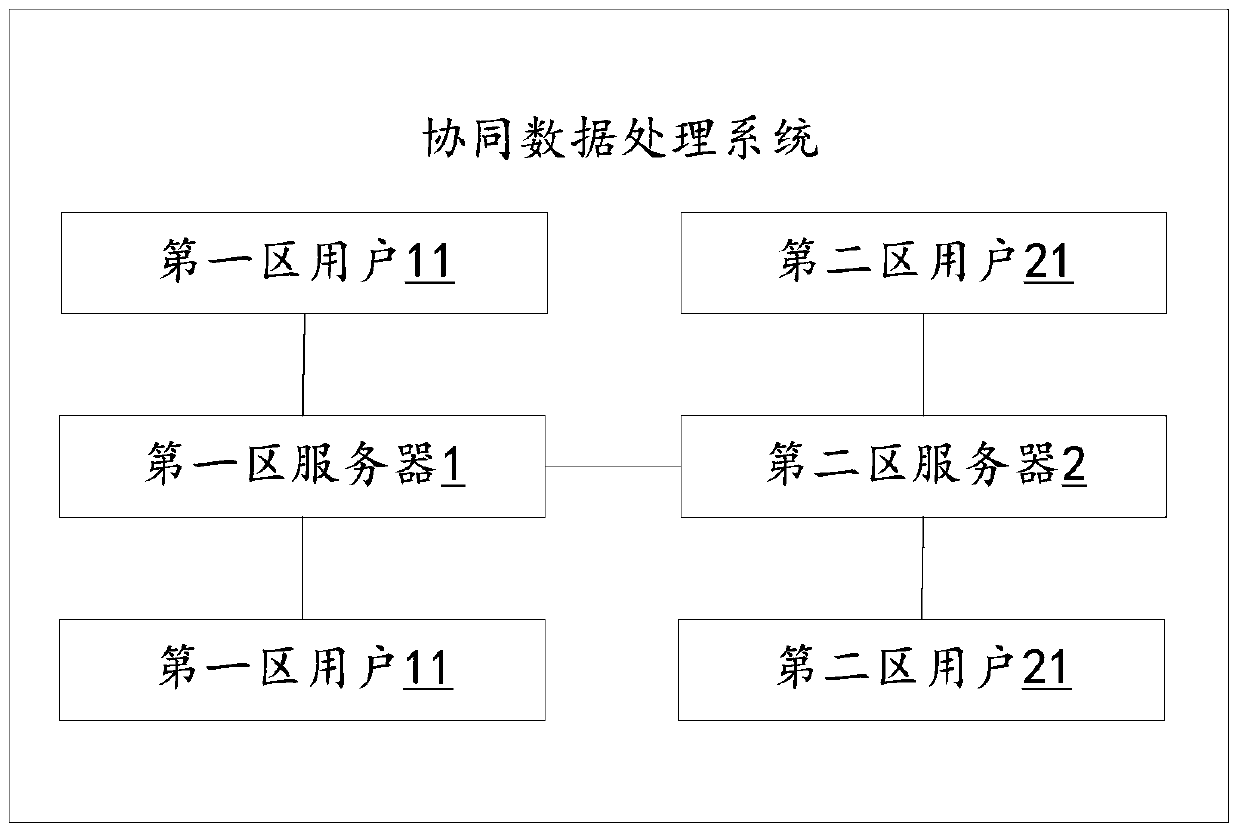

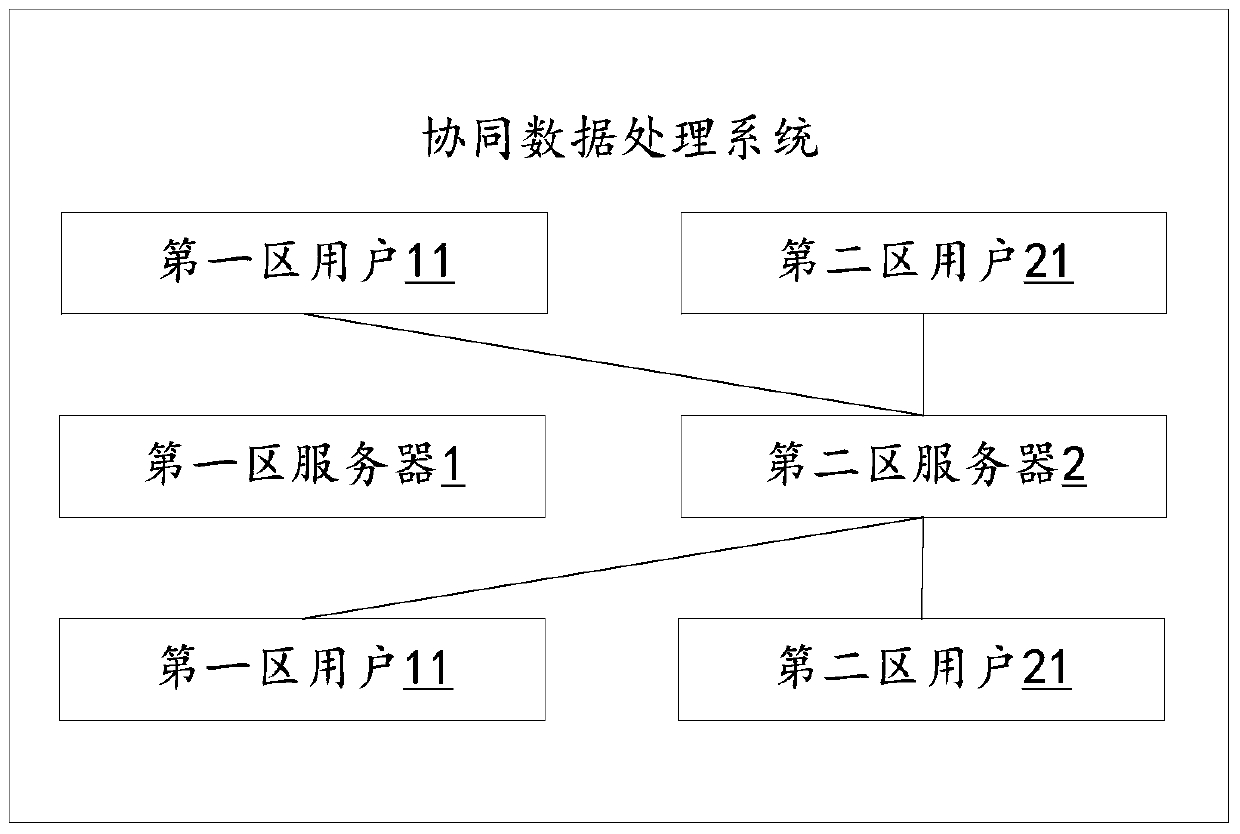

Collaborative data processing method and system

ActiveCN105608190AIncrease speedImprove hardware utilizationDatabase distribution/replicationSpecial data processing applicationsData synchronizationData consistency

The invention provides a collaborative data processing method. The method comprises the following steps: keeping data synchronization of a first-zone server and a second-zone server; setting the first-zone server to be in a first-zone data readable and writable state and a second-zone data writable state; setting the second-zone server to be in a first-zone data writable state and a second-zone device readable and writable state; when it is detected that data destruction of more than a predetermined degree occurs to the first-zone server, setting the first-zone data writable state of the second-zone server to be the first-zone data readable and writable state; or when it is detected that the data destruction of more than the predetermined degree occurs to the second-zone server, setting the second-zone data writable state of the first-zone server to be the second-zone data readable and writable state. According to the collaborative data processing scheme, the synchronization speed is high, a business service can be completely provided, and the requirement of double center data consistency can be met.

Owner:FUJIAN YIRONG INFORMATION TECH

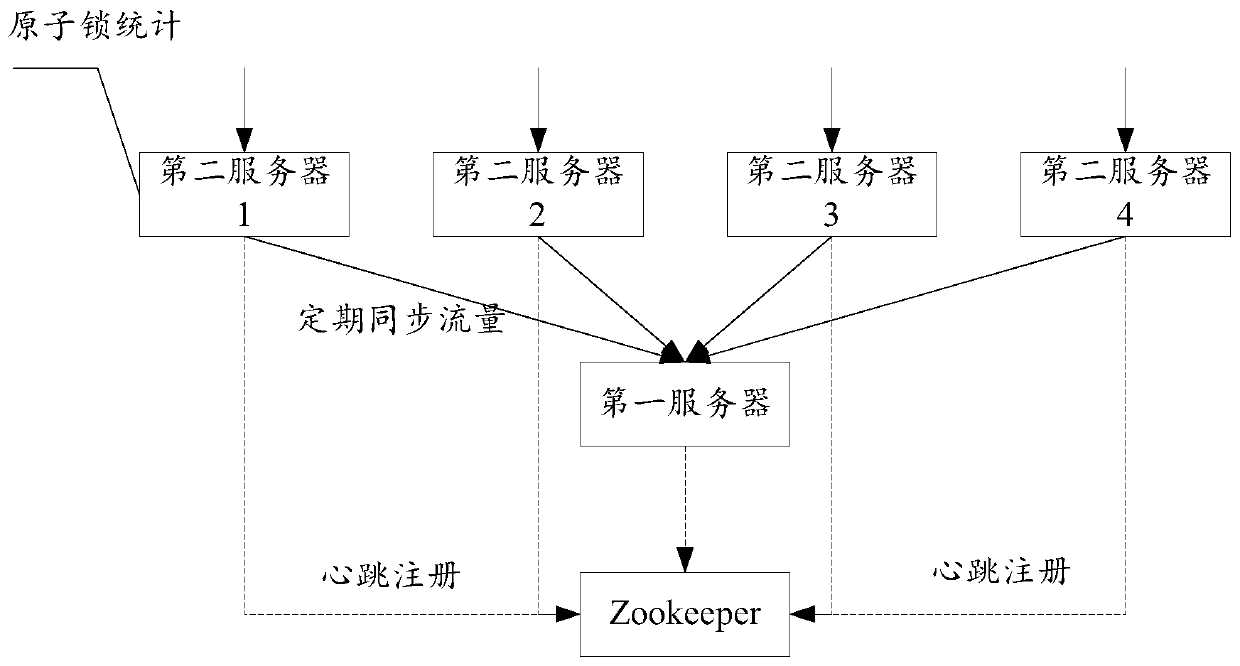

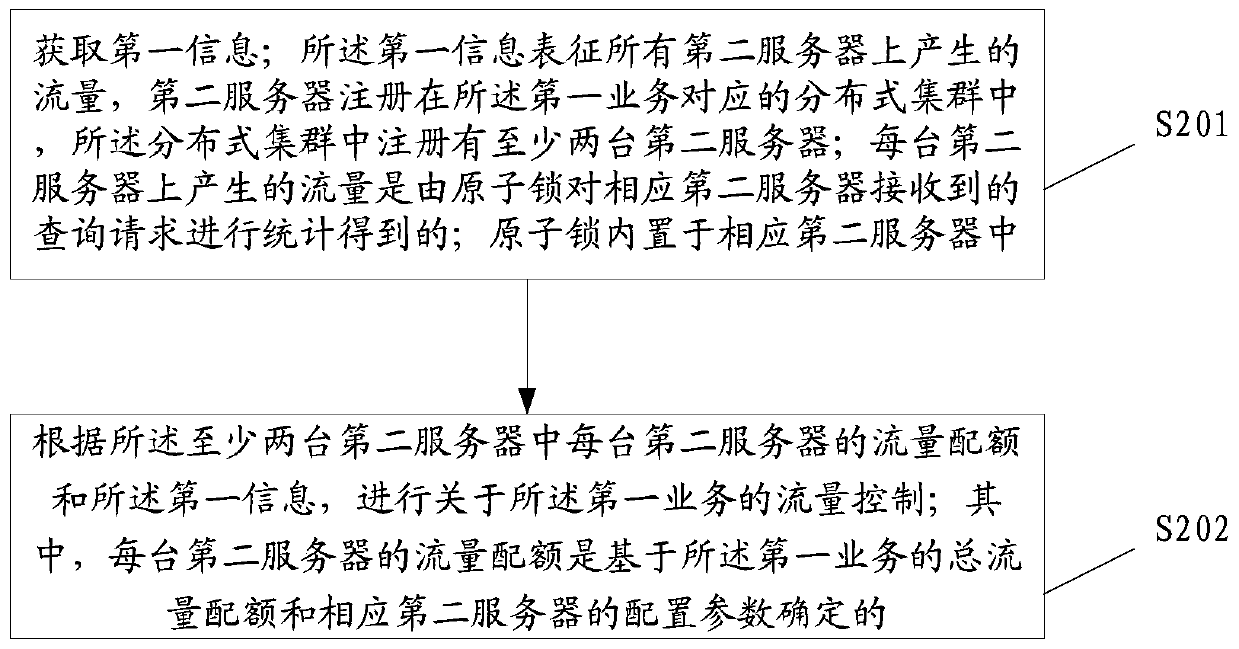

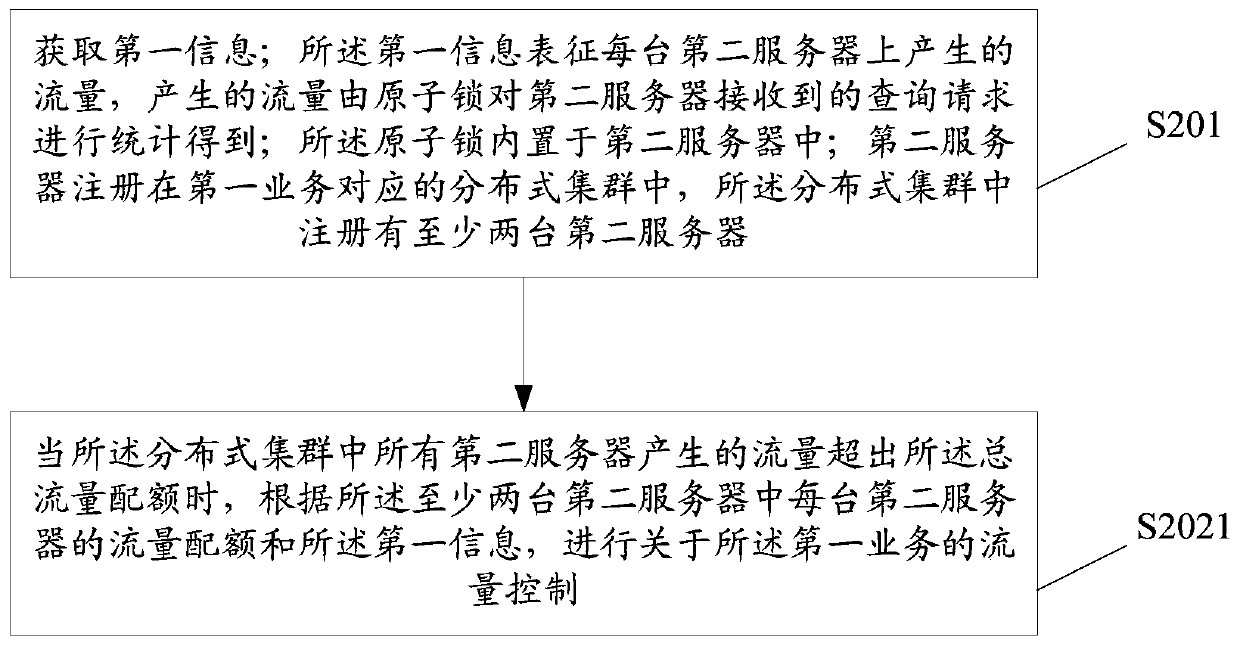

Flow control method and device, server and storage medium

PendingCN110708258AImprove hardware utilizationImprove overall throughputData switching networksEngineeringReal-time computing

The invention discloses a flow control method and device, a server and a storage medium. The method comprises the following steps: acquiring first information; wherein the first information representsflows generated on all second servers, the second servers are registered in a distributed cluster corresponding to the first service, and at least two second servers are registered in the distributedcluster; wherein the flow generated on each second server is obtained by counting the query request received by the corresponding second server by the atomic lock; the atomic locks are arranged in the corresponding second servers; according to the flow quota of each second server in the at least two second servers and the first information, flow control about the first service is carried out; wherein the traffic quota of each second server is determined based on the total traffic quota of the first service and the configuration parameters of the corresponding second server.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

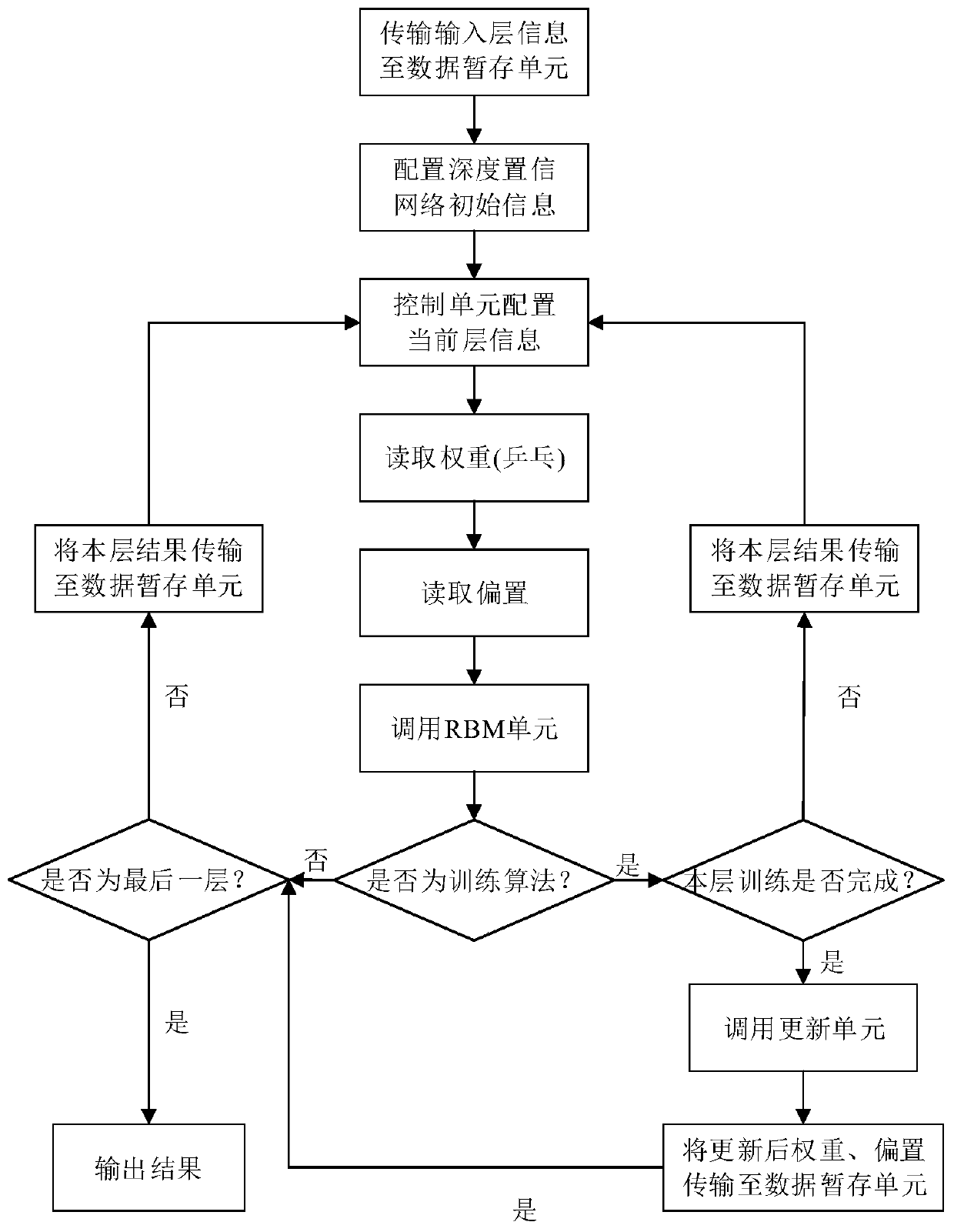

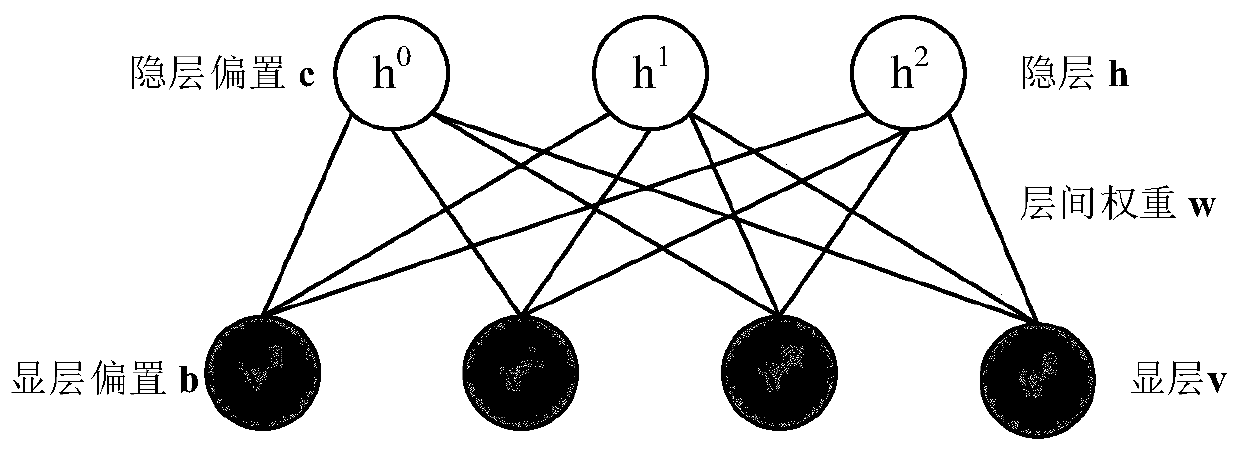

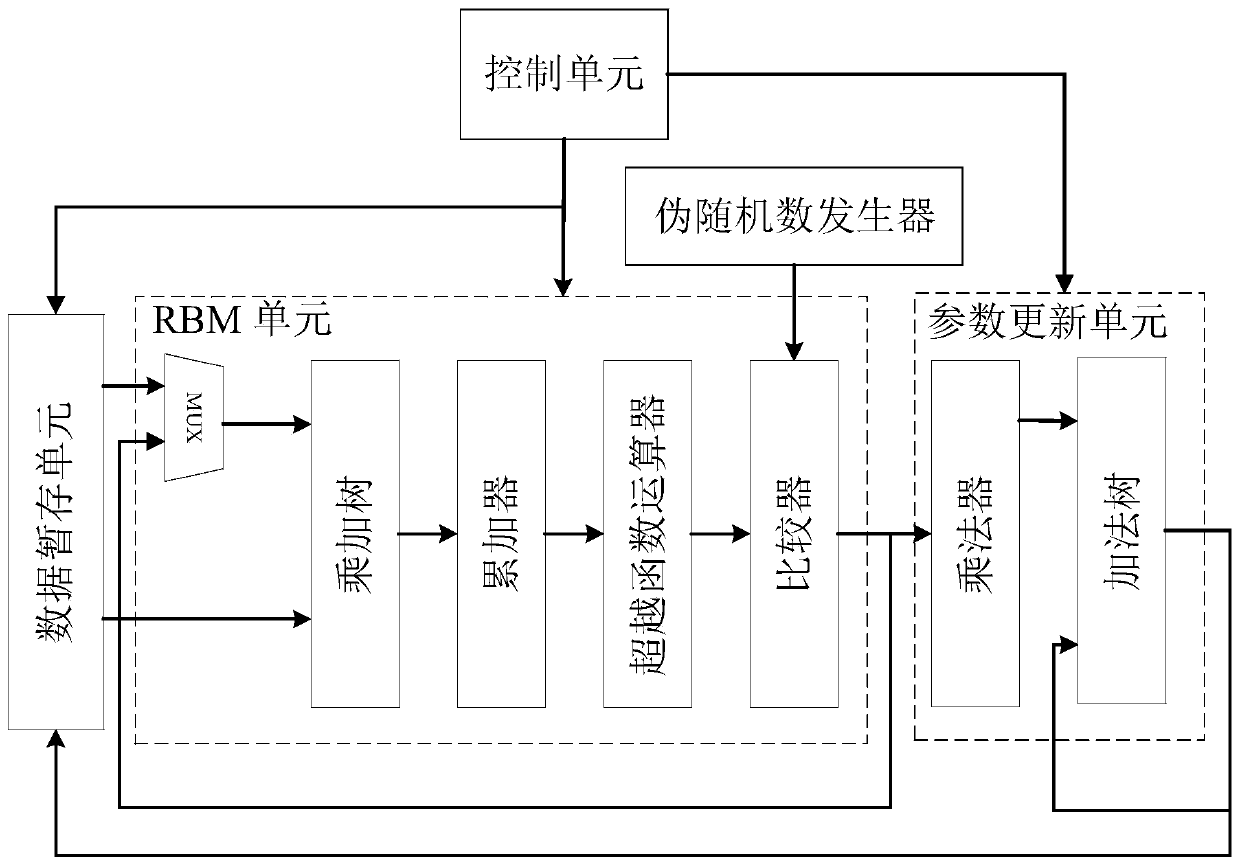

A reconfigurable deep belief network implementation system

ActiveCN109711543AApplicable to various application scenariosShort operation cyclePhysical realisationEnergy efficient computingDeep belief networkRestricted Boltzmann machine

The invention discloses a reconfigurable deep belief network implementation system. The system comprises a control unit used for controlling the operation process of a deep belief network algorithm; the data temporary storage unit is used for storing and calculating required input layer information, weights, offsets and output layer results; the restricted Boltzmann machine is used for calculatingthe activation probability of each layer of nodes in the deep belief network so as to determine the activation state; and the parameter updating unit is used for updating the weight and bias of eachlayer of nodes in the deep belief network, and is only activated in the training algorithm. The implementation system has the beneficial effects that two algorithms of training and reasoning can be supported by multiplexing the restricted Boltzmann machine and controlling the state jump of the algorithm, the hardware resource cost of the algorithm is reduced, the performance of the algorithm is ensured, and the implementation system is suitable for various artificial intelligence scenes.

Owner:NANJING UNIV

Method and apparatus of picture display

ActiveUS7257160B2Simplification and improvement of processReduce hardware costsTelevision system detailsPicture reproducers using cathode ray tubesComputer graphics (images)Computer science

A method and an apparatus of picture display. The invention displays the first picture and the second picture and displaying at least one virtual picture in between the first and the second picture. The motion compensator is included in a DVD player. The method includes: decoding the first and the second pictures from the received bit-stream; creating the virtual picture parameter according to the transition effect; and generating the virtual picture according to the virtual picture parameter by the motion compensator.

Owner:XUESHAN TECH INC

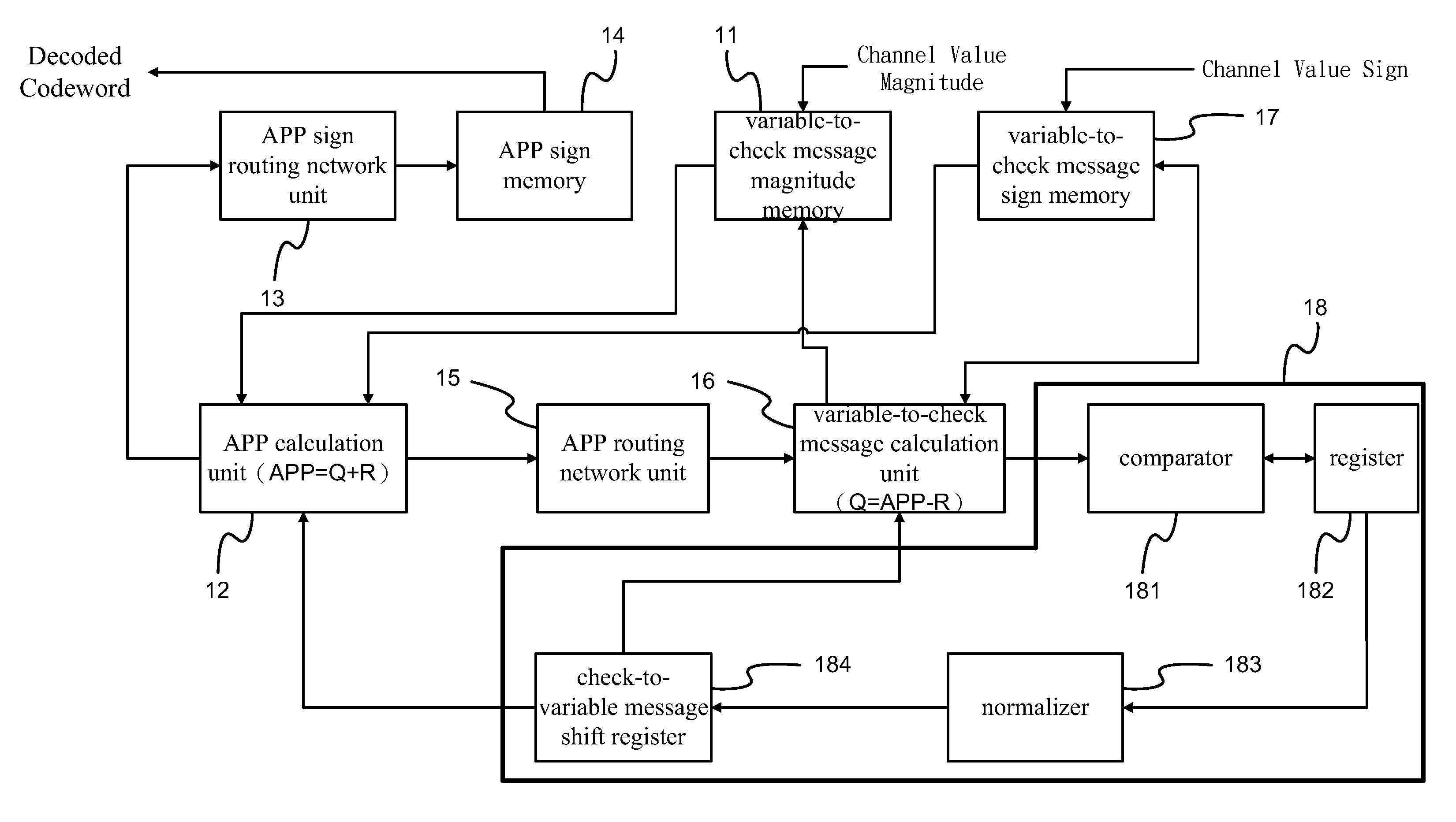

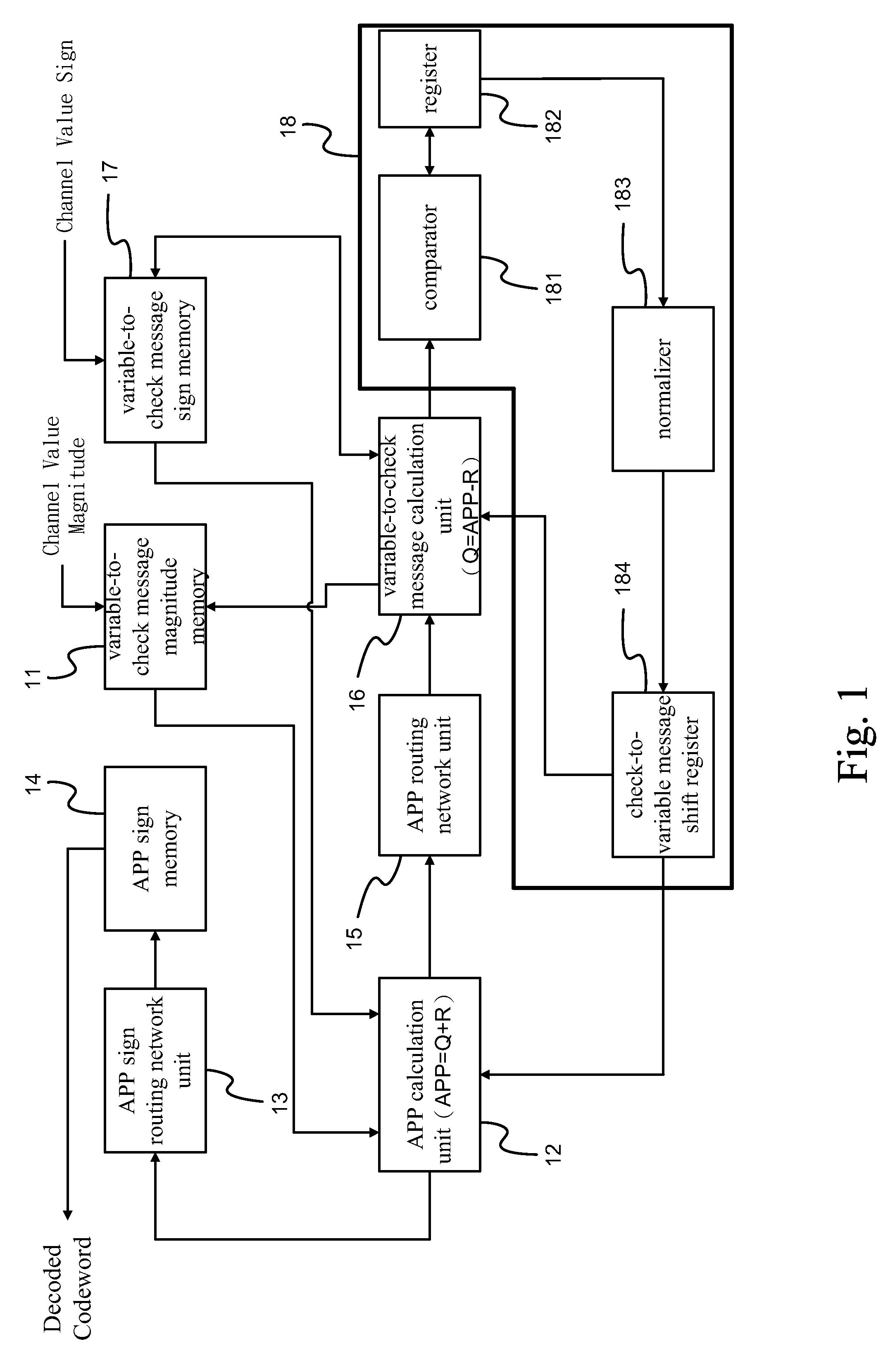

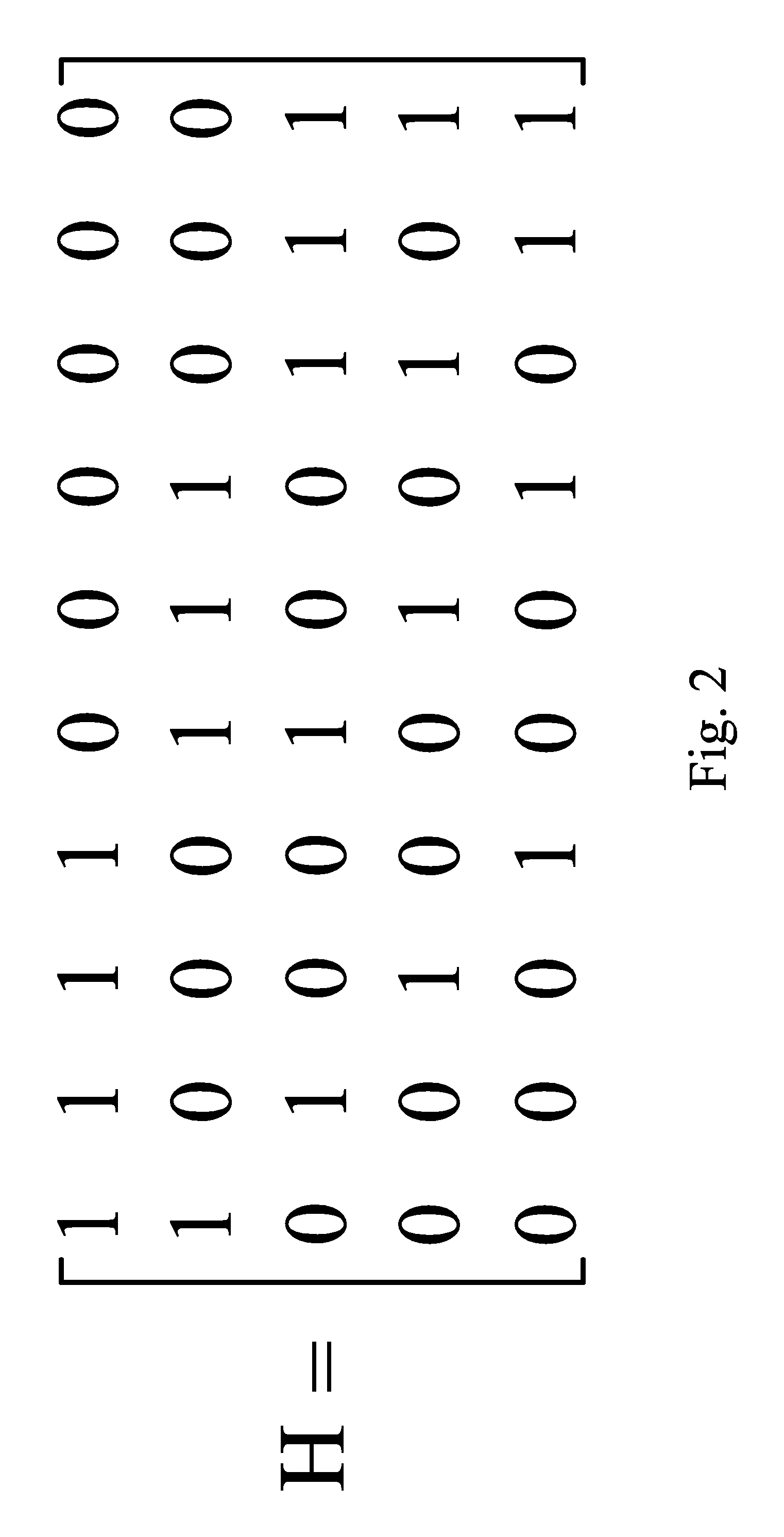

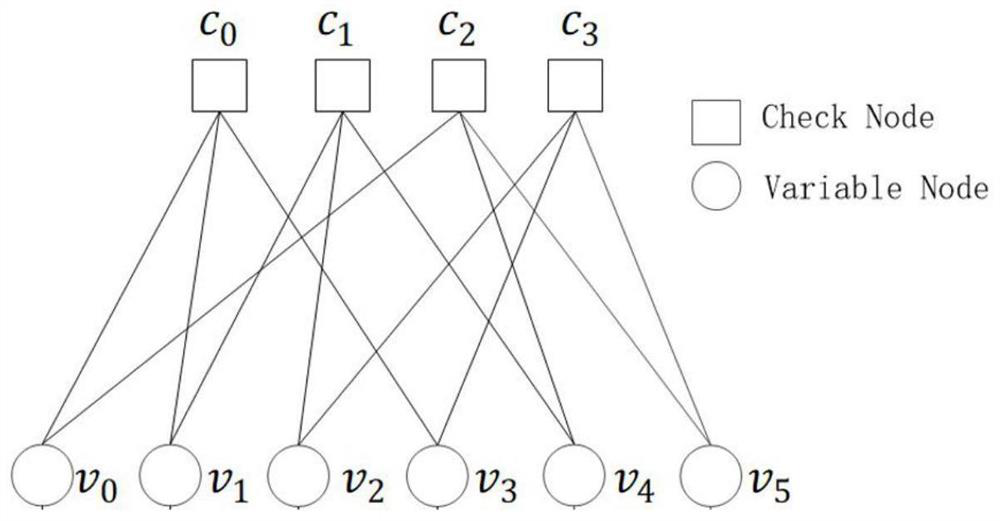

Layered decoding architecture with reduced number of hardware buffers for LDPC codes

ActiveUS9048872B2Reduce hardware areaImprove hardware utilizationError correction/detection using multiple parity bitsCode conversionShift registerProcessor register

A layered decoding architecture with a reduced number of hardware buffers for low-density parity-check (LDPC) decoding by storing a variable-to-check message. When a check node begins a new operation, a variable-to-check message (Q) is added to a check-to-variable message (R) obtained in previous check-node operation to obtain an updated APP value. Then, the R value for the check node in the layer being processed is deducted from the APP value to obtain a variable-to-check message (Q). This variable-to-check message is stored in the memory and inserted into the check node equation to obtain a check-to-variable message. Finally the check-to-variable message obtained in this operation is stored to the check-to-variable message shift register to complete the updating operation for the check node and the variable node for the layer being processed. Improved hardware utilization and fewer buffers, thus achieving a smaller hardware area while retaining the converge speed, is obtained.

Owner:NATIONAL TSING HUA UNIVERSITY

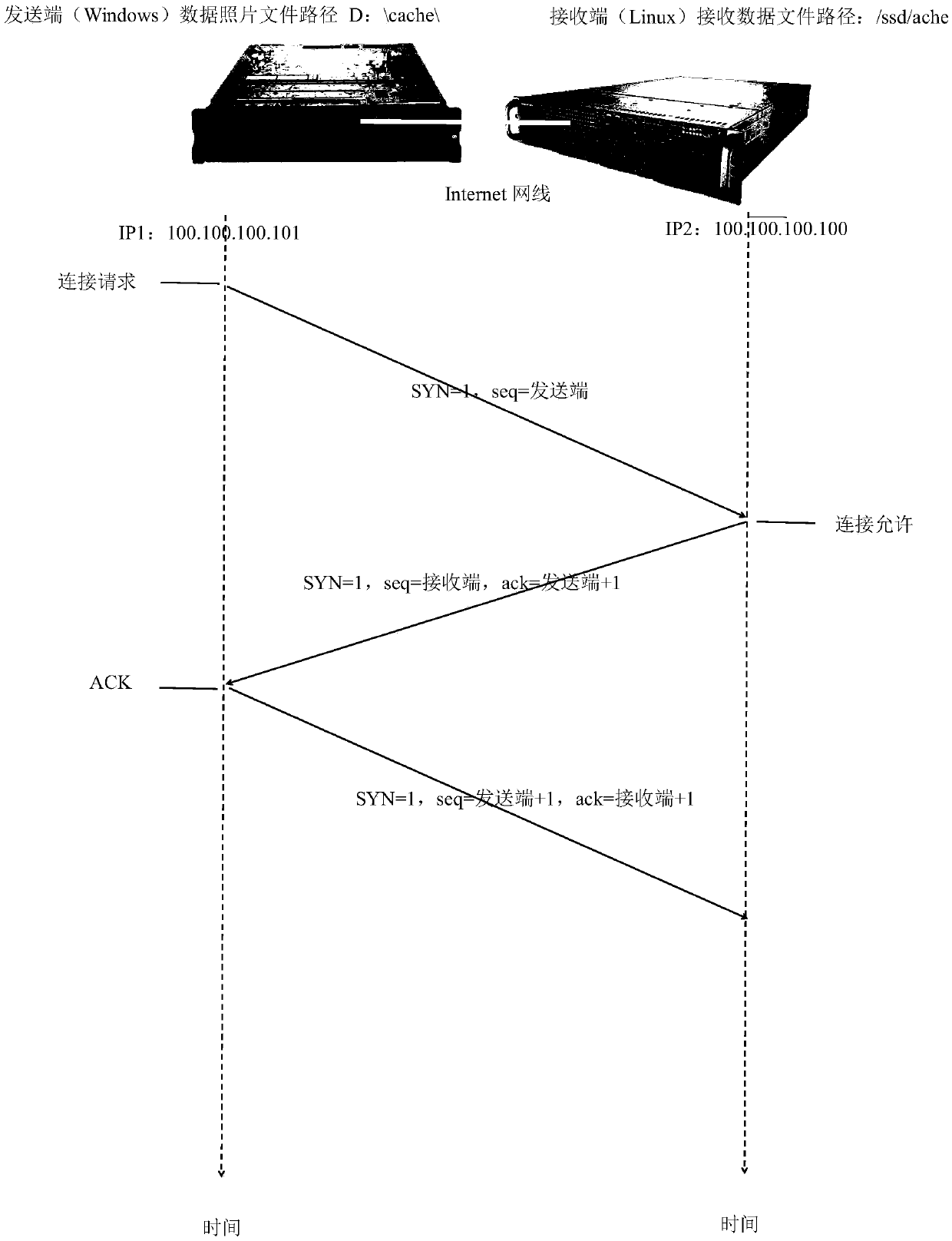

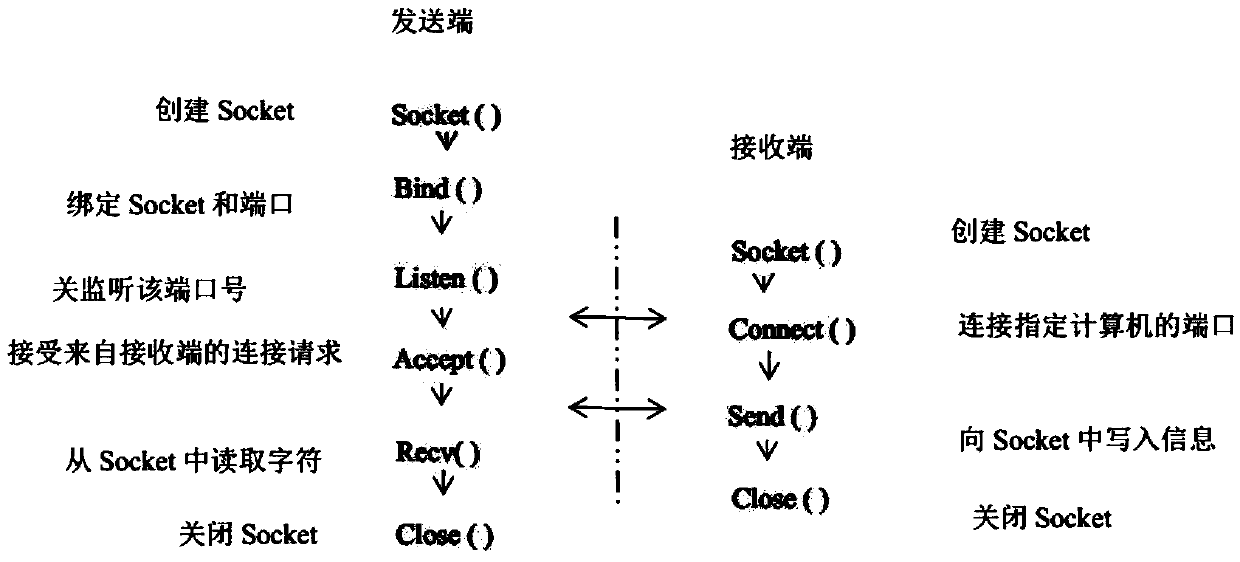

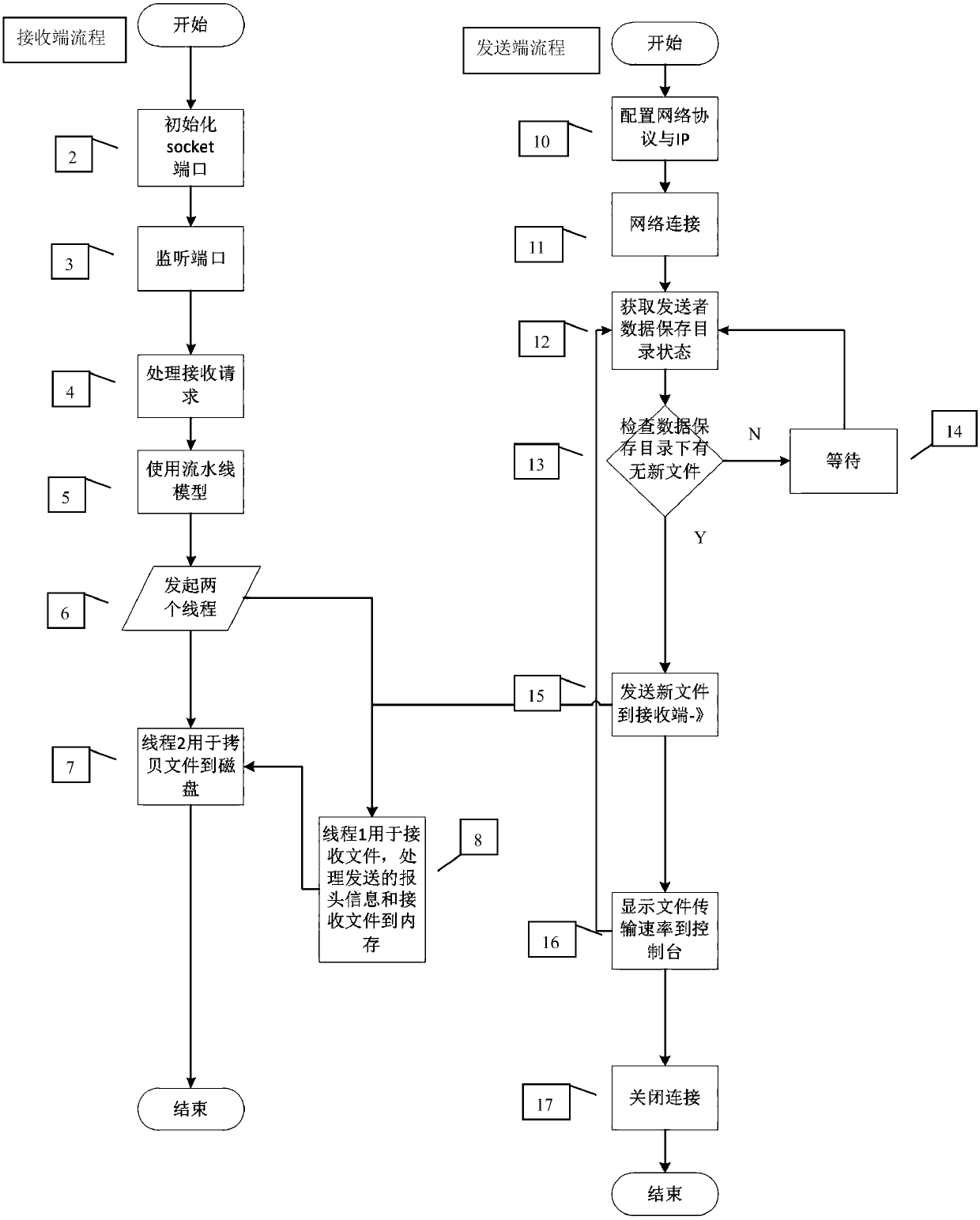

System and client for big data synchronization

InactiveCN109660562AImprove hardware utilizationLow costTransmissionData synchronizationReal-time data

The invention relates to a system and a client for big data synchronization. Compared with the traditional scheme, the hardware utilization rate is high, the cost is greatly reduced, the socket communication is adopted, the transmission rate is effectively improved, an assembly line model is used for real-time data synchronization demands of a cryo-electron microscope, and the transmission speed can be greatly improved; and the software client is already packaged, the professional does not need to build network service, thereby being convenient, fast and easy to use, and users can use directlyopen the software for use without professional training.

Owner:BLUEJAY IMAGING CO LTD

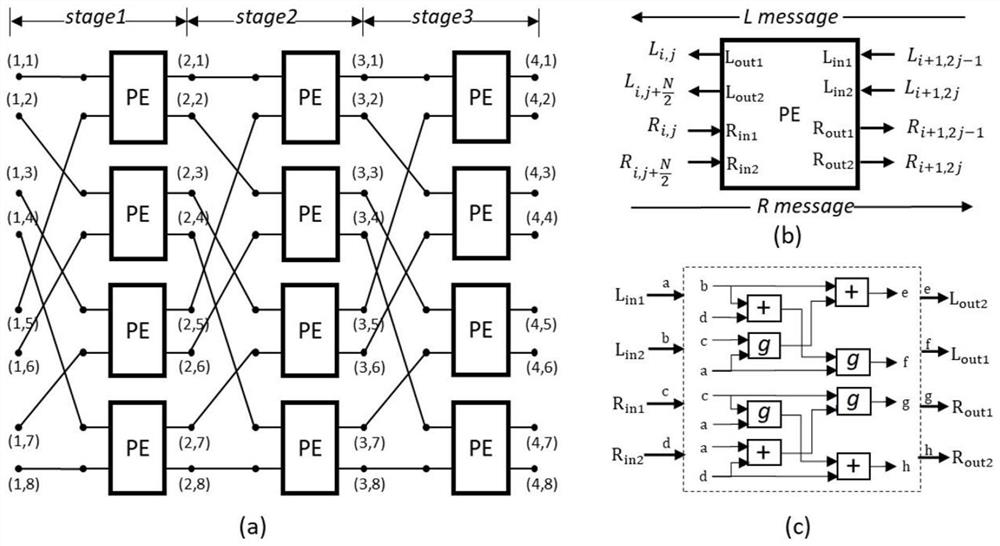

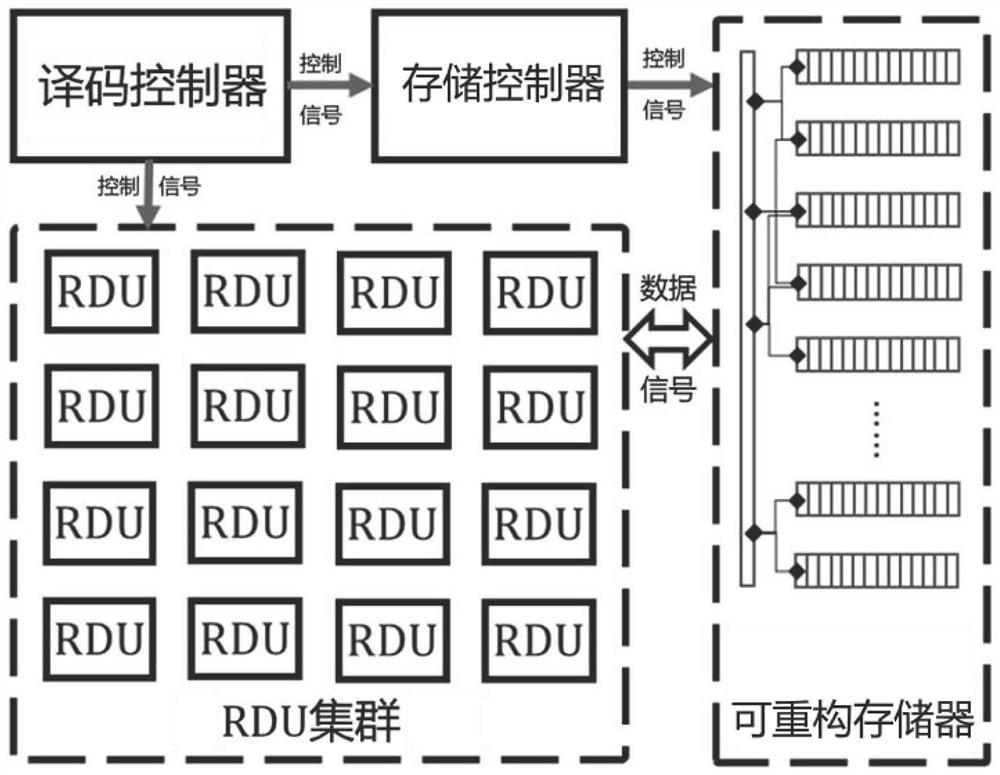

Reconfigurable polar code and low density parity check code decoder

ActiveCN113055025ASolve decodingImprove hardware utilizationError correction/detection using multiple parity bitsCode conversionComputer architectureControl store

A reconfigurable polar code and low density parity check code decoder comprises an RDU cluster, a decoding controller, a storage controller and a reconfigurable memory, the decoding controller dynamically regroups the RDU of each code word in the RDU cluster according to a decoding mode and a decoding mode, generates an instruction word and outputs the instruction word to the RDU cluster and the storage controller, the storage controller generates a corresponding read-write control signal and an address signal according to the instruction word and outputs the read-write control signal and the address signal to the reconfigurable memory for read-write control, and the reconfigurable memory reads information data from the RDU cluster and writes in or reads information and outputs the information to the RDU cluster. According to the invention, the similarity of BP decoding algorithms of an LDPC code and a polarization code is utilized, the reconfigurable decoder of the reconfigurable LDPC code and the polarization code is realized, and compared with the mode of independently realizing LDPC decoding and polarization code decoding, the decoder has the advantages that hardware resources are saved, and the utilization rate of the hardware resources is improved.

Owner:SHANGHAI UNIV

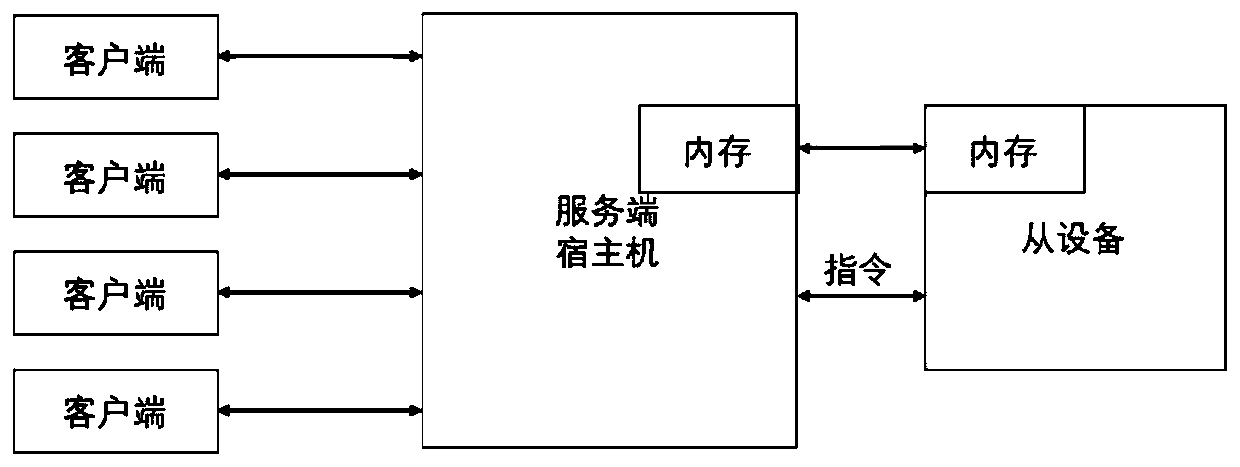

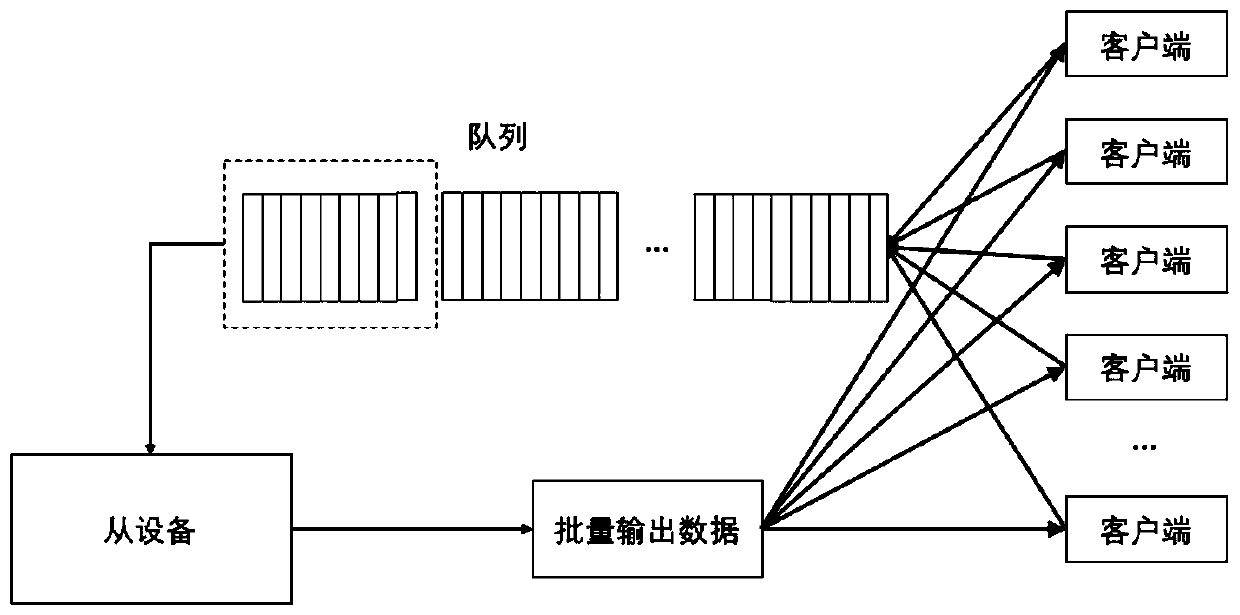

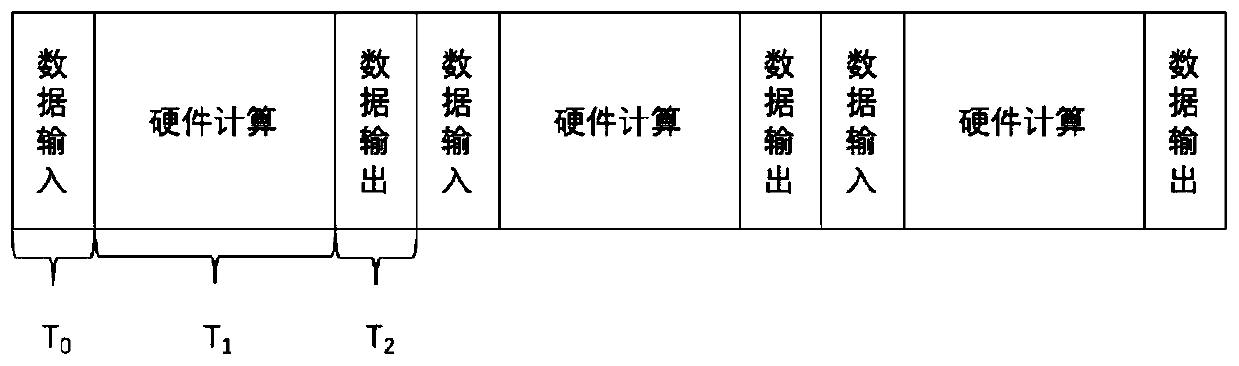

Computing task processing method, device and system, server and storage medium

PendingCN110955461AImprove hardware utilizationReduce consumptionProgram loading/initiatingParallel computingData transport

The invention discloses a computing task processing method, device and system, a server and a storage medium. A plurality of input cache regions are arranged in the server, and the method comprises the following steps of: generating a plurality of computing tasks based on a data processing request sent by a client; determining an input cache region of each calculation task, and respectively inputting task data corresponding to the calculation tasks into the input cache regions; under the condition that the input cache regions meeting the starting condition exist in the input cache regions, starting to execute the calculation tasks corresponding to the input cache regions meeting the starting condition; and returning the calculation result of the executed calculation task to the corresponding client. According to the invention, the consumption caused by data transmission can be reduced, the stable server throughput capacity is only related to the hardware computing performance of a slave device, and the hardware utilization rate of the slave device is improved.

Owner:BEIJING DAJIA INTERNET INFORMATION TECH CO LTD

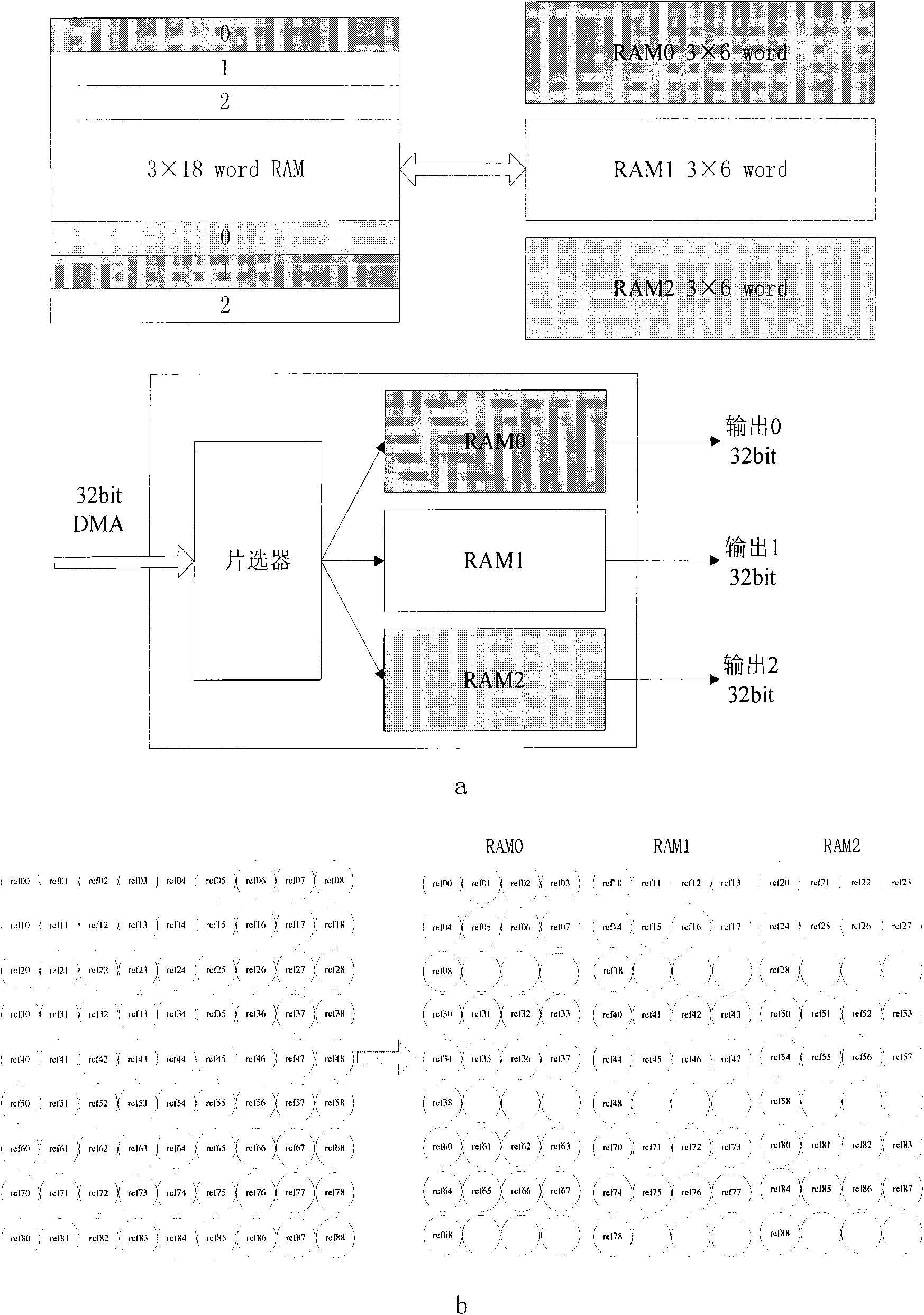

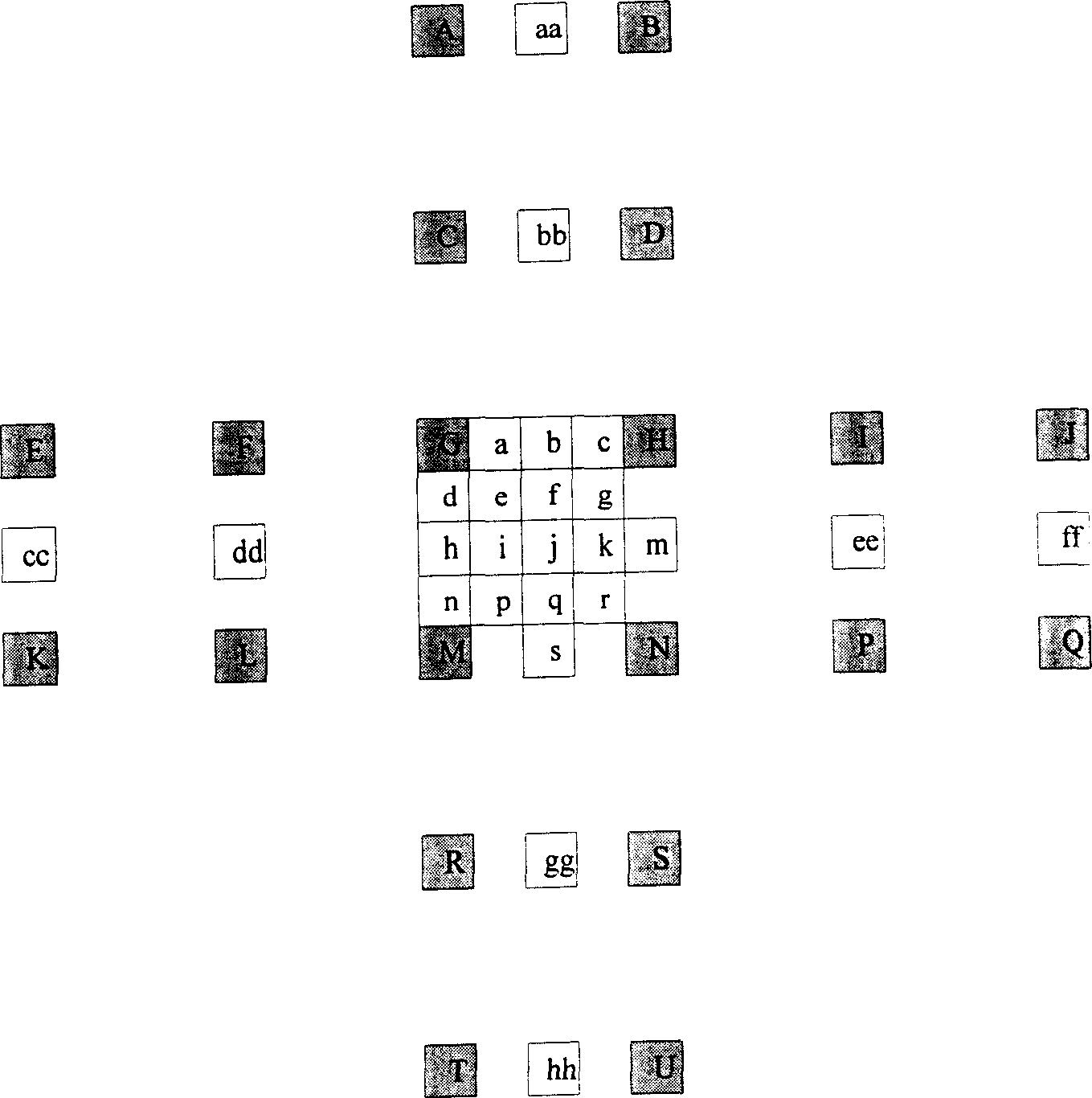

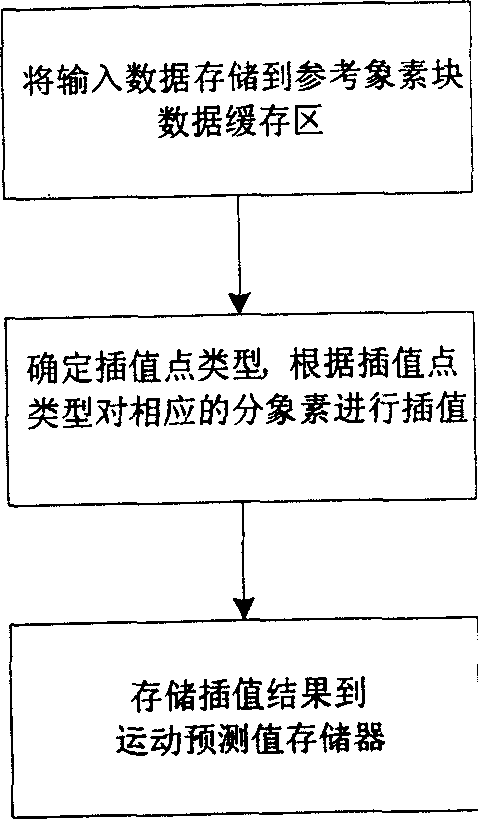

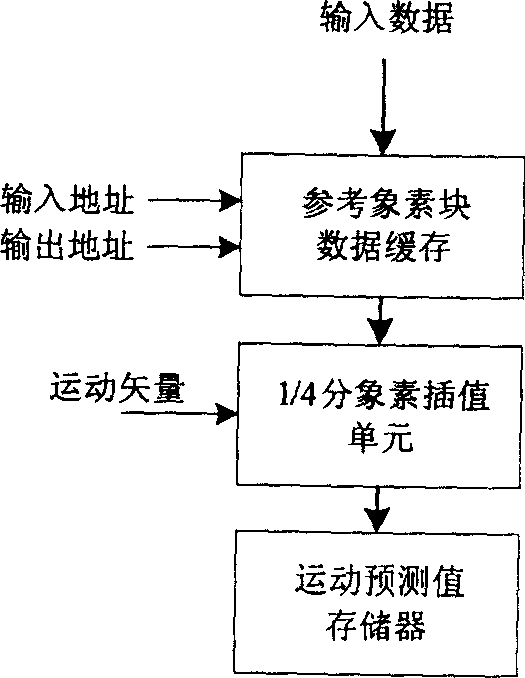

Method and device for realizing disparting pixel Interpolation for variable block size motion compensation

InactiveCN1909665AImprove hardware utilizationReduce the number of clock cyclesTelevision systemsDigital video signal modificationComputer scienceSignal processing

The invention relates to a method for variable-block motion compensation pixel interpolation, and relative device, wherein said method comprises: storing the pixel data used in interpolation into the reference pixel block data buffer area; dividing several interpolation points into several types, to interpolate on each interpolation point, to obtain the motion predict value; storing said motion predict values in row or queue into motion predict valve memory. And said device comprises: connected reference pixel block data buffer module, sub pixel interpolation unit and motion predict value memory. The invention can improve the efficiency of sub pixel interpolation.

Owner:TSINGHUA UNIV

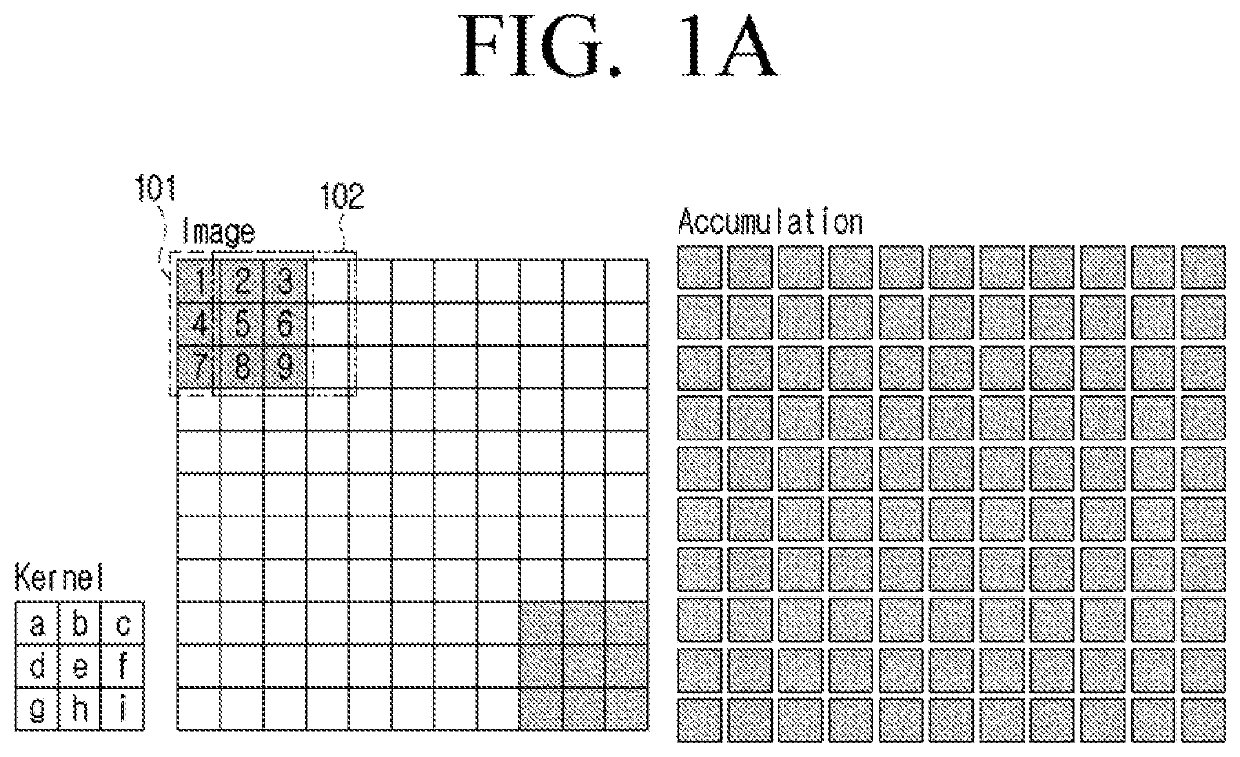

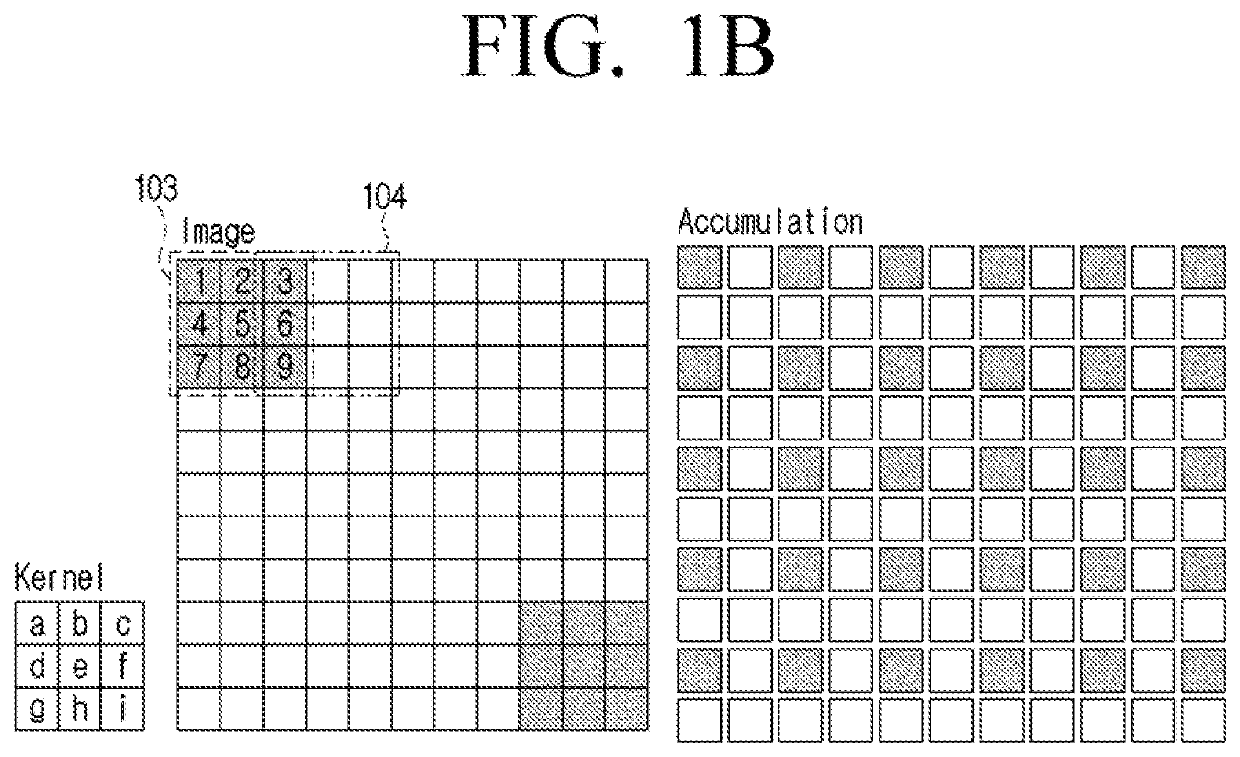

Electronic device and control method thereof

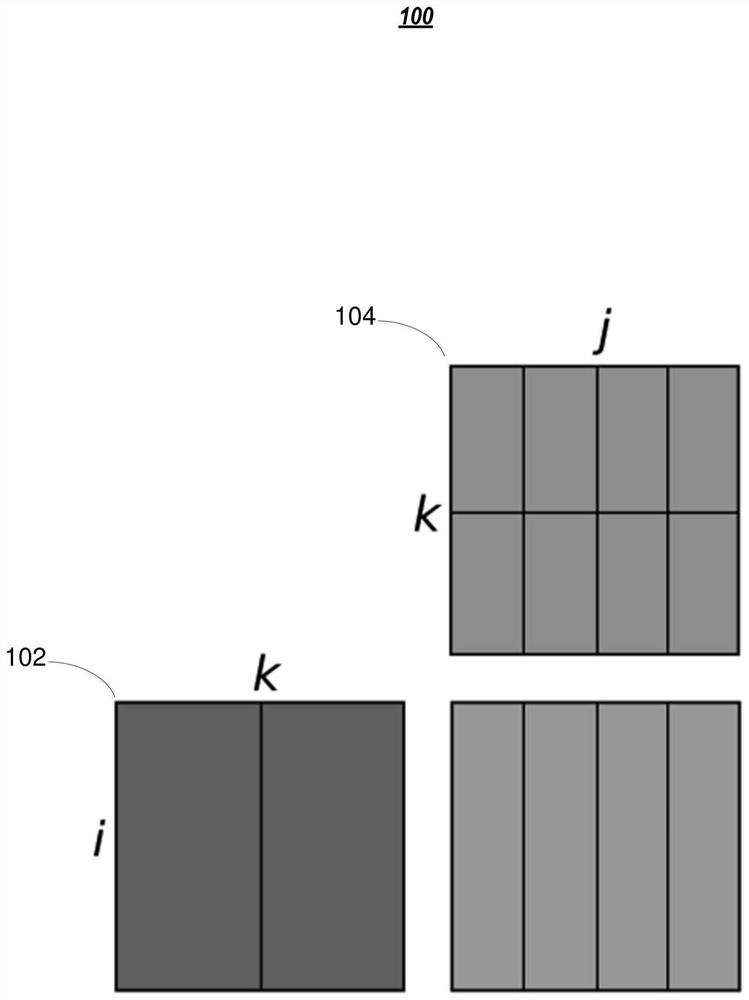

ActiveUS20200272946A1Improve hardware utilizationKernel methodsNeural architecturesInformation representationData mining

Disclosed is an electronic device. The An electronic device including a storage, and a processor configured to perform convolution processing on target data and kernel data based on stride information that indicates an interval at which the kernel data is applied to the target data stored in the storage, in which the processor is further configured to divide the target data into a plurality of pieces of sub-data based on first stride information, perform the convolution processing on the plurality of pieces of sub-data and a plurality of pieces of sub-kernel data respectively corresponding to the plurality of pieces of sub-data based on second stride information that is different from the first stride information, and combine a plurality of processing results, the plurality of pieces of sub-kernel data are obtained by dividing the kernel data based on the first stride information, and the second stride information indicates that the interval at which the kernel data is applied to the target data is 1.

Owner:SAMSUNG ELECTRONICS CO LTD

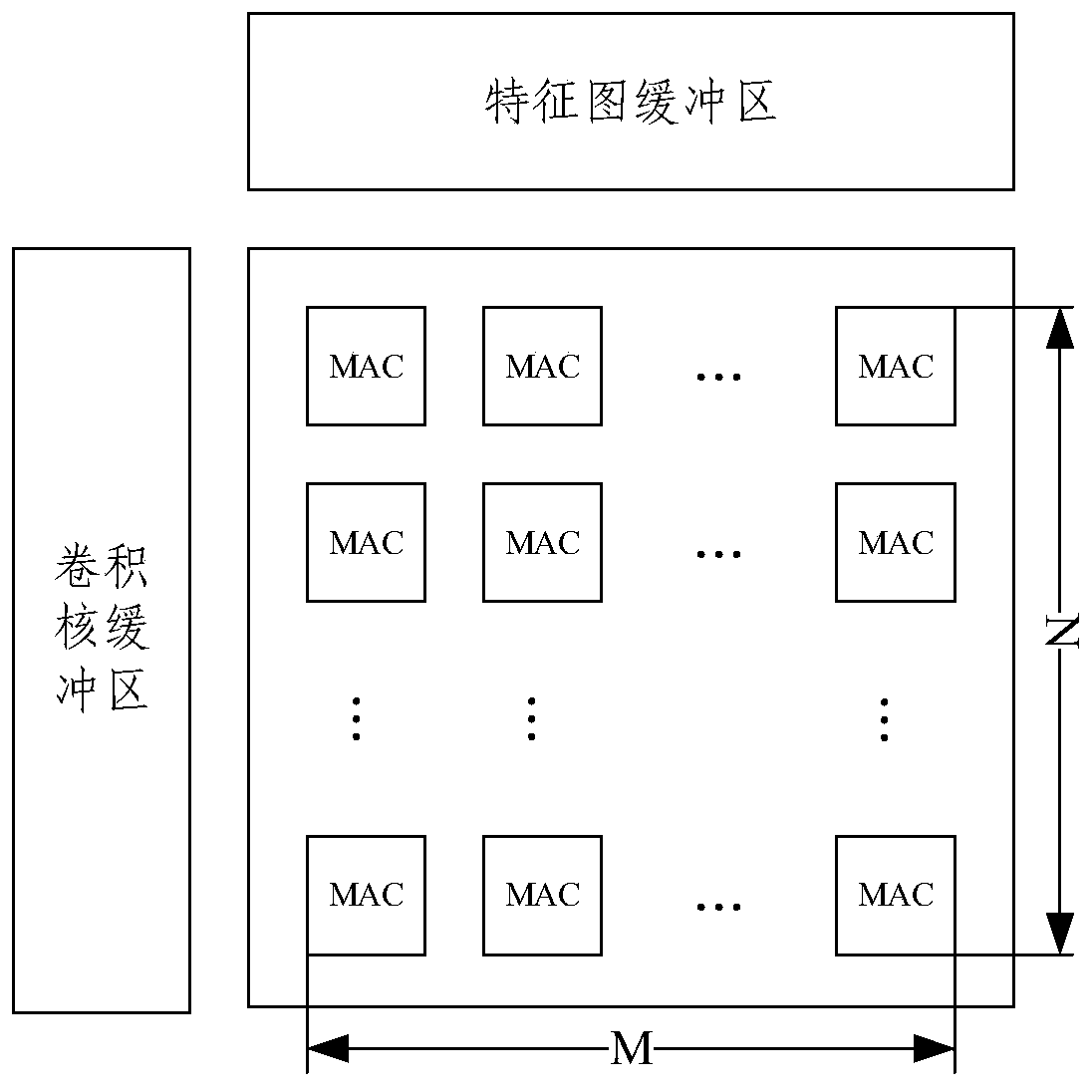

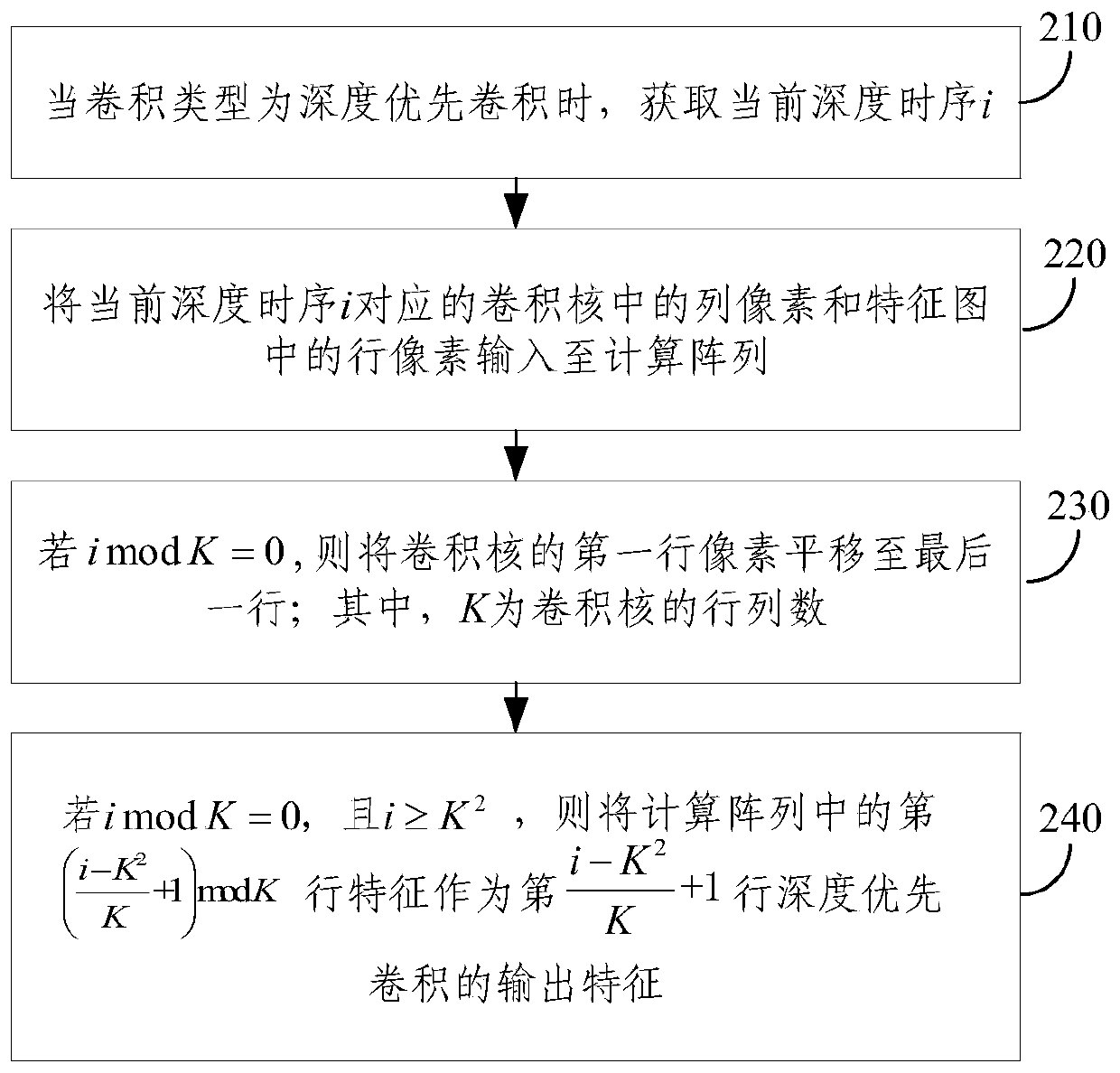

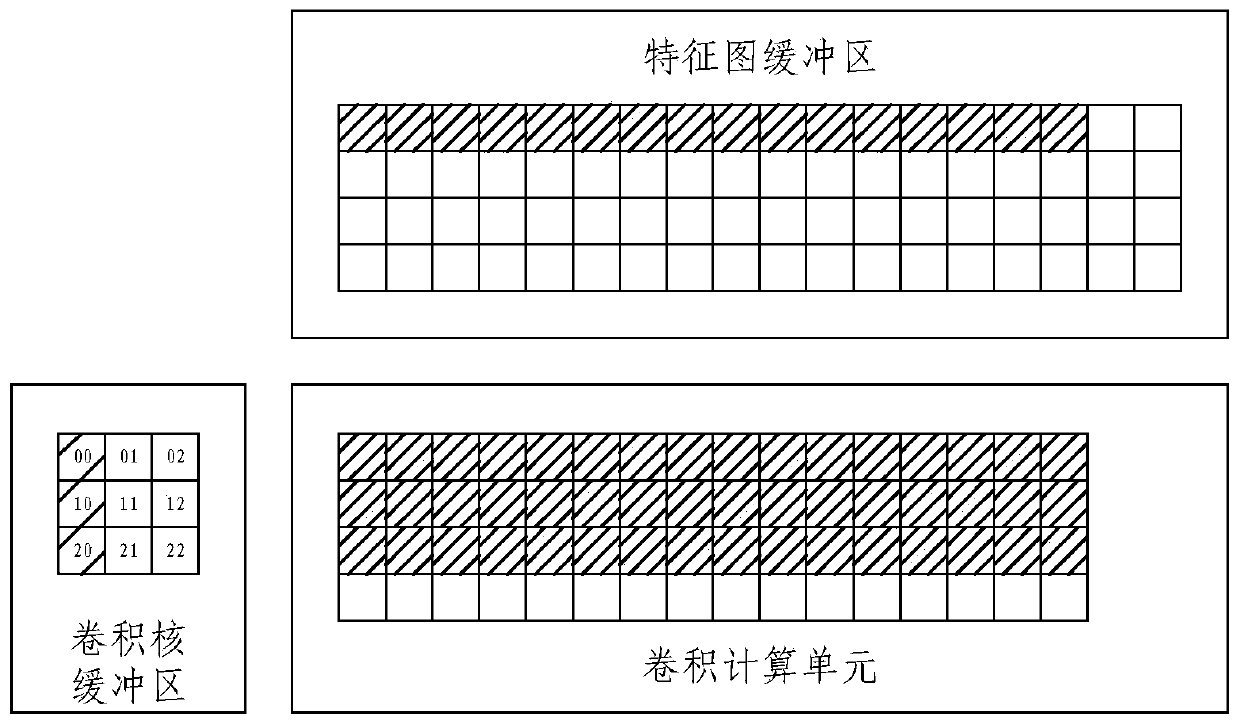

Convolution calculation acceleration method and device

ActiveCN110163793AImprove hardware utilizationAvoid wastingProcessor architectures/configurationPhysical realisationComputer scienceUtilization rate

The embodiment of the invention provides a convolution calculation acceleration method and device, and the method comprises the steps: obtaining a current depth time sequence i when the convolution type is depth-first convolution; inputting the column pixels in the convolution kernel corresponding to the current depth time sequence i and the row pixels in the feature map into a convolution calculation unit, wherein the convolution calculation unit is an array composed of multipliers and adders; if the imodK is equal to 0, translating the first row of pixels of the convolution kernel to the last row, wherein K is the number of rows and columns of the convolution kernel; and if the imodK is equal to 0 and i is greater than or equal to K<2>, taking the (i-k<2>) / k+1 modk th line feature in theconvolution calculation unit as the output feature of the (i-k<2>) / k+1 th line depth first convolution. According to the method and the device provided by the embodiment of the invention, the hardware utilization rate of the convolution calculation unit is effectively improved, the energy waste caused by the idleness of a large number of multipliers is avoided, and the depth-first convolution calculation efficiency is improved.

Owner:湃方科技(天津)有限责任公司

A method for efficient collaborative multiplexing of software and hardware resources in blockchain distributed networking

ActiveCN111770130BImprove hardware utilizationUser identity/authority verificationSoftware simulation/interpretation/emulationComputer hardwareResource pool

The invention relates to the technical field of efficient multiplexing of hardware resources and software resources, and discloses a service node, a root node, an application node and an access node. Data and hardware are abstracted into data layer and resource pool respectively, especially including software resource multiplexing method and hardware resource multiplexing method for cooperative use of software resources; full utilization of resources is realized under the efficient coordination of software and hardware, and the number of blocks is reduced. The cost of the distributed deployment of the chain.

Owner:贵阳信息技术研究院

Collaborative data processing method and system

ActiveCN105608190BIncrease speedImprove hardware utilizationDatabase distribution/replicationSpecial data processing applicationsData synchronizationEngineering

Owner:FUJIAN YIRONG INFORMATION TECH

A RFID-based indoor positioning method, device and system

ActiveCN107462249BSimple structureLow costNavigational calculation instrumentsPosition fixationControl engineeringControl theory

The embodiment of the invention discloses an indoor positioning method, device and system based on RFID (radio frequency identification). The method comprises the following steps of controlling an RFID antenna to rotate at the preset angle; obtaining the rotating angle of the RFID antenna for rotating to the current position; scanning a label; obtaining the label signal intensity corresponding to the rotating angle; determining a first elliptic equation and a second elliptic equation corresponding to the label according to the rotating angle, the label signal intensity and the rotating antenna positioning algorithm; processing the first elliptic equation and the second elliptic equation according to the elliptic intersection point calculation algorithm to obtain the corresponding two elliptic intersection points; whether the distance between the intersection point and the origin is greater than the first preset distance or not; if so, the intersection point is output; otherwise, the rotating angle when the RFID antenna rotates to another position is continuously obtained, and the cyclic operation is performed until the final intersection point is obtained. The embodiment of the invention has the advantages that only one RFID antenna is used; the advantages of simple system structure, low cost, low deployment difficulty and high hardware utilization rate are realized.

Owner:GUANGDONG UNIV OF TECH

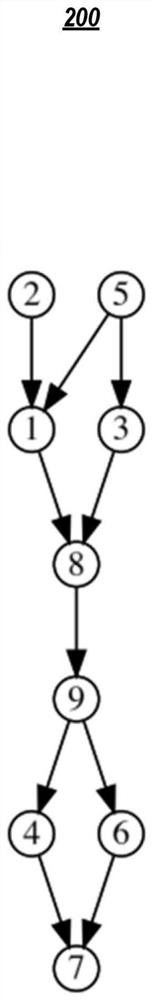

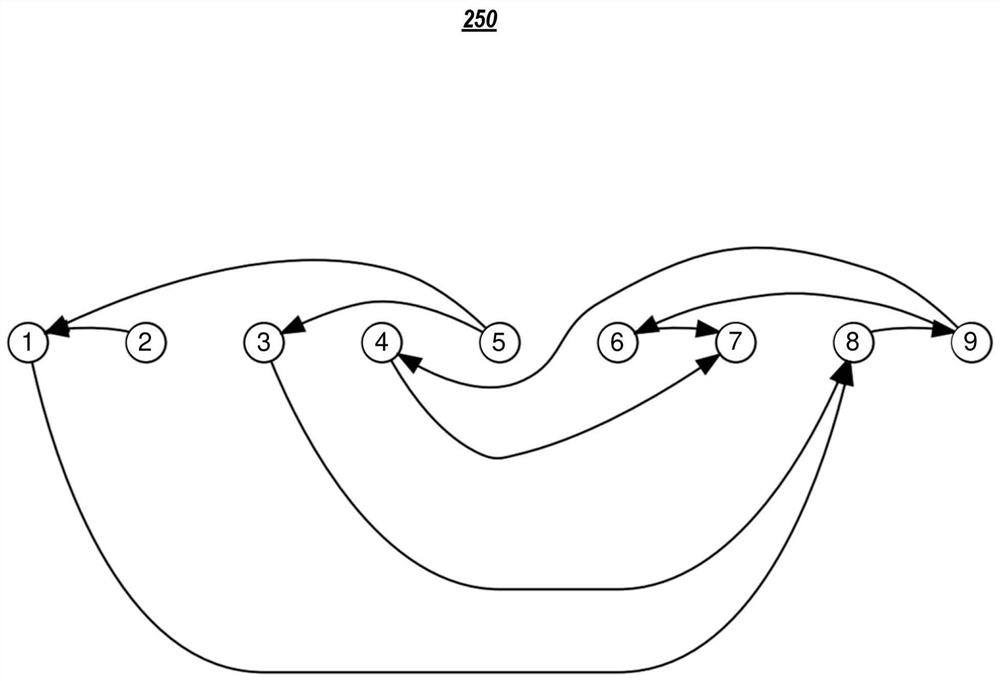

Reducing training times of deep neural networks through efficient hybrid parallelism

PendingCN112836787AImprove hardware utilizationReduce training timeMathematical modelsSoftware engineeringBaseline dataTheoretical computer science

Presented are systems and methods to automatically find efficient parallelization strategies for deep neural networks (DNNs). A computation graph comprising an efficiently ordered sequence of vertices aids in computing the best parallelizing strategy in a relatively short time. Effectiveness of the parallelization strategies is evaluated on various DNNs, and the performance of the strategies proposed by various embodiments is compared against data parallelism, expert-designed strategies, and other state-of-the-art approaches. Experimental results demonstrate that the proposed strategies outperform a baseline data parallelism strategy and achieve better performance than expert-designed strategies and state-of-the-art approaches.

Owner:BAIDU USA LLC

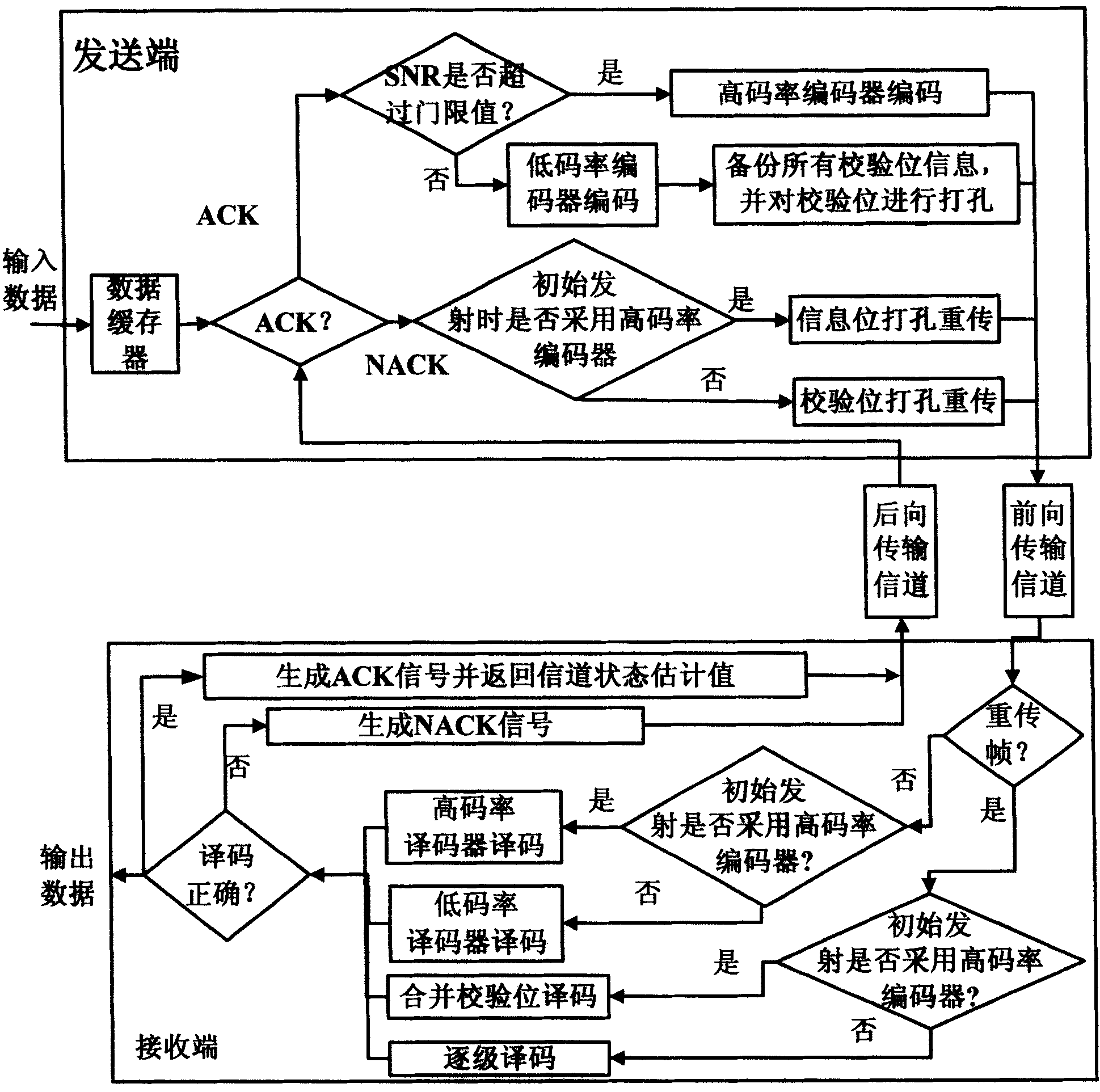

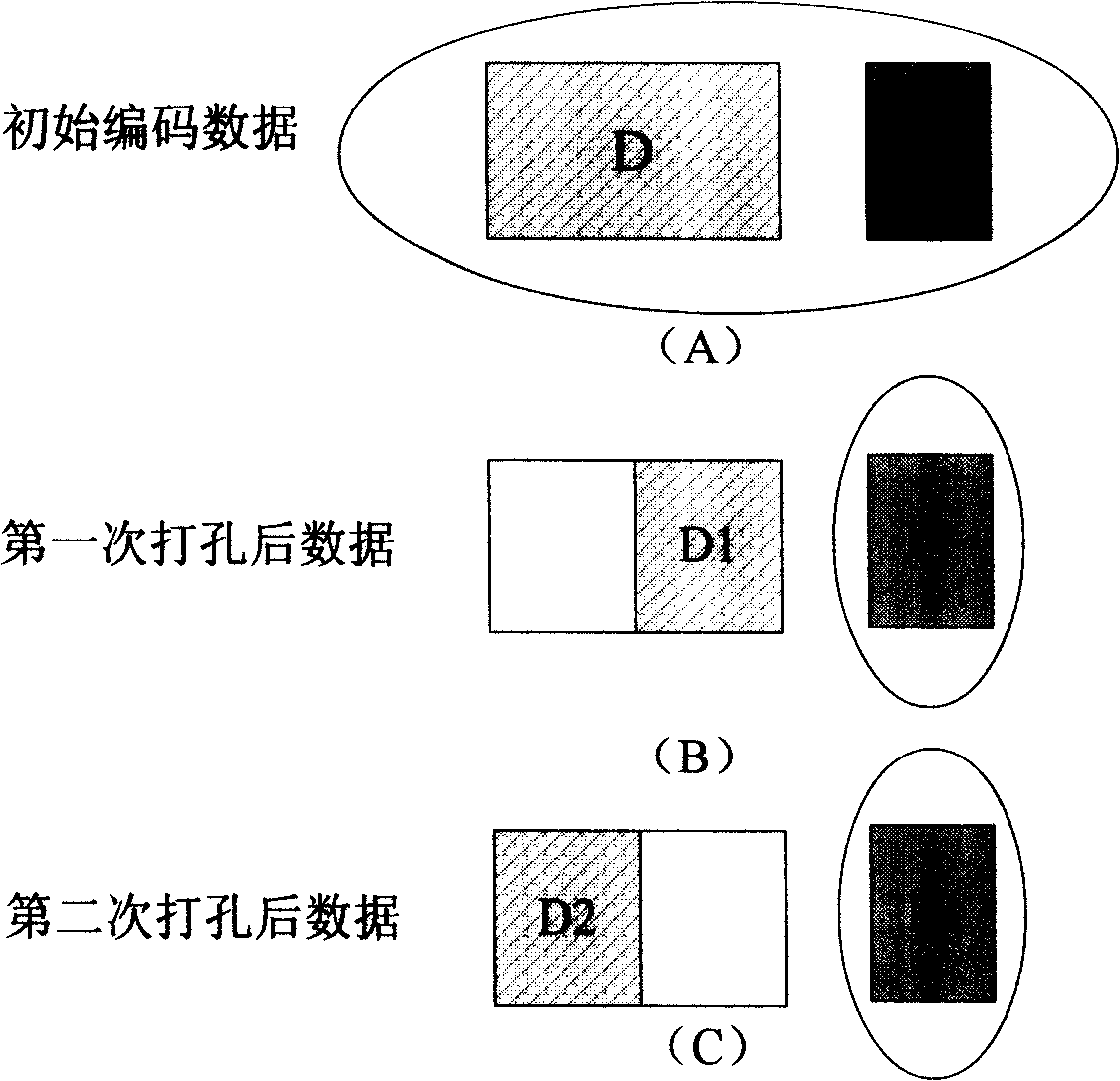

A method for enhanced self-adapted data retransfer

InactiveCN101237310BIncrease profitImprove throughputError prevention/detection by using return channelTime delaysDependability

The invention discloses a method for retransmitting enhanced self-adaptive data. The method adopting a self-adaptation technique is: when a communication channel is in good condition, to code data by means of a high bit rate coder which has a high transmission rate and few redundant error-correcting codes and to complete initial transmission of the data, or to use a method of information bit puncturing hybrid retransmission of data for improving the utilization rate of hardware and the system throughput and saving energy; and when the communication channel is in poor condition, to code data by means of a low bit rate coder which has a high transmission rate and more redundant error-correcting codes and to complete initial transmission of the data, or to use a method of parity bit puncturing hybrid retransmission of data for guaranteeing the reliability of communication transmission. The method of the invention has the combined advantages of technologies of information bit puncturing hybrid retransmission and parity bit puncturing hybrid retransmission, and thus can not only improve the utilization rate of the hardware, reduce the time delay for transmission processing, improve thesystem throughput and saves energy, but also ensure good error-correcting transmission performance in poor communication channel condition.

Owner:BEIJING UNIV OF POSTS & TELECOMM +1

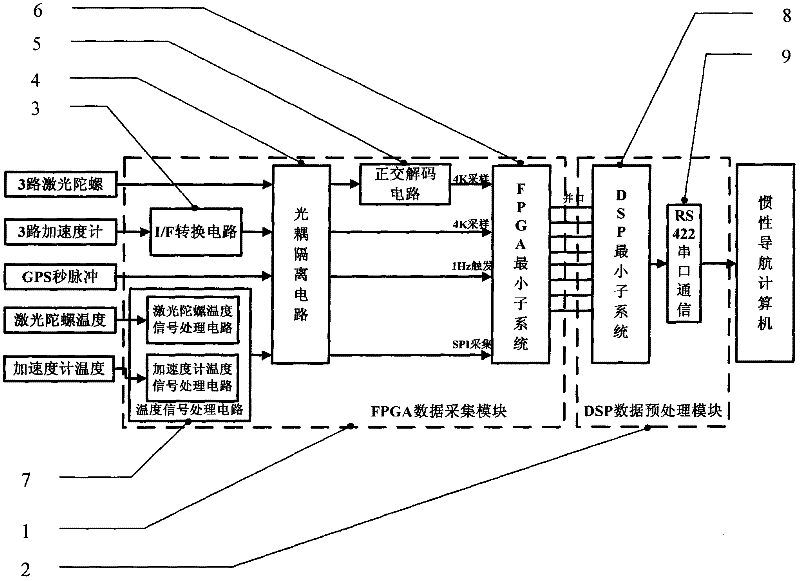

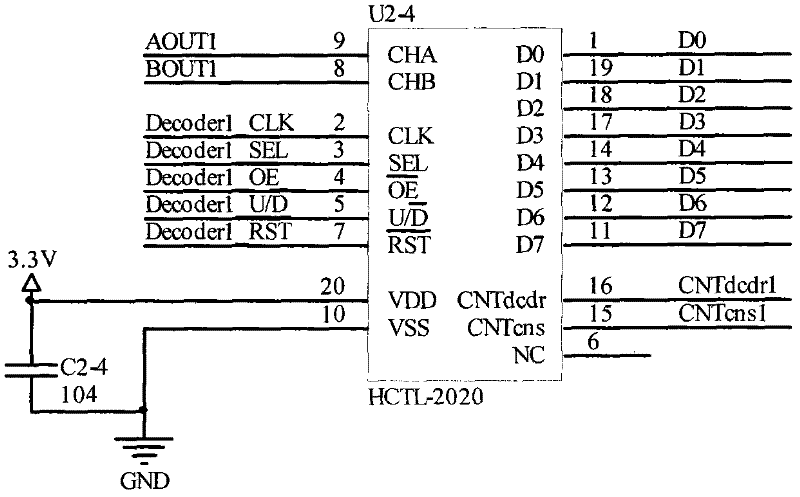

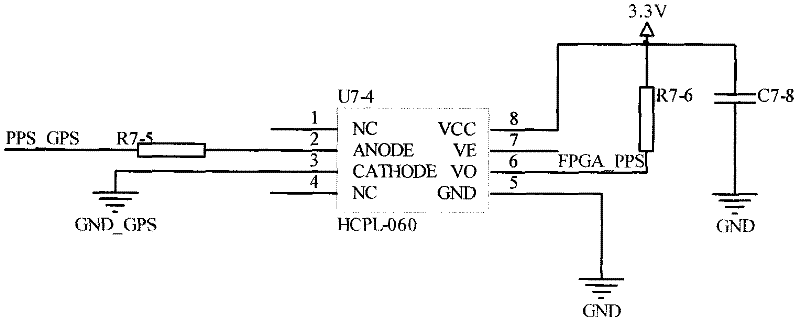

Laser gyro POS (Point of Sales) data acquisition and pre-processing system

InactiveCN102109351BImprove hardware utilizationImprove efficiencyNavigation by speed/acceleration measurementsDsp architectureData acquisition

The invention relates to a laser gyro POS data acquisition and pre-processing system which comprises a Field Programmable Gate Array (FPGA) data acquisition module and a Digital Signal Processor (DSP) data pre-processing module. The FPGA data acquisition module realizes the acquisition of laser gyro signal, accelerometer signal and temperature signal and acquires a clock by using the synchronous FPGA data of GPS second pulse. The DSP data pre-processing module reads the laser gyro data, the accelerometer data and the temperature data in the FPGA to pre-process the data and sends the pre-processing result to a navigation computer. The system realizes the integrated design of high-frequency and high-precision laser gyro POS data acquisition and pre-processing system of FPGA / DSP framework; therefore, the power consumption, the volume and the weight of the system are reduced so that the system performance can be greatly improved.

Owner:BEIHANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com