Content addressing method based on hash chain table and corresponding storage circuit

A technology of content addressing and memory, which is applied in the field of content addressable memory, and can solve the problems of high resource consumption, high cost, unfavorable expansion of search depth and width, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

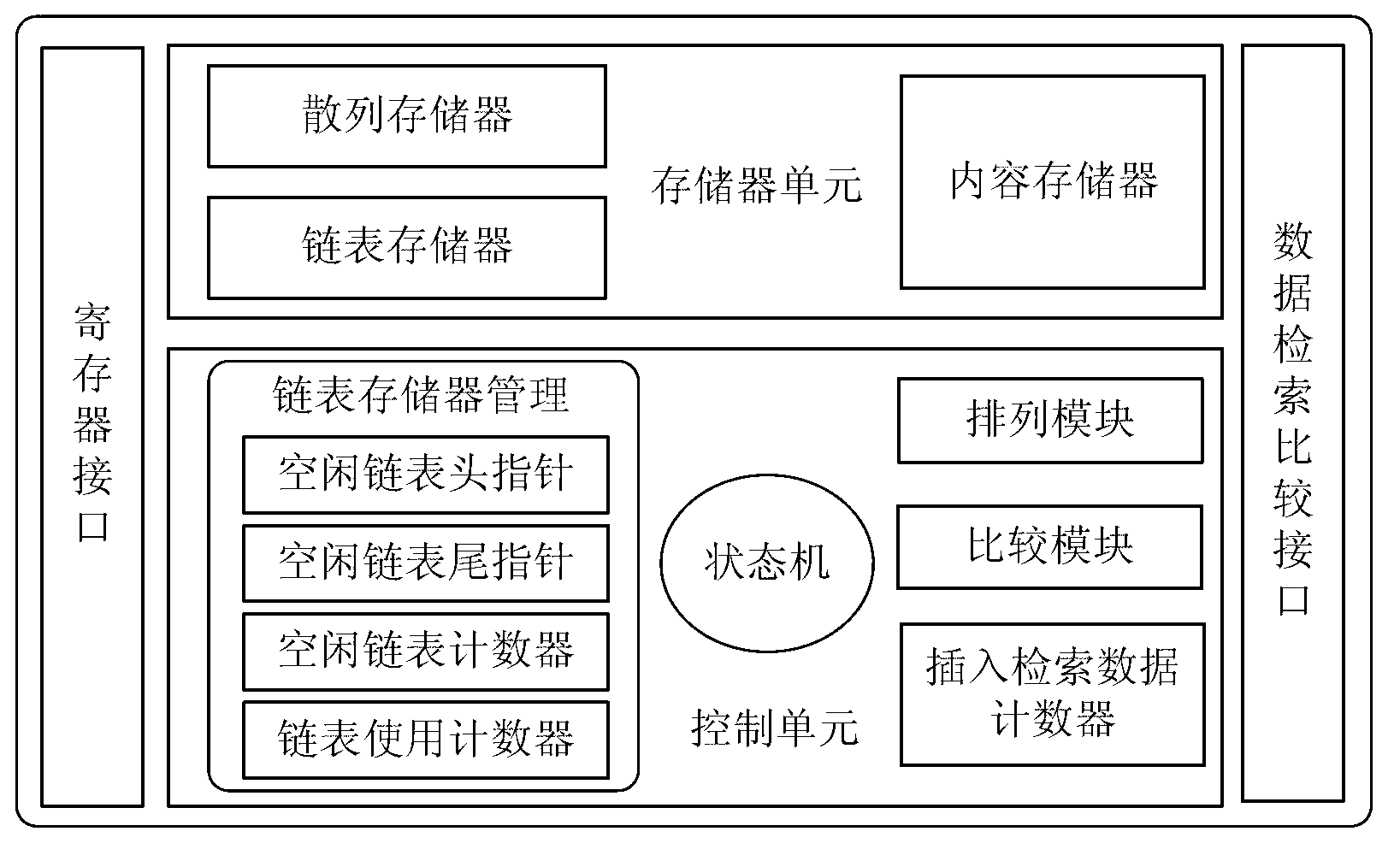

[0061] The following describes the specific implementation of the content addressable memory circuit from two aspects of functional architecture and workflow:

[0062] 1. Functional Architecture

[0063] The functional block diagram of the content addressable memory circuit is shown in figure 1 As shown, the content-addressable memory circuit includes a control unit, a memory unit, a register interface and a data retrieval and comparison interface. The specific implementation method is as follows:

[0064] 1.1 Register interface

[0065] Register read and write interface, with chip select signal CS, read and write signal WR, register address bus ADD, input data bus DATAIN[31:0], output data bus [31:0], clock CLK and reset RST, and address decoding and data selection.

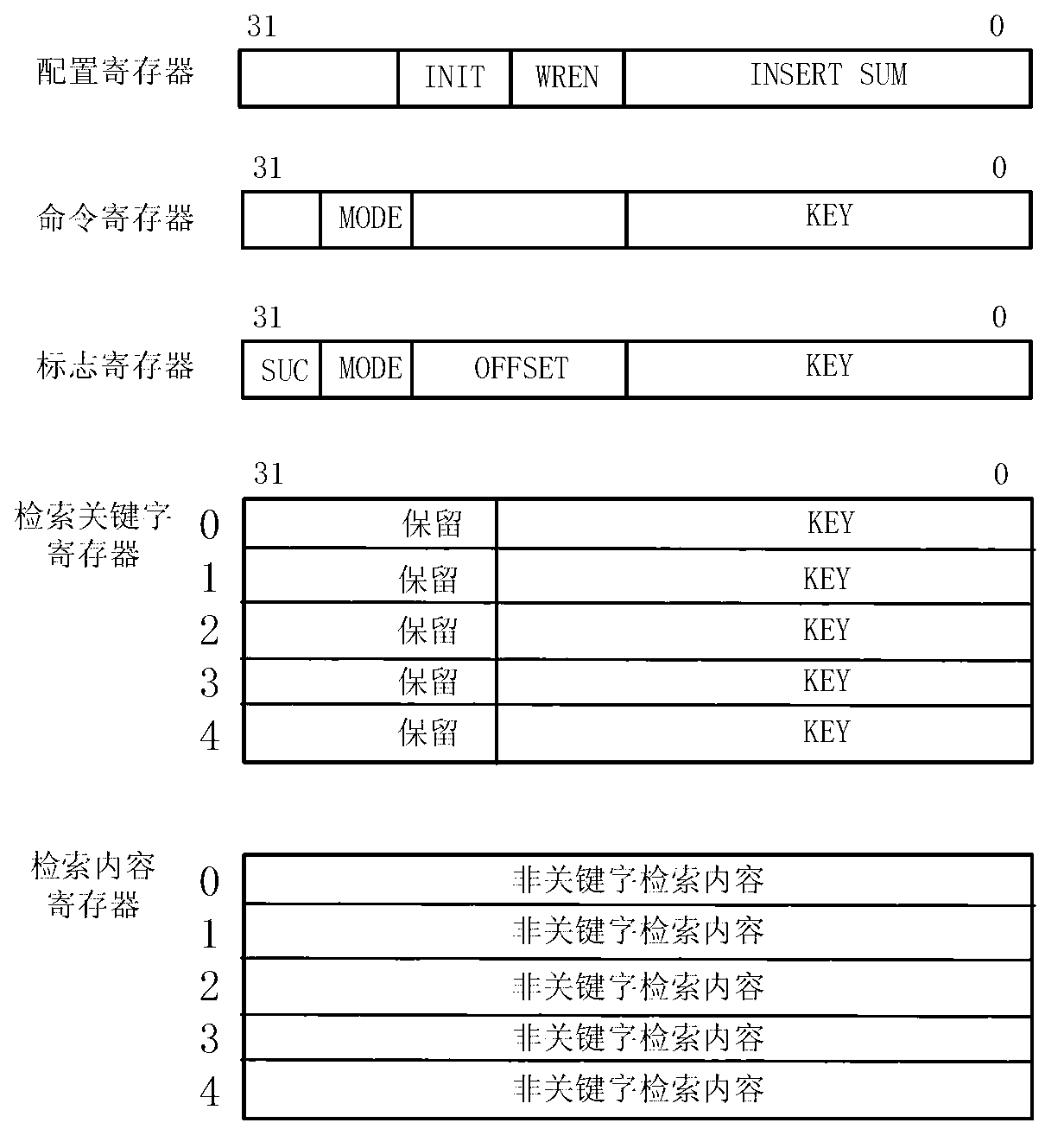

[0066] Content-addressable memory registers are defined as image 3 As shown, including configuration registers, command registers, flag registers, keyword registers and content registers, etc., the specific...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com