Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

127results about How to "Reduce floor area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

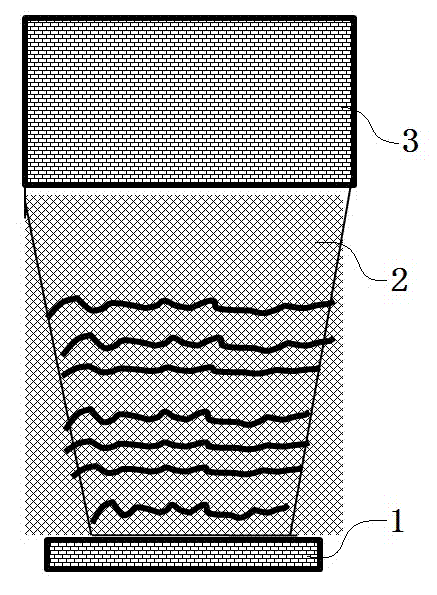

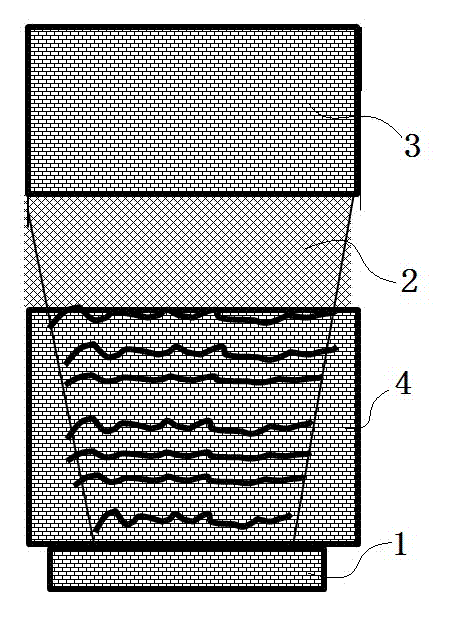

Rice field ditch integrated ecological high-value rice and soft-shelled turtle planting and breeding method

ActiveCN103027008AReduce areaReduce outputAnimal feeding stuffRice cultivationEconomic benefitsPaddy field

The invention discloses a rice field ditch integrated ecological high-value rice and soft-shelled turtle planting and breeding method which comprises the following steps: 1, ruralizing a rice field and installing fences; 2, plowing the rice field; 3, transplanting rice; 4, putting soft-shelled turtles in the rice field and raising the soft-shelled turtles; 5, conducting field management; and 6, harvesting the rice and the soft-shelled turtles in good time. The method has the advantages that: 1, the foundation works of the rice field is optimized without reducing the area of the rice; 2, the foundation works of a rice ditch is optimized without destroying the structure of the rice field; 3, the landscape of the rice field is optimized to provide a good growth environment for the soft-shelled turtles; 4, a ladder type culture method is adopted to increase the planting and breeding density; and 5, the economic benefit of the rice field in a unit area is greatly increased.

Owner:HUNAN AGRICULTURAL UNIV

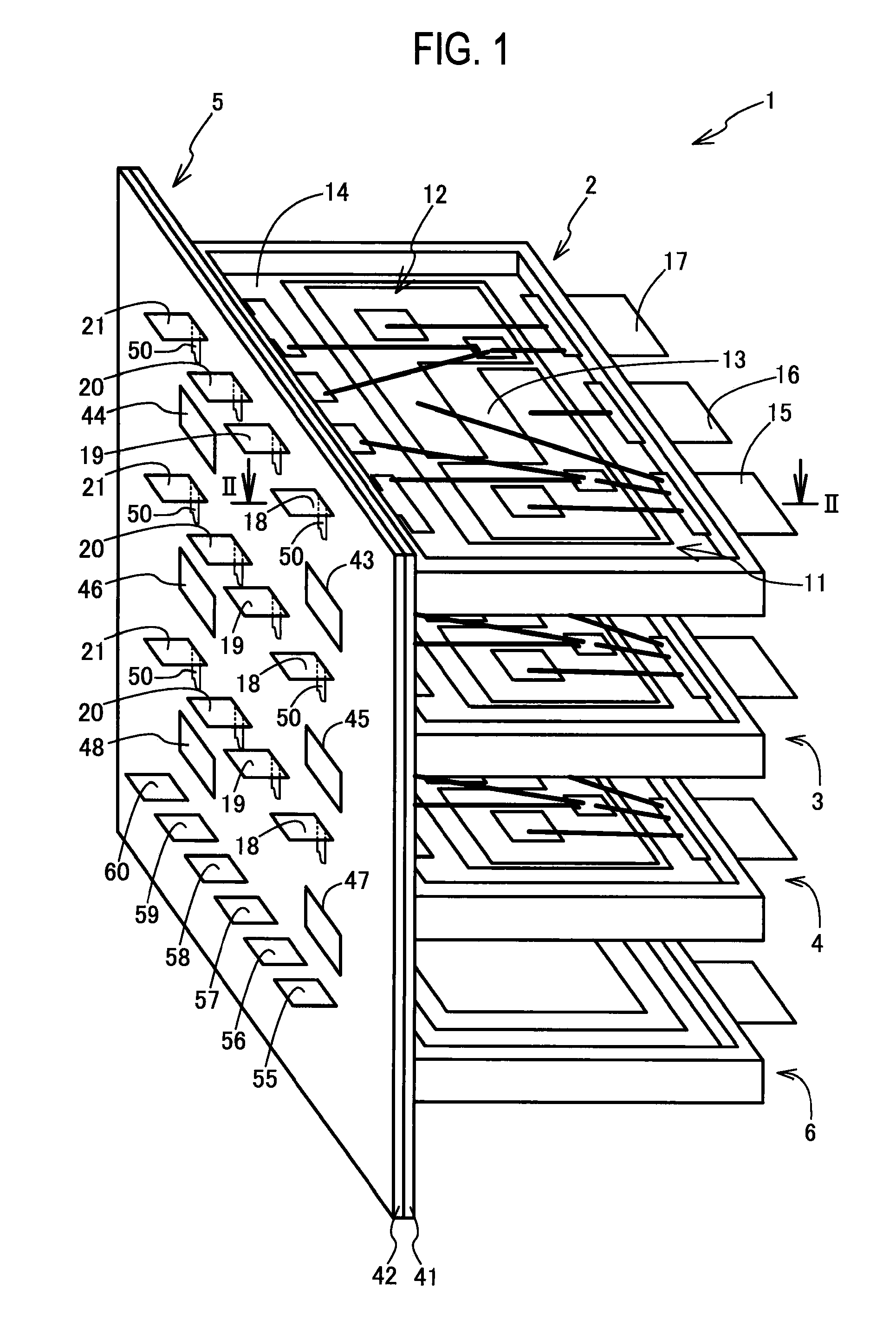

Semiconductor device

ActiveUS20090086427A1Reduce floor areaCircuit-breaking switches for excess currentsAc-dc conversion without reversalDevice materialSemiconductor

A semiconductor device includes: a first output unit configured to output a first phase; a second output unit configured to output a second phase different from the first phase, the second output unit being disposed to be stacked on the first output unit; and a controller configured to control the output units.

Owner:ROHM CO LTD

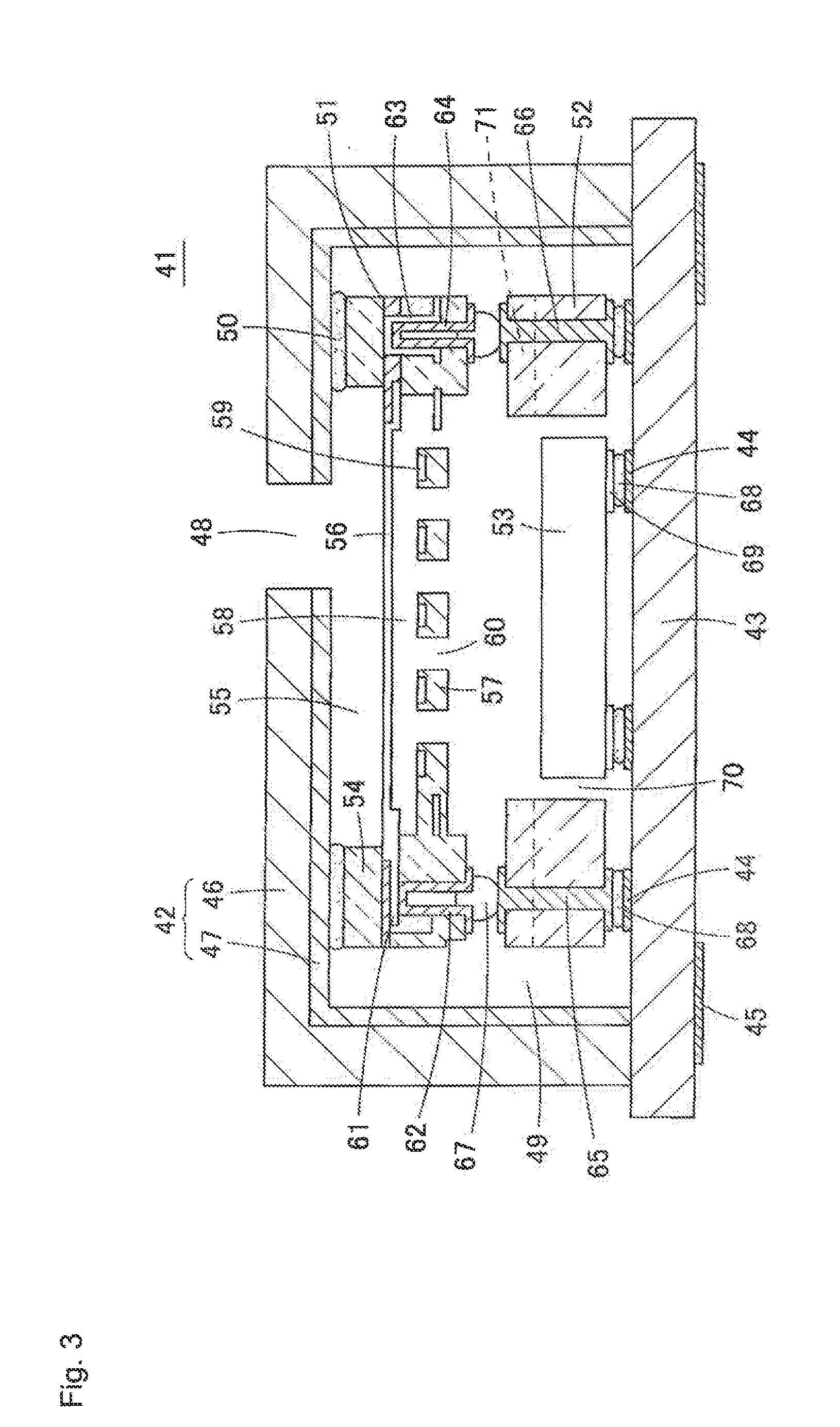

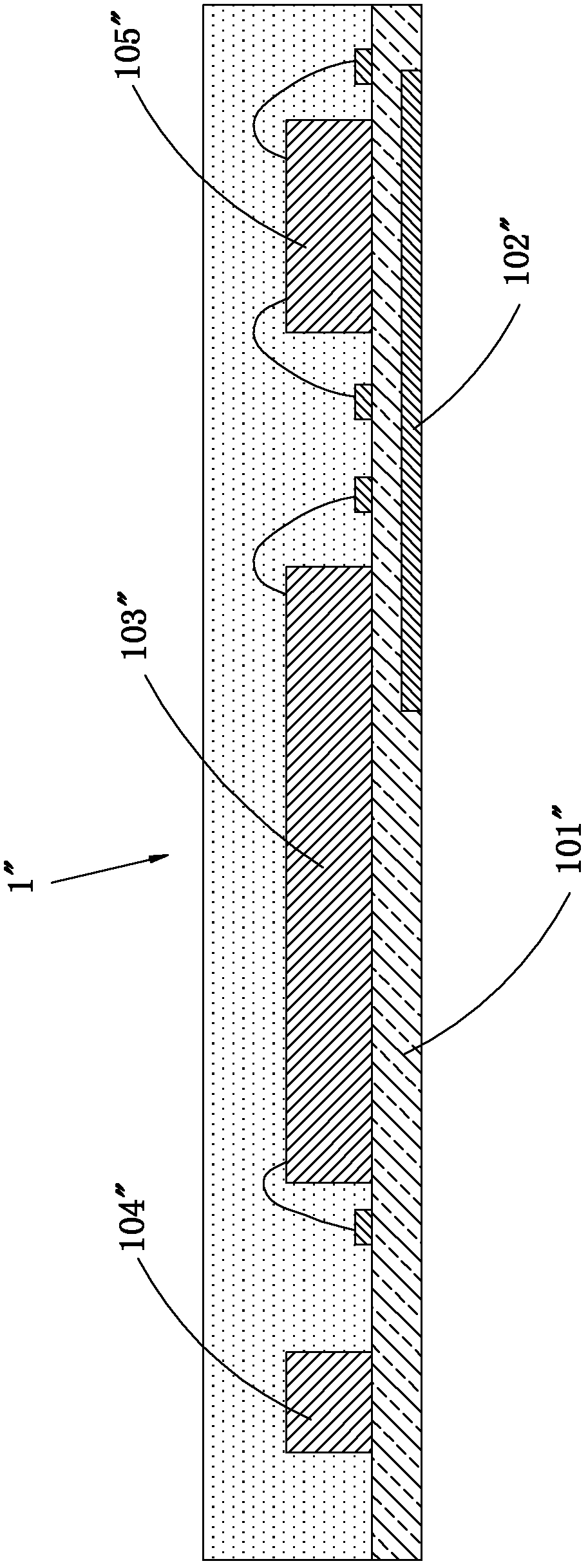

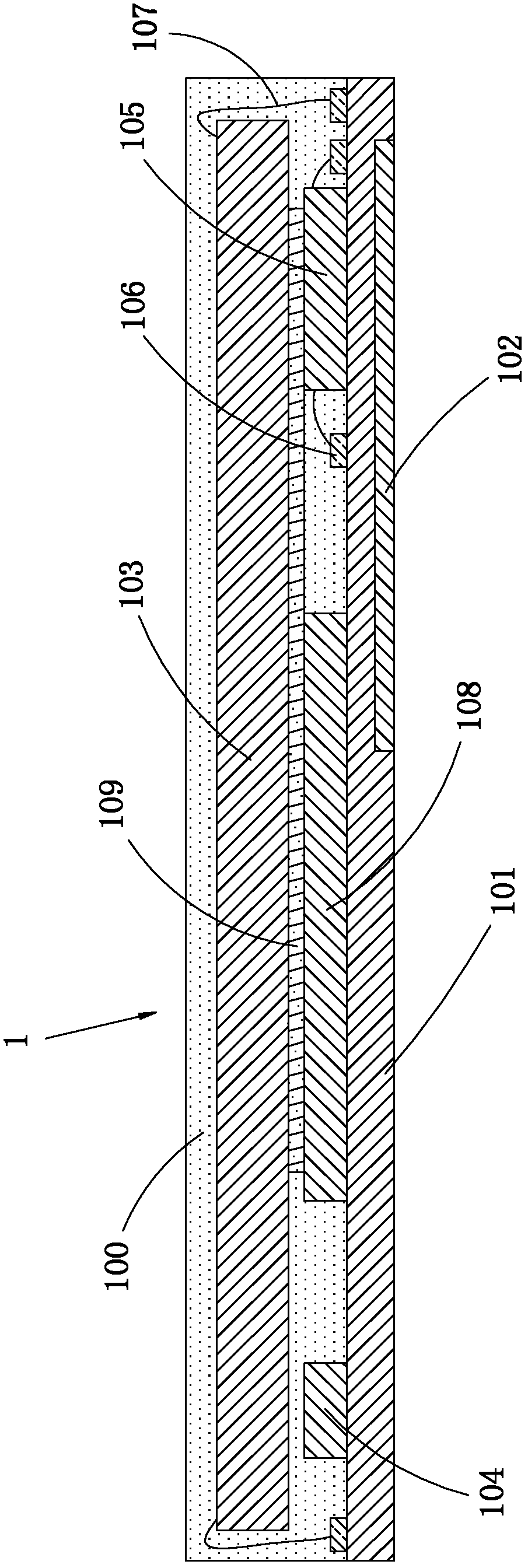

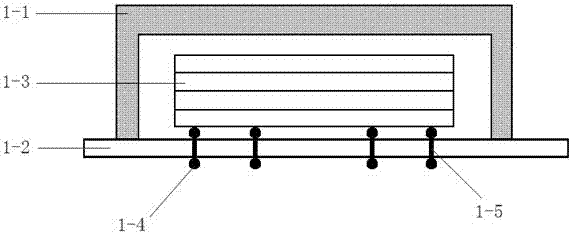

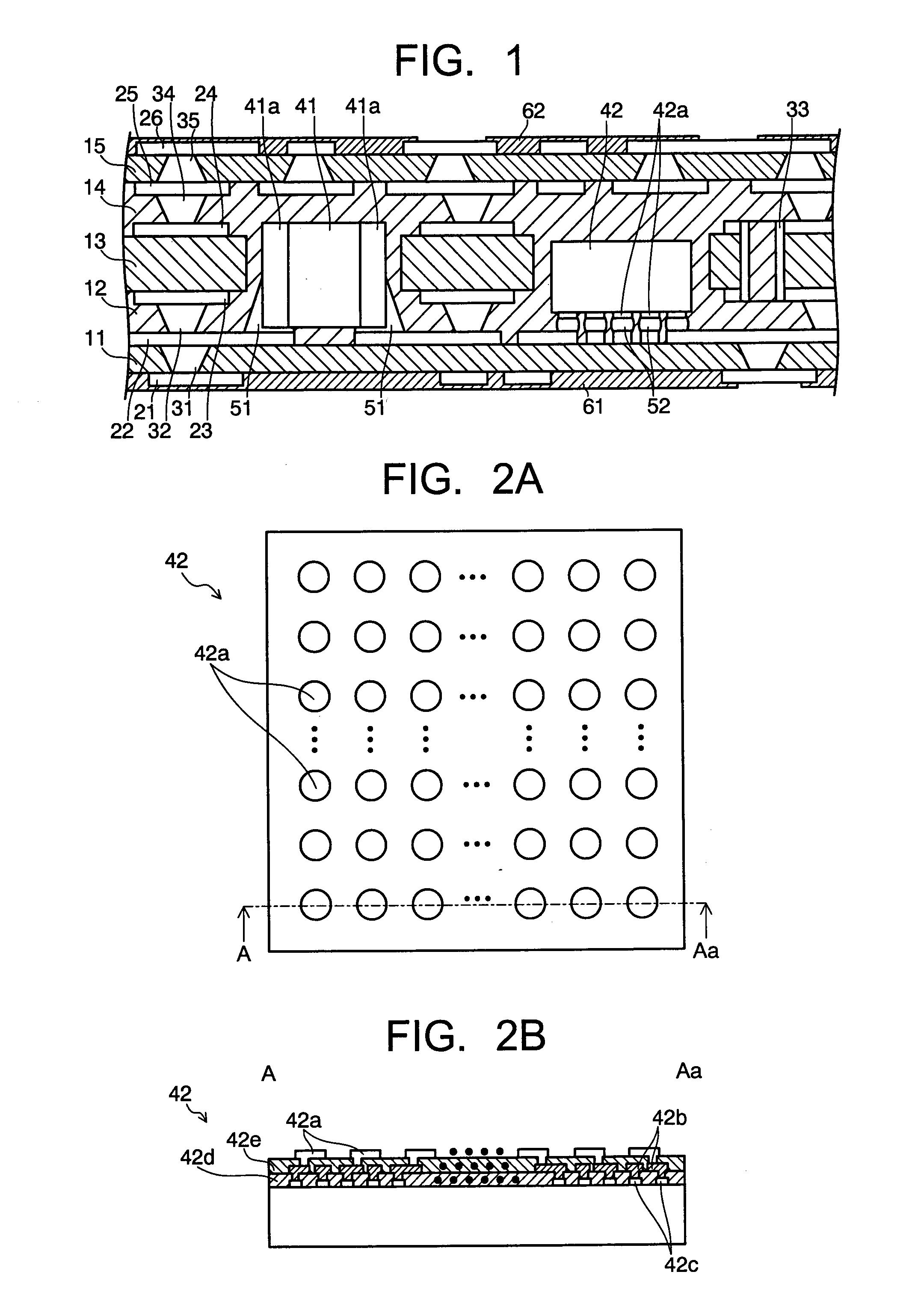

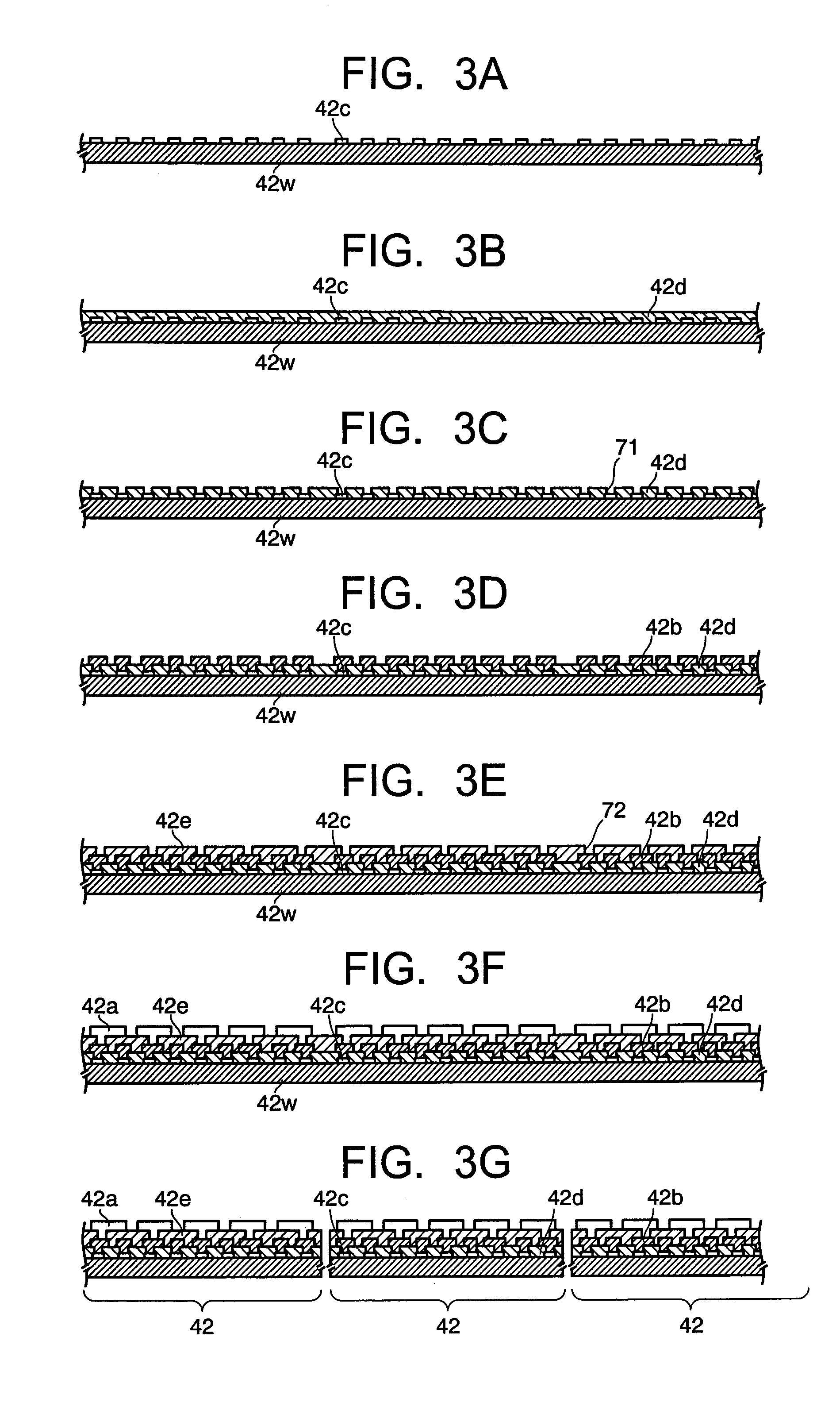

Microphone

ActiveUS20130343590A1Reduce floor areaIncrease capacityPiezoelectric/electrostrictive microphonesMicrophone structural associationSignal processing circuitsInterposer

Provided is a microphone capable of reducing a plane area seen from above, and further increasing a capacity of a back chamber of an acoustic sensor. An interposer 52 is mounted on a top surface of a circuit board 43, and an acoustic sensor 51 is mounted on the top surface thereof. A signal processing circuit 53 is accommodated in a space 70 provided in the interposer 52, and mounted on the circuit board 43. The acoustic sensor 51 is connected to the circuit board 43 through a wiring structure provided in the interposer 52. The acoustic sensor 51, the interposer 52 and the like are covered by a cover 42 put on the top surface of the circuit board 43. In the cover 42, a sound introduction hole 48 is opened in a position opposed to the front chamber of the acoustic sensor 51. The interposer 52 is formed with a ventilation notch 71 for acoustically communicating a space below a diaphragm 56 of the acoustic sensor 51 with a space inside the cover 42 and outside the interposer 52.

Owner:MMI SEMICON CO LTD

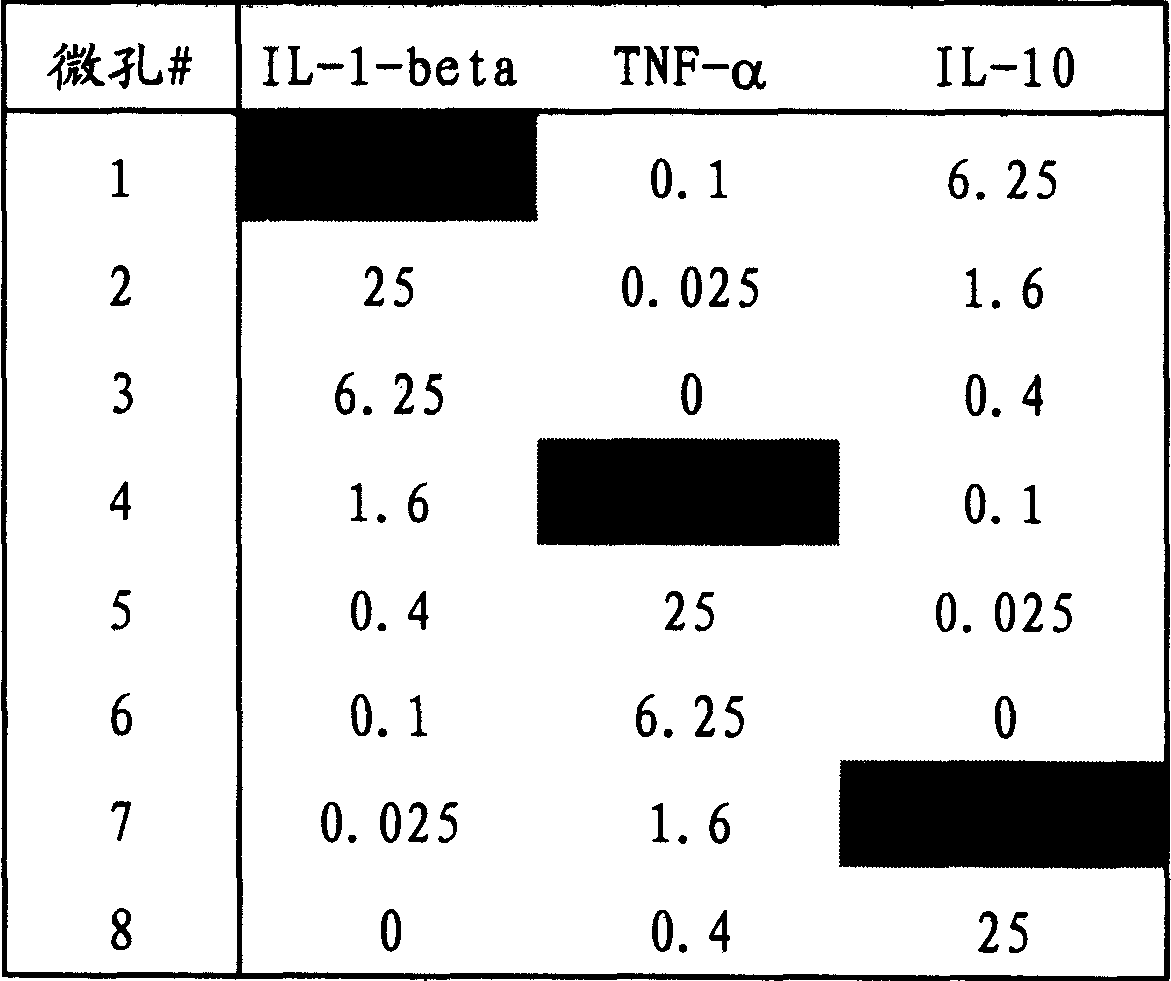

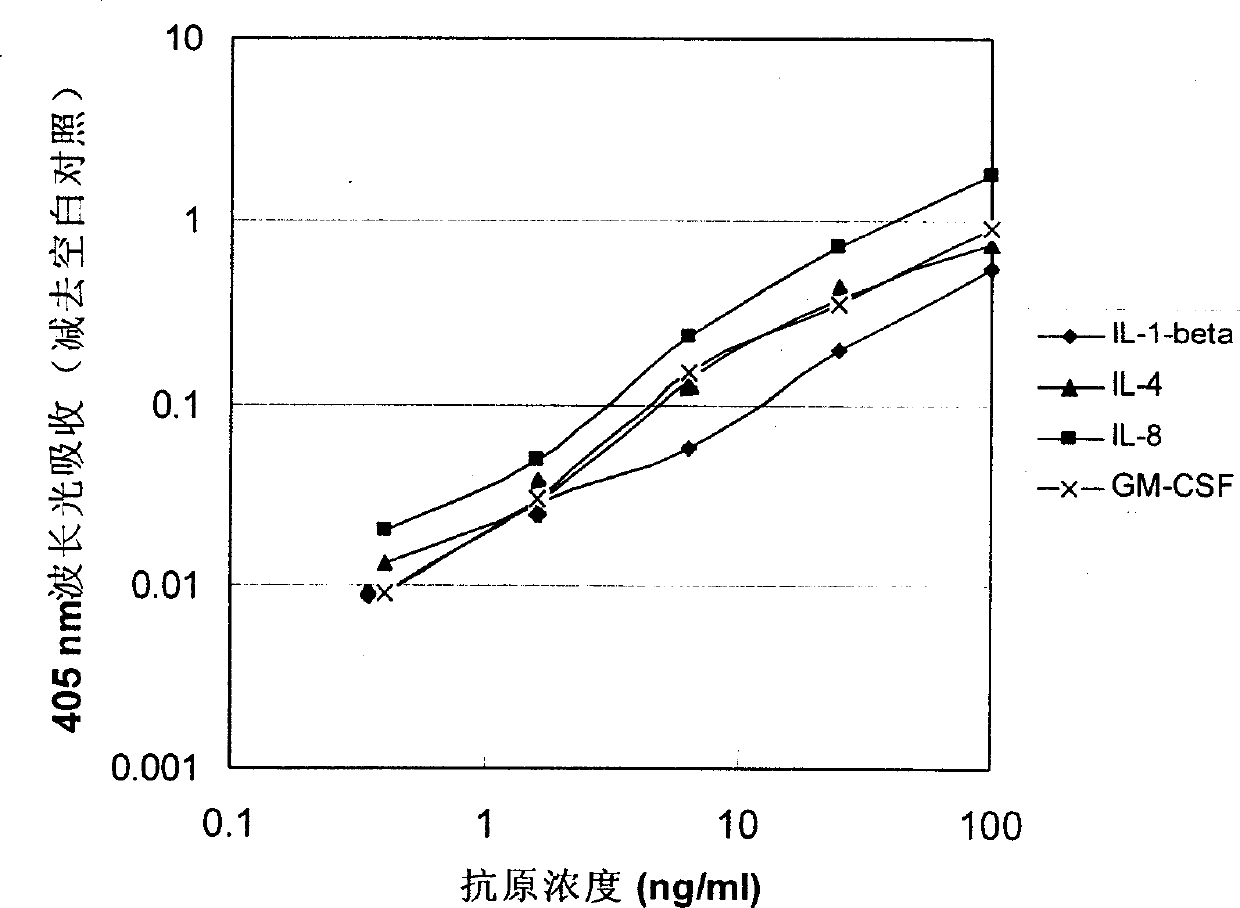

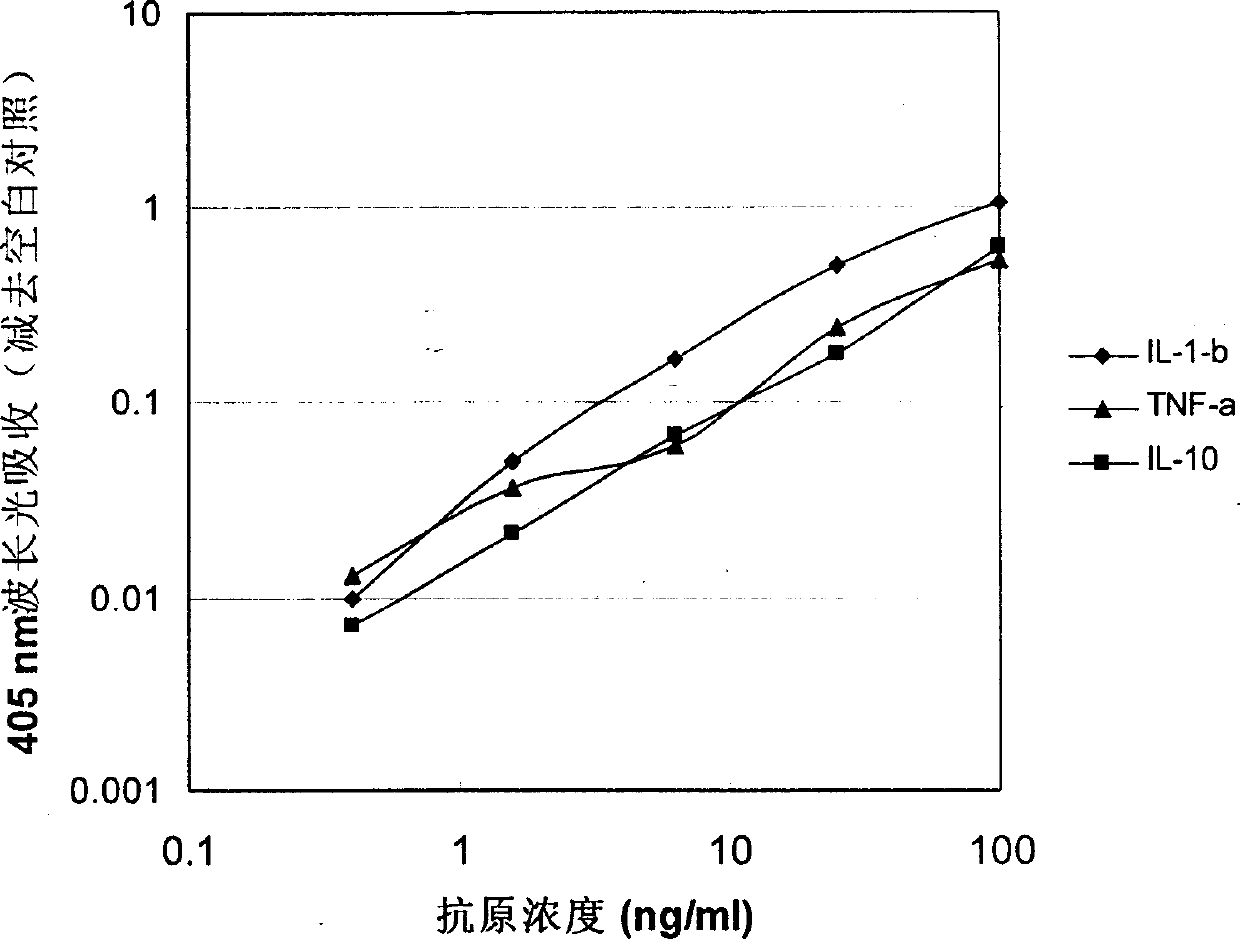

Method for quantitative determination of specific analyte with single trapping agent and reagent kit therefor

InactiveCN1700009AFacilitating the application of omics researchFacilitate disease diagnosisMaterial analysisAnalyteQuantitative determination

The invention relates to a method and its medium box for quantity measuring peculiar analysis substance by single capture medium. The method comprises the following steps: combining the tested analysis substance with solid phase capture medium, labeling analysis substance which has been captured by capture medium with report molecule, cleaning-up analysis substance from compound, recombining tested analysis substance with new solid phase capture medium, ascertaining content of analysis substance by report molecule's label signal. The medium box comprises capture device, testing device report molecule used as label and analysis substance eluent.

Owner:孙东旭

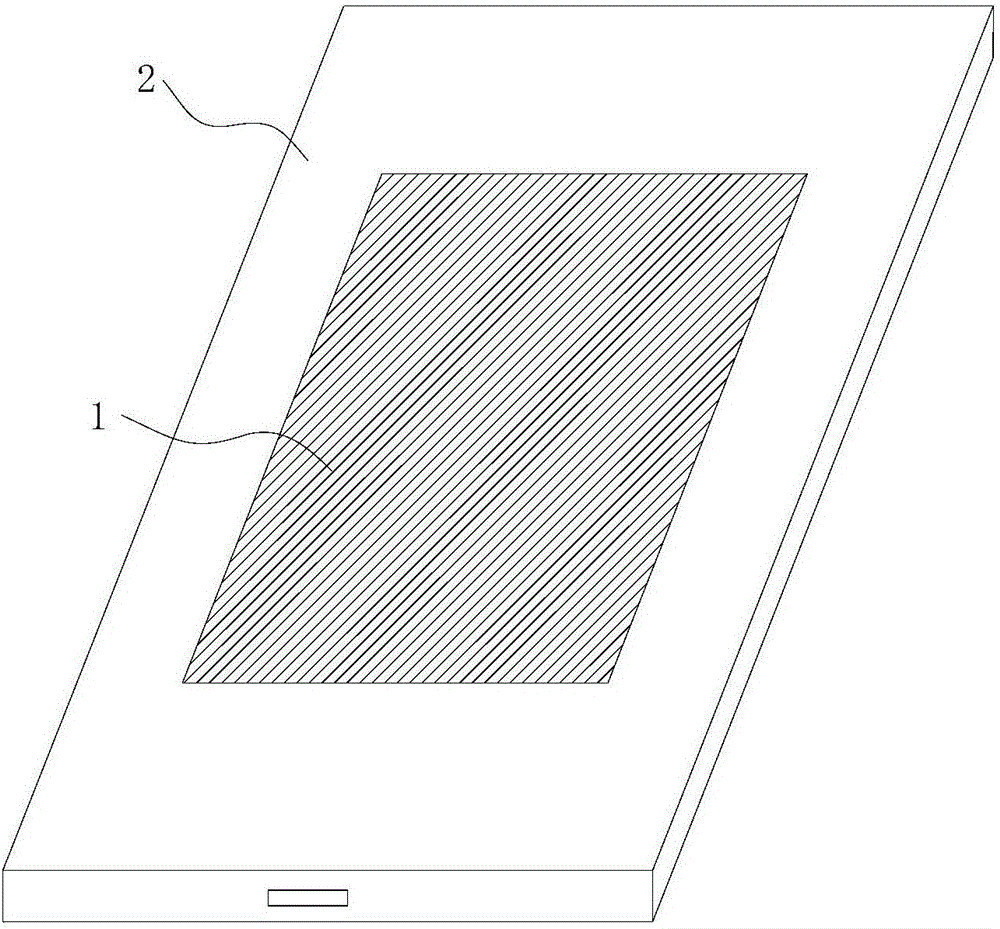

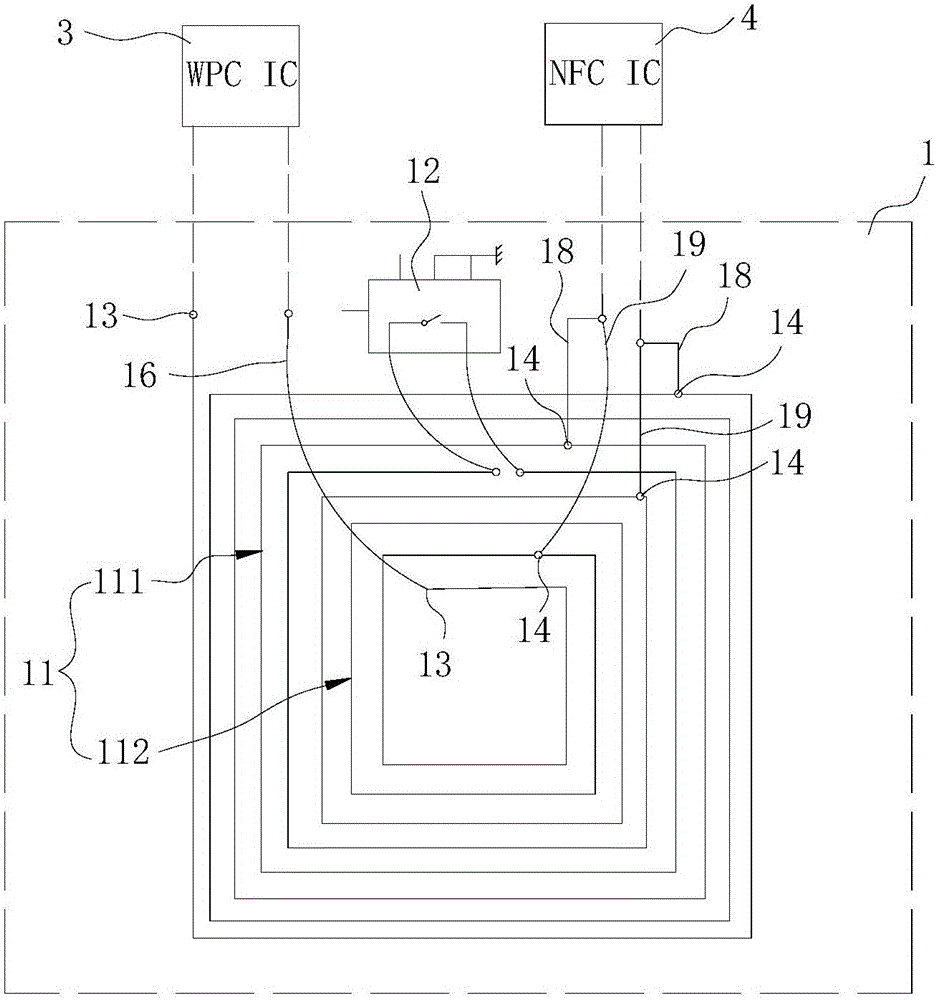

Antenna device and mobile terminal with same

ActiveCN106329114AReduced design area requirementsEnables miniaturization compatible designAntenna supports/mountingsLoop antennasMultiplexingComputer terminal

The invention provides an antenna device and a mobile terminal with the same. The antenna device comprises at least two layers of stacked coils; a second feed point electrically connected to an NFC (Near Field Communication) chip or an RFID (Radio Frequency Identification) chip is respectively arranged on the coils, and a first feed point electrically connected to a WPC (Wireless Power Consortium) chip or an FM (Frequency Modulation) chip is respectively arranged on the two coils of the surface; and the two adjacent layers of coils are isolated by an isolating unit, and the isolating unit is configured to isolate working signals of the NFC chip or the RFID chip. The antenna device realizes superposition of effective area of antennas via multilayer superposed coils, the coils can be connected or isolated to support two different functions, and multiplexing of the antenna device is realized; meanwhile, in the NFC or RFID working mode, the intensity of the radiation electromagnetic field can be improved, and the NFC or RFID communication performance is optimized.

Owner:QINGDAO HISENSE MOBILE COMM TECH CO LTD

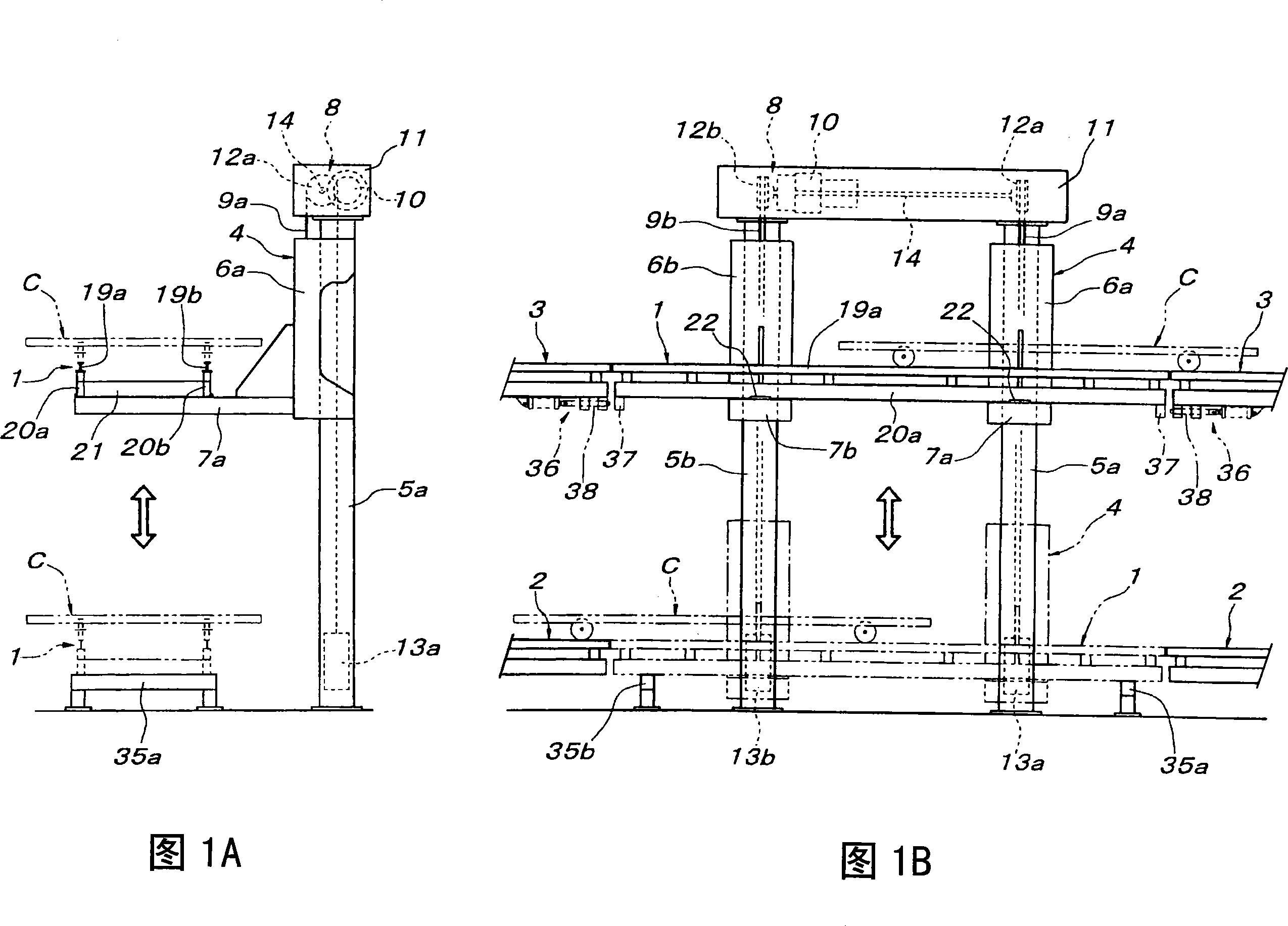

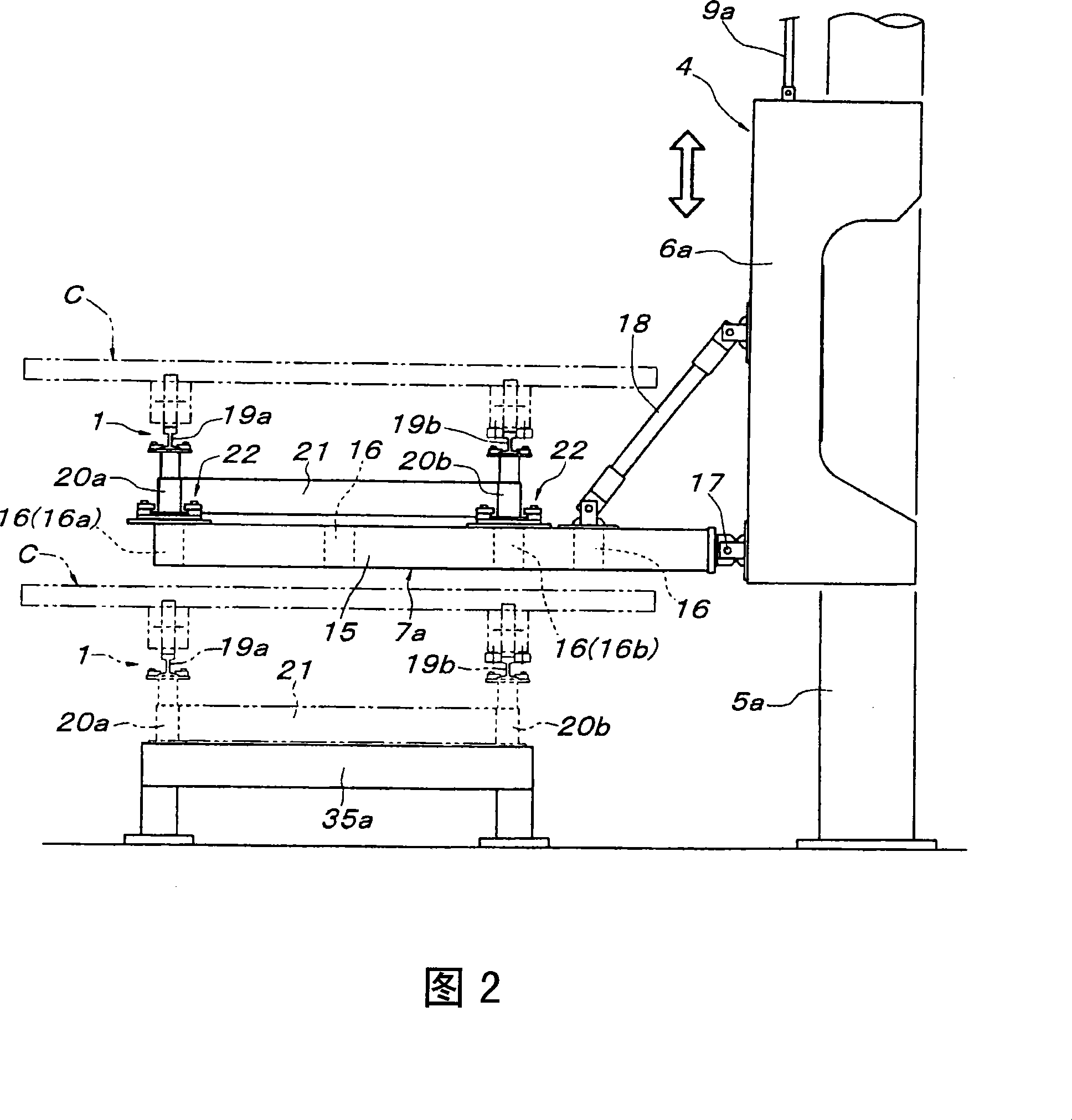

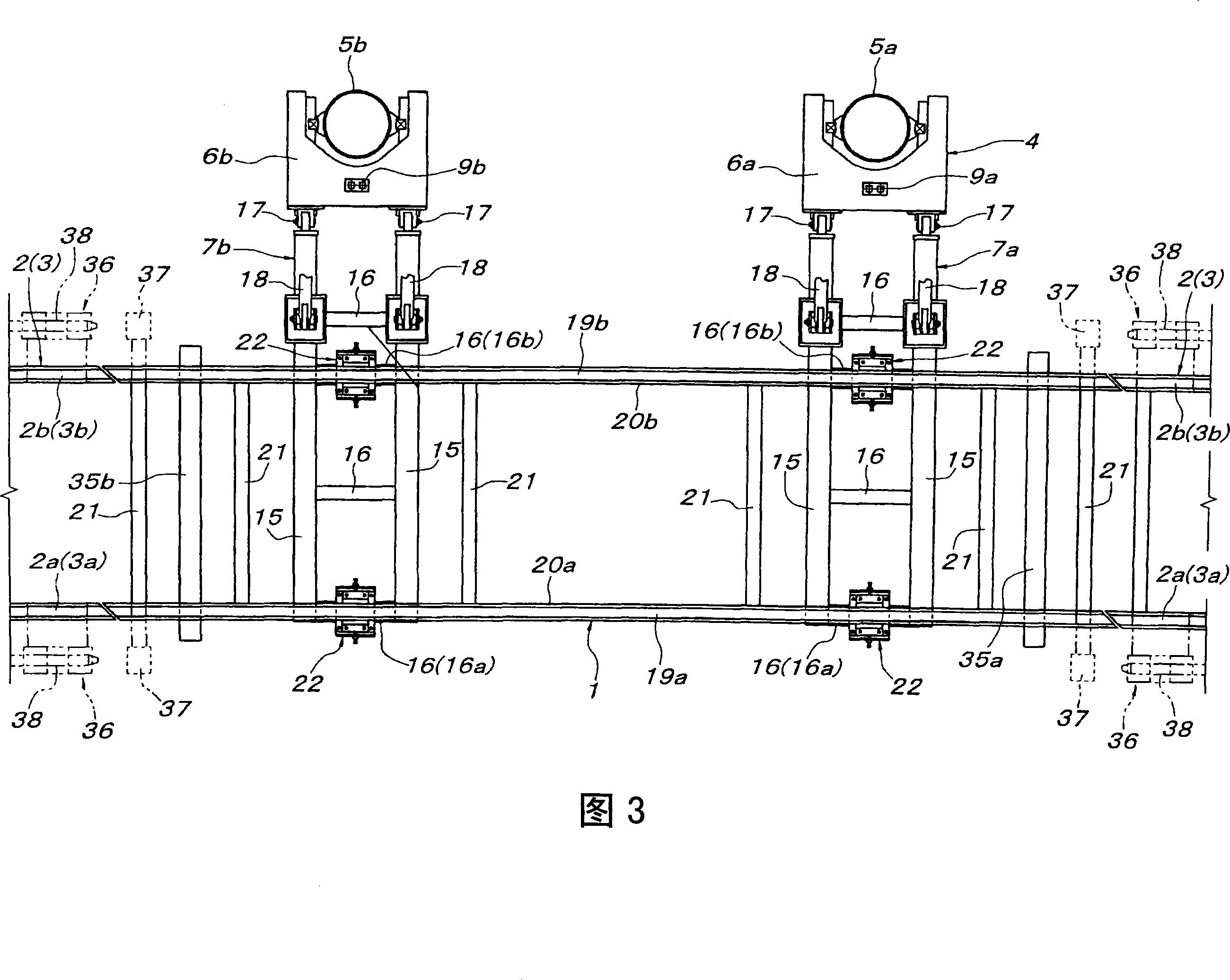

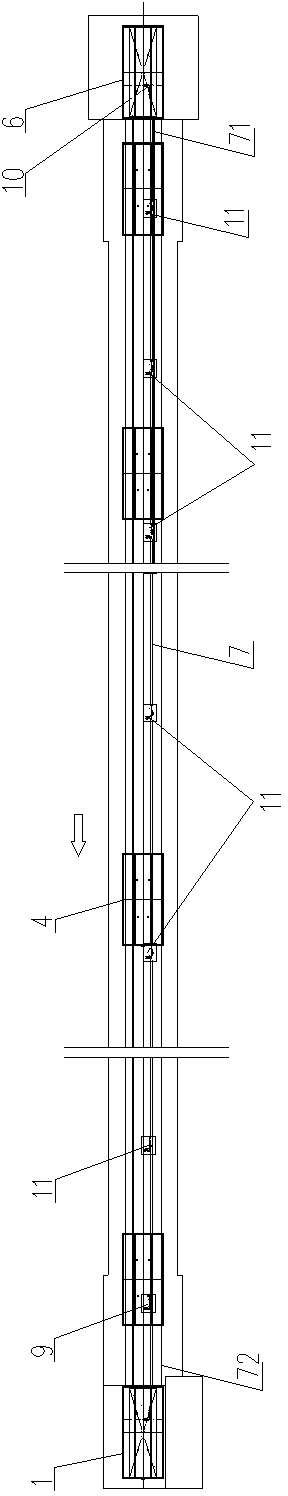

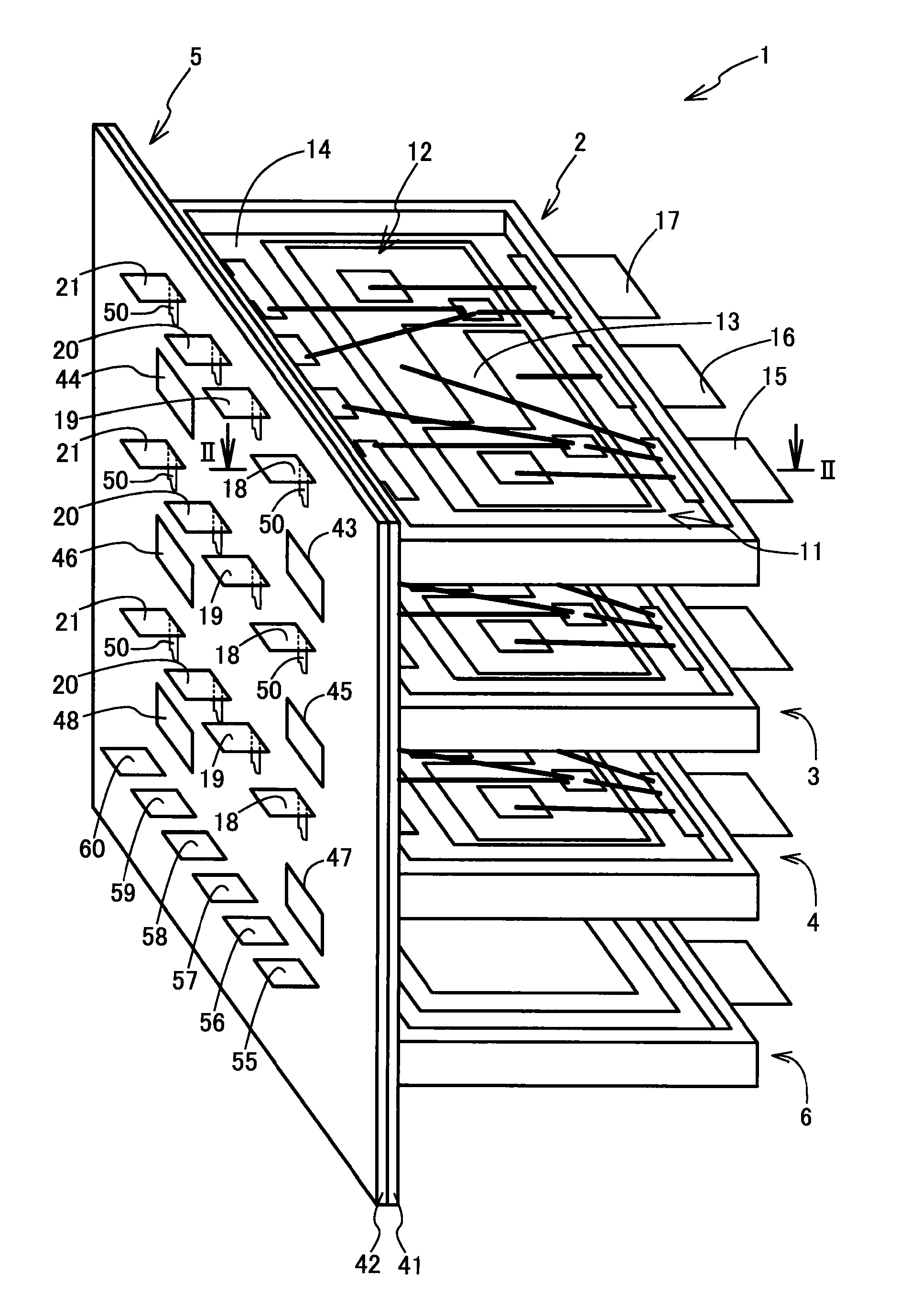

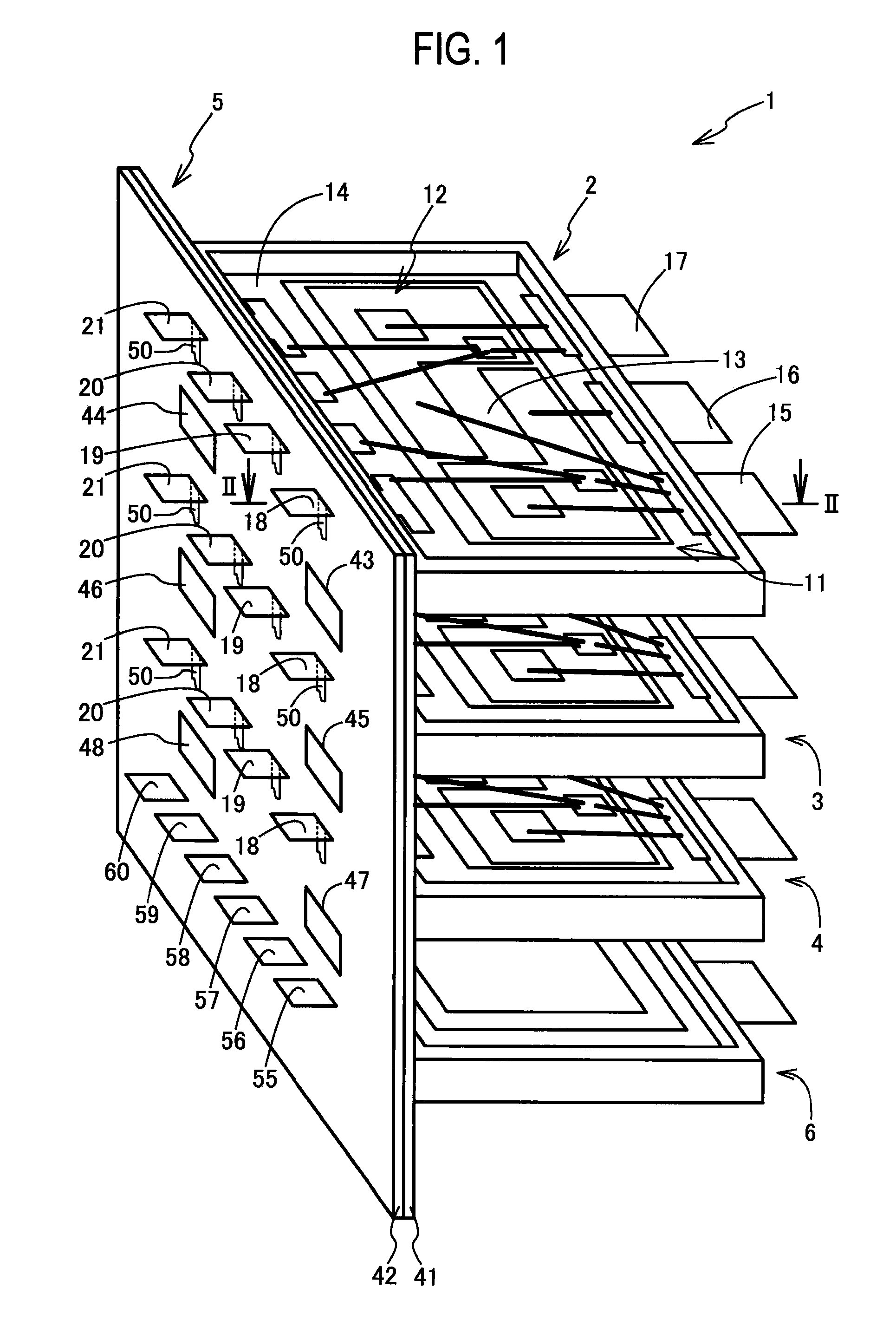

Upper and lower path switching device for traveling body for transportation

ActiveCN101229880AReduced load resistanceSafe and smooth transfer movementRailway componentsLifting framesLower limitPath switching

The present invention easily improves the accuracy of connection level alignment between an elevating guide rail and a fixed side guide rail in a path switching device which switches vertically a traveling path of a conveyance carriage or the like via an elevating guide rail, and in an upper and lower path switching device for a traveling body for transportation, including an elevating guide rail supported horizontally by an elevating body, upper fixed guide rails to be connected to the elevating guide rail at a lifted position of the elevating body, and lower fixed guide rails which are connected to the elevating guide rail at a lowered position of the elevating body, the elevating guide rail is supported movably vertically in a predetermined range with respect to the elevating body, and receiving members for receiving the elevating guide rail at a level at which the elevating guide rail is connected to the lower fixed guide rails before the elevating body reaches a lower limit thereof are provided.

Owner:DAIFUKU CO LTD

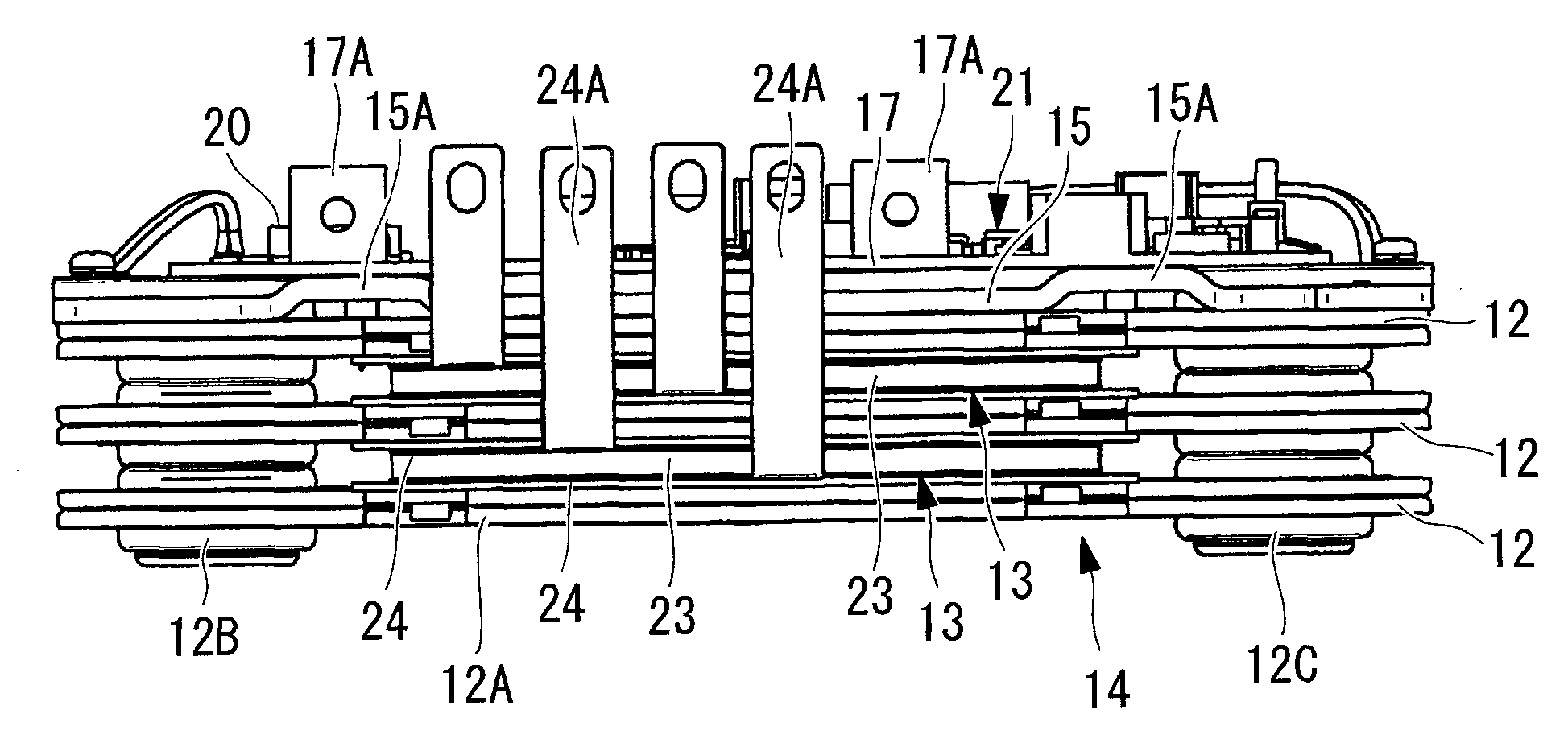

Heat medium heating apparatus and vehicular air-conditioning system including the same

InactiveUS20120237192A1Small sizeImprove performanceAir heatersVehicle heating/cooling devicesPlate heat exchangerHeat penetration

Provided is a heat medium heating apparatus including: a plurality of flat heat exchanger tubes 12; PTC heaters 13 that are respectively incorporated between flat tube parts of the flat heat exchanger tubes 12; a heat exchanger holding member 15 that press-fixes the flat heat exchanger tubes 12 and the PTC heaters 13, from one side of the flat heat exchanger tubes 12 to an inner surface of a casing 11; and a control board 17 that has a surface on which a control circuit 21 is mounted, the control circuit 21 including heat-generating electrical components 20 that control the PTC heaters 13, in which the control board 17 includes heat penetration parts that are formed so as to pass through the control board 17 correspondingly to mounting positions of the heat-generating electrical components 20, and the heat-generating electrical components 20 are mounted so as to be cooled via the heat penetration parts.

Owner:MITSUBISHI HEAVY IND LTD

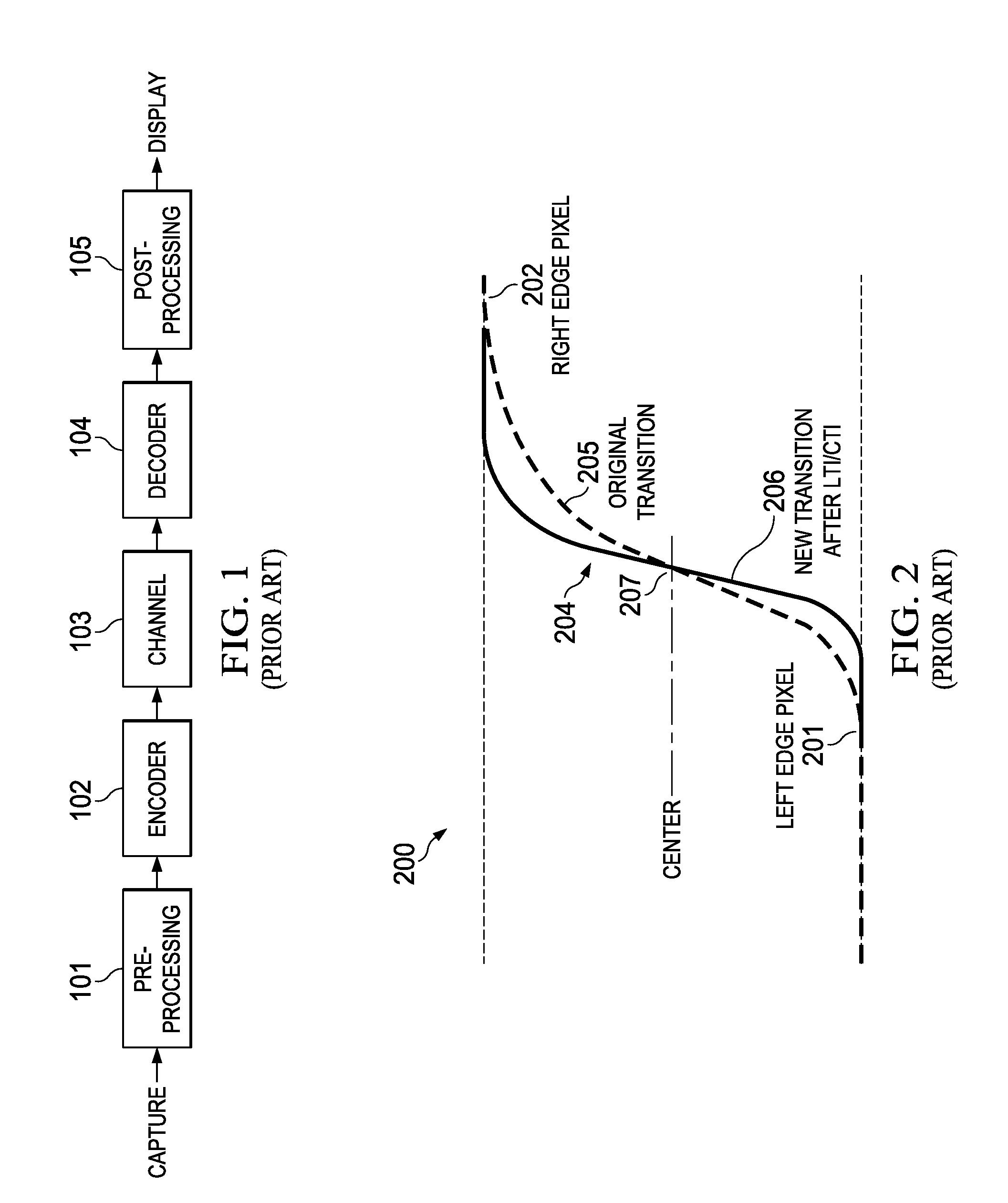

Content adaptive edge and detail enhancement for image and video processing

ActiveUS20140147057A1Reduce noiseImprove LTI/CTI qualityImage enhancementImage analysisAlgorithmImaging analysis

A content-adaptive edge and detail enhancement method is described for image / video processing. Both 2D peaking and LTI / CTI are used in sharpening pictures. Image analysis is performed to generate a mask to control the use of the two peaking techniques. The strength or likelihood of edges or transitions is measured and such a strength or likelihood measurement will be transformed into a blending factor controlling the blending of the LTI / CTI and peaking outputs.

Owner:TEXAS INSTR INC

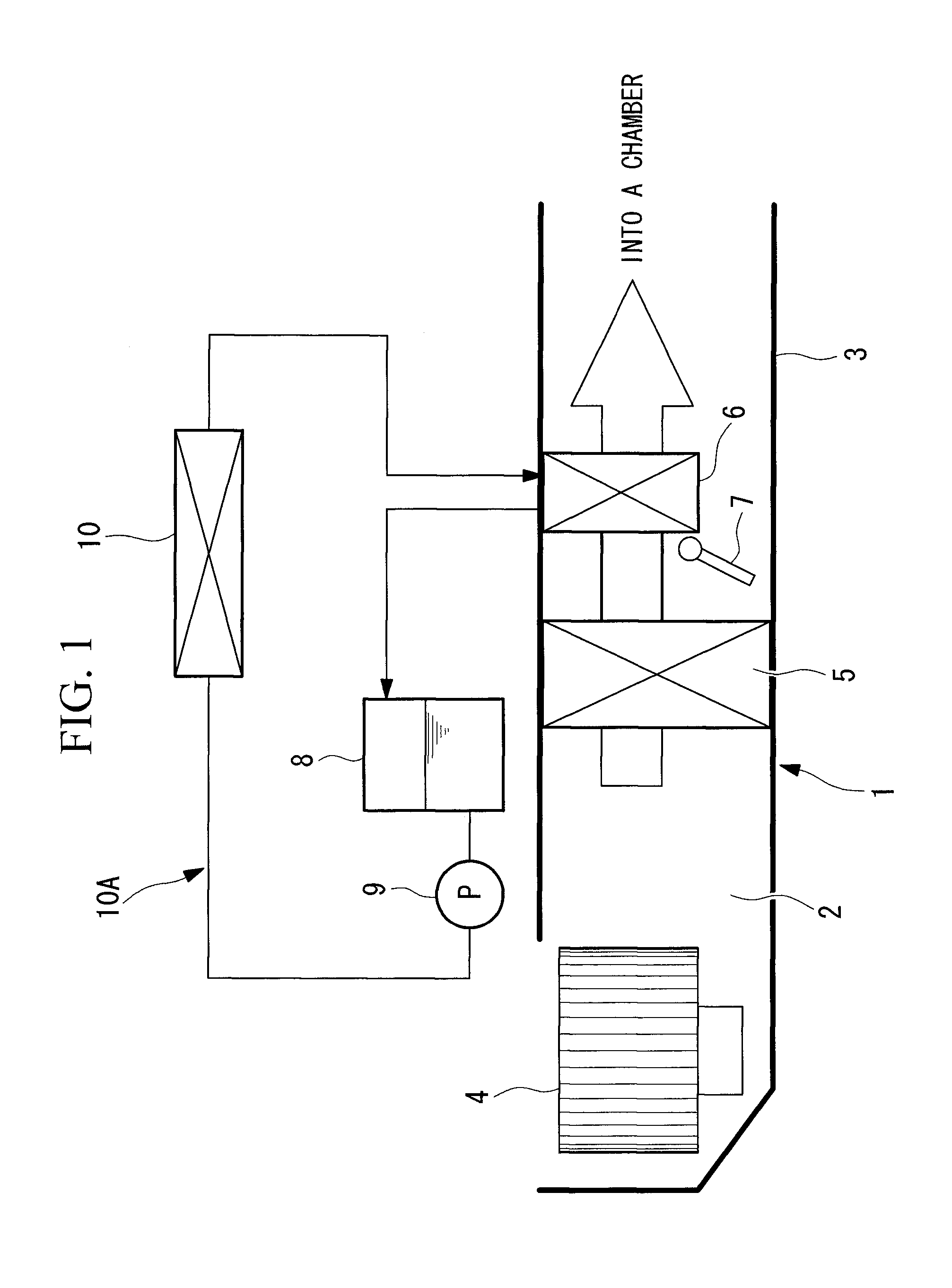

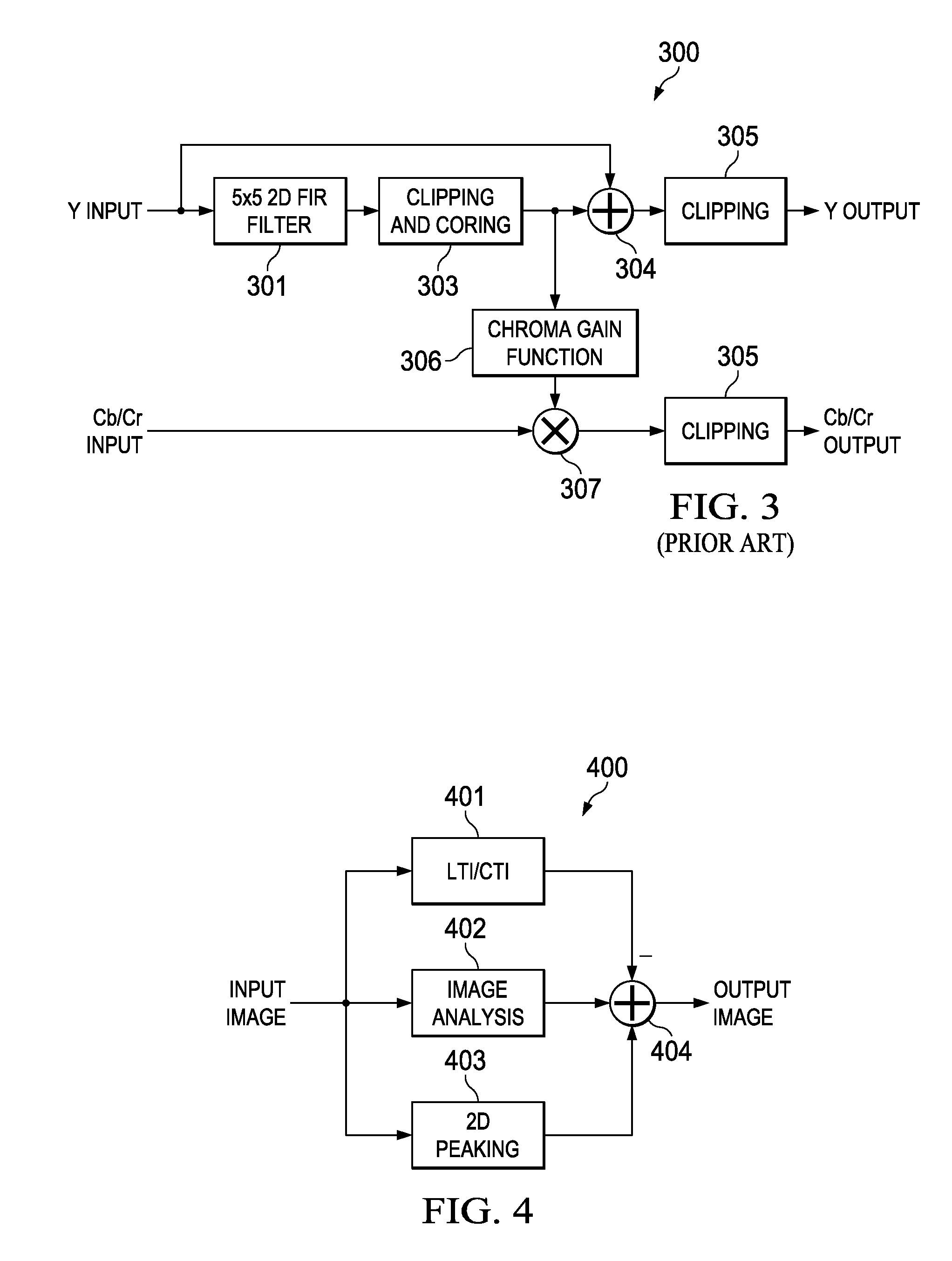

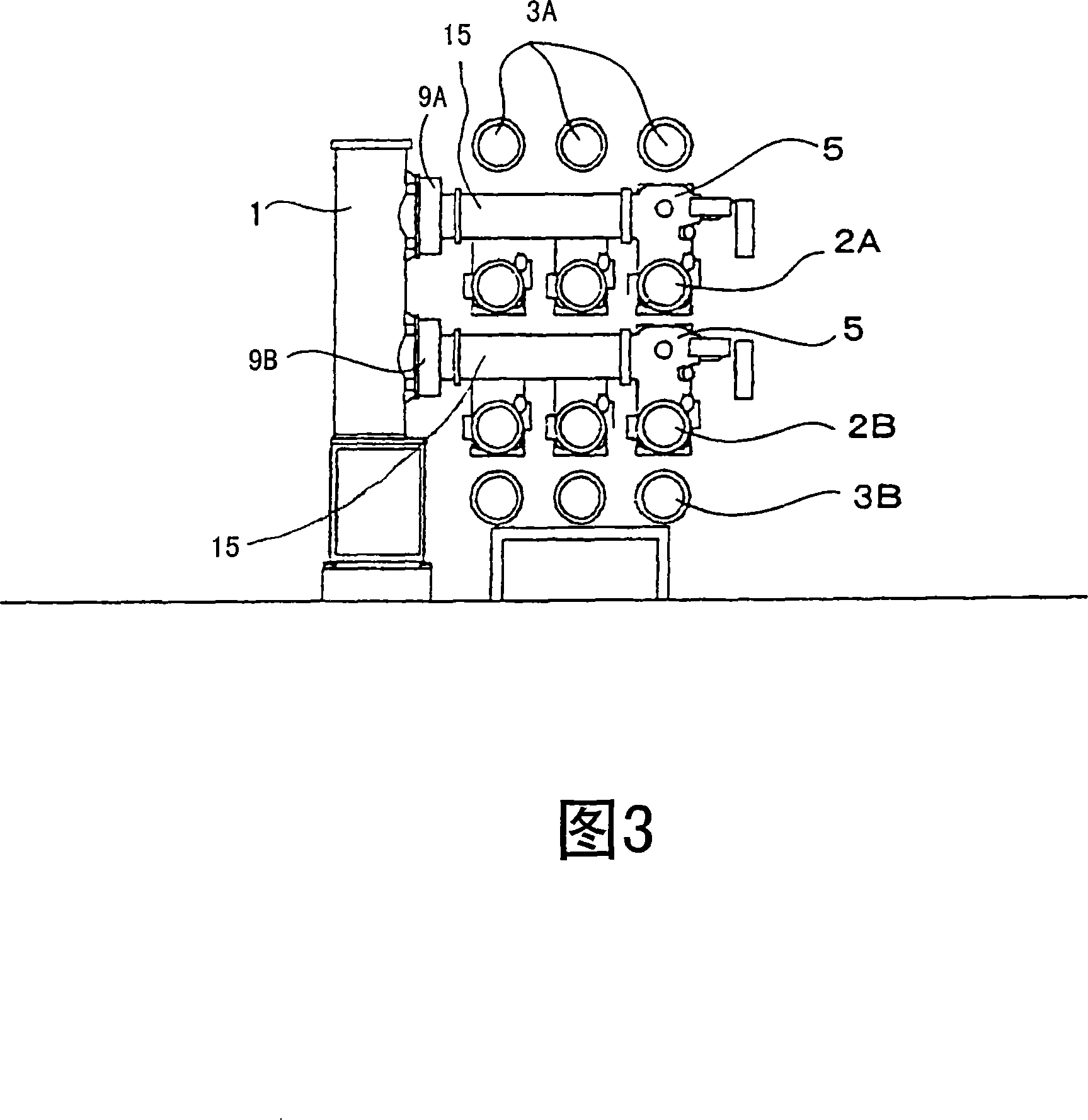

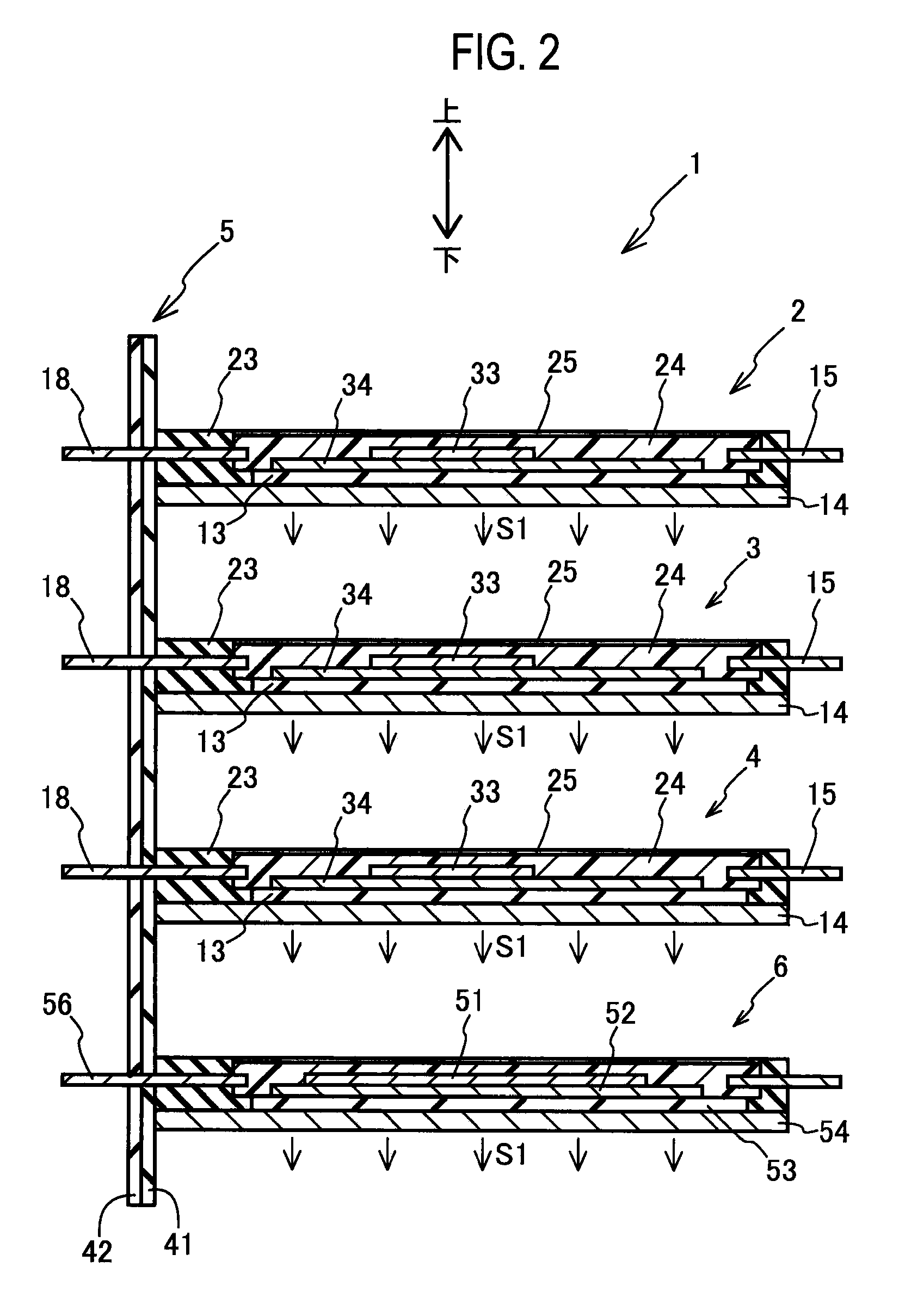

Continuous paper web duplex inkjet printing unit

InactiveUS20090189929A1Little deteriorated in qualityQuality improvementTypewritersOther printing apparatusPulp and paper industryInkjet printing

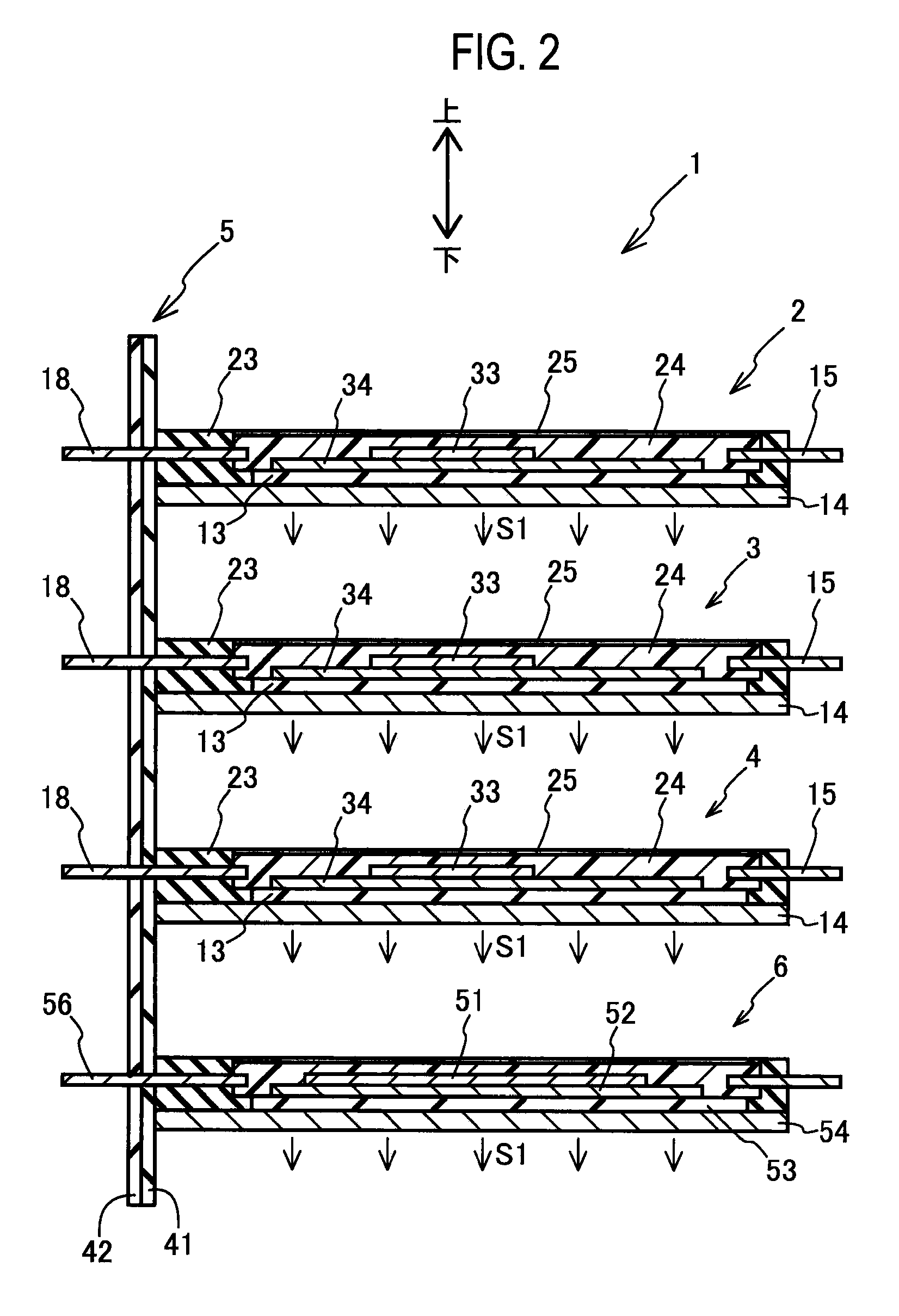

It is sought to reduce the planar area on which a continuous paper web duplex inkjet printing unit is installed. To this end, a continuous paper web duplex inkjet printing unit for inkjet printing on both sides of a continuous paper web with an inkjet printing head in an inkjet printer is configured to comprise a plurality of inkjet printers 11a-11h disposed so that they lie vertically in steps and their inkjet printing heads face downwards, and a paper threading path 15 disposed below such an inkjet printer or printers in each steps for permitting the continuous paper web to be passed zigzag from an upper to a lower step successively.

Owner:TOKYO KIKAI SEISAKUCHI LTD

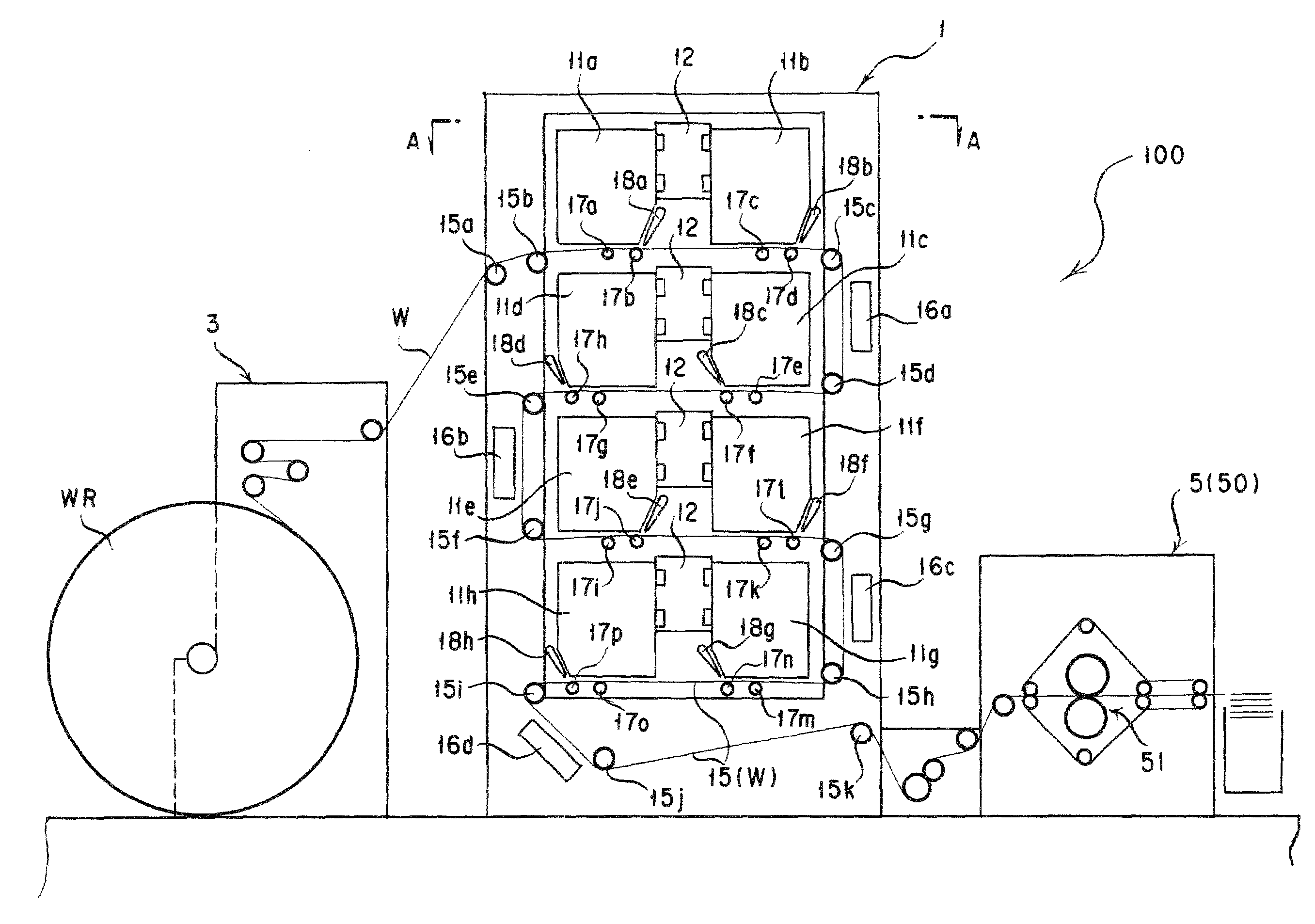

Slope aircraft landing taxi-track on aircraft-carrier deck and its using method

InactiveCN1955071AReduce floor areaReduce manufacturing difficultyAircraft carriersGround installationsAircraft landingStraight segment

An arc runway on aircraft carrier for the taking off or landing of aircraft is composed of a straight runway segment and a slope runway segment. For the taking off, said slope segment is used for the taxi and beginning acceleration and said straight segment is used for further acceleration. For the landing, said straight segment is used for the landing and deceleration sliding and said slope segment is used for further deceleration.

Owner:梁嘉麟

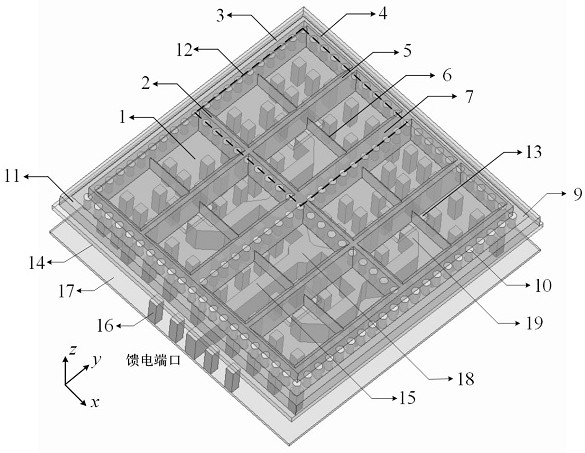

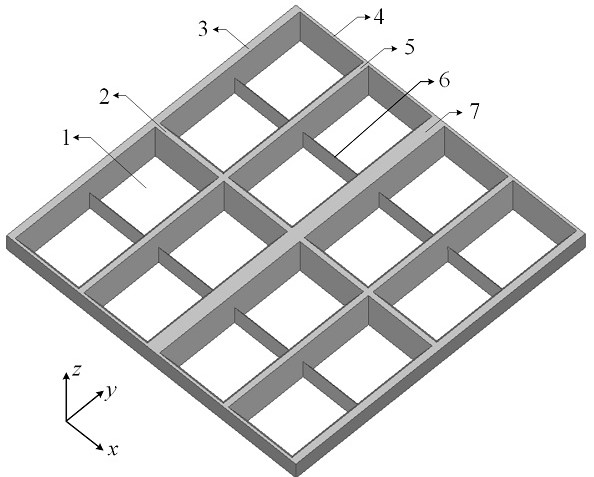

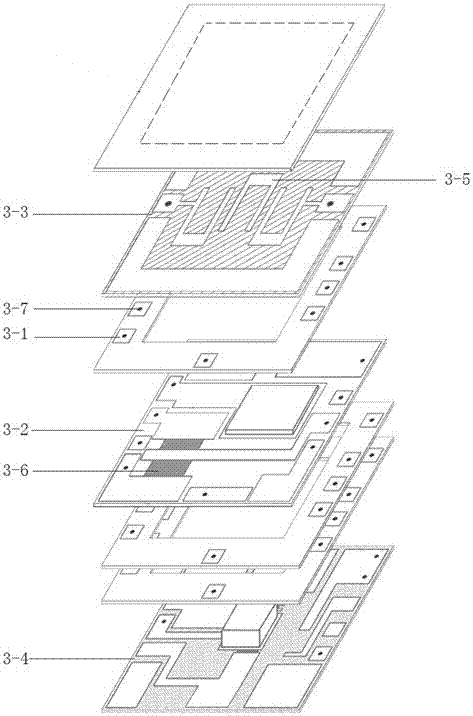

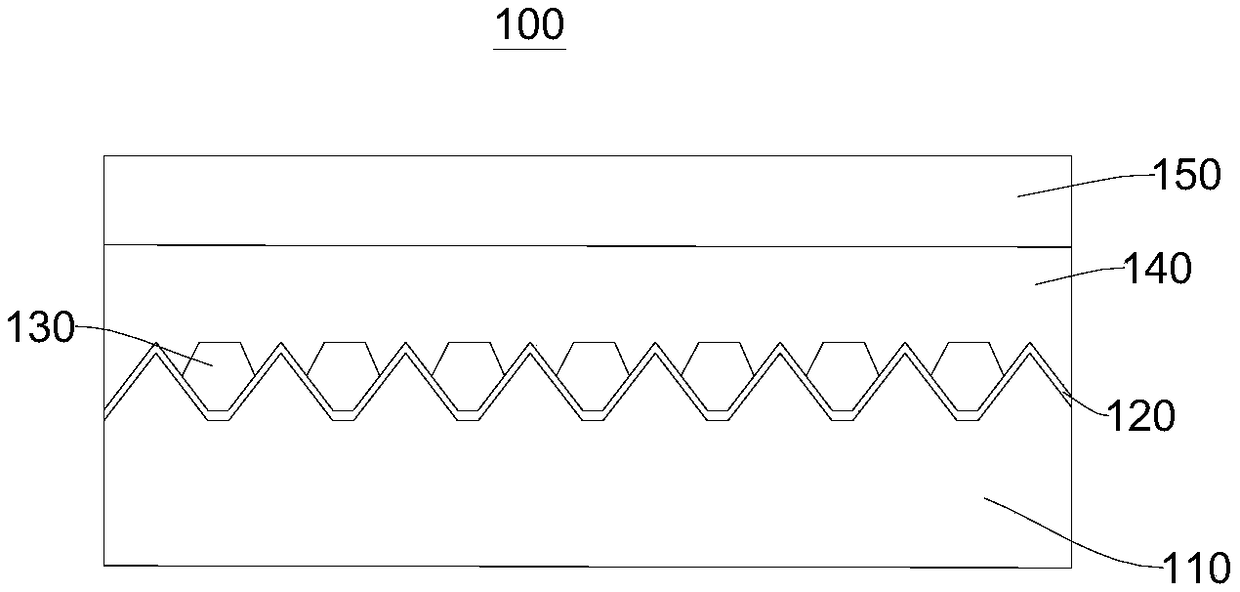

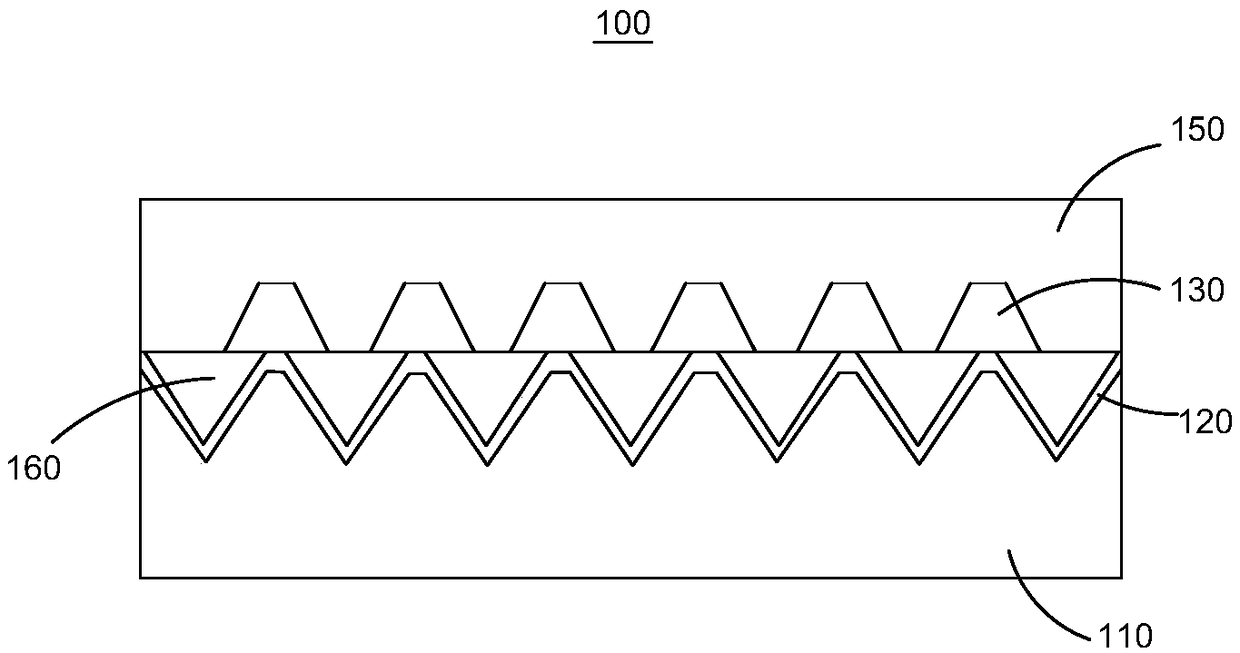

Millimeter-wave high-gain and high-radiation-efficiency slot antenna array based on ridge gap waveguide

ActiveCN112436295AImprove stabilitySimplify complexityAntenna arraysRadiating elements structural formsDielectric substrateEngineering

The present invention discloses a millimeter-wave high-gain and high-radiation-efficiency slot antenna array based on a ridge gap waveguide. The millimeter-wave high-gain high-radiation-efficiency slot antenna array comprises an upper layer structure, a middle layer structure and a lower layer structure, wherein the uppermost layer is an all-metal radiation unit layer manufactured through machining and is composed of 16 inverted trapezoidal slot radiation units at equal intervals; the middle layer is a substrate integrated waveguide high-order mode resonant cavity feed layer processed by a multilayer printed circuit board technology, and the substrate integrated waveguide high-order mode resonant cavity feed layer is composed of an upper planar structure, a middle planar structure and a lower planar structure. A metal printing surface with rectangular gaps is arranged above the substrate integrated waveguide high-order mode resonant cavity feed layer. A dielectric substrate with periodically arranged metal through holes is arranged in the middle, and a metal plate with four rectangular coupling holes is arranged below the dielectric substrate; and the bottommost layer is a machinedridge gap waveguide feed network layer and comprises a metal ridge line, metal pins surrounding the metal ridge line and a metal bottom plate. The whole antenna array is small in size, light in weight and high in integration level, and high gain and high radiation efficiency are realized in a working bandwidth.

Owner:NANJING UNIV OF SCI & TECH

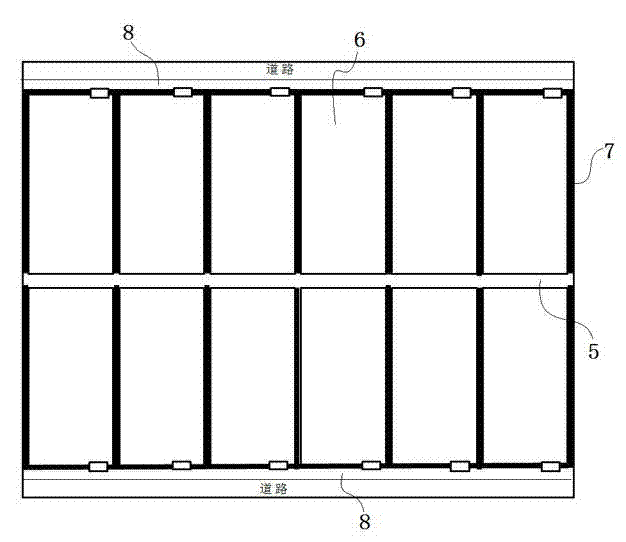

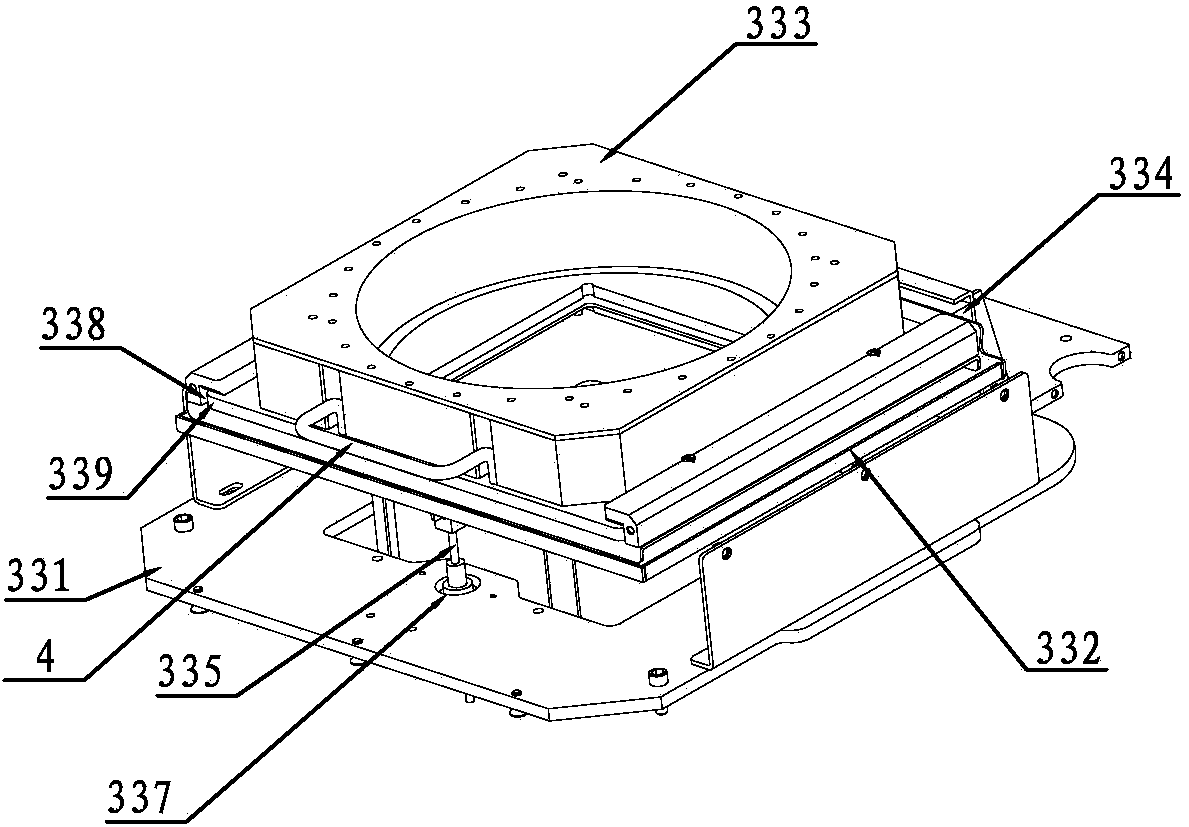

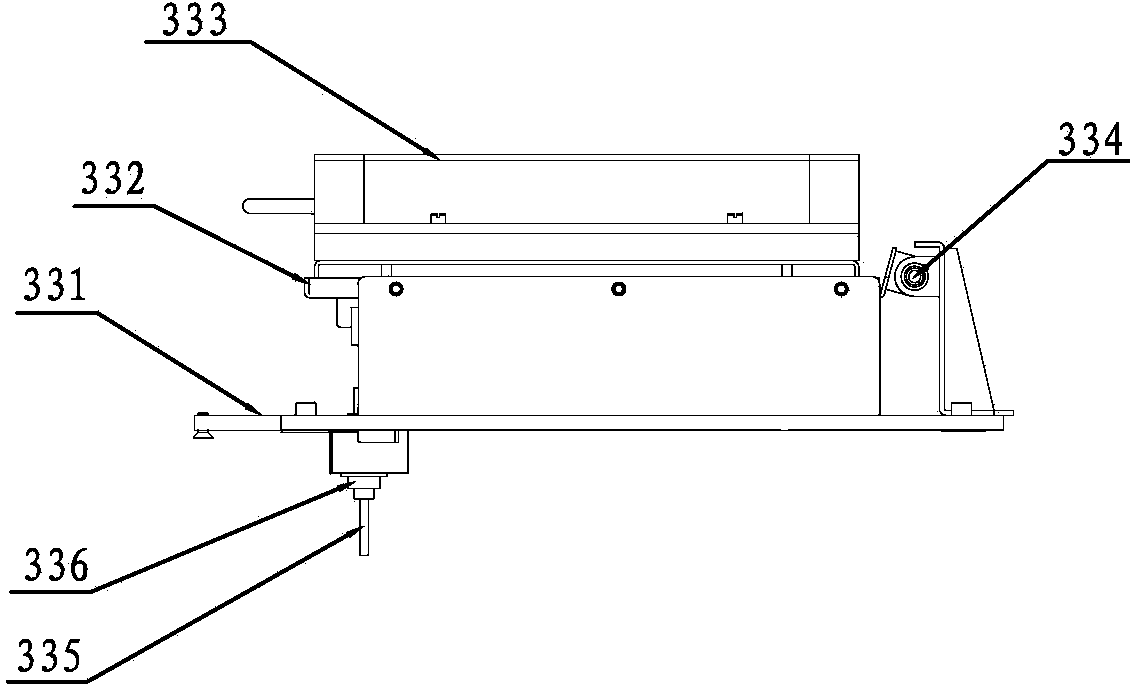

Sliding plate conveying system

The invention discloses a sliding plate conveying system which comprises a working conveying track, a return conveying device and a transfer device arranged between the working conveying track and the return conveying device and used for transferring sliding plates. The return conveying device is located under the working conveying track. The transfer device comprises a first lifting machine arranged between an outlet of the return conveying device and the input end of the working conveying track and a second lifting machine arranged between the output end of the working conveying track and an inlet of the returning conveying device. The first lifting machine and the second lifting machine are respectively provided with a high position enabling the corresponding lifting machine to be in abutting connection with the working conveying track and a low position enabling the corresponding lifting machine to be in abutting connection with the return conveying device. The returning conveying device is located under the working conveying track. The whole sliding plate conveying system is small in occupation plane area, suitable for being applied to workshops with limit space and capable of effectively expanding use range of the sliding plate conveying system.

Owner:ZHONGQI CHANGXING LUOYANG ELECTROMECHANICAL EQUIP ENG +1

Nitride-based semiconductor laser device and method of manufacturing the same

InactiveUS20090245310A1Improve flatnessStable horizontal transverse modeOptical wave guidanceSemiconductor/solid-state device manufacturingEngineeringErbium lasers

A nitride-based semiconductor laser device includes a nitride-based semiconductor layer formed on a main surface of a substrate and having an emission layer, wherein the nitride-based semiconductor layer includes a first side surface formed by a (000-1) plane and a second side surface inclined with respect to the first side surface, and a ridge having an optical waveguide extending perpendicular to a [0001] direction in an in-plane direction of the main surface of the substrate is formed by a region held between the first side surface and the second side surface.

Owner:SANYO ELECTRIC CO LTD

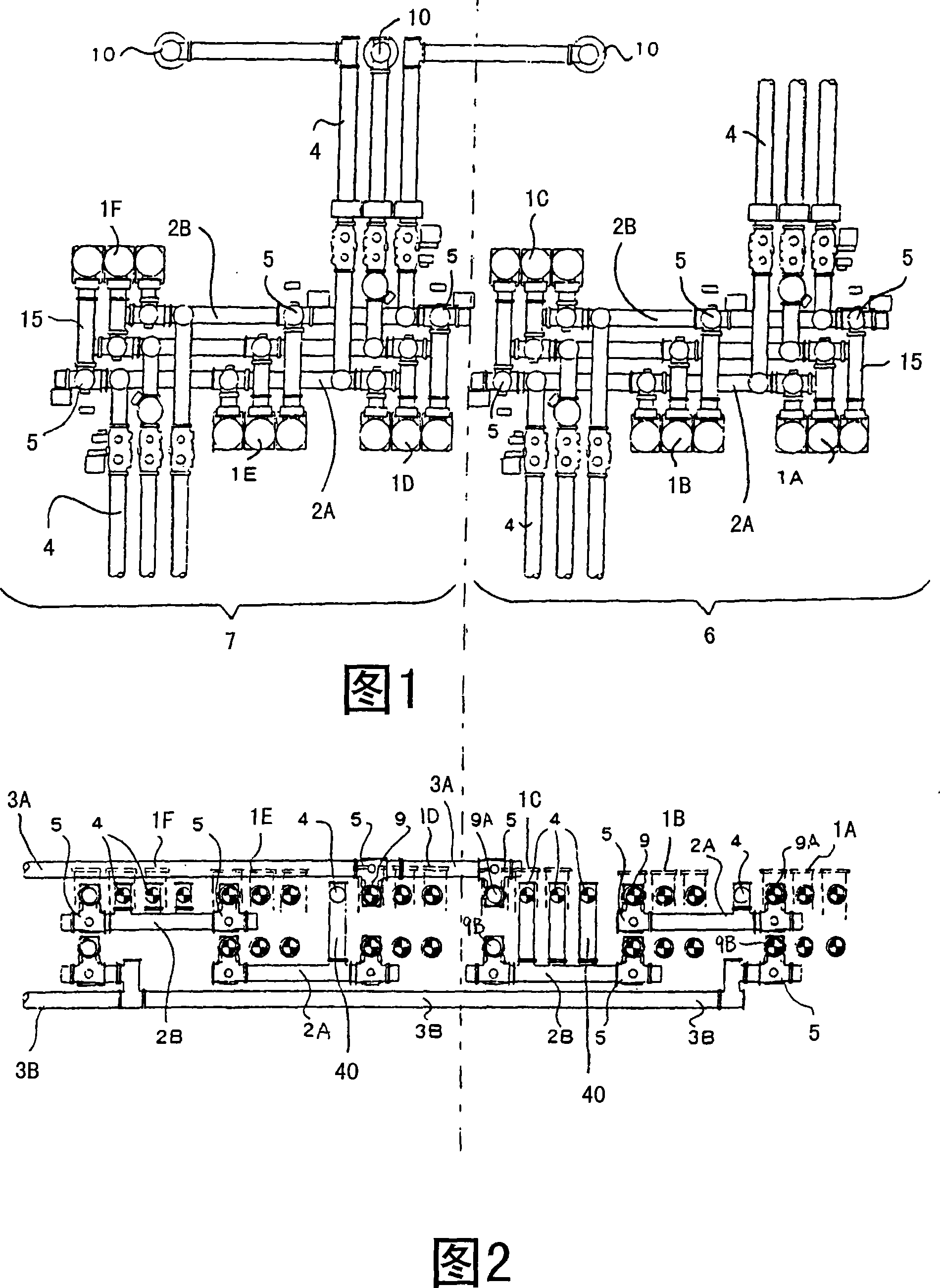

Gas insulation open-close device

InactiveCN101047304AEasy maintenanceImprove the transformation effectBus-bar/wiring layoutsSwitchgear arrangementsBusbarGas insulation

The invention provides a GIS effectively equiped with device and busbar, in order to reduce the area of applying ground and busbar length, and enhance the maintenance of breaker and recovery efficiency. The circuit in-cinnection busbar, eduction busbar, vertical breaker, and circuit among-cinnection main busbar are made by single phase device. The circuit in-cinnection busbar, vertical breaker and circuit among-cinnection main busbar make triphase divided busbar parallelly allocate on the same plane. The circuit in-cinnection busbar and circuit among-cinnection main busbar coincide up and down to make the mian axis of busbar of each phase slightly overlap at the same direction and on the same plane. The eduction busbar is coincident allocated at the direction crossed with the main axis of the circuit in-cinnection busbar and circuit among-cinnection main busbar. The vertical breaker is set beside the circuit in-cinnection busbar and circuit among-cinnection main busbar, and the orientation thereof is paralleled with the main axis of the circuit in-cinnection busbar and circuit among-cinnection main busbar.

Owner:KK TOSHIBA

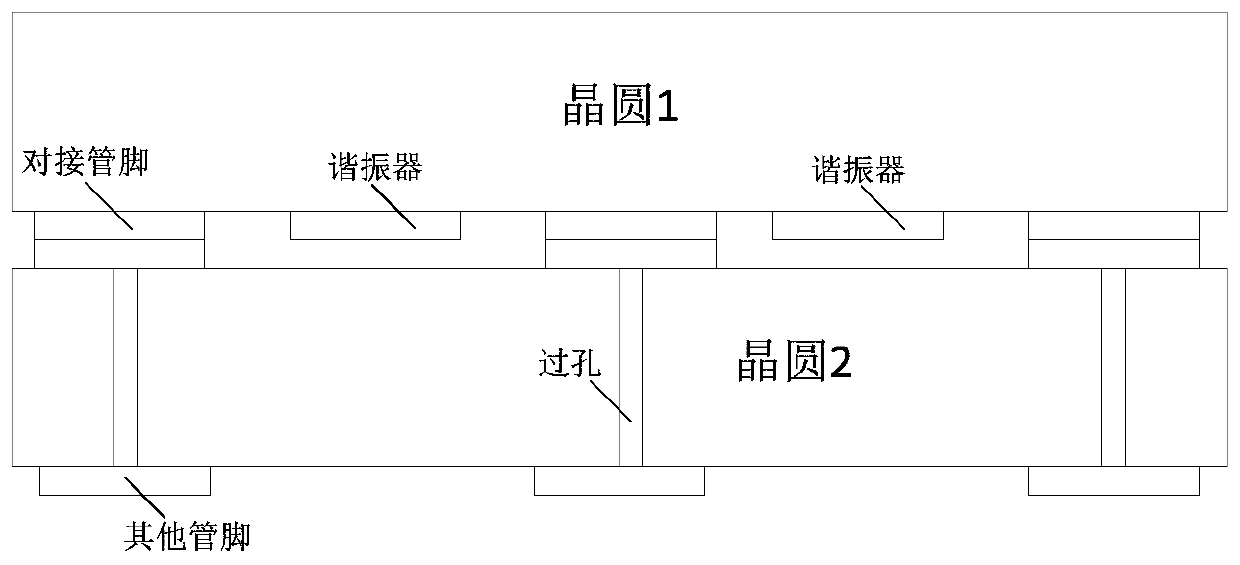

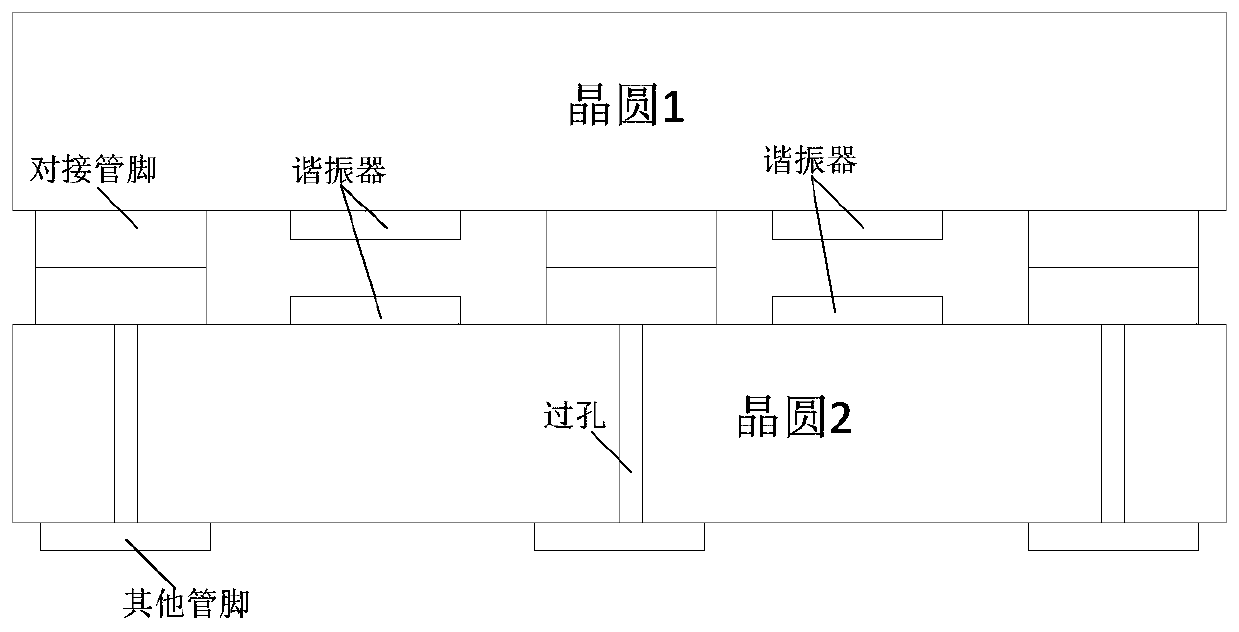

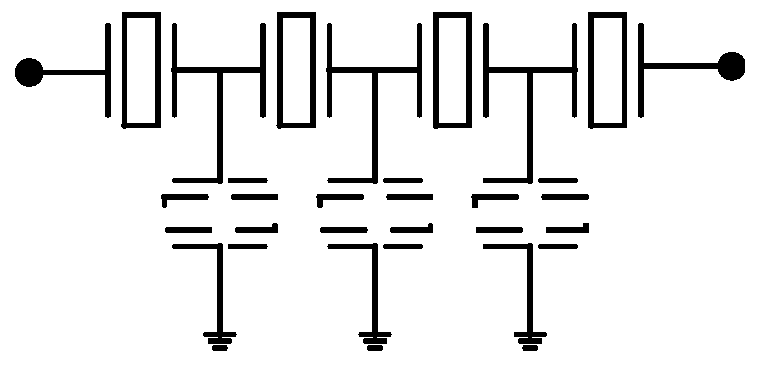

Bulk acoustic wave filter element and forming method thereof, multiplexer and communication equipment

The invention relates to the technical field of filters, in particular to a bulk acoustic wave filter element and a forming method thereof, a multiplexer and communication equipment, and the method comprises the following steps: arranging one part of resonators on an upper wafer, and arranging the other part of resonators on a lower wafer; wherein the upper wafer and the lower wafer are stacked; and the butt joint pin of the upper wafer is bonded with the butt joint pin of the lower wafer, so that the resonators of the upper wafer and the lower wafer are connected to form the filter. Accordingto the technical scheme of the invention, the resonators are respectively arranged on the upper wafer and the lower wafer, and the resonators on the upper wafer and the lower wafer are bonded throughthe butt joint pins to form the filter, so that the planar area occupied by the resonators in the upper wafer and the lower wafer can be reduced, and the size of the filter can be reduced.

Owner:ROFS MICROSYST TIANJIN CO LTD

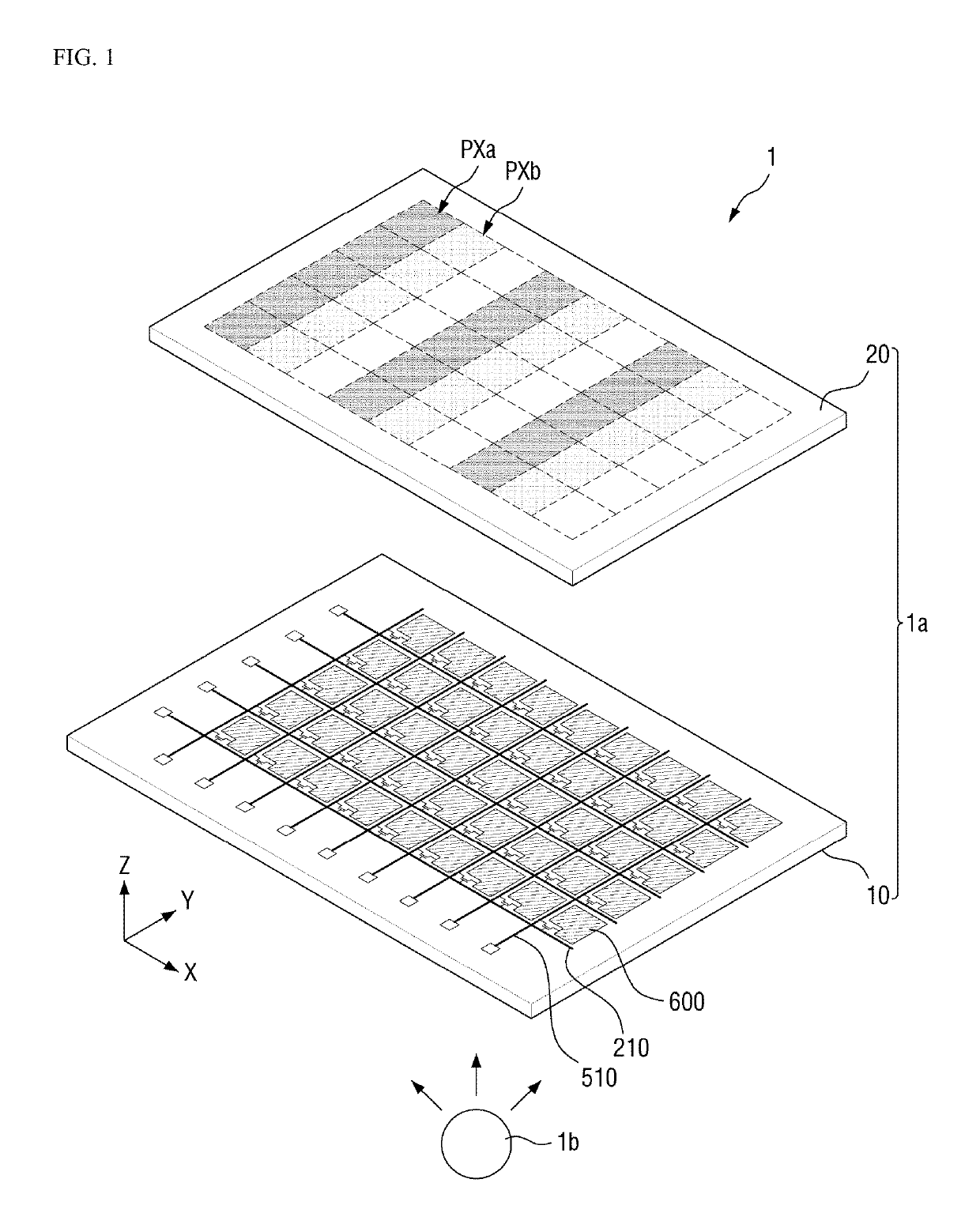

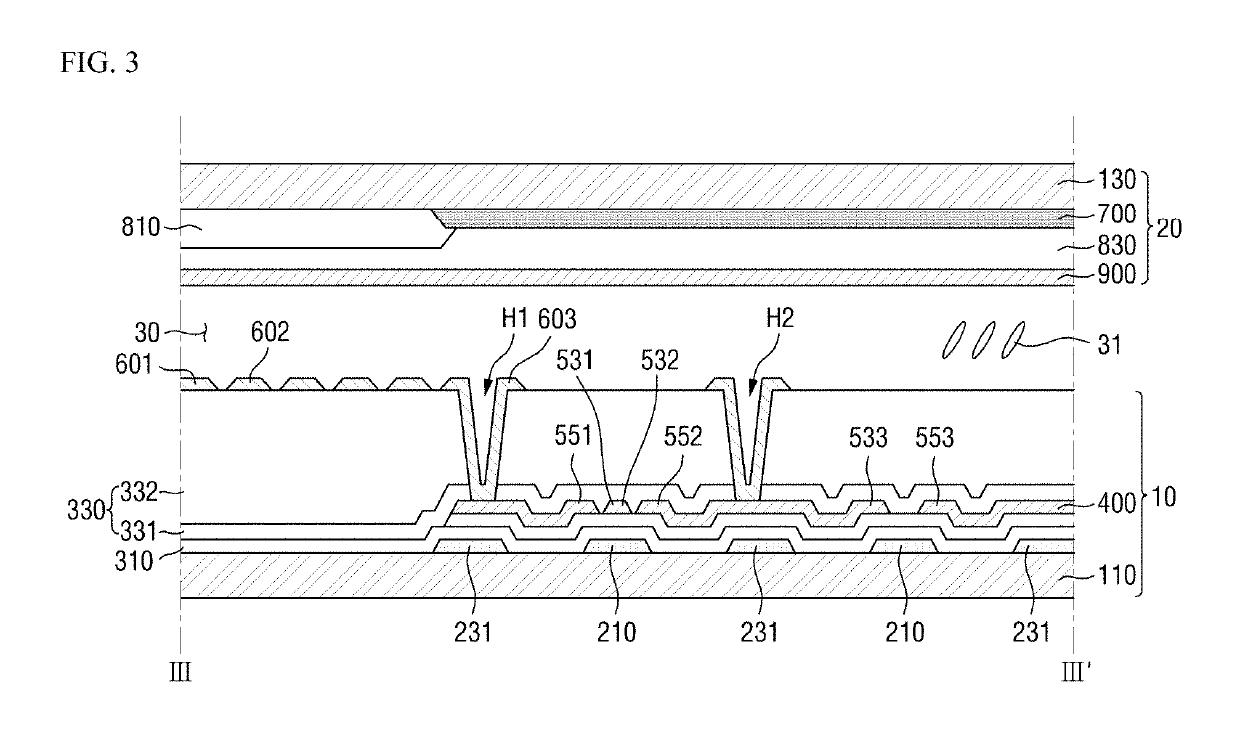

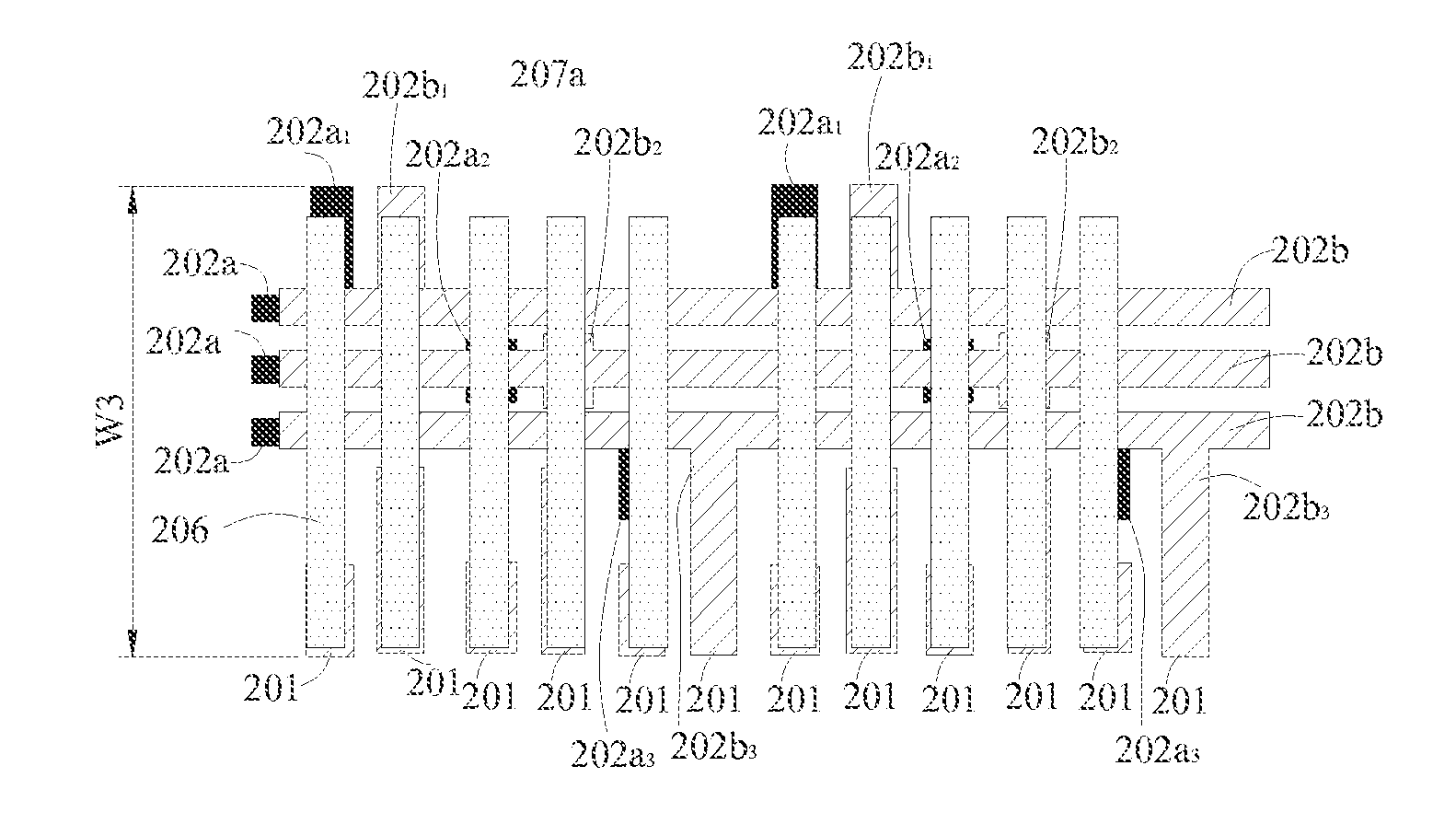

Wire substrate, display device including the same, and method of fabricating wire substrate

ActiveUS10386687B2Increase the aperture ratioSuppressing reflection of external lightSemiconductor/solid-state device detailsSolid-state devicesDisplay deviceOptoelectronics

A wire substrate, a display device including a wire substrate, and a method of fabricating a wire substrate are disclosed. The display device comprises: a first base; and a first wiring layer disposed on the first base and comprising a conductive metal layer and a metal oxide layer stacked on one another, wherein the metal oxide layer comprises MoxTayOz, wherein a content of tantalum is equal to or less than 2.0 at % (atomic percent) based on a total number of metal atoms.

Owner:SAMSUNG DISPLAY CO LTD

Display substrate and manufacture method thereof, display device and manufacture method thereof, and mobile terminal

InactiveCN108051965AReduce floor areaIncrease the screen ratioFinal product manufacturePhotovoltaic energy generationDisplay deviceEngineering

The invention discloses a display substrate and a manufacture method thereof, a display device and a manufacture method thereof, and a mobile terminal, relates to the technical field of displaying andis intended to increase screen-to-body ratio of the mobile terminal. The display substrate comprises a rigid substrate, a flexible substrate, a pixel structure and a binding terminal, wherein the rigid substrate comprises a portion corresponding to a display area of the display substrate, the flexible substrate is positioned on the rigid substrate and comprises a portion corresponding to the display area of the display substrate and a portion corresponding to a binding area of the display substrate, the pixel structure is positioned in an area of the flexible substrate corresponding to the display area of the display substrate, the binding terminal is positioned in an area of the flexible substrate corresponding to the binding area of the display substrate, and the part of the flexible substrate corresponding to the binding area is flexible. After the display device with the display substrate provided herein is applied to the mobile terminal and the part of the flexible substrate corresponding to the binding area is bent, the screen-to-body ratio of the mobile terminal is increased.

Owner:BOE HEBEI MOBILE DISPLAY TECH +1

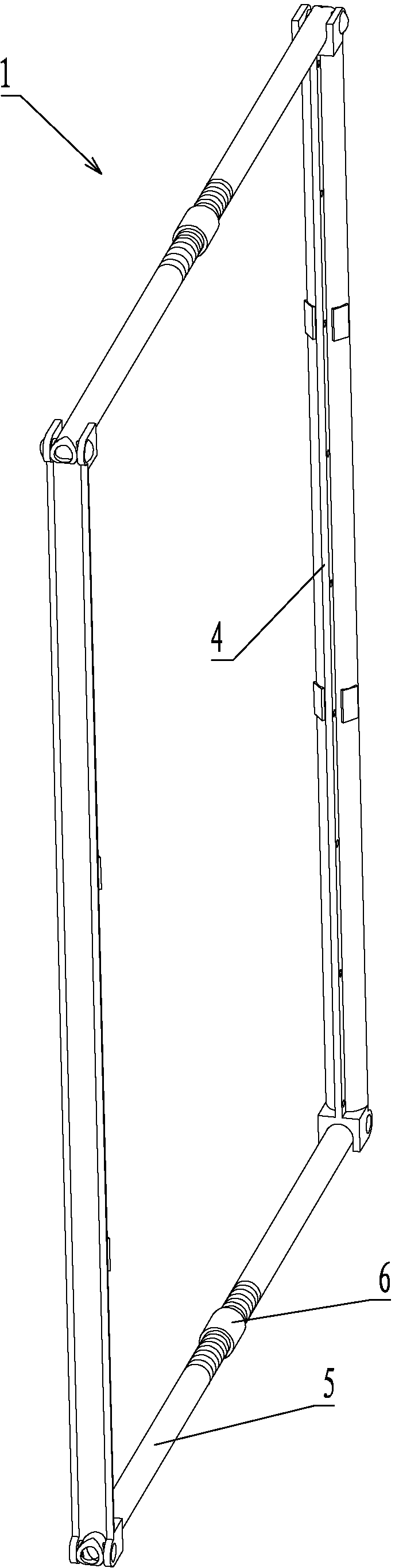

Inclined pulling assembly for 3D printing device

The utility model discloses an inclined pulling assembly for a 3D printing device. The inclined pulling assembly comprises a mounting bracket and a hollow support frame movably connected with the mounting bracket through a connecting piece, wherein a resin frame used for accommodating a printing solution is mounted on the support frame; the bottom of the resin frame is a transparent bottom plate; a pull rod is further arranged at the bottom of the side edge, opposite to the connecting piece, of the support frame, and is connected with a driving motor; the support frame is enabled to rotate along the connecting piece through the ascending and descending of the pull rod. By adopting the inclined pulling assembly, a curing layer is completely separated from the bottom of the resin frame by pulling downwards on one side slowly, translation for increasing the plane area of the resin frame is not required, friction generated by translation is avoided, the service life of a thin film on the transparent bottom plate of the resin frame is greatly prolonged, and generally, one resin frame can be used for printing for 400,000-500,000 times.

Owner:GUANGDONG SPRINTRAY 3D PRINTING TECH CO LTD

Storage module and storage equipment

The invention relates to the technical field of storage and discloses a storage module and storage equipment comprising the storage module. The storage module comprises a substrate, an interface contact group and a circuit component group packaged on an inner side face of the substrate, wherein the interface contact group is electrically connected to the circuit component group; and the circuit component group is hierarchically laminated on the inner side face of the substrate. Compared with the prior art, the circuit component group in the storage module is hierarchically laminated on the substrate, so that a designer can distribute a hierarchical structure according to dimension of a circuit component in the circuit component group, while length of the substrate is only needed to be slightly greater than the longest hierarchical structure; therefore, a plane area of the circuit component occupying the inner side face of the substrate is greatly reduced, and an effect of reducing volume of the storage module is achieved. Moreover, the circuit component group is not needed to be reduced or other lower-capacity circuit component groups are not needed to be replaced, and the problem that the capacity of the storage module is reduced due to the reduced volume of the storage module is solved.

Owner:SHENZHEN NETCOM ELECTRONICS CO LTD

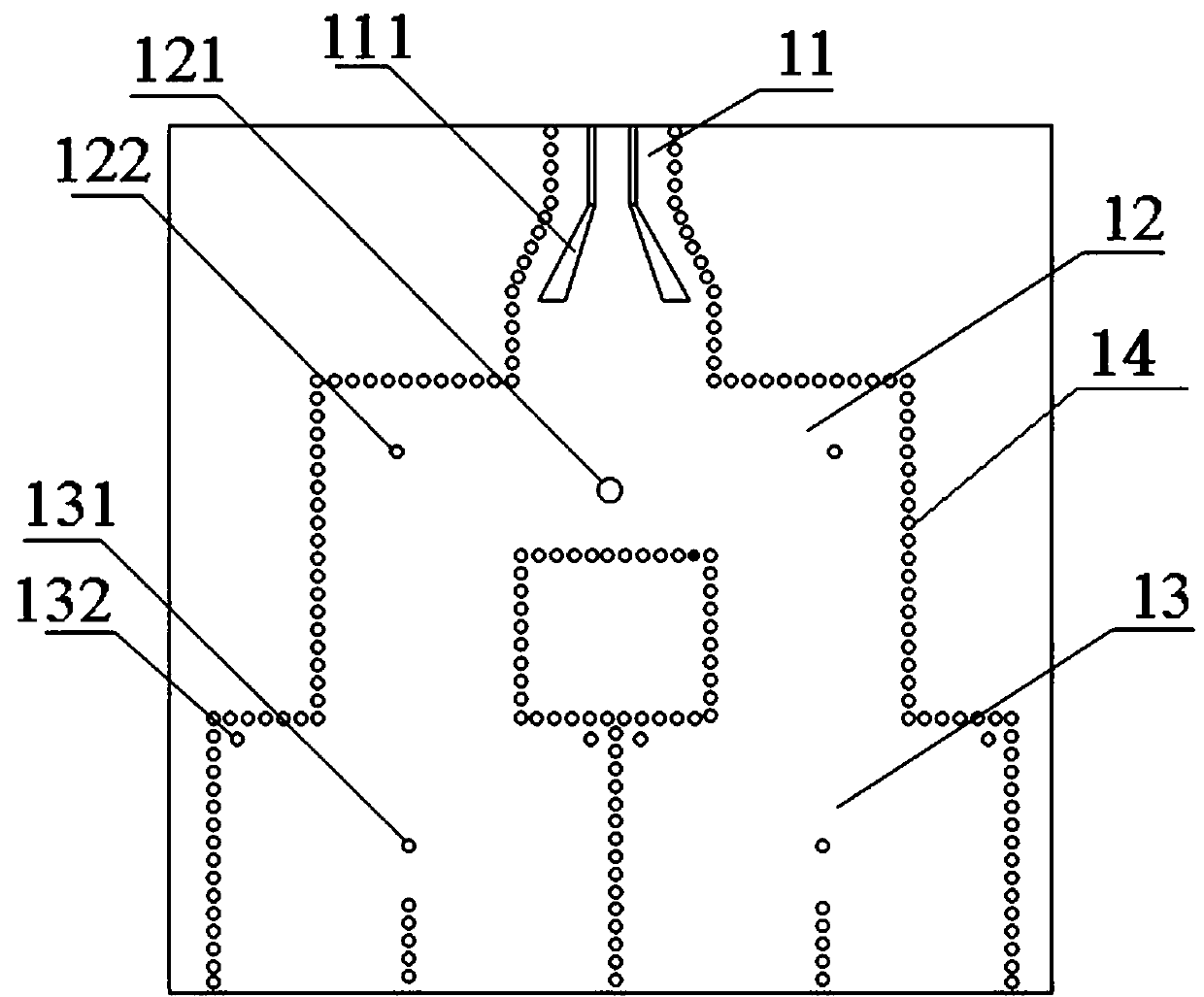

Three-dimensional stack structure of thin-film ceramic circuit

ActiveCN107275317AAchieve stackingReduce floor areaSemiconductor/solid-state device detailsSolid-state devicesBroadbandProduct integration

The invention provides a three-dimensional stack structure of a thin-film ceramic circuit. Between two adjacent thin-film ceramic substrates, through ball mounting welding or prefabricated pad welding, stacking of more than three thin-film ceramic circuit substrates is realized. Solid metal through holes are used for realizing electric connection of a random layer. The structure comprises a local electromagnetic self-shielding structure of a chip and / or a passive component. The local electromagnetic self-shielding structure comprises an upper metal layer, a lower metal layer and side surface solid metal through holes. The three-dimensional stack structure can realize stacking of the thin-film ceramic circuit so that an active chip, an RF structure, a high-power structure, a broadband switching structure and the like are integrally integrated in a three-dimensional direction, thereby reducing plan area of a function core by more than 70%, effectively improving product integration level, synchronously realizing hermetic sealing and electromagnetic self-shielding, and improving product adaptability. The three-dimensional stack structure can replace 60-70% of similar products and has advantages of saving cost by more than 60% and improving production efficiency by more than 40%.

Owner:SOUTHWEST CHINA RES INST OF ELECTRONICS EQUIP

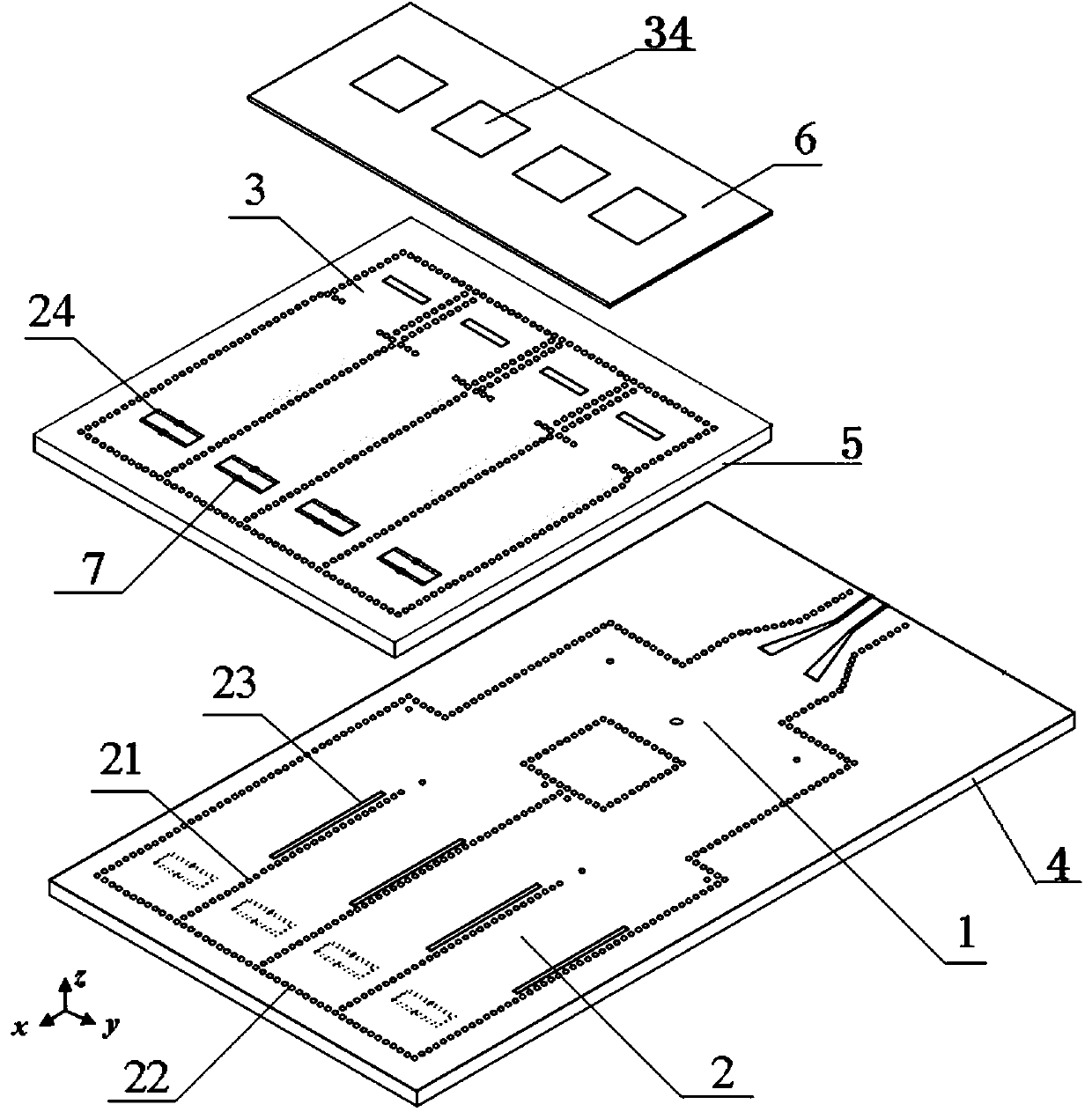

Phased array antenna based on continuously adjustable substrate integrated waveguide phase shifter

InactiveCN110571537ARealize real-time continuous scanningHighly integratedSimultaneous aerial operationsWaveguide type devicesContinuous scanningPhase array antenna

The invention belongs to the technical field of wireless communication, and relates to a phased array antenna based on a continuously adjustable substrate integrated waveguide phase shifter. The phased array antenna comprises a feed network, a phase shifter and a radiation unit, wherein the feed network is connected between the phase shifter and the radiation unit; the feed network comprises a converter, a T-shaped power divider and a Y-shaped power divider; the output end of the converter is connected with the input end of the T-shaped power divider, the output ends of the T-shaped power divider are respectively connected with the input ends of the Y-shaped power divider, and the output end of the Y-shaped power divider is connected with the phase shifter. The antenna has the advantages of low cost, compact structure, high integration level and large continuous scanning angle range.

Owner:SHENZHEN UNIV

Short-circuit unit and array substrate

ActiveUS20160252792A1Little riskSmall widthSemiconductor/solid-state device testing/measurementSolid-state devicesElectricitySignal lines

The present invention provides a short-circuit unit comprising: a plurality of signal lines divided into a plurality of groups, each group comprising multiple signal lines, and the multiple signal lines in a same group are not adjacent to each other; a plurality of short-circuit lines, each group of the signal lines correspond to one short-circuit line, and the short-circuit line electrically connects all of the signal lines in the group corresponding to the short-circuit line, the plurality of short-circuit lines are disposed in different layers and the short-circuit lines in different layers are insulated from each other. The present invention also provides an array substrate. In the short-circuit unit of the present invention, the short-circuit lines are disposed in different layers. Compared to the existing solutions in which the short-circuit lines are provided in a same layer, the width occupied by the short-circuit unit of the present invention is smaller.

Owner:BOE TECH GRP CO LTD +1

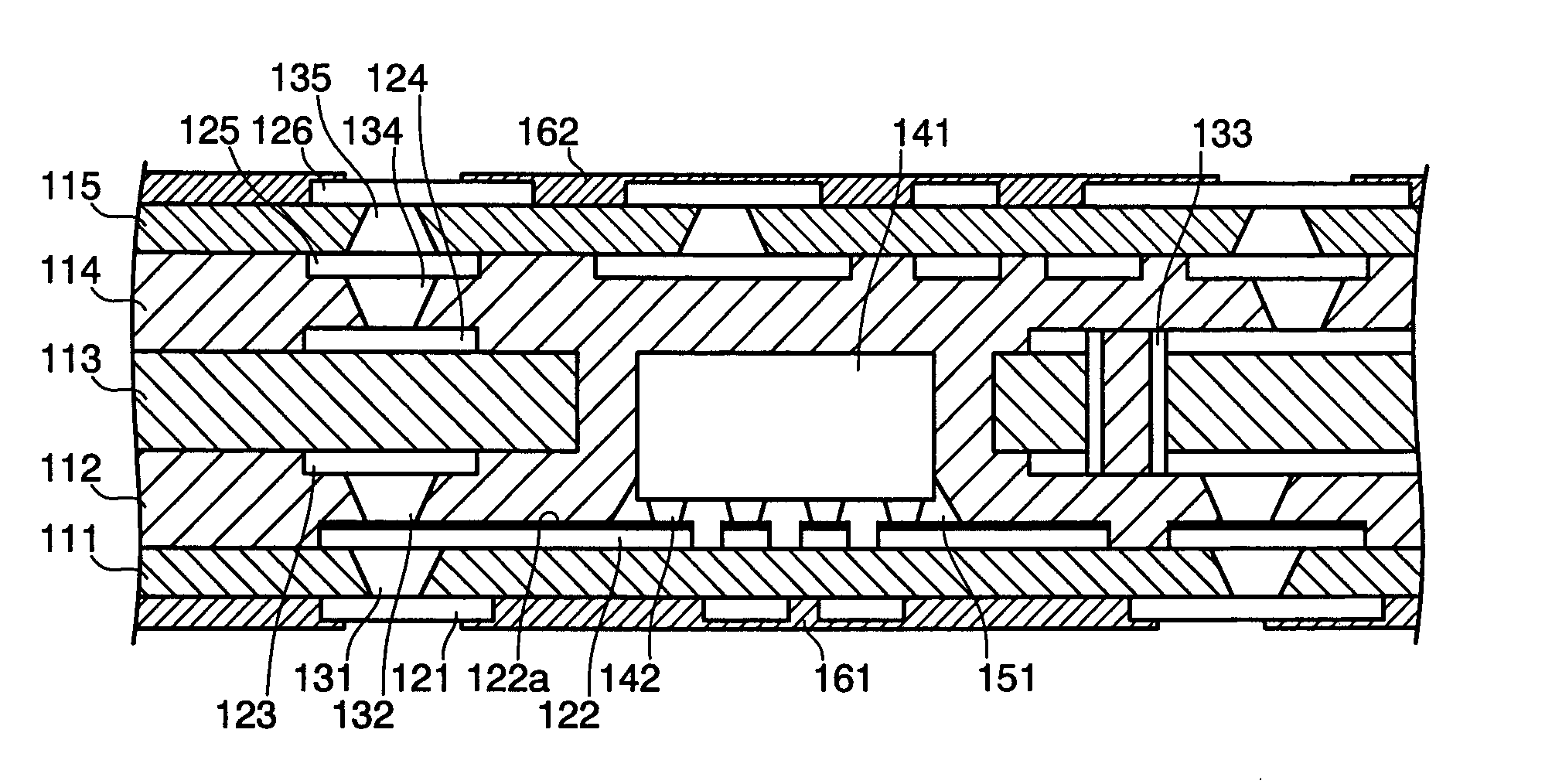

Component built-in wiring board and manufacturing method of component built-in wiring board

InactiveUS8987901B2Improve productivityLow costPrinted circuit assemblingFinal product manufactureSemiconductor chipPower strip

Disclosed is a component built-in wiring board including: a first insulating layer on a second one having laminated at least two insulating layers; a semiconductor chip buried in the second insulating layer, having a terminal pad; a wiring pattern between the first and the second insulating layers, including a mounting land and having a roughened surface facing the second insulating layer; a conductive bump between the terminal pad and the mounting land; a resin between the semiconductor chip and both the first insulating layer and the wiring pattern; a second wiring pattern between the at least two insulating layers; and an interlayer connector between surfaces of the wiring pattern and the second wiring pattern to penetrate partly through the second insulating layer in a layered direction, made of a conductive composition, and having a shape with an axis along the layered direction and a diameter varying in an axial direction.

Owner:DAI NIPPON PRINTING CO LTD

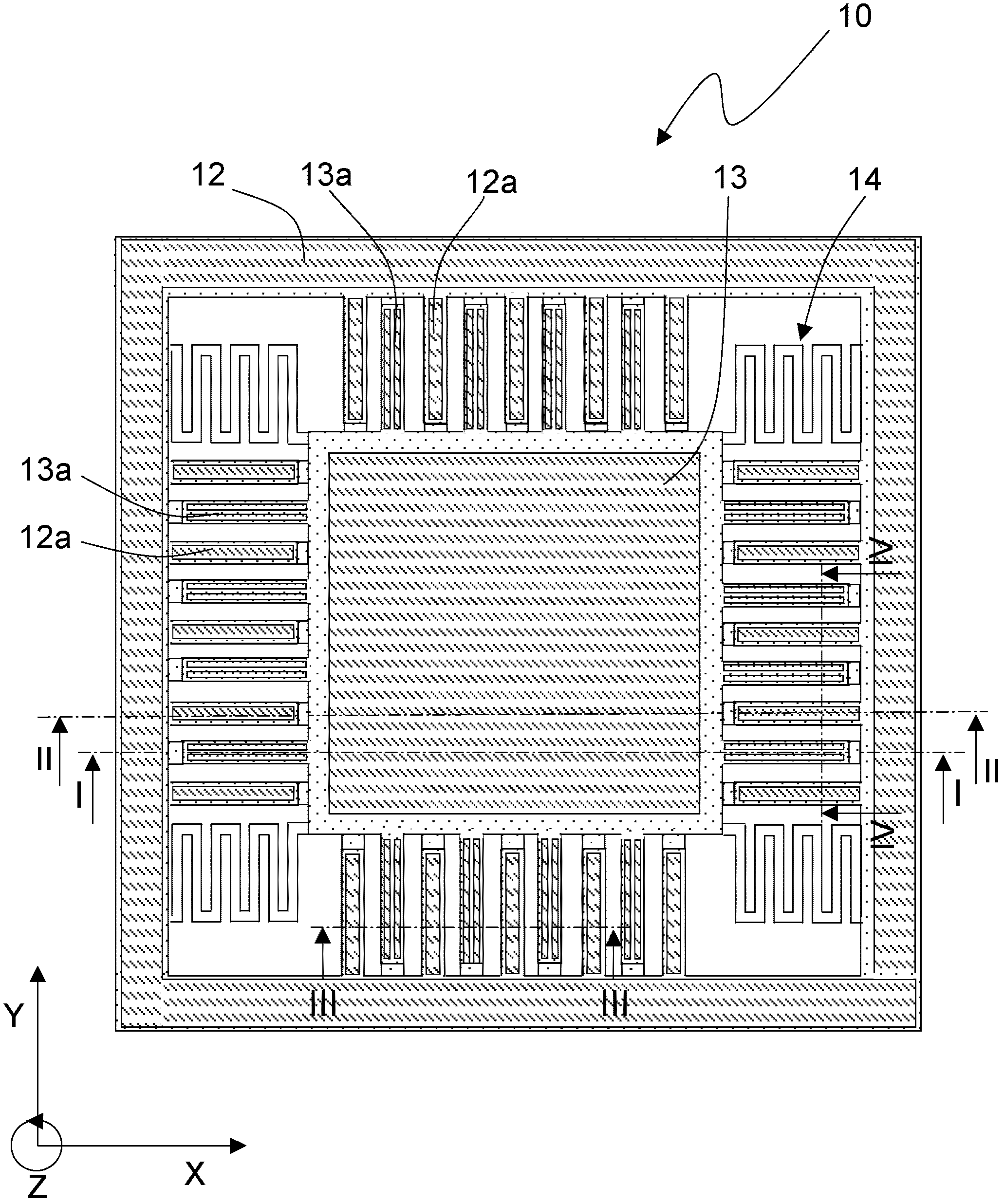

Three-dimensional microcomputer electric transducer

InactiveCN103134951AReduce floor areaAcceleration measurement using interia forcesPiezoelectric/electrostrictive devicesMicrocomputerCapacitance

The invention provides a three-dimensional microcomputer electric transducer. The three-dimensional microcomputer electric transducer comprises a plurality of movable first electrodes, a plurality of movable second electrodes, a plurality of fixed third electrodes, and a plurality of fixed fourth electrodes, wherein the first electrodes and the adjacent third electrodes form at least one first capacitor and at least one second capacitor, and the second electrodes and the adjacent fourth electrodes form at least one third capacitor. The capacitance of the first capacitor changes displacement of a mass block, the displacement is reflected in a first axis direction, the capacitance of the second capacitor changes displacement of the mass block, the displacement is reflected in a second axis direction, and the capacitance of the third capacitor changes displacement of the mass block, and the displacement is reflected in a third axis direction. The first axis, the second axis and the third axis define a three-dimensional coordinate system.

Owner:PIXART IMAGING INC

Heat medium heating apparatus and vehicular air-conditioning system including same

InactiveCN102673347AImprove air conditioning performanceImprove heating effectAir-treating devicesAir heatersPlate heat exchangerHeat penetration

Provided is a heat medium heating apparatus, which can reduce the thermal contact resistance between flat heat exchanger tubes and PTC heaters, improve the heat transfer performance, efficiently cool and control heat-generating electrical components on a board of the the PTC heaters and realize reduction in weight and low cost. The heat medium heating apparatus includes: the plurality of flat heat exchanger tubes 12; the PTC heaters 13 that are respectively incorporated between flat tube parts of the flat heat exchanger tubes 12; a heat exchanger holding member 15 that press-fixes the flat heat exchanger tubes 12 and the PTC heaters 13, from one side of the flat heat exchanger tubes 12 to an inner surface of a casing 11; and a control board 17 that has a surface on which a control circuit 21 is mounted, the control circuit 21 including heat-generating electrical components 20 that control the PTC heaters 13, in which the control board 17 includes heat penetration parts that are formed so as to pass through the control board 17 correspondingly to mounting positions of the heat-generating electrical components 20, and the heat-generating electrical components 20 are mounted so as to be cooled via the heat penetration parts.

Owner:MITSUBISHI HEAVY IND LTD

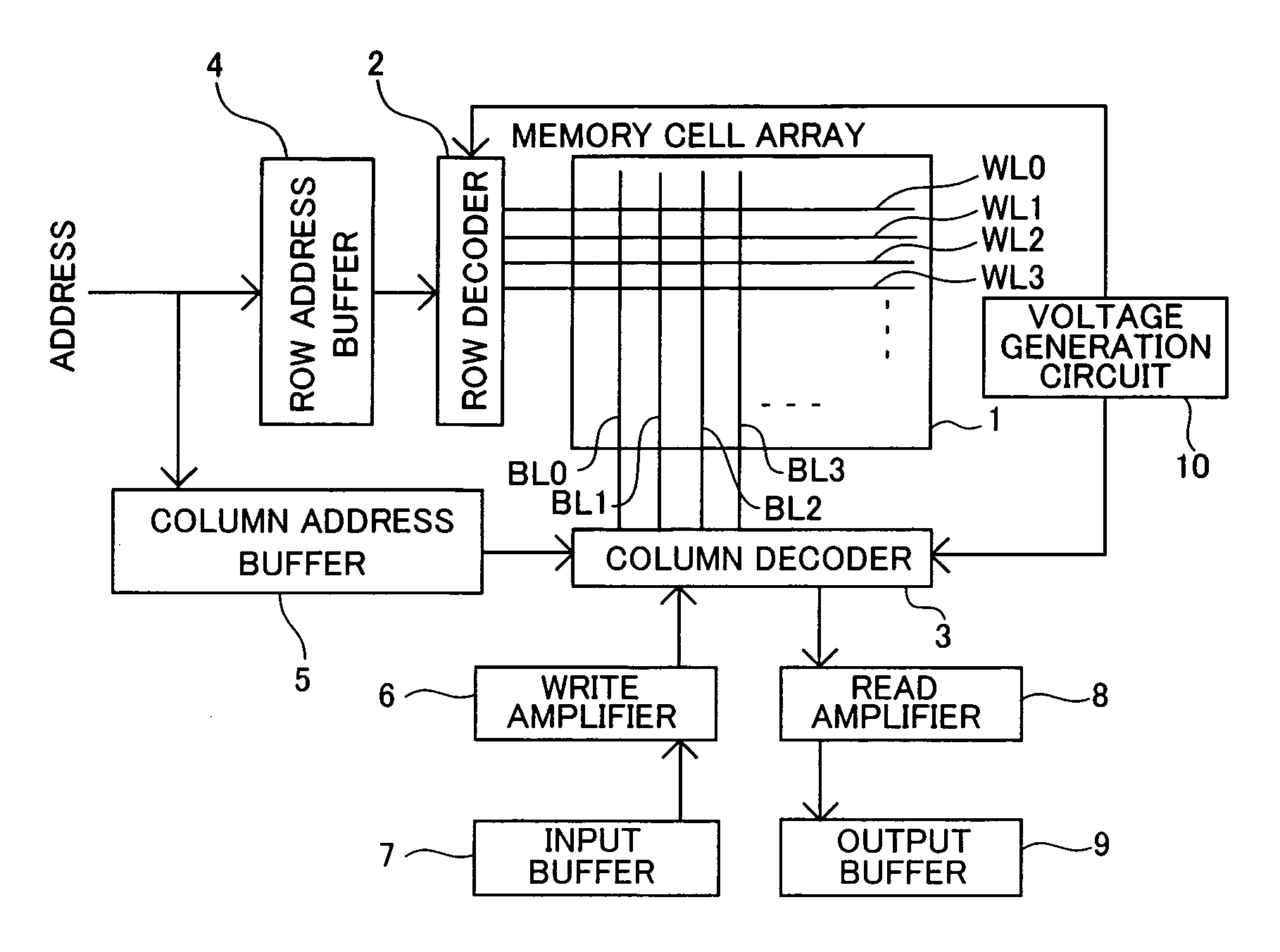

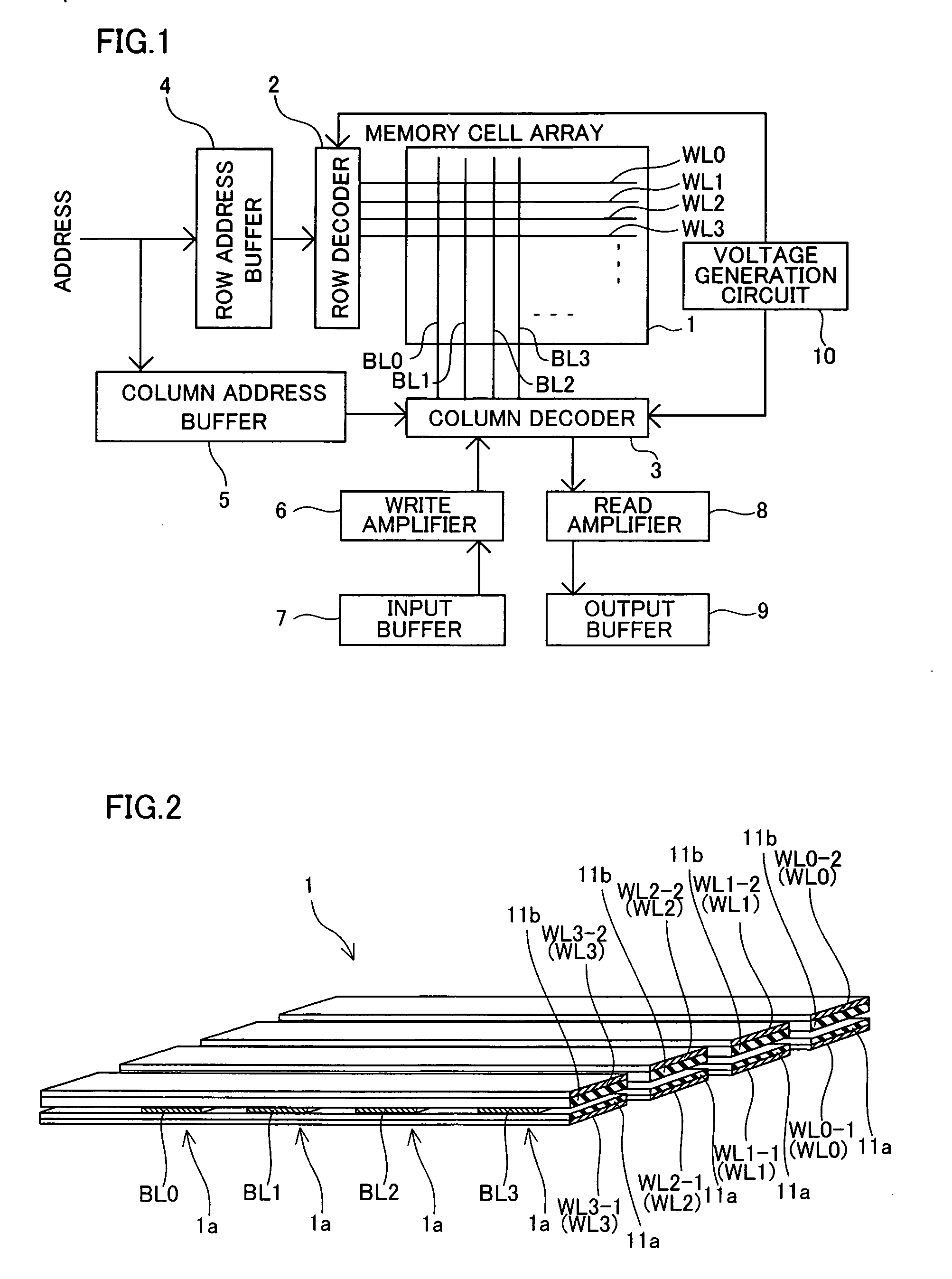

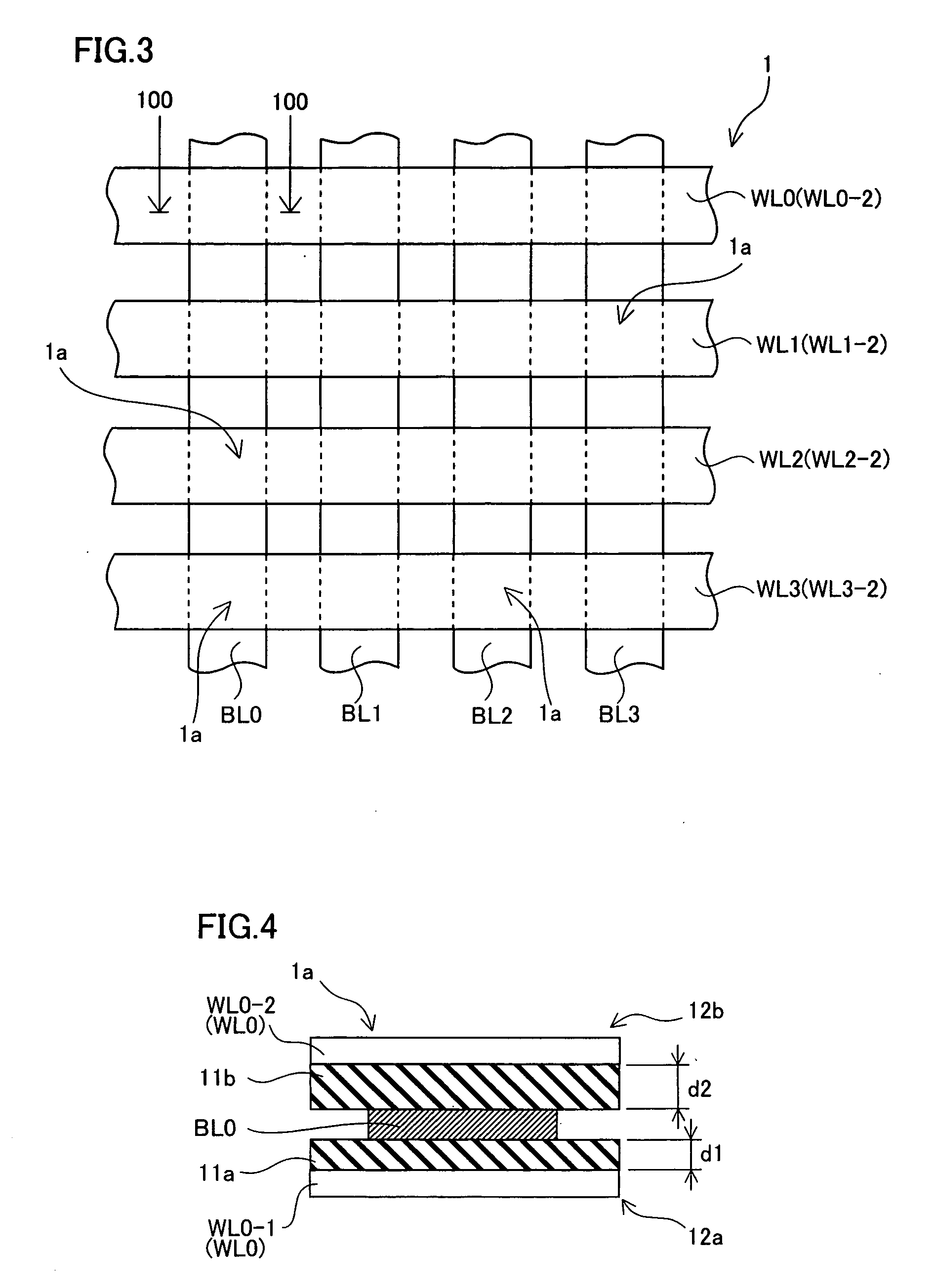

Memory

InactiveUS20070121365A1Reduce plane areaReduce floor areaDigital storageFerroelectric capacitorCapacitance

This memory comprises a bit line, a first word line and a second word line arranged to intersect with the bit line while holding the bit line therebetween and a first ferroelectric film and a second ferroelectric film, having capacitances different from each other, arranged between the bit line and the first word line and between the bit line and the second word line respectively at least on a region where the bit line and the first and second word lines intersect with each other. The bit line, the first word line and the first ferroelectric film constitute a first ferroelectric capacitor while the bit line, the second word line and the second ferroelectric film constitute a second ferroelectric capacitor, and the first ferroelectric capacitor and the second ferroelectric capacitor constitute a memory cell.

Owner:PATRENELLA CAPITAL LTD LLC

Semiconductor device

ActiveUS7773381B2Reduce floor areaCircuit-breaking switches for excess currentsAc-dc conversion without reversalEngineeringSemiconductor

Owner:ROHM CO LTD

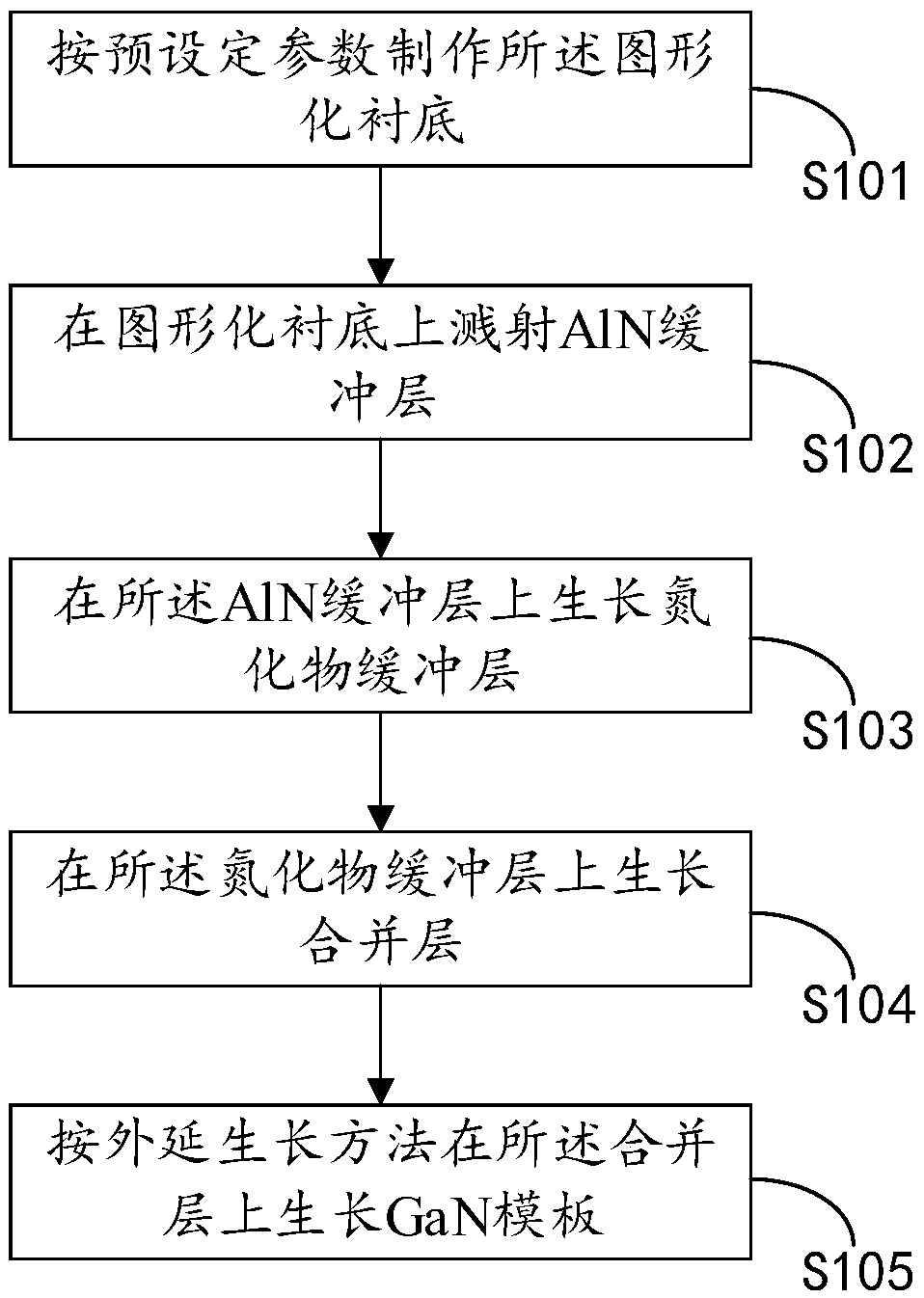

Manufacturing method of epitaxial structure of semiconductor

ActiveCN108878611AReduce floor areaLow average dislocation densitySemiconductor devicesDislocationEngineering

The invention provides a manufacturing method of an epitaxial structure of a semiconductor, and relates to the technical field of semiconductors. First, an AlN buffer layer is sputtered on a pre-set patterned substrate, wherein the surface of the patterned substrate comprises a plurality of regular hexagonal structures arranged periodically, the regular hexagonal structures are arranged accordingto preset parameters, the regular hexagonal structures comprise regular hexagonal bottom faces and cones connected to the bottom faces, and the bottom faces are parallel to the c-faces of a substratematerial; a nitride buffer layer then grows on the AlN buffer layer; the nitride buffer layer grows along the c-faces between the cones of every two adjacent regular hexagonal structures; and finally,a nitride merged layer grows on the nitride buffer layer. The manufacturing method of the epitaxial structure of the semiconductor has the effects of improving the flatness of the surface of the semiconductor, reducing the dislocation density of the semiconductor and enabling the quality of crystal lattice to be better.

Owner:GUANGDONG INST OF SEMICON IND TECH

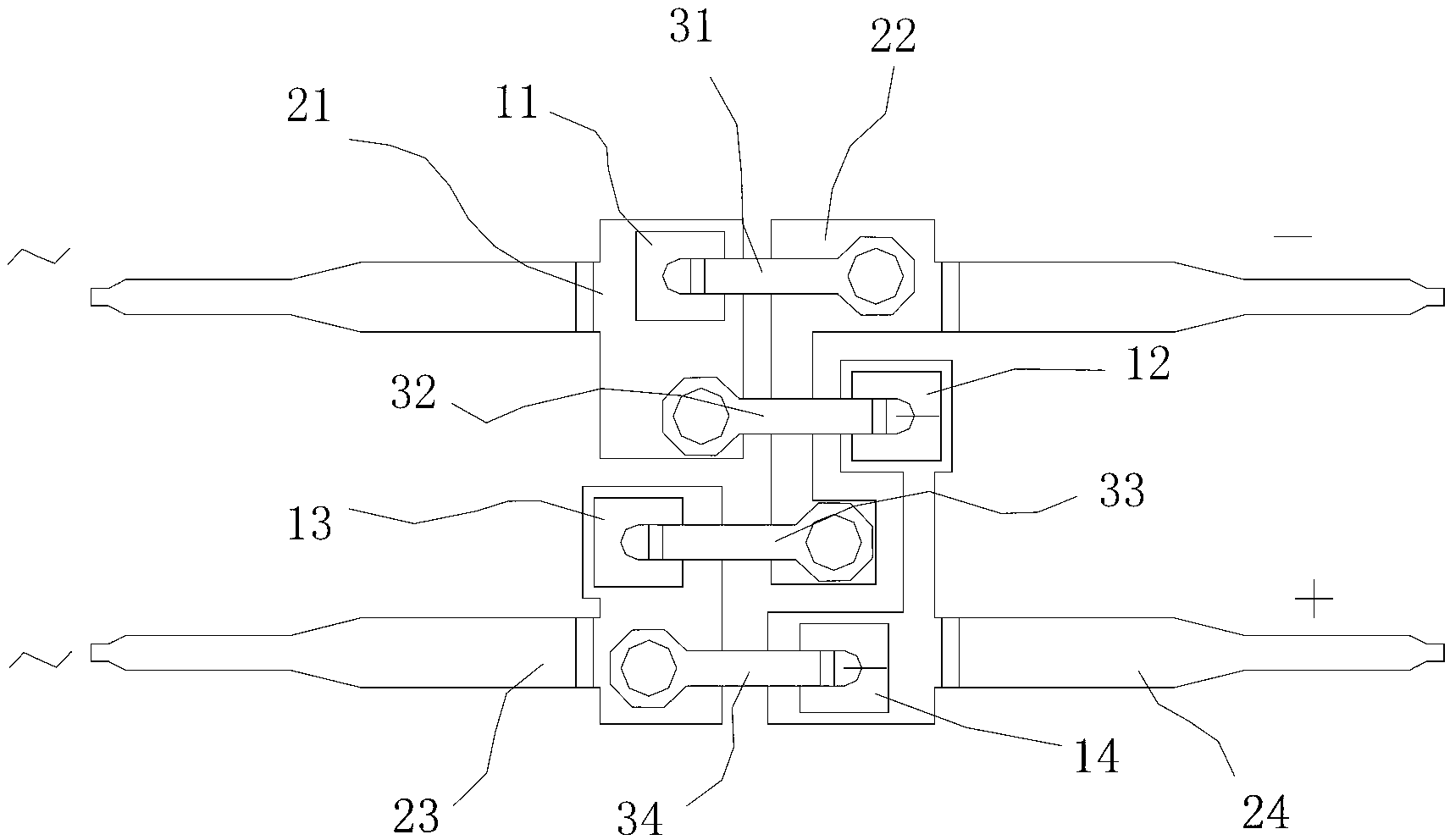

Equal-directional array type rectifier bridge stack

ActiveCN103236426AReduce floor areaReduce consumptionSemiconductor/solid-state device detailsAc-dc conversionElectrical polarityEngineering

The invention provides an equal-directional array type rectifier bridge stack which is compact in structure and more reasonable in whole layout, so that the volume and the cost of a product are effectively reduced. The equal-directional array type rectifier bridge stack comprises a chip I, a chip II, a chip III and a chip IV, a framework I, a framework II, a framework III and a framework IV, a jumper wire I, a jumper wire II, a jumper wire III and a jumper wire IV; each one of the framework I, the framework II, the framework III and the framework IV is formed by a respective body and a pin; the four frameworks are in an opposite-side layout; the bodies of the framework I and the framework III are rectangular; an insulating distance is kept between the bodies and the bodies are located at one side of the opposite-side layout; the bodies of the framework II and the framework IV are C-shaped, and the bodies are in an occlusion position relation; an insulating distance is kept between the bodies and the bodies are located at the other side of the opposite-side layout; the chip I is distributed on the front face of the body of the framework I; the chip II and the chip IV are respectively distributed on the front face of the body of the framework IV; the chip III is distributed on the front face of the body of the framework III; and the directions of polarities of the chip I, the chip II, the chip III and the chip IV are the same. According to the equal-directional array type rectifier bridge stack disclosed by the invention, the quality of a product is stable and the cost is greatly reduced.

Owner:YANGZHOU YANGJIE ELECTRONIC TECH CO LTD

Folding-leg-supported mobile phone rest station for college classroom

InactiveCN103825989AWon't breakReduce floor areaOther accessoriesTelephone set constructionsUSBMobile phone

The invention relates to a folding-leg-supported mobile phone rest station for a college classroom. The folding leg supported-mobile phone rest station, which is provided by the invention, is small in size, is suspended without nails, can be conveniently folded, moved and unfolded, brings convenience for students to charge mobile phones, can rapidly call the roll and is suitable for the college classroom. According to the technical scheme, a mobile phone access point is fixed on a folding frame, folding support legs are articulated to the lower end of the folding frame, a mobile phone fixer is fixed on the front surface and the back surface of a background layer, student numbers and name marks are arranged on the front surface of a mobile phone fixing bag sequentially, and multiple USB mobile phone charging interfaces are arranged on the front surface and the back surface of the background layer respectively.

Owner:ZHEJIANG UNIV OF WATER RESOURCES & ELECTRIC POWER +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com