Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

35results about How to "Maximize bandwidth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

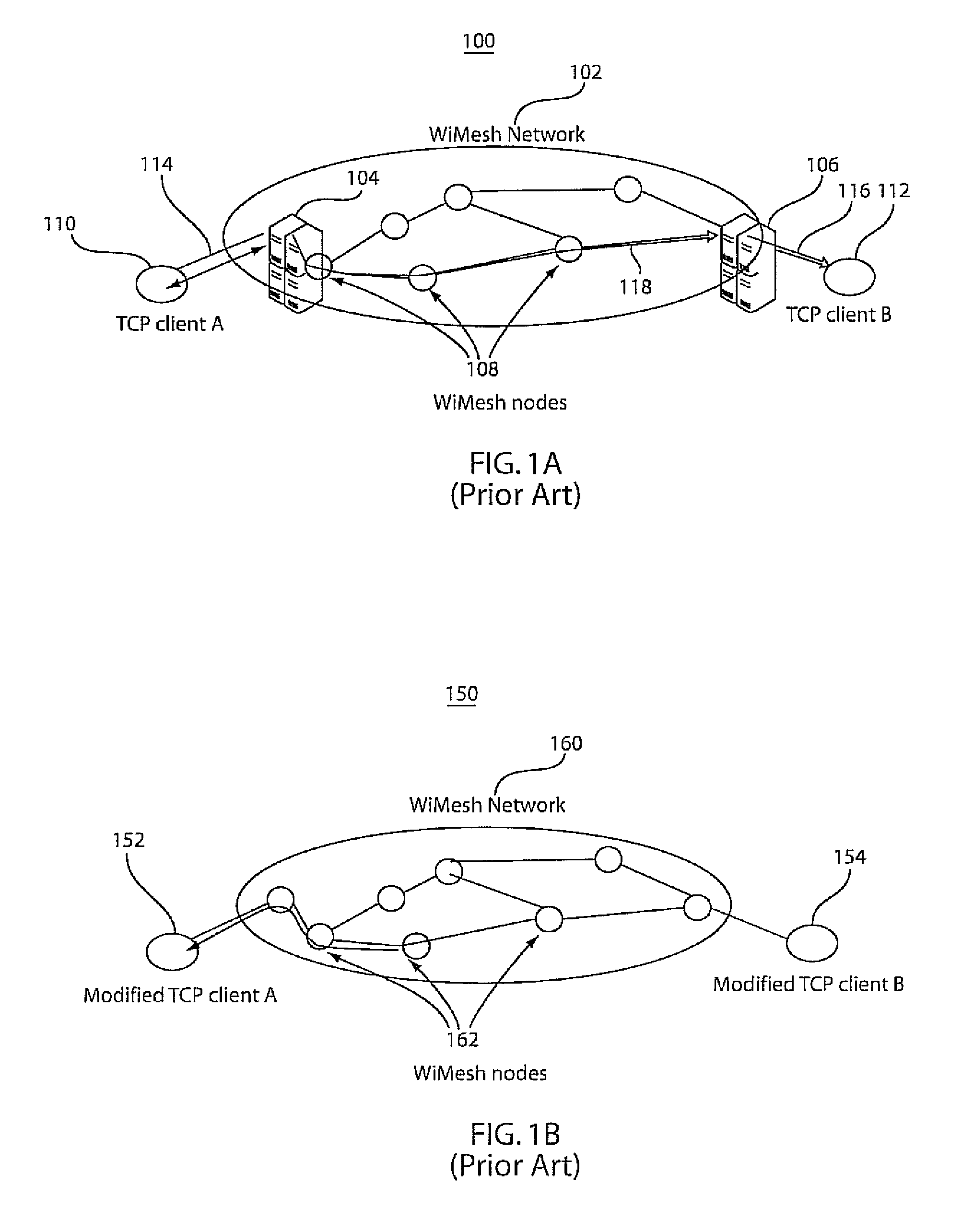

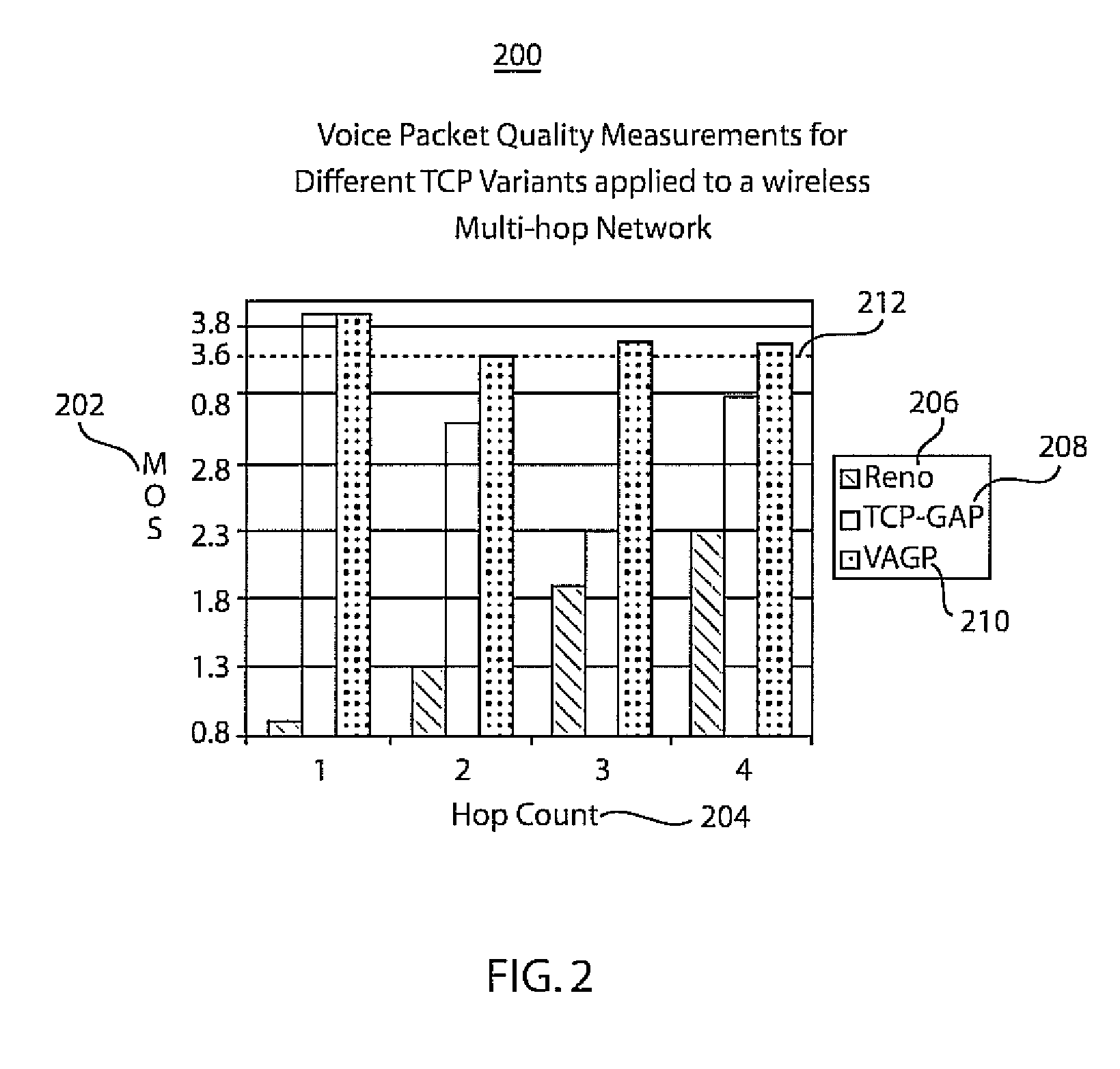

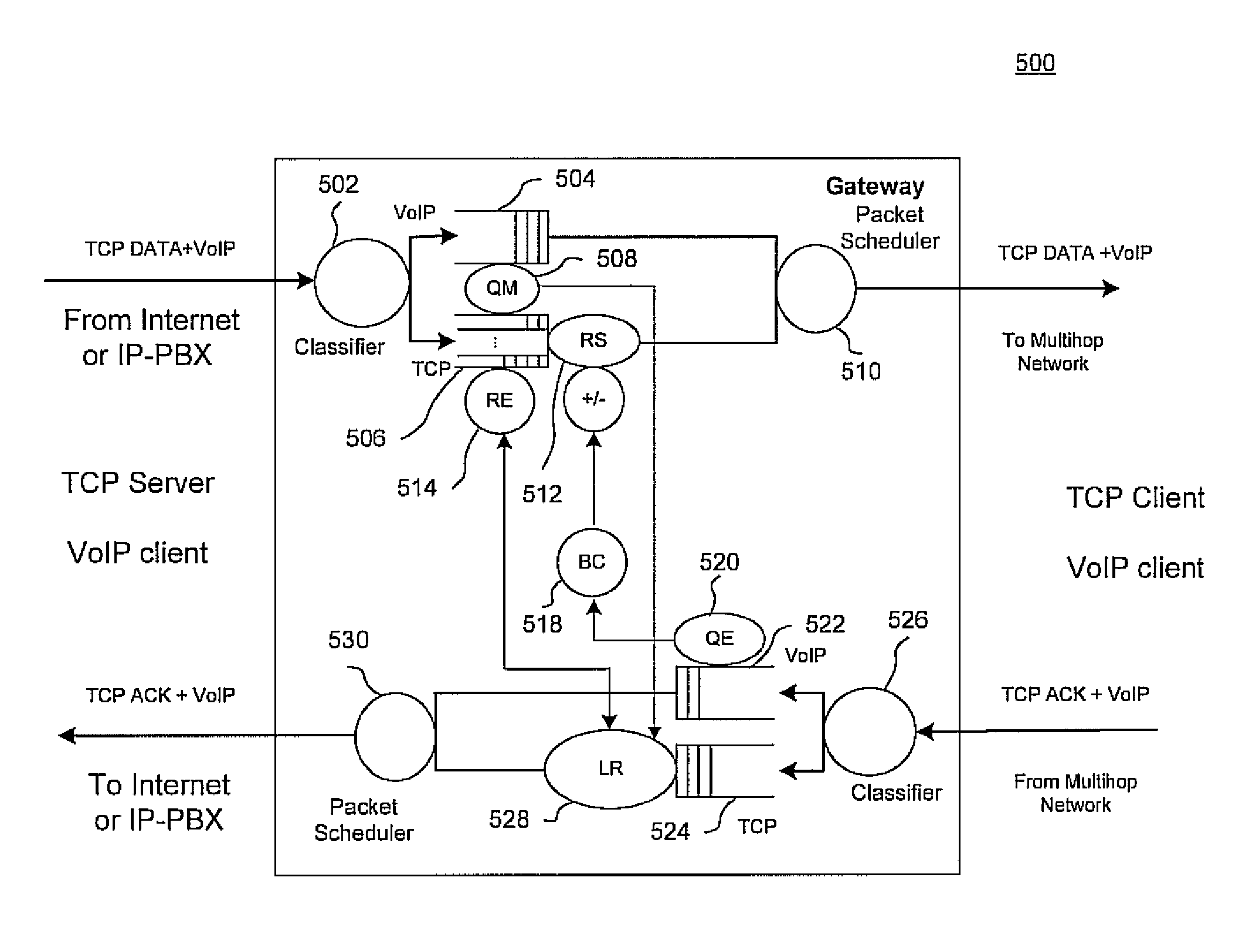

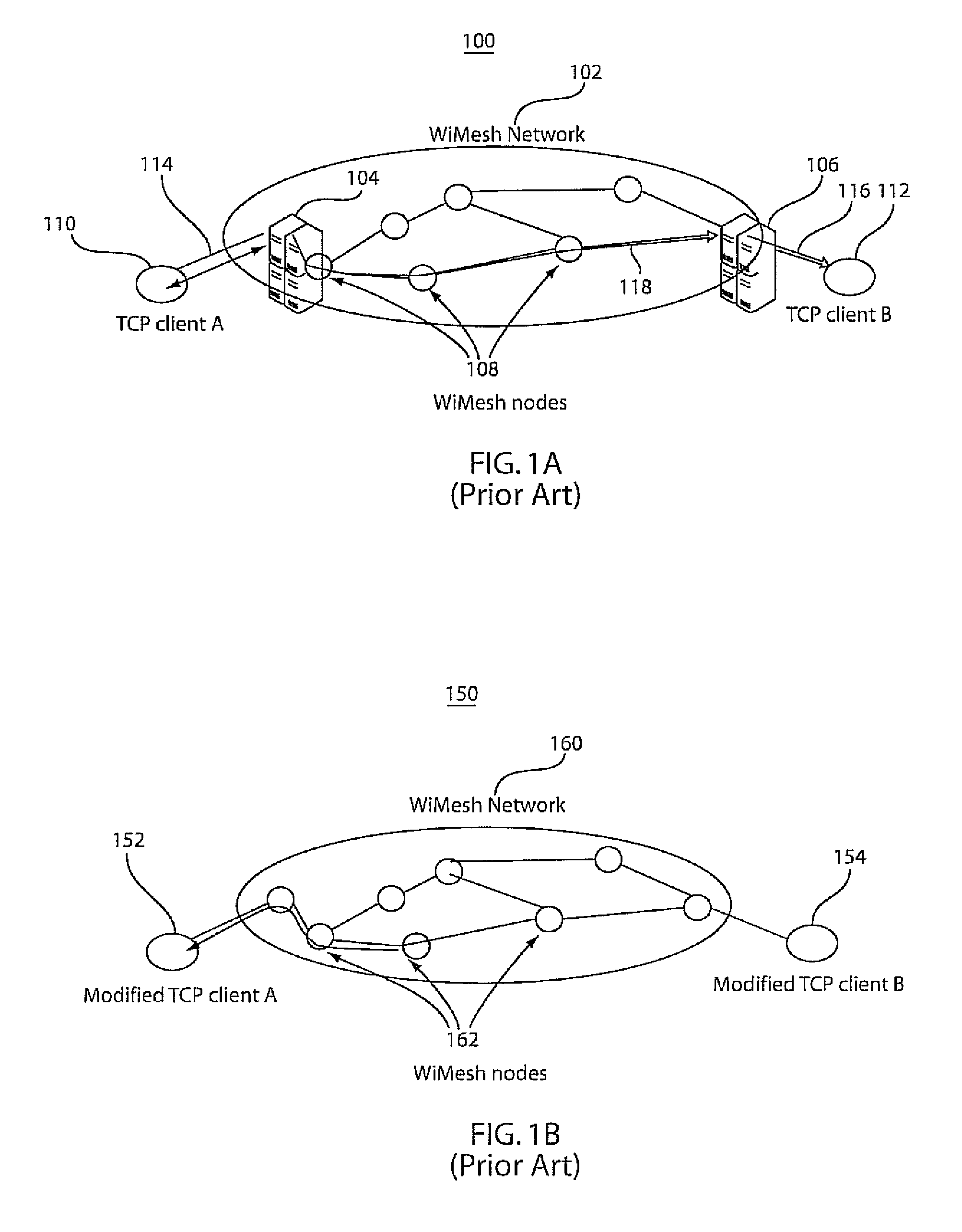

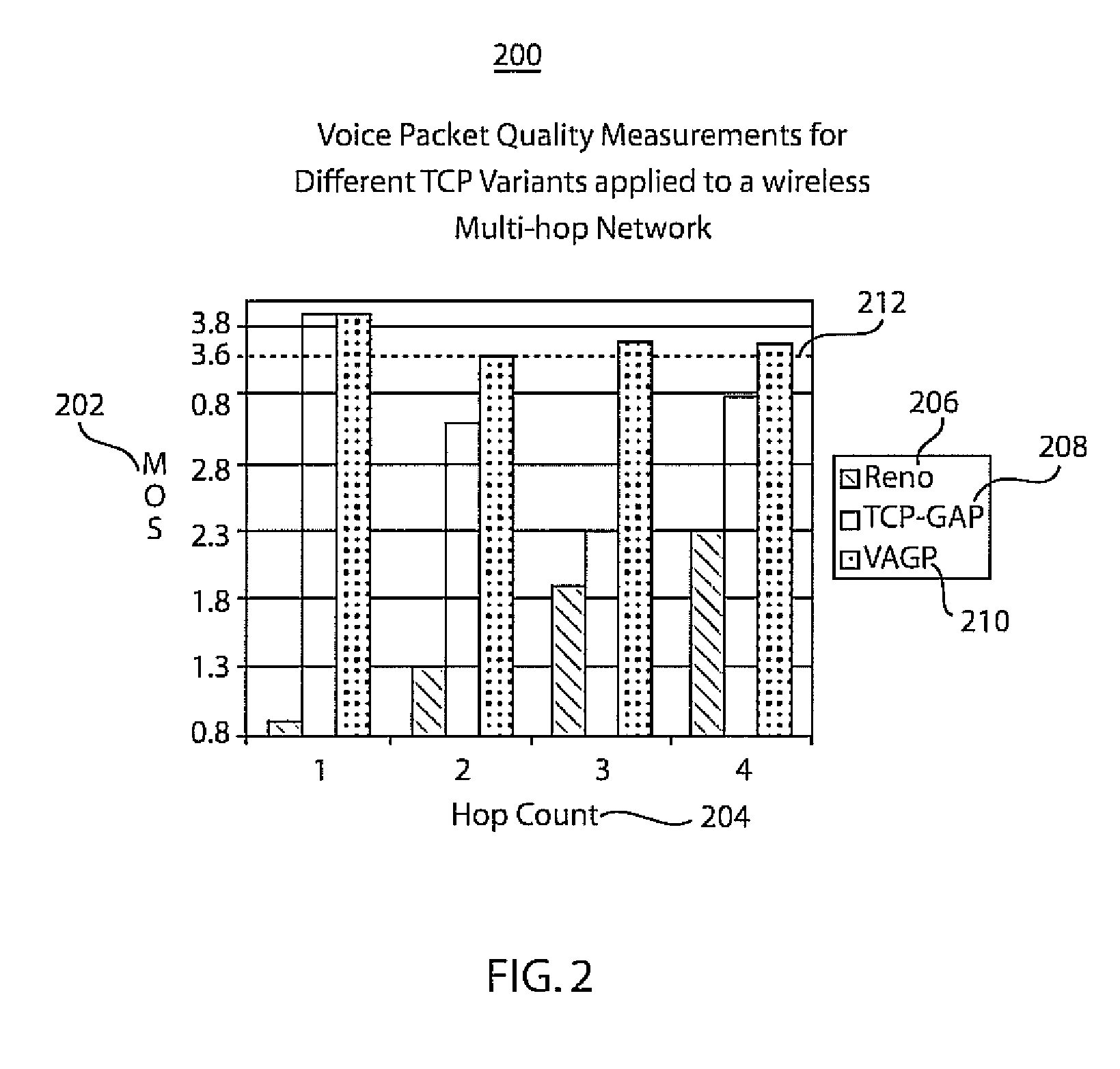

Voice adaptive gateway pacing methods and systems for wireless multi-hop networks

InactiveUS20090141631A1Sufficient VoIP traffic qualityEfficiently utilizedError preventionTransmission systemsCable networkTraffic volume

In accordance with aspects of the present principles, the quality of voice traffic and bandwidth utilization for data communication over a wireless multi-hop network may be improved. In an implementation of the present principles, a data packet transmission rate over a wireless multi-hop network may be controlled at an interface between the multi-hop network and a wired network based on a voice packet quality measure calculated from network parameters. Voice and data traffic quality and efficiency may be further improved by reordering a packet transmission queue at the interface to avoid timeout and / or varying a packet queue length at the interface using an acknowledgement window transmitted to a data packet sender.

Owner:NEC CORP

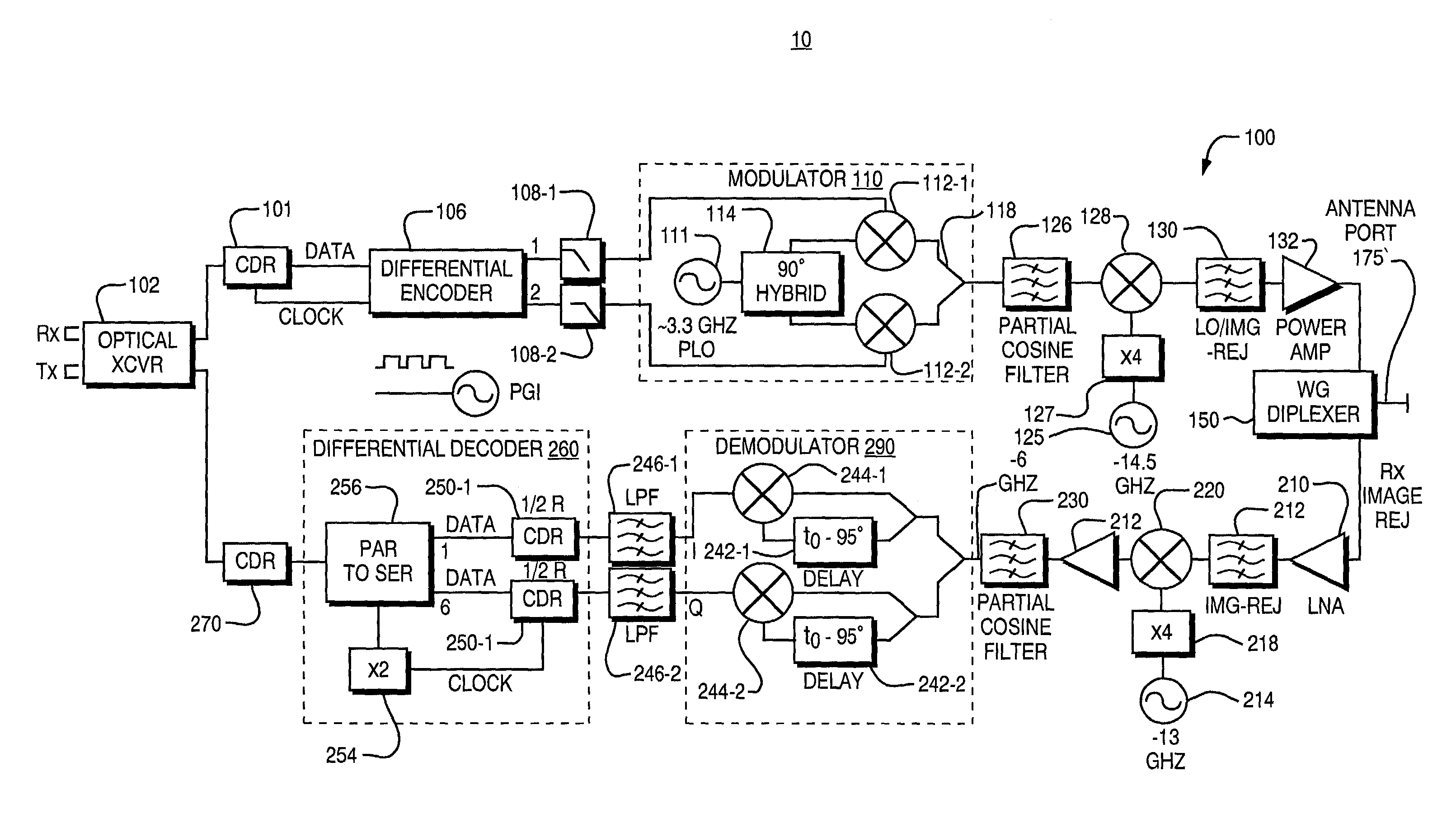

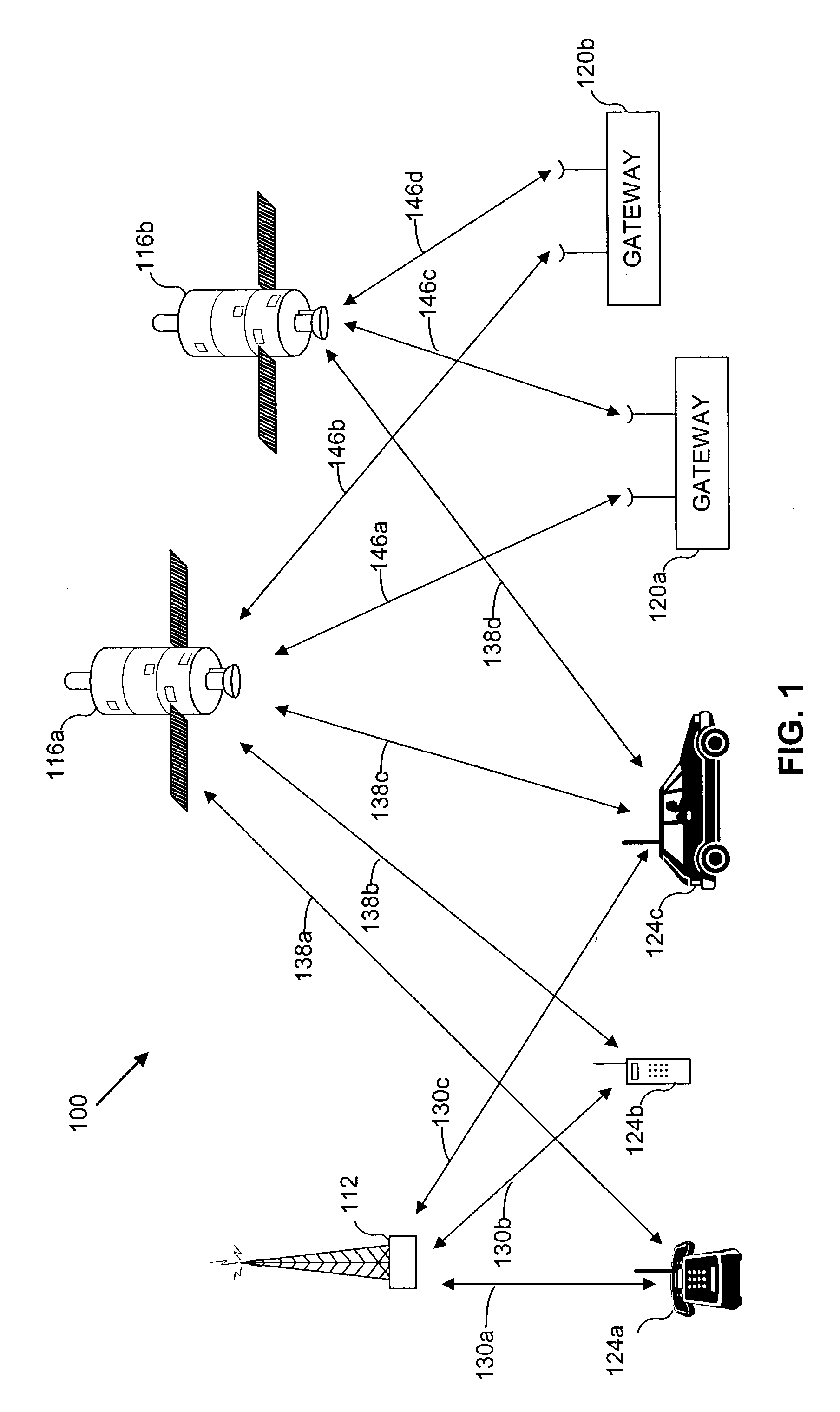

Architecture for wireless transmission of high rate optical signals

InactiveUS7103279B1Minimize intersymbol interferenceReduce noiseLine-of-sight transmissionElectromagnetic transmittersFiberHigh rate

An apparatus for a wireless transmission of high data rate signals such as received from an optical interface including gigabit fiber channel or a sonet. The architecture combines direct detection of the optical signal with clock and data recovery circuit and a differential signal encoder which is preferably a differential quadrature phase shift encoder and modulator pair. A millimeter wave, local oscillator and up conversion chain converts the optical input signal to a microwave carrier. In the opposite direction, the down converted signal is non-coherently phase detected and fed to a pair of synchronized clock and data recovery circuits to recover I and Q channel signals. These recovered signals are then combined prior to re-timing before they are fed back to the optical transceiver.

Owner:OL SECURITY LIABILITY CO

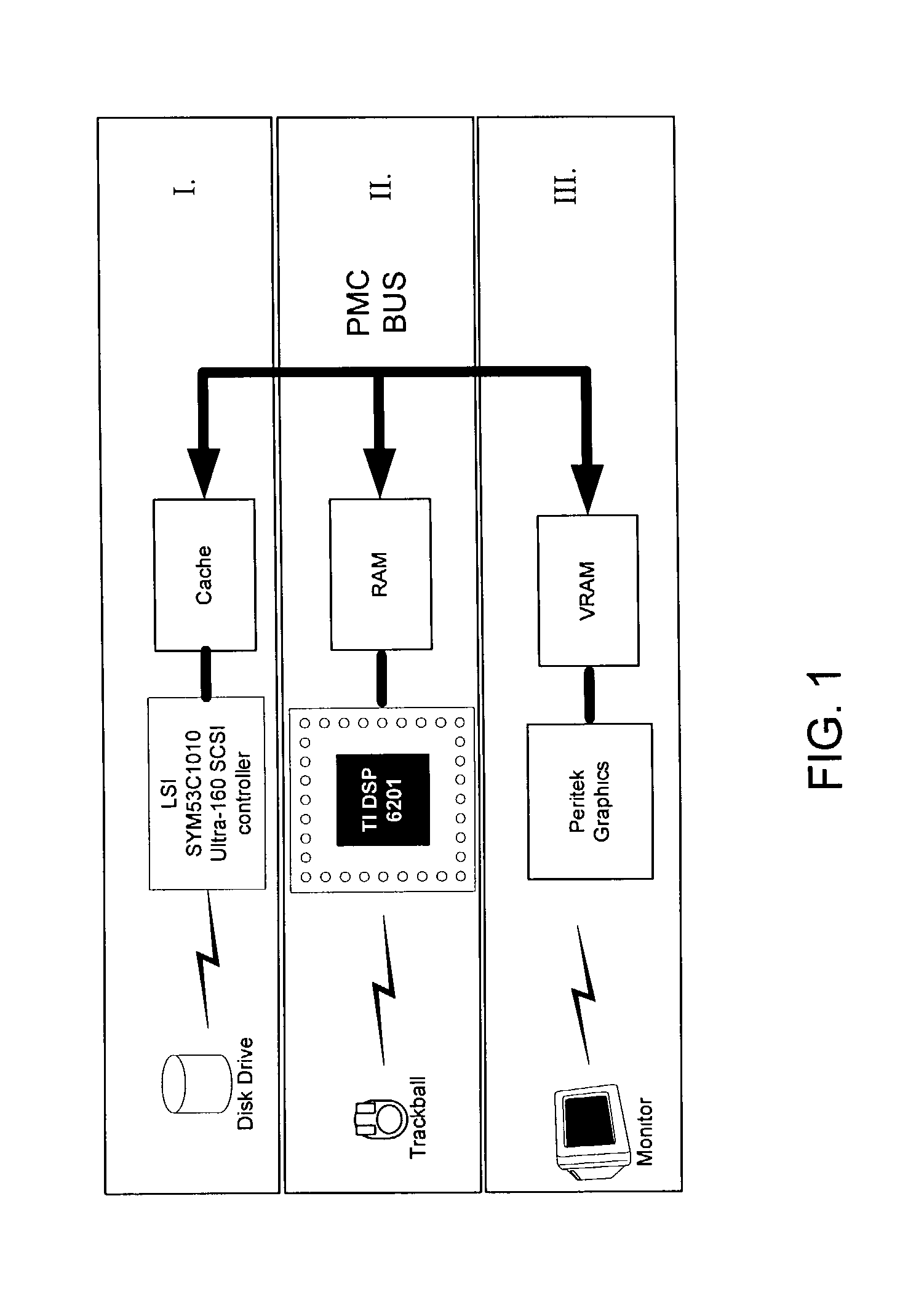

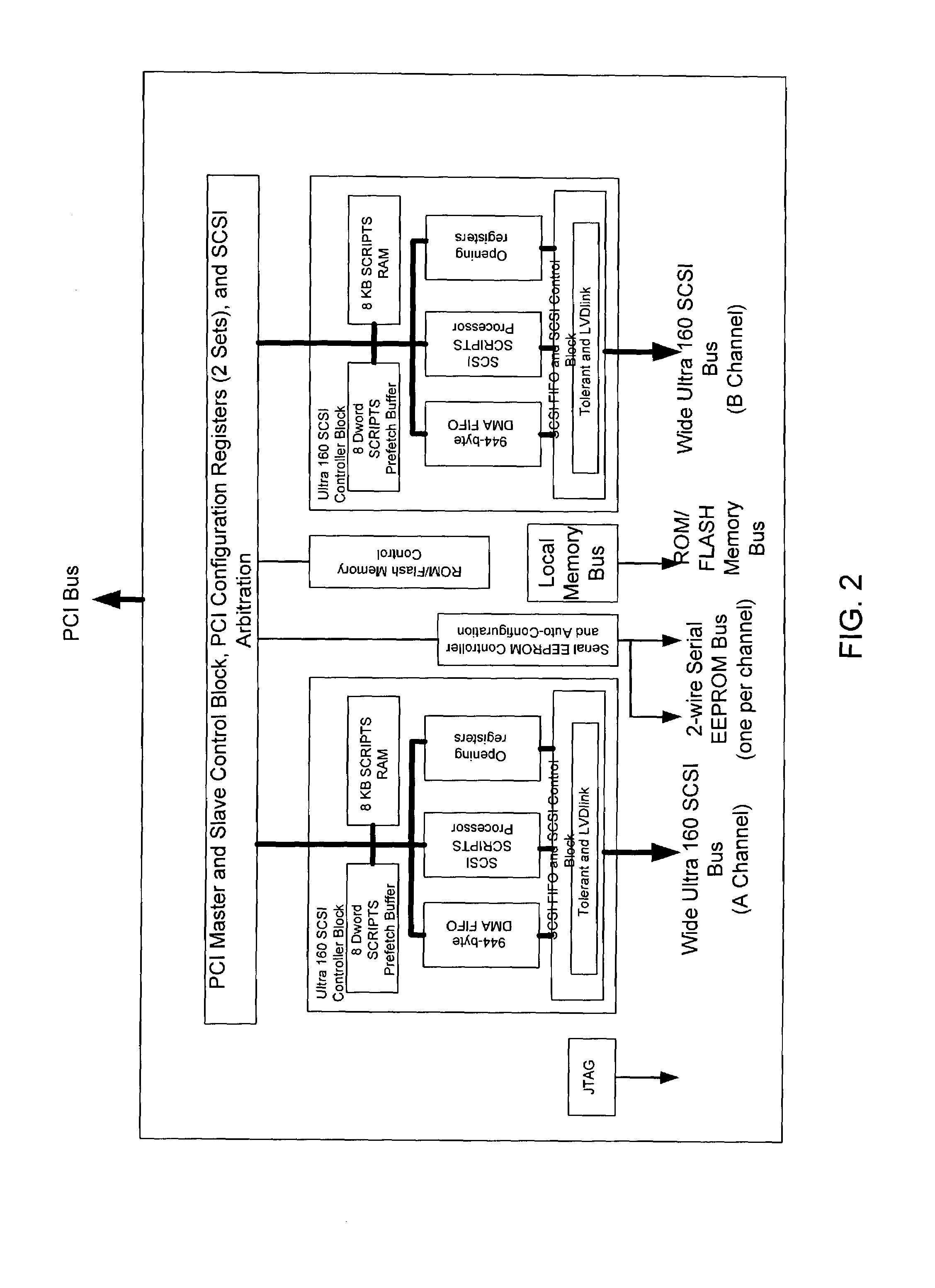

Image display system

InactiveUS7119811B2Fast imagingEasy to transformCathode-ray tube indicatorsDigital output to display deviceComputer graphics (images)Digital image

An image display system is disclosed that enables users to navigate very large digital images quickly and seamlessly. The system is optimized to transmit image data from a disk drive at high data rates. The image data is stored on the disk drive in a file format optimized for high speed retrieval, display, and seamless navigation. The image display system can be cascaded for showing two or more contiguous images.

Owner:PIXIA CORP

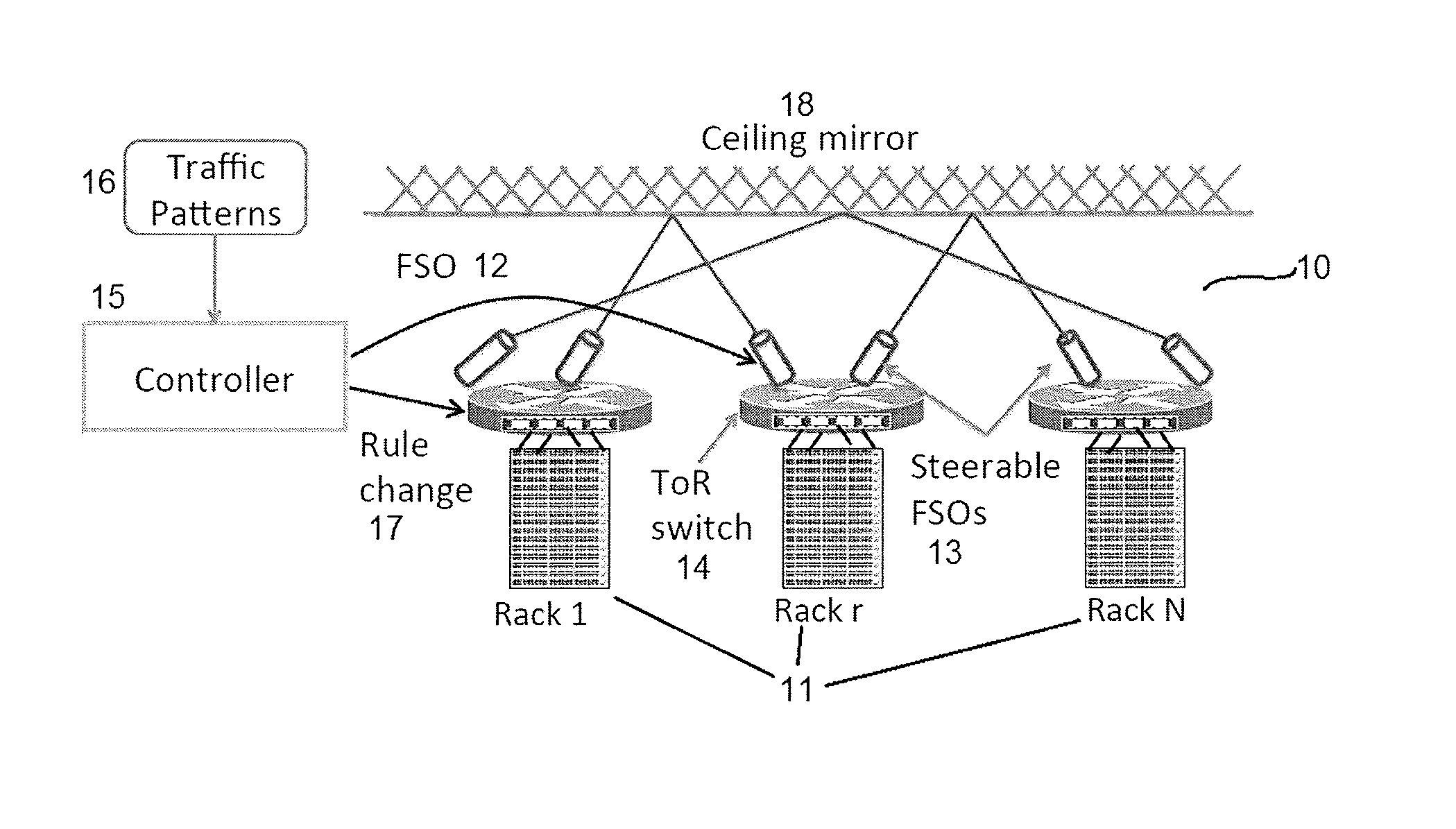

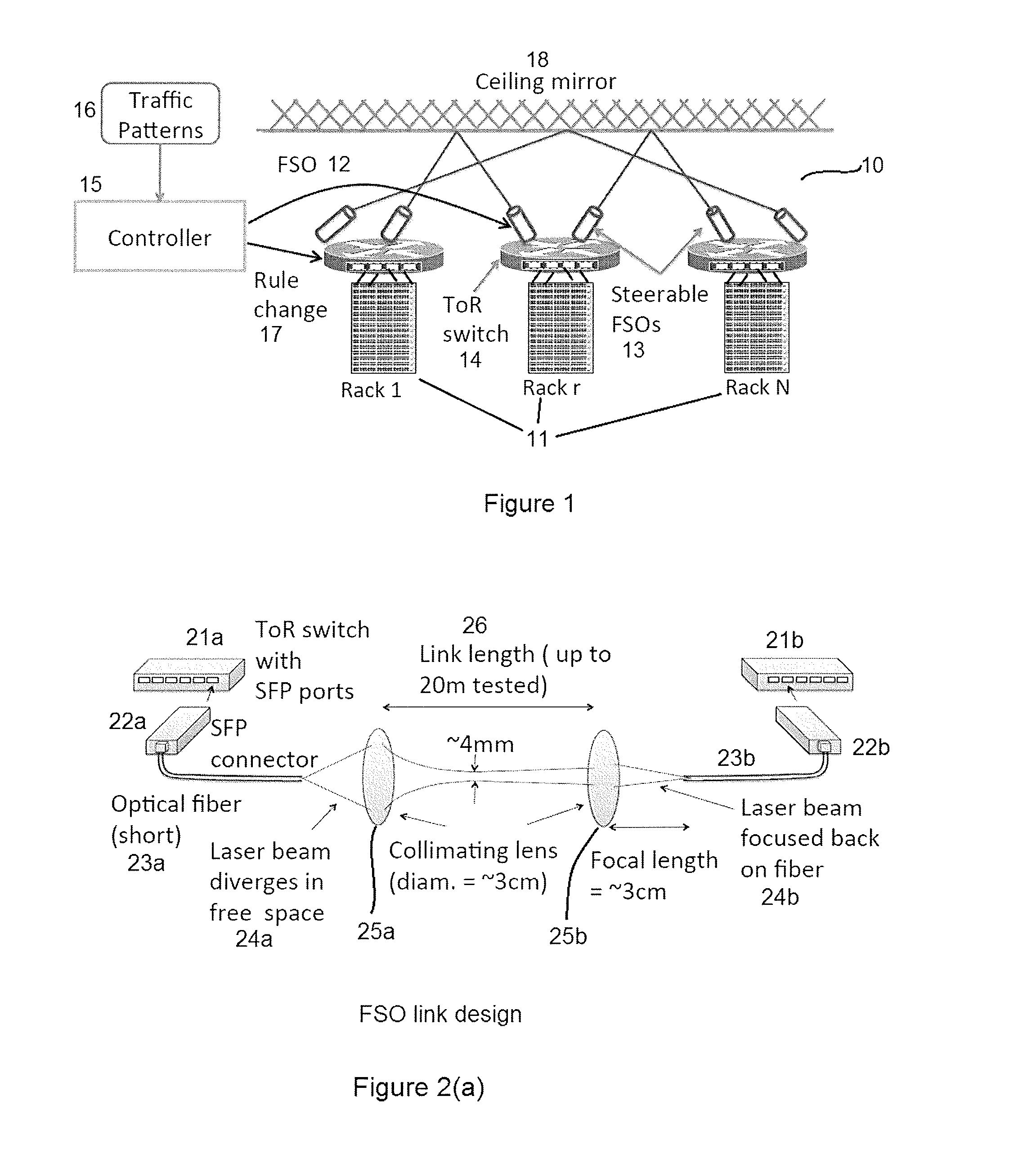

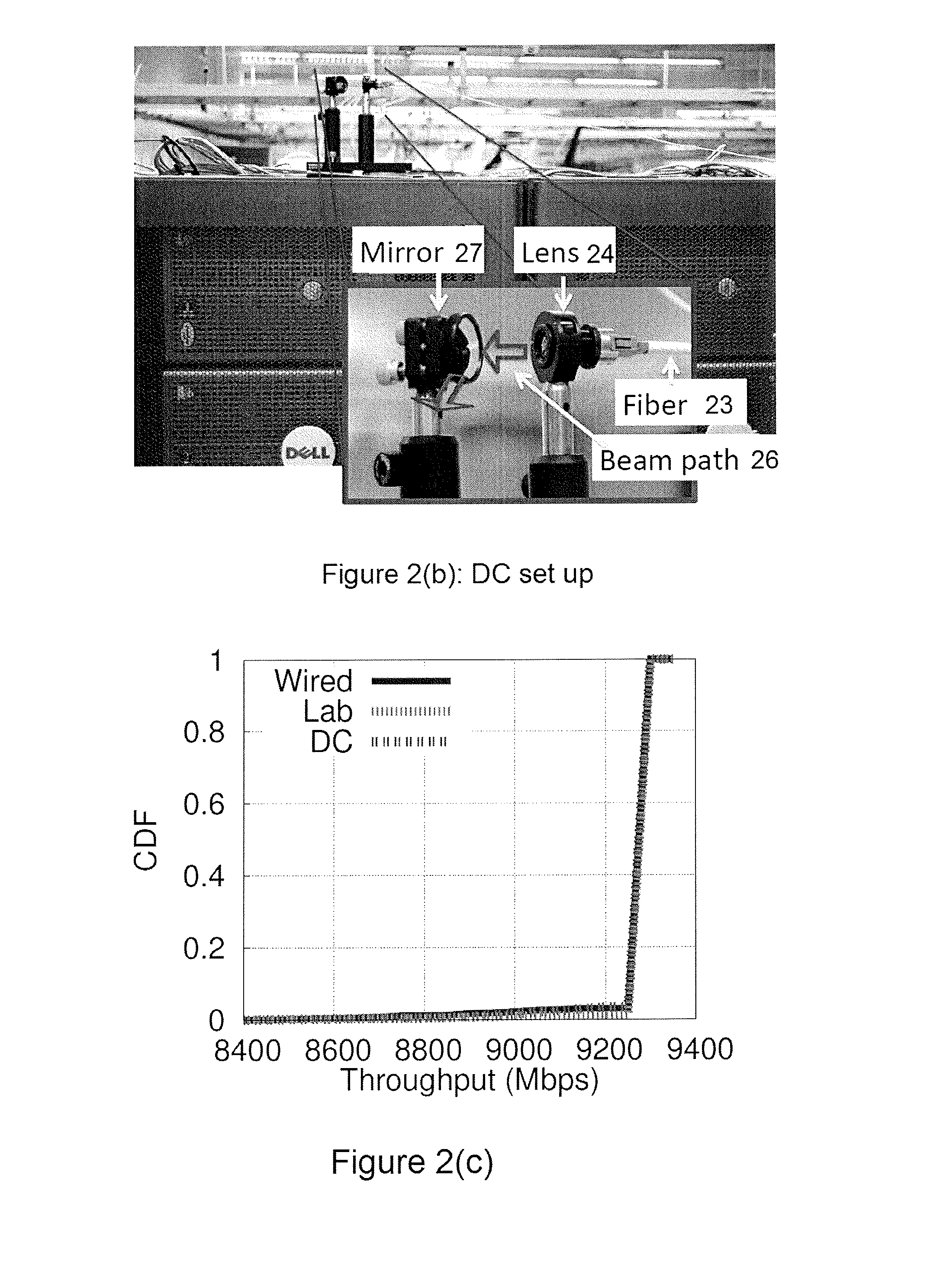

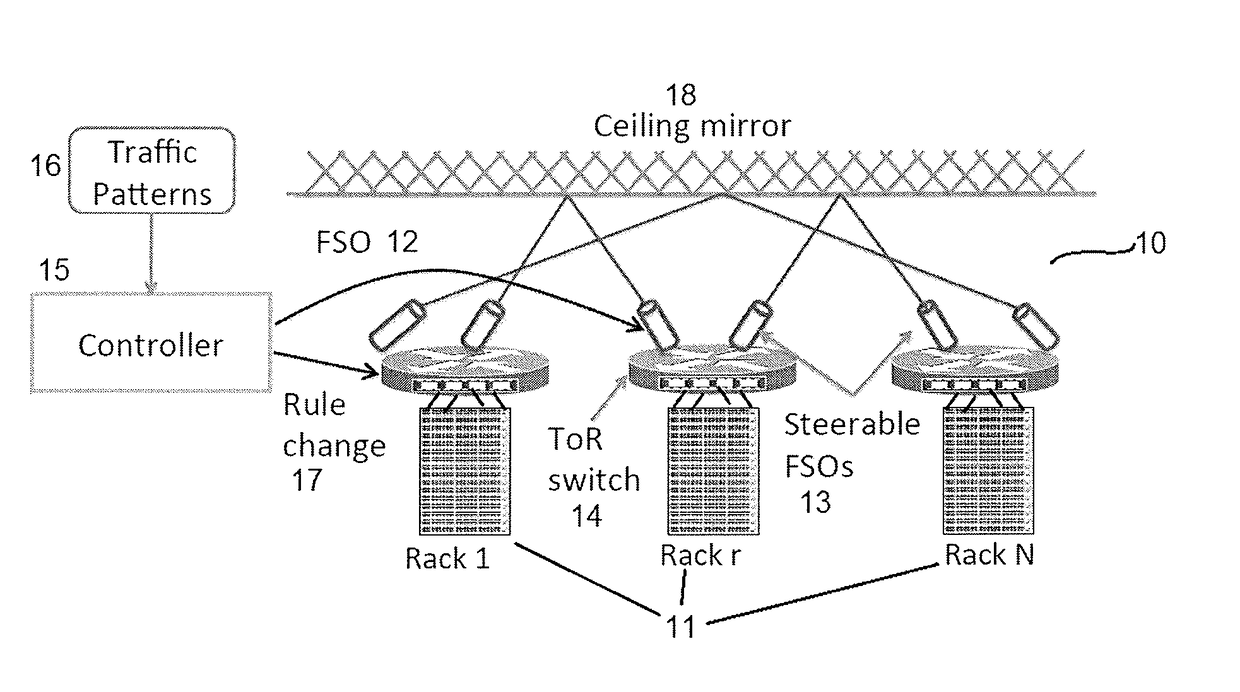

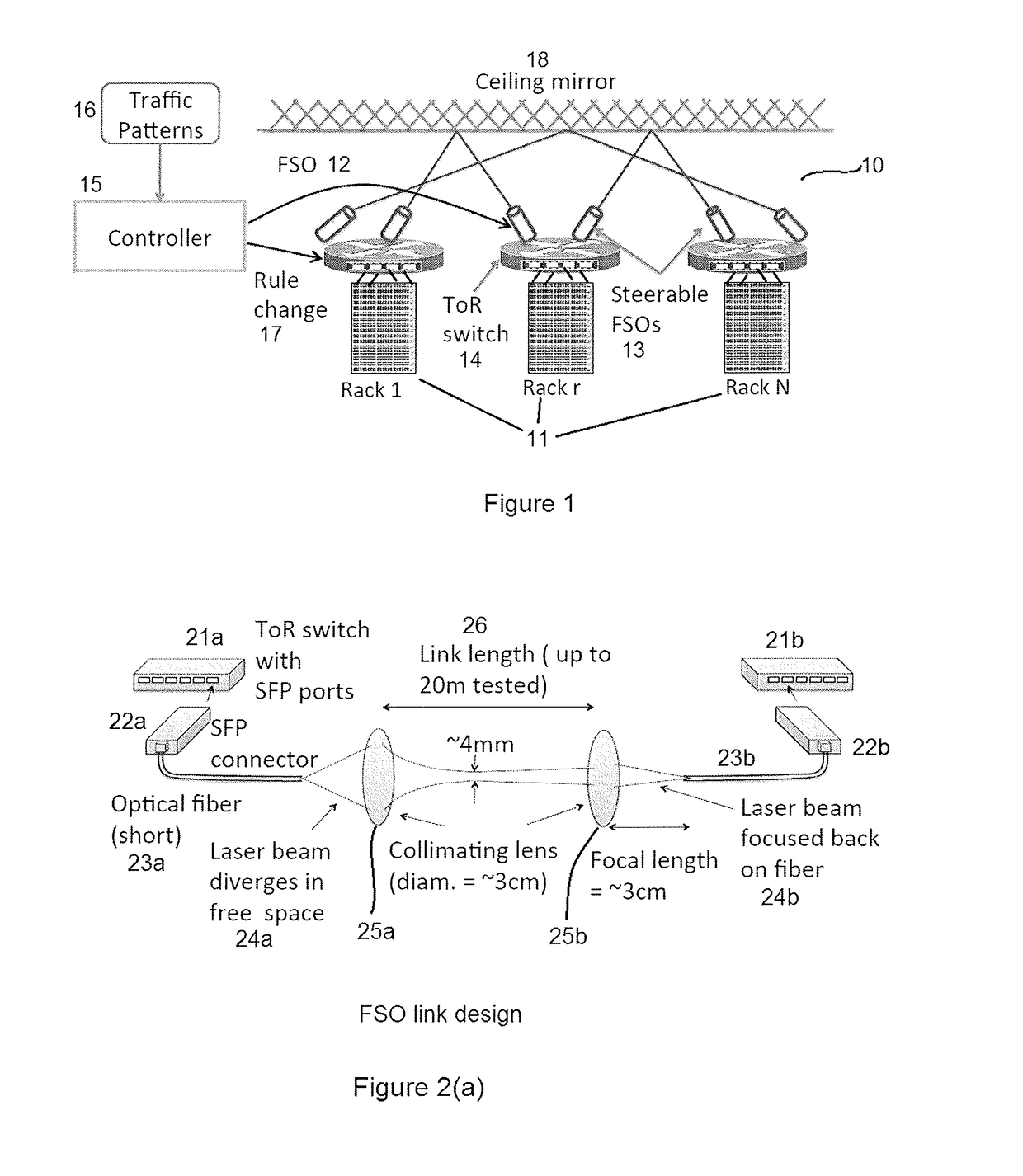

Reconfigurable wireless data center network using free-space optics

ActiveUS20160173199A1Increase data rateReduce transmit powerMultiplex system selection arrangementsFree-space transmissionInternet trafficData center

A reconfigurable free-space optical inter-rack network includes a plurality of server racks, each including at least one switch mounted on a top thereof, where each top-mounted switch includes a plurality of free-space-optic link connector, each with a free-space optical connection to a free-space-optic link connector on another top-mounted switch, a single ceiling mirror above the plurality of server racks that substantially covers the plurality of server racks, wherein the single ceiling mirror redirects optical connections between pairs of free-space-optic link connectors to provide a clear lines-of-sight between each pair of connected free-space-optic link connectors, and a controller that preconfigures a free-space optical network connecting the plurality of server racks by establishing connections between pairs of free-space-optic link connectors, and that reconfigures connections between pairs of free-space-optic link connectors in response to network traffic demands and events.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

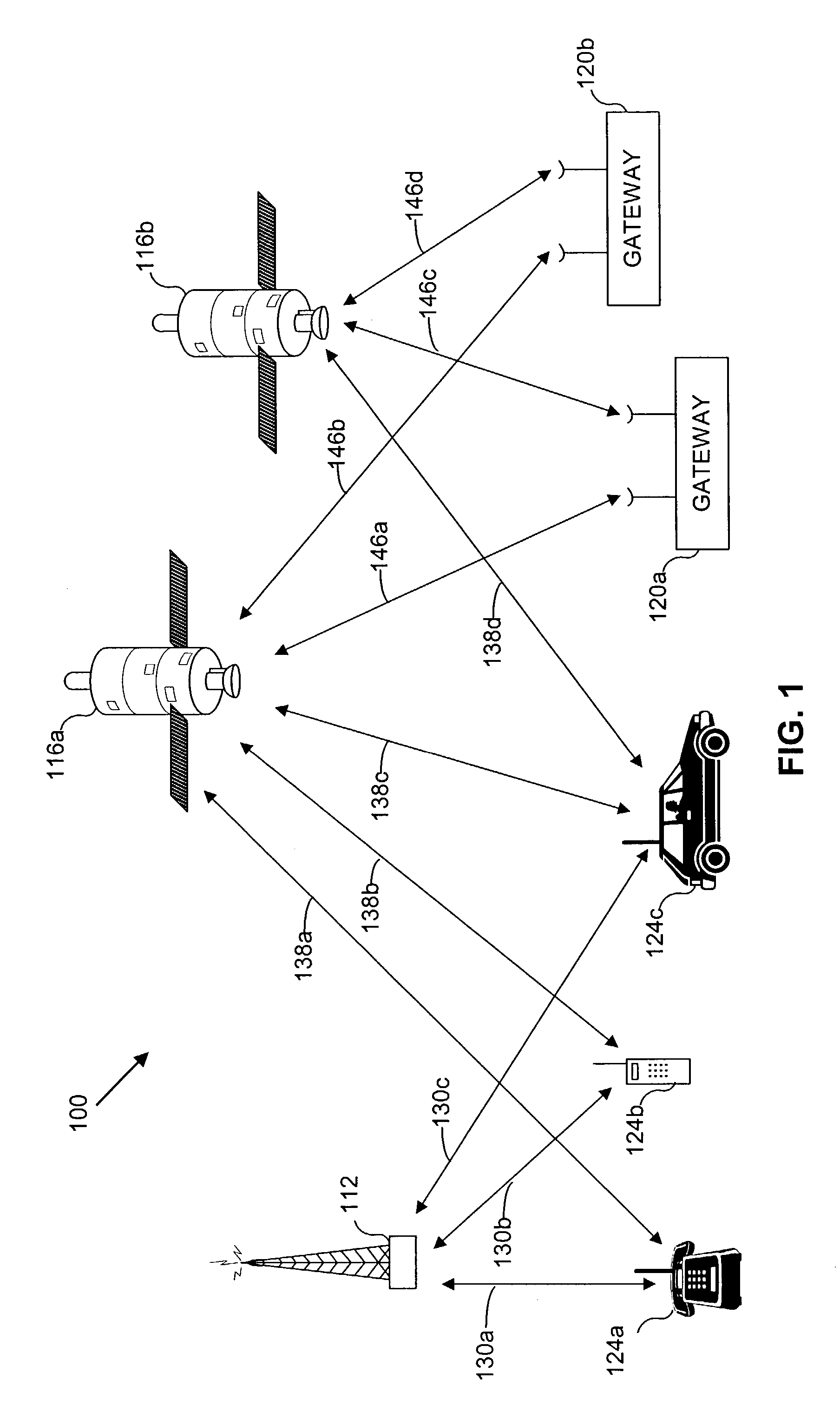

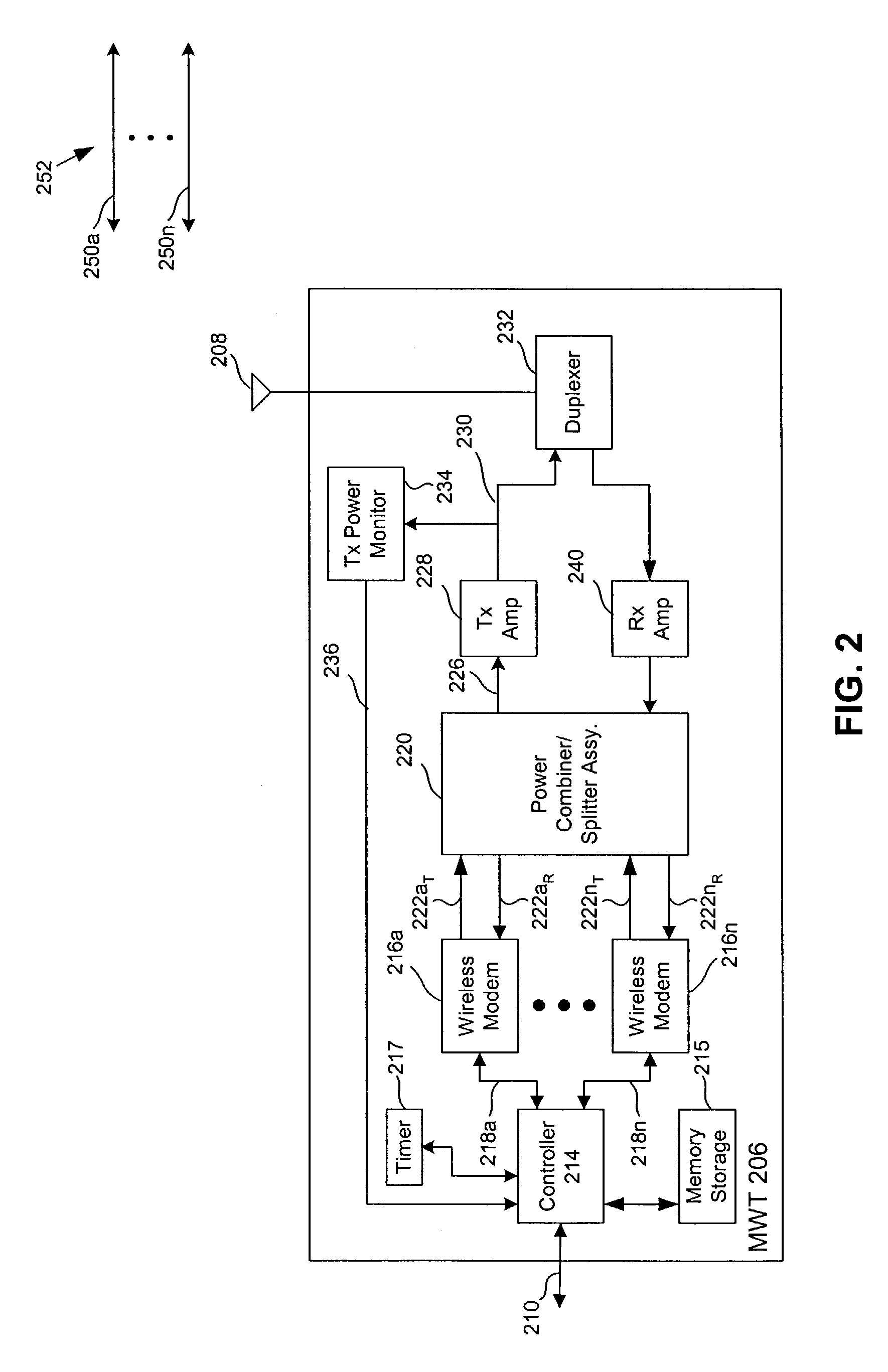

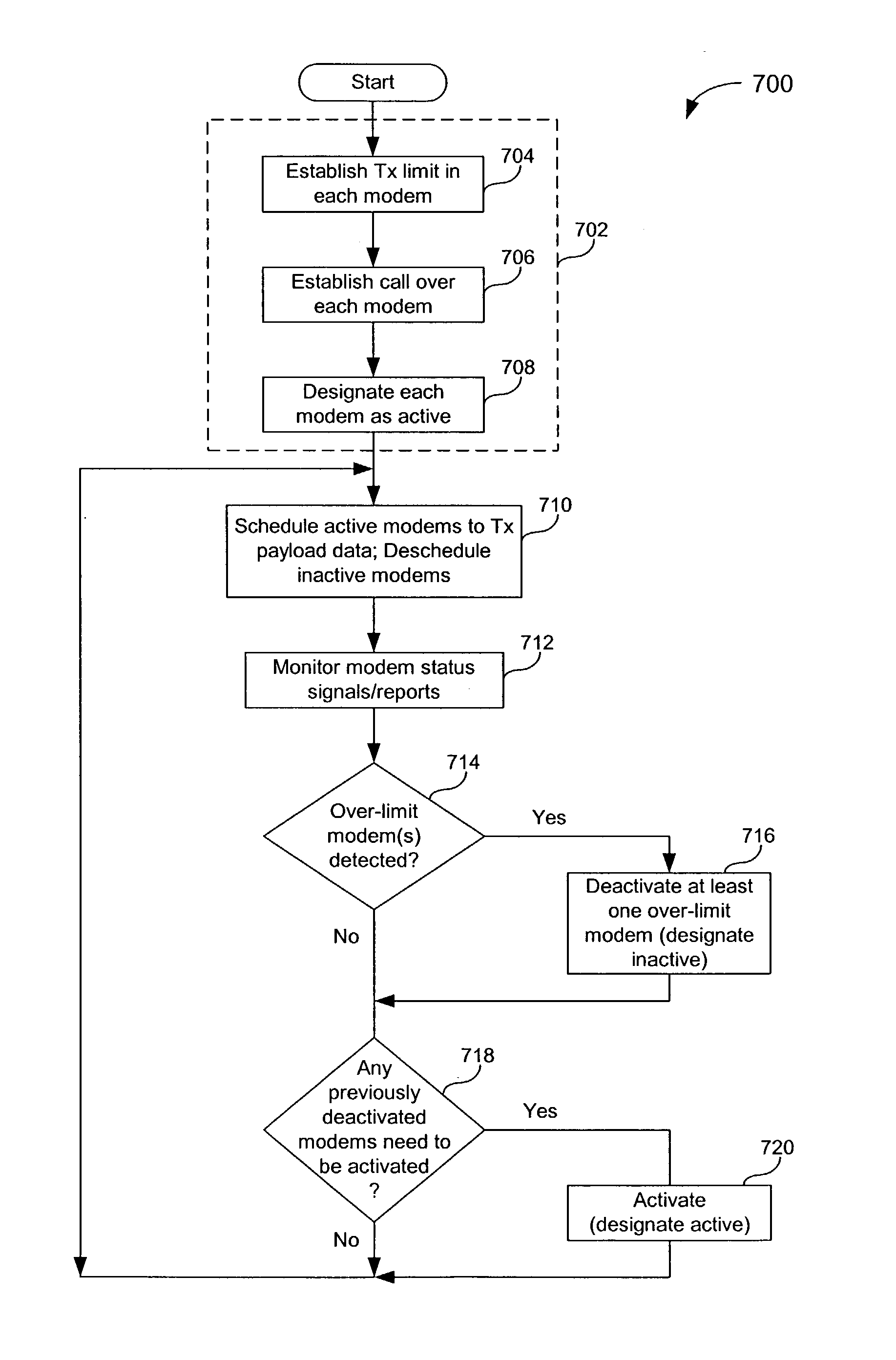

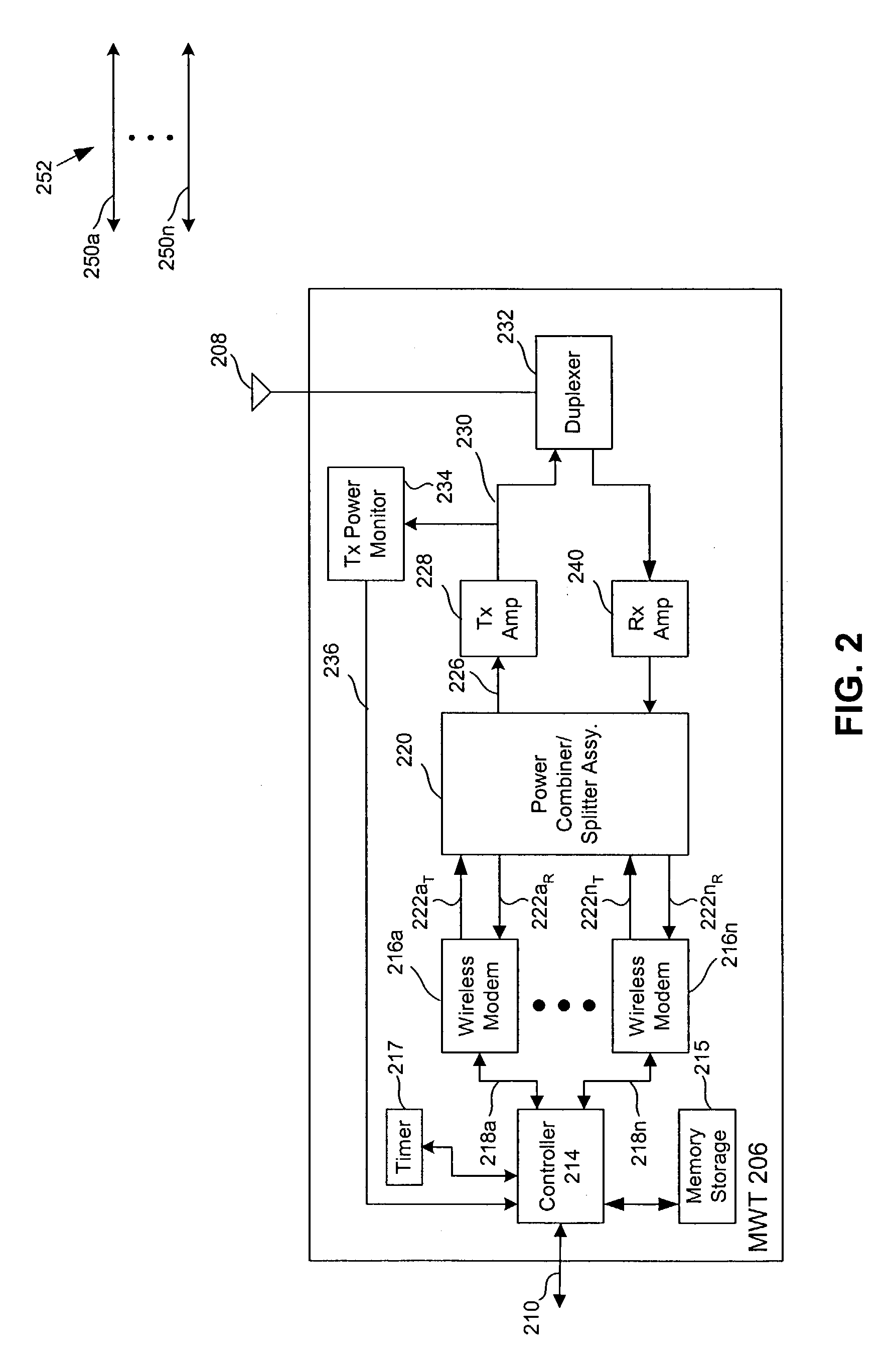

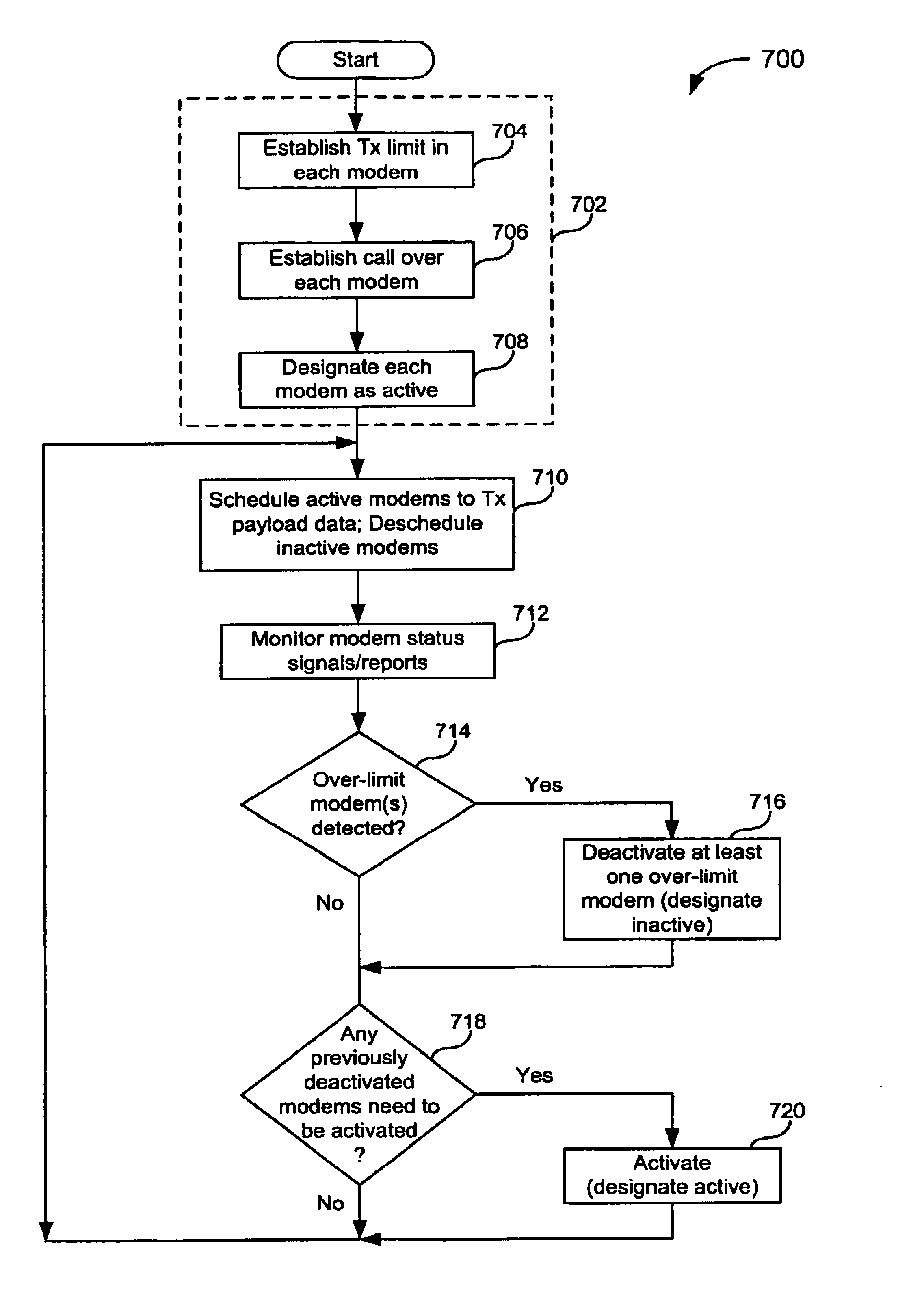

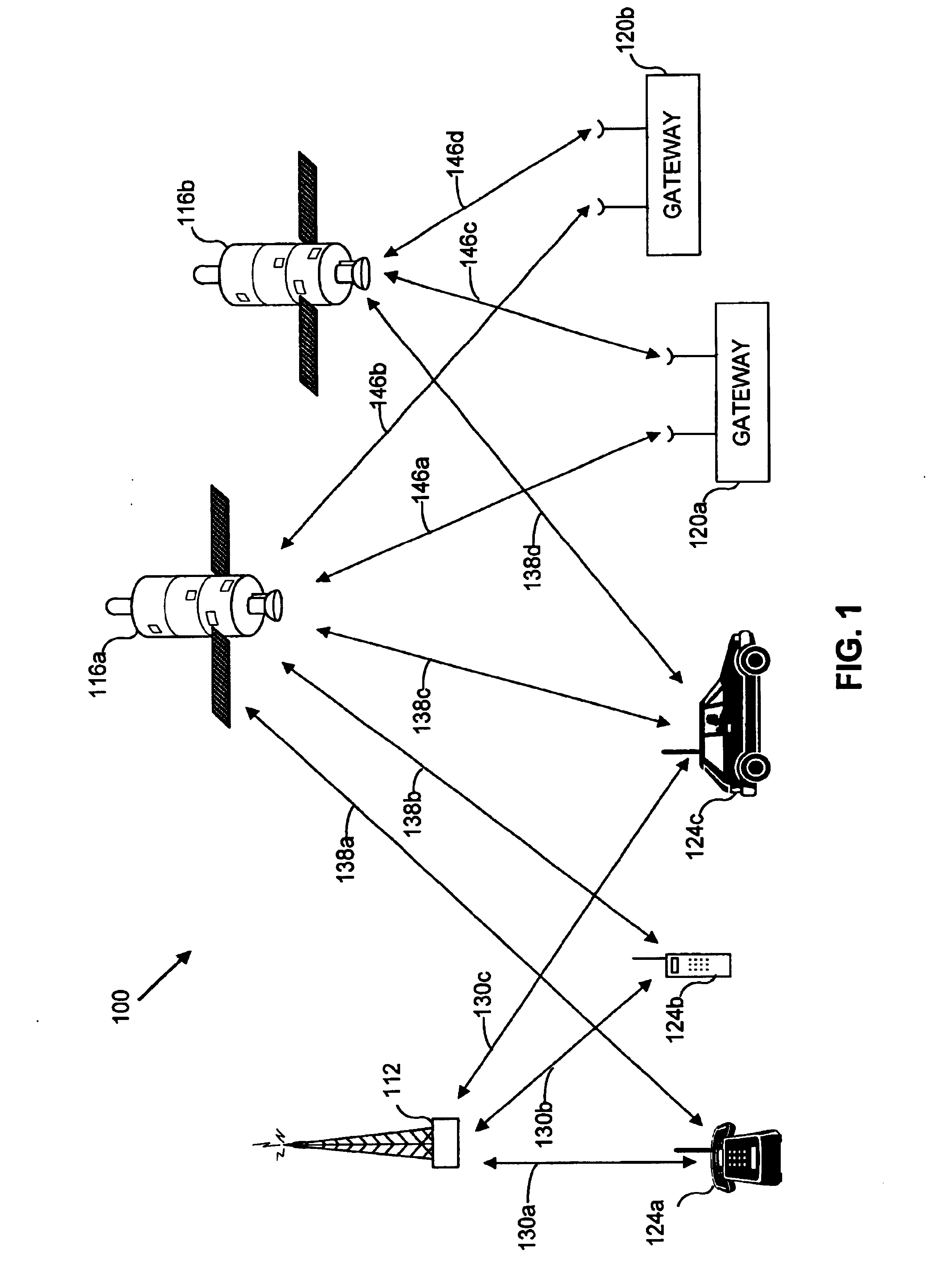

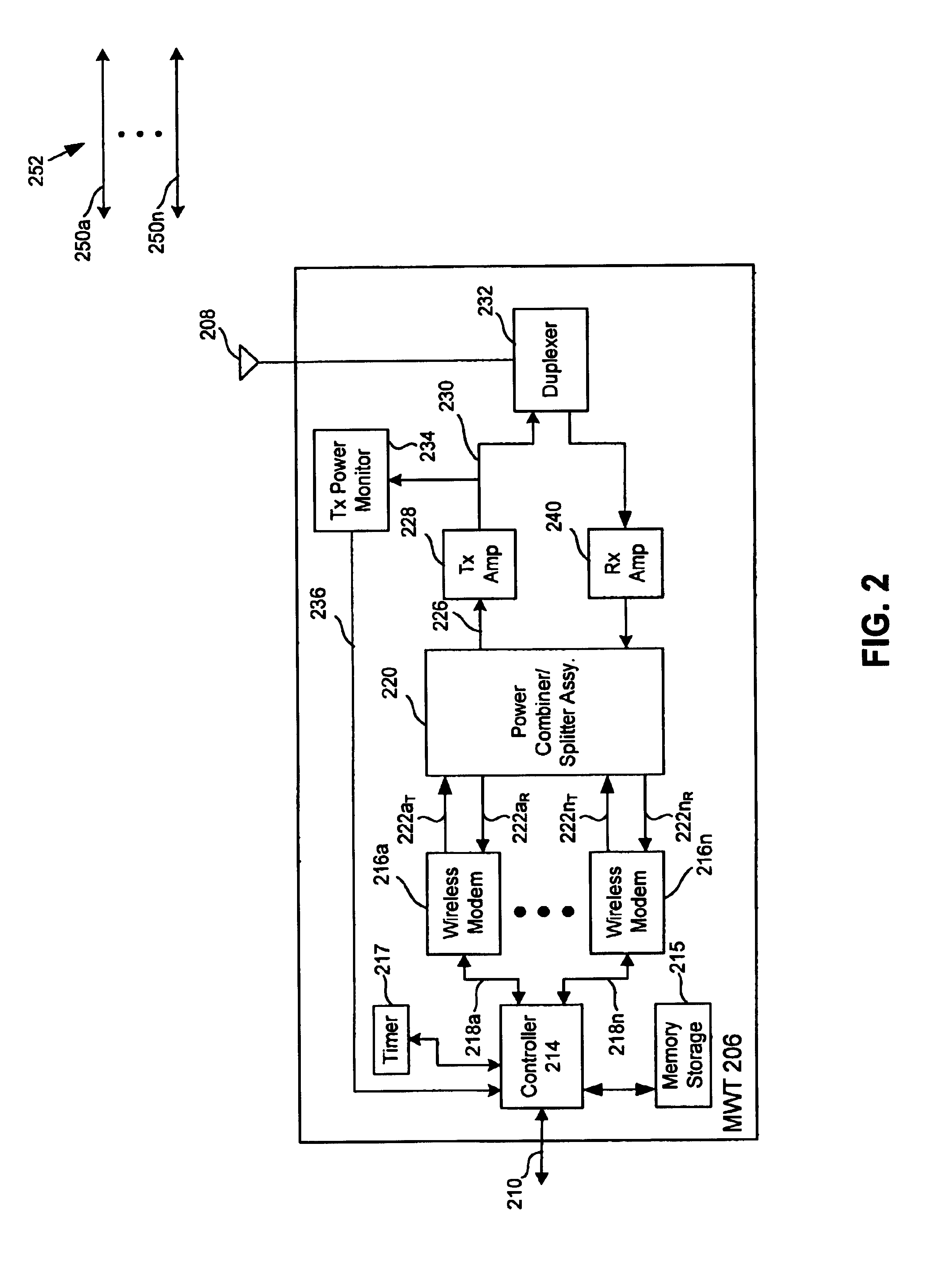

Wireless terminal operating under an aggregate transmit power limit using multiple modems having fixed individual transmit power limits

ActiveUS7058421B2Maximize communication bandwidthLow costPower managementTransmission control/equalisingModem deviceTransmitted power

A mobile wireless terminal (MWT) includes multiple wireless modems. The multiple modems have their respective transmit outputs combined to produce an aggregate transmit output. The multiple modems can concurrently transmit data in a reverse link direction and receive data in a forward link direction. The MWT is constrained to operate under an aggregate transmit power limit. Each of the multiple modems has an individual transmit limit related to the aggregate transmit power limit. When operating, over-limit ones of the multiple modems are deactivated and then reactivated to keep an aggregate transmit power of all of the modems below the aggregate limit, and to maximize data through-put on the forward and reverse links.

Owner:QUALCOMM INC

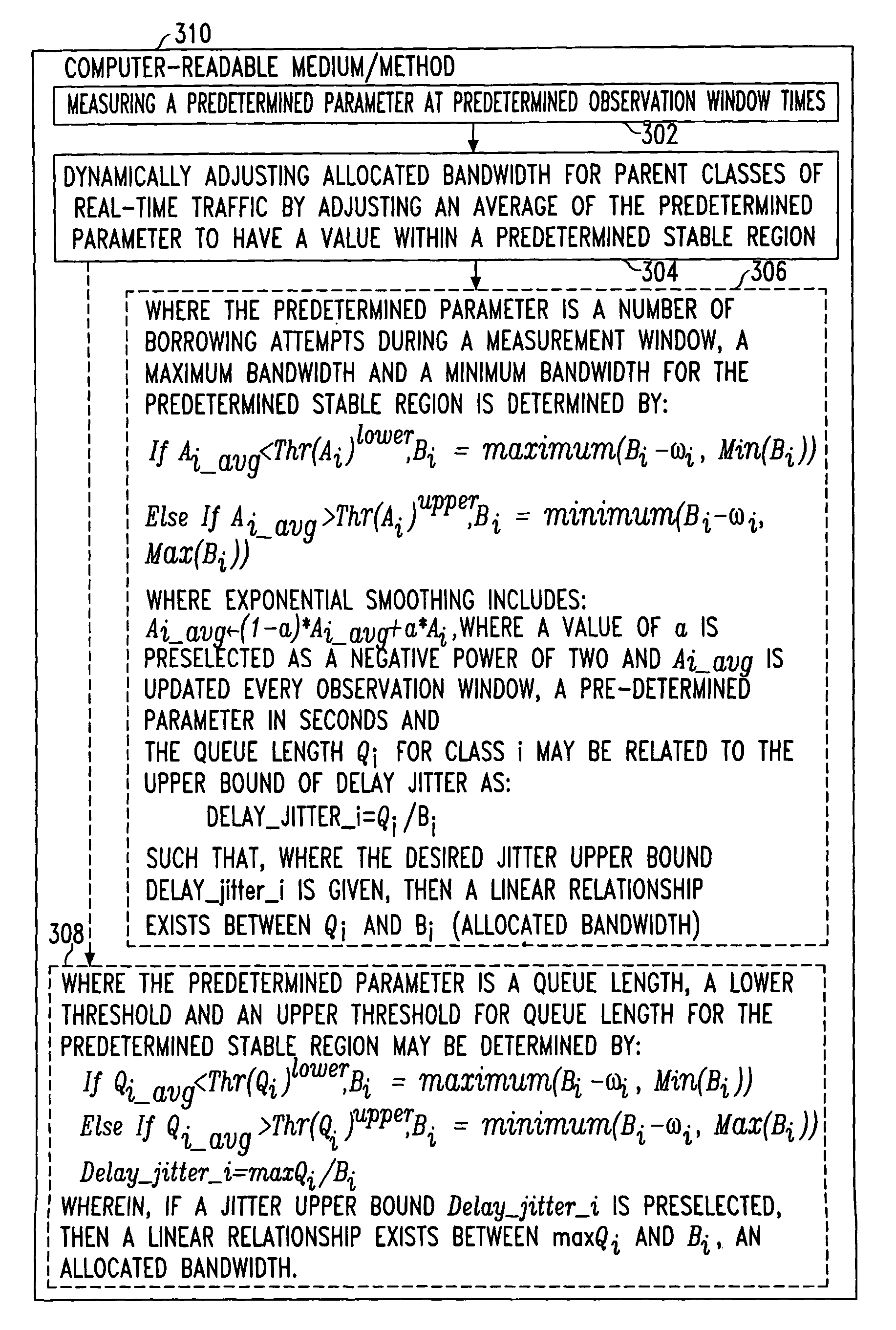

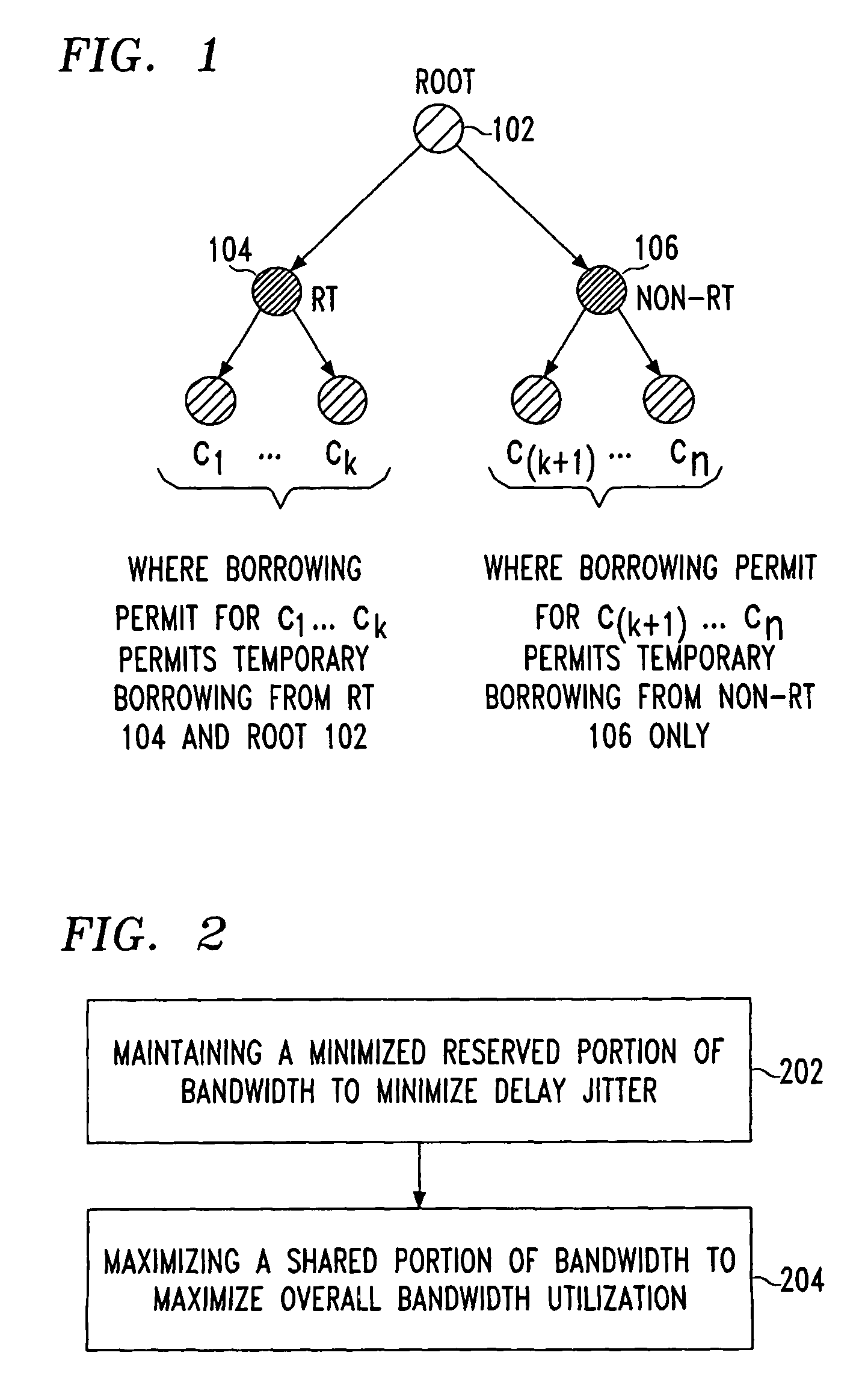

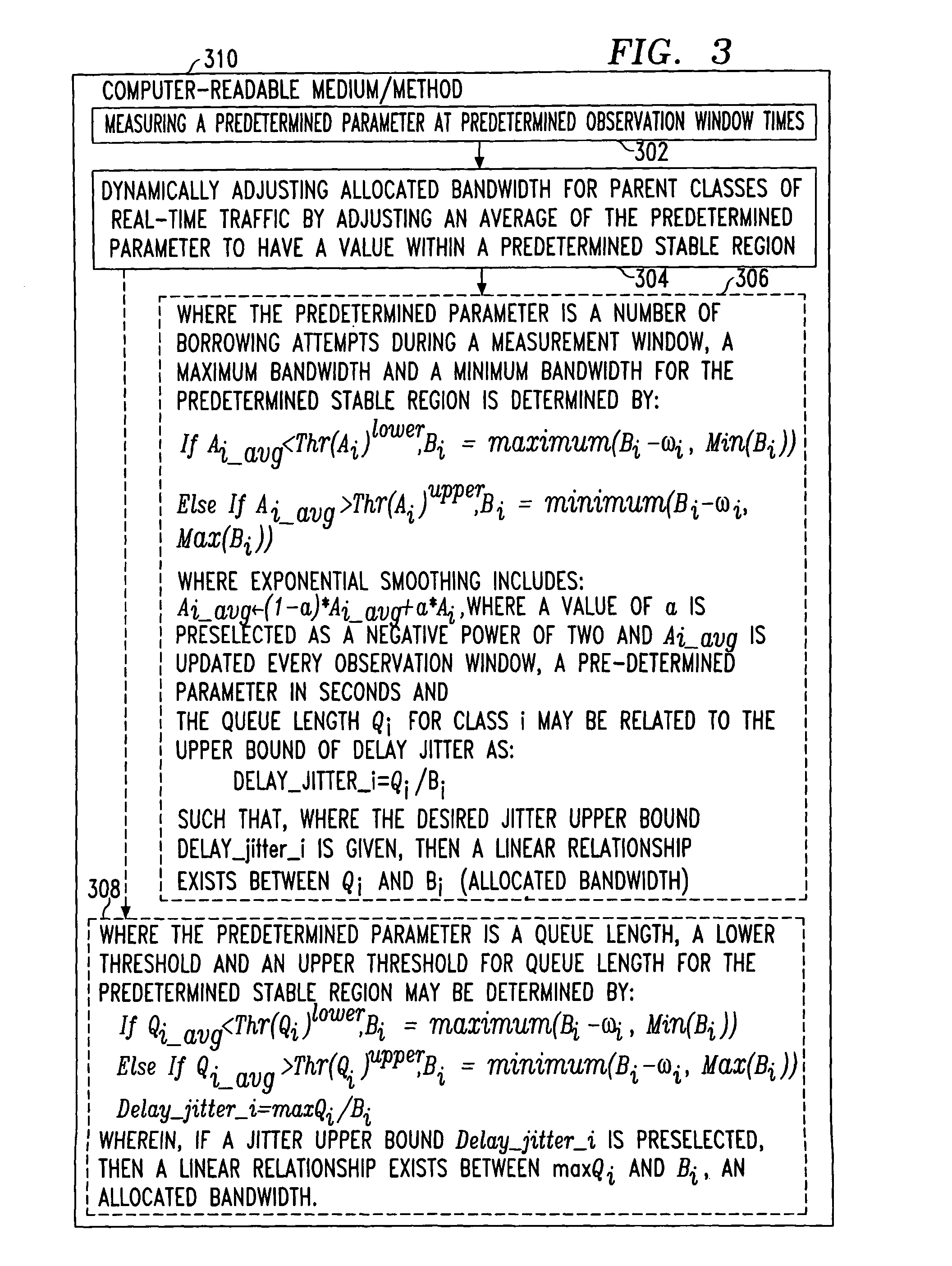

Method and device for efficient bandwidth management

InactiveUS7065048B1Minimize bandwidthMinimize delayError preventionTransmission systemsNon real timeBandwidth management

Owner:AMERICAN TELEPHONE & TELEGRAPH CO

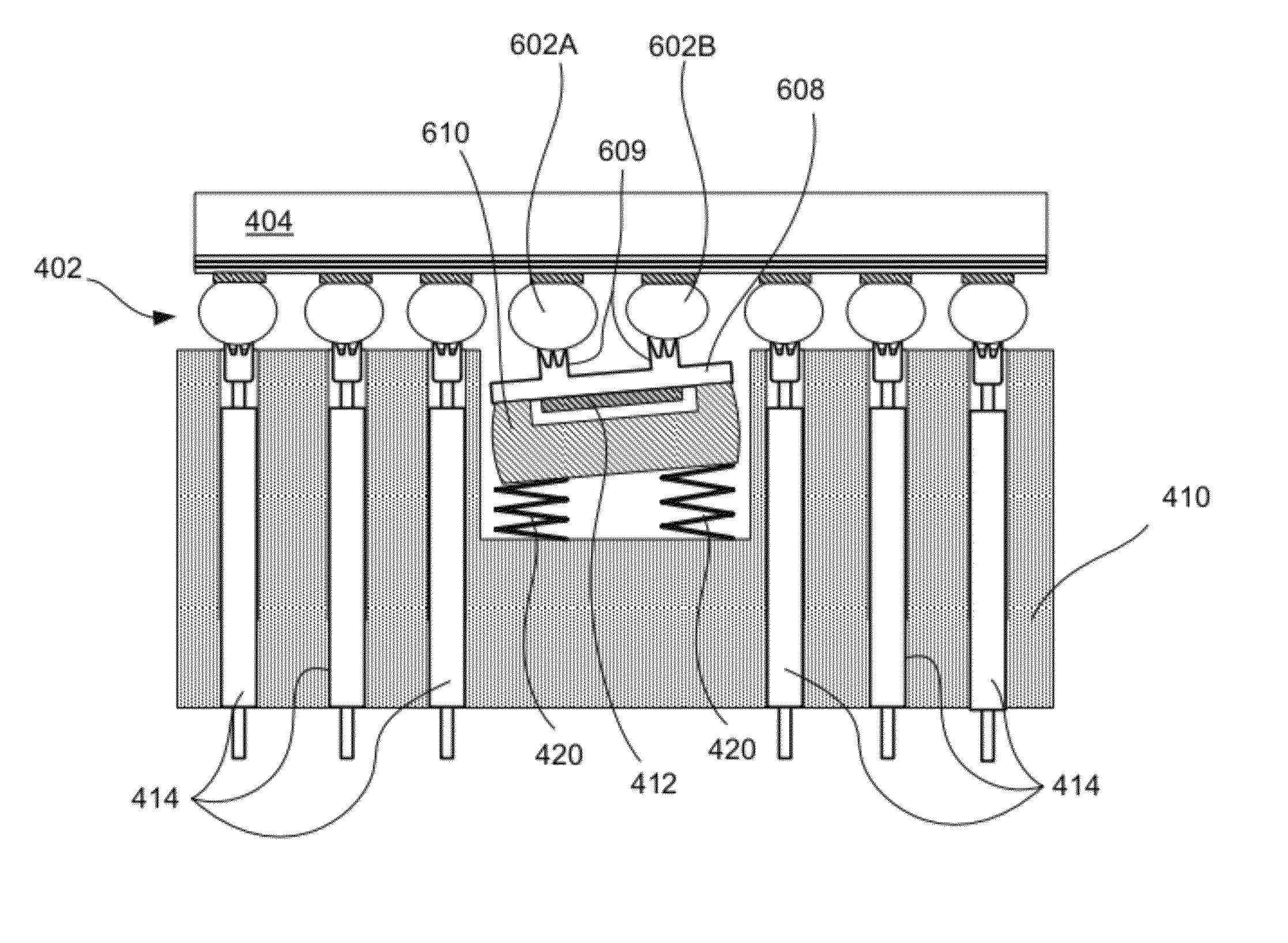

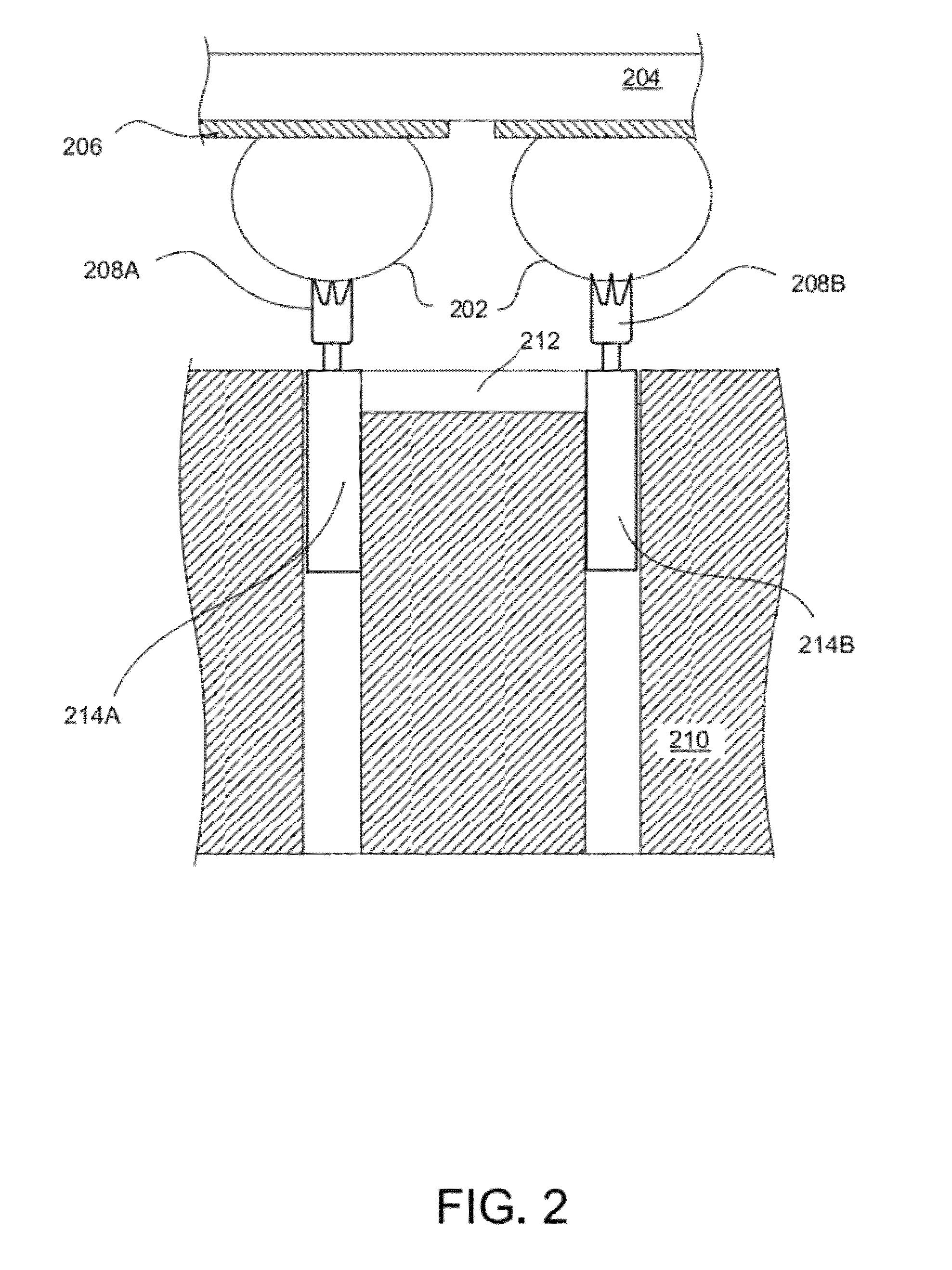

High-speed contactor interconnect with circuitry

ActiveUS8269516B1Maximize bandwidthShorten the electrical pathElectrical measurement instrument detailsElectrical testingContactorIntegrated circuit

Disclosed is a contactor interconnect in an integrated circuit device test fixture comprises a plurality of contactor pins enabled to provide electrical contact with the contact points of an integrated circuit device, the contactor pins being mounted in the test fixture; and an electrical circuit coupled to two or more of the contactor pins of the test fixture, wherein the electrical circuit is isolated from other contactor pins of the plurality of contactor pins and wherein the electrical circuit is coupled to the two or more contactor pins by an electronically direct pathway.

Owner:XILINX INC

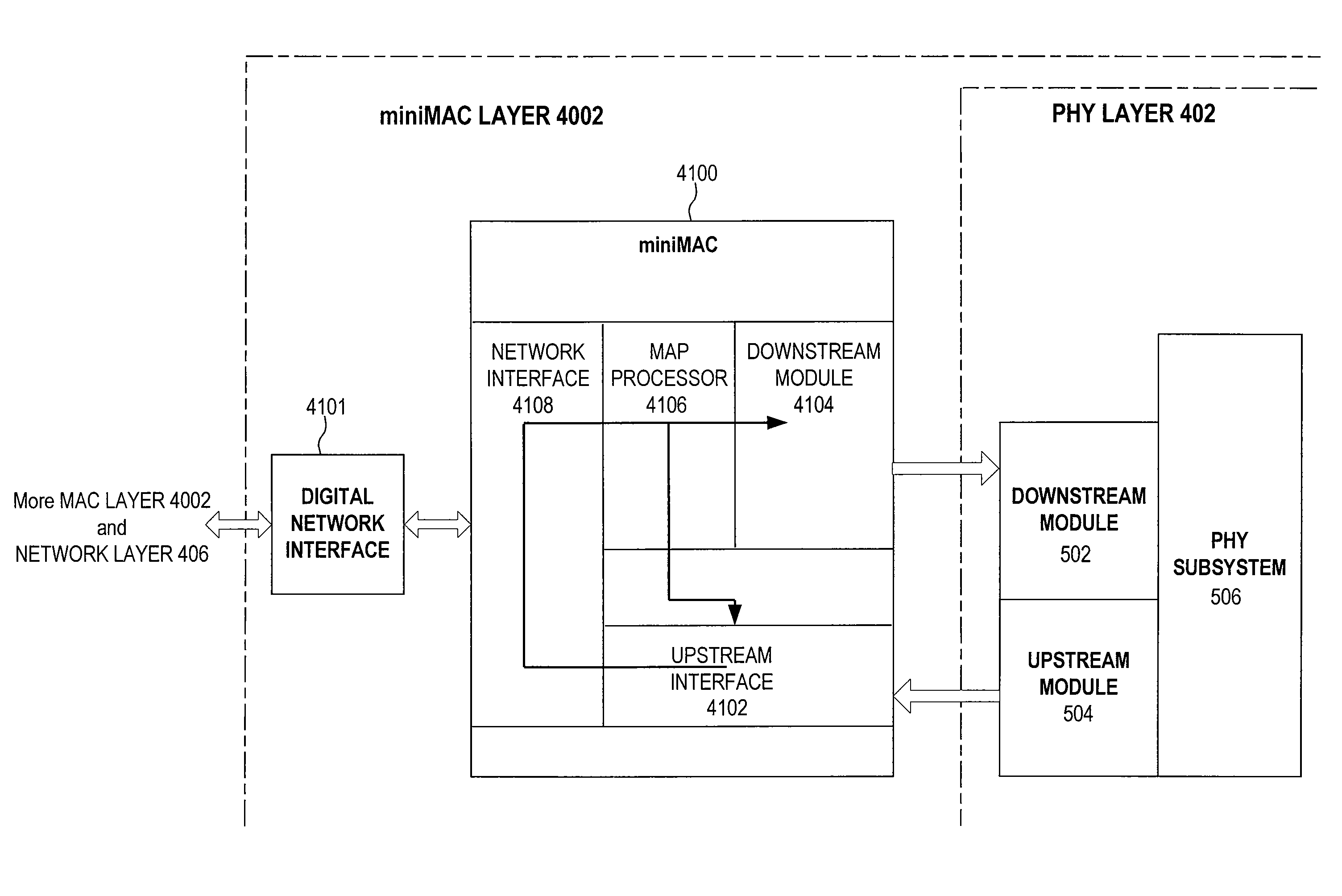

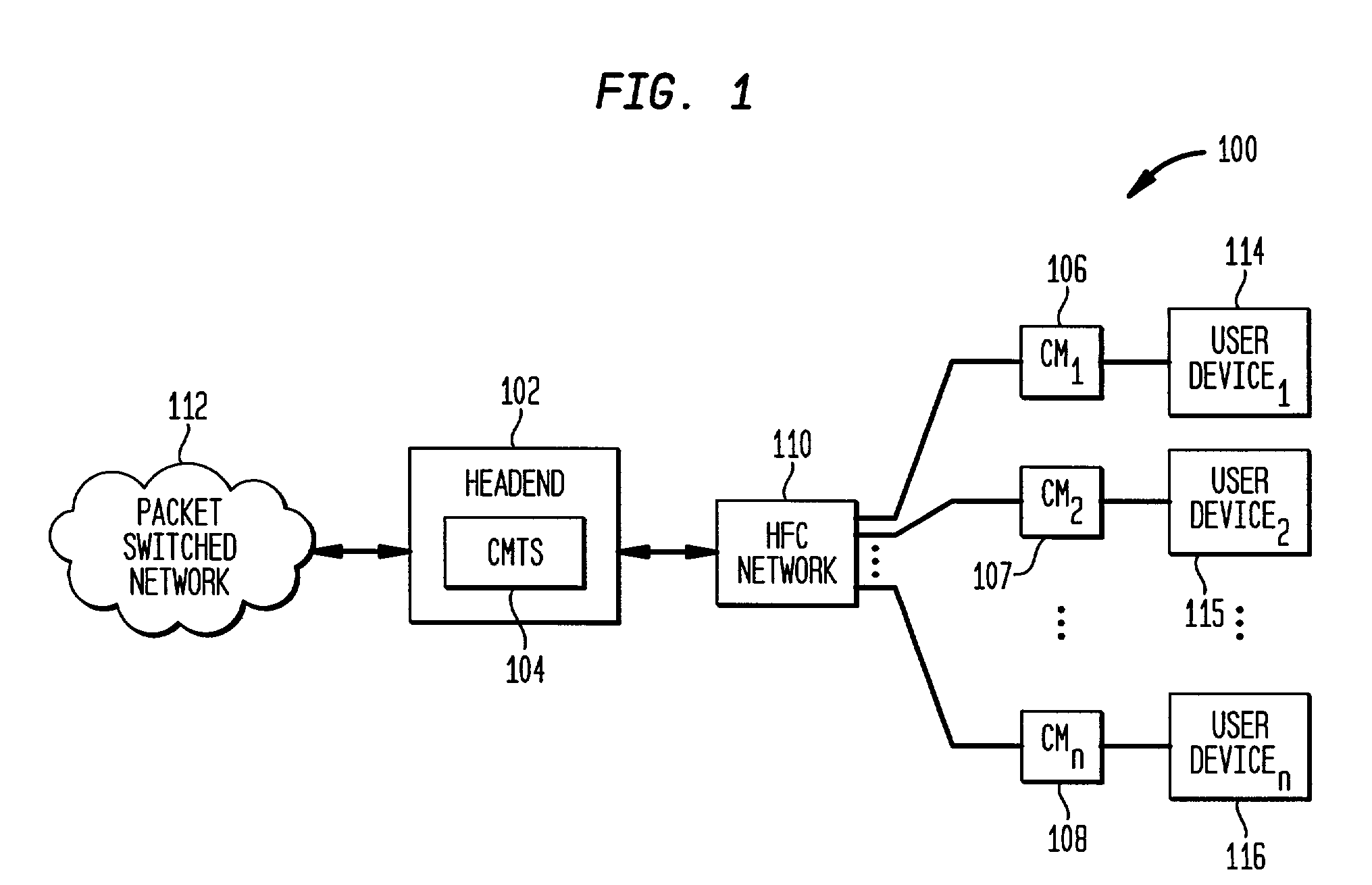

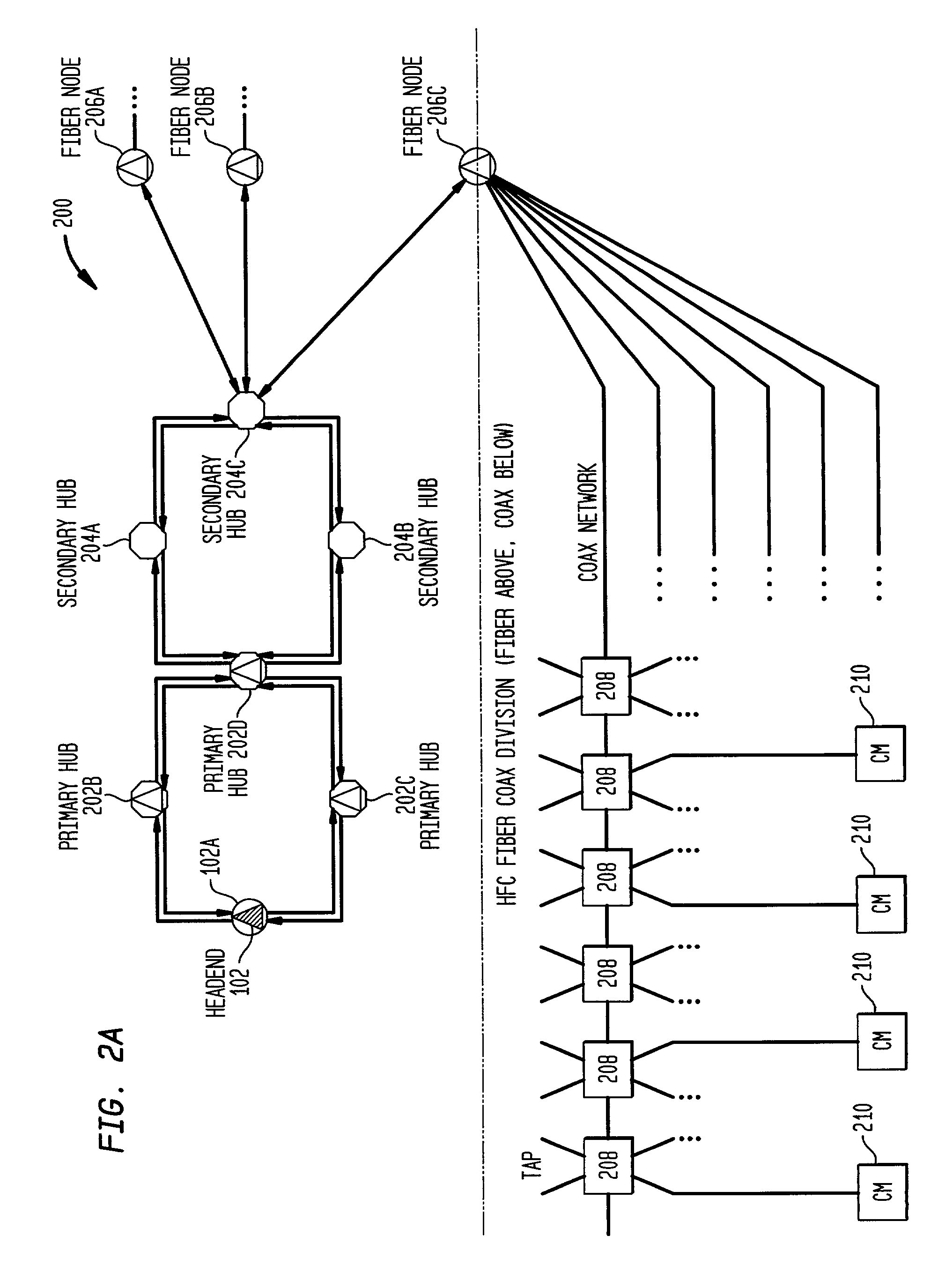

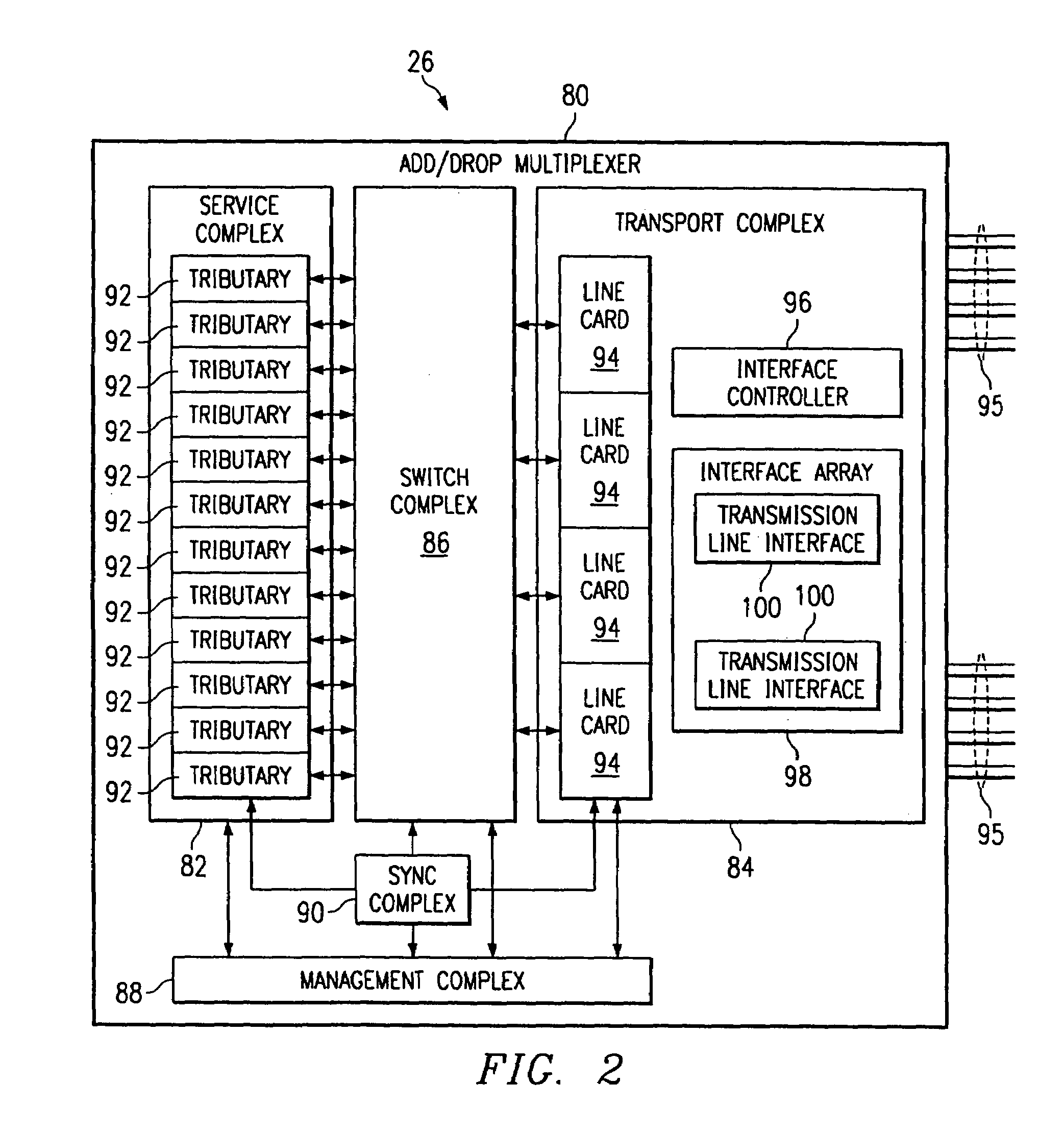

MiniMAC implementation of a distributed cable modem termination system (CMTS) architecture

ActiveUS7551610B2Easy to manageReduce distanceBroadband local area networksTime-division multiplexComputer hardwareFiber

A miniMAC implementation of a distributed CMTS in a hybrid fiber / coaxial (HFC) plant. The distributed CMTS comprises at least one network layer, at least one media access layer, and one or more physical layers. The at least one media access layer includes one or more miniMAC layers. The one or more miniMAC layers are remotely located from a remaining part of the at least one media access layer. The at least one network layer, the remaining part of the at least one media access layer, the one or more miniMAC layers, and the one or more physical layers each function as separate modules, enabling each layer to be in separate component locations of the HFC plant, yet having the at least one network layer connected to the remaining part of the at least one media access layer, the at least one media access layer connected to each of the one or more miniMAC layers, and each of the one or more physical layers connected to each of the one or more miniMAC layers. The one or more miniMAC layers are located in close proximity to the one or more physical layers in the HFC plant. The one or more miniMAC layers convert digital bit streams into packets and maintain timing constraints between the one or more miniMAC layers and the one or more physical layers.

Owner:AVAGO TECH INT SALES PTE LTD

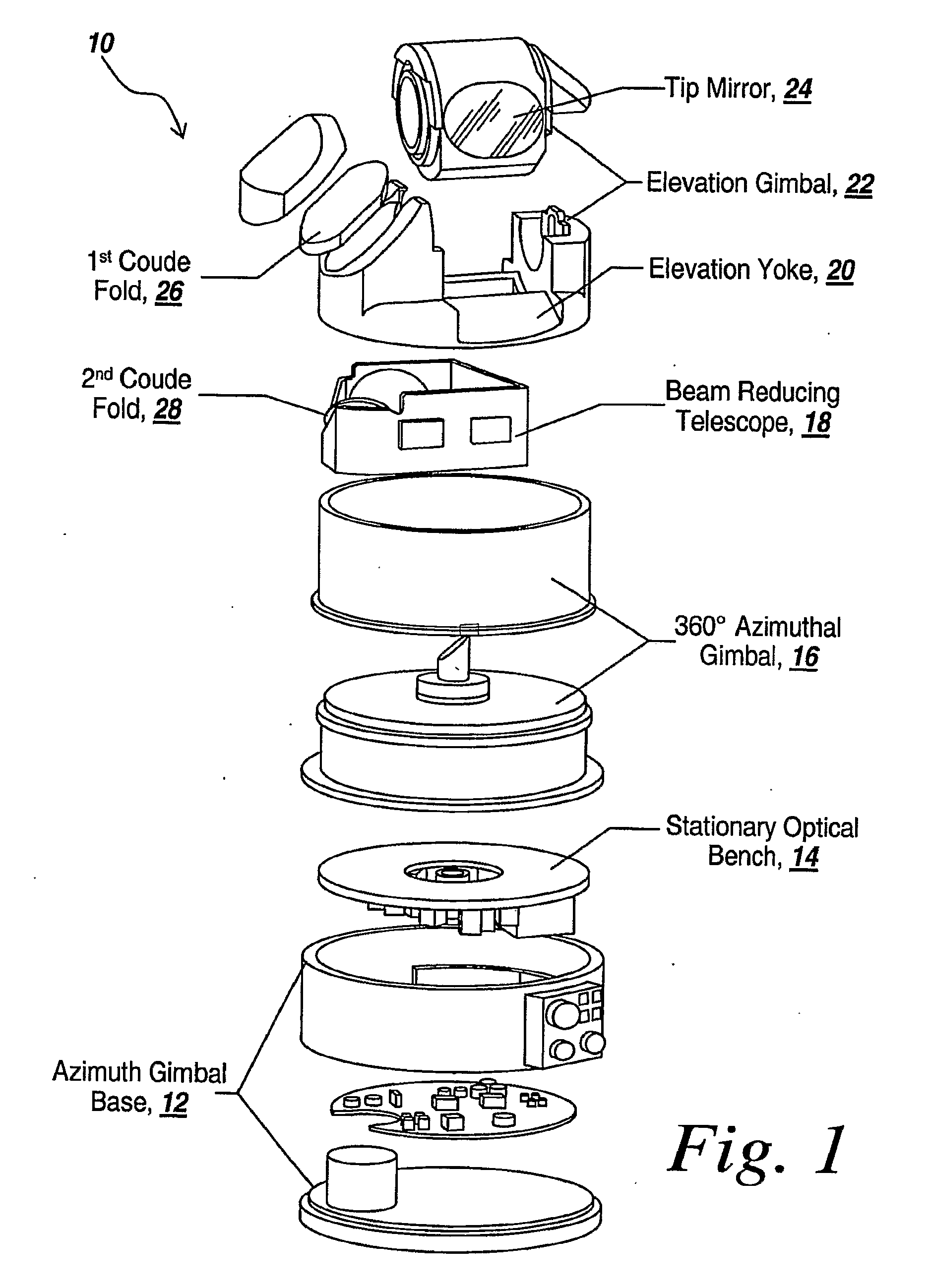

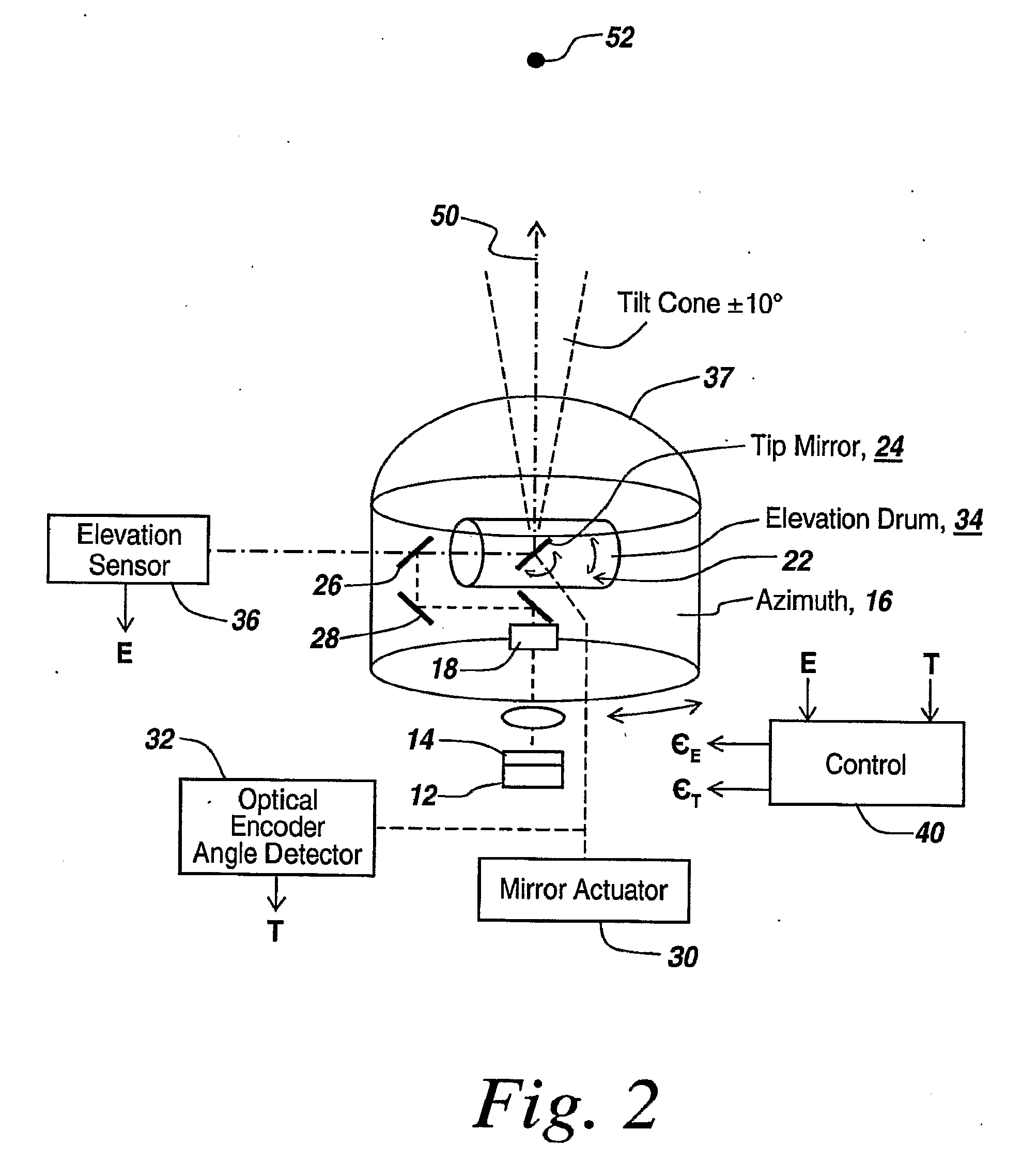

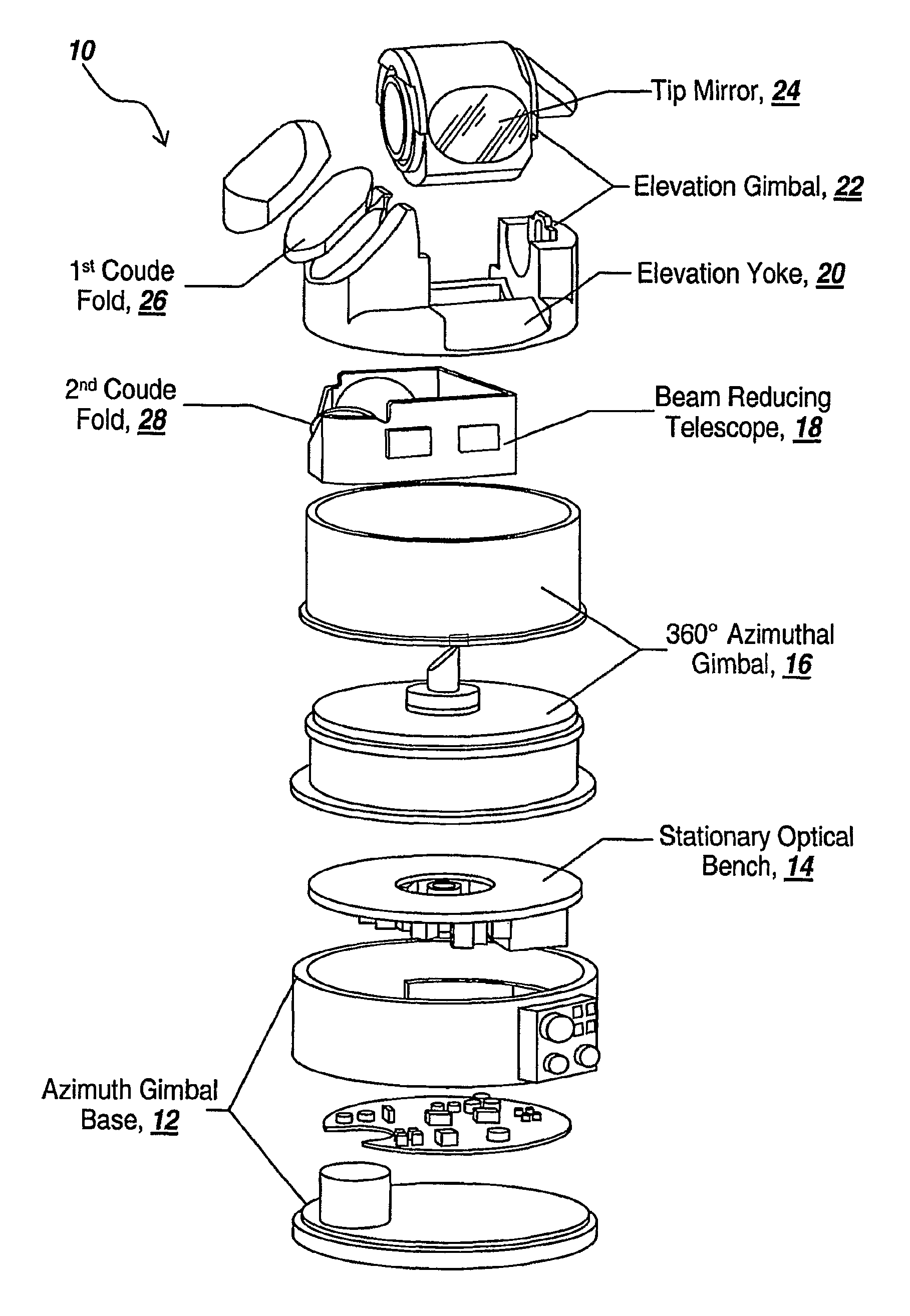

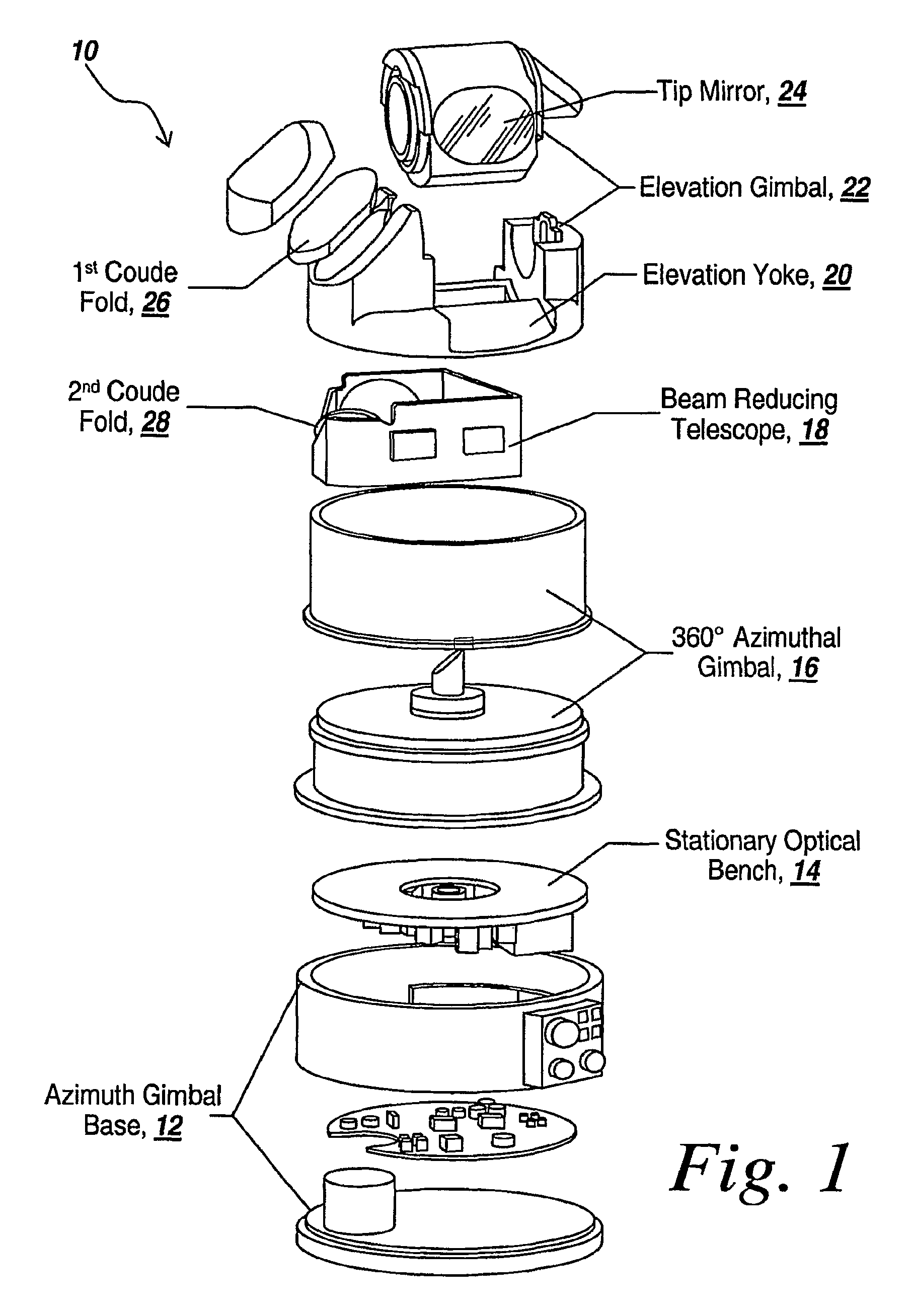

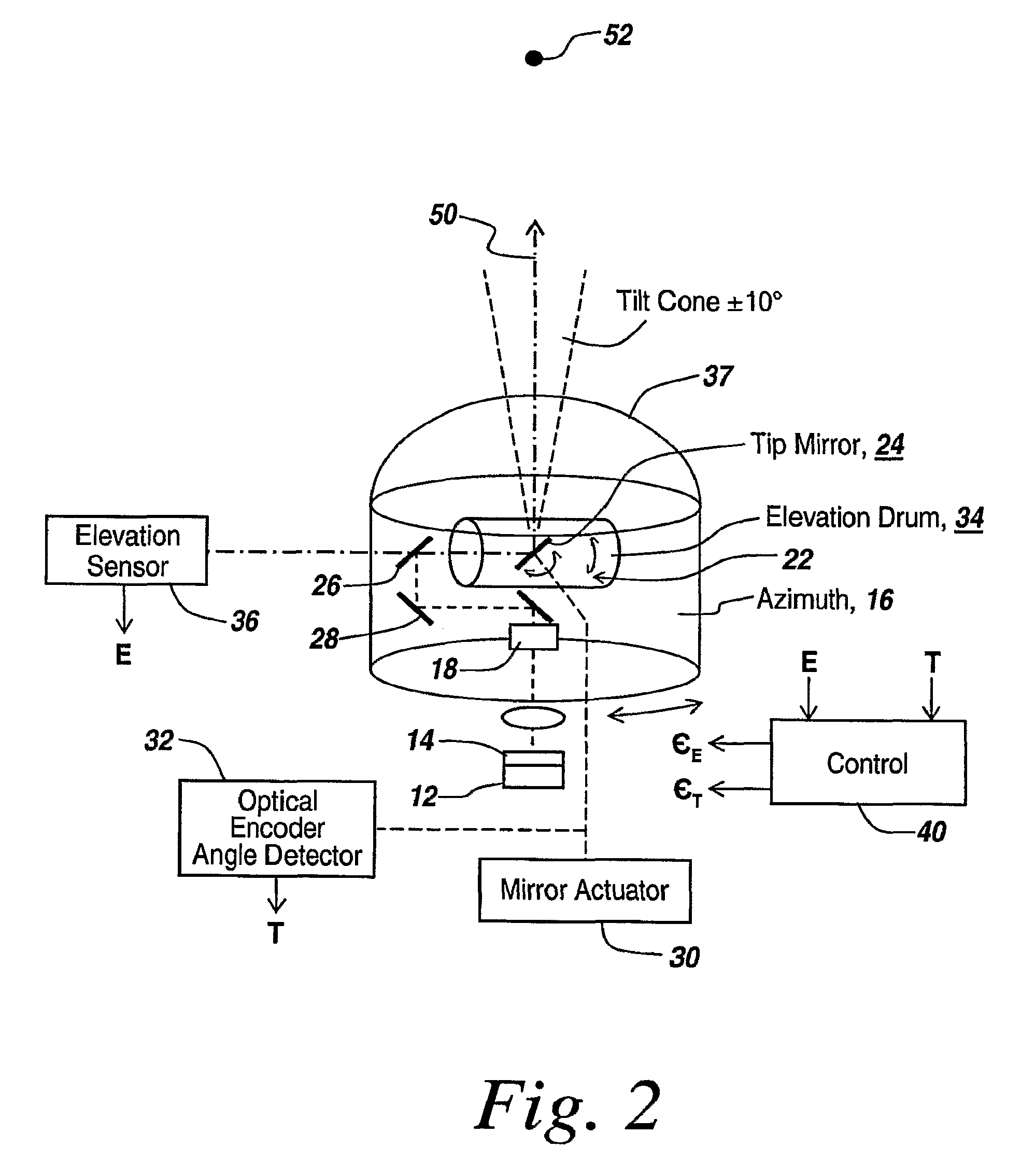

High accuracy optical pointing apparatus

ActiveUS20100220390A1Eliminate gimbal lockAvoid elevationAiming meansTelescopesHigh accelerationLight beam

In the subject three-axis pointing system, the elevation and tip mirror axes are permanently mounted with their rotation axes orthogonal to each other to eliminate gimbal lock over the hemisphere, to avoid high accelerations as the zenith or nadir pointing directions are approached, and to provide optimal two-axis beam pointing control.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

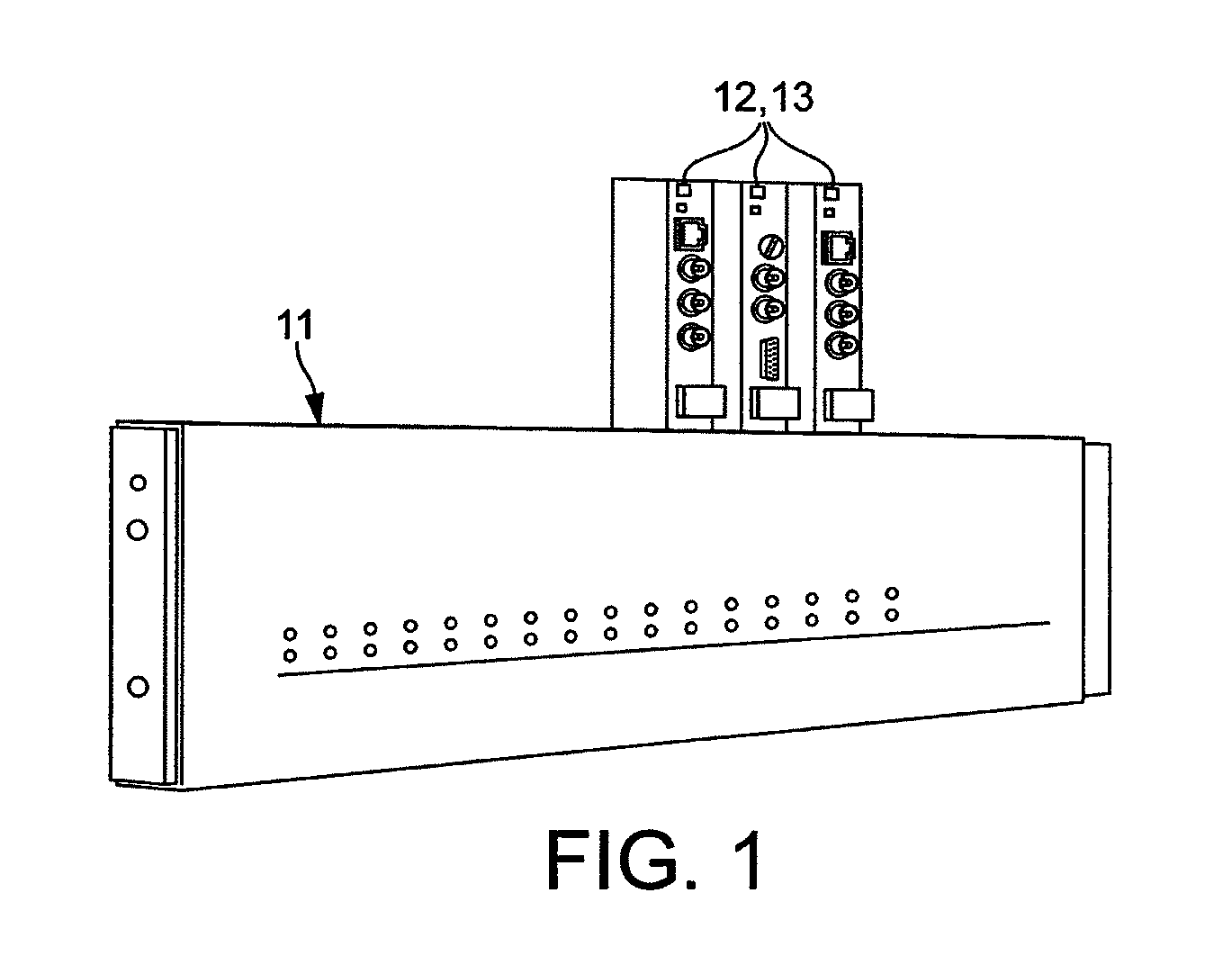

Multi-Channel Optical Communication

InactiveUS20090232505A1Maximize bandwidthSimplify creationTime-division optical multiplex systemsTime-division multiplexOperating instructionTransceiver

An optical fiber communications apparatus comprises a housing provided with a motherboard and with a support defining plurality of card receptors. A plurality of modular cards (12, 13) are provided, each of which is engageable with the motherboard via one of the card receptors. A optical card (12) includes an optical transceiver (20) for communication using a digital, optical communications signal over a single optical fiber link (17). Each modular card (12, 13) is provided with a plurality of circuit sub-assemblies (16), each circuit sub-assembly being configured for digital communication with a respective local audio, video or data electronic device via a respective connector using a respective electronic information-carrying signal. Each circuit sub-assembly (16) is configured for communication of an audio, video or data information-carrying signal with the transceiver using the digital, optical communications signal. A processor having operating instructions is provided for ascertaining the number of modular cards engaged with the motherboard and the number of circuit sub-assemblies on each of the modular cards, and for assigning time slots for the individual information-carrying signals of the circuit sub-assemblies, thereby controlling transmission of communications between the optical transceiver and the circuit sub-assemblies, and time division multiplexing those communications over the single optical fiber link to communicate a predetermined combination of audio, video and data channels multiplexed onto a single optical channel carried by the optical fiber link. A further aspect of the invention relates to controlling the power of a signal RF input into a light source used for optical communication. The power may be regulated according to a determined noise and / or distortion of a signal RF input to the amplifier or may be varied so that it lies in a predetermined range.

Owner:EMCORE INC

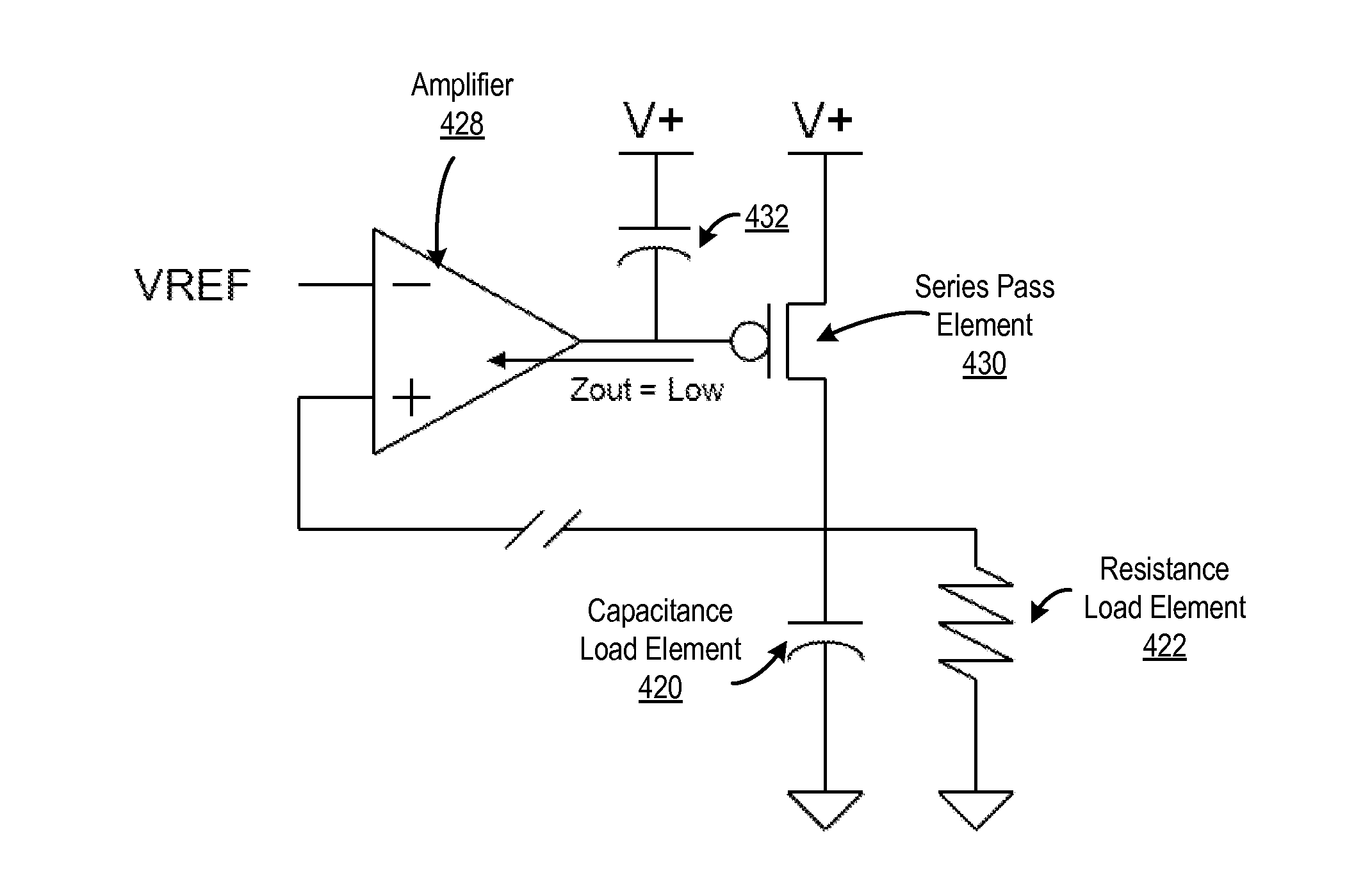

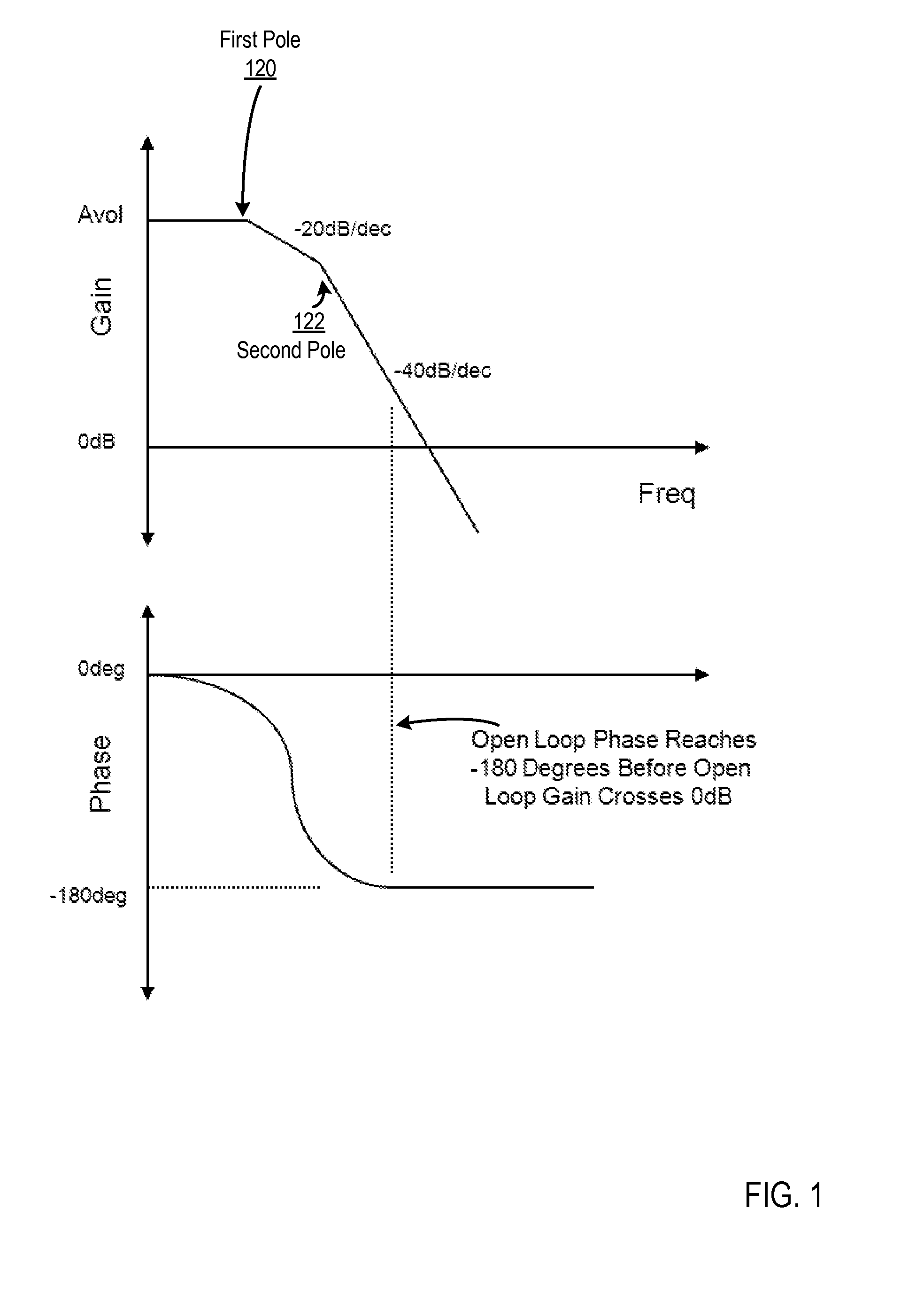

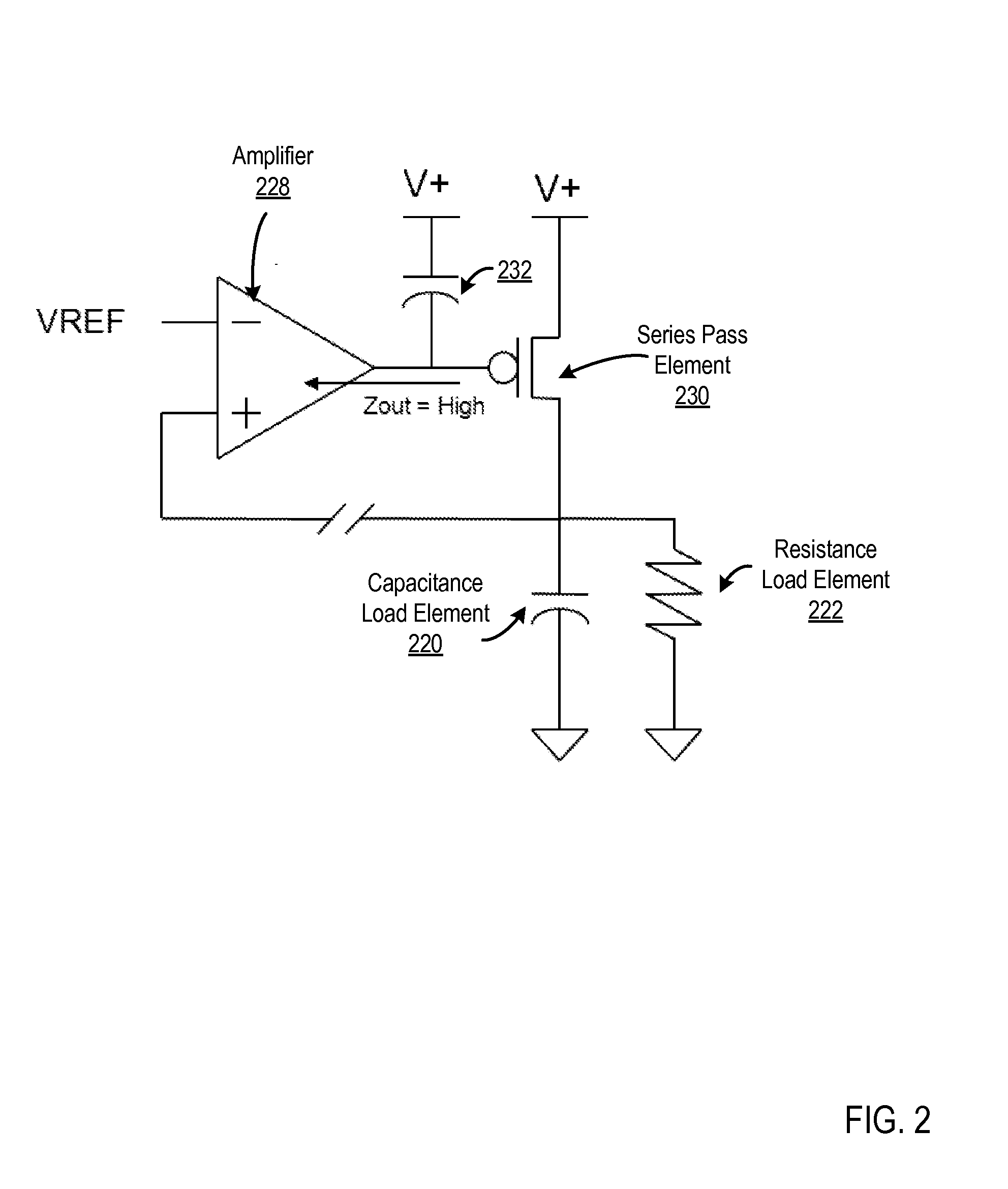

Wide-Bandwidth Linear Regulator

A linear regulator and a method of regulating a supply voltage are provided. Embodiments include a linear regulator with a first feedback loop and a second feedback loop. The first feedback loop is characterized by a first bandwidth and a first gain. The first feedback loop includes a first amplifier characterized by an output impedance which is significantly reduced in order to maximize the bandwidth of the first feedback loop when driving the capacitance of a control input of a series pass element. The second feedback loop is characterized by a second bandwidth and a second gain. The second feedback loop includes a second amplifier that controls the current in the first amplifier in the first feedback loop.

Owner:IBM CORP

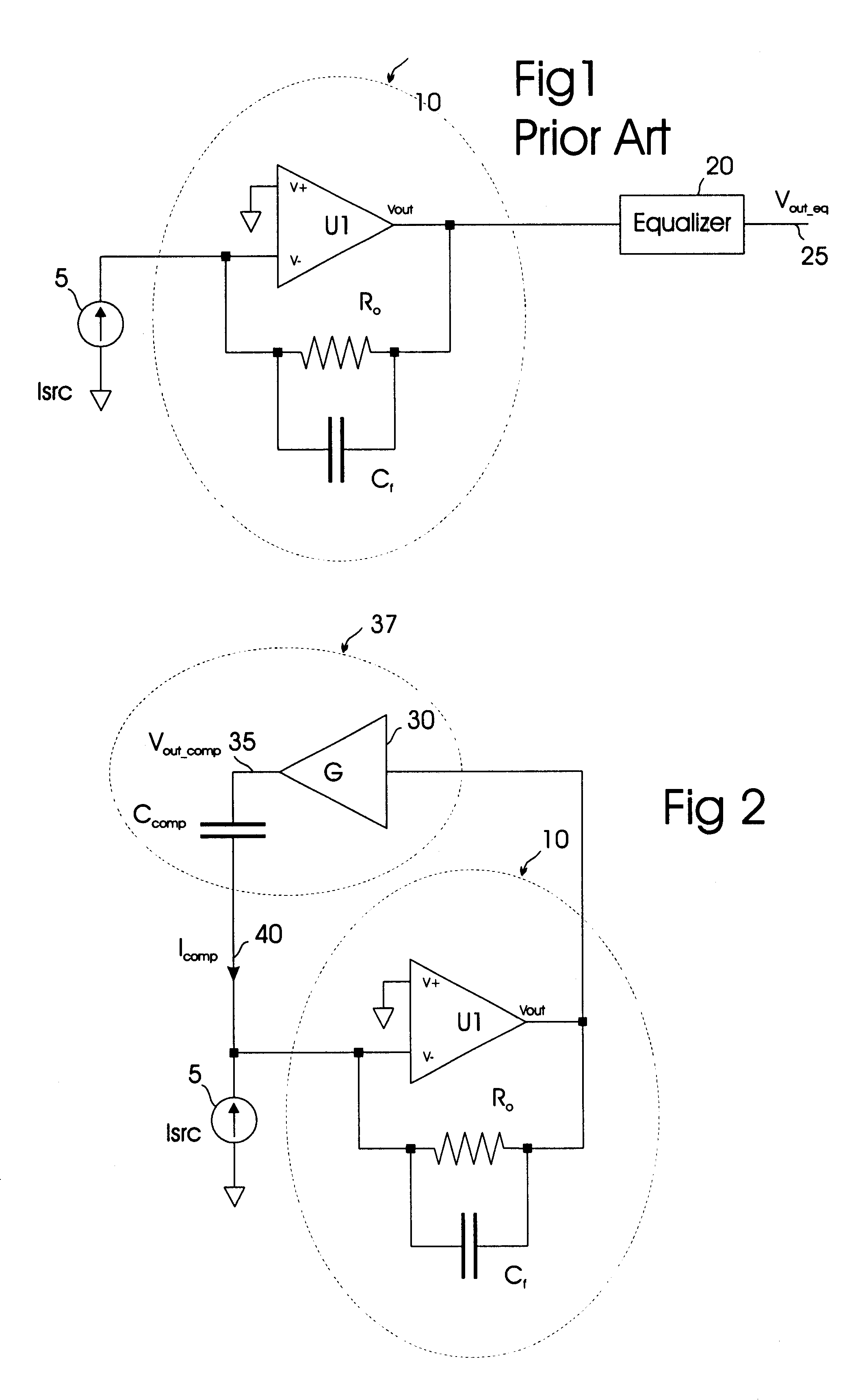

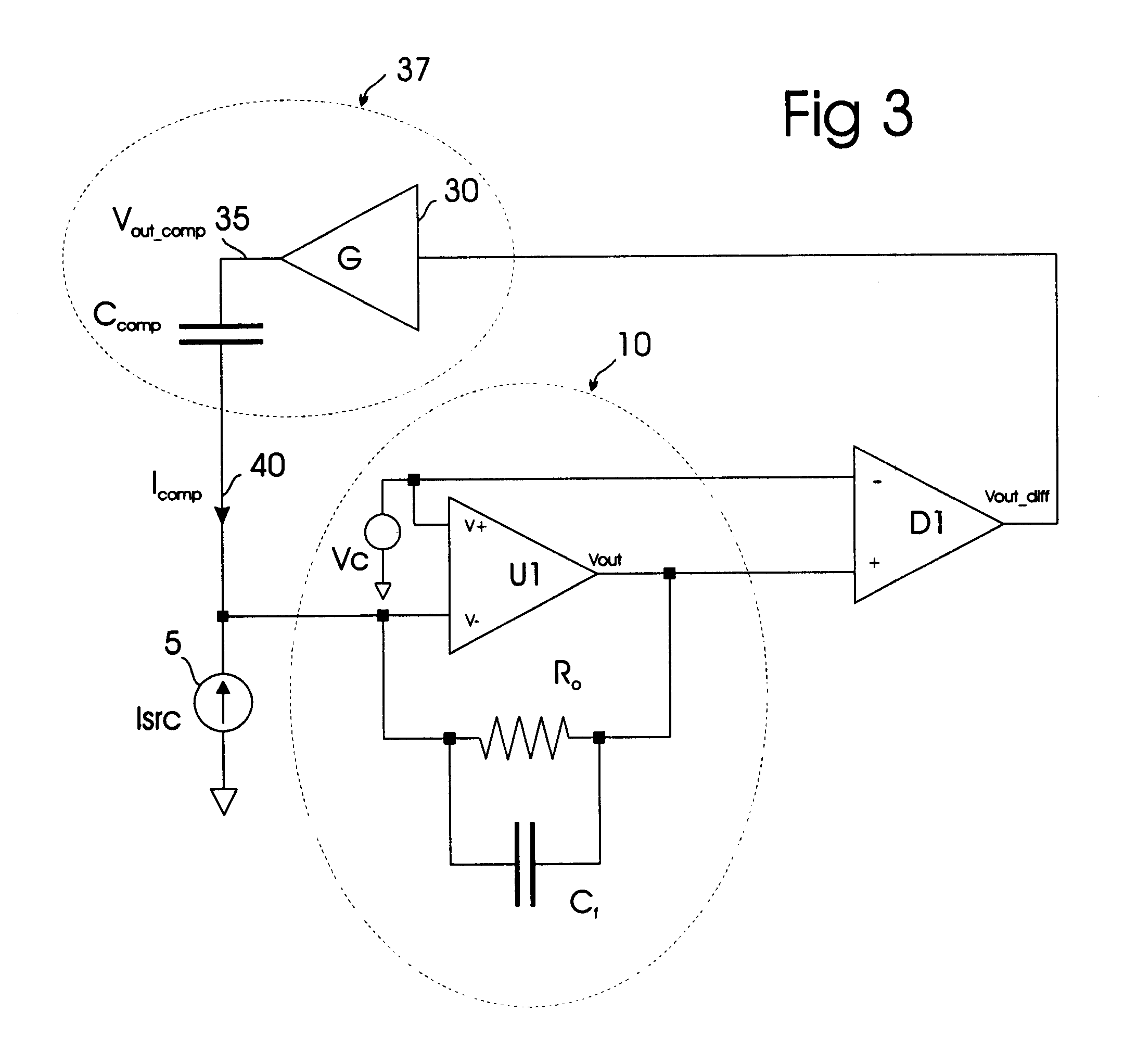

Self-compensated transimpedance amplifier

InactiveUS6611174B1Eliminates tediousEliminates costly procedureNegative-feedback-circuit arrangementsAmplifier combinationsCapacitanceLow noise

A method to increase the bandwidth of a transimpedance amplifier using capactive feedback. The resultant amplifier maintains wide bandwidth, high linearity, low noise, and low input impedance independent of component variations. These characteristics greatly facilitate the economical measurement of small currents such as those arising from photodiodes and biological preparations.

Owner:SHERMAN ADAM J

Wireless terminal operating under an aggregate transmit power limit using multiple modems having fixed individual transmit power limits

ActiveUS20040082295A1Low costReduce power consumptionPower managementTransmission control/equalisingTelecommunicationsModem device

A mobile wireless terminal (MWT) includes multiple wireless modems. The multiple modems have their respective transmit outputs combined to produce an aggregate transmit output. The multiple modems can concurrently transmit data in a reverse link direction and receive data in a forward link direction. The MWT is constrained to operate under an aggregate transmit power limit. Each of the multiple modems has an individual transmit limit related to the aggregate transmit power limit. When operating, over-limit ones of the multiple modems are deactivated and then reactivated to keep an aggregate transmit power of all of the modems below the aggregate limit, and to maximize data through-put on the forward and reverse links.

Owner:QUALCOMM INC

Voice adaptive gateway pacing methods and systems for wireless multi-hop networks

InactiveUS7839859B2Efficient use ofQuality improvementError prevention/detection by using return channelNetwork traffic/resource managementTraffic capacitySelf adaptive

Owner:NEC CORP

High accuracy optical pointing apparatus

ActiveUS7894144B2Eliminates gimbal lockHigh bandwidthAiming meansTelescopesHigh accelerationLight beam

In the subject three-axis pointing system, the elevation and tip mirror axes are permanently mounted with their rotation axes orthogonal to each other to eliminate gimbal lock over the hemisphere, to avoid high accelerations as the zenith or nadir pointing directions are approached, and to provide optimal two-axis beam pointing control.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTEGRATION INC

Controlling multiple modems in a wireless terminal using energy-per-bit determinations

InactiveUS7020484B2Maximize communication bandwidthLow costPower managementError preventionTelecommunicationsModem device

A mobile wireless terminal (MWT) includes multiple wireless modems. The multiple modems have their respective transmit outputs combined to produce an aggregate transmit output. The multiple modems can concurrently transmit data in a reverse link direction and receive data in a forward link direction. The MWT is constrained to operate under an aggregate transmit power limit. Each of the multiple modems has an individual transmit limit related to the aggregate transmit power limit. An MWT controller controls the total number of modems that transmit data at any given time, based on an average energy-per-transmitted bit, or alternatively, individual energy-per-transmitted bits of the modems.

Owner:QUALCOMM INC

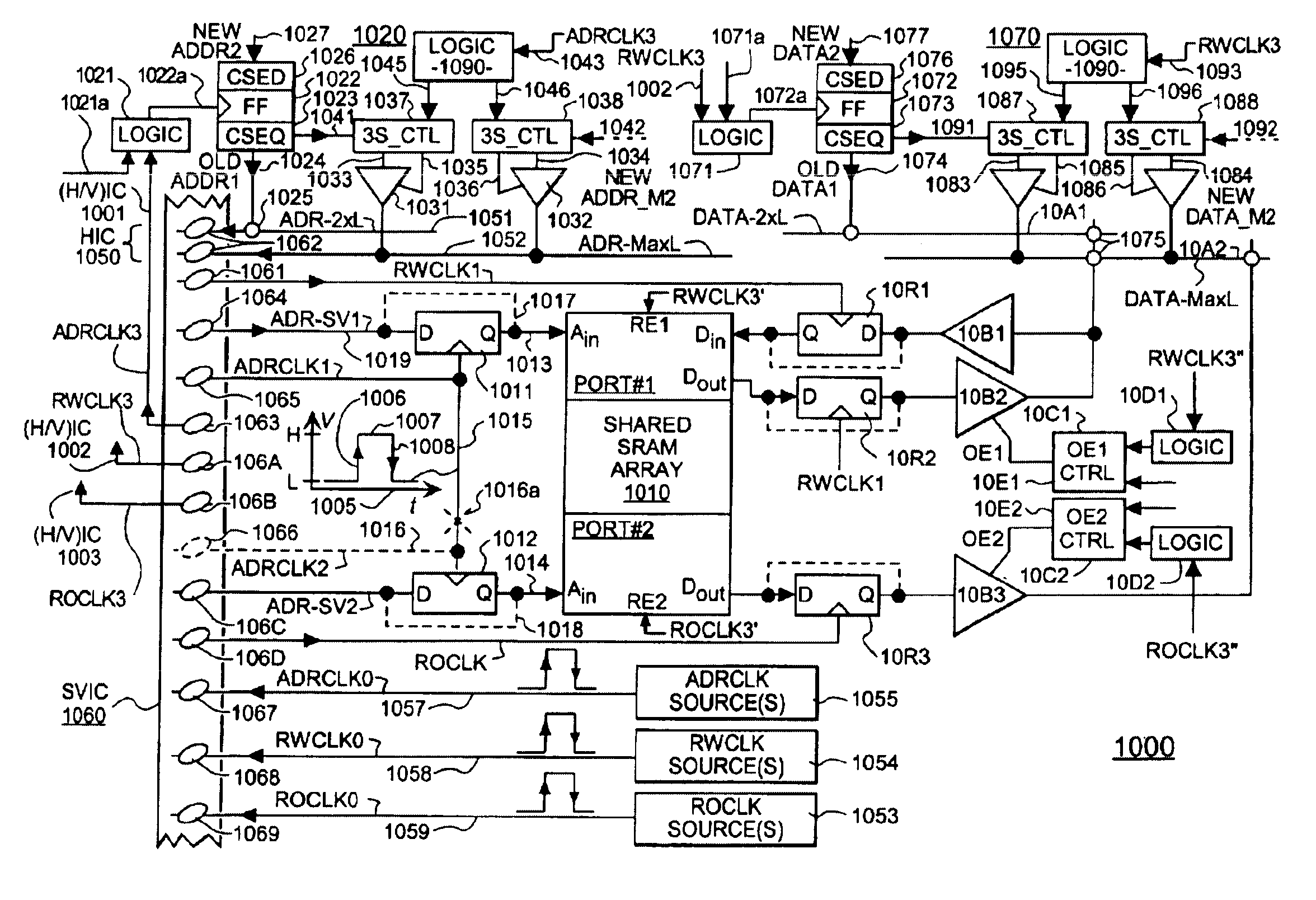

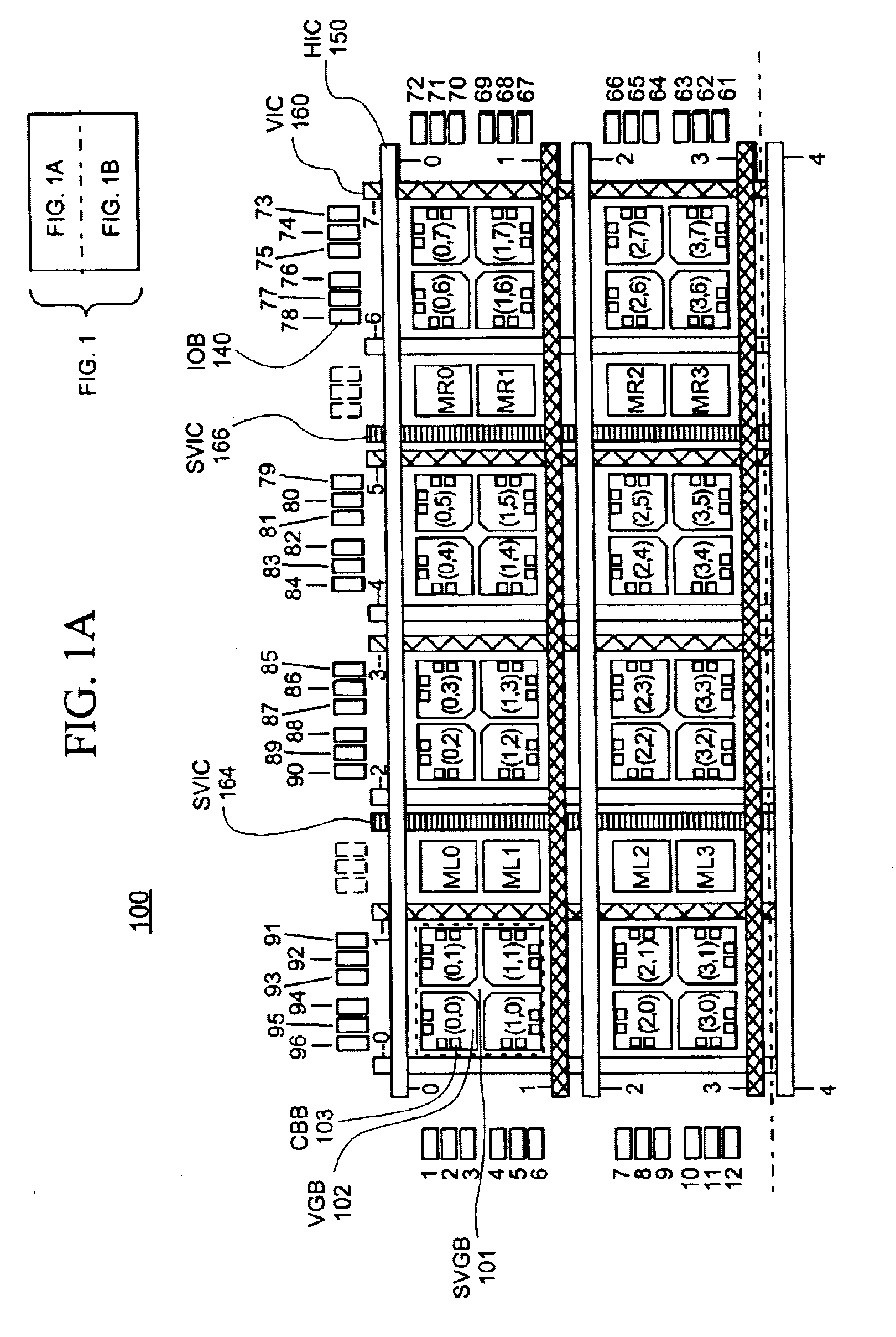

FPGA integrated circuit having embedded sram memory blocks with registered address and data input sections

InactiveUSRE39510E1Maximize bandwidthIncrease system bandwidthLogic circuits using elementary logic circuit componentsComputation using denominational number representationField-programmable gate arrayEmbedded memory

A field-programmable gate array device (FPGA) having plural rows and columns of logic function units (VGB's) further includes a plurality of embedded memory blocks, where each memory block is embedded in a corresponding row of logic function units. Each embedded memory block has a registered address port for capturing received address signals in response to further-received, address-validating clock signals. Interconnect resources are provided for conveying the address-validating clock signals to address-changing circuitry so that a next address can be generated safely in conjunction with the capturing by the registered address port of a previous address signal.

Owner:LATTICE SEMICON CORP

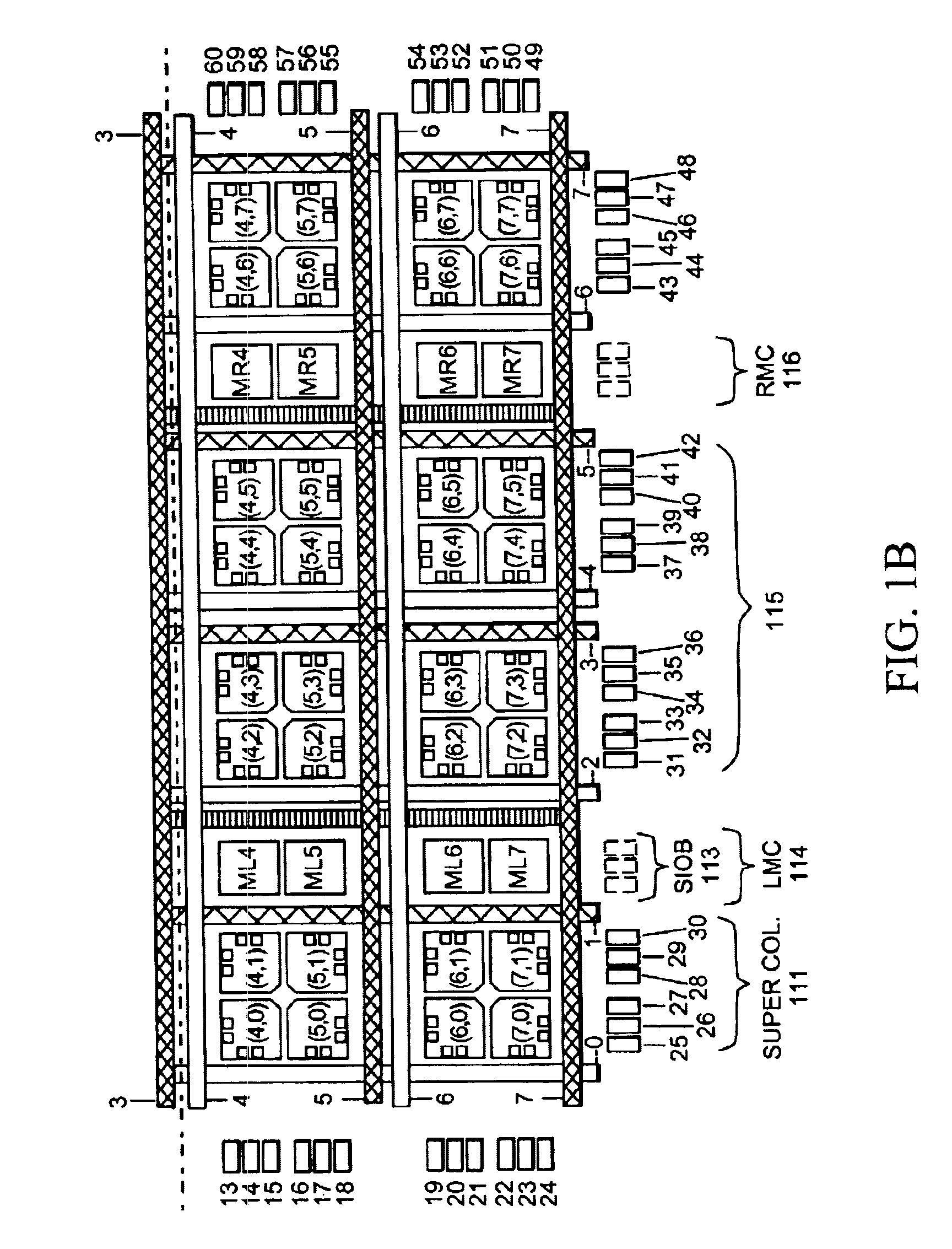

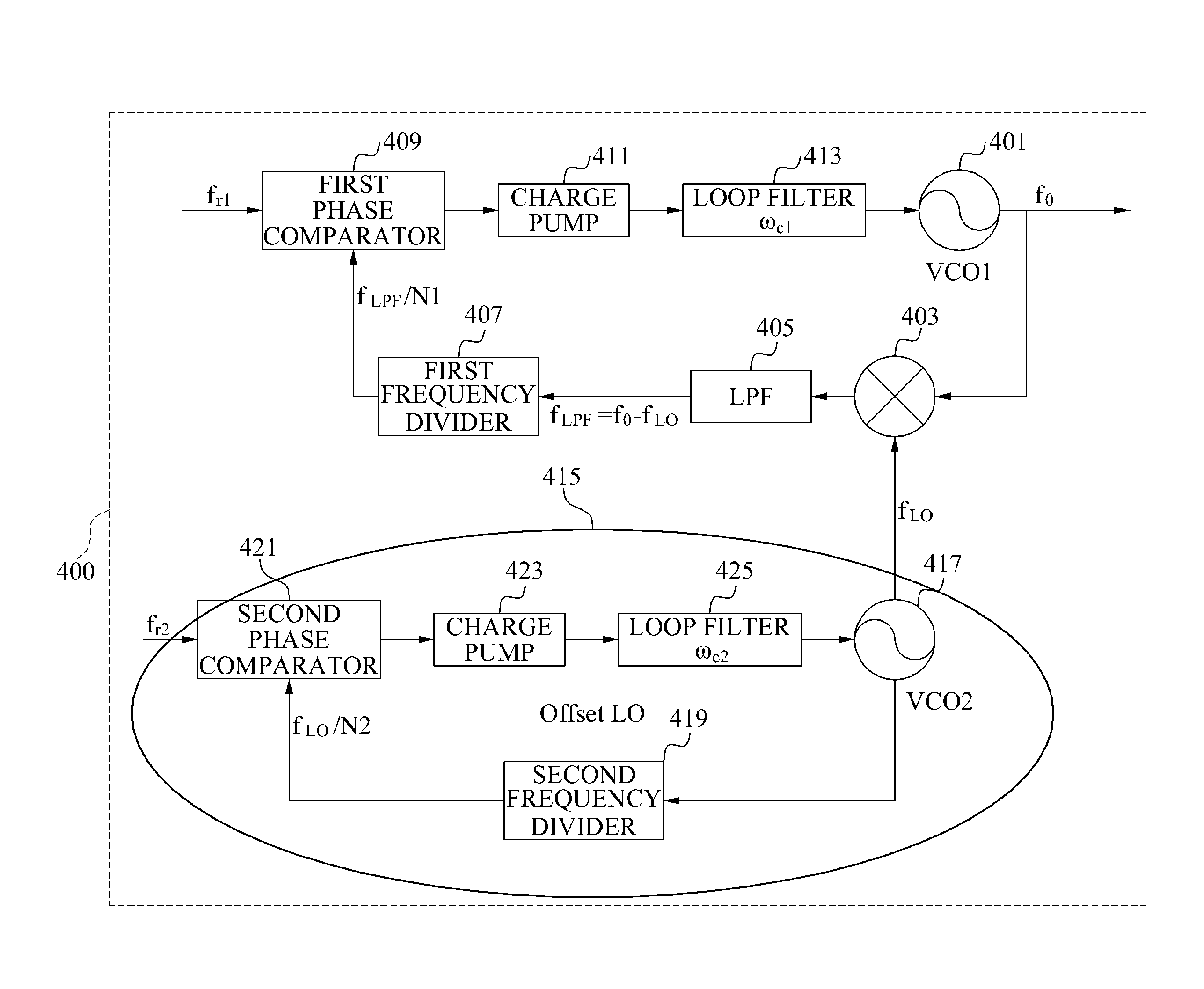

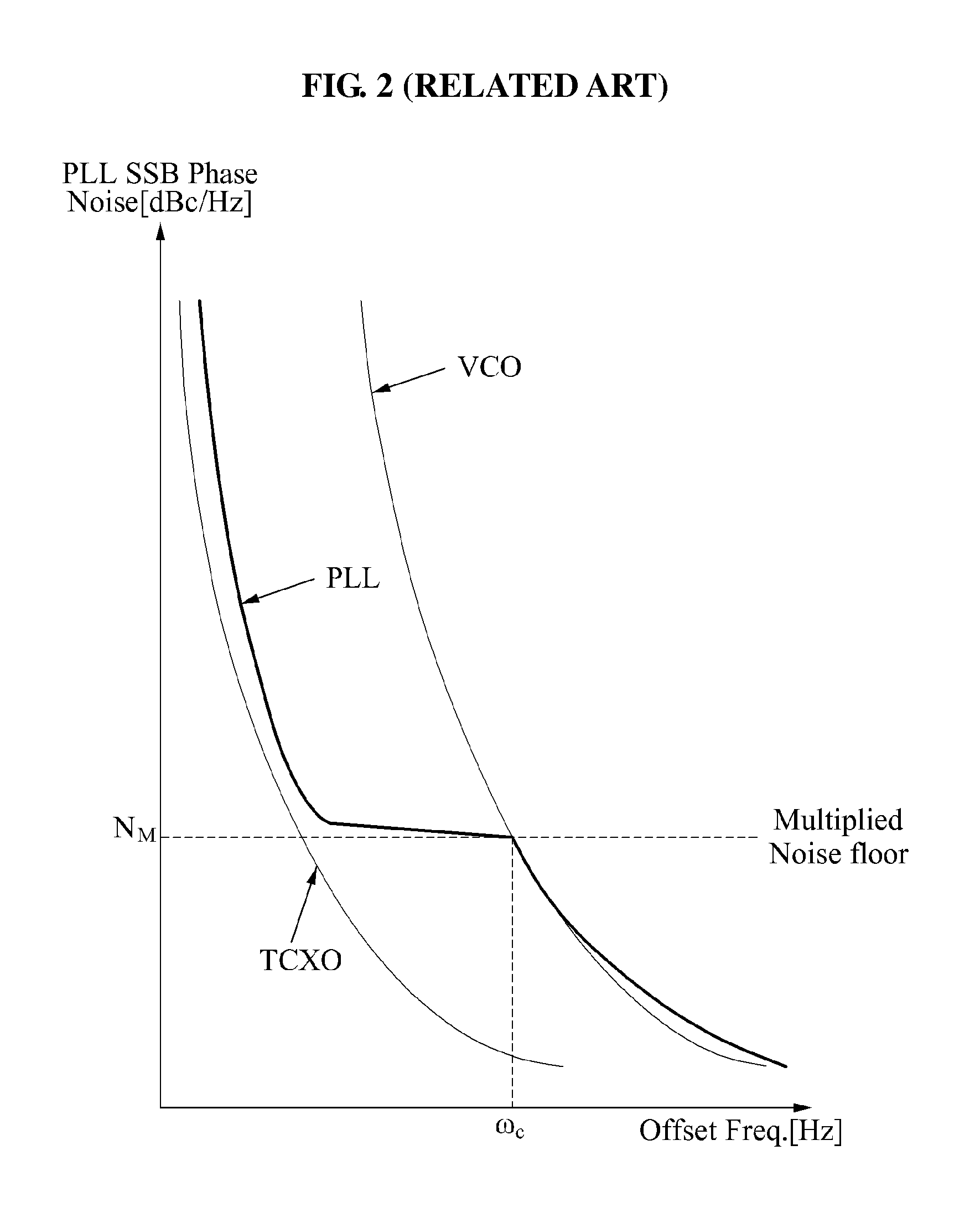

Phase locked loop (PLL) apparatus and operating method of pll apparatus

InactiveUS20150171874A1Reduce output frequencyReduce the ratioPulse automatic controlPhase differenceEngineering

Provided are a phase locked loop (PLL) apparatus and an operating method of the PLL apparatus including a PLL unit to provide a fixed frequency signal, a converter to convert, using the fixed frequency signal, a frequency of a first signal oscillated by a first voltage-controlled oscillator (VCO) based on a first control voltage, a first frequency divider to divide the converted frequency of the first signal, and a first phase comparator to compare the divided frequency of the first signal to an input first reference frequency and detect a first phase difference, wherein the first VCO may adjust the first control voltage based on the detected first phase difference to equalize the divided frequency of the first signal to the first reference frequency.

Owner:ELECTRONICS & TELECOMM RES INST

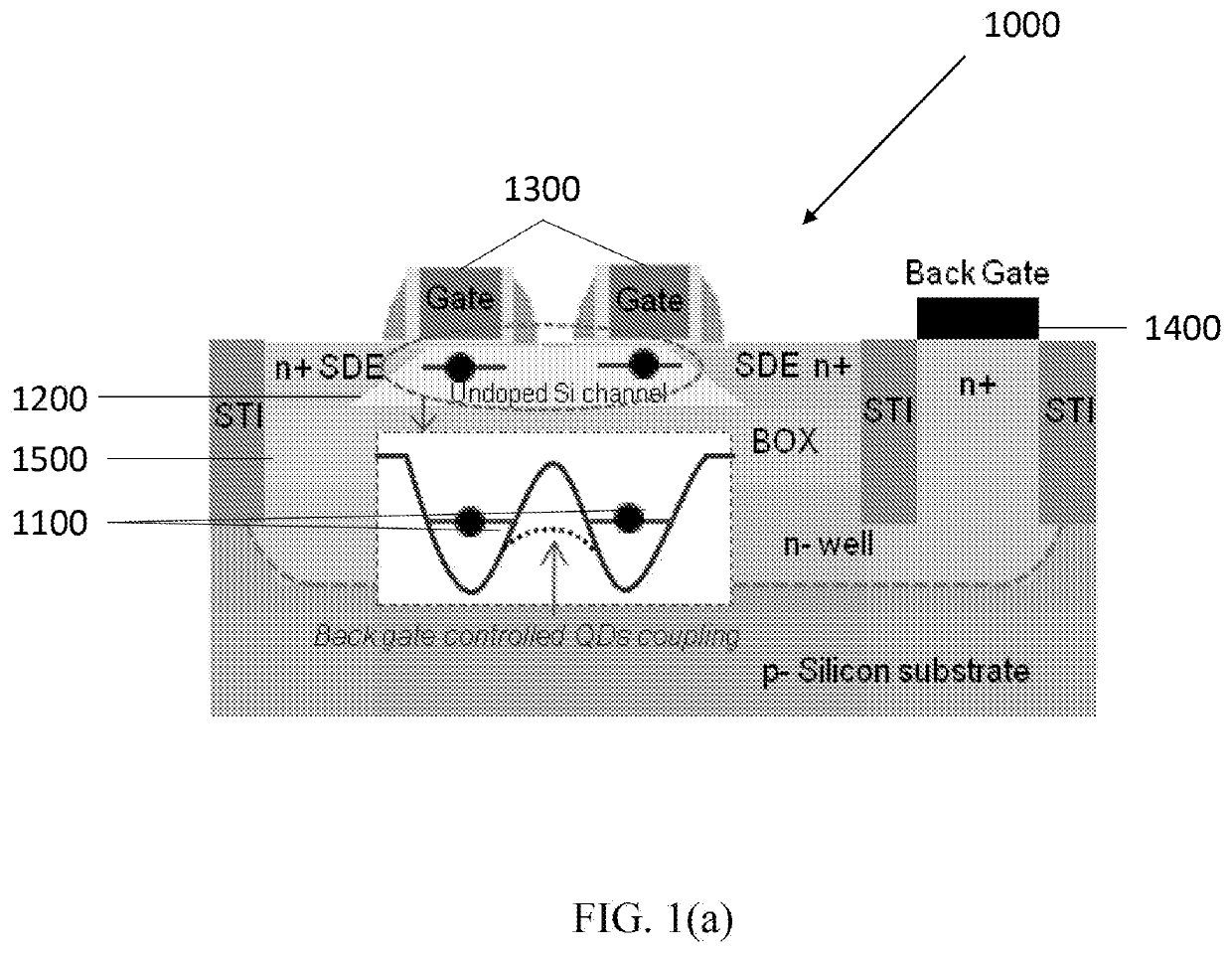

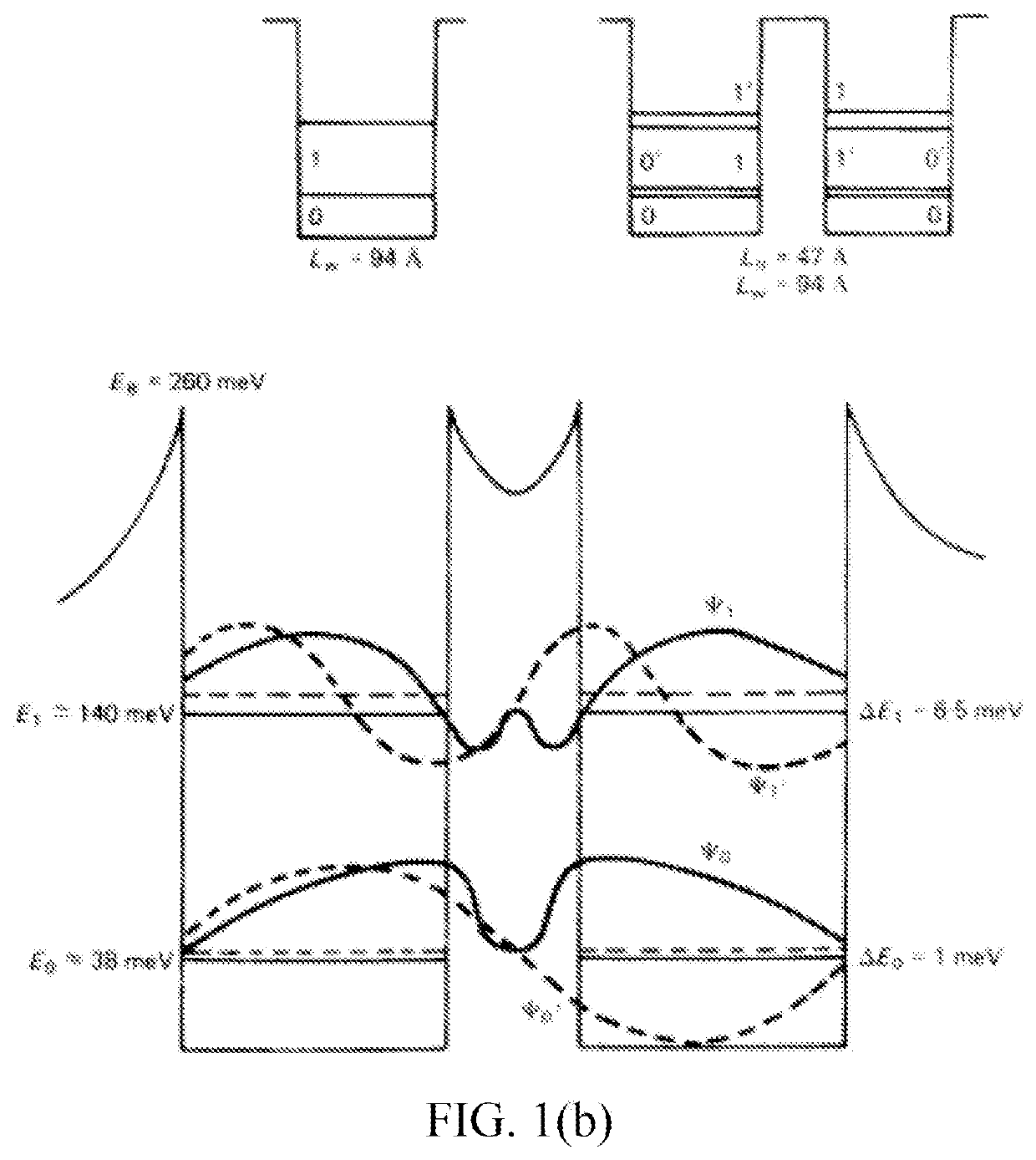

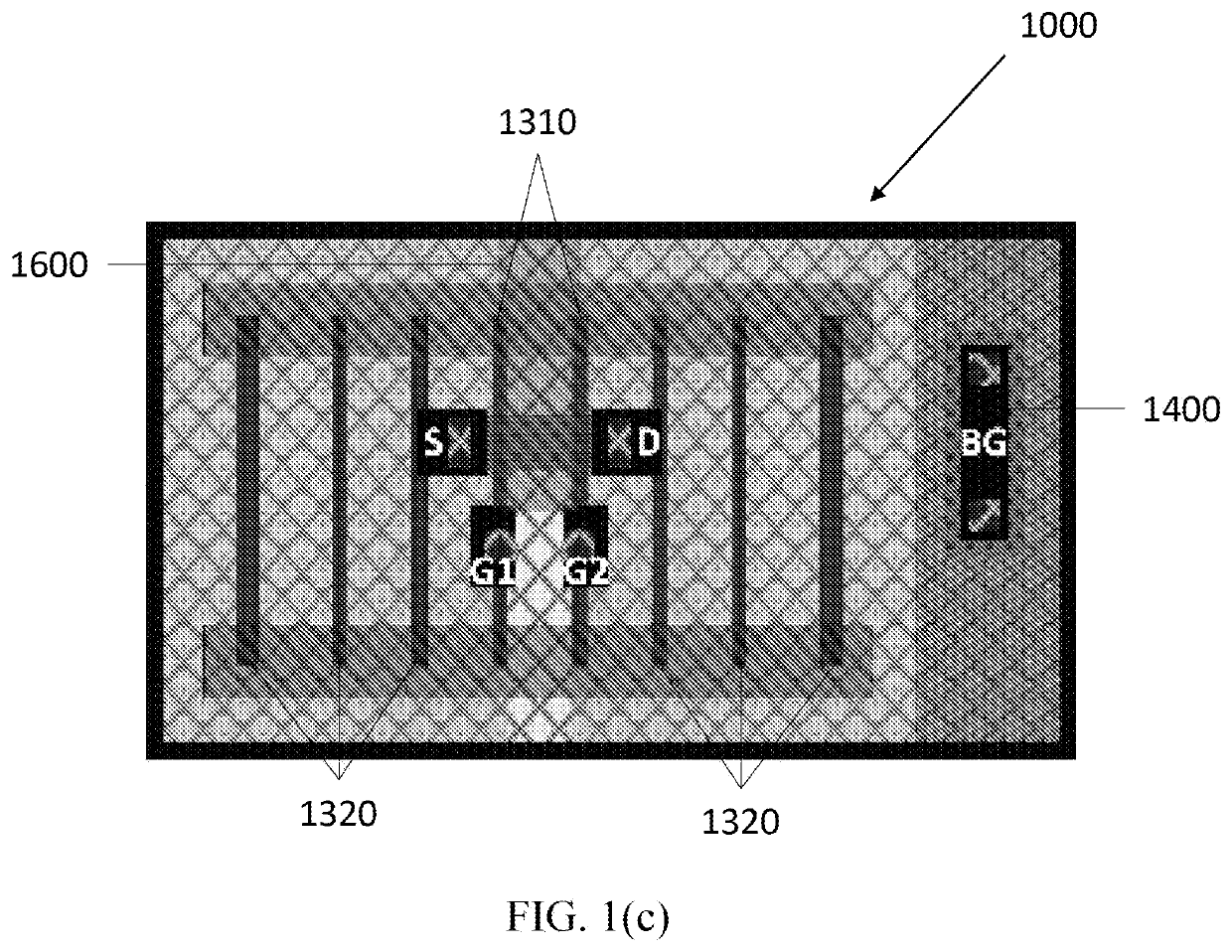

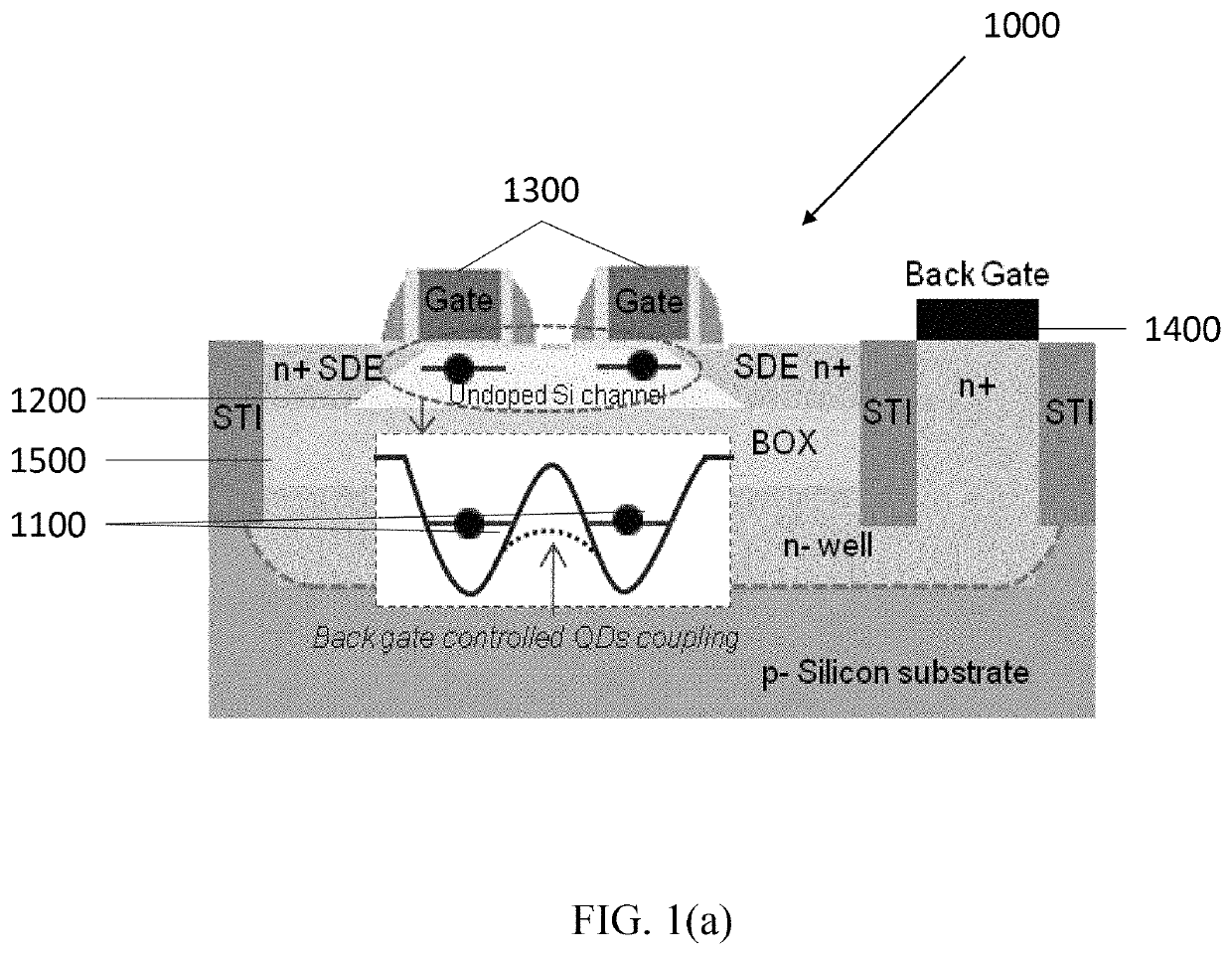

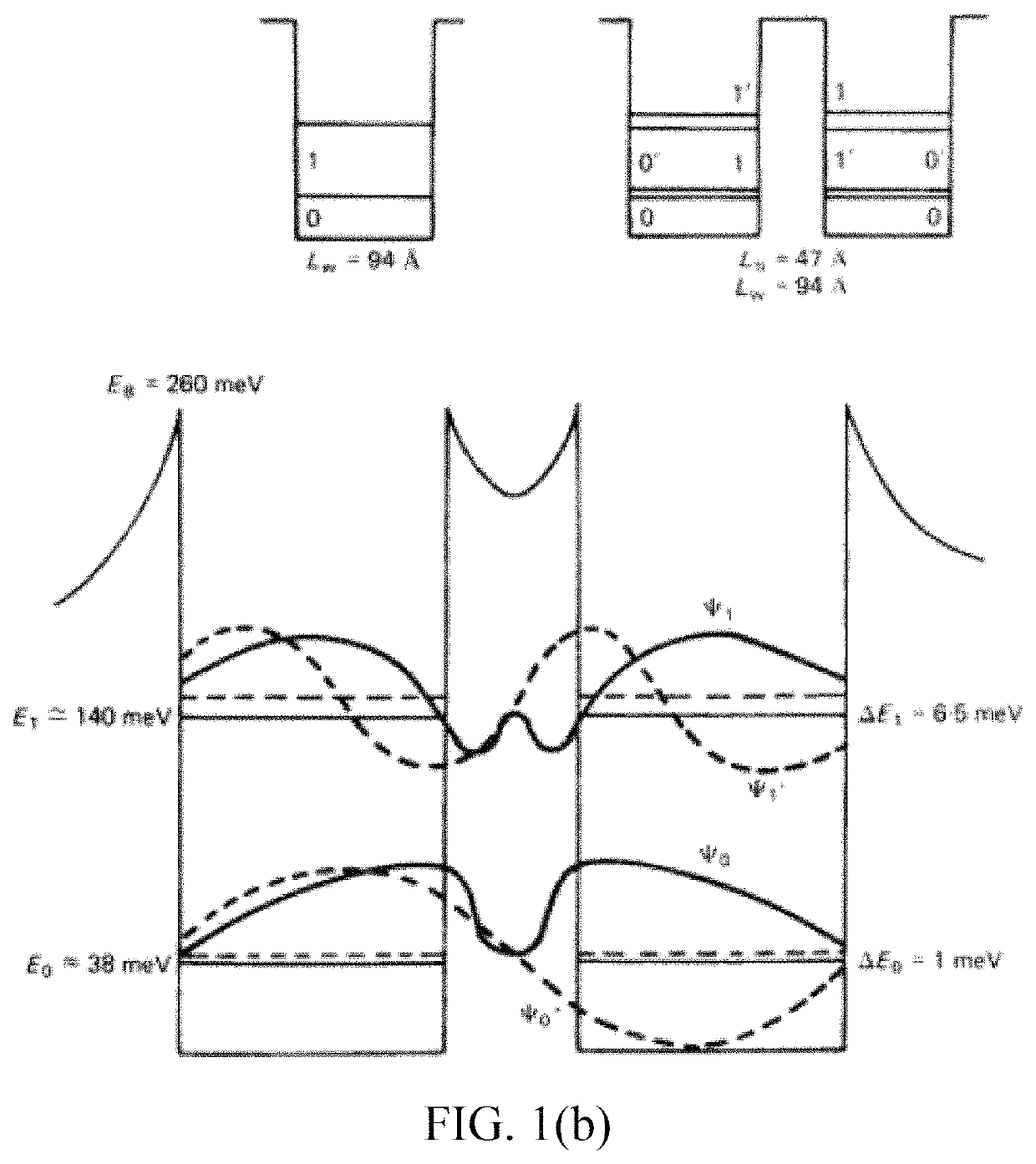

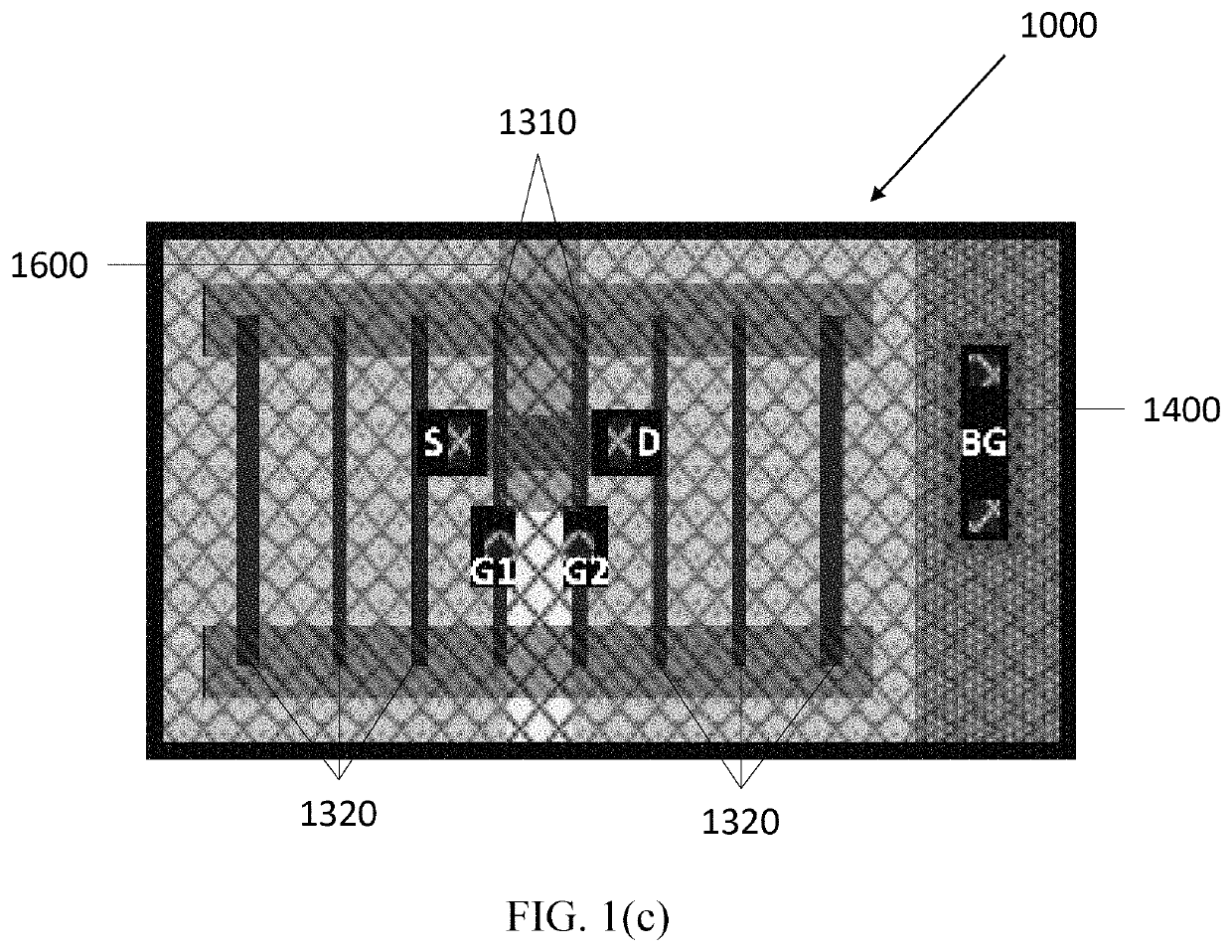

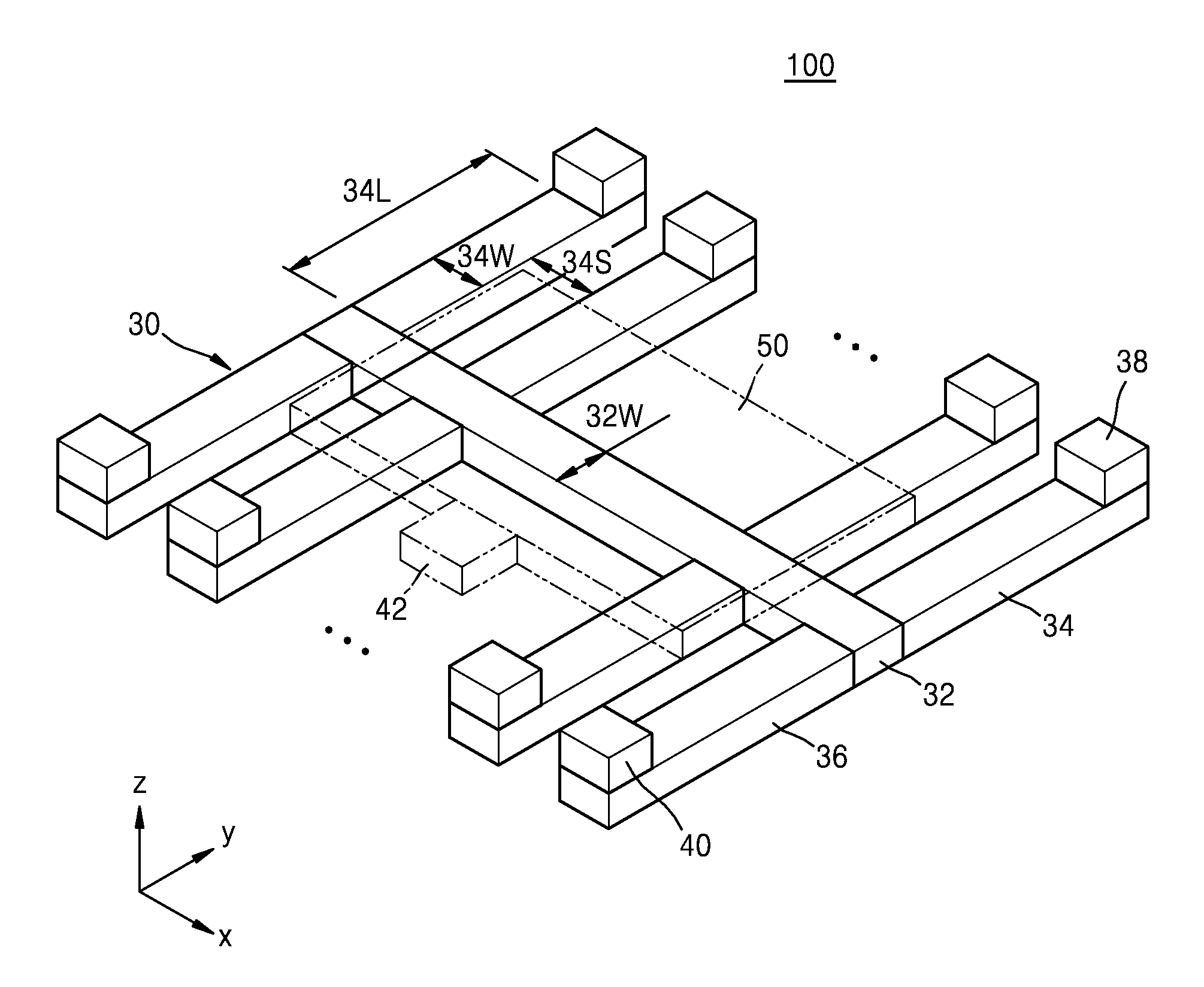

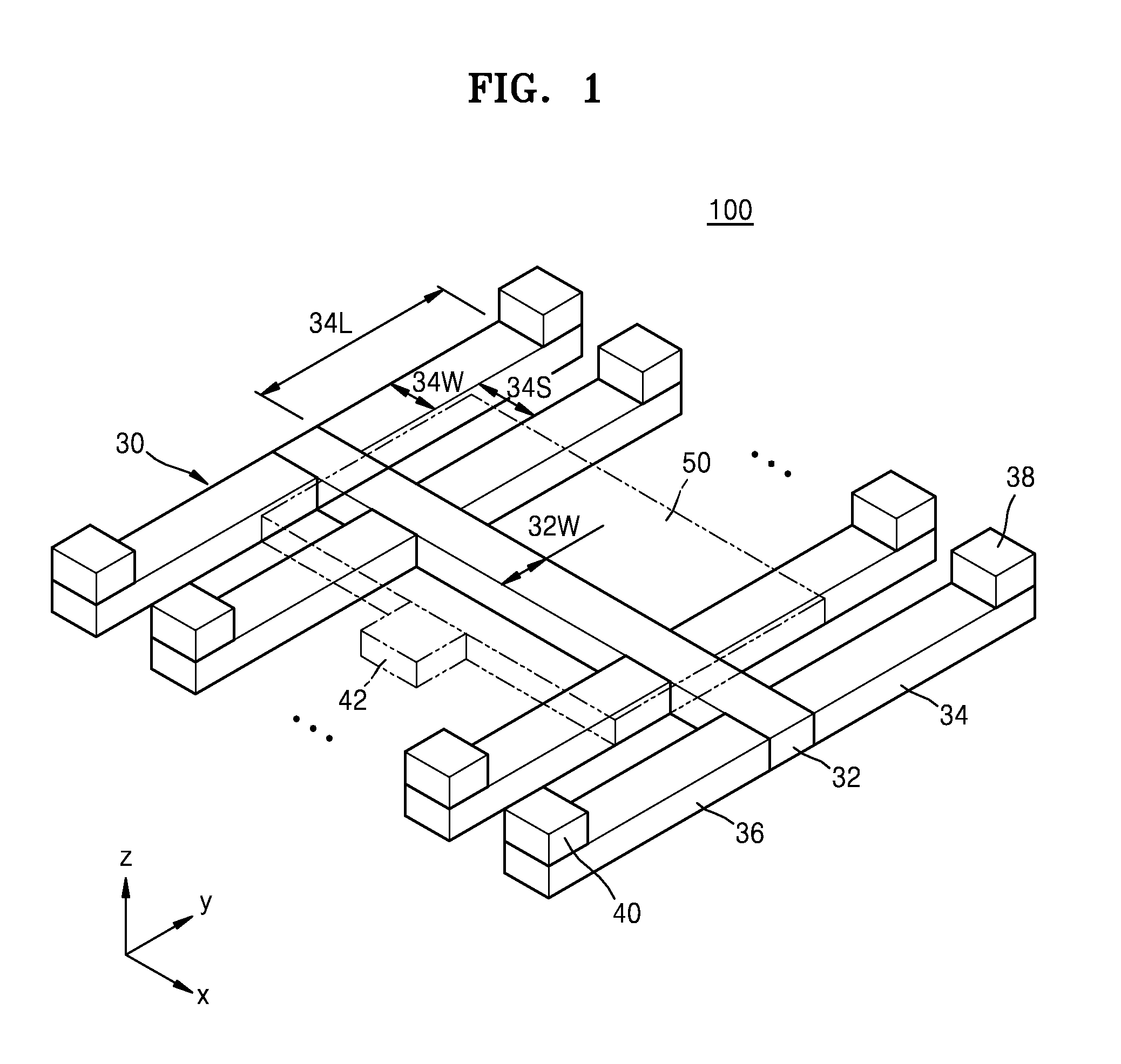

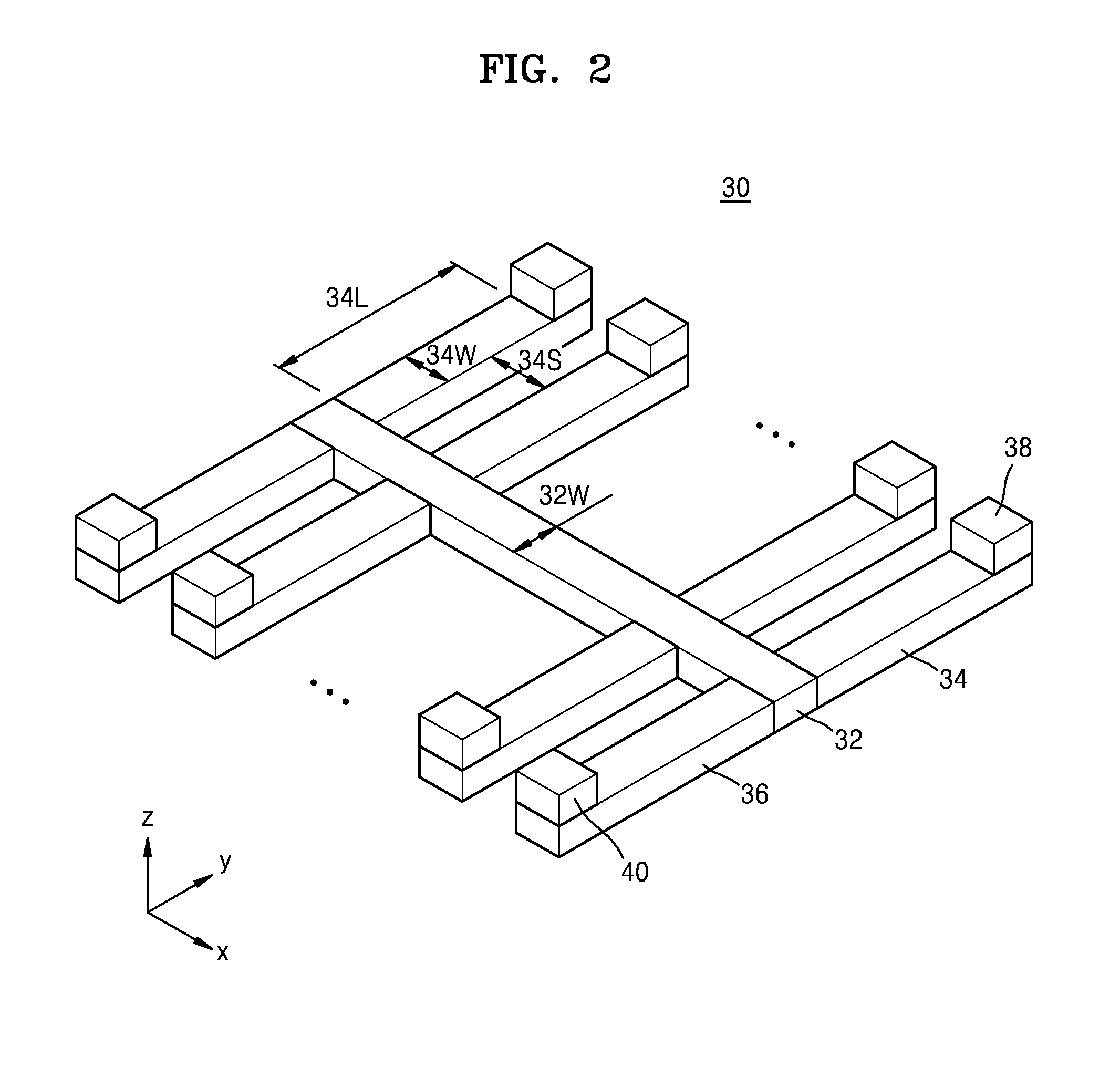

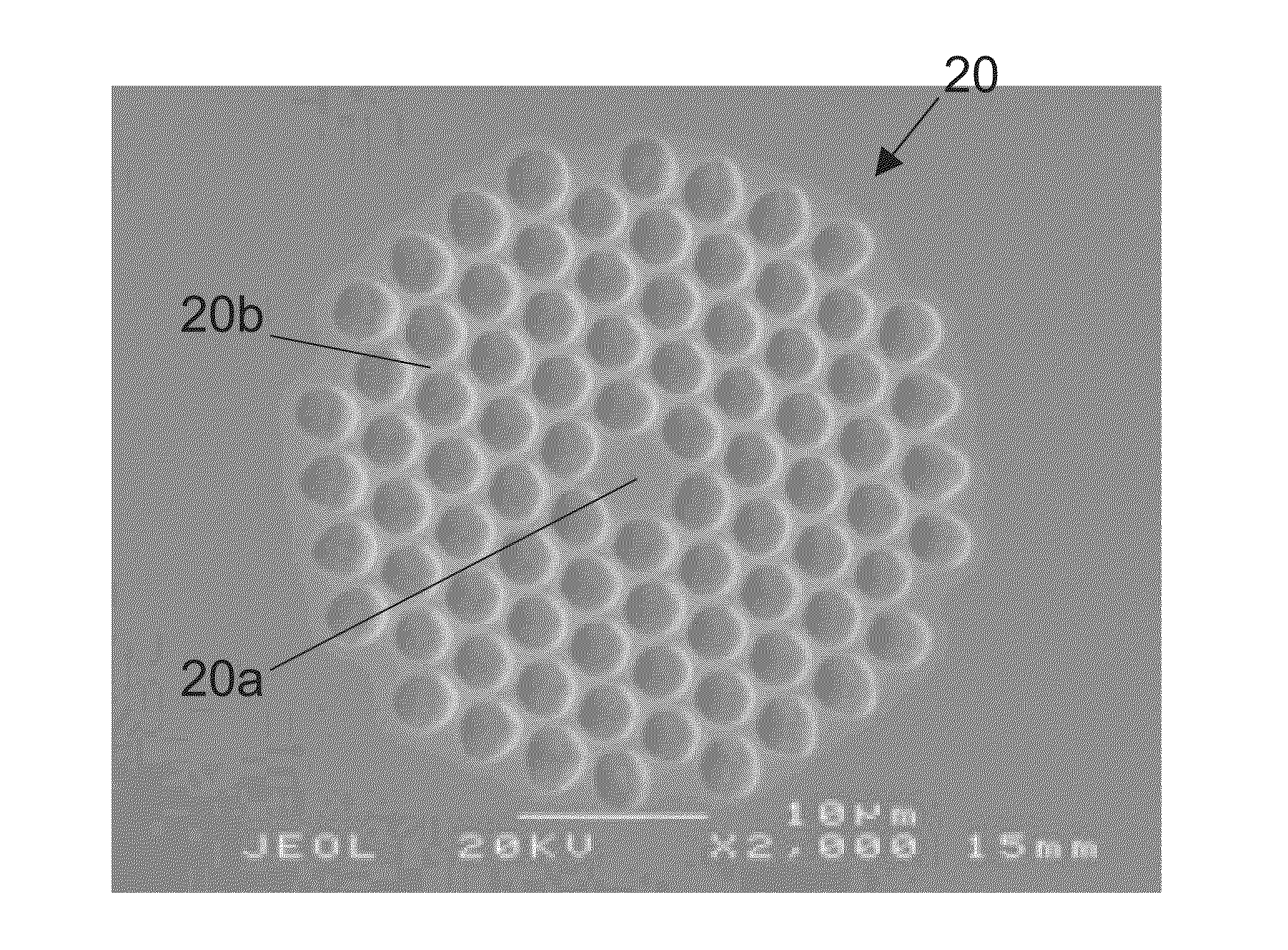

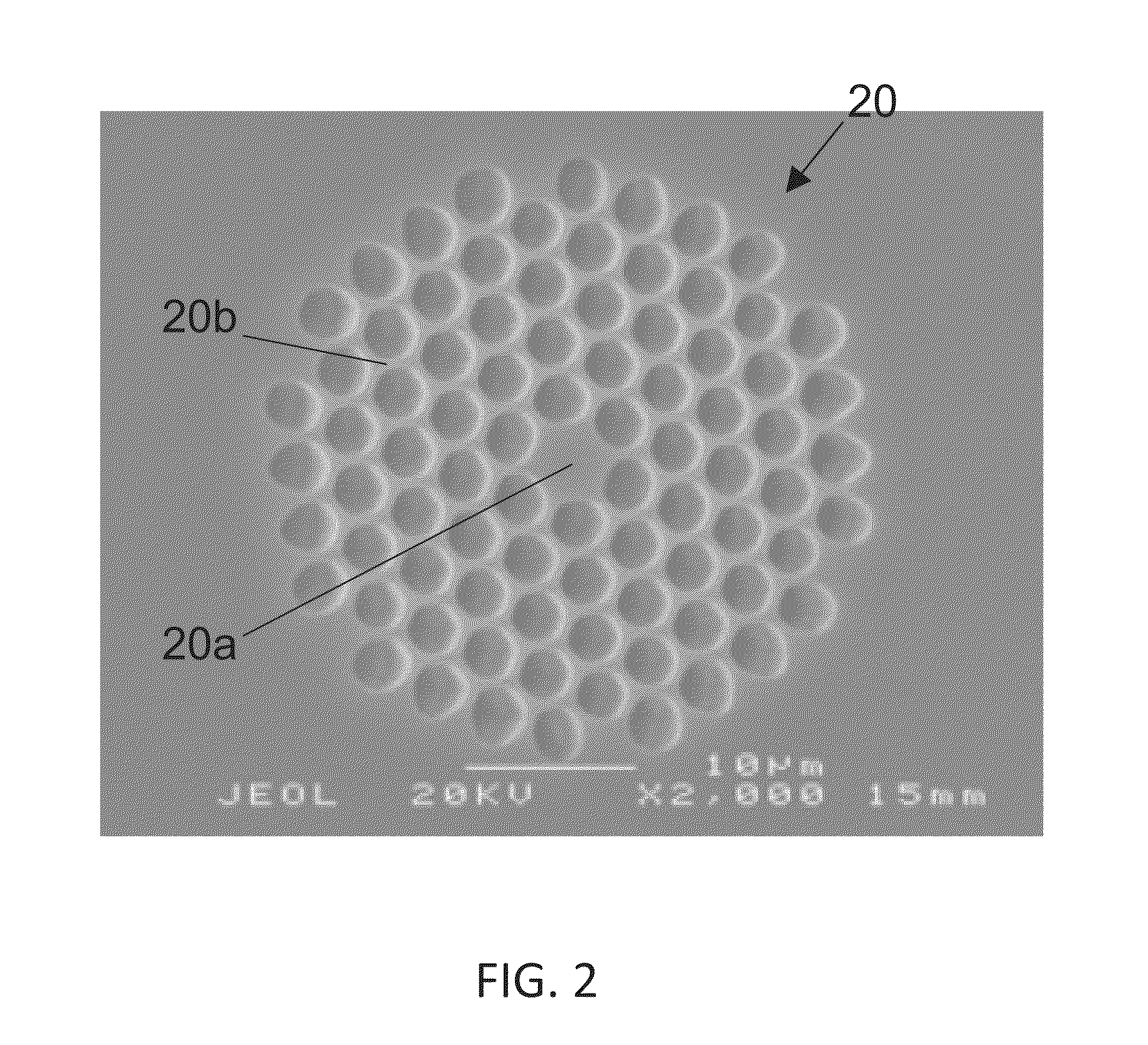

Monolithic qubit integrated circuits

ActiveUS20200185512A1Avoid qubitsMaximize spin-readout bandwidthTransistorQuantum computersMOSFETHemt circuits

Described is a monolithic integrated circuit for use in quantum computing based on single and multiple coupled quantum dot electron- and hole-spin qubits monolithically integrated with the mm-wave spin manipulation and readout circuitry in commercial complementary metal-oxide-semiconductor (CMOS) technology. The integrated circuit includes a plurality of n-channel or p-channel metal-oxide-semiconductor field-effect transistor (MOSFET) cascodes each including a single-spin qubit or two coupled quantum dot qubits formed in an undoped semiconductor film adjacent at least one top gate. There is also a back gate formed in a silicon substrate adjacent a buried oxide layer or the at least one top gate, where the back gate controls the electron or hole entanglement and exchange interaction between the two coupled quantum dot qubits. The monolithic integrated circuits described may be used for monolithically integrated semiconductor quantum processors for quantum information processing.

Owner:THE GOVERNINIG COUNCIL OF THE UNIV OF TORANTO

Monolithic qubit integrated circuits

ActiveUS11171225B2Ultra-low input capacitanceAvoid overloading qubitsTransistorQuantum computersMOSFETHemt circuits

Described is a monolithic integrated circuit for use in quantum computing based on single and multiple coupled quantum dot electron- and hole-spin qubits monolithically integrated with the mm-wave spin manipulation and readout circuitry in commercial complementary metal-oxide-semiconductor (CMOS) technology. The integrated circuit includes a plurality of n-channel or p-channel metal-oxide-semiconductor field-effect transistor (MOSFET) cascodes each including a single-spin qubit or two coupled quantum dot qubits formed in an undoped semiconductor film adjacent at least one top gate. There is also a back gate formed in a silicon substrate adjacent a buried oxide layer or the at least one top gate, where the back gate controls the electron or hole entanglement and exchange interaction between the two coupled quantum dot qubits. The monolithic integrated circuits described may be used for monolithically integrated semiconductor quantum processors for quantum information processing.

Owner:THE GOVERNING COUNCIL OF THE UNIV OF TORONTO

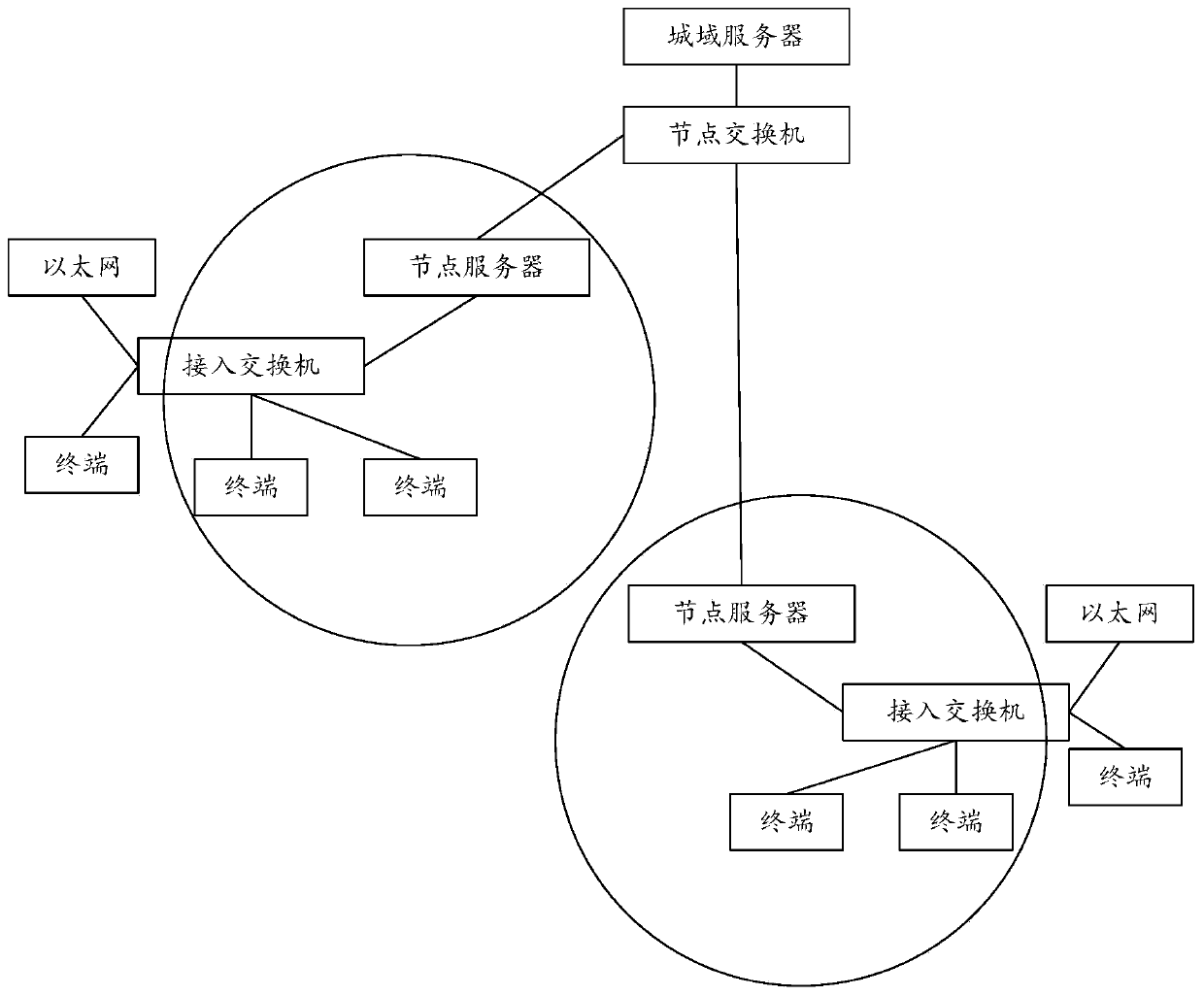

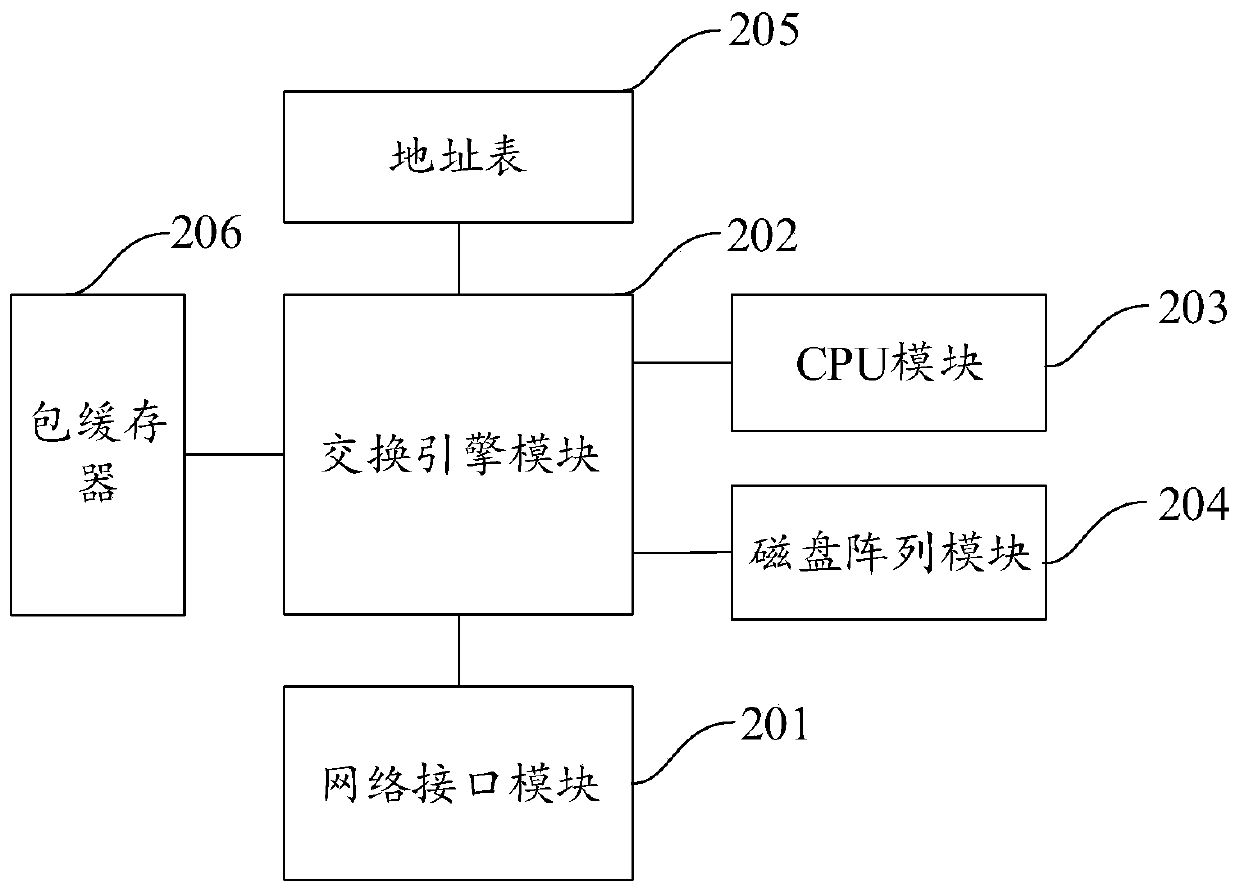

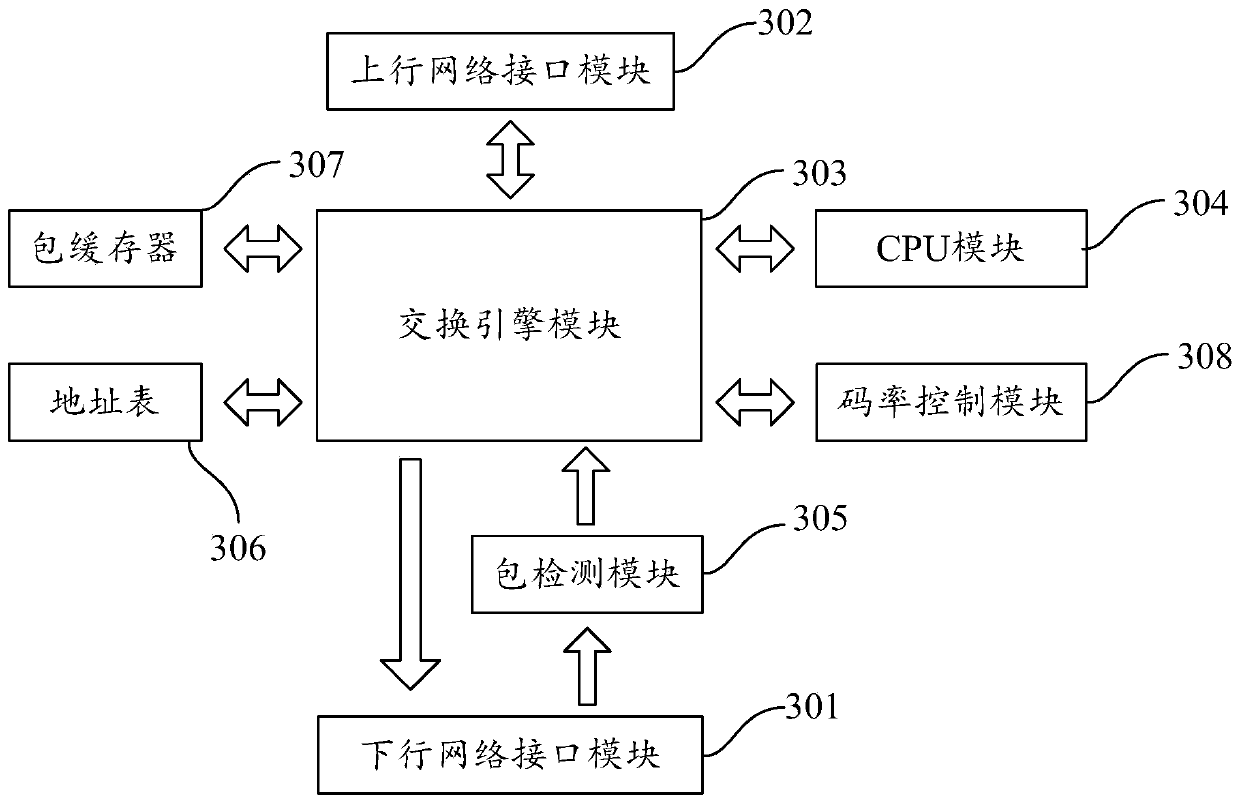

Data packet sending rate processing method and system

InactiveCN109889380ANo packet lossMaximize bandwidthNetwork traffic/resource managementData switching networksTelecommunicationsNetwork packet

The embodiment of the invention provides a data packet sending rate processing method and system, and the method comprises: a sending end sending a data packet to a receiving end according to an initial sending rate, and the initial sending rate comprises a first number of data packets sent in a unit time; the sending end receiving a second number of response messages which are returned by the receiving end and carry the data packets received by the receiving end, and judges whether the second number is equal to the first number or not; when the second number is equal to the first number, thesending end linearly increases the initial sending rate to obtain a first sending rate until the first sending rate meets a first requirement; when the second number is smaller than the first number or the first sending rate meets the first requirement, the sending end exponentially reduces the initial sending rate or the first sending rate to obtain a second sending rate until the second sendingrate meets the second requirement. According to the embodiment of the invention, the data packet sent to the receiving end by the sending end is prevented from being lost, and the bandwidth of the articulated naturality web link is utilized as much as possible.

Owner:VISIONVERA INFORMATION TECH CO LTD

Chip antenna for near field communication and method of manufacturing the same

ActiveUS20160118721A1Maximize antenna efficiencyMaximize bandwidth efficiencyAntenna arraysAntenna feed intermediatesDipole antennaAntenna element

Provided are chip antennas for near field communication and methods of manufacturing the chip antennas. A chip antenna for near field communication includes a substrate; a first antenna element on the substrate; and a second antenna element on the first antenna element. The substrate, the first antenna element, and the second antenna element are included in a single chip. The first and second antenna elements are formed outside the chip. The substrate is a lower layer including a plurality of devices. The first antenna element is a metal structure having a fish bone shape. The second antenna element is a dipole antenna.

Owner:SAMSUNG ELECTRONICS CO LTD +1

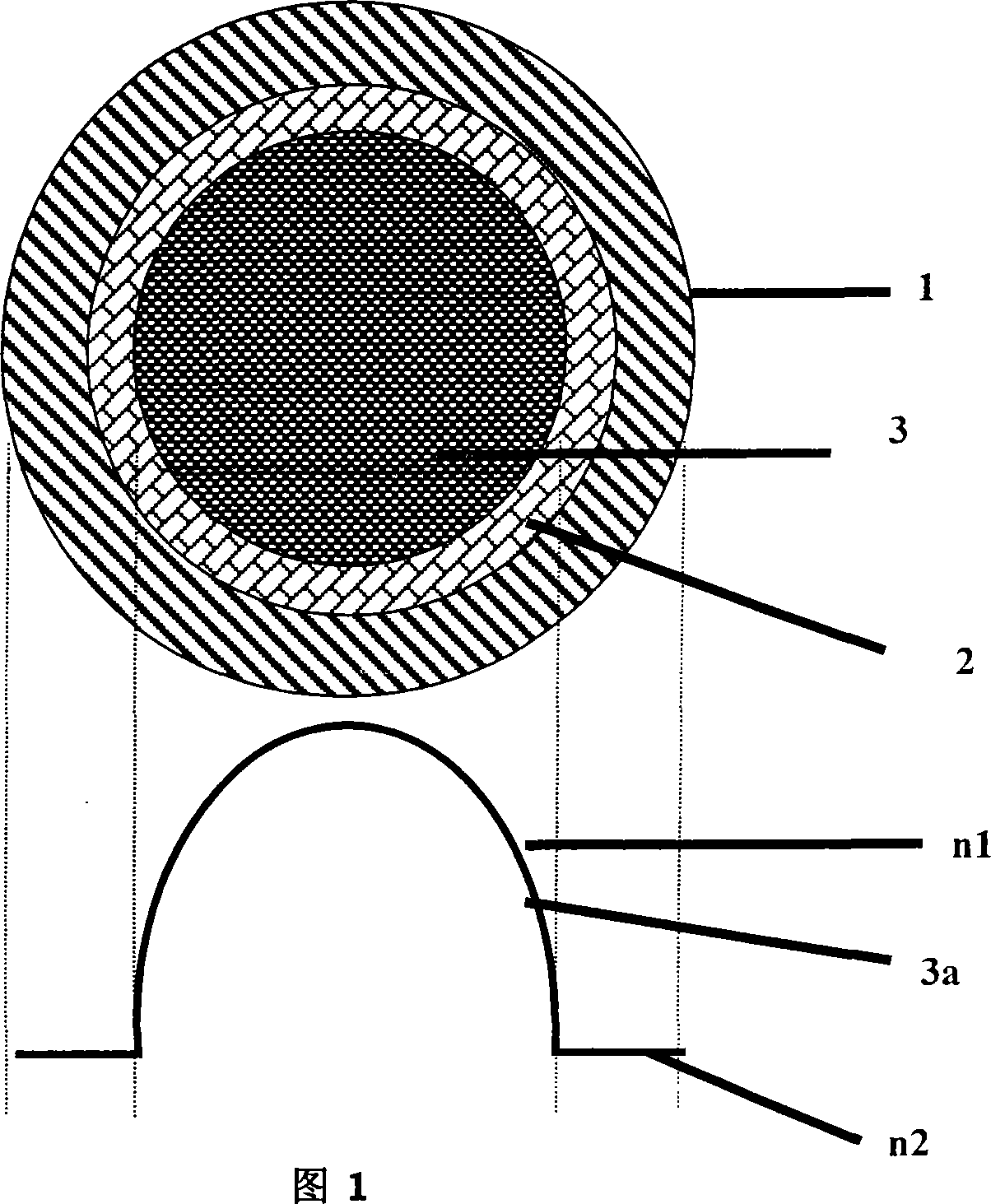

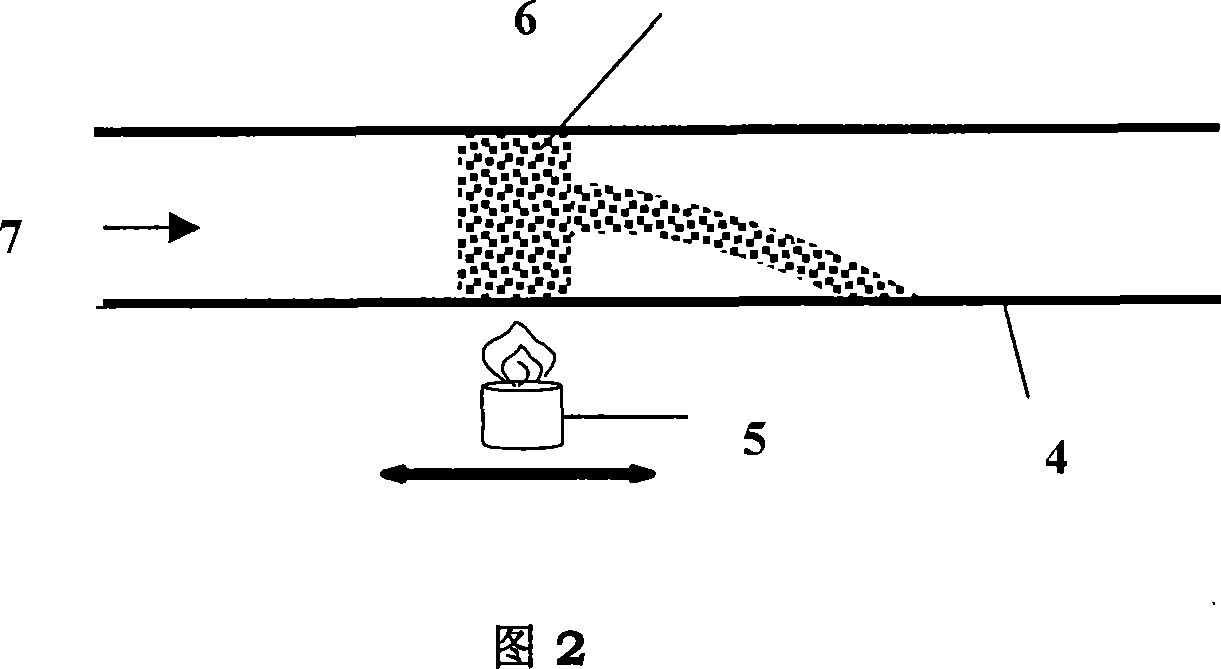

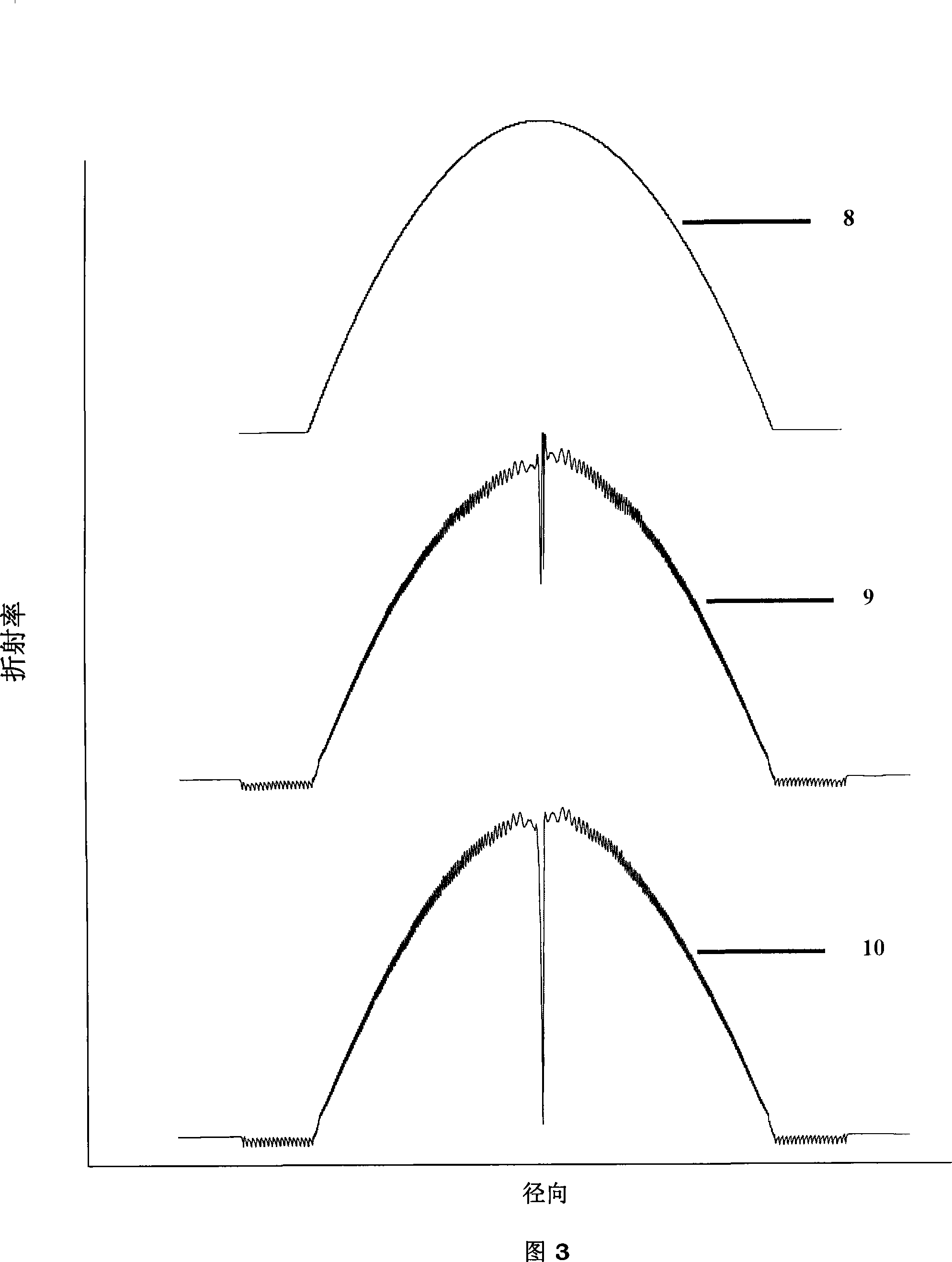

Fibre-optical with high wide-band and manufacturing method thereof

InactiveCN101052596AMaximize bandwidthHigh technical efficiencyGlass making apparatusOptical light guidesRefractive index profileNucleic acid sequencing

This invention relates to a novel protein, termed INSP152, herein identified as a secreted protein, in particular, as a MAM domain containing protein and to the use of this protein and nucleic acid sequence from the encoding gene in the diagnosis, prevention and treatment.

Owner:STERLITE OPTICAL TECH

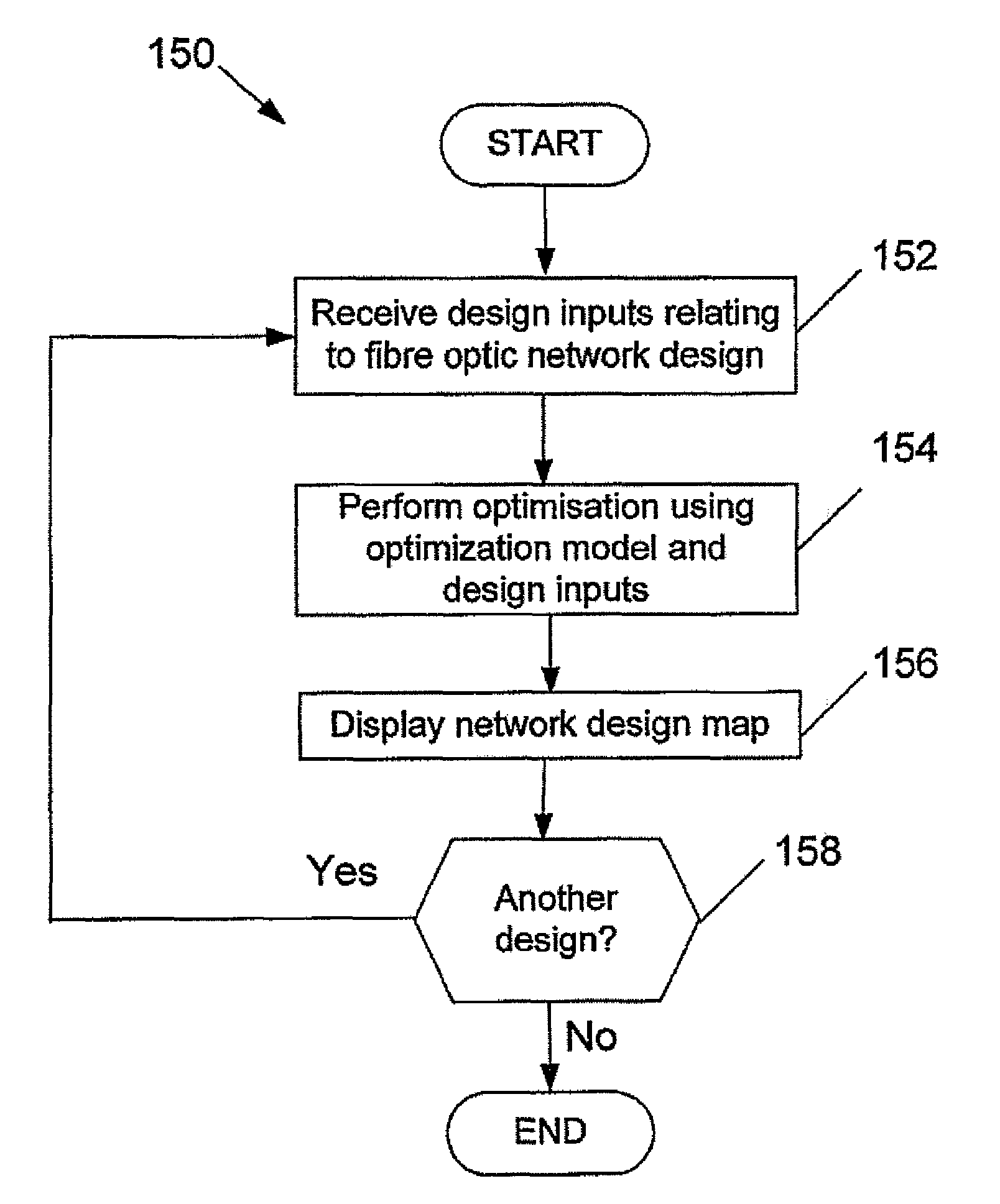

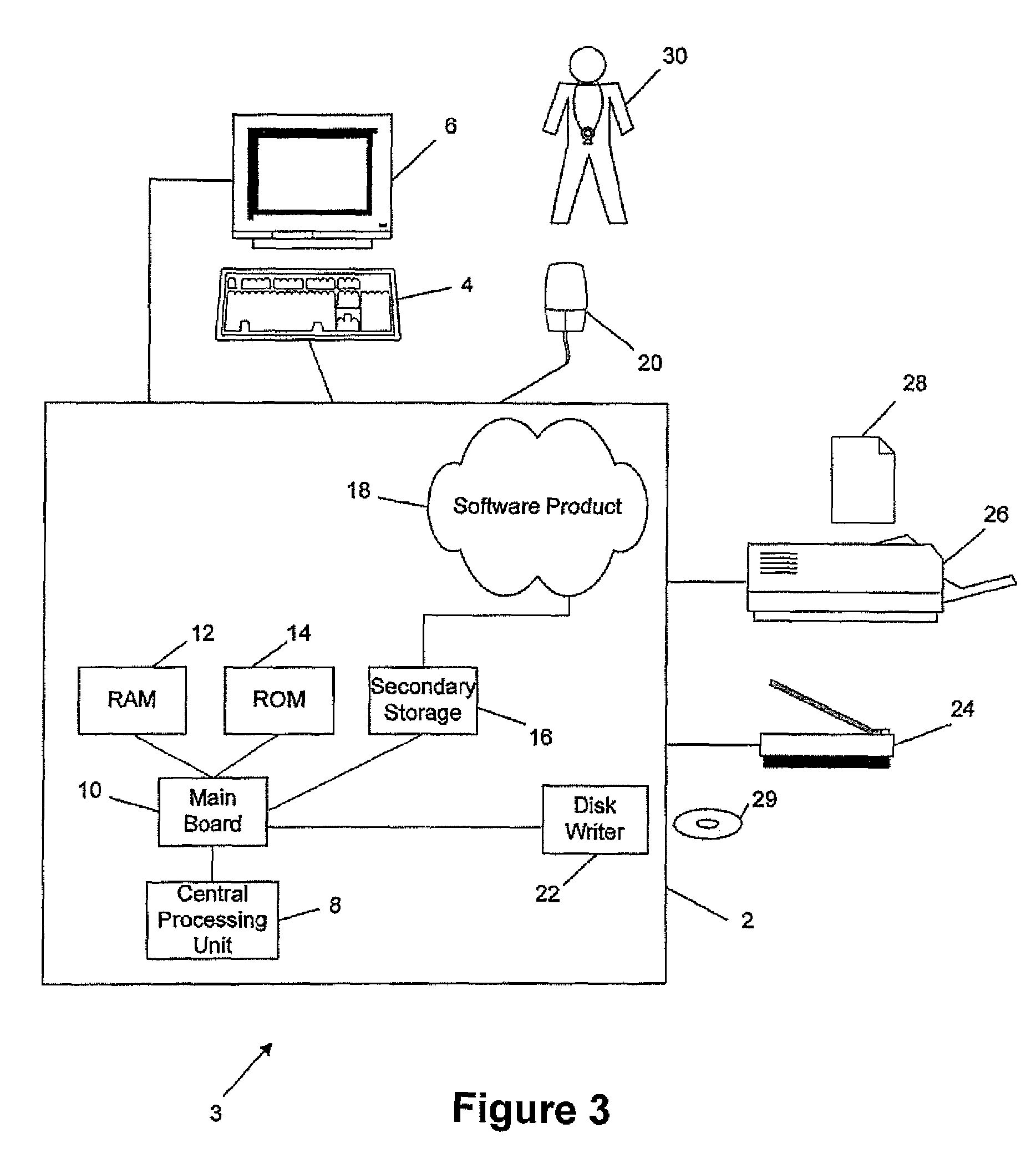

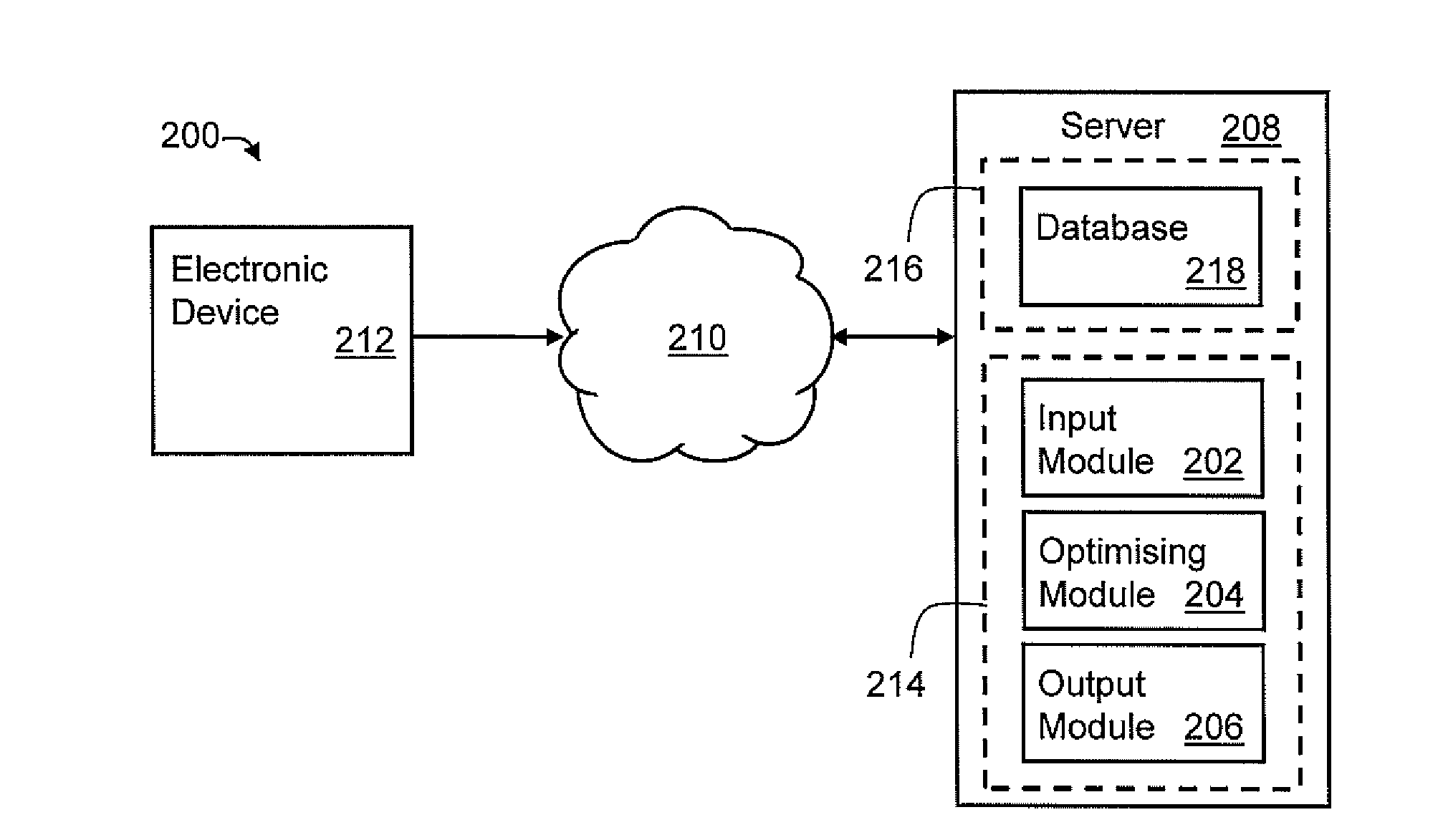

Fibre optic network design method

ActiveUS9323872B2Low costHarmful to environmentGeometric CADAnalogue computers for electric apparatusGeolocationEngineering

A system and method of designing a fiber optic network for a plurality of premises in a geographic area that has existing infrastructure is described. They include electronically receiving fiber optic network design inputs that include data indicative of a plurality of nodes in the fiber optic network and data indicative of arcs extending between said nodes in the fiber optic network based on allocated bandwidth for said premises in the geographic area, electronically receiving existing infrastructure design inputs comprising data indicative of said existing infrastructure that can be used as geographic locations for said nodes and said arcs in the fiber optic network, electronically generating design outputs by optimizing geographic locations of said nodes and said arcs in the fiber optic network using said fiber optic network design inputs and said existing infrastructure inputs, and electronically outputting the design outputs.

Owner:BIARRI NETWORKS PTY LTD

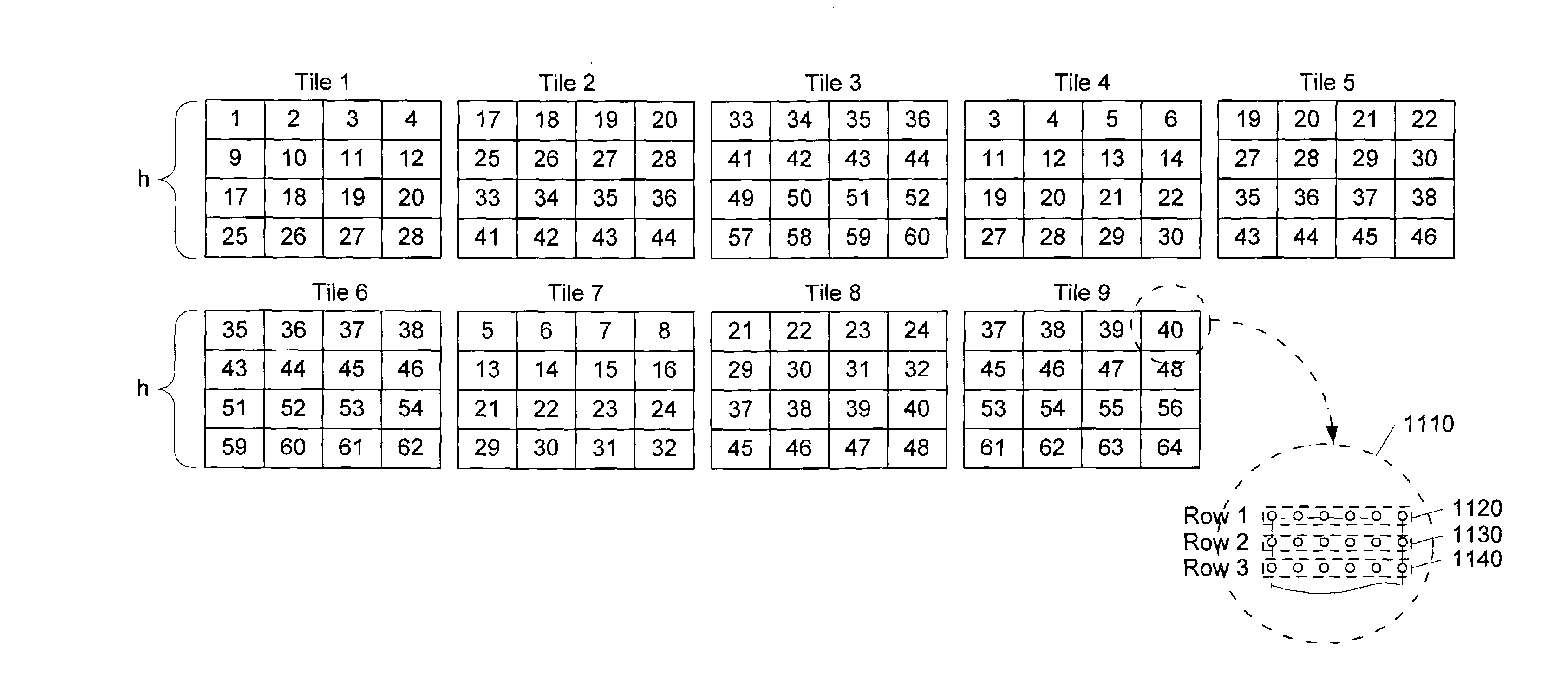

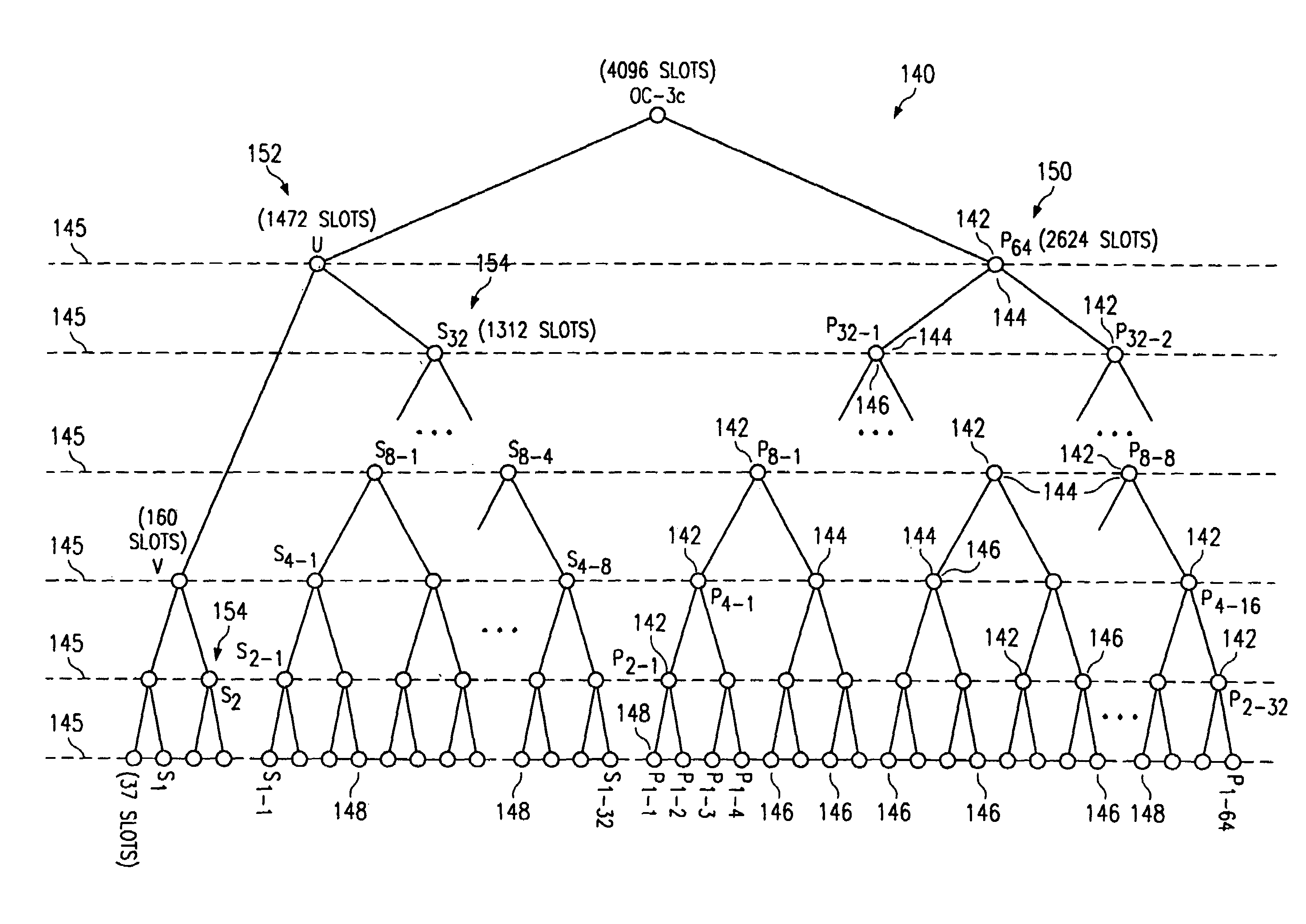

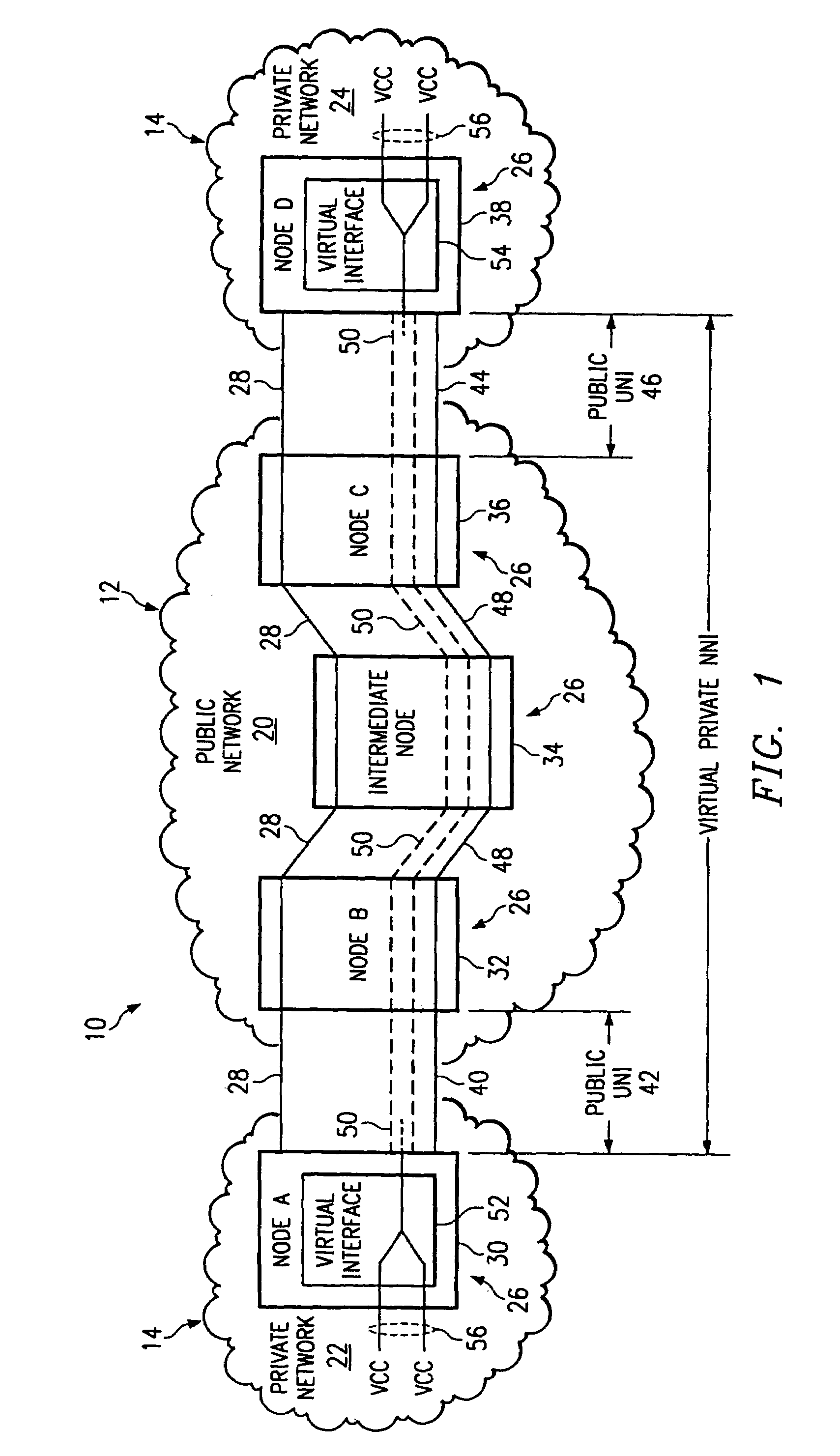

Transmission slot allocation method and map for virtual tunnels in a transmission line

InactiveUS7283487B2Eliminate and reduce disadvantageEliminate and reduce and problemTime-division multiplexData switching by path configurationEngineeringAssignment methods

In accordance with one embodiment of the present invention, a map of transmission slots for a port of a network element includes a plurality of hierarchical sets of port transmission slots. The hierarchical sets include a plurality of parent sets. Each parent set has its port transmission slots divided between a plurality of child sets. The child sets include interleaved port transmission slots.

Owner:FUJITSU LTD

Fibre Optic Network Design Method

ActiveUS20130289966A1Low costHarmful to environmentGeometric CADAnalogue computers for electric apparatusGeolocationEngineering

A system and method of designing a fibre optic network for a plurality of premises in a geographic area that has existing infrastructure is described. They include electronically receiving fibre optic network design inputs that include data indicative of a plurality of nodes in the fibre optic network and data indicative of arcs extending between said nodes in the fibre optic network based on allocated bandwidth for said premises in the geographic area, electronically receiving existing infrastructure design inputs comprising data indicative of said existing infrastructure that can be used as geographic locations for said nodes and said arcs in the fibre optic network, electronically generating design outputs by optimising geographic locations of said nodes and said arcs in the fibre optic network using said fibre optic network design inputs and said existing infrastructure inputs, and electronically outputting the design outputs.

Owner:BIARRI NETWORKS PTY LTD

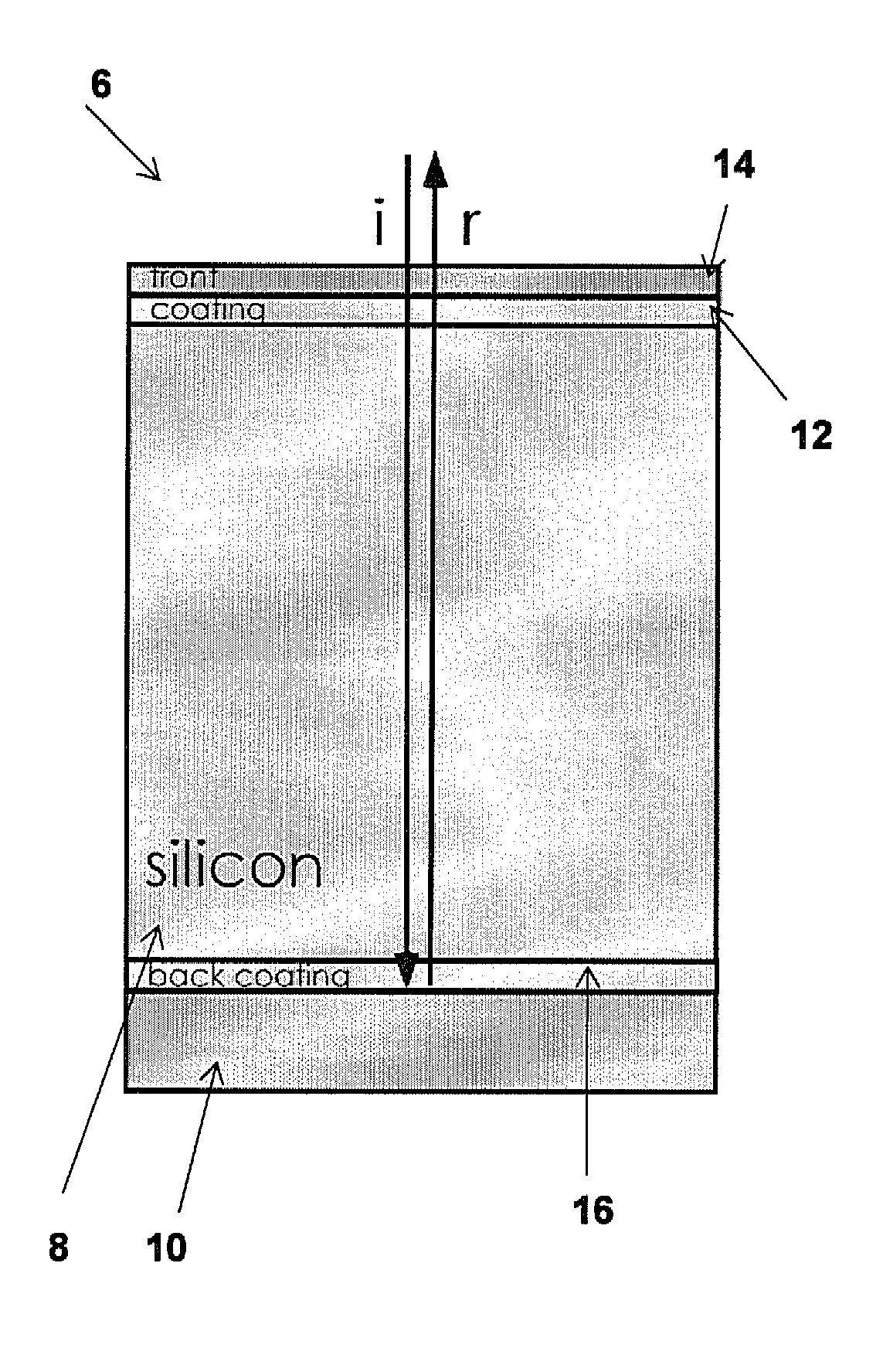

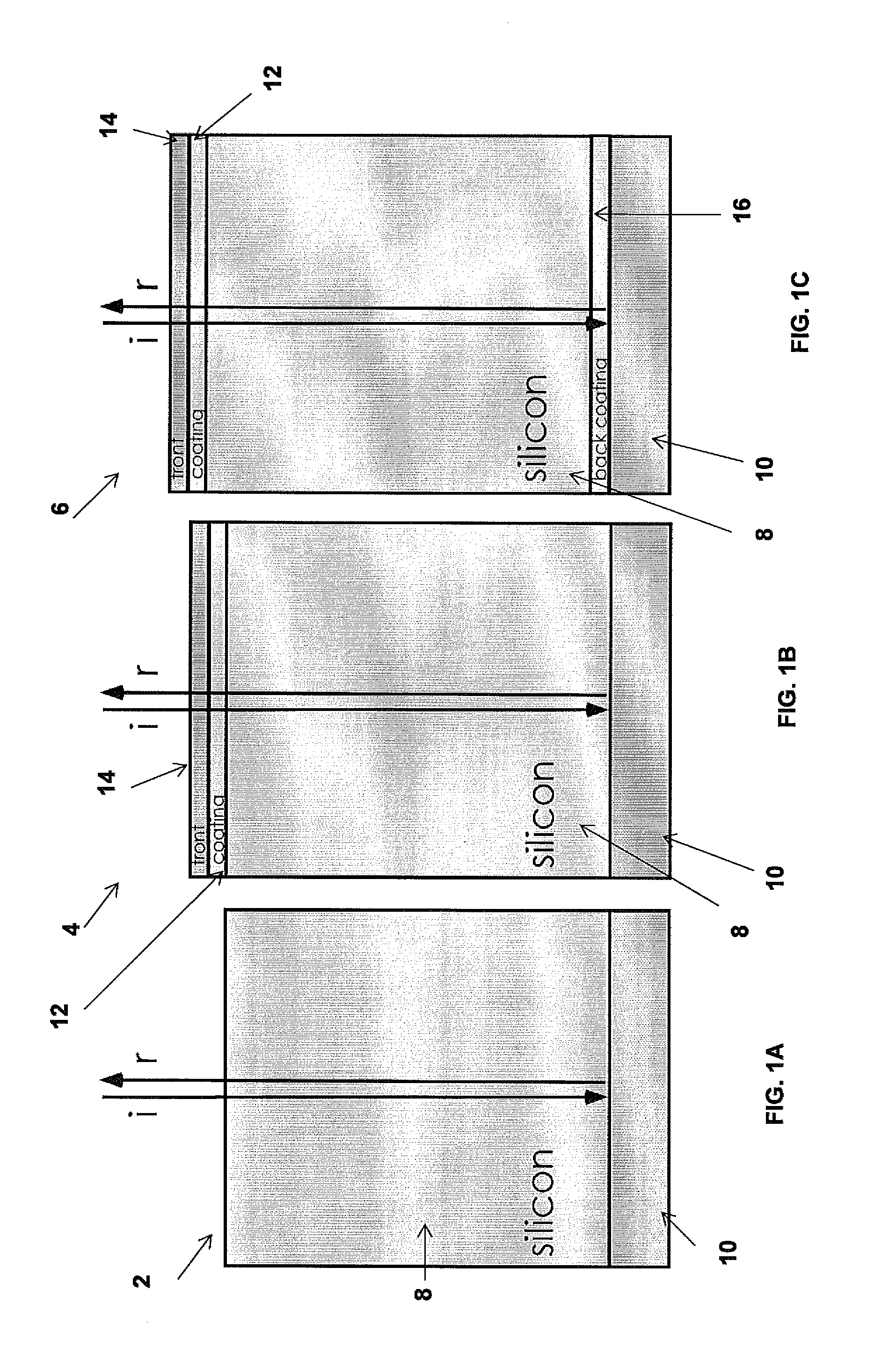

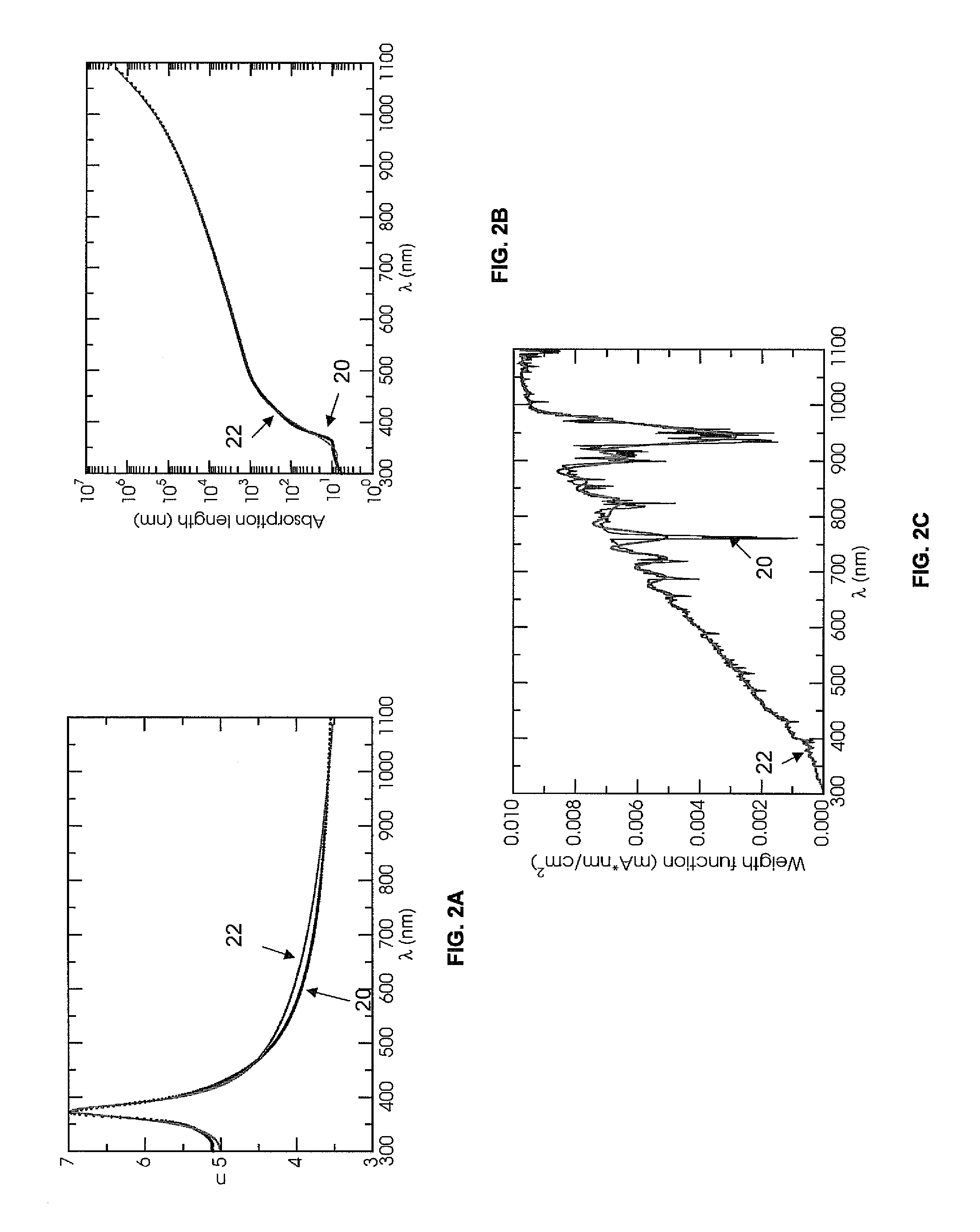

Global optimization of thin film photovoltaic cell front coatings

InactiveUS20100258174A1Maximize currentMaximize short-circuit currentSemiconductor/solid-state device manufacturingPhotovoltaic energy generationGlobal optimizationSolar cell

A solar cell includes a thin film photovoltaic material structure used in absorbing light of a selective bandwidth. A multitude of dielectric front coatings are positioned on the thin film photovoltaic material structure so as to maximize admittance over the selected bandwidth. The thicknesses and indices of each of the front coatings are chosen by a global-optimization procedure to maximize the short-circuit current of the solar cell.

Owner:MASSACHUSETTS INST OF TECH

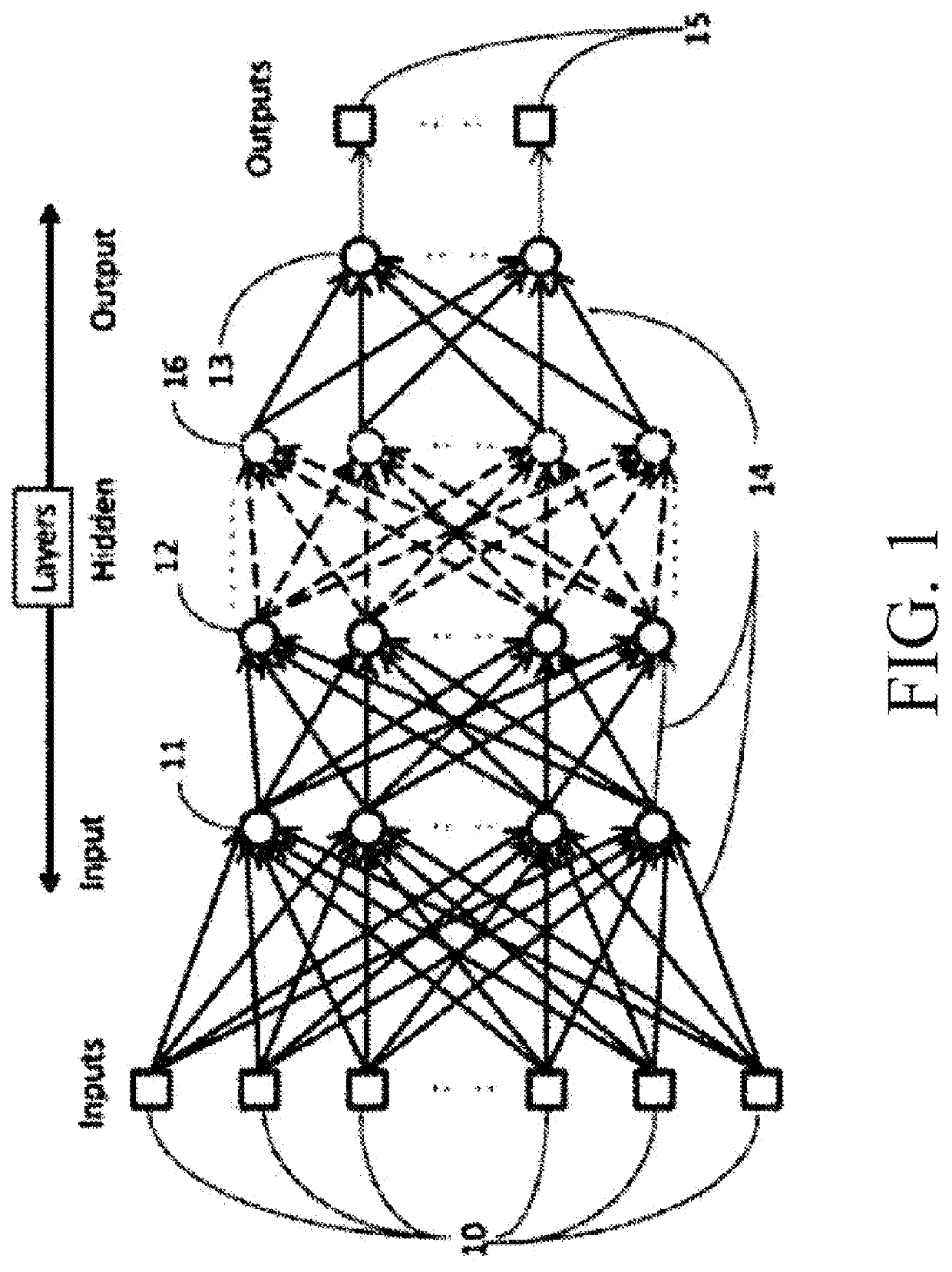

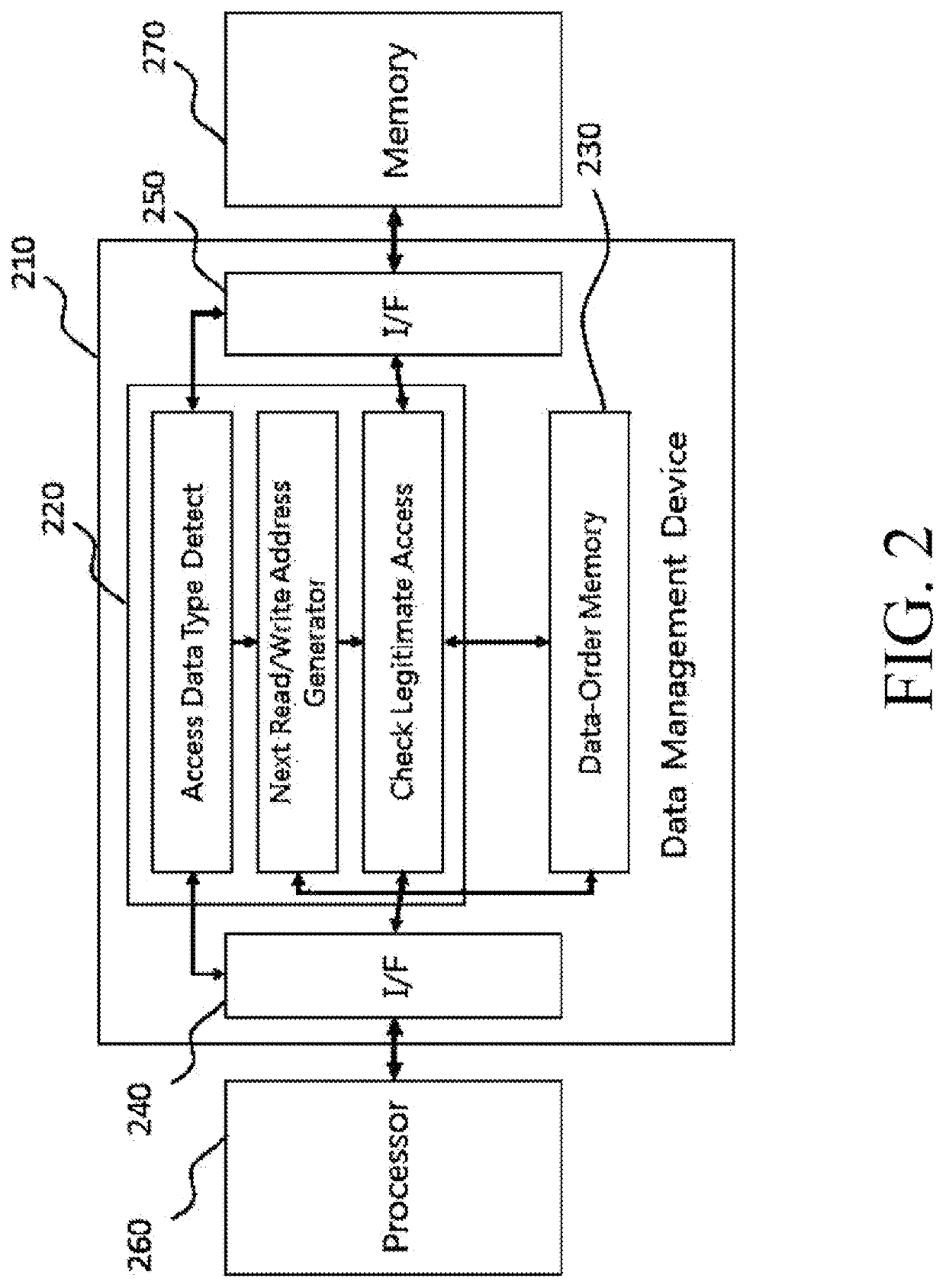

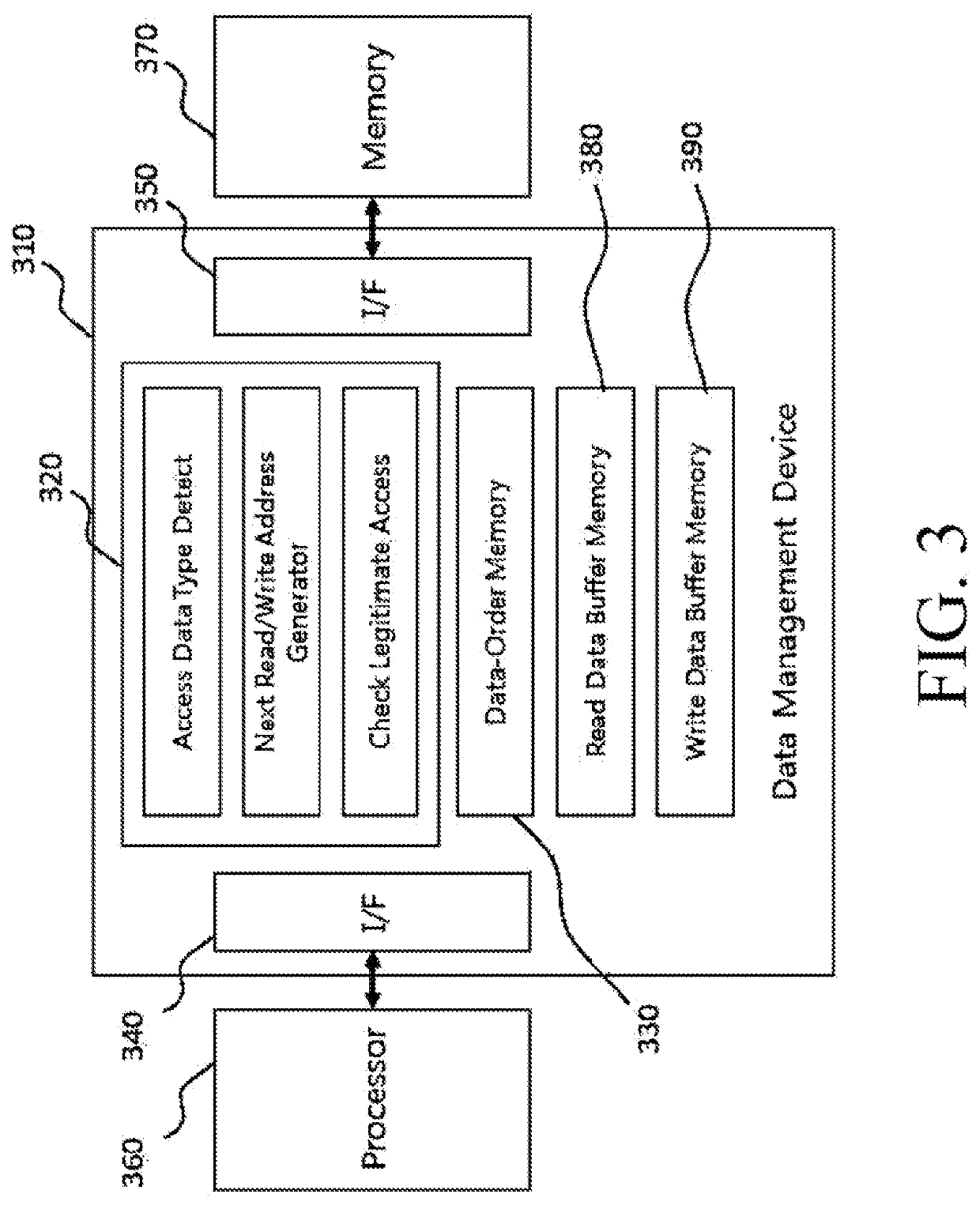

Data management device for supporting high speed artificial neural network operation by using data caching based on data locality of artificial neural network

PendingUS20210150352A1Maximize bandwidthMinimize delay timeMemory architecture accessing/allocationNeural architecturesData bufferReal-time computing

Disclosed is a data cache or data management device for caching data between at least one processor and at least one memory, and supporting an artificial neural network (ANN) operation executed by the at least one processor. The data cache device or the data management device can comprise an internal controller for predicting the next data operation request on the basis of ANN data locality of the ANN operation. The internal controller monitors data operation requests associated with the ANN operation from among data operation requests actually made between the at least one processor and the at least one memory, thereby extracting the ANN data locality of the ANN operation.

Owner:DEEPX CO LTD

Reconfigurable wireless data center network using free-space optics

ActiveUS10020880B2Maximize dynamic bisection bandwidthMaximize bandwidthMultiplex system selection arrangementsClose-range type systemsTraffic capacityData center

A reconfigurable free-space optical inter-rack network includes a plurality of server racks, each including at least one switch mounted on a top thereof, where each top-mounted switch includes a plurality of free-space-optic link connector, each with a free-space optical connection to a free-space-optic link connector on another top-mounted switch, a single ceiling mirror above the plurality of server racks that substantially covers the plurality of server racks, wherein the single ceiling mirror redirects optical connections between pairs of free-space-optic link connectors to provide a clear lines-of-sight between each pair of connected free-space-optic link connectors, and a controller that preconfigures a free-space optical network connecting the plurality of server racks by establishing connections between pairs of free-space-optic link connectors, and that reconfigures connections between pairs of free-space-optic link connectors in response to network traffic demands and events.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

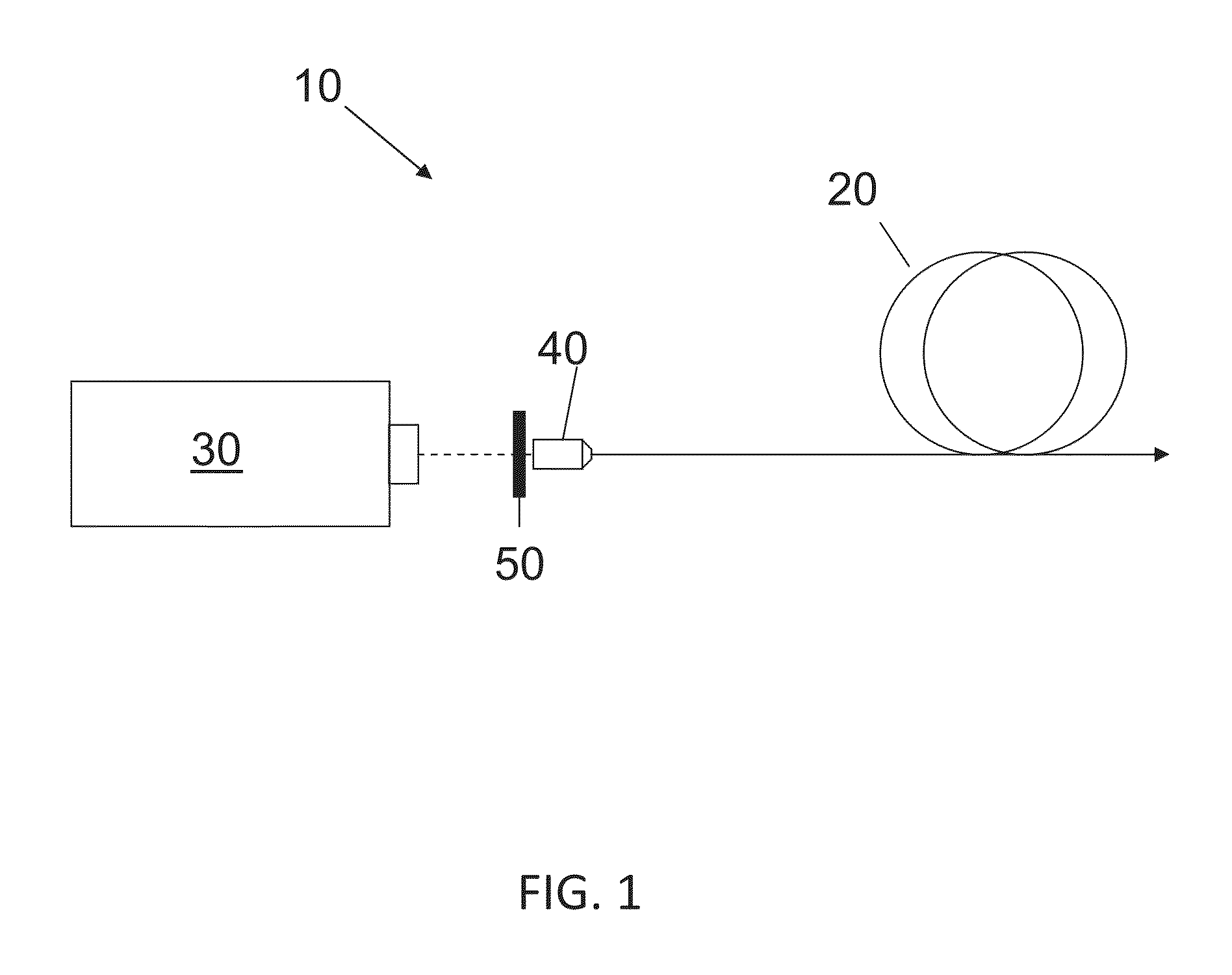

Extended spectrum supercontinuum pulse source

ActiveUS20160268758A1Short processLimited extentCladded optical fibreOptical resonator shape and constructionFrequency spectrumGroup velocity dispersion

A source of optical supercontinuum radiation comprises a length of microstructured optical fibre and a pump laser adapted to generate lasing radiation at a pump wavelength. The length of microstructured optical fibre is arranged to receive lasing radiation at the pump wavelength to generate optical supercontinuum radiation and comprises a core region and a cladding region which surrounds the core region. The source of optical supercontinuum radiation is arranged such that at a location along the length of the microstructured optical fibre (a) the microstructured optical fibre comprises a group index (GI) versus wavelength curve having a zero crossing wavelength (ZCW) at which the group velocity dispersion has a zero crossing and such that the GI increases for wavelengths away from the ZCW such that the curve includes group indices that are greater than the GI at the ZCW for wavelengths greater than as well as less than the ZCW; (b) light having a wavelength of greater than 2000 nm propagates along the length of microstructured optical fibre and has a GI that is matched to the GI of light that propagates along the length of microstructured optical fibre and that has a wavelength of less than 400 nm; and (c) the pump wavelength is within 200 nm of the ZCW.

Owner:NKT PHOTONICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com