Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

32results about How to "Eliminate DC Offset" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

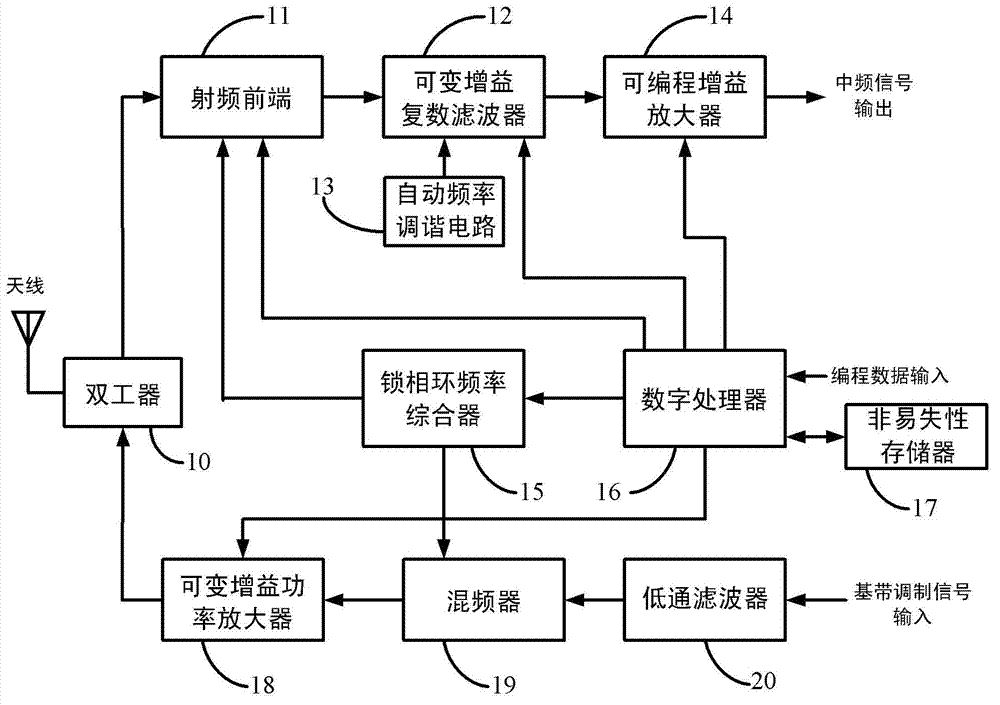

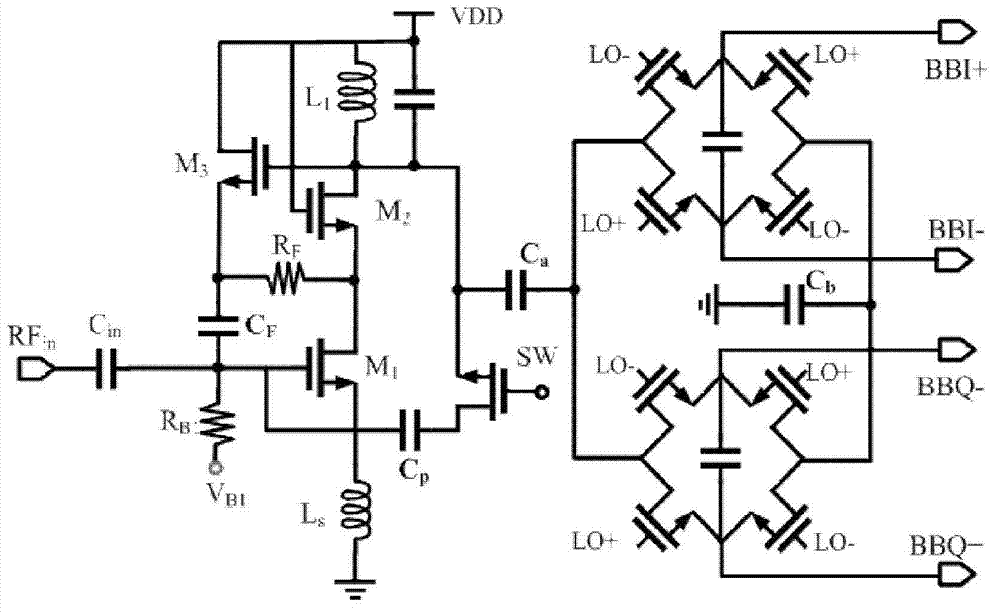

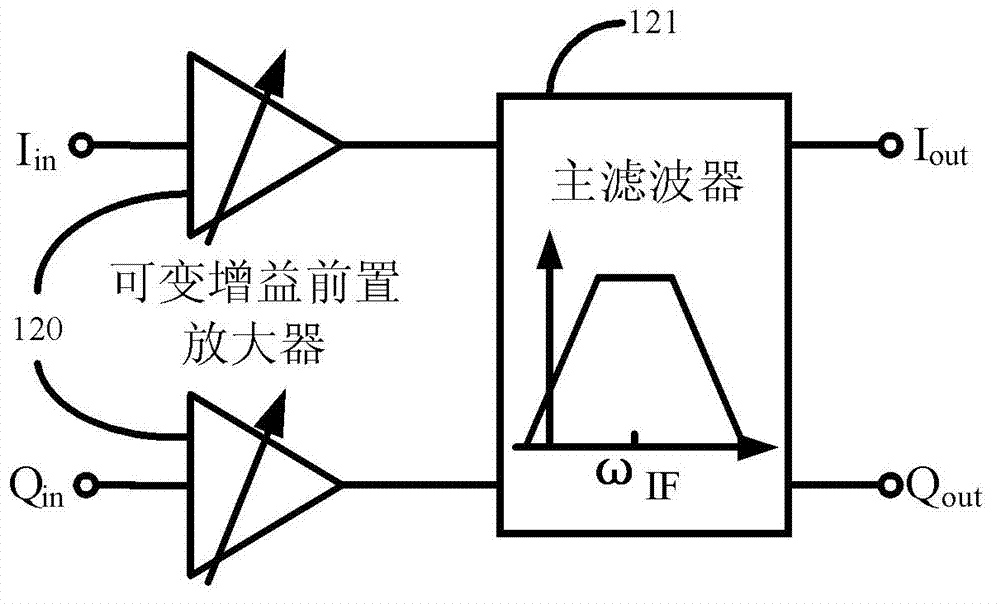

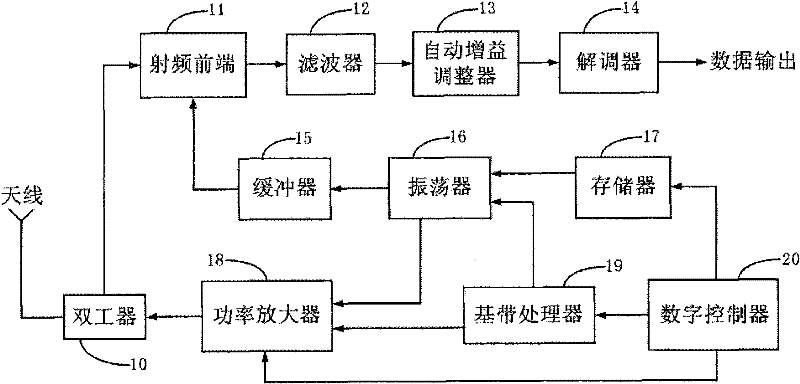

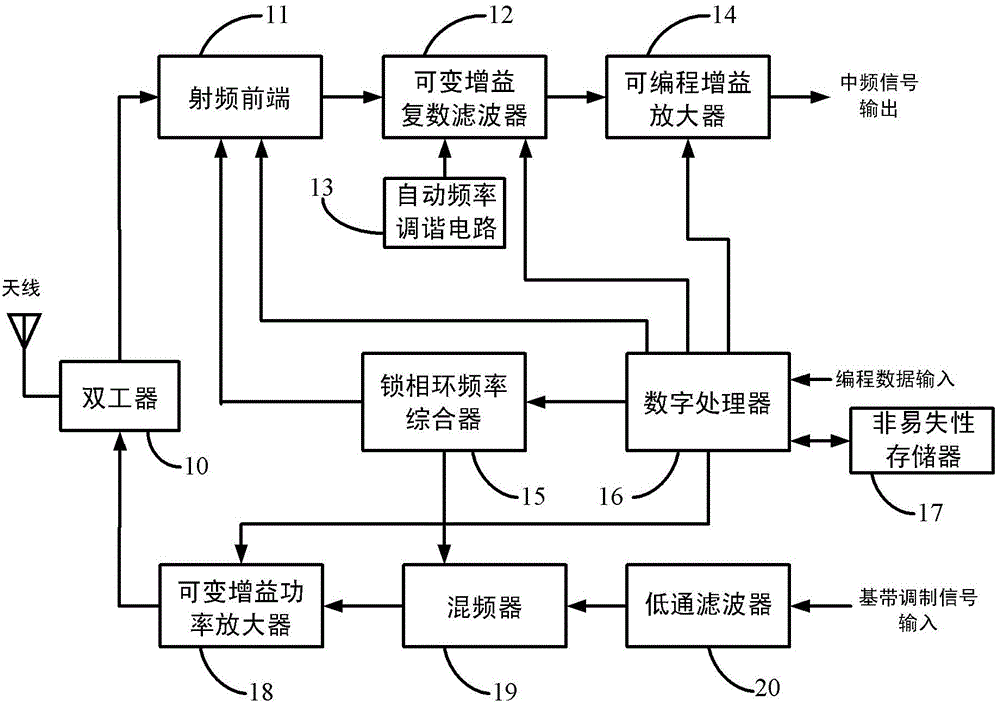

Wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device

ActiveCN102970053ALow cost requirementsReduce power consumptionNetwork topologiesTransmissionIntermediate frequencyLow-pass filter

The invention discloses a wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device which comprises a duplexer, a radio frequency front end, a variable gain complex filter, an automatic frequency tuning circuit, a programmable gain amplifier, a phase-locked loop frequency synthesizer, a digital processor, a storage, a variable gain power amplifier, a mixer and a low pass filter, wherein the duplexer, the radio frequency front end, the variable gain complex filter, the automatic frequency tuning circuit and the programmable gain amplifier form a receiving link which is used for receiving and processing a radio frequency signal and converting the radio frequency signal into a low-medium frequency digital signal so that the signal can be conveniently processed by a subsequent analog-digital converter later; the duplexer, the variable gain power amplifier, the mixer and the low pass filter form an emitting link which is used for mixing a baseband analog modulation signal into a carrier frequency and sending a wireless signal; and the receiving link and the emitting link share the duplexer. The wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device realizes singlechip integration by adopting a standard CMOS (Complementary Metal Oxide Semiconductor) process, is simple in structure and low in power consumption, and is applicable to a wireless sensor network.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

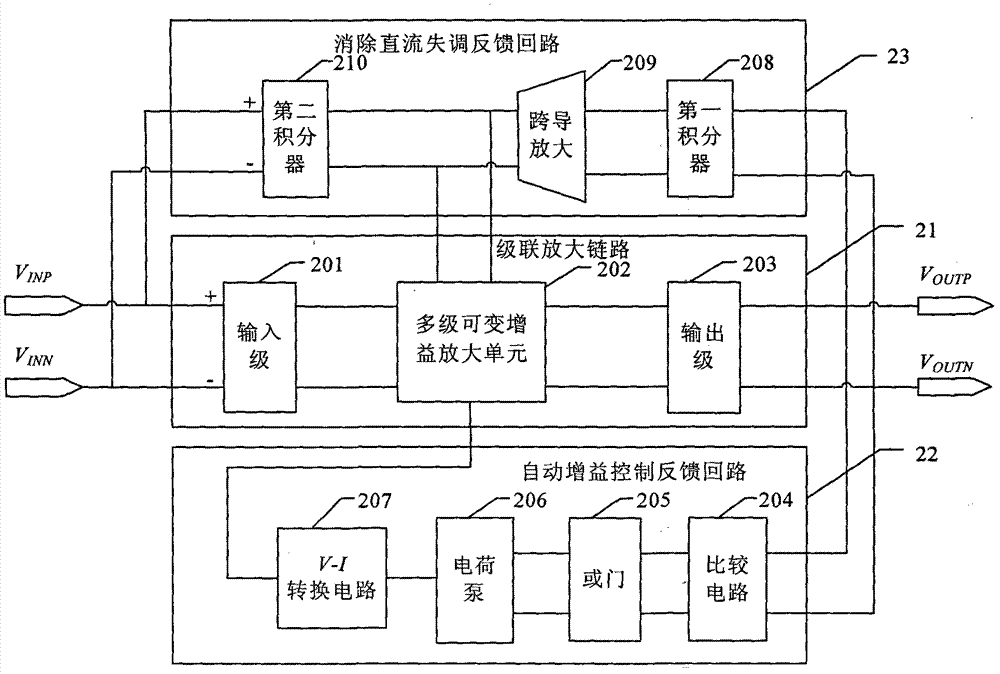

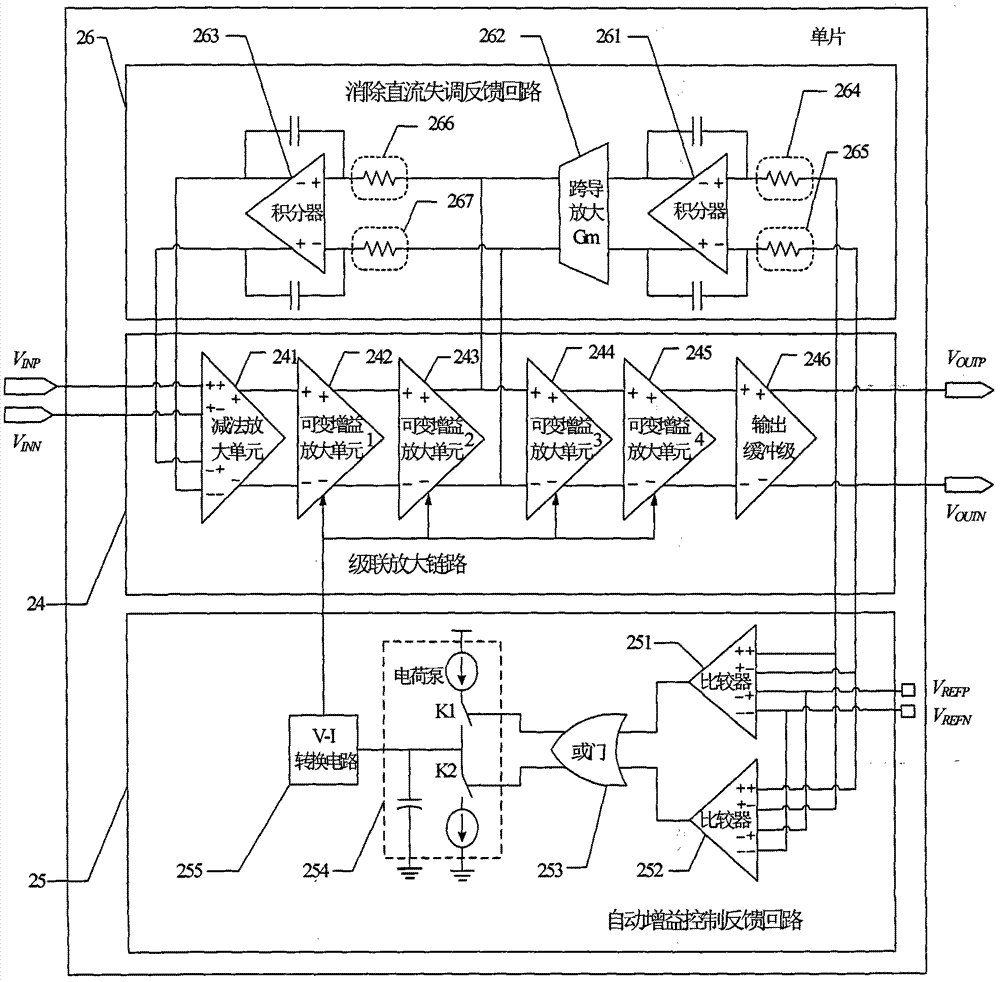

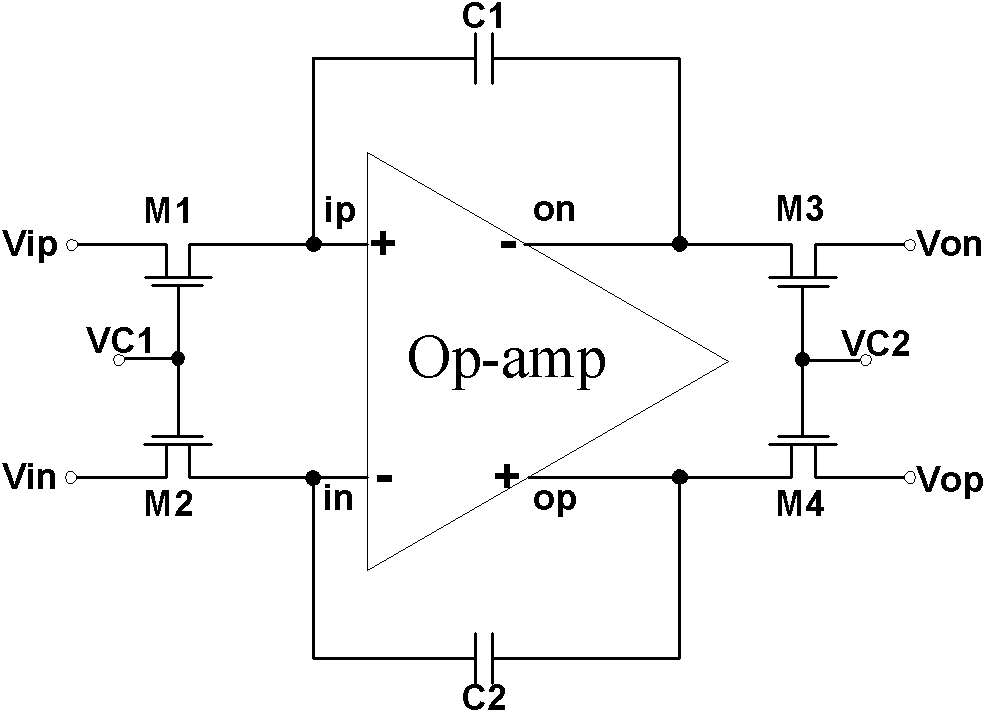

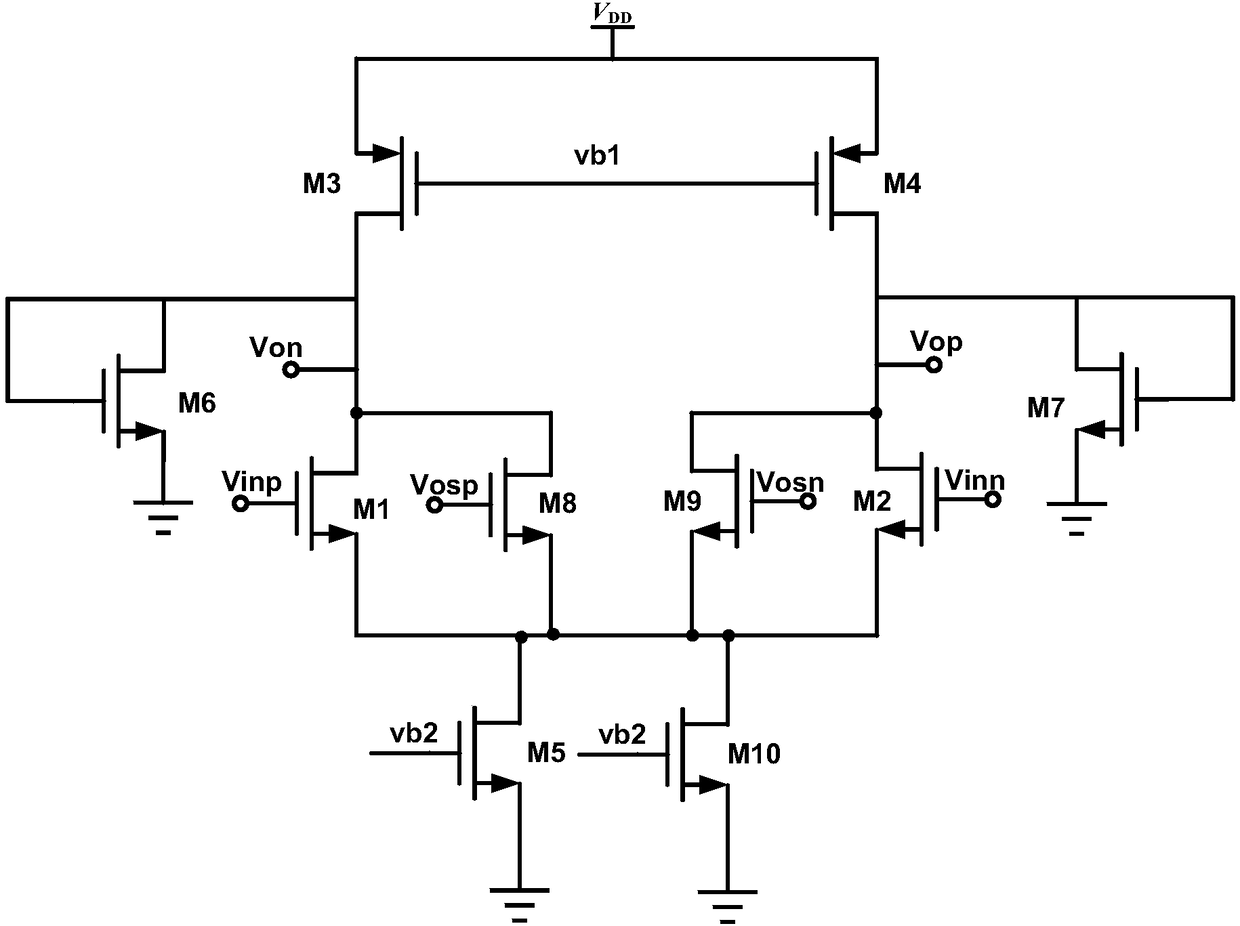

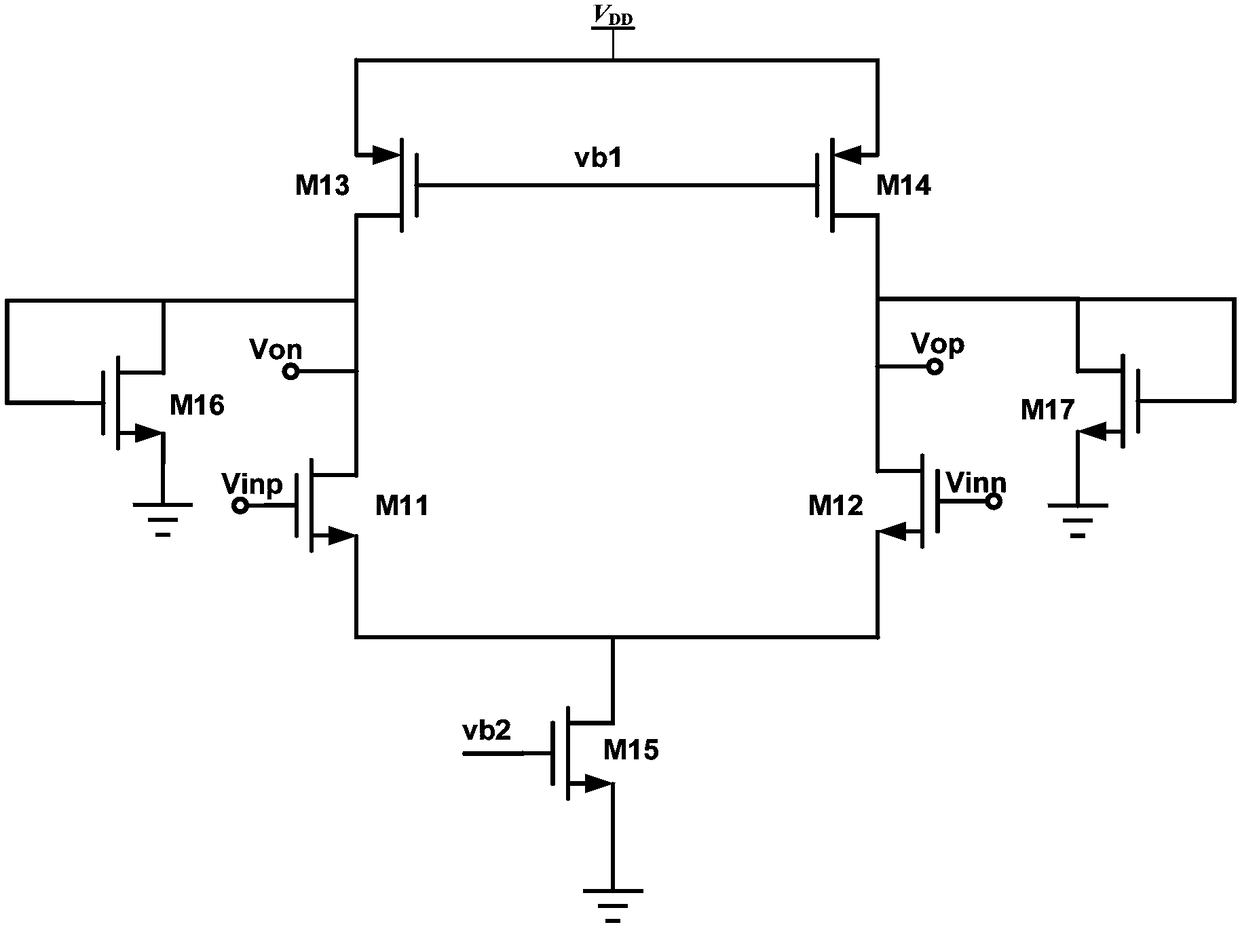

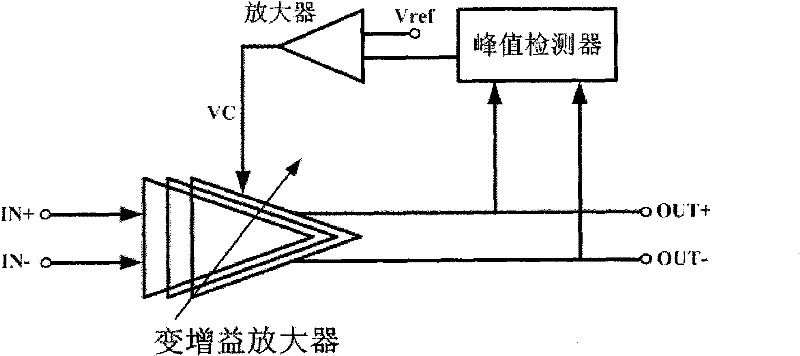

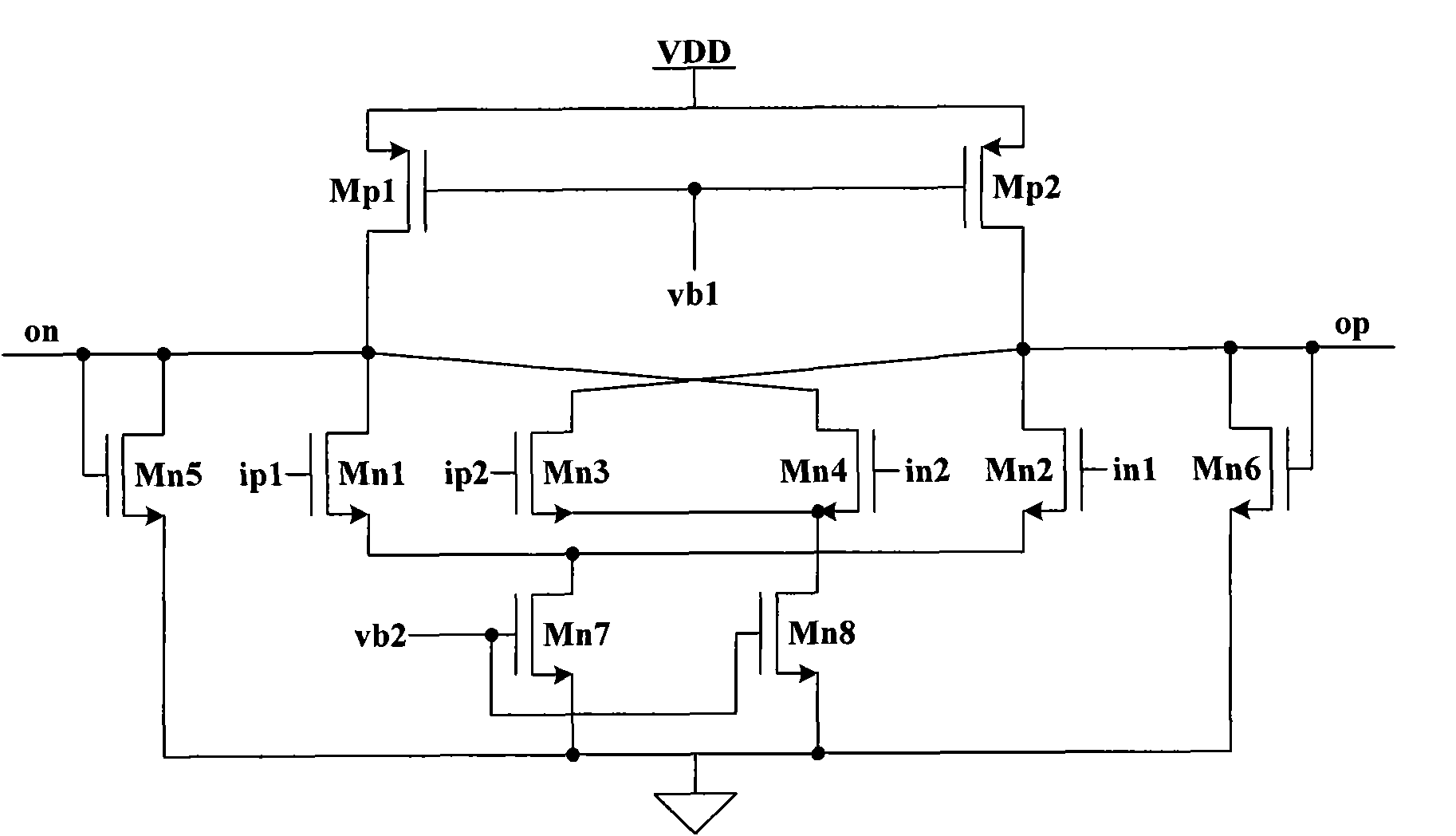

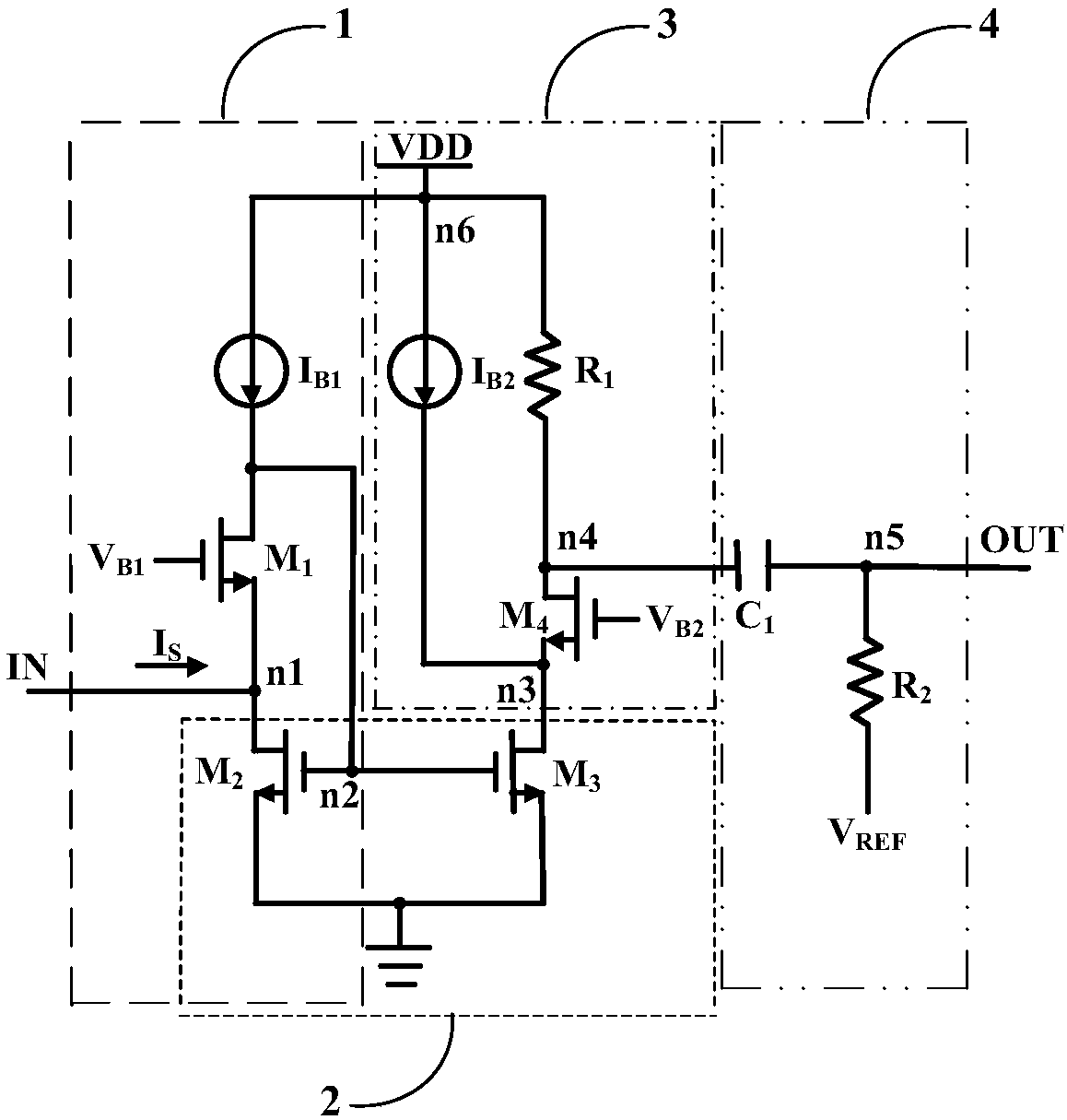

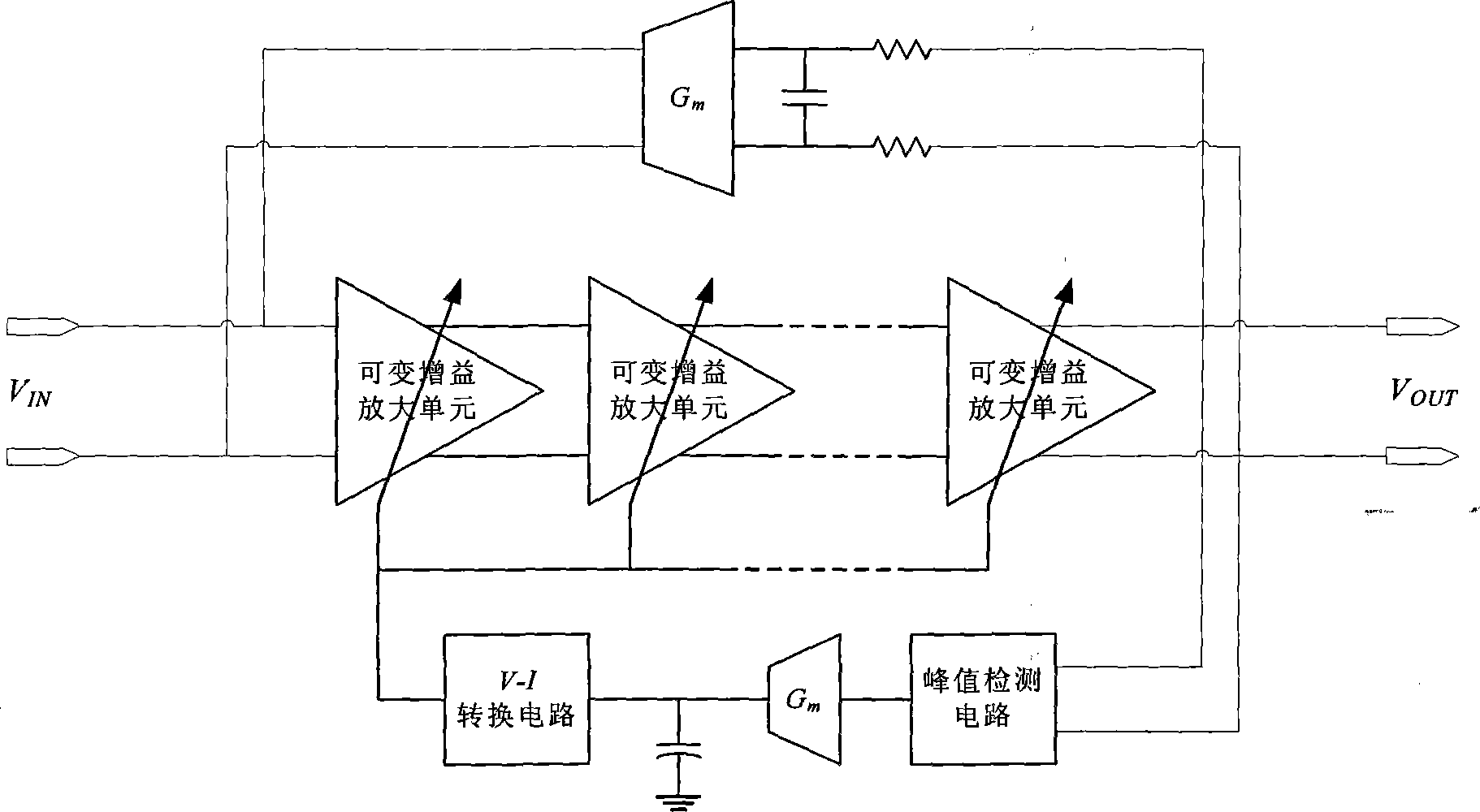

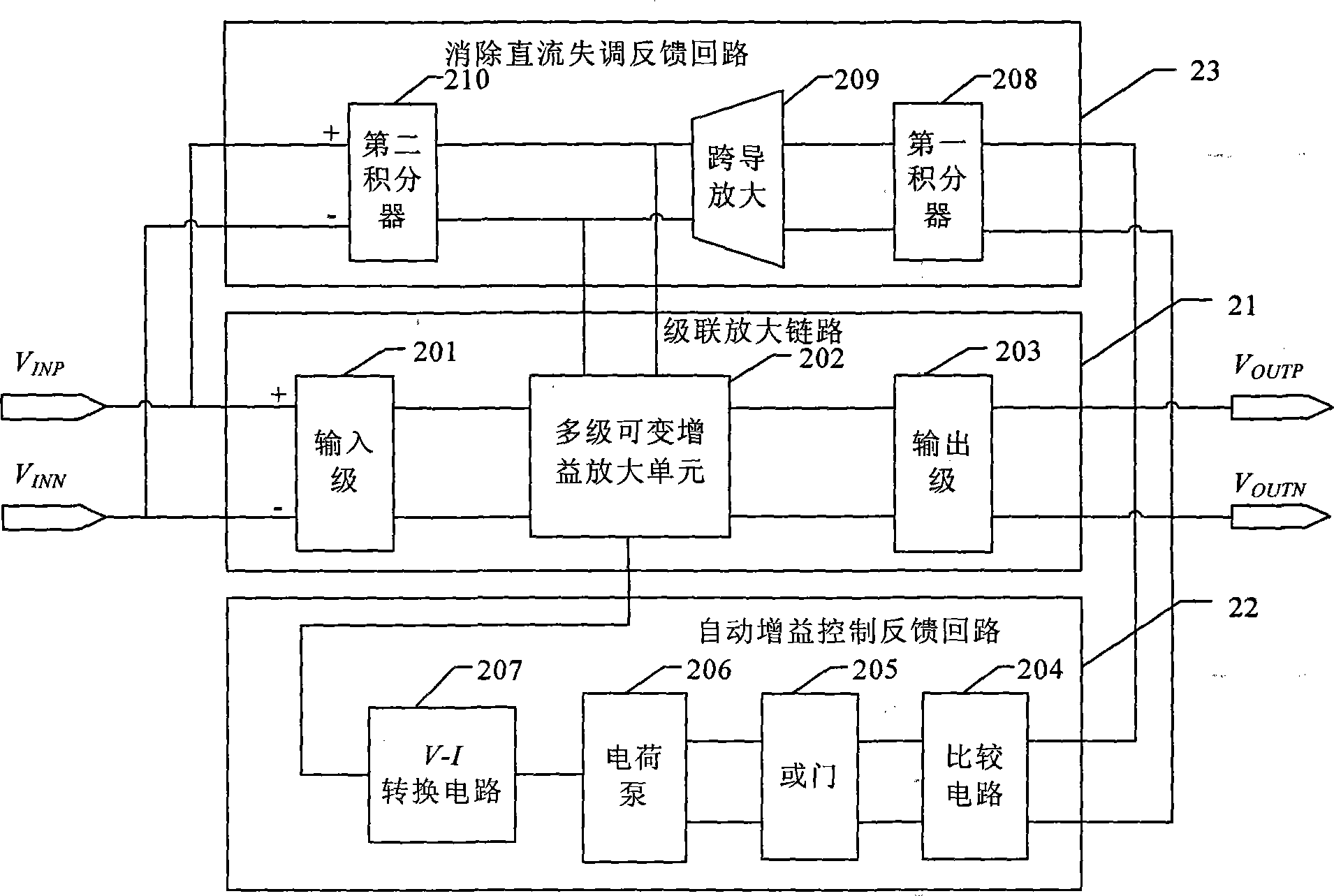

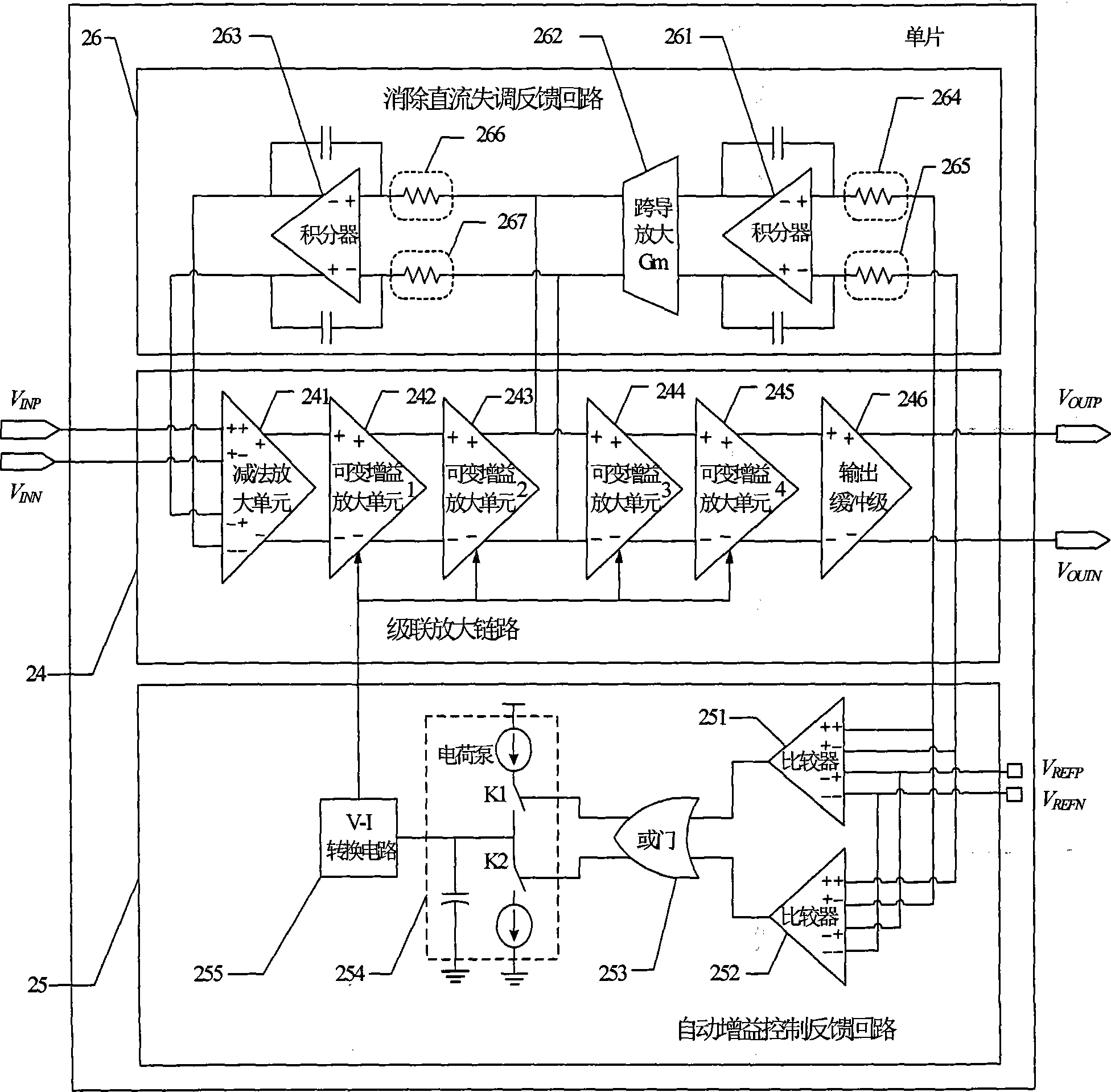

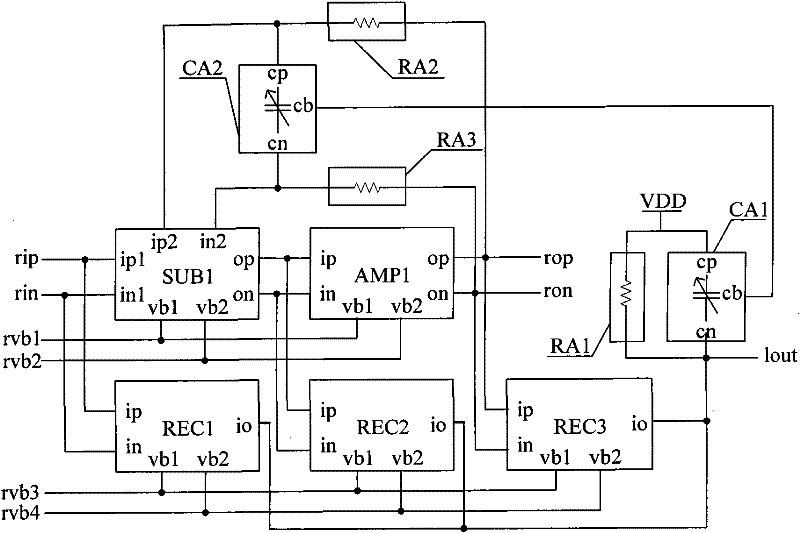

Automatic gain control amplifier for canceling direct current offset

ActiveCN102790596AThe process deviation and other factors have little influenceSimple structureGain controlCapacitanceProcess deviations

The invention discloses a complementary metal oxide semiconductor (CMOS) automatic gain control amplifier for canceling direct current offset. The CMOS automatic gain control amplifier comprises a cascade amplification link, an automatic gain control feedback loop and a direct current offset canceling feedback loop. The cascade amplification link uses multistage variable gain amplification units for cascading and can achieve high gain and enlarge high gain dynamic ranges. The automatic gain control feedback loop uses a charge pump structure and has the advantages that the automatic gain control feedback loop is less influenced by process deviation and temperature deviation, is capable of accurately detecting narrow-band and wide-band signal amplitude and is suitable for achieving CMOS processes. The direct current offset canceling feedback loop uses two-stage negative feedback loops, and each of the two-stage negative feedback loops uses an integrator as low-pass negative feedback; an active device is used as an integrator input resistor, and an equivalent resistor is provided with characteristics of temperature compensation; and the automatic gain control amplifier for canceling the direct current offset is capable of effectively canceling the direct current offset superposed by a preceding stage circuit and the direct current offset of the amplification link and is provided with a lower high pass corner frequency and a higher integrated level, and the automatic gain control amplifier for canceling the direct current offset is small in low-frequency signal loss and requires no off-chip passive devices (high value resistors or capacitors and the like). The automatic gain control amplifier is applicable to wireless communication receivers with zero intermediate frequency structures in the CMOS processes.

Owner:杭州中科微电子有限公司

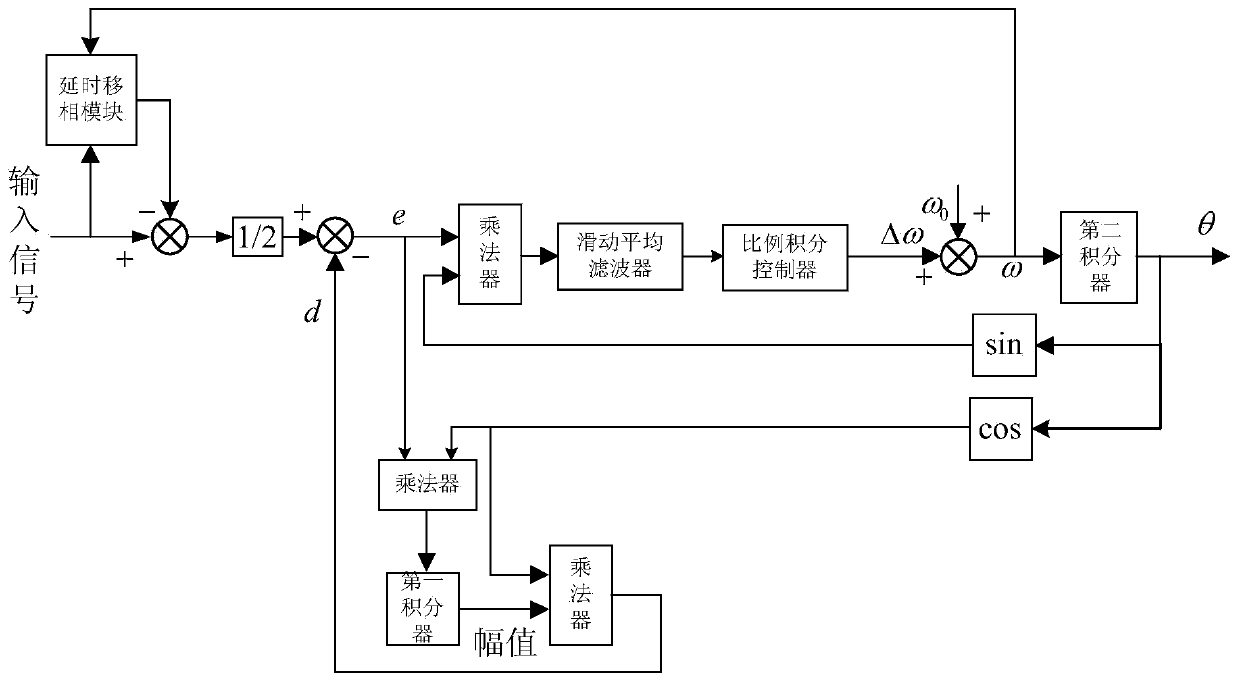

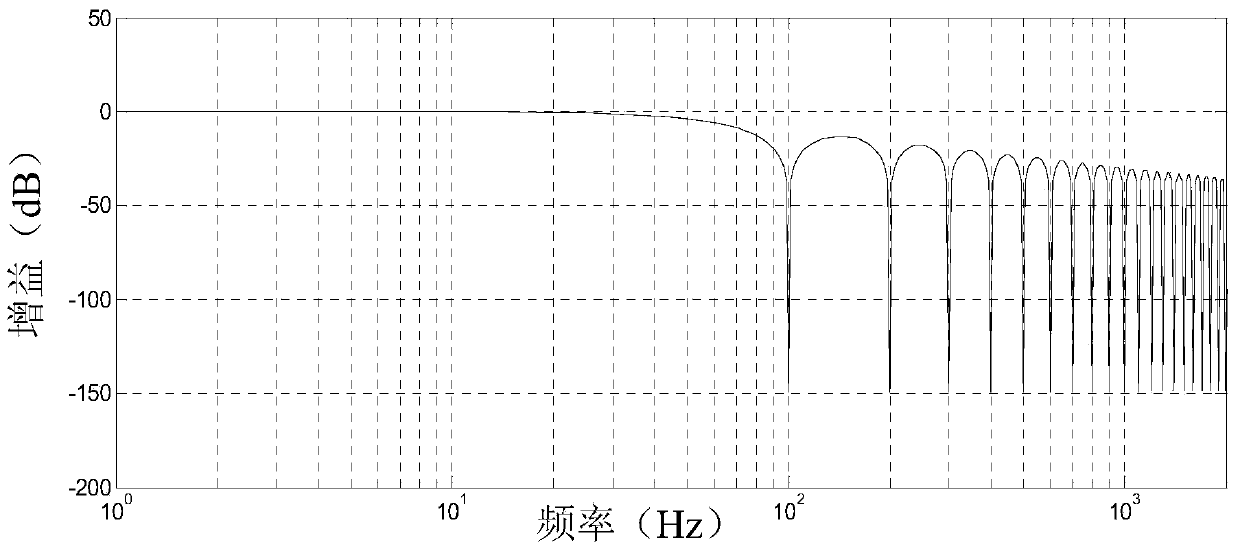

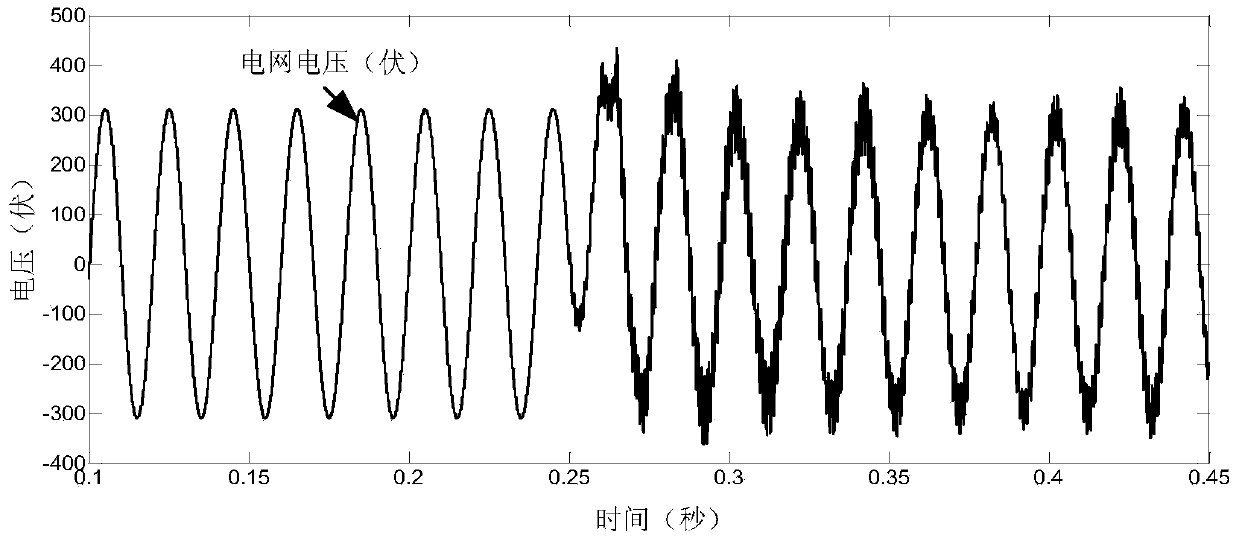

Method for network voltage amplitude, frequency and phase angle detection based on one-phase phase-locked loop algorithm

InactiveCN103558436AEliminate DC OffsetEliminate odd harmonicsMulti-tester circuitsVoltage amplitudePhysics

The invention discloses a method for network voltage amplitude, frequency and phase angle detection based on the one-phase phase-locked loop algorithm. According to the method, accurate amplitude, frequency and phase angle detection is achieved when direct current offset and harmonic waves exist in a one-phase power grid. The method comprises the steps that a network voltage signal is acquired and transmitted to a delay phase-shifting module; the delay phase-shifting module receives a network voltage frequency value obtained from the last cycle at the same time and outputs a network voltage delay signal; subtraction is carried out on the acquired network voltage signal and the network voltage delay signal to obtain a result, and the result is divided by 2 to obtain a network voltage signal free of direct current offset; the network voltage signal free of direct current offset is taken as an input signal of an enhanced phase-locked loop, and then the network voltage amplitude value, frequency value and phase angle value of the cycle are obtained. The method for network voltage amplitude, frequency and phase angle detection based on the one-phase phase-locked loop algorithm is suitable for the field of conversion of electrical energy.

Owner:HARBIN INST OF TECH

Amplifier with ultralow direct current (DC) offset at input end and analog/digital (A/D) converter

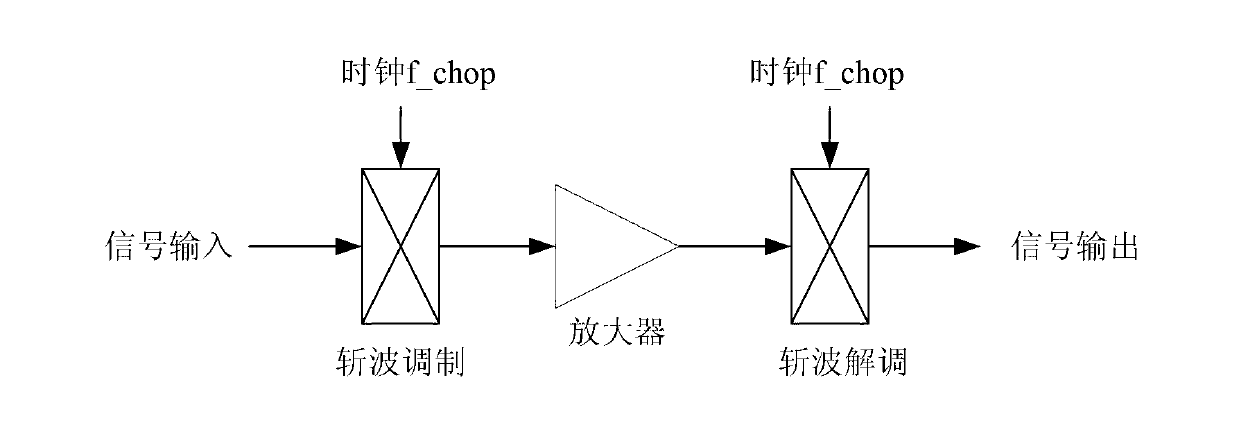

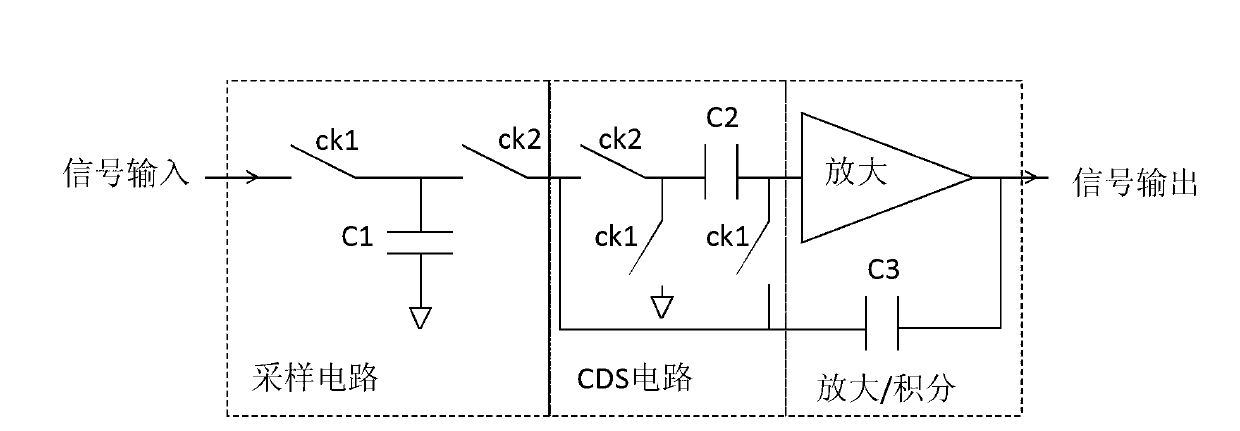

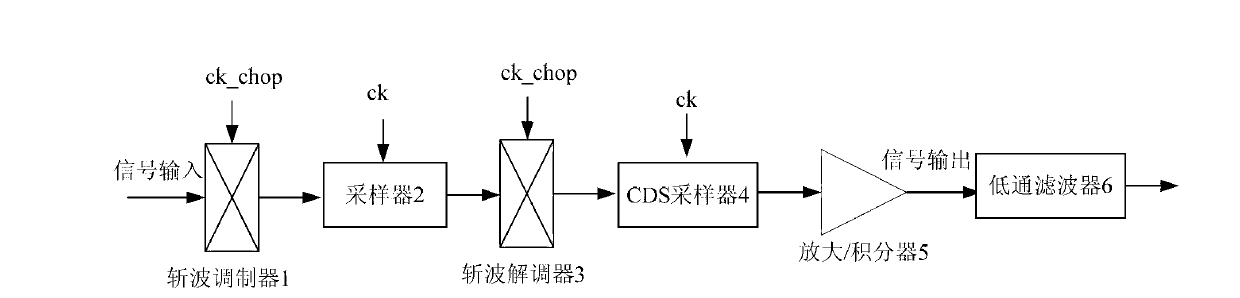

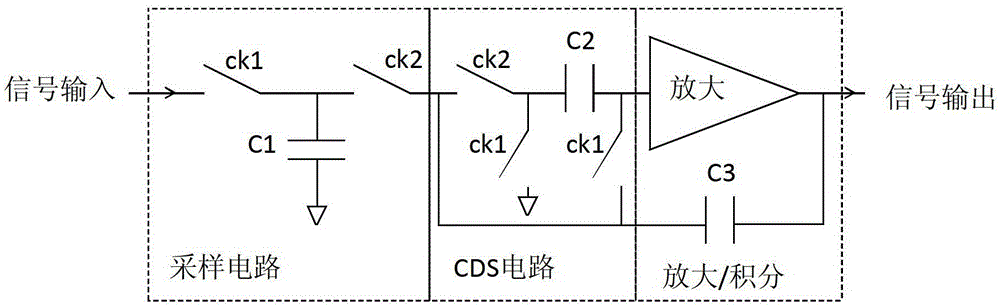

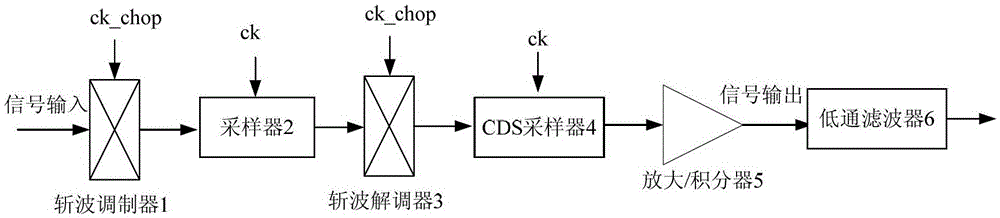

ActiveCN103138760AEliminate DC OffsetQuality is not affectedAnalogue-digital convertersA d converterIntegrator

The invention relates to an amplifier with ultralow direct current (DC) offset at an input end and an analog / digital (A / D) converter. The amplifier with the ultralow DC offset at the input end comprises a chopped wave modulator, a sampling instrument, a correlated double sampling (CDS) instrument and an amplifying / integration unit which are connected in sequence. A chopped wave demodulator is arranged in a circuit behind the sampling instrument. The chopped wave modulator and the chopped wave demodulator are used for eliminating residual DC offset generated due to imperfection of the CDS instrument and the other circuit components. On the other hand, the CDS instrument can also eliminate residual DC offset of the chopped wave modulator and the chopped wave demodulator. Due to the fact that the chopped wave modulator and the chopped wave demodulator modulate the residual DC offset of the CDS instrument and other circuit components at the clock frequency of 2*ck_chop to generate high-frequency modulating signals, input signals and the modulating signals do not overlap in a frequency domain. Consequently, the modulating signals can be eliminated at a low-pass filter which is connected with an output end of the amplifier with the ultralow DC offset at the input end. Therefore, the purpose of eliminating the residual DC offset of sampling signals is achieved.

Owner:HALO MICROELECTRONICS CO LTD

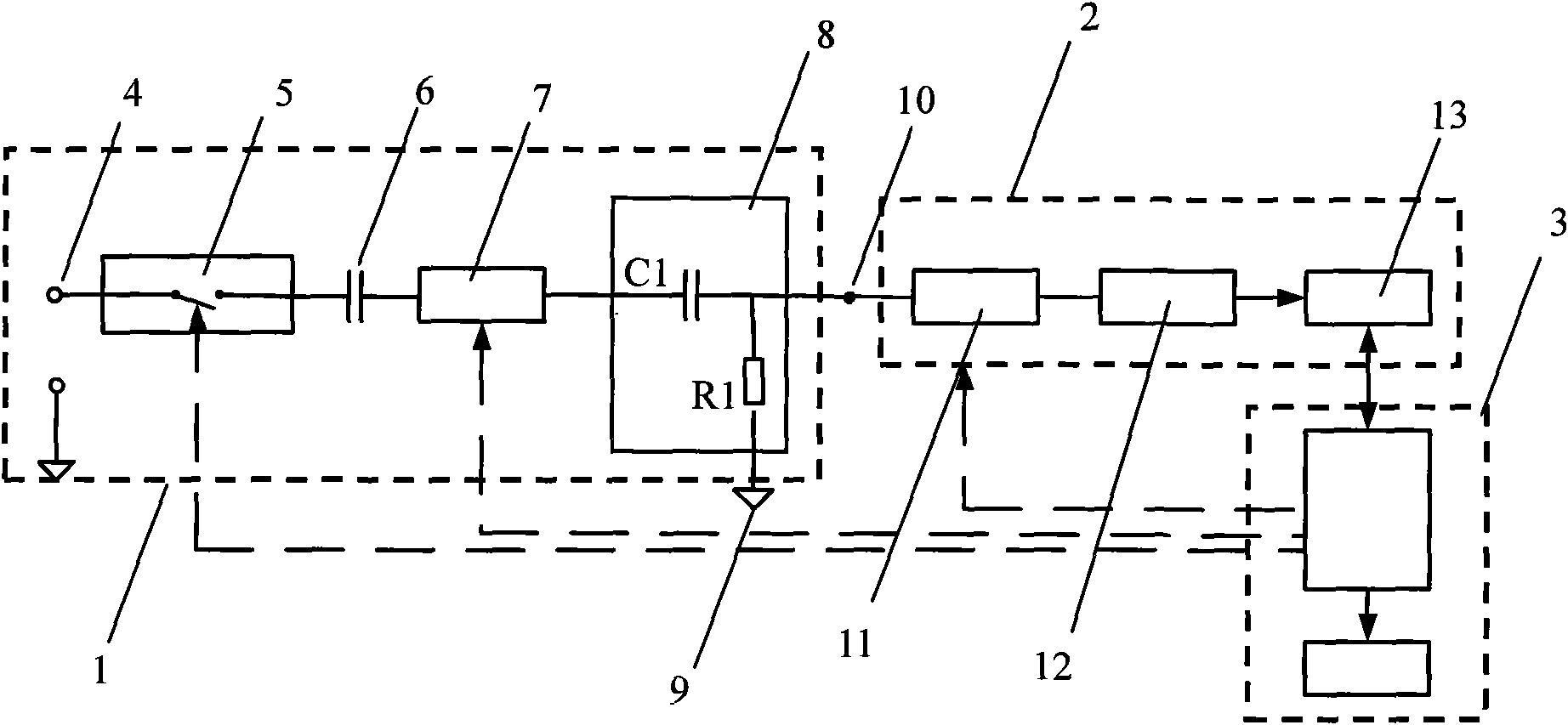

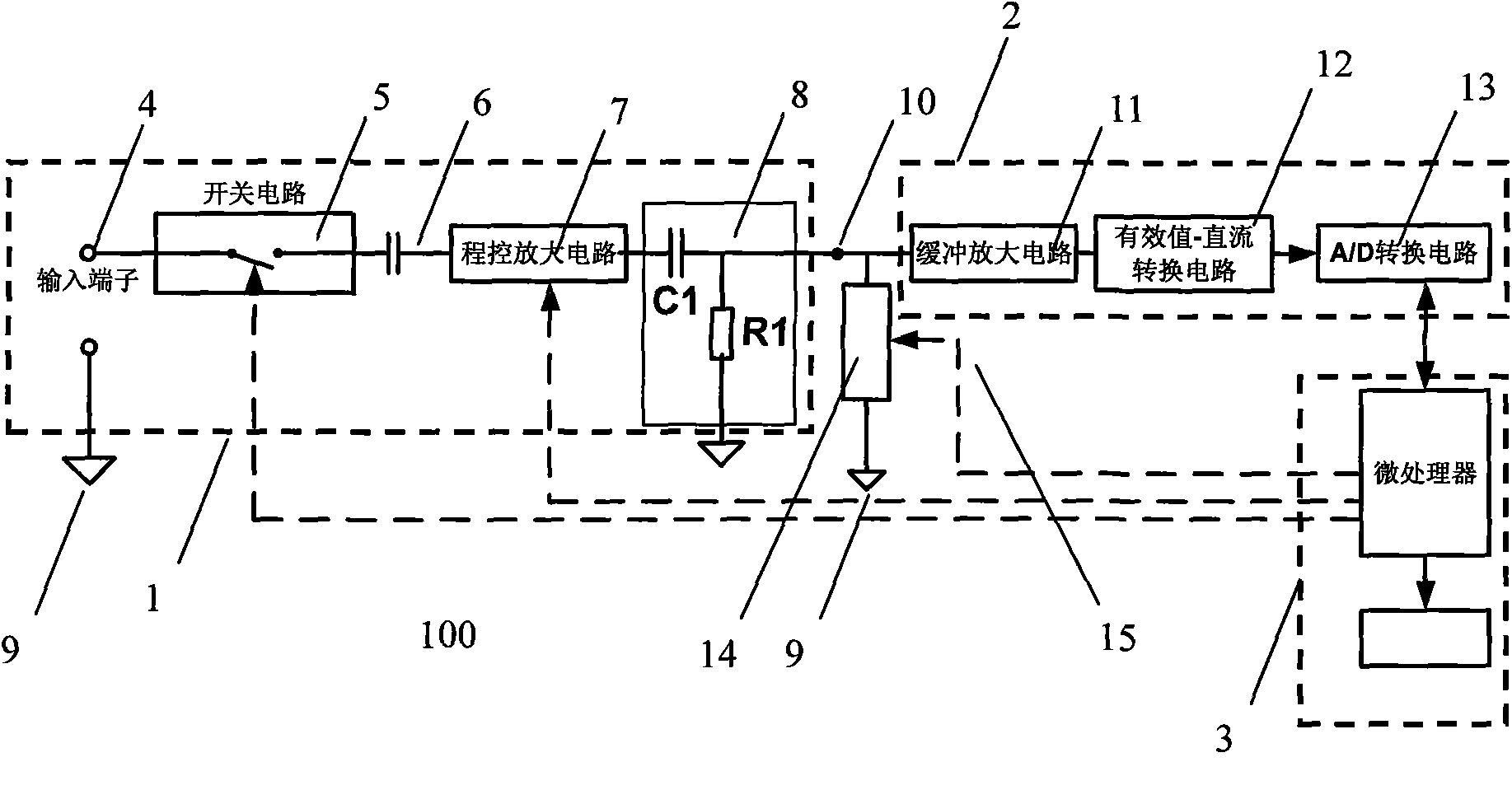

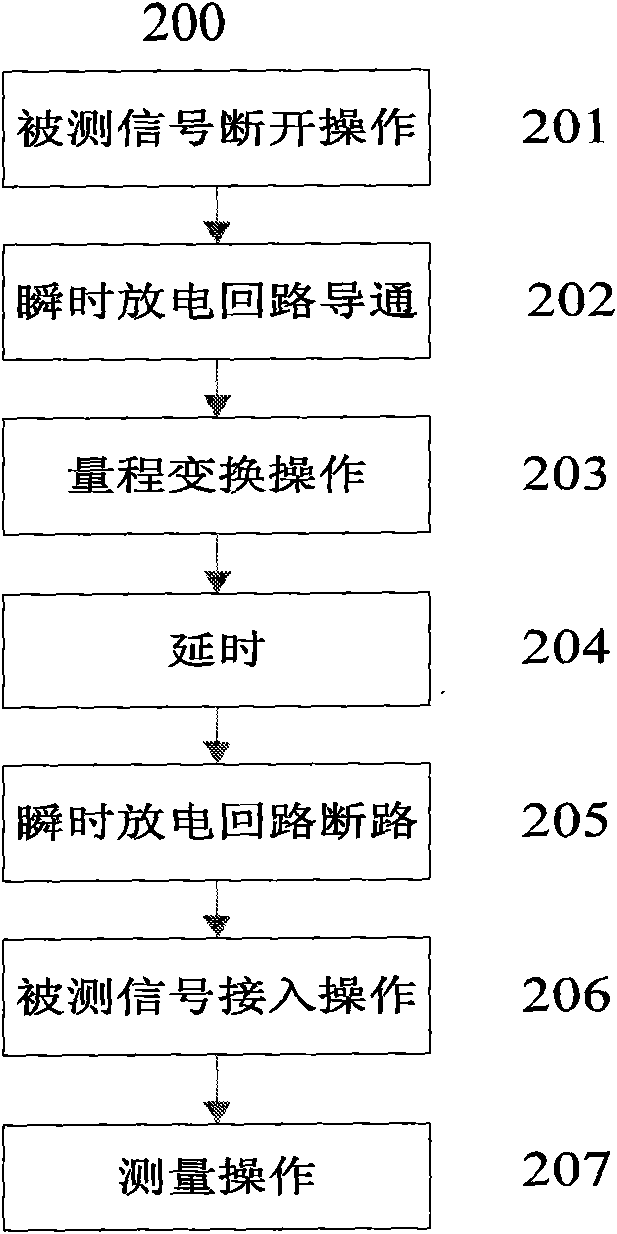

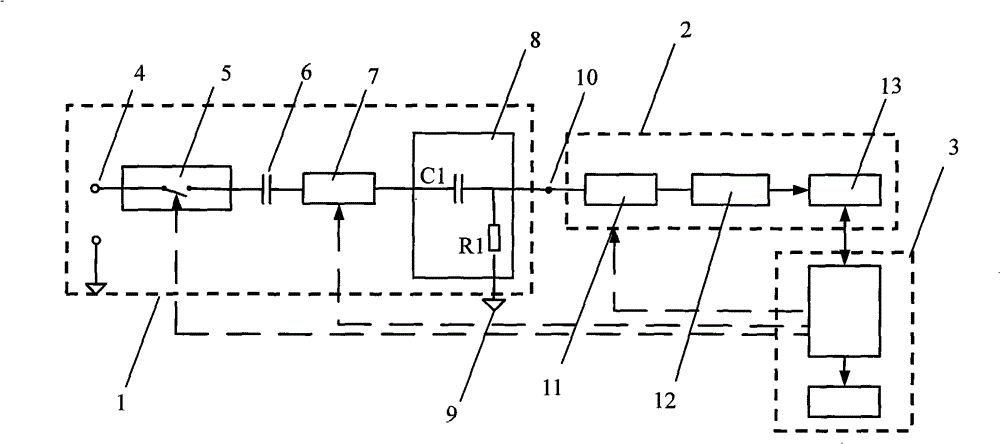

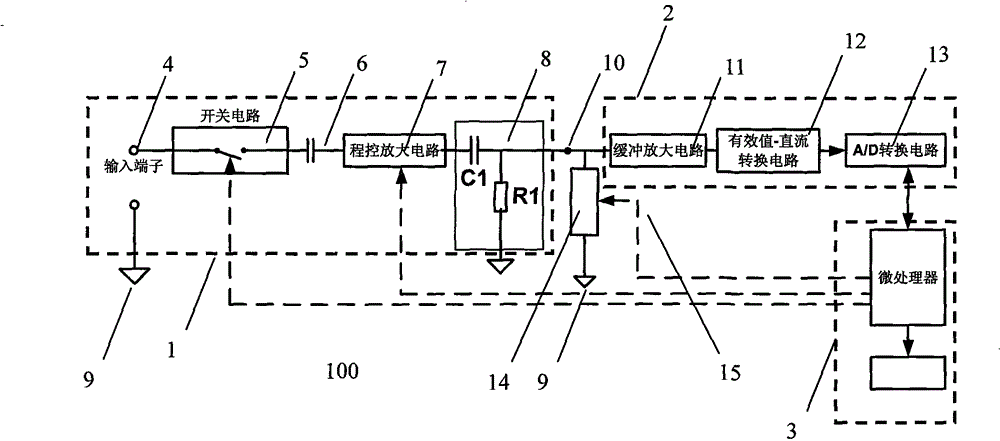

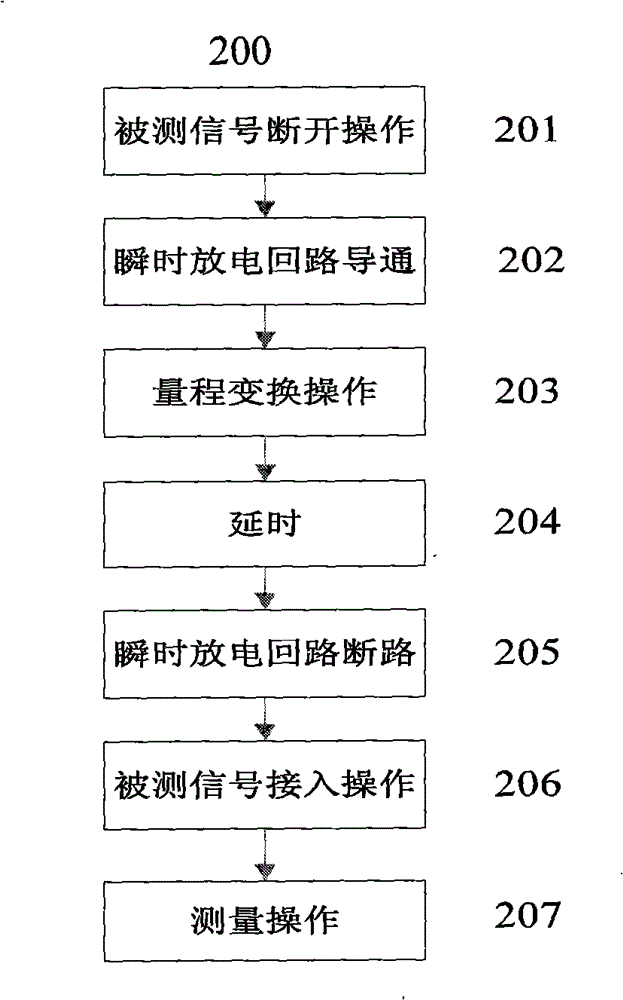

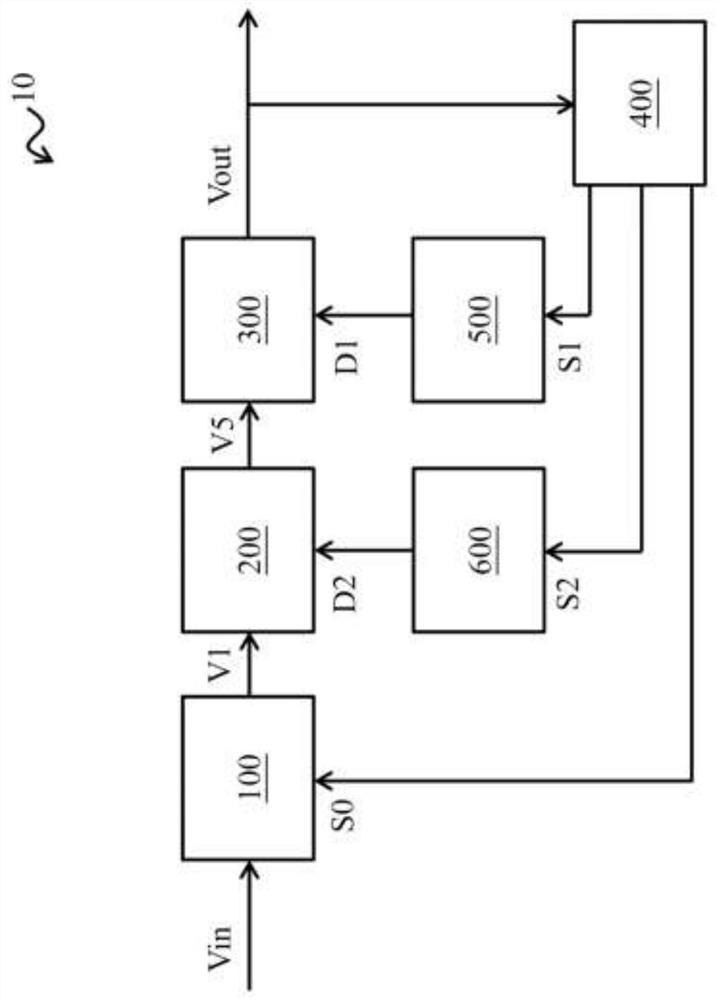

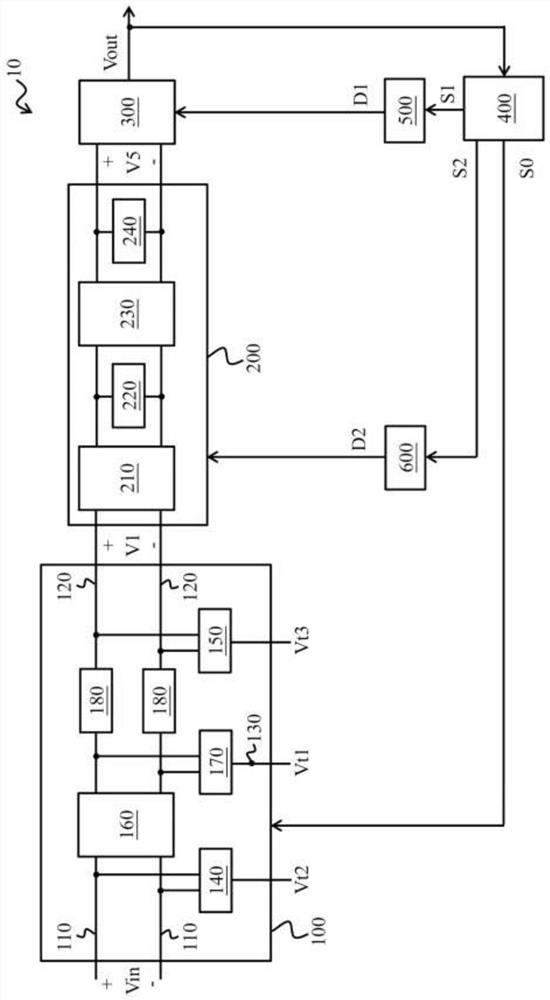

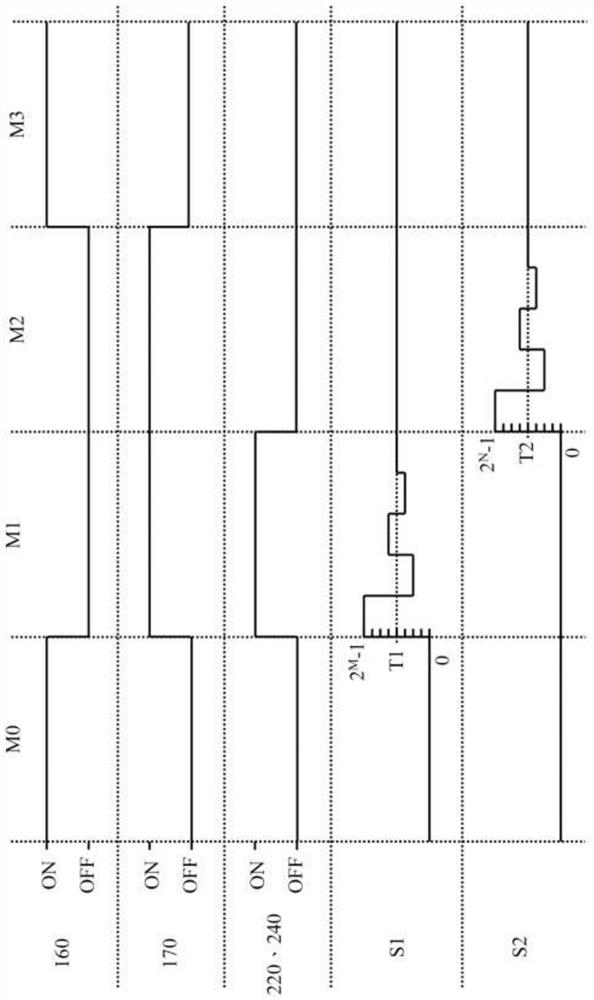

Alternating current signal measurement device, system and method

ActiveCN101839931AImprove the speed of access measurementGuaranteed accuracyAltering measuring range circuitsMulti-tester circuitsMeasurement deviceAccess time

The invention discloses an alternating current signal measurement device, an alternating current signal measurement system and an alternating current signal measurement method and relates to the field of alternating current electric signal measurement. The device is provided with an access part 1, a measurement part 2 and a control part 3, wherein the output end 10 of the access part 1 is connected with the input end of the measurement part 2 and is also connected with an instantaneous discharge circuit 14 controlled by the control part 3. The control part 3 can control the access part 1, the measurement part 2 and the instantaneous discharge circuit 14 to perform the instantaneous discharge operation of the output end 10, and adopts the following control steps: firstly, turning on the instantaneous discharge circuit; secondly, delaying a preset time period; and thirdly, turning off the instantaneous discharge circuit. The device of the invention accelerates the elimination of an abrupt signal which appears at the position of the output end 10 of the access part 1 and is caused by the quick change of the gain of a programmable amplifying circuit 7 in the access part 1. The device has the characteristics of reducing measurement access time, along with simple structure and convenient control.

Owner:RIGOL

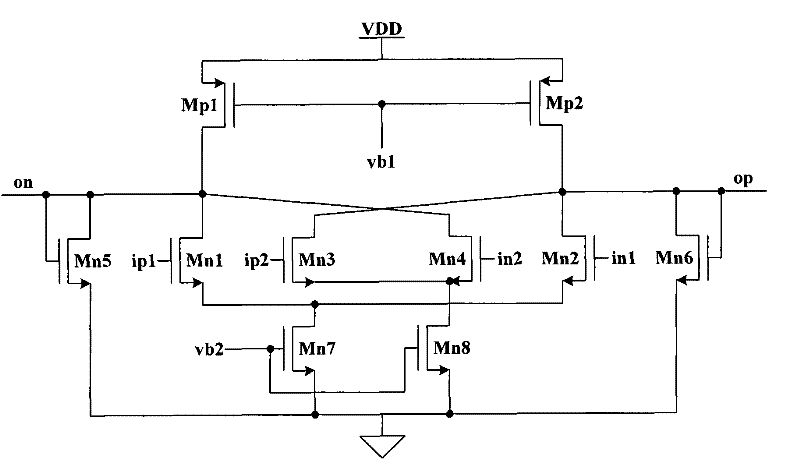

DC offset cancellation circuit

InactiveCN102130867AEliminate DC OffsetDamage reductionDc level restoring means or bias distort correctionCapacitanceEngineering

The invention discloses a DC offset cancellation circuit, which comprises a first transistor, a second transistor, a third transistor, a fourth transistor, a first feedback capacitor, a second feedback capacitor, a first voltage control signal port, a second voltage control signal port, a signal input positive end, a signal input negative end, a signal output positive end, a signal output negative end and an operational amplifier. A first voltage control signal controls the resistance of equivalent resistors of the first and second transistors, and a second voltage control signal controls the resistance of the equivalent resistors of the third and fourth transistors to fulfill the aim of adjusting equivalent high pass off frequency; therefore, the DC offset cancellation circuit can reduce damages to useful low frequency components in the signals as much as possible at the same time of suppressing or canceling DC offset. The DC offset cancellation circuit adopts active resistors instead of passive resistors, so the area of a circuit layout is reduced, and the level of integration of the circuit is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

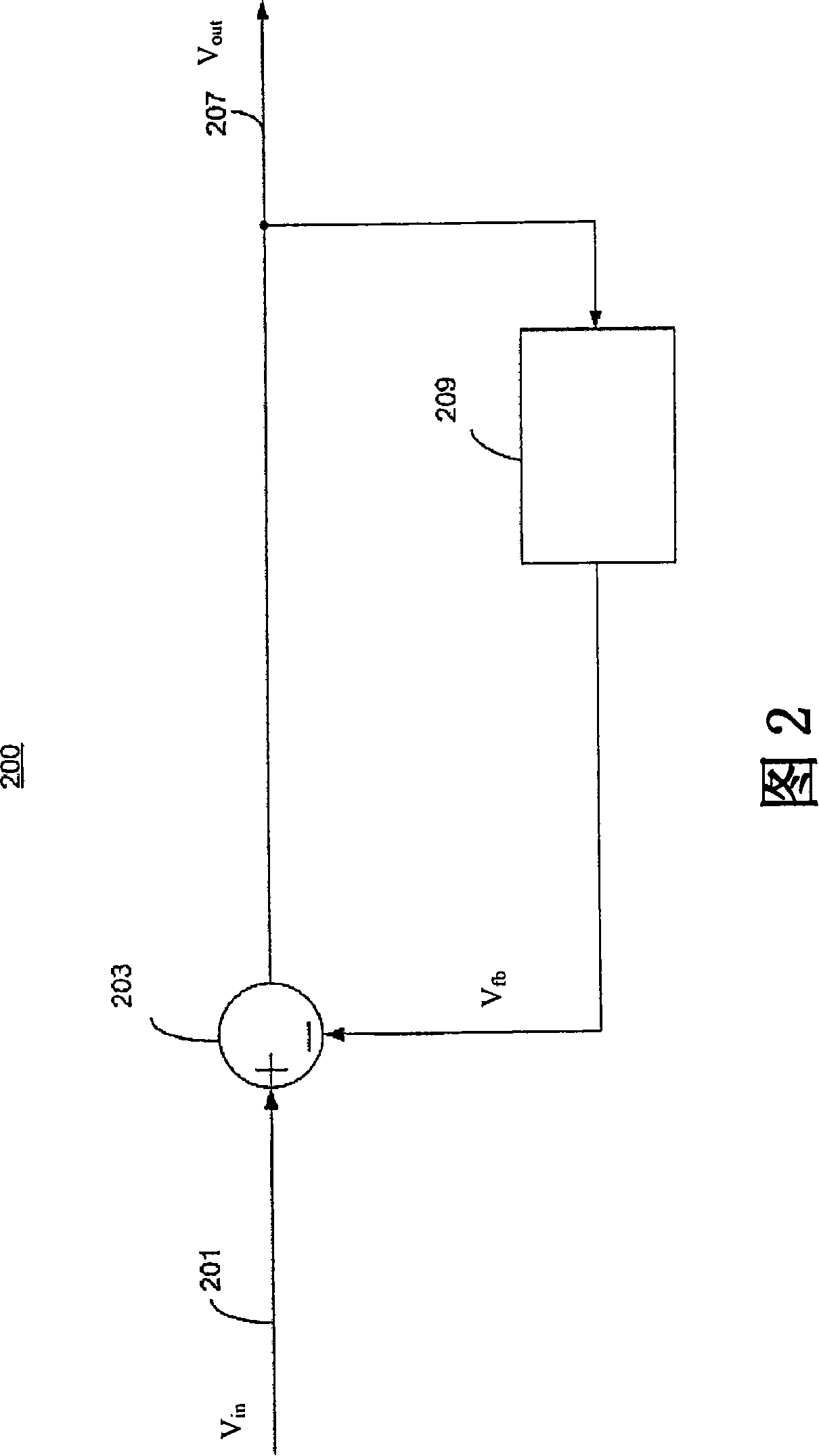

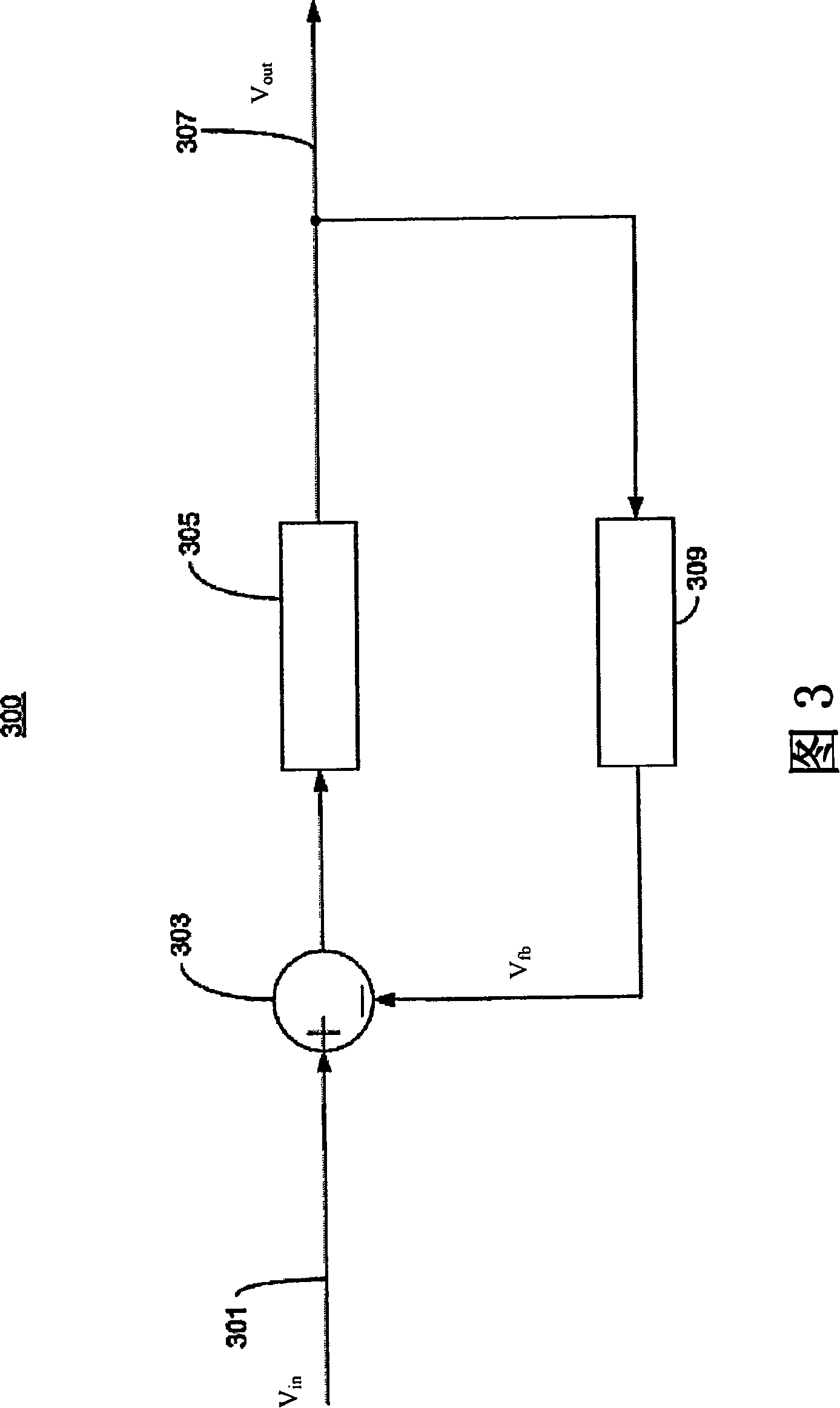

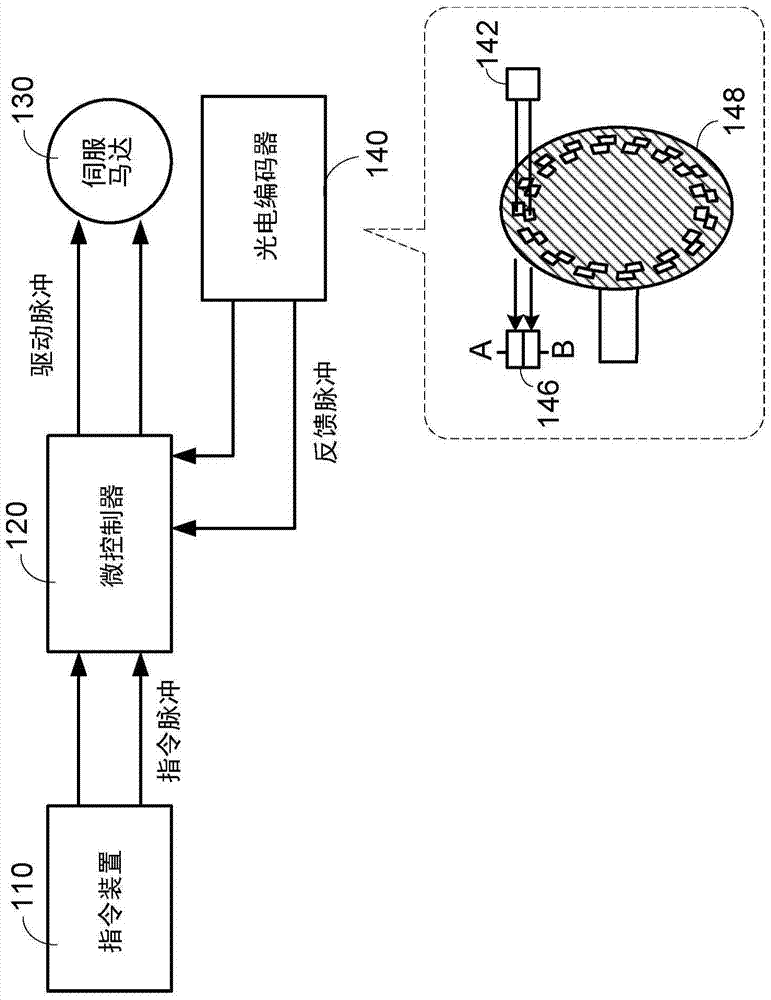

Servo loop circuit

InactiveCN101159724AEliminate generationCorner Frequency Response Time LimitDc level restoring means or bias distort correctionOffset cancellationDirect-conversion receiver

A servo loop circuit suitable for DC offset cancellation in a direct conversion receiver. The servo loop in accordance with the present invention has a low pass filtering device with a smoothly and continuously changed corner frequency, so that the response time of the low pass filtering device can be limited to a short period of time without inducing in additional DC offset. The smoothly and continuously changing of the corner frequency is performed by providing a continuously variable resistance by at least one continuously variable resistive unit, which may be implemented by transistor technique. The resistance of the continuously variable resistive unit is continuously varied by smoothly controlling the level of a voltage signal applied thereto. Thus the corner frequency response time can be limited and the extra DC offset is not admitted.

Owner:MEDIATEK INC

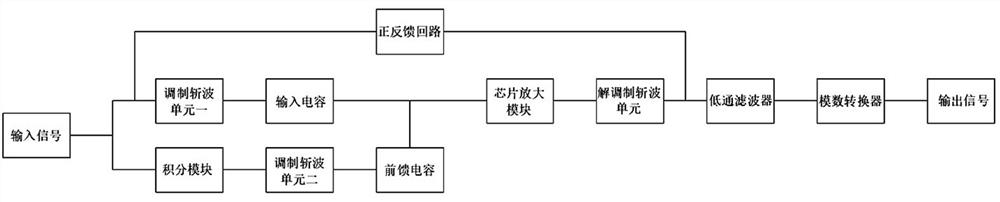

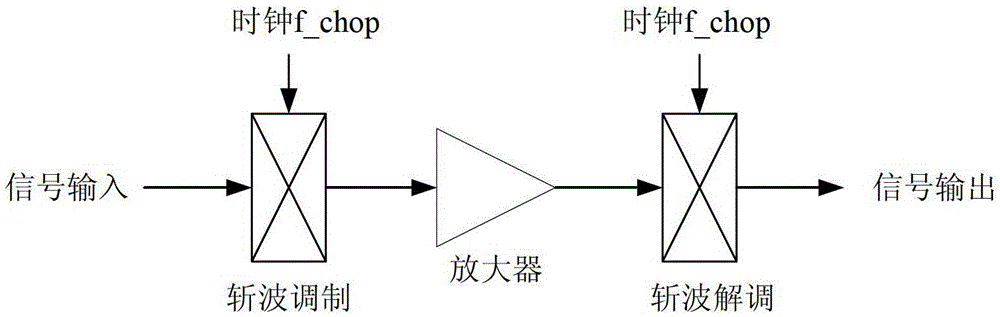

Method and system for eliminating direct current offset between electrodes based on chopping technology

ActiveCN114533087AEliminate DC OffsetDC Offset AccurateDiagnostic recording/measuringSensorsCapacitanceLow-pass filter

The invention discloses a method and a system for eliminating direct current offset between electrodes based on a chopping technology. The method comprises the following steps: step S1, outputting an electroencephalogram signal after chopping modulation and a direct current offset signal between the electrodes; s2, outputting direct current offset current between the electrodes; s3, extracting an integral direct current offset signal; s5, the electroencephalogram signals enter a chip amplification module to be amplified and demodulated, the electroencephalogram signals are returned to an original electroencephalogram signal frequency band, and original electroencephalogram signals are obtained; s6, filtering the original electroencephalogram signals through a low-pass filter to obtain noise-filtered electroencephalogram signals; and S7, transmitting the noise-filtered electroencephalogram signal into a digital-to-analog converter, and converting the noise-filtered electroencephalogram signal into a digital signal. The direct-current servo circuit effectively suppresses direct-current offset between the electrodes, compared with a traditional direct-current servo circuit, the process delay is reduced, meanwhile, the capacitance value of the input capacitor in the circuit is the same as that of the feed-forward capacitor, an ABBA type layout arrangement mode can be adopted, and process errors in the chip manufacturing process are effectively avoided.

Owner:ZHEJIANG LAB

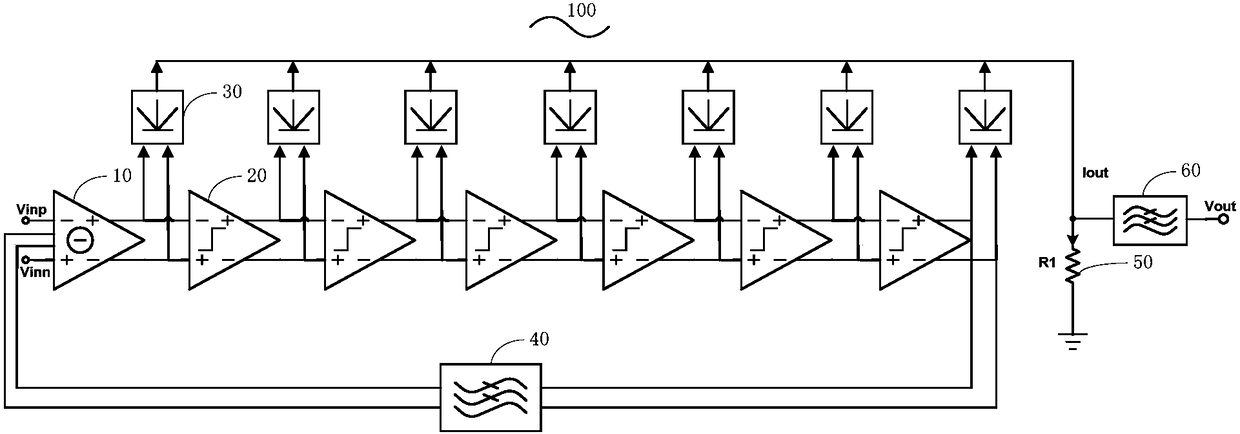

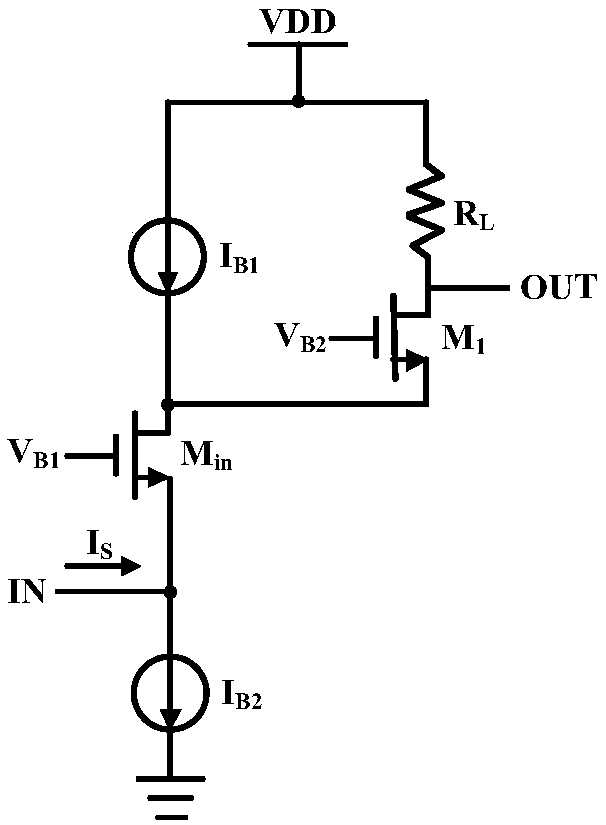

Power detection circuit

InactiveCN108365830ASimple structureEliminate DC OffsetMultiple-port networksReceivers monitoringLow-pass filterEngineering

The invention is applicable to the technical field of communication, and provides a power detection circuit. The power detection circuit comprises offset subtractors, a plurality of limiting amplifiers, a plurality of rectifiers, an active low-pass filter, an impedance device and a passive low-pass filter, wherein a detection signal is input in the first input end of the offset subtractor, the offset subtractors and the plurality of limiting amplifiers are cascaded in sequence, the output end of the offset subtractor and the output end of each level of limiting amplifier are correspondingly connected with an input end of one rectifier separately, the output end of the last level of limiting amplifier is connected with the input end of the active low-pass filter, the output ends of the plurality of rectifiers are connected in sequence and then are connected with both the input end of the impedance device and the input end of the passive low-pass filter, the output end of the active low-pass filter is connected with the second input end of the offset subtractor, and the output end of the impedance device is grounded. The power detection circuit can rapidly eliminate direct current offset of a detection signal of low frequency, and can reduce the layout area remarkably.

Owner:SHENZHEN JOINTWAY IC DESIGN CO LTD

Radio frequency transmitting-receiving device

ActiveCN101719776BReduce power consumptionSolve the problem of ultra-low power consumptionTransmissionWireless sensor networkingSystem structure

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

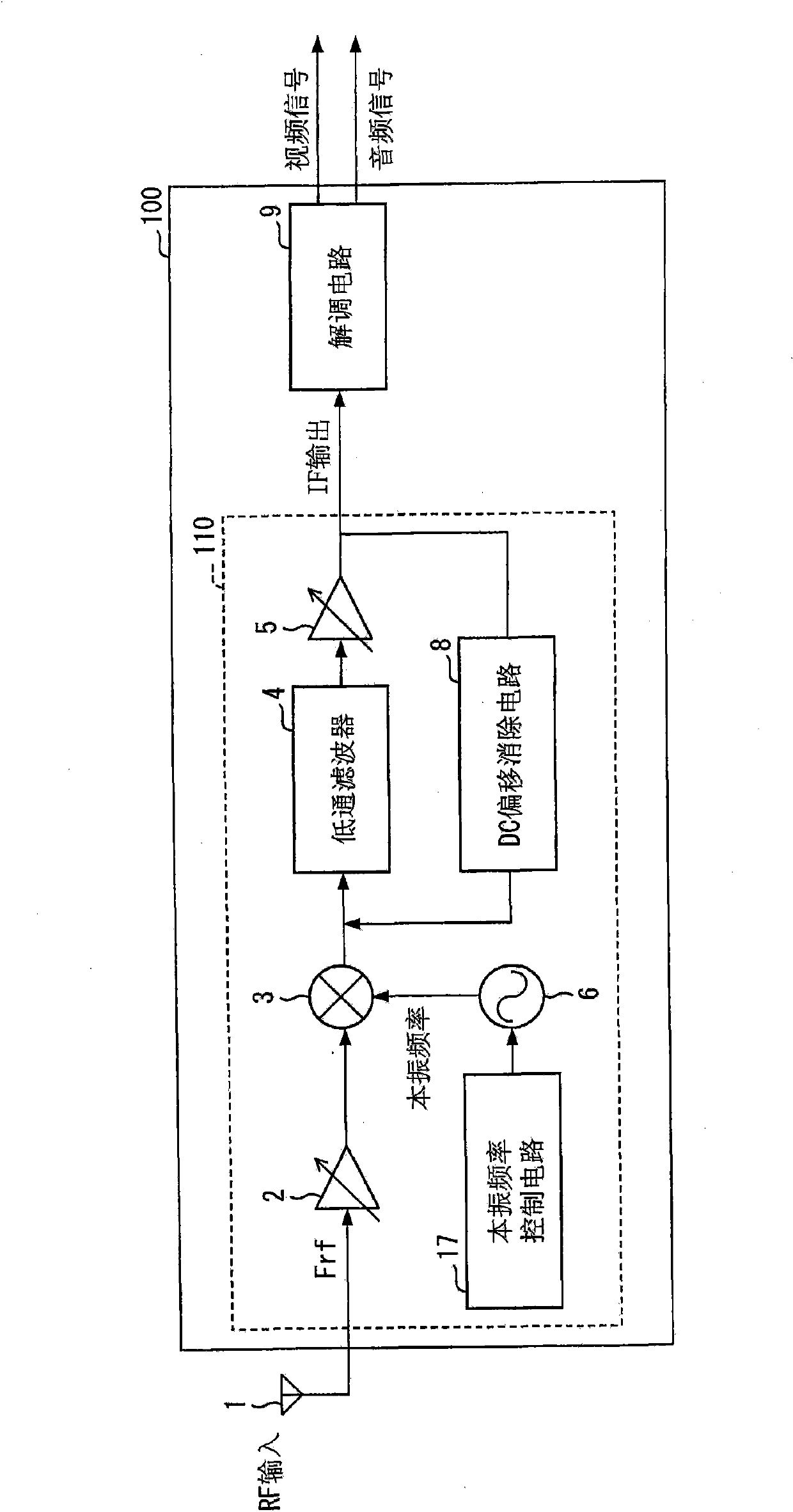

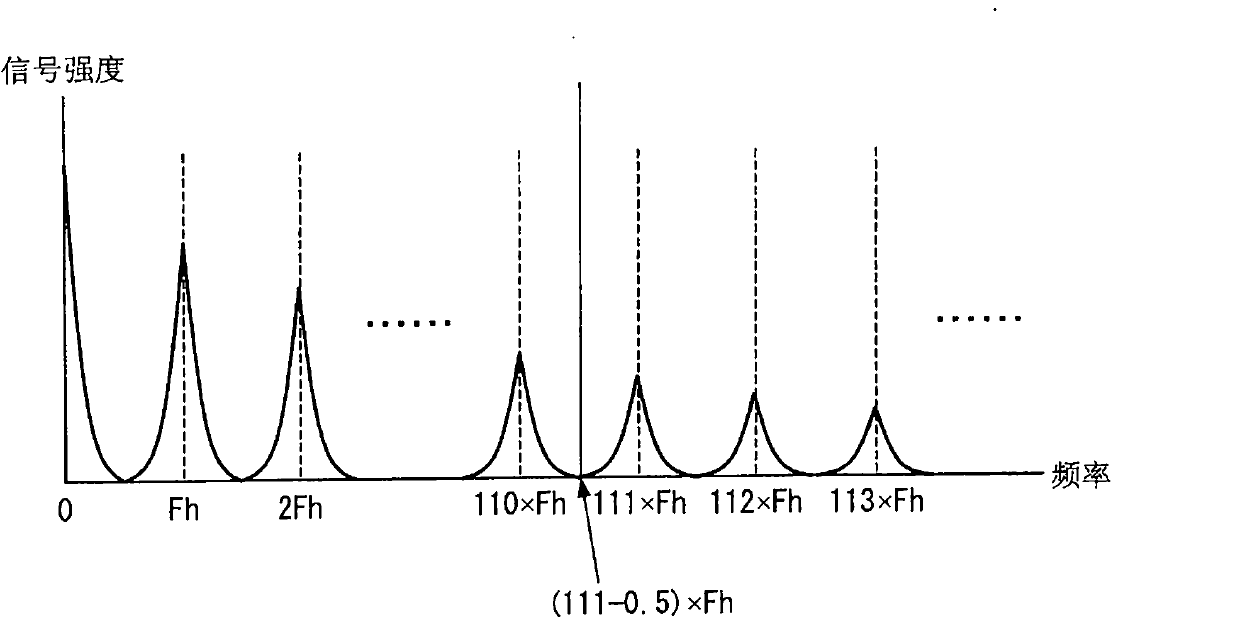

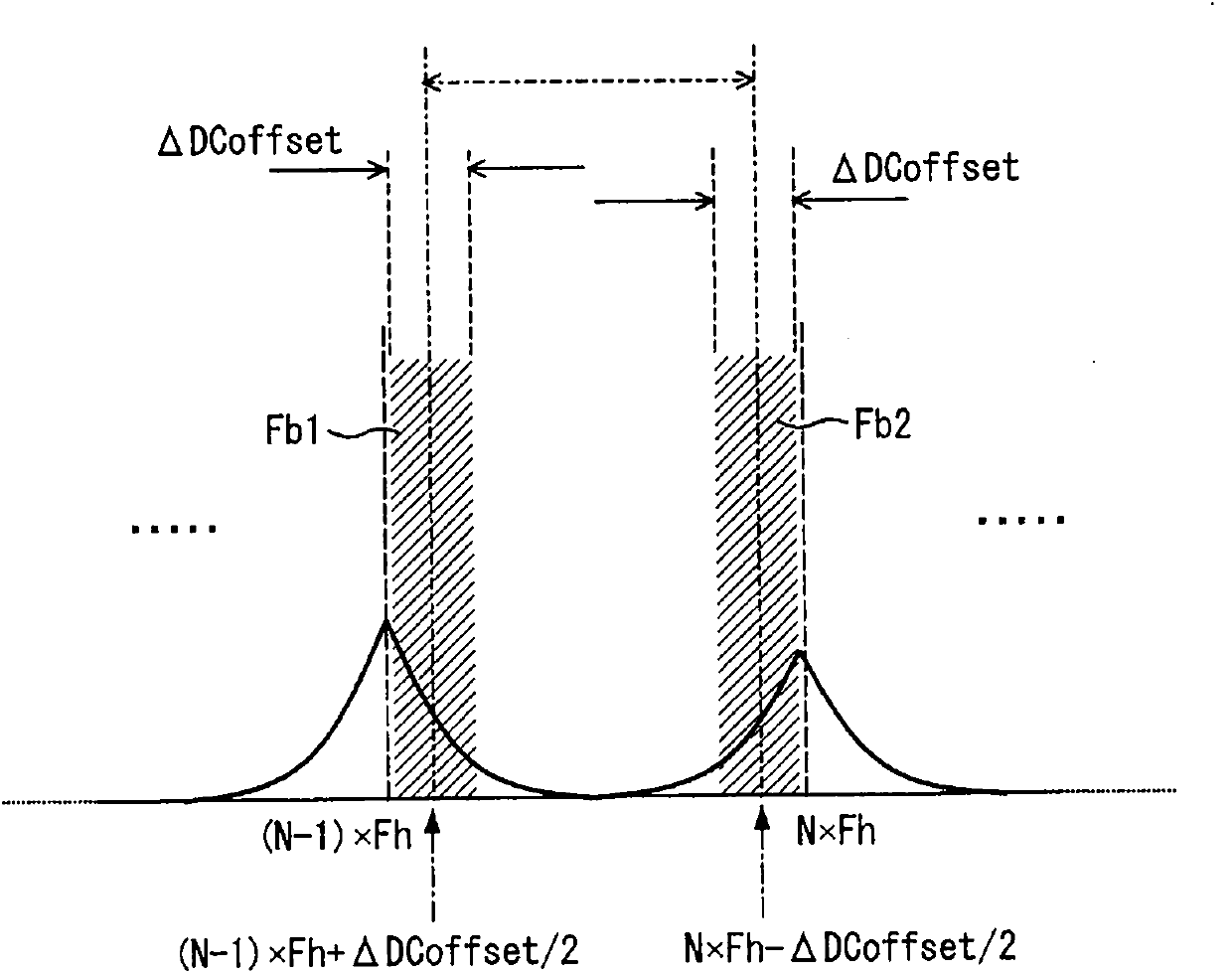

Front-end circuit, tuner, and television broadcasting receiver

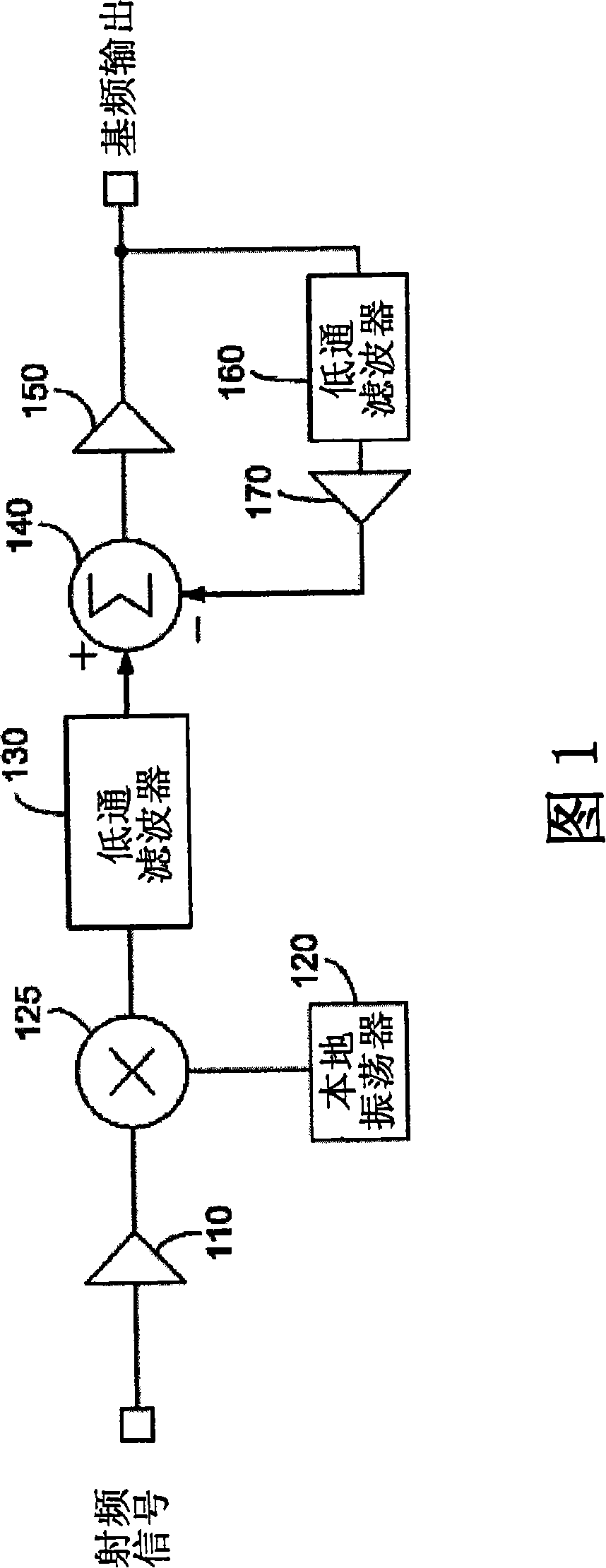

InactiveCN102006436AEliminate DC OffsetTelevision system detailsResonant circuit detailsFrequency spectrumFrequency mixer

A front-end circuit according to the present invention includes a VCO which oscillates a local signal, a mixer which converts an RF signal Frf into a baseband signal, a DC offset cancel circuit which detects a DC offset contained in the baseband signal and then eliminates the DC offset, and a local frequency control circuit which controls a frequency of the local signal. In a case where the RF signal is an analog television signal, the local frequency control circuit controls the frequency of the local signal so that a frequency of the baseband signal differs from each frequency spectrum of aluminance signal contained in a video signal which is generated by demodulating the baseband signal. This makes it possible to provide the front-end circuit which can prevent video distortion caused when a frequency spectrum is eliminated from the luminance signal.

Owner:SHARP KK

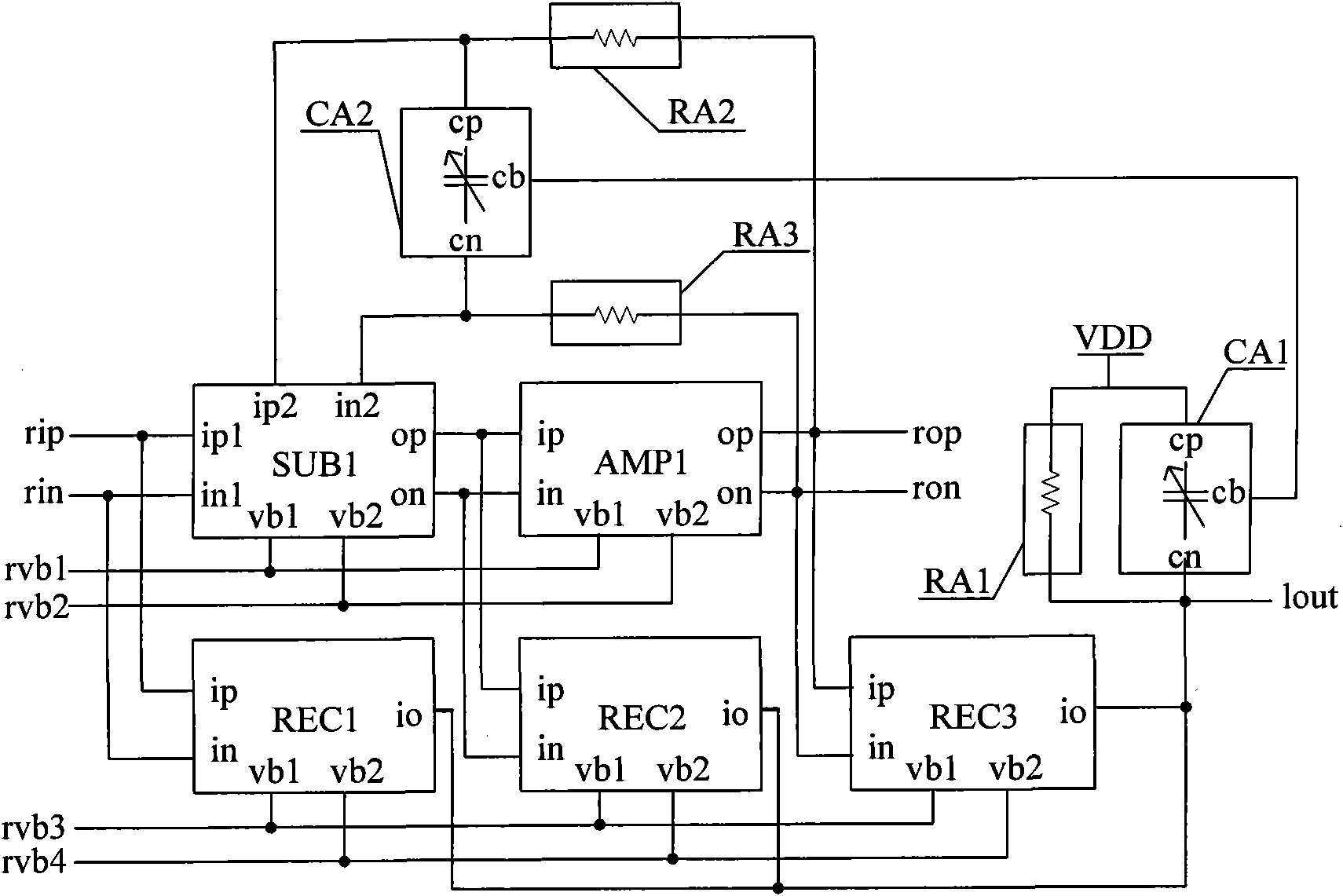

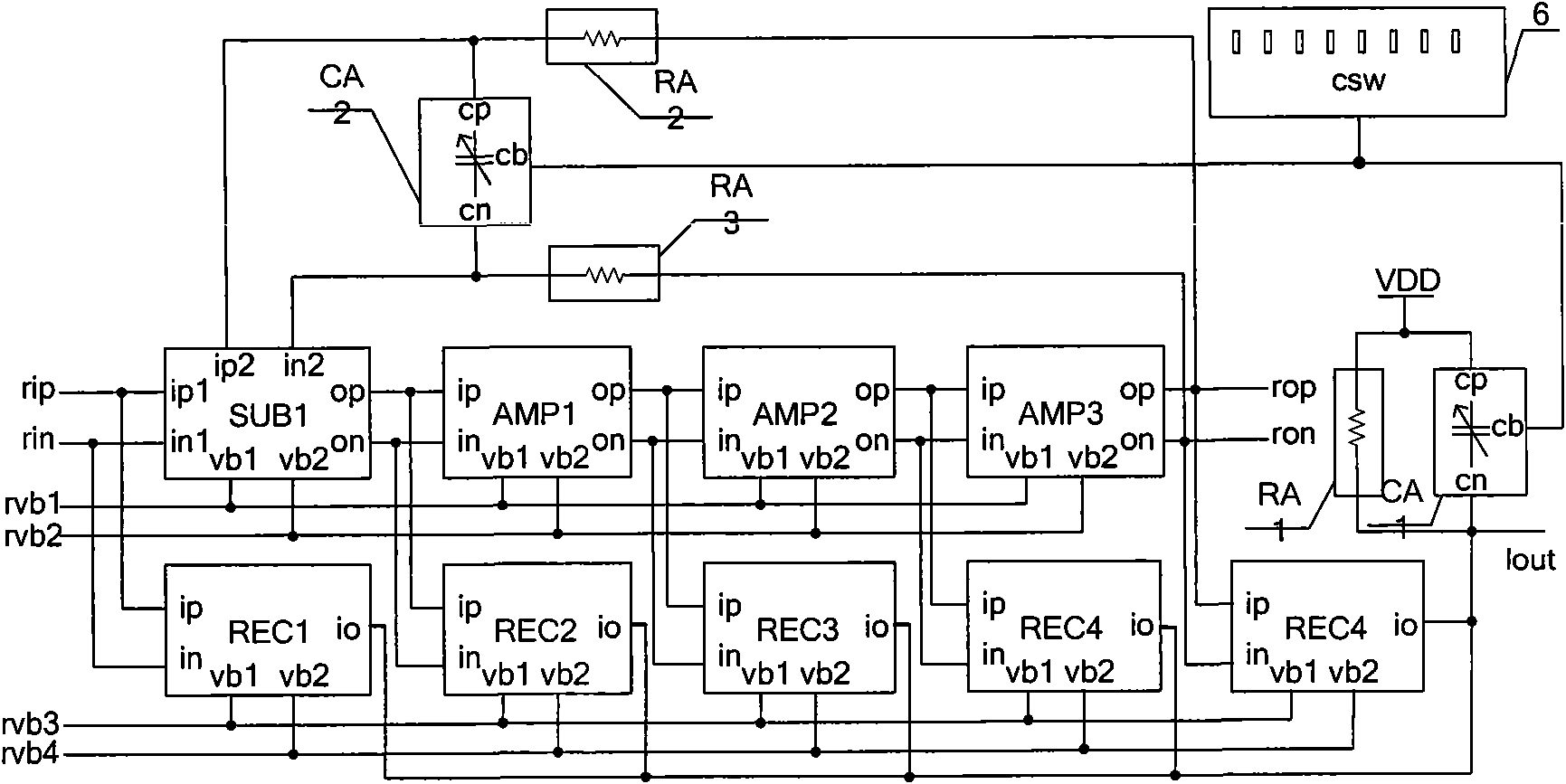

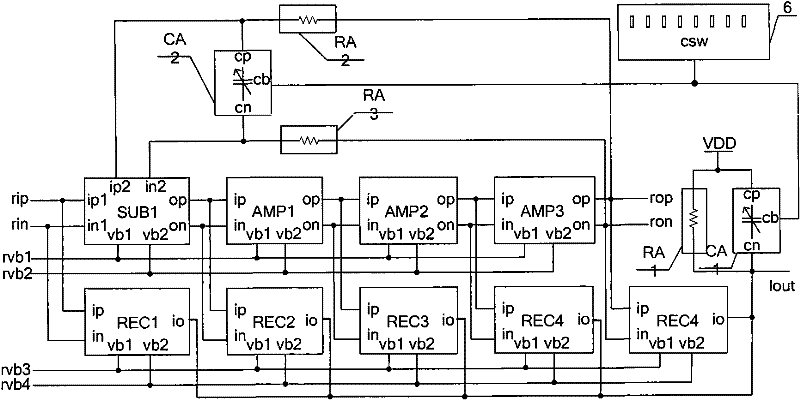

Logarithmic amplifier

ActiveCN101777876AReduce power consumptionImprove the ability to resist PVT deviationAmplifier modifications to raise efficiencyAmplifier with semiconductor-devices/discharge-tubesCapacitanceResistance capacitance

The invention discloses a logarithmic amplifier which comprises a subtracter in a folding structure, at least one amplifier in a folding structure, at least three rectifiers in a current subtracter structure, two variable capacitor arrays and three resistor arrays. The logarithmic amplifier provided by the invention has lower power and stronger anti-PVT bias capability, automatically corrects a resistance-capacitance time constant by controlling a time constant correction circuit, ensures the response speed and the ripple characteristics of an output signal in case of PVT bias, ensures the stability of the logarithmic amplifier and eliminates the direct current shift. Further, by adjusting the structures of the variable capacitor arrays, the invention improves the accuracy of the whole capacitance value and ensures that a feedback network can effectively eliminate the direct current shift of the logarithmic amplifier and ensure the stability of a feedback loop.

Owner:TSINGHUA UNIV

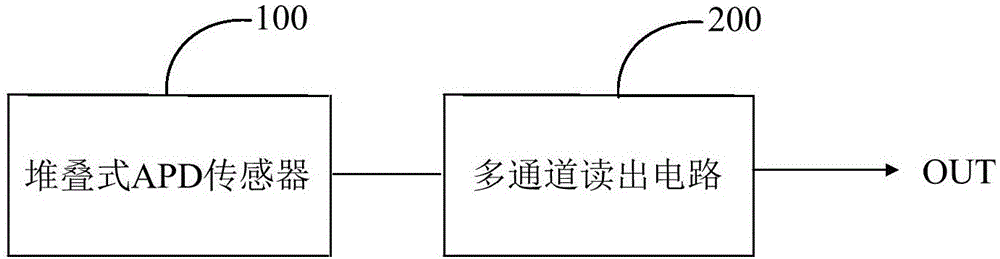

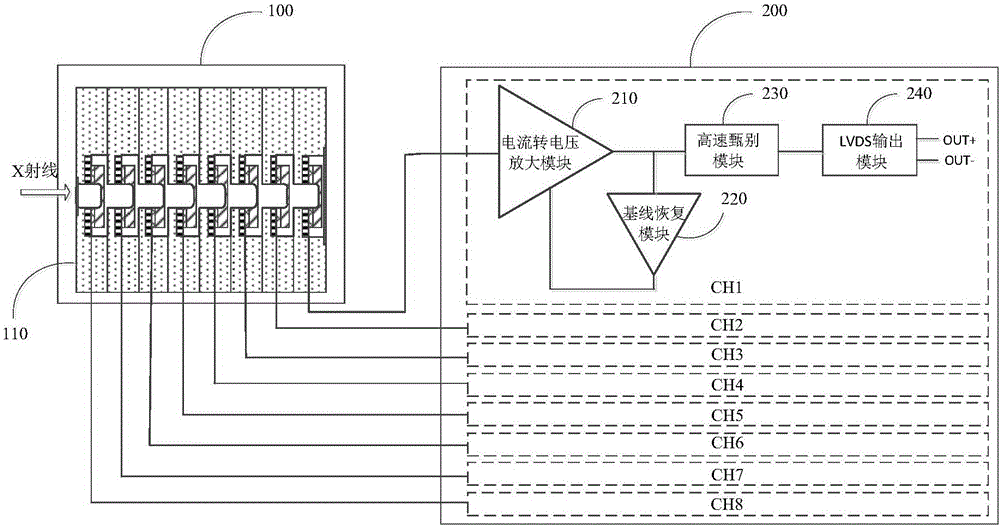

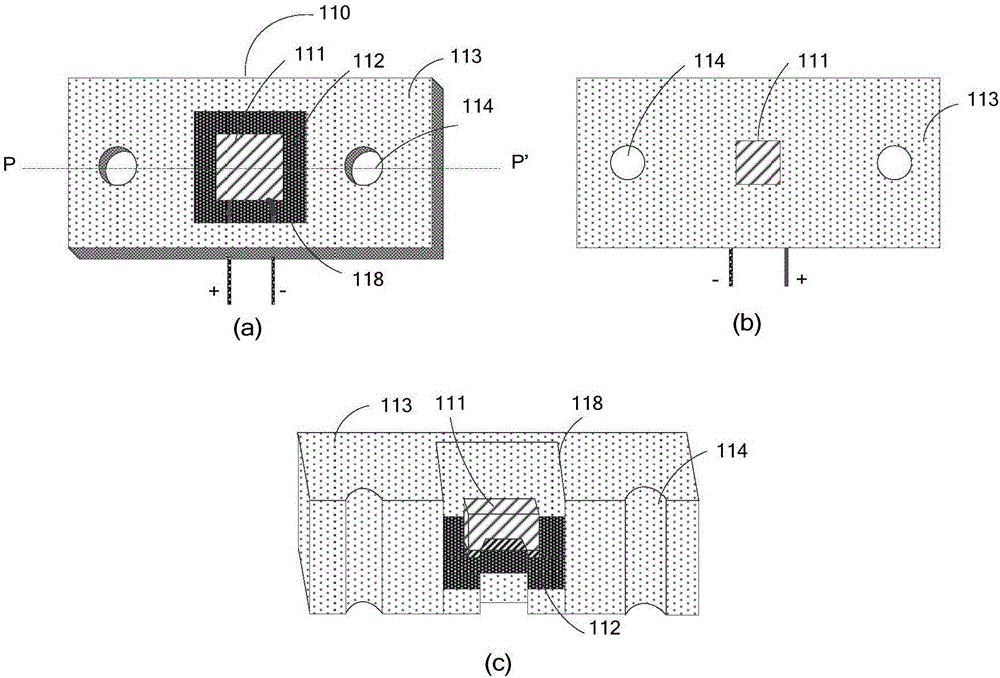

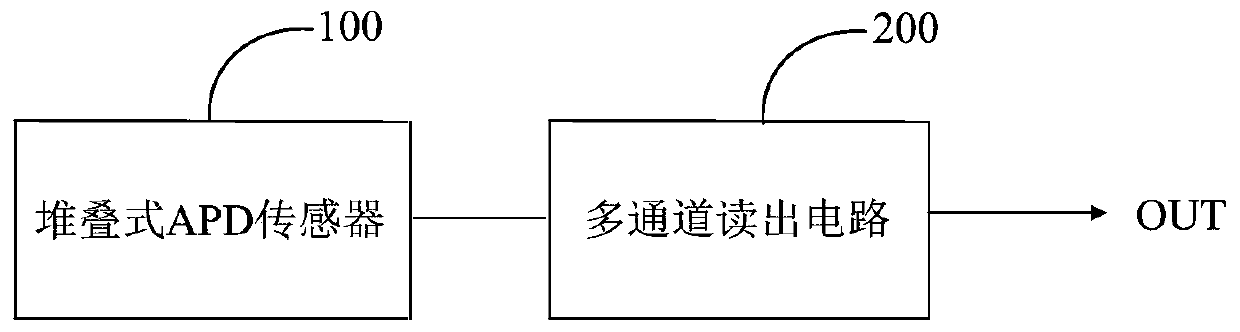

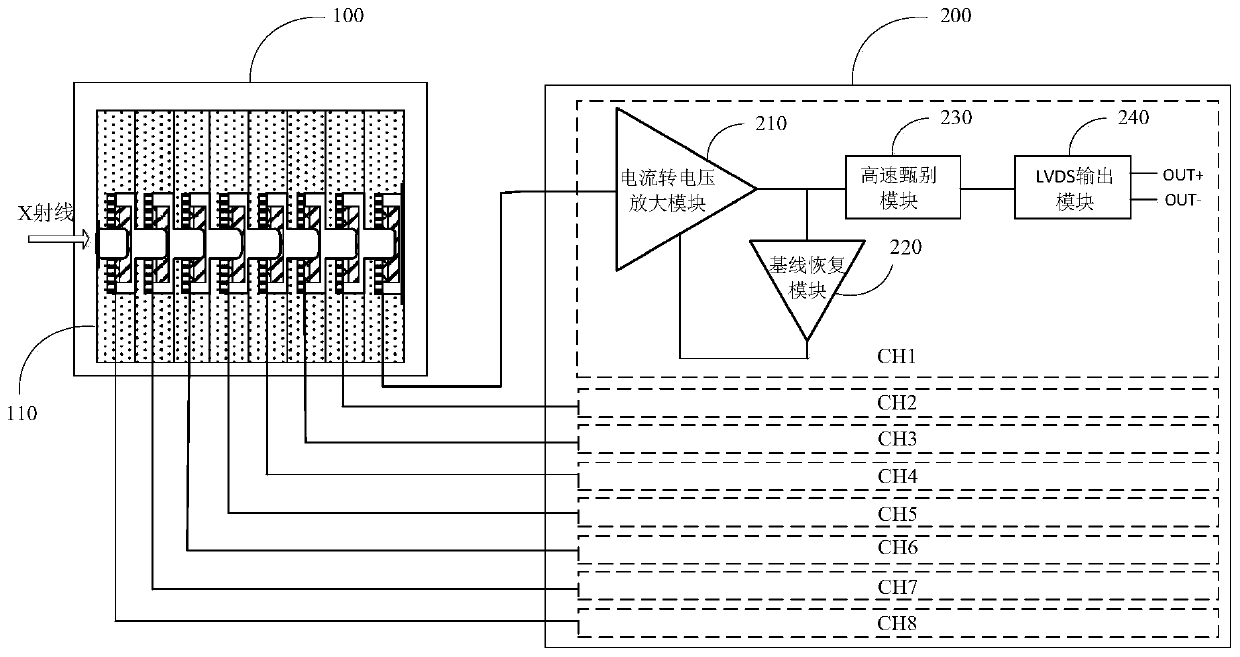

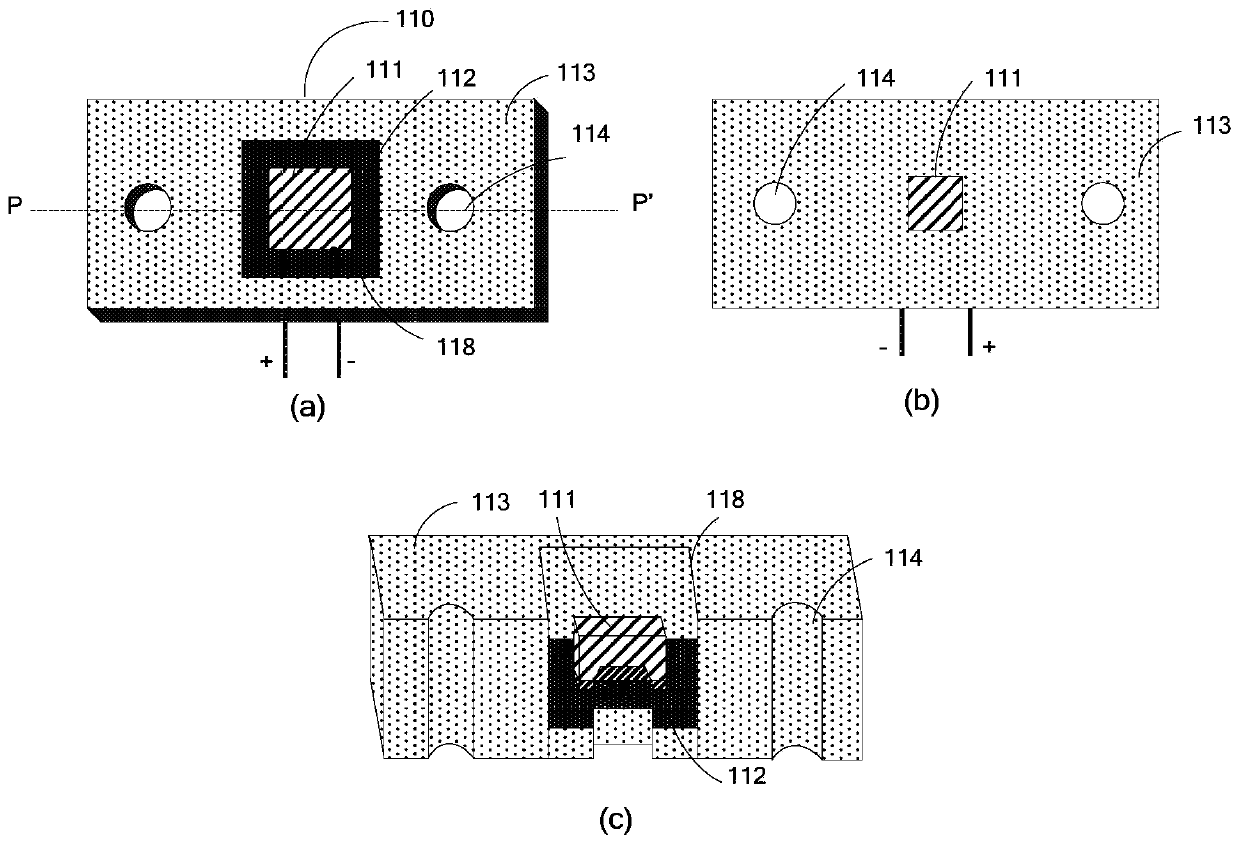

Sensor and detector on basis of avalanche photodiodes

ActiveCN106353785AImprove quantum efficiencyImprove matchX/gamma/cosmic radiation measurmentQuantum efficiencyPower flow

The invention relates to a sensor and a detector on the basis of avalanche photodiodes. The sensor comprises a plurality of APD (avalanche photodiode) sensors. The multiple APD sensors are parallelly sequentially stacked on one another and include single-tube APD sensors or array APD sensors. The detector comprises the sensor and a multi-channel reading circuit. The multi-channel reading circuit comprises current-to-voltage amplification modules and baseline restoration modules, is electrically coupled with the sensor and is used for reading out current signals outputted by the sensor. The sensor and the detector have the advantages that the sensor is configured with the multiple APD sensors which are parallelly sequentially stacked on one another, and accordingly the sensor and the detector are high in quantum efficiency under the condition of sub-nanosecond time resolution; the detector is configured with the multi-channel reading circuit, weak signals outputted by the APD sensors can be read out, the APD sensors can be effectively matched with one another, accordingly, the time resolution performance of the APD detector can be improved, and the integration level of the APD detector can be upgraded.

Owner:INST OF HIGH ENERGY PHYSICS CHINESE ACADEMY OF SCI

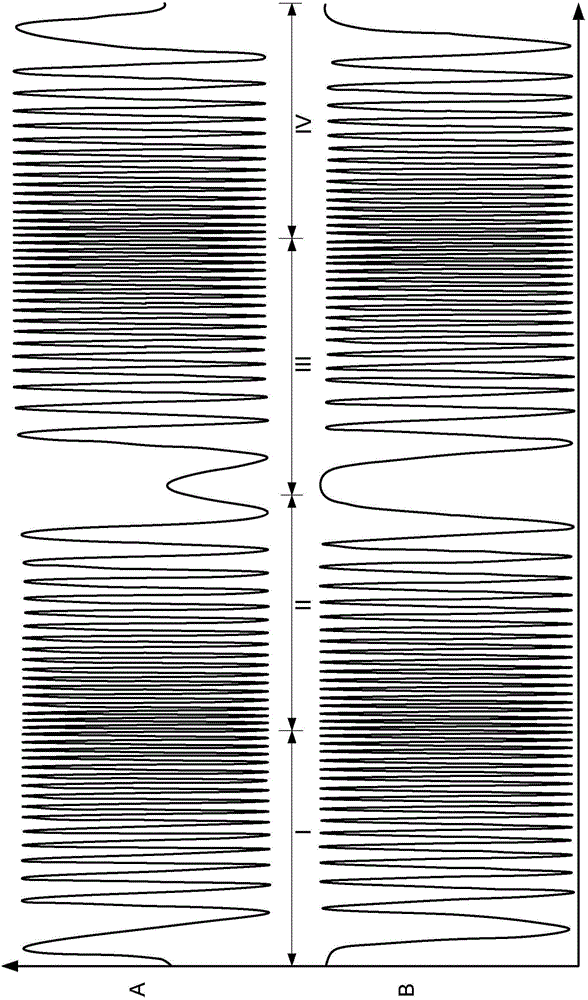

Signal processing apparatus applied to time-varying signals

The invention discloses a signal processing apparatus applied to time-varying signals. The signal processing apparatus comprises a summator and a weighting integrator. The summator is used for receiving a first input signal and an integrated signal and generating a first output signal, wherein the first output signal is equal to a result obtained by subjecting the first input signal and the integrated signal to subtraction. The weighting integrator is used for receiving the first output signal and generating the integrated signal and comprises a weighting function generator, a multiplier and an accumulator, wherein the weighting function generator is used for receiving the first output signal and generating a weighting function when the first output signal passes by the position nearby a zero crossing point, the multiplier is used for multiplying the weighting function by the first output signal, and the accumulator is connected with the multiplier and used for accumulating the result obtained by multiplying the weighting function by the first output signal and generating the integrated signal according to the accumulated result. The signal processing apparatus applied to the time-varying signals has the advantage that direct-current offset in a photoelectronic signal can be eliminated.

Owner:RDC SEMICON CO LTD

Signal processing device for time-varying signals

Owner:RDC SEMICON CO LTD

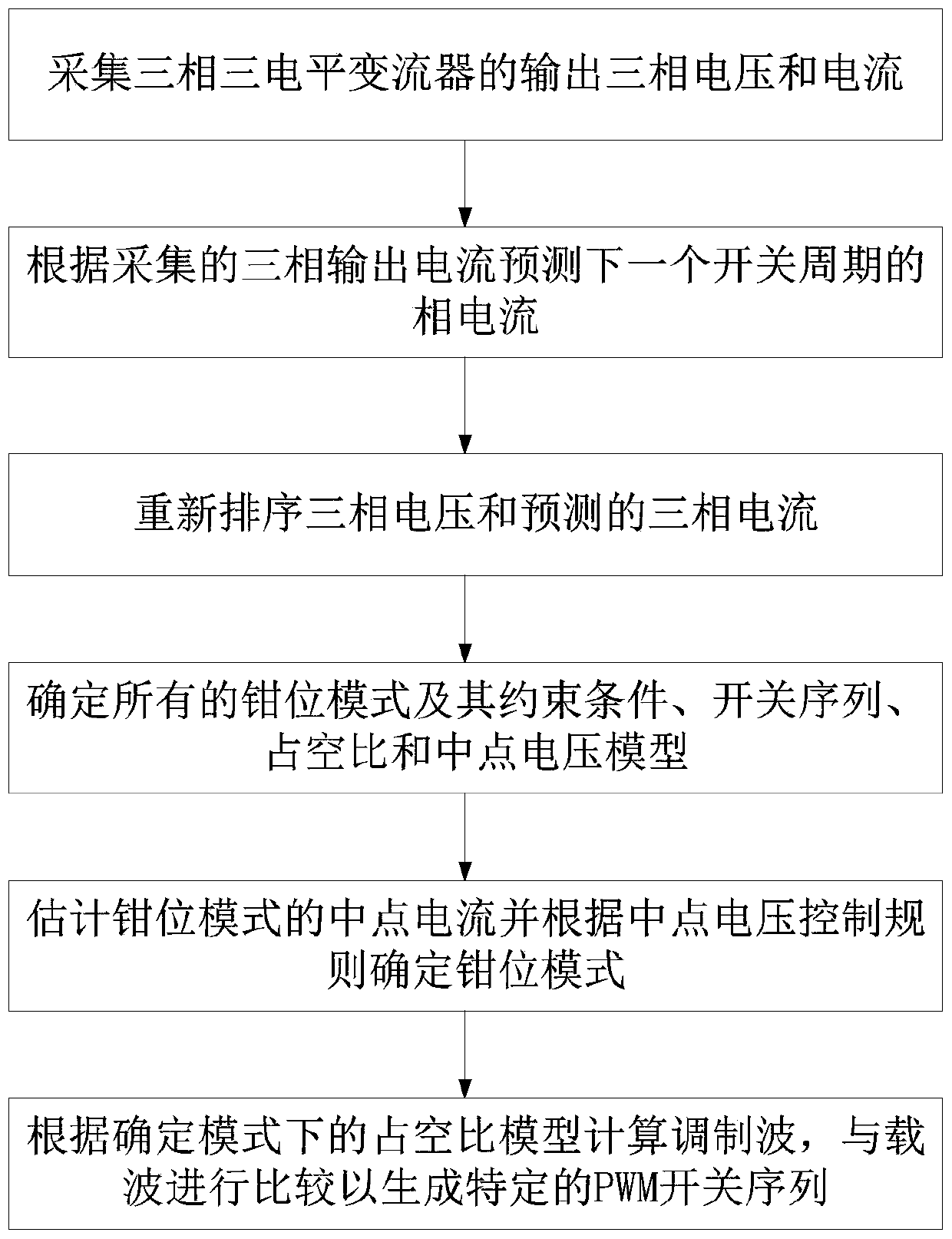

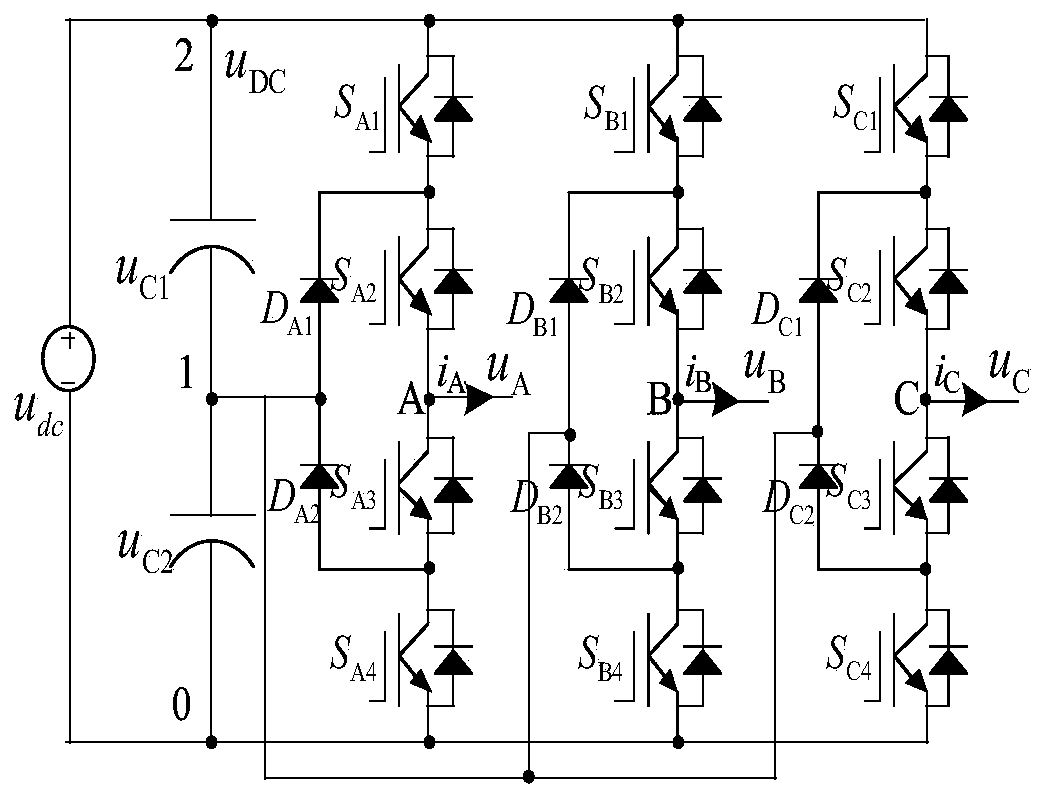

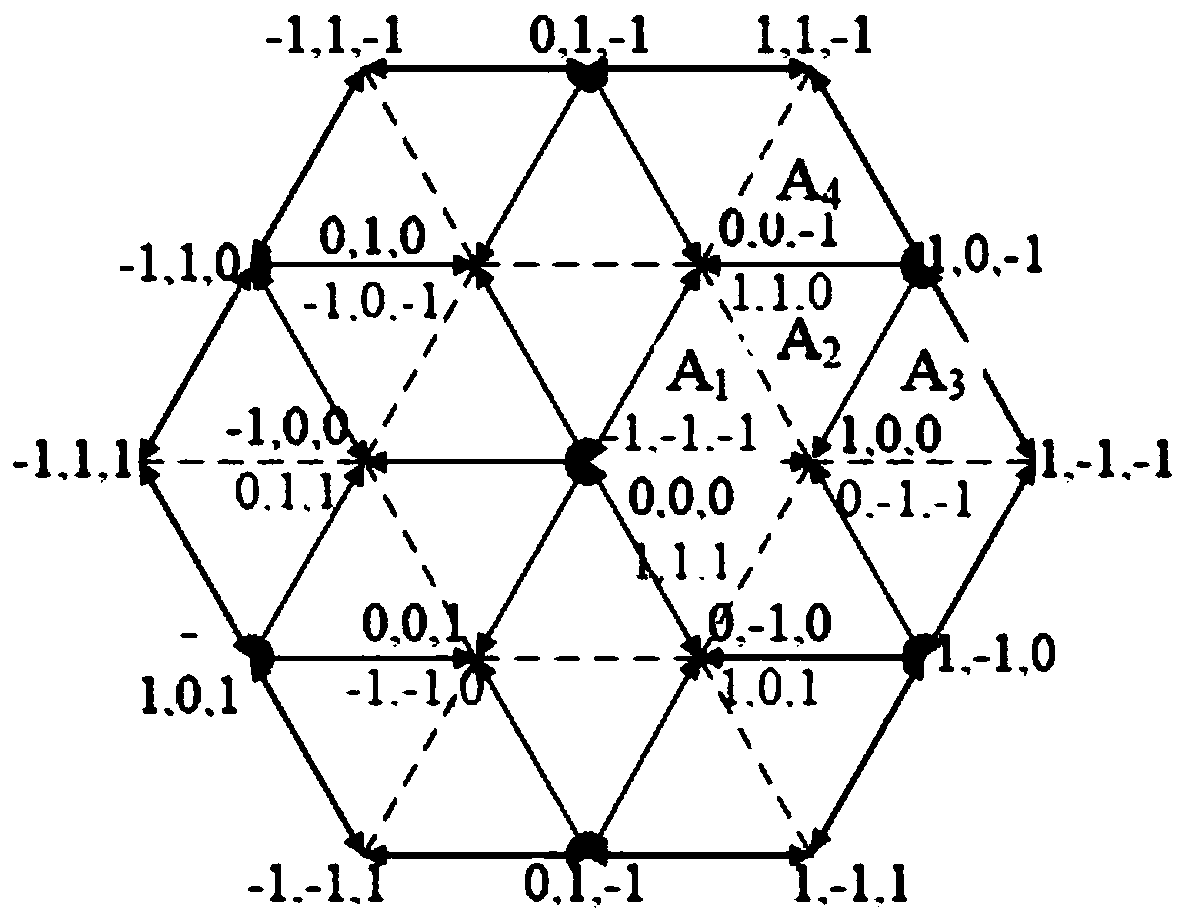

A Discontinuous Pulse Width Modulation Method for Three-level Converter

ActiveCN109600065BReduce common mode voltageReduce lossEfficient power electronics conversionAc-dc conversionPhase currentsSwitching cycle

The invention relates to a discontinuous pulse width modulation method for a three-level converter that reduces the common-mode voltage and eliminates the DC offset of the midpoint voltage. Firstly, the three-phase voltage and the three-phase current of the three-level converter are collected for preprocessing , reorder the three-phase voltages, and use the three-phase currents to predict the phase currents of the next switching cycle and reorder them, and then get all possible clamping modes according to the rearranged phase voltages, according to the rearranged phase currents of the next cycle Calculate the mid-point current, and determine the clamping mode according to the mid-point voltage control rule to control the mid-point voltage. During the modulation process, the common-mode voltage is reduced by abandoning the basic vector with high common-mode voltage, and finally according to the clamping The duty cycle model of the mode calculates the modulation wave and compares it with the carrier type determined in the clamp mode to generate a specific PWM switching sequence. The modulation method proposed by the invention can not only effectively control the balance of the midpoint voltage, but also reduce the switching loss of the system.

Owner:合肥庐阳科技创新集团有限公司

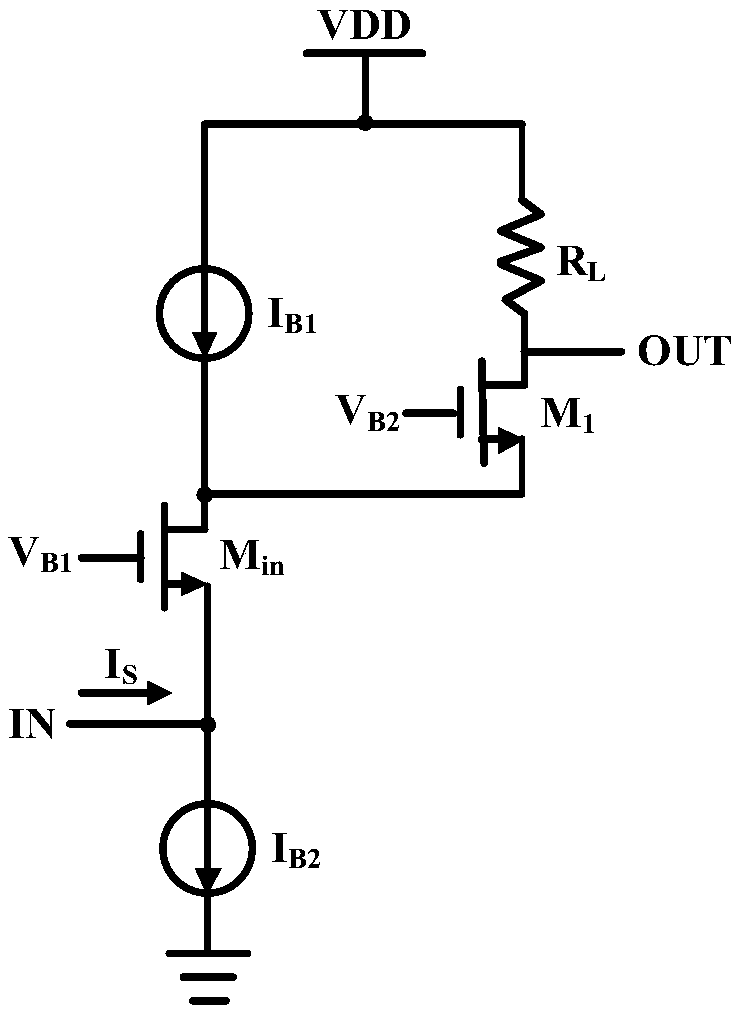

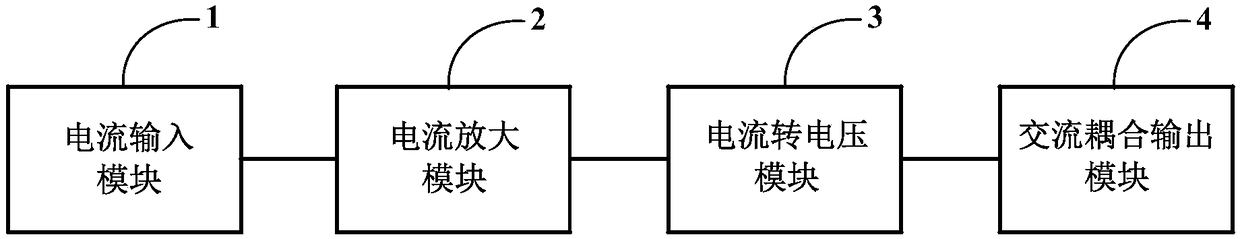

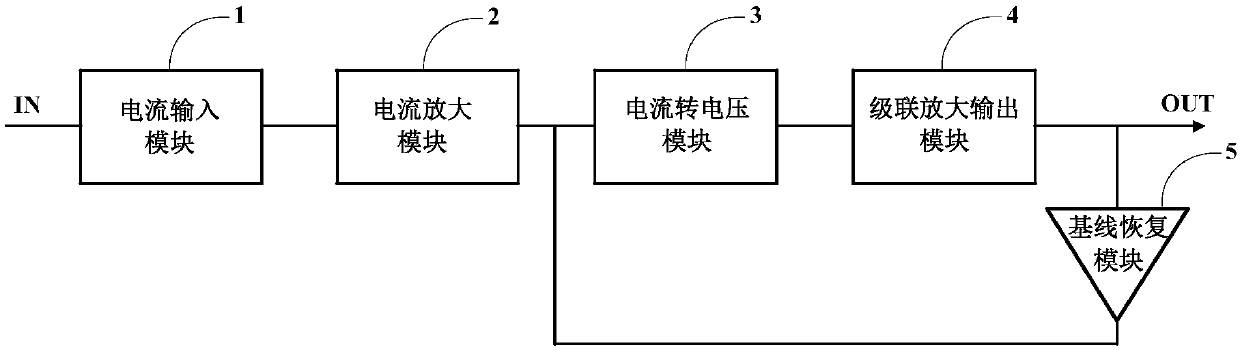

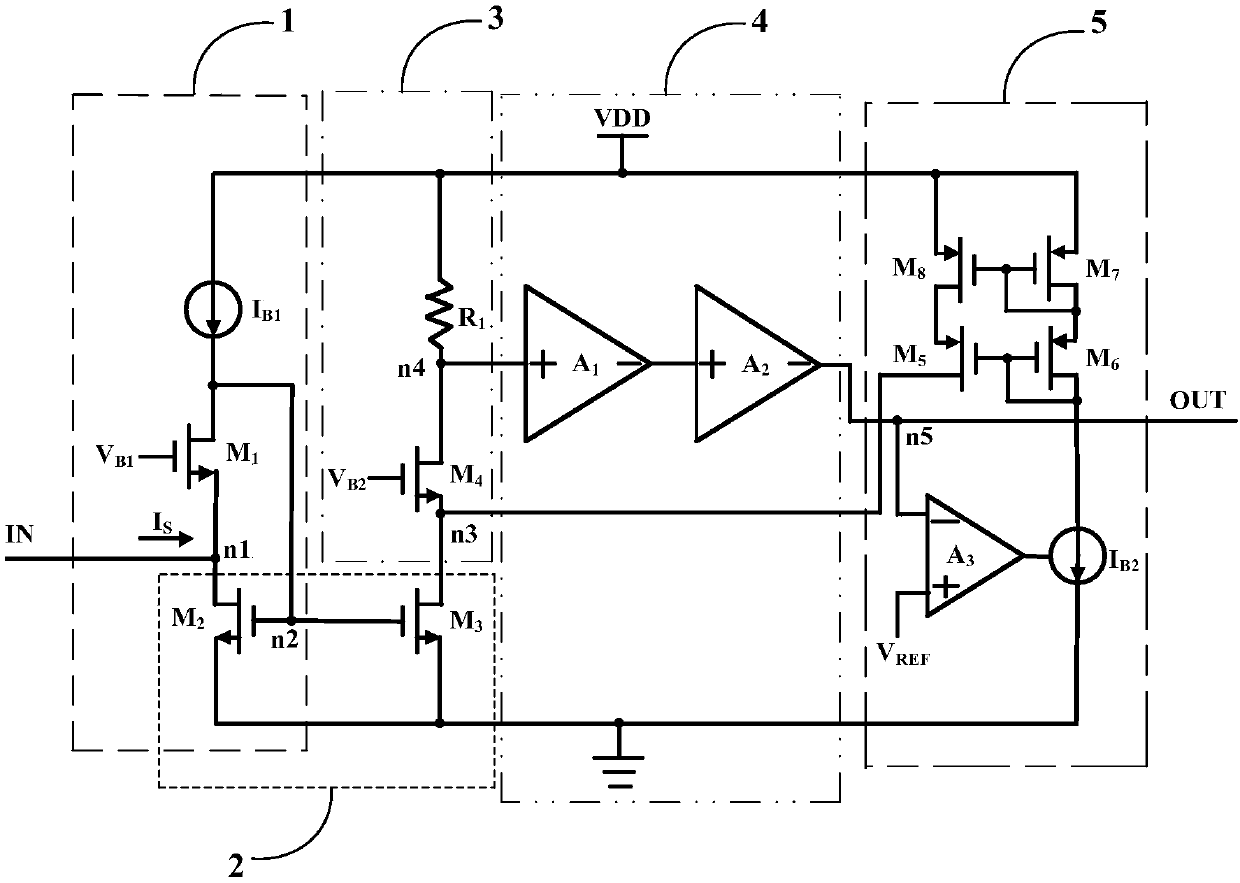

Current preamplifier, time-resolved readout circuit and time-resolved detection device

ActiveCN106341088BLow equivalent input impedanceReduce noiseAmplifier modifications to reduce noise influenceAmplifier modifications to reduce temperature/voltage variationLow noiseAudio power amplifier

The invention relates to a current pre-amplifier, a time resolution reading circuit and a time resolution detection device. The current pre-amplifier comprises a current input module, a current amplifying module, a current-to-voltage module and an alternating current coupling output module, wherein the current input module is used for receiving a current signal; the current amplifying module is used for receiving the current signal from the current input module and amplifying the current signal; the current-to-voltage module is used for receiving the current signal amplified by the current amplifying module and converting the amplified current signal into a voltage signal; and the alternating current coupling output module is used for eliminating the direct-current component of the voltage signal. The current pre-amplifier configured in the invention is easy to realize, and has the characteristics of low equivalent input impedance, low noise and the like, so that small input signals can be distinguished.

Owner:INST OF HIGH ENERGY PHYSICS CHINESE ACAD OF SCI

Burst signal detection circuit without resetting

PendingCN113489476AEliminate DC OffsetAvoid false triggersElectronic switchingElectromagnetic receiversTransconductanceCapacitance

The invention discloses a reset-free burst signal detection circuit, and the circuit is characterized in that a burst detection function is realized by charging a load capacitor through a three-input transconductance amplifier after a burst signal high-frequency component is loaded on a common-mode level of the burst signal high-frequency component. The direct-current offset of the signal can be eliminated by loading the high-frequency component of the signal to the common-mode level of the signal; for a three-input transconductance amplifier, the transconductance amplifier outputs current to charge a load capacitor in the presence of an emergent alternating current signal, so the voltage of an output node is increased, and an emergent detection signal is generated. The burst detection circuit has the advantages that reset signals are not needed, the structure is simple, the working speed is high, and power consumption is low; the number of components is reduced, the occupied chip area is smaller, the circuit integration degree is improved, the cost is reduced, and burst signal detection is easily achieved.

Owner:SOUTHEAST UNIV +1

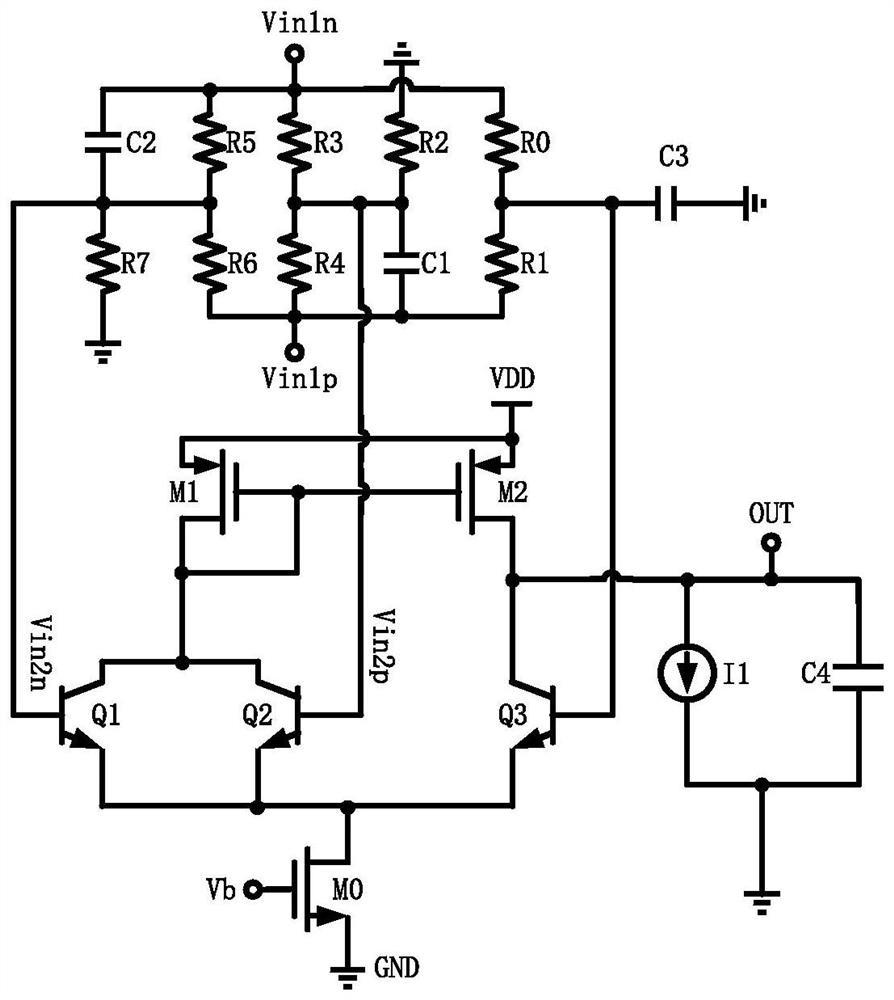

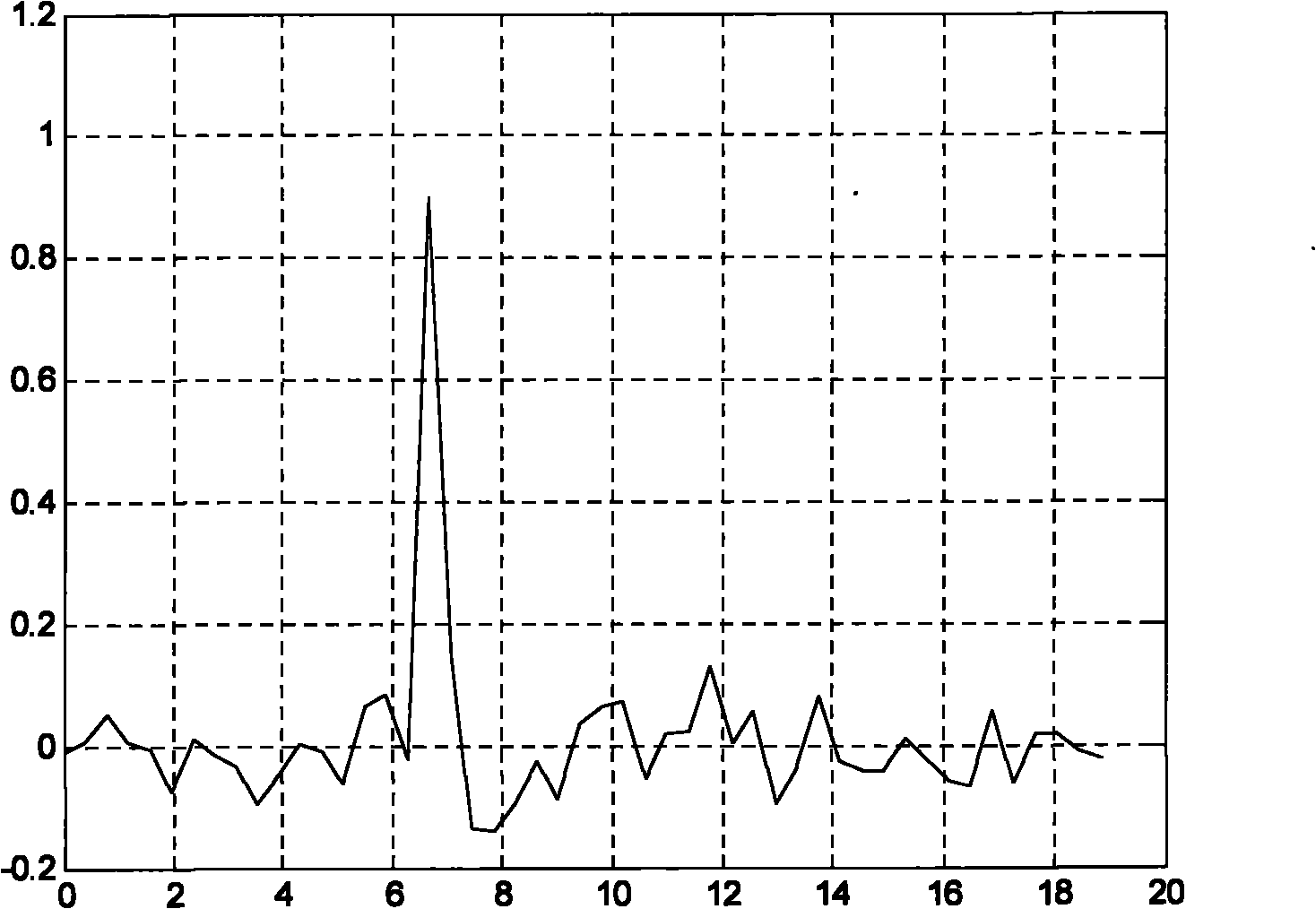

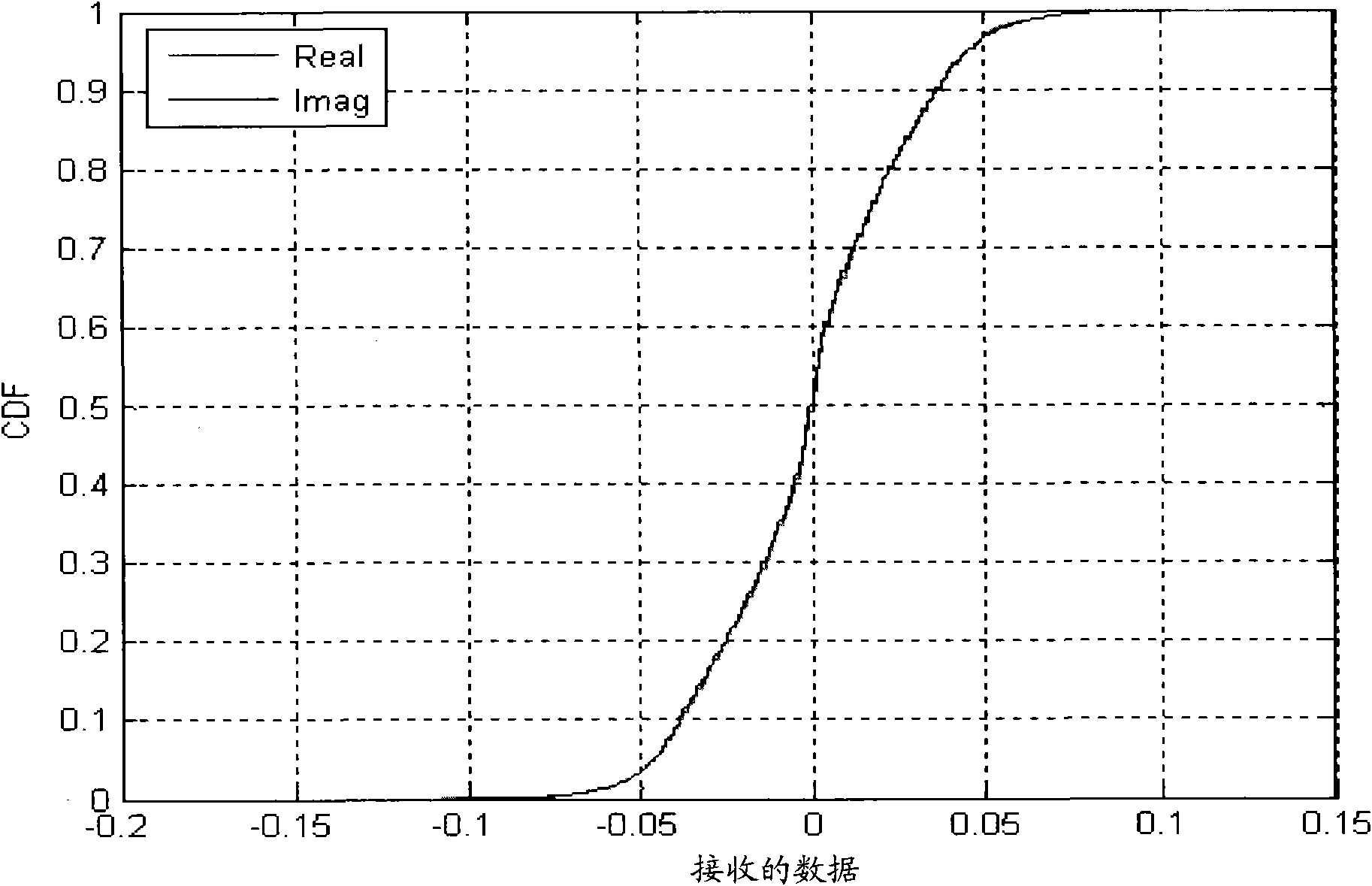

Method and device for eliminating direct current bias

ActiveCN102082750BEliminate DC OffsetImprove RF reception performanceDc level restoring means or bias distort correctionRadio frequencyComputer science

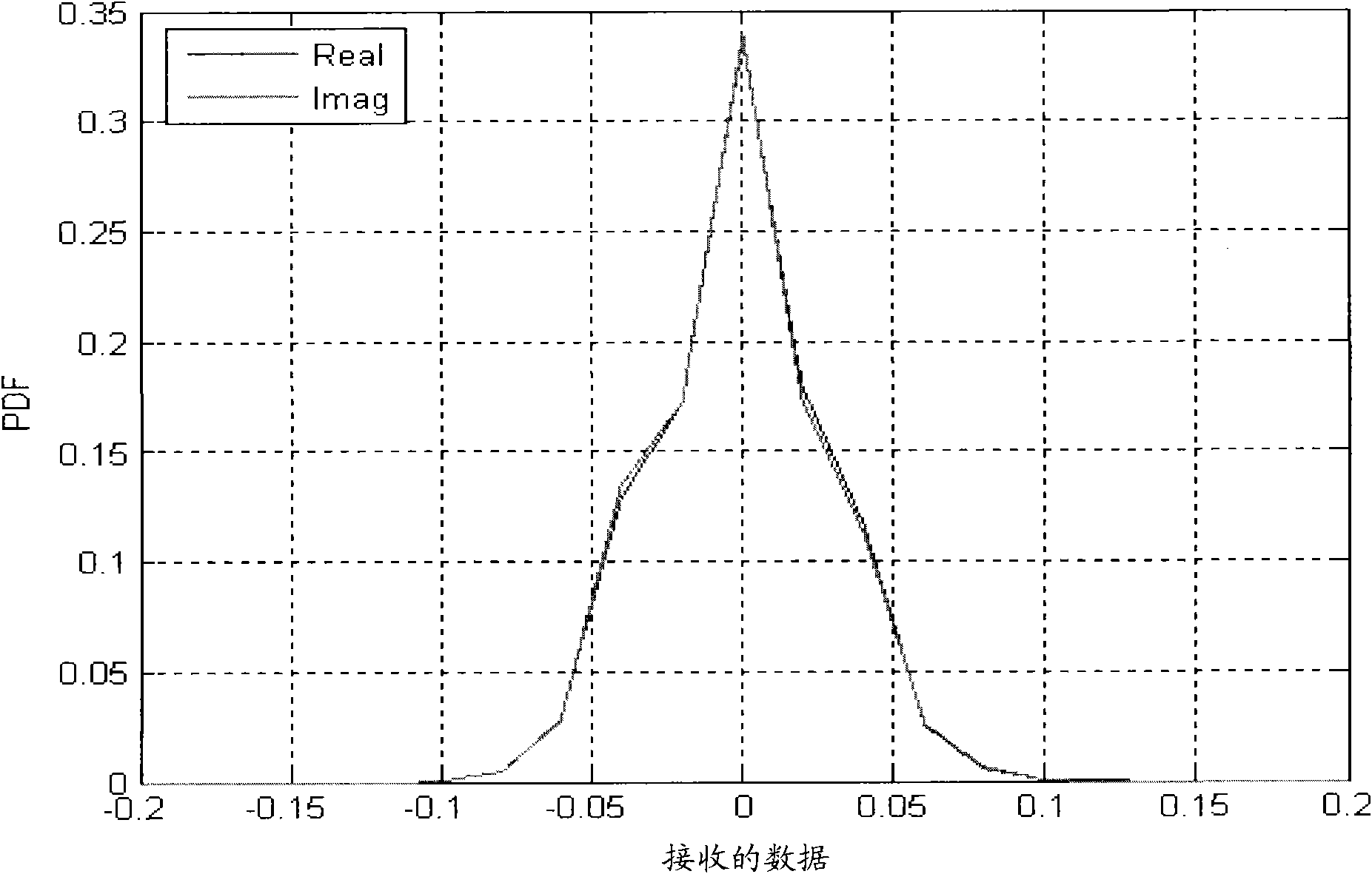

The invention relates to the technical field of radio frequency receiving, and discloses a method and device for eliminating direct current bias. The method comprises the following steps: acquiring a preset amount of data received on a digital base band; calculating the median of the preset amount of data, and adopting the median as the current direct current bias; and subtracting the direct current bias from the data received on the digital base band as the data actually received on the digital base band. By adopting the method and device provided by the invention, direct current bias in radio frequency receiving can be effectively eliminated, the radio frequency receiving performance can be improved, and the burst interference which can not be overcome by an averaging method can be inhibited.

Owner:大唐电信科技产业控股有限公司

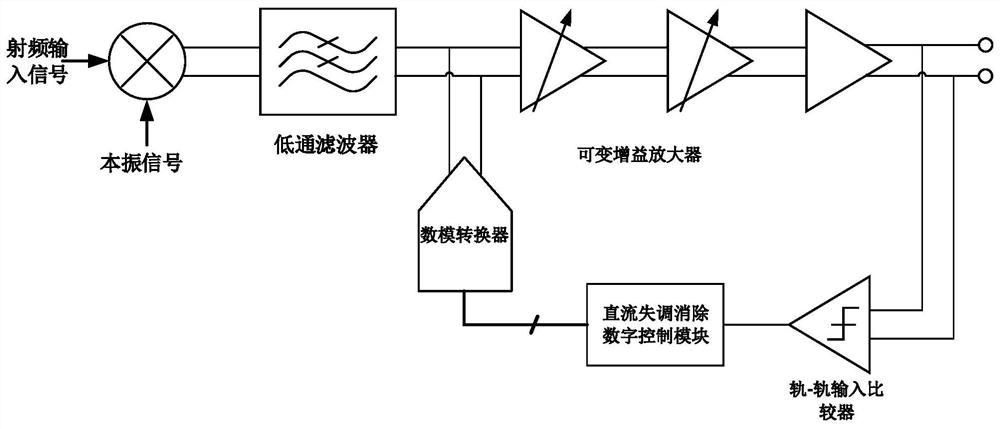

Digital-assisted direct-current offset cancellation circuit and digital control method thereof

PendingCN113242049AEliminate DC OffsetEliminate problems such as difficult compromises in response speedTransmissionOffset cancellationSoftware engineering

The invention relates to the field of integrated circuits, in particular to a digital-assisted direct-current offset cancellation circuit and a digital control method thereof. The direct-current offset cancellation circuit comprises a variable gain amplifier, a comparator with a rail-rail input voltage range, a digital control module and a 11-bit digital-to-analog converter, and an electric signal is input into the variable gain amplifier; a comparator with a rail-rail input voltage range samples differential voltage output by the variable gain amplifier in a given time window, polarity and corresponding times of the sampled differential voltage are recorded in a digital control module, the digital control module selects a direct current compensation mode according to recorded information and updates the differential voltage, the updated differential voltage is used as the input of a 11-bit digital-to-analog converter, and the output end of the 11-bit digital-to-analog converter is connected with the input end of a variable gain amplifier; and according to the invention, the direct-current offset of the receiver can be effectively eliminated.

Owner:思澈科技(上海)有限公司

An Amplifier and A/D Converter with Ultra-Low Input DC Offset

ActiveCN103138760BEliminate DC OffsetQuality is not affectedAnalogue-digital convertersIntegratorAudio power amplifier

Owner:HALO MICROELECTRONICS CO LTD

Sensors and detectors based on avalanche photodiodes

ActiveCN106353785BImprove quantum efficiencyImprove matchX/gamma/cosmic radiation measurmentQuantum efficiencyPower flow

The invention relates to a sensor and a detector on the basis of avalanche photodiodes. The sensor comprises a plurality of APD (avalanche photodiode) sensors. The multiple APD sensors are parallelly sequentially stacked on one another and include single-tube APD sensors or array APD sensors. The detector comprises the sensor and a multi-channel reading circuit. The multi-channel reading circuit comprises current-to-voltage amplification modules and baseline restoration modules, is electrically coupled with the sensor and is used for reading out current signals outputted by the sensor. The sensor and the detector have the advantages that the sensor is configured with the multiple APD sensors which are parallelly sequentially stacked on one another, and accordingly the sensor and the detector are high in quantum efficiency under the condition of sub-nanosecond time resolution; the detector is configured with the multi-channel reading circuit, weak signals outputted by the APD sensors can be read out, the APD sensors can be effectively matched with one another, accordingly, the time resolution performance of the APD detector can be improved, and the integration level of the APD detector can be upgraded.

Owner:INST OF HIGH ENERGY PHYSICS CHINESE ACAD OF SCI

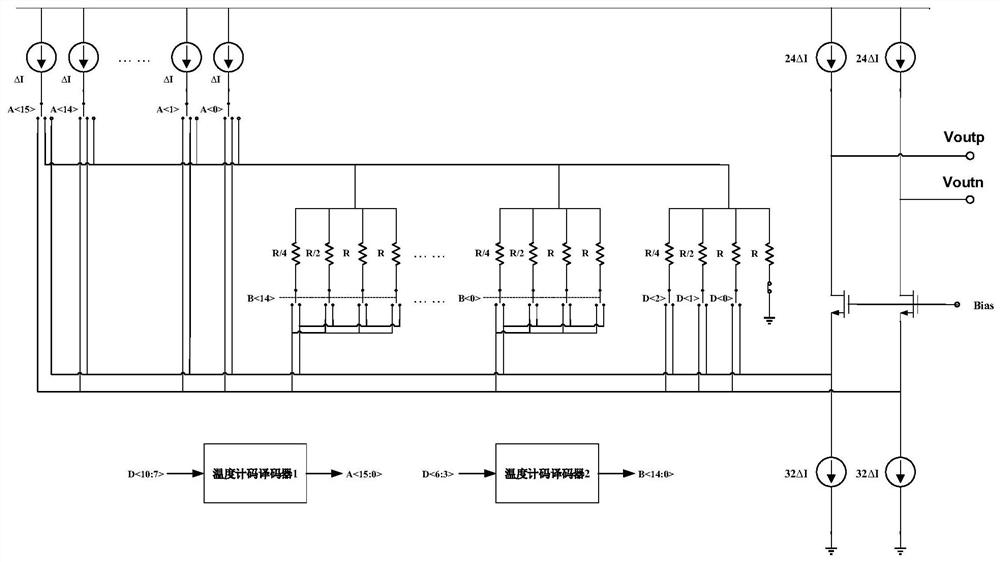

An Automatic Gain Control Amplifier for Eliminating DC Offset

ActiveCN102790596BLow temperature compensation characteristicsHighly integratedGain controlCapacitanceProcess deviations

The invention discloses a complementary metal oxide semiconductor (CMOS) automatic gain control amplifier for canceling direct current offset. The CMOS automatic gain control amplifier comprises a cascade amplification link, an automatic gain control feedback loop and a direct current offset canceling feedback loop. The cascade amplification link uses multistage variable gain amplification units for cascading and can achieve high gain and enlarge high gain dynamic ranges. The automatic gain control feedback loop uses a charge pump structure and has the advantages that the automatic gain control feedback loop is less influenced by process deviation and temperature deviation, is capable of accurately detecting narrow-band and wide-band signal amplitude and is suitable for achieving CMOS processes. The direct current offset canceling feedback loop uses two-stage negative feedback loops, and each of the two-stage negative feedback loops uses an integrator as low-pass negative feedback; an active device is used as an integrator input resistor, and an equivalent resistor is provided with characteristics of temperature compensation; and the automatic gain control amplifier for canceling the direct current offset is capable of effectively canceling the direct current offset superposed by a preceding stage circuit and the direct current offset of the amplification link and is provided with a lower high pass corner frequency and a higher integrated level, and the automatic gain control amplifier for canceling the direct current offset is small in low-frequency signal loss and requires no off-chip passive devices (high value resistors or capacitors and the like). The automatic gain control amplifier is applicable to wireless communication receivers with zero intermediate frequency structures in the CMOS processes.

Owner:杭州中科微电子有限公司

Logarithmic amplifier

ActiveCN101777876BReduce power consumptionImprove the ability to resist PVT deviationAmplifier modifications to raise efficiencyAmplifier with semiconductor-devices/discharge-tubesCapacitanceAudio power amplifier

The invention discloses a logarithmic amplifier which comprises a subtracter in a folding structure, at least one amplifier in a folding structure, at least three rectifiers in a current subtracter structure, two variable capacitor arrays and three resistor arrays. The logarithmic amplifier provided by the invention has lower power and stronger anti-PVT bias capability, automatically corrects a resistance-capacitance time constant by controlling a time constant correction circuit, ensures the response speed and the ripple characteristics of an output signal in case of PVT bias, ensures the stability of the logarithmic amplifier and eliminates the direct current shift. Further, by adjusting the structures of the variable capacitor arrays, the invention improves the accuracy of the whole capacitance value and ensures that a feedback network can effectively eliminate the direct current shift of the logarithmic amplifier and ensure the stability of a feedback loop.

Owner:TSINGHUA UNIV

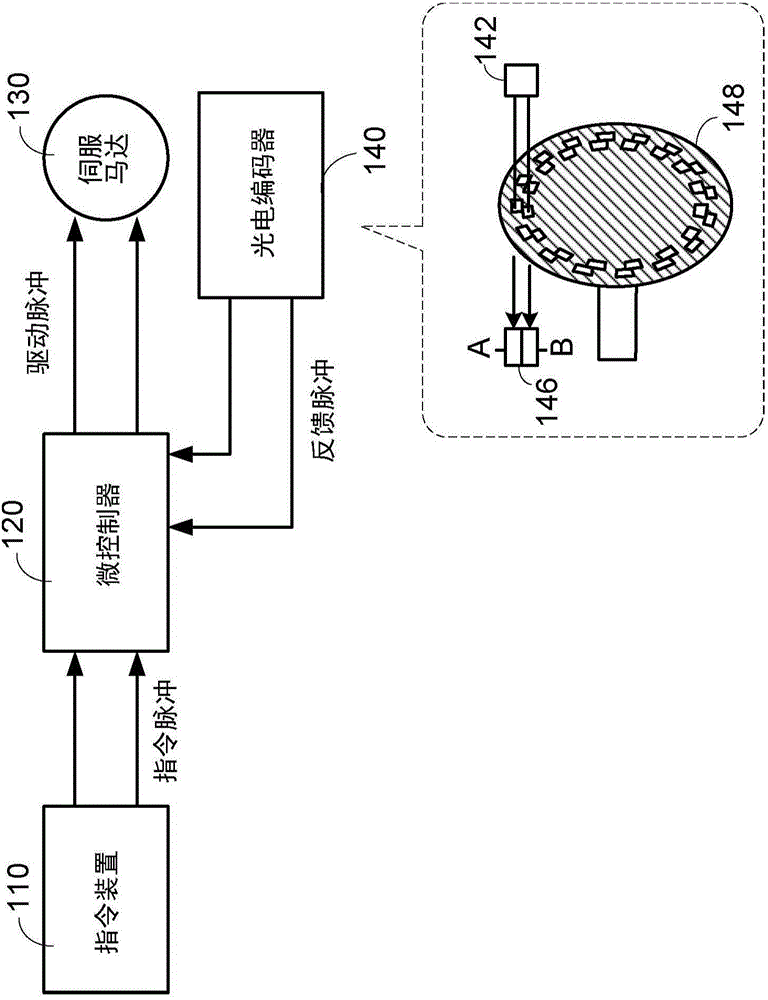

Current preamplifier, time-resolved readout circuit and time-resolved detection device

ActiveCN106374854BReduce noiseLow equivalent input impedanceNegative-feedback-circuit arrangementsAmplifier modifications to reduce noise influenceLow noiseAudio power amplifier

The invention relates to a current pre-amplifier, a time resolution reading circuit and a time resolution detection device. The current pre-amplifier comprises a current input module which is used for receiving and outputting current signals; a current amplifier module which is used for receiving the current signals output by the current input module, amplifying the current signals and then outputting the current signals; a current to voltage conversion module which is used for receiving the current signals output by the current amplifier module, adjusting the current signals, converting all received current signals into voltage signals and then outputting the voltage signals; a cascading amplifier output module which is used for receiving the voltage signals output by the current to voltage conversion module and amplifying the voltage signals, thereby providing output signals; and a base line recovery module which is used for receiving the output signals and outputting current adjusting signals to the current amplifier module according to comparison results between the output signals and a reference voltage. The current pre-amplifier provided by the invention is characterized in low noise and applicability to a high parasitic capacitance APD sensor.

Owner:INST OF HIGH ENERGY PHYSICS CHINESE ACAD OF SCI

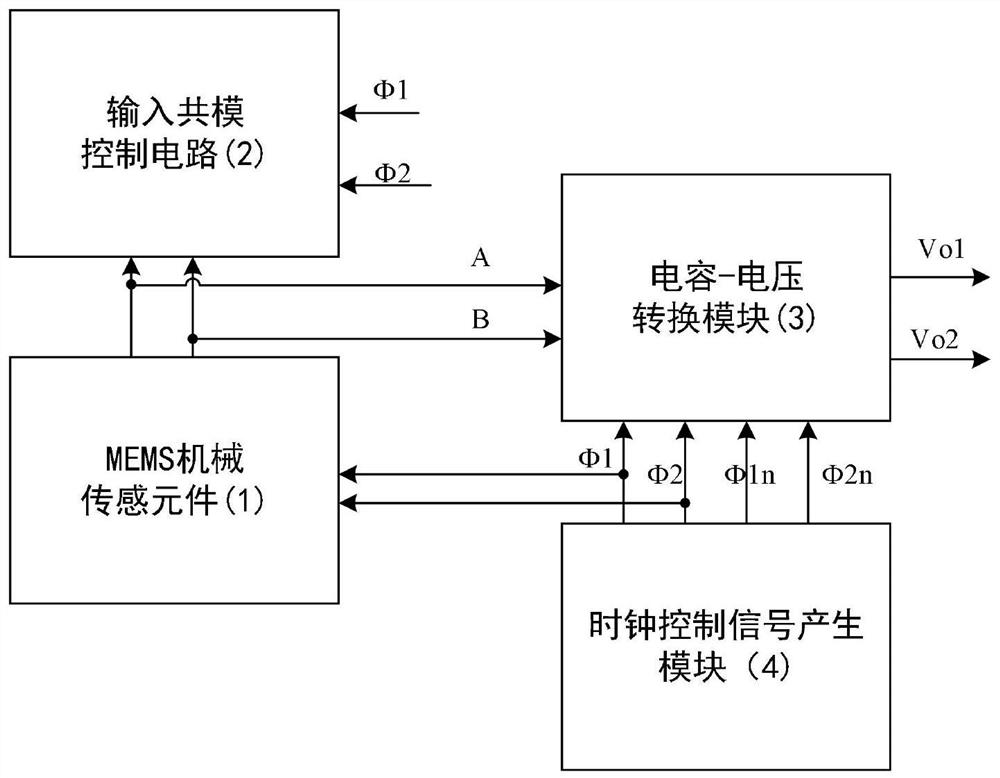

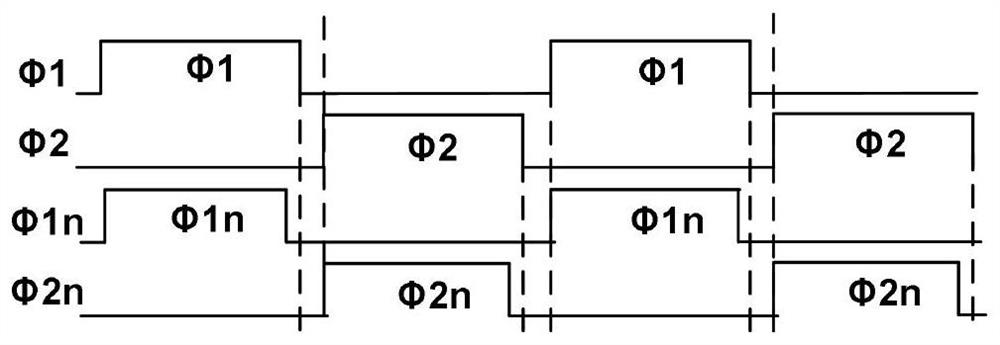

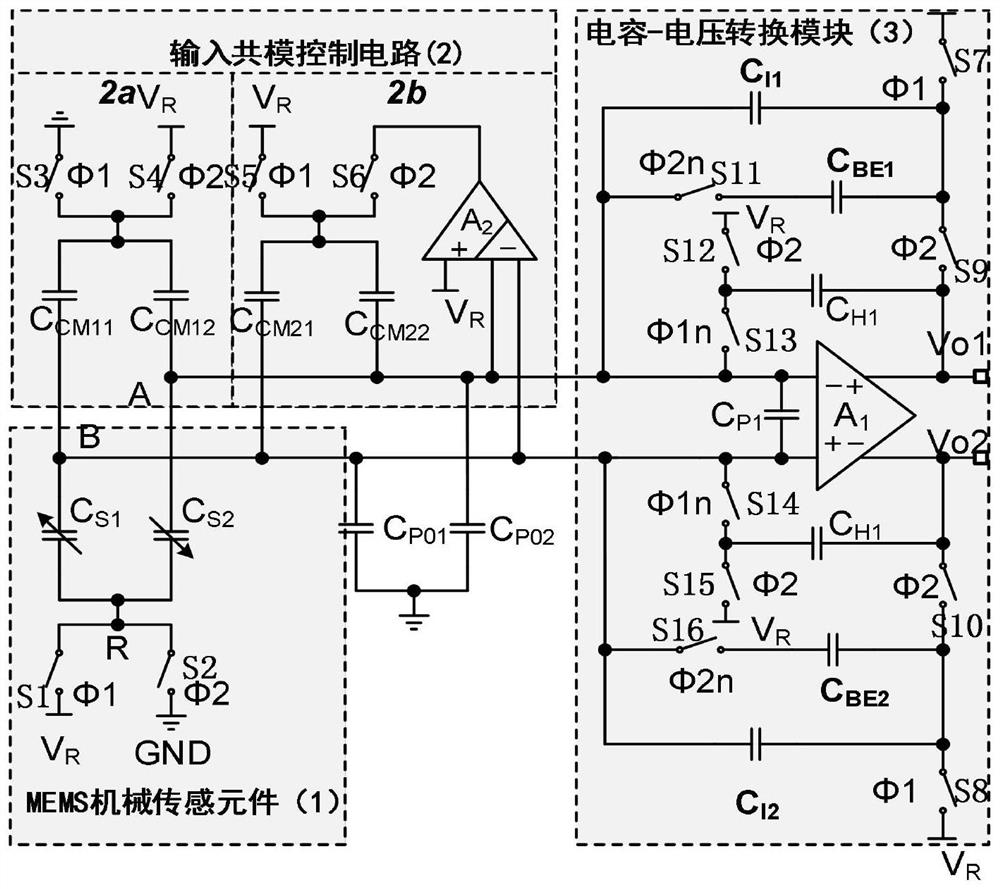

Low-noise MEMS capacitive sensor interface circuit

InactiveCN114650022AEliminate DC OffsetHigh gain accuracyAmplifier modifications to reduce noise influenceAmplifier modifications to reduce detrimental impedenceLow noiseCapacitor voltage

The invention discloses a low-noise MEMS capacitive sensor interface circuit which mainly solves the problems of gain errors and circuit noise deterioration. The device comprises an MEMS mechanical sensing element, an input common-mode control circuit, a capacitance-voltage conversion module and a clock control signal generation module. The MEMS mechanical sensing element is used for converting an external acceleration signal into a variable quantity of an MEMS mechanical capacitor and generating sensor charge signals A and B; the input common-mode control circuit is used for absorbing common-mode components of sensor charge signals, and other differential-mode components are transmitted to the integrating capacitor for signal amplification, so that conversion of capacitor voltage is realized. And the gain precision is improved by introducing the sampling holding capacitor, so that the original high-gain operational amplifier can be replaced by the low-gain operational amplifier. Due to the introduction of the bandwidth compensation capacitor, the interface circuit can work under a clock with higher frequency, and the noise floor of the interface circuit is reduced. The purposes of not additionally increasing the power consumption of the circuit and reducing the noise of the interface circuit are achieved.

Owner:西安水木芯邦半导体设计有限公司

Alternating current signal measurement device, system and method

ActiveCN101839931BImprove the speed of access measurementGuaranteed accuracyAltering measuring range circuitsMulti-tester circuitsMeasurement deviceAccess time

The invention discloses an alternating current signal measurement device, an alternating current signal measurement system and an alternating current signal measurement method and relates to the field of alternating current electric signal measurement. The device is provided with an access part 1, a measurement part 2 and a control part 3, wherein the output end 10 of the access part 1 is connected with the input end of the measurement part 2 and is also connected with an instantaneous discharge circuit 14 controlled by the control part 3. The control part 3 can control the access part 1, the measurement part 2 and the instantaneous discharge circuit 14 to perform the instantaneous discharge operation of the output end 10, and adopts the following control steps: firstly, turning on the instantaneous discharge circuit; secondly, delaying a preset time period; and thirdly, turning off the instantaneous discharge circuit. The device of the invention accelerates the elimination of an abrupt signal which appears at the position of the output end 10 of the access part 1 and is caused by the quick change of the gain of a programmable amplifying circuit 7 in the access part 1. The device has the characteristics of reducing measurement access time, along with simple structure and convenient control.

Owner:RIGOL

Direct current offset calibration system and method

ActiveCN114063699AEliminate DC OffsetReceivers monitoringElectric variable regulationEngineeringImpedance matching

The invention provides a direct current offset calibration system and method. The system is arranged at a receiver end to process differential input signals and operates in one of a working mode, a first calibration mode and a second calibration mode. The system comprises a matching circuit, an equalization circuit, an amplification circuit, a control circuit, a first digital-to-analog conversion circuit and a second digital-to-analog conversion circuit, wherein the equalization circuit is electrically connected with the matching circuit, the amplification circuit is electrically connected with the equalization circuit, and the control circuit is electrically connected with the amplification circuit. In the operating mode, the matching circuit provides impedance matching for the differential input signal. A first digital signal and a second digital signal are respectively output in the first calibration mode and the second calibration mode. The first digital-to-analog conversion circuit and the second digital-to-analog conversion circuit respectively generate a first differential calibration signal and a second differential calibration signal according to the first digital signal and the second digital signal. In the first calibration mode, the amplification circuit generates a first amplification signal according to the first differential calibration signal, and feeds back and adjusts the first digital signal; and in the second calibration mode, the equalization circuit and the amplification circuit generate a second amplification signal according to the second digital signal, and feed back and adjust the second digital signal.

Owner:SIGMASTAR TECH LTD

Wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device

ActiveCN102970053BLow cost requirementsReduce power consumptionNetwork topologiesTransmissionIntermediate frequencyLow-pass filter

The invention discloses a wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device which comprises a duplexer, a radio frequency front end, a variable gain complex filter, an automatic frequency tuning circuit, a programmable gain amplifier, a phase-locked loop frequency synthesizer, a digital processor, a storage, a variable gain power amplifier, a mixer and a low pass filter, wherein the duplexer, the radio frequency front end, the variable gain complex filter, the automatic frequency tuning circuit and the programmable gain amplifier form a receiving link which is used for receiving and processing a radio frequency signal and converting the radio frequency signal into a low-medium frequency digital signal so that the signal can be conveniently processed by a subsequent analog-digital converter later; the duplexer, the variable gain power amplifier, the mixer and the low pass filter form an emitting link which is used for mixing a baseband analog modulation signal into a carrier frequency and sending a wireless signal; and the receiving link and the emitting link share the duplexer. The wireless sensor network application-oriented low-power consumption radio frequency receiving and sending device realizes singlechip integration by adopting a standard CMOS (Complementary Metal Oxide Semiconductor) process, is simple in structure and low in power consumption, and is applicable to a wireless sensor network.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

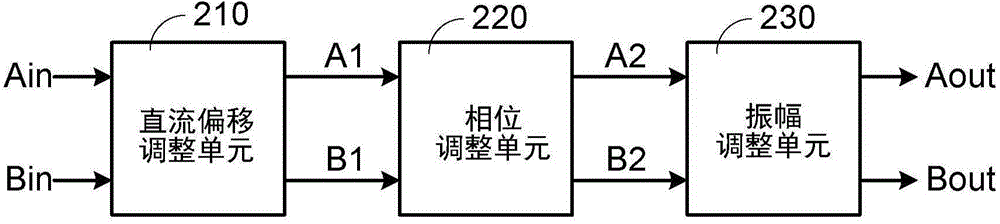

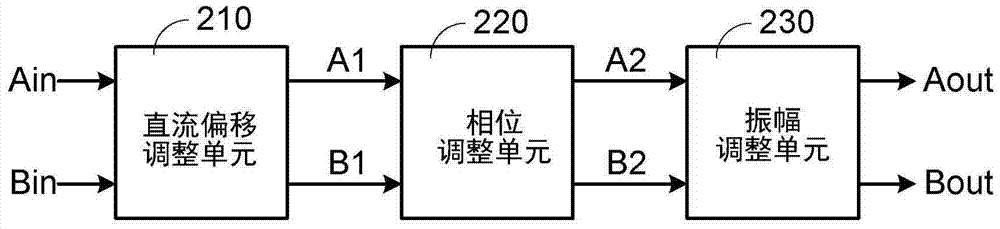

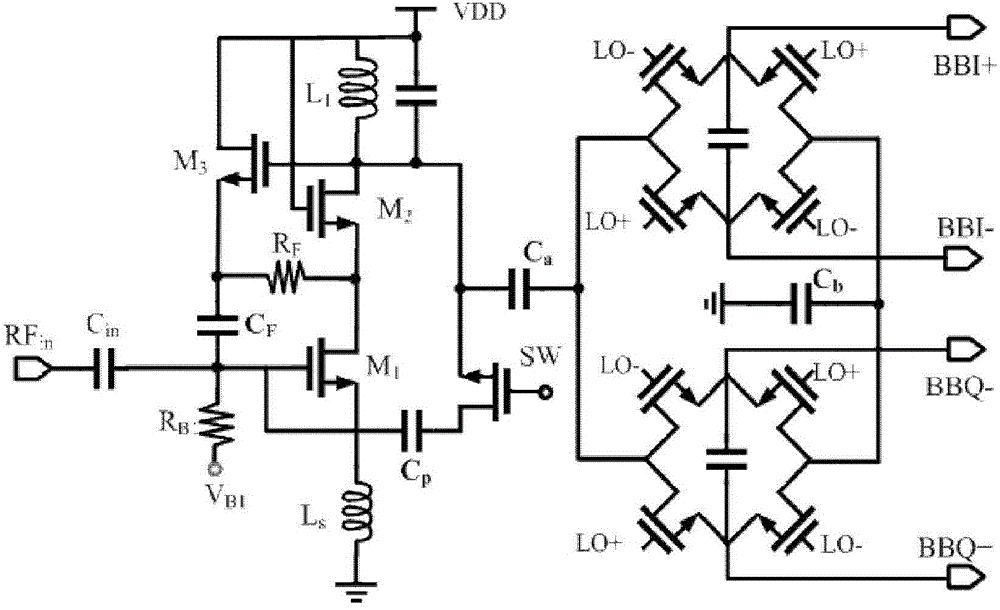

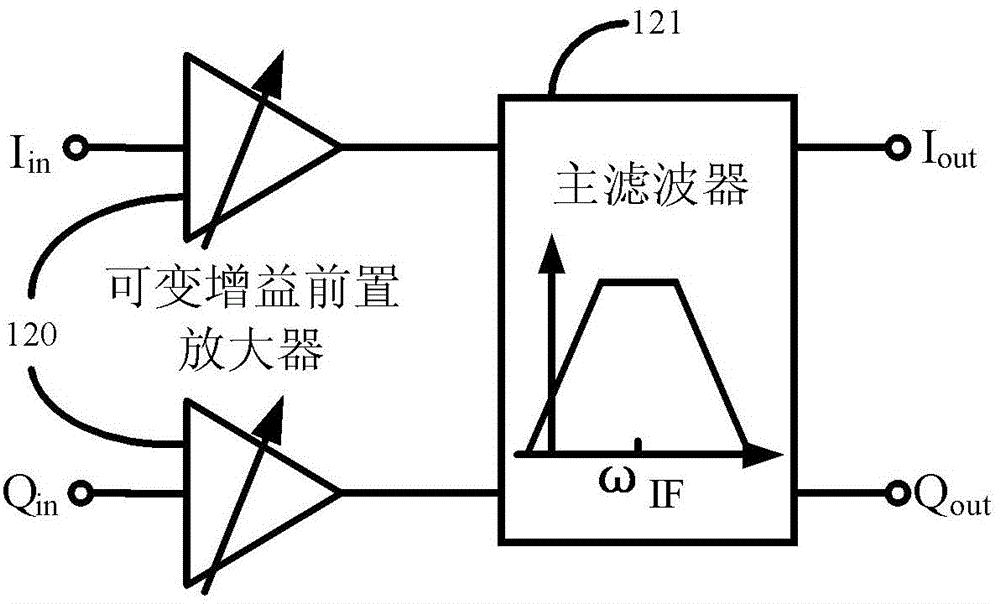

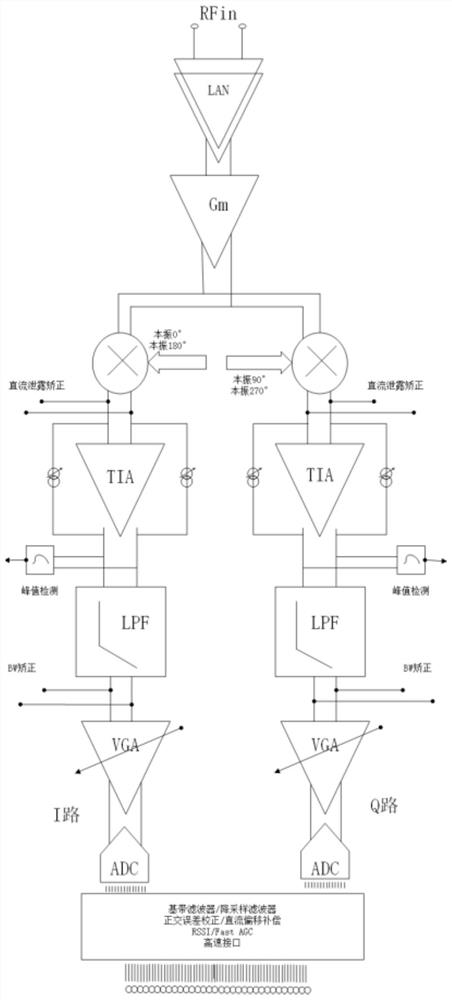

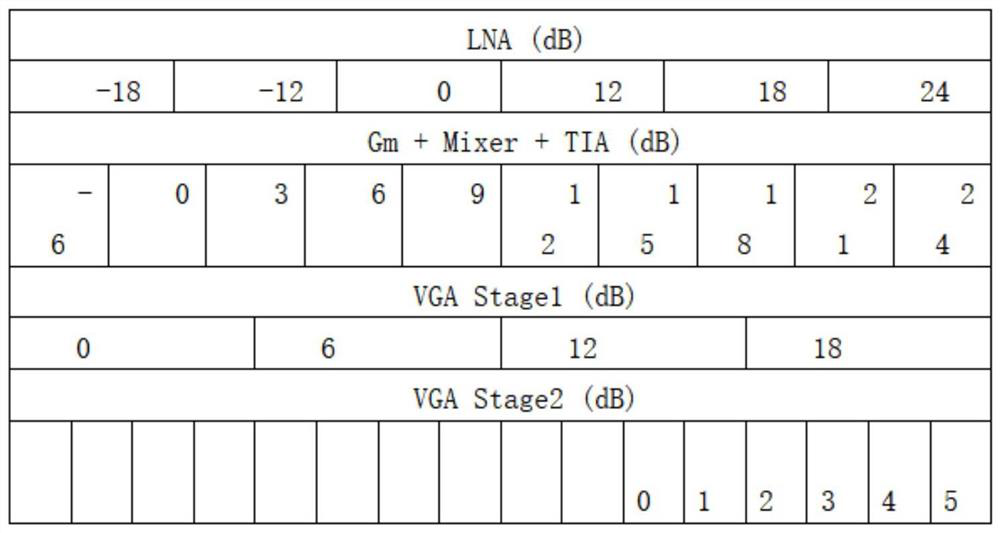

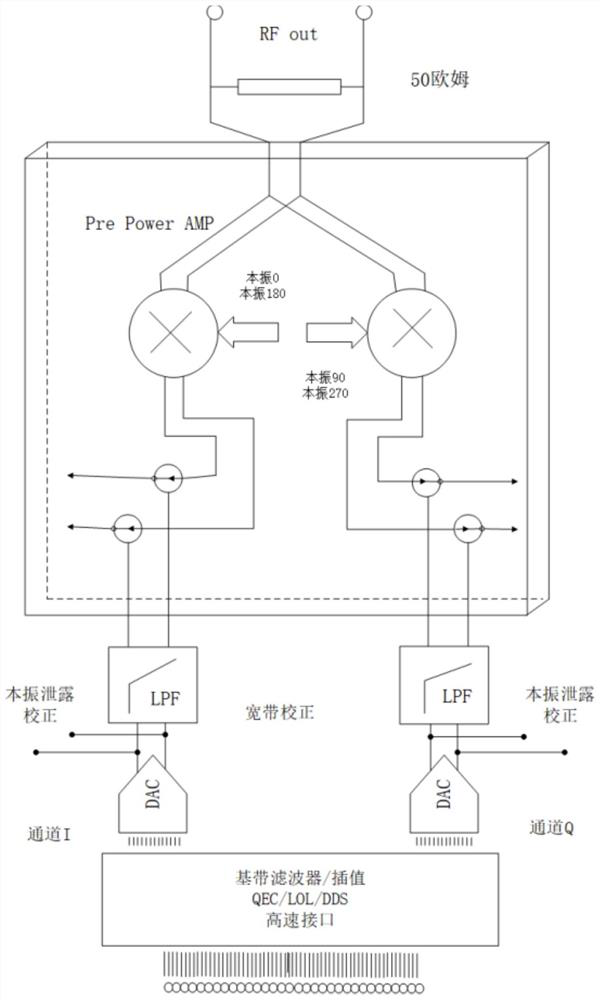

Broadband low-noise high-linearity wide-range demodulation system

The invention discloses a broadband low-noise high-linearity wide-range demodulation system, and relates to the technical field of broadband demodulation. The system comprises a receiving unit and a transmitting unit, the receiving unit comprises a low-noise amplification module, the low-noise amplification module is connected with a voltage-current conversion module, the voltage-current conversion module is connected with two down-conversion modules, the down-conversion modules are connected with a transimpedance amplification module, the transimpedance amplification module is connected with a first low-pass filtering module, and the first low-pass filtering module is connected with a second low-pass filtering module. The first low-pass filtering module is connected with a variable gain amplification module, the variable gain amplification module is connected with analog-to-digital conversion modules, the two analog-to-digital conversion modules are connected with a first integrated unit, and the transmitting unit comprises a resistor. The low-pass filter is closely followed after the transimpedance amplification module, so that out-of-band blocking is further suppressed, the pressure of the analog-to-digital converter is reduced, the bandwidth of the filter can be accurately calibrated, and controllable current is injected into the input side of the variable gain amplification module.

Owner:北京力通通信有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com