Power detection circuit

A power detection circuit and resistance technology, applied in the field of communication, can solve the problems of large layout area, inability to take into account the linear range of signal power and output voltage, bandwidth, response time, DC offset, complex circuit structure, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

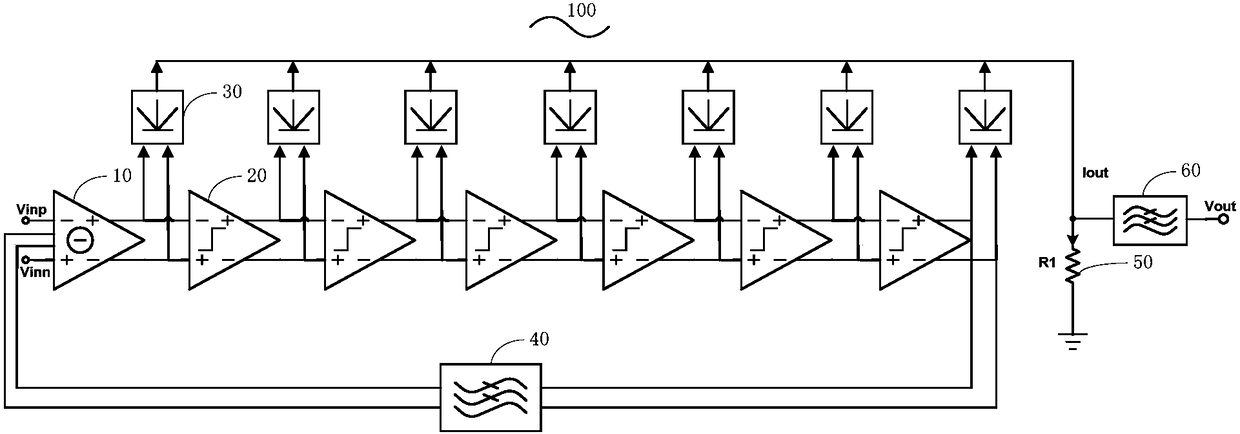

[0070] Such as figure 1 As shown, this embodiment provides a power detection circuit 100, which includes an offset subtractor 10, several limiting amplifiers 20, several rectifiers 30, an active low-pass filter 40, an impedance device 50 and a passive low-pass filter 60 .

[0071] In specific applications, any type of limiting amplifier, rectifier, impedance device and passive low-pass filter can be selected according to actual needs. For example, resistance devices can be selected as impedance devices.

[0072] In this embodiment, the impedance device 50 is a resistance device, figure 1 Expressed as the resistor R1.

[0073] In specific applications, the number of limiting amplifiers 20 and rectifiers 30 can be selected according to actual needs, and the number of rectifiers is equal to the sum of the number of limiting amplifiers and the number of offset subtractors. The number of cascaded limiting amplifiers is related to the linear detection range of the power detection...

Embodiment 2

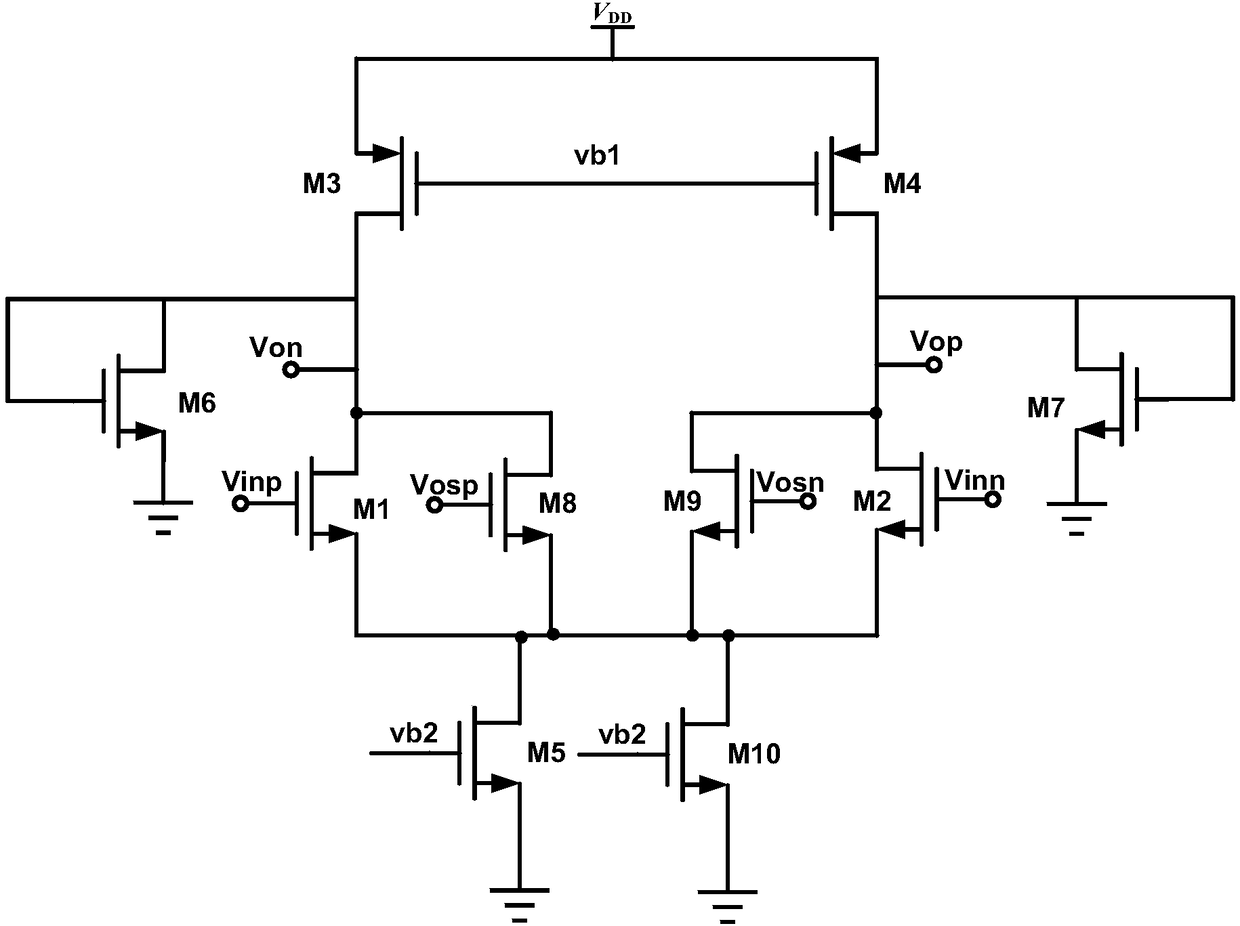

[0087] Such as figure 2 As shown, in this embodiment, the offset subtractor 10 in the first embodiment includes first to tenth field effect transistors, denoted as M1 to M10 respectively;

[0088] Wherein, the first to eighth field effect transistors M1 to M8 are N-type field effect transistors, and the ninth and tenth field effect transistors M9 and M10 are P-type field effect transistors.

[0089] Such as figure 2 As shown, the connection relationship between the devices in the offset subtractor 10 provided by this embodiment is as follows:

[0090] The gate of the first field effect transistor M1 is the negative input terminal Vinp of the offset subtractor 10, the source of the first field effect transistor M1 is connected to the source of the second field effect transistor M2, the drain of the fifth field effect transistor M5, and the second field effect transistor M5. The source of the eighth field effect transistor M8, the source of the ninth field effect transistor ...

Embodiment 3

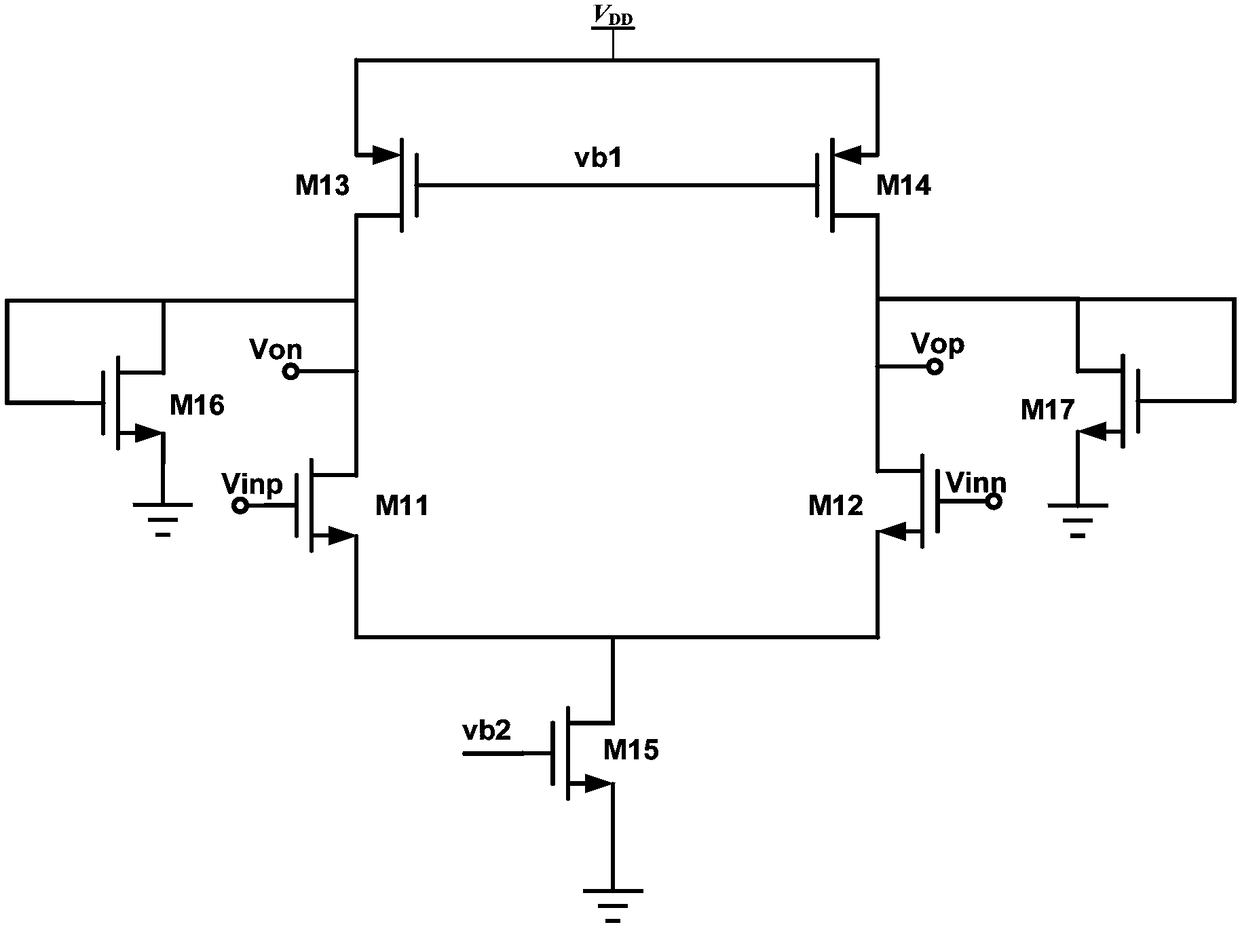

[0101] Such as image 3 As shown, in this embodiment, the limiting amplifier 20 in the first embodiment includes eleventh to seventeenth field effect transistors, denoted as M11 to M17 respectively; wherein, the eleventh field effect transistor M11, the twelfth field effect transistor The field effect transistor M12 and the fifteenth to seventeenth field effect transistors M15 to M17 are N-type field effect transistors, and the thirteenth field effect transistor M13 and the fourteenth field effect transistor M14 are P-type field effect transistors.

[0102] Such as image 3 As shown, the connection relationship between each device in the limiting amplifier 20 provided by this embodiment is as follows:

[0103] The gate of the eleventh field effect transistor M11 is the inverting input terminal Vinp of the limiting amplifier 20, the source of the eleventh field effect transistor M11 is connected to the source of the twelfth field effect transistor M12 and the fifteenth field e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com