Amplifier with ultralow direct current (DC) offset at input end and analog/digital (A/D) converter

A DC offset and input technology, applied in analog-to-digital converters, etc., can solve problems such as low temperature drift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

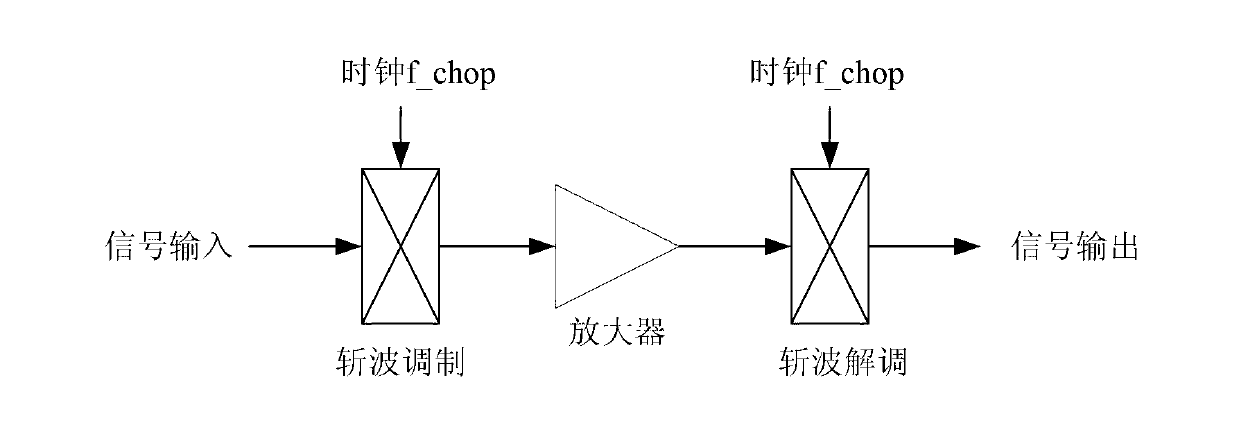

Problems solved by technology

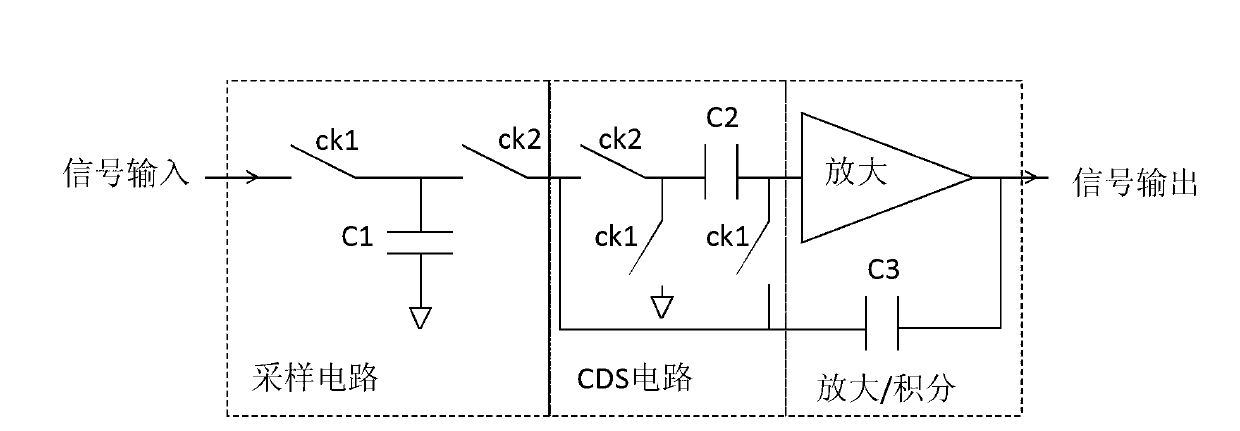

Method used

Image

Examples

Embodiment 1

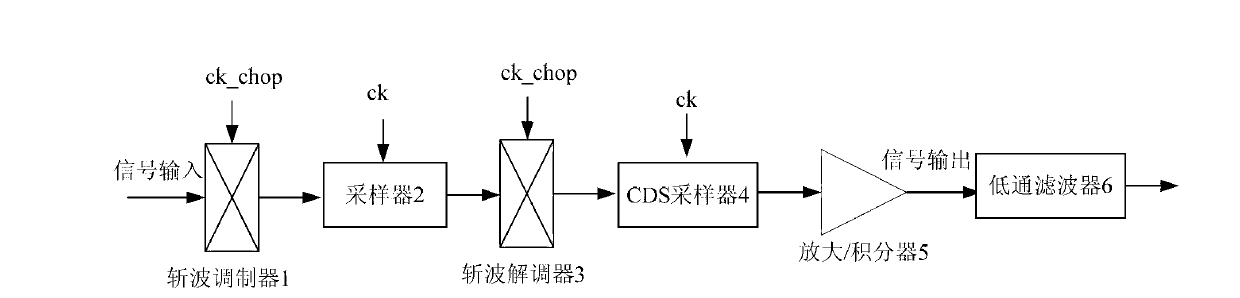

[0038] Such as image 3 , Figure 4 As shown, the amplifier with ultra-low input DC offset includes a chopper modulator 1, a sampler 2, a chopper demodulator 3, a CDS sampler 4, and an amplifier / integrator 5 connected in sequence, where the chopper modulator 1 and Chopper demodulator 3 uses chopping clock signal ck_chop, and sampler 2 and CDS sampler 4 use sampling clock signal ck. The input signal passes through the input chopper modulator 1, sampler 2, chopper demodulator 3 and CDS sampler 4 in sequence, and finally enters the amplifier / integrator 5 to complete the signal amplification and output. In this embodiment, the chopper modulator 1 and the chopper demodulator 3 are respectively arranged at the input end and the output end of the sampler 2 . The large input DC offset of the amplifier / integrator 5 itself is sampled and removed by the CDS sampler 4, while the residual DC offset caused by the non-idealities of the circuit components in the sampler 2, such as switching...

Embodiment 2

[0041] Such as Figure 4 , Figure 5As shown, the amplifier with ultra-low input DC offset includes chopper modulator 1, sampler 2, CDS sampler 4, chopper demodulator 3 and amplifier / integrator 5 connected in sequence, where chopper modulator 1 and Chopper demodulator 3 uses chopping clock signal ck_chop, and sampler 2 and CDS sampler 4 use sampling clock signal ck. The input signal passes through the input chopper modulator 1, sampler 2, CDS sampler 4 and chopper demodulator 3 in sequence, and finally enters the amplifier / integrator 5 to complete the signal amplification and output. In this embodiment, the sampler 2 and the CDS sampler 4 are arranged between the chopper modulator 1 and the chopper demodulator 3, based on the same principle as in embodiment 1, the circuit elements in the sampler 2 and the CDS sampler 4 The remaining DC offset will be modulated to a frequency of 2×ck_chop, generating a high frequency modulation signal.

[0042] The input terminal of the subs...

Embodiment 3

[0044] Such as Figure 4 , Figure 6 As shown, the amplifier with ultra-low input DC offset includes chopper modulator 1, sampler 2, CDS sampler 4, amplifier / integrator 5 and chopper demodulator 3 connected in sequence, where chopper modulator 1 and Chopper demodulator 3 uses chopping clock signal ck_chop, and sampler 2 and CDS sampler 4 use sampling clock signal ck. The input signal is sampled and amplified through the input chopper modulator 1, sampler 2, CDS sampler 4, amplifier / integrator 5 in sequence, and finally output through the chopper demodulator 3. In this embodiment, the sampler 2, the CDS sampler 4, and the amplifier / integrator 5 are all arranged between the chopper modulator 1 and the chopper demodulator 3. Based on the same principle as in Embodiment 1, the sampler 2 , CDS sampler 4 and amplifier / integrator 5 all remaining DC offsets will be modulated to a frequency of 2×ck_chop to generate a high frequency modulation signal.

[0045] Then the output signal ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com