Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

138results about How to "Deterioration of property" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

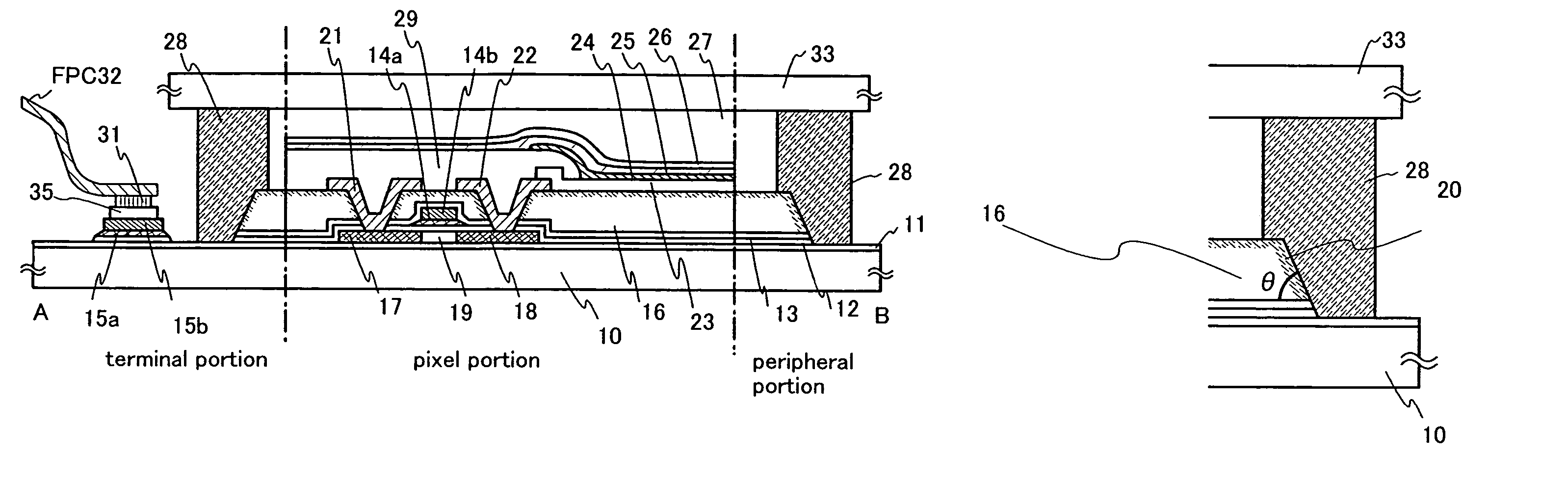

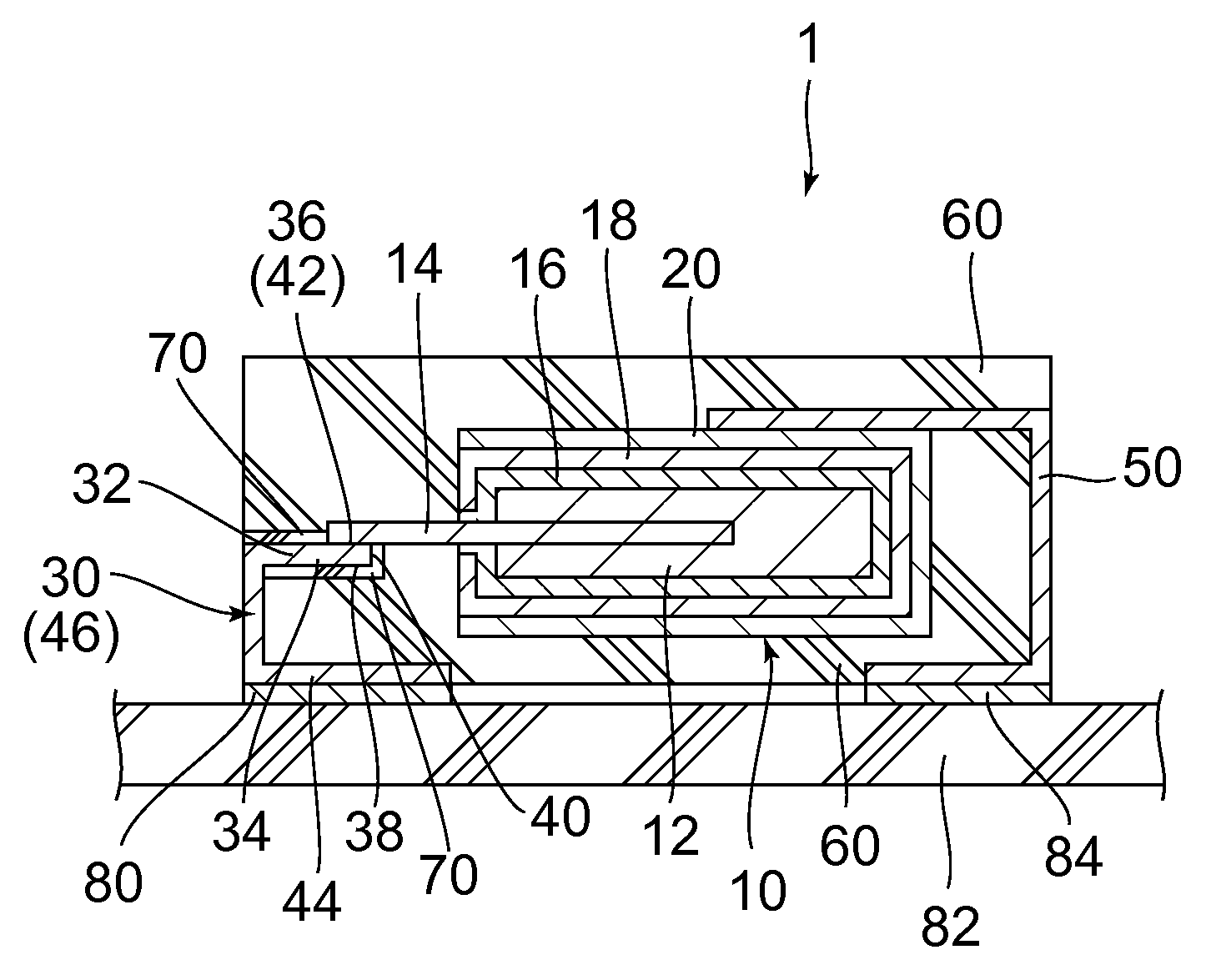

Electronics device, semiconductor deivce, and method for manufacturing the same

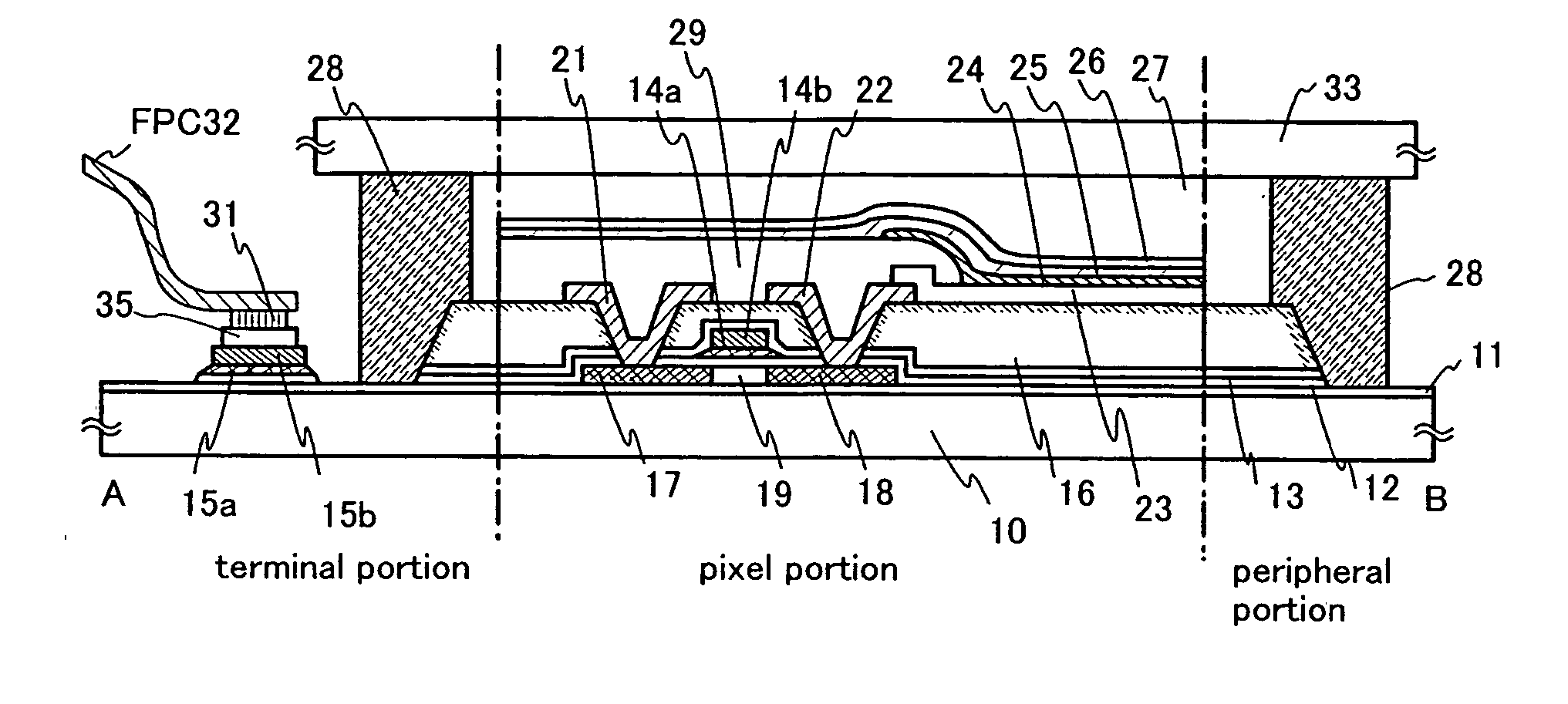

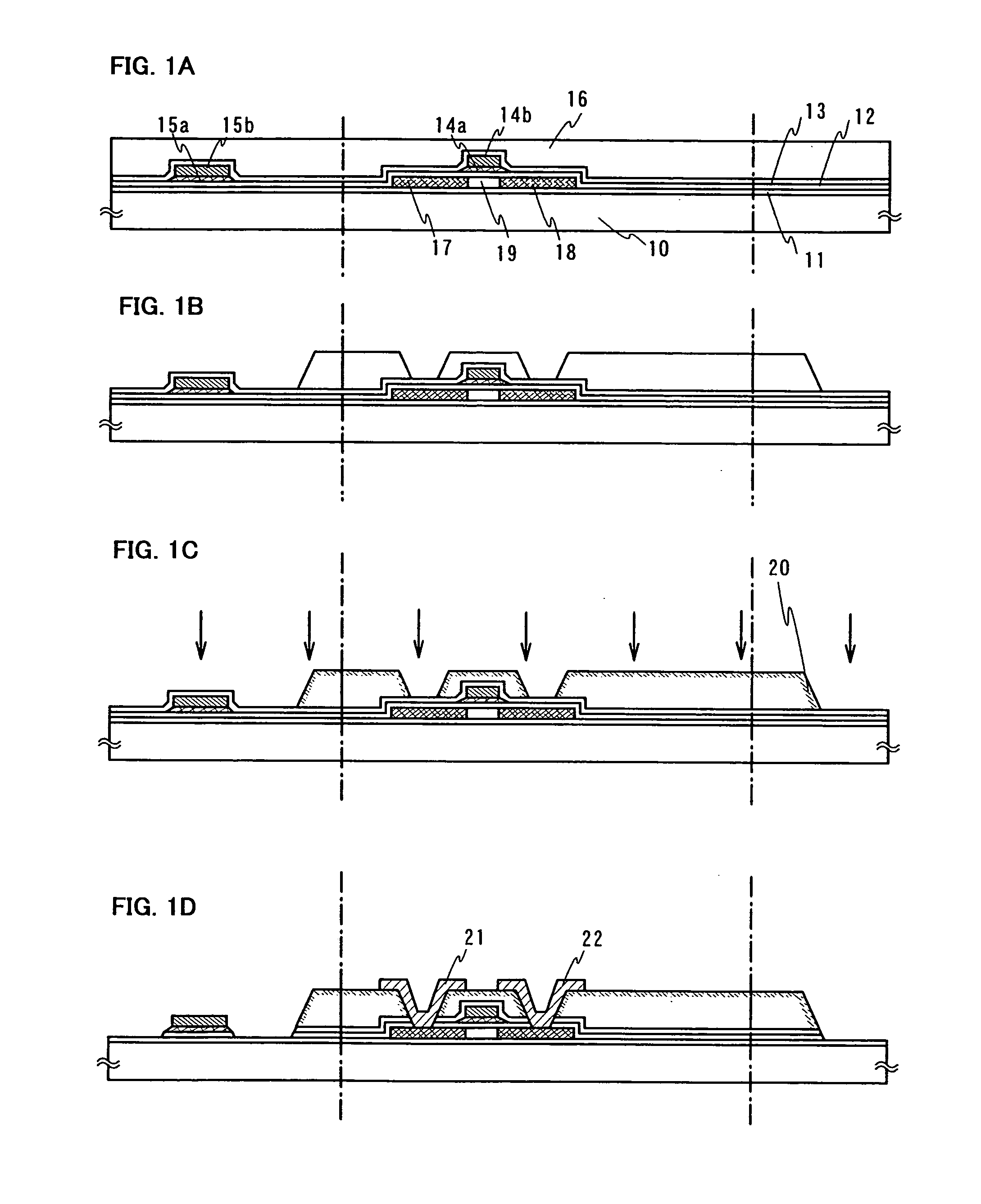

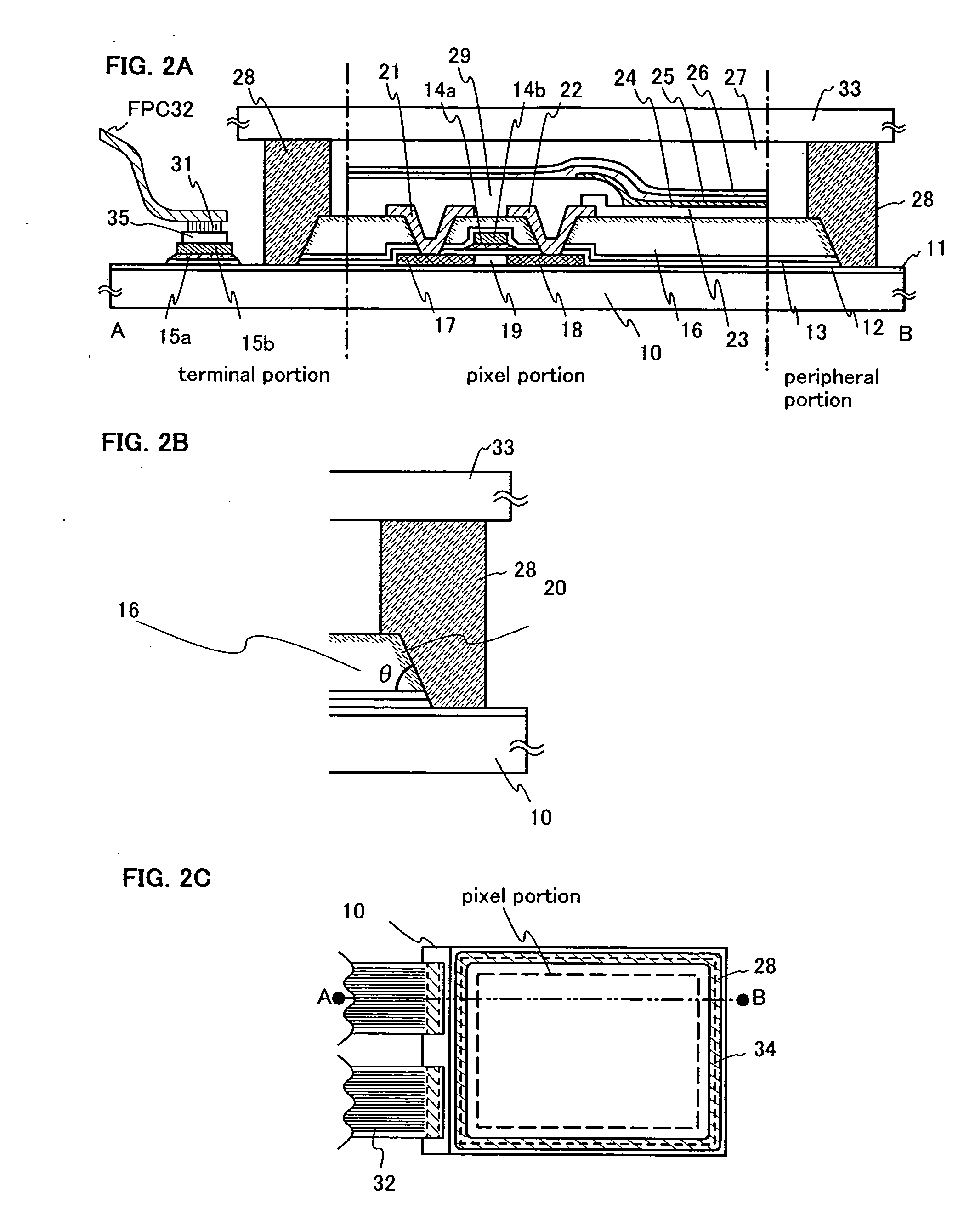

InactiveUS20050045891A1Show reliableDeterioration of propertyElectroluminescent light sourcesSolid-state devicesDisplay deviceAtomic radius

It is an object of the present invention to provide a high reliable EL display device and a manufacturing method thereof by shielding intruding moisture or oxygen which is a factor of deteriorating the property of an EL element without enlarging the EL display device. In the invention, application is used as a method for forming a high thermostability planarizing film 16, typically, an interlayer insulating film (a film which serves as a base film of a light emitting element later) of a TFT in which a skeletal structure is configured by the combination of silicon (Si) and oxygen (O). After the formation, an edge portion or an opening portion is formed to have a tapered shape. Afterwards, distortion is given by adding an inert element with a comparatively large atomic radius to modify or highly densify a surface (including a side surface) for preventing the intrusion of moisture or oxygen.

Owner:SEMICON ENERGY LAB CO LTD

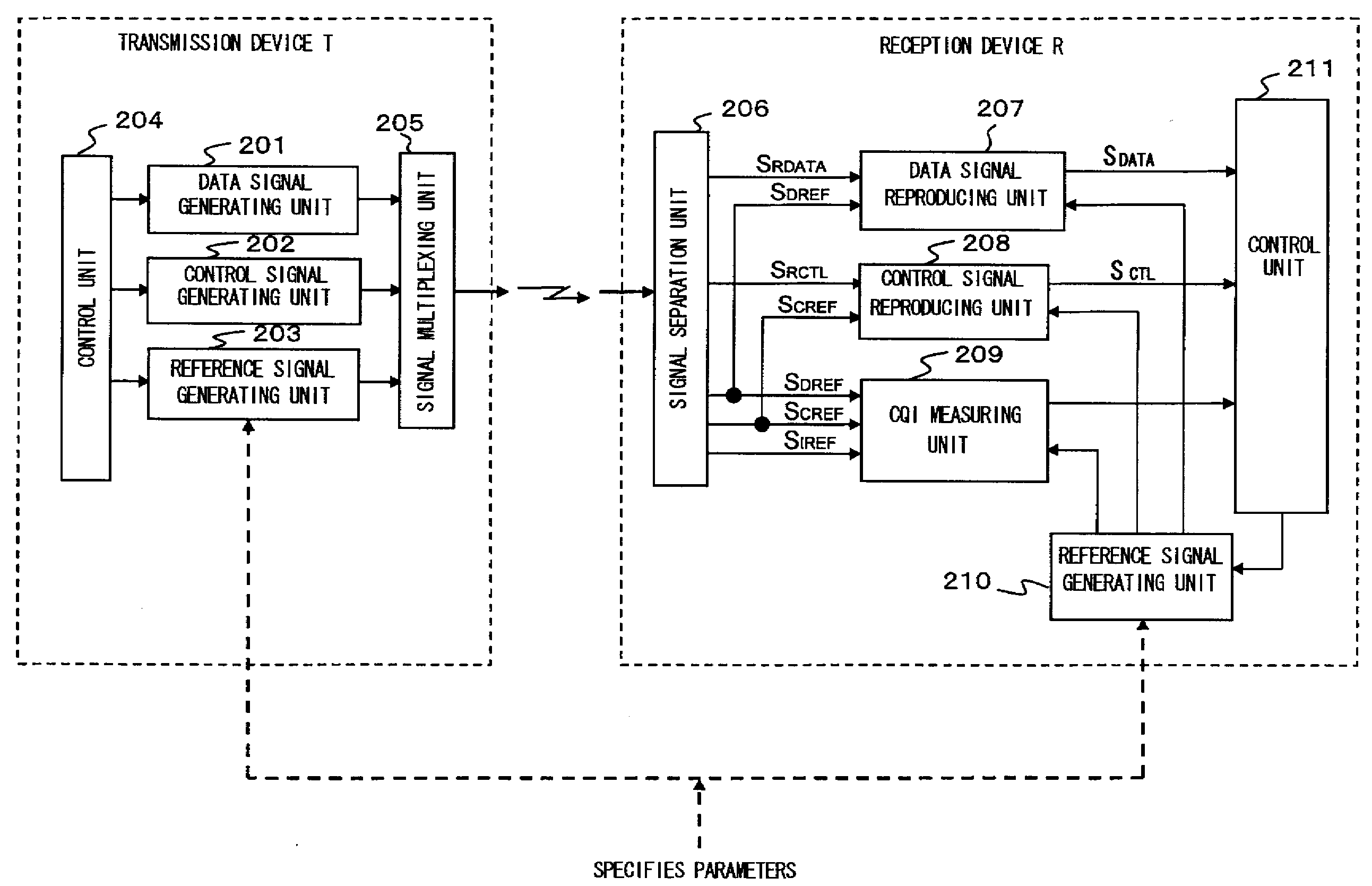

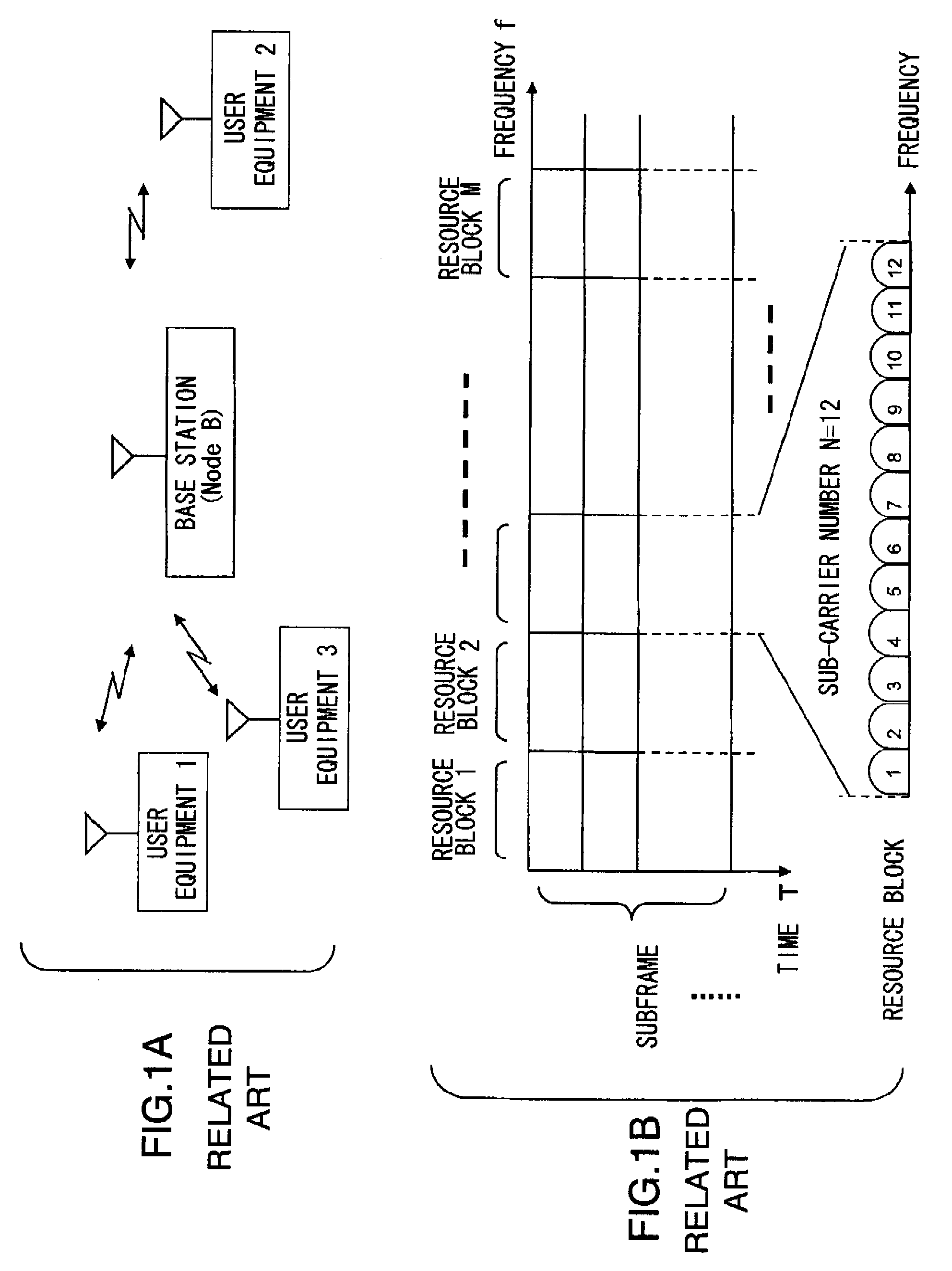

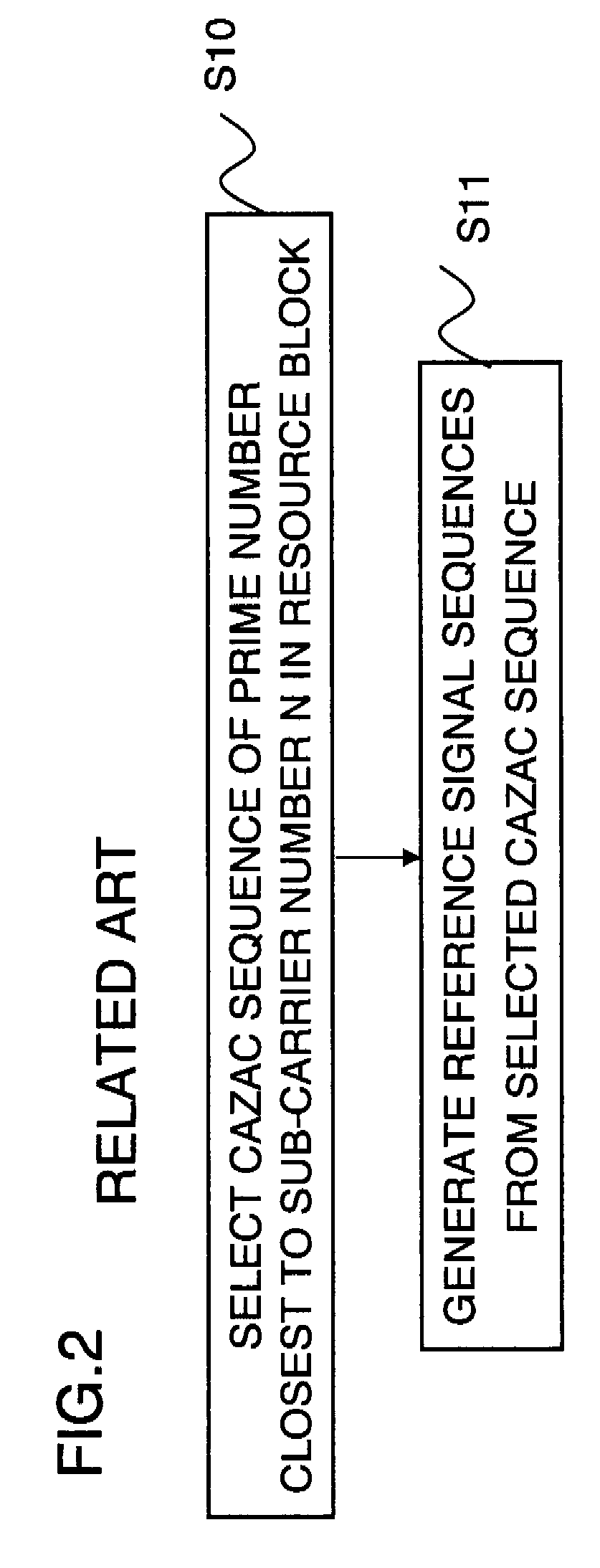

Method and apparatus for reference signal generation in wireless communication system

ActiveUS20080253484A1Excellent cross (mutual)-correlation propertyDifferenceFrequency-division multiplexAmplitude-modulated carrier systemsCommunications systemResource block

To provide a reference signal generation method and apparatus capable of obtaining many reference signal sequences having excellent properties. CAZAC sequences that satisfy the condition that the absolute value (|N−L|) of a difference between a sub-carrier number N in a resource block and a CAZAC sequence length L is not larger than a threshold value K are selected, and a sequence having a largest among greatest prime factors among the prime factors constituting the sequence length(s) is further selected from the initially selected sequences. Then, a reference signal sequence(s) is generated from a selected CAZAC sequence.

Owner:NEC CORP

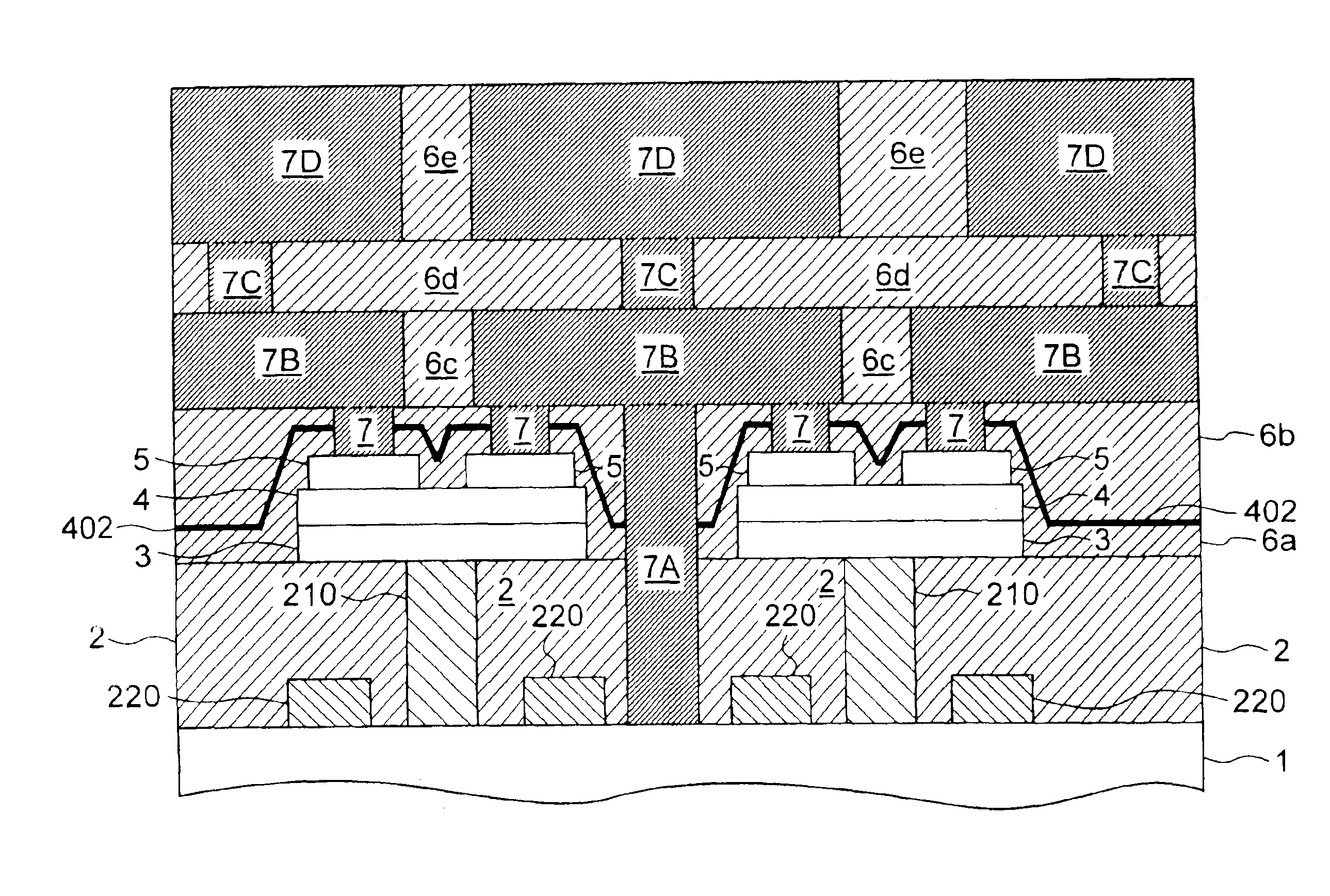

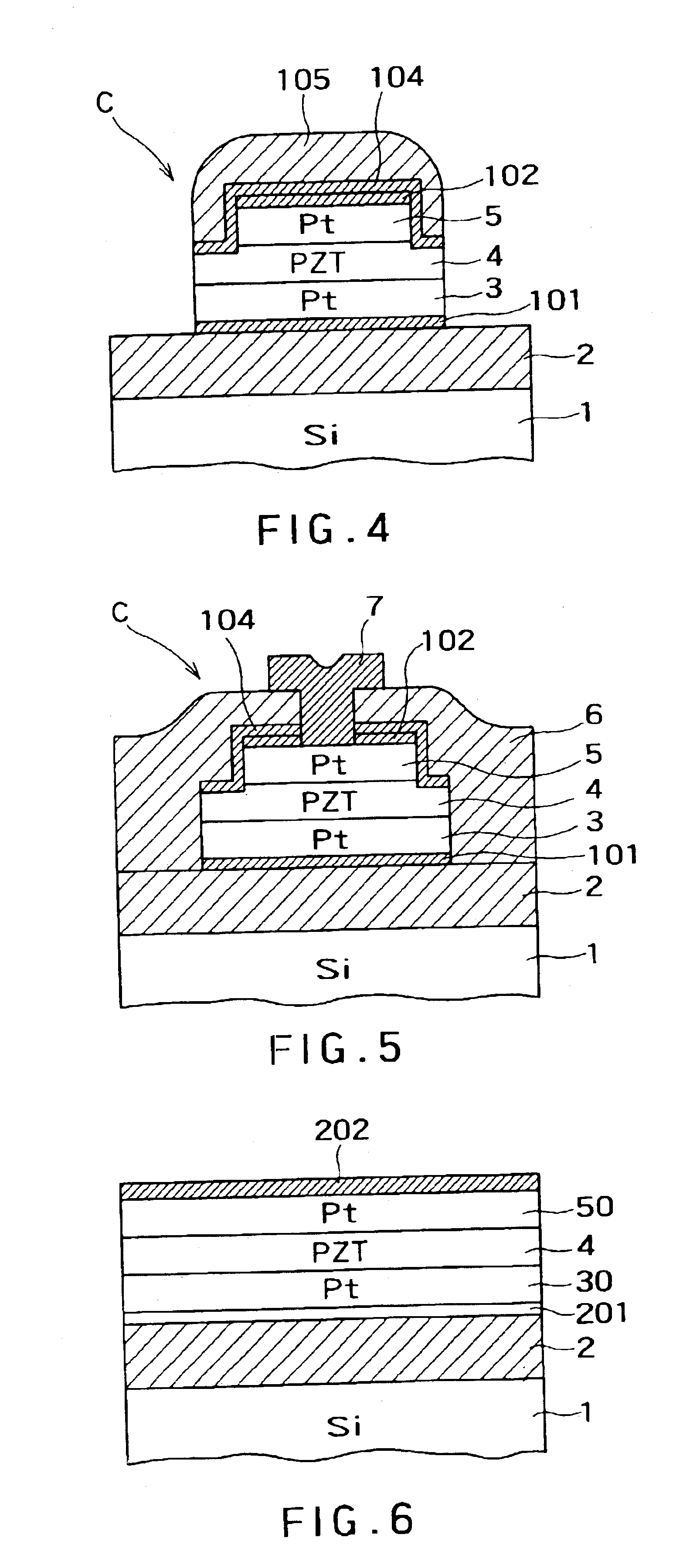

Semicondutor device having ferroelectric capacitor and hydrogen barrier film and manufacturing method thereof

InactiveUS6982453B2Effective recoveryExcellent ferroelectric capacitorTransistorSolid-state devicesHydrogenInter layer

A semiconductor device having a semiconductor substrate; an insulating film formed on said semiconductor substrate; a ferroelectric capacitor having a lower electrode, a ferroelectric film and an upper electrode which are stacked sequentially on the insulating film; a first hydrogen barrier film; a first inter-layer insulating film covering said ferroelectric capacitor; and a second inter-layer insulating film stacked on the first inter-layer insulating film, the first hydrogen barrier film being interposed between the first and second interlayer insulating films is proposed.

Owner:KK TOSHIBA

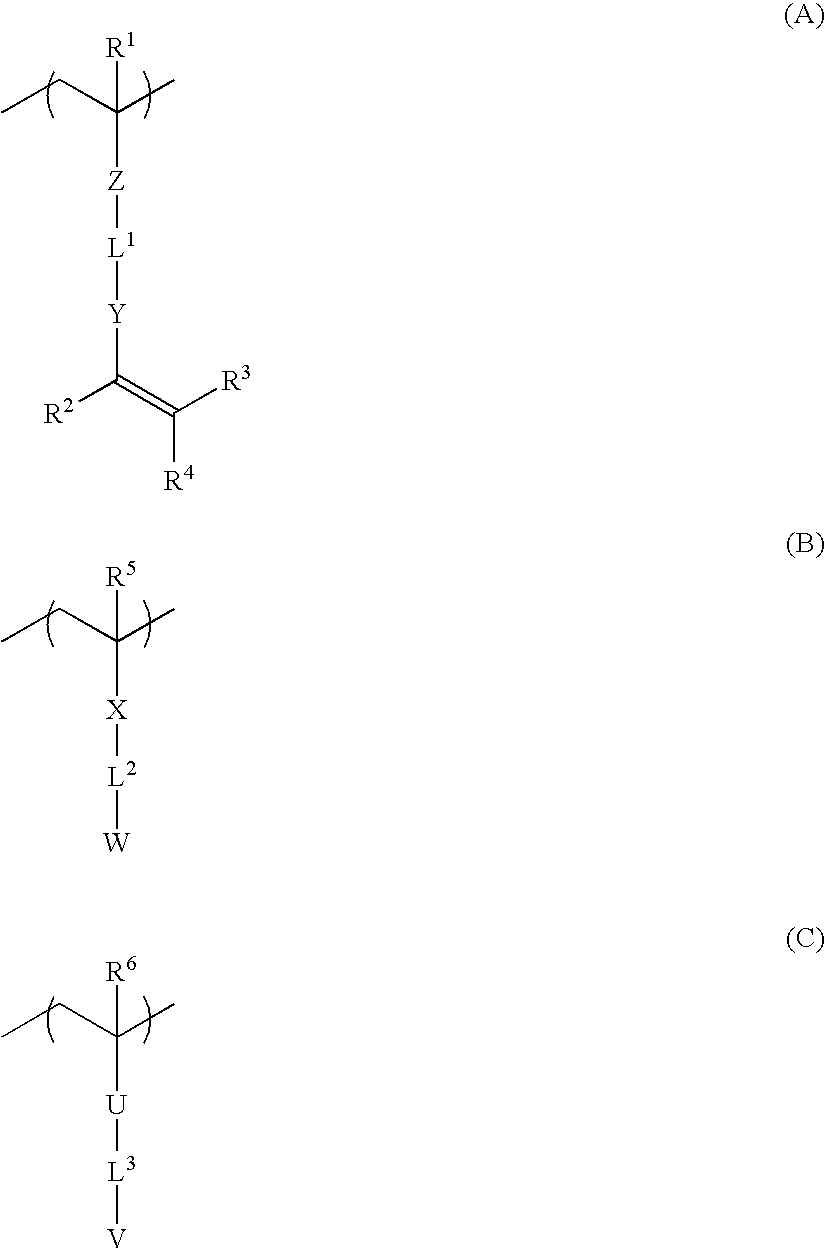

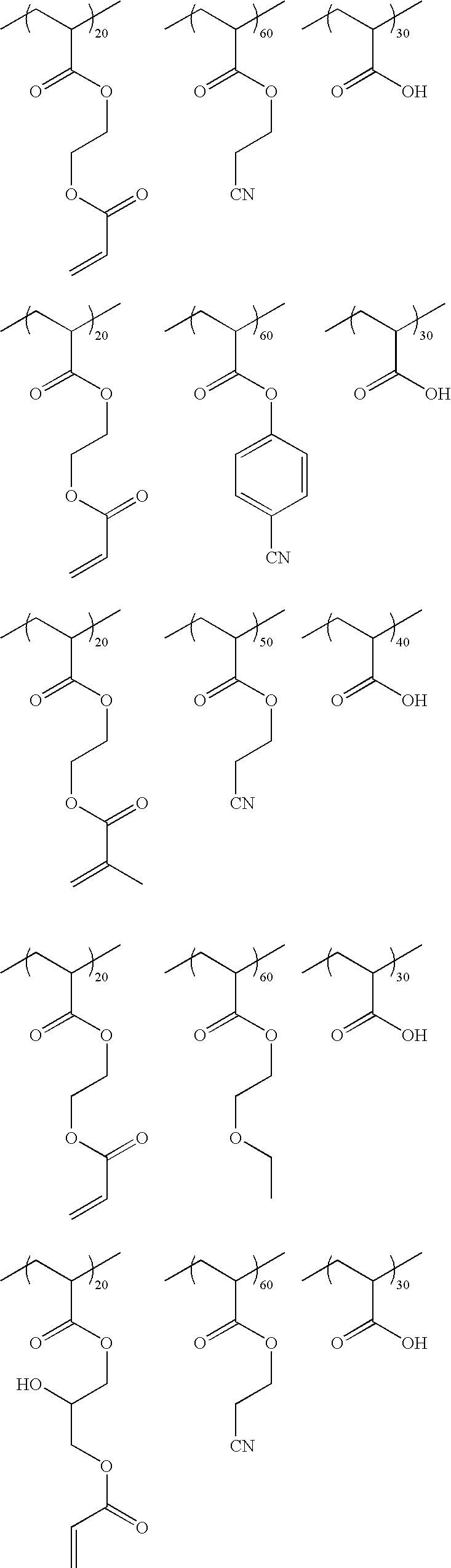

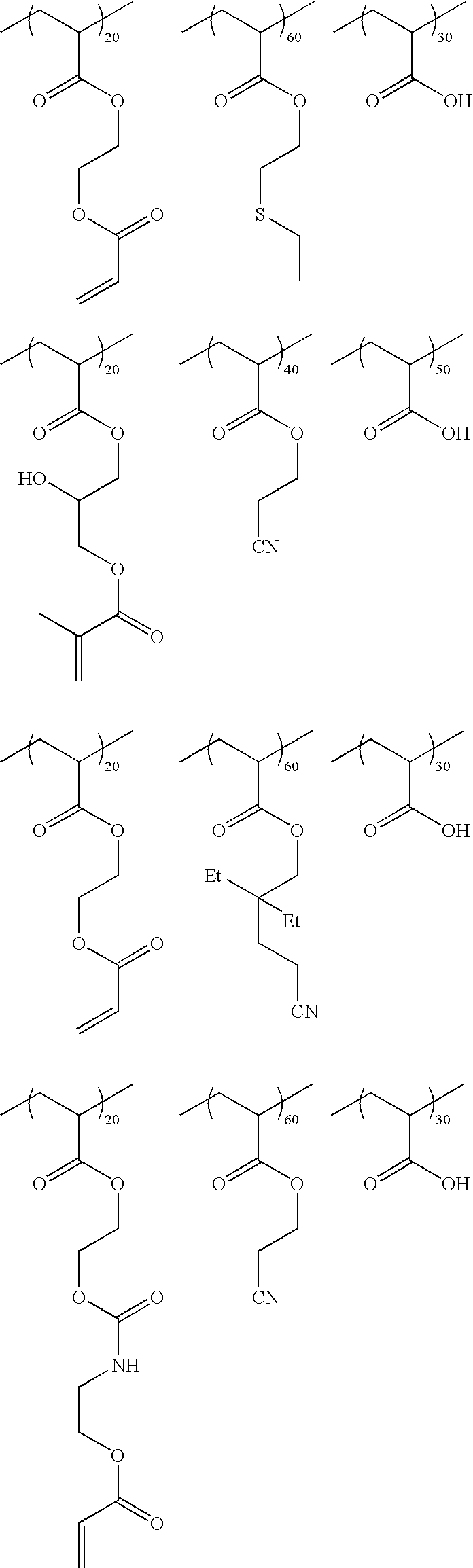

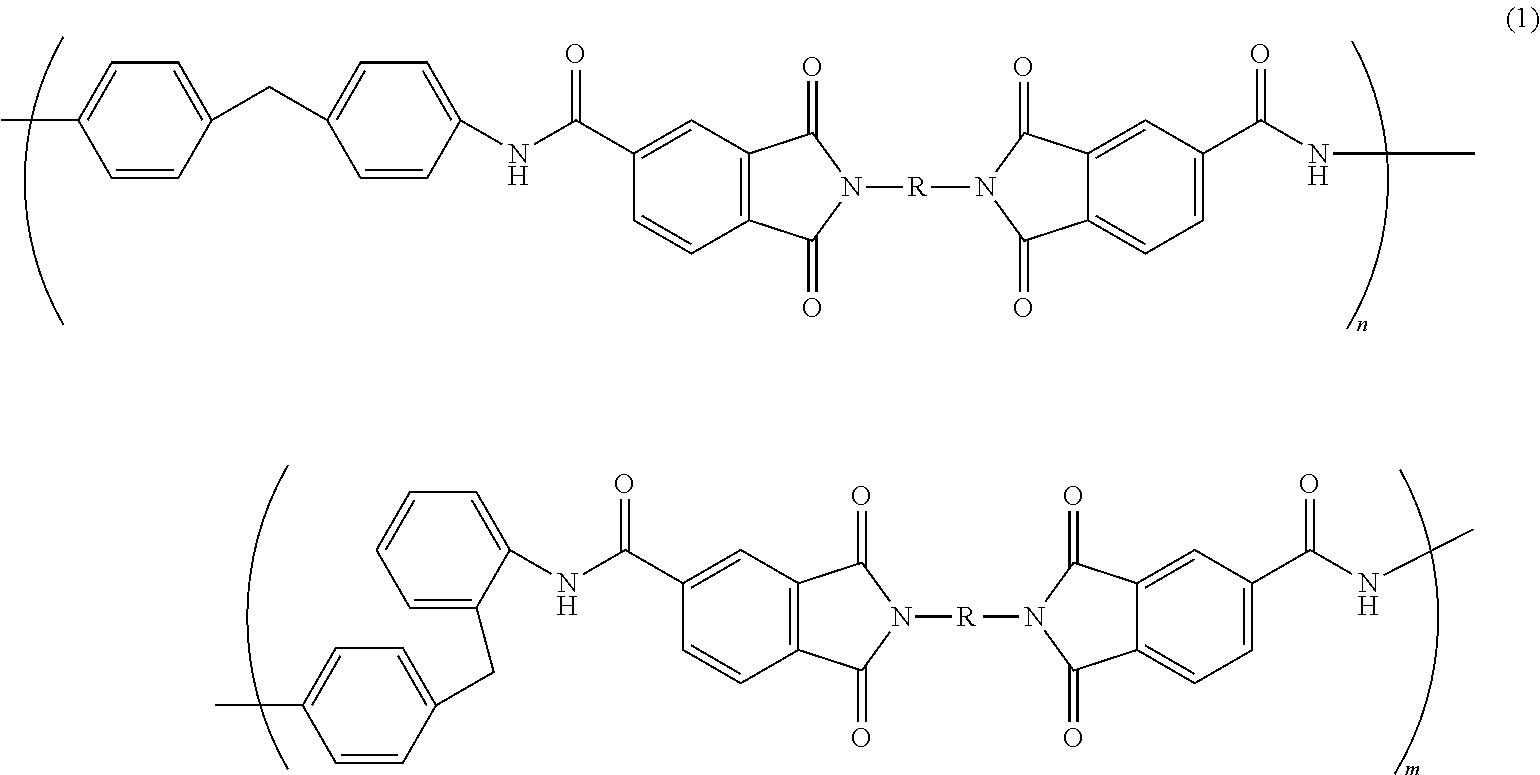

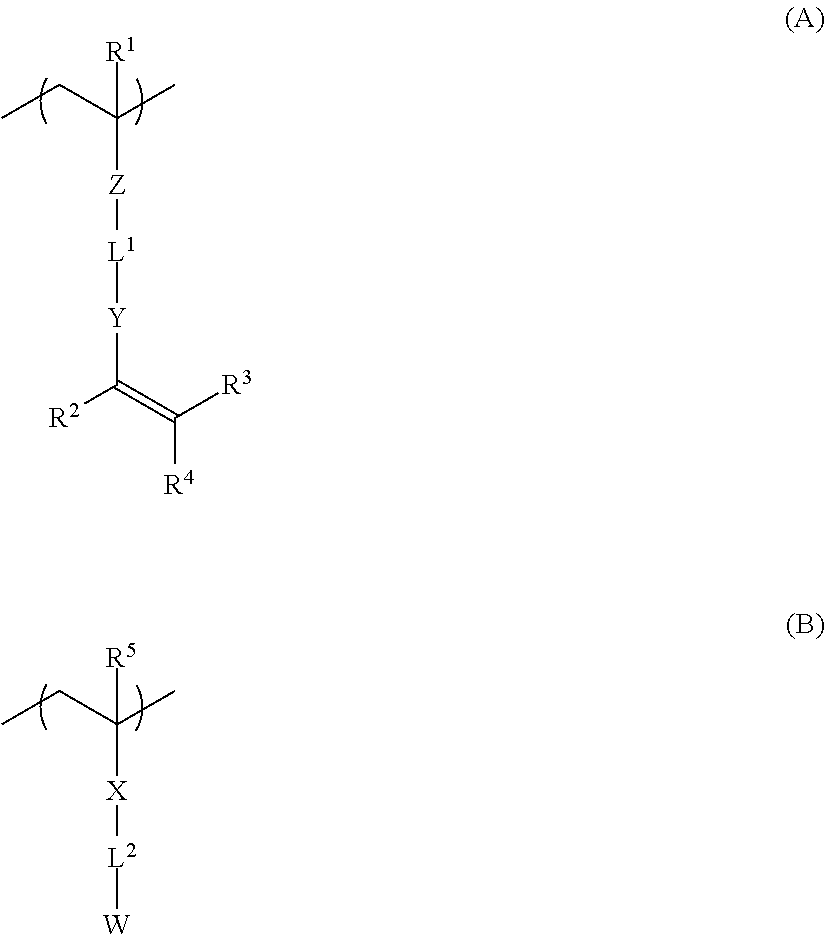

Composition for forming layer to be plated, method of producing metal pattern material, metal pattern material

ActiveUS20100080964A1Improve film propertiesImprove propertiesLayered productsDecorative surface effectsElectrical polarityPolymer

A composition including a polymer, the polymer having a non-dissociative functional group that interacts with a plating catalyst or a precursor thereof, a radical polymerizable group, and an ionic polar group; a method of producing a metal pattern material using the same: and a metal pattern material produced by the method.

Owner:FUJIFILM CORP

Electronics device, semiconductor device, and method for manufacturing the same

InactiveUS7446336B2Show reliableDeterioration of propertyElectroluminescent light sourcesSolid-state devicesDisplay deviceEngineering

It is an object of the present invention to provide a high reliable EL display device and a manufacturing method thereof by shielding intruding moisture or oxygen which is a factor of deteriorating the property of an EL element without enlarging the EL display device.In the invention, application is used as a method for forming a high thermostability planarizing film 16, typically, an interlayer insulating film (a film which serves as a base film of a light emitting element later) of a TFT in which a skeletal structure is configured by the combination of silicon (Si) and oxygen (O). After the formation, an edge portion or an opening portion is formed to have a tapered shape. Afterwards, distortion is given by adding an inert element with a comparatively large atomic radius to modify or highly densify a surface (including a side surface) for preventing the intrusion of moisture or oxygen.

Owner:SEMICON ENERGY LAB CO LTD

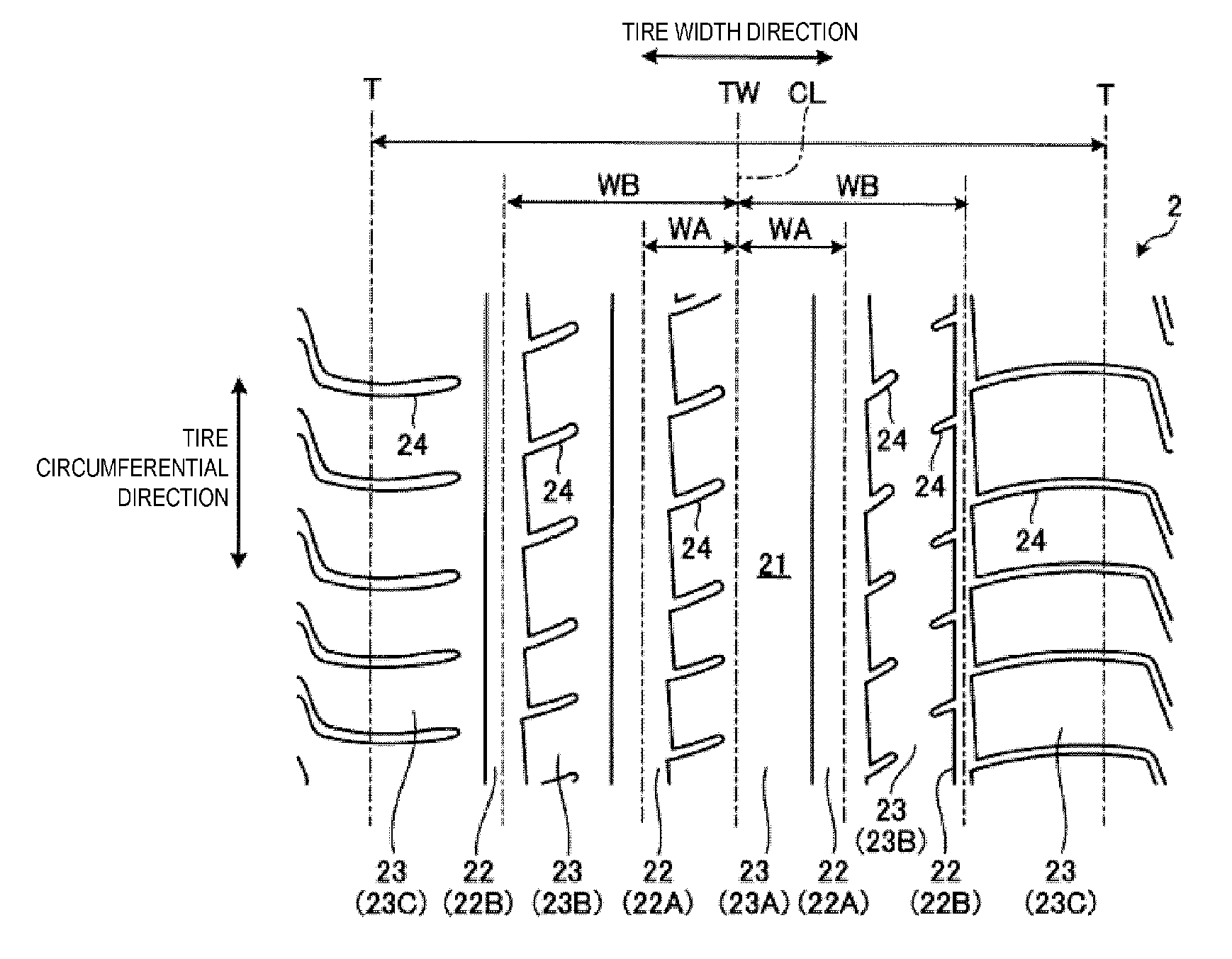

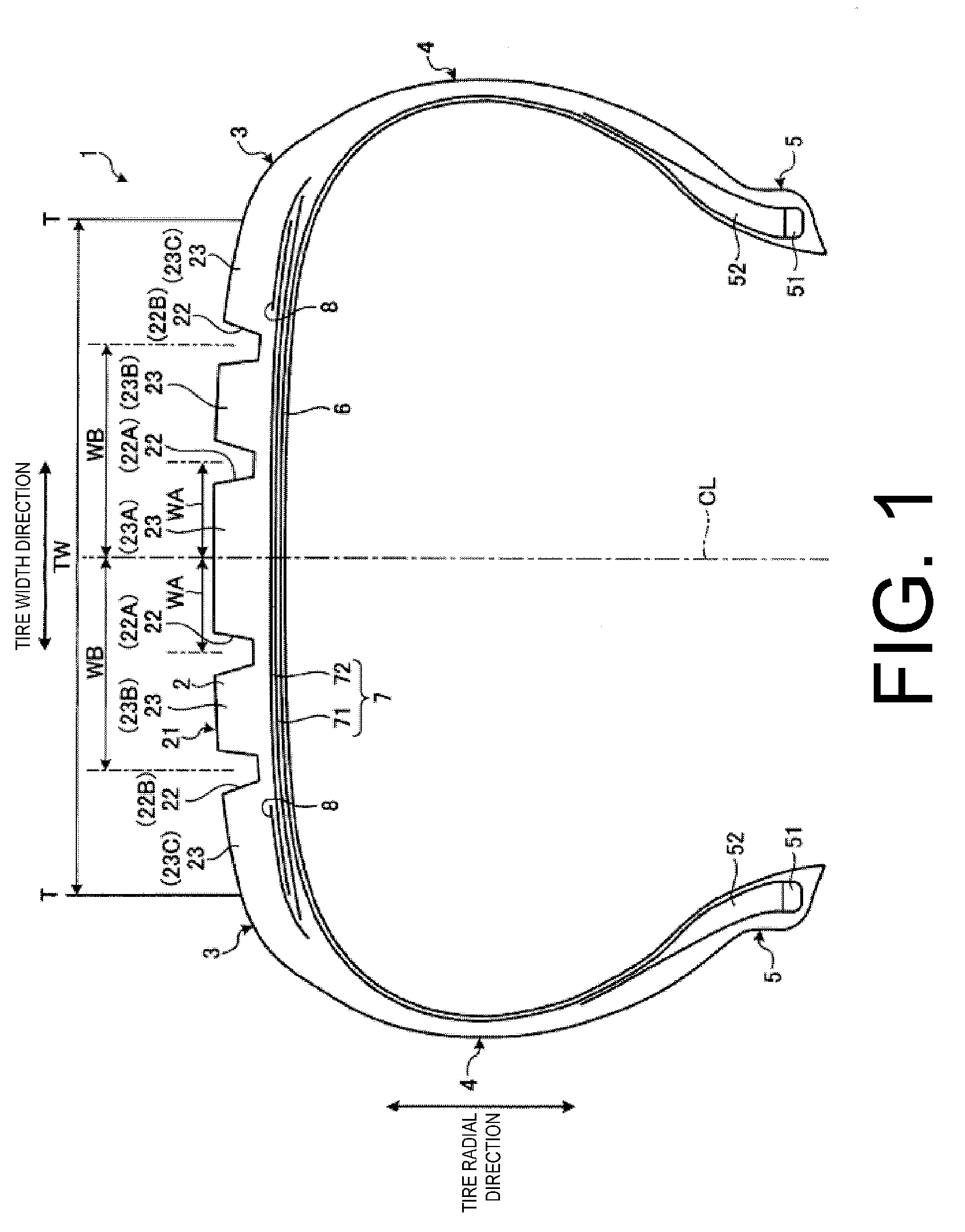

Pneumatic Tire

ActiveUS20130240101A1Improve steering stabilityImprove propertiesTyre tread bands/patternsNon-skid devicesEngineeringContact patch

The contact patch of the center land portion partitioned by the center side main grooves protrudes outward in the tire radial direction from the overall standard profile line of the tread portion. The maximum protruding amount is not less than 1.0% and not more than 2.5% of the tire width direction dimension of the center land portion. The contact patch of the intermediate land portion partitioned by the center side main groove and the shoulder side main groove protrudes outward in the tire radial direction from the standard profile line. The maximum protruding amount is not less than 0.7% and not more than 2.0% of the tire width direction dimension of the intermediate land portion. The maximum protruding amount of the center land portion is greater than the maximum protruding amount of the intermediate land portion.

Owner:YOKOHAMA RUBBER CO LTD

Multi-layer foils comprising plasticized polyvinyl acetal, featuring penetration resistance and sound-damping properties

InactiveUS20150306853A1Sure easyDeterioration of propertySynthetic resin layered productsVehicle componentsPolyvinyl alcoholTotal thickness

The invention relates to an intermediate layer film for laminated glazing, constructed from at least one first and at least one second sub-film containing plasticiser-containing polyvinyl acetal each with different plasticiser content, wherein the first sub-film consists of plasticiser-containing polyvinyl acetal with a polyvinyl alcohol content from 17 to 22% by weight, and the second sub-film consists of plasticiser-containing polyvinyl acetal with a polyvinyl alcohol content from 11 to 14% by weight, and the intermediate layer film has a total plasticiser content of less than 28% by weight. The film can be used in particular for windscreens with use of glasses with a total thickness of less than 3.7 mm.

Owner:KURARAY EURO GMBH

Polarizing plate and image display including the same

InactiveUS20070269616A1High hardnessReduce thicknessLiquid crystal compositionsPolarising elementsDisplay devicePolarizer

A polarizing plate is provided that has excellent polarization properties and high surface hardness and can have a reduced thickness. The polarizing plate includes a polarizer and a cured resin layer. The cured resin layer is formed directly on at least one surface of the polarizer. The cured resin layer is formed of a solventless photocurable composition containing the following components (A), (B), and (C): (A) at least one of a polyfunctional acrylic monomer and a polyfunctional methacrylic monomer; (B) a photocurable prepolymer; and (C) a photopolymerization initiator.

Owner:NITTO DENKO CORP

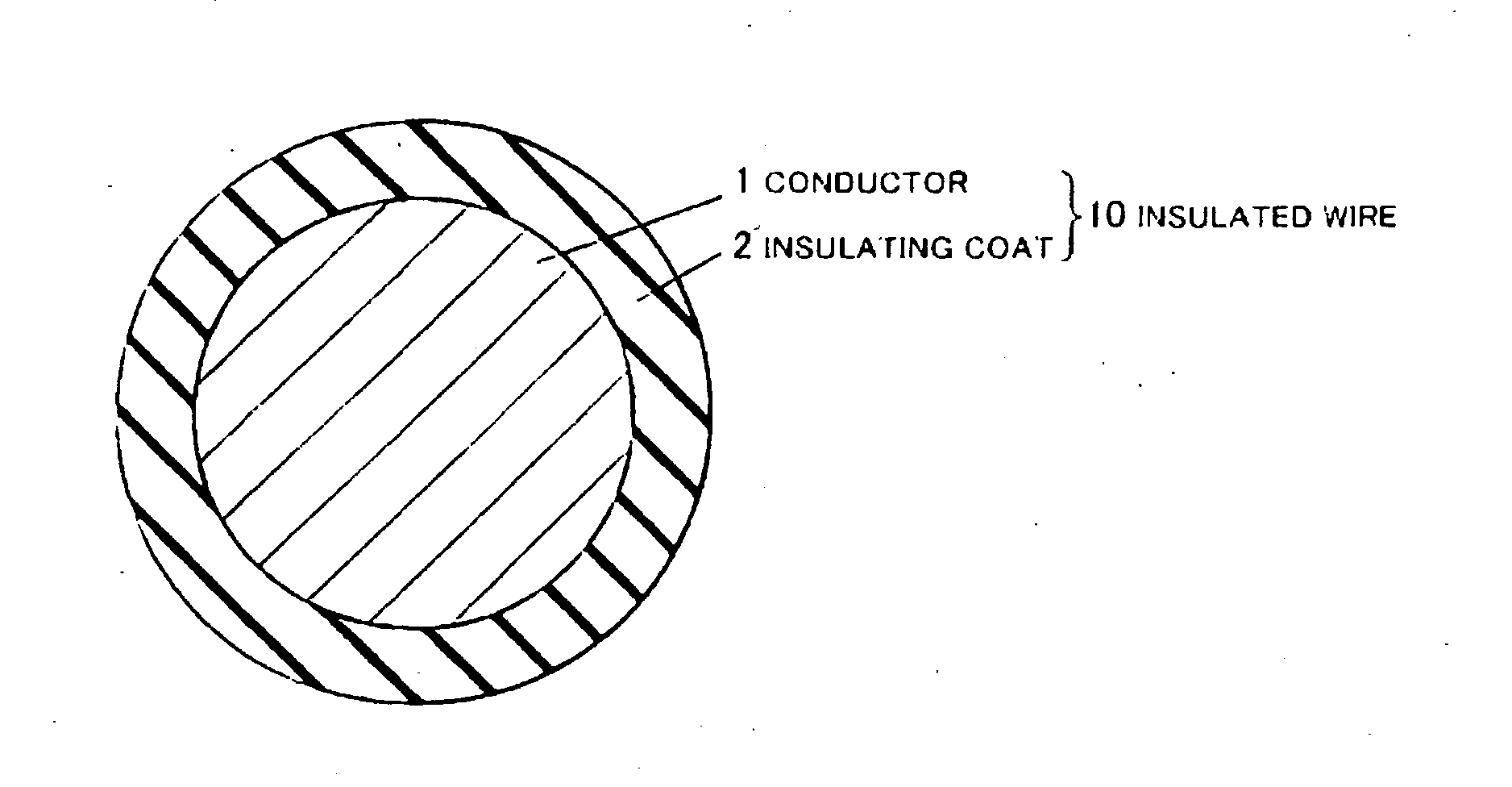

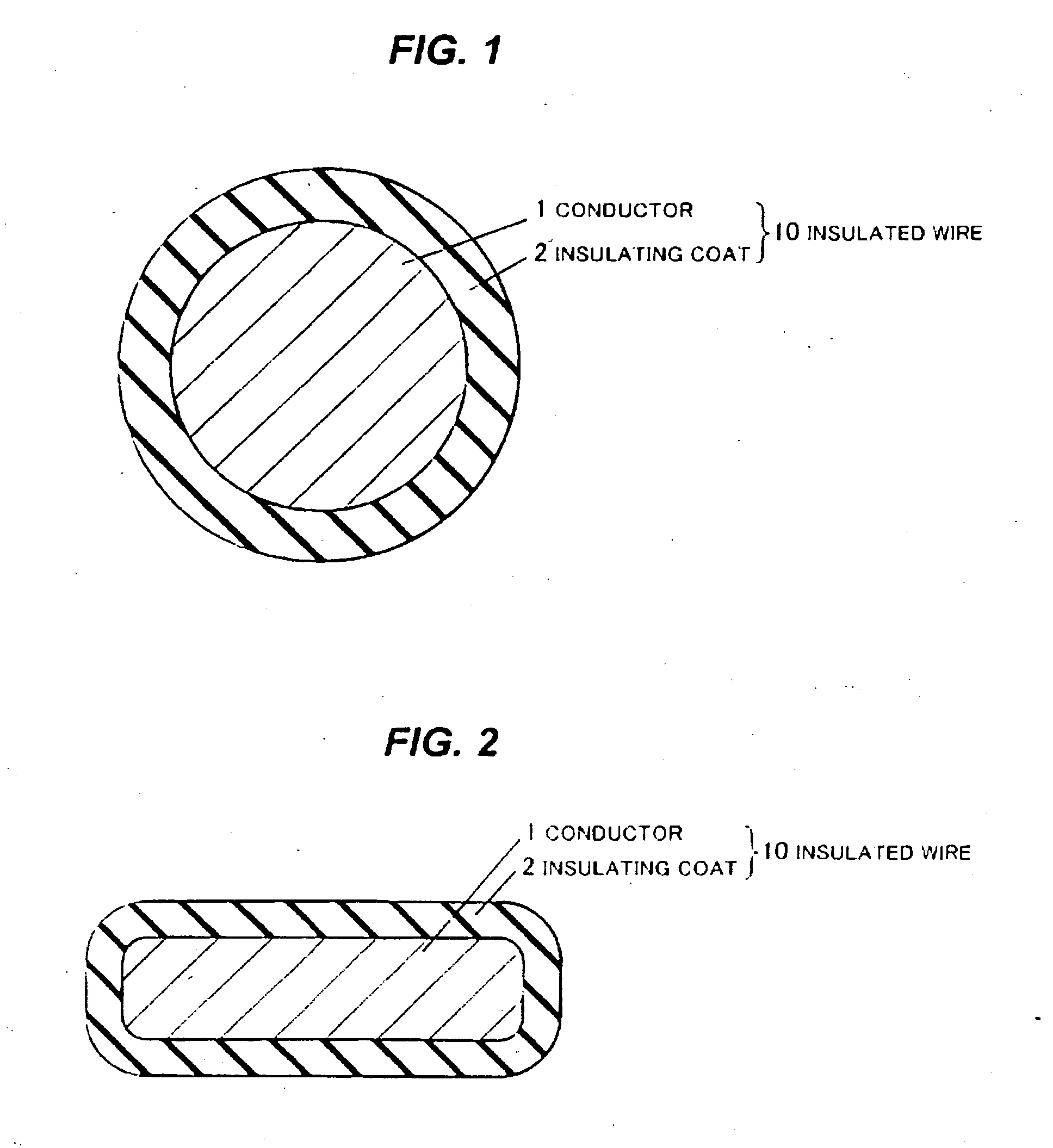

Insulating varnish and insulated wire formed by using the same

InactiveUS20110290528A1Improve compatibilityHigh partial discharge inception voltagePlastic/resin/waxes insulatorsInsulated cablesPolyamide-imideVarnish

An insulating varnish includes a polyamide-imide resin varnish including a solvent and a polyamide-imide resin, and an organosol. The polyamide-imide resin varnish is obtained by a synthesis reaction between a resin component (X) and an isocyanate component (Y). The resin component (X) is obtained by a synthesis reaction between a diamine component and an acid component in presence of an azeotropic medium. The diamine component includes aromatic diamines including a divalent aromatic group having three or more aromatic rings. The isocyanate component (Y) includes a diisocyanate (Y1) a molecule of which includes a bend structure.

Owner:HITACHI CABLE

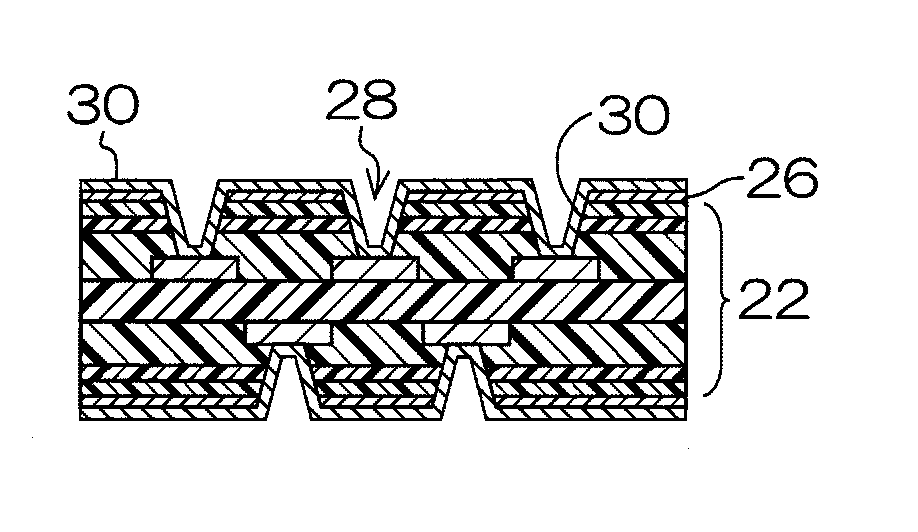

Method for producing multilayer wiring substrate and multilayer wiring substrate

InactiveUS20110247865A1Improve connection reliabilitySimple processPhototackifying patterningPretreated surfacesElectroless platingPolymer chemistry

The present invention provides a method for producing a multilayer wiring substrate, including: forming a laminated body having an insulating resin layer and a polymer adhesive layer, on a surface of a first wiring substrate wherein the polymer adhesive layer contains a polymer precursor interacting with a plating catalyst or a precursor thereof, and a reactive group bonding with an adjacent layer on the first wiring substrate side; applying energy to a region outside of a via connection portion on the surface of the laminated body, to form a patterned polymer adhesive layer; applying a plating catalyst or a precursor thereof to the patterned polymer adhesive layer, and carrying out a first electroless plating, to form a second metal wiring on the surface of the patterned polymer adhesive layer; and forming a via by utilizing the patterned second metal wiring as a mask, and subsequently carrying out a desmear treatment.

Owner:FUJIFILM CORP

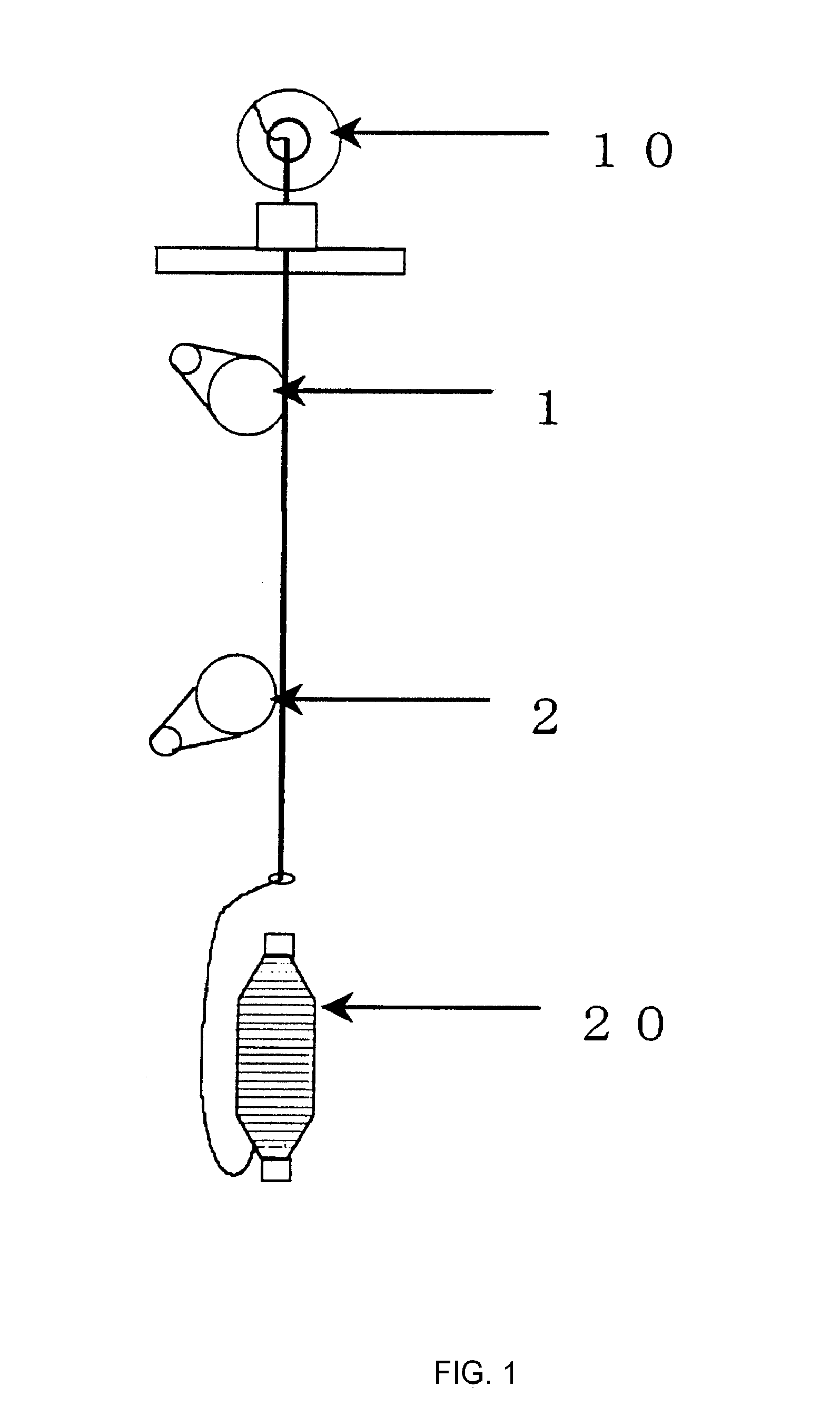

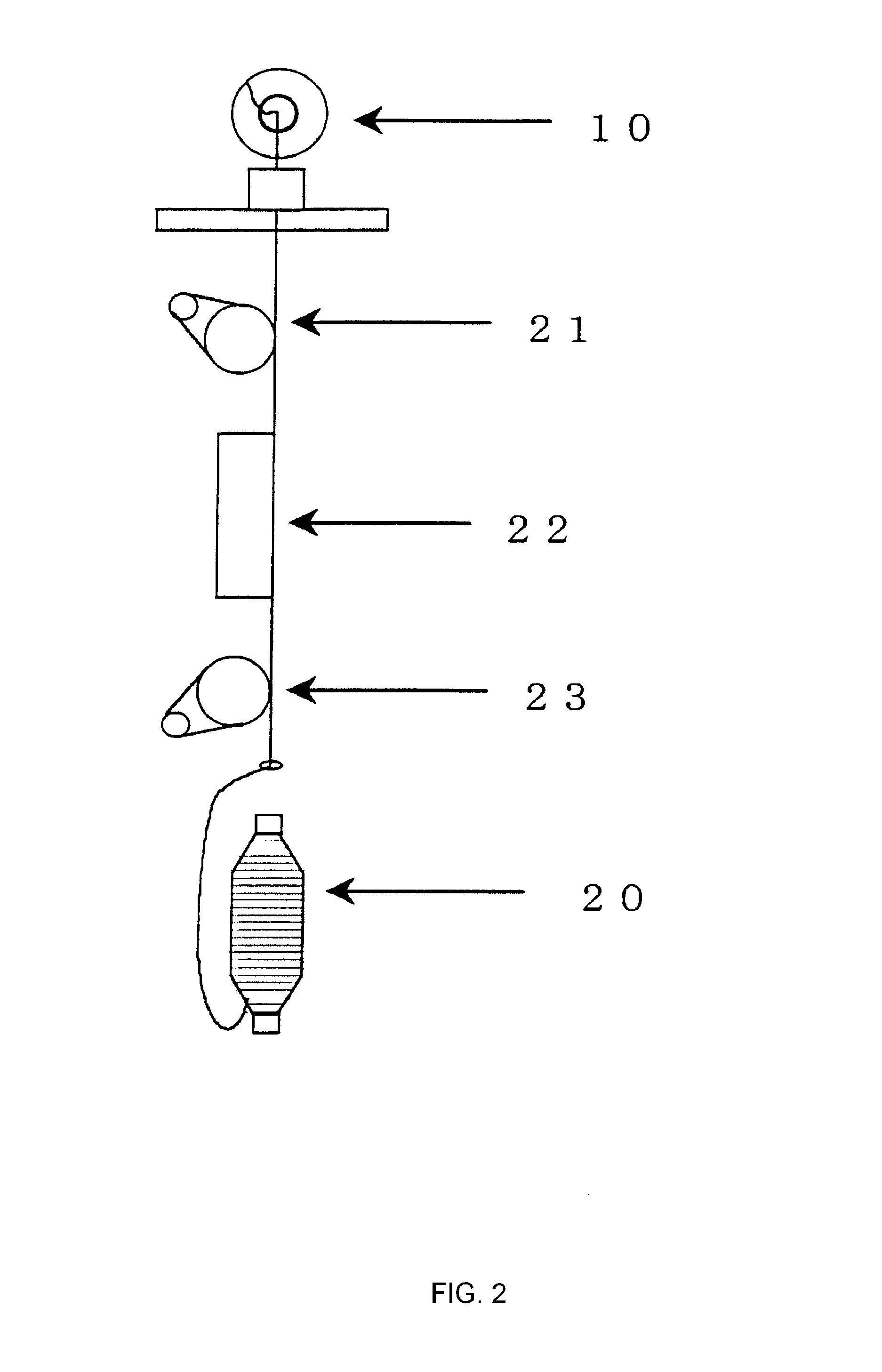

Polylactic acid resin, textile products obtained therefrom, and processes for producing textile products

InactiveUS7445841B1Deterioration of propertyLow tensile strengthEngine sealsCarpetsYarnRelative viscosity

A polylactic acid resin suitable for use especially in textile products; textile products obtained from the resin as a raw material (a fiber, multifilament, monofilament, staple, false-twist yarn, long-fiber nonwoven fabric, etc.); and processes for producing these textile products. The polylactic acid resin is a resin consisting mainly of a polylactic acid and is characterized in that it is linear, has an L-isomer content of 95 mol % or higher, an Sn content of 30 ppm or lower, a monomer content of 0.50 wt. % or lower, and has a relative viscosity of 2.7 to 3.9 or has a weight-average molecular weight of 120,000 to 220,000 and a number-average molecular weight of 60,000 to 110,000. Each of the textile products comprises the polylactic acid resin as the main material. The textile products each comprises a polylactic acid that is excellent in processability and excellent fiber properties. The free textile products are problems in practical use.

Owner:TORAY IND INC

Alkali - free glass and liquid crystal display panel

InactiveUS20070027019A1Excellent in reducing resistanceDeterioration of propertyNon-linear opticsAlkali freeLiquid-crystal display

To provide an alkali-free glass excellent in the properties for glass substrates to be used for display, excellent in the resistance to reduction, and suitable for forming by a float process. An alkali-free glass consisting essentially of, as represented by mol %: SiO2at least 60% and less than 66%,Al2O30 to 12%,B2O35 to 10%,MgO0 to 18%,CaO0 to 18%,SrO0 to 18%,BaO0 to 6%, CaO + SrO10 to 25%, MgO + CaO + SrO + BaO15.5 to 30% and containing substantially no alkali metal oxide.

Owner:ASAHI GLASS CO LTD

Heat dissipation structure

ActiveUS20150163958A1Reduce heat generationDeterioration of propertyMagnetic/electric field screeningLayered productsLiquid resinMoisture

The present invention provides a heat dissipation structure that does not cause problems such as contact failures in electronic components and that is applicable to electronic components with high heat densities. The present invention also provides a method for easily repairing an electronic device. The heat dissipation structure is obtained by filling and curing a thermally conductive curable resin composition in an electromagnetic shielding case on a substrate on which an electronic component with a heat density of 0.2 W / cm2 to 500 W / cm2 is mounted, the thermally conductive curable resin composition containing a curable liquid resin (I) and a thermally conductive filler (II), having a viscosity at 23° C. of 30 Pa·s to 3000 Pa·s and a thermal conductivity of 0.5 W / (m·K) or more, and being curable by moisture or heat.

Owner:KANEKA CORP

Aluminum alloy sheet

Disclosed is an aluminum alloy sheet resistant to deterioration through natural aging. The aluminum alloy sheet is an Al—Mg—Si aluminum alloy sheet containing 0.35 to 1.0 percent by mass of magnesium; 0.5 to 1.5 percent by mass of silicon; 0.01 to 1.0 percent by mass of manganese; and 0.001 to 1.0 percent by mass of copper, with the remainder being aluminum and inevitable impurities, in which the amount of dissolved silicon is 0.55 to 0.80 percent by mass, the amount of dissolved magnesium is 0.35 to 0.60 percent by mass, and the ratio of the former to the latter is 1.1 to 2. The aluminum alloy sheet may further contain 0.005 to 0.2 percent by mass of titanium with or without 0.0001 to 0.05 percent by mass of boron.

Owner:KOBE STEEL LTD

Latex film compound with improved tear resistance

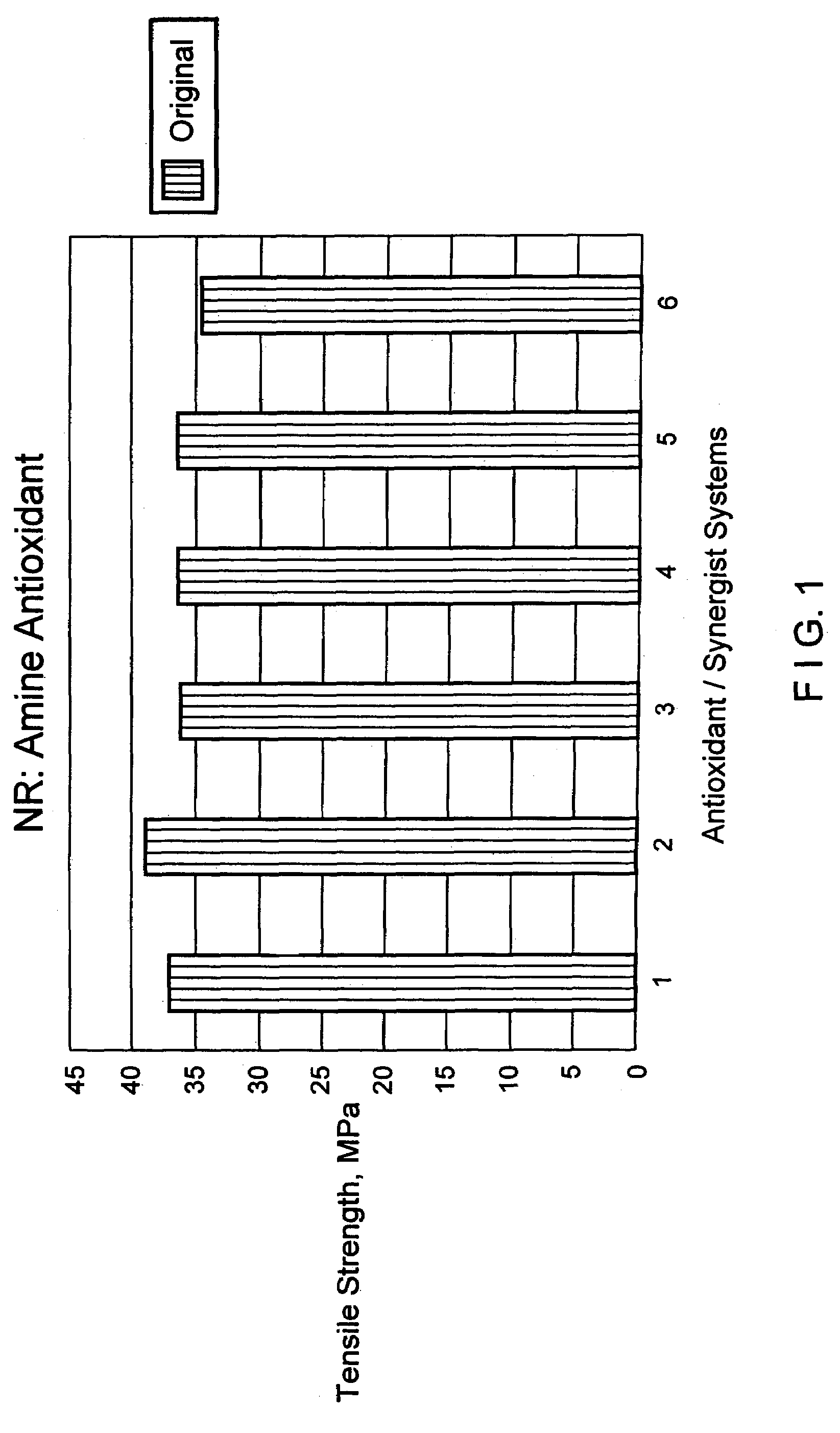

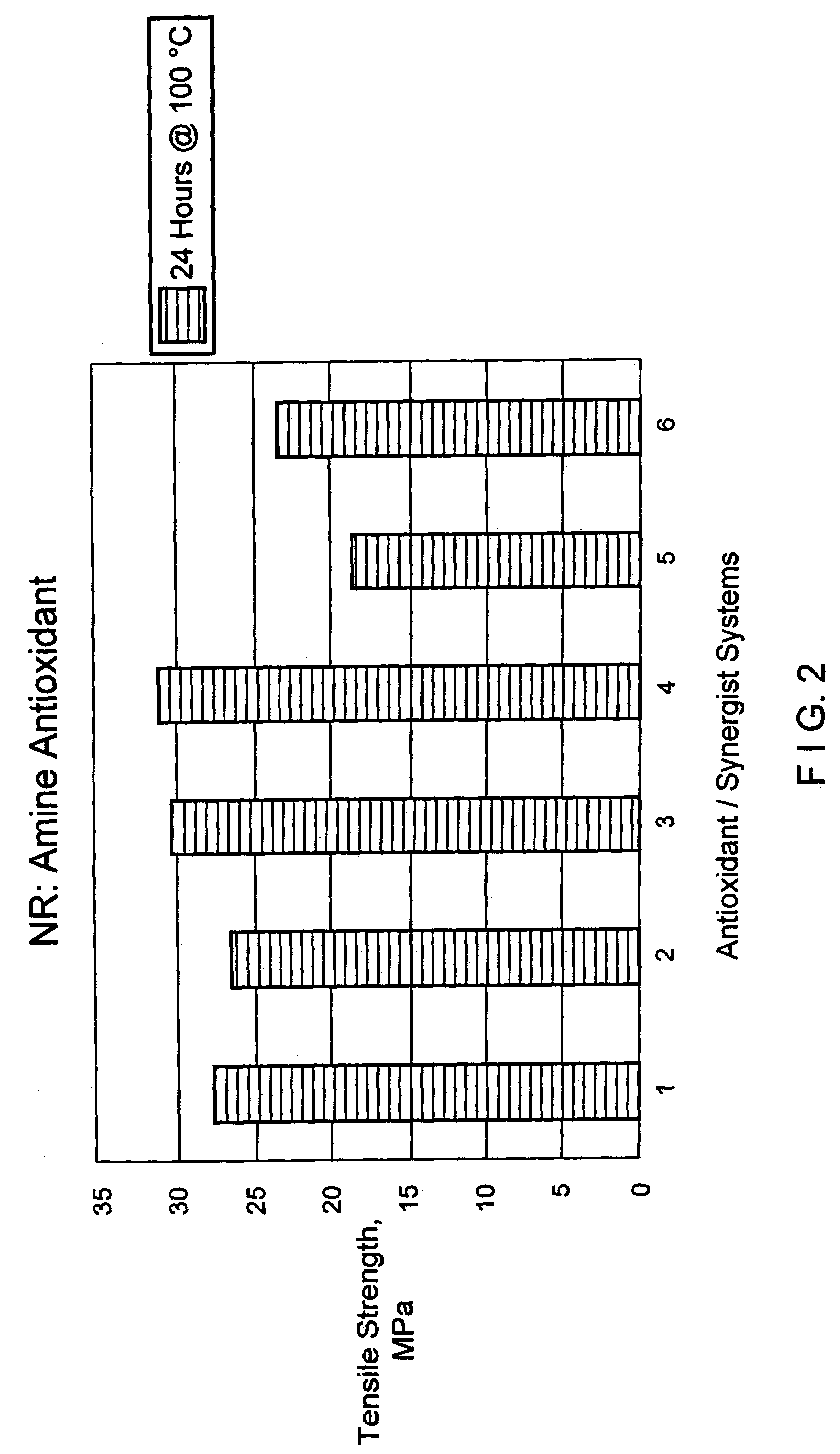

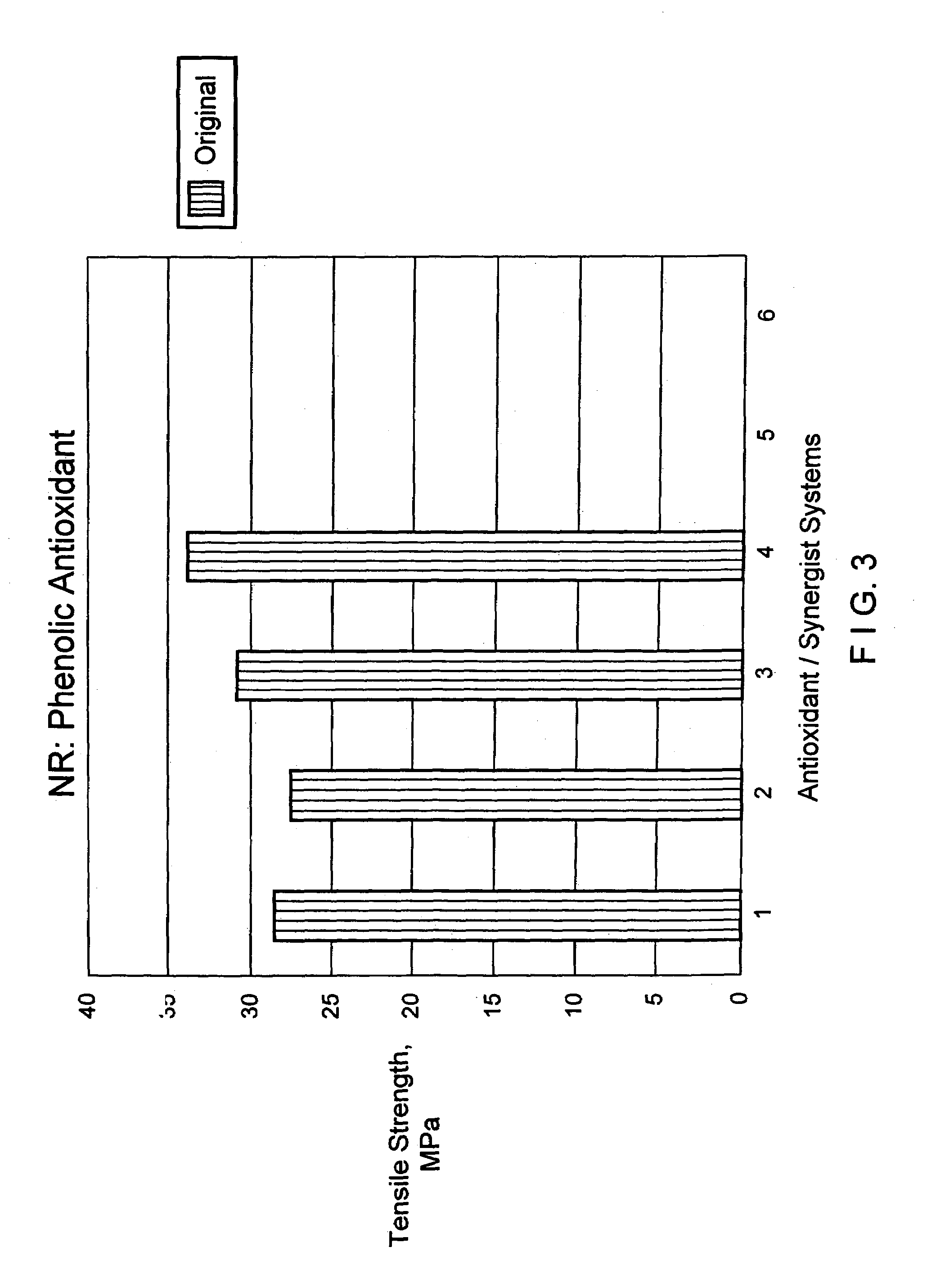

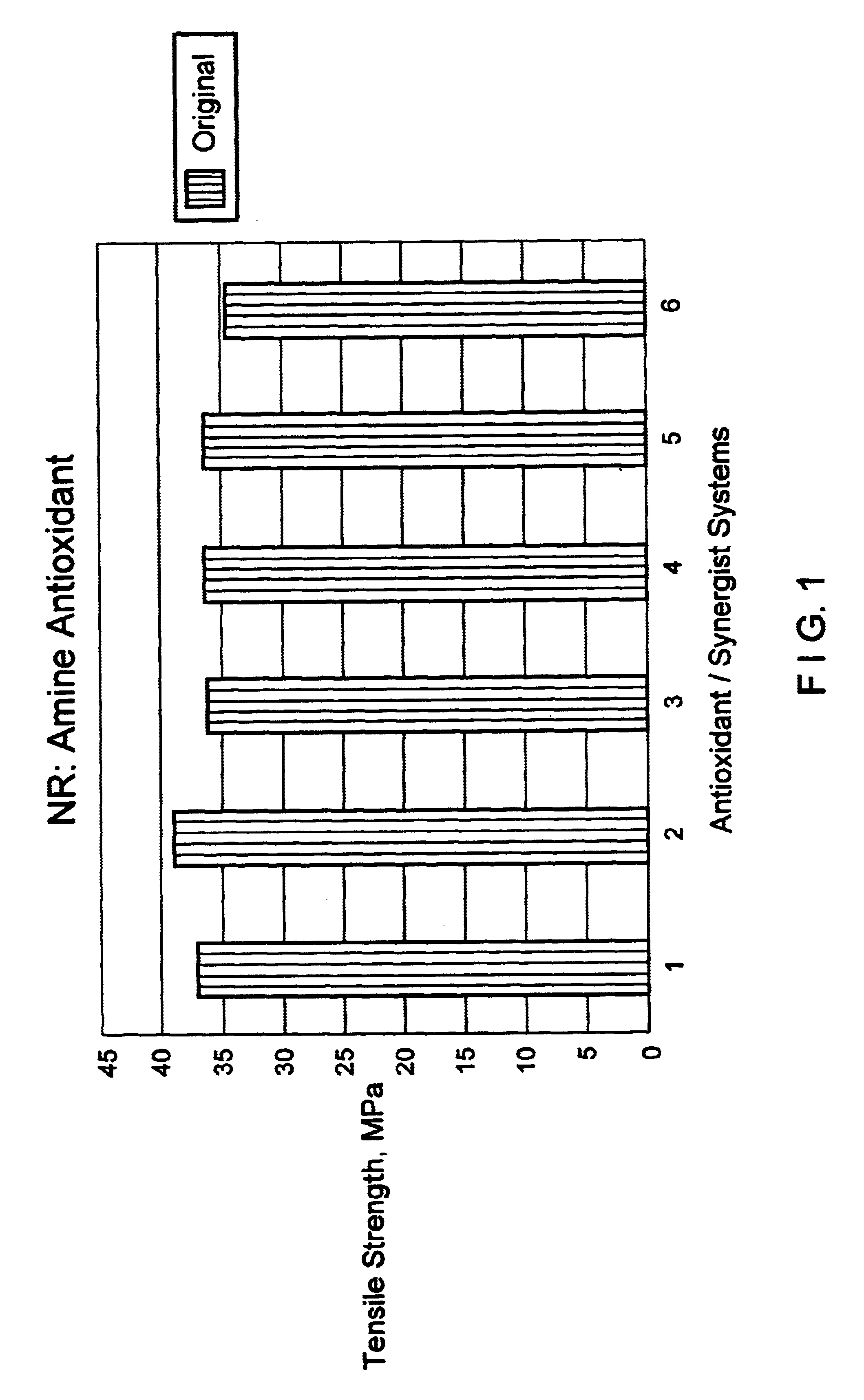

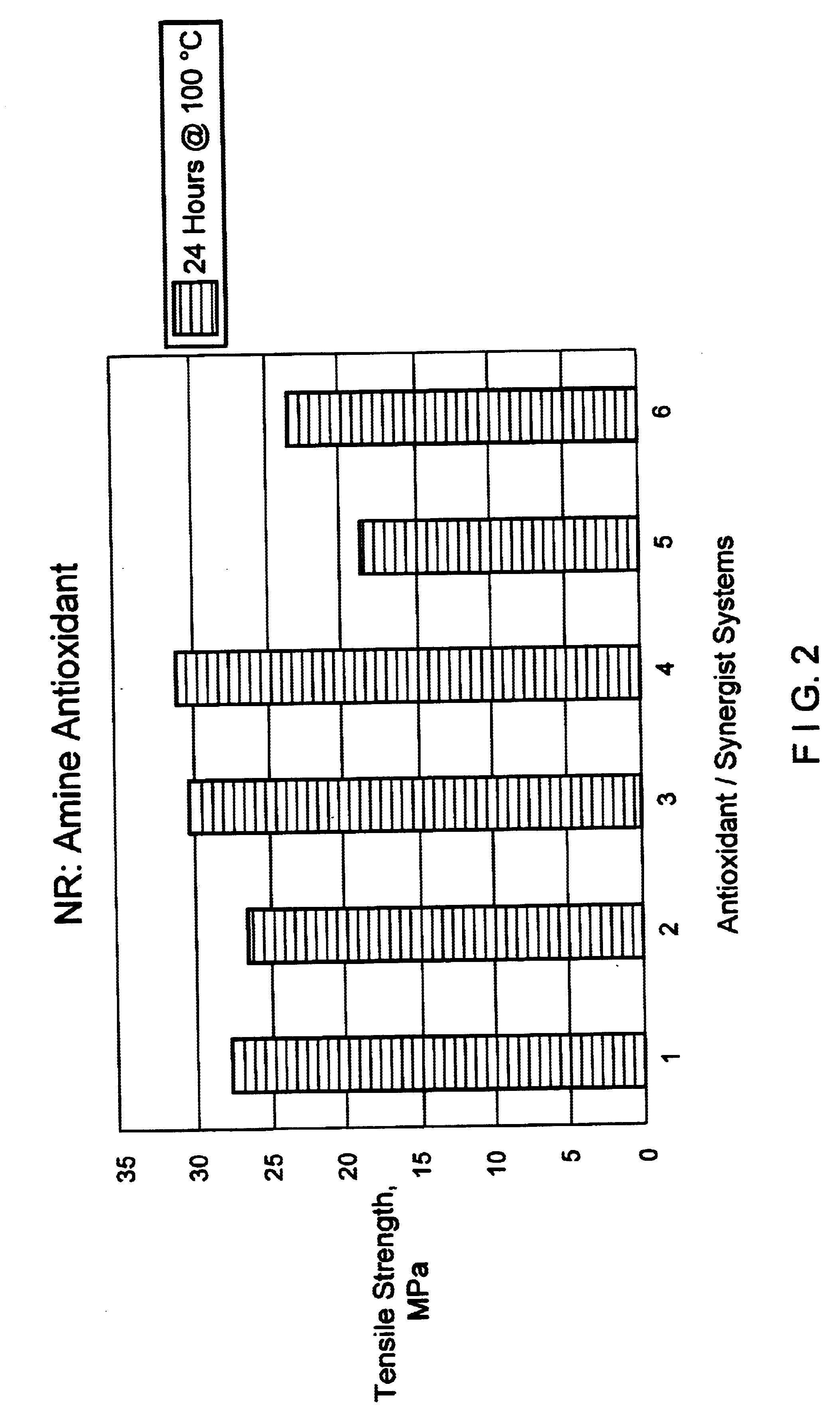

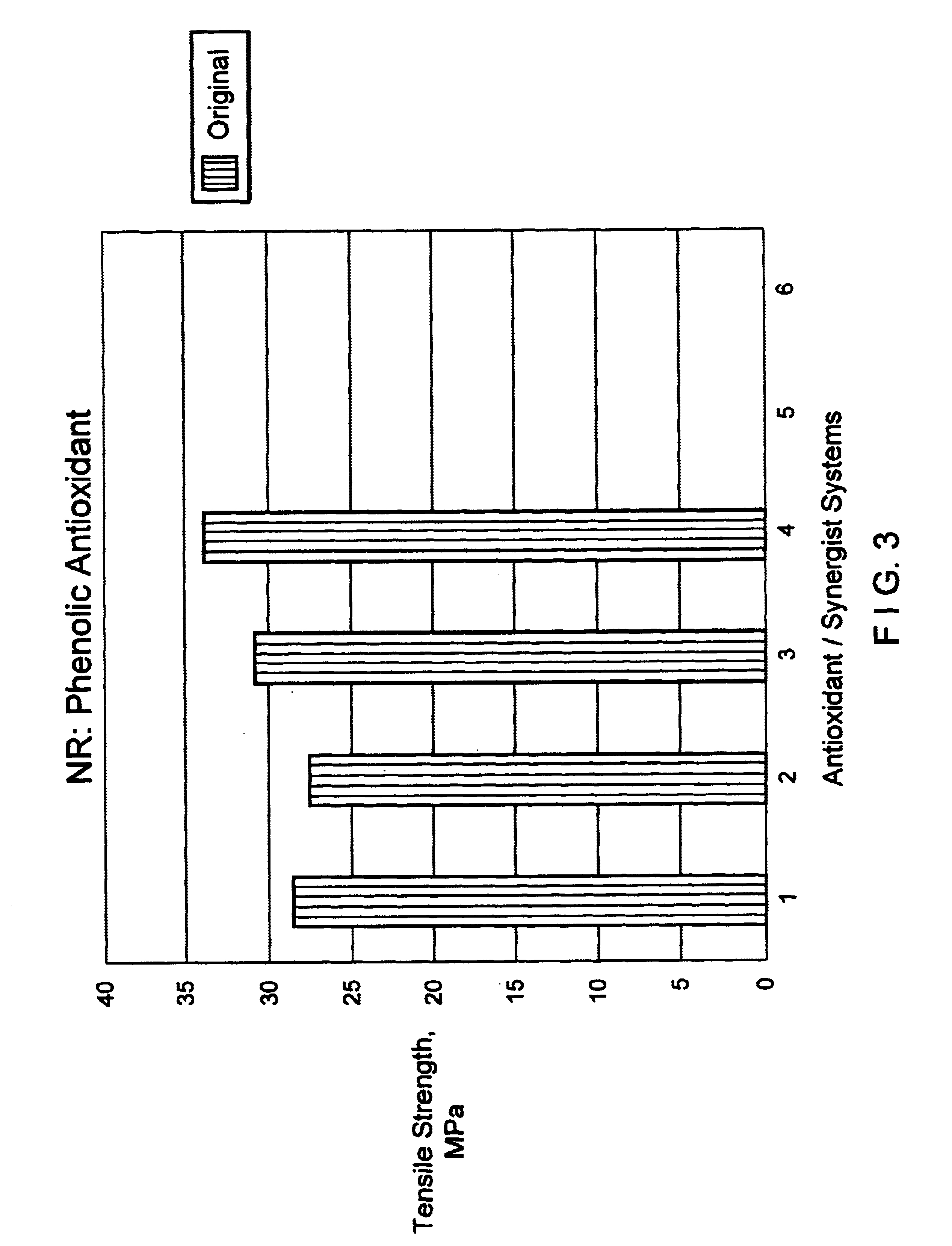

InactiveUS7048977B2Increase elasticityIncrease resistanceClosuresClosure using stoppers2-mercaptobenzimidazoleAntioxidant

The invention relates to a method of enhancing the tear resistance, tensile strength, and the aging properties of a latex product by adding an antioxidant synergist with an antioxidant to a latex compound comprising of a polymer and a curing system comprised of an activator, crosslinker and accelerator and to the latex products formed therefrom. Antioxidant synergists which can be used with the present invention include 2-mercaptobenzimidazole (MBI), 2-mercaptotoluimidazole (MTI), zinc 2-mercaptobenzimidazole (ZMBI) and zinc 2-mercaptotoluimidazole (ZMTI). The latex products formed may be gloves but can also include threads, balloons and other latex-related products.

Owner:VANDERBILT CHEM LLC

Latex film compound with improved tear resistance

InactiveUS6653380B2Good effectDeterioration of propertyGranular deliverySolid balls2-mercaptobenzimidazoleAntioxidant

The invention relates to a method of enhancing the tear resistance, tensile strength, and the aging properties of a latex product by adding an antioxidant synergist with an antioxidant to a latex compound comprising of a polymer, a stabilizing system, a film surface conditioner and a curing system comprised of an activator, crosslinker and accelerator and to the latex products formed therefrom. Antioxidant synergists which can be used with the present invention include 2-mercaptobenzimidazole (MBI), 2-mercaptotoluimidazole (MTI), zinc 2-mercaptobenzimidazole (ZMBI) and zinc 2-mercaptotoluimidazole (ZMTI). The latex products formed may be gloves but can also include threads, balloons and other latex-related products.

Owner:VANDERBILT CHEM LLC

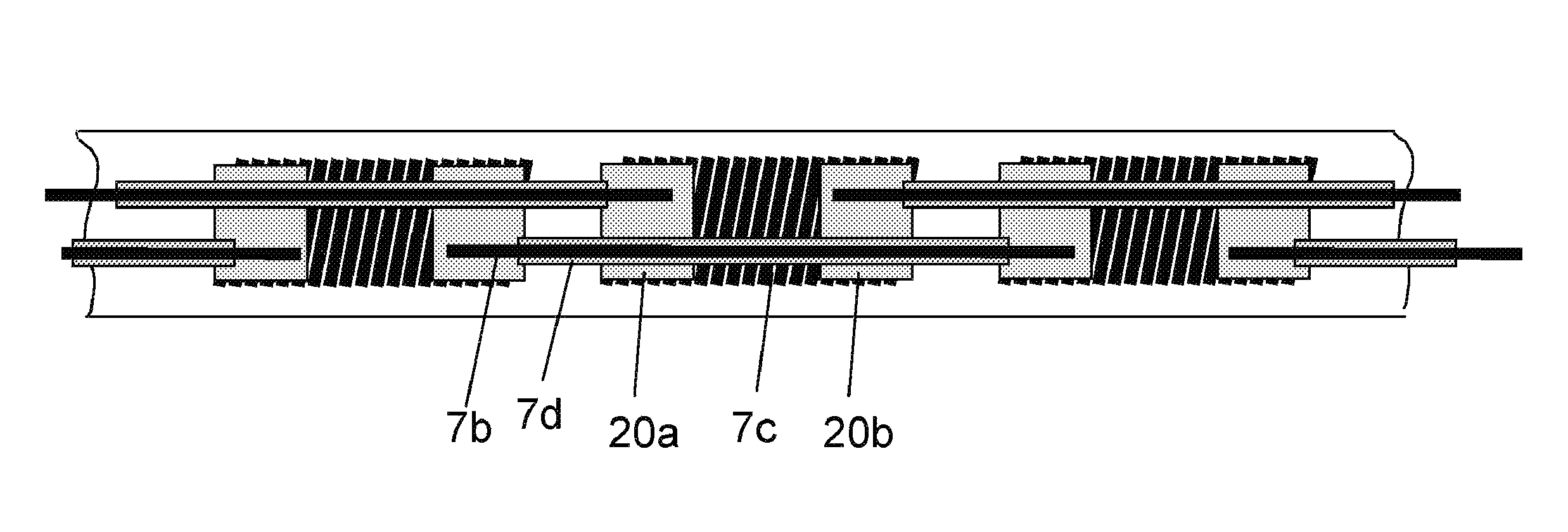

Electrode catheter for interventional use

InactiveUS8386057B2Simple and materialDeterioration of propertyTransvascular endocardial electrodesExternal electrodesCardiac pacemaker electrodeCardiac pacemaker

Owner:BIOTRONIK SE & CO KG

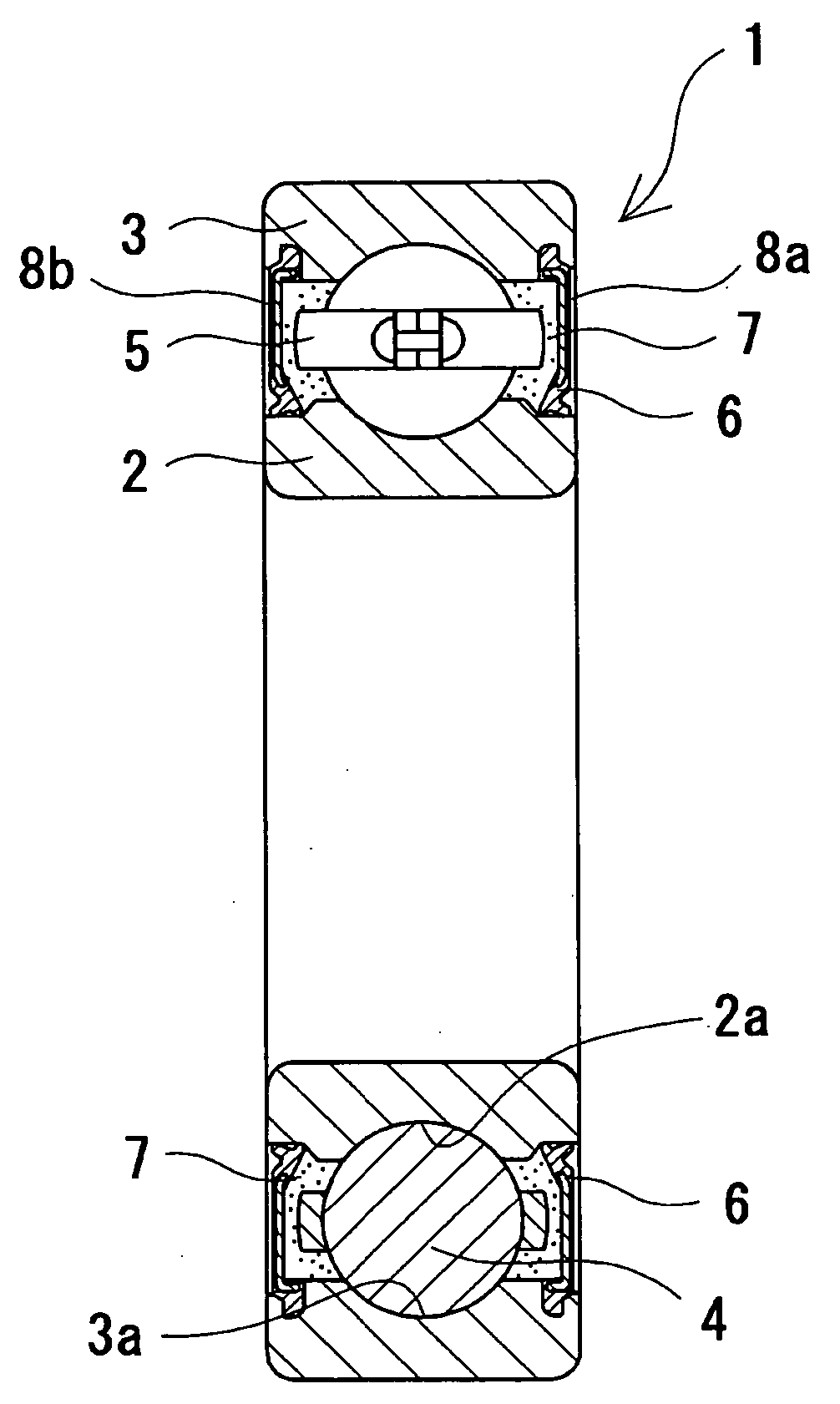

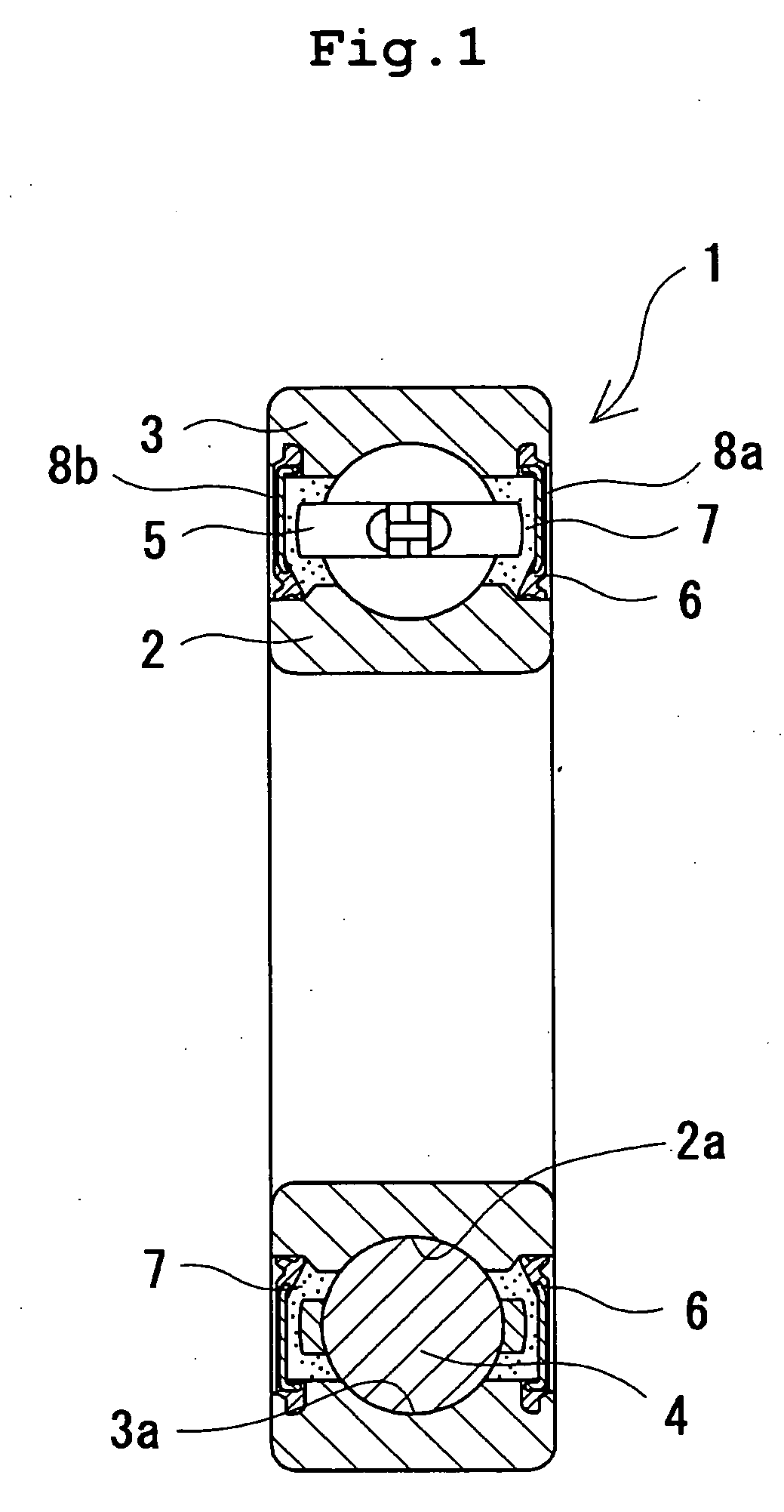

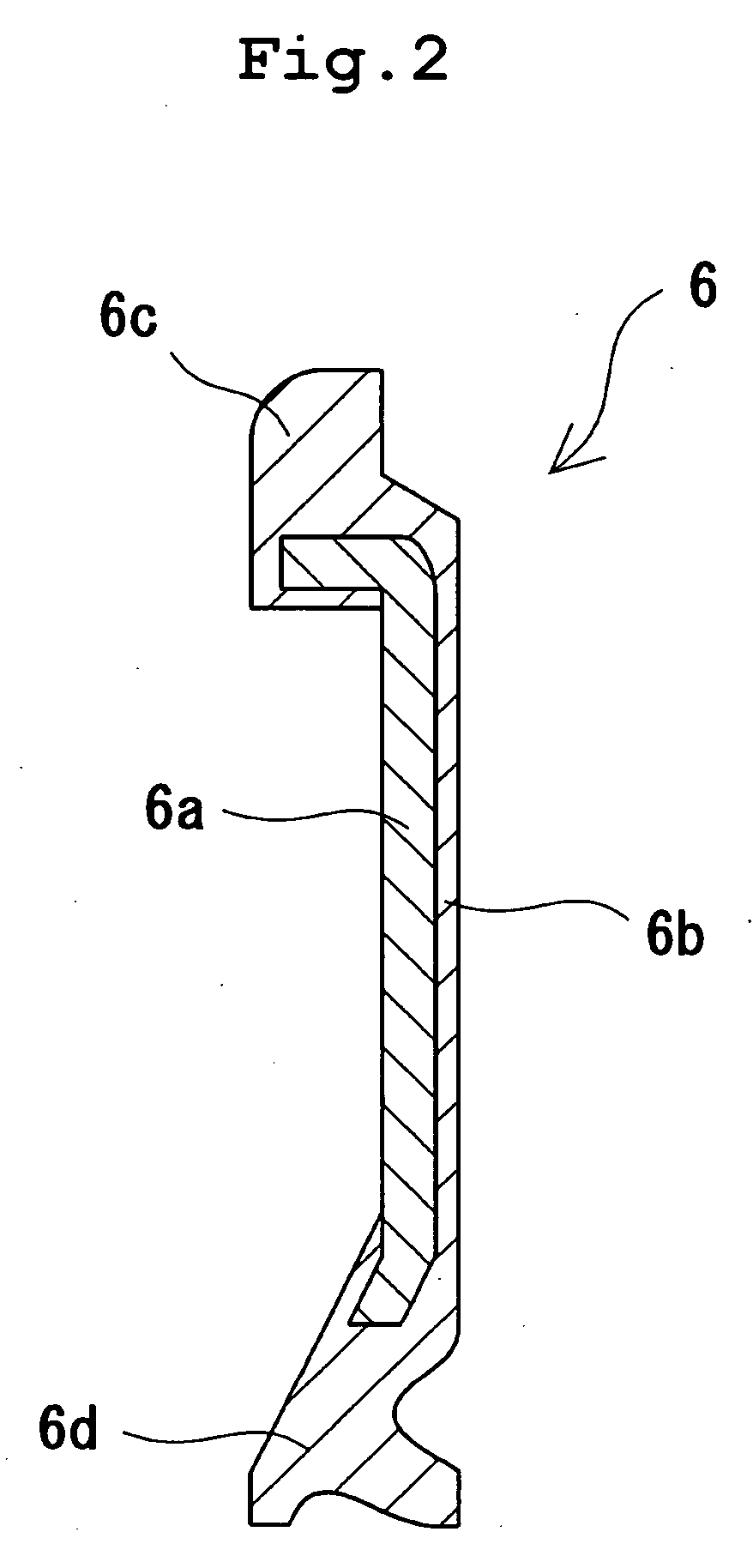

Rolling bearing for use in vehicle

A rolling bearing for use in a vehicle, particularly in an electric device on said vehicle, said bearing having a sealing member for sealing urea compound-containing grease, in which an elastic body deteriorates to a low extent when the rolling bearing is subjected to a high temperature and which is capable of maintaining a preferable sealing performance. The grease-sealing member has a rubber molding which contacts the grease. The rubber molding is formed by molding a curable fluororubber composition consisting of a copolymer containing tetrafluoroethylene, propylene, and a crosslinkable monomer consisting of unsaturated hydrocarbon, having two to four carbon atoms, in which a part of hydrogen atoms is substituted with fluorine atoms.

Owner:NTN CORP

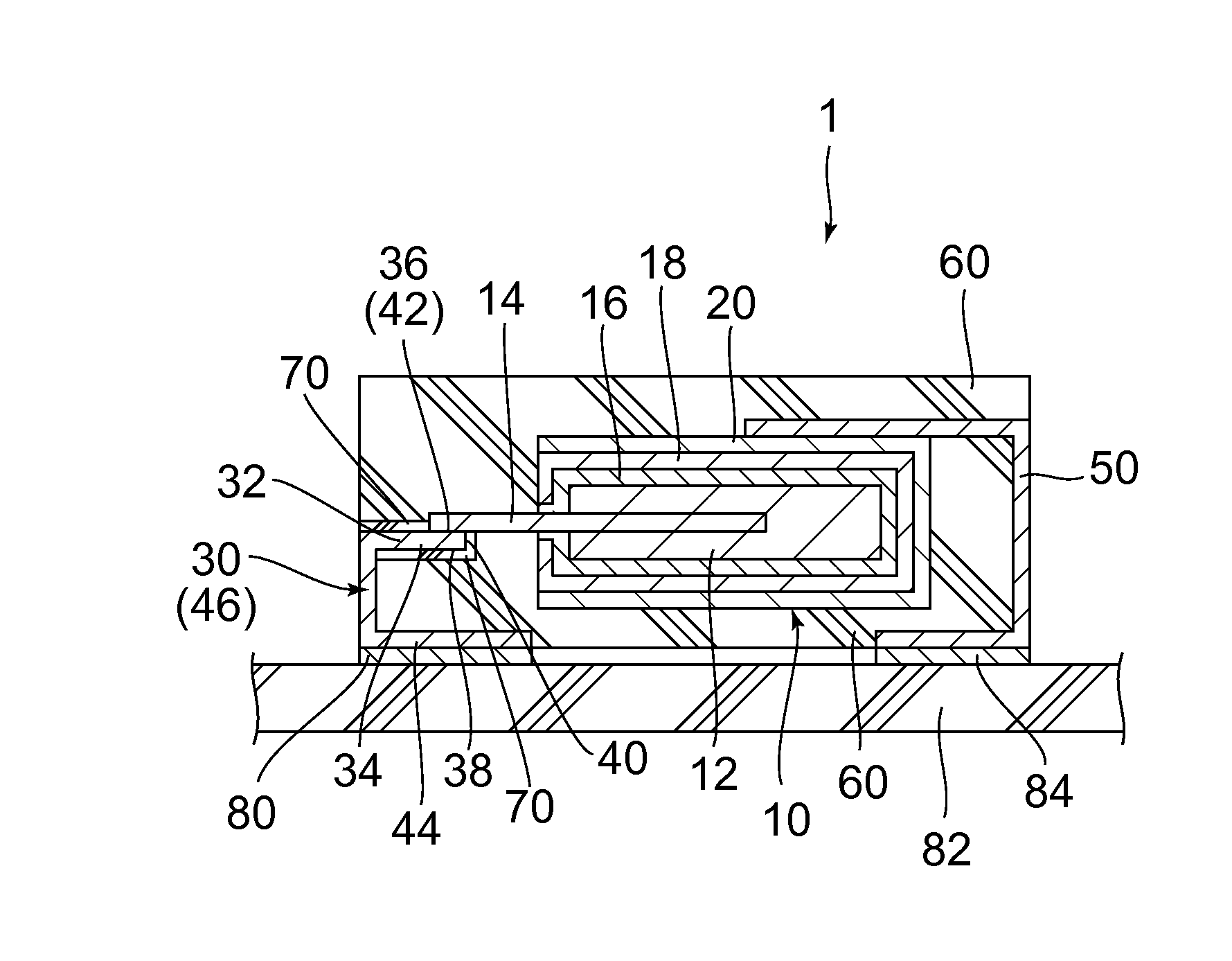

Solid electrolytic capacitor

ActiveUS9293263B2Improve moisture resistanceImprove suppression propertiesSolid electrolytic capacitorsCapacitor housing/encapsulationElectrolysisEngineering

An outer insulation member made of a first resin packs a part of an anode terminal. The packed part of the anode terminal has a predetermined section. All surfaces of the predetermined section consist of a front surface, a back surface and edges connecting between the front surface and the back surface. The front surface includes a connection area. An anode lead wire is connected to the connection area while being not connected to the anode terminal other than the connection area. The all surfaces of the predetermined section are completely covered with a mask layer made of a second resin except for the connection area. The second resin is different from the first resin in at least one of composition thereof, content of an inclusion, size of an inclusion and shape of an inclusion.

Owner:TOKIN CORP +1

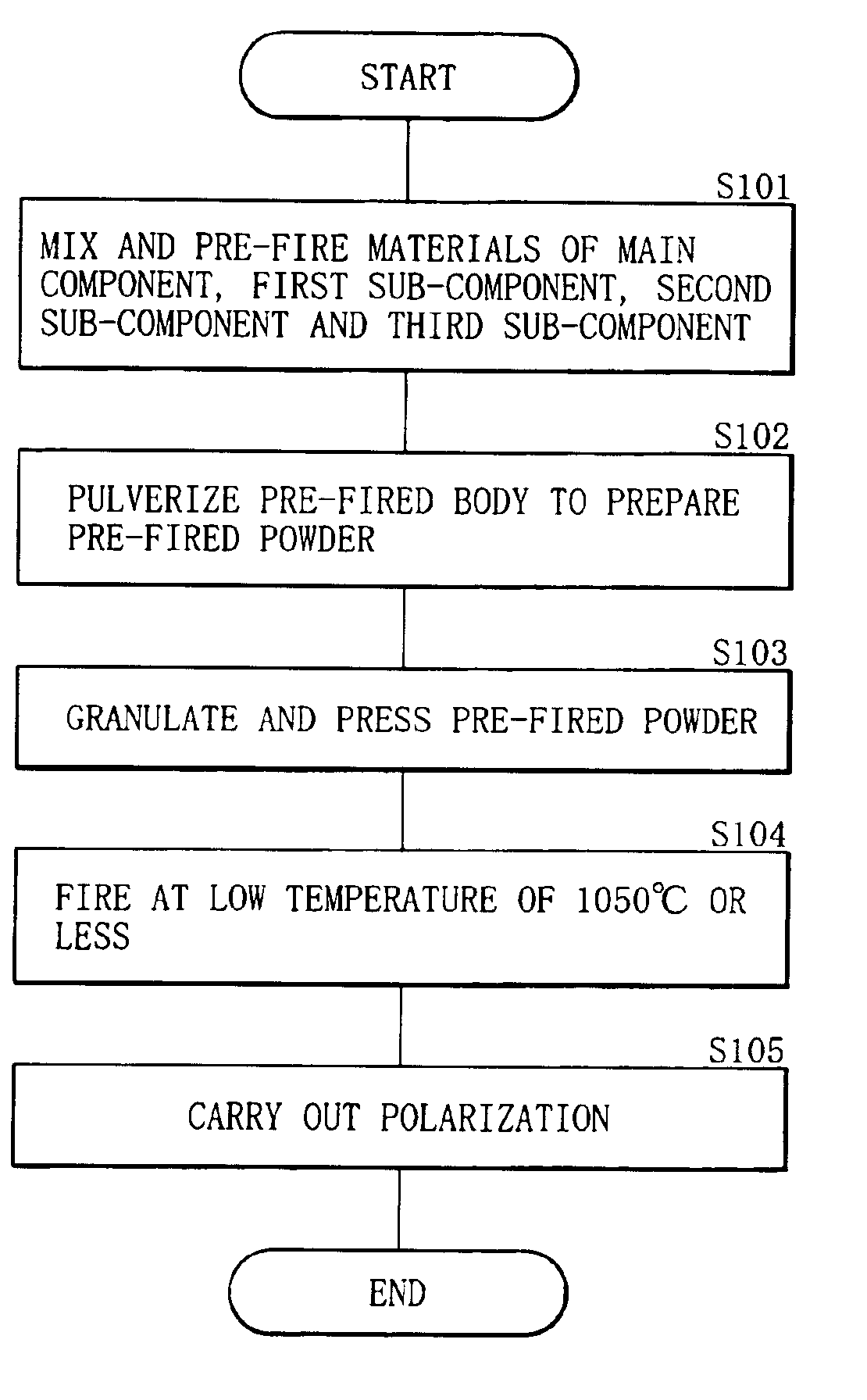

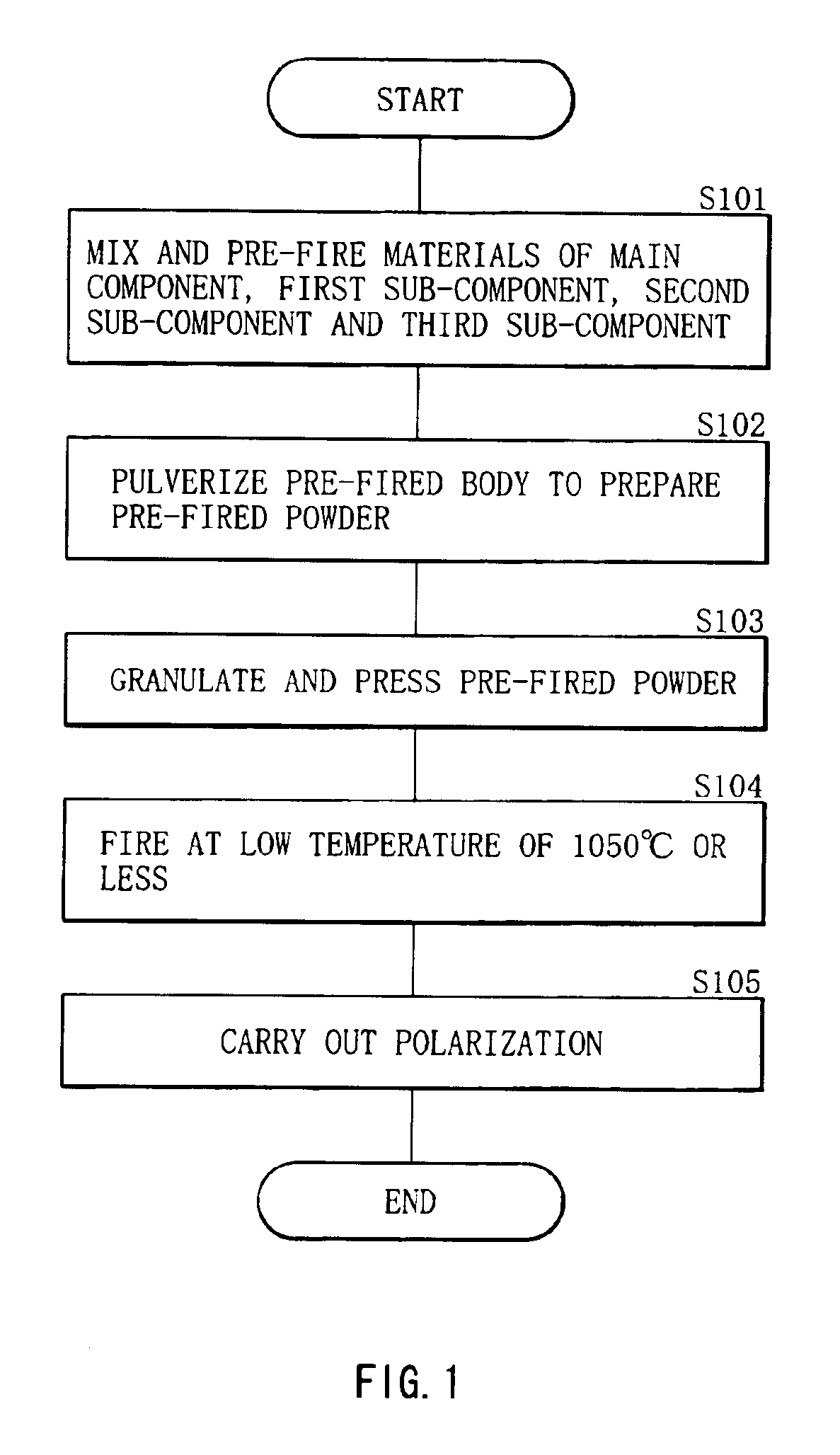

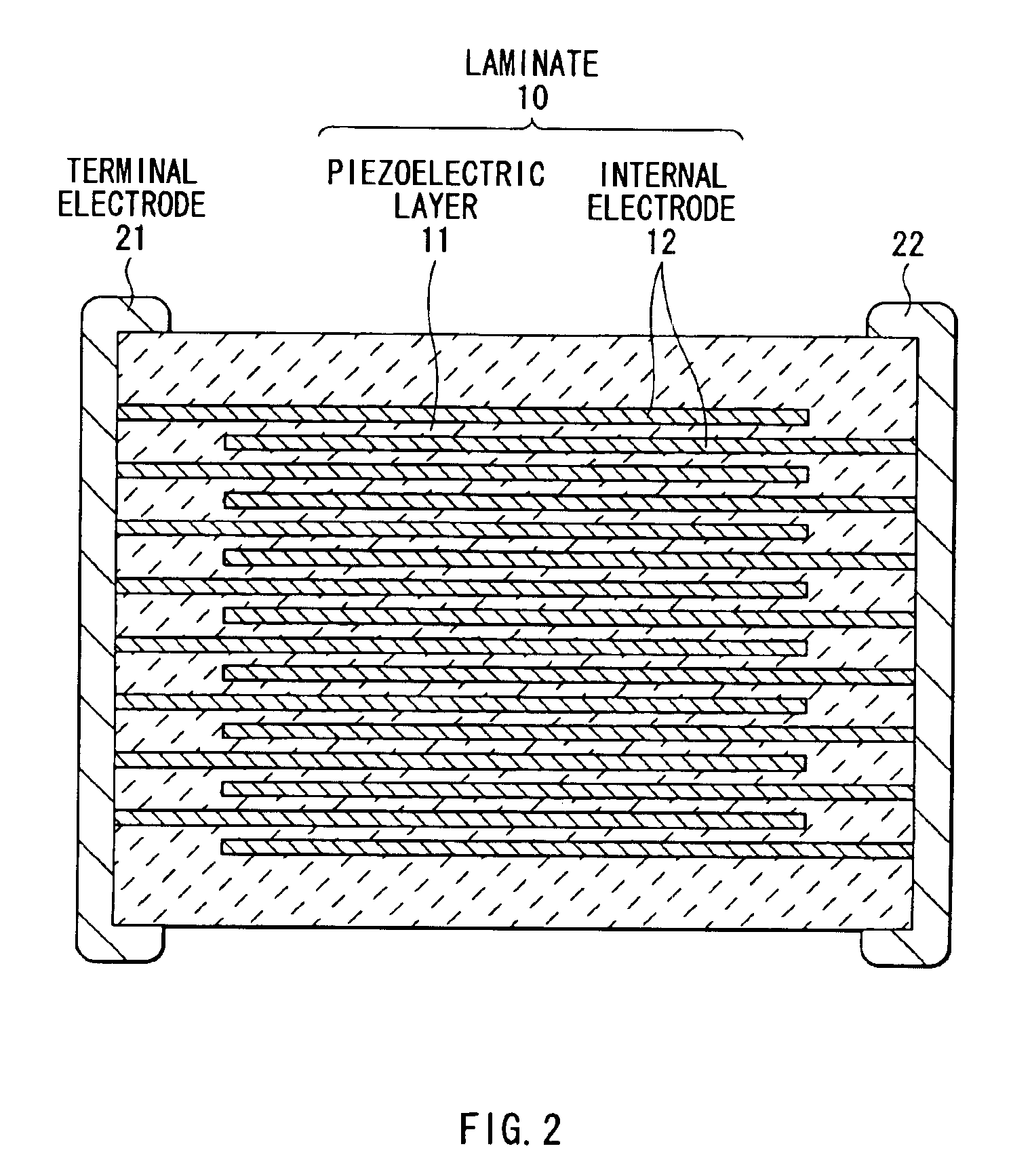

Piezoelectric ceramic, method of manufacturing the same and piezoelectric device

InactiveUS6979410B2High mechanical strengthLower firing temperaturePiezoelectric/electrostrictive/magnetostrictive devicesClaywaresCeramicMaterials science

Provided are a piezoelectric ceramic and a piezoelectric device having a larger piezoelectric strain constant and capable of being fired at a lower temperature. A main component of PbA[(Mg1 / 3Nb2 / 3)a(Zn1 / 3Nb2 / 3)bTicZrd]O3 (a+b+c+d=1, 0.99≦A≦1.01, 0.15≦a+b≦0.5, 0.05≦b≦0.25, 0.2≦c≦0.5, 0.15≦d≦0.6) and 0.01 mass % to 0.8 mass % inclusive of at least one kind selected from the group consisting of Fe, Co, Ni and Cu in the form of oxide per 1 mol of the main component as a first sub-component are comprised. Thereby, a larger piezoelectric strain constant can be obtained, and a firing temperature can be reduced. In the main component, a part of Pb may be replaced with at least one kind selected from the group consisting of Ca, Sr and Ba. Further, as a second sub-component, 0.05 mass % to 1.0 mass % inclusive of at least one kind selected from the group consisting of Sb, Nb and Ta in the form of oxide per 1 mol of the main component may be comprised.

Owner:TDK CORPARATION

Manufacturing method of display device and display device

ActiveUS20170133594A1Avoid enteringDeterioration of propertySolid-state devicesSemiconductor/solid-state device manufacturingBand shapeDisplay device

A manufacturing method of a display device includes: forming, in a resin layer including a display area where a plurality of lower electrodes is formed and a peripheral area surrounding the display area, a band-like groove which divides the resin layer in a form of surrounding the display area; forming an organic electroluminescence layer including a light emitting layer, on the resin layer and inside the band-like groove in such a way as to be placed on the plurality of lower electrodes; irradiating the organic electroluminescence layer with a pulse laser and thus eliminating the organic electroluminescence layer in such a way that a part of the organic electroluminescence layer is left in a shape of an island at least on a bottom surface of the band-like groove and that the bottom surface of the band-like groove is continuously exposed in the form of surrounding the display area.

Owner:JAPAN DISPLAY INC

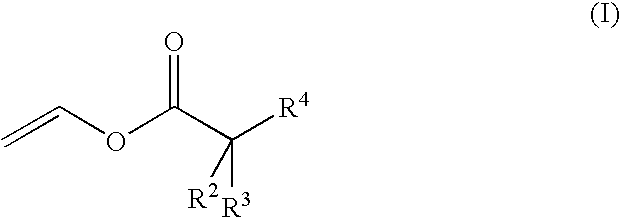

Composition for forming layer to be plated, method of producing metal pattern material, and metal pattern material

InactiveUS20110104454A1Improve film propertiesImprove propertiesPhotosensitive materialsLayered productsWater insolubleWater soluble

The present invention provide a composition for forming a layer to be plated, including a solution in which from 1% by mass to 20% by mass of a polymer having a functional group that forms an interaction with a plating catalyst or a precursor thereof and a radical polymerizable group, and a water-insoluble photopolymerization initiator are dissolved in a mixed solvent comprising from 20% by mass to 99% by mass of a water-soluble flammable liquid and water; a method of producing a metal pattern material using the composition for forming a layer to be plated; and a metal pattern material produced by the method.

Owner:FUJIFILM CORP

Aqueous copolymer dispersions with reactive diluent

ActiveUS20060205857A1Good storage stabilityImprove the level ofData processing applicationsCoatingsMeth-Polyol

The present invention relates to aqueous copolymer dispersions containing A) one or more hydroxy-functional copolymers synthesized from a) one or more OH-free (meth)acrylic esters and / or vinylaromatics, b) one or more hydroxy-functional (meth)acrylic esters, c) one or more ionic and / or potential ionic monomers capable of free-radical copolymerization, and d) one or more optionally monomers other than components a) to c) that are capable of free-radical copolymerization, and B) one or more hydroxy-functional polycarbonate polyols as reactive diluent. The present invention also relates to a process for preparing these aqueous copolymer dispersions and to their use in coating compositions.

Owner:COVESTRO DEUTSCHLAND AG

Solid Electrolytic Capacitor

ActiveUS20150213961A1Improve moisture resistanceImprove suppression propertiesSolid electrolytic capacitorsLiquid electrolytic capacitorsElectrolysisEngineering

An outer insulation member made of a first resin packs a part of an anode terminal. The packed part of the anode terminal has a predetermined section. All surfaces of the predetermined section consist of a front surface, a back surface and edges connecting between the front surface and the back surface. The front surface includes a connection area. An anode lead wire is connected to the connection area while being not connected to the anode terminal other than the connection area. The all surfaces of the predetermined section are completely covered with a mask layer made of a second resin except for the connection area. The second resin is different from the first resin in at least one of composition thereof, content of an inclusion, size of an inclusion and shape of an inclusion.

Owner:TOKIN CORP +1

Alkali-free glass and liquid crystal display panel

InactiveUS7838451B2Excellent in reducing resistanceDeterioration of propertyNon-linear opticsAlkali freeLiquid-crystal display

Owner:ASAHI GLASS CO LTD

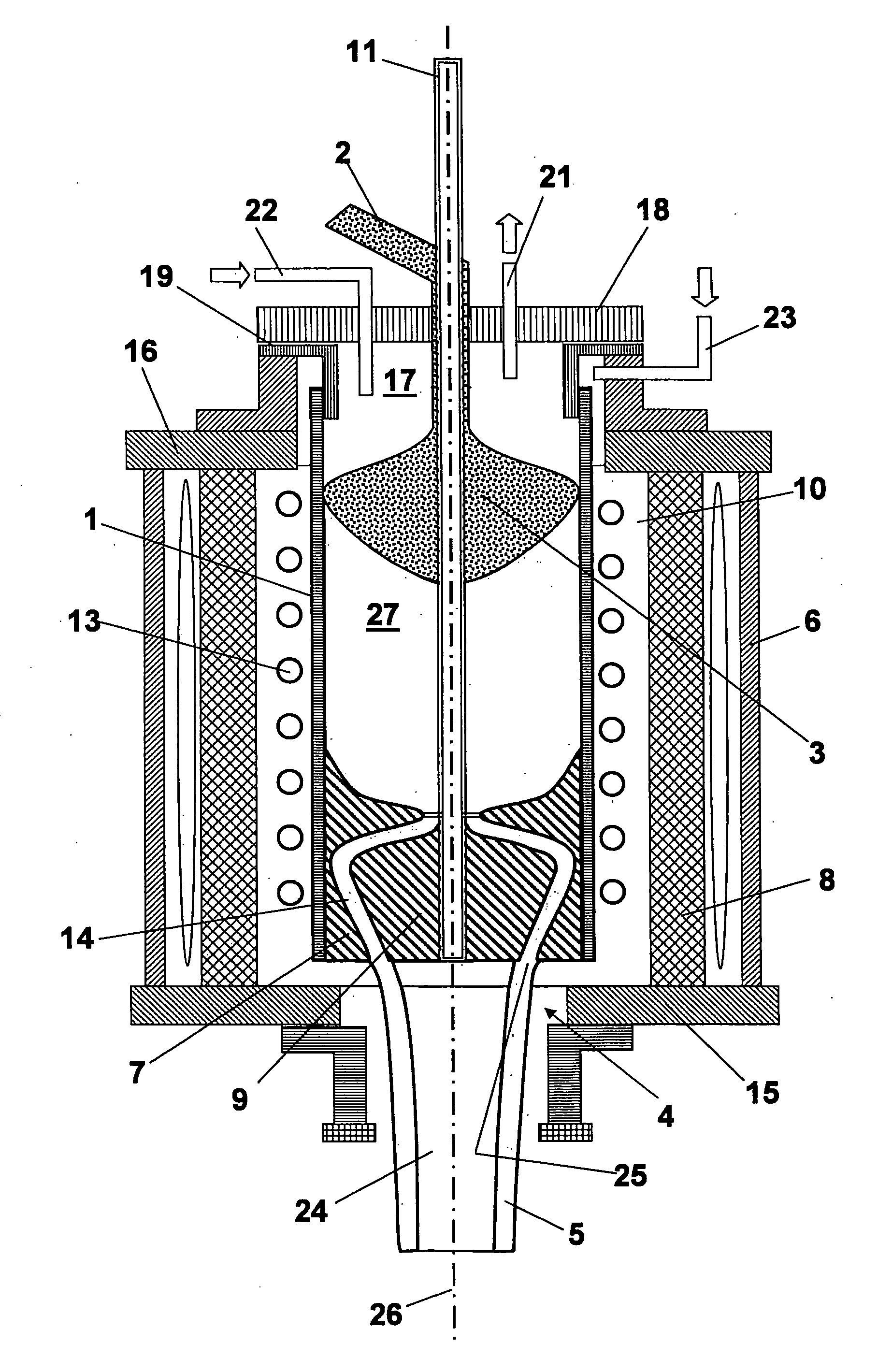

Bipolar membrane and method of manufacturing the same

To provide a bipolar membrane featuring improved adhesion between an anion-exchange membrane and a cation-exchange membrane without accompanied by an increase in the membrane voltage.[Means for Solution]A bipolar membrane comprising a cation-exchange membrane and an anion-exchange membrane joined together facing each other, wherein at least one of the ion exchange membranes contains a chlorinated polyolefin.

Owner:ASTOM CORPORATION

Method for producing quartz glass doped with nitrogen and quartz glass grains suitable for carrying out the method

InactiveUS20110183138A1Increase loadImprove responseSynthetic resin layered productsCellulosic plastic layered productsNitrogen oxideOxygen deficient

In a known method for producing quartz glass that is doped with nitrogen, an SiO2 base product is prepared in the form of SiO2 grains or in the form of a porous semi-finished product produced from the SiO2 grains and the SiO2 base product is processed into the quartz glass with the nitrogen chemically bound therein in a hot process in an atmosphere containing a reaction gas containing nitrogen. From this starting point, a method is provided for achieving nitrogen doping in quartz glass with as high a fraction of chemically bound nitrogen as possible. This object is achieved according to the invention in that a nitrogen oxide is used as the nitrogen-containing reaction gas, and that a SiO2 base product is used that in the hot process has a concentration of oxygen deficient defects of at least 2×1015 cm−3, wherein the SiO2 base product comprises SiO2 particles having an average particle size in the range of 200 nm to 300 μm (D50 value).

Owner:HERAEUS QUARZGLAS

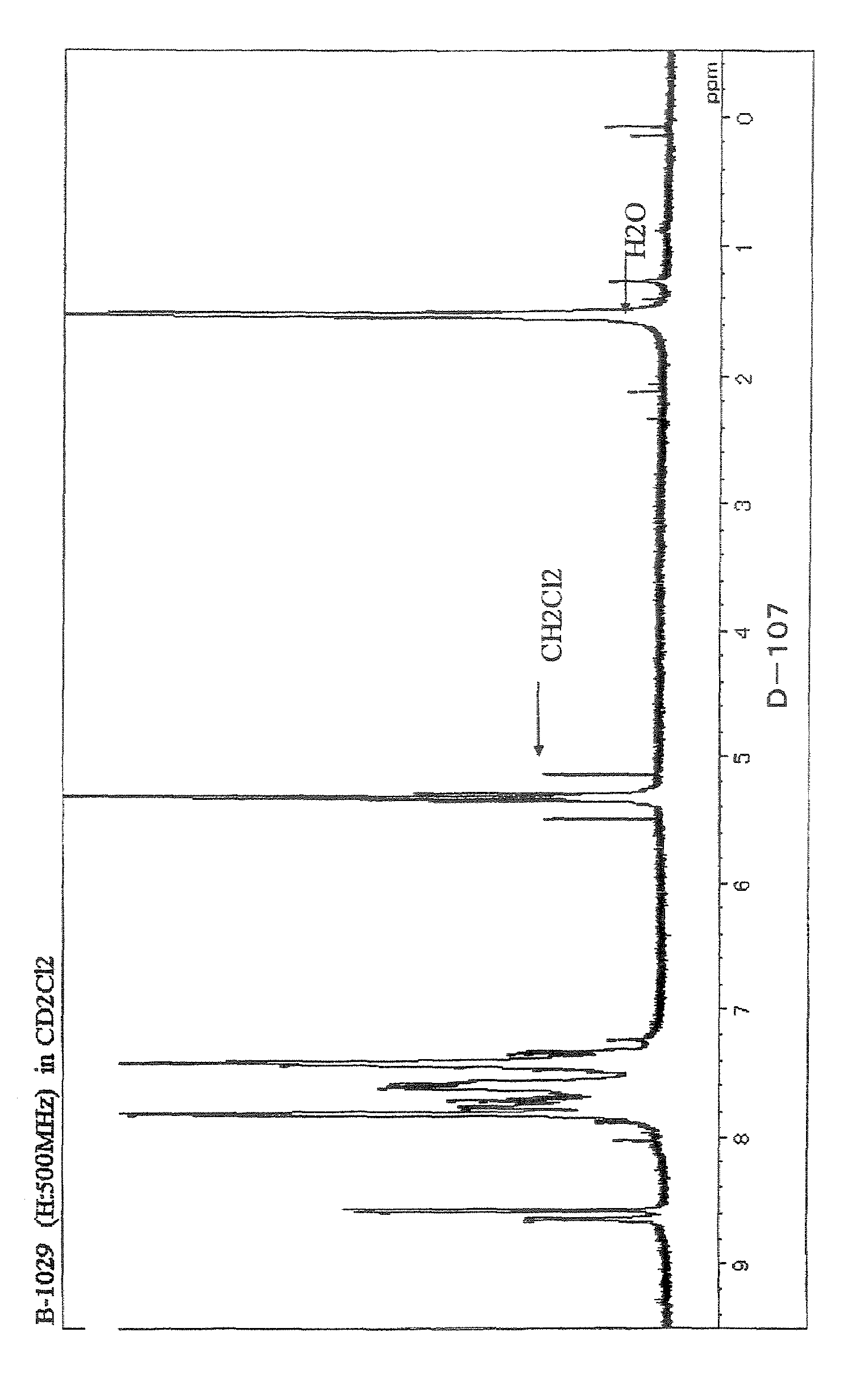

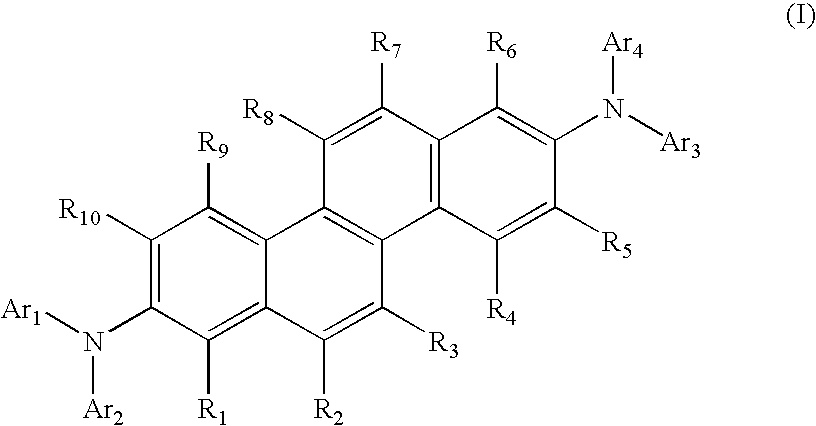

Aromatic amine derivative and organic electroluminescence device using the same

InactiveUS7642380B2Deterioration of propertySufficient luminance of lightOrganic chemistryDomestic articlesSingle substanceOrganic electroluminescence

The present invention relates to aromatic amine derivatives having a specific structure; and organic electroluminescent devices comprising a cathode, an anode and one or plural organic thin film layers including at least a light emitting layer which are sandwiched between the cathode and the anode wherein at least one of the organic thin film layers contains the above aromatic amine derivatives in the form of a single substance or a component of a mixture. There are provided the organic electroluminescent devices exhibiting a long life and a high efficiency of light emission which are capable of emitting a blue light having a high color purity, as well as the aromatic amine derivatives capable of realizing such organic electroluminescent devices.

Owner:IDEMITSU KOSAN CO LTD

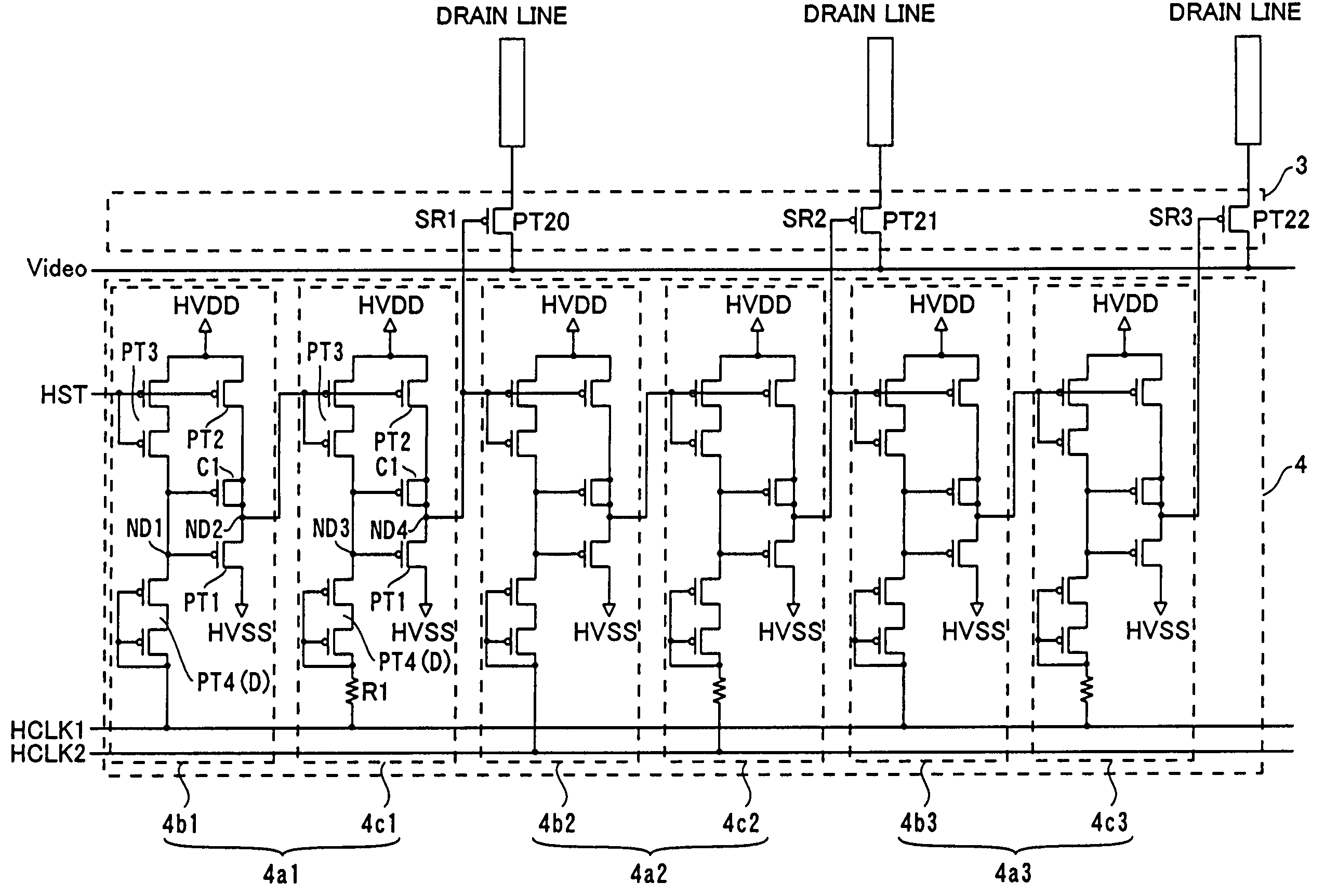

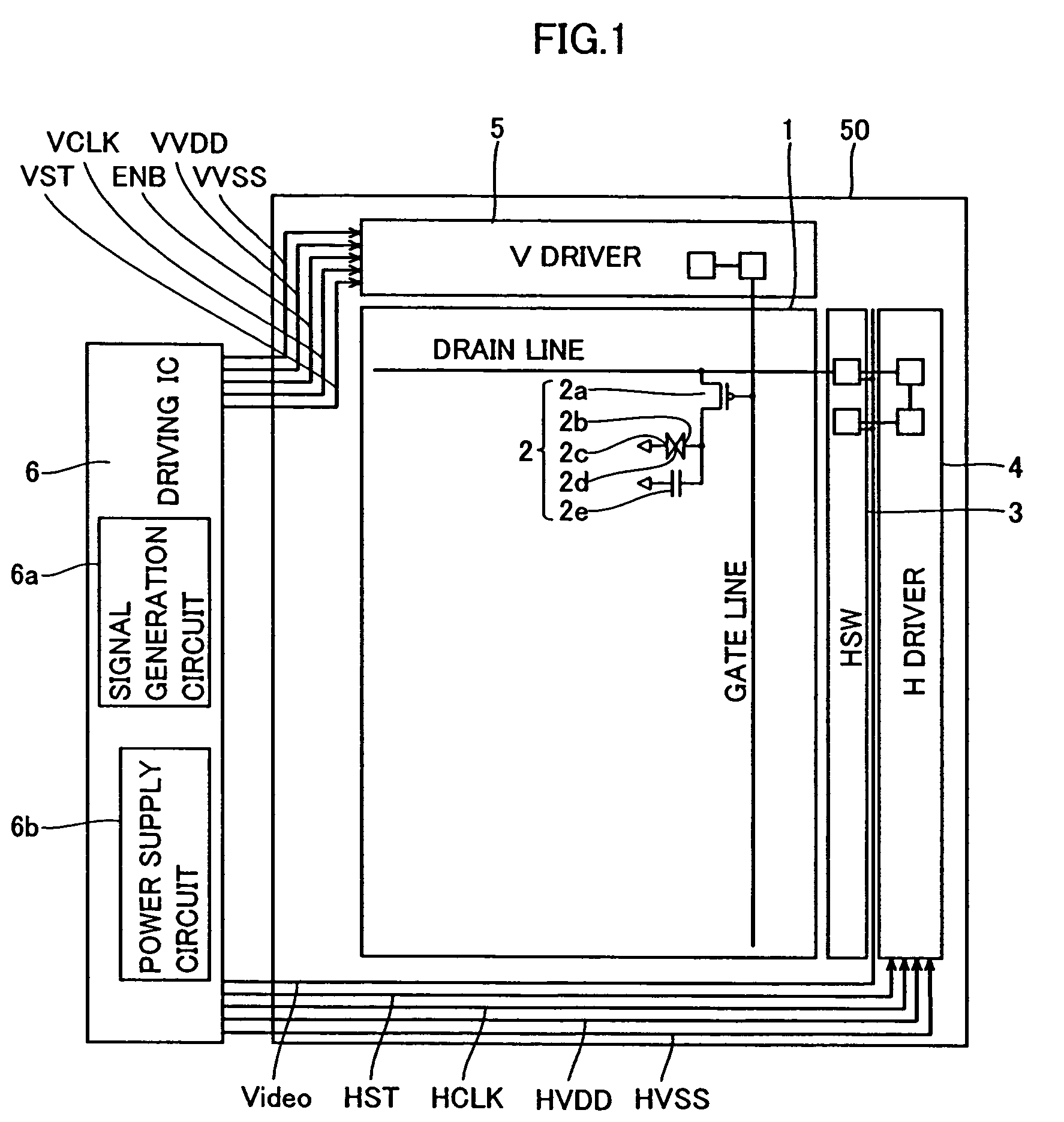

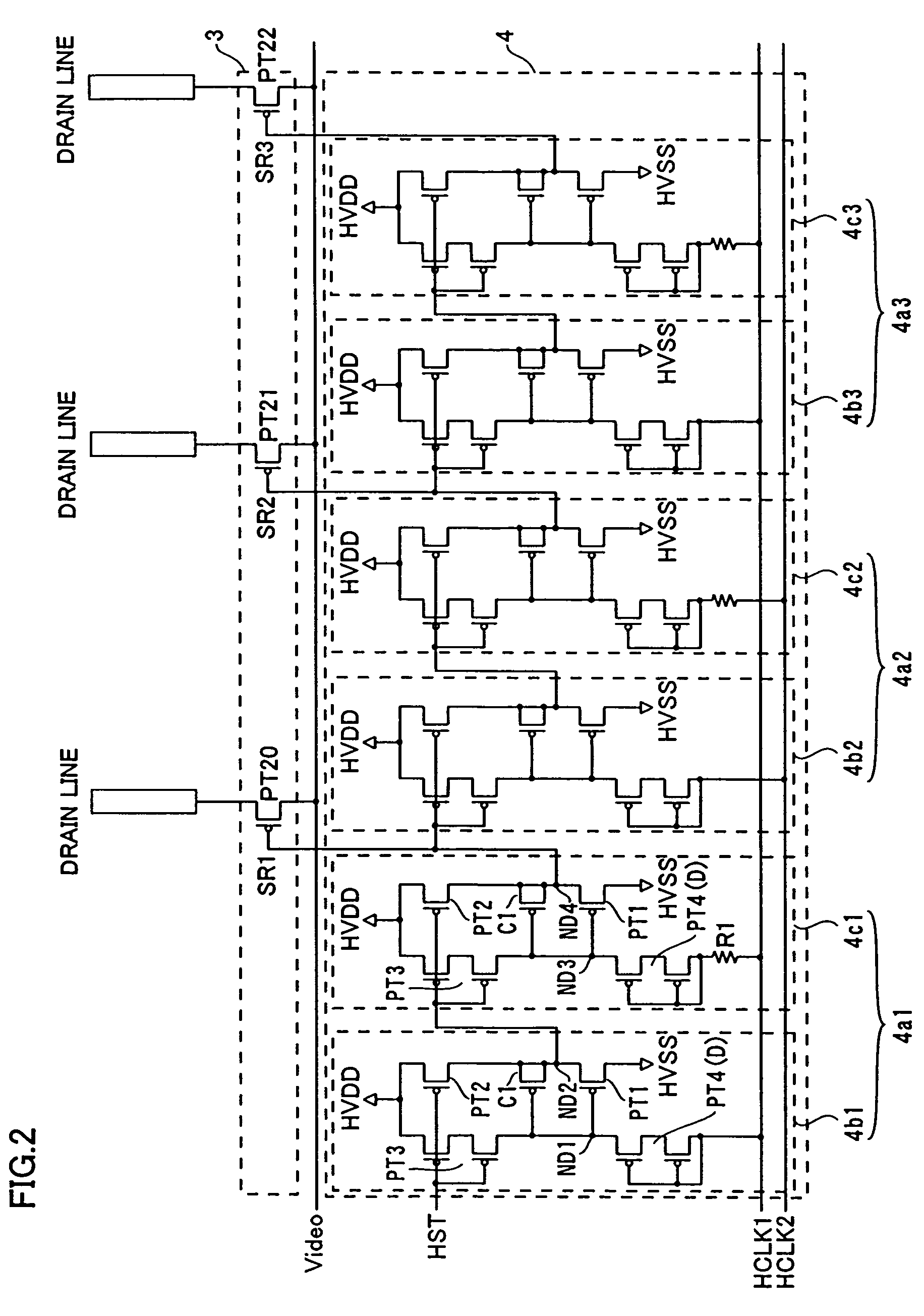

Display

ActiveUS7420535B2Preventable from deterioration of scan propertyDeterioration of propertyStatic indicating devicesSolid-state devicesElectricityEngineering

A display capable of suppressing reduction of a scanning property is provided. This display comprises a shift register circuit formed by connecting a plurality of first circuit parts each including a first conductivity type first transistor connected to a first potential and turned on in response to a clock signal, a first conductivity type second transistor connected to a second potential and a first conductivity type third transistor, connected between the gate of the first transistor and the second potential, having two gate electrodes electrically connected with each other.

Owner:SANYO ELECTRIC CO LTD

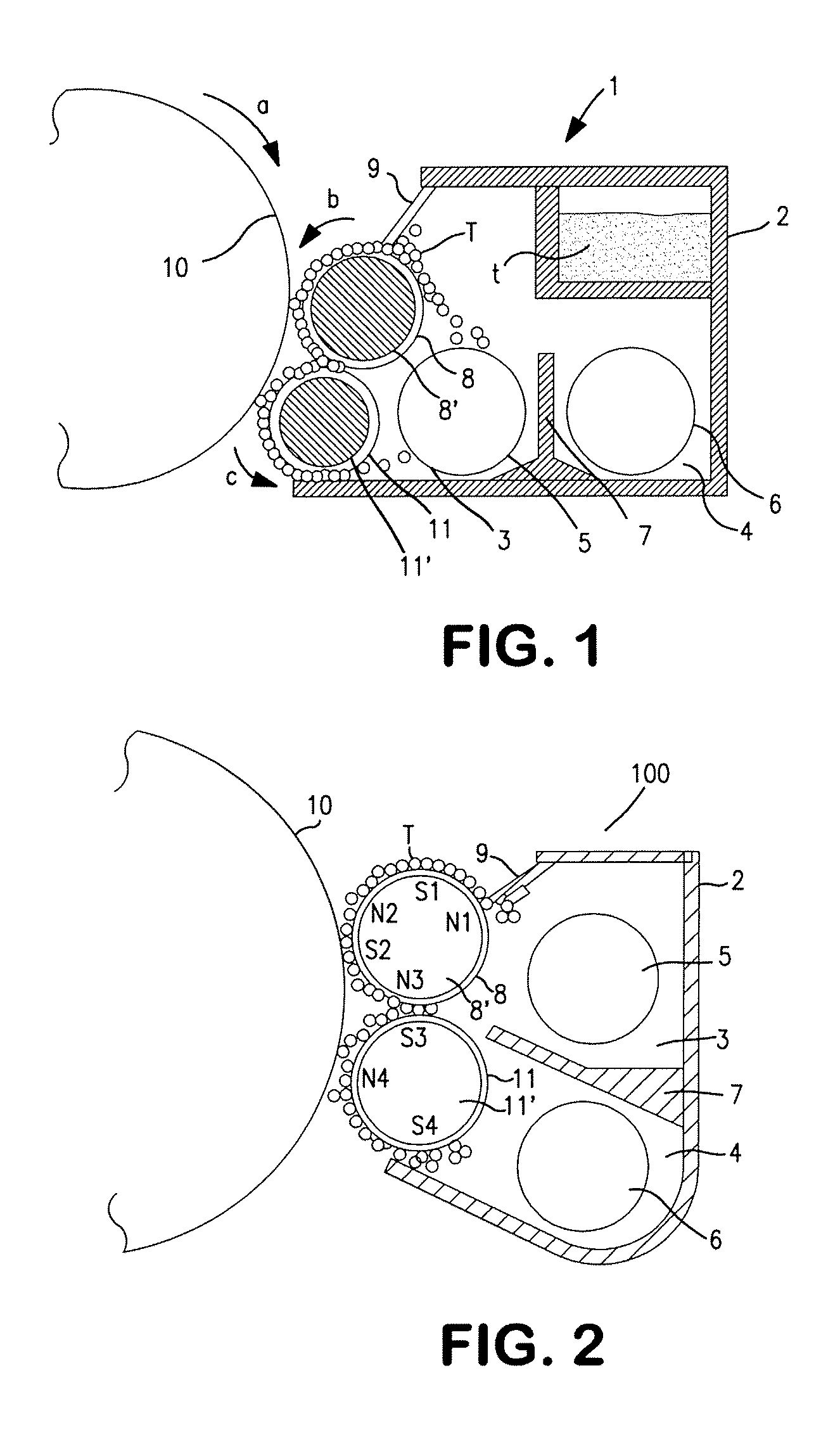

Developing method using a developer with a specified degree of compression and shearing stress

ActiveUS7272348B2High strengthAvoid problemsDevelopersElectrographic process apparatusShear stressStress measurement

A developing method using a developing device including at least: a first developer bearing member arranged to be opposed to an image bearing member; and a second developer bearing member arranged on a downstream side of a rotation direction of the image bearing member with respect to the first developer bearing member, the developing method including developing a latent image formed on the image bearing member with a developer, in which: the developer is a two-component developer having toner and a magnetic carrier; and the developer has a degree of compression C in the range of 20 to 32% and a shearing stress obtained by shearing stress measurement under a consolidation load of 4.0×10−4 N / mm2 in the range of 0.5×10−4 to 2.5×10−4 N / mm2.

Owner:CANON KK

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com