Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

96results about How to "Comprehensive verification" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Semi-physical simulation testing platform of train control network

ActiveCN102323761AReduce manufacturing costReduce technical riskSimulator controlSoftware emulationControl system

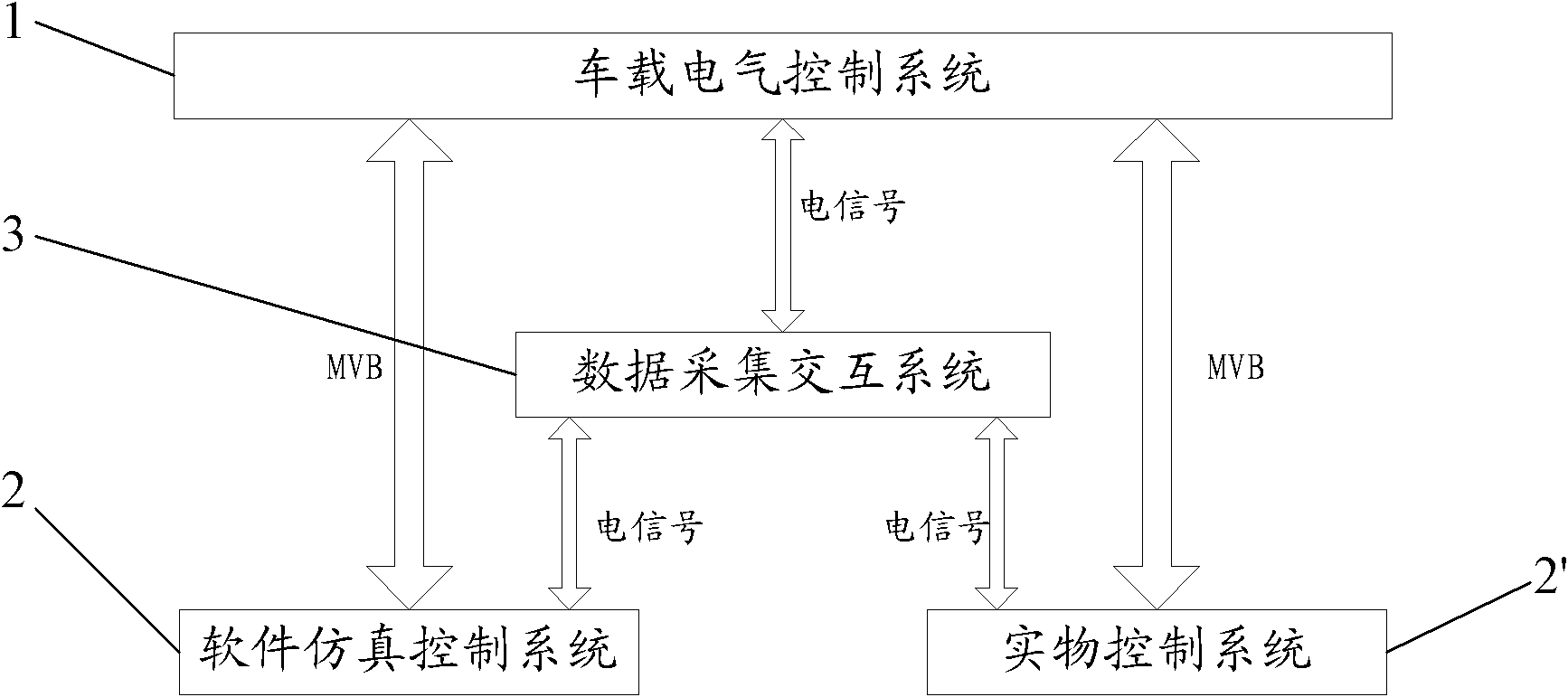

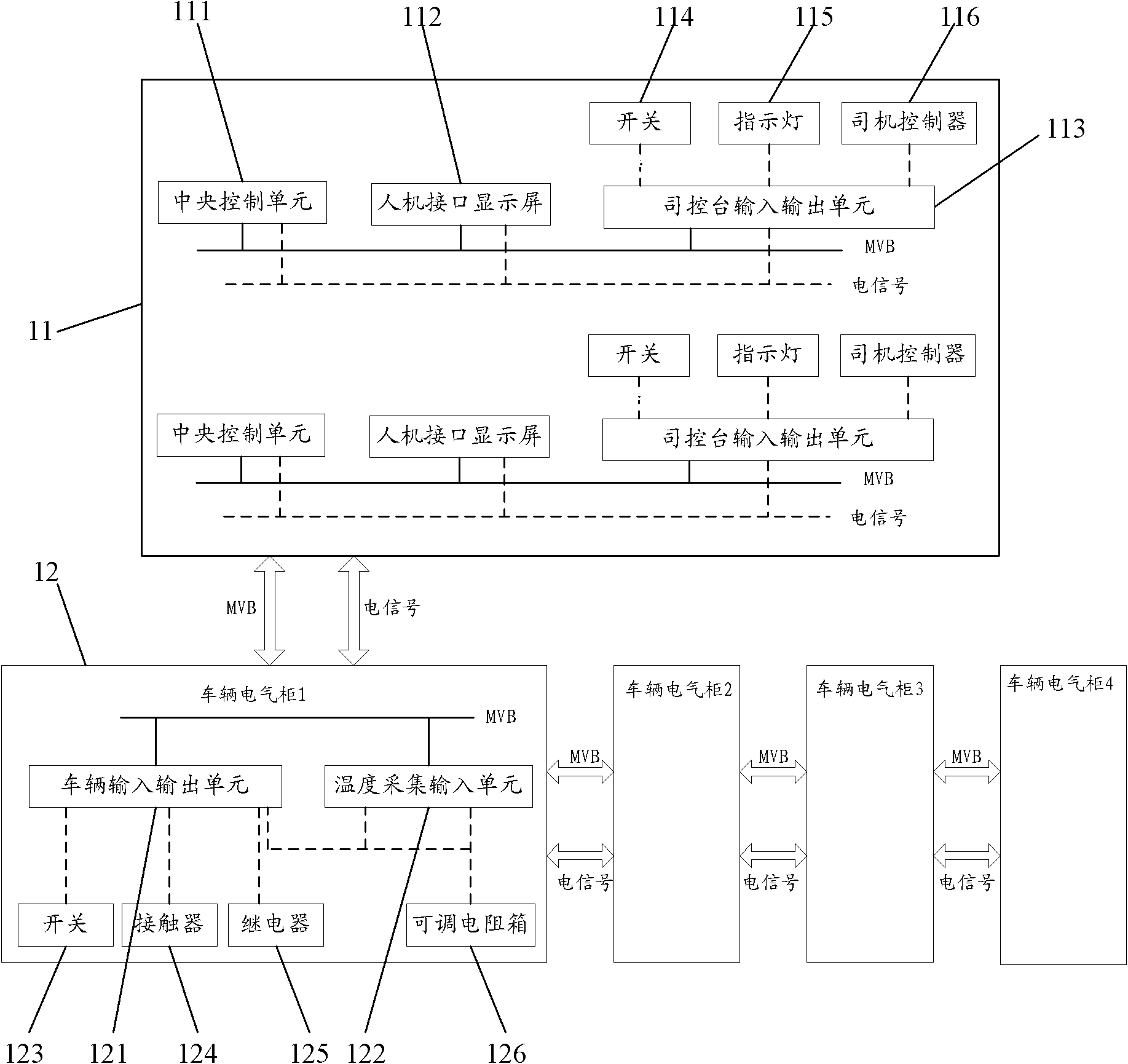

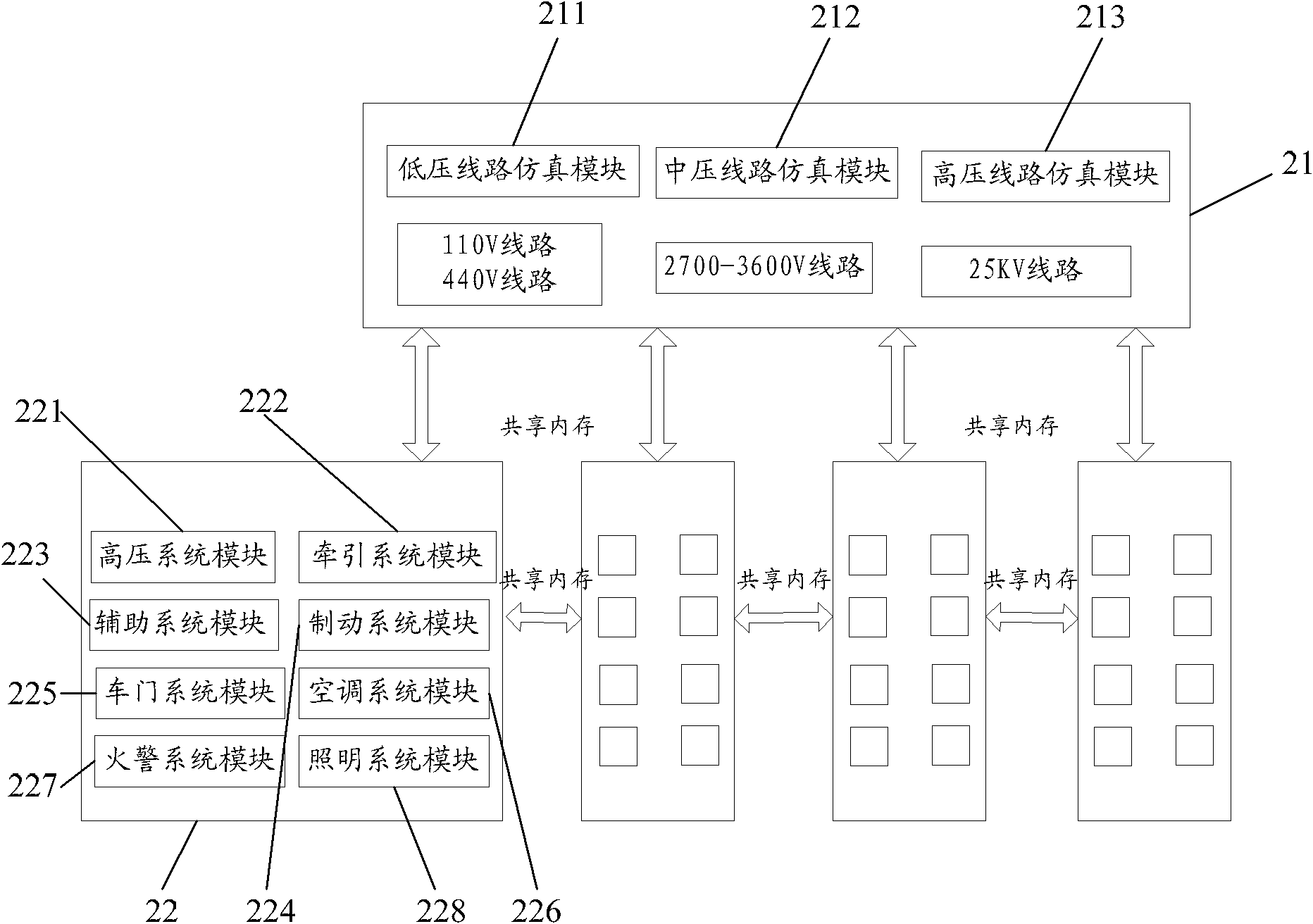

The invention discloses a semi-physical simulation testing platform of a train control network, which comprises a vehicle-mounted electrical control system, a software simulation control system and / or a physical control system and a data acquisition interactive system, wherein the software simulation control system and / or the physical control system is connected with the vehicle-mounted electrical control system; the data acquisition interactive system is connected with the vehicle-mounted electrical control system so as to convert a signal output by the vehicle-mounted electrical control system into a digital signal or convert the digital signal into an input signal required by the vehicle-mounted electrical control system; and the data acquisition interactive system is connected with the software simulation control system and / or the physical control system so as to convert the digital signal connected and output by the software simulation control system and / or the physical control system into a switching value signal or convert the switching value signal into the digital signal required by the software simulation control system and / or the physical control system. The semi-physical simulation testing platform of the train control network is capable of comprehensively implementing evaluation and verification on the design of a train network control system, eliminating possibledesign errors, rapidly positioning faults to ask for reasons, and reducing the production debugging cost and the technical risks of real trains.

Owner:CHINA RAILWAYS CORPORATION +2

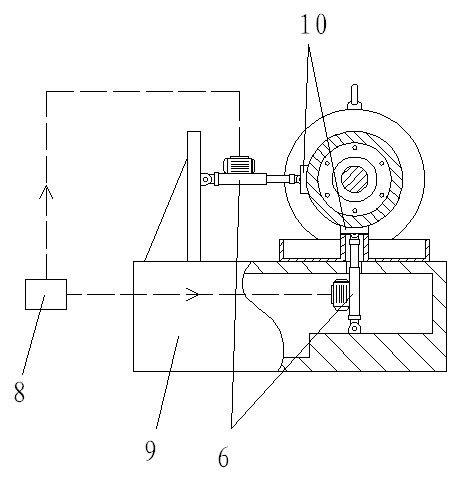

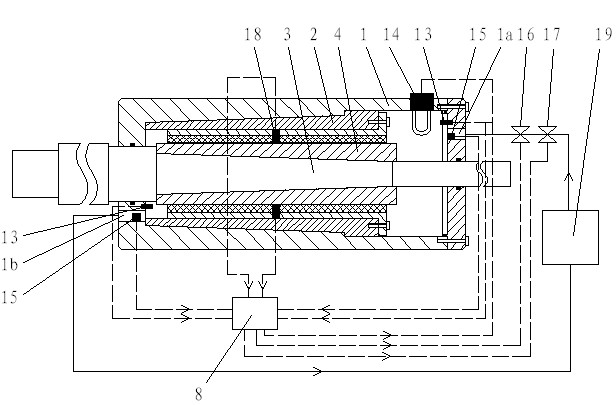

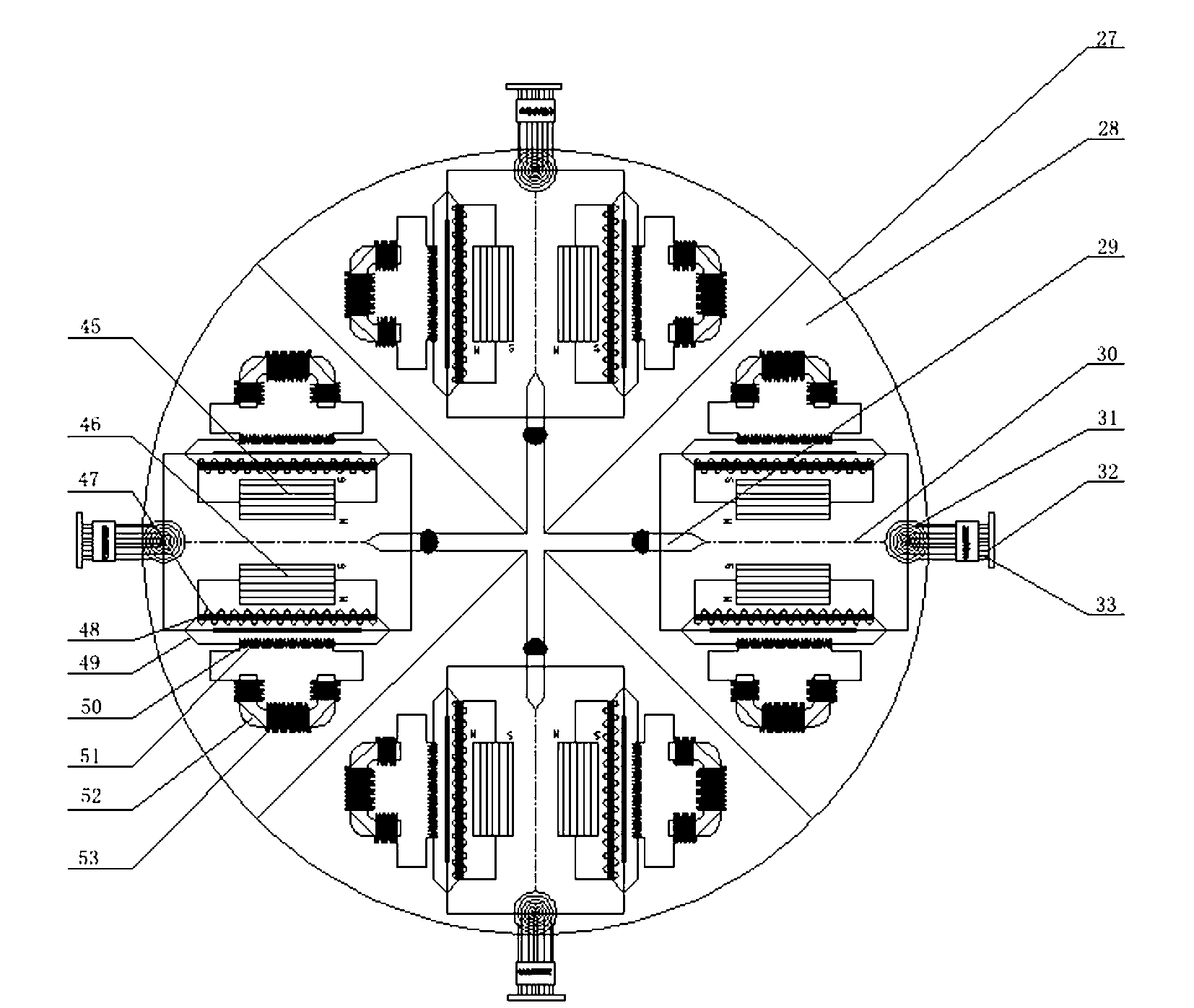

Multifunctional tribology performance test system

InactiveCN102628747AReal performance testPerformance testing is completeMachine bearings testingEngineeringTribology

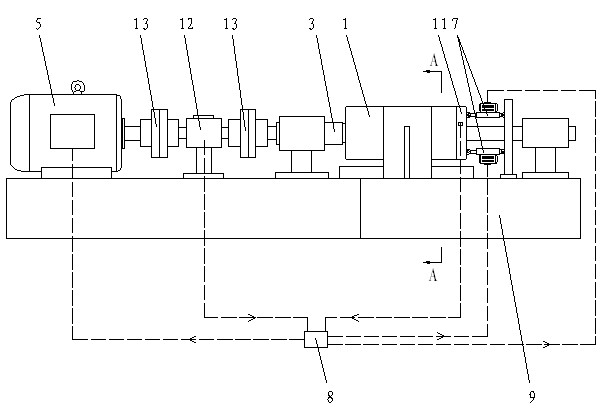

The invention discloses a multifunctional tribology performance test system, which comprises a test cabin body, a bearing sleeve, a test shaft, a shaft sleeve, a test shaft driving device, a loading device and a comprehensive performance test unit. An installation space of a piece to be tested is arranged between the shaft sleeve and the bearing sleeve. Two ends of the test cabin body are respectively in rotation sealing fit with the test shaft, and a lubricant inlet and a lubricant outlet are arranged on the test cabin body. The comprehensive performance test unit comprises a computer, a torque rotating speed detection device, a loading force detection device, a lubricant temperature detection device, a liquid film thickness detection device and a lubricant flow detection device. The multifunctional tribology performance test system can simultaneously conduct radial and axial loading, simulates actual complex working conditions of the piece to be tested truly, achieves tests of tribology comprehensive performance such as rotating speed, torque, temperature rise, friction characteristic, test loading force, production validation (PV) value, dynamic rigidity and dynamic damping, and is capable of really and comprehensively testing and verifying the comprehensive performance of the piece to be tested.

Owner:重庆奔腾智能装备技术有限公司

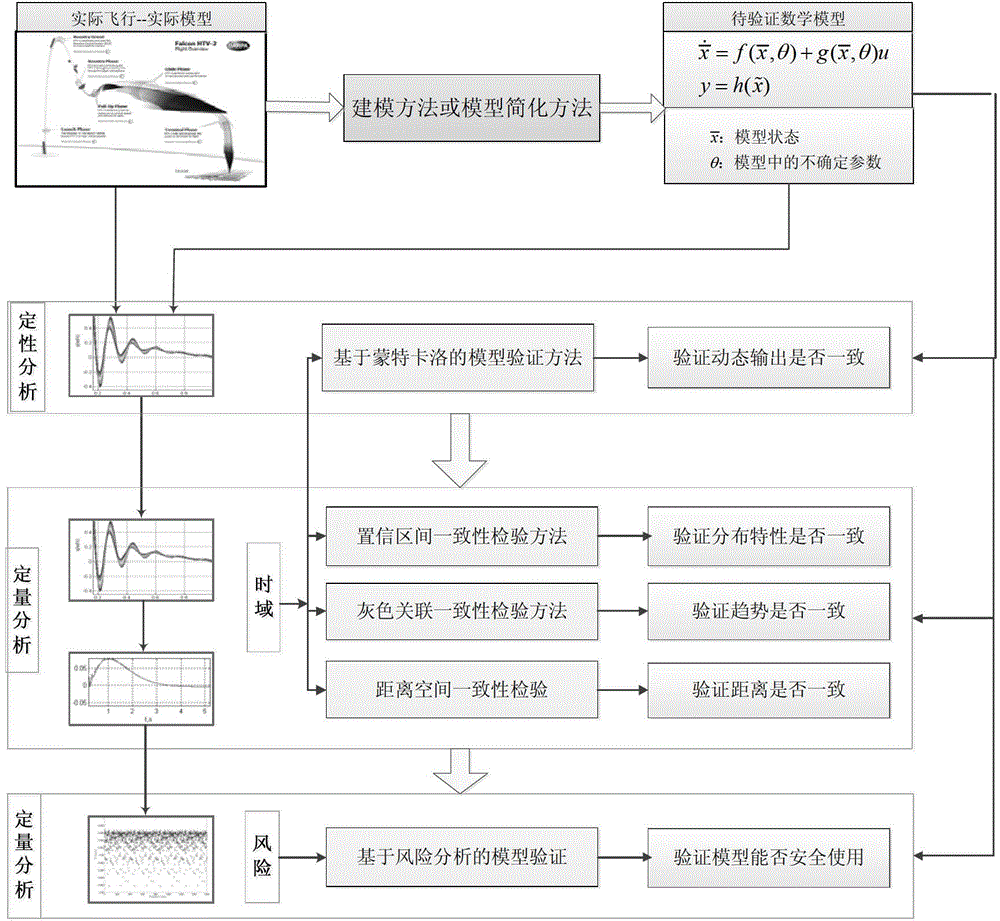

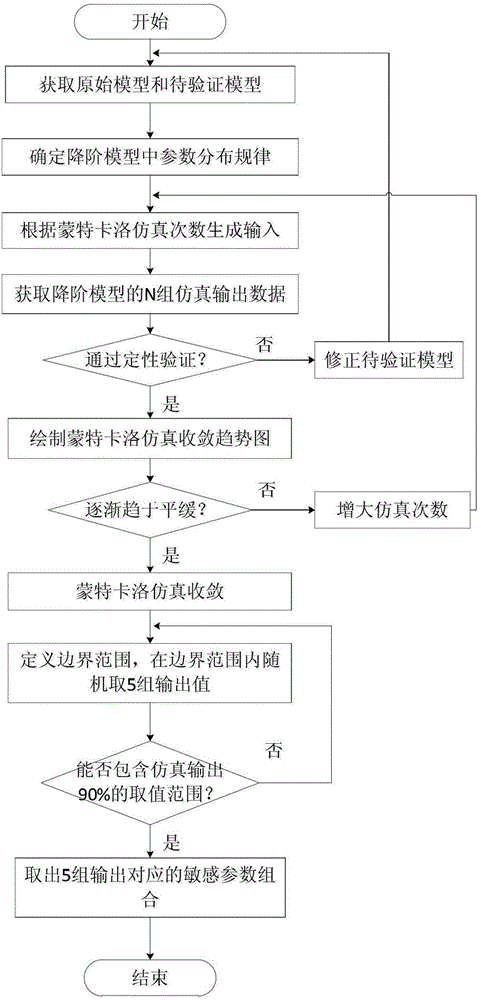

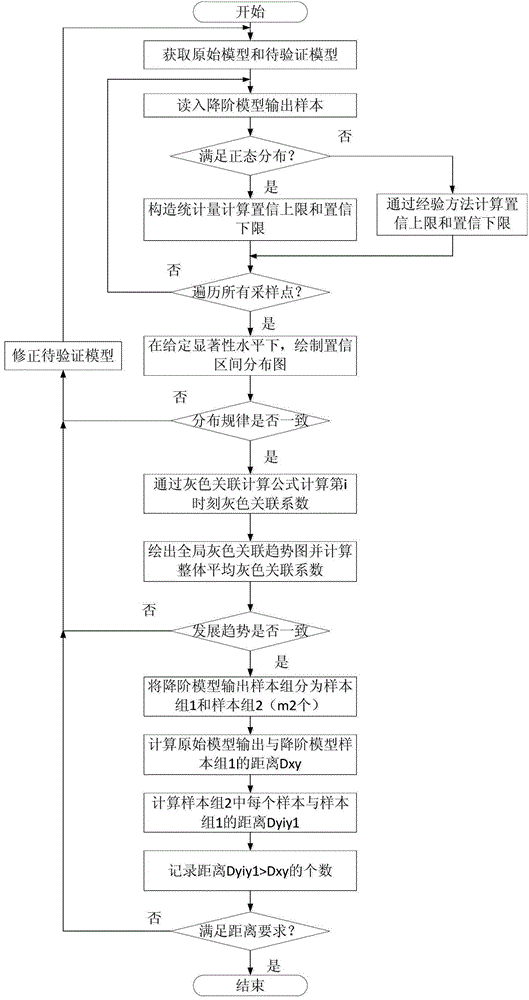

Verification and simulation realization method for near space aerocraft model

InactiveCN103150446AComprehensive verificationReduce the risk of useSpecial data processing applicationsTime domainRisk profiling

The invention relates to the technology of the near space aerocraft. In order to provide a system-level consistency check novel model verification system output on the basis of the dynamic time sequence of the near space aerocraft model, give qualitative model verification based on the monte carlo method, carry out risk analysis to the model, comprehensively carry out consistency check to a model to be verified and give a visual verification criterion, the invention adopts the technical scheme that the verification and simulation realization method for a near space aerocraft model comprises the following steps of: (1) on the basis of the monte carlo simulation method, carrying out qualitative verification; (2) carrying out the qualitative model verification based on a time domain analysis method; and (3) carrying out qualitative model verification based on risk analysis, taking a model parameter as a risk to give a visual qualitative model verification criterion, giving a model comparison standard when a plurality of models to be verified exist, verifying whether the model can be safely used, and giving a safe-use range. The verification and simulation realization method for a near space aerocraft model, which is disclosed by the invention, is mainly applied to the design of the near space aerocraft.

Owner:TIANJIN UNIV

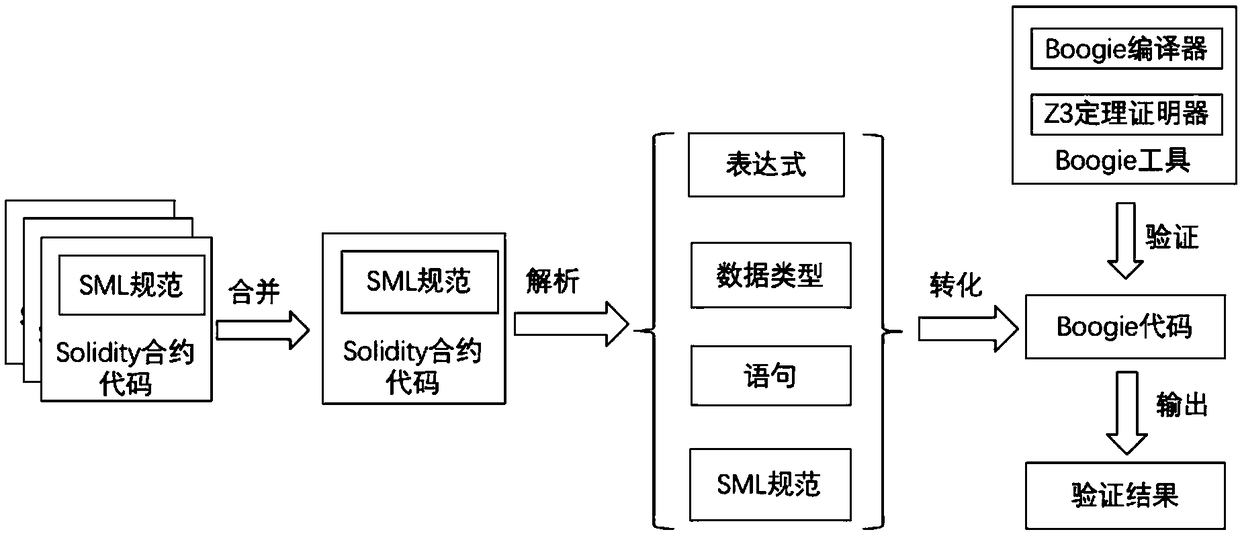

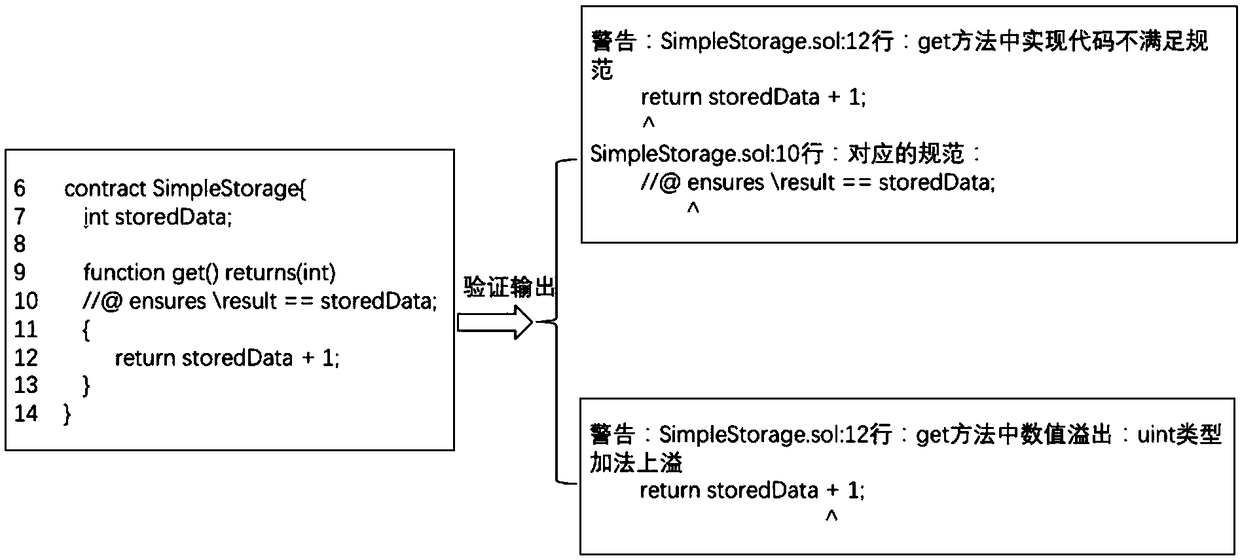

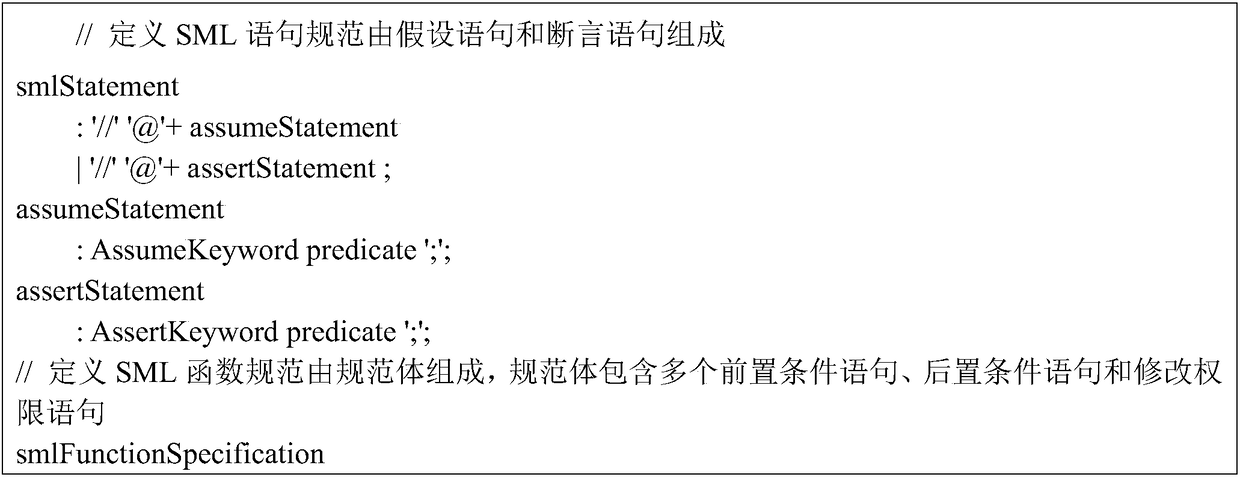

A method of formally verifying a Solidarity smart contract

ActiveCN109375899AEnsure safetySolve conversion problemsFinanceRequirement analysisMathematical modelSmart contract

The invention discloses a method for formally verifying a Solidarity intelligent contract, which establishes a model from the Solidarity intelligent contract, uses Boogie language to describe the model, and then uses a Z3 prover to verify the model. The method of the invention designs a set of universal intelligent contract model specification language, solves the conversion problem between the Solidarity intelligent contract and the mathematical model, and has important reference value for formally verifying the intelligent contract of other languages. This method can help the developer of intelligent contract to verify the function of intelligent contract quickly, comprehensively and rigorously, locate the vulnerability of intelligent contract, and ensure the security of intelligent contract.

Owner:HANGZHOU QULIAN TECH CO LTD

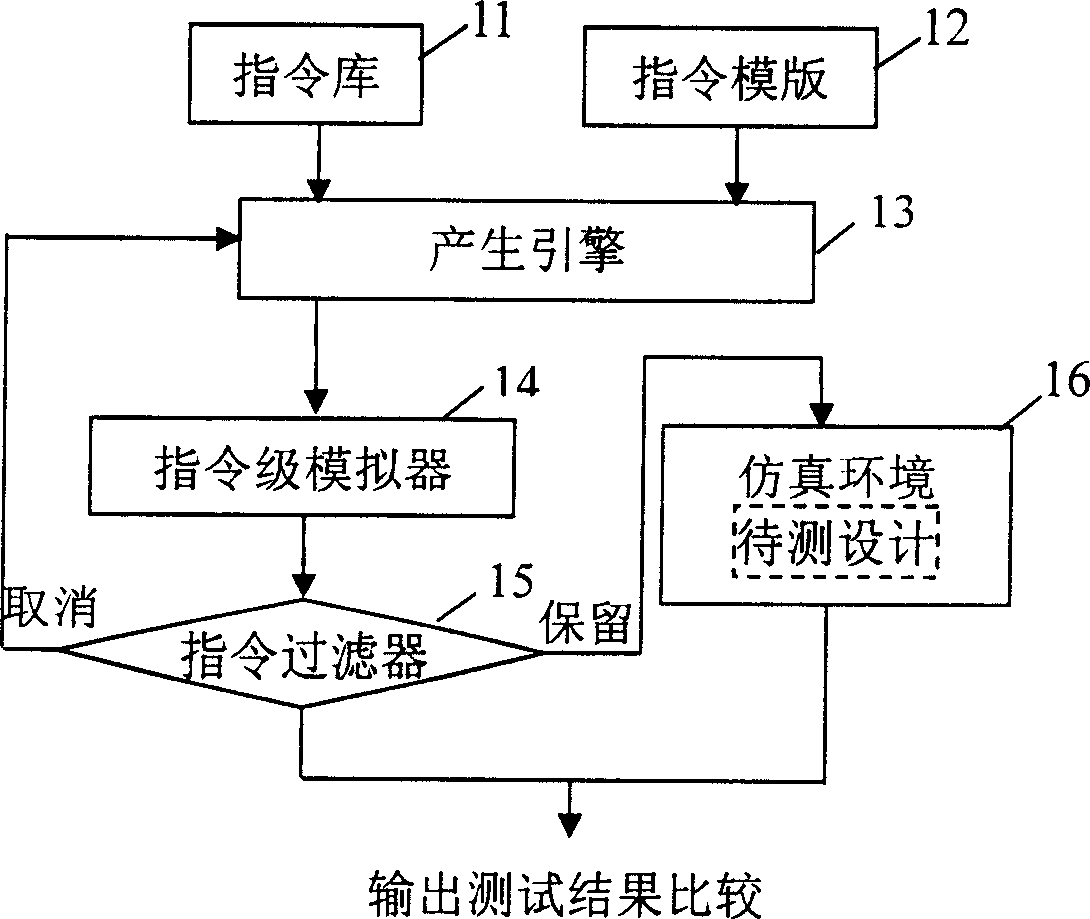

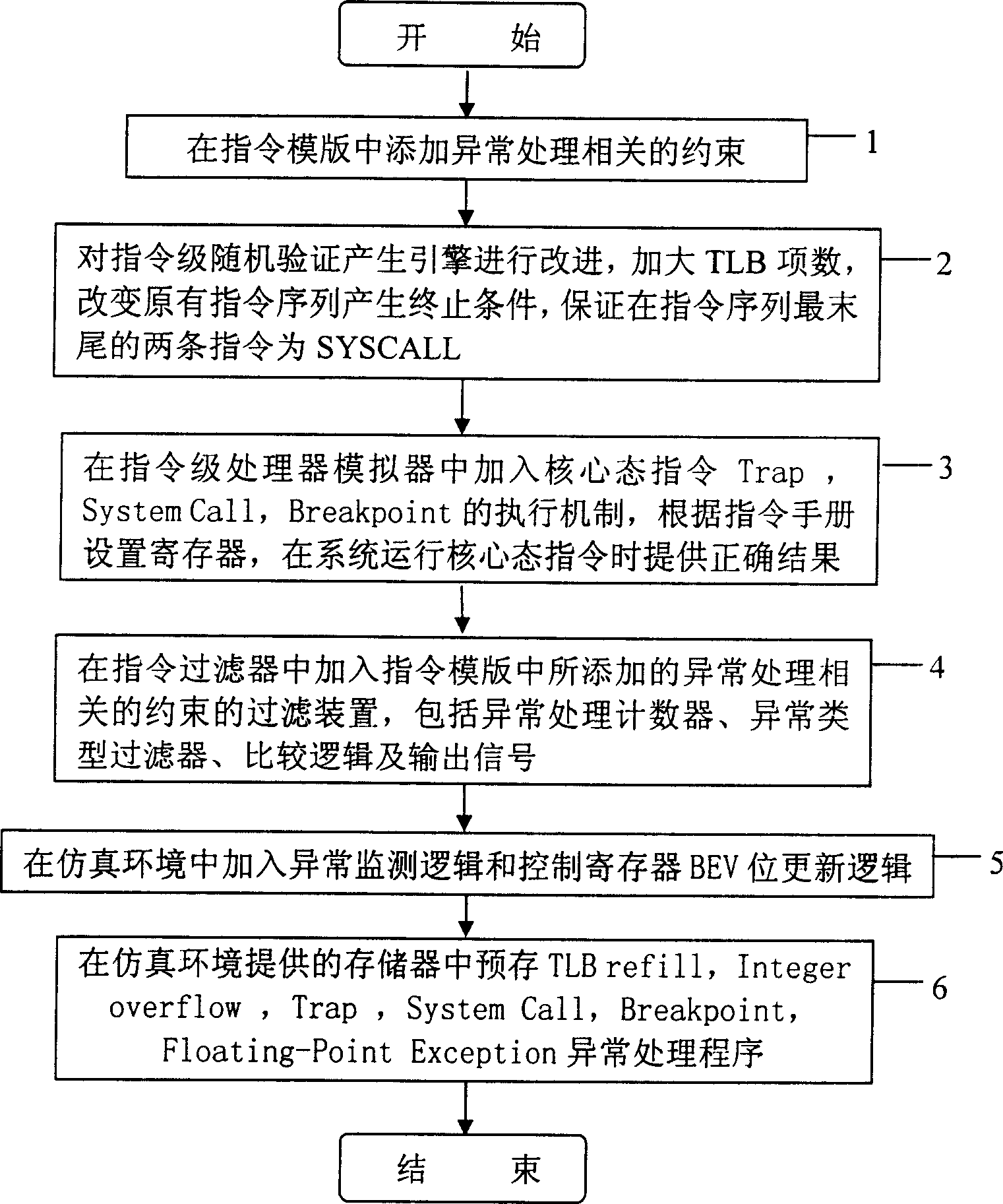

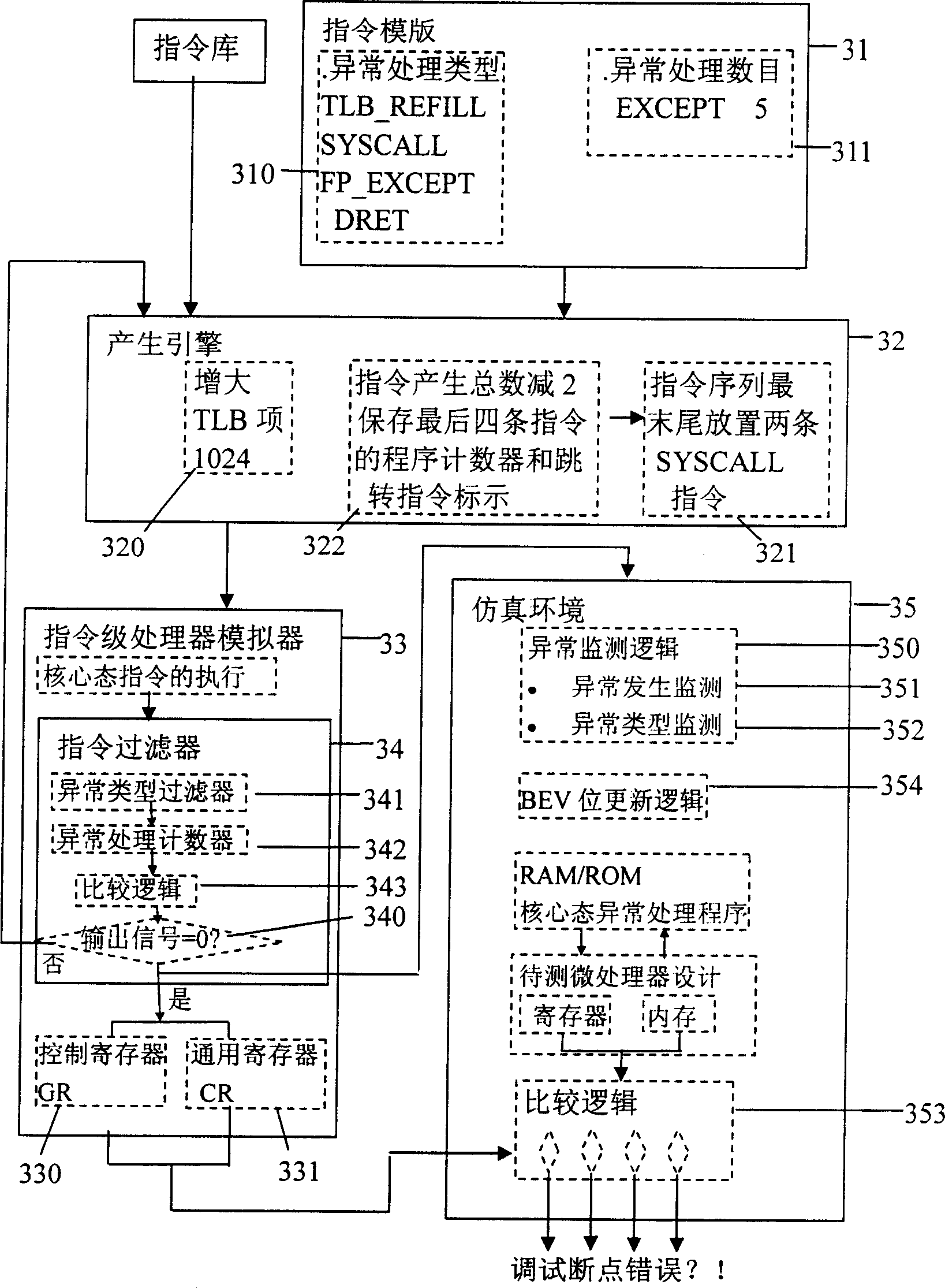

Method for realizing kernel-mode programe verification in user-mode random verification of microprocessor

ActiveCN1892616AAuthentication supportUniform coverageSoftware testing/debuggingProgram validationControl register

The present invention discloses method for realizing kernel mode program verification method in microprocessor user status random verifying. Said method includes 1, adding exception handling correlative restriction in instruction stencil-plate; 2, improving instruction grade random verifying generation engine; 3, adding kernel mode instruction execution mechanism instruction grade processor simulator, setting register, providing right result in system running kernel mode instruction; 4, adding step 1 added correlative restrictive filtering unit in instruction filter; 5, adding abnormal monitoring logic and control register updating logical in emulation environment; 6, pre-storing exception handler in emulation environment provided memory. The present invention has advantages of complete verifying and high verifying efficiency.

Owner:LOONGSON TECH CORP

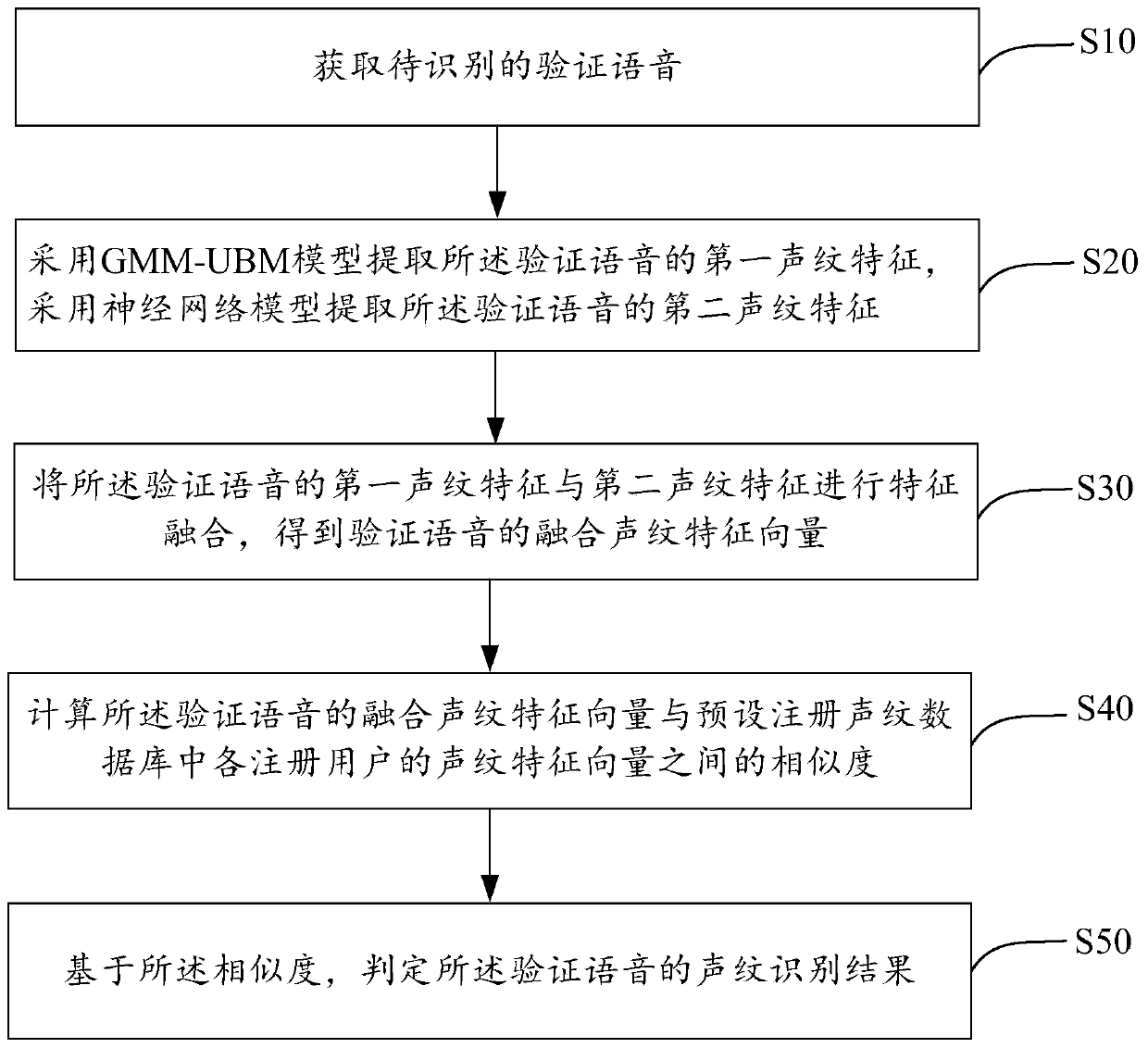

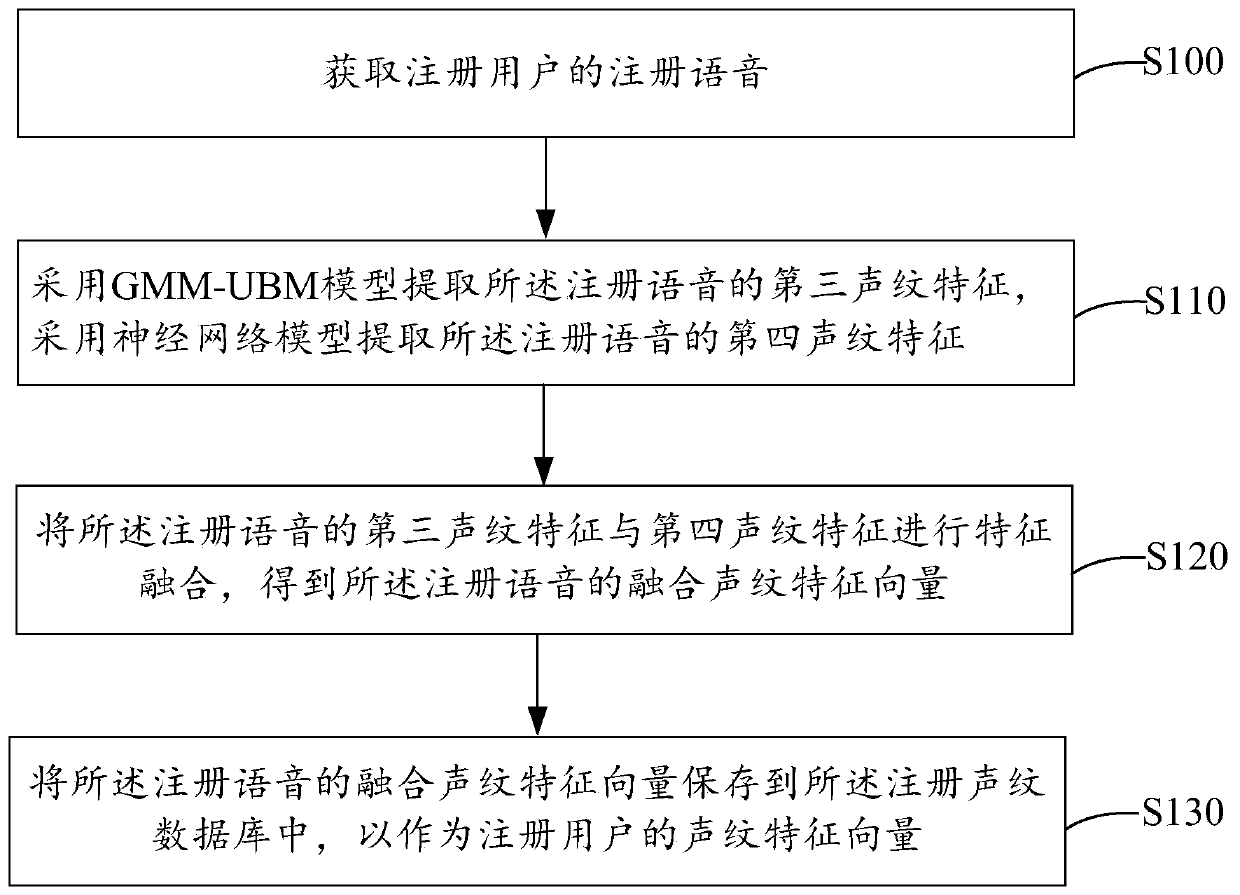

Voiceprint recognition method, device and equipment and computer readable storage medium

PendingCN110047490AImprove accuracyComprehensive verificationSpeech analysisFeature vectorNetwork model

The invention discloses a voiceprint recognition method, device and equipment and a computer readable storage medium. The voiceprint recognition method comprises the steps that to-be-recognized verification speech is acquired; a GMM-UB model is used for extracting a first voiceprint feature of the verification speech, and a neural network model is used for extracting a second voiceprint feature ofthe verification speech; feature fusion is carried out on the first voiceprint feature and second voiceprint feature of the verification speech to obtain a fusion voiceprint feature vector of the verification speech; the similarity between the fusion voiceprint feature vector of the verification speech and a voiceprint feature vector of each registered user in a preset registered voiceprint database is calculated; based on the similarity, a voiceprint recognition result of the verification speech is determined. The two models are used for performing feature extraction and speech verificationon the verification speech, compared with a single model performing feature extraction and speech verification on the verification speech, and the features extracted from the two models contain more comprehensive information, so that the accuracy rate of voiceprint recognition is improved.

Owner:PING AN TECH (SHENZHEN) CO LTD

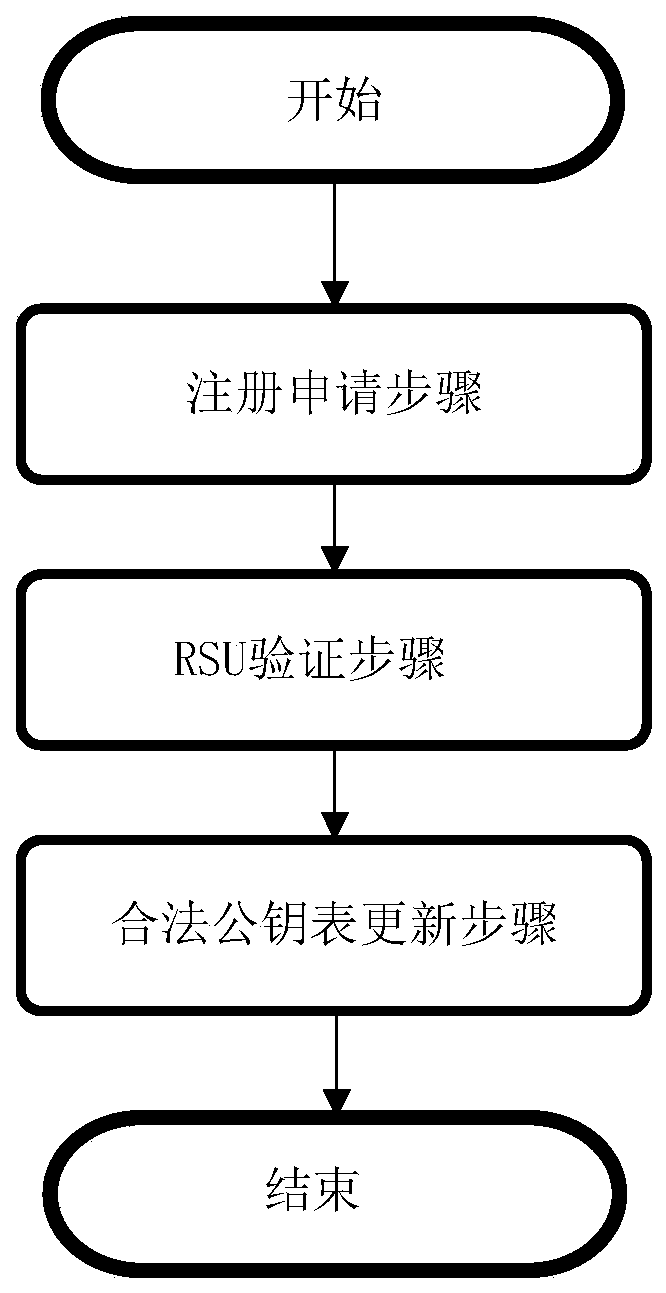

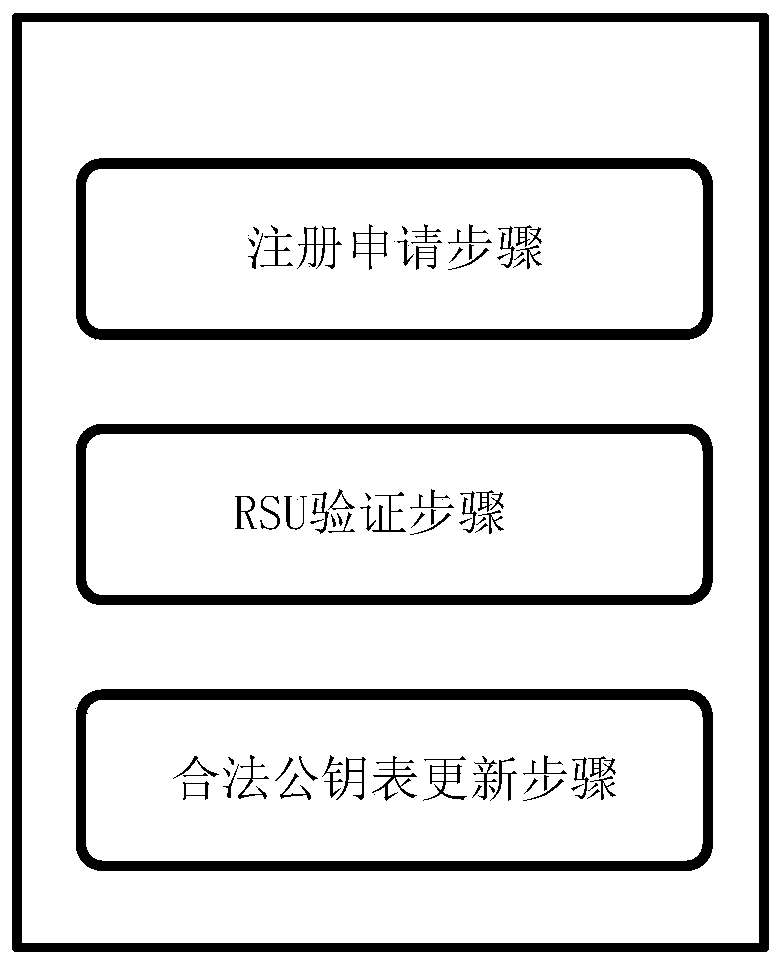

Node identity authentication method and system suitable for Internet of Vehicles

ActiveCN110831004AComprehensive verificationReduced authenticationParticular environment based servicesUser identity/authority verificationInternet privacyEngineering

The invention provides a node identity authentication method and system suitable for Internet of Vehicles, and the method comprises a registration application step: enabling a vehicle unit to apply for registration to an RSU, and obtaining registration application result information; an RSU verification step: the RSU verifies the vehicle identity corresponding to the vehicle unit, and obtains thecorresponding vehicle identity verification result information; acquiring legal public key table broadcast information according to the corresponding vehicle identity verification result information;and a legal public key table updating step: according to the legal public key table broadcast information and the vehicle local legal public key table parameters, comparing the legal public key tablebroadcast information with the vehicle local legal public key table parameters, updating the vehicle local legal public key table, and obtaining legal public key table updating result information andvehicle unit identity confirmation result information. According to the scheme based on the legal public key table, more messages can be verified in unit time, and higher efficiency is achieved.

Owner:SHANGHAI JIAO TONG UNIV +1

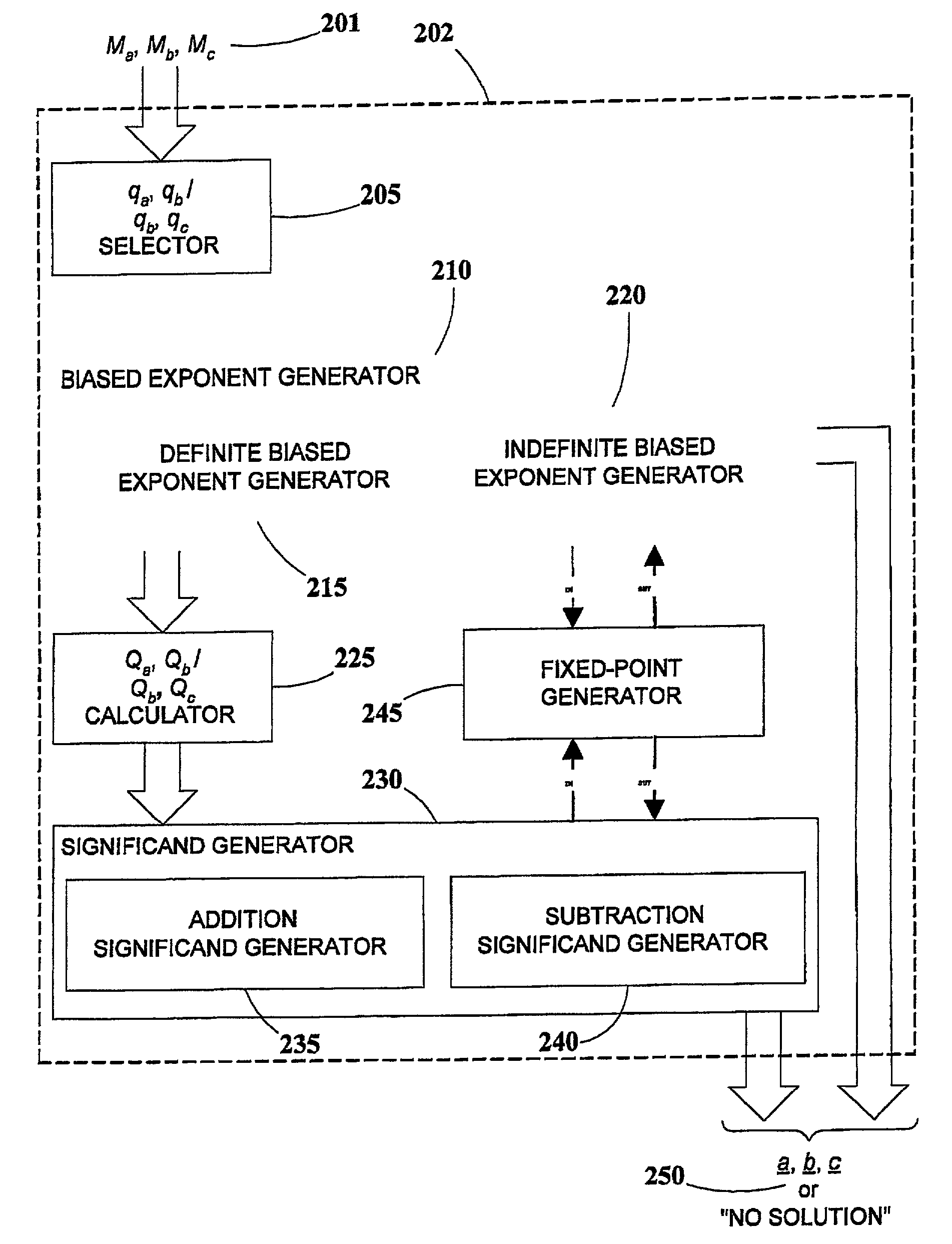

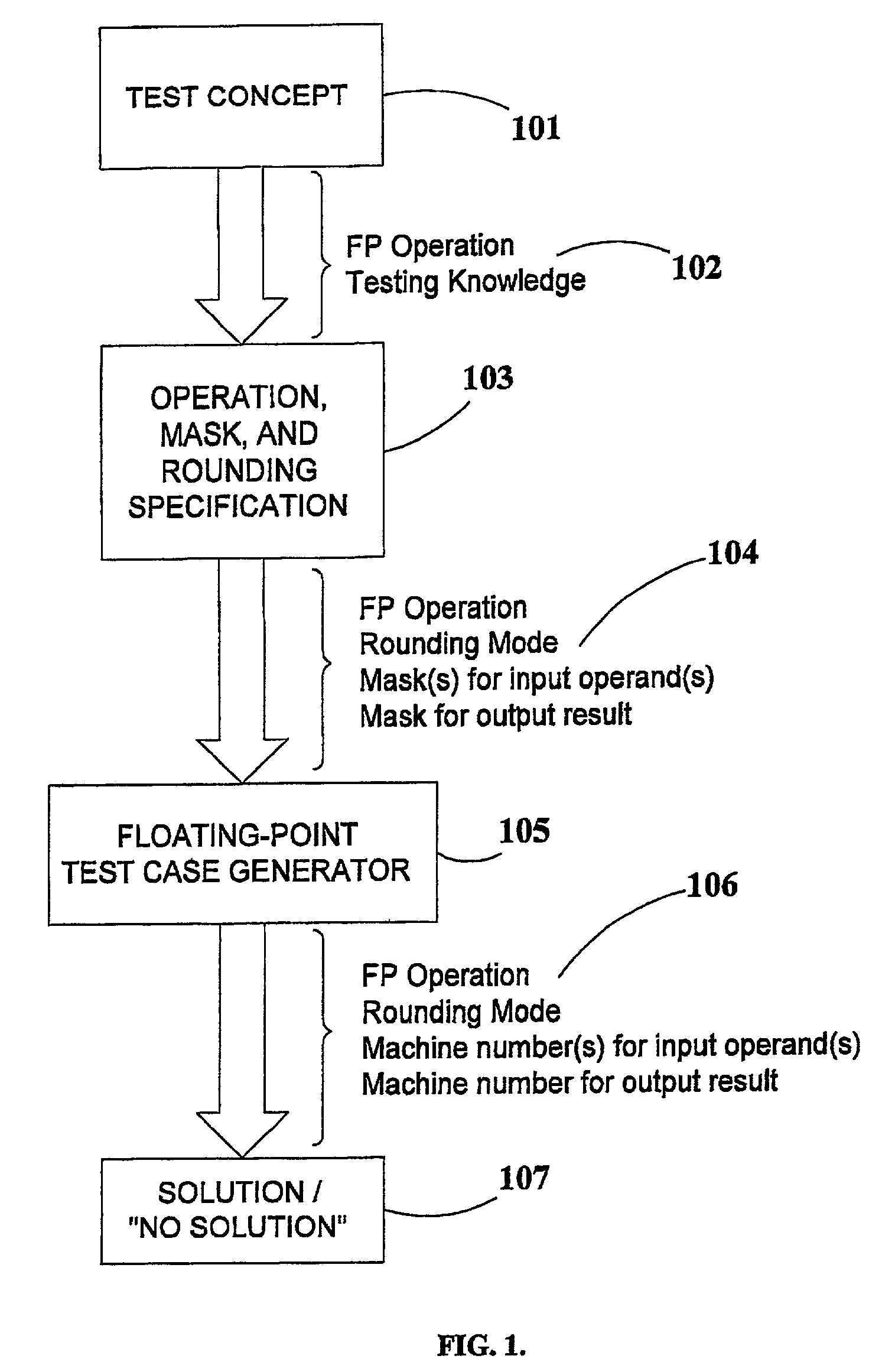

Generation of mask-constrained floating-point addition and subtraction test cases, and method and system therefor

ActiveUS7028067B2Comprehensive verificationElectronic circuit testingError detection/correctionSignificandIEEE floating point

A method and system for generating numerical test cases for testing binary floating-point arithmetic units for addition and subtraction operations, in order to verify the proper operation of the units according to a specified standard. The space for eligible test-cases is compatible with masks which stipulate the allowable forms of the operands and the result, including constant as well as variable digits in both the exponent and significand fields. The test-cases, which are generated randomly, cover the entire solution space without excluding any eligible solutions. All standard rounding modes are supported, and if a valid solution does not exist for a given set of masks, this fact is reported. The method is general and can be applied to any standard, such as the IEEE floating-point standard, in any precision. A system according to the present invention utilizes a set of sub-generators for biased exponents and significands, and also incorporates a fixed-point generator for performing calculations common to the other generators. The method relies on searching for solutions based on feasible carry sequences, and is also capable of generating test-cases for mask-constrained carry sequences.

Owner:TWITTER INC

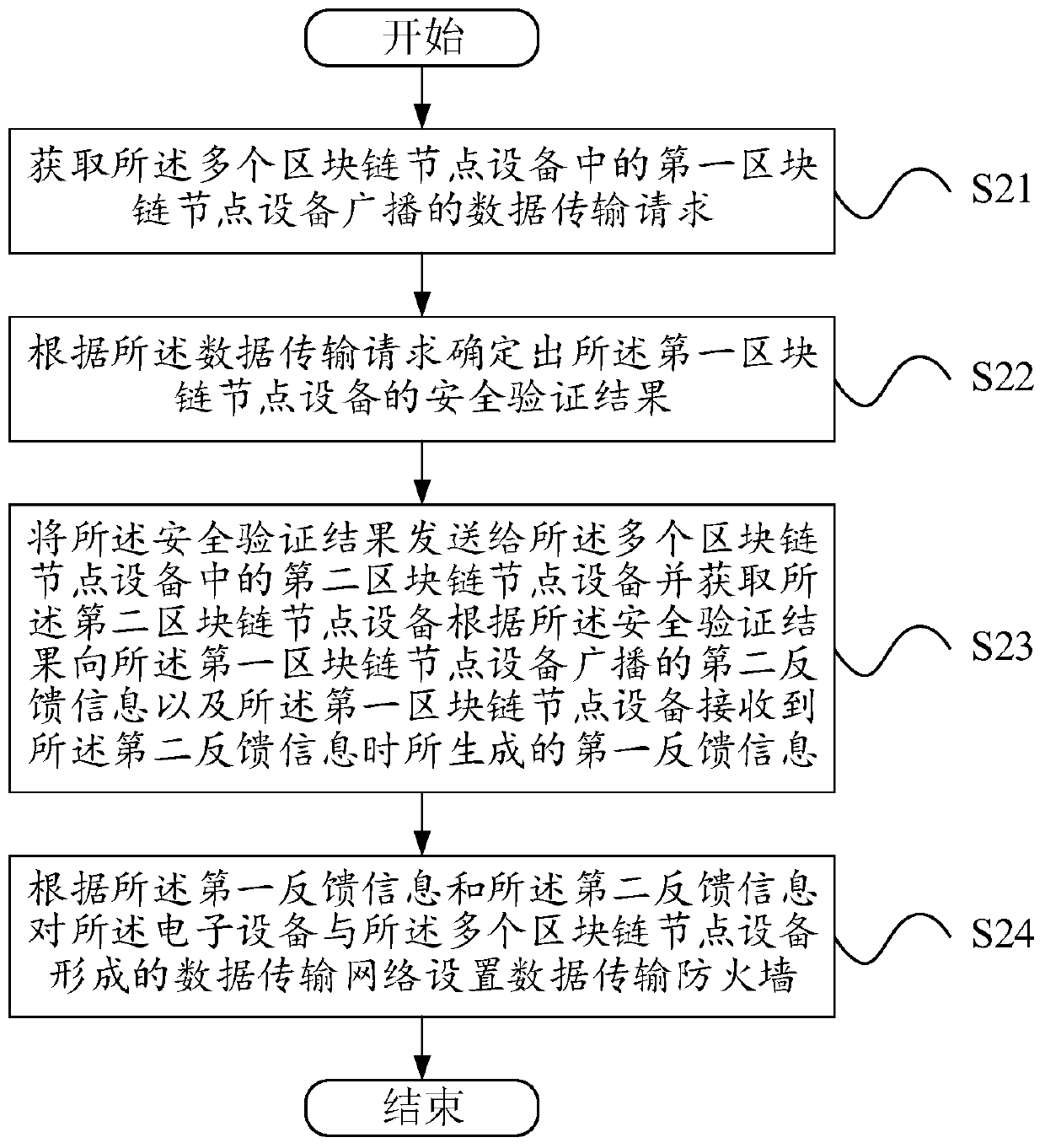

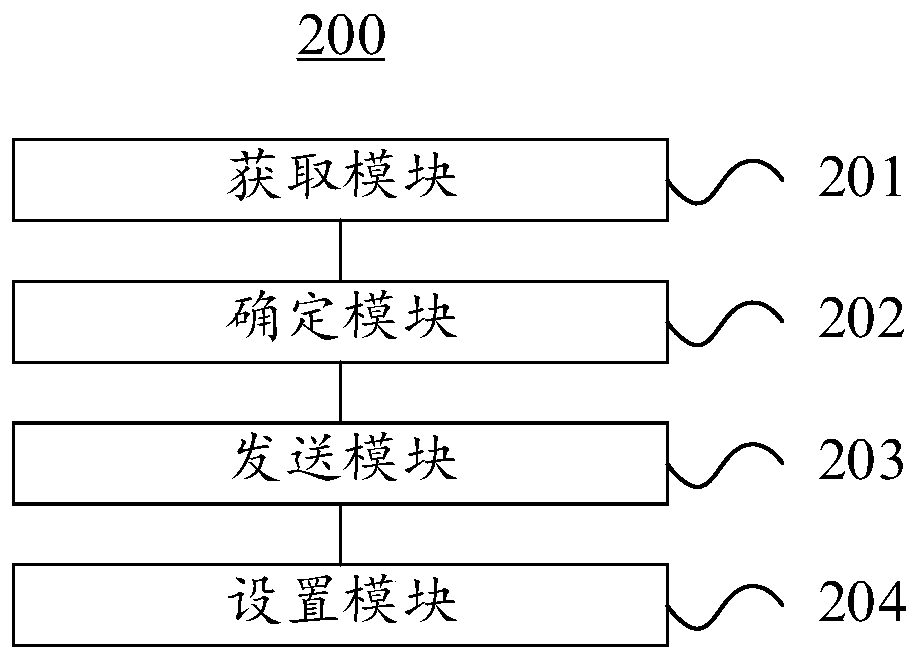

Data transmission method and device based on block chain and electronic equipment

ActiveCN110933072AImprove timelinessEnsure data transmission securityDatabase distribution/replicationDigital data protectionData transmissionSecurity validation

The embodiment of the invention discloses a data transmission method based on a block chain. In this method, the second blockchain node device is prevented from carrying out security verification on the data transmission request, so that the second blockchain node device is prevented from allocating time slice resources for security verification and encryption algorithm processing; the second blockchain node device can directly respond according to the security verification result sent by the electronic device, and the timeliness of data transmission interaction between the second blockchain node device and the first blockchain node device is improved. The electronic equipment can fully and comprehensively verify the data transmission request, thereby ensuring the data transmission security between the second blockchain node device and the first blockchain node device. By setting the data transmission firewall, the data transmission potential safety hazard between the second blockchainnode device and the first blockchain node device can be eliminated, and thus the data transmission security of the whole data transmission network is ensured.

Owner:宁波平辅寅保险科技有限公司

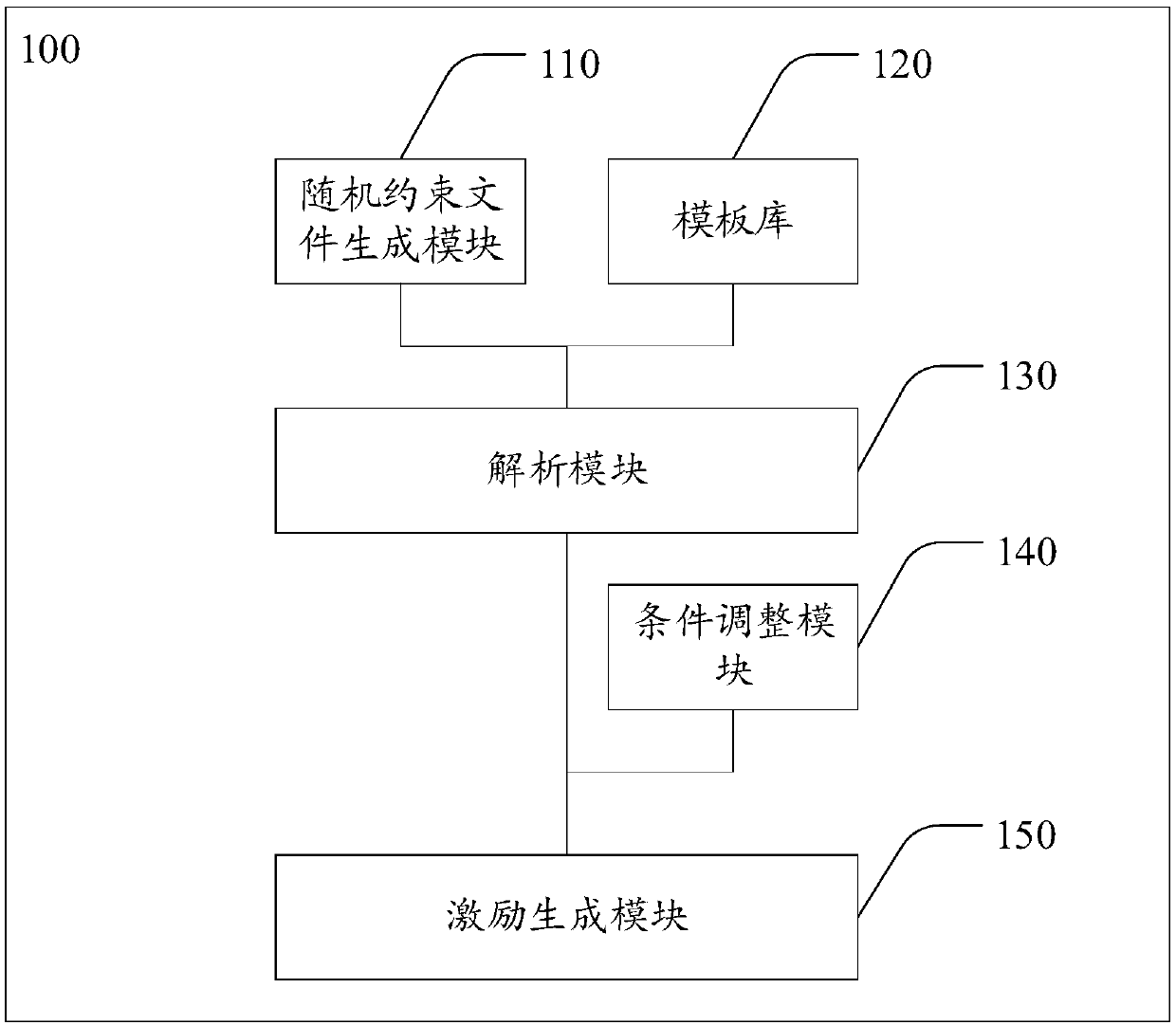

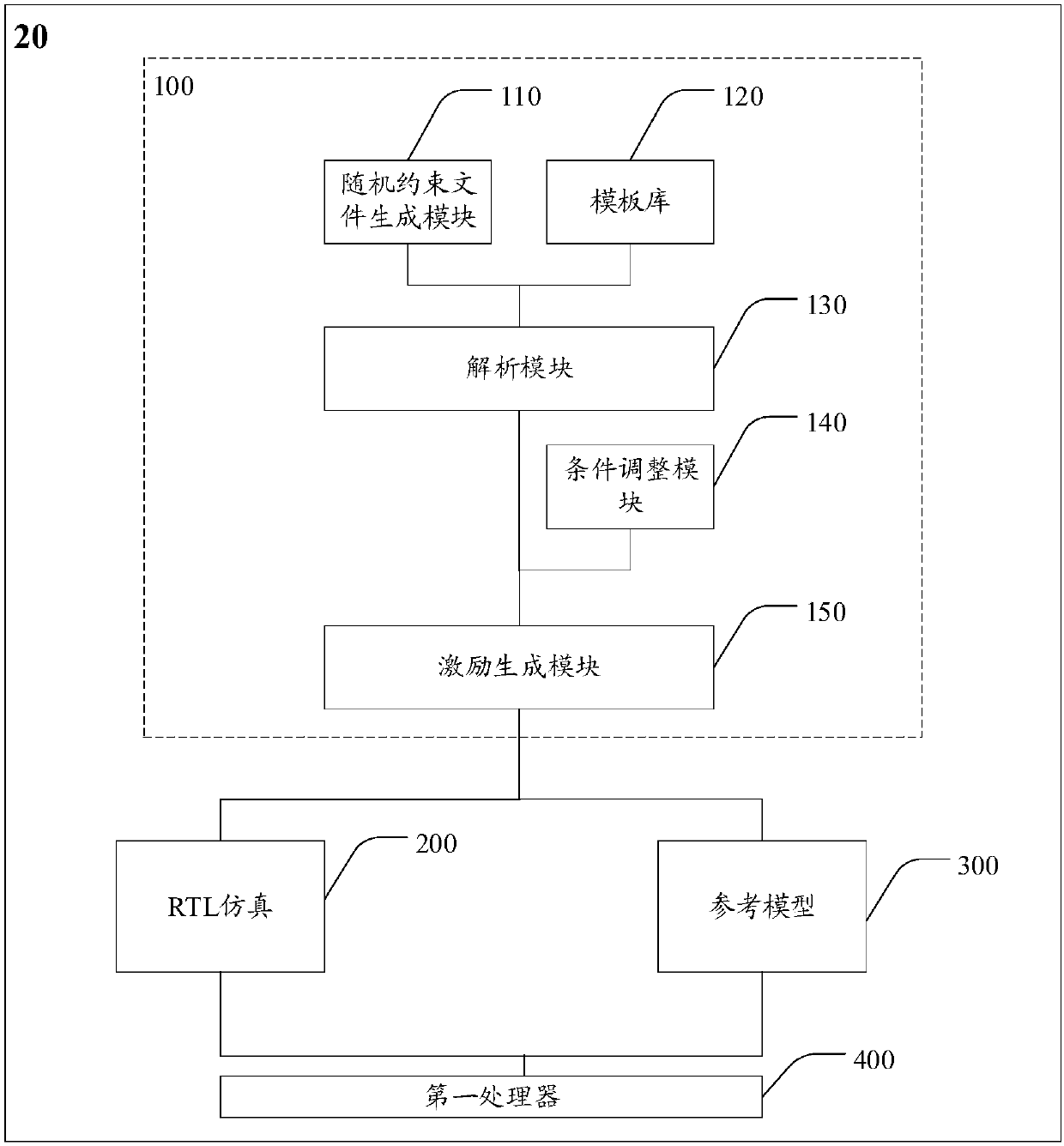

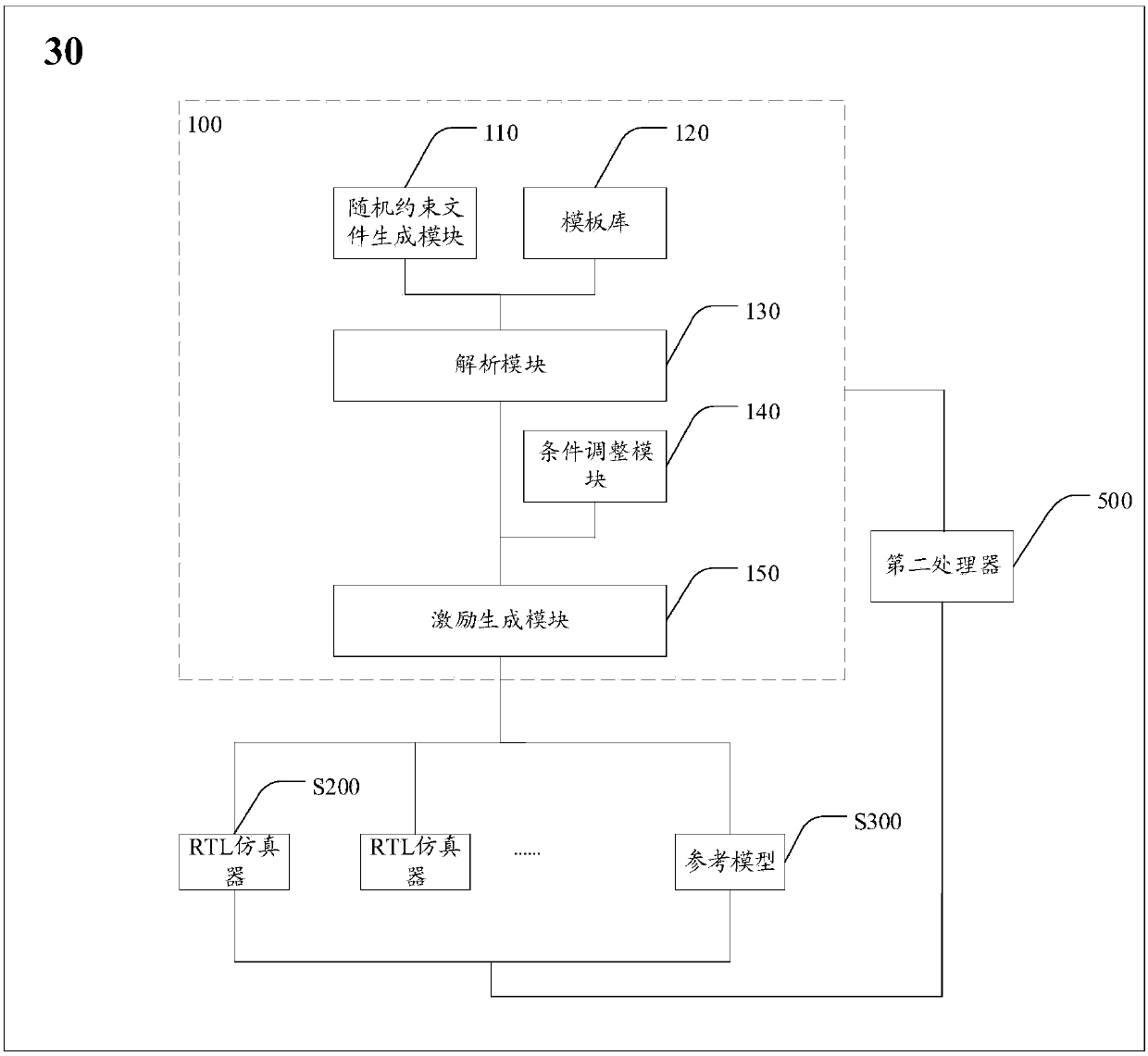

Excitation generation device, chip verification device and chip verification system

ActiveCN109992804AConvenient verificationVerification is beneficial to comprehensiveConstraint-based CADCAD circuit designComputer moduleVerification system

The invention relates to an excitation generation device, a chip verification device, a chip verification system. The excitation generation device comprises a random constraint file generation module,which is used for randomly generating a constraint file according to information to be verified of a chip; a template library used for storing the constraint file; an analysis module used for analyzing the constraint file to obtain a first constraint condition; a condition adjustment module used for adjusting a first constraint condition in the constraint file to obtain a second constraint condition; and an excitation generation module used for generating verification excitation according to the first constraint condition or the second constraint condition. According to the excitation generation device, more diverse excitation generation mechanisms can be provided, more types of verification excitation can be obtained, comprehensive chip verification is facilitated, the coverage rate canbe rapidly increased, and the chip verification efficiency is improved.

Owner:CAMBRICON TECH CO LTD

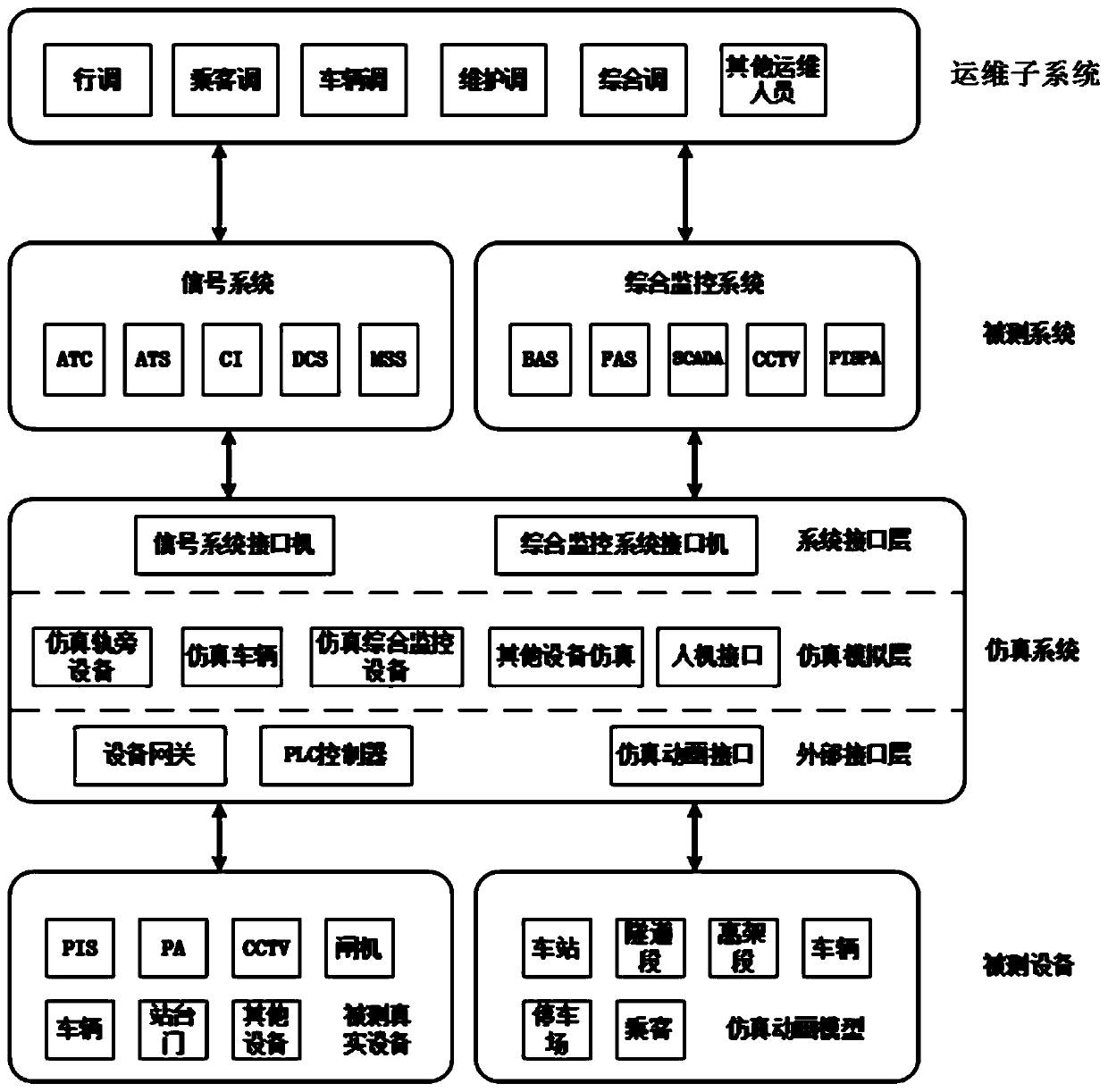

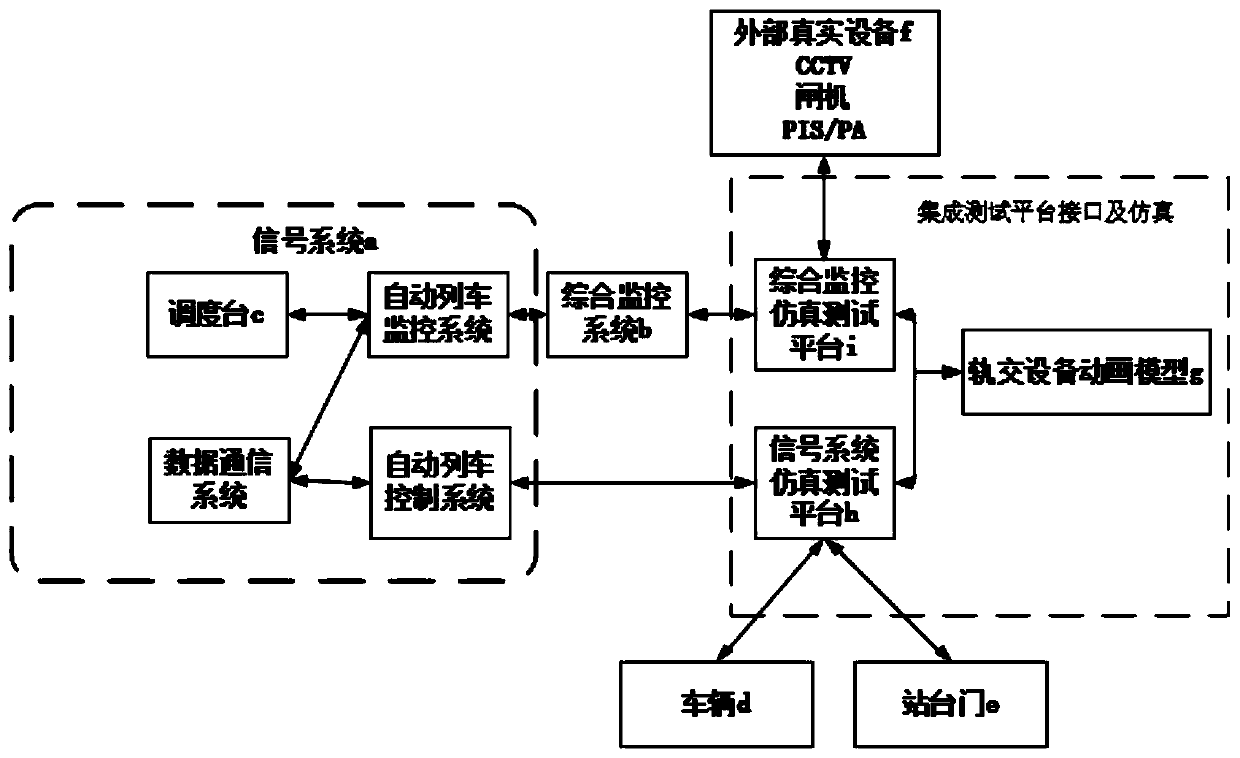

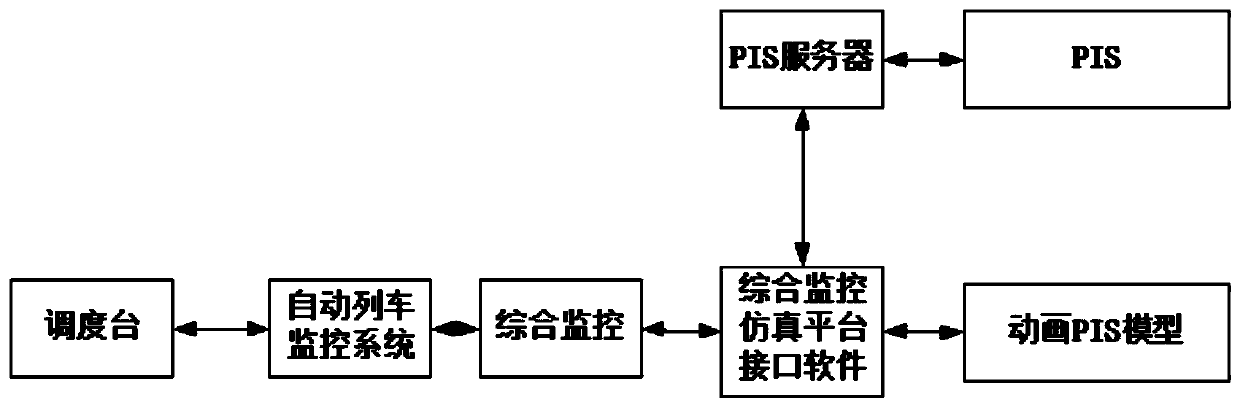

Comprehensive verification system and method for operation scene of full-automatic operating system

PendingCN110262286AIncrease credibilityComprehensive testSimulator controlEquipment under testSystem under test

The invention relates to a comprehensive verification system and a comprehensive verification method for an operation scene of a full-automatic operating system. The comprehensive verification system comprises an operation and maintenance subsystem, a tested system, a simulation system and tested equipment, wherein the operation and maintenance subsystem is connected with the tested equipment by means of the tested system and the simulation system in sequence. Through comprehensively integrating the operation and maintenance subsystem, the tested system, the simulation system and the tested equipment, the comprehensive verification system performs real-time verification on a normal scene, a faulty scene and an emergency scene of full-automatic operation of rail transit. Compared with the prior art, the comprehensive verification system has the advantages of being fully automatic, having large passenger flow, being high in integration and the like.

Owner:CASCO SIGNAL

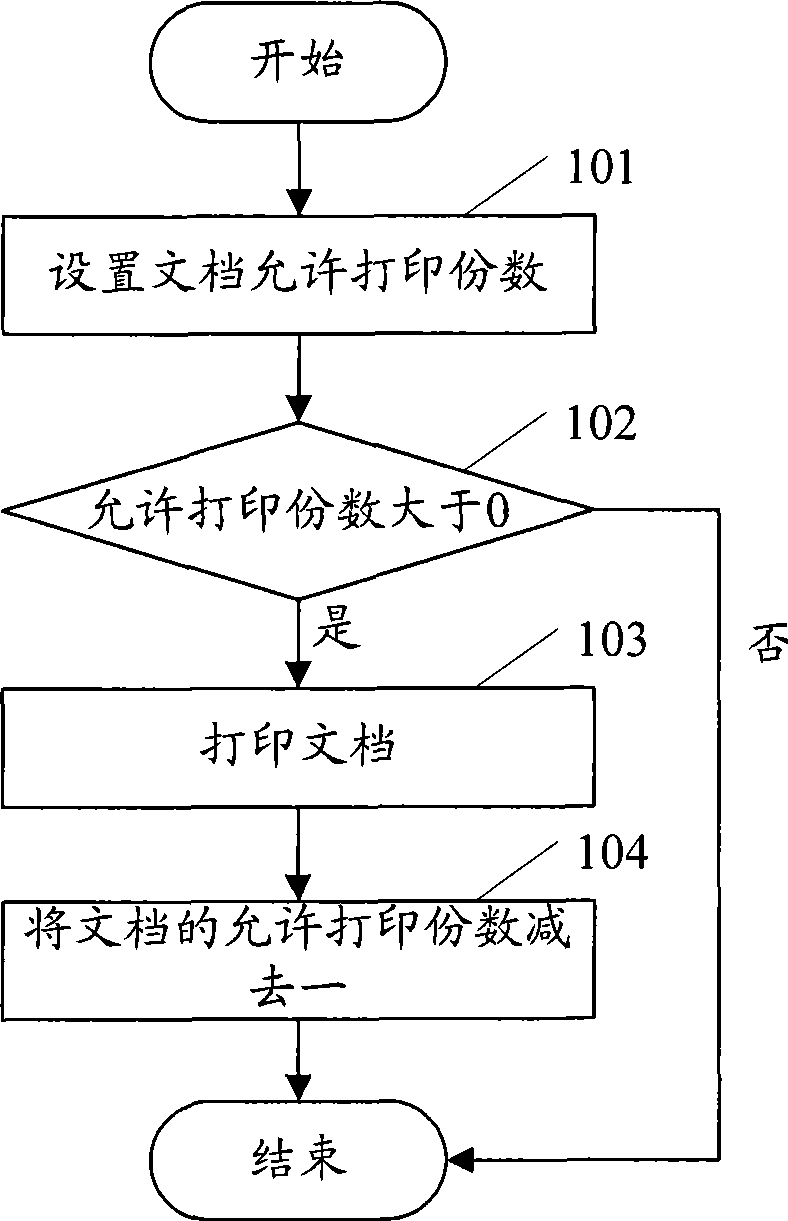

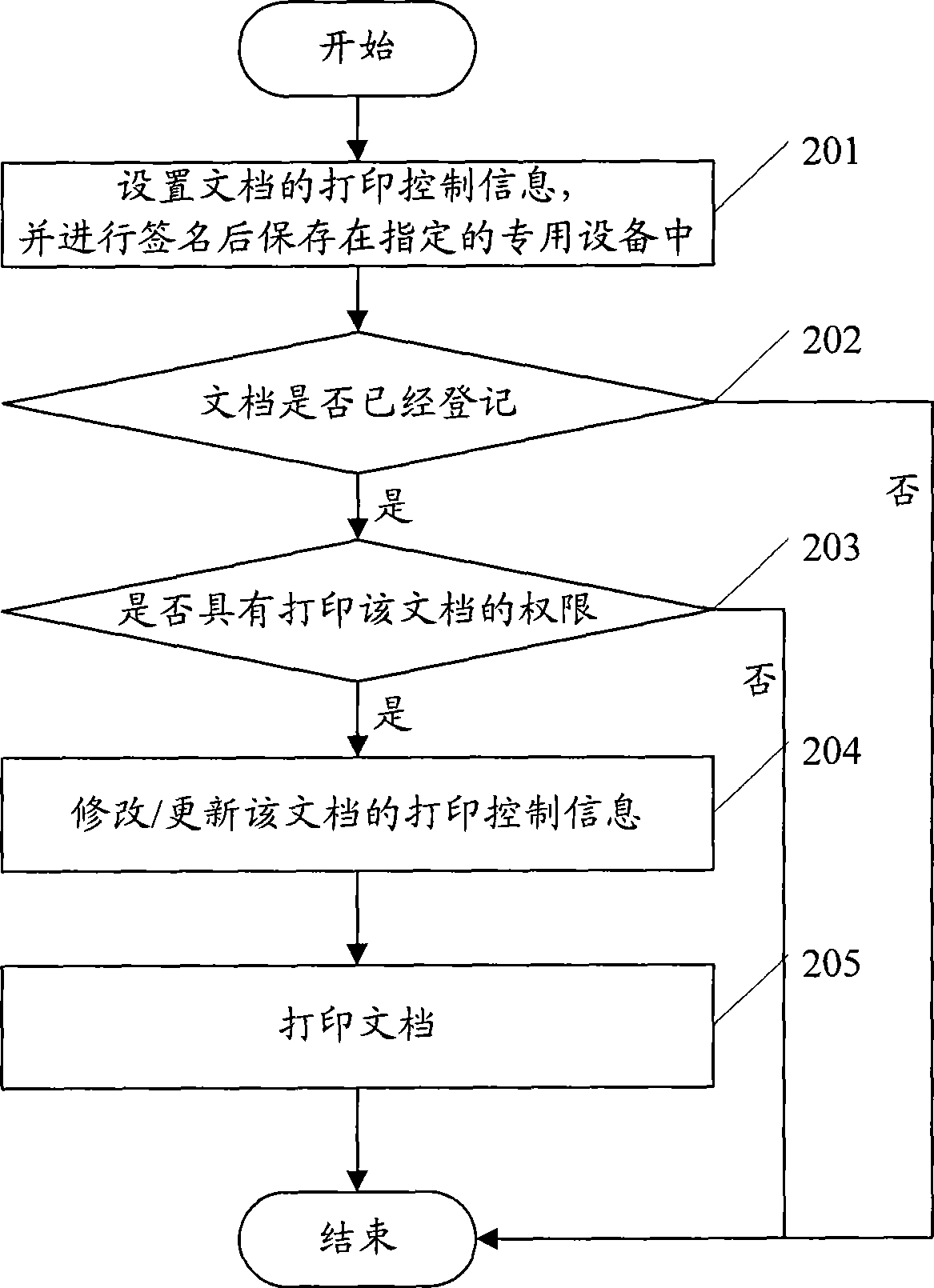

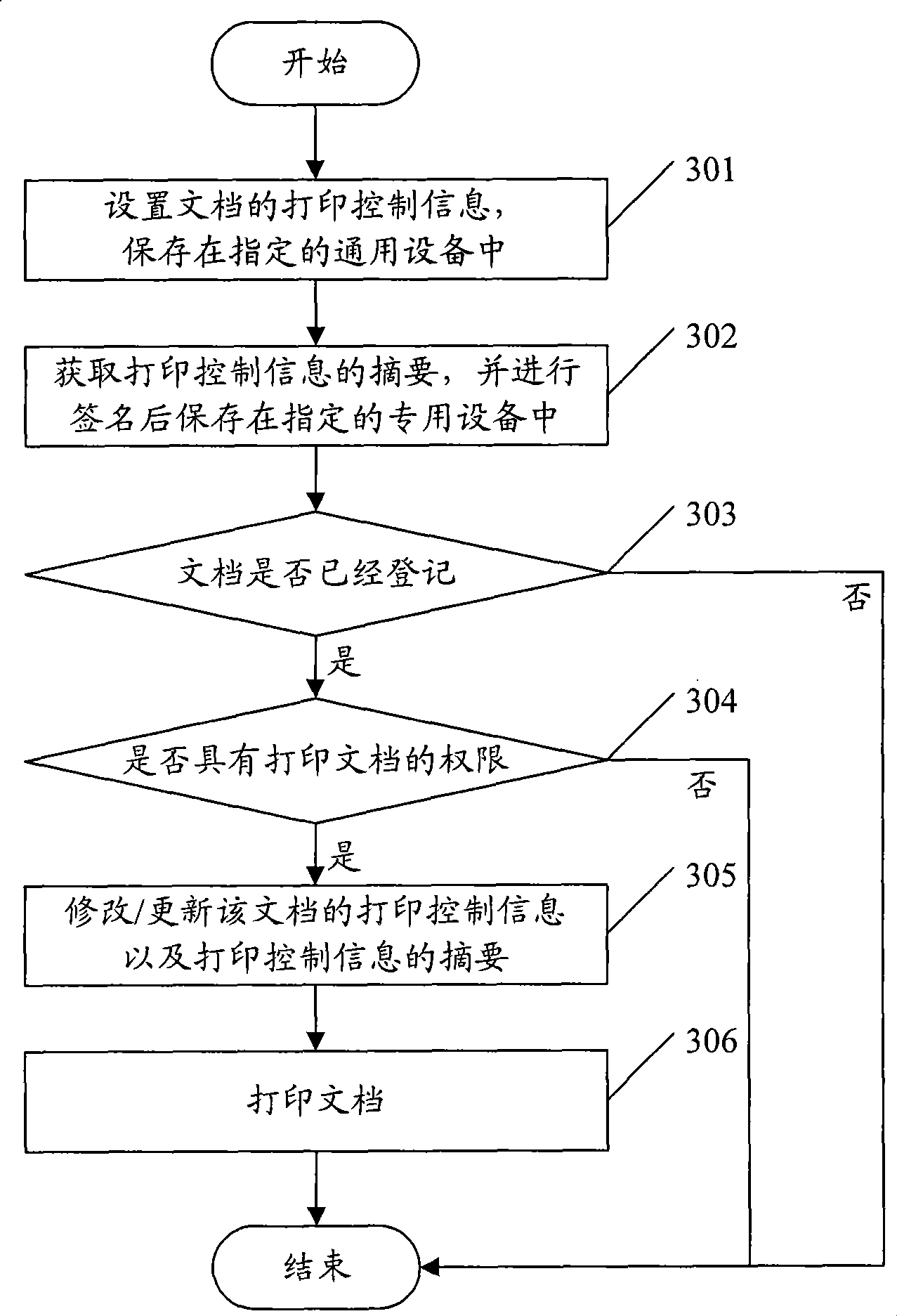

Method and system for implementing off-line printing limitation

InactiveCN101369296AEnsure safetyReduce modificationDigital data protectionDigital output to print unitsDatabase

An embodiment of the invention discloses a method of realizing off-line print constraint, comprising: registering documents in advance, storing print control information of the document; obtaining the print control information of the document when being required to print the document, performing right verification according to the print control information, and printing the document after verification. An embodiment of the invention also discloses a system of realizing print constraint. According to the method and the system in the embodiment of the invention, security of printing the document under off-line state is ensured.

Owner:BEIJING SURSEN INT TECH CO LTD

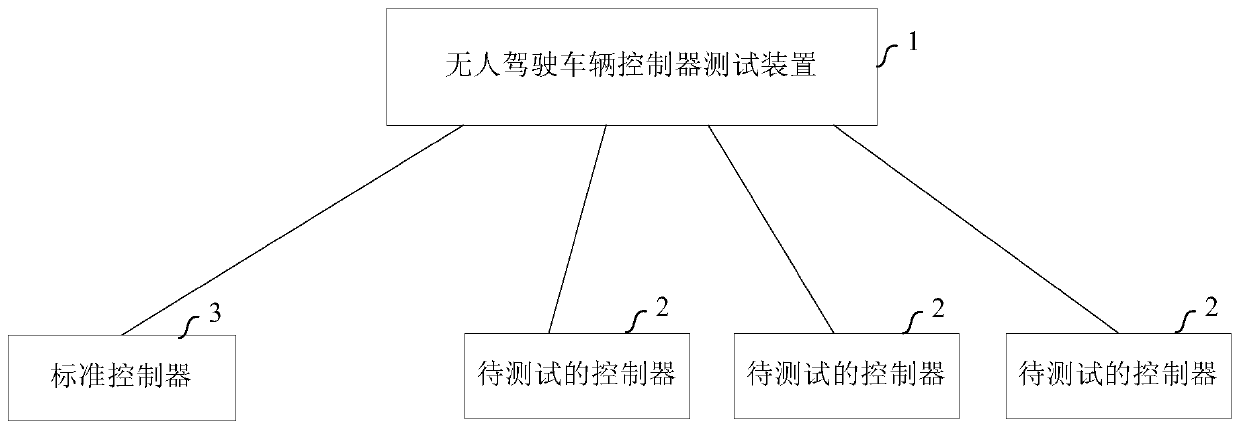

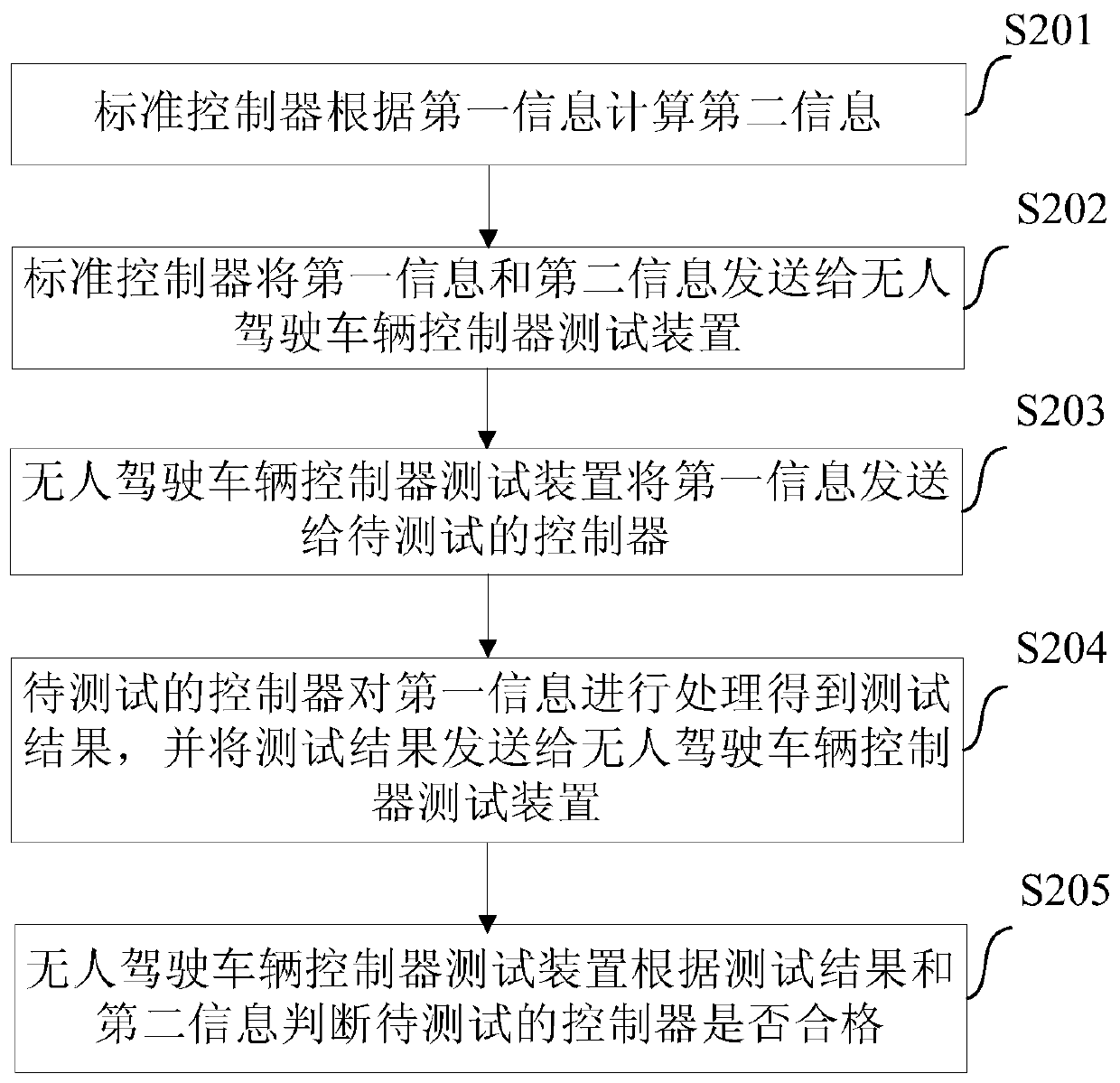

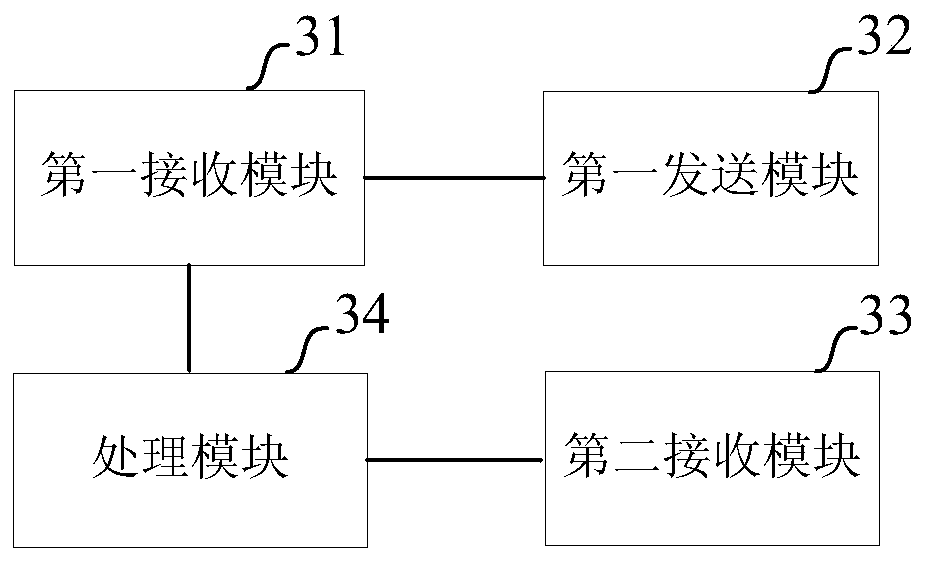

Intelligent driving vehicle controller testing method, device, server and computer readable medium

InactiveCN109725630AImprove accuracySolve the problem of too idealized test dataElectric testing/monitoringTest efficiencyEngineering

The invention provides a intelligent driving vehicle controller testing method, device, server and computer readable medium, comprising the following steps of: obtaining various sensing information detected by the intelligent driving vehicle that is actually on the road through the network, and feeding the sensing information to the local intelligent driving controller to be tested; comparing theoutput of the controller of the intelligently driven vehicle operated on the road with the output of the controller to be tested to verify the function of the controller to be tested. The intelligentdriving vehicle controller testing method, device, server and computer readable medium combines the real vehicle test and the virtual simulation software test, and adopts the sensor data of the real vehicle test, solves the problem that the virtual simulation software test data is too idealized, and improves the accuracy of the test result. Moreover, by simulating the real road reality, the verification is more comprehensive, and it is not necessary to actually mount the controller to be tested on the vehicle for road measurement, thereby reducing the test cost and improving the test efficiency.

Owner:UISEE TECH BEIJING LTD

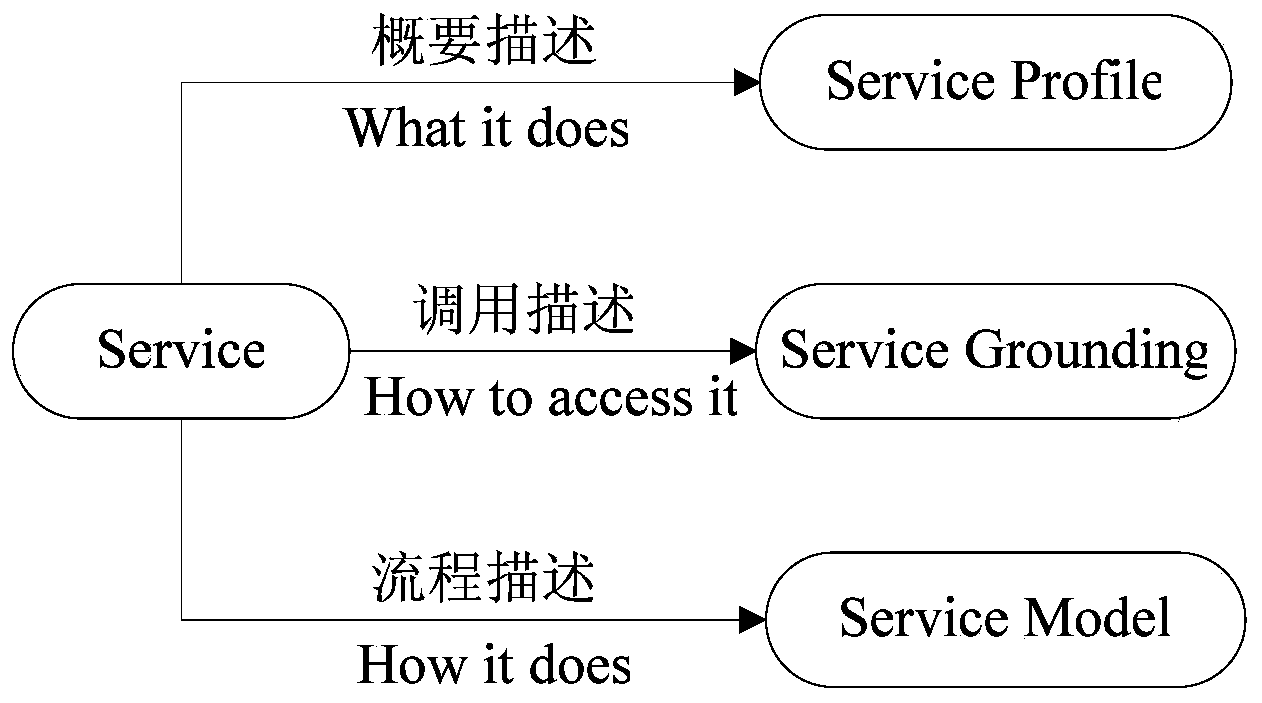

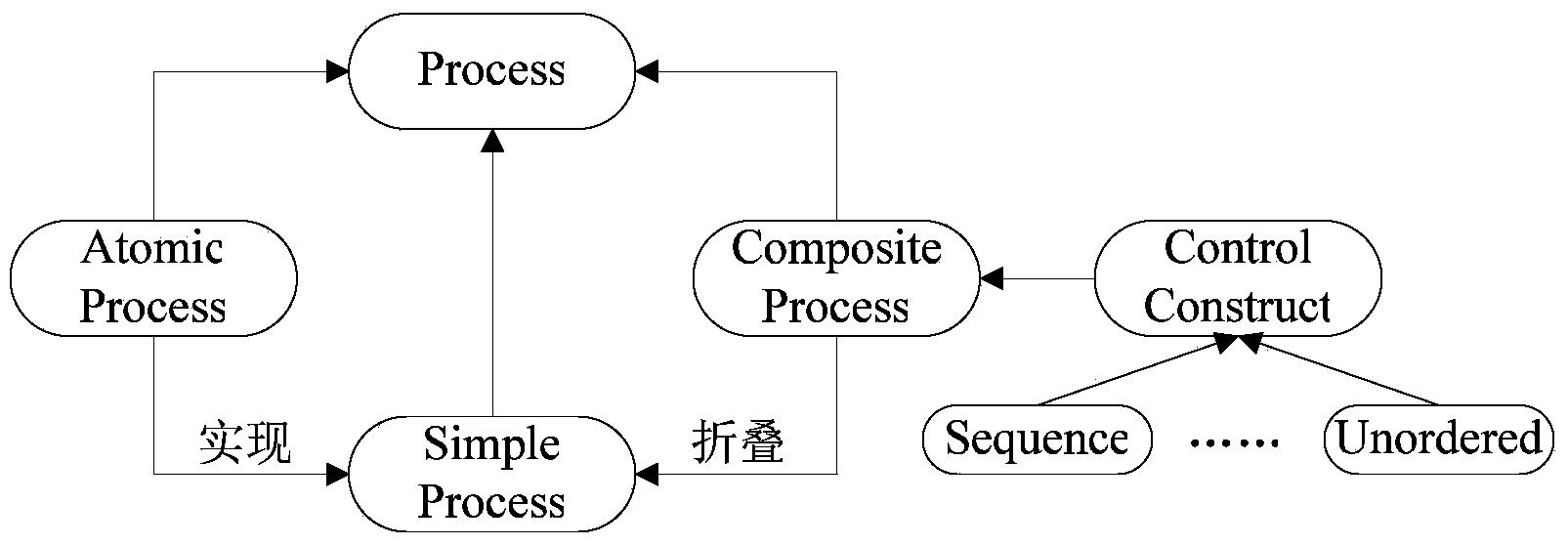

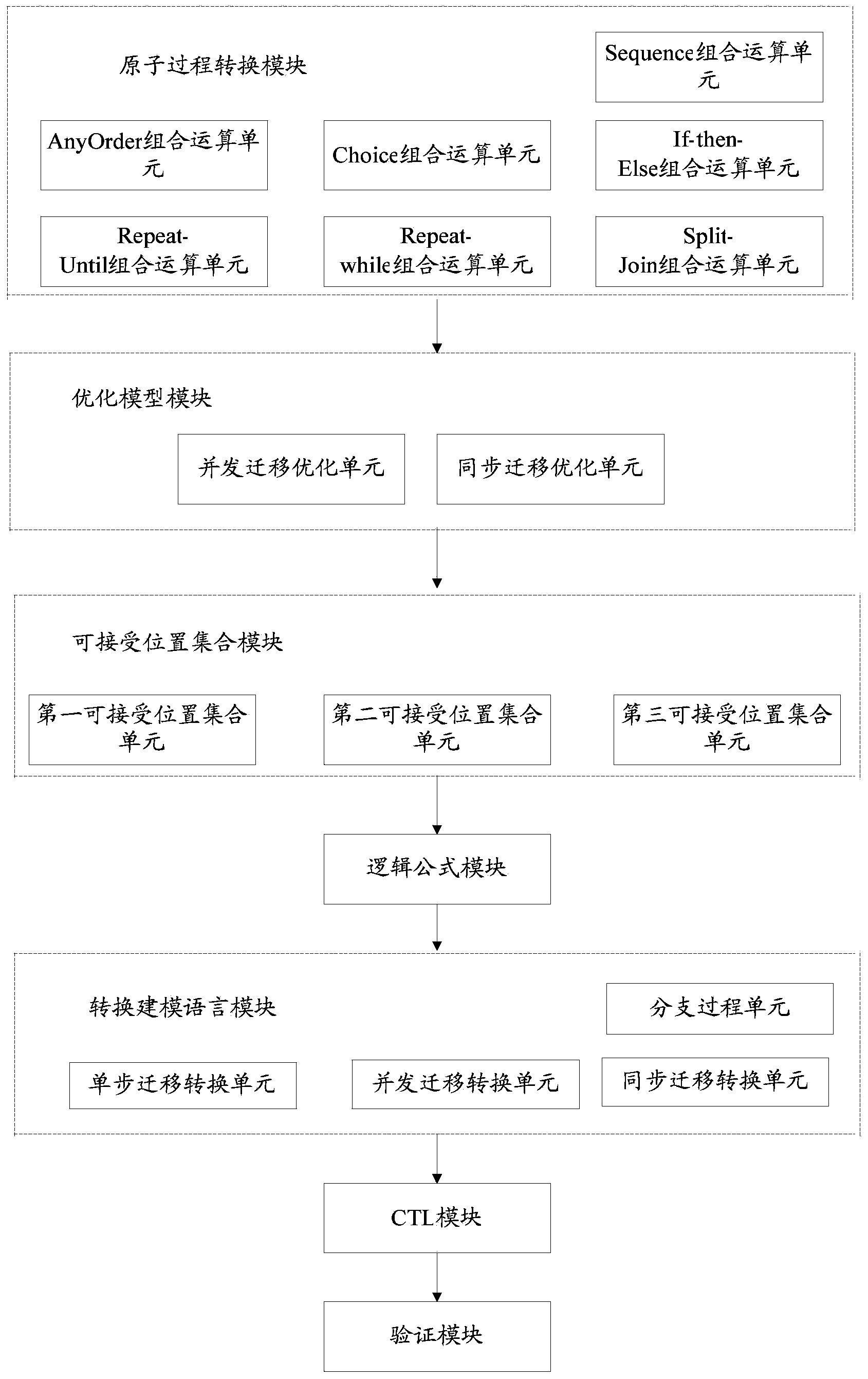

Semantic Web service composite automatic validation method and system

ActiveCN103853559AComprehensive verificationLower application thresholdSpecific program execution arrangementsOWL-SSemantic web service composition

The invention provides a semantic Web service composite automatic validation method and a semantic Web service composite automatic validation system. According to the method, the Web service of OWL-S description is converted into one atomic process automaton, and the atomic process automaton is combined into composite process automation; the redundancy concurrence and the asynchronous migration of the composite process automation are eliminated to obtain an optimized model; according to compatibility requirements limited by users, the acceptable location set of the composite process automation is determined; according to the validity requirements limited by the users, a logic formula CSV is determined; the optimized model is converted into modeling language of UPPAAL, and the acceptable location set and the logic formula CSV are expressed into a CTL formula; a composition service model described by the modeling language and the CTL formula are input into UPPAAL for validation; the description on the combination process and the atomic process in the OWL-S process is more concrete and complete, the composite operation can be taken without differences, the logic formula and the expression are supported, the description capability is higher, and the validation efficiency is improved.

Owner:FUJIAN UNIV OF TECH

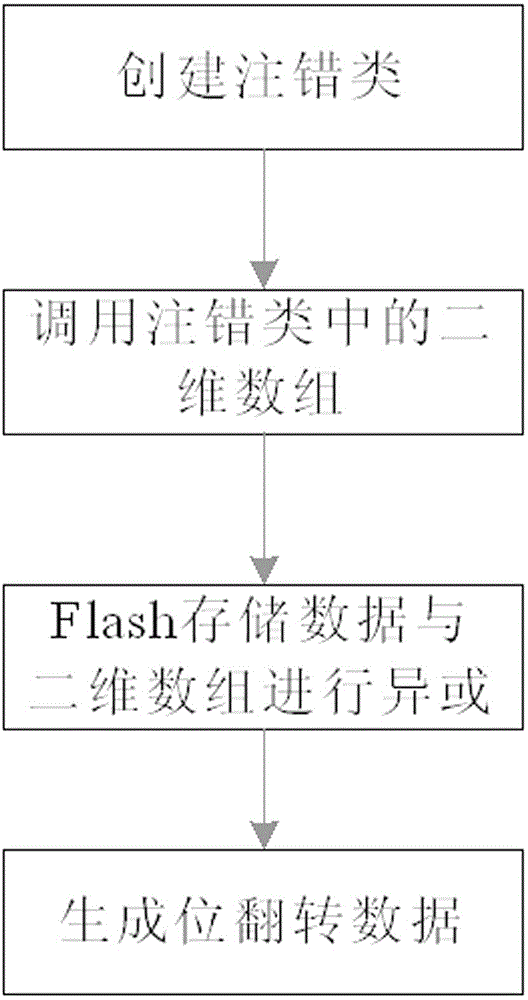

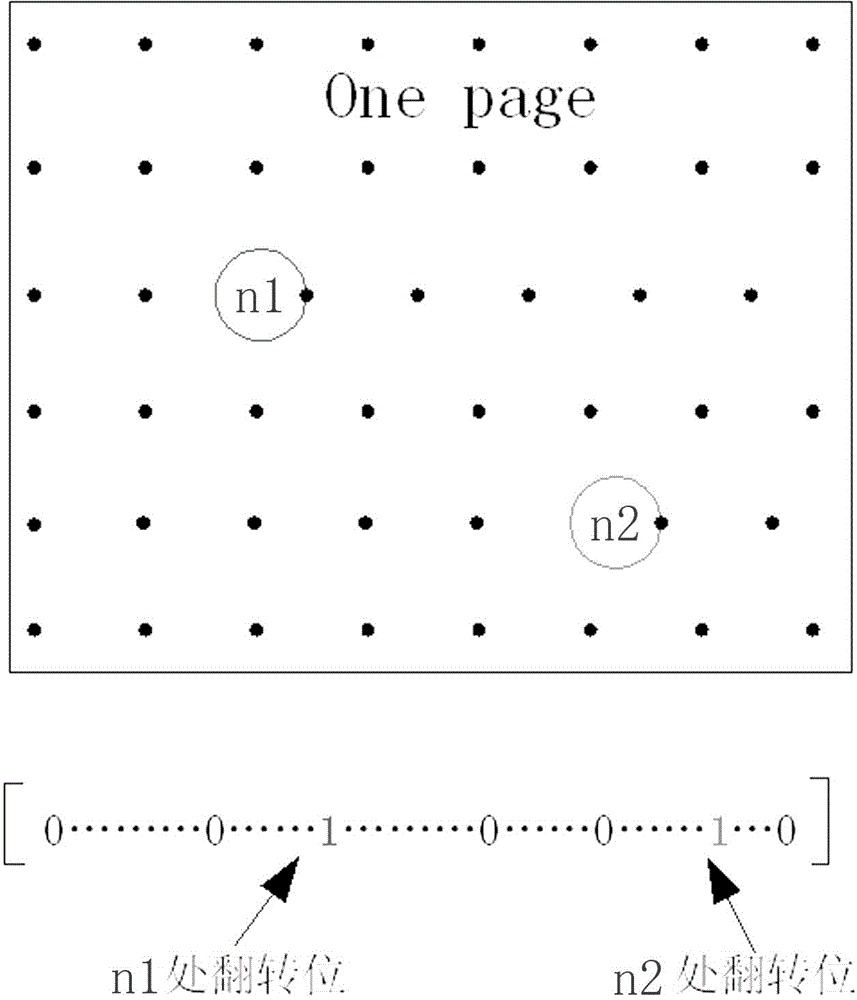

Fault injection method for Nand Flash simulation model with controllable bit flipping

ActiveCN104536864ADetect coding error correction capabilityAchieve randomizationFunctional testingStatic storageComputer architectureValidation methods

The invention discloses an injection method for a Nand Flash simulation model with controllable bit flipping. The injection method comprises the following steps: a), judging a bit flipping mode; b), randomly generating a bit flipping quantity; c),artificially setting the bit flipping quantity; d), establishing Err_pos_gen, and defining a fault position variable Err_pos; e), estabilihsing an Injet_err type, establishing a two-dimensional array which is 2<N>-1 deep and 8bit wide; f) defining a flipping bit, defining a bit flipping variable err_mum_one_byte, assigning the err-bit by utilizing a principle of corresponding a value 1 in err_mum_one_byte, to the flipping bit position of 8bit data in a Nand Flash page; g) performing data fault injection operation, performing xor operation on data in the err_bit and the data in io_data_buf; h) judging fault correcting capacity. The coding error-correcting verification method can be used for performing quantity and position controllable verification method in Nand Flash page, flexibly increasing data bit random fault inseration an beneficial to quickly completing NFC verification more comprehensively.

Owner:SHANDONG SINOCHIP SEMICON

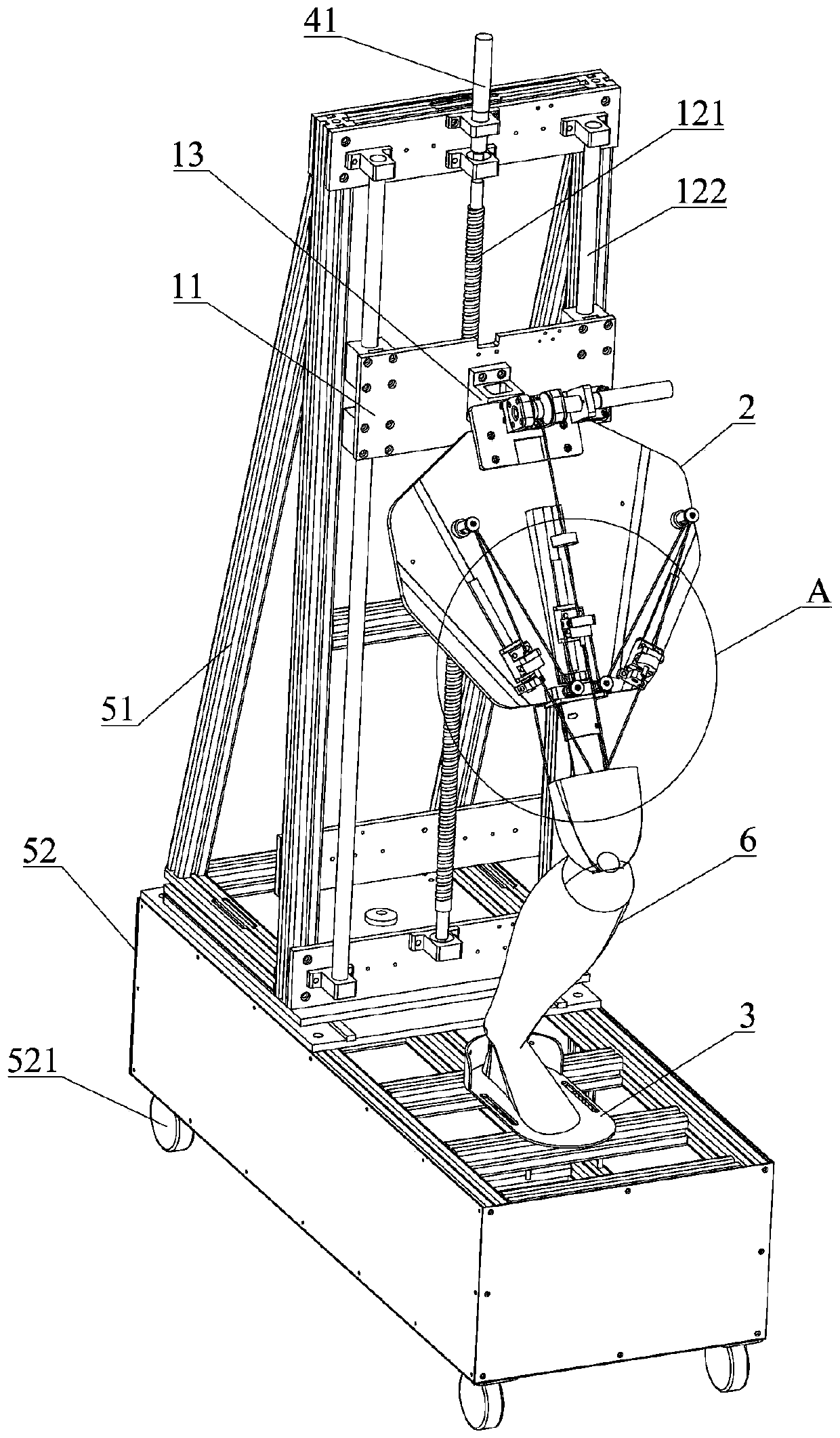

Knee joint dynamic simulation device

PendingCN109830158ASolve the problem of dynamic simulation of bucklingVerify biomechanical changesEducational modelsThigh muscleHuman body

The invention relates to a knee joint dynamic simulation device. The device comprises a hip joint simulation module, a thigh simulation module and a foot fixation module; the hip joint simulation module comprises a weight simulation block, a hip joint vertical sliding pair and a hip joint rotating pair, and is used for simulating the change of the center of gravity of squatting of a human body andhip joint movement; the thigh simulation model comprises a simulated bone plate, a quadriceps femoris connecting part and hamstring muscle connecting part, fixes specimen leg thighbone and is connected with tendons pulling the quadriceps femoris and the hamstring muscle, and is used for simulating the action of the thigh muscle in the squatting process; the foot fixation module is used for fixingthe foot of the specimen leg. By means of the weight simulation block, the device can move under the action of the gravity to bend the knee joint of the specimen leg to reproduce the movement state of the knee joint of the specimen leg, and dynamic simulation of the knee joint is completed.

Owner:PEKING UNIV THIRD HOSPITAL +1

Earthquake monitor in mine area

InactiveCN103064105ASimple structureEasy to useSeismologyElectric/magnetic detectionInfrasonic wavesEarthquake detection

An earthquake monitor in a mine area comprises a rotary base, a semispherical platform, a left and right rotary frame, an up and down rotary frame and a detector, wherein the left and right rotary frame and the up and down rotary frame are installed above the rotary base, the semispherical platform is horizontally arranged in the left and right rotary frame, the up and down rotary frame is sleeved outside the left and right rotary frame, circle centers of the semispherical platform, the up and down rotary frame and the left and right rotary frame are overlapped, the semispherical platform is fixedly connected with the left and right rotary frame, the up and down rotary frame is connected with the left and right rotary frame, the left and right rotary frame is connected to the rotary base, and a third hinged rod is inserted into the upper end of the left and right rotary frame. The detector is installed on the semispherical platform and comprises an infrasonic wave resonance device, a sphere geomagnetic field disturbance inductive device, a power source and a transformer. The earthquake monitor in the mine area is simple in structure, convenient to use, and capable of avoiding infrasonic wave disturbance due to factors of large-sized machinery working or blasting in a mine and the like. Interference factors are eliminated, earthquake detection is enabled to be more precise, and the monitor can be simultaneously regulated once more to detect and verify existence of a geological disaster when an earthquake is detected.

Owner:LIAONING TECHNICAL UNIVERSITY

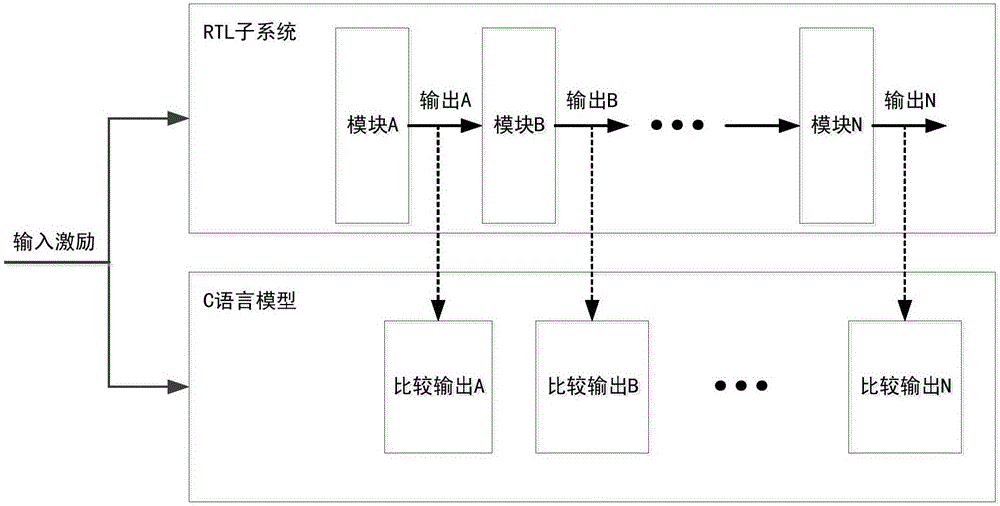

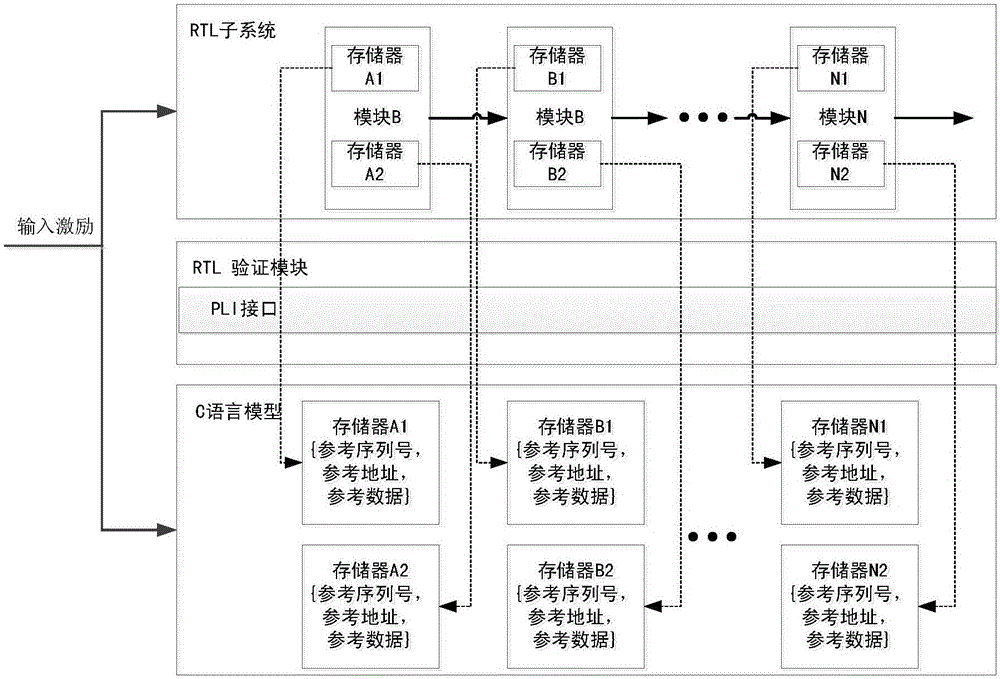

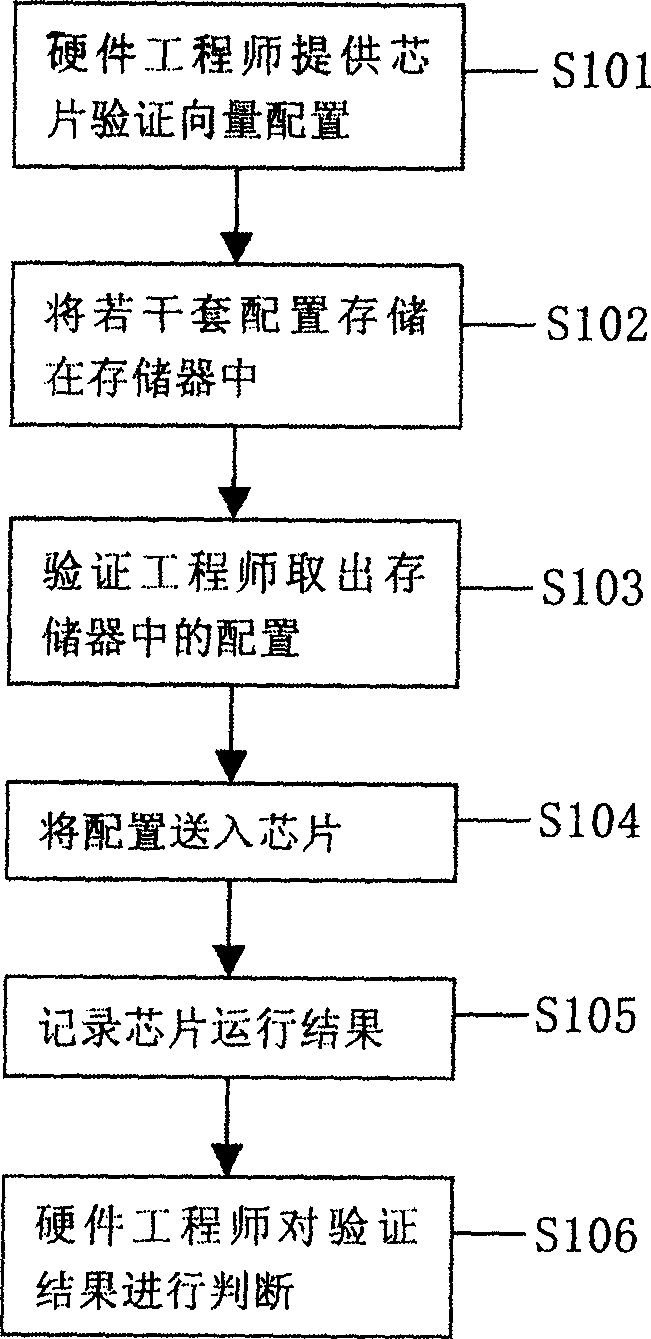

Method for building automated co-verification platform on the basis of memory access driving

ActiveCN106528364ASimple test methodEasy to debugHardware monitoringFunctional testingRelevant informationFile comparison

The invention discloses a method for building an automated co-verification platform on the basis of memory access driving. The method comprises the following steps of: according to a data processing flow, constructing a programming language function model, and storing the relevant information of an access memory as the reference information of the programming language function model; monitoring the read-write signals of all memories in an RTL (Register Transfer Level) subsystem, calling a data comparison interface by a RTL verification module if the enabling of the read-write signals is detected, comparing the relevant information of a RTL operation memory with the reference information of the programming language function model, and proving that verification is qualified if all comparison results are consistent; and if any one comparison result is consistent, generating interruption, and finishing a whole verification flow. When the method is adopted, the RTL subsystem can be accurately and efficiently tested, and the method has the advantages of being convenient in debugging and comprehensive in verification.

Owner:SUZHOU CENTEC COMM CO LTD

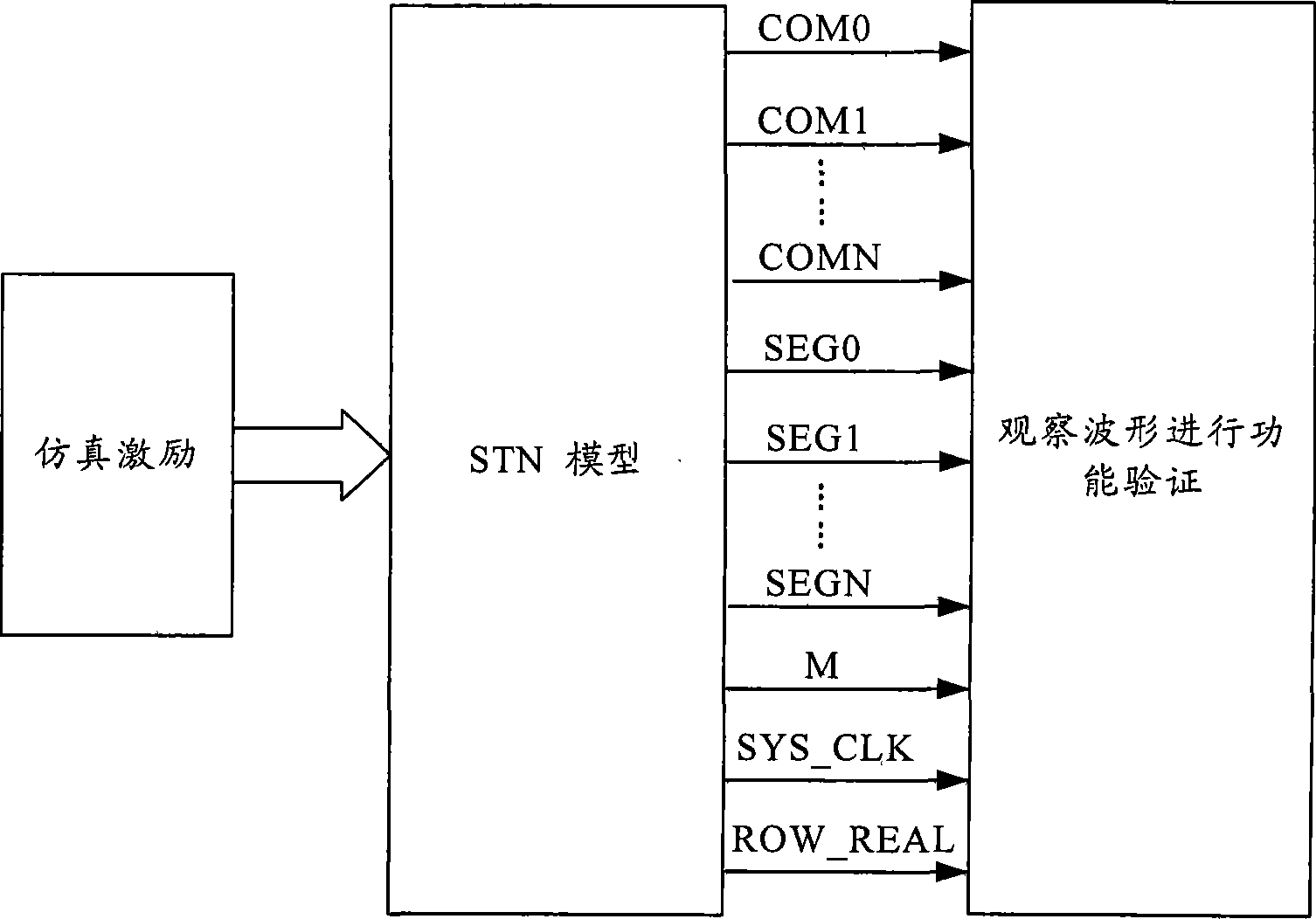

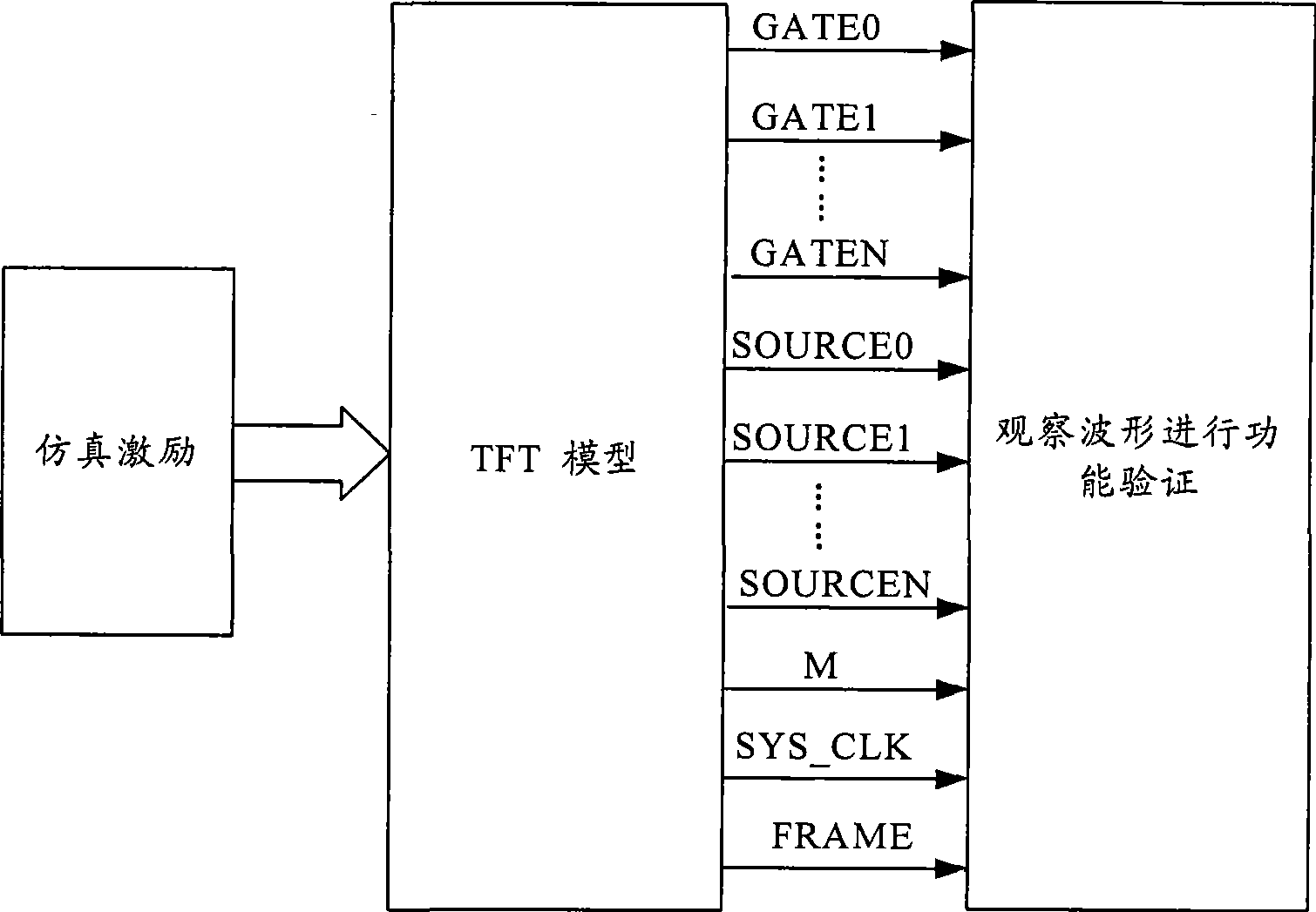

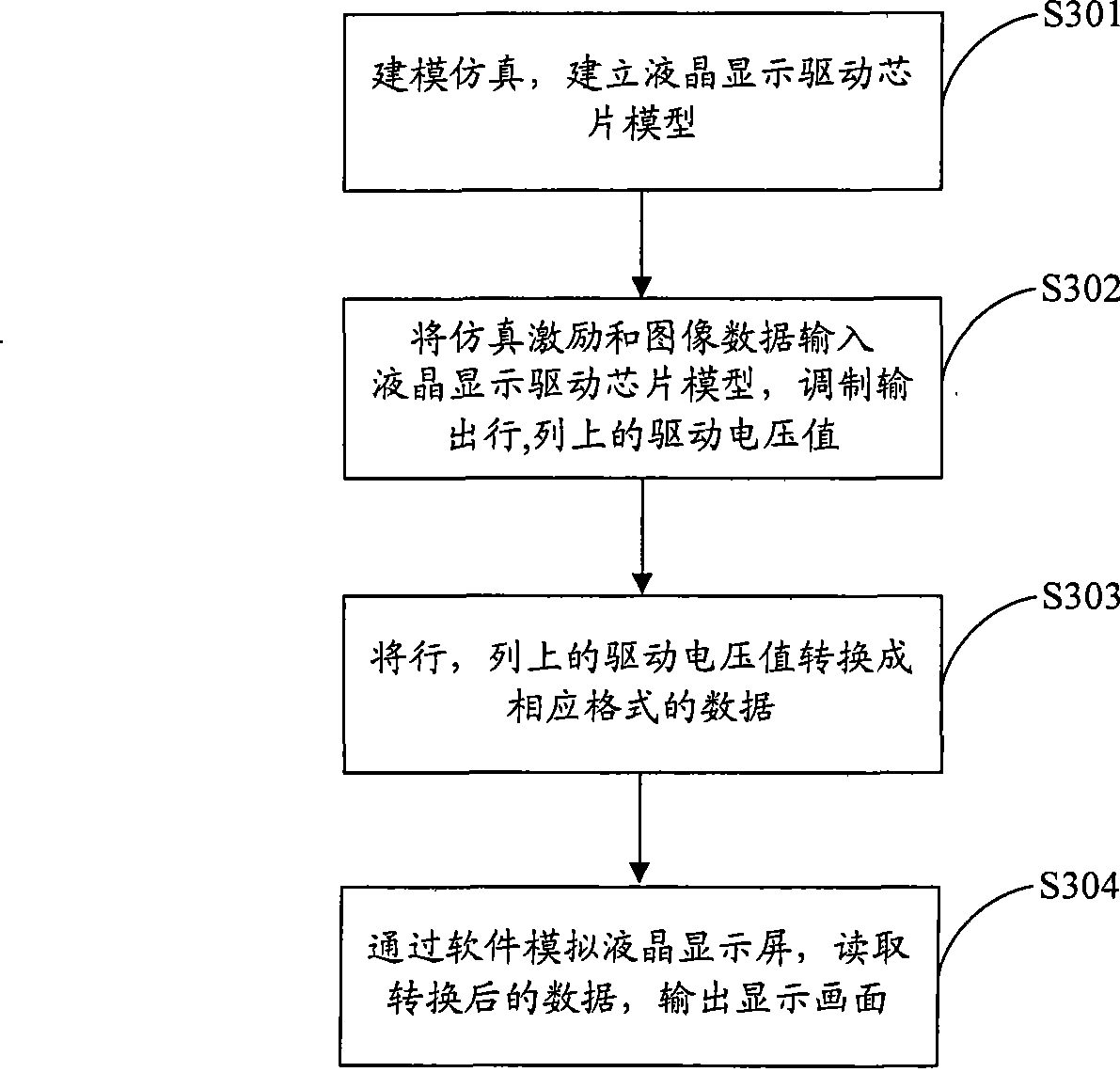

Function verification method and system for liquid crystal display drive chip

InactiveCN101369396AQuick verificationComprehensive verificationStatic indicating devicesElectrical testingLiquid-crystal displayDisplay device

The invention is suitable for display device field and provides a function verification method and system of LCD drive chip. The method comprises following steps: inputting simulation excitation and image data into LCD drive chip module, modulating and outputting drive voltage value on row and column; converting the drive voltage value on row and column into data of corresponding format; reading the converted data and simulatively outputting the corresponding display picture. Adopting the invention can perform function verification without excessively dependent on observing the wave form, the verification is fast and overall and is easy to implement, the cost is low and the operation is convenient.

Owner:BYD SEMICON CO LTD

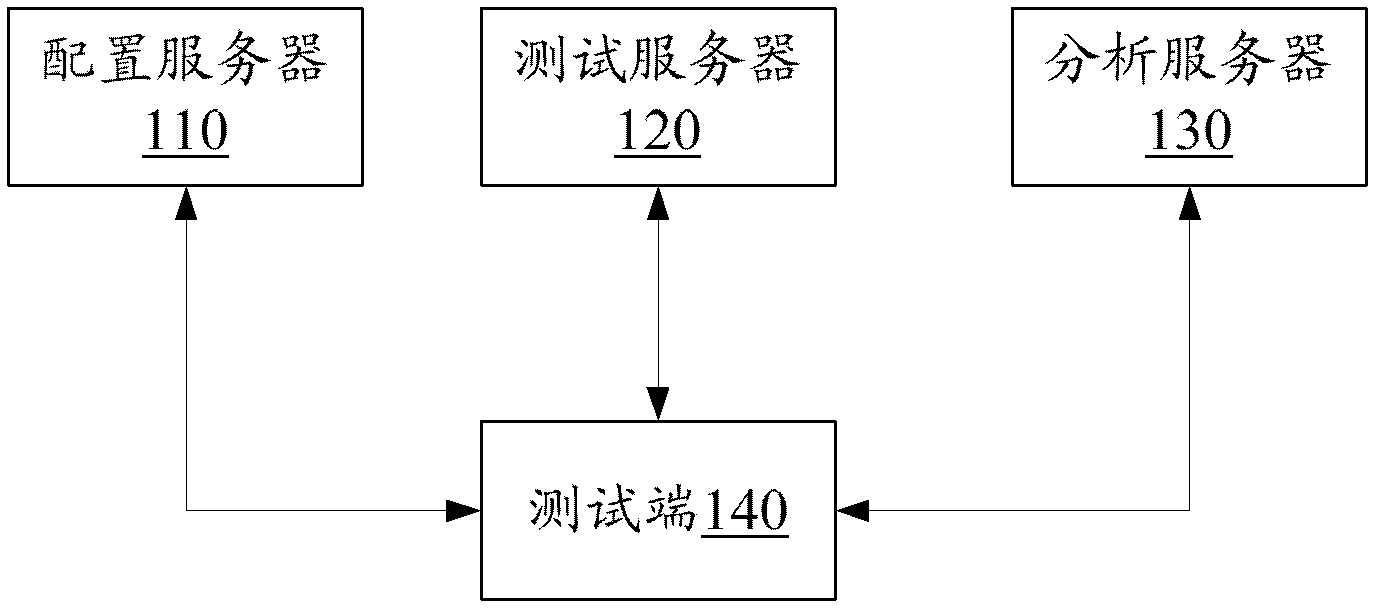

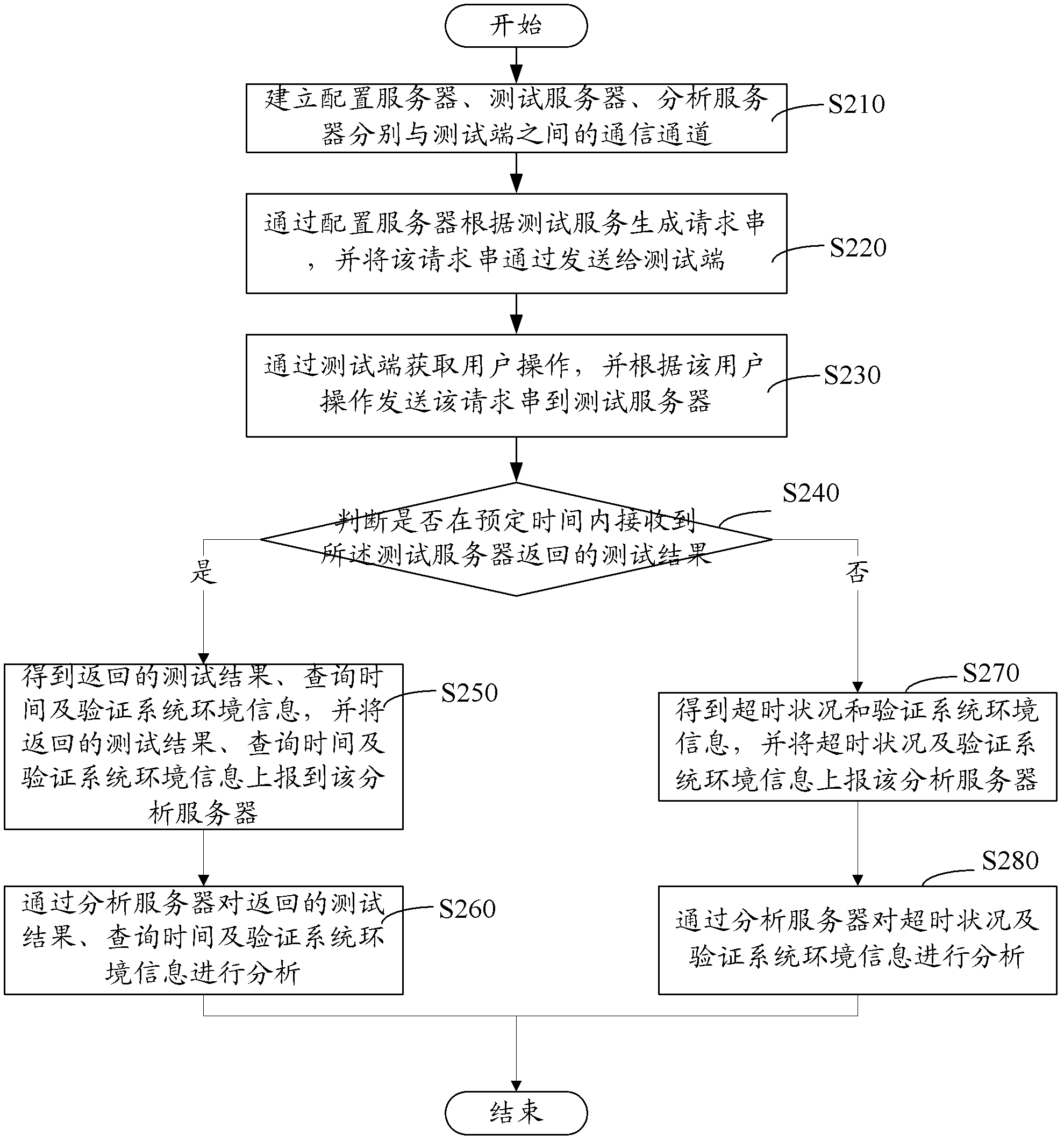

Method and system for verifying service reliability

ActiveCN103023711AComprehensive verificationVerify objectiveData switching networksComputer hardwareReal systems

The invention relates to a system for verifying the service reliability. The system comprises a configuration server, a test server, an analysis server and a test terminal, wherein a communication channel is respectively established between the configuration server and the test terminal, between the test server and the test terminal and between the analysis server and the test terminal; the configuration server is used for generating a corresponding request string according to a test service and transmitting the request string to the test terminal; the test terminal is used for acquiring user operation, transmitting the request string to the test server according to the user operation, judging whether a test result returned by the test server is received in a preset time or not, acquiring test information according to a judgment result and reporting the test information to the analysis server; and the analysis server is used for analyzing the test information. By adopting the method and the system for verifying the service reliability, a real system environment and a network environment of a user can be correctly simulated, so that the verification for testing the service reliability is comprehensive and objective.

Owner:TENCENT TECH (SHENZHEN) CO LTD

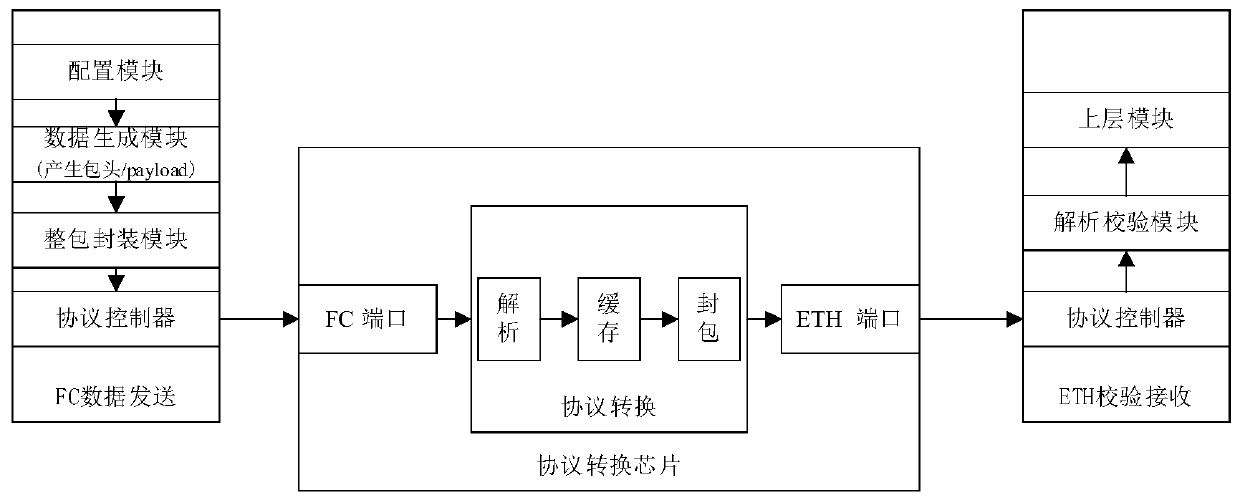

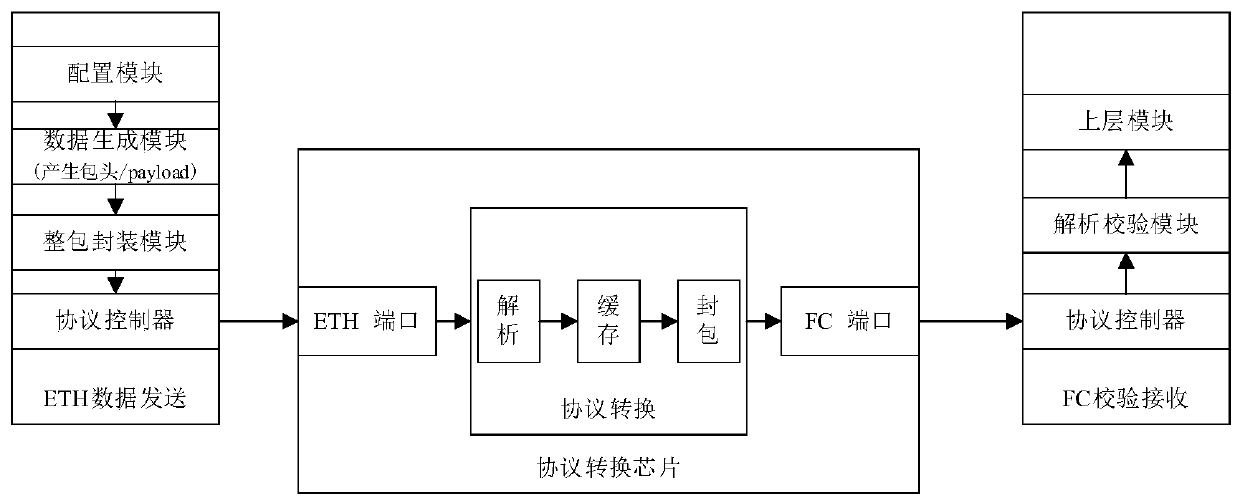

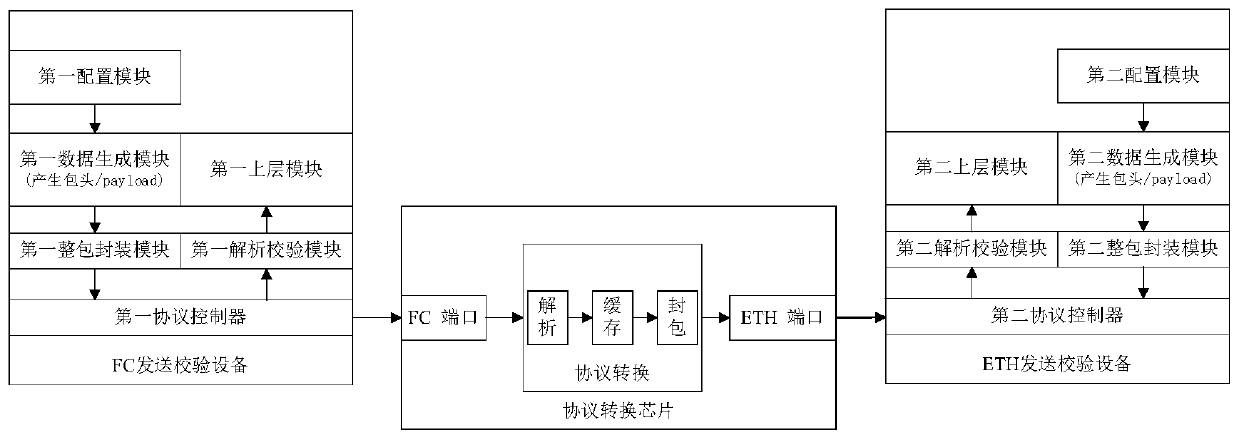

Protocol conversion function verification device and method supporting FC and Ethernet

ActiveCN110138635AFully verify protocol conversion performanceEasy to checkData switching networksEthernet protocolNetwork packet

The invention provides a protocol conversion function verification device and method supporting FC and Ethernet. The device comprises an FC sending verification device used for verifying the consistency of a first Ethernet protocol data packet and a first FC protocol data packet; and an Ethernet sending verification device which is used for verifying the consistency of the second FC protocol datapacket and the second Ethernet protocol data packet. The method comprises the following steps of randomly generating a plurality of pieces of data as payload; packaging the packet header information Header of the payload to form a first data packet according to the packet format of a protocol at the side of the sending end verification device; sending the first data packet to a target protocol conversion chip, wherein the target protocol conversion chip performs protocol conversion on the first data packet to obtain a second data packet; and backing up the payload to a receiving end verification device, wherein the receiving end verification device verifies the protocol conversion result of the target chip according to the payload and the second data packet. According to the invention, thedouble-end interconnection and intercommunication of the Header + payload can be automatically compared to verify the correctness of the target protocol conversion.

Owner:PLA STRATEGIC SUPPORT FORCE INFORMATION ENG UNIV PLA SSF IEU

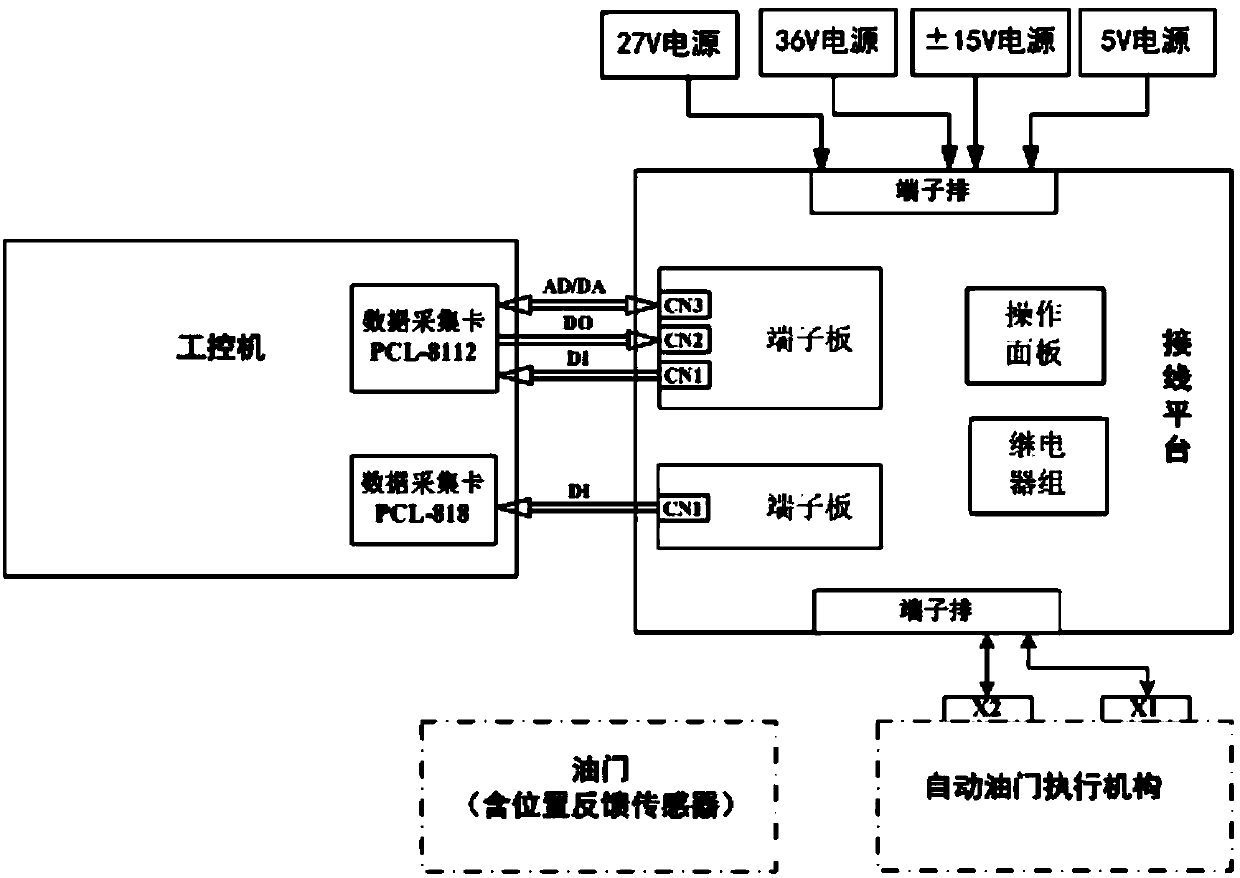

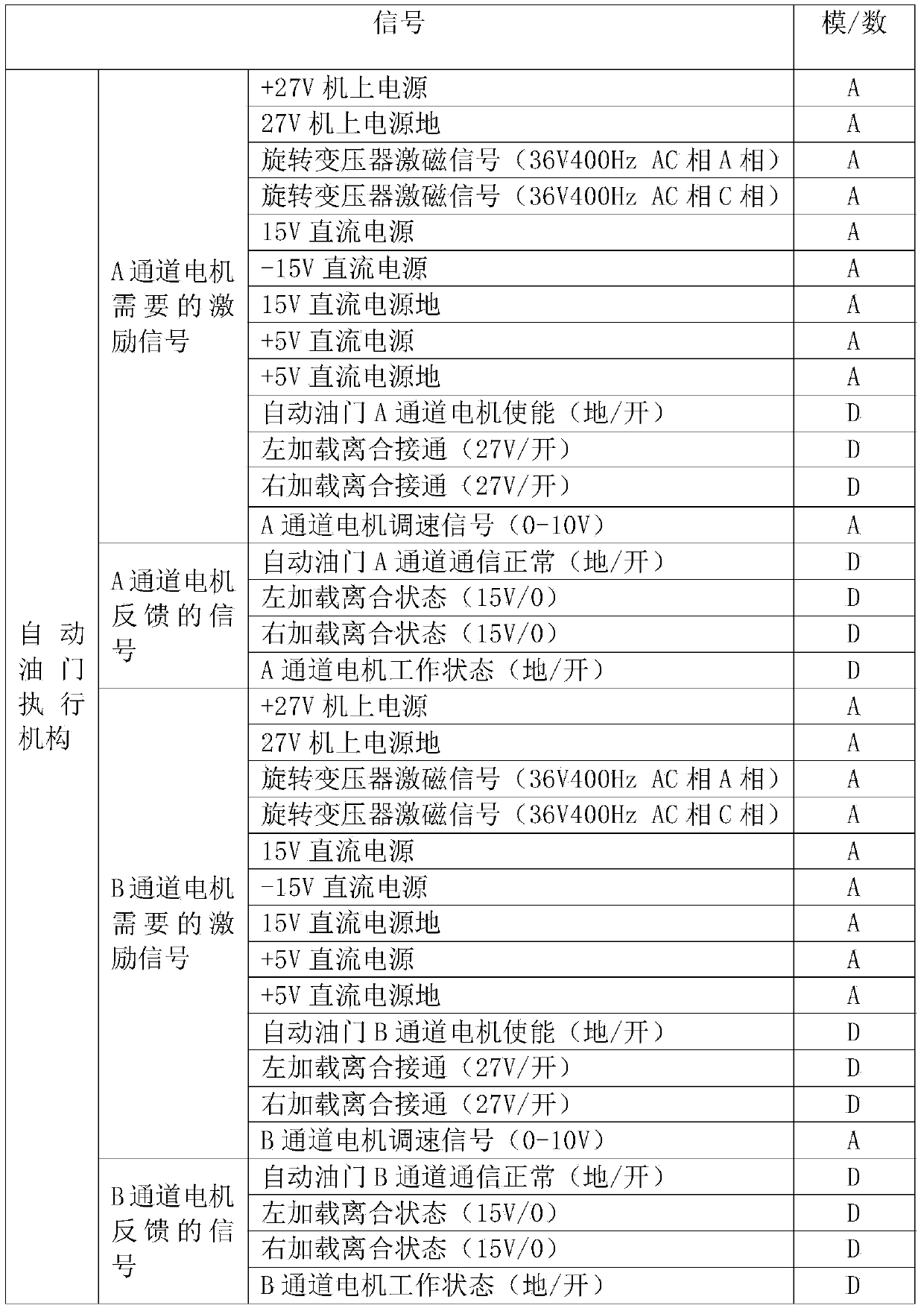

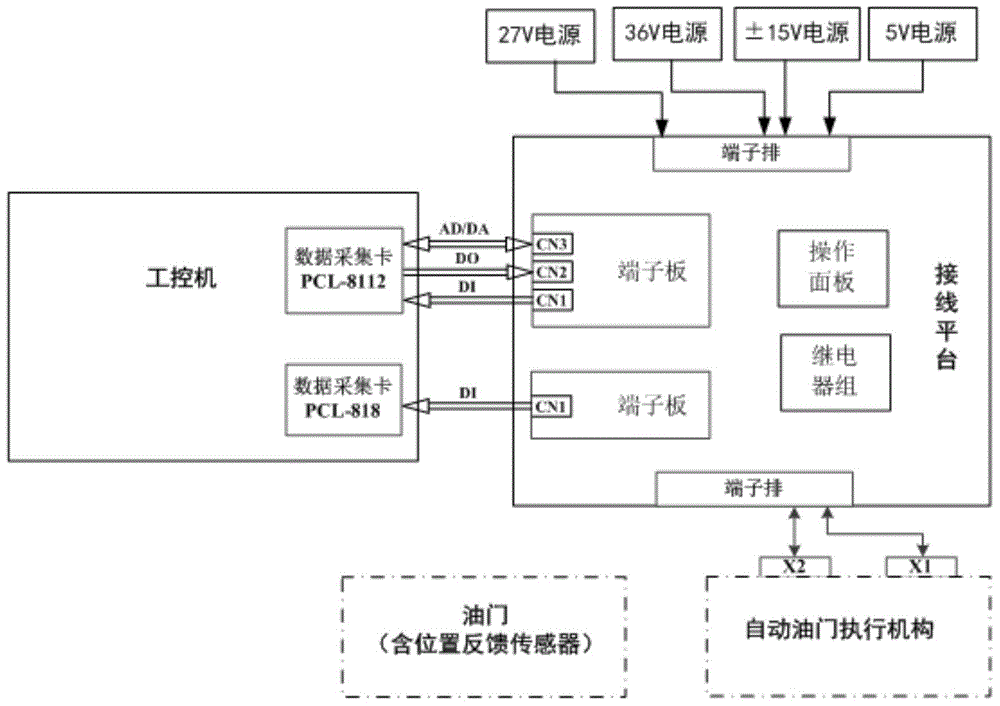

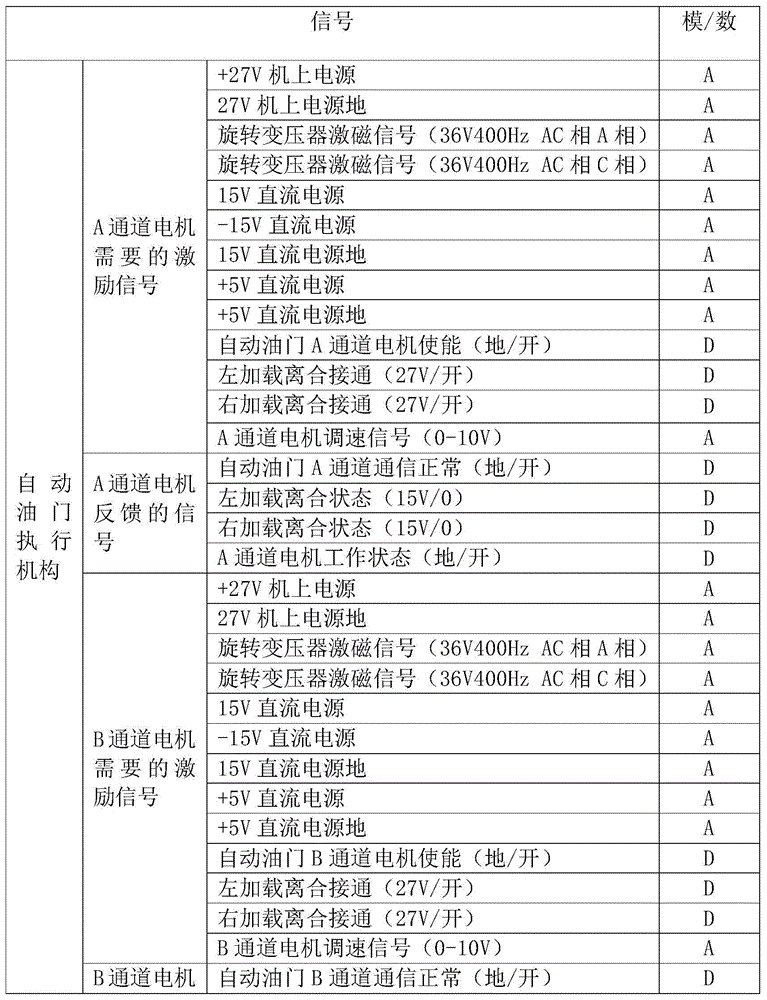

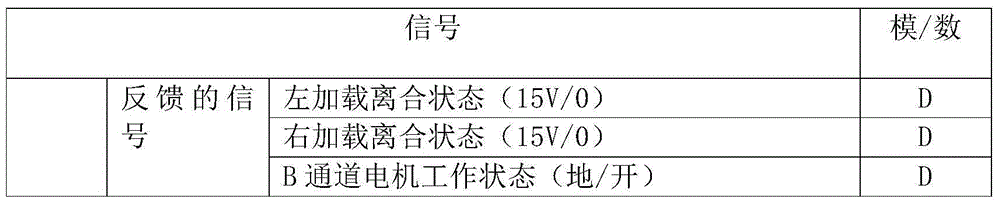

Automatic throttle actuating mechanism excitation apparatus for ground test

ActiveCN103995505ASmall scaleSave resourcesTotal factory controlProgramme total factory controlData acquisitionTest scale

The invention discloses an automatic throttle actuating mechanism excitation apparatus for a ground test, and belongs to the field of airplane designing. The apparatus comprises an industrial control computer, a wiring platform and a set of excitation power source. During an automatic throttle ground test process, an automatic throttle actuating mechanism is excited usually by use of a simulation device so as to control simulation, power supply and interface communication which are needed by an automatic throttle ground test. The apparatus is based on a system structure of the industrial control computer, a data collection card and the wiring platform and has the following advantages of shortened test scale, shortened test period, and more comprehensive verification of the automatic throttle actuating mechanism.

Owner:SHENYANG AIRCRAFT DESIGN INST AVIATION IND CORP OF CHINA

Passenger vehicle GPF reliability test method

ActiveCN112051077AVerify trueComprehensive verificationVehicle testingDriver/operatorData acquisition

The invention discloses a passenger vehicle GPF reliability test method, which comprises the following steps: a temperature sensor being installed on a vehicle GPF, wherein the GPF temperature is monitored, the weight of particles captured by the GPF is measured, and a data acquisition system is configured to perform whole-process monitoring on the state in the vehicle test process; compiling a complete assessment condition and mileage distribution; specifically decomposing the assessment working condition and mileage distribution into a vehicle driving and operation scheme according to a testfield road to form a voice prompt file, and performing vehicle driving and related operation by a driver according to the voice prompt file in the test process to ensure that the vehicle runs according to a specified working condition. and in the test process, after each working condition is finished, the GPF state and the vehicle emission result of the vehicle are checked, and the GPF reliability is judged. According to the method, the influence of vehicle driving environment factors on the GPF reliability is accurately reduced, so that the test result is more accurate, and the GPF reliability can be truly and comprehensively verified.

Owner:DONGFENG MOTOR CORP HUBEI

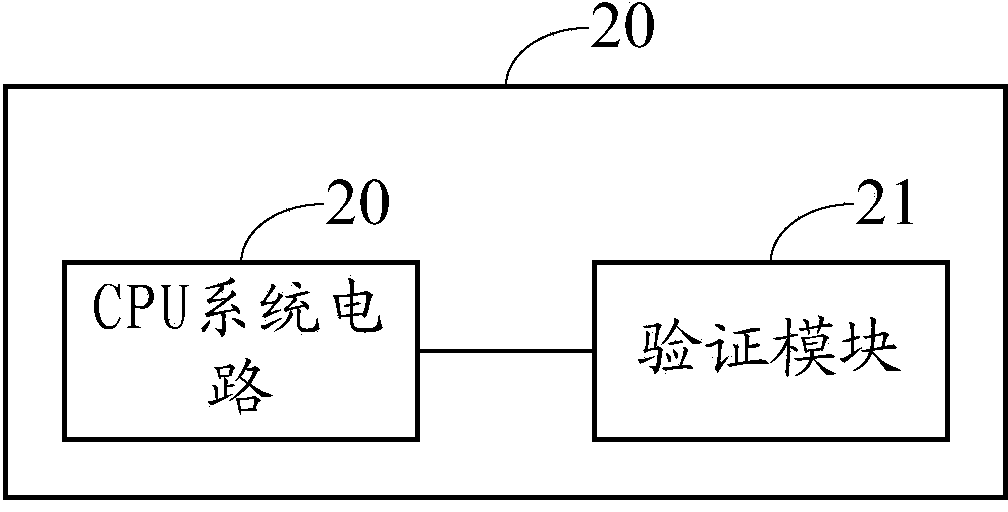

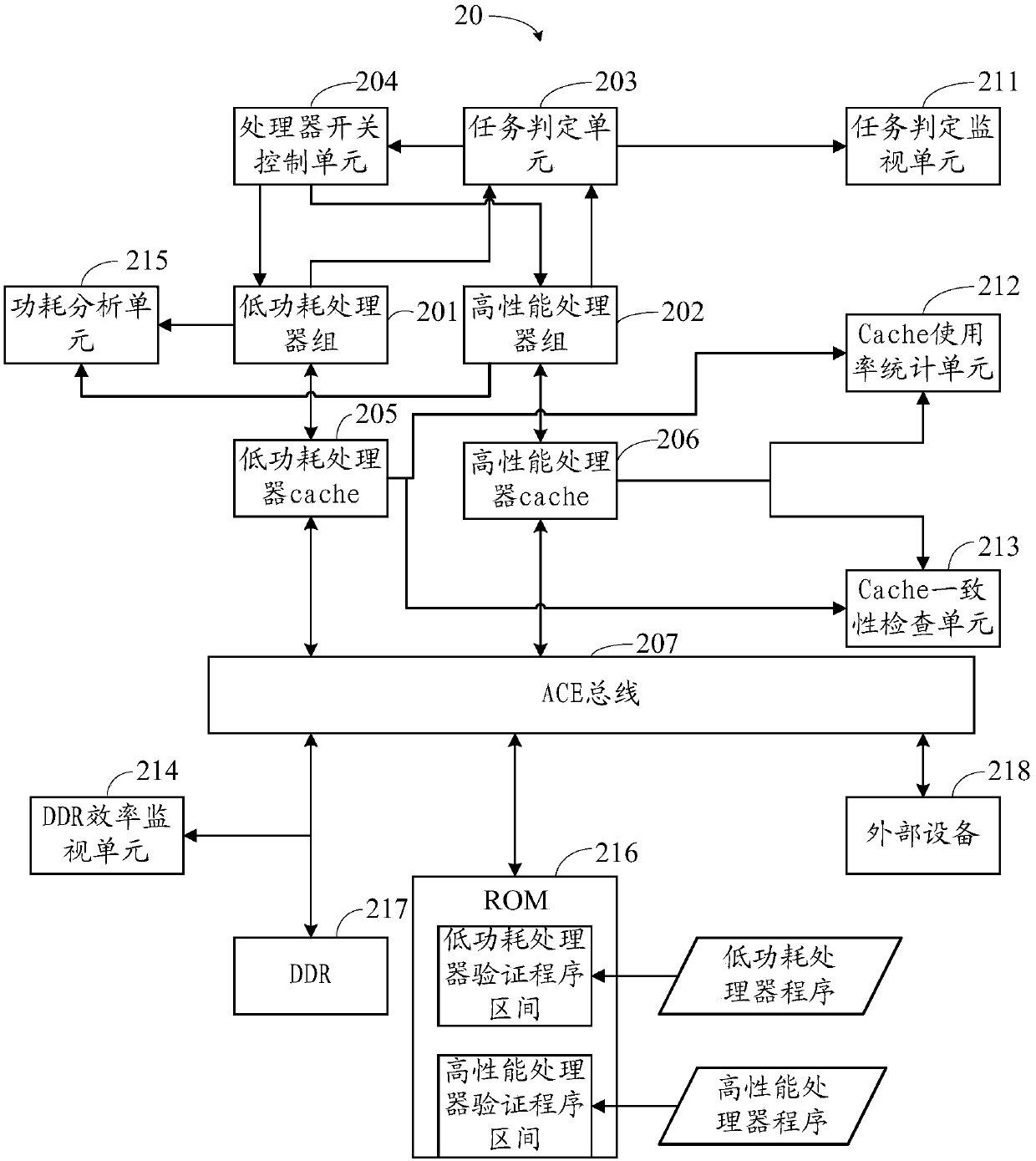

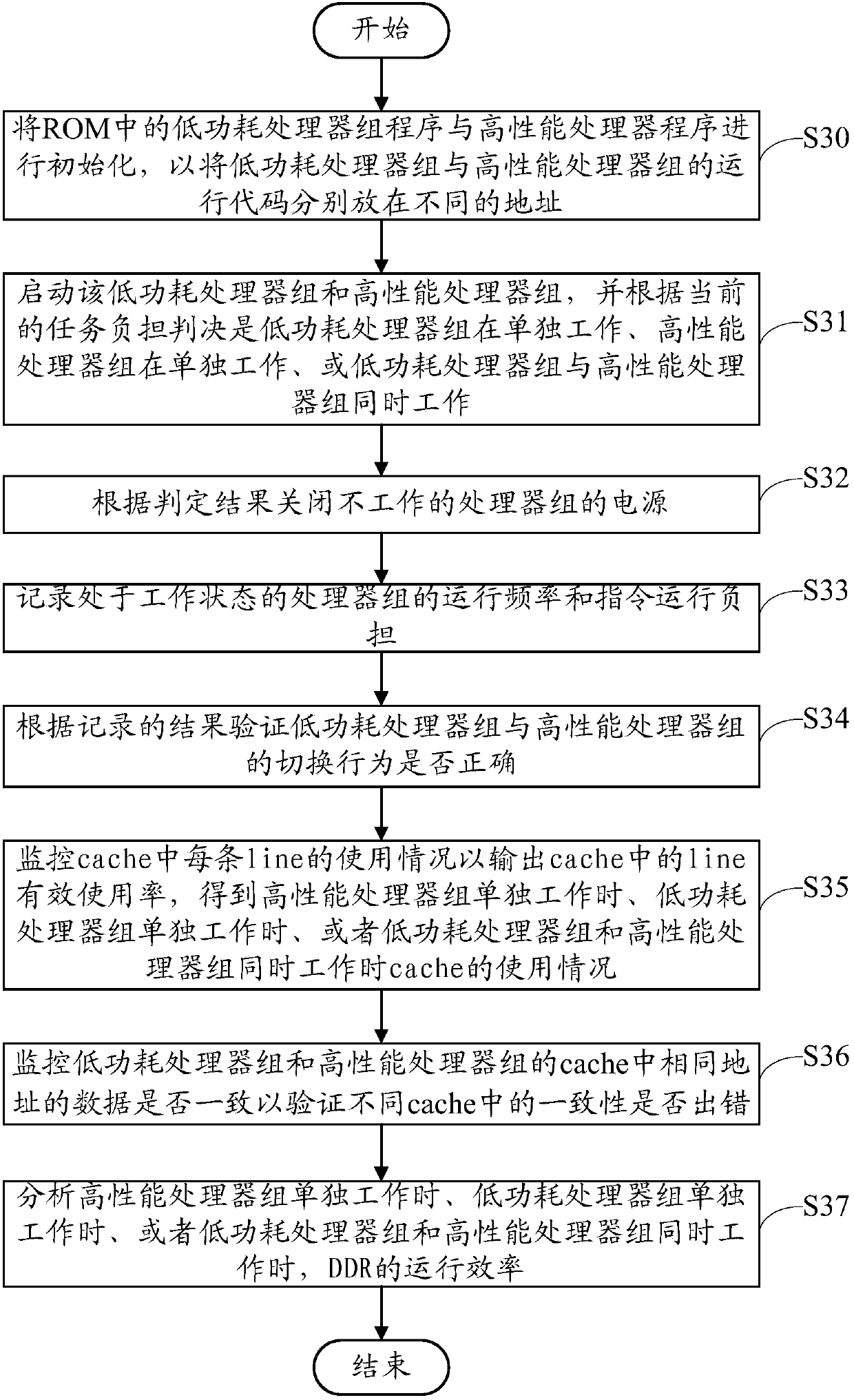

Verification method and device for central processor system

ActiveCN104199777AReduce workloadHigh degree of automationSoftware testing/debuggingValidation methodsAnalysis working

The invention provides a performance testing device and method for a central processor system. The method comprises the steps that stored low-power-consumption processor set programs and high-performance processor programs are initialized, so that corresponding processor set running codes are put on different addresses; the working processor set is judged according to the current task burden to close the power source of processor sets which do not work; the running frequency of the working processor set is recorded to verify whether the switch behavior is correct or not; storage devices are monitored to obtain the availability of the working processor set towards the storage devices; whether the data of the low-power-consumption processor sets and the data of the high-performance processor sets are consistent on the same address in the storage devices is monitored to verify whether consistencies in the different storage devices have mistakes or not; the running efficiency of a DDR of the working processor set is analyzed. Through the verification method and device for the central processor system, a circuit with heterogeneous multi-core processors can be verified, the workload is lightened for engineers, the automation degree is high, and verification is comprehensive.

Owner:FUZHOU ROCKCHIP SEMICON

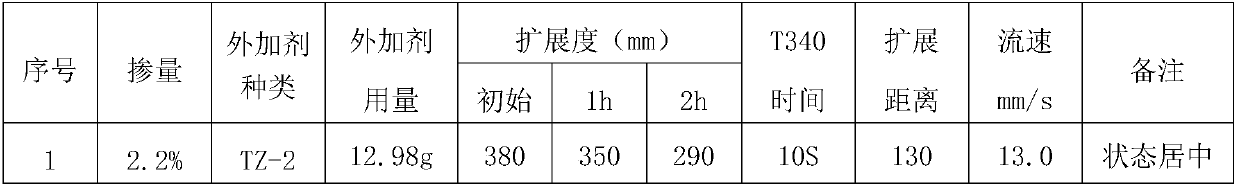

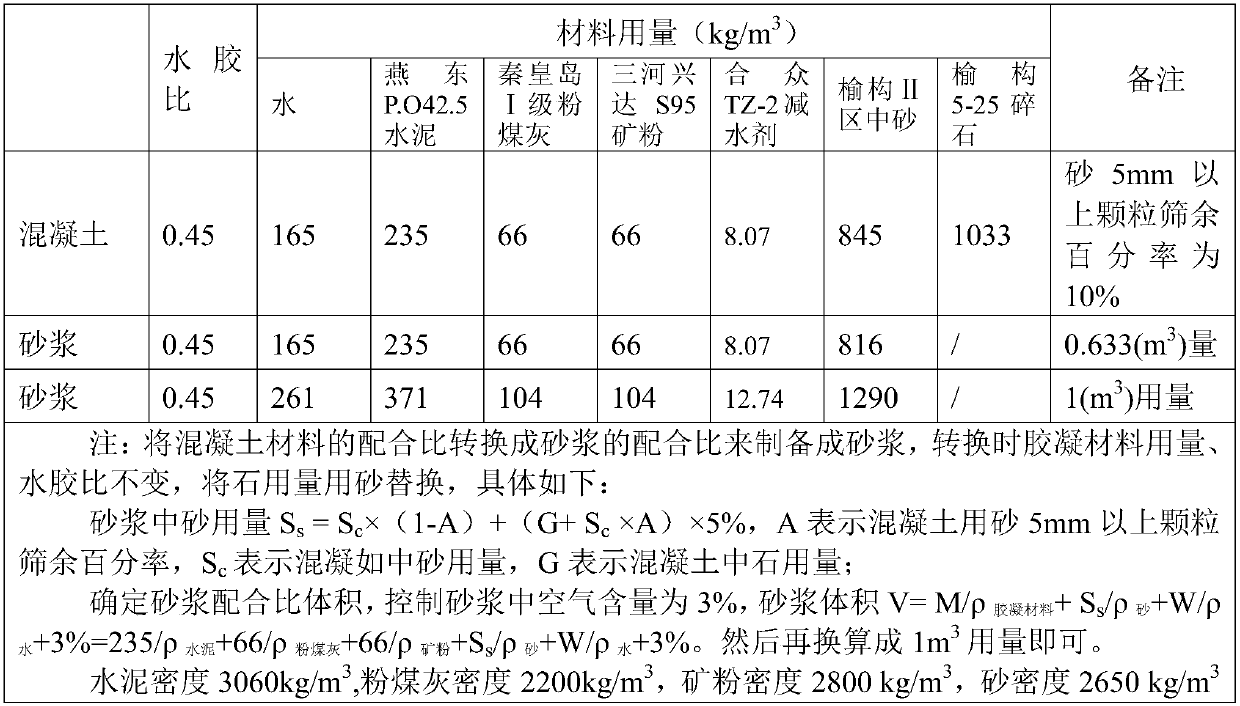

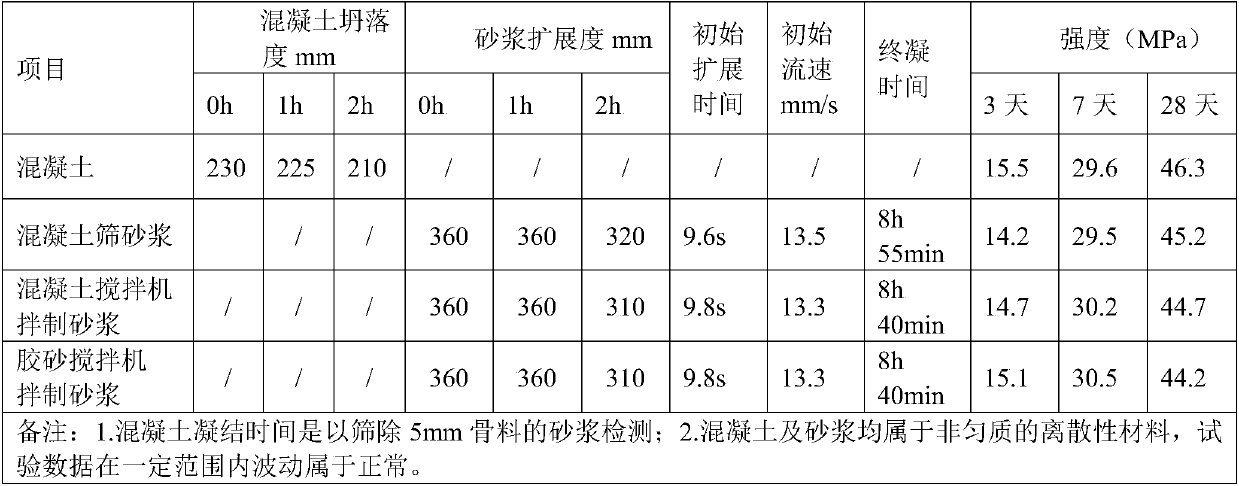

Method for detecting flow velocity of concrete additive compatible mortar

InactiveCN107843520AReduce verification timeConvenient verificationFlow propertiesGlass sheetMaterials science

The invention relates to a method for detecting flow velocity of concrete additive compatible mortar, belonging to the technical field of concrete. The method comprises the following steps: A, determining T340 time, namely putting a divergence drum in the center of a glass plate, pouring mortar added with an additive into the divergence drum, striking off after no bubble escapes and a mortar surface does not sink any more, then vertically lifting the divergence drum at a constant speed, starting timing when the divergence drum leaves the glass plate, and stopping timing when mortar divergencediameter reaches 340mm, wherein the obtained time is T340 time; and B, determining the flow velocity of the mortar, namely calculating by utilizing the formula that the flow velocity is equal to (340-inner diameter of the divergence drum) / 2 / T340 time, wherein the unit of the inner diameter of the divergence drum is mm, the unit of the T340 time is s, and the unit of the flow velocity is mm / s. Thedetection method provided by the invention is simple and is not influenced by the environment and external factors, and the detected flow velocity of the mortar is accurate.

Owner:河北合众建材有限公司

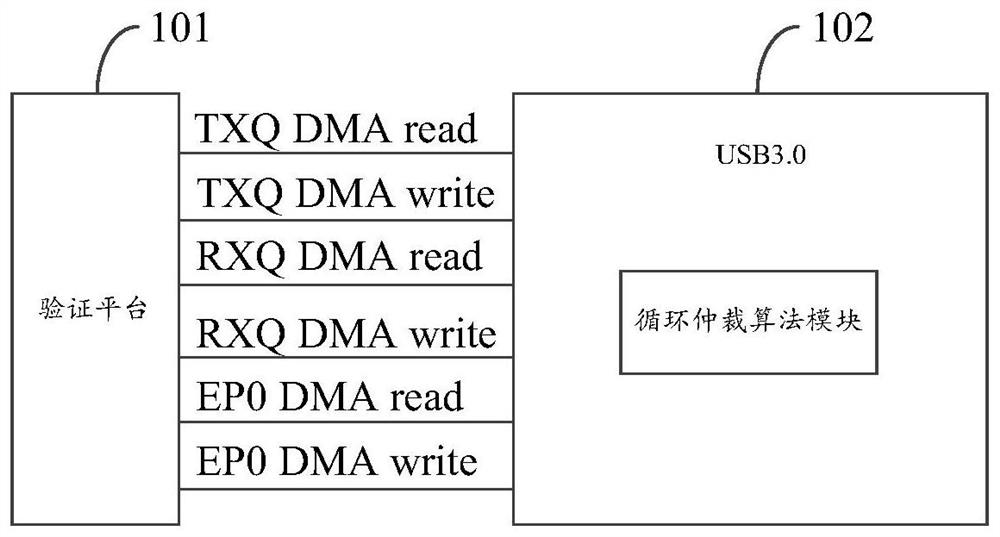

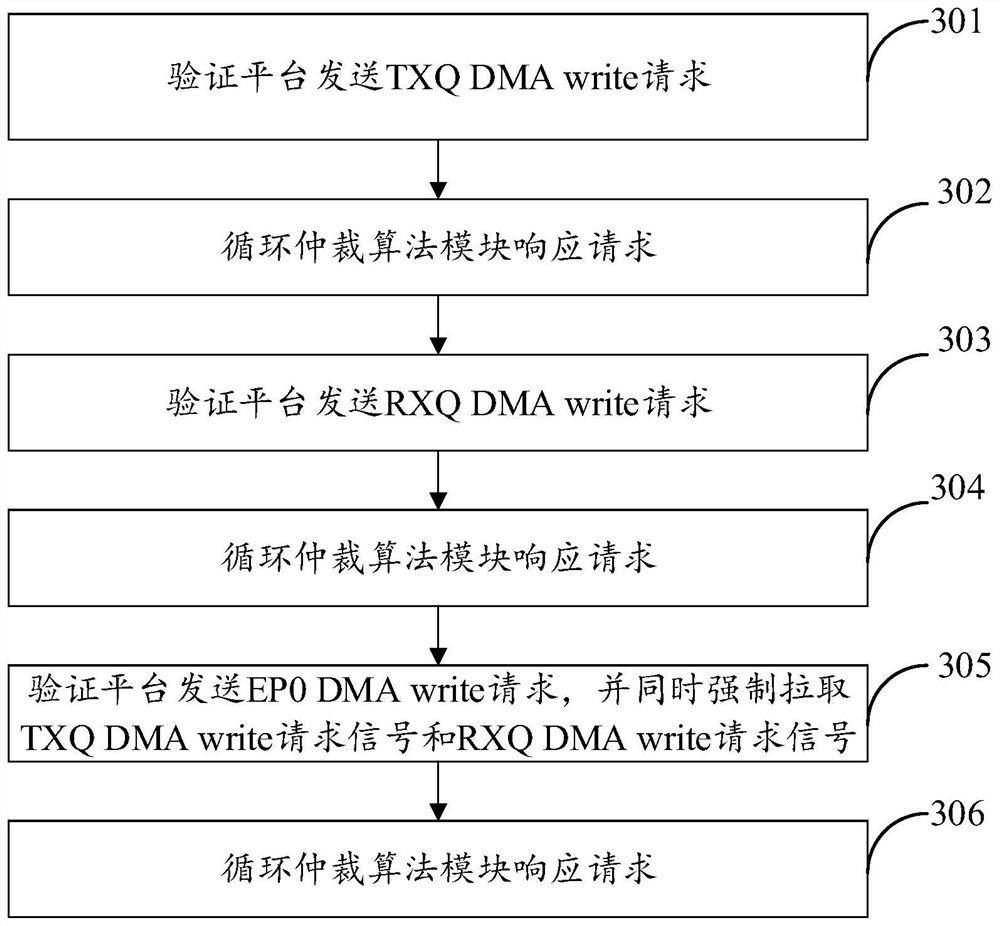

Chip verification method and device, electronic equipment and storage medium

The invention provides a chip verification method and device, electronic equipment and a storage medium. The method comprises the following steps: a verification platform sends a first verification request of a first preset channel to a chip, and forcibly pulls a signal of a second preset channel corresponding to a cyclic arbitration algorithm module, so that the cyclic arbitration algorithm module receives the request of a first preset channel and the request of a second preset channel; and the verification platform receives a first verification result sent by the chip, and the first verification result comprises a request and a response result corresponding to a target channel responded by the cyclic arbitration algorithm module according to the priority of the current channel signal soas to realize chip verification. According to the embodiment of the invention, the scene that the cyclic arbitration module receives the requests sent by the plurality of channels at the same time canbe covered, so that the chip can be verified more comprehensively.

Owner:HYGON INFORMATION TECH CO LTD

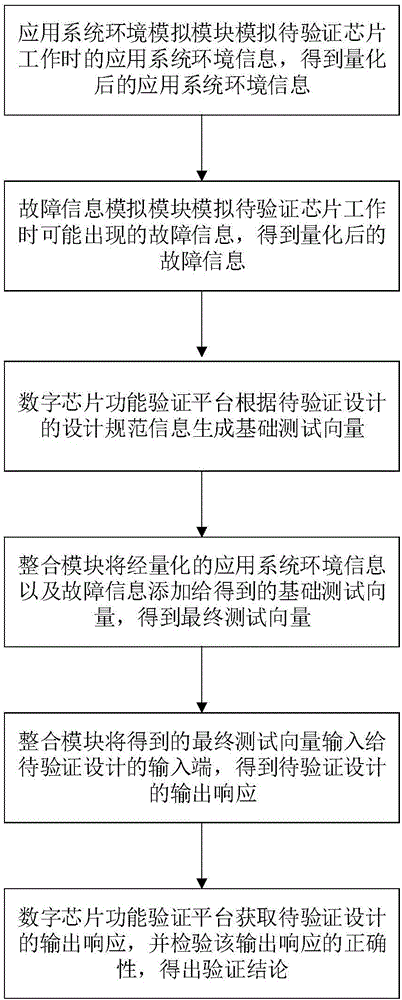

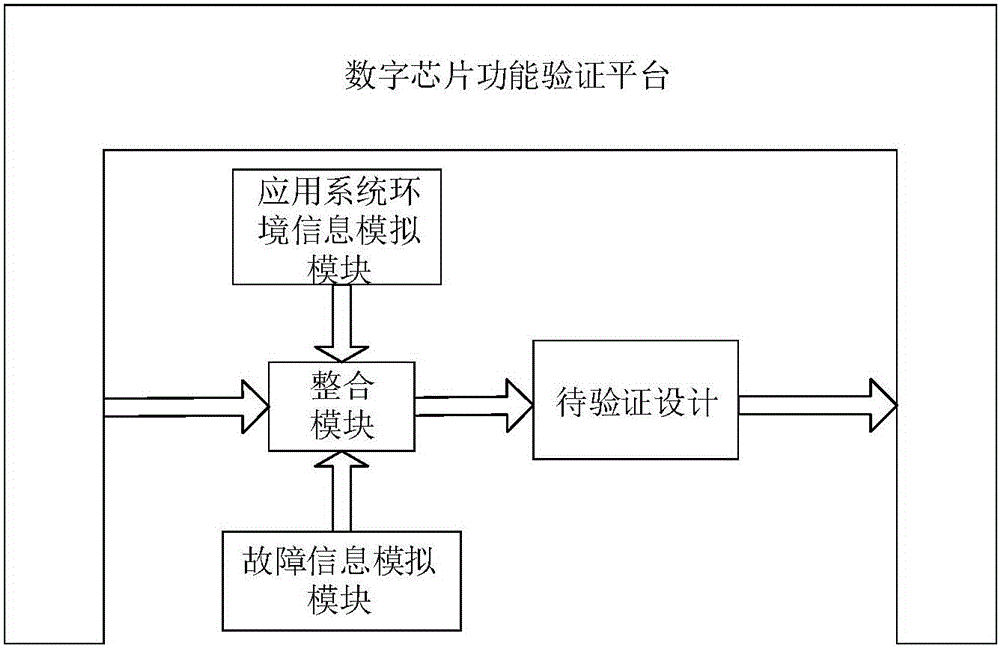

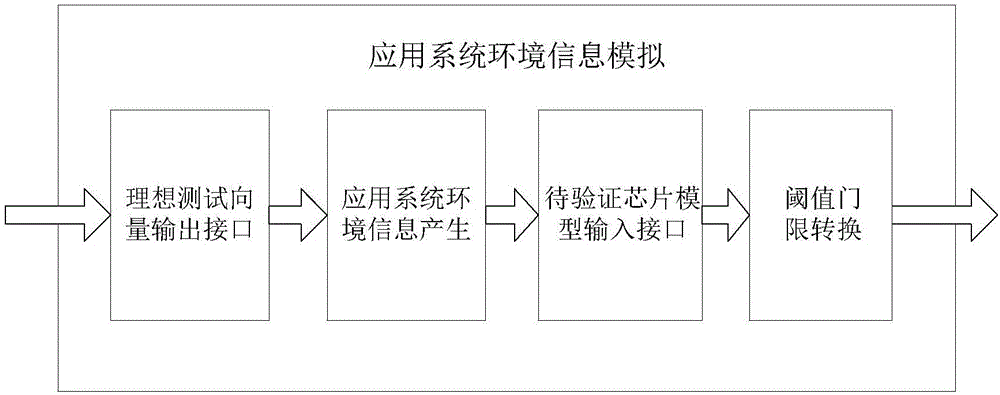

Digital chip function verifying method and system

InactiveCN106295048AComprehensive verificationImprove accuracyDesign optimisation/simulationSpecial data processing applicationsValidation methodsComputer module

The invention provides a digital chip function verifying method and system, and is used for solving the technical problems that verifying accuracy is low in the prior art. The environmental factor of an application system and influence of fault information to verifying results are considered. The verifying method comprises the following steps: simulating environmental information of the application system; simulating the fault information; generating a foundation test vector according to a design specification of a design to be verified; integrating the environmental information and the fault information with the foundation test vector; inputting the integrated vector to the design to be verified to obtain output response; and inputting the output response to a digital chip function verifying platform, and inspecting correctness of the output response to obtain verifying conclusions. The verifying system comprises a digital chip function verifying platform and the design to be verified, wherein the digital chip function verifying platform is connected with the design to be verified end to end, an output end of the digital chip function verifying platform is connected with an integrating module, an input end of the integrating module is connected with an application system environmental information simulating module and a fault information simulating module, and an output end of the integrating module is connected with an input end of the design to be verified.

Owner:XIDIAN UNIV

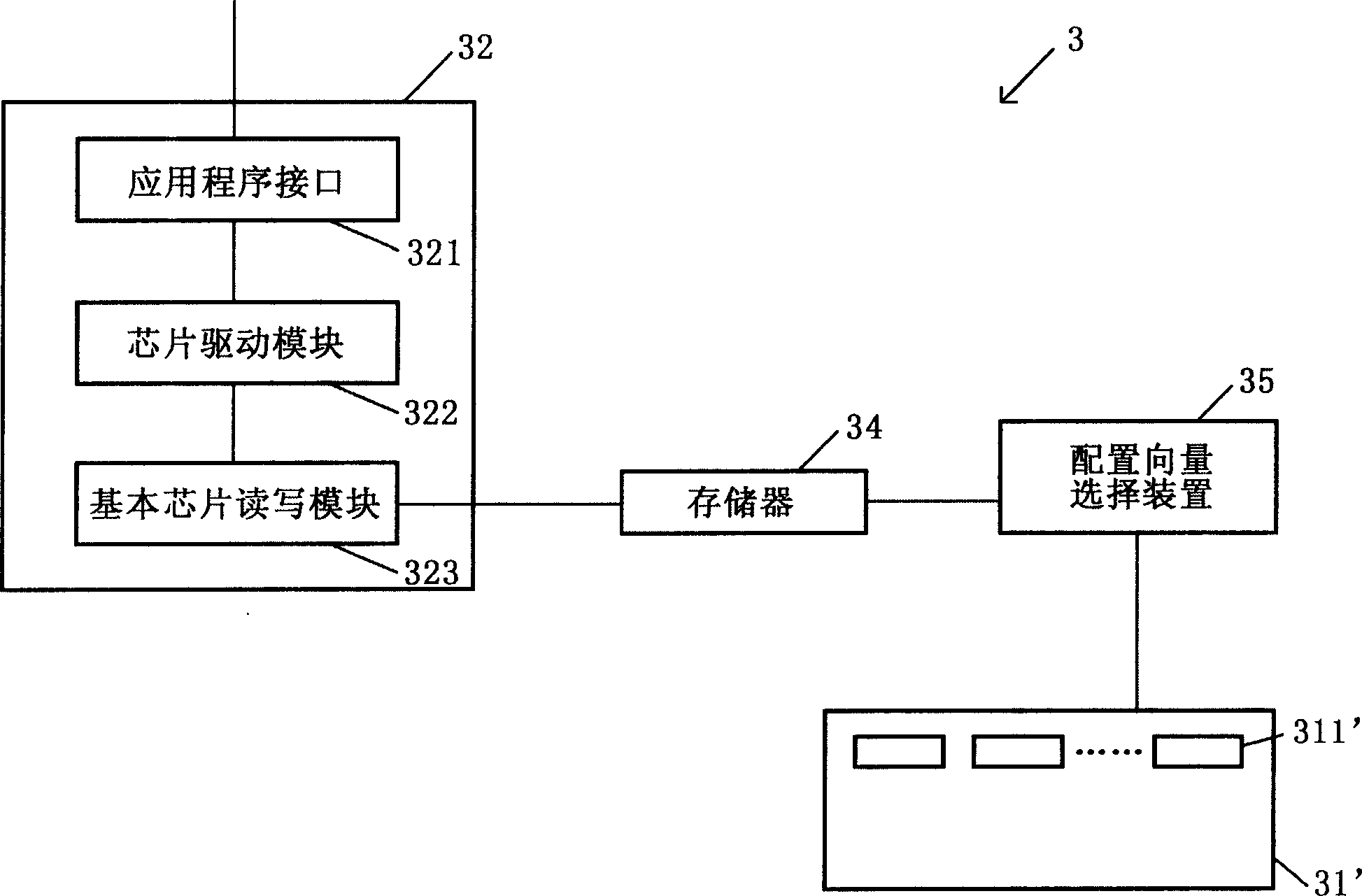

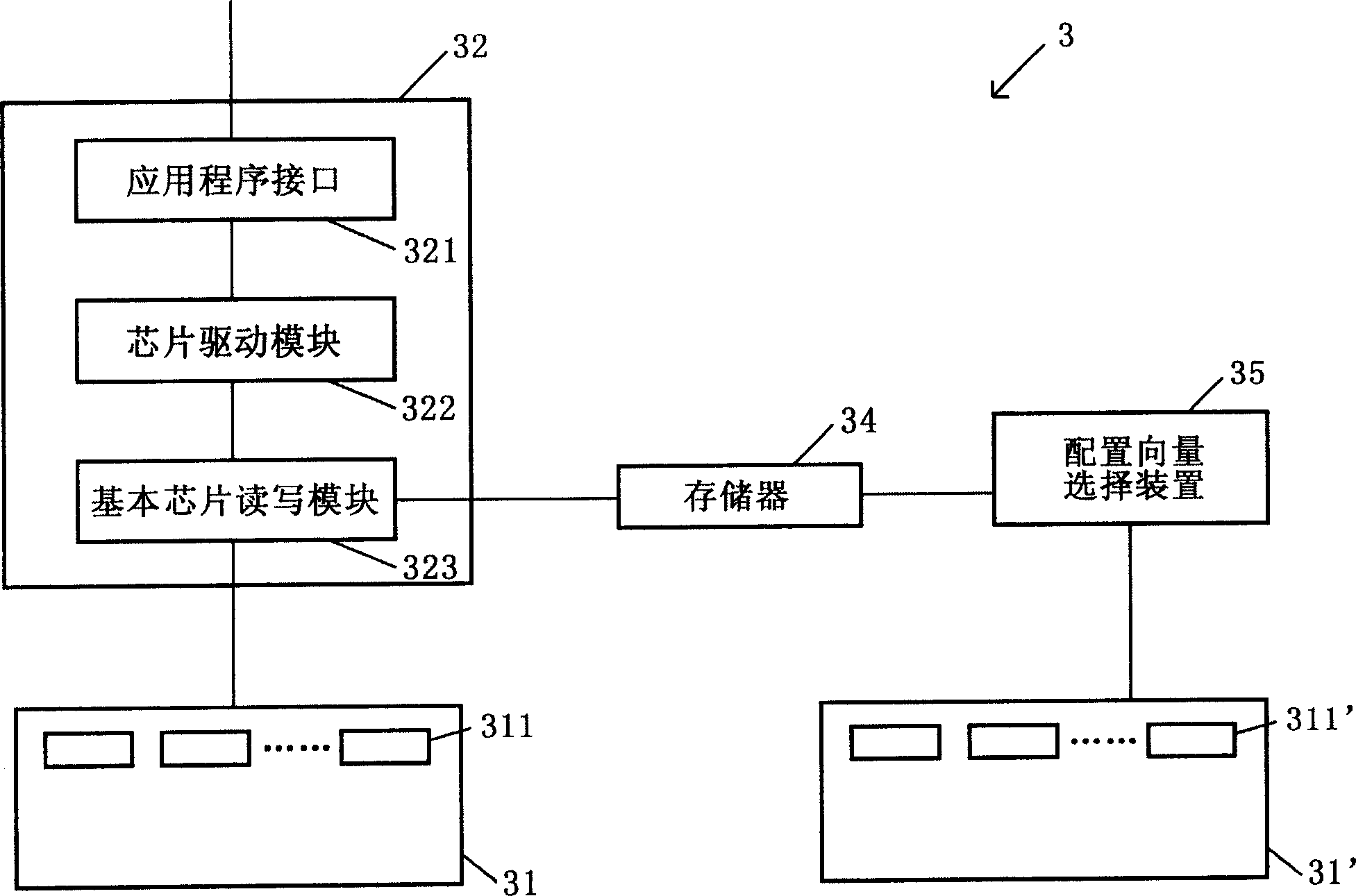

Chip examination system and method

InactiveCN1719417AComprehensive verificationIncrease the number ofError detection/correctionApplication softwareVerification system

The present invention provides a chip verification system and method. Said system includes a memory, an application program module which is used for converting the application program used in chip application into correspondent configuration vector and storing said configuration vector into the described memory and a configuration vector selection device which is used for selecting configuration vector from memory and inputting the selected configuration vector into the chip required for verification.

Owner:VIMICRO CORP

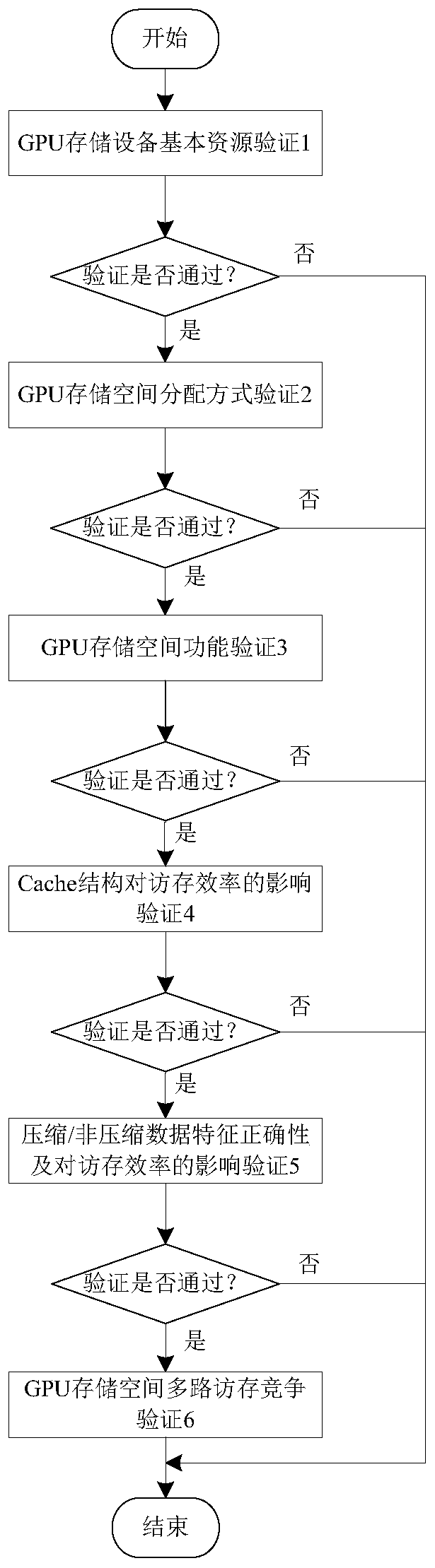

GPU storage system verification method

ActiveCN111078514AComprehensive verificationEfficient verificationHardware monitoringImage memory managementGraphicsComputer architecture

The invention belongs to the field of computer graphics, and particularly relates to a GPU storage system verification method. The verification method comprises the steps of GPU storage device basic resource verification (1), GPU storage space allocation mode verification (2), GPU storage space function verification (3), influence verification (4) of a Cache structure on memory access efficiency,verification (5) of compression / non-compression data feature correctness and influence on the memory access efficiency, and GPU storage space multipath memory access competition verification (6). Aiming at GPU storage system characteristics, comprehensive and efficient GPU storage system verification is realized from functions and performance of the storage system.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

Automatic throttle actuator excitation method for ground tests

The invention discloses an automatic throttle actuator excitation method for ground tests, and belongs to the field of aircraft design. In an automatic throttle ground test, a simulation device is often used for excitation of an automatic throttle actuator to achieve control simulation, power supply and interface communication necessary to the automatic throttle ground test. According to the invention, an automatic throttle actuator excitation device is used, in accordance with certain steps, for completing proper excitation of the automatic throttle actuator and detection, determination and disposal of fault statuses of the automatic throttle actuator. The automatic throttle actuator excitation method for the ground tests have the beneficial effects of reducing the scale of the tests, shortening the cycle of the tests and verifying the automatic throttle actuator more comprehensively.

Owner:SHENYANG AIRCRAFT DESIGN INST AVIATION IND CORP OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com