Chip verification method and device, electronic equipment and storage medium

A verification method and a verification device technology are applied in the fields of chip verification methods, devices, electronic equipment and storage media, and can solve problems such as inability to verify chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

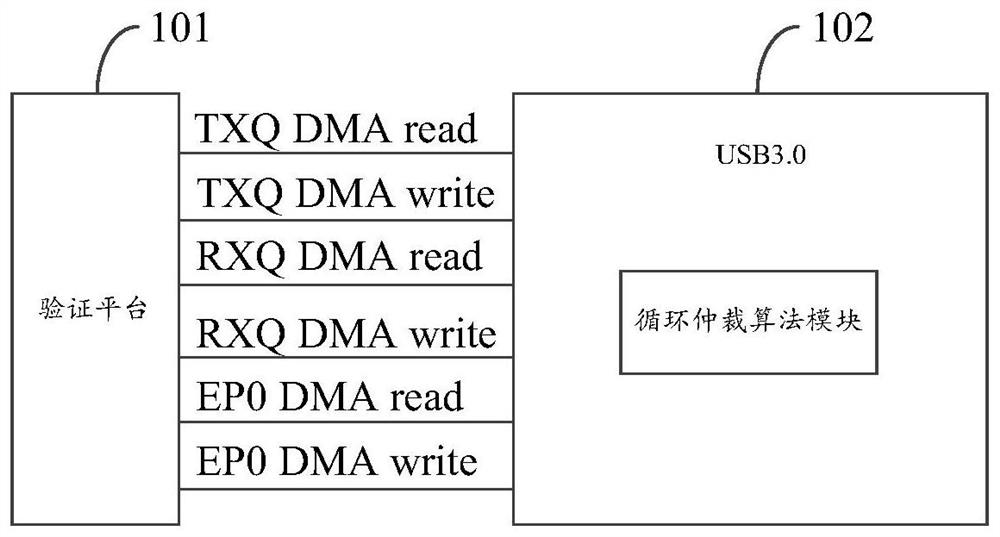

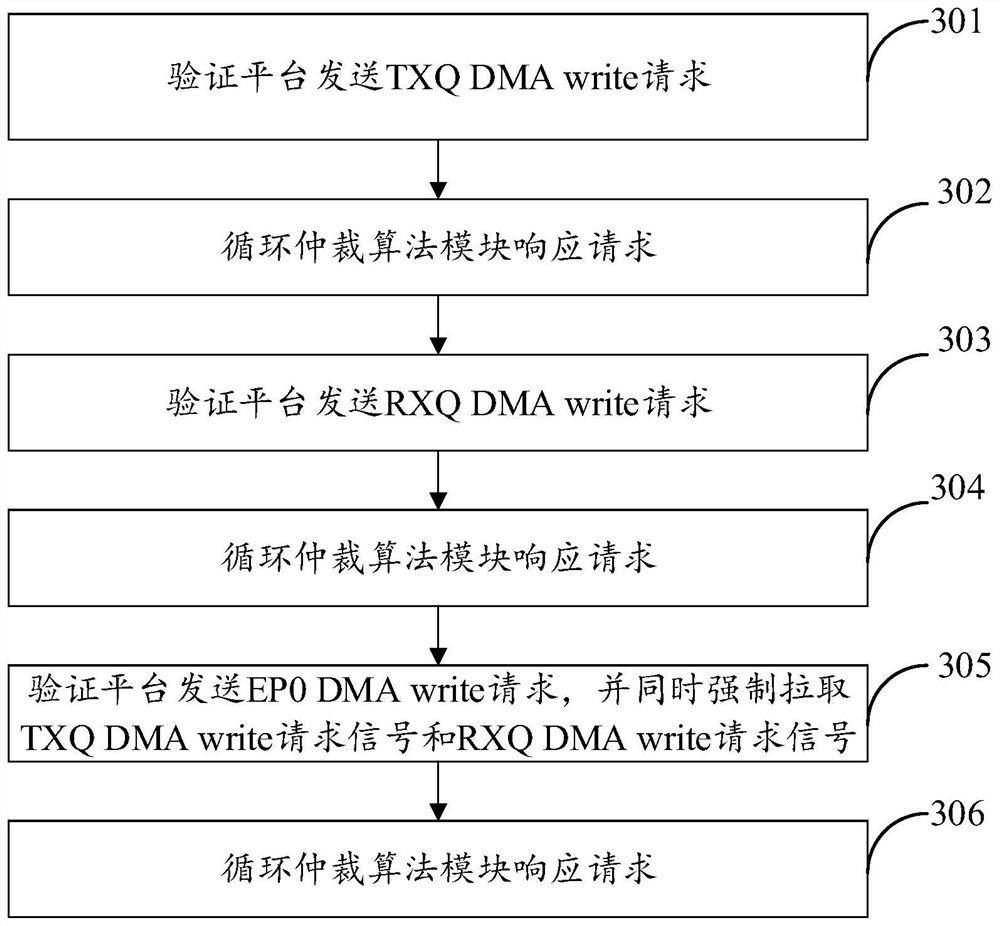

[0027] The technical solutions in the embodiments of the present application will be described below with reference to the drawings in the embodiments of the present application.

[0028] Universal Verification Methodology (Universal Verification Methodology, referred to as UVM) is a typical representative in chip verification. The most important multiplexing unit in the UVM architecture is the bus agent (Agent). The verifier generates transaction-level packets (transaction) by writing the sequence (Sequence) in the sequencer (Sequencer), and converts it into an interface stimulus through the driver (Driver). The signal acts on the bus interface, and the monitor (Monitor) collects the bus signal, converts it back into a transaction-level packet, and sends it to the scoreboard (scoreboard) for automatic comparison.

[0029] During chip verification, the UVM system is communicated with the device under test (DUT), and the UVM system sends the generated stimulus signal to the DUT...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com