Method for building automated co-verification platform on the basis of memory access driving

A memory access and collaborative verification technology, applied in the field of automatic collaborative verification platform construction, can solve problems such as inability to guarantee, increase in the number of test cases, and function B errors, and achieve the effects of convenient debugging, optimized test methods, and comprehensive verification.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In view of the deficiencies in the prior art, the inventor of this case was able to propose the technical solution of the present invention after long-term research and extensive practice. The technical solution, its implementation process and principle will be further explained as follows.

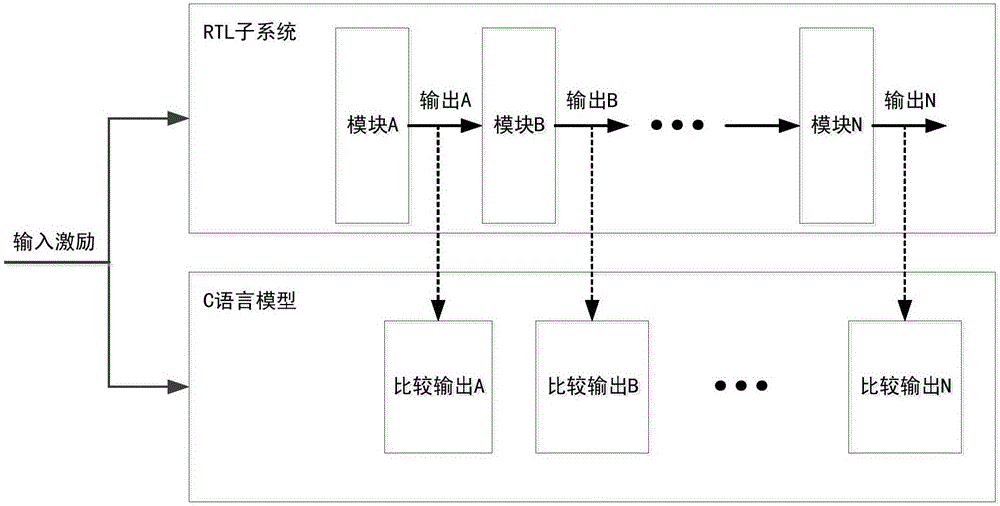

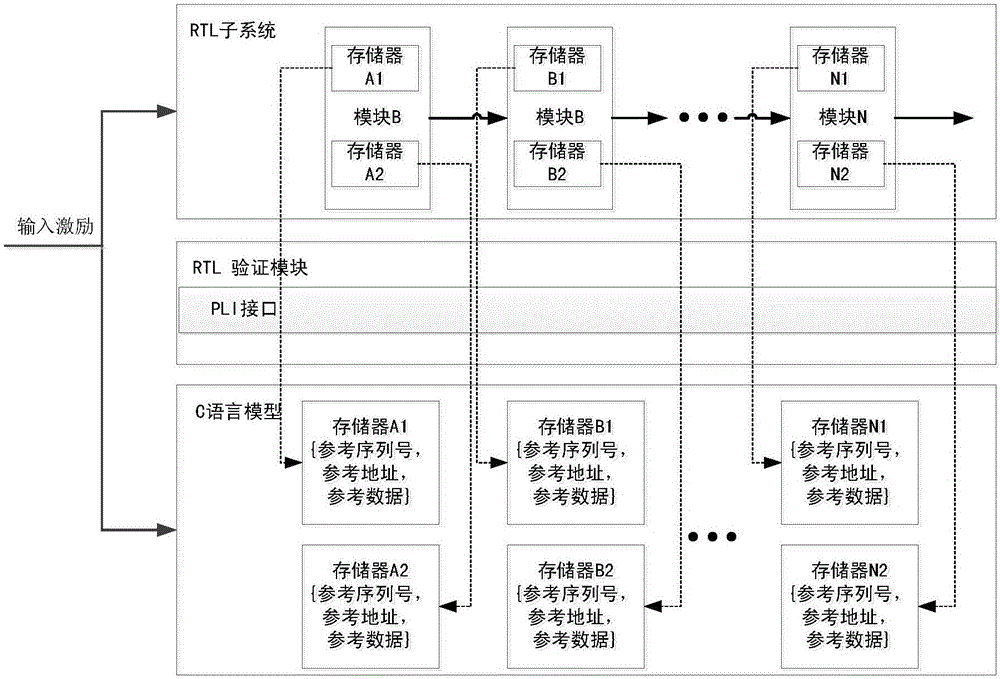

[0031] The present invention proposes a method for building an automated collaborative verification platform driven by memory access. The core of which is to use the internal memory of the module as the basic verification unit to construct an automated collaborative verification platform driven by memory access, specifically including RTL subsystems and programming languages. Functional model and RTL verification module. The memory in the RTL subsystem is used as the basic verification unit of the cooperative verification of the embodiment of the present invention; the programming language function model is used to generate reference data, so as to realize the comparison with the r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com